# Capacitive Sensors and their Interface Circuits

by

Aditi Rane

A thesis submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Master of Science

> Auburn, Alabama May 14, 2010

Keywords: Capacitive Sensors, PCB, Phase Delay

Copyright 2010 by Aditi Rane

Approved by

Robert Dean, Chair, Assistant Professor of Electrical and Computer Engineering Thaddeus Roppel, Associate Professor of Electrical and Computer Engineering John Hung, Professor of Electrical and Computer Engineering

# Abstract

An innovative technique has been developed to interface to capacitive sensors. This is a new technique where the unknown capacitance is connected with a resistance to generate a relative change of frequency in a CMOS inverter circuit. This change is proportional to the unknown capacitance. This frequency is then measured using a logical Frequency Locked Loop circuit which is programmed onto a general purpose FPGA board. This technique produces a nearly linear response, is tunable over different capacitance ranges and possesses a fast response time.

#### Acknowledgments

I would like to take this opportunity to thank Dr. Robert Dean, Charles Ellis and everyone else in the Electrical Engineering Department who have helped me during the course of my Masters Degree. I would also like to thank my friends, Sathya, Rachan, Nida, Madhu, Anant, Medha, Shweta, Trupti and Colin for all their help. A special thanks to Mithun Chandrasekhar for his constant encouragement and unwavering support and my parents, Kiran and Shubha Rane, for their constant sacrifices and for bringing me up the way they did. I would not be here without their belief in me.

# Table of Contents

| Abstrac   | et        |                                                              | ii  |

|-----------|-----------|--------------------------------------------------------------|-----|

| Acknow    | ledgme    | $\operatorname{nts}$                                         | iii |

| List of I | Figures   |                                                              | vii |

| List of ' | Tables    |                                                              | xii |

| 1 In      | troducti  | on                                                           | 1   |

| 2 Li      | terature  | e Review for Capacitive Sensors and their Interface Circuits | 2   |

| 2.1       | Capac     | itive Sensors                                                | 2   |

|           | 2.1.1     | Spacing Variation                                            | 3   |

|           | 2.1.2     | Area Variation                                               | 4   |

|           | 2.1.3     | Three Plate Systems                                          | 6   |

|           | 2.1.4     | Multiple Plate Systems                                       | 7   |

|           | 2.1.5     | 2D Sensors                                                   | 8   |

|           | 2.1.6     | Sensing of other Variables                                   | 8   |

| 2.2       | Capac     | itive Sensor Interface Circuits                              | 10  |

|           | 2.2.1     | Excitation frequency, F                                      | 10  |

|           | 2.2.2     | Oscillator                                                   | 10  |

|           | 2.2.3     | CMOS Schmitt Inverter                                        | 11  |

|           | 2.2.4     | Synchronous demodulator circuits                             | 12  |

| 2.3       | Freque    | ency Measurement Techniques                                  | 13  |

|           | 2.3.1     | Frequency Synthesizer                                        | 14  |

|           | 2.3.2     | Solid-state Digital Circuits                                 | 16  |

| 3 Os      | scillator | Circuits                                                     | 17  |

| 3.1       | Introd    | uction $\ldots$                                              | 17  |

|   |     | 3.1.1 LR Relaxation Oscillator                                            | 8          |

|---|-----|---------------------------------------------------------------------------|------------|

|   |     | 3.1.2 RC Relaxation Oscillators                                           | 9          |

|   |     | 3.1.3 Oscillators using Inverters                                         | 20         |

|   | 3.2 | Experimental Validation                                                   | 20         |

|   | 3.3 | Layout and Design 2                                                       | 27         |

|   |     | 3.3.1 PCB Layout                                                          | 27         |

|   |     | 3.3.2 PCB Board with Components                                           | 9          |

| 4 | Fre | equency Locked Loop Prototype                                             | 1          |

|   | 4.1 | Theory and Prototyping                                                    | 31         |

|   |     | 4.1.1 Introduction                                                        | 1          |

|   |     | 4.1.2 FLL Components                                                      | 1          |

|   |     | 4.1.3 FLL Circuit Prototype                                               | 5          |

|   | 4.2 | Interfacing to the FLL and GUI                                            | 2          |

|   | 4.3 | Software GUI                                                              | 4          |

|   | 4.4 | Testing with Oscillator Circuit I                                         | 8          |

|   | 4.5 | Testing with Oscillator Circuit II                                        | 1          |

| 5 | Fre | quency Locked Loop Application: Mass of Water Drop Measurement 5          | 4          |

|   | 5.1 | Sensor Circuit                                                            | 4          |

|   |     | 5.1.1 Capacitors as Sensors                                               | 5          |

|   |     | 5.1.2 Implementation                                                      | 6          |

|   |     | 5.1.3 Interfacing the Oscillator Circuit with the Fringing Field Sensor 5 | 9          |

|   | 5.2 | Testing                                                                   | 52         |

|   | 5.3 | Results                                                                   | 52         |

| 6 | Re  | lated Work [39]                                                           | '1         |

|   | 6.1 | Theory                                                                    | '1         |

|   | 6.2 | Implementation                                                            | '8         |

|   | 6.3 | Estimating Resistance and Capacitance                                     | <b>'</b> 9 |

|    | 6.4    | Experimental Validation                        | 81 |

|----|--------|------------------------------------------------|----|

|    | 6.5    | Improved Implementation of this Technique [41] | 87 |

| 7  | Со     | onclusions                                     | 90 |

| 8  | Fu     | ture Work                                      | 91 |

| Bi | bliogr | aphy                                           | 92 |

# List of Figures

| 2.1  | Illustration of Plate Spacing Variation   | 3  |

|------|-------------------------------------------|----|

| 2.2  | Examples of Overlapping Capacitive Plates | 4  |

| 2.3  | Area Variation                            | 5  |

| 2.4  | Chevron Shape to combat tilt              | 5  |

| 2.5  | Adding a Third Electrode                  | 6  |

| 2.6  | Parallel Multiplates                      | 7  |

| 2.7  | Finger Position Sensor [6]                | 8  |

| 2.8  | Equivalent Circuit                        | 9  |

| 2.9  | RC Oscillator                             | 11 |

| 2.10 | CMOS Schmitt Inverter                     | 12 |

| 2.11 | Synchronous Demodulator                   | 13 |

| 2.12 | PLL based Frequency Synthesizer           | 15 |

| 3.1  | Block Diagram of Experimental Setup       | 21 |

| 3.2  | RC Inverter Oscillator Circuit 1          | 22 |

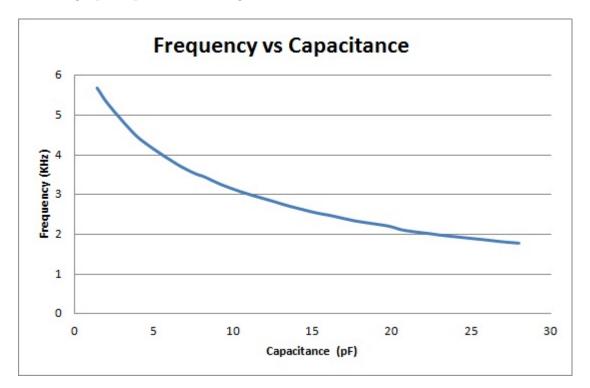

| 3.3  | Frequency vs Capacitance                  | 23 |

| 3.4  | Output Frequency at C=1pF $\dots \dots \dots$ | 23 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Output Frequency at C=15pF                                                                                                                    | 24 |

| 3.6  | Output Frequency at C=28pF                                                                                                                    | 24 |

| 3.7  | RC Inverter Oscillator Circuit 2                                                                                                              | 24 |

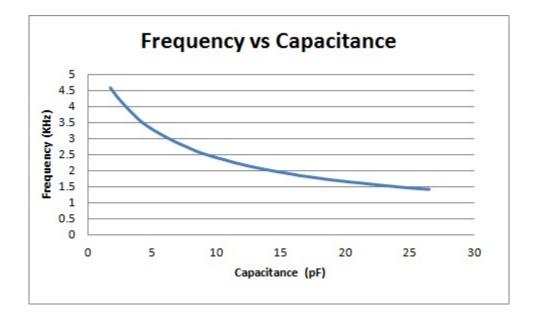

| 3.8  | Frequency vs Capacitance                                                                                                                      | 26 |

| 3.9  | Output Frequency at C=1pF                                                                                                                     | 27 |

| 3.10 | Output Frequency at C=15pF                                                                                                                    | 27 |

| 3.11 | Output Frequency at C=26pF                                                                                                                    | 27 |

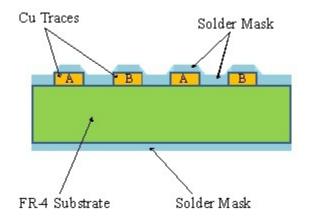

| 3.12 | Cross Section of a two-layer PCB                                                                                                              | 28 |

| 3.13 | PCB Layout of Circuit 1 in ViewMasterEZ                                                                                                       | 29 |

| 3.14 | PCB Layout of Circuit 2 in ViewMasterEZ                                                                                                       | 30 |

| 3.15 | Completed PCB                                                                                                                                 | 30 |

| 4.1  | Block Diagram of FLL                                                                                                                          | 32 |

| 4.2  | Frequency Comparator                                                                                                                          | 32 |

| 4.3  | Up/Down Counter Circuit                                                                                                                       | 33 |

| 4.4  | Synchronous Counter at Input                                                                                                                  | 34 |

| 4.5  | Synchronous Counter connected to Comparator                                                                                                   | 35 |

| 4.6  | Logical Comparator                                                                                                                            | 35 |

| 4.7  | A 4-bit FLL circuit                                                               | 37 |

|------|-----------------------------------------------------------------------------------|----|

| 4.8  | An 8-bit FLL circuit                                                              | 38 |

| 4.9  | A 12-bit FLL circuit                                                              | 39 |

| 4.10 | ATMEL Board which is attached to the parallel port on the PC                      | 40 |

| 4.11 | FPGA Board attached to the PC                                                     | 40 |

| 4.12 | The output interface for programming the EPROM                                    | 41 |

| 4.13 | Screenshot of the GUI in Visual Basic                                             | 44 |

| 4.14 | GUI Interface                                                                     | 45 |

| 4.15 | Experiment I : Frequency vs Capacitance                                           | 50 |

| 4.16 | Experiment II : Frequency vs Capacitance                                          | 53 |

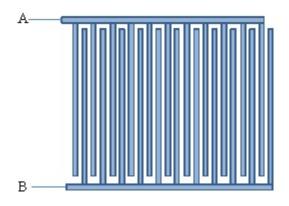

| 5.1  | Two Interdigitated Electrodes                                                     | 55 |

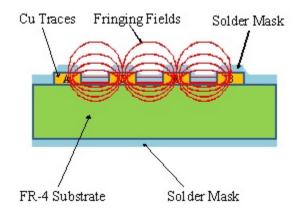

| 5.2  | A cross-sectional drawing of interdigitated electrodes realized in the Cu foil on |    |

|      | one side of a PCB                                                                 | 57 |

| 5.3  | A cross-sectional drawing of interdigitated electrodes realized in the Cu foil on |    |

|      | one side of a PCB where the red lines represent the electric field lines between  |    |

|      | the electrodes                                                                    | 57 |

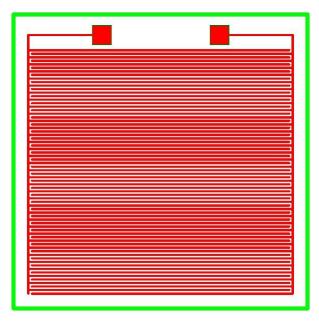

| 5.4  | The interdigitated electrode structure for the prototype device                   | 58 |

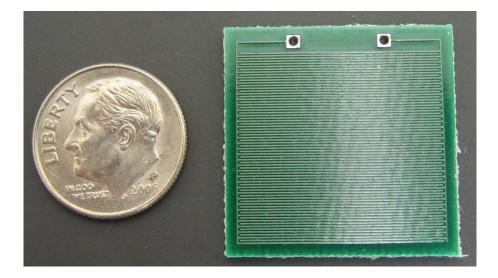

| 5.5  | The prototype device next to a dime                                               | 59 |

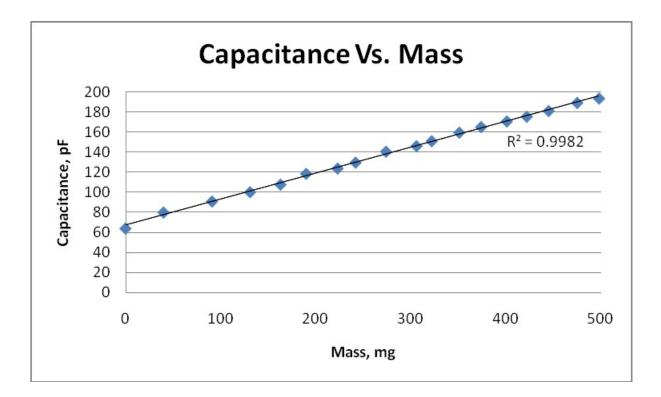

| 5.6  | Data from testing the prototype device                                            | 60 |

| 5.7  | ViewMaster layout of the Integrated Sensor                                      | 61 |

|------|---------------------------------------------------------------------------------|----|

| 5.8  | PCB with dam                                                                    | 61 |

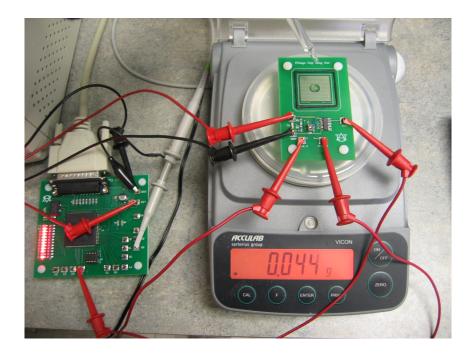

| 5.9  | Without water and weight zeroed out                                             | 63 |

| 5.10 | With water droplet                                                              | 63 |

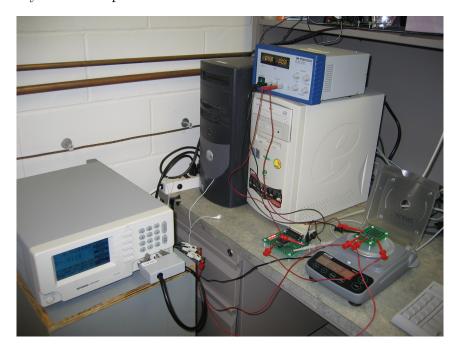

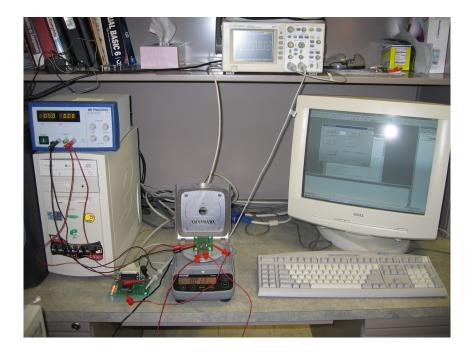

| 5.11 | Circuit connected to LCR Meter and PC                                           | 64 |

| 5.12 | Circuit connected to Oscilloscope and PC                                        | 65 |

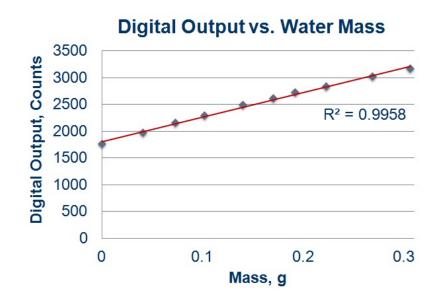

| 5.13 | Plot of Digital Output Vs. Mass of Added Water                                  | 65 |

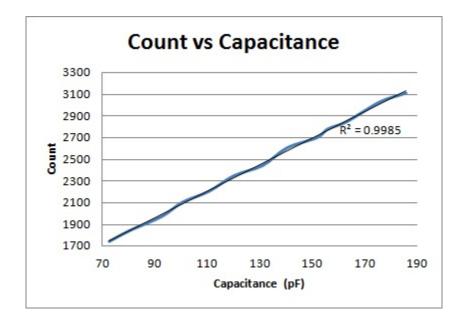

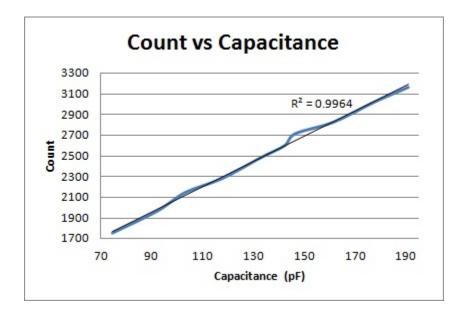

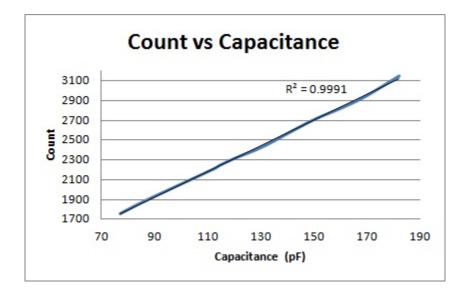

| 5.14 | Count vs Capacitance                                                            | 66 |

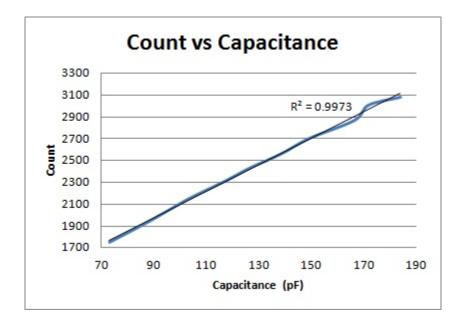

| 5.15 | Count vs Capacitance                                                            | 67 |

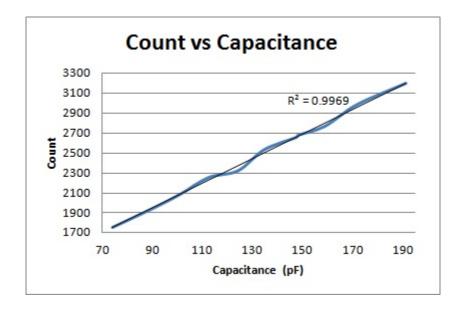

| 5.16 | Count vs Capacitance                                                            | 68 |

| 5.17 | Count vs Capacitance                                                            | 69 |

| 5.18 | Count vs Capacitance                                                            | 70 |

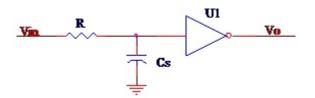

| 6.1  | Single Pole RC Low Pass Filter Circuit                                          | 71 |

| 6.2  | RC Circuit with an attached CMOS Inverter                                       | 73 |

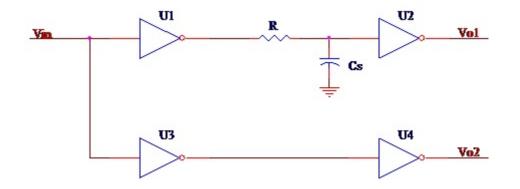

| 6.3  | Multi-Inverter Circuit                                                          | 74 |

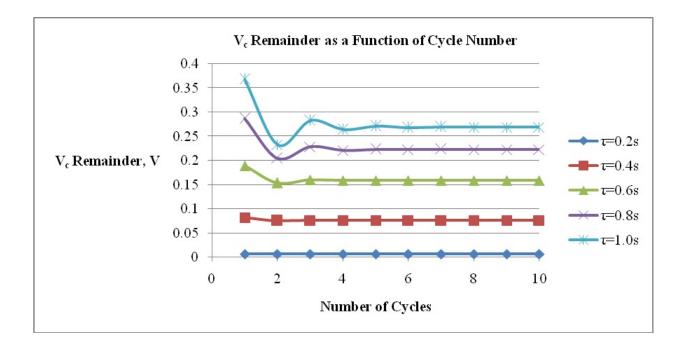

| 6.4  | A Plot Of The $V_c$ Remainder As A Function Of The Number Of State Cycles $\ .$ | 76 |

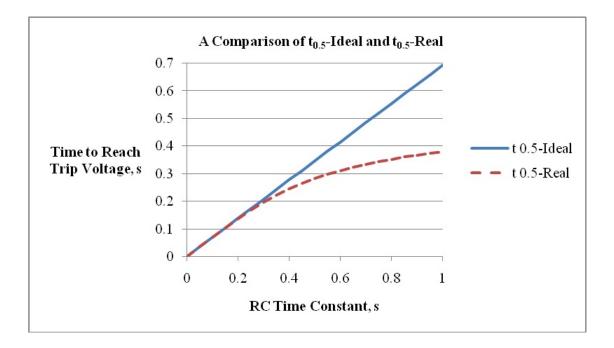

| 6.5  | A Plot Comparing $T_{0.5}$ -Ideal And $T_{0.5}$ -Real                           | 77 |

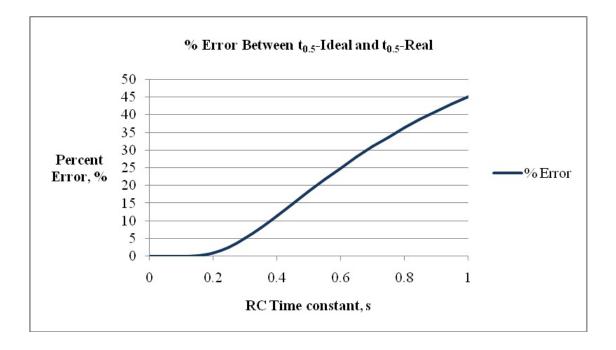

| 6.6  | A Graph Of The Percent Error Between $T_{0.5}$ -Ideal And $T_{0.5}$ -Real       | 77 |

| 6.7  | Ex-OR Gate                                                                                                                                                                                                                     | 78 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

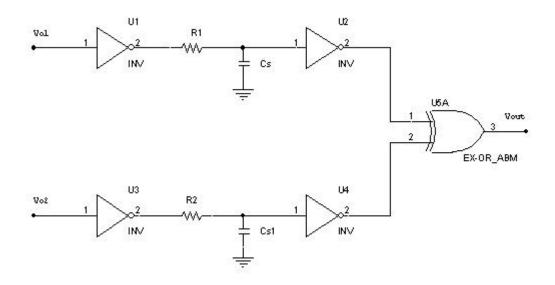

| 6.8  | Two-input RC Inverter Circuit                                                                                                                                                                                                  | 79 |

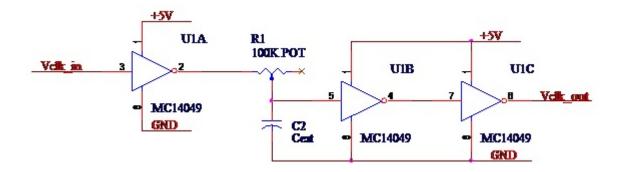

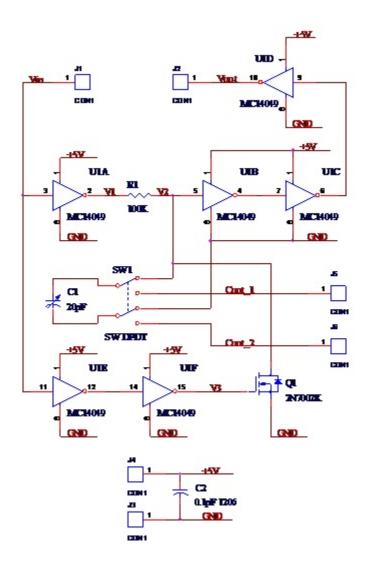

| 6.9  | A Schematic Diagram of the Implemented RC Inverter Circuit                                                                                                                                                                     | 82 |

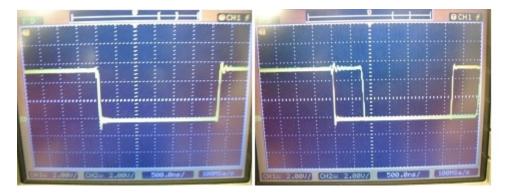

| 6.10 | Oscilloscope Images Of (I) The Two Inverter Circuit Output Voltages With $C_{ext}$<br>Removed And R Replaced By A Short (II) The Two Inverter Circuit Output                                                                   |    |

|      | Voltages With $C_{ext}$ Tuned To Its Maximum Capacitance Value $\ldots \ldots \ldots$                                                                                                                                          | 83 |

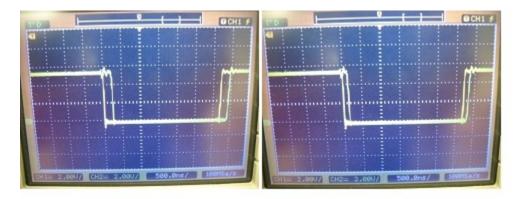

| 6.11 | Oscilloscope Images Of (I) The Two Inverter Circuit Output Voltages With $C_{ext}$<br>Tuned To Its Minimum Capacitance Value And (II) The Two Inverter Circuit<br>Output Voltages With $R = 6.07k\Omega$ And $C_{ext}$ Removed | 84 |

| 6.12 | Oscilloscope Images Of (I) The Phase Detector Output With $C_{ext}$ Tuned To Its<br>Minimum Capacitance Value And (II) The Phase Detector Output With $C_{ext}$<br>Tuned To Its Maximum Capacitance Value                      | 85 |

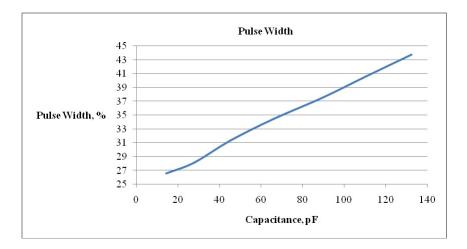

| 6.13 | A Plot Of The Percent Pulse Width Of The EX-OR Output Signal As A Function<br>Of External Capacitance                                                                                                                          | 86 |

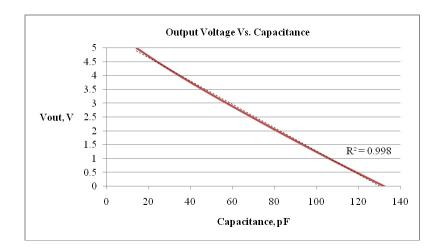

|      | A Plot Of The Capacitance Detection Circuit Output Voltage As A Function Of<br>Input Capacitance                                                                                                                               | 86 |

| 6.15 | A schematic diagram of the prototyped improved capacitance measurement cir-<br>cuit based on phase delay                                                                                                                       | 88 |

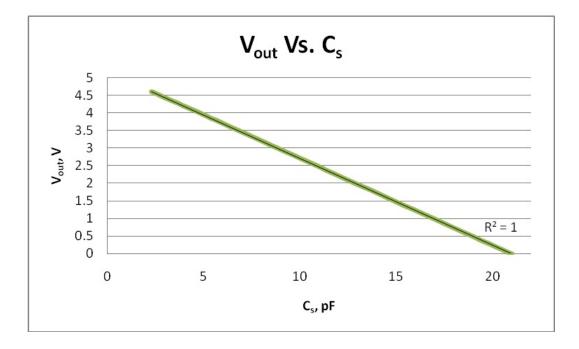

| 6.16 | A plot of the measured output voltage versus $C_s$                                                                                                                                                                             | 89 |

# List of Tables

| 3.1 | Variation of Capacitance and Resistance in terms of Frequency (in KHz) $\ldots$      | 22 |

|-----|--------------------------------------------------------------------------------------|----|

| 3.2 | Variation of Capacitance and Resistance in terms of Frequency (in KHz) $\ . \ . \ .$ | 26 |

| 4.1 | Pin Assignments of the D-Type 25 Pin Parallel Port Connector                         | 43 |

| 4.2 | Control Port                                                                         | 43 |

| 4.3 | Experimental Analysis of First Oscillator Circuit                                    | 49 |

| 4.4 | Experimental Analysis of First Oscillator Circuit                                    | 52 |

| 5.1 | Change in Capacitance and Frequency as a function of Mass - Reading I $\ . \ . \ .$  | 66 |

| 5.2 | Change in Capacitance and Frequency as a function of Mass - Reading II               | 67 |

| 5.3 | Change in Capacitance and Frequency as a function of Mass - Reading III $\ . \ .$    | 68 |

| 5.4 | Change in Capacitance and Frequency as a function of Mass - Reading IV $\ . \ . \ .$ | 69 |

| 5.5 | Change in Capacitance and Frequency as a function of Mass - Reading V                | 70 |

## Chapter 1

## Introduction

Many types of sensors convert the measurand to a change in capacitance. This is especially true for sensors realized in Microelectromechanical Systems (MEMS) technology, where one or more sets of electrodes respond to a measurand by changing the electrotrode separation distance, relative orientation or overlap area. Some sensors also perform capacitive measurand detection through detecting a change in the permittivity of the dielectric material between one of more sets of electrodes. However, the sensor described here in undergoes a change in capacitance due to an interference in fringing fields.

Many electronic techniques have also been developed to interface to capacitive sensors. In this work, the frequency locked loop (FLL) is used to track frequency variations that are related to the capacitive sensor. A 12-bit FLL is implemented in a field programmable gate array (FPGA) using combinational and sequential logic.

A capacitive fringing field sensor was also developed and tested for measuring the mass of water using Printed Circuit Board (PCB) Technology. This technology is particularly useful for realizing this type of sensor architecture. Interdigitated electrode structures are patterned in the copper cladding on one or both sides of the PCB substrate. An object that interferes with the fringing fields will then change the measurable capacitance between these electrodes. This configuration was used as a sensor for the object (water in this case) that interferes with the fringing fields. This is called a capacitive fringing field sensor. These types of sensors have been used in many applications, such as water detection [1], moisture content measurement [2] and as proximity switches [3].

#### Chapter 2

Literature Review for Capacitive Sensors and their Interface Circuits

#### 2.1 Capacitive Sensors

A capacitor consists of two conductors separated by a dielectric (solid, liquid, or gas) or a vacuum. The relationship between the charge Q and the difference in voltage V between the conductors is described by capacitance, C

$$C = Q/V \tag{2.1}$$

This capacitance depends on the geometrical design of the conductors and on the dielectric material between them,  $C(G, \epsilon)$  where G stands for Geometric Arrangement. For example, for a capacitor formed by *n* equal parallel plane plates having an overlapping area, *A*, with a distance, *d*, between each plate, and an interposed material with a relative permittivity or dielectric constant,  $\epsilon_r$ , the capacitance is

$$C \approx \epsilon_o \epsilon_r \frac{A}{d} (n-1) \tag{2.2}$$

where  $\epsilon_o = 8.85 \text{ pF/m}$  is the dielectric constant for a vacuum. Note that Equation 2.2 ignores fringing effects.

Therefore any phenomenon or quantity producing a variation in  $\epsilon_r$ , A or d, will result in a change in the capacitance, C, and can be in principle sensed by that device. In general, any change in the dielectric material or in the geometry can be considered for the sensing of the phenomenon producing it. The relative permittivity  $\epsilon_r$  for air is approximately 1; for water it changes from 88 at 0° C to 55.33 at 100° C [4]. Therefore the substitution of water for air as dielectric would result in a measurable change in capacitance. This can be applied, for example, to the measurement of the water level in a storage tank or to humidity measurement if a dielectric material is used that absorbs and dissipates water without hysteresis[5].

#### 2.1.1 Spacing Variation

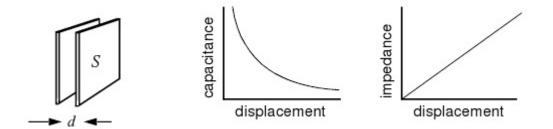

Spacing variation of parallel plates is often used for motion detection if the plate separation distance is much smaller than the square root of the plate area. The parallel plate capacitance formula shows that capacitance is inversely related to the plate separation distance. This yields a conveniently large value of capacitance at small spacing, but it does often require signal conditioning which can compensate for the parabolic capacitance-motion relationship. This can be accomplished by measuring impedance rather than capacitance, as impedance has a linear relationship related to displacement, as suggested in Figure 2.1.

Figure 2.1: Illustration of Plate Spacing Variation

Several sources of nonlinearity corrupt the performance of a simple parallel plate sensor. A simple two-plate Z-axis sensor with same-sized plates will have unwanted sensitivity to [6]-

- Transverse displacement in X or Y axes

- Coupling from the back of the plate

- Tilt of one capacitive plate with respect to the other about the Z-axis

Coupling from the back side can be handled with a shield. The shield needs to be driven by the signal conditioning circuit to the same potential as the sense plate so it does not contribute to the measured capacitance. If, for example, the back plate above is driven by a signal source and the front plate is connected to a low-impedance (virtual ground) amplifier, the shield should be connected to ground. Then, only the interplate capacitance contributes to the amplifier output signal.

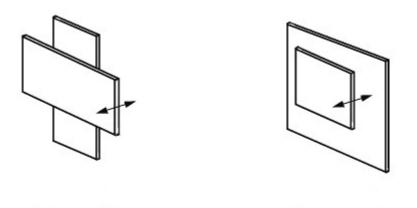

Transverse displacement sensitivity is easily handled by the methods illustrated in Figure 2.2. Having two plates of different sizes ensures that the two plates are constantly overlapping, and that any error caused due to XY axis displacement is avoided.

Figure 2.2: Examples of Overlapping Capacitive Plates

## 2.1.2 Area Variation

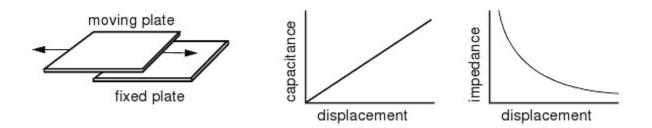

In the spacing-variation motion detectors above, when displacement increases to the dimension of the electrodes (considering that they are the same size or are square plates), measurement accuracy suffers from vanishing signal level. Area variation is then preferred. As these plates slide transversely, capacitance changes linearly with motion because the area, A, varies linearly with displacement, d. The impedance variation is of the form 1/d. Quite long excursions are possible with good linearity, but the gap needs to be small and

Figure 2.3: Area Variation

well-controlled. As with spacing variation, constant overlapping is needed so that unwanted sensitivities are minimized. Here, the unwanted sensitivities are [6]-

- Tilt in any axis

- Gap change

- Coupling from the back of the plate

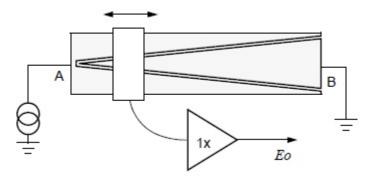

Several methods help with tilt sensitivity, such as using a small pickup plate with a chevron-shaped driven plate. The rectangular pickup plate moves laterally above the

Figure 2.4: Chevron Shape to combat tilt

chevron, and it is spaced with a small (about 0.5 mm) gap. The chevron plates are driven with a signal voltage of, 5V at 100 kHz, and a high-impedance 1X amplifier is used. The amplifier output, Eo, varies linearly from 5V at the left side to 0V at the right side, and the output voltage is insensitive to pickup plate tilt and displacement in the vertical dimension.

#### 2.1.3 Three Plate Systems

Adding a third electrode improves performance in several ways -

- Sensor capacitance is doubled

- Shielding is easier [7]

Figure 2.5: Adding a Third Electrode

The three-plate sensor can be used for either spacing-variation or area-variation sensors. With a two-plate sensor, the sensor capacitance is the measured variable. Any circuit which measures this capacitance will produce a ratio of the sensor capacitance to a discrete circuit element, a fixed capacitor or resistor. With three-plate sensors, two capacitances are formed,  $C_1$  between top and center plate and  $C_2$  between center and bottom plate (Fig. 2.5). The amplifier circuit, depending on its configuration, can generate a voltage proportional to  $C_1 - C_2$  or  $C_1/C_2$  or  $(C_1 - C_2)/(C_1 + C_2)$ . This makes ratiometric measurements possible, where one capacitor is variable with motion and the other is fixed. The ratio  $C_1/C_2$  or  $(C_1-C_2)/(C_1+C_2)$  can be arranged to track with temperature, for compensating for thermal expansion effects and to compensate for the small changes in air dielectric constants due to changes in humidity or pressure.

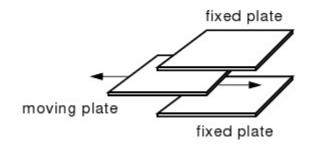

Figure 2.6: Parallel Multiplates

# 2.1.4 Multiple Plate Systems

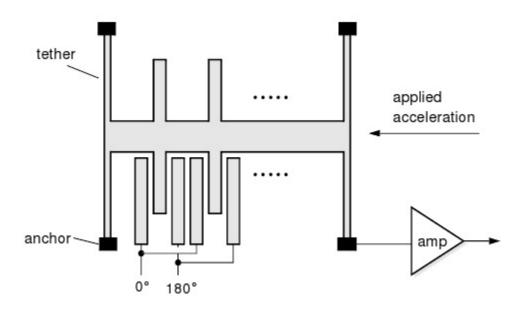

The electrode structure of an Analog Devices surface-machined silicon accelerometer, the ADXL50 [8], with an overall size of 500 x 625  $\mu$ m is illustrated in Figure 2.6. Its 42 silicon fingers are 100  $\mu$ m in length with a 2  $\mu$ m gap and a total capacitance of 0.1 pF. The H-shaped piece is elastically mounted using the good spring characteristics of silicon, and responds to acceleration in the X-direction with a small displacement. When this occurs, the common central plate or beam moves closer to one of the fixed plates while moving further from the other. The sensors fixed capacitor plates are driven deferentially by a 1 MHz square wave: the two square wave amplitudes are equal but are 180° out of phase from one another. When at rest, the values of the two capacitors are the same and therefore, the voltage output at their electrical center (i.e., at the center plate) is zero. When the sensor begins to move, a mismatch in the value of their capacitance is created producing an output signal at the central plate. The output amplitude will increase with the amount of acceleration experienced by the sensor. A demodulator (not shown) converts the displacement into acceleration [9]. As the limiting resolution of the sense amplifier is 20 × 10<sup>-18</sup>F, a beam displacement of 20 × 10<sup>-12</sup> m can be measured. Despite the high accuracy of capacitance motion detection, system imperfections such as mechanical tolerance, unwanted tilt sensitivity and thermal noise limit the reasonable performance of a simple analog sensor to about 0.1% accuracy.

#### 2.1.5 2D Sensors

Figure 2.7: Finger Position Sensor [6]

A variety of two-dimensional capacitive sensors have been produced, including the fingerposition sensor shown in Figure 2.7. This device, often found just in front of the keyboard on a laptop computer, drives a pulse in succession on each column and measures coupling to each row. By locating the coordinates of peak coupling and interpolating between adjacent rows, the location of a shielding human finger is measured to a fraction of a millimeter.

#### 2.1.6 Sensing of other Variables

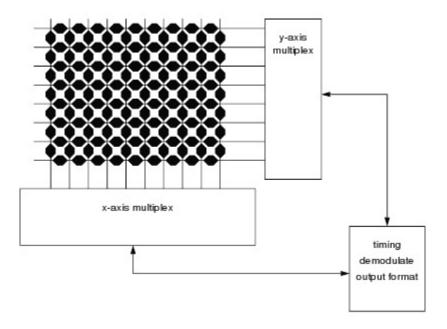

Capacitive sensors directly sense electrode motion, conductive or dielectric object motion, or the dielectric properties of a local material. All other variables must be first converted into one of these. As the technology is capable of excellent, stable, low-noise sensing, this indirect method works well. As an example, a cube of brass one cm square expands sufficiently with temperature to make a good thermometer, with better than 1°C accuracy. The

Figure 2.8: Equivalent Circuit

equivalent circuit of a capacitor can be approximated by this circuit, with small series resistance and inductance neglected for high-impedance uses. Good capacitor dielectrics have a very large shunt resistance; polypropylene capacitors have an RC product of over 300 hours [10]. Other materials have a much smaller shunt resistance, sometimes reaching 5 - 10%of the impedance of the capacitor. Although the dielectric constant K of most materials is stable, the shunt resistance or its equivalent, loss tangent (The loss tangent is a parameter of a dielectric material that quantifies its inherent dissipation of electromagnetic energy[11]), may show considerable variation with material properties or with frequency. Water has a high K (80) and a loss tangent which peaks at low frequencies and again at 1010 Hz. With this high dielectric activity, the loss tangent or the dielectric constant of water can be used to detect the moisture content of materials. A characteristic of capacitor dielectrics which may have some use in detecting material properties is dielectric absorption (Dielectric Absorption refers to the inability of a capacitor that has been charged for a long time to completely discharge when briefly discharged |12|). It is measured by charging a capacitor, discharging for 10 s, and measuring the charge which reappears after 15 min. A relatively low-quality dielectric like metallized paper has a dielectric absorption of 10%.

### 2.2 Capacitive Sensor Interface Circuits

Signal conditioning circuits convert capacitance variations into a voltage, frequency, or pulse width modulation. Very simple circuits can be used, but simple circuits may be affected by leakage or stray capacitance, and may not be suitable for applications with very small capacitance sense electrodes.

## 2.2.1 Excitation frequency, F

The excitation frequency should be reasonably high so that electrode impedance is as low as possible. Typical electrode impedance is 1-100M ohms. Ideally, the excitation frequency will be high enough to reject coupling to power waveforms and also high enough so that the overall sensor frequency response is adequate; about 50 kHz is usually acceptably high. The frequency should also be low enough for easy circuit design. CMOS switches work well at 100 kHz and below. Excitation waveshape is usually square or trapezoidal, but a triangle waveform can be used to allow a simpler amplifier with resistive feedback and a sine wave offers better accuracy at high frequency. Square wave excitation produces an output bandwidth which can be higher than the excitation frequency by 10x or more, other waveshapes usually result in an output bandwidth 2x or 3x lower than the excitation frequency. Sensors excited with a continuous wave signal usually use synchronous demodulators. This demodulator type offers high precision and good rejection of out-of-band interference.[6]

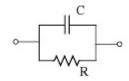

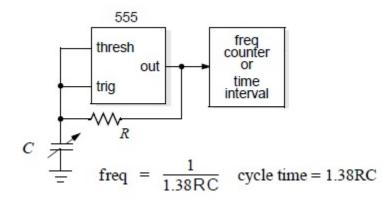

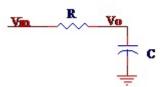

## 2.2.2 Oscillator

An R-C relaxation oscillator can be implemented using the IC 555 or its CMOS update, the 7555. This can be used to convert capacitance change into a change of frequency or pulse width. The RC oscillator used with a spacing-variation capacitor will produce a frequency output which is linear with spacing, while an area-variation capacitor is linearized by measuring pulse width. The circuit as shown has no way of accommodating stray capacitance. If, for example, the capacitor is connected by a coaxial cable, the cable capacitance adds to

Figure 2.9: RC Oscillator

the measured capacitance and spoils stability and sensitivity. Often a computer can be used to calibrate these errors, but the synchronous demodulator circuits shown below are a more accurate choice.

Another drawback with the RC oscillator is that capacitance is measured relative to the fixed resistor, and the resistor stability and temperature coefficient may not track well. Synchronous demodulators allow the use of capacitance bridges so the reference capacitance temperature coefficient will track accurately, yielding higher accuracy sensors [6]. An example of such a technique is based on the use of a novel type of oscillator whose frequency is insensitive to low and high frequency interfering signals by the application of a third order high-pass filter and special dither techniques [13].

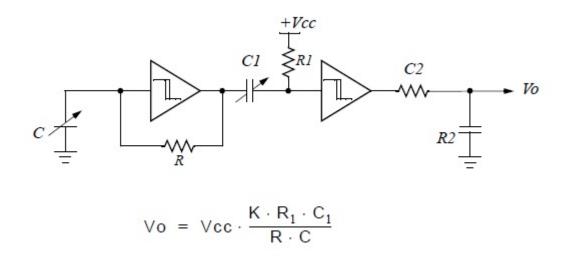

# 2.2.3 CMOS Schmitt Inverter

This circuit uses a CMOS schmitt inverter as an RC oscillator followed by a oneshot  $R_1C_1$ (with a smaller time constant) followed by lowpass  $R_2C_2$  (with a larger time constant). The output can be either capacitance-linear or 1/capacitance linear, depending on the location of the sense capacitor. It is, unfortunately, not particularly stable with temperature and power supply and it may require a floating sense capacitor [6].

Figure 2.10: CMOS Schmitt Inverter

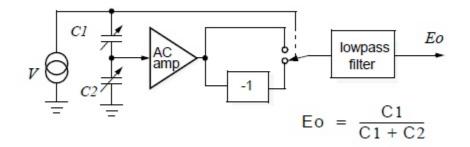

#### 2.2.4 Synchronous demodulator circuits

A square wave excitation voltage, V, at 5 Vp-p feeds the variable capacitance ( $C_1$ ,  $C_2$ , or both may be variable) and also a CMOS switch. A high-impedance unity-gain AC amplifier feeds the switch directly and also feeds an inverter. If the phase shift through the amplifier is low, the switch output is an accurate demodulation, probably contaminated by narrow spikes caused by switching transients. These transients are eliminated in the lowpass filter. An advantage of the synchronous demodulator is that out-of-band signal components are eliminated in the lowpass filter. This is important in applications where power line harmonics or other crosstalk contaminate the signal [6].

However, apart from these, many techniques have been developed to interface to capacitive sensors. One technique is using a simple digital capacitance meter which utilizes the RC discharge to test the frequency dependence of the capacitor[14]. Another technique is to realize a switched-capacitor interface for capacitive sensors based on a dual-slope analog-todigital (A/D) conversion technique. The interface consists of a switched-capacitor integrator, a comparator, and digital control circuits. The integrator samples the sensor capacitance in the form of its proportional charge [15]. Also, a single-ended readout circuit is considered,

Figure 2.11: Synchronous Demodulator

using an AC-bridge with voltage amplifier [16]. Microcontrollers have also been used in order to measure capacitances by determining the charging and discharging time of an RC Circuit [17], [18]. A charge amplifier, realized using switched capacitor techniques, can be used to measure an unknown capacitance [19]. Other types of switched capacitor circuits are also employed [20].

# 2.3 Frequency Measurement Techniques

Many physical systems demonstrate cyclic behavior, that is, one or more of their properties vary in a periodic fashion before returning to the initial value and then repeating the cycle. Examples are the angular positions of the planets and satellites in the solar system, the pressure in a cylinder in a reciprocating engine, and the heights and fields associated with surface, acoustic, and electromagnetic waves. The duration of a single cycle, the period, may vary widely. The frequency, which is the inverse of the period, is the number of cycles, including fractions, occurring in unit time. The unit of frequency is the Hertz (Hz), named after Heinrich Hertz, who investigated the nature of electromagnetic radiation. Measurement of the characteristic frequencies of a system, and their variation with time or under changing conditions, yields valuable information on its properties and behavior. Together with temperature and voltage, frequency ranks as one of the quantities most often measured in modern science and technology. The measurement of an unknown frequency requires a standard producing a fixed, stable, and known frequency, and a system or technique for the comparison of the unknown frequency with that standard. In the past, a wide variety of analog techniques and material standards have been employed. An example is the use of a tuning fork to tune a musical instrument, usually a piano. Analog frequency measurement techniques possessed two major disadvantages:

- The frequency of the standards depended upon the material properties and dimensions of critical components, which meant that they were prone to drift and affected by variations in the ambient temperature.

- In addition, optimum accuracy was achieved only when the unknown and standard frequencies were close or harmonically related.

Developments in electron-tube and later solid-state electronics improved the reliability of this technique. One example is the quartz crystal oscillator, in which a thin slice of crystalline quartz acts as the resonant element in an electronic feedback circuit. As a result of the sharpness of the resonance and the stable properties of the quartz element, this device provides a stable frequency in the range from 10 KHz to 100 MHz and remains the most common secondary frequency standard in use. In addition, a range of circuits were developed to generate more complex harmonic and subharmonic frequencies from a standard source. This led ultimately to the frequency synthesizer which, with an array of phase-locked loops, could be set to produce one of a very wide range of output frequencies. In use, however, it was still necessary to measure the beat or heterodyne frequency from the unknown frequency.

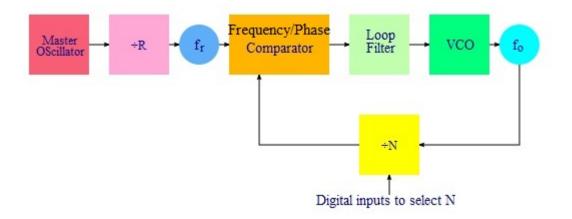

### 2.3.1 Frequency Synthesizer

A phase locked loop does for frequency what the Automatic Gain Control does for voltage. It compares the frequencies of two periodic signals and produces an error signal which is proportional to the difference between the input frequencies and phases. The error signal is then low pass filtered and integrated, and used to drive a voltage-controlled oscillator (VCO), which creates an output signal. The output signal is fed through a frequency divider back to the input of the system, resulting in a negative feedback loop. If the output frequency drifts, the error signal will increase, driving the frequency in the opposite direction so as to reduce the error. Thus the frequency and phase are locked to the input signal. This input is called the reference and is derived from a precision crystal oscillator, which is very stable in frequency. The block diagram below shows the basic elements and arrangement of a Phase Locked Loop (PLL) based frequency synthesizer.

Figure 2.12: PLL based Frequency Synthesizer

The key to the ability of a frequency synthesizer to generate multiple frequencies is the divider placed between the output and the frequency/phase comparator input. This is usually in the form of a digital counter, with the output signal acting as a clock signal. The counter is preset to some initial count value, and counts down at each cycle of the clock signal. When it reaches zero, the counter output changes state and the count value is reloaded. This circuit is straightforward to implement using combinational and sequential logic circuits, and because it is digital in nature, is very easy to interface to other digital components or a microprocessor. This allows the frequency output by the synthesizer to be easily controlled by a digital system [21].

## 2.3.2 Solid-state Digital Circuits

Fast, inexpensive solid-state digital circuits have replaced analog frequency measurement techniques and many of their associated standards. The underlying principle of the digital technique is simple: the electrical signal from the sensor or transducer observing the physical system under test generally contains, from Fourier analysis, the fundamental frequency and components at integral harmonics of this frequency. It is filtered to select the fundamental component and converted into a rectangular waveform through clipping, representing transitions between the binary logic levels 0 and 1. A frequency measurement then consists of counting the number of positive- or negative-going transitions between the two levels in a known time.

In parallel with the production of counters capable of operating at frequencies up to around 1 GHz, frequency standards based upon selected atomic transitions rather than the properties of bulk materials have been developed. These have the advantage that the frequency produced from a particular transition is in principle universal; that is, it is largely independent of the design of the standard and the materials used in its construction, and of changes in the ambient conditions. The combination of high-speed digital counters and of very stable atomic reference sources allows a wide range of frequencies to be determined simply, inexpensively, and very accurately [22].

## Chapter 3

#### Oscillator Circuits

#### 3.1 Introduction

A relaxation oscillator is an oscillator based upon the behavior of a physical system's return to equilibrium after being perturbed. That is, a dynamical system within the oscillator continuously dissipates its internal energy. Normally the system would return to its natural equilibrium; however, each time the system reaches some threshold sufficiently close to its equilibrium, a mechanism disturbs it with additional energy. Hence, the oscillator's behavior is characterized by long periods of dissipation followed by short impulses. The period of the oscillations are set by the time it takes for the system to relax from each disturbed state to the threshold that triggers the next disturbance.

The Barkhausen stability criterion is a condition to determine when an electronic circuit will oscillate. It was put forth in 1921 by German physicist Heinrich Georg Barkhausen. It is widely used in the design of electronic oscillators, and also in the design of general negative feedback circuits such as op amps, to prevent them from oscillating. Barkhausen's criterion applies to circuits with a feedback loop. Barkhausen's criterion is a necessary condition for oscillation.

It states that if A, is the gain of the amplifying element in the circuit and  $\beta(j\omega)$ , is the transfer function of the feedback path, so  $\beta$  A, is the loop gain around the feedback loop of the circuit, the circuit will sustain steady-state oscillations only at frequencies for which [24]:

• The loop gain is equal to unity in absolute magnitude, that is,  $|\beta A| = 1$ ,

• There must be a positive feedback i.e., the phase shift around the loop is zero or an integer multiple of  $2\pi$ :  $\angle \beta A = 2\pi n, n \in [0, 1, 2, ...]$

Many electronic relaxation oscillators store energy in a capacitor and then dissipate that energy repeatedly to setup the oscillations. There are many kinds of relaxation oscillators that can be implemented. For example, the capacitor can be charged toward a positive power supply until it reaches a threshold voltage sufficiently close to the supply. At that instant, the capacitor can be quickly discharged (e.g., shorted). Alternatively, when the capacitor reaches each threshold, the charging source can be switched from the positive power supply to the negative power supply or vice versa. In all such capacitor-based relaxation oscillators, the period of the oscillations is set by the dissipation rate(s) of the capacitor. Implementations of these two types of relaxation oscillators are shown here, but relaxation oscillators need not be electronic in general. Any oscillator whose oscillations are driven by a system that almost always is dissipating energy may be called a relaxation oscillator [25]. However, this study is limited only to RC relaxation oscillators using CMOS inverters.

#### 3.1.1 LR Relaxation Oscillator

Unlike RC oscillator circuits, which calculate the time constant from the product of resistance multiplied by capacitance, inductor-resistor (L/R) circuits have a time constant determined by the quotient of inductance over resistance. The time constant difference between the two configurations results in corresponding changes in the oscillator circuit response. RC units have a more rapid response when working with low resistance and a slower response with high resistance, while L/R devices offer quicker response with high resistance and slower response with lower resistance. Much like capacitors in RC oscillator systems, the transformers within an L/R oscillator provide cross-coupling and positive feedback. The transformers also have collector windings that are alternately charged from the power supply current and discharged through a series of diodes.

In some types of L/R oscillators, the oscillation frequency is determined by the wire resistance of a collector winding. However, if base resistance drops below a certain level, the oscillation frequency is no longer dependent on the collector winding resistance and instead becomes the function of flux density. This mode of operation benefits from simplicity and can be effective in low-power applications, but the dissipation of base resistance may lead to an overall decrease in efficiency, reducing the accuracy and predictability of the oscillator circuits performance [26].

# 3.1.2 RC Relaxation Oscillators

Resistor-capacitor (RC) relaxation oscillators are generally produced using operational voltage amplifiers or integrated circuits equipped with timers. When power is applied, the amplifier causes a capacitor to begin charging toward the voltage threshold under a preset time constant. As it reaches half the voltage supply, the amplifier switches operation and the capacitor starts to discharge at the same time constant. This cycle continuously repeats, independent of the supply voltage.

Relying on current sources to charge the capacitor can yield stable triangle waves, but sometimes a low-noise oscillator may be more appropriate for an application, which entails a different design strategy. A simple circuit using an inverter array to form an RC oscillator can produce square waves and reduce sideband noise density to a significant degree. Even lower noise levels can be achieved using an external circuit that modulates output frequency. This arrangement can produce asymmetrical triangle waveforms and have the inverters switch the base drive polarity at each half-cycle interval. While these circuits yield very low sideband noise, they are also more sensitive to voltage supply changes than other types of oscillators [26].

#### 3.1.3 Oscillators using Inverters

A ring oscillator is a device composed of an odd number of inverter gates whose output oscillates between two voltage levels, representing true and false. The NOT gates, or inverters, are attached in a chain; the output of the last inverter is fed back into the first. Because a single inverter computes the logical NOT of its input, it can be shown that the last output of a chain of an odd number of inverters is the logical NOT of the first input. An odd number of inverters connected in a ring can never achieve a stable state, therefore it oscillates, where as an even number is stable. This final output is asserted a finite amount of time after the first input is asserted; the feedback of this last output to the input causes oscillation.

A circular chain composed of an even number of inverters cannot be used as a ring oscillator; the last output in this case is the same as the input. An oscillator only requires power to operate; above a certain threshold voltage, oscillations begin spontaneously. To increase the frequency of oscillation, two methods may be used. Firstly, the applied voltage may be increased; this increases both the frequency of the oscillation and the power consumed, which is dissipated as heat. The heat dissipated limits the speed of a given oscillator. Secondly, an oscillator with fewer inverters may be fabricated; this results in a higher frequency of oscillation given a certain power consumption [27].

#### 3.2 Experimental Validation

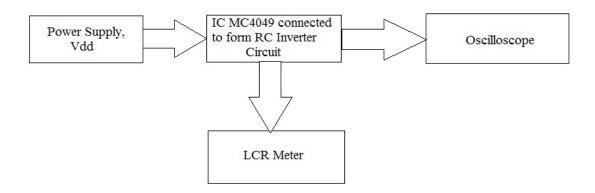

There were two adaptations of an RC Inverter Circuit that were bread-boarded and tested. A variable capacitor that ranged approximately from 8pF to 128pF was used. The oscillator circuits were connected to an oscilloscope, where the change in frequency by varying the capacitance, C and the resistance, R was measured. An LCR meter was also used to measure the change in capacitance and resistance. A power supply was also used to power up the IC chip. A block diagram of this setup is shown in Fig. 3.1.

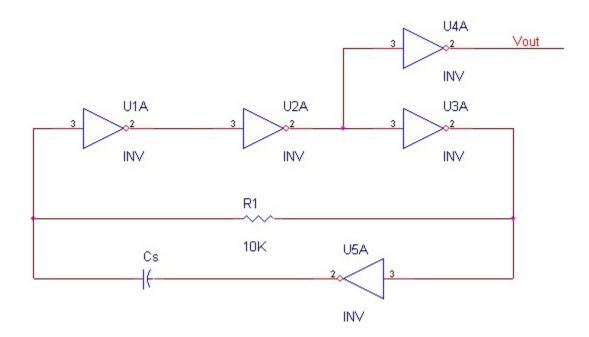

The layout of the first circuit is shown in Figure 3.2.

Figure 3.1: Block Diagram of Experimental Setup

The equation of the Frequency for this circuit in terms of the Resistance and Capacitance

Assumptions-

•  $V_{dd} = 5V$

is-

•  $V_{th} = \frac{V_{dd}}{2}$

$$T = \frac{1}{f} = RC \ln \left(\frac{V_{dd}^2}{V_{th}(V_{dd} - V_{th})}\right) [28]$$

Therefore,

$$f = \frac{1}{RC \ln\left(\frac{25}{2.5 \times 2.5}\right)}$$

$$= \frac{1}{1.386RC}$$

$$= \frac{0.721}{RC}$$

(3.1)

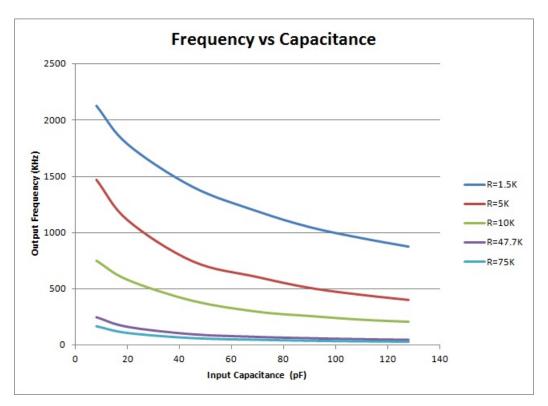

The results were also obtained in terms of frequency by using the capacitance, C and resistance R as variables (Table 3.1).

Figure 3.2: RC Inverter Oscillator Circuit 1

| Capacitance (in pF) | $R=1.5K\Omega$ | $R=5K\Omega$ | $R=10K\Omega$ | $R=47.7K\Omega$ | $R=75K\Omega$ |

|---------------------|----------------|--------------|---------------|-----------------|---------------|

| 5                   | 2674           | 1724         | 1250          | 450.5           | 312.5         |

| 8                   | 2294           | 1351         | 909.1         | 282.5           | 185.2         |

| 29                  | 1706           | 832.9        | 540.5         | 150.2           | 99.01         |

| 48                  | 1393           | 684.9        | 454.5         | 109.9           | 71.94         |

| 67                  | 1250           | 609.8        | 357.1         | 90.09           | 58.82         |

| 86                  | 1134           | 531.9        | 312.5         | 76.69           | 49.75         |

| 106                 | 1027           | 476.2        | 277.8         | 68.03           | 44.25         |

Table 3.1: Variation of Capacitance and Resistance in terms of Frequency (in KHz)

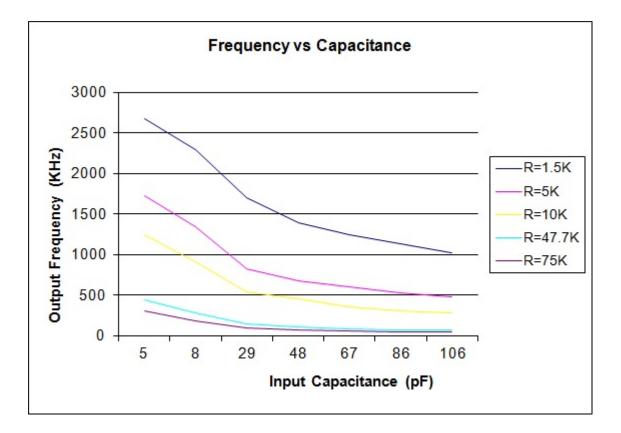

The experimental data was used to plot a graph (Figure 3.3) depicting the frequency change. This plot is most helpful, as it can be used to select a particular value of resistance for any given capacitive sensor. The ideal frequency range should be between 100KHz and 1MHz as there is a considerable amount of distortion over frequencies of 1MHz.

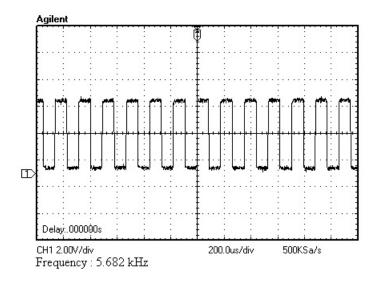

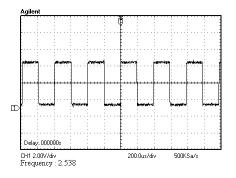

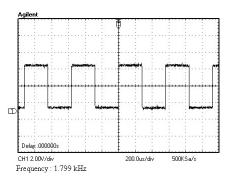

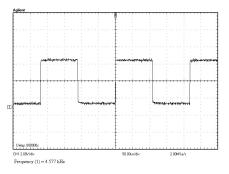

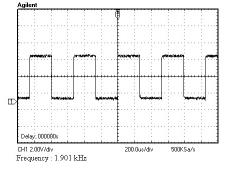

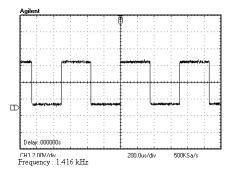

Snapshots from the oscilloscope Frequency Readout are shown in Figures 3.4, 3.5 and 3.6.

Figure 3.3: Frequency vs Capacitance

Figure 3.4: Output Frequency at C=1pF

Figure 3.5: Output Frequency at C=15pF

Figure 3.6: Output Frequency at C=28pF

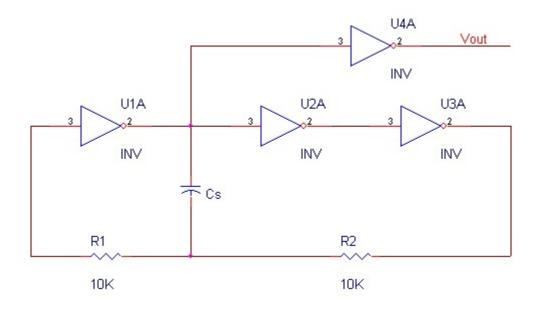

Similarly, the second circuit that was tested is shown in the Figure 3.7.

Figure 3.7: RC Inverter Oscillator Circuit 2

Equations for the frequency in terms of Resistance and Capacitance were mathematically calculated for this circuit as well-

Assumptions-

- Each inverter is "fast"

- The inverter trip voltage =  $\frac{V_{dd}}{2}$

Hence, when  $V_o = \frac{V_{dd}}{2}$  the system changes states. Therefore, RC time constant,  $\tau$  determines  $f_o$ . Let

$$V_{dd} = 5V$$

$$\frac{V_{dd}}{2} = 2.5V$$

At switching time,

$$\frac{V_o}{V_s} = \frac{R}{s + \frac{1}{sC}} = \frac{s}{s + \frac{1}{RC}}$$

$$V_s(s) = \frac{7.5}{s}$$

Therefore,

$$V_o(s) = V_s(s) \left(\frac{s}{s + \frac{1}{RC}}\right) = \frac{7.5}{s + \frac{1}{RC}}$$

$$V_o(s) = 7.5e^{\frac{-t}{RC}}$$

(3.2)

(3.3)

To find the value of t when

$$V_{o}(t) = 2.5V$$

$$2.5 = 7.5e^{\frac{-t}{RC}}$$

$$t = -RC \ln\left(\frac{2.5}{7.5}\right) = 1.0986RC$$

$$T = 2t \to f = \frac{1}{2t} = \frac{0.455}{RC}$$

$$f = \frac{0.455}{RC}$$

(3.4)

This circuit was bread-boarded using the CMOS inverter chip MC4049, and the testing results (Table 3.2) were used to obtain a plot that would show the Frequency vs Capacitance

| Capacitance (in pF) | $R=1.5K\Omega$ | $R=5K\Omega$ | $R=10K\Omega$ | $R=47.7K\Omega$ | $R=75K\Omega$ |

|---------------------|----------------|--------------|---------------|-----------------|---------------|

| 8                   | 2128           | 1471         | 751.9         | 249.4           | 169.5         |

| 20                  | 1786           | 1111         | 581.4         | 163.9           | 109.9         |

| 45                  | 1408           | 746.3        | 395.3         | 98.04           | 64.1          |

| 70                  | 1190           | 606.1        | 298.5         | 74.63           | 49.02         |

| 90                  | 1050           | 510.2        | 260.4         | 62.89           | 40.98         |

| 110                 | 952.4          | 448.4        | 227.8         | 54.64           | 35.34         |

| 128                 | 877.2          | 403.2        | 208.8         | 48.78           | 31.45         |

Table 3.2: Variation of Capacitance and Resistance in terms of Frequency (in KHz)

for different values of Resistance (Fig. 3.8). This circuit showed distortion for frequencies over 1 MHz as well. Snapshots from the oscilloscope Frequency Readout are shown in Figures 3.9, 3.10 and 3.11.

Figure 3.8: Frequency vs Capacitance

Figure 3.9: Output Frequency at C=1pF

Figure 3.10: Output Frequency at C=15pF

Figure 3.11: Output Frequency at C=26pF

# 3.3 Layout and Design

# 3.3.1 PCB Layout

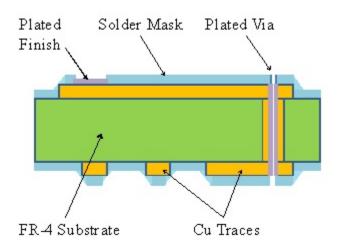

Standard printed circuit boards (PCBs) consist of a dielectric substrate that has conductive traces on at least one surface that are used for electronic component attachment and electrical interconnection. If a PCB has traces on only one side, it is called a single-sided or a single layer board. If the PCB has traces on both sides, it is called a double-sided or a 2-layer board. A PCB with additional internal layers of traces is called a multilayer PCB. The substrate can be rigid, flexible or in-between (semi-flex). FR-4 is a commonly used rigid PCB substrate material and consists of one or more layers of woven glass cloth, typically E-glass, held together by an epoxy-resin. Rigid PCB's have a fairly large range of thicknesses, from tens of mils to over 100 mils. For example, 62mils is a typical thickness for a rigid PCB. The electrical traces are usually made by patterning a solid Cu foil layer. Typical thicknesses for the Cu foil are 0.5 oz (0.7mils), 1.0 oz (1.4mils) and 2 oz (2.8mils). Traces can have minimum feature sizes as small as a few mils. Except for the portions of the traces that will be soldered to attached devices, the rest of the exposed surface of the PCB is usually coated with a polymeric material called solder mask. The primary purpose of the solder mask is to limit the flow of solder during the soldering process. Since Cu quickly oxidizes, which can make soldering difficult, the exposed Cu traces are usually plated with a surface finish such as Sn. Traces on different layers of the PCB can be electrically connected using plated through-holes. An illustration of a cross-section of a 2-layer PCB is presented in Figure 3.12.

Figure 3.12: Cross Section of a two-layer PCB

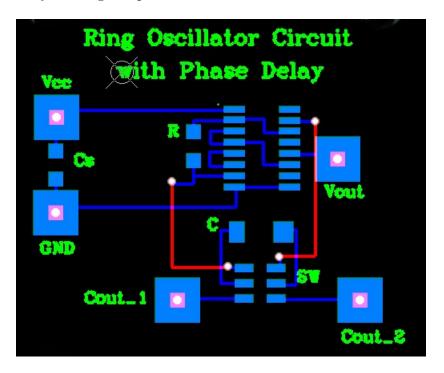

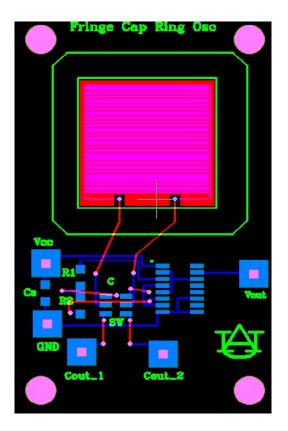

Two relaxation oscillator circuits were implemented into a single PCB board. The layout for both the circuits was done using ViewMasterEz software. For the first circuit, a resistance of  $10K\Omega$  was selected for use along with a variable capacitor of 2-20pF using the graph in Fig. 3.3. The frequency range would then be approximately equal to 270KHz to 1.25MHz which would would minimize high frequency induced distortion.

The layout of the circuit in ViewMasterEZ is as shown in Fig. 3.13. The blue traces shown are part of the copper layer. These are the interconnects and the wiring for the circuit. Also, the pads on the layout are where the components are soldered to. On top of the copper layer is the solder mask layer. The red traces are ones that are on the back side of the the PCB board and are connected to the components on the board using vias. A DPDT (Double Pole Double Throw) switch is also used so that the variable capacitance can be measured at any point of time by shifting the position of the switch.

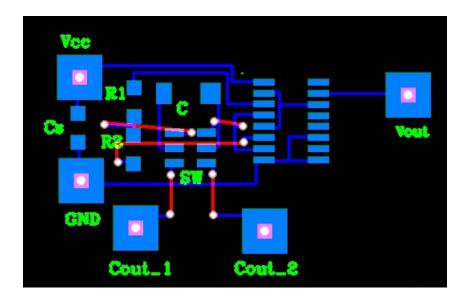

Figure 3.13: PCB Layout of Circuit 1 in ViewMasterEZ

For the second circuit, the two resistances were both selected to be  $10K\Omega$  by utilizing the Graph in Fig. 3.8. The capacitance was selected to range from 2-20pF. This gives an approximate frequency range of 200KHz to 750KHz. This circuit was laid out in the same manner as the first, with similar layers. It also used a DPDT switch as well. The layout of the circuit in ViewMasterEZ is as shown below in Fig. 3.14.

### 3.3.2 PCB Board with Components

All the components that were chosen earlier were hand soldered on to the board. The board was then ready for testing. As seen in the figure, the PCB consists of two oscillator circuits each with its own variable capacitor and DPDT switch.

Figure 3.14: PCB Layout of Circuit 2 in ViewMasterEZ

Figure 3.15: Completed PCB

# Chapter 4 Frequency Locked Loop Prototype

# 4.1 Theory and Prototyping

# 4.1.1 Introduction

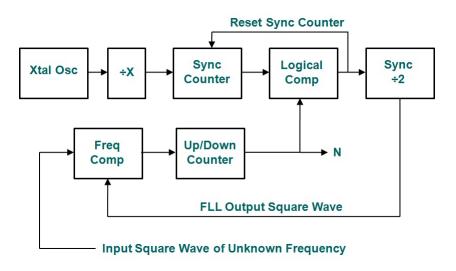

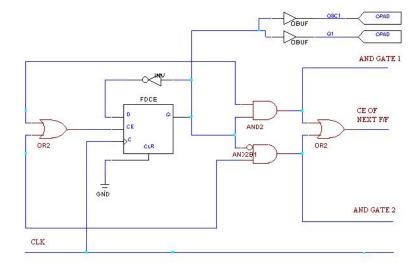

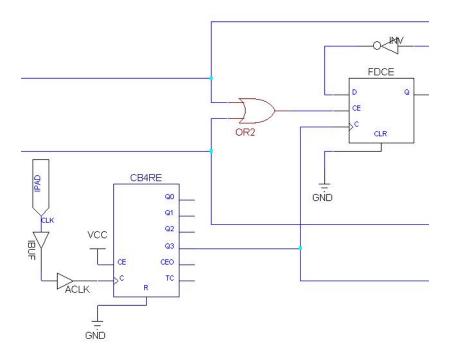

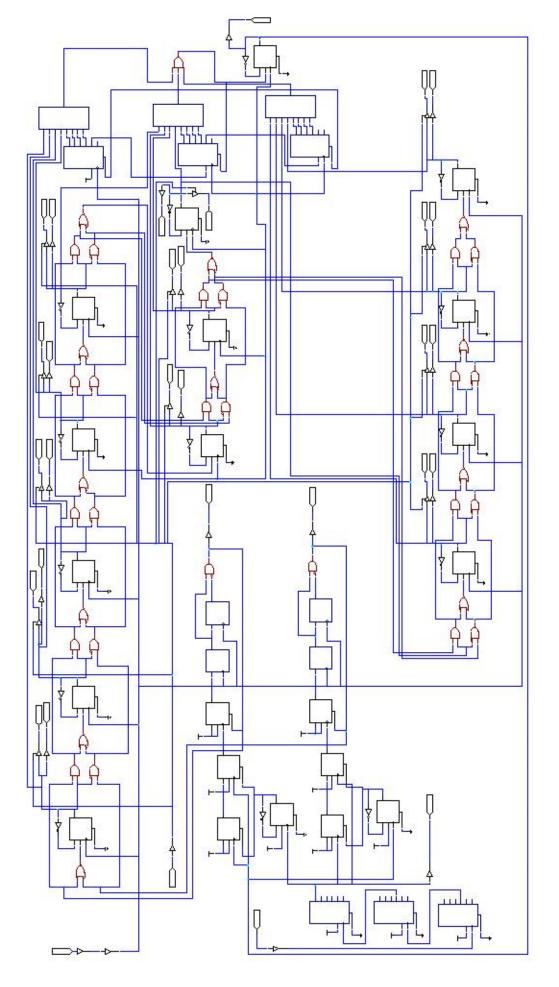

A frequency-locked loop (FLL) is a negative feedback circuit that generates a square wave that is frequency locked, but not phase locked, with an input square wave. Since logic level square waves are input and output, the circuit can be realized in sequential and combinational logic. Therefore the FLL has a finite resolution and the generated square wave dithers around the frequency of the input square wave. A frequency-locked loop is an example of a control system using negative feedback. A frequency locked loop is composed of a frequency comparator, an up down counter, a synchronous counter and a logical comparator. The FLL produces a square wave signal that dithers in frequency around the input square wave. Its digital output signal is a digital representation of the frequency of the input square waver, with a 1/f response. The FLL can be realized using just combinational and sequential logic circuits. 4-bit, 8-bit and 12-bit FLL circuits were implemented in a XC3030A Xilinx FPGA and tested. The block diagram in Fig. 4.1 shows the various stages of the FLL circuit.

### 4.1.2 FLL Components

# **Frequency Comparator**

The frequency comparator operates by comparing the state changes between the input square wave and the FLL output square wave. If either one has two state changes before a state change occurs in the other signal, the frequency comparator identifies this as a difference

Figure 4.1: Block Diagram of FLL

Figure 4.2: Frequency Comparator

in frequency. It then instructs the up/down counter to increment or decrement accordingly to reduce the difference in frequency between the two square waves.

# Up/Down Counter Circuit

Figure 4.3: Up/Down Counter Circuit

A negative feedback loop was implemented in the FLL to minimize the error between the frequency of the input square wave and the FLL output square wave. The output from the Frequency Comparator was used to increment or decrement the up/down counter to change the factor N by which the high frequency clock signal was divided to produce the FLL output square wave. This continous feedback results in the output of the circuit slowly reaching a point where it is similar to or the same as the input given its resolution. Since the digital FLL has a finite resolution, after it reaches this state, it dithers around the frequency of the input square wave. A single unit of this Up/Down Counter Circuit is shown in Figure 4.3. If these units are added in a succession to form a series, along with a feedback control, it will be able to adjust to the input frequency. The higher the number of bits, the higher the resolution of the frequency would be.

### Synchronous Counter

Figure 4.4: Synchronous Counter at Input

There were two synchronous counter chips that were used in the entire circuit. One of them was used to change the input clock frequency and divide it down by 16. The on board crystal oscillator frequency was about 10 MHz which was too high for this application. The output of the other counter was connected to the logical comparator. (Figures 4.4 and 4.5)

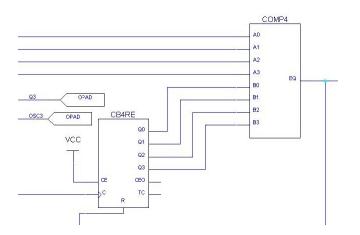

### Logical Comparator

A comparator is a device which compares two voltages or currents and switches its output to indicate which is larger. A logical comparator circuit was used to divide the high frequency clock produced by the crystal oscillator by N to produce the FLL output square wave signal. It compared the output from the synchronous counter driven by the high frequency clock with the output of the up/down counter. When the two digital words were logically equal, its output went high, which reset the synchronous counter on the next rising edge of the high frequency clock. By using a one stage flip flop divide-by-two circuit,

Figure 4.5: Synchronous Counter connected to Comparator

two of these comparator cycles produced one period of the FLL output square wave. (Refer to Fig. 4.6)

Figure 4.6: Logical Comparator

# 4.1.3 FLL Circuit Prototype

# Implementation in the Xilinx FPGA

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by the customer or designer after manufacturing, hence "field-programmable". The FPGA configuration is generally specified using a hardware description language (HDL). FPGAs contain programmable logic components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together" somewhat like a one-chip programmable breadboard. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FP-GAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory [29].

For implementation of the logic circuit, a Xilinx XC3030A FPGA chip was selected. A general-purpose FPGA board was designed for this chip. It consisted of a parallel port interconnect, 12 testing LEDs, 12 output pins, a 10MHz crystal oscillator and an EE-serial PROM insert. The EEPROM stored the FPGA configuration code used to program the FPGA when the power is first turned on. It was programmed using the ATMEL ATDH2200 FPGA Configurator and SEEPROM Programmer board. It was first plugged into this board, and using the parallel port (Fig. 4.10 and Fig. 4.11), and the ATMEL computer program (Fig. 4.12), the circuit layout data was programmed into it.

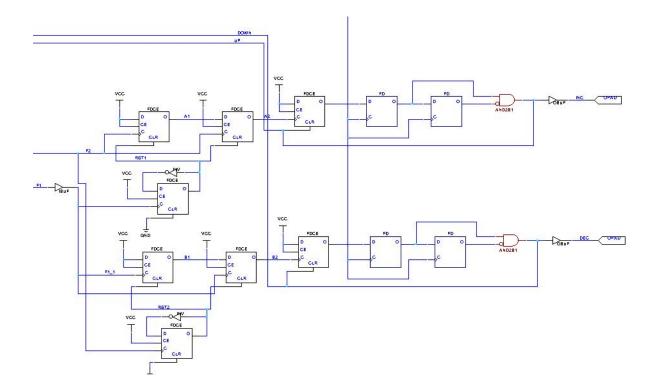

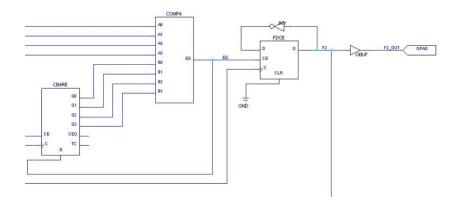

# Circuit Design

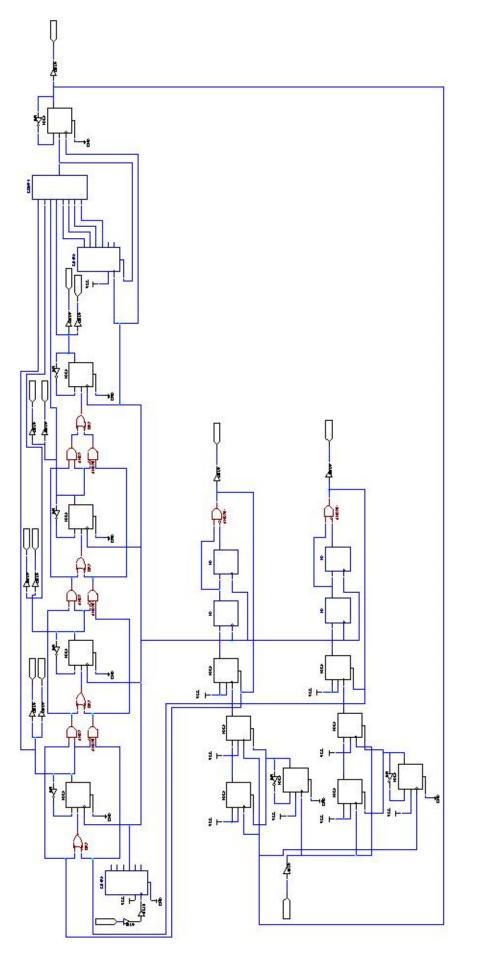

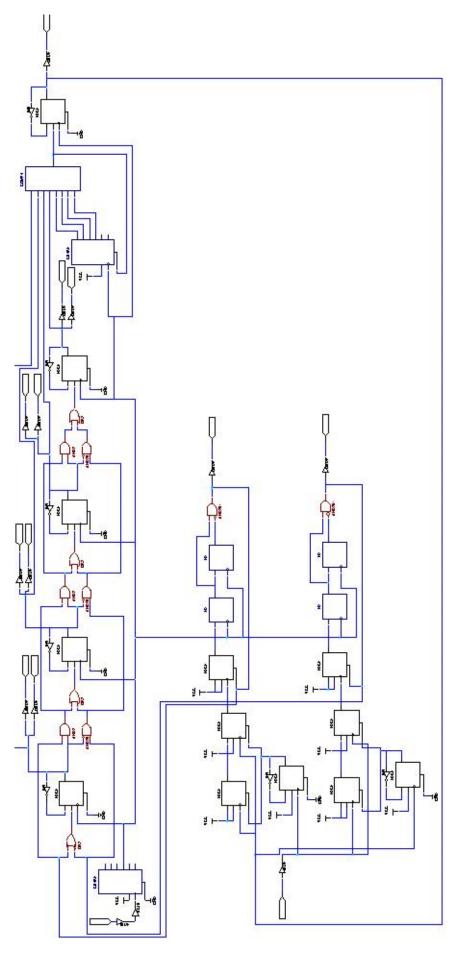

Xilinx Foundation Series Schematic layout software was used to integrate all the various parts of the FLL. The simulation in the same was then used for the first tests. The output of the circuit was checked against the input of the FLL. As predicted, the output closed in towards the input frequency over multiple clock cycles till both were the same in frequency. Figures 4.7 through 4.9 show the FLL implemented in various resolutions.

Figure 4.9: A 12-bit FLL circuit

Figure 4.10: ATMEL Board which is attached to the parallel port on the PC

Figure 4.11: FPGA Board attached to the PC

| Procedure: /E: Convert, partition, program and verify fro                                                                                                           | m a Xilinx file                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Files         Input File:       C:\Fndtn\Active\projects\fll_2\xpr <         Output File:       C:\Fndtn\Active\projects\fll_2\xpr <         Checksum:       620580 | Info<br>One or more Atmel (.bst) files are generated for<br>subsequent download sessions. The output file<br>must be of the form <file>.bst. The optional<br/>checksum can be obtained from the log output of<br/>each programming session. In this version of CPS,<br/>HEX values are only appended to the .BST output<br/>files which have been partitioned.</file> |

| Options<br>EEPROM Density: 128K<br>Reset Polarity: Low<br>FPGA: Family: AT6K/Other<br>Console                                                                       | COMM Port: LPT1                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                     | rocedure Restore Defaults View Log File.                                                                                                                                                                                                                                                                                                                              |

Figure 4.12: The output interface for programming the EPROM

#### 4.2 Interfacing to the FLL and GUI

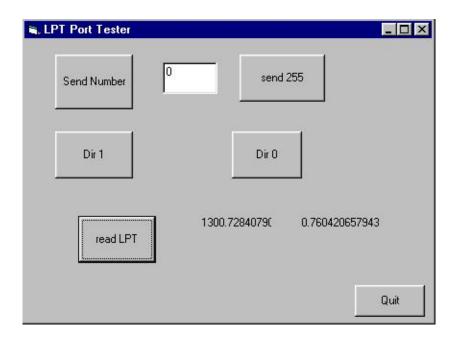

A GUI (Graphical User Interface) was designed in order to create an interface that would be able to display the output frequency, count or capacitance. This GUI was written in Visual Basic code. The parallel port was used to read in data from the FPGA board, which was then displayed as the output of the program. The biggest issue that was faced was the fact that the Parallel Port output has eight data bits, which were not enough for the twelve that were needed.

For the first 8 bits, pins 2-9 were used which are for  $D_o$ - $D_7$ . These data bits were used as input to the code, using the function Inp(PortAddress), where the PortAdress given to the parallel port was &H378. The status port was used to read the last four bits that were needed for the program. The status port can be read in by adding 1 to the base address. Therefore, the status bit data could be read in by the function Inp(PortAddress+1).

Table 4.1 and 4.2 show the pin assignment for the parallel port and the status register respectively [30]. Four of the eight status pins were chosen to work as data bits. The four that were used were Bits 3-6, as they are not inverted at the output. Note that at the beginning of the GUI, the 5th bit of the control word is kept high in order to disable the bi-directional port option of the parallel port.

The logic used in the GUI is simple. At first, the bit value for the control word is checked. After the four bits,  $C_3$ - $C_6$  were obtained, they were shifted by 5 bits by multiplying times 32. This yielded a 12-bit word with the 1st eight bits as zero, and the last four bits as  $C_3$ - $C_6$ . A logical OR function was executed with this word and the 8-bit data. The result was called the count.

Since a 10MHz clock was used, estimating the frequency was relatively easy.

$$f = \frac{10 \times 10^6}{Count \times 2} \tag{4.1}$$

| Pin No.(D-Type 25) | Signal             | Direction (In/out) | Register | Hardware Inverted |

|--------------------|--------------------|--------------------|----------|-------------------|

| 1                  | nStrobe            | In/Out             | Control  | Yes               |

| 2                  | Data               | Out                | Data     | No                |

| 3                  | Data               | Out                | Data     | No                |

| 4                  | Data               | Out                | Data     | No                |

| 5                  | Data               | Out                | Data     | No                |

| 6                  | Data               | Out                | Data     | No                |

| 7                  | Data               | Out                | Data     | No                |

| 8                  | Data               | Out                | Data     | No                |

| 9                  | Data               | Out                | Data     | No                |

| 10                 | nAck               | In                 | Status   | No                |

| 11                 | Busy               | In                 | Status   | Yes               |

| 12                 | Paper-Out/Paper-   | In                 | Status   | No                |

|                    | End                |                    |          |                   |

| 13                 | Select             | In                 | Status   | No                |

| 14                 | nAuto-Linefeed     | In/Out             | Control  | Yes               |

| 15                 | nError/nFault      | In                 | Status   | No                |

| 16                 | nInitialize        | In/Out             | Control  | No                |

| 17                 | nSelect-           | In/Out             | Control  | Yes               |

|                    | Printer/nSelect-In |                    |          |                   |

| 18-25              | Ground             | Gnd                | Gnd      | No                |

Table 4.1: Pin Assignments of the D-Type 25 Pin Parallel Port Connector

| Offset     | Name         | Read/Write | Bit No. | Properties |

|------------|--------------|------------|---------|------------|

| Base $+ 2$ | Control Port | Read/Write | Bit 7   | Busy       |

|            |              |            | Bit 6   | Ack        |

|            |              |            | Bit $5$ | Paper Out  |

|            |              |            | Bit 4   | Select In  |

|            |              |            | Bit 3   | Error      |

|            |              |            | Bit 2   | IRQ (Not)  |

|            |              |            | Bit 1   | Reserved   |

|            |              |            | Bit 0   | Reserved   |

Table 4.2: Control Port

Capacitance could also be estimated from the GUI, however, that required a curve fit. This is explained in detail in the testing section of this chapter.

# 4.3 Software GUI

The following is a copy of the GUI which was written in Visual Basic.

```

{Dim PortAddress

Private Sub Command1_Click()

a = Text1.Text

PortAddress = &H378

'Print 2 * a

Out PortAddress + 2, 0

Out PortAddress, a

```

End Sub

| Edit View                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                  |                         |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|-------------------------|