# Layout and Assembly of a High Efficiency Multi-Phase Buck Converter Utilizing Chip Scale GaN Devices

by

Stephan Wenz Henning

A thesis submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Master of Science

Auburn, Alabama August 2, 2014

Keywords: Power Conversion, Buck Converter, Switch Mode Power Supply

Copyright 2014 by Stephan Wenz Henning

Approved by

Robert N. Dean, Chair, Associate Professor of Electrical and Computer Engineering Stuart Wentworth, Associate Professor of Electrical and Computer Engineering Michael Hamilton, Assistant Professor of Electrical and Computer Engineering

### **Abstract**

As the world becomes increasingly immersed in the Information Age, more and more supercomputers and datacenters must be built to keep up with humanity's demand for electronic information. As the number of these facilities and their physical size continue to grow, so do the power demands that they place on their local power grids. Much of this demand is a direct result of the processing hardware being utilized, but a large majority of this is wasted power, lost within the system due to various areas of inefficiency.

This work will describe the implementation of a prototype design for a Point of Load voltage regulator for use in power datacenter processors using new technology GaN FETs to generate efficiencies greater than 90%. This work will detail a process used to prototype with these chip scale package GaN devices, allowing for a faster development cycle of a converter design within organizations that may not have access to advanced assembly equipment. This process details how to assemble these GaN devices in a manner that provides very high yields, while considering the possible equipment limitations of most organizations.

This process is then used in the implementation of these GaN devices in the creation of a Point of Load prototype to demonstrate the improved efficiencies possible by using these GaN devices. Design, layout, assembly, and testing stages are discussed for two versions of the prototype, detailing many of the decisions made during the design process to fully utilize these

devices. This work provides information useful to any organization considering using these new generation GaN devices in future designs by demonstrating their capabilities, discussing the features of the technology, reviewing some guidelines that may be beneficial during the design stages, and by providing a high yield assembly method that can be implemented within most well equipped organizations.

## Acknowledgments

I would like to thank my friends and family for their constant support and encouragement, without them this would not be possible. I would also like to thank Kristina for her unwavering love and faith, especially when deadlines loom large and require many late nights to stay on schedule. I would like to thank Dr. Dean for his mentorship, encouragement, and financial support over the course of this project, along with his freely given advice about life in general. I would like to thank Dr. Hamilton for the many discussions about technical matters related to this project and his support in general. I would like to thank Dr. Wentworth for his support and encouragement throughout my undergraduate carrier and his continued support of me as I continued in my academic pursuits. I would also like to thank Dr. Johnson for his management of this project, without which this work would not have been possible. I am grateful for the advice, encouragement, and assistance provided by my fellow students on this project, without them this project could not succeed. I would also like to thank John Tennant, Joe Haggerty, Linda Barresi, and Mike Palmer for their patience and assistance whenever I ran into a problem that needed their input.

# Table of Contents

| Abstract                                | ii   |

|-----------------------------------------|------|

| Acknowledgments                         | iv   |

| List of Tables                          | viii |

| List of Figures                         | ix   |

| Nomenclature                            | xiii |

| Chapter 1 Introduction                  | 1    |

| Chapter 2 Background and Previous Work  | 5    |

| 2.1 DC Distribution                     | 5    |

| 2.2 Point of Load Converters            | 7    |

| 2.3 Wide Band-Gap Devices               | 11   |

| Chapter 3 Design Goals and Approach     | 19   |

| 3.1 Scope and Goals                     | 19   |

| 3.2 Converter Selection                 | 21   |

| Chapter 4 GaN Technology Implementation | 24   |

| 4.1 EPC Device Packaging                | 24   |

| 4.2 Manual Assembly                     | 27   |

| 4.3 Primary Manual Assembly Method      | 28   |

| 4.3.1 Preparation                       |      |

| 4.3.2 Placement                         |      |

| 4.3.4 Reflow                            |      |

| 4.3.5 Inspection                        |      |

| 4.4 Secondary Manual Assembly Method    | 40   |

| 4.4.1 Preparation                       |      |

| 4.4.2 Placement and Alignment           |      |

| 4.4.3 Reflow                            |      |

| 4.4.4 Inspection                        | 45   |

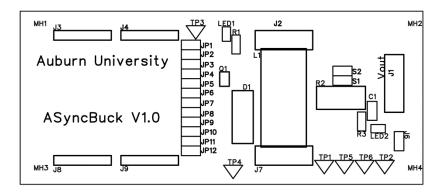

| Chapter 5 Point of Load Version 2       | 48   |

| 5.1 Design                              | 49   |

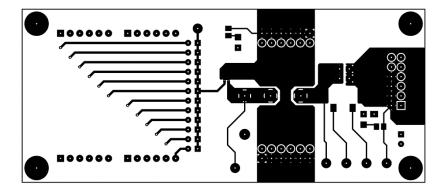

| 5.2 Layout and Implementation           | 55  |

|-----------------------------------------|-----|

| 5.3 Assembly                            | 62  |

| 5.4 Testing and Analysis                | 63  |

| 5.5 Lessons Learned                     | 72  |

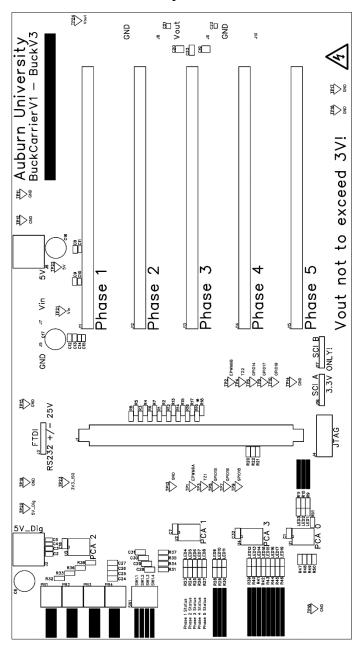

| Chapter 6 Point of Load Version 3       | 74  |

| 6.1 Design                              | 74  |

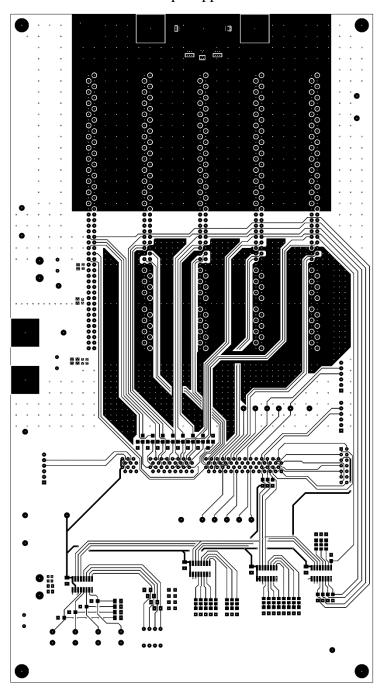

| 6.2 Layout and Implementation           | 85  |

| 6.3 Assembly                            | 91  |

| 6.4 Testing and Analysis                | 97  |

| 6.5 Conclusions                         | 108 |

| Chapter 7 Conclusions                   | 110 |

| 7.1 Summary                             | 110 |

| 7.2 Future work                         | 111 |

| References                              | 113 |

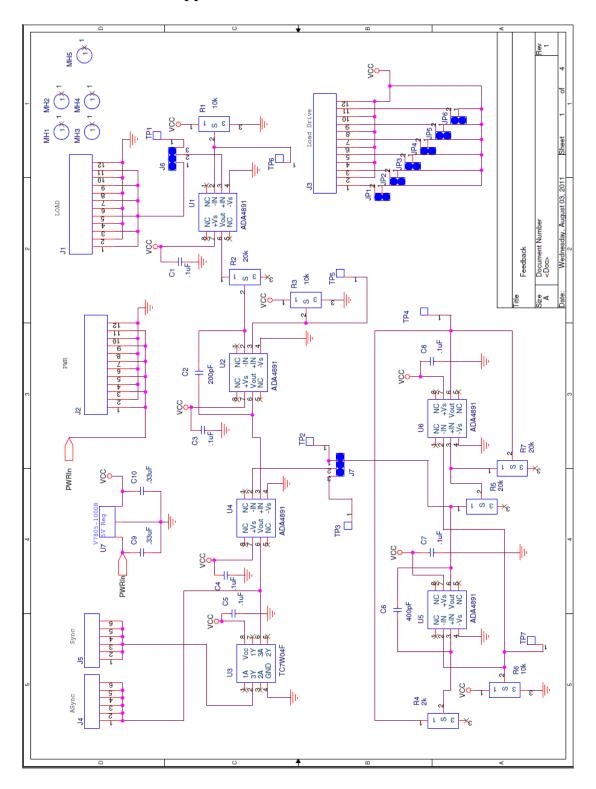

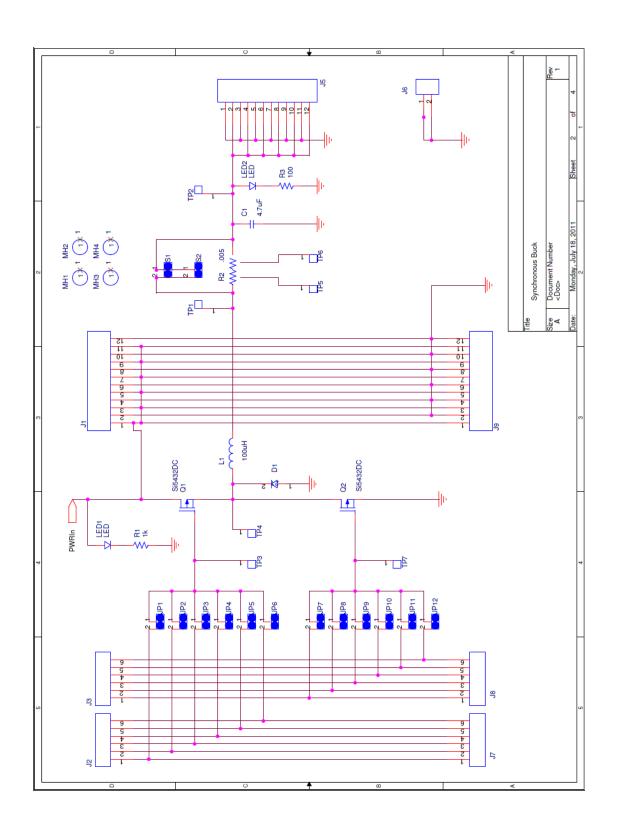

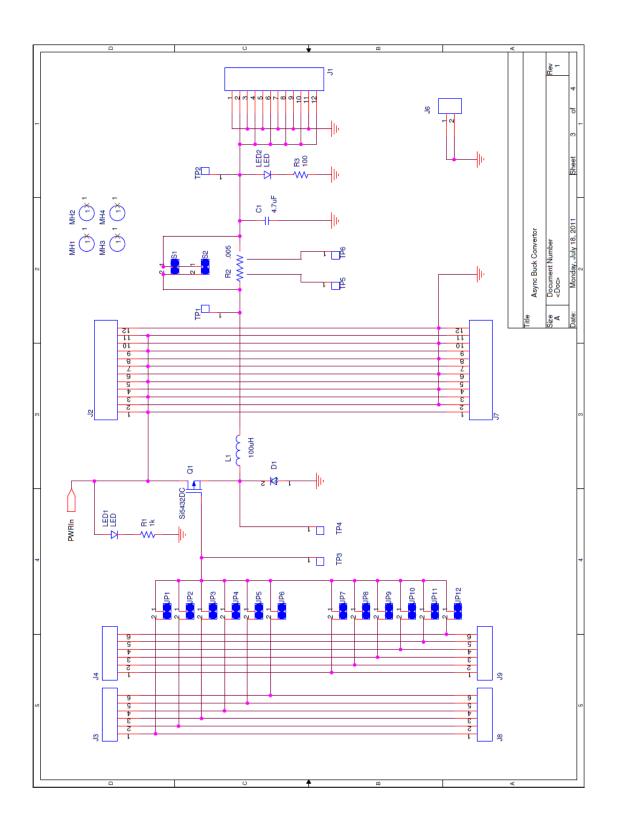

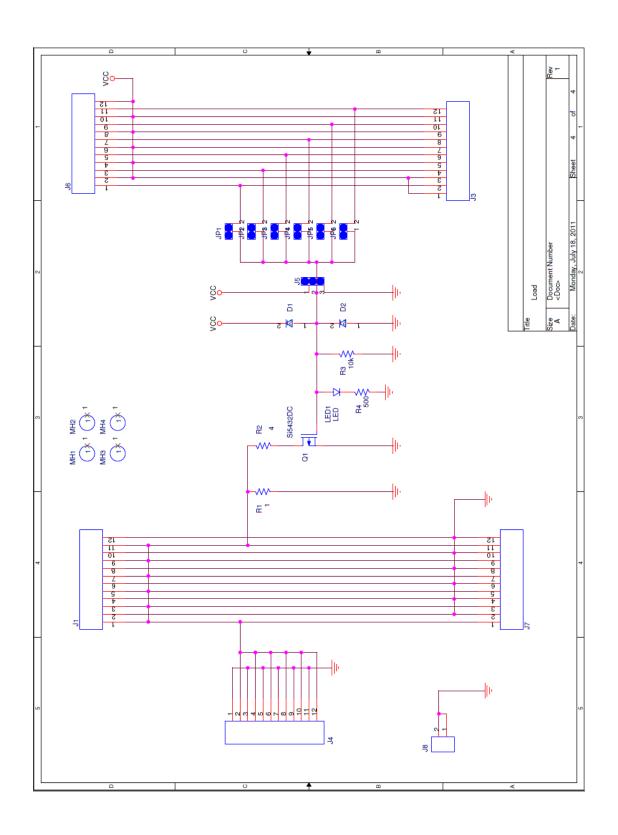

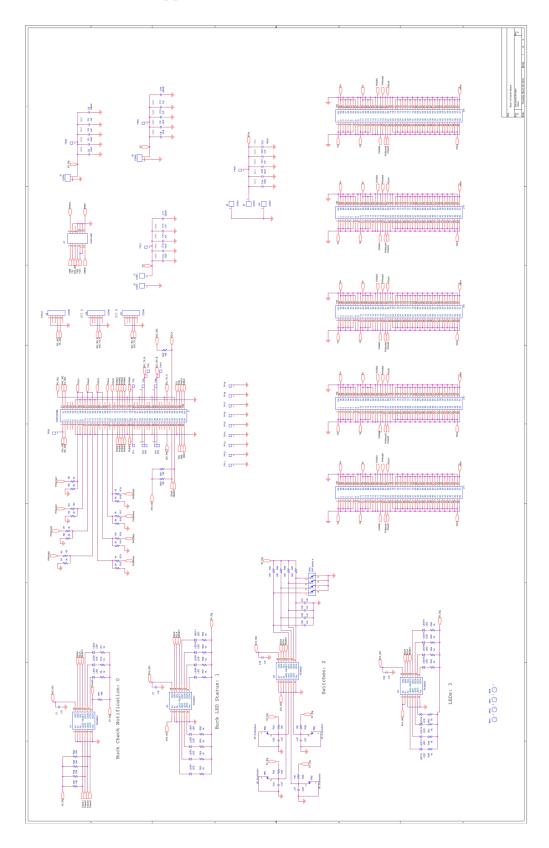

| Appendix A: POL V1 Schematics           | 120 |

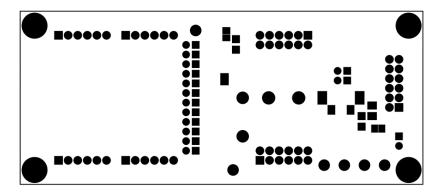

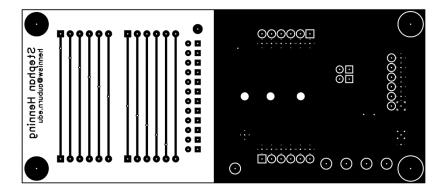

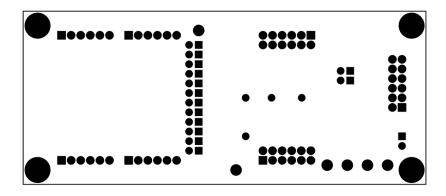

| Appendix B: POL V1 Layout               | 124 |

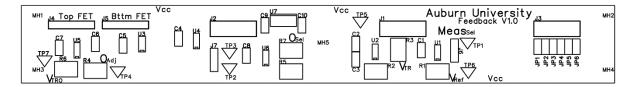

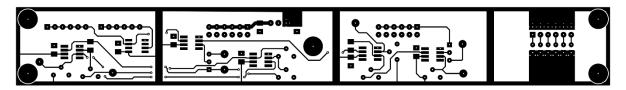

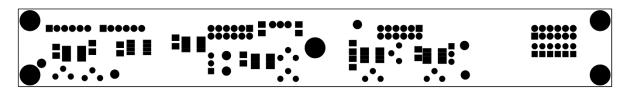

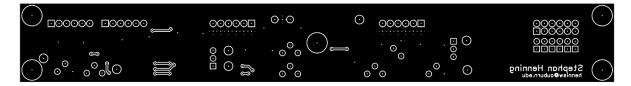

| B.1 Feedback                            | 124 |

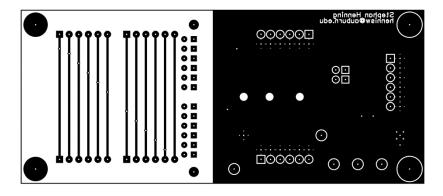

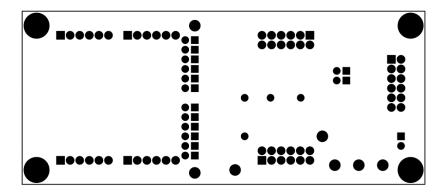

| B.2 Synchronous Buck                    | 125 |

| B.3 Asynchronous Buck                   | 126 |

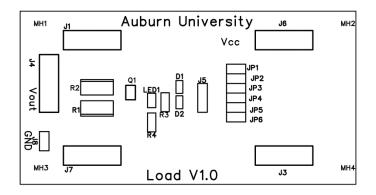

| B.4 Load                                | 128 |

| B.5 Power                               | 130 |

| Appendix C: POL V2 Schematics           |     |

| Appendix D: POL V2 Layout               | 137 |

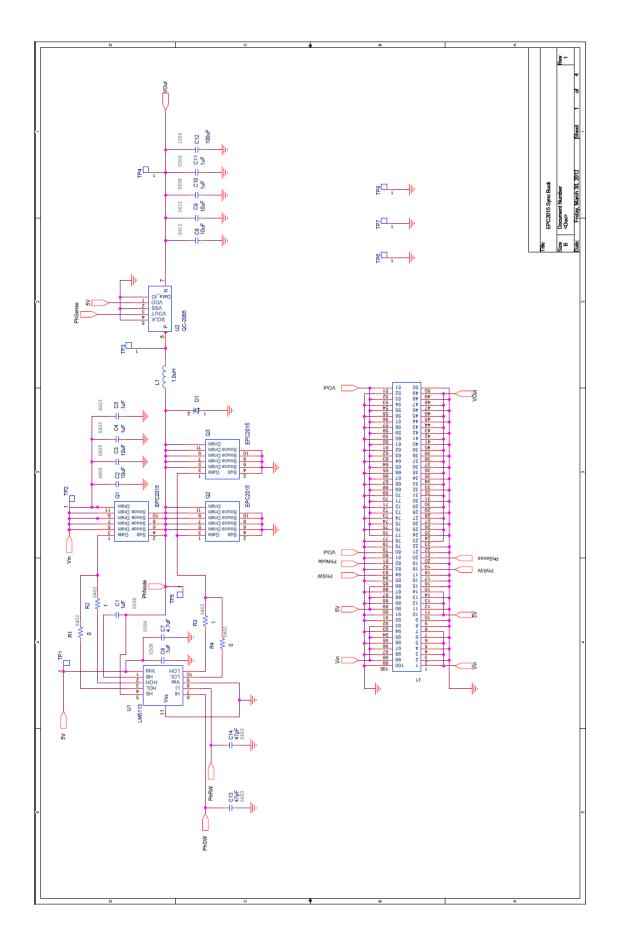

| Appendix E: POL V3 Schematics           | 143 |

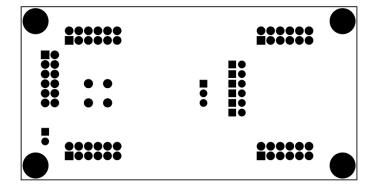

| Appendix F: POL V3 Layouts              | 145 |

| F.1 Carrier Board                       | 145 |

| F.2 Buck Daughter Card                  | 150 |

| Appendix G: Software, Scripts, and Code | 152 |

| G.1 Buck V2 Matlab Plotting Code            | .152  |

|---------------------------------------------|-------|

| G.2 Buck V3 Stages 1-3 Matlab Plotting Code | . 157 |

| G.3 Buck V3 Stages 7-9 Matlab Plotting Code | . 163 |

# List of Tables

| Table 1: Power Draw of Top Systems                 | 2   |

|----------------------------------------------------|-----|

| Table 2: Wide Band-gap Material Properties [24]    | 12  |

| Table 3: GaN Technology Advantages [25]            | 14  |

| Table 4: EPC Device Electrical Characteristics     | 17  |

| Table 5: Comparison of Device Characteristics      | 17  |

| Table 6: Point of Load Design Objectives           | 21  |

| Table 7: Comparison of Device Packages [26]        | 25  |

| Table 8: EPC Recommended Equipment and Materials   | 27  |

| Table 9: Required Equipment and Materials          | 29  |

| Table 10: Secondary Method Materials and Equipment | 41  |

| Table 11: Device Electrical Charactereistics       | 52  |

| Table 12: Version 2 Areas Requiring Improvement    | 73  |

| Table 13: Version 3 Priority Design Areas          | 74  |

| Table 14: Power stage configurations               | 102 |

# List of Figures

| Figure 1: Traditional AC Distribution System               | 6  |

|------------------------------------------------------------|----|

| Figure 2: High Voltage DC Distribution System              | 7  |

| Figure 3: Refined DC Distribution System                   | 8  |

| Figure 4: Theoretical Limits of GaN, Si, and SiC [21]      | 13 |

| Figure 5: Typical GaN Device [26]                          | 15 |

| Figure 6: EPC eGaN Device [26]                             | 16 |

| Figure 7: Auburn/UT DC Distribution System                 | 20 |

| Figure 8: Typical Multiphase Buck Circuit                  | 22 |

| Figure 9: Chip Scale Packaging used by EPC on a U.S. penny | 26 |

| Figure 10: Process Groups                                  | 29 |

| Figure 11: Footprint before pads are 'bumped'.             | 31 |

| Figure 12: Correctly 'bumped' footprint pads.              | 32 |

| Figure 13: Footprint after tacky flux application.         | 33 |

| Figure 14: X-Ray image of misaligned device.               | 36 |

| Figure 15: X-Ray image of properly aligned device.         | 36 |

| Figure 16: X-Ray image of properly soldered device.        | 39 |

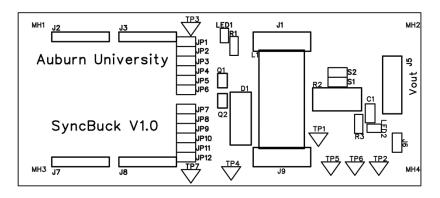

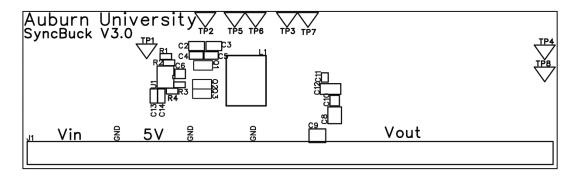

| Figure 17: Assembled Version 1 Buck Converter              | 48 |

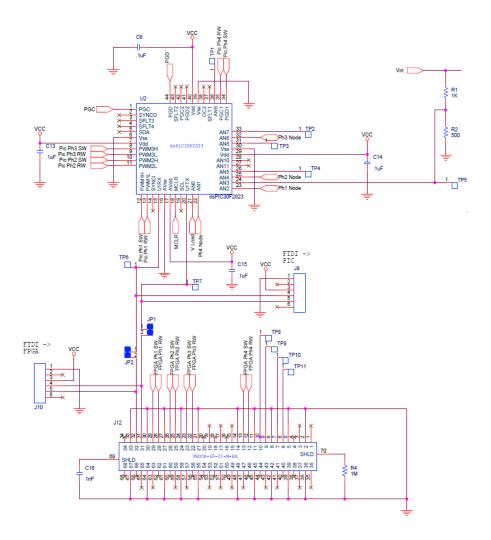

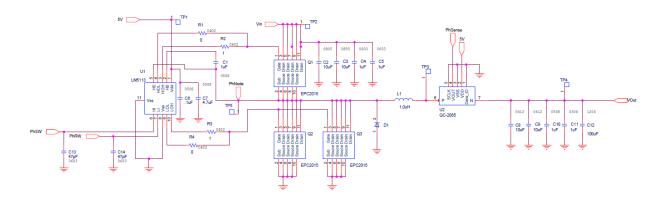

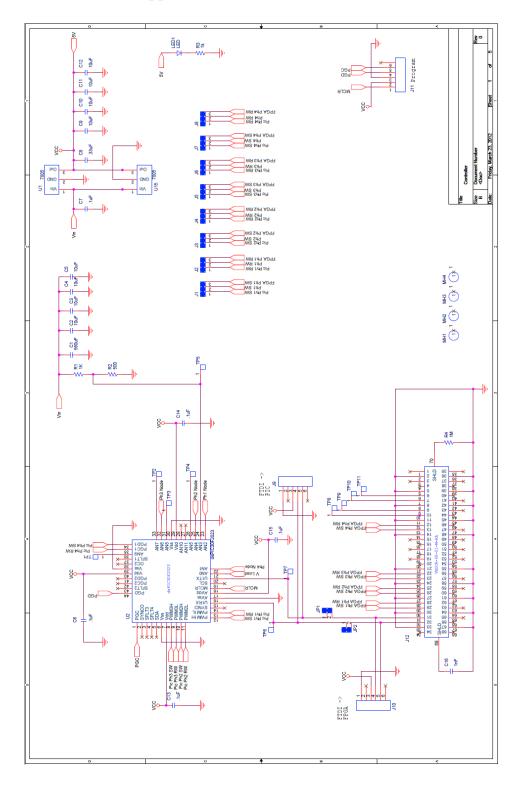

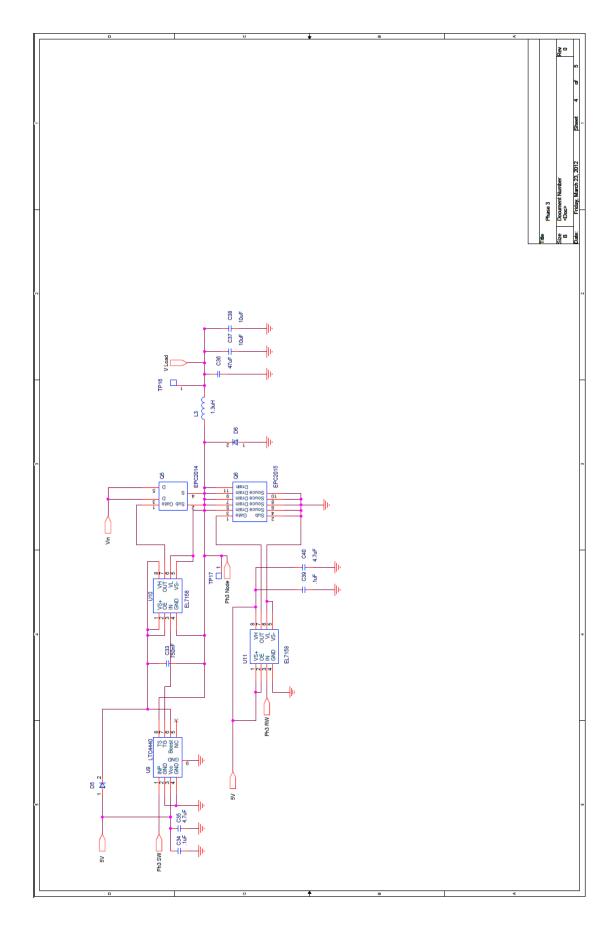

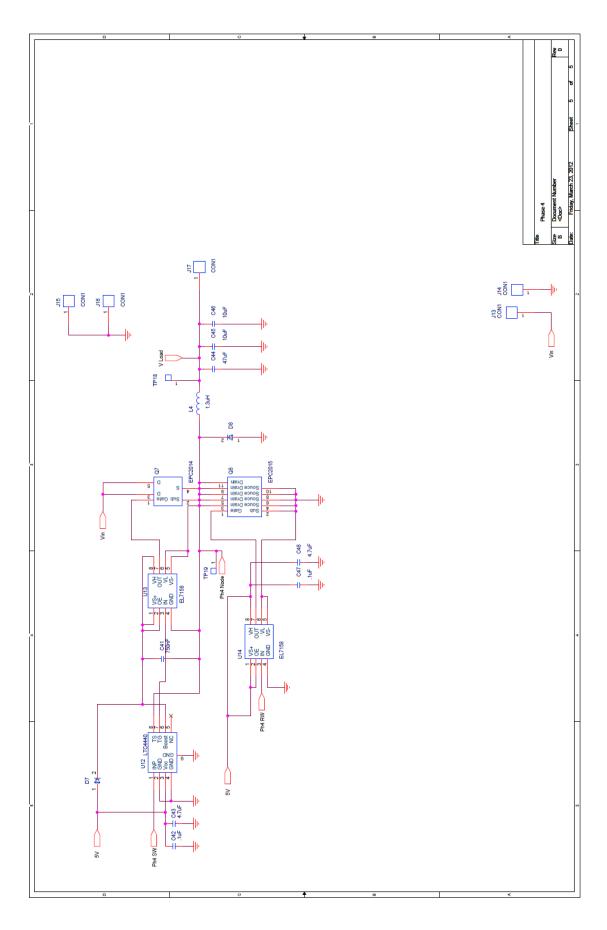

| Figure 18: Version 2 Controller, FPGA Interface & dsPIC    | 51 |

|------------------------------------------------------------|----|

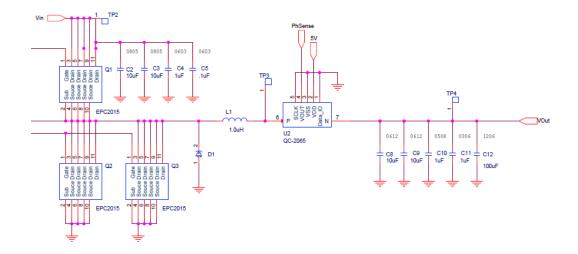

| Figure 19: Version2 Gate Drive Circuit                     | 53 |

| Figure 20: Version2 Converter Circuit                      | 54 |

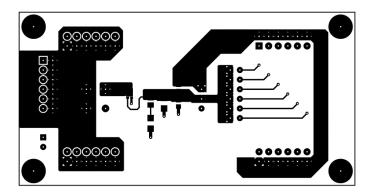

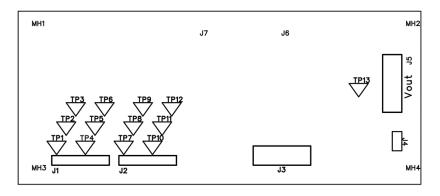

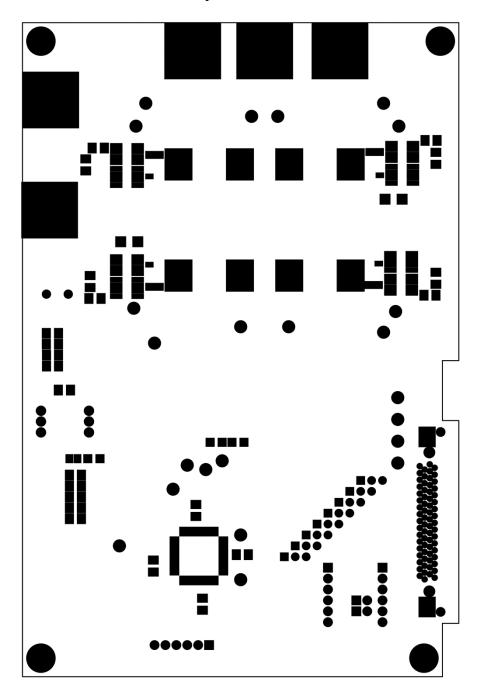

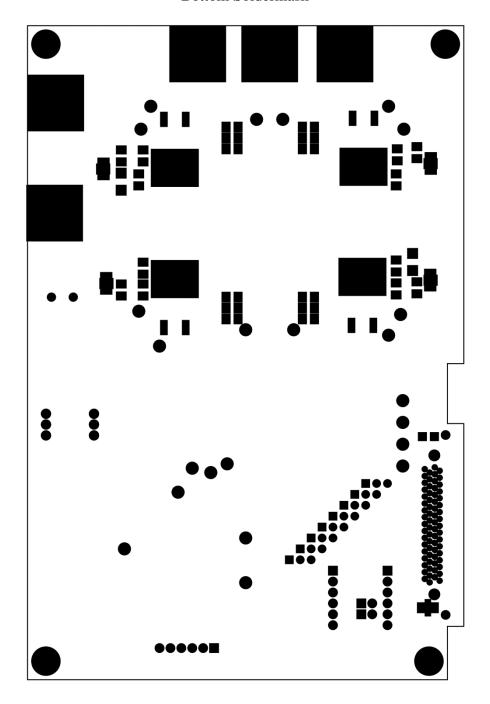

| Figure 21: Final Version2 Converter Component Placement    | 57 |

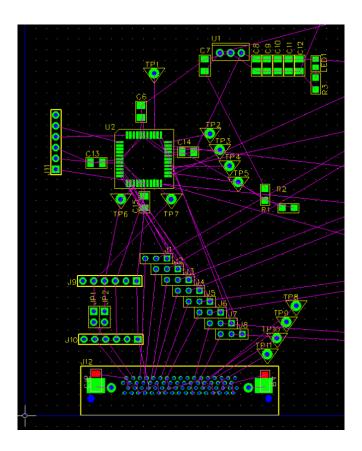

| Figure 22: Version2 Converter, 4 Phases.                   | 57 |

| Figure 23: Initial Version2 Controller Component Placement | 58 |

| Figure 24: Initial Placement, all Components               | 59 |

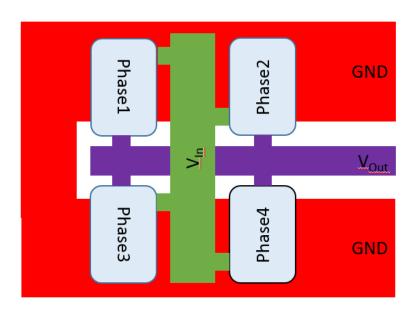

| Figure 25: 2x2 Oriented Converter Phases                   | 60 |

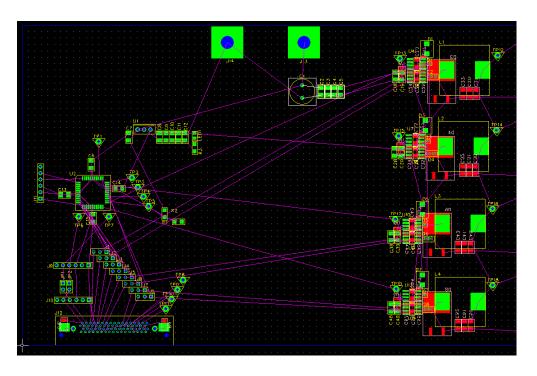

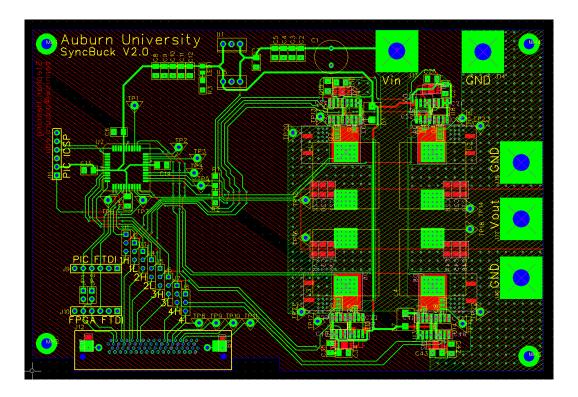

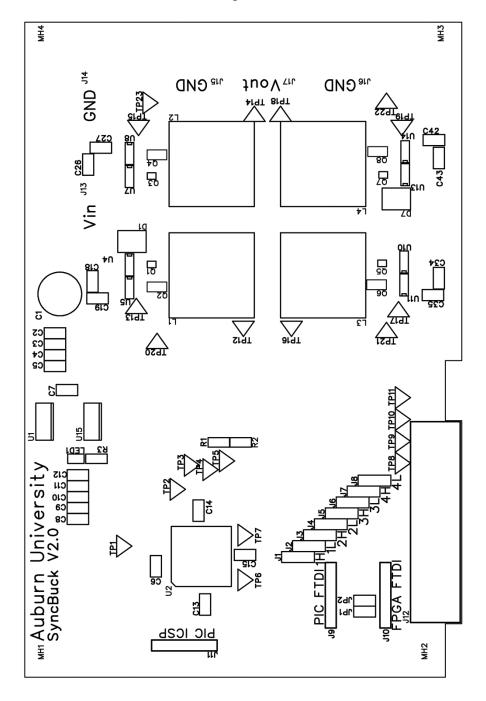

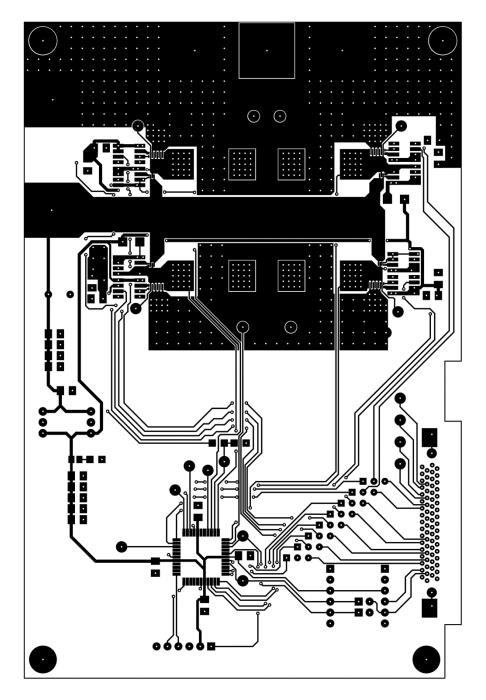

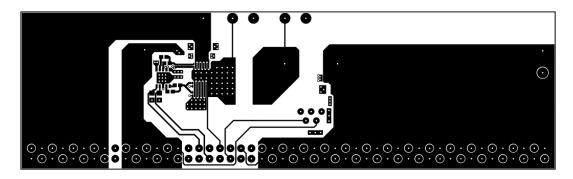

| Figure 26: Final Version2 Layout                           | 62 |

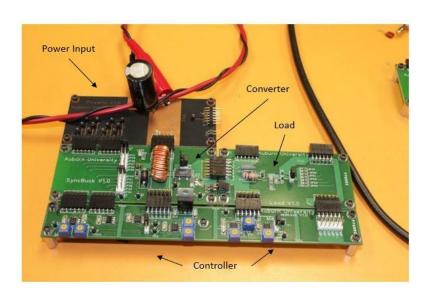

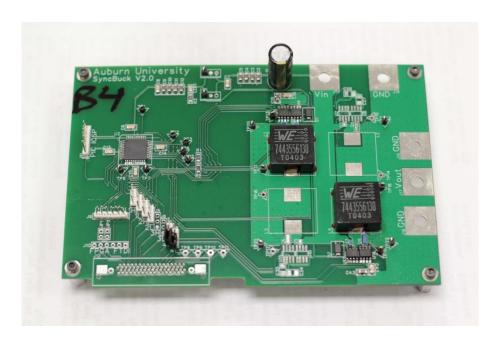

| Figure 27: Assembled Version2 Board                        | 63 |

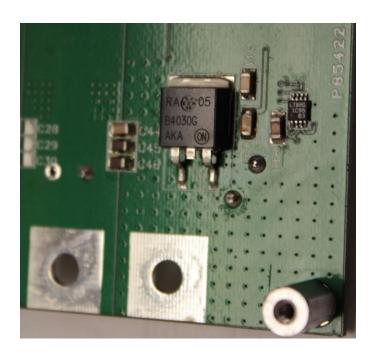

| Figure 28: Close up of Assembled Converter Phases 1 and 4  | 64 |

| Figure 29: Back of board showing assembled Phase 4         | 64 |

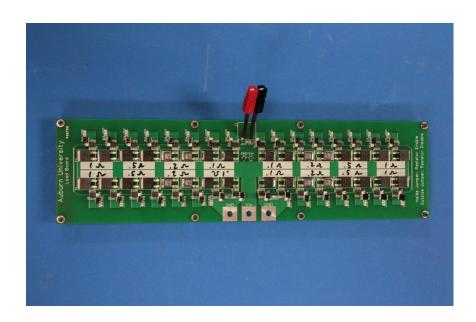

| Figure 30: Assembled load board.                           | 65 |

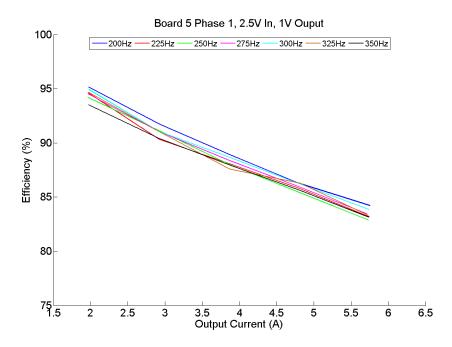

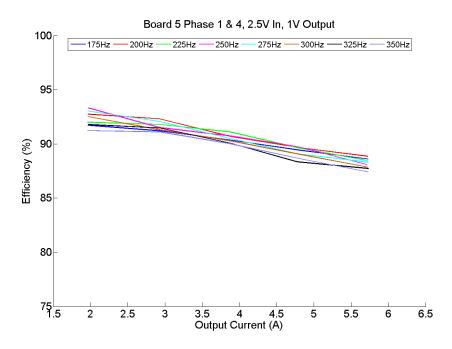

| Figure 31: Phase 1 efficiency data                         | 66 |

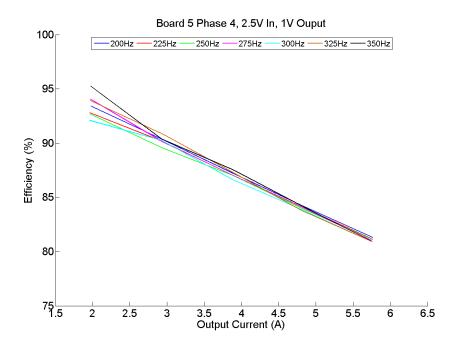

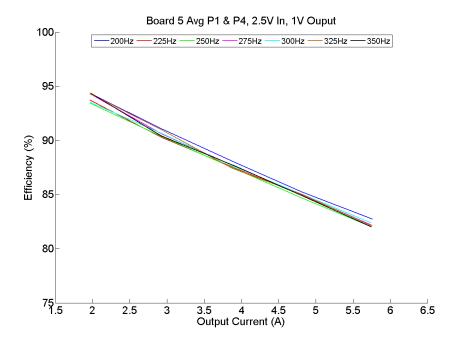

| Figure 32: Phase 4 efficiency data                         | 67 |

| Figure 33: Average of the data from Phase 1 and Phase 4    | 67 |

| Figure 34: 2 Phase operation efficiency data               | 68 |

| Figure 35: Circuit waveforms at 1.8A output                | 70 |

| Figure 36: Circuit waveforms at 5.6A out                   | 71 |

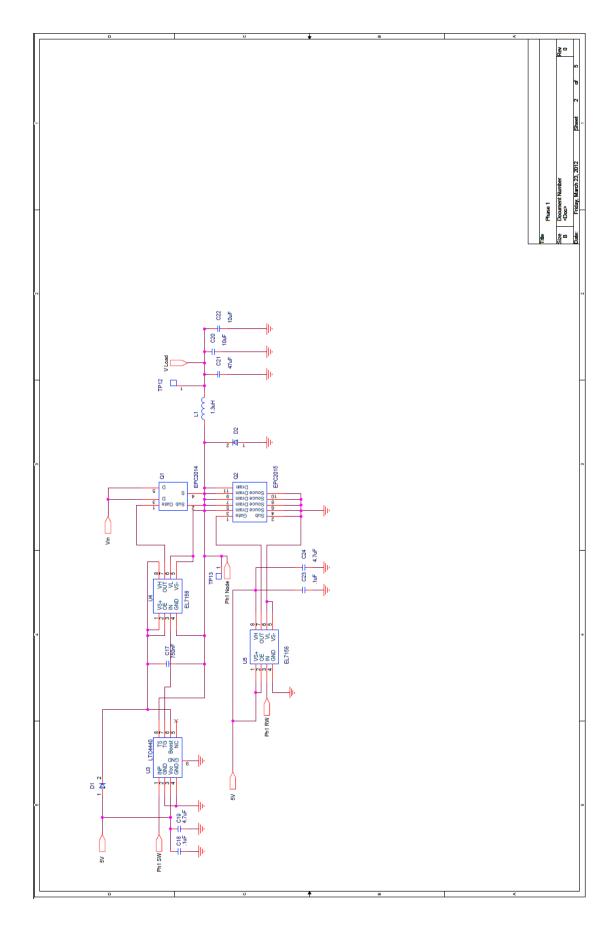

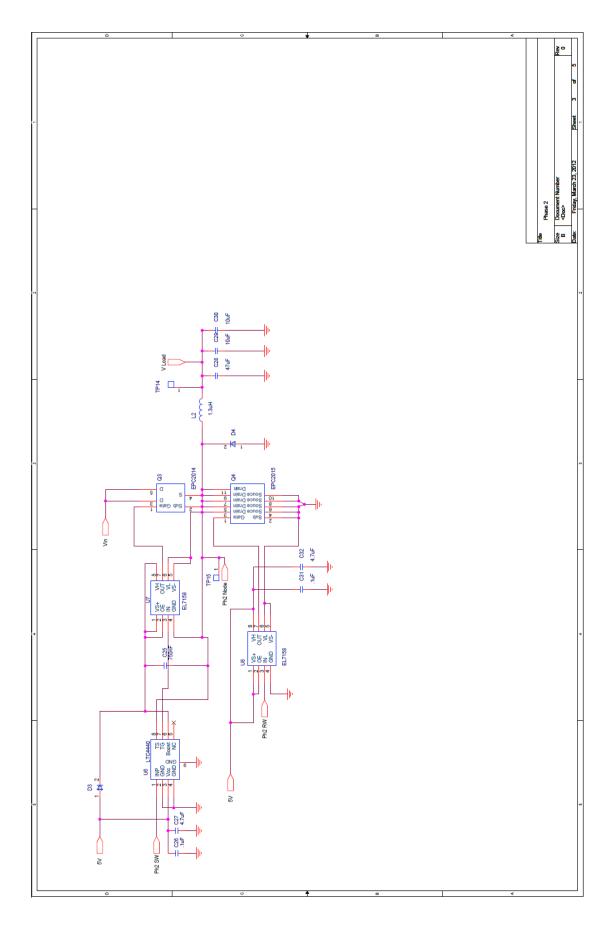

| Figure 37: Version 3 gate drive circuit                    | 76 |

| Figure 38: Version 3 converter circuit                     | 79 |

| Figure 39: Full version 3 converter stage                       | 79  |

|-----------------------------------------------------------------|-----|

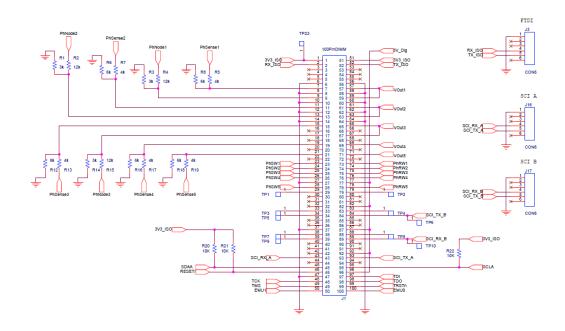

| Figure 40: Version 3 ControlCard interface                      | 81  |

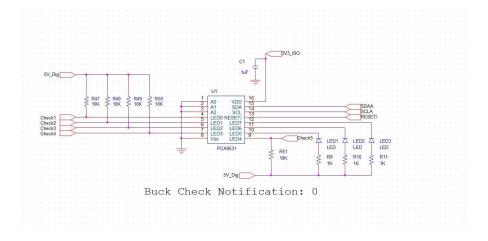

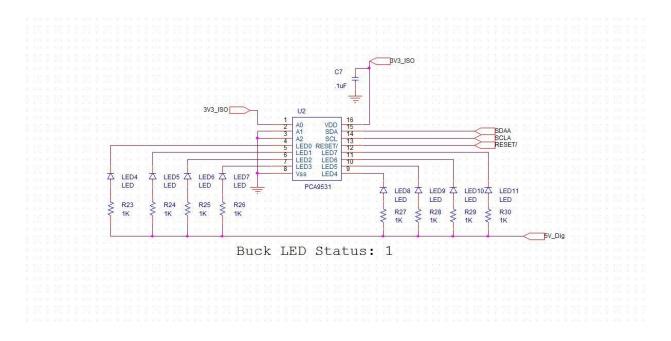

| Figure 41: Converter phase status check                         | 82  |

| Figure 42: User programmable converter status LEDs              | 82  |

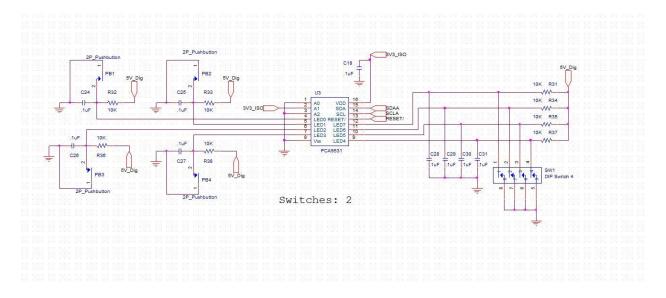

| Figure 43: User programmable pushbutton inputs                  | 83  |

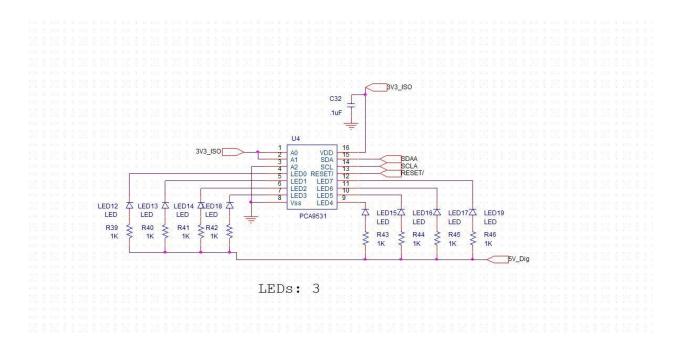

| Figure 44: Use programmable LED indicators                      | 83  |

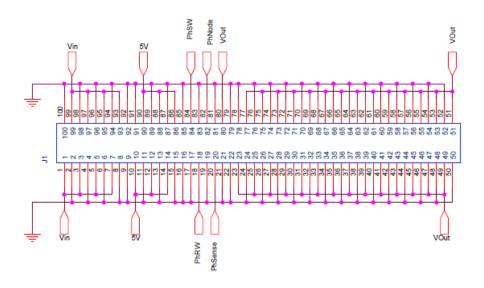

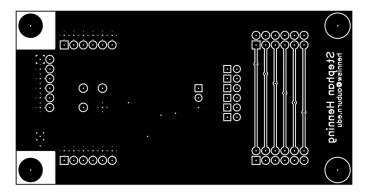

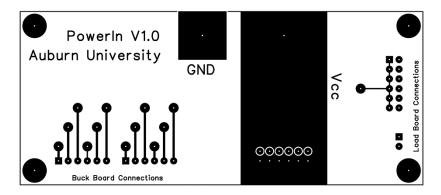

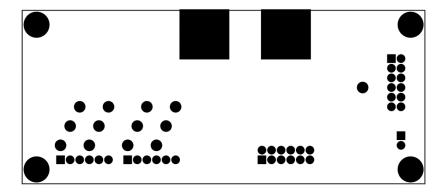

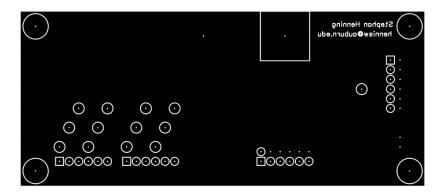

| Figure 45: Converter daughter card interface                    | 85  |

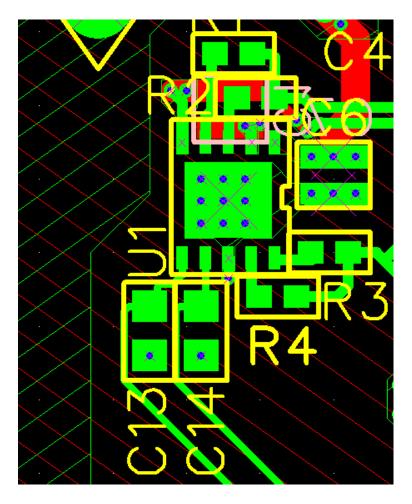

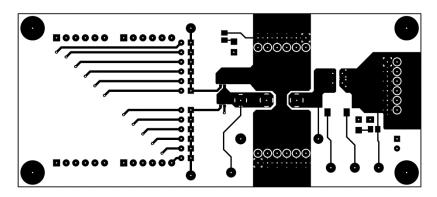

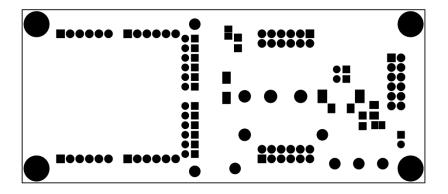

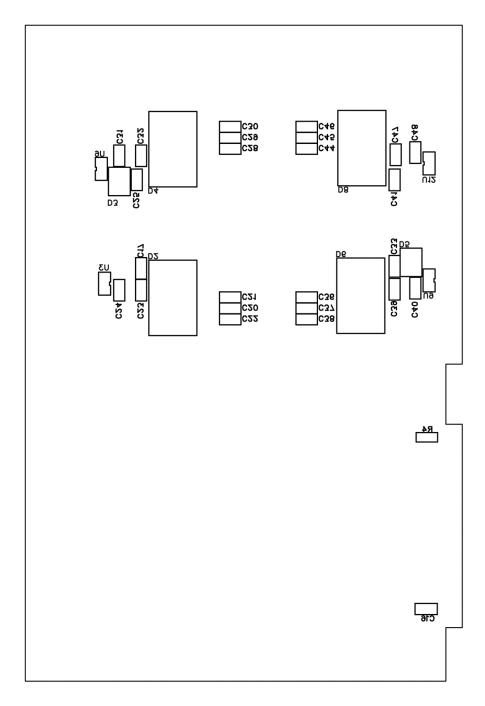

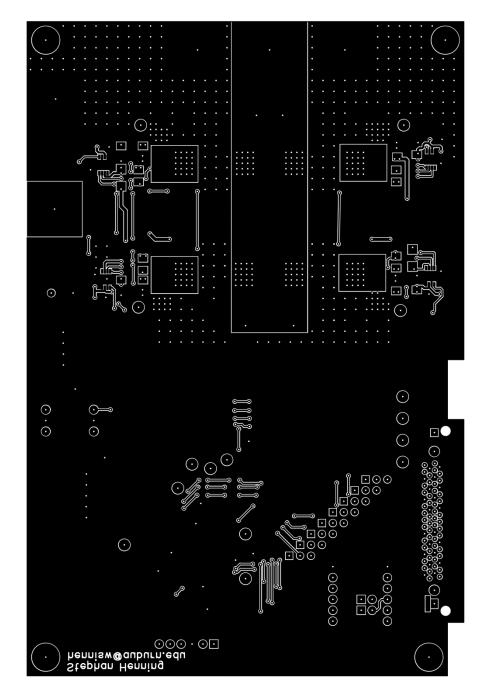

| Figure 46: Version 3 gate drive layout                          | 87  |

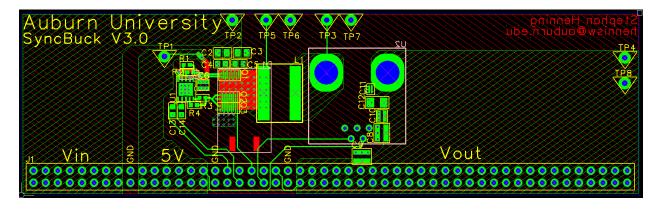

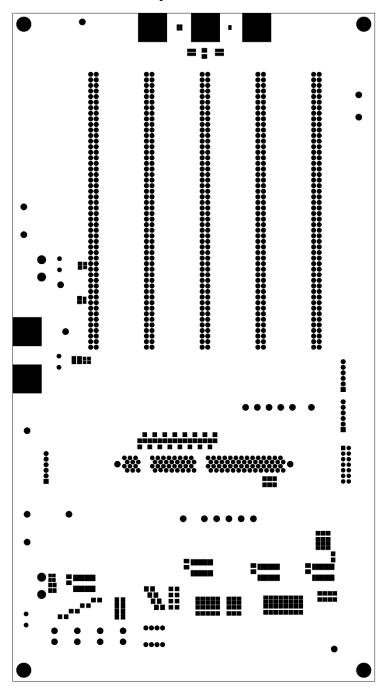

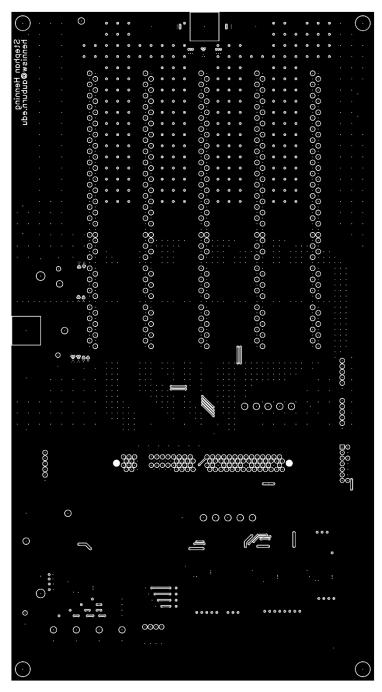

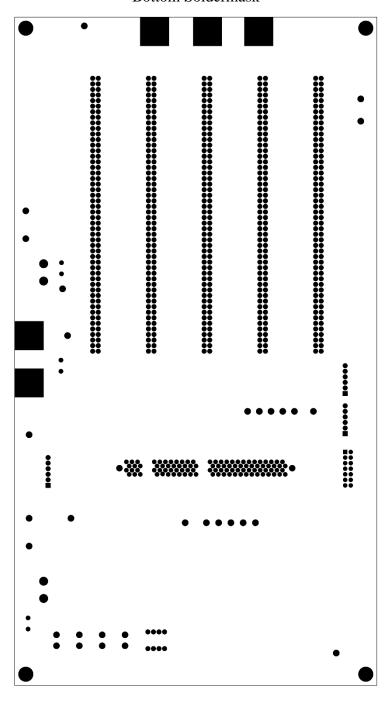

| Figure 47: Version 3 converter power stage daughter card layout | 88  |

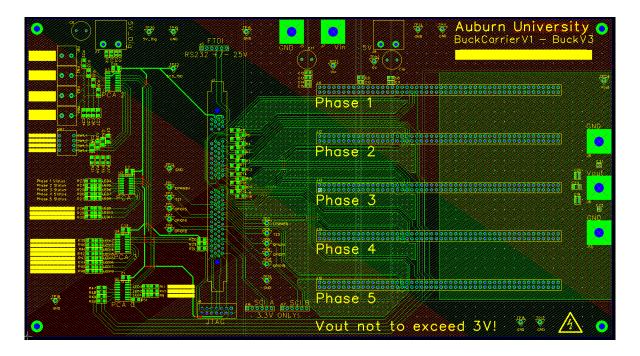

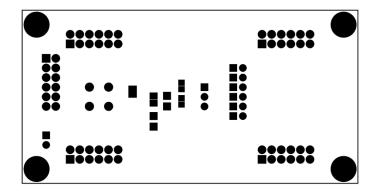

| Figure 48: Version 3 carrier board layout                       | 91  |

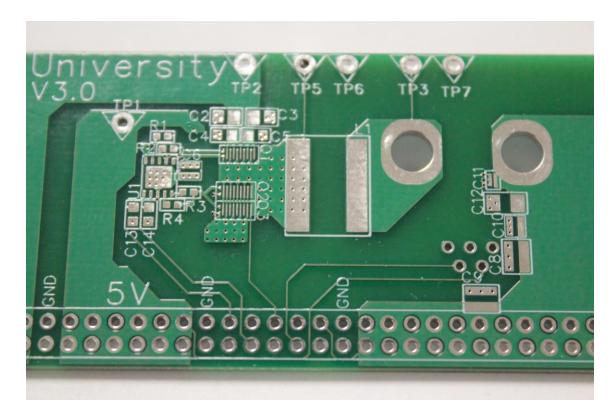

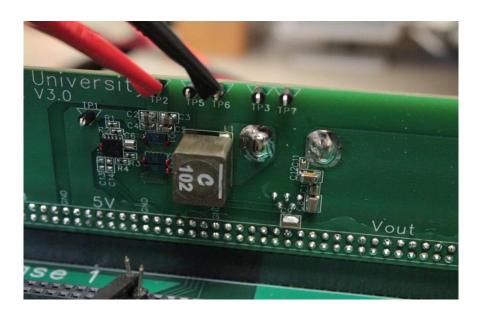

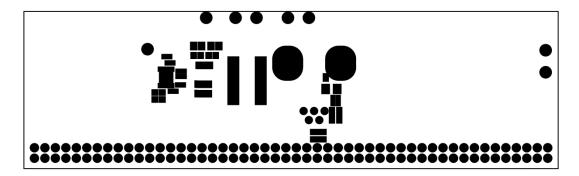

| Figure 49: Version 3 unassembled converter daughter card        | 92  |

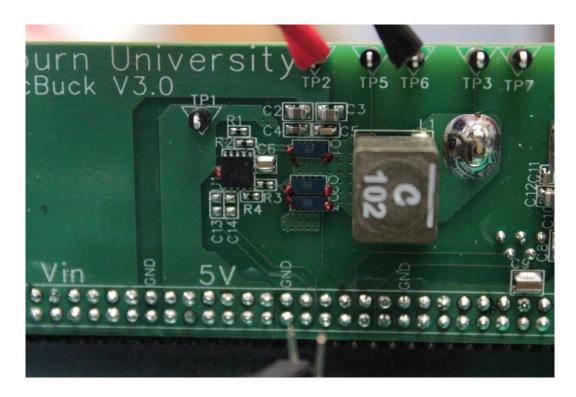

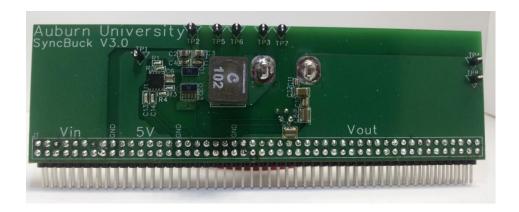

| Figure 50: Assembled version 3 converter circuit.               | 93  |

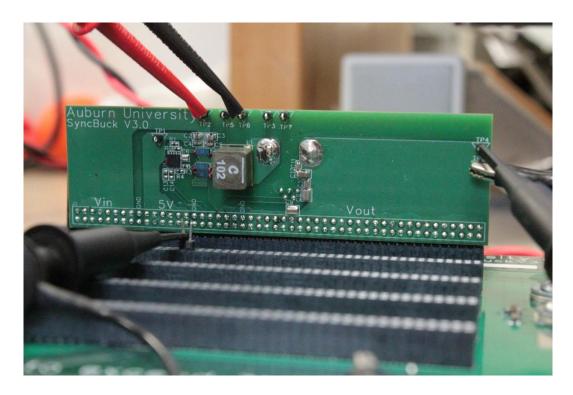

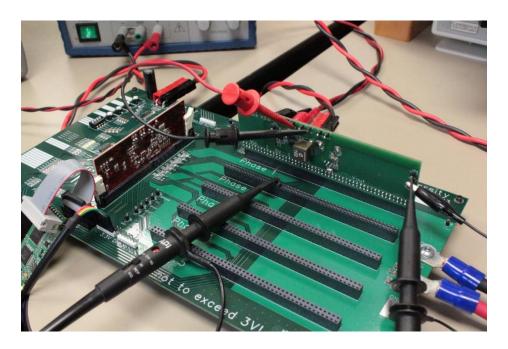

| Figure 51: Duaghter card installed in carrier board             | 94  |

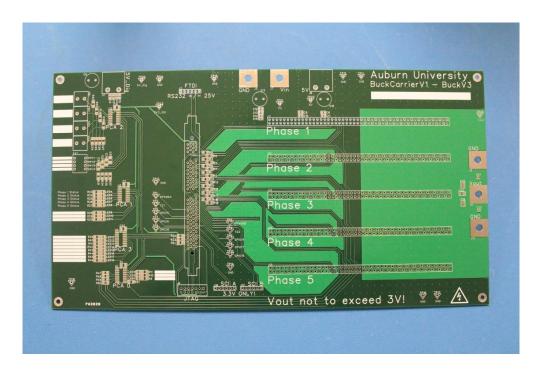

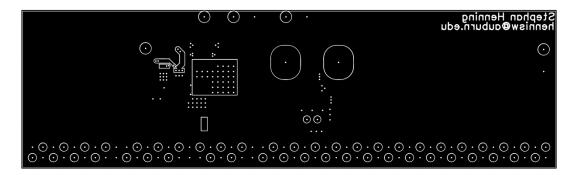

| Figure 52: Unpopulated carrier board                            | 95  |

| Figure 53: Populated control side of carrier board              | 95  |

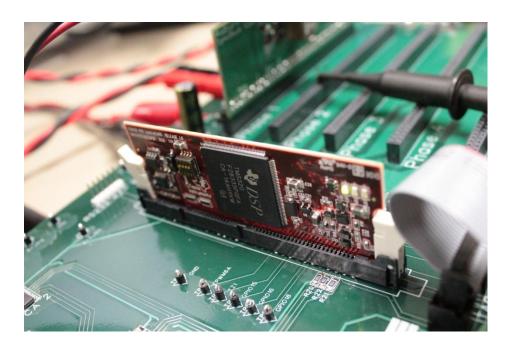

| Figure 54: ControlCard installed in carrier board               | 96  |

| Figure 55: Converter daughter card installed and being tested   | 97  |

| Figure 56: Default converter circuit assembled                  | 98  |

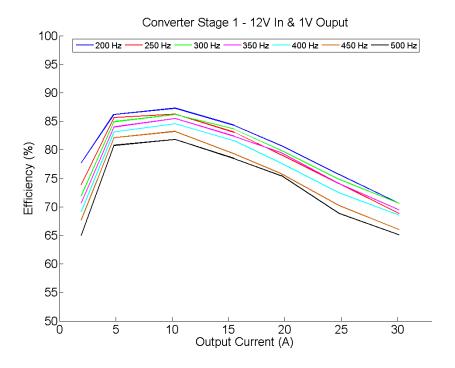

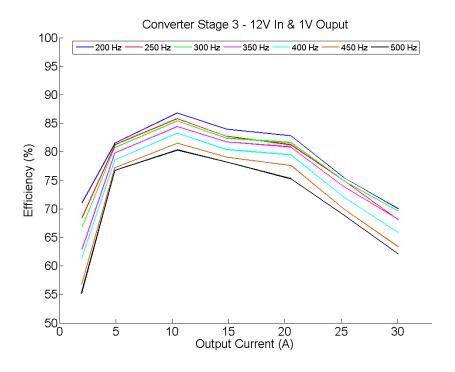

| Figure 57: Efficiency data for power stage 1                    | 99  |

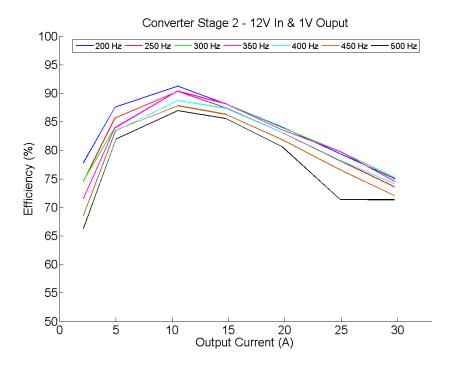

| Figure 58: Efficiency data for power stage 2                    | 99  |

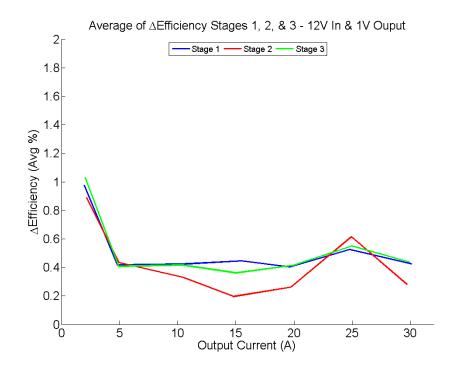

| Figure 59: Efficiency data for power stage 3                    | 100 |

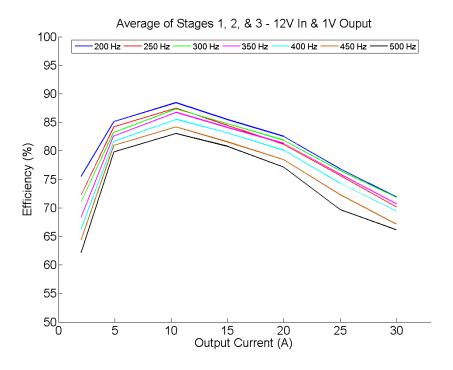

| Figure 60: Average of efficiency data stages 1, 2, and 3 | 101 |

|----------------------------------------------------------|-----|

| Figure 61: Average frequency efficiency delta            | 101 |

| Figure 62: Assembled power stage 7                       | 103 |

| Figure 63: Assembled power stage 8                       | 104 |

| Figure 64: Assembled power stage 9                       | 104 |

| Figure 65: EPC2014 under high current load               | 105 |

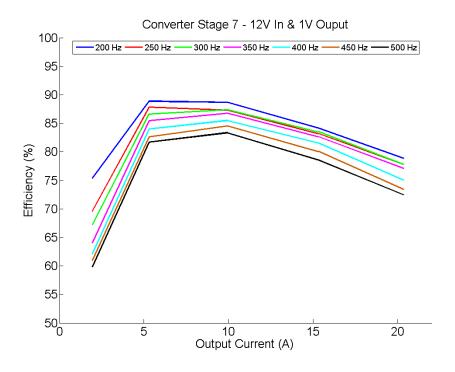

| Figure 66: Efficiency data for power stage 7             | 106 |

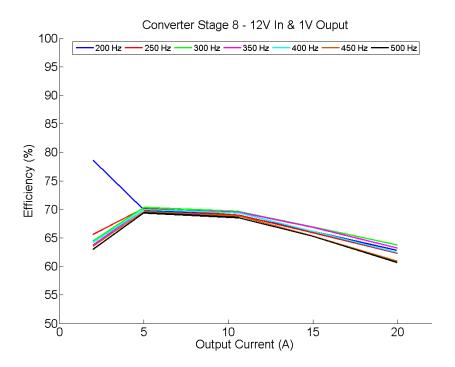

| Figure 67: Efficiency data power stage 8                 | 107 |

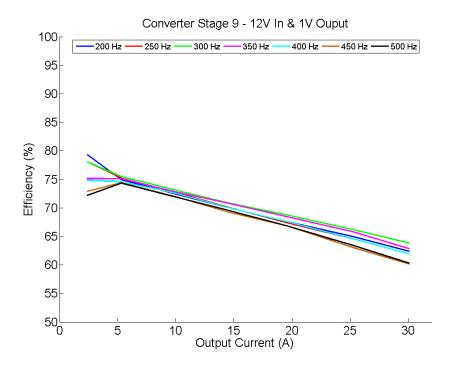

| Figure 68: Efficiency data power stage 9                 | 108 |

### Nomenclature

# Acronyms

GaN Gallium Nitride

FET Field-Effect Transistor

POL Point of Load

EPC Efficient Power Conversion

DC Direct Current

AC Alternating Current

CPU Central Processing Unit

HVDC High Voltage Direct Current

PDU Power Distribution Unit

Si Silicon

CMOS Complementary Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

SiC Silicon Carbide

BFoM Baliga's Figure of Merit

HEMT High-Electron-Mobility Transistor

RF Radio Frequency

AlN Aluminum Nitride

AlGaN Aluminum Gallium Nitride

2DEG 2 Dimensional Electron Gas

eGaN Enhancement mode Gallium Nitride

CSP Chip Scale Package

ESD Electrostatic Discharge

PCB Printed Circuit Board

BGA Ball Grid Array

IO Input/Output

FPGA Field Programmable Gate Array

ADC Analog to Digital Converter

SMT Surface Mount Technology

SMD Surface Mount Device

MLCC Multi-Layer Ceramic Capacitor

LED Light Emitting Diode

DIP Dual in-line Package

IC Integrated Circuit

DIMM Dual in-line Memory Module

RAM Random Access Memory

SMPS Switch Mode Power Supplies

### **Terms**

IR Conduction Losses

# Chapter 1 Introduction

In June of 2011 a new leader rose to the top of the TOP500 supercomputing list [1]. This newcomer to the list was the K computer built by Fujitsu and installed at the RIKEN Advanced Institute for Computational Science in Kobe, Japan. This supercomputer currently stands as the largest supercomputer in the world with a reported computing rate of 8.1 petaflops consuming 9.9MW of power, far besting its closest competitor, the Tianhe-1A with a reported rate of 2.5 petaflops which consumes 4MW. As of the most recent update of this list in November 2013 [2], the top system is now the Tianhe-2, with a computation rate of 33.86 petaflops requiring 17.8MW of power from the grid.

In this modern age, computing has become an integral part of our culture. It would be very difficult for anyone living in a technological society to make it through an average day without interacting with some kind of computer system. Not only has the level of computer integration into our daily lives increased, the scale of the computers necessary to power the daily workings of a modern world has also increased. As the scale of these large computers continues to expand, the power requirements of these systems grow as well. The largest of these supercomputer and datacenter systems have grown to the point where their power requirements are in the megawatt range, a consumption rate equivalent to that used by thousands of average suburban households. Table 1 shows the power requirements of several of the largest computing systems and their equivalent household draw. Reducing the power requirements of these facilities, thereby reducing stress on the power grid and facility operating costs, is the main reason for this push to increase power system efficiency. The implementation of more efficient

data centers becomes more and more important as energy costs continue to rise as countries like China continue to modernize at astounding rates, their energy requirements growing with them, putting pressure on global energy reserves.

Table 1: Power Draw of Top Systems

| Machine    | Location | Processing Power (TFlops/s) | Power Draw (kW) | Equivalent #<br>US Households [3] |

|------------|----------|-----------------------------|-----------------|-----------------------------------|

| Tianhe-2   | China    | 33862.7                     | 17808           | 14396                             |

| Titan      | USA      | 17590.0                     | 8209            | 6636                              |

| Sequoia    | USA      | 17173.2                     | 7890            | 6378                              |

| K computer | Japan    | 10510.0                     | 12660           | 10234                             |

| Mira       | USA      | 8,586.6                     | 3,945           | 3189                              |

Not only is the operation of these large scale computer systems very expensive, the addition of these large datacenters places increased strain on local power grids. Unfortunately, a significant portion of the power draw by these supercomputers never reaches the processors, instead being lost as heat in the electronic systems that supply the power to these processors. While large strides have been made in reducing the power requirements of the processors, as much as 35% of the power supplied to these systems may be lost in the power supplies that support them.

Addressing this relatively low overall efficiency has become vital to the development of new systems as the yearly cost of power to operate and cool these new installations begins to rival the costs associated with the construction of the facility. Additionally, any power that is wasted due to system inefficiency is burned off as heat. This only adds onto the cost of running the system as more power must now be used to operate the cooling systems needed to remove this extra heat.

Increasing the efficiency of a power system for such large facilities becomes a complicated systems problem with many separate sections that must be addressed. The focus of this work is on the Point of Load (POL) section of the power system that is being developed at Auburn University, in collaboration with the University of Tennessee where work on the other sections of the power system occurred. The POL portion of the power system typically comprises the final section of the supply, providing power directly to the processing units. Due to the lower voltages and higher currents required by modern processing units, POL stages face efficiency issues due to factors such as device resistance and circuit I<sup>2</sup>R losses, in addition to any losses inherent in the circuit topology used in a design.

This work will address these losses by looking at efficiency improvements related with the use of gallium nitride (GaN) devices in the POL power stage. Chapter 2 will provide a background on previous research in the area as well as additional discussion related to the motivation of the work. Chapter 2 will also provide an overview of wide band-gap technology, some of the features of GaN devices, and how these devices help improve efficiency when used in power converter designs. This is then followed in Chapter 3 by a discussion of design considerations for this project in the implementation of the POL power stage. Chapter 4 will discuss the implementation of these GaN devices by utilizing an assembly solution that allows for rapid prototyping of design changes. Chapter 5 will discuss the implementation of the GaN devices into version 2 of a functional converter prototype and lessons learned from the initial design. Chapter 6 provides a detailed description of the design for version 3 of the POL and discusses improvements from the version 2 design. Chapters 5 and 6 detail the design goals, provide analysis of the design and test data, and highlight areas where further improvement

could be made. Chapter 7 will provide a summary of the completed designs and describe future work that can expand on the efforts developed in this portion of the project.

## Chapter 2 Background and Previous Work

While the problem of power system efficiency is not new, the rapid rates of improvement in computer processing power and the ever increasing demands for larger and more powerful installations has begun to exceed the capabilities of the power system technology available. While it is necessary to consider the power system as a whole when discussing efficiency, the high power, low voltage – high current, nature of the POL portion of the power system creates the opportunity for large device and conduction losses within the subsystem. This chapter provides some background on high efficiency POL regulators and previous work done in this area.

#### 2.1 DC Distribution

As datacenters have grown in size and scale, their power requirements have also changed. Recent trends in processor design have created chips that are becoming ever more efficient in terms of their processing capacity per watt while also being installed in denser and denser rack system, allowing for very high CPU and core counts in current generation high density servers. While these new processors are more energy efficient, their size, and hence power demand, continue to increase, so the rest of the power system cannot be ignored when the goal is to create a power efficient datacenter.

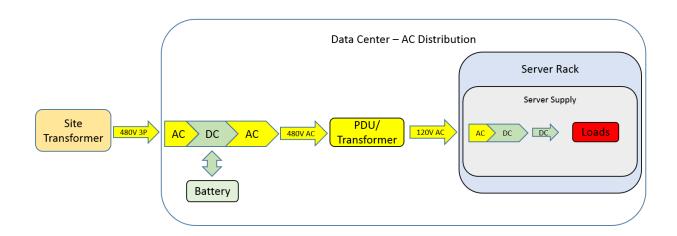

For many years the typical datacenter power system architecture was based on an AC distribution system that would then convert AC to the DC needed by the computer systems with the server rack level. An example of such an architecture is shown below in Figure 1 and is

discussed by Smedman in [4], Oliver in [5], Bindra in [6], and Murrill and Sonnenberg in [7]. While these systems are well understood and easy to implement, the multiple AC/DC conversion steps and relatively low efficiency of the rack level AC/DC power supplies can bring total system efficiency down into the 70% range.

Figure 1: Traditional AC Distribution System

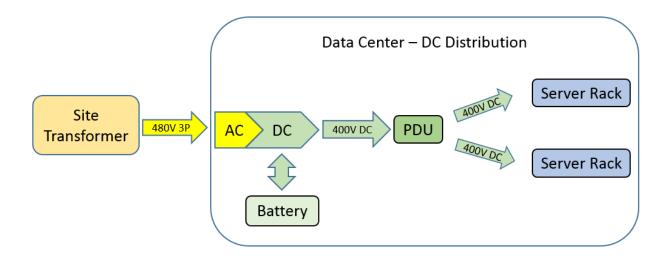

With the advancements in processing power and data storage, new power distribution systems have been developed to better power these datacenters. While some new generation systems are still utilizing AC distribution to great effect [8], many installations are beginning to transition to HVDC based distribution systems, such as the Sakura Ishikari Data Center in Japan which is utilizing a HVDC system to simplify its power system and while boosting power efficiency, generating cost savings that will allow to Sakura to compete in new technology markets [9]. While there is some variation in the specific architecture used as discussed in [10], [11], [4], [12], and [13], most facilities use a system similar to what is shown in Figure 2.

Figure 2: High Voltage DC Distribution System

This type of DC distribution system utilizes few AC/DC conversion steps, allowing for increased efficiency gains. However, this new type of system creates a need for more advanced DC supplies capable of performing DC-DC conversions to provide the computing equipment with the required DC voltages for storage media and processor cores. Companies such as Vicor [14] [5] rose to the challenge with new high efficiency DC product lines. For many large scale installations this would not be sufficient, requiring the adoption of advanced power systems using recent advancements in Si and GaN semiconductors in power converter design to further increase efficiencies within the DC supplies, providing substantial long term cost benefits considering their considerable power usage.

#### 2.2 Point of Load Converters

This newer DC distribution architecture requires the bulk of the conversion processes to occur at the rack level in the overall system. In order to achieve this, the DC power supplies used need to maintain high efficiency while maintaining a low volume, to avoid a negative impact to

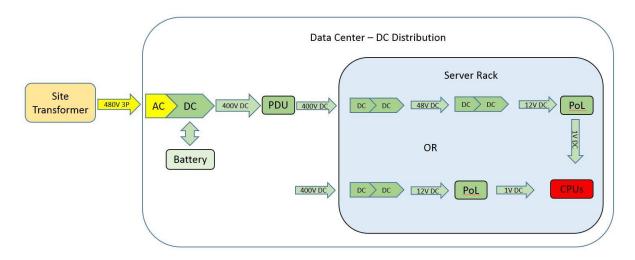

current rack processor densities. Figure 3 enhances the previous DC system diagram in and shows a further breakdown of the power system within the confines of the computation rack itself, with two possible options being shown.

Figure 3: Refined DC Distribution System

Within this DC distribution architecture, the Point of Load (POL) supply now becomes a main focus of the design due to its low output voltages and high current levels, requiring careful design in order to maintain the operating efficiencies needed to ensure overall system efficiency remains high.

In order to reach these efficiency goals, the POL supply needs to be mounted in close proximity to the processor cores in order to minimize conduction losses. This creates volumetric problems as the POL supply must have a small enough footprint to ensure that inter-card spacing can be kept small enough to maintain processor core density levels. Casey and Martin were one of the early investigators into board level POL converters and describe in [15] the utilization of a high frequency resonant converter for use as a 50W, 40V to 5V POL supply, but were limited by the components available to them at the time. Fisher et al. continued this work, using a simplified

version of the circuit in [16] and alternate fabrication methods to demonstrate a 100W 40V to 5V converter, but they also experienced fabrication issues and thermal problems due to lower than expected efficiencies of approximately 79%.

In [17] Nagar et al. provide a low output voltage ripple solution though the implementation of filter networks. Two separate options were presented, with the final recommendation utilizing a two stage LC filter in conjunction with a control system to maintain operational stability. The discussed combination of output filter and control algorithm provided a significant decrease in voltage ripple, but at a detriment to system efficiency and response rate.

Ng, Seeman, and Sanders demonstrated a CMOS based switched-capacitor POL converter with peak efficiency of 93%, with 80% over a 7mA to 1A range. This was achieved through the construction of Dickson type circuit fabricated on a chip using CMOS manufacturing techniques, as demonstrated in [18]. While the topology is impressive, the current requirements for this work are not comparable to the low current available from this implementation on the CMOS level.

Zhou, Donati, Amoroso, and Lee investigate a control system solution to improving buck topology regulators light load efficiency in [19]. They were able to demonstrate dramatic improvements at light loads of less than 1A by using drive signals specific to the load condition. This method allows for the improvement of light load efficiencies while maintaining efficiency levels at higher output currents of 8A as well. This method of control adjusts frequency as load levels increase and decrease, while also adjusting the on/off time of the synchronous rectifier, forcing the inductor to operate in discontinuous mode. This control is managed by sensing the inductor current by using changes in duty cycle in operation due to load level transitions. This requires additional logic to be implemented, either in discrete components or in the coding of the

control system. If this control method can be properly implemented, this forcing of the circuit to operate in discontinuous mode coupled with the reduced switching losses of the lower frequency operation are shown to provide great improvement at light loads without sacrificing performance at higher loads.

Xu, Wei, and Lee propose in a modification to the buck topology that allows for operation at larger duty cycles, while still maintaining the large input/output voltage ratio necessary for modern process voltage regulators. The novel topology described in [20] is called a multiphase coupled buck converter and uses coupled tapped inductors between the buck phases, combined with an active clamping circuit to handle voltage spikes that would otherwise damage the MOSFET switches. An implementation of the tested circuit resulted in a four phase 12V<sub>In</sub>, 1.5V<sub>Out</sub>, 50A converter that was operated at 300kHz with a peak efficiency of 89% and full load efficiency of 85%. This improvement over a comparable standard four phase buck converter which presented peak efficiency of 84.5% and full load efficiency of 81.5% was a result of significantly reduced switching losses, but this gain was decreased slightly from higher conduction losses in the synchronous switch.

While there has been significant work in the area of POL regulators, none of the current research solves the problem set specific to the demands of the newer generation of high current processors. Based on these previous works and other research into the area, it is believed that a combination of these methods and the implementation of next generation wide band-gap GaN devices will provide the efficiency levels needed.

### 2.3 Wide Band-Gap Devices

Silicon has been the dominant semiconductor material for most applications for many decades. Research and development in silicon technology has brought the technology to the point where devices are now near the theoretical limits for the material, and in cases such as superjunction devices and other advanced structures, past the theoretical limits as described by Lidow and Strydom in [21] and by Sherman and Herbsommer in [22]. Even with these continued advancements, as a mature technology silicon still cannot meet the needs of certain applications.

Wide band-gap devices have been in discussion since the 1950's, when William Shockley gave the introduction at the first Silicon Carbide Conference in 1958. Despite this, most research has focused on silicon devices, so much so that the first commercial wide band-gap devices were not available until 2001, with the introduction of a silicon carbide (SiC) Schottky diode by Rohm [23]. Since then fabrication processes have continued to evolve and more and more devices have reached the market, finding niche areas in which the performance advantages of wide band-gap materials make them competitive with mature silicon devices.

As research into wide band-gap devices continues, two materials have come to dominate most research and development, gallium nitride (GaN) and silicon carbide. While there are other materials that fall into the category of wide band-gap, SiC and GaN are the main materials used due to their materials properties and their relative ease of use in manufacturing as described by Kaminski in [24]. Table 2 below outlines some relevant material properties for GaN and SiC as compared to silicon (Si) and diamond.

Table 2: Wide Band-gap Material Properties [24]

| Parameter                                     |                  | Silicon             | 4H – SiC             | GaN                  | Diamond            |

|-----------------------------------------------|------------------|---------------------|----------------------|----------------------|--------------------|

| Band-gap E <sub>g</sub>                       | eV               | 1.12                | 3.26                 | 3.39                 | 5.47               |

| Intrinsic Conc. n <sub>i</sub>                | cm <sup>-3</sup> | $1.4 \cdot 10^{10}$ | 8.2·10 <sup>-9</sup> | $1.9 \cdot 10^{-10}$ | $1 \cdot 10^{-22}$ |

| Critical Field E <sub>crit</sub>              | MV/cm            | .23                 | 2.2                  | 3.3                  | 5.6                |

| Electron Mobility µn                          | $cm^2/V \cdot s$ | 1400                | 950                  | 1500                 | 1800               |

| Permittivity ε <sub>r</sub>                   | -                | 11.8                | 9.7                  | 9.0                  | 5.7                |

| Thermal Cond. λ                               | W/cm·k           | 1.5                 | 3.8                  | 1.3                  | 20                 |

| BFoM: $\varepsilon_r \cdot \mu_n \cdot E_C^3$ | rel. to Si       | 1                   | 500                  | 2400                 | 9000               |

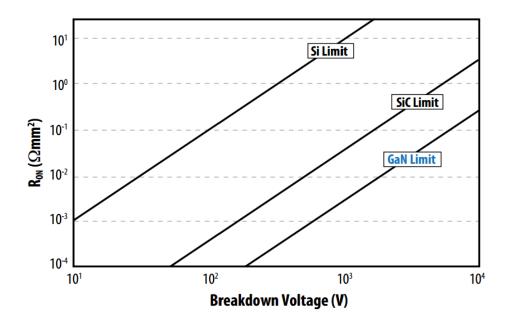

From this table several advantages to wide band-gap materials are apparent. Their lower intrinsic carrier concentration coupled with their higher band-gap, leakage currents for devices built from these materials are lower, requiring significantly higher temperature to reach comparable leakage currents to Si devices. The higher critical field of these materials means that for devices of the same width, devices manufactured with wide band-gap materials will have a higher breakdown voltage as compared to a Si device. The so called Baliga's figure of merit is a method of measuring the materials contribution to the on-resistance of a unipolar device and is defined as in (BFoM =  $\epsilon_r \cdot \mu_n \cdot E_C^3$ ) in [24]. While these values show favoritism toward the wide band-gap materials, on-resistance is based on many factors and device design must be taken into account when comparing between the materials. Figure 4 shows a comparison of theoretical on-resistance vs breakdown voltage for Si, GaN, and SiC.

Figure 4: Theoretical Limits of GaN, Si, and SiC [21]

Market penetration by wide band-gap devices is still in the early phases. In many cases Si still dominates as its low price point due to mature fabrication techniques makes it difficult for expensive wide band-gap devices to compete. GaN is beginning to gain popularity in power electronics as it has been used in the optoelectronics industry for many years and that market has helped push the advancement of the technology. In addition, fabrication processes that allow for GaN to be grown on sapphire and recently on standard silicon wafers are giving GaN a large boost in the area of materials cost as SiC remains an order of magnitude more expensive to produce. These cost issues along with challenges in the manufacturing process have largely kept SiC out of the switch market, giving GaN an opportunity to gain market share. Table 3 describes some of the needs present in power electronics design and how GaN meets these needs [25].

Table 3: GaN Technology Advantages [25]

| Need                   | Enabling Feature                     | Performance Advantage             |

|------------------------|--------------------------------------|-----------------------------------|

| High Power/Unit Width  | Wide Band-gap, High Field            | Compact, Ease of Matching         |

| High Voltage Operation | High Breakdown Field                 | Eliminate/Reduce Step Down        |

| High Linearity         | HEMT Topology                        | Optimum Band Allocation           |

| High Frequency         | High Electron Velocity               | Bandwidth, µ-Wave/mm-Wave         |

| High Efficiency        | High Operating Voltage               | Power Saving, Reduced Cooling     |

| Low Noise              | High Gain, High Velocity             | High Dynamic Range Receivers      |

| High Temp Operation    | Wide Band-gap                        | Rugged, Reliable, Reduced Cooling |

| Thermal Management     | SiC Substrate                        | High Power Devices with Reduced   |

|                        |                                      | Cooling Needs                     |

| Tech Leverage          | Direct Band-gap Enabler for Lighting | Driving Force for Technology, Low |

|                        |                                      | Cost                              |

Despite these advantages, GaN and SiC have both faced major issues in the penetration of the power electronics market. This difficulty was because of the nature of the materials, early switch devices that were fabricated from both materials were normally-on devices. While normally-on switches have their place, this is a disadvantage for most power electronics designs as additional circuitry would be needed in order to properly control these switches during operation, especially during startup sequences to ensure no short circuit faults occur before the switches can be driven into an off-state.

The first of these HEMT based depletion mode GaN devices grown on SiC appeared on the market in 2004, with the first HEMT GaN device on a Si substrate appearing in 2005. [21]. These devices were both RF transistors and GaN continued to gain more popularity in RF applications, but the difficulty in using depletion mode devices kept GaN from entering other markets, including power electronics. Usage of GaN remained confined to RF markets until the introduction of the first enhancement mode GaN device grown on a Si substrate, specifically for use as a power MOSFET, by Efficient Power Conversion (EPC) in June of 2009 [26].

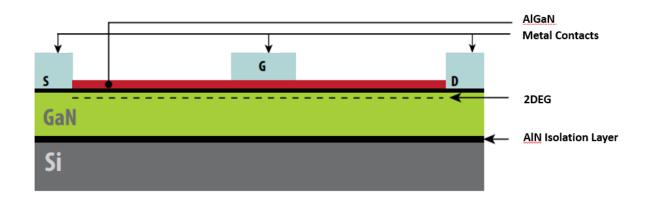

EPC begins its manufacturing process with Si wafers using a process that is similar to typical depletion mode GaN devices. In typical devices, a layer of aluminum nitride (AlN) is grown on the Si wafer. This AlN layer serves as a base onto which the GaN can be grown. Once a suitable layer of GaN is present, a layer of AlGaN is added. Drain and source contacts are then added in a manner that pieces this AlGaN layer, creating Ohmic contacts to the two dimensional electron gas (2DEG) that exists below the AlGaN layer. This creates a short circuit between the drain and source that is the basis for the normally-on behavior of these devices. In order to control the device, a gate electrode is placed on the top of the AlGaN layer, which then depletes the 2DEG when a negative voltage is applied to it. Figure 5 shows a representation of the typical construction of a GaN device.

Figure 5: Typical GaN Device [26]

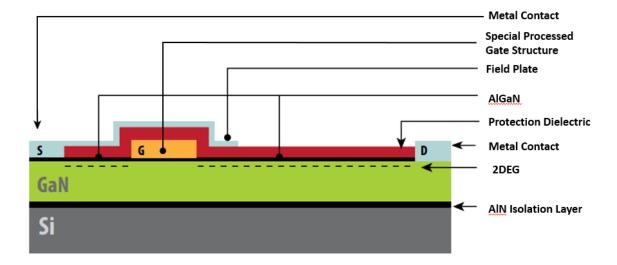

EPC's enhancement mode GaN devices utilize the same basic structure, but use a processing step to create a gate under the AlGaN layer. This creates a depletion region within the 2DEG. Appling a positive voltage to this gate structure then allows a channel to be reestablished within the 2DEG, creating the enhancement mode operation that is preferable for MOSFETs in

power electronics. The structure is then repeated laterally to create the eGaN device. Figure 6 shows a representation of this enhancement mode structure utilized by EPC.

Figure 6: EPC eGaN Device [26]

The device structure implemented by EPC allows for the creation of devices that are well suited to power electronics. These eGaN devices have  $R_{ON}$  values and  $R_{ON}$  vs  $V_{GS}$  curves that are similar to Si MOSFETs but with lower temperature coefficients, allowing for easy substitution in many designs and for better performance in higher temperature environments. Drive requirements for EPCs eGAN devices are also similar to Si parts with an expected gate voltage of 4-5V. The threshold voltage is lower than typical Si devices, which requires careful design of the gate-source path to ensure the device transitions to fully off during high speed switching operation. High speed operation is enabled by low device capacitance, allowing the device to switch high power levels in the MHz frequency range. The eGaN structure has very low  $C_{GD}$  and  $C_{GS}$ , with  $C_{GS}$  being much larger than  $C_{GD}$  but still much smaller than comparable Si devices.

The structure of the eGaN device also creates a 'body diode' that operates similar to those present in Si MOSFETs, but with a larger forward voltage than in silicon transistors [26] that may necessitate the use of a circulation diode. Table 4 lists the metrics for several EPC devices and Table 5 compares EPC devices to similar Si devices.

Table 4: EPC Device Electrical Characteristics

| Metric              | EPC2014 [27]  | EPC2015 [28]  | <b>EPC2001</b> [29] |

|---------------------|---------------|---------------|---------------------|

| $V_{DS}$            | 40 V          | 40 V          | 100 V               |

| $I_D$               | 10 A          | 33 A          | 25 A                |

| $V_{GS}$            | 5 V           | 5 V           | 5 V                 |

| $T_{J}$             | -40 to 150 °C | -40 to 150 °C | -40 to 125 °C       |

| R <sub>DS(ON)</sub> | 12 mΩ         | 3.2 mΩ        | 5.6 mΩ              |

| $Q_{G}$             | 2.48 nC       | 10.5 nC       | 8 nC                |

| $Q_{GD}$            | .48 nC        | 2.2 nC        | 2.2 nC              |

| Coss                | 150 pF        | 575 pF        | 450 pF              |

Table 5: Comparison of Device Characteristics

| Metric              | Infineon [30]<br>BSC010NE2LS | NXP [31]<br>PSMN5R6-100PS  | TI [32] CSD17306Q5A | EPC [28]<br>EPC2015 |

|---------------------|------------------------------|----------------------------|---------------------|---------------------|

| $V_{DS}$            | 25 V                         | 100 V                      | 30 V                | 40 V                |

| $I_D$               | 100 A                        | 100 A                      | 24 A                | 33 A                |

| $V_{GS}$            | 5 V                          | 5 V                        | 5 V                 | 5 V                 |

| $T_{\rm J}$         | -55 to 150 °C                | -55 to 175 °C              | -55 to 150 °C       | -40 to 150 °C       |

| R <sub>DS(ON)</sub> | 1.1 mΩ                       | 4.3 mΩ                     | 3.3 mΩ              | 3.2 mΩ              |

| $Q_{G}$             | 64 nC                        | 141 nC                     | 11.8 nC             | 10.5 nC             |

| $Q_{GD}$            | 6.8 nC                       | 43 nC                      | 2.5 nC              | 2.2 nC              |

| Coss                | 1700 pF                      | 561 pF                     | 890 pF              | 575 pF              |

| Package             | TDSON-8                      | TO-220                     | SON 5mmx6mm         | LGA 4.1x1.6         |

| Area                | $34\text{mm}^2$              | $\geq$ 48.5mm <sup>2</sup> | $30 \text{mm}^2$    | 2.5mm <sup>2</sup>  |

From the performance data in Table 4 and Table 5 it is clear that the technology of GaN devices has reached a point where they have become a viable option for use in power electronics design as they are comparable to present generation silicon devices in all performance metrics and their small board footprint is an enabling characteristic for the next generation of high power density systems. It is believed that combining devices constructed on GaN technology with well executed circuit design and system control would allow for the creation of a high efficiency, high power density system capable of supporting the increasing power demands of current and future advanced processor systems.

## Chapter 3 Design Goals and Approach

As datacenters grow larger with ever increasing power demands, the role of power system efficiency in the expected operational cost of a new facility has become more prevalent. This new attention has allowed big names in power supply design to bring new, more efficient products to market, but it has also forced facility planners to look at how to best utilize their new technology options to create the most cost effective system possible. It was from this line of thinking that Auburn University was brought in on a team with the University of Tennessee to help develop a power system for next generation datacenters. Auburn's role in this project consisted of two main tasks, first to evaluate wide band-gap devices for possible use in the various stages of the power system, and second, to develop a prototype Point of Load converter to meet the load requirements of the system processor.

### 3.1 Scope and Goals

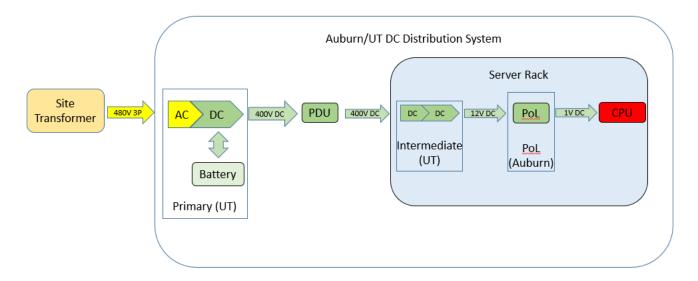

At the inception of this project, a survey was performed on the current available solutions for datacenter power systems; some of the references discovered during this survey are discussed in Chapter 2. The results from this survey demonstrated that a DC distribution based system as shown in Figure 7 using wide band-gap technologies had the potential to produce a system with an overall efficiency as high as 90%, allowing for significant operational savings for a large facility. From this architecture the input and output requirements for Auburn's POL prototype were generated based on the anticipated designs for the primary and intermediate stages.

Figure 7: Auburn/UT DC Distribution System

The requirements for the POL portion of the power system were introduced to the project team and are shown in Table 6, with an additional goal of maintaining the highest power density possible in order to reduce design size to enable the POL supply to be placed directly on the CPU card. With these requirements in hand, the team began the process of selecting a converter design best suitable to meet these requirements while taking into account the specifications of the various devices currently on the market, including the wide band-gap devices that were being evaluated.

Table 6: Point of Load Design Objectives

| Metric                | Goal     |  |

|-----------------------|----------|--|

| Output Power          | 150 W    |  |

| Input Voltage         | 12 VDC   |  |

| Output Voltage        | 1 VDC    |  |

| Output Current        | 150 A    |  |

| Output Current Ripple | ± 5%     |  |

| Max Current Slew Rate | 300 A/μs |  |

| Output Voltage Ripple | ±30 mVDC |  |

Several types of testing were done to evaluate the possible performance of a wide assortment of wide band-gap devices in the various sections of the power system. This testing included device performance metric characterization tests, switching tests, and reliability tests. From the conclusion of this testing and from a review of the literature on voltage regulator circuits, a traditional multiphase buck style converter was chosen in combination with several devices, those being the EPC eGaN devices, with the EPC2014 and EPC2015 being the primary devices under consideration for use within the POL stage.

### 3.2 Converter Selection

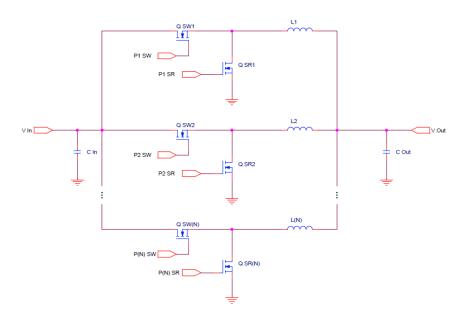

The traditional multiphase buck converter as shown in Figure 8 was chosen based on its simple design and its ability to operate well at both high and low load conditions. The buck topology is also able to maintain very high operating frequencies in order to handle potentially large transient load changes during operation, and still provide the tight output voltage regulation needed to meet the project goals [33] [34] [35] [36] [37]. The use of a multiphase system also provides advantages in that it allows for power phases to be deactivated during light load conditions, and by also providing for a measure of redundancy, allowing the system to continue operating at a reduced capacity should one phase encounter a failure.

Figure 8: Typical Multiphase Buck Circuit

Other converter topologies such as switched capacitor [38] [39] [40] and other forms of both isolated and non-isolated resonant converters were considered [41] [42] [43] [44] [45] [46] [47] [48] [49], but many of these designs have technical limitations such as lower response rate, inability to handle large load swings, or require devices with such high current or voltage capabilities that the design would grow in physical size and not provide a reasonable power density figure in the final design.

The selection of the multiphase buck converter as the topology of choice guided the selection of the EPC eGaN parts for use as the high side switch and synchronous rectifier. Unfortunately the packaging used by EPC for these devices makes them difficult to prototype with, so the initial v1 design was done as a proof of concept for the buck topology using standard

Si technology parts in a more user friendly package that allowed for the project to make forward progress while an assembly method was being developed that allowed for these EPC devices to be populated in large numbers for testing and rapid prototype development.

# Chapter 4 GaN Technology Implementation

With the decision to use the eGaN devices produced by EPC, a means of implementing the technology within the design was needed. Most typical power devices are produced in through-hole or large surface mount packages to aid in device cooling, which allows for very easy assembly operations either manually or through automated processes. The chip scale packages being utilized by EPC to aid in lowering device package parasitics and manufacturing cost are of a bumped die variety, which is very difficult to use in a prototype environment where automated assembly equipment may not be available. This created the need for a manual assembly method that would allow us to implement these eGaN devices in the POL design process and for device testing.

### 4.1 EPC Device Packaging

While the EPC eGaN devices offer better electrical characteristics than many other devices on the market, this level of performance does not come without a penalty. In order to achieve these values, EPC has chosen to package their devices as bumped die in an effort to avoiding the parasitics that are added when a device is packaged in a larger, more traditional package while also taking advantage of their high performance nature and lower cooling requirements by reducing their physical footprint. Table 7 shows an example of EPCs device packages compared to more traditional surface mount packages of devices with similar performance levels.

Table 7: Comparison of Device Packages [26]

| Device                 | LGA<br>package | Equivalent MOSFET packages             |  |

|------------------------|----------------|----------------------------------------|--|

| 40 V<br>4 mΩ max       | 4.1 x 1.6 mm   | 6.3 x 5 mm DirectFET 5 x 6 mm PolarPak |  |

| 40 V<br>16 mΩ<br>max   | 1.7 x 1.1 mm   | 4.8 x 3.9 mm<br>DirectFET              |  |

| 100 V<br>7 mΩ max      | 4.1 x 1.6 mm   |                                        |  |

| 100 V<br>30 mΩ<br>max  | 1.7 x 1.1 mm   | 5 x 6mm PQFN  4.8 x 3.9 mm  DirectFET  |  |

| 200 V<br>100 mΩ<br>max | 1.7 x 0.9 mm   | 6.3 x 5 mm DirectFET 5 x 6 mm PolarPak |  |

In many applications, these additional parasitics do not affect the device or the circuit negatively as the parasitics are minimal when compared to the characteristics of the device itself. However, the eGaN devices produced by EPC are low loss and the addition of a larger package would reduce the performance level of these devices due to the increased package inductance, capacitance, and resistance. The decision by EPC to use the device with minimal packaging after being diced from the wafer as a bumped die chip scale package (CSP) removes the possibility of

reduced device performance due to package characteristics, providing the engineer with the best foundation possible to begin their design.

While this provides the engineer with a device with outstanding electrical characteristics, the decision to use a bumped die CSP, as seen in Figure 9, may generate some difficulties during the assembly process. Due to the size and material composition of the device, automated assembly is the recommended means of assembly in order to ensure proper alignment and placement of the small device and to ensure that the rather fragile silicon substrate the device is built upon does not fracture during handling. Unfortunately, automated assembly of prototype level designs may not be feasible due to the time and costs involved with processing a design when compared to what can be accomplished manually by a skilled technician. As a result of this, a manual method must be developed that allows for rapid assembly while maintaining appropriately high levels of die attachment quality and process uniformity and repeatability.

Figure 9: Chip Scale Packaging used by EPC on a U.S. penny

### 4.2 Manual Assembly

EPC has made an effort to assist the engineer with prototype assembly by publishing guidelines for a manual assembly approach that requires precision silkscreen markings to aid in part alignment while using a hot air reflow process for die attachment [50]. This method is outlined below and Table 8 lists the materials needed.

Table 8: EPC Recommended Equipment and Materials

| Item                              | Process Group              |  |

|-----------------------------------|----------------------------|--|

| Anti-Static Mat, ESD wrist strap, | ALL                        |  |

| ESD lab coat, ESD gloves          |                            |  |

| Hot Plate or IR PCB Heater        | Prep                       |  |

| Tacky Flux                        | Prep, Placement, Alignment |  |

| Compatible Solder, spool          | Prep                       |  |

| Microscope                        | Prep                       |  |

| ESD Safe tools                    | ALL                        |  |

| Reflow Oven                       | Reflow                     |  |

| X-Ray Inspection                  | Alignment, Inspection      |  |

| Flux cleaning agent               | Prep, Inspection           |  |

| Soldering Iron                    | Prep                       |  |

This method, while being relatively simple, does not generate highly reliable or consistent results, primarily due to deviations in die placement and lack of post assembly inspection to check for defects. An alternative was needed to ensure consistent and highly reliable assembly for use in these high power prototype circuits.

In response to the issues found with the recommended process, a new method was developed to take advantage of the advanced assembly technology available to our project, while still allowing for a fully manual process that allows for very rapid assembly while maintaining the high levels of quality and uniformity necessary for prototype development of high efficiency

power converters. This method has proven itself after the assembly of many hundreds of devices and was published in [51], with less than 1% of these devices requiring rework after the initial assembly process. This process allows for defects to be found and corrected before the affected prototypes advance any further in the assembly process, preventing the significant effort needed to rework the defective devices once a circuit assembly had been fully completed. This method relies on the use of two specific pieces of equipment that may or may not be readily available to most research groups, an X-Ray inspection tool and a multi-zone reflow oven. In an effort to make this method more accessible to other groups that may wish to use these devices in a similar manner who do not have the required equipment available, a secondary method was developed that uses alternative equipment that may be more accessible for those institutions.

## 4.3 Primary Manual Assembly Method

The primary manual assembly method used in this work generates a high quality solder attachment while being a very rapid process that allows for many assemblies to be built in a short amount of time. This is accomplished through process implementations that take advantage of the material properties of solder and flux to ensure a reliable final product. The required equipment and materials for this process are listed in

Table 9. As in the original EPC process, ESD and material handling precautions must be taken into account to ensure the die are not damaged physically or electrically during the process. It is also highly recommended that this process be completed start to finish before any other components are attached to the assembly.

This process is broken down into five separate process groups as shown in

Figure 10. These groups may be assigned to separate operators and assemblies should move through the groups in a linear fashion. If a large number of assemblies are to be processed through at a given time, it is recommended that they be done in batches and passed through each process group as a batch instead of individually, unless a specific assembly requires extra attention. The PCB device footprint used in this process is a rectangular version of the standard PCB pad listed for each footprint. It is highly recommended that the PCB designer use the recommended pad layout as deviations could result in assembly defects or failures during device operation.

Figure 10: Process Groups

Table 9: Required Equipment and Materials

| Item                              | Process Group              |  |

|-----------------------------------|----------------------------|--|

| Anti-Static Mat, ESD wrist strap, | ALL                        |  |

| ESD lab coat, ESD gloves          |                            |  |

| Hot Plate or IR PCB Heater        | Prep                       |  |

| Tacky Flux                        | Prep, Placement, Alignment |  |

| Suitable Solder, spool            | Prep                       |  |

| Microscope                        | Prep                       |  |

| ESD Safe tools                    | ALL                        |  |

| Reflow Oven                       | Reflow                     |  |

| X-Ray Inspection                  | Alignment, Inspection      |  |

| Flux cleaning agent               | Prep, Inspection           |  |

| Soldering Iron                    | Prep                       |  |

#### 4.3.1 Preparation

The preparation portion of the process establishes a foundation onto which the following steps are built. Proper completion of the preparation portion is vital to ensure proper finished assembly quality. The preparation process can be completed in advance and the PCB's stored without any degradation to the process, although another cleaning step would be recommended to ensure no contaminates are present on the substrate before beginning the placement process. The preparation process is explained in detail below:

- 1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Place the following materials and equipment within easy reach of the operator: hot plate, flux, solder, soldering iron, flux cleaning agent, microscope

- 3. Place the hotplate/IR heater in the work area beneath the microscope.

- 4. Warm the assembly PCB to approximately 120°C-150°C. This temperature is dependent on the substrate used and the operator should ensure that it remains below the glass transition temperature of their substrate. Increasing the temperature beyond 150°C may yield some improvement in process completion time, but it is not advisable to exceed the published value for the substrate being used or the operator risks placing unneeded stress on the substrate.

- 5. Place a small amount of flux on the pads of the parts being assembled.

- 6. Using a small tip on the soldering iron, add a small amount of solder to each individual pad of the device footprint. There should be sufficient solder to raise the pad and form a convex surface, but not enough to cause a bridge to another pad. It is recommended that the operator attempt to achieve a uniform shape across all pads. The operator should also ensure that the solder being used is compatible with the solder used by EPC to create the

solder bumps on their devices. An incompatible alloy could generate future reliability issues.

- 7. Allow the PCB assembly to cool.

- 8. Clean any remaining flux off of the PCB assembly.

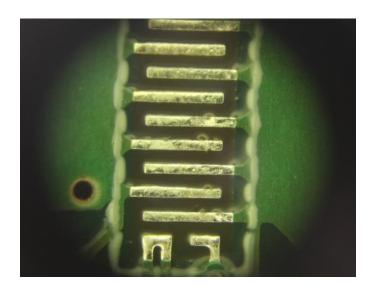

- 9. Visually inspect the 'bumped' footprint pads looking for any defects or voids in the solder areas. Any defects should be corrected before proceeding, followed by an additional cleaning step. An example of an appropriately bumped footprint can be seen in Figure 12 compared to the preprocessed footprint in Figure 11.

- 10. If a double sided design is being assembled, it is recommended that any device pads that exist on the back side be put through the prep process before the assembly is advanced any further.

Figure 11: Footprint before pads are 'bumped'.

Figure 12: Correctly 'bumped' footprint pads.

### 4.3.2 Placement

The placement process is relatively simple and may be accomplished very quickly. If only a small volume of assemblies are to be made, this process can be combined with the Prep process at a single workstation. The process steps are listed below:

- 1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Ensure the PCB assembly is clean before beginning.

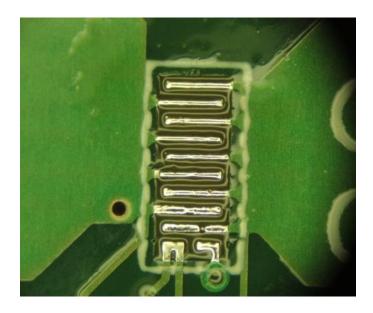

- 3. Place a small amount of tacky flux on the device footprint as shown in Figure 13. A water soluble flux is recommended for this step to aid in cleaning. RF771 tacky flux by Kester has been used successfully for this process. Tacky flux is used as it aids the operator by preventing the device from shifting should the PCB assembly be subjected to a minor bump during these processes. This step can be done for all devices on the same side of the board.

- 4. Using a set of ESD-safe fine tweezers, remove the device from its packaging and check for device orientation. The operator should be careful not to exert an excessive amount of force on the device as its exterior is very fragile and even small fractures can cause electrical malfunctions or reduce overall device performance and reliability.

- 5. Using the tweezers, place the device in its appropriate orientation in the flux over its pads.

- 6. The operator should visually align the part to the best degree possible, taking into account visual discrepancies generated by the flux.

- 7. Using very light pressure, the operator should ensure the device is making contact with the footprint pads and is not floating on the flux.

- 8. If a double sided design is being processed, the first side must be advanced through the rest of the process before the second side can be done.

Figure 13: Footprint after tacky flux application.

# 4.3.3 Alignment

The alignment process is done utilizing an X-Ray inspection device, specifically the Phoenix X-Ray pcba|analyser [52]. This machine allows the operator to exactly align the device solder bumps with the pads on the PCB assembly, generating a very high quality solder joint once sent through the reflow process. This portion of the process is vital to the quality of the solder joint and under no circumstances should any deviations from this process be done to accelerate the process unless the operator can ensure that no defects will be generated. If the alignment process is not done correctly and the assembly is sent through the reflow process it can be very difficult to remove and rework the device without damaging the PCB assembly if defects are then found in the inspection process. The alignment process is detailed below:

- 1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Place the PCB assembly in the X-Ray machine to achieve a top down view of the device. If several assemblies are to be processed, they may be inserted together, assuming the machine has a large enough capacity. It is recommended that the devices be placed on some kind of tray to make handling easier for the operator. If the reflow oven to be used has an X-ray compatible tray, it is advised to use it to help reduce the chances of the devices shifting after alignment while the assemblies are being moved.

- 3. Energize the X-Ray using appropriate safety measures for the particular machine being used. Under no circumstances should an untrained operator attempt to use the machine without proper supervision.

- 4. With the machine energized, zoom into the relevant device area of the assembly and adjust the settings on the machine until a clear view of the device and its footprint is achieved.

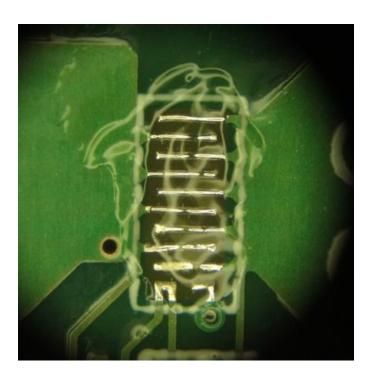

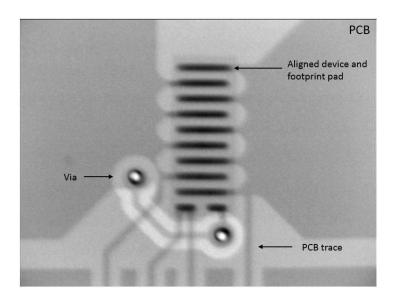

- 5. If the device is not aligned appropriately, the operator will see separation between the device and the PCB footprint as shown in Figure 14. If the device is appropriately aligned there will be very little or no distinction between the device and its footprint as seen in Figure 15. While it is not required to have a perfect overlap between the device and its footprint, it is recommended that any Theta offset be kept to the barest minimum and that there be no more then 1/4<sup>th</sup> of the narrow length of the pad offset in the corresponding dimension and no more than 1/4<sup>th</sup> of the wide length of the smallest pad on the device in the corresponding dimension. If the operator allows for any offsets larger than this, the risks of possible defects later in the process greatly increases.

- 6. De-energize the X-Ray machine and make any adjustments necessary to bring questionable devices within appropriate alignment tolerances. It is recommended to adjust devices using very light pressure on the side of the device package using a set of tweezers. The operator should be aware that the device will tend to want to sit with its solder bumps between the bumps on its footprint pad, and it may take a slightly larger amount of force to adjust the device so it is sitting on the top of the pads appropriately.

- 7. If the assembly contains more than one device, view and adjust them separately, ensure that all previously aligned devices are checked after the last device has been adjusted.

- 8. De-energize the X-Ray machine and remove the assembly from the machine.

Figure 14: X-Ray image of misaligned device.

Figure 15: X-Ray image of properly aligned device.

# 4.3.4 Reflow

The reflow process should not require much input from the operator beyond the initial creation of the reflow profile for the oven being used. It is recommended that this profile be

generated to correspond with the information provided by EPC for the solder alloy used on their devices. If the solder alloy that was used in the prep process requires a profile that differs significantly from what EPC recommends for their devices, it is recommended that the operator contact both EPC and the solder manufacture for input before proceeding. In this case a Heller 1800ESL nine zone reflow oven is being used with a general lead free solder reflow profile that is compatible with the EPC devices. The reflow process is outlined below:

- 1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Program the reflow oven to match the profile specified by EPC or a suitable alternative.

- 3. Ensure the oven has achieved proper operating temperatures before sending through any assemblies.

- 4. Place the assemblies in the oven directly or on a suitable carrier tray. If a carrier tray is used, it is recommended that temporary standoffs be placed under the board to ensure that no adhesion between the bottom side solder pads and the tray or between any excessive flux on the substrate and the tray takes place.

- 5. Allow the assembly to cool once exiting the oven.

### 4.3.5 Inspection

The inspection process is the last step and ensures that no assemblies are allowed to proceed if there are any placement defects with the devices. Extra care is recommended to ensure that all assemblies are of appropriate quality as these CSP devices are exceedingly difficult to rework once the entire circuit has been assembled, often requiring that the entire assembly be scrapped. Even if the assembly can be reworked successfully, the operator must be mindful of the fact that an assembly can only be put back through the process a finite number of times

before substrate and circuit component degradation may begin to occur. The inspection process is described below:

- 1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Clean the assembly with an appropriate flux cleaner to remove any remaining residue. While thorough cleaning can be accomplished through several methods, a combination of rinsing and ultrasonic cleaning has proven to be very effective in removing any flux residue. It is also recommended that the assembly be baked according to the flux manufactures specifications to ensure full cure of the flux to prevent the possibility of dendrite growth between pads, resulting in device and circuit failure once the assembly is in operation.

- Visually inspect the device for any physically damage and for any obvious signs of misalignment.

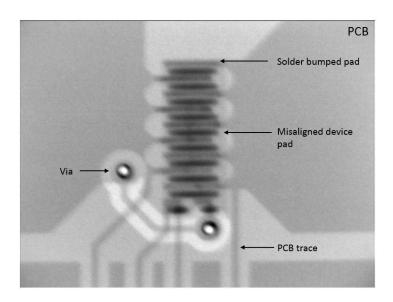

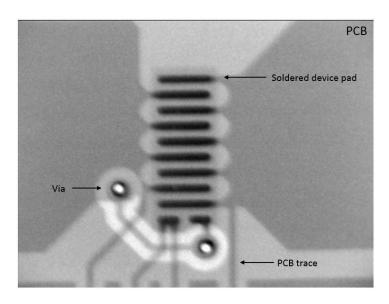

- 4. Using the X-ray machine from the alignment phase, check the device for proper alignment with the device footprint as in Figure 16. A misaligned device is usually visually obvious, but the operator should be aware that a shift in the long axis of the part could cause the part to sit properly on its pads, but with a one pin offset. This type of misalignment may not be easy to spot depending on the settings of the X-Ray, so the operator should verify that the correct number of pins is visible to ensure proper alignment.

- 5. If any defective devices are found, it is recommended that a hot air tool be used to remove the devices to prevent any damage to the device footprint from physical contact by the operator. Once the device has been removed, it is recommended that the PCB

- assembly be taken back to the prep phase of the process in order to ensure the replacement device is attached correctly.

- 6. It is recommended that once these devices have been verified by X-ray to be properly assembled that they be affixed to the substrate using an adhesive to ensure that they do not shift during any future assembly stages that they may be subjected to, such as the population of the bottom side of the board. The 'Chip Bonder' #3621 adhesive manufactured by Loctite has proven to be acceptable for this purpose. Ensure that any instructions from the manufacturer relating to proper curing of the adhesive are followed.

Figure 16: X-Ray image of properly soldered device.

Assuming that all previous steps are followed appropriately, the resulting assembly should be of the quality needed to ensure that there are no circuit failures that can be attributed to defective solder joints. Should the designer experience any issues that can only be traced back to the assembly process, it is recommended that they double check their conformance to any unique requirements of the materials they may be using. It is also recommended they insure proper

compatibility between PCB assembly plating, solder used to bump the device footprint, and the solder on the device itself with the temperature profile of the reflow oven. If the PCB assembly being processed contains many layers or if it contains higher density copper, the temperature profile may need to be adjusted to ensure that both the board and the device are achieving the required temperatures for the solder process.

### 4.4 Secondary Manual Assembly Method

The secondary method created for the assembly of these CSP EPC devices evolved from a need for an attachment solution that did not require the use of an X-Ray machine for part alignment. The X-ray machine, while allowing for very precise part placement, is a very complex and expensive piece of equipment that may not be available to many groups that wish to use these EPC devices in their projects. As discussed previously, EPC provides a solution for part placement that does not rely on an X-ray machine, but the quality and repeatability of the assembly process is not up to the levels required for these power stage prototypes. This method is the result of an effort to try and create a compromise between the two assembly techniques that allows for high quality assemblies while using more commonly available equipment.

This secondary method can be implemented with several different types of machine, but they all carry one common element necessary for this process, split optic alignment. Split optic alignment presents the viewer an overlapping view of the device footprint on the PCB as well as a view of the bottom of the pads on the device. This overlapping view allows the operator to adjust the relative position of the device versus the board to ensure that the device is in perfect alignment with its footprint on the board. The implementation of this alignment step will be relatively universal across all machines with this capability, but depending on the machine, the

reflow step may be accomplished by the machine after alignment, instead of requiring the assembly be removed and sent through a separate reflow oven. A machine such as a BGA rework machine would allow the operator to accomplish the alignment and reflow steps with a single machine, while a manual placement split optic machine will also allow for proper placement, but will require the operator to send the assembly through the reflow oven once alignment is complete. The materials and equipment needed for this method are given in Table 10 followed by a description of the procedure.

Table 10: Secondary Method Materials and Equipment

| Item                              | Process Group              |  |

|-----------------------------------|----------------------------|--|

| Anti-Static Mat, ESD wrist strap, | ALL                        |  |

| ESD lab coat, ESD gloves          |                            |  |

| Hot Plate or IR PCB Heater        | Prep                       |  |

| Tacky Flux                        | Prep, Placement, Alignment |  |

| Suitable Solder, spool            | Prep                       |  |

| Microscope                        | Prep                       |  |

| ESD Safe tools                    | ALL                        |  |

| Reflow Oven                       | Reflow                     |  |

| Split Optic Placement Machine     | Placement, Alignment       |  |

| Flux cleaning agent               | Prep, Inspection           |  |

| Soldering Iron                    | Prep                       |  |

### 4.4.1 Preparation

The preparation phase for this process is almost identical to the new method presented above. The operator may need to adjust the amount of solder added to the bumped pads based on the results of the reflow process.

1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Place the following materials and equipment within easy reach of the operator: hot plate, flux, solder, soldering iron, flux cleaning agent, microscope

- 3. Place the hotplate/IR heater in the work area beneath the microscope.

- 4. Warm the assembly PCB to approximately 120°C-150°C. This temperature is dependent on the substrate used, and the operator should ensure that it remains below the glass transition temperature of their substrate. Increasing the temperature beyond 150°C may yield some improvement in process completion time, but it is not advisable to exceed the published value for the substrate being used or the operator risks placing unneeded stress on the substrate.

- 5. Place a small amount of flux on the pads of the parts being assembled.

- 6. Using a small tip on the soldering iron, add a small amount of solder to each individual pad of the device footprint. There should be sufficient solder to raise the pad and form a convex surface, but not enough to cause a bridge to another pad. It is recommended that the operator attempt to achieve a uniform shape across all pads. The operator should also ensure that the solder being used is compatible with the solder used by EPC to create the solder bumps on their devices. An incompatible alloy could generate reliability issues further down the line.

- 7. Allow the PCB assembly to cool.

- 8. Clean any remaining flux off of the PCB assembly.

- 9. Visually inspect the 'bumped' footprint pads looking for any defects or voids in the solder areas. Any defects should be corrected before proceeding, following by an additional cleaning step.

#### 4.4.2 Placement and Alignment

The placement and alignment portion of this process differs in that both steps are combined, using the vacuum pickup and the split optic alignment to align and place the device in one step. The placement phase still includes the application of flux as described in the first method. Alignment of the device is accomplished in conjunction with placement as the split optic system aligns and then places the part. Alignment is accomplished by movement of the device in X, Y, and Theta orientations to match the orientation of the device footprint on the PCB assembly. Should the flux cause issues with viewing of the device footprint, it is advised that the operator thin out the flux layer to make the pads more visible. Should the solder bumps on the pads cause difficulties with placement once the flux has been thinned, the operator may need to reduce the amount of solder applied to the pads.

- 1. Ensure the operator is aware of and follows proper ESD protocols.

- 2. Ensure the PCB assembly is clean before beginning.

- 3. Place a small amount of tacky flux on the device footprint as shown in Figure 13. A water soluble flux is recommended for this step to aid in cleaning. The RF771 tacky flux by Kester has been used successfully for this process. Tacky flux is used as it aids the operator by preventing the device from shifting should the PCB assembly be subjected to a minor bump during these processes. This step can be done for all devices on the same layer of the board.

- 4. Program/setup the machine with an appropriate reflow profile to match the recommended solder manufacturers profiles.

- 5. Using a set of ESD-safe fine tweezers, remove the device from its packaging and check for device orientation. The operator should be careful not to exert an excessive amount of

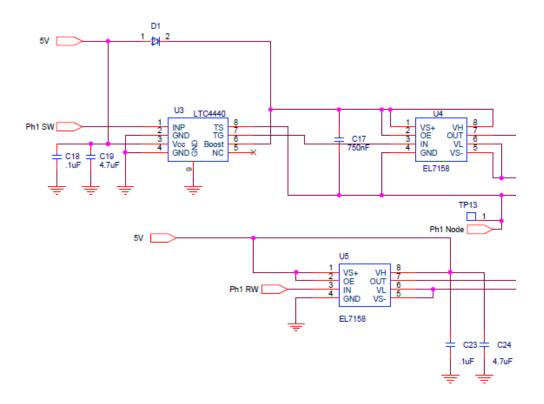

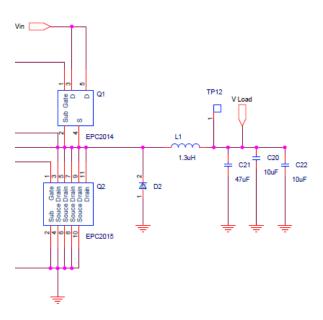

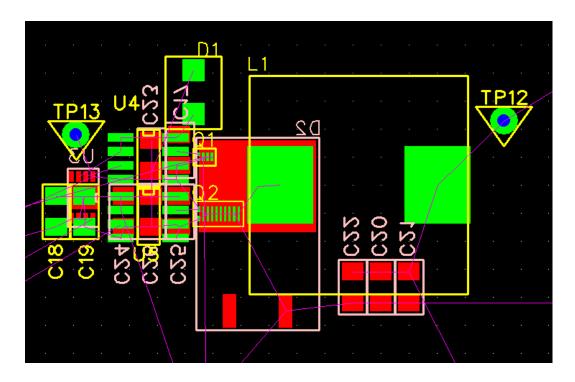

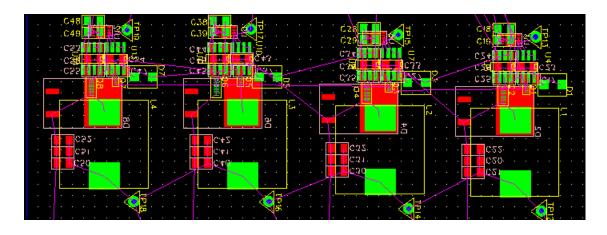

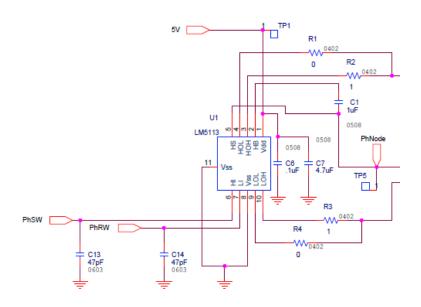

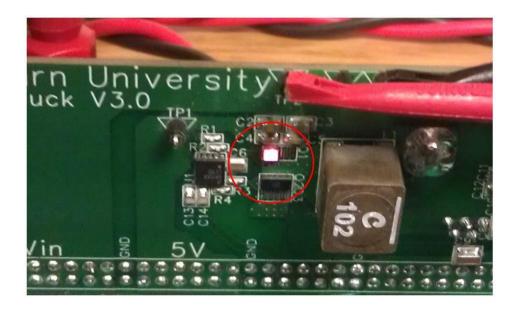

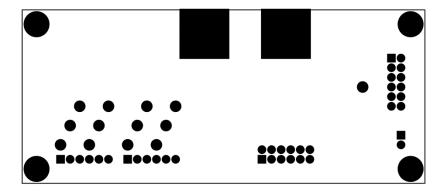

- force on the device as its exterior is very fragile and even small fractures can cause electrical malfunctions or reduce overall device performance and reliability.