## Fabrication and Characterization of Compliant Off-chip Double Helix and Carbon Nanotube Interconnect

by

Pingye Xu

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama December 13, 2014

Keywords: flip chip packaging, compliant interconnect, microelectromechanical systems (MEMS), carbon nanotube, reworkability, radio frequency

Copyright 2014 by Pingye Xu

Approved by

Michael C. Hamilton, Chair, Assistant Professor of Electrical and Computer Engineering Robert N. Dean, Associate Professor of Electrical and Computer Engineering Guofu Niu, Alumni Professor of Electrical and Computer Engineering Minseo Park, Professor of Physics

### Abstract

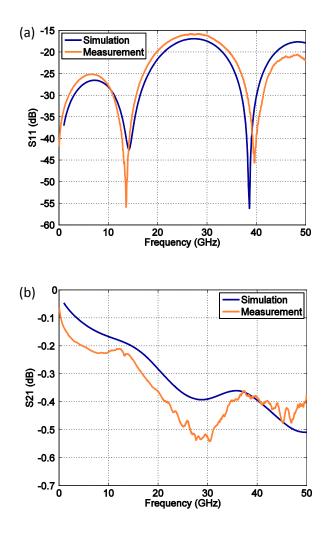

Microelectromechanical systems (MEMS) type double helix chip-level electrical interconnect structures are fabricated and characterized in this work. Due to their springlike structure, double helix interconnects have the potential to provide mechanical compliance to compensate for nonidealities, such as nonplanarity and thermal expansion mismatch between chips and substrates. A double helix configuration provides for structures with a high volumetric density of conductor for enhanced current carrying capability and lower electrical resistance. The fabrication process is compatible with wafer-level fabrication and packaging. Instead of using soldered interconnections, the double helix interconnects use pressure to make electrical connection and provide sufficiently low resistance, which is estimated to be approximately  $35 \pm$ 15 m $\Omega$  in this work. Large arrays of double helix structures have been fabricated and characterized with high yield. The mechanical and electrical models of the structures are presented. Reworkability tests were performed and the structures show a consistent resistance over 50 remating cycles. To characterize the high frequency performance, the double helix were designed and fabricated on top of coplanar waveguides (CPW) as flip-chip interconnects. The structure was characterized and simulated in High Frequency Structural Simulator (HFSS) up to 50 GHz. The measured insertion and reflection loss were less than -0.6 dB and -15 dB, respectively.

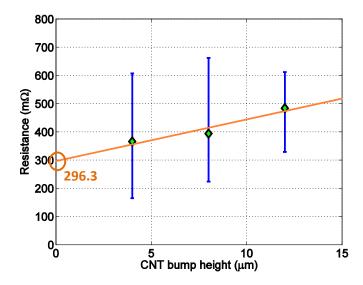

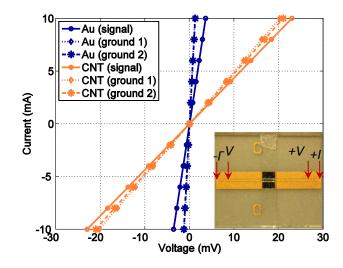

Other than using a structurally compliant interconnect, one can also use flexible material to gain compliance. A reliable solution-based process to fabricate thick carbon nanotube (CNT)

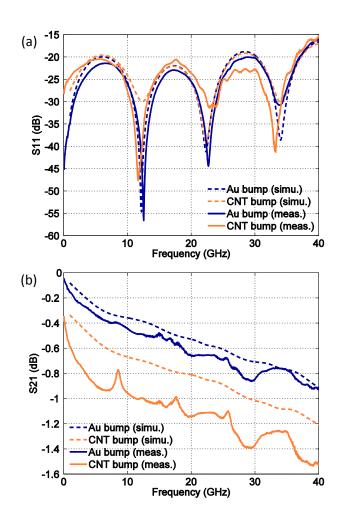

bumps has been developed and is presented in this paper. In contrast to other work of this nature, the process we have developed is capable of fabricating thick and densely packed CNT structures at room temperature with relatively high resolution and controllable film thickness or bump height. CNT structures fabricated using the developed method may find use in sensors or electrical interconnect applications. Raman spectroscopy was used to characterize the fabricated CNT bumps, verifying the CNTs are negligibly affected by the fabrication process. To study the potential application of these CNT bumps for flip-chip interconnections, we examined the deformation of the CNT bumps after flip-chip bonding and performed electrical characterization. The CNT bump interconnects display linear I-V curve with an average resistance of approximately 484 m $\Omega$  for a bump with 200  $\mu$ m diameter and height of 12  $\mu$ m. The solution deposited CNT interconnects have similar resistance to transferred CNT bumps grown by chemical vapor deposition. Temperature dependent measurements indicate that fluctuationinduced tunneling (FIT) is the most likely electrical conduction mechanism in the CNT bumps. The high frequency performance of the CNT bumps was also simulated in HFSS and characterized. The CNT bumps were deposited as flip chip interconnects on top of a CPW. The performance of the bumps were compared to similarly-sized gold interconnects. High frequency characterization was carried out up to 40 GHz. The return loss is below -15 dB and the insertion loss of the CNT interconnect is 0.3 dB higher than conventional gold bump interconnects per transition. Considering the negligible skin effect of CNT, they have the potential to out-perform conventional metal interconnects at higher frequency.

#### Acknowledgments

I would like to thank my research advisor, Dr. Michael C. Hamilton for giving me the opportunity to pursue my PhD degree under his guidance and supervision. I appreciate his support, encouragement and shared vision throughout my years in Auburn. Further, I am indebted to my committee members and university reader, Dr. Robert Dean, Dr. Guofu Niu, Dr. Minseo Park, and Dr. Daniel Harris for their support. I would also like to express gratitude to Dr. Virginia Davis for her valuable input on my carbon nanotube research.

Special thanks go to Charles Ellis, William Baugh and Michael Palmer for their help in microfabrication and measurement. I especially would like to give thanks Tamara Isaacs-Smith for training me to survive the labs.

My gratitude also extends to my lab-mates, coworkers and friends, George Hernandez, Kun Fang, Zhenzhen Shen, Simin Zou, Rujun Bai, Alexander Pfeiffenberger, Srikanth Peddada, Philip Bailey, Thomas Stegeman, Colin Stevens, Ya Guo, Fang Yu, Jinzi Cui, Zhangming Zhou, Shiqiang Wang, Harrison Burch, Hunter Burch and Kyle Owen for their research advice and encouragement.

Finally, I would like to thank my parents for being so supportive of me over the years. Words do not do justice to how thankful I am of them.

## List of Tables

| Table 1.1. Trend and performance of packaged chip                                      | 3    |

|----------------------------------------------------------------------------------------|------|

| Table 1.2. Electrical interconnect levels                                              | 4    |

| Table 1.3. Electrical property dependence of SWNT on chirality                         | 23   |

| Table 2.1. Resistance components of the measured structure                             | 45   |

| Table 2.2. Geometrical parameters of flip chip bonded CPW design                       | 53   |

| Table 3.1. A summary of fabrication parameters, measurement approcaches and results of |      |

| transferred CNT bumps                                                                  | . 69 |

# List of Figures

| Figure 1.1. Moore's law                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. Wire bonding                                                                                                                                                                  |

| Figure 1.3. Tape automated bonding                                                                                                                                                        |

| Figure 1.4. Solder ball array after reflow and ready for flip chip bonding                                                                                                                |

| Figure 1.5. MicroSpring by FormFactor                                                                                                                                                     |

| Figure 1.6. Stress engineered micro-spring structure                                                                                                                                      |

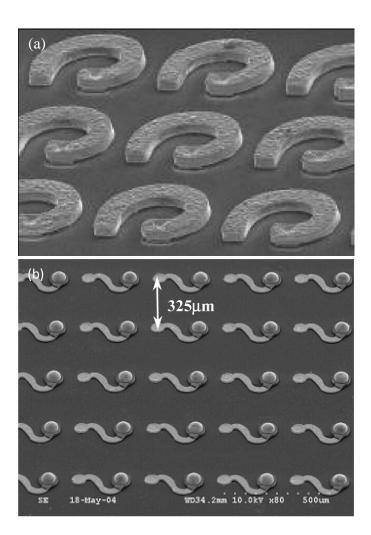

| Figure 1.7. (a) Flexconnect (b) Sea-of-Leads interconnects (c) G-helix                                                                                                                    |

| Figure 1.8. Planar microspring compliant interconnects                                                                                                                                    |

| Figure 1.9. Sea of Polymer Pillars interconnects                                                                                                                                          |

| Figure 1.10. ELASTec compliant interconnects                                                                                                                                              |

| Figure 1.11. (a) Cross-section image of PCSB. (b) Soldered PCSB after thermal cycling test. 19                                                                                            |

| Figure 1.12. (a) Transmission electron microscopy image of bundles of chemical vapor deposited carbon nanotubes and (b) Single-wall carbon nanotube (left) and multi-wall carbon nanotube |

| Figure 1.13. Graphene honeycomb lattice with the lattice vectors $a_1$ and $a_2$                                                                                                          |

| Figure 1.14. A typical CVD setup for CNT growth                                                                                                                                           |

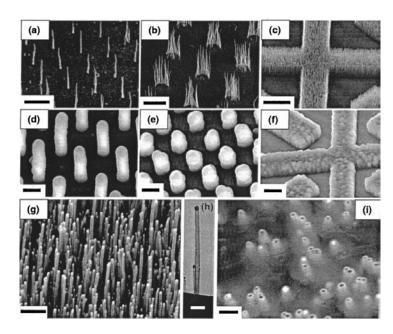

| Figure 1.15. SEM images of CVD grown MWNTs25                                                                                                                                              |

| Figure 1.16. CNT interconnects fabrication process by transferring. CNTs are first grown on one substrate and then transferring to another                                                |

| Figure 1.17. SEM images of CNTs transferred onto solder pads                                                                                                                              |

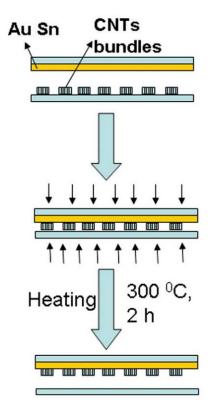

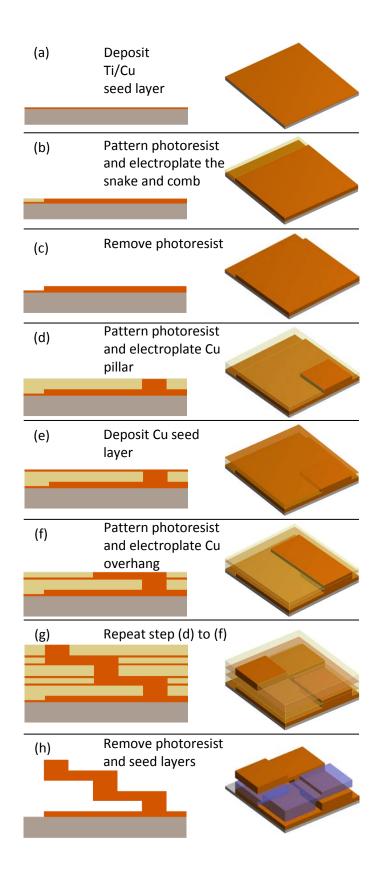

Figure 2.1. Schematic fabrication flow for double helix compliant interconnect structures. The cross-section schematics are shown on the left while the 3-D views are listed on the right. Only one helix of the pair is shown in Figure 1(a-g) for clarity purpose. Figure 1(h) shows the other helix in purple. Gray, yellow and orange represent oxidized silicon wafer, photoresist and copper, respectively.

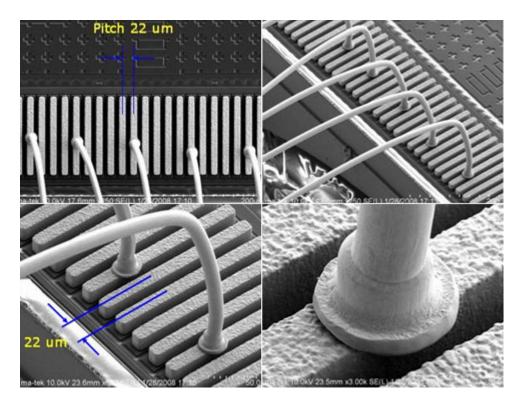

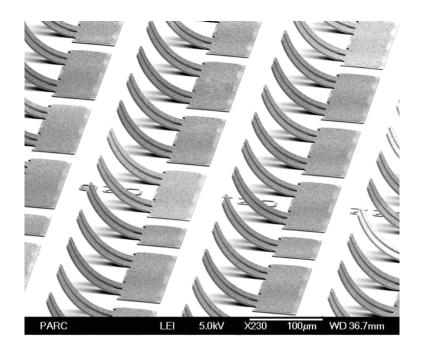

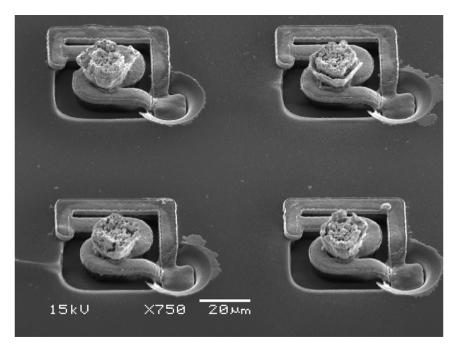

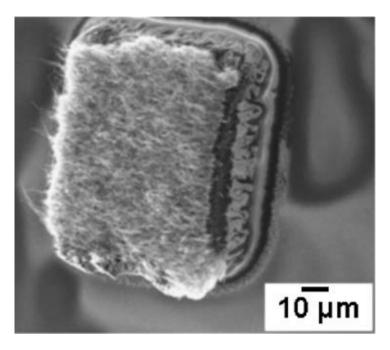

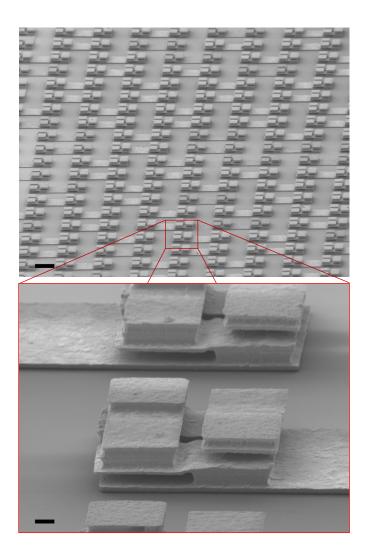

Figure 2.2. SEM images of an array of fabricated double helix contact structures prior to mechanical and electrical testing. (Scale bar:  $100 \mu m$  (top image) and  $10 \mu m$  (bottom image).) 34

| Figure 2.12. Geometry of the flip chip bonded CPW. The glass substrate, CPW lines and double helix interconnects are in blue, light orange and dark orange                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

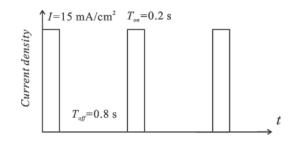

| Figure 2.13. Pulsed current indium plating waveform                                                                                                                                                                                                                            |

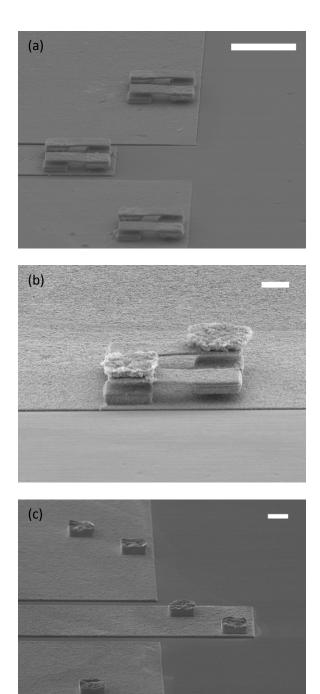

| Figure 2.14. (a) Double helix interconnects on CPW with no indium bumps. Scale bar: 100 $\mu$ m. (b) Double helix interconnects with indium bumps on top. Scale bar: 20 $\mu$ m. (c) Indium bumps electroplated on the other chip for flip-chip bonding. Scale bar: 20 $\mu$ m |

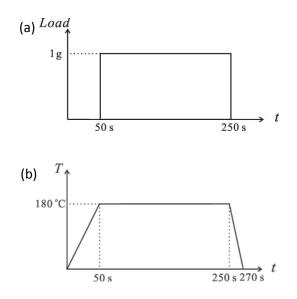

| Figure 2.15. Load and temperature profile used for flip chip bonding                                                                                                                                                                                                           |

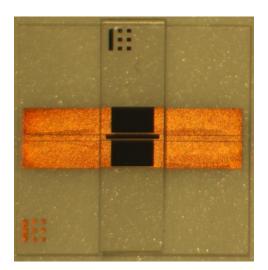

| Figure 2.16. Flip chip bonded CPW with double helix interconnects                                                                                                                                                                                                              |

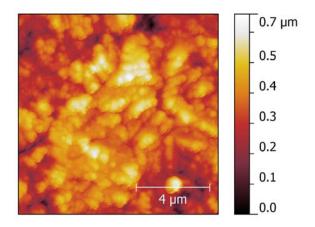

| Figure 2.17. AFM image of the electroplated copper surface                                                                                                                                                                                                                     |

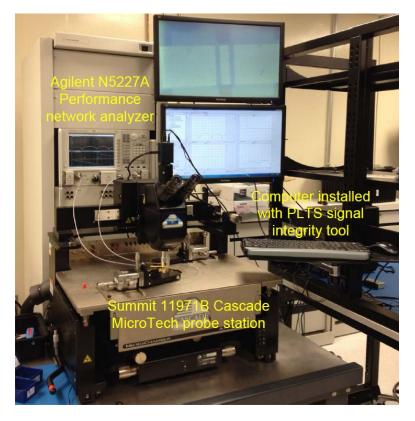

| Figure 2.18. Network analyzer setup for high frequency structure measurement                                                                                                                                                                                                   |

| Figure 2.19. S-parameters of the Flip chip bonded CPW with double helix interconnects. (a) Reflection loss S11. (b) Insertion loss S21                                                                                                                                         |

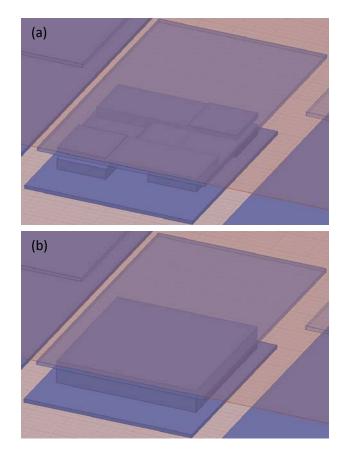

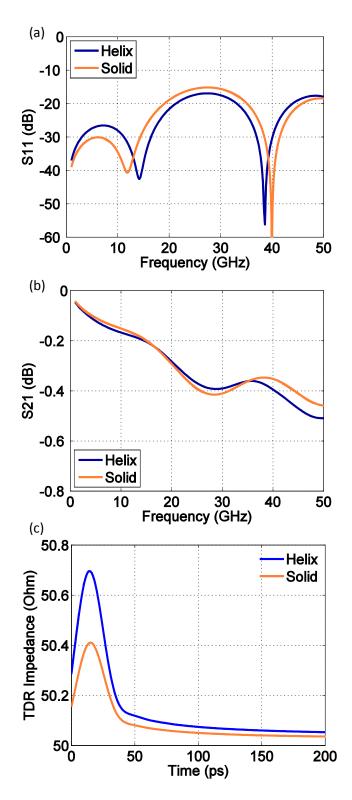

| Figure 2.20. (a) HFSS model of a double helix interconnect and (b) HFSS model of a cuboid interconnect of the same size                                                                                                                                                        |

| Figure 2.21. (a) S11, (b) S21 and (c) TDR impedance (at 50 GHz) of double helix of the double helix interconnect, compared to a cuboid shape interconnect of the same size                                                                                                     |

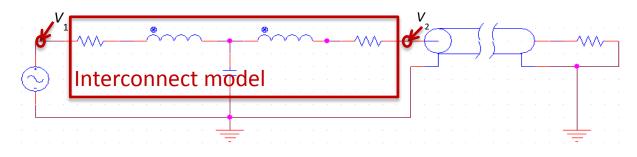

| Figure 2.22. Interconnect model in Cadence                                                                                                                                                                                                                                     |

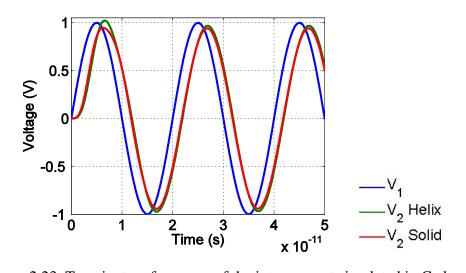

| Figure 2.23. Transient performance of the interconnect simulated in Cadence                                                                                                                                                                                                    |

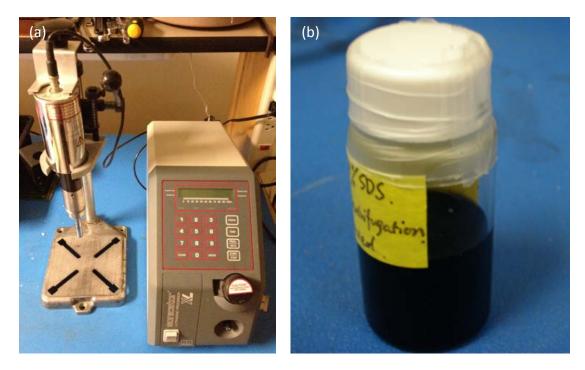

| Figure 3.1. (a) Misonix XL2020 tip sonicator and (b) CNT dispersion                                                                                                                                                                                                            |

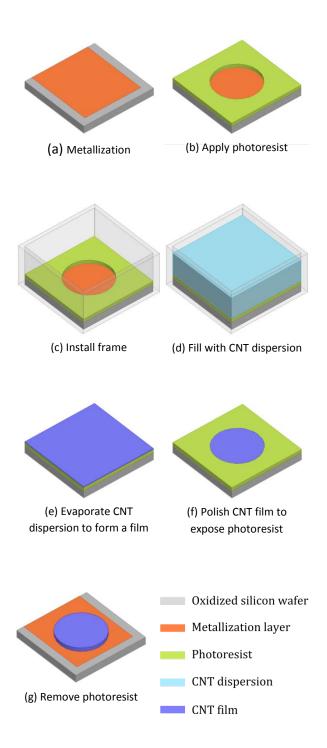

| Figure 3.2. Representative schematic of solution-based CNT bump fabrication process                                                                                                                                                                                            |

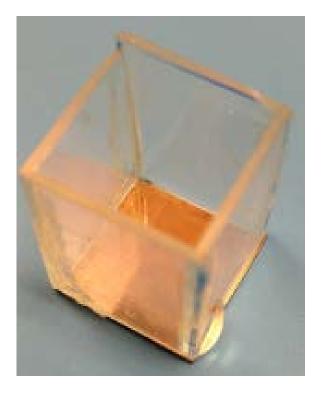

| Figure 3.3. Water tight frame for CNT bump fabrication75                                                                                                                                                                                                                       |

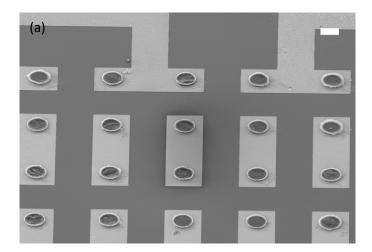

| Figure 3.4. (a) Array of CNT-SDS bumps on a gold pattern. (b) 4 $\mu$ m thick CNT-SDS bump. (c) 8 $\mu$ m thick bump. (d) 12 $\mu$ m thick bump. (Scale bar of (a): 100 $\mu$ m, (b-d): 50 $\mu$ m)                                                                            |

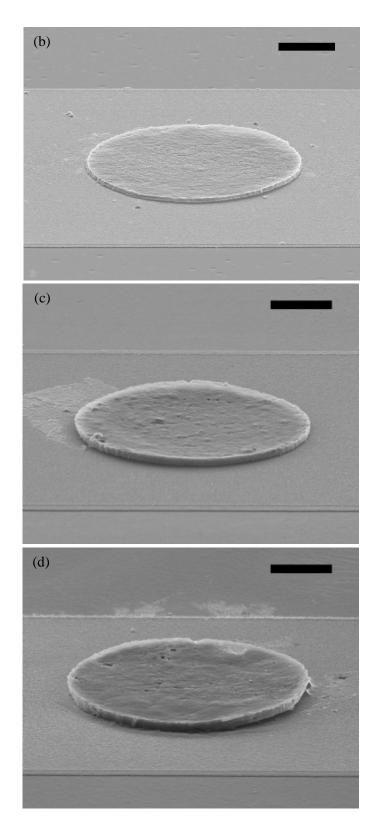

| Figure 3.5. SEM images of CNT-SDS bump surface (a) before and (b) after polishing and photoresist removal. (Scale bar: 100nm)                                                                                                                                                  |

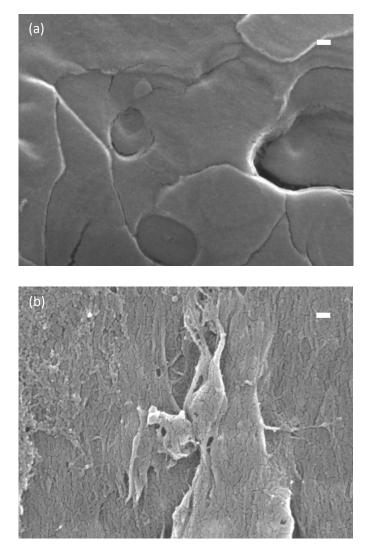

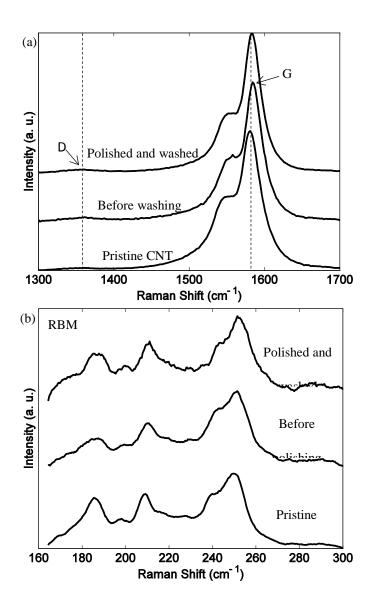

| Figure 3.6. Raman spectra of CNT-SDS bump before and after polishing and photoresist removal. Peaks are normalized. (a) G and D band. (b) Radial breathing mode                                                                                                                |

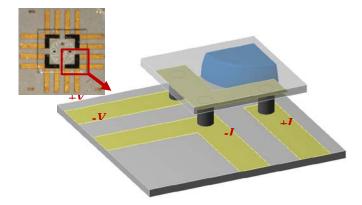

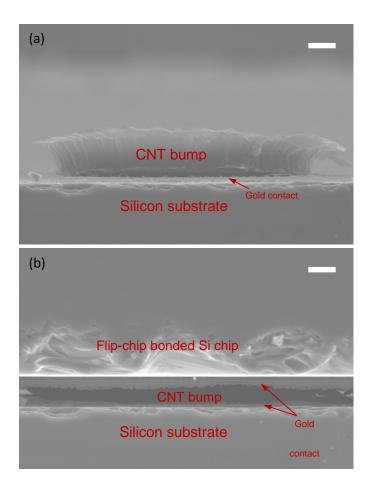

| Figure 3.8. Side view of (a) CNT bump before flip chip bonding and (b) CNT bump after flip chip bonding. (Scale bar: 10 µm)                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.9. Resistance of the measured CNT bumps of different heights with the mean, minimum and maximum values                                                                                                                       |

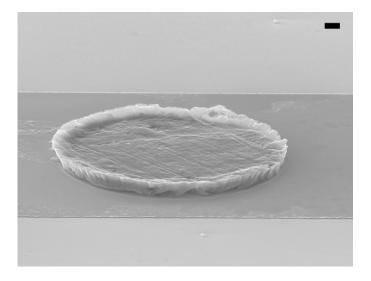

| Figure 3.10. SEM image of a CNT bump whose edge is higher than its center. (Scale bar: 10 μm)                                                                                                                                         |

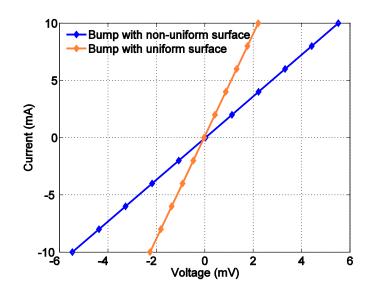

| Figure 3.11. I-V curve of the measured CNT bumps                                                                                                                                                                                      |

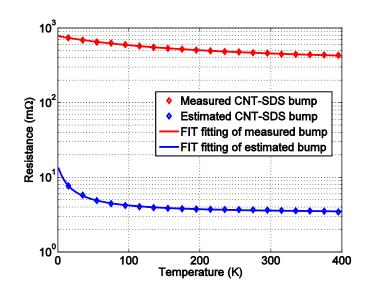

| Figure 3.12. Temperature dependence of the resistance of the flip-chip bonded CNT bump interconnects. Note that the measured values include contact resistance and estimated values do not                                            |

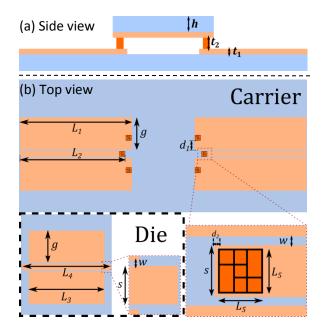

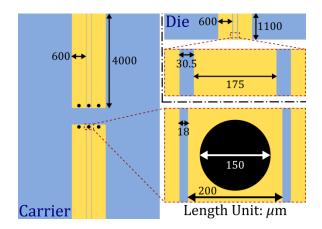

| Figure 3.13. Carrier and die layout of 50 $\Omega$ gold CPW with CNT interconnects. Glass substrate, gold CPW and CNT interconnects are in blue, yellow and black, respectively                                                       |

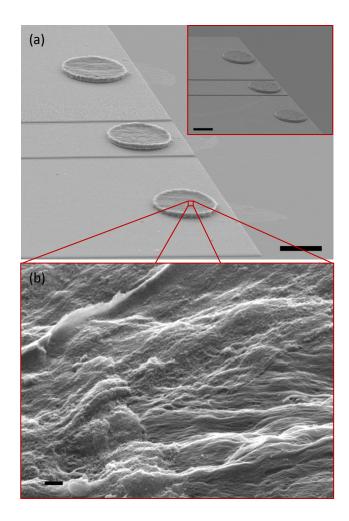

| Figure 3.14. SEM images of the fabricated structure. (a) CNT bumps as flip chip interconnects on top of a CPW. Inset: reference gold interconnects. Scale bar: $100 \ \mu m$ . (b) Top surface of the CNT bump. Scale bar: $100 \ nm$ |

| Figure 3.15. I-V curves of the signal or ground lines with CNT or gold interconnects. Inset: optical image of the flip chip bonded CPWs with CNT interconnects                                                                        |

| Figure 3.16. S-parameters of flip chip bonded CPW with CNT/Au interconnects. (1) S11 parameter. (2) S21 parameter                                                                                                                     |

## List of Abbreviations

- ITRS International Technology Roadmap for Semiconductors

- RC Resistance-Capacitance

- CTE Coefficient of the Thermal Expansion

- TAB Tape Automated Bonding

- C4 Controlled Collapse Chip Contact

- WLP Wafer Level Package

- BEOL Back End Of Line

- PCSB Polymer Core Solder Ball

- CNT Carbon Nanotube

- SWNT Single-Wall Carbon Nanotube

- MWCT Multi-Wall Carbon Nanotube

- CVD Chemical Vapor Deposition

- MMIC Monolithic Microwave Integrated Circuit

- CPW Coplanar Waveguide

- AFM Atomic Force Microscopy

- SOLT Short-Open-Load-Through

- TDR Time Domain Reflectometry

- SDS Sodium Dodecyl Sulfate

- FIT Fluctuation-Induced Tunneling

| RBM | Radial Breathing Mode        |

|-----|------------------------------|

| FEA | Finite Element Analysis      |

| LL  | Luttinger Liquid             |

| MIM | Metal-Insulator-Metal        |

| VRH | Variable-Range Hopping       |

| SEM | Scanning Electron Microscope |

|     |                              |

TEM Transmission Electron Microscopy

## Table of Contents

| Abstract                                                                                 | ii  |

|------------------------------------------------------------------------------------------|-----|

| Acknowledgments                                                                          | iv  |

| List of Tables                                                                           | v   |

| List of Figures                                                                          | vi  |

| List of Abbreviations                                                                    | X   |

| Table of Contents                                                                        | xii |

| Chapter 1 General Introduction                                                           |     |

| 1.1 Background information                                                               |     |

| 1.2 Conventional first level interconnect                                                |     |

| 1.3 Compliant off-chip interconnects                                                     | 9   |

| 1.3.1 Structurally compliant interconnects                                               | 9   |

| 1.3.2 Materially compliant interconnects                                                 |     |

| 1.4 Introduction to carbon nanotubes and carbon nanotube interconnects                   |     |

| 1.4.1 Background information of carbon nanotubes                                         |     |

| 1.4.2 Carbon nanotube interconnects                                                      |     |

| Chapter 2 Double Helix Interconnect                                                      |     |

| 2.1 Fabrication of the double helix MEMS-type interconnect                               |     |

| 2.2 DC electrical characterization                                                       |     |

| 2.2.1 Experimental setup                                                                 |     |

| 2.2.2 Electrical resistance measurement and test fixture resistance extraction           |     |

| 2.2.3 Mechanical and electrical analysis using FEA simulation                            |     |

| 2.2.4 Extraction of the lateral resistance of the snake and comb metallization           |     |

| 2.2.5 Reworkability of the double helix interconnect                                     | 50  |

| 2.3 High frequency performance of double helix interconnect                              | 52  |

| 2.3.1 Design and fabrication of the flip-chip bonded CPW with double helix interconnects | 57  |

| 2.3.2 High frequency characterization                                                    |     |

|                                                                                          |     |

| 2.3.3 Transient analysis of the double helix interconnects structure | 61  |

|----------------------------------------------------------------------|-----|

| Chapter 3 Carbon Nanotube Bump Interconnect                          | 66  |

| 3.1 Fabrication of CNT bump interconnects                            |     |

| 3.1.1 CNT dispersion                                                 |     |

| 3.1.2 Solution-based CNT bumps fabrication                           | 71  |

| 3.2 Characterization of the CNT-SDS bumps                            | 77  |

| 3.2.1 Material characterization                                      | 77  |

| 3.2.2 Electrical characterization                                    |     |

| 3.2.3 Electrical conduction mechanism                                | 85  |

| 3.3 High frequency performance of CNT bump interconnects             | 90  |

| 3.2.1 Design and fabrication of flip-chip CNT interconnects          | 90  |

| 3.2.2 High frequency characterization of flip-chip CNT interconnects |     |

| Conclusion                                                           |     |

| Future Work                                                          |     |

| Reference                                                            | 101 |

## Chapter 1 General Introduction

## **1.1 Background information**

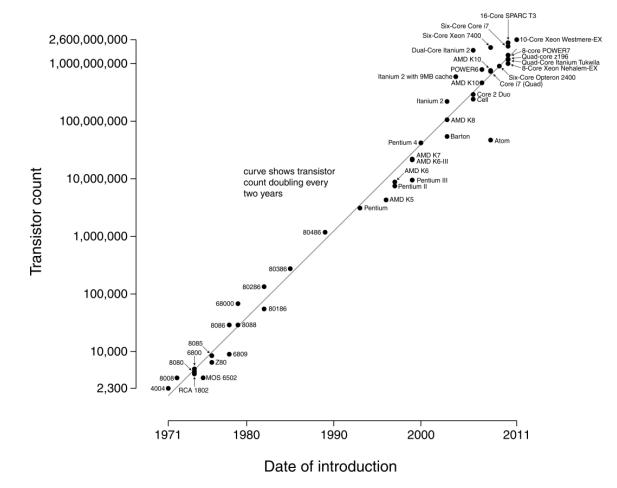

According to Gordon Moore's observation of the semiconductor industry history, the transistor count, or functionality, of a chip doubles approximately every 2 years. This observation has been known as Moore's law, as shown in Figure 1.1 [1]. The Moore's law was sustained in the last four decades due to the rapid growth of semiconductor industry, which is majorly motivated by the size reduction of transistors, also known as scaling. Smaller transistors bring about lower fabrication cost per transistor, higher transistor density, faster speed and lower power consumption etc. However, as the scaling trend continues, the I/O density increases and therefore the interconnects between chip and substrate, namely off-chip interconnects, are required to have smaller pitch size. Table 1.1 shows the requirement of interconnect pitch size as the size of transistors shrinks from International Technology Roadmap for Semiconductors (ITRS) [2]. It is shown that with the decrease of device dimensions, pins and pads counts increases accordingly. In the year of 2018, the pitch size of area array flip chip pad is expected to reduce to 95 µm. This scaling trend also contributes to lower cost of the package (per pin) and higher working frequency.

Finer pitch size imposes reliability issues on off-chip interconnects, due to the lack of mechanical strength of smaller structures. Further, to reduce the RC (Resistance-Capacitance) and transmission line delay, low-K materials has been gradually adopted by the industry. In chips with low-K dielectric material, the thermo-mechanical stresses induced by the off-chip

interconnects could crack or delaminate the dielectric material causing reliability problems [3]. Therefore, off-chip interconnects that can reduce stresses are beneficial to mitigate these coefficient of the thermal expansion (CTE) mismatch caused problems. Another solution to mitigate the reliability problem is by using underfill. Epoxy-based underfills are often used in flip chip assembly to strengthen the solder joints and hence improve reliability [4]. However, the downsides of underfill process are higher cost, poor reworkability and delamination. In addition, as the pitch size of the interconnect further decreases, the difficulty of dispense underfill material drastically increases.

## Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1.1. Moore's law [1].

| Year of Production                             | 2013     | 2014     | 2015     | 2016     | 2017     | 2018     |

|------------------------------------------------|----------|----------|----------|----------|----------|----------|

|                                                |          |          |          |          |          |          |

| Flash 1/2 Pitch (nm) (un-contacted Poly)       | 18       | 17       | 15       | 14.2     | 13.0     | 11.9     |

| DRAM 1/2 Pitch (nm) (contacted)                | 28       | 25       | 23       | 20.0     | 17.9     | 15.9     |

| Number of Chip I/Os (Number of Total Chip      |          |          |          |          |          |          |

| Pads)—Maximum                                  |          |          |          |          |          |          |

| Total pads—ASIC High Performance unchanged     | 5,400    | 5,400    | 5,600    | 6,000    | 6,000    | 6,200    |

| Signal I/O pads—ASIC high-performance (% of    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    |

| total pads)                                    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    |

| Power and ground pads—ASIC high-               | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    |

| performance (% of total pads)                  | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    | 50.0%    |

| Number of Total Package Pins—Maximum           |          |          |          |          |          |          |

| Microprocessor/controller, cost-performance    | 800–3704 | 800–4075 | 880–4482 | 880–4930 | 960–5423 | 960–5966 |

| Microprocessor/controller, high-performance    | 5616     | 5896     | 6191     | 6501     | 6826     | 7167     |

| ASIC (high-performance)                        | 5616     | 5896     | 6191     | 6501     | 6826     | 7167     |

| Chip Pad Pitch (micron)                        |          |          |          |          |          |          |

| Wedge bond                                     | 25       | 25       | 25       | 25       | 25       | 25       |

| Area array flip-chip (cost-performance, high-  | 110      | 100      | 100      | 100      | 95       | 95       |

| performance)                                   |          | 100      | 100      | 100      |          |          |

| 2-row staggered-pitch (micron)                 | 30       | 30       | 30       | 30       | 30       | 30       |

| Three-tier-pitch pitch (micron)                | 40       | 40       | 35       | 35       | 35       | 35       |

| Cost-Per-Pin                                   |          |          |          |          |          |          |

| Package cost (cents/pin) (Cost per Pin Minimum |          |          |          |          |          |          |

| for Contract Assembly—Cost-performance)—       | .51–.87  | .48–.83  | .46–.79  | .44–.75  | .42–.71  | .39–.68  |

| minimum–maximum                                |          |          |          |          |          |          |

| Package cost (cents/pin) (Low-cost, hand-held  | .20–.38  | .20–.36  | .20–.34  | .20–.32  | .20–.30  | .20–.29  |

| and memory)minimummaximum                      | .2030    | .2030    | .2034    | .2032    | .2030    | .2029    |

| Chip Frequency (GHz)                           |          |          |          |          |          |          |

| On-chip local clock                            | 4.050    | 4.211    | 4.380    | 4.555    | 4.737    | 4.927    |

| Maximum number wiring levels                   | 13       | 13       | 13       | 13       | 14       | 14       |

# Table 1.1. Trend and performance of packaged chip [2].

In a broad sense, any electrically conductive path from one component to another can be considered as an electrical interconnect, no matter if the component is passive or active. The electrical interconnects in a system can be categorized into 6 levels as shown in Table 1.2. In this work, we are concerned about the level 1 interconnects, namely the off-chip interconnect connecting the chip to the first level of packaging.

Table 1.2. Electrical interconnect levels

| Level 0 | On-chip interconnects that connect devices, such as transistors. Usually multiple     |

|---------|---------------------------------------------------------------------------------------|

|         | wiring levels are required to interconnect all devices.                               |

| Level 1 | Off-chip interconnects that connect individual chip and the first level of packaging. |

|         | The first level of packaging could be the package substrate or directly onto a board. |

| Level 2 | Interconnect from package to board.                                                   |

| Level 3 | Interconnect from board to board.                                                     |

| Level 4 | Interconnect between sub-assemblies.                                                  |

| Level 5 | Interconnect between two individual systems.                                          |

## **1.2 Conventional first level interconnect**

For the first level interconnect, the most common technologies are wire bonding, tape automated bonding (TAB) and flip chip bonding. Wire bonding is the oldest technology but is still widely in use now. Wire bonding is a process that involves attaching a wire from one pad and then using the other end of the wire to connect to another pad, as shown in Figure 1.2. The attachment of wire to pad is usually performed using thermosonic or ultrasonic welding process. Aluminum, copper, silver and gold are some of the most common bond wire materials. Wire bonding has been used extensively in the last a few decades due to its cost-effectiveness and flexibility. As the oldest bonding technology, wire bonding also has the advantage of having a complete set of infrastructure. Wire bonding has also been known as a robust and reliable process, since the thermal-mechanical stress is distributed on the relatively long bond wire, making them suitable to connect substrate and chip with large CTE mismatch. However, the wire bonding has several disadvantages inherently. First, wire bonding is a serial process, which is not time-efficient. Additionally, wire bonding is not suitable for chips with high I/O count since full area arrays are preferred and wire bonding is not applicable for area arrays. Also, wire bonding does not meet the requirement of many high frequency applications since long and thin bond wire induces large inductance and resistance to the package.

Figure 1.2. Wire bonding [5].

Tape automated bonding (TAB) process is a process that attaches metal coated polymer beam fabricated on a polymer tape, as shown in Figure 1.3. Chips are placed onto the beams and solders are applied for bonding. TAB allows gang bonding which means multiple bonds are made simultaneously, and is more time-efficient compared to wire bonding. Interconnection formed by TAB process is also robust and reliable. However, TAB process is relatively more expensive and does not support area arrays either. Further, even though the metal beam used in the TAB process is less resistive and inductive compared to bond wire, the resulted structure still has too much of inductance to be used in high frequency applications.

Figure 1.3. Tape automated bonding [6].

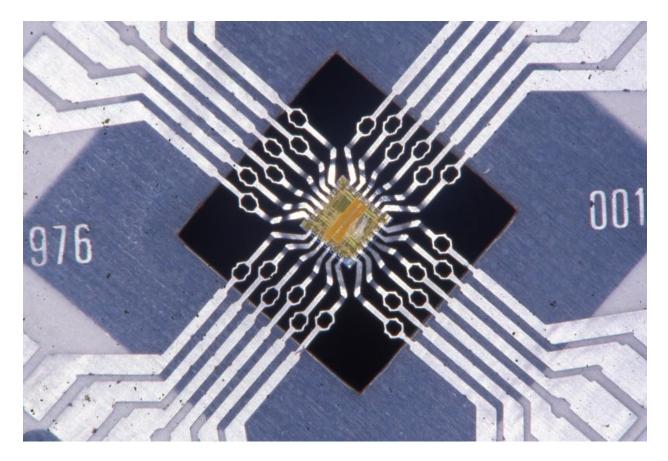

The flip chip bonding approach is gaining more popularity in recent years. The flip chip process uses C4 (controlled Collapse Chip Contact) technology. In the flip chip process, the chip is first flipped over to face down and the bonded to the substrate or board, as shown in Figure 1.4. Solder balls were applied onto the substrate or board and reflowed to form electrical connections. Flip chip has the advantage of high I/O density because it allows area array. Since the interconnects are essentially solder balls, they are short and have low inductance, which is critical for good high frequency performance. Flip chip bonding is also a cost and time efficient process. Another reason that flip chip bonding is becoming more widely accepted is because of its low profile and small footprint. However, one main issue with flip chip bonding is its

reliability. Due to the short lead, the thermal-mechanical stress caused by CTE mismatch is very detrimental which could cause crack or delamination of the low-K dielectric material. Underfill process is necessary in flip chip process, which mitigates the reliability issue. However, some concerns about using underfill are cost, reworkability and time.

Figure 1.4. Solder ball array after reflow and ready for flip chip bonding [5].

#### **1.3 Compliant off-chip interconnects**

To mitigate the reliability issues of ball grid array interconnect, one solution is to use compliant interconnects. Compliant interconnects are mechanically compliant and flexible interconnect structures that can potentially replace flip-chip bonded solder bumps due to compensation for the CTE mismatch between the silicon chip and the organic substrate. Also, the need to use underfill can be eliminated by using compliant interconnect. In the last two decades, various compliant interconnect structures have been studied. The compliance of the interconnect is either due to the spring-like geometry of the structure or flexible nature of the used materials [7]–[18]. In this work, we research both structurally and materially compliant interconnects. Structurally, we used a double helix shaped interconnect. Materially, we adopted carbon nanotube as a compliant material to enable compliance of the interconnects.

## **1.3.1** Structurally compliant interconnects

One of the first versions of MEMS based compliant interconnect called MicroSpring was developed by FormFactor, as shown in Figure 1.5 [7]. Using MicroSpring as the first level interconnect, Formfactor was able to realize wafer level package (WLP). The fabrication process of MicroSpring is similar to conventional wire bonding. Starting with the attachment of one end of the bond wire to a pad, the bonding arm was programed to shape the bond wire and then cut the bond wire without attaching the other end to a pad. Since the bond wires are usually very thin, an electroplating process was followed to thicken the bond wire. The resulted compliant interconnect structures have high yield and uniformity. The resulted interconnect also passed reliability test such as thermal shock, thermal cycling, high temperature operation life and low temperature operation life test. Another possible application of these MicroSpring are probe cards. Due to the dependence of the fabrication process on wire bonding, the fabrication process is flexible. The limitation of the fabrication of MicroSpring is that since convention serial wire bonding process is used, the fabrication process is not time efficient when large I/O count is needed.

Figure 1.5. MicroSpring by FormFactor [7].

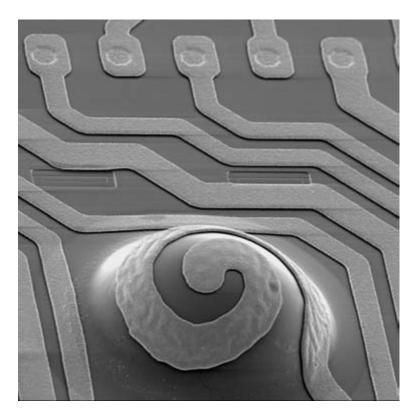

Other than using wire bonds, micro-springs can also be fabricated using conventional photolithography, sputtering and electroplating process. Using stress engineering method, the stress distributed in the metal strips can be adjusted such that one end of the metal strips stands up, and therefore the height of the micro-springs can be controlled [9], [12]–[14]. One example of the fabricated micro-spring using stress engineering is shown in Figure 1.6. The key step is the deposition of a metal layer with a large stress gradient. This is typically achieved by sputtering in changing pressure. After the stress metal layer being lithographically patterned into metal strips and subsequently released, the spring stress relaxes, lifting the tips out of the plane, forming a 3-D-compliant spring interconnect. To strengthen the metal strips, a metal electroplating process is usually preferred to thicken the

metal strips. Since the fabrication process is at low temperature, it can be integrated into the back end of line (BEOL) process. Due to the micro-fabrication based process, very high pitch size can be reached. High yield and uniformity have also been demonstrated [14].

Figure 1.6. Stress engineered micro-spring structure [14].

Compliant interconnects using other geometry have also been demonstrated. FlexConnect, helix shaped interconnect and Sea-of-Leads interconnects have been researched using similar micro-fabrication method, as shown in Figure 1.7[10], [11], [15], [16]. By alternating photoresist patterning and electroplating, FlexConnect and helix type interconnect can be fabricated. Due to the adoption of micro-fabrication process, the interconnects have high uniformity, yield and pitch size. Compared to the micro-spring interconnects, these types of compliant interconnects have the advantage of lower resistance due to larger cross-section. Another advantage of the FlexConnect and helix shaped interconnects is their greater potential

to scale down. Though the width of the micro-springs can be scaled down easily, the springs need be long enough such that they can curl to a sufficient height to provide the desired level of compliance, whereas FlexConnect and helix shaped interconnects don't have this limitation. However, the downside of FlexConnect and helix shaped interconnects is the more costly fabrication process since these structures generally require more fabrication steps and longer time.

Figure 1.7. (a) Flexconnect [10]. (b) Sea-of-Leads interconnects [11]. (c) G-helix [16].

Planar microspring is another wafer-level packaging compatible compliant interconnect developed in the past a few years, as shown in Figure 1.8 [18]. A planar structure was designed to be laterally compliant. The substrate was etched such that the cavities form under the planar structures, which enable the compliant interconnects to move vertically. CMOS BEOL-compatible wafer-level fabrication process was adopted, which allows small pitch sizes. The planar microsprings were simulated up to 35 GHz to show the potential of the interconnects to be used for high frequency application without significant power loss.

Figure 1.8. Planar microspring compliant interconnects [18].

## **1.3.2 Materially compliant interconnects**

Another category of compliant interconnects takes advantage of materials with good compliance and flexibility. These materials can be electrically conductive or insulating. For the insulating flexible materials, metallic coatings are typically applied to enable electrical conduction.

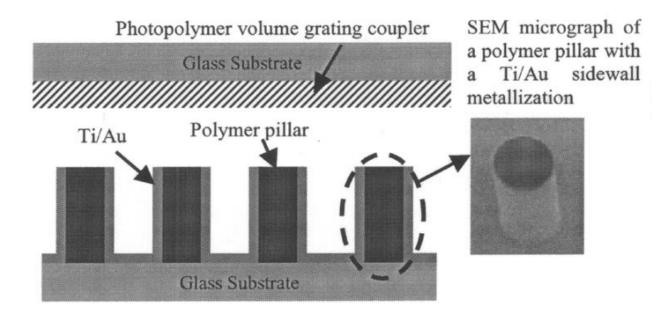

One of the typical materially compliant interconnects is a variation from the Sea-of-Leads interconnects developed in the same group from Georgia Institute of Technology, which is named Sea of Polymer Pillars [17]. Instead of using a compliant mechanical structure, compliant polymeric material is used to enable compliance. Sea of Polymer Pillars is shown in Figure 1.9. In addition to lateral compliance which minimizes the stresses on the die's lowk dielectric, Sea of Polymer Pillars allows both electrical and optical signal transmission. This dual-mode technology can mitigate some of the performance insufficiency of electrical interconnections, especially bandwidth. The reliability test shows that the polymer pillars maintain good optical alignment between the chip and the board during thermal cycling. The fabrication process of these polymer pillars includes performing photolithography on a negative tone photoresist (Avatrel 2000P), which is followed by a metal coating step. This wafer-level compatible process allows for high pitch and aspect ratio pillars and high level of electrical and optical I/O interconnect process integration. Some challenges for the Sea of Polymer Pillars include adhesion issues between the pillar and substrate and high electrical resistance due to contact resistant and thin layer of metal coating on the polymer pillars.

Figure 1.9. Sea of Polymer Pillars interconnects [17].

A wafer level packaging technology named ELASTec also uses resilient polymeric materials for compliant interconnects, as shown in Figure 1.10 [19], [20]. Compliant materials were applied under the metal interconnects, which allows an increase in reliability. Excessive strain caused by the CTE mismatch between the organic substrate and silicon chip can be mitigated because of the compliant polymeric under metal material. An additional advantage of using this contact scheme is that wafer probing is made easier due to the elastic contact system. The ELASTec interconnects have been fabricated and their reliability has been tested. For the 0.2 mm tall interconnects, a Weibull fatigue life of more than 6000 cycles was determined despite the high CTE mismatch between the FR-4 organic substrate and silicon chips. This is significantly better than conventional solder ball interconnects. One of the limitations to this ELASTec technology is the difficulty to scale down to smaller pitch sizes. The under metal material used in this case is printed silicone. Scaling down the silicone

domes laterally while maintaining their standoff height can be challenging.

Figure 1.10. ELASTec compliant interconnects [19].

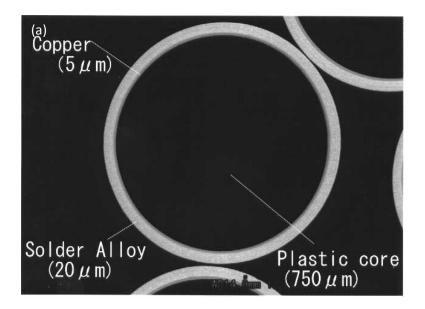

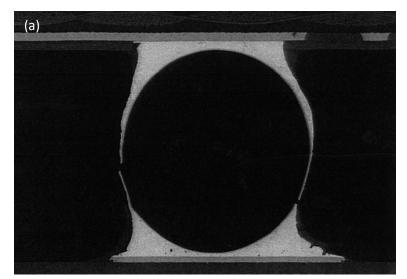

Sea of Polymer Pillars interconnects use micro-fabricated metal coated polymer pillars. A different strategy is to use ready-made metal coated polymer balls and place them onto desired locations [21]. Since the Young's modulus of these polymer core solder balls (PCSB) is much smaller than that of metal, they are more ready to relax the thermal caused strain. The PCSBs are shown in Figure 1.11. These PCSBs are fabricated by electroless plating followed by electroplating onto polymer cores. The fabrication process of these PCSB needs to be well-controlled such that uniform ball size is ensured. The test results show that the use of these compliant balls significantly enhances interconnects reliability, compared to conventional

solder balls without underfill. Full-wave electromagnetic analysis was performed, showing that these PCSB interconnect have excellent RF performance in the LTCC/BGA package up to millimeter-wave frequencies [22]. The downside of these PCSB interconnects is the slight increase of thermal and electrical resistance due to the insulating nature of the polymer cores. A 5% and an 8% increase in thermal resistance was measured for a carrier array ball grid array (CABGA) package and a plastic ball grid array (PBGA) package, respectively, compared to conventional eutectic solder balls [23]. Despite the slight increase of resistance, this PCSB interconnects are still a viable solution for applications that requires high reliability and small pitch size.

Figure 1.11. (a) Cross-section image of PCSB. (b) Soldered PCSB after thermal cycling test.

[21]

### 1.4 Introduction to carbon nanotubes and carbon nanotube interconnects

## 1.4.1 Background information of carbon nanotubes

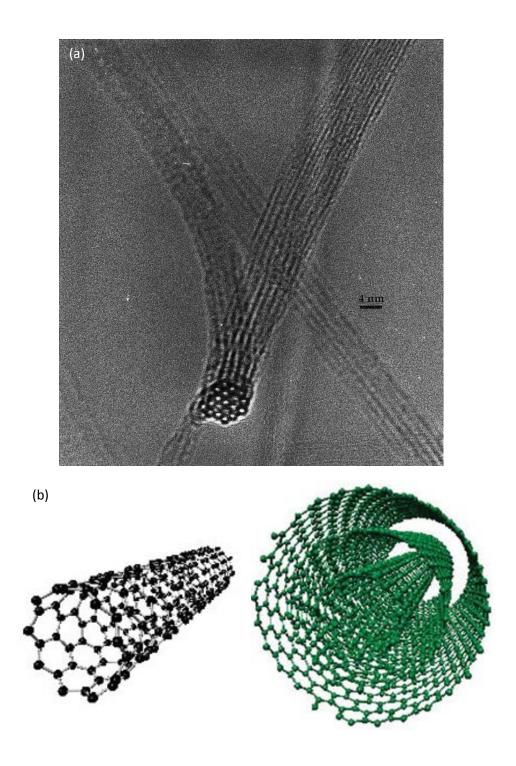

Carbon nanotubes (CNT) are wrapped up graphitic sheets with a hexagonal lattice [24], as shown in Figure 1.12. With a cylindrical shape and a typical diameter smaller than 10 nm, the carbon nanotube is considered to be one of the materials with the highest aspect ratio up to  $1.32 \times 10^8$  [25]. Depending on the number of layers of the graphitic sheets, CNTs can be categorized as single-wall carbon nanotube (SWNT) and multi-wall carbon nanotube (MWCT). Since their discovery in 1991 [26], CNTs have drawn worldwide attention of research due to their superb physical properties and therefore great potential for a huge variety of applications such scaffold materials for biomedical application, ropes, transistors, electrical interconnects, sensors/actuators, batteries and solar cells.

CNT has excellent mechanical properties and it has been known as one of the strongest materials yet discovered in terms of tensile strength and elastic modulus, with a Young's modulus an order of magnitude greater than that of stainless steel. The covalent sp<sup>2</sup> bond between carbon atoms is the main reason for CNT's strength [27]. The physical properties of CNT are different on different direction. In the axial direction, Young's modulus and the tensile strength are as high as 270-950 GPa and 11-63 GPa, respectively [28]. In comparison, CNTs are rather soft in the radial direction and radial Young's modulus is two orders of magnitude smaller than the axial modulus. In addition, it has been indicated that even the van der Waals forces between tubes can deform two adjacent CNTs [27].

Figure 1.12. (a) Transmission electron microscopy image of bundles of chemical vapor deposited carbon nanotubes [29]. (b) Single-wall carbon nanotube (left) and multi-wall carbon nanotube (right) [30].

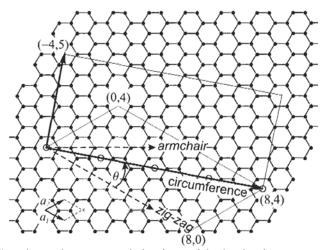

Even though all types of CNTs have cylindrical shapes, the atomic configuration of the carbon atoms is various, which has great impact on the physical properties of the CNTs. The direction the graphene sheet is wrapped is represented by a pair of chiral vectors (n,m). The integers n and m are the number of unit vectors along two directions in the crystal lattice of graphene. The unit vectors are typically chosen along the neighboring centers of the honeycomb hexagon, which a separation angle of  $60^{\circ}$ , as shown in Figure 1.13. If m = 0, the nanotubes are zigzag, and if n = m, the nanotubes are called armchair nanotubes. Otherwise, they are called chiral. The diameter of an ideal nanotube can be calculated from its (n,m) indices as shown in Equation 1.1, where a = 0.246 nm.

Figure 1.13. Graphene honeycomb lattice with the lattice vectors  $a_1$  and  $a_2$  [31].

$$d = \frac{a}{\pi}\sqrt{n^2 + nm + m^2} \tag{1.1}$$

For single wall nanotubes, the electrical properties of the nanotubes strongly depend on

the chirality. Band gaps varying from 0 to 2eV are possible. For a given (n, m) nanotube, it can be either metallic or semiconducting, as shown in Table 1.3. Ballistic conduction of electrons happens along the axial direction of metallic carbon nanotubes and therefore metallic carbon nanotube shows higher electrical conductivity along the axial direction than the most conductive metal at room temperature. Superconductivity of CNT at cryogenic temperature has also been reported [32].

| Chirality                 | Electrical Property                |

|---------------------------|------------------------------------|

| $\mathbf{n} = \mathbf{m}$ | Metallic                           |

| n - m = multiple of 3     | Semiconducting with small band gap |

| Others                    | Semiconducting                     |

Table 1.3. Electrical property dependence of SWNT on chirality

Electromigration is a common phenomenon reported that limits the current carrying capability of metals. CNTs have been known to be capable of carrying a current density as high as  $4 \times 10^9$  A/cm<sup>2</sup>, which is 3 orders of magnitudes compared to conventional copper interconnects [33].

Similar to the directional electrical conductivity of the CNT, the thermal conductivity of CNT is good along the tube. In contrast, the thermal conductivity across the wall of the tubes is low enough to be insulating [34].

#### 1.4.2 Carbon nanotube interconnects

Due to the excellent electrical and thermal conductivity of CNT, it has the potential to be used as interconnect. Also, CNT interconnects can be flexible and stress decoupled, which is beneficial to accommodate for coefficient of thermal expansion (CTE) mismatch [35]. In addition, carbon nanotube interconnects may be advantageous for high frequency application due to their reduced skin effect [36].

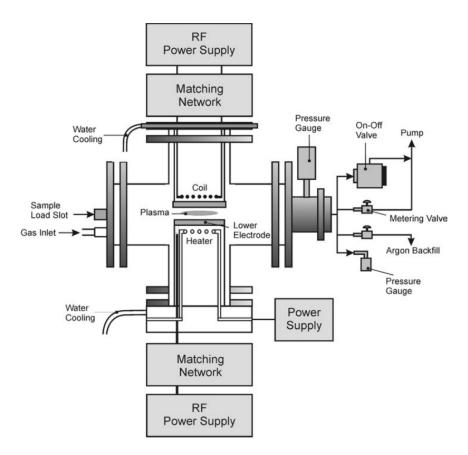

The most common method used for CNT growth on substrates is chemical vapor deposition (CVD) [37]. In a chemical vapor deposition process of CNTs, substrates are exposed to carbon containing gaseous precursors, which decompose on the areas of the substrates where catalyst layers were previously deposited to build up the CNTs. The thin catalyst layer serves as nucleating sites where carbon atoms deposits and forms tubes. By using CVD, CNT patterns are grown on predefined catalyst-seeded areas. Figure 1.14 shows a typical CVD setup for CNT growth. One limiting factor of this method is a high processing temperature, typically greater than 700 °C to yield structures of high quality CNT [37], which is not compatible with conventional microelectronics and CMOS process flows. Figure 1.15 shows SEM images of CNT interconnects grown using CVD [38].

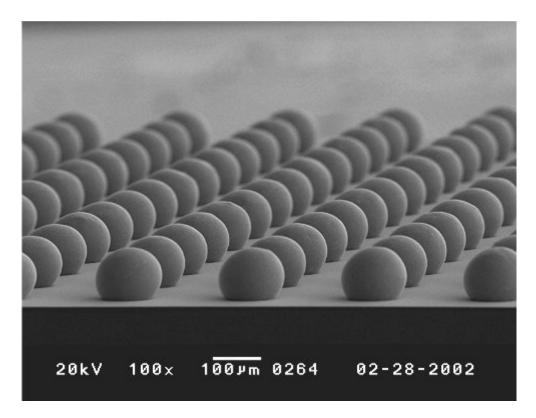

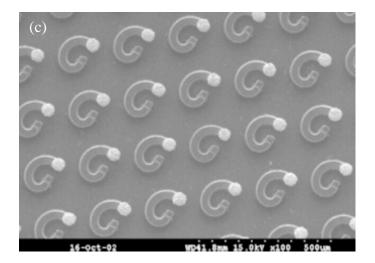

Transferring CNTs grown on another substrate can mitigate the high processing temperature issue of the CVD process at the expense of additional steps to deposit and reflow solder or conductive paste patterns which stick to and carry CNTs during transferring [39]–[42]. Additionally, since the areas to be covered with CNT forest are defined by the application of solder or conductive paste, the areas of CNT forests are not as well-defined compared to photo-lithographically defined patterns. The CNT transferring process and transferred CNT interconnects are shown in Figure 1.16 and Figure 1.17 [39].

Figure 1.14. A typical CVD setup for CNT growth [37].

Figure 1.15. SEM images of CVD grown MWNTs. The scale bars are 5, 3, 10, 2, 5, 10, 1, 0.2,

and 0.2 mm, respectively [38].

Figure 1.16. CNT interconnects fabrication process by transferring. CNTs are first grown on one

substrate and then transferring to another [39].

Figure 1.17. SEM images of CNTs transferred onto solder pads [39].

## Chapter 2 Double Helix Interconnect

In the last two decades, various structures of MEMS type interconnects have been studied [7]–[23], [43]. Two contact modes are used in these structures: soldered contact and sliding contact. Soldered contacts use solder on the MEMS based compliant interconnect structure to make connection and have been used on a number of MEMS structures including microsprings [9], [10], [12]–[14], micro-helix structure [15], [16] and Sea-of-Leads [11], [17]. Soldered contacts provide good reliability and low electrical resistance. However, soldered contacts are detrimental to the reworkability of the compliant structures.

An alternative approach to make contact between the MEMS-type interconnects and a chip without solder is to use sliding contact [12]–[14]. Stress-engineered microsprings are found to be useful for sliding contact due to their highly compliant structure. By pressing a chip with contact pads against the microsprings, the microsprings bend and the tips of the microsprings touch and slide on the contact pads to make an electrical connection. Unlike soldered contacts, since the microsprings physically touch the contact pads, the assembly is easily disassembled and capable to be reused. We note that generally, implementations using the sliding mode contact require additional packaging structures to hold the chips in place and in contact with the substrate or interposer.

One downside of the stress-engineered microsprings is their relatively high electrical resistance. Cheng et al. designed and fabricated one of the most electrically conductive

compliant microsprings, which demonstrates a resistance of approximately 70 m $\Omega$  [14]. Their microsprings are essentially long thin and narrow pieces of curled-up metal fabricated on top of a chip. The tips of the microsprings touch the contact pads on a second chip to provide an electrical connection. The electrical performance is largely limited by the geometry because the cross-sectional area of the microspring and contact area to the contact pad are small. Another issue with the microspring is its inability to scale down. Though the width of the springs can be scaled down easily, the springs need be long enough such that they can curl to a sufficient height to provide the desired level of compliance.

In this work, we describe a double helix MEMS-type interconnect structure. Single-helix MEMS-type interconnects of different shapes (G-helix,  $\beta$ -helix etc.) have been studied in the last decade [15], [16]. However, all these interconnect use solder for permanent bonding and the geometry of the structures shows high resistance even in simulation [10]. The double helix compliant interconnect reported in this paper has low resistance and uses pressure to make electrical connection such that the need for solder and underfill is minimized or eliminated.

Due to the development of wireless applications in recent years, many research works have focused on millimeter-wave frequency range systems. One important aspect of these systems is module packaging. The proper strategy to assemble and interconnect monolithic microwave integrated circuits (MMICs) is critical to the performance of the system [44]. Flipchip approach is considered to be the most promising approach to make interconnects and assemble chips due to its low reflection and insertion loss as well as low fabrication cost. The vertical off-chip compliant interconnects are used in combination with flip-chip bonding technology.

Despite the works on various structures of the compliant interconnect, to the best of our

knowledge, none of them focused on the high frequency performance of the compliant structure. This work also presents the design and fabrication a flip chip bonded coplanar waveguide (CPW) structure using compliant double helix structures as interconnects [45]. The CPW serves as a test structure for characterization of the double helix interconnects. The performance of the structure was simulated and measured up to 50 GHz. The insertion loss and reflection loss were simulated and measured to be reasonably low.

In section 2.1, the fabrication process of the double helix MEMS-type compliant interconnects is described. Section 2.2 presents electrical characterization and reworkability results of the structure. Electrical and mechanical simulation results are included for comparison purpose. Section 2.3 includes the simulation and measurement results of the structure working at high frequency.

## 2.1 Fabrication of the double helix MEMS-type interconnect

Figure 2.1 schematically illustrates the fabrication procedure used to form the double helix MEMS-type interconnects, or double helix contacts. Only one helix of the pair is shown in Figure 2.1(a-g) for clarity purpose. The other helix is colored in semi-transparent purple in Figure 2.1(h). Starting with an oxidized silicon wafer, 50 nm Ti and 400 nm Cu were deposited as a seed layer for copper electroplating (Figure 2.1(a)). An AZ 9245 photoresist layer was applied to define the structure used for characterization, namely the underlying lateral metallization of a snake and comb structure (as described in the electrical characterization section), onto which the double helix structure was to be fabricated. Copper was electroplated to construct a 3 µm thick snake and comb structure (Figure 2.1(b)) and the applied photoresist was then removed (Figure 2.1(c)). Sequentially, another lithography step was performed to coat the snake and comb structure with an 8 µm thick photoresist pattern. This layer of photoresist was 5 µm taller than the snake and comb to allow the formation of patterns on top of the snake and comb. The photoresist was then exposed and developed followed by hard bake at 90 °C for 20 min and copper electroplating to form the bottom pillars of the double helix structure (Figure 2.1(d)). The hard bake of the photoresist is necessary before copper electroplating to prevent the possible outgassing and cracking of the photoresist caused by the following steps. The baking temperature was kept much lower than the softening temperature of the photoresist to avoid reflow. Careful preparation and tuning of the Cu electroplating resulted in uniform plating of the Cu to a level even with the defined photoresist. Without removing the photoresist, 200 nm of Cu was deposited to serve as a second seed layer for copper electroplating (Figure 2.1(e)). Similar to the electroplated bottom pillars, patterns were defined with 2.5 µm of photoresist and electroplated with copper to form lateral overhang

structures (Figure 2.1(f)). Steps from Figure 2.1(d) to Figure 2.1(f) were repeated to build up the structure to form a full turn of the double helix structure (Figure 2.1(g)). Note also that these steps could continue to be repeated to form taller structures with higher vertical compliance, which may be useful for chips that are to be mounted onto substrates with uneven surfaces. Additionally, the thickness of the lateral overhangs is a variable that can be optimized to balance electrical and mechanical performance, as well as ability to be fabricated. After finishing a complete turn of the double helix structures, seed layers and photoresist must be removed to expose the double helix structure. The structure was soaked in acetone, methanol and copper etchant alternatively with mild agitation until the seed layers and photoresist were completely removed. To ensure a thorough removal of photoresist, an oxygen plasma descum process was then performed. After etching the initial Ti seed layer using BOE, the double helix compliant interconnect structures are complete and ready for use (Figure 2.1(h)).

All of the copper electroplating steps were performed at a current density of 8 mA/cm2. Before each electroplating step, the substrate was dipped in 1% hydrochloric acid to remove any copper oxide on the surface of the Cu that was to be electroplated to ensure uniform plating. The copper electroplating solution used was an acidic copper plating solution consisting of copper sulfate (60 g/L), sulfuric acid (100 g/L), hydrochloric acid (0.2 g/L) and small amounts of brightener and suppressor (Cu electroplating additives). Note that since the photoresist layers were not removed before the complete double helix structure was fabricated, it is critical to control the copper plating time so that the height of the electroplated copper layers is close to that of the photoresist layers to allow a planar and uniform surface and facilitate the subsequent fabrication steps.

The fabricated double helix interconnects are uniform and of high yield, as shown in the

SEM image of Figure 2.2. The fabrication process is based on conventional photolithography and electroplating of Cu. All the steps were completed at the wafer level and performed at room temperature. Therefore, this process can be an extension of the standard back-end-of-line (BEOL) or wafer-level packaging process to provide chip interconnection with high I/O density [11]. At this point, the top surface of the Cu double helix is the native Cu surface and has not been optimized for best electrical performance. As described in the electrical performance section below, this surface is a source of considerable electrical resistance that can possibly be minimized through further fabrication and characterization efforts such as coating with Au or Cr or intentional nano-tailoring.

Figure 2.1. Schematic fabrication flow for double helix compliant interconnect structures. The cross-section schematics are shown on the left while the 3-D views are listed on the right. Only one helix of the pair is shown in Figure 1(a-g) for clarity purpose. Figure 1(h) shows the other helix in purple. Gray, yellow and orange represent oxidized silicon wafer, photoresist and

copper, respectively.

Figure 2.2. SEM images of an array of fabricated double helix contact structures prior to mechanical and electrical testing. (Scale bar:  $100 \ \mu m$  (top image) and  $10 \ \mu m$  (bottom image).)

## 2.2 DC electrical characterization

#### 2.2.1 Experimental setup

Applying pressure is necessary for the double helix interconnects to electrically connect with contact pads on a corresponding second chip. Therefore it is useful to explore the impact of the applied load on the electrical resistance of the structure. To measure the resistance of the structure under varying forces, a flip chip bonder (FC-150) was used to apply various loads onto the double helix compliant structures.

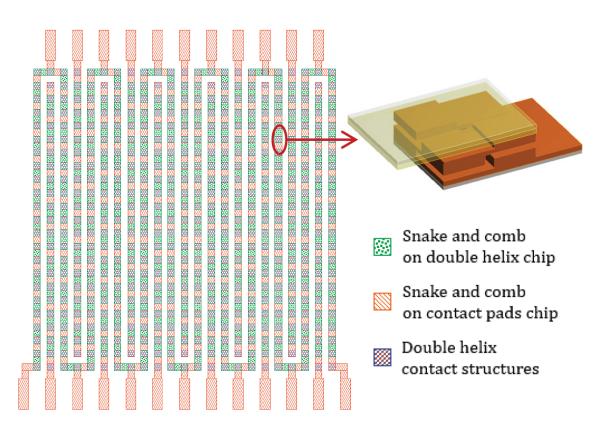

The snake and comb structure for electrical characterization is illustrated in Figure 2.3. The snake is used for measuring resistance while the comb is used for detecting unwanted shorts. Note that the double helix interconnects chip described in the previous section only has half of the lateral metallization of the snake and comb structure (blue and green in Figure 2.3). A complementary snake and comb contact pads chip, with lateral metallization that completes the daisy-chain structure (blue and orange in Figure 2.3), is necessary to be assembled onto the double helix interconnect chip in order to make a complete snake and comb structure for resistance measurements. To fabricate the complementary contact pads chip, photolithography was again used to define the pattern on an oxidized silicon substrate and gold was electroplated on a previously deposited gold seed layer to make an approximately 1  $\mu$ m thick gold contact pads pattern. The substrate was diced into chips after the photoresist and the seed layer were removed.

Figure 2.3. Mask layers of snake and comb test structure and double helix interconnects for electrical measurements. The double helix contacts are pressed against matching contact pads during measurement to form a complete chain. In the top right inset, gray, gold and orange represent oxidized silicon wafer, gold and copper, respectively.

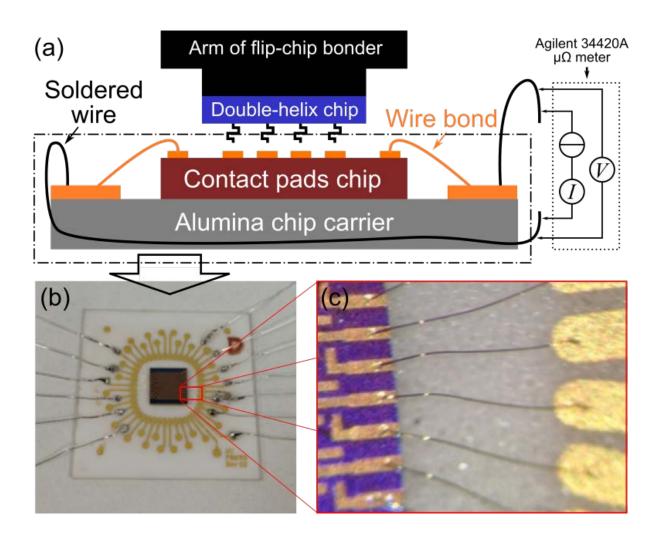

Figure 2.4(a) shows a schematic of the electrical measurement set-up. The double helix interconnect chip was picked up by the arm of the flip chip bonder, held inverted, then aligned to and pressed against the matching contact pads chip. Since it is not practical to use micro-manipulated probes inside a flip-chip bonder to probe the chip, especially when 4-point resistance measurement is needed, electrical contacts to the contact pads on the edge of the contact pads chip need to be extended so that measurement can be performed using equipment outside of the flip-chip bonder. In order to do so, the contact pads chip was attached to an

alumina substrate and wire bonds were used to connect the pads of the contact pads chip to gold pads on the alumina substrate, as shown in Figure 2.4(c). Soldered wires were used to further extend electrical connections to the structure outside the flip-chip bonder, as shown in Figure 2.4(b). An Agilent 34420A Micro-Ohm meter was used to perform 4-point measurements.

Figure 2.4. (a) The schematics of the electrical characterization. (b) Contact pads chip was attached to the alumina chip carrier with wire bonds and soldered wires to extend electrical access to the structure outside the flip-chip bonder for electrical measurement. The soldered wires were clipped and connected to the Micro-Ohm meter. (c) Zoom view of the wire bond between the contact pads chip and the alumina chip carrier. (d) FC-150 flip chip bonder.

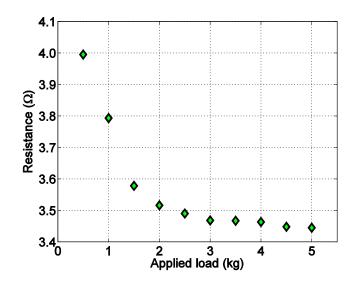

## 2.2.2 Electrical resistance measurement and test fixture resistance extraction

The FC-150 was used to provide a controlled load onto the double helix interconnect chip over the range of 0 to 5 kg. The corresponding average applied force on each double helix structure ranged from 0 to 92.6 mN, considering that there are 529 double helix structures on each chip. Using the snake and comb structure, no shorts were detected, indicating a complete removal of seed layers. The measured resistance of 22 double helix structures in series, including the resistance of the test fixture, is shown in Figure 2.5.

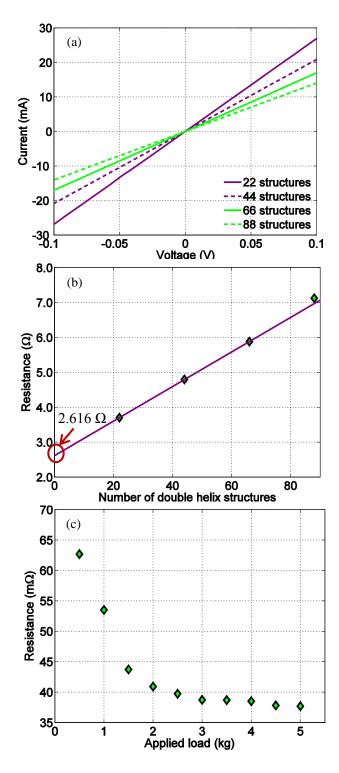

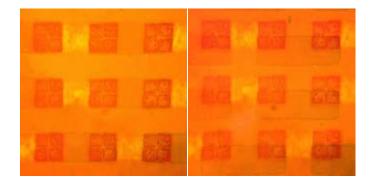

Since the measured resistance data includes the resistance of the lateral metallization and resistance of the test fixture (wire bonds and soldered wires), the resistance of individual double helix contact structure cannot be calculated by simply dividing the total resistance by the number of double helix structures. To accurately extract the resistance of individual double helix structures from the experiment data, an extrapolation method was used, as shown in Figure 2.6(a) and (b). The I-V curve was measured using a Keithley 4200 semiconductor characterization system. The I-V curve is linear, demonstrating high quality electrical interconnection. Consecutive chains of double helix structures were measured and the data points were linearly fitted and plotted against the number of double helix structures. As a result, the intercept of the fitted line and y-axis should approximate the resistance of the test fixture. The extrapolated resistance of the wire bonds and the soldered lead wire of the test fixture was found to be approximately 2.616  $\Omega$ , as shown in Figure 2.6(b). Direct measurement of the test fixture (lead wires, wire bonds and a small section of lateral metallization), using a four-wire method, gave a resistance value that was within 10% of the extrapolated value. Since the resistance of the test fixture is similar to the resistance of the string of double helix structures, it is necessary to account for it in the analysis of the resistance of individual double helix interconnect structures. By subtracting the resistance of the test fixture from the total resistance and then dividing the resulting resistance by the number of the double helix structures, the resistance of individual double helix structures (including a small portion of lateral metallization) was obtained as a function of applied load, as shown in Figure 2.6(c).

Figure 2.5. Measured resistance of 22 double helix structures in series under different forces. Note that this includes the resistance of the lateral snake and comb metallization, as well as that

of the test fixture.

Figure 2.6. (a) I-V characteristics of the resistance of the double helix structures, including the test fixture. (b) Extrapolation of the resistance of the test fixture. (c) Resistance of one double helix interconnect structure versus load applied to full chip.

## 2.2.3 Mechanical and electrical analysis using FEA simulation

## 2.2.3.1 Mechanical

A representative structure was modeled and simulated using finite element analysis (FEA) software ANSYS Workbench 14.5, as shown in Figure 2.7(a). Since both the snake and comb structure and the double helix compliant interconnect contribute to the measured resistance, the contact pads of the snake and comb are included in the FEA model. The time independent plastic behavior of electroplated Cu was modeled using a bilinear kinematic hardening rule. The yield strength of electroplated copper was assumed to be 280 MPa. The Young's modulus and the tangent modulus were assumed to be 140 GPa and 4.67 GPa, respectively [46]. The maximum deformation in the vertical direction was approximately  $2.6 \,\mu m$  when  $0.5 \,\text{kg}$  of load was applied to the structure (this corresponds to approximately 9.26 mN of force per double helix structure). The compliance of the fabricated double helix structures is approximately 0.28 mm/N, comparably lower than other reported values [15]. However, we note that the compliance is adjustable by modifying the geometric parameters of the structure, such as overhang thickness, pillar length and height. When the applied load on each structure was greater than 0.62 kg, the gold contact pad chip touched the upper lateral overhang and created a shorter electrical path. This explains the significant resistance drop when the applied load increased from 0.5 kg to 1.5 kg, as shown in Figure 2.6(c). The presented results for chains of multiple structures are smoothed, due to an assumed slight variation in structure height due to fabrication tolerances. Additionally, more compression is expected to lead to more complete contact between the vertical and lateral sections of the double helix structure and is another reason that the resistance drops as the applied force increases. Although the low resistance at higher loads is helpful, the compliance of the structure is degraded. Therefore, the structure is

recommended to be used under low compressive load. The issue of resistance change due to varying loads at low compressive loads can be solved by using additional fixtures such as the balls/pits fixtures [14] to clamp the compliant structure at a fixed load.

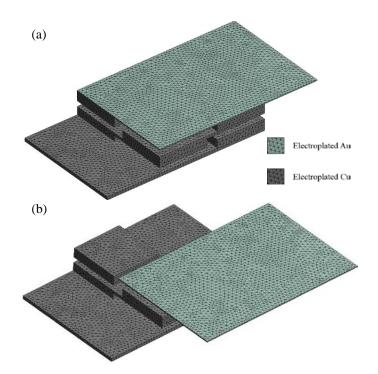

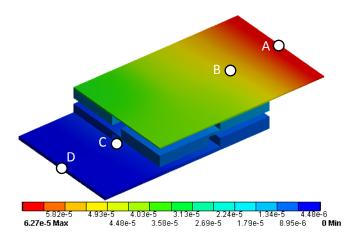

## 2.2.3.2 Electrical

The resistance of the structure is also modeled in ANSYS Workbench. The electrical potential distribution was modeled by feeding a source current of 1 mA through the structure, as shown in Figure 2.8. The resistance was calculated by dividing the sensed voltage drop by the source current. The top contact pad is made of electroplated gold with a resistivity of 3  $\mu\Omega$ ·cm. The rest of the structure uses electroplated copper with a resistivity of 2.4  $\mu\Omega$ ·cm. The resistivity of the electroplated gold and copper was obtained from resistivity measurement using a corresponding Van der Pauw structure. All the components contributing to the total resistance of the structure were modeled except for the contact resistance between the contact pad and the double helix structure. Even though there are models for contact resistance, these models require additional parameters such as effective contact area and asperity deformation [47], [48]. To simplify the modeling, we modeled the contact resistance of the interface as a resistor and used it to fit the total measured resistance. The simulated resistance results are listed in Table 2.1.

Figure 2.7. (a) The meshed 3-D FEA models of a double helix structure in full contact with the contact pads of the snake and comb. (b) The meshed 3-D FEA models of a double helix structure with only one of the two helixes making contact to the contact pads. (bottom contact pad size: 150 μm × 100 μm × 3 μm; top contact pad size: 150 μm × 100 μm × 1 μm; size of the pillar of the double helix: 45 μm × 45 μm × 5 μm; size of the lateral overhang structure of the double

helix:  $45 \,\mu\text{m} \times 100 \,\mu\text{m} \times 2.5 \,\mu\text{m}$ .)

Figure 2.8. Electrical potential distribution of the double helix structure when a source current of 1 mA is fed through.

| Component                              | Resistance  |

|----------------------------------------|-------------|

|                                        | $(m\Omega)$ |

| Simulated top Au lead, $R_{AB}$        | 15.1        |

| Simulated bottom Cu lead, $R_{\rm CD}$ | 4.0         |

| Simulated double helix, $R_{\rm BC}$   | 11.4        |

| (no contact resistance)                |             |

| Simulated double helix, $R_{\rm BC}$ ' | 43.6        |

| (including contact resistance)         |             |

| Measured double helix, $r_{\rm BC}$    | 19.5-51.3   |

| (including contact resistance)         |             |

| Measured total resistance, $r_{AD}$    | 61-87       |

Table 2.1. Resistance components of the measured structure

#### 2.2.3.3 Scalability

Without considering the contact resistance, the simulated double helix structure has a resistance of 11.4 m $\Omega$  ( $r_{BC}$  in Table 2.1). To study the scalability of the interconnect structure, the structure was scaled laterally to half of its size and simulated. The scaled structure has a small increase of resistance to 12.7 m $\Omega$ . The mechanical compliance of the scaled-down structure was reduced. Therefore we further reduced the widths of the overhangs and pillars by approximately 3% to match the compliance of the original, non-scaled structure. By doing so, the resistance increased slightly to 13.5 m $\Omega$ . A small increase in resistance for structures with reduced lateral dimensions indicates the potential of the structure to be scaled down.

#### 2.2.4 Extraction of the lateral resistance of the snake and comb metallization

Since the structure is only slightly bent at a load of 0.5 kg, the resistance at 0.5 kg was used and the contact resistance was swept to fit it in the ANSYS modeling. 10 chips were measured at 0.5 kg load and the resistance ranges from 61 m $\Omega$  to 87 m $\Omega$  with an average of 69.4 m $\Omega$ . In order to extract the resistance of the double helix structure without the lateral resistance of the snake and comb structure, an offset measurement was performed by slightly moving the top double helix chip during flip-chip pressing to only contact one of the two helixes of the double helix structure, as shown in Figure 2.9. The load on the structure was halved since only half of the structure was pressed. As a result, the resistance of both the single helix and the double helix structure, including the test fixture resistance and the lateral metal resistance, can be measured, as in (2.1) and (2.2). The single helix structure was assumed to have twice the resistance of the double helix, as in (2.3), because in the double helix the two single helixes are in parallel.

$$R_{\rm M1} = R_{\rm L} + R_{\rm t} + n \cdot R_{\rm SH} \tag{2.1}$$

$$R_{\rm M2} = R_{\rm L} + R_{\rm t} + n \cdot R_{\rm DH} \tag{2.2}$$

$$R_{\rm SH} = 2 \cdot R_{\rm DH} \tag{2.3}$$

$R_{\rm M1}$ ,  $R_{\rm M2}$ ,  $R_{\rm L}$ ,  $R_{\rm t}$ ,  $R_{\rm SH}$ ,  $R_{\rm DH}$  are the resistance of the measured single and double helix test structure chains, lateral metal, test fixture, a single helix and a double helix, respectively. n is the number of the measured helix structures. The resistance of the double helix can be extracted by subtracting (2.1) by (2.2), as in:

$$R_{\rm DH} = (R_{\rm M1} - R_{\rm M2})/n \tag{2.4}$$

Equation (2.4) was verified using ANSYS simulation. The top chip was moved such that only one of the two helixes is making contact, as shown in Figure 2.7(b). Resistance of the single and double helix test structure chains ( $R_{M1}$  and  $R_{M2}$ ) was simulated. The resistance of one double helix was calculated using (2.4). The calculated double helix resistance is 12.0 m $\Omega$ , which is close to the simulated resistance value of 11.4 m $\Omega$ , as shown in Table 2.1, indicating that equation (2.4) is valid for lateral resistance extraction.

Using (2.4), the measured resistance of the double helix structure was calculated, which varies from 19.5 to 51.3 m $\Omega$ , with an average of 35.4 m $\Omega$ , as shown in Table 2.1. This

variation is assumed to be mainly due to contact resistance variation. Therefore, the resistance of the structure has the potential to be significantly reduced if an improved contacting strategy or surface treatment is implemented. One method to improve contact resistance is by using closed-loop copper electroplating since it can provide a smoother contact region and make the fabrication process more controllable. Additionally, a difference in the actual structure between the fabricated structure and the simulated one and the natural copper oxide can lead to the resistance difference found between measurement and simulation as shown in Table 2.1. Given these sources of variation, as well as the fabrication-induced variation, we find that our measured and simulated performance is a reasonable match.

In comparison to other reported compliant interconnect structures that can be integrated into BEOL process or wafer level packaging processes [10], [11], [14], [15], the presented double helix structure shows relatively low resistance. Simulation results show that the Flexconnect [10] and  $\beta$ -helix [15] have a resistance lower than 50 m $\Omega$ , but no contact resistance was considered. Measurement data shows that the Sea-of-Leads has a low total resistance of 2.52  $\Omega$  per 54 interconnects [11], while the microspring interconnect has a resistance of approximately 70 m $\Omega$  [14].

Despite the low resistance of the double helix structure, the presented structure can be further improved in several aspects. First, the fabrication process is comparably more complex. One possibility to simplify the fabrication process is to replace the pillar and overhang structure with electroplated curved metal layers [49], [50]. By doing so, the number of metal deposition and electroplating steps can be reduced. Second, the stand-off height of the structure is comparably shorter. This geometric shortcoming can be mitigated by modifying the design of the pillar and the overhang. Furthermore, more refined fabrication processes are desired so that higher performing and more uniform structures can be fabricated.

Figure 2.9. Flip chip bonding alignment observed from the microscope of the flip chip bonder.(a) Resistance measurement without offset. (b) Offset resistance measurement. Note that only half of the double helix structure was aligned to be in contact.

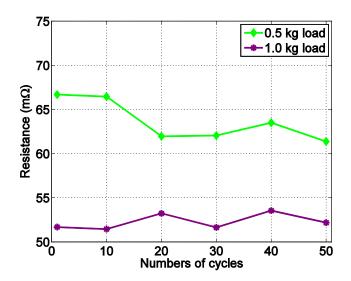

Figure 2.10. The resistance of the double helix interconnect (including lateral resistance of the snake and comb structure) after remating cycles.

## 2.2.5 Reworkability of the double helix interconnect