# PACKAGING OF SILICON CARBIDE HIGH TEMPERATURE, HIGH POWER **DEVICES - PROCESSES AND MATERIALS**

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

|                                                                         | Yi Liu       |                                                                                                     |

|-------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------|

| Certificate of Approval:                                                |              |                                                                                                     |

| John Evans<br>Associate Professor<br>Industrial and Systems Engineering |              | R. Wayne Johnson, Chair<br>Samuel Ginn Distinguished Professor<br>Electrical & Computer Engineering |

| Thomas A. Baginski Professor Electrical & Computer Engineering          |              | Stuart M. Wentworth Associate Professor Electrical & Computer Engineering                           |

|                                                                         | Stephen L. M |                                                                                                     |

Graduate School

# PACKAGING OF SILICON CARBIDE HIGH TEMPERATURE, HIGH POWER DEVICES - PROCESSES AND MATERIALS

# Yi Liu

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama May 11, 2006

# PACKAGING OF SILICON CARBIDE HIGH TEMPERATURE, HIGH POWER DEVICES - PROCESSES AND MATERIALS

| <b>T</b> 7.    | • | •   |

|----------------|---|-----|

| V <sub>1</sub> |   | 111 |

|                |   |     |

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon the request of individuals or institutions and at their expense.

The author reserves all publication rights

| Signature of Author |

|---------------------|

|                     |

|                     |

|                     |

| Date of Graduation  |

# **VITA**

Yi Liu, son of Yucheng Liu and Yufang Zhou, was born in March 10, 1973 in Jilin, P.R.China. He attended Tianjin University in September 1991 and graduated with a Bachelor of Science degree in Mechanical Engineering in July 1995. After working as a mechanical engineer in Tianjin Yizhong Vehicle Safety Belt Factory for two years, he entered the Graduate School, Tianjin University in September 1997. He received the Master of Science degree in Mechanical Engineering in March 2000. Then he worked at Tianjin Assembly and Test Factory, Motorola China Inc. as a process engineer. In August 2001, he joined Ph.D. program of the Department of Electrical and Computer Engineering, Auburn University.

### DISSERTATION ABSTRACT

# PACKAGING OF SILICON CARBIDE HIGH TEMPERATURE, HIGH POWER DEVICES - PROCESSES AND MATERIALS

# Yi Liu

Doctor of Philosophy, May 11, 2006 (M.S., Tianjin University, 2000) (B.S., Tianjin University, 1995)

132 Typed Pages

Directed by R. Wayne Johnson

Silicon carbide (SiC) has unique electrical, thermal and physical properties compared to the Si and GaAs conventionally used in microelectronics as it can operate in the temperature range from 350°C to 500°C. However, there is a lack of reliable packaging techniques and materials for SiC, in particular substrates, die attach, die metallization and die passivation that can survive temperatures as high as 500°C.

Direct bond copper (DBC)  $Al_2O_3$  substrates in which a thick Cu foil is cladded on  $Al_2O_3$  has been used for power electronics for many years because of its acceptable heat dissipation capability, high current carrying capability, low coefficient of thermal expansion (CTE) and high mechanical strength. AlN has a very high thermal conductivity and a CTE approximating that of SiC (AlN = 4.5ppm/°C vs. SiC = 4.4ppm/°C [1]).

However, with thick Cu metallization, the AlN is prone to fracture during thermal cycling due to its low flex strength and fracture toughness [2]. While  $Si_3N_4$  does not have the thermal conductivity of AlN ( $Si_3N_4$ = 60W/m•K vs. AlN= 170-250W/m•K), the high fracture toughness of  $Si_3N_4$  (2.4X AlN) allows thick Cu metallization and provides better thermal cycling performance.

Die attach is another key issue for high temperature operation. This study examined a transient liquid phase bonding technique using eutectic Au-Sn braze with a thick Au (20μm) layer electroplated on the DBC Al<sub>2</sub>O<sub>3</sub> substrate. After brazing and annealing at 400°C, the Sn from the eutectic preform diffused into the substrate Au, lowering the Sn concentration to less than 10% and raising the braze joint melting point to over 400°C. Au-Ge and Au-Ge-Ag braze alloys were also evaluated.

Die metallization plays a role as an adhesion layer and diffusion barrier. It should not degrade during high temperature storage. A sputtered thin film stack of Ti/Ti-W/Au was examined to assess its performance, including its stability during high temperature storage.

In high voltage applications, insulation is required to prevent the breakdown of SiC device passivation or arcing around the edge of the die. Phthalonitrile and polyhedral oligomeric silsesquioxanes (POSS) nanoreinforced polyimides were characterized as high temperature high voltage passivation materials. Ceramic capacitors, one of the passive components needed in a power electronics module, were also examined for high temperature applications up to 300°C.

### **ACKNOWLEDGMENTS**

I would like to express my appreciation and sincere thanks to my research advisor, Dr. R. Wayne Johnson, who guided and encouraged me throughout my studies. His advice and research attitude have provided me with a model for my entire future career. I also wish to thank my advisory committee members, Dr. John Evans, Dr. Stuart M. Wentworth, and Dr. Thomas A. Baginski, for their advice on this work.

Appreciation is also expressed to those who have made contributions to my research. I am especially indebted to Dr. John R. Williams, Dr. Michael J. Bozack, Dr. Hyacinth S. Gale, Michael J. Palmer, Guoyun Tian, John Marcell, Cai Wang, Hongtao Ma, Tan Zhang and Zhenwei Hou for their cooperation and continued assistance throughout the course of this research.

Finally, I would like to thank, although this is too weak a word, my wife Xuan Li and my parents for their continual encouragement and support throughout this work.

Style manual or journal used: <u>IEEE Transaction on Components and Packaging</u>

<u>Technology</u>

Computer software used: Microsoft Word 2003

# TABLE OF CONTENTS

| LIST OF TABLES.                                           | xi  |

|-----------------------------------------------------------|-----|

| LIST OF FIGURES.                                          | xii |

| CHAPTER 1 INTRODUCTION                                    | 1   |

| 1.1 SiC Properties                                        |     |

| 1.2 SiC Processing                                        |     |

| 1.2.1 SiC Crystal Growth                                  |     |

| 1.2.2 SiC Defects                                         |     |

| 1.2.3 SiC Doping.                                         |     |

| 1.2.4 SiC Etching, Dicing and Polishing                   |     |

| 1.2.5 SiC Contacts                                        | 6   |

| 1.3 SiC High Temperature, High Power Devices              | 9   |

| 1.4 Electromigration                                      |     |

| 1.5 Packaging of SiC High Temperature, High Power Devices | 11  |

| 1.5.1 Substrate Materials for SiC Power Electronics       | 12  |

| 1.5.2 Die Attach                                          |     |

| 1.5.3 Wire Bonding                                        |     |

| 1.5.4 High Voltage Passivation                            |     |

| 1.6 Research Objectives                                   |     |

| CHAPTER 2 DIE ATTACH FOR SILICON CARBIDE PACKAGE          | 30  |

| 2.1 Introduction                                          |     |

| 2.2 Chip Metallization                                    |     |

| 2.3 Die Attach                                            |     |

| 2.3.1 Introduction                                        |     |

| 2.3.2 Au-Sn Eutectic Alloy                                |     |

| 2.3.3 Electroplating                                      |     |

| 2.3.4 High Temperature Brazing.                           |     |

| 2.4 Reliability Test                                      |     |

| 2.4.1 High Temperature Storage Test                       |     |

| 2.4.2 Thermal Cycle Test                                  |     |

| 2.5 Au-Ge Braze                                           |     |

| 2.6 Au-Ge-Ag Braze                                        |     |

|                                                           |     |

| CHAPTER 3 CHARACTERIZATION OF HIGH TEMPERATURE            |     |

| ELECTRICAL INSULATION POLYMERS                            | 78  |

| 3.1 Introduction                                          | 78  |

| 3.2 Experimental Procedure and Results                       | 81  |

|--------------------------------------------------------------|-----|

| CHAPTER 4 CHARACTERIZATION OF HIGH TEMPERATURE               |     |

| CAPACITORS                                                   | 90  |

| 4.1 Introduction                                             |     |

| 4.2 Experimental Procedure                                   |     |

| 4.3 Results and Discussions                                  |     |

| CHAPTER 5 CONCLUSIONS                                        | 107 |

| 5.1 Die Attach for SiC Packaging                             | 107 |

| 5.2 Substrates for SiC Packaging                             | 108 |

| 5.3 High Temperature, High Voltage Passivation               | 108 |

| 5.4 Ceramic Capacitors for High Temperature Applications     | 109 |

| 5.5 Recommendations for Packaging SiC High Temperature, High |     |

| Power Devices                                                | 109 |

| 5.6 Recommendations for Future Work                          |     |

| BIBLIOGRAPHY                                                 | 111 |

# LIST OF TABLES

| Table 1-1 Properties of semiconductor materials | 3  |

|-------------------------------------------------|----|

| Table 1-2 High temperature applications         | 10 |

| Table 1-3 High temperature substrate properties | 13 |

| Table 1-4 Adhesive properties                   | 19 |

| Table 1-5 Brazes properties                     | 20 |

| Table 1-6 Wire bonding process comparision      | 22 |

| Table 2-1 Substrates dimensions                 | 53 |

| Table 3-1 Properties of PI-2611                 | 84 |

# LIST OF FIGURES

| Figure 1-1 Common SiC defects.                                                                                                            | 5  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2 Total resistance as a function of d                                                                                            | 8  |

| Figure 1-3 DBC Al <sub>2</sub> O <sub>3</sub> process                                                                                     | 14 |

| Figure 1-4 DBC AIN process                                                                                                                | 16 |

| Figure 1-5 First bond and second bond comparison, (a) ball bonding and (b) wedge bonding                                                  | 24 |

| Figure 1-6 POSS structures                                                                                                                | 28 |

| Figure 2-1 Metallization stack for Ag-In die attach                                                                                       | 32 |

| Figure 2-2 Au-Sn phase diagram                                                                                                            | 34 |

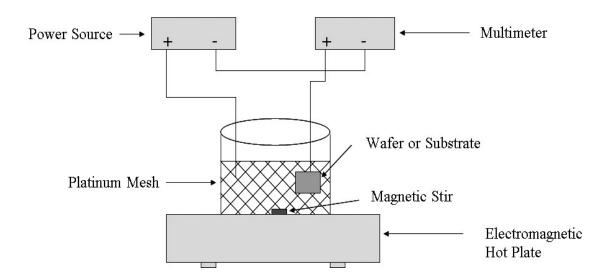

| Figure 2-3 Gold plating setup                                                                                                             | 36 |

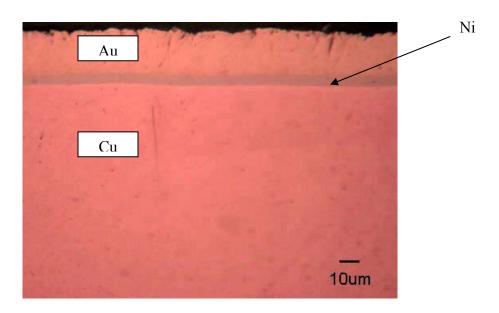

| Figure 2-4 DBC Al <sub>2</sub> O <sub>3</sub> substrate electroplated with 20μm Au                                                        | 37 |

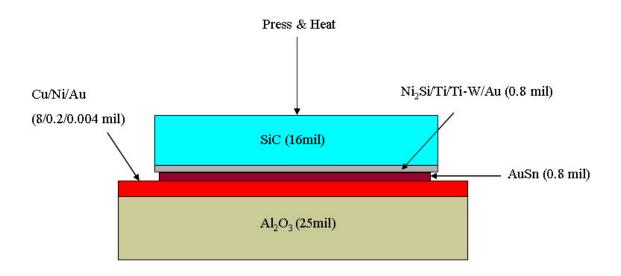

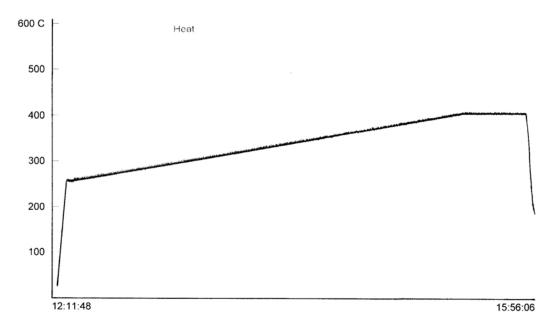

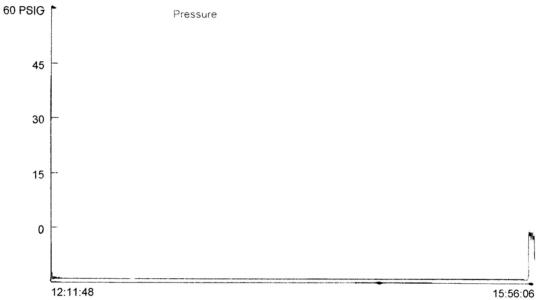

| Figure 2-5 Brazing setup.                                                                                                                 | 38 |

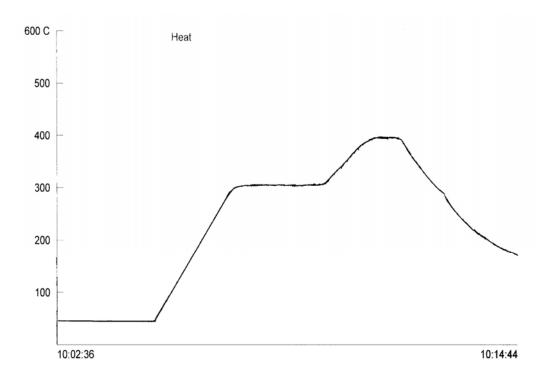

| Figure 2-6 AuSn brazing profile                                                                                                           | 39 |

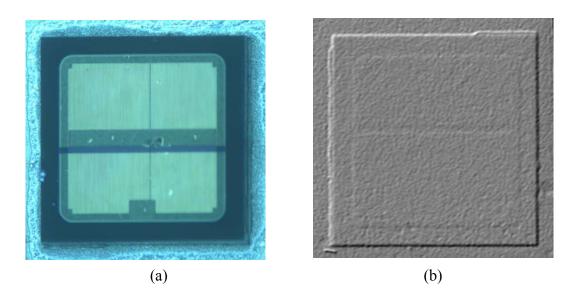

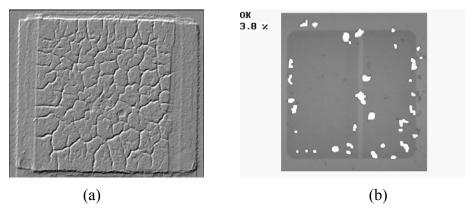

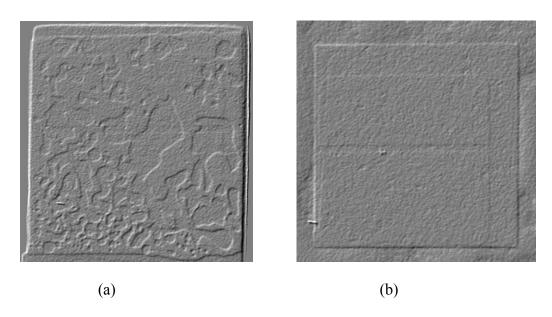

| Figure 2-7 (a) as-brazed sample and (b) x-ray relief mode picture of as-brazed sample                                                     | 40 |

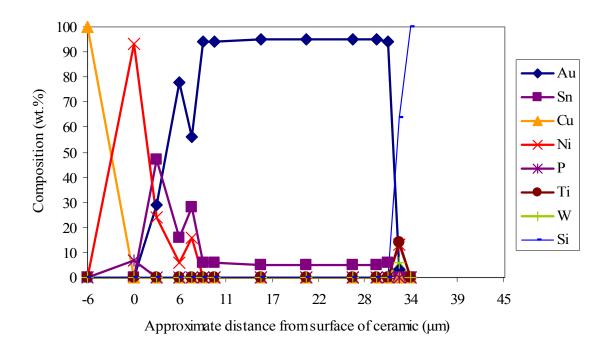

| Figure 2-8 Element concentration plot across an AuSn as-brazed sample                                                                     | 41 |

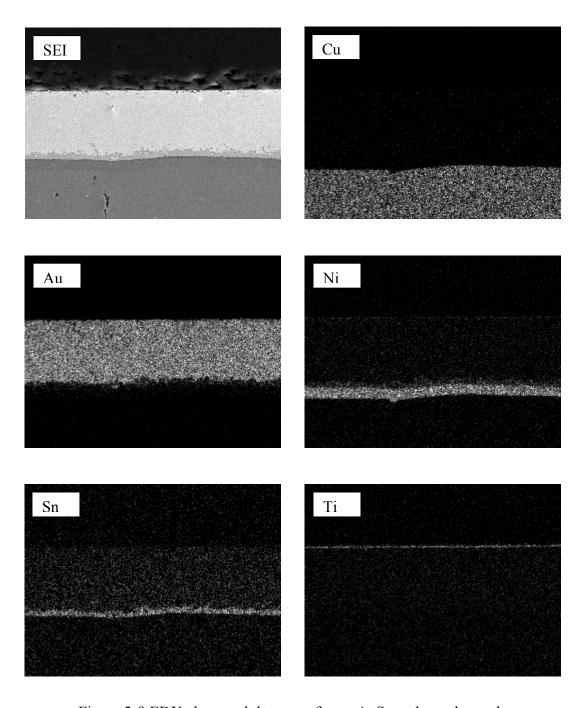

| Figure 2-9 EDX elemental dot maps for an AuSn as-brazed sample                                                                            | 42 |

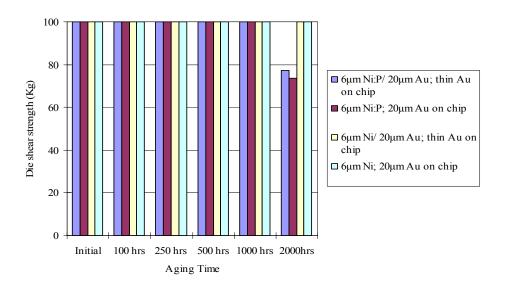

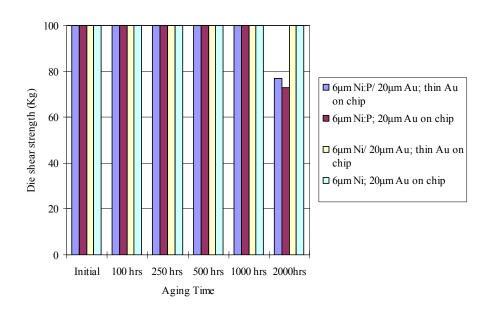

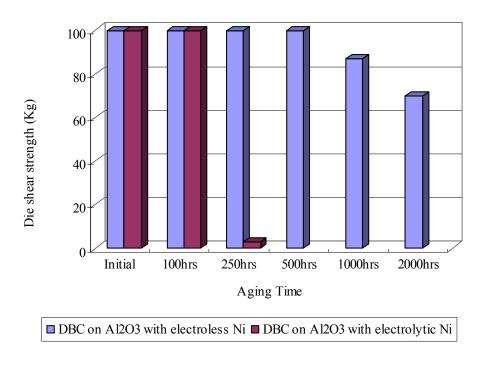

| Figure 2-10 Die shear strength as a function of aging at 400°C in air                                                                     | 44 |

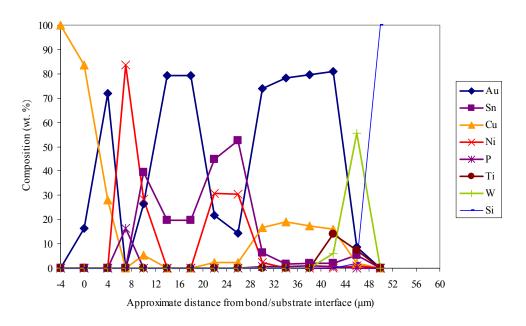

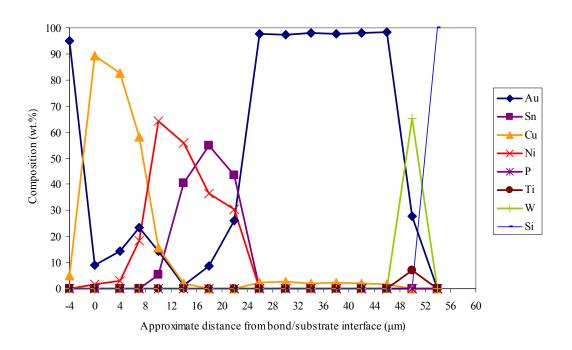

| Figure 2-11 Element concentration plot across an AuSn brazed sample after 2000 hours storage at 400°C, electroless Ni:P, thick Au on chip | 45 |

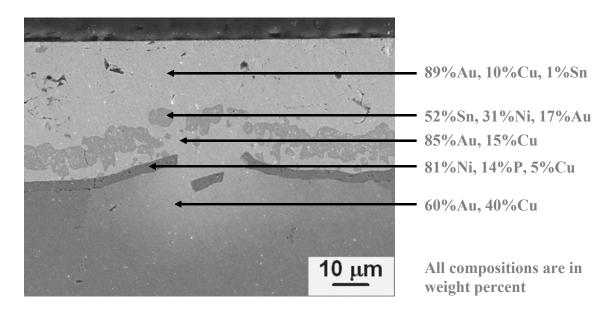

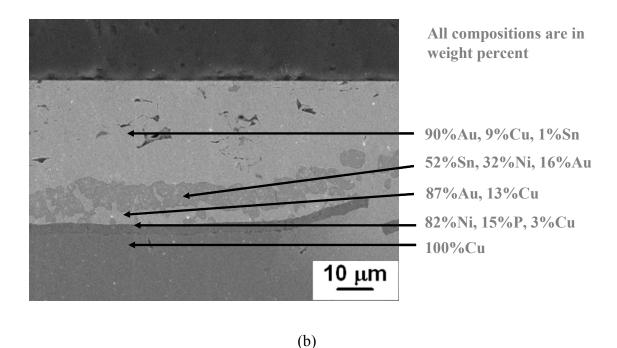

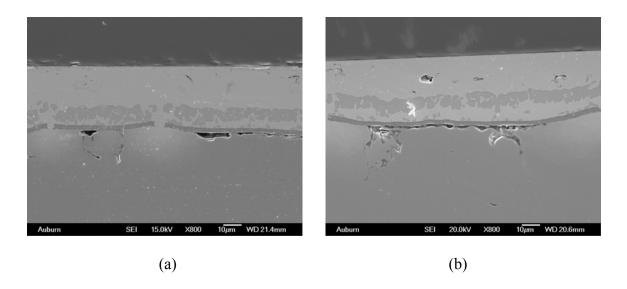

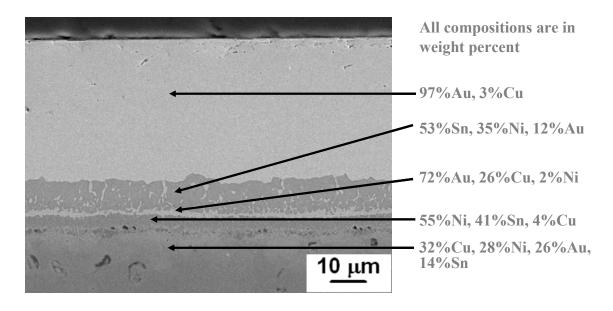

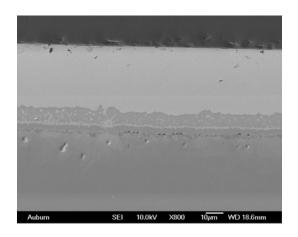

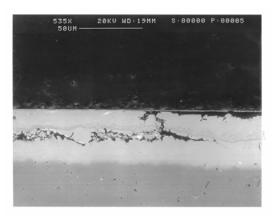

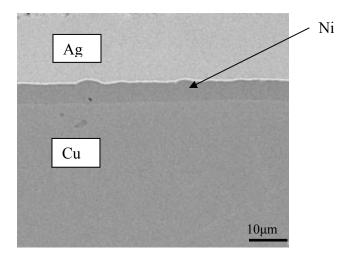

| Figure 2-12 | Cross-section of die attach after 2000 hours at 400°C, electroless Ni:P, thick Au on chip, (a) at Ni:P:Cu broken area and (b) at Ni:P:Cu continous area                                    | 46 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

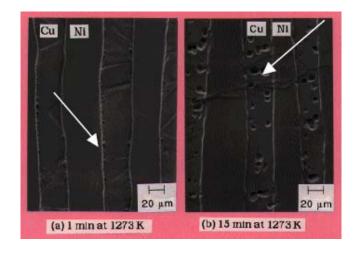

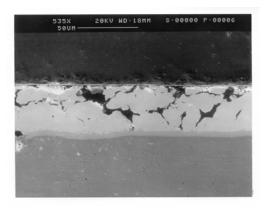

| Figure 2-13 | Cross-section of the die attach, (a) voids at Cu-Ni:P interface after 1000 hours aging and (b) cracks at Cu-Ni:P interface after 2000 hours aging at 400°C                                 | 47 |

| Figure 2-14 | Kirkendall effect of Cu-Ni couple after 1 minute and 15 minutes aging at 1000°C                                                                                                            | 48 |

| Figure 2-15 | Element concentration plot across an AuSn brazed sample after 2000 hours storage at 400°C; electrolytic Ni, thick Au on substrate                                                          | 49 |

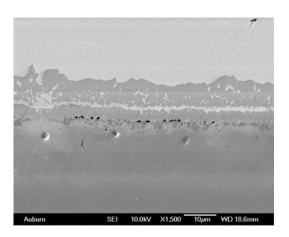

| Figure 2-16 | Cross-section of die attach after 2000 hours at 400°C, electrolytic Ni, thick Au on substrate                                                                                              | 49 |

| Figure 2-17 | Cross-section of the die attach, showing voids at Cu-Ni interface after 2000 hours aging at 400°C                                                                                          | 50 |

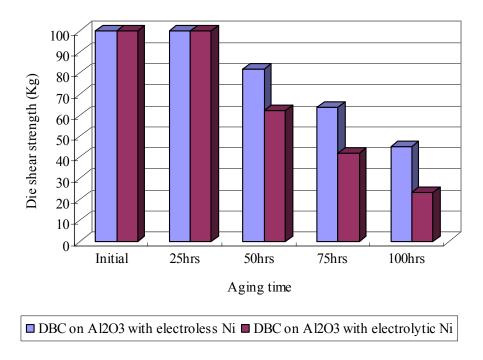

| Figure 2-18 | Die shear strength as a function of aging, confirmation test, 6 $\mu m$ Ni DBC Al <sub>2</sub> O <sub>3</sub> substrates, 400°C in air                                                     | 51 |

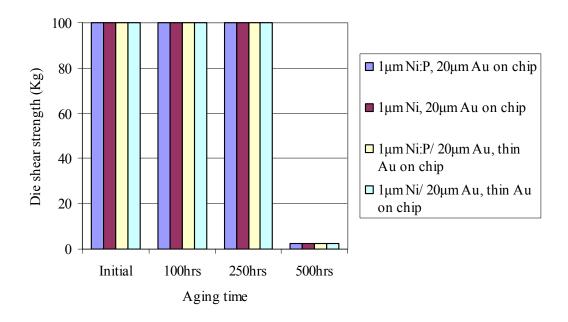

| Figure 2-19 | Die shear strength as a function of aging, confirmation test, $1\mu m$ Ni DBC $Al_2O_3$ substrates, $400^{\circ}C$ in air                                                                  | 51 |

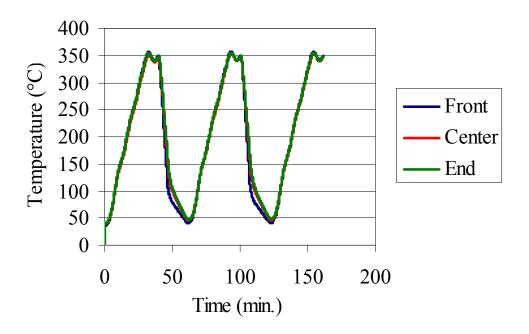

| Figure 2-20 | Thermal cycle test profile                                                                                                                                                                 | 52 |

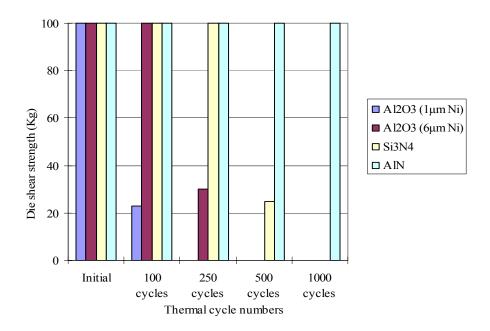

| Figure 2-21 | Die shear strength as a function of thermal cycle numbers                                                                                                                                  | 54 |

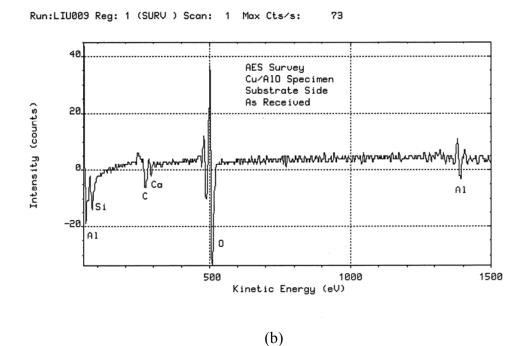

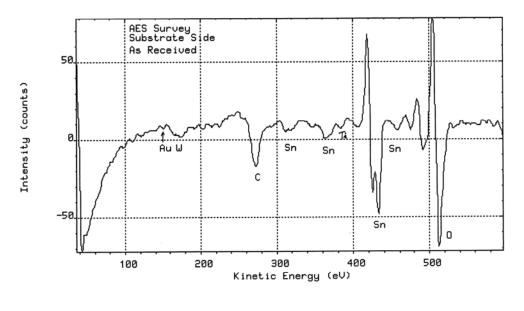

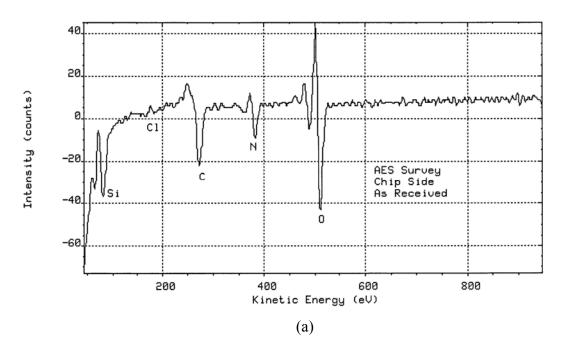

| Figure 2-22 | AES results after 100 thermal cycles, DBC $Al_2O_3$ substrate with 1 $\mu$ m electroless Ni:P, (a) Cu foil surface and (b) substrate surface                                               | 55 |

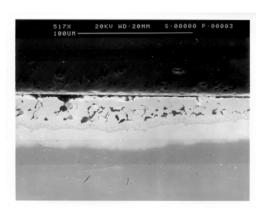

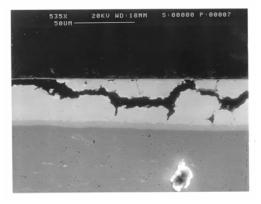

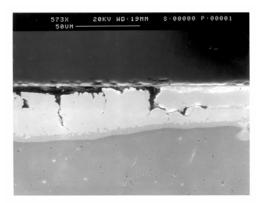

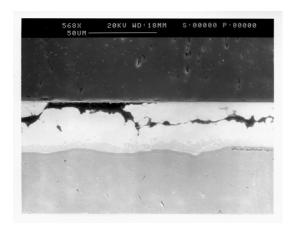

| Figure 2-23 | Cross-section of braze layer after 100 thermal cycles, showing crack in braze layer and braze-TiW delamination. DBC $Al_2O_3$ with $1\mu m$ electrolytic $Ni$                              | 56 |

| Figure 2-24 | Cross-section of braze layer after 100 thermal cycles, showing crack in braze layer and braze-TiW delamination. DBC $Al_2O_3$ with $1\mu m$ electroless Ni:P                               | 56 |

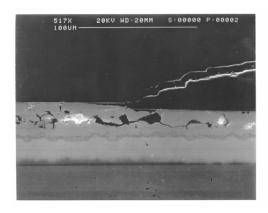

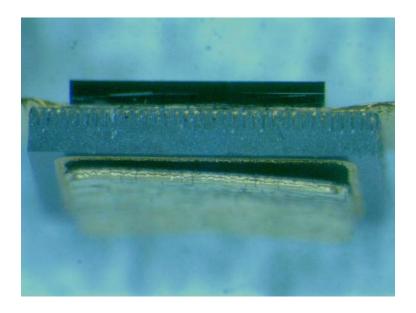

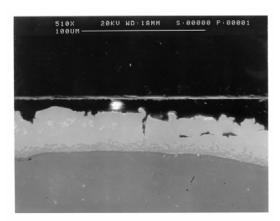

| Figure 2-25 | Cu foil delamination after 250 thermal cycles                                                                                                                                              | 57 |

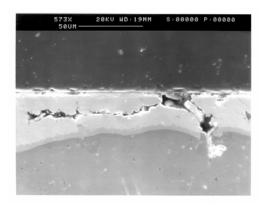

| Figure 2-26 | Cross-section of braze layer after 250 thermal cycles, showing cracks in the braze layer and braze-TiW delamination. DBC Al <sub>2</sub> O <sub>3</sub> substrate with 6um electrolytic Ni | 57 |

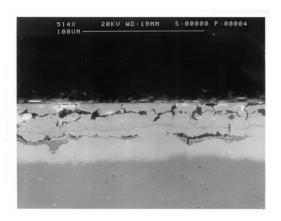

| Figure 2-27 | Cross-section of braze layer after 250 thermal cycles, showing cracks in the braze layer and braze-TiW delamination. DBC Al <sub>2</sub> O <sub>3</sub> substrate with 6μm electroless Ni:P                                                                 | 58 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

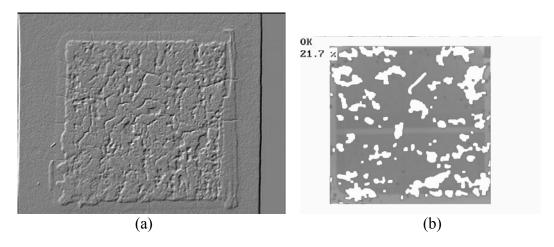

| Figure 2-28 | (a) X-ray image in relief mode, showing cracks in the braze layer and (b) x-ray image in voids calculation mode, calculating braze residue area percentage on chip surface; DBC $Al_2O_3$ substrate with $6\mu m$ electroless Ni:P after 250 thermal cycles | 59 |

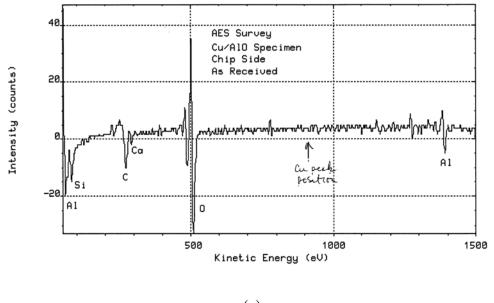

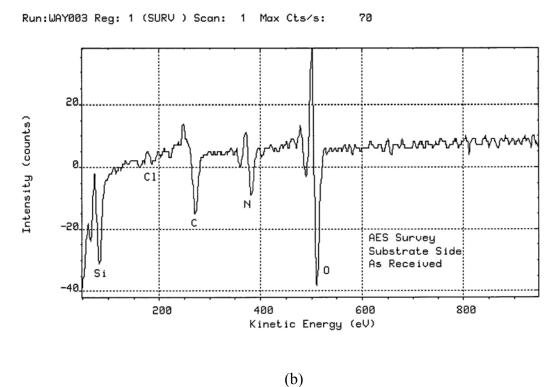

| Figure 2-29 | AES results after 250 thermal cycles, DBC Al <sub>2</sub> O <sub>3</sub> with 6μm electroless Ni:P, (a) substrate side and (b) chip side                                                                                                                    | 60 |

| Figure 2-30 | Si <sub>3</sub> N <sub>4</sub> assembly after 500 cycles, showing the Cu foil delamination                                                                                                                                                                  | 61 |

| Figure 2-31 | AES results of Si <sub>3</sub> N <sub>4</sub> substrate after 500 thermal cycles, (a) Cu foil surface and (b) substrate surface                                                                                                                             | 62 |

| Figure 2-32 | Cross-section of the braze layer after 500 thermal cycles, showing cracks in the braze layer and braze-TiW delamination. Si <sub>3</sub> N <sub>4</sub> substrate after 500 thermal cycles                                                                  | 63 |

| Figure 2-33 | (a) X-ray image in relief mode, showing cracks in the braze layer and (b) x-ray image in voids calculation mode, calculating braze residue area percentage on chip surface; AMB $\mathrm{Si_3N_4}$ substrate after 500 thermal cycles                       | 64 |

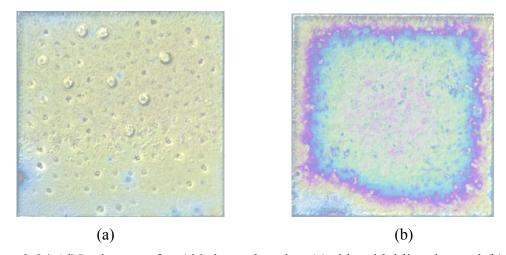

| Figure 2-34 | AlN substrate after 100 thermal cycles, (a) side with blistering and (b) side without blistering                                                                                                                                                            | 64 |

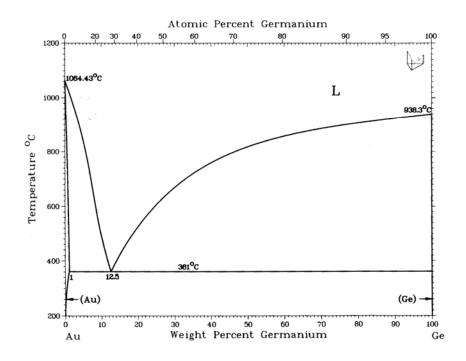

| Figure 2-35 | Au-Ge phase diagram                                                                                                                                                                                                                                         | 66 |

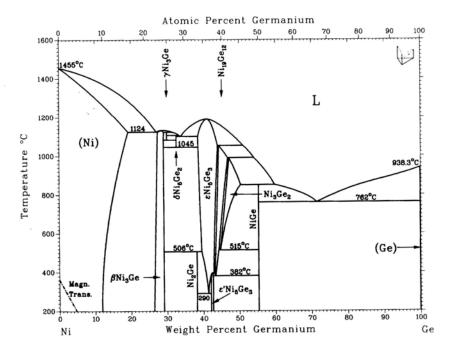

| Figure 2-36 | Ni-Ge phase diagram                                                                                                                                                                                                                                         | 66 |

| Figure 2-37 | Au-Ge braze reflow profile                                                                                                                                                                                                                                  | 67 |

| Figure 2-38 | X-ray relief mode images of Au-Ge bond (a) before optimization and (b) after optimization                                                                                                                                                                   | 68 |

| Figure 2-39 | AuGe braze die shear strength as a function of aging at 300°C                                                                                                                                                                                               | 68 |

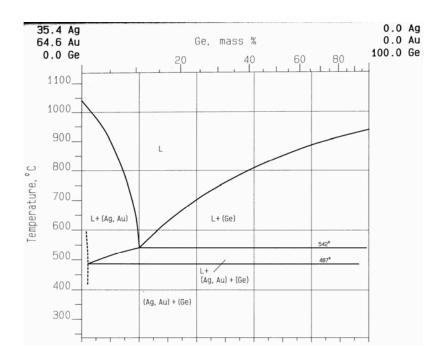

| Figure 2-40 | Au-Ge-Ag phase diagram                                                                                                                                                                                                                                      | 70 |

| Figure 2-41 | DBC Al <sub>2</sub> O <sub>3</sub> substrate plated with 20μm Ag                                                                                                                                                                                            | 70 |

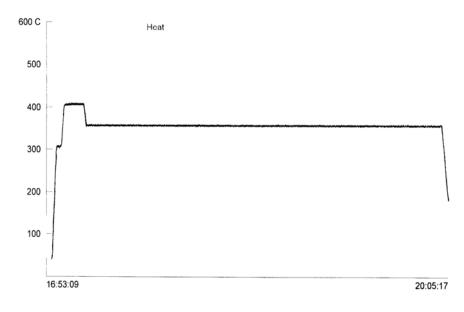

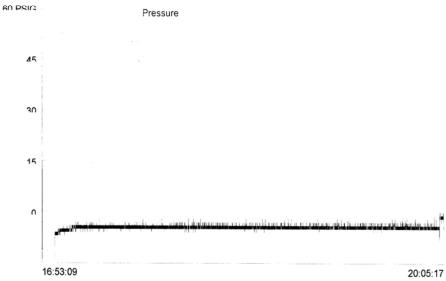

| Figure 2-42 | Au-Ge-Ag brazing profile                                                                                                                                                                                                                                    | 72 |

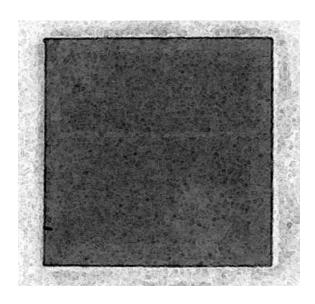

| Figure 2-43 | X-ray picture of Au-Ge-Ag as-brazed sample                                                                                                                                                                                                                  | 73 |

| Figure 2-44 Au-Ge-Ag die shear strength as a function of aging at 400°C                                       | 73       |

|---------------------------------------------------------------------------------------------------------------|----------|

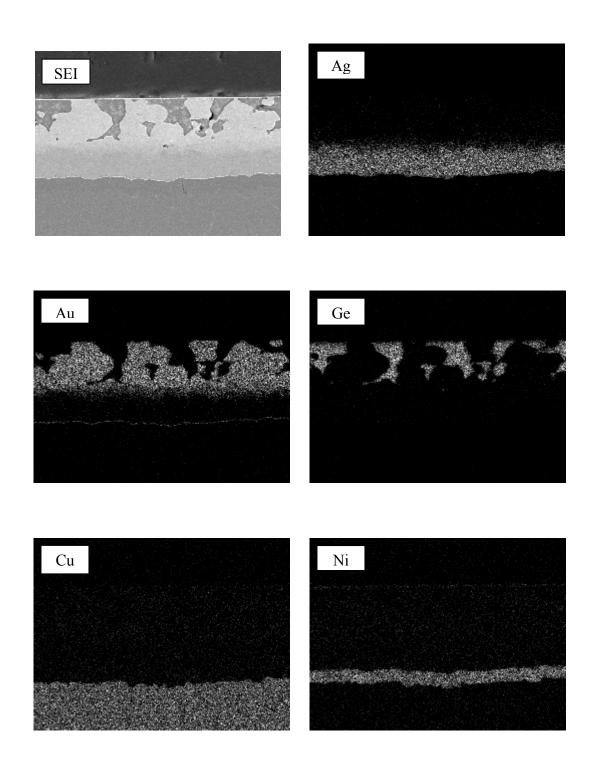

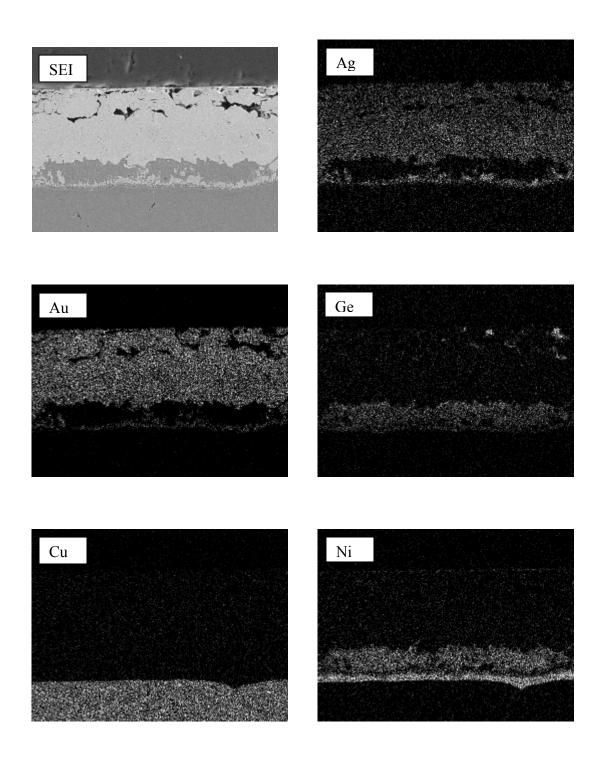

| Figure 2-45 EDX elemental dot maps for Au-Ge-Ag on electroless Ni:P/Au, as-brazed sample                      | 74       |

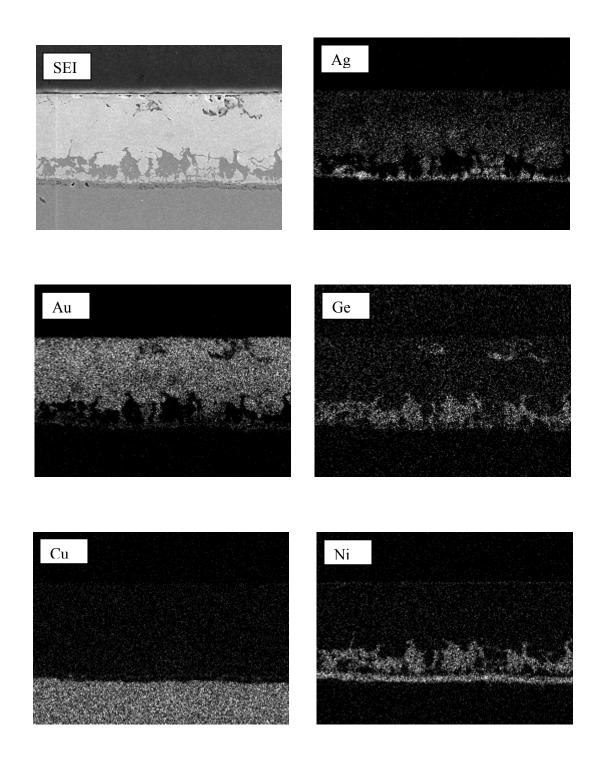

| Figure 2-46 EDX elemental dot maps for Au-Ge-Ag on electroless Ni:P/Au, 100 hours storage at 400°C            | 75       |

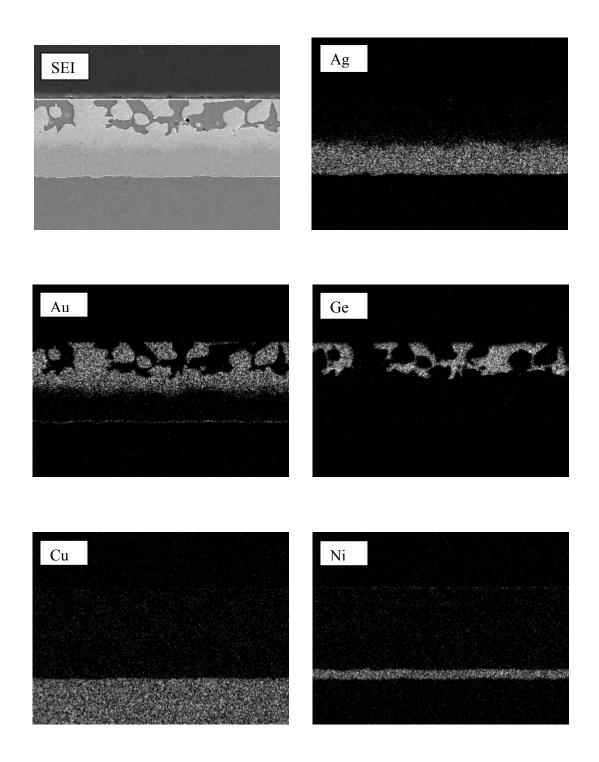

| Figure 2-47 EDX elemental dot maps for Au-Ge-Ag on electrolytic Ni/Au, as-brazed sample                       | 76       |

| Figure 2-48 EDX elemental dot maps for Au-Ge-Ag on electrolytic Ni/Au, 100 hours storage at 400°C             | 77       |

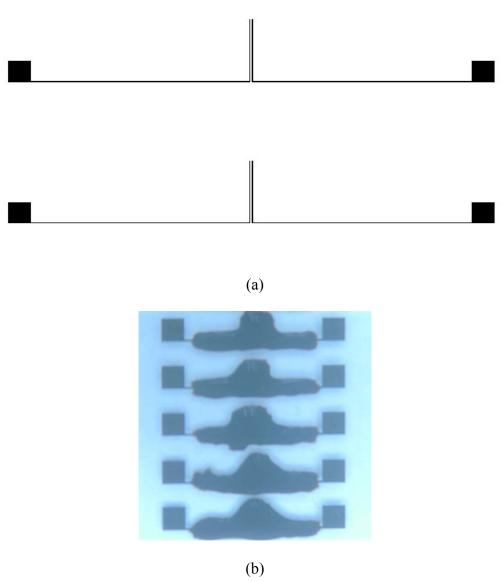

| Figure 3-1 (a) Test pattern, (b) test pattern with cured PT material                                          | 82       |

| Figure 3-2 Breakdown voltage test setup                                                                       | 83       |

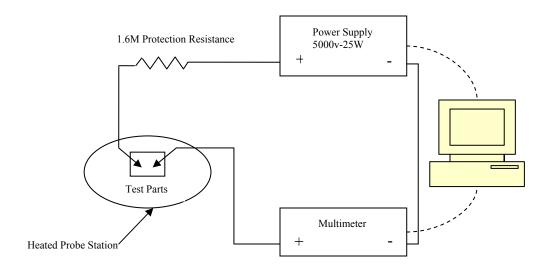

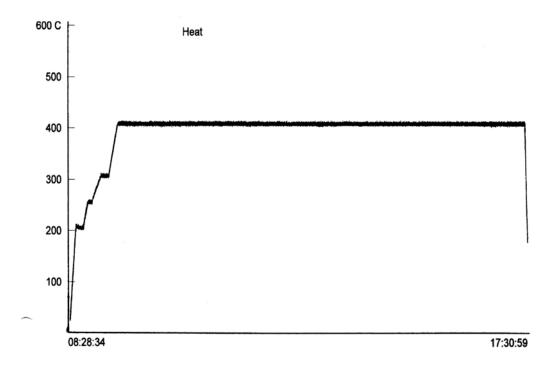

| Figure 3-3 PT curing profile                                                                                  | 85       |

| Figure 3-4 Curing profile of PI-2611 with POSS additive                                                       | 86       |

| Figure 3-5 Leakage current vs. applied electrical field strength                                              | 87       |

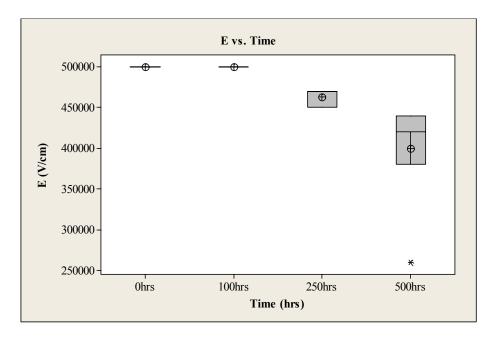

| Figure 3-6 Electrical breakdown field strength for PT thermally aged at 300°C                                 | C 88     |

| Figure 3-7 Electrical breakdown field strength for PM1215 thermally aged at                                   | 300°C 89 |

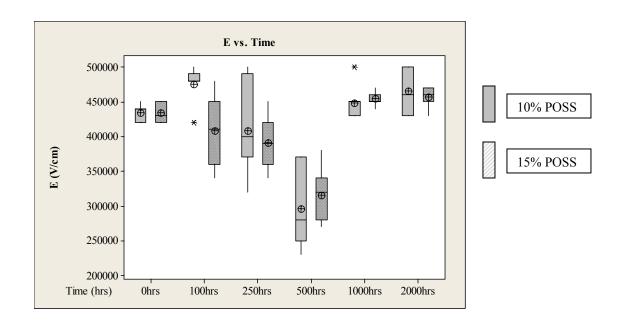

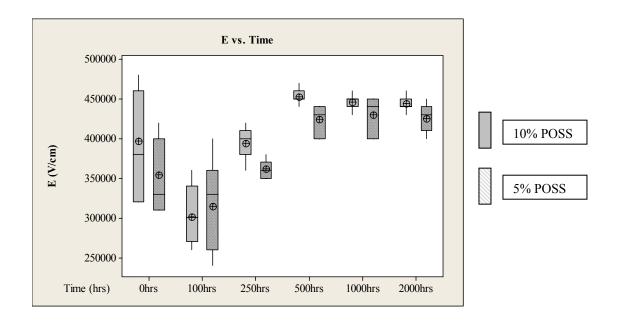

| Figure 3-8 Electrical breakdown field strength for POSS-modified PI2611 thermally aged at 300°C               | 89       |

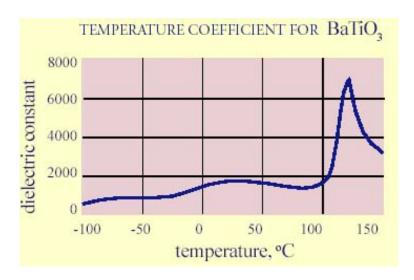

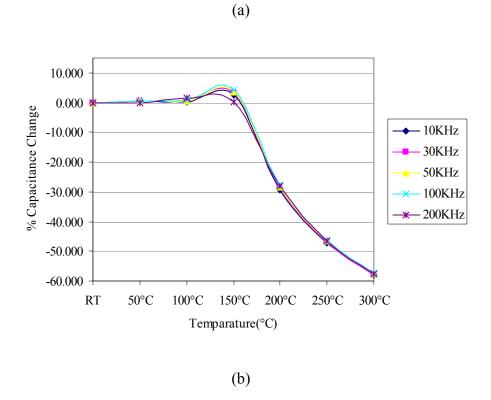

| Figure 4-1 Dielectric vs. temperature for BaTiO <sub>3</sub>                                                  | 92       |

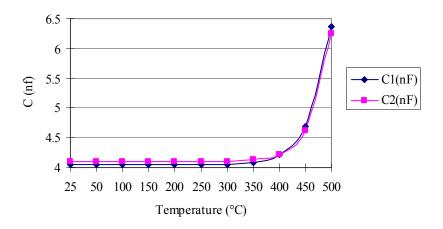

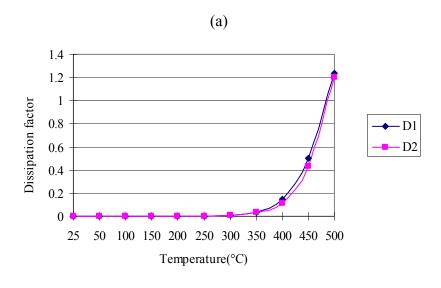

| Figure 4-2 (a) Capacitance vs. temperature and (b) dissipation factor vs. temperature for class I capacitor   |          |

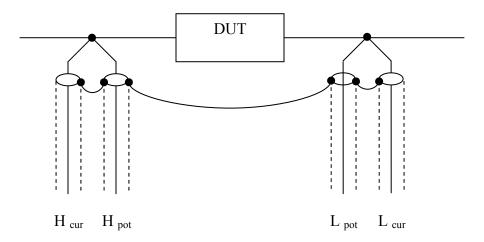

| Figure 4-3 Four terminal pair connection                                                                      | 96       |

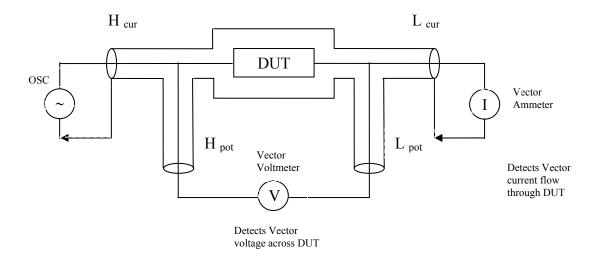

| Figure 4-4 Four terminal pair measurement principle                                                           | 97       |

| Figure 4-5 Experimental setup                                                                                 | 98       |

| Figure 4-6 Ceramic capacitor                                                                                  | 99       |

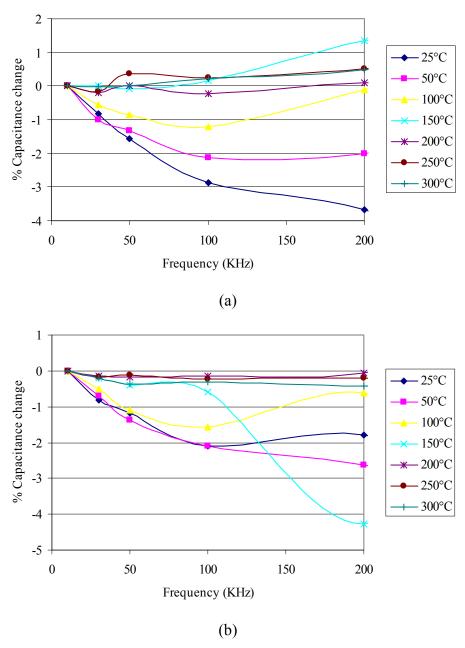

| Figure 4-7 Capacitance vs. temperature for different frequencies, (a) initially (b) after 2000 hours of aging |          |

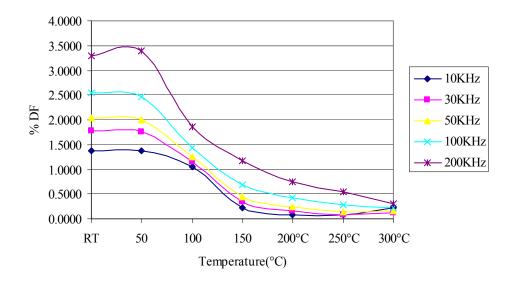

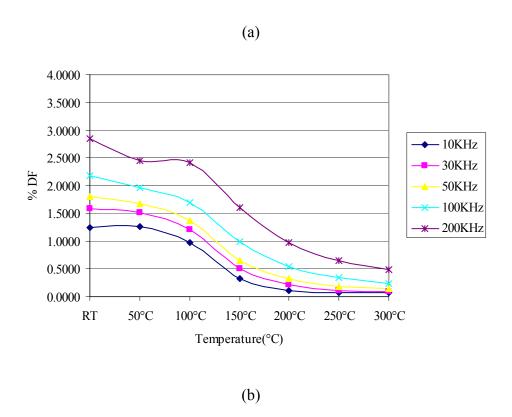

| _            | Dissipation factor vs. temperature for different frequencies, (a) initially and (b) after 2000 hours of aging | 102 |

|--------------|---------------------------------------------------------------------------------------------------------------|-----|

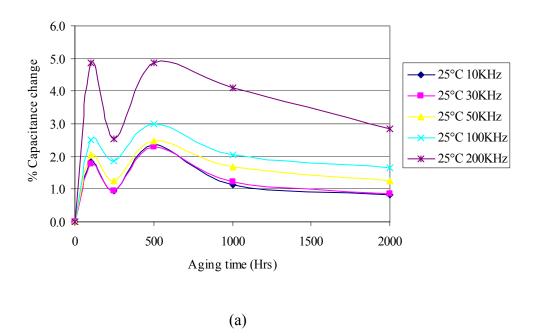

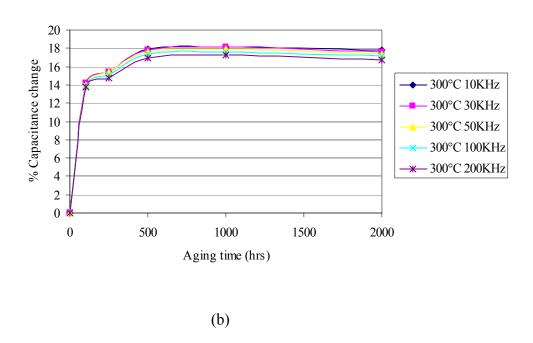

| Figure 4-9 ( | Capacitance vs. aging time, (a) at 25°C and (b) at 300 °C                                                     | 103 |

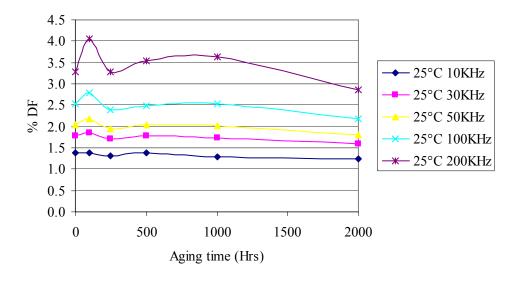

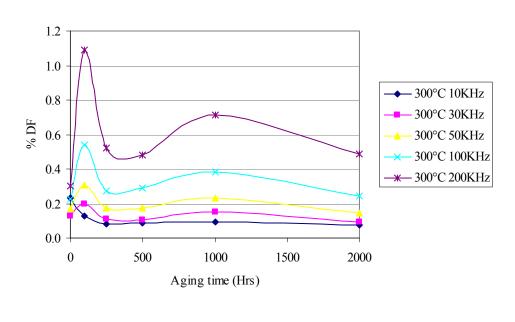

| Figure 4-10  | Dissipation factor vs. time for different frequencies, (a) at 25 °C and (b) at 300°C                          | 104 |

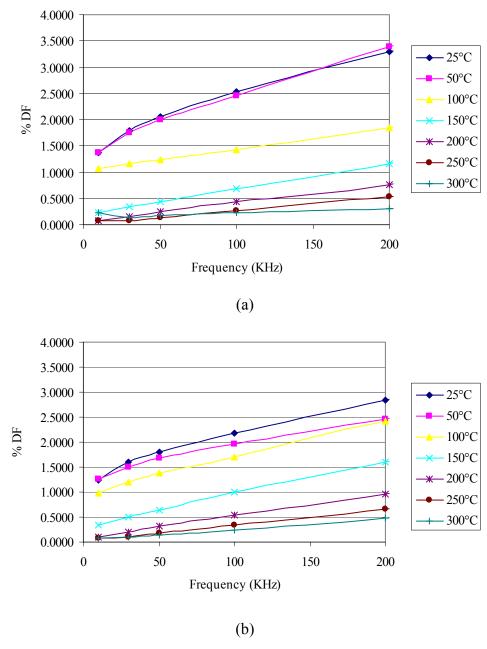

| Figure 4-11  | Dissipation factor vs. frequency at different temperatures, (a) initially and (b) after 2000 hours of aging   | 105 |

| Figure 4-12  | Capacitance vs. frequency at different temperatures, (a) initially and (b) after 2000 hours of aging          | 106 |

#### CHAPTER 1

#### **INTRODUCTION**

# 1.1 SiC Properties

Silicon has long been the dominant semiconductor material because of its major processing advantages: it can easily be oxidized to form silicon dioxide, which is not only a high-quality insulator but also an excellent diffusion barrier layer. GaAs is another widely used semiconductor material which has found many applications in analog and digital devices that require very high frequency operation. However, both Si and GaAs have relative narrow band gaps (the energy difference between the conduction band minimum and valence band maximum) which limit their applications in harsh environments. Wide bandgap semiconductors (SiC, GaN, etc.) are currently moving out of the laboratory into real world applications. The commercialization of SiC that started a decade ago has accelerated over the past few years. The improvements made in SiC semiconductor device technology for power electronics and optoelectronic applications are partially due to the commercial availability of SiC substrates of ever-increasing diameter and quality [3]. SiC offers unique electrical and thermophysical properties compared to Si and GaAs, these include [4]:

1. Wide bandgap. SiC can operate at extremely high temperatures without suffering from intrinsic conduction effects because of its wide energy bandgap. 4H-SiC has an intrinsic temperature of 1650°C for an extrinsic doping level of 10<sup>16</sup>cm<sup>-3</sup>.

- Another advantage of the large bandgap is the negligible leakage current up to 400°C [5]. Also, this property allows SiC to emit and detect short wavelength light which makes the fabrication of blue LEDs and UV photodetectors possible.

- 2. High critical breakdown electric field. With a higher breakdown electric field, SiC power devices can be designed to have 1/10<sup>th</sup> of the thickness of equivalent silicon devices and with more than 10 times higher doped voltage blocking layers. For the majority carrier modulated devices such as power Schottky diodes and MOSFETs, 1/10<sup>th</sup> the blocking layer thickness combined with 10 times the doping concentration can give SiC devices a factor of 100 advantage in resistance over that of the analogous Si majority carrier devices. For the minority carrier modulated devices such as PiN diodes, BJTs, and thyristors, a 1/10<sup>th</sup> blocking layer thickness can yield a 100 times faster switching speed compared to the Si devices [6].

- 3. High saturated electron velocity. This property enables SiC microwave devices to operate at higher cut-off frequencies.

- 4. Significantly higher thermal conductivity. This allows enhanced thermal management for high power devices. Heat flows more readily through SiC than through other semiconductor materials, which enables SiC devices to operate at extremely high power levels while still dissipating a large amount of heat.

Silicon carbide (SiC), aluminum nitride (AlN), gallium nitride (GaN), boron nitride (BN), and zinc selenium (ZnSe) are wide bandgap materials that are now under development for high temperature, high frequency applications. However, SiC offers several advantages over other wide bandgap materials including the commercial

availability of the substrate, well understood device processing techniques, and the ability to grow a thermal oxide for use as a mask during fabrication, device passivation layers and gate dielectrics [7].

In addition to the SiC substrate providing the basis for SiC homoepitaxial device structures, SiC substrates are used for heteroepitaxy of GaN device structures, due to the close lattice match to GaN and excellent thermal conductivity. The properties of common semiconductor materials are presented in Table 1-1 [3].

Table 1-1 Properties of semiconductor materials [3]

| Materials                                         | GaN   | 4H- SiC | 6H- SiC | Si   | GaAs |

|---------------------------------------------------|-------|---------|---------|------|------|

| Properties                                        |       |         |         |      |      |

| Thermal conductivity (W/m•K)                      | 130   | 490     | 490     | 130  | 50   |

| Bandgap (Ev)                                      | 3.44  | 3.2     | 3.0     | 1.12 | 1.42 |

| Saturated electron velocity (10 <sup>7</sup> m/s) | 2.7   | 2.0     | 2.0     | 1.0  | 2.0  |

| Electron mobility (cm <sup>2</sup> /V•s)          | 900   | 1000    | 600     | 1450 | 8500 |

| E <sub>b</sub> (Mv/cm)                            | 12.2  | 9.7     | 10      | 11.8 | 12.8 |

| Lattice constant (Å)                              | 3.189 | 3.073   | 3.081   | 3.94 | 4.00 |

# 1.2 SiC Processing

Silicon carbide has more than 170 polytypes, the most common of which are cubic 3C-SiC, also referred to as  $\beta$ -SiC, the hexagonal 4H-SiC and 6H-SiC ( $\alpha$ -SiC), and the rhombohedral 15R-SiC structures. These polytypes are differentiated by the stacking sequence of the biatom layers of the SiC structure [3]. Although 4H-SiC and 6H-SiC are commercially available, 4H-SiC is preferred over 6H-SiC because it has a higher and more isotropic electron mobility compared to 6H-SiC [5].

# 1.2.1 SiC Crystal Growth

Most single crystal semiconductor boules are grown by crystal pulling or seeded solidification from a melt composed of Si or Ge, or from compound semiconductors, such as GaAs. However, it is impractical to manufacture industrial quantities of monocrystalline SiC using these methods because of the thermodynamic properties of SiC. The SiC phase diagram exhibits a peritectic reaction at 2830°C with a total pressure of ~10<sup>5</sup>Pa, calculations also indicate that the stoichiometric melting occurs only at pressures exceeding 10<sup>5</sup>atm and temperatures above 3200°C [8]. It is possible to create extreme growth conditions such as this for small diamond boules, but such conditions are currently not feasible for commercial production of large diameter semiconductor grade SiC [3].

Large diameter SiC crystal growth technology has evolved from the original SiC sublimation method first developed by Lely [9] and lately modified as a seeded sublimation technique, physical vapor transport (PVT) process by Tairov and Tsvetkov [10]. This latter method has been further refined for the production of large diameter SiC boules, and various modifications of these techniques are now used at many laboratories worldwide [3].

In order to reduce the cost of SiC devices and gain the advantages of Si and GaAs device infrastructures, a large amount of effort has been given to grow high quality, large diameter SiC substrate materials [3]. Recently, 3 inch 6H and 4H SiC substrates have been offered commercially by Cree, Inc., and 4 inch 6H and 4H SiC substrates are under development.

# 1.2.2 SiC Defects

Defects in SiC include: 1) open-core dislocations (called micropipes); 2) low-angle boundaries; and 3) conventional dislocations [3]. Micropipes have been the main factor preventing the commercialization of many types of SiC devices. Several mechanisms have been identified as causing micropipes, including the seed surface quality, the growth process stability and cleanliness, and the specific parameters controlling nucleation density and growth rate. Recent developments in fabrication techniques have decreased the density of micropipes to 0.9 pipes/cm<sup>2</sup>.

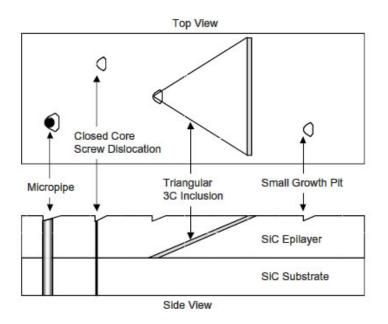

Low-angle boundaries near the crystal periphery caused by unoptimized process conditions are visible to the naked eye and sometimes extend through the entire thickness of the wafer. Recent efforts have result in substrates of up to 4 inch without low angle grain boundary defects [3]. Figure 1-1 shows these common SiC substrate defects [11].

Figure 1-1 Common SiC defects [11]

# 1.2.3 SiC Doping

Epitaxial growth is used to deposit high quality active device layers. Ion implantation is often utilized for doping profiles, but epitaxy is required to form the starting material. Implants directly into substrates have generally been of poor electrical quality [12]. However, implantation is used for selective area doping because dopant diffusion is not feasible due to the high temperatures required. Both n-type and p-type doping have been achieved for SiC during vapor phase epitaxy (VPE). Dopants for n-type SiC include N, P, As and B; Al and Ga can be p-type dopants, with Al being the most common. Undoped SiC is typically n-type because of residual nitrogen. Both the n-type and p-type doping density of 4H and 6H SiC can be adjusted between 10<sup>14</sup> and 10<sup>19</sup> cm<sup>-3</sup>.

# 1.2.4 SiC Etching, Dicing and Polishing

Wet etching of SiC is relatively difficult due to its high bonding energy which requires molten KOH at 450°C. Instead, reactive ion etching (RIE) has been found to be an effective dry etching method. For wafer slicing, a diamond abrasive cutting tool can be used. A diamond based polishing regime can be used for wafer polishing. However, it is often preferable to use an RIE treatment in order to remove residual subsurface damage, which is detrimental to the subsequent SiC epitaxial process [13]. Chemical mechanical polish (CMP) removes material at an even slower rate and is used for final processing after diamond slurry polishing. An RIE treatment followed by a CMP can significantly reduce subsurface damage [14].

#### 1.2.5 SiC Contacts

All semiconductor devices have contacts and all contacts exhibit contact resistance, thus it is important to characterize the contact resistance. Contacts are

generally metal-semiconductor contacts. The first widely accepted theory for metal-semiconductor contact was developed by Schottky in the late 1930's [15]. True ohmic contacts exhibit a straight line current-voltage characteristic with a low value of resistance. The contacts must be able to supply the necessary device current, but at the same time the voltage drop across the contact should be small compared to the voltage drops across the active device regions, and the contact should not inject minority carriers. For high temperature, high power devices, an ohmic contact should not degrade under extreme conditions.

One of the primary uses of Schottky contacts on SiC is in efficient, solid state, high-voltage switching applications [16]. Most of the elemental metal layers deposited on n-type SiC exhibit a Schottky contact with a high barrier height in the as-deposited condition. Pt, Au, Ag, Ni, Cr and Al sputtered on n-type SiC produce a rectifying contact [17], while Au, Al, Ag, Ti and Ni form a Schottky contact on p-type SiC. Barrier heights on p-type SiC tend to be higher than those on n-types [18].

Many metals form Schottky contacts in the as-deposited form, but a short-term (2 minutes), high-temperature (>900°C) anneal can convert the Schottky contact to ohmic. After high temperature annealing, metals that form some kind of silicide. Ni, Ni/Cr, Co and Ti are widely used for the fabrication of ohmic contacts. The lowest reported value of contact resistivity to n-type SiC was less than  $1x10^{-6} \ \Omega \cdot \text{cm}^2$  [19]. It is difficult to form ohmic contacts for a p-type substrate because of the large band gap and work function of SiC. Al/Ti contacts are commonly used for p-type ohmic contact, being deposited either subsequently or simultaneously [20-22]. Spieb et al. [21] fabricated Al/Ti ohmic contacts

for p-type 6H-SiC with specific contact resistance values ranging from  $5x10^{-6} \Omega \cdot \text{cm}^2$  to  $5x10^{-3} \Omega \cdot \text{cm}^2$ .

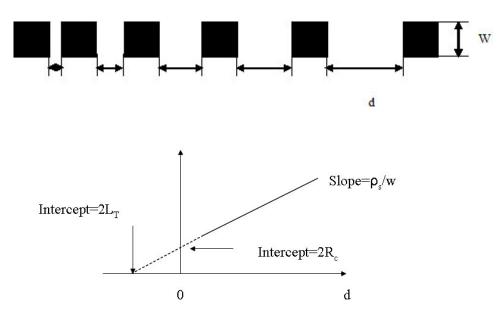

Contact resistance measurement techniques fall into four main categories: two-contact two-terminal, multiple-contact two-terminal, four-terminal and six-terminal methods. The transmission line method (TLM) is widely used to characterize ohmic contacts. A TLM test structure and a plot of total resistance as a function of contact spacing are shown in Figure 1-2 [22]:

Figure 1-2 Total resistance as a function of d

Total resistance between any two adjacent contacts is expressed by:

$$R_T = \frac{\rho_s \times d}{w} + 2R_c \tag{1.1}$$

- The slope  $\rho_s/w$  describes the sheet resistance

- The intercept at d=0 is  $R_T=2R_c$ , giving the contact resistance

The transmission line model thus gives a complete characterization of the contact by providing both the semiconductor sheet resistance and the specific contact resistance.

# 1.3 SiC High Temperature, High Power Devices

Most traditional silicon integrated circuit devices are not suitable for applications at temperatures above 250°C. At low operational temperatures, the intrinsic carriers are negligible compared to the doping concentration, but the number of intrinsic carriers exponentially increases with temperature, which results in unacceptably high junction reverse leakage currents [23]. Eventually the semiconductor device operation is overcome by uncontrolled leakage current. SiC devices, however, can operate above 350 °C because of their higher bandgap energy, which requires greater energy to excite the electron from the valence band into the conduction band. High temperature devices operating from 350°C-500°C are in great demand for aerospace applications, nuclear power instruments, satellites, space exploration, geothermal wells and sensors. Table 1-2 shows some typical high temperature applications and technologies [24].

A variety of SiC devices has been demonstrated, including p-n junction diodes, Schottky diodes, bipolar junction transistors (BJTs), insulated gate bipolar transistors (IGBTs), MESFET, JFET and thyristors. MOSFETs with lifetimes of >700 years at 2 MV/cm and 350°C have been reported [25]. SiC has the potential to replace Si diodes and Si insulated gate bipolar transistors (IGBTs) because the on-state and switching losses are drastically reduced in SiC [26]. A 4H-SiC Schottky barrier diode (1400V) with a forward current density of 700 A/cm² at 2V has been demonstrated, and packaged SITs have produced 57W of output power at 500MHz [27]. Additionally, heterojunction devices such as the heterojunction FET (HFET) and heterojunction bipolar transistor (HBT) have been proposed and fabricated [28]. SiC bipolar junction transistors typically have low current gain in the common emitter mode due to minority carrier recombination

in their npn structures [29]. Heavily doping the emitter does not produce any significant improvement of the current gain due to the effect of bandgap narrowing (BGN). However, heterojunction structures using wide bandgap emitters or III-V nitride semiconductors may be able to improve the current gain and high-frequency response [7].

Table 1-2 High temperature applications [24]

| High Temperature Applications                 | Peak<br>Ambient<br>Temp. (°C) | Chip Power                 | Current<br>Technology | Future<br>Technology |

|-----------------------------------------------|-------------------------------|----------------------------|-----------------------|----------------------|

| Automotive                                    |                               |                            |                       |                      |

| Engine control Electronic                     | 150                           | < 1kW                      | BS & SOI              | BS & SOI             |

| On-cylinder& Exhaust Pipe                     | 600                           | < 1kW                      | N/A                   | WBG                  |

| Electric Suspension & Brakes                  | 250                           | > 10kW                     | BS                    | WBG                  |

| Electric/Hybrid Vehicle PMAD                  | 150                           | > 10kW                     | BS                    | WBG                  |

| Turbine Engine<br>Sensors, Telemetry, Control | 300<br>600                    | < 1kW<br>< 1kW             | BS & SOI<br>N/A       | SOI &<br>WBG<br>WBG  |

| Electric Actuation                            | 150<br>600                    | > 10kW<br>> 10kW<br>> 10kW | BS & SOI<br>N/A       | WBG<br>WBG           |

| Spacecraft                                    |                               |                            |                       |                      |

| Power Management                              | 150                           | > 1kW                      | BS & SOI              | WBG                  |

|                                               | 300                           | > 10kW                     | N/A                   | WBG                  |

| Venus & Mercury Exploration                   | 550                           | ~ 1kW                      | N/A                   | WBG                  |

| Industrial                                    |                               |                            |                       |                      |

| High Temperature Processing                   | 300                           | < 1kW                      | SOI                   | SOI                  |

|                                               | 600                           | < 1kW                      | N/A                   | WBG                  |

| Deep-Well Drilling Telemetry                  |                               |                            |                       |                      |

| Oil and Gas<br>Geothermal                     | 300<br>600                    | < 1kW<br>< 1kW             | SOI<br>N/A            | SOI &<br>WBG<br>WBG  |

BS= bulk silicon, SOI= silicon on insulator, WBG= wide bandgap (semiconductor)

# 1.4 Electromigration

SiC power devices designed for use in harsh environments must take into account the electromigration phenomena. Electromigration is the movement of atoms in a metal film due to the momentum transfer from the electrons carrying the current. When a potential is applied along a conductor trace, two forces act on metal ions: one is due to the electric field along the trace, and the other is due to the electron "wind" effect. The two forces act in opposite directions, and the combined result is the metal ion being in the direction of the electron motion. Under high current density conditions, this metal-atom movement causes voids in some regions which can eventually result in open circuits and metal pileups or "hillocks" in other regions which can cause short circuits between closely spaced conductors [30]. Failure modes are typically characterized by a certain percentage increase in the line resistance, by a line becoming an open circuit, or by adjacent lines becoming short circuited. Line degradation is a slow process and under normal device operating conditions can take many years. Hence, measurements are made under accelerated conditions at higher than normal temperatures and/or current densities. Accelerated tests typically use temperatures above 200°C and current density above 10<sup>6</sup> A/cm<sup>2</sup> [22].

# 1.5 Packaging of SiC High Temperature, High Power Devices

SiC high temperature, high power devices are of little advantage if they can not be reliably packaged to form a complete system capable of operation under harsh environments. The major challenges for such packaging technologies are the mechanical, physical and electrical stability of the packaging materials and the interactions among these materials [31]. The key issues involved in packaging high temperature, high power

SiC devices include: material oxidation, decomposition and intermetallic compound (IMC) formation under high temperature conditions, along with heat generation and dissipation (cooling technology) and coefficient of thermal expansion (CTE) mismatches between different materials.

In order to function correctly in high temperature, high power applications, innovative packaging material and packaging design concepts are required. Additionally, high temperature passive components, such as resistors, inductors, capacitors and transformers, must also be developed for operation in hostile conditions before the full system-level benefits of high ambient temperature power electronics can be realized [31].

# 1.5.1 Substrate Materials for SiC Power Electronics

The substrate plays a key role in heat removal, in addition to the mechanical support it provides and its use in chip backside electrical connections. Commonly used substrate materials include beryllium oxide (BeO), silicon nitride (Si<sub>3</sub>N<sub>4</sub>), aluminum nitride (AlN) and aluminum oxide (Al<sub>2</sub>O<sub>3</sub>).

BeO has the highest thermal conductivity commercially available for high power hybrid applications. Although it provides the best performance for heat dissipation, the high cost and toxicity issues associated with beryllium have led to its replacement with alternate ceramic substrate materials [32]. One alternative substrate material that is being considered, Si<sub>3</sub>N<sub>4</sub>, has a reasonable thermal conductivity and a lower CTE and 2.4X the fracture toughness of AlN.

AlN offers another alternative to BeO without the toxicity concerns. AlN has excellent electrical properties (dielectric constant, loss tangent, resistivity, and dielectric strength), mechanical properties and a near perfect CTE match to SiC. The thermal

conductivity of AlN decreases with temperature, however it is still slightly better than that of BeO in the high temperature range [33]. The thermal conductivity of AlN is significantly influenced by its chemical purity and density, the key to producing a high thermal conductivity AlN substrate is to fabricate an extremely pure and very dense AlN ceramic material [34].

Al<sub>2</sub>O<sub>3</sub> based ceramics are popular as substrates because of their availability, low cost, good electrical properties and acceptable thermal conductivity. Al<sub>2</sub>O<sub>3</sub> compositions range from 90 to 99 weight percent purity, with the other constituents being SiO<sub>2</sub>, MgO and CaO. Typical substrate properties are presented in Table 1-3[35].

Table 1-3 High temperature substrate properties [35]

| Materials                    | Al <sub>2</sub> O <sub>3</sub> | Si <sub>3</sub> N <sub>4</sub> | AlN     | SiC     |

|------------------------------|--------------------------------|--------------------------------|---------|---------|

| Properties                   |                                |                                |         |         |

| Thermal conductivity(W/m•°C) | 20                             | 30-90                          | 170-230 | 490     |

| CTE (ppm/°C)                 | 6.7-7.1                        | 2.7                            | 4.5     | 4.2-4.8 |

| Young's modulus (GPa)        | 380                            | 310                            | 330     | 450     |

| Fracture toughness (MPa•m ½) | 3.3-3.7                        | 5-6.5                          | 2.7     | 4.6     |

| Flexural strength (MPa)      | 274                            | 850                            | 400     | 550     |

In order to carry a large current, thick copper metallization is required. Joining between metals and ceramics is difficult due to the dissimilar nature of the atomic bonding of the two materials. Direct bond copper (DBC), active metal brazing (AMB) and thin film/plated Cu have been developed to attach thick Cu to ceramic substrates.

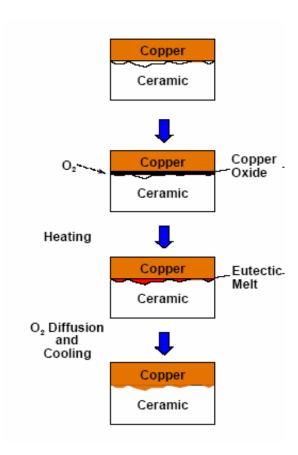

The basic development of DBC process was undertaken by General Electric 30 years ago, and steady research and development in DBC technology has made possible the mass production of 5.5" x 7.5" substrates using a highly automated process [36]. The

DBC process was initially developed on Al<sub>2</sub>O<sub>3</sub> substrates. The principle of the DBC technique relies on the phenomenon that oxygen decreases the melting temperature of pure Cu (1085°C), the eutectic Cu/O melts at 1065°C in 1.4 at% oxygen. The Cu foil is in close contact with the Al<sub>2</sub>O<sub>3</sub> and is heated to 1065°C to 1085°C, as illustrated in Figure 1-3 [37]. During this process, the Cu sheet forms a thin oxidation layer and a eutectic melt at the CuO and Al<sub>2</sub>O<sub>3</sub> interface, while the Cu sheet itself remains solid. After cooling to room temperature, an excellent CuO to Al<sub>2</sub>O<sub>3</sub> joint can be achieved due to the following spinell reaction: [37].

$$CuO + Al2O3 = CuAl2O4$$

(1-2)

Figure 1-3 DBC Al<sub>2</sub>O<sub>3</sub> process [37]

Direct Bond Copper (DBC) substrates have been used for power electronics for many years because of the following advantages:

- Low CTE in spite of the relatively thick copper cladding layer

- High current carrying capability due to copper's low resistivity

- High mechanical strength

- High heat dissipation capability

The excellent electrical conductivity and heat dissipation properties of DBC allow very high current flows; a 0.3mm DBC on 0.63mm thick Al<sub>2</sub>O<sub>3</sub> only shows an increase in temperature of 17°C with conventional cooling and 100 A continuous current. Due to the high temperature involved in fusing of Cu to Al<sub>2</sub>O<sub>3</sub>, the adhesion of Cu to Al<sub>2</sub>O<sub>3</sub> is very strong, and the strong joint between Cu and Al<sub>2</sub>O<sub>3</sub> significantly constrains the CTE of the Cu surface to 7.2 ppm/°c which is only slightly higher than that of Al<sub>2</sub>O<sub>3</sub> (6.8 ppm/°c) [37]. The DBC Al<sub>2</sub>O<sub>3</sub> thus has excellent reliability under thermal cycling conditions. Experiments have shown that DBC Al<sub>2</sub>O<sub>3</sub> can survive 1000 cycles from -55°C to +150°C test conditions [36].

Compared to a conventional metal package, DBC packages combine very high current carrying capability with only about 30% of the weight. Thus DBC substrates have become more and more important for aviation, military and space power electronic applications.

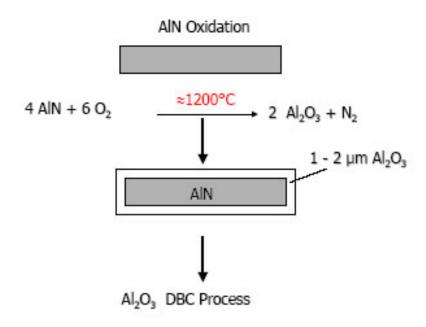

In order to increase the thermal properties of power modules, the DBC process has also been investigated on AlN substrates. An oxidation treatment of the AlN prior to the DBC process is needed to achieve good adhesion [38]. The process is illustrated in Figure 1-4 [37]. BeO substrate is also compatible with DBC process.

Figure 1-4 DBC AlN process [37]

The low surface tension of Si<sub>3</sub>N<sub>4</sub> makes it difficult for many molten metals to satisfy the wetting condition in order for reactions to take place at the ceramic interface. The active metal brazing (AMB) method brazes copper foil on Si<sub>3</sub>N<sub>4</sub> with a Cu-Ag eutectic alloy with the addition of about 8 wt% Ti. The high chemical reactivity of Ti with the Si<sub>3</sub>N<sub>4</sub> enhances the wetting and bonding characteristics [39]. Recently, Kyocera announced its AMB Si<sub>3</sub>N<sub>4</sub> substrate which achieved 5000 cycles of air-to-air temperature cycling from -60°C to 175°C without any failure [40]. The AMB Si<sub>3</sub>N<sub>4</sub> substrate is much stronger mechanically than conventional DBC Al<sub>2</sub>O<sub>3</sub> and DBC AlN substrates [40].

NiCr/Cu/Au thin film metallization has recently been studied [33] on AlN substrates, thick Cu layer can be achieved by subsequent electroplating of Cu to the required thickness. However, with a thick Cu layer, the AlN is prone to fracture during thermal cycling due to its low flexural strength and fracture toughness [2].

Copper metallized ceramic substrates ( $Si_3N_4$ , AlN and  $Al_2O_3$ ) can be supplied with a standard Ni/Au surface finish. Typically 200 $\mu$ inch of Ni is electrolessly plated or electrolytically plated over the copper foil. On top of the Ni layer, a thin layer of gold is immersing plated to a thickness of 5-20 $\mu$ inch to prevent Ni oxidation.

Electroless nickel (EN) plating is also known as chemical or autocatalytic nickel plating. In contrast to the traditional electrolytic (galvanic) technique, chemical nickel plating baths work without an external current source. The plating operation is based upon the catalytic reduction of nickel ions on the surface being plated. Electroless nickel has the following advantages [41]:

- The need for complicated trace routing is avoided

- The unique throwing power of the solution

- The coating grows uniformly over the exposed surface

There are three main types of electroless nickel coatings: nickel-phosphorus, nickel-boron and poly alloys. Nickel-phosphorus is generally used for engineering applications. In the most widely used electroless technique, nickel is deposited by the catalytic reduction of nickel ions with sodium hypophosphite in acid baths at a pH of 4.9 and at a temperature of 88°C. The deposit typically contains 3 to 13wt % phosphorus depending on the chemical composition of the solution and the operating conditions. The phosphorus content significantly influences the nickel's chemical and physical properties in both the as-plated and after heat treatment conditions. Based on the phosphorus composition, electroless Ni:P can be divided into three categories [41]:

1. Phosphorus content between 3 and 7 wt %. These coatings have excellent wear resistance.

- 2. Phosphorus content between 9 and 12 wt %. Corrosion protection and abrasion resistance are good enough for most applications. The plating bath works particularly economically.

- 3. Phosphorus content between 10 and 13 wt %. The coatings are very ductile and corrosion resistant. They have the highest performances for corrosion resistance against chlorides and simultaneous mechanical stress.

# 1.5.2 Die Attach

Die attach is another key issue for high temperature operations. The joint must survive the high temperature while maintaining good electrical conductivity if the chip backside requires electrical connection. In order to achieve good die bonding, three methods can be chosen: adhesive bonding, diffusion bonding and braze bonding.

Adhesive bonding is a material jointing process in which an adhesive is dispensed between two facing surfaces, and cured to produce an adhesive bond. Based on its conductivity properties, the die adhesive can be categorized into two types: conductive and non-conductive. An electrically conductive adhesive is made by loading metallic particles in a polymer matrix. Table 1-4 presents typical conductive adhesives' compositions and properties. Conductive adhesives are not suitable for use above 250°C [42].

Table 1-4 Adhesive properties [42]

| Basic     | Filling      | Configuration | Glass      | Volume               | Operating   | Curing      |

|-----------|--------------|---------------|------------|----------------------|-------------|-------------|

| resins    | materials    | of particles  | transition | resistivity          | temperature | conditions  |

|           |              |               | temp. (Tg) | (Ω•cm)               | range       |             |

| Epoxy     | Ag           | Flakes        | 90°C       | 6e10 <sup>-5</sup>   | -65~150°C   | 1h/130°C    |

| Epoxy     | Ag-plated Cu | Flakes        | N/A        | 4.5e10 <sup>-3</sup> | 20~160°C    | 30min/125°C |

| Epoxy     | Ni           | other         | N/A        | 1                    | -50~150°C   | 2h/65°C     |

| Polyimide | Ag           | Flakes        | 249°C      | 5e10 <sup>-4</sup>   | 20~250°C    | 1h/140°C    |

| Silicone  | Ag-plated Cu | Flakes/balls  | -55°C      | 1e10 <sup>-2</sup>   | -55~125°C   | 168h/25°C   |

| Silicone  | Ag           | Flakes        | N/A        | 6e10 <sup>-4</sup>   | -50~200°C   | 1h/150°C    |

Diffusion bonding is a method of joining metallic or non-metallic materials that relies only on interface solid state diffusion to create new metallurgical grains and bridge the gap, with no braze alloy or bonding agent required [43]. A seamless joint can be made by controlling the temperature, pressure, and time. Normally, a temperature of 50% - 70% of the melting point of the most fusible metal is used, and pressure is applied to aid in deformation of the interface and to remove any oxidation film. The bonding is usually done in a vacuum or in an inert gas environment.

Diffusion bonding has found applications in weapons industry, where the welding materials need to be isolated from the atmosphere, generally in a vacuum [44]. A technique has been developed where a thin film of silver (on the order of microns) is placed between the surfaces to be bonded. The temperature is raised to near silver's melting point to facilitate diffusion. The advantages of this process over traditional welding include the small amount of bonding material needed and it generate little particulate matter so it is a relatively clean process [44].

Braze bonding is a heating process in which two or more like or unlike materials are joined together by means of another metal alloy with a lower melting point. Usually the metal alloy has a eutectic composition. The term "eutectic" is from the Greek word eutektos, meaning "easily melted". To prevent oxidation, brazing is normally conducted in an inert gas or in a vacuum. Braze joints can be made exceptionally strong, sometimes stronger than the two metals being joined, and are able to withstand shock, vibration and normal temperature changes, providing good electrical conductivity and heat transfer between the die and the substrate.

Commonly used braze alloys include Au-Sn (80/20), Au-Ge (88/12), Au-Si (96.85/3.15) and Au-In (81/19) (composition in wt%) which have eutectic melting points of 280°C, 361°C, 363°C and 487°C, respectively. Au based brazes have good electrical conductivity, good thermal conductivity and good resistance to oxidation. Au based brazes can usually be bonded with good results in an inert (N<sub>2</sub>) environment. Table 1-5 presents a list of the properties of common brazes [45]:

Table 1-5 Brazes properties [45]

| Braze<br>Composition | Liquidus<br>°C | Density<br>(g/cc) | Electrical<br>Conductivity<br>(% of IACS) | Thermal<br>Conductivity<br>(W/m•K) | Thermal<br>Coefficient of<br>Expansion<br>(ppm/°C) (20°C) | Tensile<br>Strength<br>(psi) |

|----------------------|----------------|-------------------|-------------------------------------------|------------------------------------|-----------------------------------------------------------|------------------------------|

| 80Au, 20Sn           | 280            | 14.51             | 7.7                                       | 57                                 | 15.9                                                      | 40000                        |

| 88Au, 12Ge           | 361            | 14.67             | 11.4                                      | 44                                 | 13.4                                                      | 26900                        |

| 96.85Au, 3.15Si      | 363            | 15.7              | 46.4                                      | 27                                 | 12.3                                                      | 37000                        |

| 81Au, 19In           | 487            | 14.72             | 8.4                                       | 28                                 | 14.7                                                      | 33700                        |

To achieve good wetting, the braze thickness and footprint must be carefully chosen. The following are the rules of thumb for small dies being joined using Au based brazes [46]:

- Thickness =  $25 \sim 40 \mu m$

- Length = 90 percent of die length

- Width = 90 percent of die width

There are several methods that can be used to present the braze for bonding [46]:

Preforms: Preforms are pre-shaped brazes that are placed at the joint area before heating. This is the most common method because of its quick set-up time. Singulated preforms can be expensive to procure, but they enable flexible production because substrate designs and feed mechanisms do not need to be changed. Preforms are supplied in a variety of shapes and sizes, although they are difficult to handle at very small sizes.

Die backside metallization: Here, a metallization layer is applied to the back of the wafer as a part of the wafer fabrication process. The metallization layer can be plated, sputtered or evaporated.

Pre-deposition of braze on the substrate: In this process, the braze is electroplated on the bond pad when the substrate is produced. This is a cost-effective method, but deposits on individual substrates can be time-consuming.

Braze ribbon or automatic preform feeder: This is a cost-effective method to produce custom preforms using a ribbon spool feeder and a punch mechanism. The preforms are produced in a high-volume environment and the scrap braze ribbon is recycled. There is often a materials handling issue, however, as most preforms are only about 40µm thick, and ribbon less than 125µm thick is difficult to feed because the

material frequently folds over itself and jams the feeder (commonly referred to as "shingling") [46].

# 1.5.3 Wire Bonding

Wire bonding is an electrical interconnection technique using wire and a combination of heat, pressure, and/or ultrasonic energy. Wire bonding is a solid phase diffusion process. By bringing two metallic materials (usually Au and Al) into intimate contact, electron sharing or interdiffusion of atoms takes place, resulting in the formation of the wire bond. In the wire bonding process, the bonding force required leads to material deformation, breaking up the contamination layer and smoothing out surface asperity, which can be enhanced by the application of ultrasonic energy. Heat can accelerate atoms interdiffusion, and thus the bond formation [47]. There are three major types of wire bonding: thermocompression bonding, ultrasonic bonding, and thermosonic bonding, as shown in Table 1-6 [47].

Table 1-6 Wire bonding process comparision [47]

| Wirebonding       | Pressure | Temperature | Ultrasonic<br>energy | Wire   | Bonding pad metallization |

|-------------------|----------|-------------|----------------------|--------|---------------------------|

| Thermocompression | High     | 300-500°C   | No                   | Au     | Al, Au                    |

| Ultrasonic        | Low      | 25°C        | Yes                  | Au, Al | Al, Au                    |

| Thermosonic       | Low      | 100~240°C   | Yes                  | Au     | Al, Au                    |

There are two basic forms of wire bonds: ball bonds and wedge bonds. In ball bonding, a free air ball (FAB) is formed after the second bond, and the first bond is achieved by bonding the FAB to the pad. Consistent and symmetrical FAB is important to produce a consistent first bond. To achieve a consistent FAB size requires a consistent

tail length after the second bond formation and consistent electronic flaming off (EFO) firing. A certain amount of tail bond, which is formed by the inside chamfer of the capillary, is left to allow pulling of the wire out of the capillary after the second bond (stitch bond) formation in preparation for the next FAB formation [48].

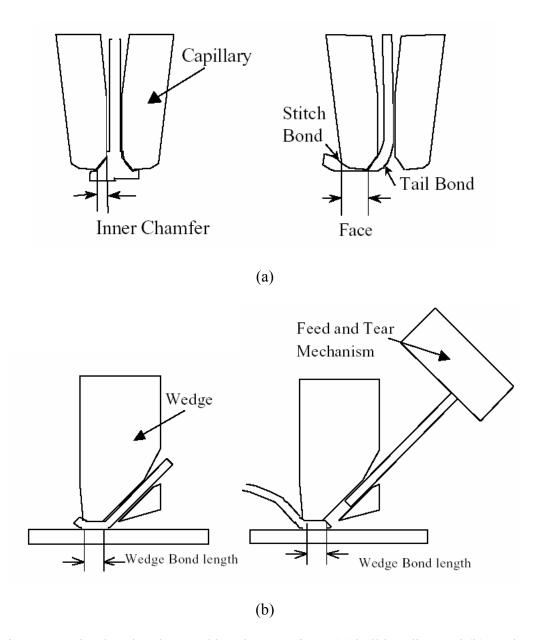

In wedge bonding, the wire is bonded directly to the pad by applying force and ultrasonic energy. The wire is broken by a cutter and the wire is then fed underneath the wedge. No tail bond is involved in wedge bonding. Figure 1-4 shows the first bond and second bond comparisons of ball bonding and wedge bonding [48].

Large diameter Al wire bonding is often used with silicon power devices. However at high temperatures, the mechanical strength of the Al decreases. Also, Al is incompatible with the Au wire bond pads used on SiC dies due to intermetallic formation and Kirkendall voiding at high temperature. In order to carry high current, large diameter wedge bonding with 250µm Au and Pt was developed for power packaging. Au wire provides higher conductivity than Pt, but Pt has a higher mechanical strength at high temperatures. Large Au wire has been successfully bonded to dies and to the Cu/Ni/Au substrate metallization [2].

Figure 1-5 First bond and second bond comparison, (a) ball bonding and (b) wedge bonding [48]

# 1.5.4 High Voltage Passivation

Devices operating at high power conditions may be exposed to high voltages, and as a result high voltage breakdown may occur between adjacent high voltage electrical connections and/or between high voltage electrical connections and the surrounding air.

An effective dielectric passivation coating must be applied to ensure reliable package

operation. Suitable candidates are preferred that can be applied by dispensing or spincoating, have a high dielectric breakdown voltage and high temperature stability. Polymers with easy processability, good mechanical properties, high thermal stability and high electrical breakdown voltage are usually chosen for electronic packaging applications.

Because of its long term thermal-oxidative stability in both nitrogen gas and in air, low moisture absorption, outstanding flame resistance and extreme high glass transition temperature (T<sub>g</sub>) of 510°C, phthalonitriles have shown promise as materials that can be potentially used for a variety of high temperature applications [49]. In order to lower the initial processing temperature to less than 150°C and to increase the processing window between the melting point of the phthalonitrile and its polymerization temperature, low melting phthalonitrile oligomers which have aromatic ether groups linking the phthalonitrile endcaps have been developed. A larger processing window means that a higher concentration of curing additive can be used to control the polymerization rate and the viscosity changes that accompany the phthalonitrile cure. Flexible ether linkages were chosen for incorporation into the polymeric backbone to increase processability without sacrificing the exceptional thermal, mechanical and flammability properties of phthalonitriles. With a decrease in the cross-link density of the polymer and an increased flexibility due to multiple aromatic ether linkages, the low melting phthalonitrile polymers show an improved toughness when compared to the standard phthalonitrile system. When used alone or blended with phthalonitrile, the enhanced toughness of the low melting phthalonitrile polymer may alleviate potential micro-cracking problems that

could arise from thermal-cycling in aerospace and other high temperature applications [49].

The thermal-oxidative stability of the phthalonitrile polymers has been evaluated in nitrogen gas and in air by TGA analysis. Oligomeric phthalonitrile and phthalonitrile exhibit similar thermal stability up to 500 °C [49].

Polyimides are high temperature engineering polymers with a transparent, amber color. When compared to most other organic or polymeric materials, polyimides exhibit an exceptional combination of thermal stability (>500°C), mechanical toughness, chemical resistance and excellent dielectric properties. Because of their high degree of ductility and inherently low CTE, polyimides can be readily implemented into a variety of microelectronic applications [50].

In the fabrication of microelectronic devices, polyimide coatings are typically spin applied to the substrate and then thermally cured into a smooth, rigid, intractable polymeric film or structural layer. For optimal adhesion to silicon, oxides and most metals, adhesion promoters are required. Some polyimides have built in adhesion promoters, while others require the application of a separate adhesion promoter or coupler prior to polyimide application. Adhesion promoters are also applied by spin coating. While spin coating assures the best uniformity and coating quality, other application techniques that have been used for applying polyimides include draw, spray, extrusion, roller, dip and drop coating [50].

Curing the polyimide film involves the removal of the solvent carrier or other volatiles from the layer and the imidization or hardening of the polymer into an intractable polyimide film. This curing process is typically done in steps. Hot plates are

commonly used for the initial bake after the polyimide has been applied. Post apply bakes can range from 50°C to 150°C on one or more in-line hot plates. A furnace or programmable oven is used for the final cure. Final curing is usually done between 280°C - 400°C, depending on the application [50].

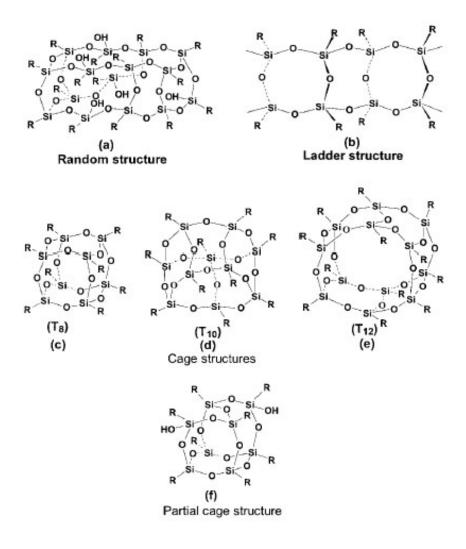

Polyhedral oligomeric silsesquioxanes (POSS) are a class of nanofillers for polymers. The term silsesquioxane refers to all structures with the empirical formula RSiO<sub>1.5</sub>, where R is hydrogen or any alkyl, alkylene, aryl, arylene, or organofunctional derivatives of alkyl, alkylene, aryl and arylene groups. The silsesquioxanes include random structures, ladder structures, cage structures and partial cage structures, as indicated in Figure 1-6 [51].

POSS compounds embody a truly hybrid (inorganic-organic) architecture, which contains an inner inorganic framework of  $(SiO_{1.5})_x$  that is externally covered by organic substituents. These substituents can be purely made up of hydrocarbon or may include a range of polar structures and functional groups, and making the POSS nanostructure compatible with polymer and biological systems [51].

Figure 1-6 POSS structures [51]

A variety of POSS nanostructured chemicals have been prepared which contain one or more covalently bonded reactive functionalities that are suitable for polymerization, grafting, surface bonding or other transformation. The incorporation of POSS derivatives into polymeric materials can lead to dramatic improvements in polymer properties, including increases in the glass transition temperature, oxidation resistance, and abrasion resistance, as well as reductions in flammability, heat evolution and viscosity during processing. The POSS nanocomposites show great promise for use in semiconductor processing, bio-medical development and space applications [51].

# 1.6 Research Objectives

The goal of the project is to develop the assembly materials and processes for packaging silicon carbide power electronics, which will be used under extreme environments. As a part of the project, the dissertation work includes a study of die attach materials and processes, the substrates, the polymer passivations and capacitors for high temperature applications.

In Chapter 1, the properties, processing and device technology of SiC have been reviewed and some key issues in packaging of power electronics discussed, including: substrates technology, die attach materials, high temperature braze bonding and high temperature, high voltage passivation coatings.

Chapter 2 present details of the die attach technology, which includes the selection of a suitable braze, SiC die metallization, substrate preparation and mechanical strength and metallurgy investigations of the braze joint during high temperature storage and thermal cycling.

The electrical breakdown property of several polymers that may be suitable for the high temperature passivation coating is reported in Chapter 3. The electrical breakdown mechanism is also discussed.

In Chapter 4, the dissipation factor and capacitance of ceramic capacitors during high temperature storage are discussed.

Chapter 5 concludes the dissertation by summarizing the results and findings, and suggesting topics for future work.

### **CHAPTER 2**

### DIE ATTCH FOR SILICON CARBIDE PACKAGE

### 2.1 Introduction

The challenges of packaging SiC power devices for high temperature applications include their high operating temperatures, wide thermal cycle ranges, high currents and high voltages. In addition to providing the electrical interfaces between the contact pads on the SiC device and other components, the packaging also provides electrical insulation, mechanical and environmental protection and a path for heat conduction and removal. In SiC power packages, consideration must also be given to current carrying capability and high voltage insulation. As a result, the selections of chip metallization, die attach, substrate and insulation dielectric are crucial to a successful package design.

### 2.2 Chip Metallization

An effective chip metallization should provide the following features:

- Good adhesion to the wafer passivation and the contact (Ohmic or Schottky)

- Low contact resistance

- An effective diffusion barrier

- A metal stack that is compatible with wire bonding and braze metallurgy

- High temperature reliability

Evaporation and sputtering are two of the most important physical vapor deposition (PVD) methods used for depositing thin metal films. Sputtering offers several

advantages over evaporation due to its better film adhesion and ability to deposit alloys. A sputtered three layer thin film stack composed of Ti/Ti-W/Au (1000 Å /2000 Å /2000 Å) was evaluated as the chip metallization in this project. Ti provides good adhesion to the device contacts (Ni<sub>2</sub>Si, an ohmic contact); Ti-90W functions as a diffusion barrier layer; and Au protects the underlying Ti-W from oxidation, as well as serving as a wire bondable and braze wettable surface.

### 2.3 Die Attach

#### 2.3.1 Introduction

Polymer die attach materials are limited to operating temperatures below about 250°C, while Au-Ge and Au-Si are not suitable die attachment materials for operating temperatures over 350°C. The use of thick film Au conductor material fired at 600°C as a die attach material has been demonstrated by Auburn researchers [52]. However, the firing is performed in air, and the SiC contact pad stacks were not compatible with such high temperatures (600°C) in air, the pads are not wire bondable after die attach. This process has been refined by researchers at NASA Glenn Research Center [53].

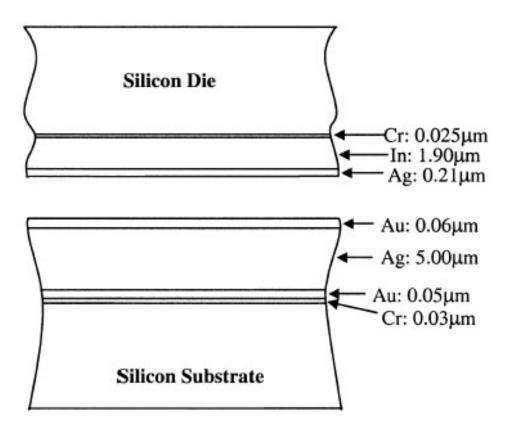

Chuang and Lee have recently demonstrated a low temperature die attach process using Ag and In [54]. The In layer initially melts at low temperature, and then diffuses into the Ag layer, forming an Ag-rich phase and intermetallic crystals. The process can be performed around 200°C by selecting the proper thickness ratio of Ag and In (Figure 2-1), and the resulting melting point after diffusion is over 600°C.

Figure 2-1 Metallization stack for Ag-In die attach [54]

While promising, there is significant concern over possible Ag migration under electrical bias at high temperatures. Auburn researchers have observed Ag migration between thick film Pd-Ag conductors during bias testing of thick film resistors at 300°C with a bias as low as 10Vdc [55].

The technique developed (transient liquid phase bonding) in this work uses a eutectic Au-Sn preform with thick Au (20 $\mu$ m) plating either on the substrate or on the chip. With high temperature brazing and annealing at 400°C, the Sn from the eutectic Au-Sn preform diffuses into the thick Au layer, lowering the Sn concentration to less than 10 wt% and raising the alloy melting point to over 400°C.

# 2.3.2 Au-Sn Eutectic Alloy

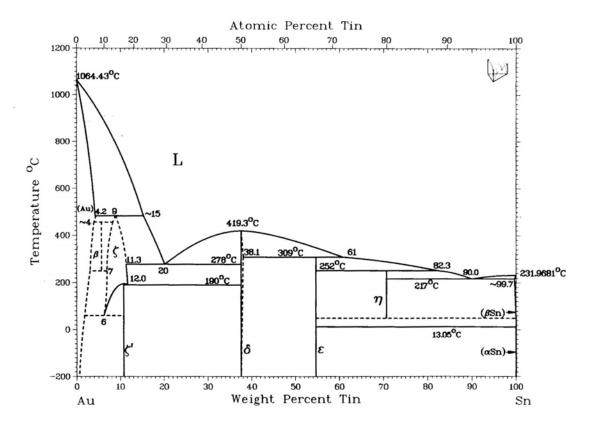

The Au-Sn phase diagram is presented in Figure 2-2 [57]. The equilibrium phases are briefly described as follows [57]-[58]:

- 1. The liquid phase L.

- 2. The fcc solid solution, Au, having a maximum solid solubility of about 4.2 wt% Sn at 498°C.

- 3. The  $\beta$  phase, which is composed of Au<sub>10</sub>Sn and is stable above 250°C.

- 4. The  $\zeta$  phase, which exists between 12 and 16 at% Sn at 225°C and extends from 11.07 to 16.31 at% Sn at 275°C, where the peritectic temperature of the L+ Au-  $\zeta$  is 498°C. The  $\zeta$   $\zeta$ ' + Sn eutectoid composition appears to consist of 18.5 at% Sn at 190°C. The L-  $\zeta$  + AuSn eutectic occurs at 278°C with 29.5 at% Sn. This is the most commonly used eutectic braze alloy, with Au 80 wt% and Sn 20 wt%.

- 5. The  $\zeta$ ' phase, which is stable at 17 at% Sn and below 160 °C.

- 6. The  $\delta$  phase, which is an AuSn intermetallic compound with a melting point of 419.3 °C. The homogeneity range is 50~50.5 at% Sn.

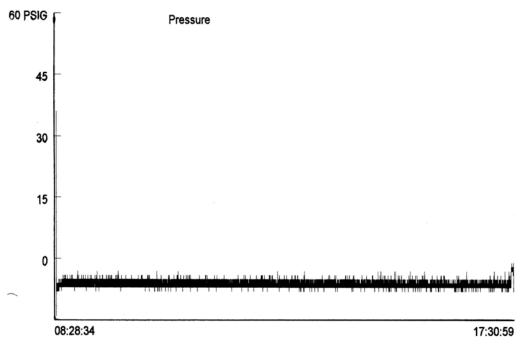

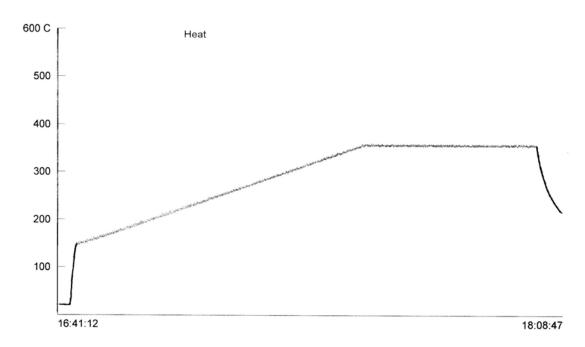

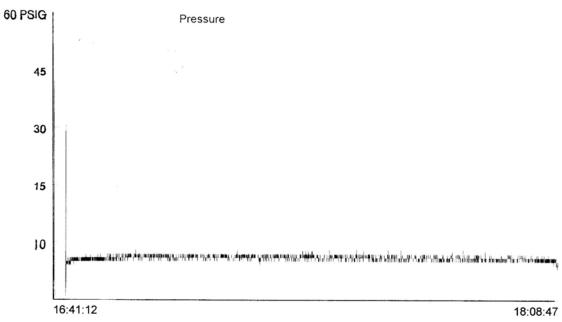

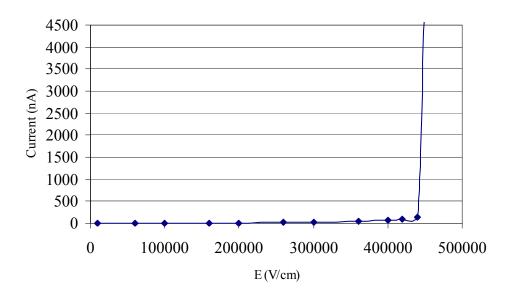

- 7. The ε phase, which is the orthorhombic intermetallic compound AuSn<sub>2</sub>; the peritectic L+ δ--- ε reacts at 309 °C, giving a composition of about 72 at% Sn. The homogeneity range of this phase is very narrow.