## BUILT-IN SELF-TEST CONFIGURATIONS FOR FIELD PROGRAMMABLE GATE ARRAY CORES IN SYSTEMS-ON-CHIP

| my own or was done in colla   |                          | work described in this thesis is ommittee. This thesis does not ormation. |

|-------------------------------|--------------------------|---------------------------------------------------------------------------|

|                               | Jonathan McKinley Harris |                                                                           |

|                               | Johannan Wekinley Harris |                                                                           |

|                               |                          |                                                                           |

|                               |                          |                                                                           |

|                               |                          |                                                                           |

| Certificate of Approval:      |                          |                                                                           |

|                               |                          |                                                                           |

|                               | _                        |                                                                           |

| Victor P. Nelson<br>Professor |                          | Charles E. Stroud, Chair<br>Professor                                     |

| Electrical and Computer       |                          | Electrical and Computer                                                   |

| Engineering                   |                          | Engineering                                                               |

|                               |                          |                                                                           |

| Adit D. Singh                 | _                        | Stephen L. McFarland                                                      |

Acting Dean Graduate School

Professor

Engineering

**Electrical And Computer**

#### BUILT-IN SELF-TEST CONFIGURATIONS FOR FIELD PROGRAMMABLE GATE

## ARRAY CORES IN SYSTEMS-ON-CHIP

Jonathan McKinley Harris

A Thesis

Submitted to

the Graduate Faculty of

**Auburn University**

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama December 17, 2004

# BUILT-IN SELF-TEST CONFIGURATIONS FOR FIELD PROGRAMMABLE GATE ${\sf ARRAY\ CORES\ IN\ SYSTEMS-ON-CHIP}$

## Jonathan McKinley Harris

|               | _    | • | ies of this thesis at its discretion, xpense. The author reserves all |

|---------------|------|---|-----------------------------------------------------------------------|

|               |      |   | Signature of Author                                                   |

|               |      |   | Date                                                                  |

| Copy sent to: |      |   |                                                                       |

|               | Name |   | Date                                                                  |

#### **VITA**

Jonathan McKinley Harris, son of Ralph and Cathy Harris, was born June 25, 1979, in Winston-Salem, NC. He graduated from Forbush High School with high honors in 1997. He graduated cum laude with a Bachelor of Science degree in Electrical Engineering at the University of North Carolina at Charlotte in May 2003. After completion of his undergraduate degree, he entered the graduate program in Electrical Engineering at Auburn University in August 2003. While in pursuit of his Master of Science degree at Auburn University, he worked under the advisement of Dr. Charles Stroud as a graduate research assistant in the Electrical and Computer Engineering department. On June 12, 2004, he married Melinda L. Beaver, daughter of Bobby and Wanda Beaver.

#### THESIS ABSTRACT

## BUILT-IN SELF-TEST CONFIGURATIONS FOR FIELD PROGRAMMABLE GATE ARRAY CORES IN SYSTEMS-ON-CHIP

Jonathan McKinley Harris Master of Science, December 17, 2004 (B.S.E.E, University of North Carolina at Charlotte, 2003)

#### 125 Typed Pages

#### Directed by Charles E. Stroud

Built-In Self-Test configurations for the logic and routing resources present in the Field Programmable Gate Array core of a System-on-Chip is presented in this Thesis. These configurations completely test the Programmable Logic Blocks and Programmable Routing Resources present in the Field Programmable Gate Array Core. A vendor-specific CAD tool, Atmel System Designer software suite, is used in conjunction with custom design automation tools to generate a complete set of logic and routing BIST configurations for any size Atmel AT94K series FPGA core as well as any size Atmel AT40K series FPGA.

#### **ACKNOWLEDGEMENTS**

The author would like to thank Dr. Charles Stroud for assistance with the development and application of the BIST configurations completed in the work for this thesis. The author would also like to thank master's committee members Dr. Victor Nelson and Dr. Adit Singh for their advice and contributions to this thesis. Many thanks are due to family members Ralph, Cathy, Gray, and Kristy for their continued support during the course of the completion of the work for this thesis. A special thanks is due to my wife, Melinda, who has given so much of herself and her time during the completion of this thesis. Above all, thanks to God for the strength and persistence to complete this thesis and the work involved therein.

IEEE (Institute of Electrical and Electronic Engineers) Format

Microsoft Word

## TABLE OF CONTENTS

| CHAPTER ONE                                                                      | 1   |

|----------------------------------------------------------------------------------|-----|

| 1.1 Systems on Chip (SoCs)                                                       | 3   |

| 1.2 Field Programmable Gate Arrays (FPGAs)                                       | 4   |

| 1.3 The Testing Problem                                                          |     |

| 1.4 Built-In Self-Test (BIST) Techniques                                         | 7   |

| 1.5 BIST for FPGAs                                                               |     |

| 1.6 Thesis Statement                                                             | 12  |

| CHAPTER TWO                                                                      | 15  |

| 2.1 Atmel AT94K Series FPSLIC                                                    | 15  |

| 2.2 Atmel AT40K Series FPGA                                                      | 17  |

| 2.2.1 PLB Architecture                                                           | 18  |

| 2.2.2 Programmable Interconnect Points (PIPs) in FPGAs                           | 20  |

| 2.2.3 Routing Architecture                                                       | 22  |

| 2.3 Overview of Testing Methods for FPGAs                                        | 27  |

| 2.4 Previous Work in BIST for FPGAs                                              | 28  |

| 2.4.1 Logic BIST                                                                 | 28  |

| 2.4.2 Routing BIST                                                               | 31  |

| 2.4.3 BIST for the ORCA FPGAs                                                    | 33  |

| 2.4.4 BIST for the Xilinx 4000 and Spartan Series FPGAs                          | 34  |

| 2.4.5 Previous Work In Logic BIST for the Atmel AT94K Series FPGA Core           | 36  |

| 2.5 ORCA, Xilinx, and Atmel FPGA Comparison                                      | 36  |

| 2.6 BIST Configuration Comparison                                                | 39  |

| 2.7 BIST Development                                                             |     |

| 2.7.1 Macro Generation Language (MGL)                                            | 42  |

| 2.8 Thesis Restatement                                                           |     |

| CHAPTER THREE                                                                    | 46  |

| 3.1 Architectural Implications on Logic BIST Architecture                        | 46  |

| 3.2 Modeling the PLB for Fault Simulations                                       | 54  |

| 3.2.1 MGL Generated BIST Configurations                                          | 55  |

| 3.2.2 Theoretical Best Case                                                      | 61  |

| 3.2.3 Manually Generated BUT Configurations with Bitstream Manipulation          | 63  |

| 3.3 MGL's Effects on Logic BIST Development and Application                      | 71  |

| 3.4 Comparison of Logic BIST for Atmel, ORCA, and Xilinx FPGAs                   | 72  |

| CHAPTER FOUR                                                                     | 74  |

| 4.1 Fault Models for FPGA Routing Resources                                      | 74  |

| 4.2 Modifications to Routing BIST Methodology                                    | 75  |

| 4.3 Overview of Routing BIST Configurations                                      |     |

| 4.4 BIST Configurations for Cross-Point PIPs                                     | 82  |

| 4.5 BIST Configurations for Repeaters                                            | 87  |

| 4.6 BIST Configurations for the Tri-Stated L Output and the X Direct Connections | 104 |

| 4.8 Summary of Routing BIST Configurations                                       |     |

| 4.9 MGL's Effect on Routing BIST Development and Application                     | 113 |

| 4.10 Comparison of the Routing BIST for Atmel, ORCA, and Xilinx FPGAs            | 115 |

| CHAPTER FIVE                                                                     |     |

| 5.1 Comparison of Work |     |

|------------------------|-----|

| 5.2 Future Work        | 121 |

| 5.3 Conclusion         | 122 |

| REFERENCES             |     |

## LIST OF TABLES AND FIGURES

| Figure 1.1 Example System on Chip (SoC) Architecture                     | 3  |

|--------------------------------------------------------------------------|----|

| Figure 1.2 Example FPGA Block Diagram                                    |    |

| Figure 1.3 Typical BIST Structure                                        |    |

| Figure 1.4 Basic Logic BIST Architecture for FPGAs                       |    |

| Figure 1.5 Test Sessions for logic BIST for FPGAs                        | 11 |

| Figure 1.6 Example Interconnect BIST Architecture for FPGAs              | 12 |

| Figure 2.1 Atmel AT94K Series FPSLIC Architecture                        |    |

| Table 2.1 Atmel FPGA and FPGA Core Sizes                                 | 17 |

| Figure 2.2 Atmel AT94K Series FPGA Core Architecture                     | 18 |

| Figure 2.3 Atmel AT40K Series PLB                                        |    |

| Figure 2.4 PIP Structures Typically Found in FPGAs                       | 20 |

| Figure 2.5 Local Interconnect Associated with the Atmel PLB              | 23 |

| Figure 2.6 PLB-to-PLB Adjacent Connections                               | 24 |

| Figure 2.7 PLB-to-Bus Connections                                        | 25 |

| Figure 2.8 Staggered Repeaters in Atmel Routing Architecture             | 26 |

| Figure 2.9 Logic BIST Architecture                                       | 29 |

| Figure 2.10 Basic ORA Structure in Logic BIST                            | 31 |

| Figure 2.11 Routing BIST Architecture                                    | 32 |

| Figure 2.12 Parity check-based Routing BIST                              | 32 |

| Table 2.2 Comparison of PLBs                                             | 37 |

| Table 2.3 Comparison of Routing Resources                                | 38 |

| Table 2.4 Percent Composition of PIPs in Routing Resources               | 39 |

| Table 2.5 BIST Configurations for ORCA and Xilinx FPGAs                  |    |

| Figure 3.1 Clock and Set/Reset Routing Structure in Atmel FPGA           | 47 |

| Figure 3.2 ORA Structure for Logic BIST                                  | 49 |

| Figure 3.3 BUT to ORA Connections During Logic BIST                      |    |

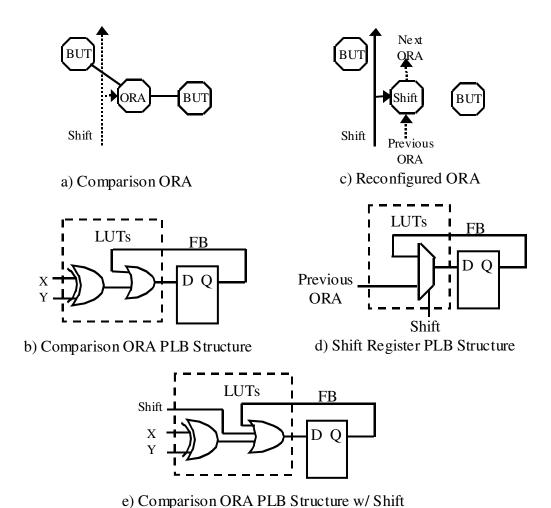

| Figure 3.4 Comparison ORA and Reconfigured ORA for Shift Register        | 52 |

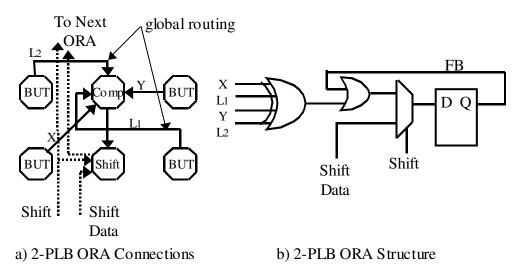

| Figure 3.5 2-PLB ORA with Shift Register                                 | 53 |

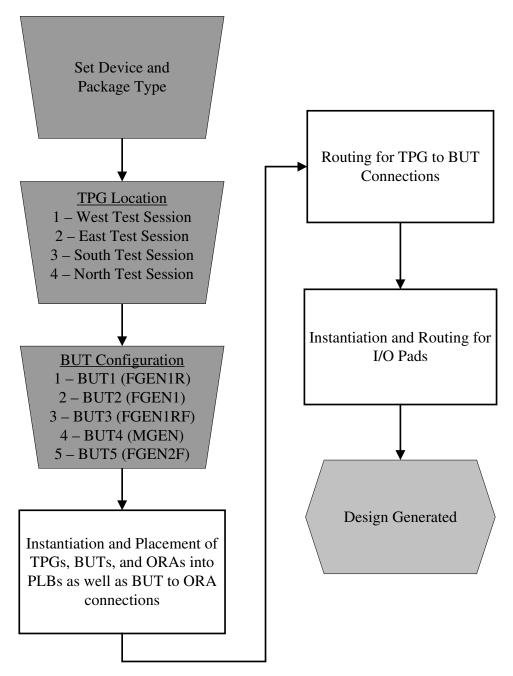

| Figure 3.6 Logic BIST MGL Program Flow Diagram                           |    |

| Table 3.1 Pin Numbers for I/O Cells for Logic BIST                       |    |

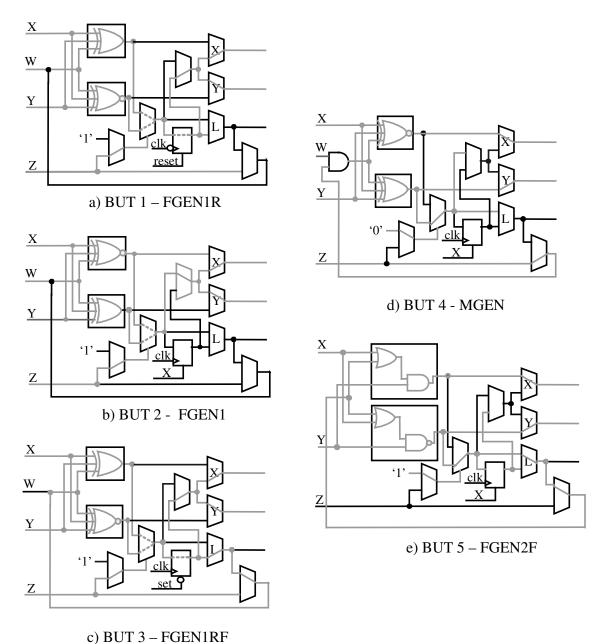

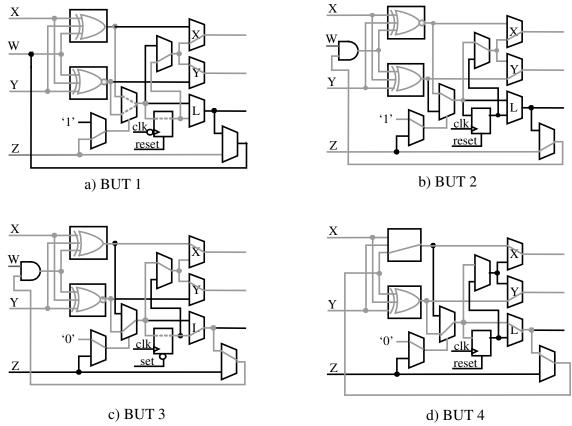

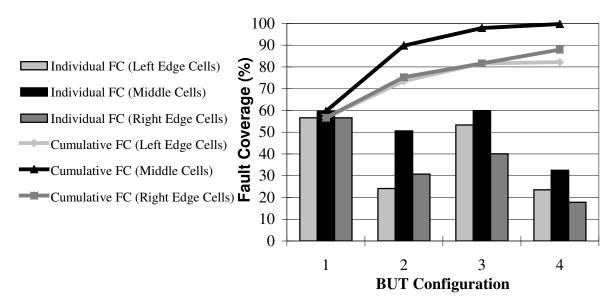

| Figure 3.7 MGL Generated BUT Configurations                              | 59 |

| Table 3.2 MGL Generated BUT Configurations                               | 60 |

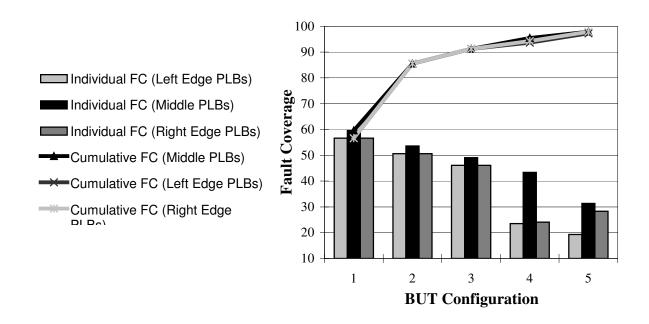

| Figure 3.8 Middle and Edge Fault Coverage (Five BUT Configurations)      |    |

| Figure 3.9 Theoretical Minimum Three BUT Configurations                  | 63 |

| Table 3.3 Manually Produced BUT Configurations                           |    |

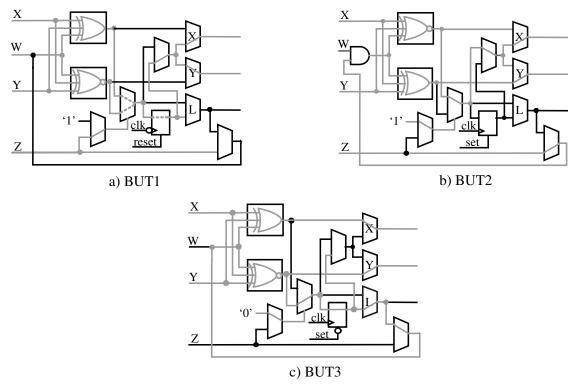

| Figure 3.10 Manually Generated Four BUT Configurations                   | 66 |

| Figure 3.11 Middle and Edge PLB Fault Coverage (Four BUT Configurations) | 67 |

| Figure 3.12 Column-Based to Row-Based Rotation for Logic BIST            | 68 |

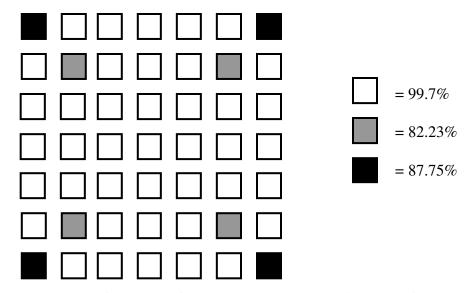

| Figure 3.13 Fault Coverage of PLBs Located in Four Corners of the Array  | 69 |

| Table 3.4 Total Fault Coverage for PLB and Local Interconnect            |    |

| Table 3.5 FPGA Logic BIST Configuration Comparison                       |    |

| Figure 4.1 Routing BIST Architecture                                     |    |

| Table 4.1 Test Pattern Sequences for Routing BIST                        |    |

| Figure 4.2 ORA Structure for Routing BIST                                | 79 |

| Table 4.2 Pin Numbers for I/O Cells for Routing BIST                       | 81  |

|----------------------------------------------------------------------------|-----|

| Figure 4.3 Global Routing Associated with the PLB                          | 83  |

| Figure 4.4 Cross-Point PIP Routing BIST Architecture                       |     |

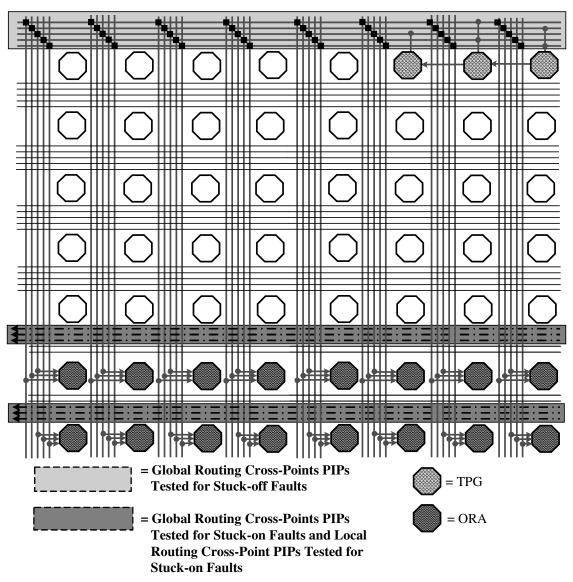

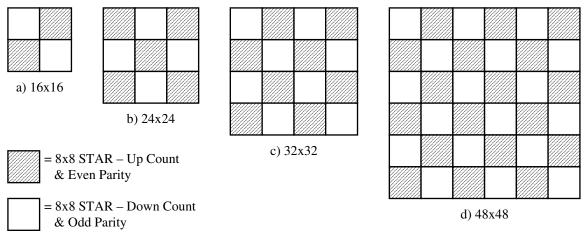

| Figure 4.5 Abus Cross-Point STAR Tiles for all FPGA Array Sizes            | 86  |

| Figure 4.6 Ebus Cross-Point STAR Tiles for all FPGA Array Sizes            | 87  |

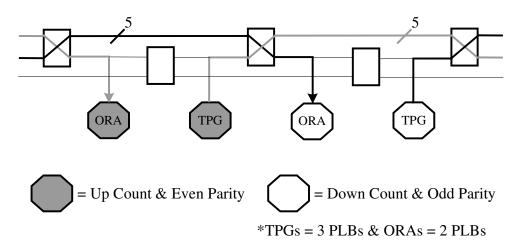

| Figure 4.7 Repeater Connections and Targeted Fault Types                   | 88  |

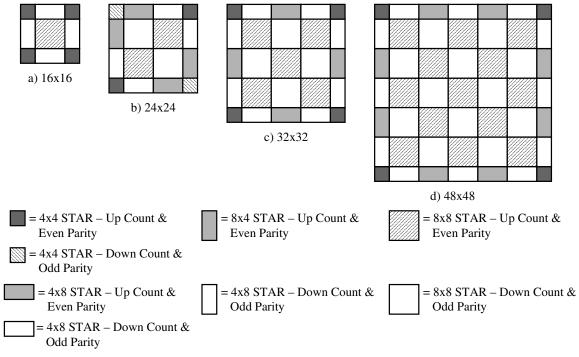

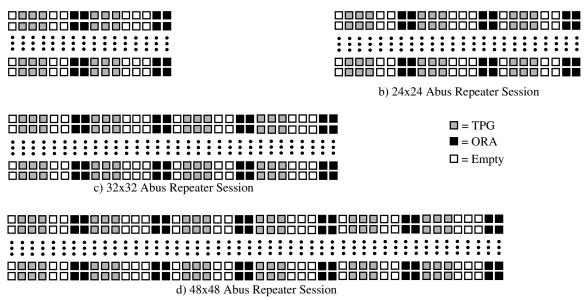

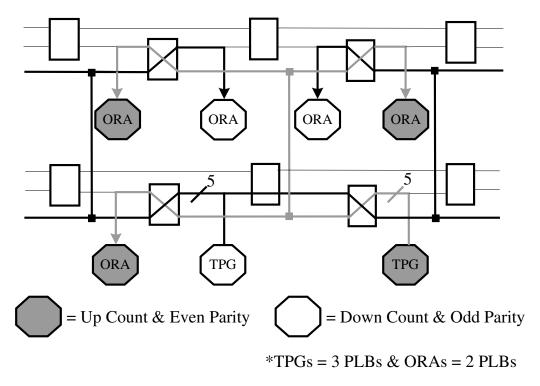

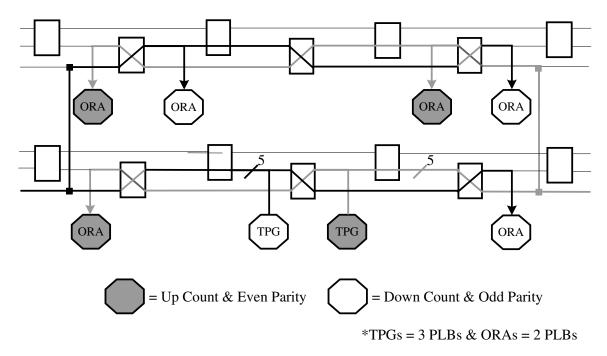

| Figure 4.8 Repeater Set 1 Configuration Architecture                       | 90  |

| Figure 4.9 Repeater Set 2 Configuration Architecture                       | 91  |

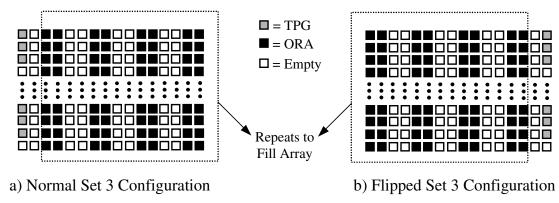

| Figure 4.10 Repeater Set 3 Configuration Architecture                      | 92  |

| Figure 4.11 Abus Repeater Set 1 Configuration Architecture                 | 93  |

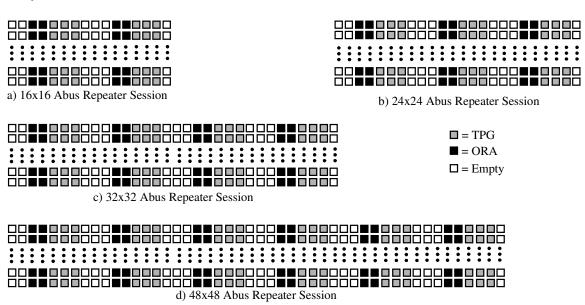

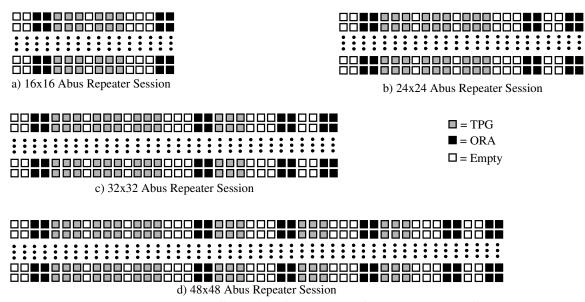

| Figure 4.12 Abus Set 1 Configurations for All Array Sizes                  | 94  |

| Figure 4.13 Flipped Abus Set 1 Configurations for All Array Sizes          | 95  |

| Figure 4.14 Ebus Repeater Set 1 Configuration Architecture                 | 96  |

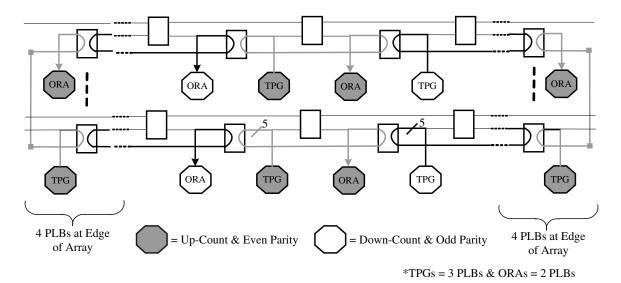

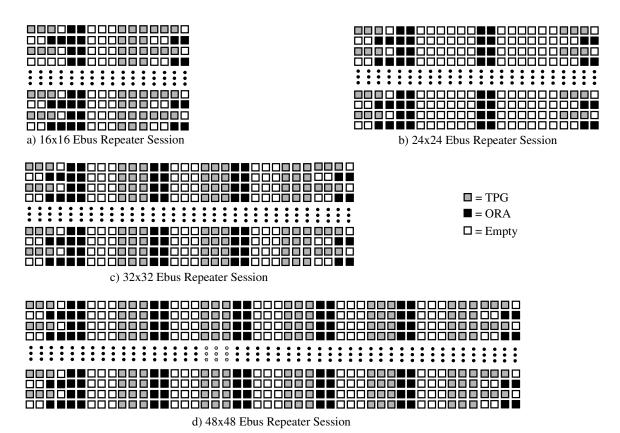

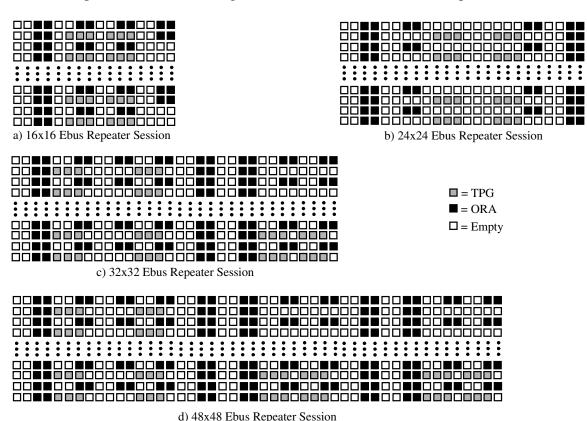

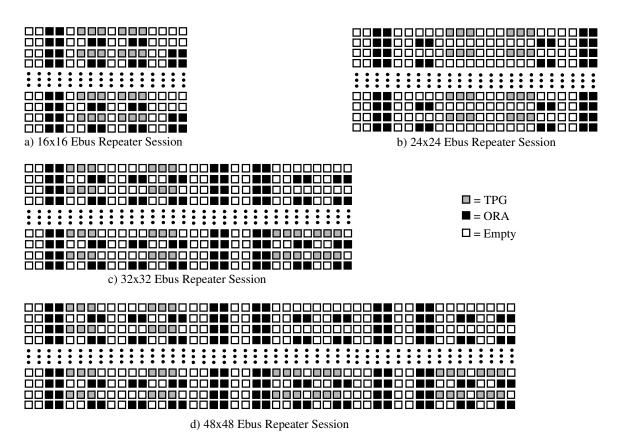

| Figure 4.15 Ebus Set 1 Configurations for Each Array Size                  | 97  |

| Figure 4.16 Flipped Ebus Set 1 Configurations for Each Array Size          | 98  |

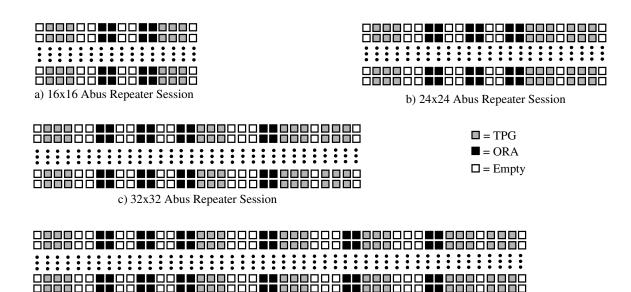

| Figure 4.17 Abus Repeater Set 2 Configuration Architecture                 | 99  |

| Figure 4.18 Abus Set 2 Configurations for Each Array Size                  | 99  |

| Figure 4.19 Flipped Abus Set 2 Configurations for Each Array Size          | 100 |

| Figure 4.20 Ebus Line Repeater Set 2 Configuration (16x16, 32x32, & 48x48) | 101 |

| Figure 4.21 Ebus Line Repeater Set 2 Configuration (24x24)                 | 101 |

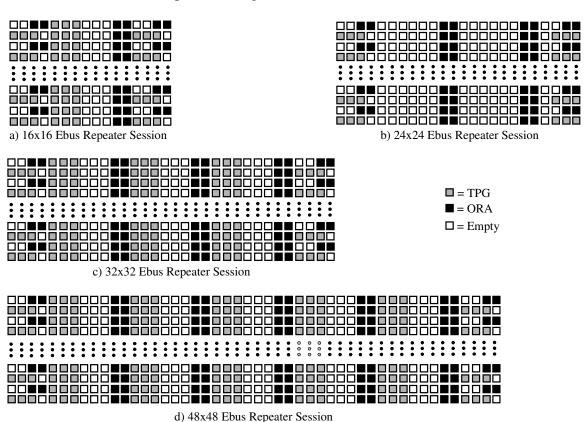

| Figure 4.22 Ebus Set 2 Configuration for Each Array Size                   | 102 |

| Figure 4.23 Flipped Ebus Set 2 Configuration for Each Array Size           | 103 |

| Figure 4.24 Abus and Ebus Set 3 Configuration for Each Array Size          | 104 |

| Figure 4.25 L Output Configuration Architecture                            | 105 |

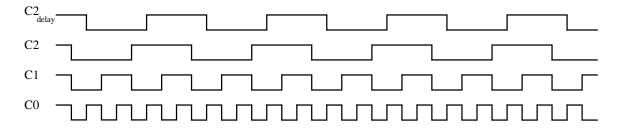

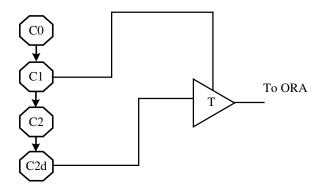

| Figure 4.26 L Output Configuration Structure and Timing Diagram            | 107 |

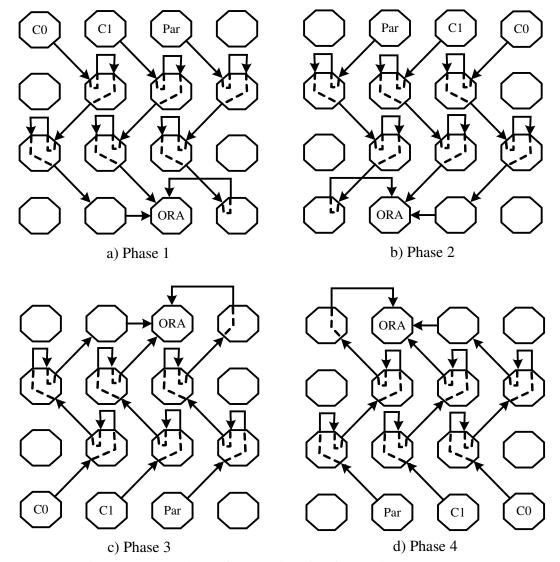

| Figure 4.27 X Direct Connection Configuration Test Phases                  |     |

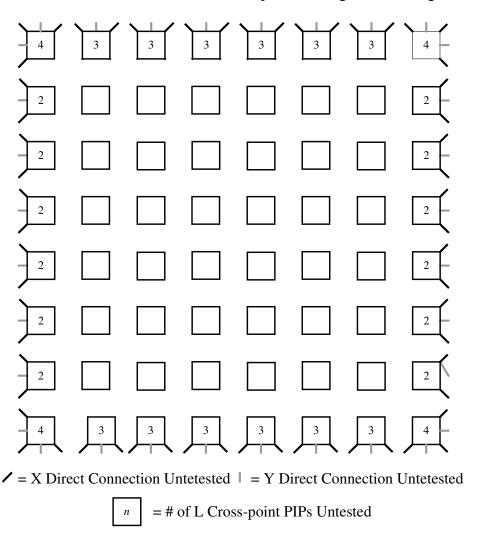

| Figure 4.28 Untested Direct Connections and L Output Cross-point PIPs      | 110 |

| Table 4.3 Summary of Routing BIST MGL and C Programs                       |     |

| Table 4.4 FPGA Routing BIST Comparison                                     | 116 |

## LIST OF ACRONYMS

| ASIC -   | Application Specific Integrated Circuit            |

|----------|----------------------------------------------------|

| AVR -    | Advanced Virtual RISC                              |

| BIST -   | Built-In Self-Test                                 |

| BUT -    | Block Under Test                                   |

| CAD -    | Computer Automated Design                          |

| CLB -    | Configurable Logic Block                           |

| CPU -    | Central Processing Unit                            |

| CUT -    | Circuit Under Test                                 |

| DCT -    | Discrete Cosine Transform                          |

| DSP -    | Digital Signal Processing                          |

| FIR -    | Finite Impulse Response                            |

| FFT -    | Fast Fourier Transform                             |

| FPGA -   | Field Programmable Gate Array                      |

| FPSLIC - | Field Programmable System Level Integrated Circuit |

| HDL -    | Hardware Description Language                      |

| IC -     | Integrated Circuit                                 |

|          |                                                    |

Integrated Development System

Input/Output

Intellectual Property

IDS -

I/O -

IP -

LUT - Look Up Table

MGL - Macro Generation Language

MUX - Multiplexer

NCD - NeoCAD Design Language

ORA - Output Response Analyzer

PAR - Place and Route

PCB - Printed Circuit Board

PIP - Programmable Interconnect Point

PLB - Programmable Logic Block

RISC - Reduced Instruction Set Computer

SoC - System-on-Chip

SRAM - Static Random Access Memory

STAR - Self Test ARea

TPG - Test Pattern Generator

VLSI - Very Large Scale Integration

WUT - Wire Under Test

XDL - Xilinx Design Language

#### **CHAPTER ONE**

#### **INTRODUCTION**

Meeting time to market demands and profitability requirements of digital electronics systems is increasingly important in the current economy [1]. In the past, systems have been designed at the board level, meaning a system may comprise many integrated circuits (ICs) interconnected on a printed circuit board (PCB). Currently, IC process technologies are allowing transistor sizes to pass under the 100 nanometer threshold, thus making the designs much more dense and allowing on the order of a hundred million transistors to be fabricated on a single IC [2], [3]. With the availability to comprise an entire system on a single IC, an increase in the overall device speed and reduction of device power can be achieved. This integration of a system down to the IC level is referred to as System-on-Chip (SoC). In addition to the aforementioned advantages, an SoC implementation significantly reduces the cost of the system. Therefore, SoCs have been gaining popularity in the electronic design industry due to the attractiveness of attaining a complete system level design in an IC.

Primarily, there are two types of SoC design implementations; Application Specific Integrated Circuit (ASIC) based SoCs and generic SoCs containing user-programmable logic. A typical ASIC-based SoC would incorporate standard cell and regular structure based components and, therefore, be limited to one particular application, having no programmability to make it adaptable. In contrast, a generic SoC

contains user-programmable logic allowing it to be easily reprogrammed to adapt to such changes as updated industry standards. ASIC-based SoCs have primarily dominated the drive into SoC design implementations; however, generic SoCs containing Field Programmable Gate Arrays (FPGAs) as the user-programmable logic have been increasing in popularity [2]. Generic SoC designs have many advantages over the ASIC-based SoC designs. These advantages include [4]:

- ☐ The SoC does not suffer from expensive redesigns and long time to market.

- □ The embedded FPGA may be used for different functions at different times.

- □ Due to the FPGA's massive parallelism, many algorithms (such as image or signal processing and cryptography) can be implemented.

- ☐ The same SoC can be used for multiple applications.

- □ The FPGA can be used to implement protocols and algorithms likely to change.

- □ The FPGA can support remote and internet based field upgrades.

These generic SoC designs are very attractive to designers as their reconfigurability provides low design cost, shorter time to market, and possibly increased testability [2], [1]. As a result of the advantages mentioned above, the incorporation of an FPGA is increasingly becoming the standard technique in the design of an SoC [2]. This thesis will focus on the testing of FPGA core logic and routing resources within a specific generic SoC; however, the overall approach is applicable to most SoCs with user-programmable logic.

### 1.1 Systems on Chip (SoCs)

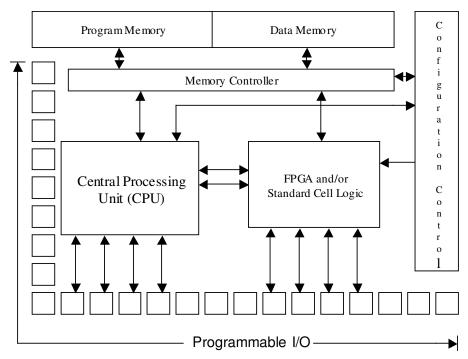

An example structure of an SoC includes user programmable or standard cell logic, memory (for data and program), Central Processing Units (CPUs), and possibly some analog circuitry [5]. SoCs are usually designed around Intellectual Property (IP) cores that generally fall into two categories, Hard IP cores and Soft IP cores. Hard IP cores are supplied as a predesigned physical layout of a particular circuit, whereas Soft IP cores are available in synthesizable modules described in a Hardware Description Language (HDL), such as VHDL or Verilog [5]. These Soft IP cores would be synthesized into standard cell logic or into an FPGA core and, having performed the physical layout based on the logic implementation, be incorporated into the SoC. Any combination of Hard and/or Soft IP cores may be used in the design of an SoC. An example structure comprised in an SoC is shown in Figure 1.1. This figure shows the components mentioned previously and illustrates their interconnections.

Figure 1.1 Example System on Chip (SoC) Architecture

The CPU allows complex algorithms to be implemented in software, which is almost a necessity in modern day digital systems. The CPU can either have a predefined set of operating conditions, or may be user-configurable to allow for more flexibility [5]. The user programmable logic, shown in Figure 1.1 as an FPGA, allows various hardware functions to be implemented using the programmability of the FPGA, to be discussed in the next section. Program and data memories exist to store the algorithms for execution by the CPU and to provide a place to store operands and data to be manipulated, respectively [5]. Also shown in the figure is a memory controller interface, which serves to control the interaction of the CPU and FPGA with the program and data memories. In addition to the memory controller, the configuration control can allow the FPGA to be programmed via the CPU or directly from the user.

#### 1.2 Field Programmable Gate Arrays (FPGAs)

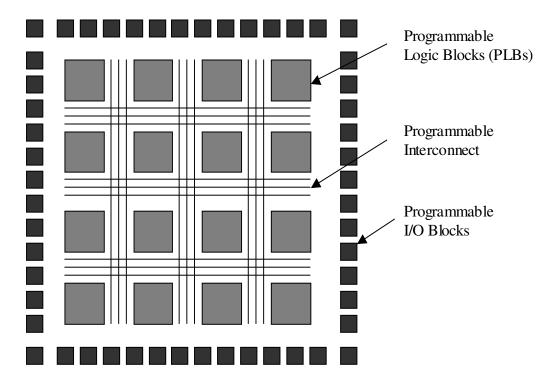

The FPGA portion of the SoC typically consists of four components, configurable logic blocks (CLBs) also known as programmable logic blocks (PLBs), programmable interconnect, programmable Input/Output (I/O) cells, and a configuration memory [6]. An example FPGA structure is shown in Figure 1.2. The PLBs serve as the user programmable logic and allows for the implementation of various digital logic functions. The PLBs are typically arranged in an *NxN* array and are connected via the programmable interconnect network to allow multiple logic functions to be performed. The programmable I/O cells can function as inputs or outputs, depending on the requirements of the design. The programming bits necessary to configure the CPU and/or the FPGA for the desired system function are stored in the configuration memory.

Figure 1.2 Example FPGA Block Diagram

Typically, a PLB will consist of two to eight k-input Look Up Tables (LUTs), one flip-flop per LUT, and various multiplexers and logic gates [7]. Each LUT can realize any combinational logic function of k inputs and each PLB can simultaneously execute m different k-input logic functions where m is the number of LUTs in the PLB. The flip-flop(s) give the user the flexibility of performing sequential logic functions as well as combinational logic functions. The multiplexers serve to set up the data paths in the PLB. These make the paths through which the appropriate input signals propagate through the PLB in order to implement the desired digital function.

The programmable interconnect consists of various wire segments controlled by programmable interconnect points (PIPs) to form connections between two or more PLBs and/or between the PLBs and the programmable I/O cells [6]. The routing resources used to make connections between adjacent PLBs are usually referred to as *local routing* and

those resources used to make connections between non-adjacent PLBs are typically referred to as *global routing*. The PIPs control the connections of the various wire segments to make or break these local or global connections between PLBs [6]. Data bits stored in the configuration memory are used to control the PIPs. The PIPs act similar to switches where the data bits from the configuration memory are used to turn the PIP on and off, thus making or breaking connections between the associated wire segments.

The configuration memory stores all the configuration bits for the PLBs, I/O cells, and the programmable interconnect network and is loaded via a configuration interface. The configuration memory is typically comprised of Static Random Access Memory (SRAM) cells that contain configuration bits for each of the LUTs, multiplexers, flip-flop reset/set, and various PIPs in the FPGA [6].

Due to the volatility of the SRAM-based configuration memory, the configuration bits must be loaded each time the device is powered on and, therefore, must be stored in an external memory device or loaded from a computer [6]. However, the advantage of using an SRAM-based memory is that it allows in-system reprogramming to change the system function whenever desired.

## 1.3 The Testing Problem

Testing combinational and sequential logic components is an intricate process and involves many interacting aspects [8]. The primary issues in testing include the cost of the test development, the quality of the generated test and the cost and time of applying the test [8]. Other factors influencing testing are the increasing number of transistors present in an IC, which can currently number in the millions. Over the past two to three

decades, the number of I/O pins on most very large scale integration (VLSI) devices has increased by an order of magnitude while the number of transistors contained in those VLSI devices has increased by about four orders of magnitude [7]. This has inherently reduced the accessibility and, therefore, the testability of the circuits within these VLSI devices [7]. In order to develop and evaluate the quality of a test for a device, a fault model is used to emulate the various types of faults that can be encountered in VLSI devices.

Typically, fault models that model gate, transistor, and other physical faults and defects are used to perform fault simulations to determine the ability of a given set of test patterns to detect faults within a circuit [7]. Testing is performed by using test patterns designed to test for the specific type of fault model and applying these patterns to the circuit under test (CUT). Once these test patterns have been applied to the CUT, the output responses are compared against responses of a fault-free circuit obtained from simulation. If all the output responses match, the CUT is assumed to be fault-free, however, in case of a mismatch, the CUT is determined to be faulty and is typically discarded.

## 1.4 Built-In Self-Test (BIST) Techniques

Built-In Self-Test (BIST) is a method of testing a given circuit wherein additional circuitry is added such that the circuit can test itself. BIST can be broken into two categories, on-line BIST and off-line BIST. When performing on-line BIST, the CUT is operating in its normal system mode of operation. During off-line BIST the CUT is placed in a test mode that is typically not a normal system mode of operation. The

advantage of off-line BIST is that it can be applied at the manufacturing, field, depot, and operational levels [7], [8]. The primary focus of this thesis will be off-line BIST.

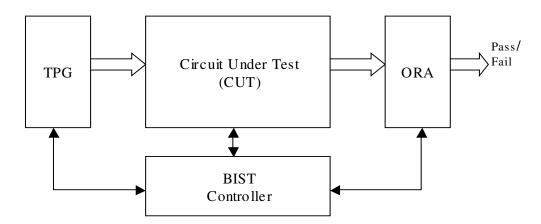

The particular form of off-line BIST that will be applied for the research involved in this thesis will be a form of off-line BIST where no additional circuitry outside the chip itself is required for testing, but existing flip-flops and registers within the CUT are manipulated and used for testing [7]. A typical BIST structure comprises a test controller, test pattern generator (TPG), circuit under test (CUT), and an output response analyzer (ORA) as illustrated in Figure 1.3 [9].

**Figure 1.3 Typical BIST Structure**

The TPG supplies test patterns to the CUT and the ORA analyzes the results to indicate a pass or fail condition for the CUT. Typically, the TPG generates exhaustive or pseudo-exhaustive test patterns and may be as simple as a binary *n*-bit counter or an *n*-bit linear feedback shift register (LFSR) with a primitive polynomial or as complex as an algorithmic test patter generator [7]. The ORA can be as simple as a comparator that compares known good responses with the actual responses of the CUT or can be as complex as a multiple input data compactor that may use signature analysis to indicate a fault occurrence [7]. If the TPG and ORA are separated from the CUT, they can be used

to test multiple CUTs concurrently. Using this approach imposes no performance penalties on the CUT other than additional set-up time when controlling the CUT to operate in its BIST mode of operation [7].

#### 1.5 BIST for FPGAs

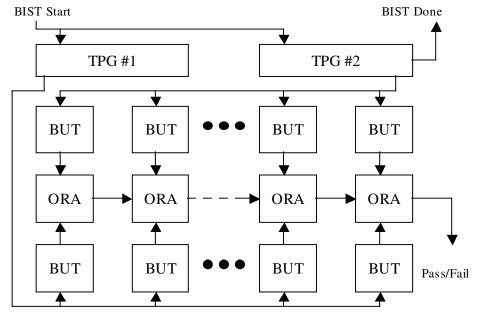

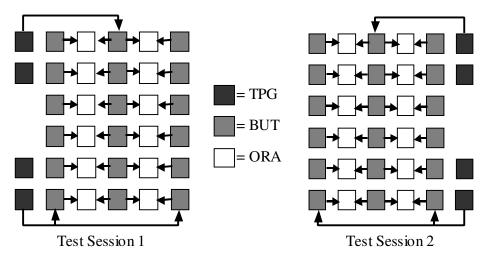

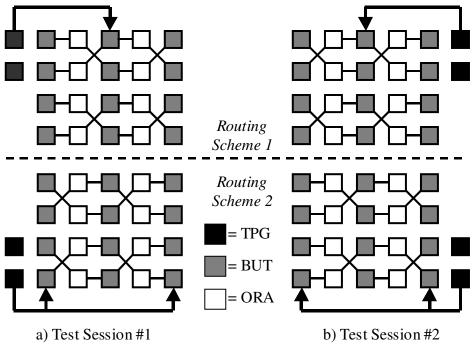

Typical BIST approaches for FPGAs involve taking the FPGA off-line, testing the device, and, if found fault-free, placing the FPGA back on-line within the system. This is possible since most current FPGAs use an SRAM-based configuration memory, which is inherently in-system reprogrammable. As a result, the FPGA is reconfigured to create a BIST structure, the device is tested, and is then reprogrammed for the system function before being returned to the system operation [7]. Due to the reconfigurability and multiple modes of operation and combinations of interconnection of an FPGA, many test configurations will be required to completely test an FPGA's programmable logic and routing resources. The basic idea in BIST for the programmable logic of an FPGA is to configure rows (or columns) of PLBs as TPGs and ORAs, and other rows (or columns) of PLBs as blocks under test (BUTs), as illustrated in Figure 1.4. [7]

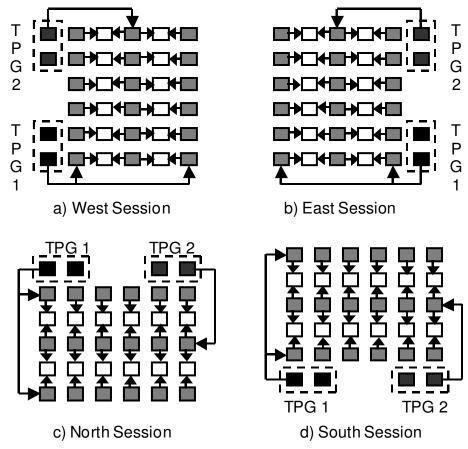

Figure 1.4 Basic Logic BIST Architecture for FPGAs [7]

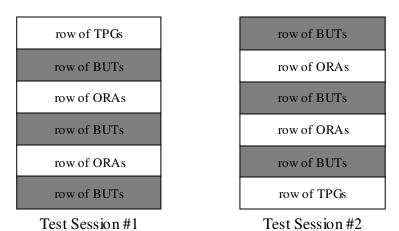

The BUTs are reconfigured several times such that they are tested in all their modes of operation. Each time the BUT is reconfigured to test a different PLB mode, it is referred to as a *test phase* [7]. A collection of test phases that completely test the BUTs in all their modes of operation is referred to as a *test session* [7]. Once the BUTs have been completely tested in all their modes of operation, the test session is repeated such that the PLBs that were previously TPGs and ORAs become BUTs, and vice versa as illustrated for a 6×N array of PLBs in Figure 1.5 [7]. As a result, the programmable logic resources in the FPGA can be tested in a minimum of two test sessions.

Figure 1.5 Test Sessions for logic BIST for FPGAs

Each test phase consists of the following steps: 1) the FPGA is reconfigured with a BIST configuration, 2) the BIST sequence is executed, which involves initialization, test pattern generation, and output response compaction, and 3) the BIST results are read from the ORAs [7]. In step 1, the test controller interacts with the FPGA to reconfigure the FPGA for testing. This is done when the controller retrieves the current BIST configuration from a storage device, such as a computer, and downloads this information to the configuration memory of the FPGA. The controller also initializes the TPGs, ORAs, and BUTs and provides a BIST Start signal to initiate the test in step 2. In step 3, the Pass/Fail results from the test phase are read from the ORAs in the FPGA to indicate the condition of the device. For this type of BIST, comparator-based ORAs are used because of the nature of the BIST architecture. Since the BUTs are receiving indentical inputs from two TPGs, their outputs should match and a fault condition can be determined simply by seeing a match or mismatch between the respective BUT outputs [7].

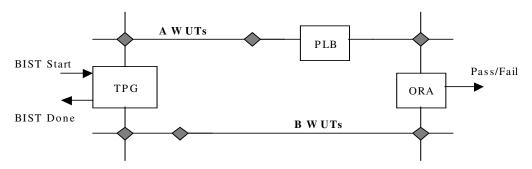

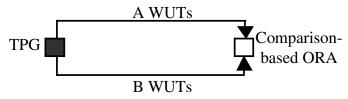

One approach in BIST for the programmable interconnect of an FPGA is to configure a subset of the routing resources (wire segments and PIPs) to form two groups

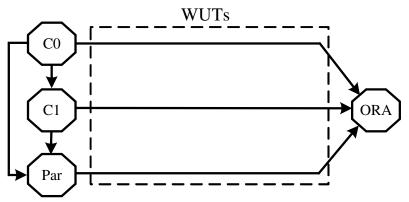

of wires under test (WUTs). The WUTs receive identical test patterns from a TPG and the values are compared at the other end of the WUTs by one or more comparison-based ORAs [7]. A set of WUTs may be composed of several wire segments connected by closed PIPs and may also include PLBs to check local routing to/from the PLBs. An example of this type of BIST architecture for programmable interconnect is shown in Figure 1.6 [7].

Figure 1.6 Example Interconnect BIST Architecture for FPGAs [7]

#### 1.6 Thesis Statement

The off-line BIST approach to testing FPGAs offers the advantage of no additional circuitry, thus no area overhead in the design of the chip as well as no performance penalty in the system mode of operation [7]. Theoretically, the same BIST approach can be implemented in the FPGA core of a generic SoC. Once the BIST has been performed on the FPGA and the FPGA determined fault-free, the FPGA core can then be used to test the other cores in the SoC [4].

When applied to FPGA core logic and routing resources in an SoC, the benefits of an off-line BIST approach can be fully utilized. Since the FPGA can be reprogrammed, it can be removed from system operation, reprogrammed for BIST, tested for faults, and if no failures, reprogrammed for system operation. If faults are detected, the system function can be reconfigured to avoid the faults present in the FPGA. A disadvantage of testing an FPGA core with this approach is the requirement of multiple test configurations. Since the PLBs and routing resources must be configured in many different modes of operation, complete testing requires multiple configurations of the device [7]. Despite the disadvantage of multiple test configurations, the use of BIST for testing FPGA core logic provides the most benefits for complete testing of any test methods to date.

The research to be presented in this thesis is based upon a previously proposed SoC BIST methodology [4] and previous work completed in BIST for FPGA logic and routing resources, in [10] and [11] respectively. The work to be presented is a continuation of these two previous BIST approaches in relation to testing FPGA core logic and routing resources that are a part of a generic SoC. The BIST approach is developed for and applied to a commercially available SoC, specifically the Atmel AT94K series Field Programmable System Level Integrated Circuit (FPSLIC).

The remaining chapters of this thesis are structured in the following manner: Chapter 2 presents a detailed overview of the Atmel AT94K FPSLIC FPGA core architecture as well as a review of previous work completed in BIST for other FPGAs. Chapter 3 presents the BIST approach used in the testing of the FPGA core logic resources and the results obtained with the Atmel AT94K Series SoC. Chapter 4 presents the BIST approach used for the routing resources in the Atmel AT94K Series FPSLIC FPGA core and the obtained results. Chapters 3 and 4 also give an overview of the testing obstacles encountered with the Atmel FPSLIC and the methods used to overcome

these obstacles and how they can be applied to testing other SoCs. Chapter 5 provides a summary of the work completed as well as suggestions for future work in testing FPGA core logic and routing resources in SoCs.

#### **CHAPTER TWO**

#### **BACKGROUND INFORMATION**

Presented within this chapter is an overview of the AT94K series Field Programmable System Level Integrated Circuit (FPSLIC) architecture (a generic SoC) and the FPGA architecture incorporated in the Atmel AT40K series FPGAs and the FPGA core of the FPSLIC. A review of prior work completed in the testing of FPGAs as well as work in BIST for FPGAs is presented. In addition, a comparison of the FPGA architectures in the prior BIST work to that of the Atmel FPGA is also presented. The development process of the previous applications of BIST for FPGAs will be discussed and background material for the proposed development process of BIST for application to the Atmel FPGA will be presented.

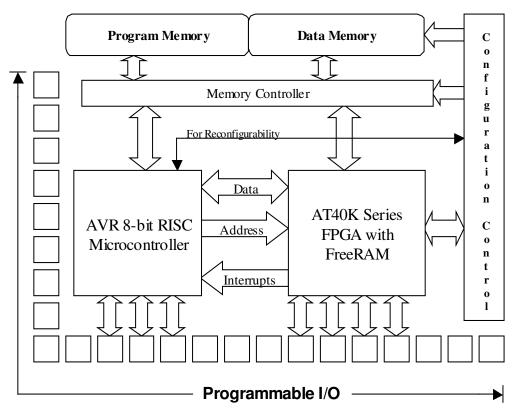

#### 2.1 Atmel AT94K Series FPSLIC

The Atmel AT94K series FPSLIC incorporates an FPGA core utilized in the AT40K series FPGAs along with an AVR (Advanced Virtual RISC) 8-bit Reduced Instruction Set Computer (RISC) microcontroller unit, a configuration controller, a memory controller, and program and data memories [14]. The combination of the AVR and configuration controller allows for in-system reprogramming of the desired operation of the device by downloading a configuration in to the FPGA core or by utilizing the AVR to dynamically reprogram the FPGA core of the device [14]. Figure 2.1 illustrates

the interconnections in the FPSLIC device between the FPGA and the AVR with the memory and configuration controller components.

Figure 2.1 Atmel AT94K Series FPSLIC Architecture [14]

The AVR 8-bit RISC Microcontroller supports over 120 instructions, of which most execute within a single clock cycle [14]. The microcontroller architecture is optimized for C code, but may be programmed in assembly language as well [14]. For storage, up to 36 Kbytes of memory can be partitioned for up to 16 Kbytes x 16-bit program memory and up to 16 Kbytes x 8-bit data memory [14]. Between the AVR and the FPGA there are 16 address lines (8 lines for the AT94K05) decoded from 4 bits in the AVR memory map and an 8-bit bi-directional data bus to allow for accessibility from the AVR core of the device to the FPGA core [14]. In addition, 16 internal interrupt lines are supplied from the FPGA to the AVR and up to four external interrupts are available

through user I/O [14]. The FPGA core of the FPSLIC can be one of four sizes of the AT40K series FPGA, ranging in usable gate count from 5,000 to 40,000 gates [14], [15]. These four sizes are summarized in Table 2.1, which details the AT40K FPGA and the associated AT94K FPGA core sizes in terms of the number of PLBs. The primary focus of the FPSLIC architecture will be on the FPGA portion of the device since this portion of the device is the focal point of the research and development work described in this thesis.

**Table 2.1 Atmel FPGA and FPGA Core Sizes**

| FPGA    | FPSLIC                  | Number of PLBs NxN |

|---------|-------------------------|--------------------|

| AT40K05 | AT94K05                 | 16x16              |

| AT40K10 | AT94K10                 | 24x24              |

| AT40K20 | Not Currently Available | 32x32              |

| AT40K40 | AT94K40                 | 48x48              |

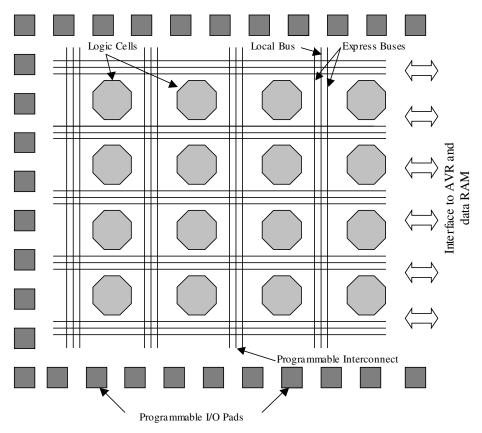

#### 2.2 Atmel AT40K Series FPGA

The AT40K FPGA is designed for rapid implementation of high-performance, large gate count designs through the use of synthesis- and schematic-based tools either on a PC or Sun platform [15]. Designs can be implemented in the AT40K series FPGA through common design software such as Synplicity, ModelSim, Exemplar, and Viewlogic since the Atmel design tools are devised to integrate with these and other industry standard design software [15]. The FPGA can be used to implement arithmetic-intensive functions, which include applications for high-speed Digital Signal Processing (DSP) functions. Examples of such DSP functions include Finite Input Response (FIR) filters, Fast Fourier Transforms (FFT), convolvers, interpolators, and Discrete Cosine Transforms (DCT) [15].

The basic AT94K series FPGA core architecture is illustrated in Figure 2.2. The device consists of an array of PLBs, two planes of programmable interconnect (vertical and horizontal) and programmable I/O pads. The PLBs are arranged in an  $N\times N$  array where N is given in Table 2.1.

Figure 2.2 Atmel AT94K Series FPGA Core Architecture [15]

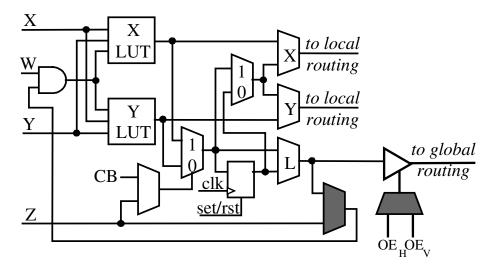

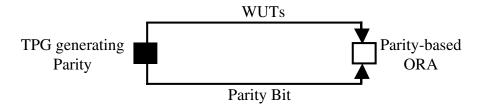

#### 2.2.1 PLB Architecture

The logic within the PLB is shown in Figure 2.3 and, as can be seen, various combinations of functions can be implemented within the PLB. Configuration bits stored in the configuration memory of the device determine the logic function performed by the PLB. Any n-input logic function, where  $1 \le n \le 4$ , can be realized within the PLB utilizing the two 3-input LUTs simultaneously. If  $n \le 3$ , up to two logic functions can be

obtained using one LUT for each function, since each LUT contains eight bits [15]. The logic function(s) implemented can be either sequential or combinational, by using or not using the D flip-flop, respectively [15]. A logic function with feedback may also be realized within the PLB and can be either sequential or combinational [15]. The AND gate present on the W input is important for logic functions implementing arrays of multipliers [15]. The multiplexers shown in gray produce a default logic value of '1' when no input is selected; otherwise, they behave similar to non-decoded multiplexers where a control bit is associated with each input to the multiplexer [7]. The multiplexer with CB (configuration bit) shown as an input has a configuration bit from the configuration memory driving one of its inputs. The remaining multiplexers shown behave as decoded multiplexers with a single configuration bit selecting one of the mulitplexer's two inputs. In addition to the various types of logic functions available, the PLB output L can be optionally tri-stated for bi-directional bus implementations when the PLB output needs to be in a high impedance state [15]. The X, W, Y, and Z inputs are selected from multiplexers that are a part of the local routing resources, which are discussed in more detail in the next section. In addition to X, W, Y, and Z inputs there is a clock and a set/reset input to the flip-flop and a horizontal and vertical output enable to the tri-state buffer of each PLB for a total of eight inputs. The outputs of the PLB include the X and Y outputs to adjacent PLBs and the L output which connects to the global routing resources for a total of three outputs.

Figure 2.3 Atmel AT40K Series PLB [15]

### 2.2.2 Programmable Interconnect Points (PIPs) in FPGAs

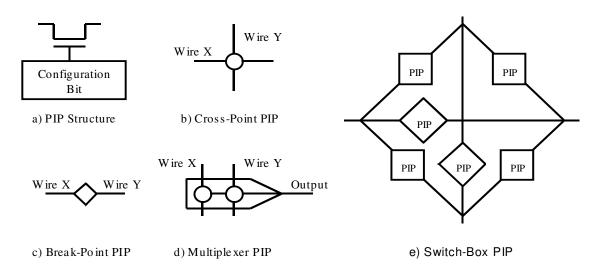

In order to understand the routing architecture present in an FPGA, it is important to understand the types of PIPs and wire segments commonly found in FPGAs. The basic structure of a PIP is shown in Figure 2.4a, where a pass transistor (transmission gate) is turned on/off by the logic value of a configuration memory bit. A connection can be made or broken by setting the configuration bit to the desired logic value.

Figure 2.4 PIP Structures Typically Found in FPGAs [7]

The general types of PIPs found in FPGAs fall into four categories, cross-point PIPs, break-point PIPs, multiplexer PIPs, and switch-box PIPs [7]. The cross-point PIPs (Figure 2.4b) connect wire segments perpendicular to one another; for example, a vertical wire segment and horizontal wire segment are connected. A break-point PIP (Figure 2.4c) connects or disconnects wire segments within the same plane, such as a verticalvertical connection or a horizontal-horizontal connection [7]. The multiplexer PIP (Figure 2.4d) can either be decoded or non-decoded and selects one of multiple input wire segments to make a connection to an output wire segment [7]. Non-decoded multiplexer PIPs are controlled by k configuration bits, where k is the number of input wire segments to the PIP [7], such that there exists one bit per wire segment and that bit controls the connection for its respective wire segment. The decoded multiplexer PIP has  $2^k$  input wire segments and is controlled by k configuration bits [7]. For the decoded multiplexer, the binary code formed by the configuration bits controls the connection between a given input and the output wire segments as in a basic multiplexer. The last type of PIP, the switch-box PIP (Figure 2.4e), also referred to as a compound cross-point PIP, is usually made of an array of pass transistors making connections in various directions between different wire segments [7].

Typically, the types of PIPs and wire segments found in an FPGA can be separated into global and local routing resources. The multiplexer PIPs are typically found in the local routing resources while the cross-point, break-point, and switch-box PIPs are usually found in the global routing resources. The local routing resources are those associated with a given PLB and its adjacent PLBs. The PLB inputs and outputs enter and exit through the local routing resources and can make connections either to

adjacent PLBs or to other PLBs or I/O cells through the global routing resources. Global routing resources allow connections to be made between PLBs that are typically at distances of more than one PLB apart in the array. These resources can also be used to route long distances from PLBs to I/O cells. The global routing resources commonly comprise longer wire segments and their associated PIPs. The wire segments present in the global routing resources span differing lengths of the FPGA array and connections can be made between these wire segments by the various types of PIPs that are present within the global routing network.

The wire segments in the programmable interconnect in the FPGA have various lengths which are typically associated with the number of PLBs that a given wire segment spans. These include short to medium length wire segments denoted as xI lines, x2 lines, x4 lines, and x8 lines which span one, two, four, and eight PLBs, respectively. Longer wire segments may span a quarter (xQ lines), one half (xH lines), or the full length (xL lines) of the FPGA array.

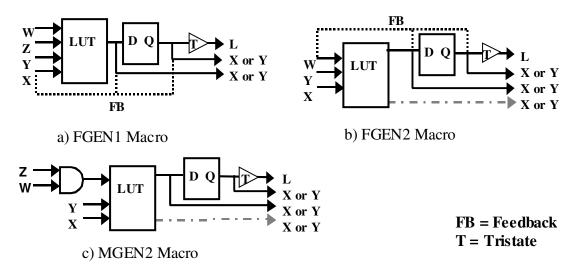

#### 2.2.3 Routing Architecture

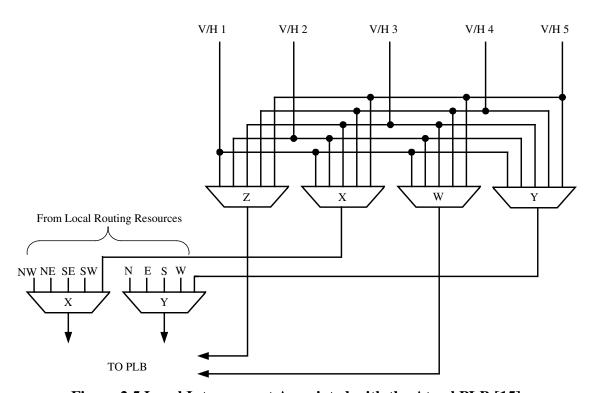

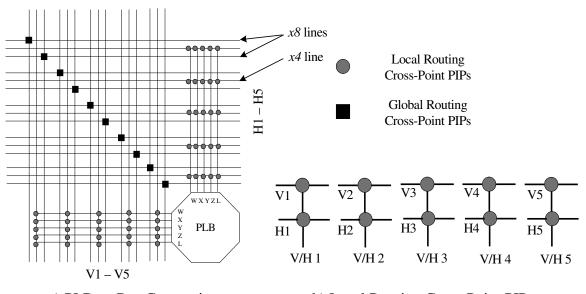

The routing architecture present in the Atmel FPGA core consists of both local and global routing resources. The local routing resources are formed by wire segments and PIPs that make connections to adjacent PLBs and allow access to/from the global routing resources. The global routing resources comprise busses of wire segments that span either four PLBs (x4 lines, which are referred to as local busses in Atmel terminology) or span eight PLBs (x8 lines, referred to as express busses in Atmel terminology) in the array before reaching repeaters, which will be discussed shortly.

The local routing resources consist of non-decoded multiplexer PIPs, which select inputs from one of the five x4 lines or from direct PLB connections from adjacent PLBs, as illustrated in Figure 2.5. The five inputs to each multiplexer PIP, denoted as V/H 1 through V/H 5 in Figure 2.5, come from the five vertical and five horizontal x4 lines in the global routing resources. The **W** and **Z** inputs to PLB can come from any one of the five vertical x4 lines or of the five horizontal x4 lines and are selected by their respective multiplexer PIPs. In the case of the **X** and **Y** inputs, additional multiplexer PIPs select a signal either from the inputs from the x4 lines or from one of the direct connections from an adjacent PLB.

Figure 2.5 Local Interconnect Associated with the Atmel PLB [15]

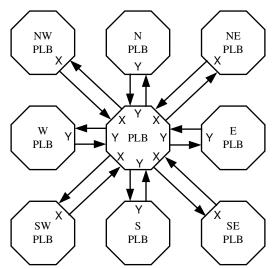

The available direct PLB connections are illustrated in Figure 2.6, which shows the eight possible direct PLB connections. Only one input from any given direction can be selected at one time. The available connections denoted as **X** in Figure 2.6 include

both the **X** input to the PLB and the **X** output from the PLB and make it possible to connect to a diagonally adjacent PLB [15]. It is possible to connect to adjacent PLBs located northwest, northeast, southeast, and southwest (denoted NW, NE, SE, and SW, respectively, in Figures 2.5 and 2.6) using local **X**. The connections denoted as **Y** in Figure 2.6 include both the **Y** input to the PLB and the **Y** output from the PLB and can make connections to orthogonally adjacent PLBs to the north, east, south, and west (denoted as N, E, S, and W, respectively, in Figures 2.5 and 2.6).

Figure 2.6 PLB-to-PLB Adjacent Connections [15]

Each PLB has connections as shown in Figure 2.6 to and from the adjacent PLBs both orthogonally and diagonally except for those PLBs that are along the edges of the PLB array. The PLBs along the edges have direct connections to and from I/O cells in place of the respective direct PLB connections.

The PLB connections to the global routing resources are shown in Figure 2.7 and are denoted as W, X, Y, Z, and L [15]. Here, W, X, Y, and Z serve as inputs to the PLB and L is a PLB output. The PLB inputs can connect to one, and only one, of the five vertical x4 lines or of the five horizontal x4 lines at a time [15]. The same is also true for

the **L** output of the PLB. It is important to note that the **X** and **Y** inputs can enter the PLB through one and only one of the connections from either one of the *x4* lines or one of the adjacent PLB connections such that both connections cannot be made simultaneously. Therefore, if a connection is made to **X** or **Y** from a *x4* line, no connection can be made from the direct inputs connected to an adjacent PLB [15].

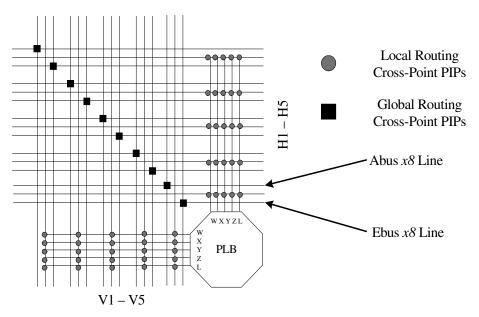

a) PLB-to-Bus Connections b) Local Routing Cross-Point PIPs Figure 2.7 PLB-to-Bus Connections [15]

A connection is made to the x4 lines in the five vertical or horizontal busses through the cross-point PIPs shown in Figure 2.7b, denoted as V1 - V5 and H1 - H5. When the cross-point PIP is turned on, the x4 line is available to the PLB and multiplexer PIPs, shown in Figure 2.5, present on the **W**, **X**, **Y**, and **Z** inputs as well as the **L** output select the bus as an input or output, respectively. Cross-point PIPs in the global routing resources, illustrated in Figure 2.7a diagonally from the PLB, can be used to make connections between the horizontal x8 and vertical x8 lines. Connections between horizontal and vertical x4 lines are made through the cross-point PIPs shown in Figure 2.7b.

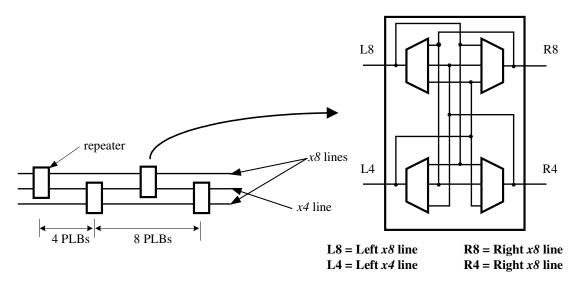

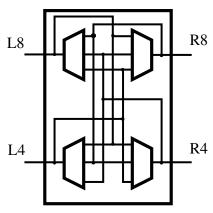

The x8 lines span eight PLBs before reaching a repeater and the x4 lines span four PLBs before coming to a repeater [15]. The x8 lines that are located furthest from the PLB shall be referred to as Abus lines while the x8 lines closest to the PLB shall be referred to as Ebus lines. Repeaters are staggered throughout the array, meaning that every other span of eight cells the repeaters alternate which x8 and x4 lines can be connected as is illustrated in Figure 2.8a. These repeaters allow selected types of connections to be made between wire segments. For simplicity only one of the five busses of x4 lines and x8 lines is shown. The internal organization of the repeater is illustrated in Figure 2.8b and consists of four 3-input non-decoded multiplexer PIPs.

a) Staggered Repeaters b) Repeater Connections

Figure 2.8 Staggered Repeaters in Atmel Routing Architecture

Connections can be made in multiple directions through the repeater. A connection can be made from one x4 line through the repeater to the adjacent x4 line or from one x4 line to either of the x8 lines (where L4 and R4 denote left and right x4 lines and L8 and R8 denote left and right x8 lines as shown in Figure 2.8b). The repeaters are staggered such that the orientation of the repeater is flipped about the horizontal axis from one repeater to the next such that the x4 lines and x8 lines alternate entry/exit points

of the repeater. As can be seen in the figure, four multiplexers within the repeater allow for the various combinations of connections to be made. The high-level functionality of the repeater is similar to that of the switch-box PIPs, however, the actual internal organization utilizes multiplexer PIPs instead of pass transistors to complete connections between the different wire segments. This provides buffering for long or heavily loaded signals and also implies directionality of the signal.

### 2.3 Overview of Testing Methods for FPGAs

Many previous methods for testing FPGAs rely on externally applied test vectors, hence these various testing approaches are limited to device-level testing only [16]-[18]. In addition, there also exist many restrictions in controllability and observability due to the number of I/O cells present in a particular package that can be used for testing the FPGA. This problem is further complicated in generic SoCs since a large portion of the FPGA core I/O is internally connected to other SoC components. As a result, even more controllability and observability restriction exists in the FPGA core of a generic SoC.

In BIST-based approaches, such as in [9]-[10], [19], [20], the testing configurations do not rely on externally applied test vectors, but instead use the internal circuitry of the FPGA to generate test patterns for the purpose of testing the FPGA. Multiple test configurations may be required, but the advantage is the ability to use the same test procedure from device-level testing through system-level testing, since BIST is applicable to all these levels [10]. The BIST approach results in less total test development time since BIST can be applied from device-level testing through system-level testing without the need for developing different tests for different levels of testing.

Therefore, there is less final cost since test development is applicable to the various levels of testing of electronic devices, which, in turn, is a significant portion of device cost [21].

#### 2.4 Previous Work in BIST for FPGAs

Previous implementations of BIST for FPGAs have been applied to devices such as the Lucent Technologies Optimized Reconfigurable Cell Array (ORCA) 2C and 2CA FPGAs [9], [20] and to the Xilinx 4000 and Spartan series FPGAs [10]. Typically BIST is separated into logic and routing BIST, which test the PLBs and programmable interconnect present in an FPGA, respectively. In these previous works, there are specific architectural issues that have a large impact on the implementation of BIST in the respective device [10].

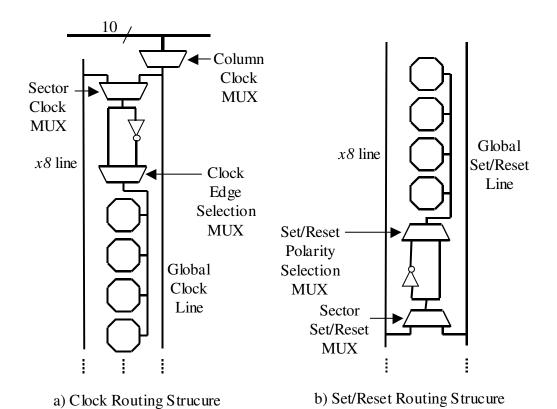

# 2.4.1 Logic BIST

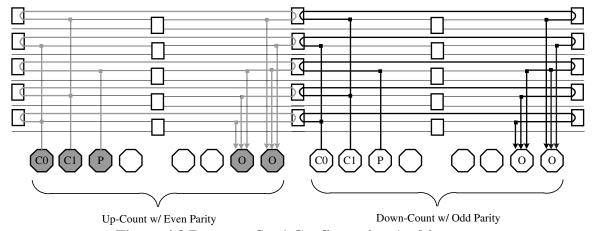

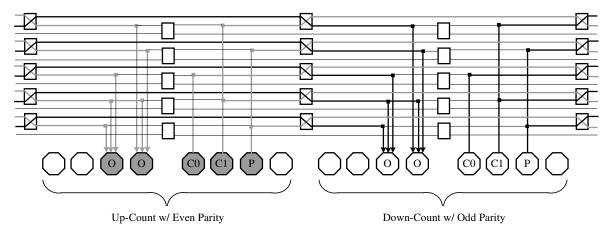

In the previous implementations of BIST for FPGAs the basic idea for logic BIST is illustrated in Figure 2.9, where some columns (or rows) of the PLBs are configured as TPGs and ORAs and other columns (or rows) of PLBs are configured as BUTs. This architecture is flipped from the first test session to the second test session. The flipping of the architecture ensures that all PLBs become BUTs during testing as long as at least half the PLBs are BUTs during each test session.

Figure 2.9 Logic BIST Architecture

Typically a binary counter is utilized as the TPG for the logic BIST test sessions since it generates exhaustive test patterns and can be used to apply all possible 2<sup>n</sup> test patterns for an *n*-input logic function [7]. This type of TPG is the most economical choice since a counter mode is common in the PLBs of most FPGAs [7]. An LFSR (Linear Feedback Shift Register) could also be used; however, additional logic is required to obtain an all 0's state, which makes the TPG more difficult to implement, when compared to a binary counter [7]. Algorithmic TPGs are used to test PLBs that have RAM modes of operation such as the ORCA and Xilinx FPGAs [10]. These algorithmic TPGs are also more difficult to implement and require more logic, hence more PLBs, than a binary counter.

There are two important features to note pertaining to this logic BIST architecture. First, multiple TPGs are used in order to source identical test patterns to alternating rows or columns of identically configured BUTs [7]. Second, every BUT, except for the first and last two columns, has its corresponding outputs observed by two different ORAs and compared with different BUTs [7]. The combination of these two factors guarantees that any single faulty PLB can be guaranteed to be detected [7]. In

addition, the conditions that allow multiple faulty PLBs to avoid detection are so limiting that, in practice, the chances of occurrence are very unlikely [7].

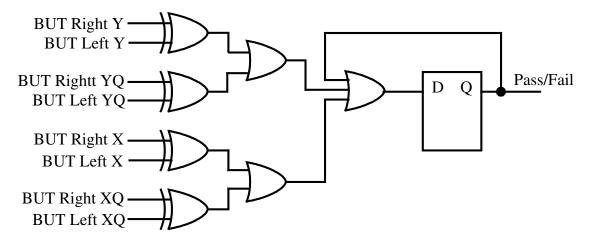

Multiple test phases are applied during each test session in order to completely test the PLBs configured as BUTs in all of their modes of operation [9], [11], [20]. The number of configurations depends on the number of modes of operation available in the PLB. Hence, the more available modes of operation that can be implemented in a PLB, the greater the number of configurations that are required to test the PLB. It is desired to minimize the number of configurations required to test an FPGA in order to minimize testing time and test development effort and time.

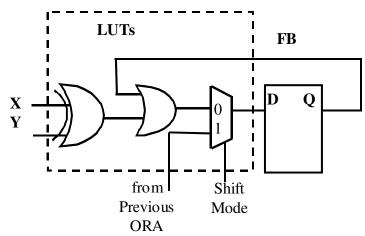

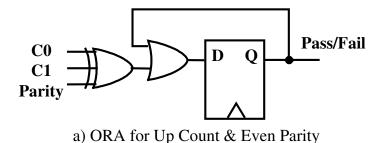

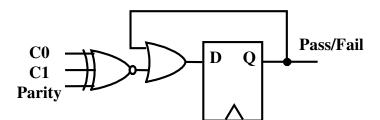

Since identical test patterns are applied to identically configured BUTs, the ORAs employed are comparison-based in order to compare the responses of the BUTs located in the adjacent rows or columns [7]. The basic architecture of the comparison-based ORA previously used is illustrated in Figure 2.10 where four sets of outputs from adjacent BUTs are compared [10], [19]. The feedback, OR gate, and flip-flop in the PLBs configured as ORAs latch any mismatch detected in the corresponding BUT outputs so that the faulty indication result is stored [7]. To retrieve the results, the ORAs can be connected as a shift register to shift out the results at the end of each BIST sequence or the configuration memory can be read to obtain the contents of the ORA flip-flops at the end of a BIST sequence [7].

Figure 2.10 Basic ORA Structure in Logic BIST [10], [19]

### **2.4.2 Routing BIST**

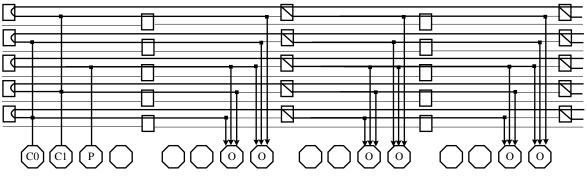

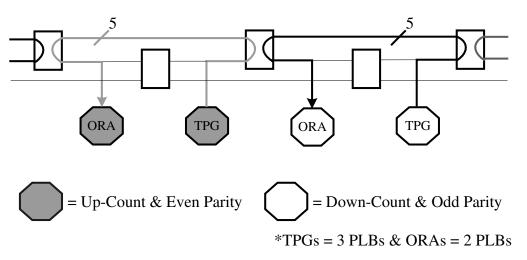

One methodology applied in the routing BIST in previous implementations consists of a counter-based TPG that sources test patterns over two sets of WUTs that have their signals compared at a destination by a comparison-based ORA, as illustrated in Figure 2.11. Groups of PLBs are configured as the TPGs in order to source the test patterns over the sets of WUTs [22]. These WUTs are configured from a subset of the routing resources of the FPGA and include selected wire segments and PIPs that are targeted for testing [22]. The ORAs receive the test patterns sourced over the WUTs by the TPGs and detect mismatches between the sets of WUTs to give a Pass/Fail indication at the end of the BIST sequence to determine if the WUTs are faulty or fault-free [22]. The ORA results can be retrieved in a similar fashion as in the logic BIST: the ORAs can be connected as a shift register and the results shifted out at the end of the BIST sequence or the results can be read directly from the configuration memory [7].

**Figure 2.11 Routing BIST Architecture**

Another approach to testing interconnect is demonstrated in Figure 2.12 where the counter-based TPG also generates parity over the binary count sent over a set of WUTs and, over some other routing resources, the parity bit is routed to the destination parity check-based ORA which also receives the signals from the WUTs [23]. In this routing BIST architecture, which is similar to that shown in Figure 2.11, some PLBs are configured as TPGs and some PLBs are configured as ORAs with selected wire segments and PIPs selected for testing configured as WUTs. However, in this case, the TPG generates a parity bit associated with its test pattern and the ORA is configured accordingly to check the parity bit associated with the output response of the WUTs, as illustrated in Figure 2.12. The parity bit is sent from the TPG to the ORA over known good routing resources [23].

Figure 2.12 Parity check-based Routing BIST

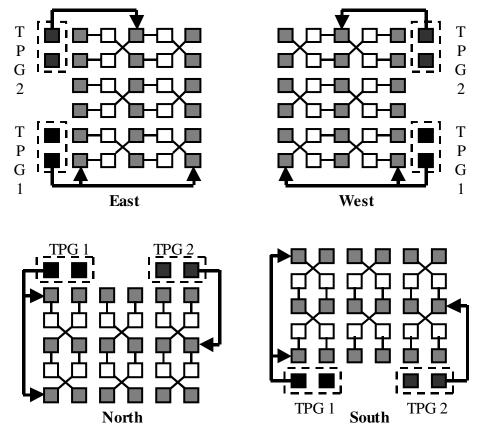

In both the comparison- and parity check-based routing BIST approaches, Self Test AReas (STARs) have been used to implement the BIST configurations within the routing resources of the FPGA [10]. These STARs consist of selected subsets of the programmable logic and routing resources within the FPGA configured as TPGs, ORAs,

and WUTs [28]. These STARs are scalable to the architecture of the device to which the approach is applied and can be as large as the entire array. The number of configurations depends on the size of the STARs and the number of routing resources to be tested within the STAR during a given test session. The size of the STAR during a given test session impacts both the speed of the test and the diagnostic resolution of the test [10]. A large STAR or a STAR with a high number of routing resources has larger resistive and capacitive loading. This is due to the finite on resistance and gate capacitance of the transmission gates in the various PIPs in the set of WUTs. These factors cause longer delays in signal propagation, which affects the speed of the test. In addition, a large STAR makes fault diagnosis more difficult since a larger number of routing resources is under test in a given test phase and determining which of the wire segments is faulty is made much more difficult.

#### 2.4.3 BIST for the ORCA FPGAs

The logic BIST approach implemented in [9], [11], [20] for the ORCA 2C and 2CA FPGAs uses the logic BIST architecture illustrated in Figure 2.9. It is important to note the impact of the PLB and interconnect architectures on the number of configurations and testability of the FPGA. A total of 9 and 14 phases per test session were required to completely test the PLBs in the 2C and 2CA FPGAs, respectively [9], [20]. The ORCA 2CA FPGA has more modes of operation than the ORCA 2C FPGA, which include multiplier and comparator modes as well dual-port RAM modes of operation. This increased number of modes translates to more BIST configurations required to test the PLB in all its modes of operation. The PLB in the ORCA 2C and

2CA FPGAs device consists of four 16-bit LUTs, four flip-flops, a fast-carry circuit, and several multiplexers [25]. The inputs to the flip-flops can be fed in through four primary inputs to the PLB or can be driven by the four LUTs [25]. There are five primary outputs of the PLB, which can be driven either from the flip-flops or the LUTs to allow for combinational or sequential functions to be performed [25]. The LUTs can be programmed in one of three modes: logic (LUT), arithmetic (fast-adders/subtractors), and memory (RAM) [25]. The two RAM modes allow the LUTs in the PLB to function as either a 16x4 RAM or as a two 16x2 RAMs. The four flip-flops present in the PLB can be configured to act as level sensitive latches or to act as edge-triggered flip-flops [25].

The routing resources of the ORCA FPGAs required 27 and 44 BIST configurations, respectively, for the two BIST approaches described in [11] and [22]. Both approaches used the routing BIST architecture shown in Figure 2.11. The approach in [22] required more configurations due to the use smaller STARs in the application of routing BIST which were chosen to increase diagnostic resolution. The routing resources associated with each PLB in the ORCA FPGA include six horizontal and six vertical 4-bit global routing busses and four sets of direct 5-bit local routing busses to adjacent PLBs [22]. Along the horizontal and vertical direction, there are two 4-bit busses of *x1* lines , two 4-bit busses of *x4* lines, one 4-bit bus of *xH* lines, and one 4-bit bus of *xL* lines associated with each PLB.

# 2.4.4 BIST for the Xilinx 4000 and Spartan Series FPGAs

The logic BIST illustrated in Figure 2.9 was also applied to the Xilinx 4000 and Spartan series FPGAs [10]. For the case of these Xilinx FPGAs, a total of 12 test phases

per test session were needed to completely test the PLBs. The PLB consists of two 4-input LUTs, one 3-input LUT, two flip-flops, dedicated carry logic, and various multiplexers to configure the cell interconnections and functions [26]. The two 4-input LUTs can function together as a single 32x1 RAM or as two 16x1 RAMs [26]. The two flip-flops can function as edge-triggered flip-flops or as level-sensitive latches [26]. The additional logic associated with the PLBs is the carry logic circuitry used to implement fast adders, subtractors, and counters [26].

The routing resources within the Xilinx 4000 and Spartan series FPGAs consist of a specific number of wire segments dependent upon the particular type of device, either 4000E/Spartan or a 4000XL/XLA series FPGAs. Both types of devices include an 8-bit bus of x1 lines and a 4-bit bus of x2 lines. The 4000E/Spartan FPGAs include ten vertical and six horizontal long lines (including xQ, xH, and xL lines) while the 4000XL/XLA FPGAs have 18 vertical and six horizontal long lines. The 4000XL/XLA FPGAs also include three 4-bit busses of x4 lines and 2 direct connections to each adjacent PLB. The comparison-based routing BIST approach in Figure 2.11 was applied to all routing resources in the 4000E/Spartan and 4000XL/XLA series FPGAs [10]. A total of 128 BIST configurations were required to test all routing resources in the 4000E/Spartan series FPGAs while a total of 206 BIST configurations were required to test all of the routing resources in the 4000XL/XLA series FPGAs [10].

The parity-based routing BIST configuration was proposed in [23] to test the x1 lines and their associated switch-box PIPs in the 4000 series FPGAs. It was theorized that these resources could be tested in three BIST configurations. However, this BIST approach was never implemented in the actual FPGA to verify that three BIST

configurations were sufficient. In addition, the xI lines and their associated switch-box PIPs the easiest to test routing resources [10].

## 2.4.5 Previous Work In Logic BIST for the Atmel AT94K Series FPGA Core

The only previous work for logic BIST for the FPGA core in the AT94K series FPSLIC was proposed in [27]. This work involved on-line testing of the LUTs in the PLBs where two test configurations were required per LUT in each PLB [27]. In this approach, only the LUTs in the PLBs are tested and the remaining logic is left untested, as are the routing resources within the FPGA. In the work reported in [27], the total number of configurations to test the NxN PLB array in the FPGA is  $2N^2$  since the PLBs are tested one at a time. In addition, it appears that the AVR core would perform the TPG and ORA functions.

#### 2.5 ORCA, Xilinx, and Atmel FPGA Comparison

The composition of the PLBs and the complexity of the routing resources are considerably different in the Atmel AT40K series FPGAs than in the ORCA and Xilinx FPGAs. The PLBs in the ORCA and Xilinx FPGAs consist of more logic and hence more programmability and functionality than the Atmel FPGA, as is summarized in Table 2.2. The ORCA and Xilinx PLBs have approximately twice the number of primary inputs as the Atmel PLB and also have more outputs. In addition, the LUTs in the ORCA and Xilinx PLBs have more bits than contained in the LUTs in the Atmel PLB. There are also more configuration multiplexers and additional logic gates (including carry logic) in the ORCA and Xilinx PLBs than in the Atmel.

Table 2.2 Comparison of PLBs [14], [15], [25], [26]

| 1 usic 212 Comparison of 1 225 [1 1], [10], [20] |       |         |                 |  |  |

|--------------------------------------------------|-------|---------|-----------------|--|--|

| PLB                                              | Atmel | ORCA 2C | Xilinx 4000     |  |  |

| Component                                        | AT40K | and 2CA | and Spartan     |  |  |

| # Inputs                                         | 8     | 19      | 13              |  |  |

| # Outputs                                        | 3     | 6       | 4               |  |  |

| # LUTs                                           | 2     | 4       | 3               |  |  |

| # Bits/LUT                                       | 8x1   | 16x1    | (2)16x1, (1)8x1 |  |  |

| Config. Multiplexers (incl. Carry Logic)         | 11    | 17      | 26              |  |  |

| # Flip-Flops                                     | 1     | 4       | 2               |  |  |

| # Addt'l Logic Gates<br>(incl. Carry Logic)      | 1     | 3       | 6               |  |  |

The routing resources dispersed within the ORCA and Xilinx FPGAs are more numerous and comprise more types of wire segments and PIPs than the Atmel FPGA, as summarized in Table 2.3. The ORCA and Xilinx FPGAs contain about twice as many total types of routing resources as the Atmel FPGA. The diagonal direct lines are unique to the Atmel FPGA and are not found in either the ORCA or Xilinx FPGAs. The Atmel and ORCA routing resources are symmetrically aligned horizontally and vertically meaning that the number and interconnections of vertical and horizontal planes of wire segments is the same. However, in the Xilinx FPGA, the routing resources do not have rotational symmetry. This asymmetry contributes to the test complexity for the Xilinx since there are different numbers of horizontal and vertical bussing planes depending on the type of routing resource [10]. In addition, some of the busses in the Xilinx routing resources are shared between PLBs and create obstacles in the development of logic and routing BIST configurations [10]. There also exists dedicated carry routing in the ORCA and Xilinx FPGAs that is not present in the Atmel FPGA. Carry routing can be implemented with the direct routing (orthogonal or diagonal direct lines) in the Atmel device, but at the expense of a PLB output since there is no dedicated logic or routing for carry circuitry within the Atmel FPGA. The conclusion drawn in [10] is that the routing architecture of the FPGA is the primary component in the number of BIST configurations required to completely test the device. This was demonstrated by the total number of test configurations required for the Xilinx routing resources (128 and 206) compared to that required for the ORCA routing resources (27 and 44) [10].

Table 2.3 Comparison of Routing Resources [10], [15]

| = =                   |          |            |          |            |              |            |               |            |

|-----------------------|----------|------------|----------|------------|--------------|------------|---------------|------------|

| Routing               | A        | tmel       | ORCA 2C  |            | Xilinx 4000E |            | Xilinx 4000XL |            |

| Resource              | A'.      | Г40К       | ORCA 2CA |            | and Spartan  |            | and XLA       |            |

| Type                  | vertical | horizontal | vertical | horizontal | vertical     | horizontal | vertical      | horizontal |

| x1 lines              | 0        | 0          | 8        | 8          | 8            | 8          | 8             | 8          |

| x2 lines              | 0        | 0          | 0        | 0          | 4            | 4          | 4             | 4          |

| <i>x4</i> lines       | 5        | 5          | 8        | 8          | 0            | 0          | 12            | 12         |

| x8 lines              | 10       | 10         | 0        | 0          | 0            | 0          | 0             | 0          |

| long lines            | 0        | 0          | 8        | 8          | 10           | 6          | 18            | 6          |

| direct lines          | 1        | 1          | 5        | 5          | 0            | 0          | 2             | 2          |

| diagonal direct lines |          | 1          | 0        |            | 0            |            | 0             |            |

| carry lines           |          | 0          | 0        |            | 2            |            | 2             |            |

| Total                 | 17       | 17         | 29       | 29         | 24           | 20         | 46            | 34         |

Another important point to consider in the comparison of the ORCA, Xilinx, and Atmel FPGAs is the percent composition of the types of PIPs present in the routing resources of the devices, as illustrated in Table 2.4. The Atmel FPGA is more similar in certain aspects to the Xilinx than the ORCA FPGAs. In terms of break-point PIPs and multiplexer (MUX) PIPs, the Atmel FPGA is more similar in composition to the Xilinx FPGA, however, as in the ORCA FPGA, there are no true switch-box PIPs in the Atmel FPGA. The closest routing resource that the Atmel FPGA has to the switch-box PIPs in the Xilinx FPGA are the repeaters and they are more similar to multiplexer PIPs than to switch-box PIPs as illustrated in Figure 2.8b.

Table 2.4 Percent Composition of PIPs in Routing Resources [10], [15]

|                    | Xilinx | ORCA   | Atmel |

|--------------------|--------|--------|-------|

| Type of PIP        | 4000   | 2C/2CA | AT40K |

| <b>Break-Point</b> | 1.5%   | 12%    | N/A   |

| <b>Cross-Point</b> | 11.3%  | 69%    | 34.8% |

| MUX                | 72.5%  | 19%    | 60.9% |

| Switch-Box         | 14.7%  | N/A    | N/A   |

| Repeaters          | N/A    | N/A    | 4.3%  |

## 2.6 BIST Configuration Comparison

As found in [10], the routing architecture is the primary influence on the total number of test configurations and on the total test time. The comparisons of the routing architecture presented in Tables 2.2, 2.3, and 2.4, therefore, allow a good relative comparison of the total number of BIST configurations for the ORCA and Xilinx FPGAs. Table 2.5 summarizes the total number of logic and routing BIST configurations for the ORCA and Xilinx FPGAs.

Table 2.5 BIST Configurations for ORCA and Xilinx FPGAs [10]

|                        |         | ORCA  | Xilinx      | Xilinx  |

|------------------------|---------|-------|-------------|---------|

|                        | ORCA 2C | 2CA   | 4000E       | 4000XL  |

|                        |         |       | and Spartan | and XLA |

| # logic BIST configs   | 9       | 14    | 12          | 12      |

| # routing BIST configs | 27/44   | 27/44 | 128         | 206     |

As Table 2.5 demonstrates, the primary component in the total number of BIST configurations is the number of routing BIST configurations. The ORCA 2C and 2CA FPGAs required 27 and 44 routing BIST configurations, with the differing numbers due to the size of the STARS [10]. The Xilinx 4000E and Spartan FPGAs required 128 routing BIST configurations while the Xilinx 4000XL/XLA FPGAs required 206 routing BIST configurations. The Atmel device has a fine-grain PLB architecture, with a rotationally symmetrical routing architecture. In addition, the composition of routing

resources in the Atmel FPGA, as illustrated in Table 2.3 and Table 2.4, is somewhere between the percentages found in the ORCA and Xilinx FPGAs, and will have an impact on the total number of configurations since the routing architecture is the primary influence. The differences between the architectures of these FPGAs affect the number of test configurations for the respective FPGA architectures to completely test the routing resources. One of these differences is that the main types of PIPs within the respective FPGAs differ in their percent composition and in their amount of inputs [10]. The crosspoint and break-point PIPs make up 81% of the total PIPs in the ORCA FPGAs and the remaining 19% comprises the multiplexer PIPs [10]. In addition, there are no switch-box PIPS in the ORCA routing resources [10]. The more difficult to test PIPs are the multiplexer and switch-box PIPs. In addition, the size of the multiplexer PIPs is smaller in the ORCA FPGAs in comparison with the Xilinx FPGAs, 5 inputs compared to 35 inputs [10]. Consequently, more configurations are required to completely test these types of PIPs in comparison to the break-point or cross-point PIPs.

Another difference arises in the carry logic where, in the ORCA FPGAs, there is dedicated carry routing to the four adjacent cells but the carry-out output can also be placed on one of the five PLB outputs, allowing for better observability of the signal [10]. In the Xilinx FPGAs the carry-out can only be observed on dedicated routing that goes from a given PLB to only one PLB located directly above that PLB. A third difference is the sharing of the routing resources associated with the PLBs [10]. In the ORCA FPGAs, the routing resources are not shared between two adjacent PLBs whereas in the Xilinx FPGAs, the routing resources are shared between the two adjacent PLBs [10]. In addition to the effect of PIP types in the ORCA and Xilinx FPGAs, the routing resources

in the two FPGAs contain rotating and staggered busses, which make testing the busses more difficult and increase the number of configurations required to test the FPGA interconnect [10]. Finally, the inputs and outputs to and from the ORCA FPGAs can be connected to all routing resources on any side of the PLB while in the Xilinx FPGAs, the inputs and outputs can be connected to and from a subset of the routing resources on only two sides of the PLB making testing more complex [10].

### 2.7 BIST Development