# LEAD-FREE ASSEMBLY AND RELIABILITY OF CHIP SCALE PACKAGES AND 01005 COMPONENTS

### Yueli Liu

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama May 11, 2006

# LEAD-FREE ASSEMBLY AND RELIABILITY OF CHIP SCALE PACKAGES AND 01005 COMPONENTS

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee.

This dissertation does not include proprietary or classified information.

|                                                                  | Yueli Liu                                                                           |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Certificate of Approval:                                         |                                                                                     |

| Thomas A. Baginski Professor Electrical and Computer Engineering | R. Wayne Johnson, Chairman<br>Ginn Professor<br>Electrical and Computer Engineering |

| Pradeep Lall Associate Professor Mechanical Engineering          | John L. Evans Associate Professor Industry and Systems Engineering                  |

| Stephen L. M<br>Dean<br>Graduate Sc                              |                                                                                     |

# LEAD-FREE ASSEMBLY AND RELIABILITY OF CHIP SCALE PACKAGES AND 01005 COMPONENTS

| T 7 1 | ٠. | _ |      |

|-------|----|---|------|

| Yue   | 1  | - | .111 |

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon request of individuals or institutions and at their expense.

The author reserves all publication rights.

| Signature of | Author |

|--------------|--------|

|              |        |

|              |        |

|              |        |

|              |        |

| Date of Grad | uation |

#### **VITA**

Yueli Liu, daughter of Shixun Liu and Yulian Yang, was born Sept. 15, 1973, in Shihezi, China. She entered Nanchang Institute of Aeronautical Technology in September, 1991, and graduated with a Bachelor of Science degree in Material Engineering in July 1995. She then entered Graduate School, Tianjin University, in September 1995. She received the degree of Ph. D. in Material Engineering in February 2000. She married Dong Wei, son of Qinghe Wei and Heai Wang, in November 2003. She worked at the Motorola Advanced Technology Center - Asia, China, as a Research & Development Engineer from Feb. 2000 until Aug. 2001. In Aug. 2002, she joined the Electrical and Computer Engineering Department's Ph.D. program at Auburn University.

#### DISSERTATION ABSTRACT

# LEAD-FREE ASSEMBLY AND RELIABILITY OF CHIP SCALE PACKAGES AND 01005 COMPONENTS

#### Yueli Liu

Doctor of Philosophy, May 11, 2006 (Ph.D., Tianjin University, 2000) (B.S., Nanchang Institute of Aeronautical Technology, 1995)

### 165 Typed Pages

Directed by R. Wayne Johnson

Chip Scale Packages (CSPs) are widely used in portable and hand-held electronic devices due to their small size and availability. Consumers expect portable products to survive being dropped repeatedly, and drop testing is now common in the reliability evaluation of portable product designs. Lead-free assembly is another trend in electronics industries because of legislation and market factors.

Underfill materials are often used to improve the reliability of a variety of electronic components. In this research, the assembly processes for three underfill options (capillary underfill, fluxing underfill and corner bond underfill) compatible with lead-free assembly have been developed and evaluated. CSPs with eutectic SnPb and without

underfill were compared with lead-free and underfilled CSPs. Drop tests were carried out to evaluate the drop reliability of the CSPs as a function of assembly materials. Failure analysis was performed to reveal the typical failure modes for different underfills.

The mechanical shock reliability over the life of the product is very important to the customer. The effects of different surface finishes (Immersion Sn and Immersion Ag), reflow profiles (two cooling rates) and thermal aging on the drop reliability of lead-free CSPs were investigated. Drop test results for assemblies as-built and as a function of aging at 125°C were correlated with cross sectional analyses of the solder joints. Microstructural and failure analyses were also conducted to study IMC evolution and the formation of Kirkendall void and the effect of these changes on drop reliability.

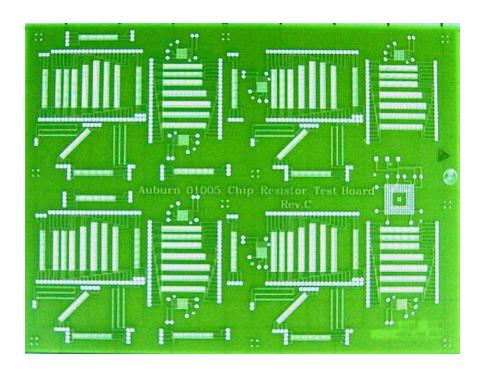

Reducing the size of the passive components and the spacing between them increases the package density and is an efficient way to miniaturize many electronic products. To satisfy this demand, 01005 chip components are now commercially available. However the implementation of such tiny components in new products presents some novel design and assembly process issues. A 01005 test vehicle was designed to investigate the effect of PCB pad design on assembly yield. Process capability of 01005 test board manufacturing was evaluated. A Design of Experiment (DOE) was used to optimize the solder paste printing based on 3D solder paste inspection. Lead-free solder was used for all assembly trials. Several tests were performed to explore the influence of process parameters on placement accuracy and reflow defects. As a results of this analyses of experimental results and a post-reflow inspection for assembly defects, recommendations for PCB design and assembly processes are made.

#### **ACKNOWLEDGMENTS**

I would like to express my appreciation and sincere thanks to my research advisor, Dr. R. Wayne Johnson, who has provided me with guidance and encouragement throughout the pursuit of this degree. His advice has been invaluable and kept my motivation and determination at the highest level. I also wish to thank my advisory committee members Dr. Thomas A. Baginshki, Dr. Pradeep Lall and Dr. John L. Evans for their advice on this work.

I would like to recognize the help of several key members of the technical staff, industrial partners and fellow graduate students. Special thanks are due to Guoyun Tian, Mike Palmer and John Marcell for their assistance throughout the process of this research.

Finally, I would like to express my profound gratitude to my husband, Dong Wei, my daughter, Katherine Liu Wei and my parents for their encouragement and support throughout this work.

| Style manual or journal used: | IEEE Transactions on Components and Packaging |

|-------------------------------|-----------------------------------------------|

| Technologies                  |                                               |

Computer software used: Microsoft Word 2000 SR-1

# TABLE OF CONTENTS

| LIST OF TABLES                                                       | xii    |

|----------------------------------------------------------------------|--------|

| LIST OF FIGURES                                                      | . xiii |

| CHAPTER 1. INTRODUCTION                                              | 1      |

| 1.1 IC Packaging Trends                                              | 1      |

| 1.2 Chip Scale Package (CSP)                                         |        |

| 1.2.1 Advantages of CSPs                                             |        |

| 1.2.2 Types and Application of CSPs                                  |        |

| 1.3 Lead-free Technology                                             |        |

| 1.3.1 Driving Forces for Lead-free Technology                        |        |

| 1.3.2 Lead-free Solder Alloy                                         |        |

| 1.3.3 Issues in Implementing Lead-free Technology                    |        |

| 1.4 Board Level Reliability of Lead-free Solder                      |        |

| 1.4.1 Currently Lacking Sufficient Database                          |        |

| 1.4.2 Drop Reliability of Lead-free Components                       |        |

| 1.5 Research Objectives                                              |        |

| CHAPTER 2. PROCESSING AND RELIABILITY OF CORNER BONDING CHIP         |        |

| SCALE PACKAGES                                                       | 29     |

| 2.1 Introduction                                                     | 29     |

| 2.2 Assembly Process of Corner Bonding CSPs                          | 31     |

| 2.2.1 Test Vehicle                                                   |        |

| 2.2.2 Process Issues of Corner Bonding Underfill                     | 34     |

| 2.2.3 Effect of Dispensing Pressure on Underfill Volume Consistency. |        |

| 2.2.4 Reflow Profile and Underfill Cure                              |        |

| 2.2.5 Self-alignment Capability of Corner Bonding CSPs               | 44     |

| 2.2.6 Rework of Corner Bonding CSPs                                  |        |

| 2.3 Drop Test                                                        |        |

| 2.4 Failure Analysis                                                 |        |

| 2.5 Summary                                                          |        |

| CHAPTER 3. LEAD-FREE ASSEMBLY AND DROP RELIABILITY OF CHIP             |     |

|------------------------------------------------------------------------|-----|

| SCALE PACKAGES                                                         | 55  |

| 3.1 Introduction                                                       | 55  |

| 3.2 Test Vehicle                                                       | 56  |

| 3.3 Assembly Process                                                   | 57  |

| 3.3.1 No-Underfill                                                     | 57  |

| 3.3.2 Capillary Underfill                                              | 62  |

| 3.3.3 Fluxing Underfill                                                | 63  |

| 3.3.4 Corner Bond Underfill                                            | 72  |

| 3.4 Drop Test Results                                                  | 74  |

| 3.5 Failure Analysis                                                   | 79  |

| 3.6 Summary                                                            | 83  |

| CHAPTER 4. EFFECT OF SURFACE FINISH, REFLOW PROFILE, AND               |     |

| THERMAL AGING ON DROP RELIABILITY OF LEAD-FREE CSPS                    | 85  |

| 4.1 Introduction                                                       | 85  |

| 4.2 Test Vehicle                                                       | 86  |

| 4.3 Assembly Process                                                   | 88  |

| 4.4 Drop Test Results                                                  | 92  |

| 4.5 Kirkendall Voids Formation with Aging Time                         | 94  |

| 4.6 Failure Analysis                                                   | 98  |

| 4.7 Summary                                                            | 104 |

| CHAPTER 5. PCB DESIGN AND ASSEMBLY PROCESS DEVELOPMENT OF              |     |

| 01005 COMPONENTS WITH LEAD-FREE SODLER                                 | 106 |

| 5.1 Introduction                                                       | 106 |

| 5.2 Test Vehicle Design                                                | 108 |

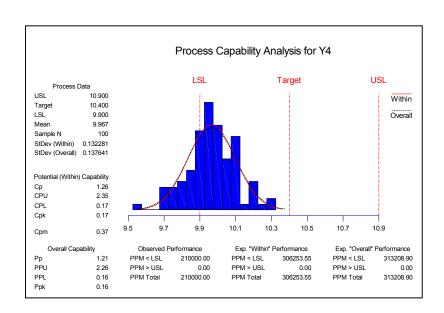

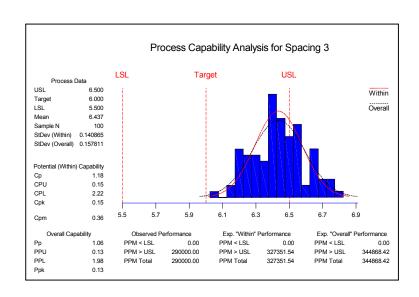

| 5.3 Process Capability Evaluation of Board Manufacturing               |     |

| 5.4 Printing Optimization                                              | 114 |

| 5.5 Placement Accuracy Evaluation                                      | 119 |

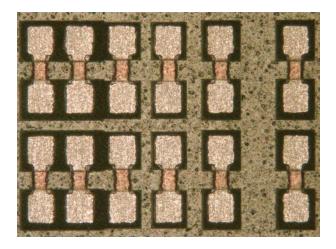

| 5.6 Reflow                                                             |     |

|                                                                        | 122 |

| 5.7 Post Reflow Inspection                                             |     |

| 5.7.1 Bridging                                                         |     |

| 5.7.2 Tombstones                                                       |     |

| 5.7.3 Missing Parts                                                    |     |

| 5.7.4 Edge-standing and Upside-down Components                         |     |

| 5.8 Summary                                                            | 132 |

| CHAPTER ( CONCLUCION                                                   | 12: |

| CHAPTER 6. CONCLUSION                                                  |     |

| 6.1 Processing and Drop Reliability of Corner Bond Chip Scale Packages |     |

| 6.2 Lead-free Assembly and Drop Reliability of Chip Scale Packages     | 135 |

| 6.3 Effect of Surface Finish, Reflow Profile, and High Temperature Aging on |     |

|-----------------------------------------------------------------------------|-----|

| Drop Test Reliability of Lead-free CSPs                                     | 136 |

| 6.4 PCB Design and Assembly Process Development of 01005 Components         |     |

| with Lead-free Solder                                                       | 136 |

| 6.5 Recommendations for Future Work                                         | 138 |

| BIBLOGRAPHY                                                                 | 139 |

# LIST OF TABLES

| Table 1.1 Effect of Higher Process Temperatures on Various Microelectronic Board Assembly | 11    |

|-------------------------------------------------------------------------------------------|-------|

| Table 3.1 The Properties of the Underfill Investigated                                    | 57    |

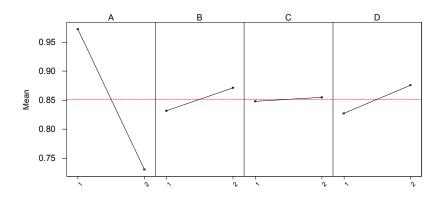

| Table 3.2 Controllable Factors.                                                           | 67    |

| Table 3.3 Taguchi L9 Test Matrix                                                          | 67    |

| Table 3.4 Response Table for Means                                                        | 68    |

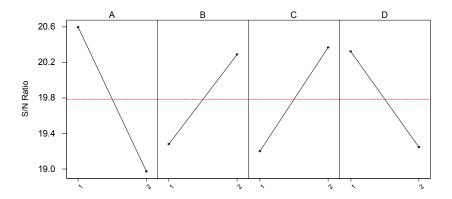

| Table 3.5 Response Table for S/N                                                          | 70    |

| Table 4.1 Factors and levels investigated in this DOE                                     | 88    |

| Table 4.2 Full Factorial DOE for 2 <sup>2</sup> 1 <sup>4</sup>                            | 88    |

| Table 5.1 Pad Dimensions (unit: mil)                                                      | . 108 |

| Table 5.2 Process Capability Statistics of the Pad Dimensions (unit:mil)                  | . 111 |

| Table 5.3 Process Capability Statistics of the Pad Spacings (unit:mil)                    | . 112 |

| Table 5.4 Factors and Levels for 01005 Printing DOE                                       | . 114 |

| Table 5.5 Taguchi's L8 OA for Printing DOE                                                | . 115 |

| Table 5.6 The Means and C <sub>PK</sub> for Placement Accuracy Evaluation                 | . 122 |

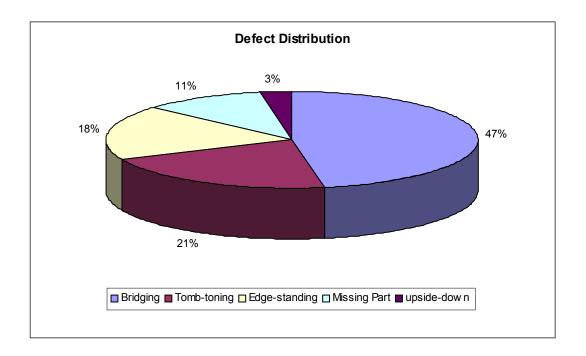

| Table 5.7 Defect Distribution in All Samples                                              | 126   |

# LIST OF FIGURES

| Figure 1.1 Unit Shipments Growth YR2000 through YR2006                                                                                                  | 2    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2 IC Package Evolution and the area reductions achieved with CSP/FBGA                                                                          | 2    |

| Figure 1.3 Dominant Passive Component Dimensions (mm)                                                                                                   | 3    |

| Figure 1.4 Trends in Size of Monolithic Ceramic Capacitors                                                                                              | 4    |

| Figure 1.5 Main CSP Types                                                                                                                               | 6    |

| Figure 1.6 Lead-free Impact on SMT Assembly                                                                                                             | . 10 |

| Figure 1.7 Lead-free Tighter Process Window                                                                                                             | . 17 |

| Figure 2.1 Corner Bonding Underfill Process                                                                                                             | . 30 |

| Figure 2.2 Photographs of Test Board (front and back) with Weight (31.8g) Attached to Backside (non-CSP side) for Drop Test                             | . 32 |

| Figure 2.3 Cross Section (a) and Close-up (b) of Failed Solder Joint after Drop Test Using Printed Wiring Board with Electroless Ni/Immersion Au Finish | . 33 |

| Figure 2.4 X-ray Pictures of Underfill Contacting the Solder Paste Sn-Ag-Cu                                                                             | . 35 |

| Figure 2.5 Underfill was Pushed into the Solder Paste, Causing Solder Joint Failure                                                                     | . 35 |

| Figure 2.6 Underfill Touching Solder Paste, Causing a Bad Solder Joint Shape                                                                            | . 36 |

| Figure 2.7 Corner Dot Dispensing Pattern                                                                                                                | . 37 |

| Figure 2.8 CSP Placed into Corner Dot Underfill                                                                                                         | . 37 |

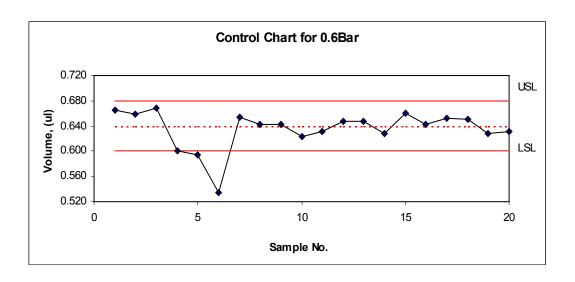

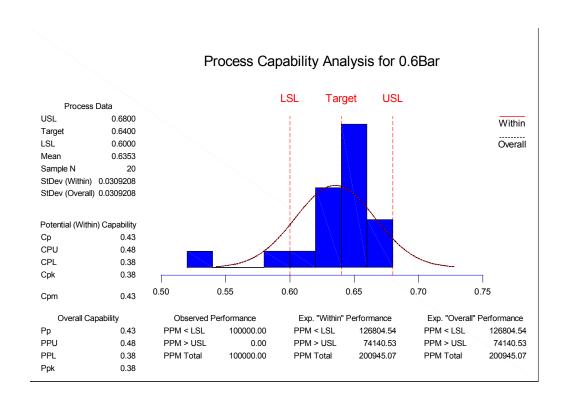

| Figure 2.9 Control Chart of Underfill Volume at 0.6 Bar                                                                                                 | . 39 |

| Figure 2.10 Process Capability Analysis of Underfill Volume at 0.6 Bar                                                                                  | . 40 |

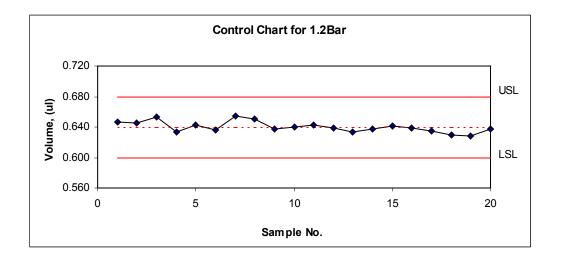

| Figure 2.11 Control Chart of Underfill Volume at 1.2 Bar                                                                                  | . 40 |

|-------------------------------------------------------------------------------------------------------------------------------------------|------|

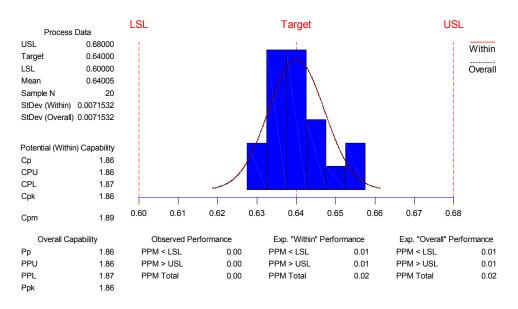

| Figure 2.12 Process Capability Analysis of Underfill Volume at 1.2 Bar                                                                    | . 41 |

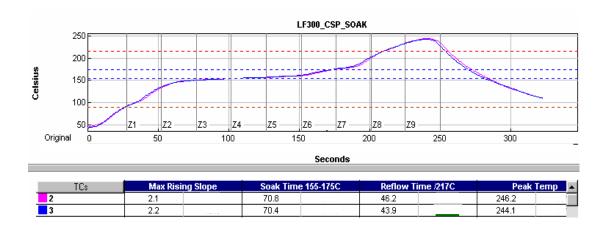

| Figure 2.13 Conventional Soak Reflow Profile                                                                                              | . 42 |

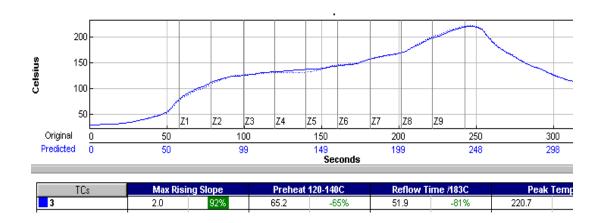

| Figure 2.14 Ramp Reflow Profile                                                                                                           | . 42 |

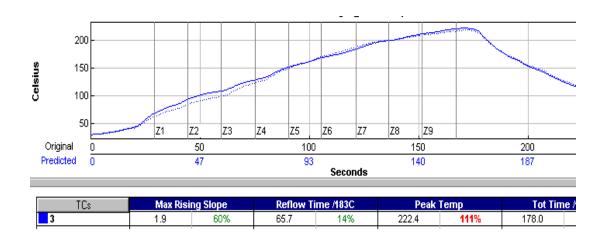

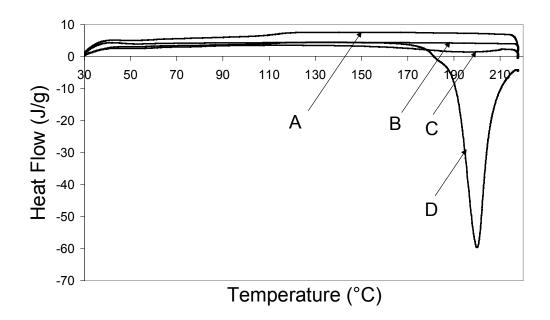

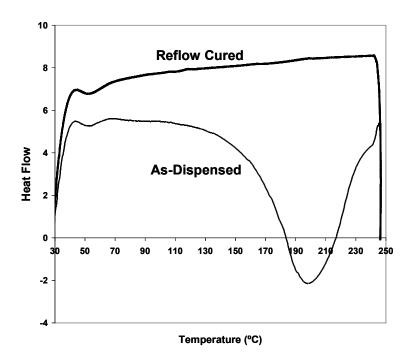

| Figure 2.15 DSC of Loctite 3515 (A- Soak, , B - Ramp, C - Box Oven, D - Uncured); Instrument Model - TA Instruments DSC2920 Modulated DSC |      |

| Figure 2.16 Cross Section of Solder Joint Showing Excellent Wetting with Soak Profile                                                     | . 44 |

| Figure 2.17 Cross Section of Solder Joint Showing Excellent Wetting with Ramp Profile                                                     | . 44 |

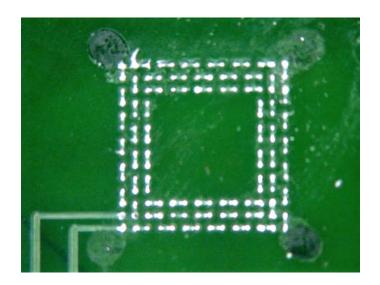

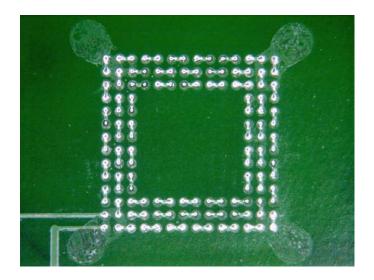

| Figure 2.18 X-ray Image of a CSP Intentionally Placed with a 5 mil (50%) Offset                                                           | . 45 |

| Figure 2.19 X-ray of CSP after Reflow                                                                                                     | . 45 |

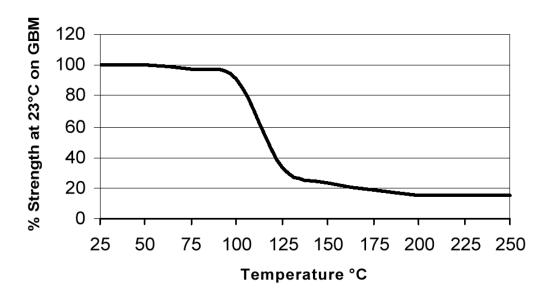

| Figure 2.20. Lap Shear Strength as a Function of Temperature                                                                              | . 47 |

| Figure 2.21 CSP Site after CSP Removal                                                                                                    | . 48 |

| Figure 2.22 CSP Site after Dressing                                                                                                       | . 48 |

| Figure 2.23 Drop Test Results                                                                                                             | . 49 |

| Figure 2.24 Cross Section of Failed Solder Joint (No Underfill).                                                                          | . 50 |

| Figure 2.25 Crack in Laminate under Solder Pad (No Underfill)                                                                             | . 51 |

| Figure 2.26 Photograph of Cracked Corner Bond Underfill after Drop Testing                                                                | . 52 |

| Figure 2.27 Cracking of Copper and Laminate after Drop Testing. Sample was Corner Bonded                                                  |      |

| Figure 2.28. Cross Section of Crack in Capillary Underfilled CSP after Drop Test                                                          | . 53 |

| Figure 3.1 No-Underfill Process                                                                                                           | . 58 |

| Figure 3.2 'Soak' Reflow Profile for Lead-free Assembly                                                                                   | . 59 |

| Figure 3.3 Ramp-to-Peak Lead-free Reflow Profile                                                                                                                  | 59 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

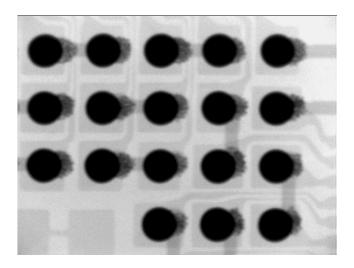

| Figure 3.4 X-Ray Image of Lead-free Solder Joints (Ramp-to-Peak Profile)                                                                                          | 60 |

| Figure 3.5 Cross Section of Solder Joint Showing Excellent Wetting with Ramp and Soak Profile                                                                     | 60 |

| Figure 3.6 Eutectic Sn/Pb Reflow Profile                                                                                                                          | 61 |

| Figure 3.7 X-Ray Image of CSP Intentionally Placed 50% Off-pad in Both the X and Y Directions                                                                     | 61 |

| Figure 3.8 X-Ray Image after Reflow                                                                                                                               | 62 |

| Figure 3.9 Capillary Underfill Process                                                                                                                            | 62 |

| Figure 3.10 Fluxing Underfill Process                                                                                                                             | 64 |

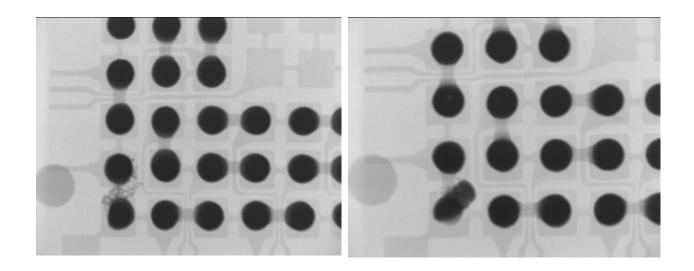

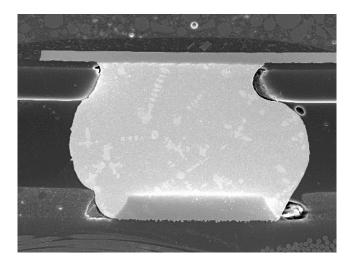

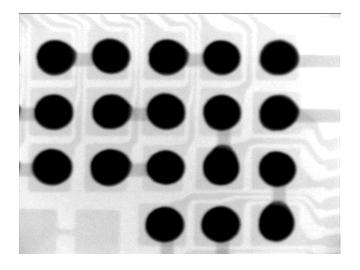

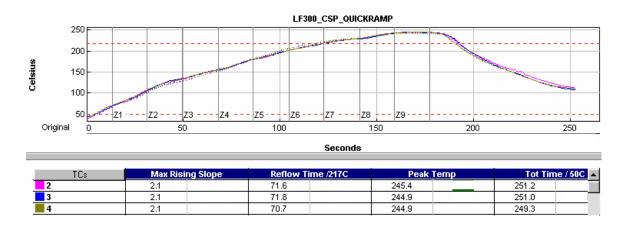

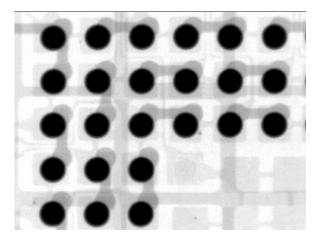

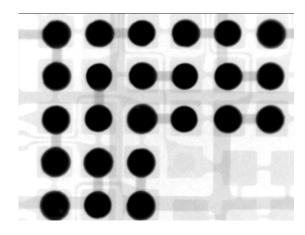

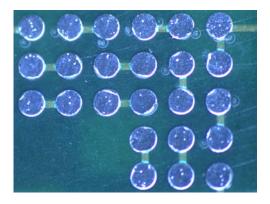

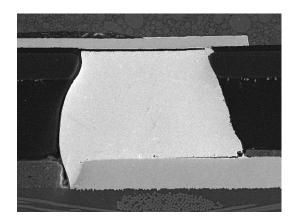

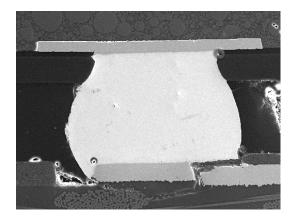

| Figure 3.11 Flat Section (CSP Polished Away) of Fluxing Underfill Showing Voiding Before Placement Optimization                                                   | 66 |

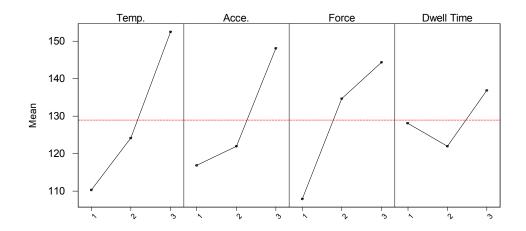

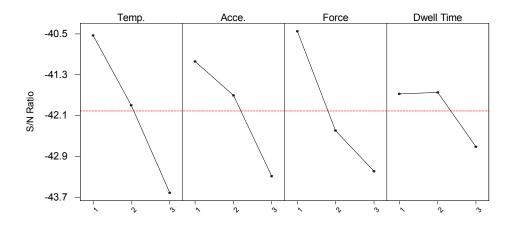

| Figure 3.12 Main Effects Plot for Means.                                                                                                                          | 69 |

| Figure 3.13 Main Effects Plot For S/N Ratios                                                                                                                      | 70 |

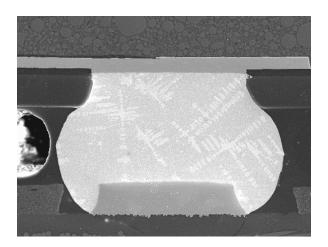

| Figure 3.14 Flat Section of Fluxing Underfill Showing Reduced Voiding After Placement Optimization                                                                | 71 |

| Figure 3.15 DSC Curves for Uncured and Reflow Cured Fluxing Underfill                                                                                             | 72 |

| Figure 3.16 X-Ray Image After Reflow for CSP Intentionally Mis-placed by 50% in Both the X and Y Directions with Corner Bond Underfill                            | 74 |

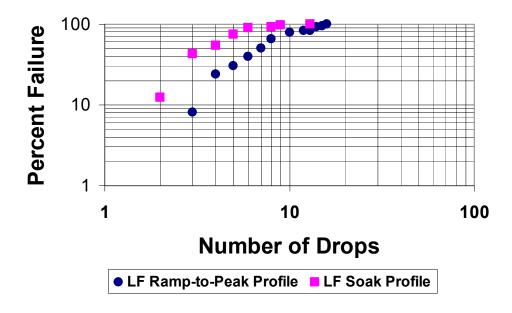

| Figure 3.17 Drop Test Results for Non-Underfilled Sn/Ag/Cu CSPs with Two Reflow Profiles                                                                          | 75 |

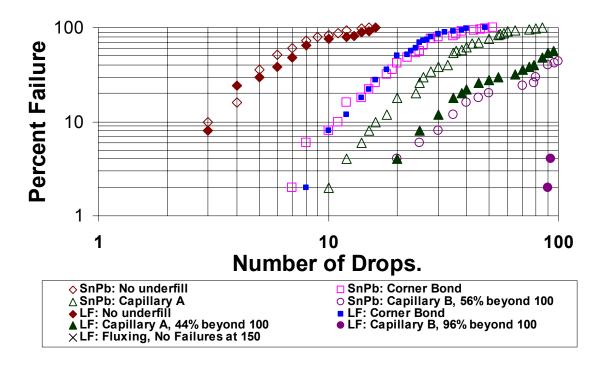

| Figure 3.18 Drop Test Results for Sn/Pb and Sn/Ag/Cu Solders and Different Underfills                                                                             | 76 |

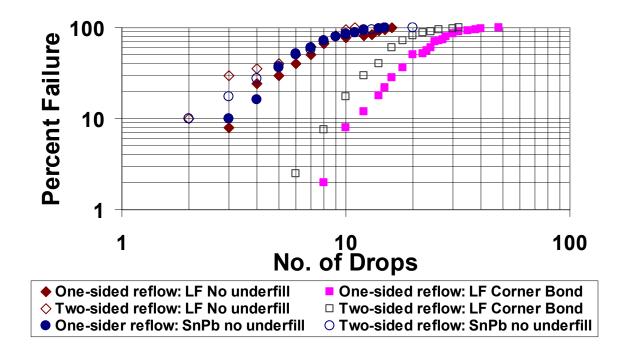

| Figure 3.19 Drop Test Results for Single and Double Reflow Cycles                                                                                                 | 77 |

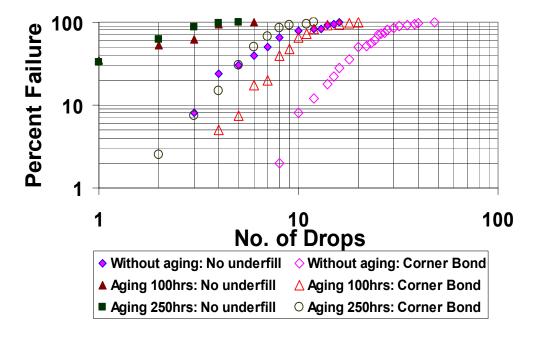

| Figure 3.20 Drop Test Results for Sn/Ag/Cu Solder With No Underfill and With Corner Bond Underfill After 0, 100 and 250 Hours of Aging at 125°C Prior to Dropping | 78 |

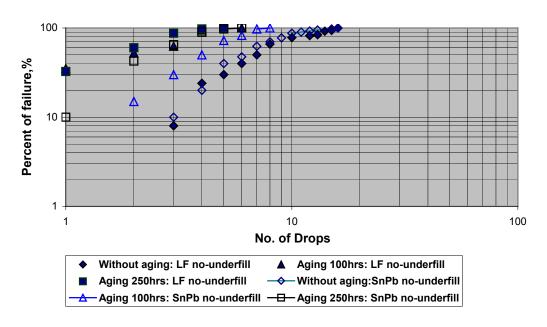

| Figure 3.21 Drop Test Results for Sn/Pb and Sn/Ag/Cu Solder with No Underfill After 0, 100 and 250 Hours Aging at 125°C Prior to Dropping         | 79 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

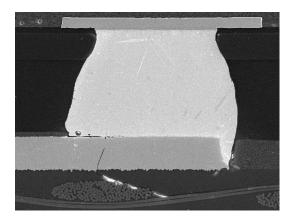

| Figure 3.22 Cross Section of a Typical Drop Test Failure of a Sn/Ag/Cu Solder Joint (no Underfill) Reflowed With the Ramp-to-Peak Profile         | 80 |

| Figure 3.23 Cross Section of a Typical Drop Test Failure of a Sn/Ag/Cu Solder Joint (no Underfill) Reflowed With the Soak Profile                 | 80 |

| Figure 3.24 Cross Section of Sn/Ag/Cu Failure with Capillary Underfill A                                                                          | 81 |

| Figure 3.25 Cross Section of Sn/Ag/Cu Failure with Capillary Underfill B                                                                          | 82 |

| Figure 3.26 Cross Section of Sn/Ag/Cu CSP (No-Underfill) Failure Assembled With Two Reflow Cycles                                                 | 82 |

| Figure 3.27 Cross Section of Sn/Ag/Cu CSP Failure After 250 Hours at 125°C Storage Prior to Drop Testing                                          | 83 |

| Figure 4.1 Test Vehicle                                                                                                                           | 86 |

| Figure 4.2 Cross Section of As-Received Sn Finish                                                                                                 | 87 |

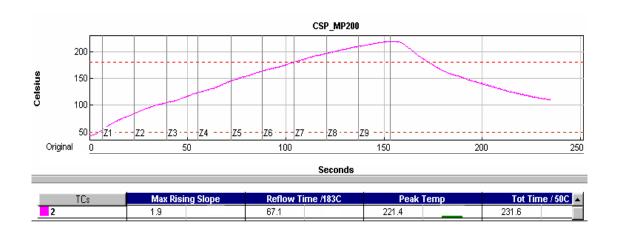

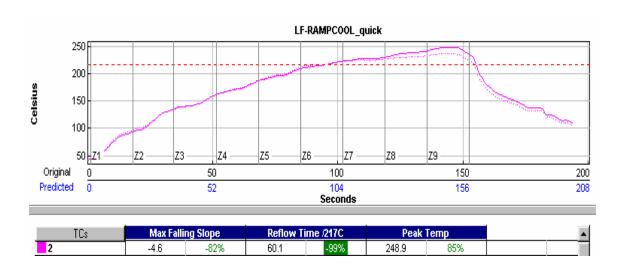

| Figure 4.3. 'Quick' Cool Down Reflow Profile                                                                                                      | 89 |

| Figure 4.4 'Moderate' Cool Down Reflow Profile                                                                                                    | 90 |

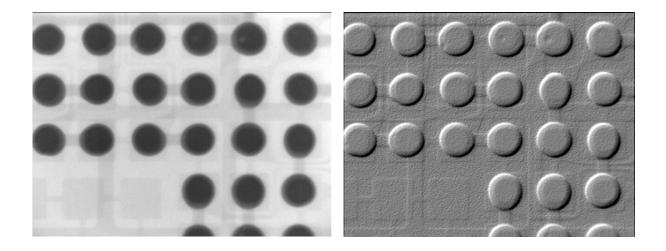

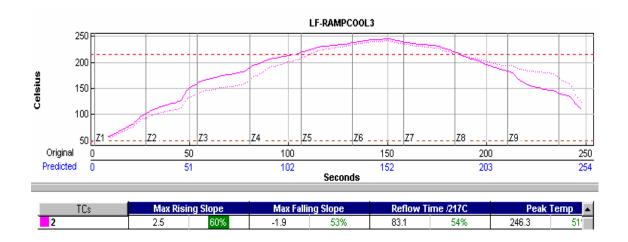

| Figure 4.5 Optical Micrograph for the "Quick" and "Moderate" Cool Down Profiles for Solder Joints on the Sn Surface Finish 90                     |    |

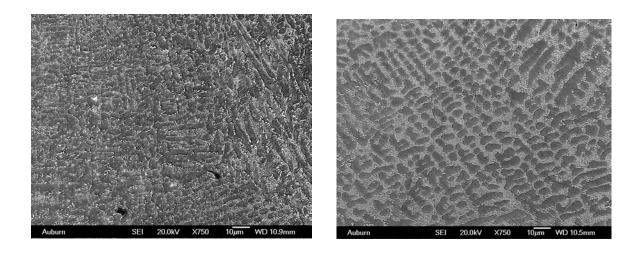

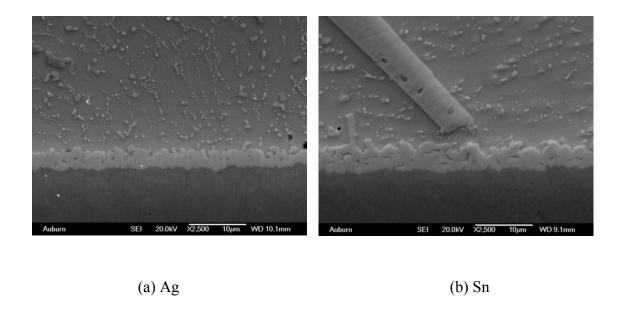

| Figure 4.6 As-built Intermetallic Structure for Ag and Sn Finishes, Moderate Reflow Profile                                                       | 91 |

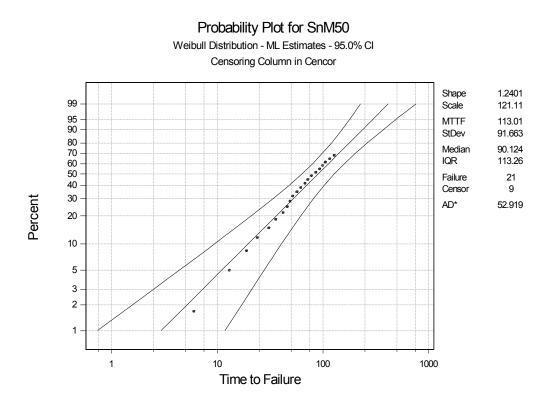

| Figure 4.7 Weibull Plot for Sn Surface Finish, Moderate Cooling, Aging 50hrs                                                                      | 92 |

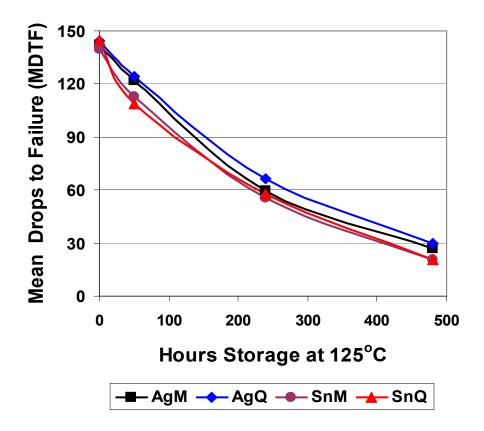

| Figure 4.8 Mean Number of Drops to Failure as a Function of Aging at 125°C, Surface Finish and Reflow Profile                                     | 93 |

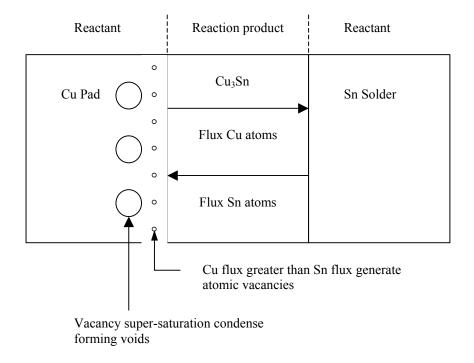

| Figure 4.9 Schematic Representation Depicting the Formation of Kirkendall Voids During the Reaction of Cu with Sn to Form Intermetallic Compounds | 95 |

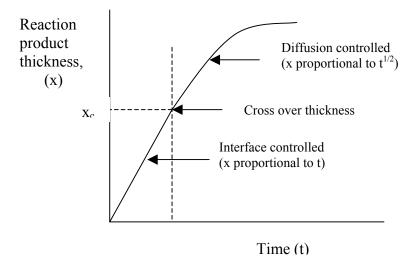

| Figure 4.10 Graphic Representation of Change in Reaction Kinetics with Reaction Product Thickness                                                 | 95 |

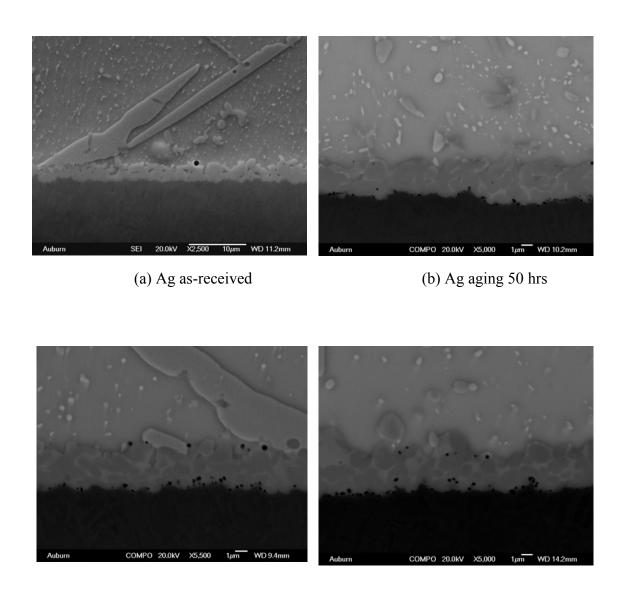

| Figure 4.11 Kirkendall Void Formation and Increasing as Aging Time Increases at 125°C, Ag Finish, Quick Profile                                                                 | 96    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

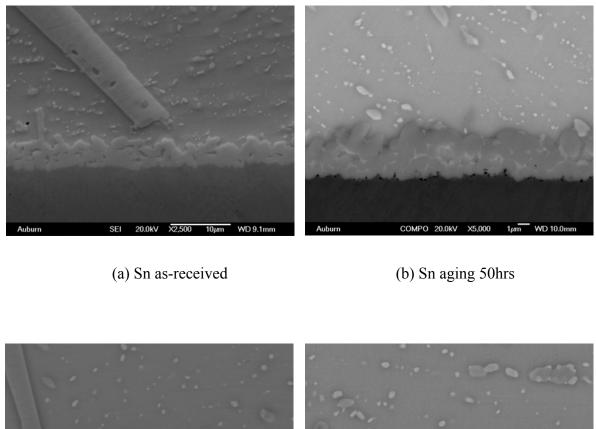

| Figure 4.12 Kirkendall Void Formation and Increasing as Aging Time Increases at 125°C, Sn Finish, Quick Profile                                                                 | 97    |

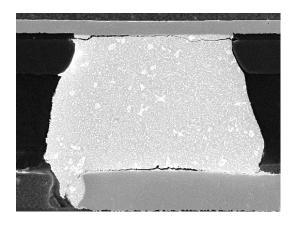

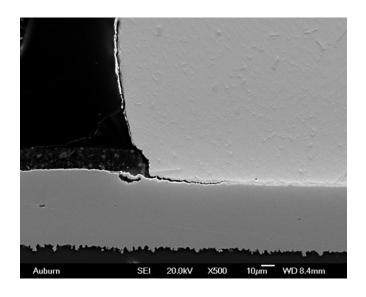

| Figure 4.13 Typical Crack Propagating Through the Cu-Sn Intermetallic (No Aging, Sn Finish, Quick Profile                                                                       | 99    |

| Figure 4.14 Close-up of Crack in Figure 4.13                                                                                                                                    | 99    |

| Figure 4.15 Typical Crack Propagating Through the Cu-Sn Intemetallic, then Turning into Cu (No Aging, Ag Finish, Moderate Profile)                                              | . 100 |

| Figure 4.16. Close-up of Crack in Figure 4.15                                                                                                                                   | . 100 |

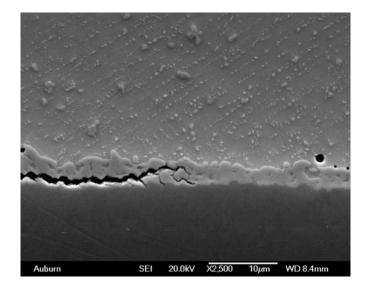

| Figure 4.17. Example of Crack Propagation With the Ag Finish, Quick Reflow Profile after 50 hours at 125°C                                                                      | . 101 |

| Figure 4.18. Example of Crack Propagation With the Sn Finish, Quick Reflow Profile after 50 hours at 125°C                                                                      | . 102 |

| Figure 4.19. Example of Crack Propagation in the Intermetallic Layer With the Ag Finish, Quick Reflow Profile after 240 hours at 125°C                                          | . 102 |

| Figure 4.20 Example of Crack Propagation in the Intermetallic Layer With the Ag Finish, Quick Reflow Profile after 480 hours at 125°C                                           | . 103 |

| Figure 4.21 Example of Crack Propagation in the Intermetallic Layer Turning into the Cu With the Ag Finish, Moderate Reflow Profile after 480 hours at 125°C                    | . 103 |

| Figure 4.22 Example of Crack Propagation in the Ni-Sn Intermetallic Layer on the CSP Side of the Solder Joint With the Ag Finish, Quick Reflow Profile after 480 hours at 125°C | . 104 |

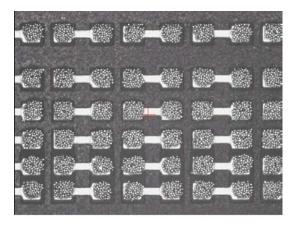

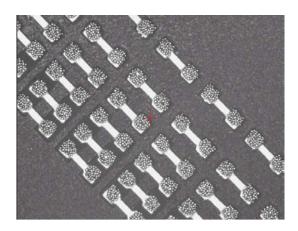

| Figure 5.1 01005 Test Vehicle                                                                                                                                                   | . 109 |

| Figure 5.2 Capability Histogram for Y4 (Pad Size 4)                                                                                                                             | . 111 |

| Figure 5.3 Capability Histogram for Pad-to-Pad Spacing 3                                                                                                                        | . 112 |

| Figure 5.4. Photograph of Pads and Solder Mask Showing Lack of Solder Mask between Pads with 4mil and 5 mil spacing. The other pad spacings are 6mils, 8mils and 15mils         | . 113 |

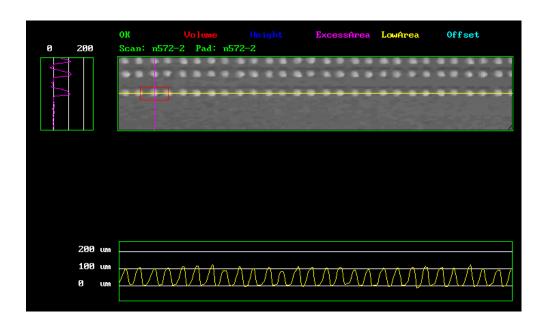

| Figure 5.5 3D Solder Paste Inspection Using the MVT SP-1 after Calibration                      | . 116 |

|-------------------------------------------------------------------------------------------------|-------|

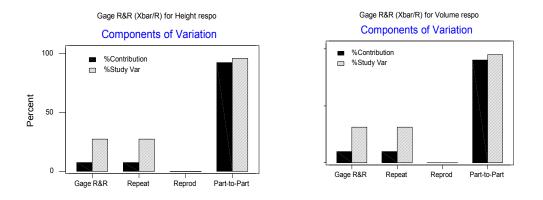

| Figure 5.6 Gage R&R for Height and Volume Response                                              | . 116 |

| Figure 5.7 Main Effects Plot for Means Based on Volume Transfer Efficiency                      | . 118 |

| Figure 5.8 Main Effects for S/N Ratio Based on Volume Transfer Efficiency                       | . 118 |

| Figure 5.9 Printing Performance Using Optimized Print Settings                                  | . 118 |

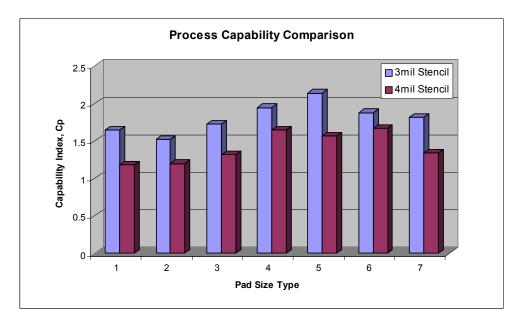

| Figure 5.10 Process Capability Comparison for Two Stencils and Pad Size Types                   | . 119 |

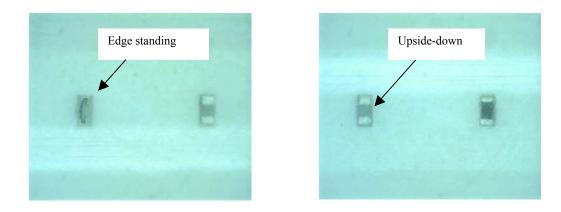

| Figure 5.11 Two Common Orientation Defects in As-received 01005 Components in Carrier Tape      |       |

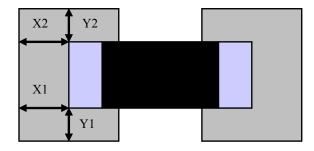

| Figure 5.12 Schematic of Distances X1, Y1, X2 and Y2                                            | . 121 |

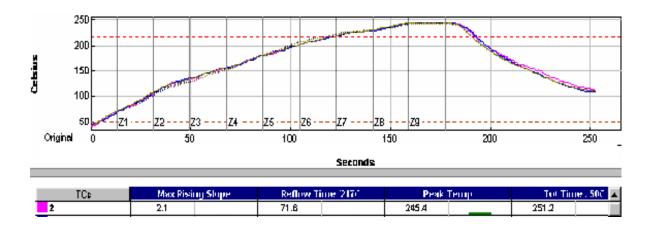

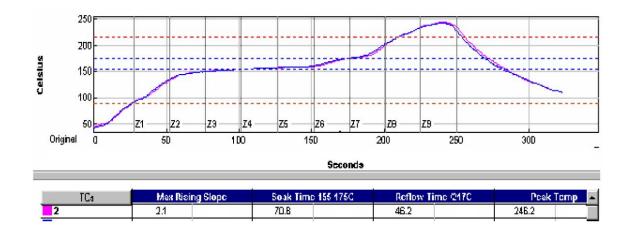

| Figure 5.13 Lead-free Quick-ramp Reflow Profile                                                 | . 123 |

| Figure 5.14 Lead-free Soak Reflow Profile                                                       | . 123 |

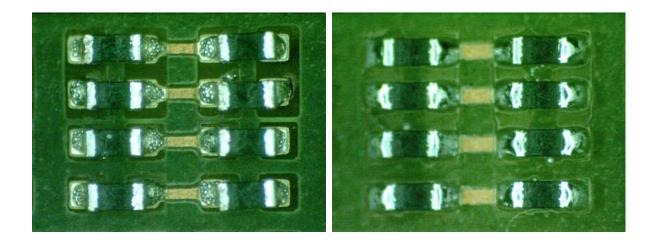

| Figure 5.15 Wetting Comparison in Air (a) or Nitrogen (b)                                       | . 124 |

| Figure 5.16 X-ray of Solder Joints for Ramp (a) and Soak (b) Profiles in Nitrogen               | . 124 |

| Figure 5.17. Defect Distribution in for all Build Combinations                                  | . 125 |

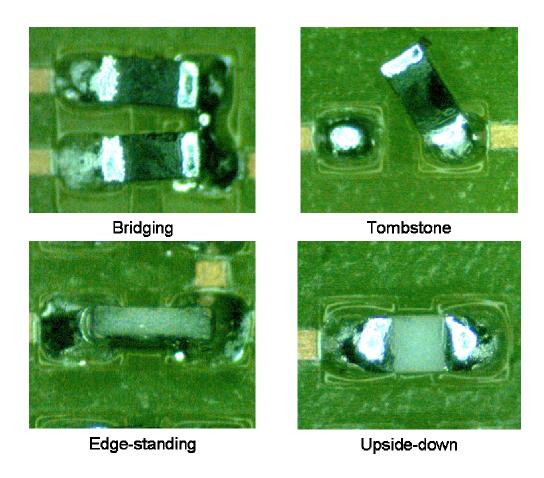

| Figure 5.18 Example of Different Defects                                                        | . 126 |

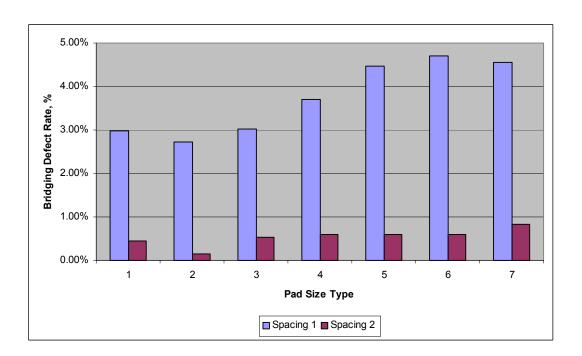

| Figure 5.19 Bridging Defect Rate Comparison for Different Pad Size Types                        | . 127 |

| Figure 5.20 Tombstone Defect Rate Comparison for Pad Size Type 1 with and without Vias-in-Pad   | . 128 |

| Figure 5.21 Tombstone Defect Rate as a Function of Reflow Profile                               | . 129 |

| Figure 5.22 Tombstone Defect Rate as a Function of Resistor Orientation for Type 1 Size Pads.   | . 129 |

| Figure 5.23 Tombstone Defect Rate as a Function of Pad Size Type                                | . 130 |

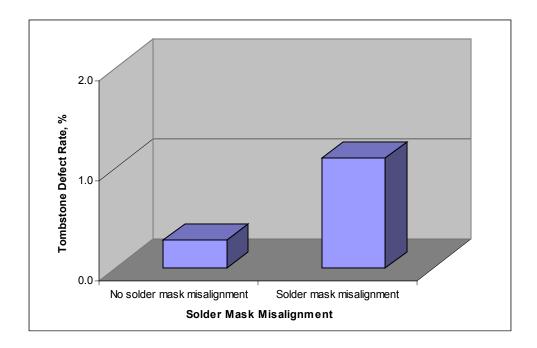

| Figure 5.24 Tombstone Defect Rate as a Function of Solder Mask Misalignment for Pad Size Type 1 | . 131 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Integrated Circuit (IC) Package Trends

The electronics industry is mainly driven by the demand for "smaller, lighter, faster, higher complexity, lower power consumption, and cheaper technology" [1]. Miniaturization continues to accelerate for portable consumer electronics, particularly for consumer electronic products like cell phones, personal data assistants (PDA), camcorders, laptops, cameras and MP3 players. In fact, another driving force in product miniaturization is the increasing complexity of features and functions, accompanied by a lower cost. This market dynamic has accelerated the development and use of finer pitch and smaller components with higher density, both in design and manufacturing technologies.

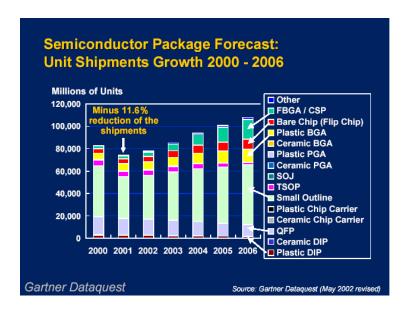

Chip Scale Packages (CSPs) and Fine-Pitch Ball Grid Array Packages (FBGAs) are the two package types that are most prevalent in portable hand held consumer electronics today [2]. If the area required by the die is more than 80% of the total package area, the industry typically refers to this as a CSP. FBGAs on the other hand are typically defined by their ball pitch, i.e. 1.0mm and below. As shown in Figure 1.1, over the next few years, it is likely that CSPs/FBGAs will experience the largest growth within mainstream IC packages. Much of the this growth will come by way of new

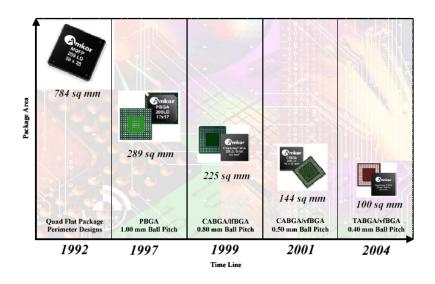

product introductions, although some of the growth will be due to Plastic Ball Grid Array (PBGA) and Quad Flat Package (QFP) migration. Figure 2 shows how a CSP/FBGA can significantly reduce the package area for roughly the same ball/lead count [2].

Figure 1.1 Unit Shipments Growth YR2000 through YR2006 [2]

Figure 1.2 IC Package Evolution and the area reductions achieved with CSPs/FBGAs [2]

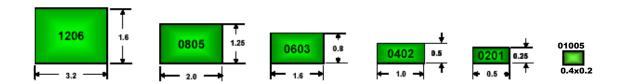

Passive components occupy a significant area on the printed circuit board (PCB), especially for analog and mix-signal applications, which use a larger number of passives compared to a typical digital system [3]. Reducing the size of the passive components and the spacing between them would increase the package density, and is an efficient way to miniaturize many electronic products.

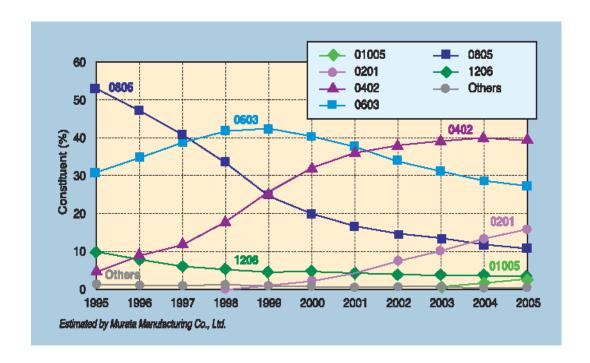

Figure 1.3 shows the dimensions of dominant passive components. An example of the size evolution of multi-layer ceramic chip capacitors is given in Figure 1.4 [4]. The chip size of the most commonly used passive components gradually decreased from 0805 chip in 1995, to 0603 (1.6-0.8mm) in 1998. With the increasing adoption of ultrasmall capacitors for mobile phones, digital cameras and digital camcorders and other compact portable products, set makers have begun to adopt 0402 (1.0-0.5mm), format products as general-purpose capacitors, so 0402 was projected to be the most popular size in 2003. 0201 (0.5-0.25mm) emerged in 1998 and is rapidly gaining market acceptance. Set makers are now demanding that monolithic ceramic capacitors be downsized still further to 01005 (0.4-0.2mm) size, and products of this size are expected to be used in 2004 for modular products that contain capacitors.

Figure 1.3 Dominant Passive Component Dimensions (mm) [2]

Figure 1.4 Trends in Size of Monolithic Ceramic Capacitors [4]

## 1.2 Chip Scale Package (CSP)

## 1.2.1 Advantages of CSPs

Chip Scale Packages combine the best of flip chip assembly and surface mount technology. It gives almost the same size and performance benefits as a bare die chip assembly, while offering the advantages of an encapsulated package. In comparison to standard surface mount technology, CSPs have the following advantages [5]:

- Reduced package footprint

- Thin profile and reduced weight

- Better electrical performance

- Area array distribution of connections (for most CSPs)

In comparison to standard flip chip technology assembly, CSPs have the following advantages:

- Encapsulated packages

- Easily testable with fast testing for known good dies

- Mountable using a conventional assembly line

- Accommodates die shrink without changing package footprint

- Reworkable

- Some CSPs do not require underfill when mounted on organic substrates

## 1.2.2 Types and Application of CSPs

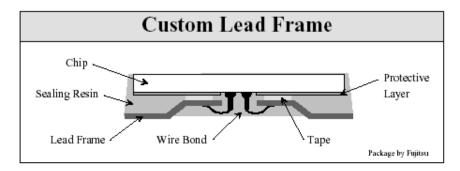

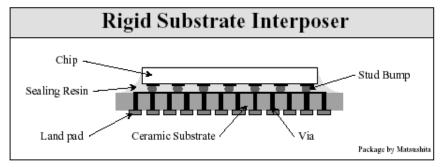

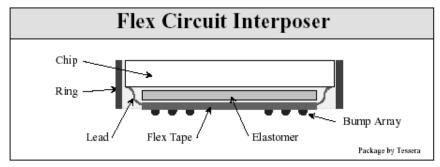

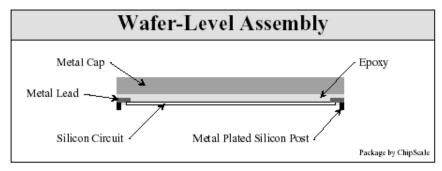

The package may use an interposer/carrier, and the interposer may be ceramic, polymer, or flex-film. Depending on the CSP design, the interconnection [7] between the IC and the carrier may be wire bonding, TAB, Au stud, soldering, or conductive adhesives. CSPs are generally classified into four major types based on their structure: flex circuit interposer, rigid substrate interposer, custom lead frame, and wafer-level assembly. Examples of packages of these types are shown in Figure 1.5 [6].

Reduction of size and weight are the most important factors during initial adoption of CSP technology. Consequently, consumer products such as camcorders, mobile phones, and laptops are among the products that have been first to use CSPs.

The electrical improvement and high-speed architecture development for memory also make them attractive for DRAM applications.

Figure 1.5 Main CSP Types [6]

### 1.3 Lead-free Technology

#### 1.3.1 Driving Forces for Lead-free Technology

Electronic products currently contain lead (Pb) in their components, printed circuit boards (PCBs) and solder joints. The eutectic tin-lead alloy (63%Sn37%Pb, wt%) has been practically the only alloy used for soldering purposes in electronics. Although electronics manufacturing accounts for less than 0.6% of lead consumption in the world [8], electronic products often end up in landfills after their disposal, and lead can potentially leach out from the landfills into water supplies. In the USA, the regulatory limit for lead in drinking water is set at 0.015 mg/l, as per EPA40 CFR141. The limit is set at 5 mg/l if the test follows the Toxicity Characteristics Leaching Procedure (TCLP), as per EPA40 CFR261 [9]. A recent study [10] demonstrates that the lead that leaches out from solder can be several hundred times higher than these limits.

Lead is dangerous to human health. The most common types of lead poisoning are classified as alimentary, neuromotor, and encephalic [11]. Lead poisoning often occurs following a prolonged exposure to lead or lead-containing materials [12]. Therefore, the risk of lead leaching from landfills into water supplies must be eliminated.

There are several forces driving the movement toward the elimination of Pb.

The initial driving force is the fear of legislation, for example, the proposal of (RoHS) and WEEE directives in Europe to restrict the sale of lead-bearing electronic products,

effective July 1, 2006; recycling laws in Japan; and pending regulations in both China and California. However, recently other forces such as the market-driven commercial advantages associated with environmental-friendly electronics have raised a great deal of interest in the industry and have accelerated this process. "Green electronics" is gaining greater appreciation from consumers [13]; so green marketing is now rapidly being viewed as a powerful and effective marketing tool.

#### 1.3.2 Lead-free Solder Alloy

The criteria for screening candidate lead-free alloys can be summarized as follows:

- Nontoxic

- Available and affordable in sufficient quantities

- Exhibit sufficient electrical and thermal conductivity

- Possess adequate mechanical properties: strength, toughness, fatigue and creep resistance

- Compatible with typical terminal metallizations (eg. Cu, Ni, Ag, Au, Sn, etc.)

- Have acceptable melt and process temperatures

Several review papers have been published on the development of lead-free solders. [13-19]. Vincent and Humpston summarized their research on electronic assembly using binary lead-free solder. The factors they considered were economic and supply limitations, as well as the technical questions such as solderability and reliability [19]. Hwang systematically illustrated important solder properties for practical applications, especially those properties that are important to ensure solder joint integrity in surface

mount technology. The comparisons between lead-free alternatives and conventional Sn-Pb or Sn-Pb-Ag eutectic solders were emphasized [17]. Glazer reviewed the physical metallurgy aspects, including the physical properties and microstructure, mechanical properties, and oxidation and corrosion behavior of binary lead-free solders [15]. This database was later updated and expanded to include the Sn-Ag-, Sn-Zn-, and Sn-Bi-based ternary solders. The manufacturability issues for applications of these lead-free solders in low-cost electronic assembly were also presented [16]. Abtew and Slvaduray discussed the properties of the binary lead-free solders and technical issues of solder joints [14]. Suganuma reviewed recent developments in ternary lead-free solders and the interaction of these solders with metallization [18].

A great deal of effort has been directed to the development of a eutectic Sn-Ag-Cu solder. Based on the above criteria, eutectic Sn-Ag-Cu alloy is considered to be the most promising candidate for replacing eutectic Sn/Pb systems. Cu is added to Sn/Ag in order to lower the melting temperature, and improve the wettability, creep and thermal fatigue characteristics. The ternary eutectic temperature is at 217°C. Its thermomechanical properties are also better than those of the conventional Sn-Pb solder [20]. In 2000, NEMI recommended the use of eutectic Sn-Ag-Cu alloy (Sn3.9 Ag0.6Cu) to replace eutectic Sn-Pb alloy in reflow processing and eutectic Sn0.7Cu alloy in wave soldering [21]. These alloys have already been used successfully in production and have demonstrated exceptional reliability in thermal cycling compared to eutectic Sn-Pb.

### 1.3.3. Issues in Implementing Lead-free Technology

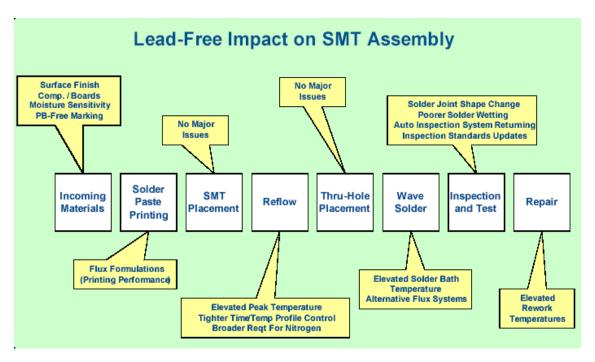

The impact of using lead-free technology for SMT assembly is shown in Figure 1.6 [22]. There are several important issues that arise as a consequence of switching from eutectic Sn-Pb to a lead-free solder technology for microelectronic chips, packages, and assemblies. The key issues are discussed in this section.

Figure 1.6 Lead-free Impact on SMT Assembly [22]

#### 1.3.3.1 Higher Process Temperatures

Most lead-free alloys of interest have a melting temperature that is 35-40°C higher than eutectic Sn-Pb (Melting Point = 183°C), which often has a drastic effect on the integrity, reliability, and functionality of printed wiring boards, components, and other attachments [23]. The bulk of lead-free research has focused on identifying suitable solder candidate alloys to replace eutectic Sn-Pb. The effects of higher process

temperatures on various microelectronic board assemblies when utilizing most lead-free solders are listed in Table 1.1 [41], and other issues related to higher process temperature will be discussed in the following section.

TABLE 1.1 Effect of Higher Process Temperatures on Various Microelectronic Board Assembly [41]

| Board assembly items               | Effects                                                                           |

|------------------------------------|-----------------------------------------------------------------------------------|

| Components                         |                                                                                   |

| Ceramic chip carriers              | Little to none                                                                    |

| Organic chip carriers              | Degradation can be substantial, depends on $T_{\text{\scriptsize g}}$ of material |

|                                    | Increased moisture sensitivity level                                              |

| Specials: electrolytic capacitors, | Susceptible to damage, typically designed for 230°                                |

| wound components, etc.             | maximum temperature, some up to 260°C                                             |

| Printed circuit board material     | Standard FR-4, $T_g \sim 140^{\circ}C$                                            |

|                                    | Subject to degradation                                                            |

|                                    | Higher T <sub>g</sub> materials                                                   |

|                                    | Will survive proposed ~ 240°C                                                     |

|                                    | Typically will not survive ≥ 260°C                                                |

| Plastic overmold material          | Thermal plastics may undergo shrinking or warping                                 |

|                                    | or cause critical features to move (creep)                                        |

|                                    | Thermal setting compounds, typically not affected                                 |

|                                    | by MSL-related effects                                                            |

| Fluxes                             | Must be formulated to be active near and at the alloy                             |

|                                    | melt point temperature                                                            |

|                                    | Must not create charred masses that hinder soldering,                             |

|                                    | or allow surface reoxidation                                                      |

Higher reflow temperatures increase dissolution rates, which may result in an increased concentration of termination pads and surface finish elements in solder joints.

Copper is the main circuit material utilized for PCBs and also some component lead frames (e.g., small outline—SO; quad flat pack—QFP; plastic leaded chip carrier—PLCC) owing to its good electrical conductivity and solder wetting properties. Tin has a high affinity for copper, so the high tin composition of many lead-free solders and their high melt temperatures lead to a much increased tendency to dissolve copper termination pads compare to eutectic Sn-Pb. The lead-free alloys have significantly greater Sn contents and melting points than eutectic Sn-Pb, which both serve to boost the Cu dissolution rate to between two and seven times faster compared to 60Sn-40Pb [100]. Excessive intermetallic compound formation (Cu<sub>6</sub>Sn<sub>5</sub>) can also adversely affect the solder joint reliability due to the brittle nature of this compound, particularly under impulsive load conditions [24].

Nickel/gold is another popular board finish. However, care must be exercised to not exceed the rule-of-thumb Au threshold concentration in a solder joint, which is approximately 3% [25].

#### 1.3.3.2 Component Finishes

Lead-free manufacturing not only pertains to solder pastes and solder bars for wave soldering, but also as a substitute for the lead-bearing finishes used for component leads and solder bumps. In general, the change to lead-free finishes for components is expected to be a substantial part of the conversion of electronic assemblies to lead-free manufacturing, and may well be the most difficult to implement. Component manufacturers have reliability concerns related to both the impact of devising suitable

processes to provide consistent, high-quality finishes with new materials, and also the effects these finishes will have on the integrity of solder joints. As noted earlier, there is also some concern about the possible effects that increased process temperatures will have on the components themselves [26].

Many peripherally leaded components utilize Sn-Pb finishes for the leads. In general, it is relatively easy to eliminate lead from surface finishes on the leads of components. Examples of alternatives include Pd/Ni, Sn, Au, Ag, Ni/Au, Ag/Pt, Ag/Pd, Pt/Pd/Ag, Pd, and Ni. These finishes have all been used in the past and are likely to be key contenders for use in completely lead-free systems [27]. Ni/Pd finished terminations have previously been evaluated with several lead-free solders and found to provide solderability comparable to eutectic Sn-Pb [28]. Sn-Bi-based finishes have also been utilized with component lead frames for some time. These finishes exhibit excellent mechanical properties when used with Sn-Ag-Bi solders. [29]. Several plated, tin-based lead-free finishes, such as Sn, Sn-Bi and Sn-Cu among others have been found to be suitable for component terminations (i.e., lead frames) [30].

Area array components (i.e., Ball Grid Arrays) typically consist of eutectic Sn-Pb or Sn-Pb-2%Ag solder ball terminations. It appears that the major lead-free solder candidates are also suitable as BGA solder ball materials. However, if the melting temperature for the later interconnections is set around 220°C, then the first level interconnection needs to have a melting point of at least above 260-270°C in order to avoid remelting during subsequent reflow processes. A suitable high melt, lead-free alloy that meets the condition of low cost and whose melting point is within the range of

250-300°C has not yet been identified. The only well-established lead-free alloy in this temperature range is 80Au-20Sn, which is too expensive to be utilized for this application [31]. There are also concerns with lead-free terminated BGA components, among which are their wetting and self-centering characteristics, both of which impact placement accuracy requirements and manufacturing yields [32].

Some lead-free component finishes are eutectic Sn-Cu or pure Sn. Sn whiskers readily grow on high Sn content finishes under certain condition, which may cause shorts, so Sn whiskers are major concern for components with high Sn finishes.

#### 1.3.3.3 Board Surface Finishes

The PCB industry currently produces a number of lead-free finishes including electroless nickel/immersion gold (ENIG), Immersion Ag (Im Ag), Sn, Ni/Pd, and organic solderability protectants (OSPs).

a. Hot Air Solder Leveling (HASL). It is a physical deposition process using bulk liquid metal into which the board is dipped to apply coatings. A secondary step (hot air blow) is used to level or reduce the amount of material retained on the surface [31]. Hot air solder leveling accounts for over 60% of the surface finishes on printed circuit assemblies. The PCB industry has been exploring alternatives to HASL that eliminate thermal shock for boards, which is further aggravated by the increased process temperature required by most lead-free alloys.

- b. *Plated Finishes*. The trend here is to provide thinner, more uniform, and planar finishes that facilitate fine-pitch assembly. These conditions are more easily achieved by utilizing plated finish solutions:

- 1. Electroless Nickel/Immersion gold—The Interconnection Technology Research Institute (ITRI) and others have investigated the failure of SMT parts, particularly eutectic Sn-Pb BGA component solder joint failures associated with electroless Ni/Immersion Au metallization on board pads [37]. These failures general occur under mechanical shock test conditions. Given the root cause theory of this type of failure, it is anticipated that lead-free solders will experience the same failure mechanism. Nickel/gold finishes are often utilized for higher temperatures and multisoldering purposes. The cost of Ni/Au is about 25% higher than for OSP finishes [26].

- 2. Electroplated tin—Electroplated Sn exhibits excellent solderability and corrosion resistance, but is prone to Sn whisker growth. Thin, hair-like whiskers grow from the surface and pose a potential reliability problem due to the electrical shorts they may cause in the field [38-40]. Heat fusing or reflow is used to eliminate tin whiskers [26].

- c. *Organic Solderability Protection (OSP)*. OSP is an anti-tarnish coating of an organic compound over a copper surface to prevent oxidation. It is a water-based organic compound that selectively bonds with copper to provide an organometallic layer that protects the copper. OSP keeps the copper surface solderable and flat, and it is lead-free and hence may be considered more environmentally friendly [31].

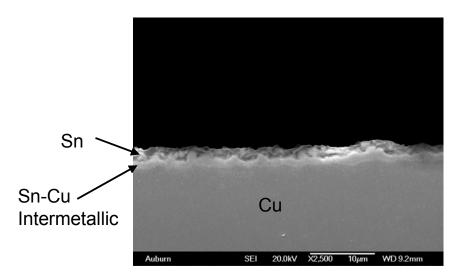

Effects of Higher Process Temperatures. The higher process temperatures typical of lead-free solders may cause some lead-free surface finishes to react more rapidly compared to eutectic Sn-Pb conditions. If the board finish is Sn finish, it can be consumed in Cu-Sn intermetallics and then lose solderability with multiple high temperature reflows.

Oxidation problems with OSPs can result upon exposure to several soldering processes, particularly at elevated lead-free soldering temperature conditions. Utilizing an inert atmosphere and reformulating OSPs to withstand higher process temperatures will reduce this risk [26].

Another area of concern is the reaction rate between lead-free solders and terminal metallurgy systems. The formation of Ni-Sn IMCs at the interface is considerably slower than the formation of Cu-Sn IMCs. This is an important aspect that must be taken into consideration because the Sn content and process temperature are both significantly higher for lead-free solders compared to eutectic Sn-Pb, so the reaction rates are quicker. The formulation of excessively thick IMC layers should be avoided to prevent weak solder joints. However, even with a reduced formation rate, a thicker Ni layer is required than for eutectic Sn-Pb solders [28].

## 1.3.3.4 Process Challenges

As noted previously, the preliminary challenge that lead-free solders present for IC and component manufacturers, and electronic assemblers is the higher process temperatures typically required of lead-free solders. The generally accepted limit that

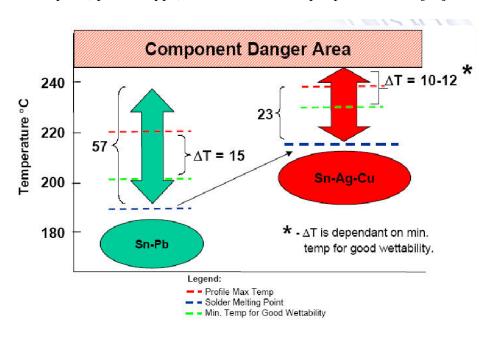

IC packages can withstand is approximately 240°C, and the lower limit to reliably reflow eutectic Sn-Pb solders is about 205°C. This provides approximately a 35°C process window, which is sufficient in a properly monitored line to produce a low-defect-rate, high-yield product with a low risk of creating process drift-related defects. However, with lead-free assemblies, the process window shrinks dramatically, as illustrated in Figure 1.7 [22]. For Sn-Ag-Cu alloys, whose liquidus is 217°C, the process window is reduced to only 10°C. Given that assemblers, prefer to remain within 5°C of their control limits, the actual process window is therefore very small. However, it has been determined that the soldering process can be significantly improved by obtaining and analyzing data on a real-time basis in a reflow oven. Process control can be aided by utilizing prediction software that customizes the profile for a specific solder paste, product type, and user-defined input process limit [33].

Figure 1.7 Lead-free Tighter Process Window [22]

#### 1.3.3.5 Rework

Rework is the term in the electronics industry that pertains to removing and subsequently replacing one or more of the components or other attachments on a PWB. The procedure typically consists of locally heating the solder joints of the component. When the solder joints melt, the component is lifted away from the board either by mechanical means or by a vacuum-activated device. A replacement component is locally reflowed to the same site. Typically the board is also heated from the underside to lower the thermal gradient and to reduce warping.

Rework is an important aspect of manufacturing that helps meet required yields to achieve economic viability—another aspect that is expected to be substantially affected by the change to lead-free technology. Rework operators will require additional training, and further development work will be necessary because the properties and melting points of the solders can be significantly altered from component to component across an assembly because of elemental additions introduced to the solder from the PWB and terminal pad metallization systems.

Several studies focusing on rework practices for solders have been reported [34, 35, 36, 44]. The rework of lead-free solder joints has been shown to be technically feasible. Concerns associated with locally heating printing circuit boards or attachments at high temperatures are mostly associated with the need to reflow heavy and complex components such as BGAs that require a high level of heat to effectively achieve removal and reflow. With careful optimization, it appears that rework can be

accomplished without damaging temperature-sensitive parts with minimal board warpage. The same issues apply to rework of general assembly operations, soldering temperatures and other parameters must be tightly controlled.

#### 1.4 Board Level Reliability of Lead-free Solders

#### 1.4.1 Limited Database

Long-term reliability remains a major unknown, since there is currently only a limited database for lead-free solders. Even with accelerated testing, it will take years to generate an understanding equivalent to that presently available for eutectic Sn-Pb. The need for this level of understanding is admittedly less critical for relatively short-lived consumer electronics applications such as games, mobile telephones, or other handheld telecommunication devices, but for applications whose service lifetimes are expected to span from a few years to a decade or more, this lack of information is a real concern. Numerous studies have indicated that, in general, lead-free alloys including Sn-Ag-Cu exhibit a level of reliability under accelerated testing conditions that is at least equivalent to that of eutectic Sn-Pb solder joints, and in many cases is substantially better [41]. The field data for the lead-free solders utilized in several niche products such as phones (Nortel), minidisc players (Panasonic), laptop and tabletop personal computers available from several manufacturer have not indicated any major reliability problems [41]. However, more accelerated laboratory tests and field data are necessary before drawing conclusions about the long-term reliability of these solder materials, as

they have so far been used in a limited number of solder joint configurations and field conditions [41-43].

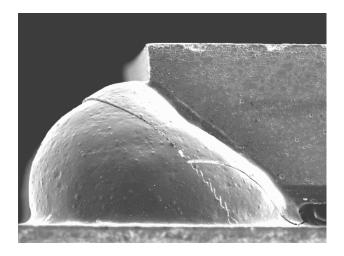

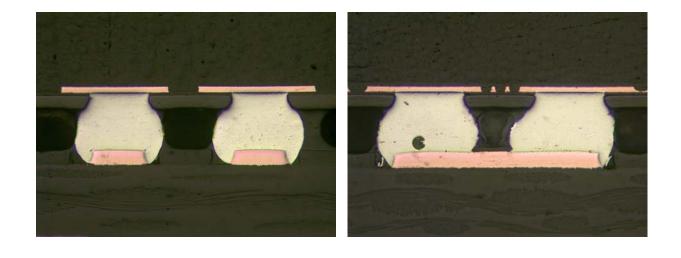

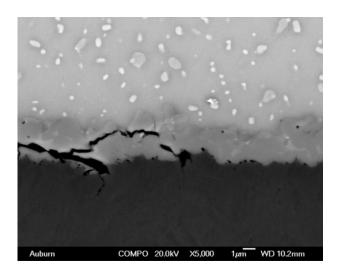

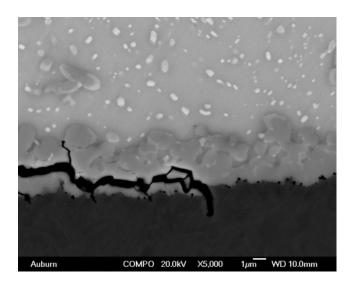

## 1.4.2 Drop Reliability of Lead-free Components

Two of the main failure modes for packages to board solder joint interconnects are low cycle solder fatigue due to thermal excursions and brittle fracture caused by static and dynamic loads such as impact shock, vibration, and bending. Traditionally, the critical failure mode of interest has been solder fatigue, which is driven by the coefficient of thermal expansion (CTE) mismatch between the component and motherboard. However, due to the continuous push for device miniaturization and new applications in portable electronics, which are subjected to human clumsiness, solder joint failure under drop or shock conditions has now become a critical reliability issue. Instead of ductile fatigue cracking through the bulk solder that is typically observed in thermal cycle loading, the typical failure mode for a solder joint under drop impact is brittle fracture of the intermetallic compound (IMC) between the board pad and bulk solder joint [69].

Researchers are now starting to pay more attention to drop test studies and analyses due to urgent industrial demands to understand the failure mechanisms involved [45-50]. A new JEDEC standard for board level drop tests of handheld electronic products has just been released that specifies the drop test procedure and conditions that should be used for such tests [51-53].

New reliability concerns are also arising due to the increasing complexity of solder metallurgies, since as a result of the new environmental requirements novel combinations of solder paste, printed circuited boards (PCB) surface finishes and component terminal metallizations are being employed. Therefore, it is important to have a systematic study of the metallurgical reactions and the evolution of the related microstructures of solder interconnections, as well as their impact on reliability, especially when soldered assemblies are tested under mechanical shock loading conditions.

## 1.4.2.1 Effect of the Surface Finish on Drop Reliability

The compatibility of PWB surface finishes with solder compositions is an important factor governing the reliability of solder joints. Extensive work has been conducted to study the effect of PCB surface finish on the thermal fatigue reliability performance of lead-free solder joints and their underlying failure mechanism. However, very few papers have been published on the board level reliability under drop conditions [55-61]. The influence of surface finish on drop impact reliability has not been comprehensively documented and the failure mechanism not yet well understood.

Samhit et al. [54] discussed the reliability implications of the incompatibility between 96.5Sn3.5Ag solder and two PWB surface finishes (Electroless Ni/Immersion Au and pre-tinned Cu) for the case of a Cu terminated component. Their work illustrates how surface finish combinations involving Cu and Electroless Ni/Immersion Au on the component and board, respectively or vice versa, can present reliability risks

in thin (30-100*um*) solder joint assemblies in portable electronic products that are subjected to mechanical drop environments.

Chong et al. [55] studied the effects of drop impact on the reliability of solder interconnects of leaded (36Pb62Sn2Ag) and lead-free (Sn4Ag0.5Cu) compositions. The influence of different package types and the impact of PCB surface finishes of OSP and ENIG (electroless Ni/Immersion Au) were also examined. The drop test results showed that lead-free solder joints on the ENIG finish have weaker drop reliability performance compared to the leaded and lead-free solders on an OSP finish.

Mikko et al. [60] investigate two different types of wafer level chip scale package (WL-CSP) components with eutectic Sn3.8Ag0.7Cu and eutectic SnPb solder paste on Ni (P)/Au and OSP surface finishes under standard drop test. The failure analyses revealed that the primary failure mode in the component side was the cracking of interconnections along a brittle NiSnP layer between the electroless Ni(P) of high P-content and the solder alloy, while components with (Al)Ni(V)/Cu UBM failed by cracking along the [Cu, Ni]<sub>6</sub>Sn<sub>5</sub> intermetallic layer. On the board side the cracking occurred in the porous NiSnP layer formed between the electroless Ni(P) metallization and the (Cu, Ni)<sub>6</sub>Sn<sub>5</sub> intermetallic layer. The fact that the cracking occurred predominantly on the component side reaction layer was though to be due to three factors: higher normal stresses on the component side, brittleness of the reaction layer(s) and the strain-rate hardening of the bulk solder interconnections.

Jiang et al. [61] compared the reliability of two solder compositions (Sn-Pb and Sn-Ag-Cu) and two surface finishes (Ni/Au and OSP). The results indicated Sn-Ag-Cu

solder showed lower fracture toughness then SnPb solder during drop impact. The crack path in the SnPb solder joint almost always went through bulk solder near the substrate side. However, IMC interfacial failure near the substrate side was found in the Sn-Ag-Cu solder. The Ni/Au surface finish showed a better drop performance than OSP in both Sn-Pb and Sn-Ag-Cu solder joints.

## 1.4.2.2 Effect of Underfill on Drop Reliability

Underfill materials are often used to enhance the reliability of a variety of component types, including flip-chips, chip scale packages (CSPs), and ball grid arrays (BGAs) [62-67]. Most manufacturers that use flip-chips on boards (FCOB) or a flip-chip in a package (e.g. FC-BGA) underfill them due to the large CTE mismatch between the silicon die and the substrates. The other packages may only be underfilled if there is either a perceived risk to the products (e.g. a cell phone may undergo frequent drops) or for a high reliability application (e.g. avionics). The CTE matching of the underfill materials is typically achieved through the addition of silica-based fillers. This addition lowers the CTE and thus provides a gradient between the silicon chip and the substrate.

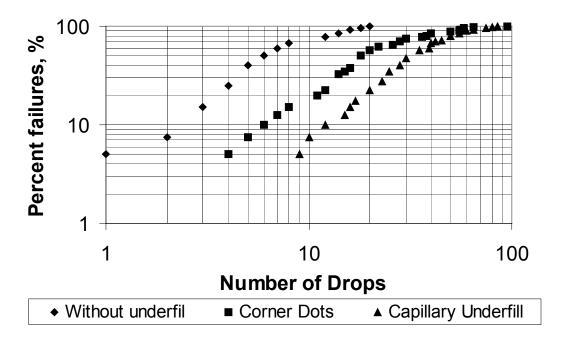

Liu et al. [65] examined the assembly process with capillary and fluxing underfills. Issues of solder paste versus flux only, solder flux residue cleaning and reworkability were investigated for the capillary flow underfills. Drop tests were performed to evaluate the relative performance of the underfills, and the results indicated that all of the underfills significantly (5-6x) improved the reliability in the

drop test compared to nonunderfilled parts. Test vehicles were also subjected to liquid-to-liquid thermal shock testing. The use of underfill improved the thermal shock performance by 5x.

Ghaffrian et al. [67] studied the effect of underfill on CSP reliability. Three package structures were tested: leadless CSP, flex-on-chip CSP and TAB CSP. The results showed that underfill improved the reliability of leadless packages, had a minimal impact on flex-on-chip CSPs, and was negative for TAB CSP reliability.

The most common reason to underfill CSPs is to improve their shock and vibration reliability (drop testing). However, their widespread use has been limited due to complex application requirements that restrict the integration of underfills into SMT assemblies, and also complicate repair and rework [68]. New developments in underfill materials that can be pre-applied to the CSP prior to board-level assembly will eliminate the uncertainties and imprecision of liquid underfill dispensing, a concept that is most often associated with wafer-level package.

## 1.4.2.3 Effects of Thermal Aging and Kirkendall Void on Drop Reliability

Drop tests are typically performed on as-built samples. However, customers expect their portable products to survive dropping after some use time in the field, so portable electronic products such as cellular phone should undergo thermal aging prior to the drop and bend tests.

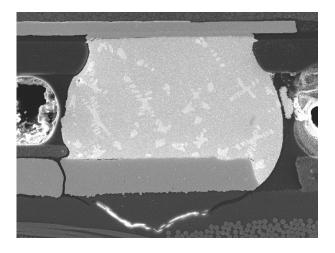

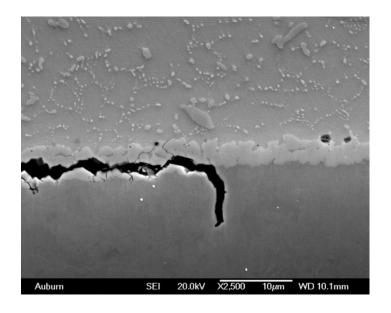

Chiu et al. [69] conducted drop tests and shear tests of ball grid arrays (BGAs) with Sn-Ag-Cu solder balls on Cu pads after thermal aging at 100°C, 125°C, 150°C,

175°C for 3, 10, 20, 40 and 80 days. Kirkendall voids were observed at the Cu to Cu<sub>3</sub>Sn interface. Voids occupied 25% of pad/solder interface after only 3 days of 125°C aging, and the void density increased with the aging time and temperature. The drop performance degraded 80% from time 0 to 10 days at 125°C.

Date et al. [70] performed miniature Charpy tests on solder balls of eutectic Sn-Pb and Sn-Ag-Cu bonded to Cu, which were subsequently aged at 150°C for up to 1000hrs. A large number of voids were observed in the Cu<sub>3</sub>Sn phase after 500hrs aging at the interface between solder and Cu. A ductile to brittle transition associated with the fracture inside the solder to within the interfacial intermetallic compound (IMC) phase was seen as the aging time increased.

The formation of Kirkendall voids at the solder/Cu interface had been reported by earlier researcher. In 1994, Yang and Mussel [71] reported observation of voids at the interface between a eutectic Sn-Ag solder joint and electroplated Cu after aging at 190°C for 3 days. It is interesting that they also aged the same solder on rolled Cu at 190°C for 12 days. Although the Cu<sub>3</sub>Sn phase existed, no voids were found in either the Cu<sub>3</sub>Sn phase or the Cu<sub>6</sub>Sn<sub>5</sub> phase. Their explanation was that during the formation of the Cu<sub>3</sub>Sn phase, the mass imbalance due to the different diffusion rates of Sn and Cu induced the formation of vacancies or fine Kirkendall voids, which may be accelerated by the hydrogen introduced during the electroplating process.

Ahat et al. [72] reported a study of interface microstructure and shear strength of 96.5Sn3.5Ag and 62Sn36Pb2Ag on Cu after aging at 250°C for 0, 50, 250, 500, and 1000 hrs. As the aging time increased, more voids formed in the Cu<sub>3</sub>Sn phase. The

shear strength of both the Sn-Ag and Sn-Pb-Ag decreased with aging time, and the fracture mode changed from mixture of solder and IMC at zero aging time, to a complete fracture of the IMC layer after 1000 hrs aging.

Mei et al. [73] carried out a study that focused on two issues: the conditions for void formation, and the effect of voids on solder joint reliability. There were a total of 9 cases studied based on the different combinations of components, component finish, solder and board surface finish. Voids were seen in high, low, and zero densities in samples under different conditions, after aging either for 20 days at 125°C or for 5 days at 145°C. For Case 4, leaded component (10 µm electroplated SnPb over lead-frame of 97Cu2.5Ni0.5Si aged 5 days at 145°C), very few voids were seen and the Cu<sub>3</sub>Sn phase was not visible. For case 7, leaded component with 10 µm electroplated matt Sn over Cu-3Ni lead-frame, attached onto the motherboard with OSP Cu pads, -40°C-125°C 2000 cycles, there were few voids at the interface between the solder and the mother board; no voids were visible at the interface between the solder and component lead. It seems that the Cu plating process and the small concentration of Ni in either the solder or substrate influenced the void density and distribution. Voids were seen in the thermal cycled assemblies. Drop tests showed that aged BGAs did not fail at the voided interface; rather the failures occurred inside the solder joint or PCB laminate. The shock strength at 400G of BGAs packages aged for 20 days at 125°C did not degrade.

## 1.5 Research Objectives

The main objective of this research was to develop and optimize the assembly processes for chip scale packages (SnPb/lead-free) and very tiny 01005 components (lead-free), and to evaluate the drop reliability of CSPs. Four projects were conducted and are presented in the following chapters.

Chapter 2 examines the SnPb CSP assembly processes with corner bonding underfill including underfill dispensing, CSP placement and reflow. SnPb CSPs were used as a baseline to compare with lead-free CSPs in the latter chapters. Drop tests were carried out to evaluate the drop reliability of CSPs with corner bonding underfill and the results compared with those obtained with conventional capillary underfill and non-underfilled CSPs. Failure analysis was performed to find the typical failure modes and the location of solder joint cracks for different underfill processes using cross-sectioning and SEM technologies.

The assembly processes for three underfill options (capillary underfill, fluxing underfill and corner bond underfill) compatible with lead-free assembly were developed and are discussed in Chapter 3. CSPs with eutectic SnPb were compared with lead-free CSPs. Drop tests and failure analyses are also included.

Chapter 4 investigates the effects of surface finishes (Immersion Sn and Immersion Ag), reflow profiles (two cooling rates) and thermal aging on the drop reliability of lead-free CSPs. The test vehicles were assembled and then subjected to thermal aging to simulate IMC growth under application conditions. Drop test results for assemblies as-built and as a function of aging at 125°C were correlated with cross

sectional analyses of the solder joints. Microstructural and failure analysis were also conducted to study IMC evolution and the formation of Kirkendall voids, as well as the effect of those changes on drop reliability.

Chapter 5 describes a test vehicle designed to investigate the effect of PCB pad design on 01005 chip resistor assembly yield. The process capability for 01005 test board manufacturing was evaluated. A Design of Experiment (DOE) was used to optimize the solder paste printing based on 3D solder paste inspection. Lead-free solder was used for all assembly trials. Several tests were performed to explore the influences of process parameters on placement accuracy and reflow defects. As a result of a through analyses of the experimental results and post-reflow inspection for assembly defects, recommendations for PCB design and assembly processes are provided.

Chapter 6 concludes the dissertation results and findings and discusses the topics for future work.

#### **CHAPTER 2**

# PROCESSING AND RELIABILITY OF CORNER BONDING CHIP SCALE PACKAGES

#### 2.1 Introduction

Chip scale packages (CSPs) are now widely used for many electronic applications, especially in portable products. Usually CSP designs are expected to meet the necessary thermal cycle or thermal shock reliability requirements for those applications. However, with decreasing pad sizes and solder joint volumes, the mechanical shock (drop) and bending resulting from mishandling during transportation or customer usage, may cause solder joint failure, which eventually leads to product malfunctions. Therefore, board level solder reliability during drop impact is a great concern to semiconductor and electronic product manufacturers, especially for handheld or portable telecommunication devices such as mobile phones and PDAs.

The use of underfills is known to increase the mechanical strength of CSP-to-board connections [62-67]. The most common underfills used in the electronics industry today are capillary underfills with low viscosity, which are developed to flow underneath a component by capillary action after reflow, and are then cured at elevated temperatures to form a bond with high adhesion to both the component and the substrate. If moisture is present in the PCB, a dehydration bake is required prior to

underfilling to eliminate voids in the underfill [74]. Since capillary underfills need additional board dehydration, underfill dispensing, flow and cure steps and the associated equipment for the assembly process, this process increases the cost of materials, capital equipment, and process time. Consequently, manufacturers of portable electronics are looking for other solutions that would not only improve drop performance but also reduce cost.

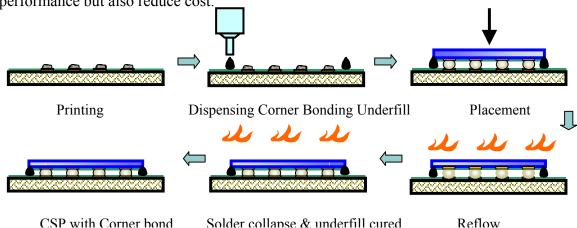

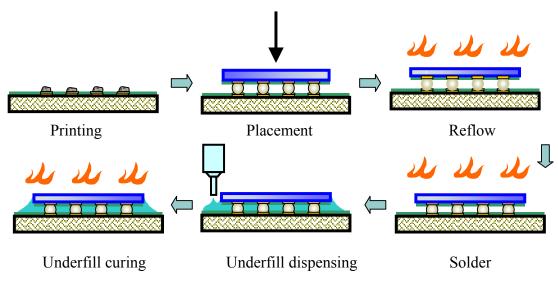

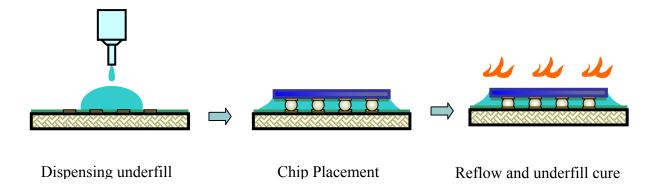

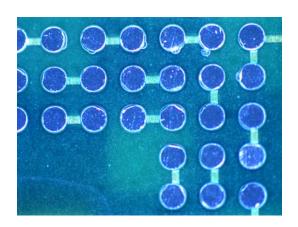

Figure 2.1 Corner Bonding Underfill Process

Corner bonding underfill offer an alternate approach, as shown in Figure 2.1. In this approach a high-viscosity underfill is dispensed at the four corners of the CSP site after solder paste printing, just prior to CSP placement. The CSP is then placed and reflowed. During the reflow cycle the solder balls collapse and the underfill cures, providing reinforcement at the four corners of the CSP. Since the underfill dots are relatively small, a dehydration bake is not required. With a smaller contact area compared to full capillary underfill, the assembled CSPs can be removed using a standard hot air rework station, so this process is reworkable. The whole assembly cycle

time is reduced due to no post-reflow dispensing and a cure step.

In this chapter, the SnPb assembly processes for corner bonding including underfill dispensing, CSP placement and reflow are examined. Drop tests were carried out to evaluate the drop reliability of CSPs with corner bonding underfill and compared with conventional capillary underfill and non-underfilled CSPs. Failure analysis was performed to find the typical failure modes and the locations of solder joint cracks for different underfill processes using cross-sectioning and SEM technologies.

#### 2.2 Assembly Process of Corner Bonding CSPs

#### 2.2.1 Test Vehicle

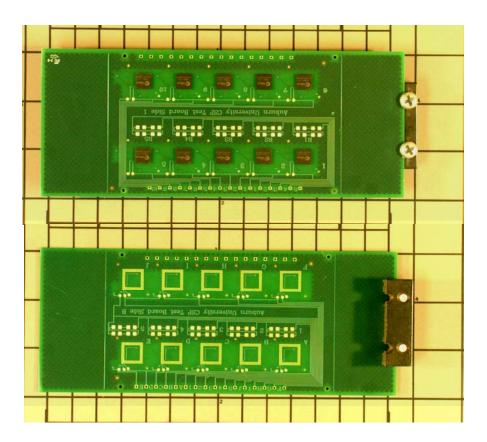

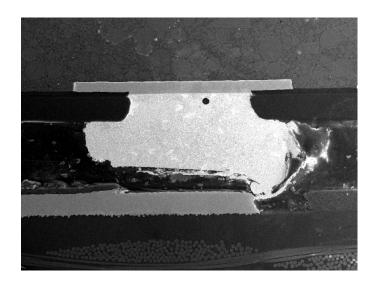

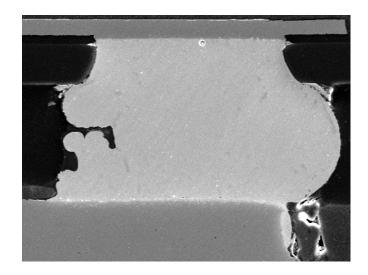

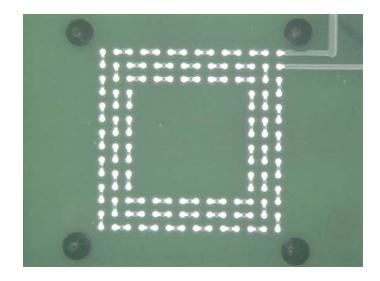

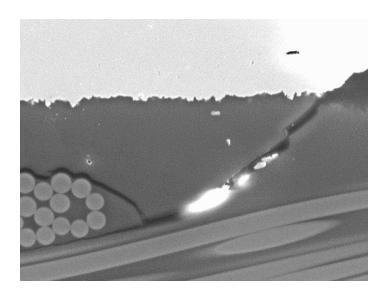

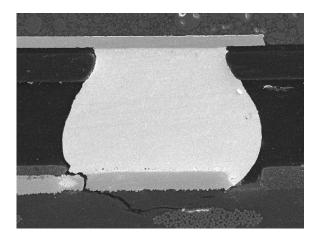

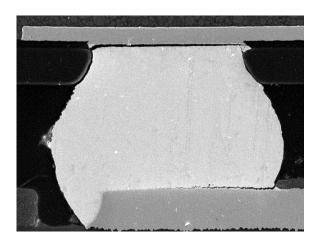

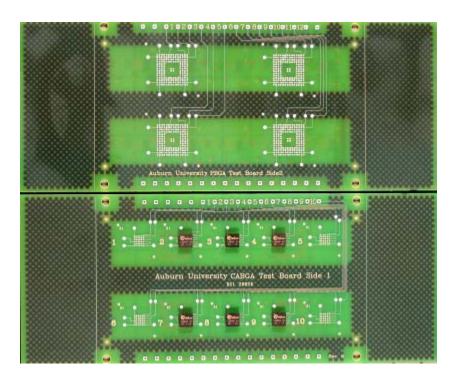

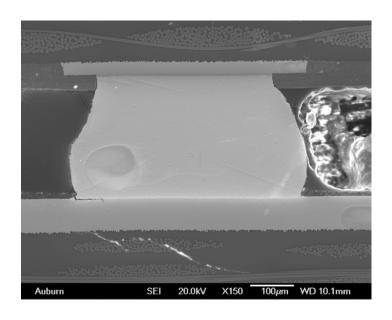

A test vehicle designed at Auburn University was used in this study, as shown in Figure 2.2. The test board dimensions were 2.95" by 7.24" by 0.042" thick, with a four-layer construction of FR-4 epoxy with glass fiber reinforcement. Each side had 10 CSPs attachment sites with one side for 12mm CSPs and another side for 8mm CSPs. Only the 8mm CSPs were used in this study. Standard technology was used for board fabrication, with no build-up or HDI layers. Drill holes (0.013" drill) under the 12mm CSP were plugged and tented to prevent underfill from flowing through the hole during dispensing. The pads were 0.010" in diameter, NSMD (non-solder mask defined) with an electroless nickel/immersion gold finish. Initial drop testing experiments yielded inconsistent results. Failure analysis revealed failure at the interface between the nickel and the intermetallic layer (Figure 2.3), which is indicative of black pad associated with

electroless nickel/immersion gold [75]. Boards were therefore obtained from a second supplier with an immersion silver finish and used for the remaining experiments.

Figure 2.2 Photographs of Test Board (front and back) with Weight (31.8g) Attached to Backside (non-CSP side) for Drop Test.

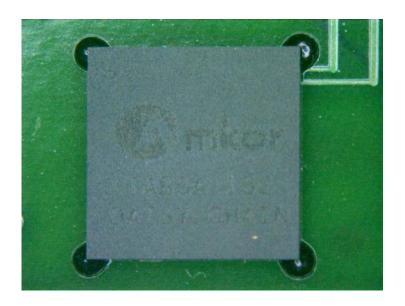

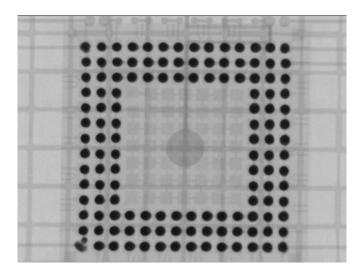

The CSP, manufactured by Amkor Technology, was an 8mm, 0.5mm pitch, 132 I/O TapeArray and was purchased from Practical Components (A-TArray132-.5mm-8mm-DC). The I/O was on a 14 x 14 array with only the outer three rows populated. The CSP was a daisy chain test part for continuity measurements. The silicon die was 3.98mm x 3.98mm.

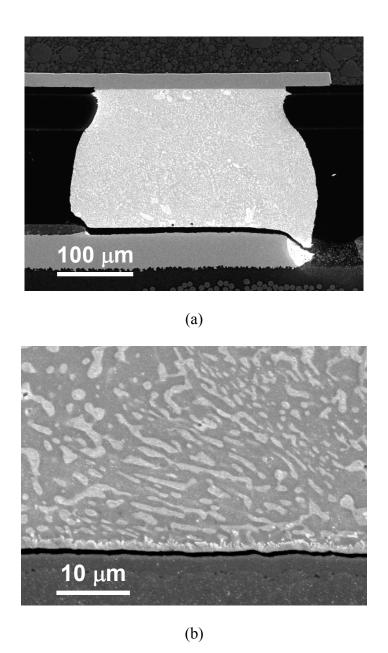

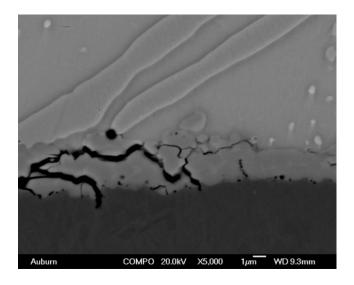

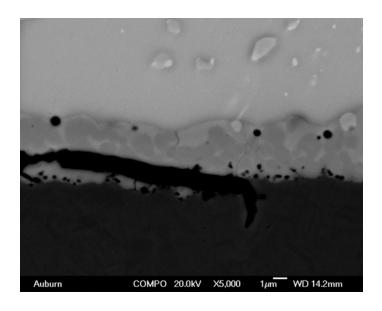

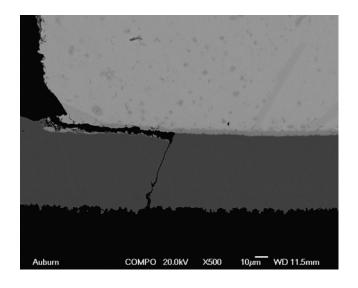

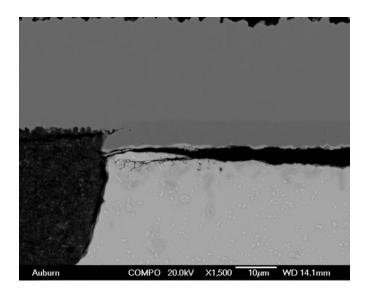

Figure 2.3 Cross Section (a) and Close-up (b) of Failed Solder Joint after Drop Test

Using Printed Wiring Board with Electroless Ni/Immersion Au Finish.

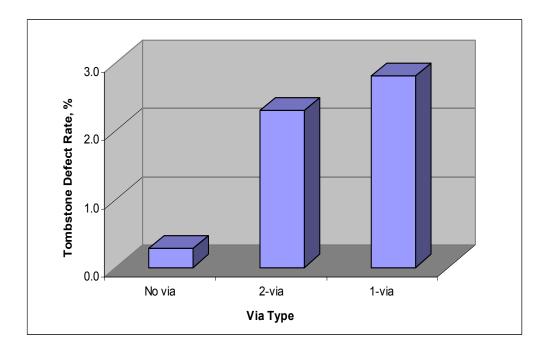

## 2.2.2 Process Issues of Corner Bonding Underfill