# BUILT-IN SELF TEST OF CONFIGURABLE MEMORY RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS

| Except where reference is made to the work of others, the work describ | oed in this thesis is |

|------------------------------------------------------------------------|-----------------------|

| my own or was done in collaboration with my advisory committee. The    | his thesis does not   |

| include proprietary or classified information.                         |                       |

| Da                                  | niel Milton                         |

|-------------------------------------|-------------------------------------|

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

| Certificate of Approval:            |                                     |

|                                     |                                     |

|                                     |                                     |

| Victor P. Nelson                    | Charles E. Stroud, Chair            |

| Professor                           | Professor                           |

| Electrical and Computer Engineering | Electrical and Computer Engineering |

|                                     |                                     |

| Thaddeus A. Roppel                  | George T. Flowers                   |

| Associate Professor                 | Interim Dean                        |

| Electrical and Computer Engineering | Graduate School                     |

# BUILT-IN SELF TEST OF CONFIGURABLE MEMORY RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS

Daniel Milton

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama December 17, 2007

# BUILT-IN SELF TEST OF CONFIGURABLE MEMORY RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS

# Daniel Milton

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights.

| Signature of Author |  |

|---------------------|--|

|                     |  |

|                     |  |

|                     |  |

|                     |  |

| Date of Graduation  |  |

# $V_{\rm ITA}$

Daniel Milton, son of Thomas and Diane Milton, was born in Birmingham, Alabama on April 25, 1983. In the Fall of 2005, he graduated Summa cum Laude with a Bachelor of Electrical Engineering majoring in Computer Engineering. Upon graduation he immediately began working on his Master of Science degree at Auburn University under the advisement of Dr. Charles E. Stroud.

#### Thesis Abstract

# BUILT-IN SELF TEST OF CONFIGURABLE MEMORY RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS

### Daniel Milton

Master of Science, December 17, 2007 (B.E.E., Auburn University, 2005)

# 151 Typed Pages

### Directed by Charles E. Stroud

Testing embedded memory resources in Field Programmable Gate Arrays (FPGAs) is difficult because the collective signal fan-in and fan-out is much greater than the available external I/O. A testing approach is needed that can test all of the memory resources in parallel without out being limited to external I/O. Built-in Self Test (BIST) is a testing method that incorporates test circuitry around the devices under test (DUT). The programmable nature of FPGAs allows the BIST circuitry to have no performance and size overhead because the BIST circuitry can be downloaded to the FPGA while the system is offline. Once offline, resources inside the FPGA can be tested and the results retrieved. If the FPGA is found to be fault-free then the system function can be downloaded again and brought back online.

BIST for embedded memory resources in Virtex 4 FPGAs is developed and test configurations are generated for all Virtex 4 devices. Twenty-five total BIST configurations are developed to test memories operating in RAM, FIFO, ECC, and cascade modes. To test each operating mode, a hardware design language (HDL) based test pattern generator

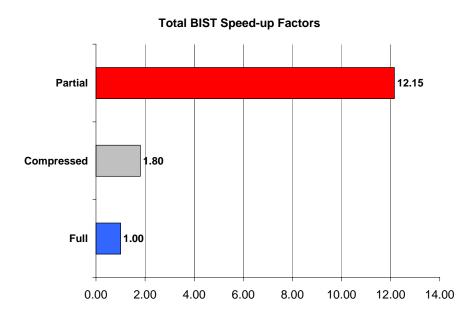

(TPG) is developed and then incorporated into an algorithmically placed BIST template that contains two TPGs, DUTs, and output response analyzers (ORAs) to observe DUT outputs. Partial reconfiguration is used to reduce both configuration bitstream storage and test time. A total speed-up factor of 12 is observed when utilizing partial reconfiguration.

#### ACKNOWLEDGMENTS

I would like to thank Dr. Stroud for his support and advise during my tenure at Auburn University during both my undergraduate and graduate studies. I would also like to thank Dr. Nelson and Dr. Roppel for their contribution to this thesis by serving on my graduate committee. To my research colleagues, Sachin, Sudheer, Bobby, Lee, Mustafa, Brad, David, and Noah, I am grateful for all of your help and assistance throughout my research. Lastly, I would like to acknowledge my parents, as their ever present support has always inspired my to fulfill my potential.

Style manual or journal used <u>Journal of Approximation Theory (together with the style</u> known as "aums"). Bibliography follows IEEE Transactions.

Computer software used <u>The document preparation package TeX</u> (specifically <u>Microsoft Excel</u> and figures were drawn in *Microsoft Visio*.

# Table of Contents

| Lis | ST OF | FIGURES                                    | xi  |

|-----|-------|--------------------------------------------|-----|

| Lis | ST OF | TABLES                                     | xiv |

| 1   | Intr  | RODUCTION                                  | 1   |

|     | 1.1   | Built-In Self Test (BIST)                  | 2   |

|     |       | FPGAs                                      | 3   |

|     | 1.3   | Embedded Memory Resources in FPGAs         | 5   |

|     | 1.4   | Thesis Statement                           | 6   |

| 2   |       | KGROUND                                    | 8   |

|     | 2.1   | Introduction to FPGAs                      | 8   |

|     | 2.2   | Virtex 4 Architecture                      | 12  |

|     |       | 2.2.1 Virtex 4 PLBs                        | 14  |

|     |       | 2.2.2 Virtex 4 BRAMs                       | 15  |

|     |       | 2.2.3 Virtex 4 FIFOs                       | 22  |

|     |       | 2.2.4 Virtex 4 CAD Tools                   | 27  |

|     |       | 2.2.5 Virtex 4 Boundary Scan               | 27  |

|     | 2.3   | SRAM Testing                               | 30  |

|     |       | 2.3.1 SRAM Fault Models                    | 31  |

|     |       | 2.3.2 March Tests for Single-Port Memories | 32  |

|     |       | 2.3.3 March Tests for Dual-Port Memories   | 35  |

|     | 2.4   | Overview of BIST for FPGAs                 | 37  |

|     |       | 2.4.1 BIST for BRAMs                       | 40  |

|     | 2.5   | Thesis Restatement                         | 42  |

| 3   | Virt  | TEX 4 BLOCK RAM BIST IMPLEMENTATION        | 44  |

|     | 3.1   | Virtex 4 BRAM BIST Architecture            | 44  |

|     | 3.2   | TPG Development                            | 48  |

|     | 3.3   | BRAM BIST Configurations                   | 51  |

|     | 3.4   | Running BIST Configurations                | 61  |

|     | 3.5   | ORA Results Retrieval                      | 62  |

|     | 3.6   | BIST Results                               | 63  |

|     | 3.7   | BRAM BIST Summary                          | 68  |

| 4  | VIRTEX 4 FIFO BIST IMPLEMENTATION            | 69  |

|----|----------------------------------------------|-----|

|    | 4.1 Virtex 4 FIFO BIST Architecture          | 69  |

|    | 4.2 FIFO TPG Development                     | 69  |

|    | 4.3 FIFO BIST Configuration Development      | 74  |

|    | 4.4 Running FIFO BIST Configurations         | 77  |

|    | 4.5 FIFO BIST Results                        | 78  |

| 5  | VIRTEX 4 ECC AND CASCADE BIST IMPLEMENTATION | 82  |

|    | 5.1 ECC and Cascade BIST Architecture        | 82  |

|    | 5.2 ECC BRAM BIST Development                | 85  |

|    | 5.3 Cascade TPG Development                  | 89  |

|    | 5.4 BIST Configurations                      | 91  |

|    | 5.5 Running BIST Configurations              | 91  |

|    | 5.6 BIST Results                             | 93  |

| 6  | Summary and Conclusion                       | 98  |

|    | 6.1 Summary of Virtex 4 BIST Results         | 98  |

|    | 6.2 Application to Virtex 5                  | 100 |

| Ві | IBLIOGRAPHY                                  | 101 |

| AF | PPENDICES                                    | 104 |

| Λ  | MMTPG VHDL Source code                       | 105 |

| А  | MM1FG VHDL SOURCE CODE                       | 105 |

| В  | FIFOTPG VHDL Source code                     | 123 |

| С  | ECCTPG VHDL Source code                      | 127 |

| D  | CASTPG VHDL Source code                      | 131 |

| Ε  | List of Acronyms                             | 135 |

# LIST OF FIGURES

| 1.1  | General BIST Architecture                     | 3  |

|------|-----------------------------------------------|----|

| 1.2  | FPGA Architecture                             | 4  |

| 1.3  | Basic PLB Architecture                        | 4  |

| 2.1  | Configuration Bits in FPGAs                   | 10 |

| 2.2  | A Five Transistor Configuration SRAM Cell [1] | 11 |

| 2.3  | A Six Transistor Configuration SRAM Cell [1]  | 11 |

| 2.4  | Basic Virtex 4 Architecture                   | 14 |

| 2.5  | Virtex 4 PLB [2]                              | 15 |

| 2.6  | Simplified Virtex 4 Slice Diagram [2]         | 16 |

| 2.7  | Virtex 4 BRAM [2]                             | 18 |

| 2.8  | ECC BRAM Architecture [2]                     | 22 |

| 2.9  | BRAM Cascade Operational Diagram [2]          | 23 |

| 2.10 | Virtex 4 FIFO Implementation [2]              | 25 |

| 2.11 | Virtex 4 FIFO [2]                             | 25 |

| 2.12 | TAP Controller State Diagram [3]              | 29 |

| 2.13 | SRAM Memory Functional Model                  | 30 |

| 2.14 | Structural Model of a two-port SRAM cell      | 31 |

| 2.15 | March LR with 4-bit BDS [4]                   | 35 |

| 2.16 | March s2pf [5]                                | 36 |

| 2.17 | March d2pf [5]                                | 37 |

|------|-----------------------------------------------|----|

| 2.18 | A General Comparison Based BIST Architecture  | 38 |

| 2.19 | A Circular Comparison Based BIST Architecture | 39 |

| 2.20 | Comparison Based ORA with Shift Chain         | 40 |

| 2.21 | Comparison Based ORA without a Shift Chain    | 40 |

| 3.1  | BRAM BIST Architecture                        | 45 |

| 3.2  | BRAM ORA Orientation                          | 46 |

| 3.3  | ORA Placement and Comparison in SX devices    | 47 |

| 3.4  | ORA Placement and Comparison in FX devices    | 48 |

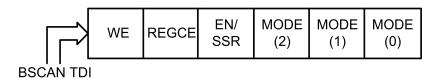

| 3.5  | MMTPG Control Shift Register                  | 51 |

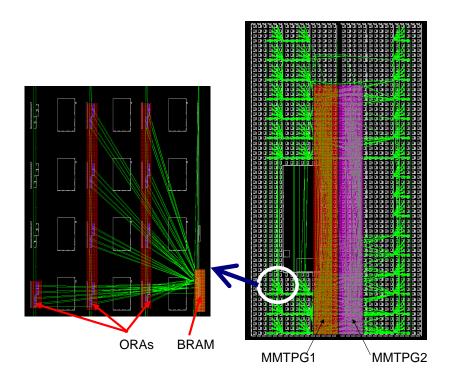

| 3.6  | FX12 BRAM BIST                                | 55 |

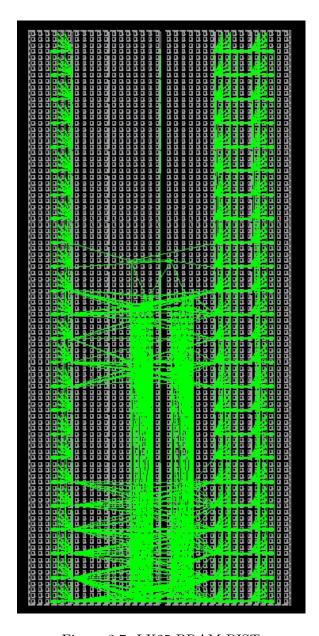

| 3.7  | LX25 BRAM BIST                                | 56 |

| 3.8  | V4BRAMTPG Syntax                              | 59 |

| 3.9  | V4BRAMBIST Syntax                             | 59 |

| 3.10 | V4BRAMMOD Syntax                              | 59 |

| 3.11 | Example BIST program execution                | 59 |

| 3.12 | Partial BRAM BIST in LX60                     | 60 |

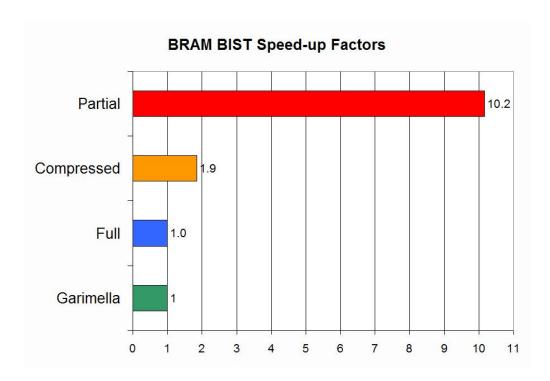

| 3.13 | LX60 BRAM BIST Speed-up factors               | 64 |

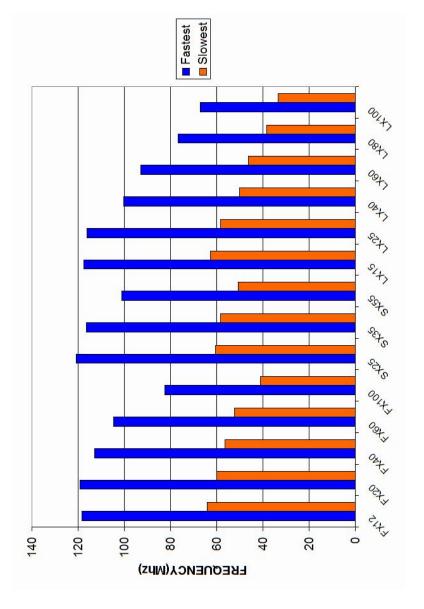

| 3.14 | Timing Analysis (Slowest / Fastest )          | 66 |

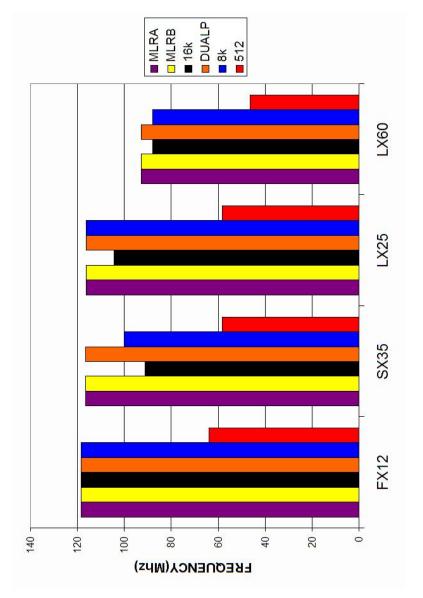

| 3.15 | Timing Analysis per BRAM BIST Configuration   | 67 |

| 4.1  | FIFO ORA Placement                            | 70 |

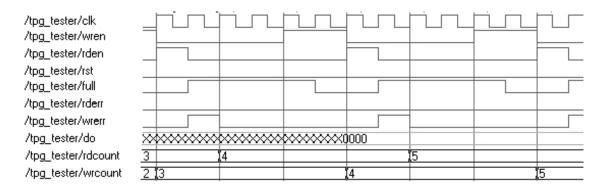

| 12   | FILL Flag Transition Timing                   | 73 |

| 4.3  | FIFOTPG Control Register               | 74 |

|------|----------------------------------------|----|

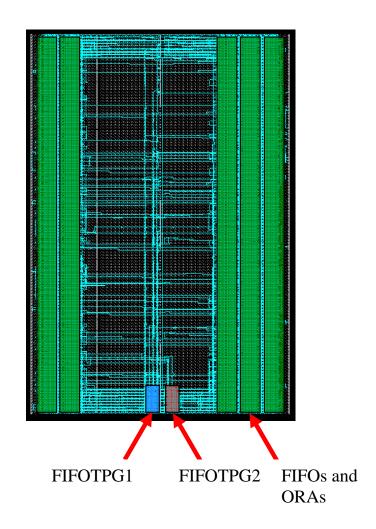

| 4.4  | LX60 FIFO BIST Configuration           | 75 |

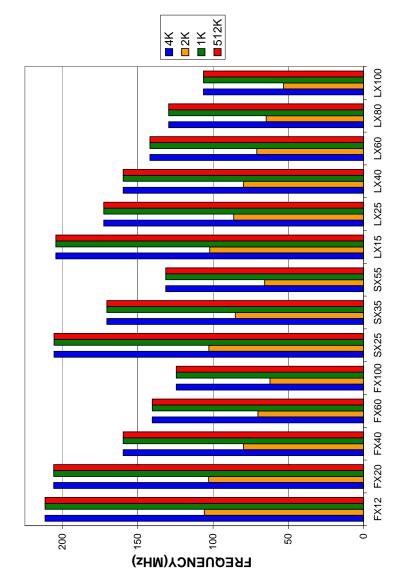

| 4.5  | FIFO BIST Timing Analysis              | 79 |

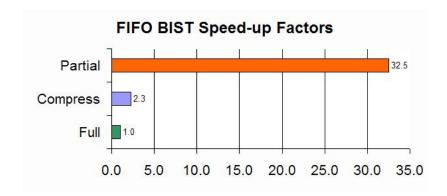

| 4.6  | LX60 FIFO Speed-up Factors             | 81 |

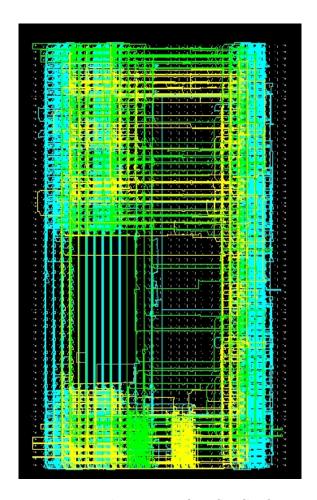

| 4.7  | Routed FX12 FIFO BIST Configuration    | 81 |

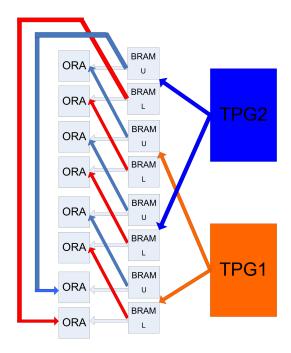

| 5.1  | ECC and Cascade BIST Architecture      | 84 |

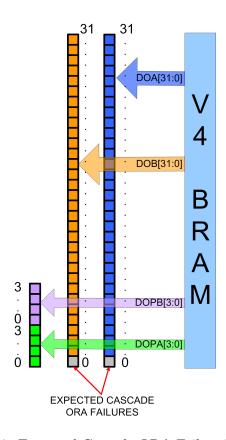

| 5.2  | Expected Cascade ORA Failure Locations | 85 |

| 5.3  | Parity Tree TPG [6]                    | 87 |

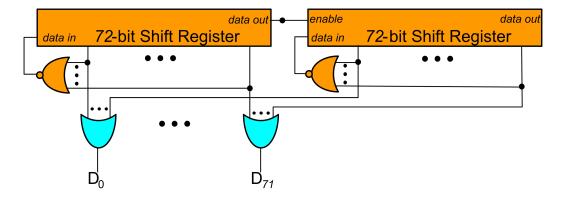

| 5.4  | Cascade BRAM Operational Diagram       | 90 |

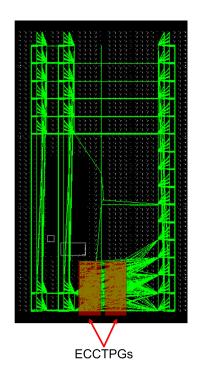

| 5.5  | FX12 ECC BIST                          | 92 |

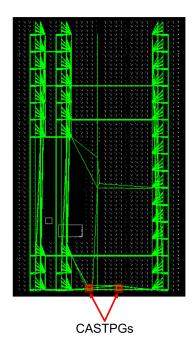

| 5.6  | FX12 Cascade BIST                      | 92 |

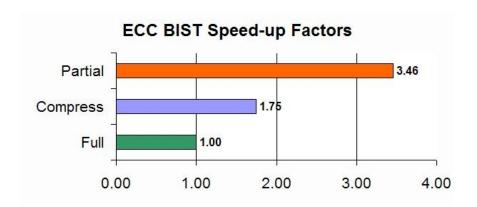

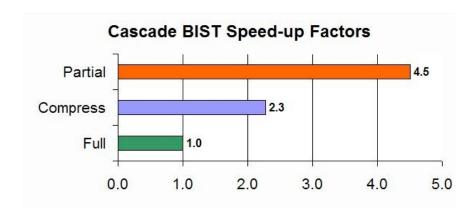

| 5.7  | LX60 ECC BIST Speed-up Factors         | 95 |

| 5.8  | LX60 CAS BIST Speed-up Factors         | 95 |

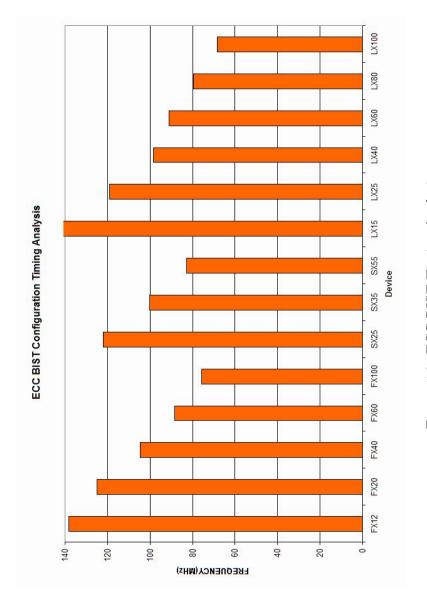

| 5.9  | ECC BIST Timing Analysis               | 96 |

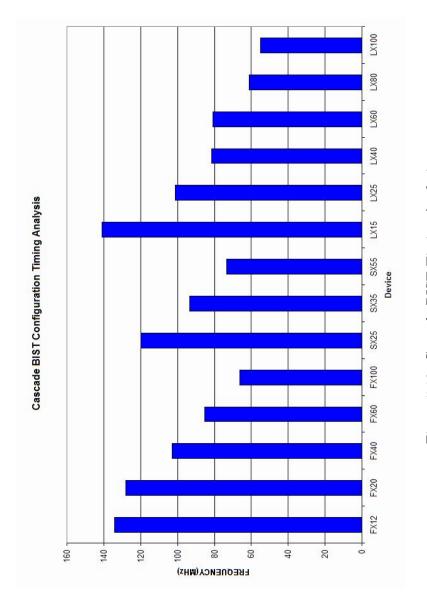

| 5.10 | Cascade BIST Timing Analysis           | 97 |

| 6 1  | BIST Speed-up for LX60                 | 99 |

# LIST OF TABLES

| 2.1  | Overview of Resources in Virtex 4 Family Devices [2] | 13 |

|------|------------------------------------------------------|----|

| 2.2  | Summary of Virtex 2 and 4 BRAM Aspect Ratios         | 17 |

| 2.3  | BRAM Signal Descriptions [2]                         | 19 |

| 2.4  | BRAM Configuration Options [2]                       | 20 |

| 2.5  | ECC Status Description                               | 22 |

| 2.6  | FIFO Configuration Options [2]                       | 24 |

| 2.7  | Virtex 4 Status Flag Clock Cycle Latency [2]         | 26 |

| 2.8  | FIFO Port Signal Descriptions [2]                    | 26 |

| 2.9  | Summary of Xilinx Design Tools                       | 28 |

| 2.10 | Virtex 4 BSCAN Module Access Commands [3]            | 29 |

| 2.11 | Common SRAM Fault Types                              | 32 |

| 2.12 | March Test Notation Descriptions                     | 33 |

| 2.13 | Common March Tests for Single Port Memories          | 34 |

| 2.14 | Background Data Sequence for 8-bits                  | 35 |

| 2.15 | Virtex 2 BRAM Summary                                | 41 |

| 3.1  | Virtex 4 TPG March Test Algorithms                   | 50 |

| 3.2  | BRAM BIST Configuration Detail                       | 52 |

| 3.3  | BRAM Initialization Values                           | 53 |

| 3.4  | XDL Argument Summary                                 | 58 |

| 3.5  | BRAM BIST Execution Detail                           | 62 |

| 3.6 | Summary of LX60 BRAM BIST Download Size and Test Times | 65 |

|-----|--------------------------------------------------------|----|

| 4.1 | Summary of Virtex 4 FIFO Configurations                | 76 |

| 4.2 | Summary of LX60 FIFO BIST Download Size and Test Times | 80 |

| 5.1 | ECC BRAM BIST Configuration Settings                   | 88 |

| 5.2 | Summary of Cascade BIST Configuration Settings         | 91 |

| 5.3 | Summary of LX60 CAS BIST Download Size and Test Times  | 94 |

| 5.4 | Summary of LX60 ECC BIST Download Size and Test Times  | 94 |

#### Chapter 1

#### INTRODUCTION

Moore's Law states that the complexity of Integrated Circuits (ICs) tends to double every 24 months [7]. While this empirical observation was first observed in 1965, more recently, the International Technology Roadmap for Semiconductors has predicted Moore's Law will persist at least until 2016 based upon industry data and forecasts [8]. One of the earliest microprocessors, the Intel 4004, had approximately 2300 transistors [9]. For contrast, recent state-of-the-art Field Programmable Gate Arrays (FPGAs) may contain more than one billion transistors [10]. Clearly, one can see the exponential growth in transistor count over the last four decades. The continuing problem with these higher density ICs is that developing tests for such complex devices is becoming progressively more difficult with each generation of new ICs. Recent IC fabrication technology has led to larger chip sizes with smaller feature sizes, but also has introduced new types of defects and subsequently increased the probability of defects [6].

Developing good tests for ICs is becoming a major factor in the cost of producing working silicon ICs. One of the reasons for high costs is the disparity between the number of Input/Output (I/O) pins in packaged ICs verses the number of transistors in the package. Using external 'bed-of-nails' test equipment, the costs of testing are generally attributed to the fixed cost of the test equipment and the speed at which the actual tests can be performed. IC manufactures generally employ tests that minimize the cost of the test equipment while minimizing the device test time [11]. Improvements in Design for Test (DFT) methodology have produced scan design and Built-in Self Test (BIST) [6][11].

### 1.1 Built-In Self Test (BIST)

DFT is a common practice in the VLSI design process. Traditionally, DFT for ICs has involved using scan flip-flops. Scan flip-flops reduce the amount of time needed to generate tests for sequential circuits because they can operate as a shift register to shift in a test vector from an external Automated Test Equipment (ATE). When shifting a new test vector into a scan chain, the output response from the previous vector is shifted out, which is then can be compared to an expected value. Scan design eliminates the possibility of being unable to initialize a flip-flop to a desired value. However, for many large VLSI circuits, the number of test vectors that must be applied to achieve a necessary fault coverage percentage has also increased. Coupled with a growing amount of test vectors and ATE not being able to test at speed for newer ICs, a different approach for applying test vectors was introduced [11].

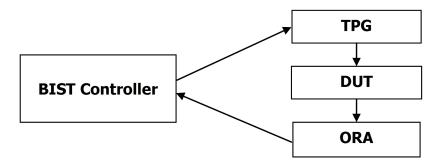

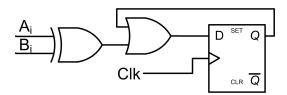

BIST is a DFT technique that allows the Device Under Test (DUT) or a portion of the DUT to tell the tester if it is fully functional. BIST implementations include a Test Pattern Generator (TPG) which drives a DUT or many DUTs in parallel. The outputs of the DUTs are then analyzed by an Output Response Analyzer (ORA) which determines the correctness of the DUT. The general BIST architecture can be seen in Figure 1.1. BIST solves two of the major issues with ATE based testing. First, the BIST circuitry is implemented in the chip itself, and therefore it can perform at speed. Secondly, since the BIST circuitry generates test vectors, the external tester merely needs to tell the device to perform BIST and then report whether the device is faulty or not [6].

Figure 1.1: General BIST Architecture

Traditionally, BIST has been used to test logic and memory resources in VLSI circuits [6]. One caveat of BIST is that it usually implies an overhead in terms of increased chip area which may in turn reduce the yield of the chip [6]. One may wonder if it is possible to implement BIST with no overhead. BIST implementations proposed in [12][13][14][15][16][17][18][19][20][21][22] suggest BIST for FPGAs can incur no overhead penalty in terms of speed and area.

## 1.2 FPGAs

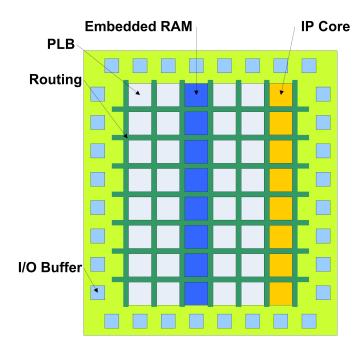

An FPGA can be described as "an array of logic blocks that can be programmably interconnected to realize different designs" [23]. A general FPGA architecture, as seen in Figure 1.2, contains I/O cells that facilitate signals entering and exiting the device. Programmable Logic Blocks (PLBs) perform the necessary digital logic functions and the programmable routing resources direct signals both between PLBs and the overall signal path from inputs to outputs.

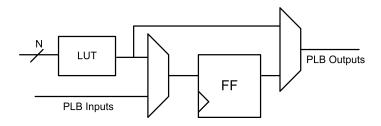

PLBs vary among manufactures, but a simple PLB can contain Look-up Tables (LUTs), flip-flops/latches, and multiplexers. A simple PLB architecture is illustrated in Figure

Figure 1.2: FPGA Architecture

Figure 1.3: Basic PLB Architecture

1.3. LUTs can be configured as the truth table for a given logical function and they can implement small distributed random access memories (RAMs). The interconnection or routing between PLBs is realized by configuring Programmable Interconnect Points (PIPs) to create signal paths from wire segments inside the FPGA [23].

FPGA programming techniques vary among manufacturers, and include static RAM (SRAM), fuse/anti-ifuse, and floating gate methods. SRAM is the most popular programming technique for advanced FPGAs because SRAM based designs allow high density and fast configuration [23]. SRAM based FPGAs contain a configuration memory that, when written to, specifies the operation of PLBS, I/O cells, and routing resources. Besides logic blocks and routing resources, the configuration memory may configure other embedded resources in the FPGA such as embedded RAMs, multipliers, and digital signal processors (DSP). The inclusion of additional embedded resources allows for higher PLB utilization because the embedded resources can offload much of the functionality of digital systems.

# 1.3 Embedded Memory Resources in FPGAs

FPGA manufacturers have incorporated embedded memories for many product generations [10][24]. Previously, storing large quantities of data internally required an appreciable amount of PLB resources to implement a memory resource. While most designers frequently utilize the memory resources as regular RAM modules, several FPGAs now allow system designers to configure memory resources as multi-port RAMs and First-In-First-Out (FIFO) modules. The advent of dedicated memory resources extends the potential of FPGAs to act as a programmable System-on-Chip (SoC). However, as advantageous as memory resources

are, there are testability concerns that must be addressed. Traditionally, testing RAMs requires applying test patterns that read and write data in such an order that within a set of faults being tested, any such fault will be sensitized if present. These testing algorithms are generally known as march tests. There have been many march tests developed for detecting certain types of faults within memory resources [25][26]. Unfortunately, applying march tests to embedded memories is complicated. ATE is generally used to verify production ICs. However, ATEs usually provide test patterns to the external I/O pins of an IC. A better testing approach is needed because most FPGAs contain many memory resources whose collective fan-in and fan-out are much greater than the available I/O pins [10][24]. BIST is an ideal solution for testing embedded resources in FPGAs. A BIST approach offers more flexibility for testing than an external ATE because test pattern generation is not limited by the external I/O availability. Previous implementations have shown that this approach is quite feasible and efficient for testing embedded memories [27][17][28].

# 1.4 Thesis Statement

The goal of this thesis is to develop a BIST architecture and BIST configurations for testing embedded memories in Xilinx Virtex 4 FPGAs. This BIST architecture will address minimizing both the test time required and the memory required to store the BIST configurations. This minimization is achieved by designing the BIST architecture to efficiently utilize an FPGA configuration technique known as partial reconfiguration. The remainder of this thesis is organized as follows: In Chapter 2, additional background information on BIST for FPGAs will be given along with details toward testing SRAMs in general and a detailed overview of the Virtex 4 FPGA architecture. In Chapter 3, a

BIST architecture for Virtex 4 embedded memories will be presented with applications to memory resources configured to operate in a basic RAM mode of operation. Chapters 4 and 5 will apply the presented BIST architecture to memory resources configured to operate as FIFOs and Error-Correcting Code (ECC) RAMs, respectively. Chapter 6 will summarize the work presented in this thesis and include ideas for future research in this field.

#### Chapter 2

#### BACKGROUND

This chapter presents an overview of different BIST techniques for FPGAs found in the literature. The architecture of the Xilinx Virtex 4 FPGA will also be presented with an emphasis on the dedicated memory resources referred to as block RAMs (BRAMs). Background on SRAM testing will be presented that predominately focuses on march tests and the associated fault models for which they are designed.

## 2.1 Introduction to FPGAs

FPGAs differ from Application Specific Integrated Circuits (ASICs) because they are made of logic and routing resources capable of implementing most digital systems while not being explicitly fabricated for a specific task. For example, one might buy a microprocessor, an ASIC, as part of a digital system while another designer might use an FPGA to implement a microprocessor and other supporting functions all in the same IC. Furthermore, another designer might use the exact same FPGA in a DSP application. Clearly, the flexibility of FPGAs is its main advantage. Another advantage is the reduced non-recurring engineering costs by eliminating the need to design and fabricate custom ASICs. The main disadvantage, however, of FPGAs is higher chip area, higher power consumption, and lower operational speeds as compared to a custom ASIC which is due to extra programming circuitry overhead. Also, FPGAs typically are more expensive than traditional ASICs so they are usually relegated to low volume or prototype designs [23].

In order for an FPGA to realize a digital system, it must be programmed [23]. Several programming technologies exist, but SRAM based FPGAs are currently the most common and popular. Other older programming technologies exist such as fuse or anti-fuse based and mask-programmable FPGAs. However, these programming technologies only allow for one-time programmability, either at the factory in the case of mask-programmed FPGAs or in the field as is the case with fuse or anti-fuse based FPGAs. While SRAM based FPGAs are advantageous in their capabilities of being programmed more than once, they also must be reprogrammed each time the chip is power cycled. This is necessary because SRAM is inherently a volatile storage medium [1].

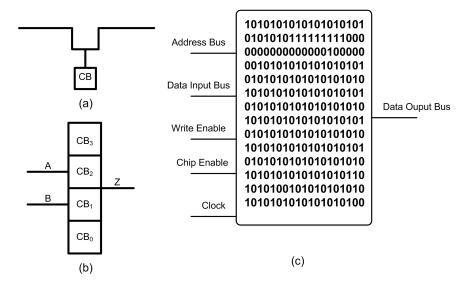

When a FPGA is configured, the configuration data, also known as a bitstream, is downloaded to the device. The bitstream contains all of the configuration bits that, when downloaded, implement a desired logic function. Configuration bits can control many resources inside the FPGA such as a LUTs' contents, routing resources, and the operational mode of embedded intellectual property (IP) cores such as BRAMs and DSP modules. Configuration bits also can determine the initialization values of flip-flops in PLBs and data values stored in BRAMs [29][2]. Figure 2.1 illustrates the use of configuration bits. In Figure 2.1a, a configuration bit is used to block or pass a signal for implementing programmable routing resources. In Figure 2.1b, configuration bits are used to implement a LUT such that a 2-input truth table can be realized for a logical function. Configuration bits can also initialize a BRAM as seen in Figure 2.1c.

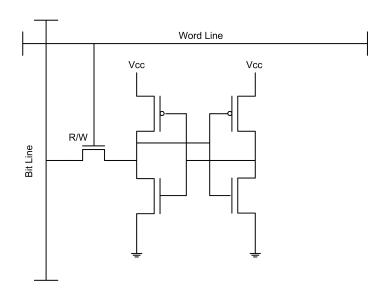

As described in [1], configuration memory SRAM cells do not require fast read and write performance, which allows FPGA designers to use a five transistor SRAM as shown

Figure 2.1: Configuration Bits in FPGAs

in Figure 2.2 instead of a more standard six transistor SRAM cell that provides both the complemented and uncomplemented form as seen in Figure 2.3.

Another important attribute concerning FPGA configuration is the ability for FPGAs to be partially reconfigured. Most modern FPGAs like the Xilinx Virtex series support partial reconfiguration [3][29]. Partial reconfiguration allows for a reduction in bitstream size by only storing the difference between a previous full download and the changes needed to implement the modified system function. Partial reconfiguration allows a designer to extract more functionality from a smaller FPGA for usage scenarios where a subset of implemented system functions can be swapped in and out of the FPGA without compromising critical performance parameters. In terms of testing FPGAs, partial reconfiguration is a valuable tool that allows the test configuration download time to be reduced.

Figure 2.2: A Five Transistor Configuration SRAM Cell  $\left[1\right]$

Figure 2.3: A Six Transistor Configuration SRAM Cell [1]

#### 2.2 Virtex 4 Architecture

Xilinx released the Virtex 4 FPGA family in 2004 and, at the time of its introduction, it was one of the most complex FPGAs available on the market. For its production, Xilinx used a 1.2V, 90nm, triple-oxide process and it is only available in a flip-chip BGA package [10]. The Virtex 4 PLB contains four slices and each slice features two 4-input LUTs and two flip-flops. Dedicated memory storage is provided via a programmable 18K-bit SRAM called a block RAM. Previously in Virtex 2, an 18 x 18 multiplier module was available [29]. In Virtex 4, the multiplier has grown into a complete DSP module that incorporates a 48-bit accumulator attached to the 18 x 18 multiplier. The accumulator can also perform addition and subtraction on two data words without first being processed by the multiplier. Virtex 4 is available in three distinct product families: LX, SX, and FX as summarized in Table 2.1. The LX family contains eight devices that have been tailored toward design implementations that have high PLB usage. The SX family consists of three devices and is targeted toward DSP-oriented designs due to higher number of DSP modules. The FX family is a blend of the SX and LX family and provides more specialized modules which include PowerPC (PPC) and high performance I/O Serial/Deserial (SERDES) modules.

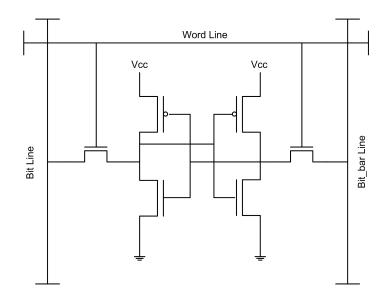

Virtex 4 employs a column based architecture. Each device has a center column which divides the FPGA into two halves. Beginning from the center column and moving in either direction, first there are columns of PLBs. The width of the first columns of PLBs differs by device size and family. Moving outward again, the next resource will either be a column of DSP or BRAM modules as illustrated in Figure 2.4. In FX family devices, either one or two PPC modules will be positioned to the left of the center column.

Table 2.1: Overview of Resources in Virtex 4 Family Devices [2]

| Device    | Row x Col | Slices | DSPs | BRAMs | PPCs | I/O |

|-----------|-----------|--------|------|-------|------|-----|

| XC4VLX15  | 64 x 24   | 6,144  | 32   | 48    | -    | 320 |

| XC4VLX25  | 96 x 28   | 10,752 | 48   | 72    | -    | 448 |

| XC4VLX40  | 128 x 36  | 18,432 | 64   | 96    | -    | 640 |

| XC4VLX60  | 128 x 52  | 26,624 | 64   | 160   | -    | 640 |

| XC4VLX80  | 160 x 56  | 35,840 | 80   | 200   | -    | 768 |

| XC4VLX100 | 192 x 64  | 49,152 | 96   | 240   | -    | 960 |

| XC4VLX160 | 192 x 88  | 67,584 | 96   | 288   | -    | 960 |

| XC4VLX200 | 192 x 116 | 89,088 | 96   | 336   | -    | 960 |

| XC4VSX25  | 64 x 40   | 10,240 | 128  | 128   | -    | 320 |

| XC4VSX35  | 96 x 40   | 15,360 | 192  | 192   | -    | 448 |

| XC4VSX55  | 128 x 48  | 24,576 | 512  | 320   | -    | 640 |

| XC4VFX12  | 64 x 24   | 5,472  | 32   | 36    | 1    | 320 |

| XC4VFX20  | 64 x 36   | 8,544  | 32   | 68    | 1    | 320 |

| XC4VFX40  | 96 x 52   | 18,624 | 48   | 144   | 2    | 448 |

| XC4VFX60  | 128 x 52  | 25,280 | 128  | 232   | 2    | 576 |

| XC4VFX100 | 160 x 68  | 42,176 | 160  | 376   | 2    | 768 |

| XC4VFX140 | 192 x 84  | 63,168 | 192  | 552   | 2    | 896 |

The smallest addressable unit of configuration memory in Virtex 4 is referred to as a frame, and each frame consists of 41 32-bit words. During the creation of a configuration bitstream, successive frame data along with frame addresses are written to the configuration bitstream. Designs utilizing regular structures, such as multiple identically configured BRAMs or replicated system logic in fault tolerant designs, can take further advantages of multi-frame write capabilities. Multi-frame write capabilities allow the configuration bitstream to specify multiple frame addresses to be given the same frame data. This can allow substantial reductions in configuration bitstream sizes and can be beneficial to reducing the time to perform BIST as discussed in Chapter 3.

All or parts of the configuration memory can also be read back. Configuration memory readback can be performed for various reasons such as configuration download verification,

but for BIST, readback is used to retrieve ORA results. In order to capture the contents of flip-flops, the *CAPTURE* module must be instantiated in the design. The *CAPTURE* module permits the current contents of flip-flops to overwrite their initial specified state stored in the configuration memory. Once the current flip-flop values have been captured, the ORA results can be retrieved via configuration memory readback.

Figure 2.4: Basic Virtex 4 Architecture

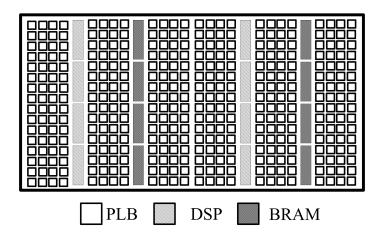

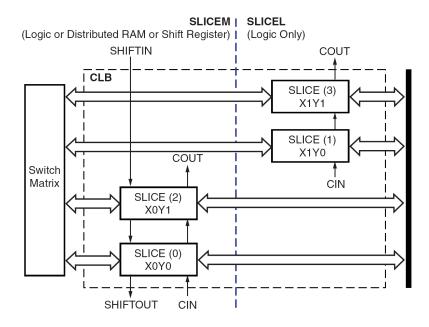

# 2.2.1 Virtex 4 PLBs

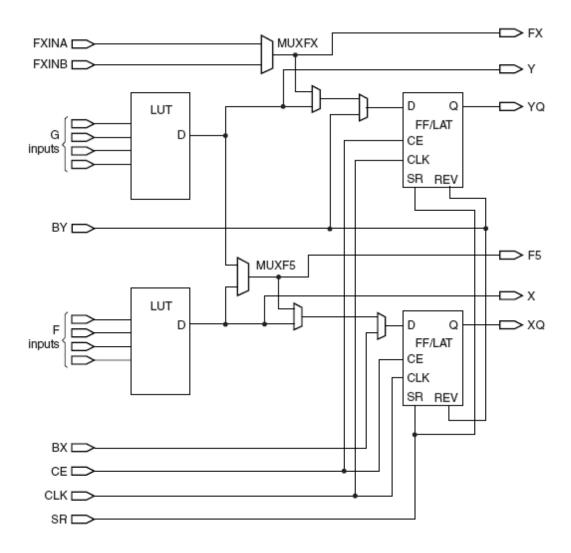

Virtex 4 PLBs each consist of 2 SLICEMs and 2 SLICELs as pictured in Figure 2.5. A simplified representation of a SLICE is shown in Figure 2.6. A SLICEL contains 2 LUTs and 2 flip-flops plus multiplexers and logic gates to allow implementation of complex switching functions that span multiple SLICELs and even multiple PLBs. SLICEMs are a superset of SLICELs and have additional specialized features that enable them to be used as small distributed memories or function as a fast shift register. This thesis does not focus on testing PLBs and the slices within them. PLBs will be used in the work presented in this

thesis, however their use will only be to implement TPG and ORA components to facilitate testing BRAMs.

Figure 2.5: Virtex 4 PLB [2]

#### 2.2.2 Virtex 4 BRAMs

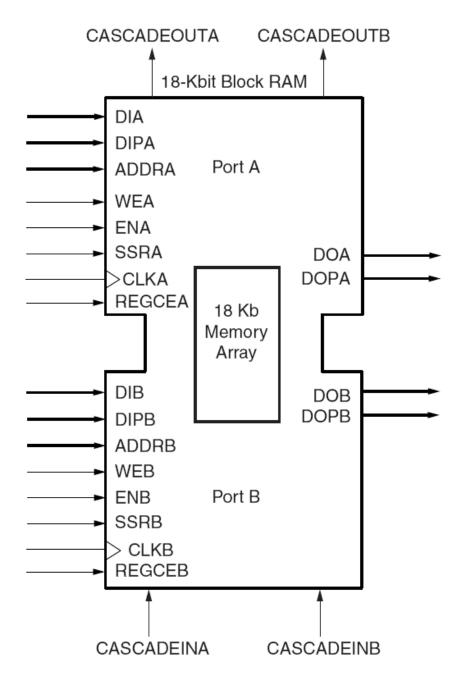

This thesis concentrates on the development of BIST for BRAMs in Virtex 4 FPGAs. In [14], BIST was implemented for distributed RAMs, BRAMs, and multipliers in Xilinx's Virtex 2 series FPGAs. Distributed RAMs are memory resources created by using PLBs to create small memories. The BRAMs available in both Virtex 2 and 4 share much of the same functionality. The BRAM features present in Virtex 2 can be viewed as a subset of those present in Virtex 4. The Virtex 4 BRAM, as seen in Figure 2.7, is a true dual-port RAM meaning that is has dual address and data input and output buses. The memory array can be configured in multiple aspect ratios that utilize up to 18K of addressable memory as

Figure 2.6: Simplified Virtex 4 Slice Diagram [2]

outlined in Table 2.2. For word sizes of eight bits and larger there are additional parity bits associated with each word. It is important to note, however, that the user is responsible for writing data to the parity bit locations since parity over the written data word is not calculated automatically. As for BRAM performance, all BRAM read and write operations can be completed in a single clock period unless using a registered output mode.

Table 2.2: Summary of Virtex 2 and 4 BRAM Aspect Ratios

| Word Depth | Word Width | Parity Width |

|------------|------------|--------------|

| 512        | 32         | 4            |

| 1K         | 16         | 2            |

| 2K         | 8          | 1            |

| 4K         | 4          | -            |

| 8K         | 2          | -            |

| 16K        | 1          | -            |

Table 2.3 lists all of the input and output signal names and functionality found in a Virtex 4 BRAM. It should be noted that the Virtex 2 BRAM uses the same signal names except for the cascade input and outputs. Unlike Virtex 2, Virtex 4 BRAMs support cascading two 16K x 1-bit configured BRAMs to create a 32K x 1-bit memory without utilizing additional PLBs. All of the inputs are captured at either the rising or falling edge of the input clock depending if the BRAM clock input is programmed to be rising or falling edge triggered. Also, the following signals are programmable in their active levels: WE, EN, SSR, and REGCE. The WE signal is actually a 4-bit bus which enables the ability to write a single byte to a BRAM when configured to have a data word wider than a byte. This feature is most commonly used in conjunction with combining a PPC module and several BRAMs such that they implement program and data storage for the processor.

Table 2.4 summarizes additional configuration parameters for each BRAM. The SAVE-DATA configuration option determines if a partial reconfiguration will overwrite the present

Figure 2.7: Virtex 4 BRAM [2]

Table 2.3: BRAM Signal Descriptions [2]

| Port Name       | Description [2]                     |

|-----------------|-------------------------------------|

| DI[A,B]         | Data Input Bus                      |

| DIP[A,B]        | Data Input Parity Bus               |

| ADDR[A,B]       | Address Bus                         |

| WE[A,B]         | Write Enable                        |

| EN[A,B]         | Port Enable                         |

| SSR[A,B]        | Set/Reset                           |

| CLK[A,B]        | Clock Input                         |

| DO[A,B]         | Data Output Bus                     |

| DOP[A,B]        | Data Output Parity Bus              |

| REGCE[A,B]      | Output Register Clock Enable        |

| CASCADEIN[A,B]  | Cascade input pin for 32K x 1 mode  |

| CASCADEOUT[A,B] | Cascade output pin for 32K x 1 mode |

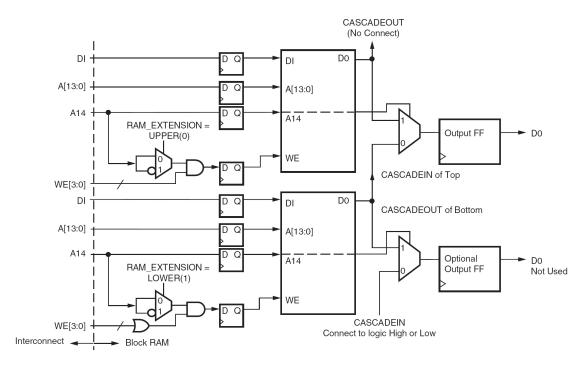

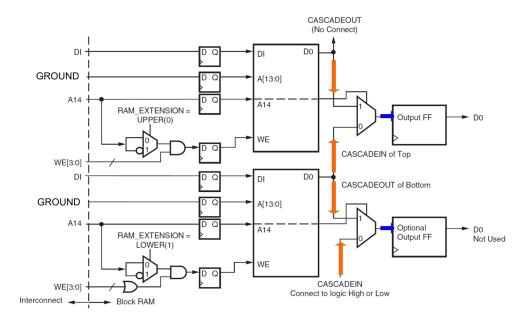

contents of a BRAM. This option is useful if the reconfiguration is targeted at changing the system function that operates on data stored in the BRAM. The RAM\_EXTENSION parameter for each port determines which BRAM is the UPPER or LOWER BRAM when configured in the cascade mode of operation. There are no restrictions on whether a particular BRAM can be UPPER or LOWER. This designation is decided by either the designer or the constraints associated with the available resources during resource placement. It is important to point out that the BRAMs located on a bottom row or directly above a PPC modules do not have CASCADEIN[A,B] inputs. Likewise, BRAMs located on the top row or directly below a PPC module do not have CASCADEOUT[A,B] ports. The DO\_REG parameter determines if the output data bus is either latched or sent through an extra flip-flop. The READ\_WIDTH and WRITE\_WIDTH parameters determines the selected BRAM aspect ratio per port. The WRITE\_MODE parameter selects one of three supported write modes. READ\_FIRST brings the current contents of the addressed word to the output during a write operation. Likewise, WRITE\_FRIST writes the input data to the addressed

location while it also forces the input data to the output of the BRAM. The NO\_CHANGE write mode prevents the data output from changing during a write operation. Only a read operation will change the output data.

Table 2.4: BRAM Configuration Options [2]

| Configuration Attribute | Parameters                         |

|-------------------------|------------------------------------|

| SAVEDATA                | TRUE, FALSE                        |

| RAM_EXTENSION_[A,B]     | LOWER, UPPER, NONE                 |

| DO_[A,B]_REG            | 0,1                                |

| INVERT_CLK_DO[A,B]_REG  | TRUE, FALSE                        |

| READ_WIDTH_[A,B]        | 36,18,9,4,2,1,0                    |

| WRITE_WIDTH_[A,B]       | 36,18,9,4,2,1,0                    |

| WRITE_MODE_[A,B]        | READ_FIRST, WRITE_FIRST, NO_CHANGE |

### BRAM Error Checking Code (ECC) and Cascade Operational Modes

A pair of BRAMs can be configured to either implement a 512 x 72-bit ECC RAM or a 32K x 1-bit RAM. However, there are several restrictions for these additional modes concerning the actual placement during design implementation. An ECC BRAM can be placed in a Virtex 4 so long as the bottom BRAM is located on an even row. For clarity, the numbering convention Xilinx uses sets the bottom most row to be row zero. If an FX devices is being used, an ECC BRAM can not use the BRAM directly below or above the PowerPC core. Restrictions on the placement for cascaded BRAMs are somewhat less strict. Any pair of BRAMs in a column can be cascaded so long as the two BRAMs are physically adjacent and the pair does not span a PPC module when using FX family devices [2].

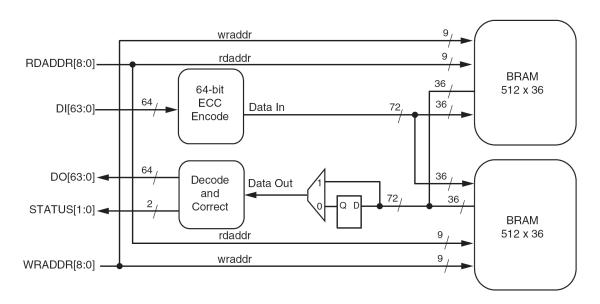

An ECC RAM is commonly used in systems that are designed to be fault tolerant. In Virtex 4, when a data word is written to an ECC RAM, a Hamming code is generated for the written data word and stored alongside the data. A Hamming code is a form of an error checking code that inserts Hamming bits throughout a data word. Each Hamming bit contains parity over a subset of the data word. The contents of all the Hamming bits for a given data word is what is referred to as the Hamming code associated with a data word. The Hamming code is designed such that any single bit error in the Hamming code or in the data word will be able to indicate the presence of a single-bit error and indicate which bit is incorrect. If a Hamming bit is allocated to generate parity over the entire Hamming code and the data, then it is possible to provide single-bit error correction and double-bit error detection [30].

Virtex 4 uses what is termed a (72,64) Hamming code, meaning the Hamming codeword is 72 bits with 64 of those bits being the actual data. Seven of the eight Hamming bits are used to provide single-bit correction and the eighth bit is used to provide parity over the entire Hamming codeword which enables double-bit error detection [30]. Figure 2.8 illustrates the architecture of an ECC BRAM. An ECC BRAM also generates status bits that indicate if a single bit error was corrected or a double bit error was detected. Table 2.5 gives a description of the three valid ECC status words. It is important to note, however, that when a single bit error is corrected in the Virtex 4 ECC implementation, only the data at the output registers of the ECC BRAM are corrected. The contents stored in the BRAM are not corrected automatically [2].

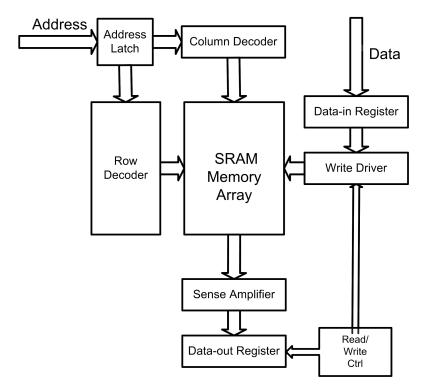

The cascade mode of operation is implemented by using the MSB of the ADDR[A,B] bus, a single configuration bit, and dedicated routing to send the lower BRAM data output to the upper BRAM in the cascade pair. Figure 2.9 illustrates two BRAMs configured as a cascade pair. Data written to a cascaded pair is routed to either the lower or upper BRAM by the MSB of the address bus. In addition, the MSB of the address bus selects the data

from either the lower or upper BRAM during read operations. The lower BRAM outputs its data to the dedicated routing between a cascade pair and is then output via a multiplexer that is selected by the MSB of the address bus. Both lower and upper BRAMs in a cascade pair output data during every read operation but the output of the upper BRAM is the only valid output for a cascade configured BRAM pair [2].

Table 2.5: ECC Status Description

| Status[1:0] | Condition                  |

|-------------|----------------------------|

| 00          | No error                   |

| 01          | Single Bit error corrected |

| 10          | Double Bit error detected  |

| 11          | Invalid status condition   |

Figure 2.8: ECC BRAM Architecture [2]

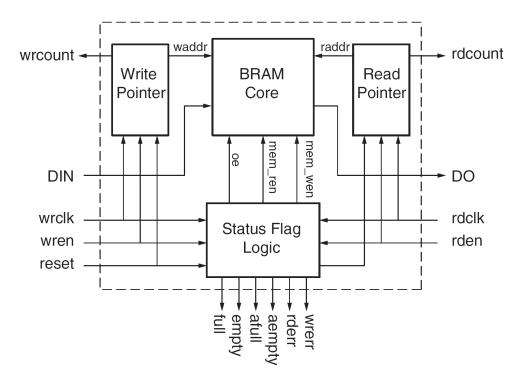

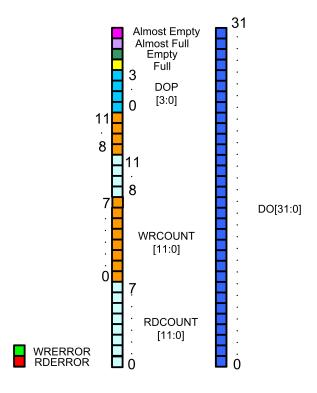

### 2.2.3 Virtex 4 FIFOs

A First In, First Out (FIFO) memory is commonly used in digital systems to handle data flow control and buffering. A FIFO holds data in a queue such that the first data stored

Figure 2.9: BRAM Cascade Operational Diagram [2]

is also the first data able to be retrieved. In Virtex 4 each BRAM can be configured as a FIFO without utilizing any surrounding PLBs. The FIFO implementation, as illustrated in Figures 2.10 and 2.11, generates both read and write pointers used to retrieve and store data from the BRAM [2]. A description of each FIFO input and output is given in Table 2.8. Also, status flags are generated to determine the state of the FIFO. In earlier FPGAs, such as Virtex 2, implementing a FIFO required using a substantial number of PLBs for this supporting logic.

Each Virtex 4 FIFO can be independently configured to four different depths as summarized in Table 2.6. Like BRAMs, the FIFO control signals RDCLK, WRCLK, RDEN, WREN, and RST also have programmable active levels. The first-word fall-through (FWFT) operational mode extends the depth of a FIFO by one data word. In this mode, the first

data item written to the FIFO is not stored in the BRAM, but is immediately available at the registered outputs. The remaining configuration options pertain to the programmable Almost Full/Empty flag limits. These programmable flags are set by the designer to help coordinate the status of the FIFO with surrounding logic.

Table 2.6: FIFO Configuration Options [2]

| Configuration | ALMOST_EMPTY_OFFSET |           | ALMOST_FULL_OFFSET |

|---------------|---------------------|-----------|--------------------|

|               | Standard            | FWFT      |                    |

| 4k x 4        | 5 to 4092           | 6 to 4093 | 4 to 4091          |

| 2k x 9        | 5 to 2044           | 6 to 2045 | 4 to 2043          |

| 1k x 18       | 5 to 1020           | 6 to 1021 | 4 to 1019          |

| 512 x 36      | 5 to 508            | 6 to 509  | 4 to 507           |

The timing characteristics of the various FIFO status flags are given in Table 2.7. The most interesting attribute in this table is the assertion of the FULL flag. The FULL flag is asserted one clock cycle after the last possible data entry is written and deasserts 3 to 4 clock cycles later depending on whether the standard or FWFT operational modes is used. This latency means that one could accidentally write to a FIFO when in actuality it is already full. To remedy this problem, Xilinx recommends using the ALMOST FULL flag to signal the FIFO is full [2]. In terms of testing, the FIFO's status flag timing creates several problems in terms of the ability to create test algorithms that fully test the device in all modes of operation. This issue will be discussed in detail in Chapter 4.

Figure 2.10: Virtex 4 FIFO Implementation [2]

Figure 2.11: Virtex 4 FIFO [2]

Table 2.7: Virtex 4 Status Flag Clock Cycle Latency [2]

|                     |               |   |             | ·    |

|---------------------|---------------|---|-------------|------|

| Clock Cycle Latency | Assertion     |   | Deassertion |      |

|                     | Standard FWFT |   | Standard    | FWFT |

| EMPTY               | 0             | 0 | 3           | 4    |

| FULL                | 1             | 1 | 3           | 3    |

| ALMOST EMPTY        | 1             | 1 | 3           | 3    |

| ALMOST FULL         | 1             | 1 | 3           | 3    |

| READ ERROR          | 0             | 0 | 0           | 0    |

| WRITE ERROR         | 0             | 0 | 0           | 0    |

Table 2.8: FIFO Port Signal Descriptions [2]

|             |           | O Port Signal Descriptions [2]                   |  |  |

|-------------|-----------|--------------------------------------------------|--|--|

| Port Name   | Direction | Description                                      |  |  |

| DI          | Input     | Data input.                                      |  |  |

| DIP         | Input     | Parity-bit input.                                |  |  |

| WREN        | Input     | Write enable, Active high or low.                |  |  |

| WRCLK       | Input     | Clock for write domain operation. Rising or      |  |  |

|             |           | falling edge triggered.                          |  |  |

| RDEN        | Input     | Read enable, Active high or low.                 |  |  |

| RDCLK       | Input     | Clock for read domain operation. Rising or       |  |  |

|             |           | falling edge triggered.                          |  |  |

| RESET       | Input     | Asynchronous reset of all FIFO functions, flags, |  |  |

|             |           | and pointers. Active high or low.                |  |  |

| DO          | Output    | Data output.                                     |  |  |

| DOP         | Output    | Parity-bit output.                               |  |  |

| FULL        | Output    | All entries in FIFO memory are filled. No addi-  |  |  |

|             |           | tional write enable is performed.                |  |  |

| ALMOSTFULL  | Output    | Almost all entries in FIFO memory have been      |  |  |

|             |           | filled.                                          |  |  |

| EMPTY       | Output    | FIFO is empty. No additional read can be per-    |  |  |

|             | _         | formed.                                          |  |  |

| ALMOSTEMPTY | Output    | Almost all valid entries in FIFO have been read. |  |  |

| RDCOUNT     | Output    | The FIFO data read pointer.                      |  |  |

| WRCOUNT     | Output    | The FIFO data write pointer.                     |  |  |

| WRERR       | Output    | When the FIFO is full, any additional write op-  |  |  |

|             |           | eration generates an error flag.                 |  |  |

| RDERR       | Output    | When the FIFO is empty, any additional read      |  |  |

|             | -         | operation generates an error flag.               |  |  |

| L           |           | i – – – – – – – – – – – – – – – – – – –          |  |  |

#### 2.2.4 Virtex 4 CAD Tools

Xilinx provides a complete set of computer-aided design (CAD) tools that enable a designer to implement digital systems using a high-level design methodology that supports schematic entry, hardware description language (HDL) synthesis, and IP core integration. A designer can either use a graphical user-interface (GUI), Project Navigator, to implement designs, or command-line tools can be used. By using command-line tools and batch files, one can automate the BIST configuration generation process. Table 2.9 summarizes several Xilinx tools that are used to implement the BIST configurations presented in this thesis. BITGEN has several options that can be utilized in BIST configuration generation. BITGEN supports the creation of partial configuration bitstream from a set of regular full configuration bit-files. During the creation of partial bit-files BITGEN compares two NCD design files and generates a bit-file containing the difference between the two. The XDL command-line tool allows the conversion between an NCD file and an XDL file. An XDL file type contains a human-readable netlist description of a FPGA configuration. XDL can convert an XDL file to an NCD file type which describes a given FPGA configuration, but this file type is a binary file which is not human-readable [31].

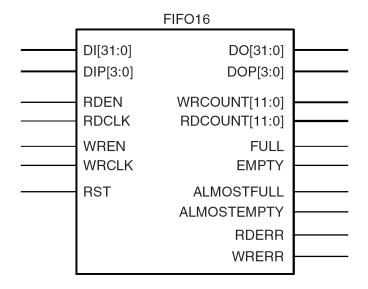

### 2.2.5 Virtex 4 Boundary Scan

Virtex 4 implements boundary scan, also called JTAG, that meets IEEE Standard 1149.1-2001 [3]. Boundary scan was originally intended as a mechanism for testing interconnect between multiple IC chips on a system board. A boundary scan implementation includes the following four signals: Test Clock (TCK), Test Mode Select (TMS), Test Data In (TDI), and Test Data Out (TDO). By asserting TMS to either a logic high or low during

Table 2.9: Summary of Xilinx Design Tools

|             | Table 2.5. Summary of Annix Design Tools |            |                                            |  |  |

|-------------|------------------------------------------|------------|--------------------------------------------|--|--|

| Application | Input                                    | Output     | Description                                |  |  |

|             | File Type                                | File Type  |                                            |  |  |

| XST         | VHDL, Verilog                            | NGC        | Synthesis Tool - Compiles HDL and gener-   |  |  |

|             |                                          |            | ates a design netlist compatible with Xil- |  |  |

|             |                                          |            | inx devices                                |  |  |

| NGDbuild    | NGC                                      | NGD        | Compiles designs to common format          |  |  |

| MAP         | NGD                                      | NCD        | Translates post-synthesis design to a de-  |  |  |

|             |                                          |            | vice specific implementation               |  |  |

| PAR         | NCD                                      | NCD        | Places and routes device specific designs  |  |  |

| BITGEN      | NCD                                      | .BIT, .RBT | Creates bitstream configuration files for  |  |  |

|             |                                          |            | download                                   |  |  |

| XDL         | XDL, NCD                                 | NCD, XDL   | Converts in between XDL and NCD de-        |  |  |

|             |                                          |            | sign formats                               |  |  |

| TRCE        | NCD                                      | TWR        | TRACE - Generates configuration timing     |  |  |

|             |                                          |            | analysis report                            |  |  |

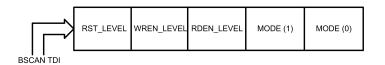

a rising transition on TCK, one can navigate a state machine termed the test access port (TAP) controller as illustrated in Figure 2.12 [11]. However, the technology has evolved and now most FPGAs allow for device programming via boundary scan [29][3]. Xilinx's Virtex series of FPGAs also allow connecting boundary scan signals to internal FPGA logic. This connection is made via what Xilinx calls boundary scan (BSCAN) modules. In Virtex 4, four BSCAN modules are available for use and each module is selected by shifting a specific data word into TAP's instruction register as shown in Table 2.10. The convention that is used when shifting data either into the data register when in state Shift-DR or the instruction register when in state Shift-IR is to assert TMS to a '1' on the last data bit transmitted over TDI.

NOTE: The value shown adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.

Figure 2.12: TAP Controller State Diagram [3]

Table 2.10: Virtex 4 BSCAN Module Access Commands [3]

| Boundary Scan | Binary Code | Description                    |

|---------------|-------------|--------------------------------|

| Command       | (9:0)       |                                |

| USER1         | 1111000010  | Access user-defined register 1 |

| USER2         | 1111000011  | Access user-defined register 2 |

| USER3         | 1111100010  | Access user-defined register 3 |

| USER4         | 1111100011  | Access user-defined register 4 |

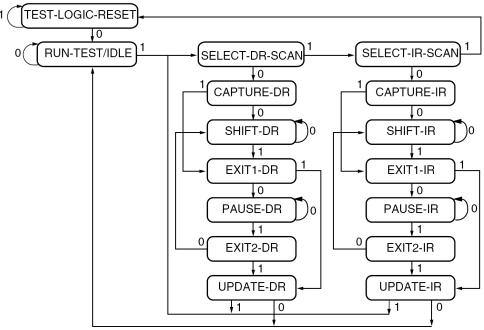

# 2.3 SRAM Testing

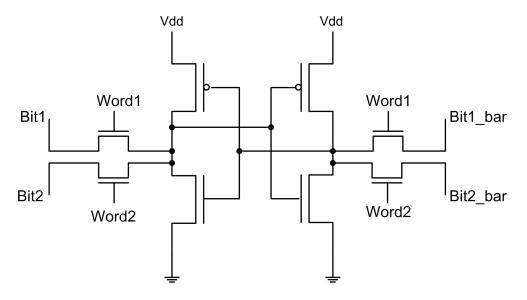

Most digital systems incorporate some type of memory element whether it is an embedded SRAM in a microprocessor's cache or a standalone memory in a digital system. Applications that utilize memories are quite abundant and thus there is a need to ensure that memory devices such as SRAMs are fault-free. Figure 2.13 illustrates a functional model of a common SRAM. As seen in this figure, an array of memory cells and supporting functions such as decoders, sense amplifiers, and storage registers are all components integral to a SRAM. Figure 2.14 shows how a two-port memory can be made by additional word and bit lines that connect the the cross-coupled inverters.

Figure 2.13: SRAM Memory Functional Model

Figure 2.14: Structural Model of a two-port SRAM cell

#### 2.3.1 SRAM Fault Models

In [26], van de Goor shows that a simple stuck-at fault (SAF) model is not sufficient for modeling faults found in memory devices. Table 2.11 lists common types of faults for SRAMs and are sometimes referred to as simple faults. Coupling faults can be further classified into four subtypes: inversion coupling faults (CFin), idempotent coupling faults (CFid), state coupling faults (CFst), and disturb coupling fault (CFdst). A CFin refers to a  $\uparrow$  and/or  $\downarrow$  write operation in a coupling cell that causes an inversion in the coupled cell. For example, if cell A and cell B are both '1' and a '0' is written to cell A, a CFin fault in cell B would invert its value to a '0' as well. In this case cell A is considered the coupling cell and cell B is deemed the coupled cell. A CFid is similar to a CFin except that the coupled cell is forced to either a 1 or 0 instead of an inversion. A CFst is slightly more complicated as the coupled cell is only affected if the coupling cell is in a certain state. For example, a '1' in cell A could force cell B to either a '1' or '0', but if cell A is a '0', no fault

effect would be observed. Finally, a CFdst refers to a fault where the coupled cell undergoes a transition due to a read or write operation to the coupling cell [32]. When coupling faults are considered as part of a memory's fault model, often the occurrence of multiple faults is considered. These multiple faults are said to be linked and are referred to as linked faults. The term linked is used because in the presence of multiple faults, each fault can possibly influence the effect of the other faults [11].

Table 2.11: Common SRAM Fault Types

| Fault Type        | Description                                                 |

|-------------------|-------------------------------------------------------------|

| Stuck-At (SAF)    | A logic value of a memory cell always being 1 or 0          |

| Transition Faults | Memory cell not able to make a 0 to 1 or 1 to 0 transition  |

| (TF)              |                                                             |

| Coupling Faults   | A change in one memory cell, the coupling cell, causes an-  |

| (CF)              | other cell , the coupled cell, to change its value          |

| Address Decoder   | The expected memory cell is not selected or another cell is |

| Faults (AF)       | selected                                                    |

| Data Retention    | The expected stored data is corrupted                       |

| Faults (DRF)      |                                                             |

| Pattern Sensitive | The contents of a memory cell changes the value of another  |

| Faults (PSF)      | memory cell                                                 |

### 2.3.2 March Tests for Single-Port Memories

Memory devices are traditionally tested with march tests. March tests apply defined test patterns consisting of writing and reading varying patterns of 1s and 0s to and from a memory device. Table 2.12 lists common notations used to describe march tests while Table 2.13 lists several march tests of varying complexity. For example, when running the MATS+ march test on a memory device, a '0' is written to each memory location in either a descending or ascending traversal. Next, starting at the lowest addressed memory location and traversing upward, a '0' is read and a '1' is written to each memory location. The next

Table 2.12: March Test Notation Descriptions

| Notation   | Description                                     |

|------------|-------------------------------------------------|

| Notation   | *                                               |

| r          | A read operation                                |

| W          | A write operation                               |

| r0         | Read a 0                                        |

| w0         | Write a 0                                       |

| w1         | Write a 1                                       |

| 1          | Traverse upward through memory addresses        |

| <b></b>    | Traverse downward through memory addresses      |

| $\uparrow$ | Traverse any direction through memory addresses |

sequence begins at the highest memory location and traverses downward while reading a '1' and then finally writing a '0' to each memory location.

In terms of fault detection, MATS+ is able to detect all SAF and all AF [11]. More complex tests such as March Y can detect additional faults, those being TF and CF in and some linked faults. In addition, March C- can detect most all types of CFs. The general trend for march test fault detection is that longer, more complex tests offer higher fault detection. While high fault detection is obviously desired, some tests like those used specifically to target pattern sensitive faults can be unpractical, especially if the DUT is of any sufficient size.

In [32], van de Goor presents March LR as "a test for simple faults and realistic linked faults." The set of realistic linked faults further reduces the universe of possible linked faults by removing combinations that are not likely to occur in actual devices. Realistic linked faults do not include linked faults containing one or more CFins and linked faults containing two CFids or two CFdsts are also removed. Van de Goor shows that March LR is superior to March C- as it can also detect some neighborhood PSFs (NPSFs)[32].

Table 2.13: Common March Tests for Single Port Memories

| March Test | Description                                                                                                                | Test time |

|------------|----------------------------------------------------------------------------------------------------------------------------|-----------|

| MATS+      | $\{ \uparrow(w0); \uparrow(r0,w1); \downarrow(r1,w0) \}$                                                                   | 5N        |

| March C-   | $\{\updownarrow(w0);\uparrow(r0,w1);\uparrow(r1,w0);\downarrow(r0,w1);\downarrow(r1,w0);\updownarrow(r0)\}$                | 10N       |

| March Y    | $\{\updownarrow(w0);\uparrow(r0,w1,r1);\downarrow(r1,w0,r0);\updownarrow(r0)\}$                                            | 8N        |

| March LR   | $\{\updownarrow(w0); \downarrow(r0,w1); \uparrow(r1,w0,r0,w1); \uparrow(r1,w0); \uparrow(r0,w1,r1,w0); \updownarrow(r0)\}$ | 14N       |

Note: N = Number of address locations

All of the march tests listed in Table 2.13 are designed for bit-oriented memories (BOMs), meaning each memory word is a single bit. However, many memories, including the Virtex 4 BRAM, perform as a word-oriented memory (WOM), meaning each word is more than a single bit. Executing BOM-based march tests on WOM involves extending the bit operation to the entire word. For example, if a  $w\theta$  operation is to be applied to a BOM of 4-bits it could be interpreted as w0000, meaning write all zeros to each bit in the data word. Writing and reading either all zeros or ones in a WOM does not sufficiently detect CF between cells in a data word. In [4], van de Goor et al. develop methods for converting BOM march tests, specifically March LR, to WOM march tests by using background data sequences (BDS). Instead of writing either all zeros or ones, BDS involve writing binary patterns consisting of alternating ones and zeros and alternating sets of ones and zeros. Table 2.14 list all possible BDS for an eight bit word. The number of BDS for a M-bit word is given by Equation 2.1. Figure 2.15 illustrates converting March LR to March LR with 4-bit BDS. The test length increases from 14N to 30N, where N is number of words in the memory. In general, Equation 2.2 gives the expected test length for a WOM march test derived from a BOM march test. The variable 'M' in Equation 2.2 refers to the number of bits in a data word. Converting March LR to incorporate BDS requires running

```

\begin{split} & \{ [\updownarrow(w0000); \downarrow(r0000,wl111); \uparrow(r1111,w0000,r0000,wl111); \\ & \uparrow(r1111,w0000); \\ & \uparrow(r0000,w1111,r1111,w0000); \updownarrow(r0000) ] \\ & [\uparrow(r0000,w1111,r1111); \downarrow(r1111,w0000,r0000); \\ & \uparrow(r0000,w0101,w1010,r1010); \downarrow(r1010,w0101,r0101); \\ & \uparrow(r0101,w0011,w1100,r1100); \downarrow(r1100,w0011,r0011); \uparrow(r0011) ] \} \end{split}

```

Figure 2.15: March LR with 4-bit BDS [4]

Table 2.14: Background Data Sequence for 8-bits

| # | Normal   | # | Inverse  |

|---|----------|---|----------|

| 0 | 00000000 | 1 | 11111111 |

| 2 | 01010101 | 3 | 10101010 |

| 4 | 00110011 | 5 | 11001100 |

| 6 | 00001111 | 7 | 11110000 |

the original March LR test as enclosed in the first set of square brackets in Figure 2.15 and then addition additional marches that incorporate BDS.

$$#BDS = \lceil \log_2(M) \rceil + 1 \tag{2.1}$$

$$Test \ Length = (16 + 7 * \lceil \log_2(M) \rceil$$

(2.2)

## 2.3.3 March Tests for Dual-Port Memories

In [5], Hamddioui and van de Goor describe two march tests for dual-port memories. Specific march tests are required for both ports in order to detect specific faults in dual-port memories. Dual-port memories generally support the following operations by the two ports[5]:

• Simultaneous read and write operations to different addresses.

- Simultaneous read and write operations to the same address. For this case, however, the write operation is assumed to have higher priority over the read operation.

- Two simultaneous reads to either the same or different addresses.

- Two simultaneous write operations to different addresses.

The only operation not allowed is simultaneous write operations to the same address location. The Virtex 4 BRAM supports the same operations and limitations discussed above. The faults associated with dual-port memories are classified as 2PF1 and 2PF2[5]. Faults classified as 2PF1 are sensitized by two simultaneous reads or both a read and write operation. Two types of faults are associated with two simultaneous reads. In one case, the correct data value is read through the sense amplifier in the SRAM cell, but the actual data stored in the cell will flip. The other case is when sense amplifier reads an incorrect value and the actual data stored is also flipped. Simultaneous read and write operations can also cause the intended write operation to not occur. March s2pf, as seen in Figure 2.16, detects all 2PF1 type faults. The ':' symbol used in Figure 2.16 separates the operation on each port. For example, 'r1:-' would indicate a read operation on one port and any allowed operation on the second port.

```

\left\{ \begin{array}{c} \diamondsuit\left(w0:n\right) \;\; ; \\ M_0 \\ & \uparrow (r0:r0,r0:-,w1:r0) \;\; ; \;\; \uparrow (r1:r1,r1:-,w0:r1) \;\; ; \\ M_1 \\ & \downarrow (r0:r0,r0:-,w1:r0) \;\; ; \;\; \downarrow (r1:r1,r1:-,w0:r1) \;\; ; \\ M_3 \\ & \downarrow (r0:-) \;\; \right\} \\ M_5 \\ \end{array}

```

Figure 2.16: March s2pf [5]

2PF2 faults are similar to the 2PF1 type faults except the affected cell is a neighboring cell. For example, a fault may flip a neighboring  $cell_i$  if two read operations occur on  $cell_j$ . Another type of fault occurs when a read occurs at  $cell_i$  and a write to  $cell_j$ . During this scenario, the fault will cause the read to return the wrong value [5]. March d2pf, as seen in Figure 2.17, is able to detect all 2PF2 faults. The the variables 'c' and 'r' correspond to the memory cell column and row location, respectively. The variables 'C' and 'R' represent the number of memory cell columns and rows, respectively. The widest word size, 36-bits, is assumed to be the memory array column size. When this march test is applied to BRAMs in Virtex 4, 'C' is considered to be zero and R is '512'.

Figure 2.17: March d2pf [5]

### 2.4 Overview of BIST for FPGAs

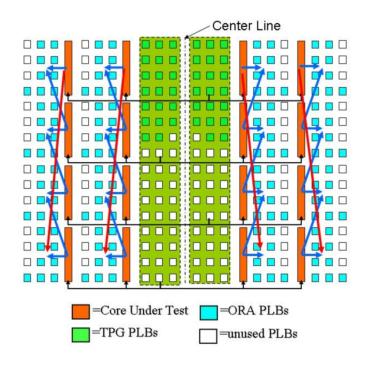

Developing BIST for FPGAs consists of designing test configurations that fully test all components within a FPGA. Traditionally, these components have been grouped into the following types of tests: BIST for PLBs, BIST for I/O Buffers, BIST for programmable routing resources, and BIST for specialized embedded cores such as large SRAMs [14][18][33]. The work presented in this thesis concentrates on testing Virtex 4 BRAMs which fall into the category of testing specialized embedded cores. BIST for PLBs is also called Logic BIST

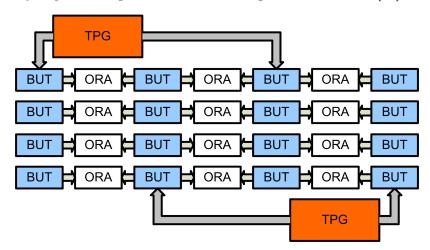

and this is the most common BIST found in the literature. Logic BIST usually requires repeatedly configuring PLBs in different modes of operations and applying test patterns the PLBs under test. A general BIST architecture is illustrated in Figure 2.18. Two identical TPGs drive alternating columns of blocks under tests (BUTs) whose outputs are observed by two adjacent ORAs. For Logic BIST, all of the BIST components are implemented using PLBs. In certain implementations such as in [34], the TPGs can be implemented using other available specialized cores. In order to test all PLBs in a FPGA, the entire BIST architecture must be flipped such that the PLBs acting as BUTs are now ORAs and the PLBs previously implementing ORAs are now configured to be BUTs [34].

Figure 2.18: A General Comparison Based BIST Architecture

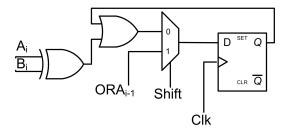

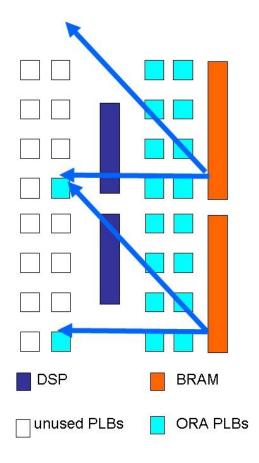

Several different types of ORAs are used in BIST for FPGAs. A comparison-based ORA design is the most common. Figures 2.20 and 2.21 illustrate two types of comparison-based ORAs: one with a shift chain and one without a shift chain. Using an ORA design without shift chains reduces the size of an ORA and can allow for more ORAs to be used which increases diagnostic resolution [21]. In both designs, any mismatch from the BUTs will cause the flip-flop to latch to a '1' until the end of the test. The addition of the

shift chain allows the results to be shifted out of the device at the end of testing [14]. A comparison-based ORA with no shift chain can be used when the FPGA supports read back of the contents of the flip-flops in the each PLB via configuration memory readback. Modern FPGAs such as the Virtex family from Xilinx support this readback operation [29][3].

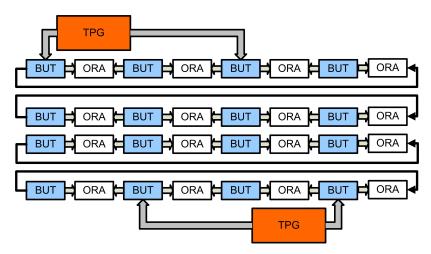

Figure 2.18 also presents an example of a general comparison-based ORA BIST architecture. This type of comparison has limitations in terms of diagnostic resolution for BUTs located at the outer columns since they are only compared by a single ORA. In [14], cases where a fault could escape detection are discussed. A circular-comparison based BIST architecture, as seen in Figure 2.19, eliminates the loss of fault detection around outer columns. Circular-comparison based BIST architectures require a minimum of three BUTs for fault detection and four BUTs for fault diagnosis [28]. The only condition for a fault to escape detection is for all BUTs in a circular comparison chain to have identical equivalent faults. If the comparison chain is sufficiently long, then the probability of multiple equivalent fault occurring is negligible.

Figure 2.19: A Circular Comparison Based BIST Architecture

Figure 2.20: Comparison Based ORA with Shift Chain

Figure 2.21: Comparison Based ORA without a Shift Chain

## 2.4.1 BIST for BRAMs

In [17], Garimella developed BIST configurations to test BRAMs in Virtex 2 FPGAs. The work presented in this thesis borrows many of the same concepts and applies them to BIST for BRAMs in Virtex 4. BRAMs in Virtex 2 only operate as a dual-port memory. There are no built-in FIFOs or ECC or cascade modes of operation. Garimella's approach was to create a portable BIST architecture that could be adapted to different FPGAs. A HDL was used to model, synthesize, and implement the entire BIST architecture. Garimella used the comparison-based ORA design that includes the shift chain. The end of the shift chain was connected to the boundary scan port TDO. The boundary scan pin TDI was connected to each ORA such that a '1' on TDI enabled all of the ORAs to become a shift register. Likewise, a '0' on TDI would disable the shift operation and the ORAs would

Table 2.15: Virtex 2 BRAM Summary

| Table 2.10. Virtex 2 Digital Summary |                 |               |           |        |  |  |

|--------------------------------------|-----------------|---------------|-----------|--------|--|--|

| BIST                                 | Test            | Address       | Data      | Clock  |  |  |

| Configuration                        | Algorithm       | Locations (A) | Width (D) | Cycles |  |  |

| 1                                    | March LR w/ BDS | 512           | 36        | 58A    |  |  |

| 2                                    |                 | 1K            | 18        | 14A    |  |  |

| 3                                    |                 | 2K            | 9         | 14A    |  |  |

| 4                                    | March LR        | 4K            | 4         | 14A    |  |  |

| 5                                    |                 | 8K            | 2         | 14A    |  |  |

| 6                                    |                 | 16K           | 1         | 14A    |  |  |

| 7                                    | March s2pf      | 512           | 36        | 14A    |  |  |

| 8                                    | March d2pf      | 512           | 36        | 9A     |  |  |

TOTAL BIST CLOCKS= 485,888

continue to compare BUT responses on each clock cycle. The system clock for the ORAs, BUTs, and TPG was sent through the TCK port on the Boundary Scan port.

Table 2.15 summarizes the eight BIST configurations generated by Garimella for Virtex 2 BRAMs. March LR was implemented as a TPG and used for each of the programmable aspect ratios. March LR was chosen primarily because of its relatively low complexity and high fault coverage. The 512 x 36 addressing mode used March LR modified to generate BDS so that fault detection of intra-word coupling faults was maximized. March s2pf and d2pf were also used to test dual-port functionality.

The advantages of Garimella's approach was that the BIST architecture was described in a HDL which allowed for very rapid development. There are, however, some important disadvantages. BIST approaches such as in [34] take advantage of partial reconfiguration FPGA techniques in order to reduce test time and the amount of configuration data needed to download to a device during multiple BIST configurations. In order for several FPGA configurations to use partial reconfiguration efficiently, there needs to be only small regular changes between each configuration. In terms of BIST for PLBs, the changes made between

each configuration is only to change the operational mode of the BUT and keep the rest of the BIST circuitry static [34]. This approach yielded substantial test time and configuration storage reductions when applied to BIST for PLBs in Virtex 2 and Virtex 4.

Garimella's approach is not compatible with partial reconfiguration. The use of a HDL to develop BIST configurations removes the control over the placement of BIST circuitry. The CAD tools that transform a HDL to a configuration ready for download are not able to take advantage of the regularity of BIST architectures. The result is that the TPG and ORA portions of the BIST circuitry are intermingled amongst the available logic resources surrounding BRAMs. CAD tools also do not obtain identical results in repeated implementations. This severely limits the use of partial reconfiguration because at no time are subsequent BIST configurations guaranteed to be similar to previous configurations. For this reason, Garimella used full configuration downloads for each BIST configuration. Another disadvantage with the HDL approach is that developing BIST at a high level reduces the controllability over the resource being tested. For example, in BIST configurations that used active low signals, the synthesis tool inverted the signals connected to the BRAM instead of configuring the BRAM ports to the opposite level. This behavior was observed when determining the portability of Garimella's BIST approach to Virtex 4. As a result, configuration bits and logic inverting BRAM control signals are not tested by Garimella's approach.

### 2.5 Thesis Restatement

The work by Garimella in developing BIST configurations for Virtex 2 BRAMs is a basis for the work presented in this thesis. The main disadvantage of Garimella's approach

is not being able to take advantage of partial reconfiguration techniques between each BIST configuration following the initial full BIST configuration download. Downloading BIST configurations is the most time expensive portion of the entire time required for BIST. The time spent applying BIST clock cycles is nominal compared to the configuration time required. This thesis presents the development of BIST configurations for Virtex 4 BRAMs compatible with partial reconfiguration. Using partial reconfiguration, a large portion of the time needed to perform BIST can be reduced. Unlike Garimella, the BIST architecture presented in this thesis does not rely on a HDL to describe the overall BIST architecture. Instead, this approach uses custom created BIST programs to implement BIST configurations which enables much greater control of each BIST configuration as compared to the HDL approach by Garimella. This improvement allows for testing BRAMs in all of their configuration options gives higher fault coverage. Chapter 3 will introduce the general BIST architecture for testing BRAMs. Also in Chapter 3, BIST configurations testing BRAMs in single and dual-port modes are presented. BIST configurations for FIFO operational modes are developed in Chapter 4 while ECC and cascade mode BIST configurations are presented in Chapter 5.

### Chapter 3

### VIRTEX 4 BLOCK RAM BIST IMPLEMENTATION

A BIST approach developed for BRAMs in Virtex 4 FPGAs is presented in this chapter. The BIST architecture will be discussed as well as a TPG which is able to generate multiple march tests. Finally, results from applying BIST to Virtex 4 devices are given and compared to results obtained by Garimella in [17].

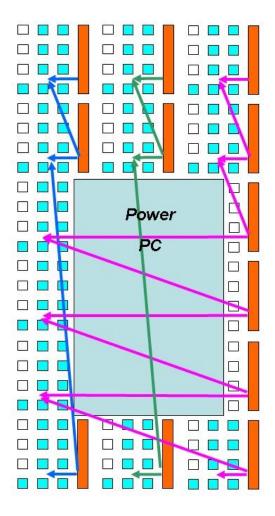

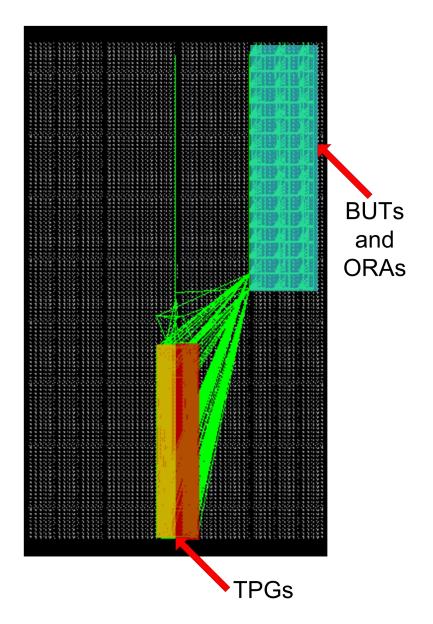

### 3.1 Virtex 4 BRAM BIST Architecture