# Thick Film Packaging Techniques for 300°C Operation

by

# Rui Zhang

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama December 12, 2011

Keywords: thick film, Silicon Carbide, die attach, high temperature packaging

Copyright 2011 by Rui Zhang

# Approved by

Robert W Johnson, Chair, Professor of Electrical & Computer Engineering Robert N Dean, Assistant Professor of Electrical & Computer Engineering Guofu Niu, Professor of Electrical & Computer Engineering John Evans, Professor of Industrial and Systems Engineering

#### **Abstract**

Geothermal well logging and instrumentation applications require electronics capable of 300°C operation. SiC device technology enables the design and fabrication of analog circuits that can operate at these temperatures. However, to build functional systems operating at high temperatures, an interconnection and packaging technology must be developed to provide interconnectivity between different SiC devices and passive components. Key elements of a high temperature packaging technology include the interconnection substrate, die attach and wire bonding. New developments in each of these areas for high temperature operation are discussed in this work.

Thick film technology based on ceramics and metals has potential for higher operating temperatures. In this work, the effect of 300°C storage on the adhesion of different thick film conductors and multilayer dielectrics has been studied. In addition, the electrical properties of the dielectric, including leakage current, capacitance, and dissipation factor, have been studied as a function of temperature and of high temperature aging. The leakage current was also investigated as a function of high temperature aging under DC bias voltage.

Eutectic AuSn die attach was used with a Ti/TiW/Au backside die metallization for 300°C operation. Liquid Phase Transient (LPT) die attach process was developed. Results of die attach reliability based on shear strength were discussed after thermal

storage and thermal cycling tests. Investigation of Au wire bonding on different SiC die metallization was reported. Failure analysis after reliability testing was also performed.

Passive components were selected for this high temperature application and an attach process was developed. After an initial test, one resistor and one capacitor were selected for reliability testing after 300°C storage and thermal cycling tests. External lead attach was also investigated for next level device connection.

Before building the final amplifier module, a SiC die was attached in a ceramic DIP package and tested functional at 300°C. An amplifier module was fabricated on a multilayer thick film ceramic substrate. Passive components and the SiC chip were then assembled. The amplifier was tested as-built and after high temperature storage.

## Acknowledgments

First and foremost, I would like to express my sincere gratitude to my advisor, Dr. R. Wayne Johnson. He has been a constant source of inspiration and ideas, given me great challenges and been very supportive with all kinds of help. His advice and research attitude have provided me with a model for my future career. I would also like to thank my advisory committee members, Dr. Robert Dean, Dr. Guofu Niu and Dr. John Evans for their support.

Appreciation is also expressed to cooperative support and continual assistance from Dr. Michael Bozack, Michael J. Palmer, John Marcell, Ping Zheng, Huihua Shu, Kun Fang, and ZhenZhen Shen throughout the course of this research. The support for this research provided by GE Global Research is also acknowledged.

This material is based upon work supported by the Department of Energy's Geothermal Technologies Program, under Award DE-FC36-08GO18181.

Finally, I would like to thank my parents for their continuous encouragement and support throughout my life.

# **Table of Contents**

| Abstract                                                        | ii |

|-----------------------------------------------------------------|----|

| Acknowledgments.                                                | iv |

| List of Tables                                                  | ix |

| List of Figures                                                 | x  |

| Chapter 1 Introduction                                          | 1  |

| 1.1 High Temperature Electronics (HTE)                          | 1  |

| 1.2 Applications of High Temperature Electronics                | 1  |

| 1.3 High Temperature Electronics in Enhanced Geothermal Systems | 3  |

| 1.4 High Temperature Electronics Packaging                      | 4  |

| 1.4.1 SiC Device                                                | 5  |

| 1.4.2 Substrate Materials                                       | 8  |

| 1.4.3 Thick Film Metallization                                  | 9  |

| 1.4.4 Die Metallization                                         | 10 |

| 1.4.5 Die Attach and Wire Bonding                               | 11 |

| 1.4.6 Passive Components Attach                                 | 13 |

| 1.5 Research Outline                                            | 13 |

| Chapter 2 Thick Film Paste Selection                            | 15 |

| 2.1 Introduction to Thick Film Technology                       | 15 |

| 2.2 Thick Film Conductor Paste                                  | 16 |

| 2.3 Thick Film Dielectric Paste                                            | 18       |

|----------------------------------------------------------------------------|----------|

| 2.4 Adhesion Test                                                          | 18       |

| 2.5 Electrical Testing                                                     | 33       |

| 2.5.1 Leak Current Measurement                                             | 34       |

| 2.5.2 Dissipation Factor and Capacitance Measurement                       | 40       |

| 2.5.3 Biased Measurement                                                   | 42       |

| 2.6 Summary                                                                | 46       |

| Chapter 3 High Temperature Die Attach and Wirebonding of Silicon Carbide D | evices48 |

| 3.1 Introduction                                                           | 48       |

| 3.2 SiC Die Metallization                                                  | 48       |

| 3.3 Off-eutectic AuSn Liquid Phase Transient (LPT) Die Attach              | 50       |

| 3.3.1 Liquid Phase Transient Bonding                                       | 51       |

| 3.3.2 Die Attach with Eutectic AuSn Paste                                  | 54       |

| 3.3.3 Die Attach with Eutectic AuSn Preform                                | 55       |

| 3.4 Die Attach Reliability Test                                            | 57       |

| 3.4.1 High Temperature Thermal Aging Test                                  | 57       |

| 3.4.2 Thermal Cycling Test                                                 | 63       |

| 3.5 Wire Bonding                                                           | 64       |

| 3.5.1 Wire Bond Pad Metallurgy                                             | 64       |

| 3.5.2 Wire Bond Pull Test                                                  | 65       |

| 3.5.3 Wire Bond Ball Shear Test                                            | 66       |

| 3.5.4 Daisy Chain Electrical Resistance                                    | 68       |

| 3 5 5 New Metallization Evaluation                                         | 69       |

| 3.6 Summary                                          | 72 |

|------------------------------------------------------|----|

| Chapter 4 Passive Components Attach                  | 73 |

| 4.1 Introduction                                     | 73 |

| 4.2 Passive Components Selection                     | 73 |

| 4.3 Resistor and Capacitor Attach                    | 76 |

| 4.3.1 Process Development                            | 77 |

| 4.3.2 High Temperature Thermal Aging Test            | 79 |

| 4.3.3 Thermal Cycling Test                           | 85 |

| 4.4 External Lead Attach                             | 88 |

| 4.4.1 Background                                     | 88 |

| 4.4.2 Moly Tab Attach                                | 89 |

| 4.4.3 External Lead Attach                           | 90 |

| 4.5 Summary                                          | 91 |

| Chapter 5 High Temperature Electronics Packaging     | 92 |

| 5.1 Single Chip DIP Packaging                        | 92 |

| 5.2 Amplifier Module                                 | 94 |

| 5.2.1 Substrate Fabrication                          | 94 |

| 5.2.2 Passive Components Attach                      | 96 |

| 5.2.3 Die Attach and Wire Bonding                    | 96 |

| 5.2.4 AmplifierTesting                               | 97 |

| Chapter 6 Conclusion and Future Work Recommendation  | 98 |

| 6.1 Thick Film Technology for 300°C Applications     | 98 |

| 6.2 Packaging for High Temperature SiC Based Devices | 98 |

| 6.3 Passive Compon | ents for 300°C Applications | 98  |

|--------------------|-----------------------------|-----|

| 6.4 Recommendation | ns for Future Work          | 99  |

| References         |                             | 100 |

# List of Tables

| Table 1.1 Application Area and Parameters for High Temperature Electronics | 1  |

|----------------------------------------------------------------------------|----|

| Table 1.2 Physical Properties of Semiconductor Materials                   | 6  |

| Table 1.3 Physical Properties of Semiconductor and Substrates Materials    | 9  |

| Table 2.1 Properties of Selected Thick Film Conductors                     | 19 |

| Table 2.2 Properties of Selected Thick Film Dielectric                     | 19 |

| Table 2.3 Test Pattern for Electrical Test Vehicle                         | 34 |

| Table 2.4 Measured Line Width and Spacing on Comb Pattern                  | 38 |

| Table 3.1 High Temperature Solder and Braze Alloys                         | 50 |

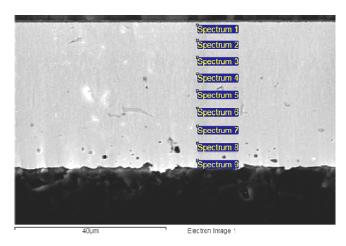

| Table 3.2 EDS Analysis on the Initial Bonding Layer                        | 57 |

| Table 3.3 EDS Analysis on the 320°C Aged Bonding Layer                     | 60 |

| Table 3.4 Average Daisy Chain Resistance (Ω)                               | 69 |

# List of Figures

| Figure 1.1 Diagram of an Enhanced Geothermal System                                                                | 4  |

|--------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 Intrinsic Carrier Density Versus Temperature for Si, GaAs, GaN, and SiC                                 | 7  |

| Figure 1.3 Metallization Scheme for Semiconductor in HTE                                                           | 10 |

| Figure 2.1 Basic Screen Printing Process                                                                           | 16 |

| Figure 2.2 Adhesion Test Vehicle                                                                                   | 20 |

| Figure 2.3 Standard 850°C Firing Profile                                                                           | 21 |

| Figure 2.4 Illustration of Pull Test                                                                               | 22 |

| Figure 2.5 Ceramic Surface after Pull Test                                                                         | 22 |

| Figure 2.6 SEM Photos of DuraStrate Substrate in Comparison with Standard Al <sub>2</sub> O <sub>3</sub>           | 23 |

| Figure 2.7 Metal Surface after 500 hours Aging at 320°C                                                            | 23 |

| Figure 2.8 Auger Analysis on Samples as Build and after 500 hours Aging at 320°C                                   | 24 |

| Figure 2.9 Pull Strength as a Function of Aging (320°C) for Conductor C101 and Dielectric D1 Fired at 850°C        | 25 |

| Figure 2.10 Pull Strength as a Function of Aging (320°C) for Conductor C101 and Dielectric D1 with Co-fire Process | 26 |

| Figure 2.11 Pull Strength as a Function of Aging (320°C) for Conductor C101 and Dielectric D1 Fired at 980°C       | 27 |

| Figure 2.12 Pull Strength as a Function of Aging (320°C) for Conductor C105 and Dielectric D1 fired at 850°C       | 28 |

| Figure 2.13 Pull Strength as a Function of Aging (320°C) for                                                       |    |

| Conductor C110, C101 and Dielectric D1, D4 fired at 850°C                                                                  | 29 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.14 Pull Strength as a Function of Aging (320°C) for Conductor C109 and Dielectric D1 fired at 850°C               | 30 |

| Figure 2.15 Pull Strength as a Function of Aging (320°C) for Conductor C109 on Ceramic fired at Different Conditions       | 31 |

| Figure 2.16 Pull Strength as a Function of Aging (320°C) for Conductor C109 on Dielectric D1 fired at Different Conditions | 32 |

| Figure 2.17 Conductor C109 Pulled off from Ceramic and Dielectric D1 fired at 980°C                                        | 32 |

| Figure 2.18 Electrical Test Vehicle                                                                                        | 34 |

| Figure 2.19 Capacitor Leakage Current Density at 100V Bias as a Function of Storage Time at 320°C                          | 35 |

| Figure 2.20 Capacitor Leakage Current Density at 100V Bias as a Function of Temperature (Test Vehicle Fired at 980°C)      | 36 |

| Figure 2.21 Designed Comb Test Pattern                                                                                     | 38 |

| Figure 2.22 Initial Leakage Current at 100V Bias as a Function of Temperature (Test Vehicle Fired at 980°C)                | 39 |

| Figure 2.23 Test Fixture for Capacitance and Dissipation Factor Measurement                                                | 40 |

| Figure 2.24 Initial Capacitance as a Function of Frequency and Temperature (Test Vehicle Fired at 980°C)                   | 41 |

| Figure 2.25 Initial Dissipation Factor as a Function of Frequency and Temperature (Test Vehicle Fired at 980°C)            |    |

| Figure 2.26 Test Pattern for Leakage Current under Bias                                                                    | 42 |

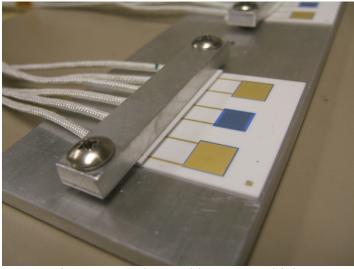

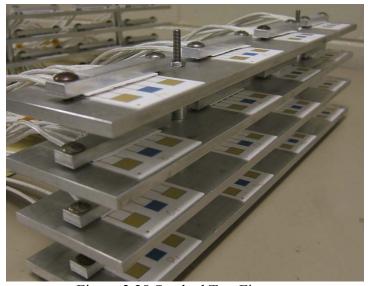

| Figure 2.27 Wires Held on Test Vehicle                                                                                     | 43 |

| Figure 2.28 Stacked Test Fixtures                                                                                          | 43 |

| Figure 2.29 Leakage Current as a Function of Aging Time                                                                    | 44 |

| Figure 2.30 Comb Pattern after 1000 hours Biased Aging                                                                     | 45 |

| Figure 2.31 Corner of Capacitor after 1000 hours Biased Aging                                                              | 45 |

| Figure 2.32 Leakage Current as a Function of Aging Time for 300 Minutes                      | 46 |

|----------------------------------------------------------------------------------------------|----|

| Figure 3.1 SiC Test Die with Daisy Chain Pattern                                             | 49 |

| Figure 3.2 Au-Sn Phase Diagram                                                               | 52 |

| Figure 3.3 Wire bonding and Die Shear Test Vehicle                                           | 53 |

| Figure 3.4 Typical X-Ray Result for SiC Die Attach with AuSn Paste                           | 55 |

| Figure 3.5 X-Ray Result for SiC Die Attach with AuSn Preform                                 | 56 |

| Figure 3.6 Cross-section Micrograph of Initial Die Attach with AuSn Preform                  | 57 |

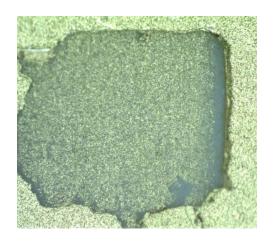

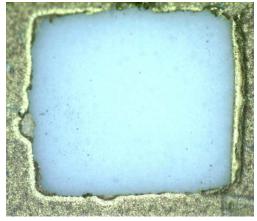

| Figure 3.7 Failure Mode on Substrate after Shear Test                                        | 58 |

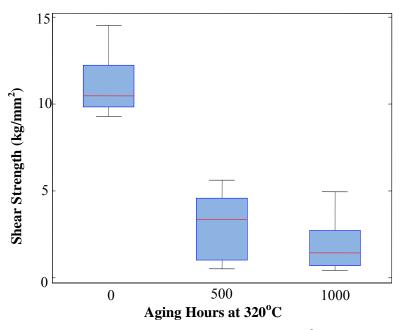

| Figure 3.8 Shear Strength as a Function of Aging (320°C) with C101 on $Al_2O_3$              | 59 |

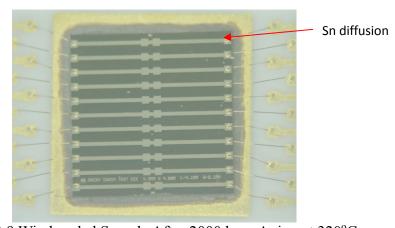

| Figure 3.9 Wirebonded Sample After 2000 hour Aging at 320°C                                  | 59 |

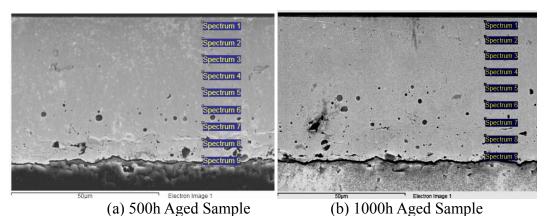

| Figure 3.10 Cross-section Micrograph of 320°C Aged Die Attach with AuSn Preform              | 60 |

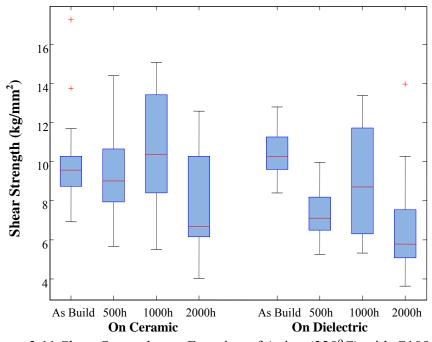

| Figure 3.11 Shear Strength as a Function of Aging (320°C) with C109 and D1                   | 61 |

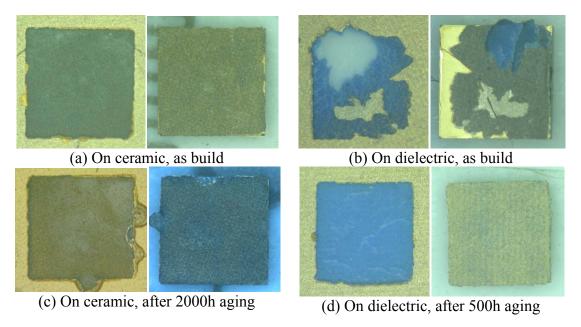

| Figure 3.12 Failure Mode for Die Shear as Built and after Aging                              | 62 |

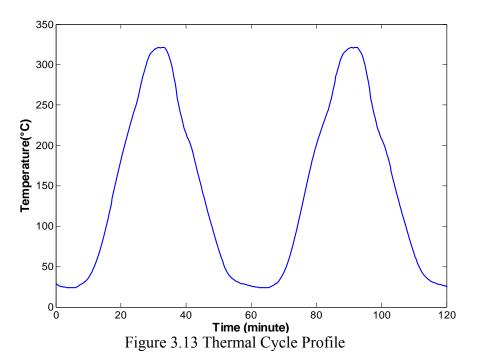

| Figure 3.13 Thermal Cycle Profile                                                            | 63 |

| Figure 3.14 Schematic Sequence of Ball-Stitch Wire Bonding                                   | 64 |

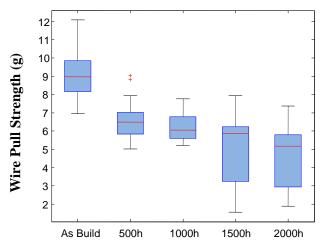

| Figure 3.15 Wire Pull Strength as a Function of Aging (320°C)                                | 66 |

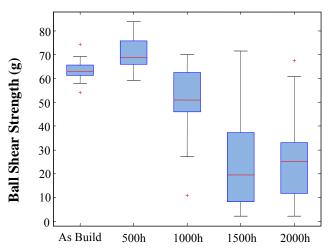

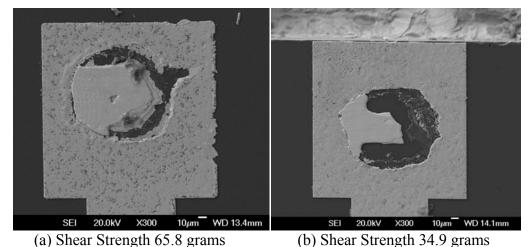

| Figure 3.16 Ball Shear Strength as a Function of Aging (320°C)                               | 67 |

| Figure 3.17 Wire Bonding Pad after Ball Shear Test on Sample after 1000 Hours Aging at 320°C | 68 |

| Figure 3.18 Auger Test Result for 0 hour Sample and 500 hour Aged Sample (320°C)             | 68 |

| Figure 3.19 Test Vehicle for Daisy Chain Resistance Measurement                              | 69 |

| Figure 3.20 Wire Pull Strength as a Function of Aging (320°C) with New Metallization.        | 70 |

| Figure 3.21 Ball Shear Strength as a Function of Aging (320°C) with New Metallization                                         | 71 |

|-------------------------------------------------------------------------------------------------------------------------------|----|

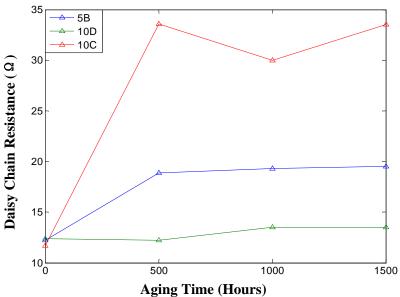

| Figure 3.22 Average Daisy Chain Resistance ( $\Omega$ ) as Function of Aging (320°C) with New Metallization                   | 72 |

| Figure 4.1 Vishay WSC4527 Resistor                                                                                            | 74 |

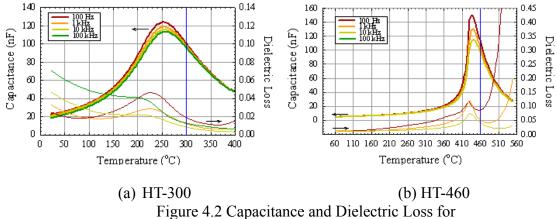

| Figure 4.2 Capacitance and Dielectric Loss for TRS High Temperature Capacitor                                                 | 75 |

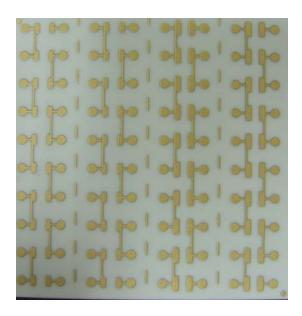

| Figure 4.3 Passive Component Attach Test Vehicle                                                                              | 77 |

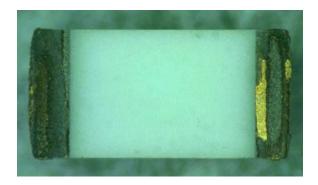

| Figure 4.4 X-Ray Result of Passive Component Attach with AuSn Paste                                                           | 77 |

| Figure 4.5 X-Ray Result of Passive Component Attach with AuSn Preform                                                         | 78 |

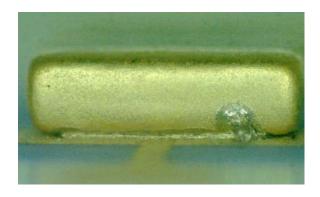

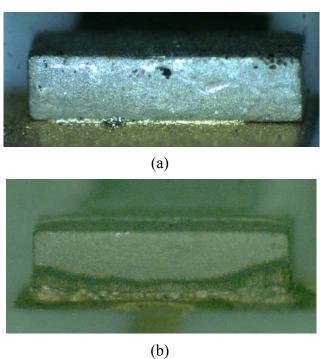

| Figure 4.6 Side View of KEMET Capacitor after Bonding                                                                         | 79 |

| Figure 4.7 Test Vehicle for Mini-Systems Resistor and KEMET Capacitor                                                         | 81 |

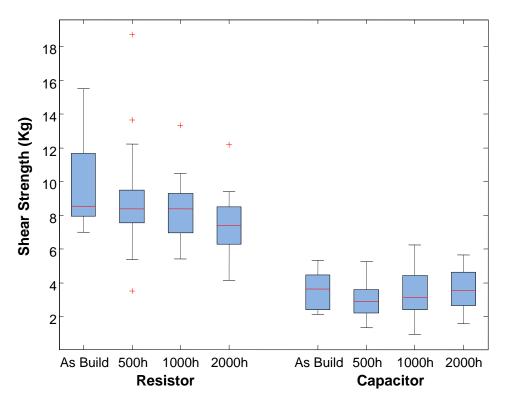

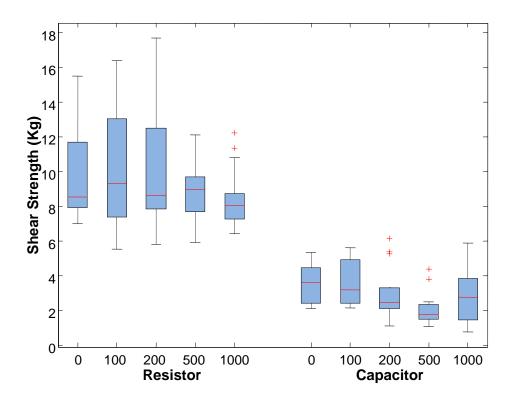

| Figure 4.8 Shear Strength of Passive Component after Aging at 320°C                                                           | 82 |

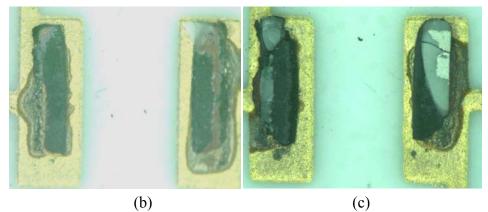

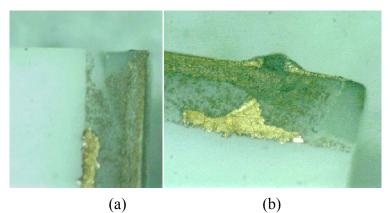

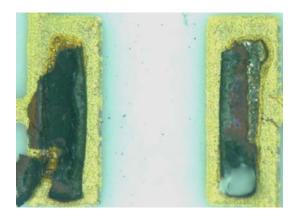

| Figure 4.9 Failure Mode on the Thick Film Metallization after (a) 500 (b) 1000 (c) 2000 Hours Aging at 320°C                  | 82 |

| Figure 4.10 Failure Mode on Resistor after 2000 Hours Aging at 320°C                                                          | 83 |

| Figure 4.11 Resistor Solder Joint (a) As Built (b) After 2000 Hours Aging at 320°C                                            | 83 |

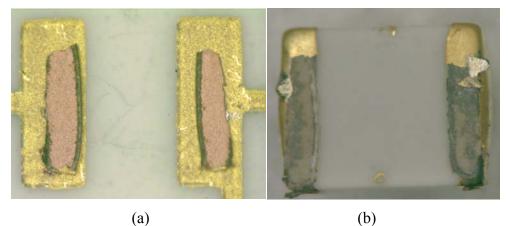

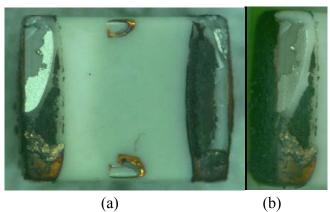

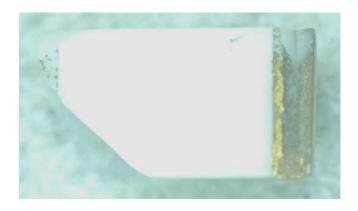

| Figure 4.12 Initial Failure Mode for KEMET Capacitor on (a) Thick Film Metallization (b) Capacitor Body                       | 84 |

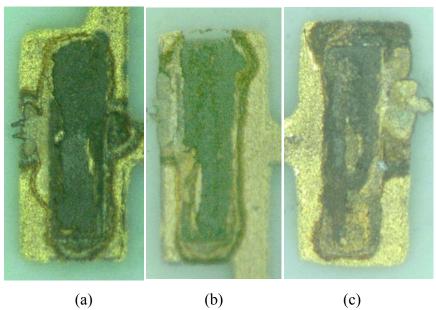

| Figure 4.13 KEMET Capacitor Failure Mode on the Thick Film Metallization after (a) 500 (b) 1000 (c) 2000 Hours Aging at 320°C | 84 |

| Figure 4.14 KEMET Capacitor Sheared after 2000 Hours<br>Aging at 320°C (a) Top View (b) Side View                             | 85 |

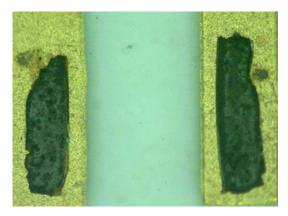

| Figure 4.15 Shear Strength of Passive Component after Thermal Cycles                                                          | 86 |

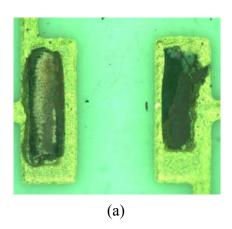

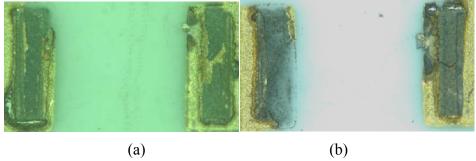

| Figure 4.16 Failure Mode on the Thick Film Metallization after (a) 200 (b) 1000 Thermal Cycles                                | 86 |

| Figure 4.17 Mini-System Resistor Sheared after 500 Thermal Cycles                                                             | 87 |

| Figure 4.18 Mini-System Resistor Sheared after 1000 Thermal Cycles         | 87 |

|----------------------------------------------------------------------------|----|

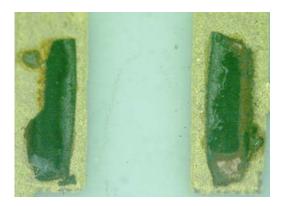

| Figure 4.19 Failure Mode on the Thick Film Metallization after 100 cycles  | 88 |

| Figure 4.20 Failure Mode on the Thick Film Metallization after 500 cycles  | 88 |

| Figure 4.21 Failure Mode on the Thick Film Metallization after 1000 cycles | 88 |

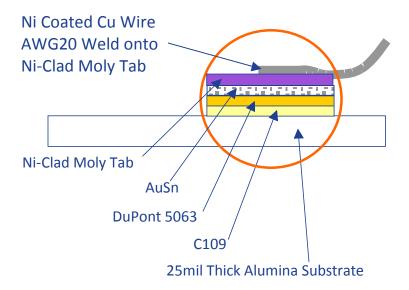

| Figure 4.22 Configuration of Wire Welding Substrate                        | 90 |

| Figure 4.23 Wire Welding Substrates with Peripheral Moly Tabs Attached     | 90 |

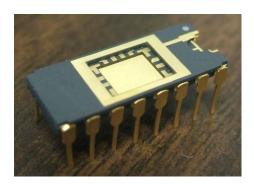

| Figure 5.1 16-Pin Ceramic DIP Package                                      | 92 |

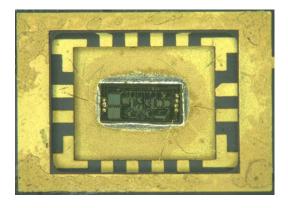

| Figure 5.2 X-Ray on Amplifier Attached to DIP Package                      | 93 |

| Figure 5.3 Amplifier Attached and Wirebonded to DIP Package                | 93 |

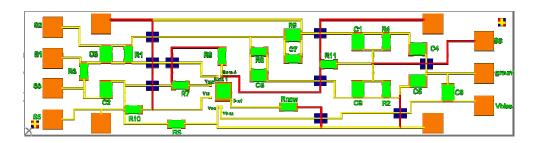

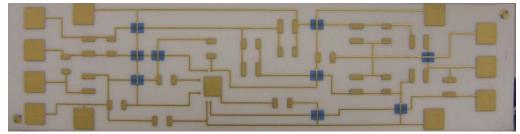

| Figure 5.4 Designed Amplifier Test Board                                   | 94 |

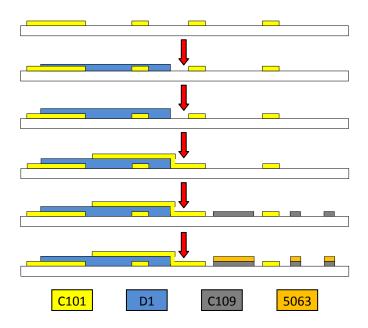

| Figure 5.5 Substrate Fabrication Process                                   | 95 |

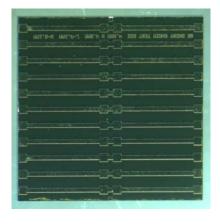

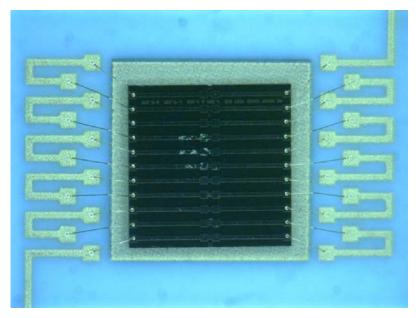

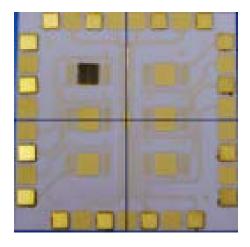

| Figure 5.6 Fabricated Substrate                                            | 96 |

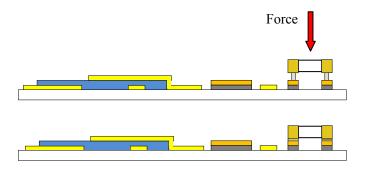

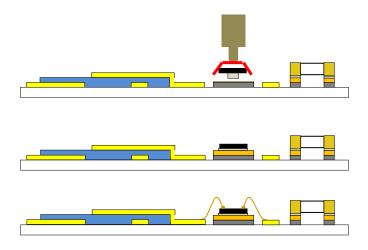

| Figure 5.7 Resistor Attachment Process                                     | 96 |

| Figure 5.8 Die Attach and Wirebonding Process                              | 97 |

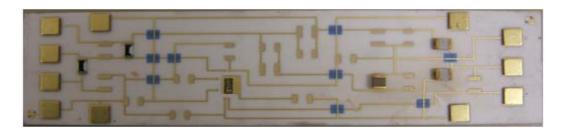

| Figure 5.9 Assembled Test Board                                            | 97 |

#### CHAPTER 1 INTRODUCTION

### 1.1 High Temperature Electronics (HTE)

The term "high temperature electronics" (HTE) is defined in various ways in the literature, depending on the areas of application. For this thesis, HTE is taken to mean "electronic operation at temperatures in excess of those normally encountered by conventional, silicon-based semiconductors [1]". This temperature limit has been set by convention at 75°C, with some military systems being operated at a maximum temperature of 125°C. However, there are growing demands for electronics that must operate at a much higher temperature.

# 1.2 Application of High Temperature Electronics

Interest in the area of high temperature electronics has increased dramatically in recent years. The primary applications for high temperature electronics include automotive, well logging, power grid, nuclear reactors, aircraft, and space exploration. For example, the temperature of the instrumentation of combustion engine environments is typically greater than 300°C [2]; Measurement-While-Drilling (MWD) tools for oil, natural gas, and geothermal wells have to withstand reservoir ambient temperatures up to 350°C; Applications for Venus planetary exploration require electronics operating at 500°C. Table 1.1 lists a number of high temperature applications and summarizes their temperature, operating times, and other requirements [3].

Table 1.1 Application Area and Parameters for High Temperature Electronics. [3]

| Application                                        | Temperature (°C)    | Minimum<br>Duration                          | Duty                                        | Other Environmental Factors                                                              |

|----------------------------------------------------|---------------------|----------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------|

| Well-logging-gas & oil (down-hole) instrumentation | 150 to 300          | Few<br>hours-years                           | Intermittent/cyclical, or continuous        | Temperature cycling,<br>chemicals, pressure,<br>mechanical stress,<br>possibly radiation |

| Well-logging-geoth<br>ermal                        | 150 to 400          | Few-100 hours                                | Intermittent/cyclical                       | Temperature cycling chemicals, pressure, mechanical stress                               |

| Aircraft systems-on engines & smart transducers    | 300 to 500          | 1000 hours                                   | Intermittent/cyclical                       | Temperature cycling, vibration, stress, fuel/oil/chemicals                               |

| Aircraft engine R & D                              | 500 to 600          | 100 hours                                    | Intermittent/cyclical (one-shot acceptable) | Temperature cycling,shock/vibration                                                      |

| Automobiles                                        | 150 to 250<br>(700) | 8000 operating<br>hours, 10 years<br>"shelf" | Intermittent/cyclical                       | Temperature cycling,vibration, fuel/oil/chemicals, rough handling                        |

| Fossil-fuel energy plants                          | 400 to 500          | Months-years                                 | S Continuous Radiation                      |                                                                                          |

| Nuclear reactors                                   | 200 to 450          | Months-years                                 | Continuous                                  | Radiation                                                                                |

| Space Exploration                                  | 125 to 485          | Month - years                                | Intermittent/cyclical, or continuous        | Temperature cycling chemicals, pressure, Radiation                                       |

The elevated temperature may be a result of high environment temperature or it may develop due to high power dissipation and difficulties of effective heat removal. Heat buildup in dense electronics and the concept of un-cooled high power electronics have been an attractive research topic over the years. Operating electronic devices at higher temperature could eliminate or reduce the need for bulky heat transfer hardware and cooling systems. For example, in the aircraft industry, where weight reduction is a major cost driver, elimination of the heavy hydraulic cooling systems for lighter electrical systems is always desired [2].

There is a growing body of evidence that high temperature electronics have greatly improved operating lifetimes at lower temperatures. Honeywell HT SOI electronics rated for 5 years at 225°C have a potential for 10 years at 200°C and 20 years at 150°C [4]. The

improvement of electronics reliability at high temperature can be of substantial benefit to the reliability and lifetime of electronics used at conventional temperatures. High temperature exposure and operation has also been an important part of the reliability evaluation and improvement for conventional temperature electronics.

## 1.3 High Temperature Electronics in Enhanced Geothermal Systems

Until recently, geothermal systems have only exploited resources where naturally existing hot fluid and rock permeability is sufficient to allow heat extraction from production wells. However, the vast majority of geothermal energy within reach of conventional techniques is in dry and non-permeable rock [5].

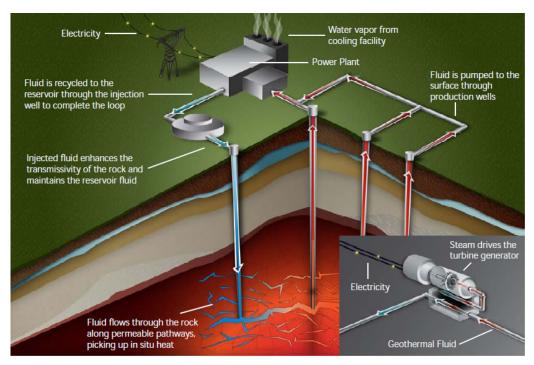

A DOE sponsored study by MIT concluded that geothermal energy could provide 100,000 MWe or more in 50 years by using advanced technology known as Enhanced Geothermal Systems (EGS) [6][7]. EGS reservoirs are made by drilling wells into hot but dry rock and fracturing the rock sufficiently to enable a fluid (water) to flow between the wells. The fluid circulates along permeable pathways, picking up in situ heat, and is then pumped to the surface through the production wells. At the surface, the hot fluid passes through a power plant where electricity is generated. The fluid is recycled into the reservoir through the injection well to complete the circulation, as shown in Figure 1.1 [6]. EGS may be expanded by adding additional production and injection wells, which could allow heat harvesting from large areas and increase power generation capacities. EGS in multiple geological environments at various depths will enable geothermal energy to increase in scale and be an important contributor to the U.S. energy portfolio as a source of clean and renewable energy. [8].

Figure 1.1 Diagram of an Enhanced Geothermal System [6]

In EGS, typical measurements made by a measurement-while-drilling (MWD) tool include: azimuth, inclination, temperature, pressure, and strain. For maintenance and monitoring purpose, fluid flow, data logging, and data transmission are also required. The control of these parameters enables the productivity of the EGS to be optimized.

The MIT study indicates that high temperature instrumentation for geothermal is a key technology deficiency [6][7]. Today most geothermal tools use conventional oil patch electronics operating in a heat shield or dewar flask [9]. The heat shields used in geothermal tools are highly specialized and relatively large and expensive. Shielded or flasked devices do not provide for long term operation and there are also many sensors that cannot be flasked. Logging and well monitoring instruments capable of operation at high temperatures for days or even years remain commercially unavailable.

# 1.4 High Temperature Electronics

The keys to successful high temperature circuits are the availability of stable high

temperature electronic components (integrated circuits, resistors, capacitors, etc.) and the packaging of these components using the proper materials [2]. In the following sections the semiconductor, packaging materials and processes, and passive components for high temperature electronics are discussed.

#### 1.4.1 SiC Device

Silicon has been the dominant semiconductor material over the last 50 years. However, the long term operating temperature for devices made with Si is not more than 150°C. Beyond this temperature, Si-based devices are not able to function efficiently, especially when the high temperature is combined with a high power, high frequency and high radiation environment [10]. Silicon on insulator (SOI) technology extends the performance of electronics toward higher temperature up to 300°C. Beyond 300°C, SOI devices would not be applicable.

To solve this problem, a semiconductor with a wider band gap is a better choice to fabricate devices for high temperature applications. The band gap energy, Eg, is a measure of the amount of thermal energy needed to ionize the particular semiconductor material. Wide band gap (WBG) semiconductors offer various advantages over traditional Si-based devices, including high thermal conductivity, high breakdown voltage, high temperature stability, and low chemical reaction rates. Examples of WBG semiconductors are silicon carbide (SiC), gallium nitride (GaN), gallium phosphide (GaP) and diamond. Table 1.2 summarizes some of the physical properties of these materials in comparison with traditional semiconductors [11] [12] [13]. Due to the dependence of the physical properties on the doping level, impurities, temperature, and structural defects, these values can be different from other published literature.

Table 1.2 Physical Properties of Semiconductor Materials [11] [12] [13]

|                                         | Silicon | GaAs | AlGaAs | GaN  | SiC  | Diamond |

|-----------------------------------------|---------|------|--------|------|------|---------|

| Band Gap (eV)                           | 1.1     | 1.3  | 1.9    | 3.39 | 2.9  | 5.5     |

| Breakdown Field (kV/cm)                 | 250     | 300  | 500    | 3300 | 2500 | 10000   |

| Thermal Conductivity                    | 1.5     | 0.5  | 0.1    | 1.3  | 4.9  | 20      |

| (W/cm/K)                                |         |      |        |      |      |         |

| Electron Mobility (RT)                  | 1400    | 4000 | 3000   | 1250 | 250  | 2200    |

| $cm^2/v-s$                              |         |      |        |      |      |         |

| Hole Mobility (RT) cm <sup>2</sup> /v-s | 600     | 400  |        | 250  | 50   | 1600    |

| Electron Sat Velocity (10 <sup>7</sup>  | 1.0     | 1.0  | 1.0    | 2.7  | 2.0  | 2.7     |

| cm/s)                                   |         |      |        |      |      |         |

| Dislocation Energy (eV)                 | 13      | 9    | 9      | \    | 22   | \       |

| Melting Point (°C)                      | 1412    | 1238 | 1304   | 1800 | 2700 | >3300   |

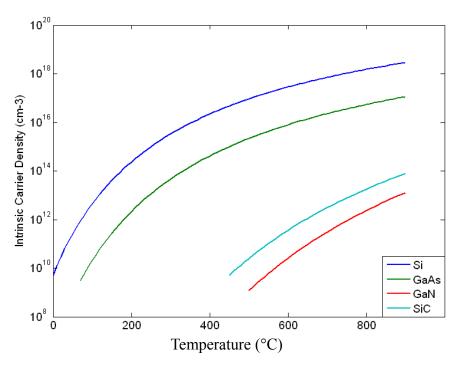

The intrinsic carrier density  $n_i$  is the most important physical property that increases exponentially with temperature, which leads to increased leakage current and finally the failure of the junction once the density of intrinsic carrier exceeds the doping density. The intrinsic carrier density  $n_i$  of a semiconductor depends on temperature and the band gap energy of the semiconductor [11],

$$n_i = \left(\frac{2\pi kT}{h^2}\right)^{3/2} (m_{dh}m_{de})^{3/4} e^{-E_g/2kT}$$

where k and h are Planck's and Boltzmann's constants, T is the absolute temperature,  $m_{de}$  and  $m_{dh}$  are the electron and hole effective masses, and  $E_g$  is the band gap energy. The intrinsic carrier density is plotted in Fig 1.1 for Si, GaAs, GaN, and SiC, showing an exponentially increase with temperature and decrease with band gap. As an example, a carrier density of  $10^{14}$ cm<sup>-3</sup> is reached at 200°C for Si but not until 900°C for SiC.

Figure 1.2 Intrinsic Carrier Density Versus Temperature for Si, GaAs, GaN, and SiC

Among all the candidates, SiC is by far the most developed wide band-gap semiconductor due to the commercial availability of high quality SiC bulk wafers, known device processing techniques, and the ability to grow thermal oxides. Various SiC semiconductor devices have recently been demonstrated to be functional at temperatures as high as 600°C [14] [15]. The most beneficial properties that make SiC an attractive semiconductor material are [16] [17]:

- Wide band gap energy: SiC based electronic devices can operate at extremely high temperatures without suffering from intrinsic conduction effects because of the wide band gap energy. The much smaller intrinsic carrier concentration of SiC theoretically permits device operation at temperatures exceeding 800°C. Also, this property allows SiC to emit and detect short wavelength light which makes the fabrication of blue light emitting diodes and ultraviolet detectors possible.

- High breakdown electric field: SiC can withstand a voltage gradient over eight

times greater than Si or GaAs without undergoing avalanche breakdown. This property enables the fabrication of very high-voltage, high-power devices such as diodes, power transistors, power thyristors and surge suppressors, as well as high power microwave devices. Additionally, it enables the blocking voltage region of a power device to be roughly 10 times thinner and 10 times more heavily doped, permitting roughly a 100-fold decrease in the blocking region resistance. It allows the devices to be placed very close together, providing high density packing for integrated circuits.

- High thermal conductivity: SiC is an excellent thermal conductor. Heat will flow more readily through SiC than other semiconductor materials. This property enables SiC devices to operate at extremely high power levels and still dissipate the large amounts of excess heat generated. SiC power devices can be made smaller and require less cooling, which lead to extremely high power densities and efficiencies.

- High saturated electron drift velocity: SiC devices can operate at high frequencies (RF and microwave) because of the high saturated electron drift velocity of SiC.

- High bonding energy between Si and C: This property gives SiC high mechanical strength, chemical inertness, and radiation resistance.

These properties allow SiC devices to offer tremendous benefits over other available semiconductor devices in a large number of industrial and military applications and make SiC the leading candidate for high power, high temperature electronics.

#### 1.4.2 Substrate Materials

Organic based substrates have a glass transition temperature ( $T_g$ ) in the 125°C to 200°C range. Above this temperature there is a significant increase in CTE and a decrease in mechanical properties. For high temperature applications, ceramic based technologies

must be considered. Table 1.3 [2] presents the properties of Si and SiC materials along with aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) and aluminum nitride (AlN) ceramic substrates. It suggests that AlN is an ideal candidate for packaging SiC devices for high temperature applications, since its coefficient of thermal expansion (CTE) is closely matched to SiC. This matched CTE will provide excellent reliability for high temperature application that requires a large number of thermal cycles.

$Al_2O_3$  is the most widely used ceramic substrate and a wide variety of  $Al_2O_3$  packages are commercially available. The CTE of  $Al_2O_3$  is relatively high compared to that of SiC, which will limit the number of thermal cycles to failure. However, for applications that do not require large numbers of thermal cycles,  $Al_2O_3$  could be a better choice considering the mature metallization technology on  $Al_2O_3$  and the high cost of AlN.

Table 1.3 Physical Properties of Semiconductor and Substrates Materials [2]

|                                | Si   | SiC  | Al <sub>2</sub> O <sub>3</sub> | AlN     |

|--------------------------------|------|------|--------------------------------|---------|

| Density, g/cm <sup>3</sup>     | 2.3  | 3.21 | 3.75                           | 3.31    |

| Hardness, GPa                  | 11.5 | 24.0 | 19.0                           | 12.0    |

| Strength, MPa                  | 250  | 450  | 350-400                        | 350-400 |

| Elastic modulus, GPa           | 130  | 470  | 397                            | 320     |

| Thermal conductivity, W/mK     | 150  | 300  | 25                             | 200     |

| Thermal expansion coefficient, | 3.5  | 3.7  | 7.2                            | 4.1     |

| ppm/°C                         |      |      |                                |         |

| Dielectric constant (@1MHz)    | 11.0 | 42   | 9.4                            | 8.9     |

| Dissipation Factor(@1MHz)      | 0.09 | 0.05 | 0.0004                         | 0.0005  |

#### 1.4.3 Thick Film Metallization

The term "thick film" is derived from the fact that the fired film is fairly thick, varying from 0.2 mil  $(5.08\mu\text{m})$  to 2 mils  $(50.8~\mu\text{m})$  [18]. In the thick film process, the individual layer is deposited by screen printing. The thick film material to be printed is

referred to as an ink or paste. The ink contains three components [19]: a functional phase which defines the electrical properties of the fired film (e.g.: conductor, dielectric, resistor), a binder which provides adhesion between the fired film and the substrate, and the vehicle which established the printing characteristics. More details about thick film technology will be given in Chapter 2.1.

Thick film metallization that is intended for high temperature operation must resist surface oxidation and migration while maintaining good adhesion to the substrate. Gold-based thick film materials were preferred for electrical interconnections and conductive die attach for high temperature applications.

#### 1.4.4 Die Metallization

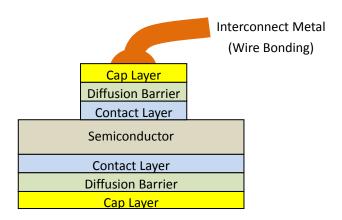

The semiconductor must be connected to the substrate with other components to provide a functional system. The temperature limit for devices is imposed by the die metallization rather than the semiconductor's inherent capability. A typical metallization scheme for a semiconductor used in high temperature application consists of a contact layer, a diffusion barrier layer, and a cap layer, as sketched in Figure 1.3.

Figure 1.3 Metallization Scheme for Semiconductor in HTE.

Metals with high electrical conductivity needed for interconnections often do not

form chemically stable semiconductor interfaces [11]. The solution is to separate the two functions of making a contact and interconnecting devices by inserting a diffusion barrier and a cap layer. The contact is made with a material that is thermodynamically stable in contact with the semiconductor, providing good adhesion, high environmental resistance, as well as high electrical conductivity. The diffusion barrier must be inert to the contact and the cap layer. The cap layer must have good wettability with the die attach material, or, in the case of die surface metallization, must have good wire bonding properties or solder ball attach properties (for flip chip). For example, in this proposed research, Ti/TiW/Au is selected as the backside metallization. The Ti is used as a contact layer that provides strong adhesion to the semiconductor, and the TiW layer is used as the diffusion barrier.

To develop such a multilayer structure, it is not only the choice of materials that is important but also the way in which they are prepared [11]. The micro-fabrication techniques used affect the metallurgical properties of the layers, which may further affect diffusion rates or intermetallic formation. Developing a suitable metallization stack compatible with high temperature operation is difficult, and a great deal remains to be done.

## 1.4.5 Die Attach and Wire Bonding

Die attach (also known as die mount or die bond) is the process of attaching the chip to the substrate or the semiconductor package. The die attach material must be compatible with the substrate and die backside metallization, have a sufficiently high melting point after die attach, and not form intermetallics which degrade the bond strength with time at temperature [20]. Furthermore, thermal cycling must also be

considered depending on the application. Although in some applications the device might require only a few temperature cycles (such as in well logging, power plant monitoring, and space exploration), in other applications they may face many cycles (such as in automobiles and aircraft). Temperature cycling can be a more severe issue than continuous operation at an elevated temperature, due to the strain from thermal expansion differences [3].

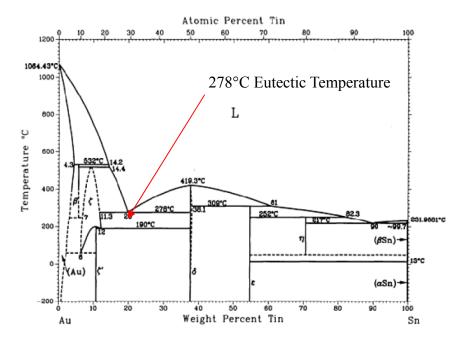

For high temperature applications, Au based eutectic alloys have been proposed as promising die attach materials because of their good compatibility with the die and substrate metallization, excellent electrical conductivity, thermal conductivity and corrosion resistance [10][20]. The die attach material used in this research was eutectic AuSn. A eutectic alloy is an alloy with the lowest melting point possible for the metals combined in the alloy. The idea is to dissolve Au from both the substrate and die into the molten eutectic AuSn perform, increasing the Au concentration and thus increasing the melting point.

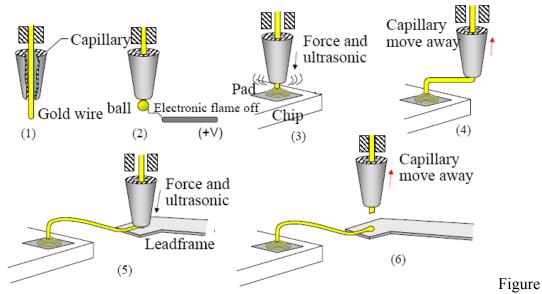

Wire bonding is the process of providing electrical interconnection between the semiconductor I/O pads and the corresponding substrate pads using very fine wires. This is accomplished using a combination of heat, pressure and/or ultrasonic energy. Once the surfaces are in intimate contact, electron sharing or interdiffusion of atoms takes place, resulting in the formation of a metallurgical bond. [21]

The wire used in wirebonding is usually made of gold (Au), aluminum (Al), and sometimes copper (Cu) and platinum (Pt). In general, it is desirable that the bonding pad and wire be of the same material because intermetallic growth due to interdiffusion and interface corrosion can occur between dissimilar metals at high temperatures [22]. For

example, Al wire cannot be used on a Au pad in high temperature applications due to diffusion, formation of brittle Au-Al intermetallics, as well as Kirkendall voiding, which can lower the physical and mechanical properties of the bond [20]. Au possesses higher strength at high temperature than Al, and Au ball bonding on gold pad provides a more reliable option for devices operated at high temperature.

### 1.4.6 Passive Components Attach

Passive components are a necessary part in most electronic systems. Although modern semiconductor technology can build on-chip resistors and capacitors, those passive component usually have a loose tolerance and only very small capacitors can be fabricated on chip. This on-chip fabrication process becomes much more difficult for passive component that need to work at high temperature, due to the very limited choice of dielectric materials. Passive components have received relatively little attention compared to semiconductor materials and processing techniques. As a result, capacitors are often the weakest point in designing electronics for high temperature applications.

The passive components selection, termination material selection, and reliability assessment for this research was done by GE Global Research [23] at Niskayuna, NY. Here the focus is on the component attachment process. AuSn was used for passive attach.

#### 1.5 Research Outline

The goal of the project was to identify and develop packaging materials and processes for high-temperature electronics that can be used to monitor wellbore conditions in enhanced geothermal systems. The environmental conditions of temperature (300°C) and depth (10 km) pose significant challenges to the sensor and electronic

systems necessary to monitor wellbore conditions.

In Chapter 2, thick film technology is briefly discussed. The adhesion of several thick film conductor and dielectric pastes on Al<sub>2</sub>O<sub>3</sub> substrates and on each other were tested. The adhesion as a function of aging at 300°C was also investigated. The dielectric properties: leakage current, capacitance and dissipation factor as a function of temperature as-built and after aging is also reported.

Chapter 3 describes the die attach and wire bonding of SiC test die. Off-eutectic AuSn solder was used for die attach and the results of die shear strength are discussed after 300°C storage and thermal cycling tests. Investigation of Au wire bonding on different SiC die metallization is also reported. Failure analysis after reliability testing was also performed.

Chapter 4 discusses the passive component attach process. Four components from various vendors were tested initially and two of them were selected for reliability test after 300°C storage and thermal cycling tests. External lead attach were also investigated for next level device connection.

Chapter 5 reports the SiC die attach in a ceramic DIP package. Then an amplifier module was fabricated on a multilayer thick film ceramic substrate. The substrate metallization was selected based on the results from Chapter 2. Passive components and the SiC chip were then assembled. The amplifier was tested as-built and after high temperature storage.

Chapter 6 summarizes the conclusion from this work and proposed ideas for future work.

#### CHAPTER 2 THICK FILM PASTE SELECTION

#### 2.1 Introduction to Thick Film Technology

The technology used to manufacture thick film hybrid microelectronic circuits was introduced in the 1950s [24]. At that time it was considered an alternative approach to printed circuit boards (PCBs). With years of research and advances in materials technology, the current thick film technology is favored for high reliability, high power, and high temperature application.

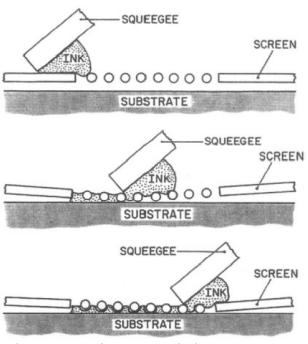

In the thick film process, the individual layer is deposited by screen printing, which deposits a viscous ink (or paste) on to a base material (substrate) through a woven screen with a photo defined polymer pattern of the desired geometry. Figure 2.1[25] illustrates the process for screen printing. The substrate is usually held by vacuum and its position can be finely adjusted to ensure good alignment between consecutive layers. The ink is applied to the surface of the screen and the flexible squeegee travels across the screen, pushing the ink through the open areas of the screen mesh. At a point immediately behind the squeegee, the screen peels away from the substrate and, due to the surface tension between the ink and the substrate, leaves a deposit of paste in the desired pattern on the substrate [24].

Figure 2.1 Basic Screen Printing Process [25]

After printing, the pastes are usually dried at 150°C for 15 minutes to remove the organic solvents. Then the films proceed to the firing stage. In some circumstances, however, they may be overprinted with another thick film paste, dried, and fired together, known as a co-fire process. The firing temperature profile typically includes 10 min at a peak temperature of 850°C and an overall firing cycle time of 30 to 60 minutes.

At the initial firing stage, the remaining organic carrier is removed from the film. At a temperature between 300°C and 500°C, the nonvolatile resin portion of the vehicle is pyrolyzed [19]. In the temperature range 600°C to 850°C, the glass flows, sintering of particles occurs, and chemical reactions take place to form the final film and to provide adhesion to the substrate. Precious metal conductors are fired in air while copper conductors require firing in an inert atmosphere such as nitrogen. The print, dry and fire steps are repeated to fabricate the interconnection structure.

## 2.2 Thick Film Conductor Paste

Thick film conductors provide interconnection between the components, attachment pads for passive components as well as bare die, wirebonding pads and terminations for thick film resistors. The three main components in a thick film paste are: a functional phase which defines the electrical properties of the fired film (e.g.: conductor, dielectric, resistor), a binder which provides adhesion between the fired film and the substrate, and the organic vehicle which established the printing characteristics.

For conductors, the functional phase may be gold, silver, copper, palladium-silver, platinum-silver, palladium-gold, or platinum-gold [19]. The metallurgy chosen depends on a number of engineering factors including wire bondability, solderability, environmental requirements, electrical conductivity, and cost.

The binder systems for thick film conductors are usually composed of glass compositions and oxide additives. Numerous oxides such as copper oxide and cadmium oxide promote adhesion to alumina substrates by formation of spinel compounds such as copper aluminate (CuAl<sub>2</sub>O<sub>4</sub>) [26]. This type of bonding mechanism is a chemical or reactive bond, which generally requires firing temperatures of 900°C or higher for the chemical reaction [19]. However, the detailed composition used in any commercial thick film ink, especially the binder system, is never published for proprietary reasons.

Thick film metallization that is intended for high temperature operation must resist surface oxidation and migration while maintaining good adhesion to the substrate. Silver based thick film conductor has poor solder leach resistance and has an inherent tendency to migrate in the presence of an electric field. Gold based thick film conductors exhibit high conductivity, excellent resistance to oxidation, corrosion and migration. It also has excellent wire bondability with Au wire and the ability to be die attached with Au based

die attach materials. Additions of platinum to Au conductor formulations can result in materials with excellent solderability and leach resistance at the expense of conductivity.

[27]

#### 2.3 Thick Film Dielectric Paste

Dielectrics serve three primary roles in thick film hybrid circuit applications: cross-over insulation between conductor layers, formation of capacitors, and encapsulation of the hybrid substrate.

Screen printed parallel plate capacitors are not widely used due to a low capacitance density compared to chip capacitors. It is also difficult to achieve the designed capacitance value. The trimming process can help but the cost is too high.

Thick film dielectric encapsulations are mainly used to protect resistors during trimming and the circuit from harsh environmental condition during operation. Encapsulant dielectrics are formulated with low melting point glasses to allow a reduced firing temperature (500°C) since it is usually the last layer to be processed.

For this research, the main function of the dielectric was to provide cross-over insulation between two conductive layers. Cross-over dielectrics are comprised of a ceramic material, a glass serving as the binder, and an organic vehicle. These films are required to have a low dielectric constant, low dissipation factor (low electrical loss), high breakdown voltage, high insulation resistance, a CTE matched to the substrate, and a smooth, pinhole-free surface finish [19].

#### 2.4 Adhesion Test

A multilayer thick film circuit built with conductors and dielectrics for high temperature operation must maintain good adhesion to the substrate and to each other after high temperature exposure. To achieve this requirement, several thick film conductor and dielectric inks that contain different binding systems were evaluated for use in high temperature applications. Their properties were summarized in Table 2.1 and Table 2.2. Some of them have previously been demonstrated for  $500^{\circ}$ C use on  $Al_2O_3$  substrates [28], the others are recommended by the vendors.

Table 2.1 Properties of Selected Thick Film Conductors

| Ink No. | Property        | Fired     | Lin Resolution | Resistivity      | Viscosity |

|---------|-----------------|-----------|----------------|------------------|-----------|

|         |                 | thickness | (Lines/Spaces) | $(m \Omega/sq)$  | (Pa.S)*   |

| C101    | Cd free, Au     | 6-9µm     | 125/125μm      | ≤7.0 (@10μm      | 350-500   |

|         | wire bondable   |           |                | fired thickness) |           |

| C105    | Mixed bonded    | 8-11µm    | 125/125μm      | ≤7.0 (@10µm      | 240-260   |

|         | Au and Al wire  |           |                | fired thickness) |           |

|         | bondable        |           |                |                  |           |

| C110    | High density.   | 5μm       | 75/75μm        | ≤5.0 (@10μm      | 240-360   |

|         | Fine printing,  |           |                | fired thickness) |           |

|         | ultra fine line |           |                |                  |           |

|         | etching.        |           |                |                  |           |

| C109    | Pb, Cd, Ni      | 12-16μm   | 200μm          | ≤9.5 (@12μm      | 200-280   |

|         | free.           |           |                | fired thickness) |           |

<sup>\*</sup> Brookfield 2xHA, UC&SP, SC4-14/6r, 10rpm, 25°C

Table 2.2 Properties of Selected Thick Film Dielectric

| Ink No.                          | D1                     | D4                     |

|----------------------------------|------------------------|------------------------|

| Fired thickness (µm)             | 40-60 (3 fired layers) | 45-50 (3 fired layers) |

| Breakdown voltage (Vdc/mil)      | >700 (minimum)         | >400                   |

| Dielectric Constant              | 6-10                   | 8-10                   |

| Dissipation Factor (%)           | ≤0.5                   | <0.5                   |

| Insulation Resistance (Ω@100Vdc) | >10 <sup>11</sup>      | >10 <sup>12</sup>      |

| Viscosity (Pa.S)*                | 220-295                | 150-250                |

<sup>\*</sup>Brookfield HBT, UC&SP, 10rpm, 25°C

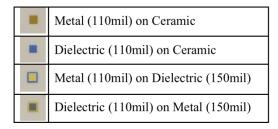

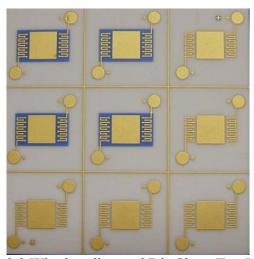

An adhesion test vehicle was designed and fabricated to characterize the adhesion of thick film materials on a 2" by 2" alumina substrate. The three-layer test vehicle provided adhesion testing of metal to ceramic, metal to dielectric, dielectric to ceramic, and dielectric to metal. A test vehicle sample along with pad dimensions is shown in Figure

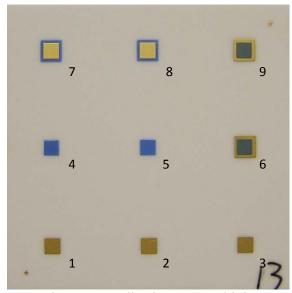

2.2. Each layer was printed, and then fired. Two dielectric layers were sequentially printed and fired as is common in multilayer thick film processing to eliminate pinholes. The inks were printed and dried at 150°C for 15 minutes. The standard firing profile was a 60-minutes profile with an 850°C peak temperature held for 10 minutes. The actual profile used here was recorded with a thermocouple and plotted in Figure 2.3.

Figure 2.2 Adhesion Test Vehicle

Figure 2.3 Standard 850°C Firing Profile

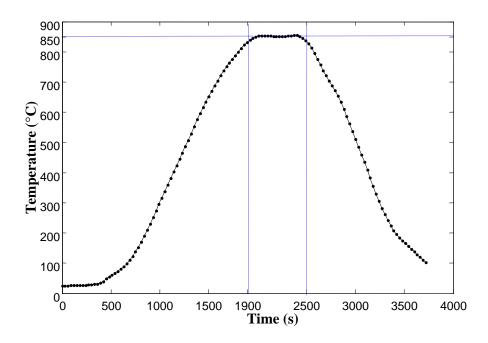

Then the substrate was diced into 9 pieces (0.67" by 0.67"). To evaluate the adhesion of the thick film inks, aluminum studs with epoxy coated ends from Quad Group were cured to the thick film pad and the bottom substrate was attached and cured to a ceramic plate coated with epoxy to reinforce the substrate. The pull stud end had a diameter of 106 mils and the epoxy coated on it had a tensile strength of 10,000 to 13,000 psi. Based on the pull stud diameter and epoxy tensile strength, the epoxy will start to fail when the pull strength reaches 88.2lb to 114.7lb. A clamp was used to clamp the part and the ceramic plate together during epoxy cure at 150°C for an hour. The pull test was conducted on a Sabastian-V Mechanical tester and this process is illustrated in Figure 2.4. The most severe tests that ultimately limit the number of applications for the thick film conductors are aging tests, including storage at elevated temperatures [26]. The pull test was conducted on samples as built and samples after aging at 320°C for 500, 1000, 1500 and 2000 hours. All of the pull tests were performed at room temperature.

Figure 2.4 Illustration of Pull Test

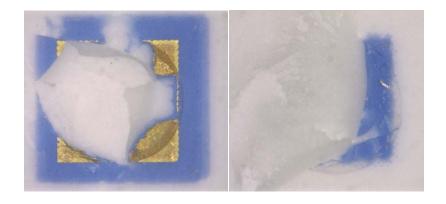

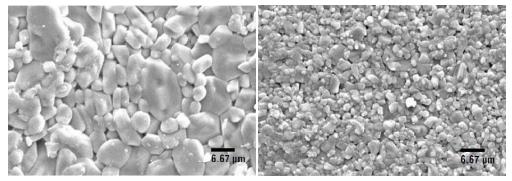

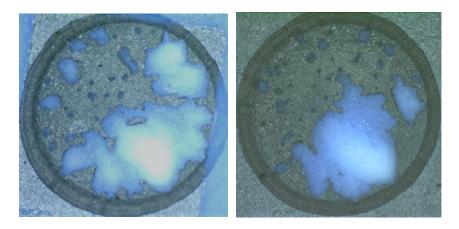

In the initial test, conductor C101 with dielectric D1 was investigated (fired at 850°C). The initial failure was all in the epoxy for all four combinations. However, after 500 hours aging at 320°C, chunks of substrate were pulled off during the pull test, as shown in Figure 2.5. These failures were not expected since 320°C aging should not affect the strength of the ceramic substrate. To better evaluate the thick film adhesion, DuraStrate Thick-Film Substrates from CoorsTEK were selected for future adhesion tests. The fine-grained DuraStrate offers a 20% increase in strength and superior reliability over traditional Al<sub>2</sub>O<sub>3</sub> [29]. Figure 2.6 are the SEM photos showing the difference of the DuraStrate Substrate in comparison with standard Al<sub>2</sub>O<sub>3</sub>.

Figure 2.5 Ceramic Surface after Pull Test

Standard 96% Alumina Substrate Material

Figure 2.6 SEM Photos of DuraStrate Substrate

in Comparison with Standard Al<sub>2</sub>O<sub>3</sub> [29]

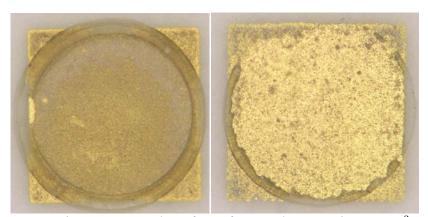

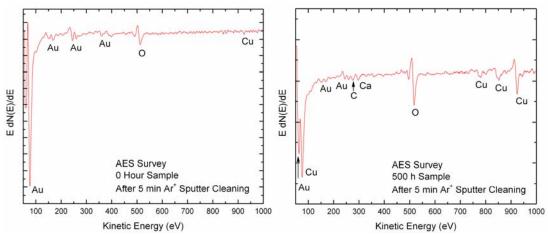

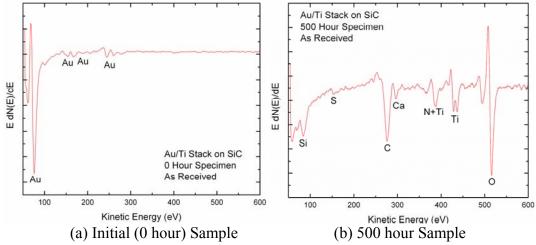

For metal on ceramic, our initial pull test on 500 hours aged sample have low pull strength, with the failure still in the epoxy. A dark layer was observed on the metal surface, as shown in Figure 2.7. To identify the dark layer, Auger test is done on 0 hour and 500 hours sample. Five minutes of Ar sputtering was used, which corresponds to about 150 Å of the surface removed. Carbon was found on the aged sample, which explains the lower pull strength. Cu was also observed, likely from the copper oxide used in the reactive binding system. The results are shown in Figure 2.8. The pull test was repeated for metal on ceramic after cleaning the metal surface with carbon eraser.

Figure 2.7 Metal Surface after 500 hours Aging at 320°C

Figure 2.8 Auger Analysis on Samples as Build and after 500 hours Aging at 320°C

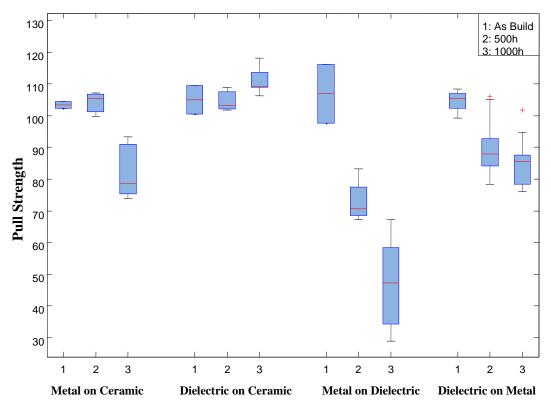

The investigation was continued with conductor C101 and dielectric D1 (fired at 850°C). The results are shown in Figure 2.9. All initial failures were in the epoxy layer. There was a significant drop in pull strength for conductor C101 on dielectric D1 after 1000 hours at 320°C and the failure mode shifted to metal-to-dielectric failure. There were also smaller decreases in pull strength for C101 on ceramic and D1 on C101 after aging.

Figure 2.9 Pull Strength as a Function of Aging (320°C) for Conductor C101 and Dielectric D1 Fired at 850°C

Alternate processing of C101 and D1 was then evaluated. Two layers of D1 dielectric were printed and fired (the standard process), then a third layer of D1 was printed and dried, but not fired. The layer of C101 conductor was printed over the dried D1 and the two layers were co-fired. The adhesion was good after 500 hours aging, but after 1000 hours the metal adhesion degraded significantly. The test results are presented in Figure 2.10.

Figure 2.10 Pull Strength as a Function of Aging (320°C) for Conductor C101 and Dielectric D1 with Co-fire Process

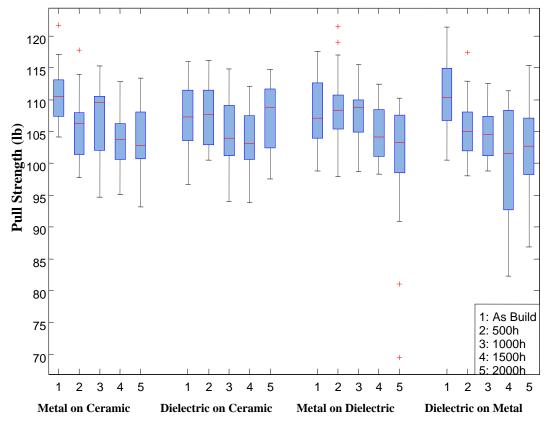

Conductor C101 is a mixed bonded (both glass and reactive bonding) conductor ink. At 850°C, only the glass contributes to the bonding process. A higher firing temperature is required for the reactive bonding to occur. Thus a firing profile with a 980°C peak temperature was evaluated with conductor C101. The pull test results as a function of aging at 320°C are plotted in Figure 2.11. There was no degradation after 1000 hours at 320°C – all failures were in the epoxy layer. After 1500 hours, there were some samples with very small areas of dielectric that pulled off from the metal during pull testing, but the pull strength remained high. After 2000 hours the pull strength remained high. Again, there were some samples with very small areas of dielectric that pulled off from the metal during pull testing. In addition, a few samples exhibited a small amount of metal pulling off from the dielectric during pull testing. The results indicate that firing C101 and D1 at 980°C is the preferred profile for high temperature application.

Figure 2.11 Pull Strength as a Function of Aging (320°C) for Conductor C101 and Dielectric D1 Fired at 980°C

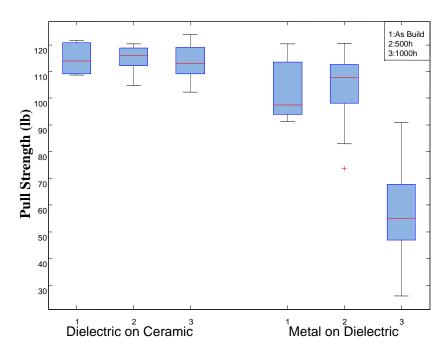

Conductor C105 with dielectric D1 was also evaluated (fired at 850°C). The pull test results as a function of aging at 320°C are plotted in Figure 2.12. The initial pull test failures were all within the epoxy used to adhere the aluminum pull stud to the test pad. After 500 hours aging, all the metal has been pulled off from the ceramic and from the dielectric with low strength. The dielectric on ceramic showed no degradation after 1500 hour aging, confirming the dielectric results from the previous test with C101. However, low pull strength of the dielectric on metal after 500 hour aging was observed, with all the dielectric D1 pulling off from the C105 metal.

Figure 2.12 Pull Strength as a Function of Aging (320°C) for Conductor C105 and Dielectric D1 fired at 850°C

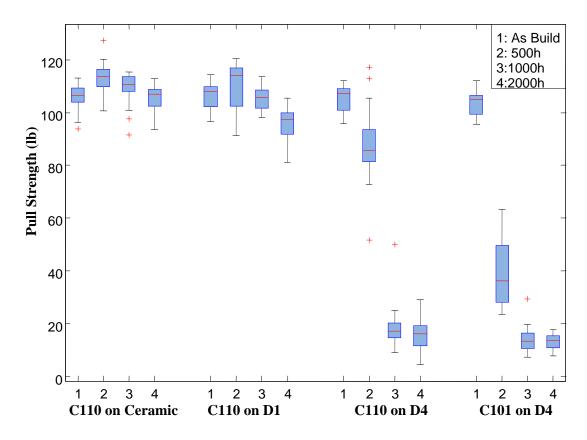

While improving adhesion with different process parameters, new materials were also evaluated. Au conductor C110 and dielectric D4 were tested with standard processes. C110 was printed on ceramic, on new dielectric D4, and on previously tested dielectric D1. New dielectric D4 was also tested with conductor C101 printed on it. The test results are shown in Figure 2.13. The initial pull test failures were all within the epoxy. After 500 hour aging, both C110 and C111 on dielectric D4 show degradation. The conductor C110 on ceramic did not degrade after 2000 hours aging and C110 on dielectric D1 also shows good adhesion after 2000 hour aging.

Figure 2.13 Pull Strength as a Function of Aging (320°C) for Conductor C110, C101 and Dielectric D1, D4 fired at 850°C

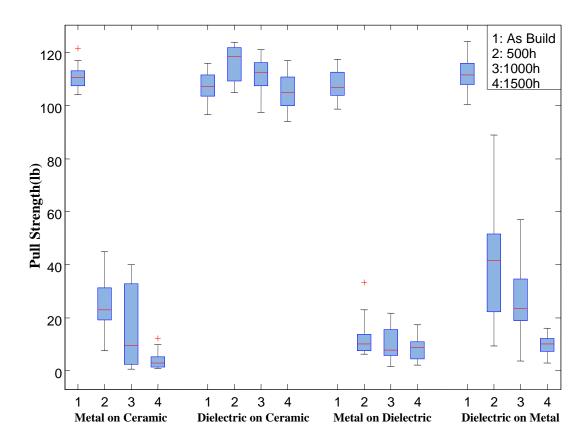

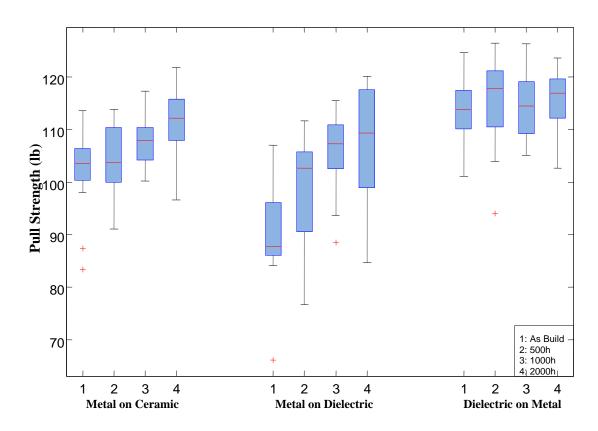

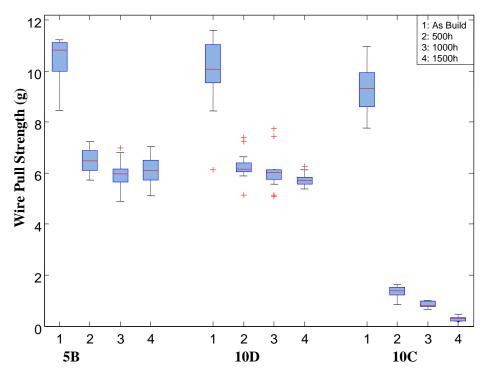

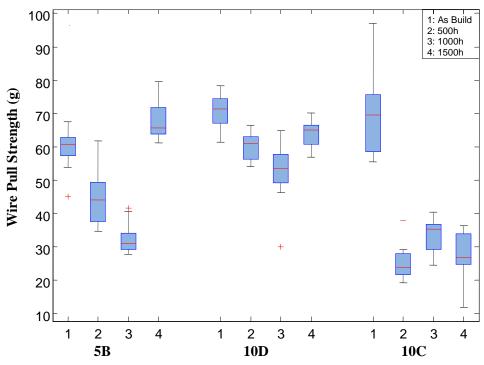

C109 Au/Pt/Pd conductor was tested with standard processes on ceramic and on dielectric D1. The test results are shown in Figure 2.14. The results show an improved adhesion after aging, with all failure in the epoxy after 2000 hours aging. Initially nearly half the samples had a small area of metal and dielectric pulled off. After 1000 hours aging, the failures were all within the epoxy. This failure mode remained the same after 2000 hours aging. This indicates that if fired at a higher temperature, the initial adhesion might be improved and all the failure would be in the epoxy.

Figure 2.14 Pull Strength as a Function of Aging (320°C) for Conductor C109 and Dielectric D1 fired at 850°C

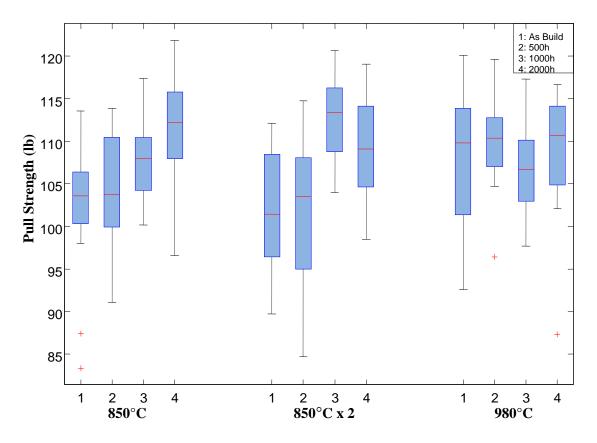

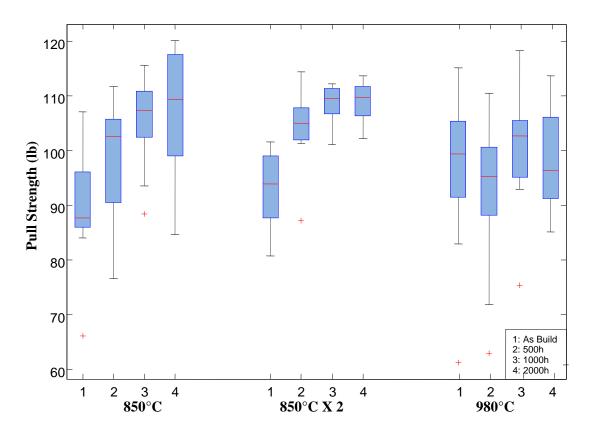

Conductor C109 on ceramic and on dielectric D1 with a firing profile with a 980°C peak temperature was evaluated. Also a group of samples were fired twice with the original 850°C profile. The test results are shown in Figure 2.15 (on ceramic) and Figure 2.16 (on dielectric D1). The second firing at 850°C does not improve the adhesion for C109 on ceramic or on dielectric D1. For conductor C109 fired with a 980°C peak temperature, although the initial pull strength was increased on both ceramic and dielectric D1, there were large areas of metal and dielectric pulled off during the pull test, as shown in Figure 2.17. A closer examination of the failure surface indicates that it was not just the metal that pulled off, but also ceramic and dielectric were found on the pulled conductor C109. It is suspected that a firing profile with 980°C peak temperature may cause excessive Pt diffusion into the ceramic and dielectric, which caused the above

failure. Since the detailed conductor composition remain proprietary, the exact reason is not clear.

Figure 2.15 Pull Strength as a Function of Aging (320°C) for Conductor C109 on Ceramic fired at Different Conditions

Figure 2.16 Pull Strength as a Function of Aging (320°C) for Conductor C109 on Dielectric D1 fired at Different Conditions

Figure 2.17 Conductor C109 Pulled off from Ceramic and Dielectric D1 fired at 980°C

From the adhesion perspective, the combination of C101/D1 fired at 980°C, C110/D1 fired at 850°C show satisfactory adhesion and should be used as our metal and dielectric for the multilayer thick film metallization. However, after the study of die attach, it was found that the Au based conductor C101 is not compatible with the die attach material

selected for high temperature application (details will be given in Chapter 3).

The combination of conductor C109 and dielectric D1 fired at 850°C provided satisfactory adhesion after 2000 hours aging at 320°C. Thus, C101 with C109 was selected for use on the die attach pads and the passive components attach pads. Since conductor C101 had good wire bonding results and lower resistivity than C109, it was used for wire bonding pads and interconnections.

## 2.5 Electrical Testing

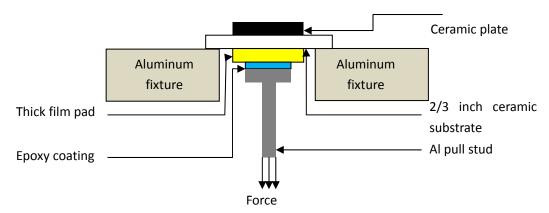

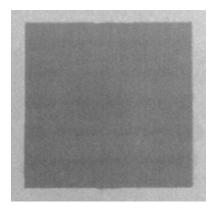

The electrical properties and reliability of the dielectric at 300°C is important for circuit design and performance. To characterize dielectric properties of the thick film materials, an electrical test vehicle was designed and fabricated on 2" by 2" alumina substrates. Gold conductor C101 and dielectric D1 were evaluated. A bottom conductor layer, two dielectric layers, and a top conductor layer were printed, dried, and fired separately. Initial test vehicles were fired at 850°C. Based on the adhesion test results, subsequent test vehicles were fired at 980°C.

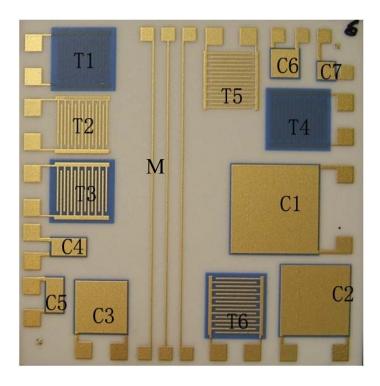

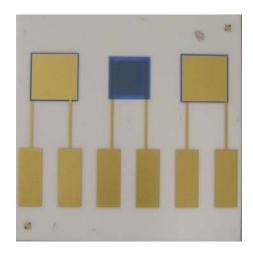

This three-layer test vehicle provided electrical test structures for leakage current, capacitance, dissipation factor, and a metal electromigration tests. The test pattern is shown in Figure 2.18. On the test vehicle there are 7 capacitors, 6 comb patterns, and 3 migration test lines. These structures are labeled in Figure 2.18 and their properties are summarized in Table 2.3. The metal migration patterns were 1730 mils long, but were not evaluated in this test as the anticipated application current levels were low and metal electromigration was not anticipated.

Figure 2.18 Electrical Test Vehicle

Table 2.3 Test Pattern for Electrical Test Vehicle

| Capacitor | size (mil) | Comb Pattern (line width 10mil) |                               |  |

|-----------|------------|---------------------------------|-------------------------------|--|

| C1        | 500 by 500 | T1                              | 10mil space; under dielectric |  |

| C2        | 400 by 400 | T2                              | 10mil space; no dielectric    |  |

| C3        | 300 by 300 | Т3                              | 10mil space; on dielectric    |  |

| C4        | 100 by 200 | T4                              | 12mil space; under dielectric |  |

| C5        | 200 by 100 | T5                              | 12mil space; no dielectric    |  |

| C6        | 160 by 160 | T6                              | 12mil space; on dielectric    |  |

| C7        | 100 by 100 |                                 |                               |  |

## 2.5.1 Leak Current Measurement

Leakage currents were measured on the various sized capacitors and comb patterns with a bias voltage up to 100V at different temperatures. An HP 4145 Semiconductor Parameter Analyzer was used. The measurement current includes two components: the transient capacitor charging current, and the steady state leakage current. The voltage was increased from 0V to 100V, in 5V steps. To reduce the error due to the charging current,

the leakage current was measured at each step after the voltage had been applied for 20 seconds.

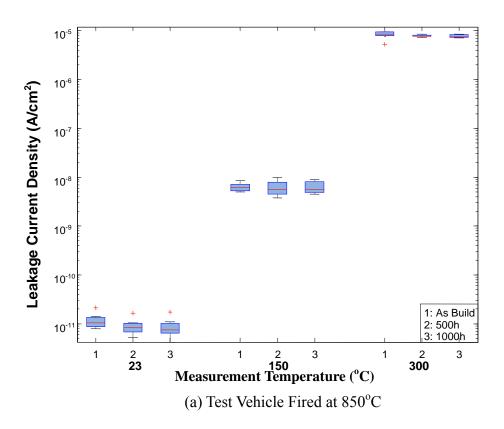

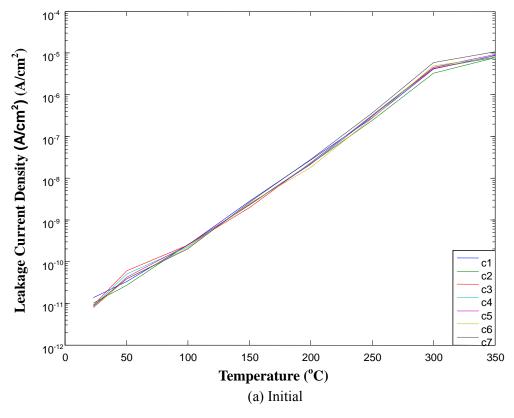

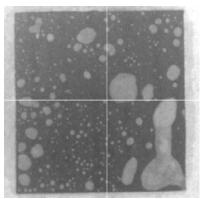

Aging data up to 1000 hours has been collected for test vehicles fired with a peak temperature of 850°C and test vehicles fired with a peak temperature of 980°C. Figure 2.19 plots the results of 100V bias capacitor leakage current density (leakage current/capacitor area) measurements initially and after 500 and 1000 hours of unbiased aging at 320°C. No significant change was found with aging.

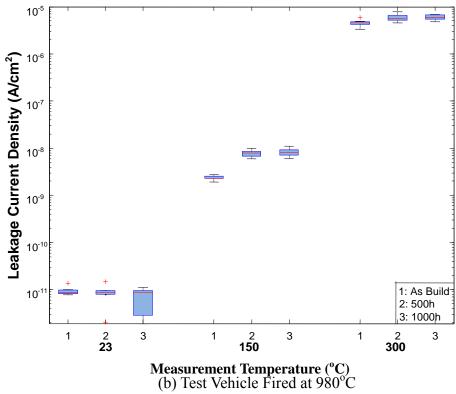

Figure 2.20 plots capacitor leakage current density as a function of temperature measured at 100V bias with test vehicles fired at a peak of 980°C, with samples as-built (a) and after 1000 hours aging (b). No significant change was found with aging, and compared with Figure 2.19, firing at 980°C does not change the electrical properties.

Figure 2.19 Capacitor Leakage Current Density at 100V Bias as a Function of Storage Time at 320°C (a) Test Vehicle Fired at 850°C (b) Test Vehicle Fired at 980°C

Figure 2.20 Capacitor Leakage Current Density at 100V Bias as a Function of Temperature (Test Vehicle Fired at 980°C)

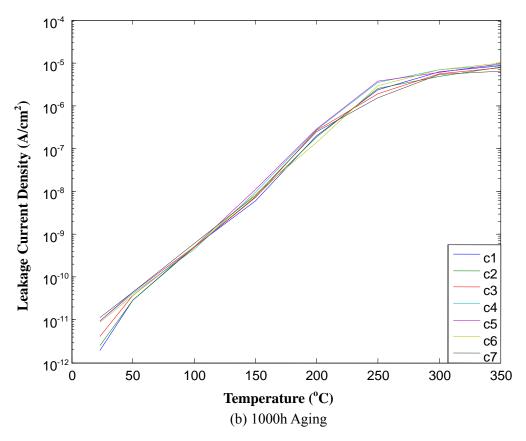

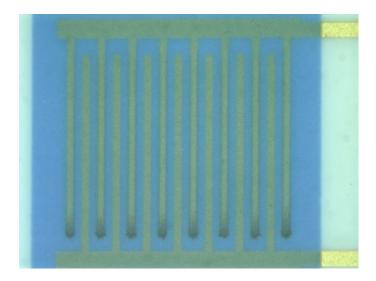

The comb pattern was designed to have 8 lines on one comb and 7 lines on the other. Each line was 10mil wide, with a 10 mil space for T1, T2, and T3, and 12 mil space for T4, T5, and T6. Each line had a length of 250 mil, with 225 mil overlapped to the next line, as shown in Figure 2.21. Each comb pattern had 225x14 = 3150 mil of overlapped length. For comb pattern T2 and T5, lines were printed onto the ceramic; for pattern T1 and T4, a dielectric layer was printed on top of the lines; for comb pattern T3 and T6, lines were printed on top of a dielectric layer. Table 2.1 shows the measured line width and spacing compared to the designed value, which indicates that after firing the conductor shrank on ceramic and expanded on dielectric.

Figure 2.21 Designed Comb Test Pattern

Table 2.4 Measured Line Width and Spacing on Comb Pattern

| Designed           | Measured Line/Spacing (mil) |               |  |  |

|--------------------|-----------------------------|---------------|--|--|

| Line/Spacing (mil) | On Ceramic                  | On Dielectric |  |  |

| 10/12              | 9.70/12.6                   | 10.65/11.2    |  |  |

| 10/10              | 9.65/10.7                   | 10.15/9.8     |  |  |

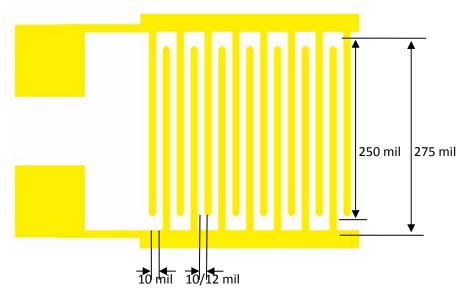

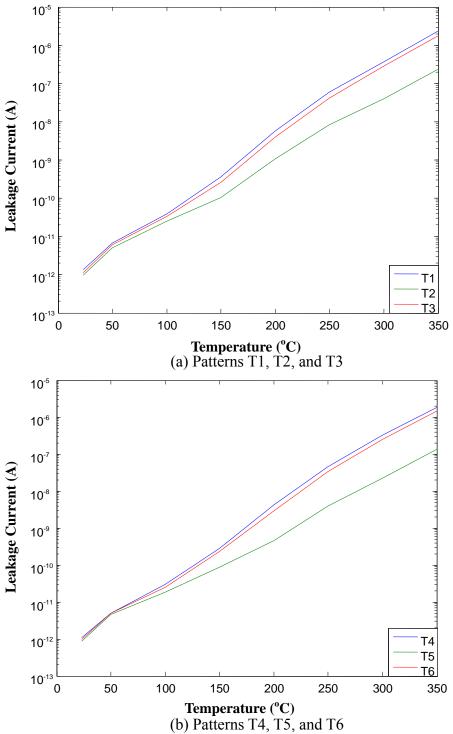

Figure 2.22 plots the initial result of the leakage current measurements at 100V bias. The results are the average of seven test vehicles fired with a peak temperature of 980°C. The results indicate that comb patterns printed in contact with the dielectric D1 had slightly higher leakage currents at elevated temperatures.

Figure 2.22 Initial Leakage Current at 100V Bias as a Function of Temperature (Test Vehicle Fired at 980°C)

The comb pattern leakage current has also been measured on samples fired with a peak temperature of 850°C. The results were similar to the samples fired with peak

temperature of 980°C. There was no change in leakage current for both the 850°C fired and 980°C fired samples after 1000 hours unbiased aging at 320°C.

# 2.5.2 Dissipation Factor and Capacitance Measurement

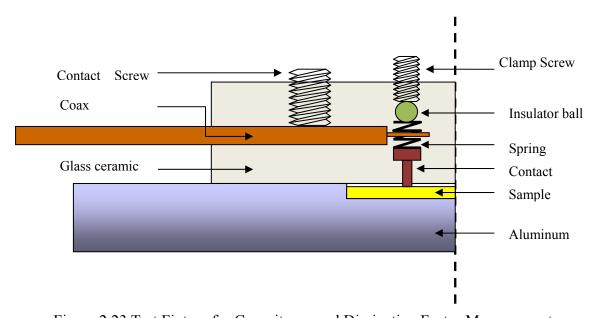

For capacitance and dissipation factor measurements, a test fixture was designed to hold the sample and provide stable contact to the coax cable, as shown in Figure 2.23. Four 1-meter (electrical length) coax cables were connected to the capacitor through a glass ceramic (Macor). A contact screw was fixed on each cable to prevent twisting. Another screw was used to provide pressure on the spring (inconel) through an insulator ball (silicon nitride). The sample was held on an aluminum substrate and the substrate was attached to the glass ceramic by screws (not shown in the illustration). Due to the design complexity and space limitation, only capacitor C1 (500 mil by 500 mil) was measured.

Figure 2.23 Test Fixture for Capacitance and Dissipation Factor Measurement

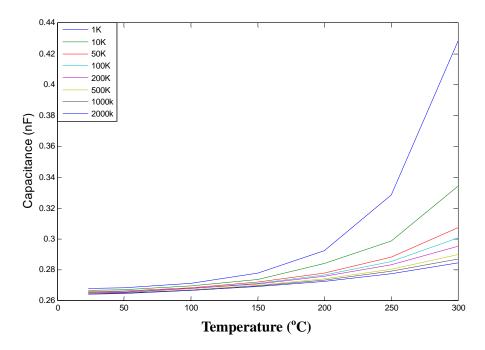

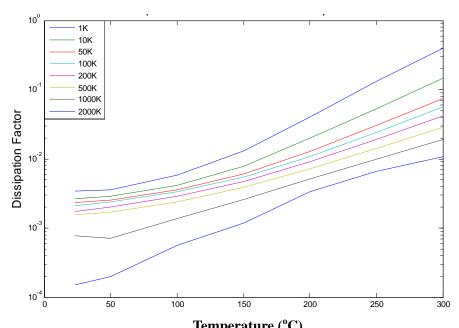

The fixture was placed inside a Delta Design 9023 oven. Dissipation factor and capacitance were measured with an Agilent 4192A LF Impedance Analyzer as the

temperature was stepped from room temperature to 350°C. The initial results for 980°C fired test vehicles are shown in Figures 2.24 and 2.25, which is the average value from six test vehicles. The capacitance and dissipation factor has also been measured on test vehicles fired with peak temperature of 850°C. The results were similar to the samples fired with peak temperature of 980°C. There was no significant change in capacitance or dissipation factor for both the 850°C fired and 980°C fired samples after 1000 hours unbiased aging at 320°C.

Figure 2.24 Initial Capacitance as a Function of Frequency and Temperature (Test Vehicle Fired at 980°C)

Temperature (°C)

Figure 2.25 Initial Dissipation Factor as a Function of Frequency and Temperature

(Test Vehicle Fired at 980°C)

# 2.5.3 Biased Measurement

To further investigate the dielectric properties after high temperature storage, the leakage current test was repeated with a modified test pattern, and aging test was conducted under 100V DC and 60V DC bias voltage. Two capacitors (400mil square) and one comb pattern (10mil line/space) under dielectric were fabricated on 2" by 2" alumina substrates, as shown in Figure 2.26.

Figure 2.26 Test Pattern for Leakage Current under Bias

Au conductor C101, Au/Pt/Pd conductor C109, and dielectric D1 were evaluated. A bottom conductor layer, two dielectric layers, and a top conductor layer were printed, dried, and fired separately. The bottom and top conductor layer used the same conductor paste, either Au or Au/Pt/Pd. The test vehicles includes four groups: Au conductor under 100V bias voltage, Au conductor under 60V bias voltage, Au/Pt/Pd conductor under 100V bias voltage, and Au/Pt/Pd conductor under 60V bias voltage. Each group has eight substrates, which include 16 capacitor patterns and 8 comb patterns.

Figure 2.27 Wires Held on Test Vehicle

Figure 2.28 Stacked Test Fixtures

To measure leakage current with bias voltage on multiple test patterns, a  $100k\Omega$  resistor was connected in series with each test pattern. Leakage current was calculated from the voltage measurement across this resistor. High temperature wires were held by crimps and pushed into tight contact with the test pattern by an aluminum bar, as shown in Figure 2.27. A ceramic substrate was used between the aluminum bar and the wires to prevent electrical shorting. Four substrates were placed on a large aluminum fixture, and four of these fixtures were stacked together, as shown in Figure 2.28. The wires were connected to the resistors and power supplies on a breadboard outside the aging oven.

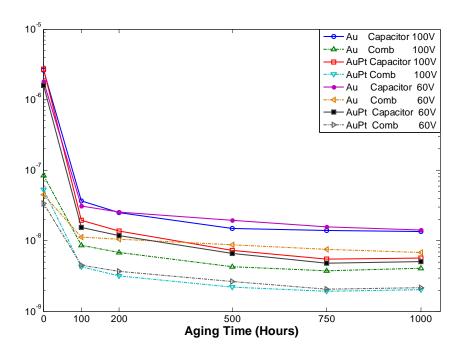

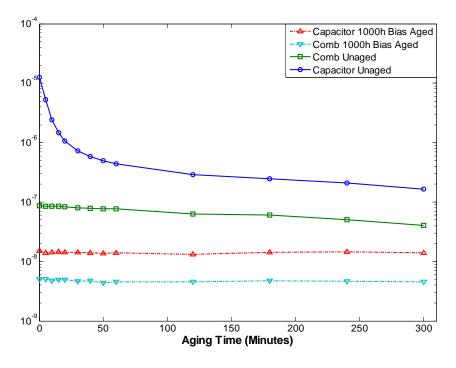

The test vehicles were placed in a 300°C oven, with 100V and 60V power supplied continuously. Leakage current was calculated from voltage measurements initially, after 100, 200, 500, and 1000 hours aging. The results were plotted in Figure 2.29.

Figure 2.29 Leakage Current as a Function of Aging Time

After 100 hours aging at 300°C, the leakage current exhibited a significant decrease on all the test patterns, and a slow decrease continued through 750 hours. Test vehicles

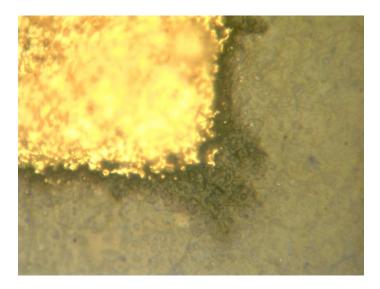

were removed from the oven after 1000 hours aging at 300°C. On the comb pattern from all four groups, discoloration of the ground connected comb fingers was observed, as shown in Figure 2.30. There was no difference with bias voltage (100V/60V). Samples will be cross-sectioned for SEM/EDS analysis. The similar discoloration was found on the corner of the capacitor, as shown in Figure 2.31.

Figure 2.30 Comb Pattern after 1000 hours Biased Aging

Figure 2.31 Corner of Capacitor after 1000 hours Biased Aging

The significant leakage current decreasing was not expected. To understand the mechanism, two aged samples (with 100V bias voltage) and two unaged samples were

wired onto the same test fixture. Since the thick film metal conductor did not show a large difference from Figure 2.29, the samples fabricated with Au conductor C101 were tested. 100V DC bias voltage was applied to the samples after the oven had reached 300°C for 20 minutes. The leakage current was then measured immediately. The initial leakage current from the unaged sample was higher than we measured in the initial test. This was because in the previous test, the initial leakage current was measured after applying bias voltage for some time, which is not an accurate initial value. The test result shows that 1000h bias aged samples have a relatively constant leakage current during the 300 minutes test time, while the unaged samples show a rapid decreasing leakage current, as shown in Figure 2.32. This test continued for 24 hours and no discoloration was found on the samples.

Figure 2.32 Leakage Current as a Function of Aging Time for 300 Minutes

### 2.6 Summary

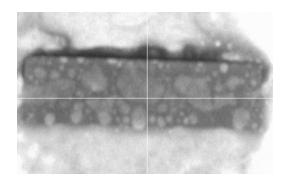

Several conductor and dielectric inks were investigated for application at 300°C. For