## Design of 3.33GHz CML Processor Datapath

by

Abdullah Al Owahid

A thesis submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Master of Science

> Auburn, Alabama May 7, 2012

Keywords: CML, CMOS, Processor

Copyright 2012 by Abdullah Al Owahid

Approved by

Fa Foster Dai, Chair, Professor of Electrical and Computer Engineering Vishwani D. Agrawal, James J. Danaher Professor of Electrical and Computer Engineering Victor P. Nelson, Professor of Electrical and Computer Engineering Abstract

Almost a decade processor speed has been stuck at operating frequency 2-3GHz due to excessive power consumption of CMOS logic gate at higher frequency whereas predicted speed at present was 10-15GHz. This leads the idea of multi-core design in today's processor architecture. However it increases the communication overhead  $\beta$  and there exist data dependency which cannot fully exploit the advantage of many-core design. Further many core design is increasing number of dark silicon and number of core cannot be increased after certain limit. Therefore a novel approaches in processor design using CML logic gate has been proposed.

Handcrafted 16-bit CML microprocessor datapath has been developed at operating frequency 3.33GHz using 130nm CMOS technology. With the same feature size, CMOS gate is incapable to operate beyond 1GHz whereas CML logic gates were optimized for 12GHz using bias current of 70% of peak  $f_t$  current with a logic swing of 600mV. Considering critical path delay, circuit has been slowed down to operate at 3.33GHz.

All the processor components - decoder, mux, register file, ALU was deliberately handcrafted due to lack of analog synthesizer tool. Reported static power consumption of multicycle CML processor datapath is 41.264W. However it is not the best case and could have been reduced to 50% by implementing multi-input CML logic. Expected chip area is 2.2mm x 3.45mm and power density per unit area is  $5.44\mu W/\mu m^2$ . Estimated performance evaluated is 892 MIPS. Supply voltage used is 2.8V. CML logic was defined as, logic-1 = 2.8V and logic-0 = 2.2V. 1V reference voltage was used to constant bias the current source and reset signal uses 1.3V and 0.7V for high and low logics respectively. It has been observed that it is possible to realize ultra-high speed processor using existing technology with minimum power consumption in CML logic.

#### Acknowledgments

I would like to acknowledge the continuous support and guidance of Dr. Fa Foster Dai. Without his suggestion and direction it would have been impossible to complete this thesis work. I would also like to thank my committee members Dr. Vishwani D. Agrawal for his meaningful suggestions regarding processor architecture and Dr. Victor P. Nelson.

I thank my friends and colleagues - James Clark, Shannon Price, Xin Jin and Baohu Li for being with me and making life at Auburn enjoyable.

Last but not the least, I would like to thank my family members - my parents whose love brought me so far, my brother and sister, and especially my wife for her patience.

# Table of Contents

|     |        | t                                                    | ii  |

|-----|--------|------------------------------------------------------|-----|

| Acl | know   | ledgments                                            | iii |

| Lis | t of I | Figures                                              | vii |

| Lis | t of [ | Tables                                               | xi  |

| Lis | t of A | Abbreviations                                        | xii |

| 1   | Int    | roduction                                            | 1   |

|     | 1.1    | Problem Statement                                    | 1   |

|     | 1.2    | Background and Motivation                            | 1   |

|     | 1.3    | Contribution                                         | 4   |

|     | 1.4    | Organization                                         | 5   |

| 2   | Ba     | ckground and High Speed CML Logic Realization        | 6   |

|     | 2.1    | CML Inverter                                         | 8   |

|     |        | 2.1.1 CML Inverter Optimization                      | 9   |

|     | 2.2    | CML Universal Gate                                   | 16  |

|     |        | 2.2.1 Universal CML Gate Optimization                | 19  |

|     | 2.3    | CML XOR/XNOR Gate                                    | 21  |

|     | 2.4    | CML Mux Realization                                  | 24  |

|     | 2.5    | CML D-latch Realization                              | 26  |

|     | 2.6    | Speed, Power, Area and Delay of Basic CML Components | 28  |

| 3   | Da     | tapath                                               | 29  |

|     | 3.1    | First Clock Cycle of Every Instruction               | 31  |

|     | 3.2    | R-type Instruction                                   | 32  |

|     |        | 3.2.1 R-type ADD/SUB/AND/XOR                         | 32  |

|   |      | 3.2.2   | R-type SLT                                                                                                           | 33 |

|---|------|---------|----------------------------------------------------------------------------------------------------------------------|----|

|   |      | 3.2.3   | R-type SEQ                                                                                                           | 34 |

|   | 3.3  | I-type  | Instruction                                                                                                          | 35 |

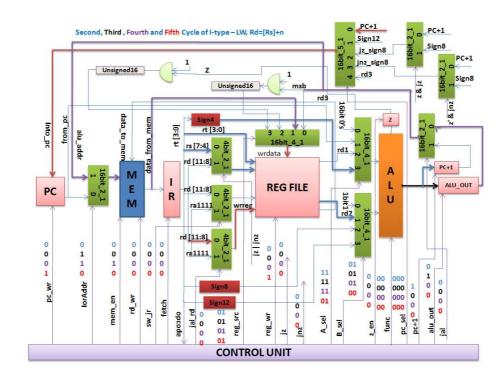

|   |      | 3.3.1   | I-type LW                                                                                                            | 35 |

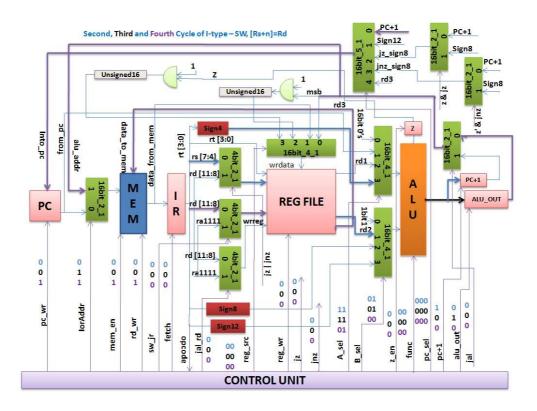

|   |      | 3.3.2   | I-type SW                                                                                                            | 36 |

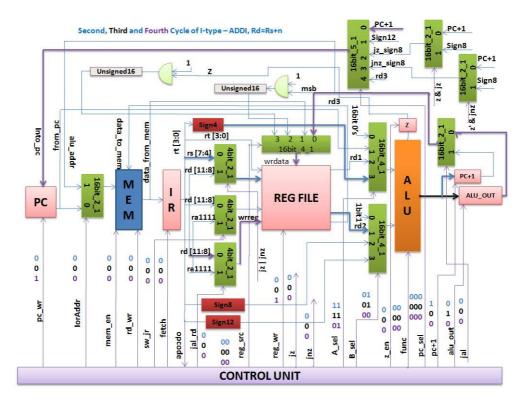

|   |      | 3.3.3   | I-type ADDI                                                                                                          | 37 |

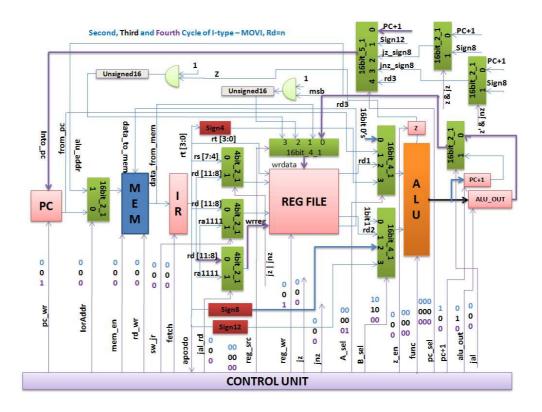

|   |      | 3.3.4   | I-type MOVI                                                                                                          | 37 |

|   | 3.4  | J-type  | e Instruction                                                                                                        | 38 |

|   |      | 3.4.1   | J-type J LABEL                                                                                                       | 39 |

|   |      | 3.4.2   | J-type JZ LABEL                                                                                                      | 40 |

|   |      | 3.4.3   | J-type JNZ LABEL                                                                                                     | 41 |

|   |      | 3.4.4   | J-type JAL                                                                                                           | 41 |

|   |      | 3.4.5   | J-type JR                                                                                                            | 42 |

|   | 3.5  | Contro  | ol Signals                                                                                                           | 43 |

| 4 | Со   | mpone   | nt Realization                                                                                                       | 46 |

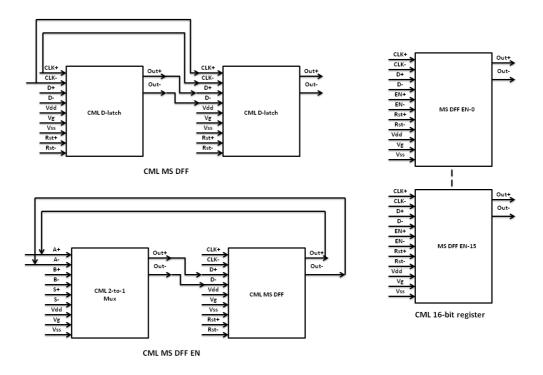

|   | 4.1  | 16-bit  | Register With Enable Input                                                                                           | 47 |

|   | 4.2  | Z Regi  | ister (1-bit Register With Enable Input)                                                                             | 49 |

|   | 4.3  | 4 16-b  | oit 2-to-1 Mux                                                                                                       | 49 |

|   | 4.4  | 3 4-bit | t 2-to-1 Mux                                                                                                         | 50 |

|   | 4.5  | 3 16-b  | oit 4-to-1 Mux                                                                                                       | 50 |

|   | 4.6  | 16-bit  | 5-to-1 mux                                                                                                           | 51 |

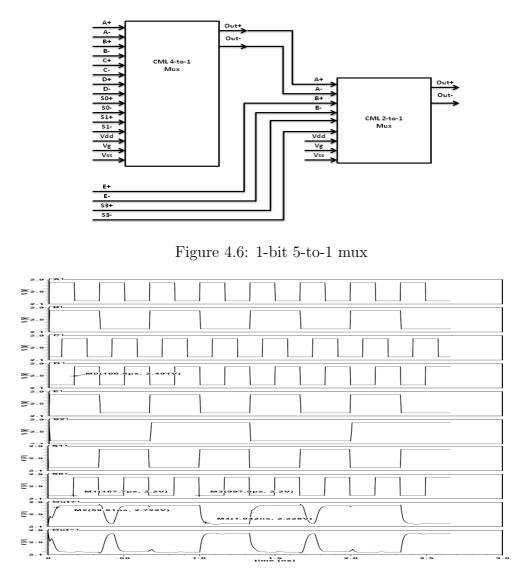

|   | 4.7  | 16-bit  | ALU                                                                                                                  | 52 |

|   | 4.8  | 16x16   | Register File                                                                                                        | 57 |

|   | 4.9  | Sign 4  | -to-16 extension (Sign 4) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                             | 62 |

|   | 4.10 | Sign 8- | B-to-16 extension (Sign 8) $\ldots$ | 63 |

|   | 4.11 | Sign 1  | 2-to-16 extension (Sign 12)                                                                                          | 63 |

|   | 4.12 | 2 unsig | gned 1-to-16 extension (Unsigned 16)                                                                                 | 64 |

|    | 4.13   | 4 1-bit AND gate                     | 65 |

|----|--------|--------------------------------------|----|

|    | 4.14   | 1 1-bit OR gate                      | 65 |

| 5  | Pr     | ocessor Verification and Performance | 67 |

|    | 5.1    | Processor Verification               | 67 |

|    | 5.2    | Performance                          | 70 |

|    | 5.3    | Comparison                           | 72 |

| 6  | Со     | nclusions                            | 74 |

|    | 6.1    | Future Work                          | 74 |

| Bi | bliogr | aphy                                 | 76 |

# List of Figures

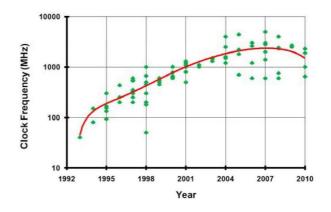

| 1.1  | Operating frequency over time                                                | 2  |

|------|------------------------------------------------------------------------------|----|

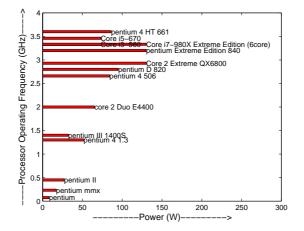

| 1.2  | Operating Frequency vs. Power of Intel Processor                             | 2  |

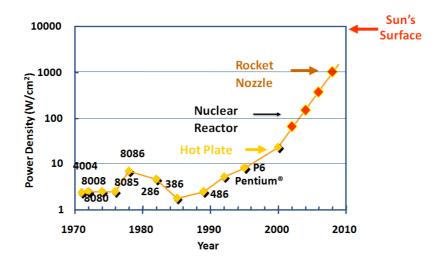

| 1.3  | Power density per unit area                                                  | 3  |

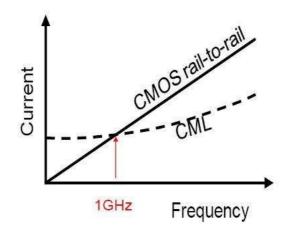

| 2.1  | Current consumptions for CMOS vs. CML logic                                  | 6  |

| 2.2  | CMOS vs. CML power consumption                                               | 7  |

| 2.3  | CML Inverter                                                                 | 8  |

| 2.4  | Normalized current for CML inverter                                          | 13 |

| 2.5  | CML inverter half-circuit small-signal model                                 | 15 |

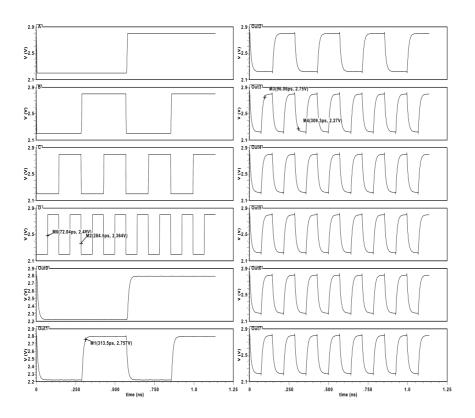

| 2.6  | Post vs. pre layout simulation of CML inverter with 18fF input/output load   |    |

|      | capacitance (input changes at 83ps)                                          | 16 |

| 2.7  | CML inverter layout                                                          | 16 |

| 2.8  | Universal CML gate                                                           | 17 |

| 2.9  | Universal CML gate with embedded level shifter                               | 18 |

| 2.10 | Normalized current for CML universal gate                                    | 20 |

| 2.11 | Post vs. pre layout simulation of CML AND with 18fF input/output load capac- |    |

|      | itance (input changes at 83ps)                                               | 20 |

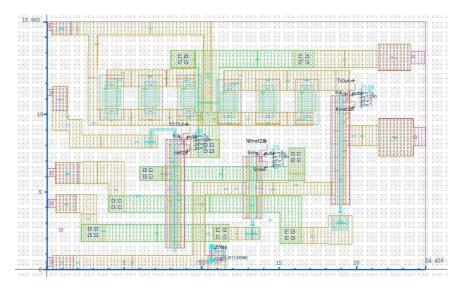

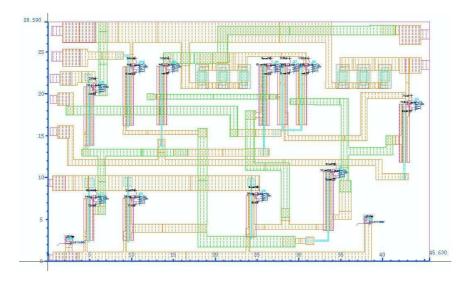

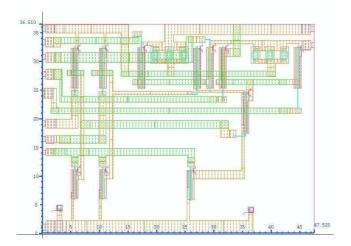

| 2.12 | CML AND layout                                                                                                 | 21 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2.13 | CML XOR gate                                                                                                   | 22 |

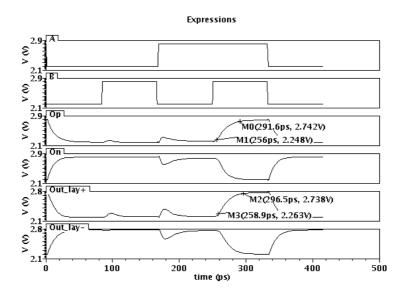

| 2.14 | Post vs. pre layout simulation of CML XOR with 18fF input/output load capac-<br>itance (input changes at 83ps) | 23 |

| 2.15 | CML XOR layout                                                                                                 | 23 |

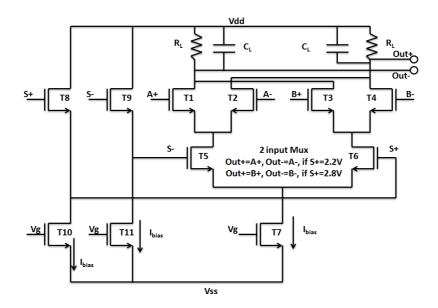

| 2.16 | CML Mux realization                                                                                            | 24 |

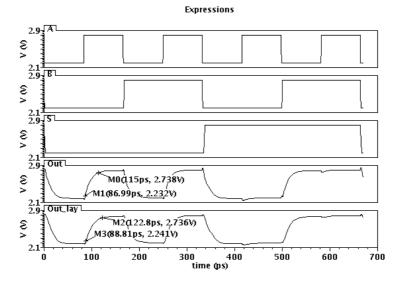

| 2.17 | Post vs. pre layout simulation of CML Mux with 18fF input/output load capac-<br>itance (input changes at 83ps) | 25 |

| 2.18 | CML Mux layout                                                                                                 | 25 |

| 2.19 | CML D-latch                                                                                                    | 26 |

| 2.20 | Post vs. pre layout simulation of CML D-latch with 18fF input/output load capacitance at 6GHz (166ps)          | 27 |

| 2.21 | CML D-latch layout                                                                                             | 27 |

| 3.1  | Processor datapath                                                                                             | 29 |

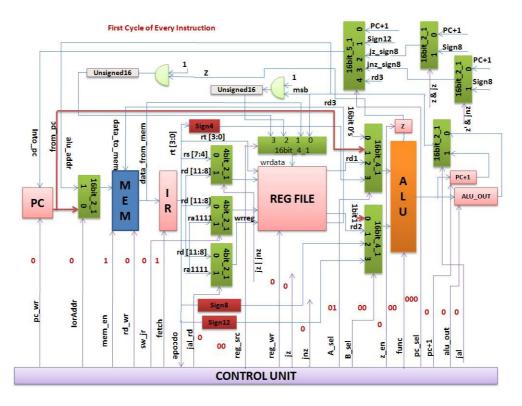

| 3.2  | First clock cycle of any instruction                                                                           | 31 |

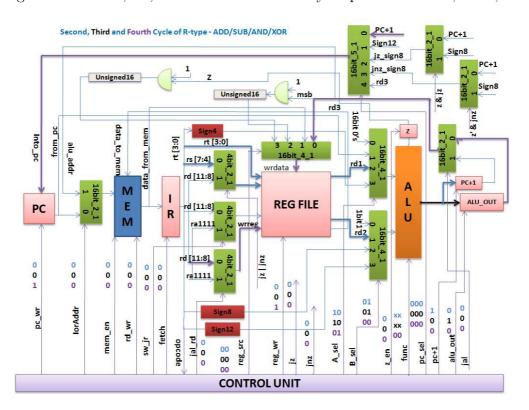

| 3.3  | R-type ADD/SUB/AND/XOR                                                                                         | 32 |

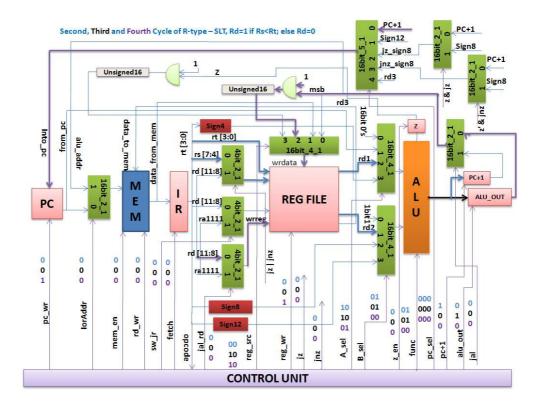

| 3.4  | R-type SLT                                                                                                     | 33 |

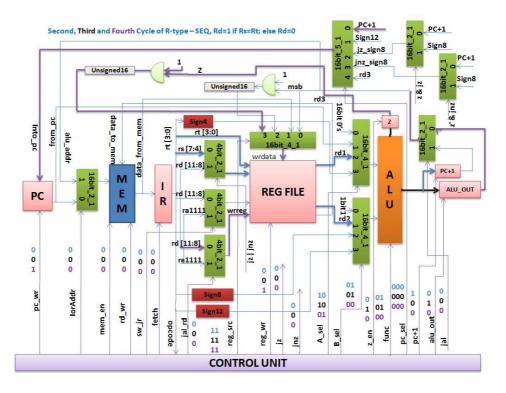

| 3.5  | R-type SEQ                                                                                                     | 34 |

| 3.6  | I-type LW                                                                                                      | 35 |

| 3.7  | I-type SW                                                                                                                         | 36 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8  | I-type ADDI                                                                                                                       | 37 |

| 3.9  | I-type MOVI                                                                                                                       | 38 |

| 3.10 | J-type J LABEL                                                                                                                    | 39 |

| 3.11 | J-type JZ LABEL                                                                                                                   | 40 |

| 3.12 | J-type JNZ LABEL                                                                                                                  | 41 |

| 3.13 | J-type JAL                                                                                                                        | 42 |

| 3.14 | J-type JR                                                                                                                         | 43 |

| 4.1  | Datapath Components                                                                                                               | 46 |

| 4.2  | Block diagram of MS DFF, MS DFF-EN, 16-bit register                                                                               | 48 |

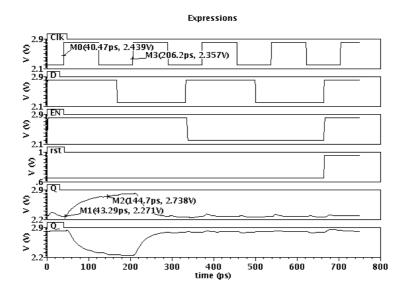

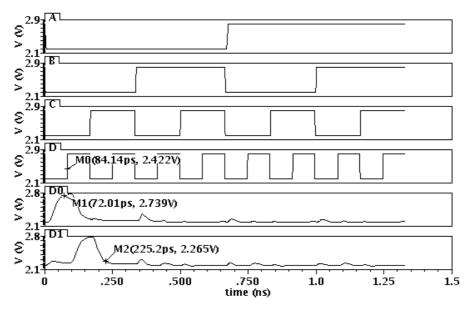

| 4.3  | 1-bit register output at 6GHz with 20fF load capacitance (clock period 166ps) $% \left( 1,1,2,2,2,3,2,3,3,3,3,3,3,3,3,3,3,3,3,3,$ | 49 |

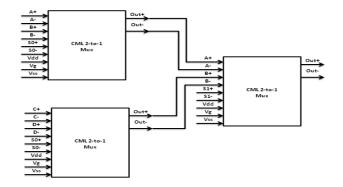

| 4.4  | 1-bit 4-to-1 mux                                                                                                                  | 50 |

| 4.5  | 1-bit 4-to-1 mux output with 20fF load capacitance (input changes at 83ps) $$                                                     | 51 |

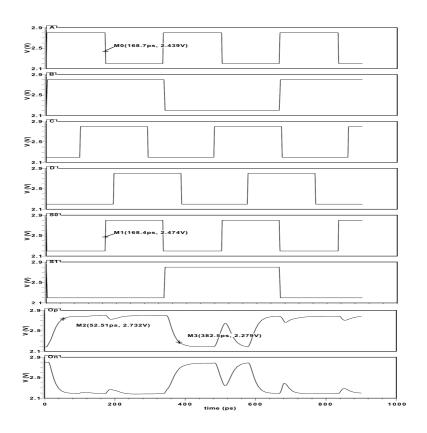

| 4.6  | 1-bit 5-to-1 mux                                                                                                                  | 52 |

| 4.7  | 1-bit 5-to-1 Mux output with 20fF load capacitance (input changes at 166ps)                                                       | 52 |

| 4.8  | Block diagram of 16-bit ALU                                                                                                       | 53 |

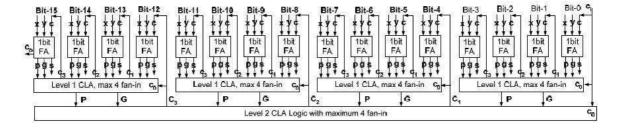

| 4.9  | 16-bit CLA block diagram                                                                                                          | 53 |

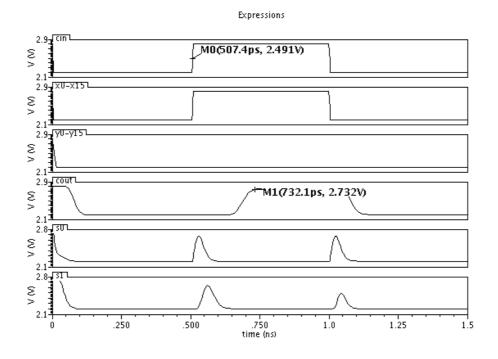

| 4.10 | Critical path delay in 16-bit CLA is 224.7ps (input changes at 500ps)                                                             | 55 |

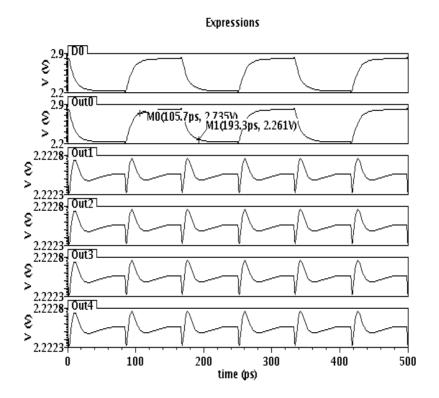

| 4.11 | 16-bit ALU Output (input changes at 300ps)                                            | 56 |

|------|---------------------------------------------------------------------------------------|----|

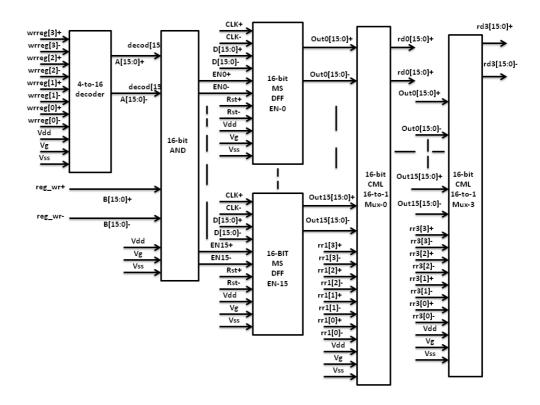

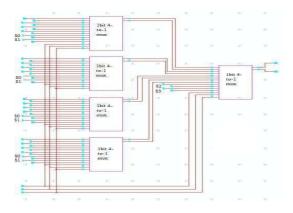

| 4.12 | 16x16 Register File Schematic                                                         | 58 |

| 4.13 | 4-to-16 Deocoder (input changes at 83ps)                                              | 59 |

| 4.14 | 1-bit 16-to-1 Mux Schematic                                                           | 59 |

| 4.15 | 1-bit 16-to-1 Mux Output (input changes at 144ps)                                     | 60 |

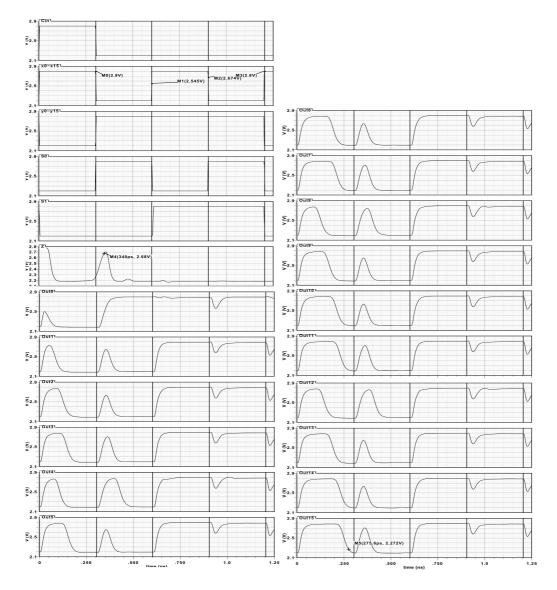

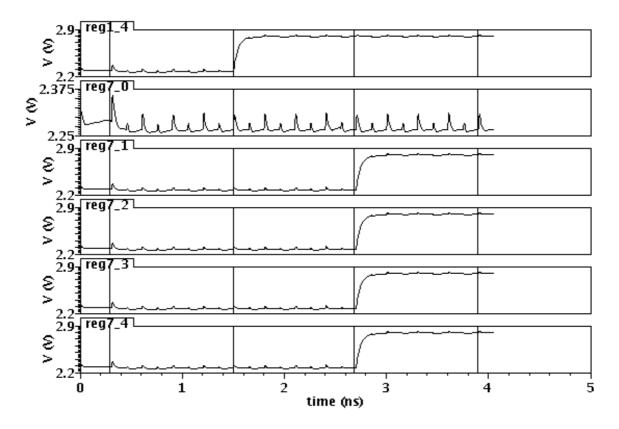

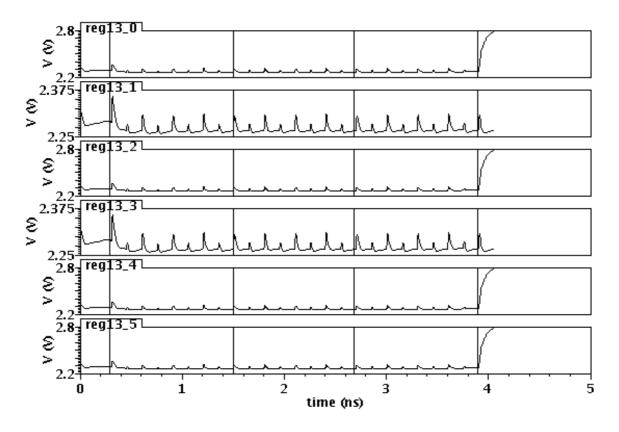

| 4.16 | 16x16 Register File Output at 3.33GHz                                                 | 61 |

| 4.17 | Sign 4 to 16 Extension Output (input changes at 72ps)                                 | 63 |

| 4.18 | Unsigned 1 to 16 Extension Output (input changes at 83ps)                             | 64 |

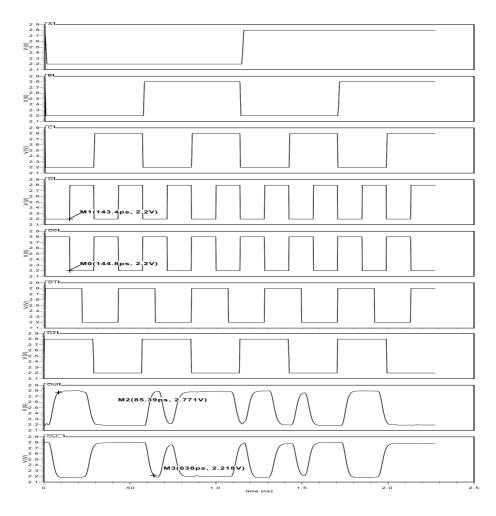

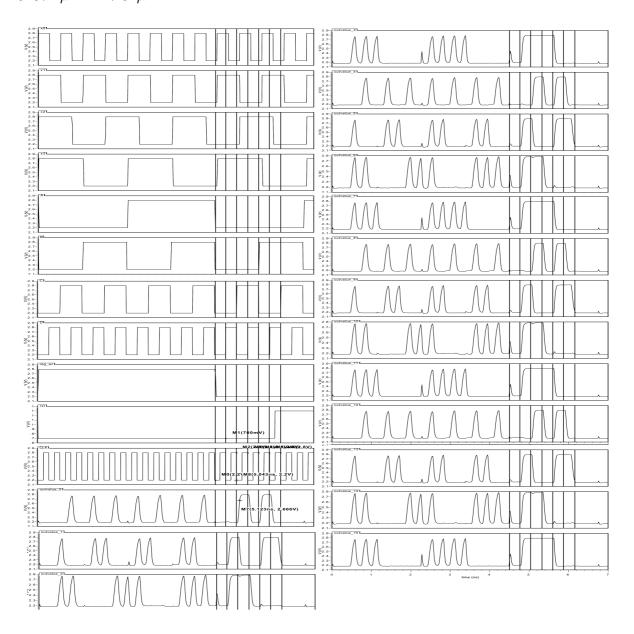

| 5.1  | Handcrafted Processor Schematic                                                       | 67 |

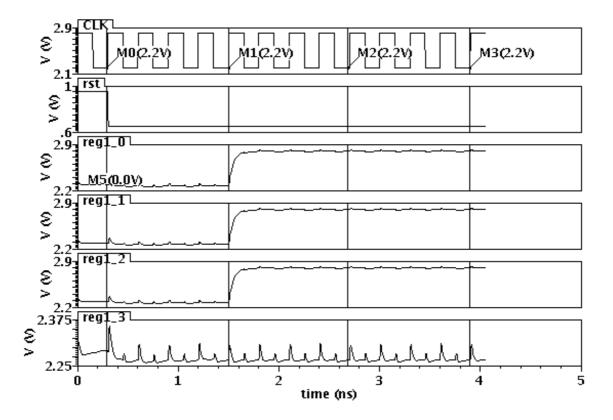

| 5.2  | MOVI instruction                                                                      | 68 |

| 5.3  | ADDI instruction                                                                      | 69 |

| 5.4  | ADD instruction                                                                       | 70 |

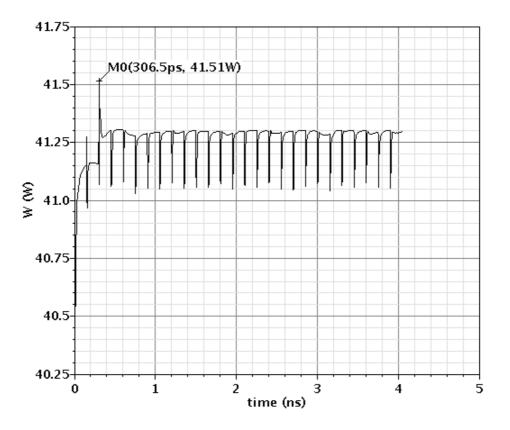

| 5.5  | Static power consumption of CML processor data<br>path over 13 clock cycles $\ . \ .$ | 71 |

# List of Tables

| 2.1 | Inverter Operation                                                                            | 8  |

|-----|-----------------------------------------------------------------------------------------------|----|

| 2.2 | CML AND Operation                                                                             | 19 |

| 2.3 | CML XOR Operation                                                                             | 22 |

| 2.4 | CML Mux Operation                                                                             | 24 |

| 2.5 | CML D-latch Operation                                                                         | 26 |

| 2.6 | Power, Area and Delay of Basic Components (post layout simulation with 18fF load capacitance) | 28 |

| 3.1 | Instruction Set Architecture                                                                  | 29 |

| 3.2 | Opcode and 15 Different Operations                                                            | 30 |

| 3.3 | Control Signal Table Part-1                                                                   | 44 |

| 3.4 | Control Signal Table Part-2                                                                   | 45 |

| 4.1 | Component Power Dissipation, Expected Area and Delay                                          | 65 |

### List of Abbreviations

- ALU Arithmetic Logic Unit

- BiCMOS Bipolar and CMOS in same integrated chip

- BJT Bipolar Junction Transistor

- CML Current Mode Logic

- CMOS Complementary Metal Oxide Semi-conductor

- ECL Emitter Coupled Logic

- ISA Instruction Set Architecture

- MCML Mos Current Mode Logic

- MIPS Million Instructions Per Second

- nMOS n-type Metal Oxide Semi-conductor

- RISC Reduced Instruction Set Computing

- SoC System on Chip

- SPICE Simulation Program with Integrated Circuit Emphasis

- SRAM Static Random Access Memory

#### Chapter 1

#### Introduction

This thesis presents the design of a handcrafted 3.33GHz CML processor datapath. RISC architecture has been adopted in designing the multi-cycle processor datapath and the ISA is 16-bits long. It is the first ever MCML processor that requires constant power dissipation unlike CMOS processors. Also, once optimized, power dissipation does not increase with increasing operating frequency. Optimizing CML logic for higher operating frequency requires higher power than optimizing for lower frequency. Therefore, once CML logic has been optimized for a targeted maximum frequency, operating the circuit at lower frequency will lose the benefits in terms of power.

Due to larger switching noise associated with CMOS circuits, CML is a better choice for high speed circuit realization [1]. BJT based CML gates are faster than MOSFET CML due to higher  $g_m$  and lower power but have been avoided for process difficulty and uncommonness in designing digital circuits. Therefore MOSFET-CML (MCML) logic has been used.

### 1.1 Problem Statement

The problem solved in this thesis: Design a high speed low power processor datapath.

### 1.2 Background and Motivation

Processor speed has been stuck at 2-3GHz due to excessive power consumption, as indicated in Figure 1.1 for the last 10 years [2]. Therefore multi-core design has evolved to increase performance. But the number of cores cannot be increased after a certain limit and there exists communication overhead  $\beta$ . Further, due to data dependency, programs cannot be fully parallelized, which inhibits proper exploitation of multi-core design.

Figure 1.1: Operating frequency over time

Intel processor speed vs power have been obtained and plotted in Matlab as depicted in Figure 1.2 [3].

Figure 1.2: Operating Frequency vs. Power of Intel Processor

In Figure 1.2 it is observed that processor power consumption has been increased almost exponentially at operating frequencies beyond 2GHz. Also notable is that, core i-5 has higher operating frequency than core-i7 but the power consumption in core i-7 is almost double due to a higher number of cores. So reducing the number of cores will not only reduce power but can result in higher performance due to less data dependency. Power consumption can also be reduced by moving to deep submicron technology. However, the main drawback to reducing feature size is it increases unit power density and chips cannot sustain that power, as shown in Figure 1.3 [4].

Figure 1.3: Power density per unit area

In CML, per unit power density is lower as it requires greater area than CMOS due to load resistances in CML logic. Therefore in CML, we can achieve higher operating frequency with less power density.

A previous mixed signal superscalar processor was developed in 1997, using  $0.5\mu$ m BiC-MOS process and required 3.6V and 2.1V power supplies. The reported operating frequency was 533MHz and the design used a PowerPC architecture that contained three pipelines and a large on-chip secondary cache to achieve a peak performance of 1600 MIPS. The 15mm x 10 mm die contained 2.7M transistors (2M CMOS and 0.7M bipolar) and dissipated less than 85W [5]. All logic circuits were implemented in three-level emitter coupled logic (ECL) and only RAM structures were implemented with CMOS circuits.

Although BJT has less switching noise and are faster than MOS transistors they are expensive and not frequently used in digital circuits [1]. This led to the idea to design a high speed processor datapath using MCML logic. Further CMOS SRAM cannot operate at 3.33GHz using  $0.12\mu$ m technology. Therefore only high speed datapath was developed in this thesis.

#### 1.3 Contribution

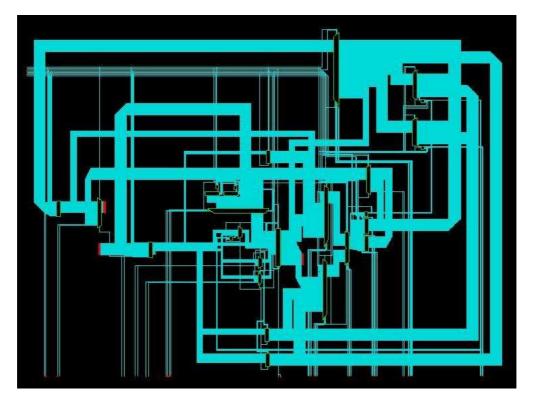

CML logic architecture has been discussed in the literatures but it is not guaranteed that it can realize digital functions unless optimization has been performed [6]-[8]. Optimized CML logic can steer full bias current at different input combinations, resulting in full voltage swing that differentiate logic states. Also, technology files provide only transistors, unlike digital technology files that provides optimized CMOS logic gates. Therefore, due to lack of analog synthesizer tools handcrafting of CML logic architecture is necessary and then optimization is required for CML logic to realize digital function for a targeted frequency. All the basic components have been derived first, with maximum operating frequency 12GHz using 130nm CMOS technology. Bias current was chosen to be 70% of peak  $f_t$  current that gives us highest possible operating frequency without burning transistors when operate. Further, biasing CML gates with 70% of peak  $f_t$  or less may incur 10% propagation delay but can save more than 40% power [1] and [7]. Logic swing was determined to be 600mV, assuming it will be advantageous than CMOS logic at this frequency that has fixed swing 1V. These basic CML logic designs were later used in realizing 16-bit 3.33GHz datapath components. All the processor components - mux, register file, ALU were deliberately handcrafted in Cadence Virtuoso. Reported static power consumption of the multi-cycle CML processor is 41.264W and power density per unit area is  $5.44 \mu W/\mu m^2 = 544 W/cm^2$ , below traditional CMOS processor power density per unit area, as indicated in Figure 1.3. Estimated performance of the multi cycle CML processor datapath is 892 MIPS and expected chip area is 2.2mm x 3.45mm.

This work has been accepted at IEEE International Symposium On Circuits and Systems (ISCAS) 2012 Conference [9].

## 1.4 Organization

The thesis has been organized as follows: Chapter 2 provides background and describes high speed CML logic realization. Chapter 3 introduces datapath design. Chapter 4 describes CML datapath component realization and verification. Chapter 5 represents processor verification, performance and comparison. Chapter 6 draws conclusions and discusses future work.

#### Chapter 2

Background and High Speed CML Logic Realization

Recently, interest in high speed digital circuit baseds on MCML/BJT-CML is increasing due to low power consumption [10]. Noise coupling between digital circuitry and sensitive analog blocks has always been a major obstacle in complete system on chip design (SoC) [11]. MOS current mode logic (MCML) is a promising alternative to conventional MOS in mixed signal applications. Many efforts were exhausted to realize the potential of MCML [12]-[17]. Even though MCML has been shown to dissipate less power than CMOS at operation frequencies of more than 300MHz, designers have been reluctant to exchange MCML for CMOS [14]. The high complexity of MCML and the lack of automation tools made it impossible to produce robust and power-efficient designs while maintaining low cost and reasonable time to market.

Figure 2.1: Current consumptions for CMOS vs. CML logic

Figure 2.1 shows typical current consumption for CMOS and CML logics [18]. As indicated, typically at slower frequency CMOS is beneficial whereas CML takes less power

at higher operating frequency. Figure 2.1 is based on assumption, and not according to circuit measurements, and is not shown in scale. It is supposed that typically beyond 1GHz CML is beneficial than CMOS.

Figure 2.2: CMOS vs. CML power consumption

A divide by two circuits was realized in CMOS (W = 160nm, 160nm, 200nm, 600nm, 1m, 1.5m, 2.5m, 3m, 7m and 10m for 0.5, 1, 1.2, 1.4, 1.5, 1.6, 1.8, 2, 2.3 and 2.5GHz respectively) and CML (W = 160nm, 160nm, 160nm, 200nm, 250nm, 300nm each having  $W_{tail} = 120$ nm for 0.5, 1, 2, 2.5, 3 and 4GHz respectively) architecture. Channel length, L = 120nm was fixed for both cases and power has been plotted in Figure 2.2. At 2.5GHz CMOS D filp-flop propagation delay reaches 50% of input clock cycle whereas CML D flip-flop was able to generate correct output till 6GHz. It is obvious that CML dominates over CMOS beyond 1.5GHz. Benefits of MCML circuit topology over CMOS are largely independent of technology [6].

Many successful attempts have been made to expose the relationships between the MCML gate delay and the various design parameters [19]-[21]. These efforts have provided insight into the design considerations and have been described briefly for CML inverters and universal CML logic. There is no straight forward method to optimize CML logic and modeling accurate propagation delay for CML logic with pen and paper is very hard to

derive due to higher order effects. Therefore, we will rely on some approximation in the later subsections and compare with the simulation results in designing high speed CML gates.

#### 2.1 CML Inverter

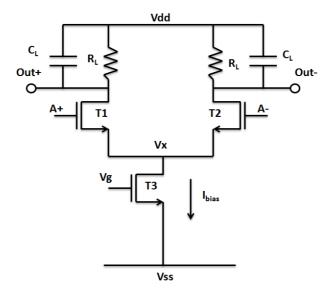

Figure 2.3: CML Inverter

Figure 2.3 shows a CML Inverter which is typically a differential pair. There exists a particular biasing voltage  $V_{in}$  (quiescent point), for which  $I_{d1} = I_{d2} = I_{bias}/2$ . For differential input, which is our logic swing  $\Delta V$ , it is necessary to tune the circuit such that when logic-1  $(V_{in} + \Delta V/2)$  is applied to A+ and logic-0  $(V_{in} - \Delta V/2)$  is applied to A-, T1 turns on and T2 turns off resulting in  $I_{d1}=I_{bias}$ ,  $I_{d2}=0$ ; steering all the current through T1. A Summary of CML inverter operation has been given in Table 2.1

| A+                      | A-                      | T on | T off | Out+                    | Out-                    |

|-------------------------|-------------------------|------|-------|-------------------------|-------------------------|

| $V_{in}$ - $\Delta V/2$ | $V_{in} + \Delta V/2$   | 2, 3 | 1     | $V_{in} + \Delta V/2$   | $V_{in}$ - $\Delta V/2$ |

| $V_{in} + \Delta V/2$   | $V_{in}$ - $\Delta V/2$ | 1, 3 | 2     | $V_{in}$ - $\Delta V/2$ | $V_{in} + \Delta V/2$   |

Table 2.1: Inverter Operation

#### 2.1.1 CML Inverter Optimization

If our supply voltage is  $V_{dd}$  as indicated in Figure 2.3, and the output of the CML gate drives another gate, then we must have to maintain:

Logic-1 =

$$V_{dd} = V_{in} + \Delta V/2$$

and Logic-0 =  $V_{dd}$ -  $\Delta V = V_{in}$ -  $\Delta V/2$

Let us assume logic-1  $(V_{in}+\Delta V/2)$  is applied to A+ and logic-0  $(V_{in}-\Delta V/2)$  is applied to A-. Therefore, to keep T1 in its forward-active region and T2 in its cut-off region, necessary conditions are:

$$V_{gs1} > V_{th1}; V_{gd1} < V_{th1}; V_{ds1} > V_{gs1} - V_{th1}$$

$V_{gs2} < V_{th2}; V_{gd2} < V_{th2}$

If we assume that the magnitude of the voltage swing is just large enough to steer all the current from one side to the other then  $\Delta V = \Delta V_{min}$ , which is the minimum swing required (just large enough to turn off T2),

$$V_{gs2} = V_{th2}$$

$$V_{g2} - V_x = V_{th2}$$

$$V_{in} - \Delta V_{min}/2 - V_x = V_{th2}$$

$$V_{dd} - \Delta V_{min}/2 - \Delta V_x = V_{th2}$$

$$V_x = V_{dd} - \Delta V_{min} - V_{th2} \qquad (2.1)$$

$$V_{gs1} = V_{g1} - V_x$$

$$V_{gs1} = V_{in} + \Delta V_{min}/2 - V_x$$

$$V_{gs1} = V_{dd} - V_x \qquad (2.2)$$

$$I_{bias} = (\mu_n C_{ox}/2)(W/L)(V_{gs1} - V_{th1})^{\alpha} \qquad (2.3)$$

where  $\mu_n$  is electron mobility in nMOS device and  $C_{ox}$  is capacitance per unit area of gate oxide,  $C_{ox} = \epsilon_{ox}/t_{ox}$ . Permittivity of  $SiO_2$ ,  $\epsilon_{ox} = 3.9\epsilon_0$ ; where permittivity of free space  $\epsilon_0 = 8.85 \cdot 10^{-14}$  F/cm and  $t_{ox}$  is thickness of gate oxide. For a short channel device, like  $0.12\mu$ m feature size  $\alpha \simeq 1.25$ . For easiness of our pen and paper calcuation, sometimes we will assume either  $\alpha$  is 2.

For matching purposes, T1 and T2 have to be same feature size such that an equal amount of current flows on both sides at the quiescent point. Therefore equation 2.1 yields

$$V_{th1} = V_{dd} - \Delta V_{min} - V_x$$

and,  $V_{gs1} - V_{th1} = V_{dd} - V_x - V_{dd} + \Delta V_{min} + V_x$

$$= \Delta V_{min}$$

(2.4)

$I_{bias} = (\mu_n C_{ox}/2) (W/L) (\Delta V_{min})^{\alpha}$ (2.5)

Therefore,  $I_{bias}$  can be realized as a function of minimum logic swing  $\Delta V_{min}$ , with  $I_{bias} \propto \Delta V_{min}$ . It means, the less logic swing we define, the less bias current we need to realize a CML inverter. The minimum amount of current that will be required to realize this logic swing occurs when W is minimum. In other words, we can realize this full swing at high bias current which is true but we will burn more power. The minimum amount of  $W_n$  that can provide just large enough (smallest) bias current to realize full swing is:

$$I_L = (\mu_n C_{ox}/2) (W_n/L) (\Delta V_{min})^{\alpha}$$

(2.6)

Again, let us consider a CML inverter circuit at its quiescent point, as indicated in Figure 2.3. In determining our minimum logic swing  $\Delta V_{min}$  we need to consider how we are going to forward bias the transistors, meaning what our overdrive should be. Typically, for overdrive votage,  $V_{ov} \geq 300$ mV, the transistor reaches soft saturation and when  $V_{ov} \geq$ 500mV, the transistor reaches hard saturation. Overdrive voltage is referred to as  $V_{ov} = V_{gs}$  -  $V_t$ . It is necessary to determine overdrive voltage because, if we apply logic-1 at A+ and logic-0 at A- and try to turn off T2 but if T2 at quiescent point reached velocity saturation then  $(\Delta V)/2$  is small enough to completely turn off T2. The consequence will be we cannot realize full swing. Making our logic swing large can turn T2 off but we will end up in greater RC constant and high propagation delay. Therefore, we need overdrive voltage such that it can push the transistor slightly in to the forward active region. A careful consideration was made such that  $V_{ov} = V_{gs} - V_t = 263.9$ mV. Therefore it is necessary to expose the relation between logic swing and overdrive voltage. For an input voltage Vg1 at gate terminal of T1,

$$V_{gs1} = Vg1 - V_x$$

$$V_{g1} = V_{gs1} + V_x$$

and

$$V_{g2} = V_{gs2} + V_x$$

For differential input voltage, which is our logic swing,

$$\begin{split} \Delta V &= V_{g1} - V_{g2} \\ \Delta V &= V_{gs1} - V_{gs2} \\ I_{d1} &= (1/2)\mu C_{ox}(W/L)(V_{gs1} - V_t)^2 \; \alpha = 2 \; \text{for simplicity} \quad (2.7) \\ I_{d2} &= (1/2)\mu C_{ox}(W/L)(V_{gs2} - V_t)^2 \\ \sqrt{Id1} - \sqrt{Id2} &= \Delta V \sqrt{(1/2)(\mu C_{ox}(W/L))} \\ I_{d1} + I_{d2} - 2\sqrt{Id1.Id2} &= (1/2)(\mu C_{ox}(W/L))\Delta V^2 \\ I_{bias} - 2\sqrt{Id1.Id2} &= (1/2)(\mu C_{ox}(W/L))\Delta V^2 \\ 2\sqrt{Id1.Id2} &= I_{bias} - (1/2)(\mu C_{ox}(W/L))\Delta V^2 \\ 2\sqrt{Id1.(Ibias - Id1)} &= I_{bias} - (1/2)(\mu C_{ox}(W/L))\Delta V^2 \\ -4I_{d1}^2 + 4I_{d1}.I_{bias} &= I_{bias}^2 - I_{bias}(\mu C_{ox}(W/L))\Delta V^2 + (1/4)(\mu C_{ox}(W/L))^2\Delta V^4 \end{split}$$

$$-4I_{d1}^{2} + 4I_{d1} \cdot I_{bias} = I_{bias}^{2} - I_{bias} \cdot K\Delta V^{2} + (1/4)K^{2}\Delta V^{4} \text{ K} = \mu \text{Cox}(W/L)$$

$$4I_{d1}^2 - 4Id1 \cdot I_{bias} + I_{bias}^2 - I_{bias}K\Delta V^2 + (1/4)K^2\Delta V^4 = 0$$

$$I_{d1} = [4I_{bias} \pm \sqrt{(16I_{bias}^2 - 16I_{bias}^2 + 16I_{bias}K\Delta V^2 - 4K^2\Delta V^4)}]/8$$

$$I_{d1} = [2I_{bias} \pm \Delta V \sqrt{(4I_{bias}K - K^2\Delta V^2)}]/4$$

$$I_{d1} = I_{bias}/2 \pm (1/4)\Delta V 2 \sqrt{(I_{bias}.K)} \sqrt{[1 - K\Delta V^2/4I_{bias}]}$$

$$I_{d1} = I_{bias}/2 \pm (\Delta V/2) \sqrt{(I_{bias}.K)} \sqrt{[1 - (\Delta V/2)^2/(I_{bias}/K)]}$$

As Logic 1 was applied to A+ and Logic-0 at A-, then differential input Vid > 0 resulting Id1 > Id2.

$$I_{d1} = I_{bias}/2 + (\Delta V/2)\sqrt{(I_{bias}.K)}\sqrt{[1 - (\Delta V/2)^2/(I_{bias}/K)]}$$

(2.8)

$$I_{d2} = I_{bias}/2 - (\Delta V/2)\sqrt{(I_{bias}.K)}\sqrt{[1 - (\Delta V/2)^2/(I_{bias}/K)]}$$

(2.9)

At the biasing (quiescent) point,  $V_{id} = 0$ , resulting  $I_{d1} = I_{d2} = I_{bias}/2$ . Therefore equation 2.7 yields

$$I_{bias}/2 = (1/2)\mu C_{ox}(W/L)(V_{gs1} - V_t)^2$$

$$I_{bias}/2 = (K/2)V_{ov}^2$$

$$K = I_{bias}/V_{ov}^2$$

Plugging in the value of K in equation 2.8 we get

$$I_{d1} = I_{bias}/2 + (\Delta V/2)(I_{bias}/V_{ov})\sqrt{[1 - ((\Delta V/2)/V_{ov})^2]}$$

(2.10)

$$I_{d2} = I_{bias}/2 - (\Delta V/2)(I_{bias}/V_{ov})\sqrt{[1 - ((\Delta V/2)/V_{ov})^2]}$$

(2.11)

Now if we want to steer full current through T1, resulting  $I_{d1} = I_{bias}$  and  $I_{d2} = 0$ , then equation 2.10 yields

$$I_{bias} = I_{bias}/2 + (\Delta V/2)(I_{bias}/V_{ov})\sqrt{[1 - ((\Delta V/2)/V_{ov})^2]}$$

$$I_{bias}/2 = (\Delta V/2)(I_{bias}/V_{ov})\sqrt{[1 - ((\Delta V/2)/V_{ov})^2]}$$

$$1 = \frac{\Delta V}{V_{ov}} \cdot \sqrt{1 - (\frac{\Delta V}{4V_{ov}})^2}$$

$$= (\frac{\Delta V}{V_{ov}})^2 - \frac{1}{4} \cdot (\frac{\Delta V}{V_{ov}})^4$$

$$= \left(\frac{\Delta V}{V_{ov}}\right)^2 \left(1 - \frac{\Delta V^2}{4V_{ov}^2}\right)$$

$$\left(\frac{V_{ov}}{\Delta V}\right)^2 = \frac{4V_{ov}^2 - \Delta V^2}{4V_{ov}^2}$$

$$4V_{ov}^4 = 4V_{ov}^2 \cdot \Delta V^2 - \Delta V^4$$

$$\left(2V_{ov}^2 - \Delta V^2\right)^2 = 0$$

$$\Delta V = \pm \sqrt{2}V_{ov} \qquad (2.12)$$

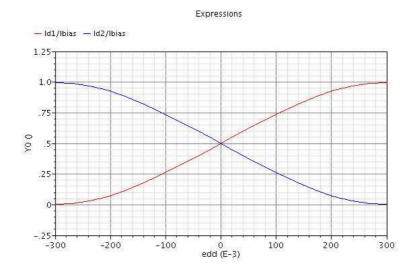

It means for  $\Delta V = +\sqrt{2}V_{ov}$  swing either one of the transistor will turn on pushing other one to be off and at  $\Delta V = -\sqrt{2}V_{ov}$  it will be reversed, as indicated in Figure 2.4.

Figure 2.4: Normalized current for CML inverter

At the biasing point shown earlier,  $V_{ov} = 263.9$ mV, therefore our minimum logic swing from the biasing point will be  $\Delta V/2 = \sqrt{2} \cdot 263.9$ mV =  $\pm 373.21$ mV. In Figure 2.4 it is shown, at  $\pm 300$ mV swing from the biasing point, T1 passes all the bias current and at -300mV from the biasing point, T2 completely turns on resulting in a total logic swing  $\Delta V = 600$ mV. 73mV discrepancy occurs because it is a short channel device and  $\alpha$  is not 2, but rather close to 1.25. Equation 2.12 can further be extended by plugging  $V_{ov}$  in terms of bias current and W.

$$\Delta V = \pm \sqrt{2} V_{ov}$$

$$\Delta V = \pm \sqrt{2} \sqrt{\frac{I_{bias}}{K}}$$

$$\Delta V = \pm \sqrt{\frac{2I_{bias}}{\mu C_{ox} \frac{W}{L}}}$$

(2.13)

It means the more W/L ratio we have, the faster we can move in switching region. But making W larger will increase parasitic capacitance at higher operating frequency and the RC constant will be dominating.

In order to achieve faster full swing,  $\Delta V = I_{bias} * R_L$ , we can increase bias current to reduce  $R_L$ . Bias current was tuned to 1.65mA for W=7 $\mu$ m and L=120nm, which is 70% of peak  $f_t$  current, and load resistance  $R_L$  was tuned to 348 $\Omega$ .

Input gate capacitance of each CML basic component is,  $C_{gg} = 8$ fF. It is stated that wire capacitance is 0.10ps/ $\mu$ m [22]. Assuming  $100\mu$ m is required to connect next stage then 10ps delay should be added and typically 1fF is necessary to mimic 1ps delay. Therefore 10+8 = 18fF was added as output load capacitance ( $C_L$ ).

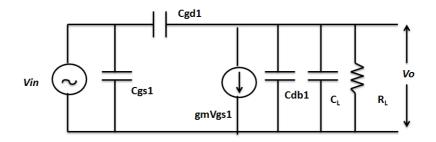

Propagation delay,  $P_d = 0.69$  RC, where C is the capacitance looking in to Drain of T1/T2.

$$P_{d} = 0.69R_{L}(C_{intr} + C_{L})$$

$$P_{d} = 0.69R_{L}(C_{gd1} + C_{db1} + C_{L})$$

$$= 0.69 \frac{\Delta V}{I_{bias}} (C_{gd1} + C_{db1} + C_L)$$

(2.14)

Figure 2.5: CML inverter half-circuit small-signal model

Where  $C_{intr}$  is intrinsic capacitance which equals the gate to drain  $(C_{gd1})$  plus drain to bulk  $(C_{db1})$  capacitance as shown in Figure 2.5. Equation 2.14 means, the higher the bias current, the lower the propagation delay. But, bias can be increased by increasing W, and at higher frequency further increasing bias current will not reduce propagation delay and parasitic capacitance will dominate. Hence, optimized width obtained for the upper level transistors are  $7\mu$ m and  $4\mu$ m width for the current source, all having channel length = 120nm with bias current,  $I_{bias}=1.65$ mA.

All these intuitive design considerations were included in designing CML logic circuits that can achieve maximum operating frequency of 12GHz with 0.12 $\mu$ m feature size. Supply voltage used was  $V_{dd}=2.8$ V, logic-1 = 2.8V, logic-0 = 2.2V, constant biasing voltage,  $V_g =$ 1V to bias the current source and logic swing  $\Delta V = 600$ mV.

Figure 2.6 shows post vs. pre layout simulation of a CML inverter operating at 12GHz (input changes at 83ps) with 18fF input/output load capacitance. Rising delay of inverter in circuit level simulation is 17.47ps and extracted layout delay is 24.79ps. The power consumption of the CML inverter is  $P = V_{dd}*I_{bias} = 2.8V * 1.65mA = 4.62mW$ , which is constant. Operating this optimized CML inverter at 1MHz and 12GHz will dissipate the same amount of power. Therefore power consumption is independent of operating frequency. Figure 2.6 also shows layout simulation varies with circuit level simulation by an amount of

Figure 2.6: Post vs. pre layout simulation of CML inverter with 18fF input/output load capacitance (input changes at 83ps)

7.32ps. Layout of the CML inverter was also performed and the reported area is  $15.960 \mu m$  x  $24.450 \mu m$ , as indicated in Figure 2.7.

Figure 2.7: CML inverter layout

### 2.2 CML Universal Gate

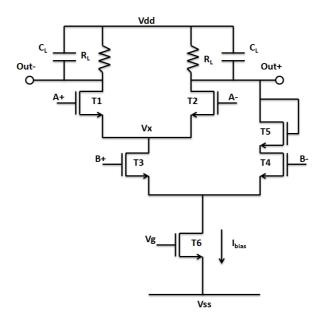

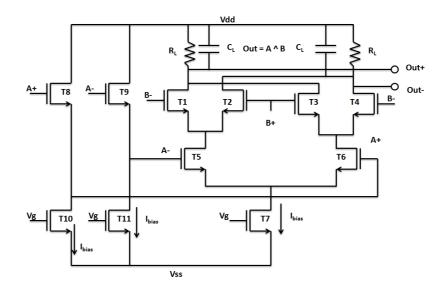

A universal CML gate is represented in Figure 2.8 that can realize AND, NAND, OR and NOR functions. According to input logic combination as indicated in Figure 2.8, the universal gate can realize an AND function. Reversing the output will realize a NAND function. Reversing all the inputs and outputs will realize an OR function and thus a NOR can be realized as well.

Figure 2.8: Universal CML gate

Careful consideration was made to choose  $V_{in}=2.5$ V and  $\Delta$ V=600mV, leading Logic-1=2.8V and Logic-0=2.5V as shown earlier in CML inverter section. The biasing conditions are same as before. If we assume Logic-1 has applied in A+ and Logic-0 has been applied in A- then,

$$V_{gs1} > V_{th1}; V_{gd1} < V_{th1}; V_{ds1} > V_{gs1} - V_{th1}$$

$V_{gs2} < V_{th2}; V_{gd2} < V_{th2}$

For input B, levels have to be at least  $V_{DS}$  amount down such that the condition  $V_{GD3}$  $< V_{th}$  and  $V_{GD4} < V_{th}$  is met when T3 and T4 operate (are in the forward active region). Therefore logic-1 for input B is  $V_{in} + \Delta V - V_{DS}$  and Logic-0 is  $V_{in} - \Delta V - V_{DS}$ .

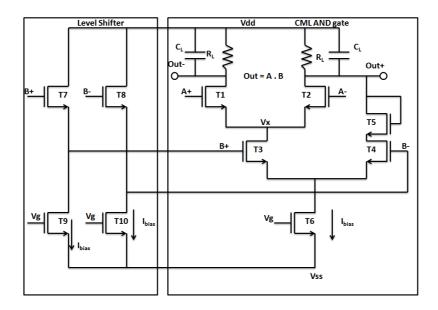

Due to the discrepancy of logic levels for the second input, a level shifter is necessary and has been embedded with in each gate as indicated in Figure 2.9. The previous power

Figure 2.9: Universal CML gate with embedded level shifter

of the CML gate was  $V_{dd}*I_{bias}$  and now with the level shifter it is  $V_{dd}*3I_{bias}$ ; total power increased by a factor of 3.

T7 and T8 have to be the same size as T1 and T2 for matching purposes, such that T7/T8 can mimic the voltage drop  $V_{DS}$  by T1/T2. To balance the differential architecture, T5 is necessary with T4; because T3 sees either T1 or T2 as a load and is also used for preventing breakdown. T6, T9 and T10 are of same size and constant biasing voltage (Vg) is applied to act as a current source.

There are three paths in the universal CML gate and it is necessary to make sure total bias current ( $I_{bias}$ ) flows in any of these path from  $V_{dd}$  to  $V_{ss}$  depending on logic combination from. Splitting of  $I_{bias}$  is not acceptable because full swing realization will not be possible.

Table 2.2 shows the path that will be turned on, depending on input logic combination and realization of the CML AND function. It is notable that the entry at B+/B- is unshifted logic. It is applied to input B at the level shifter and eventually it gets shifted down by an amount  $V_{DS}$  and propagates to input B of CML AND. It is indicated in Table 2.2 that lowest level (2<sup>nd</sup> level, input B) dominates in path selection.

| A+                    | A-                    | B+                    | B-                    | Out+                  | Out-                  | T off   | T on      | Path       |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------|-----------|------------|

| $V_{dd}$ - $\Delta V$ | $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | 1, 2, 3 | 5, 4, 6   | T5, T4, T6 |

| $V_{dd}$ - $\Delta V$ | $V_{dd}$              | $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | 1, 4, 5 | 2, 3, 6   | T2, T3, T6 |

| $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | 1, 2, 3 | 5, 4, 6   | T5, T4, T6 |

| $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | $V_{dd}$ - $\Delta V$ | $V_{dd}$              | $V_{dd}$ - $\Delta V$ | 2, 4, 5 | 1,  3,  6 | T1, T3, T6 |

#### Table 2.2: CML AND Operation

#### 2.2.1 Universal CML Gate Optimization

When a path turns on, it is necessary to steer all the bias current  $(I_{bias})$  to that path, as stated before, to realize full logic swing,  $\Delta V = R_L * I_{bias}$ . The more bias current we have, the faster the swing realized. Intuitive techniques to optimize the CML gate have been shown in the CML inverter optimization subsection. It was found, using 130nm CMOS technology, the highest operating frequency we can obtain for CML inverter is 12GHz with upper transistor W=7 $\mu$ m, L=120nm for bias current of 1.65mA for which current source size is W=4 $\mu$ m, L=120nm. As we cannot exceed this operating frequency for particular logic swing  $\Delta V$ =600mV, supply voltage  $V_{dd}$ =2.8V, logic-1=2.8V, logic-0=2.2V parameters, the same size has been used in CML universal gate for upper transistors. But in this case, it has second level of input and here it contributes more parasitic capacitance, bias current has been increased very little from 1.65mA to 1.753mA (for which current source size is W=7 $\mu$ m, L=120nm) to operate at 12GHz.

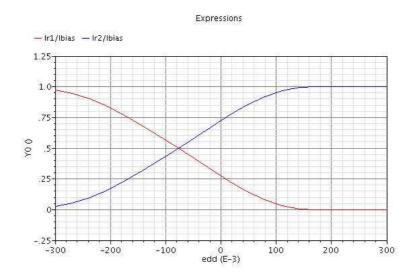

For upper level (and  $2^{nd}$  level) transistors, around  $V_{ov}=200$ mV has been provided such that a 300mV swing from the biasing point can turn off and on the transistors. It should be noted, at quiescent point  $I_{r1} \neq I_{r2}$ , as indicated in Figure 2.10. The reason is, Out+ has 2 paths at Q point but Out- has 1 path to  $V_{ss}$ . Therefore, typically  $I_{r1} = \frac{1}{3}I_{r2}$ , as it is observed in Figure 2.10. It is shown that  $I_{r1} = 517.5\mu$ A and  $I_{r2} = 1.238$ mA out of total bias current 1.753mA. Therefore, initially, Out+ tends to be close to logic-0 (2.2V), which is 2.371V and Out- tends to be close to logic-1 (2.8V), which 2.62V at Q point. As it can be seen in normalized current plot of universal CML gate in Figure 2.10 that  $I_{d1} \neq I_{d2}$  at

Figure 2.10: Normalized current for CML universal gate

biasing point. But full current steering was made possible at -300 mV to +300 mV swing, which is our objective.

Figure 2.11: Post vs. pre layout simulation of CML AND with 18fF input/output load capacitance (input changes at 83ps)

Figure 2.11 shows post vs. pre layout simulation of the CML AND gate at 12GHz (input changes at 83ps). Load capacitance,  $(C_L) = 18$ fF was added to mimic next stage input capacitance,  $C_{gg} = 8$ fF plus 10fF to mimic 100 $\mu$ m wire for connecting next stage similar to the CML inverter [22]. The circuit level simulation shows rising delay is 35.6ps whereas

extracted layout simulation has rising delay of 37.6ps. Bias current  $I_{bias}=1.759$ mA and 2 other current source supply 2.019mA each, for a total power consumption of 2.8V \* (1.753 + 2.019 + 2.019)mA = 16.2148mW.

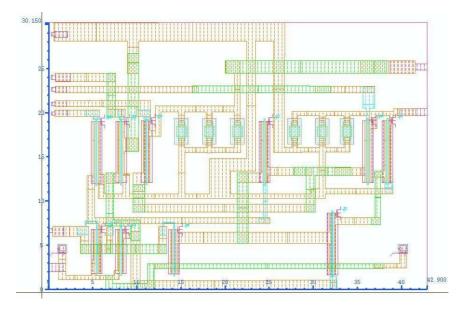

Figure 2.12: CML AND layout

The reported area of CML AND gate is  $30.150\mu m \ge 42.900\mu m$ , as indicated in Figure 2.12 and this area should be the same for CML NAND/OR/NOR. Layouts of all these gates have been performed and have been simulated but not included because their architectures are not different from CML AND, just the reverse of inputs or outputs.

#### 2.3 CML XOR/XNOR Gate

A CML XOR gate is shown in Figure 2.13 with an embedded level shifter. Table 2.3 briefly describes CML XOR operation and paths.

Logic-1 represented by  $V_{in}+\Delta V/2 = 2.8V$  and logic-0 is  $V_{in}-\Delta V/2 = 2.2V$ , where  $V_{in} = 2.5V$  is the biasing (quiescent) voltage and  $\Delta V=600$ mV is the logic swing. Bias current  $I_{bias}=1.757$ mA and two other current sources supply 2.019mA each, having total power consumption of 2.8V \* (1.757+2.019+2.019)mA = 16.226mW. Power consumption of the

Figure 2.13: CML XOR gate

CML XOR is even less than the CML AND gate, which is impractical in CMOS realization but possible in CML architecture.

| A+ | A- | B+ | B- | Out+ | Out- | T on    | T off      |

|----|----|----|----|------|------|---------|------------|

| 0  | 1  | 0  | 1  | 0    | 1    | 7, 5, 1 | 2, 3, 4, 6 |

| 0  | 1  | 1  | 0  | 1    | 0    | 7, 5, 2 | 1, 3, 4, 6 |

| 1  | 0  | 0  | 1  | 1    | 0    | 7, 6, 4 | 1, 2, 3, 4 |

| 1  | 0  | 1  | 0  | 0    | 1    | 7, 6, 3 | 1, 2, 4, 5 |

Table 2.3: CML XOR Operation

For the 00 combination, T1, T5 and T7 will turn on and  $I_{bias}$  will flow down to Vss, resulting in all other paths being turned off. For the 01 combination, either T2 or T3 will turn on; depending on A. As A+ is 0 and A- is 1, T5 will be on and T6 will be off, and the path will be T2, T5 and T7.

As the lowest level dominates the path, for the 10 combination T6 will be on, and as B+ is 0 and B-=1, T4 will turn on and the path will be T4, T6 and T7. For 11 combinations, T3, T6 and T7 will be turned on.

Figure 2.14 shows post vs. pre layout simulation of CML XOR gate with 18fF input/output load capacitance at 12GHz (input changes at 83ps). It is observed that circuit

Figure 2.14: Post vs. pre layout simulation of CML XOR with 18fF input/output load capacitance (input changes at 83ps)

level rise delay is 33.7ps whereas extracted layout delay is 41.5ps. Therefore, 7.8ps discrepancy exists in between circuit level and device level simulation.

Figure 2.15: CML XOR layout

Reported area of CML XOR is  $28.590\mu m \ge 45.630\mu m$  as indicated in Figure 2.15.

#### 2.4 CML Mux Realization

A CML mux has been realized at the transistor level as indicated in Figure 2.16. The architecture is very similar to the XOR and the power dissipation is less than the CML AND/XOR gate. Realizing a CML mux with transistors reduces power at least  $\frac{1}{3}$  over realizing the mux by cascading CML AND gates. Realizing mux with transistor has two fold benefits; one is less power and the other one is delay reduced by  $\frac{1}{2}$ . Table 2.4 describes CML mux operation.

Figure 2.16: CML Mux realization

| B+(V) | A+(V) | S+(V) | Out+(V) | T on | T off      |

|-------|-------|-------|---------|------|------------|

| 2.2   | 2.2   | 2.2   | 2.2     | 5, 2 | 6, 1, 3, 4 |

| 2.2   | 2.8   | 2.2   | 2.8     | 5, 1 | 6, 2, 3, 4 |

| 2.8   | 2.2   | 2.2   | 2.2     | 5, 2 | 6, 1, 3, 4 |

| 2.8   | 2.8   | 2.2   | 2.8     | 5, 1 | 6, 2, 3, 4 |

| 2.2   | 2.2   | 2.8   | 2.2     | 6, 4 | 5, 1, 2, 3 |

| 2.2   | 2.8   | 2.8   | 2.2     | 6, 4 | 5, 2, 2, 3 |

| 2.8   | 2.2   | 2.8   | 2.8     | 6, 5 | 4, 1, 2, 3 |

| 2.8   | 2.8   | 2.8   | 2.8     | 6, 5 | 4, 2, 2, 3 |

Table 2.4: CML Mux Operation

Figure 2.17 shows post vs. pre layout simulation of CML mux with 18fF input/output load capacitance at 12GHz (input changes at 83ps). It is observed that circuit level rise delay is 28.01ps whereas extracted layout delay is 33.99ps. Therefore, 5.98ps discrepancy exists in between circuit level and device level simulation.

Figure 2.17: Post vs. pre layout simulation of CML Mux with 18fF input/output load capacitance (input changes at 83ps)

Figure 2.18: CML Mux layout

The reported area for the CML Mux is  $36.510\mu$ m x  $47.520\mu$ m, as indicated in Figure 2.18. Total power consumption of the CML Mux is 2.8V \* (2.019 + 2.019 + 1.757)mA = 16.226mW.

### 2.5 CML D-latch Realization

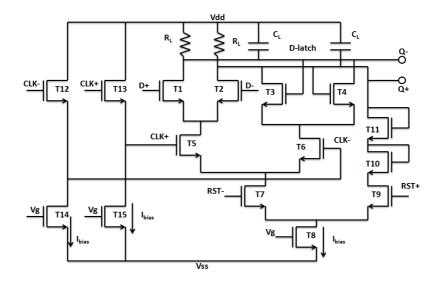

A CML D-latch has been realized in transistors, as indicated in Figure 2.20, with four levels of hierarchy with a reset input, not by cascading CML AND gates, in contrast to CMOS architecture. This architecture not only reduces power consumption but also reduces

Figure 2.19: CML D-latch

delay. Very surprisingly power consumption is less than the CML AND gate, which cannot be realized in CMOS architecture. It is notable that, the lowest level dominates in selecting upper level paths. RST+=1.3V (RST-=0.7V) turns on T9 (T7 off) and ties Q+ to Vss, irrespective of any input combination.

| CLK+(V) | D+(V) | RST+(V) | $Q_{t+1} + (\mathbf{V})$ | T on             | T off                       |

|---------|-------|---------|--------------------------|------------------|-----------------------------|

| 2.2     | 2.2   | 2.2     | $Q_t +$                  | 8, 7, 6, (3 / 4) | 9, 5, (4 / 3), 1, 2, 10, 11 |

| 2.2     | 2.8   | 2.2     | $Q_t +$                  | 8, 7, 6, (3 / 4) | 9, 5, (4 / 3), 1, 2, 10, 11 |

| 2.8     | 2.2   | 2.2     | 2.2                      | 8, 7, 5, 2       | 9,6,1,3,4,10,11             |

| 2.8     | 2.8   | 2.2     | 2.8                      | 8, 7, 5, 1       | 9, 6, 2, 3, 4, 10, 11       |

| X       | Х     | 2.8     | 2.2                      | 8, 9, 10, 11     | 1, 2, 3, 4, 5, 6, 7, 8      |

Table 2.5: CML D-latch Operation

Table 2.5 briefly describes the operation of the CML D-latch. Initially Q+ tends to be logic-0 (the reason explained for the CML AND gate). If the clock is high, then whichever

data comes at D+ is passes to the output Q+. Also, the present state pushes lower level transistors to retain their logic states when clock is not high. Therefore at beginning, reset is not necessary in CML architecture.

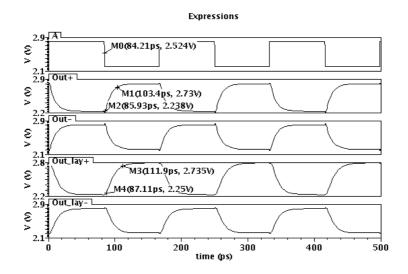

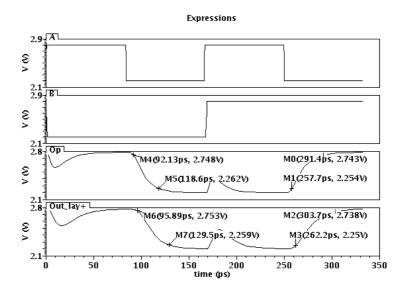

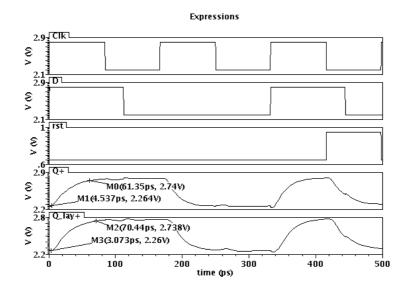

Figure 2.20: Post vs. pre layout simulation of CML D-latch with 18fF input/output load capacitance at 6GHz (166ps)

Figure 2.20 shows post vs. pre layout simulation of CML D-latch with 18fF input/output load capacitance at 6GHz. It is observed that circuit level rise delay is 56.813ps whereas extracted layout delay is 67.367ps. Therefore, 10.554ps discrepancy exists in between circuit level and device level simulation.

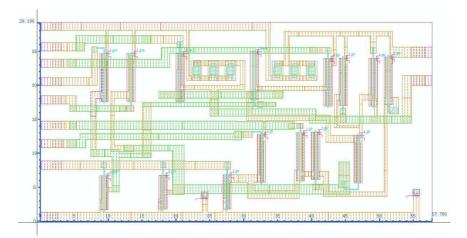

Figure 2.21: CML D-latch layout

Power consumption of the CML D-latch is 2.8V \* (2.019 + 2.019 + 1.431)mA = 15.3132mW. Reported area for CML D-latch is 29.190 $\mu$ m x 57.780 $\mu$ m, as indicated in Figure 2.21.

# 2.6 Speed, Power, Area and Delay of Basic CML Components

Table 2.6 summarizes post simulation power, area and delay with 18fF load (10fF for wire 8fF for next stage  $C_{gg}$ ) capacitance of each CML basic components. In later chapters, higher level circuit realization has been performed using these basic components to develop a CML processor datapath. Therefore, in measuring theoretical worst case delay it has assumed that delay is additive, meaning if the output of a CML AND gate drives the input of a CML Mux, the total delay is the sum of the two. Total delay of any complex component in simulation is found to match the number of basic components in the critical path and assigning delay to each of them.

| Component      | Power (mW) | Area ( $\mu m x \mu m$ ) | Delay (ps) |

|----------------|------------|--------------------------|------------|

| Inverter       | 4.62       | 15.96x24.45              | 24.79      |

| AND/NAND       | 16.2148    | 30.15x42.90              | 37.6       |

| OR/NOR         | 16.2148    | 30.15x42.90              | 46.09      |

| XOR/XNOR       | 16.226     | 28.59x45.63              | 41.5       |

| CML 2-to-1 Mux | 16.226     | 36.51x47.52              | 33.99      |

| CML D-latch    | 15.3132    | 29.19x57.78              | 67.367     |

Table 2.6: Power, Area and Delay of Basic Components (post layout simulation with 18fF load capacitance)

Layout of the processor datapath has not been performed but the circuit level simulation. It is observed that post vs. pre layout simulation differs maximum 10ps and wire delay is 10ps (for 100 $\mu$ m wire connecting next stage and assuming wire delay is 0.10ps/ $\mu$ m) [22]. Therefore 20fF load capacitance was added inside every CML logic in datapath simulation to mimic post layout + wire delay (in intermediate stages  $C_{gg} = 8$ fF has already been considered by simulation tool). Area was predicted by counting the number of gates \* area of each gate + 50% area for wiring.

# Chapter 3

# Datapath

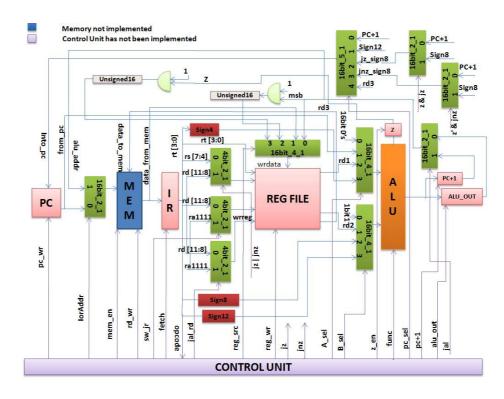

A multi-cycle 16-bit processor datapath has been designed using a RISC architecture that can execute 15 different operations and a 4-bit opcode has been used. Three different types of instructions can be performed and instruction set architecture is given in Table 3.1.

| Address bus (16-bit) |      |     |                   |  |  |  |  |  |  |  |  |

|----------------------|------|-----|-------------------|--|--|--|--|--|--|--|--|

| 15-12                | 11-8 | 7-4 | 3-0               |  |  |  |  |  |  |  |  |

| Opcode R-type        | Rd   | Rs  | Rt                |  |  |  |  |  |  |  |  |

| Opcode I-type        | Rd   | Rs  | Immediate operand |  |  |  |  |  |  |  |  |

| Opcode J-type        |      |     | Address           |  |  |  |  |  |  |  |  |

| Table $3.1$ : | Instruction | Set | Architecture |  |

|---------------|-------------|-----|--------------|--|

|               |             |     |              |  |

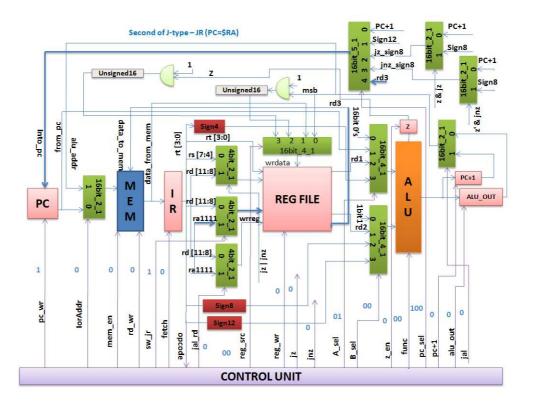

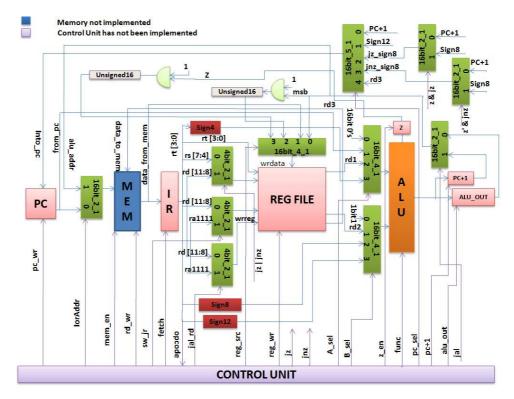

Figure 3.1: Processor datapath

The processor datapath is shown in Figure 3.1, where all the components have been realized in CML logic except the cache memory and control unit. Correct operation of the datapath has been verified by providing external control stimulus in every clock cycle and observing/providing data to/from memory. Fifteen different operations that can be performed are listed in Table 3.2. The Processor datapath does not contain any novel approach. However this datapath can be re-structured such that power consumption will be less and operating frequency can be increased.

| Type   | Opcode                                                                                                                                                                         | Description                                          | Cycle |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------|

|        | 0000 ADD                                                                                                                                                                       | Rd=Rs+Rt                                             | 4     |

|        | 0001 SUB                                                                                                                                                                       | Rd=Rs-Rt                                             | 4     |

|        | 0010 AND                                                                                                                                                                       | Rd=Rs●Rt                                             | 4     |

| R-type | 0011 XOR                                                                                                                                                                       | $Rd=Rs\oplus Rt$                                     | 4     |

|        | 0100 SLT                                                                                                                                                                       | Rd=1 if Rs <rt else="" rd="0&lt;/td"><td>4</td></rt> | 4     |

|        | $0101  \mathrm{SEQ}$                                                                                                                                                           | Rd=1 if $Rs=Rt$ else $Rd=0$                          | 4     |

|        | 0110 LW                                                                                                                                                                        | Rd=[Rs]+n; n=4bit                                    | 5     |

|        | 0111 SW                                                                                                                                                                        | [Rs+n]=Rd; n=4bit                                    | 4     |

| I-type | 1000 ADDI                                                                                                                                                                      | Rd=Rs+n; n=4bit                                      | 4     |

|        | 1001 MOVI                                                                                                                                                                      | Rd=n; n=8bit                                         | 4     |

|        | 1010 J LABEL                                                                                                                                                                   | PC = LABEL; n=12bit                                  | 2     |

|        | 1011 JZ                                                                                                                                                                        | PC=LABEL if $Rd=0; n=8bit$                           | 4     |

| J-type | $0000 \text{ ADD}$ $Rd=Rs+Rt$ $0001 \text{ SUB}$ $Rd=Rs-Rt$ $0010 \text{ AND}$ $Rd=Rs\bullet Rt$ $0011 \text{ XOR}$ $Rd=Rs\bullet Rt$ $0010 \text{ SLT}$ $Rd=1 \text{ if } Rs$ | 4                                                    |       |

|        | 1101 JAL                                                                                                                                                                       | \$RA=PC+1 &PC=LABEL; n=12bit                         | 3     |

|        | 1110 JR                                                                                                                                                                        | PC=RA; least 12-bit unused                           | 2     |

Table 3.2: Opcode and 15 Different Operations

The datapath contains 16-bit program counter register, 16-bit instruction register, 16x16 register file, 16-bit ALU, 16-bit pc+1 register and 16-bit ALU\_out register. PC, IR, ALU\_out, PC+1 are 16-bit registers with enable input that controls the write operation. The 16-bit ALU contains 16-bit CLA, BLA, AND and XOR. In the 16x16 register file, 4-bit rr1, rr2 and rr3 can address any of 16 register (16-bit each) and propagates the content of addressed register in 16-bit rd1, rd2 and rd3 through 3 16-bit 16-to-1 mux. 4-bit wrreg is used for addressing the write register and 1-bit reg\_wr is used to enable the write operation. It is assumed, for mem\_en=1 and rd\_wr=0, that memory can be read and for mem\_en=1 and

rd\_wr=1 memory can perform write operation. It takes 2-5 cycles to perform any of the 15 instructions as listed in Table 3.2 with brief description.

In Table 3.2 RA is register-15 implemented in hardware. Also, register-0, which contains 0 is implemented in hardware as well. The critical path delay is 5 clock cycles for the LW instruction and the path is  $PC \Rightarrow IR \Rightarrow Reg_file \Rightarrow ALU_out \Rightarrow MEM \Rightarrow Reg_file.$

# 3.1 First Clock Cycle of Every Instruction

The first clock cycle is same for any instruction and the selected path is shown in Figure 3.2, with control logic. As indicated in Figure 3.2, in the first cycle men\_en = 1 and fetch = 1 and data comes into IR register, assuming that memory is fast enough to be read in one clock cycle. Also, at the same time,  $A\_sel = 01$ ,  $B\_sel=00$  selects the content of PC and 1-bit value 1 (from first input of 16bit\_4\_to\_1 mux) and the ALU performs PC+1.

Figure 3.2: First clock cycle of any instruction

#### 3.2 R-type Instruction

Six different type of instruction can be performed in R-type operation. They are ADD, SUB, AND, XOR, SLT and SEQ. ADD, SUB, AND, XOR instructions perform addition, subtraction, binary bitwise AND and binary bitwise XOR respectively. SLT stores  $R_d = 1$ if  $R_s < R_t$ , else  $R_d = 0$  (performs  $R_s - R_t$  and checks MSB). SEQ stores  $R_d = 1$  if  $R_s = R_t$ , else  $R_d = 0$  (performs  $R_s - R_t$  and checks Z flag). It takes four cycles to perform any R-type instruction.

# 3.2.1 R-type ADD/SUB/AND/XOR

In the second cycle of R-type ADD/SUB/AND/XOR instructions,  $A\_sel = 10$ ,  $B\_sel = 01$  selects rd1 and rd2 and pc+1 = 1 signal enables PC+1 to be saved in the PC+1 register. Control signal func = 00, 01, 10 and 11 at second cycle performs ADD, SUB, AND and

Figure 3.3: R-type ADD/SUB/AND/XOR

XOR respectively. The third clock cycle saves the ALU result in the ALU\_OUT register and

control signal is alu\_out = 1. Control signal jal = 1 passes the content of the ALU\_OUT register through 16-bit 2-to-1 mux. At the fourth clock cycle reg\_wr = 1 enables the register file to be written which was addressed by  $R_d[11:8] = \text{wrreg}[3:0]$  for control signal jal\_rd = 0. At the same cycle pc\_wr =1 enables PC register to be updated at the end of fourth clock cycle that can be used for next instruction. Second cycle to fourth cycle of R-type ADD/SUB/AND/XOR is shown in Figure 3.3 with control logic.

# 3.2.2 R-type SLT

At the second cycle PC+1 (computed in first cycle) gets updated in the PC+1 register and  $A\_sel = 10$ ,  $B\_sel = 01$  selects rd1 and rd2 as operands to the ALU, as indicated in Figure 3.4. Function of the ALU is func = 01, meaning it performs subtraction at the second cycle.

Figure 3.4: R-type SLT

At third clock cycle the result is stored in ALU\_OUT register, holding control signal alu\_out = 1. Control signal jal = 1 passes the content of the ALU\_OUT register through the mux

and the MSB gets ANDed with 1. If  $R_s < R_t$  then MSB = 1 and the AND result is 1 else MSB = 0. This result geta unsigned extension to 16-bit data. At fourth clock cycle, reg\_wr = 1 enables the addressed register to be written by the data and PC is upadated as well as indicated in Figure 3.4.

# 3.2.3 R-type SEQ

At the second cycle PC+1 gets updated in the PC+1 register and rd1 and rd2 gets selected as operands to the ALU and the ALU performs the subtraction. At the third cycle

Figure 3.5: R-type SEQ

the ALU result gets updated in ALU\_OUT and also control signal z = 1 enables the Z register to be updated. 1-bit zero flag register (Z) is used to hold the value, either 0 or 1 to indicate that the resultant bits are all zero or not, respectively. The content of the Z register (Z = 1 means rd1 = rd2 else rd1  $\neq$  rd2) is ANDed with 1-bit 1 at the third cycle. This result gets unsigned extension to 16-bit data and fed to fourth input of 16-bit 4-to-1 mux. At the fourth clock cycle reg\_src = 11 selects that 4<sup>th</sup> input to that mux and reg\_wr = 1 enables the write operation to the register file addressed by  $R_d[11:8] = \text{wrreg}[3:0]$ , which is selected by control signal jal\_rd = 0, as shown in Figure 3.5.

### 3.3 I-type Instruction

Four different types of instruction can be performed as immediate type operations. LW computes the contents of the  $R_s$  register and added to the sign extended 16-bit immediate data. The computed address is used to point to a location in memory and the data at this address is loaded into register,  $R_d = [R_s] + n$ . Likewise, SW computes the address but stores the content of the register addressed by 4-bit  $R_d$  into memory location,  $[R_s+n] = R_d$ . ADDI adds the content of register  $R_s$  to 4-bit immediate operand n (sign extended) and stores it to register  $R_d$ ,  $R_d = R_s+n$ . MOVI converts 8-bit immediate operand to sign extended 16-bit data and moves it into register  $R_d$ ,  $R_d = n$ .

# 3.3.1 I-type LW

Figure 3.6: I-type LW

LW takes 5 clock cycles to complete and the second to fifth clock cycle is shown in Figure 3.6. At the second cycle, A\_sel = 11 and B\_sel = 01, selects sign extended rt[3:0] bits and content of register rs[3:0] through rd2. It also performs addition in second cycle. At the third clock cycle the result is stored in ALU\_OUT register and at the fourth clock cycle the computed address (result) points to an address location in memory and memory is being when control signal IorAddr = 1 and mem\_en = 1. Data from memory is written into register file at the fifth clock cycle and PC is updated while reg\_wr = 1 and pc\_wr = 1. The destination register is addressed by rd[11:8] and mux selection signal jal\_rd = 0.

#### 3.3.2 I-type SW

At the second cycle control signal A\_sel = 11 and B\_sel = 01 selects sign extended least significant 4-bits and the content of  $R_s$  register as operands to the ALU and performs addition. The computed address (result) is then updated in ALU\_OUT in the third clock

Figure 3.7: I-type SW

cycle, as indicated in Figure 3.7. At the fourth clock cycle, content of register file output  $rd3 = data_to_mem$  is written to the memory (MEM) addressed by computed result  $(R_s+n)$  when IorAddr = 1, mem\_en = 1 and rd\_wr = 1 and PC gets updated.

# 3.3.3 I-type ADDI

Figure 3.8: I-type ADDI

The second and third clock cycles for ADDI are the same as LW/SW, but this time the sum is considered as a result rather than an address and gets updated in ALU\_OUT in the third clock cycle. The result is then saved to register  $R_d$  by selecting the path through reg\_src = 00 and reg\_wr =1 at the fourth clock cycle as indicated in Figure 3.8.

### 3.3.4 I-type MOVI

The MOVI operation moves least 8-bit data into register- $R_d$  with sign extension as indicated in Figure 3.9. At the second clock cycle control signal A\_sel = 00, B\_sel = 10

Figure 3.9: I-type MOVI

selects 16-bit 0 (from first input of 4-to-1 mux) and sign-extended 8-bit data as operands to ALU and performs addition, meaning 8-bit data is added with 0 and PC+1 is updated in the PC+1 register. At the third clock cycle the ALU result is saved into ALU\_OUT register and control signal alu\_out = 1. At the fourth clock cycle data is written into register file addressed by  $R_d[11:8] = \text{wrreg}[3:0]$  and reg\_wr =1 and PC is updated.

### 3.4 J-type Instruction

J-type can perform five different types of jump instruction based on opcode. J LABEL performs jump unconditionally and does not save the program counter value. It takes 12-bit as an immediate operand and can jump in [-2048 - +2047] bit memory location. JZ and JNZ perform jump based on the contents of  $R_d$ . If  $R_d = 0$  then JZ performs jump and if  $R_d = 1$  then JNZ performs jump. If the condition is not satisfied then the program counter increments by one. Both JZ and JNZ take n = 8-bits as an immediate operand and can jump in [-128 - +127] bit memory location. JAL instruction performs the jump operation unconditionally but it saves (jump and link) the incremented program counter into RA =1111 register in the register file. RA is the fifteenth register in the register file that was implemented in hardware. The JR instruction returns from any location by loading the program counter from RA that was saved earlier by some other instruction and can jump (return) in between [-32768 - +32767] bit memory location.

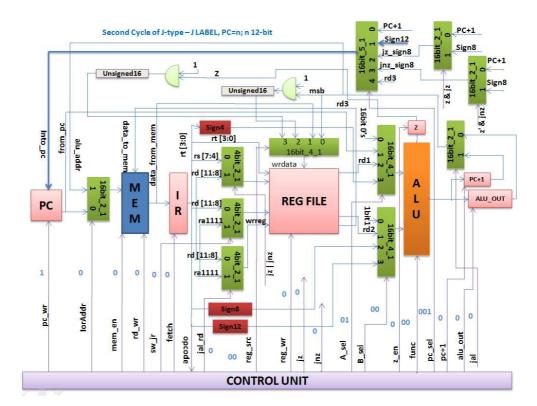

# 3.4.1 J-type J LABEL

As indicated in Figure 3.10, J LABEL can be executed in two clock cycles. The first

Figure 3.10: J-type J LABEL

cycle is the same as any instruction. At the second clock cycle, sign-extended 12-bit gets selected through 16-bit 5-to-1 mux by control signal  $pc\_sel = 001$ . Also, at the second clock cycle control signal  $pc\_wr = 1$  lets PC register be updated.

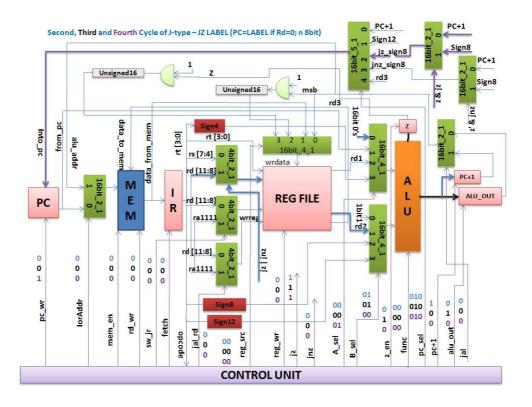

#### 3.4.2 J-type JZ LABEL

JZ LABEL can be executed in four clock cycles as indicated in Figure 3.11. At the second clock cycle computed PC+1 gets updated in the PC+1 register and control signal jz = 1 is activated and remains high until the fourth clock cycle. Also in the second clock

Figure 3.11: J-type JZ LABEL

cycle A\_sel = 00 and B\_sel = 01 selects 16-bit 0 (first input of 16-bit 4-to-1 mux) and the content of  $R_d$  register through rd2. Input to register file rr2 (which is  $R_d$ [11:8]) was selected through mux signal bit jz | jnz. The ALU performs addition and if the result is 0 then ALU output z will go high. At the third clock cycle z\_en =1 activates z register to be updated. At the fourth clock cycle z & jz = 1 (if z = 1) selects 16-bit 2-to-1 mux control bit to pass Sign8 in the datapath and pc\_sel = 010 lets it pass through 16-bit 5-to-1 mux and LABEL is updated in PC register.

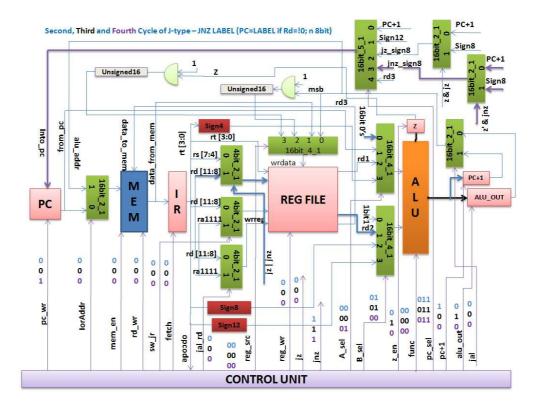

# 3.4.3 J-type JNZ LABEL

JNZ can perform jump operation to 8-bit LABEL if  $R_d \neq 0$ , as indicated in Figure 3.12. At the second cycle control signal jnz = 1 enables  $R_d$  to be connected as input rr2 of register

Figure 3.12: J-type JNZ LABEL

file through 4-bit 2-to-1 mux. Input rr2 of reg file generates content of this register at rr2 signal. A\_sel = 00, B\_sel = 01 selects 16-bit 0 and rr2 and func = 00 performs addition in this cycle. At the third cycle  $z_{en} = 1$  let z register to be updated. At fourth clock cycle, z & jnz determines whether PC+1 or Sign8 will be passed through 16-bit 2-to-1 mux and pc\_sel = 011 lets it pass. Also in this cycle pc\_wr =1 lets PC register be updated.

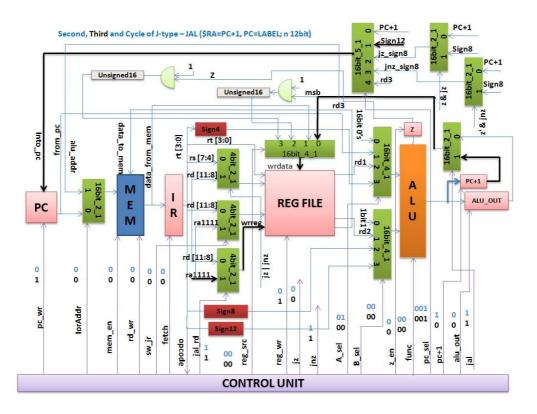

### 3.4.4 J-type JAL

JAL can be performed in three clock cycles as indicated in Figure 3.13. At the first cycle the instruction is fetched to IR register and PC is incremented by 1 as stated before. At the second clock cycle control signal jal\_rd =1 selects wrreg[3:0] =  $R_d$ [11:8], addressing

Figure 3.13: J-type JAL

which register needs to be written. Also at this cycle PC+1 register gets updated because of pc+1 = 1. At third clock cycle control signal jal = 1 selects PC+1 to pass through the 16-bit 2-to-1 mux and reg\_wr = 1 lets it be written to the addressed register. Also Sign12 (12-bit sign extended LABEL) gets selected in the 16-bit 5-to-1 mux as control signal pc\_sel = 001 and pc\_wr = 1 enables updating of PC register.

#### 3.4.5 J-type JR

JR can be executed in two clock cycles as indicated in Figure 3.14. At the second clock cycle, input to Ref file rr3[3:0] = ra[1111] gets selected as control signal sw\_jr = 1. The corresponding content of rr3 becomes available at the rd3 16-bit output and gets passed through the 16-bit 5-to-1 mux as control signal is pc\_sel = 100. At the same time result (return address coming through rd3) gets updated in PC register and control signal is pc\_wr = 1.

Figure 3.14: J-type JR

# 3.5 Control Signals

Control signals have been summarized for all fifteen instructions and listed in Table 3.3 and Table 3.4 for every clock cycle.

| С      | n      | I      | 100    |        | f   | G      | ;      |          |        | A                                      | В      | f      | 7      | n                                      | 0                                      | ;      | n                                     | J | J      |

|--------|--------|--------|--------|--------|-----|--------|--------|----------|--------|----------------------------------------|--------|--------|--------|----------------------------------------|----------------------------------------|--------|---------------------------------------|---|--------|

|        | р<br>с |        | m<br>e | r<br>d | e I | S      | j      | r<br>e   | r<br>e |                                        |        |        | Z      | p<br>c                                 | $\begin{vmatrix} a \\ 1 \end{vmatrix}$ | j<br>a | p<br>c                                |   |        |

| У      |        | 0<br>r | -      |        | t t | W      | a<br>1 |          |        | -                                      | -      | u      | -      |                                        |                                        |        |                                       | Z | n<br>z |

| c<br>l | -<br>W | r<br>A | m      | -<br>W | c   | -<br>j |        | g        | g      | s<br>e                                 | s<br>e | n<br>c | e<br>n | $\begin{vmatrix} + \\ 1 \end{vmatrix}$ | u                                      | 1      | -<br>S                                |   | Z      |

| e      | r      | d      | -<br>e | r      | h   | r<br>J | -<br>r | -<br>  S | -<br>W | $\begin{vmatrix} c \\ 1 \end{vmatrix}$ | 1      | C      | 11     | 1                                      | -<br>0                                 |        | e                                     |   |        |

| C      | 1      | d      | n      | 1      | 11  | 1      | d      | r        | r      |                                        | 1      |        |        |                                        | u u                                    |        | 1                                     |   |        |

|        |        | r      | 11     |        |     |        | u      | c        |        |                                        |        |        |        |                                        | t                                      |        | 1                                     |   |        |

| All    | 0      | 0      | 1      | 0      | 1   | 0      | 0      | 00       | 0      | 01                                     | 00     | 00     | 0      | 0                                      | 0                                      | 0      | 00                                    | 0 | 0      |

| 1      |        |        | 1      |        |     |        |        |          |        |                                        | 00     | 00     | Ŭ      |                                        |                                        |        | $\begin{vmatrix} 00\\0 \end{vmatrix}$ |   | 0      |