#### Low Noise, Low Power Capacitive-Coupling Quadrature Voltage-Controlled Oscillator for Phase-Locked Loops

by

Feng Zhao

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama December 8, 2012

Keywords: quadrature voltage-controlled oscillator (QVCO), phase-locked loop (PLL), phase noise, phase accuracy, bi-modal oscillation

Copyright 2012 by Feng Zhao

Approved by

Fa Foster Dai, Chair, Professor of Electrical and Computer Engineering Guofu Niu, Alumni Professor of Electrical and Computer Engineering Bogdan M. Wilamowski, Professor of Electrical and Computer Engineering Stanley J. Reeves, Professor of Electrical and Computer Engineering

#### Abstract

This dissertation presents the analytical results and design details of two quadrature voltage-controlled oscillators (QVCO). It uses capacitive quadrature-coupling technique to couple two voltage-controlled oscillator (VCO) cores. The proposed capacitive-coupling QVCO (CC-QVCO) architecture provides the advantage of low phase noise performance and elimination of the bi-modal oscillation. Different from conventional quadrature-coupling mechanism with active devices, CC-QVCO utilizes noiseless capacitors to form QVCO allowing shaped gate voltage and reduced thermal noise.

A differential Colpitts CC-QVCO with enhanced swing is proposed to offer excellent phase noise performance under a 0.6-V power supply. It achieves 4.5dB lower phase noise than its single-phase counterpart at 3-MHz offset. Optimized capacitive coupling combined with source inductive enhance-swing technique enables low power and low phase noise simultaneously. The QVCO achieves a measured phase noise of - 132.3dBc/Hz @ 3MHz offset with a center frequency of 5.6GHz and consumes 4.2mW from a 0.6-V supply. This performance corresponds to a Figure-of-Merit (FoM) of 191.5dB. Due to the inherent phase shift in the proposed quadrature-coupling path, the problem associated with  $\pm 90$  °phase ambiguity between the quadrature outputs has been avoided.

Capacitive-coupling technique is also applied to classic NMOS cross-coupled VCO

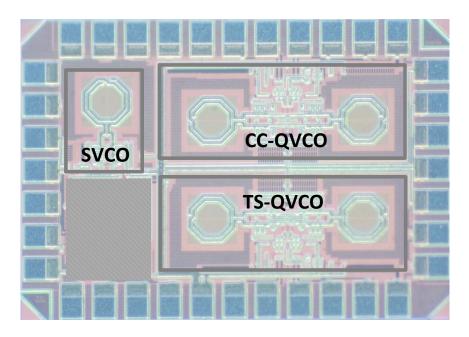

with current tail to demonstrate its advantages over other quadrature-coupling technique. The problem of phase ambiguity for this QVCO has also been successfully avoided by the inherent leading phase shifter. Silicon implementations and measurement results of this CC-QVCO and another class-C mode top-series QVCO (TS-QVCO) for comparison have been discussed. The CC-QVCO has been fabricated in a 0.13  $\mu$ m CMOS technology and occupies an area of 1.0 ×0.35 mm<sup>2</sup>. With 1.2-V supply voltage, it achieves 0.23-0.91 ° phase error in the frequency range of 4.3-5.27GHz. It demonstrates the effectiveness of the capacitive-coupling technique for wide frequency range quadrature signal generation and low phase noise performance.

$\Sigma\Delta$  modulator based fractional-N PLL is widely used to produce frequency reference for wireless communication systems. Quantization noise caused by  $\Sigma\Delta$  modulator will degrade the phase noise spectrum at the PLL output, and the situation becomes worse when the loop is nonlinear. Techniques and structures for noise improvement have been proposed to address the problem of noise degradation caused by  $\Sigma\Delta$  modulator. Also included is the design of a wideband PLL with power optimized divider. An intuitive but useful power optimization methodology is proposed for dividers.

#### Acknowledgments

I have been extremely fortunate to be a graduate student in the ECE department at Auburn University and work closely with my academic advisor, Prof. Fa Foster Dai. I would like to express my deepest gratitude and appreciation to him for his invaluable guidance, discussions, encouragement, and assistance during my study and research. His instruction and motivation lead to the completion of this research work. He is also an important friend to me in my personal lives and career because he is like a beacon, lighting up my way.

I would like to take this opportunity to thank my committee members, Prof. Bogdan M. Wilamowski, Prof. Stanley J. Reeves, and Prof. Guofu Niu for taking their valuable times out of their busy schedule to serve in the committee. I want to thank Prof. Bogdan Wilamowski for leading me into the area of neural networks and Prof. Stanley Reeves for the technical discussions in DSP area. I would like to express my gratitude to Prof. Guofu Niu for his invaluable discussion and advice to my career. I would also like to thank Dr. Stuart M. Wentworth for consolidating my understanding of microwave operation and Mike Palmer for his help in chip bonding. I would like to thank Dr. David Irwin and Dr. Richard Jaeger for their guidance and discussions during my PhD study.

I extend my thanks to those great friends who have made graduate study life intellectually and socially enriched. I would like to express my sincere gratitude to the friendship of Xueyang Geng, Desheng Ma, Xuefeng Yu, Yuan Yao, Yuehai Jin, Jianjun Yu, Joseph Cali, Michael Pukish, Xin Jin, Kaijun Li, Zachary Hubbard, Siyu Yang, Rong Jiang, Hechen Wang, and Zhan Su for their accompanying through many difficult and delighted times.

All of the work was made possible by the love and encouragement of my family. I would like to appreciate my parents and family members for their support. Finally I would like to express my cordial appreciation to my wife Yumei Tang and my Son Kevin K. Zhao for their continuous love and support.

### Table of Contents

| Abstract  | :ii                                                         |  |  |

|-----------|-------------------------------------------------------------|--|--|

| Acknow    | Acknowledgmentsiv                                           |  |  |

| List of F | iguresix                                                    |  |  |

| List of T | Sables                                                      |  |  |

| Chapter   | 1 Introduction                                              |  |  |

| 1.1       | Prior Art of QVCO Structures                                |  |  |

| 1.2       | Analysis of QVCO for Deterministic Quadrature Outputs       |  |  |

| 1.3       | Phase-Locked Loop Frequency Synthesizer                     |  |  |

| 1.4       | Outline and Contribution                                    |  |  |

| Chapter   | 2 A 0.6-V Low-Phase Noise CC-QVCO with Enhanced Swing 14    |  |  |

| 2.1       | Introduction                                                |  |  |

| 2.2       | CC-QVCO with Noise Reduction and Stable Oscillation         |  |  |

| 2.2.      | 1 Architecture of the CC-QVCO                               |  |  |

| 2.2.      | 2 Colpitts VCO Core with G <sub>m</sub> -Enhancement        |  |  |

| 2.2.      | 3 Noise Reduction for the CC-QVCO                           |  |  |

| 2.2.      | 4 Optimization of Capacitive Coupling                       |  |  |

| 2.2.      | 5 Intrinsic Phase Shift to Avoid Phase Ambiguity            |  |  |

| 2.2.      | 6 Quadrature Inaccuracy                                     |  |  |

| 2.3       | Implementation and Measured Results                         |  |  |

| 2.4       | Conclusions                                                 |  |  |

| Chapter   | 3 A 0.23-0.91 °4.3-5.27GHz NMOS LC CC-QVCO without Bi-Modal |  |  |

| Oscillati | ion                                                         |  |  |

| 3.1       | Introduction                                                |  |  |

| 3.2       | Important Aspects of QVCO and Prior QVCO Structures         |  |  |

| 3.3       | CC-QVCO with Leading Phase Delay                                 | 55  |

|-----------|------------------------------------------------------------------|-----|

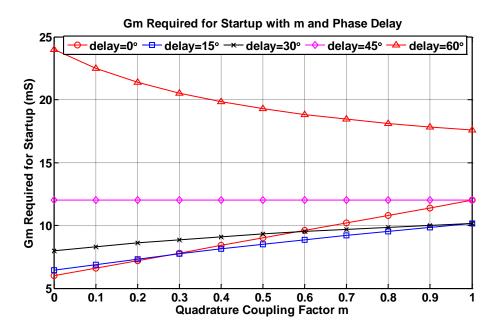

| 3.3.1     | Linear Model of the CC-QVCO and Start-up Conditions              | 56  |

| 3.3.2     | 2 Mode Rejection for Stable Operation                            | 61  |

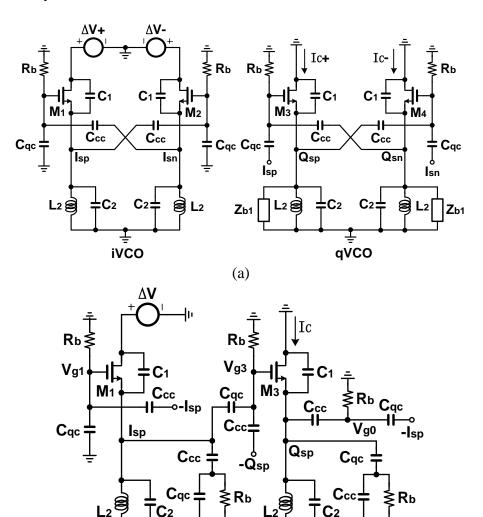

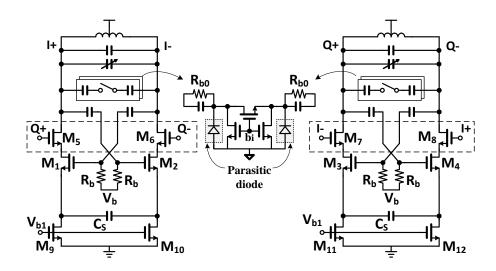

| 3.4       | Design and Simulation Results of a 5.6GHz CC-QVCO                | 64  |

| 3.4.1     | Design Procedure of a CC-QVCO                                    | 64  |

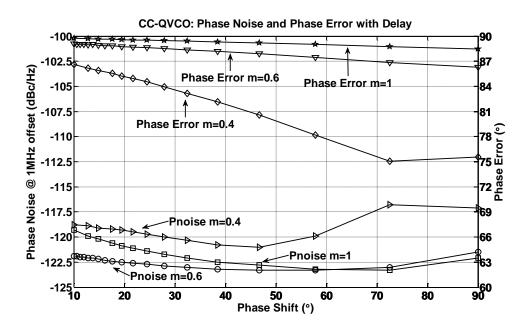

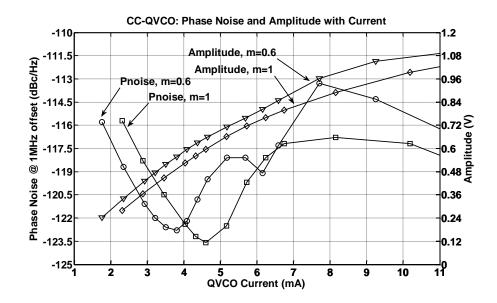

| 3.4.2     | 2 Choice of Quadrature Coupling Factor m and Phase Delay         | 68  |

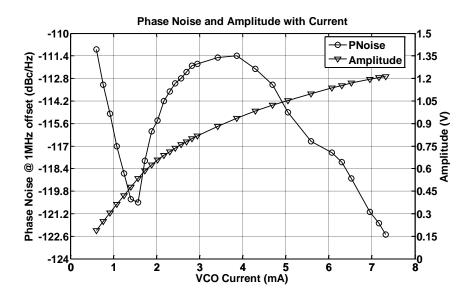

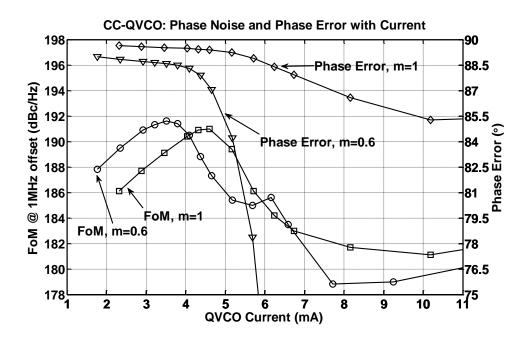

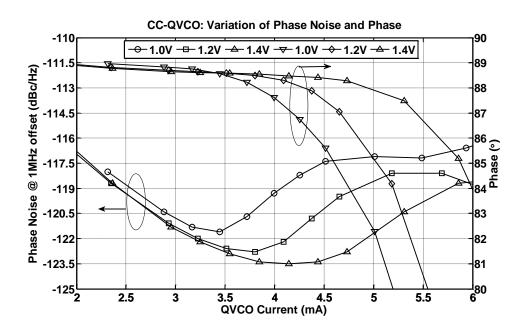

| 3.4.3     | B Phase Noise and Phase Error with Current Bias                  | 69  |

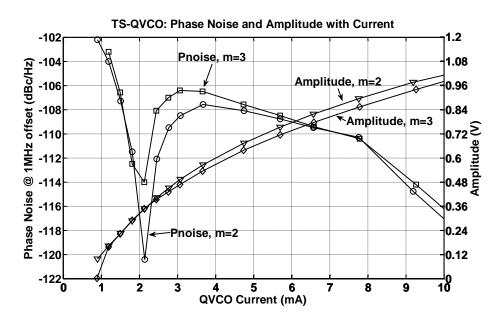

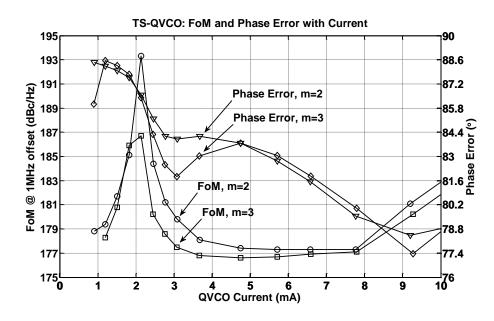

| 3.4.4     | Class-C Mode TS-QVCO for Comparison                              | 73  |

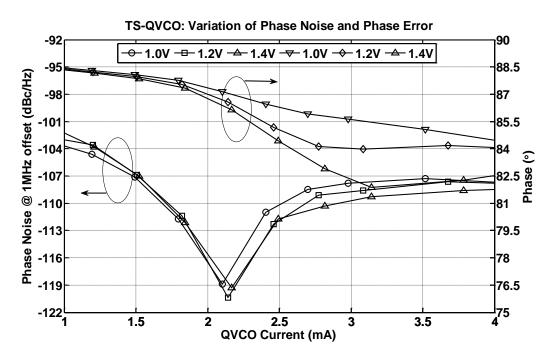

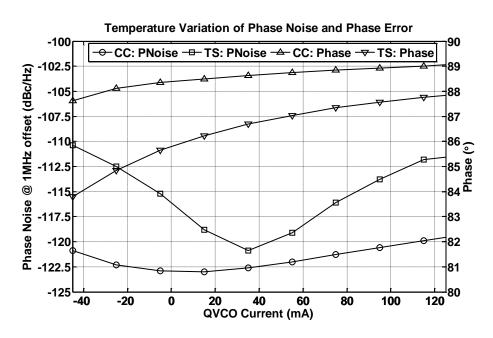

| 3.4.5     | 5 Performance Tolerance to Voltage and Temperature Variations    | 76  |

| 3.5       | Implementation and Measurement Results                           | 79  |

| 3.5.1     | Upconversion Mixer and IF Baseband Signal Generation             | 80  |

| 3.5.2     | Phase Noise and Frequency Range                                  |     |

| 3.5.3     | B Phase Accuracy                                                 | 84  |

| 3.6       | Conclusion                                                       | 85  |

| Chapter 4 | 4 Quantization Noise Reduction Techniques for Fractional-N PLL   | 87  |

| 4.1       | Introduction                                                     | 87  |

| 4.2       | $\Sigma\Delta$ Modulators and Noise Folding from Nonlinearity    |     |

| 4.2.1     | $\Sigma\Delta$ Modulator Structures and Phase Noise Contribution | 90  |

| 4.2.2     | 2 Nonlinearity Analysis for $\Sigma\Delta$ Modulators            |     |

| 4.2.3     | B Discussion of Simple Noise Reduction Techniques                |     |

| 4.3       | Proposed Fractional-N PLL with Noise Cancellation                |     |

| 4.4       | Conclusion                                                       | 101 |

| Chapter 5 | 5 A Wide-Band Integer-N PLL Design                               | 102 |

| 5.1       | Introduction                                                     | 102 |

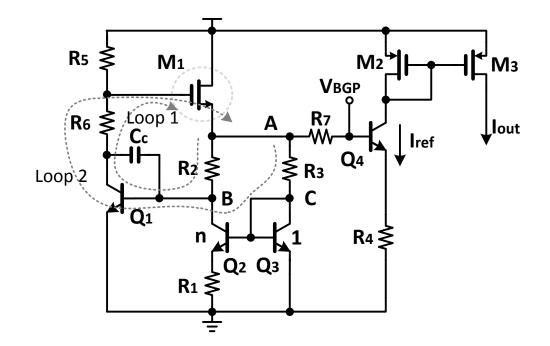

| 5.2       | Analysis of Bandgap Reference for Current Generation             | 105 |

| 5.3       | Circuit Design                                                   |     |

| 5.3.1     | VCO with Extended Frequency Range                                |     |

| 5.3.2     | Power and Speed Optimization for DTC                             | 109 |

| 5.3.3     | B Design Divide-by-2/3 and MMD                                   | 113 |

| 5.4                               | Experimental Results of the Wide-Band PLL |  |

|-----------------------------------|-------------------------------------------|--|

| 5.4                               | .1 Phase Noise and Frequency Tuning Range |  |

| 5.4                               | .2 Output Spectrum and Lock Time          |  |

| 5.5                               | Conclusion                                |  |

| Chapter 6 Summary and Future Work |                                           |  |

| 6.1                               | Summary of the Works                      |  |

| 6.2                               | Future Work                               |  |

| Bibliography                      |                                           |  |

# List of Figures

| Fig. 1.1 A radar transceiver with image rejection capability                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2 Typical QVCO structure                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 1.3 Prototype circuits of VCO cores and coupling circuit for QVCO: (a) parallel coupling, (b) back-gate coupling [10], (c) transformer coupling [9], (d) 2 <sup>nd</sup> -harmonic coupling [2] [11] [12], and (e) top-series coupling [8]. Components in dashed boxes are used for quadrature coupling. The connections at Q stage are similar to I stage with I+ coupled to Q- and I- coupled to Q+. For simplicity, the bias circuitry is not shown 4 |

| Fig. 1.4 Quadrature phase directivity circuits for QVCO: (a) cascode transistor for quadrature coupling [16], (b) source coupling [19], (c) resistor based parallel coupling [21], (d) source degenerated quadrature coupling [20][23][24], (e) capacitive source degeneration VCO core [17], and (f) RC poly-phase filter for 90 degree phase shift [18]. For simplicity, the bias circuitry is not shown                                                    |

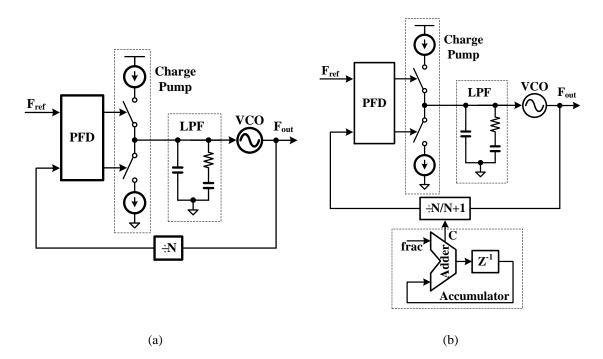

| Fig. 1.5 (a) Integer-N PLL, and (b) $\Sigma\Delta$ modulator based Fractional-N PLL 10                                                                                                                                                                                                                                                                                                                                                                        |

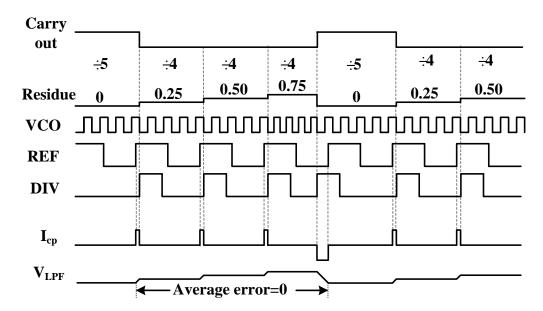

| Fig. 1.6 Classic accumulator based fractional-N PLL example waveforms for n=4.2511                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 2.1 Conventional quadrature VCO with parallel coupling transistors                                                                                                                                                                                                                                                                                                                                                                                       |

| Fig. 2.2 Proposed QVCO with optimized capacitive coupling and intrinsic phase shift. 17                                                                                                                                                                                                                                                                                                                                                                       |

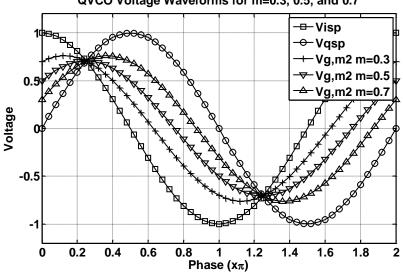

| Fig. 2.3 Voltage waveforms for different coupling-strength factor m                                                                                                                                                                                                                                                                                                                                                                                           |

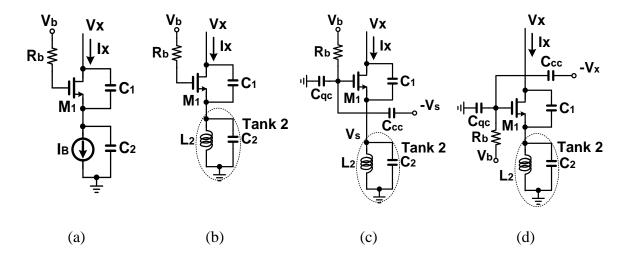

| Fig. 2.4 Half circuits of differential Colpitts VCOs used to analyze the start-up condition and resonance frequency: (a) Conventional structure with current tail; (b) ES VCO; (c) ES VCO with cross-coupled positive feedback at source; (d) ES VCO with cross-coupled positive feedback at drain                                                                                                                                                            |

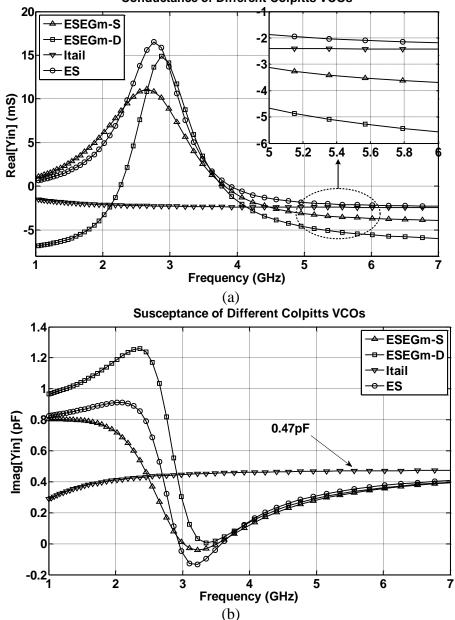

| Fig. 2.5 Calculation results of (a) Conductance; and (b) Susceptance for different Colpitts VCOs. Component values used for calculation are as following: C1=0.8 pF, C2=1.2 pF, L2=1.25 nH, gm=10.3 mS, QL2=15                                                                                                                                                                                                                                                |

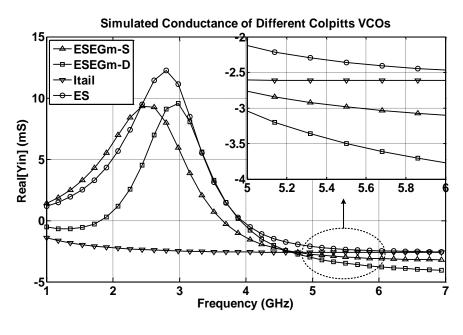

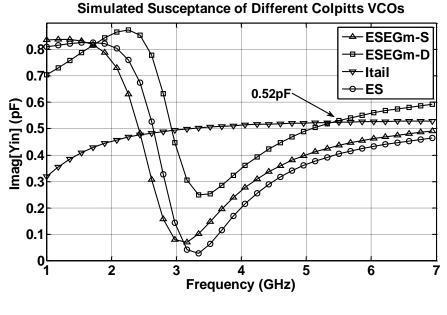

| Fig. 2.6 Simulation results of (a) Conductance; and (b) Susceptance for different Colpitts VCOs. Components used for simulation are the same as calculation                                                                                                                                                                                                                                                                                                   |

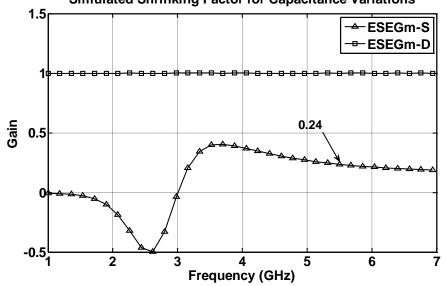

| Fig. 2.7 Simulation results of the shrinking factors for ESEGm-D VCO and ESEGm-S VCO                                                                                                                                                                                                                                                                                                                                                                          |

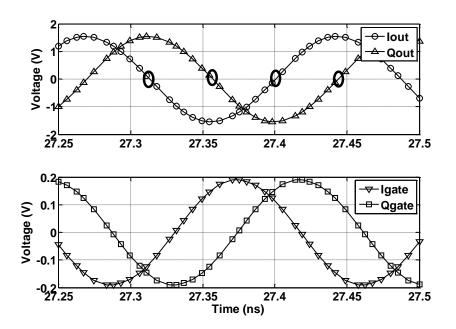

| Fig. 2.8 Simulation results of CC-QVCO outputs and coupling signals with m=0.4. The phase difference between the zero-crossing of Iout or Qout and the peak of Igate or Qgate is about 55 °                                                                                                                                                                                                                                                                   |

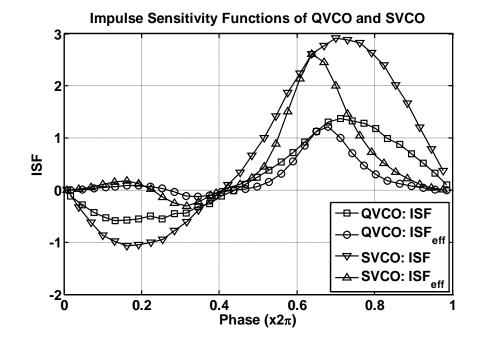

| Fig. 2.9 ISF and ISF <sub>eff</sub> for CC-QVCO and SVCO with m=0.4, respectively                                                                                                                                                                                                                                                                                                                                                                             |

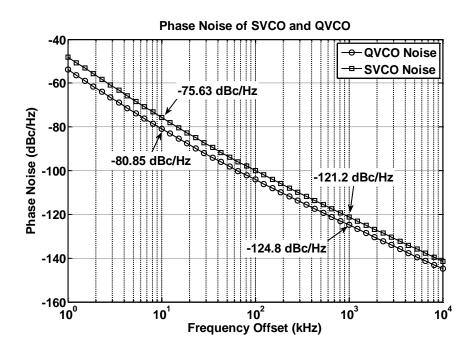

| Fig. 2.10 Simulation results of phase noise for SVCO and CC-QVCO with m=0.4 29                                                                                                                                                                                                                                                                                                                                                                                |

| Fig. 2.11 Simulation results of phase noise improvement and phase error for different coupling strength factor m with $C_{tankq}=1.01C_{tanki}$                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

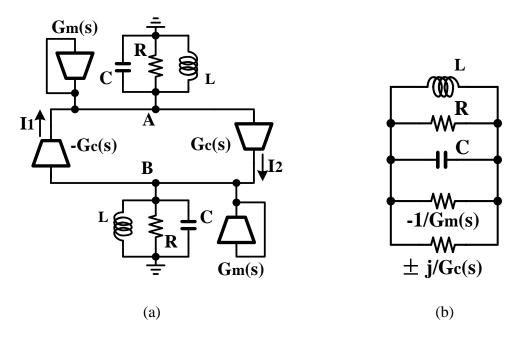

| Fig. 2.12 (a) Linear model of quadrature oscillator; and (b) equivalent model of individual VCO with coupling effects                                                                                                                           |

| Fig. 2.13 (a) CC-QVCO circuit for the derivation of Gc(s); and (b) simplified half-circuit model for the derivation of Gc(s). The DC bias and varactors (included in C2) are not shown in the figure and the ground symbols represent ac ground |

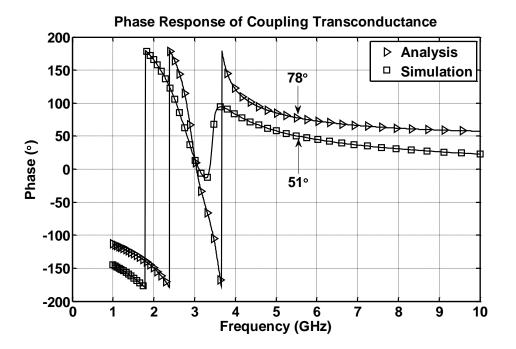

| Fig. 2.14 Simulation results of phase shift versus analytical formula for quadrature-<br>coupling transconductance                                                                                                                              |

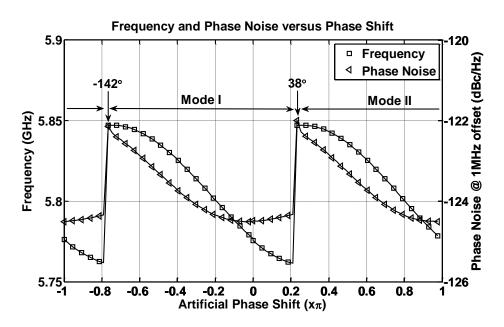

| Fig. 2.15 Simulation results of oscillation frequency and phase noise with artificial phase shift introduced in the coupling path                                                                                                               |

| Fig. 2.16 Simulation result of output phases with artificial phase shift introduced in the coupling path (with $C_{tankq}=1.01C_{tanki}$ )                                                                                                      |

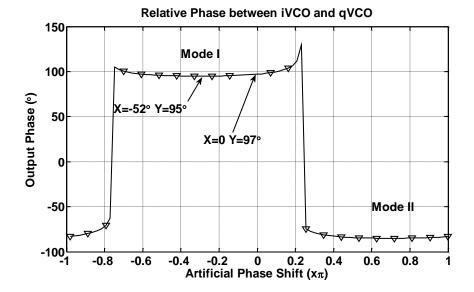

| Fig. 2.17 Die photo of the implemented QVCO RFIC (1.2×1.2mm <sup>2</sup> including pads) 42                                                                                                                                                     |

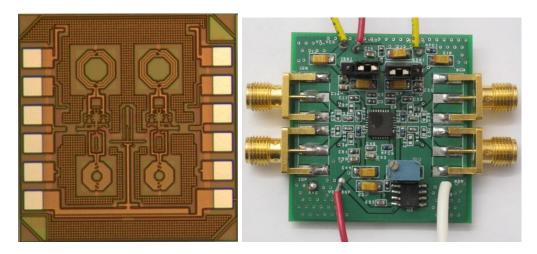

| Fig. 2.18 Measured phase noise of (a) SVCO, and (b) QVCO                                                                                                                                                                                        |

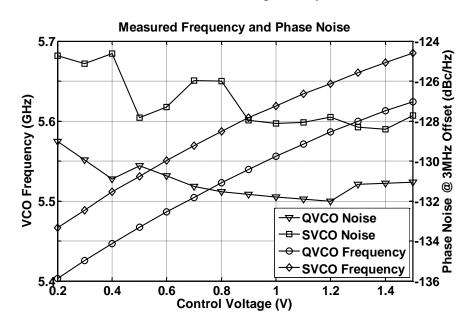

| Fig. 2.19 Measured frequency tuning range and phase noise of QVCO and SVCO 43                                                                                                                                                                   |

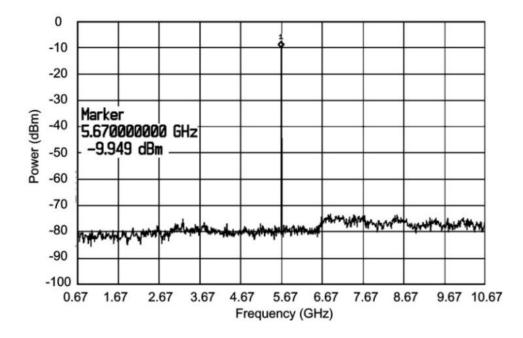

| Fig. 2.20 Measured output spectrum for the CC-QVCO                                                                                                                                                                                              |

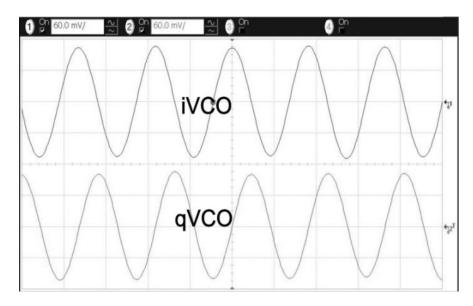

| Fig. 2.21 Measured output voltage waveforms for the CC-QVCO                                                                                                                                                                                     |

| Fig. 3.1 Classic QVCO structure utilizing parallel coupling                                                                                                                                                                                     |

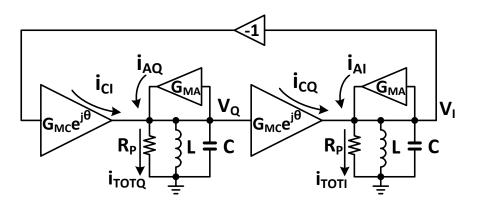

| Fig. 3.2 (a) linear model of conventional QVCO, and (b) Phasor diagram illustration of voltage and current for two phase relationships                                                                                                          |

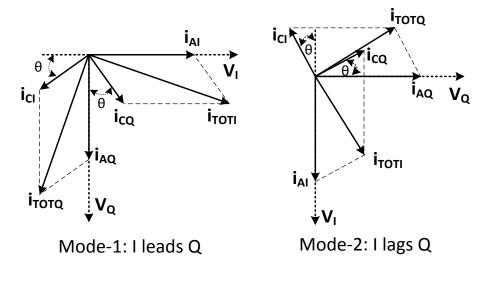

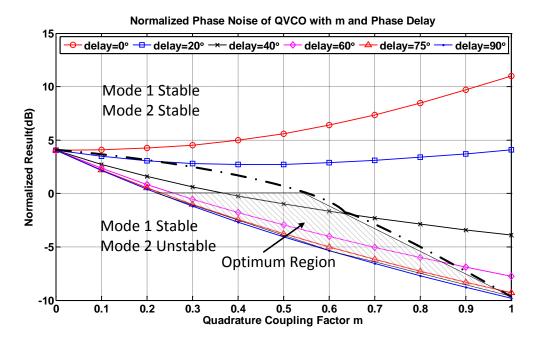

| Fig. 3.3 QVCO phase noise normalized to SVCO noise for different m and phase delay (phase noise of SVCO is at 0dB), and $\gamma$ is assumed to be 2 for short-channel MOS transistors. 53                                                       |

| Fig. 3.4 QVCO phase noise without MC devices normalized to QVCO noise with MC devices for different m and phase delay, and $\gamma$ is assumed to be 2 for short-channel MOS transistors. 54                                                    |

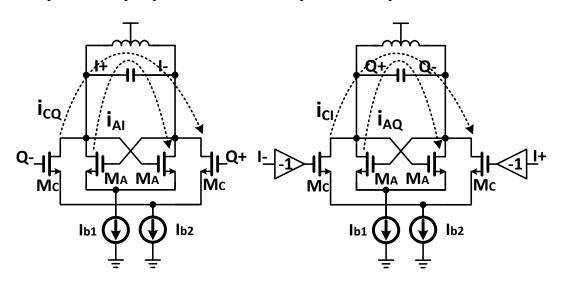

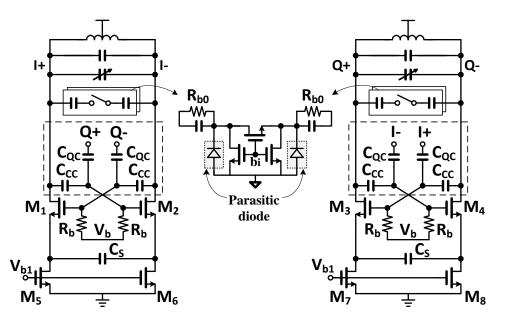

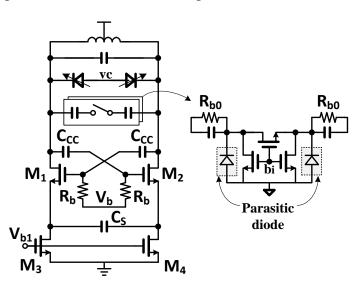

| Fig. 3.5 Proposed CC-QVCO with inherent leading phase shifter for quadrature signal generation                                                                                                                                                  |

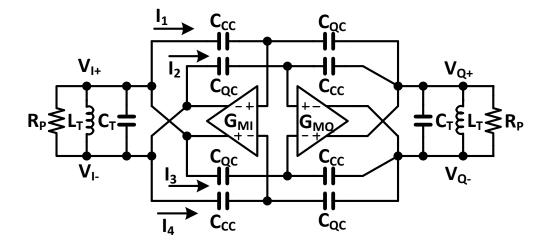

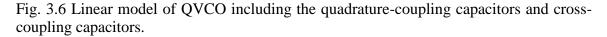

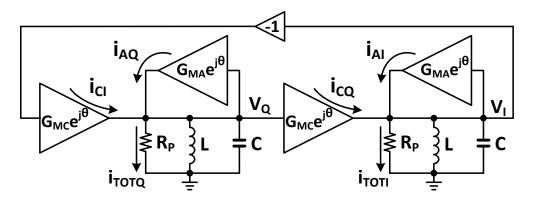

| Fig. 3.6 Linear model of QVCO including the quadrature-coupling capacitors and cross-<br>coupling capacitors                                                                                                                                    |

| Fig. 3.7 Simplified linear model of the proposed QVCO with phase shifter                                                                                                                                                                        |

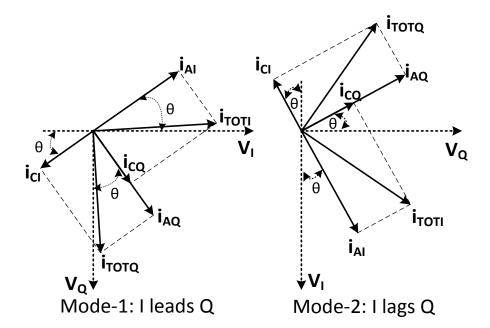

| Fig. 3.8 Phasor diagram of the voltage and current relationships in the proposed CC-<br>QVCO                                                                                                                                                    |

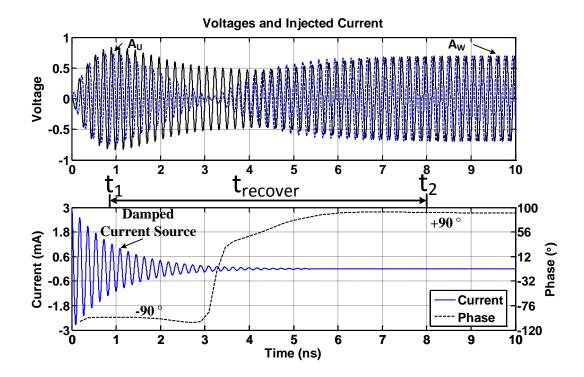

| Fig. 3.9 Transient waveforms for MRR calculation                                                                                                                                                                                                |

| Fig. 3.10 Minimum $g_{m1,2}$ required to meet the start-up condition                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.11 Phase noise and phase error with different m and phase shift for CC-QVCO68                                                                                              |

| Fig. 3.12 Single-phase VCO (SVCO) for comparison                                                                                                                                  |

| Fig. 3.13 Simulated signal amplitudes and phase noise for SVCO                                                                                                                    |

| Fig. 3.14 Simulated signal amplitudes of the CC-QVCO71                                                                                                                            |

| Fig. 3.15 Simulated phase noise and phase error of the proposed QVCO with bias current for 1.2V and 1.5V supply (1% capacitor mismatch is artificially introduced to the LC tank) |

| Fig. 3.16 Proposed QVCO with top-series transistor for quadrature coupling                                                                                                        |

| Fig. 3.17 Simulated phase noise and output amplitude of the proposed TS-QVCO 74                                                                                                   |

| Fig. 3.18 TS-QVCO: simulated phase error and FoM for m=2 and m=3 (1% capacitor mismatch is artificially introduced into the LC tank)                                              |

| Fig. 3.19 CC-QVCO: simulated phase noise and phase error with bias and supply voltage (1% capacitor mismatch is artificially introduced into the LC tank)                         |

| Fig. 3.20 TS-QVCO: simulated phase error and phase noise with bias and supply voltage (1% capacitor mismatch is artificially introduced into the LC tank)                         |

| Fig. 3.21 QVCO phase error and phase noise with temperature (1% capacitor mismatch is artificially introduced into the LC tank)                                                   |

| Fig. 3.22 Die photos of the implemented CC-QVCO, class-C mode TS-QVCO, and SVCO                                                                                                   |

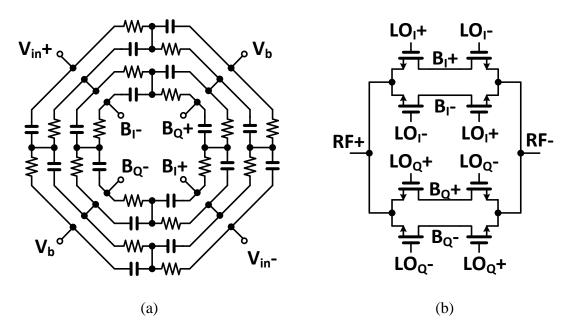

| Fig. 3.23 Auxiliary circuits for phase error measurement: (a) 4 stages of RC poly-phase filter for IQ baseband signal generation, (b) upconversion mixer                          |

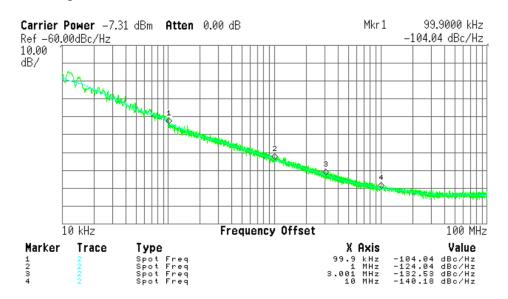

| Fig. 3.24 Measured phase noise performance of the proposed CC-QVCO at 4.7GHz with a 1.2V power supply and 8.5mA total current                                                     |

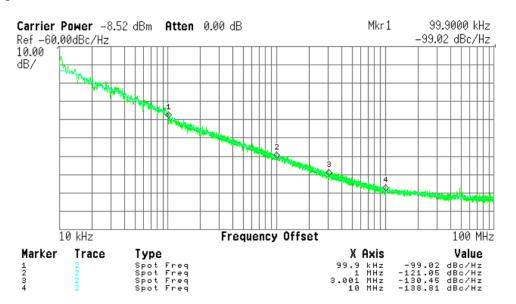

| Fig. 3.25 Measured phase noise performance of the proposed TS-QVCO at 4.9GHz with a 1.2V power supply and 9mA total current                                                       |

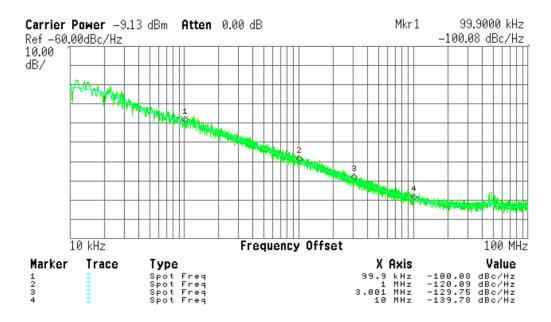

| Fig. 3.26 Measured phase noise of the implemented SVCO at 5.35GHz with a 1.2V power supply and 4.6mA current                                                                      |

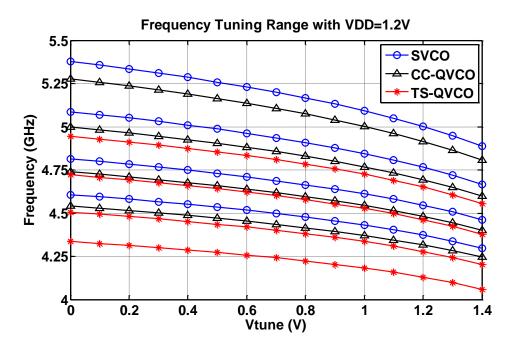

| Fig. 3.27 Measured frequency tuning range of SVCO, CC-QVCO, and TS-QVCO with 1.2V power supply                                                                                    |

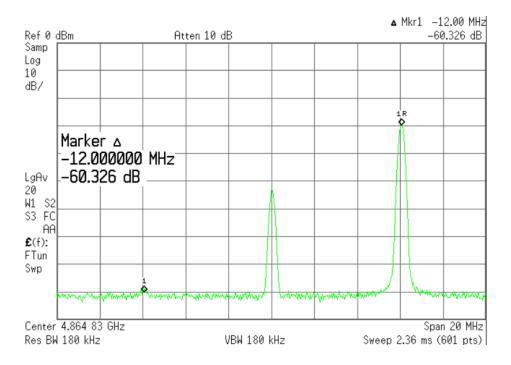

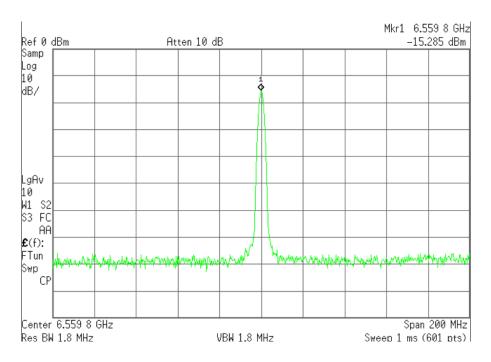

| Fig. 3.28 Measured output spectrum at the output of upconversion mixer where the frequency is 4.86GHz                                                                             |

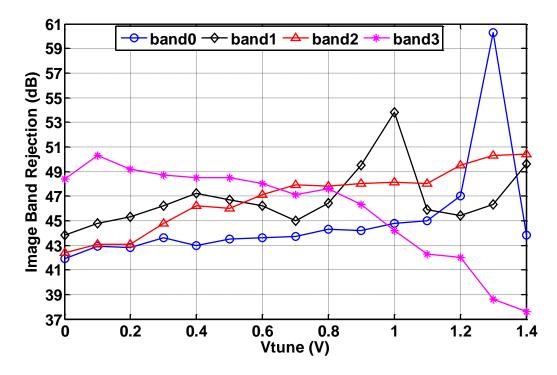

| Fig. 3.29 Measured SBR of CC-QVCO across the tuning range with 1.2V VDD                                                                                                           |

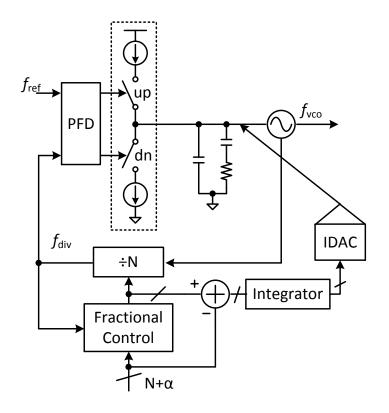

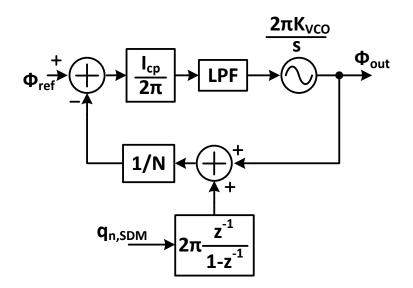

| Fig. 4.1 System diagram of fractional-N PLL with quantization noise cancelling                                                                                                    |

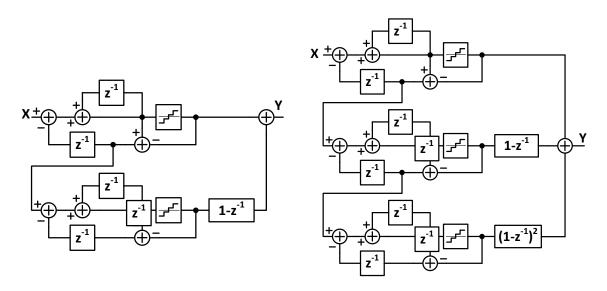

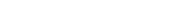

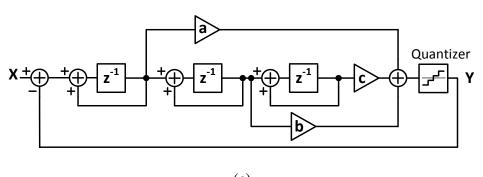

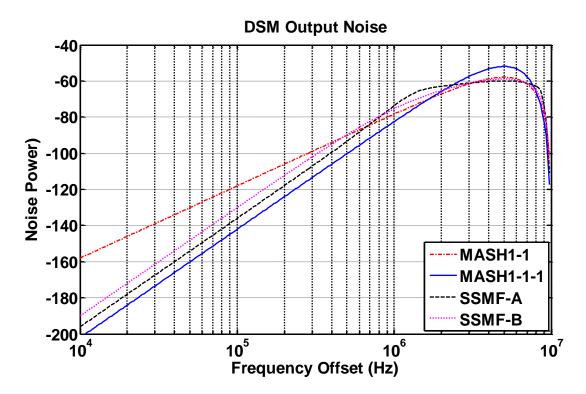

| Fig. 4.2 $\Sigma\Delta$ modulator structures: (a) MASH1-1, (b) MASH1-1-1, and (c) SSMF                                                                                            |

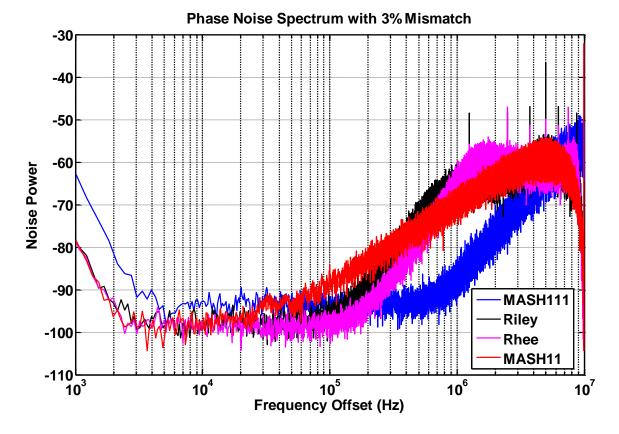

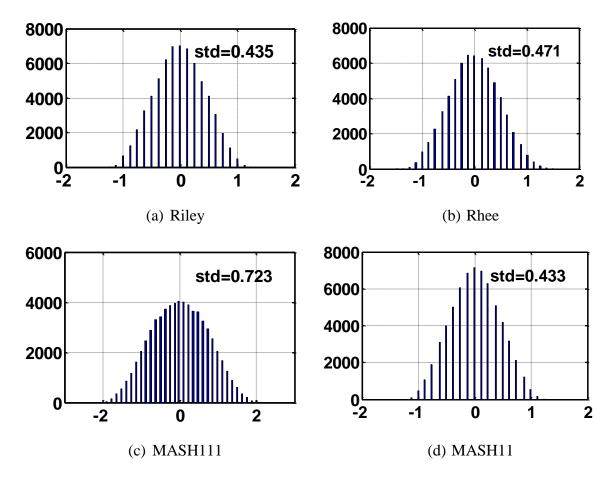

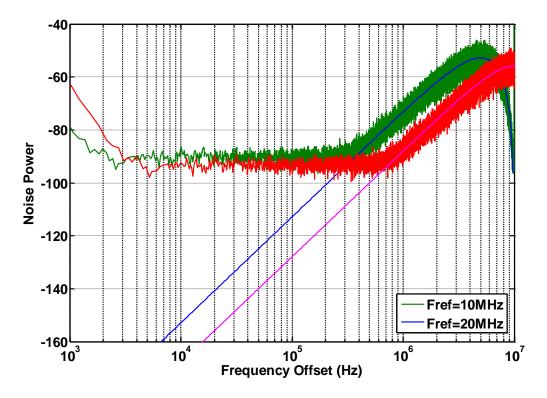

| Fig. 4.3 Output noise power of $\Sigma\Delta$ modulators with 10MHz sampling clock frequency. 92                                       |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.4 PLL model including $\Sigma\Delta$ modulator noise                                                                            |

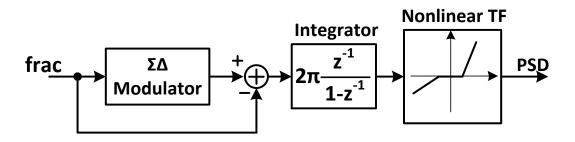

| Fig. 4.5 Behavioral model to examine the nonlinearity effect on the quantization noise. 94                                             |

| Fig. 4.6 Phase noise spectrum of MASH1-1 and MASH1-1-1 with 3% gain mismatch. 95                                                       |

| Fig. 4.7 Distribution of phase error at the input of PFD for different $\Sigma\Delta$ modulators96                                     |

| Fig. 4.8 Simulated noise improvements by doubling the clock frequency under 3% gain mismatch                                           |

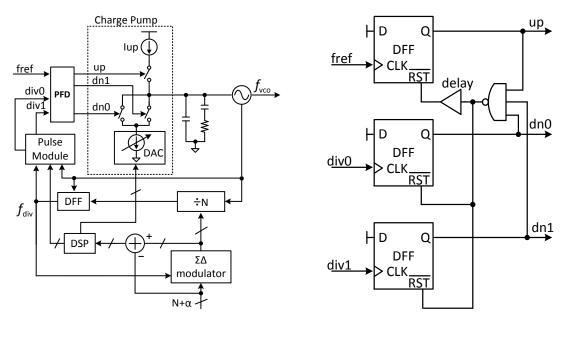

| Fig. 4.9 (a) System diagram of the proposed fractional-N PLL with quantization noise cancellation technique; (b) PFD circuit           |

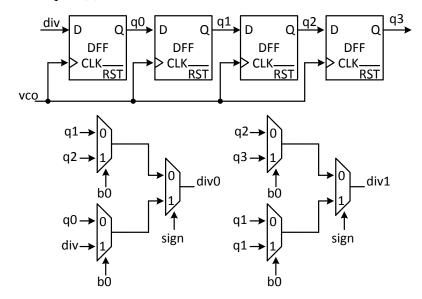

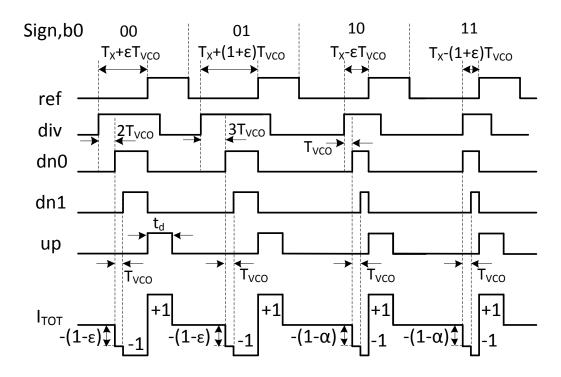

| Fig. 4.10 Pulse control module used to generate PWM signal                                                                             |

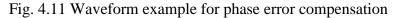

| Fig. 4.11 Waveform example for phase error compensation                                                                                |

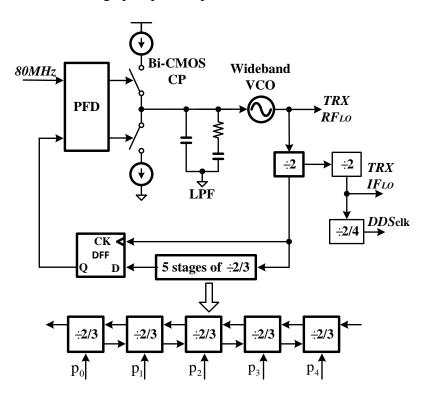

| Fig. 5.1 System diagram of the proposed PLL system                                                                                     |

| Fig. 5.2 Bandgap circuit utilized to generate voltage reference and current reference . 105                                            |

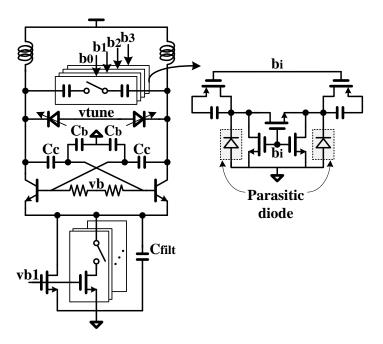

| Fig. 5.3 Schematic of the proposed VCO with extended tuning range 108                                                                  |

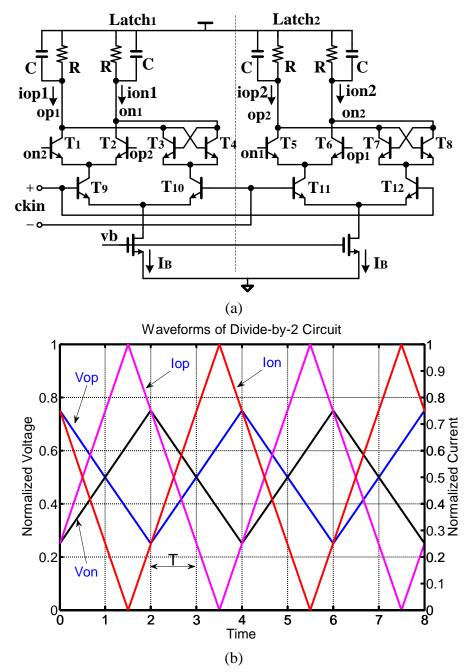

| Fig. 5.4 Divide-by-2 circuit: (a) Circuit schematic and (b) simplified waveforms for derivation of self-oscillation frequency          |

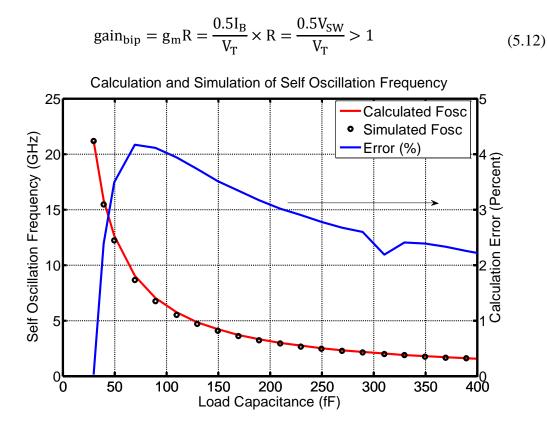

| Fig. 5.5 Comparison of calculated and simulated self-oscillation frequency of DTC with $R=250\Omega$ , and $IB=0.8mA$                  |

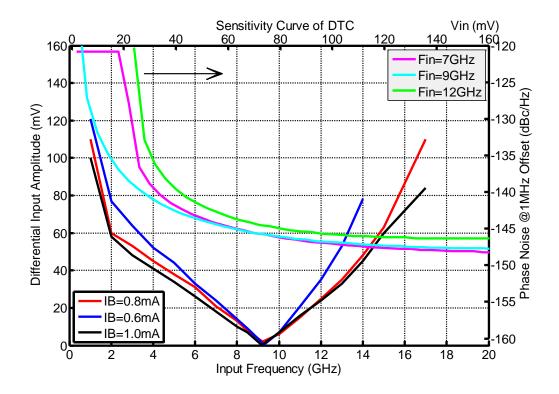

| Fig. 5.6 Simulated sensitivity curves of the DTC with R=250 $\Omega$ , C=130fF and phase noise performance with different input signal |

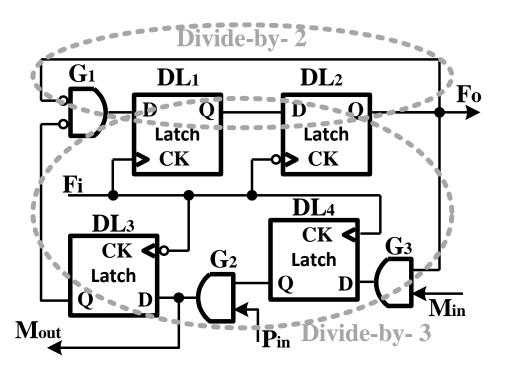

| Fig. 5.7 Circuit schematic of divide-by-2/3                                                                                            |

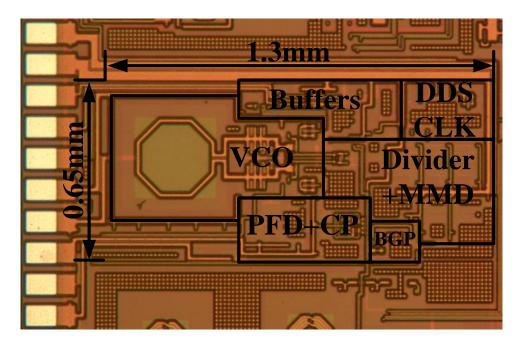

| Fig. 5.8 Die photo of the implemented PLL                                                                                              |

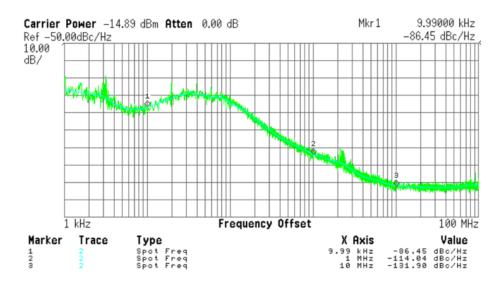

| Fig. 5.9 Measured phase noise of the PLL with BW=100kHz, Fref=80MHz 116                                                                |

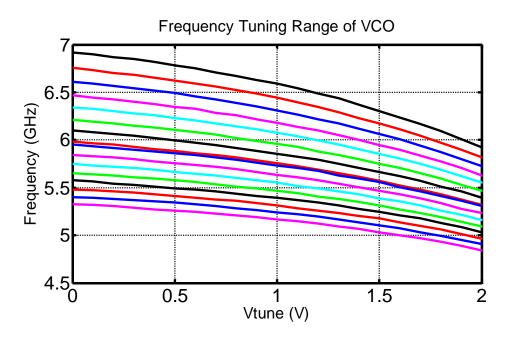

| Fig. 5.10 Measured VCO frequency tuning range                                                                                          |

| Fig. 5.11 PLL output spectrum 117                                                                                                      |

#### List of Tables

| Table 2.1: Performance Summary and Comparison of QVCOs with Different Coupling | 5    |

|--------------------------------------------------------------------------------|------|

| Techniques                                                                     | . 46 |

| Table 3.1: Performance Summary of the implemented VCO and QVCOs                |      |

| Table 5.1: Performance Summary of the PLL    1                                 | 117  |

# **Chapter 1 Introduction**

Single chip implementation of wireless transceivers gain popularity as the fabrication process is gradually developing to smaller feature size since it allows tens of GHz circuit integration. Among the many building blocks of a radio frequency (RF) transceiver, clock signal generation is indispensable to provide clean and accurate carrier for reference. Integer-N or fractional-N phase-locked loop (PLL) frequency synthesizer is usually utilized to produce such high performance clock signals due to its low power consumption and accurate frequency synthesis. LC VCO plays a very important role in providing clean clock signals because of its low power and low noise performance.

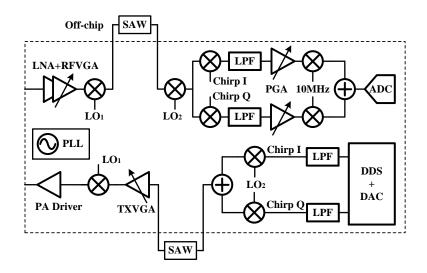

Fig. 1.1 A radar transceiver with image rejection capability.

Many RF transceivers usually adopt complex signal modulation and demodulation scheme because of its potential to carry more information in a limited bandwidth. Fig. 1.1

shows a radar transceiver system that is able to provide gain for the signal at frequency of  $f_{LO}+f_{IF}$  while reject the image signal at frequency of  $f_{LO}-f_{IF}$  [1]. It requires a quadrature local oscillator (LO) signals to upconvert the baseband signal into RF. On the receiver side, the 10-MHz clock signals are also of quadrature type. Two possible phase relationships exist for quadrature output, i.e., +90 ° and -90 °, but it is desirable to maintain the phase relationships in one of the two possible forms since the wrong mode will amplify the image signal instead of the wanted frequency signal. It is entirely possible to embed automatic detecting circuit to find the right phase and then select the right LO signal, but it requires additional circuit. Moreover, the quadrature accuracy directly affects the signal quality in the transmitted or received signal. Therefore, a quadrature signal generating mechanism that is able to provide deterministic and accurate quadrature outputs is essential for image-rejection transceivers.

Several techniques can be employed to produce quadrature signals [2]-[5], i.e., (i) a voltage-controlled oscillator (VCO) with a doubled frequency followed by a divide-by-two circuit; (ii) a poly-phase filter; (iii) a quadrature VCO (QVCO). The first method requires a VCO operating at twice of the desired frequency which consumes more power because of the additional divide-by-two circuit. The poly-phase filter is a narrow-band technique with large loss. Compared with the first two techniques, QVCO comprises two VCO cores coupled with each other and can take advantage of low power consumption. In addition, its high voltage swing eases the design of the prescaler and the mixer. The coupling mechanism for a QVCO can be implemented using active devices or passive components like inductors, transformers, and capacitors. One popular QVCO

implementation is coupled with parallel transistors due to its simplicity and low cost of area [6]. This coupling technique, however, suffers from a trade-off between phase noise and phase accuracy because the coupling needs to be strong enough to provide decent phase accuracy, which degrades the quality factor of LC tank and phase noise performance [5], [7]. Also extra power consumption is required to properly bias the coupling transistors. In order to improve the phase noise performance, transistors in series can be placed at the top or bottom of the main amplifying transistors [5], [8]; however, the parasitic capacitance introduced by the coupling transistors will reduce the frequency tuning range and the voltage headroom for the signal output is also decreased. Moreover, extra power consumption is required to maintain the signal amplitude since the coupling strength required to maintain phase accuracy lowers the signal swing. Another disadvantage of the QVCO coupling using active devices, especially with parallel transistors, is the noise degradation resulted from the current noise introduced by the coupling transistors.

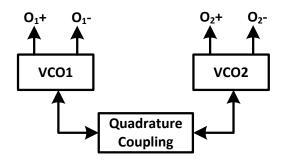

Fig. 1.2 Typical QVCO structure.

A typical QVCO usually consist of two VCO cores and quadrature coupling devices, as shown Fig. 1.2. To provide the same output amplitude and oscillation frequency, the two VCO cores should have the same structure and device size. Either active device or passive components is indispensable to form quadrature coupling between the two VCO cores such that the output can produce quadrature signals. It is obvious that the two outputs  $O_1$  and  $O_2$  are symmetric if the quadrature-coupling block is symmetric. Therefore, the problem of phase ambiguity, meaning that the output phase relations can be +90 ° or -90 °, may exist in the above QVCO structure. Fortunately this problem can be addressed by introducing a phase delay in the quadrature-coupling path.

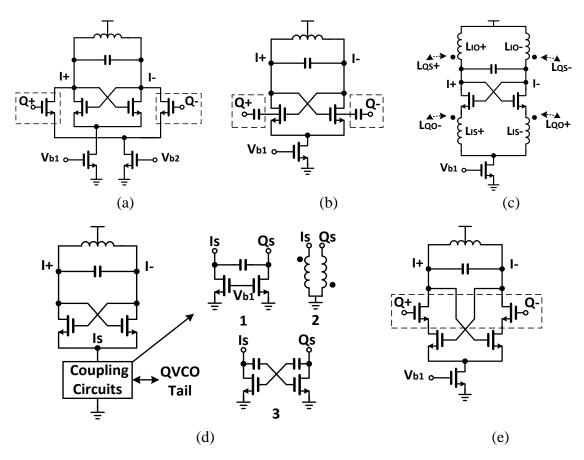

Fig. 1.3 Prototype circuits of VCO cores and coupling circuit for QVCO: (a) parallel coupling, (b) back-gate coupling [10], (c) transformer coupling [9], (d)  $2^{nd}$ -harmonic coupling [2] [11] [12], and (e) top-series coupling [8]. Components in dashed boxes are used for quadrature coupling. The connections at Q stage are similar to I stage with I+ coupled to Q- and I- coupled to Q+. For simplicity, the bias circuitry is not shown.

## **1.1 Prior Art of QVCO Structures**

Fig. 1.3 shows six types of VCO cores used in prior QVCO topologies. Fig. 1.3 (a) shows the VCO cores used in parallel-coupling QVCO [6]. This structure is simple but suffers from the noise degradation of the active quadrature-coupling devices. In addition, the phase delay is limited to the intrinsic delay resulted from the parasitics and thus cannot successfully avoid bi-modal oscillation.

Back-gate coupling: Fig. 1.3(b) shows the VCO core for QVCO with back-gate coupling. This technique features the advantages of compact design and low power consumption by sharing the amplifier transistors with quadrature-coupling path. However, it requires triple-well CMOS process and is prone to the possibility of forward biasing the intrinsic bulk-substrate diode. Similar to parallel-coupling technique, it also suffers from limited phase delay in the quadrature-coupling path.

Transformer coupling: a VCO core used for QVCO with transformer coupling [9] is shown in Fig. 1.3(c). The noise source for quadrature-coupling has been eliminated in this structure. The area cost this QVCO does not increase much because the transformer only occupies a little more metal area. Another advantage of this structure is that the phase delay in the quadrature-coupling path can be larger than the parallel coupled QVCO since the quadrature-coupling signal should go through a cascode transistor on top of before reaching the LC tank, where cascode structure means one transistor is on top of the other transistor. The remaining problem for such a QVCO design is the difficulty of constructing a proper transformer model.

Second-harmonic coupling: this technique uses the second harmonic waveform to

form the coupling between the two VCO cores. Three coupling examples [2] [11] [12] with this technique are shown in Fig. 1.3(d). A QVCO design using this technique can be compact with capacitive coupling. However, the problem of phase ambiguity requires additional circuit to provide correct directivity.

Top series coupling: Fig. 1.3(e) shows the VCO cores for QVCO with top series coupling [8] [13]. The noise contribution from the active devices in quadrature-coupling path can be reduced by utilizing top or bottom series coupling. The active coupling device is in cascode form and its noise can be degenerated by the bottom transistor. One advantage of this structure is its capability of rejecting the unwanted oscillation mode. But the voltage headroom is reduced because of the series transistors. The phase noise performance is sensitive to bias current and temperature change, which will be demonstrated by simulation results in Chapter 3.

The resonant frequency of a QVCO varies with the coupling strength and this feature can be utilized to achieve wide-band frequency tuning range [14] [15]; but the power consumption is much higher than the classic QVCO structures. As a result, this structure is not so popular for quadrature generation.

## **1.2 Analysis of QVCO for Deterministic Quadrature Outputs**

As mentioned, the QVCO outputs can be ambiguous if not designed properly, especially under the influence of PVT variations. Directivity circuits, such as a ring of transistors [2], can be used to help produce correct output phases. Phase delay is usually introduced in the quadrature-coupling path to avoid the problem of phase ambiguity, or

bi-modal oscillation [2] [16]-[22]. Most phase-shifting circuits achieve a phase delay much less than the optimum value of 90 °, but those phase shifters at least can provide some safe margin to avoid the problem of bi-modal oscillation.

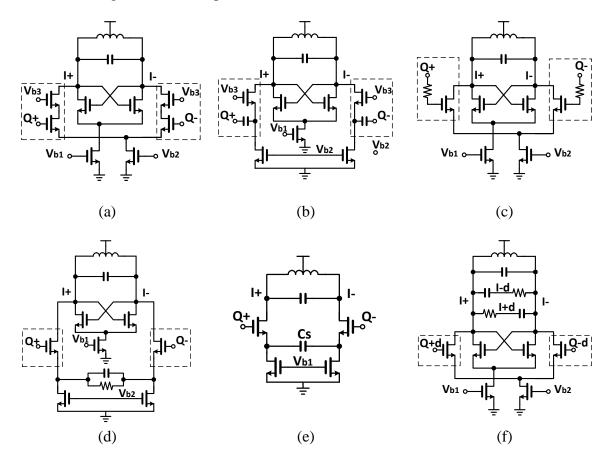

Fig. 1.4 Quadrature phase directivity circuits for QVCO: (a) cascode transistor for quadrature coupling [16], (b) source coupling [19], (c) resistor based parallel coupling [21], (d) source degenerated quadrature coupling [20][23][24], (e) capacitive source degeneration VCO core [17], and (f) RC poly-phase filter for 90 degree phase shift [18]. For simplicity, the bias circuitry is not shown.

Five types of circuit with VCO cores for used for QVCO are shown in Fig. 1.4(a)-(e). Cascode topology as shown in (a) with a phase delay of 20° is proposed to move the QVCO operation away from the unstable boundary, therefore giving sufficient phase margin to avoid bi-modal oscillation [16]. The phase shift is introduced by a pole at high frequency which can be easily found from the following equivalent transconductance

$$G_{m,cascode} = \frac{g_{m1}}{1 + \frac{sC_P}{g_{m2}}} \tag{1.1}$$

where  $C_P$  is the parasitic capacitance or artificially introduced capacitor at the source terminal of the cascode transistor, and  $g_{m2}$  is the transconductance of the cascode transistor.

The phase shifter shown in Fig. 1.4 (b) and (c) can provide phase delay for stable operation of QVCO but both suffer from noise degradation. The quality factor of the LC tank in (b) is decreased because the source input impedance of  $1/g_m$  will load the resonant tank; while the series resistors in the quadrature-coupling path add to the output noise.

Another type of phase shifter uses RC source degeneration network to provide phase delay [20] [23] [24], as shown in Fig. 1.4(d). It is advantageous over cascode phase shifter because it does not suffer from the problem of degraded voltage headroom and can be embedded into the main VCO cores as shown in (e) [17]. The effective transconductance of the quadrature-coupling circuits for (d) and (e) are

$$G_{m,RC \ deg} = \frac{g_{m1}(1 + sR_SC_S)}{1 + g_{m1}R_S/2 + sR_SC_S} \tag{1.2}$$

$$G_{m,C \ deg} = \frac{g_{m1} s C_S}{g_{m1}/2 + s C_S}$$

(1.3)

Usually, the phase shifters mentioned above only achieves a phase shift around 45  $^{\circ}$  in practical QVCO design and it is still far away from the optimum condition of 90  $^{\circ}$ . Mirzaei [18] suggested RC poly phase shifter to produce the 90  $^{\circ}$  phase shift for optimum operation of QVCO as shown in Fig. 1.4(f). A phase shift of 72  $^{\circ}$  has been achieved due to the load effect in the real implementation according to the publication. However, the quality factor of the LC tank can be easily degraded by the RC poly-phase filter, especially when a high quality tank is required.

# **1.3 Phase-Locked Loop Frequency Synthesizer**

PLL circuits are widely used to generate a precise frequency signal from a very high precision reference signal. It has wide application in wired and wireless communications systems to provide accurate carrier that is phase aligned with the incoming high-precision reference clock signal. The VCO signal is divided and compared with the high-precision reference by the phase frequency detector (PFD). Then the error signal is fed into charge pump to transform the phase error into current pulses. The pulses are filtered by the loop filter and then the filtered voltage is used to control the VCO to stabilize its phase and frequency variations. The negative feedback mechanism results in the generation of a tunable and stable output signal at the desired frequency.

Two types of PLL structures with negative feedback loop, integer-N and fractional-N, have been widely used for frequency synthesis. Integer-N PLL, as shown in Fig. 1.5 (a), provide an output frequency equals to N times the reference frequency whereas N is the divider ratio. However, this architecture limits the frequency resolution to the PFD comparison frequency.

Another architecture named as fractional-N PLL has become increasingly popular since its invention because it can achieve fine frequency resolution with larger loop bandwidth than integer-N PLL. Unlike integer-N PLL, fractional-N PLL allows a division ratio of fractional number by using a control module to dynamically adjust the divide factor to different integer numbers so that the long-term averaged division ratio is a fractional number. The principle of the fractional-N PLL is therefore a result of averaging, since only integer-N division ratio can be achieved with nowadays devices.

Fig. 1.5 (a) Integer-N PLL, and (b)  $\Sigma\Delta$  modulator based Fractional-N PLL.

Conventional fractional-N PLL contains an accumulator or  $\Sigma\Delta$  modulator as the fractional control module to dynamically control the divide factor [25]. Fig. 1.5 (b) shows an accumulator based fractional-N PLL. Take it as example, as long as the content of the accumulator is lower than its capacity, the divide ratio in the divider path is N; the frequency divider is adjusted to implement a division ratio of N+1 every time the accumulator overflows. For example, with a 2-bit adder and fractional input number is 1, the adder overflows every four reference clock periods and the division ratio is

$$m = \frac{[3 \times N + (N+1)]}{4} = N + 0.25 \tag{1.4}$$

Assuming that the PLL is locked and the average voltage on the loop filter becomes zero under steady-state conditions. Fig. 1.6 illustrates the resulting steady-state waveforms produced by the PLL with N=4 and m=4.25. We see that, while the integrated current over four reference periods is zero on average, the residue value at the output of the accumulator instantaneously varies with time in a periodic manner. This periodicity leads to the fractional spur that plagues the classical fractional-N approach.

Fig. 1.6 Classic accumulator based fractional-N PLL example waveforms for n=4.25.

Then  $\Sigma\Delta$  modulator based fractional-N PLL is proposed to address the problem of fractional spur [26]. It can randomize the spur and shape the phase noise to high frequency offset which is filtered by the loop. However, the instantaneous phase error still exists at the input of PFD since the  $\Sigma\Delta$  fractional-N PLL is still use long-term averaging effect to achieve fractional frequency control. In order to lower the noise degradation caused by the  $\Sigma\Delta$  modulator, a phase error compensation mechanism is therefore indispensable to achieve the goal of wide-bandwidth modulation in fractional-N PLL.

In attempt to reduce the noise caused by  $\Sigma\Delta$  modulators, a compensating pulseamplitude-modulated (PAM) current can be injected into the loop filter and efficiently compensated the phase error. The current is generated from a current digital-to-analog converter (DAC) with fixed pulse width. This technique can be applied to accumulator based and  $\Sigma\Delta$  modulator based fractional-N PLL [25] [27]. The compensation technique based on PAM requires high-precision DAC current generator to completely compensate the phase error. It needs more complicate control technique like dynamical element match (DEM) to reduce the mismatch of DAC current generator. PFD/DAC can be embedded to improve the compensating accuracy [25]; however, it can be only applied to first order  $\Sigma\Delta$  modulator or modulators with a phase error less than one VCO period. Therefore, it is desirable to develop a PLL system that is able to suppress the quantization noise caused by high order  $\Sigma\Delta$  modulator.

#### **1.4 Outline and Contribution**

This dissertation focuses on the topic of capacitive-coupling quadrature VCO, with a particular on phase noise reduction and elimination of phase ambiguity. Chapter 2 aims to develop a differential Colpitts QVCO with enhanced swing technique and capacitive quadrature-coupling mechanism for low phase noise performance under 0.6-V power supply. Silicon verification results are also given to demonstrate the proposed technique.

In chapter 3, quadrature-coupling technique, combined with inherent phase shifter, is applied to classic NMOS VCO with current tail for quadrature generation. The proposed structure demonstrates excellent phase noise and phase error performance over a wide frequency range. Implementation and measurement results are given to show the robustness of the proposed QVCO structure.

Chapter 4 explores several quantization reduction techniques for fractional-N PLL. Nonlinearity analysis of four types of popular  $\Sigma\Delta$  modulator structures and simple noise reduction technique have been discussed. A concept for high-order  $\Sigma\Delta$  modulator noise cancellation is proposed for fractional-N PLL.

Chapter 5 describes a wideband integer-N PLL with 4.8-6.8GHz output frequency range. The design details about the VCO, multi-modulus divider, and bandgap reference are explained. A power optimization methodology is developed for divider design.

Chapter 6 summarizes this dissertation and suggests future research topics.

# Chapter 2 A 0.6-V Low-Phase Noise CC-QVCO with Enhanced Swing

# **2.1 Introduction**

Phase noise and phase accuracy are two essential specifications for quadrature signal generation since the two aspects directly affect the quality of the received or transmitted signal in a wireless communication system. The ever-growing demand for chip-level integration of multi-band transceiver continues imposing tighter phase noise performance specifications for radio-frequency (RF) carrier generation. Quadrature signals with phase accuracy and no phase ambiguity are critical for image-rejection transceivers since they directly affect the polarity and the outcome of the complex mixers. Phase error existed in the quadrature signals will add to the error of a baseband signal and deteriorate the bit error rate (BER) of a communication system. Thus, a high performance quadrature signal generation technique with both low noise and decent phase accuracy is highly desirable for complex signal modulation and demodulation.

To eliminate noise degradation introduced by the coupling mechanism, noiseless components such as transformer, inductor, and capacitor can be used for coupling. A QVCO with transformer coupling which is based on the technique of super-harmonic coupling [2] shows good phase noise performance with the expense of inductor area. An energy-circulating QVCO with inductive coupling can achieve even much better phase noise performance than the single-phase VCO of the same kind [28], yet it comes at the cost of additional area of two inductors. In order to reduce the area of a coupling transformer, the secondary coupling tank can share the tank area with the resonant tank and it can achieve a decent figure-of-merit (FoM) [9]. However, transformer models are either not accurate or not available in most commercial CMOS technology and it requires extra effort to develop an accurate transformer model. Therefore, QVCO with capacitive coupling techniques [11] [29] [30] have been developed to simplify the circuit design with good noise performance and small area.

Various QVCO coupling mechanisms have been developed in search of improved phase noise performance, yet another important aspect of the QVCO design, the phase ambiguity, is often overlooked. The understanding of the phase ambiguity and the stability is critical since a typical QVCO may operate at either one of its two stable modes with different phase relationships. Each stable mode corresponds to +90 °or -90 ° phase relationship between the two outputs of the QVCO. However, quadrature signals with deterministic phase relationship are often required for proper image rejection in RF receivers [24]. The phenomenon of the bimodal oscillation has been observed and phase shifter in the coupling path can help solving this problem [16]-[18]. Theoretical analysis and experimental results prove that the phase shift of 90 °introduced in the quadrature-coupling path provides optimum phase noise performance and minimum phase error arising from mismatch between two VCO cores [18]. However, the phase shift of 90 °has

to be implemented with poly-phase shifters [18], or additional active devices stages [19], or source degenerated phase shifter [20] for QVCO using parallel coupling transistors.

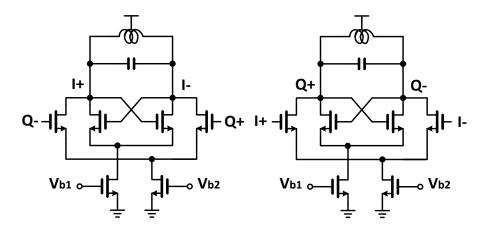

For a conventional QVCO with parallel coupling transistors as shown in Fig. 2.1, the iVCO and the qVCO couple with each other at the gate of the coupling transistors and the largest energy injection happens at the zero-crossings of the VCO output swing. According to the impulse sensitivity function (ISF) theory [31], the VCO phase noise is most sensitive to disturbance near the zero-crossings of the oscillation. Consequently the phase noise of the quadrature outputs is degraded due to the fact that the amplitude-to-phase noise conversion in this topology is largest at their zero-crossings. It's for this reason that a QVCO with parallel coupling ends up with worse phase noise than that of its single-phase counterpart.

Fig. 2.1 Conventional quadrature VCO with parallel coupling transistors.

The current trend of technology scaling presents challenges for circuit designs. Feature size shrinking forces the power supply drop below 1 V. Lowered supply voltage limits the output swing that can be generated, which further limits the phase noise that an oscillator can achieve. A Colpitts QVCO with enhanced swing and capacitive coupling technique [32] for low phase noise performance has been proposed for a 0.6-V supply voltage. The capacitive coupling (CC)-QVCO, as shown in Fig. 2.2, not only achieves low phase noise performance under a low supply voltage, but also guarantees stable oscillation with an intrinsic phase shift in the coupling path.

Fig. 2.2 Proposed QVCO with optimized capacitive coupling and intrinsic phase shift.

This chapter will present the details of the proposed capacitive-coupled QVCO (CC-QVCO) [32]. In section 2.2, we will introduce the architecture of the CC-QVCO, the noise-reduction technique and the optimization of the capacitive coupling. Moreover, the transconductance- (effective  $G_m$ -) enhancement technique for power reduction and the intrinsic phase shift for stable oscillation will be analyzed in section 2.2. Section 2.3 provides the implementation and experimental results for the proposed CC-QVCO. Finally, conclusions are drawn in section 2.4.

# 2.2 CC-QVCO with Noise Reduction and Stable Oscillation

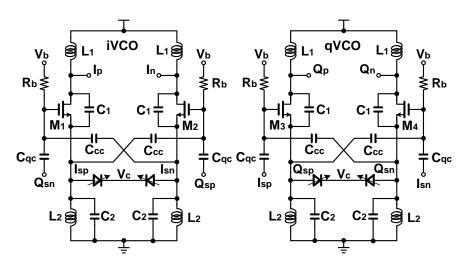

### 2.2.1 Architecture of the CC-QVCO

As shown in Fig. 2.2, instead of using noisy transistors for quadrature signal coupling, capacitive coupling is employed to improve the phase noise performance of the QVCO. To achieve large output swing required for good phase noise performance under a low supply voltage around 0.6 V, an enhance-swing (ES) Colpitts VCO structure similar to [33] is adopted. Different from simple ES Colpitts VCO,  $G_m$ - enhancement technique is employed using the cross-coupled capacitors  $C_{cc}$  to reduce the power consumption. The proposed CC-QVCO is composed of two such  $G_m$ -enhanced VCO cores and four quadrature-coupling capacitors  $C_{qc}$ . The coupling-strength factor m between the iVCO and qVCO is defined as

$$m = \frac{C_{qc}}{C_{cc} + C_{qc}}$$

(2.1)

Assuming the transient voltages of the quadrature output signals as  $V_{isp}=V_0cos(\omega_0 t)$ and  $V_{qsp}=V_0sin(\omega_0 t)$ , the voltage signal at the gate of  $M_2$  is

$$V_{g,M2}(t) = mV_{qsp}(t) + (1 - m)V_{isp}(t)$$

(2.2)

The voltage waveforms with different coupling-strength factor are illustrated inFig. 2.3. As it can be seen from the figure, the smaller the coupling strength factor m is, the farther the peak of  $V_{g,M2}$  deviate from the zero-crossing of  $V_{isp}$  and  $V_{qsp}$ . Because the voltage at the drain of each transistor has the same phase as its source voltage, the voltage peak on the gates can also be shifted away from the zero-crossings of the output voltage. As a result, the amplitude of the gate voltage is no longer the maximum during the zero-crossings of the VCO output swing. Moreover, the effective ISF for the CC-QVCO can also be improved. Therefore, the amplitude-to-phase noise conversion between the two

VCO cores is reduced and the phase noise performance of the CC-QVCO is improved.

QVCO Voltage Waveforms for m=0.3, 0.5, and 0.7

Fig. 2.3 Voltage waveforms for different coupling-strength factor m.

In addition, phase noise is further improved by placing diode junction varactors with reference to the ground. The quality factor reduction caused by the parasitic diodes has been avoided because the VCO tank on n-type anode has been isolated from substrate since the p-type cathode is connected to a DC bias voltage [34] [35]. The combination of these techniques described above enables the proposed CC-QVCO with low phase noise (-122 dBc/Hz @ 1-MHz offset) and low power consumption (4.2 mW).

#### 2.2.2 Colpitts VCO Core with G<sub>m</sub>-Enhancement

A Colpitts VCO features superior phase noise characteristics than cross-coupled VCO since the noise injection from active devices for the former structure is at the minimum of the tank voltage when the ISF is low [3], [31]. Unfortunately, a Colpitts VCO requires large trans-conductance which means more power to meet the start-up conditions in the presence of process-voltage-temperature (PVT) variations. Therefore,

high power dissipation is necessary to ensure reliable start-up.

Fig. 2.4 shows the half circuits of different Colpitts VCO topologies. The derivation of the small-signal admittance for Colpitts VCO with current tail as shown in Fig. 4(a) is straightforward and can be written as

$$Y_{in,Itail} = \frac{s^2 C_1 C_2}{g_m + s(C_1 + C_2)}$$

(2.3)

where the  $g_m$  is the transconductance of  $M_1$ . The admittance of an ES-Colpitts VCO shown in Fig. 2.4(b) with tank 2 to enhance the signal swing is given by

$$Y_{\text{in,ES}} = \frac{sC_1}{1 + g_m Z_{L2} + sC_1 Z_{L2}} = \frac{sC_1(1 + s^2 L_2 C_2)}{1 + s^2 L_2 (C_1 + C_2) + g_m sL_2}$$

(2.4)

$$Z_{L2} = sL_2 \parallel \frac{1}{sC_2} \parallel R_{P2}$$

(2.5)

Fig. 2.4 Half circuits of differential Colpitts VCOs used to analyze the start-up condition and resonance frequency: (a) Conventional structure with current tail; (b) ES VCO; (c) ES VCO with cross-coupled positive feedback at source; (d) ES VCO with cross-coupled positive feedback at drain.

Equation (2.4) is based on ideal lossless inductor  $L_2$ , i.e.  $R_{P2}=\infty$ . Shown in Fig. 2.4 (c) and (d) are other two Colpitts VCO structures with  $G_m$ -enhancement. ES VCO of Fig.

2.4 (c) places the cross-coupled capacitor at the source. The admittance looking into the half-circuit can be derived with the Kirchhoff's circuit laws (KCL). The voltage at the drain can be expressed as

$$I_{X}\frac{1}{sC_{1}} + I_{X}g_{m}(2-m)Z_{L2}\frac{1}{sC_{1}} + I_{X}Z_{L2} = V_{X}$$

(2.6)

The admittance for the ES VCO with  $G_m$ -enhancement placed at source (ESEG<sub>m</sub>-S) is defined as

$$Y_{in,ESEGm-S} = \frac{I_X}{V_X} = \frac{sC_1}{1 + (2 - m)g_m Z_{L2} + sC_1 Z_{L2}}$$

(2.7)

where the  $g_m$  is the transconductance of  $M_1$ . By assuming an ideal lossless inductor  $L_2$ , the admittance for ESEG<sub>m</sub>-S VCO can be rewritten as

$$Y_{in,ESEGm-S} = \frac{sC_1(1+s^2L_2C_2)}{1+s^2L_2(C_1+C_2)+(2-m)g_msL_2}$$

(2.8)

Similarly, the admittance for ESEG<sub>m</sub>-D VCO as shown in Fig. 4(d) can be derived

as

$$Y_{in,ESEGm-D} = \frac{sC_1 - (1 - m)g_m}{1 + (g_m + sC_1)Z_2} = \frac{[sC_1 - (1 - m)g_m](1 + s^2L_2C_2)}{1 + s^2L_2(C_1 + C_2) + g_msL_2}$$

(2.9)

The real parts of those equations represent the negative transconductance required to start the oscillator. The larger the absolute value of the transconductance is, the smaller the power consumption is required for start-up. Oscillators will fail to start oscillation when the negative admittance cannot compensate the tank loss. The real admittances for the four VCO topologies are expressed as follows.

$$Re[Y_{in,Itail}] = \frac{-g_m \omega^2 C_1 C_2}{g_m^2 + \omega^2 (C_1 + C_2)}$$

(2.10)

$$Re[Y_{in,ES}] = \frac{-g_m \omega^2 L_2 C_1(\omega^2 L_2 C_2 - 1)}{[1 - \omega^2 L_2 (C_1 + C_2)]^2 + (g_m \omega L_2)^2}$$

(2.11)

$$Re[Y_{in,ESEGm-S}] = \frac{-(2-m)g_m\omega^2 L_2 C_1(\omega^2 L_2 C_2 - 1)}{[1-\omega^2 L_2 (C_1 + C_2)]^2 + [(2-m)g_m\omega L_2]^2}$$

(2.12)

$$Re[Y_{in,ESEGm-D}] \tag{2.13}$$

$$= -g_m(\omega^2 L_2 C_2 - 1)$$

$$\times \frac{\omega^2 L_2 C_1 - (1 - m)[1 - \omega^2 L_2 (C_1 + C_2)]}{[1 - \omega^2 L_2 (C_1 + C_2)]^2 + (g_m \omega L_2)^2}$$

Fig. 2.5 (a) shows the calculated real admittances of the four VCO structures. As shown in the frequency range of 5~6 GHz, the conductance of ESEG<sub>m</sub>-S VCO is about 1.5 times that of ES VCO and thus relaxes the start-up requirement. Compared with conventional Colpitts VCO with ideal current tail, the improvement at f=5.5 GHz is about 35%. Therefore, the power consumption is reduced and improved FoM can be achieved. The improvement has been verified through simulation and the simulated admittances are shown in Fig. 2.6. Although the simulated conductance improvement is smaller than the calculation result, the Colpitts VCOs with G<sub>m</sub>- enhancement as shown in Fig. 2.4 (c) and (d) still achieve lower power consumption than the other two structures. The discrepancies between the Fig. 2.5 and Fig. 2.6 are caused not only by using simplified small-signal transistor models with first-order approximation, but also by neglecting C<sub>qc</sub>, C<sub>cc</sub>, and other parasitic capacitances for deriving the analytic expressions. However, Fig. 2.5 gives first-order approximation of the admittances. The magnitude of negative G<sub>m</sub> decreases when frequency is reduced, i.e., it becomes more difficult for the VCOs to meet the start-up condition as frequency decreases. After a certain frequency value, the G<sub>m</sub>

becomes positive and peaks at the resonant frequency of Tank 2 as shown in Fig. 2.5 (a) and Fig. 2.6 (a). The resonant frequency of Tank 2 should be placed far below the VCO resonance frequency to maintain a sufficient margin for stable oscillation.

**Conductance of Different Colpitts VCOs**

Fig. 2.5 Calculation results of (a) Conductance; and (b) Susceptance for different Colpitts VCOs. Component values used for calculation are as following:  $C_1=0.8$  pF,  $C_2=1.2$  pF,  $L_2=1.25$  nH,  $g_m=10.3$  mS,  $Q_{L2}=15$ .

(b)

Fig. 2.6 Simulation results of (a) Conductance; and (b) Susceptance for different Colpitts VCOs. Components used for simulation are the same as calculation.

The resonance frequency of the Colpitts VCO core is determined by the inductor  $L_1$ and the equivalent capacitance looking into the drain terminal. The equivalent capacitor without considering parasitic capacitances can be obtained from the imaginary part of Equation (2.3), (2.4), (2.8), and (2.9), as shown in Fig. 2.5(b), while the simulation result for the equivalent capacitor is shown in Fig. 2.6 (b). The simulated equivalent capacitor for ESEG<sub>m</sub>-D VCO is larger than the other two VCOs with bottom inductors because of the directly added quadrature-coupling capacitors. For the two Colpitts VCO structures shown in Fig. 2.4 (b) and (c), which have inductors at source terminals, the equivalent capacitor at the cost of the bottom inductor. However, the primary goal of the bottom inductor in this design is to enhance the signal swing under a low supply voltage. As a result, the resonance frequency is increased compared with a conventional Colpitts VCO. This feature is very useful for RF frequency VCO design since the parasitic capacitance starts to dominate at high frequency.

Although the conductance of  $ESEG_m$ -D VCO can save much more power than that of  $ESEG_m$ -S VCO, the latter structure is used because its performance is less sensitive to the mismatches produced by the quadrature-coupling path than the former. This can be understood by observing the Colpitts VCO structure given in Fig. 2.4 (a). The equivalent capacitance at the drain can be approximate as  $C_{tot} = C_{drain} + C_1 \parallel C_2$  around resonant frequency. The capacitance variation  $\Delta C_2$  at the source is shrunk by a factor of  $n^2 = C_1^2/(C_1 + C_2)^2$  and n is usually smaller than 0.4 for good phase noise performance. However, the capacitance variation  $\Delta C_{drain}$  at the drain directly adds to the total capacitance. Fig. 2.7 shows the shrinking factor of capacitance variations for  $ESEG_m$ -S VCO and  $ESEG_m$ -D VCO. The capacitance variations are applied to the source for  $ESEG_m$ -S VCO and the drain for  $ESEG_m$ -D VCO. From the Fig. 2.7, it is known that the shrinking factor for the  $ESEG_m$ -S VCO is about one fourth of that of the  $ESEG_m$ -D VCO around the target frequency. Therefore, the  $ESEG_m$ -S VCO suffers less from the mismatch in the quadrature-coupling path than the  $ESEG_m$ -D VCO.

Simulated Shrinking Factor for Capacitance Variations

Fig. 2.7 Simulation results of the shrinking factors for ESEGm-D VCO and ESEGm-S VCO.

### 2.2.3 Noise Reduction for the CC-QVCO

Ideally the phase noise of a QVCO can be reduced by 3 dB compared to a singlephase VCO that draw half of the current of the QVCO, and a phase noise normalized to the power consumption would be the same as its single phase counterpart [8]. This assumption does not take into account of various effects that have impact on the phase noise performance, such as additional noise generated by the coupling devices and the reduction of effective quality factor of the LC tanks. On the other hand, the coupled signal is usually at its maximum when the QVCO is most susceptible to noise, i.e., when the two VCO cores inject noise to each other during the zero-crossing point of their output swings. Due to both the additional noise introduced by coupling transistors and noise injection around the most sensitive time of output signals, the phase noise normalized to power consumption of the QVCO based on series or parallel coupling [5]-[8] can only be close, but not as good as that of its single-phase counterpart.

Fig. 2.8 Simulation results of CC-QVCO outputs and coupling signals with m=0.4. The phase difference between the zero-crossing of  $I_{out}$  or  $Q_{out}$  and the peak of  $I_{gate}$  or  $Q_{gate}$  is about 55 °.

In order to lower the phase noise, it is beneficial to reduce the voltage swings of the coupled signals at their zero-crossing time. By using cross-coupled capacitors for  $G_m$ -enhancement and quadrature-coupling capacitors for quadrature generation, the voltages on the gate can be shaped for better noise performance. Fig. 2.8 shows the simulated transient voltages for the CC-QVCO with m=0.4. It is obvious that the voltage maxima of the coupling signal have been shifted away from the zero-crossings of the output signals.

As a result, the amplitude-to-phase noise conversion between the two VCO cores is reduced and the phase noise performance of the CC-QVCO is improved beyond what can be achieved by its single-phase counterpart.

Fig. 2.9 ISF and ISF<sub>eff</sub> for CC-QVCO and SVCO with m=0.4, respectively.

In order to verify the noise improvement, the ISF and effective ISF (ISF<sub>eff</sub>) of the QVCO and SVCO are obtained using the direct impulse response measurement method of [31] implemented in MMSIM 10.2. The QVCO and SVCO are simulated using the same tank inductance and are tuned to oscillate at a center frequency of 5.8 GHz. The QVCO including two VCO cores draws twice the current of the SVCO. Fig. 2.9 shows the simulated ISFs of the QVCO versus that of the single-phase VCO (SVCO). The noise-modulating function (NMF) is defined as the instantaneous drain current divided by the peak drain current over an output signal cycle. The ISF<sub>eff</sub> is defined as the product of ISF and NMF. The simulation result shows that the proposed CC-QVCO achieves lower

ISF and effective  $ISF_{eff}$  than its SVCO core. The corresponding coefficient ratio of  $c_{0svco}$  to  $c_{0qvco}$  is about 2.1, which means the noise power resulted from the transistors used in CC-QVCO will be improved by 6.4 dB.

Fig. 2.10 Simulation results of phase noise for SVCO and CC-QVCO with m=0.4.

Fig. 2.10 shows the phase noise simulation results of the CC-QVCO and its SVCO core. The proposed CC-QVCO achieves 3.6~5.2-dB phase noise improvement at the frequency offset of 10 kHz to 1 MHz when compared with its SVCO of the same kind. The noise summary for 1-MHz offset shows that each of the four transistors for the CC-QVCO contributes a noise power of  $4.90 \times 10^{-14} V^2/Hz$ , while each of the two transistors contributes a noise power of  $1.92 \times 10^{-13} V^2/Hz$  for the SVCO. Therefore, the noise improvement resulted from the transistors can be approximate as

$$c_{0,improve}(dB) = 10\log \frac{1.92 \times 10^{-13}}{4.90 \times 10^{-14}} = 5.93dB$$

(2.14)

This value is very close to the simulated  $ISF_{eff}$  improvement of 6.4 dB. It proves that the CC-QVCO can achieve better phase noise performance than its SVCO core because of the reduced  $ISF_{eff}$ . Since the capacitive coupling does not use devices that introduce extra noise, the CC-QVCO accomplishes 3-dB phase noise improvement predicted by the theory under ideal condition [8]. The additional noise improvement beyond 3 dB for the proposed CC-QVCO is caused by the reduced  $ISF_{eff}$  as shown in Fig. 2.7. At lower frequency offset, the noise improvement becomes more obvious than that obtained at high frequency offset, since the flicker noise of transistors dominates the overall noise performance at low frequency offset and the improvement can be more than 3 dB.

It is for the mechanism described above, that the proposed CC-QVCO outperforms the most of QVCOs published so far with good phase noise, low power consumption and small area.

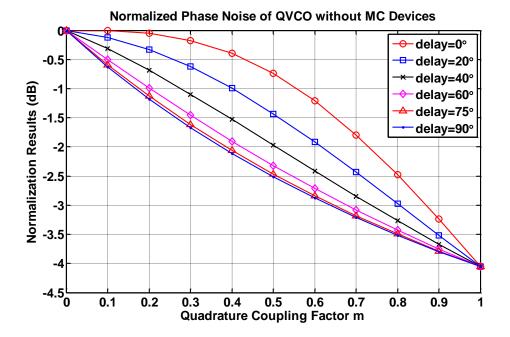

## 2.2.4 Optimization of Capacitive Coupling

In this section, the optimization of capacitive coupling strength factor m as defined in Equation (2.1) is discussed. The phase noise improvement of CC-QVCO compared with its SVCO counterpart depends on the coupling-strength factor m. On the other hand, the coupling strength should be as large as possible to reduce the phase error. Thus, the selection of m is a trade-off between noise improvement and phase error. Regardless of the trade-off, the proposed CC-QVCO is advantageous over conventional QVCO structure for the following two reasons: (i) it completely eliminates the noise sources associated with the transistors used for quadrature coupling; (ii) it provides phase noise improvement beyond 3-dB theoretical prediction; especially the flicker noise can be

further improved further because of the reduced ISF<sub>eff</sub>.

Fig. 2.11 Simulation results of phase noise improvement and phase error for different coupling strength factor m with  $C_{tankq}=1.01C_{tanki}$ .

Shown in Fig. 2.11 are the simulated phase noise improvement and the phase errors for different coupling strength factor m. The simulation for both the phase noise and the phase error is based on the assumption of 1% mismatch for the LC tank. It can be seen that the phase noise improvement is relatively constant around 3.5 dB @ 1-MHz offset when m is between 0.3 and 0.5. The phase noise improvement for lower offsets reaches their peaks when m is around 0.25. The phase noise improvement gradually disappears as m approaches 1. When m is equal to 0, i.e. quadrature coupling disappears, the two VCO cores become independent to each other and hence fail to produce quadrature outputs. With the mismatch included in the LC tank, the noise improvement has dropped to 0 when m becomes 0.1 instead of 0. Given the 1% tank mismatch, the two VCO cores are relatively independent from each other and cannot produce quadrature outputs when m is

smaller than 0.1. On the other hand, the phase error increase rapidly as m approaches 0. Therefore, there is an optimum point of m to achieve the best phase noise improvement with acceptable phase error. Furthermore, the VCO design cares more about the out-of-band noise at large offset frequency since the close-in noise can be filtered by the phase-locked-loop (PLL). Considering all the factors described above, the coupling strength factor of 0.4 is chosen to implement the proposed CC-QVCO.

Fig. 2.12 (a) Linear model of quadrature oscillator; and (b) equivalent model of individual VCO with coupling effects.

#### 2.2.5 Intrinsic Phase Shift to Avoid Phase Ambiguity

This section starts with an introduction to the linear QVCO model followed by derivations for the intrinsic phase shift of the proposed CC-QVCO.

To generate quadrature outputs, two stand-alone, nominally identical VCO cores have to be coupled with each other with active devices or passive components. However, the oscillation frequency of a QVCO will depart from the resonance frequency of individual VCO cores because of the coupling mechanisms. The behavior of the two VCO cores including coupling effects can be modeled by a simplified linear model [8] [17] [19], as shown in Fig. 2.12 (a), where  $G_m(s)$  provides a negative resistance compensating the energy loss due to the equivalent resistance R of a LC tank, and  $G_c(s)$  represents the transconductance of the coupling mechanism between the two VCO cores.

Fig. 2.12 (b) presents the equivalent model for each VCO with quadrature-coupling mechanism. Since one VCO core may lead or lag the other VCO core by 90 °phase,  $\pm j$  is introduced to the coupling transconductance. For a conventional QVCO with parallel coupling transistors [13], the frequency deviation can be found with steady state analysis as

$$\Delta \omega = \omega_0 \pm \frac{G_c(j\omega_0)}{2C} \tag{2.15}$$

where the positive or negative sign depends on whether the iVCO leads or lags the qVCO by 90°;  $\omega_0$  is the resonance frequency of individual LC tank; C is the capacitor of the LC tank; and G<sub>c</sub> is the equivalent transconductance of the quadrature-coupling mechanism between the two VCO cores. From Equation (2.15), it is obvious that the larger the G<sub>c</sub> is, the larger the frequency deviation from  $\omega_0$  becomes, which worsens the quality factor of the LC tank. It is desirable to decrease the coupling strength to improve the phase noise performance. The trade-off between the phase noise and phase error calls for a solution that can maintain the phase noise performance without sacrificing the phase error.

Another commonly seen problem for a QVCO design is the phase ambiguity, i.e., the phase relations between the QVCO outputs could be either +90 °or -90 °. It is essential to provide 90 °quadrature phase signals with deterministic phase relationship since a receiver or transmitter which has been hard-wired to the QVCO outputs cannot distinguish complex signals if the output phases are ambiguous, i.e. the wanted sideband might be suppressed and instead the image signal might be detected after the image rejection receiver. Although the asymmetry between two VCO cores can help the QVCO to operate in one of the two stable modes, the bimodal oscillation can still exist due to PVT variations. Usually, a phase shifter could be introduced in the quadrature-coupling path to allow only one deterministic stable quadrature outputs, either +90 ° or -90 °[16]-[20]. To allow only one modal oscillation, the phase shift can be introduced by using cascode transistor [16]. From theoretical point of view, 90 °phase shift in the coupling path achieves not only the minimum phase noise performance, but also the best tolerance to component mismatches between the two VCO cores [18], [19]. However, those coupling mechanism with phase shifter still deteriorate the phase noise performance because of the extra noise from the coupling transistors.

The noise degradation and phase ambiguity between the two VCO cores can be solved simultaneously with the proposed Colpitts CC-QVCO. The CC-QVCO has an intrinsic phase shift in the quadrature-coupling path and it can avoid the problem associated with the bimodal oscillation. To illustrate this effect, a linear model similar to the one shown in Fig. 2.12 (a) needs to be developed. Unlike a conventional QVCO with parallel coupling, the proposed CC-QVCO is based on Colpitts VCO structure and the quadrature-coupling transconductance  $G_c(s)$  is not intuitive.

According to the linear model of Fig. 2.12 (a), the  $G_c(s)$  can be found by grounding node B and applying a voltage source  $\Delta V$  at node A. The  $G_c(s)$  can be defined as the ratio

of the current  $I_2$  flowing into ground to the voltage source applied at node A. Similar method can be used to find the quadrature- coupling transconductance for the CC-QVCO. Fig. 2.13 (a) shows the circuit schematic used to analyze the quadrature -coupling transconductance, where DC bias circuitry and LC tanks are not shown as they do not affect the analysis.

Fig. 2.13 (a) CC-QVCO circuit for the derivation of Gc(s); and (b) simplified half-circuit model for the derivation of Gc(s). The DC bias and varactors (included in C2) are not shown in the figure and the ground symbols represent ac ground.

(b)

The coupling path from qVCO to iVCO has been disconnected and the loading effect resulted from capacitor  $C_{cc}$  and  $C_{qc}$  is model by impedance  $Z_{b1}$  expressed as

$$Z_{b1} = \frac{1 + sR_b(C_{cc} + C_{qc})}{sC_{qc}(1 + sR_bC_{cc})}$$

(2.16)

In order to find the transconductance, the outputs of the second VCO are grounded and a differential voltage is applied to the iVCO as shown in Fig. 2.13 (a). The  $G_c(s)$  can be found with the following expression:

$$G_{c}(s) = \frac{\Delta I_{C}}{\Delta V} = \frac{I_{C+} - I_{C-}}{\Delta V_{+} - \Delta V_{-}}$$

(2.17)

The circuit in Fig. 2.13 (a) is differential, and it can be simplified to half circuit as shown in Fig. 2.13 (b). The following two equations are defined to simplify the derivations: