# Power-Aware System-on-Chip Test Optimization through Frequency and Voltage Scaling

by

Vijay Sheshadri

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama May 4, 2014

Keywords: System-on-Chip, Test Schedule Optimization, Voltage and Frequency Scaling, Session-Based Test Schedule, Sessionless Test Schedule

Copyright 2014 by Vijay Sheshadri

Approved by

Prathima Agrawal, Samuel Ginn Distinguished Professor of Electrical and Computer Engineering Vishwani D. Agrawal, James J. Danaher Professor of Electrical and Computer Engineering Adit Singh, James B. Davis Professor of Electrical and Computer Engineering

#### Abstract

A System-on-Chip (SoC) is a complete system that has been integrated onto a single chip. An SoC is often designed by embedding reusable blocks called cores. With shrinking device sizes, SoC cores are growing in number and complexity, which has led to high volumes of test data and resulted in long test times. Therefore, reducing test cost by minimizing the overall test time is one of the main goals of System-on-Chip (SoC) testing. Power dissipation during test mode is often much higher than that of functional mode and hence, test power management is also a major concern in SoC testing. To efficiently manage test resources and power dissipation, tests for the SoC cores are arranged into test schedules. Within these test schedules, the core tests may (as in the case of session-based test schedule) or may not (as in the case of sessionless test schedule) be grouped into test sessions. Traditional SoC test methods assume a constant test frequency and supply voltage ( $V_{DD}$ ) for the entire test schedule. However, test time and test power can be regulated by  $V_{DD}$  and test clock frequency to optimize SoC test schedules for a given power budget.

The research presented in this dissertation focuses on power-aware optimization of SoC test schedules to minimize test time by scaling the supply voltage and test clock rate. This scaling can be session wise (in the case of a session-based test schedule) or dynamic (in case of sessionless test schedule). SoC testing can be sped up by increasing the test clock rate. However, test clock is constrained by the rated power limit (power constraint) and the critical path delay (structure constraint) of the SoC cores. These constraints can be manipulated using  $V_{DD}$ . Therefore, by scaling  $V_{DD}$  and clock rate, an optimal test time and schedule can be obtained for an SoC.

For the session-based test scheduling, the optimization problem is mathematically formulated and solved through Integer Linear Program (ILP) based methods to provide optimal solutions. For SoCs with large number of cores, Integer Linear Programs are NP-hard and, in general, computationally expensive. To overcome this difficulty, a simulated annealing based heuristic method capable of providing near-optimal solutions is developed. Results show that the overall SoC test time can be considerably shortened by scaling the test clock and supply voltage. A similar heuristic method that is based on simulated annealing algorithm, is developed for the optimization of sessionless test schedules. The heuristic approach is capable of both preemptive (tests can be halted and resumed at will) and non-preemptive scheduling (tests cannot be interrupted at any time). Here also, the optimization results show a significant test time reduction over conventional reference test schedules where  $V_{DD}$ and clock are fixed at given nominal values.

# Acknowledgments

There are many people to whom I would like to express my gratitude for their help during the pursuit of my doctoral dreams. Foremost among them are Professors Prathima Agrawal and Vishwani D. Agrawal, without whose constant support and guidance this dissertation would not have been possible.

I would like to thank Dr. Adit Singh, for serving as a member of my advisory committee, and Dr. Sanjeev Baskiyar, the external reader for this dissertation. I am also thankful to Dr. Victor Nelson, for teaching me the various VLSI-CAD tools through his course 'CAD for VLSI'. Thanks are in order, as well, for Dr. Alice Smith and Dr. Chase Murray from the Dept. of Industrial Engineering. I have immensely benefited from their courses on Adaptive Optimization and Linear Programming. I would also like to acknowledge the support of Ms. Shelia Collis and the Wireless Engineering Research and Education Center (WEREC), Ms. Jo Ann Loden, Ms. Penny Christopher and Ms. Carol Lovvorn in helping me keep my school and immigration paper work in order.

My heartfelt thanks go out to my colleagues in Broun Hall, in particular, Dr. Pratap Prasad, Dr. Santosh Kulkarni, Dr. Suraj Sindia, Praveen Venkataramani, Gopalkrishna Iyer and Muralidharan. I owe much gratitude to all my friends, especially to the Auburn Kannada Koota gang.

Above all, I would like to express my deepest gratitude to my caring parents and my loving wife for their constant love compassion and support.

Finally, I must acknowledge that the research presented in this dissertation, is supported in part by the National Science Foundation Grants CCF-1116213, IIP-0738088 and IIP-1266036.

# Table of Contents

| Abstract                                                   | ii  |

|------------------------------------------------------------|-----|

| Acknowledgments                                            | iv  |

| List of Figures                                            | vii |

| List of Tables                                             | ix  |

| 1 Introduction                                             | 1   |

| 1.1 Problem Statement                                      | 2   |

| 1.2 Organization of Dissertation                           | 3   |

| 2 Background and Prior Work on SoC Testing                 | 4   |

| 2.1 Test Infrastructure                                    | 5   |

| 2.1.1 Core Test Wrapper                                    | 6   |

| 2.1.2 Test Access Mechanism (TAM)                          | 7   |

| 2.2 Test Scheduling                                        | 7   |

| 2.3 Power Constrained Testing                              | 9   |

| 2.4 Frequency and Voltage Scaling                          | 10  |

| 3 Optimization of Session-Based Test Schedules             | 12  |

| 3.1 Background                                             | 12  |

| 3.2 Mixed-Integer Linear Program (MILP) Based Optimization | 18  |

| 3.2.1 Introduction                                         | 18  |

| 3.2.2 MILP Formulation                                     | 19  |

| 3.3 Heuristic Based Optimization                           | 21  |

| 3.3.1 Simulated Annealing (SA)                             | 21  |

| 3.4 Results                                                | 25  |

| 3.4.1 Experimental Setup                                   | 25  |

|    |        | 3.4.2    | MILP Results                      | 27 |

|----|--------|----------|-----------------------------------|----|

|    |        | 3.4.3    | Heuristic Algorithm Results       | 30 |

|    |        | 3.4.4    | Lower Bounds on SoC Test Time     | 31 |

|    |        | 3.4.5    | SoC Power Budget                  | 33 |

|    |        | 3.4.6    | Multiple Supply Voltages          | 35 |

| 4  | Op     | otimizat | ion of Sessionless Test Schedules | 36 |

|    | 4.1    | Heuris   | tic Approach to Optimization      | 36 |

|    | 4.2    | Optim    | ization Results                   | 38 |

|    |        | 4.2.1    | Lower Bound on SoC Test Time      | 42 |

|    |        | 4.2.2    | SoC Power Budget                  | 43 |

|    |        | 4.2.3    | Multiple Supply Voltages          | 44 |

|    | 4.3    | Compa    | arison With Session-Based Testing | 45 |

| 5  | Со     | onclusio | n and Future Work                 | 50 |

|    | 5.1    | Future   | Work                              | 53 |

| Bi | bliogr | aphy     |                                   | 54 |

| Ap | opend  | ix: SoC  | Test Benchmarks                   | 59 |

# List of Figures

| 2.1 | A simple test set-up showing the SoC under test, the test source and sink. The         |        |

|-----|----------------------------------------------------------------------------------------|--------|

|     | test data from the test source to different cores and from the cores to the test       |        |

|     | sink, is carried over the test bus.                                                    | 4      |

| 2.2 | SoC Test scheduling modeled as 3D optimization problem                                 | 5      |

| 2.3 | Overview of IEEE1500 wrapper [40]. (WBR = wrapper boundary register; WBY               |        |

|     | = wrapper by<br>pass; WP(I/O) = wrapper parallel (input/output); WS(I/O) =             |        |

|     | wrapper serial (input/output); WIR = wrapper instruction register.) $\ldots$ .         | 6      |

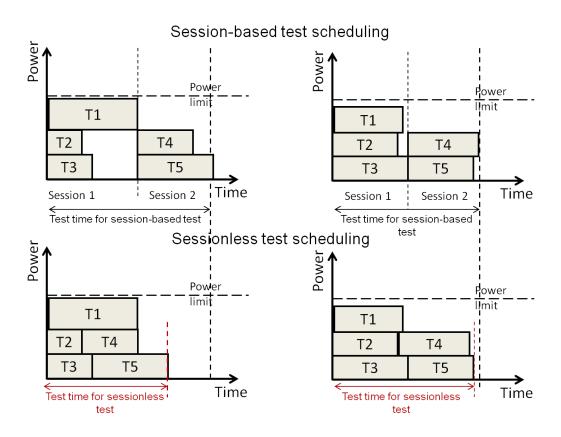

| 2.4 | Two test scheduling strategies, session-based (non-partitioned) and sessionless(partit | ioned) |

|     | are illustrated. Sessionless testing can be non-preemptive (b) or preemptive (c)       |        |

|     | [33, 35]                                                                               | 8      |

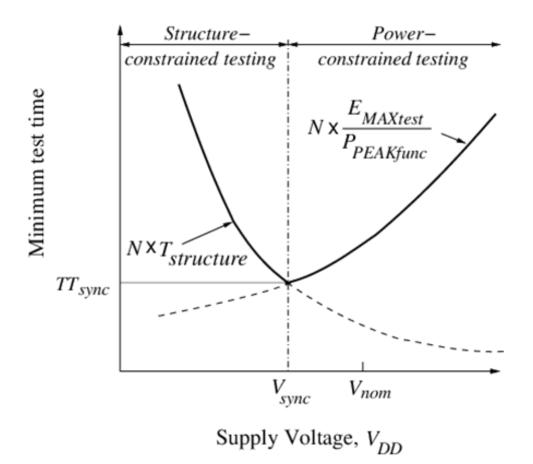

| 2.5 | Test time as a function of $V_{DD}$ [65]. The nominal and the optimal $V_{DD}$ are     |        |

|     | denoted by $V_{nom}$ and $V_{sync}$ , respectively                                     | 11     |

| 3.1 | Overview of the SA heuristic algorithm.                                                | 22     |

| 3.2 | Generating the initial solution for the SA algorithm.                                  | 23     |

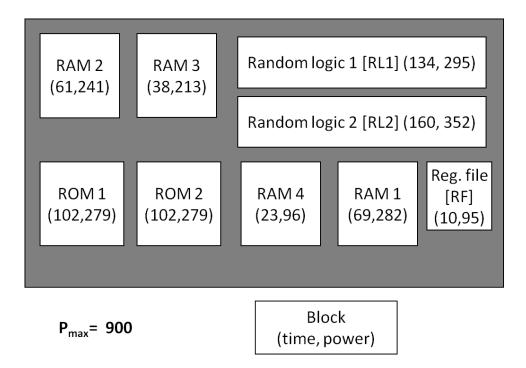

| 3.3 | Components of ASIC Z and their test time (in arbitrary units) and test power           |        |

|     | (in mW)                                                                                | 25     |

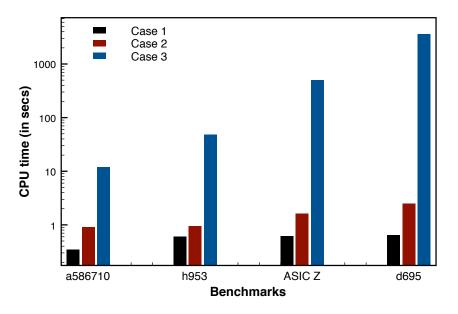

| 3.4 | CPU time (in seconds) of the MILP optimization method for the ITC benchmarks.          | 30     |

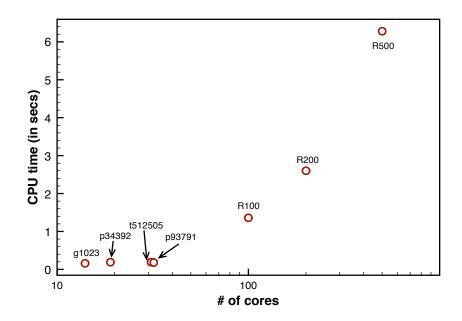

| 3.5 | CPU time (in seconds) of the heuristic optimization method for the SoC bench-              |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | marks                                                                                      | 32 |

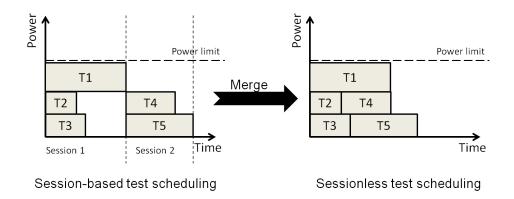

| 4.1 | 'Merging' test sessions to convert a session based test schedule into a sessionless        |    |

|     | test schedule.                                                                             | 37 |

| 4.2 | The 'Merge' function erases the session boundaries in a session based test schedule        |    |

|     | and combines the tests together to form a sessionless test schedule. $\ldots$ . $\ldots$ . | 38 |

| 4.3 | Best-fit decreasing (BFD) algorithm for sessionless test scheduling. Test schedules        |    |

|     | obtained from this algorithm are used as reference cases in this paper where               |    |

|     | voltage and frequency are fixed at their nominal values for the entire schedule            | 39 |

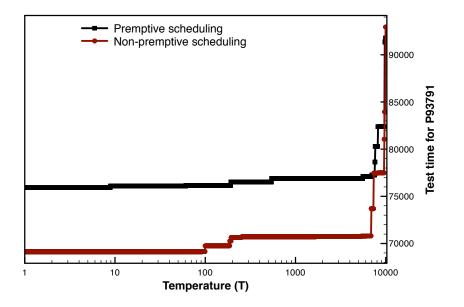

| 4.4 | Convergence of the SA based optimization algorithm. The plot shows the heuris-             |    |

|     | tic algorithm converging towards the optimum test time as the temperature pa-              |    |

|     | rameter $(T)$ reduces                                                                      | 40 |

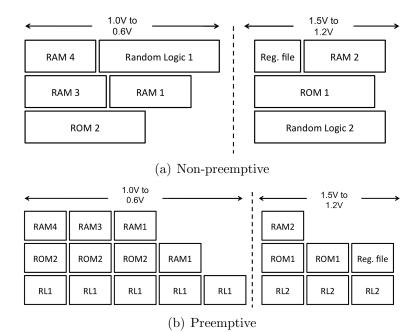

| 4.5 | Optimized sessionless test schedules for ASIC Z, under non-overlapping voltage             |    |

|     | range condition, for both (a) non-preemptive and (b) preemptive cases. (Note:              |    |

|     | Diagram not to scale.)                                                                     | 45 |

| 4.6 | Comparing session-based and sessionless test schedules                                     | 47 |

# List of Tables

| 3.1  | Test Data set for ASIC Z at nominal supply voltage $(1.0V)$                                                                                                   | 26 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Optimized Test Schedule for ASIC Z for nominal and custom clock rate (Cases 1 and 2). The supply voltage is at nominal value for both cases                   | 28 |

| 3.3  | Test times (in arbitrary units) of ASIC Z system for custom $V_{DD}$ and clock rate (Case 3).                                                                 | 29 |

| 3.4  | Test times (in arbitrary units) for benchmark SoCs, obtained by MILP optimiza-<br>tion method for the three optimization cases considered.                    | 29 |

| 3.5  | Test times (in arbitrary units) for MILP and heuristic test scheduling methods, with customized $V_{DD}$ and clock rates.                                     | 30 |

| 3.6  | Test times (in arbitrary units) for benchmark SoCs, obtained by the heuristic optimization method for the three optimization cases considered.                | 31 |

| 3.7  | Optimal test times (in arbitrary units) for nominal and custom clock rate (Cases 1 and 2) compared with the lower bound on test time at nominal $V_{DD}$      | 33 |

| 3.8  | Optimal test times (in arbitrary units) for custom $V_{DD}$ and clock frequency (Optimization Case 3) compared with the lower bound on test time at $V_{min}$ | 34 |

| 3.9  | Optimized test times (in arbitrary units) for ASIC Z, for various power budget values                                                                         | 34 |

| 3.10 | Test times (in arbitrary units) and optimal voltages of ASIC Z system, for dual voltage ranges.                                                               | 35 |

| 4.1  | Test times (in arbitrary units) for sessionless test scheduling with voltage and frequency scaling.                                                           | 41 |

| 4.2  | CPU times <sup>*</sup> for all the benchmarks SoCs for the heuristic optimization algorithm.                                                                  | 42 |

| 4.3  | Test times (in arbitrary units) for sessionless test scheduling with voltage and frequency scaling.                                                           | 43 |

| 4.4  | Sessionless test schedule optimization for ASIC Z, subject to various power budget values.                                                                    | 44 |

| 4.5 | Comparing test time results for session-based and sessionless test schedule opti-<br>mization.                   | 46 |

|-----|------------------------------------------------------------------------------------------------------------------|----|

| 4.6 | Comparison of CPU times between session-based and sessionless testing, for the heuristic optimization algorithm. | 48 |

| 1   | Overview of the benchmarks used in this dissertation                                                             | 60 |

# Chapter 1

## Introduction

Technological developments have made it possible to integrate an entire system onto a single chip. Termed as 'System-On-Chip' (or SoC for short), these devices have core based architecture where each core is often a reusable logic or memory block. Owing to their modularity, small area, high performance and low power consumption, SoC devices are becoming increasingly popular. In recent times, SoCs are extensively used in networking and communication applications. Emerging cellular and wireless technologies, such as WiMAX and LTE require high data rates, low latency at very low power budgets. SoCs are well suited for such requirements as they offer low power, programmable and cost-effective hardware solutions. SoCs are the driving force behind modern-day smart phones and tablets, and can also be found in other wireless applications such as radios, wireless access points, Bluetooth, etc.

The number of cores being embedded in SoC devices is increasing due to device size miniaturization. The resulting complexity and increase in the number of fault-sites has complicated testing of SoCs. Consequentially, the test data volume also grows in proportion to the number of cores in the SoC, since each core is associated with one or more tests, leading to longer test times. Thus, test time minimization has become a major challenge in the field of SoC testing. While testing multiple cores simultaneously can reduce the test time significantly, such concurrent execution is limited by excessive power dissipation due to increased switching activity. The power dissipation of a circuit during test mode is often higher than functional mode. Elevated power levels and heat dissipation by neighbouring cores can lead to the formation of thermal hotspots and undesirable power droops. Thermal hotspots may eventually cause irreversible damages to the chip whereas power droops induce clock stretching which may lead to a good chip incorrectly failing a timing test [18]. Therefore, power-aware test strategies are needed for efficient test power management.

#### 1.1 Problem Statement

The complexity of SoC testing is mitigated to an extent by adopting modular testing, which is equivalent to a "divide-and-conquer" approach. In modular testing, block-level tests can be applied to individual blocks (cores) of the SoC, such that these blocks can be tested almost independent of one another. As discussed earlier, concurrent testing of cores presents a trade-off between test time and test power. Hence, an optimal arrangement of core tests can be formed so as to yield a minimal test time while maintaining the test power under a safe limit. Such an arrangement is termed as SoC test schedule (discussed in detail in the next chapter).

The general SoC test scheduling problem can be stated as: Given an SoC with N cores, where each core may be associated with one or more tests, and a test power budget, find a test schedule (concurrency and sequence of test application) to:

- a. Test all cores.

- b. Reduce the overall test time.

- c. Conform to the SoC test power budget.

The contribution of this work is a power-aware test scheme that optimizes the overall test time of an SoC by exploiting the influence of  $V_{DD}$  and clock over test power and test time of individual cores. In this work, both exact and heuristic approaches for test optimization are provided; while the exact method provides the most optimal result, the heuristic method achieves near-optimal results but addresses the problem of scalability.

## 1.2 Organization of Dissertation

The rest of this dissertation is organized as follows: Chapter 2 discusses the basics of SoC testing methodologies and summarizes the previous work in this field. Optimization techniques for SoC test schedules are presented in Chapters 3 and 4. Chapter 5 concludes the research work presented in this dissertation. The details of the SoC benchmarks, used in this research work, are provided in the appendix.

#### Chapter 2

## Background and Prior Work on SoC Testing

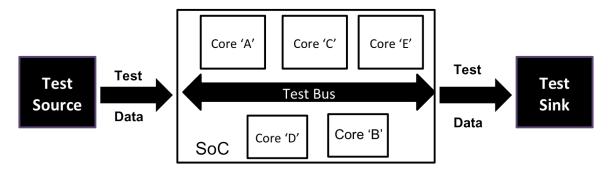

As mentioned previously, in SoC testing, the modularity of an SoC is exploited by treating each core as a testable unit. A simple test set-up for an SoC is shown in Figure 2.1. The test source stores and provides the test stimuli for all the cores. The test bus relays the stimuli to the corresponding core and the test response of the cores to test sink. The test sink stores all responses which are then compared to the response of a fault-free version of the device to identify the faults.

Figure 2.1: A simple test set-up showing the SoC under test, the test source and sink. The test data from the test source to different cores and from the cores to the test sink, is carried over the test bus.

It is easily seen that as the number of cores increases, the overall test time of the SoC also increases. While concurrent testing of cores may cut down the overall test time, there may be other factors influencing it. For instance, there may be some test resources, such as test bus, external pins of the SoC, etc., that may be commonly shared among cores. This may lead to a conflict when such cores are tested simultaneously. Test power may also limit concurrent testing of cores.

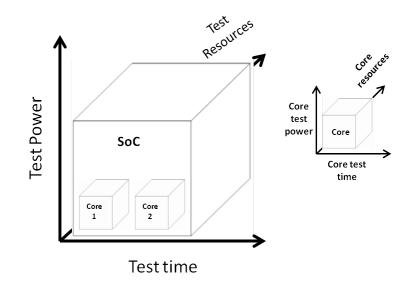

The SoC testing problem can be modeled as a 3-dimensional optimization problem, where the SoCs power limit, test time and resources (such as pin count, etc.) form the three

Figure 2.2: SoC Test scheduling modeled as 3D optimization problem.

axes. The power limit is fixed for the SoC and the resources have a limited availability. The objective of the 3-D optimization would be to minimize the test time by effective allocation of resources such that the power limit is not exceeded. This optimization problem has been modeled as a 3-D bin packing problem [24] as shown in Figure 2.2. Each core in the SoC can be modeled as a cuboid, where the core's test power, test time and test resources, such as BIST resources, wrapper width, etc., constitute the three dimensions. The idea here is to place the cores in the cuboid representing the SoC in such a way that the test time is minimized while satisfying the power and resource constraints. This bin packing problem differs from the general bin packing problem in that if two cores are tested simultaneously, they overlap only on the time axis and not on the other two axes.

# 2.1 Test Infrastructure

The test infrastructure of SoC consists of a wrapper and a test access mechanism (TAM) [7].

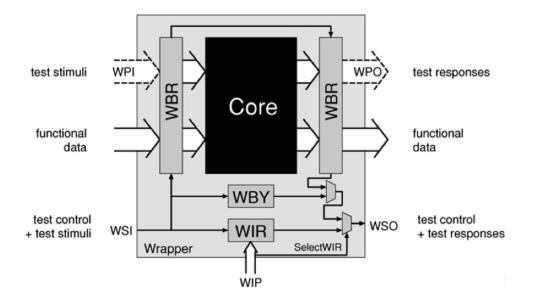

Figure 2.3: Overview of IEEE1500 wrapper [40]. (WBR = wrapper boundary register; WBY = wrapper bypass; WP(I/O) = wrapper parallel (input/output); WS(I/O) = wrapper serial (input/output); WIR = wrapper instruction register.)

# 2.1.1 Core Test Wrapper

The test wrapper aides in the access and isolation of embedded cores. It acts as an interface between the core and the on-chip structure for test data transportation (TAM). The IEEE 1500 standard for embedded cores defines a standardized, scalable and configurable core wrapper for both logic and memory cores [1]. This wrapper consists of scan and control registers, data and control signals and instruction set. The IEEE 1500 wrapper architecture is shown in Figure 2.3. The boundary registers (WBR) form the wrapper chains which interface the TAM with the internal scan chains through the parallel pins (WPI/WPO). The instruction register (WIR) provides the necessary control information.

The wrapper may also perform serial-parallel or parallel-serial conversion to provide width adaptation in case of a mismatch between the available TAM width and the core input/output terminals. Wrapper configuration can be optimized for effective utilization of test bandwidth [20, 21, 31, 35, 39, 47, 48].

#### 2.1.2 Test Access Mechanism (TAM)

TAM is the infrastructure responsible for transporting the test data between SoC external pins and embedded cores. The TAM can be dedicated solely for test purposes or can be an existing on-chip bus structure. TAM design involves trade-offs between the transport capacity of the mechanism and the test application cost incurred in terms of test time, area overhead, etc.

Multiple TAM architectures have been proposed in the past. Aerts and Marinissen introduce [5]:

- A multiplexing architecture, where the entire TAM width is allocated to each core and the cores are tested sequentially,

- A distributed architecture, where a fixed TAM width is assigned to each core,

- A daisy chain architecture, where all the TAM width is assigned to every core but a bypass structure is added to shorten the access path for the cores.

More recently, a flexible TAM architecture has been proposed, where the TAM assignment to the cores is flexible; hence the TAM varies dynamically after each core test [26, 27, 71].

Previously published work formulates the test time as a function of TAM width and optimizes TAM allocation among cores, to achieve test time minimization. It has been shown [27] that the relation between the test time and TAM width is that of a 'staircase' function, meaning that the test time will only reduce after the TAM assignment to a core exceeds a certain core threshold value. Some of the published references on TAM optimization are [25–27, 34, 48, 71].

# 2.2 Test Scheduling

As mentioned earlier, a test schedule is an ordered arrangement of core tests often optimized for lowering test time and/or test power. A simple test schedule can be sequential

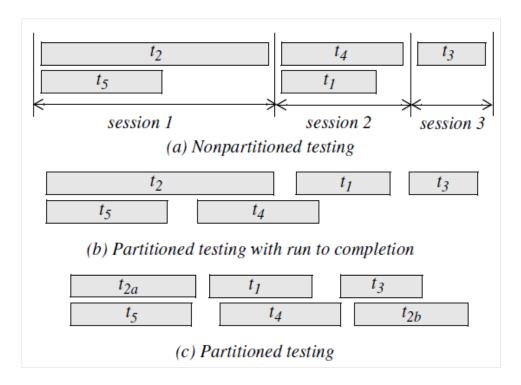

Figure 2.4: Two test scheduling strategies, session-based (non-partitioned) and session-less(partitioned) are illustrated. Sessionless testing can be non-preemptive (b) or preemptive (c) [33,35].

or concurrent. In sequential scheduling, only one core is tested at a time. As a result, the overall test time is simply the sum of all individual core test times. While this is the simplest scheme to implement, the overall test time is longest. Concurrent scheduling, on the other hand, makes use of concurrency by simultaneously testing multiple cores. Existing concurrent scheduling strategies may be broadly categorized into:

- Session-based (non-partitioned) test scheduling, where no new test is allowed to start until all tests of a previous session are completed. A test session refers of a set of tests initiated simultaneously and run concurrently [13,14,35,55,56,73]. See the illustration in Figure 2.4(a).

- Sessionless (partitioned) test scheduling, where test session boundaries are ignored and a test may be scheduled to start as soon as possible [23,44,54,57,58,74]. The sessionless or partitioned test scheduling can be further divided into preemptive and non preemptive scheduling. In the preemptive strategy, tests can be interrupted or restarted at

any time [25,34]. The non preemptive strategy does not allow such interruptions, i.e., a test once initiated must be completed. Figures 2.4(b) and (c) illustrate non-preemptive and preemptive schedules, respectively.

#### 2.3 Power Constrained Testing

To be used during test mode, the test vectors are so designed as to maximize switching activity in the circuit, in order to detect more faults per vector and hence minimize the test time. Therefore, test power can be up to four times the functional power [68]. To guarantee that this increased power dissipation will not cause heat induced failures in the device, a peak power budget for the entire SoC is defined. Power constrained test scheduling focuses on optimizing the overall test time of the SoC for a given power budget.

Many power-constrained testing strategies have been studied in the past [13, 14, 18, 25, 34, 53, 55, 56, 71]. The concept of fixing a single power budget for the SoC is known as the global peak power model and has been widely used. However, this model is regarded as a pessimistic approach since the single power limit value is based on the peak power consumption of the circuit and the circuit's power consumption may not often reach peak power. Samii *et al.* proposed a cycle-accurate power model where there is a power value for every clock cycle [52]. While this model is more accurate than the global peak power model, it is more complex and computationally expensive. Alternatively, Larsson [32] proposed a power grid model aimed at countering local hot spots. This model allocates cores to a set of power grids. During test scheduling, cores are selected such that not only the global peak power limit, but also the grid's power limit is not exceeded.

In the research presented in this dissertation, we adopt a global peak power model where the power consumption during simultaneous execution of multiple tests is given by the sum of their peak powers, and this value must not exceed the peak power budget of the SoC at any given time. The additive model for estimating power consumption was introduced by Chou *et al.* [13,14]. In this model, the test power consumption of a block is approximated to a single value corresponding to the peak power consumption over the test time of the block.

#### 2.4 Frequency and Voltage Scaling

The idea of scaling voltage and frequency has been prevalent in the field of microprocessors and SoCs. In [60], a locally placed configurable dynamic voltage and frequency scaling (DVFS) controller enables a large number of on-chip processors to switch  $V_{DD}$  by selecting from two power grids and also independently controls their clock rates, in order to improve the energy efficiency of the multi-processor SoC (MPSoC). Voltage and frequency scaling techniques have also been employed in testing of SoCs.

Recently, multi-frequency SoC testing has been investigated. Sehgal *et al.* [53] have focused on the use of a multi-channel ATE capable of providing multiple frequencies. Zhao *et al.* [70] discuss test optimization through wrapper design in order to perform bandwidth matching between the ATE's clock input and the core's frequency. The PMScan system, introduced by Devanathan *et al.* [16], utilizes an adaptive supply voltage regulation scheme that lowers the  $V_{DD}$  to balance the power dissipation and the frequency during the shift operation, while satisfying the timing requirements. Scheduling with multiple voltage islands and testing of cores at multiple voltages has also been considered [29]. These authors schedule core tests at multiple voltage levels and clock domains and reduce the clock frequency during low voltage testing to enable a time division multiplexing scheme for concurrent testing of cores.

Venkataramani *et al.* [62–66] discuss two aspects of testing, namely, power constrained testing where the test clock speed is limited by the circuit's rated power and structure constrained testing where the test clock speed is limited by the critical path or other timing constraints of the circuit. The supply voltage is used for the purpose of balancing these two constraints to allow higher test clock rates in order to achieve test time reduction. Since test power is two to four times higher than the functional power, test clock is often power constrained, i.e., any increase in the clock would cause the power to exceed the device's rated

Figure 2.5: Test time as a function of  $V_{DD}$  [65]. The nominal and the optimal  $V_{DD}$  are denoted by  $V_{nom}$  and  $V_{sync}$ , respectively.

maximum. The power consumption can be reduced by lowering the operating voltage. As a result, the clock rate can be increased without exceeding the power constraint of the core. However, reducing the voltage causes the delay of a circuit to increase, hence, elongating the critical path of the device. Thus, as we reduce  $V_{DD}$ , on one hand, the lowered power consumption allows higher clock rates thereby shrinking the test time but, on the other hand, the increased circuit delay requires slower clock rate and a longer test time. As Figure 2.5 [62, 64, 65] shows there exists an optimal point where the two constraints are satisfied and at the same time test time is significantly reduced. Experiments on ISCAS benchmark circuits by those authors show test time reductions of up to 62% at optimal values of  $V_{DD}$  [63].

# Chapter 3

#### Optimization of Session-Based Test Schedules

#### 3.1 Background

Objectives of SoC testing, as outlined previously, are to test all cores of the SoC while managing the power dissipation so as to avoid thermal stress. Consider an SoC with n cores  $C_1, \dots, C_n$ , where each core  $C_i$  is associated with a test  $t_i$ , and a peak power budget. The power budget for an SoC,  $P_{max}$ , is defined as the maximum allowable power dissipation during the testing of SoC. The power budget is chosen so as to account for power droops and thermal hotspots that may occur due to peak activity during testing. Let there be n cores,  $C_1, \dots, C_n$  in an SoC and let the test corresponding to a core  $C_i$  be  $t_i$ , where  $i \in 1, 2, \dots, n$ . Each test is associated with test time and test power, which have been characterized at nominal operating conditions (nominal voltage and clock rate). Let  $T_{t_i}$  and  $P_{t_i}$  be the time and power of the test  $t_i$ . Let tests,  $t_1, \dots, t_n$ , be distributed among k sessions,  $S_1, \dots,$  $S_k$  such that each session,  $S_j$  contains one or more tests. The test time of a session  $S_j$ , given by  $T_{S_j} = \max(T_{t_i} | \forall t_i \in S_j)$  and the power dissipated during session,  $S_j$  is given by  $P_{S_j} = \sum(P_{t_i}), \forall t_i \in S_j$ .

The general test scheduling problem can be expressed as an optimization problem: *Objective:*

Minimize

$$\sum_{j=1}^{k} T_{S_j} \cdot x_j$$

where

$$x_j = \begin{cases} 1, & \text{if } S_j \text{ is scheduled} \\ 0, & \text{otherwise} \end{cases}$$

#### Subject to:

- 1) Power constraint:  $P_{S_j} \cdot x_j \leq P_{max}$ ,  $P_{max}$  being the power budget for the SoC.

- 2) Test completeness constraint: each test,  $t_i, i \in \{1, 2, \dots, n\}$  is executed at least once.

The test time and test power can, however, be influenced by the test clock. A faster clock reduces the test time but increases the power consumption. Lowering the clock frequency, on the other hand, reduces the test power but leads to longer test time. Thus, there exists a trade-off between the test time and test power. However, the energy spent during testing remains constant. Energy spent per core test,  $E_{t_i} = P_{t_i} \times T_{t_i}$ . The total energy spent during the testing of the entire SoC can then be expressed as,  $E_{total} = \sum_{i=1}^{n} P_{t_i} \times T_{t_i}$ . In [62, 64, 65], the authors have proved that a lower bound on the total test time is given by the ratio of the total energy spent during the test and the power budget,

$$TT_{LB1} = \frac{E_{total}}{P_{max}} = \frac{\sum_{i=1}^{n} P_{t_i} \times T_{t_i}}{P_{max}} = \sum_{i=1}^{n} \frac{P_{t_i}}{P_{max}} T_{t_i},$$

(3.1)

where  $TT_{LB1}$  is the lower bound on SoC test time.

Let  $\frac{P_{max}}{P_{t_i}} = F_{t_i}$ , where  $F_{t_i}$  is the scaling factor by which the clock frequency of a test  $t_i$  is varied with respect to the nominal value. This scaling factor shall be referred to as *frequency* factor for the remainder of this work. Hence, the total test time of an SoC is lowest when each core test is scheduled sequentially at a clock rate equal to  $\frac{P_{max}}{P_{t_i}} f_{nom}$ .

**Theorem 3.1** Concurrent scheduling of core tests at a test clock rate  $\frac{P_{max}}{P_{t_i}} f_{nom}$ , cannot improve the lower bound on the total test time of the SoC, obtained by the sequential test schedule at the same clock rate.

Proof: Let there be n tests,  $t_1, \dots, t_n$ . Let  $T_{t_i}$  and  $P_{t_i}$  be the test,  $t_i$ 's test time and power dissipated, respectively. Let  $P_{max}$  be the power budget.

Case 1: Sequential test scheduling (One test scheduled per session).

Let each session  $S_i$  contain a single test,  $t_i$ . This implies that the session's test time and power are the same as that of the test, i.e.,  $T_{S_i} = T_{t_i} = T_i$  and  $P_{S_i} = P_{t_i} = P_i$ . Now, if the clock frequency is altered, for speeding up the testing, the frequency factor,  $F_i = P_{max}/P_i$ . The modified session test time, now, is  $T_i/F_i$  or,  $T_i.P_i/P_{max}$ . The total test time (say TT1), therefore, is  $\sum_{i=1}^{n} T_i.P_i/P_{max}$  or,

$$TT1 = (T_1 \cdot P_1 + \dots + T_n \cdot P_n) / P_{max}$$

(3.2)

#### Case 2: Concurrent test scheduling (Multiple tests scheduled in each session).

Let the n tests be scheduled in k sessions such that every test is covered by exactly one test session. The test time and power of a session,  $S_j$  are given by  $T_{S_j} = \max\{T_i\}$  and  $P_{S_j} = \sum(P_i), \forall t_i \in S_j$ , respectively. If the clock frequency per session is varied, the frequency factor per session,  $F_j = P_{max}/P_{S_j} = P_{max}/\sum P_i, \forall t_i \in S_j$ . The modified session test time for session,  $S_j$  is given by,  $(\max\{T_i\}, \sum P_i)/P_{max}, \forall t_i \in S_j$ . The total test time (say TT2), therefore, is  $[\sum_{i=1}^k T_{S_j}(\sum P_i)]/P_{max}, \forall t_i \in S_j$  or,

$$TT2 = [T_{S_1} \cdot (P_1 + \dots + P_x) + \dots + T_{S_k} \cdot (P_y + \dots + P_n)] / P_{max}, \text{ where } x, y \in \{1, \dots, n\}$$

(3.3)

For any session,  $S_j$ ,  $T_{S_j} \ge T_i$ ,  $\forall t_i \in S_j$ , i.e, the session's test time is always greater than or equal to the test times of the tests in that session. This implies that, if tests  $t_x, t_y, t_z \in S_j$ , then  $T_{S_j}.P_x + T_{S_j}.P_y + T_{S_j}.P_z \ge T_x.P_x + T_y.P_y + T_z.P_z$ . The LHS of this inequality resembles 3.3 and the RHS resembles that of 3.2. Hence, from this and 3.2 and 3.3, we can say that  $TT2 \ge TT1$  and therefore, the total test time of concurrent scheduling is at most as small as the lower bound when the test clock rate is  $\frac{P_{max}}{P_{t_i}} f_{nom}$ .

The test power of a core test, characterized at nominal supply voltage  $(V_{nom})$ , is dependent on voltage. As  $E \propto P \propto V^2$ , the energy per core test and hence the total test energy also varies with the supply voltage. Therefore, the lower bound on test time given in Equation 3.1 is applicable at the nominal supply voltage. The energy per core test is given by,  $E_{t_i} = P_{t_i} (\frac{V_{min}}{V_{nom}})^2 T_{t_i}$ , where  $V_{min}$  is the lowest value to which the supply voltage can be reduced, without disrupting the circuit's functionality. Hence, the new lower bound for the total test time of the SoC is,

$$TT_{LB2} = \frac{\sum_{i=1}^{n} P_{t_i}(\frac{V_{min}}{V_{nom}})^2 T_{t_i}}{P_{max}},$$

(3.4)

where  $TT_{LB2}$  is the new lower bound on SoC test time.

Note that here a constant  $V_{min}$  is assumed for all SoC cores; however, the value of  $V_{min}$  may vary among the cores.

The theorem showed that scheduling core tests at a clock frequency such that the power consumed per test is the same as the power budget, yields the lower bound and that concurrent test scheduling cannot improve this lower bound. This is under the assumption that the power dissipation of a core can be raised to equal the power budget without any physical limitation on the individual core power limit or the clock. In reality, the clock rate of individual cores is often limited by their structural constraints (e.g., critical path delay) and power constraints(rated maximum power). Consequentially, the maximum clock frequency of a session is decided by the maximum clock frequency of the slowest core in that session, i.e.,  $f(S_j) \leq \min\{f_{max}(t_i) | \forall t_i \in S_j\}$ , where  $f(S_j)$  is the clock rate of session  $S_j$  and  $f_{max}(t_i)$ is the maximum clock frequency of a test  $t_i$ . Since all cores of the SoC are tested at the nominal clock frequency,  $f_{nom}$ , it is valid to assume that  $f_{nom}$  is the clock rate of the slowest core in the SoC (say  $f_0$ ). Then, frequency factor of a session,  $F_j = \frac{f(S_j)}{f_0}$ . Note that the test session containing the slowest core of the SoC will possess a unity frequency factor. The maximum frequency factor is given by:

$$\max\{F_j\} = \min[\frac{\min\{f_{max}(t_i) | \forall t_i \in S_j\}}{f_0}, \frac{P_{max}}{P_{S_j}}]$$

(3.5)

The structural and power constraints that limit a core's maximum frequency are also influenced by the supply voltage. The power consumed (P) varies in direct relation with supply voltage  $(V_{DD})$  and clock frequency (f),

$$P \propto V_{DD}^2.f \tag{3.6}$$

This implies that power consumption can be reduced by lowering the operating voltage. As a result, the clock rate can be increased without exceeding the power constraint of the core. However, the delay of a circuit also varies with the voltage, as given by the alpha power law [46, 50, 51]:

$$delay \propto \frac{V_{DD}}{(V_{DD} - V_{TH})^{\alpha}},\tag{3.7}$$

where  $\alpha$  is the velocity saturation index. The value of  $\alpha$  lies between 1 (for complete velocity saturation) and 2 (no velocity saturation) [46, 50, 51]. As seen from the above expression, reducing the voltage causes the delay to increase, which in turn, slows down the execution speed and hence, results in longer a test time. Thus, as we reduce V<sub>DD</sub>, on one hand, the lowered power consumption allows higher clock rates thereby shrinking the total test time and on the other hand, the increased circuit delay results in slower clock rate and a longer test time. Therefore, it is required to find an optimal V<sub>DD</sub> that will allow us to balance the two trade-offs and at the same time achieve a test time reduction.

Let  $f_p$  and  $f_s$  be the frequency limits corresponding to the power and structural constraints of a core, respectively. The relationship given in Equation 3.6 can now be written as:

$$P_{core} \propto V_{DD}^2.f_p$$

where  $P_{core}$  and  $f_p$  are the power rating and the power constrained frequency limit for a core, respectively. Since the power rating for a core is a constant, the  $f_p - V_{DD}$  relation can be rewritten as:

$$f_p \propto 1/V_{DD}^2 \tag{3.8}$$

The  $f_s - V_{DD}$  relationship can be expressed, in accordance with the alpha power law (Equation 3.7), as:

$$f_s \propto \frac{(V_{DD} - V_{TH})^{\alpha}}{V_{DD}} \tag{3.9}$$

From these expressions it can be noted that as  $V_{DD}$  is decreased,  $f_p$  increases allowing higher clock rates. At the same time,  $f_s$  decreases with decreasing  $V_{DD}$ , thus restricting the clock rate. Both these constraint limits are independent of each other, i.e., the power constraint limit  $f_p$  is only decided by the rated power of the core, with no regards to the critical path of the core and similarly, the critical path of the core dictates the structure constraint limit, ignoring the rated power limit of the core. The maximum clock rate of a core, therefore, is the minimum of the two frequency limits. Now, the clock frequency of a session, which is the same as the slowest core in that session, is given by  $f(S_j) \leq \min\{f_p(t_i), f_s(t_i) | \forall t_i \in S_j\}$ and since the frequency factor of a session,  $F_j = \frac{f(S_j)}{f_0}$ , its maximum value is given by,

$$\max\{F_j\} = \min[\frac{\min\{f_p(t_i), f_s(t_i) | \forall t_i \in S_j\}}{f_0}, \frac{P_{max}}{P_{S_j}}]$$

(3.10)

The lower bound for the SoC test time, defined in Equation 3.4, does not take into account, the structure constraint of the clock rate. As a result, the equation predicts that the test time continually reduces as  $V_{DD}$  is lowered. However, from Figure 2.5, we know that beyond an optimal  $V_{DD}$  point, the test time increases with decreasing  $V_{DD}$ . Therefore, Equation 3.4 is revised to include the optimal voltage,  $V_{opt}$ , instead of  $V_{min}$ .

$$TT_{LB2} = \frac{\sum_{i=1}^{n} P_{t_i} (\frac{V_{opt}}{V_{nom}})^2 T_{t_i}}{P_{max}},$$

(3.11)

It can be noted that Equation 3.4 would be the same as Equation 3.11, when  $V_{opt} = V_{min}$ .

Let us assume that  $f_s = k \cdot f_p$  at  $V_{nom}$ . As  $V_{DD}$  is lowered, both  $f_s$  and  $f_p$  vary accordingly. At  $V_{opt}$ ,  $f_{s(V_{opt})} = f_{p(V_{opt})}$ , i.e.,  $f_s \cdot \frac{V_{nom}}{V_{opt}} \cdot (\frac{V_{opt} - V_{th}}{V_{nom} - V_{th}})^{\alpha} = f_p \cdot (\frac{V_{nom}}{V_{opt}})^2$ . Since

$$f_s/f_p = k,$$

$$k = \frac{V_{nom}}{V_{opt}} \cdot \left(\frac{V_{nom} - V_{th}}{V_{opt} - V_{th}}\right)^{\alpha}$$

(3.12)

The value of  $\alpha$  for recent short-channel MOSFETs is 1.3 [50]. For the sake of simplicity, let us assume the value of  $\alpha$  as 1. Now, Equation 3.12 can be written as,  $k(V_{opt})^2 - kV_{th}V_{opt} - V_{nom}(V_{nom} - V_{th}) = 0$ , which is of the form  $ax^2 + bx + c = 0$ . Solving for  $V_{opt}$ ,

$$V_{opt} = \frac{kV_{th} \pm \sqrt{(kV_{th})^2 + 4kV_{nom}(V_{nom} - V_{th})}}{2k}$$

(3.13)

#### 3.2 Mixed-Integer Linear Program (MILP) Based Optimization

#### 3.2.1 Introduction

Linear Programming (LP) [28] is an optimization tool designed to achieve the best outcome in a mathematical model where the relationship among the factors involved in the model can be formulated as linear equalities or inequalities. Linear programming consists of a linear objective function that has to be optimized under restrictive conditions that are expressed as linear equalities or inequalities. The canonical form of LP problems is:

> maximize  $c^T x$ Subject to  $Ax \le b$  and  $x \ge 0$

where c and b are vectors of constant coefficients and A is a matrix of pre-determined coefficients whereas x is a vector of variables (known as decision variables) whose values are to be determined.

Integer linear programming (ILP) is a special case of linear programming wherein all the variables are restricted to integers. ILP problems are NP-complete and hence, large optimization problems are intractable through this method. Similar to ILP, MILP (mixed integer linear programming) is also a special case of linear programming since it contains a combination of integral and real-valued decision variable. MILP problems are also NPcomplete and solving them can be cumbersome and time consuming. In the past, MILP based optimization techniques have been used for SoC test scheduling [8–10, 27, 29]. The MILP model presented in this section takes into account the influence of  $V_{DD}$  and clock on the test time and test power and optimizes the overall test time of the SoC for a pre-defined peak power limit.

#### 3.2.2 MILP Formulation

The mixed-ILP model for optimizing  $V_{DD}$  and clock rate per test session is formulated in this section. The voltage range is divided into multiple steps of voltages and for each step, the test power and frequency limits (structure and power constraint) of each test session is pre-computed. Let  $P_{ij}$  be the test power of  $j^{th}$  session at  $i^{th}$  voltage. Similarly, let  $F_{s_{ij}}$  and  $F_{p_{ij}}$  be the frequency limit imposed by the structure and power constraints, respectively, for the  $j^{th}$  session at  $i^{th}$  voltage. For each session, the  $V_{DD}$  is chosen by a binary variable whereas the clock rate of the session is a real-valued variable.  $T_j$  and  $F_j$  are the test time and frequency factor of a test session.  $x_{ij}$  is a binary variable that selects a test session and its optimal  $V_{DD}$  among all possible test sessions and voltage steps. The test schedule optimization can then be described as follows:

Objective:

Minimize

$$\sum_{i,j} (T_j/F_j) \cdot x_{ij}$$

,

where

$$x_{ij} = \begin{cases} 1, & \text{if } j^{th} \text{session is scheduled at } i^{th} voltage \\ 0, & \text{otherwise} \end{cases}$$

Subject to:

1.  $F_j \cdot \sum_i (P_{ij} \cdot x_{ij}) \leq P_{max}$ 2.  $\sum_i x_{ij} = 1$ 3. a.  $F_j \cdot x_{ij} \leq F_{s_{ij}}$  b.  $F_j \cdot x_{ij} \leq F_{p_{ij}}$  4. each test,  $t_i, i \in \{1, .., n\}$  is executed at least once.

The first constraint of the ILP ensures that the power consumption of the test session does not exceed the power budget. The second constraint specifies that each session should be associated with exactly one voltage value. The clock frequency is bounded by the structure constraint  $(F_{s_{ij}})$  and the power constraint  $(F_{p_{ij}})$  in the ILP's third constraint. The fourth one is a test completeness constraint which ensures that all the core tests are scheduled.

The above non-linear model is linearized using simple substitutions. Let  $1/F_j = u_j$  and  $u_j \cdot x_{ij} = q_j, \forall i, j$ . These substitutions necessitate the inclusion of two more constraints: 1)  $q_j \ge u_j - M(1 - x_{ij}), \forall i, j$ , where M is a large number such that M >>  $u_j, 2) q_j \ge 0$ . The new ILP formulation is as follows:

Objective:

Minimize

$$\sum_{j} T_j . q_j$$

Subject to:

- 1.  $\sum_{i} (P_{ij}.x_{ij}) \leq P_{max}.u_j$

- 2.  $\sum_{i} x_{ij} = 1$

- 3. a.  $x_{ij} \leq F_{s_{ij}}.u_j$  b.  $x_{ij} \leq F_{p_{ij}}.u_j$

- 4. each test,  $t_i, i \in \{1, ..., n\}$  is executed at least once.

- 5.  $q_j \ge u_j M(1 x_{ij}), \forall i, j$

- 6.  $q_j \ge 0$

Note that the voltage step size determines the precision of the solution. However, reducing the step size to enhance the precision would increase the number of variables in the formulation and hence render the problem intractable through ILP.

#### 3.3 Heuristic Based Optimization

Integer Linear Programs are NP-hard, in general and are computationally expensive for large SoCs. The CPU time required to obtain an optimal solution increases exponentially as the number of cores and the complexity of the SoC increases. The proposed MILP method also shares the same issues with scalability in terms of the problem size. Hence, a simulated annealing (SA) based optimization technique is presented that is much faster than ILP for larger SoCs and also capable of producing results similar to that of the ILP method. Heuristic algorithms, often employing greedy approaches, perform much better in terms of CPU time as compared to exact methods such as ILP. While a heuristic method does not guarantee an optimal solution, a good algorithm can produce near-optimal values consistently. Many heuristic optimization approaches in the field of SoC testing have been published in the past [15, 19, 23, 35, 44, 57, 74].

#### 3.3.1 Simulated Annealing (SA)

Simulated annealing is a directed search algorithm inspired from the annealing process in metallurgy, first proposed by Kirkpatrick *et al.* [30] has been used in the past for SoC test scheduling [23, 35, 74]. The algorithm accepts a non-improving solution with a finite probability so as to avoid getting stuck at a local optimum. The probability of accepting worse solutions is controlled by the temperature parameter (T). As the temperature of the process cools down, it becomes less and less likely for the algorithm to accept non-improving solutions. Theoretical studies on simulated annealing have shown that simulated annealing based algorithms converge to a global optimum with a probability of 1 under certain specified conditions on the updating and iteration of temperature values [61]. The overview of our SA based optimization algorithm is as shown in Figure 3.1.

#### Simulated Annealing Heuristic

T = temperature K = cooling parameter  $T_f$  = final temperature  $X_B$  = best solution obtained so far  $X_C$  = current solution

generate initial solution,  $X_0$  (test schedule and corresponding test time)  $X_B = X_0, X_C = X_0$ while  $T \ge T_f$  do perform SA move operation (swapping of tests) on  $X_C$ scale clock rate and voltage to optimize the new test schedule compute test time of the optimized test schedule,  $X_{new}$   $Diff = X_{new} - X_C$ if  $Diff \le 0$  or  $\exp(\frac{-Diff}{KT}) \ge random(0, 1)$  then  $X_B = X_{new}, X_C = X_{new}$ else discard  $X_{new}$  and retain  $X_C$ end if  $T = K \times T$

end while

Figure 3.1: Overview of the SA heuristic algorithm.

# Initial solution

The initial solution is developed by inserting a randomly selected test into a session until the session's power consumption  $(P_{ses})$  is close to the peak power budget  $(P_{max})$ . This step is repeated until all the tests are grouped into sessions such that no two sessions contain the same test.

The test schedule, thus generated, serves as the starting point for the simulated annealing heuristic. Frequency and voltage scaling (described in Cost Calculation) are also applied to optimize the test time obtained through Figure 3.2.

#### SA move operator

The move operator in our simulated annealing algorithm is a swapping of tests between two sessions. Among the many test sessions of the test schedule, two sessions  $s_1$  and  $s_2$  are

#### **Initial Solution**

list1 = list of core tests to be scheduled {initially contains all core tests} list2 = list of core tests currently executed {initially empty}  $t_{sch} = 0$  {overall test time of the test schedule} while list1 is not empty do list2 = empty list while  $P_{ses} < P_{max}$  do insert random test *i* into list2 delete test *i* from list1  $P_{ses} = \Sigma P_i, \forall i \in list2$ end while if  $P_{ses} > P_{max}$  then remove recently added test from list2 end if  $t_{sch} = t_{sch} + max(t_i, \forall i \in list2)$ end while

Figure 3.2: Generating the initial solution for the SA algorithm.

selected at random, such that  $s_1 \neq s_2$ . A randomly chosen test in each session is swapped with each other, thus forming a new test schedule. The cost of the resultant solution, which is the test time of the new test schedule, is computed. The new test schedule is accepted if the new solution is better than the best solution obtained so far or if their difference (d) is such that  $\exp(\frac{-d}{KT}) \geq random(0, 1)$ , where K is the cooling parameter and T is the annealing temperature (described in Annealing Schedule), else the swap is discarded.

Simulated annealing is a neighborhood evaluation based class of algorithms where neighboring solutions are examined and accepted or discarded. The neighboring solutions, in this case, are obtained by swapping of the tests in the sessions. In the worst case, the number of sessions may be the same as the number of tests implying that each session will contain one unique test. Hence, the number of neighboring solutions for an SoC with 'n' core tests would be  $\frac{n(n-1)}{2}$ .

# Cost calculation

The cost in this optimization problem refers to the test time of the test schedule. The overall test time for the session-based test schedule is the sum of the test time of the longest test in the session. The test clock frequency and the supply voltage are scaled to optimize the test time. The scaling factor for the clock, referred to as the frequency factor (F), is updated after addition of every test during the initial solution phase and after every swap, in the SA move operation phase. The frequency factor is limited by both the peak power budget and the clock rate constraints of individual core of the SoC, as given in Equation 3.5.

Voltage scaling is done for each session as given below:

- $\bullet\,$  reduce  $V_{DD}$  by one step.

- Calculate the power and structure constraint limits of the tests using Equations 3.8 and 3.9 respectively.

- Update the frequency factor using Equation 3.10.

- Repeat the steps if the resulting session test time is lower than before, else quit the voltage scaling procedure.

#### Annealing schedule

Annealing schedule refers to the temperature (T), the cooling parameter (K) and their effects on the optimization procedure. True to the metallurgical annealing process, the initial value of the temperature is high. Each iteration of the heuristic, which produces a new solution, corresponds to a value of the temperature. After each iteration, the temperature is reduced according to  $T_{new} = K \times T$ , where  $K \leq 1$ . Hence, the number of iterations is dependent on both, the temperature and the cooling parameter. The stopping criteria for the procedure would be the temperature value reducing below a certain specified limit.

Figure 3.3: Components of ASIC Z and their test time (in arbitrary units) and test power (in mW).

# 3.4 Results

# 3.4.1 Experimental Setup

The exact and the heuristic optimization methods were experimented on several ITC'02 benchmarks [3] and ASIC Z. The ASIC Z was introduced by Y. Zorian in [73] and consists of RAM, ROM and other blocks. These blocks, along with their test time and power are shown in Figure 3.3. The peak power budget for the ASIC Z is given as 900 mW.

The test time and test power data for the ITC benchmark SoCs have been provided by Millican and Saluja [41]. The peak power budget for these SoCs were assigned based on the test power information of individual cores in the SoCs. To account for power and structure constrained limits on the frequency of individual cores, maximum clock rates are allocated for each core. The values for the power constrained limit ( $f_p$ ) are computed based on the test length and test power of the blocks/cores. The block with the highest test power and longest time is regarded as the slowest and the rest of the cores in the SoC are

|       | Test | Test  | Freque    | ncy constraints |

|-------|------|-------|-----------|-----------------|

| Block | time | power | $(f_p^+)$ | $(f_s^{++})$    |

| RAM1  | 69   | 282   | 1.75      | 6.65            |

| RAM2  | 61   | 241   | 2         | 7.55            |

| RAM3  | 38   | 213   | 3         | 5.6             |

| RAM4  | 23   | 96    | 5         | 8.8             |

| ROM1  | 102  | 279   | 1.5       | 4.6             |

| ROM2  | 102  | 279   | 1.5       | 3.83            |

| *RL1  | 134  | 295   | 1.2       | 2.74            |

| *RL2  | 160  | 352   | 1         | 2               |

| **RF  | 95   | 10    | 8         | 17.6            |

Table 3.1: Test Data set for ASIC Z at nominal supply voltage (1.0V)

+ power constraint ++ structure constraint \*Random Logic \*\* Register File

normalized with respect to the slowest core. Hence, the test with a low test power value can be clocked at a faster rate. For assigning the structure constraint limit  $(f_s)$ , the fact that the test power can be as high as four times the functional power is taken into account, i.e.,  $P_{func} \leq P_{test} \leq 4P_{func}$ .  $P_{test} \propto f_p$  and since the structure constraint limit decides the functional clock rate,  $P_{func} \propto f_s$ . Hence, the structure constraint limit  $(f_s)$  for each core is set to  $k \times f_p$ , where k is a uniform random number generated in the range(1,4). For illustration, the complete data of ASIC Z, including the frequency limits, is given in Table 3.1. This test data set for ASIC Z is specified at a nominal supply voltage. The test time, test power and the power budget were provided by Y. Zorian in [73]. The frequency constraints for each block were derived by the steps described previously. Similarly, the test data for the remaining benchmarks is given in the Appendix section.

Further, the range of operating voltage, in this work, is assumed to be between 1.0V (nominal) and 0.6V (minimum). The other parameters for the alpha-power law, namely,

$V_{th}$  and  $\alpha$  are assumed to be 0.5V and 1.0. These values are in tune with the 45-nm technology [72]. In [59], Tran and Baas show the operation of a 32-bit adder, designed in 45-nm technology node, for a range of  $V_{DD}$ , starting from 1.0V all the way down to 0.1V. The authors note that the operation of the circuit enters sub-threshold region below 0.5V. Other related work have reported the functioning of memory and logic circuits, for sub-70nm technology, at voltages as low as 0.6V (non sub-threshold operation) [6,49,67]. Keeping this in mind, let us revisit the lower bound on SoC test time. As mentioned earlier, the structure constraint of the SoC cores' clock rate limits the scaling of  $V_{DD}$ . Assuming the least restrictive condition on the structure constraint, we have  $f_s = 4f_p$ . Substituting  $V_{nom} = 1.0V$ ,  $V_{th} = 0.5V$  and k = 4in Equation 3.13 yields a  $V_{opt} \approx 0.69V$ . This value of  $V_{opt}$  can be used in Equation 3.11 to derive the lower bound on the test time of the SoC benchmarks considered in this work.

The experiments were preformed on a Dell workstation with a 3.4GHz Intel Pentium processor and 2GB memory. The MILP models were solved using IBM CPLEX Optimization Solver (student edition) whereas the SA based heuristic algorithm was developed using the Python scripting language [4].

# 3.4.2 MILP Results

The results for the proposed MILP method are presented in this section. In order to evaluate the optimization results, three optimization cases are considered. The first one, referred to as Case 1, is the nominal case where the  $V_{DD}$  and the test clock are fixed at a nominal value. In the second case (Case 2), the  $V_{DD}$  is fixed at a nominal value but the clock frequency is optimized per test session [55]. Finally, in Case 3, both  $V_{DD}$  and the clock are optimized [56].

Let us consider the ASIC Z system. Previously published optimal test times for the ASIC Z include 392 by Zorian [73], 330 by Chou *et al.* [13, 14] and 300 by Larsson and Peng [35]. For the nominal case (Case 1), the test schedule and test time (300 units) are similar to the one obtained by Larsson and Peng [35]. Customizing the test clock per session

|         |                     | Test |         |            | Freq.  | Test                  |

|---------|---------------------|------|---------|------------|--------|-----------------------|

| Session | Block               | time | Session | Block      | factor | $\operatorname{time}$ |

| 1       | RL1, RL2            | 160  | 1       | RAM1, ROM2 | 1.5    | 68                    |

|         | RAM2                |      |         |            |        |                       |

| 2       | RAM1, ROM1,         | 102  | 2       | RAM2, RAM3 | 1.98   | 30.77                 |

|         | ROM2                |      |         |            |        |                       |

| 3       | RAM1, RAM4,         | 38   | 3       | RAM4, RF   | 4.71   | 4.88                  |

|         | $\operatorname{RF}$ |      |         |            |        |                       |

|         |                     |      | 4       | ROM1, RL1, | 0.97   | 164.624               |

|         |                     |      |         | RL2        |        |                       |

|         | Total test time =   | 300  |         | Total test | time = | 268.274               |

Table 3.2: Optimized Test Schedule for ASIC Z for nominal and custom clock rate (Cases 1 and 2). The supply voltage is at nominal value for both cases.

(Case 2) reduces the test time by 10.5% (Table 3.2). The frequency factor in the table indicates the speed-up of the clock, done to reduce the test time. A frequency factor of 1.5 implies that the test clock frequency of that session was increased to 1.5 times the nominal value. The lower bound on the overall test time for ASIC Z at nominal V<sub>DD</sub>, calculated using Equation 3.1, is 220.2 units. The difference between the lower bound and the test time at nominal clock rate and voltage (case 1) is 26.6% and the difference between the lower bound and the test time for optimization case 2 (customized test clock frequency) is 17.9%. One can observe that by customizing the clock rate, the test scheduling result moves closer to the lower bound but is constrained by the maximum clock rate of individual cores.

Table 3.3 shows, however, that customizing both  $V_{DD}$  and the test clock (Case 3) lowers the test time by as much as 50%. It can also be noted from the table that the sessions in the schedule not only have different clock rates but also different  $V_{DD}$  (which is the optimum  $V_{DD}$ for that session). The lower bound in Equation 3.4, calculated at  $V_{min} = 0.6V$  is 79.27 units. The difference between this lower bound and the optimal test time as seen in Table 3.3 is 46.5%. The test time from optimization case 3 deviates from the lower bound as the optimal  $V_{DD}$  for each session in the test schedule is higher than  $V_{min}$ .

| Session | Block      | Freq. factor | $\mathbf{V}_{\mathbf{D}\mathbf{D}}$ | Test time |

|---------|------------|--------------|-------------------------------------|-----------|

| 1       | RF         | 12.5         | 0.8V                                | 0.8       |

| 2       | RAM1,RAM2, |              |                                     |           |

|         | RAM3,RAM4  | 2.56         | $0.65\mathrm{V}$                    | 26.95     |

| 3       | ROM1,ROM2, |              |                                     |           |

|         | RL1, RL2   | 1.33         | $0.75\mathrm{V}$                    | 120.5     |

|         | 148.25     |              |                                     |           |

Table 3.3: Test times (in arbitrary units) of ASIC Z system for custom  $V_{DD}$  and clock rate (Case 3).

Table 3.4: Test times (in arbitrary units) for benchmark SoCs, obtained by MILP optimization method for the three optimization cases considered.

|           |        |                 | Case 1   | Case 2      | Case 3     |        |            |

|-----------|--------|-----------------|----------|-------------|------------|--------|------------|

| Benchmark | No. of | $P_{max}$       | Test     | Test        | Test       | % Redu | ction over |

|           | cores  | $(\mathrm{mW})$ | time     | time        | time       | Case 1 | Case 2     |

| a586710   | 7      | 800             | 14271856 | 13011130.61 | 6799115.12 | 52.36  | 47.74      |

| h953      | 8      | 800             | 122636   | 121715.34   | 79318.76   | 35.32  | 34.84      |

| ASIC Z    | 9      | 900             | 300      | 268.274     | 148.25     | 50.58  | 44.74      |

| d695      | 10     | 400             | 15188    | 12733.2     | 7173       | 52.77  | 43.67      |

Case  $1 = V_{DD}$  and test clock fixed at nominal value; Case  $2 = V_{DD}$  fixed at nominal value, clock scaled per test session; Case  $3 = V_{DD}$  and clock scaled per test session.

Similarly, the optimized test times for the benchmarks for the various optimization cases considered, is tabulated in Table 3.4. The percent reduction specified in the last two columns of the table refer to the reduction in test time achieved by case 3 ( $V_{DD}$  and clock scaling) with respect to the other two optimization cases. For instance, in case of ASIC Z, the test time for the optimization case 3 is about 50% lower than that of case 1 (fixed  $V_{DD}$  and clock) and 45% lower than case 2 (only frequency scaling). From the table it can be noted that by customizing both voltage and frequency can reduce the test time in half.

The plot in Figure 3.4 shows the CPU time of the MILP optimization method. As seen from the plot, optimization through frequency and voltage scaling consumes most CPU time and also the run time grows very quickly with the SoC size.

Figure 3.4: CPU time (in seconds) of the MILP optimization method for the ITC benchmarks. The CPU times reported are with respect to a 4GHz Intel Pentium processor with 2GB memory.

# 3.4.3 Heuristic Algorithm Results

A comparison of optimized test times obtained from the MILP and the SA based test scheduling algorithm is provided in Table 3.5. Since the heuristic can be dependent on the initial solution, the algorithm is repeated for hundred starting points and the best solution among them is selected. The CPU time of the algorithm is averaged over the hundred simulations. As seen from the table, the difference between the heuristic solution and the exact solution is marginal. The table also shows that the CPU time for the heuristic does not vary much with respect to the SoC size.

To emphasize this point, the heuristic methods was employed to solve the test scheduling problem for larger ITC benchmarks, for which the MILP solver would struggle to provide a solution. In order to further evaluate the performance of the heuristic, SoCs with 100, 200 and 500 cores (referred to from now on as R100, R200 and R500, respectively) were created. The test time and test power data for the R100 SoC was generated using a uniform random number generator, in the range (10, 100) and (50, 500), respectively. The R200 and the

|           | SA based he | euristic method      | MILP method |                 |  |

|-----------|-------------|----------------------|-------------|-----------------|--|

| Benchmark | Test time   | CPU time             | Test time   | CPU time        |  |

| a586710   | 6799118.34  | 0.12 sec             | 6799115.12  | 12.03 sec       |  |

| h953      | 79319.12    | 0.09 sec             | 79318.76    | $48.17  \sec$   |  |

| ASIC Z    | 150.26      | 0.11 sec             | 148.25      | 501.18  sec     |  |

| d695      | 7177.53     | $0.17  \mathrm{sec}$ | 7173        | $3649.52  \sec$ |  |

Table 3.5: Test times (in arbitrary units) for MILP and heuristic test scheduling methods, with customized  $V_{DD}$  and clock rates.

Table 3.6: Test times (in arbitrary units) for benchmark SoCs, obtained by the heuristic optimization method for the three optimization cases considered.

|           |        |                 | Case 1  | Case 2     | Case 3    |        |            |

|-----------|--------|-----------------|---------|------------|-----------|--------|------------|

| Benchmark | No. of | $P_{max}$       | Test    | Test       | Test      | % Redu | ction over |

|           | cores  | $(\mathrm{mW})$ | time    | time       | time      | Case 1 | Case 2     |

| g1023     | 14     | 400             | 21245   | 19888.7    | 12193.05  | 42.6   | 38.7       |

| p34392    | 19     | 400             | 952199  | 758199.76  | 369692.1  | 61.17  | 51.24      |

| t512505   | 31     | 400             | 5589002 | 5414047.16 | 3038172.5 | 45.64  | 43.88      |

| p93791    | 32     | 400             | 178568  | 160618.71  | 90391.8   | 49.38  | 43.72      |

| R100      | 100    | 900             | 1347    | 1213.56    | 730.4     | 45.77  | 39.81      |

| R200      | 200    | 900             | 2837    | 2502.29    | 1536.35   | 45.84  | 38.60      |

| R500      | 500    | 900             | 7706    | 6653.01    | 4212.27   | 45.34  | 36.68      |

R500 are multiple copies of the R100 SoC. The peak power budget for these SoCs was set to 900mW. Table 3.6 summarizes the optimized test times obtained through the heuristic method for these SoCs. From the table, it can be noted that the heuristic method also achieves a test time reduction of up to 60%.

The CPU time for the heuristic optimization is plotted in Figure 3.5. As seen from the figure, the heuristic algorithm is able provide an optimized test schedule for the 500 core SoC in just over 6 seconds.

Figure 3.5: CPU time (in seconds) of the heuristic optimization method for the SoC benchmarks. The CPU times reported are with respect to a 4GHz Intel Pentium processor with 2GB memory.

# 3.4.4 Lower Bounds on SoC Test Time

Section 3.1 introduced two lower bounds on the SoC test time; one applicable at nominal value and the other at the optimum point of the supply voltage. In Table 3.7, the SoC test time for optimization Cases 1 and 2 (nominal and custom clock rate at nominal  $V_{DD}$ ) is compared with the lower bound on test time at nominal  $V_{DD}$  (Equation 3.1). From the table one can observe that, as the test clock rate is scaled, the optimal test time moves closer to the lower bound but this progression is hindered by limits on the individual clock rates of the SoC cores. It can be noted from Table 3.7 that, for benchmarks h953 and t512505, the difference between the lower bound and the optimal test time is much larger than the rest of the benchmarks. This because, from the theorem, we know that the lower bound on test time is reached by scaling the test clock at the rate  $P_{max}/P_{test}$ . For some cores in these two benchmarks, this ratio is as large as 2000. The individual clock constraints, however, are not as high as the ratio,  $P_{max}/P_{test}$ . As a result, there is a marked difference between the lower bound and the optimal clock constraints, however, are not as high as the ratio,  $P_{max}/P_{test}$ . As a result, there is a marked difference between the lower bound and the optimal test times for these two benchmarks.

|           |        |                 | Lower      | Heuristic | optimization | % Diff  | erence |

|-----------|--------|-----------------|------------|-----------|--------------|---------|--------|

| Benchmark | No. of | $P_{max}$       | Bound      | test t    | times for    | from LB |        |

|           | cores  | $(\mathrm{mW})$ | $(LB)^*$   | Case 1    | Case 2       | Case 1  | Case 2 |

| a586710   | 7      | 800             | 11476950.1 | 14271856  | 13011130.61  | 19.58   | 11.79  |

| h953      | 8      | 800             | 41511.06   | 122636    | 121715.34    | 66.15   | 65.89  |

| ASIC Z    | 9      | 900             | 220.2      | 300       | 268.274      | 26.60   | 17.92  |

| d695      | 10     | 400             | 9193.4     | 15188     | 12733.2      | 39.47   | 27.78  |

| g1023     | 14     | 400             | 11400.31   | 21245     | 19888.7      | 46.34   | 42.7   |

| p34392    | 19     | 400             | 516245.20  | 952199    | 758199.76    | 45.7    | 31.91  |

| t512505   | 31     | 400             | 1587297.02 | 5589002   | 5414047.158  | 71.6    | 70.68  |

| p93791    | 32     | 400             | 121480.20  | 178568    | 160618.71    | 31.98   | 24.37  |

| R100      | 100    | 900             | 1132.26    | 1347      | 1213.56      | 15.94   | 6.7    |

| R200      | 200    | 900             | 2264.52    | 2837      | 2502.29      | 20.2    | 9.5    |

| R500      | 500    | 900             | 5661.3     | 7706      | 6653.01      | 26.53   | 14.9   |

Table 3.7: Optimal test times (in arbitrary units) for nominal and custom clock rate (Cases 1 and 2) compared with the lower bound on test time at nominal  $V_{DD}$ .

The lower bound on SoC test time defined by Equation 3.1 does not apply for optimization Case 3, since the supply voltage is also scaled along with the clock rate and the lower bound on the scaling of  $V_{DD}$  would be  $V_{opt}$ . The results for optimization Case 3 (both  $V_{DD}$  and clock scaled per test session) are compared with the lower bound computed at  $V_{opt} = 0.69V$  (Equation 3.11) in Table 3.8. The difference between the lower bound and the optimal test time can be attributed to the fact that while calculating the optimal  $V_{DD}$ point, a least restrictive condition was assumed for the structure constraint. This, however, is not the case for all cores of the SoC and therefore,  $V_{opt}$  for such cores will be higher than the calculated value of 0.69V.

Once again, one can notice that there is a large gap between the lower bound and the optimal test times for benchmarks h953 and t512505, which could not be bridged by voltage scaling.

<sup>\*</sup>Lower Bound calculated at nominal  $V_{DD}$ , by Equation 3.1; Case 1:  $V_{DD}$  and test clock fixed at nominal value; Case 2:  $V_{DD}$  fixed at nominal value, clock scaled per test session.

| zation Case 5) compared with the lower bound on test time at $v_{\min}$ . |        |                 |               |            |              |

|---------------------------------------------------------------------------|--------|-----------------|---------------|------------|--------------|

|                                                                           | No. of | $P_{max}$       | Lower         | Optimal    | % Difference |

| Benchmark                                                                 | cores  | $(\mathrm{mW})$ | $Bound(LB)^*$ | test time  | from LB      |

| a586710                                                                   | 7      | 800             | 5464175.96    | 6799115.12 | 19.63        |

| h953                                                                      | 8      | 800             | 19763.41      | 79318.76   | 75.08        |

| ASIC Z                                                                    | 9      | 900             | 104.83        | 148.25     | 30.23        |

| d695                                                                      | 10     | 400             | 4376.98       | 7173       | 39.02        |

| g1023                                                                     | 14     | 400             | 5427.69       | 12193.05   | 55.48        |

| p34392                                                                    | 19     | 400             | 245784.34     | 369692.1   | 33.5         |

| t512505                                                                   | 31     | 400             | 755712.11     | 3038172.5  | 75.12        |

| p93791                                                                    | 32     | 400             | 57836.72      | 90391.77   | 36.01        |

| R100                                                                      | 100    | 900             | 539.07        | 730.40     | 26.2         |

| R200                                                                      | 200    | 900             | 1078.14       | 1536.34    | 29.82        |

| R500                                                                      | 500    | 900             | 2695.35       | 4212.27    | 36.01        |

Table 3.8: Optimal test times (in arbitrary units) for custom  $V_{DD}$  and clock frequency (Optimization Case 3) compared with the lower bound on test time at  $V_{min}$ .

\*Lower Bound calculated at  $V_{opt} = 0.69V$ , by Equation 3.11.

## 3.4.5 SoC Power Budget

The optimization techniques proposed in this work increase the test power consumption close to the power budget. While this strategy may not come across as a low-power testing method, it can be noted that by controlling the power budget, one can choose to make savings in the test power. However, there will always be a trade-off between the test time and the test power. This phenomenon is evident in Table 3.9, which gives the optimum test time for ASIC Z for power budgets. As seen from the table, lower value of  $P_{max}$  increases the test time whereas a higher value reduces the test time. However, the percent reduction in test time for the different power budgets is similar.

# 3.4.6 Multiple Supply Voltages

Modern SoCs are typically heterogeneous and may consist of mixed-signal circuits, logic and memory blocks, each of which may function at separate voltages and clock frequencies.