## Testing and Diagnosis of CMOS Open Defects in the Presence of Common Hazards

by

Chao Han

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama Aug 01, 2015

Copyright 2015 by Chao Han

Approved by

Adit D. Singh, Chair, James B. Davis Professor of Electrical and Computer Engineering Vishwani D. Agrawal, James J. Danaher Professor of Electrical and Computer Engineering Victor P. Nelson, Professor of Electrical and Computer Engineering Fa Foster Dai, Professor of Electrical and Computer Engineering

#### Abstract

CMOS open defects are breaks in wires or defective transistors within some library cell causing pull up or pull down failure of the defective gates. Traditionally, TSOF (transistor stuck-open fault) is used to model such open defects, and two pattern tests are required to detect the fault. The first pattern initializes the faulty gate output, while the second pattern activates the fault and propagates the fault effect to an observable output. It has been assumed that since delay caused by such open faults is generally very large, the test patterns are only sequence dependent instead of also being timing dependent as is the case in transition delay fault (TDF) testing. Thus these opens can be detected by either stuck-at tests (for the easy to initialize faults) or two-pattern TDF tests. However, due to the significant leakage current observed in current advanced CMOS technology, stuck-at (DC) tests are no long effective in detecting many open defects which, in effect, behave like delay faults. In addition, recent studies have shown that high quality TDF tests do not detect many open faults due to the fact that the detecting conditions for TDFs cannot always guarantee the explicit targeting of TSOFs. Furthermore, a large number of TSOFs are still undetected by even targeted TSOFs in the LOC scan test mode; many of these can actually cause circuit malfunction. This is because common hazards during normal circuit transitions may activate TSOFs that do not appear to be activated from a functional state in timing unware analysis.

In this work we propose a circuit transformation scheme to use existing ATPG to generate targeted tests for TSOFs in primitive and complex gates in a scan test environment, using both LOC and LOS test modes. To allow the LOS tests to be applied at the highest achievable speed

when an at-speed scan enable is not supported, we present a scan enable timing evaluation methodology. A key contribution of this work is the development of hazard initialized tests for targeting TSOFs undetected by traditional LOC and LOS timing unware tests but can be activated by hazards. To improve test efficiency we also present a new DFT scheme with multiple independent scan enable control signals that allows mixed LOC and LOS tests to be applied to the CUTs to boost TSOF coverage beyond that that achievable from traditional LOC and LOS tests.

Finally, in order to understand the yield loss due to systematic process and layout effects early in the manufacturing process, and assist with yield ramp, it is also important to locate the physical open failures inside the defective chip. The few studies that have addressed TSOF diagnosis so far have been primarily based on stuck-at tests or have employed stuck-at diagnosis tools. We present an improved TSOF diagnosis scheme employing two-pattern scan test that generates diagnostic tests for the all non-redundant TSOFs, including those undetected by stuck-at and TDF tests.

#### Acknowledgments

This dissertation would not have been completed without the help of so many people in so many ways. First of all I would like to express my gratitude to Dr. Adit Singh. Without his expertise, research ideas and support there was no way I could finish this work. He guided me the importance of independent research which is essential for one to pursue a Ph.D. degree.

I appreciate Dr. Vishwani Agrawal, Dr. Victor Nelson and Dr. Fa Dai for being my committee member and offering the brilliant courses and ideas during my Ph.D. study. From Dr. Vishwani Agrawal's courses I have learned the foundation of computer architecture and all kinds of advanced VLSI design methodologies. I have a fully understanding of the basic flow of front and back end VLSI design using various tools and softwares from Dr. Victor Nelson's courses. It is Dr. Fa Dai's courses made me realize the great importance of analog circuit design.

I also thank my colleagues, without whom my study and research at Auburn University would not have been enjoyable. Yu Zhang, Bei Zhang, Xi Qian, Wei Jiang, Jie Zou and many more were there to help me with both my study and life.

My parents always stand behind me and I own my greatest gratitude to their selfless love and support.

Finally, I would like to acknowledge that the dissertation is based upon work supported by the National Science Foundation under Grants No. EECS-0903449 and CCF-1319529.

## **Table of Contents**

| A  | bstract                                                         | ii   |

|----|-----------------------------------------------------------------|------|

| A  | cknowledgments                                                  | iv   |

| Li | ist of Tables                                                   | vii  |

| Li | ist of Figures                                                  | viii |

| 1  | Introduction                                                    | 1    |

| 2  | Background and Prior Works                                      | 6    |

|    | 2.1 Scan Based Delay Testing                                    | 6    |

|    | 2.2 Transistor Stuck Open Fault and Transition Delay Fault      | 8    |

|    | 2.3 Special Case – Cross Wire Open Fault in Complex gate        | 13   |

|    | 2.4 Hazard activated Transistor Stuck Open Fault                | 16   |

|    | 2.5 Diagnosis of Transistor Stuck Open Fault                    | 18   |

| 3  | Gate Modification for Directly Targeting Open Fault             | 21   |

|    | 3.1 Gate Modification for Targeting Transistor Stuck Open Fault | 21   |

|    | 3.2 Gate Modification for Targeting Cross Wire Open Fault       | 26   |

| 4  | Timing Evaluation Tests for Scan Enable Signals                 | 31   |

|    | 4.1 Scan Enable Timing Test Generation Scheme                   | 32   |

|    | 4.2 Experimental Results for Scan Enable Timing Tests                            | 34 |

|----|----------------------------------------------------------------------------------|----|

| 5  | Experimental results of LOC and LOS Targeted Tests for Open Faults               | 37 |

|    | 5.1 Test Coverage for Transistor Stuck Open Fault                                | 37 |

|    | 5.2 Test Coverage for Cross Wire Open Fault                                      | 40 |

| 6  | Hazard Initialized Test Generation for Transistor Stuck Open Fault               | 44 |

|    | 6.1 ATPG Hazard Initialized Test Generation                                      | 45 |

|    | 6.2 SPICE Simulation for Verifying the Effectiveness of Hazard Initialized Tests | 48 |

|    | 6.3 Experimental Results of Hazard Initialized Test                              | 50 |

| 7  | Mixed LOC and LOS Tests for Targeting Hazard Activated Open Fault                | 55 |

|    | 7.1 The Mixed LOC and LOS Test Scheme                                            | 55 |

|    | 7.2 Experimental Results of Mixed Tests for Targeting Opens                      | 57 |

|    | 7.3 Mixed LOC and LOS Tests Experimental Results for Cross Wire Open Fault       | 59 |

| 8  | Transistor Stuck Open Fault Diagnosis                                            | 62 |

|    | 8.1 Diagnostic Fault Simulation for Transistor Stuck Open faults                 | 62 |

|    | 8.2 Distinguished Test Generation for Transistor Stuck Open faults               | 62 |

|    | 8.3 TSOF Diagnosis Experimental Results                                          | 66 |

| 9  | Conclusion and Future Work                                                       | 69 |

| Ri | hliography                                                                       | 73 |

# List of Tables

| 3.1 | Number of possible cross wire open (CWO) faults for sample AOI complex gates with and without layout information     | . 28 |

|-----|----------------------------------------------------------------------------------------------------------------------|------|

| 4.1 | Number of test patterns for scan enable timing evaluation                                                            | . 35 |

| 5.1 | LOC and LOS TSOF coverage for re-synthesized circuits with complex gates                                             | . 38 |

| 5.2 | Number of test vectors for TDF, LOC and LOS Open tests                                                               | . 38 |

| 5.3 | Incidental CWO coverage of LOC TDF tests and coverage increase from targeting undetected CWOs in LOC and LOS modes   | . 41 |

| 5.4 | Incidental CWO coverage of TDF tests and improvement from targeted LOC and LOS testsfor a fixed layout configuration | . 42 |

| 5.5 | Number of test patterns applied in each test mode                                                                    | . 43 |

| 6.1 | Potential coverages of hazard initialized test for LOC and LOS undetectable TSOFs                                    | . 49 |

| 6.2 | Number of TSOFs potentially detected for varying gate inertia values as a % of nominal inverter delay                |      |

|     | Potential coverages of hazard initialized test for LOC and LOS test undetectable TSOFs                               |      |

| 7.1 | TSOF coverage improvement for multiple scan enable and enhanced scan design                                          | . 57 |

| 7.2 | TSOF fault coverage considering only non-redundant faults                                                            | . 58 |

| 7.3 | Number of test vectors for each test type                                                                            | . 59 |

| 7.4 | CWO coverage improvement with multiple scan enables tests and enhanced scan tests                                    | . 59 |

| 7.5 | CWO coverage improvement with multiple scan enables tests and enhanced scan tests 6 | 0 |

|-----|-------------------------------------------------------------------------------------|---|

| 7.6 | Number of multiple scan enables tests for each test type                            | 0 |

| 8.1 | Experimental results for LOC mode                                                   | 7 |

| 8.2 | Experimental results for 2 scan enables mixed LOC and LOS mode                      | 8 |

# List of Figures

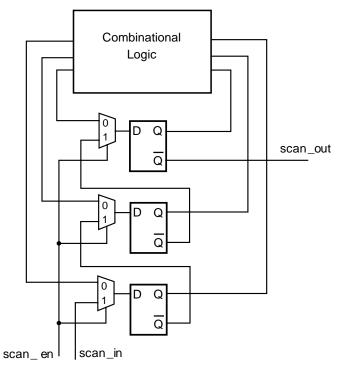

| 2.1 | Full Scan Architecture for CUT                                               | 6  |

|-----|------------------------------------------------------------------------------|----|

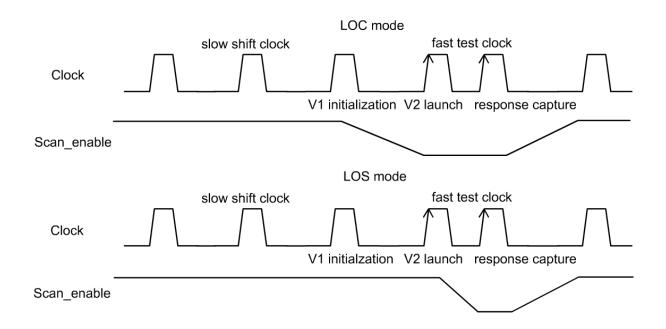

| 2.2 | LOC and LOS scan_enable timing waveforms                                     | 7  |

| 2.3 | Possible Open Defects inside a NAND2 Gate                                    | 9  |

| 2.4 | Miss of TSOF by TDF Test                                                     | 11 |

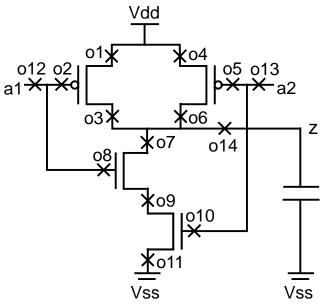

| 2.5 | AOI_21 Gate Transistor Schematic                                             | 12 |

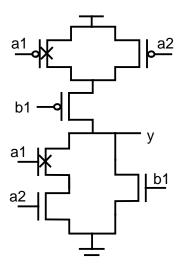

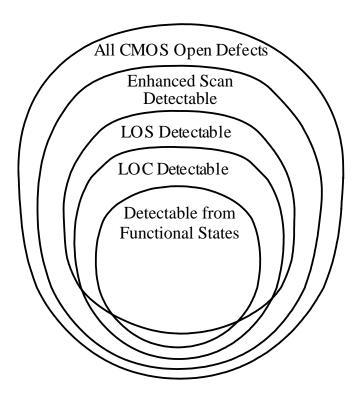

| 2.6 | CMOS Open Fault Coverages for Different Tests                                | 13 |

| 2.7 | Hazard activations of TSOF in NAND2 Gate                                     | 14 |

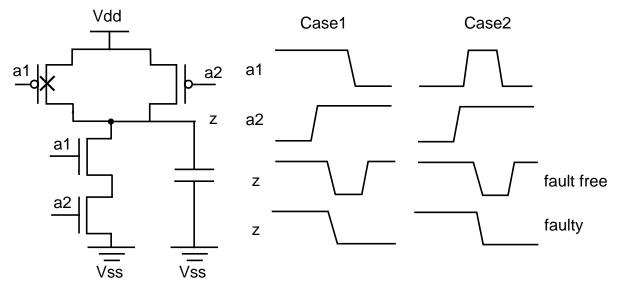

| 2.8 | Transistor stuck-open fault activation by switching hazard                   | 15 |

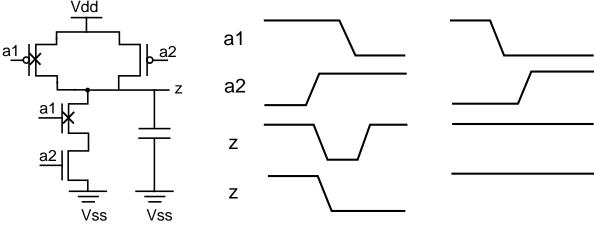

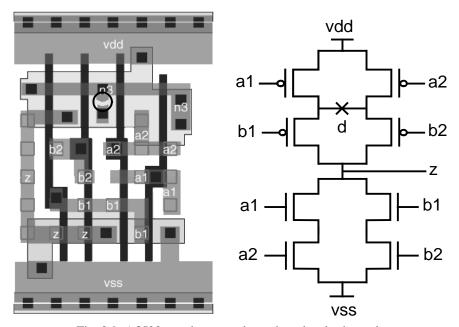

| 2.9 | AOI22 gate layout and transistor level schematic                             | 17 |

| 3.1 | NAND2 transistor level schematic                                             | 21 |

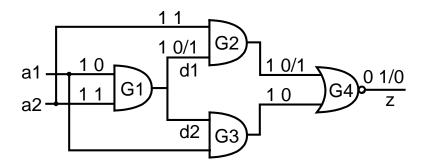

| 3.2 | 2 input NAND gate modification and test generation for PMOS TSOF at input a1 | 22 |

| 3.3 | 2 input NAND gate modification and test generation for NMOS TSOF at input a1 | 22 |

| 3.4 | 2 input NOR gate modification and test generation for NMOS TSOF at input a1  | 23 |

| 3.5 | AOI21 transistor level schematic                                             | 23 |

| 3.6 | AOI21 Complex Gate modification structure and test generation for PMOS TSOF  | 24 |

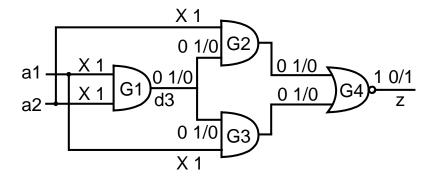

| 3.7 | Gate modification for test generation of NMOS TSOFs in AOI21 gate            | 25 |

| 3.8 Possible PMOS network configurations for an AOI22 gate                 | 26  |

|----------------------------------------------------------------------------|-----|

| 3.9 Possible PMOS network configurations for an AOI33 gate                 | 26  |

| 3.10 Possible PMOS network configurations for an AOI44 gate                | 28  |

| 3.11 AOI33 gate transformation for targeting CWOF                          | 29  |

| 4.1 Scan enable waveforms for LOC and LOS tests                            | 31  |

| 4.2 Condition for LOS test evaluation of scan enable timing                | 32  |

| 4.3 Modified Logic for Scan enable LOS Test Generation                     | 33  |

| 4.4 Scan enable timing test generation under the context of slow scan path | ı34 |

| 6.1 Hazard activation of PMOS TSOF at input a1                             | 45  |

| 6.2 Hazard initialized test for NMOS TSOFs at input a1 and a2              | 46  |

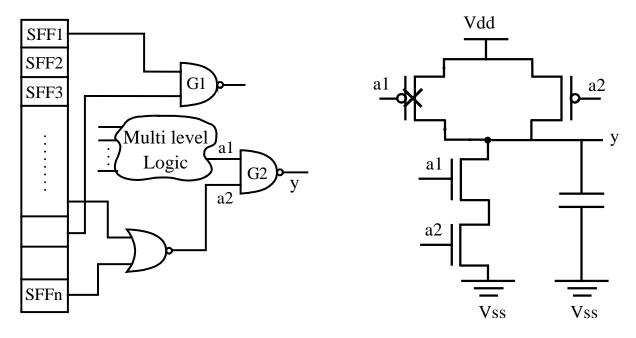

| 7.1 Multiple Scan Enables Structure for Mix LOC and LOS Tests              | 56  |

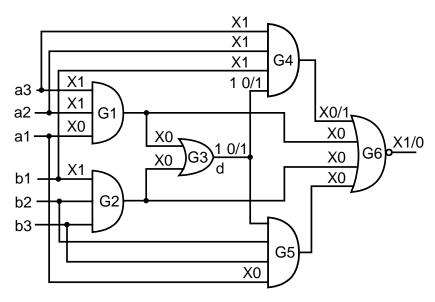

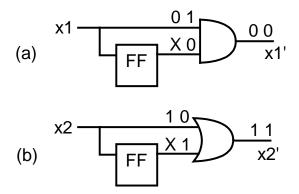

| 8.1 Logics modeling of TDF faults                                          | 63  |

| 8.2 Exclusive test generation for detecting TDF                            | 64  |

| 8.3 Exclusive test generation logic for a pair TDFs                        | 64  |

| 8.4 TSOF diagnosis flow                                                    | 65  |

#### CHAPTER 1

#### Introduction

The quality of modern ASICs manufactured with advanced technology feature size of 45nm and below has been significantly influenced by defects and parameter variations induced from manufacturing process. One important category of the manufacturing defects is open. Open defects can result from missing of via or break of wires at both interconnects between library cells or connections within library cells. An open defect within the library cell will cause certain transistor fail or difficult to be turned on. Transistor stuck-open fault (TSOF) has been used to model such open defect. The victim transistor will cause the faulty gate output fail or difficult to be pulled up or pulled down by the intended input vectors, and thus the output either becomes floating or keeps its previous value.

To detect a transistor stuck-open fault we need a two pattern test [1] of which the first vector initializes the gate output to the state during which the target transistor is off and the second vector attempts to turn on the transistor and flip the initial state for fault activation and propagates the fault effect to the circuit's output. It was assumed that as delays caused by the transistor stuck-open faults are very large (due to small leakage current), they are only sequence dependent [1,2], and many of them can be detected by scan based stuck-at test [3,45] as the gate output initialization can be accomplished during test pattern shift in operation; and for those open faults whose gate outputs are difficult to be initialized by the stuck at tests, the widely used two pattern TDF (transition delay fault) timing test [4] can catch them.

However, due to the significant leakage current of the today's advanced CMOS manufacturing technology, many open faults behave like delay faults. The net leakage current at the gate output can charge or discharge the output capacitance within a much smaller time such that the stuck-test may fail to capture the fault effect. For example, more than 70% of the timing faults identified in the industrial study in [6] were detectable by scan based TDF tests at just half the operational clock frequency but not by very slow speed stuck-at tests, suggesting open defects with long charging time constants from leakage currents.

Recall that the two pattern TDF tests are guaranteed to detect any lumped "gross" (large) slowto-rise or slow-to-fall transition fault at the target circuit node. Thus, a LOC (Launch on Capture) test set that covers all LOC detectable TDF faults, at first glance, appears to detect all functionally relevant large physical delay defects. However, it has become increasingly apparent that high quality transition delay tests fail to detect many open defects causing circuit malfunctions. A recent industrial study [7] has shown that performing detailed "cell aware" testing which targets defects inside the standard cells for high end production parts, resulted in the detection of additional defectivity of as much as 885 DPPM beyond what was screened by industrial grade stuck-at and N-detect (N=5) TDF tests; approximately 87% of these additional defects required two pattern tests for detection, suggesting they are likely to be opens. TSOFs are normally expected to be covered by TDF tests at the transistor inputs; as slow-to-rise faults for NMOS transistors and slowto-fall faults for PMOS transistors. This appears to be reasonable, since a stuck-open transistor is very (up to infinitely) slow to turn on, and therefore should be adequately modeled by a slow-torise or slow-to-fall input at the gate of the transistor. However, in practice a TSOF does not impact delays at the input of the transistor, but only delays the transition at the output of the logic gate containing the stuck-open transistor. This gate output is a different node than the input node which

is the target of the TDF tests. Since TDF tests only require a transition at the target node, and not at all nodes along the detection path to the output, a TDF test for the transistor input node may not require the corresponding gate output to switch, thereby failing to detect a stuck-open fault in that transistor. Although by targeting TDF at the gate output node will create the desired output transition, only one TSOF is targeted by the test and the TDF is dropped from ATPG. However, we need to generate tests for targeting all the TSOFs at the parallel transistor branches. The failure of LOC TDF tests to detect large delays caused by commonly occurring open defects was addressed in [8,9] by explicitly targeting the TSOFs missed by the TDF tests. This was done by modifying the circuit to additionally force ATPG to generate a transition at the gate output when targeting the TDFs at the gate inputs.

However, a significant number of CMOS open faults are still undetected by ATPG targeted open tests. While some of these faults could be functionally redundant, many are undetectable because of the architectural limitations of scan design that restrict two pattern tests to either the launch on capture (LOC) or the launch on shift (LOS) modes. Since LOC tests are launched from a superset of all circuit functional states, it is commonly assumed that only opens that are LOC detectable need be targeted during the test, and any opens undetectable by LOC tests are functionally redundant and cannot cause circuit malfunctions. However, traditional scan based LOC and LOS tests are timing unware tests and transient circuit states are not considered during test generation. In practice CMOS circuits experience many transient states from large number of hazards which may occur during signal transitions. This is because gate delays for individual CMOS gates are strongly input dependent, causing signal arrival at the inputs of the internal gates in a logic block to be highly uncorrelated, therefore generating hazards at the gate output. In fact, hazards in CMOS circuits are so prevalent that they are well known to contribute to nearly half the

switching power consumption. Such hazards can easily initialize a gate output to a faulty value and thereby activate a logical fault that does not appear to be activated from a functional state under timing unware analysis.

It is known that, generally speaking, LOS tests have higher fault coverage than LOC tests. Thus some of the LOC tests undetectable hazard-activated opens can be detected by employing LOS tests. However the requirement of high speed scan enable for LOS tests makes it less favorable for industrial application. Although one can apply clock tree synthesis to the scan enable for fast signal switching, it may result in significant routing overhead.

When targeting TSOFs we can take the advantage of the slower LOS tests as the delay caused by open faults are normally large (such delay can still vary significantly depending on threshold voltages variation and trapped voltage at the open gate terminal of the defective transistor) such that even slow LOS tests can detect many open faults. In practice we would like the LOS tests to be launched at the highest clock rate for detecting as many TSOFs as possible. This requires evaluating the timing of the scan enable signal to find out how fast it can switch.

Furthermore, to ensure the IC quality and reliability for very low DPPM application like automotive industry, all opens must be targeted during test, unless proven benign, not just those that are detectable from functional states or by LOC and LOS tests.

Once the defective chips are identified, it is also important to identify the physical locations of the open defects to help study the yield loss due to systematic process and layout variations in the early stage of the manufacturing process. Recall that due to the significant leakage current of current advanced CMOS technology, stuck-at tests are no longer sufficient to target TSOFs. However, most of the current open diagnosis studies are based on stuck-at tests or stuck-at diagnosis tool. Although diagnosis of TDFs has been recently proposed in [10], the test condition

difference between TDF and TSOF and hazards activation issue for opens makes it difficult to directly apply to TSOFs.

In this work, we address two problems: detection test generation and diagnostic test generation for CMOS open faults, including those hazard-activated faults which are undetectable by LOC and LOS tests. Chapter 2 presents the background and prior works for CMOS open faults detection and diagnosis. We introduce our circuit modification scheme for explicitly targeting opens in Chapter 3. Chapter 4 introduces our methodology for scan enable signal timing evaluation. Experimental results of LOC and LOS tests for targeting open faults are presented in Chapter 5. Chapter 6 discusses the hazard initialized test generation for opens undetected by traditional LOC and LOS tests. Chapter 7 introduces our mixed LOC and LOS test DFT scheme that employs multiple independent scan enable signals for targeting opens undetected by traditional LOC and LOS tests. We present our TSOF diagnosis scheme in Chapter 8. Chapter 9 presents a summary and conclusion of our work, along with suggestions for future work.

#### CHAPTER 2

#### **Background and Prior Works**

### 2.1 Scan Based Delay Test

Scan structure has been the most widely used DFT schemes for decades. In a full-scan design, all storage elements are replaced with scan cells, which are configured as one or more shift registers (also call scan chains) during the shift operation. As a result, all inputs to the combinational logic, including those driven by the scan cells, can be controlled and all outputs from the combinational logic, including those driving the scan cells, can be observed. The main advantage of full-scan design is that it converts the difficult problem of sequential ATPG into the simpler problem of combinational ATPG. Figure 2.1 shows the full scan design scheme. When

Fig. 2.1 Full Scan Architecture for CUT

scan\_en = 0, the circuit operates in the functional mode; when scan\_en = 1, the circuit operates in the scan mode where test vector can be shifted in for test launch or test response can be shifted out for observation.

Scan based delay testing involves the application of two test vectors <V1, V2> via the scan chains. The first vector V1, which is used to initialize the internal logic values of CUT (circuit under test), is first scanned into the scan chain when scan\_en = 1, typically using a slow scan clock. The second vector V2 is then used to launch transitions at the inputs of the combinational part of the circuit. These transitions propagate to the outputs of the logic block and are then captured back into the scan chain by a fast capture clock pulse, reflecting operational frequency. Finally, the response captured in the scan chain is scanned out of the CUT and compared with the expected correct test response.

Unfortunately, because of the architectural limitations of scan, not all <V1, V2> combinations can be applied by a scan delay test. Depending on how the V2 vector is generated, scan delay tests

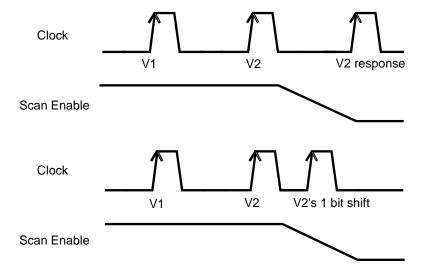

Fig 2.2 LOC and LOS scan\_enable timing waveforms

are classified as Launch-on-Shift (LOS) [11, 12], or Launch-on-Capture (LOC)[13, 14]. For the Launch-on-Shift tests, the V2 vector is restricted to a one-bit shift from V1. For the Launch-on-Capture tests, V2 is the response of the CUT to vector V1. In practice, LOS tests are not always supported because they require the scan enable signal to transit at-speed between the shift mode required to launch the test, and the functional mode required to capture the response of the timing test, all safely within a functional clock period. Figure 2.2 shows the clock and scan enable signal waveforms for LOC and LOS tests. Such high speed scan enable signals are expensive to implement, although several CAD vendors now offer tools to support such an implementation. Another concern with LOS tests is that V2 vectors are not obtained from functional operation, which may result in over testing, as some detected delay faults are not supposed to be activated from functional operation. Nevertheless, low cost LOC test are generally preferred. The restrictions on the V2 vector generally limit the TDF and TSOF coverage achievable using both LOC and LOS scan tests. We believe to achieve very high coverage needed for high quality delay testing, greater flexibility in choosing the V2 vector is required.

#### 2.2 Transistor Stuck-Open Fault and the Relationship with Transition Delay Fault

As one important category of CMOS manufacturing defect, transistor open defect has been studied for several decades. Basically it is some open (break) at the terminals of a transistor causing the switching on failure of the transistor. Here we assume the transistor open defect causes a complete break. Figure 2.3 shows all the possible open defects that could occur in a NAND2 gate. Note that Opens o12, o13 and o14 can be seen as interconnect opens and thus we only target o1 to o11 type transistor open defects, which can be modeled as transistor stuck-open faults.

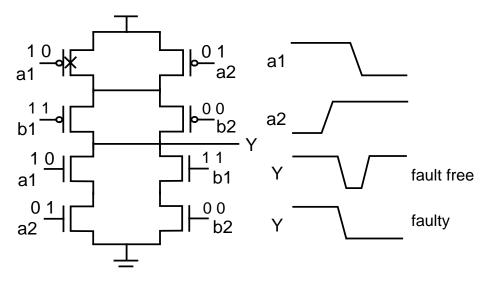

Suppose we would like to detect the PMOS stuck-open fault at input a1 (this fault models the o1,

o2 and o3 open defects). A two pattern test is required of which the V1 vector initializes the gate

Fig. 2.3 Possible Open Defects inside a NAND2 Gate

output to 0, and the V2 vector attempts to turn on the faulty PMOS transistor and to pull up the gate output to 1. The V2 pattern must also be a test for a stuck-at-1 (s-a-1) test at input a1, i.e. V2 must propagate any incorrect faulty value at output of the gate to an observable node (primary output or scan flip-flop input). If there is a PMOS stuck-open fault at input a1, the gate output will be in a floating (high impedance) state retaining the voltage of the previous state 0 for certain amount of time. Note that the net leakage current from the PMOS transistor at input a2 may still slowly charge the load capacitance to a certain voltage level. For old technologies with large load capacitance and minimal transistor leakage current, the time constants of the gate output retains its previous state would be on the order of micro-seconds [5]. Thus earlier papers [1-3] assumed that transistor stuck-open fault is only test sequence dependent and many of them can be detected by stuck-at tests. However, for today's advanced technology with small load capacitance and relative large leakage current, this time constant could be reduced to the order of nano-seconds [5], depending on the threshold voltages of the pull up and pull down transistors. Thus stuck-at tests are no longer effective for targeting transistor stuck-open fault at the parallel pull up or pull down

branches. In addition, we need to consider a particular situation when the open defect is near the gate terminal of a transistor (etc. o8 or o10 open defect) with certain amount of trapped charges at the floating gate terminal. Such charges might partially turn on the victim transistor, which results in a much higher leakage current and thus much faster charging/discharging time constant at the load capacitance. Depending on the amount of the trapped charges, the time constant could vary up to three order of magnitude. This particular situation makes such open defect much more difficult to detect and at-speed delay fault tests are a must for targeting transistor stuck-open faults result from such open defects. Note for a stuck-open fault due to the o7, o9 or o11 open defect, a stuck-at test is likely to detect it as the open breaks the only pull down path and there is no leakage current discharging the load capacitance.

The commonly used TDF delay fault model assumes a single gross transistion fault at some circuit node. The ATPG tool generates two pattern <V1,V2> delay tests capable of detecting both slow-to-rise and slow-to-fall transition faults at the circuit nodes. The V1 to V2 change creates a rising (falling) transition at the target node, while V2 is also a s-a-0 (s-a-1) test for the target node. Note that while TSOFs are not directly targeted, TDF testing implicitly assumes that TSOFs will be covered by the TDF tests for the transistor gate input. Thus, in the example in Figure 2.1, the PMOS transistor stuck-open fault is expected to be covered by the TDF test for the slow-to-fall delay fault at input a1. If the two pattern TDF test for the slow-to-fall delay fault at input a1 sets a1=1, a2=1 for V1, and a1=0, a2=1 for V2, the TSOF will indeed be detected; the gate output will be initialized low by V1 vector, and fail to be pulled up by V2 vector because of the stuck-open fault. However, not all TDF tests for a slow-to-fall delay fault on input a1 will detect the open fault. A slow-to-fall delay fault at input a1 can also be detected by a TDF test that sets a1=1, a2=0 for V1, and a1=0, a2=1 for V2. Observe that the V1 to V2 change again causes the falling transition

at a1, and the fault effect is sensitized to the NAND output by V2. However, in this case the gate output is initialized high by V1, and remains high for V2 in a fault free circuit. To detect the open fault with such test pattern pair, certain timing constraint needs to be satisfied for the transition from V1 to V2 vector to initialize the gate output to low. The signal waveforms in Figure 2.4 show such condition. As we can see only when the 1 to 0 transition at input a1 occurs later than the 0 to 1 transition at input a2, a transient state in which both a1 and a2 equals 1 can be generated to initialize the gate output to 0, and the fault will be activated by the V2 vector. (This is also the basic idea for our hazard initialized test which will be discussed later in our work). Consequently, a TDF test for input a1 cannot ensure the detection of the PMOS TSOF at input a1. Note that while

Fig. 2.4 Miss of TSOF by TDF Test

a slow-to-rise TDF test targeting the gate output node z will indeed create a 0 to 1 transition at node z to satisfy the initialization condition for detecting the PMOS TSOF, only one of the two PMOS TSOFs in the NAND2 gate is covered by such test. The detection of TSOFs that are missed by TDF testing has been addressed in earlier papers [8, 9]. The methodology involves first identifying the list of transistor stuck open faults that are not detected by the generated TDF test set, and then rerunning the TDF ATPG for the target faults with the additional constraint that the generated TDF tests also create a transition at the output of the faulty gate. For example, if the

initially generated TDF test set included a test vector pair <V1,V2> for covering the slow-to-fall transition at input a1 in Figure 2.4 that set a1=1, a2=0 for V1, and a1=0, a2=1 for V2, the corresponding transistor stuck-open fault would not be detected as explained above. In this case that TDF ATPG would be rerun with the additional constraint that the test also requires a transition at the output of the NAND gate. This would generate a test vector pair <V1,V2> that sets a1=1, a2=1 for V1, and a1=0, a2=1 for V2, if the structural constraints of scan and the circuit characteristics allow such a test.

Fig. 2.5 AOI\_21 Gate Transistor Schematic

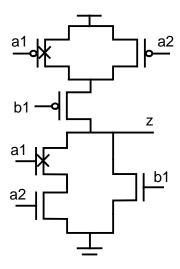

Modern ASIC consists of not only primitive gates but also a large number of complex gates. Figure 2.5 shows a transistor level schematic of AOI\_21 gate. A two pattern test for the PMOS TSOF at input a1 would be V1 (a1,a2) = 1 1 or V1 (b1) = 1 to initialize the gate output to 0, and V2 (a1,a2) = 0 1 and V2 (b1) = 0 to activate the fault. However, a slow-to-fall TDF test targeting input a1 would be V1 (a1) = 1, V2 (a1a2) = 0 1 and V2 (b1) = 0. This suggest that the fault coverage of TSOFs in complex gates from TDF tests can be even lower than coverages of TSOFs in primitive gates. Although both tests have the same V2 vector, the V1 vectors are quite different between the two tests and by simply adding some constraints to the ATPG cannot generate the

required V1 vector for the TSOF. Therefore we need new methodologies for targeting TSOFs in complex gates.

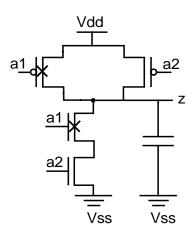

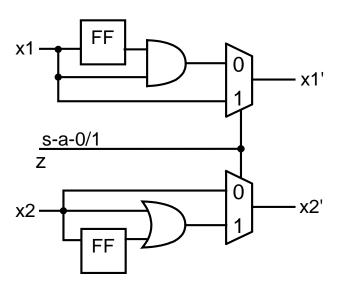

## 2.3 Hazard Activated Transistor Stuck-Open Fault

Even though prior research [8,9] has been proposed to target TSOFs missed by TDF tests (in the context of primitive gates), a significant number of TSOFs in large circuits are undetectable by even ATPG targeted TSOF tests. Some of these faults could be functionally redundant, but many are undetectable because of the architectural limitations of scan that restrict two pattern tests to either the launch-on-capture (LOC) or the launch-on-shift (LOS) modes. Since we can shift in any value into the scan chains as V1 vector, the V1 vectors set is a superset of CUT's functional states.

Fig. 2.6 CMOS Open Fault Coverages for Different Tests

And for LOC tests the V2 vectors are the responses of the V1 vectors, V2 vectors set is also a superset of CUT's functional states. Thus LOC tests are launched from a superset of all circuit

functional states, as illustrated in Figure 2.6. And it is commonly assumed that only TSOFs that are LOC detectable need to be targeted during the test, and that any open faults undetectable by LOC testing are functionally redundant and cannot impact circuit operation.

However, traditional test generation and fault simulation only considers timing unware Boolean signal values and ignores transient circuit states. In practice CMOS circuits experience many more transient states from large number of hazards that occur during functional transitions. This is because gate delays for individual CMOS gates are strongly input dependent (e.g. the best and worst case output rise time for a 3-input CMOS NAND gate can vary by a factor of 3), causing signal arrival at the inputs of the internal gates in a logic block to be highly uncorrelated, thereby giving rise to transient logic values at the gate output.

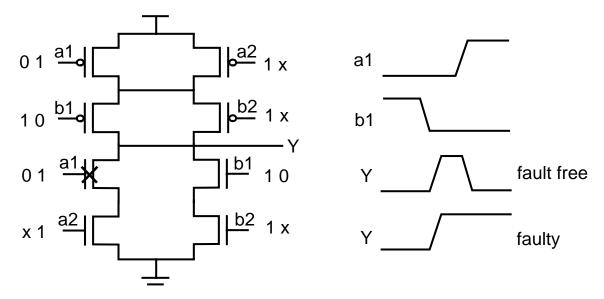

Take a two input NAND gate as an example. Assume two adjacent functional states with V1 = 1 1, V2 = 0 1 at the inputs of the NAND gate does not exist to activate the PMOS TSOF in Figure 2.7. The fault can still be activated by two functional states with V1 = 1 0, V2 = 0 1 which create a transient state (hazard) shown in the figure (Case 1). Such a local hazard can be easily generated if the NAND gate sits deeply inside the combinational logic. Actually even first level

Fig. 2.7 Hazard activations of TSOF in NAND2 Gate

gates driven directly by clocked flip-flops (e.g. Gate 1 in Figure 2.8) are subject to clock skews that can sometimes exceed a gate delay in current designs, resulting in spurious glitches at the gate output before signals stabilize. Furthermore, even two functional states with V1 = 0.0, V2 = 0.1 may activate the open fault if input all receives a propagating hazard (Case 2 in Figure 2.7), although the probability of Case 2 to cause circuit errors would be much lower than that for Case 1, as the probability of satisfying both hazard propagating and fault effect sensitizing conditions for Case 2 is generally very rare under normal operation. Note while TSOF at the parallel branches could be activated by both local hazards and propagating hazards, only propagating hazard may activate TSOF at the serial branch (e.g. NMOS TSOF at input a1) to cause errors.

Fig. 2.8 Transistor stuck-open fault activation by switching hazard

Hazards can easily initialize opens to a faulty value and thereby activate a logical fault that does not appear to be activated from a functional state under timing unware analysis. In fact, hazards in CMOS are so prevalent that they are well known to contribute to nearly half the switching power consumption.

One efficient way of targeting LOC undetected opens that could be activated by hazards is to employ LOS tests. It is known that LOS tests can achieve higher fault coverage due to the lower correlation between V1 and V2 vectors for LOS tests than that of LOC tests. Although many designs do not support LOS tests running at the functional clock speed due to the limitation of slow scan enable signal, we can still take advantage of the LOS tests, since many TSOFs behave like relative large delay faults and at-speed clock is not required to capture the faulty effects. To make full use of LOS tests, it is still necessary to find out how fast the scan enable signal can switch from 1 to 0 before the arrival of the capture clock cycle, such that the tests can be applied at the highest speed to achieve its maximum coverage for TSOFs.

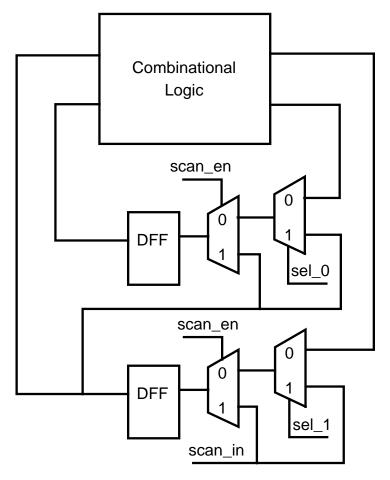

To ensure the IC quality and reliability and achieve very low DPPM, all open defects must be targeted during test, unless proven benign, not just those that are detectable from functional states or by LOC and LOS tests. Some studies have been proposed to target delay faults not detectable by traditional LOC and LOS tests. [15,16] used multiple cycle tests to target undetected TSOFs and TDFs. Partial enhanced scan design was proposed in [17,18] to target undetected TDFs from LOC and LOS tests as well. In this work, we propose two methodologies for targeting TSOFs. The first one employs ATPG to generate potential hazards for targeting TSOFs, known as hazard initialized tests generation. The second one utilizes multiple independent scan enable control signals to generate mixed LOC and LOS tests with additional reachable test launch states to target TSOFs.

### 2.4 Special Case – Cross Wire Open Fault within Complex gate

For primitive gates, TSOFs are the only type of open faults that need to be considered because they can model any open defects in the pull up or pull down path. However, modern ASIC consists of not only primitive gates but also a large number of complex gates, and an additional type of

open faults are found in complex gates only which behave differently from traditional TSOFs – we call them the cross wire open (CWO) faults. This important fault type has not been studied as a target for test generation so far.

Figure 2.9 shows a cross wire open fault d in the schematic of an AOI22 complex gate. To detect this fault, in addition to a V1 vector that initializes the Z output low, we need a V2 vector that either activates only the pull up path a1, b2 or only the pull up path a2, b1, both of which contain the open defect. Thus with V2 (a1, a2) = 01 and V2 (b1, b2) = 10, or V2 (a1, a2) = 10 and V2 (b1, b2) =  $\frac{10}{2}$  and V2 (b1, b2) =  $\frac{10}{2}$

Fig. 2.9 AOI22 gate layout and transistor level schematic

b2) = 01, the cross wire open fault can be activated, as the gate output will stay at its initialized low value and not be pulled up, indicating a fault. Existing TDF timing tests and TSOF tests supported by the commercial ATPG cannot generate test vectors to satisfy the required conditions for V2 described above, and the detection of such faults generally depend on chance.

The recently proposed defect-oriented cell aware tests [7] target all possible defects within the library cells and therefore cross wire open faults are assumed to be included. However, these tests are not explicitly focused on such opens, and target very many other possible defects in the cell

layout, leading to a large increase in the test set. Furthermore, detailed cell level layout information is not always available at test generation. There is, therefore, a need to develop compact and effective tests from a gate level model of the circuit. Note further that the proposed cell aware tests [7] currently only consider open detection under timing unaware Boolean analysis that ignores hazards. They are unable to generate tests for many open faults that appear undetectable from functional states but can actually be activated by hazards and cause circuit errors. Thus in addition to targeting of cross wire opens with traditional LOC and LOS scan tests, it is necessary to target CWOFs that can only be potentially activated by common hazards.

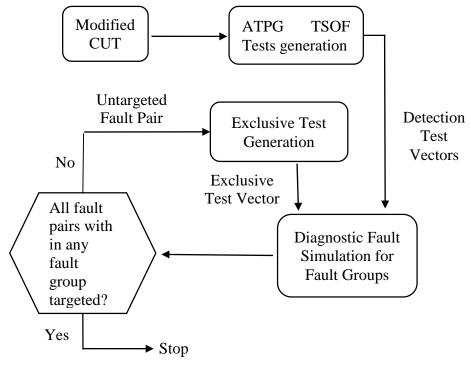

#### 2.5 Diagnosis of Transistor Stuck Open Fault

In order to study the yield loss due to systematic process and layout variations in the early stage of the IC manufacturing process, it is important to not only detect the open defects, but also diagnose these open defects. There are two most commonly used diagnosis methodologies—namely, cause–effect analysis and effect–cause analysis. Cause–effect analysis assumes the causes of failure are due to a specific fault type (generally stuck-at faults). Extensive fault simulation is required to build a fault dictionary for deriving and recording the test responses with respect to the applied test set and fault type. Each fault (or group of faults) inside the dictionary has its unique syndrome with the information of which vectors detecting the fault and at which outputs the fault effect is observed. Once this dictionary is built, the syndrome of the failing chip is compared with the syndromes of the dictionary to find which faults match up with the recorded possible syndromes in the dictionary. Therefore, it is often also referred to as the fault-dictionary based analysis. The problem with this methodology is large memory is required to store the dictionary, since for large circuit with large number of faults and test vectors the size of the dictionary could become significant large, although some fault dictionary compression schemes have been

proposed to reduce dictionary size. Unlike the fault-dictionary-based analysis, effect—cause analysis directly examines the syndrome of the failing chip to derive the fault candidates through Boolean reasoning on the CUD (circuit under diagnosis). The minor drawback of effect—cause analysis is that it takes longer to complete because a unique round of analysis is required for each failing chip. In this work we focus on cause-effect analysis for transistor stuck-open fault diagnosis and diagnose test generation.

Diagnosis of TSOFs has been addressed in papers [21, 22, 23]. [21] discussed TSOF diagnosis based on SAF (stuck-at fault) diagnosis tool and the experiments were conducted on combinational circuit only. Further research [22] improved the method proposed in [21] and full scan test strategy was used in the experiment. But [22] still requires information from SAF diagnosis tool. While these diagnosis methodologies can be applied to circuits with large feature size technology which has very large time constants of charging or discharging of load capacitances from leakage current, for sub-micron or even nanometer feature size technology, due to the large threshold to power supply voltage ratio, the relative large net leakage current can charge or discharge the gate output capacitance within a short amount of time to invalidate the fault effects, such that many TSOFs may behave like large delay faults possibly missed by SAF tests. Thus the stuck-at test based TSOF diagnosis mythologies are no longer effective to target TSOFs found in modern ICs manufactured with advanced technology. A SAT based diagnostic ATPG was proposed in [23] to target arbitrary faults in combinational circuits, including TSOFs. However significant effort has to be made to such ATPG to support large circuits with full scan design. In addition, as what has been discussed in Section 2.4, CMOS circuits experience a large number of hazards during normal operations and many open defects that are assumed to be functionally redundant from timing unaware analysis can in fact be activated by such hazards and cause circuit failure. It is necessary to diagnose these

hazard activated TSOFs as well. TDF diagnosis methodology has been proposed in recent papers [10], but it is now apparent that a large number of TSOFs are missed by high quality TDF tests.

In order to effectively diagnose TSOFs, we use targeted TSOF tests to conduct fault simulation for building an initial fault diagnosis dictionary to separate faults into different groups such that faults from different groups can be distinguished by their own syndromes consisting of indexes of vectors detecting the faults and indexes of the outputs observing the faults effect. We then borrow the exclusive tests generation scheme from [10] to generate exclusive test for undistinguished TSOF fault pairs inside a group and further improve the resolution of the dictionary.

#### **CHAPTER 3**

#### Gate Modification for Directly Targeting Open Fault

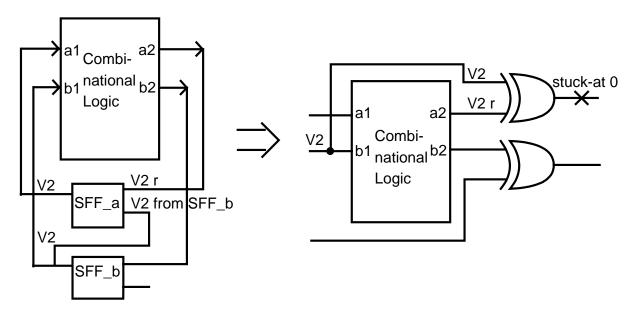

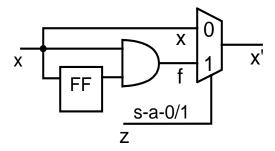

Since many TSOFs are undetected by traditional TDF tests, it is necessary to develop methodology to generate tests specifically target TSOFs. Instead of developing new constraints into the ATPG for targeting TSOFs, we modify the circuit logic structure to allow the use of conventional ATPG to target TSOFs. This is done by using the modified logic to convert the test detection conditions of TSOF into the conditions for TDF. Earlier research [8,9] has proposed a similar scheme but it can only be applied to circuits implemented with primitive gates. The following two sections will discuss our gate modification schemes for targeting TSOFs [47] and CWOFs [49] (cross wire open fault).

### 3.1 Gate Modification for Targeting Transistor Stuck Open Fault

Figure 3.1 shows the transistor level schematic of a two input NAND gate. A test for the PMOS

Fig. 3.1 NAND2 transistor level schematic

TSOF at input a1 would be V1 (a1a2) = 1 1, to initialize the gate output to 0, and V2 = 0 1, to

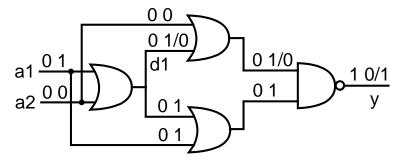

activate the fault. By using the logic structure in Figure 3.2, the ATPG can generate such a test by targeting the slow-to-fall TDF at node d1. Since the V1 vector for node d1 is 1 and d1 is a fan-out branch of gate G1's output, the V1 vector for input a1 and a2 would be a1a2 = 11. For the purpose of fault effect activation and sensitization, we need V2 (a1a2) = 0 1. This vector pair is exactly the test for the PMOS TSOF at input a1. Similarly, by targeting the slow-to-fall TDF at node d2, we can generate the test for PMOS TSOF at input a2. To generate a test for the NMOS TSOFs at the serial NMOS path, we can target the slow-to-rise TDF at node d3 (G1's output) of the same logic structure, which is shown in Figure 3.3. To have V1 (d3) = 0, at least one of inputs a1 and a2 need to be 0, and this will initialize the gate output to 1. V2 (d3) = 1 requires a1 = a2 = 1 to pull down the gate output to 0. An NMOS TSOF at a1 or a2 will be activated by this vector pair.

The logic structure in Figure 3.2 is for a NAND type gate. By replacing the AND/NOR gate in the structure with OR/NAND gate, we have the logic structure for a NOR type gate. Figure 3.4

Fig. 3.2 2 input NAND gate modification and test generation for PMOS TSOF at input a1

Fig. 3.3 2 input NAND gate modification and test generation for NMOS TSOF at input a1

shows the logic and test generation for a NMOS TSOF in a two input NOR gate by targeting the slow to rise TDF at node d1.

Fig. 3.4 2 input NOR gate modification and test generation for NMOS TSOF at input a1

Now let us discuss the test generation conditions for TSOFs in complex gates. Figure 3.5 shows the transistor level schematic for an AOI21 complex gate. To target a PMOS stuck open fault at

Fig. 3.5 AOI21 transistor level schematic

input a1, the V1 vector must first turn on at least one of the parallel NMOS paths (a1 = 1; a2 = 1 or b1= 1) to pull down output z to 0, and the V2 vector must then turn on the faulty PMOS pull up path (a1 = 0 and a2 = 1 and b1 =0) which contains the target transistor to pull up output Y to 1; additionally Y must be sensitized to an observable circuit output. Note that the PMOS TSOF at input b1 dominates either PMOS TSOF at input a1 or PMOS TSOF at input a2. This is because the PMOS at input b1 is in series with either PMOS at a1 or PMOS at a2, and the detection of

either one will ensure the detection of the PMOS TSOF at b1, therefore there is no need to generate specific test for targeting this fault. To target an NMOS stuck open fault at the input a1 (and input a2, since they are in series), the V1 vector must turn on either one of the PMOS paths (a1 or a2 = 0 and b1 = 0) to pull up the gate output and the V2 vector must turn on the NMOS path containing the target transistor (a1 & a2 = 1 and b1 = 0). As we can see, although the V2 vector requirement for targeting the PMOS TSOF and the NMOS TSOF is the same as the requirement for slow-to-fall TDF and slow-to-rise TDF, the V1 vector for the TSOF test is quite different from the V1 vector for the TDF test. Consequently, TDF test patterns may not be very effective for TSOF detection in complex gates; explicitly targeting the stuck open faults is necessary.

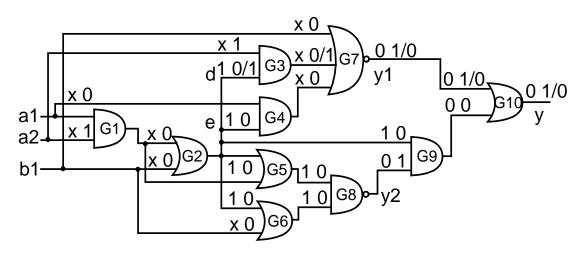

To deterministically target both PMOS and NMOS TSOFs in an AOI21 gate, we replace the complex gate by the structure shown in Figure 3.6. The signal values in Figure 3.6 show the test generation for the PMOS TSOF at the a1 input by targeting node d (second input of G3 gate) slow-

Fig. 3.6 AOI21 Complex Gate Modification Structure for Both PMOS and NMOS TSOFs

to-fall TDF. The resulting two-pattern test V1 V2 must have d = 1 0 and a2 = x 1. Since the node d is a fan-out of gate G2's output, at least one of G2's inputs (G1 output and b1) must be 1 for the V1 vector and both must be 0 for the V2 vector to make d = 1 0. Since G1 output = A1 & A2, (V1 V2) d = 1 0 would give us either a1 = 1; a2 = 1 or b1 = 1 for V1 vector, and A1 = 0; A2 = 1; b1

=0 for V2 vector. Now we have a1 = 1; a2 = 1 or b1 = 1 for the V1 vector (to pull down the AOI21 gate output to 0), and a1 = 0; a2 = 1 and b1 = 0 (to pull up the gate output to 1) for the V2 vector. These are precisely the conditions for the test for PMOS stuck-open fault at A1. Similarly, by targeting slow-to-fall TDF at node e (gate G4's second input), we have the test for PMOS TSOF at a2 input.

To generate the test for the NMOS TSOF at a1 input (and a2, since the two NMOS transistors are in series), we target the slow-to-rise TDF at node f (G6's first input) as shown in Figure 3.7. Node f is also a fan-out of the G2 output. With f = 0.1 it is easy to derive G1 output = 0.1 and b1 = 0.0. Thus we have (V1 V2) a1 & a2 = 0.1 and b1 = 0.0. These are the conditions for detecting NMOS TSOFs at a1 and a2. Similarly the test for the NMOS TSOF at b1 input can be generated by targeting node g (G5's first input) slow-to-rise TDF.

Fig. 3.7 Gate modification for test generation of NMOS TSOFs in AOI21 gate

All the other AOI or OAI type complex gates can be replaced by the corresponding structures accordingly. Note that the functionality of the replacing structure is equivalent to the corresponding original complex gate (i.e. the circuit in Figure 3.7 is functionally equivalent to the AOI21 gate). This allow us to replace all the complex gates with the logic structures and employ ATPG to target all the corresponding TDFs which represent the TSOFs at one time.

## 3.2 Cross Wire Open Fault Identification and Gate Modification for Detection

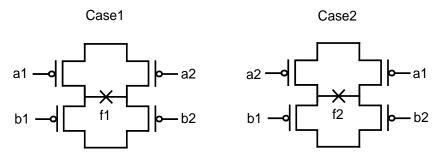

To target the CWO faults within the complex gates independent of library cell layout, we need to identify all the possible open faults for all input configurations of the complex gates. This is because without layout information, it is impossible to tell how inputs from the netlist map to physical transistor locations in silicon. For example, Figure 3.8 shows the PMOS networks of an AOI22 gate. It is obvious that by exchanging input a1 and a2 we have two possible network configurations, which create two possible open faults f1 and f2. To activate fault f1 the V2 vector

Fig. 3.8 Possible PMOS network configurations for an AOI22 gate

needs to turn on PMOS at input a1 and b2 (a1, b2) only or a2 and b1 (a2, b1) only. Similarly for fault f2 we need PMOS at (a2, b2) or (a1, b1) to be turned on. If the layout information is unavailable, both these CWOs must be targeted during test generation to guarantee fault detection.

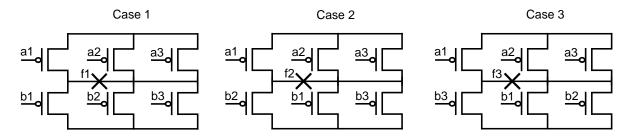

Now consider the PMOS network of an AOI33 gate. Figure 3.9 shows some different input configurations. As can be seen in Case 1, the CWO fault f1 separates the upper and lower level of

Fig. 3.9 Possible PMOS network configurations for AOI33 gate

inputs into two groups respectively: input a1 on the left side and input a2, a3 on the right side; input b1 on the left side and inputs b2, b3 on the right side. If we keep the input configuration for the upper level inputs the same and list all the possible configurations for the lower level inputs based on different grouping, we have three possible PMOS networks. For Case 1, fault f1 separates input b1 and b2, b3; for Case 2, fault f2 separates input b2 and b1, b3; for Case 3, fault f3 separates input b3 and b1, b2. To activate fault f1 in Case 1, the V2 vector should turn on PMOS at a1 and b2 or b3 (a1, (b2 + b3)), or PMOS at a2 or a3 and b1 ((a2 + a3), b1). Similarly, for fault f2 in Case 2 we need (a1, (b1 + b3)) or ((a2 + a3), b2), and for fault f3 in Case 3 we need (a1, (b1 + b2)) or ((a2 + a3), b3). Since we also have three possible configurations for the upper level inputs, totally we have a total of 3x3 = 9 faults for all possible input configurations of the AOI33 gate. Similarly, for the AOI333 gate, when we consider the open faults at the first and second level of inputs, we have 3x3 = 9 faults; when we consider the second and third level, we have another 9 faults. Thus for the AOI333 gate we have 18 possible faults to target.

Figure 3.10 shows the different PMOS network configurations of an AOI44 gate. For fault f0 which is at the side of the network, the analysis is similar to our discussion of AOI33 gate; for each level of inputs we have 4 possible configurations and totally we have 4x4 = 16 possible side open faults for the AOI44 gate. Now consider fault f1 which is at the center of the network. It separates the upper and lower inputs into two groups respectively: input a1, a2 and a3, a4 for the upper level; input b1, b2 and b3, b4 for the lower level. If we keep the upper level network the same and interchange the lower level network, we have six possible configurations (as shown in Figure 3.10) based on different groups of inputs: input b1, b2 and b3, b4 separated by fault f1; input b3, b4 and b1, b2 separated by fault f2; input b1, b3 and b2, b4 separated by fault f3; input b2, b4 and b1, b3 separated by f4, input b1, b4 and b2, b3 separated by f5, input b2, b3 and b1, b4 separated by f6.

Fig. 3.10 Possible PMOS network configurations for AOI44 gate

As there can be three possible configurations for the upper level network (the reason there are three instead of six configurations as in the lower level is that we interchange the two groups in the lower level to have six configurations, and the interchanging of input groups in the upper level network is redundant since the network is symmetrical), in total we have 6x3 = 18 possible faults at the center of the AOI44 network. Thus the AOI44 gate have 18 + 16 = 34 possible CWO faults.

| AO<br>AO | I22,<br>I221 | AO<br>2 |          | AO<br>AO | I32,<br>I32 | AOI322 |     | AOI33 |     |

|----------|--------------|---------|----------|----------|-------------|--------|-----|-------|-----|

| 2        | 1            | 4       | 2        | 6        | 2           | 8      | 3   | 9     | 2   |

| AOI332   |              | AO      | I33<br>3 | AO       | I42<br>2    | AO     | I43 | AO    | I44 |

| 15       | 4            | 18      | 4        | 16       | 4           | 30     | 3   | 34    | 3   |

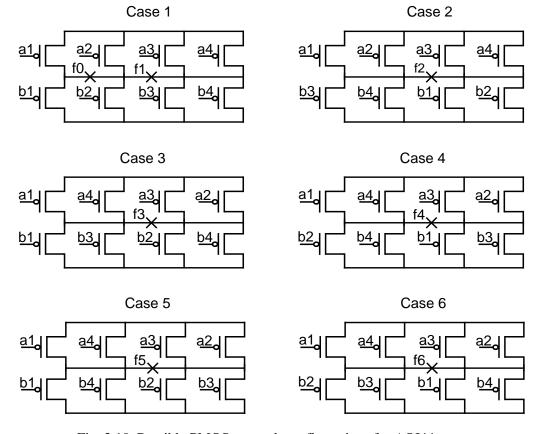

Table 3.1 Number of possible cross wire open (CWO) faults for sample AOI complex gates with and without layout information

Table 3.1 shows the number of cross wire open faults possible for varying sizes of AOI complex gate cells. The number on the left is the total possible faults from all layout configurations, while the number on the right is the number of faults from a particular configuration assuming we have the cell layout information.

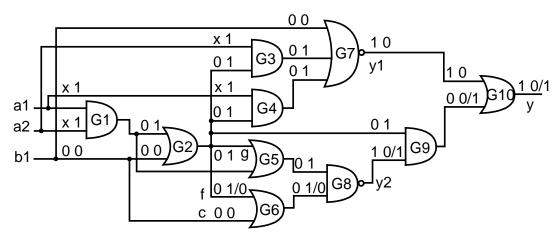

We use a commercial ATPG tool to generate deterministic tests for the timing un-aware cross wire opens in complex gates. This is done by transforming the complex gates into another circuit structure for the purposes of test generation. This converts the detection of open faults into the detection of corresponding transition delay faults with additional test activation conditions. Figure 3.11 shows an example of AOI33 gate transformation. The function of the transformed structure

Fig. 3.11 AOI33 gate transformation for targeting CWOF

is the same as that of the AOI33 gate. In the figure we target node d (output of gate G3) slow-to-fall TDF in the transformed circuit. Since (V1) d = 1 and d = (a1 AND a2 AND a3) OR (b1 AND b2 AND b3), we have either (V1) a1 = a2 = a3 = 1 or b1 = b2 = b3 = 1 to initialize the output y to 0. The fault effect has two paths (gate G4 or G5) to sensitize to output y. Suppose it sensitizes through gate G4, then we have (V2) a2 = 1, a3 = 1 and b1 = 1. Since (V2) d = 0, we have gate

G1's output = 0 and G2's output = 0, which give us a1 = 0 and b2 or b3 = 0. Thus the V2 vector will try to turn on PMOS at input a1 and input b2 or b3 only. This is exactly one test for the cross wire open fault f1 in Figure 3.10. Similarly, if the fault effect sensitizes through gate G5, we have the V2 vector to set a1 = 1, a2 = 0 or a3 = 0 and b1 = 0, b2 = 1, b3 = 1, which is the other test for fault f1. Thus by using ATPG to target the TDF fault, we have the test for the corresponding cross wire open (CWO) fault. The transformed sub-circuits circuits for other complex gates can be created in a similar way. We use a small script to automate the transformation before the circuit is given to ATPG.

Using the transformed circuit each time we can only run a single test generation for one cross wire open fault of every complex gate. To target all the possible faults within all the complex gates, we need to run test generation on multiple transformed copies of the CUT. The total number of test generation runs needed equals the total number of possible cross wire opens faults in the largest complex gate. This results in a somewhat large fault list and test data volume for the CUTs, which can be greatly reduced if layout information is available.

Note that while we have worked with a traditional circuit structure based commercial ATPG tool, adding the required constraints on two pattern TDF tests to target opens can perhaps be more easily implemented in SAT based ATPG, and also using new commercial tools that support user defined fault models.

#### **CHAPTER 4**

## **Timing Evaluation Tests for Scan Enable Signals**

One simple way of targeting those hazard activated TSOFs that are undetectable by LOC open tests is to employ LOS open tests. Recall what has been discussed in Chapter 2, the delay caused by the TSOF can vary several orders depending on the threshold voltage variations and trapped voltage level at the open gate terminal of a transistor. To effectively target the open faults with varying delay effects, it is necessary to find out the maximum speed supported by the LOS test. The speed of the fastest LOS tests that can be applied to the circuits is determined by the speed of the global scan enable signal switching from 1 to 0 during the launch and capture cycle of the test. Since it is a broadcast control signal that fans out to all the scan flip-flops, it's switching speed is generally quite slow compare to clock signals, unless employs clock tree synthesis to the scan enable signal or implements a scan enable pipeline structure into the circuit, both of which will

Fig. 4.1 Scan enable waveforms for LOC and LOS tests

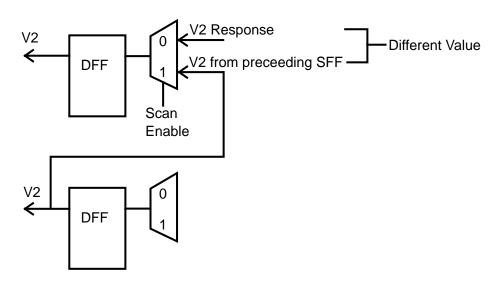

result in considerable design overhead. Figure 4.1 shows the timing waveforms of the LOS tests with slow and fast capturing clock. Observe that if the scan enable signal meets timing constraint and switches from 1 to 0 fast enough, the combinational logic's response to the V2 pattern will be captured into scan flip flops. If it does not switch fast enough, the scan flip flop will once again operate in the shift mode and capture the result from the content of the preceding scan flip flop. As the circuit clock speed is increased, narrowing the launch-to-capture window, in any circuit at some point the scan enable will fail to switch in time. Our goal is to develop a test to determine this maximum clock frequency at which the LOS test still works correctly.

# 4.1 Scan Enable Timing Test Generation Scheme

To detect scan enable signal timing failure during a LOS test, the scan input value at one scan flip-flop should be different from the expected V2 response of the combinational logic. In such a case, scan enable timing failure at any flip flop will cause the incorrect (scan input) value to be captured, and the failure will be detected. Figure 4.2 illustrates the conditions required for the LOS tests to create different values at the scan in and data inputs. Thus developing the desired timing

Fig. 4.2 Condition for LOS test evaluation of scan enable timing

tests for the scan enable signal involves developing a LOS test pattern set such that every scan flipflop is covered by the test set by ensuring different scan-in and functional signals at the scan multiplexer inputs. This LOS test is then repeatedly run at different launch-to-capture frequencies to determine the highest frequency where the test passes [50].

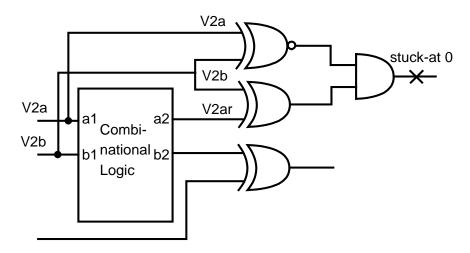

In order to generate such LOS tests, we modify the combinational circuits into the structure shown in Figure 4.3 and employ ATPG to target the corresponding stuck-at 0 faults in the structure. Since our goal is to generate different values at the data input and scan\_in input of the MUX when V2 vector is applied to the circuit, we add a XOR gate for each state output of the combinational logic and feed the XOR gate's inputs with value at data input (V2) and value at scan\_in input (V2 from preceding flip-flop), the required LOS test can be generated when we use ATPG to target the stuck-at 0 fault at the output of the XOR gate. This is because to detect the stuck-at fault, ATPG

Fig. 4.3 Modified Logic for Scan Earble LOS Test Generation

needs to set the output to 1, which will in turn set different values at the XOR gate's inputs and give us different V2 response and V2 from preceding flip-flop. If all the stuck-at 0 faults are detected, the generated test set is a scan enable signal timing test set.

However, there remains a further potential problem. Often in designs the scan interconnects are routed with the lowest priority, and a few can be extremely slow. It is possible that if the scan enable is also slow to switch, such a slow scan interconnect between SFF\_a and SFF\_b in this example may not allow the new V2 value from the output of SFF\_b to arrive at the scan\_in input of SFF\_a before the capture edge, resulting in the capture of the earlier V1 value. If this V1 is different from V2, the XOR gate will always produce a 1 at the output and the scan enable timing error will go undetected. To overcome this problem, a more robust test would require that the test patterns guarantee SFF\_b has same logic value for both the V1 and V2 vectors, so that no signal transition and/or propagation is needed during application of V2; furthermore these two identical logic values must be different from circuit response feeding into SFF\_a. Figure 4.4 shows the

Fig. 4.4 Scan enable timing test generation under the context of slow scan path

structure to generate the more restricted tests. Note that the V1 for SFF\_b would be the V2 for SFF\_a, as V2 is a one bit shift of V1, thus the test needs to generate identical V2 values for both a1 and b1 state inputs. By adding a XNOR gate for the two inputs and targeting stuck-at 0 fault at the output of the NAND gate, ATPG can generate the more robust test for scan enable signals at each flip-flop.

# **4.2 Experimental Results for Scan Enable Timing Tests**

The experimental results for the test set testing the speed of the scan enable signal are shown in Table 4.1. There are two cases that we considered in the experiments performed on the larger benchmark circuits. In Case 1 in Table 2, we assume that the scan shift paths are always faster than the scan enable signal. Recall that in this case the test only requires that the final steady state values at the data and scan\_in inputs at the target flip flop be different during the launch (V2) cycle, because the scan shift signal will not be delayed. Case 2 considers the further constrained case where the scan shift into the target flip flop may be delayed. In this case we do not allow any

| CUT    | # Gates | # DFF | # Test Patterns |        |  |

|--------|---------|-------|-----------------|--------|--|

| COT    | # Gates | # DFF | Case 1          | Case 2 |  |

| s13207 | 2573    | 638   | 7               | 16     |  |

| s15850 | 3448    | 534   | 6               | 12     |  |

| s35932 | 12204   | 1728  | 11              | 15     |  |

| b14    | 8567    | 245   | 7               | 15     |  |

| b15    | 10871   | 449   | 8               | 28     |  |

| b20    | 17158   | 490   | 10              | 29     |  |

| b21    | 17482   | 490   | 7               | 23     |  |

| b22    | 17482   | 490   | 10              | 31     |  |

| b17    | 27852   | 1415  | 10              | 62     |  |

Table 4.1 Number of test patterns for scan enable timing evaluation

transition at the scan\_in input during the launch cycle, which still ensures that the data and scan\_in inputs differ. Obviously Case 2, being further constrained, requires larger test sets because, on average, fewer circuit flip-flops will be simultaneously set up to the needed test conditions by a single two pattern test – more tests will be need to cover all the flip flops. Note however that even for Case 2, the number of tests needed to test the scan enable signal speed at all flip flop in the large benchmarks circuit is quite small; in all cases less than 100. This suggests that the tests can

be repeated at multiple clock frequencies to determine the point of failure at affordable cost. CMOS Open LOS tests can then be run at the fastest speed to detect faults with the smallest delays [50].

#### CHAPTER 5

### Experimental results of LOC and LOS targeted tests for Open Faults

The experiments reported in this chapter were all conducted with commercial ATPG tools on the re-synthesized large ISCAS89 and ITC99 benchmark circuits using an open source 250nm technology standard cell library containing a rich set of complex gates. The XOR, XNOR and multiplexers are implemented using inverters, AOI and OAI gates in our experiments. The ATPG is allowed to switch the primary inputs between the V1 and V2 vectors. Note that in this experiment we not only target the TSOFs at the parallel branches of the gates, but also the those at the serial branch since an open defect near the gate terminal of the transistor in the serial branch may also behave like a delay fault which is undetected by DC tests. Section 5.1 reports the test coverages for transistor stuck open faults and Section 5.2 reports the test coverages for cross wire open faults.

## 5.1 Test Coverage for Transistor Stuck Open Fault

Tables 5.1 shows the TDF and TSOF fault coverages of TDF and TSOF tests for the circuits under LOC and LOS test modes. Columns 2 and 3 show the TDF and TSOF fault coverages of the LOC TDF tests; Columns 4 and 5 show the TDF and TSOF fault coverages of LOC TSOF tests. Column 6 shows the additional TSOF fault coverage improvement from the LOS TSOF tests; Column 7 shows the combined TSOF fault coverages of the LOC and LOS TSOF tests. It can be seen that although we get more than 90% TDF coverage with LOC TDF tests, the actual TSOF coverage of TDF tests is only 83.76% on average and many TSOFs are not detected. By applying

targeted LOC TSOF tests, on average we get 3.3% TSOF coverage improvement. By comparing Columns 3 and 5 we know with LOC TSOF tests alone we lose about 3% TDF fault coverage. The coverage loss can be easily recovered by applying additional TDF tests for the undetected TDF faults. Allowing tests to be also generated from the LOS mode adds between 5% to 20% additional TSOF coverage. Thus LOS test are very effective for detecting those hazard activated TSOFs to improve open fault coverages.

| CUT     | LOC TI | OF Tests | LOC TS | OF Tests | Δ LOS   | Combined |

|---------|--------|----------|--------|----------|---------|----------|

| CUT     | TDF FC | TSOF FC  | TDF FC | TSOF FC  | TSOF FC | TSOF FC  |

| s1423   | 92.20% | 85.88%   | 90.60% | 92.01%   | 4.71%   | 96.72%   |

| s9234   | 94.35% | 84.85%   | 91.60% | 91.78%   | 7.59%   | 99.38%   |

| s13207  | 89.22% | 73.93%   | 85.76% | 79.19%   | 19.72%  | 98.91%   |

| s15850  | 86.09% | 79.01%   | 84.36% | 83.06%   | 16.04%  | 99.10%   |

| s35932  | 95.61% | 94.94%   | 95.46% | 96.39%   | 0.88%   | 97.27%   |

| s38417  | 98.22% | 83.30%   | 96.42% | 85.05%   | 13.79%  | 98.83%   |

| s38584  | 95.52% | 91.27%   | 93.49% | 93.90%   | 5.19%   | 99.08%   |

| b14     | 91.31% | 84.76%   | 89.15% | 87.61%   | 8.31%   | 95.92%   |

| b15     | 88.20% | 80.03%   | 83.83% | 83.54%   | 8.58%   | 92.13%   |

| b20     | 92.85% | 86.61%   | 91.16% | 89.53%   | 7.87%   | 97.40%   |

| b21     | 92.86% | 86.42%   | 91.25% | 89.43%   | 7.69%   | 97.11%   |

| b22     | 91.93% | 86.42%   | 90.40% | 88.50%   | 7.46%   | 95.96%   |

| b17     | 86.03% | 78.45%   | 80.67% | 80.37%   | 10.41%  | 90.78%   |

| b18     | 92.98% | 76.78%   | 80.13% | 78.67%   | 16.67%  | 95.35%   |

| Average | 91.96% | 83.76%   | 88.88% | 87.07%   | 9.64%   | 96.71%   |

Table 5.1 LOC and LOS TSOF coverage for re-synthesized circuits with complex gates

Note that for the ITC99 benchmark circuits a significant number of TSOFs are still undetected by the LOC and LOS tests. These TSOFs can still be potentially activated by common hazards and new methodologies need to be developed for targeting them. In the later sections we will discuss our proposed method for targeting these undetected faults.

Table 5.2 shows the number of test vectors for each test type. Column 5 shows the percentage of additional number of LOC TSOF and top off TDF tests to the number of LOC TDF tests alone for each CUT. On average with 37% more tests, we get the same TDF coverage and 3.3%

| CUT     | #LOC TDF<br>Tests | # LOC TSOF<br>Tests | # Top Up<br>TDF Tests | Additional<br>% to LOC<br>TDF Tests | △# LOS<br>TSOF Tests |

|---------|-------------------|---------------------|-----------------------|-------------------------------------|----------------------|

| s1423   | 117               | 122                 | 29                    | 29.06%                              | 23                   |

| s9234   | 200               | 225                 | 57                    | 41.00%                              | 29                   |

| s13207  | 291               | 278                 | 102                   | 30.58%                              | 127                  |

| s15850  | 243               | 264                 | 69                    | 37.04%                              | 116                  |

| s35932  | 102               | 118                 | 10                    | 25.49%                              | 11                   |

| s38417  | 256               | 231                 | 86                    | 23.83%                              | 69                   |

| s38584  | 379               | 373                 | 128                   | 32.19%                              | 95                   |

| b14     | 835               | 935                 | 249                   | 41.80%                              | 165                  |

| b15     | 977               | 907                 | 473                   | 41.25%                              | 289                  |

| b20     | 1316              | 1390                | 366                   | 33.43%                              | 182                  |

| b21     | 1568              | 1775                | 416                   | 39.73%                              | 179                  |

| b22     | 1253              | 1405                | 407                   | 44.61%                              | 201                  |

| b17     | 1428              | 1283                | 850                   | 49.37%                              | 492                  |

| b18     | 1643              | 1638                | 767                   | 46.38%                              | 886                  |

| Average | NA                | NA                  | NA                    | 36.84%                              | NA                   |

Table 5.2 Number of test vectors for TDF, LOC and LOS Open tests

additional TSOF coverage. Although the test cost overhead is relative high, the coverage improvement is for the hard to detect faults. Note that significant coverage boost is achieved for each CUT from moderate number of LOS TSOF tests. A drawback is that we may not be able to apply LOS tests at-speed as it requires fast scan enable control signal.

# **5.2** Test Coverage for Cross Wire Open Faults

The experimental results for targeting CWO faults are shown in Table 5.3 and Table 5.4. Results in Table 5.3 are for all possible CWO faults in a circuit when cell layout information is not available. Results in Table 5.4 are for one set of CWO faults in a circuit with known fixed cell layout information. We initially employ LOC TDF tests to conduct the open fault simulation using the transformed circuit structure discussed in Chapter 3. We then incrementally allow LOC and LOS cross wire open fault test generation to target the faults undetected by LOC TDF tests. The rationale for this order is to maximize the test speed with which most of tests are applied. LOC tests can always be run at speed, so the LOC tests are used to target as many opens as can be detected by such tests. The remaining faults are still targeted by LOS tests because even when LOS tests must be run much slower because of a slow scan enable signal, they can still detect many opens that display very large delay fault behavior.

In Table 5.3, Column 2 shows the total number of possible CWO faults in the absence of layout information. Column 3 shows the percentages of total number of possible CWO faults to the total number of TSOFs for each CUT. Note the percentages are relatively large since we consider all possible inputs configurations of the complex gates. Note that for ITC99 benchmark circuits the percentages of COW faults count are larger than the percentages of COW faults for the ISCAS89 benchmark circuits. This is because ITC99 circuits consist of a larger percentage of complex gates. Column 4 shows the CWO fault coverage (as percentage of the total number of possible CWO

faults) of the TDF LOC tests for the original circuits with complex gates. Column 5 and 6 show the incremental coverage improvement over TDF LOC tests by LOC and LOS cross wire open tests. As we can see, by applying TDF tests alone, on average only 50% of the CWO faults are

| CUT     | Total<br>CWOs | CWO % of total TSOFs | CWO FC<br>of<br>TDF Tests | ΔLOC<br>CWO<br>FC | ΔLOS<br>CWO<br>FC | Total<br>FC |

|---------|---------------|----------------------|---------------------------|-------------------|-------------------|-------------|

| s1423   | 82            | 4.75%                | 69.51%                    | 19.51%            | 0%                | 89.02%      |

| s9234   | 148           | 4.91%                | 45.27%                    | 48.65%            | 2.03%             | 95.95%      |

| s13207  | 580           | 7.61%                | 54.83%                    | 22.41%            | 18.97%            | 96.21%      |

| s15850  | 734           | 7.37%                | 43.19%                    | 37.87%            | 11.04%            | 92.10%      |

| s35932  | 1674          | 4.96%                | 97.85%                    | 2.15%             | 0%                | 100%        |

| s38417  | 2080          | 6.99%                | 63.94%                    | 31.54%            | 1.20%             | 96.68%      |

| s38584  | 2653          | 7.77%                | 69.05%                    | 21.75%            | 2.86%             | 93.67%      |

| b14     | 2347          | 12.45%               | 47.59%                    | 34.73%            | 8.27%             | 90.58%      |

| b15     | 3976          | 15.04%               | 31.34%                    | 40.34%            | 12.60%            | 84.28%      |

| b20     | 4395          | 11.39%               | 53.11%                    | 32.38%            | 7.87%             | 93.36%      |