# **Stress Analysis in Bipolar Transistors**

by

Parameshwaran Gnanachchelvi

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama May 7, 2016

#### Approved by

Bogdan M. Wilamowski, Chair, Professor, Electrical and Computer Engineering Richard C. Jaeger, Co-chair, Distinguished University Professor (Emeritus), Electrical and Computer Engineering Jeffrey C. Suhling, Quina Distinguished Professor, Mechanical Engineering Michael Hamilton, Associate Professor, Electrical and Computer Engineering Vishwani Agrawal, James J. Danaher Professor, Electrical and Computer Engineering

#### Abstract

Stress effects in semiconductor devices have gained significant attention in semiconductor industry nowadays. Stress effect in semiconductor devices is used as a beneficial effect in sensor applications and strain engineering and efforts are taken to increase these effects. Strain engineering is widely used for MOSFETs. Performance of SiGe based heterostructure bipolar transistors (HBTs) is improved by bandgap and strain engineering. However this approach is not fully developed for Si bipolar junction transistors (BJTs). While stress effects are useful in some areas there are some unwanted stress effects as well. The unintentional stresses developed during fabrication, processing and packaging are harmful in semiconductor devices and efforts are taken to mitigate these stress effects.

In this research work, stress-induced changes were investigated in the perspective of improvement for strain engineering in Si BJTs as well as mitigation of stress effects in precision analog circuits. npn and pnp BJTs on (100) and (111) planes were studied using experimental and modeling approaches. Modeling approach was mainly used for this study in order to overcome the practical difficulties associated with fabrication of devices with different orientation and sizes and controlled application of stress in various orientations for measurements. Measurements were taken for in-plane normal stress and the validity of the model was verified. A new one-dimensional numerical model was developed in Matlab in order to make the stress analysis easier and more in-depth with short running time. Simulation results of the 1-D model and Sentaurus TCAD tool were compared and both results showed very good

agreement. While commercial TCAD tools usually takes tens of minutes for 2-D or hours for 3-D simulations for this type of stress analysis, the newly developed 1-D model gives comparable results in seconds and without any loss of information generated. This model can be used for fast stress analysis/prediction in vertical or lateral npn/pnp BJTs in any plane and will help in developing optimal design for strain engineering in BJTs or stress mitigation in analog circuits.

The stress induced changes in vertical and lateral bipolar transistors on (100) plane were quantitatively analyzed for different stress orientations. Our analysis revealed that for a vertical npn transistor substantial enhancement in collector current (I<sub>C</sub>), dc current gain ( $\beta$ ), cutoff frequency (f<sub>T</sub>), and maximum oscillation frequency (f<sub>max</sub>) can be achieved using an uniaxial inplane compressive or an out-of-plane tensile stress. In a vertical pnp considerable improvement in I<sub>C</sub> can be achieved with an in-plane or an out-of-plane compressive stress while the changes in  $\beta$ , f<sub>T</sub> and f<sub>max</sub> are minimal. Lateral pnp BJTs showed much higher improvement for in-plane longitudinal compressive stress. In addition, lateral npn BJTs showed higher improvement for out-of-plane compressive stress. These results revealed a promising opportunity for strain engineering in both vertical and lateral Si BJTs.

This study also revealed that the transport limited BJTs are less sensitive to stress than injection limited BJTs. In addition, vertical pnp on (100) silicon is less sensitive to stress than the vertical npn on (100) plane or vertical npn or pnp on (111) plane. On (111) silicon vertical npn BJTs are less sensitive than the vertical pnp BJTs. Finally, stress effects in precision analog circuits have been explored with the help of Spice simulations incorporating the 1-D theoretical model. Some methods for stress mitigation in precision analog circuits are also suggested including usage of less sensitive BJTs whenever possible, keeping the matching BJTs in close

proximity to avoid stress gradients, avoiding high stress regions in chips, usage of enclosed lateral devices for stress compensation.

## Acknowledgement

I am always thankful to Auburn University and the Department of Electrical and Computer Engineering for providing me a good environment for my graduate studies. First, I would like to express my sincere gratitude to my major advisor, Dr. Bogdan Wilamowski, for providing me an opportunity for PhD study at Auburn University, and for his guidance, encouragement, understanding and support throughout my study. Without his full support I would have not achieved this success in my life. I am grateful for his enthusiasm for Electrical Engineering and his belief in me as a researcher. I would also like to specifically thank my Coadvisor, Dr. Richard Jaeger, for providing me continuous support and patient guidance for my research work and the publications. I also would like to express my heartfelt gratitude to my graduate committee members Dr. Jeffrey Suhling, Dr. Michael Hamilton, Dr. Viswani Agrawal and the University reader of this dissertation Dr. Vitaly Vodyanoy for their constructive inputs, support and guidance. I would like to thank Dr. Guofu Niu for his help in Sentaurus simulations, radio frequency analysis and great support in providing valuable input for my research publication.

I would like to thank Dr. Safina Hussain for helping and training me in 4-point bending fixture measurements, for developing flex connector for measurements, and also proving me some experimental data for comparison with the simulation results. I also would like to thank Dr. Wu Xing for his extended help in solving any programming issues throughout my research work.

v

I also express my sincere thanks to my fellow graduate students Dr. Michael Pukish, Jordan Richardson, Dr. Philip Reiner, Jiao Yu, Dr. Hao Yu, Dr. Tiantian Xie and Tim Brown for their support and for making work hours pleasant and motivating. I am also thankful to Charles Ellis, Mike Palmer and all other staff in Electrical and Computer Engineering Department for their support.

I would like to thank my family members who provided moral support during the pursuit of this academic goal. I would like to thank my mother Kanagambikai Thirunavukkarasu and my brothers Kathirvel Thirunavukkarasu, Dr. Gnanavel Thirunavukkarasu and Thangavel Thirunavukkarasu for their encouragement. I dedicate my success to my late father Velupillai Thirunavukkarasu who was always proud of my achievements. I also would like to thank my husband Dr. Kodeeswaran Parameshwaran for his continuous inspiration. Finally, but not least, I am also greatly thankful for my lovely son Mayooran Selliah who always been a ray of hope and happiness in my life, for his understanding, unwavering love and help, during my doctoral studies.

This research work was supported by the Semiconductor Research Corporation (SRC), The Center for Advanced Vehicle and Extreme Environment Electronics (CAVE<sup>3</sup>) and Alabama Microelectronics Science and Technology Center (AMNSTC).

# Table of Contents

| Abs  | tract                                                                                | ii       |

|------|--------------------------------------------------------------------------------------|----------|

| Ack  | nowledgments                                                                         | v        |

| List | of Tables                                                                            | xi       |

| List | of Figures                                                                           | xii      |

| INT  | RODUCTION                                                                            | 1        |

| 1.1  | Stress effects in semiconductor devices                                              | 1        |

| 1.2  | Previous research works on stress effects in bipolar transistors and analog circuits | 6        |

| 1.3  | Scope of the research                                                                | 9        |

| 1.4  | Structure of this dissertation                                                       |          |

|      | EVIEW ON STRESS EFFECTS ON SEMICONDUCTOR BAND STRUCTURE<br>RRIER MOBILITY            |          |

| 2.1  | Introduction                                                                         | 12       |

| 2.2  | Stress, strain and tensors                                                           | 12       |

| 2.3  | Stress effects on semiconductor band structure                                       |          |

| 2.4  | Deformation potential theory                                                         | 16       |

| 2.5  | Stress effect in mobility                                                            | 19       |

| 2.6  | Piezoresistive concept development                                                   |          |

| 2.7  | Piezoresistive theory                                                                | 23       |

| 2.8  | Summary                                                                              |          |

| STR  | RESS EFFECTS IN BIPOLAR TRANSISTORS-THEORETICAL AND EXPERI                           | MENTAL32 |

| 3.1  | Introduction                                                                         |          |

| 3.2   | Bipolar devices used for characterization and simulation                   | 32 |

|-------|----------------------------------------------------------------------------|----|

| 3.2.1 | Vertical transistors                                                       | 32 |

| 3.2.2 | Lateral transistors                                                        | 33 |

| 3.3   | Modeling the mechanical stress effects in bipolar transistor               | 34 |

| 3.3.1 | Vertical npn transistors on (100) silicon                                  | 37 |

| 3.3.2 | Vertical pnp transistors on (100) silicon                                  |    |

| 3.3.3 | Vertical npn transistors on (111) silicon                                  | 40 |

| 3.3.4 | Vertical pnp transistors on (111) silicon                                  | 41 |

| 3.4   | Characterization                                                           | 41 |

| 3.4.1 | Conventional experimental set-up                                           | 42 |

| 3.4.2 | Improvement with new flex connector                                        | 47 |

| 3.5   | Summary                                                                    | 53 |

| MOE   | DELING OF STRESS EFFECT WITH SENTAURUS TCAD SIMULATOR                      | 54 |

| 4.1   | Introduction                                                               | 54 |

| 4.2   | Introduction to Sentaurus TCAD simulator                                   | 54 |

| 4.3   | Creating and meshing device structures                                     | 55 |

| 4.4   | Device equations and physical models                                       | 56 |

| 4.5   | Stress simulation with 2-D bipolar transistor model                        | 69 |

| 4.6   | Stress simulation results for all 6 directions for npn and pnp transistors | 79 |

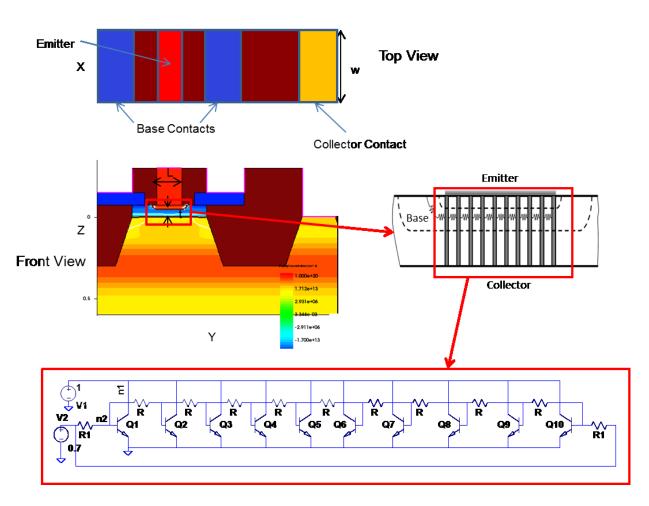

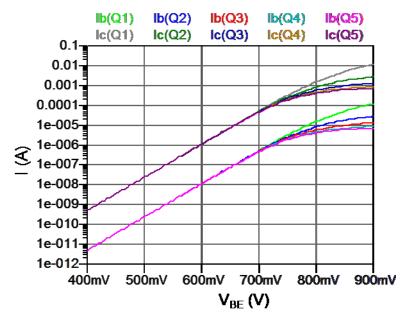

| 4.7   | Stress simulation with 3-D bipolar transistor model                        | 81 |

| 4.8   | Summary                                                                    | 84 |

|       | NUMERICAL MODELLING FOR RAPID STRESS ANALYSIS IN BIPOLAR<br>NSISTORS       | 85 |

| 5.1   | Introduction                                                               | 85 |

| 5.2   | Device equations                                                           | 87 |

| 5.3   | Modeling of an npn transistor with MATLAB                                  | 88 |

| 5.3.1 | Initialization                                                             |    |

| 5.3.2   | Solving Poisson equation for base-collector and base-emitter junctions                      |     |

|---------|---------------------------------------------------------------------------------------------|-----|

| 5.3.3   | Electrostatic potential and electric field calculations for the entire region               |     |

| 5.3.4   | Field dependent mobility and velocity calculations                                          |     |

| 5.3.5   | Novel Integrated approach for calculating carrier concentration in base                     |     |

| 5.3.6   | Calculation of carrier concentrations in emitter and collector                              |     |

| 5.3.7   | EQFP, HQFP calculations                                                                     |     |

| 5.4     | Modeling of a pnp transistor with MATLAB                                                    | 111 |

| 5.5     | Application of 1-D model to verify text book approaches                                     | 115 |

| 5.6     | Modeling the mechanical stress effect                                                       |     |

| 5.7     | Verifying the validity of the model with experimental results and theoretical expectations  |     |

| 5.8     | Residual stresses in bipolar transistors                                                    |     |

| 5.9     | Stress effects in saturation current for vertical and lateral transistors in (100) plane    |     |

| 5.10    | Stress effects in bipolar transistors on (111) plane                                        |     |

| 5.11    | Summary                                                                                     |     |

|         | FORMANCE ENHANCEMENT IN BIPOLAR TRANSISTORS ON (100) PLA<br>AXIAL STRESS                    |     |

| 6.1     | Introduction                                                                                |     |

| 6.2     | Vertical transistors on (100) plane                                                         |     |

| 6.2.1   | dc characteristics                                                                          |     |

| 6.2.1.  | 1 Modeling for dc analysis (with Matlab)                                                    |     |

| 6.2.1.2 | 2 Theoretical expectations (extended theory)                                                |     |

| 6.2.1.  | 3 Understanding the impact of in-plane normal stress on vertical transistors on (100) plane |     |

| 6.2.1.4 | 4 Analysis of impact of in-plane and out-of-plane normal stresses                           |     |

| 6.2.2   | rf characteristics                                                                          |     |

| 6.2.2.  | 1 Modeling for ac analysis (with Sentaurus)                                                 |     |

| 6.2.2.2 | 2 Theoretical expectations                                                                  |     |

| 6.2.2.  | 3 Analysis of impact of in-plane and out-of-plane normal stresses                           | 154 |

| 6.3     | Lateral Transistors on (100) plane                                                          |     |

| 6.3.1 | Theoretical Expectations                                                      | 158 |

|-------|-------------------------------------------------------------------------------|-----|

| 6.3.2 | Analysis of impact of in-plane and out-of-plane normal stresses               |     |

| 6.3   | Summary                                                                       | 163 |

| MITI  | IGATION OF STRESS EFFECTS IN PRECISION ANALOG CIRCUITS                        | 164 |

| 7.1   | Introduction                                                                  | 164 |

| 7.2   | Magnitudes of stress and stress gradients in integrated circuits              | 164 |

| 7.3   | Impact of stress on analog integrated circuit building blocks                 |     |

| 7.4   | Approaches for minimizing the impact of stress on bipolar integrated circuits | 175 |

| 7.5   | Summary                                                                       | 176 |

| CON   | ICLUSION                                                                      | 177 |

| Refe  | rences                                                                        |     |

| Appe  | endices                                                                       | 185 |

| A     | Doping profile.                                                               | 185 |

| В     | Current crowding effects in 2-D and 3-D simulations                           |     |

| С     | MATLAB Code of 1-D npn bipolar transistor model                               | 194 |

| D     | Piezoresistive coefficients in Si.                                            | 206 |

| E     | Spice Netlists for simulation of stress effects in analog circuits.           | 208 |

| F     | Publications of the Author.                                                   |     |

# List of Tables

| 2.1 | Different notations of stress subscripts and reduced forms                                         | 14  |

|-----|----------------------------------------------------------------------------------------------------|-----|

| 2.2 | The compliance and stiffness coefficients of silicon                                               | 15  |

| 2.3 | Quadratic fits to simulation results of Creemer & French                                           | 19  |

| 2.4 | Piezoresistive coefficient values for lightly doped silicon                                        | 23  |

| 4.1 | SRH doping and temperature dependent parameters                                                    | 58  |

| 4.2 | Mobility model parameters at T=300 K                                                               | 59  |

| 4.3 | Canali model parameters for Si at T=300 K                                                          | 60  |

| 4.4 | Lattice scattering model parameters for silicon at T=300K                                          | 61  |

| 4.5 | Bangap model parameters for silicon                                                                | 65  |

| 4.6 | Deformation potential parameters                                                                   | 66  |

| 4.7 | Models selected for Sentaurus simulations                                                          | 68  |

| 4.8 | Piezoresistive coefficient estimates for vertical BJTs on (100) and (111) planes                   | 75  |

| 5.1 | Stress induced changes in $\Delta n_i^2/n_i^2$ (including residual stress)                         | 127 |

| 6.1 | Piezoresistive coefficient estimates for vertical BJTs on (100) plane                              | 137 |

| 6.2 | Increase in collector current and current gain of a vertical transistor for 150 MPa                | 153 |

| 6.3 | Piezoresistive coefficient estimates for vertical and lateral BJTs on (100) plane                  | 161 |

| 6.4 | Increase in collector current and current gain of a lateral transistor for 150 MPa                 | 163 |

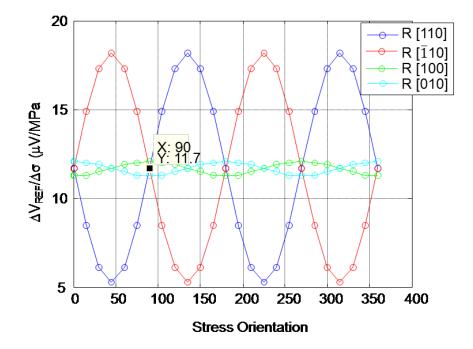

| 7.1 | $(\Delta V_{ref}/\Delta\sigma)$ for an in-plane stress in different orientations with respect to R | 174 |

# List of Figures

| 1.1. | Sources of mechanical stress generation in integrated circuits                                                                                                                                                      | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2. | Transmission electron micrographs of 45-nm p-type and n-channel transistors                                                                                                                                         | 5  |

| 2.1. | Stress states on an infinitesimal unit element (for clarity, stresses on negative faces are not depicted)                                                                                                           | 13 |

| 2.2. | Schematic band structure of silicon in the (a) stress-free and the (b) stressed case                                                                                                                                | 16 |

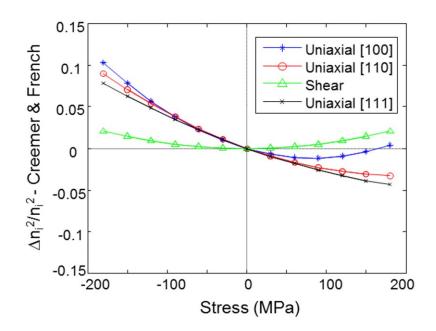

| 2.3. | Stress induced change in $\Delta n_i^2/n_i^2$ from Creemer & French [57, 68]                                                                                                                                        | 18 |

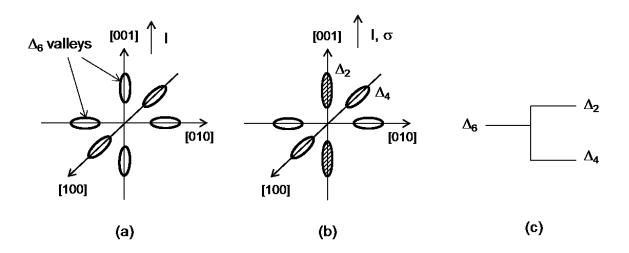

| 2.4. | Conduction band (a) unstrained (b) uniaxial tensile strain in [001] direction (c) band energy splitting.                                                                                                            | 20 |

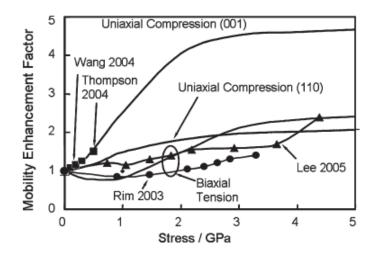

| 2.5. | Calculated and experimental data for uniaxial longitudinal compressive and biaxial tensile-stress-enhanced hole mobility versus stress (biaxial stress = $\sigma_{XX} + \sigma_{YY}$ )                              | 21 |

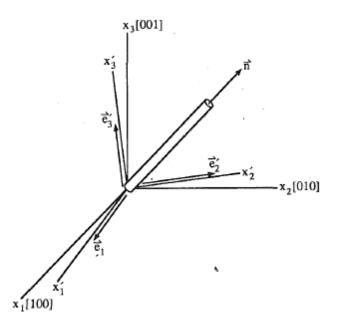

| 2.6. | Filamentary conductor arbitrarily oriented with respect to an off-axis coordinate system.                                                                                                                           | 27 |

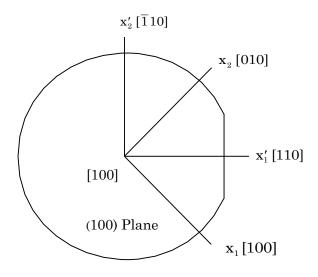

| 2.7. | (100) Wafer plane                                                                                                                                                                                                   | 28 |

| 2.8. | (111) Wafer plane                                                                                                                                                                                                   | 30 |

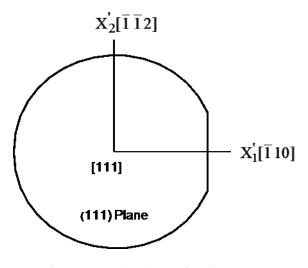

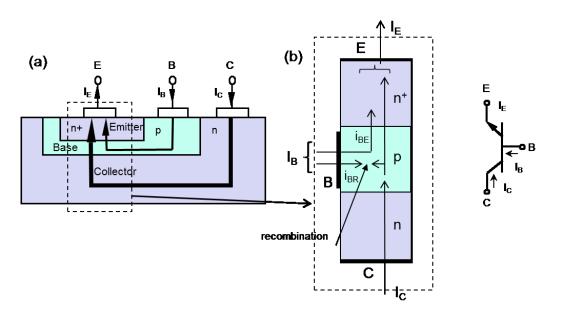

| 3.1. | Vertical bipolar devices (a) vertical npn transistor (b) vertical pnp transistor (substrate pnp transistor). The main current flow directions are indicated, C is the collector, B is the base and E is the emitter | 33 |

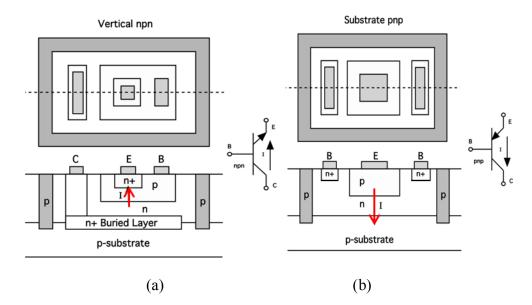

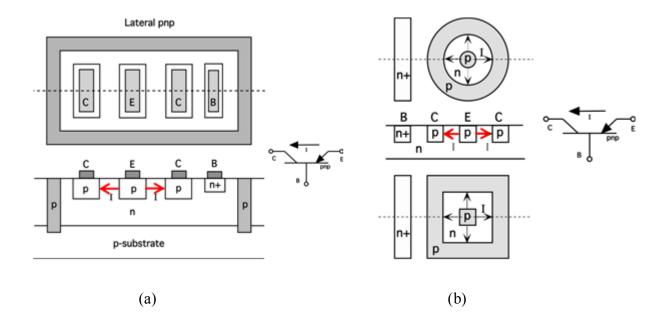

| 3.2. | Lateral bipolar devices (a) unidirectional pnp transistor (b) multidirectional pnp transistor. The main current flow directions are indicated, C is the collector, B is the base and E is the emitter               | 34 |

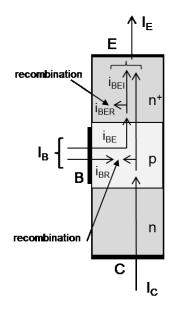

| 3.3. | A vertical npn transistor (a) simplified cross-section (b) simplified block model showing the current components                                                                                                    | 35 |

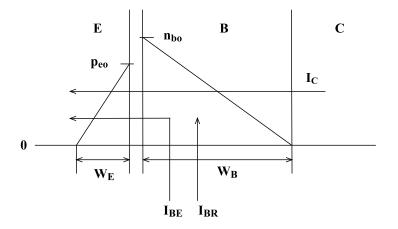

| 3.4. | One dimensional npn transistor                                                                                                                                                                                      | 36 |

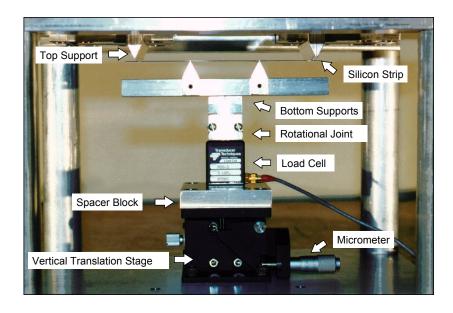

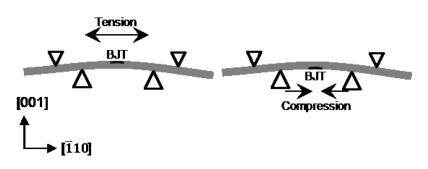

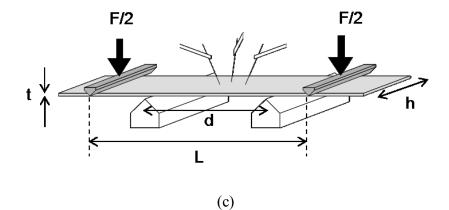

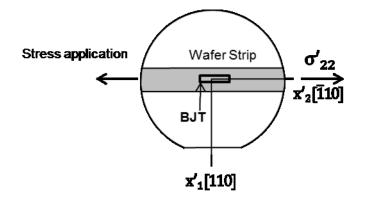

| 3.5. | (a) Four-point bending fixture (b) configurations for tensile and compressive stress applications (c) four-point bending geometry                                                                                   | 43 |

| 3.6.  | Stress application direction                                                                                                                                                    | 44 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7.  | Changes in I <sub>C</sub> -V <sub>CE</sub> Characteristics with stress $\sigma[\overline{1}10]$ for an npn BJT with probing                                                     | 45 |

| 3.8.  | Changes in Gummel plot with stress $\sigma[\overline{1}10]$ for an npn BJT with probing showing non-uniform changes                                                             | 45 |

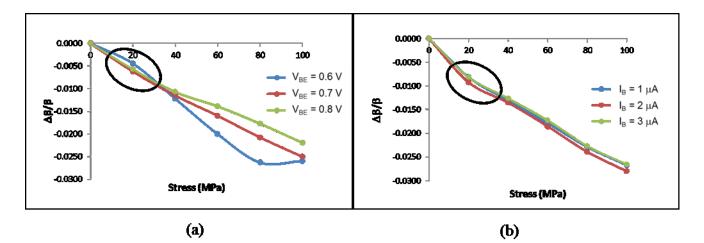

| 3.9.  | Fractional change in dc current gain with stress $\sigma[\overline{1}10]$ for npn BJT with probing (a) using fixed V <sub>BE</sub> method (b) using fixed I <sub>B</sub> method | 46 |

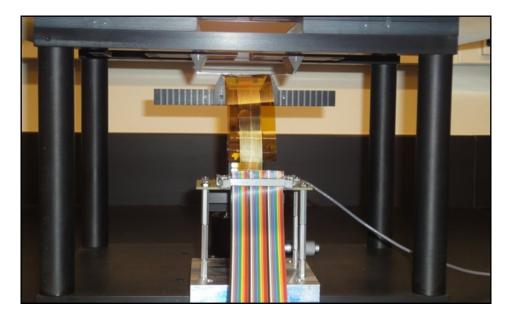

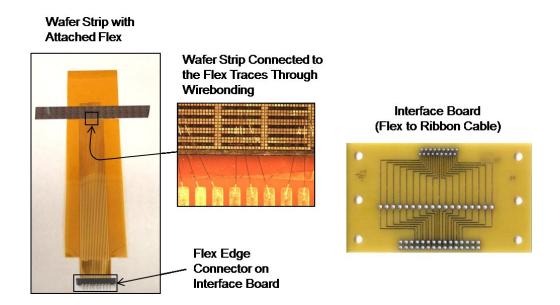

| 3.10. | 4 PB set up with new flex connector and a flexible carrier                                                                                                                      | 48 |

| 3.11. | Flex connector and interface board                                                                                                                                              | 48 |

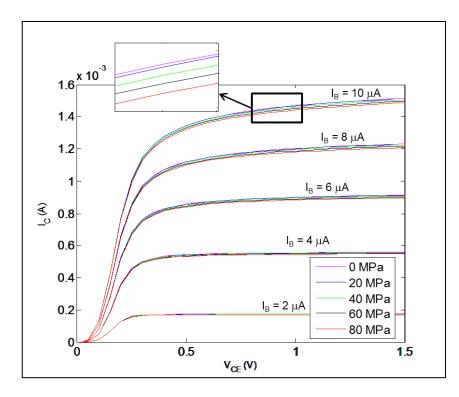

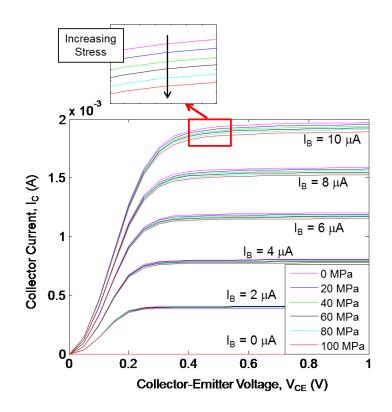

| 3.12. | Changes in I <sub>C</sub> -V <sub>CE</sub> Characteristics with stress $\sigma[\overline{1}10]$ for an npn BJT showing uniform changes                                          | 49 |

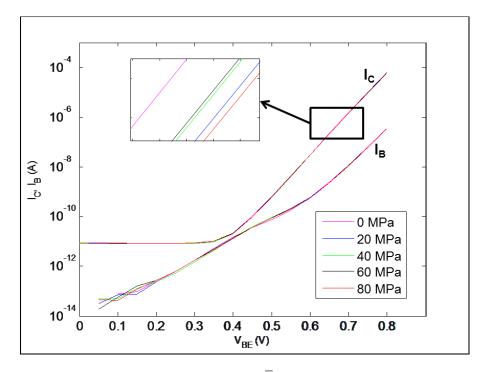

| 3.13. | Changes in Gummel plot with stress $\sigma[\overline{1}10]$ for an npn BJT showing uniform changes                                                                              | 49 |

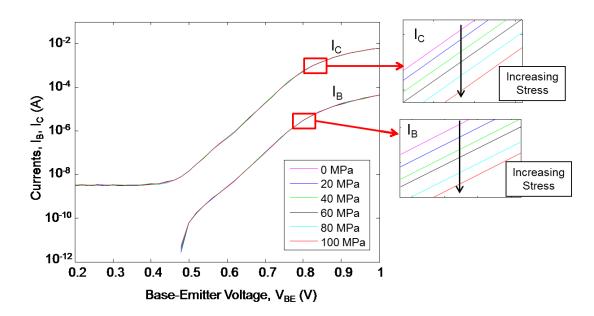

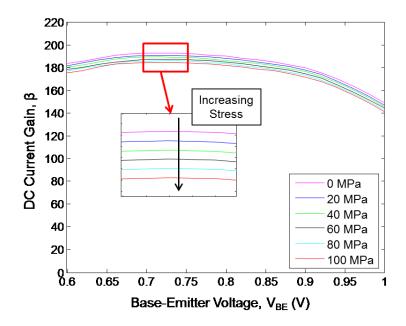

| 3.14. | Changes in dc current gain with stress $\sigma[\overline{1}10]$ for an npn BJT showing uniform changes                                                                          | 50 |

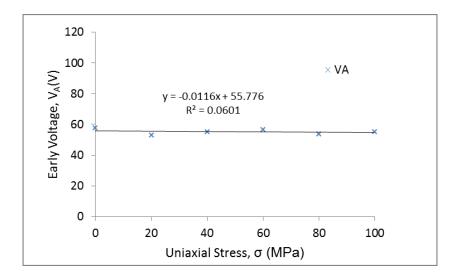

| 3.15. | Changes in Early voltage with stress $\sigma[\overline{1}10]$                                                                                                                   | 51 |

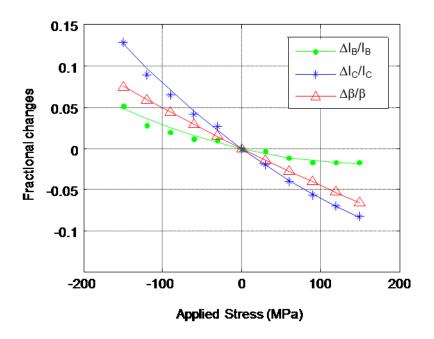

| 3.16. | Changes in currents and current gain with stress (npn # 1).                                                                                                                     | 52 |

| 3.17. | Changes in currents and current gain with stress (npn # 2)                                                                                                                      | 52 |

| 4.1.  | Temperature dependence of the energy bandgap of silicon                                                                                                                         | 63 |

| 4.2.  | Doping dependence of the energy bandgap of silicon                                                                                                                              | 64 |

| 4.3.  | Stress induced change in $\Delta n_i^2/n_i^2$ with stress using deformation potential model (default) in Sentaurus                                                              | 67 |

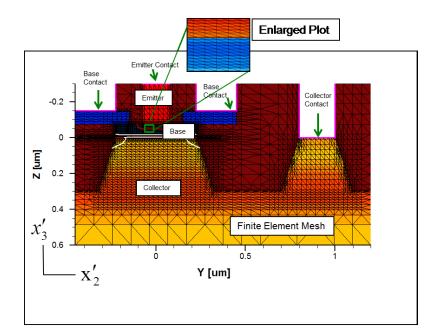

| 4.4.  | 2-D mesh structure of a vertical npn transistor developed in Sentaurus                                                                                                          | 69 |

| 4.5.  | Doping profile along the centerline                                                                                                                                             | 70 |

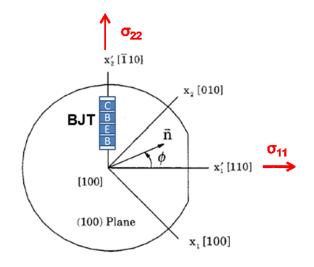

| 4.6.  | Illustration of transistor arrangement and stress application                                                                                                                   | 71 |

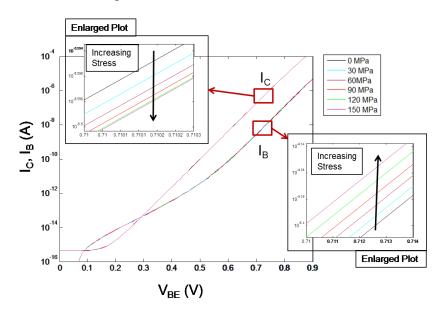

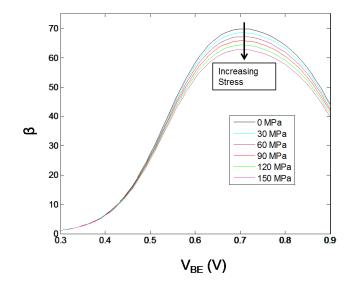

| 4.7.  | Stress induced change in Gummel plot for an npn vertical transistor in (100) plane                                                                                              | 72 |

| 4.8.  | Stress induced change in dc current gain for an npn vertical transistor in (100) plane                                                                                          | 72 |

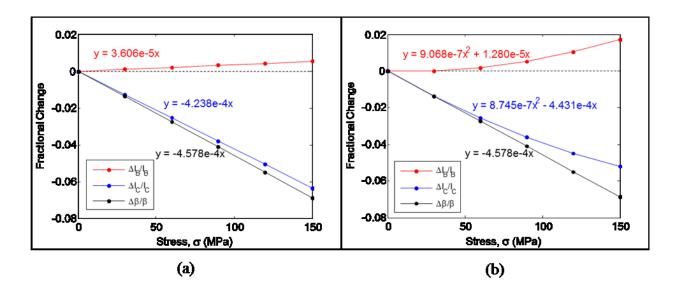

| 4.9.  | Stress inducted changes of an npn vertical transistor in (100) plane (a) change in currents (b) change in dc current gain                                                       | 73 |

| 4.10. | Another 2-D vertical npn transistor developed in Sentaurus (a) mesh of bipolar structure 2 (b) doping profile along AA                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .74 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11. | Stress induced change in currents and current gain of an npn vertical transistor to match the experimental results (a) experimental results [83] (b) simulated results with estimated piezoresistance values and deformation potential model of Sentaurus with a residual stress of -320 MPa (c) simulated results with estimated piezoresistance values and ( $\Delta ni2/ni2$ ) from Creemer and French's model with a residual stress of +160 MPa.                                                                                                                            | .76 |

| 4.12. | Stress induced change in current and dc current gain for structure 2 (a) accounts for stress induced change in mobility only (b) accounts for change in mobility as well as intrinsic carrier concentration from Creemer and French's model (residual stress = $+160$ MPa)                                                                                                                                                                                                                                                                                                       | .77 |

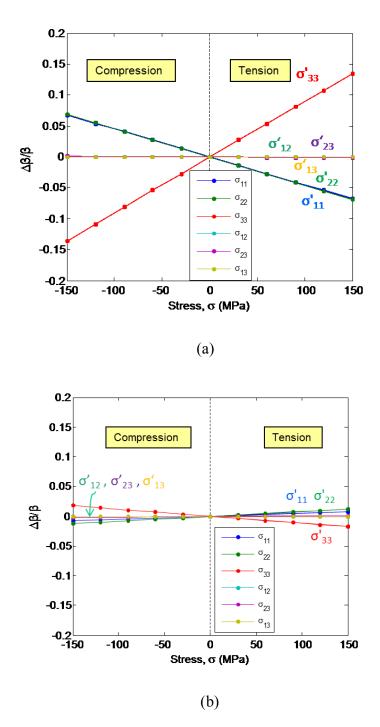

| 4.13. | Stress induced change in dc current gain of a pnp transistor for all 6 stress components .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .79 |

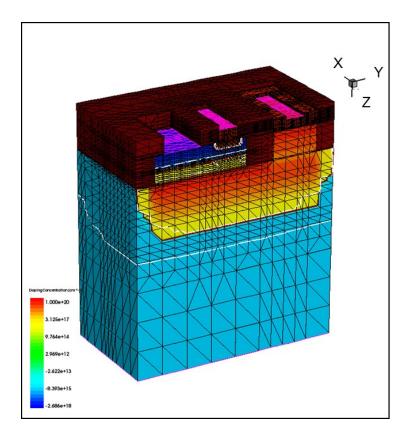

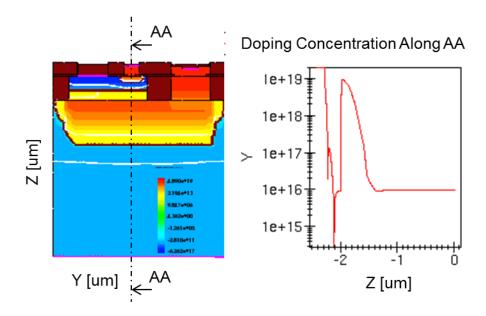

| 4.14. | 3-D mesh (structure 3) of a vertical npn transistor developed in Sentaurus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .82 |

| 4.15. | Doping profile of 3-D model (structure 3) along AA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .82 |

| 4.16. | Stress induced change in dc current gain of an npn transistor for all 6 stress components (a) with 3-D model (b) with 2-D model                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .84 |

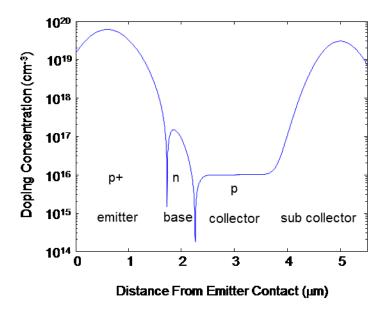

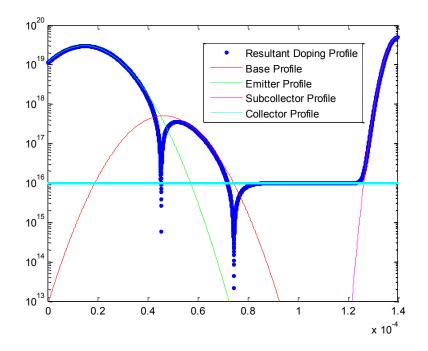

| 5.1.  | Doping profile of an npn transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .91 |

| 5.2.  | Fermi potential of an npn transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .92 |

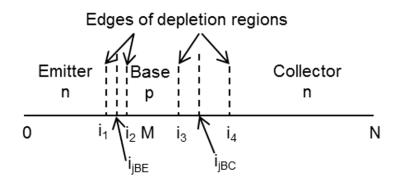

| 5.3.  | 1-D representation of a BJT illustrating terms and symbols. $i_{jBE}$ , $i_{jBC}$ - metallurgical junctions; $i_4$ , $i_3$ - start, end points of BC depletion region calculations (used in Figure 5.4, 5.5); $i_2$ , $i_1$ - start, end points of BE depletion region calculations; $i_3$ , $i_2$ - start, end points for base transport calculations (used in Figure 5.12).                                                                                                                                                                                                    | .93 |

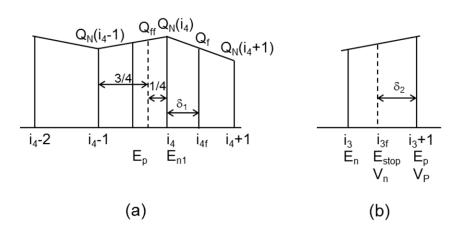

| 5.4.  | Pseudocodes for BC depletion-region calculations (a) Subroutine A - calculating<br>the depletion start point, built-in potential between the depletion start and end points,<br>desired voltage drop across the junction, and checking whether the accuracy is<br>reached (b) Subroutine B - calculating the potentials, charges and field at and between<br>the fractional start and end points, and returning the end point and the potential at the<br>fractional end point to (a), and also returning the potential between the start and end<br>points to the main program. | .95 |

| 5.5.  | BC depletion-region fractional start and end point illustrations (a) showing the fractional and whole number start points $(i_{4f}, i_{4)}$ decimal part $(\delta_1)$ and the charges $(Q_N, Q_f, Q_{ff})$ (b) showing the fractional and whole number end points $(i_{3f}, i_{3)}$ , decimal part $(\delta_2)$ , potentials $(V_n, V_p)$ and electric fields $(E_n, E_{stop}, E_p)$ .                                                                                                                                                                                           | .96 |

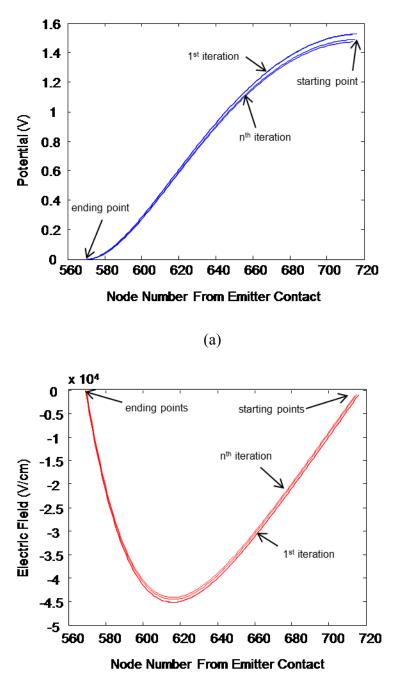

| 5.6.  | Base-collector depletion region (a) potential with iteration (b) electric field with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|       | iteration                                                                                                                                                                                                                                                                                                                                                                        | 97  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

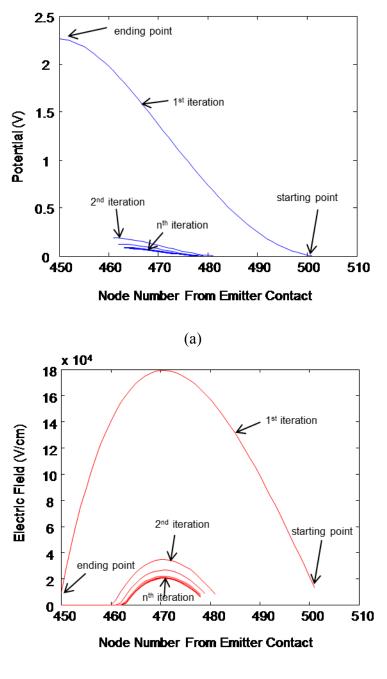

| 5.7.  | Base-emitter depletion region (a) potential with iteration (b) electric field with iteration                                                                                                                                                                                                                                                                                     | 98  |

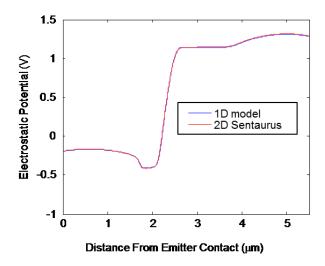

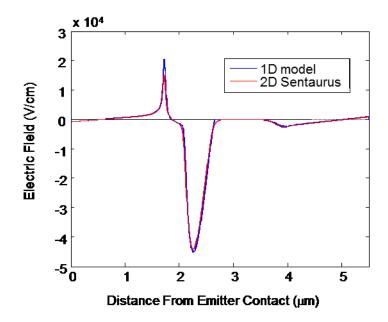

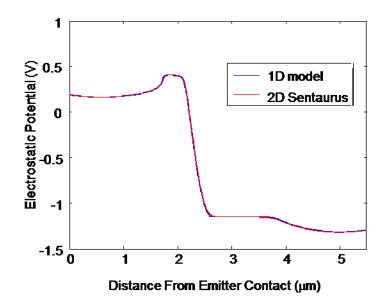

| 5.8.  | Electrostatic potential for the entire region                                                                                                                                                                                                                                                                                                                                    | 100 |

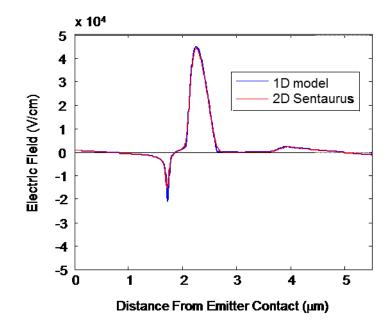

| 5.9.  | Electric field for the entire region                                                                                                                                                                                                                                                                                                                                             | 101 |

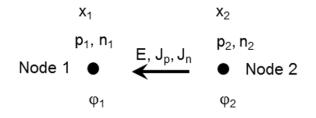

| 5.10. | Illustration of nodes 1 and 2, positions $(x_1, x_2)$ , hole, electron densities $(p_1, p_2, n_1, n_2)$ , potentials $(\phi_1, \phi_2)$ , current densities $(J_p, J_n)$ and electric field (E).                                                                                                                                                                                 |     |

| 5.11. | Subroutine C - new iterative approach for calculating carrier concentration in base.<br>Starting from electron current density $J_n=0$ at the BC depletion edge (i <sub>3</sub> ), and increasing by steps for each iteration, the electron concentration distribution in the base is computed until achieving the required accuracy at the BE depletion edge (i <sub>2</sub> ). | 106 |

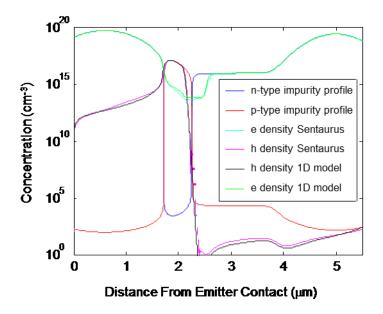

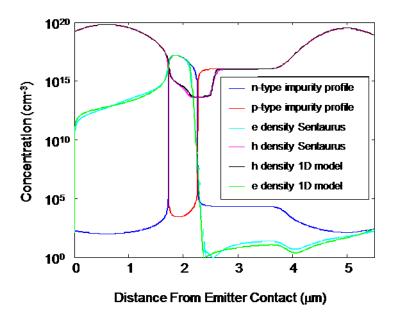

| 5.12. | Impurity profiles, electron density and hole density of an npn transistor                                                                                                                                                                                                                                                                                                        | 111 |

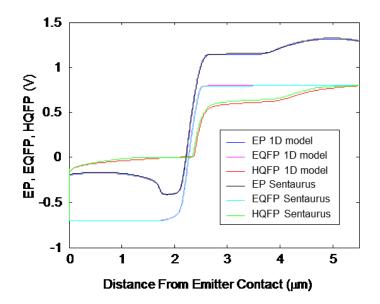

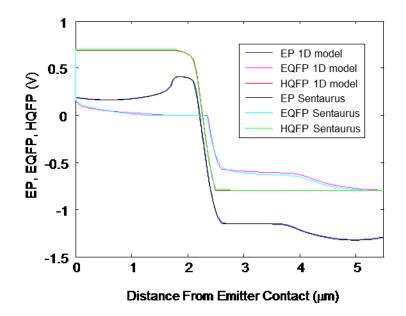

| 5.13. | EP, EQFP and HQFP of an npn transistor                                                                                                                                                                                                                                                                                                                                           | 111 |

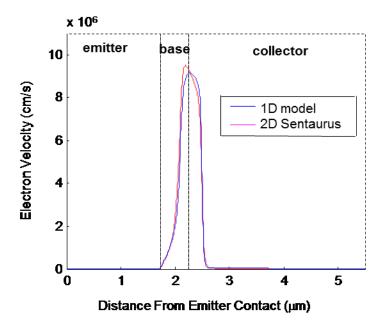

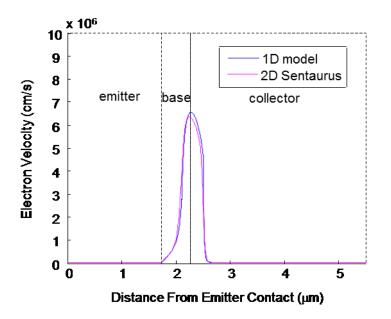

| 5.14. | Electron velocity of an npn transistor                                                                                                                                                                                                                                                                                                                                           | 112 |

| 5.15. | Doping profile of the pnp transistor                                                                                                                                                                                                                                                                                                                                             | 113 |

| 5.16. | Electrostatic potential of a pnp transistor                                                                                                                                                                                                                                                                                                                                      | 113 |

| 5.17. | Electric field of a pnp transistor                                                                                                                                                                                                                                                                                                                                               | 114 |

| 5.18. | Impurity profiles, electron density and hole density of a pnp transistor                                                                                                                                                                                                                                                                                                         | 115 |

| 5.19. | Hole velocity of a pnp transistor                                                                                                                                                                                                                                                                                                                                                | 115 |

| 5.20. | EP, EQFP and HQFP of a pnp transistor                                                                                                                                                                                                                                                                                                                                            | 116 |

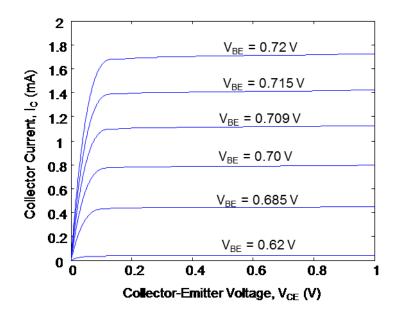

| 5.21. | I-V characteristics of an npn transistor                                                                                                                                                                                                                                                                                                                                         | 117 |

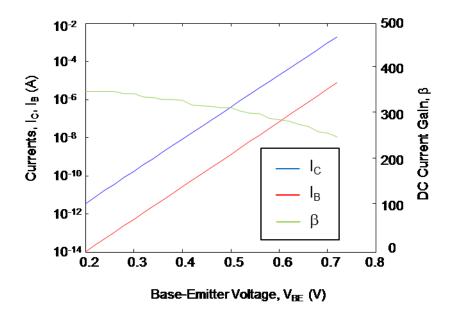

| 5.22. | Gummel plot and dc current gain of an npn transistor                                                                                                                                                                                                                                                                                                                             | 117 |

| 5.23. | Gummel plot and dc current gain of an npn transistor                                                                                                                                                                                                                                                                                                                             | 119 |

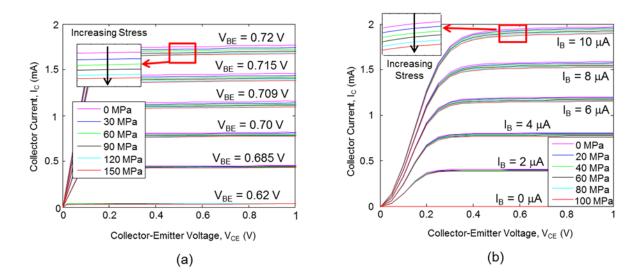

| 5.24. | Stress-induced change in $I_C$ - $V_{CE}$ characteristics of an npn bipolar transistor<br>For $\sigma'_{22}[\overline{1}10]$ (a) 1-D Simulation results (b) Experimental results                                                                                                                                                                                                 | 122 |

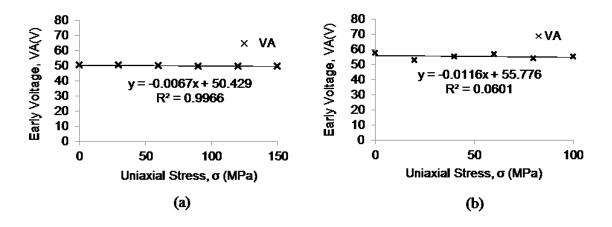

| 5.25. | Stress-Induced change in Early voltage of an npn bipolar transistor for $\sigma'_{22}$<br>(a) 1-D Simulation results (b) Experimental results                                                                                                                                                                                                                                    | 122 |

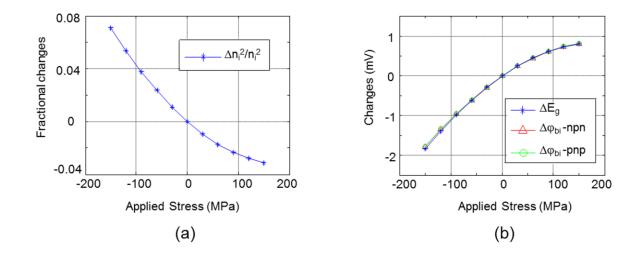

| 5.26. | Stress-induced changes for $\sigma'_{22}[\bar{1}10]$ (a) Fractional changes $\Delta ni2/ni2$<br>(b) Changes in bandgap ( $\Delta E_g$ ), barrier height of npn BJT ( $\Delta \phi_{bi}$ - npn) and barrier                                                                                                                                                                       |     |

|       | height of pnp BJT ( $\Delta \phi_{bi}$ - pnp).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .123 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

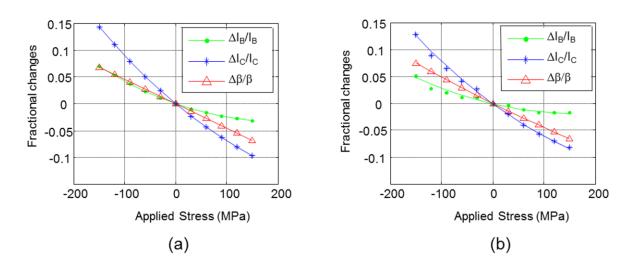

| 5.27. | Fractional changes in collector, base currents and current gain of an npn BJT for $\sigma'_{22}[\bar{1}10]$ (a) 1-D simulation results (b) Experimental results                                                                                                                                                                                                                                                                                                                                                       | .124 |

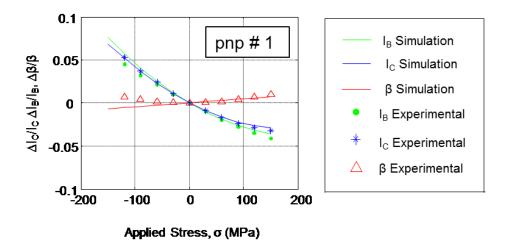

| 5.28. | Fractional changes in collector, base currents and current gain of a pnp BJT for $\sigma'_{22}[\bar{1}10]$ (a) 1-D simulation results (b) Experimental results                                                                                                                                                                                                                                                                                                                                                        | .126 |

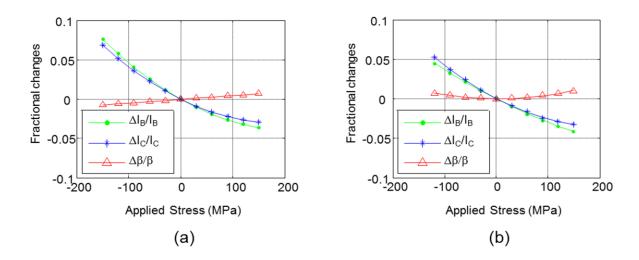

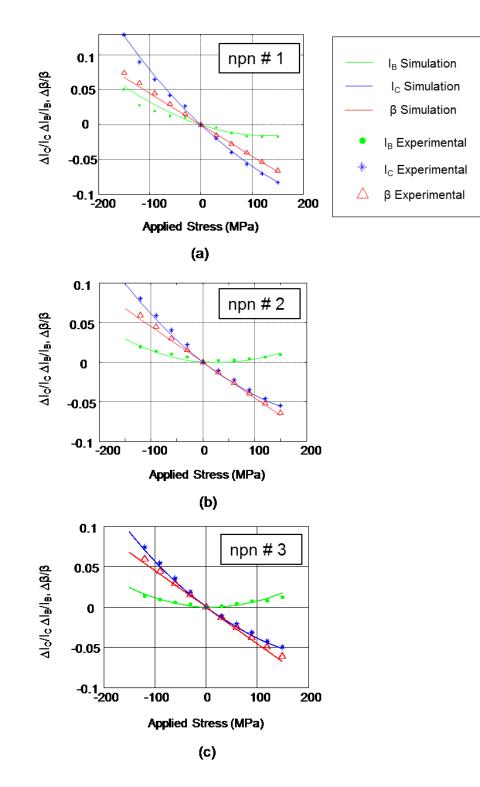

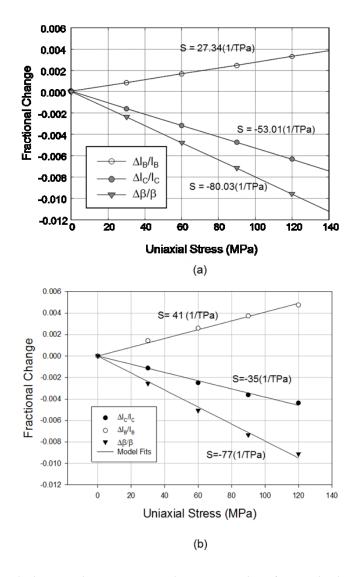

| 5.29. | Comparison of experimental and simulation results for different npn BJTs with same profile in similar/same strips ( $\pi 12n = 455$ /TPa, $\pi 12p = -8$ /TPa)<br>(a) residual = +70 MPa (b) residual stress = +160 MPa (c) residual stress = +180 MPa. Residual stresses were added in simulation to match the experimental results.                                                                                                                                                                                 | .128 |

| 5.30. | Comparison of experimental and simulation results for pnp BJT in similar/same strips ( $\pi 12n = 200/\text{TPa}$ , $\pi 12p = -15/\text{TPa}$ ). Simulation and experimental results matched without adding any residual stress.                                                                                                                                                                                                                                                                                     | .129 |

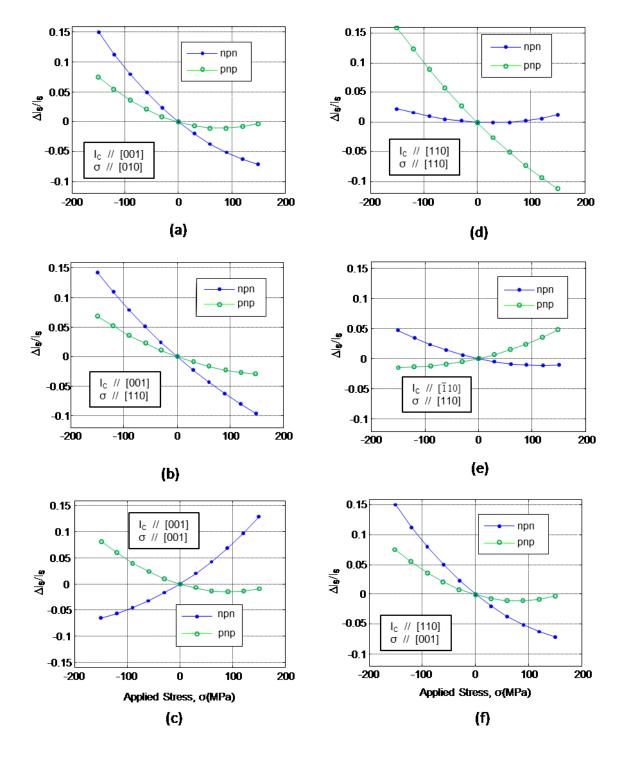

| 5.31. | Simulated changes in saturation current for npn and pnp transistors as a function of uniaxial normal stress for various current and stress orientations                                                                                                                                                                                                                                                                                                                                                               | .131 |

| 5.32. | Fractional changes in currents and current gain of a vertical npn transistor on (111) plane for an in-plane normal stress $\sigma$ [110] (a) simulation results (b) experimental data                                                                                                                                                                                                                                                                                                                                 | .134 |

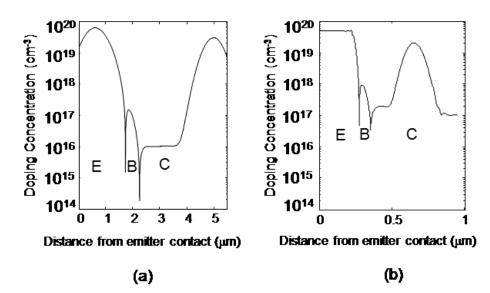

| 6.1.  | Doping profiles used for simulations (a) profile 1 and (b) profile 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .136 |

| 6.2.  | Simplified block model of a vertical npn BJT showing the current components.<br>E-emitter, B-base, C-collector                                                                                                                                                                                                                                                                                                                                                                                                        | .138 |

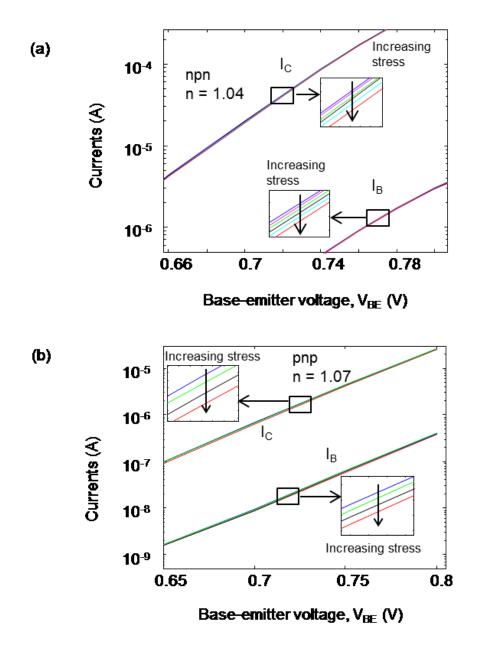

| 6.3.  | Experimental results of Gummel plots for in-plane tensile stress, $\sigma 22'$ [110],<br>(a) for an npn BJT and (b) a pnp BJT. The ideality factor (n) of collector current<br>for the plotted V <sub>BE</sub> range is indicated. $\beta_{npn} \cong 200$ , $\beta_{pnp} \cong 80$ corresponding well with<br>the ratio of estimated mobility in the npn and pnp base regions.                                                                                                                                       | .142 |

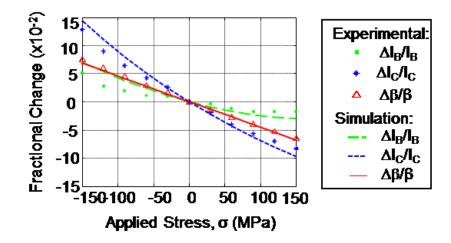

| 6.4.  | Comparison of experimental and simulated fractional changes in $I_C$ , $I_B$ and $\beta$ of an npn BJT for $\sigma$ [110]. Simulation was performed without adding any residual stress ( $\sigma_0 = 0$ ).                                                                                                                                                                                                                                                                                                            | .143 |

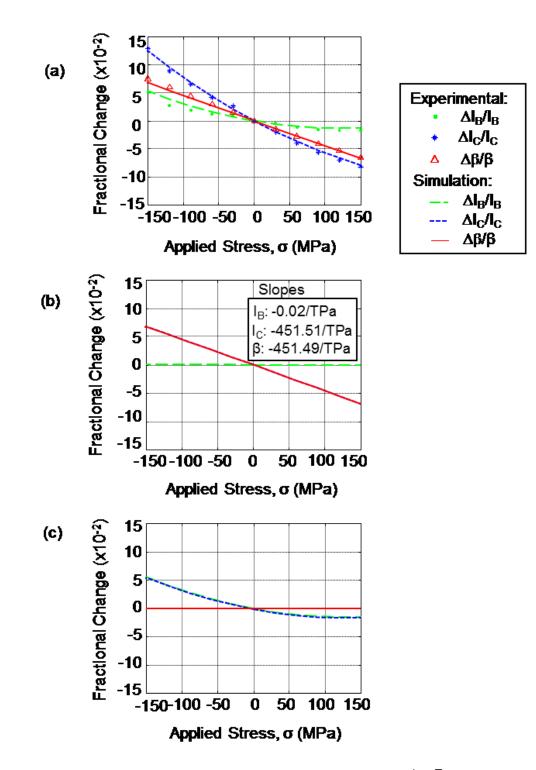

| 6.5.  | Fractional changes in $I_C$ , $I_B$ and $\beta$ for an npn BJT for $\sigma 22'$ [110]. Residual stress of +70 MPa was added in simulations to match the experimental results (a) comparison with the experimental results (both piezoresistance mobility model and the deformation potential models are included for simulation) (b) simulation with piezoresistance mobility model only (plots of $I_C$ and $\beta$ overlap) (c) simulation with deformation potential model only (plots of $I_C$ and $I_B$ overlap) | .144 |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

6.6. Simulated fractional changes in base current components of an npn BJT for tensile

|       | stress. (a) with piezoresistance mobility model only; (b) with deformation potential model only; (c) with both models together. $\delta_1 = 0.08$ , $\delta_2 = 0.82$ and $\delta_3 = 0.10$ in simulations.                                                                                                                          | 145 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7.  | Fractional changes in $I_C$ , $I_B$ and $\beta$ for a pnp BJT for $\sigma 22'$ [110]. (a) comparison with the experimental results (both stress models are included for simulation) (b) simulation with piezoresistance mobility model only (c) simulation with deformation potential model only (plots of $I_C$ and $I_B$ overlap). | 148 |

| 6.8.  | Simulated fractional changes in base current components of a pnp BJT for tensile stress (a) with piezoresistance mobility model only (b) with deformation potential model only (all plots overlap) (c) with both models together. Simulations yields $\delta_1 = 0.15$ , $\delta_2 = 0.74$ and $\delta_3 = 0.11$ .                   | 149 |

| 6.9.  | Simulated fractional changes in injection limited and transport limited current gain components of an npn and a pnp BJTs.                                                                                                                                                                                                            | 151 |

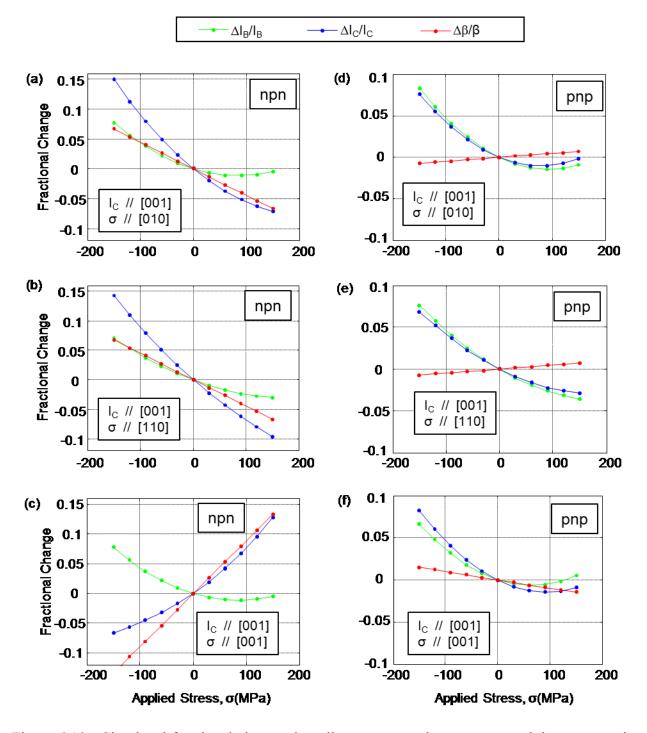

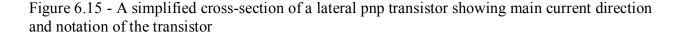

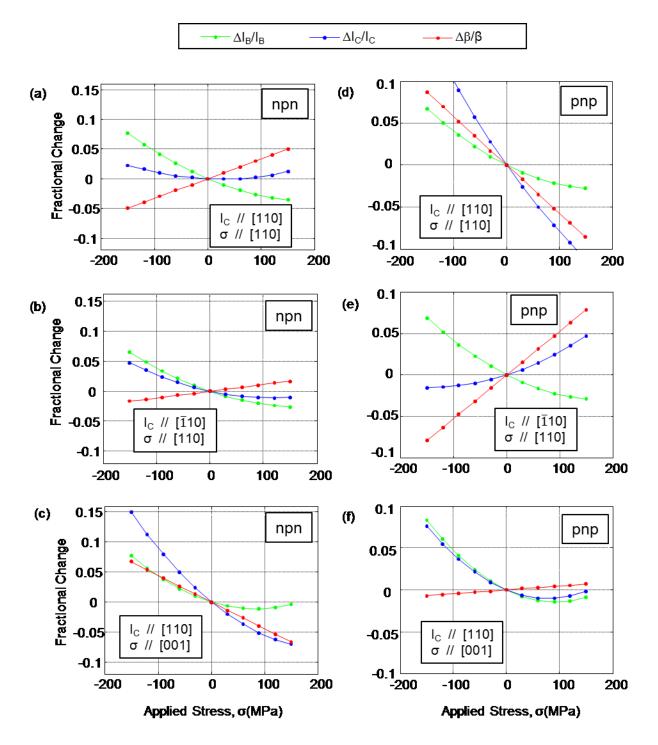

| 6.10. | Simulated fractional changes in collector current, base current and dc current gain of vertical transistors on (100) plane as a function of uniaxial stress (a), (b), (c) for npn transistors (d), (e), (f) for pnp transistors                                                                                                      | 152 |

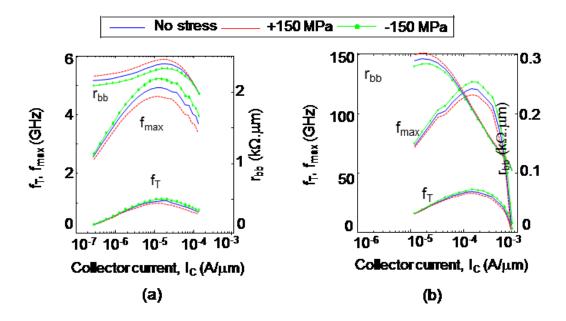

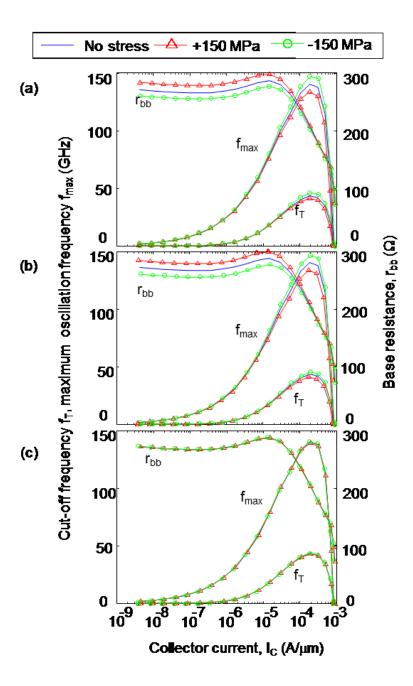

| 6.11. | Simulation results of stress induced changes in $f_T$ , $f_{max}$ and $r_{bb}$ of npn BJT for $\sigma'_{22}[110]$ (a) for profile 1 and (b) for profile 2                                                                                                                                                                            | 155 |

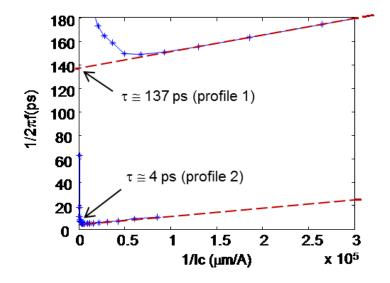

| 6.12. | $1/2\pi f_T$ vs $1/I_C$ plots of profile 1 and profile 2 showing the transit time extraction at zero stress.                                                                                                                                                                                                                         | 156 |

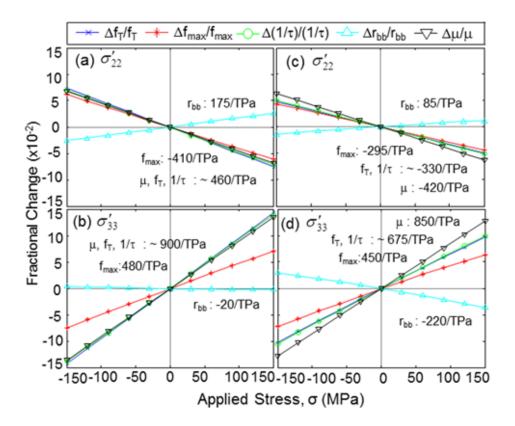

| 6.13. | Fractional changes in $f_T$ , $f_{max}$ , $1/\tau$ , and $r_{bb}$ along with changes in $\mu$ at peak $f_T$ point.<br>(a) & (b) are the results of npn profile 1. (c) & (d) are the results of npn profile 2.<br>Stress directions and the slopes are indicated                                                                      | 156 |

| 6.14. | Simulated stress induced changes in $f_T$ , $f_{max}$ and $r_{bb}$ (a) combined effects;<br>(b) with piezoresistance mobility model only; (c) with deformation potential model only.                                                                                                                                                 | 158 |

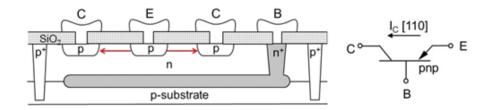

| 6.15. | A simplified cross-section of a lateral pnp transistor showing main current direction and notation of the transistor                                                                                                                                                                                                                 | 159 |

| 6.16. | Simulated fractional changes in collector current, base current and dc current gain of lateral transistors on (100) plane as a function of uniaxial stress (a), (b), (c) for npn transistors (d), (e), (f) for pnp transistors                                                                                                       | 162 |

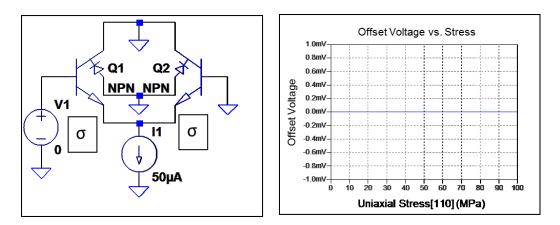

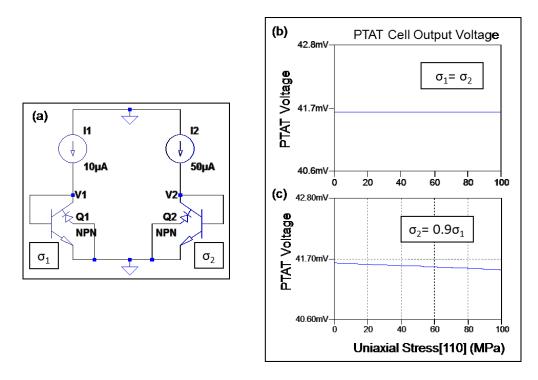

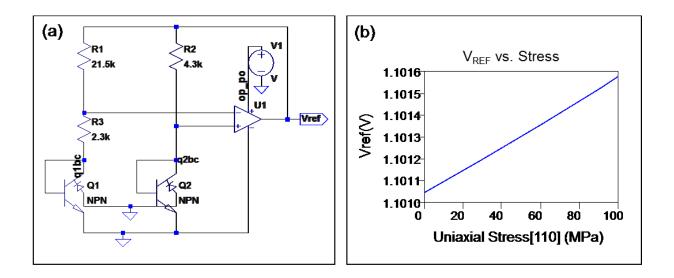

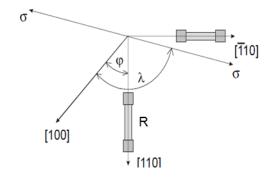

| 7.1.  | A differential pair circuit (a); and simulated offset voltage versus uniaxial [110] Stress (b)                                                                                                                                                                                                                                       | 166 |

| 7.2.  | Simulated output voltage of a PTAT circuit versus uniaxial [110] Stress<br>(a) circuit (b) output when both transistors experience equal stress ( $\sigma_1 = \sigma_2$ )<br>(c) output when transistors experience different stress ( $\sigma_2 = 0.9 \sigma_1$ )                                                                   | 169 |

| 7.3. | A simple op-amp circuit (a); and simulated offset voltage versus uniaxial [110] stress (b).                                                                        | 169 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.4. | Simulated output voltage of a bandgap reference circuit versus uniaxial [110]<br>Stress (a) circuit diagram (b) SPICE simulation output for resistors in [110] and |     |

|      | stress in [110] directions.                                                                                                                                        | 171 |

| 7.5. | Resistor (R) and stress ( $\sigma$ ) orientations in a (100) plane                                                                                                 | 173 |

| 7.6. | Relative stress induced change V <sub>REF</sub> for different resistor orientations                                                                                | 175 |

# CHAPTER 1

#### INTRODUCTION

## 1.1 Stress effects in semiconductor devices

Stress induced mobility improvement in semiconductors have been known since 1950s [1]. However, until 1990s the main attention was focused on sensor applications only [2-4]. Several research works have reported on two main types of stress sensors, the piezoresistive stress sensors and the piezojunction stress sensors [5-10]. The piezoresistive stress sensors are based on the stress-induced changes in the majority-carrier mobility of a device and utilize majority-carrier devices such as resistors and MOSFETs. However, piezojunction stress sensors are based on the mechanical stress-induced changes in the saturation current of a minority-carrier device and use bipolar junction transistors or p-n junctions. Initially sensors were fabricated with resistors and bipolar transistors. Later in 1960s with the introduction of MOSFETs, piezoresistive stress sensors based on MOSFETs were introduced to replace the resistor based stress sensors. As stress sensors both MOSFETs and bipolar transistors offer certain advantages over the traditional resistor based sensors. Such potential advantages include size reduction, better sensitivity, wide temperature range capability and easier integration with circuits [9]. Solid-state sensors based on piezoresistive and piezojunction effects are widely used for structural stress analysis in microelectronic fabrication in industrial applications [11, 12].

During the past 50 years the semiconductor industry has achieved a massive development in areas such as smaller sized devices, low power consumption and cost effective designs. In 1965, the Intel co-founder Gordon Moore predicted that the number of transistors on a microprocessor chip will nearly double every 2 years or so [13]. With technological innovations

1

and scaling down of transistor geometries Moore's law had prevailed for several decades. This has resulted in chips that are significantly faster and have greater complexity in each generation while continuously bringing the cost per transistor down. Until 2000 scaling down was the main technology for improving the performance of MOSFETs. As the transistors scale down to nm technology, due to the practical limitations such as short channel effects, semiconductor industry emerged to seek for other alternatives. Several new innovative technologies such as strained-silicon, high-K gate dielectric, ultrathin body SOI MOSFET, double-gate MOSFETs, double-gate on Si Fin, multi-gate transistor on multiple fins, and tri-gate MOSFETs were developed to keep up with the trend of emerging market demand. The introduction of new technologies, materials and advanced processing steps all together increased the complexity of the chips and packages. The stress distribution also changed rapidly over small scales and the mechanical stress effects become more significant in IC circuits.

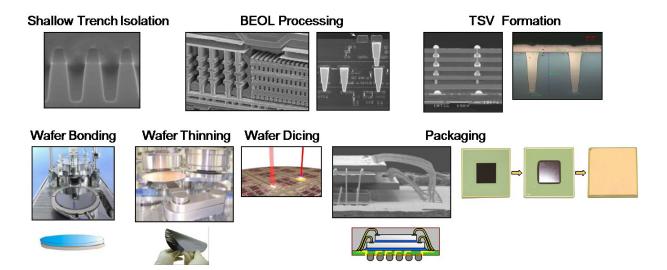

Figure 1.1 – Sources of mechanical stress generation in integrated circuits

Stresses are produced in integrated circuits (IC) by thermal and mechanical loadings. IC chip processing involves several steps with a variety of materials of different thermal and elastic properties. Stress develops during thermal cycling of the chips. Formation of many structural elements such as chemical vapor deposition (CVD) process of silicon dioxide, silicon nitride, polycrystalline silicon, etc. exhibits intrinsic stresses. Large localized stresses are induced in the silicon substrate near the corners and edges of such structural elements [14]. Another cause for mechanical stress is the lattice mismatch of materials used in different processes. Furthermore, shallow trench isolation (STI), back-end-of-line (BEOL) processing, through-silicon-via (TSV), wafer bonding, wafer thinning, wafer dicing, and electronic packaging etc. results mechanical stresses (Figure 1.1). All these stresses may significantly influence the reliability of the semiconductor devices [14-18]. These stresses may collectively lead to failure of the package resulting in cracking of the die, breaking of connections, bond failure, solder fatigue, and encapsulant cracking [6]. Even without producing these adverse effects, stresses may lead to parametric shifts that affect the performance and tolerances of integrated circuits and make them to work out of the specifications [6].

Stress effects are more significant in precision analog circuits such as temperature sensors, bandgap references, current mirrors, PTAT (proportional to absolute temperature) circuits and operational amplifiers. Stress induced parametric shifts affect the reliability of these circuits which mainly work upon precise matching of the transistors. In bipolar transistors the stress induced changes in the mobility and the bandgap affect various parameters such as saturation current, base emitter voltage, dc current gain and make them to work out of specification. Hence, it is extremely important to take steps to mitigate these stress effects.

3

With the advancements in technology, reducing the process and packaging induced stress effects has become extremely important. Hence, stress investigation and mitigation has become an important area of research. Several researchers have demonstrated the use of silicon stress test chips based on piezoresistive and piezojunction stress sensors to investigate die stresses in electronic packages [6-10]. Currently, in most of the IC processing, stress sensors are incorporated for real-time monitoring of the stress-induced changes during fabrication, processing and packaging to ensure high quality and reliability.

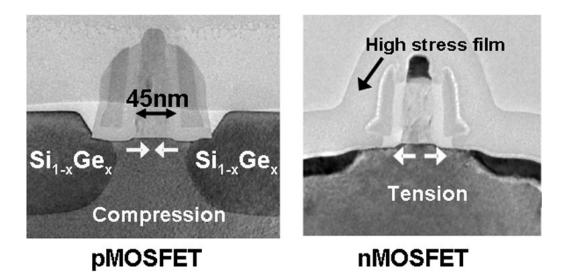

Stress investigations in semiconductor devices gained special attention in 2000s with the introduction of strain engineering. The stress effects in semiconductors differ depending on the direction of current flow, orientation of stress and the type of material. This property is used as an advantage to enhance the mobility of MOSFETs, which is known as strain engineering. Strain-induced mobility enhancement was introduced for MOSFETs at the 90 nm technology node and has since been an active area of research [19]. This is an intentional stress induction widely used in industry at present. For example, SiGe pockets are introduced into the source and drain of PMOS to create the compressive stress in the p-channel area in order to increase the mobility. In the case of NMOS, a highly tensile silicon-nitride capping layer is deposited at the end of the NMOS process covering the source, drain, and gate stack in order to create tensile stresses in the n-channel (Figure 1.2) [19-21]. Currently, strain-induced mobility enhancement is used as an efficient and practical aid for downscaling of MOSFETs.

Figure 1.2 – Transmission electron micrographs of 45-nm p-type and n-channel transistors [21]

Similar concept is applicable for bipolar transistors as well. Bandgap and strain engineering is used in SiGe based heterostructure bipolar transistors (HBTs) to improve the performance [22]. In the base of these heterostructures addition of Ge to Si makes the effective base bandgap smaller. Furthermore the compressive stress associated with SiGe alloys produces additional bandgap shrinkage. It is estimated that for each 10% of Ge introduced there will be a net base bandgap reduction of about 75 meV [23]. The major goal of the above processes is the improvement of current gain and frequency by reducing the bandgap of base of BJT. Another way for improvement is mechanical stress induced performance enhancement. Though some studies reported mechanical strain-induced performance enhancement in Si based BJTs [24-28], this approach is not fully developed. Most of these investigations in BJTs or HBTs are focused on the influence of biaxial stresses. However, in fabrication processes biaxial stresses are less preferred because of their integration challenges, process complexity, and higher cost involvement [20]. In contrast uniaxial stresses are more preferred over biaxial stress due to easy integration, higher percentage enhancement [29, 30] and cost effectiveness. Uniaxial stresses can

be introduced using an extrinsic stress layer [24] or post fabrication using a cap layer or with packaging [20].

As described above stress effect needs to be improved and applied as beneficial effects in some instances and needs reduced when deemed undesirable in other instances. Main beneficial effects are their usage in sensor applications and strain engineering. However, unintentional stress effects generated during fabrication, processing and packaging are more deleterious in analog and digital circuits. Overall a comprehensive understanding of stress effects in semiconductor devices is necessary to improve the stress effects for sensor applications or strain engineering or to reduce the stress effects when deemed harmful.

#### 1.2 Previous research works on stress effects in bipolar transistors and analog circuits

The saturation current of the bipolar transistor is modified by mechanical stress through the piezojunction effect [31]. Piezojunction effect was first described by Hall, Bardeen, and Pearson in 1951 for hydrostatic pressure on p-n junctions [32]. The theory was based on bandgap widening caused by isotropic stress. In 1962 Rindner observed that the resistance of shallow p-n junction was highly stress-sensitive for anisotropic elastic stresses [33]. During 1960s researchers repeated and extended the experiments where they produced the stress by pressing a stylus on a point of a p-n junction [34-45]. They often reported impressive results including the changes in the current-voltage characteristics, base current, break down voltage, and generationrecombination currents [46-50]. For several years the researchers used very high compressive stress with large stress gradient generated by styli. In 1973 Monteith and Wortman obtained much smaller stresses using cantilever beams instead of styli and reported different behavior for tensile and compressive stress [51].

In 1964 Wortman, Hauser and Burger extended the piezojunction theory to anisotropic high stresses in the range of GPa based upon the stress-induced variations in energy band structure and their effect on minority carrier densities [50]. They developed the equations for the current-voltage characteristics of diodes and transistors under stress. Their results showed that at stress levels greater than 1 GPa the device currents can change by several orders of magnitude when stress levels are changed by a factor of 2. In 1967, the theory was further refined by Kanda considering the changes in effective masses for stresses over 1GPa [52]. Kanda calculated the current change in p-n junction by considering the stress-induced change in minority carrier concentration and mobility. The difference of heavy-hole mass and light-hole mass and their stress dependence were taken into account in addition to the stress dependence of band edge energies when calculating the change in minority carrier concentration. In 1973, Kanda developed a basic framework for the stress dependence of the common-emitter transistor current gain and showed that the stress dependence of current gain of the npn and pnp transistors can be explained by the combined effects of the stress dependence of the emitter efficiency and the stress dependence of the base transport factor [53]. All above research work and models were based on hydrostatic pressure and stress-inducing styli, quite successful for high stress levels, usually over 1 GPa. However, they were not intended for the moderate stress levels usually occur during the fabrication, processing and packaging of semiconductor devices. Until 1980, most investigations of the piezojunction effect have been focused on the design of mechanical sensors.

In 1980s a research group from Delft University started to focus their research work on moderate stress levels ( $\approx 200$  MPa) that usually occur during the semiconductor fabrication processes. In 1982, Meijer proposed that the mechanical stress might be a dominant factor limiting the accuracy of bandgap references and temperature transducers based on his experimental work [54, 55]. Fruett researched on piezojunction effect in silicon, its consequences and its applications for integrated circuits and sensors and it's temperature dependences [56] and proposed a new test structure based on cantilever technique to characterize the devices under stress at different temperatures. He used the characterization results of vertical and lateral bipolar transistors on (100) silicon wafers to extract the first- and second-order piezojunction coefficients and temperature dependence and compared with the piezoresistive coefficients. He also investigated about the piezojunction effect related errors caused in temperature-reference voltages used in bandgap references and temperature transducers. He suggested methods to minimize the piezojunction effect in integrated circuits based on the fact that the transistor stress sensitivity depends on the type of the transistor and the stress orientation. He also showed that appropriate transistor selection and proper layout design can be used to mitigate the piezojunction effect in analog circuits [56].

In 2002 Creemer and French developed an analytical model of the effect of mechanical stress on the saturation current of bipolar transistors [31, 57]. They recommended the model for circuit and sensor design, which can be used for tensile as well as compressive stress and suitable for lower than 200 MPa that generally developed during the semiconductor fabrication processes. This model can be used for any orientation with respect to the axis of crystal from which the transistor is fabricated. The model was verified by comparing the results with experimental results of npn and pnp transistors under different stress levels. They extracted the piezojunction and piezoresistive parameters and compared with literature values. Their research focused on the transistor saturation current at normal, forward bias, and at low-level injection. Fruett, Creemer, French and co-workers of Delft University extensively published their research

work on stress effect in saturation current and base emitter voltage of silicon bipolar transistors [5, 57].

In another study Creemer and French modeled the piezojunction effect as a combination of the stress-induced effects in the intrinsic carrier concentration and the carrier mobility. Here the stress effects on the saturation current were expressed as an equivalent change in the baseemitter voltage. Theory was verified with experimental results for npn vertical and pnp lateral transistors for a stress range of -155 MPa to 155 MPa. They observed that, while stress-induced changes in the mobility strongly depended on the orientation of current flow in the base, the changes in intrinsic carrier concentration did not. Based on this observation it was suggested that for a given stress orientation the changes in intrinsic concentration is fixed, but the mobility can still be influenced by giving the transistor a different orientation with respect to the crystal axes. In this way, the mobility change could either amplify or compensate for the intrinsic concentration effect [58].

#### 1.3 Scope of the research

Even though several theoretical and experimental studies have been conducted in stress induced effects in bipolar transistors, the models were based on traditional "piezojunction effect" that characterizes the variation of the saturation current of a pn junction device in terms of a second order set of piezojunction coefficients. This approach provides a solid experimental characterization of the device and allows very good fitting of the stress dependent changes in transistor characteristics. Combined effect of all stress induced variations is straight forwardly modeled by the piezojunction approach. Much of the underlying device behavior may however be masked by merging of variations in mobility and intrinsic carrier concentration in the piezojunction formulation. This results in the loss of predictive understanding for optimum design. Separation of stress dependent mobility variations from the stress dependent intrinsic carrier concentration in modelling would avoid this short coming. This approach would provide a direct insight regarding transistor design and layout necessary to improve the stress effects for strain engineering or to mitigate the impact of process or packaging induced stress effects on analog circuits.

The focus of this research is as follows:

- To develop a numerical model for rapid stress analysis in bipolar transistors

- To investigate and include appropriate models to represent the stress effects on bipolar transistors

- To characterize the possibility for potential strain engineering in bipolar transistors

- To provide techniques to mitigate the stress effects on bipolar transistors and precision analog circuits.

# 1.4 Structure of this dissertation

The dissertation is structured as follows:

In chapter 1 an introduction and an overview of stress effects in semiconductor devices especially bipolar transistors, a review of previous research work in this area and the scope of this research work are presented.

Chapter 2 provides a review of the theories on the stress effect on band structure and the carrier mobility.

Chapter 3 describes the theoretical and experimental work of this study. Improved experimental methods used for this work and the characterization results of npn and pnp bipolar transistors in (100) plane are also presented.

Chapter 4 describes the 2-D and 3-D model development with Sentaurus to interpret the stress effect in bipolar transistors. It also includes the comparison of 2-D and 3-D simulation results. Chapter 5 illustrates a 1-D numerical model development with MATLAB for rapid stress analysis in bipolar transistors and comparison of results with the Sentaurus simulation, and experimental results. It also presents the application of 1-D model to verify the textbook approaches. The early voltage and the current based on Gummel approach are verified in this section. Then stress models are included and the simulation results are analyzed and compared with the experimental results. The residual stresses in bipolar transistors are successfully quantified using this 1-D model. Stress dependent changes in saturation current of npn and pnp transistors are analyzed and compared.

Chapter 6 describes an analysis of opportunities for performance enhancement in vertical and lateral npn and pnp bipolar transistors using uniaxial stress on (100) plane.

Chapter 7 presents a study of stress effects in analog circuits and methods to minimize these stress induced unwanted effects. Spice simulation was performed for some simple analog circuits by including the theoretical models developed in chapter 3 to include the stress effect and the results are presented here.

Finally, Chapter 8 provides the summary and conclusion.

#### CHAPTER 2

# A REVIEW ON STRESS EFFECTS ON SEMICONDUCTOR BAND STRUCTURE AND CARRIER MOBILITY

#### 2.1 Introduction

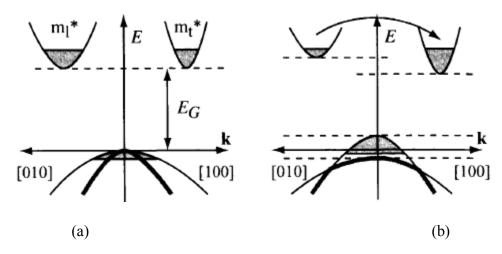

Mechanical stress in semiconductor devices influences the band structure and the carrier mobility. First the stress generates a mechanical strain, which deforms the band structure. The changes in bands modify the parameters of carrier transport such as the bandgap, intrinsic carrier concentration and carrier mobility through which they change the electrical characteristics of semiconductor devices. This chapter reviews the theories behind the stress effects in semiconductor devices such as the deformation potential theory and piezoresistive theory.

## 2.2 Stress, strain and tensors

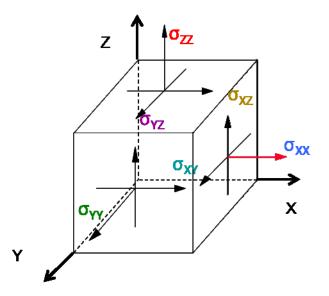

The general state of stress for an infinitesimal unit element (Figure 2.1) can be represented by a symmetric 3 x 3 matrix stress tensor as follows [59, 60]:

$$\sigma_{ij} = \begin{bmatrix} \sigma_{XX} & \sigma_{XY} & \sigma_{XZ} \\ \sigma_{YX} & \sigma_{YY} & \sigma_{YZ} \\ \sigma_{ZX} & \sigma_{ZY} & \sigma_{ZZ} \end{bmatrix}$$

(2.1)

where the diagonal elements  $\sigma_{XX}$ ,  $\sigma_{YY}$  and  $\sigma_{ZZ}$  are called the normal stresses and, the off-diagonal elements are called the shear stresses. Because of the static equilibrium requirements the stress tensor is always symmetric and it yields:

$$\sigma_{XY} = \sigma_{YX}, \quad \sigma_{XZ} = \sigma_{ZX} \quad \text{and} \quad \sigma_{YZ} = \sigma_{ZY} \quad (2.2)$$

Hence the stress tensor has only 6 independent stress components: 3 normal stress components  $\sigma_{XX}, \sigma_{YY}, \sigma_{ZZ}$  and 3 shear components  $\sigma_{XY}, \sigma_{YZ}, \sigma_{XZ}$ .

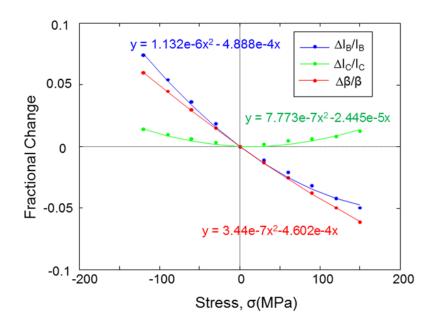

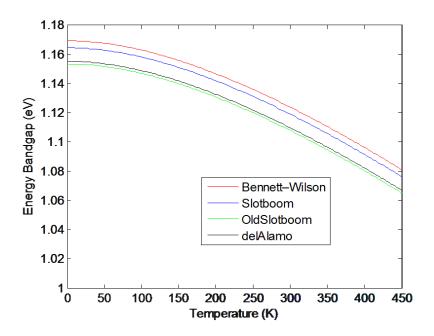

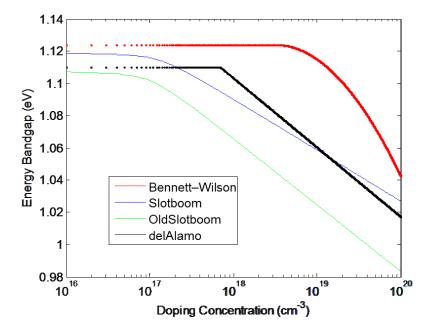

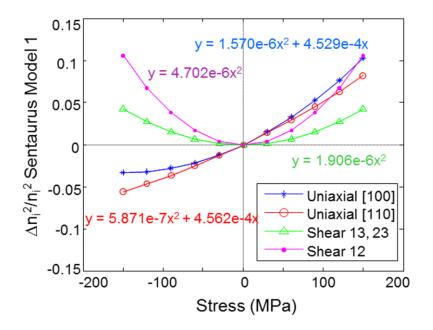

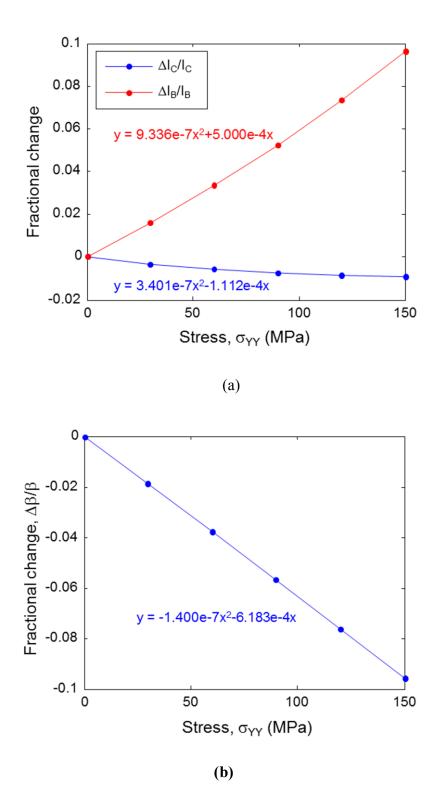

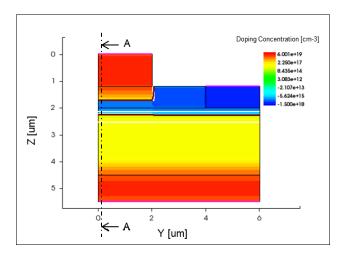

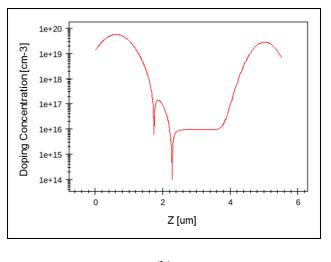

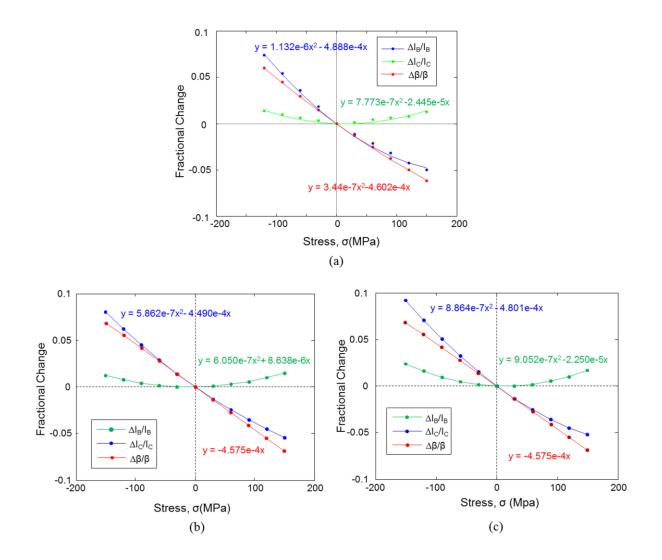

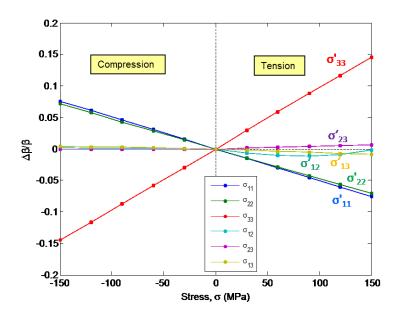

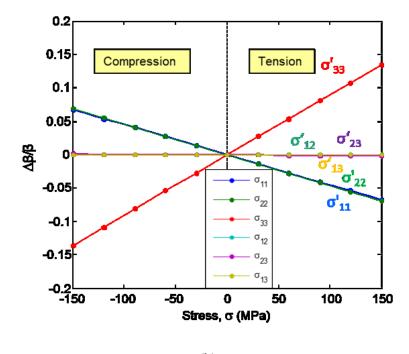

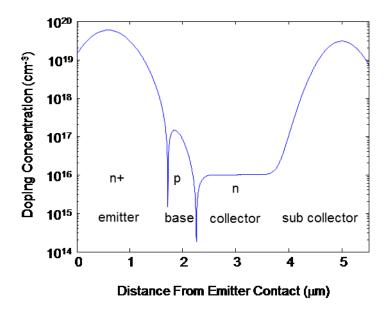

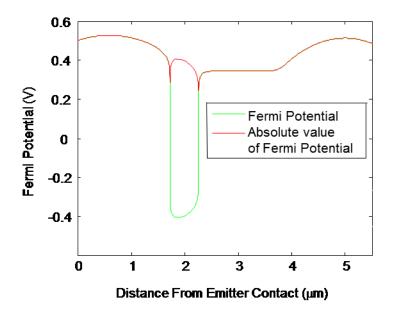

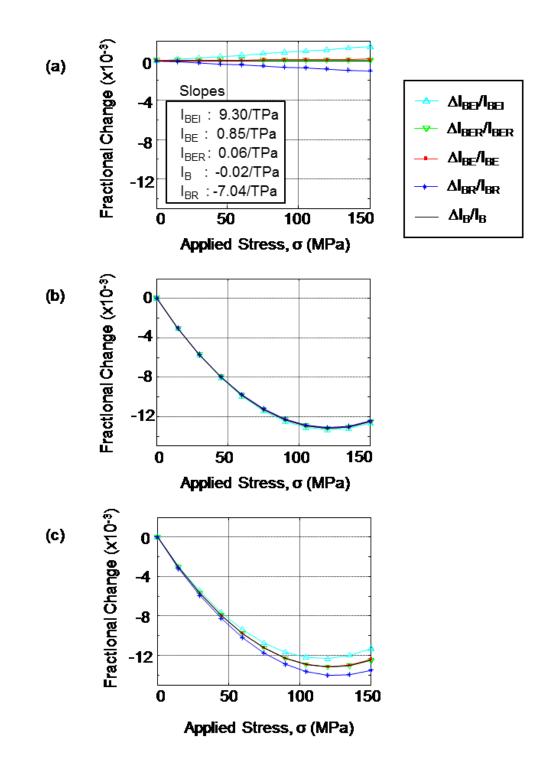

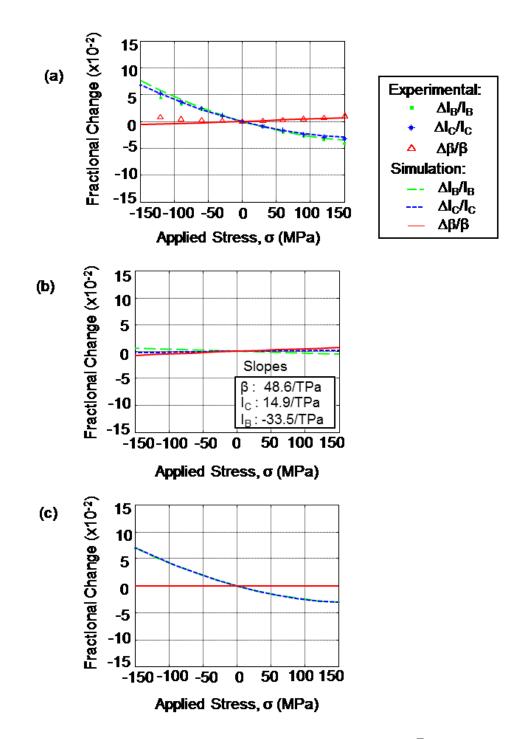

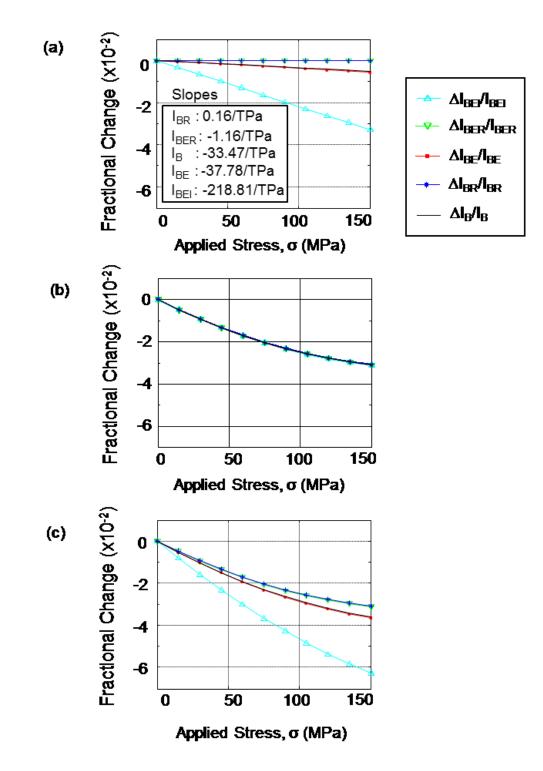

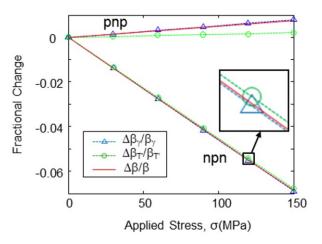

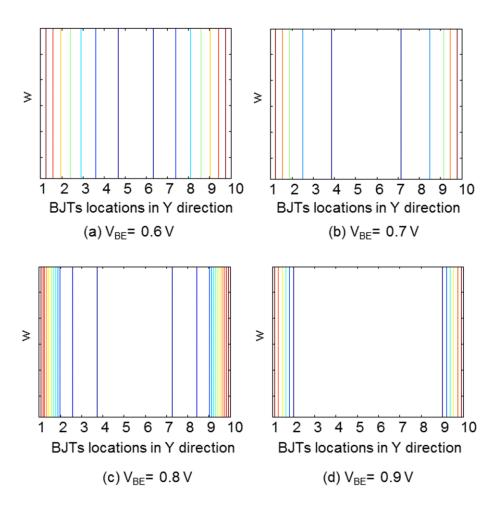

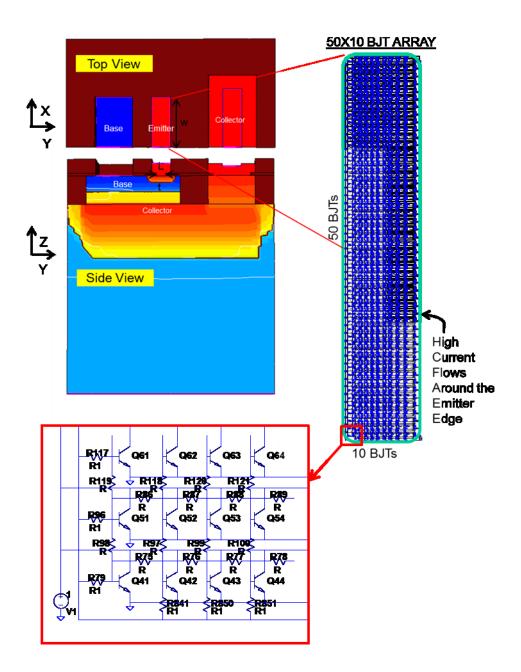

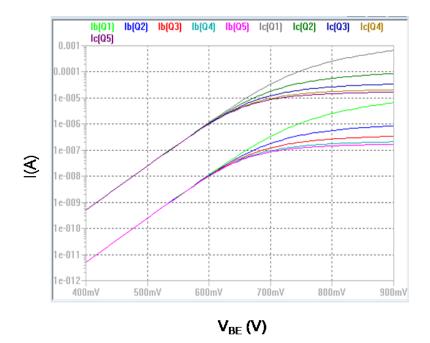

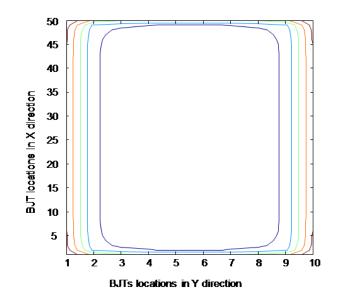

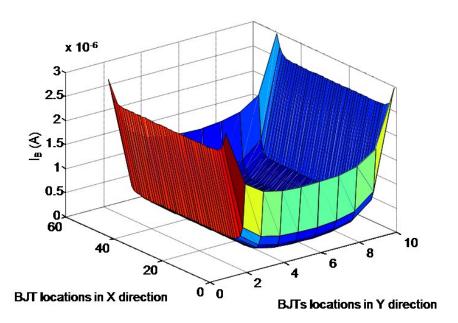

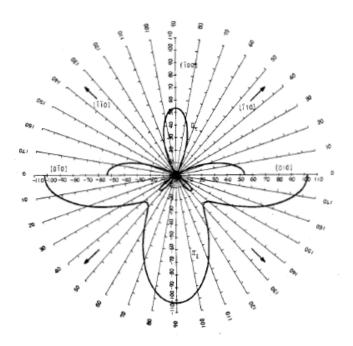

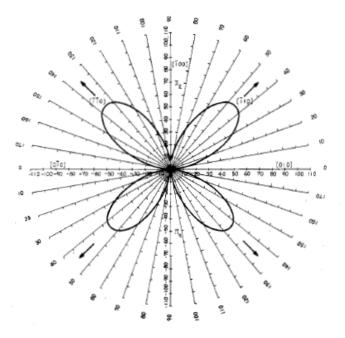

Figure 2.1 – Stress states on an infinitesimal unit element (for clarity, stresses on negative faces are not depicted)