# Extreme Environment Reliability of Components for Computing with SAC305 and Alternative High Reliability Solders

by

### **Thomas Edward Sanders**

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama May 7, 2016

Keywords: Reliability, Lead-Free Solder, Isothermal Aging, Electronics Packaging, Failure Analysis

Copyright 2016 by Thomas Edward Sanders

### Approved by

John L. Evans, Chair, Thomas Walter Professor of Industrial and Systems Engineering Michael Bozack, Professor, Physics

R. Wayne Johnson, Professor and Chair, Electrical and Computer Engineering, Tennessee Tech University

Fadel Megahed, Assistant Professor, Industrial and Systems Engineering Mark Schall, Assistant Professor, Industrial and Systems Engineering

#### **Abstract**

The semiconductor and packaging industries have been moving away from the use of Lead (Pb) due to the increasing awareness of the health and safety concerns surrounding its use. For many applications, the industry has moved from eutectic Sn-Pb solder to the near-eutectic Sn-Ag-Cu (SAC) solders, and more applications – including those considered "extreme environment" – are likely to take place in the near future. However, the reliability of electronic assemblies with SAC solder joints has proven hard to predict based on previous experience with SnPb solders.

The reliability of electronic solder joints is determined by a variety of factors including bulk solder properties and failure mechanics. Both the composition and microstructure of the solder joint will affect its bulk properties. Although an initial microstructure will be present following assembly – which will involve one or more soldering steps – this structure will continue to evolve over the lifetime of the joint. The microstructure and microstructural evolution of the Sn-Ag-Cu solders differ significantly from that of eutectic SnPb solders. Because of the risks and uncertainties involved, a new body of reliability engineering knowledge must be built of for the Sn-Ag-Cu solders based on application-specific process and service parameters.

This experiment considers the thermal cycle reliability of an assortment of different electronic components and evaluates them on a 0.200" (200 mils) thick printed circuit board. Two substrate materials are tested: FR4-06 and Megtron6. Organic

Solderability Preservative (OSP) surface finish is used with all test vehicles. The primary solders for package attachment in this experiment are SnPb and SAC305. Two solders designed for high-temperature reliability are also considered, including a Bi-doped SAC material and the six-element alloy Innolot (Sn3.8Ag0.7Cu3Bi1.4Sb0.15Ni).

Isothermal storage at high temperature was used to accelerate the aging of the assemblies. Aging Temperatures are 25°C, 50°C, and 75°C. Aging durations are 0-Months (No Aging, baseline), 6-Months, 12-Months, and 24-Months. The test vehicles were then subjected thermal cycles of -40°C to +125°C on a 120-minute thermal profile in a single-zone environmental chamber to assess the solder joint performance.

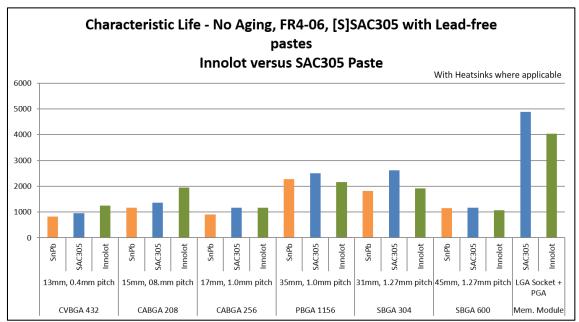

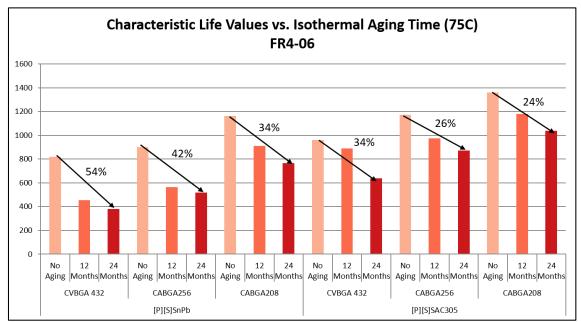

The as-reflowed failure data (No Aging Group) was found to follow specific reliability trends depending on the type and size of the component. The smaller plastic ball grid array (BGA) packages show the following pattern in Characteristic Life value, listed from best to worst: (1) Matched Innolot, (2) [S]SAC305 doped with [P]Innolot, (3) Matched SAC305, and (4) Matched SnPb. However, when considering the effects of isothermal aging on the relative reliability of various packages, the data indicate that even components that show similar initial reliability trends may display differences following aging. Following isothermal aging, several components exhibit higher reliability when paired with SnPb solder than with the SAC solder materials.

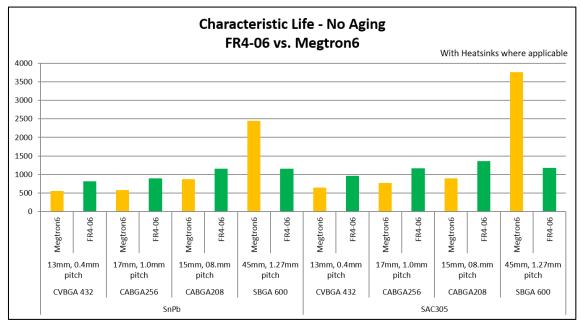

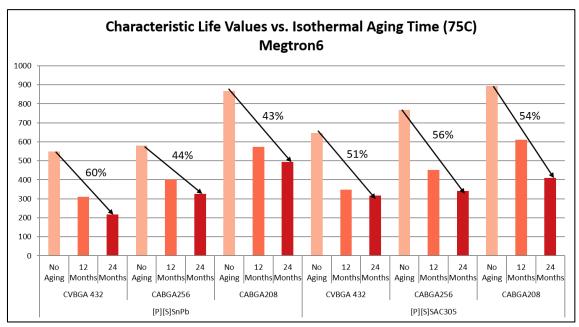

Significant differences in reliability were seen between equivalent packages mounted to the two substrate materials tested (FR4-06 and Megtron6). For all of the over-molded plastic BGA components, reliability was higher on the standard glass-epoxy material (FR4-06). Performance for these packages on the high-electrical-performance polyphenylene oxide (PPO) blend material (Megtron6) was much worse. The degradation

in reliability with aging were also found to be worse on Megtron6 for the Sn-Ag-Cu materials when paired with these components. However, the two Super-BGA components – SBGA 304 and SBGA 600 – dramatically reverse this substrate-based reliability trend.

For the smaller plastic BGA packages, Innolot doping (micro-alloying) appears to be an effective strategy for improving characteristic life. However, as component size and pitch increase, this improvement seems to wane (and in some cases reverse itself altogether). This may be attributable to under-doping of the large-component joints.

Based on assembly-level reliability, the "paste doping" strategy appears to be a promising approach to improve reliability in high-stress environments, but one that requires significant further study.

### Acknowledgments

I would like to express profound gratitude to my advisor, Dr. John L. Evans, for years of support, guidance, and mentorship throughout the ups and downs of research and graduate study. I would also like to extend my appreciation to my committee members, Dr. Michael Bozack, Dr. R. Wayne Johnson, Dr. Fadel Magahed, and Dr. Mark Schall for their valuable time and insight. Particular thanks are due to Dr. Bozack for his editorial guidance during the writing of this dissertation, and for many useful discussions concerning various topics related to lead-free soldering. I would also like to thank all my lab-mates, coworkers, and friends: Dr. Sivasubramanian Thirugnanasambandam, Dr. Zhou Hai, Dr. Namo Pankaj, Anto Raj, Sharath Sridhar, Chaobo Shen, Cong Zhao, and Seth Gordon. Special thanks go to Dr. Colin Stevens for his help with the initial LabVIEW program coding and system deployment, and to Erica Snipes for her help in cross-sectioning and microscopic analysis. Finally, I am, of course, indebted to my siblings, Robert and Emily, my mother Janet, and my father Thomas, who is lost to us but not forgotten.

### Table of Contents

| Abstract                                                    | ii   |

|-------------------------------------------------------------|------|

| Acknowledgments                                             | V    |

| List of Tables                                              | xii  |

| List of Figures                                             | xiii |

| List of Abbreviations                                       | xix  |

| Chapter 1                                                   | 1    |

| 1.1 Printed Circuit Assemblies                              | 1    |

| 1.2 Printed Circuit Assemblies: Introduction                | 6    |

| 1.2.1 Through-Hole Mount Technology (THMT)                  | 7    |

| 1.2.2 Surface Mount Technology (SMT)                        | 9    |

| 1.2.3 Area Arrays                                           | 14   |

| 1.2.4 No-Lead (Lead-Less) Components                        | 17   |

| 1.2.5 Internal Structure of Common Surface Mount Components | 18   |

| 1.3 Substrates for Electronic Assemblies                    | 20   |

| 1.3.1 Types of PCBs                                         | 21   |

| 1.3.2 Laminate Substrates                                   | 23   |

| 1.3.3 Solder Mask                                              | 24 |

|----------------------------------------------------------------|----|

| 1.3.4 PCB Surface Finishes                                     | 25 |

| 1.4 Trends in Electronic Packaging                             | 27 |

| Chapter 2                                                      | 31 |

| 2.1 Soldering                                                  | 31 |

| 2.2 Solder Joints for Electronic Assemblies                    | 32 |

| 2.2.1 Overview of Surface Mount Manufacturing Process          | 33 |

| 2.2.2 Solder Paste and Flux                                    | 35 |

| 2.3 Solder Joint Properties                                    | 37 |

| 2.3.1 Properties Important to Manufacturability                | 41 |

| 2.3.2 Properties Important to Reliability                      | 42 |

| 2.4 A Brief History of Solder in Electronic Assemblies         | 42 |

| 2.4.1 Tin-Lead Solder: An Industry Dominating Solution         | 43 |

| 2.4.2 Tin-Lead Solders: The Decline                            | 46 |

| 2.4.3 Tin-Lead Solder: Searching for a Replacement             | 48 |

| 2.4.4 Electronic Solders: Near-Eutectic Sn-Ag-Cu (SAC) Solders | 49 |

| 2.5 Eutectic SnPb Solder: A Closer Look                        | 51 |

| 2.5.1 Eutectic SnPb Solder: Material Properties                | 53 |

| 2.5.2 Eutectic SnPb Solder: Microstructural Evolution          | 53 |

| 2.6 Near-Eutectic Sn-Ag-Cu (SAC) Solder: A Closer Look         | 56 |

| 2.6.1 Near-Eutectic Sn-Ag-Cu (SAC) Solder: Material Properties       | 61 |

|----------------------------------------------------------------------|----|

| 2.6.2 Near-Eutectic Sn-Ag-Cu (SAC) Solder: Microstructural Evolution | 62 |

| 2.7 Other Elements commonly found in Tin-Rich Solders                | 63 |

| 2.7.1 Silver (Ag)                                                    | 64 |

| 2.7.2 Bismuth (Bi)                                                   | 65 |

| 2.7.3 Copper (Cu)                                                    | 65 |

| 2.7.4 Indium (In)                                                    | 65 |

| 2.7.5 Antimony (Sb)                                                  | 66 |

| 2.7.6 Zinc (Zn)                                                      | 66 |

| Chapter 3                                                            | 67 |

| 3.1 Introduction                                                     | 67 |

| 3.2 Failure Modes in Electronic Assemblies                           | 68 |

| 3.3 Characteristic Solder Joint Failures                             | 70 |

| 3.3.1 Typical BGA Joint Failure Locations                            | 71 |

| 3.3.2 Some Factors Affecting BGA Solder Joint Failures               | 73 |

| 3.3.3 Experimentally Locating BGA Solder Joint Failures              | 74 |

| 3.4 Understanding Solder Joint Failures                              | 76 |

| 3.4.1 Fatigue                                                        | 78 |

| 3.4.2 Creep & Grain Boundary Sliding                                 | 79 |

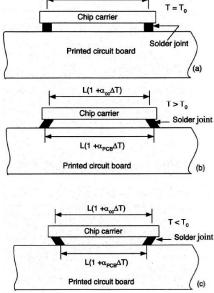

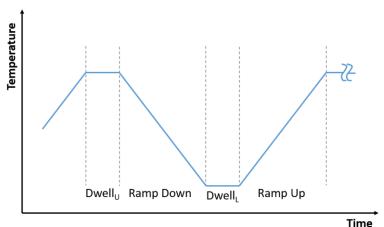

| 3.4.4 Effects of Thermal Cycling on Solder Joints                    | 82 |

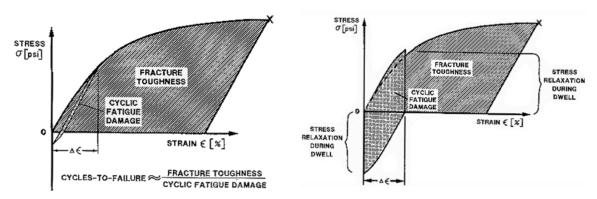

| 3.4.5 Failure Mechanics                                                      | 83  |

|------------------------------------------------------------------------------|-----|

| 3.5 Predicting Solder Joint Reliability under Thermal Cycling                | 85  |

| 3.5.1 Analytical Solutions                                                   | 86  |

| 3.5.2 Numerical Methods                                                      | 88  |

| 3.5.3 Experimental Methods                                                   | 90  |

| 3.6 Experimental Methods: Thermal Cycle Testing                              | 91  |

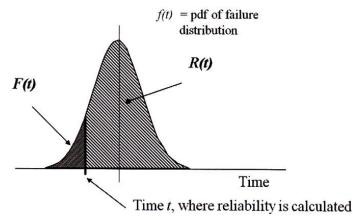

| 3.6.1 Thermal Cycle Testing: Statistical Analysis                            | 94  |

| Chapter 4                                                                    | 100 |

| 4.1 Introduction                                                             | 100 |

| 4.2 Thermal Cycle Reliability of Sn-Pb and Sn-Ag-Cu Solders, As Reflowed     | 101 |

| 4.3 Reliability Effects of Composition on Sn-Ag-Cu (SAC) Solders             | 102 |

| 4.4 Reliability Effects of Process Parameters on Sn-Ag-Cu Solders            | 104 |

| 4.5 Reliability Effects of Test Parameters on Sn-Ag-Cu Solders               | 105 |

| 4.6 Effects of Isothermal Aging on Sn-Pb and Sn-Ag-Cu Solders                | 108 |

| 4.6.1 Effects of Isothermal Aging on Sn-Ag-Cu Solders: Mechanical Properties | 109 |

| 4.6.2 Effects of Isothermal Aging on Sn-Ag-Cu Solders: Reliability Data      | 112 |

| 4.7 Impact of Current Work                                                   | 114 |

| Chapter 5                                                                    | 116 |

| 5.1 Electronic Assemblies and Solder Joints                                  | 116 |

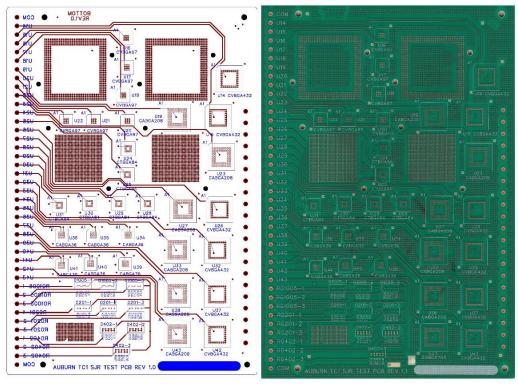

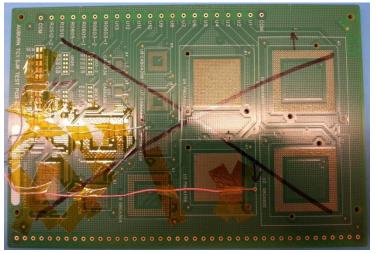

| 5.2 Test Vehicle Design – TC1-SR I Test Board                                | 117 |

| 5.3 Test Vehicle: Components and Circuit Board Assemblies (CBAs)        | 121 |

|-------------------------------------------------------------------------|-----|

| 5.4 Test Plan                                                           | 124 |

| 5.5 Surface Mount Assembly                                              | 127 |

| 5.6 Experimental Methods                                                | 133 |

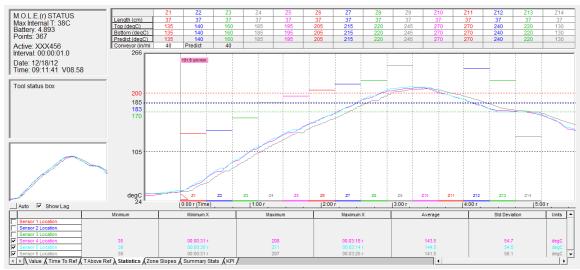

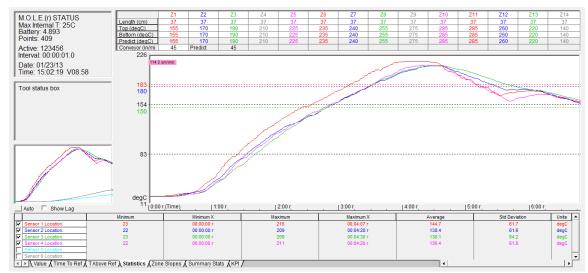

| 5.6.1 Experimental Methods: Thermal Cycle Test Parameters and Equipment | 134 |

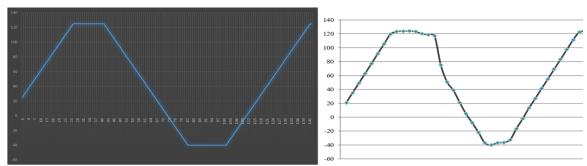

| 5.6.1 Experimental Methods: The Effects of Test Magnitude               | 137 |

| 5.6.2 Experimental Methods: Data Acquisition and Monitoring Equipment   | 143 |

| 5.6.3 Experimental Methods: Data Analysis Techniques and Software       | 149 |

| 5.6.4 Experimental Methods: Failure Analysis Protocol and Methods       | 151 |

| Chapter 6                                                               | 153 |

| 6.1 Weibull Graphs and Results                                          | 153 |

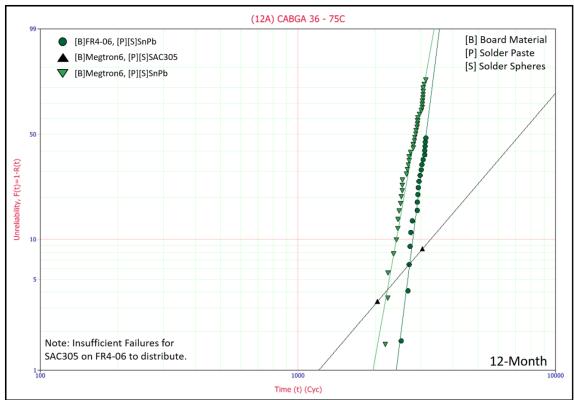

| 6.2 CABGA 36 [6mm, 0.8mm pitch]                                         | 154 |

| 6.3 CABGA 208 [15mm, 0.8mm pitch]                                       | 155 |

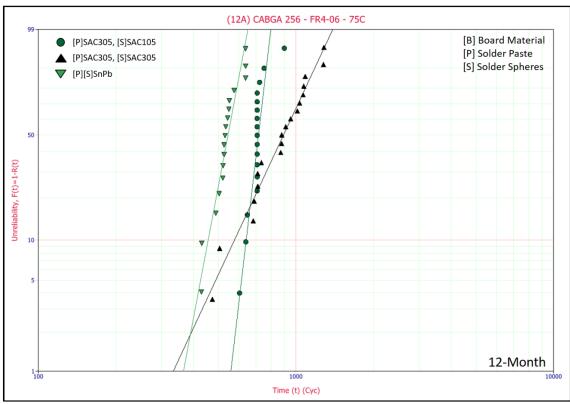

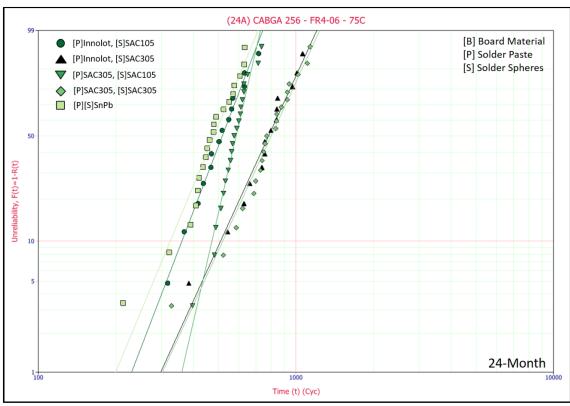

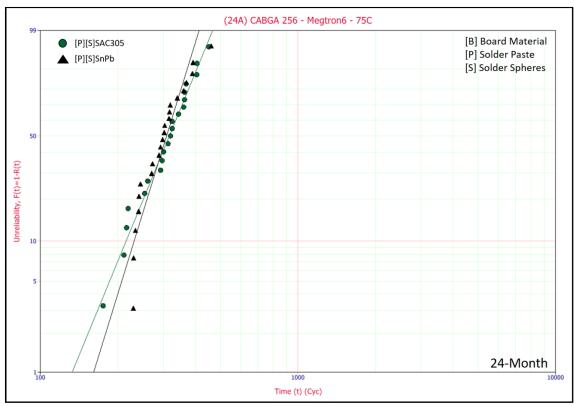

| 6.4 CABGA 256 [17mm, 1.0mm pitch]                                       | 162 |

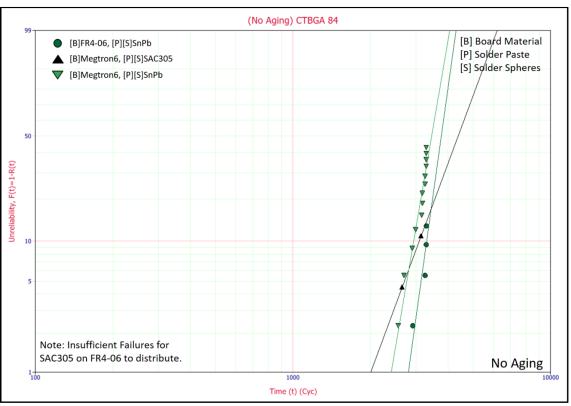

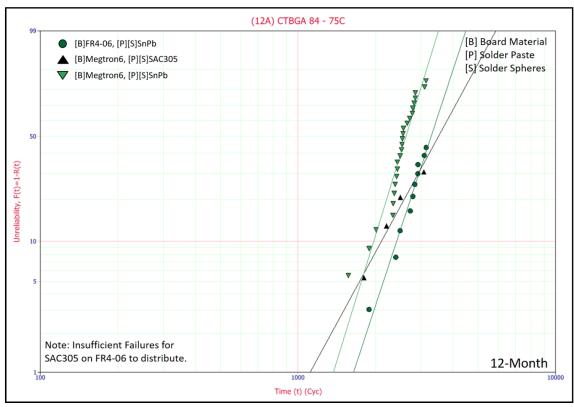

| 6.5 CTBGA 84 [6mm, 0.5mm pitch]                                         | 166 |

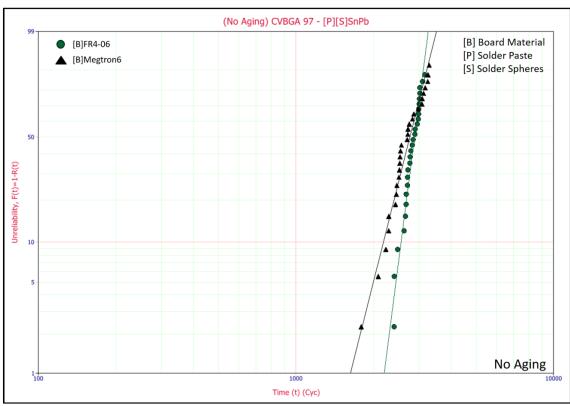

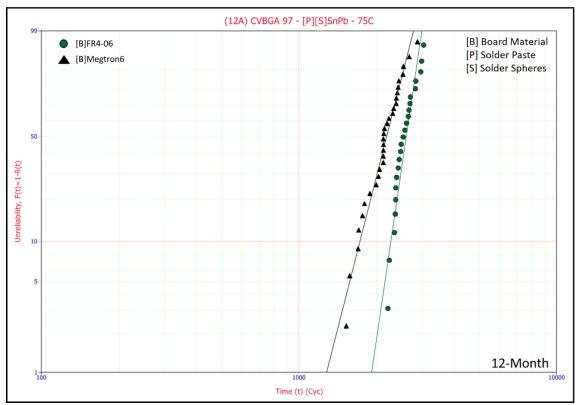

| 6.6 CVBGA 97 [5mm, 0.4mm pitch]                                         | 169 |

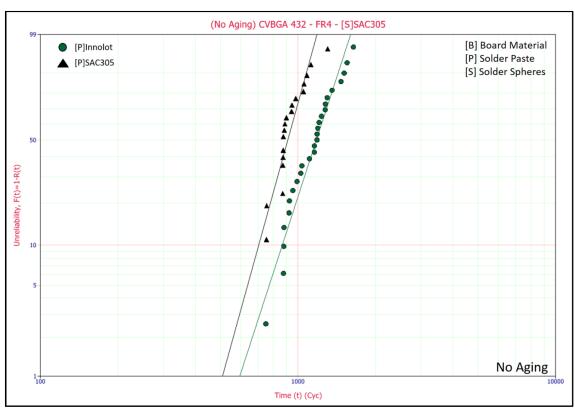

| 6.7 CVBGA 432 [13mm, 0.4mm pitch]                                       | 171 |

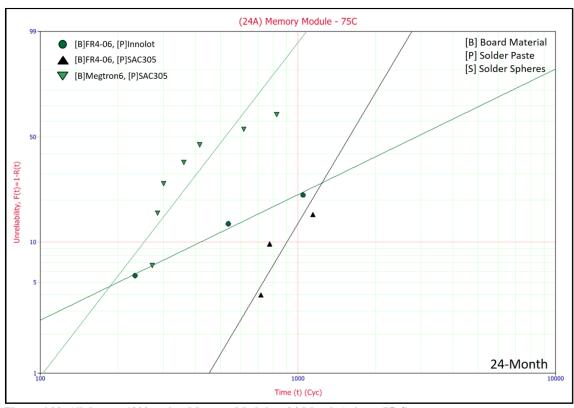

| 6.8 Memory Module [LGA Socket + PGA]                                    | 174 |

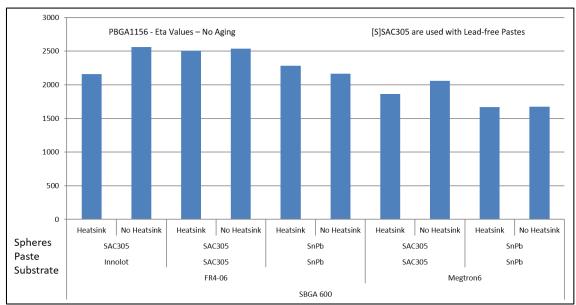

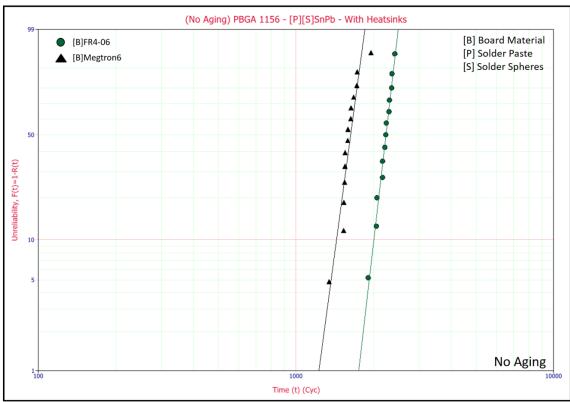

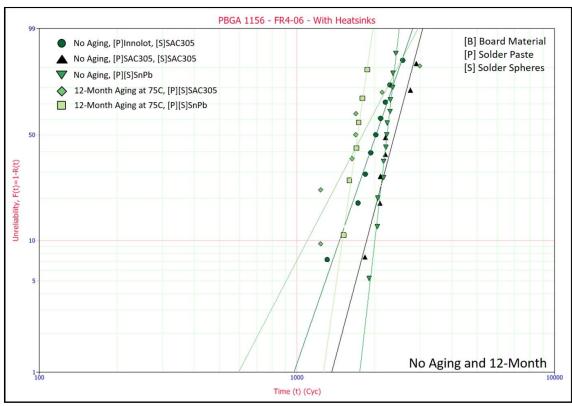

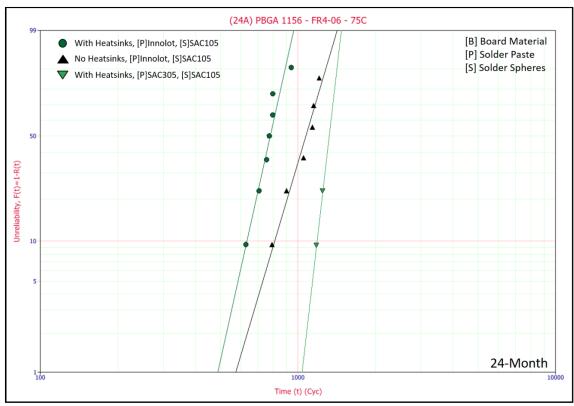

| 6.9 PBGA 1156 [35mm, 1.0mm pitch]                                       | 177 |

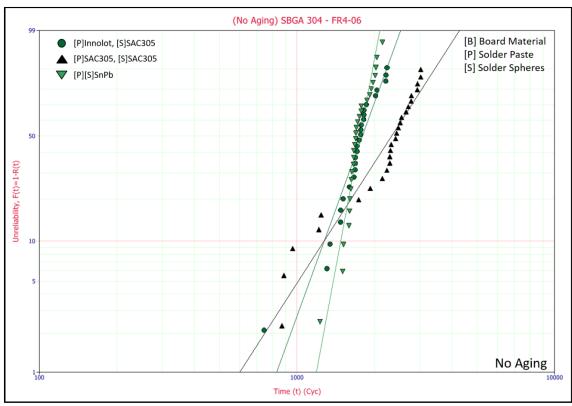

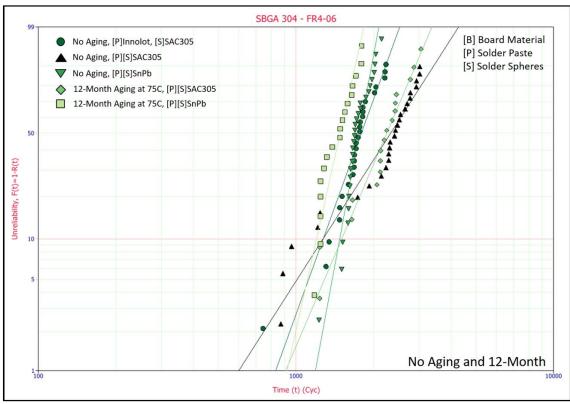

| 6.10 SBGA 304 [31mm, 1.27mm pitch]                                      | 181 |

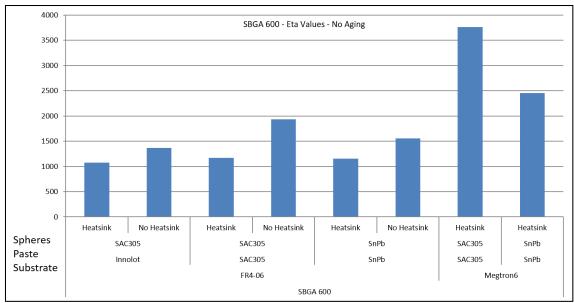

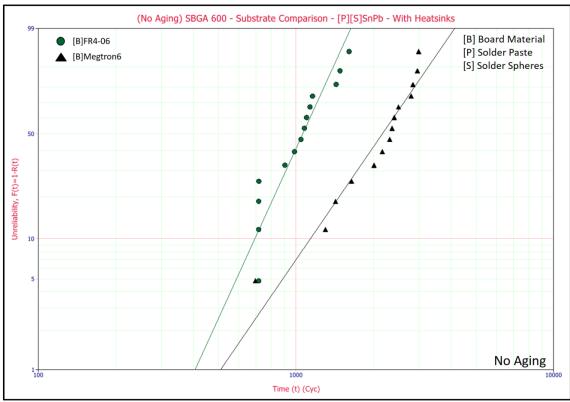

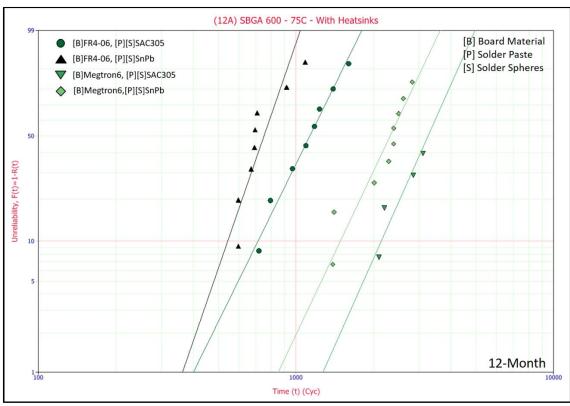

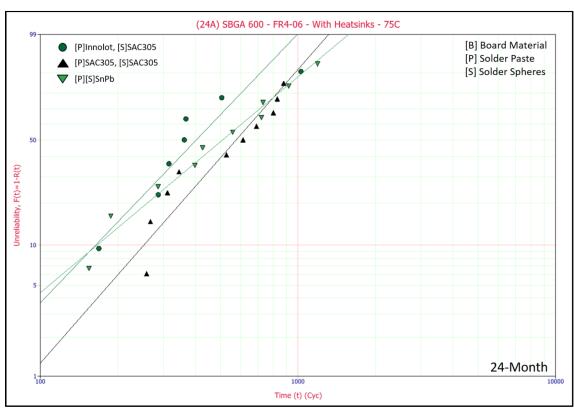

| 6.11 SBGA 600 [45mm, 1.27mm pitch]                                | 183 |

|-------------------------------------------------------------------|-----|

| Chapter 7                                                         | 188 |

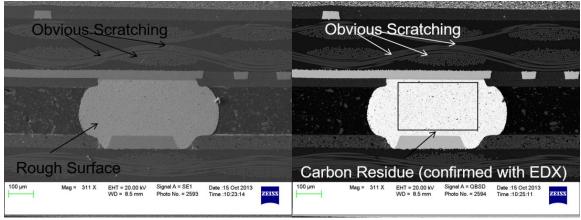

| 7.1 Failure Analysis                                              | 188 |

| 7.2 Preliminary Failure Analysis: FR4-06 Substrates               | 188 |

| 7.2.1 FR4-06: No Aging Group (0 Cycles)                           | 189 |

| 7.2.2 FR4-06: No Aging Group (1000 Cycles)                        | 194 |

| 7.2.3 FR4-06: No Aging Group (2000 Cycles)                        | 195 |

| 7.2.4 FR4-06: No Aging Group (3000 Cycles)                        | 197 |

| 7.3 Preliminary Failure Analysis: Megtron6, No Aging, 3000 Cycles | 201 |

| 7.3.1 Megtron6: CABGA 208, [P]SAC305, [S]SAC105                   | 202 |

| 7.3.2 Megtron6: CABGA 208, [P]SAC305, [S]SAC305                   | 204 |

| 7.3.3 Megtron6: SBGA 304, [P]SAC305, [S]SAC305                    | 206 |

| 7.3.4 Megtron6: CABGA 256, [P]SAC305, [S]SAC305                   | 208 |

| Chapter 8                                                         | 210 |

| 8.1 Results and Conclusions: TC1-SRJ Project                      | 210 |

| 8.2 Ongoing and Future Work: TC1-SRJ Project                      | 217 |

| 8.3 Ongoing and Future Work: Follow-On and Related Projects       | 218 |

| References                                                        | 220 |

### List of Tables

| Table 1.1. Principal Types of Gull Wing and J-Lead Packages [2,6]               | 9          |

|---------------------------------------------------------------------------------|------------|

| Table 1.2. Principal Types of Gull Wing and J-Lead Packages [2,6]               | 14         |

| Table 1.3. Area Array Packages [5,6]                                            | 16         |

| Table 1.5. Some Important Properties of Printed Circuit Boards                  | 22         |

| Table 2.1. Large Organizational efforts to find Pb-Free solutions [28]          | 49         |

| Table 2.2. Select properties of 63Sn-37Pb [2].                                  | 53         |

| Table 2.3. Phases in Sn-Ag-Cu Solder [from NIST]                                | 58         |

| Table 2.4. Properties of some component materials [3].                          | 61         |

| Table 3.1. Effects of some Design Parameters on BGA Package Fatigue Life [6,55] | <b>7</b> 4 |

| Table 3.2. Common Non-destructive and Destructive Interconnect FA Methods [56]  | 75         |

| Table 3.3. CTE values of some circuit assembly materials [3].                   | 79         |

| Table 3.4. Dwell Temperatures for TC testing by application [3,13,51,65]        | 93         |

| Table 4.1. Summary of Lead-Free and Sn-Pb Thermal Cycle data from [51]          | 01         |

| Table 5.1. Top-Side CBAs. 1                                                     | 23         |

| Table 4.2. Bottom-Side CBAs                                                     | 24         |

| Table 4.3. Test Plan                                                            | 26         |

| Table 5.4. Thermal Cycle Chambers used for testing the TC1-SRJ test vehicle     | 37         |

| Table 5.5. US and European Grip Paper standard systems [112]                    | 51         |

| Table 8.1. Rough joint composition numbers. [S]SAC305 with [P]Innolot           | 12         |

## List of Figures

| Figure 1.1. Levels of Packaging. Adapted from [2].                                    |

|---------------------------------------------------------------------------------------|

| Figure 1.2. Dual In-Line Package (DIP) [2].                                           |

| Figure 1.3. First Level Packaging options [2]                                         |

| Figure 1.4. Printed Circuit Board.                                                    |

| Figure 1.5. Through-Hole Mount vs. Surface Mount Attachment. Adapted from [2]         |

| Figure 1.6. Through-Hole Mount Technology Component and Solder Joint [2,5]            |

| Figure 1.7. Gull Wing Leads (left) and J-Leads (right) [2].                           |

| Figure 1.8. Area Array Component and Solder Joint [5]                                 |

| Figure 1.9. No-Lead Component and Solder Joint [5]                                    |

| Figure 1.10. Standard BGA (left) and Cavity-Down BGA (right)                          |

| Figure 1.11. Some Ball Grid Array Structure Options [5]                               |

| Figure 1.12. NSMD versus SMD PCB lands                                                |

| Figure 1.13. Increases in Packaging Density over time [5].                            |

| Figure 2.1. Key steps in SMT Assembly [3].                                            |

| Figure 2.2. Solder Paste (modified from [3])                                          |

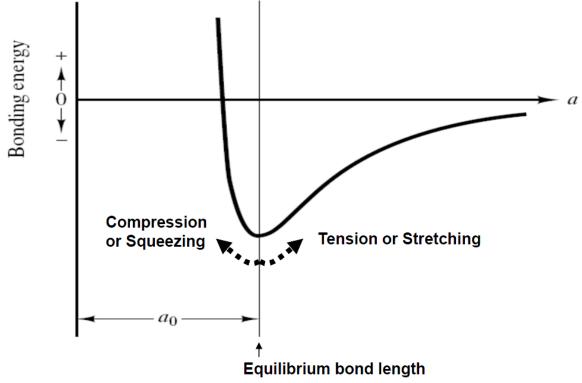

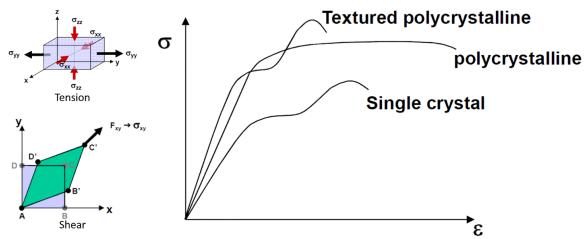

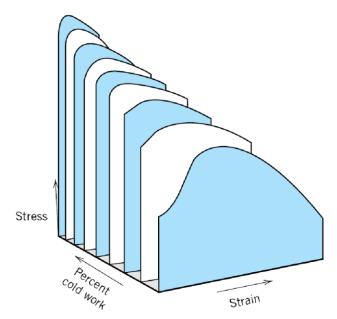

| Figure 2.3. (Conceptual) Equilibrium Bond Length vs. Bonding Energy [20]              |

| Figure 2.4. Tension and Shear (left) and typical Stress-Strain curves (right) [20] 40 |

| Figure 2.5. Strain Hardening [20].                                                    |

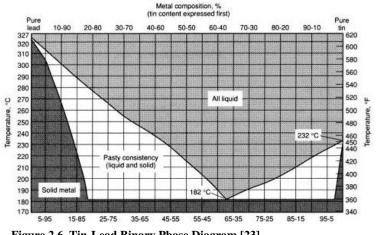

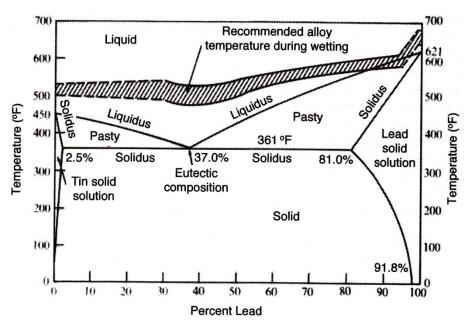

| Figure 2.6. Tin-Lead Binary Phase Diagram [23].                                       |

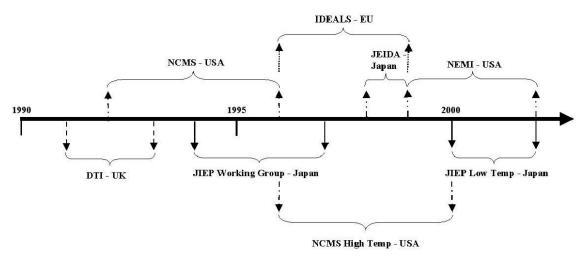

| Figure 2.7. Rough Time-Line of Major Lead-Free Solder Consortia [28].                   | 49  |

|-----------------------------------------------------------------------------------------|-----|

| Figure 2.8. Tin-Lead Binary Eutectic Phase Diagram [2].                                 | 51  |

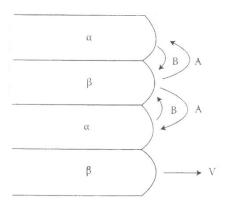

| Figure 2.9. Interdiffusion in Lamellar Solidification [30].                             | 52  |

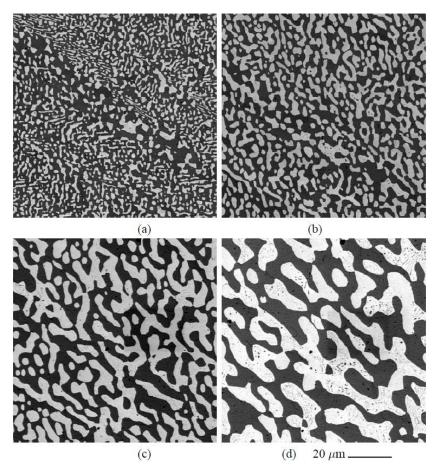

| Figure 2.10. Microstructural Evolution in Eutectic SnPb Solder [17]                     | 55  |

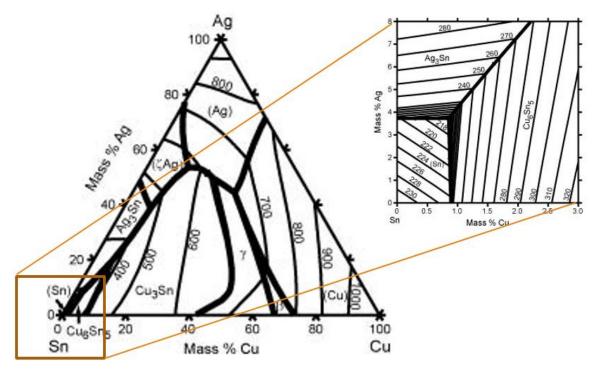

| Figure 2.11. From NIST: Sn-Ag-Cu Phase Diagrams.                                        | 57  |

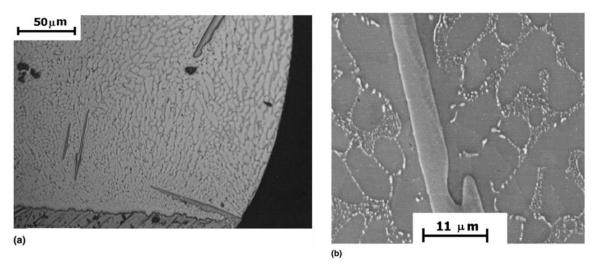

| Figure 2.12. (a) Optical and (b) BSE images of typical SAC Joint Microstructure [32]    | 60  |

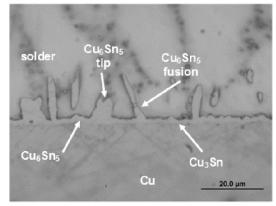

| Figure 2.13. Cu pad IMCs with HASL after 500 hours of aging [37]                        | 60  |

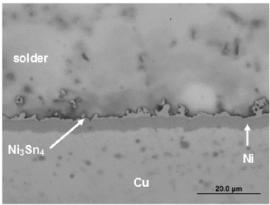

| Figure 2.14. Cu pad IMCs with Ni/Ag after 1000 hours of aging [37].                     | 60  |

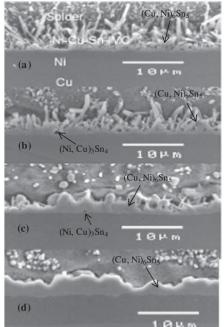

| Figure 2.15. IMC Evolution at Ni Pad [36].                                              | 62  |

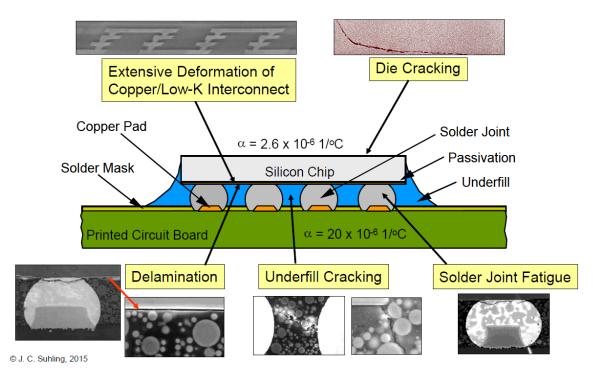

| Figure 3.1. Common Flip-Chip Failure Modes [6]                                          | 70  |

| Figure 3.2. Common Joint Failure Modes.                                                 | 71  |

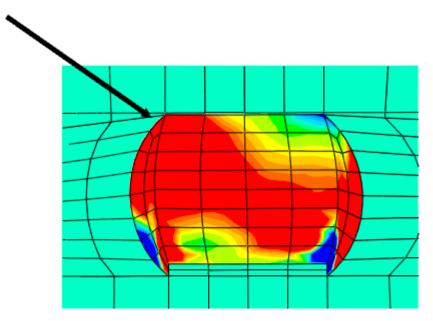

| Figure 3.3. FEA model: Induced stress maximized at the upper corner of the joint [6]    | 72  |

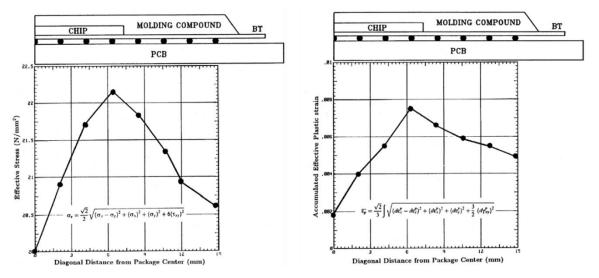

| Figure 3.4. Stress and Strain vs. DNP [6].                                              | 73  |

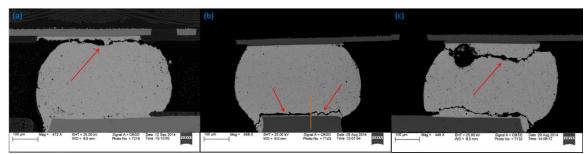

| Figure 3.5. Some Failure Modes seen in BGA-type solder joints.                          | 77  |

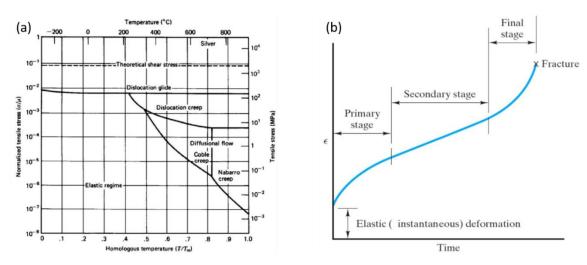

| Figure 3.6. (a) Deformation Mechanism Map for Silver [61], (b) Stages of Creep [20]     | 81  |

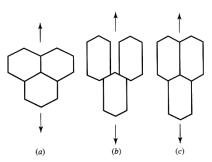

| Figure 3.7. Grain Boundary Sliding [61].                                                | 81  |

| Figure 3.8. DNP Model [2].                                                              | 86  |

| Figure 3.9. Schematic of Thermal Cycle.                                                 | 91  |

| Figure 3.10. Cyclic Fatigue Damage during Thermal Cycling [3].                          | 92  |

| Figure 3.11. Probability Density Function (pdf) and its application to Reliability [66] | 94  |

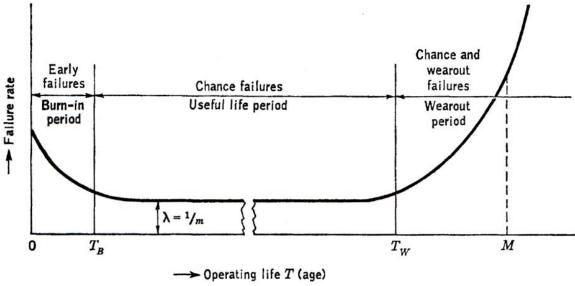

| Figure 3.12. Bathtub Curve [67].                                                        | 95  |

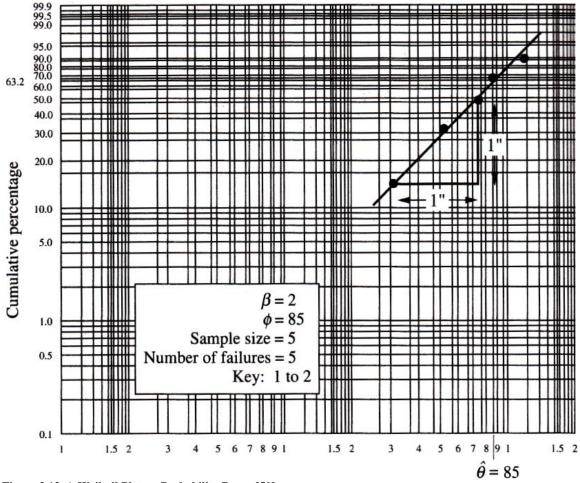

| Figure 3.13. A Weibull Plot on Probability Paper [50].                                  | 99  |

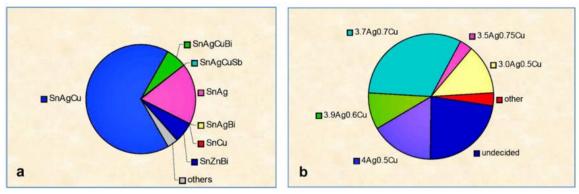

| Figure 4.1. From [68]. Survey of the market share of lead-free solders                  | 100 |

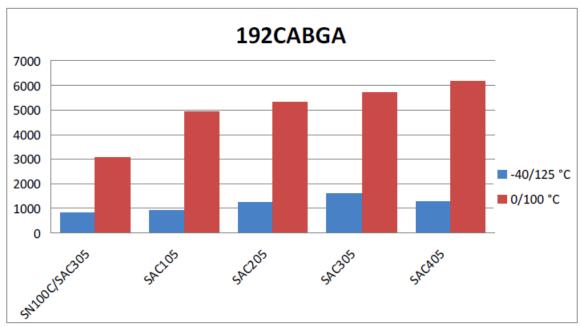

| Figure 4.2. From [51]. TC Characteristic life vs. Silver content, CABGA192            | 3 |

|---------------------------------------------------------------------------------------|---|

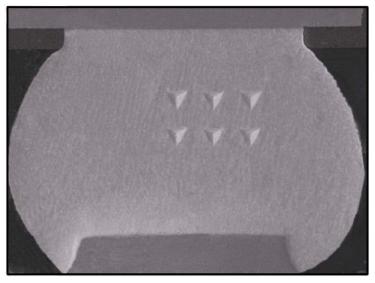

| Figure 4.3. A series of Nanoindentations in a SAC solder joint [104]                  | 1 |

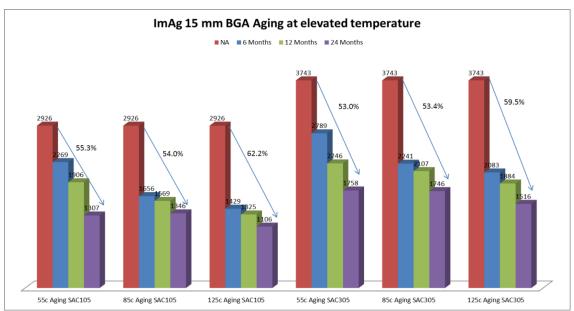

| Figure 4.4. TV7 Project: Characteristic Life degradation with aging for CABGA 208. 11 | 3 |

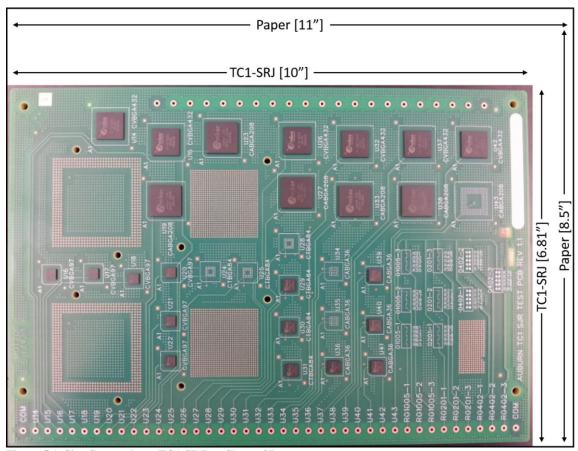

| Figure 5.1. Size Comparison: TC1-SRJ vs. Sheet of Paper                               | 8 |

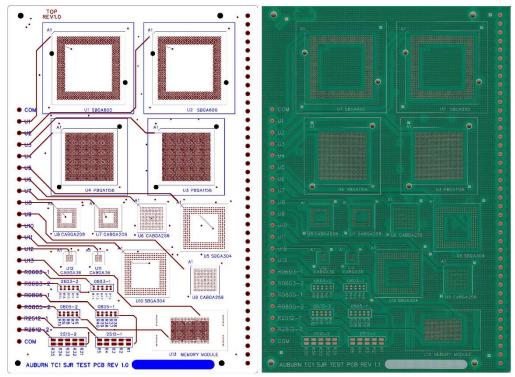

| Figure 5.2. TC1-SRJ Test Vehicle: Top-Side (Schematic and Un-assembled PCB) 12        | 0 |

| Figure 5.3. TC1-SRJ Test Vehicle: Bottom-Side (Schematic and Un-assembled PCB).12     | 0 |

| Figure 5.4. Summary of some important sub-groups from the Test Matrix                 | 6 |

| Figure 5.5. Speedline Technologies MPM Momentum. 12                                   | 7 |

| Figure 5.6. Juki KE-2080L (left) and Juki JX3 (right) pick-and-place machines 12      | 8 |

| Figure 5.7. Heller a1913 MKIII Reflow Oven                                            | 9 |

| Figure 5.8. Setup Board used for Thermal Profiling of the Reflow Oven                 | 9 |

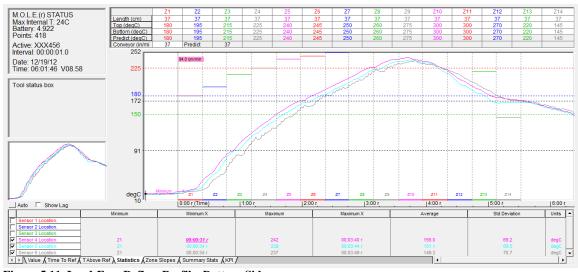

| Figure 5.9. SnPb Reflow Profile, Bottom-Side                                          | 0 |

| Figure 5.10. SnPb Reflow Profile, Top-Side                                            | 1 |

| Figure 5.11. Lead-Free Reflow Profile, Bottom-Side                                    | 1 |

| Figure 5.12. Lead-Free Reflow Profile, Top-Side                                       | 2 |

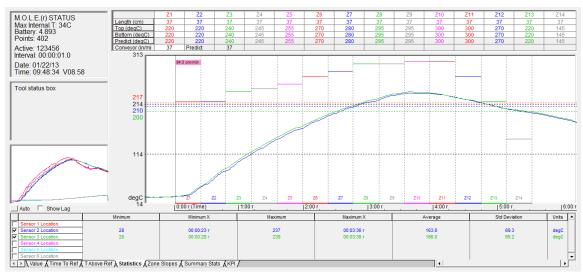

| Figure 5.13. TC1-SRJ Assemblies being stacked for Isothermal Aging                    | 4 |

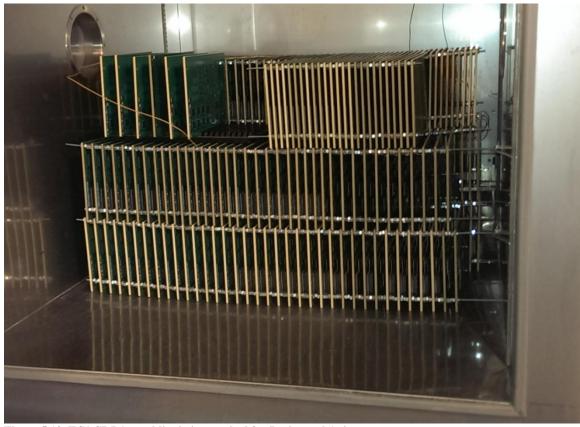

| Figure 5.14. TC1-SRJ Thermal Profile, Theoretical (left) vs Experimental (right) 13   | 5 |

| Figure 5.15. Thermotron, 16 cft (left) and ETC16 (right) Thermal Cycling Chambers. 13 | 6 |

| Figure 5.16. Several hundred TC1-SRJ boards being sorted at Auburn University 13      | 8 |

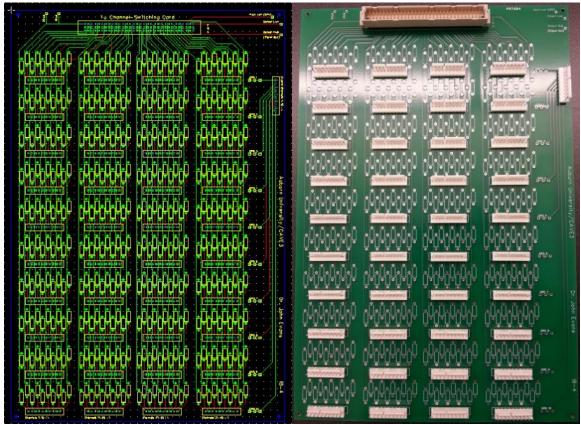

| Figure 5.17. IB-4 Interface Board (Schematic and PCA)                                 | 0 |

| Figure 5.18. GRD-IB-1 Ground Interface Board (Schematic and PCA)                      | 1 |

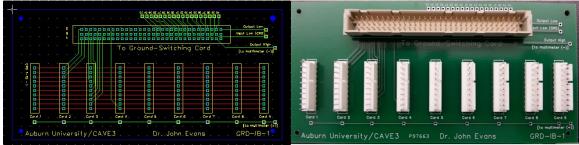

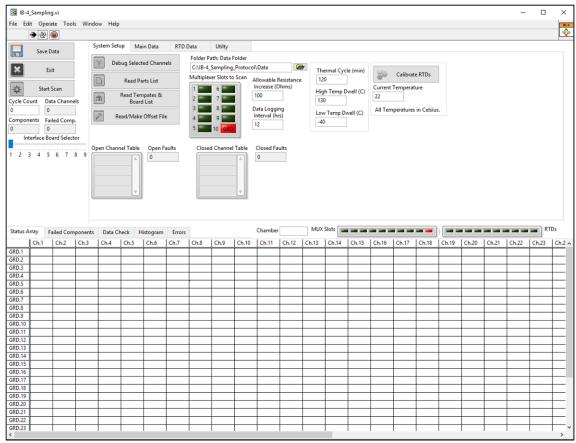

| Figure 5.19. Setup Page of IB-4 Sampling Program                                      | 2 |

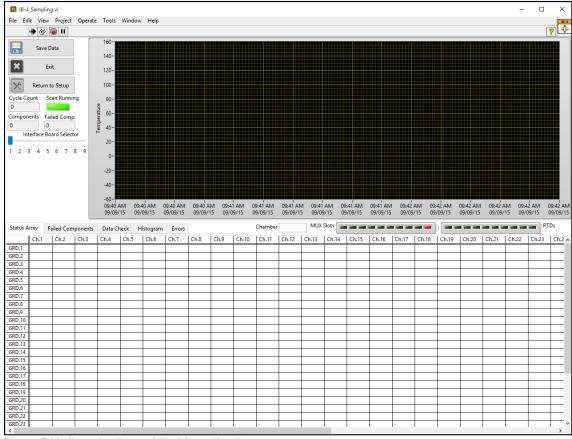

| Figure 5.20. Scanning Page of IB-4 Sampling Program                                   | 3 |

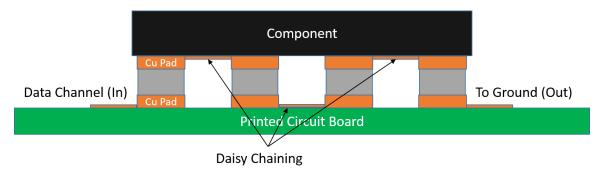

| Figure 5.21. Electrical Daisy Chaining for continuity testing                    |

|----------------------------------------------------------------------------------|

| Figure 5.22. TC1-SRJ boards stacked (left) and corresponding wiring (right) 145  |

| Figure 5.23. Monitoring System for the TC1-SRJ experiment (24A Group, LHS) 146   |

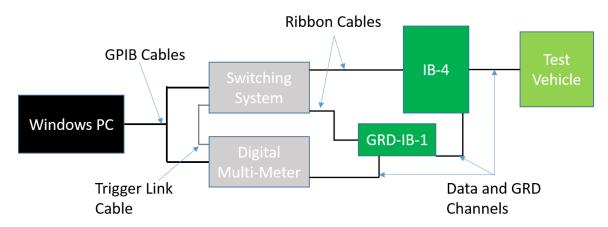

| Figure 5.24. Diagram of the TC1-SRJ Monitoring System. 147                       |

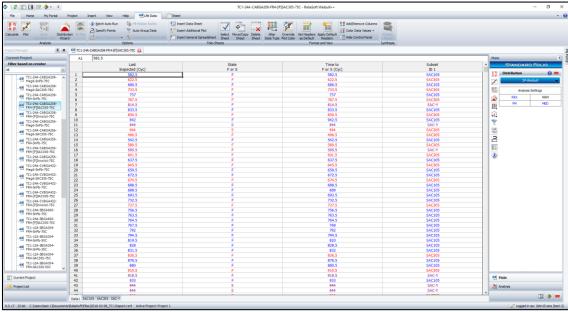

| Figure 5.25. Weibull++ Software User Interface                                   |

| Figure 6.1. All data at 12-Months of Aging (75°C). CABGA 36 – [P][S]SnPb         |

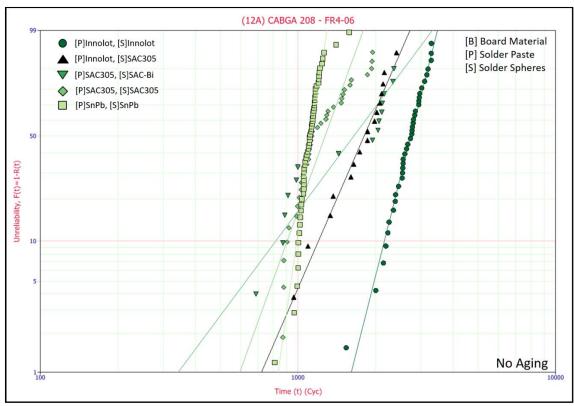

| Figure 6.2. Key Groups on FR4-06. CABGA 208 – No Aging                           |

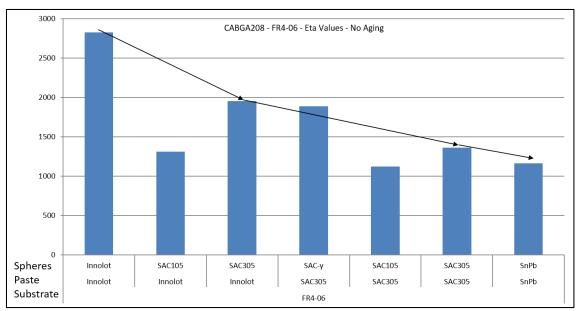

| Figure 6.3. Characteristic Life values. CABGA 208 – FR4-06 – No Aging 157        |

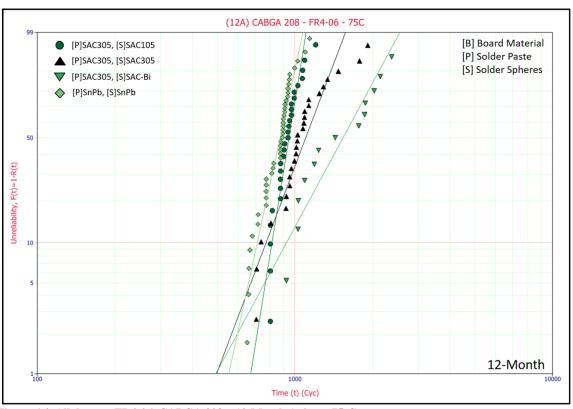

| Figure 6.4. All data on FR4-06. CABGA 208 – 12-Month Aging – 75°C                |

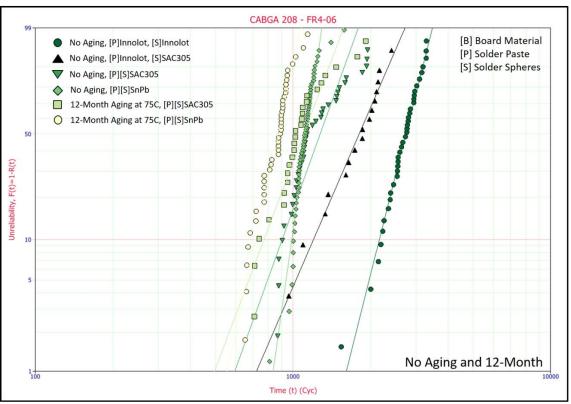

| Figure 6.5. Key groups on FR4-06. CABGA208 – No Aging and 12-Month (75°C) 159    |

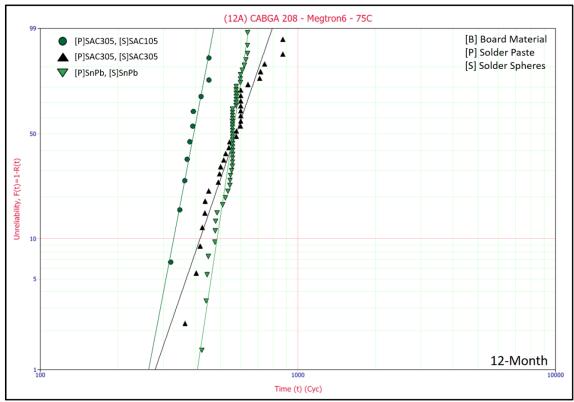

| Figure 6.6. All data on Megtron6. CABGA 208 – 12-Month Aging – 75°C 160          |

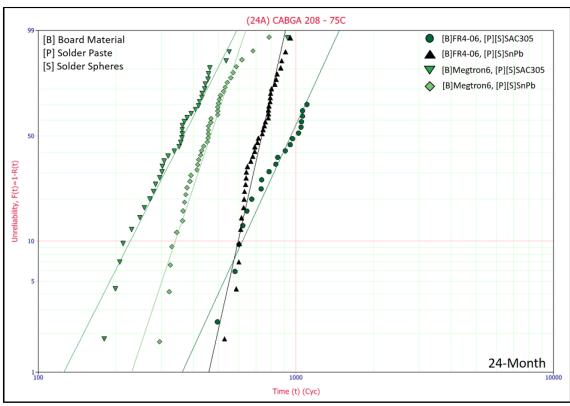

| Figure 6.7. Key Groups at 24-Months Aging (75°C). CABGA 208                      |

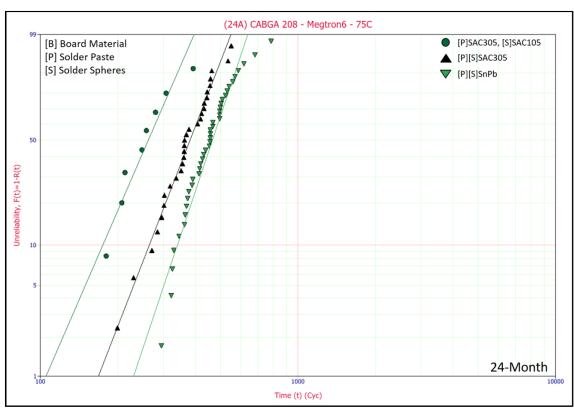

| Figure 6.8. All data on Megtron6. CABGA 208 – 24-Month Aging – 75°C 162          |

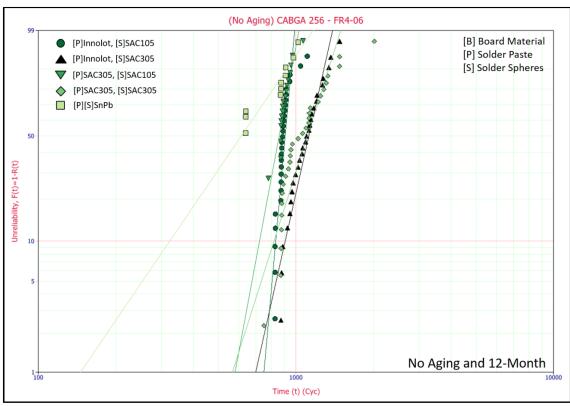

| Figure 6.9. All data on FR4-06. CABGA 256 – No Aging                             |

| Figure 6.10. All data on FR4-06. CABGA 256 – 12-Month Aging – 75°C               |

| Figure 6.11. All data on FR4-06. CABGA 256 – 24-Month Aging – 75°C               |

| Figure 6.12. All data on Megtron6. CABGA 256 – 24-Month Aging – 75°C 166         |

| Figure 6.13. All data at No Aging. CTBGA 84 – 12-Month Aging – 75°C 167          |

| Figure 6.14. All data at 12-Months of Aging (75°C). CTBGA 84                     |

| Figure 6.15. Substrate Comparison. CVBGA 97 – [P][S]SnPb – No Aging 169          |

| Figure 6.16. Substrate Comparison. CVBGA 97 – [P][S]SnPb – 12-Months at 75°C 170 |

| Figure 6.17. Solder Paste Comparison. CVBGA 432 – FR4-06 – No Aging 172          |

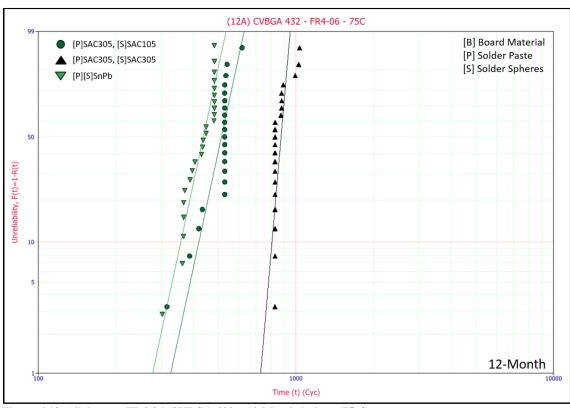

| Figure 6.18. All data on FR4-06. CVBGA 432 – 12-Month Aging – 75°C               |

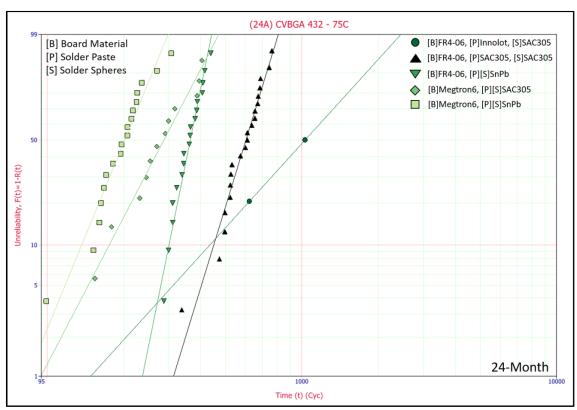

| Figure 6.19. All data at 24-Months (75°C). CVBGA 432. Note horizontal axis 174        |

|---------------------------------------------------------------------------------------|

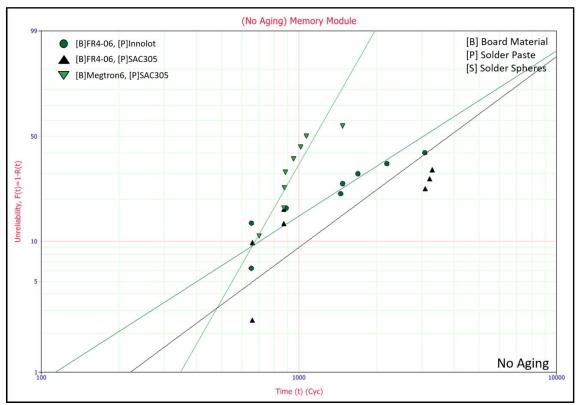

| Figure 6.20. All data at No Aging. Memory Module                                      |

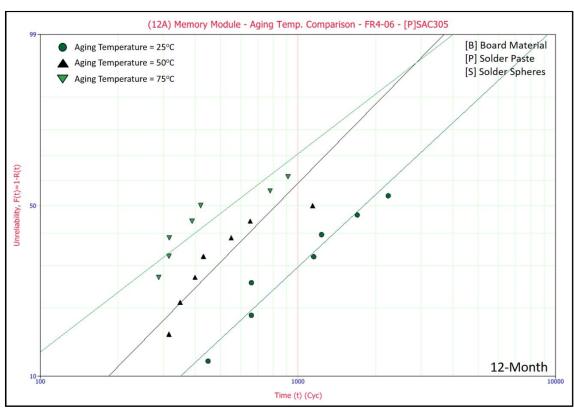

| Figure 6.21. Aging Temperature Comparison. Memory Module – 12-Month Aging 176         |

| Figure 6.22. All data at 1300 cycles. Memory Module – 24-Month Aging – 75°C 177       |

| Figure 6.23. Characteristic Life values. PBGA 1156 – FR4-06 – No Aging 178            |

| Figure 6.24. Substrate Comparison. PBGA 1156 – [P][S]SnPb – No Aging 179              |

| Figure 6.25. Key groups on FR4-06. PBGA 1156 – No Aging and 12-Month (75°C) 180       |

| Figure 6.26. All data on FR4-06. PBGA 1156 – 24-Month Aging – 75°C                    |

| Figure 6.27. SBGA 304 – FR4-06 – No Aging                                             |

| Figure 6.28. Weibull Plot: SBGA304 – No Aging and 12-Month (75°C)                     |

| Figure 6.29. Characteristic Life values. SBGA 600 – FR4-06 – No Aging                 |

| Figure 6.30. Substrate Comparison. SBGA 600 – No Aging – [P][S]SnPb                   |

| Figure 6.31. SBGA 600 – FR4-06 – With Heatsinks – 12-Month Aging – 75°C 186           |

| Figure 6.32. SBGA 600 – FR4-06 – With Heatsinks – 24-Months Aging – 75°C 187          |

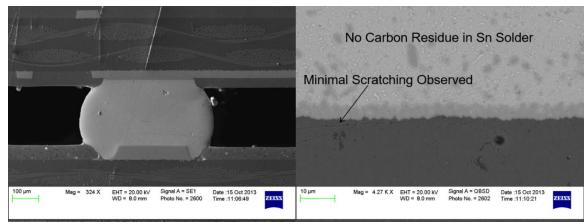

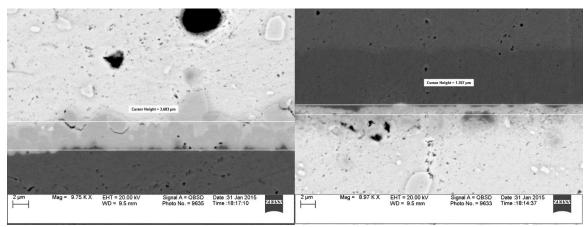

| Figure 7.1. SE (left) and BSE (right) micrographs, Polishing Procedure 1              |

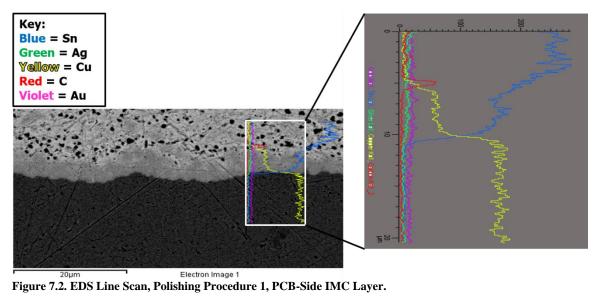

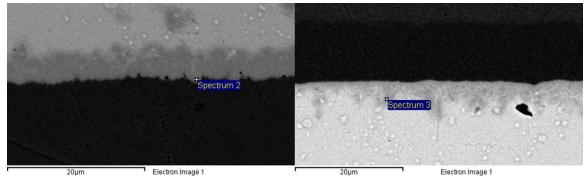

| Figure 7.2. EDS Line Scan, Polishing Procedure 1, PCB-Side IMC Layer                  |

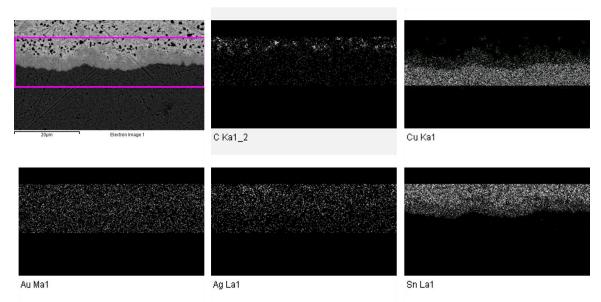

| Figure 7.3. EDS MAPS, Polishing Procedure 1, PCB-Side IMC Layer                       |

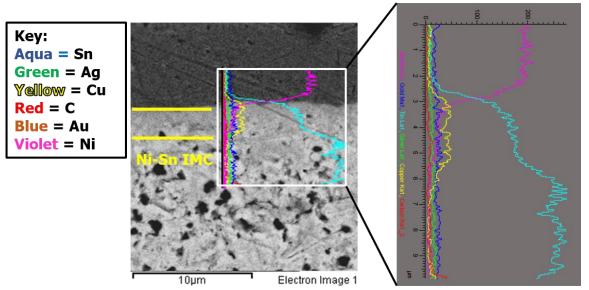

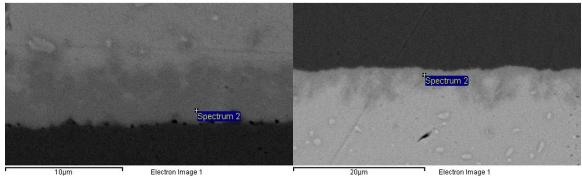

| Figure 7.4. EDS Line Scan, Polishing Procedure 1, Component-Side IMC Layer 192        |

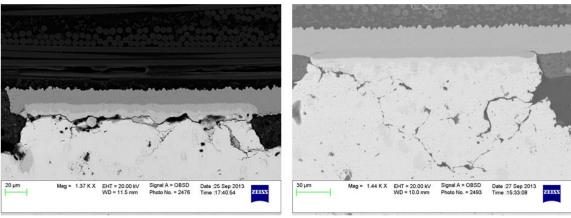

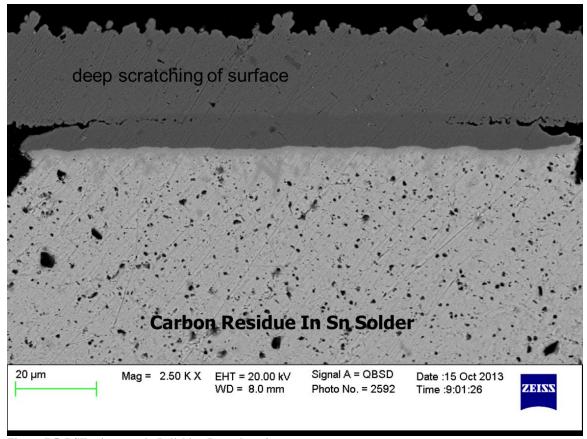

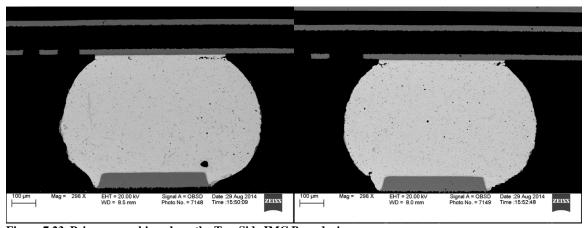

| Figure 7.5. BSE micrograph, Polishing Procedure 2                                     |

| Figure 7.6. SE (left) and BSE (right) electron micrographs. Polishing Procedure 3 194 |

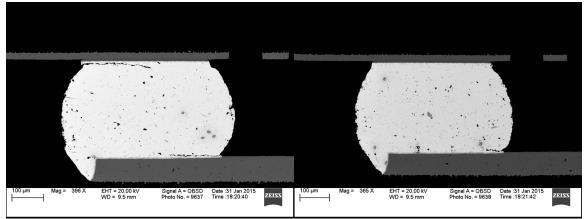

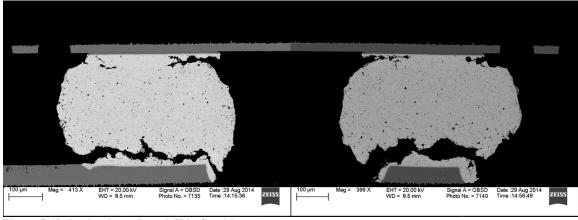

| Figure 7.7. Board- (left) and Component-Side (right) IMC, SAC305, 1000 TCs 195        |

| Figure 7.8. Board- (left) and Component-Side (right) IMC, Innolot, 1000 TCs 195       |

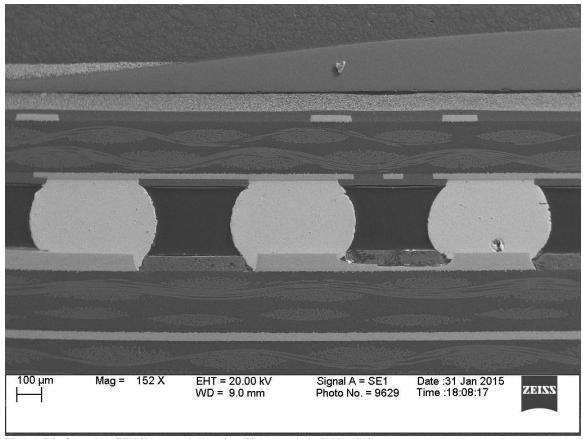

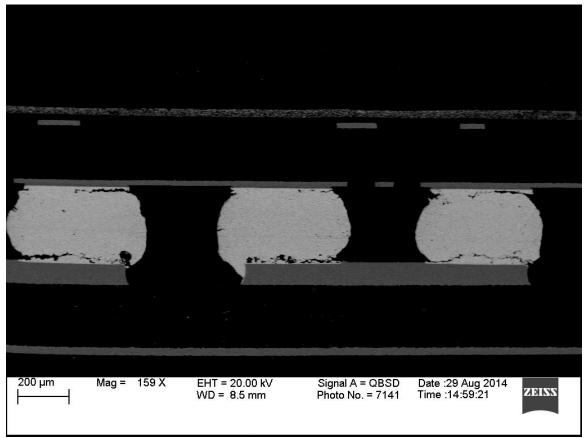

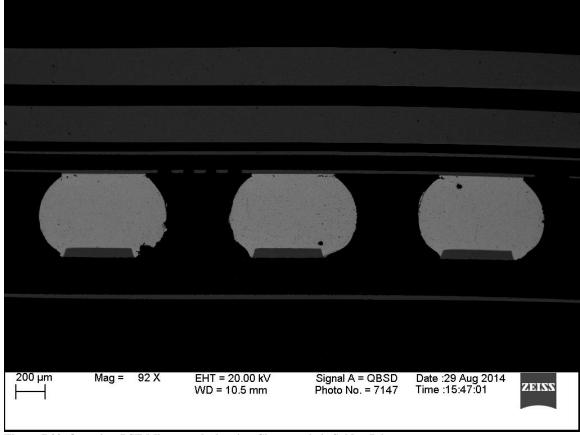

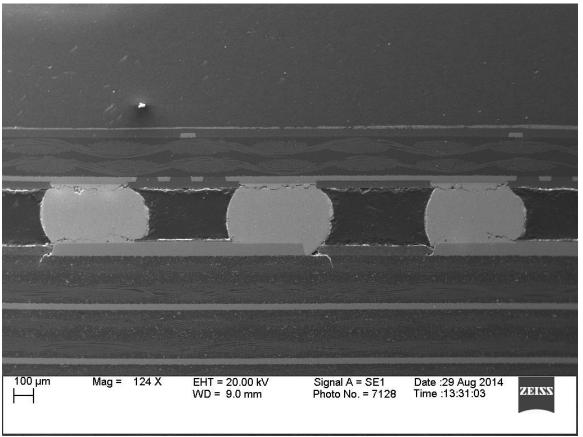

| Figure 7.9. Overview SE Micrograph showing Characteristic Solder Joints               |

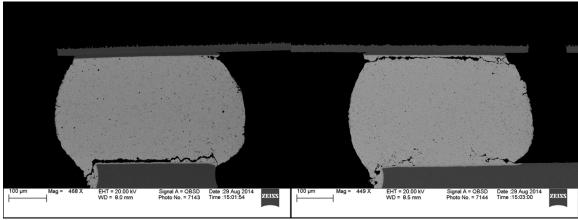

| Figure 7.10. Board- (left) and Component-Side (right) IMC, SAC305, 2000 TCs 196            |

|--------------------------------------------------------------------------------------------|

| Figure 7.11. Roughly equivalent cracking (left); crack initiation at board-side (right) 19 |

| Figure 7.12. Overview SE Micrograph showing Characteristic Solder Joints                   |

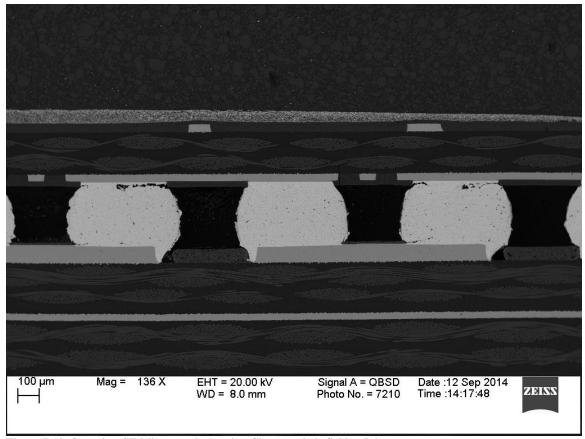

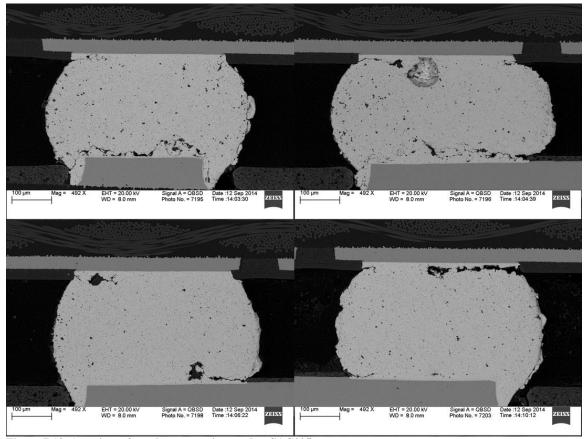

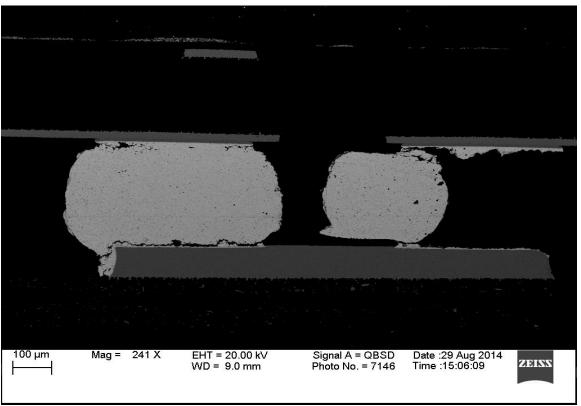

| Figure 7.13. A variety of crack propagation modes, SAC305-paste                            |

| Figure 7.14. Overview SE Micrograph showing Characteristic Solder Joints                   |

| Figure 7.15. A variety of crack propagation modes, Innolot-paste                           |

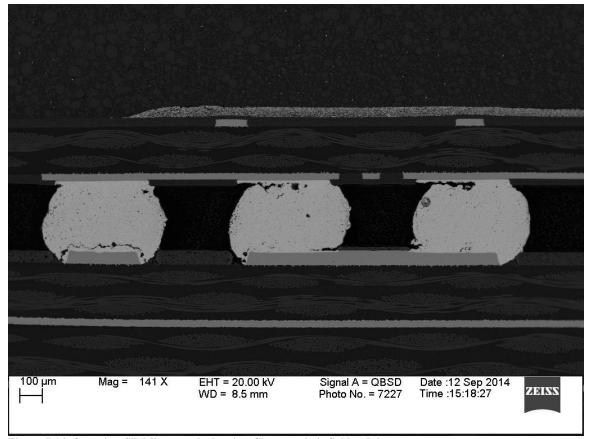

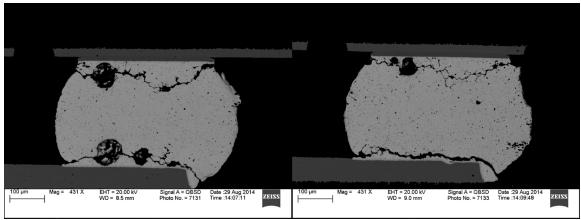

| Figure 7.16. Overview BSE Micrograph showing Characteristic Failure Modes 202              |

| Figure 7.17. Roughly equivalent cracking at Board/Component-Side of two joints 200         |

| Figure 7.18. Predominant Board-Side Cracking                                               |

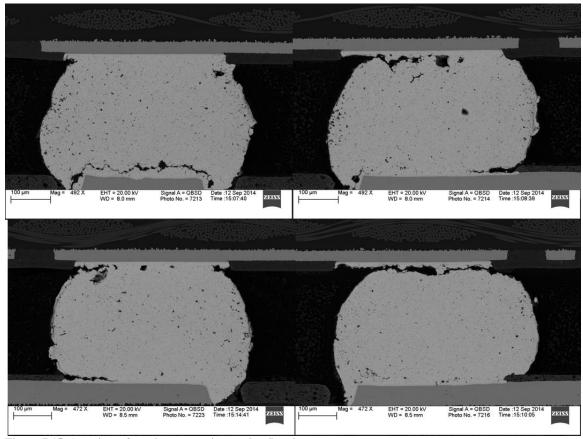

| Figure 7.19. Overview BSE Micrograph showing Characteristic Failure Modes 204              |

| Figure 7.20. Primary cracking at IMC Boundaries                                            |

| Figure 7.21. Traumatic failure in Right-most Joint                                         |

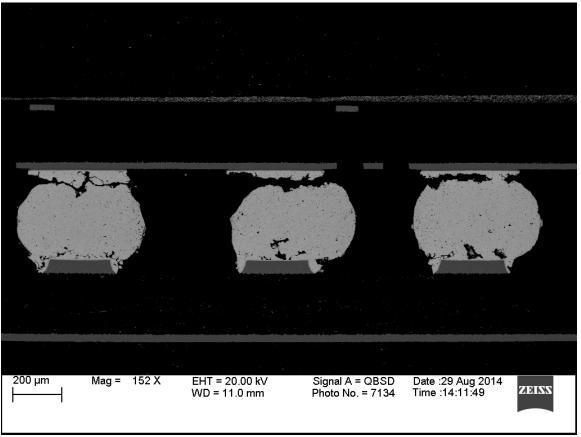

| Figure 7.22. Overview BSE Micrograph showing Characteristic Solder Joints 20               |

| Figure 7.23. Primary cracking along the Top-Side IMC Boundaries                            |

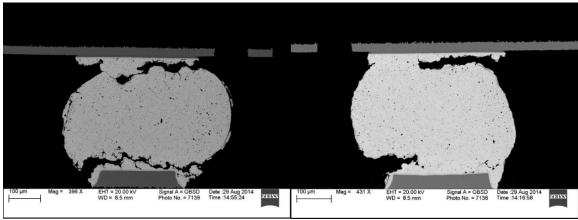

| Figure 7.24. Overview SE Micrograph showing Characteristic Failure Modes 208               |

| Figure 7.25. Roughly equivalent cracking at Top and Bottom                                 |

| Figure 8.1. Solder Paste Comparison, No Aging Group                                        |

| Figure 8.2. Substrate Comparison, No Aging Group                                           |

| Figure 8.3. Characteristic life vs. Isothermal Aging Time. Key packages, FR4-06 213        |

| Figure 8.4. Characteristic life vs. Isothermal Aging Time. Key packages, Megtron6 215      |

### List of Abbreviations

BGA Ball Grid Array

BSE Back-Scattered Electron

GPIB General Purpose Interface Bus

LGA Land Grid Array

PCA Printed Circuit Assembly

PCB Printed Circuit Board

PGA Pin Grid Array

RTD Resistance Temperature Detector

SAC Tin(Sn) - Silver(Ag) - Copper(Cu)

SCPI Standard Commands for Programmable Instruments

SEM Scanning Electron Microscope

SE Secondary Electron

SMC Surface Mount Component

SMR Surface Mount Resistor

SnPb Tin – Lead

THMC Through-Hole Mount Component

UBM Under-Bump Metallurgy

# Chapter 1 A Brief Introduction to Electronic Assemblies

#### 1.1 Printed Circuit Assemblies

In 1996, the Electronic Industry surpassed the Automotive Industry to become the largest industry in the world [1]. Since that time, the industry has continued to grow and mature, finding new applications such as smartphones and wearables that have transformed and may continue to transform the way that people interact with each other and incorporate information into their lives. Electronics have come become indispensable in industry, consumer applications, and for public record keeping and civic involvement, and they show little sign of slowing down their ever expanding influence.

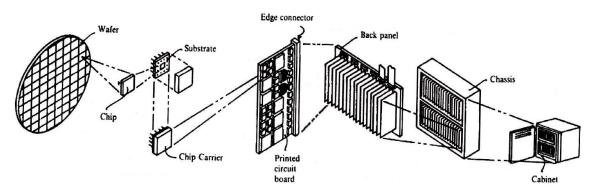

Active electronic components begin life as a Silicon "die," or chip, which is diced from a single-crystal Silicon Wafer. The silicon chip contains many solid-state electronic devices (transistors, resistors, inductors, and capacitors) that have been defined and connected to form functional electrical circuitry [2]. The production of such semi-conductor-based electronic devices is one of the crowning technological achievements of the modern era, involving a laundry list of fields including semiconductor physics, chemical and materials engineering, surface science and thin-film physics and engineering, electrical engineering and design, very large systems integration, and advanced optical processing technologies, to name a few. Continuing advancements in photolithography, materials, and manufacturing practices have enabled seemingly endless increases in the functional density of silicon chips – immortalized in the public

imagination via Moore's Law – and provided the driving force for many of the necessities and conveniences of modern life.

However, the story of the silicon chip does not end at wafer dicing. The silicon dies need protection from the outside environment and will often need to be combined with other electrical elements so as to create the desired circuit. This is where the Packaging of the electrical components comes in. Here, by packaging, we are not referencing containers intended for shipping. Rather, we mean "the placement and connection of many electronic and electro-mechanical components...in an enclosure which protects the system from the environment and provides easy access for routine maintenance" [2]. There are four (4) main functions of electronic packaging [2]:

- 1. Signal Distribution

- 2. Power Distribution

- 3. Heat Dissipation

- 4. Protection (Mechanical, Chemical, & Electromagnetic)

Figure 1.1. Levels of Packaging. Adapted from [2].

The first level of electronic packaging is the Chip Carrier. Typically, the silicon die is mechanically affixed to a lead-frame or interposer layer, and electrical connections are made between the chip and carrier using small wires ("wire bonding") or solder joints

("flip-chip BGA", etc.) [2,3]. Chip Carriers come in a vast array of options, differentiated by the type of attachment to the substrate, internal structure, materials used for construction, as well as other factors such shape, size, vertical standoff, and lead pitch.

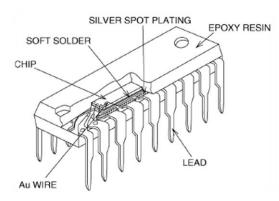

Figure 1.2. Dual In-Line Package (DIP) [2].

In addition to active components (i.e.

components that involve some form of gate or switching action), a variety of passive components – such as resistors, capacitors, or inductors – are available. These can also range significantly in their internal complexity, and are found in a plethora of sizes and shapes [3].

Figure 1Error! No text of specified style in document..3. First Level Packaging options [2].

The second level of packaging is the electronic assembly, or Printed Circuit Assembly (PCA). Anyone who has opened up their PC to view its "motherboard" has

experience in dealing with electronic assemblies. Just as a chip carrier has an interposer layer or lead-frame, an electronic assembly has a substrate – usually called a Printed

Circuit Board, or PCB. The Printed Circuit Board is typically a rigid laminate constructed of layers of fiberglass-epoxy composite. (Other materials, such as ceramic, metal/metal-core, and flexible polymer are also possible.) This substrate also contains external – and often internal – Copper metallization layers. The Copper

Figure 1.4. Printed Circuit Board.

layers are photolithographically defined so as to provide the 'wires' for the electrical circuit (as well as to provide thermal design enhancements, etc.). Thus, the Printed Circuit Board provides a flat surface for mechanical fixturing of the components, thermal redistribution and dissipation, electrical isolation (bulk substrate, typically) and electrical connection (via the copper traces) where needed to form the appropriate circuit [2,3].

The components are attached to the substrate using solder. The solder is a metal — typically an alloy — of reasonable melting point that is used to form a metallurgical bond between the component-side leads or terminations and the corresponding copper pads (known as "lands") on the Printed Circuit Board surface. The solder joints formed during assembly provide an electrical, thermal, and mechanical connection between the PCB and the component [2,3]. Solder and its use in Printed Circuit Assemblies will be discussed in Chapter 2.

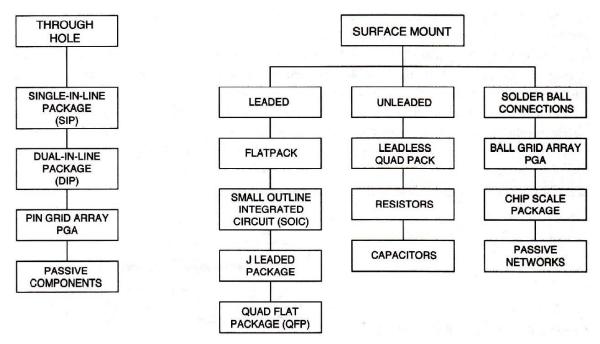

Since the 1970s, the electronics packaging industry has been dominated by two component "mounting" technologies: each of which has its own associated soldering technology, manufacturing process, component design restrictions, etc. Through-hole

Mount Technology, or THMT, is typified by component leads that pass through the Printed Circuit Board and are clinched on the backside prior to soldering via the Wave Soldering process. Surface Mount Technology, or SMT, involves components that are attached to the copper pads ("lands") on the same side of the PCB using a Reflow Soldering process [3].

### **Through-Hole Mount Attachment**

### **Surface Mount Attachment**

Figure 1.5. Through-Hole Mount vs. Surface Mount Attachment. Adapted from [2].

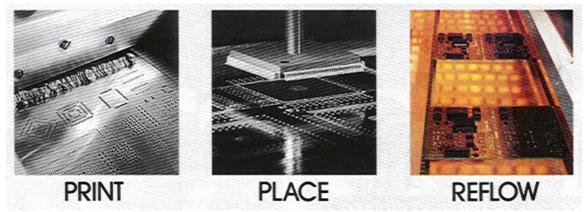

For a typical Printed Circuit Assembly (PCA) containing only surface mount components, some of the key assembly steps include paste printing, component placement and solder reflow. Solder paste is a thickened flux/solvent vehicle containing small (around 35-45 microns in diameter for Type 3 paste) spheres of the solder alloy. It is applied to the substrate's exposed copper pads, or "lands," via a screen printing process. In modern applications, this mostly involves a metal stencil and squeegee blade. Components are carefully placed so that their leads, BGA balls, or metalized pads are sitting (ideally) directly on top of the appropriate paste deposit. During solder reflow, the assembly passes through a multi-zone reflow oven/furnace, culminating with the solder alloy exceeding its Liquidus temperature for a short period of time – typically 30-90 seconds. Above liquidus, the solder is fully melted, and it "wets" to the metal surfaces. Upon cooling a solid and continuous metallic joint has been formed [3].

### 1.2 Printed Circuit Assemblies: Introduction

Although computers existed before its invention, the advent of the modern electronics industry depends principally on the invention of the transistor in 1947. Prior to the creation of the transistor, electronics were famously dominated by slow, large, power-hungry, and failure-prone Vacuum Tubes. Electronics were traditionally wired and assembled by hand. This process was slow and inefficient, and reliability was dismal, so the incentives to keep things simple were numerous. J. R. Pierce, the Bell Labs engineer credited with coining the term "transistor" is quoted as saying "Nature abhors the vacuum tube" [4]. Once unencumbered of the limitations of the vacuum tube, engineers were freed to imagine circuits of ever-growing complexity.

Although this was a significant boon, it soon became clear that a new approach to the traditional hand-assembly and wiring approaches was needed in order to deal with the large number of high-quality interconnects ("wires") needed. Additionally, smaller transistors (and other circuit components) and shorter interconnects were desirable so as to increase circuit response speed (reduce propagation delay) [4].

In response, the monolithic semiconductor "integrated circuit," or IC, was invented by Jack Kilby of Texas Instruments in 1958. The integrated circuit was also separately developed by Robert Noyce, one of the co-founders of Intel, about half a year later. Noyce also developed techniques for depositing interconnects by adding a top layer of metal and then etching away unused areas, making his device more practical than Kilby's [4].

To fully realize the potential of the integrated circuit, electronic packaging designers now needed to solve many of the same challenges that motivated its invention. The assembly of electronics at the time involved hand-wired, "point-to-point," interconnects, and (often) no substrate of any kind [3]. The creation of the printed circuit board – or PCB – predates the invention of the transistor, but printed circuit boards initially had few uses. Now, suddenly, the printed circuit board became a very attractive option as a mounting surface, and new types of integrated circuit "packages" and techniques for mounting them to PCBs were needed [4].

### 1.2.1 Through-Hole Mount Technology (THMT)

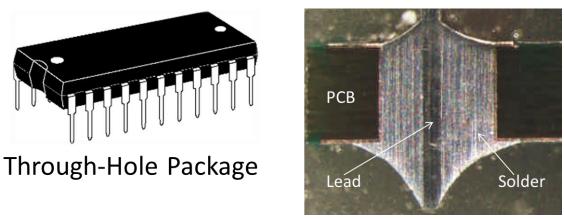

The basic idea of through-hole mount technology consists of drilling vias (through-holes) in the Printed Circuit Board, passing component leads through these vias, and crimping them on the backside. This is followed by soldering (adding solder around) the component leads, which joins them to the appropriate metal traces of the PCB [3]. The principal method of soldering in through-hole mount assembly is 'wave soldering' technique, which involves a standing wave of molten solder. The PCB is passed over the wave, soldering all of the through-hole connections at once. After some initial quality concerns had been allayed, the electronic packaging industry was quick to adopt wave soldering technology, as the throughput advantages were overwhelming.

Later, techniques for metal plating of the through-holes were created, and the need for greater component densities was met by first adding a second metal interconnect layer (on the component side of the board) and eventually by adding multiple interconnect layers built into the printed circuit board. Automated placement machines

were also developed that would take a THMT component and quickly place it on the PCB (including all necessary wire cutting, forming, and crimping).

One of the enduring advantages of THMT, even when compared to more modern approaches, is the excellent reliability of the solder joints. Assuming voiding is controlled, the soldered through-hole connection is extremely sound mechanically, and the lead/pin attached to the through-hole mount component (THMC) effectively takes up stresses resulting from thermal expansion in the PCB substrate, etc. These advantages allowed THMT to dominate the electronic packaging arena from the 1950s to the 1980s. Even to the present day, THMT is still used in certain applications, such as when components are too large for surface-mounting technology due to high power requirements or mechanical limitations, or subjected to very high mechanical stress.

On the downside, since through-hole mount technology requires vias to be drilled through the printed circuit board, I/O connections can only be placed along two edges of the components without compromising the mechanical integrity of the PCB. Lead pitch reductions are limited by the same concern, as well as by the fact that smaller through-hole leads will not support the (generally heavy) though-hole mount components.

Additionally, since the through-holes pass all the way through the PCB, all metal interconnects must be routed around them to avoid shorting. Eventually, it became clear that a new technology was needed to achieve higher I/O and component densities and keep pace with IC advances.

The basic form of a Through-Hole Mount Technology Component and Solder

Joint are shown below in Figure 1.6. These solder joints are typically the easiest joints to

inspect by eye, with metallic luster, surface appearance, wetting/feathering angle, wetting/filleting coverage, etc. all being readily apparent to the unaided eye.

Figure 1.6. Through-Hole Mount Technology Component and Solder Joint [2,5].

There are a variety of Through-Hole Mount Components, including varieties of the package types listed below. The Dual In-Line Package (DIP) was the most popular THMC, with many forms available such as PDIP (Plastic DIP), CDIP (Ceramic DIP), CERDIP (CDIP, Glass Sealed), SDIP (Skinny DIP), etc. Table 1.1 lists a few of the primary types of THMC.

Table 1.1. Principal Types of Gull Wing and J-Lead Packages [2,6]

| Single In-Line<br>Package (SIP) | Zig-Zag In-Line<br>Package (ZIP) | CARRIER CO. |

|---------------------------------|----------------------------------|-------------|

| Dual In-Line<br>Package (DIP)   |                                  |             |

### 1.2.2 Surface Mount Technology (SMT)

Surface Mount Technology was originally developed in the 1960s, but was ahead of its time. High component prices (due largely to low production volumes), high capital

investment requirements during switchover, a lack of widespread technical knowledge on how to effectively use it, and other factors led to SMT being used only in niche applications (primarily military and aerospace) until the 1980s. As THMT ran aground of its physical limitations, however, SMT became more attractive [3]. By the 1980s, the development of VLSI integrated circuit technology meant that through-hole packaging techniques simply could no longer provide for the necessary I/O capabilities to keep up with industry and consumer demand.

In general, Surface Mount Technology can be described as a process for soldering components directly to the surface of a printed circuit board, foregoing the need for a through-hole. Surface mount components (SMC) were initially similar to through-hole mount components, re-engineered to have short leads of various design ("leaded") or contact pads ("lead-less"). Rather than using a wave soldering process, surface mount components typically have solder paste pre-applied to the PCB contact pads (through a silk-screening or stencil process). After components are placed on the board, the paste is 'reflowed' (heated above Liquidus and then allowed to cool) in a reflow oven, causing it to form a solid joint [3].

SMT brings with it several design advantages compared to THMT. Since no through-holes are required, components can be placed on both sides of a printed circuit board more easily, significantly increasing the useable PCB surface area. Surface Mount Components also provide finer lead pitches, and I/O can be placed around all four sides of the component. SMCs are also typically smaller than their THMC contemporaries, often less than half as large. These allow for significant increases in component and

input/output density. Smaller, lightweight components are also highly desirable in certain applications such as aerospace [3,7].

The cost of Surface Mount Components was initially significantly higher than that for Through-Hole Mount Components, but much of this was eventually offset by cost savings via maturation of the part production processes and economies of scale. Today SMCs are typically less costly than their THMC equivalents. Since surface mount components have higher I/O capabilities, the number of functions per component can also be higher, meaning that the cost per function is even more heavily weighted in favor of SMCs. However, more precise interconnect layout technologies are also required, which have offsetting costs associated with them. Since fewer vias need to be drilled into the PCB for surface mount technology-based boards, time and money are saved here. Rework of defective parts is also easier and faster (and therefore lower cost), although it typically requires more expensive equipment up front [3].

The manufacturing process is generally simpler and faster for surface mount technology, although process parameters need to be determined and maintained to fairly exacting standards. Material handling is easier and fewer placement machines are typically needed, as a single 'pick-and-place' machine can install essentially any surface mount component. During the solder reflow operation, the surface tension of the molten solder will cause surface mount components to "self-align" (align correctly to the corresponding PCB pads), leading to higher quality than during THM production. However, reliability can be an issue, as SMT joints tend to be more mechanically fragile [2,3]. One hidden benefit of surface mount manufacturing is worker safety: the most dangerous piece of equipment is generally the pick-and-place machine, which can

significantly damage hands placed unwarily into it. Through-hole mount technology, on the other hand, generally requires the use of a wave solder machine, which contains a vat of liquid metal solder. Accidents involving a wave soldering apparatus can be quite severe.

The electrical performance of surface mount interconnects is typically better, due to the shorter leads employed. On the other hand, thermal management can become more complicated, as thinner leads – necessary for finer pitch I/O – also have higher thermal resistance [3]. Smaller components also lead to a higher concentration of thermal energy, exacerbating this problem. Thermal damage during reflow is also a concern. Although the temperature of the solder bath is higher in wave soldering systems, the heating and cooling is somewhat limited to the leads of the through-hole mount components. Surface mount components, on the other hand, experience a mostly identical thermal profile to the reflowed joints themselves.

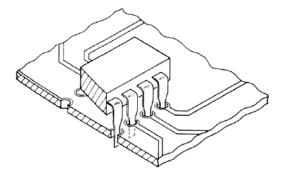

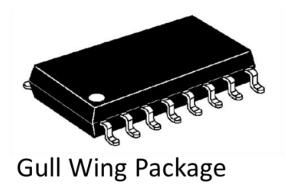

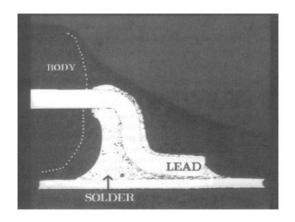

There are a variety of (perimeter array) surface mount solder joints, each of which will be dictated by the type of lead/attachment to the PCB land. For leaded packages (excluding BGAs), the two most important lead types/shapes are Gull Wing and J-Lead. These are shown schematically in Figure 1.7, below. Note that the geometry of the solder joint differs between the two lead types: the main solder fillet on the Gull Wing joint reaches back toward the body of the component, whereas the main fillet on the J-Lead joint reaches outward away from the component [3].

Figure 1.7. Gull Wing Leads (left) and J-Leads (right) [2].

A large variety of Surface Mount Components exist, including both Gull Wing packages, J-Lead packages, and other types yet to be discussed. Table 1.2 lists only a few of the primary categories for Gull Wing and J-Lead packages.

Table 1.2. Principal Types of Gull Wing and J-Lead Packages [2,6]

| Gull Wing Packages                |           | J-Lead Packages                          |           |

|-----------------------------------|-----------|------------------------------------------|-----------|

| Small Outline IC (SOIC)           | CARREST . | Small Outline<br>J-Lead (SOJ)            |           |

| Quad Flat Pack<br>(QFP)           |           | Plastic Leaded<br>Chip Carrier<br>(PLCC) | RALLARIA. |

| Small Outline<br>Transistor (SOT) |           |                                          |           |

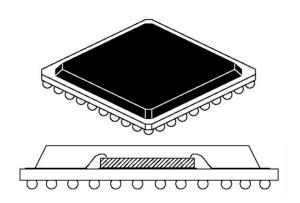

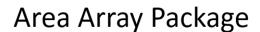

### 1.2.3 Area Arrays

As input/output requirements for ever more advanced IC components continued to grow, finer pitch I/O interconnects were needed. However, finer pitches come with a range of manufacturability concerns, including increasing fragility of finer-pitch leads and "bridging" (unwanted electrical connection, generally via reflowing solder) between closely spaced contact pads on the Printed Circuit Boards. Eventually, it becomes prohibitively difficult to further decrease the lead pitches for standard SMC chip carriers. Fortunately, a solution had been around for some time.

Once one has made the transition to surface mounted technology, there is no fundamental reason that I/O should be limited to the perimeter of a component. Since no through-holes have to be drilled, I/O can be installed in a full 2-dimensional lattice, or Area Array, under a surface mounted component. For a square component with n leads

along each edge, this approach increases the number of potential I/O channels from approximately 4n to n<sup>2</sup> (although, depending on the component, I/O may cover only part of the allowable area). Area arrays allows one to dramatically increase I/O capabilities without having to decrease the lead pitch [5].

Since Surface Mount Technology had already been developed by the time Area Arrays became popular, the underlying manufacturing and cost structures were fairly similar. (Although time and money had to be spent adapting the existing processes to new I/O strategies such as the Ball Grid Array.) However, higher interconnect counts require more board level wiring, raising per-assembly prices. (As before, per-function prices continued to decrease.) When using BGAs, yield and manufacturability increase with respect to fine pitch chip carriers, as the solder balls used are more robust than traditional leads. As always, shorter interconnects lead to improved electrical performance.

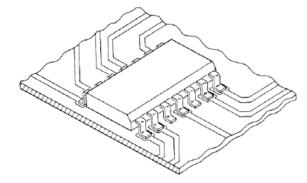

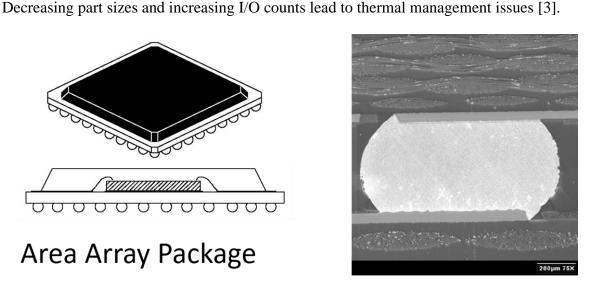

Figure 1.8. Area Array Component and Solder Joint [5].

The predominate Area Array component is the Ball Grid Array, or BGA. Ball Grid Arrays have small spheres of solder ("solder bumps") applied to the grid of contact pads built into the bottom of the component. These solder bumps are placed onto

corresponding solder paste deposits as if they were component leads. Typically, during reflow soldering, the bumps reflow (i.e. melt) and wet together with the solder paste to form a hamburger shaped solder joint. This "ball collapse" process means that lead Coplanarity is not an issue for BGA packages, although other problems – such as head-in-pillow – can occur.

There are, however, applications in which a higher standoff distance from the printed circuit board is preferred. In such circumstances, a higher melting-point solder can be used for the solder bumps. This substitution increases the standoff height of the component because only the solder paste will reflow during soldering. A similar strategy can be used, except with small columns of (high-T<sub>m</sub>) solder instead of spheres, resulting in an even more exaggerated stand-off. This type of component is known as a Column Grid Array (CGA). Another area array is the Pin Grid Array, where thick metal pins (similar to through-hole leads) are attached in lieu of solder spheres or columns [2,3]. This type of package often used in conjunction with socket into which the pins are inserted.

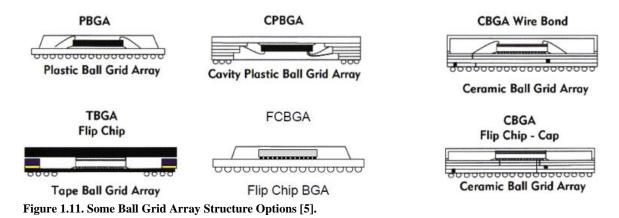

As with the previously described packages, a variety of BGA packages are available, including Plastic BGA (PBGA), Ceramic BGA (CBGA), Thin Chip BGA (CTBGA), Very Thin Chip (CVBGA), Super-BGA (SBGA), and Flip-Chip BGA (FCBGA) packages, among others.

Table 1.3. Area Array Packages [5,6]

| Ball Grid Array<br>(BGA) | Pin Grid Array<br>(PGA) |  |

|--------------------------|-------------------------|--|

|                          |                         |  |

### 1.2.4 No-Lead (Lead-Less) Components

The leads on a component (most often made of copper) can flex, and thereby take up the stress generated by linear Coefficient of Thermal Expansion mismatches between a component and printed circuit board. However, for Surface Mount attachment, there is no conceptual reason that one cannot do away with the component leads entirely. In such cases, the bare metal terminations on the bottom of the component are placed directly onto the solder paste deposit atop the corresponding copper lands of the Printed Circuit Board.

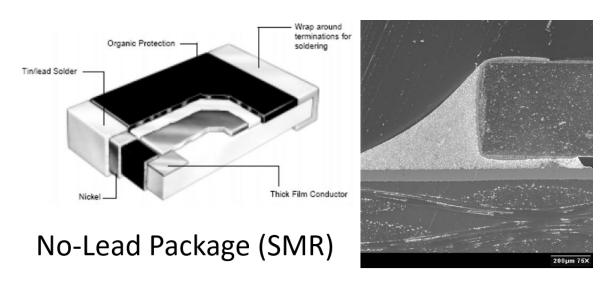

Figure 1.9. No-Lead Component and Solder Joint [5].

Components of this type that lack leads are called Lead-less or No-Lead packages. Typically, the PCB land extends beyond the shadow of the component termination, causing the major solder fillet of the resulting joint to point outward away from the package. Since the solder deposit typically starts at only a few mils in height and slump occurs during reflow soldering, the standoff height of the component is quite low. This low standoff can be a disadvantage for larger packages, as contaminants such as flux residue become difficult to clean from between the PCB and component [2,3].

There are a variety of lead-less components common to surface mount assembly. These include the Surface Mount Resistor (SMR), Metal Electrode Leadless Face (MELF), and Quad Flat No-Lead (QFN) packages. Another type of No-Lead package is the Land Grid Array, or LGA. This is a type of area array the closely resembles the Ball Grid Array, with the key difference that no solder spheres are added to the component terminations.

# 1.2.5 Internal Structure of Common Surface Mount Components

The production of a typical active Surface Mount Components starts with an appropriate Interposer Layer. The Interposer is a small substrate, with functions similar to those described for the Printed Circuit Board (discussed below), except at the component level (i.e. first level of packaging). In most applications, a rigid organic or ceramic interposer is used. Bismaleimide Triazine (BT) is a common base material for organic laminates, whereas most ceramic interposers are made from a sintered mixture of alumina and glass with a low Coefficient of Thermal Expansion close to that of the silicon die. Other interposer options include the use of a metal lead-frame (generally copper) or a flexible organic film (such as polyimide). Interposers will have one or more copper metallization layers for transferring power and electrical signals between various circuit points [2,3].

The most common method of electrical connection between the Interposer and Silicon Die is the Wire-Bond. Wire-bonding involves connecting an (electrical) pad on the die to a matching pad on the interposer using a thin (10s of microns in diameter) metal wire. The bonding pads are generally 40 or 50 microns on a side. The wire is

bonded to the first pad, drawn out, bonded to the second pad, and clipped. The bonding normally takes place in around 1/10 of a second, and wire-bonding equipment must be able to accurately form many wire-bonds in quick succession. The most common wire material used is Gold (>90% prevalence), with Aluminum being used in some applications. Aluminum wire is used in certain applications, with additional strong interest in copper as a material of the future. The bonding process is performed using thermo-compression in the case of Gold wire-bond and using ultrasonic bonding in the case of Aluminum wire-bonds [2,3].

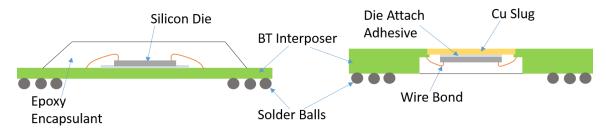

There are two main internal structures employed for plastic BGA packages with wire-bonded silicon dies. Figure 1.10 shows the standard ("cavity up") configuration on the left and the "cavity down" configuration on the left. The cavity-down package in this figure incorporates a head-slug, which would aid in heat transfer out the 'top' of the component.

Figure 1.10. Standard BGA (left) and Cavity-Down BGA (right)

Two other options for forming connections between the die and interposer are Flip-Chip attachment and Tape-Automated Bonding (TAB). In Flip-Chip attachment, the silicon die has small solder bumps added to its electrical contact pads. The chip is then inverted and reflow mounted onto the interposer similar to the attachment of a BGA package to the PCB. Tape-Automated Bonding involves the use of a thin, flexible tape onto which the pattern of wire-bonds has been built up using patterned gold-plated

copper film. The die is placed in the same orientation as in wire-bonding, and the tape is aligned above the die and then pressed down such that all electrical connections are made at once using thermo-compression [2,3].

In the case of wire-bonding or tape-automated bonding, the mechanical connection between the die and interposer is made by affixing the bottom of the die to the interposer using a thermally conductive adhesive. In Flip-Chip attachment, and 'underfill' material (typically a glass-filled epoxy) is injected under the die and fills the spaces between the solder joints. The solder joints and underfill jointly provide the mechanical attachment. Ceramic packages are then generally hermetically sealed using a ceramic lid. In plastic (organic) packages, the silicon die is over-molded using an epoxy-based molding compound. A variety of internal structures can be created using largely similar production processes [2,3]. A few of the structure options are shown below in Figure 1.11.

### 1.3 Substrates for Electronic Assemblies

A Printed Circuit Board, or PCB, consists of a (generally rigid) substrate material with flat metal traces on one or both sides and (potentially) incorporated internally into the substrate itself. Passive and active circuit components then need to be attached

mechanically to the substrate "board" and electrically to the metal traces. The printed circuit board provides mechanical support for the components, while the built-in metal traces provide electrical interconnect between the components. The PCB is also responsible for thermal conduction and dissipation and electrical isolation (anywhere no metal traces are placed). Modern PCBs also incorporate a range of secondary features, including the special markings used in component alignment (fiducials), additional electrical access points for circuit testing, and text and visual markings to aid in identification, service, and maintenance [2,3,7].

## 1.3.1 Types of PCBs

Printed Circuit Boards are typically classified as either Rigid Laminate, (Organic) Flexible, or Ceramic, with Metal Core Substrates as an additional option. Substrates of each type exhibit very different properties, and the selection of an appropriate substrate for a given product will depend on matching these properties to the application in question, the components to be used, and the processing windows available. One of the most important material properties to be considered in substrate selection is the PCB's linear Coefficient of Thermal Expansion (CTE). One of the most common strategies for increasing assembly reliability is to match the CTE of the Printed Circuit Board to that of the components, for reasons that will be discussed in Chapter 3 [2,3,7]. Other important properties include:

**Table 1.5. Some Important Properties of Printed Circuit Boards.**

| General Properties              | Material Properties                          |

|---------------------------------|----------------------------------------------|

| Meets Performance Requirements  | Coefficient of Thermal Expansion (CTE)       |

| (Low) Cost                      | Glass Transition Temperature (if applicable) |

| Ease of Use / Manufacturability | Stiffness (Modulus)                          |

| Durability                      | Strength and Toughness                       |

|                                 | Electrical Properties                        |

Ceramic substrates are normally used with ceramic components, as this provides nearly-ideal matching between the Coefficient of Thermal Expansion (CTE) of the component and PCB. The CTE of ceramic substrates is also sufficiently close to that of silicon that flip-chip reliability is significantly improved versus a rigid laminate. The base materials used are metal oxides such as alumina and beryllia. The conductive traces are added using either a thick-film, additive process or a thin-film, subtractive process. The thin-film process allows for finer line-widths and tolerances, but is more expensive.

Ceramic substrates are made up of many layers and there are two processes for combining the various layers together to form the full PCB. The conventional method used with thick-film is a sequential process where each ceramic sheet and conductive layer is applied one at a time, with a firing step between each sheet addition. However, a co-firing process can also be used: wherein all sheets are aligned and fired at the same time. This improves yield and substrate planarity, at the expense of the conductor trimming step [2,3,7].

Flexible (organic) substrates are manufactured by attaching a thin metal foil to a flexible polymer film using an adhesive. As with the ceramic substrates, several layers

can be bonded together to allow for multiple copper layers. This is necessary to form complex circuitry. As with the rigid laminates (discussed below), the copper layers are defined photolithographically. The main advantages over rigid laminates are thinness and the ability to bend or roll-up the substrate, which allows for very different product designs than either ceramic or rigid laminate [2,3,7].

One other type of Printed Circuit Board worth noting is the constraining core substrate. Constraining core substrates, a category that includes metal-core substrates, incorporate a central "core" that is CTE-matched to some other structure (e.g. components, copper traces). In the case of metal core substrates, this core would be a metal sheet or metal-matrix composite material. Outer layers are added above and below the core using conventional rigid laminate construction techniques [2,3,7].

#### 1.3.2 Laminate Substrates

For most commercial applications, a Rigid Laminate substrate is used. As with ceramic substrates, rigid laminates are typically constructed of many layers. In this case, however, each of the layers is composed of a reinforcing cloth that has been impregnated with a polymer matrix material. These composite sheets come in two varieties, known as core and prepreg layers, which are stacked in an alternating fashion and then laminated together (i.e. joined using temperature and pressure) [2,3,7].

The core sheets are (potentially) clad in a copper layer that is photolithographically defined so as to create the appropriate electrical circuitry or thermal distribution layers. These layers are fully cured, allowing them to maintain their shape during the copper processing steps. The copper cladding is typically denoted using

"weights" such as half-ounce or one-ounce: these are meant to represent the weight of copper over a 1 ft<sup>2</sup> area. A one-ounce foil will, therefore, be 1.34 mils or about 34 microns thick [2,3,7].

The prepreg layers are partially cured sheets that will not be fully polymerized until the lamination process takes place. This allows them to conform topologically to the copper traces from the abutting core sheets. Following the lamination process, throughholes are drilled and plated in order to allow for vertical electrical or thermal interconnects [2,3,7].

#### 1.3.3 Solder Mask

The copper traces on the Printed Circuit Board surface must be protected from oxidation and corrosion. In areas where no electrical contact needs to be made, the traces are coated with a Solder Mask, which both protects them from the elements and prevents solder from wetting to them. Solder masks are typically applied either as dry films or wet (screen) printed onto the PCB surface. Common solder mask materials are acrylic or epoxy polymers [2,3,7].

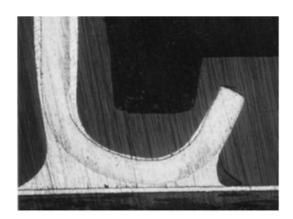

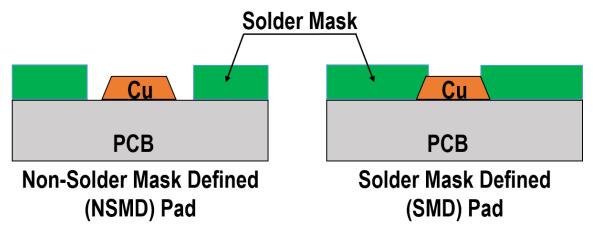

As one of the purposes of the solder mask is to prevent wetting of solder onto the copper during reflow, the contact pads ("lands") on the Printed Circuit Board surface must be kept clear of solder mask. However, the pads can be 'defined' in two different manners. One method is to print the solder mask around the copper pad, leaving a space between the two. Pads that are defined in this way are known as Non-Solder Mask Defined (NSMD). NSMD pads have been shown to provide higher resistance to thermal-mechanical fatigue, as the geometry of the solder-pad interface creates lower stress

concentrations. This has contributed to NSMD pads becoming the standard for PCB lands. Copper pads can also by defined by printing the solder mask such that only the desired pad area is exposed. This type of pad is known as Solder Mask Defined (SMD). SMD pads are used on the bottom pads of component interposers, in large part because they can help prevent delamination between the pads and substrate ("pad lifting/peeling") and tearing of the copper traces [2,3]. Figure 1.11, below, shows the difference between NSMD and SMD pads.

Figure 1.12. NSMD versus SMD PCB lands.

## 1.3.4 PCB Surface Finishes

Since the Solder Mask cannot extend over the areas where electrical contact needs to be made, a separate "surface finish" is therefore applied to remaining exposed copper areas. This surface finish allows them to be preserved as either conductive test points, fiducials, or lands for solder wetting. Ideally, the surface finish will allow for multiple reflow soldering steps while maintaining the Solderability of the copper lands. A variety of different surface finishes have been developed over the years [2,3,7].

The primary surface finish used with Tin-Lead (SnPb) solder was a thin solder coating applied via the Hot Air Solder Leveling (HASL) process. In the HASL process,

the Printed Circuit Board is dipped into a molten solder bath. The solder clings to any exposed metal surfaces not covered by the solder mask. As the board is pulled up out of the solder bath, a hot air 'knife' is used to blow off most of the solder, clearing the vias and through-holes and leaving only a thin coating on the copper surfaces. Historically, the HASL process was primarily used with a Tin-Lead solder bath. The process is more challenging to use with (higher melting temperature) Lead-Free solders, and it does not produce the very flat and uniform coatings needed for fine-pitch components. Therefore, the HASL process has fallen significantly in popularity in recent years [2,3].

A variety of alternative surface finishes are now available that facilitate the production of Lead-Free assemblies and are provide better compatibility with modern components due to their superior planarity and uniformity. Some of the alternative surface finishes now available include:

- Organic Solderability Preservative (OSP)

- Electroless Nickel / Immersion Gold (ENIG)

- Electroless Nickel / Electroless Palladium / Immersion Gold (ENEPIG)

- Immersion Silver (ImmAg, ImAg, IAg)

- Immersion Tin (ImmSn, ImSn, ISn)

Organic Solderability Preservative (OSP) is substantially different from the other coating options, which are all metal-based. OSP is an organic compound-based antitarnish coating that relies on a thin (0.7-1.0 microns, typically) carbon-based layer to protect the copper pads from oxidation and contamination. These coatings are the lowest cost surface finish option available. They also provide excellent planarity and solderability, easy visual inspection, and multiple reflow capabilities [2,3].

The other alternative surface finishes rely on the deposition of one or more metals using three primary film deposition processes: Electroplating, Electroless Plating, and Immersion Plating. All three plating processes involve a buffer solution, or plating bath, into which ions of the desired metal are dissolved from an appropriate chemical precursor. The ions will physically impinge on the exposed metal surfaces, but must be bonded in place to produce the coating. The metal ions have a positive electric charge, and providing them with electrons causes them to become neutralized and plate the metal surfaces (a process known as reduction). In Electroplating, the necessary electrons are supplied by passing an electrical current through the existing metal traces. This process is cheap and fast, but each surface to be plated must receive current, so it is not generally used when many discrete pads need to be coated. Electroless Plating replaces the external current (as a source of electrons) with a chemical added to the bath called a Reducing Agent. In Immersion Plating, a reducing agent is not used. Instead, the base metal (generally Copper) surrenders electrons to the bath, ionizing some of the surface. A more noble metal such as Tin or Silver absorbs the electrons and replaces the surface ions. This replacement reaction is self-limiting and produces a coating that is non-porous, extremely thin, and dense [2].

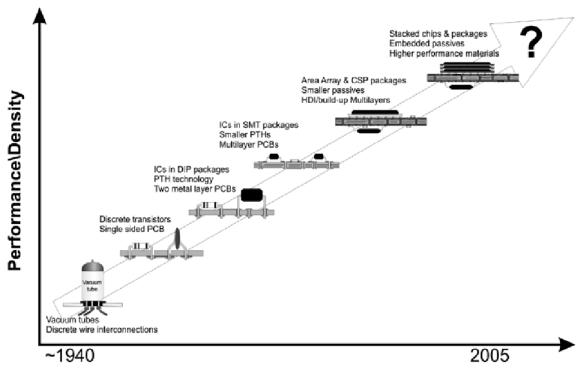

## 1.4 Trends in Electronic Packaging

Subsequent to the invention of the integrated circuit, the history of the IC industry can largely be described by a continuous decrease in the size of transistors (and other circuit components) and a corresponding increase in their density, leading to an exponential increase in the number of circuit components in each IC. In a 1965 paper,

Gordon Moore (one of the co-founders of Intel) noted that the number of components per IC had doubled every year since 1958, and confidently predicted that this trend would continue "for at least 10 years. [8]" Few could have predicted that the doubling predicted by Moore would continue all the way to the present day, a span of nearly 50 years.

As the electronics industry blossomed, advances in IC technology had a dramatic effect on the corresponding electronic packaging technologies required. Smaller components allowed for increasing IC complexity. To connect these increasingly complex IC components, larger and larger numbers of input/output (I/O) channels are needed. At the same time, smaller components also allow identical circuits to be built into a continually shrinking silicon wafer (or "die"), a process known as die shrink.

Component and die shrink also allow for improved circuit response time and lower power usage (in general), by lowing threshold voltages and reducing parasitics (unwanted resistive, capacitive, and inductive losses in metal interconnects). As a result, the overall dynamic is one of packaging technology forced to continually improve to keep pace with shrinking IC components (feature size reductions of approximately 15% per year) [9].

Traditional trends in the electronic packaging industry include: [6]

- Smaller and Lighter Packages

- Faster Circuit Responses

- Increased Circuit Density

- Higher Power Density

- Larger Semiconductor Dies

- More Inputs/Outputs (I/O's)

- Lower Cost per functional unit

## • Higher Reliability

**Note:** Complexity has increased significantly over the years but there are limits to what extrapolated technologies can offer in terms of cost and performance

Figure 1.13. Increases in Packaging Density over time [5].

As IC technologies continued to advance, the push to achieve higher I/O counts and lower package sizes continues. Consequently, electronic packaging technologies will need to continue to advance to keep pace with improvements in integrated circuits. In 2009, the International Technology Roadmap for Semiconductors (ITRS), determined that "[i]nnovation in assembly and packaging is accelerating in response to the realization that packaging is now the limiting factor in cost and performance for many types of devices" [10]. However, many of the currently available or next generation technologies, such as the Multi-Chip Module (MCM) and System-in-Package (SiP), are easily understood in the overall historical context of finding ways to improve the functional density of components. Moreover, the main processing breakthrough involved in cutting-

edge applications such as 2.5D and 3D packaging is the through-silicon via (TSV), which is fundamentally an IC technology.

# Chapter 2 A Brief Introduction to Electronic Solders

## 2.1 Soldering

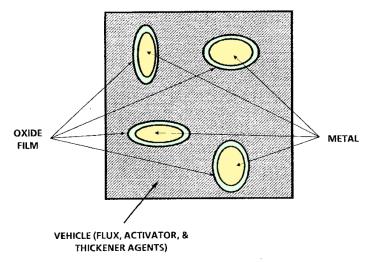

An assortment of techniques has been developed over the years for joining separate metal work pieces. These include Welding, Brazing, and Soldering. In soldering, the surfaces to be joined are heated in the presence of a distinct filler material, called the Solder. The solder melts and flows between the surfaces and, upon cooling, forms a metallurgical bond between them. A chemical agent known as a flux, which removes oxides and contamination to leave behind a readily solderable surface, is often used when soldering [3,11,12].

Soldering takes place at temperatures below 450°C – otherwise, it would be considered Brazing – and, additionally, must be done at temperature low enough to avoid damaging other components of the system that is being soldered [3,13]. Solders are therefore generally alloys with a low melting temperature. Alloys are solid solutions of two or more metals (or mixtures of several phases that are solid solutions) that exhibit metallic bonding. Alloys are typically stronger than pure metals, and can have much lower melting points, making them extremely useful for solder applications [14,15].

In order for a robust joint to be formed during soldering, a metallurgical bond must be created between the solder material and the work pieces that are being soldered. To forge this bond, the solder must flow easily (low viscosity) and 'wet' rapidly (have low surface energy) with the surface finish. Additionally, an intermetallic compound layer must be formed at the solder-surface interface – this is what provides the

metallurgical bonding between the two materials [16]. Because most Intermetallics are brittle, however, the thickness of the IMC layer should be controlled. Such control is typically accomplished by limiting the time-above-liquidus of the solder during the soldering process [17].

## 2.2 Solder Joints for Electronic Assemblies

Solder joints are vital to the quality, performance, and reliability of Electronic Assemblies. Solder joints enable electrical power and signals to pass into and out of electronic components. Signals route through the joints and out through the copper traces of the substrate to other components and connectors. The loss of a single key signal pathway could dramatically alter the behavior of a circuit, or cause it to fail entirely. Therefore, quality and reliability are highly desirable. Electrical "parasitics" – unwanted resistive, capacitive, and inductive losses in metal interconnects – are also clearly undesirable in an electronic solder joint [3].