## Accelerated Life-Cycle Testing of Various Lead-Free Solder Alloys by Mechanical Shock and Thermal Cycling Techniques

## by Sharath Sridhar

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama Dec 16, 2017

Keywords: Reliability, Lead-Free Solder, Electronics Packaging, Drop Testing, Thermal Cycling, Failure Analysis

Copyright 2017 by Sharath Sridhar

## Approved by

John L. Evans, Charles D. Miller Endowed Chair, Professor,

Industrial and Systems Engineering

Michael Bozack, Professor, Physics

Sa'd Hamasha, Assistant Professor, Industrial and Systems Engineering

Gregory Harris, Associate Professor, Industrial and Systems Engineering

## **Abstract**

For the last couple of decades, our inclination towards computer technology has increased broadly. Personal device assistants also known as PDA's have become a part of our daily needs. Hence, the reliability of these handheld electronic devices has become a major concern for the manufacturers as they are subjected to drop, shock and thermal cycling conditions during their day-to-day operation.

Board level drop impact testing is one of the most important methods of evaluating the reliability of electronic assemblies. The first phase of this study examines the drop impact performance of no-aged and isothermally aged flip chip packages on laminate assemblies for various doped lead-free solder paste alloys. A potential solution to replace the industrial standard solder paste Sn96.5 Ag3.0 Cu0.5 (SAC305) is carried out. The test vehicle consists of 16 ball grid array packages (BGA) which are 15mm chip array ball grid array's (CABGA208) with perimeter solder balls on 0.8mm pitch. In this experimental study, SAC305 solder spheres and SAC305 solder paste are selected to be the baseline, Solder pastes with 12 different dopants are investigated in comparison with the baseline to determine their reliability. Two sets of printed circuit boards (PCB) are manufactured, the first being no-aged and the second set of boards are isothermally aged at 125C for 6 months prior to testing. The boards are further categorized into 3 different reflow

temperatures and 2 different stencil thicknesses, 4 mil and 6 mil respectively. JEDEC BS111 test standard is followed to conduct the drop testing where the half sine impact pulse duration of 0.5ms with peak acceleration at 1500G's is maintained. The boards are subjected to accelerated life testing where the test end state is 300 drops, and the data is collected at an interval of every 20 drops. The results of no-aged and aged samples are categorized and compared using data analytics and Weibull analysis. Failure analysis is carried out to determine best solder paste, solder ball, reflow temperature profile and stencil size.

In the second phase of the study, the reliability performance of various electronic assemblies during thermal cycling testing are investigated. Best performed doped low creep lead free solder alloys designed for high-temperature reliability from phase 1 testing are used. The test boards are 0.200" thick power computing printed circuit boards with MEGTRON6 substrate material and OSP coating. Single-sided assemblies are built separately for the Top-side and Bottom-side of the boards. JEDEC JESD22-A104-B test standard is followed; the test boards are subjected for thermal cycling between the temperatures -40°C and +125°C respectively, 120-minute cycle profile with 45-minute transitions and 15-minute dwells at peak temperatures is maintained. The test assemblies include surface mount resistors, 5mm, 6mm, 13mm, 15mm, 17mm, 31mm, 35mm and 45mm ball grid array packages respectively. The failure data of the test

| assemblies are used in this study to understand the effect of solder paste composition on the solder |

|------------------------------------------------------------------------------------------------------|

| joint reliability during thermal cycling testing.                                                    |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

## **Acknowledgements**

The author would like to express his deepest thanks his advisor Dr. John L. Evans, for providing this great opportunity to further his education and granting the privilege to work under his leadership. The author extends his gratitude to the committee members, Dr. Michael Bozack, Dr. Saad Hamasha, Dr. Gregory Harris and Dr. PK. Raju for their valuable insight and time. The author also would like to thank Dr. Jorge Valenzuela, Dr. PK Raju, Mr. Tom Devall and their families for the moral support and valuable guidance provided during many instances.

The author would like to thank his colleagues, Dr. Thomas Sanders, James Heurich, Will Malone, Anto Raj, Siva Thiru and Seth Gordon for their contributions in performing the testing and analysis of the data as well as their valuable inputs throughout the research and coursework.

Finally, the author would like to thank his beautiful wife Ashwini for supporting him in this journey. Author also would like to thank his wonderful parents Uma and Sridhar for all the sacrifices they have done over the years to provide the best. Deepest sense of gratitude to Dr. Seshan Sivam and Dr. Satish V. Kailas for providing precious guidance and invaluable support.

## **Table of Contents**

| Abstract                                                 | ii    |

|----------------------------------------------------------|-------|

| Acknowledgements                                         | V     |

| List of Figures                                          | xii   |

| List of Tables                                           | xviii |

| List of Abbreviations                                    | xix   |

| Chapter 1. A Brief Introduction to Electronic Assemblies | 1     |

| 1.1 Electronics Packaging                                | 1     |

| 1.2 Packaging Classification                             | 3     |

| 1.2.1 Through Hole Mount Technology                      | 3     |

| 1.2.2 Surface Mount Technology                           | 5     |

| 1.2.3 Leaded Components                                  | 6     |

| 1.2.4 No-lead Lead-Less Components                       | 7     |

| 1.2.5 Area Arrays                                        | 9     |

| 1.3 Ball Grid Array                                      | 9     |

| 1.4 Substrates for Electronic Packaging                  | 12    |

|   | 1.4.1 Laminate Substrates                       | 14 |

|---|-------------------------------------------------|----|

|   | 1.4.2 Solder mask                               | 15 |

|   | 1.4.3 Surface Finishes                          | 16 |

|   | 1.5 Electronic Packaging Trends                 | 18 |

|   | 1.6 Evolution of Solder                         | 23 |

|   | 1.7 Soldering                                   | 23 |

|   | 1.8 Solder Joints for Electronic Assemblies     | 24 |

|   | 1.9 Rise and fall of tin-lead solder            | 25 |

|   | 1.10 Eutectic Alloy and 63Sn-37Pb               | 26 |

|   | 1.10 Near-Eutectic Sn-Ag-Cu (SAC) Solder        | 29 |

|   | 1.12 Solder Paste and Flux                      | 32 |

|   | 1.13 Overview of SMT Process                    | 35 |

| C | hapter 2. Literature Review                     | 40 |

|   | 2.1 Properties of a Solder Joint                | 40 |

|   | 2.1.1 Properties Important to Manufacturability | 41 |

|   | 2.1.2 Reliability of a Solder Joint             | 42 |

|   | 2.1.3 Properties Important for Reliability      | 43 |

|   | 2.2 Failure Modes in Electronic Assemblies      | 44 |

|   | 2.3 Characteristic Solder Joint Failures in BGA's | 45 |

|---|---------------------------------------------------|----|

|   | 2.3.1 Fatigue                                     | 48 |

|   | 2.3.2 Creep                                       | 49 |

|   | 2.3.3 Coefficient of Thermal Expansion            | 51 |

|   | 2.3.4 Tensile Properties                          | 52 |

|   | 2.3.5 Shear Properties                            | 53 |

|   | 2.3.6 Intermetallic Compound Layer (IMC)          | 55 |

|   | 2.3.7 Effect of Aging on Solder                   | 55 |

|   | 2.3.8 Effect of Aging on the Intermetallics       | 57 |

|   | 2.4 Drop/Mechanical Shock Testing.                | 58 |

|   | 2.5 Thermal Cycling Testing                       | 60 |

|   | 2.6 Accelerated Lifecycle Testing                 | 61 |

|   | 2.7 Failure Mechanics                             | 61 |

|   | 2.8 Solder Doping                                 | 64 |

|   | 2.9 Weibull Analysis                              | 67 |

| ( | Chapter 3. Experimental Setup                     | 69 |

|   | 3.1 Why BGA?                                      | 69 |

|   | 3.2 Purpose of Study                              | 69 |

| 3.3 Test Vehicle Design and Assembly                                       | 70 |

|----------------------------------------------------------------------------|----|

| 3.3.1.1 Drop Test Board Design – Phase 1                                   | 70 |

| 3.3.1.2 Test Components                                                    | 71 |

| 3.3.1.3 Build Matrix                                                       | 74 |

| 3.3.1.4 Drop Test Board SMT Assembly                                       | 76 |

| 3.3.1.5 Drop Test Setup                                                    | 78 |

| 3.3.1.6 Test Method                                                        | 79 |

| 3.3.2.1 Thermal Cycling Test Board Design – Phase 2 – (TC2 SRJ Test Board) | 82 |

| 3.3.2.3 Test Vehicle Design and Specifications                             | 83 |

| 3.3.2.3 Test Plan                                                          | 84 |

| 3.3.2.4 General Build Matrix/Assembly Information                          | 86 |

| 3.3.2.5 Solder Paste and Screen Printing                                   | 89 |

| 3.3.2.6 Component Placement                                                | 89 |

| 3.3.2.7 TC2-SRJ Reflow Profiles                                            | 90 |

| 3.3.2.8 Quality Assurance                                                  | 92 |

| 3.3.2.9 Thermal Cycling Test Parameters and Equipment                      | 93 |

| 3.3.2.10 Data Acquisition System                                           | 94 |

| 3.4 Failure Analysis and Sample Preparation Protocol                       | 96 |

| Chapter 4. Reliability Test Results                  | 98  |

|------------------------------------------------------|-----|

| 4.1 Introduction                                     | 98  |

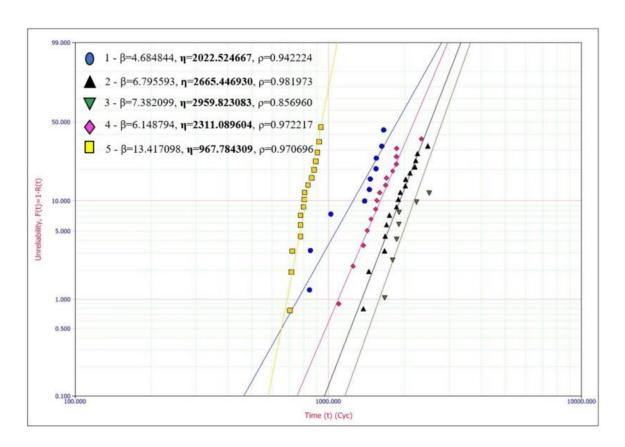

| 4.2 Weibull Graphs and Results                       | 98  |

| 4.2.1 Phase 1 Results                                | 98  |

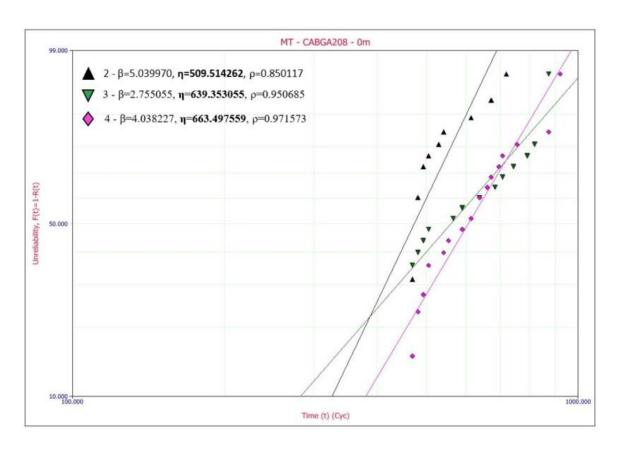

| 4.2.1.1. CABGA 208 [15mm, 0.8mm pitch]               | 99  |

| 4.2.2. Phase 2 Results                               | 107 |

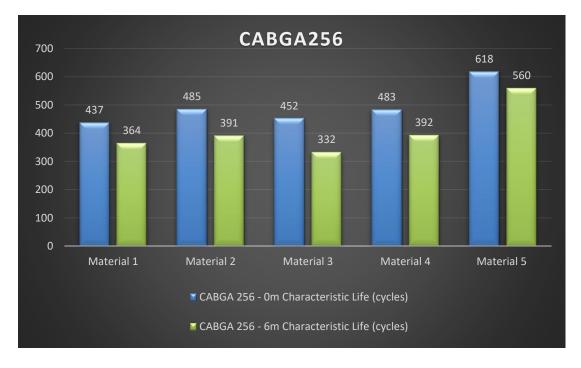

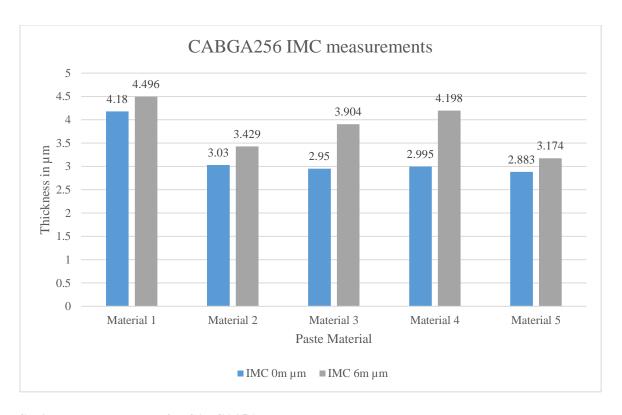

| 4.2.2.1 CABGA 256 [17mm, 1.0mm pitch]                | 108 |

| 4.2.2.2 CABGA 208 [15mm, 0.8mm Pitch]                | 112 |

| 4.2.2.3 CVBGA 432 [13mm, 0.4mm Pitch]                | 117 |

| Chapter 5. Failure Analysis                          | 122 |

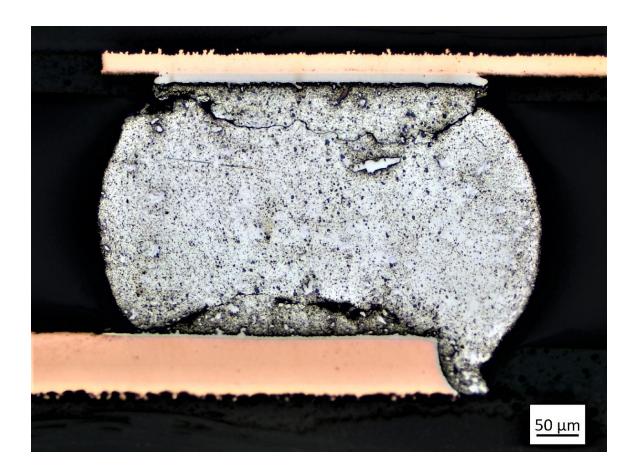

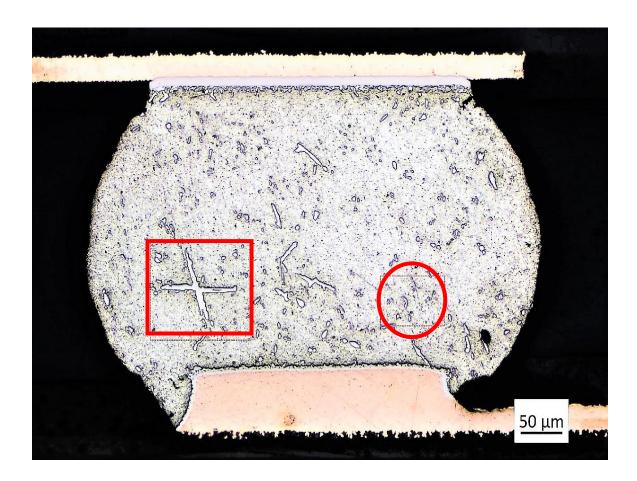

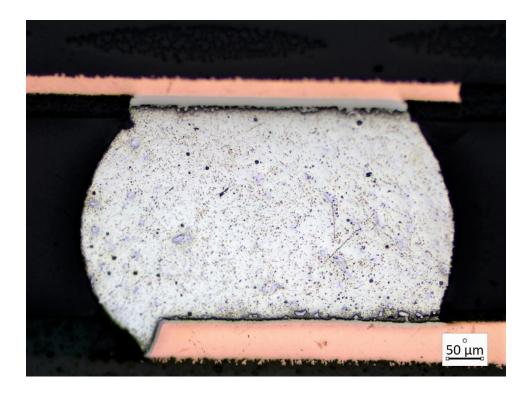

| 5.1 Cross Sectioning and Failure Analysis            | 122 |

| 5.3 Failure Modes                                    | 124 |

| 5.3.1 Paste Material 1 CABGA208                      | 125 |

| 5.3.2 Paste Material 2 (Baseline - Innolot) CABGA208 | 129 |

| 5.3.3 Paste Material 3 CABGA208                      | 131 |

| 5.3.4 Paste Material 4 CABGA208                      | 133 |

| 5.3.5 Paste Material 5 CABGA208                      | 135 |

| Chapter 6. Summary and Conclusion                    | 138 |

| 6.1 Phase 1 Summary | . 138 |

|---------------------|-------|

| 6.2 Phase 2 Summary | . 139 |

| 6.3 Conclusion      | . 139 |

| 6.4 Future work     | . 141 |

# **List of Figures**

| Figure 1.1 Levels of Packaging. Adapted from [2]                                       | 3   |

|----------------------------------------------------------------------------------------|-----|

| Figure 1.2 Packaging classification [2]                                                | 3   |

| Figure 1.3 DIP and Its Side View [2]                                                   | 4   |

| Figure 1.4 Through-Hole Mount Attachment vs. Surface Mount Attachment Adapted from [2] | 6   |

| Figure 1.5 DIP, Gull Wing Component and J-Lead Component [2,5]                         | 7   |

| Figure 1.6 QFN Component and SMR Component[116]                                        | 8   |

| Figure 1.7 BGA package and Solder Joint [5]                                            | .10 |

| Figure 1.8 Some Ball Grid Array Structure Options [5]                                  | .11 |

| Figure 1.9 A PGA Component Used in Motorola 68020 Microprocessor                       | .11 |

| Figure 1.10 Cross-section view of a PCB with different types of vias [116]             | .13 |

| Figure 1.11 NSMD versus SMD PCB lands [116]                                            | .15 |

| Figure 1.12 Integration development of packages in the last decades [14,15,16]         | .19 |

| Figure 1.13 Trends of semiconductor packages [17]                                      | .21 |

| Figure 1.14 High density 3D semiconductor packaging [17]                               | .22 |

| Figure 1.15 Trends in System-in-Package technology [18]                                | .22 |

| Figure 1.16 Phase Diagram for Tin-Lead Solder Alloy                                    | .27 |

| Figure 1.17 Tin-Lead Binary Phase Diagram [23]                                                             | 27 |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 1.18 From NIST: Sn-Ag-Cu Phase Diagrams                                                             | 30 |

| Figure 1.19 SEM Micrograph of Typical Sn-Ag-Cu Solder, Ag3Sn and Cu <sub>6</sub> Sn <sub>5</sub> Morpholog | 31 |

| Figure 1.20 Solder Paste [116]                                                                             | 33 |

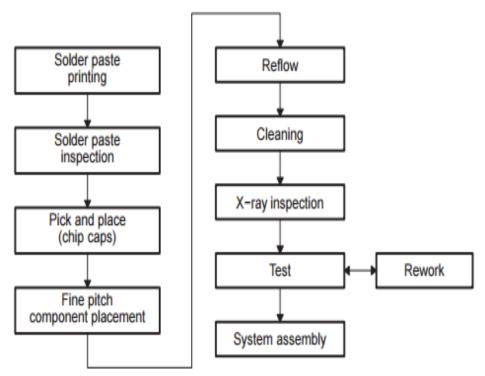

| Figure 1.20 Typical SMT Assembly Process Flow                                                              | 35 |

| Figure 1.21 Picture of Solder Paste [116]                                                                  | 34 |

| Figure 1.22 A Picture of Stencil Printer [116]                                                             | 36 |

| Figure 1.23 Different Types of Unsatisfied Printing Result [116]                                           | 37 |

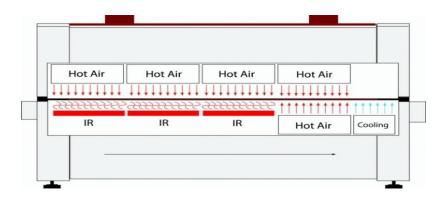

| Figure 1.24 Example of a Reflow Oven, With Its Cross-Section View of Structure                             | 38 |

| Figure 1.25 A Typical Reflow Thermal Profile [33]                                                          | 38 |

| Figure 1.26 A Typical SMT Assembly Production Line                                                         | 39 |

| Figure 2.1 Common Flip-Chip Failure Modes [6]                                                              | 44 |

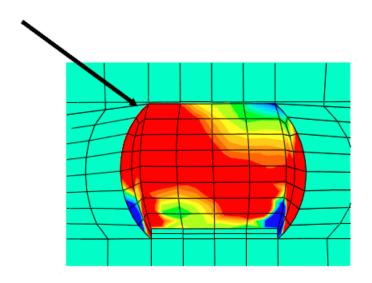

| Figure 2.2 FEA model showing induced stress [6]                                                            | 46 |

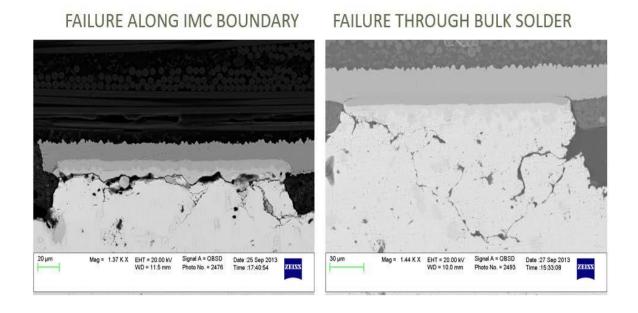

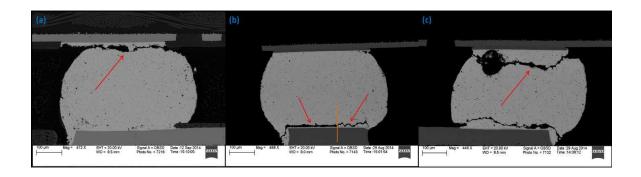

| Figure 2.3 Common Joint Failure Modes                                                                      | 46 |

| Figure 2.4 Characteristic fatigue failure                                                                  | 47 |

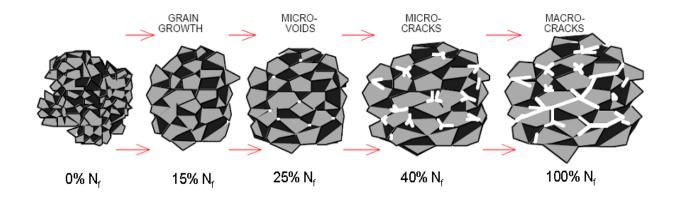

| Figure 2.5 Depiction of the Effects of the Accumulating Fatigue Damage [101]                               | 48 |

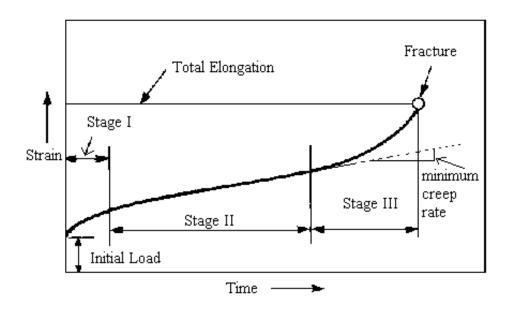

| Figure 2.6 Different stages of creep                                                                       | 50 |

| Figure 2.7 a) Cyclic Stress Induced by CTE Mismatch after expansion                                        | 51 |

| Figure 2.8 Tensile loading [36]                                                  | 52 |

|----------------------------------------------------------------------------------|----|

| Figure 2.9 Stress-Strain relationship                                            | 52 |

| Figure 2.10 Solder Joints Subjected to Shear Strain due to CTE Mismatch [36]     | 54 |

| Figure 2.11 Solder state under shear load                                        | 54 |

| Figure 2.12 Effect of Aging at Room temperature for Sn-Pb solder [65]            | 56 |

| Figure 2.13 Expected Failure Modes from Drop Testing [99]                        | 59 |

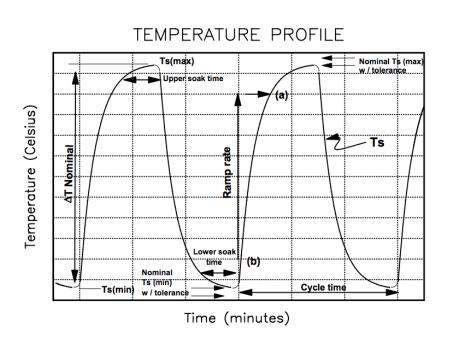

| Figure 2.14 Representative Temperature Profile for Thermal Cycle Test Conditions | 60 |

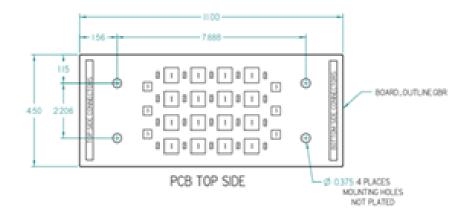

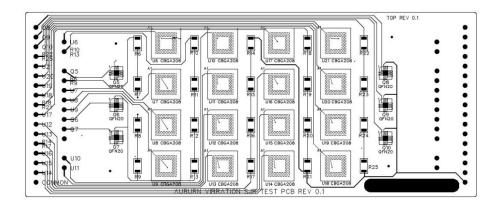

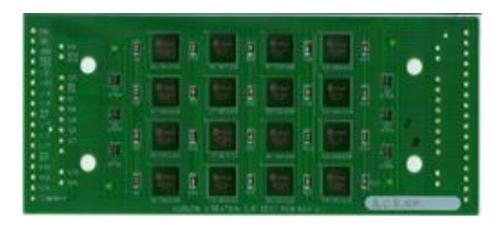

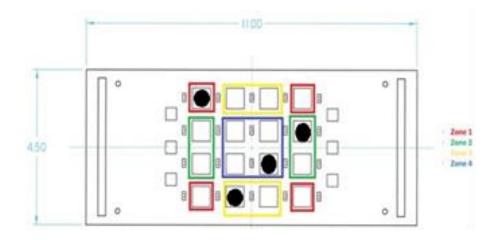

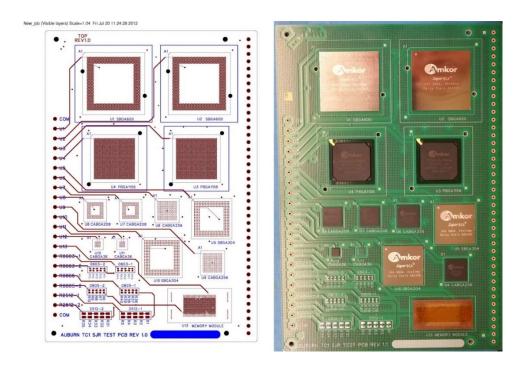

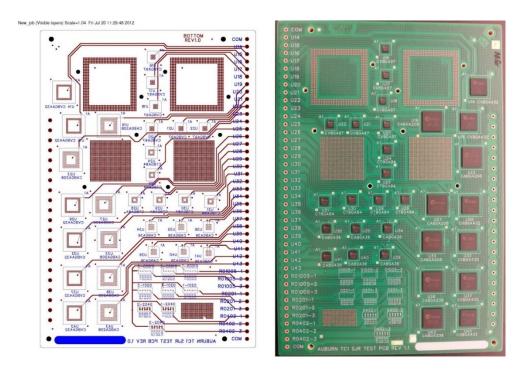

| Figure 3.1 Test board design and finished board                                  | 71 |

| Figure 3.2 Zone wise distribution of BGA packages                                | 72 |

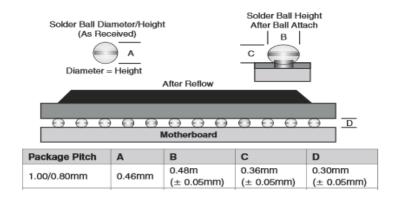

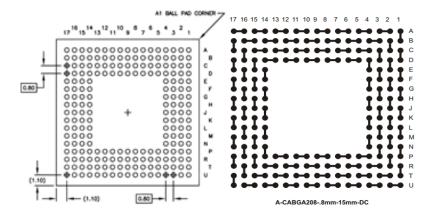

| Figure.3.3 BGA Design [8-9]                                                      | 73 |

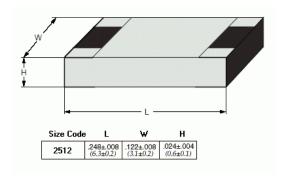

| Figure.3.4 Resistor Design [10]                                                  | 73 |

| Figure 3.5 QFN Design [11]                                                       | 74 |

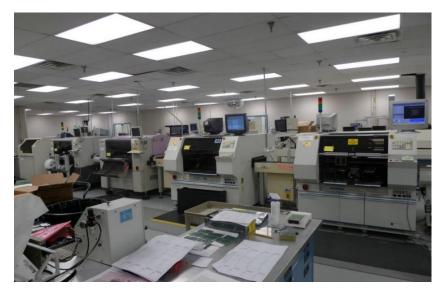

| Figure 3.6 SMT Assembly Line at UAH                                              | 77 |

| Figure 3.7 Reflow Oven                                                           | 77 |

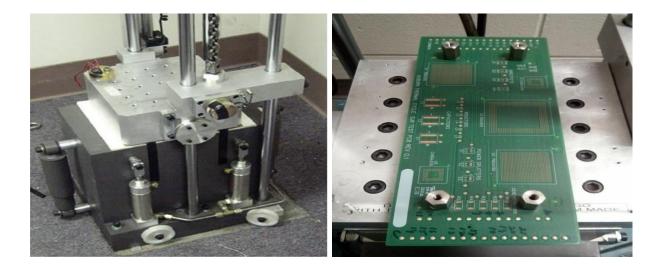

| Figure 3.8 Drop tower base and fixture                                           | 79 |

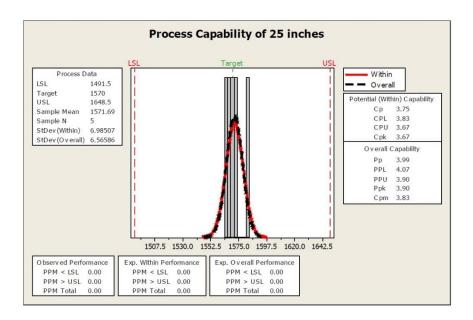

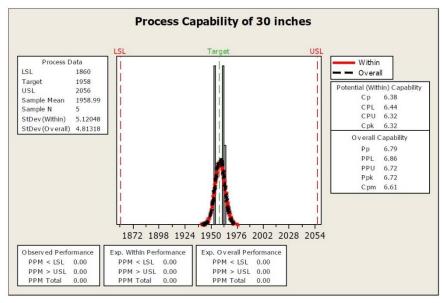

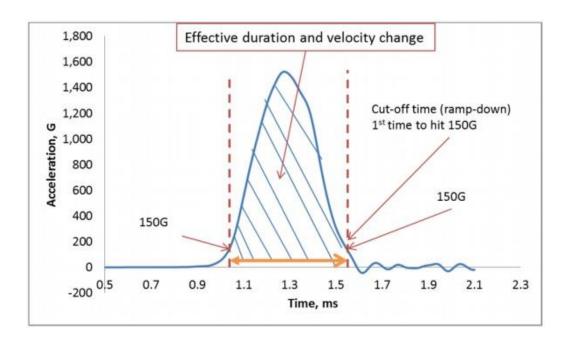

| Figure 3.9 Process capability test results                                       | 80 |

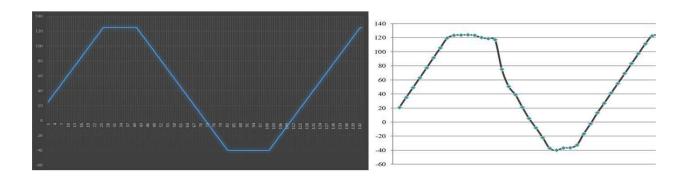

| Figure 3.10 Drop test profile                                                    | 81 |

| Figure 3.11 TC2-SRI Test Vehicle: Top-Side View                                  | 83 |

| Figure 3.12 TC2-SRJ Test Vehicle: Bottom-Side View                                          | .84 |

|---------------------------------------------------------------------------------------------|-----|

| Figure 3.13 Phase II Board Aging Groups                                                     | .84 |

| Figure 3.14 Screen printing machine                                                         | .89 |

| Figure 3.15 Pick and Place machines                                                         | .90 |

| Figure 3.16 Reflow oven                                                                     | .90 |

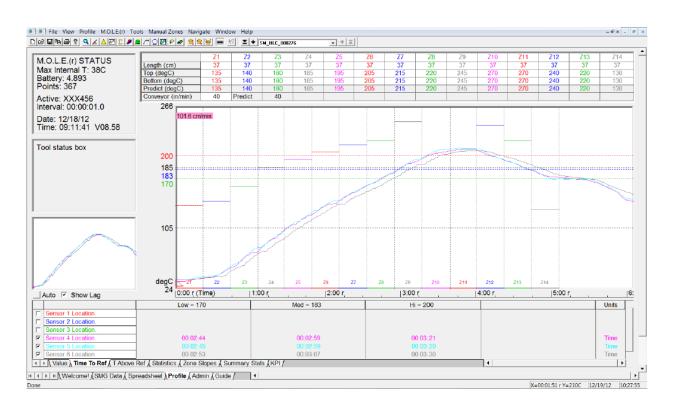

| Figure 3.17 Phase II Top-Side Reflow Profile                                                | .91 |

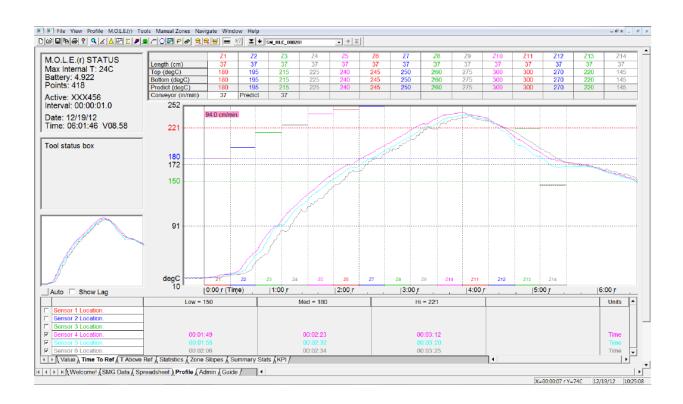

| Figure 3.18 Phase II Bottom-Side Reflow Profile                                             | .92 |

| Figure 3.19 Thermal Profile used                                                            | .93 |

| Figure 3.20 Thermotron Thermal cycling test chambers                                        | .94 |

| Figure 3.21 Full Monitoring System                                                          | .95 |

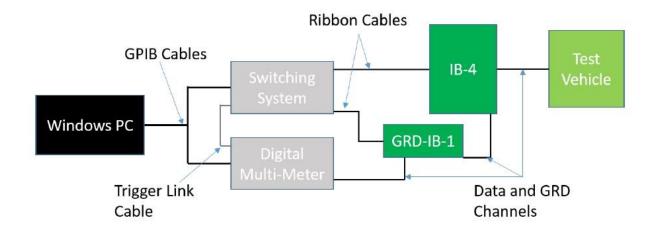

| Figure 3.22 Diagram of the TC2-SRJ Monitoring System                                        | .95 |

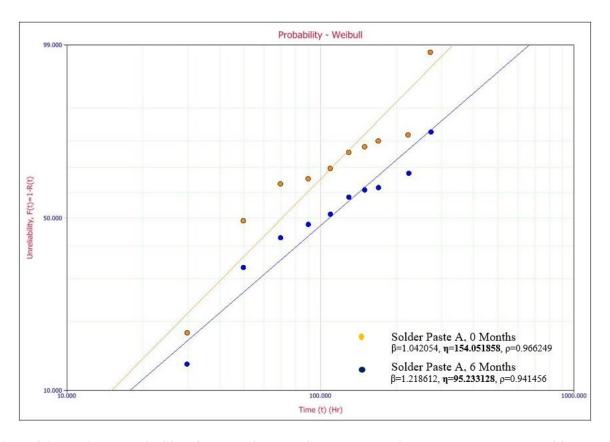

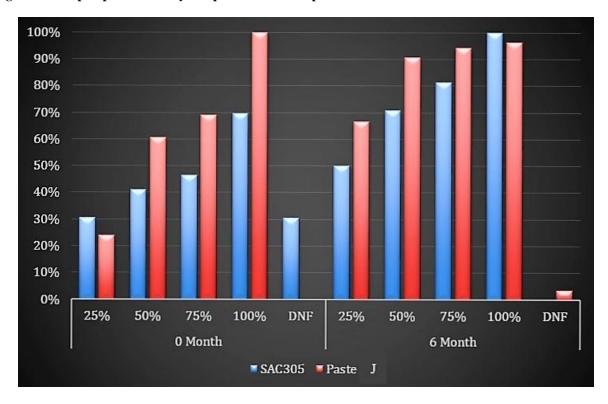

| Figure 4.1 Drop reliability of the baseline material paste A at no aged and aged conditions | .99 |

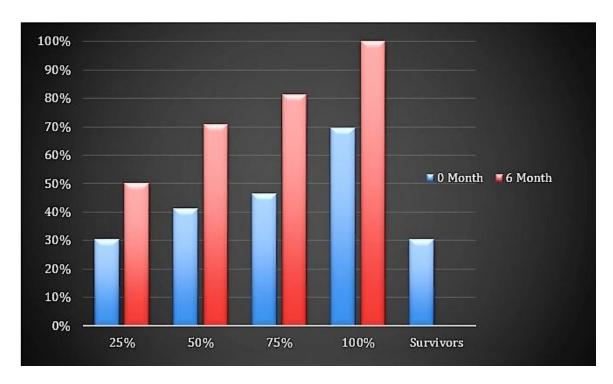

| Figure 4.2 Percentage failure comparison of the baseline                                    | 100 |

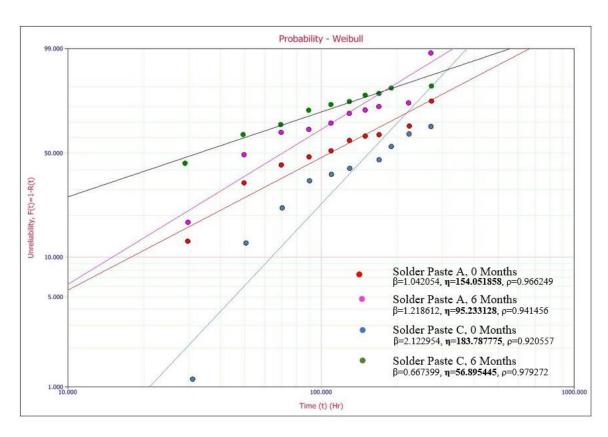

| Figure 4.3 Drop impact reliability comparison of solder paste C with the baseline           | 101 |

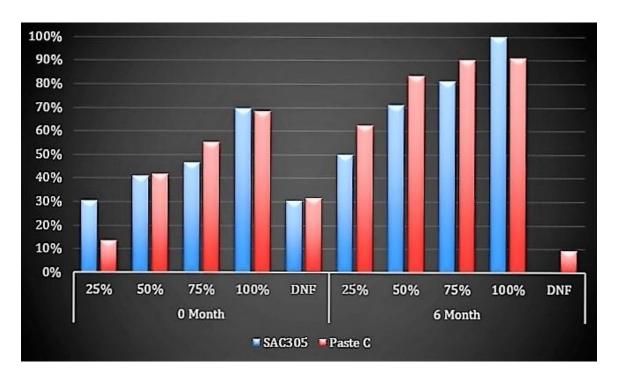

| Figure 4.4 Percentage failure comparison of solder paste C with the baseline                | 101 |

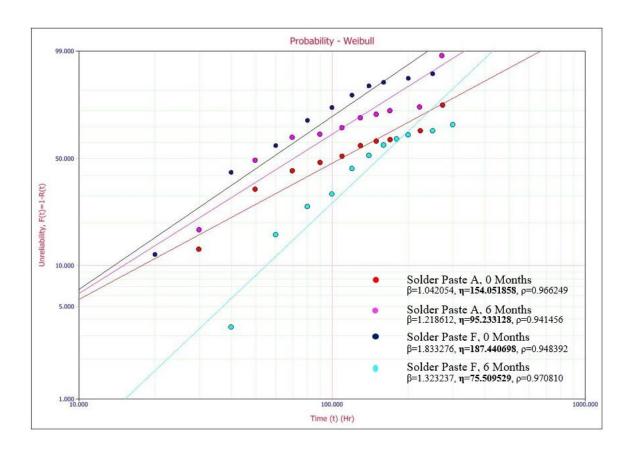

| Figure 4.5 Drop impact reliability comparison of solder paste F with the baseline           | 102 |

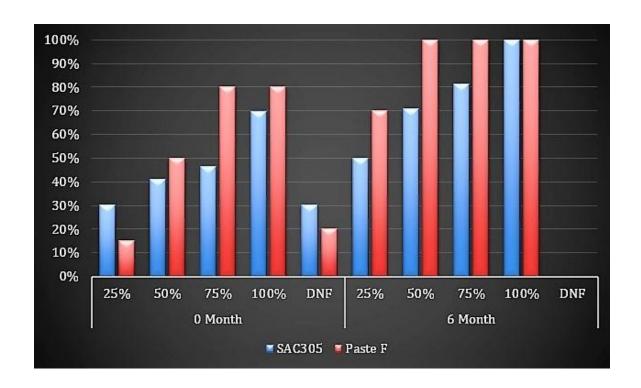

| Figure 4.6 Percentage failure comparison of solder paste F with the baseline                | 103 |

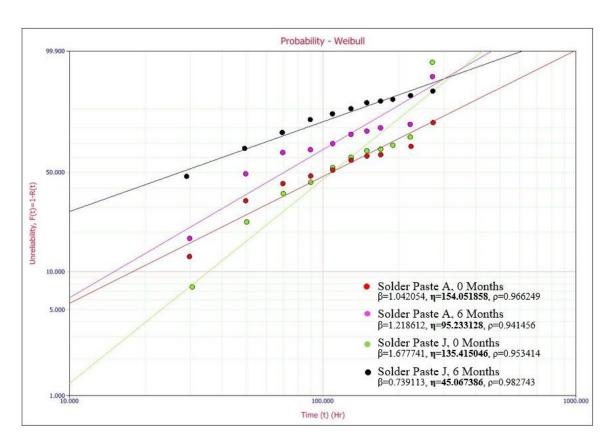

| Figure 4.7 Drop impact reliability comparison of solder paste J with the baseline           | 104 |

| Figure 4.8 Percentage failure comparison of solder paste J with the baseline              | 104 |

|-------------------------------------------------------------------------------------------|-----|

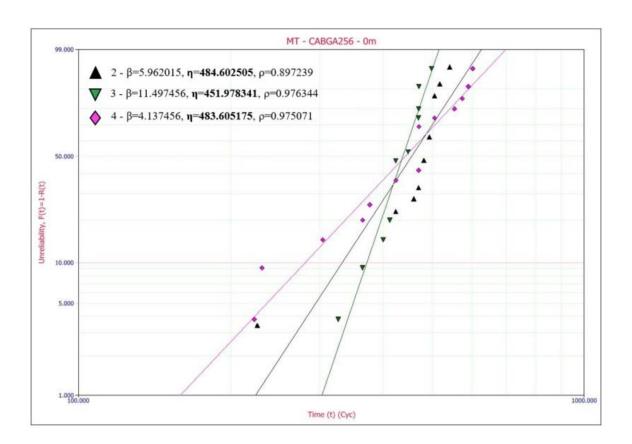

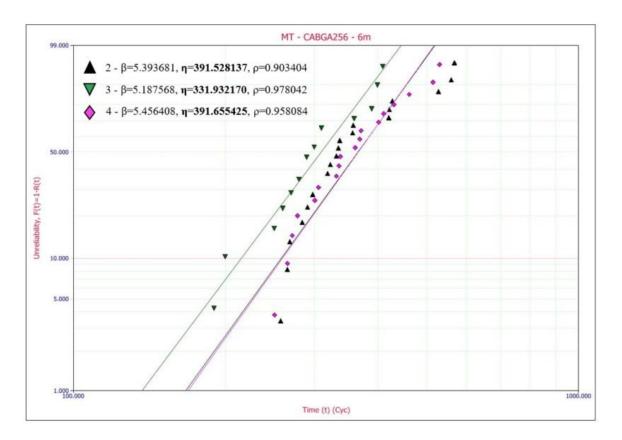

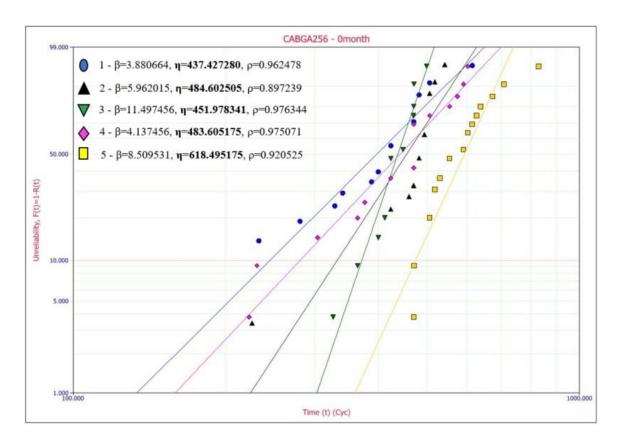

| Figure 4.9 Thermal Cycling reliability comparison of materials 3 and 4 with the baseline  | 108 |

| Figure 4.10 Thermal Cycling reliability comparison of materials 3 and 4 with the baseline | 109 |

| Figure 4.11 Thermal Cycling reliability comparison at no-aging                            | 110 |

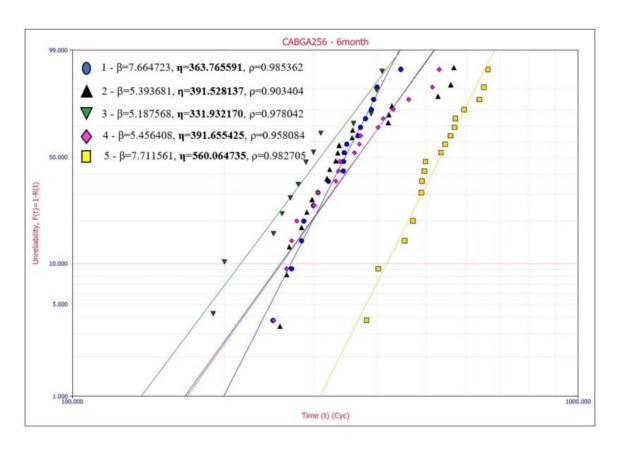

| Figure 4.12 Thermal Cycling reliability comparison after 6-months aging                   | 111 |

| Figure 4.13 Thermal Cycling reliability comparison of materials 3 and 4 with the baseline | 113 |

| Figure 4.14 Thermal Cycling reliability comparison of materials 3 and 4 with the baseline | 114 |

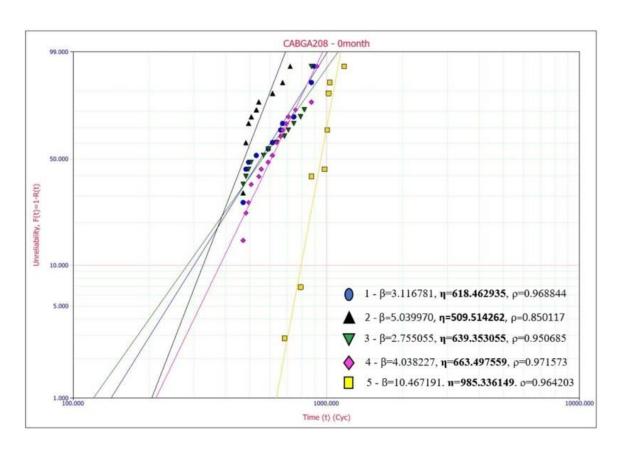

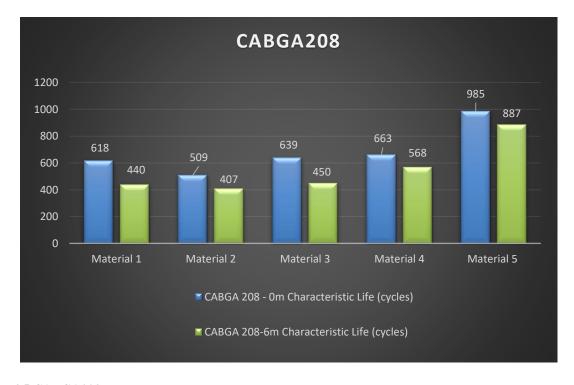

| Figure 4.15 Thermal Cycling reliability comparison at no-aging                            | 115 |

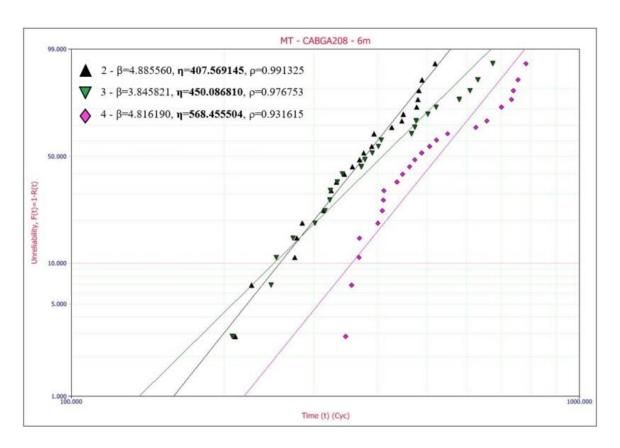

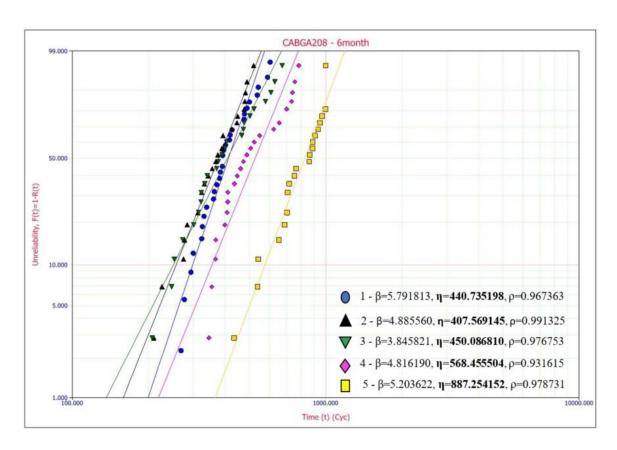

| Figure 4.16 Thermal Cycling reliability comparison after 6-months aging                   | 116 |

| Figure 4.17 Thermal Cycling reliability comparison at no-aging                            | 118 |

| Figure 4.18 Thermal Cycling reliability comparison after 6-months aging                   | 119 |

| Figure 4.19 Thermal Cycling reliability comparison at no-aging                            | 120 |

| Figure 4.20 Thermal Cycling reliability comparison after 6-months aging                   | 121 |

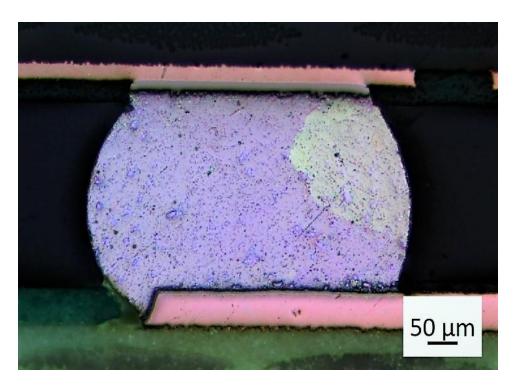

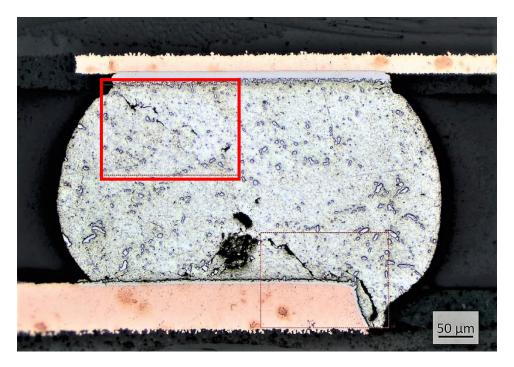

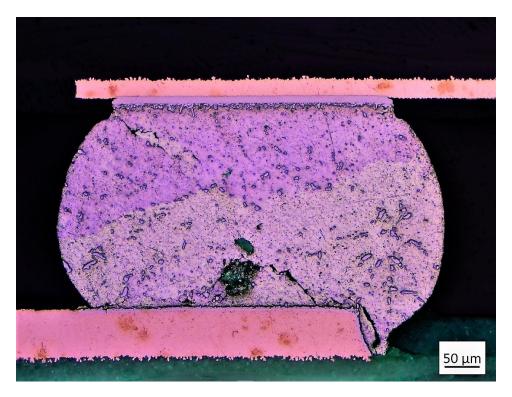

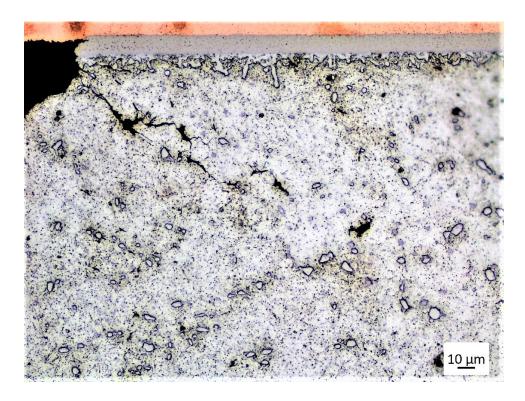

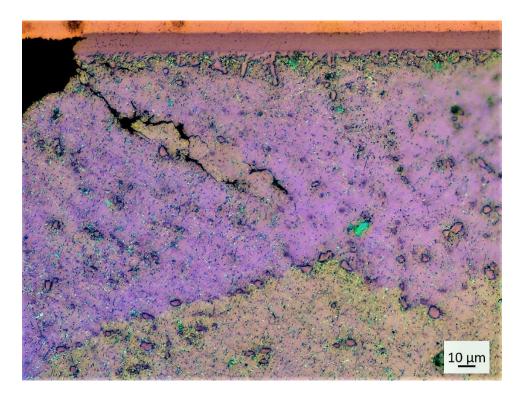

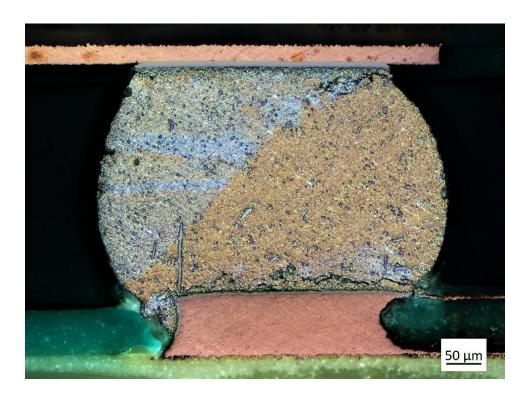

| Figure 5.1 Microstructure of a BGA Solder Joint                                           | 123 |

| Figure 5.2 CABGA208 SAC350 Solder Join                                                    | 124 |

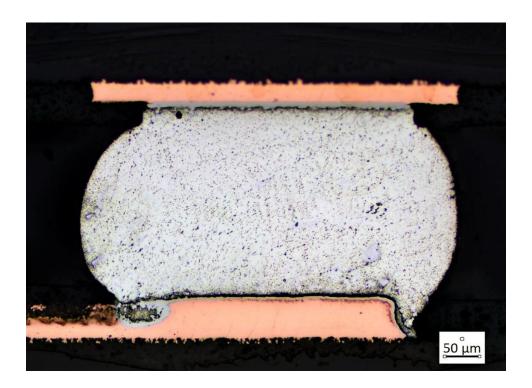

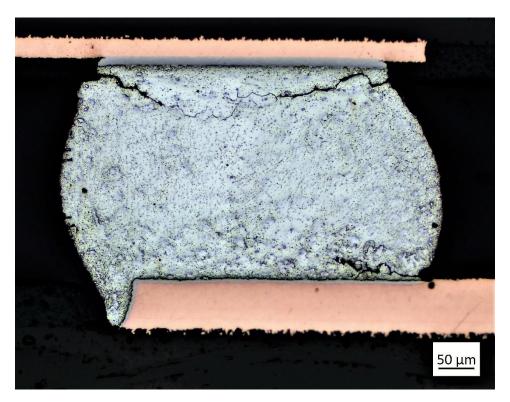

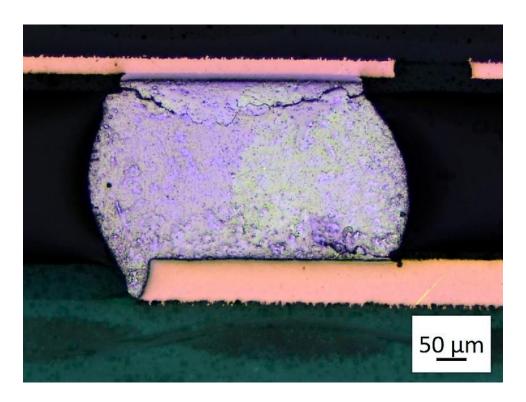

| Figure 5.3 Paste Material 1 CABGA208                                                      | 125 |

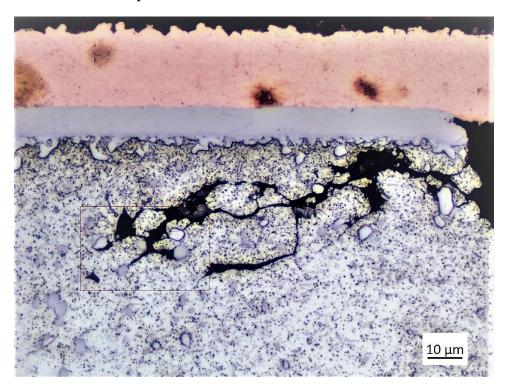

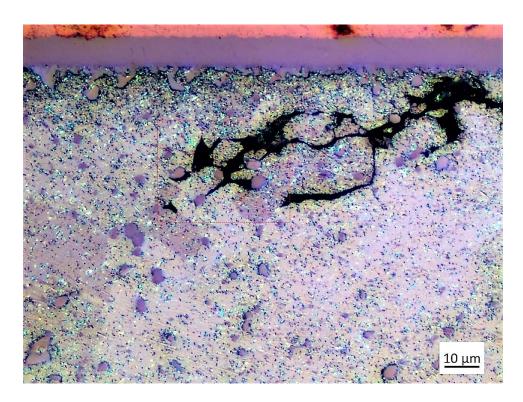

| Figure 5.4 Paste Material 1 CABGA208 polarized                                            | 126 |

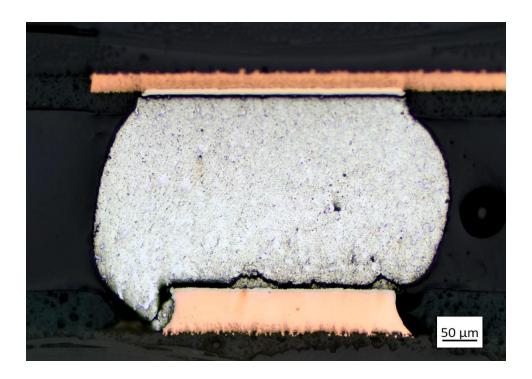

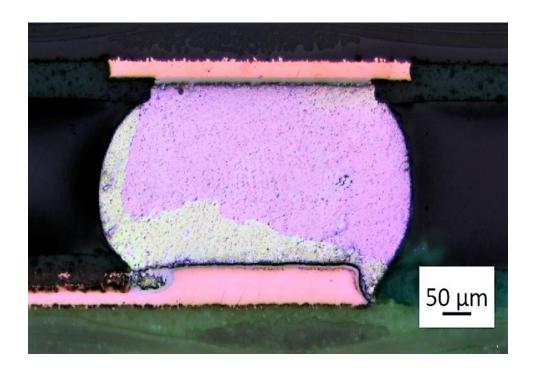

| Figure 5.5 Paste Material 1 CABGA208                                                      | 126 |

| Figure 5.6 Paste Material 1 CABGA208 polarized                       | 127 |

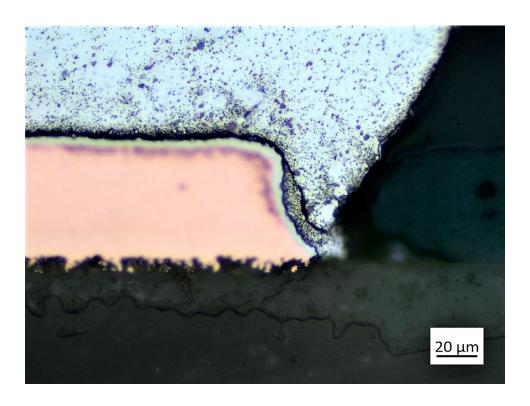

|----------------------------------------------------------------------|-----|

| Figure 5.7 Paste Material 1 CABGA208                                 | 128 |

| Figure 5.8 Paste Material 1 CABGA208 polarized                       | 128 |

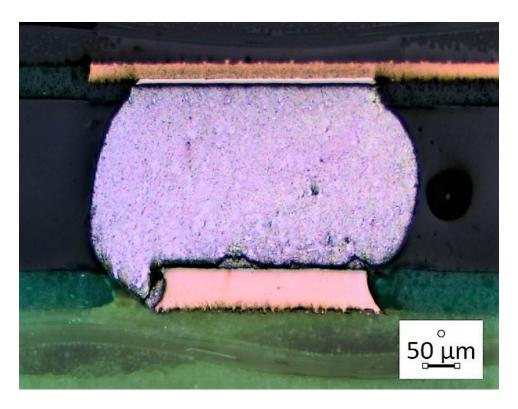

| Figure 5.9 Paste Material 2 (Baseline - Innolot) CABGA208            | 129 |

| Figure 5.10 Paste Material 2 (Baseline - Innolot) CABGA208 polarized | 130 |

| Figure 5.11 Paste Material 2 (Baseline - Innolot) CABGA208 polarized | 130 |

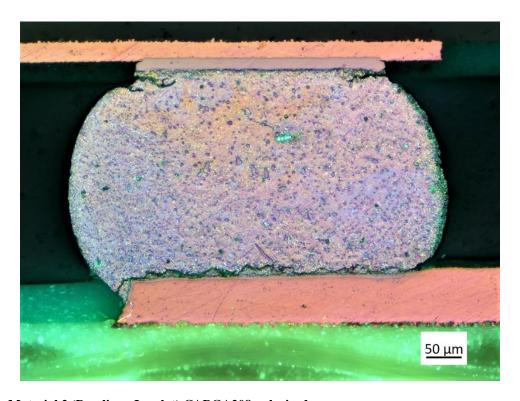

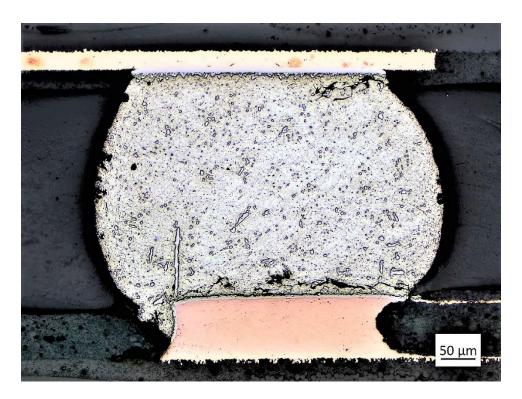

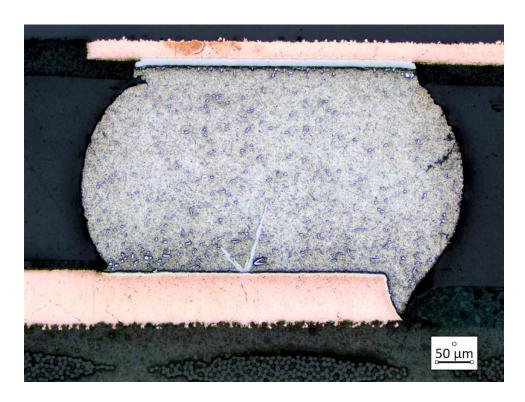

| Figure 5.12 Paste Material 3 CABGA208                                | 131 |

| Figure 5.13 Paste Material 3 CABGA208 polarized                      | 132 |

| Figure 5.14 Paste Material 3 CABGA208                                | 132 |

| Figure 5.15 Paste Material 4 CABGA208                                | 133 |

| Figure 5.16 Paste Material 4 CABGA208 polarized                      | 134 |

| Figure 5.17 Paste Material 4 CABGA208                                | 134 |

| Figure 5.18 Paste Material 4 CABGA208 polarized                      | 135 |

| Figure 5.19 Paste Material 5 CABGA208                                | 136 |

| Figure 5 20 Paste Material 5 CABGA208                                | 137 |

## **List of Tables**

| Table 1.1 Summary of Properties of Surface Finishes                         | 17  |

|-----------------------------------------------------------------------------|-----|

| Table 1.2 Summary of Properties to be Considered for Solder Alloy Selection | 25  |

| Table 2.1 Factor affect BGA solder joint reliability                        | 43  |

| Table 3.1 Test board/Solder Paste build matrix                              | 75  |

| Table 3.2 Reflow profile process window                                     | 77  |

| Γable 3.3 Reflow profile zone set point temperatures                        | 77  |

| Гable 3.4 Test board build matrix                                           | 85  |

| Table 3.5 Phase II Top-Side component matrix                                | 86  |

| Гable 3.6 Phase II Bottom-Side component matrix                             | 88  |

| Table 3.7 US and European Grip Paper standard systems [112]                 | 96  |

| Table 4.1 Drop test summary                                                 | 105 |

| Гable 4.2 Vibration test summary                                            | 106 |

| Гable 4.3 Liquid shock test summary                                         | 107 |

| Table 4.4 CABGA256 test summary                                             | 112 |

| Table 4.5 CABGA208 test summary                                             | 117 |

## **List of Abbreviations**

BGA Ball Grid Array

BSE Back-Scattered Electron

GPIB General Purpose Interface Bus

LGA Land Grid Array

PCA Printed Circuit Assembly

PCB Printed Circuit Board

PGA Pin Grid Array

RTD Resistance Temperature Detector

SAC Tin (Sn) - Silver (Ag) - Copper (Cu)

SCPI Standard Commands for Programmable Instruments

SEM Scanning Electron Microscope

SE Secondary Electron

SMC Surface Mount Component

SMR Surface Mount Resistor

SnPb Tin-Lead

THMC hrough-Hole Mount Component

#### **Chapter 1. A Brief Introduction to Electronic Assemblies**

#### 1.1 Electronics Packaging

Electronic Packaging Industry is the largest industry in the world [1]. The term of "Package" in electronic manufacturing industry refers to a supportive case that encloses a semiconducting material to prevent it from corrosion and physical damages. Electronic packaging refers to the method of enclosing, protecting or providing physical structure to either electronic components, assemblies of components or finished electronic devices. The manufacturing of this package is known as electronic packaging.

The manufacturing phase of an integrated circuit can be divided into two steps. The first, wafer fabrication, is a sophisticated and intricate process of manufacturing the silicon chip. The second, is a highly precise and automated process of packaging the die. Those two phases are commonly known as "Front-End" and "Back-End", respectively. Each electronic package should provide circuit support and protection, heat dissipation, signal distribution, manufacturability, serviceability and power distribution. This is a multi-disciplinary subject among Mechanical, Electrical and Industrial Engineering, Chemistry, Physics and even Marketing [2]. Market dictates the demand, then the engineers design, chemists and physicists investigate new materials and methods and Industrial engineers work on the manufacturing of the parts. Although more functional and smaller packages are desirable, they also are required to be qualified based on

reliability and feasible pricing. More functional devices produce more heat and require complex cooling system which both increases the price and complexity. There is a tradeoff among functionality, reliability, size and price which always makes challenges for engineers.

An IC chip which is enclosed inside the package is a very delicate and complex device. It has thousands of transistors and I/Os (input/output links) which are spaced very closely (within nanometers) to reduce electrical delay and current leakage. Contrary to popular opinion, IC chips are not being shrunk in size simply because they need to be made more compact. The primary purpose of miniaturization is to reduce electrical delay. When two switches/transistors/logic devices communicate with each other, their speed of communication depends on how far they are from each other. Higher the distance, slower the communication (which will increase computation speed in turn), it is essential to bring the logic devices as close to each other as possible [3]. This is the primary goal of miniaturization. An inevitable consequence of miniaturization is that billions of transistors are placed on a single chip, which means lots of input/output links (I/Os) inside a single chip which need to be connected to other devices such as memories, connectors, power devices etc. One of the biggest challenges in the electronics industry is figuring out how to protect these delicate ICs, at the same time successfully connecting all the I/Os from the chip to the board and to other chips. Scaling the interconnects to achieve reliable connectivity with acceptable delay is the main challenge. Figures 1.1&1.2 show the hierarchy of packaging

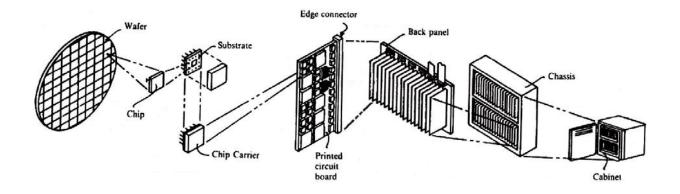

Figure 1.1 Levels of Packaging. Adapted from [2]

## 1.2 Packaging Classification

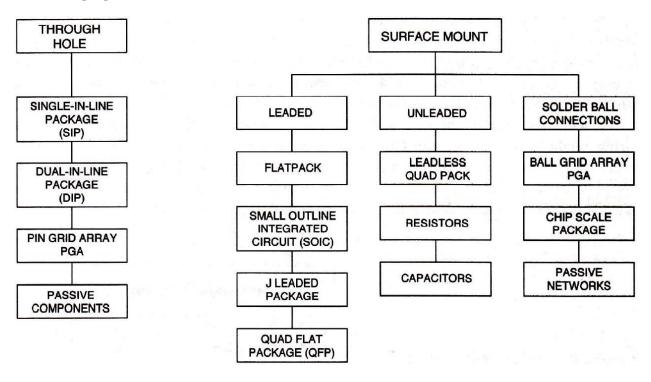

Figure 1.2 Packaging classification [2]

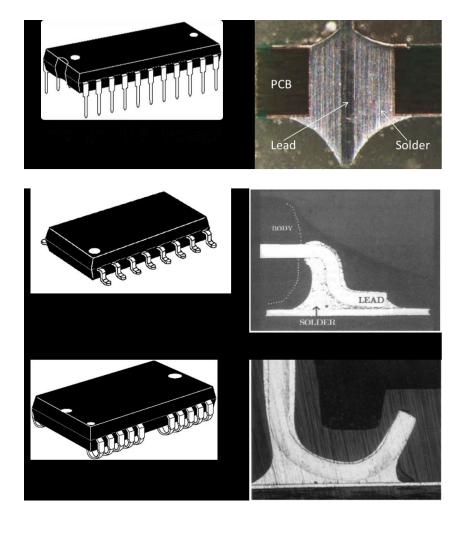

## 1.2.1 Through Hole Mount Technology

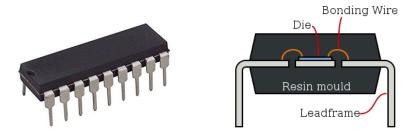

It is a mounting scheme used for electronic components that involves the use of leads on the components that are inserted into holes drilled in printed circuit boards (PCB). This is followed by soldering (adding solder around) the component leads, which joins them to the appropriate metal traces of the PCB [3]. The principal method of soldering in through-hole mount assembly is 'wave soldering' technique, which involves a standing wave of molten solder. The PCB is passed over the wave, soldering all the through-hole connections at once. The electronic packaging industry was quick to adopt wave soldering technology, as the throughput advantages was overwhelming. A typical THMT Component is Dual In-Line Package (DIP). Figure 1.3 shows an example of a DIP, and its side-view [4].

Figure 1.3 DIP and Its Side View [2]

While through-hole mounting provides strong mechanical bonds when compared to SMT techniques due to its lead frame structure effectively taking up stresses resulting from thermal expansion in the PCB substrate, additional drilling required makes the boards more expensive to produce. They also limit the available routing area for signal traces on layers immediately below the top layer on multilayer boards since the holes must pass through all layers to the opposite side. Through-hole mounting techniques are now usually reserved for that which require the additional mounting strength, or for components such as plug connectors or electromechanical relays that require great strength in support. On the downside, it became clear that a new technology was needed to achieve higher I/Os, component densities and keep pace with IC advances.

#### 1.2.2 Surface Mount Technology

The increase in demand for the leads and surface area constraints in the board led to development of Surface Mount Technology. It is a method for constructing electronic circuits in which the components are mounted directly onto the surface of the printed circuit boards. This largely replaced the through-hole technology construction method of fitting components with wire leads into holes in the circuit board. An SMT component is usually smaller than through-hole component because it has either smaller leads or no leads. SMT components can be placed on both sides of the PCB since no through-holes are required, which increases the usage of the surface area significantly.

The electrical performance of surface mount interconnects is typically better due to the shorter leads employed. On the other hand, thermal management can become more complicated, as thinner leads – necessary for finer pitch I/O – also have higher thermal resistance [5]. Also, with less solder for each joint, reliability of solders joints is more of a concern [6].

SMT components normally have flat profile made of tin-lead, silver, or gold-plated copper pads without holes, called solder pads. Solder paste is first applied to all the solder pads using a screen printing process. These are then conveyed into the reflow soldering oven where the component leads are bonded with the pads on the circuit board [5]. Figure 1.4 shows THMT vs SMT

## **Through-Hole Mount Attachment**

## **Surface Mount Attachment**

Figure 1.4 Through-Hole Mount Attachment vs. Surface Mount Attachment. Adapted from [2]

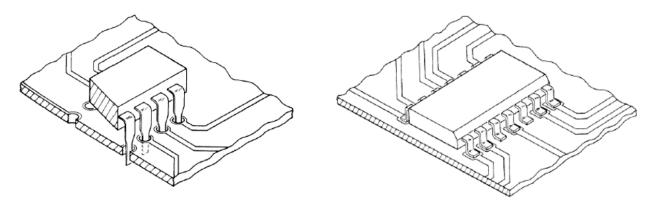

## **1.2.3 Leaded Components**

There are variety of leaded components: Gull Wing and J-Lead are the most common ones. It can be noticed that a Gull Wing device is a surface mount component and has leads folded out from its body in the shape of a 'L', while a J-leaded device is a surface mount component that has it's leads folded under its body in the shape of a 'J' [5]. Finally, all the THMT components are leaded components. The figure 1.5 shows some of the leaded components that are widely used.

Figure 1.5 DIP, Gull Wing Component and J-Lead Component [2,5]

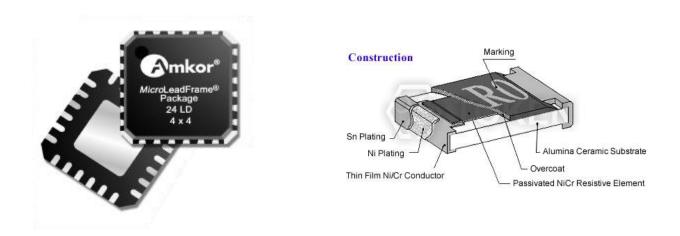

#### 1.2.4 No-lead Lead-Less Components

Components with no leads are called Lead-Less or No-Leads components. There are a variety of lead-less components common to surface mount assembly. These include the Surface Mount Resistor (SMR), Metal Electrode Leadless Face (MELF), and Quad Flat No-Lead (QFN) packages. These components are designed to be placed flat on the PCB. They have bare metal terminations on the bottom of the component and are placed directly onto the solder paste printed on the copper pad of PCB [5].

SMT components are usually plastic encapsulated, in which the die is wire bonded with planar copper lead frame. The copper lead frame forms perimeter lands on the component bottom to provide electrical connections to the PCB. Flat no-lead Components usually are square or rectangular, and includes an exposed thermal pad at center of the component bottom to improve heat transfer out [7]. Figure 1.6 shows the side view of a QFN Component.

The advantages for No-Leads Components include reduced lead inductance, a small sized (near chip scale) footprint, and low weight, so that they have good thermal and electrical performance. Disadvantage for No-Leads Components, especially the one with small sized of exposed contact as well as large area of exposed thermal pad that they are easy to float on the pool of molten solder under the thermal pad during reflow assembly.

Figure 1.6 QFN Component and SMR Component [116]

#### 1.2.5 Area Arrays

These types of SMT Components have finer pitch I/O interconnects which allows greater number of connections than lead type component where only the outer perimeter is used [8]. Their need increased as the requirement for advanced IC components continue to grow. Since no through-holes are needed, I/O's can be installed in a full 2-dimensional lattice, or Area Array, under a surface mounted component. For a square component with n leads along each edge, this approach increases the number of potential I/O channels from approximately 4n to n2 (although, depending on the component, I/O may cover only part of the allowable area). Area arrays allows one to dramatically increase I/O capabilities without having to decrease the lead pitch [9].

However, finer pitches come with a range of manufacturability concerns, including increasing fragility of finer-pitch leads and "bridging" between closely spaced contact pads on the Printed Circuit Boards. Eventually, it becomes difficult to further decrease the lead pitches for standard SMC chip carriers.

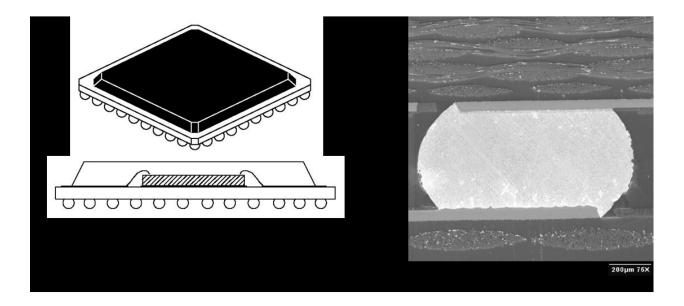

#### 1.3 Ball Grid Array

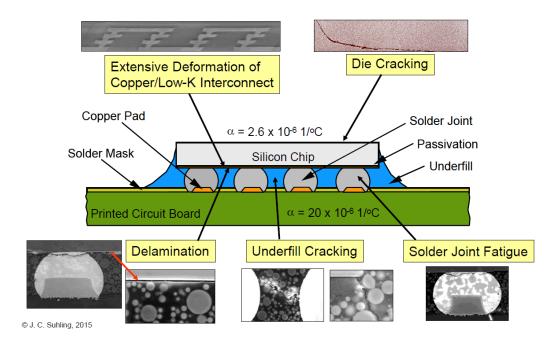

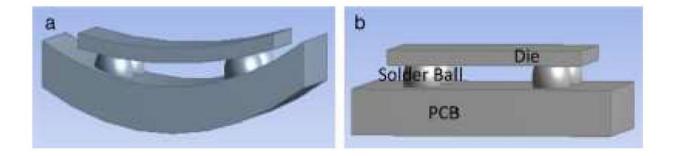

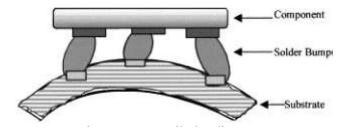

Ball grid array or BGA packages are predominant area array packages, they do not have solderable leads in a few straight rows. Instead, their leads are solder spears applied to the grid of contact pads built into the bottom of the component. These solder bumps are placed onto corresponding solder paste deposits as if they were component leads. Typically, during reflow soldering, the bumps melt and wet together with the solder paste to form a hamburger shaped solder joint as shown in the figure 1.7 thus eliminating the lead coplanarity issue. On the contrary, BGA Components are not mechanically compliant, given that the solder balls are as flexible as leads are. These joints are prone to failure due to CTE mismatch between PCB and BGA when the

package is exposed to thermal or mechanical harsh environments. This reliability issue can be overcome in a process called Underfilling, where epoxy material is filled under the BGA after soldering it on to the PCB.

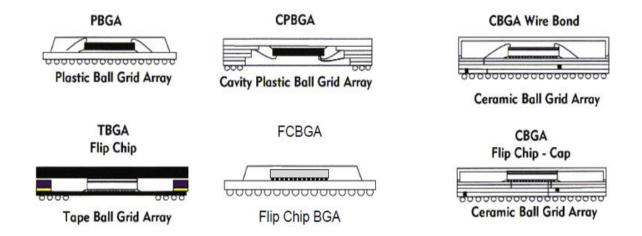

Figure 1.7 BGA package and Solder Joint [5].

A variety of BGA packages are available, including Plastic BGA (PBGA), Ceramic BGA (CBGA), Thin Chip BGA (CTBGA), Very Thin Chip (CVBGA), Super-BGA (SBGA), and Flip-Chip BGA (FCBGA) packages, among others. Figure 1.8 shows some of the cross-sectional views of some components listed above.

Figure 1.8 Some Ball Grid Array Structure Options [5]

Another area array is the Pin Grid Array, where thick metal pins (like through-hole leads) are attached in lieu of solder spheres or columns [2,5]. This type of package often used in conjunction with socket into which the pins are inserted.

Compared to traditional DIP, PGA allows for more I/O. There are different types of PGA, including Plastic Pin Grid Array (PPGA), Flip-Chip Pin Grid Array (FCPGA), Ceramic Pin Grid Array (CPGA), and Organic Pin Grid Array (OPGA).

Figure 1.9 A PGA Component Used in Motorola 68020 Microprocessor [116]

## 1.4 Substrates for Electronic Packaging

Substrates used for PCB manufacturing is a multibillion dollar industry. They can be typically classified into Rigid Laminate, (Organic) Flexible, or Ceramic, with Metal Core Substrates as an additional option. Each substrate type exhibit different properties and the selection of an appropriate one depends on the requirement. The primary requirement to be considered during substrate selection is PCB's coefficient of thermal expansion. Some of the other properties are listed below –

| General properties            | Material properties              |  |  |

|-------------------------------|----------------------------------|--|--|

| Meets Performance Requirement | Coefficient of thermal expansion |  |  |

| Cost                          | Glass Transition temperature     |  |  |

| Ease of use                   | Stiffness                        |  |  |

| Durability                    | Strength and toughness           |  |  |

| Machinability                 | Good Static dissipation          |  |  |

| Dimensional stability         | Reduce creep and warp            |  |  |

| Resistance to moisture        | Dielectric performance           |  |  |

Typically, a PCB consists of a non-conductive substrate, on which conductive traces are etched from copper sheets which are laminated. PCBs can be single sided, double sided, or a multi-layer of laminated substrates. Conductive parts on different layers are electronically connected with each other through vias. A via can be through hole, or a blind one exposed on one side, and or sometimes buried inside to connect internal layers without being exposed on either surface [10]. Figure 1.10 shows a cross-section view of a PCB with all three types of vias.

Figure 1.10 Cross-section view of a PCB with different types of vias: (1) Through hole; (2) Blind via; (3) Buried via. The green and gray layers are non-conducting, while the thin orange layers and vias are conductive.

Laminate substrates are most widely used ones in the industry. Ceramic substrates are normally used with ceramic components, as the CTE match is ideal between them. Flexible organic substrates are used to form complex circuitry. They are manufactured by attaching a thin metal foil to a flexible film using an adhesive. Constraining core substrates are metal core substrates. They incorporate a core that is CTE matched to components and other structures. The metal core used in these would be metal sheet or metal matrix composite material.

#### 1.4.1 Laminate Substrates

Most commercial applications use rigid laminate substrates. They are typically constructed with many layers. The raw materials involved in the manufacturing process are Glass Fabric, Resin and Copper Foil. The different raw materials are rolled onto each other to form a strong sturdy single layer. This process is called impregnation. The layer that comes out of the impregnation process is treated to make the material homogenous. The lamination lay-up is followed by another process where the copper foil is embedded to the Pressplates and Presspregs. The different layers of laminates obtained are compressed and pressed by applying pressure and heat for a long period in the Laminate Pressing step. The resulting product is an inseparable single unit product. The resulting layers are broken down in the breakdown process. The core sheets are (potentially) clad in a copper layer that is photolithographically defined to create the appropriate electrical circuitry or thermal distribution layers. The finished product is subjected to lamination process, throughholes are drilled and plated to allow for vertical electrical or thermal interconnects [2,5,11] and a final inspection to check for errors.

The primary advantage of utilizing laminate substrate is higher layer counts which help in increasing the routing capability of the embedded components and the component density. The main advantage that pushes the laminate substrate printed circuit boards to the forefront is the relatively lower cost of manufacturing and better utility. [2]

#### 1.4.2 Solder mask

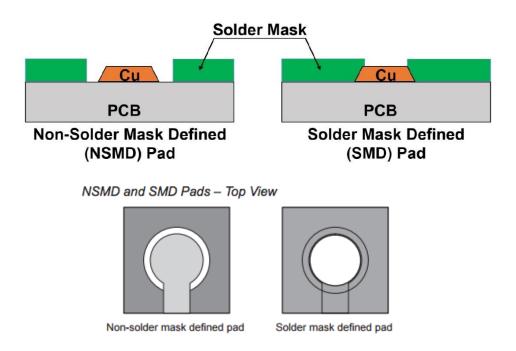

Copper traces on the PCB must be protected from oxidation, corrosion and bridging. Solder mask is a thin lacquer like layer commonly made of acrylic or epoxy polymers coated where no electrical contact is needed on the PCB [2,5,11].

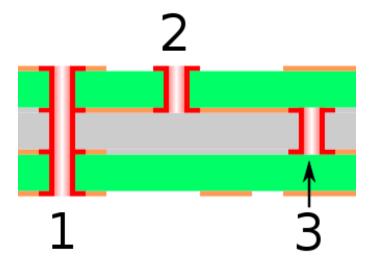

One of the purposes of the solder mask is to prevent wetting of solder onto the copper during reflow, the contact pads ("lands") on the Printed Circuit Board surface must be kept clear of solder mask. There are two types of solder mask designs for a PCB. One is to print the solder mask around the copper pad and it is called Non-Solder Mask Defined(NSMD). The other is to print solder mask such that just the desired pad area is exposed and it is called Solder Mask Defined(SMD). In NSMD, a small space is left while printing the mask around the copper pad, whereas in SMD the desired exposed area is smaller than the copper pad. Figure 1.11 shows difference between NSMD and SMD PCB design.

Figure 1.11 NSMD versus SMD PCB lands.

#### 1.4.3 Surface Finishes

Surface finishes are applied over the exposed copper pad areas as the solder mask can only protect copper traces. This finish allows them to be preserved as either conductive test points, fiducials or lands for solder wetting. Besides protecting copper pad from corrosion and oxidization, surface finish can also increase solderability of solder paste to the copper pad, by dissolving the outermost layer of surface finish during reflow or wave soldering. A variety of different surface finishes have been developed over the years and some of them are discussed below [2,5,11,12].

Hot Air Solder Leveling (HASL): In this process the PCB is immersed into a molten tinlead bath. The solder clings on to the exposed metal surfaces that are not covered by the solder mask. Hot air "knives" are used to blow off the excess solder, clearing the through holes and vias and leaving only a thin coat on the copper surfaces. This is one of the least expensive surface finishes available and facilitates excellent solderability. This process was primarily used with tinlead baths, and proved challenging to use with lead-free solders as their melting temperature was higher. Another drawback of this process is the coating is not even and the coplanarity of the surface is poor. Also, thermal shock damage to the PCB is a common issue therefore, the popularity of HASL has fallen significantly in recent years.

Organic Solderability Preservative (OSP): is an organic compound-based anti-tarnish coating. It uses a thin protective layer (typically 0.7-1microns) of carbon-based organic layer to protect the copper pad oxidation and contamination. OSP finish is the leader in low cost surface finishes, has superior co-planarity and solderability, facilitates easy visual inspection and multiple reflow capabilities [2,5]. Disadvantage of OSP finish including poor shelf life, sensitive to handling, and difficulty during circuit testing because the coating is non-conductive.

A variety of alternative surface finishes are available to support the production of lead-free assemblies. They are more compatible with newer packages and have superior planarity and uniformity. They rely on deposition of one or more metals using Electroplating, Electroless Plating, and Immersion Plating. A buffer solution or a plating bath is used into which ions of desired metal are dissolved. When the boards are dipped the metal ions impinge the exposed metal surface and bond in place to produce the coating. Below is the list of alternative surface finishes available -

- Immersion Tin (ImSn, ImmSn, ISn)

- Immersion Silver (ImAg, ImmAg, IAg)

- Electroless Nickel Immersion Gold (ENIG)

- Electroless Nickel/Electroless Palladium/Immersion Gold (ENEPIG)

PCB Surface finishes are chosen depending on the application, cost, quality and reliability. Every Surface Finish has its strengths weaknesses; the Table 1.1 lists some of the properties of Surface Finishes discussed in this topic.

| Туре    | Planarity | Solderability | Al Wire<br>Bondable | Au Wire<br>Bondable | Contact<br>Surface |

|---------|-----------|---------------|---------------------|---------------------|--------------------|

| HASL    | POOR      | GOOD          | NO                  | NO                  | NO                 |

| LFHASL  | FAIR      | GOOD          | NO                  | NO                  | NO                 |

| OSP     | GOOD      | GOOD          | NO                  | NO                  | NO                 |

| IMM Ag  | GOOD      | GOOD          | YES                 | NO                  | NO                 |

| IMM Sn  | GOOD      | GOOD          | NO                  | NO                  | NO                 |

| ENIG    | GOOD      | GOOD          | YES                 | NO                  | YES                |

| ENEPIG  | GOOD      | GOOD          | YES                 | YES                 | YES                |

| Elec Au | GOOD      | GOOD          | YES                 | (soft only)         | YES                |

<sup>\*</sup> Finish cost factor only, all other features being equal.

**Table 1.1 Summary of Properties of Surface Finishes**

## 1.5 Electronic Packaging Trends

The achievements in electronics packaging so far has helped to reach higher state of integrity by utilizing new materials, employing more accurate processes and configurations. This needs a new methodology to electronic design and layout of semiconductor chips, circuits and systems. In this section the roadmap of modern packaging that shows the path to system integration is presented [2].

"Electronic packaging is traditionally defined as the back-end process that transforms bare integrated circuits (IC) into functional products." [15] Electronics packaging technologies are not mature technologies, and many technological aspects will still affect the application possibilities. Strongly, it can be stated that by technological driving forces, the electronics and information technologies have changed and it will change the manufacturing technologies [13]. The electronics industries through the past few decades have tried to reduce the dimensions of components as well as complete electronics systems. To reach a reliable and cost-effective system, the size and weight is being reduced by employing lower voltages and higher speeds. The recent progress in electronic manufacturing tends includes achievements in higher integration such as better materials, process, and configurations which leads to the design of more efficient and better layout of semiconductor chips, circuits and systems. Furthermore, the quality and cost should be considered as essential factors. Since all the components such as semiconductor chips and passives must be placed inside the system, all the concerns such as electrical (signal processing), physical (heat transfer and cooling), mechanical, chemical and technological should be solved [14].

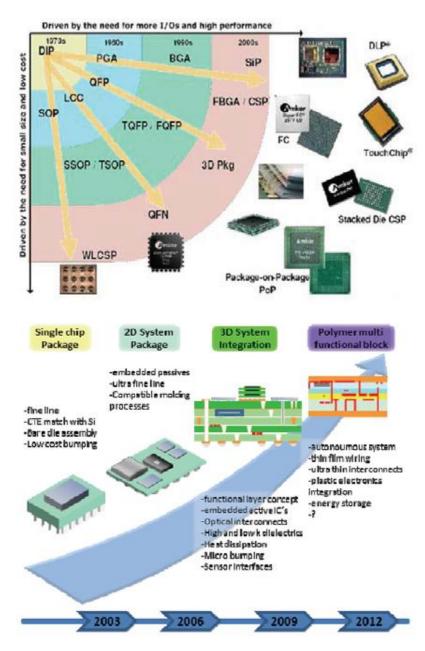

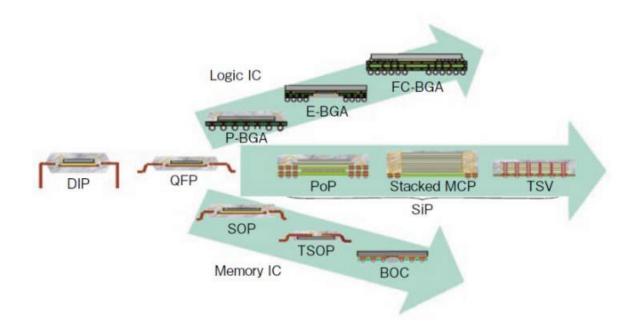

In figure 1.12 and 1.13 shows the integration development of packages where the industry moved from Dual in Line (DIL) to Leaded Chip Carrier (LCC) and other (PGA, QFP etc.) which cause dramatic changes in components such as microprocessors, memories, etc.

Figure 1.12 Integration development of packages in the last decades [14,15,16]

In the past, two types of packaging have been used for semiconductor chips non-hermetic (plastic) and hermetic (metal and ceramic). Plastic packages were more commercial applications due to low cost (one half to one tenth the cost of ceramic and metal packages) and small size comparing to the ceramic and metal packages. While the Hermetic packages have been used mostly for military, space and medical applications because of their perceived reliability advantage over plastic packages [14]. The new packaging process focusing on three-dimensional (3-D) packaging including interconnection to provide better electrical performance and packaging density comparing to the two-dimensional (2-D) packages which was popular in the past is here.

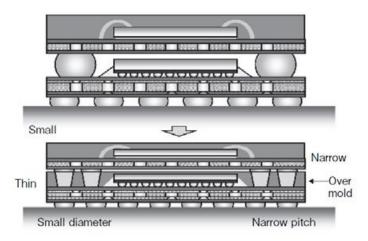

Besides, three-dimensional packaging has potential to increase the density more than 50 times by stacking ICs. Figure 1.13 shows the packaging trends through the time: single chip packaging, 2-D system packaging, 3-D system packaging and future polymer multifunctional solution [14]. Eventually, electronic packaging is developing very fast through the coming soon future [14]. Moreover, the cost is focused more today as the most significant factor with increasing the number of elements on chip [14].

In another study, Nakamura and Katogi studied the evolution of packaging technology through the time. As shown in figure 1.14, the trends of semiconductor packages have been traced differently in their work. They divided the trends into three main categories: Logic IC; System in a Package (SIP); and Memory IC [17]. Moreover, they suppose that three-dimensional packages will be popular in near future. Good example for three dimensional packages would be Package on Package (POP) for stacking logic and memory IC, stacking Multi Chip Packages (MCP) for stacking multiple semiconductor chips, and Chip on Chip (COC) for connecting two semiconductor chips directly [17]. Typical POP stacks the memory packaging on the logic packaging which is popular for mobile information terminals such as smartphones. BGA can be

good example of POP which is used for lower packaging. Moreover, the materials have become thinner according to the requirements of structural components. Besides, packaging wrap and reflow resistance have been focused to improve the packaging process. For example, the rate of pin count increase is 8% to 11% per year since 1997; the cost per pin has been reduced only 5% per year; and the original size from year 1997 to 2001 decreased to 60%. In general, electronics technology will continue to progress in various fields such as robotics, automobile industries, medical equipment etc. and its progress is very depend on many factors, but one of the most important one is development on materials technology in 20 years ahead which based on chemistry and some other technologies such as: polymer synthesis technology; interface control technology in molecular units; bonding technology for different kinds of materials; development of signal transmission technology; and super-fine photosensitivity technology [17].

Figure 1.13 Trends of semiconductor packages [17]

Figure 1.14 High density 3D semiconductor packaging [17]

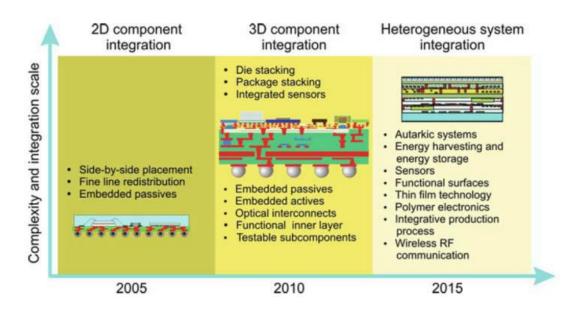

Gerlatch et al. in their book named "Bio and Nano Packaging Techniques for Electronic Devices" studied on System on Chip (SoC) technology and its trend through the electronics manufacturing history. It states that SoC technology was developed for high volume custom devices by using design elements from different semiconductor devices or by using of reprogrammable logic [18]. Figure 1.15 shows the trend of SoC from 2005 to 2015.

Figure 1.15 Trends in System-in-Package technology [18]

#### 1.6 Evolution of Solder

Many techniques have been developed over the years for joining metal work pieces. Some of the common ones are welding, brazing and soldering. In all the 3 techniques, the surfaces of the metals to be joined are heated in the presence of a filler material which forms a metallurgical bond and upon cooling turns into a sold joint and in-turn joining the work pieces. A chemical agent known as a flux, which removes oxides and contamination to leave behind a readily fusible surface, is often used during this process [5,19,20].

Solder is derived from old French, soudure, which means fasten together. Its use in English as a noun meaning "a fusible metallic alloy used for uniting less fusible metal surface or parts" and dates to 1350. Lead was first obtained as a by-product of silver production, during cupellation of lead from ores. The softness and malleability of lead was later recognized. Lead was used as a setting agent to fix posts in ground and lock mortised stones. Solders containing alloys of lead and tin were found from surviving artifacts and literary source of the Roman Imperial Period. Analysis of solder joints have revealed that both tin-rich and lead-rich alloys were used. In the 20th Century, modern practices developed with the improvement of extraction techniques gave raise to exotic metal at affordable cost along with the alloy phase diagrams paving the path for diversity in alloy making today.

## 1.7 Soldering

Soldering is a process of joining two metal surfaces using a molten filler metal with or without the use of a flux agent. A metallurgical bond is formed as soon as the filler metal solidifies. This metal joining techniques amongst many others can be called as Soldering only when the filler metal melt below 450°C [5] additionally, must be done at temperature low enough to avoid

damaging other components of the system that is being soldered [5,6]. Therefore, solders are generally alloys with low melting temperature. Often in this process fluxes are used to clean the mating surfaces and remove most of oxides and organic films before soldering process.

To forge this bond, the solder must flow easily (low viscosity) and 'wet' rapidly (have low surface energy) with the surface finish. Additionally, an intermetallic compound layer must be formed at the solder-surface interface. This is what provides the metallurgical bonding between the two materials [21]. Most Intermetallics are brittle, however, the thickness of the IMC layer should be controlled. Such control is typically accomplished by limiting the time-above-liquidus of the solder during the soldering process [22].

#### 1.8 Solder Joints for Electronic Assemblies

Electronics soldering is a process where the components are attached to the PCB. Most common methods followed to do it are wave soldering process and reflow soldering process. In both processes a strong mechanical connection is created between the components and the PCB. This joint provides electrical, thermal and mechanical continuity in the assembly. The properties of the joint vary with solder and substrate material. Additionally, they must take up mechanical stresses from CTE (coefficient of thermal expansion) mismatches, and be strong enough to deal with vibration and drop conditions. Also, they must maintain their strength over an extensive period, during which they must resist degradation due to environmental factors, electro migration, and diffusion-based microstructure evolution [5]. Table 1.2 is the summary of properties to be considered for the solder alloy selection.

| Manufacturing                             | Reliability                        |  |

|-------------------------------------------|------------------------------------|--|

| Melting/liquidus temperature              | Electrical conductivity            |  |

| Wettabilitty (of copper)                  | Thermal conductivity               |  |

| Cost                                      | Coefficient of thermal expansion   |  |

| Environmental friendliness                | Shear properties                   |  |

| Availability and number of suppliers      | Tensile properties                 |  |

| Manufacturability using current processes | Creep resistance                   |  |

| Ability to be made into balls             | Fatigue properties                 |  |

| Copper pick-up rate                       | Corrosion and oxidation resistance |  |

| Recyclability                             | Intermetallic compound formation   |  |

| Ability to be made into paste             |                                    |  |

Table 1.2 Summary of Properties to be Considered for Solder Alloy Selection

## 1.9 Rise and fall of tin-lead solder

Tin-Lead (SnPb) solder alloys has been the material of choice for the electronic industry and its history dates to thousands of years to prove its popularity. For electronics manufacturing industry, the eutectic Tin-Lead solder with 63% Tin and 37% lead (63Sn37Pb) by weight is the most universal option. A fine-pitch micro-electronic package assembled in the U.S. in the late 1990s (or even today, for some applications) has the same general composition and properties as

that used by the ancient Romans to seal their sewer pipes [5,20,23]. Tin-Lead solders have a variety of advantages in electronic applications [24,25].

- Lead (Pb) is inexpensive and plentiful. Tin-Lead (Sn-Pb) alloys have relatively low melting temperatures suitable for the soldering of electronic assemblies.

- Sn-Pb alloys have low surface tension (which is advantageous to the solder wetting process), with Lead (Pb) acting to reduce the surface tension of pure Tin (Sn).

- Sn-Pb alloys form strong intermetallic bonds with the copper pads used in electronics, with Lead (Pb) acting as a solvent metal during IMC formation.

- Sn-Pb alloys have good mechanical properties, with Lead (Pb) acting to improve the ductility of pure Tin (Sn). The most popular tin-lead solder for electronics manufacturing is the mixture of 63% Tin and 37% Lead by weight [2,5,20].

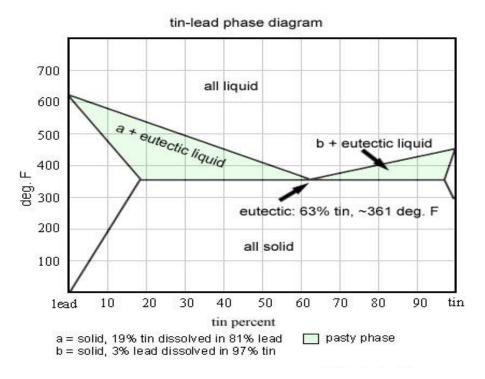

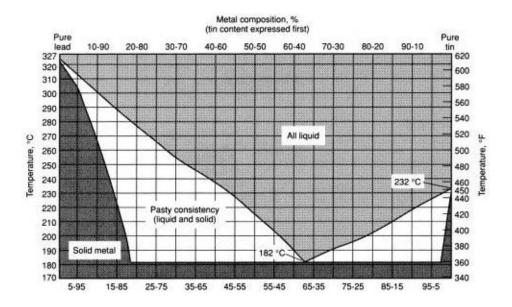

# 1.10 Eutectic Alloy and 63Sn-37Pb

The term eutectic is derived from the Greek word eutektos, meaning 'easily melted'. Eutectic alloys have a single temperature at which the entire alloy melts (when increasing temperature) and solidifies (when decreasing temperature) which makes it easy to predict and work with. These alloys have a pasty range and behave very differently from most alloy compositions. Pasty range is a range of temperatures in which the alloys is partially solid and partially liquid and this is not recommended in electronics. Figure 1.16 shows the pasty range and eutectic point of SnPb alloy.

Figure 1.16 Phase Diagram for Tin-Lead Solder Alloy

Eutectic alloys have more homogenous compositions and provide lowest possible melting temperatures. The phase diagram below shows binary alloy system of tin-lead.

Figure 1.17 Tin-Lead Binary Phase Diagram [23]

From the Figure 1.17 we can see that the 63%Tin,37%Lead composition has the lowest melting temperature of 183°C which is very favorable. Any temperature lower than this will weaken the joint and any higher will be damaging the parts of the assembly. Advantages of 63Sn-37Pb solder include [2,5,20,26]

- Eutectic Composition (i.e. single transition temperature)

- Low melting point (183oC)

- Low Cost (made from relatively abundant/cheap elements)

- Good Wetting and Manufacturability

- Adequate Fatigue Resistant

- Good joint integrity

- Excellent electrical conductivity

Despite the many advantages of the Sn-Pb solder alloys, it has a fatal flaw. Lead (Pb), presents a grave danger of toxicity. The effects are mostly long term, cumulative exposure and a threat to children. Symptoms of high lead exposure can include: [27]

- Anemia

- Decreased renal function

- Increased blood pressure and cardiovascular disease

- Anti-social behavior

- Learning disabilities

- Mental retardation

Given the nature of these effects, attracted a lot of attention and concern. Finally, in Japan, the advisory committee of Japan Institute of Electronics Industry Development Association (JEIDA) created a roadmap in 1998 for the commercialization of lead-free solders. Although no direct governmental action has been taken in Japan, the Japanese electronics industry has been ahead of the curve in the implementation of lead-free products. In 2000, the EU adopted two directives that were designed to stop the use of lead in electronics. The Waste of Electrical and Electronic Equipment (WEEE) directive stipulated that lead needed to be removed from all electrical and electronic components at their end-of-life. The Directive of the Restriction of the Use of Certain Hazardous Substances (RoHS) prohibits the use of lead in electrical and electronic components manufactured after July 1, 2006 [28]. In the Unites States, no direct governmental action has been taken, but market forces have pushed the US electronics industry toward the adoption of lead-free practices. In 2000, the IPC developed a roadmap for lead-free research and development in the United States [29].

## 1.10 Near-Eutectic Sn-Ag-Cu (SAC) Solder

With the bans of Sn-Pb, researchers started replacing Pb with copper (Cu), Silver (Ag), Bismuth (Bi), Indium (In), Zinc (Zn), Antimony (Sb) and others. Tin was still chosen as the base element because of its ability to wet and excellent ability to form intermetallic compounds with other metals. Amongst all the combinations Sn-Ag-Cu was chosen as the quick fix in the electronic industry. SAC alloys are near eutectic with melting temperatures range between 232°C and 183°C. both silver and copper have face centered cubic crystal structure which provides high thermal, electrical conductivity and metallic luster to their properties. The Equilibrium Ternary Phase Diagram of the Sn-Ag-Cu system is shown in Figure 1.18. The phase diagram shows the ternary eutectic point in the Tin-rich region, at a composition of approximately 95.6Sn-3.5Ag-0.9Cu

(SAC359), which has a melting temperature of about 217.2 <sup>o</sup>C. This near-eutectic composition with sufficiently low melting temperature was considered a viable lead-free solder candidate [32].

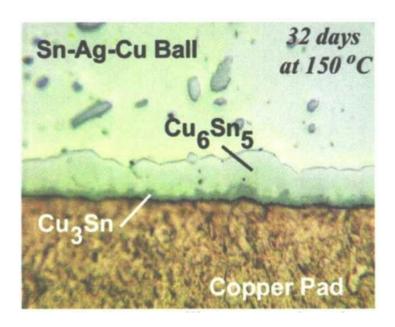

The ternary phase diagram Figure 1.18 also shows three possible precipitates near the eutectic SnAgCu region: Ag<sub>3</sub>Sn, Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn. IMC, Cu<sub>3</sub>Sn, exists, but does not form except at higher copper contents and therefore, is not seen within the bulk of the solder. No Intermetallics exist between Silver (Ag) and Copper (Cu) [30].

Figure 1.18 From NIST: Sn-Ag-Cu Phase Diagrams

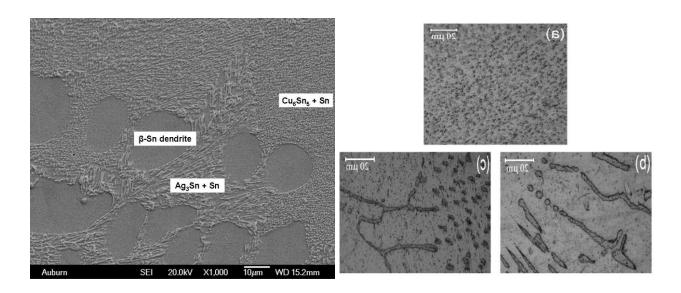

The ternary eutectic microstructure of SAC solders consists of  $\beta$ -Sn dendrites (primary phase), eutectic Sn-Ag regions (needle-shape Ag<sub>3</sub>Sn intermetallic dispersed within  $\beta$ -Sn matrix), and eutectic Sn-Cu regions (scallop-shape Cu<sub>6</sub>Sn<sub>5</sub> intermetallic dispersed within  $\beta$ -Sn matrix), as shown in Figure 1.19. These interspersed fine intermetallic particles are capable of pinning and blocking the movement of dislocations, and will thus enhance mechanical strength and reliability of solder joints when compared to eutectic Sn-Pb alloy [96,97].

Figure 1.19 SEM Micrograph of Typical Sn-Ag-Cu Solder, Ag3Sn and Cu<sub>6</sub>Sn<sub>5</sub> Morphology

The Intermetallic Compounds ( $Ag_3Sn$  and  $Cu_6Sn_5$ ) have higher strength and higher modulus than the  $\beta$ -Sn. Therefore, a higher concentration of  $Cu_6Sn_5$  rods and (particularly)  $Ag_3Sn$  platelets increases the effective modulus (stiffness) of a Sn-Ag-Cu solder joint. Overly large  $Ag_3Sn$  plates should be avoided, as they act as crack initiation sites under tensile and shear stresses. For a typical SAC solder (3–4 % Ag and 0.5–1 % Cu),  $Ag_3Sn$  plates outnumber  $Cu_6Sn_5$  rods. Since,

the IMC Ag<sub>3</sub>Sn is the only phase containing Silver (Ag) in a SAC solder, an increase in Ag content results in a corresponding increase of Ag<sub>3</sub>Sn IMC precipitates [98,99,100].

Following are some of the SAC-family solders that were developed as a lead-free replacement:

- SAC305 (Sn96.5Ag3.0Cu0.5): most popular SAC solder alloy, especially in automotive and consumable electronics industry. Pasty melting range is around 217°C to 220°C. Low cost, excellent fatigue resistance, good mechanical characteristics, best wetting SAC alloy.

- SAC105 (Sn98.5Ag1.0Cu0.5): popular in automotive and cellphone industry, because of superior drop and vibration resistance. Pasty melting range is around 220°C to 225°C. Low cost.

- SAC405 (Sn95.5Ag4.0Cu0.5): contains more Silver. More thermal fatigue resistance and expensive than SAC305.

- SAC387 (Sn95.5Ag3.8Cu0.7): recommendation of the European IDEALS Consortium.

Not commonly used in the United States.

- SAC396 (Sn95.5Ag3.9Cu0.6): recommendation of the U.S. NEMI group. Used in the United States occasionally.

- SnCu Eutectic (Sn99.3Cu0.7): eutectic mixture of Tin and Copper. Eutectic melting point is 227°C. Low cost, but poor mechanical properties, and easy to have Tin Whiskers.

- SnAg Eutectic (Sn96.5Ag3.5): eutectic mixture of Tin and Silver. Eutectic melting point is 221°C.

### 1.12 Solder Paste and Flux

In the reflow soldering of surface mount assemblies, solder paste is used for the connection between the leads of the surface mount components and the lands on the PCB. Solder paste is a

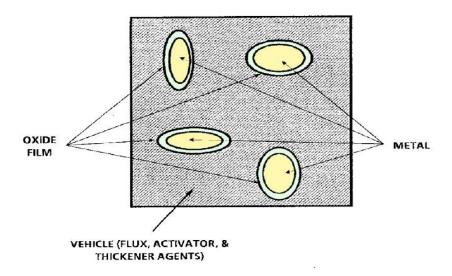

suspension of solder alloy particles in a fluid vehicle or a carrier that contains solvents, flux activators, rheological modifiers and other additives. Figure 1.19 shows the solder paste system.

Figure 1.19 Solder Paste

The size of the solder particles in the solder paste is an important factor, couple of effects commonly seen are listed below

- Irregularly shaped and larger solder particles tend to clog the screens and the stencils.

- Smaller particles are more susceptible to oxidation and other surface effects.

- Smaller particles allow small pockets of paste to separate from the main paste deposit. This can lead to electrical isolation of the lands on the PCB.

The usual rule-of-thumb is to use the largest particle size that works with the solder bumps in question, as this reduces problems with solder balls and reduces overall cost [5].

Solder pastes have high solder content, typically 90% by weight. However, because of difference in the density, it amounts to about 50% by volume. The additional 50% is taken up by the flux vehicle.

Flux vehicle is a viscous fluid containing 'activators' – usually mild acids to promote wetting of the solder material during reflow by removing oxides and other surface contaminants. Fluxes also contain solvents, which dissolve the flux and impart the pasty characteristic that allows it to be screen printed, and additives (e.g. rheological modifiers). Solvents must be carefully selected, as they are a key element in the formation of voids (unfilled volumes) within solder joints. The flux vehicle must also coat the exposed metal surface to prevent re-oxidation and provide a sump for the byproducts produced during flux activation [5].

Joint Industry Standard for Fluxes, J-STD-004, classifies fluxes into three categories – low, medium and high, based on their level of activity (I.E how acidic they are). Flux compositions are: Rosin (RO), Resin (RE), Organic (OR) and Inorganic (IN) [5].

Figure 1.21 Picture of Solder Paste

### 1.13 Overview of SMT Process

In this process, the electronic components are attached on to the copper pads of the PCB. SMT is the central part of the entire SMP packaging technology [31]. The figure below shows the typical SMT assembly process flow.

Figure 1.20 Typical SMT Assembly Process Flow

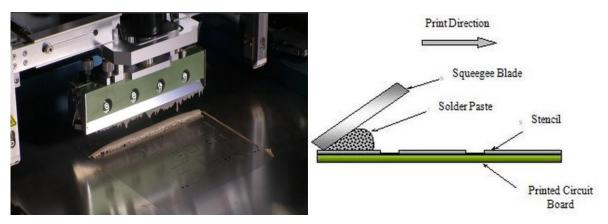

The first step of the SMT assembly process is solder past printing. In this step, solder paste is printed onto the copper pads of the PCB. The figure 1.21 shows the picture of solder paste. Typically, the consistency of it is like toothpaste. This paste is applied on to the copper pads located on the PCB through a process called Stencil printing. Stencil is a sheet of material (usually made of stainless steel) manufactured with desired thickness and with series of apertures cut into it to match the PCB on to which it need to be printed. The main aim for Stencil Printing Process is to accurately deposit correct amount of solder paste onto the copper pads of the PCB surface so that

the solder joint between PCB and component terminal have acceptable electrical contact and mechanical strength. In this process a squeegee blade is used to apply the solder paste. Necessary force is applied on the squeegee to move the paste across the stencil to deposited the paste on to the pad. Figures 1.21 show the squeegee in the assembly line waiting for a PCB to print the paste. The other figure shows the side view of the printing process where squeegee blade is dragging the paste across the stencil to get a good print on the copper pads.

Figure 1.21 A Picture of Stencil Printer and Cross-Section View of a Squeegee Printing Solder Paste on Stencil

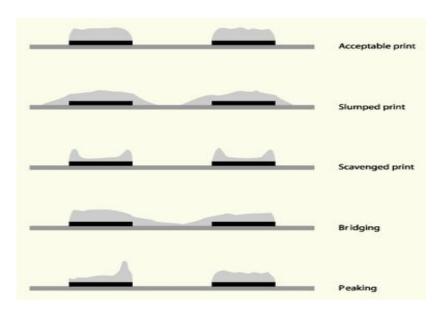

Some of the important parameters that need to be taken care of during this process is squeegee speed, squeegee pressure, stencil separation speed, stencil cleaning, print stroke, storage and handling. Figure 1.22 shows unsatisfying prints

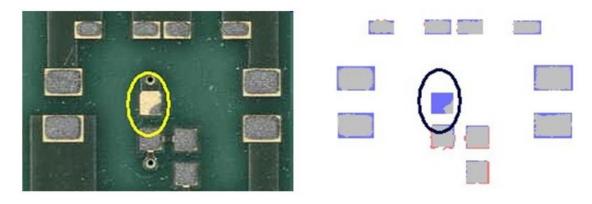

The quality of the paste print is evaluated by a 2D & 3D inspection process. In 2D process the area of the paste deposit is inspected and for the 3D volume of the paste deposited is inspected. The figures below show the images of 2D and 3D inspection processes.

Figure 1.22 Example of Fault Found by 2D and 3D inspection respectively

Figure 1.23 Different Types of Unsatisfied Printing Result

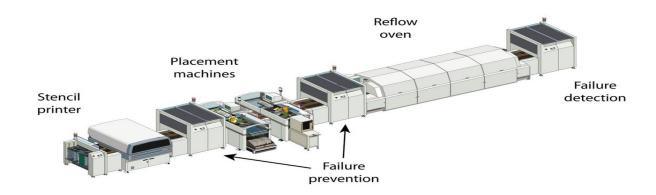

Various automatic machines are used to place different electronic assemblies on to the PCB. There are many Pick-and-place machines and are differentiated by lot of variables, the important ones being placement, speed and accuracy. Others include, types of feeders, serviceable board size, inspection capabilities, cost and many more [9].

Reflow soldering process – In this process the PCB with paste printed and electronic assemblies mounted on them enter an oven where the solder joint melt and upon cooling a

permanent metallurgical bond between the copper pad on the PCB and the electronic assembly is formed. The reflow oven uses either infrared or convection as a source of heat. It consists of multiple zones and the temperature of these zones can be individually controlled. The PCB assembly moves across these zones on a conveyor belt, and is therefore subjected to a controlled time-temperature profile [32]. The figure 1.24 show an example of a reflow oven and its labeled sectional view.

Figure 1.24 Example of a Reflow Oven, With Its Cross-Section View of Structure

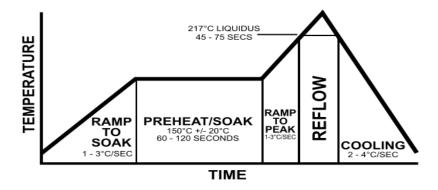

The controlled time-temperature profile in the reflow soldering process helps to create a good metallurgical bond between the component and the PCB without overheating and damaging the assembly. Figure below shows a typical reflow profile of an SMT process.

Figure 1.25 A Typical Reflow Thermal Profile [33]

The boards coming out the reflow oven is thoroughly cleaned which is followed by inspection and testing. In this step, either X-Ray inspection or Automated Optical Inspection is performed, to look for the defects that may have occurred in the SMT process [47]. Areas inspected in this phase include component presence, polarity, solder deposition, dry joints, solder shorts to name some. Mechanical and electrical tests are finally conducted to assure the quality of the soldering process. The figure 1.26 shows a typical SMT assembly line.

Figure 1.26 A Typical SMT Assembly Production Line

## **Chapter 2. Literature Review**

## 2.1 Properties of a Solder Joint

Solder alloy selection for a printed circuit assembly involves in understanding and balancing a wide array of properties. Though some of the properties are universally desirable but others depend on the area of application. Some factors that needs to be concerned for the selection of solder materials include, processing of components and substrates, solder strength as a function of temperature, cost, restrictions concerning health and environmental factors.

Solder materials must provide good thermal and electrical conductivity, be easily manufacturable, and have adequate reliability for the intended application [2,5,6]. There are many physical and mechanical properties that are highly desirable in solder joint of electronic assemblies. These properties affect the manufacturability, quality, strength and reliability of the solder joints. Depending on the physical or mechanical properties that one is interested in, it will be important to consider the material composition and processing.

## 2.1.1 Properties Important to Manufacturability

Some of the properties of a solder material that are important for manufacturability include: [2,5,6,24]

- Cost

- Melting Temperature Range

- Solderability (wetting, adhesion)

- Drossing

- Compatibility with the substrate metallization and component UBM

- Compatibility with common Flux Systems

- Compatibility with manufacturing processes of solder balls and powder

- External Visual Appearance (for inspection)

- Health and Environmental Concerns

Melting temperature range of a solder material is an important form property from manufacturability standpoint. Higher temperatures can result in printed circuit board warping, component or die cracking and many other defects. Also, it can add up the energy expenditure of the soldering process. Therefore, lower melting temperatures are preferred and considered advantageous from a manufacturing perspective.

# 2.1.2 Reliability of a Solder Joint

By now, we know that the electronics industry is after higher component density, better mechanical performance, higher real-estate and lower cost of an SMT assembly. This sort after qualities make reliability of an electronics package more critical and essential for consideration. Reliability can be defined as the ability of a system or a component to function under stated conditions for a specific period [34].

Reliability of a surface mount assembly considers Wafer Level Reliability, Chip Level Reliability, and Board Level Reliability (BLR), corresponding to hierarchy of interconnection levels [35]. Azira, et al. [36] mention that Board Level Reliability is also known as an interconnect reliability testing and is used to evaluate the quality and reliability of solder connections (BGA, QFN, SMT Resistor, and others) after mounting an IC package to a printed circuit board (PCB). Matin, et al. [37] mention that during a product life cycle, solder joint is exposed to an environment of thermal-mechanical fatigue, including temperature excursions, vibration, drop and shock, which will cause failure of solder joint. Especially when the environment is harsh it will have a severe influence on the Board Level Reliability. Shen, et al. [38] found that fatigue can cause microstructure evolution and deformation due to Coefficient of Thermal Expansion (CTE) between SMT components and the Printed Circuit Board. Zhang, et al. [39] investigated solder joint crack propagation along intermetallic layer between interfaces of the solder joint with component as well as PCB substrate. Zhou, et al. [40] studied the effect of long-term isothermal aging at elevated temperatures on package characteristic lifetime reliability. Basit, et al. [41] developed Finite Element Analysis (FEA) models to simulate solder alloys behavior during thermal aging and cycling. Table 2.1 summaries factors that affect BGA solder joint reliability.

| Feature                | Lower Reliability | Moderate Reliability | Higher Reliability |

|------------------------|-------------------|----------------------|--------------------|

|                        |                   |                      |                    |

| Part Type              | CBGA              | CCGA                 | PBGA               |

| Die size to part ratio | Largest           |                      | Smallest           |

| Ball to pad ratio      | Smaller           |                      | Larger             |

| Pad type               | SMD               |                      | NSMD               |

| Via type               | In-pad unfilled   | In-pad filled        | Interstitial open  |

| Via size, min.         | < 0.020" (> 4:1)  |                      | ≥ 0.020" (≤ 4:1)   |

| (aspect ratio)         |                   |                      |                    |

| Ball size              | Smaller           |                      | Larger             |

| Stencil thickness      | < 0.006"          |                      | ≥ 0.006"           |

| Underfill              | Reworkable UF     | No UF                | Non-reworkable UF  |

Table 2.1 Factor affect BGA solder joint reliability

# 2.1.3 Properties Important for Reliability

The melting temperature range of the solder material is an important property from reliability perspective. However, here higher temperatures are considered advantageous, which make it resistant against thermally-driven failures (Creep). Other important reliability properties include: [2,5,26,24]

- Coefficient of thermal Expansion (CTE)

- Voiding

- Aging

- Grain Growth and Microstructure

- Intermetallic Formation

- Mechanical Properties (Modulus, Tensile and Shear properties)

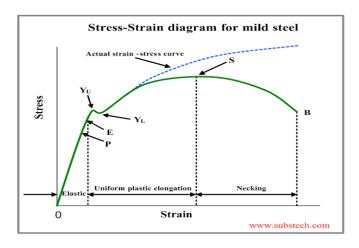

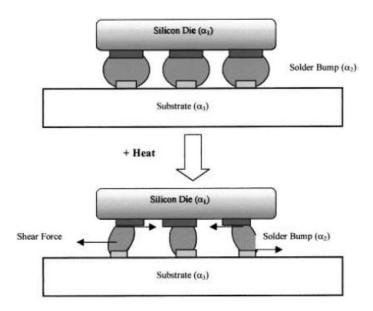

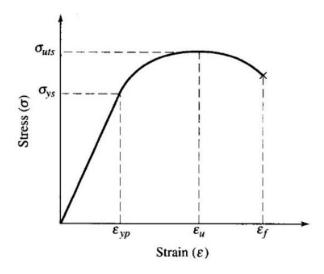

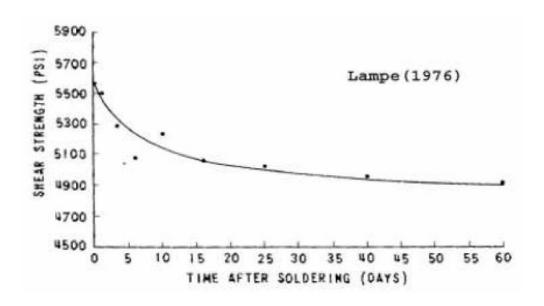

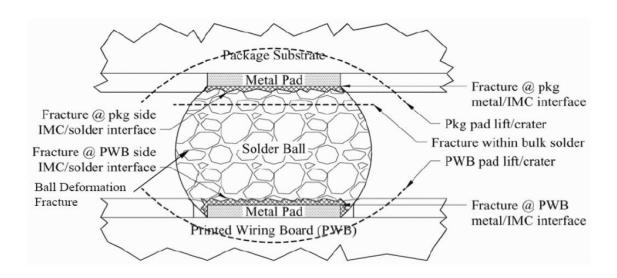

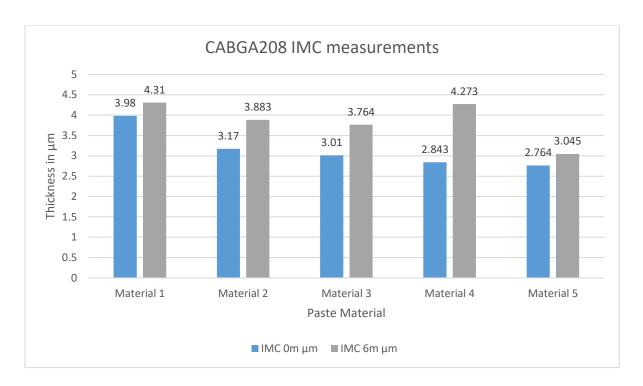

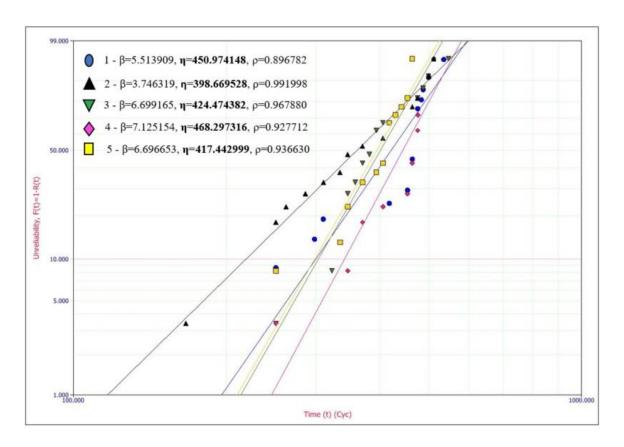

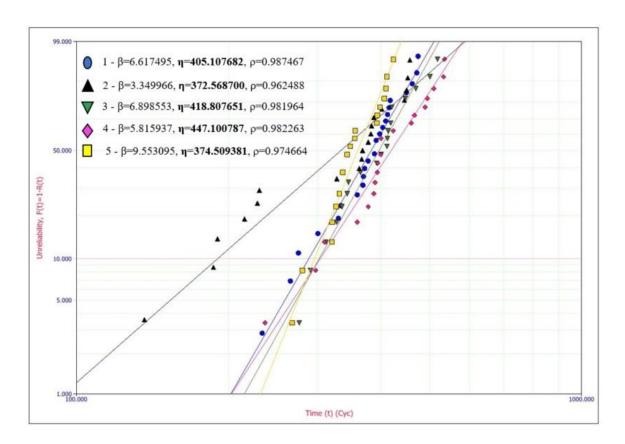

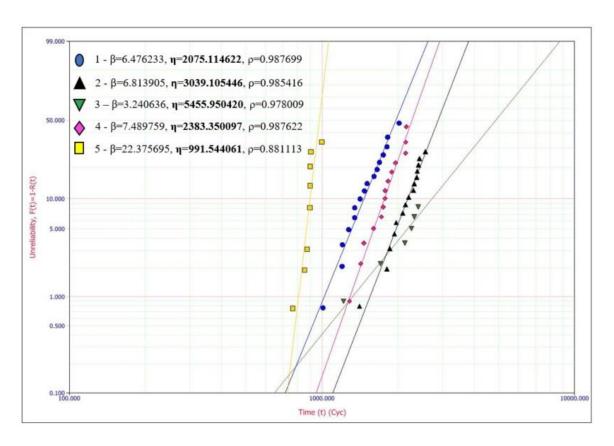

- Failure Modes (Crack initiation and growth, Creep, Fatigue)