# Wireless Communication Demonstration in Hardware Using an Exactly Solvable Chaotic System

by

D. Aaron Whitney

A thesis submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Master of Science

> Auburn, Alabama May 4, 2019

Keywords: chaos, chaotic oscillator, communication, wireless, matched filter, mixed-signal processing

Copyright 2019 by D. Aaron Whitney

Approved by

Robert N. Dean, Chair, McWane Professor of Electrical and Computer Engineering Victor P. Nelson, Professor of Electrical and Computer Engineering Thaddeus Roppel, Associate Professor of Electrical and Computer Engineering

#### Abstract

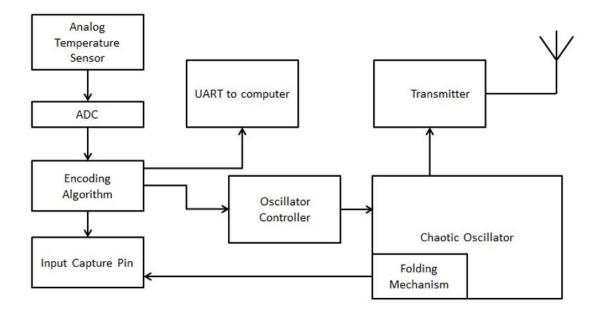

This work presents a hardware demonstration of a mixed-signal wireless communication system that utilizes a chaotic oscillator based on an exactly solvable piecewise linear set of differential equations, along with a matched filter derived from its exact analytical solution. An analog temperature sensor serves as the input for the system. The analog output from the sensor is converted to an 8-bit value via a microcontroller; this value is then encoded into an analog chaotic waveform via a linear controller, and data is transmitted serially over a wireless transmitter and receiver at 2.3 GHz. A matched filter defined in software extracts the binary data from the received analog signal, and a second microcontroller samples this binary data and sends it to a computer for verification. Tests show that the system is able to accurately transmit and receive the sensor data in the intended manner. Included in this work is relevant background information and theory for the system, a description of the design, function, and implementation of each component in the system, hardware test results and verification of the system's intended function, and the results of multiple bit-error-rate (BER) tests in varying ambient conditions.

# Table of Contents

| Abstract        |     |                         |                                                                    |    |

|-----------------|-----|-------------------------|--------------------------------------------------------------------|----|

| List of Figures |     |                         | v                                                                  |    |

| 1               | Int | troduction              |                                                                    | 1  |

| 2               | Ba  | Background              |                                                                    | 5  |

|                 | 2.1 | Beginn                  | ings of Chaos Theory                                               | 5  |

|                 |     | 2.1.1                   | The Lorenz System                                                  | 5  |

|                 |     | 2.1.2                   | Universality and The Logistic Map                                  | 7  |

|                 | 2.2 | Saito a                 | nd Fujita's System                                                 | 9  |

|                 | 2.3 | The Ex                  | xactly Solvable Chaotic System                                     | 12 |

|                 | 2.4 | The Ex                  | xactly Solvable System in Communications                           | 14 |

|                 | 2.5 | A Mat                   | ched Filter for the Chaotic System                                 | 16 |

| 3               | De  | evelopme                | ent                                                                | 18 |

|                 | 3.1 | Chaoti                  | c Oscillator Realization                                           | 18 |

|                 |     | 3.1.1                   | Low-Frequency Oscillator in Electronics                            | 18 |

|                 |     | 3.1.2                   | High-Frequency Oscillator in Electronics                           | 26 |

|                 |     | 3.1.3                   | The Single-Transistor Chaotic Oscillator and its Implementation in |    |

|                 |     |                         | Hardware                                                           | 28 |

|                 | 3.2 | 2 Oscillator Controller |                                                                    | 33 |

|                 | 3.3 | Matche                  | ed Filter Realization                                              | 39 |

|                 | 3.4 | Encoding and Decoding   |                                                                    | 53 |

|                 |     | 3.4.1                   | Encoding                                                           | 53 |

|                 |     | 3.4.2                   | Decoder                                                            | 57 |

| 4               | Te  | sting                   |                                                                    | 60 |

| 5     | Results                                                 | 64  |

|-------|---------------------------------------------------------|-----|

| 6     | Conclusion                                              | 65  |

| 7     | Future Work                                             | 67  |

| Bibli | iography                                                | 68  |

| Appe  | endices                                                 | 72  |

| А     | MATLAB program for digital matched filter demonstration | 73  |

| В     | Program for Software-Defined Matched Filter             | 76  |

| С     | Program for Encoder                                     | 100 |

| D     | Program for Decoder                                     | 129 |

# List of Figures

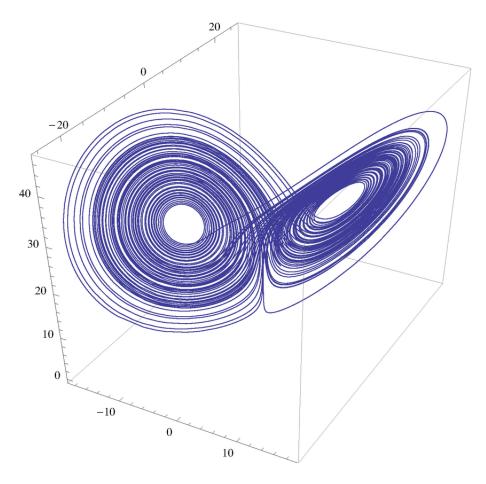

| 2.1 | Phase-space representation of the Lorenz system exhibiting chaotic behavior.                       |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | Note the two orbits, giving the system the appearance of a butterfly. Source:                      |    |

|     | Adapted from [27]                                                                                  | 6  |

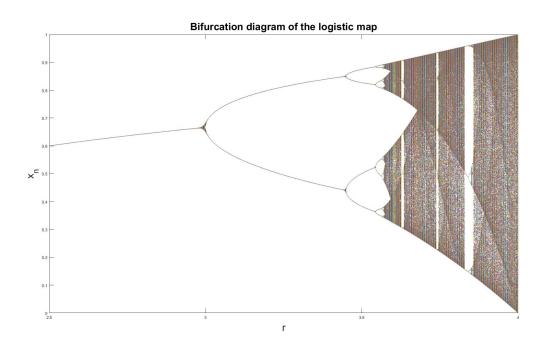

| 2.2 | Bifurcation diagram showing the value of a population given its growth rate. A                     |    |

|     | single cycle exists until $r \approx 3.0$ . The single cycle becomes unstable and is replaced      |    |

|     | by a period-doubled cycle. The pattern of instability being replaced by period                     |    |

|     | doubling continues until $r\approx 3.6$ when the system tends to an infinite number of             |    |

|     | values. Source: Adapted from [32]                                                                  | 8  |

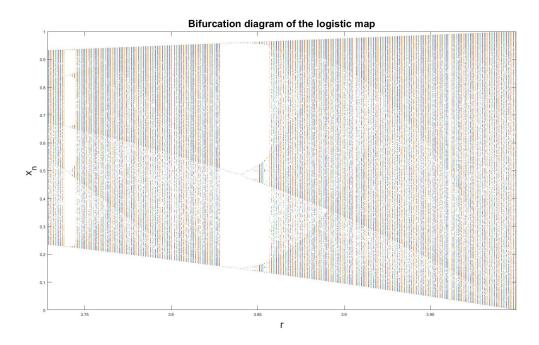

| 2.3 | Zoomed view of bifurcation diagram. Notice the sudden transition from chaotic                      |    |

|     | behavior to period-5 at $r \approx 3.74$ , and the transition to period-3 at $r \approx 3.83$ . It |    |

|     | has been shown that any system which exhibits period-3 at any particular value                     |    |

|     | is capable of chaotic behavior at other values. [33] Note the bifurcations after                   |    |

|     | period-3, which are scaled duplicates of the initial bifurcation. Source: Adapted                  |    |

|     | from [32]                                                                                          | 9  |

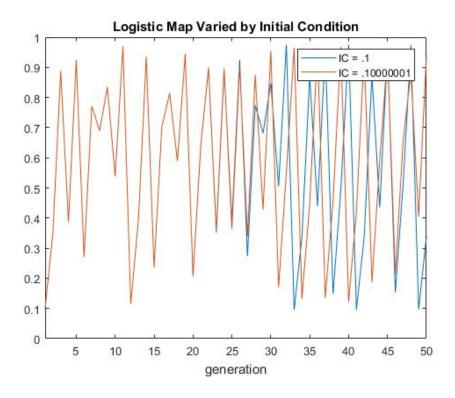

| 2.4 | Plot of two initial conditions of a dynamic population model with a positive                       |    |

|     | Lyapunov exponent. Slight variance in initial condition causes divergence at                       |    |

|     | roughly the 33rd generation. Source: Adapted from $[32]$                                           | 10 |

| 2.5 | Physical representation of the manifold piecewise linear system as a resonant                      |    |

|     | circuit with a negative resistance. Source: Adapted from [10]                                      | 10 |

| 2.6 | Phase-space plot of the solution to Eq. 2.11, with $\delta = 0.11$ , $\beta = 0$ , and all initial conditions set to 0. Source: Adapted from [10] | 12 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | conditions set to 0. Source: Adapted from [10]                                                                                                    | 12 |

| 2.7 | Basis function that can be superposed over a binary sequence to form a chaotic                                                                    |    |

|     | wave. Source: Adapted from $[25]$                                                                                                                 | 14 |

| 2.8 | Plot of the output of the exactly solvable system. The growing oscillation occurs                                                                 |    |

|     | around one of two equilibrium points until a zero crossing of the output and its                                                                  |    |

|     | derivative, and the oscillation is forced to the equilibrium point with opposite                                                                  |    |

|     | sign. Source: Adapted from $[36]$                                                                                                                 | 15 |

| 3.1 | Operation of the exactly solvable folded-band oscillator. The oscillation grows                                                                   |    |

|     | until the amplitude surpasses $+1$ , then at the local maximum of the oscillation                                                                 |    |

|     | (roughly $t = 7.5$ ) the equilibrium point is switched to 0 for one half period. The                                                              |    |

|     | equilibrium point is then switched back to 1, effectively removing energy from                                                                    |    |

|     | the oscillation and allowing it to continue without becoming unbounded. Source:                                                                   |    |

|     | Adapted from [12]                                                                                                                                 | 19 |

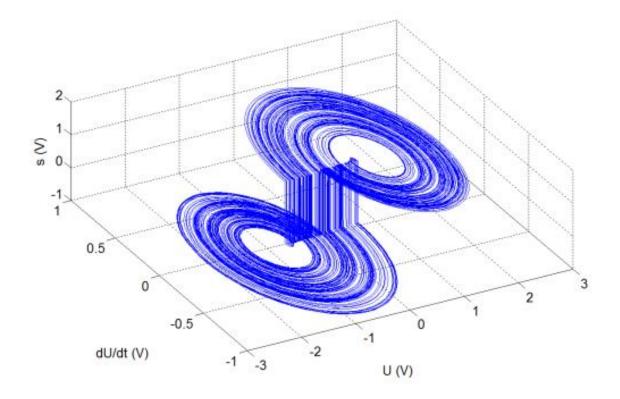

| 3.2 | Phase-space representation of the function of the chaotic system. Source: Adapted                                                                 |    |

|     | from [12]                                                                                                                                         | 20 |

| 3.3 | Return map for the chaotic system. Source: Adapted from $[12]$                                                                                    | 21 |

| 3.4 | Schematic of low-frequency oscillator circuit. Source: Adapted from $[42]$                                                                        | 23 |

| 3.5 | Simulated output of low-frequency electronic oscillator. Source: Adapted from [42]                                                                | 24 |

| 3.6 | Phase-space representation of the electronic chaotic oscillator. Source: Adapted                                                                  |    |

|     | from [42]                                                                                                                                         | 25 |

| 3.7 | Electronic schematic for the high-frequency chaotic oscillator. Source: Adapted                                                                   |    |

|     | from $[5]$                                                                                                                                        | 26 |

| 3.8  | Output of the high-frequency chaotic oscillator. Source: Adapted from $[5]$ $\ .$ .   | 26 |

|------|---------------------------------------------------------------------------------------|----|

| 3.9  | Symbolic content of the high-frequency chaotic oscillator. Source: Adapted from [5]   | 27 |

| 3.10 | Phase-space representation of the high-frequency oscillator. Source: Adapted          |    |

|      | from [5]                                                                              | 28 |

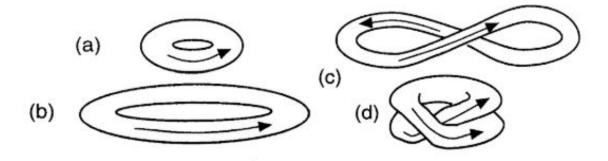

| 3.11 | Stretch-twist-fold phenomenon. Source: Adapted from [44]                              | 29 |

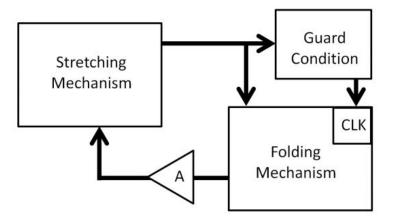

| 3.12 | Block diagram of approach to oscillator design. Source: Adapted from $[45]$           | 30 |

| 3.13 | Schematic of 18.4 kHz resonant circuit. Source: Adapted from [45] $\ldots$ .          | 30 |

| 3.14 | Equivalent circuit for single-transistor resonant circuit. Source: Adapted from [45]  | 31 |

| 3.15 | Schematic of single-transistor chaotic oscillator in SPICE. Source: Adapted from [45] | 34 |

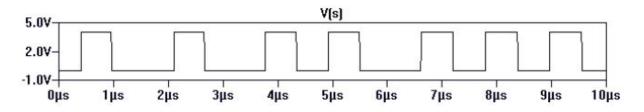

| 3.16 | Time-domain output of oscillator. Source: Adapted from [45]                           | 35 |

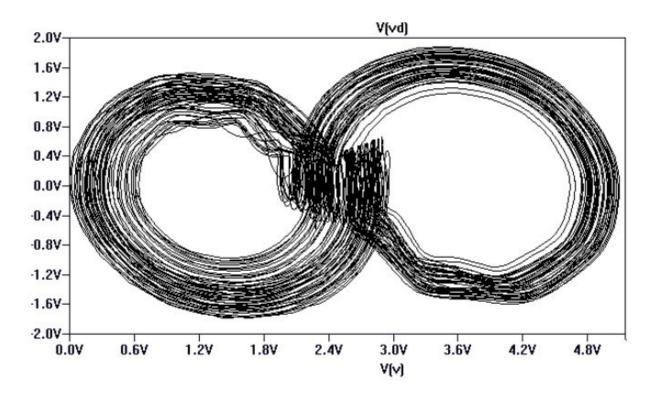

| 3.17 | Phase plot of simulation. Source: Adapted from [45]                                   | 35 |

| 3.18 | Time-domain oscilloscope capture of hardware oscillator output, overlaid with         |    |

|      | s(t) (blue). Source: Adapted from [45]                                                | 36 |

| 3.19 | Phase-space oscilloscope capture of hardware oscillator. Source: Adapted from [45]    | 36 |

| 3.20 | Oscillator controller block diagram                                                   | 37 |

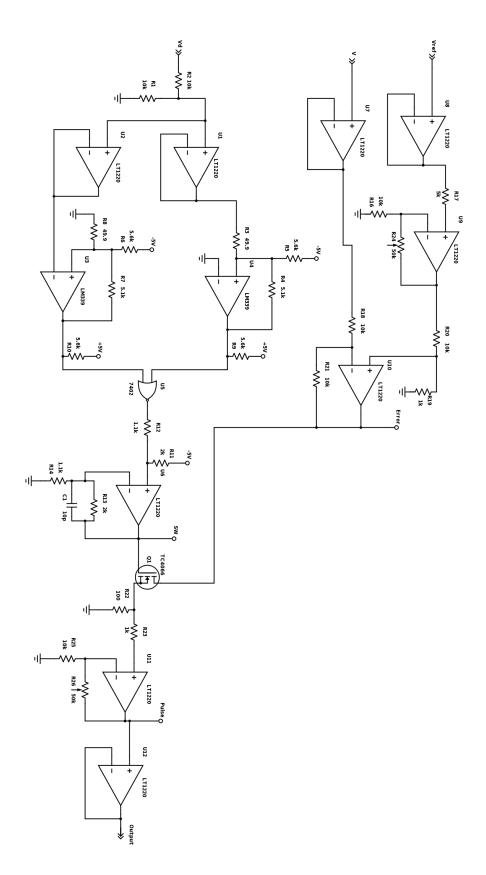

| 3.21 | Oscillator controller schematic.                                                      | 40 |

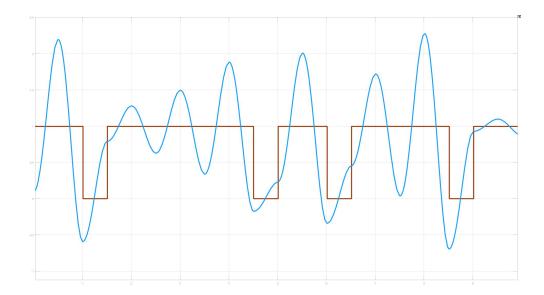

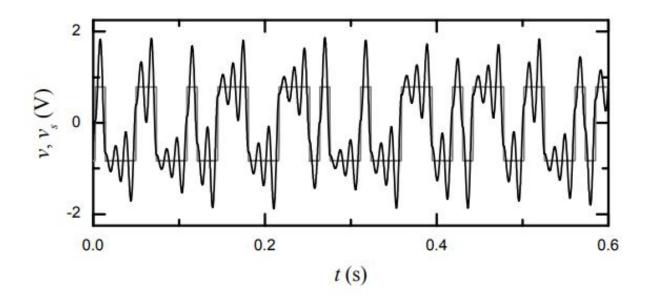

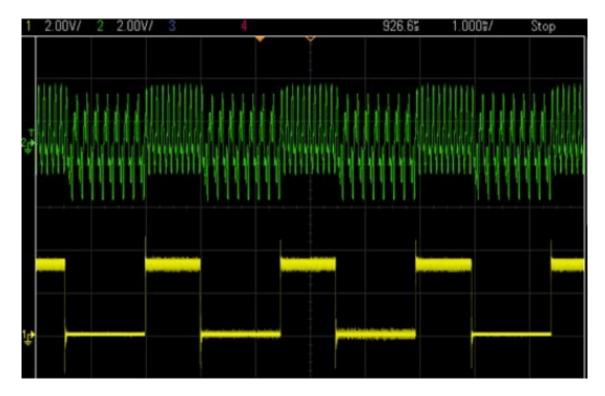

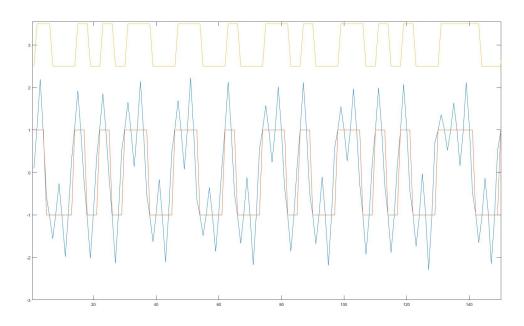

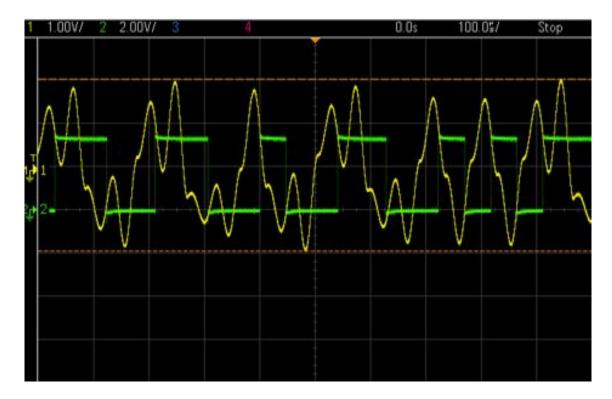

| 3.22 | Oscilloscope capture of the oscillator output when the controller receives a 1-0-1-0  |    |

|      | pattern. Source: Adapted from [46]                                                    | 41 |

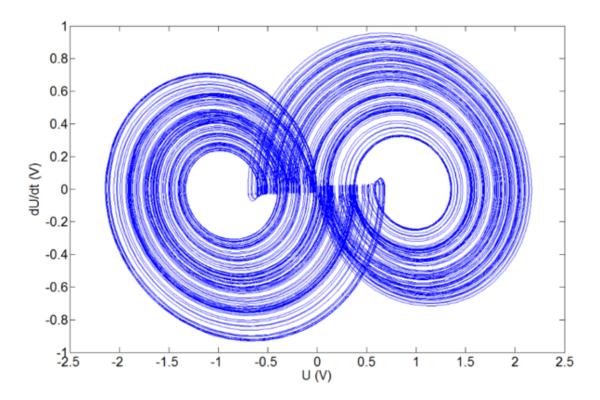

| 3.23 | Phase-space capture of the oscillator receiving a 1-0-1-0 pattern. Source: Adapted    |    |

|      | from [46]                                                                             | 41 |

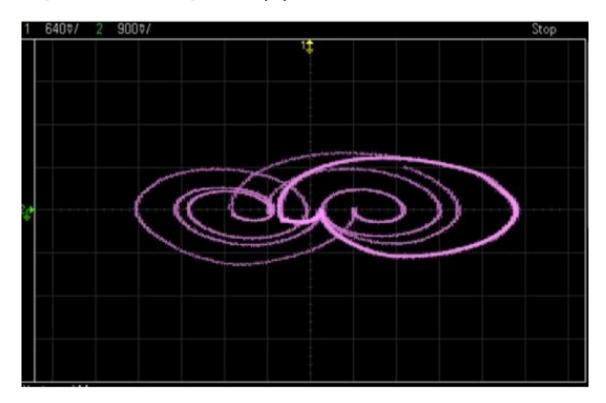

| 3.24 | Oscilloscope capture of the function of the controller                                                                                                                         | 42 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

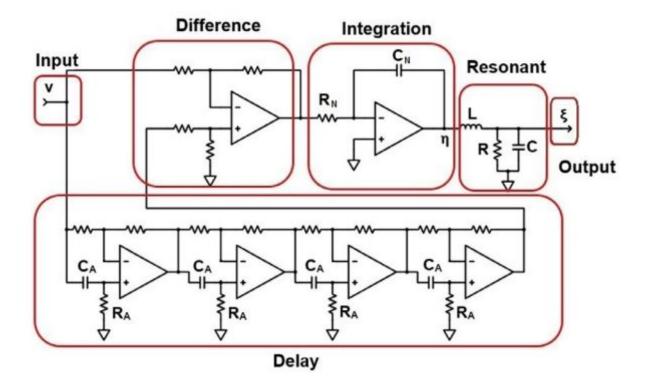

| 3.25 | Generalized schematic of the analog matched filter. Source: Adapted from $\left[ 36 \right]$ .                                                                                 | 43 |

| 3.26 | Results of the simulation of showing the output of matched filter when supplied with a noisy input signal. Source: Adapted from [36]                                           | 44 |

| 3.27 | Simulation with falsified symbolic content and matched filter correction of falsified data. Source: Adapted from [36]                                                          | 44 |

| 3.28 | Oscilloscope capture of oscillator output overlaid with symbolic content, and the matched filter output $\xi$ overlaid with symbolic output $\eta$ . Source: Adapted from [36] | 45 |

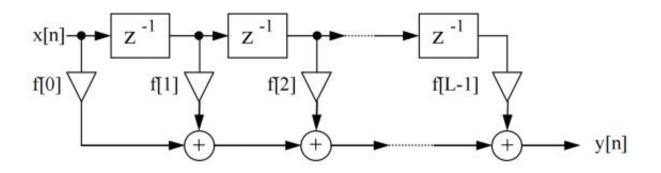

| 3.29 | General diagram of an FIR filter. Source: Adapted from [50]                                                                                                                    | 46 |

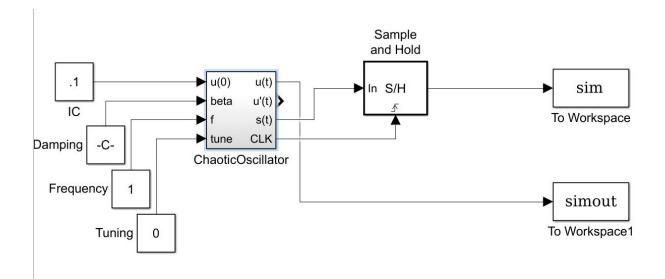

| 3.30 | Simulink model of the oscillator with tunable parameters and outputs to the MATLAB workspace.                                                                                  | 47 |

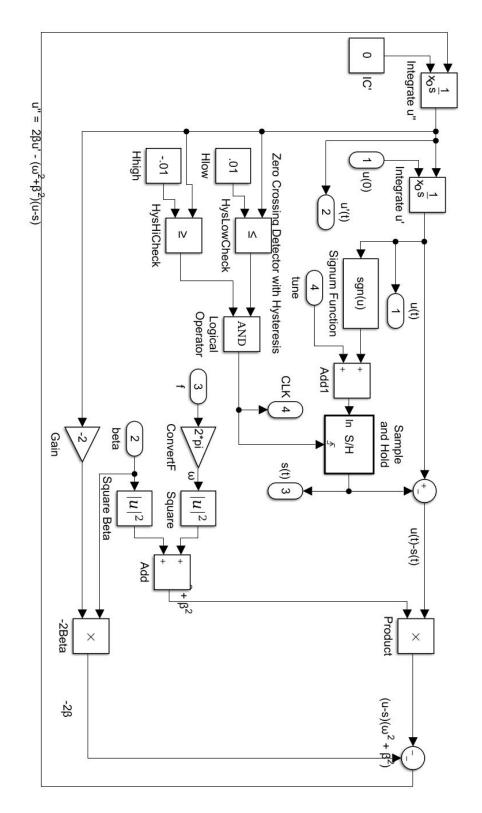

| 3.31 | Simulink model of the chaotic equation block diagram.                                                                                                                          | 48 |

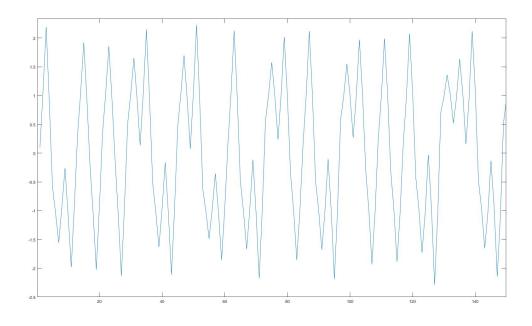

| 3.32 | Decimated oscillator output to simulate sampling                                                                                                                               | 49 |

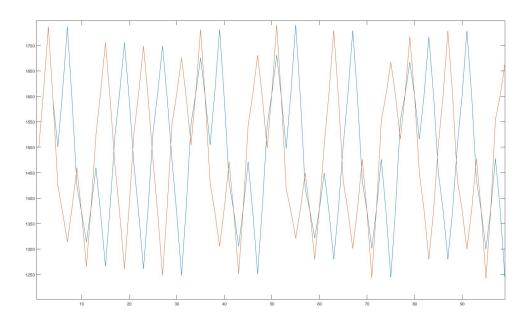

| 3.33 | Sampled level-shifted and scaled oscillator signal (red) and delayed signal (blue).                                                                                            | 49 |

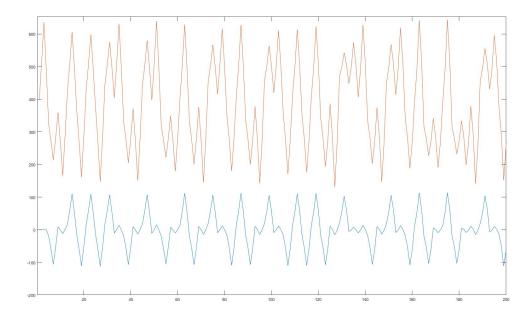

| 3.34 | Sampled oscillator output (red) with output of subtraction operation                                                                                                           | 50 |

| 3.35 | Output of subtractor (red) with output of integrator (blue)                                                                                                                    | 50 |

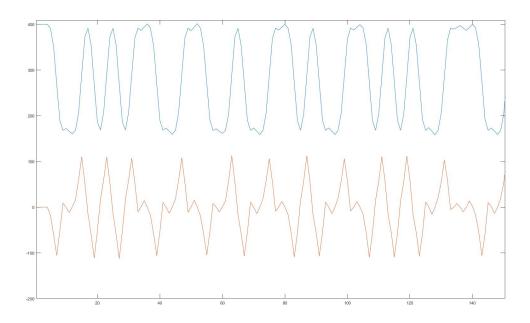

| 3.36 | Sampled oscillator signal overlaid with symbolic content, and digital matched filter algorithm output (yellow)                                                                 | 51 |

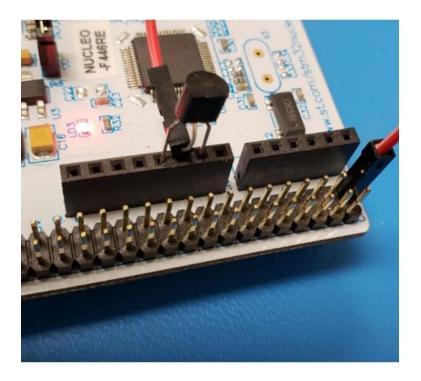

| 3.37 | Development platform used to implement the software matched filter                                                                                                             | 52 |

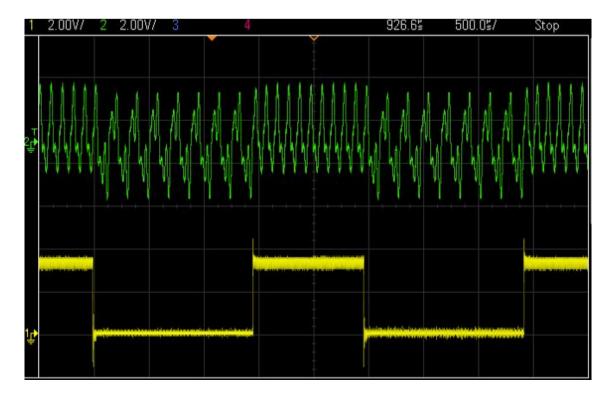

| 3.38 | Software-defined matched filter (green) shown extracting correct symbolic data from oscillator output (yellow).                                                                | 53 |

| 3.39 | Symbolic content of oscillator (yellow) compared with software matched filter                      |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | (green). Notice the small delay in the matched filter's output. $\ldots$ . $\ldots$ .              | 54 |

| 3.40 | Temperature sensor connected to encoder microcontroller                                            | 55 |

| 3.41 | Controller input (yellow) and oscillator output given the binary sequence (green).                 |    |

|      | Note the transient periods between oscillator states                                               | 56 |

| 3.42 | Block diagram of the encoder and its interfaces with the oscillator and controller.                | 57 |

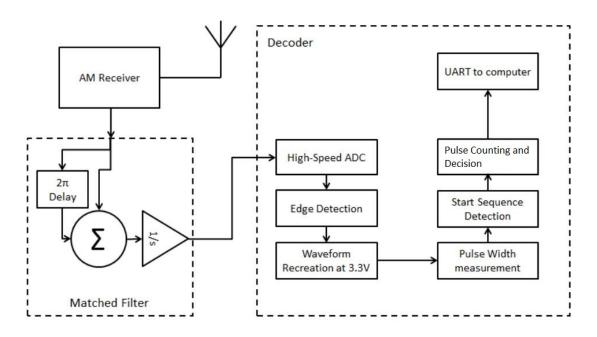

| 3.43 | Block diagram of the decoder and its interface with the receive side                               | 58 |

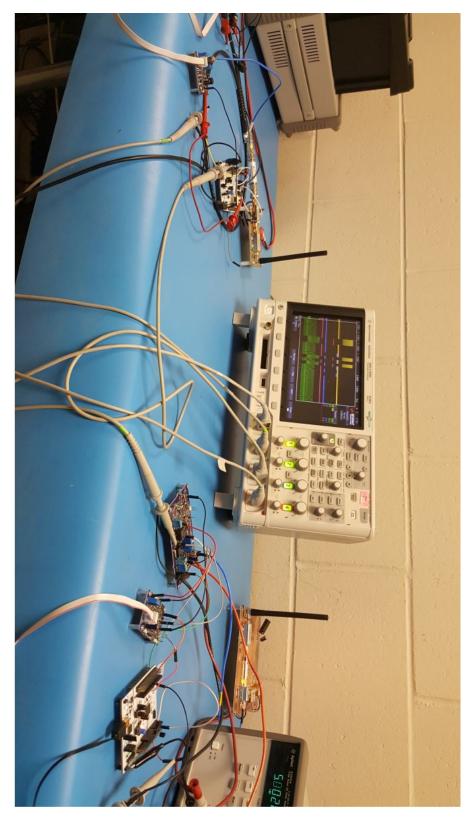

| 4.1  | Testing environment for the full communication system. Transmit side (right)                       |    |

|      | and receive side (left).                                                                           | 62 |

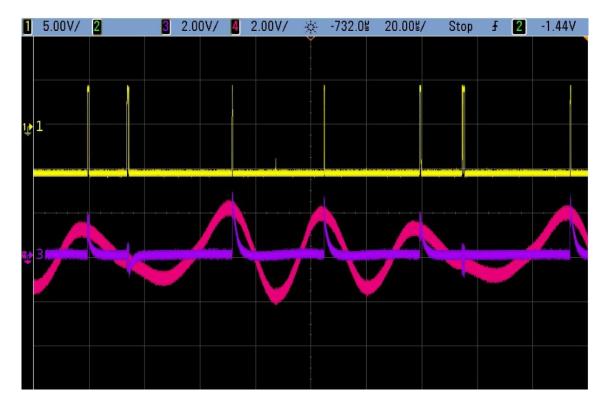

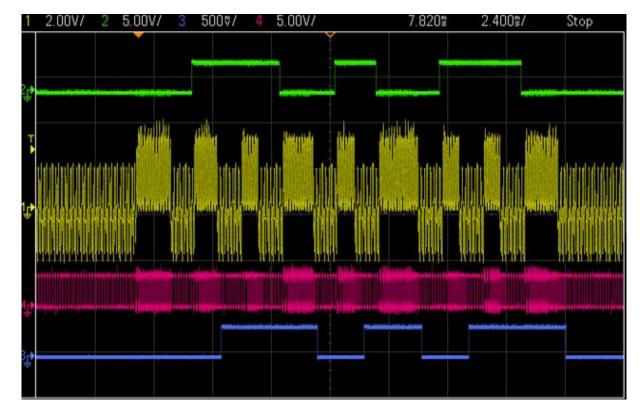

| 4.2  | Oscilloscope capture of the function of the communication system. Oscillator                       |    |

|      | output (yellow), binary data sent serially to oscillator controller (green), matched               |    |

|      | filter output (pink), and decoded binary data (blue). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 63 |

| 5.1  | Bit-error rate test results from both tests.                                                       | 64 |

# Chapter 1

## Introduction

Initially, the area of chaos was primarily studied by mathematicians and physicists in order to describe or model physical, chemical, or naturally occurring phenomena [1, 2, 3]. This motivation has now shifted towards taking advantage of the inherent properties found in chaos for various applications, such as communication systems, radar, random number generation (RNG), and noise signal generation. Some of the advantageous properties include continuous power spectral density for communication, radar, and noise signal generation. In particular, communication systems can utilize the spread spectrum properties in order to minimize the detectability of the signal. This is because the transmitted power is spread out over a large range of frequencies, which gives the illusion of an increase in the noise floor. There is a large amount of theory involved in taking advantage of chaotic dynamics; however, there is room for applying chaos theory to real-world systems. Utilizing chaos theory in electronic circuitry allows for the realization of complex waveforms and functionality with minimal electronic circuitry, potentially reducing size, weight, and cost, while enhancing reliability.

A wireless communication system based on an exactly solvable chaotic equation has been demonstrated. The system consists of a data input from a temperature sensor, a chaos oscillator controller, an exactly solvable chaotic oscillator, an AM wireless communication system, a matched filter, and a data output section. Accurate transmission and reception of the sensor data is verified via serial buses from ST microcontrollers on both ends of the system.

The exactly solvable chaotic oscillator has a fundamental frequency of approximately 18.4 kHz. It produces a baseband chaotic signal using a single-transistor sinusoidal oscillator circuit where the signum function-based nonlinearity is generated using operational amplifiers (op amps), comparators, and digital logic devices. The oscillator is controlled into two distinct orbits, representing 1s and 0s, using proportional feedback control. This type of controller compares the measured waveform with a desired waveform and applies a voltage pulse that is proportional to the magnitude of the difference between these two waveforms. This voltage pulse is then applied at regular intervals to the chaotic waveform in order to steer the trajectory to the desired orbit.

A standard frequency modulated (FM) transmitter up-converts the chaotic modulated signal onto a 2.3 GHz carrier for wireless transmission to a receiver that down converts it back to baseband. For the purposes of simplicity and reliability, as well as to maintain focus of work on the novel portions of the system, an off-the-shelf transmitter and receiver were used in the final iteration.

A matched filter for the exactly solvable system was previously developed. The matched filter was developed utilizing the exact analytical solution of the chaotic waveform, which is written as a linear convolution of a fixed basis function. It was shown that the matched filter could be written as a delay differential equation. The electronic matched filter was realized using a difference amplifier and an analog integrator, and utilizes all-pass filters to generate the necessary delay circuit that recovers the information from the received signal. The matched filter was also realized in software using an ST microcontroller. The matched filter's output waveform was sampled by a second ST microcontroller that communicates over a serial bus to recover the encoded information.

Chaotic oscillators have a wide range of possible applications, including random number generation [4], communication systems [5, 6], ranging for vehicle collision detection [7], and noise signal generation [8]. Some distinct characteristics of chaotic systems include topological mixing, determinism, long-term aperiodic behavior, sensitivity to initial conditions, as well as a spread spectrum response. The theoretical uniform power density of a chaotic system is one of the key characteristics that could be taken advantage of in their designs. A majority of these chaotic systems are defined by a an ideal set of differential equations. One of the problems with implementing these in electronics is having to account for the nonideal properties, such as temperature dependencies and limited bandwidth, of the electrical components. In addition, many of these systems are typically based on a set of higher order nonlinear dynamical equations. These systems often lack an exact analytical solution, limiting their applications in communication systems. To improve the performance of these systems in the presence of additive white Gaussian noise (AWGN), a matched filter is often used. This requires an exactly solvable solution to develop. However, there are some lower order linear systems that exhibit chaotic behavior that have been developed. An example of this can be seen in the piecewise linear system developed [10]. This system is of particular interest, due to the fact that an exact analytical solution has already been developed [12, 11].

This system is defined by a linear second-order set of differential equations with discrete states that provide a third dimension of freedom. This chaotic system has been used in the lower audio frequency range (approximately 84 Hz) for vehicle ranging and detection applications [20, 21]. It has been shown that a relatively simple matched filter can be derived and implemented at this low frequency making the system suitable for communication applications [22]. However, the low operating frequency of this design limits its practical use in a communication system that typically operate in the RF range. For this reason, the frequency of the oscillator design needs to be increased.

The low frequency oscillator featured analog and discrete components implemented on a non-permanent prototype board. One of the key components was a negative resistanceinductor-capacitor (RLC) resonance circuit realized using a negative impedance converter (NIC). The limited bandwidth of the NIC and prototype layout board proved to be one of the limiting factors in scaling the frequency. An alternative approach to the NIC has been developed with an emphasis on the hardware implementation.

Presented is a mixed-signal electronic implementation of an exactly solvable chaotic oscillator. The design is based on a single transistor in a common-base amplifier configuration

combined with an parallel inductor and capacitor (LC) resonance tank circuit and a mixedsignal feedback network. The oscillator features a simple topology that is implemented using commercial-off-the-shelf (COTS) parts. This approach is intended to increase the operating frequency of the oscillator through careful board design. The intended application for this design is for it to be used in a communication system. Included is a circuit based model of the system and simulation results.

This approach reduces cost by replacing the NIC, which requires a high bandwidth operational amplifier, with a single transistor circuit. This design takes careful consideration of the layout of the oscillator to minimize trace lengths and to reduce the overall footprint of the components.

#### Chapter 2

#### Background

#### 2.1 Beginnings of Chaos Theory

The discovery of the conditions in which random behavior occurs is generally attributed to H. Poincaré and his study of the three-body problem using Newtonian assumptions. Poincaré noted that the trajectories of the bodies was dependent on initial conditions, and for certain initial conditions, the behavior of the system was difficult to predict. Numerous studies on the three-body problem were performed [29], [30]; the prevailing consensus for some time was that the unpredictable behavior was due to noise and/or measurement error.

#### 2.1.1 The Lorenz System

An early mathematical representation for chaotic behavior in nature was that of a model of atmospheric convection developed by E. Lorenz. [24] This model showed that a fluid placed within a box that is heated in a uniform manner from the bottom and cooled from the top is a nonlinear and deterministic system, as modeled by Lorenz's simplification of the three-dimensional Navier-Stokes equations,

$$dx/dt = \sigma(y - x) \tag{2.1}$$

$$dy/dt = -x(\rho - z) - y \tag{2.2}$$

$$dz/dt = xy - \beta z \tag{2.3}$$

where  $\sigma$  corresponds to the Prandtl number,  $\rho$  corresponds to the Rayleigh number, and  $\beta$  corresponds to a physical dimension of the system. x(t) represents the rotational speed of the

Figure 2.1: Phase-space representation of the Lorenz system exhibiting chaotic behavior. Note the two orbits, giving the system the appearance of a butterfly. Source: Adapted from [27]

system, and y(t) and z(t) represent the distribution of temperature. The Rayleigh number is of particular interest in this model; it represents the amount of turbulence present in the system dynamics. At high values of p, the convection in the system becomes unstable. [28] Lorenz showed that the system exhibited chaotic behavior when  $\sigma = 10$ ,  $\rho = 28$ , and  $\beta = 8/3$ . The trajectory of this system is highly sensitive to initial conditions, though nearly all initial conditions will tend to a strange attractor trajectory known as the "Lorenz attractor". A three-dimensional phase-space representation of this attractor is shown in Fig. 2.1.

The sensitivity of this system to initial conditions led to the acceptance of the "Butterfly Effect" in which a small change in initial conditions can greatly vary the behavior of a large system. Lorenz hypothesized that further understanding of this system could lead to improved understanding and prediction of large-scale weather patterns.

#### 2.1.2 Universality and The Logistic Map

Though chaos had been mathematically modeled, the manner in which it emerges had yet to be theorized. An early demonstration of the conditions in which chaotic behavior arises was shown by M. Feigenbaum. [31] Feigenbaum showed that chaotic behavior exists throughout nature and natural phenomena, specifically citing a population of organisms with a static birth rate. To demonstrate this, a model for a dilute population of organisms was modeled as:

$$p_{n+1} = bp_n \tag{2.4}$$

where  $p_{n+1}$  is the population value dependent on the previous population value  $p_n$  multiplied by a constant birthrate *b*. Eq. 2.4 accurately describes the growth of the organism population with the solution  $p_n = p_0 b^n$  so long as there is no mutual interference or competition and the environment is fixed. When these conditions inevitably break down, the population is determined by a varying growth rate, shown in Eq. 2.5:

$$p_{n+1} = b_{eff} p_n \tag{2.5}$$

where  $b_{eff} < b$ , and  $b_{eff}$  is a function of p. One can infer that given a limited amount of resources,  $b_{eff} \cong 0$  when the population is sufficiently large. If  $p_n$  is defined as  $(b/a)x_n$ , where a is some scaling factor, then the equation can be written in the general form of a logistic map:

$$x_{n+1} = bx_n(1 - x_n) \tag{2.6}$$

Figure 2.2: Bifurcation diagram showing the value of a population given its growth rate. A single cycle exists until  $r \approx 3.0$ . The single cycle becomes unstable and is replaced by a period-doubled cycle. The pattern of instability being replaced by period doubling continues until  $r \approx 3.6$  when the system tends to an infinite number of values. Source: Adapted from [32]

By varying the growth rate, the population value can become unstable. Typically, new population values emerge as previous cycles become unstable, causing the system to oscillate between these new paths, until the system tends to an infinite number of values. This phenomena is shown as a bifurcation diagram in Fig. 2.2. Fig. 2.3 shows that the seemingly random oscillations can be brought back in to order at certain growth rates, and then quickly bifurcate back to chaotic behavior. Feigenbaum discovered that any system which exhibits this period-doubling path to chaotic behavior also exhibits the following characteristic – the distance between bifurcations asymptotically approaches the number 4.669. [32] Additionally, the strange attractors of these systems are fractals: each new bifurcation is a scaled duplicate of the original bifurcation.

These models, in addition to Lorenz's model, also display a characteristic that is often taken advantage of in its applications – sensitivity to initial conditions. Fig. 2.4 shows a

Figure 2.3: Zoomed view of bifurcation diagram. Notice the sudden transition from chaotic behavior to period-5 at  $r \approx 3.74$ , and the transition to period-3 at  $r \approx 3.83$ . It has been shown that any system which exhibits period-3 at any particular value is capable of chaotic behavior at other values. [33] Note the bifurcations after period-3, which are scaled duplicates of the initial bifurcation. Source: Adapted from [32]

plot of the values of a population for a given generation, with two initial conditions that vary by a small amount. The system dynamics, including a positive Lyapunov exponent, are identical, but a minute change in initial conditions produces a divergence that, if one did not have access to the underlying system parameters, one could not infer with any certainty that the two systems were identical.

# 2.2 Saito and Fujita's System

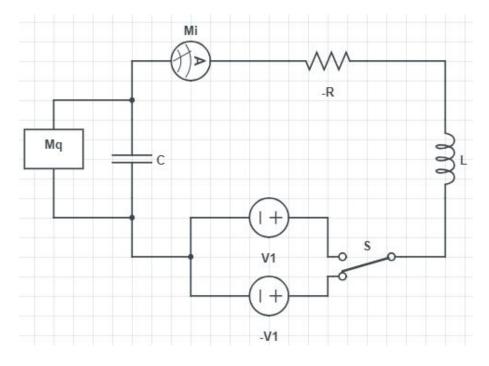

Although chaotic behavior had been identified and studied to a significant degree [13, 14, 15, 16, 17, 18, 19], there still existed difficulty in performing mathematical analysis on the systems when chaotic. Saito and Fujita proposed a novel differential equation that exhibited chaotic behavior, called the manifold piecewise linear system. [10] This system was described in physical form as a resonant circuit with a negative resistance, shown in Fig. 6.

Figure 2.4: Plot of two initial conditions of a dynamic population model with a positive Lyapunov exponent. Slight variance in initial condition causes divergence at roughly the 33rd generation. Source: Adapted from [32]

Figure 2.5: Physical representation of the manifold piecewise linear system as a resonant circuit with a negative resistance. Source: Adapted from [10]

In this circuit, -R is some negative resistance/impedance, L is and inductance, and Cis a capacitance.  $V_1$  and  $-V_1$  represent two identical voltage sources with opposite signs.  $M_q$ and  $M_i$  are charge and current measuring devices, respectively, and S is a switch dependent on a number of characteristics of the circuit at a given time. The general function of the circuit can be described as follows: When the switch is closed upward, the bias in the circuit is equal to  $V_1$ . When the charge measuring device detects that the charge on the capacitor  $q \leq q_{th}$ , where  $q_t h$  is an arbitrary charge threshold, and the current measuring device detects i = 0, the switch is flipped and the polarity of the circuit is reversed. Once the circuit, now biased at  $-V_1$  reaches the condition i = 0 and  $q > q_{th}$ , as detected by the charge and current measuring devices, the switch will return to its original position. The circuit is governed by the following parameters and equation:

$$x = \frac{q}{CV} \tag{2.7}$$

$$\tau = \frac{1}{\sqrt{LC}}t\tag{2.8}$$

$$2\delta = R\sqrt{\frac{C}{L}} \tag{2.9}$$

$$\beta = \frac{q_{th}}{CV} \tag{2.10}$$

$$\ddot{x} - 2\delta \dot{x} + x = \begin{cases} 1\\ -1 \end{cases}$$

(2.11)

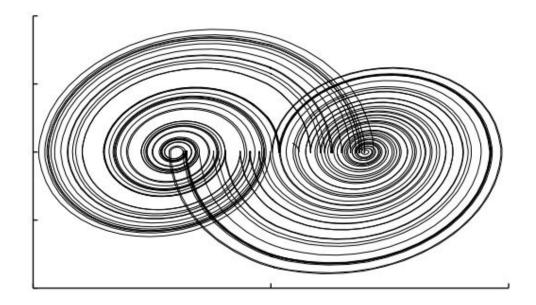

Fig. 2.6 shows the solution of Eq. 2.11 in phase-space representation, with  $\delta = 0.11$ ,  $\beta = 0$ , and initial conditions x(0) = 0.6 and  $\dot{x}(0) = 0$ . The thick bands show the presence of chaotic behavior, and the overall space resembles Lorenz's two-spiral chaos. Saito and

Figure 2.6: Phase-space plot of the solution to Eq. 2.11, with  $\delta = 0.11$ ,  $\beta = 0$ , and all initial conditions set to 0. Source: Adapted from [10]

Fujita's system showed that multi-dimensional sets of linear differential equations were not the only path to chaotic behavior – chaos could be achieved using a single equation with piecewise components. Additionally, these equations could be represented with relatively simple circuitry, as nonlinear electrical components could handle the discrete-time caveat to these systems. This analytical and simplistic approach is the basis on which the theory for the presented communication system is derived.

# 2.3 The Exactly Solvable Chaotic System

Despite the long-standing assumption that the inherent nature of chaotic systems produced no exact solution, [34] a novel chaotic oscillator system was conceived that yielded an exact analytical solution. [25]. The system is based on a linear, constant-coefficient ordinary differential equation with a discrete-time forcing function

$$\ddot{x} - 2\beta \dot{x} + (\beta^2 + \omega^2)x = (\beta^2 + \omega^2)s(t)$$

(2.12)

where s(t) is a binary waveform. For the initial conditions  $x(0) = x_0$  and  $\dot{x}(0) = y_0$ , and the parameter values  $\beta = ln(2) \ \omega = 2\pi$ . The general solution to this system takes the following form:

$$x(t) = x_b(t) + x_u(t)$$

(2.13)

where  $x_b(t)$  is a bounded particular solution and  $x_u(t)$  is a homogeneous solution. To achieve an exact solution, there must be a condition for which  $x_u(t) = 0$  for any time t. Upon analysis of the system, it was found that the term  $\beta$  was equivalent to a positive Lyapunov exponent, indicating chaotic behavior. Additionally, this condition was shown to take the form of a shift map, and it has been shown that shift maps have the chaotic characteristics of dense orbits, sensitivity to initial conditions, and topological transitivity. [35]

A significant advantage of this derivation of chaos is that the bounded solution can be realized as a linear superposition of a basis function, and the waveform can be realized in full for any binary sequence s(t). This approach to the system is defined in Eq. 2.14 and Eq. 2.15:

$$x_b(t) = \sum_{i=0}^{\infty} s_i P(t-i)$$

(2.14)

$$P(t) = \begin{cases} 2^{t-1}(\cos\omega t - \frac{\beta}{\omega}\sin\omega t), & t < 0\\ 1 - 2^{t-1}(\cos\omega t - \frac{\beta}{\omega}\sin\omega t), & t = 0\\ 0, & t > 0 \end{cases}$$

(2.15)

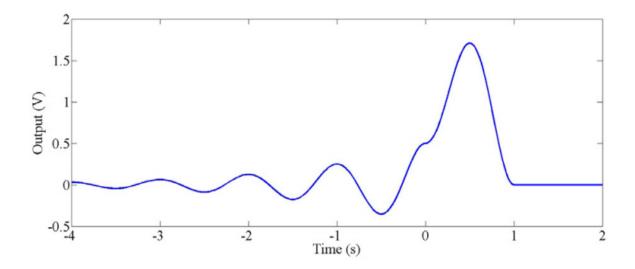

where  $x_b(t)$  is the bounded general solution and P(t) is the basis function. A plot of the basis function for the considered system is shown in Fig. 2.7. So, for any given sequence s(t) an initial condition exists that yields a bounded particular solution. It stands to reason, then, that there must exist an initial condition for which a certain binary sequence yields a bounded particular solution.

Figure 2.7: Basis function that can be superposed over a binary sequence to form a chaotic wave. Source: Adapted from [25]

# 2.4 The Exactly Solvable System in Communications

From this defined set of linear differential equations, a nonlinear system was considered based on the fact that the mapping of initial conditions to binary sequences constitutes a present nonlinearity in the general system. A nonlinear ordinary differential equation was considered:

$$\ddot{u} - 2\beta \dot{u} + (\beta^2 + \omega^2)u = (\beta)^2 + \omega^2)[2s(t)]$$

(2.16)

where x(t) is the output of the system,  $\omega$  is the fundamental frequency, and  $\beta$  corresponds to a Lyapunov exponent. In order for the system to exhibit chaotic behavior, the Lyapunov exponent must remain positive; for this system,  $0 < \beta \leq ln(2)$  constitutes a positive lyapunov exponent. s(t) is a nonlinear forcing function described as the piecewise function:

$$s(t) = \begin{cases} +1, & x(t) \ge 0\\ -1, & x(t) < 0 \end{cases}$$

(2.17)

Figure 2.8: Plot of the output of the exactly solvable system. The growing oscillation occurs around one of two equilibrium points until a zero crossing of the output and its derivative, and the oscillation is forced to the equilibrium point with opposite sign. Source: Adapted from [36]

with the initial conditions defined as  $s(0) = u_0$  and  $\dot{u}(0) = v_0$ , with  $\beta = \ln 2$  and  $\omega = 2\pi$ . The piecewise portion s(t) can be treated as a feedback applied to an oscillator, and can be represented practically as a signum function that constitutes the equilibrium point about which the unstable oscillation occurs. The oscillation will increase about an equilibrium point until the guard condition is reached, at which time the equilibrium point will switch, and the unstable oscillation will continue with lower energy around the new equilibrium point. The guard condition is defined as the point at which the output of the system u(t) and the derivative of the output  $\dot{u}(t)$  both cross zero. This means that the oscillation will grow until it reaches the energy required to maintain an amplitude of 1, and once a local maximum/minimum of oscillation is reached, the oscillation will be steered to a new equilibrium point, and the energy of the oscillation will be lost, allowing it to grow again. A graphical representation of the function of the system is shown in Fig. 2.8.

It has been demonstrated that an oscillation of this type can be controlled without knowledge of the system dynamics by using small perturbations to prevent the guard condition from forcing the oscillation to the next equilibrium point. [37] This effectively enables s(t) to be controlled externally, and this ability is the basis on which data is injected into the communication system. If s(t) can be controlled, then it follows that a sequence of data could be used as the basis of operation of a control system, and the oscillations would occur around the desired equilibrium point.

### 2.5 A Matched Filter for the Chaotic System

In order for communication to occur, it is necessary that the binary data injected into the oscillator be separated from the oscillatory portion of the signal [40, 41]. This is achieved by inserting a matched filter on the receive side of the system, which is designed to maximize signal-to-noise ratio. [38] Chaotic systems are known to have the property of flat power-spectral density, an attribute shared with AWGN. [39] Therefore, a matched filter designed to separate the desired signal, which resembles noise, from any noise present in the environment should be extremely effective in noise-laden environments. A mathematical representation of a matched filter for this exact purpose was developed by Corron et al. [22] This derivation utilizes the fact that the chaotic system has an exact solution and can be written as a convolution of a basis function with a series of binary symbols, and the fact that the matched filter can be realized as a finite-impulse response (FIR) filter, using the time-reversed basis function as the impulse response. P(-t) is defined as:

$$\ddot{P} + 2\beta \dot{P} + (\omega^2 + \beta^2)P = (\omega^2 + \beta^2)h(t)$$

(2.18)

where h(t) is a pulse,

$$h(t) = \begin{cases} 1, & -1 \le t < 0\\ 0, & all \ other \ t \end{cases}$$

(2.19)

Differentiation of Eq. 2.19 yields a time-shifted unit impulse function combined with another unit impulse function at t = 0. This is a general form of the impulse response of the matched filter for the basis function, and therefore the equation of the matched filter can be described by the following:

$$\dot{\eta} = v(t+1) - v(t) \tag{2.20}$$

$$\ddot{\xi} + 2\beta \dot{x}i + (\omega^2 + \beta^2)\xi = (\omega^2 + \beta^2)\eta(t)$$

(2.21)

where v(t) is the input to the matched filter,  $\eta(t)$  is an intermediate state, and  $\xi(t)$  is the output of the matched filter. The intermediate state  $\eta(t)$  is defined as:

$$\eta(t) = \int v(t' + 1 - v(t')dt'.$$

(2.22)

The intermediate state is equivalent to the input to the filter subtracted from the input delayed by one period. The output of the intermediate stage is then compared to a threshold to recreate the symbolic data of the original waveform. This generated waveform is then fed to a resonant circuit that matches the resonant circuit present in the original system, to recreate the original chaotic waveform. This waveform is then compared to a threshold to extract the symbolic data.

## Chapter 3

#### Development

# 3.1 Chaotic Oscillator Realization

#### 3.1.1 Low-Frequency Oscillator in Electronics

Due to the simplicity of the discussed exactly solvable chaotic system, successful design and implementation in electronics can be achieved with relative ease. A low-frequency oscillator was developed by Corron et al. [12], and the design was based on the construction of an exactly solvable system with respect to a folded band map, instead of a shift map. This allowed for the process of encoding data to be executed with less difficulty. This system can also be written as a linear convolution of a basis function and symbolic data, allowing for the same derivation of a matched filter. The continuous-time portion of the oscillator is described by the following:

$$\frac{d^2u}{dt^2} - 2\beta \frac{du}{dt} + (\omega^2 + \beta^2) \cdot (u - s) = 0$$

(3.1)

where  $\omega = 2\pi$  and  $\beta = 0$ . The transitions of the discrete-time portion of the system are described as:

$$\frac{du}{dt}(t) = 0 \Rightarrow s(t) = H(u(t) - 1)$$

(3.2)

where H(t) is the left-continuous Heaviside function,

$$H(t) = \begin{cases} 1, & x > 0 \\ 0, & x \le 0 \end{cases}$$

(3.3)

Figure 3.1: Operation of the exactly solvable folded-band oscillator. The oscillation grows until the amplitude surpasses +1, then at the local maximum of the oscillation (roughly t = 7.5) the equilibrium point is switched to 0 for one half period. The equilibrium point is then switched back to 1, effectively removing energy from the oscillation and allowing it to continue without becoming unbounded. Source: Adapted from [12]

This describes the guard condition for the system, as the binary state s(t) is assigned the value of the shown Heaviside function shifted by unity when the derivative of the output of the system reaches zero. This system operates in a similar manner to the previously discussed system based on a shift map. Energy is injected into the system until the guard condition is triggered. The equilibrium point is switched, and the oscillation continues for half the oscillation period about the new equilibrium point, at which time the point switches back. This effectively removes energy from the system to a value below the guard condition, and allows it to continue functioning in a bounded manner. This operation is shown in Fig. 3.1.

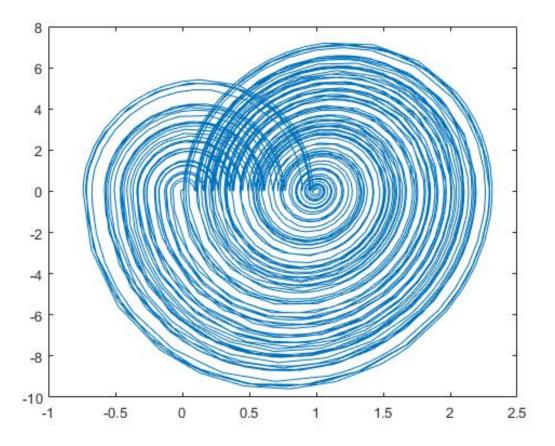

The dynamics of this system can also be viewed from the perspective of a phase space, with a clockwise spiral outward about an attractor at the origin until the x-value passes one, and once the spiral crosses the y-axis (derivative equal to zero), the attractor shifts to 1, and the radius of the spiral tightens around the new attractor for half a rotation, then the attractor shifts back to the origin and the spiral "folds" back on itself and continues its

Figure 3.2: Phase-space representation of the function of the chaotic system. Source: Adapted from [12]

original clockwise spiral about the origin. The phase-space representation is shown in Fig. 3.2.

Another way to grasp the function of this system is through a Poincaré return map. The map is generated using the local maxima of the oscillator's waveform (Fig 3.1). For any  $t_n$  where the s(t) remains the same, the solution

$$u(t) = s_n + (u_n - s_n)e^{\beta(t - t_n)}\cos\omega(t - t_n) - \frac{\beta}{w}\sin\omega(t - t_n)$$

(3.4)

is valid. The times at which the guard condition allows the state to change are described by

$$u(t_n + 1/2) = s_n - e^{\beta/2}(u_n - s_n).$$

(3.5)

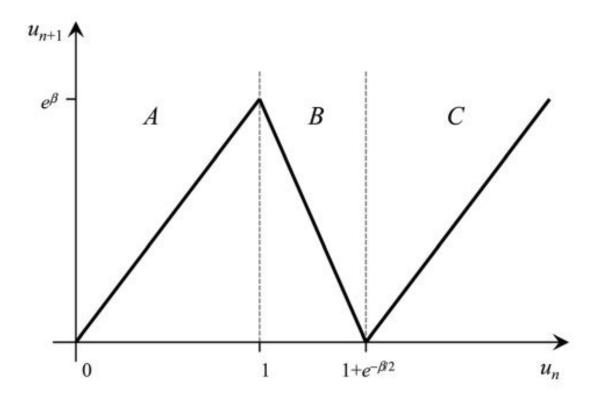

Figure 3.3: Return map for the chaotic system. Source: Adapted from [12]

The return map can then be derived by comparing each local maximum with the next local maximum in time. This relationship is modeled by

$$u(t_n + 1) = e^{\beta} u_n > 0, (3.6)$$

which describes the first segment of the return map. The second and third segments are modeled by

$$u(t_n + 3/2) = (e^{\beta} + e^{3\beta/2}) - e^{3\beta/2}u_n > 0$$

(3.7)

and

$$u(t_n + 1) = e^{\beta} u_n - (e^{\beta/2} + e^{\beta}), \qquad (3.8)$$

respectively. The return map generated by these three parameters is shown in Fig. 3.3. The slopes of segments A and C are identical, and the slop of segment B is negative, but greater in magnitude than A and C. Segment B corresponds to the "folding" shown in the phase-space representation. Each segment has a slope magnitude greater than one, indicating chaotic behavior [42].

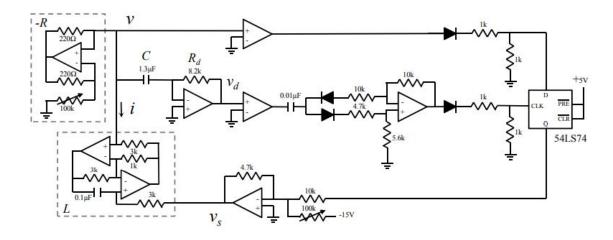

This chaotic system was also developed in circuitry [42]. This circuit was constructed using commercially available analog and digital electronic components, and the schematic for this circuit is shown in Fig 3.4. Notable off-the-shelf components are as follows: omamps are all of type TL082, diodes 1N4148. The circuit is comprised of three stages: an RLC resonant circuit, a guard condition evaluation stage, and a switching stage. The box denoted by -R corresponds to the realization of a negative resistor using an op-amp circuit, and the box denoted by L corresponds to the realization of an inductance by a negative impedance converter (NIC). The resonant portion of the oscillator circuit is modeled by

$$C\frac{dv}{dt} - \frac{v}{R} + i = 0 \tag{3.9}$$

and

$$L\frac{di}{dt} = v - v_s \tag{3.10}$$

where v is the voltage of the tank circuit, i is the inductor current, and  $v_s$  is a feedback term generated by the switching stage. This stage is responsible for adding oscillatory energy in the system. The value of -R is paramount to generating chaotic behavior, and through tuning it was found that a magnitude of  $R \approx 6.5k\Omega$  yielded the desired function. The tank voltage is fed to an op-amp configured as a comparator with the negative terminal tied to ground, which measures the sign of the tank voltage. The comparator op-amp is railed, so a positive tank voltage will correspond to a digital high value, and a negative tank voltage to a digital low. The diode and voltage divider bring the op-amp output voltage down to

Figure 3.4: Schematic of low-frequency oscillator circuit. Source: Adapted from [42]

standard logic levels. The current through the capacitor is converted to a voltage  $v_d$  using an op-amp configured as a voltage-to-current converter;  $v_d$  is described by

$$v_d = -R_d C \frac{dv}{dt} \tag{3.11}$$

A comparator, configured in the same manner as the one first discussed, checks the sign of  $v_d$ . The DC logical output of the comparator is blocked by the  $0.01\mu$ F capacitor, and is converted into a short pulse when the output of the comparator changes. This pulse is brought to the appropriate logic levels by the diodes and difference amplifier. Concisely put, the middle trace of the circuit generates a pulse when the sign of the derivative of v changes. This pulse is treated as the clock input to the flip-flop. The sign of the output voltage is treated as the input of the flip-flop, and the output is fed back to the resonant circuit. The flip-flop serves the function of holding the sign of the output voltage at every change in sign of the derivative of the output voltage. The output is fed to an op-amp configured as a summer; this amplifies and level-shifts the output of the flip-flop to symmetrical voltages, in this case  $\pm 15$ V. The feedback circuit can effectively be modeled mathematically as a signum function

$$v_s = V sgn(v) + V_0 \tag{3.12}$$

Figure 3.5: Simulated output of low-frequency electronic oscillator. Source: Adapted from [42]

where  $V_0$  is a small offset to account for asymmetries in the physical implementation of the circuit. A simulated output of this circuit is shown in Fig. 3.5.

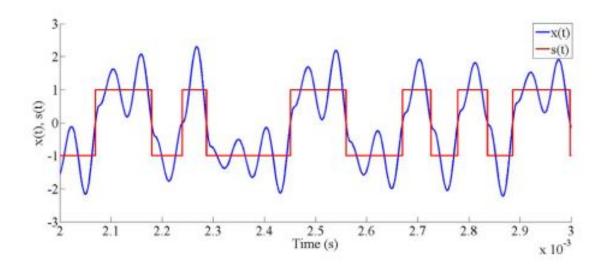

This circuit operates in a similar manner as those previously discussed: an oscillation is centered around  $\pm 1$ V, the oscillation grows until the amplitude is greater than 1V and the oscillation reaches a local maximum. The guard condition forces the circuit to the other attractor and the oscillation begins to grow again. The location of the attractors over time defines the binary sequence, and this sequence is overlaid on the oscillator output. The operation of the circuit can also be understood through the phase-space representation, as shown in Fig. 3.6.

Examining the phase-space representation, assuming a starting position around the negative attractor, it can be seen that the trajectory spirals clockwise outward from the attractor until its radius from the attractor is greater than 1, and when the spiral reaches a y-axis value of zero, the feedback network forces the oscillation to take place around the opposite attractor, causing a fold in the trajectory. The trajectory then continues around the new attractor until the guard condition is met again. Upon simple visual examination, the presence of chaos can be deduced from the thick, dense bands around each attractor.

Figure 3.6: Phase-space representation of the electronic chaotic oscillator. Source: Adapted from [42]

Figure 3.7: Electronic schematic for the high-frequency chaotic oscillator. Source: Adapted from [5]

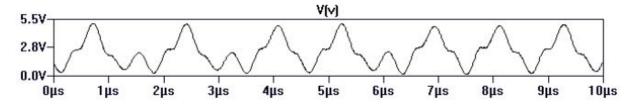

Figure 3.8: Output of the high-frequency chaotic oscillator. Source: Adapted from [5]

## 3.1.2 High-Frequency Oscillator in Electronics

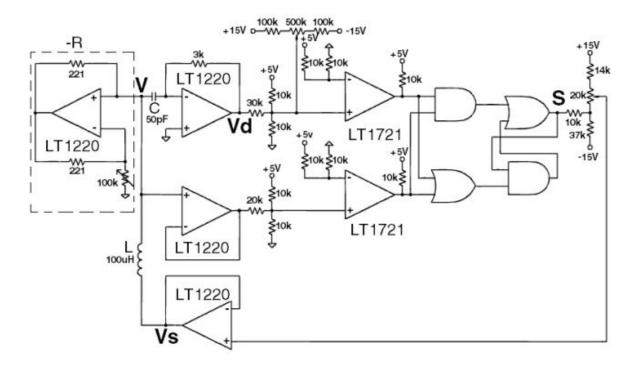

Whereas the original system was derived and proved as a low-frequency system (roughly 84 Hz), a similar chaotic system has been realized at high-frequency, allowing for feasible use in communication systems. This high-frequency system was realized by Beal et al. [5] as an exact folded-band chaotic oscillator, with a similar theoretical derivation to the circuit developed by Corron et al. The schematic for the implementation in electronics of the high-frequency chaotic system is shown in Fig. 3.7.

Components were chosen for the specific purpose of high-frequency operation. All opamps utilized in this design are Linear Technology LT1220, due to its favorable characteristics

Figure 3.9: Symbolic content of the high-frequency chaotic oscillator. Source: Adapted from [5]

at the desired operating frequency of 1 MHz. The impedance converter used to simulate inductance in the low-frequency design was replaced with a real inductor, with a value of 100uH and a series resistance of 1 $\Omega$ . Potentiometers were added to allow for tuning of various parameters to ensure the sensitive conditions that result in chaotic behavior are met. These adjustments included scaling the value of  $v_d$  and  $v_s$ , and adjusting the value of -R. The flip-flop used for the generation of the symbolic content in the low-frequency design was replaced with a network of logic gates. This network is fed by v and  $v_d$  converted to logic levels. The output of the oscillator is shown in Fig. 3.8 and the symbolic content is shown in Fig. 3.9. Additionally, a phase-space plot of the circuit simulated with real components is shown in Fig. 3.10.

Due to the circuit being simulated with non-ideal components, there are a few noticeable differences in the resulting phase plot as compared to the phase plot of the low-frequency oscillator. Perhaps the most obvious difference is the "wrinkling" of the plot near the folding action. This is likely caused by non-ideal switching within the logic network, causing some secondary oscillations in the resonant circuit. These oscillations are quickly damped and do not have a major effect on the desired operation of the system. Secondly, the folding condition does not take place exactly along the x-axis, and this can perhaps be attributed to hysteresis within the non-ideal active components present. Lastly, the attractors are no longer centered around  $\pm 1$ ; this is certainly caused by the lack of chaotic behavior during the simulation being remedied by an adjustment of the potentiometer controlling the levels

Figure 3.10: Phase-space representation of the high-frequency oscillator. Source: Adapted from [5]

of the symbolic content s. Overall, this system functions within the necessary parameters to allow for use in communication systems.

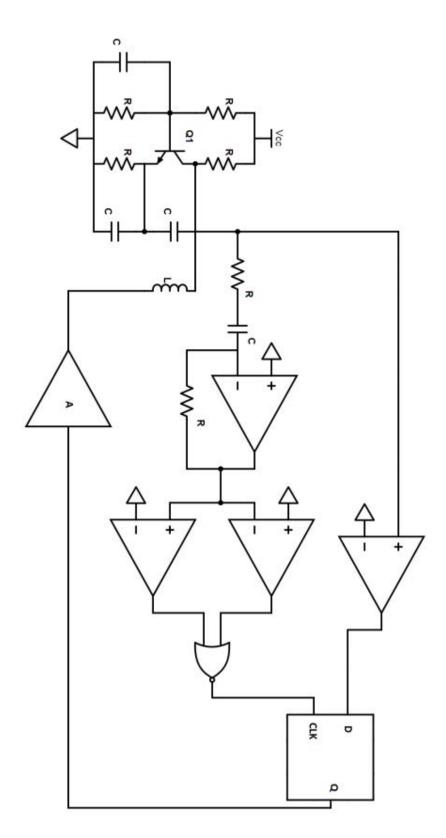

# 3.1.3 The Single-Transistor Chaotic Oscillator and its Implementation in Hardware

While the previously discussed high-frequency system simulated with real components is able to function properly within the simulation environment, implementation in hardware is somewhat difficult due to the narrow band of tuned parameters that allow for chaotic operations, and the inherent variance of virtually every component with respect to the ambient conditions. For this reason, a lower-frequency system was designed by Rhea et al. [45] to somewhat account for the variations in the ambient conditions in which the physical oscillator would be placed, and allow for the system to be re-tuned relatively infrequently.

Figure 3.11: Stretch-twist-fold phenomenon. Source: Adapted from [44]

This system is based on the previously discussed exactly solvable chaotic system that can be considered a convolution of a linear basis function and a binary sequence. In this system, the two attractors are defined as  $\pm 1$ . The design of this particular system is based on an easy-to-grasp description of chaotic behavior by E. Ott [26]. The process described is that of the manipulation of a circle. To begin, a circle is stretched until it reaches a certain size, then it is twisted into a figure-8, and finally folded back on itself, at which point the two stacked circles merge and become a single, smaller circle. A visual representation is shown in Fig. 3.11, and it is known that this phenomenon can describe the behavior of various systems. [44]. The "stretching" corresponds to the exponential sinusoidal growth of the system. In the implementation of this design, this is performed by a negative RLC circuit. A negative impedance implies the addition of energy into the system. This growth is unstable, so there must be a limiter in place to prevent failure of components. This is performed by a clock signal that is generated to trigger the "twisting" and "folding" processes, which are analogous to the changing of attractors and removal of energy from the system. A block diagram of this process is shown in Fig. 3.12.

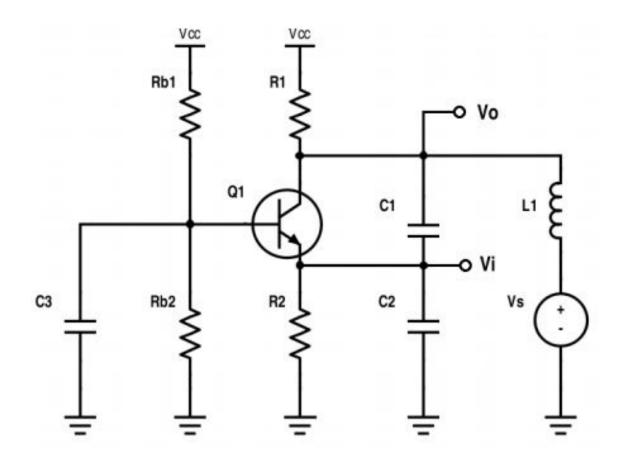

A feature of this design is the replacing of the op-amp NIC with a single bipolar junction transistor (BJT) in common-base configuration. A schematic of the resulting resonant circuit is shown in Fig. 3.13. The relevant components were selected with respect to a resonant frequency of 18.4 kHz. The capacitors C1 and C2 function as both bypass capacitors for the

Figure 3.12: Block diagram of approach to oscillator design. Source: Adapted from [45]

Figure 3.13: Schematic of 18.4 kHz resonant circuit. Source: Adapted from [45]

Figure 3.14: Equivalent circuit for single-transistor resonant circuit. Source: Adapted from [45]

bias network of the transistor, and as a component of the resonant circuit formed with L1. The voltage source  $V_s$  is defined by the piecewise linear function previously discussed, and it corresponds to the feedback voltage that serves to center the oscillation at one of the two defined attractors. Modeling the transistor in its application as a voltage-controlled voltage source, and knowing the states of the discrete-time signal, nodal analysis can be performed on the equivalent circuit, shown in Fig. 3.14, yielding

$$\frac{V_i}{\frac{1}{sC_1}} + \frac{V_i}{R_1} + \frac{V_i - V_0}{\frac{1}{sC_2}} = 0$$

(3.13)

$$\frac{V_0 - V_s}{sL} + \frac{v_0 - V_i}{\frac{1}{sC_2}} + \frac{V_0 - A_0 V_i}{R_2} = 0$$

(3.14)

where  $V_0$  is the output taken from the collector of the BJT,  $V_i$  is the input to the emitter, and  $V_s$  is a known binary sequence. The transfer function for this circuit is described by

$$\frac{V_0}{V_s} = \frac{s(C_1 + C_2) + \frac{1}{R_1}}{s^3(LC_1C_2) + s^2(B) + s(C_1 + C_2 + \frac{L}{R_1R_2}) + \frac{1}{R_1}}$$

(3.15)

where

$$B = \left(\frac{C_2L}{R_1} + \frac{L(C_1 + C_2)}{R_2} - A_V C_2 L\right).$$

(3.16)

One drawback to the design approach for this system is that the resonant circuit being replaced by the single BJT and the tank circuit constructed with a physical inductor and capacitor effectively make this system third-order, though the third order terms are many orders of magnitude smaller than the first and second order terms. To ensure this behavior would not render the previously developed approach to the design of a matched filter ineffective, the circuit was constructed and further simulated.

For evaluation, a SPICE model of the circuit was designed and tested. The circuit utilizes the single transistor model in combination with an LC tank circuit to create the required -RLC component. The resonant circuit effectively adds energy to the system, creating a growing oscillation. This oscillation is fed into a comparator with the negative reference terminal grounded. The output of the comparator is fed into a D-latch as the input D, which functions as the folding mechanism of the system. The clock signal of the latch is controlled via a network that determines the sign of the derivative of the resonant circuit output. This network acts as the guard condition and functions by feeding the output of the resonant circuit into an op-amp configured as a differentiator. To detect a zero-crossing of the derivative, two differentiators, one with the positive terminal as a reference and the other with the negative terminal as a reference, take the output of the differentiator and compare it to ground. The outputs of these comparators are fed into a NOR gate, which then acts as the clock signal for the latch. The function of this center trace is to create a pulse that will cause the latch to accept a new input from the comparator on the top trace. This pulse is created due to the hysteresis present in the dual-comparator configuration, which means that during any zero-crossing event, there will be a short time when both comparators are driven low, which will drive the output of the NOR gate high. A schematic of the full circuit is shown in Fig. 3.15, and the simulation results are shown as a time-domain plot (Fig. 3.16) and a phase plot (Fig. 3.17).

From visual inspection of the simulation results, it is not possible to detect the presence of third-order dynamics. The system behaves in a more desirable manner, in fact, as the transient periods and noticeable hysteresis present in the high-frequency design are not present in this design.

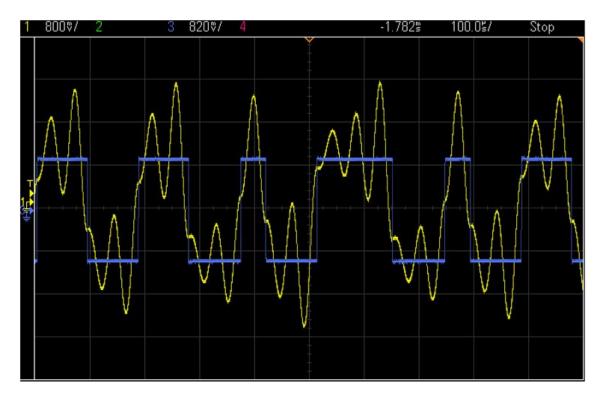

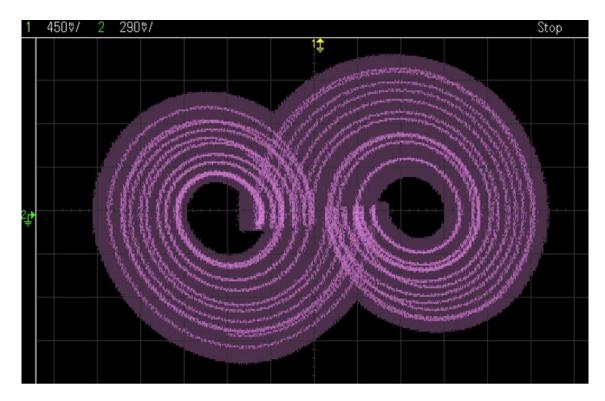

This circuit was implemented in hardware via a four-layer PCB. To ensure proper operation, the components were laid out with consideration to reducing the average trace length. Additionally, the second and fourth layers were configured as ground planes to isolate the components on the top layer from the power rails on the third layer. Potentiometers were placed at the base, collector, and emitter of the BJT, as well as on the SMA output of the oscillator, to ensure compatibility with transmitter and receiver components. Trimmer pots were also used on the  $V_s$  output to ensure the levels could always be tuned to  $\pm 1$ V. These design considerations made the physical oscillator relatively easy to tune to account for changes in hardware component parameters due to ambient conditions. A time-domain oscilloscope capture is shown in Fig 3.18, and a phase space capture is shown in Fig. 3.19. The time-domain capture shows probes of the output V and the symbolic content  $V_s$ . This operation, along with the presence of the double-scroll signature in the phase-space capture, is consistent with the representation of the dynamics of the theoretical systems.

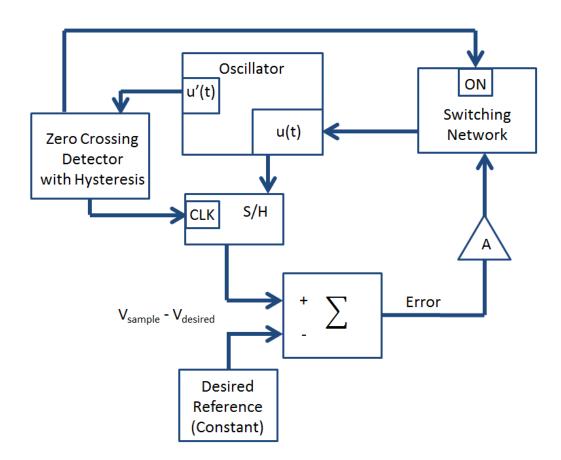

#### 3.2 Oscillator Controller

To allow the oscillator to act appropriately upon a desired serial sequence of binary data, a controller was developed by Rhea et al [46]. The design approach to the controller is based on "steering" the oscillator output value toward a desired value using proportional control, based on the difference between the oscillator's output and the desired reference

Figure 3.15: Schematic of single-transistor chaotic oscillator in SPICE. Source: Adapted from [45]

Figure 3.16: Time-domain output of oscillator. Source: Adapted from [45]

Figure 3.17: Phase plot of simulation. Source: Adapted from [45]

Figure 3.18: Time-domain oscilloscope capture of hardware oscillator output, overlaid with s(t) (blue). Source: Adapted from [45]

Figure 3.19: Phase-space oscilloscope capture of hardware oscillator. Source: Adapted from [45]

Figure 3.20: Oscillator controller block diagram.

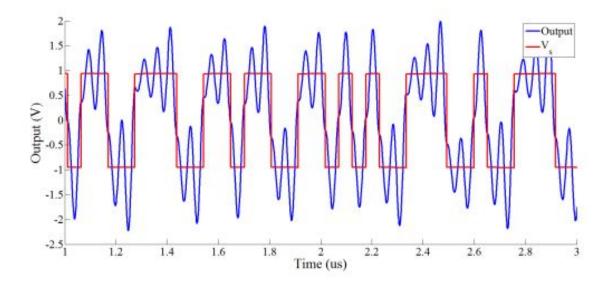

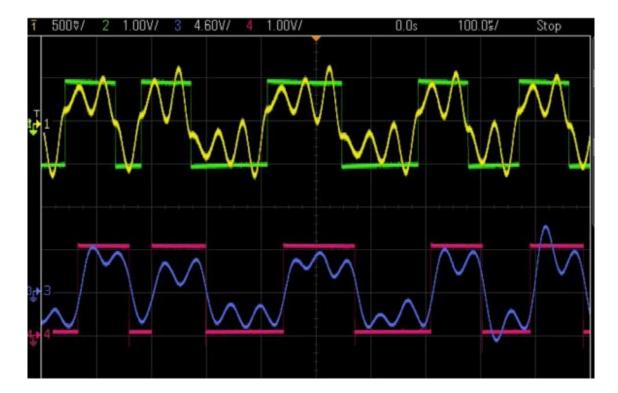

voltage. This allows the reference voltage to be controlled externally, giving the system the ability to accept an input of symbolic data. This controller uses the oscillator output v and the output derivative  $v_d$  as inputs. A reference voltage is applied to the controller given the desired state of the symbolic portion of the oscillator s(t). Both the reference voltage and the oscillator output voltage are buffered, and the reference voltage is scaled via an op-amp in a non-inverting configuration. A potentiometer is placed in the feedback path to allow for tuning of the value of the reference voltage. The oscillator output voltage and the reference voltage are then compared, and an error value is generated. Meanwhile, the derivative of the oscillator output is fed into two parallel amplifiers; one inverting and the other noninverting. The outputs of the parallel amplifiers are then used as the inputs to a NOR gate. This network takes advantage of the hysteresis present in the amplifier configuration to generate a short pulse as the derivative of the oscillator output crosses zero. This pulse is fed into the gate of an N-channel MOSFET, while the drain is driven by the previously generated error value. The output is taken at the source of the MOSFET, and is a pulse that varies in magnitude depending on the error magnitude and is allowed to conduct when given a pulse from the NOR gate. This pulse is fed into a non-inverting op-amp circuit, which contains a potentiometer to allow for the adjustment of pulse length. This effectively "steers" the oscillator back to the desired trajectory when the oscillator is nearing the triggering of the guard condition. It is necessary to adjust the pulse length somewhat infrequently due to the small variances that can appear in the oscillator output caused by changing ambient conditions. A block diagram for the controller is shown in Fig. 3.20, and the schematic is shown in Fig. 3.21. The controller was implemented in hardware via a 4-layer PCB, with attention paid to overall trace length. The second and fourth layers were configured as ground planes to isolate the components from the power rails, as well as to ensure the variation in the ground reference for all components was as small as possible. An oscilloscope capture of the controlled oscillator is shown in Fig. 3.22. This shows the reference voltage given to the controller (green), and the corresponding hardware oscillator output (yellow). A more detailed view of the controller function is shown in Fig. 3.23. This shows the hardware oscillator output (pink), the pulses generated at the points where the derivative of the output crosses zero (yellow) and the magnitude of the error (purple) when the MOSFET is allowed to conduct.

#### 3.3 Matched Filter Realization

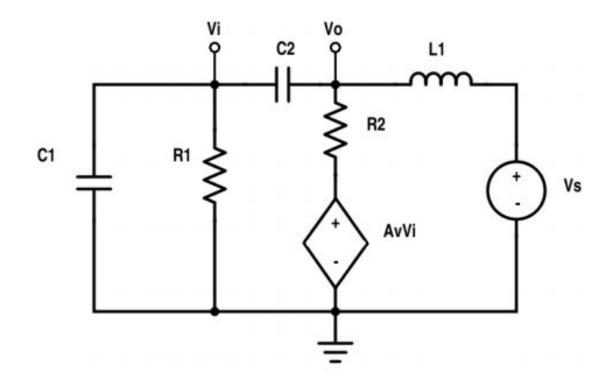

To allow for the extraction of the symbolic content of the waveform, a matched filter was developed by Werner et al. [36], using the theory for the matched filter derived by Corron et al [22]. The matched filter is designed to be the ideal filter for a particular system by correlating the filter input with a basis function known to represent the dynamics of the transmitting system. The derived equation for the intermediate stage of a matched filter, discussed previously, is

$$\eta(t) = \int v(t'+1) - v(t')dt'.$$

(3.17)

This corresponds to the signal being passed through a delay line that delays the signal by one period, then subtracts that delayed signal from the origininal signal, and integrates. The subtraction of the delayed signal with the current signal cancels most of the periodic content of the received waveform, leaving only the large shifts between attractors. The integration stage acts as a low-pass filter, further removing the higher-frequency information left over after the subtraction stage. This description of the filter allows for easy implementation in analog electronics. A schematic showing the various stages present in the matched filter is shown in Fig. 3.24. The received waveform v is input into a delay line, consisting of four amplifier stages with unity gain. These op-amps are configured as inverting first-order all-pass filters. Four stages were chosen due to the fact that the oscillator waveform contains various frequency components, and the change in delay with frequency leads to some distortion in the output. This is especially notable with two stages, where each stage must

Figure 3.21: Oscillator controller schematic.

Figure 3.22: Oscilloscope capture of the oscillator output when the controller receives a 1-0-1-0 pattern. Source: Adapted from [46]

Figure 3.23: Phase-space capture of the oscillator receiving a 1-0-1-0 pattern. Source: Adapted from [46]

Figure 3.24: Oscilloscope capture of the function of the controller.

shift the signal through 180 degrees. To reduce distortion, the amount of delay required from each stage needs to be reduced. This leads to a small increase in complexity from the need for more stages, but the signal quality at the delay output is increased. This delayed signal, along with the original input, are fed into a difference amplifier, which subtracts the original input from the delayed input. This value is then fed to an op-amp configured as a low-pass filter, which acts as the transfer function  $\frac{1}{s}$ , which is integration in the frequency domain. The output of this integrator is  $\eta$ , the symbolic content of the original waveform. Additionally, a resonant circuit is present as the final stage of the design. This is used for verification purposes, to show the mathematically derived output  $\xi$ , which should contain the same oscillatory dynamics as the original chaotic system.

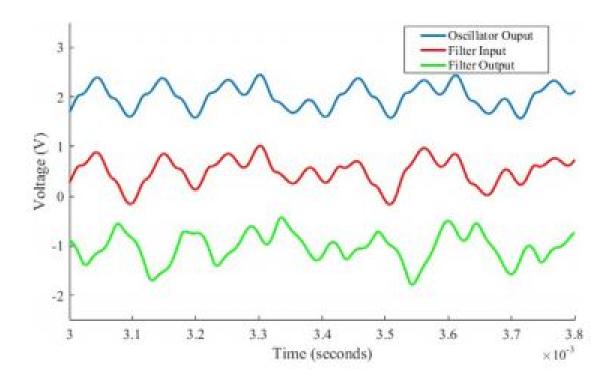

To verify this design and conjecture, a simulation of the electronic matched filter was created and tested using a simulated chaotic oscillator output mixed with noise. The results of this test are shown in Fig. 3.26. The original waveform (blue) is injected with noise

Figure 3.25: Generalized schematic of the analog matched filter. Source: Adapted from [36]

(red), and the matched filter is able to roughly produce a waveform with the original system dynamics. Discrepancies between the two waveforms are due to the fact that real filters have a limited passband, which will inevitably eliminate some high-frequency components of the spread-spectrum chaotic waveform, and also to the small variations in real components used to create the resonant circuit in the matched filter designed to replicate the resonant circuit in the oscillator. Additionally, the simulation was performed with deliberate alterations to the symbolic content of the waveforms using noise. The results of this test are shown in Fig. 3.27. The matched filter is able to remove the falsified data from the test waveform and reconstruct the original bitstream.

After demonstration of the successful function of the electronic design, the filter was constructed in hardware. To ensure the correct delay time, care must be taken in component selection. To ensure the fundamental frequency of the oscillator is not attenuated,  $C_N$  and  $R_N$  must be selected to ensure the gain bandwidth product is appropriate. To ensure each

Figure 3.26: Results of the simulation of showing the output of matched filter when supplied with a noisy input signal. Source: Adapted from [36]

Figure 3.27: Simulation with falsified symbolic content and matched filter correction of falsified data. Source: Adapted from [36]

Figure 3.28: Oscilloscope capture of oscillator output overlaid with symbolic content, and the matched filter output  $\xi$  overlaid with symbolic output  $\eta$ . Source: Adapted from [36]

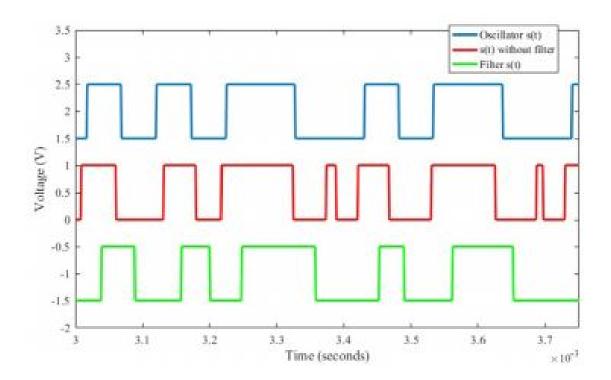

stage of the delay line produces a phase shift of 90 degrees, the physical components  $C_A$ and  $R_A$  must be selected to be as close to identical as possible Additionally, to recreate the original chaotic waveform as accurately as possible, the R, L, and C, present in the resonant circuit must match the resonant circuit of the oscillator. Given the oscillator's operation at 18.4 kHz, the component values were chosen to be  $C_A = 0.1$ ,  $R_A = 75\omega$ ,  $C_N = 0.1$ ,  $R_N = 84\omega$ , C = 0.5,  $R = 18k\omega$ , and L = 150. This hardware matched filter was then tested with a hardware oscillator injected with a generated noise signal. Fig. 3.28 shows an oscilloscope capture of this test. The oscillator (yellow) is injected with a noise signal and its symbolic content (green) is altered. The matched filter is able to extract the correct symbolic data (red) and roughly reconstruct the original system dynamics (blue).

In addition to this analog filter, a digital matched filter was developed. This was done to increase the flexibility of the matched filter design for possible use in updated systems with oscillators that have different parameters to the one used in this system. The digital

Figure 3.29: General diagram of an FIR filter. Source: Adapted from [50]

filter was implemented as a software-defined finite-impulse-response (FIR) filter. The general equation for an  $N^{th}$  order FIR filter is

$$Y[n] = X[n] * H[n] = \sum_{k=0}^{N-1} H[k] * X[n-k], \qquad (3.18)$$

which is a sum of convolutions, and the exact function is described by the values of the FIR coefficients, H. [49]. A block diagram depicting the general form of an FIR is shown in Fig. 3.29. While this approach is implementable in hardware, it is less than desirable due to the use of multipliers; however, taking a software approach to this problem alleviates any issues using certain undesirable hardware components.

To lay out the algorithmic approach to the design of the matched filter in software, a MATLAB script was written to perform the operations required in an intuitive way. A Simulink model was designed to simulate the function of the oscillator. The model hierarchy is shown in Fig. 3.30 and Fig. 3.31. The simulated output of this oscillator was then decimated to simulate the waveform being sampled at a rate of 4 samples/second, which, at a fundamental frequency of 18.4 kHz, amounts to a sample rate of 36.8 kSamples/s; this sampling rate can be handled easily by commonly available hardware. Additionally, this sampling rate allows a sample to be stored until four more samples are taken, which will amount to a delay of 360 degrees. The decimated simulink output is shown in Fig. 3.32.

Figure 3.30: Simulink model of the oscillator with tunable parameters and outputs to the MATLAB workspace.

be interpreted properly by a 12-bit analog-digital converter (ADC). The array of data is then subtracted from the array shifted by 4 (for example, Arr[k-4]-Arr[k]) to simulate the current signal being subtracted from the period-delayed signal. The delayed signal is shown in Fig. 3.33 and the subtracted signal is shown in Fig. 3.34. The subtraction operation will show a spike when a change in attractor occurs, and will have a relatively small output when the attractor does not change between samples. To manipulate these spikes into the desired sequence of bits, a numeric integration stage is used. This creates a signal in which the spikes in the subtractor output cause the integrator's output to change, and the points at which no spikes occur cause little change in the final output. The output of the integrator stage compared with the subtraction stage is shown in Fig. 3.35. The output of the integrator is then compared to a threshold, and a digital output is generated. The digital output compared with the symbolic content of the initial waveform are shown in Fig. 3.36. By examining these results, it can be seen that the digital matched filter algorithm is able to successfully reproduce the symbolic content of the oscillator waveform. The MATLAB program used to demonstrate this algorithm is contained in Appendix A.

Figure 3.31: Simulink model of the chaotic equation block diagram.

Figure 3.32: Decimated oscillator output to simulate sampling.

Figure 3.33: Sampled level-shifted and scaled oscillator signal (red) and delayed signal (blue).

Figure 3.34: Sampled oscillator output (red) with output of subtraction operation.

Figure 3.35: Output of subtractor (red) with output of integrator (blue).

Figure 3.36: Sampled oscillator signal overlaid with symbolic content, and digital matched filter algorithm output (yellow).

While it may be relatively simple to implement this algorithm in an environment where nothing has to be done in real-time, far more considerations must be taken into account when implementing this system in real hardware. For this task, an ST microcontroller was chosen as the platform to implement the filtering algorithm. The STM32 Nucleo F446 was chosen for this task because of the onboard ADC, robust processor, and low cost. The development board is shown in Fig. 3.37. The ARMKeil MDK toolchain was used to set up the various layers of software and firmware; this toolchain has the advantage of easy instantiation of peripherals and other components necessary to the physical implementation of this design. The various programs used are included in Appedix B.

To allow the microcontroller's hardware to perform any operations on the signal, it must be converted to a digital waveform. This was accomplished by configuring a 12-bit ADC to sample the analog signal at a defined general purpose input-output (GPIO) pin on the microcontroller development board; the incoming signal was tested to ensure its compliance with the 0-3.3V operating range of the microcontroller hardware. An external timer was

Figure 3.37: Development platform used to implement the software matched filter.