## True Random Number Generation from a High Frequency Chaotic Jerk Circuit

by

Remington Chase Harrison

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama December 14, 2019

Keywords: chaos theory, nonlinear dynamics, random number generation, Dieharder, jerk chaos

Copyright 2019 by Remington Chase Harrison

Approved by

Robert N. Dean, Chair, McWane Endowed Professor of Electrical and Computer Engineering Edmon Perkins, Assistant Professor of Mechanical Engineering Lloyd Riggs, Professor of Electrical and Computer Engineering Thaddeus Roppel, Associate Professor of Electrical and Computer Engineering

#### Abstract

Shown in this work is a method for true random number generation by directly sampling a high frequency chaotic jerk circuit. A method for determination of the maximum Lyapunov exponent, and thus the maximum bit rate for true random number generation, of the jerk system of interest is shown. The system is tested over a wide range of sampling parameters in order to simulate possible hardware configurations. The system is then implemented in high speed electronics on a small printed circuit board to verify its performance over the chosen parameters. The resulting circuit is well suited for random number generation due to its high dynamic complexity, long term aperiodicity, and extreme sensitivity to initial conditions. Also, a framework for evaluating other random number generation schemes based on chaotic systems is been given and is applicable to a wide variety of potential RNG solutions. This specific system passes the Dieharder RNG test suite at 3.125 Mbps.

## Acknowledgments

I would like to thank my wife, Abbie, for supporting me over the course of our time at Auburn. We have made so many new friends here that have helped us and made our time here really special.

I would also like to thank my advisor, Robert Dean, for guidance through the graduate and doctoral process, and his help on a multitude of details relating to this work.

I would like to thank my advising committee of Thad Roppel, Lloyd Riggs, and Edmon Perkins, in their aid as well.

A special thanks goes to all of the members of the Nonlinear Dynamics Lab. I've enjoyed working with all of you.

## Table of Contents

| Ał | ostract |                                               | ii  |

|----|---------|-----------------------------------------------|-----|

| Ac | know    | edgments                                      | iii |

| 1  | Info    | nation, Entropy, and Randomness               | 1   |

|    | 1.1     | Compression                                   | 2   |

|    | 1.2     | The Coin Toss                                 | 6   |

|    | 1.3     | Entropy                                       | 8   |

| 2  | Over    | iew of Chaos and Random Number Generators     | 11  |

|    | 2.1     | Chaos                                         | 11  |

|    | 2.2     | Random Number Generation                      | 13  |

|    | 2.3     | Laser Chaos and Random Number Generation      | 15  |

| 3  | The     | haotic Jerk System                            | 18  |

|    | 3.1     | Background                                    | 19  |

| 4  | Harc    | vare Circuit Design                           | 23  |

|    | 4.1     | Circuit Simulation                            | 23  |

|    | 4.2     | Circuit Hardware                              | 26  |

|    | 4.3     | Compact and Low Power Implementation          | 32  |

|    |         | 4.3.1 Efficient Design of Chaotic Oscillators | 32  |

|    | 4.4     | Smaller Board Design                          | 33  |

|    |         | 4.4.1 PCB Implementation                      | 34  |

|    | 4.4.2 Low Power Improvements                     | 38 |

|----|--------------------------------------------------|----|

| 5  | Hardware Random Number Generation Results        | 41 |

| 6  | Other Methods Of Obtaining Randomness From Chaos | 48 |

|    | 6.1 Von Neumann Corrector                        | 48 |

|    | 6.2 XOR Operation                                | 55 |

| 7  | Conclusion                                       | 59 |

| 8  | Future Work                                      | 60 |

| Re | ferences                                         | 62 |

| Ap | pendices                                         | 70 |

| A  | Compiling and Using Dieharder on Windows         | 71 |

| В  | Creating a Printed Circuit Board using KiCad     | 75 |

| С  | Code Sections for Various Functions              | 96 |

| D  | Dieharder Output                                 | 14 |

# List of Figures

| 1.1  | A 256x256 pixel black image, containing very little information                                                                                     | 4  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | A 256x256 pixel image in a checkerboard pattern, also containing very little information                                                            | 5  |

| 1.3  | A 256x256 pixel image generated randomly, containing much more information                                                                          | 6  |

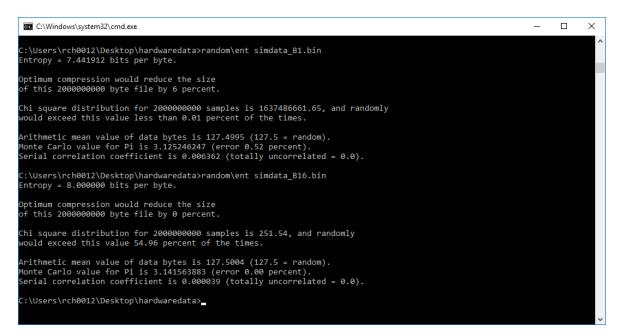

| 1.4  | A screenshot of the ent program running on two different files                                                                                      | 10 |

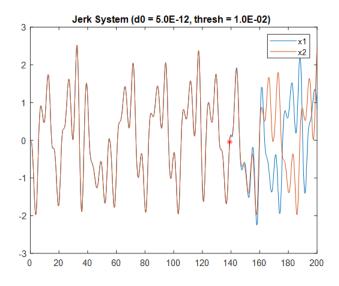

| 3.1  | Sensitivity to initial conditions in the jerk equation. The red asterisk denotes the point of divergence.                                           | 21 |

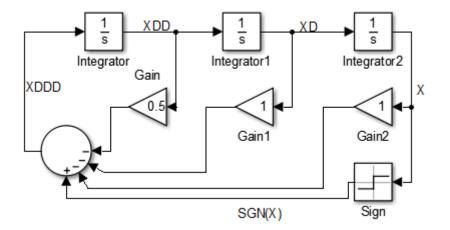

| 4.1  | Block diagram of (3.2)                                                                                                                              | 23 |

| 4.2  | LTSpice simulation of an ideal circuit implementation of (3.2)                                                                                      | 24 |

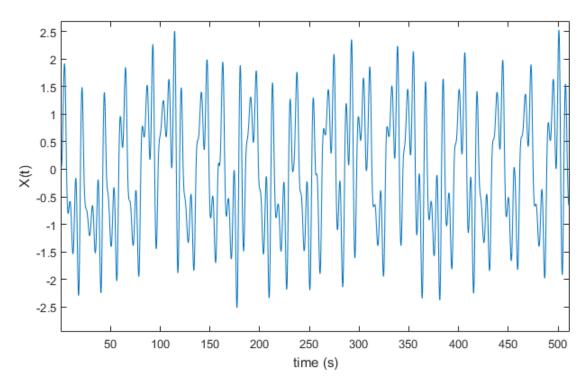

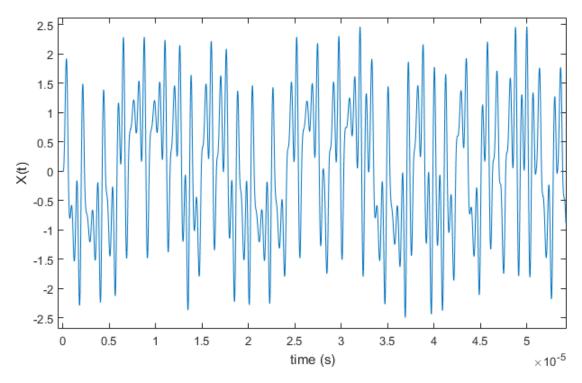

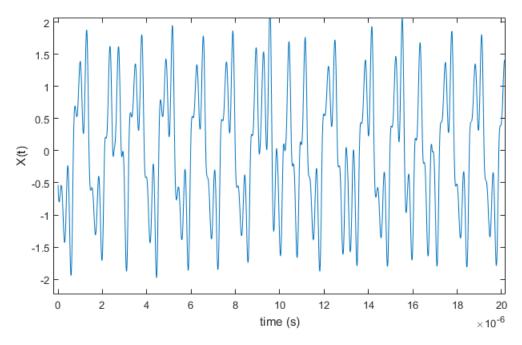

| 4.3  | Time domain plot of $x(t)$ with $G = 1 \dots \dots$ | 24 |

| 4.4  | Time domain plot of $x(t)$ with $G = 10 M$                                                                                                          | 25 |

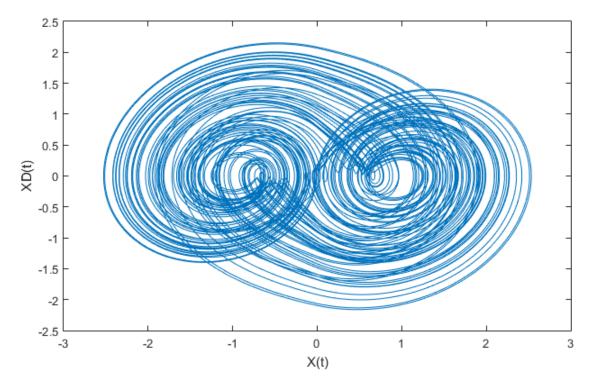

| 4.5  | Phase space of the chaotic equation                                                                                                                 | 25 |

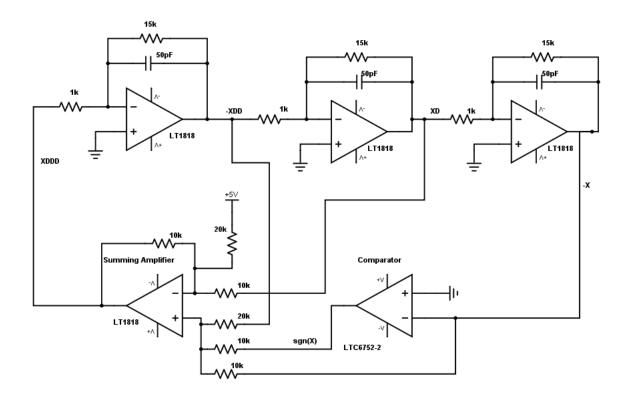

| 4.6  | Real component implementation of (3.2)                                                                                                              | 27 |

| 4.7  | LTSpice simulation of (3.2) with real components                                                                                                    | 28 |

| 4.8  | Time domain plot of $x(t)$ for the simulated system                                                                                                 | 29 |

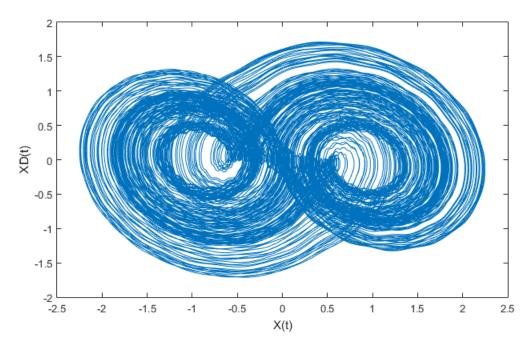

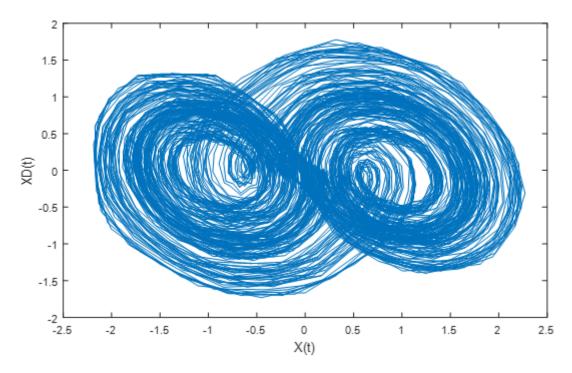

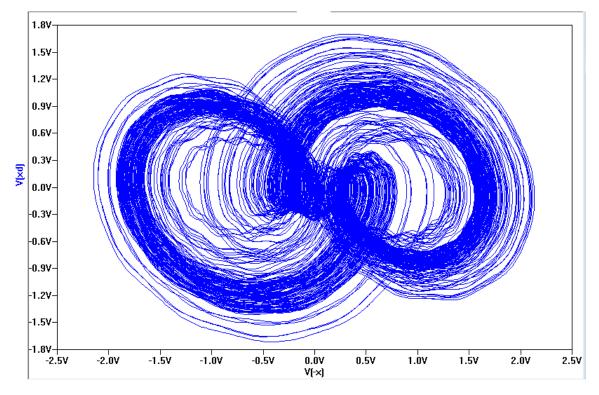

| 4.9  | Phase space $(\dot{x} \text{ vs } x)$ for the simulated system $\ldots \ldots \ldots \ldots \ldots \ldots$                                          | 29 |

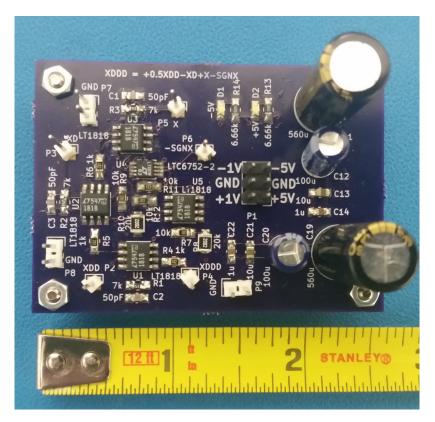

| 4.10 | Populated printed circuit board                                                                                                                     | 30 |

| 4.11 | Time domain plot of $x(t)$                                                                                                                          | 30 |

| 4.12 | Phase space $(\dot{x} \text{ vs } x) \dots $  | 31 |

| 4.13 | x(t) and $sgn(x(t))$                                                                                                                                | 31 |

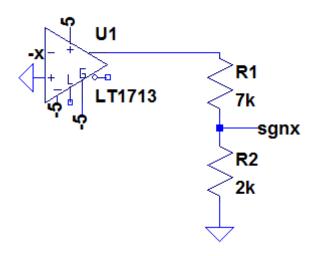

| 4.14 | Schematic of the resistor divider scaling the signum function                                                                                       | 34 |

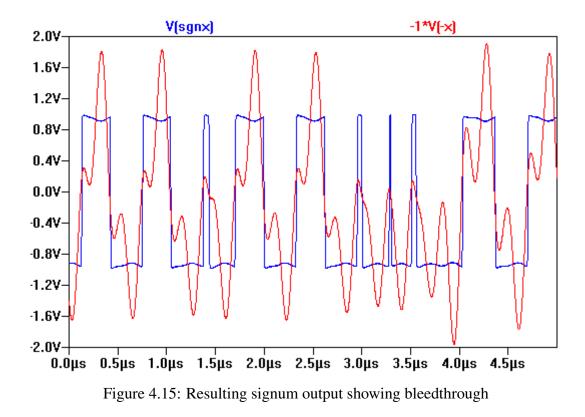

| 4.15 | Resulting signum output showing bleedthrough                                                                                                        | 35 |

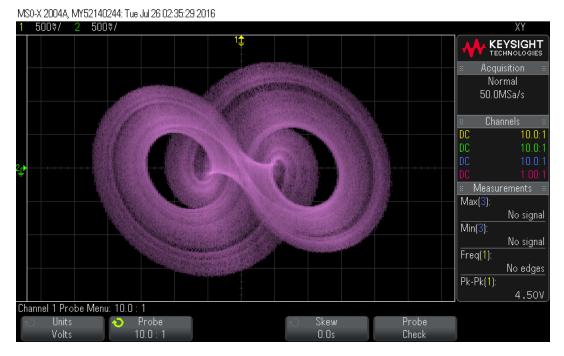

| 4.16 | Simulated phase space $\dot{x}(t)$ vs. $x(t)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.17 | System schematic of the improved oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

| 4.18 | Photograph of the assembled board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37 |

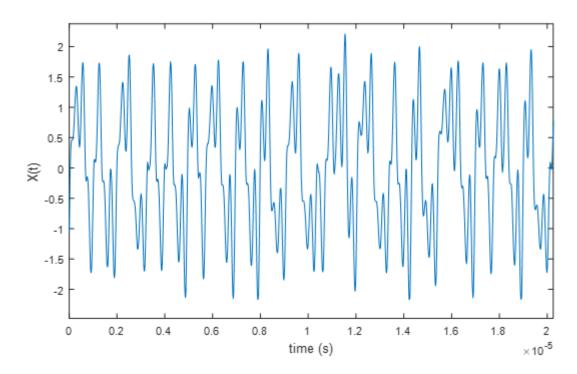

| 4.19 | Captured continuous output $x(t)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37 |

| 4.20 | Captured phase space of the assembled circuit board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

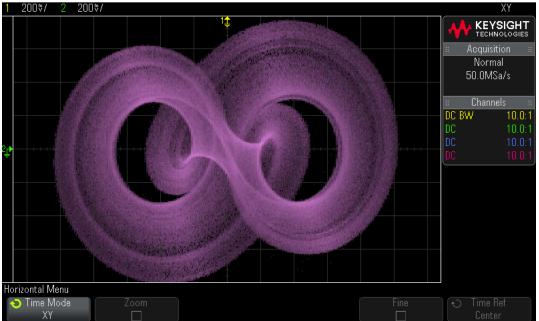

| 4.21 | Captured phase space of the assembled circuit board operating at 2.5 VDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |

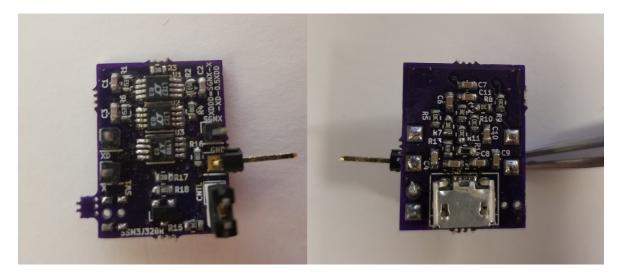

| 4.22 | The front and back of the populated circuit board which implements the jerk equation at 4 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40 |

| 5.1  | Partial output of Dieharder testing. More tests and results are given in Appendix D than are shown here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42 |

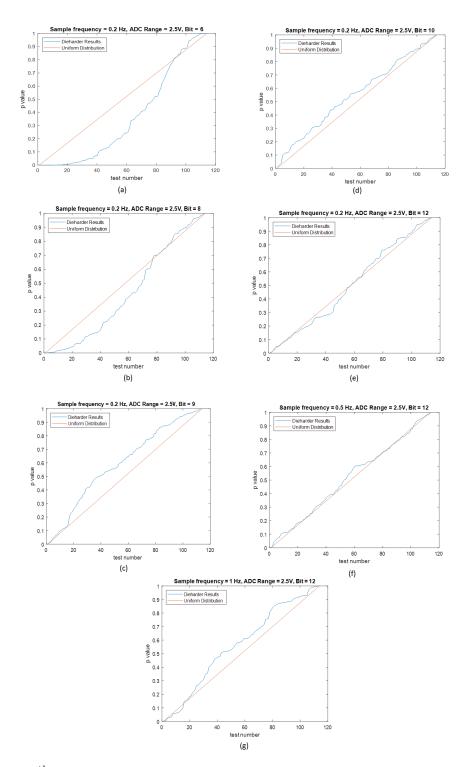

| 5.2  | (a) $6^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (b) $8^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (c) $9^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (d) $10^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (e) $12^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (e) $12^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (f) $12^{th}$ bit of an ADC sample of the system at 0.2 Hz with a full scale range of 2.5V. (g) $12^{th}$ bit of an ADC sample of the system at 0.5 Hz with a full scale range of 2.5V. (g) $12^{th}$ bit of an ADC sample of the system at 1 Hz with a full scale range of 2.5V. | 44 |

| 5.3  | The hardware circuit board sampled by the Handyscope HS6 inside of Multi-Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46 |

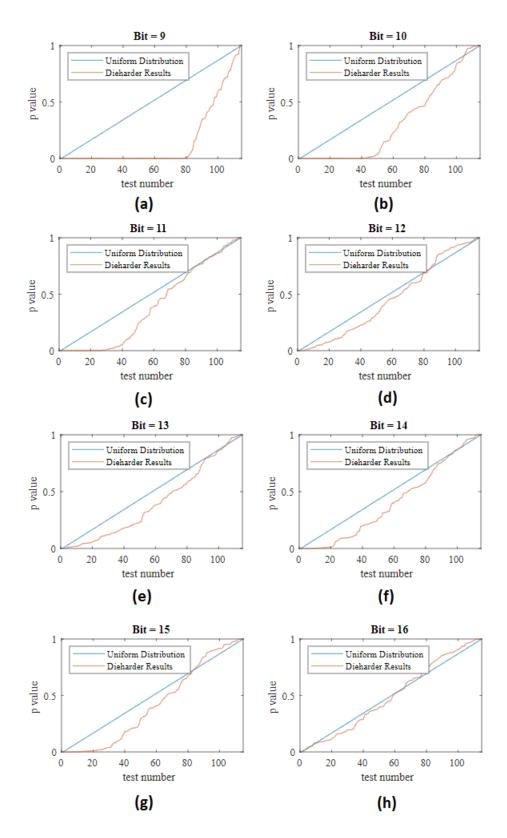

| 5.4  | Results from Dieharder testing of the hardware circuit. All bits were collected at 3.25 MHz with a full scale voltage of $\pm 2V$ . (a) 9th bit of each 16 bit sample (b) 10th bit of each 16 bit sample (c) 11th bit of each 16 bit sample (d) 12th bit of each 16 bit sample (e) 13th bit of each 16 bit sample (f) 14th bit of each 16 bit sample (g) 15th bit of each 16 bit sample (h) 16th bit of each 16 bit sample .                                                                                                                                                                                                                                                                                                                                                                                                                           | 47 |

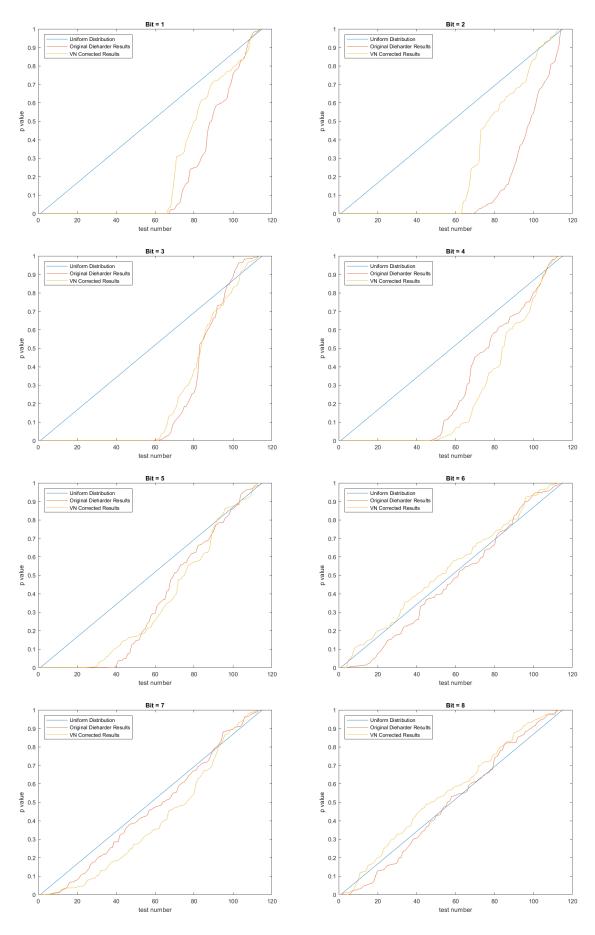

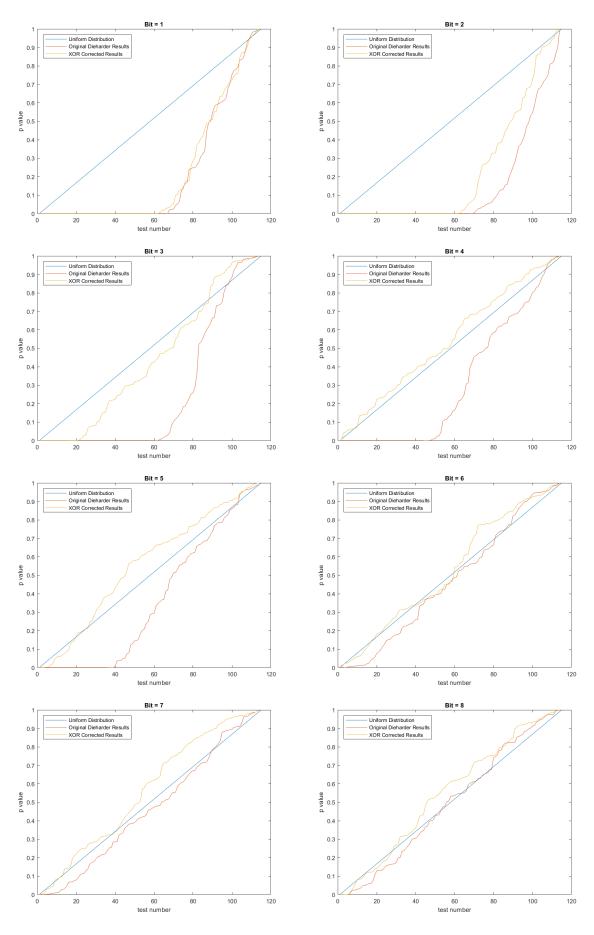

| 6.1  | Results from simulated data with Von Neumann correction (bits 1-8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51 |

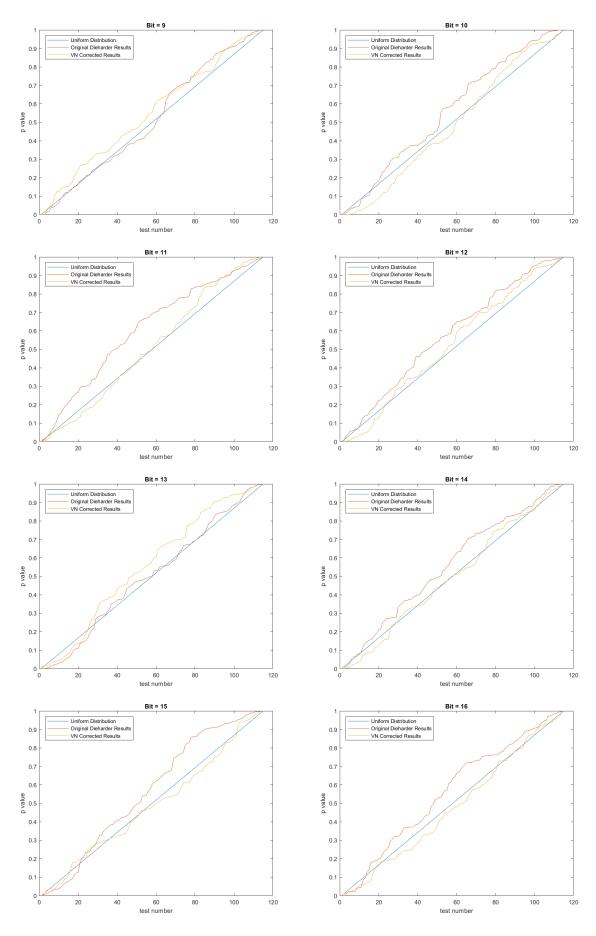

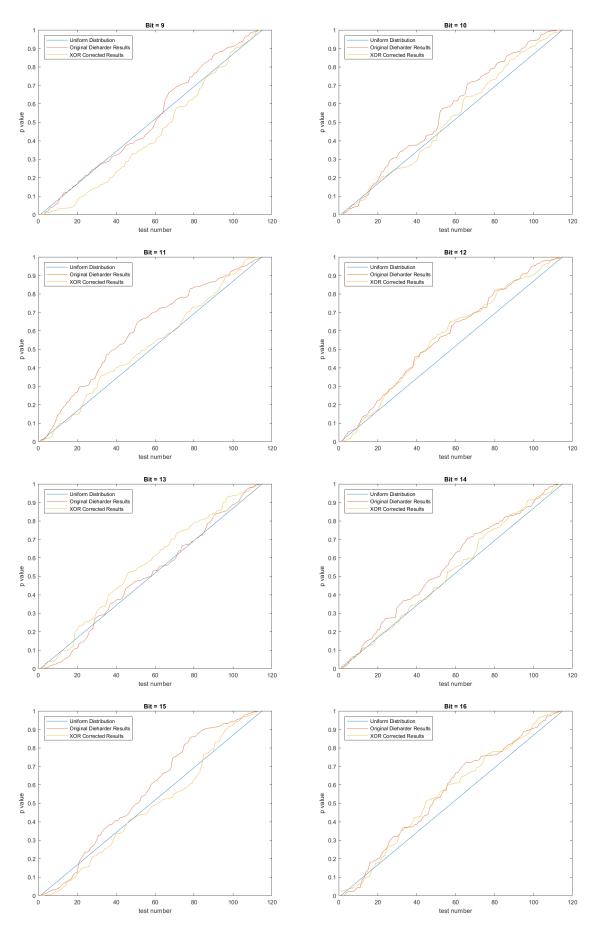

| 6.2  | Results from simulated data with Von Neumann correction (bits 9-16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53 |

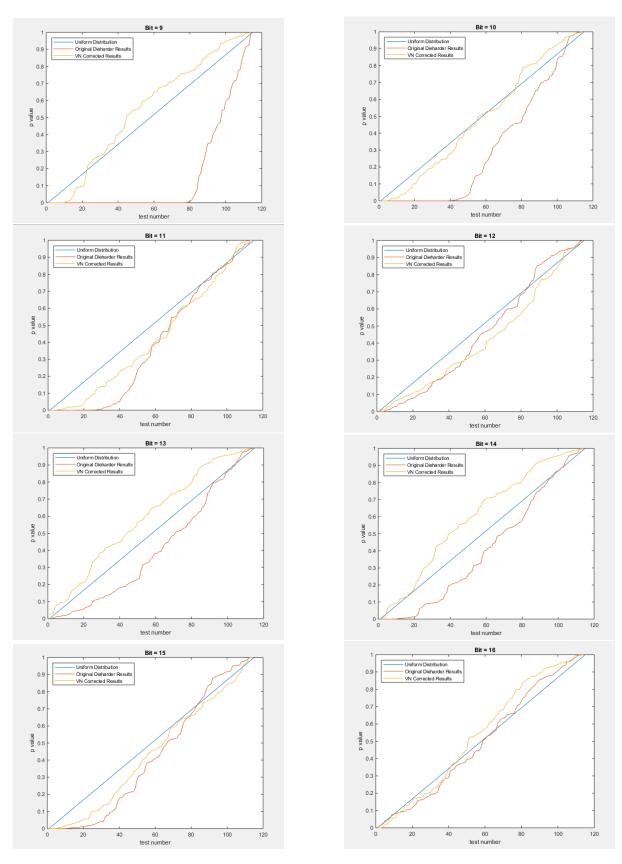

| 6.3  | Results from hardware data with Von Neumann correction (bits 9-16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54 |

| 6.4  | Results from simulated data with XOR correction (bits 1-8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56 |

| 6.5  | Results from simulated data with XOR correction (bits 9-16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |

| A.1  | The select packages screen within Cygwin Setup. Make sure that at least these packages are installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

| A.2  | Cygwin's terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 73 |

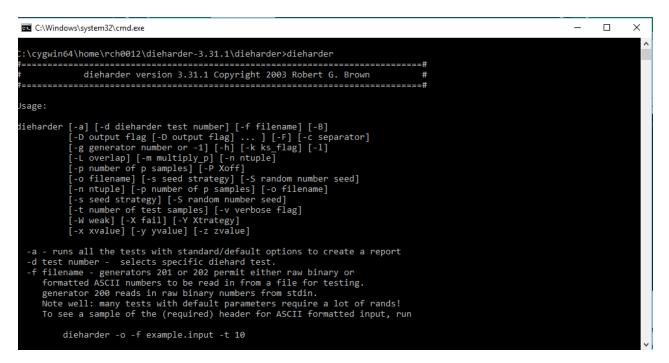

| A.3          | Dieharder output with no commands given                                     | 74 |

|--------------|-----------------------------------------------------------------------------|----|

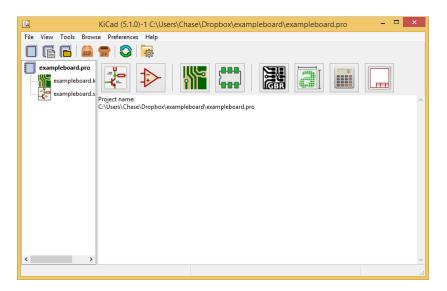

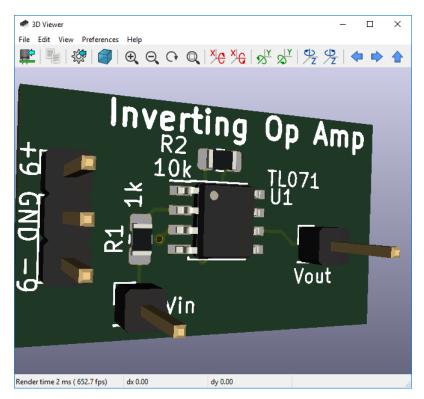

| <b>B.</b> 1  | The homescreen of KiCad after a new blank project has been created          | 76 |

| B.2          | A blank EESchema schematic, with labelled items                             | 76 |

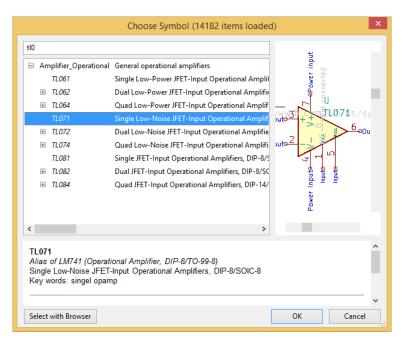

| B.3          | Picking and placing a part withing EESchema                                 | 77 |

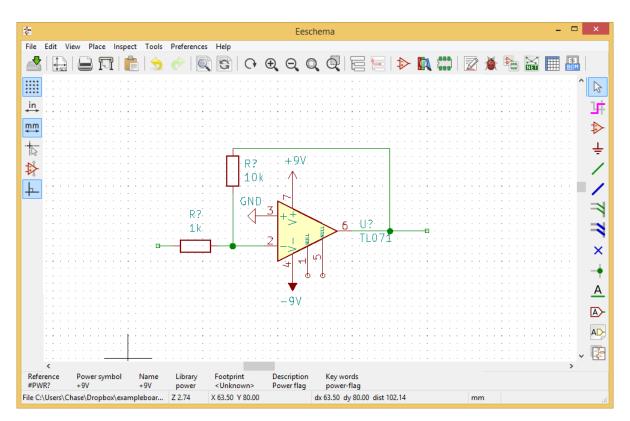

| B.4          | A basic EESchema schematic of the op amp circuit                            | 77 |

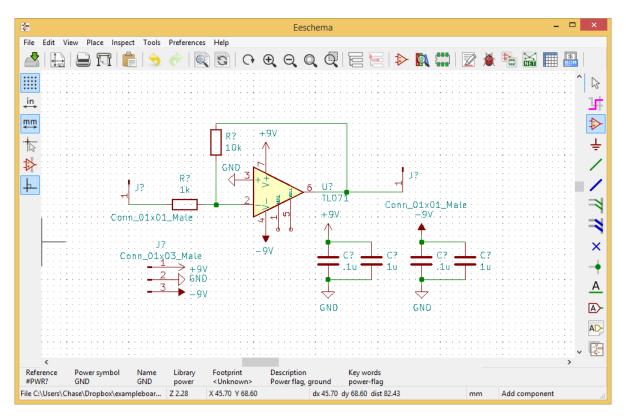

| B.5          | A better EESchema schematic of the op amp circuit                           | 78 |

| B.6          | Annotating the schematic                                                    | 79 |

| B.7          | A screenshot of the Design Rules Check output with some warnings            | 79 |

| B.8          | A screenshot of the blank footprint assignment screen                       | 81 |

| B.9          | A screenshot of the filled footprint assignment screen                      | 81 |

| B.10         | A screenshot of the "Generate Netlist" screen in EESchema                   | 82 |

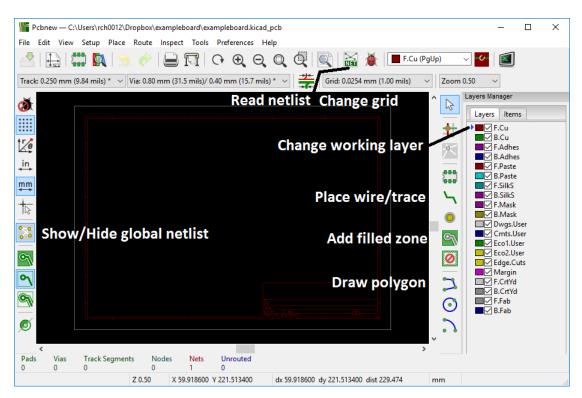

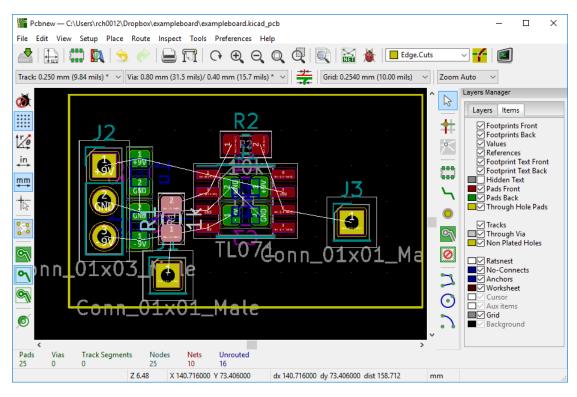

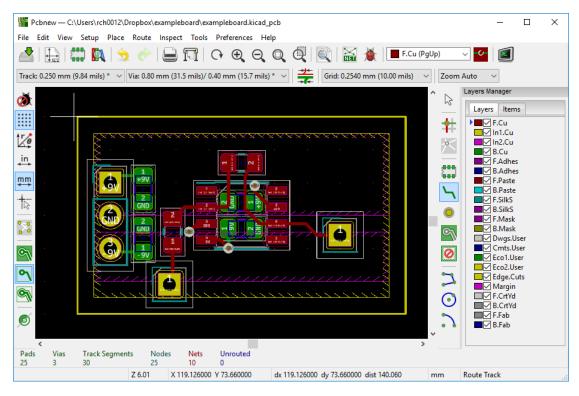

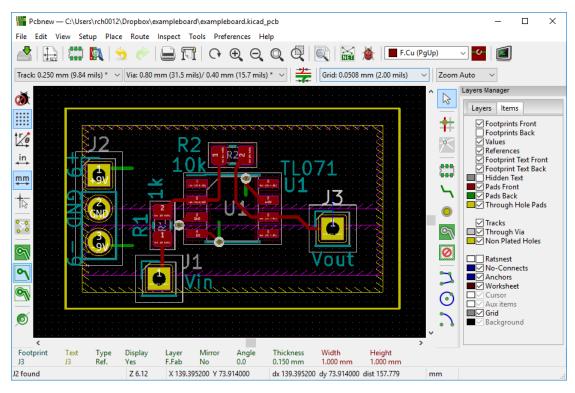

| <b>B</b> .11 | A screenshot of the blank PCB layout in PCBnew                              | 82 |

| B.12         | A screenshot of the read netlist window in PCBnew                           | 83 |

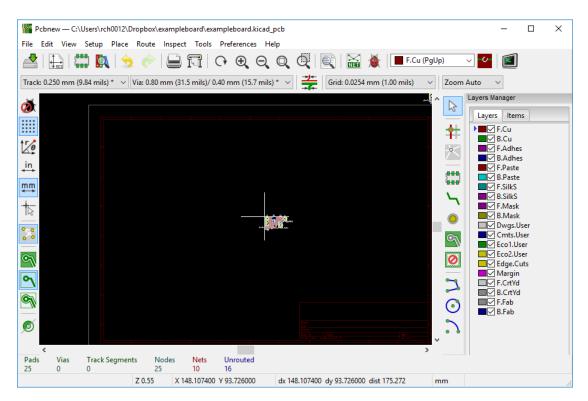

| B.13         | A screenshot of the components ready to be placed in PCBnew                 | 83 |

| B.14         | A screenshot of the layer setup in PCBnew                                   | 84 |

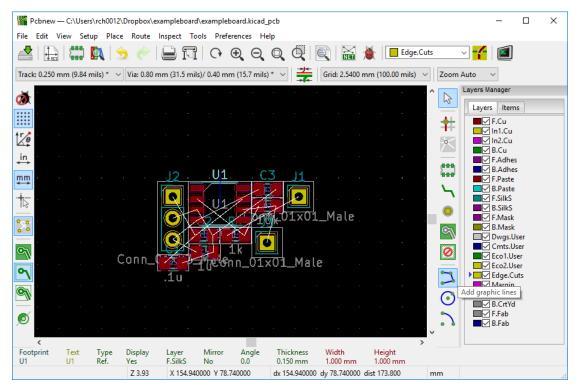

| B.15         | Beginning step of creating the edges of the PCB                             | 85 |

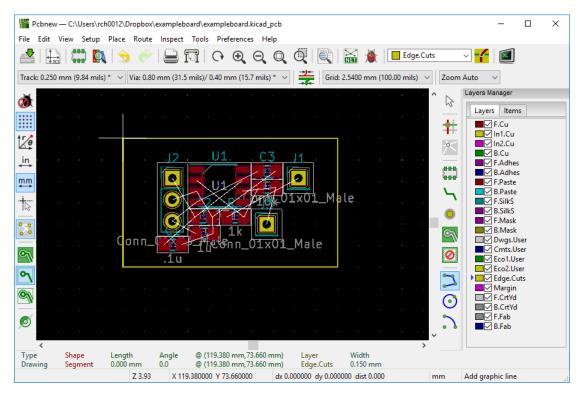

| B.16         | A completed border that defines the edges of the PCB                        | 85 |

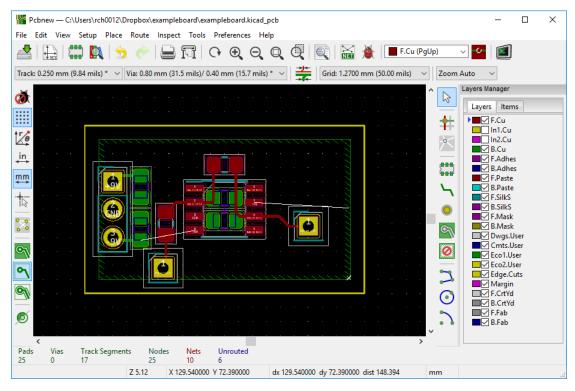

| B.17         | The components moved to their desired locations, but unrouted               | 86 |

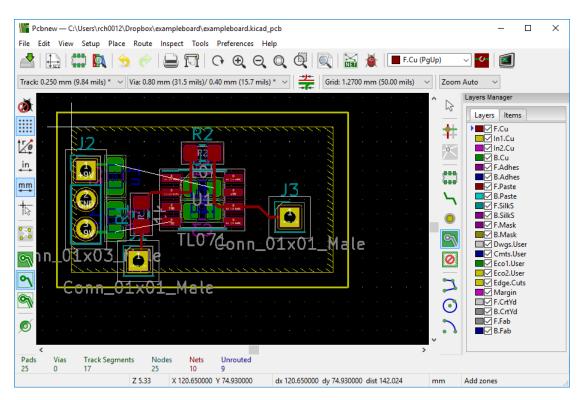

| B.18         | Selecting a copper zone to begin drawing                                    | 88 |

| B.19         | A copper zone drawn on inner layer 1                                        | 88 |

| B.20         | A copper zone drawn on the bottom layer                                     | 89 |

| B.21         | A copper zone drawn on the second inner layer for the power planes          | 89 |

| B.22         | A completed layout where all components are connected with no unrouted nets | 90 |

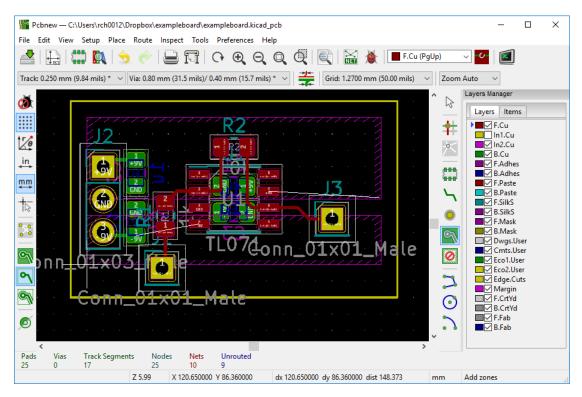

| B.23         | Changing the names of the connectors on the PCB                             | 91 |

| B.24         | The front silk screen with designators, references, and values              | 92 |

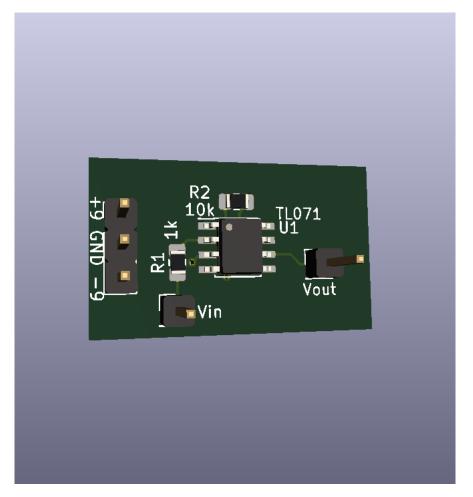

| B.25         | The front silk screen in 3D                                                 | 93 |

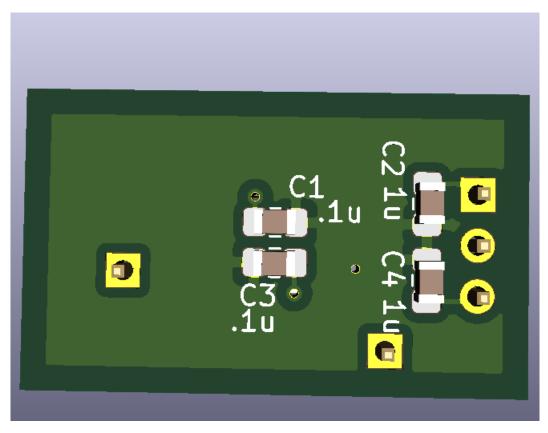

| B.26 The back silk screen in 3D                   | 94 |

|---------------------------------------------------|----|

| B.27 The completed board in 3D                    | 94 |

| B.28 Plotting each of the layers as a gerber file | 95 |

| B.29 Plotting the drill locations for the PCB     | 95 |

## List of Tables

| 1.1 | Summary of file sizes resulting from the previous exercise | 5  |

|-----|------------------------------------------------------------|----|

| 6.1 | Bit Pair Probabilities of an Unbiased Sequence             | 49 |

| 6.2 | Bit Pair Probabilities of a Biased Sequence                | 49 |

| 6.3 | Von Neumann Corrected Sequence                             | 49 |

| 6.4 | The exclusive-OR truth table                               | 55 |

## Chapter 1

#### Information, Entropy, and Randomness

In order to discuss the technical aspects of a random number generator based on a chaotic system, the term random needs to be investigated first. Unfortunately, trying to simply define "random in a meaningful way proves easier said than done. A more apt approach perhaps is to look how randomness is derived from information. This somewhat philosophical method of approach is more roundabout than most, but hopefully will be fruitful in attempting to delve into this topic appropriately.

Information, for the purposes of this discussion, can be assumed to be infinitely precise and available. More specifically, any value that can be described, measured, or transferred can be done so to infinite precision, and there are an infinite number of such values. Of course, this assumption is highly debatable and not meant to build into a proof of anything. It is merely a baseline upon which to build an understanding of how humans understand and interpret information. One could argue that the total information contained in any fixed space is by definition not infinite by quantum limits, but even then the total information is so large that it is effectively freely available for the systems of interest. By making this assumption, a gradual building of this understanding into a framework for a random number generator can be achieved.

What, then, is information? In the modern digital age, information is usually measured in bits and bytes. There is a constant demand for both a higher throughput of data (colloquially referred to as "bandwidth", and measured in megabits per second), and reducing the amount of data needed (referred to as compression). Often the abundance of available data for consumption gives rise to an "information overload" where it is difficult to sort through what is desired and what is not needed. Information itself is valuable to certain parties, most recently in the form of user data sold to third parties without consent. "Big Data" has become a rising area

of innovation in order to sort large amounts of data and see trends that otherwise could not be seen without accumulating these massive databases.

All of these are examples of what information can be, but none really capture the essence of what information is in a meaningful way as far as a random number generator. Information is an intuitive idea that most would be able to identify, yet would struggle to adequately and concretely describe without a reference. However, by building upon an understanding of this reference, certain properties of the reference will come to light and help form an understanding of information itself. For this discussion, data compression will serve as a technical reference to aid in realizing this definition.

## 1.1 Compression

Compression, in terms of a digital system, is the process of reducing the amount of data needed to store a particular piece of information, whether it be a picture, music, or text. There are a multitude of different algorithms for compression of data; a good resource for covering these algorithms specifically is [1].

First, consider some data that is uncompressed. This data need not be infinite or capture every minute detail of the pre-digitized work. This data is considered "raw", meaning there has been no futher processing of this data other than the original digitization into bits. The data is more than likely a direct conversion using an analog to digital converter with a set resolution. The resulting data file is merely a "list" of these samples in sequential order, perhaps with some header information and metadata. Of course, this data format is not the most efficient form for storing the data since these raw formats do not take into account information about the data itself.

In order to increase the storage efficiency of this data, a compression algorithm is used to condense the stored data down to a smaller size. Instead of going into specifics on how these algorithms work, we will focus on what these algorithms achieve: lower storage requirements by simply describing the data in a different way. We will also consider what is left and what is discarded in the compression process.

Some compression algorithms are "lossless", meaning that they reduce the required amount of data needed to store all of the information without losing any information. This is most readily seen in the PNG and FLAC storage formats for images and music, respectively. This is achieved by removing redundant data that can be exactly replicated in the future or by storing differences in sequential bytes (which are usually much smaller than the full byte value). There are also "lossy" compression algorithms, such as JPG and MP3. These algorithms remove some information contained in the data in exchange for a much lower storage requirement. The "discarded" information is usually high frequency information that is at the extreme end of human hearing (in the case of music) or hard edge information in pictures, resulting in some blurring and "compression artefacts", but when viewed from a distance are not noticeable. Note that information is always lost in the original digitization process.

As an example, consider a completely black square image to be stored digitally (shown in Fig.1.1). This image was generated in Matlab by converting an array of zeros into a figure using imshow, and then saved in various file formats. The first file format, .bmp, is the stored sequential array of the values, and is uncompressed. The second file format, .png, is the image stored with lossless compression specifically for images. The third file format, .jpg, is a lossy compression algorithm for images. The fourth file format, .zip, is a generic lossless compression function given in Windows as Send to -> Compressed (zipped) folder in the .bmp file's right-click context menu. The .bmp format takes 65 kB of data to store digitally (close to 256\*256\*8 bits per pixel). The .jpg format is able to reduce this file size down to 1100 bytes. The .png format further reduces the file size to merely 160 bytes. The .zip format achieves a file size slightly higher than the .png format at 221 bytes (the extra data coming from increased header information). From the drastic reduction in file size by using these various compression algorithms, we can see that the original image contained very little information. This makes sense intellectually as well, since the entire image could be described with a few words (e.g. "256 pixel square entirely black"), which is a small amount of information.

Next, consider the same size image with a black and white checkerboard pattern (i.e. every pixel is opposite the ones next to it, with colors limited to black and white), as shown in Fig.1.2. This image was generated similarly to the previous one and again saved in the four different

Figure 1.1: A 256x256 pixel black image, containing very little information

formats. The .bmp format takes 8.1 kB to store uncompressed. The .jpg format is unable to compress the picture and ends up taking 28.8 kB to store. In addition, it introduces artifacts (e.g. colors other than black and white) into the picture. However, the .png format is able to losslessly compress the image down to 135 bytes, with the .zip format taking up 211 bytes. Even though there is some "information" in this image (more so than the completely black image), the compression algorithms are able to reduce this image into a very small amount of "real" data that can completely replicate the picture. Again, this exact pattern is easily described in words, so the only unique properties of the image are the size and starting pixel color. These properties are able to precisely define the image.

Finally, consider an image with a random choice of black and white in each pixel (shown in Fig.1.3), the pattern being created using the rand function in Matlab and then processed in the same way as with the previous two images. The uncompressed .bmp again takes 8.1 kB to store. The .jpg format, much like the checkerboard pattern, fails at compressing the image and takes 44 kB to store (over 5 times the original size). Interestingly, the .png and .zip formats also both fail to compress the image, taking 8.2 kB to store. These results are summarized in Table 1.1.

Figure 1.2: A 256x256 pixel image in a checkerboard pattern, also containing very little information

Table 1.1: Summary of file sizes resulting from the previous exercise.

|              | .bmp   | .jpg    | .png   | .zip   |

|--------------|--------|---------|--------|--------|

| black square | 65 kB  | 1100 B  | 160 B  | 221 B  |

| checkerboard | 8.1 kB | 28.8 kB | 135 B  | 211 B  |

| random       | 8.1 kB | 44 kB   | 8.2 kB | 8.2 kB |

Why do all of the compression attempts fail on the last image? It is the same size as the other images and even has the same ratio of pixel color as the checkerboard image. Of course, it is because of the pattern of the individual pixels. In the checkerboard image, information about one pixel completely defines every other pixel. In the random image, there is no information gained about one pixel from examining any other (or all!) of the other pixels. Thus, the best that the compression algorithms can do it simply list each pixel in order. Hence, the storage requirement is very near the uncompressed .bmp size.

At this point, it can be said that information about something can be split into two parts. First, there is information that is unknown, unique, or "random". This is the information that in incompressible and cannot be reduced without removing properties of the item. Second,

Figure 1.3: A 256x256 pixel image generated randomly, containing much more information

there is information that is known, predictable, or patterned. This is the part that compression algorithms attempt to reduce to the base "unique" part of the information, which can then be decompressed later. Some items, such as the black square, are almost entirely predictable. Others, like the checkerboard, are some balance between unique and patterned. Finally, there is the "random", which is the focus of much interest and research. The main goal of studying randomness and random phenomena is to learn what parts can be understood as patterned, and what parts are truly random. If one is able to remove the patterned part and only keep the random, then a random number generator can be built.

## 1.2 The Coin Toss

Perhaps the most iconic random number generator known today is the simple coin toss. This "heads or tails" device has decided outcomes with varying degrees of importance throughout history, from choosing between places to eat with friends or deciding team placement in sporting events, all the way to determining presidential candidates and other elected positions in the United States. A large emphasis is placed on the fairness of the chosen coin, with a weighted or even "double-headed" coin universally seen as unfair as the outcome is skewed from a fifty-fifty distribution.

Despite the extensive use of the coin toss as a random number generator, its dynamics have been thoroughly studied and have been found to be quite predictable [2][3]. In order to perform a coin flip, the coin is placed either heads up or heads down on the thumb, and then the thumb flicks it upward. After the point at which the coin loses contact with the thumb, the "initial conditions" are set, meaning that the dynamics of the coin flip are allowed to propogate forward without further input. Air resistance, gravity, and impact with the ground are the forces that act upon the coin to ultimately determine the ending heads or tails decision.

By measuring the initial conditions of the coin (e.g. side initially up, rotational velocity, upward velocity, mass of the coin, etc.) with enough accuracy, and by knowing certain properties of the environment (e.g. coefficients of friction and restitution of the ground and coin, initial height above ground, etc.), the outcome of the coin flip can be confidently predicted [4]. With enough sophistication in equipment, multiple sets of initial conditions can be measured and mapped to their final outcomes, allowing rapid predictions in real time while the coin is still in the air. These heads or tails "basins" of initial conditions show that various ranges in specific initial conditions end up with the same outcome, meaning that measurement errors or inaccuracy within these ranges do not affect the predicted outcome.

Given that the coin toss is so readily predictable by modern standards, it seems odd that it is still so widely used with the assumption that the outcome is fifty-fifty. Most would realize that the coin toss somehow "predictable", but would continue to trust in the process for decision making. Of course, in reality there is an understanding also that no one is measuring the coin's initial conditions (beyond the the side up perhaps), and no one has ready access to equations of dynamics for the coin into which to input the conditions. Hence, there is a mutual *lack* of information during the coin toss among parties that prevents one from gaining a predictive advantage over the other. The information is technically available to any observer, and the final outcome *could* be calculated, but rarely would anyone pursue attempting to perform the prediction in real time.

So is the coin toss random? On one hand, there are accurate models for the coin toss dynamics that take into account a multitude of different toss variables and scenarios, and measuring these variables is fairly straight forward. With modern equipment, real time prediction is certainly feasible. In this sense, the coin toss is not random: Given enough information about the initial system, the outcome is confidently known. On the other hand, the dynamics of the coin toss map the initial conditions to an even distribution of heads and tails, and the initial conditions of the system are mostly unknown to the parties and unable to be accurately measured or influenced by a human to confidently move them between the basins of initial conditions. Even if steps were taken to measure the initial conditions, uncertainty in these measurements could be enough to change the predicted outcome such that the confidence in the prediction is no better than the original fifty-fifty chance.

In essence, there are parts of the coin toss that are "known", and there are parts that are "random". Specifically, the equations governing the trajectory of the coin while in the air and when impacting the ground have been thoroughly researched and can be considered known. The unknown part of the coin toss is only the initial condition of the system. The initial conditions could be known with enough determination, and thus an accurate prediction could be made, but in most situations this aspect of the coin toss remains hidden from all parties. This is the random part that most rely on in order to make decisions. Even though the coin toss is not precisely the ideal fifty-fifty chance that it is expected to be, it is good enough for most purposes.

## 1.3 Entropy

"Entropy" is a term that is sometimes interchangeably used with randomness and information in order to describe a sense of disorder or unpredictability. For this discussion, we will focus instead on the more tangible aspects of entropy as it relates to random number generation.

A system that has entropy tends to move from states of order to states of disorder. Order is denoted by stability, periodicity, or predictability. Disorder is denoted by instability, aperiodicity, or unpredictability. The entropy of a system is then a measure of the amount of that disorder compared to the order in the system, or the tendency of the order to transition into disorder. Entropy has a well established background using thermodynamic principles. When considering each individual molecule of a system and the properties of them (known as "microstates") as they relate to the properties of the overall system (known as "macrostates"), the thermodynamic definition of entropy S can be written as 1.1.

$$S = k_B \ln(\Omega) \tag{1.1}$$

In this definition,  $k_B$  is Boltzmann's constant  $(1.381 \times 10^{-23} J/K)$ , and  $\Omega$  is the number of equiprobable microstates. It follows from this definition that a system with a large number of microstates has a high entropy, regardless of the macrostate of the system. Likewise, given the macrostate of the system, the entropy S is a measure of how much more information is needed to completely describe the system down to the microstate level.

This thermodynamic definition is very similar to the communication theory definition given by Shannon [5, 6]:

$$H = -\sum_{i=1}^{n} p_i \log_2(p_i)$$

(1.2)

Here, H is the Shannon entropy, and the  $p_i$  are the individual probabilities of each symbol. For a binary system, the entropy is maximized when  $p_0 = p_1 = 0.5$ . That is, when all probabilities are equally likely, then the least amount of information is known about the system until it is sampled. Likewise, once it is sampled, the maximum amount of new information is learned. For example, a communication scheme that only sends 0's ( $p_0 = 1, p_1 = 0$ ) has zero entropy since no information is actually communicated.

In a technical sense, the entropy of a certain bit sequence is a measure of the information contained in that sequence compared to the length of that sequence. This is usually measured in bits per byte, with 8 bits per byte being the maximum entropy measure possible. ent is a program available on Linux to quickly examine a bit stream or file and evaluate various aspects related to its randomness [7]. An example of this program running is shown in Fig. 1.4.

In the first file tested, the data in the file could technically have been represented with 6% less data (i.e. 6% of the data is redundant). This amounts to an entropy of approximately 7.44

Figure 1.4: A screenshot of the ent program running on two different files

bits per byte. The second file, however, is uncompressible. The data within this file has the maximum entropy possible at 8 bits per byte. For both files, other metrics of randomness are given in addition to the entropy. The arithmetic mean of the file is the mean of all of the 8 bit byte values from 0 to 255 that are represented in the file. The Monte Carlo value for  $\pi$  is a calculation based on using successive byte values as 24-bit XY coordinate pairs within a unit square, and then measuring how many of those pairs land within the unit circle. The serial correlation is a measure of how each byte relates to the previous byte; correlation denotes predictability in the bit stream and thus redundant data.

#### Chapter 2

#### Overview of Chaos and Random Number Generators

#### 2.1 Chaos

In the 1960's, in an attempt to create a model for weather patterns that had phenomena that were unexplained by previous linear models, Edward Lorenz discovered a system that had very peculiar properties [8]. When his system was simulated with very close initial conditions, the future outputs were vastly different. Robert May, when describing population densities, found an equation that did not have a steady state solution, was not periodic, and yet did not become globally unstable [9]. These, along with other discoveries in the field of nonlinear dynamics, ultimately led to the coining of the term "chaos" in order to describe these phenomena.

Today, chaos can be found in multiple areas, including phenomena in both natural and artificial events. For example, weather patterns are chaotic in the sense that they are able to be accurately predicted a few days in advance, but forecasts longer than a week suffer a drastic decrease in confidence. A normal pendulum has a simple periodic orbit dependent only on gravity and the length of the pendulum, but when an extra joint is added to the pendulum to make it a double pendulum, the motion of the end mass is complex and can complete full revolutions around the second joint. Fluid mixing results in an overall homogeneous mixture but has chaotic trajectories for the individual particles. Chaos also has strong similarities to fractal geometry found in many plants and rock formations.

Chaos, before the formal recognition that it currently has, was mostly bundled into the term "noise" and its effects were disregarded as unavoidable. While chaos does share a number of characteristics with noise, some properties set chaos apart as a unique phenomenon. There are also qualities of chaos that can be measured in a system of interest to quantify the existence of chaos in that system.

One of the first properties of chaos is known as sensitivity to initial conditions. As the designation implies, chaotic systems' future states have an extreme dependence on the starting conditions of the systems. Small changes in these conditions quickly multiply into large deviations in the eventual trajectories that the system will take, even in the absence of any other influence such as noise. Furthermore, extremely small perturbations in the system state at any time will cause the same divergence in trajectories.

Chaotic systems also exhibit long term aperiodicity even though they are cyclic. Specifically, chaotic systems can have a number of orbits that trajectories of the system will follow. Certain trajectories will take different amounts of time to complete one cycle of an orbit. Other trajectories will switch from one orbit to another for a time and then switch back. Each cycle of an orbit takes a slightly different amount of time, and thus there is no fixed period of the system. Phase space portraits and Poincare sections can shed greater insight into different orbits that a chaotic system can have.

From this, chaotic systems have a spread spectrum power density. Whereas normal periodic systems have their spectral power mostly at a natural or resonant frequency, chaotic systems have this power over a large frequency band or set of bands. Often this can extend from near 0 Hertz to the fundamental frequency of the system without having a large defined peak at any one point in that range.

Chaotic systems also exhibit what is known as topological mixing. This is an extension of both the properties of sensitivity to initial conditions and aperiodicity. A set of points close together on any trajectory of the system will, given enough time, become spread out over all of the orbits of the system. An analogy is mixing food coloring into a pudding: once it starts to be mixed, the color quickly becomes dispersed throughout the pudding until the mixture is homogeneous. At this point, the color and the pudding cannot be unmixed. Likewise, it is extremely difficult to determine the starting positions of the points in a chaotic system after this mixing has occurred.

All of these properties gives rise to another useful characteristic of chaotic systems: they are impossible to predict in the long term. For chaotic systems that can be defined as differential equations, the short term behavior can be predicted with high accuracy. This accuracy quickly

drops off due to sensitivity to initial conditions and aperiodicity to the point that long term behavior is essentially a random guess. At that point, new information needs to be gathered in order to be able to predict the system again.

Thus, chaotic systems are ideal for random number generation. They are naturally unstable and are aperiodic, which prevents prior information about the system from being used to determine long term behavior in the output. However, care must be taken so that random numbers are extracted from the system correctly such that statistical randomness is preserved.

## 2.2 Random Number Generation

Most randomly generated numbers today are generated with an algorithm designed to provide these numbers in a statistically uniform order. These algorithms are referred to as pseudorandom number generators. The increase in the reliance on random numbers has caused pseudorandom number generators to be present in almost every digital electronic system. Pseudorandom number generators are extremely fast and efficient, only limited by the clock speed of the algorithm and the power budget of the system. There are multiple different designs of these generators, including linear feedback shift registers, block ciphers, and stream ciphers [10][11].

However, as the name implies, pseudorandom number generators are not actually random. Pseudorandom number generators are meant to provide a source of statistical randomness, not true randomness. These generators are suitable for most everyday applications given that most generators are isolated enough from user interface, and most consumers are only concerned with the statistical randomness of random numbers. For extremely secure systems, this compromise is not acceptable.

There are a number of weaknesses in pseudorandom number generators that prevent them from being truly random. One of the most prominent issues of a pseudorandom number generator is that it will eventually repeat itself. Some of these generators have extremely long cycle lengths. Hence, there is a set amount of bits that can be taken from the generator before it is guaranteed to start its output sequence over. Also, some configurations of a pseudorandom number generator will not produce statistically random numbers. This is most prominently seen in early configurations of linear feedback shift registers, where not only did the output repeat itself, it did so before all combinations of output were given. Pseudorandom number generator designs today go to great lengths to ensure that the output of the generator is as uniform as possible and as long as possible before it repeats itself.

Ultimately the output of every pseudorandom number generator can be predetermined given the initial states of the generator and the configuration of the generator. Since there are no outside states or influences to the generator, only an algorithm stored in memory, the future output is fixed. If an outside entity wanted to predict the output sequence from a pseudorandom number generator before they were actually generated, all that would be required would be to take the state of the generator and run the algorithm faster until the future output of the first generator was given by the second; no further information would be required. Normally, it is very difficult to get any information from a pseudorandom number generator aside from the output sequence, but once that information is known, the generator can be broken.

On the other hand, true random numbers are not based on a digital algorithm but rather on a physical process. The true randomness comes from the inability to get full information about either the system or the system state. For example, even if the dynamics of a physical system were hypothetically known exactly, the system output would still be unable to be predicted because the exact initial conditions cannot be measured. Likewise, if hypothetically the initial conditions could be exactly known, the future output would still be unable to be predicted because the system itself is never exactly known. In this way, physical processes provide a source of true randomness in that nothing can be fully known or predicted.

In order to be useful random number generators, physical processes still must provide statistical randomness as well as providing true randomness. Usually, the random numbers taken straight from the system will be biased in one way or another, and thus must be compensated for in a post-processing step. The most famous of these steps is the Von Neumann corrector, which takes a number sequence with a bit level bias and returns a new sequence where the bits are weighted equally.

Statistical randomness can be examined using a number of tests designed to evaluate large bit sequences for uniformity. Some programs that are publicly available include NIST and Dieharder [12][13]. Ideally, a true random number generator will pass all of the performed tests with every bit sequence tested. A large amount of data must be given to these programs in order to assess randomness, and the physical process must be swept over its operating parameters in order to ensure that the system maintains its randomness throughout operation.

#### 2.3 Laser Chaos and Random Number Generation

Lasers have provided incredible improvements and applications to a multitude of different areas, including manufacturing, medical, chemical, entertainment, and metrology [14][15][16][17][18]. Lasers' naturally small wavelengths allow extremely precise resolution when controlling the laser output spatially, while still being able to lase with a high output power. Usually, in order to keep the laser within a desired frequency range, a feedback mechanism is required; however, this is readily achieved with various techniques [19][20][21].

Random number generation is one of the foundations of modern cryptosecurity. Without a reliably random number source, encryption schemes for monetary and communication purposes would be much easier to break. As such, random number generators need to be inherently unstable, unable to be predicted, and yet easy to implement in a real system such that they can efficiently be used.

Stability in laser frequency is normally desired for most applications, since for these applications the laser energy needs to be confined to a small bandwidth compared to the natural frequency of the laser. However, for random number generation, the natural instability of the laser can be exploited. In addition, a laser can be made more unstable by placing certain feedback paths in the system that multiply the natural instability.

Note that laser instability for random number generation does not mean instability in the sense of lasing. Instability in normal laser systems means that there is no coherent beam because certain frequencies that the laser is designed to operate at are not supported by the optical geometry of the system or by any electronics providing amplification of the beam. Instability in these systems refers to a phenomenon where the system is globally stable but not locally stable, and is also not periodic. In a sense the laser output is random over a set of parameters, usually frequency or amplitude. Laser systems that exhibit this behavior are referred to as chaotic systems. Chaotic phenomena in lasers have been reported and studied extensively in recent decades [22][23][24][25]. Chaos can be present in laser systems through various means, most of which involve a feedback mechanism [26]. In normal laser operation, feedback is used to keep laser frequency locked into a very narrow bandwidth. Chaotic laser operation requires this feedback to enhance the instability of the laser to the point that the nonlinear dynamics of the system overwhelm the normal operation. A large amount of research in laser chaos has been performed to mitigate or eliminate the effects of chaos in normal laser systems [27][28][29].

One method to induce chaos in a laser system is to couple a coherent, but much weaker, output of the laser back into the system [30]. By doing this, coherence in the system collapses and the laser is now no longer one specific frequency, but rather a broad range of frequencies, ultimately resulting in a noiselike spectra. The gradual increase in frequency content of a signal, noting higher order periodicity, is also known as period doubling [31].

Laser radar using a chaotically modulated carrier has been shown to provide a number of advantages over conventional radar, including low probability of intercept and increased resolution [32]. Creating a wideband signal for modulation at microwave frequencies presents a challenge for most radar systems, but chaotic signals have the necessary properties to give these benefits. Chaotic radar systems also have the ability to be synchronized with each other under certain conditions, which allows for a transmitter and receiver pair to operate theoretically undetected while still maintaining high resolution [33][34].

A lasers' naturally high frequency allows the chaotic phenomena to have a very high bandwidth, on the order of 1 GHz. This allows for random numbers to be generated more quickly than chaos found in other systems at lower frequencies, since a high throughput of random numbers in a random number generator is desirable. Some schemes for extracting random numbers from chaotic laser systems are shown below. Importantly, these schemes pass the random number generator tests to ensure that the output is statistically random in addition to being truly random.

One method of obtaining random numbers from a chaotic laser signal is to sample it with an analog to digital converter. This method is suitable for high speed random number generation because no post processing is necessary with a well designed system, which reduces system complexity and increases robustness [35][36]. In these systems, the signal is sampled at a high sample rate in order to acquire a number of bits, e.g. an 8-bit sample. One of these bits is extracted and taken as a random bit. Then, another sample is taken and another bit extracted. The continuous operation of sampling and extraction creates a bit stream that can then be used as random numbers. Bit rates on the order of 10 Gbps are reported using this method. Additionally, by taking more than one bit per sample, higher bit rates can be achieved, but some statistical tests fail with the inclusion of more bits.

Another method is to sample the laser signal and then compare it with a time delayed version of the laser signal [37]. This requires storage of the laser signal for later processing, which might prohibit real time operation. First, the derivative of the laser signal amplitude is taken as the new signal in order to avoid biases in the final output. Then, a bit-wise XOR operation is performed between the signal sample and its time delayed derivative sample, and then a subset of the bits are taken as the random bits. In this system, where the lowest 5 bits of the XOR operation are taken at a sampling rate of 2.5 GHz, bit rates of 12.5 Gbps are achieved while passing all statistical tests.

Additionally, by sampling both the clockwise and counterclockwise lasing modes within a single cavity, multi-bit samples can be taken and then post processed similarly as above. This is an improvement to other similar systems that use two separate laser cavities to achieve the same statistical results [38]. Moreover, the optical feedback path chosen can be easily constructed in a semiconductor, which allows ready implementation with an analog to digital converter and any digital communication necessary. By taking 4 bits per sample, 40 Gbps is achieved in practice.

### Chapter 3

## The Chaotic Jerk System

Electronic implementations of chaotic systems offer a variety of useful applications. The deterministic yet unpredictable behavior of these types of systems lends well to inclusion in areas such as acoustic ranging [39] and automotive collision avoidance radar systems [40][41], random stimulating noise sources for MEMS [42], spread spectrum communication systems [43], and random number generation (RNG)[44] [45]. These chaotic systems have shown promise in having continuous power spectral density [46] as well as potential security against various attacks under which other systems could be susceptible [47][48].

The primary application of interest for the oscillator in this paper is true RNG. RNGs with high bit rates are increasingly needed as various areas of security become more reliant on electronic means. Chaotic oscillators are especially well suited for use as RNGs due to the long term unpredictable nature of the waveforms that are generated [49]. Moreover, these oscillators can be used as seeds for pseudo-RNG (PRNG). This allows for the relatively higher speed PRNG systems to be used more effectively [50, 51]. Different implementations of chaotic oscillators into RNGs have been shown to pass the NIST test [52]. In addition, chaotic circuits can be realized using minimal components and system footprint. [53].

Specifically, "double scroll" systems with discrete states similar to the one developed by Saito et. al [54] have an advantage in that one "scroll" can be mapped to a "1" and the other to a "0". These types of chaotic oscillators potentially could require deskewing [55]; however many developed systems achieve high bit rates without post processing any bits, thereby decreasing the delay in the desired bit stream [56].

#### 3.1 Background

This work explores chaotic jerk systems, which are defined by a third order ordinary differential equation (ODE). These autonomous dissipative systems contain the lowest order derivative that can produce continuous timed chaos. The term jerk comes from the definition of successive derivatives in mechanical systems where x is the displacement,  $\dot{x}$  is the velocity,  $\ddot{x}$  is the acceleration, and  $\ddot{x}$  is called the "jerk" [57].

Chaotic systems must include a nonlinear term in order to generate chaos. The intended application of interest is a RNG, so careful consideration was taken with regard to the potential nonlinearity. In order to be able to more easily produce random bits, discrete nonlinearities were considered. A candidate choice of a discrete nonlinearity can introduce discrete states to a continuous time equation, making it easier to generate a random bit stream from an autonomous system [58]. Sprott [58] gives many third order equations that exhibit chaos, but most contain nonlinearities that are difficult to implement accurately in electronics, such as multiplicative relationships, exponential functions, and trigonometric functions. However, one specific nonlinearity listed is the nonlinear switching event defined by the signum function, as defined in (3.1).

$$sgn(x) = \begin{cases} +1, & x \ge 0\\ -1, & x < 0 \end{cases}$$

(3.1)

By using this nonlinearity in a continuous time system, this system is less complex and yet more robust than an equivalent discrete time system, even though continuous time systems can potentially undergo synchronization using a master-slave oscillator system [59].

Taking this specific nonlinearity into consideration, one of the equations given in [58], is much simpler than the others:

$$\ddot{x} = -0.5\ddot{x} - \dot{x} - x + sgn(x) \tag{3.2}$$

This system was carefully chosen because these functions can easily be implemented in mixed signal electronic circuitry. The advantage of this discrete nonlinearity is that it can be implemented in electronic circuitry by using a single comparator. This system's structure and its state feedback topology are composed of a weighted summation of the system's states and the output from the discrete nonlinearity. These mathematical functions can be implemented in electronics by using a string of operational amplifier (op amp) integrators, a comparator, and an analog summing amplifier. Implementation of this system in MOS has been proposed and designed with desirable simulation results in the kHz frequency range, but has yet to be physically realized [60]. These circuits could potentially require specialized MOS fabrication techniques in order to reach high frequencies. The electronic design presented here requires a small number of commercial off-the-shelf (COTS) components in order to be implemented. This is advantageous in scaling the frequency of the design up to 4 MHz since the propagation delay required to complete the feedback path is minimized.

Next, the maximum Lyapunov exponent (MLE) of the system needs to be estimated so that the maximum bit rate for random number generation can be found. The method chosen to accomplish this is a direct measurement of the divergence rate of many pairs of almost identical trajectories in simulation. The sensitivity of these chaotic systems to initial conditions causes trajectories that are different only by an amount well below measurement thresholds of real systems to quickly diverge. The MLE is then calculated by comparing the inital offset between the two systems with the time it takes for the difference in trajectories to reach a chosen threshold. This calculation is given with the following equation

$$MLE = \frac{ln(\frac{threshold}{offset})}{time}$$

(3.3)

where threshold is the chosen divergence limit, offset is the initial difference in states of the two trajectories, time is the final time taken to reach the threshold, and ln is the natural logarithm. Then, this translates into a theoretical maximum bit rate as follows

$$bitrate = \frac{MLE}{\ln 2} \approx 1.443 * MLE \tag{3.4}$$

The bit rate given in (3.4) has units of  $s^{-1}$ .

For the jerk system, many time domain simulations were performed in order to determine the MLE by using a MATLAB script to implement the differential equations with a fixed time step. Initial conditions for both systems (the x,  $\dot{x}$ , and  $\ddot{x}$  states) were randomized such that they were between -1 and +1 so that the trajectories remained in the chaotic region of the attractor rather than becoming globally unstable. Then an very small offset (between  $10^{-12}$  and  $10^{-8}$ ) was applied to the second system's x state. The threshold limit was chosen to be between  $10^{-4}$ and  $10^{-1}$ . An example plot of divergence in the two trajectories for one set of the chosen offset and threshold is shown in Fig. 3.1. In this figure, an initial condition for the systems is chosen and then one is separated by a small amount ( $d0 = 5*10^{-12}$  for this example). Then the systems are simulated forward in time until they reach the specified threshold (here,  $thresh = 1*10^{-2}$ and is marked with an asterisk). After this point, the systems visibly diverge quickly.

Figure 3.1: Sensitivity to initial conditions in the jerk equation. The red asterisk denotes the point of divergence.

The resulting MLE from many simulations with various initial conditions, thresholds, and offsets was between 0.152 and 0.153 for the jerk system. This then gives a bit rate of 0.218 and 0.221 bits per second. Sprott reaches a very similar result for an MLE of the same system when using another method with some approximations [61]. It can be seen visually that the system has a natural "frequency" of oscillation (when considering the time to complete one orbit around half of the attractor) of approximately 0.2Hz. Thus, the bit rate of the system

itself is around 1 bit per cycle. By framing the bit rate this way, the system can be scaled to any frequency and the bit rate will remain constant with respect to the system. Specifically, when the system is implemented at high frequency in an electronic circuit, the circuit will be able to generate random bits at this higher natural frequency, as long as the system is represented accurately.

## Chapter 4

### Hardware Circuit Design

#### 4.1 Circuit Simulation

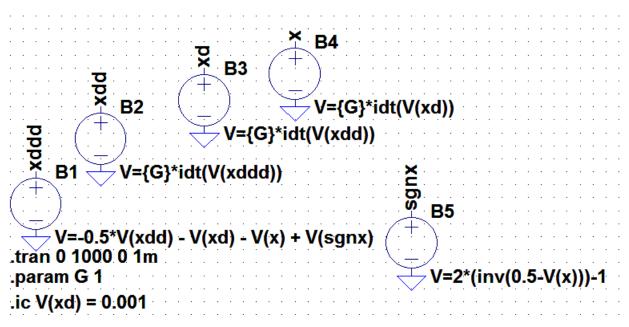

A block diagram of the chaotic jerk system in state feedback form is shown in Fig. 4.1. The system's ideal dynamics were first simulated using ideal component models in LTSpice as shown in Fig. 4.2. The parameter "G" sets the overall loop gain of each of the integrating stages. Figs. 4.3 and 4.4 show the time domain of x(t) for various values of G. The phase space  $(\dot{x} \ vs. x)$  of the chaotic equation is shown in Fig. 4.5. Demonstration that the fundamental frequency of oscillation increases as the loop gain G increases is shown in Figs. 4.3 and 4.4.

Thus, in order to achieve the highest possible frequency in the real circuit, the gains of the integrating stages must be very high. A standard operational amplifier integrator has a transfer equation of (4.1).

$$v_o = \frac{-1}{RC} \int_0^t v_{in} dt \tag{4.1}$$

Figure 4.1: Block diagram of (3.2)

Figure 4.2: LTSpice simulation of an ideal circuit implementation of (3.2)

Figure 4.3: Time domain plot of x(t) with G = 1

Figure 4.4: Time domain plot of x(t) with G = 10 M

Figure 4.5: Phase space of the chaotic equation

Hence, the gain of each of the integrating stages is set by the values of the input resistor (R) and feedback capacitor (C), and also is always negative. This is accounted for in the summing amplifier as the polarity of each stage will be the opposite of the stage before, but the polarity of each term in (3.2) is referenced to  $\ddot{x}$ .

However, the frequency of oscillation cannot be increased indefinitely. Real operational amplifiers have finite gain bandwidth products (GBP) and slew rate limitations. Since the gain of the op amp integrators must be high, the primary frequency limitation of this implementation is the GBP of the op amp. Equation (3.2) assumes that there is no propagation delay through the string of integrators and comparator. In practice, the propagation delay through these devices can cause signals that are assumed to be "in sync" to be "out of sync". Additionally, non-ideal op amp phase responses become more pronounced at higher frequencies that could potentially be detrimental to the desired chaotic operation.

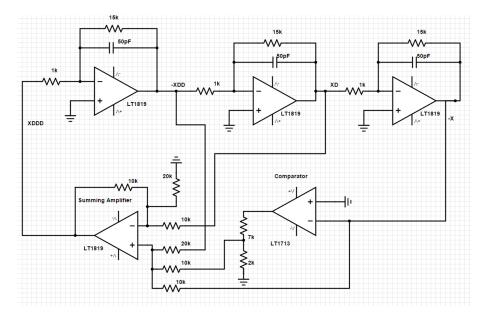

A simulation with models for real components is shown in Fig. 4.6. This circuit was simulated in LTSpice as shown in Fig. 4.7. LT1818 op amps were chosen for their high bandwidth, low propagation delay, and ability to operate from differential power supplies. The LTC6752-2 comparator has separate input and output power supply power rails. This means that the comparator's output can be scaled to  $\pm 1V$  to achieve proper scaling of the signum function. Also, feedback resistors were added in parallel with the feedback capacitors in order to prevent integrator latch up. Figs. 4.8 and 4.9 show the time domain and phase space of this circuit simulation, respectively. These component model simulations are in agreement with the ideal simulations at the target frequency of 4 MHz. Unfortunately, when the resonant frequency is made any higher by decreasing the feedback capacitor value, the phase space becomes increasingly distorted until the circuit is no longer chaotic. Thus, although the circuit could potentially be made to oscillate at a higher frequency, the component values were chosen so that the circuit maintains a clean phase space and time domain signal.

## 4.2 Circuit Hardware

A 4-layer printed circuit board (PCB) was developed using KiCad. A tutorial for creating PCBs within KiCad is given in Appendix B. This prototype maintains the core components

Figure 4.6: Real component implementation of (3.2)

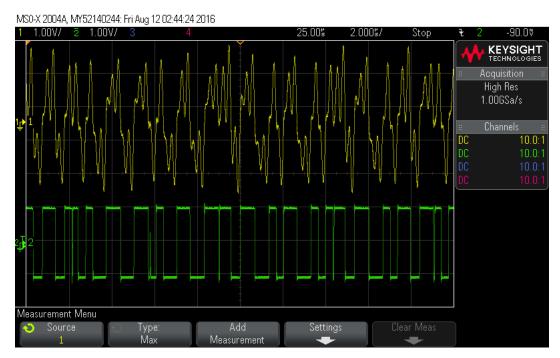

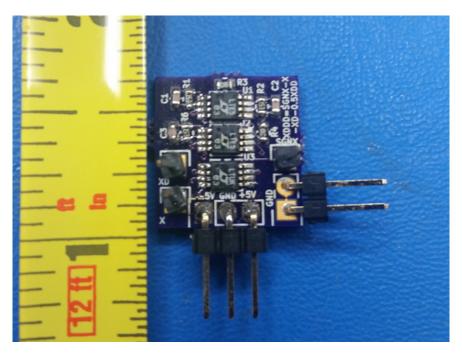

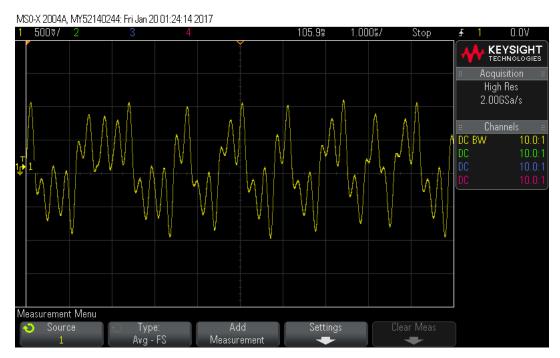

from the schematic in Fig. 4.7; however, additional components such as headers and decoupling capacitors were added for probing and filtering the power supply. A photograph of the populated PCB is shown in Fig. 4.10. Time domain and phase space plots of the hardware circuit are shown in Figs. 4.11 and 4.20, respectively. An oscilloscope screen capture of the signum function output of the circuit is shown in Fig. 4.13. This circuit is shown populated to oscillate at the target 4 MHz fundamental frequency.

The hardware circuit is in close agreement with both the ideal simulation and the real component simulation when comparing both the time domain and phase space plots. Moreover, the signum output shown can be used as the random bit stream for a RNG. The circuit draws approximately 40 mA from both the +5V and -5V power supplies, and draws approximately 2mA from both the +1V and -1V power supplies.

Figure 4.7: LTSpice simulation of (3.2) with real components

Figure 4.8: Time domain plot of x(t) for the simulated system

Figure 4.9: Phase space ( $\dot{x}$  vs x) for the simulated system

Figure 4.10: Populated printed circuit board

Figure 4.11: Time domain plot of x(t)

Figure 4.12: Phase space ( $\dot{x}$  vs x)

Figure 4.13: x(t) and sgn(x(t))

## 4.3 Compact and Low Power Implementation

The circuit board previously described was improved in order to reduce the form factor and to decrease the required power consumption. The system requires both a positive and a negative supply voltage, which would require buck-boost converters in low power/embedded systems to provide these additional rails. This design utilized the LTC6752-2 comparator that required separate 1V and -1V rails; the coefficients of (3.2) are not kept in proportion when the +5V and -5V rails lower from their nominal value. This could result from either an increase in current requirements elsewhere or from battery voltage dropping during discharge. While the circuit may still chaotically oscillate, it would no longer be an accurate representation of the design equation.

# 4.3.1 Efficient Design of Chaotic Oscillators

As electronics and manufacturing technology improves, a premium is placed on cost, component count, and the physical dimensions of the overall system. Electronic subsystems should occupy the minimum area possible while still achieving high functionality. This includes consolidation of component values, using smaller size components, component layout optimization, and careful design of feedback paths for signal integrity. Chaotic circuits have the advantage of rich dynamics in a relatively small electronic implementation when compared to other traditional topologies. This simplicity should be taken advantage of as much as possible. Specifically, chaotic circuits requiring multiple operational amplifiers should aim to group these devices into a single package, and standard component values should be used instead of nonstandard values if the design requirements of the system can still be met. Also, component values should be reused throughout the design to reduce both component and manufacturing cost. However, the precision and functionality of the chaotic oscillator should not be sacrificed for the sake of cost. If the system design dictates that a specific component is necessary, it should not be replaced with another component that would impact the performance of the system negatively.

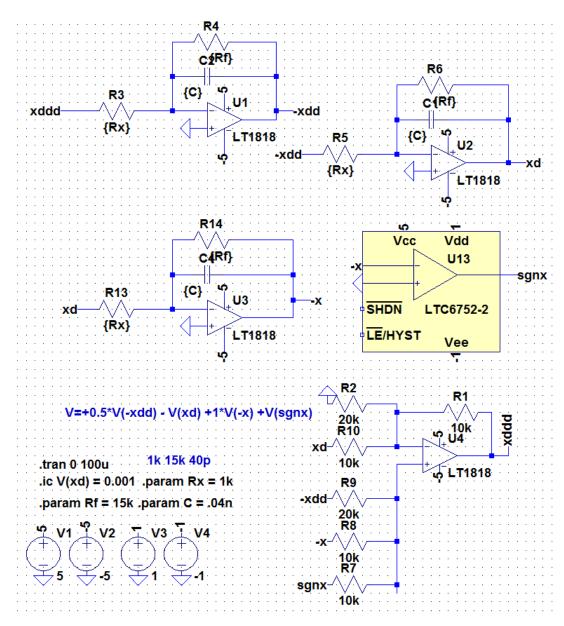

# 4.4 Smaller Board Design

The previous oscillator used discrete operational amplifier (op amp) chips in order to implement the three integrators and summing amplifier. These four chips have been replaced with two LT1819 dual op amp chips in micro small outline packages (MSOP). These are functionally the same as the LT1818, but the reduced size allows for a much smaller trace length in the feedback path and fewer power filtering capacitors. The feedback path of the circuit is routed in a counterclockwise direction in order to take advantage of the pinout of these smaller chips.