## When Alice meets the "Hardware" Bob — Attacks and Solutions in the Digital World

by

# Yadi Zhong

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama May 4, 2024

Keywords: Cryptanalysis, GIFT-COFB, Fault Attacks, Boolean Satisfiability (SAT), Test Pattern Generation, Zero-Knowledge Succinct Non-Interactive Argument of Knowledge (zk-SNARK)

Copyright 2024 by Yadi Zhong

# Approved by

Ujjwal Guin, Chair, Associate Professor of Electrical and Computer Engineering Vishwani D. Agrawal, Professor Emeritus of Electrical and Computer Engineering Adit D. Singh, Professor of Electrical and Computer Engineering Mehdi Sadi, Assistant Professor of Electrical and Computer Engineering Akond Rahman, Assistant Professor of Computer Science and Software Engineering

#### **Abstract**

Modern cryptography and the digital world (CMOS mainly) have been advancing side-by-side. Although cryptographic algorithms only need to be proven with theoretical soundness, cryptographic engineering on digital device requires more efforts to achieve a secure implementation than simply just design theories. Although properties like energy-efficiency, low-latency, and minimal area overhead are desired in hardware-based implementations for cryptographic modules, they could potentially weaken the theoretical justification of cryptosystems, where adversaries can break the secret key inside the hardware.

In this dissertation, we develop novel attack to uniquely determine the secret key for hardware implementation of GIFT-COFB, one of the ten finalists for National Institute of Standards and Technology (NIST) Lightweight Cryptography Standardization Process. The 2-round partial unrolled design of GIFT-COFB is shown to be the most energy-efficient among all other r-round partial unrolling and fully unrolled settings. Our proposed chosen-plaintext attack can effectively break the master key K on this 2-round partial unrolled GIFT-COFB. In addition, we present two chosen-plaintext attacks on multicycle AES implementations with fault-based attacks. Both attacks on GIFT-COFB and multicycle AES include explanations from algebraic cryptanalysis perspective.

In parallel, the adoption of horizontal business models in semiconductor manufacturing is negatively affected by the overproduction of integrated circuits (ICs) and the piracy of intellectual properties (IPs), which compromised the integrity of the digital world's semiconductor supply chain. Logic locking emerges as a primary design-for-security measure to counter these threats, where ICs become fully functional only when unlocked with a secret key. However, Boolean satisfiability-based attacks have rendered most locking schemes ineffective. This gives rise to numerous defenses and new locking methods to achieve SAT resiliency. Subsequent attacks have been proposed to target these newly proposed solutions. The reasons behind the effectiveness of SAT attack and the following SAT-based attack have yet to be explored. In this

dissertation, we provide a unique perspective on SAT attack efficiency based on conjunctive normal form (CNF) stored in SAT solver. We demonstrate how this attack learns new relations between keys in every iteration using distinguishing input patterns and the corresponding oracle responses. Each input-output pair gives additional CNF clauses of unknown keys to be appended to SAT formulation, which leads to an exponential reduction in incorrect key values. Overall, SAT attack is shown to break most locking scheme within the linear iteration complexity of key size. Our analysis provides a new perspective on the capabilities of SAT attack against multiplier benchmark c6288 with possibly new directions to achieve SAT resiliency.

In the digital world, it is also crucial to reduce manufacturing defect escapes in today's safety-critical applications requires increased fault coverage. However, generating a test set using commercial automatic test pattern generation (ATPG) tools that lead to zero-defect escape is still an open problem. It is challenging to detect all stuck-at faults to reach 100% fault coverage. It remains challenging to detect hard-to-detect and redundant faults for large VLSI circuits. More optimization needs to be done as undetected faults still exist under the stateof-the-art commercial ATPG tools. Rather than attacking logic locking with SAT solvers, in this dissertation, we propose a novel test pattern generation approach constructively using the powerful SAT attack on logic locking. A stuck-at fault is modeled as a locked gate with a secret key, where it can effectively deduce the satisfiable assignment with reduced backtracks under key initialization of the SAT attack. The input pattern that determines the key is a test for the stuck-at fault. We propose two different approaches for test pattern generation. First, a single stuck-at fault is targeted, and a corresponding locked circuit with one key bit is created. This approach generated one test pattern per fault. We also consider a group of faults and convert the circuit to its locked version with multiple key bits. The inputs obtained from the SAT attack tool are the test set for detecting this group of faults. Our approach finds test patterns for all hardto-detect faults that were previously undetected in commercial ATPG tools. The proposed test pattern generation approach can efficiently detect redundant faults with ITC'99 benchmarks. The results show that we can detect all the hard-to-detect faults and identify redundant faults, and a 100% stuck fault coverage is achieved.

Finally, we consider privacy-enhancing solutions to offer additional benefits for securing the digital world. In this dissertation, we develop an efficient, secure, and on-demand communication protocol using zero-knowledge proofs (ZKPs) that allow the prover to provide evidence of its secret without revealing that to the verifier. The edge device, acting as the prover, convinces the central server, the verifier, of the unique PUF response stored inside the device without requiring the actual storage of PUF responses on the server. The non-interactive characteristic of zk-SNARK, Zero-Knowledge Succinct Non-Interactive Argument of Knowledge, offers better optimization to authentication frequency, communication bandwidth between device and server, and protection of device-specific secret, all of which contribute to constructing our proposed device authentication framework.

## Dedication

# Dedicated to my dear parents.

Dear Lord Jesus Christ, the everlasting Light. "And so I come to the realization that I cannot fully trust in anyone to help me in my necessities save only You – my hope, my trust, my comfort, and my most faithful Friend ... Only You Yourself, my God, can stand by me, help me, comfort, counsel, teach, and defend me."

— The Imitation of Christ by St. Thomas A Kempis

And singing the canticle of Moses, the servant of God, and the canticle of the Lamb, saying: Great and wonderful are Thy works, O Lord God Almighty; Just and true are Thy ways, O King of ages. Who shall not fear Thee, O Lord, and magnify Thy name? For Thou only art Holy: for all nations shall come, and shall adore in Thy sight, because Thy judgments are manifest.

— Revelation 15:4-5 (Douay-Rheims)

Galatians 6:7-9, Philippians 4:6-7, Ephesians 6:10-12.

I really appreciate the anonymous individuals who wrote the following Bible verses on the steps outside of Broun Hall, which I saw on April 22, 2024. These verses (Colossians 1:16, Philippians 1:6) mean very much to me and I am grateful that the Lord has planned all these.

# ALL HAIL KING JESUS!

For in Him were all things created in heaven and on earth, visible and invisible, whether thrones, or dominations, or principalities, or powers. All things were created by Him and in Him. — Colossians 1:16

Being confident of this very thing: that He who hath begun a good work in you will perfect it unto the day of Christ Jesus. — Philippians 1:6

#### Acknowledgments

Praise be to the Almighty God for this PhD journey! You are the Way, the Truth, and the Life, and You are the source that keep me going! This PhD is made possible only because of You.

I would like to express my gratitude to my parents for continually uplifting me through my journey through graduate school at Auburn, without your support, I could not have made it this far. I really appreciate my dad for patiently waiting for me every day to finish my daily tasks; and my mom for teaching me a whole lot more with her own experience as a professor. It is great blessings from God that to learn Thy way of righteousness and daily strive toward Thy heavenly bliss! Words cannot express the goodness of the Lord and His plan in this journey as we grow in trusting Him in everything, and experiencing that God is in control of everything, both small and great. Christ Jesus is the ruler of all and Thy works are manifest! I am grateful for your constant warning, encouragement, and advice!

Thank you to my advisor Dr. Ujjwal Guin for providing me the opportunity both as an undergrad researcher (thanks to Alex Jones for turning down the opportunity in the first place) and a graduate student at Auburn. Thank you for heavy editing on my plethora of paper drafts. I appreciate the encouragement, and scolding as well (these all helped me to improve my research), for all rejections and major revisions and minor revisions, and I learned the importance of consistent revising to improve these papers.

I would like to extend my gratitude and appreciation to the committee members of my dissertation: Dr. Vishwani D. Agrawal, Dr. Adit D. Singh, and Dr. Mehdi Sadi. Thank you all for your interest, valuable suggestions, and time which makes this thesis possible. I learned a lot from your research and professional expertise. I am particularly grateful of having the opportunity to

take your classes in both undergraduate and graduate studies. These include Dr. Singh's Digital Logic Circuits (ELEC 2200), where I was first introduced to recycled ICs and SRAM power-up states, VLSI Design (ELEC 6770) and Advanced VLSI Design (ELEC 7770), and Dr. Sadi's Computer Aided-Design of Digital Integrated Circuits (ELEC 6250) and AI and Neuromorphic Hardware (ELEC 6970). In addition, Dr. Agrawal's excellent VLSI testing book has been an valuable resource to me. Thank you to my university reader Dr. Akond Rahman for detailed comments and feedback that helped improve the quality of this dissertation.

I would also like to thank my colleagues in the System Engineering and Security Lab, Ayush and Yuqiao, for assisting and teaching me a great amount in areas I was unfamiliar with when I first started my graduate school. I appreciate all the help I received from my colleagues, Pratiksha, Kaniz, Austin, Caleb, Josh, Colton, and Chris, during my time working towards a PhD. I am grateful for the insightful/funny discussions I had with all the undergrads in our lab, William, Holden, Craig, Mukarram, Pascal, Farrok, Gaines (now Master student in the same lab), Ammar, and Josh. You are great friends to me.

A big Thank You goes to my coauthors, Josh and Ammar. I enjoyed working with you all and I am grateful for all collaborations, brainstorming, discussions, and writings.

I would like to express my gratitude to all excellent faculty members in Department of Electrical and Computer Engineering. In both my undergraduate and graduate studies, I have taken many exciting and intensive courses, which were critical in strengthening my foundation in various diverse topics related to signal processing, electronics, embedded systems, computer networks, VLSI design, digital system designs, and hardware security. These academic courses helped me comprehend and describe the novelty in my research work. I appreciate all the technical support I received from Mr. Autry May, Mr. Michael Eddy, and Mr. John Tennant of ECE Department. My sincere appreciate to Mrs. Linda Allgood, Mrs. Mary Lloyd, Mrs. Elizabeth Gowan, and Mrs. Faith Fain in the ECE Department for their excellent administrative support, guidance, and help in both my undergraduate and graduate years. I am grateful for everything the department has provided during my studies.

Finally, my sincere thanks to all of my labmates for making the research experience more enjoyable and rewarding. Your help ranging from brainstorming new ideas to simply assisting with menial tasks when I am busy means very much to me. Y'all made my day.

Dear Lord, the ruler of all, the King of kings, the Lord of lords, and also the Advisor of advisors, no one can start this PhD journey or make it to completion save You. It is truly a joyful thing, always and everywhere, to give thanks to You and count the blessings You have bestowed upon me. Lord, I praise You for the numerous graces You have showered on your daughter on this journey and guided me through the rejections, storms, temptations of relying on others instead of fully trust in You, who knows both the visible and invisible things, past, present, and future.

# Contents

| Ał | ostract | :                                                                                                         | 11  |

|----|---------|-----------------------------------------------------------------------------------------------------------|-----|

| Dε | edicati | on                                                                                                        | V   |

| Αc | know    | ledgments                                                                                                 | vii |

| Li | st of A | Abbreviations                                                                                             | xix |

| Ι  | Ali     | ce and the "Hardware" Bob                                                                                 | 1   |

| 1  | Intro   | duction                                                                                                   | 2   |

|    | 1.1     | Thesis Statement and Research Questions                                                                   | 5   |

|    | 1.2     | Contributions                                                                                             | 6   |

|    | 1.3     | Organization of this Thesis                                                                               | 9   |

| 2  | Back    | ground and Preliminaries                                                                                  | 15  |

|    | 2.1     | Substitution-Permutation Network, Authenticated Encryption, Authenticated Encryption with Associated Data | 15  |

|    | 2.2     | Globalization of Semiconductor Supply Chain                                                               | 16  |

|    | 2.3     | Zero-Knowledge Proof                                                                                      | 18  |

| II | На      | ardware-Based Attacks                                                                                     | 20  |

| 3  | Cho     | sen-Plaintext Attack on Energy-Efficient Hardware Implementation of GIFT-COFB                             | 21  |

|    | 3.1     | Introduction                                                                                              | 21  |

|    | 3.2     | NIST Lightweight Cryptography Finalist GOFT-COFB                                                          | 23  |

|    |         | 3.2.1 Threat Model                                                                                        | 23  |

|   |      | 3.2.2     | Lightweight Hardware Implementation of GIFT-COFB                     | 24 |

|---|------|-----------|----------------------------------------------------------------------|----|

|   | 3.3  | Chose     | n-Plaintext Attack on GIFT-COFB                                      | 25 |

|   | 3.4  | Result    | and Discussions                                                      | 29 |

|   | 3.5  | Summ      | ary                                                                  | 30 |

| 4 | Faul | t-Injecti | ion Based Chosen-Plaintext Attacks on Multicycle AES Implementations | 31 |

|   | 4.1  | Existin   | ng AES Implementation, Notations, and Threat Model                   | 32 |

|   |      | 4.1.1     | Threat Model                                                         | 34 |

|   | 4.2  | Propos    | sed Attacks on Multicycle AES Implementations                        | 35 |

|   |      | 4.2.1     | Proposed Exhaustive Key-Byte Search Attack                           | 35 |

|   |      | 4.2.2     | Proposed Fault-Injection Attack                                      | 42 |

|   |      | 4.2.3     | Extending the Proposed Attacks to AES-192 and AES-256                | 44 |

|   |      | 4.2.4     | Number of Plaintext Requirement                                      | 46 |

|   | 4.3  | Theore    | etical Justification of Double-Solution for Equation 4.5             | 46 |

|   | 4.4  | Summ      | ary                                                                  | 48 |

| 5 | Com  | plexity   | Analysis of the SAT Attack on Logic Locking                          | 49 |

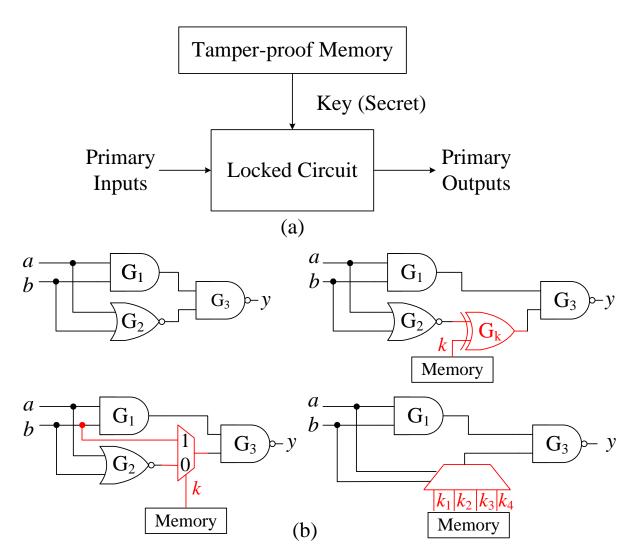

|   | 5.1  | Backg     | round                                                                | 51 |

|   |      | 5.1.1     | SAT attack on Logic Locking                                          | 51 |

|   |      | 5.1.2     | SAT Resistant Logic Locking Techniques and Attacks                   | 54 |

|   | 5.2  | SAT A     | attack Analysis: Pruning of Incorrect Key with CNF Update            | 54 |

|   |      | 5.2.1     | SAT Attack for a Locked Cone with One Output                         | 56 |

|   |      | 5.2.2     | SAT Attack against Multiple Overlapping Logic Cones                  | 59 |

|   | 5.3  | SAT A     | Attack Analysis: Iteration Complexity                                | 62 |

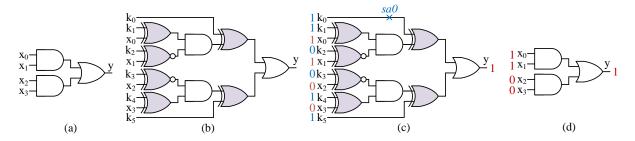

|   | 5.4  | Case S    | Study: Locking with Point Functions                                  | 70 |

|   |      | 5.4.1     | Deterministic Property of SAT Attack with Constraints                | 70 |

|   |      | 542       | Extending the point function analysis to TTLock and SFLL             | 74 |

|   | 5.5 | Future  | Directions                                                       | 75  |

|---|-----|---------|------------------------------------------------------------------|-----|

|   |     | 5.5.1   | Achieving Higher Time Complexity Against SAT Solvers             | 75  |

|   |     | 5.5.2   | Controllability Analysis                                         | 77  |

|   |     | 5.5.3   | Extension of the Proposed Complexity Analysis to the SMT Attacks | 78  |

|   | 5.6 | Summ    | ary                                                              | 79  |

| 6 | AFL | A: ATP  | G-Guided Fault Injection Attack on Secure Logic Locking          | 80  |

|   | 6.1 | Prior V | Work in existing logic locking and attacks                       | 83  |

|   |     | 6.1.1   | Comparison of AFIA with CLIC-A                                   | 85  |

|   |     | 6.1.2   | Comparison of AFIA with Key Sensitization Attack                 | 86  |

|   |     | 6.1.3   | Dissimilarities between Logic Locking and Cryptosystems          | 87  |

|   |     | 6.1.4   | Fault Injection Methods                                          | 88  |

|   | 6.2 | Differe | ential Fault Analysis (DFA) attack                               | 90  |

|   |     | 6.2.1   | Threat Model                                                     | 90  |

|   |     | 6.2.2   | Differential Fault Analysis (DFA) Attack Methodology             | 92  |

|   |     | 6.2.3   | Example                                                          | 94  |

|   |     | 6.2.4   | Test Pattern Generation                                          | 95  |

|   | 6.3 | AFIA:   | ATPG-guided Fault Injection Attack                               | 97  |

|   |     | 6.3.1   | Overall Approach                                                 | 98  |

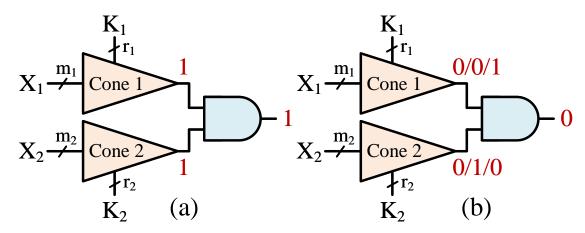

|   |     | 6.3.2   | Cone Analysis                                                    | 99  |

|   |     | 6.3.3   | Test Pattern Generation                                          | 101 |

|   |     | 6.3.4   | Fault Injection                                                  | 102 |

|   |     | 6.3.5   | Proposed Algorithm for AFIA                                      | 102 |

|   |     | 6.3.6   | Example                                                          | 104 |

|   |     | 6.3.7   | AFIA Complexity Analysis                                         | 106 |

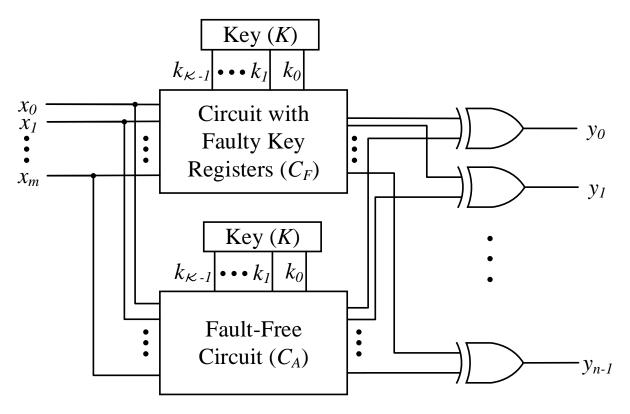

|   |     | 638     | AFIA on Fault-Tolerant Circuit                                   | 107 |

|    |      | 6.3.9   | AFIA on Non-Functional-Based Locking Techniques                                         | 18 |

|----|------|---------|-----------------------------------------------------------------------------------------|----|

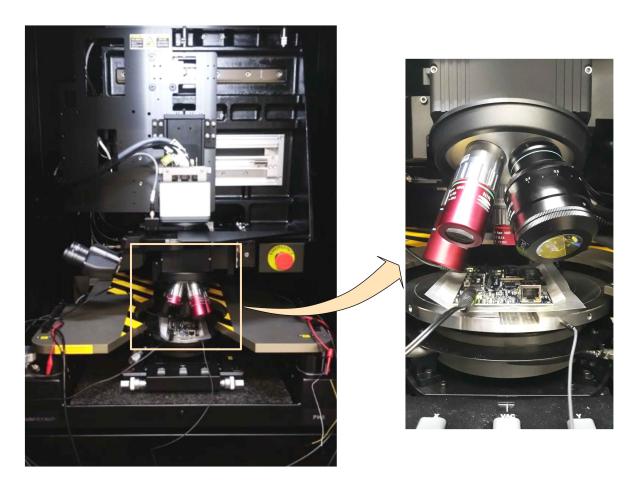

|    | 6.4  | Experi  | mental Results                                                                          | )8 |

|    |      | 6.4.1   | Laser Fault Injection                                                                   | )9 |

|    |      | 6.4.2   | Fault Count Comparison                                                                  | 0  |

|    | 6.5  | Summa   | ary                                                                                     | 2  |

| II | I H  | [ardwa  | are-Based Solutions                                                                     | 4  |

| 7  | A C  | omprehe | ensive Test Pattern Generation Approach Exploiting the SAT Attack for                   |    |

| ,  |      | -       | ng                                                                                      | 5  |

|    | 7.1  | Prior V | Vorks                                                                                   | 8  |

|    |      | 7.1.1   | SAT attack on Logic Locking                                                             | 9  |

|    | 7.2  | Propos  | ed SAT-based Test Generation Approach                                                   | 21 |

|    |      | 7.2.1   | Novel miter construction for stuck-at fault with key-dependent circuit in logic locking | 22 |

|    |      | 7.2.2   | Identification of Redundant Faults                                                      | 25 |

|    |      | 7.2.3   | ATPG using the SAT Attack on Logic Locking                                              | 26 |

|    |      | 7.2.4   | Test Pattern Generation and Redundant Fault Identification Algorithm . 13               | 31 |

|    | 7.3  | Result  | and Analysis                                                                            | 5  |

|    | 7.4  | Summa   | ary                                                                                     | 1  |

| 8  | On-I | Demand  | Device Authentication using Zero-Knowledge Proofs for Smart Systems 14                  | 12 |

|    | 8.1  | Backgr  | round                                                                                   | 13 |

|    |      | 8.1.1   | Physically Unclonable Functions                                                         | 13 |

|    |      | 8.1.2   | Zero-Knowledge Proofs                                                                   | 4  |

|    |      | 8.1.3   | Pairing-based zk-SNARKs                                                                 | -5 |

|    | 8.2  | Propos  | ed Approach                                                                             | 15 |

|    |      | 8.2.1   | Threat Model                                                                            | 6  |

|    |      | 822     | Registration Phase                                                                      | 16 |

|    |        | 8.2.3    | Operational Phase            | 150 |

|----|--------|----------|------------------------------|-----|

|    |        | 8.2.4    | Security Analysis            | 152 |

|    | 8.3    | Experi   | mental Results               | 153 |

|    |        | 8.3.1    | Performance Analysis         | 154 |

|    | 8.4    | Summ     | ary                          | 155 |

| 9  | Cond   | clusions | and Future Work              | 157 |

|    | 9.1    | Future   | Work and Possible Directions | 158 |

| Bi | bliogr | aphy     |                              | 160 |

| Δr | nendi  | ix       |                              | 194 |

# List of Figures

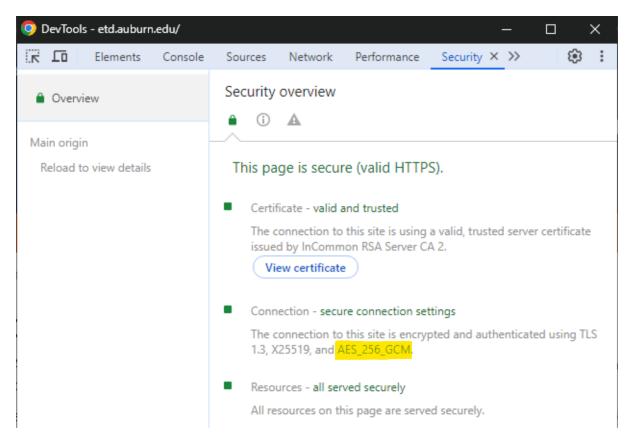

| 1.1 | TLS 1.3 and authenticated encryption scheme AES_256_GCM are used to secure communications with AUETD server, https://etd.auburn.edu/. Screenshot was taken with Google Chrome                                                                                                                | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

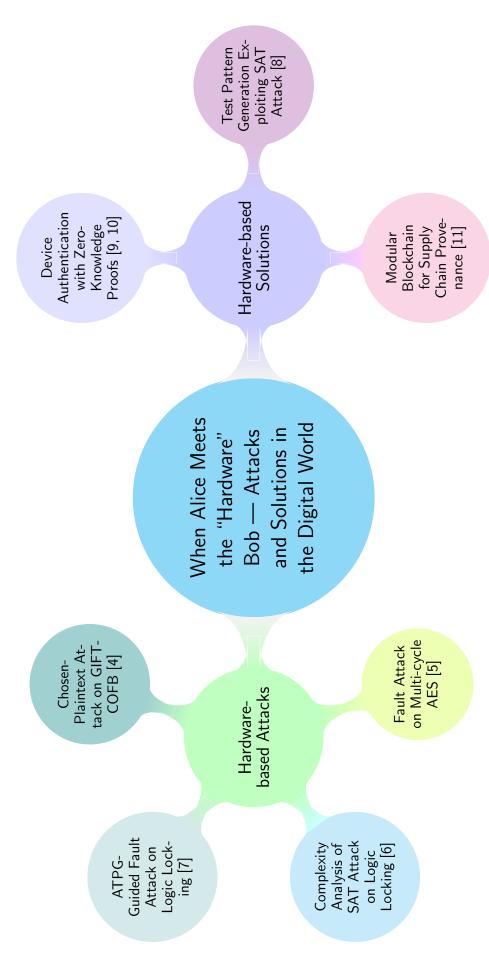

| 1.2 | Overview of publications included in this dissertation                                                                                                                                                                                                                                       | 10 |

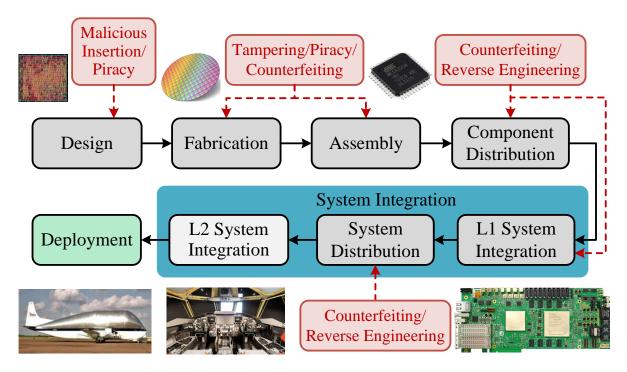

| 2.1 | Overview of electronics supply chain and possible attack surface                                                                                                                                                                                                                             | 17 |

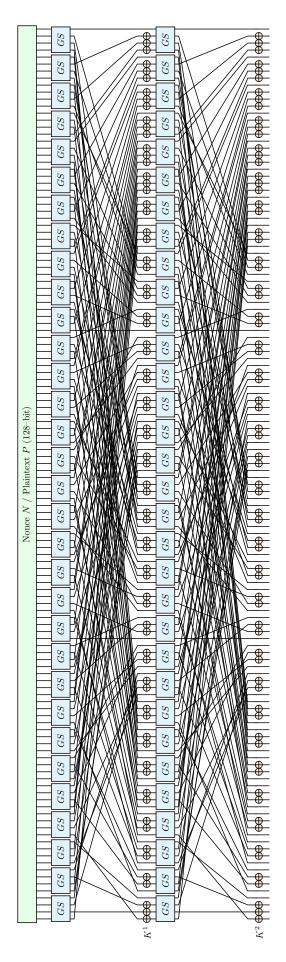

| 3.1 | GIFT-128 block cipher                                                                                                                                                                                                                                                                        | 22 |

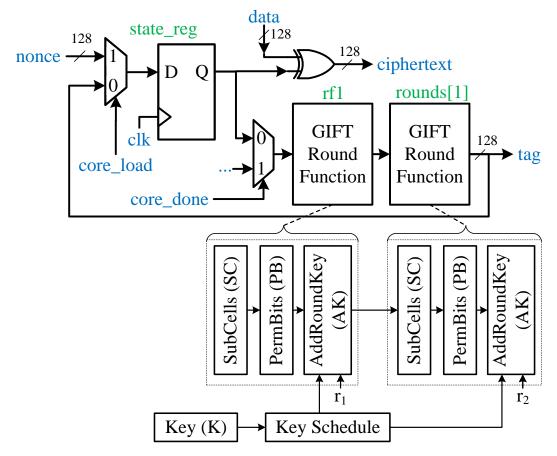

| 3.2 | Hardware implementation of 2-round partial unrolled GIFT-COFB                                                                                                                                                                                                                                | 25 |

| 3.3 | Differential Distribution Table (DDT) of GIFT Sbox                                                                                                                                                                                                                                           | 26 |

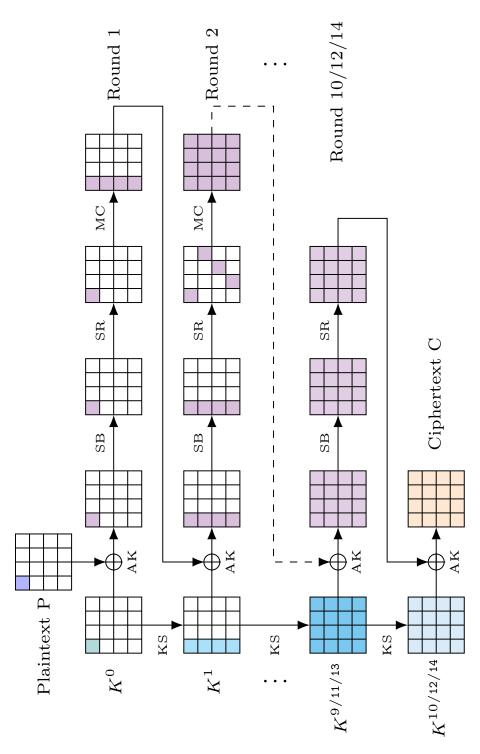

| 4.1 | Encryption rounds in AES-128, AES-192, and AES-256                                                                                                                                                                                                                                           | 33 |

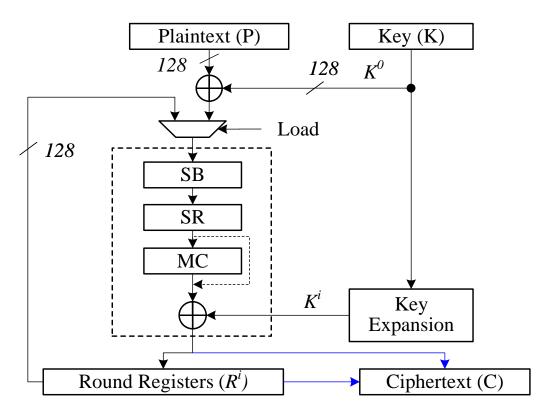

| 4.2 | Hardware implementation of multicycle AES-128.*                                                                                                                                                                                                                                              | 36 |

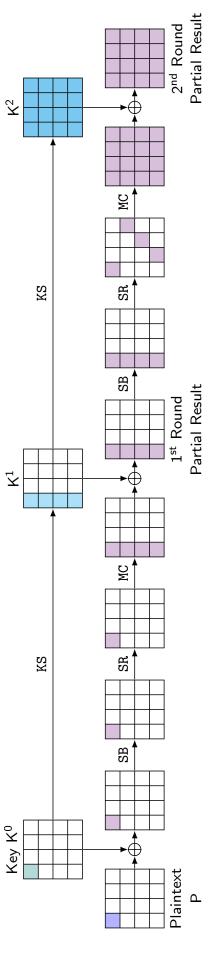

| 4.3 | First two encryption rounds of AES                                                                                                                                                                                                                                                           | 37 |

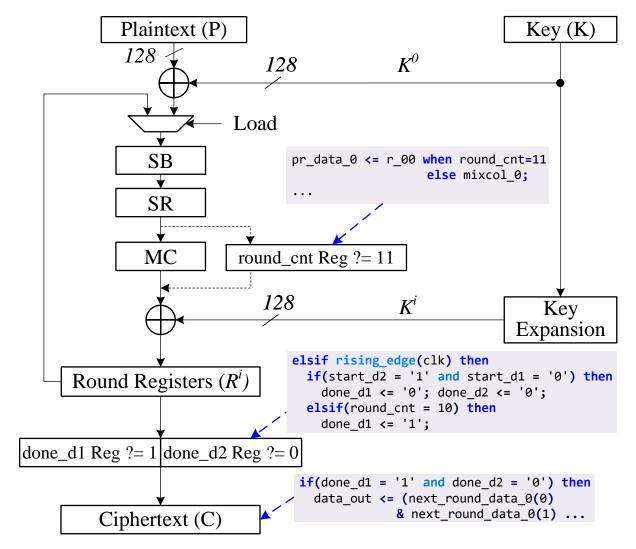

| 4.4 | Structure of multicycle AES-128, where round result $R^i$ is sent to ciphertext $C$ only after the last round of encryption, code segment from Lines 319-326, 399-428.*                                                                                                                      | 43 |

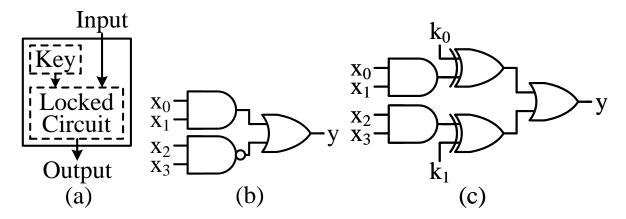

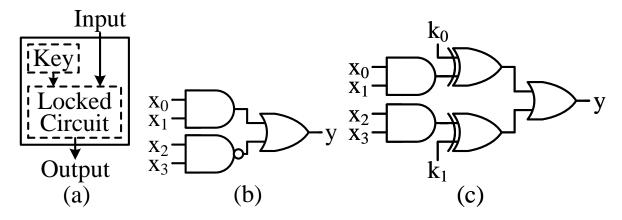

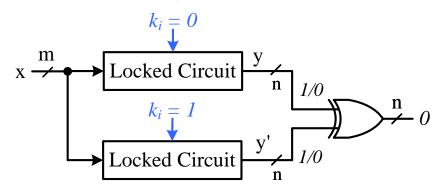

| 5.1 | Overview of logic locking. (a) Architecture of a locked circuit. (b) Original design. (c) XOR-based locking, with secret key of $k_0k_1=01$                                                                                                                                                  | 50 |

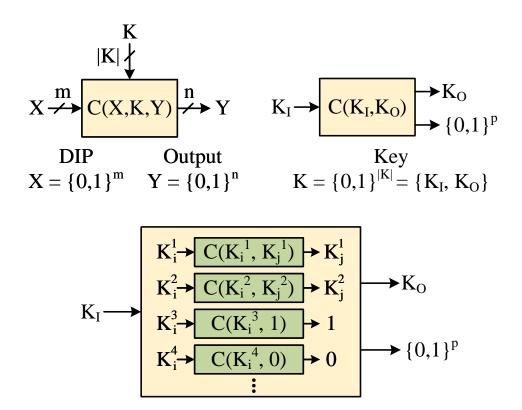

| 5.2 | Abstract representation of functions of key bits derived from an IO pair. (a) Locked circuit with an IO pair, (b) function of keys, and (c) subfunctions                                                                                                                                     | 55 |

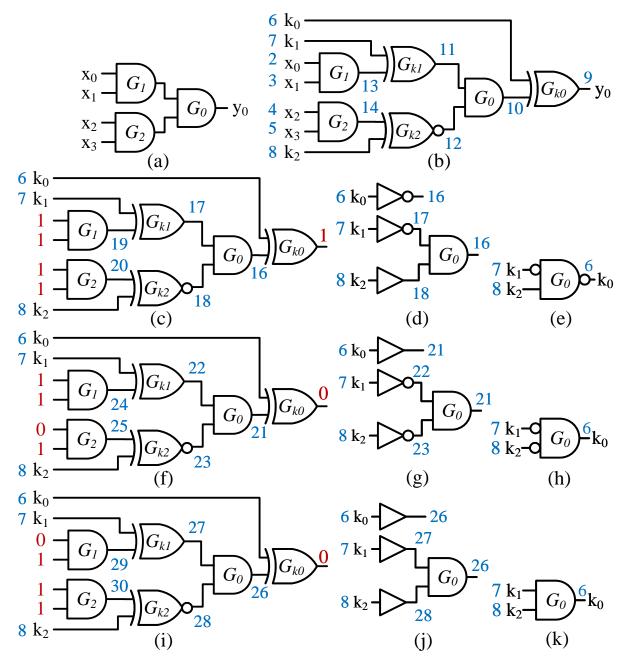

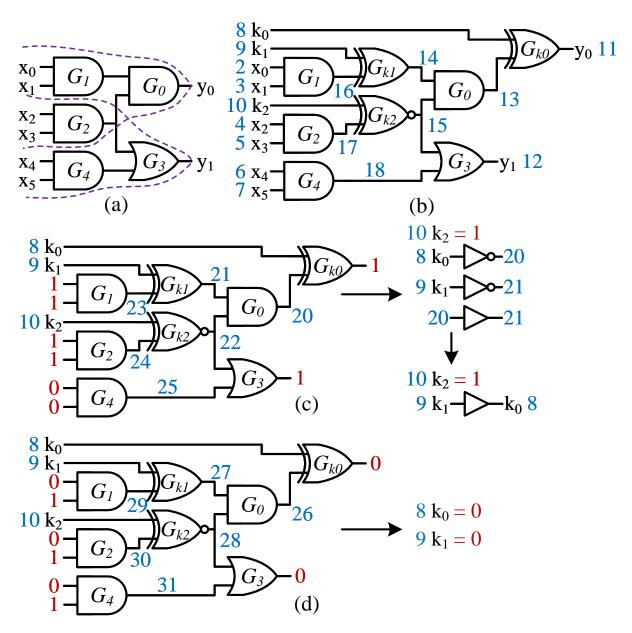

| 5.3 | Step-by-step SAT attack analysis. (a) Original circuit. (b) Locked circuit with $K = \{001\}$ . CNF update and key-pruning for (c-e) 1 <sup>st</sup> IO pair $P_1 = \{1111; 1\}$ ; (f-h) 2 <sup>nd</sup> IO pair $P_2 = \{1101; 0\}$ , and (i-k) 3 <sup>rd</sup> IO pair $P_3 = \{0111; 0\}$ | 56 |

| 5.4 | SAT attack on 2 intersecting cones with $K = \{001\}$ . (a) Original circuit. (b) Locked circuit. CNF update and key-pruning for (c) $1^{\text{st}}$ pair $P_1 = \{111100; 11\}$ , (d) $2^{\text{nd}}$ IO pair $P_2 = \{010101; 00\}$                                                        | 59 |

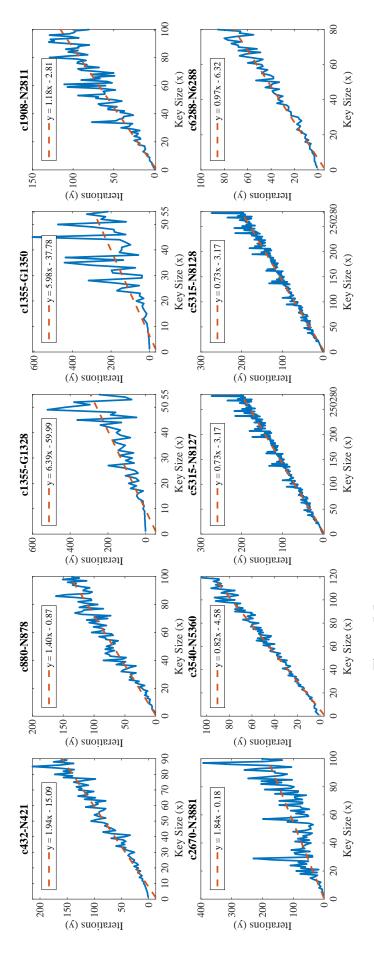

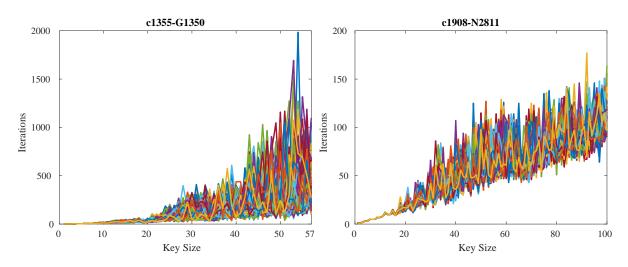

| 5.5 | SAT attack total iterations for ISCAS'85 benchmarks                                                                                                                                                                                                                                          | 63 |

| 5.6 | The zoomed-in view of SAT attack Iterations for ISCAS'85 benchmarks                                                                                                                                                                                                                          | 65 |

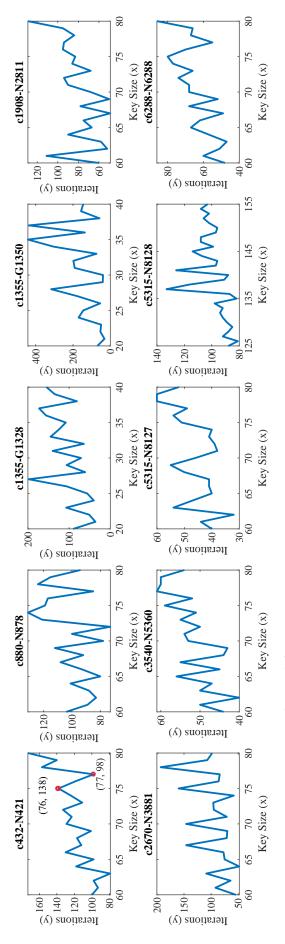

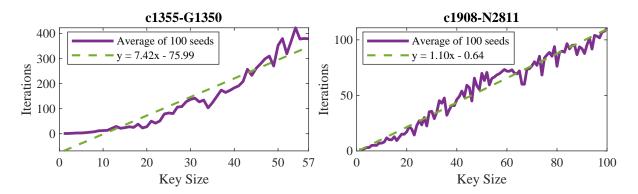

| 5.7  | and c1908-N2811 with 6 randomized seed setups for SAT solver Lingeling                                                                                                                                                                                                             | 66  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.8  | The iteration complexity of SAT attack on locked benchmarks c1355-G1350 and c1908-N2811 with 100 randomized seed setups for SAT solver Lingeling                                                                                                                                   | 66  |

| 5.9  | The average iteration complexity of SAT attack on locked benchmarks c1355-G1350 and c1908-N2811 with 100 different seed setups for SAT solver Lingeling.                                                                                                                           | 67  |

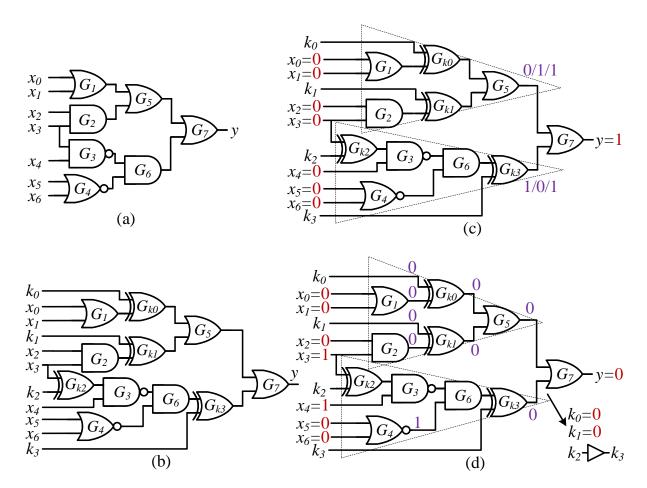

| 5.10 | Key elimination. (a) original circuit, (b) locked circuit with 4 keys, (c) the $1^{st}$ IO pair $P_1=\{0000000;1\}$ from SAT attack (d) the second IO pair $P_2=\{0001100;0\}$ and equivalent relation of $k_0,k_1,k_2,k_3$ under $P_2$ only, where $k_0$ and $k_1$ are determined | 68  |

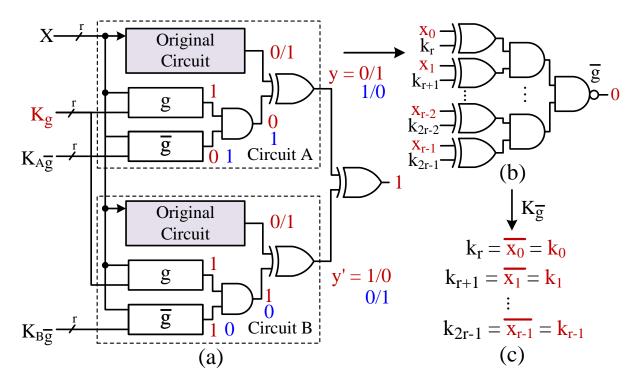

| 5.11 | SAT attack on AntiSAT with fixed key $K_g$ . (a) Miter construction. (b) CNF update. (c) $K_{\overline{g}}=\{k_r-k_{2r-1}\}$ is determined                                                                                                                                         | 71  |

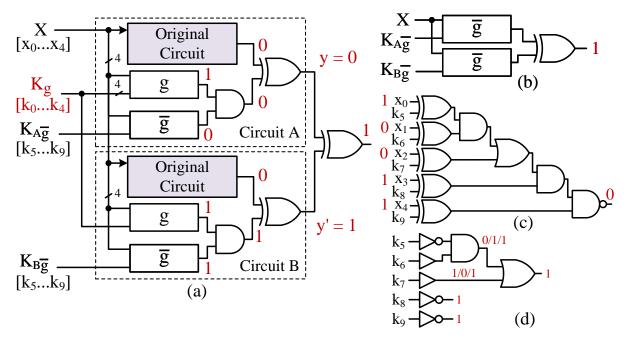

| 5.12 | SAT attack on CAS-Lock with fixed $K_g$ . (a) Miter construction and (b) Equivalent representation. (c) CNF update at SAT attack iteration 1. (d) Key pruning after iteration 1.                                                                                                   | 73  |

| 5.13 | Generalized architecture of stripped functionality logic locking (SFLL). The functions $F$ and $G$ can be configured to implement $TTLock$ and $SFLL-HD^h$                                                                                                                         | 75  |

| 5.14 | SAT attack key evaluation of circuit with an AND gate at the output. Oracle response of (a) logic 1, (b) logic 0                                                                                                                                                                   | 78  |

| 6.1  | Logic Locking: (a) An abstract view of the logic locking. (b) Different types of logic locking techniques with XOR/XNOR, MUX and LUT                                                                                                                                               | 81  |

| 6.2  | The inefficiency of CLIC-A attack. (a) Original circuit. (b) Locked circuit with 6 dependent key gates, where correct key $\{k_0,, k_5\} = \{001100\}$ . (c) Key assignment and input pattern returned by Constraint-based CLIC-A. (d) The oracle response $y = 1$                 | 83  |

| 6.3  | The abstract representation of our DFA attack                                                                                                                                                                                                                                      | 92  |

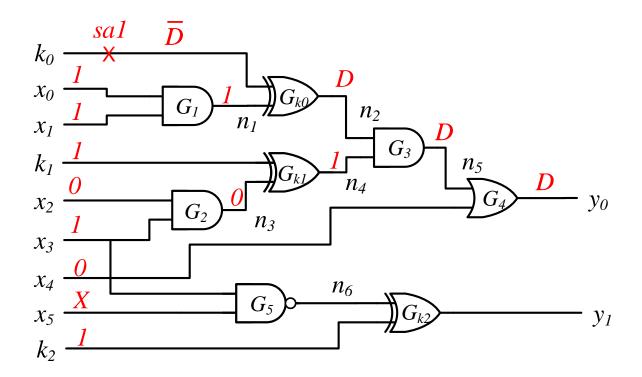

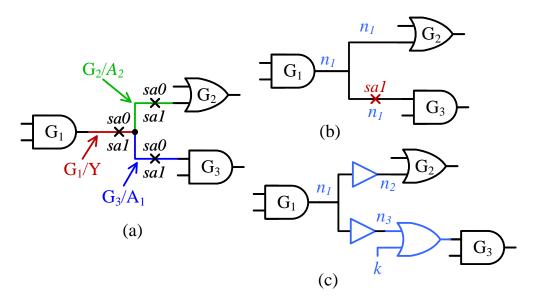

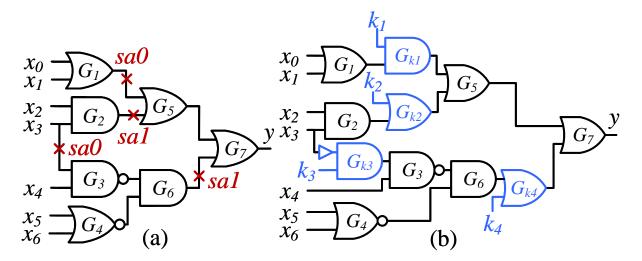

| 6.4  | Test pattern generation considering a $sal$ at key line $k_0$ with constraint $k_1 = 1$ and $k_2 = 1$ . Test pattern, $P_1 = [11010X]$ can detect a $sal$ at $k_0$                                                                                                                 | 95  |

| 6.5  | An abstract view of a locked circuit                                                                                                                                                                                                                                               | 97  |

| 6.6  | Directed graph of locked c432-RN320 netlist with a 32-bit key                                                                                                                                                                                                                      | .01 |

| 6.7  | Test Pattern Generations for AFIA. (a) Test Pattern $P_0 = [XXXXXX0]$ for $sa1$ at $k_2$ . (b) Test Pattern $P_1 = [0X0X0X]$ for $sa1$ at $k_0$ with injected fault $k_1 = 1$ .                                                                                                    | 04  |

| 6.8  | The FPGA board placed under the lens for laser-fault injection at the target registers                                                                                                                                                                                             | 09  |

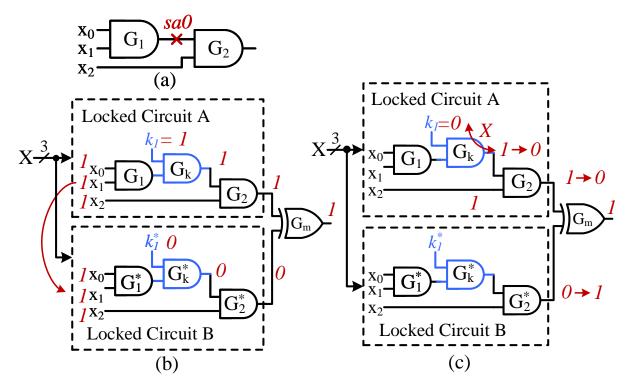

| 7.1 | Logic Locking. (a) Overview of logic locking (b) Original circuit. (c) XOR-based locking with $\{k_0k_1\} = \{01\}1$                                                                                                                                                                                                        | 16 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

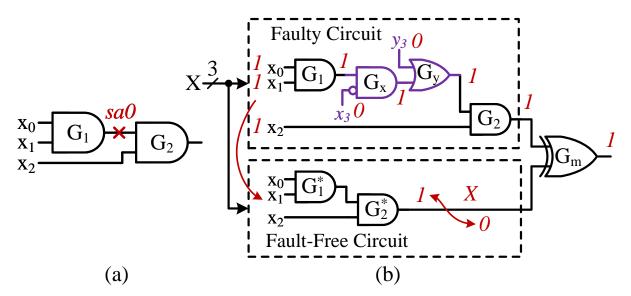

| 7.2 | Conflicts in solving miter circuit presented in Fujita et al (a) A simple circuit with a <i>sa0</i> fault. (b) Conflict during SAT assignment                                                                                                                                                                               | 18 |

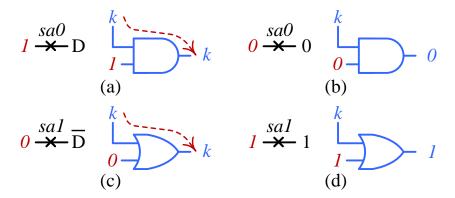

| 7.3 | Logic locking-based modeling of a $saf$ with AND or OR key gate. Converting a $sa0$ to AND key gate, (a) successful propagation of key $k$ with logic 1, (b) failed propagation of $k$ with logic 0; a $sa1$ to OR key gate, (c) successful propagation of $k$ with logic 0, and (d) failed propagation of $k$ with logic 1 | 23 |

| 7.4 | Stuck-at-faults in the presence of multiple fanout branches. (a) Fanout branch naming with TetraMAX. (b) Naming convention used in <i>.bench</i> file. (c) Fanout branch renaming using buffers                                                                                                                             | 24 |

| 7.5 | SAT attack's miter circuit with 1-bit key $k_i$ for $i^{th}$ saf (redundant fault) 12                                                                                                                                                                                                                                       | 26 |

| 7.6 | The proposed test pattern generation with the SAT attack miter. (a) A simple circuit with a $sa0$ fault. (b) No backtrack in deriving the satisfiable assignment with $k_1 = 1$ . (c) Backtrack at an earlier stage with $k_1 = 0$                                                                                          | 28 |

| 7.7 | Test generation with a group of faults. (a) circuit with multiple faults (b) the safs equivalence with logic locking                                                                                                                                                                                                        | 29 |

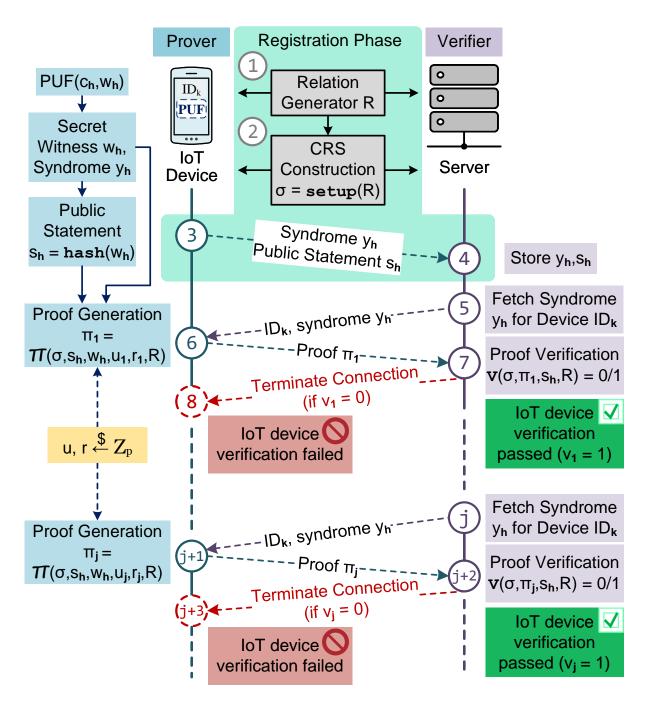

| 8.1 | The proposed device authentication scheme using ZKPs                                                                                                                                                                                                                                                                        | 47 |

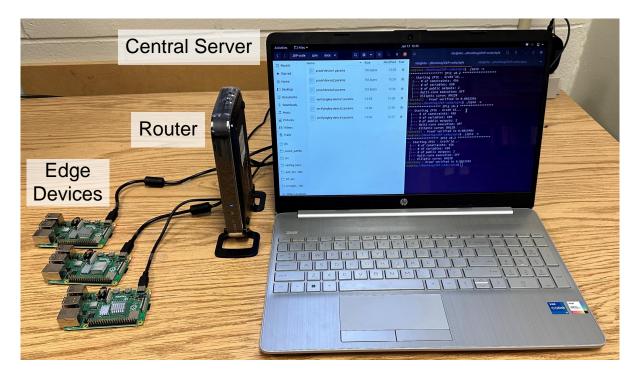

| 8.2 | Implementation setup with Raspberry Pi 4 Model B as edge devices and laptop as the central server                                                                                                                                                                                                                           | 54 |

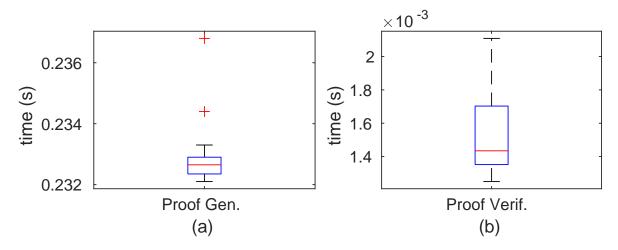

| 8.3 | Box plots of (a) proof generation time by Raspberry Pi as IoT devices, (b) proof verification time by a laptop as a server                                                                                                                                                                                                  | 55 |

# List of Tables

| 5.1                               | Summary of post-SAT logic locking techniques and corresponding attacks 51                                                                                                           |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2                               | Comparison of SAT attack iterations $(TI)$ between multiple primary outputs $( PO )$ and single cone                                                                                |

| <ul><li>5.3</li><li>5.4</li></ul> | SAT attack uses 2 patterns to eliminate all 15 incorrect keys from keypace. If output differs from the oracle's, <b>X</b> is placed, else <b>✓</b> . The correct key is highlighted |

| 6.1                               | Comparison of Number of Injected Faults                                                                                                                                             |

| 7.1                               | The SAT attack uses only 2 patterns to eliminate the incorrect keys from the search space. If the output matches the correct output, we put ✓, else ✗ 130                           |

| 7.2                               | Stuck-at Faults Summary for ITC'99 Benchmarks                                                                                                                                       |

| 7.3                               | Hard-to-Detect Faults summary in ITC'99 Benchmarks                                                                                                                                  |

| 7.4                               | Comparison on number of test patterns on SAT detected faults between Approach 1 and Approach 2                                                                                      |

| 7.5                               | Test Generation Time Summary for ITC'99 Benchmarks                                                                                                                                  |

## List of Abbreviations

**AES-NI** Intel Advanced Encryption Standard New Insturctions

**AES** Advanced Encryption Standard

**ASIC** Application-Specific Integrated Circuit

**ATPG** Automatic Test Pattern Generation

**CCA** Chosen-Ciphertext Attack

**CMOS** Complementary Metal Oxide Semiconductor

**CNF** Conjunctive Normal Form

**COFB** Combined Output Feedback Mode

**CPA** Chosen Plaintext Attack

**CRP** Challenge-Response Pair

**CRS** Common Reference String

**DFA** Differential Fault Analysis

**DFT** Design-for-Testability

**DIP** Distinguishing Input Pattern

**ECDHE** Elliptic Curve Diffie-Hellman Key Exchange

**EUF-CMA** Existential Unforgeability under Chosen-Message Attack

**FA** Fault Attack

**FPGA** Field Programmable Gate Array

**FSM** Finite State Machine

**HLS** High-Level Sythesis

IC Integrated Circuit

**IoT** Internet of Things

**IP** Intellectual Property

**LUT** Look-Up Table

**LWC** Lightweight Cryptography

MAC Message Authentication Code

**NIST** National Institute of Standards and Technology

**NP** Non-Deterministic Polynomial Time Complexity

**NVM** Non-Volatile Memory

**PET** Privacy Enhancing Technology

**PPT** Probabilistic Polynomial Time

**PRNG** Pseudo Random Number Generator

**PUF** Physically Unclonable Function

**QAP** Quadratic Arithmetic Program

**R1CS** Rank-1 Constraint System

**RE** Reverse Engineering

sa0 Stuck-at 0

sa1 Stuck-at 1

**SAT** Boolean Satisfiability

**SCA** Side-Channel Attack

**SoC** System-on-a-Chip

**SRAM** Static Random Access Memory

**TLS** Transport Layer Security

**zk-SNARK** Zero-Knowledge Succinct Non-Interactive Argument of Knowledge

**ZKP** Zero-Knowledge Proof

# Part I

Alice and the "Hardware" Bob

# Chapter 1

#### Introduction

Cryptography is everywhere. Whether in checking the latest weather updates, sending emails, or downloading software packages, we are using cryptography, however implicit it may seem, every day. Dear reader, you are now reading this dissertation in pdf format obtained from Auburn University Electronic Theses and Dissertations (AUETD) database, https://etd. auburn.edu/. You have already made a secure connection with AUETD server before you can download the dissertation to your electronic device, i.e., PC, laptop, tablet, or phone. How is this connection established between your device and the server, you may ask? Or how this dissertation is downloaded securely without malicious modifications by potential adversarial parties in-transit? The answer is in Transport Layer Security (TLS) 1.3. TLS 1.3 protects network communications with client initiating the handshake protocol with server using Elliptic Curve Diffie-Hellman key exchange (ECDHE) server to agree on shared secret and subsequently the session keys; then it proceeds with record layer for both parties, where authenticated encryption with associated data (AEAD) is performed based on shared secret keys for secure communication. As shown in Figure 1.1, the authenticated encryption scheme AES\_256\_GCM is applied to encrypt the following communications with AUETD server, which is how the dissertation is delivered to your digital device.

In the abstract view, one may consider the main business of cryptography in TLS 1.3 as securing messages transmitted between two parties, A and B, in the midst of passive and active adversaries. Parties A and B, on the other hand, are generally referred to as Alice and Bob, since Ron Rivest coined them in the seminal work of RSA in 1978 [1]. With a plethora of attackers trying to break cryptographic schemes which Alice and Bob are using in order

Figure 1.1: TLS 1.3 and authenticated encryption scheme AES\_256\_GCM are used to secure communications with AUETD server, https://etd.auburn.edu/. Screenshot was taken with Google Chrome.

to extract their secret messages, these adversaries are given various names according to their roles, *i.e.*, Eve the eavesdropper, Mallory the malicious attacker, Oscar the opponent, Trudy the intruder, etc. They can launch network-based attacks such as message injection attack, message dropping attack, re-ordering attack, reflection attack, replay attack, etc. In theory, on the other hand, they are categorized by ciphertext-only attacks, known-plaintext attacks, chosen-plaintext attacks (CPA), chosen-ciphertext attacks (CCA), or existential unforgeability under chosen-message attacks (EUF-CMA) for digital signatures. Correspondingly, security notions for passive and active attacks have been developed by cryptographic community: EAV–security, CPA–security, CCA–security, and EUF-CMA–security, etc.

Digital world, in parallel with the timing for development of modern cryptography, has been advancing with complementary metal oxide semiconductor (CMOS) technology and the ever-shrinking technology nodes based on Moore's law. The transformation in the digital realm, dear reader, brings the technical innovations in PCs, laptops, tablets, phones, etc., which you are now using it to read this dissertation. In addition, the incentive to achieve power efficiency and reducing energy consumption drives the development and designs of microcontrollers, embedded device, Internet of Things (IoTs), low-power application-specific integrated circuits (ASICs) and field programmable gate arrays (FPGAs).

Considering from cryptographic engineering perspective, the digital world has certainly facilitated algorithmic development of efficient implementations for both power reduction, performance increase, and area/footprint minimization on diverse platform from servers to PCs, embedded systems, ASICs, and FPGAs. Intel's Advanced Encryption Standard (AES) New Instructions (AES-NI)\* is one notable example which runs round-based AES in dedicated hardware inside the CPU. It achieves up to  $10\times$  performance increase than the software counterparts. Processor families since Intel Westmere and AMD Bulldozer of 2010 support AES-NI for cryptographic hardware accelerations. This exemplifies the fact that optimizations in hardware implementations offer better performance in cryptographic engineering than software implementations.

Nevertheless, digital world also brings new sets of attacks to cryptosystem designs as never before. In addition to passively or actively attacking through communication channels, ubiquitous hardware provides novel attack venues to adversaries. Side-channel attacks (SCAs) and fault attacks (FAs) give attackers the additional capabilities to recover the secret inside hardware device, *e.g.*, encryption/decryption keys for cryptographic algorithms. These include power-based SCA, electromagnetic-based SCA, timing-based SCA, Flush+Reload attacks, cache template attacks, speculative execution attacks, load value injection attacks, clock glitching attacks, voltage glitching attacks, undervolting attacks, laser injection attacks, to just name a few. Attacks like above exploits the hardware the adversaries are currently in possession of, *i.e.*, ASICs, FPGAs, microcontrollers, and DRAMs, or even launch these attack remotely for some SCAs (hardware is required still). One of the earliest record of SCA attacks can be dated back to World War II, where scientists from Bell Labs decoded Signal Corps teletypewriter's encrypted message with 75% accuracy [2]. This demonstrates the successful

<sup>\*</sup>Breakthrough AES Performance with Intel® AES New Instructions, Intel Corporation, 2010.

side-channel based attack on hardware, *i.e.*, the typewriter, where key press happened about 80 feet away from the observation site.

#### 1.1 Thesis Statement and Research Questions

In the dissertation, we follow two main themes: (i) hardware-based attacks, and (ii) hardware-based solutions. This section explains the intuitions behind our title "When Alice meets the 'Hardware' Bob — Attacks and Solutions in the Digital World" and Part I of this dissertation, including the roles which Alice and Bob played in each theme.

When focusing on hardware-based attacks, Alice, our main character, will become the adversary in this dissertation, who is launching attacks to break the secret key and derive its secret value with a series of challenge-response pairs via interactions with the "Hardware" Bob. This challenge-response pair can be thought of as plaintext-ciphertext pairs from a cryptographic module, or simply input-output response of a hardware locked circuit. Note that in Kerchoff's principle, information about cryptographic designs or systems are public save the secret key. In hardware security domain, the locked circuit generally can be obtained by some means or from specific entities (may or may not be malicious), while the key which locks the design is kept secure, *i.e.*, tamper-proof memory. The goal for Alice the adversary, on the other hand, is to break these keys and successfully determine their values with the help of some challenge-response pairs, known or chosen by purpose.

We consider hardware-based solutions in the last part of this dissertation. Our character Alice, then, returns to its former benign profession. In VLSI testing, Alice is mainly concerned with increasing stuck-at faults coverage for Bob the hardware (hardware circuits) in automatic test pattern generation (ATPG). More specifically, two paths are considered: (i) test pattern generation for hard-to-detect faults where commercial ATPG tools failed to find suitable patterns, and (ii) identification of redundant faults where no test pattern will be needed. Another solution we explore in this dissertation is device authentication performed in a large digital-ecosystem, such as IoT nodes for an in-field applications. The "hardware" Bob represents the IoT edge node that is required to prove and demonstrate to Alice, acting as server

and the verifier, of its authenticity. In this scenario, Alice is applying privacy-enhancing cryptography to build achieve authentications of edge device for central server, while taking into consideration the malicious parties' potential disruptions of authentication process or attempts to stole device-specific proprietary information. Her overarching goals are to find solutions to hardware-related problems in VLSI testing and hardware security.

Therefore, we expand the scope of Alice and Bob, along with their interactions, though traditional defined in cryptography alone, into hardware security and VLSI testing realms as well. The digital world, on the other hand, relies heavily on hardware as its foundation, along with the ever-evolving development and advancement in chip design, manufacturing, testing, assembly and packaging process. For the above reasons, the dissertation aims to look at research problems from the hardware perspective. In particular, (i) how hardware can be exploited or facilitate additional attack vectors to break the internal secret? (ii) How would hardware be a core benefit to help form new solutions for hardware assurance and quality assurance?

#### 1.2 Contributions

This dissertation proposes novel attacks and/or solutions in cryptography, hardware security, VLSI testing as mentioned above. The contributions of this dissertation are summarized as follows:

In Part I (Chapters 1, 2), we begin this dissertation with introductory discussions on Alice and the "Hardware" Bob, the big picture of attacks and solutions in the digital world, as well as preliminaries. Background and necessary preliminaries in cryptography's substitution-permutation network, authenticated encryption with associated data, semiconductor supply chain, zero-knowledge proof (ZKP) and its properties are introduced in Chapter 2.

In Part II (Chapters 3, 4, 5, 6), we discuss multiple hardware-based attacks in broader scope of cryptography and hardware security. It ranges from algebraic cryptanalysis on hardware-based GIFT-COFB and multicycle AES; the analysis of Boolean satisfiability (SAT) attack, its iteration complexity on various logic locking schemes; to fault-based attack on logic locking from ATPG perspective to retrieve its internally programmed secret key. These chapters include the following publications:

## **Hardware-based Attacks**

- Y. Zhong, and U. Guin, "Chosen-Plaintext Attack on Energy-Efficient Hardware Implementation of GIFT-COFB," in IEEE International Symposium on Hardware Oriented Security and Trust (HOST), pp. 1-4, 2022.

- Y. Zhong, and U. Guin, "Fault-Injection Based Chosen-Plaintext Attacks on Multicycle AES Implementations," in ACM Great Lakes Symposium on VLSI (GLSVLSI), pp. 1-6, 2022.

- Y. Zhong, and U. Guin, "Complexity Analysis of the SAT Attack on Logic Locking," in IEEE Transactions on Computer-Aided Design of Integrated Circuits, pp. 1-14, 2023.

- Y. Zhong, A. Jain, M.T. Rahman, N. Adadi, J. Xie, and U. Guin, "AFIA: ATPG-Guided Fault Injection Attack on Secure Logic Locking," Journal of Electronic Testing: Theory and Applications, pp. 1-20, 2022.

Chapter 3 develops the chosen-plaintext attack (CPA) on the most-energy-efficient hardware implementation of GIFT-COFB, one of the ten finalists in the NIST Lightweight Cryptography Standardization Process [3]. Only a constant number of nonce-tag pairs is required to break the 128-bit key with  $O(2^4)$  attack complexity [4]. Chapter 4 presents the fault injection attacks on Advanced Encryption Standard (AES), a widely adopted symmetric cipher standardized by NIST in 2000. By injecting faults on a single-bit register, the overall attack complexity to break a 128-bit key is  $O(2^8)$ . This complexity can be further extended to 192-bit and 256-bit keys as well [5]. Chapter 5 describes the full anatomy of the SAT attack, one the most effective break against logic locking. Linear iteration complexity is observed for the traditional locking on ISCAS'85 benchmarks. Analysis and explanations are given to provide additional insights into the SAT-based attacks on post-SAT solutions [6]. Chapter 6 introduces AFIA: ATPG-guided fault injection attack on secure logic locking [7]. The average complexity to break the secret key of a locked circuit is linear to the key length. A quadratic complexity is only needed in the worst-case scenario to completely determine the key bits.

In Part III (Chapters 7, 8, 9), we target hardware-based solutions in VLSI testing and device authentication. In addition, future work with possible solutions and mitigation in hardware security and VLSI testing are discussed. Papers included in this theme are listed as follows:

## **Hardware-based Solutions**

- Y. Zhong, and U. Guin, "A Comprehensive Test Pattern Generation Approach Exploiting SAT Attack for Logic Locking," in IEEE Transactions on Computers, pp. 1-13, 2023.

- Y. Zhong, J. Hovanes, and U. Guin, "On-Demand Device Authentication using Zero-Knowledge Proofs for Smart Systems," in Great Lakes Symposium on VLSI (GLSVLSI), pp. 569-574, 2023.

- J. Hovanes, **Y. Zhong**, and U. Guin, "A Novel IoT Device Authentication Scheme Using Zero-Knowledge Proofs," in GOMACTech, pp. 1-4, 2023.

- Y. Zhong, A. Ebrahim, U. Guin, and V. Menon, "A Modular Blockchain Framework for Enabling Supply Chain Provenance," in IEEE Physical Assurance and Inspection of Electronics (PAINE), pp. 1-7, 2023.

Chapter 7 proposes novel test pattern generation approaches using the efficient SAT attack on logic locking. We exploit the linear iteration complexity in the SAT attack for generating tests for undetected faults, of which the commercial ATPG tools, *e.g.*, TetraMAX II, failed to find suitable test patterns or determine as reduced faults. The equivalence of a stuck-at fault (*sa0*, *sa1*) is converted to its equivalent key gates. Our proposed approaches achieve 100% fault coverage by identifying redundant faults and producing test patterns for undetected faults [8]. Chapter 8 provides a novel device authentication protocol to for IoT devices [9,10]. The widely available SRAM PUF on each edge device is its device fingerprint. This proposed zk-SNARK-based approach protects secrecy of the PUF response even if the central server is compromised by adversaries. It is also resilient against machine learning-based PUF attacks since it is impossible for an adversary to observe any challenge-response pair in a meaningful way. Chapter 9 concludes the dissertation and discusses possible future directions in cryptography, hardware security, and VLSI testing.

A list of all 9 co-authored peer-reviewed publications along with links to source code are included in the Appendix.

# 1.3 Organization of this Thesis

The rest of this dissertation is organized as follows and shown in Figure 1.2.

#### Part II: Hardware-based Attacks

In Chapter 3, we propose a chosen-plaintext attack on the most-energy-efficient hardware implementation of GIFT-COFB by Caforio et al. As any attacker could have access to the IoT device, he/she can apply a nonce to the GIFT-COFB encryption oracle and observe the 2-round update from the 128-bit output tag. Multiple nonce-tag pairs can be captured through resetting the oracle and assigning new values to the input nonce. With only a few nonce-tag pairs, the adversary can recover both round keys of round 1 and 2, and use them to derive the 128-bit secret key, K, through the reverse of key schedule. The attack was published at HOST 2022 (Washington DC) and has been cited in NIST IR 8454\*:

Y. Zhong, and U. Guin, "Chosen-Plaintext Attack on Energy-Efficient Hardware Implementation of GIFT-COFB," in IEEE International Symposium on Hardware Oriented Security and Trust (HOST), pp. 1-4, 2022.

In Chapter 4, we propose two attacks to break the multicycle AES implementations. Both attacks take three plaintext-ciphertext pairs to evaluate one key byte. The first attack is designed to break vulnerable AES implementations which leaks round operation to the output. An adversary can also access the internal scan chains and observe the round register value. By varying one byte in plaintext, we showed that the effect of three other key bytes of the same MixColumns operation, along with key addition, can be eliminated by XORing the same output byte using only two plaintext-ciphertext pairs. However, one more plaintext-ciphertext pair is necessary to remove the redundant solution to uniquely determine the correct key byte. The second attack focuses on breaking a multicycle AES implementation where the contents in

<sup>\*</sup>NIST IR 8454: Status Report on the Final Round of the NIST Lightweight Cryptography Standardization Process, June 2023.

Figure 1.2: Overview of publications included in this dissertation.

ciphertext registers are updated once all the round computations are complete. The adversary can launch the attack by injecting a fault in the flag register which signals the completion of all computations (e.g., done). Once a fault is injected, the internal states of the round registers are dumped as the ciphertext. An adversary can perform the same steps mentioned in the first attack to determine the key after observing the first round result from the ciphertext. This attack is also applicable to the encryption round that skips MixColumns. As no faults are injected in the internal computations of AES, the traditional fault detection schemes can not identify this attack. We demonstrated both attacks on different AES implementations with 128-bit key size (AES-128) from the OpenCores benchmarks with the key search space complexity of  $O(2^8)$ . The same attacks can be applied to other AES implementations with 192/256-bit keys. Our attack was published at GLSVLSI 2022 (Irvine, CA):

Y. Zhong, and U. Guin, "Fault-Injection Based Chosen-Plaintext Attacks on Multicycle AES Implementations," in ACM Great Lakes Symposium on VLSI (GLSVLSI), pp. 1-6, 2022.

In Chapter 5, we present two novel aspects to analyze the iteration complexity of the oracle-guided SAT attack. First, we provide a detailed analysis of the SAT attack based on the conjunctive normal form (CNF) clauses stored in the SAT solver. The SAT attack iteratively finds DIPs to eliminate an equivalent class of incorrect keys. We explore what the attack learned after finding a DIP at each iteration. We show that the SAT tool is implicitly constructing a relationship between different key bits by applying the DIP to the oracle and observing the correct response. Please note that the desired goal for any logic locking technique is to achieve an exponential iteration complexity of key size so that an adversary cannot determine the correct key value within given time constraints. However, our analysis points to the linear growth of the required patterns or iterations rather than the desired exponential increase with keys. Using examples, we showed how the attack uses a DIP to eliminate a class of equivalent keys which results in the linear iteration complexity. We also confirmed that the complexity gets even lower for circuits with multiple overlapping logic cones. Note that a logic cone can be described as a directed graph where the input nodes and gates point toward the sole output.

Second, one interesting observation is that the complexity (*i.e.*, number of iterations/DIPs) of the SAT attack often reduces with increasing key size. We provided detailed explanations of why it takes fewer iterations to find the correct key when we locked a circuit with a larger key size. Finally, we analyzed the SAT attack complexity for a circuit locked with point functions. Our complexity analysis was published at IEEE Transactions on Computer-Aided Design of Integrated Circuits, 2023:

Y. Zhong, and U. Guin, "Complexity Analysis of the SAT Attack on Logic Locking," in IEEE Transactions on Computer-Aided Design of Integrated Circuits, pp. 1-14, 2023.

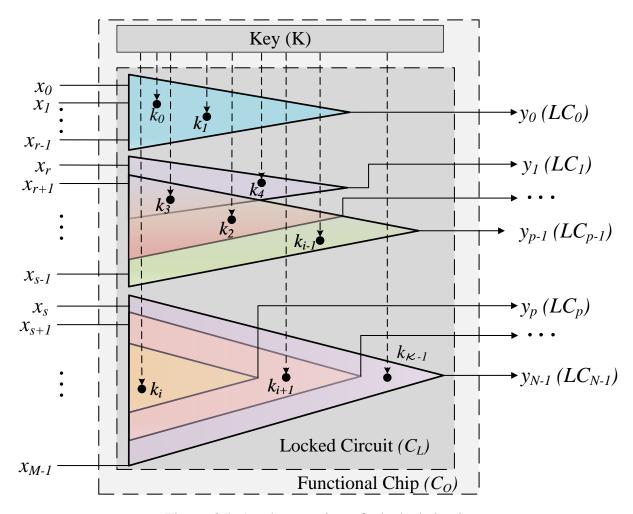

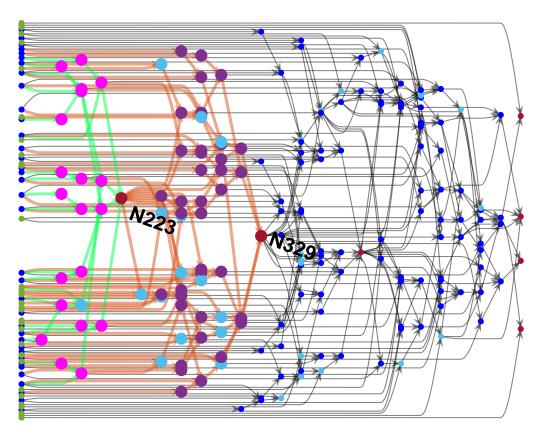

In Chapter 6, we details how an adversary can extract the secret key from a locked netlist, even if all the existing countermeasures are in place. An adversary can determine the secret key by injecting faults at the key registers, which hold the key value during normal operation, and performing differential fault analysis. We present a key sensitization-based ATPG-guided fault injection attack (AFIA), to break any locking scheme. The entire process can be performed in three steps. First, we processed the locked netlist and converted it into a directed graph to extract all logic cones and construct a key-cone association matrix that records the distribution of keys among different cones. This structural analysis facilitates total fault reduction for the subsequent test pattern generation. Second, it is necessary to select an input pattern that produces an incorrect response for the target key bit only while keeping its dependent keys at faulty states. This can be achieved by using a constrained automatic test pattern generation (ATPG) to generate such a test pattern, which is widely popular for testing VLSI circuits. A 1-bit key value can be determined by generating a test pattern that can detect the stuck-at fault (saf) at the target key (corresponds to that key bit) while keeping its dependent keys at logic 1 (or logic 0). This is due to the fact that dependencies are often inserted to prevent direct sensitization of a key bit to the output by test patterns due to other key lines blocking its path. In our proposed approach, the pattern which detects a stuck-at 1 (sal) fault at one key line with logical constraints for the recovered key lines is sufficient to determine that key bit. One can also use stuck-at 0 (sa0) fault to derive such pattern. Note that the fault-free and faulty responses are always the complements under the test pattern which detects that fault, which in turn can to derive the

key-bit value. The same process needs to be applied for other key bits to generate similar input patterns, and this results in at most  $\mathcal{K}$  patterns for determining the entire key of size  $\mathcal{K}$ . Note that one test pattern can detect multiple key bits when they are placed in different logic cones (of no dependencies). Third, we applied these test patterns to only one instance of unlocked chip and collect the responses. Faults can be injected at the blocking key registers using laser fault injection equipment and obtain the key value by comparing the output responses with test patterns' generated by constrained ATPG. Our fault attack on logic locking was published at Journal of Electronic Testing: Theory and Applications, 2022:

Y. Zhong, A. Jain, M.T. Rahman, N. Adadi, J. Xie, and U. Guin, "AFIA: ATPG-Guided Fault Injection Attack on Secure Logic Locking," Journal of Electronic Testing: Theory and Applications, pp. 1-20, 2022.

#### **Part III: Hardware-based Solutions**

In Chapter 7, we demonstrate the novel miter construction for test pattern generation of stuck-at-0 (sa0) and stuck-at-1 (sa1) faults, where each fault has its equivalent locked circuit to be applied with the existing SAT-based attack. We target undetected faults where commercial ATPG tools TetraMAX II fall short in producing test patterns. Our work focuses on identifying the redundant ones from these undetected faults and finding suitable patterns for detecting non-redundant faults to increase fault coverage further. The equivalence of a stuck-at fault (sa0, sa1) is an AND or OR key-gate, respectively. Once the stuck fault is converted to a key-dependent AND/OR gate, SAT attack is applied to solve the key and return the distinguishing input patterns it used in deriving the key value. A distinguishing input pattern returned by the SAT attack allows us to sensitize a stuck fault and propagate the faulty response to the output. To the best of our knowledge, this research was the first attempt to apply the SAT-based logic locking attack on the equivalent keyed circuit to (i) find test patterns for undetected faults, (ii) identify redundant faults, and (iii) reduce test pattern count for the combination of multiple faults. Our SAT attack-based test pattern generation was published at IEEE Transactions on Computers, 2023:

Y. Zhong, and U. Guin, "A Comprehensive Test Pattern Generation Approach Exploiting SAT Attack for Logic Locking," in IEEE Transactions on Computers, pp. 1-13, 2023.

Chapter 8 proposes an efficient, secure, and on-demand device authentication protocol using Zero-Knowledge Succinct Non-Interactive Argument of Knowledge (zk-SNARK). The signature from a physically unclonable function (PUF) is used to create the proof, which can be verified by the central server acting as a verifier without storing the actual PUF response. The edge device periodically generates proofs using a self-generated random seed. The proof can then be made public for verification for anyone with the common reference string (CRS). This allows repeated authentication by verifying the identity of an edge device without access to the PUF secret. This work was done in collaboration with my colleague Joshua Hovanes. Our zk-SNARK-based solutions were published at GLSVLSI 2023 (Knoxville, TN) and GOMACTech 2023 (San Diego, CA):

- Y. Zhong, J. Hovanes, and U. Guin, "On-Demand Device Authentication using Zero-Knowledge Proofs for Smart Systems," in Great Lakes Symposium on VLSI (GLSVLSI), pp. 569-574, 2023.

- J. Hovanes, **Y. Zhong**, and U. Guin, "A Novel IoT Device Authentication Scheme Using Zero-Knowledge Proofs," in GOMACTech, pp. 1-4, 2023.

In Chapter 9, we conclude the dissertation and discuss possible future directions. This include possible solutions to secure semiconductor supply chain with modular blockchain-based approaches [11], future work in heterogeneous integration, 3D packaging, as well as possible hardware-based applications with privacy-enhancing technologies (PETs).

# Chapter 2

# **Background and Preliminaries**

2.1 Substitution-Permutation Network, Authenticated Encryption, Authenticated Encryption with Associated Data

Modern cryptography and digital world (CMOS mainly) have grown side-by-side. Although cryptographic designs only need to be proven sound theoretically, cryptographic engineering on digital device requires more efforts to achieve a secure implementation than just theoretical soundness.

Since NIST's standardization of Advanced Encryption Standard (AES), block ciphers subsequently designed are largely based on substitution-permutation network (SPN) or its tweakable version. AES has 10, 12, or 14 encryption rounds for 128-bit, 192-bit, or 256-bit key, respectively. Each encryption round includes SubBytes, ShiftRows, MixColumns, and AddRoundKey. All are linear operations except SubBytes, where sixteen 8-bit Sboxes have nonlinear property between its input and output byte. Similarly, GIFT–128 is a 128-bit SPN block cipher with 40 encryption rounds [12]. Each round contains, SubCells, PermBits, AddRound-Key. GIFT Sbox (GS) is a non-linear function of 4-bit input/output with algebraic degree of 3.

Authenticated Encryption (AE) achieves secrecy and integrity simultaneously in the presence of an active adversary. It consists of symmetric encryption and Message Authentication Code (MAC), where generally encrypt-then-MAC is adopted. In terms of secrecy, AE need to satisfy CCA-Security. For authentication, unforgeability must be met, where any tampered

encrypted messages by attackers will be discovered. Authenticated Encryption with Associated Data (AEAD), on the other hand, also includes associated data as the input, which is authenticated but not encrypted, e.g., packet header. AEAD has nonce N, message M, and associated data A as inputs; ciphertext C of the same length as the original message, and message authentication tag T (fixed length) as outputs. NIST initiated the process to standardize lightweight cryptography (LWC) back in 2015 requiring submissions in AEAD with optional hashing functionalities. Emphasis is placed on schemes suitable for constrained environment like RFID tags, industrial controllers, sensor nodes and smart cards [13]. GIFT-128 with combined output feedback mode (COFB) was selected as one of the ten finalists in the third round of NIST LWC competition.

# 2.2 Globalization of Semiconductor Supply Chain

The integrated circuits (ICs) are fundamental to virtually every technology in the Department of Defense (DoD), industrial and commercial spaces. Moore's Law has guided the microelectronics industry for decades to enhance the performance of ICs. The continuous addition of new functionalities in SoCs has forced design houses to adopt newer technology nodes everdecreasing transistor size to continuously improve operational speed, reduce power consumption, overall die area, and the resultant cost of a chip. The exponential growth of electronics becomes feasible due to the globalization of semiconductor design, manufacturing, and test processes, and the markets and nation-state incentives which support the much needed investments production capability and capacity. Building and maintaining a fabrication unit (foundry) requires a multi-billion dollar investment [14]. As a result, a system-on-a-chip (SoC) design house acquires intellectual properties (IPs) from many vendors and sends the design to a foundry for manufacturing, typically located offshore due to the horizontal integration in the semiconductor industry. At present, the majority of the SoC design houses no longer design the complete SoC and/or manufacture chips on their own. As a result, the trusted foundry model is no longer assumed to be valid for producing ICs, where the trustworthiness of microelectronic parts is often questioned.

Figure 2.1: Overview of electronics supply chain and possible attack surface.

With horizontal business model in semiconductor supply chain, ensuring the security, integrity, and authenticity of electronic components, systems, and the supply chain that delivers them becomes highly challenging. Unfortunately, the same globalization opens Pandora's box of threats, including (i) counterfeit ICs [15–19], (ii) piracy of intellectual properties (IPs) and cloning [20–23], and (iii) malicious modifications or tampering with hardware Trojans [24–26], as shown in Figure 2.1. These threats could present in multiple stages in the electronics supply chain, including design, fabrication, assembly, distribution, and system integration, etc. Due to the sophistication of today's critical infrastructures, electronic products could be manufactured from multiple levels of system integration. For example, smaller systems, such as FPGAs and microcontroller boards, can be assembled first using discrete components, and we call it level-1 (L1) system integration. Complex systems, such as helicopter electronics, require the integration of multiple smaller L1 systems, and we denote it as level-2 (L2) system integration. Due to the complex globalized supply chain, an adversary could control or disrupt the supply chain or launch cyber attacks by exploiting hardware vulnerabilities. The hardware hack reported by Bloomberg shows a tiny chip, the size of a grain of rice, can be covertly hidden in a larger

system to infiltrate data in U.S. companies [27,28]. The threat was undetected due to the difficulty of observing and understanding the complete functionality of the electronic system and its supply chain. Observing and understanding the electronics and supply chain operations has many challenges and, if improperly conducted, can expose further vulnerabilities and threats to intellectual property and trade secrets.

# 2.3 Zero-Knowledge Proof

First developed in 1980s by Goldwasser, Micali, and Rackoff [29], a zero-knowledge proof (ZKP) allows the prover (P) to convince the verifier (V) that a statement is true, yet without revealing any details about its secret witness. The verifier learns no additional information beyond the validity of the statement. In addition, Goldreich et al. [30] showed that ZKP proof systems exist for all non-deterministic polynomial (NP) languages.

The definition for ZKP is described as follows:

#### **Definition**

- Let L be a NP-language, with witness relation  $\mathcal{R}$ , s.t.  $L = \{x | \exists w : \mathcal{R}(x, w) = 1\}$

- Let P be the prover and V be the verifier.

- P needs to convince V that  $x \in L$  and also that P knows w.

Details of how P proves a statement or how V convinces of the validity of the statement itself are associated with the three properties of ZKP [29] – completeness, soundness, and zero-knowledge. The definition below is based on Groth'16 [31] and Bünz et al. [32]:

## **Properties of ZKP**

• Completeness: For every  $x \in L$ ,

$$\Pr \big[ (\sigma,\tau) \leftarrow \mathsf{Setup}(R); \pi \leftarrow \mathsf{Prove}(R,\sigma,x,w) : \mathsf{Vrf}(R,\sigma,x,\pi) = 1 \big] = 1 - \epsilon.$$

Note that  $\epsilon$  is negligible, and  $\epsilon=0$  for perfect completeness for honest provers. (i.e., honest prover P convinces the verifier V of the secret w.)

• Soundness: For all probabilistic polynomial time (PPT) adversary A,

$$\Pr\left[\begin{array}{c} (R,z) \leftarrow \mathcal{R}(1^{\lambda}); (\sigma,\tau) \leftarrow \mathsf{Setup}(R); (x,\pi) \leftarrow \mathcal{A}(R,z,\sigma) : \\ x \notin L_R \text{ and } \mathsf{Vrf}(R,\sigma,x,\pi) = 1 \end{array}\right] \rightarrow 0,$$

where  $\lambda$  is the security parameter. (i.e., cheating prover or adversary  $\mathcal{A}$  fakes proofs with negligible probability.)

• Zero-Knowledge: For every PPT verifier  $\mathcal{V}$ , there exist a PPT simulator  $\mathcal{S}$  with  $\forall x \in L$ , probability ensembles of  $\left\{\mathsf{View}_{\mathcal{V}}\big(<\!P,\mathcal{V}\!>\!(x)\big)\right\}$  and  $\left\{\mathcal{S}(\mathcal{V},x)\right\}$  are computationally indistinguishable. Equivalently, For all PPT adversary  $\mathcal{A}$ ,

$$\begin{split} \Pr \left[ \begin{array}{l} (\sigma,\tau) \leftarrow \mathsf{Setup}(R); \\ \pi \leftarrow \mathsf{Prove}(R,\sigma,x,w) \end{array} \right. &: \mathcal{A}(R,z,\sigma,\tau,\pi) = 1 \\ \\ \Pr \left[ \begin{array}{l} (\sigma,\tau) \leftarrow \mathsf{Setup}(R); \\ \pi \leftarrow \mathcal{S}(R,\tau,x) \end{array} \right. &: \mathcal{A}(R,z,\sigma,\tau,\pi) = 1 \\ \end{array} \right]. \end{split}$$

In other words, the proof reveals nothing to the verifier V except  $x \in L$ . In particularly, proofs should not reveal prover P's secret witness w. (i.e., verifier learns nothing except the validity of proofs.)

# Part II

**Hardware-Based Attacks**

## Chapter 3

Chosen-Plaintext Attack on Energy-Efficient Hardware Implementation of GIFT-COFB

#### 3.1 Introduction

The recent advancement of the Internet of Things (IoT) results in more connected electronic devices than ever. Vast chunks of data are being transferred over the unsecured channel for increasingly ubiquitous computing. This may give rise to the potential breach of confidentiality, integrity, and authentication if, somehow, the devices transmit information without the proper protection mechanism. As IoT devices are resource-constrained and low-cost, have limited area, and less computation power, the previously standardized Advanced Encryption Standard (AES) block cipher is not suited for these devices. Thus, NIST instantiated the process to standardize lightweight cryptographic algorithm, stressing its importance on RFID tags, sensor nodes, industrial controllers, and smart cards [33]. Among all the candidates submitted to NIST, ten were selected as the finalists [34]. All finalists ensured tight security bounds and ensured efficient implementation in both hardware and software. One of the ten finalists is GIFT-COFB [35], which integrates combined-feedback mode (COFB) with GIFT-128 cipher [12] to offer authenticated encryption with associated data.