FAULT DETECTION AND DIAGNOSTIC TEST SET MINIMIZATION

Except where reference is made to the work of others, the work described in this thesis is my own or was done in collaboration with my advisory committee. This thesis does not include proprietary or classified information.

Mohammed Ashfaq Shukoor

Certificate of Approval:

Victor P. Nelson Professor Electrical and Computer Engineering Vishwani D. Agrawal, Chair James J. Danaher Professor Electrical and Computer Engineering

Adit D. Singh James B. Davis Professor Electrical and Computer Engineering George T. Flowers Dean Graduate School

# FAULT DETECTION AND DIAGNOSTIC TEST SET MINIMIZATION

Mohammed Ashfaq Shukoor

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama May 9, 2009 FAULT DETECTION AND DIAGNOSTIC TEST SET MINIMIZATION

Mohammed Ashfaq Shukoor

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights.

Signature of Author

Date of Graduation

Mohammed Ashfaq Shukoor, son of Mrs. Rasheeda Begum and Mr. S. Mohammad Iqbal, was born on October 2, 1983, in Bangalore, Karnataka, India. He graduated from St. Joseph's College, Bangalore in 2001. He earned the degree Bachelor of Engineering in Electronics and Communication from Bangalore Institute of Technology affiliated to Visvesvaraya Technological University, Belgaum, India in 2005. He then worked at Cognizant Technology Solutions for about a year as a Programmer Analyst in the domain of Customer Relationship Management. He joined the graduate program in Electrical & Computer Engineering at Auburn University in January 2007. At Auburn University, as a graduate research assistant he received support in parts from an Intel Corporation grant and from the Wireless Engineering Research and Education Center (WEREC). During the summer of 2008, he held an internship at Texas Instruments, Bangalore, India, working on low power testing of VLSI circuits.

#### THESIS ABSTRACT

# FAULT DETECTION AND DIAGNOSTIC TEST SET MINIMIZATION

Mohammed Ashfaq Shukoor

Master of Science, May 9, 2009 (B.E., Bangalore Institute of Technology, 2005)

101 Typed Pages

Directed by Vishwani D. Agrawal

The objective of the research reported in this thesis is to develop new test generation algorithms using mathematical optimization techniques. These algorithms minimize test vector sets of a combinational logic circuit for fault detection and diagnosis, respectively.

The first algorithm generates a minimized fault detection test set. The *test minimization Integer Linear Program (ILP)* described in the literature guarantees an absolute minimal test set only when we start with the exhaustive set of test vectors. As it is impractical to work with exhaustive test sets for large circuits, the quality of the result will depend upon the starting test set. We use the concept of *independent fault set (IFS)* defined in the literature to find a non-exhaustive vector set from which the test minimization ILP will give an improved (often minimal) test set. An IFS is a set of faults such that no two faults in the set can be detected by the same vector. The largest IFS gives a lower bound on the size of the test set since at least one vector is needed to detect each fault in the IFS. This lower bound can be closely achieved by selecting tests from the test vectors derived for the faults in the IFS. Using the theory of primal-dual linear programs, we model the IFS identification as the *dual* of the test minimization problem. A solution of the dual problem, whose existence is guaranteed by the duality theorem, gives us a conditionally independent fault set (CIFS). A CIFS is an IFS relative to a non-exhaustive vector set. Our CIFS is, therefore, not absolute but is specific to the starting vector set. Successively adding more vectors to test the faults in the identified CIFS and solving the dual problem, we bring the CIFS closer to its minimal size. In the process of reaching the absolute IFS we have accumulated a non-exhaustive set of vectors that can now be minimized by the test minimization ILP (now referred to as the primal problem) to get a minimal test set. Thus the newly proposed primal-dual solution to the minimal test generation problem is based on (1) identifying independent faults, (2) generating tests for them, and (3) minimizing the tests. The primal-dual method, when applied to the ISCAS85 benchmark circuits, produces better results compared to an earlier primal ILP-alone test minimization method [47]. For the largest benchmark circuit c7552, the earlier minimization method (primal ILP) produced a test set of 145 vectors in 151 CPU seconds, while our method (primal-dual ILP) produced a test set of 139 vectors in just 71 CPU seconds.

In the second part of this research, we address the minimization of a diagnostic test set without reduction in diagnostic resolution. A full-response dictionary is considered for diagnosis. The *full-response dictionary* distinguishes between faults detected by exactly the same test vectors but at different outputs of the circuit. A new diagnostic ILP is formulated from a *diagnostic table* obtained by fault simulation without fault dropping. This ILP can become intractable for large circuits due to very large number of constraints that typically grows quadratically with the number of faults. We make the complexity manageable by two innovations. First, we define *diagnostic independence relation* for fault-pairs with no common test vector and also for faults-pairs detected by a common vector but at different outputs of the circuit. These fault-pairs require no constraint in the ILP, thus reducing the number of constraints. Second, we propose a two-phase ILP approach. An initial ILP phase, using an existing ILP procedure that requires a smaller set of constraints (linear in the number of faults), preselects a minimal detection test set from the given unoptimized vector set. Fault-pairs that are already distinguished by the preselected detection vectors then do not require distinguishing constraints in the diagnostic ILP of the final phase, which selects a minimal set of additional vectors for distinguishing between the remaining fault-pairs. The overall minimized diagnostic test set obtained by the two phase method may be only slightly longer than a one-step diagnostic ILP optimization, but it has the advantages of significantly reduced computation complexity and reduced test application time. The two-phase method, when applied to the ISCAS85 benchmark circuits, produces very compact diagnostic test sets. For the largest benchmark circuit c7552, an earlier compaction method [41] has reported a test set of 198 vectors obtained in 33.8 seconds. Our method produced a test set of 128 vectors in 18.57 seconds.

#### Acknowledgments

A lot of people have either directly or indirectly contributed towards this thesis, and I owe a debt of gratitude to each and every one.

This work may not have been possible without the strong support, constant guidance and remarkable patience of my advisor Dr. Vishwani Agrawal. His approach to research and an in-depth knowledge of the subject will continue to inspire me. I thank Dr. Adit Singh and Dr. Victor Nelson for being on my committee. I would like to express my gratitude to Auburn University for giving me the opportunity to pursue my ambitions. I appreciate the support from the Wireless Engineering Research and Education Center (WEREC) and the encouragement I received from its director, Dr. Prathima Agrawal. The patient advice and helpful attitude of Dr. Srivaths Ravi, Dr. Rubin Parekhji, and other coworkers at Texas Instruments, Bangalore, added significantly to my understanding of VLSI testing.

Throughout the course of my Master's degree, I have received a lot of support from my colleagues especially Nitin, Wei, Khushboo, Jins, Fan, Kim, and Manish. I am thankful for all their help and suggestions.

No words are enough to express my gratitude to my family for their unconditional love and support. My parents Mohammad Iqbal and Rasheeda Begum, my brother Musheer, and sister Zeba have provided me the best possible love and support.

Finally my special thanks to all my friends back home and at Auburn who have stood by me during my good and bad times. Style manual or journal used <u>Journal of Approximation Theory (together with the style</u> known as "aums"). Bibliograpy follows van Leunen's *A Handbook for Scholars*.

Computer software used <u>The document preparation package  $T_EX$  (specifically  $\underline{\mathbb{A}}T_EX$ )</u> together with the departmental style-file aums.sty.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                                                 | xii                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| LIST OF TABLES                                                                                                                                  | xiii                                                  |

| 1       INTRODUCTION         1.1       Problem Statement         1.2       Original Contributions         1.3       Organization of the Thesis  | . 2                                                   |

| <ul> <li>2 BACKGROUND</li> <li>2.1 Types of Circuits</li></ul>                                                                                  | 6<br>6<br>8<br>8                                      |

| 2.4.2       Other Fault Models                                                                                                                  | 9<br>10<br>10<br>11                                   |

| 2.6Fault Collapsing                                                                                                                             | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 2.11.1 Standard LP Problems2.12 Primal and Dual Problems2.13 Integer Linear Programming (ILP)2.14 Applications of Linear Programming in Testing | . 21<br>. 22                                          |

| <ul> <li>3 PREVIOUS WORK ON DETECTION TEST SET MINIMIZATION</li> <li>3.1 Independent Fault Set</li></ul>                                        | . 24<br>. 27                                          |

|    |      | 3.4.1 Static Compaction                                      |

|----|------|--------------------------------------------------------------|

|    |      | 3.4.2 Dynamic Compaction                                     |

|    | 3.5  | Methods of Finding Maximal IFS                               |

|    |      |                                                              |

| 4  | Min  | IIMAL TEST GENERATION USING PRIMAL-DUAL ILP ALGORITHM 3      |

|    | 4.1  | Test Minimization ILP                                        |

|    | 4.2  | Dual ILP                                                     |

|    | 4.3  | A Primal-Dual ILP Algorithm                                  |

|    | 4.4  | Results                                                      |

|    |      | 4.4.1 Example 1: c1355                                       |

|    |      | 4.4.2 Example 2: c2670                                       |

|    | 4.5  | Benchmark Results                                            |

|    | 4.6  | Primal LP with Recursive Rounding 5                          |

|    | 4.7  | Analysis of Duality for Integer Linear Programs              |

|    |      |                                                              |

| 5  | BAG  | CKGROUND ON FAULT DIAGNOSIS 5                                |

|    | 5.1  | Fault Diagnosis    5                                         |

|    |      | 5.1.1 Cause-Effect Diagnosis                                 |

|    |      | 5.1.2 Effect-Cause Diagnosis                                 |

|    | 5.2  | Diagnosis Using Fault Dictionaries                           |

|    |      | 5.2.1 Full-Response (FR) Dictionary 54                       |

|    |      | 5.2.2 Pass-Fail (PF) Dictionary                              |

|    | 5.3  | Dictionary Compaction                                        |

| 6  | Dai  | gnostic Test Set Minimization 6                              |

| -  | 6.1  | ILP for Diagnostic Test Set Minimization                     |

|    |      | 6.1.1 Fault Diagnostic Table for Diagnostic ILP              |

|    |      | 6.1.2 Diagnostic ILP Formulation                             |

|    | 6.2  | Generalized Fault Independence                               |

|    | 6.3  | Two-Phase Minimization   7                                   |

|    | 6.4  | Results                                                      |

|    | 6.5  | Analysis of Undistinguished Fault Pairs of c432              |

|    | 0.0  |                                                              |

| 7  | Cor  | NCLUSION 7                                                   |

|    | 7.1  | Future Work                                                  |

|    |      | 7.1.1 Primal-Dual Algorithm with Partially Specified Vectors |

| Bı | BLIO | GRAPHY 8                                                     |

|    |      |                                                              |

| A  | PPEN | DIX 8                                                        |

# LIST OF FIGURES

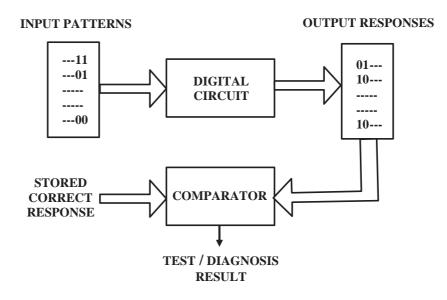

| 2.1 | Testing/Diagnosis Process                                                                            | 7  |

|-----|------------------------------------------------------------------------------------------------------|----|

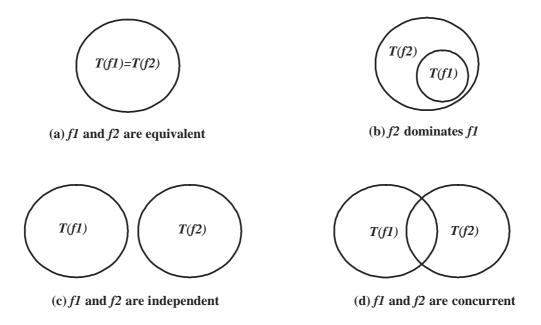

| 2.2 | Relations Between Faults $f1$ and $f2$                                                               | 10 |

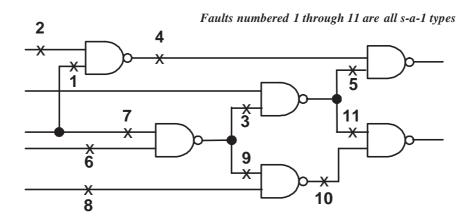

| 3.1 | c17 Circuit with 11 Functional Dominance Collapsed Faults $[69]$                                     | 25 |

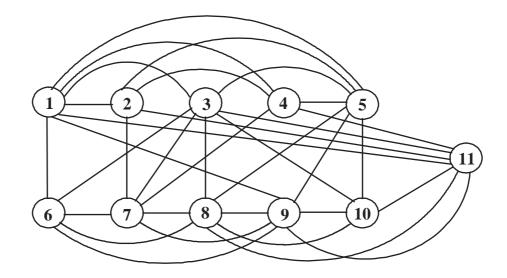

| 3.2 | Independence Graph for c17 Benchmark Circuit                                                         | 26 |

| 3.3 | Largest Clique in the Independence Graph of Figure 3.2                                               | 27 |

| 3.4 | Multiple Maximum Cliques in the Independence Graph of Figure 3.2                                     | 28 |

| 4.1 | Detection Matrix $a_{kj}$                                                                            | 39 |

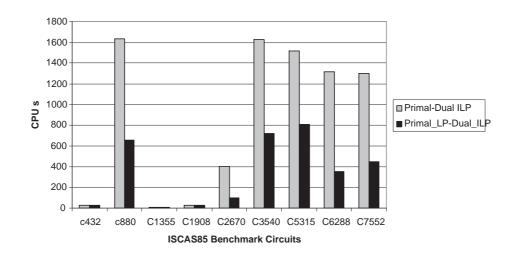

| 4.2 | CPU Time Comparison Between Primal_LP-Dual_ILP Solution with Pri-<br>mal_ILP-Dual_ILP Solution.      | 52 |

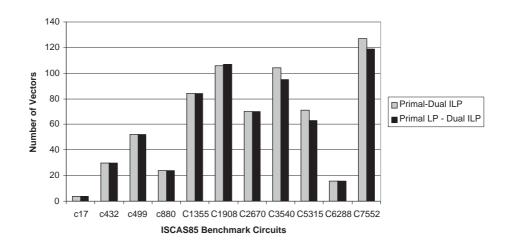

| 4.3 | Test Set Size Comparison Between Primal_LP-Dual_ILP Solution with Pri-<br>mal_ILP-Dual_ILP Solution. | 53 |

| 5.1 | Tests and Their Fault Free Responses                                                                 | 59 |

| 5.2 | Full-Response Fault Dictionary                                                                       | 59 |

| 5.3 | Pass-Fail Fault Dictionary                                                                           | 60 |

| 6.1 | Full-Response Fault Dictionary.                                                                      | 64 |

| 6.2 | Fault Diagnostic Table.                                                                              | 64 |

| 6.3 | Fault Detection Table.                                                                               | 67 |

| 6.4 | Fault Diagnostic Table.                                                                              | 68 |

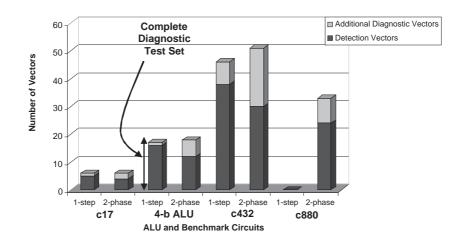

| 6.5 | Comparison Between 1-Step Diagnostic ILP Minimization and 2-Phase Approach                           | 72 |

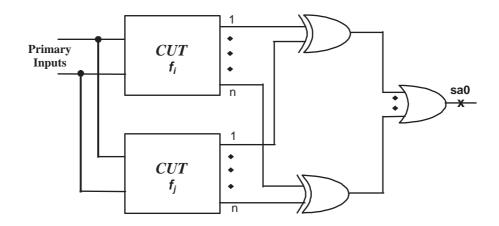

| 6.6 | An ATPG-based Method for Examining a Fault Pair $(f_i, f_j)$                                         | 78 |

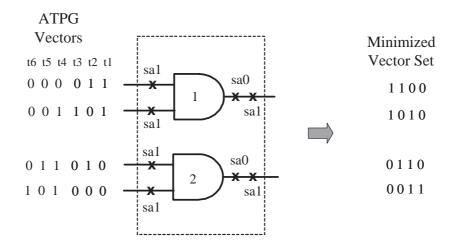

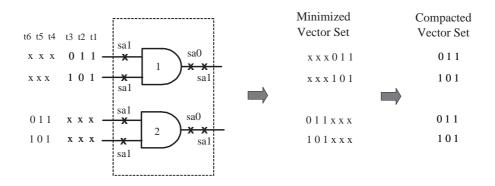

| 7.1 | Non-optimal Solution Obtained Using ILP Minimization.                                                | 81 |

| 7.2 | Minimizing Partially Specified Vectors and then Vector Merging                                       | 82 |

# LIST OF TABLES

| 2.1 | Primal and Dual Problem Definition                                                     | 22 |

|-----|----------------------------------------------------------------------------------------|----|

| 4.1 | Four-bit ALU and Benchmark Circuits - Initial ATPG Vectors and Target Fault Set.       | 46 |

| 4.2 | Example 1: Dual ILP Iterations and Primal ILP Solution for c1355                       | 47 |

| 4.3 | Example 2: Dual ILP Iterations and Primal ILP Solution for c2670. $\ldots$             | 48 |

| 4.4 | Test Sets Obtained by Primal-Dual ILP for 4bit ALU and Benchmark Circuits.             | 49 |

| 4.5 | Comparing Primal-Dual ILP Solution With ILP-Alone Solution [47]                        | 50 |

| 4.6 | Test Sets Obtained by Primal_LP-Dual_ILP Solution for 4bit ALU and Benchmark Circuits. | 51 |

| 4.7 | Comparing Primal_LP-Dual_ILP Solution with LP-Alone Solution [48]                      | 54 |

| 4.8 | Comparison of Optimized Values of Relaxed LP and ILP.                                  | 55 |

| 6.1 | Independence Relation.                                                                 | 68 |

| 6.2 | Generalized Independence Relation.                                                     | 68 |

| 6.3 | Constraint Set Sizes.                                                                  | 69 |

| 6.4 | Phase-1: Diagnosis With Minimal Detection Test Sets                                    | 74 |

| 6.5 | Phase-2: Diagnostic ILP Minimization                                                   | 75 |

| 6.6 | Diagnosis with Complete Daignostic Test Set                                            | 76 |

| 6.7 | Two-phase Minimization vs. Previous Work [41].                                         | 77 |

#### Chapter 1

# INTRODUCTION

With increasing integration levels in today's VLSI chips, the complexity of testing them is also increasing. This is because the internal chip modules have become increasingly difficult to access. Testing costs have become a significant fraction of the total manufacturing cost. Hence there is a necessity to reduce the testing cost. The factor that has the biggest impact on testing cost of a chip is the time required to test it. This time can be decreased if the number of tests required to test the chip is reduced. So, we simply need to devise a test set that is small in size. One way to generate a small test set is to compact a large test set. But, the result of compaction depends on the quality of the original test set. This aspect of compaction has motivated the work presented in the initial part of this thesis.

Another important aspect of the VLSI process is *Failure Analysis*, the process of determining the cause of failure of a chip. Once a chip has failed a test, it is important to determine the cause of its failure as this can lead to improvement in the design of the chip and/or the manufacturing process. This in turn can increase the yield of the chips. *Fault diagnosis* is the first step in failure analysis, which by logical analysis gives a list of likely defect sites or regions. Basically, fault diagnosis narrows down the area of the chip on which physical examination needs to be done to locate defects. Fault dictionary based diagnosis has been the most popular method, as it facilitates faster diagnosis by comparing the observed behaviors with pre-computed signatures in the dictionary. Here again the size of the fault dictionary becomes prohibitive for large circuits. We explore the idea of managing the diagnostic data in a *full-response dictionary* by optimizing the diagnostic test set.

#### 1.1 Problem Statement

The problems solved in this thesis are:

- Finding a minimal set of vectors to cover all stuck-at faults in a combinational circuit

- Formulating an exact method for minimizing a given diagnostic test set.

- Devising a polynomial time approach to overcome the computational limitations of the exact method of item 2.

## 1.2 Original Contributions

We have developed a new test generation algorithm to produce minimal test sets for combinational circuits. This method is based on (1) identifying independent faults, (2) generating tests for them, and (3) minimizing the tests. The parts 1 and 2, give us a nonexhaustive vector set, which on compaction will give a minimal test set. Using the theory of primal-dual linear programs, we have modeled the independent fault set identification as the dual of the already known test minimization integer linear program (ILP) [29]. A solution of the *dual ILP*, whose existence is guaranteed by the duality theorem, gives us a conditionally independent fault set (CIFS). The third part, test minimization, is accomplished by the already known test minimization ILP, now called the *primal ILP*. Benchmark results show potential for both smaller test sets and lower CPU times.

To address the problem of the fault dictionary size, we have given a *Diagnostic ILP* formulation to minimize test sets for a full-response dictionary based diagnosis. The ILP solution is a smaller test set with diagnostic characteristics identical to the unoptimized test set. An ideal test set for diagnosis is one which distinguishes all faults. Thus during

diagnostic test set minimization it should be ensured that the resulting test set consists of at least one vector to distinguish every pair of faults. This is done by having a constraint for every fault pair to be distinguished. Note that the number of fault pairs is proportional to the square of the number of faults. This results in a very large number of constraints in the diagnostic ILP, making its computational complexity exponential. To overcome the constraint problem we have defined a *diagnostic fault independence* relation which reduces the number of fault pairs to be distinguished and thus the number of constraints. Finally we have developed a two-phase method for generating a minimal diagnostic test set from any given test set. In the first phase we used existing ILP minimization techniques to obtain a minimal detection test set and found the faults not diagnosed by this test set. In the second phase we used the diagnostic ILP to select a minimal set of vectors capable of diagnosing the undiagnosed faults of phase-1. The resulting minimized test set combined with the minimal detection test set of phase-1 serves as our complete diagnostic test set.

A paper [73] describing the primal-dual ILP algorithm was presented at the 12th VLSI Design and Test Symposium (VDAT-2008) in July 2008. Another paper [74] on the twophase method of diagnostic test set minimization has been accepted for presentation at the Fourteenth IEEE European Test Symposium (ETS-2009) to be held in May 2009.

#### **1.3** Organization of the Thesis

The thesis is organized as follows. In Chapter 2, we discuss the basics of testing and fault diagnosis. In Chapter 3, the previous work on test set compaction is discussed. In Chapter 4, the new primal-dual ILP algorithm is introduced and results for some benchmark circuits are presented. To prepare the reader for the second part of research in the thesis, Chapter 5 provides the background material on fault diagnosis. Chapter 6 then discusses the original two-phase approach for diagnostic test set minimization with results on benchmark circuits. Conclusions and ideas about future work directions are discussed in Chapter 7.

#### Chapter 2

# BACKGROUND

This chapter gives the basic background material on *VLSI testing* and *fault diagnosis*, which includes fault models, fault collapsing, test generation, fault simulation, etc. We also touch upon some basics of *Linear Programming*, the optimization technique used in this research for minimizing test sets for both testing and diagnosis. Our discussion begins with a description of the types of circuits that will and will not be addressed by the testing and diagnosis methods discussed in this thesis.

### 2.1 Types of Circuits

This thesis will address the problem of minimal test set generation for testing and diagnosis in *combinational logic circuits* only. However, it should be noted that nearly all *sequential* logic, i.e., circuits containing state-holding elements (flip-flops) are tested in a way that transforms their operation under test from sequential to combinational. This is usually accomplished by implementing scan-based design [13] in which all flip-flops in the circuit are modified and are stitched together to from one or more *scan chains*, so that they can be controlled and observed by shifting data through these scan chains. During scan based testing, input data is scanned into the flip-flops via the scan chains and other input data is applied to the input pins (or primary inputs) of the circuit. Once these inputs are applied and the circuit (now fully combinational) has stabilized its response, the circuit is clocked to capture the results back into the flip-flops, and the data values at the output pins (or primary outputs) of the circuit are recorded. The combination of values at the primary

outputs and the values scanned out of the scan chains make up the response of the circuit to the test. Like for testing, the scan based environment is also used for fault diagnosis.

#### 2.2 Testing/Diagnosis Process

The basic process of testing or diagnosing a digital circuit is shown in Figure 2.1 [13]. During testing the digital circuit is referred to as *Circuit under Test* (CUT), and during diagnosis it is referred as *Circuit under Diagnosis* (CUD). Binary test vectors are applied to the CUT/CUD. The response of the CUT/CUD to a test vector is compared with the stored correct response. A mismatch between the stored and observed responses indicates a bad circuit.

The input data to the CUT/CUD is referred to as the *test pattern* or *test vector*. A collection of test vectors designed to exercise whole or part of the circuit is called a *test set*. There are two kinds of tests: *fault detection tests* and *fault diagnostic tests* [16]. Fault detection tests are used for the purpose of testing and they tell us whether the CUT is faulty or fault-free. They do not give any information on the identity (type, location) of the fault. A diagnostic test is applied after a circuit has failed the testing process. Its aim is to identify the fault that caused the circuit to fail.

### 2.3 Testing

Testing is the process of verifying if the manufactured chip has the intended functionality and timing. The test inputs to a digital IC (Integrated Circuit) are developed to exercise the implemented function or to detect modeled faults [6].

Figure 2.1: Testing/Diagnosis Process

Testing can be of two types - functional and structural testing. Functional tests are used to completely exercise the circuit function. A complete functional test for a circuit will check all entries of the truth table for the circuit function. The problem with this approach is the number of the tests needed to completely exercise even simple functions. For example, a 64-bit ripple carry adder has 129 inputs and 65 outputs. To completely exercise its function, we need  $2^{129}$  input patterns. An Automatic Test Equipment (ATE) operating at 1GHz would take about  $10^{22}$  years to apply all of these patterns to the CUT [13]. Thus an exhaustive functional test is impractical even for moderate sized circuits. Structural tests on the other hand are used to verify the topology of the CUT. A structural test can be used to verify if all connections are intact and all gate-level truth tables are correct [35]. Structural testing is entirely based on fault models.

#### 2.4 Fault Modeling

A defect is the unintended difference between implemented hardware and its intended design [13]. Defects are those that could occur in a fabricated IC. A fabricated chip could have many types of defects, for example, breaks in signal lines, lines shorted to ground, lines shorted to VDD, etc. Fault modeling is the translation of real world defects to a mathematical construct that can be operated upon algorithmically and understood by a software simulator for the purpose of providing a metric for quality measurement [21]. Thus physical defects are modeled as faults because the analysis of faults is much simpler. Also, fault models greatly simplify the test generation process. Physical defects can be modeled as either logical faults or delay faults, depending on whether the defect affects the logical behavior or the time of operation. Fault models can represent many, though not all physical defects.

## 2.4.1 Single Stuck-at Fault Model

This is the earliest and most widely used fault model to date. Eldred's 1959 paper [27] laid the foundation for the stuck-at fault model, though that paper did not make any mention of the stuck-at fault. The term "stuck-at fault" first appeared in the 1961 paper by Galey, Norby and Roth [33].

Stuck-at faults are gate-level faults modeled by assigning a fixed '0' or '1' value to an input or an output of a logic gate or a flipflop [13]. Each interconnection in a circuit can have two faults, stuck-at-1 (sa1, s-a-1) and stuck-at-0 (sa0, s-a-0). If we assume that there can be several simultaneous stuck-at faults, then in a circuit with n interconnections between gates there are  $3^n - 1$  possible multiple stuck-at faults. All combinations except the one having

all lines as fault-free are treated as faults. It is evident that even for moderate values of n, the number of multiple stuck-at faults could be very large. Thus it is a common practice to model only single stuck-at faults. Therefore the assumption is that only one stuck-at fault is present in a circuit at a time. In a circuit with n interconnections there can be no more than 2n single stuck-at faults. This number can be further reduced using fault collapsing techniques [13, 69] discussed in Section 2.6. Numerous algorithms have been developed and programmed to efficiently generate tests for single stuck-at faults [66, 36, 31, 65, 43, 71, 72].

### 2.4.2 Other Fault Models

Other than stuck-at faults there are *bridging faults* that model electrical shorts between signal lines occurring at the wafer level. Then there are *transition delay faults* that model gross delay defects (such as pinched metal lines, resistive contacts, etc.) at gate terminals. *Path delay faults* model small distributed delay defects which cause timing failures in the chip. The detection of transition and path delay fault requires a pair of vectors. The *IDDQ faults* are those that elevate the steady state current in the circuit. For example, transistor shorts can be effectively modeled as IDDQ faults. As can be seen each fault model, models unique types of defects. Details of these fault models can be found in [13].

#### 2.5 Relations among Faults

Consider two faults f1 and f2. Let T(f1) and T(f2) be the sets of all the test vectors that detect f1 and f2 respectively. The following relations can be defined for a pair of faults.

Figure 2.2: Relations Between Faults f1 and f2

#### 2.5.1 Fault Equivalence

Two faults are said to be equivalent, if and only if the corresponding faulty circuits have identical output functions [13]. Equivalent faults cannot be distinguished by any test vector, i.e., a test for one fault will also detect the other fault. Thus the two faults have the exact same test sets as shown in Figure 2.2(a).

## 2.5.2 Fault Dominance

If all tests of fault f1 detect another fault f2, then f2 is said to dominate f1. This relation is shown in Figure 2.2(b), where  $T(f1) \subseteq T(f2)$ . Thus any test for the *dominated* fault (f1) will also be a test for the *dominating fault* (f2). Notice that fault equivalence is a special condition of fault dominance in which two faults dominate each other. So, dominance is a more basic relation than equivalence.

#### 2.5.3 Fault Independence

Two faults are said to be independent if and only if they cannot be detected by the same test vector [7, 8], i.e., they have no common test. Thus, if f1 and f2 are independent then T(f1) and T(f2) are disjoint sets as shown in Figure 2.2(c).

## 2.5.4 Fault Concurrence

Two faults that neither have a dominance relationship nor are independent are defined as concurrently-testable faults [24]. The concurrently-testable faults can have two types of tests as depicted in Figure 2.2(d):

1. Each fault has an exclusive test that does not detect the other fault [3].

2. A common test called the *concurrent test* in [24], that detects both faults.

Concurrently-testable faults have also been referred to as compatible faults in the literature [7].

## 2.6 Fault Collapsing

We had seen that for a circuit with n interconnections we would have 2n stuck-at faults. Clearly this number would become very large for big circuits, and would result in longer test set generation times. Fault Collapsing is the process of reducing the number of faults that need to be targeted for test generation, without any penalty on the fault coverage. It is done by utilizing the relations defined in the previous section. The relative size of the collapsed set with respect to the set of all faults is called the collapse ratio [13]:

$$Collapse \ ratio \ = \ \frac{|Set \ of \ collapsed \ faults|}{|Set \ of \ all \ faults|}$$

Fault collapsing can be classified into two types, *Equivalence collapsing* and *Dominance Collapsing*. Equivalent fault collapsing involves partitioning all faults into disjoint equivalent fault sets such that all faults in a set are equivalent to each other, and selecting one representative fault from each set. The resulting set of faults is called an equivalence collapsed fault set. A test vector which detects the representative fault of an equivalent fault set will also detect all other faults belonging to that set. So we need to generate a test only for the representative fault. This reduces the test generation time. It should be noted that equivalence collapsing does not affect the diagnostic resolution, i.e., the ability to distinguish between faults.

In the case of large circuits, where coverage (detection) of faults is more important than their exact location (diagnosis), dominance fault collapsing may be desirable [23]. For a pair of faults having a dominance relation, a test for the dominated fault will also detect the dominating fault. Thus the dominating fault can be dropped from the target fault list. However there is a drawback to dominance fault collapsing. In case the dominated fault is *redundant*, i.e., it does not modify the input-output function of the circuit and cannot be detected by any test, there would be no test for the dominating fault even if it is detectable. Dominance collapsing always results in a smaller set than the equivalence collapsed set. Though dominance collapsing produces a smaller collapsed fault set, the tests for the collapsed faults may not guarantee 100% fault coverage. Hence equivalence collapsing is more popular.

For example, consider an n-input AND gate. The total number of stuck-at faults is 2n + 2. All single s-a-0 faults on the inputs and output of the AND gate are equivalent. Thus, using equivalence collapsing, the number of stuck-at faults is reduced to n + 2. Also, the output s-a-1 fault dominates a single s-a-1 fault on any input and hence the output s-a-1 can be left out of the target fault set. Thus, dominance fault collapsing further reduces the number of faults for an *n*-input AND gate to n + 1. Similar results for dominance and equivalence fault collapsing can be derived for other Boolean gates as well. It must be noted that faults on a fanout stem and branches cannot be collapsed.

Equivalence and dominance fault collapsing can either be performed at a functional or structural level. Functional collapsing is based on the effect of faults on the Boolean function of the circuit [4]. For an *n*-line circuit there are 2n single stuck-at faults, and the Boolean equation has to be applied to  $2n^2 - 1$  pairs of faults to determine all equivalence/dominance relations [13]. Also, it will be cumbersome to manipulate large Boolean functions. For these reasons structural collapsing is used in practice. In structural collapsing relations between faults are determined for simple Boolean gates and are then applied to larger circuits.

The size of the fault set can be further reduced by performing hierarchical fault collapsing as described in [4, 5, 63, 68, 70]. Most definitions for fault equivalence and dominance, appearing in the literature, correspond to single output circuits. For such circuits, fault equivalence defined on the basis of indistinguishability (identical faulty functions) implies that the equivalent faults have identical tests. However, for multiple output circuits, two faults that have identical tests can be distinguishable if their output responses are not the same. This leads to *diagnostic equivalence* and *diagnostic dominance* which are extended definitions for equivalence and dominance respectively [68, 70].

## 2.7 Fault Simulation

Fault simulation is the process of computing the response of a faulty circuit to given input stimuli. The program that performs fault simulation is called a *fault simulator*. The basic operation of a fault simulator is as follows: Given a circuit, a test input and a fault, the fault simulator inserts the fault into the circuit and computes its output response for the test input. It also computes the good circuit response to the same test input. Finally it declares the fault as detected if there is mismatch between the good and faulty responses. Thus for a test set and a fault list the fault simulator can give the fault coverage of the test set. Fault coverage is defined as [13],

# $Fault Coverage = \frac{Number of faults detected}{Number of faults in initial fault list}$

Notice that the fault simulator can determine which faults are detected by which test vectors. We have used this feature of the fault simulator extensively in our work. Also, a fault simulator is used along with an *Automatic Test Pattern Generator* (ATPG) for test generation.

There are several algorithms for fault simulation, the simplest being the serial fault simulation. Here fault simulation is performed for one fault at a time. As soon as one fault is detected, the simulation is stopped and a new simulation is started for another fault. This fault simulation method, though simple, is very time consuming. Another technique of fault simulation, which simulates more than one fault in one pass is called parallel fault simulation. It makes use of the bit-parallelism of logical operations in a digital computer [13]. The parallel fault simulator can simulate a maximum of w - 1faults in one pass, where w is the machine word size. So, a parallel fault simulator may run w - 1 times faster than a serial fault simulator. Other fault simulation algorithms include Test-Detect [67], Deductive [9], Concurrent [77, 78], Differential [18], etc.

#### 2.8 Test Generation

Automatic test pattern generation is the process of generating input patterns to test a circuit, which is described strictly with a logic-level netlist [13]. These programs usually operate with a fault generator program, which creates the collapsed fault list. Test generation approaches can be classified into three categories: *exhaustive*, *random* and *deterministic*.

In the exhaustive approach, for an *n*-input circuit,  $2^n$  input patterns are generated. The exhaustive test set guarantees 100% fault coverage (ignoring the redundant faults if any). It is evident that this approach is feasible only for circuits with very small number of primary inputs.

Random test generation is a simple approach in which the input patterns are generated randomly. Fault simulation is performed for every randomly generated pattern. A pattern is selected only if it detects new faults. In a typical test generation process, random patterns are used for achieving an initial 60-80% fault coverage, after which deterministic test pattern generation can be employed to achieve the remaining coverage [2].

Deterministic Automatic Test Pattern Generator (D-ATPG) algorithms are based on injecting a fault into a circuit, and determining values for the primary inputs of the circuit that would activate that fault and propagate its effect to the circuit output. In deterministic test generation, the search for a solution involves a decision process for selecting an input vector from the set of partial solutions using an algorithmic procedure known as backtracking. In backtracking, all previously assigned signal values are recorded, so that the search process is able to avoid those signal assignments that are inconsistent with the test requirement. The exhaustive nature of the search causes the worst-case complexity to be exponential in the number of signals in the circuit [32, 42]. To minimize the total time, a typical test generation program is allowed to do only a limited search in the number of trials or backtracks, or the CPU time.

The most widely used deterministic automatic test pattern generation algorithms are: D-algorithm [66], PODEM (Path-Oriented Decision Making) [36] and FAN (Fanout-Oriented Test Generator) [31]. The faults left undetected after the D-ATPG phase are either redundant faults for which no test exists, or aborted faults that could not be detected due to CPU time limit.

### 2.9 Failure Analysis

Testing of fabricated chips prevents the shipment of defective parts, but improving the production quality of the chips depends on effective *failure analysis*. A better quality production process means higher yield, i.e., more usable die. Typically, an IC product goes through two manufacturing stages [52]: (1) prototype stage, and (2) high-volume manufacturing stage.

During the prototype stage, a small number of sample chips are produced to verify the functionality and timing of the design. The chips may fail badly due to design bugs or manufacturing imperfections. All issues that cause the chip to fail must be addressed so that these do not recur when the design goes into mass production. It is here that failure analysis comes into play.

After the prototype stage, the product is ready for high-volume production. In this stage there could be fluctuations in the yield mainly due to manufacturing errors. Continuous yield monitoring is necessary from time to time to respond to unexpected low-yield situations [50]. Here again failure analysis is the means for yield improvement.

Some of the methods of failure analysis consist of etching away certain layers, imaging the silicon surface by scanning electron microscopy (SEM) or focused ion beam (FIB) systems, particle beams, etc. [52]. Any analysis performed directly on the defective chip is called physical analysis. With millions of transistors and several layers of metals, physical analysis process is often laborious and time consuming. Thus physical inspection of the chip is not feasible without an initial suspect list of defect sites. It is the job of *fault diagnosis* to guide the physical analysis process by providing the suspected defect locations.

# 2.10 Fault Diagnosis

Fault diagnosis is the first step in failure analysis which by logical analysis gives a list of likely defect sites or regions. Basically, fault diagnosis narrows down the area of the chip on which physical examination needs to be done to locate defects. Fault diagnosis involves applying tests to failed chips and analyzing the test results to determine the nature of the fault. A test set used for the purpose of diagnosis is referred to as a *diagnostic test set* [16]. The test sets are constructed so as to ideally pin-point to a single fault candidate. Such a characteristic of a diagnostic test set is called its *diagnostic resolution*. The highest number of fault candidates reported for a test in the diagnostic test set is referred to as its diagnostic resolution. Precision of fault diagnosis is very critical as it leads to physical analysis. If a wrong site or location is predicted then the actual defect site could be damaged during the physical inspection process of the predicted site.

# 2.11 Linear Programming

In the work described in this thesis, the optimization of detection and diagnostic test sets is done using linear programming techniques. Thus, the current and the subsequent sections of this chapter give a brief review of linear programming.

Linear Programming (LP) is the method of selecting the best solutions from the available solutions to a problem. It is the most widely used method of constrained optimization in economics and engineering fields.

The main elements of any linear program are,

- Variables: The goal is to find the values for the variables that provide the best value of the objective function. These values are unknown at the start of the problem. LP assumes that all variables are real valued, meaning that they can take fractional values.

- 2. **Objective function:** This is a linear mathematical expression that uses the variables to express the goal of optimization. The goal of the LP problem is to either *maximize* or *minimize* the value of the objective function.

- 3. Functional Constraints: These are linear mathematical expressions that use the variables to express certain conditions that need to be met while looking for the possible optimum solution

4. Variable Constraints: Usually variables have bounds. Very rarely are the variables unconstrained.

With the advancements in computing power and algorithms for solving LPs, the largest optimization problems today could have millions of variables and hundreds of thousands of constraints. These large problems can be solved in practical amounts of time.

# 2.11.1 Standard LP Problems

LP problems can have objective functions to be maximized or minimized, constraints may be inequalities  $(\leq, \geq)$  or equalities (=), and variables can have upper or lower bounds. There are two standard classes of problems - the *standard maximum problem* and the *standard minimum problem* [28]. In these problems all variables are constrained to be nonnegative, and all functional constraints are inequalities. These two play an important role because any LP problem can be converted to one of these two standard forms.

We are given an *m*-vector,  $b = (b_1, \ldots, b_m)^T$ , an *n*-vector,  $c = (c_1, \ldots, c_n)^T$ , and an  $m \times n$  matrix of real numbers,

$$A = \begin{bmatrix} a_{11} & a_{12} & \dots & a_{1n} \\ a_{21} & a_{22} & \dots & a_{2n} \\ & & \ddots & \ddots & & \ddots \\ & & & \ddots & \ddots & & \ddots \\ a_{m1} & a_{m2} & \dots & a_{mn} \end{bmatrix}$$

The **Standard Maximum Problem** [28] is to find an *n*-vector,  $x = (x_1, \ldots, x_n)^T$ , to Maximize

$$P = c_1 x_1 + c_2 x_2 + \dots + c_n x_n$$

(or  $P = c^T x$ )

subject to the constraints,

$$a_{11}x_{1} + a_{12}x_{2} + \ldots + a_{1n}x_{n} \leq b_{1}$$

$$a_{21}x_{1} + a_{22}x_{2} + \ldots + a_{2n}x_{n} \leq b_{2}$$

$$. \qquad (or \ Ax \leq b)$$

$$.$$

$a_{m1}x_1 + a_{m2}x_2 + \ldots + a_{mn}x_n \leq b_m$

and

$x_1 \ge 0, x_2 \ge 0, \ldots, x_n \ge 0$  (or  $x \ge 0$ )

Here,  $x_j$  and  $c_j$  (where j = 1, 2, ..., n) are the variables and coefficients respectively in the objective function. P is the objective function value that needs to be maximized.  $b_i$  are the limits, and  $a_{ij}$  (where i = 1, 2, ..., m) are the coefficients of the functional constraint equations.

Similarly the **Standard Minimum Problem** [28] is to find an *m*-vector,  $y = (y_1, \ldots, y_n)^T$ , to Minimize

$$Q = b_1 y_1 + b_2 y_2 + \dots + b_m y_m$$

(or  $Q = y^T b$ )

subject to the constraints,

$$a_{11}y_1 + a_{12}y_2 + \ldots + a_{m1}y_n \ge c_1$$

$a_{12}y_1 + a_{22}y_2 + \ldots + a_{m2}y_n \ge c_2$

. (or  $y^T A \ge c^T$ )

$a_{1n}y_1 + a_{2n}y_2 + \ldots + a_{mn}y_n \geq c_n$

and

$$y_1 \geq 0, y_2 \geq 0, \ldots, y_m \geq 0$$

(or  $y \geq 0$ )

Here,  $y_i$  and  $b_i$  (where i = 1, 2, ..., m) are the variables and coefficients respectively in the objective function. Q is the objective function value that needs to be minimized.  $c_j$  are the limits, and  $a_{ij}$  (where j = 1, 2, ..., n) are the coefficients of the functional constraint equations.

Many algorithms have been proposed to solve linear programs. One of the oldest and most popular methods is the *simplex method* [10, 22] invented by George Dantzig in 1947. It is a robust method as it can solve any linear program. *Interior-point method* found by Karmarkar [49] is a polynomial time method and is preferred over the simplex method for extremely large problems.

### 2.12 Primal and Dual Problems

If we have an optimization problem defined for an application, we could define another optimization problem called the *dual problem*. The original problem now will be called the *primal problem*. These two problems share a common set of coefficients and constants. If the primal minimizes one objective function of one set of variables then its dual maximizes another objective function of the other set of variables

Let us look at the duality for the standard problems defined previously. As in Section 2.11.1, c and x are n-vectors, b and y are m-vectors, and A is an  $m \times n$  matrix. We assume  $m \ge 1$  and  $n \ge 1$ .

The dual of the *standard maximum problem* is the *standard minimum problem*. The definitions of the primal maximum problem and the dual minimum problem are given in

Table 2.1: Primal and Dual Problem Definition

| Standard Maximum     | Standard Minimum     |

|----------------------|----------------------|

| Problem (Primal)     | Problem (Dual)       |

| Maximize $P = c^T x$ | Minimize $Q = y^T b$ |

| subject to,          | subject to,          |

| $Ax \le b$           | $y^T A \ge c^T$      |

| and $x \ge 0$        | and $y \ge 0$        |

Table 2.1. Another way to look at this is the dual of the *standard minimum problem* is the *standard maximum problem*. Hence the two problems are called *duals*.

The primal and dual LP problems are related by an important property called *duality*. This property indicates that we may in fact solve the dual problem in place of or in conjunction with the primal problem.

Duality theorem states that if the primal problem has an optimal solution, then the dual also has an optimal solution, and the optimized values of the two objective functions are equal [75].

There is a twofold advantage in studying the dual problem. First, its implementation enhances the understanding of the original (primal) model. Second, it is sometimes computationally easier to solve the dual model than the original model, and likewise provides the optimal solution to the latter at no extra cost.

## 2.13 Integer Linear Programming (ILP)

ILP is a variant of LP where the variables can take on only integer values. In ILP the number of solutions grows extremely rapidly as the number of variables in the problem increases. This is because of the numerous possible ways of combining these variables. Thus the worst case computational complexity of ILP problems is exponential. Special algorithms such as branch and bound method [10] have been developed to find optimal integer solutions. However, the size of problem that can be solved successfully by these algorithms is an order of magnitude smaller than the size of linear programs that can easily be solved. The LP problem has polynomial complexity due to its continuous decision space, as the variables can take fractional values. Thus in some cases the ILP problem is converted to a *relaxed-LP* problem by allowing the variables to take on real values, after which rounding algorithms are used to obtain an integer solution.

The primal-dual problems of LP described in the previous section can be transformed into two ILP problems by treating the variables as integers. The ILP problems share several of the duality properties.

### 2.14 Applications of Linear Programming in Testing

The ILP techniques have been used to optimize various aspects of testing. They have been used to obtain optimization of test sets for both combinational [29] and sequential circuits [26] as well as for globally minimizing N-detect tests [47, 46] and multiple fault model tests [81]. Other applications for the ILP techniques include test resource optimization [14, 58] and test data compression [15] for the testing of SoCs.

As stated earlier the computational complexity of the ILP would be too high to obtain an optimum solution for even medium size circuits. For this reason reduced-complexity LP variations such as the recursive rounding technique [48] can be used. The recursive rounding technique has been described in detail in the appendix.

### Chapter 3

# PREVIOUS WORK ON DETECTION TEST SET MINIMIZATION

This chapter gives a background of the various compaction techniques that have been proposed for detection test set minimization. In this chapter test set minimization/compaction is in the context of detection test sets only.

Before discussing the various test minimization techniques described in the literature let us look at the concept of *independent fault set* (IFS), which plays an important role in test minimization.

#### 3.1 Independent Fault Set

In Section 2.5 we had seen the definition of the independence relation between a pair of faults. Two faults are called independent if no vector can detect both [7]. An *independent fault set* (IFS) contains faults that are pair-wise independent. Thus we need one vector for every fault in the IFS. Hence the cardinality of the largest IFS for a circuit provides a lower bound on the size of a complete fault detection test set [7].

### 3.2 Independence Graph

The independence relations among faults can be represented graphically as an *inde*pendence graph (also known as *incompatibility graph*). In an independence graph the nodes represent faults, and the edges between nodes represent the pair-wise independence relations between faults. As independence is a symmetric relation the edge does not require a direction. Thus an edge between two nodes means that the two corresponding faults cannot be detected by a common vector. And the absence of an edge between two nodes indicates that the corresponding two faults can be detected by a common test vector, i.e., the two faults could have equivalence, dominance or concurrence relation.

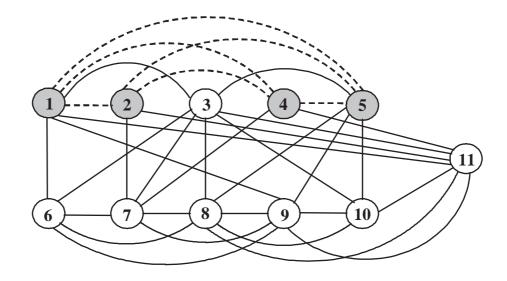

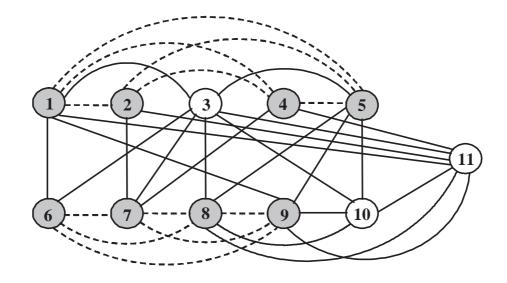

Figure 3.2 shows the independence graph for ISCAS85 [40] benchmark circuit c17 [23]. The circuit has 17 nets, so there will be 34 single stuck-at faults. Using functional dominance collapsing of [69] the number of faults is reduced to eleven. Figure 3.1 shows the eleven faults in the c17 circuit, numbered 1 through 11. The edges in the independence graph represent functional independences and were found using the ATPG-based procedure described in [23]. Here it should noted that if the independence graph is for a dominance collapsed fault set, then the absence of an edge between two nodes means that the two faults are concurrentlytestable.

Figure 3.1: c17 Circuit with 11 Functional Dominance Collapsed Faults [69]

In an independence graph the nodes belonging to a clique form an IFS. A clique is a subgraph in which every node is connected to every other node [20]. A maximum clique is

Figure 3.2: Independence Graph for c17 Benchmark Circuit

a clique of largest size i.e., with the highest number of nodes. Thus the maximum clique of an independence graph will give the largest IFS.

From the independence graph of c17, redrawn in Figure 3.3, it is clear that nodes (faults) 1, 2, 4 and 5 form an independent fault set (IFS). So, in order to detect all faults in c17, we need at least 4 vectors. Actually, the minimum possible test set for c17 has four vectors. In general, however, the size of largest IFS is only a theoretical minimum and such a test set whose size equals the lower bound may not be achieved in practice for many circuits. This was shown in [46] where, for a 5-bit and 6-bit multiplier a minimum test set of 7 test vectors was obtained, whereas the theoretical lower bound for these multipliers is 6.

One important point to make note of is that a circuit can have multiple maximal independent fault sets. For example, Figure 3.4 shows the same independence graph for c17

Figure 3.3: Largest Clique in the Independence Graph of Figure 3.2

with another maximum clique formed by nodes numbered 6, 7, 8 and 9. The four faults corresponding to these nodes also form a maximal IFS.

#### 3.3 Need for Test Minimization

Compact test sets are very important for reducing the cost of testing VLSI circuits by reducing test application time and test storage requirements of the tester. This is especially important for scan-based circuits as the test application time for such circuits is directly proportional to the test set size and number of flip-flops used in the scan chain.

## 3.4 Test Set Compaction

The test minimization problem for combinational circuits has been proven to be NPcomplete [51, 34]. Most ATPGs are not concerned with generating minimal test sets, as test

Figure 3.4: Multiple Maximum Cliques in the Independence Graph of Figure 3.2

generation is in itself computationally difficult. Thus ATPGs adopt a localized approach by targeting a single fault and generating a test vector for that fault. So heuristic methods based on compaction algorithms are used to obtain a minimal test set.

There are two types of compaction techniques - *static compaction* and *dynamic compaction*.

### 3.4.1 Static Compaction

Static compaction, also known as *post-generation compaction* [17], techniques are used to compact a given test set. Static compaction techniques work only with already generated test vectors. Hence these techniques are usually independent of the test generation process. Several static compaction algorithms based on different heuristics exist in the literature and are discussed next. One of the most popular static compaction techniques is reverse order fault simulation [72], where the generated test vectors are simulated in the reverse order, hoping to eliminate some of the initially generated vectors. This method is very effective because the normal test generation often starts with a random phase, where random vectors are simulated until no new faults are being detected and then a deterministic ATPG phase begins, where fault-specific vectors are generated. This is done so that the test pattern generation effort is not wasted on the easy to detect faults that can be detected by random vectors. The random vector generation phase is one of the main sources of redundant test vectors. Fault simulation of the test vectors in the reverse order removes most of the initially generated random vectors, which are made redundant by the deterministic vectors.

Another static compaction technique is described by Goel and Rosales [37], where pairs of compatible test vectors, that do not conflict in their specified (0, 1) values, are repeatedly merged into single vectors. This method is suitable only for patterns in which the unassigned inputs are left as don't care (X) by the ATPG program. Also, the compacted test set will vary depending on the order in which vectors are compacted. One drawback of this technique is that little reduction in test set size can be achieved for a highly incompatible test set.

The paper [45] describes a test ordering technique called *double detection* which combines static and dynamic compaction. In this technique, during test generation a fault is not dropped from the fault list until it is detected twice. Each vector is assigned a variable to keep a count of the number of faults it uniquely detects. At the end of the test generation if a vector has a count 0 it means that all the faults detected by it are also detected by other vectors. But this does not mean that the vector is redundant, because it may become an *essential vector* for a fault on eliminating some other vector after fault simulation. Fault simulation is performed during which all vectors with non-zero counts are simulated first, followed by the vectors with zero counts in the reverse order. This time many vectors with 0 counts become redundant, i.e., those that do not detect any new fault, and can be eliminated.

In all of the techniques described above, the size of the compacted test set depends on the order in which the vectors are compacted. One static compaction technique in which the order of vectors does not influence the final compacted test set size is the *integer linear programming* (ILP) method called the *Test Minimization ILP* [29]. The test minimization ILP gives the most compact test set possible for the given test set. However, it should be noted that the complexity of the ILP is exponential. Other *linear programming* (LP) based techniques like *recursive rounding* [48] that have polynomial time complexity can be used to obtain a close to optimum test set. The work presented in this thesis makes extensive use of the test minimization ILP along with recursive rounding. The test minimization ILP is described in the next chapter and the details of the recursive rounding technique can be found in Appendix A.

One of the main advantages of static compaction is that no modification of the ATPG is needed, as it is independent of the test generation process. Though static compaction adds to the test generation time, this time is usually small compared to the total test generation time. However optimal static compaction algorithms are impractical, so heuristic algorithms are used. Static compaction can also be used after dynamic compaction to further compact the test sets.

#### 3.4.2 Dynamic Compaction

In the literature techniques that attempt to reduce the number of test vectors during test generation have been classified as dynamic compaction techniques. There are some other techniques in literature classified as static which work after test generation and significantly modify or replace previously generated vectors based on the fault simulation information. We have classified such techniques as dynamic. Thus there are two sub categories of dynamic compaction.

#### Dynamic Compaction during Test Generation

Dynamic compaction techniques under this category attempt to reduce the number of test vectors while they are being generated. These techniques require modifications in the test generation process and algorithms. The key idea of compaction during test generation is that if the fault coverage of each test pattern is maximized during test generation, then the total number of patterns can be reduced.

The first dynamic compaction procedure was proposed by Goel and Rosales [37] in which every partially specified test vector is processed immediately after its generation by trying to use only the unspecified inputs in the test vector to derive a test to detect additional faults by the same vector.

Akers and Krishnamurthy were the first to present test generation and compaction techniques based on independent faults [7]. As the minimum test set size cannot be smaller than the size of the largest independent fault set (IFS), the tests for independent faults can be considered necessary. For every fault in a maximal IFS, partially specified tests are found using the test value propagation technique. Each partially specified test also gives information on which other faults can be potentially detected by it. This process is repeated for a different maximal IFS. While each pair of faults within an IFS requires separate tests, there is a definite possibility that a pair of faults from different IFSs can be detected by a single test. Thus a fault matching procedure was used to find sets of *compatible faults*, i.e., faults that can be detected by a single test vector, from the independent fault sets. The authors suggested that the information on compatible fault sets and independent fault sets could be used to decide the order of faults to be targeted during test generation. Thus these techniques could be used as a pre-processing step to the test generation step. However they did not provide any specific technique for fault ordering. Results for benchmark circuits are also not given. Though this paper did not provide any results, it became the basis for later work on independent faults.

COMPACTEST [59] was the first technique to make use of independent faults for fault ordering. The target faults are ordered such that the faults present in largest maximum independent fault sets (MIFS) appear at the beginning of the fault list. Later Kajihara *et al.* [45] proposed *dynamic fault ordering* which is an enhancement of the fault ordering technique of COMPACTEST. Here the fault list is reordered whenever a test is generated. The independent fault set with largest number of undetected faults at that point is put at the beginning of the fault list.

The "double detection algorithm" [45] described earlier in the section on static compaction is also a dynamic compaction technique. Here the processing done during test generation falls under the dynamic compaction category.

A redundant vector elimination (RVE) algorithm, which identifies redundant vectors during test generation and dynamically drops them from the test set, was developed by Hamzaoglu and Patel [38]. The RVE algorithm fault simulates all the faults in the fault list except the ones that are proven to be untestable, and it keeps track of the faults detected by each vector, the number of essential faults of each vector and the number of times a fault is detected. The essential faults of a vector are those that cannot be detected by any other vector in the vector set [17, 45]. During test generation if the number of essential faults of a vector reduces to zero, i.e. the vector becomes redundant, and it is dropped from the test set. The compaction results of RVE algorithm were similar to those of the double detection algorithm of [45].

Another recent work on dynamic compaction involves *independence fault collapsing* [25, 23] and *concurrent test generation* [24, 23], which collapses faults into groups based on independence relation, and then for each group tries to generate either a single vector, or as few vectors as possible, which can detect all faults in that group. In the independence fault collapsing algorithm an independence graph is constructed for a dominance collapsed fault set. In such a graph the absence of an edge between two nodes indicates that the corresponding two faults are concurrently testable. Thus two nodes that are not connected by an independence edge can form a single node whose label combines the fault labels of both nodes. Then, all nodes that had edges connecting to the two nodes will have edges to the combined node. This collapsing procedure ends when the graph becomes fully-connected. However, depending on the order in which the nodes are collapsed the size of the collapsed graph can vary. Thus the collapsing of faults in the independence graph is done using metrics - *degree of independence* defined for every fault and *similarity metric* defined for every pair of faults. This algorithm groups faults into nodes such that the similarity metrics among faults within each group are minimized. This increases the possibility of finding a

single concurrent test for the group. Concurrent test generation technique is used to find a single or as few test vectors as possible to detect all faults in each group. However these two techniques were very computationally intensive and could not provide optimum results.

#### **Dynamic Compaction after Test Generation**

Compaction methods under this category are mainly based on essential fault pruning, and have been classified in the literature as static techniques as they are applied after the test generation process. But, we will consider them as dynamic techniques as the test vectors are modified or even replaced by new vectors during the compaction process. The main advantage of the dynamic compaction techniques in this category is that the level of compaction achievable is not dependent on the quality of the original test set, as opposed to static compaction.

Chang and Lin [17] proposed the *forced pair-merging* algorithm which involves modification of one vector to cover the essential faults of another vector. The essential faults of a vector are those that cannot be detected by any other vector in the vector set. For a vector say t1, as many specified (0s and 1s) bits as possible are replaced with Xs such that the vector still detects its essential faults. Then, for each of the remaining vectors, say t2, the algorithm tries to change the bits that are incompatible with the new t1 to Xs. If the process succeeds, the pair is merged into a single vector. The authors also propose *essential fault pruning* (EFP) method to achieve further compaction by removing a vector by modifying other vectors of the test set to detect all the essential faults of the target vector. A limitation of this method is its narrow view of the problem; it is not possible to remove all the essential faults of a vector. Kajihara, et al. give the *essential fault extraction* (EFE) algorithm in [44]. The EFE is similar to EFP, wherein instead of modifying existing vectors, new vectors are generated by targeting essential faults. The authors also propose the *Two-by-one* algorithm in which addition of a new test vector removes two other vectors in a given test set. After determinimng two tests to be removed the essential faults of these vectors are used as target faults for the vector to be added.

In [39] the essential fault reduction (EFR) algorithm [39] is proposed which is an improved version of the EFP method of [17]. EFR uses a multiple target test generation (MTTG) procedure [17, 45] to generate a test vector that will detect a given set of faults. The EFR algorithm makes use of the independence (incompatibility) graph to decide which faults in a vector can be pruned through detection by another vector. The EFR algorithm, redundant vector elimination (RVE) algorithm described in the previous sub-section, along with dynamic compaction [37] and a heuristic for estimating the lower bound are incorporated into an advanced ATPG system for combinational circuits, and is called *MinTest*. MinTest produced some of the smallest reported single-detect test sets for the ISCAS85 [12] and ISCAS89 [11] (scan versions) benchmark circuits. However this technique was computationally expensive.

### 3.5 Methods of Finding Maximal IFS

The importance of independent fault sets (IFS) in the reduction of test set size has been established in the previous sections. We also saw that the largest IFS provides a lower bound on the test set size. This lower bound can be closely achieved by selecting tests from the test vectors derived for the faults in the IFS [7, 8]. However, the problem of finding the largest IFS is complex, and heuristics have to be used to find a maximal independent fault set.

Akers and Krishnamurthy [7] were the first to describe the derivation of maximal IFS from a set of faults within a given circuit by combining the notions of fault dominance and fault independence. For a given circuit their procedure involved finding dominance and independence relations among faults for primitive gates forming the circuit. Then use the transitive property of fault dominance to find additional dominance relations among faults in the entire circuit. The transitive property of fault dominance is, if a fault f1 dominates f2 and f2 in turn dominates f3, then f1 dominates f3. They then create a graph with undirected edges between nodes representing the independence relations between faults of the primitive gates of the circuit. The authors give a theorem stating that if fault f1dominates f2, f3 dominates f4, and f1 and f3 are independent then f2 and f4 are also independent. Using this theorem, additional edges are added to the graph. In the final graph a maximal clique gives the maximal IFS. It was here that the notion of an independent fault graph was first introduced, though the term "independence fault graph" was not used.

In the paper by Tromp [76] a maximal independent fault set was found using a graph, constructed based on *necessary assignments* [64] of all faults. Necessary assignments are line values that must be set for a fault to be detected. There is an edge between two nodes in the graph, if the necessary assignments of the faults corresponding to the nodes have conflicting values, implying the faults are independent. A maximal IFS was found as a maximal clique in the graph. The main problem with this technique is that it has high computational complexity, as all pairs of faults have to be considered, and then a maximal clique problem has to be solved over all pairs of faults. The paper [60] gives an improved

technique to compute independent fault sets based on necessary assignments. It allows construction of an IFS incrementally, thus resulting in reduced computational complexity.

In the paper on COMPACTEST [59], due to the complexity of computing independent faults sets for the entire circuit, independent faults sets are computed only within *maximal fanout free regions* using a labeling procedure. It also shows that the IFS for a fanout free region is also the IFS for the complete circuit.

Kajihara, et al. [45] give an improved method to find the necessary assignments utilizing *static learning* [31] and *unique sensitization* [31, 72]. The use of these techniques increases the number of necessary assignments, thereby increasing the potential to compute larger maximal IFS. Heuristics are used to store the necessary assignments efficiently and to simplify the identification process for independence of two faults.

In [39] a *minimum test set size* (MTSS) estimation technique is given to find lower bounds on test set sizes. As the size of maximal IFS gives the lower bound on the test set size, it computes the maximal IFS by finding the maximal clique in the independence graph initially only for essential faults and then enlarging this clique by considering other faults.

## Chapter 4

MINIMAL TEST GENERATION USING PRIMAL-DUAL ILP ALGORITHM

In the previous chapters we saw that the size of the largest IFS gives a lower bound on the test set size. This lower bound can be closely achieved by selecting tests from the test vectors derived for the faults in the IFS. This chapter describes the formulation of a dual ILP whose solution gives the largest IFS. The dual ILP is obtained by treating the test minimization ILP as the primal problem. The latter part of this chapter gives the primal-dual ILP based algorithm for generating a minimal detection test set, followed by the results of the algorithm.

#### 4.1 Test Minimization ILP

The Test Minimization ILP [29] falls under the category of static compaction as explained in Section 3.4.1. It is an exact solution to the problem of creating a minimum detection test set. The level of compaction achievable by this method is conditional to the original unoptimized test set. Thus, an absolute minimum test set for a circuit would be given by the test minimization ILP solution if we start with the exhaustive vector set for that circuit.

Suppose a combinational circuit has K faults. We are given a vector set V of J vectors and we assign a [0, 1] integer variable  $v_j$ ,  $j = 1, 2, \ldots, J$  to each vector. Without loss of generality, we assume that all K faults are detected by these vectors. Our problem then is to find the smallest subset of these vectors that detects all faults. The variables  $v_j$  have the following meaning:

- If  $v_j = 1$ , then vector j is included in the selected vector set.

- If  $v_j = 0$ , then vector j is discarded.

| Fault        | Vector number $(j)$ |          |   |   |   |   |   |   |   |   |

|--------------|---------------------|----------|---|---|---|---|---|---|---|---|

| number $(k)$ | 1                   | <b>2</b> | 3 | 4 | • | • | • | • |   | J |

| 1            | 0                   | 1        | 1 | 0 |   |   |   |   |   | 1 |

| <b>2</b>     | 0                   | 0        | 1 | 0 |   |   |   |   |   | 1 |

| 3            | 1                   | 0        | 0 | 1 |   |   |   |   |   | 0 |

| 4            | 0                   | 1        | 0 | 0 |   |   |   | • | • | 0 |

| •            | •                   | •        | • | • | • |   | • | • | • |   |

| •            | •                   | •        | • | • | • | • | • | • | • | • |

| K            | 1                   | 1        | 0 | 0 | • | • | • | • | • | 1 |

Figure 4.1: Detection Matrix  $a_{kj}$ .

We simulate the fault set and the vector set without dropping faults. The result is represented as a detection table (matrix) of 0s and 1s, shown in Figure 4.1. In this matrix, an element  $a_{kj} = 1$  only if fault k is detected by vector j.

The test minimization ILP problem is stated as,

$$\text{Minimize } \sum_{j=1}^{J} v_j \tag{4.1}$$

subject to,

$$\sum_{j=1}^{J} v_j \ a_{kj} \ge 1; \qquad for \ k = 1, 2, ..., K$$

(4.2)

$$v_j \in integer[0,1], \quad j = 1, ..., J$$

(4.3)

The constraint set given by equation (4.2) ensures that the  $k^{th}$  fault is detected by at least one vector in the selected vector set. The fact that we start with a vector set Vthat detects all faults in the set F and the direction of inequality in constraints that allow us to set any or all  $v_j$ 's to 1, guarantee the existence of a solution [26, 47]. Additionally, the provable ability of the ILP to find the optimum, provided its execution is allowed to complete, and the minimum requirement of 1 for every constraint guarantees the smallest size test set.

# 4.2 Dual ILP

Treating the test minimization ILP problem described in the previous section as the *primal*, we formulate another ILP called the *dual ILP* to obtain the largest IFS.