# FREQUENCY SYNTHESES WITH DELTA-SIGMA MODULATIONS AND THEIR

# APPLICATIONS FOR MIXED SIGNAL TESTING

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

Dayu Yang

Certificate of Approval:

Richard C. Jaeger Distinguished University Professor Electrical & Computer Engineering

Charles E. Stroud Professor Electrical & Computer Engineering Fa Foster Dai, Chair Associate Professor Electrical & Computer Engineering

Guofu Niu Alumni Professor Electrical & Computer Engineering

Stephen L. McFarland Acting Dean Graduate School

# FREQUENCY SYNTHESES WITH DELTA-SIGMA MODULATIONS AND THEIR APPLICATIONS FOR MIXED SIGNAL TESTING

Dayu Yang

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama December 15, 2006

# FREQUENCY SYNTHESES WITH DELTA-SIGMA MODULATIONS AND THEIR APPLICATIONS FOR MIXED SIGNAL TESTING

Dayu Yang

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights.

Signature of Author

Date of Graduation

VITA

Dayu Yang, son of Shangda Yang and Meilin Yao, was born in April 02, 1977 in Shanghai, P. R. China. He attended Shanghai Jiao Tong University in May 1995 and graduated with a Bachelor of Engineering degree in Communication Engineering in July 1999. He entered the Graduate School, Shanghai Jiao Tong University in September 1999 and received the Master of Science degree in Circuits and Systems in March 2002. Then he worked at Pericom Technology (Shanghai) Co. Ltd. as a mixed signal circuit design engineer. In January 2003, he joined Ph.D. program of the Department of Electrical and Computer Engineering, Auburn University.

## DISSERTATION ABSTRACT

# FREQUENCY SYNTHESES WITH DELTA-SIGMA MODULATIONS AND THEIR APPLICATIONS FOR MIXED SIGNAL TESTING

Dayu Yang

Doctor of Philosophy, December 15, 2006 (M.S., Shanghai Jiao Tong University, 2002) (B.S., Shanghai Jiao Tong University, 1999)

129 Typed Pages

Directed by Fa Foster Dai

This dissertation presents design and application of two popular frequency synthesizers, namely, the direct digital frequency synthesis (DDS) and phase lock loop (PLL) synthesis.

DDS is a digital technique for frequency synthesis, waveform generation, sensor excitation, and digital modulation/demodulation in modern communication systems. DDS provides many advantages including fine frequency-tuning resolution, continuous-phase switching and accurate matched quadrature signals. DDS can directly generate and modulate signal at microwave frequencies. A high-speed DDS can be significantly simplified the transceiver architecture. Thus the cost of radio and radar systems can be reduced considerably.

High speed DDS over GHz is demanding for wireless communication systems. This research proposes work on designing a high speed DDS chip with nonlinear DAC in Silicon Germanium (SiGe) process and using DDS as test pattern generator for analog circuitry built-in self test.

Nonlinear DAC is needed for high speed DDS for it replaces conventional ROM and linear DAC. The structure and system performance are analyzed with experimental data for a DDS with nonlinear DAC. Tradeoffs should be made to gain the best performance with feasible hardware implementation.

Spurious components in the DDS output spectrum introduced by the phase truncation are problems and delta-sigma modulators can be used either in phase or frequency domain to suppress in-band spurs. The formula deductions of delta-sigma modulation in both phase and frequency domain are presented and various delta-sigma modulators such as MASH, feed-forward, feedback and error feedback have been implemented in both phase and frequency in a CMOS DDS chip and their performances are compared.

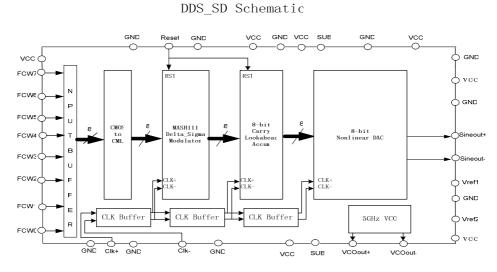

Circuit and layout designs using SiGe technology of DDS building blocks such as current mode logic (CML), 11-bit pipe-lined accumulator, 12-bit carry look-ahead accumulator, 1-1-1 Mash type delta-sigma modulator and a nonlinear DAC are discussed.

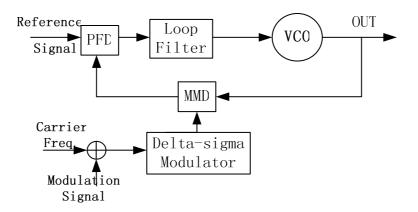

A DDS-based built-in-self-test (BIST) is presented for analogy circuit test. It uses DDS for test pattern generator (TPG) and a multiplier and accumulator as output response analyzer (ORA) and thus avoids traditional FFT-based spectrum analysis. Detail methods of frequency response and linearity test are introduced and verified by a field programmable gate array (FPGA) experimental results. PLL is another important frequency synthesis for its small area and power consumption. Fractional-N type PLL can have a wide loop bandwidth and fast settling time. The fractional spurs are reduced by delta-sigma modulators with new coefficients that have less out-band noise in order to suppress the modulators output bit pattern. A 2.5 GHz fractional-N PLL is designed in silicon on insulator (SOI) technology for its full dielectric device isolation, less junction capacitances, lower average device threshold voltages and less body effect and source follower effect.

#### ACKNOWLEDGMENTS

I would like to express my appreciation and sincere thanks to my advisor, Dr. Fa Foster Dai, who guided and encouraged me throughout my studies. His advice and research attitude have provided me with a model for my entire future career. I also wish to thank my advisory committee members, Dr. Charles E. Stroud, Dr. Richard C. Jaeger, Dr. Guofu Niu and Dr. Alvin Lim, for their guidance and advices on this work.

Appreciation is also expressed to those who have made contributions to my research. I am especially indebted to Shengfang Wei, Shuying Qi, Vasanth Kakani, Xuefeng Yu, Weining Ni, Yuan Yao, Wenting Deng, Xueyang Geng and Yi Liu for their cooperation and continued assistance throughout the course of this research.

Finally, I would like to thank, although this is too weak a word, my parents and family members for their continual encouragement and support throughout this work.

Style manual or journal used: IEEE Journal on Solid State Circuits

Computer software used: Microsoft Word 2003

# TABLE OF CONTENTS

| 4.6 Ultra High Speed DDS with MASH Delta-sigma Modulation   | 58  |

|-------------------------------------------------------------|-----|

| 4.7 Conclusions                                             | 63  |

| CHAPTER 5 DDS BASED BUILT-IN SELF TEST                      | 64  |

| 5.1 Introduction                                            | 64  |

| 5.2 Linearity Test Using DDS                                |     |

| 5.3 Implementation and Test Results                         |     |

| 5.4 Frequency Response Test Using DDS                       |     |

| 5.5 BIST Measurement of Frequency Response                  |     |

| 5.6 Conclusions                                             |     |

| CHAPTER 6 PHASE LOCKED LOOP FREQUENCY SYNTHESIZER           | 80  |

| 6.1 Introduction                                            |     |

| 6.2 Charge Pump PLL                                         | 81  |

| 6.3 Fractional-N Frequency Synthesizer                      | 84  |

| 6.4 Fractional Spurs                                        | 86  |

| 6.5 Delta-sigma Modulation in Fractional-N PLL              | 88  |

| 6.5.1 Dynamic Range of Modulator                            | 88  |

| 6.5.2 Multibit Quantizer                                    | 89  |

| 6.5.3 NTF Optimization                                      | 89  |

| 6.6 Digital Modulations in PLL and Band-Widening Techniques |     |

| 6.7 Circuit Design of a Fractional-N PLL in SOI             | 95  |

| 6.7.1 SOI Technology                                        | 95  |

| 6.7.2 SOI Devices                                           | 96  |

| 6.7.3 MOS Current Mode Logic                                | 98  |

| 6.7.4 Phase Frequency Detector                              | 99  |

| 6.7.5 Charge Pump and Loop Filter                           |     |

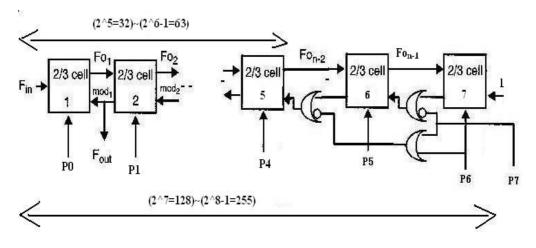

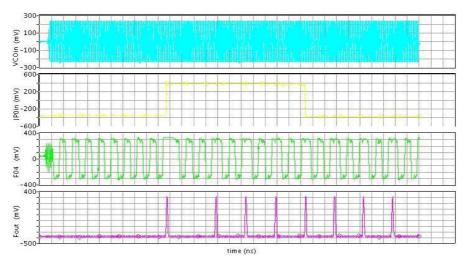

| 6.7.6 Multi-Modulus Divider                                 | 103 |

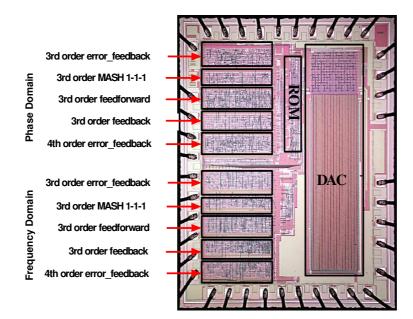

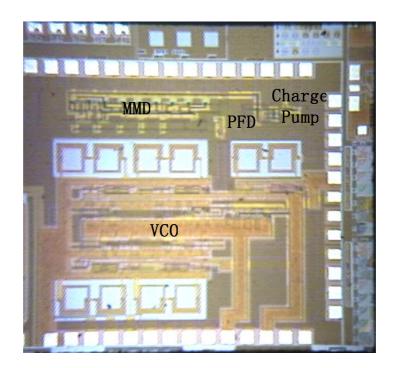

| 6.7.9 Die Photo                                             | 106 |

| 6.8 Conclusion                                              | 107 |

| CHAPTER 7 CONCLUSIONS                                       | 108 |

| BIBLIOGRAPHY                                                | 110 |

# LIST OF TABLES

| Table 2-1 Quadrant table of a sine wave in one period                             | 10 |

|-----------------------------------------------------------------------------------|----|

| Table 2-2 Flipping Operations from first quadrant to other quadrants              | 10 |

| Table 3-1 Performance comparison of delta-sigma modulators in frequency and phase |    |

| domains of DDS. (In-band SFDR and SINAD are measured from NCO)                    | 40 |

| Table 4-1 Thermometer-code representation of 2-bit binary values                  | 55 |

# LIST OF FIGURES

| Figure 1-1 Frequency synthesizer in a super-heterodyne receiver                                    |

|----------------------------------------------------------------------------------------------------|

| Figure 2-1 Conventional ROM-based DDS7                                                             |

| Figure 2-2 Spurs and noise in output spectrum caused by phase, amplitude quantization              |

| (L=16, W=10, D=12)                                                                                 |

| Figure 2-3 Quadrant compression of sine ROM 10                                                     |

| Figure 2-4 High-speed DDS with a nonlinear DAC11                                                   |

| Figure 2-5 First quadrant sine wave construction using nonlinear DAC cells 12                      |

| Figure 2-6 Worst case spur versus phase bit W and output bits D of nonlinear DAC 14                |

| Figure 2-7 SINAD with different DAC bits <i>D</i> and phase bits $W$ (BW=0.25·f <sub>clk</sub> )15 |

| Figure 2-8 Structure design of DDS with nonlinear DAC with $L=16$ , $W=12$ , $D=11$ 16             |

| Figure 3-1 Linear model of delta-sigma modulator                                                   |

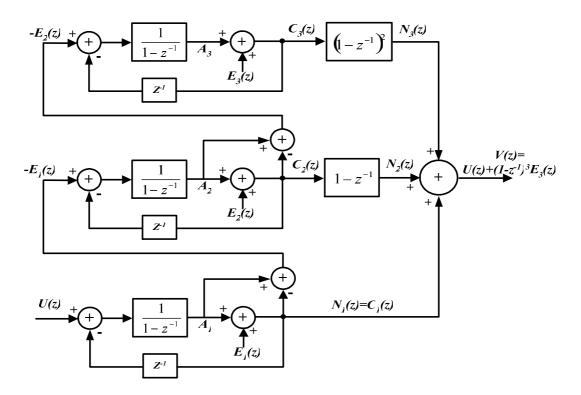

| Figure 3-2 MASH delta-sigma modulator with quantization noise e[n] at each stage 22                |

| Figure 3-3 Autocorrelation of second order MASH type modulator's quantization error.               |

|                                                                                                    |

| Figure 3-4 DDS with NCO and DAC                                                                    |

| Figure 3-5 Phase domain delta-sigma modulation in DDS                                              |

| Figure 3-6 Error feedback modulator in phase domain                                                |

| Figure 3-7 Proposed DDS with frequency domain delta-sigma modulation                               |

| Figure 3-8 Four types delta-sigma modulators implemented in a DDS and NCO for       |

|-------------------------------------------------------------------------------------|

| comparison                                                                          |

| Figure 3-9 Measured in-band SINAD and SFDR of the NCO output with various           |

| delta-sigma modulators in frequency and phase domains                               |

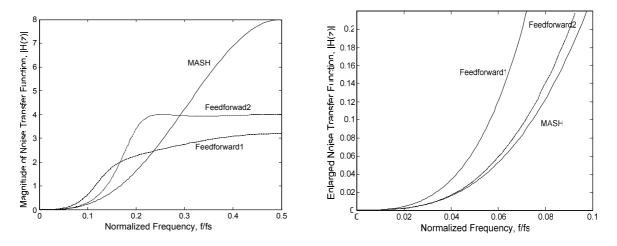

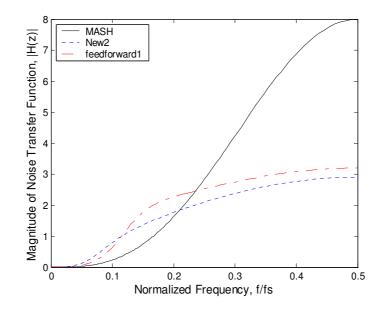

| Figure 3-10 simulated noise transfer function of MASH and feedforward delta-sigma   |

| modulators                                                                          |

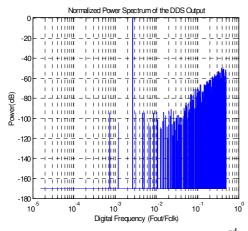

| Figure 3-11 Comparison of measured NCO output spectrum with different noise shaping |

| effects                                                                             |

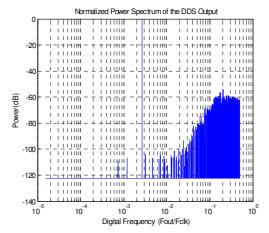

| Figure 3-12 Die photo of the CMOS DDS prototype chip with various delta-sigma       |

| modulators in frequency and phase domain                                            |

| Figure 3-13 Comparison of the measured output spectra for (a) conventional DDS      |

| without delta-sigma modulation and (b) proposed DDS with frequency domain           |

| delta-sigma modulation, f <sub>o</sub> =750KHz, F <sub>clk</sub> =30MHz39           |

| Figure 3-14 Measured DDS output spectra (FCW=0000000,11111111) 41                   |

| Figure 3-15 Measured DDS output spectra with third order MASH type delta-sigma      |

| modulation                                                                          |

| Figure 3-16 Measured DDS output spectra with third order feedback type delta-sigma  |

| modulation                                                                          |

| Figure 4-1 A four-level AND CML logic 44                                            |

| Figure 4-2 Output resistance of emitter follower at high bias and high frequency    |

| Figure 4-3 Oscillation caused by emitter followers inductive output                 |

| Figure 4-4 A generic architecture of an N×M pipelined accumulator                   |

| Figure 4-5 1-bit CML full adder                                                     |

|                                                                                     |

| Figure 4-6 A 12-bit carry look-ahead adder using CML logics                           | . 52 |

|---------------------------------------------------------------------------------------|------|

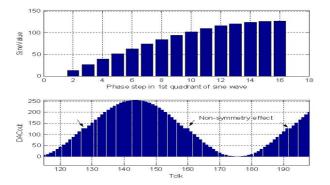

| Figure 4-7 Architecture of the nonlinear DAC in DDS                                   | . 54 |

| Figure 4-8 Non-symmetry effect of sine waveform.                                      | . 55 |

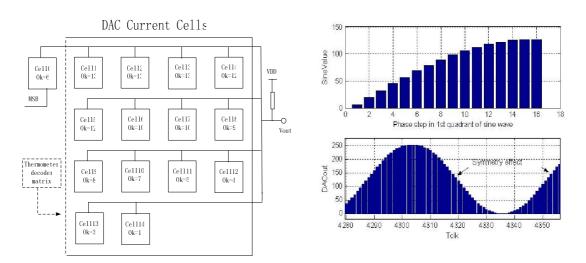

| Figure 4-9 DAC cell matrix structure and its symmetry effect.                         | . 56 |

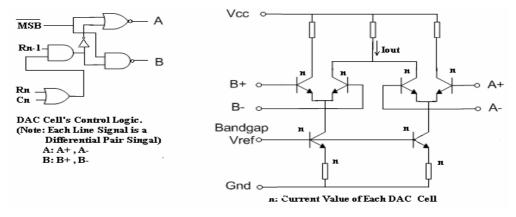

| Figure 4-10 DAC current cell circuit.                                                 | . 57 |

| Figure 4-11 Simulated DAC output waveform at 10GHz.                                   | . 58 |

| Figure 4-12 Schematic of DDS with delta-sigma modulation                              | . 58 |

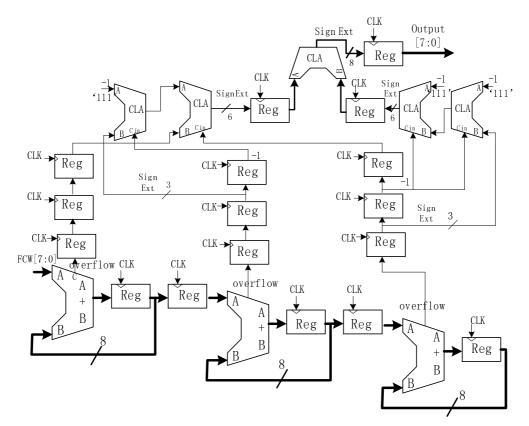

| Figure 4-13 Third order MASH delta-sigma modulator architecture                       | . 60 |

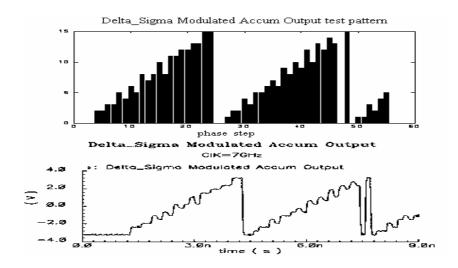

| Figure 4-14 Delta-sigma modulated accumulator output running at 7GHz.                 | . 61 |

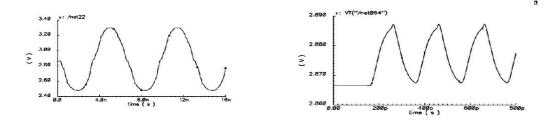

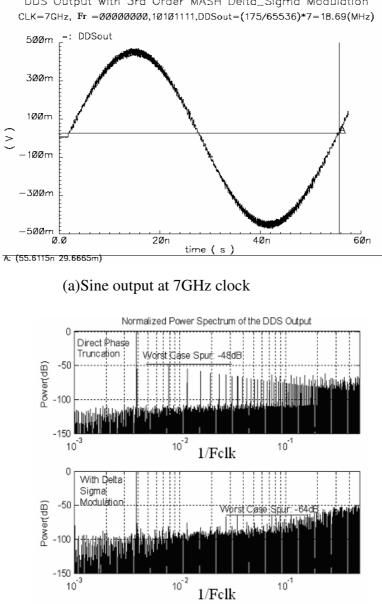

| Figure 4-15 Delta-sigma modulated DDS output waveform and spectrum ( $F_{clk}$ =7GHz) | . 62 |

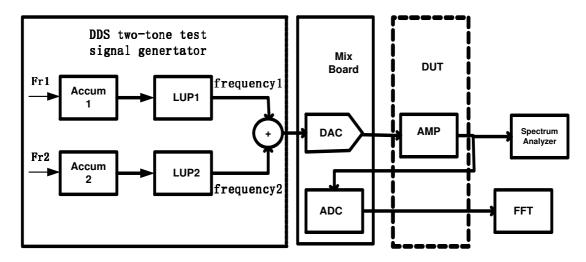

| Figure 5-1 Two-tone test using DDS for linearity test.                                | . 66 |

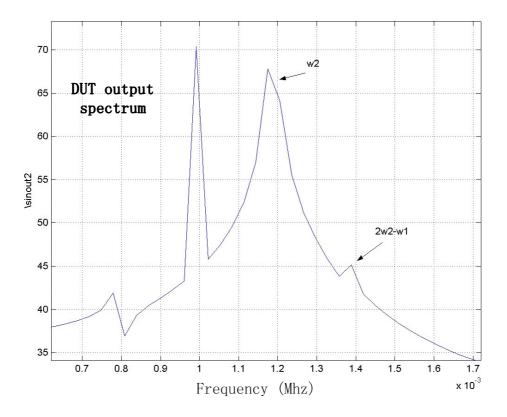

| Figure 5-2 DUT output spectrum measured by FFT                                        | . 66 |

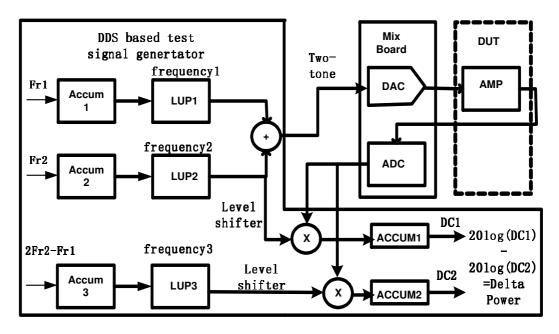

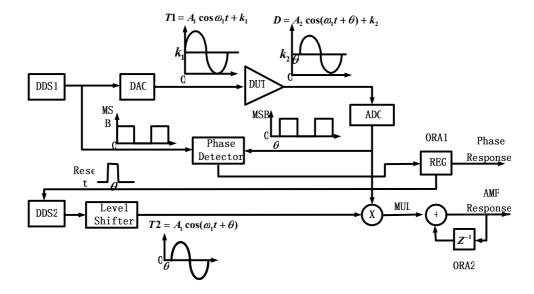

| Figure 5-3 Automatic Linearity (IP3) Test using DDS.                                  | . 68 |

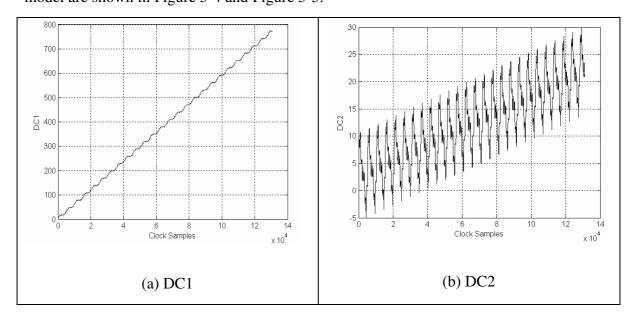

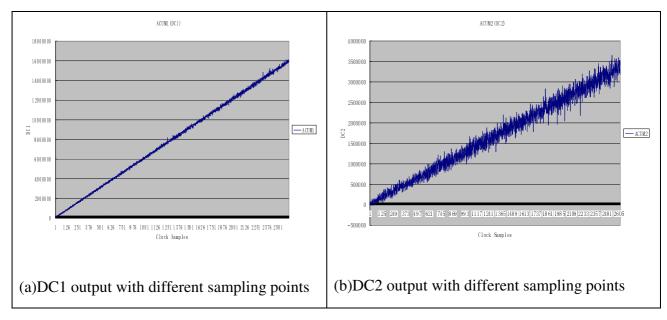

| Figure 5-4 DC from the accumulator at different sampling points                       | . 70 |

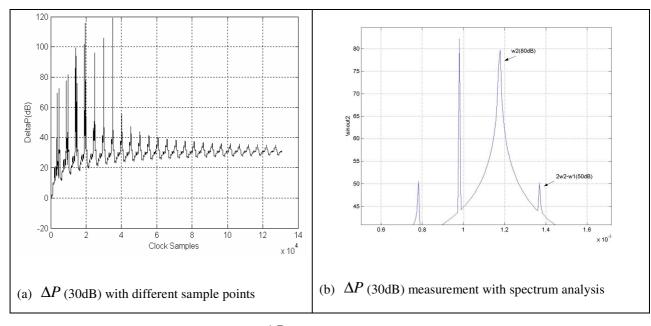

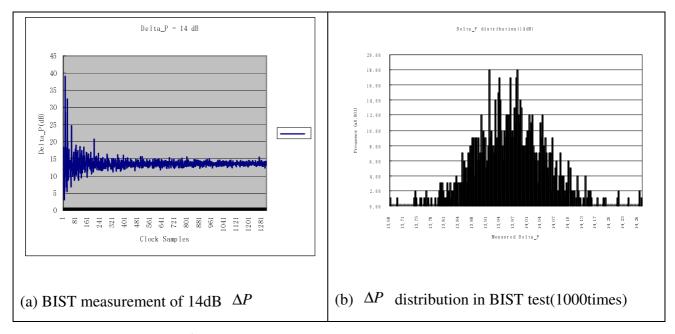

| Figure 5-5 $\Delta P$ (30dB) measurement                                              | . 71 |

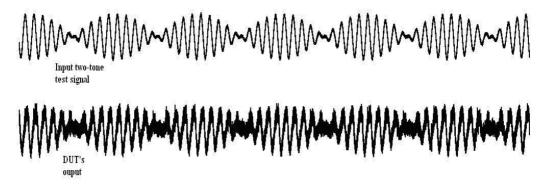

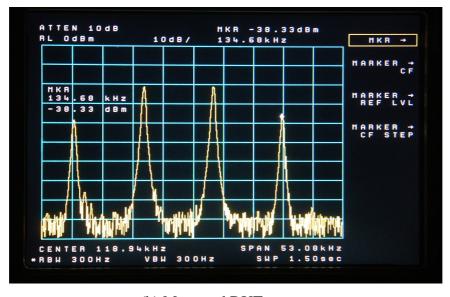

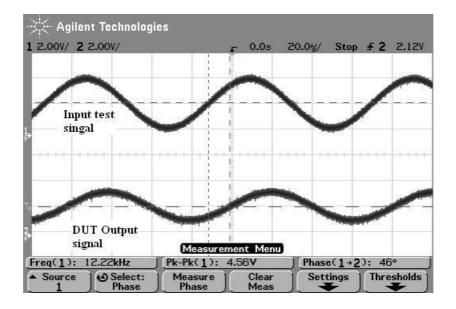

| Figure 5-6 Hardware measurements of two-tone test at the DUT output                   | . 72 |

| Figure 5-7 Hardware measurements of DC1 and DC2                                       | . 73 |

| Figure 5-8 $\Delta P$ measurement per 100 points and its distribution                 | . 73 |

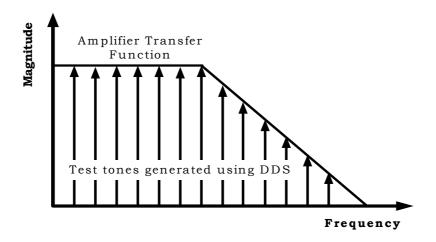

| Figure 5-9 Frequency response test using DDS                                          | . 75 |

| Figure 5-10 BIST of frequency response of an analog circuit                           | . 76 |

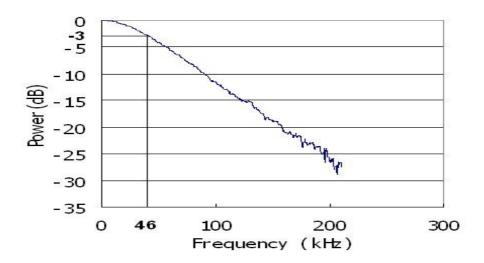

| Figure 5-11 BIST measured frequency response of a low pass filter                     | . 78 |

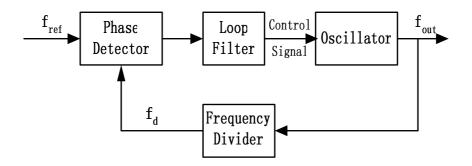

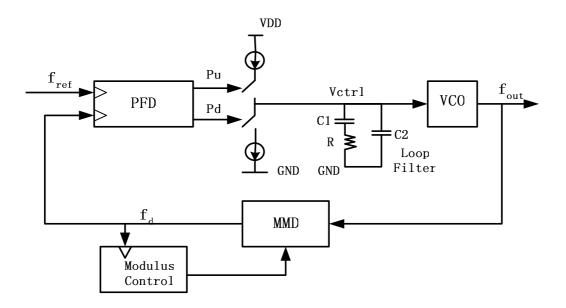

| Figure 6-1 Typical PLL frequency synthesizer.                                         | . 80 |

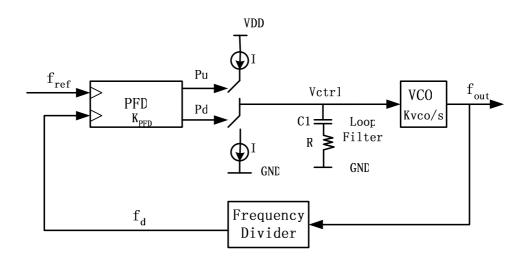

| Figure 6-2 Charge pump PLL.                                                           | . 82 |

| Figure 6-3 Fractional-N PLL frequency synthesizer.                                    | . 84 |

|---------------------------------------------------------------------------------------|------|

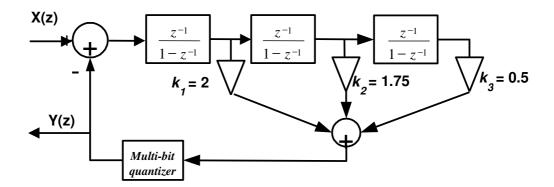

| Figure 6-4 Block diagrams illustrating the proposed 3rd order feedforward delta-sigma | l    |

| modulators in PLL.                                                                    | . 90 |

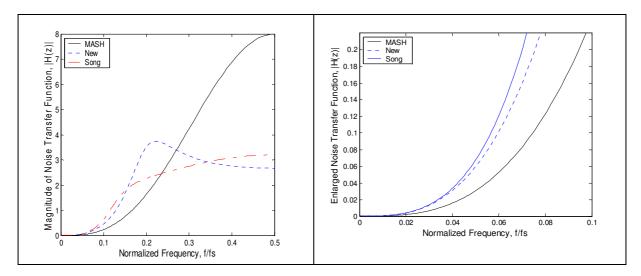

| Figure 6-5 Simulated noise transfer function of MASH and feedforward delta-sigma      |      |

| modulators ( $k_1 = 2, k_2 = 1.75, k_3 = 0.5$ )                                       | . 91 |

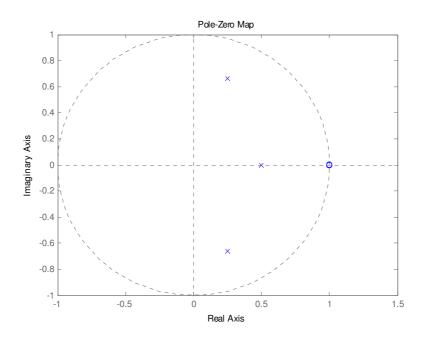

| Figure 6-6 The PZ map of the new transfer function (Stable)                           | . 91 |

| Figure 6-7 Simulated noise transfer function of MASH and new feedforward delta-sign   | ma   |

| modulators ( $k_1 = 1.75, k_2 = 1, k_3 = 0.25$ )                                      | . 92 |

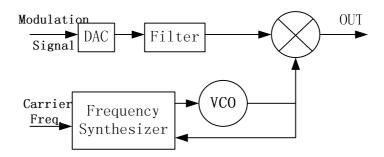

| Figure 6-8 Modulation frequency up-conversion using mixer.                            | . 92 |

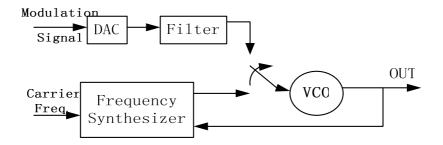

| Figure 6-9 Modulation frequency up-conversion using direct modulation of VCO          | . 93 |

| Figure 6-10 Modulation frequency up-conversion using indirect modulation of VCO       | . 94 |

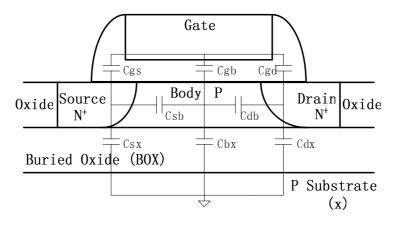

| Figure 6-11 Cross-section of SOI NMOS                                                 | . 96 |

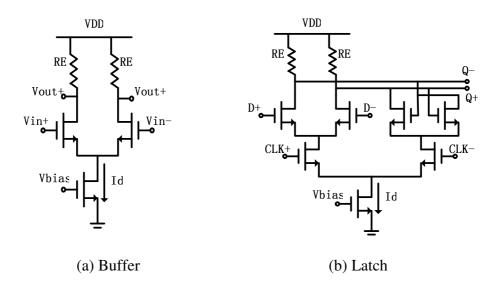

| Figure 6-12 MOS Current Mode Logic.                                                   | . 98 |

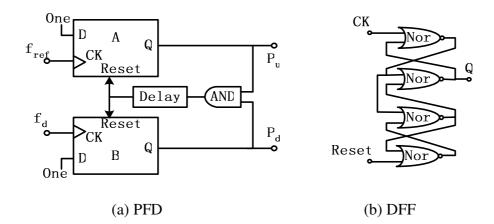

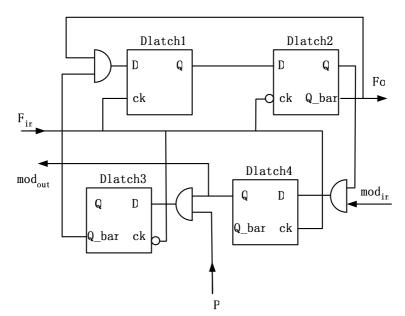

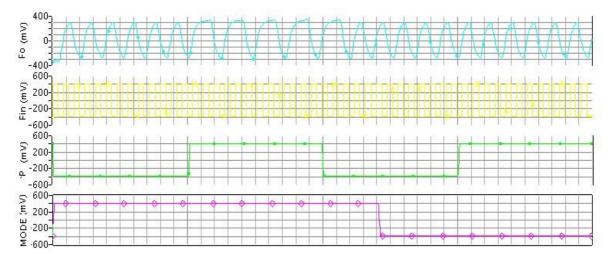

| Figure 6-13 PFD and its D flip-flop implementation                                    | 100  |

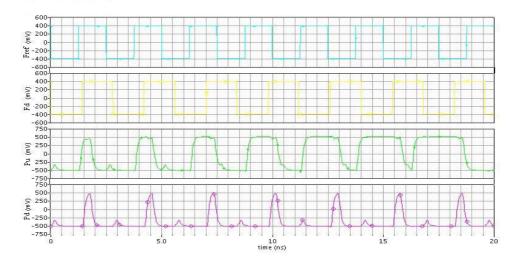

| Figure 6-14 PFD simulation results.                                                   | 100  |

| Figure 6-15 Charge pump schematic.                                                    | 101  |

| Figure 6-16 Charge pump simulation results                                            | 102  |

| Figure 6-17 Divider by 2 or 3 cell.                                                   | 103  |

| Figure 6-18 Simulation result of Divider by 2 or 3 cell                               | 104  |

| Figure 6-19 Multi-modulus divider.                                                    | 105  |

| Figure 6-20 MMD simulation result                                                     | 106  |

| Figure 6-21 Die photo of the PLL in SOI.                                              | 106  |

## **CHAPTER 1 INTRODUCTION**

# 1.1 RFIC Design

Radio frequency integrated circuit (RFIC) design becomes challenging with the growing demand of wireless and communication market. The competence resides in high performance, high compatibility [1], lower cost and low power dissipation. In addition, high levels of integration, which may include all of the analog and digital functions related to transceiver and built-in self-test (BIST) are the design goals to achieve better performance. The thesis presents research work on one of the building blocks of RFIC--- frequency synthesizer design and its application for analog circuit build-in-self-test (BIST).

Device technology plays an important role in RF IC design. Bipolar device takes its advantages in high speed, high trans-conductance  $(g_m)$ , low noise of its npn transistor, but it has a slow pnp transistor and high power consumption [2].

CMOS technology is gaining its popularity in RF circuits [3][4]. It's preferred for low quiescent power dissipation, complementary transistors, low cost and easy scaling. Its disadvantage is its low speed and large noise, the limited set of available passive devices. The modeling for the CMOS technology is mainly optimized for digital design and it needs accurate model for RF design [5].

Bipolar complementary metal-oxide-semiconductor (BiCMOS) technology can provide high integration capability of both digital and analog circuitry as well as high performance levels. BiCMOS IC technology is viewed as a good candidate for implementing the relatively complex digital functions because the high current-drive capability of the bipolar transistors greatly facilitates driving large capacitive loads. The hetero-junction bipolar transistor uses two different materials such as Si and Ge to form a pn junction inside the transistor to reach higher unity gain-bandwidth product (f<sub>T</sub>), low noise, good linearity and low power consumption compared to BJT. Mature SiGe technology [6] that has many generations provides a full device suite for RF IC design, including a trench isolated, highly planar SiGe hetero-junction bipolar transistor (HBT), n-MOS and p-MOS devices, poly-silicon and diffused resistors, high-density MOS and high quality-factor metal-insulator-metal (MIM) capacitors, varactor diodes, and spiral inductors. It makes it possible to achieve full mixed-signal design and high levels of integration in RF IC design.

Silicon-On-Insulator (SOI) CMOS circuits differentiate from conventional bulk CMOS for its device is built on a thin silicon layer placed upon an insulator. Circuits fabricated in a SOI process can operate with higher speed and lower power consumption than circuits fabricated with bulk CMOS because the reduced parasitic capacitances intrinsic to the device structure is isolated from the substrate. The buried insulator layer allows the use of a high resistance substrate, which significantly reduces the device capacitance and the loss of passive components, such as inductors, that are commonly used in analog and RF circuits. Thus, SOI provides an advantage over bulk MOS to realize complete systems on a chip by integrating high speed digital devices with high performance analog and RF devices.

#### 1.2 Frequency Syntheses

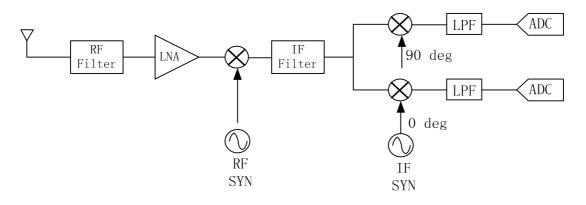

Figure 1-1 Frequency synthesizer in a super-heterodyne receiver.

In a RF transceiver, a frequency synthesizer is needed to generate the local oscillation (LO) frequency to mix with the received RF signal and down-convert it to IF and base band. A typical super-heterodyne receiver is shown in Figure 1-1, two frequency synthesizers are used to provide different local oscillation signals. Quadrant signals from the IF synthesizer are used to get rid of the image signal from the mixers. Ideal frequency synthesizer generates a pure sinusoidal wave form for frequency translation. Its purity is highly demanded such that no image signal caused by synthesizer after mixer. But due to systematic design, repetitive pattern disturbance and noise from circuits, the synthesizer output's amplitude and phase varies from the desired design values, the output spectrum is never an ideal single tone. It usually contains of unwanted spurious frequency components and phase noise and it could mix with the input signal and produce side bands and noise in the desired channel. This reduces the sensitivity and selectivity of a receiver. So the main frequency synthesizer design goal is to get low spurious tones and low phase noise in the output spectrum with minimum power and area consumption. On other aspects, fine channel spacing in transceivers require high frequency resolution as low as Hz and quick frequency toggling needs fast frequency switching speed as high as GHz. Besides generating pure local oscillation frequency, synthesizers need to combine modulation techniques to realize a modulated transmitter.

There are mainly two types of frequency synthesizer, namely, the phase locked loop (PLL) and direct digital synthesizer (DDS). PLL is a conventional way to realize low phase noise and low spurious tone frequency synthesizer. But the need of high-Q passive component and off chip components makes it a hard for a full integration. Besides, narrow bandwidth of the integer-N type PLL makes it relatively low frequency switching speed of the system. Fractional-N type PLL achieves fine step size since the output frequency can vary by a fraction of the input reference frequency. As a result, the fractional-N PLL can have high reference frequency and low division ratio, which leads to lower in-band noise. However, it also generates fractional spurs in the output spectrum due to periodic switching of the divider ratio.

DDS can provide fast frequency switching, fine resolution and wide tuning range in frequency-agile communication systems and it is suitable for integration for no need of off-chip components. It can also provide various direct modulations such as chirp, MSK, FSK and GMSK. DDS is also flexible as a test pattern generator in testing area and addresses an application in BIST for RF circuits. Its drawback is that high speed and high resolution is usually achieved at the cost of big area and huge power consumption.

These two types of frequency synthesizers both suffer from unwanted spurs in the vicinity of the main output frequency. These spurs are caused by the periodic disturbance due to their own mechanisms. Delta-sigma modulation technique is used to decrease the

periodic disturbance without affecting the synthesizer's function. Various types of delta-sigma modulators in frequency synthesizers can have different effects in spur reduction.

#### 1.3 Dissertation Organization

In Chapter 2, the fundamentals of direct digital synthesis including the spurs and quantization noises introduced by phase and amplitude truncation are reviewed. Nonlinear DAC is introduced to DDS to replace the speed bottle neck ROM lookup table and linear DAC. Top level structure and system performance are analyzed and design tradeoffs are evaluated.

In Chapter 3, the basics of delta-sigma modulation are introduced and its white noise linear model is examined. The effectiveness of various types of delta-sigma modulators in both frequency domain and phase domain of DDS is verified by math deduction and real implementation in a CMOS chip. Their performances including spur reduction effect, area, speed and stability are compared.

In Chapter 4, the RF circuit designs of DDS building blocks such as CML digital circuits, phase accumulators, delta-sigma modulator and nonlinear DAC are discussed

In Chapter 5, a DDS-based BIST approach for analog frequency response and linearity test is proposed.

In Chapter 6, a fractional-N type wide-band PLL in SOI technology is presented. Chapter 7 concludes the thesis with a summary.

# **CHAPTER 2 DIRECT DIGITAL SYNTHESIS**

### 2.1 Introduction

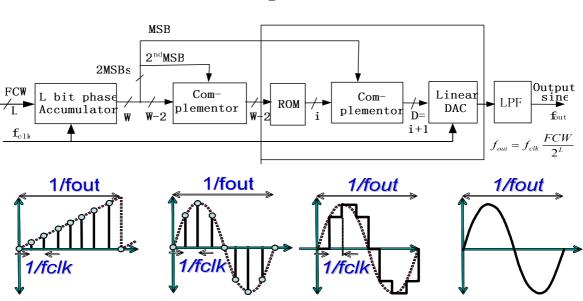

In this chapter, basic ROM-based the direct digital synthesis(DDS) and its mechanism are first reviewed in section 2.2. Phase truncation after the accumulator and DAC's amplitude quantization can cause unwanted the spurs and noise in the output spectrum. The location and strength of the spurs can be determined by the phase accumulator's length Land phase word W that addresses the ROM. Increasing the W and DAC bits D can lead to reduction of spur and noise but may cause bigger area and power consumption. Standard Sine ROM compression technique stores only first quadrant amplitude value to reduce 75% the ROM.

In section 2.3, a nonlinear DAC replaces the conventional ROM lookup table and linear DAC in DDS to reach high speed. In section 2.4, the structure and system performance such as SNR and SFDR of DDS with a nonlinear DAC are analyzed. An experimental structure design is given in section 2.5.

# 2.2 DDS Fundamentals

### 2.2.1 Conventional ROM-based DDS

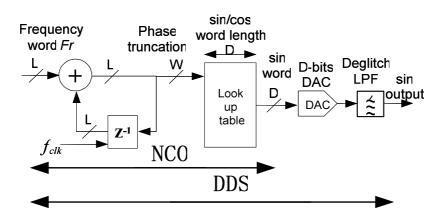

Figure 2-1 shows a conventional ROM-based DDS, The output frequency of the DDS depends on the input *L*-bit word named frequency control word (FCW). At each positive

edge of the reference clock cycle the FCW is added to an accumulator. At any instant, the value in the accumulator represents the phase of the output sinusoid, so it is referred as phase accumulator register. The value in the phase accumulator register is used to address the ROM storing the values of the sinusoid in digital domain. The DAC and filter are used to reconstruct the waveform in analog domain. The frequency resolution is determined by the word length of the phase accumulator which is L.

$$f_{out} = f_{clk} \cdot \frac{FCW}{2^L} \tag{2.1}$$

Figure 2-1 Conventional ROM-based DDS.

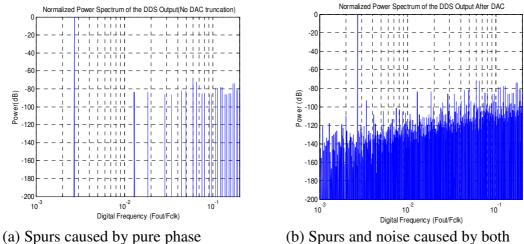

Finite phase word length and amplitude word length will cause quantization errors and thus lead to unwanted spurs and noises in the output wave form. The actual word length of the phase information in the sine ROM will determine the phase quantization error, while the number of the bits in the digital-to-analog converter (DAC) will determine the amplitude quantization error. Therefore, it is desirable to increase the resolution of the ROM and DAC. Unfortunately, larger ROM and DAC resolutions mean larger area, higher power consumption, lower reliability, lower speed, and greatly increased costs. Some memory compression techniques can be used to alleviate the problem and will be introduced later. However, the truncation of the phase accumulator bits dressing the sine ROM is necessary. This "phase truncation error" corrupts the output sinusoid and it's periodic and results in spurs in output spectrum of DDS as shown in Figure 2-2(a). The location and magnitude of these spurious spurs have been calculated by Nicholas and Samueli[7]. Knowing that FCW is the input frequency control word, *L* is the accumulator's size, *W* is the number of bits addressing the ROM. *B=L-W* is the truncated phase word bits. The number of spurs is:

$$N = \frac{2^{B-1}}{(FCW, 2^L)}$$

(2.2)

where (FCW,  $2^L$ ) represents the greatest common divisor of the FCW and  $2^L$ .

These spurs are equally spaced between 0 and  $f_{clk}/2(FCW, 2^L)$  in the spectrum. The magnitude of the largest spur in the spectrum is given by:

$$\zeta_{worst} = 2^{B-L} \frac{\pi (FCW, 2^B) / 2^B}{\sin(\pi (FCW, 2^B) / 2^B)}$$

(2.3)

There is something important between the magnitude of the largest spur and (FCW,  $2^B$ ). The magnitude of the worst case spur in the spectrum is a decreasing function of (FCW,  $2^B$ ) with the maximum value provided by (FCW,  $2^B$ ) =  $2^{B-1}$ . If (FCW,  $2^B$ ) =1, the worst case spur would be 3.933dB lower than the spur caused by same *B*, but unrestricted values of FCW. Nicholas has proposed an architecture to force the (FCW,  $2^B$ )=1 to get the half bit improvement in worst case spur [7]. Under this situation, when *B* is bigger than 4, the magnitude of the worst case spur can be approximately estimated as  $2^{-W}$ . Similarly, the amplitude truncation of ROM to DAC can also introduce quantization to the output. The spurious spurs caused by the quantization effects both in phase and amplitude are shown in Figure 2-2(b), the locations of the spurs are mainly determined by phase truncation. ROM and DAC would affect the magnitudes of the spurs and also increase the noise power density in band by 6dB per bit. The in-band noise plus spurs close to the main signal cannot be filtered by the low pass filter afterward.

(a) Spurs caused by pure phase quantization

(b) Spurs and noise caused by both phase and amplitude quantization

Figure 2-2 Spurs and noise in output spectrum caused by phase, amplitude quantization (L=16, W=10, D=12).

# 2.2.2 Quadrant Compression of ROM

The size of the ROM can be reduced by more than 75 percent by taking advantage of the fact that only one quadrant of the sine wave form needs to be stored. As shown in Table 2-1 [8], the second, third and fourth quadrants of a sine waveform can be constructed by using the phase to amplitude information of first quadrant and the two MSBs of the phase information W.

| Phase                                                              | MSB | MSB-1 | Sine       |

|--------------------------------------------------------------------|-----|-------|------------|

| 0 <a<90< td=""><td>1</td><td>0</td><td>sinA</td></a<90<>           | 1   | 0     | sinA       |

| 90 <a<180< td=""><td>1</td><td>1</td><td>sin(90-A)</td></a<180<>   | 1   | 1     | sin(90-A)  |

| 180 <a<270< td=""><td>0</td><td>0</td><td>-sinA</td></a<270<>      | 0   | 0     | -sinA      |

| 270 <a<360< td=""><td>0</td><td>1</td><td>-sin(90-A)</td></a<360<> | 0   | 1     | -sin(90-A) |

Table 2-1 Quadrant table of a sine wave in one period

Thus, given a sin(A) over only the first quadrant, the operations necessary to flip to the

other quadrants are as shown in Table 2-2.[8]:

Table 2-2 Flipping Operations from first quadrant to other quadrants

| Quadrant I   | 0.5+0.5sin(k) (k is running index from 0 to $2^{W-2}$ -1)                 |

|--------------|---------------------------------------------------------------------------|

| Quadrant II  | $0.5+0.5\sin(k)$ (k is complemented running index from 0 to $2^{W-2}-1$ ) |

| Quadrant III | $0.5-0.5\sin(k)$ (k is running index from 0 to $2^{W-2}-1$ )              |

| Quadrant IV  | $0.5-0.5\sin(k)$ (k is complemented running index from 0 to $2^{W-2}-1$ ) |

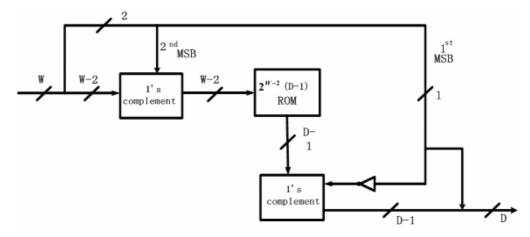

Figure 2-3 shows the hardware implementation of a quadrant compressed sine ROM, the second MSB of the phase word is used to switch on and off the 1's complement of the rest phase word. The inverse of the first MSB of the phase word is used to switch on and off the 1's complement of ROM output. The first MSB of the phase word is also the MSB of the final digital amplitude output.

Figure 2-3 Quadrant compression of sine ROM.

#### 2.3 DDS with Nonlinear DAC

In conventional ROM-based digital frequency synthesizer, it's not easy to achieve output frequency bigger than 2GHz because of the time and area consumed by ROM look up table. At present, ROM-less DDS gains popularity because it uses a nonlinear DAC to replace the ROM lookup table and the linear DAC and thus can generate much higher output frequency [9][10].

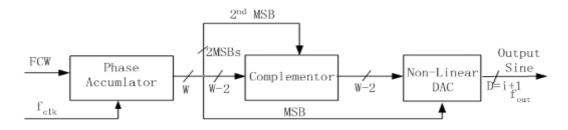

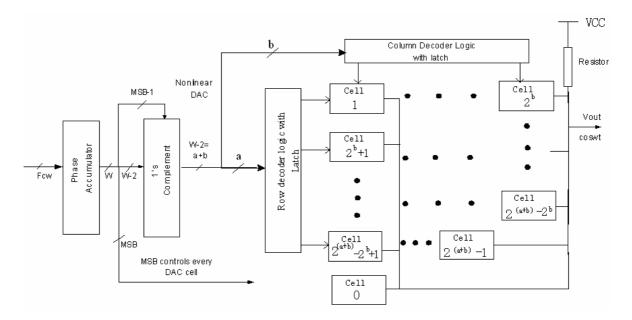

Figure 2-4 High-speed DDS with a nonlinear DAC.

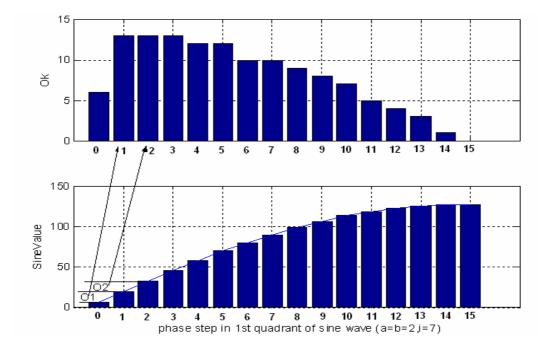

The function of a nonlinear DAC in DDS is to convert the linear phase information W at the output of the accumulator directly into analog sine waveform as shown in Figure 2-4. The truncated phase information W is divided into several parts. The first two MSBs are used to select different quadrants of the sine wave. The rest bits are segmented into a, b two parts. The whole phase  $0 \sim \pi/2$  in the first quadrant is divided equally into  $2^{(a+b)}$  phase steps. With the corresponding DAC bits D=i+1, each phase step corresponds to a DAC output magnitude. The difference of each phase step magnitude forms basic DAC cells and each cell's output value is  $O_K$  given as [11]

$$O_{k=} \begin{cases} \inf\left[ (2^{i}-1)\sin\frac{\pi(0.5)}{2(2^{a+b}-1)} \right] , \text{ for } k=0 \\ \inf\left[ (2^{i}-1)\sin\frac{\pi(k+0.5)}{2(2^{a+b}-1)} - \sum_{n=0}^{k-1} O_{n} \right], \text{ for } 1 \le k \le 2^{a+b}-1 \end{cases}$$

$$(2.4)$$

A switching matrix with row and column thermo-meter decoders is used to switch on and off each DAC cell according to the phase information *W*. The DAC output is the sum of all the DAC cells that the output of thermo-decoder turns on. As shown in Figure 2-5, the value of sine wave at phase step k is formed by summing the outputs form DAC cell<sub>0</sub> to DAC cell<sub>k</sub>.

Figure 2-5 First quadrant sine wave construction using nonlinear DAC cells.

The first the quadrant sine wave form thus can be reconstructed by switching on and off different DAC cells with different values. Same as the ROM storing the first quadrant sine value, the other quadrants of sine wave form can be built by flipping the phase and output waveforms as shown in Figure 2-3. The MSB output of the phase accumulator is used to provide the proper mirroring of the sine waveform at the  $\pi$  phase point. The second MSB is used to invert the remaining bits for the second and fourth quadrant of sine wave.

In next section, structure parameters of a DDS with nonlinear DAC such as the accumulator length L, nonlinear DAC's input phase word W, DAC's output resolution D are evaluated according to the tradeoffs between system performance and hardware implementation.

#### 2.4 **Optimization of DDS Structure Parameters**

DDS structure parameters directly impact its speed, area, power consumption and its output performance. Spurious free dynamic range (SFDR) is defined as the difference in decibels between the *root-mean-square* (*rms*) power of the fundamental and the largest spurious signal within a specified frequency band. SINAD is the difference in decibels between the rms power of the fundamental and the noise and distortion that falls within the Nyquist frequency.

There are several ways to improve these two targets. One is to increase the phase bit W to reduce spurs and Nonlinear DAC bit (D = i+1) to decrease the quantization noise effect. However, increase the W and D will also increase the complexity of the implementation. The other way is to add a delta-sigma modulator to shape the quantization noise and this will be discussed in next chapter. Higher order delta-sigma modulator has higher noise shaping effect of the quantization noise. But it also leads to bigger circuit implementation and may cause un-stability. So there is a tradeoff between the output performance and the complexity.

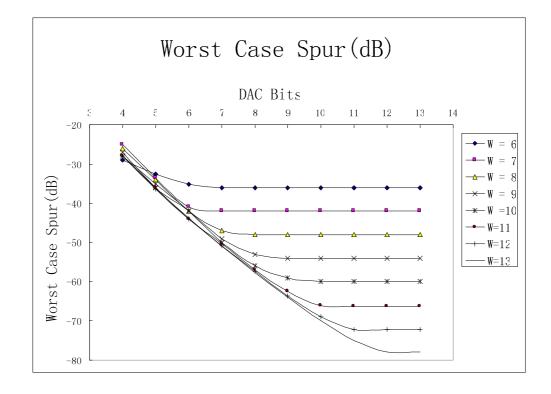

Different W and D combinations are compared in simulations to test the magnitude of the worst case spur and the result is shown in Figure 2-6. It plots the decibel difference

between the largest spurious (the worst case spur) and the fundamental signal versus the number of phase bits W and the number of nonlinear DAC output bits. It's shown that the worst-case spur decreases as the number of DAC bits or the number of phase bit W increase.

Figure 2-6 Worst case spur versus phase bit W and output bits D of nonlinear DAC.

From Figure 2-6 we can see that when the DAC bit D is bigger than the phase bit W, the Worst case spur is mainly determined by the DAC bit D and the phase bit W has little effect on it. When the phase bit W is bigger than DAC bit D, the increase of the phase bits W will decrease the worst spur.

When nonlinear DAC bit D and phase bit W are all bigger than 10, the worst case spur in dB with respect to carrier can be restricted below the -60dB.

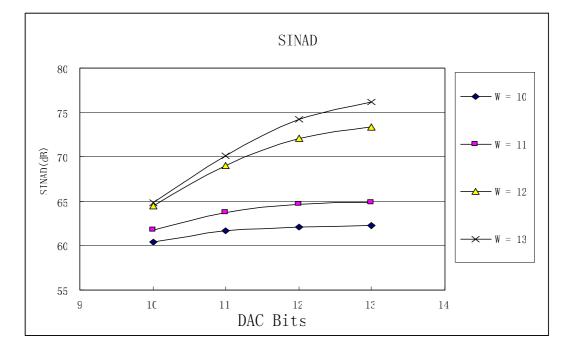

From the viewpoint of the implementation, it's needed to keep DAC output bits D

small for less power consuming. Besides, the total current output will double with one bit increase in D and this will bring to the headroom design problem of the circuit. SINAD is used to determine the DAC output bits D. The SINAD at the output with different nonlinear DAC bits D and phase bits W is shown in Figure 2-7. The band of interest is  $0.25 \cdot f_{clk}$ .

Figure 2-7 SINAD with different DAC bits D and phase bits W (BW=0.25·f<sub>clk</sub>).

SINAD increases with the increase of the DAC bits D and phase bits W. Normally, the number of phase bits W is chosen slightly larger than that of the DAC output bits such that the overall quantization noise is dominated by the number of DAC bits D.

According to the discussion of tradeoffs between SFDR, SNR and hardware implementation, the phase bits W is first determined by the in-band worst case spur requirement. Then the DAC output is determined using the SINAD within the band.

### 2.5 Experimental Structure Design and Results

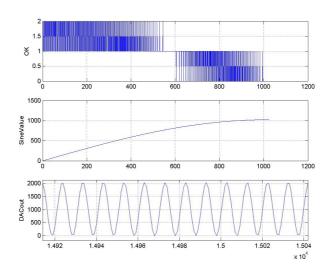

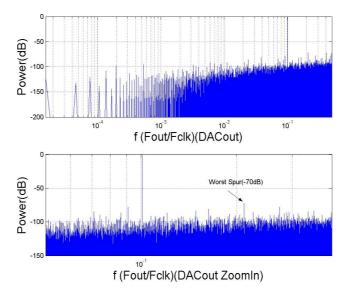

Figure 2-8 shows a design example with parameters L=16, W=12, D=11 of the nonlinear DAC. The basic DAC cells values, first quadrant waveform and whole time domain waveform is shown in Figure 2-8 (a)and the output spectrum is shown in Figure 2-8 (b)

(a) The output sine wave form (L=16, W=12, D=11)

Figure 2-8 Structure design of DDS with nonlinear DAC with L=16, W=12, D=11

In this design, the SINAD would be 68dB in a relative wide band-with which is  $0.25 \cdot f_{clk}$  and the worst case spur can reach -70dB.

# CHAPTER 3 DELTA-SIGMA MODULATION IN DIRECT DIGITAL SYNTHESIS

### 3.1 Introduction

Delta-sigma modulation has been used in high-performance ADC, DAC and fractional-N frequency synthesizer and begins to appear in the DDS recently [12][13]. Section 3.2 first reviews the basic concepts of delta-sigma modulator. Section 3.3 discusses its linear white noise model. Based on the linear model, formula deductions of delta-sigma modulation in both phase and frequency domain for DDS are presented. Section 3.4 presents comparisons of various delta-sigma modulations in DDS. Delta-sigma modulators such as MASH, feed-forward, feedback and error feedback have been implemented in both phase and frequency domains in a CMOS DDS. The DDS prototype is fabricated in a 0.35µm CMOS technology with core area of 1.7x2.1 mm<sup>2</sup> and total 75 mA current. Measured DDS output demonstrates that frequency domain delta-sigma modulation.

#### 3.2 Delta-Sigma Modulation Basics

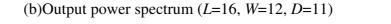

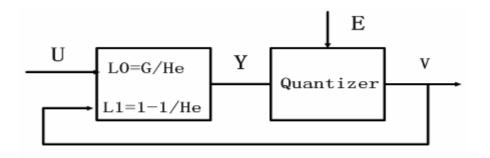

A common linear model of delta-sigma modulator is shown in figure 3-1 [14].

It consists of a quantizer and feedback loop. The system transfer function obtained from Figure 3-1 is given as follows

$$V(z)=G(z)U(z)+He(z)E(z)$$

(3.1)

Figure 3-1 Linear model of delta-sigma modulator.

In equation (3.1), U(z) is the input signal, V(z) is the output signal, E(z) is the quantization noise, H(z) is *Noise Transfer Function* (NTF), G(z) is *Signal Transfer Function* (STF). STF can pass the base-band signal from input to output directly. NTF is usually a high-pass filter (HPF), it can restrain the base-band noise and let the high frequency noise pass. In this way, the quantization error is shaped away for the band of interest. For an L<sup>th</sup> order MASH type, feedback, and error-feedback type delta-sigma modulator, their noise transfer function is given by

$$He(z) = (1 - Z^{-1})^{L}$$

(3.2)

Assuming the quantization error e[n] is an additive white noise, its power is evenly distributed through the whole bandwidth:

$$\sigma_{e}^{2} = \mathbb{E}[(e(n))^{2}] = \frac{1}{2\pi} \int_{-\pi}^{\pi} P_{e}(\omega) d\omega$$

(3.3)

Using transformation  $z=e^{j\omega}$  and  $\omega=2\pi f/f_s$ , the modulated quantization noise from the L<sub>th</sub> modulator is

$$P_{\rm L}(\omega) = (2\sin\frac{\omega}{2})^{2\rm L} \delta_{\rm e}^{2}$$

(3.4)

The sampling clock  $f_s$ , the baseband  $f_b$  and the frequency of the signal satisfy over-sampling condition, namely,  $f_s >> f_b \ge f$ :

$$P_{L}(f) = \frac{2P_{L}(\omega)}{f_{s}} = 2(\sin\frac{\pi f}{f_{s}})^{2L} \delta_{e}^{2} / f_{s} \approx 2^{2L+1} (\frac{\pi f}{f_{s}})^{2L} \delta_{e}^{2} / f_{s}$$

(3.5)

The total quantization noise in the band of interest  $[0, f_b]$  is:

$$\varepsilon_{\rm L}^{2} = \int_{0}^{f_{b}} P_{L}(f) df = \frac{\pi^{2L}}{2L+1} \, \delta_{\rm e}^{2} (\frac{2f_{b}}{f_{s}})^{2L+1} = \frac{\pi^{2L}}{2L+1} \, \delta_{\rm e}^{2} (\frac{1}{R})^{2L+1}$$

(3.6)

For an input sine wave form with power  $\sigma_x^2 = E^2/2$ , the signal to noise ratio (SNR) and dynamic range (DR) of L<sup>th</sup> order delta-sigma modulator are:

SNR<sub>L</sub>=

$$\sigma_x^2 / \varepsilon_L^2 = \frac{3 \cdot 2^{2n-1}}{\pi^{2L}} (2L+1) R^{2L+1}$$

(3.7)

$$DR_{L} = E^{2} / \varepsilon_{L}^{2} = \frac{3 \cdot 2^{2n}}{\pi^{2L}} (2L+1) R^{2L+1}$$

(3.8)

$$SNR(dB) = 10lg3 + 10(2n-1)lg2 + 10lg(2L+1) + 10(2L+1)lgR - 20Llg\pi$$

(3.9)

From above deductions, increasing the modulator order *L* can increase the in-band SNR. When the order L is fixed, doubling the over-sampling ratio *R* will increase the SNR a value of 3(2L+1).

If the quantizer inside the modulator is multi-bit (n>2), the SNR can be improved by 6dB with one more bit increase in quantizer.

In practice, the modulator's order L cannot be increased without limit for it would introduce instability and cause the modulator to oscillate. Usually, L is less than 3 to make sure the stability of the modulator.

#### 3.3 Linear Model of Delta-Sigma Modulator

The above deductions are based on the linear model of the delta-sigma modulator. The question remains that under what condition does the linear model of the delta-sigma modulator holds. The function of the quantizer inside a delta-sigma modulator is to

truncate its input into quantized signal which represent the input signal. The quantization process is an inherently non-linear operation and introduces errors to the conversion. In order to make the analysis tractable, the quantizer is often linearized by using an input-independent additive white noise model.

In this white noise model, a number of assumptions are traditionally made on the error process and its statistics. They follow:

1. The quantization error sequence e[n] is statistically independent of the input sequence.

2. The Probability Density Function (PDF) of e[n] is uniform over the range of half the bin width.

3. The random variables of the error process are uncorrelated.

If all the above assumptions hold, the linear model of delta-sigma modulator holds.

In order to get the delta-sigma modulator which is capable of complying with the signal-independent white noise assumption, the characteristics of the quantization error e[n] introduced inside the delta-sigma modulator is studied. Most of all, the input to the delta-sigma modulator is preferred to be DC so that math equations of the e[n] and its statistical performance can be derived.

On the other hand, MASH type delta-sigma modulator (Figure 3-2 [23]) is a widely used for its easy implementation and stability. A rigorous analysis of MASH delta-sigma modulators with DC input and initial values of each accumulator have been proposed in [15]. It mainly examines the statistics of the quantizer error sequences.

First of all, the quantization error from different stage is derived:

$$e_{l}[n] = \frac{1}{2} - \left\langle \frac{V_{l,0}}{2b} + \sum_{Kl=0}^{n-1} \left( \frac{V_{l-1,0}}{2b} + \dots + \sum_{K_{2}=0}^{K_{3}-1} \left( \frac{V_{l,0}}{2b} + \sum_{Kl=0}^{K_{2}-1} \beta \right) \right) \right\rangle$$

(3.10)

In (3.10), 1 represents MASH type modulator's order.  $\pm b$  is the output levels of the single-bit (or binary) quantizer.  $V_{i,0}(i=1\cdots l)$  are the initial values in each stage's accumulator.  $\beta$  is the normalized the DC input to the delta-sigma modulator.

Figure 3-2 MASH delta-sigma modulator with quantization noise e[n] at each stage. Assume  $e_l[n]$  is a stationary ergodic random process, its sample mean, average power and auto-correlation are evaluated below.

Sample mean:

$$M(\hat{x}) = \lim_{N \to \infty} \frac{1}{N} \sum_{n=0}^{N-1} \hat{x}[n]$$

(3.11)

Average power:

$$M\left(\hat{x}^2\right) = \lim_{N \to \infty} \frac{1}{N} \sum_{n=0}^{N-1} \hat{x}^2[n]$$

(3.12)

Auto-correlation:

$$r_{\hat{x}}(r) = \lim_{N \to \infty} \frac{1}{N} \sum_{n=0}^{N-1} \hat{x}[n] \hat{x}[n+r]$$

(3.13)

Let the  $V_{1,0}$  be an irrational number, the following results are important. [15]

(1) For modulator's order l > 2, the sample mean and average power of the binary quantizer error from the last stage are :

$$M(\varepsilon_i) = 0 \tag{3.14}$$

$$M(\varepsilon_l^{2}) = \frac{1}{12}$$

(3.15)

The autocorrelation is different from second order MASH with higher order MASH type modulators. For second order MASH type, the autocorrelation of the binary quantizer error from the second stage is found:

$$r_{\varepsilon^{2}}(r) = \begin{cases} \frac{1}{12}, r = 0\\ \frac{1}{2\pi^{2}\mu^{2}} \left(\frac{1}{4}(\gamma - \pi)^{2} - \frac{1}{12}\pi^{2}\right), r \neq 0 \end{cases}$$

(3.16)

(2) For third or higher order MASH type, the autocorrelation of the binary quantizer error from the last stage is found:

$$r_{\varepsilon l}(r) = \begin{cases} \frac{1}{12}, r = 0\\ 0, r \neq 0 \end{cases}$$

(3.17)

From all the math equations, a conclusion is drawn that an irrational initial condition imposed in the 1st accumulator guarantees a linear white noise model for a third or higher order MASH delta-sigma modulator. The real implementation for the irrational number is based on the fact that a rational number, which is represented by a ratio of two relatively prime integer numbers, will tend to an irrational number when the number in the denominator is made very large. Usually, it is desirable to utilize the minimum odd number "1" in the first accumulator as the initial seed. This is accomplished by setting "1" LSB in the first accumulator each time the circuit is reset [15].

(3) For second order MASH type delta-sigma modulator, the autocorrelation is not zero and the linear model does not hold. However, dithering can be added to the LSB of the first accumulator to dither the autocorrelation effect in (3.16) and thus to make its linear model hold.

We used a second order MASH type delta-sigma modulator to test initial seed and dithering effect. We set L=30, Fr=3. First initial values of all accumulators in the modulator are set to be zero and the autocorrelation of the second MASH type modulator's quantization error is shown in Figure 3-3.

(a) Normal autocorrelation of (b) With initial seed '1' added to (c) With dithering quantization error

the 1<sup>st</sup> accumulator

added to the LSB of 1<sup>st</sup> accumulator

Figure 3-3 Autocorrelation of second order MASH type modulator's quantization error.

First initial values of all accumulators in the modulator are set to be zero and the autocorrelation of the second order MASH type modulator's quantization error is shown in Figure 3-3 (a). Next an initial seed "1" is added to the first accumulator in the modulator and the result is shown in Figure 3-3 (b). There're some improvements in the quantization error autocorrelation in (b) but it's still not a white noise. So a 16-bit pseudo random series is added to dither the LSB of the 1<sup>st</sup> accumulator and the result is shown in (c). This is almost a white noise and the linear model of delta-sigma modulator holds. For higher order delta-sigma modulator, the results are even better.

In this section, a MASH type delta-sigma modulator with DC input is studied and the quantization errors for its quantizers are examined using the math autocorrelation to verify the effectiveness of linear model of delta-sigma modulator. Modulator with order higher than 3 satisfies the linear white noise model. Lower order modulator needs dithering to approach the linear model. The linear model of delta-sigma modulator is the basis of its use in DDS in next section.

#### 3.4 Delta-sigma Modulation in DDS

#### 3.4.1 Introduction

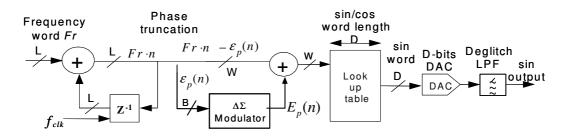

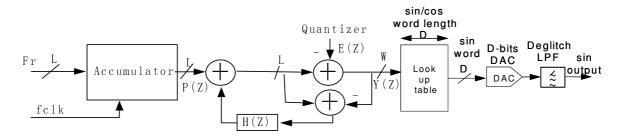

As illustrated in Figure 3-4, a conventional direct digital synthesizer (DDS) consists of a numerically controlled oscillator (NCO) and a digital-to-analog converter (DAC). The NCO further includes a phase accumulator and a lookup table that transforms digital phase information to digital amplitude information. The DDS output spectrum contains spurious components mainly due to phase word truncation before the ROM lookup table. The periodic truncated phase error sequence causes spurs in its output spectrum. Delta-sigma modulators have been implemented in both frequency [16] and phase [17] domains in DDS to reduce the spurs, their noise shaping effects and design tradeoffs have been compared [18]. In this section, we go details of comparison and implementation of eight different delta-sigma modulators including MASH, feed-forward, feedback and error feedback in both frequency and phase domains in a CMOS DDS chip. The noise shaping effects, in-band SFDR, SINAD, operation speeds, area and stability are compared according to measured results.

Figure 3-4 DDS with NCO and DAC.

## 3.4.2 Phase Domain Modulation

In an ideal DDS without phase truncation (L = W) and with infinite amplitude precision, the output sequence of the NCO is given by

$$S(n) = \sin\left(2\pi \frac{Fr}{2^L}n\right) \tag{3.18}$$

where  $F_r$  is the input frequency control word with *L* bits and *W* is the length of phase word to address the accumulator.

In order to reduce the ROM size, one can either truncate the phase accumulator output from *L* bits to *W* bits. With a phase word truncation, we define *B* to be the number of bits truncated such that L-W=B. The output of the DDS becomes

$$S_{t}(n) = \sin\left(2\pi \frac{2^{B}}{2^{L}} \left[\frac{Fr}{2^{B}}n\right]\right)$$

(3.19)

where the operator [] represents truncation to integer values. Equation (3.19) can alternatively be expressed as

$$S_{t}(n) = \sin\left(\frac{2\pi}{2^{L}} \left[Fr \cdot n - \varepsilon_{p}(n)\right]\right)$$

(3.20)

where  $\varepsilon_p(n)$  represents the phase error sequence. Applying trigonometric identities, Equation (3.20) can be rewritten as

$$S_{t}(n) = \sin\left(2\pi \frac{Fr \cdot n}{2^{L}}\right) \cos\left(2\pi \frac{\varepsilon_{p}(n)}{2^{L}}\right) - \cos\left(2\pi \frac{Fr \cdot n}{2^{L}}\right) \sin\left(2\pi \frac{\varepsilon_{p}(n)}{2^{L}}\right)$$

(3.21)

Assuming  $\mathcal{E}_p(n) \ll 2^L$ , we get

$$S_{t}(n) = \sin\left(2\pi \frac{Fr \cdot n}{2^{L}}\right) - 2\pi \frac{\varepsilon_{p}(n)}{2^{L}} \cdot \cos\left(2\pi \frac{Fr \cdot n}{2^{L}}\right)$$

(3.22)

Therefore, the output spectrum of the DDS is composed of a sine wave at the desired output frequency corrupted by the cosine modulated harmonics of the phase error  $\varepsilon_p(n)$ . The periodic sequence  $\varepsilon_p(n)$  can be expressed as Fourier series. Thus, the conventional DDS with phase truncation ends up with spurs at different places in its output spectrum.

Figure 3-5 Phase domain delta-sigma modulation in DDS.

In order to reduce spurs due to phase truncation, we apply delta-sigma modulation in phase domain. There are two ways of adding delta-sigma modulator in phase domain. One is shown in Figure 3-5. The phase word  $Fr \cdot n$  after the accumulator is truncated into  $Fr \cdot n -\varepsilon_p(n)(W \text{ bits})$  and  $\varepsilon_p(n)$  (*B* bits). The phase error  $\varepsilon_p(n)$  is fed into a delta-sigma modulator. The modulator's output  $E_p(n)$  is expressed as a single-bit or multi-bit word and added back to the truncated phase.

Using a linear model for delta-sigma modulators, we get

$$E_{p}(z) = \mathcal{E}_{p}(z) + Q(z)(1 - z^{-1})^{k} = \mathcal{E}_{p}(z) + Noise(z)$$

(3.23)

where Q(z) is the quantization noise from the quantizer inside the modulator and k is the order of the modulator. We can rewrite (3.23) as

$$E_p(n) = \mathcal{E}_p(n) + Noise(n)$$

(3.24)

where the modulated quantization noise, Noise(n), is the inverse Z-transform of  $Q(z)(1-z^{-1})^k$ .

The DDS output is thus given by

$$S_{t}(n) = \sin\left(\frac{2\pi}{2^{L}} \left[Fr \cdot n - \varepsilon_{p}(n) + Ep(n)\right]\right)$$

=  $\sin\left(\frac{2\pi}{2^{L}} \left(Fr \cdot n + Noise(n)\right)\right)$  (3.25)

Assuming  $Noise(n) \ll 2^{L}$ , we obtain

$$S_t(n) = \sin\left(2\pi \frac{Fr \cdot n}{2^L}\right) - 2\pi \frac{Noise(n)}{2^L} \cdot \cos\left(2\pi \frac{Fr \cdot n}{2^L}\right)$$

(3.26)

The second type of delta-sigma modulation in phase domain is phase error feedback as shown in Figure 3-6:

Figure 3-6 Error feedback modulator in phase domain.

From the linear model of error feedback delta-sigma modulator shown in Figure3-6, we can write the modulator's transfer function:

$$Y(z) = P(z) + (1 - H(z))E(z)$$

(3.27)

Error feedback delta-sigma modulator actually has a single bit quantizer and the output Y(z) represents the input P(z) added with the modulated quantization noise (1 - H(z))E(z). The order of the modulator can be changed with different transfer function H(z).

In DDS application, the input *L*-bit phase is truncated to *W*-bit. It is a single bit quantization except that the remaining is *W*-bit in word length.

Shown in Figure 3-6, the error feedback modulator's input is the phase information  $Fr \cdot n$  but not the phase error  $\varepsilon_p(n)$  as the case in the type phase domain modulation shown in figure 3-5.

The modulator's output is  $Fr \cdot n + Noise(n)$  where Noise(n) is the modulated quantization noise which has high frequency shaping effect. In this way we can get DDS's output S<sub>t</sub>(n) that is same as (3.25) and (3.26).

$$S_{t}(n) = \sin\left(\frac{2\pi}{2^{L}}(Fr \cdot n + Noise(n))\right)$$

$$= \sin\left(2\pi \frac{Fr \cdot n}{2^{L}}\right) - 2\pi \frac{Noise(n)}{2^{L}} \cdot \cos\left(2\pi \frac{Fr \cdot n}{2^{L}}\right)$$

(3.28)

In equation (3.28), the modulated quantization Noise(n) takes place of the original phase error  $\varepsilon_p(n)$ . Thus, spurs introduced by the phase truncation are reduced, and modulated quantization noise with high frequency shaping shows up in the spectrum. Delta-sigma modulators with different noise transfer functions thus lead to different DDS output spectra.

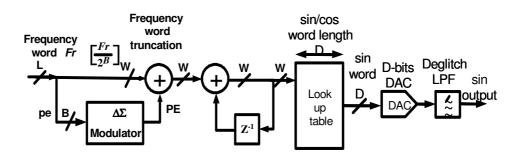

#### 3.4.3 Frequency Domain Modulation

Delta-sigma modulation can also be implemented in the frequency domain of a DDS. For frequency word truncation, the frequency word Fr is truncated from L bits to W bits before the phase accumulator. The discarded frequency bits B=L-W, and the output sequence of the DDS ROM become

$$S(n) = \sin\left(2\pi \frac{Fr}{2^{L}}n\right) = \sin\left(2\pi \frac{(Fr/2^{B})}{2^{W}} \cdot n\right)$$

$$= \sin\left(2^{1-W}\pi\left(\left[\frac{Fr}{2^{B}}\right] \cdot n + \left(Fr - \left[\frac{Fr}{2^{B}}\right] \cdot 2^{B}\right) \cdot n / (2^{B})\right)\right)$$

$$= \sin\left(2\pi\left(\left[\frac{Fr}{2^{B}}\right]n + pe \cdot n\right) / 2^{W}\right)$$

(3.29)

where the operator [] represents truncation to an integer and the frequency error due to frequency word truncation is

$$\left(\left(Fr - \left[\frac{Fr}{2^{B}}\right] \cdot 2^{B}\right) \middle/ 2^{B}\right) = pe$$

(3.30)

As shown in (3.29), the phase accumulator size can be reduced to *W* bits if the input frequency word *Fr* is truncated to  $[Fr/2^{B}]$ .

The frequency word truncation will also cause a phase error  $(pe \cdot n)$  which is periodic in nature and thus leads to spurs at the DDS output. If the input word  $Fr \le 2^B$ , then  $[Fr/2^B] = 0$ , there will be no DDS output due to frequency word truncation. However, to avoid losing frequency information, the constant frequency error *pe* needs to be modulated and added back to the accumulator.

Figure 3-7 Proposed DDS with frequency domain delta-sigma modulation.

As shown in Figure 3-7, the modulated frequency error pe is added back to the truncated Fr that is represented by  $[Fr/2^B]$ . Note that in Figure 3-7, the delta-sigma modulator's input pe is constant, which benefits the modulator design with improved stability, input range and speed. The noise shaped frequency error is thus a series of numbers and is given by

$$PE(z) = pe(z) + Q(z)(1 - z^{-3}) = pe(z) + Noise(z)$$

(3.31)

where Q(z) is the quantization noise introduced by the delta-sigma modulator.

With the frequency domain delta-sigma modulation, the DDS output is given by

$$S_{t}(n) = \sin 2\pi \left( \left[ \frac{Fr}{2^{B}} \right] n + PE(n) \cdot n \right) / 2^{W}$$

$$= \sin 2\pi \left( \left[ \frac{Fr}{2^{B}} \right] n + pe \cdot n + Noise(n) \cdot n \right) / 2^{W}$$

$$\approx \sin \left( 2\pi \frac{Fr \cdot n}{2^{L}} \right) - \cos \left( 2\pi \frac{Fr \cdot n}{2^{L}} \right) \cdot \left( 2\pi \frac{Noise(n) \cdot n}{2^{W}} \right)$$

(3.32)

Thus, the DDS output spectrum is composed of a sine wave at the desired output frequency and a cosine wave that is modulated by the quantization noise shaped by the delta-sigma modulator. Based on the linear model of a delta-sigma modulator, the periodic phase error due to frequency word truncation is reduced. Instead, the modulated quantization noise from the modulator occurs at the DDS output.

## 3.4.4 Comparison of Measured NCO Output Spectra for Various Delta-sigma Modulators

Although various delta-sigma modulators in both the phase domain and frequency domain can move the spurs and quantization noise to a high frequency band, their performances on noise shaping are different. To compare various delta-sigma modulator performances, we consider factors such as the modulator topology, the order of the modulator, the modulator input, the in-band spurious tones, the number of quantizer bits, the modulator speed and area, etc. We first implemented an NCO with several types of delta-sigma modulators in both frequency and phase domain in FPGA as shown in Figure 3-8. The NCO output is captured into a PC for analysis. First we analyze the output characteristics such as the spurious-free-dynamic-range (SFDR), defined as the ratio between the fundamental signal and the highest spurs and the signal-to-noise-and-distortion ratio (SINAD) shown in (3.33).

$$SINAD = 20 \cdot \log\left(\frac{Signal}{SUM (Noise + Harmonics)}\right)$$

(3.33)

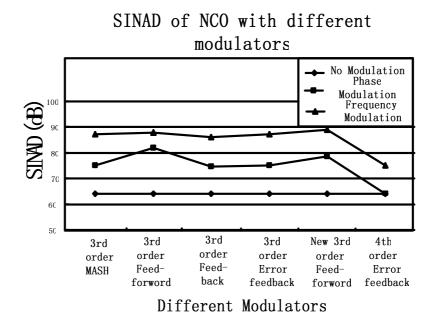

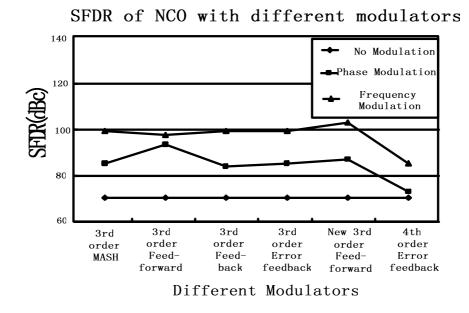

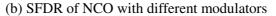

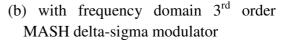

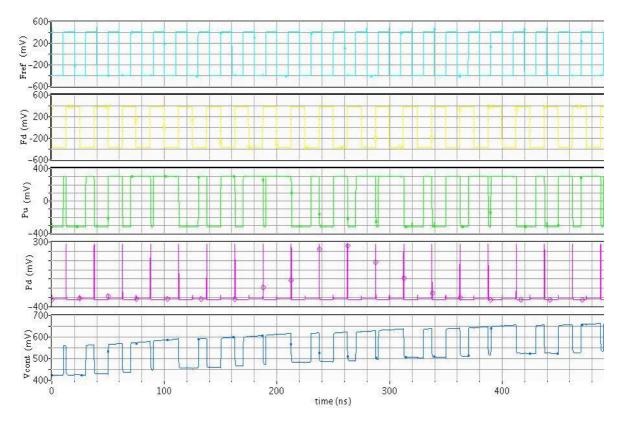

The oversampling ratio (OSR) of the delta-sigma modulator is chosen as 64 and the band of interest is from zero to 1/64 of the clock frequency. The measured in-band SINAD and SFDR of the NCO output with various delta-sigma modulators are given in Figure 3-9. The measurements show that without delta-sigma modulation, direct phase truncation has a low SFDR and SINAD. With delta-sigma modulation, in-band SFDR and SINAD increase. In phase domain modulation, the phase error pe (*L*-*W* bits LSBs) has different repeating periods with respect to different Fr, which leads to a varying the input to the modulator. In contrast, frequency domain modulators have constant dc input.

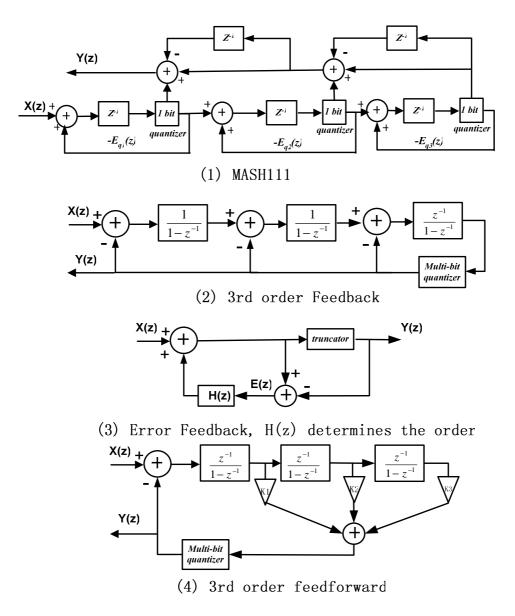

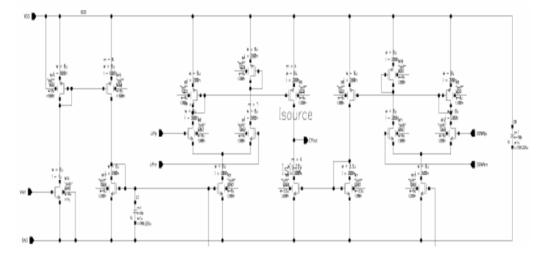

Figure 3-8 Four types delta-sigma modulators implemented in a DDS and NCO for comparison.

As a result, the frequency domain delta-sigma modulation has higher SFDR and SINAD than phase domain. Although using a high-order delta-sigma modulator results in sharper noise shaping effect, it suffers from degraded SFDR and SINAD.

(a) SINAD of NCO with different modulators

Figure 3-9 Measured in-band SINAD and SFDR of the NCO output with various delta-sigma modulators in frequency and phase domains.

Since the modulated quantization noise dominates the DDS output spectrum, its noise transfer function He(Z) can greatly affect the DDS output. We implemented four types of delta-sigma modulators, i.e., MASH, feedforward, feedback and error feedback as shown

in Figure 3-8. MASH, feedback and error feedback type delta-sigma modulators have the same noise transfer function of  $He(Z)=(1-Z^{-1})^k$ , where k is the order of the modulator. MASH-111 has three 1-bit quantizers, while the feedback type modulator has a multi-bit quantizer and the error feedback delta-sigma modulator has one single-bit quantizer. A feedforward type delta-sigma modulator is first presented in the frequency domain in [16]. It's a second order feedforward type with a multi-bit quantizer. The modulator's order can be increased by adding more accumulators in cascade and different noise transfer functions can be obtained by varying the feedforward coefficients  $k_1$ ,  $k_2$ ,  $k_3$ . We propose a *feedforward2* delta-sigma modulator with coefficients of  $k_1 = 2.5$ ,  $k_2 = 2.5$ ,  $k_3 = 1$ .

Figure 3-10 compares the noise transfer function of MASH, *feedforward1* [19], and the proposed *feedforward2* modulator. It's clear that MASH has much sharper noise shaping effect in-band. But it has high out-of-band noise that requires a high-order LPF for noise rejection. The *feedforward2* modulator has lower in-band noise compared with existing *feedforward1* modulator and has flat out-of-band noise compared with MASH type.

Figure 3-10 simulated noise transfer function of MASH and feedforward delta-sigma modulators.

Figure 3-11 gives the measured NCO output spectrum for two types of delta-sigma modulators. The measured spectra of the two delta-sigma modulators are almost identical with the modulated noise. Multi-bit quantizer inside the modulator can make feedback signal match input signal more accurately and make the quantization noise more random, which better fits the liner model for delta-sigma modulators.

Although feedforward modulator can increase in-band SINAD by a few dB, it has drawback of instability. In contrast, a MASH type modulator is good for its high speed, sharp slope and full input dynamic range, and it is always stable. The drawback of a MASH modulator lies on its fixed number of output bits. The error feedback has the same noise transfer function as that of MASH except for its lower speed. However, error feedback modulator can flexibly choose the number of output bits. Feedback modulator also has the same noise transfer function as MASH and it also has an advantage of a multi-bit quantizer, but it has stability problem.

(a) NCO output spectrum with 3<sup>rd</sup> order MASH type delta-sigma modulation in frequency domain(1-bit quantizer)

(b) NCO output spectrum with frequency domain 3<sup>rd</sup> order *feedforward2* delta-sigma modulation (multi-bit quantizer)

Figure 3-11 Comparison of measured NCO output spectrum with different noise shaping effects.

The proposed *feedforward2* delta-sigma modulator is good in both in-band and out-of-band performances, but its implementation requires more hardware and its speed is lower.

# 3.4.5 Implementation of DDS with Various Delta-sigma Modulators in 0.35µm CMOS Technology

To compare the DDS performance with various delta-sigma modulations, we designed delta-sigma modulators including MASH1-1-1, 3<sup>rd</sup> order feedforward, feedback and error feedback delta-sigma modulators and error feedback delta-sigma modulator as shown in Figure 3-8 in both frequency and phase domains. Different delta-sigma modulators can be selected individually while other delta-sigma modulators are turned off.

The proposed DDS with frequency domain and phase domain delta-sigma modulator was implemented in 0.35 $\mu$ m CMOS technology with two poly and four metal layers. A 16-bit accumulator is designed, and 8 phase bits are used for addressing the look-up ROM. The 12-bit current steering DAC is integrated to convert the ROM output to an analog signal. For 12-bit amplitude resolution in a conventional DDS without a delta-sigma modulator, at least 12 phase bits should be used, which requires a look-up ROM with 2<sup>12</sup>x12 bits. The use of a delta-sigma noise shaper effectively reduces the required number of phase bits. Thus, we use only 8 phase bits to address the ROM, which reduces the ROM size by a factor of 2<sup>4</sup> or 16 times compared to that of a conventional DDS without a delta-sigma modulator.

Figure 3-12 Die photo of the CMOS DDS prototype chip with various delta-sigma modulators in frequency and phase domain.

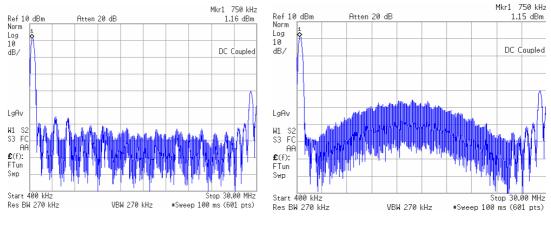

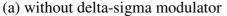

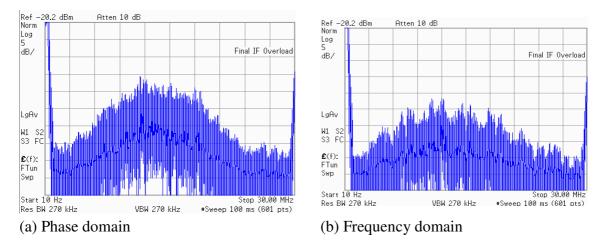

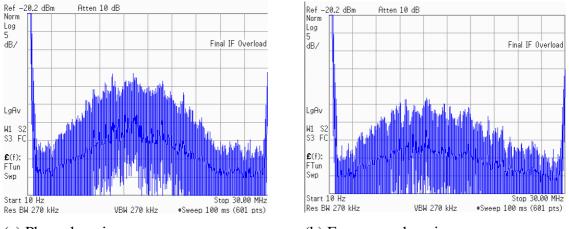

The die photo of the fabricated CMOS delta-sigma DDS prototype chip is shown in Figure 3-12. The total die area is  $2x2.5mm^2$ , in which the DDS active core area is  $1.7 x 2.1mm^2$  including the DAC, and the rest of the die area is used for pads and ESD diodes. The 16-bit phase accumulator and ten delta-sigma modulators occupy  $0.7x2.1mm^2$  die area. The  $2^8x12$ -bit ROM occupies only  $0.1x0.8mm^2$ , which would be 16 times larger without the delta-sigma noise shaper. In a conventional DDS, the ROM normally takes the majority of the die area, whereas the ROM takes only a small portion of the total area in this DDS implementation, which clearly demonstrates the advantage of using delta-sigma noise shaping in DDS designs. The measured DDS output spectra with and without delta-sigma modulators are shown in Figure 3-13(a). It's clear that the in-band spurs shown in figure 3-13(b).

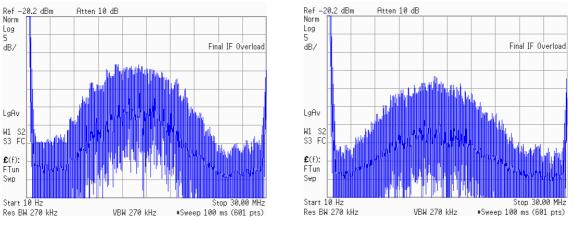

Figure 3-13 Comparison of the measured output spectra for (a) conventional DDS without delta-sigma modulation and (b) proposed DDS with frequency domain delta-sigma modulation,  $f_0=750$ KHz,  $F_{clk}=30$ MHz.

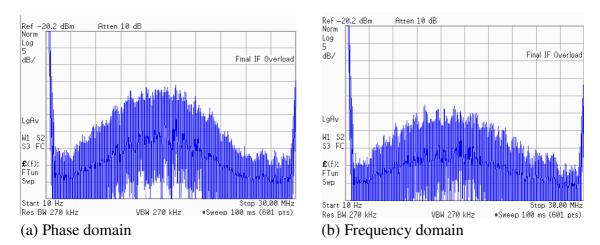

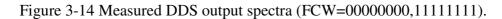

We have implemented various delta-sigma modulators in both frequency and phase domains in a CMOS DDS chip. The measured data demonstrates that frequency domain modulations have better SFDR and SINAD than their phase domain counterparts. Measurements results of output spectrum with different delta-sigma modulators either in frequency domain and phase domain are shown in Figure 3-14 ~Figure 3-18. For clear comparison , they all have a same frequency control word FCW=00000000,11111111. We have also compare factors such as input range, quantizer bits, speed and stability for different type of delta-sigma modulators (Table 3-1).

| Frequency<br>domain                  | High freq<br>noise | No. of<br>output<br>bits | In-band<br>SFDR<br>(dBc) | In-band<br>SINAD<br>(dB) | Stability            | Area<br>(mm <sup>2</sup> ) | Speed<br>(MHz) |

|--------------------------------------|--------------------|--------------------------|--------------------------|--------------------------|----------------------|----------------------------|----------------|

| 3 <sup>rd</sup> order<br>MASH 111    | poor               | 3                        | 99.5                     | 87.23                    | ABSOLUTELY<br>STABLE | 0.112                      | 180            |

| 3 <sup>rd</sup> order<br>Feedback    | fair               | ≥3                       | 99.4                     | 86.11                    | FAIR                 | 0.126                      | 140            |

| 3 <sup>rd</sup> order<br>Feedforward | good               | ≥3                       | 103                      | 89.03                    | POOR                 | 0.161                      | 150            |

| 3 <sup>rd</sup> order EF             | poor               | ≥3                       | 99.5                     | 87.23                    | GOOD                 | 0.147                      | 140            |

| 4 <sup>th</sup> order EF             | poor               | ≥4                       | 85.4                     | 75.15                    | GOOD                 | 0.148                      | 160            |

| Phase<br>domain                      |                    |                          |                          |                          |                      |                            |                |

| 3 <sup>rd</sup> order<br>MASH 111    | poor               | 3                        | 85.4                     | 75.15                    | ABSOLUTELY<br>STABLE | 0.112                      | 180            |

| 3 <sup>rd</sup> order<br>Feedback    | fair               | ≥3                       | 84                       | 74.57                    | FAIR                 | 0.126                      | 140            |

| 3 <sup>rd</sup> order<br>Feedforward | good               | ≥3                       | 87                       | 78.59                    | POOR                 | 0.161                      | 150            |

| 3 <sup>rd</sup> order EF             | fair               | ≥3                       | 85.4                     | 75.15                    | GOOD                 | 0.147                      | 140            |

| 4 <sup>th</sup> order EF             | poor               | ≥4                       | 73                       | 64.10                    | GOOD                 | 0.148                      | 160            |

Table 3-1 Performance comparison of delta-sigma modulators in frequency and phase domains of DDS. (In-band SFDR and SINAD are measured from NCO)

## 3.4.6 Conclusions

Mash 1-1-1 delta-sigma modulator in frequency domain provides a good noise shaping means for DDS application with optimal speed, stability and input dynamic range. Feed-forward delta-sigma modulator can provide both good in-band noise shaping and flat high frequency performance. Error-feedback takes advantage in its flexible output bit numbers.

(a) Without modulation

(b) Third order feedforward type delta-sigma modulation in phase domain

Figure 3-15 Measured DDS output spectra with third order MASH type delta-sigma modulation.

Figure 3-16 Measured DDS output spectra with third order feedback type delta-sigma modulation.

(a) Phase domain

(b) Frequency domain

Figure 3-17 Measured DDS output spectra with third order error feedback type delta-sigma modulation.

(a) Phase domain

(b) Frequency domain

Figure 3-18 Measured DDS output spectra with fourth order error feedback type delta-sigma modulation.

#### **CHAPTER 4 HIGH SPEED DDS DESIGN**

## 4.1 Introduction

This chapter discusses the RF circuit design of high speed DDS basic building blocks such as current mode logics, pipelined and carry look-ahead phase accumulators, delta-sigma modulator and a nonlinear DAC that have been discussed in previous chapters. SiGe BiCMOS technology is adopted for its high speed and low noise performance.

## 4.2.SiGe BiCMOS

In contrast to conventional Si bipolar transistors, SiGe bipolar transistor [20] is formed by adding some germanium to its base. The SiGe compound in base has a narrower band-gap compared to the pure silicon one. The relatively large band gap in the emitter can be used to increase the potential barrier to holes that can be injected from the base back to the emitter. Therefore, the emitter doping is can be decreased which leads to the increase of the base-emitter width and hence to reduce the  $C_{je}$ . Meantime, the base doping can be increased which lead to reduction of base width and base-collector depletion region. All these changes bring to higher operating frequency  $f_T$ , higher gain, increased early voltage VA and lower base resistance  $r_b$  which are needed for RF circuit design.

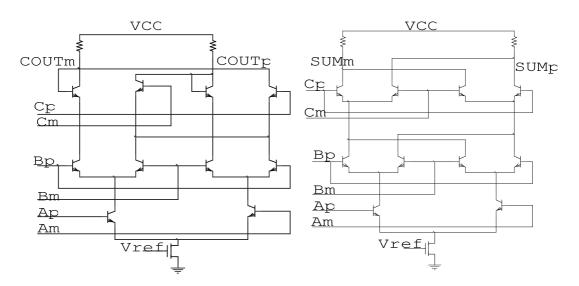

### 4.3 CML Digital Blocks

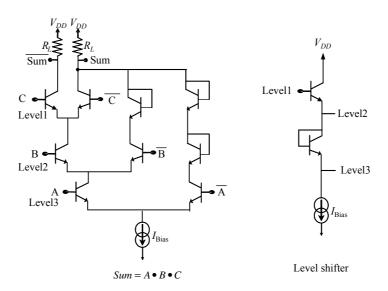

Current mode logic (CML) has been employed in the high-speed digital systems for it very fast switching property. The circuit topology is composed of several single current switch pairs which are tied together either in series or parallel with a common current source at the bottom. A current switch pair consists of two bipolar transistors with common emitter connected together. The digital signal in CML circuits is differential and switches on and off each current switch pair at one time. The current is flowing through only one branch from power (VDD) to ground. Figure 4-1 shows a four level 3-input 'AND' circuit. One of the two resistors pulls down the output voltage from VDD to VDD-I<sub>Bias</sub>R<sub>L</sub> when bias current flowing through it. The output differential swing is thus 2I<sub>Bias</sub>R<sub>L</sub> which many range from 100mv~400mv [21]. So the resistance of R<sub>L</sub> mainly depends on the swing requirement when the bias current is determined.

Figure 4-1 A four-level AND CML logic.

The four-level CML logic (with one current source level) has up to 3 different inputs levels and 3~4 current branches to realize complex combinational logic with less hardware

and power compared to ECL logics. The input level voltage of A, B, C under a 3.3V supply is 1.3V, 2.2V and 3.1V so as to make sure the transistors not work in saturation mode. Additional transistors are connected as diode to let each current branch have same voltage drop at each input level. It is necessary for high speed SiGe bipolar transistor has a relatively low  $BV_{CEO}$ . A level shifter made of emitter follower buffer to shift down the output voltage level 1 to level2 or level3 to the next stage CML logics.

CML circuit's speed is mainly determined by its propagation delay which is contributed by the base-emitter capacitance, the Miller effect on the intrinsic base-collector capacitance, the inner collector node parasitic such as the collector-substrate capacitance  $C_s$  and parasitic resistance  $r_c$  and of course the load capacitance  $C_L$  and resistance  $R_L$  at the output node. SiGe technology has taken its advantages in reducing the parasitics such as  $r_b$ ,  $C_{je}$  and so to  $C_{\pi}$  and high current gain. Transistor's unity current gain-bandwidth product  $f_T$  is the frequency at which the short-circuit current gain  $\beta$  is equal to 1.

$$f_{T} = \frac{g_{m}}{2\pi(c_{\pi} + c_{\mu})}$$

(4.1)

In order to achieve maximum speed, it's a good decision to make the bias current as large as possible by setting it to peak  $f_T$ . Next, simulations are made to get tradeoff between power consumption and the minimum propagation delay of the CML circuits. For each 3-input AND circuit with minimum transistor size in 0.18um and 0.12um, the bias current is biased at near 70% to its peak  $f_T$ . With the same AND circuit as load, the propagation delays is 10ps and 5ps.

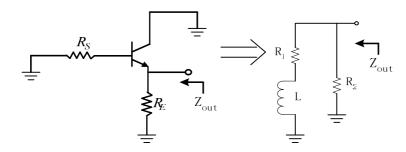

When the emitter follower stage inside the level shifter is running at very high speed,

its output impedance would increase with increasing frequency and appear to be inductive

[22].

Figure 4-2 Output resistance of emitter follower at high bias and high frequency.

For the quite large DC biasing condition:  $\frac{1}{gm} < R_s + r_b$

The output impedance can be approximated by the equivalent circuit of Figure 4-2, where:

$$R_1 = \frac{1}{gm} + \frac{Rs + r_b}{\beta_0} \tag{4.2}$$

$$R_2 = R_s + r_b \tag{4.3}$$

$$L = \frac{1}{\omega_T} (R_s + r_b) \tag{4.4}$$

Because there are inductive components in the output resistance, when the level shifter is to drive the next stage with quite large capacitive load, it may cause peaking or instability in the overall circuit response as shown in Figure 4-3.

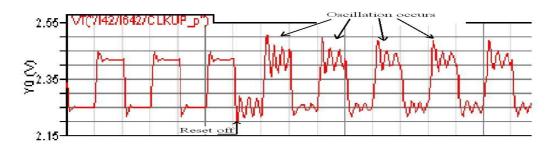

Figure 4-3 Oscillation caused by emitter followers inductive output.

The edge of the clock signal starts to oscillate when the reset is turn off and circuit begins to work. That's one reason normally the transistor with minimum size used. Meantime, we need to shrink the load capacitance as small as possible and thus try not let level shifter drive too much loads.

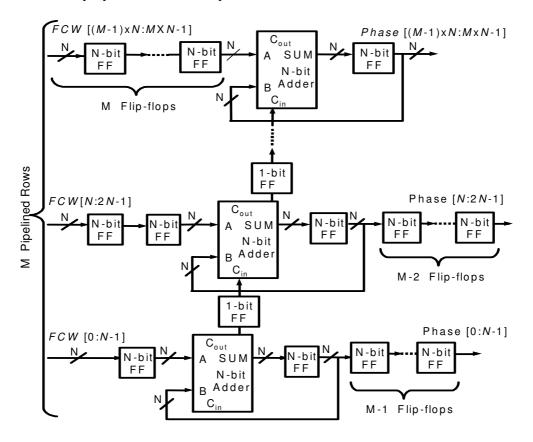

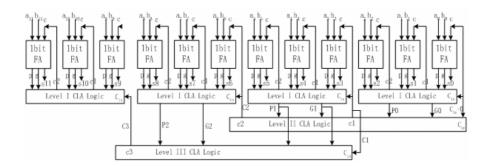

## 4.4 Pipeline and Carry Look-Ahead Accumulators

Accumulator is a major block in the DDS. Phase accumulator in DDS adds up a frequency control word FCW at each clock cycle and generates a phase word of a sine wave at the output. Therefore, accumulator output 0 refers phase 0 and output  $2^{L}$ -1 refers  $2\pi$ . The accumulator's size L determines the final output frequency resolution. The output frequency resolution doubles with one bit increase in accumulator's length. As discussed in Chapter 2, the phase bits L is truncated to W bits before it goes to ROM or nonlinear DAC and this combined with FCW also determines the spurious spurs. With DAC output bits D, the truncated phase bits W which is connected to ROM determined the quantization noise floor. As a rule of thumb in practical applications, the number bits at the ROM input W should be bigger than or equal to D+2.