# ENERGY AWARE TASK SCHEDULING ON HETEROGENEOUS SYSTEMS

| Except where reference is made to the work of others, the work described in this     |

|--------------------------------------------------------------------------------------|

| dissertation is my own or was done in collaboration with my advisory committee. This |

| dissertation does not include proprietary or classified information.                 |

|                                                                             | Rabab Farouk Abdo | el-Kader                                                                                       |

|-----------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------|

| Certificate of Approval:                                                    |                   |                                                                                                |

| Cheryl Seals Assistant Professor Computer Science and Software Engineering  |                   | Sanjeev Baskiyar, Chair<br>Associate Professor<br>Computer Science<br>and Software Engineering |

| Levent Yilmaz Assistant Professor Computer Science and Software Engineering |                   | George T. Flowers<br>Interim Dean<br>Graduate School                                           |

# ENERGY AWARE TASK SCHEDULING ON HETEROGENEOUS SYSTEMS

Rabab F. Abdel-Kader

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama December 17, 2007

# ENERGY AWARE TASK SCHEDULING ON HETEROGENEOUS SYSTEMS

| Rahah F | A hdo | Vadar    |

|---------|-------|----------|

| Kanan F | A DOE | I-K XAET |

| Permission is granted to Auburn University to make copies of this dissertation and its   |

|------------------------------------------------------------------------------------------|

| discretion, upon request of individuals or institutions and at their expense. The author |

| reserves all publication rights.                                                         |

| Signature of Author |  |

|---------------------|--|

|                     |  |

|                     |  |

| Date of Graduation  |  |

#### DISSERTATION ABSTRACT

#### ENERGY AWARE TASK SCHEDULING ON HETEROGENEOUS SYSTEMS

Rabab F. Abdel-Kader

Doctor of Philosophy December 17, 2007 (M.S. Tuskegee University 2002) (B.S. Suez Canal University, 1998)

128 Typed Pages

Directed by Sanjeev Baskiyar

We consider the problem of scheduling directed a-cyclic task graphs (DAG) on heterogeneous distributed processor systems with the twin objectives of minimizing finish time and energy consumption. Previous scheduling heuristics have assigned DAGs to processors to minimize overall run-time of applications. But due to many new applications on embedded systems such as high performance DSP in image processing, multimedia, and wireless security, there is a strong need for scheduling algorithms which lower energy consumption and yet attain good finish times.

In this research, we employ dynamic voltage scaling (DVS) within the scheduling heuristics to achieve the twin objectives. The processors used can run on different discrete operating voltages. Processors can scale down their voltages to slow down in

iv

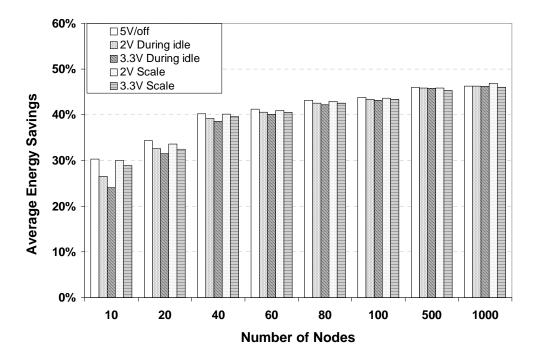

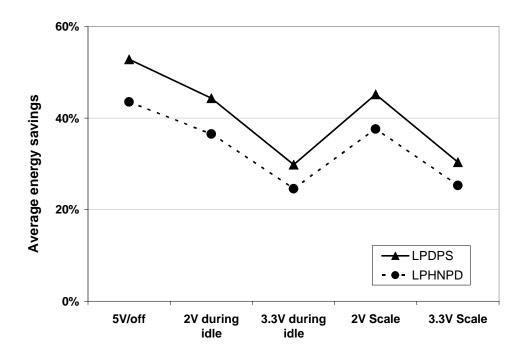

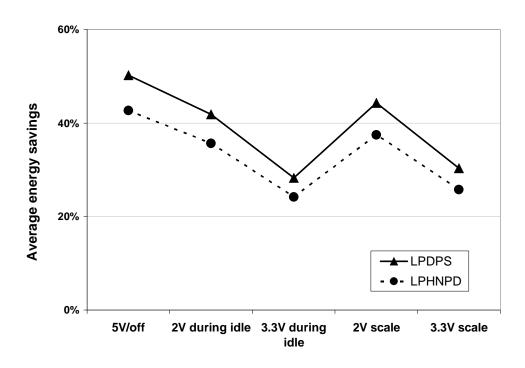

order to reduce energy consumption whenever they idle due to task dependencies. Specifically, we combine Decisive Path Scheduling (DPS) and Heterogeneous N-predecessor Duplication (HNPD) with DVS. Using simulations, we show average energy consumption reductions of 40% over DPS and 28% over HNPD.

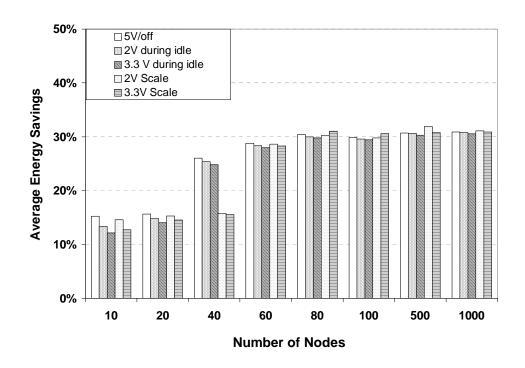

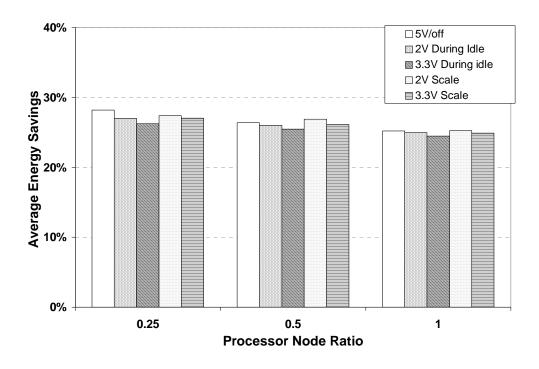

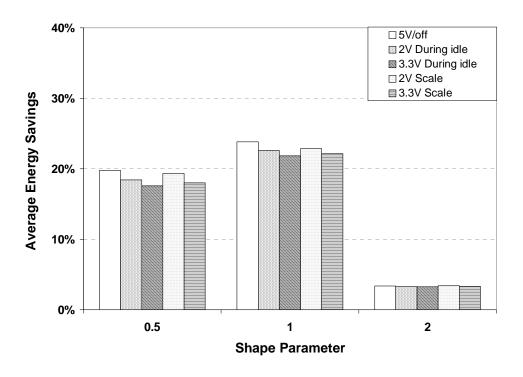

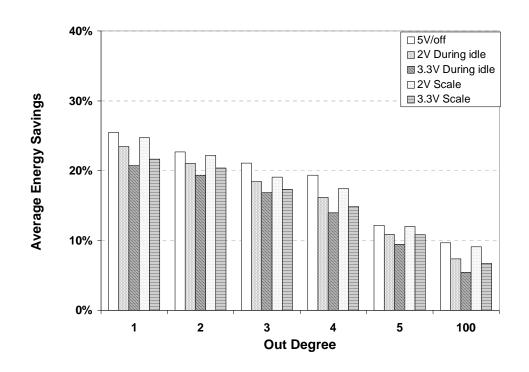

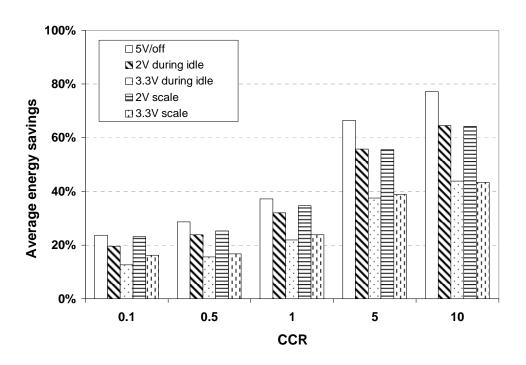

The simulations used large number of randomly generated DAGs with various characteristics as well as DAGs of real world problems. Energy savings increased with increasing number of nodes or increasing Communication to Computation Ratios (CCR) whereas it decreased with increasing parallelism (out-degree) or increasing number of available processors. Increasing nodes, increase tasks dependencies and thus idle times. When CCR increases, processors are idle longer due to communication between tasks. Our algorithms used such idle times to achieve energy savings. An increase in out-degree resulted in smaller average energy savings. A larger out-degree allows more processors to run in parallel, reducing idle times.

Style manual: IEEE Standard

Software used: Microsoft Word 2007, Microsoft Excel 2007, Microsoft Visual Studio

2003,and C++

# TABLE OF CONTENTS

| LIST OF FIGURES                                 | ix   |

|-------------------------------------------------|------|

| LIST OF TABLES                                  | xiii |

| 1. INTRODUCTION                                 | 1    |

| 1.1 Contributions                               | 3    |

| 2. RELATED WORKS                                | 5    |

| 2.1 Power Estimation Techniques                 | 6    |

| 2.2 Power Optimization Techniques               | 8    |

| 2.3 Software power optimization on system level | 9    |

| 2.4 Scheduling to lower energy consumption      | 10   |

| 3. DYNAMIC VOLTAGE SCALING                      | 15   |

| 3.1 Power Management Implementation             | 19   |

| 4. DIRECTED A-CYCLIC GRAPH                      | 21   |

| 4.1 Performance                                 | 24   |

| 5. SCHEDULING ALGORITHMS                        | 28   |

| 5.1 EADAGS algorithm                            | 28   |

| 5.2 EAGS-D algorithm                            | 37   |

| 5.3 Voltage scaling strategies                  | 46   |

| 6. RESULTS AND DISCUSSION           | 51  |

|-------------------------------------|-----|

| 6.1 Results for random DAGs         | 51  |

| 6.1.1 Results for EADAGS            | 52  |

| 6.1.2 Results for EAGS-D            | 60  |

| 6.2 Results for real world problems | 68  |

| 6.2.1 Gaussian elimination          | 68  |

| 6.2.2 Molecular dynamic code        | 79  |

| 6.2.3 Fast Fourier transforms       | 88  |

| 6.2.4 Sieve of Eratosthenes         | 98  |

| 7. CONCLUSIONS                      | 108 |

| BIBLIOGRAPHY                        | 110 |

# LIST OF FIGURES

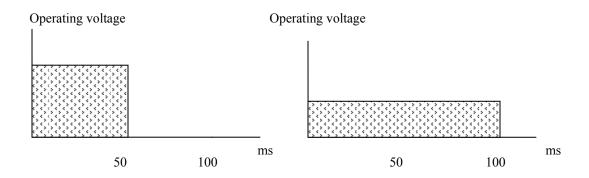

| 3.1. Different operating rates for the same task           | 17 |

|------------------------------------------------------------|----|

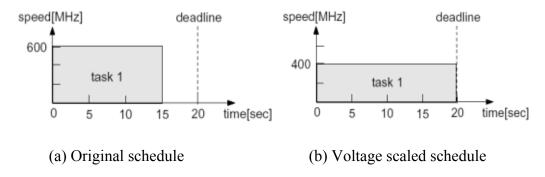

| 3.2. Voltage Scaling graph                                 | 19 |

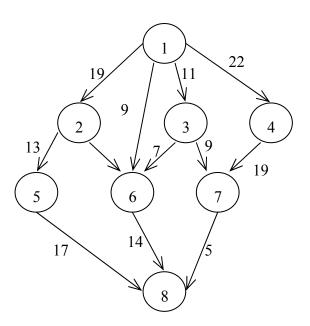

| 4.1. A sample DAG                                          | 21 |

| 5.1. EADAGS algorithm                                      | 36 |

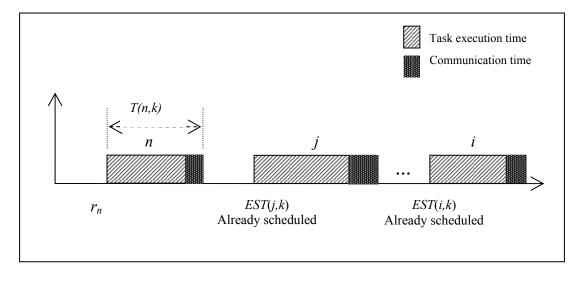

| 5.2. Timeline for machine k                                | 36 |

| 5.3. EAGS-D algorithm                                      | 45 |

| 5.4. Timeline for machine k (case 1)                       | 45 |

| 5.5. Timeline for machine k (case 2)                       | 46 |

| 5.6. Timeline for machine k (case 3)                       | 46 |

| 5.7. Different finish times with different execution rates | 49 |

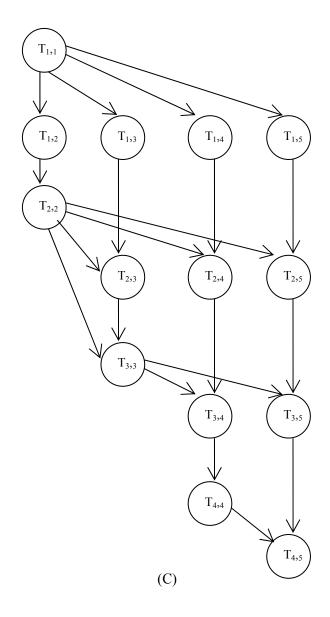

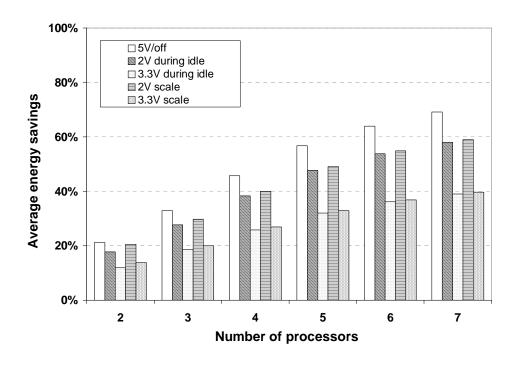

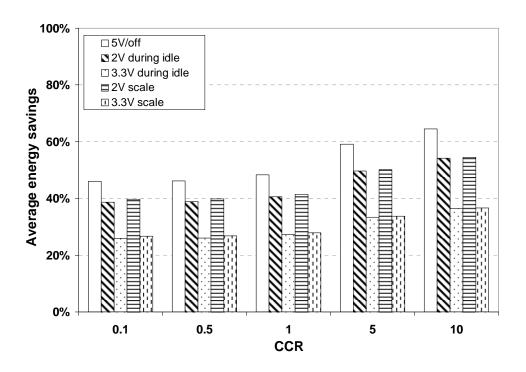

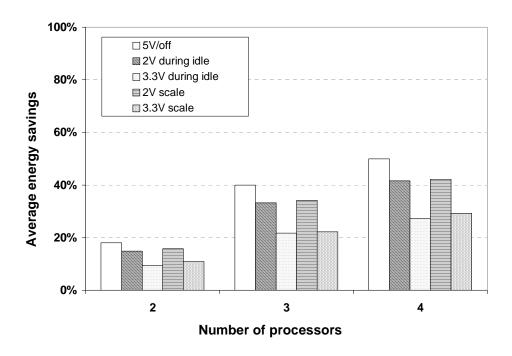

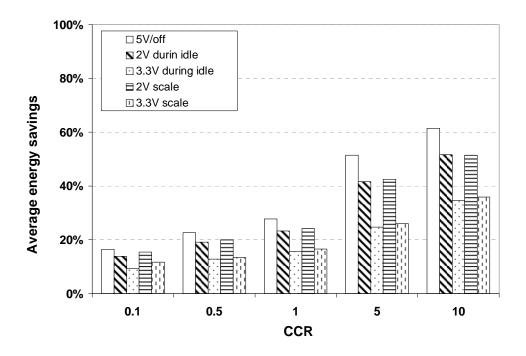

| 6.1. Average power savings with respect to number of nodes | 53 |

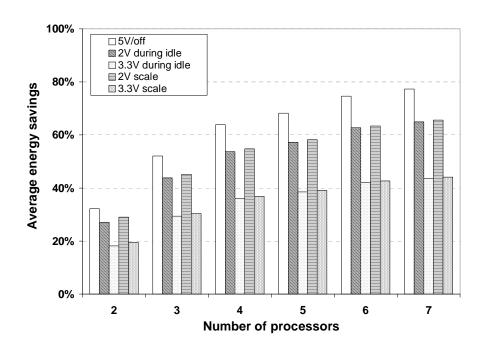

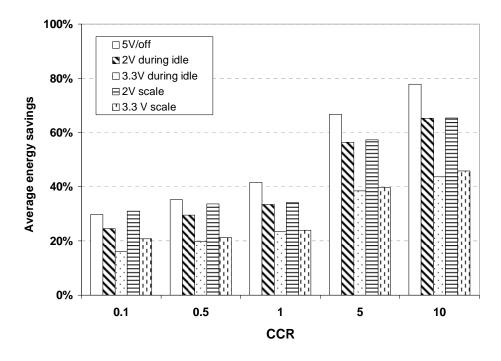

| 6.2. Average power savings with respect of CCR             | 55 |

| 6.3. Average power savings with respect to PNR             | 56 |

| 6.4. Average power savings with respect to shape parameter | 57 |

| 6.5. Average power savings with respect to out-degree      | 59 |

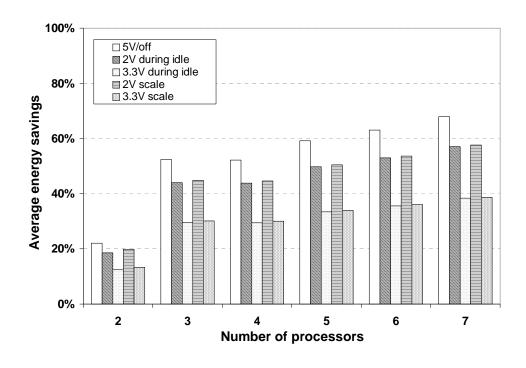

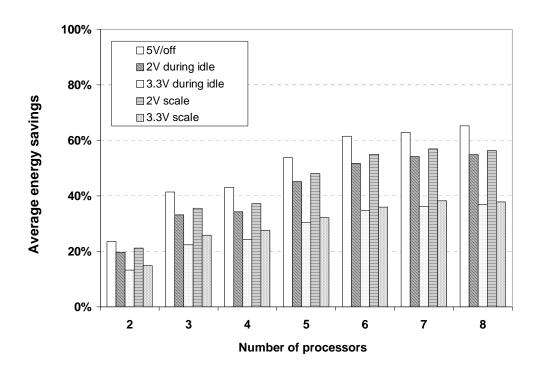

| 6.6. Average power savings with respect to number of nodes | 61 |

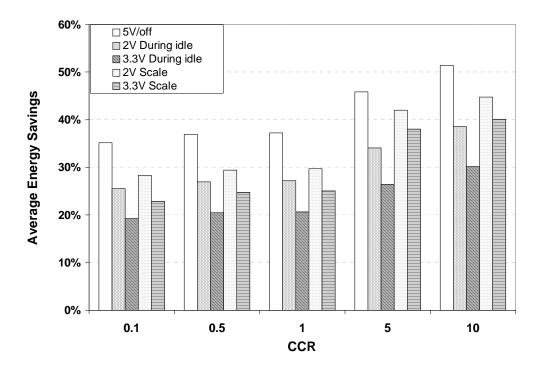

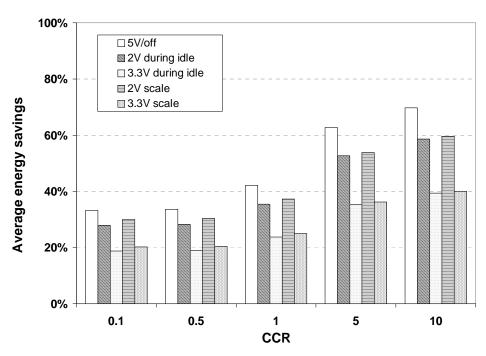

| 6.7. Average power savings with respect of CCR             | 63 |

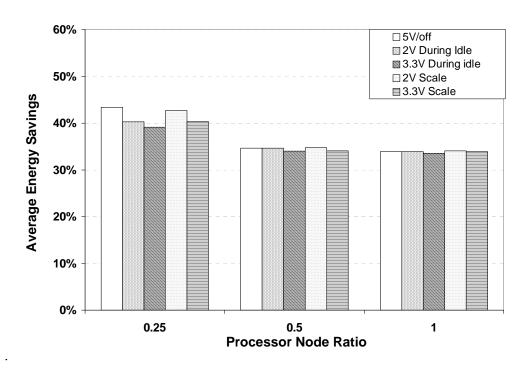

| 6.8. Average power savings with respect to PNR64                                 |

|----------------------------------------------------------------------------------|

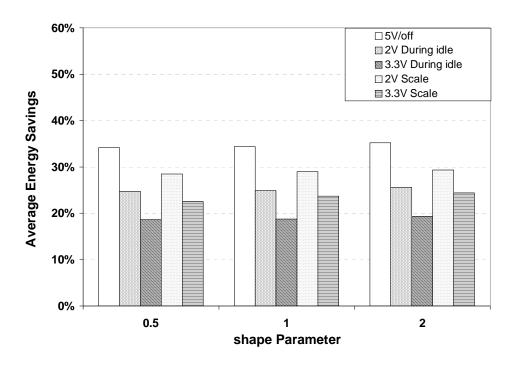

| 6.9. Average power savings with respect to shape parameter                       |

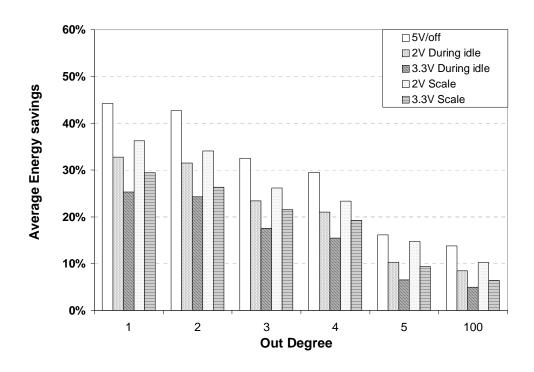

| 6.10. Average power savings with respect to out-degree                           |

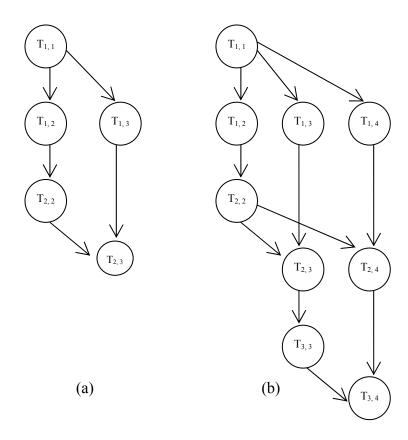

| 5.11. Gaussian elimination task graph71                                          |

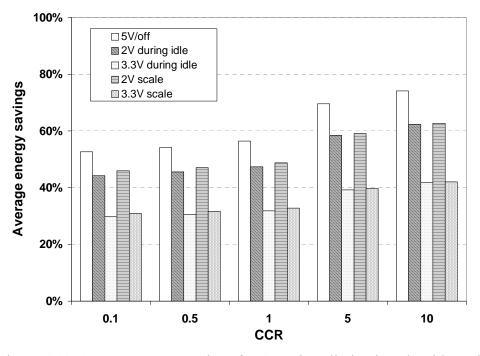

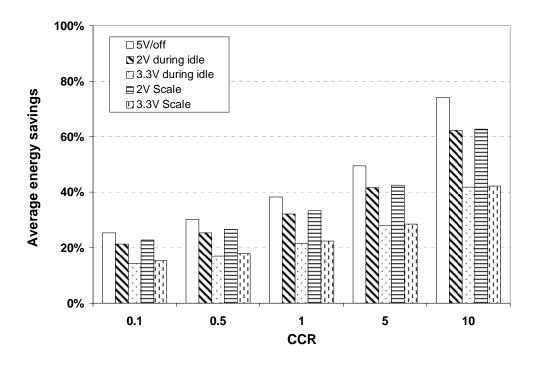

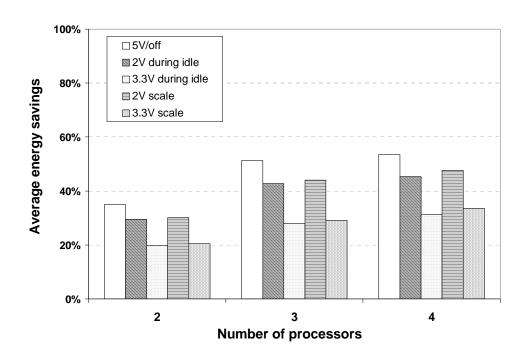

| 6.12. Average power savings for Gaussian elimination algorithm with EADAGS with  |

| different number of processors                                                   |

| 6.13. Average power savings for Gaussian elimination algorithm with EADAGS with  |

| different CCR values                                                             |

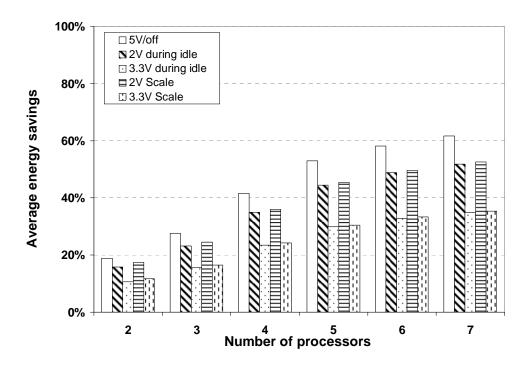

| 5.14. Average power savings for Gaussian elimination algorithm with EAGS-D with  |

| different number of processors                                                   |

| 5.15. Average power savings for Gaussian elimination algorithm with EAGS-D with  |

| different CCR values                                                             |

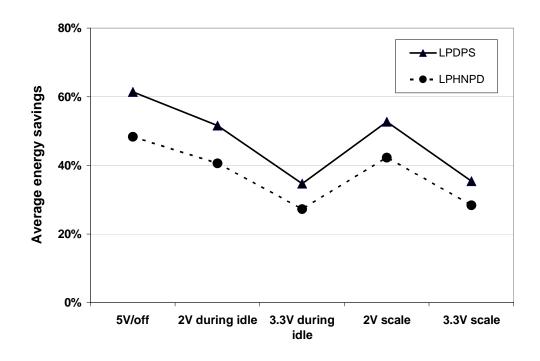

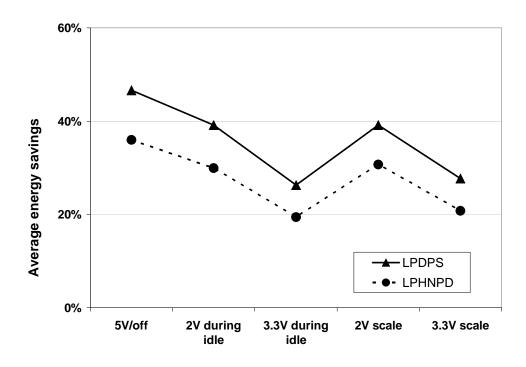

| 5.16. Average power savings for Gaussian elimination algorithm with EADAGS and   |

| EAGS-D with voltage scaling levels                                               |

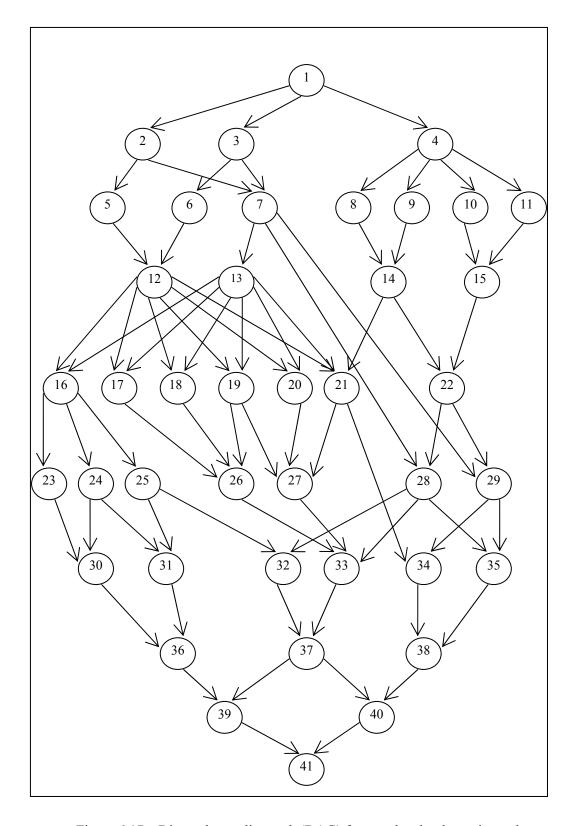

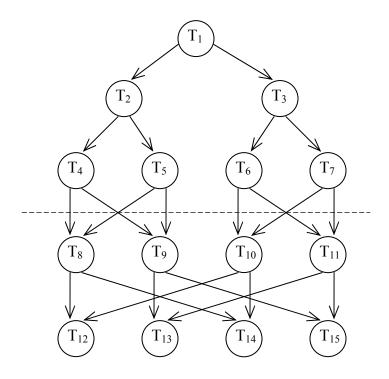

| 5.17. Directed Acyclic graph (DAG) for a molecular dynamics code                 |

| 5.18. Average power savings for molecular dynamic code with EADAGS with differen |

| number of processors82                                                           |

| 5.19. Average power savings for molecular dynamic code with EADAGS with differen |

| CCR values82                                                                     |

| 5.20. Average power savings for molecular dynamic code with EAGS-D with differen |

| number of processors8                                                            |

| 6.21. Average power savings for molecular dynamic code with EAGS-D with different        |

|------------------------------------------------------------------------------------------|

| CCR values86                                                                             |

| 6.22. Average power savings for molecular dynamic code algorithm with EADAGS and         |

| EAGS-D with voltage scaling levels                                                       |

| 6.23. The generated DAG for FFT with four points90                                       |

| 6.24. Average power savings for FFT with EADAGS with different number of processors92    |

| 6.25. Average power savings for FFT with EADAGS with different CCR values93              |

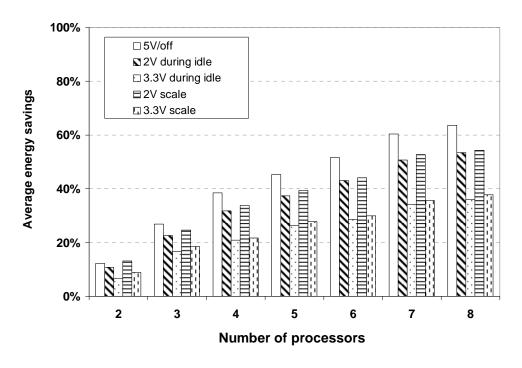

| 6.26. Average power savings for FFT with EAGS-D with different number of processor       |

| 95                                                                                       |

| 6.27. Average power savings for FFT with EAGS-D with different CCR values96              |

| 6.28. Average power savings for FFT with EADAGS and EAGS-D with voltage scaling          |

| levels                                                                                   |

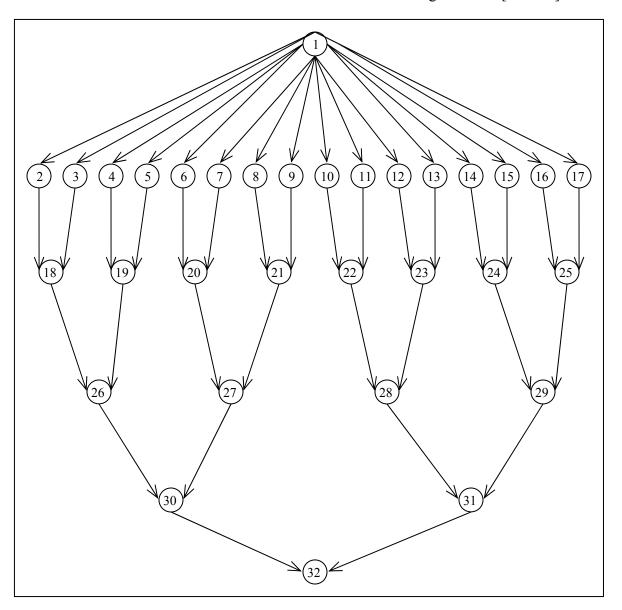

| 6.29. Sieve of Eratosthenes task graph for $N=32$                                        |

| 6.30. Average power savings for different number of processors for Sieve of Eratosthenes |

| with EADAGS101                                                                           |

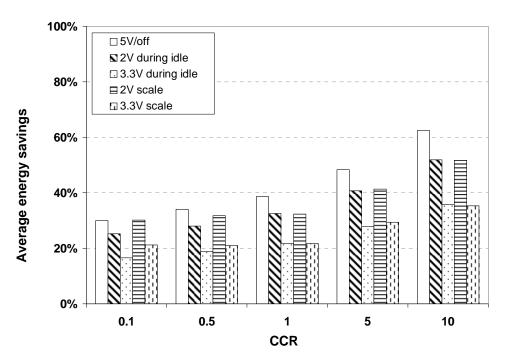

| 6.31. Average power savings for different CCR values for Sieve of Eratosthenes with      |

| EADAGS                                                                                   |

| 6.32. Average power savings for Sieve of Eratosthenes with EAGS-D with different         |

| number of processors                                                                     |

| 6.33. Average power savings for Sieve of Eratosthenes with EAGS-D with different CCR     |

| values105                                                                                |

| 6.34. | Average    | power  | savings | for Sie | ve of I | Eratosthe | nes wi | h EAD | AGS | and | EAGS-I | D with |

|-------|------------|--------|---------|---------|---------|-----------|--------|-------|-----|-----|--------|--------|

| volta | ge scaling | levels |         |         |         |           |        |       |     |     |        | 107    |

# LIST OF TABLES

| 3.1. The relationship between clock frequencies, supply voltage, and power dissipation of |

|-------------------------------------------------------------------------------------------|

| Transmeta's Crusoe TM5400 microprocessor                                                  |

| 5.1. EADAGS algorithm                                                                     |

| 5.2. EAGS-D algorithm40                                                                   |

| 6.1 Makespan and average power savings with respect to number of nodes for EADAGS         |

| 54                                                                                        |

| 6.2. Makespan and average power savings for different CCR values for EADAGS55             |

| 6.3. Makespan and average power savings for different shape parameter for EADAGS .58      |

| 6.4. Makespan and average power savings with respect to out-degree for EADAGS59           |

| 6.5. Makespan and average power savings with respect to number of nodes for EAGS-D        |

| 61                                                                                        |

| 6.6. Makespan and average power savings for different CCR values for EAGS-D63             |

| 6.7. Makespan and average power savings for different shape parameters for EAGS-D .66     |

| 6.8. Makespan and average power savings with respect the out-degree for EAGS-D67          |

| 6.9. Gaussian elimination algorithm69                                                     |

| 6.10. Makespan and average power savings for different number of processors for           |

| Gaussian elimination with EADAGS74                                                        |

| 6.11. Makespan and average power savings with respect to CCR for Gaussian elimination |

|---------------------------------------------------------------------------------------|

| with EADAGS75                                                                         |

| 6.12. Makespan and average power savings for different number of processors for       |

| Gaussian elimination with EAGS-D77                                                    |

| 6.13. Makespan and average power savings with respect to CCR for Gaussian elimination |

| with EAGS-D78                                                                         |

| 6.14. Makespan and average power savings for different number of processors for       |

| molecular dynamic code with EADAGS82                                                  |

| 6.15. Makespan and average power savings with respect to CCR for molecular dynamic    |

| code with EADAGS84                                                                    |

| 6.16. Makespan and average power savings for different number of processors for       |

| molecular dynamic code with EAGS-D85                                                  |

| 6.17. Makespan and average power savings with respect to CCR for molecular dynamic    |

| code with EAGS-D                                                                      |

| 6.18. Makespan and average power savings with respect to number of processors for FFT |

| with EADAGS92                                                                         |

| 6.19. Makespan and average power savings with respect to CCR for FFT with EADAGS .    |

| 94                                                                                    |

| 6.20. Makespan and average power savings for different number of processors for FFT   |

| with EAGS-D96                                                                         |

| 6.21. Makespan and average power savings with respect to CCR for FFT with EAGS-D.     |

| 97                                                                                    |

| 6.22. Makespan and average power savings for different number of processors for Siev | ve |

|--------------------------------------------------------------------------------------|----|

| of Eratosthenes with EADAGS10                                                        | )1 |

| 6.23. Makespan and average power savings for different CCR values for Sieve          | of |

| Eratosthenes with EADAGS10                                                           | )3 |

| 6.24. Makespan and average power savings for different number of processors for Siev | ve |

| of Eratosthenes with EAGS-D10                                                        | )4 |

| 6.25. Makespan and average power savings for different CCR values for Sieve          | of |

| Eratosthenes with EAGS-D10                                                           | )6 |

#### **CHAPTER 1**

#### INTRODUCTION

We consider scheduling on heterogeneous distributed computing systems interconnected by high-speed networks. Such systems are promising for fast processing of computationally intensive applications with diverse computation needs.

One of the challenges in heterogeneous computing is to develop scheduling algorithms that assign the tasks of applications to processors [Reut97]. Therefore, researchers have proposed many static, dynamic and even hybrid algorithms to minimize execution time of applications running on a heterogeneous system [Iver98][Kwok99] [Radu00][Seig97][Topc99][Wang97]. Another challenge facing distributed computing is energy consumption [Dong01]

There are many applications which require both low finish time and low energy consumption. Energy consumption is a major issue in many real-time distributed embedded systems. Furthermore, most applications running on an energy limited system inherently constrain the finish time. Low-cost, low-energy sensor networks composed of Smart Dust Mote [Smar06] are examples of such systems. New wireless communication systems are expected to evolve using this system. These networks are distributed networks operating on energy constraints, also called energy-aware distributed systems

(PADS). Hence there is a need for scheduling algorithms which would effectively reduce the overall energy consumed and yet attain the best possible finish time.

We consider the problem of scheduling a directed a-cyclic task graph (DAG) on a heterogeneous distributed processor system with the twin objectives of minimizing finish time and energy consumption. The DAG structure is important as it occurs in many regular and irregular applications in forms of Cholesky factorization, LU decomposition, Gaussian elimination, FFT, Laplace transforms, and instruction level parallelism. Such low energy schedules can help run such applications in multi-hop sensor radio networks.

Traditionally, priority has been on performance, and consequently the supply voltage has been set at the maximum allowable level based on device breakdown potentials to enable fast operation. However, applications may not require the maximum achievable speed at all times. The top energy consumers in a computer system [Kump94] are display (68%), disk (20%), and CPU (12%). There seems little which can be done to minimize screen energy-consumption, beyond employing a screen-saver and relying on hardware improvements. Disk energy consumption is minimized by spinning down the disk when it has been inactive.

However, in the future, we may well see ubiquitous computing devices with neither disks nor conventional displays. For such devices, minimizing the energy consumed by the CPU will be critical if the replacements of disks and displays consume relatively smaller fractions of total energy.

A study by Argonne National Laboratory has indicated that a 2.5 petaflop supercomputer, made of over a hundred thousand CPUs, will be available by 2010. The

study predicts that such a system will cost \$16 million and would require 8 mega watts of energy to operate at a cost of about \$8 million per year. Hence, high energy prices and rising concerns about the environmental impact of electronics systems highlight the importance of incorporating low energy design schemes at all levels of such systems. Current microprocessors from AMD, Intel and Transmeta allow the speed of the microprocessor to be set dynamically.

Another study by NASA in 1998 predicted energy need of 25 megawatts for Japan's NEC earth simulator, which is capable of executing 40 Tflops. That amount increased to 100 megawatts in a more recent study that much energy is enough to light 1.6 million 60-watts light bulbs, the lighting requirements of a small city.

Reducing systems components energy and energy consumption decrease systems expenses. Assuming a rate of \$100 per megawatt a Pflops machine consuming 100 megawatts of energy would cost \$10,000 per hour approximate \$85 million dollar a year.

These estimates do not include air cooling expenses which are commonly 40% of systems operating cost. For such systems even small reduction in overall energy consumption would significantly impact Pflops systems' operational costs.

#### 1.1 Contributions

In this dissertation we presented two scheduling algorithms for scheduling Directed Acyclic Graphs on a distributed computing system for low energy.

The first proposed algorithm combines Decisive Path Scheduling (DPS) with dynamic voltage scaling for the twin objectives of low energy consumption and minimum execution time. We call it Energy Aware DAG Scheduling (EADAGS). The second algorism proposed combines Heterogeneous N-predecessor Duplication (HNPD) with dynamic voltage scaling to minimize both finish time and consumed energy, we identify that algorithm as Energy Aware Graph Scheduling with Duplication (EAGS-D).

In both cases first the initial algorithm is completed using either DPS or HNPD for minimum finish time, then the amount of consumed energy is estimated and the voltage scaling algorithm is simulated to minimize the consumed energy without affecting the finish time.

The remainder of this dissertation is organized as follows. In the next Chapter, we describe different types of scheduling on both homogenous and heterogeneous systems, energy estimation and energy optimization techniques, and prior work on scheduling for low energy are discussed. Chapter 3 explains the concept of dynamic voltage scaling and how it can be used to reduce the consumed energy in computing systems. Chapter 4 defines DAG and explains some of the definitions and terminology used by the scheduling algorithms. Chapter 5 introduces both scheduling algorithms presented in this work EADAGS and EAGS-D. Chapter 6 is for the simulation and analysis of results. Finally the conclusion and suggestions for future work are presented in Chapter 7.

#### **CHAPTER 2**

#### RELATED WORK

Traditional scheduling algorithms did not consider the amount of energy consumption. Instead, they focus on performance or fairness. Recently, low energy system design has gained significant attention largely due to demands from the portable electronics industry. System design for low energy is also very important for other industries such as automotive, telecommunications, information technology, etc. This is due to the fact that low energy designs can offer significant reduction in system packaging costs and improvement in reliability.

Two main design aspects of scheduling are how to build the scheduling queue and how to choose the optimal processor. List and cluster scheduling are primary techniques to schedule tasks on heterogeneous systems.

In list scheduling, tasks are ordered in a scheduling queue based on the priority assigned to free tasks. List scheduling algorithms have been shown to have good cost-performance trade-offs.

Cluster scheduling involves merging nodes/paths to form clusters that can be scheduled on the same processor so as to get closer to the objectives of schedule length, number of processors, etc.

Several algorithms for static scheduling on heterogeneous multiprocessors systems are available: Dynamic Level Scheduling (DLS), Generalized Dynamic Level Scheduling (GDLS), Best Imaginary Level (BIL), Mapping Heuristics (MH), Heterogonous Earliest Finish Time (HEFT), Task Duplication Scheduling (TDS), Static Task Duplication Scheduling (STDS), Fast Critical Path (FCP), and Fast Load Balancing (FLB). Among the above TDS and STDS employ task duplication to suppress communication whereas others do not. A brief description of these algorithms is available in [Topc02].

Heterogeneous N-predecessors Decisive Path (HNPD) is based on DPS but with Task duplication. The performance of HNPD was proven to outperform two of the best existing heuristics, Heterogeneous Earliest Finish Time (HEFT) and Static Task Duplication Scheduling (STDS), in terms of finish time and the number of processors employed over a wide range of parameters.

Low energy scheduling research can be classified in two major categories

- 1. Energy estimation techniques (energy model)

- 2. Energy optimization techniques.

# **2.1 Power Estimation Techniques**

Existing energy estimation methodologies can be classified based on their level of abstraction, namely instruction level, architecture level, and gate level.

• Instruction level: application for this can be for embedded processing systems as presented by Nikoladis in [Niko02]. He uses an assembly or machine level

program as input and gives an estimate of the energy consumed for that specific program on a specific processing system. This provided an accurate estimation of energy consumption even in the presence of instantaneous energy supply variation.

- Architecture level: it provides cycle-by-cycle energy consumption data of the architecture on the basis of the instruction/data flow stream. At the architecture level a technique presented by Landman uses the black box energy model for the architecture level components to estimate the energy consumed while preserving the accuracy of the gate or circuit level estimation [Land94].

- Gate level: Ishehara summarized and compared different techniques for energy estimation and proved that gate level estimation of energy consumption is the most accurate measurement [Ishe96]. The techniques for energy estimation at the gate level and low levels of abstraction can be classified into

- o Simulation based techniques: the earliest techniques proposed suggested monitoring both the supply voltage and current waveforms. These techniques were to slow to handle very large circuits so other techniques were introduced assuming that the supply and ground voltages are constant and estimate only the supply current waveform.

- o Probabilistic techniques: most of the probabilistic techniques are

applicable to combinational circuits only. In these techniques user supplied input signal probabilities are propagated into the circuit. To achieve this, special models for the components have to be developed and stored in a module library.

Statistical techniques: they do not require any specialized model for the components. The idea is to simulate the circuit with randomly generated input vectors until energy converges to the average energy. The convergence is tested by statistical mean estimation techniques.

## 2.2 Power Optimization Techniques

Competition is driving the requirement for energy optimization. Systems are designed with low energy consumption as one of the important criteria. Energy optimization can be achieved through both hardware and software.

## • Hardware Optimization:

- o Behavior level: transformations, scheduling, resource allocation, etc.

- o Architecture level: low energy flip-flops, low energy adder, etc.

- o Circuit level: low energy circuits.

# • Software Optimization

Instruction level: low energy compiling, low energy instruction scheduling.  System level: Dynamic energy management, low energy memory management, etc.

## 2.3 Software energy optimization on system level

There are two techniques that can reduce energy consumption on system level scheduling: Dynamic Energy Management (DPM) and Dynamic Voltage Scaling (DVS).

The DPM technique dynamically reconfigures an electronic system by reducing number of active components and/or load on such components while providing services. DPM is used in various forms usually in portable devices. However, the complexity of interfacing heterogeneous components has limited designers to simple solutions in DPM. An example of a simple policy, mostly applied to laptops and PDA, is a timeout policy, which turns off a component after a fixed inactivity period, under the assumption that it is highly likely that a component remains idle if it has been idle for the timeout period.

The fundamental premise for the applicability of DPM is that systems (and their components) experience non-uniform workloads during operation time. Such an assumption is valid for most systems, both when considered in isolation and when systems are connected via internet. A second assumption of DPM is that it is possible to predict, with a certain degree of confidence, the fluctuations of workload. The analytical process of prediction should not consume significant energy. Typically, a energy manager (PM) implements a control procedure based on some observations and/or assumptions on the workload.

In DVS technique, computation and communication tasks are run at reduced voltages and clock frequencies which fill idle periods but reduce energy dissipation

while providing required performance. The key idea of DVS is to dynamically scale the supply voltage of CPU while meeting total computation time and/or throughput. It is a trade-off between processor speed and energy consumption which is especially useful in real-time systems. The energy consumption of a processor running at high speed and high voltage is much larger than running at low speed and low voltage. For example, reducing the supply voltage from 5 V to 3.3 V in some cases has reduced energy by 56% [Pouw01].

DVS essentially fills the slack times by elongated computation or communication times. There are two types of slack times: Worst Slack Time (WST) and Workload-Variation Slack time (WVST). WST results from low processor utilization. WVST occurs due to execution time variations caused by data-dependent computation. WST can be roughly estimated from the scheduling results before task execution whereas WVST can be known only after execution.

## 2.4 Scheduling to lower energy consumption

For uniprocessor real-time systems, many schemes have been proposed to manage energy consumption. Mosse et. al. [Moss00] proposed and analyzed several schemes to dynamically adjust processor speed for slack reclamation. They used a compiler to assist the operating system in changing the CPU operating levels to reduce energy consumption.

Weiser [Weis94] discussed several methods for varying the clock speed dynamically under control of the operating system. He proved that by adjusting the clock

speed at a fine grain, substantial CPU energy can be saved with a limited impact on performance.

Chandrakasan [Chan96] has shown that for periodic tasks, a few voltage/frequency levels are sufficient to achieve almost the same energy savings as infinite voltage/speed levels.

Yang [Yang01] proposed a two-phase scheduling scheme which contains a design time scheduler and a runtime scheduler that minimizes energy consumption while meeting timing constraints. By choosing different scheduling options at compile time they achieved 20-40% average energy savings.

Zhang and Chen [Zhan02] proposed a priority based task mapping and scheduling for a fixed task graph applying the earliest deadline first scheduling and formulating the voltage scaling problem as an integer programming problem. They proved that their framework can slow 8% of cycles in very short time.

The main concern in DVS is to increase slack time utilization as much as possible and to make resultant energy consumption as low as possible. Two types of slack time are defined as worst slack time (WST) and workload-variation slack time (VST). WST results from processors utilization that is less than 100%. Low processor utilization is always the case even if all tasks exhibit their worst-case execution time. VST occurs due to execution time variations caused by data-dependent computation. WST can be estimated from the scheduling results before task execution whereas VST can be known only after actual task execution.

Shin et. al. [Shin01] proposed a low-energy, priority-based scheduling which

consists of two parts: an off-line component which determines minimum processor speed while guaranteeing deadlines of all tasks and an online component which dynamically varies processor speed to utilize both WST and WVST.

Shang et. al. [Shan03] proposed a history-based DVS for interconnected networks. Their technique leverages network history to predict future network needs, judiciously controlling the frequency (and voltage) of links to track actual network utilization. Such mechanisms resulted in 46% average energy savings at the cost of 15.2% increase in network latency and 2.5% decrease in network throughput.

Theoretical investigations of speed scaling algorithms were initiated by Yao, Demers, and Shankar [Yao 95]. Yao et al. propose formulating speed scaling problems as scheduling problems. They assumed that each task has a release time when it arrives into the system, an amount of work that must be performed to complete the task and also a deadline that specifies the time by which the task should be completed. A schedule specifies which task to run at each time, and at what speed that task should be run. In some settings, for example, the playing of a video or other multimedia presentation, there may be natural deadlines for the various tasks imposed by the application. In other settings, the system may impose deadlines to better manage tasks or ensure a certain quality of service to each task. They studied the problem of minimizing the total energy used subject to the deadline feasibility constraints

Few other literatures have considered energy saving in addition to the performance. Lu, Benini and Micheli [Lu00] presented a greedy on-line scheduling algorithm to facilitate energy management for multiple devices. They ordered the

execution of tasks so that devices can have continuous long idle periods during which they can be shut down. They achieved an average energy savings of 33%.

Mishra et. al. [Mish03] proposed two novel techniques for energy management in distributed systems. The first is a static technique which uses a greedy algorithm to manage energy in presence of parallelism. The second technique uses task reallocation that enhances the first algorithm by allowing out-of-order execution where preemption is allowed. Their technique saved an average of 10-20% more savings than a simple static energy management technique.

Shiue and Chakrabarti in [Shiu00] presented polynomial time algorithms for (i) resource-constrained scheduling and (ii) latency-constrained scheduling for the case when the resources operate at multiple voltages. Both scheduling schemes try to reduce the overall energy consumption. The resource-constrained scheduling scheme tries to balance the conflicting requirements of reducing the latency and maximally utilizing resources operating at reduced voltages. The latency-constrained scheduling scheme assigns as many nodes as possible to the resources operating at low voltages without violating the timing constraint.

Kirovski and M. Potkonjak [Kiro97] developed a system-level approach for energy minimization of cost-constrained hard real-time designs. The approach simultaneously optimizes all three degrees of freedom for energy minimization, namely switching activity, effective capacity and supply voltage.

Srivastava in [Sriv96] described three broad architectural approaches for energy efficient programmable computation: predictive shutdown, concurrency driven supply

voltage reduction, and switching activity reduction. A significant reduction in energy consumption can be obtained by employing these architectural techniques. They have shown that an aggressive shut down strategy based on a predictive technique can reduce the energy consumption by a large factor compared to the straightforward conventional schemes where the energy decision is based solely on a predetermined idle time threshold.

An example where the idea embodied in their techniques can be applied is the combination of parallelism-driven voltage reduction with switching activity reduction to increase the energy efficient of memory operations when the access pattern is sequential in nature. Such sequential access patterns occur, for example, when fetching video data from a frame buffer memory or when writing a page of virtual memory back to disk. Instead of accessing data from memory in a serial fashion, several words can be read from memory and the memory can be clocked at a lower rate for the same throughput. If the serial implementation runs at a supply of 3V to meet a given throughput, then the parallel version can run at a supply voltage of 1.3 V while meeting throughput requirements.

Chaeseok and Ha. [ImHa04] proposed an energy efficient real-time multi-task scheduling by the use of buffers with DVS. They saved an average energy of 44% with reasonable machine specifications. The buffers increase CPU utilization by averaging the workload. Their technique was designed for multimedia applications where a slight buffering delay is tolerable.

#### **CHAPTER 3**

#### DYNAMIC VOLTAGE SCALING

For most energy-conscious designs, a major source of energy savings is voltage scaling, which scales operating voltages of processors and corresponding maximum clock speeds. The dominant source of energy consumption in digital CMOS circuits is the dynamic energy dissipation P, characterized by

$$P \propto CV^2 f$$

where C is the effective switching capacitance, V is the supply voltage, and f is the clock speed [Burd96].

Since energy varies linearly with the clock speed and the square of the voltage, adjusting the voltage can result in significant energy reductions, at least in theory. However, reducing the supply voltage requires a corresponding decrease in clock speed and increase in task execution latency.

The settling time for a gate is proportional to the voltage; the lower the voltage drop across the gate, the longer the gate takes to stabilize. To lower the voltage and still operate correctly, the cycle time must be lowered first. When raising the clock rate, the voltage must be increased first. Given that the voltage and the cycle time of a chip could be adjusted together, it should be clear now that the lower-voltage, slower-clock chip will

dissipate less energy per cycle. If the voltage level can be reduced linearly as the clock rate is reduced, then the energy savings per instruction will be proportional to the square of the voltage reduction. Of course, for a real chip it may not be possible to reduce the voltage linear with the clock reduction. However, if it is possible to reduce the voltage at all by running slower, then there will be a net energy savings per cycle.

Currently manufacturers do not test and rate their chips across a smooth range of voltages. However, some data is available for chips at a set of voltage levels. For example, a Motorola CMOS 6805 microcontroller is rated at 6 MHz at 5.0 Volts, 4.5 MHz at 3.3 Volts, and 3 MHz at 2.2 Volts. This is a close to linear relationship between voltage and clock rate. Thus there is seemingly no technical objection to designing a variable-voltage system provided that the input reference voltage to the processor's voltage regulator may be a digital word writable by the processor.

The other important factor is the time it takes to change the voltage. The main time-cost would be for the converter or regulator to ramp the supply voltage up or down. The ramping time is determined by the time constants of the converter. The frequency for voltage regulators is on the order of 200 KHz [Weis94], so we speculate that it will take a few tens of microseconds to boost the voltage on the chip. Moreover the CPU should be able to continue working during a voltage ramp and ramping should not have any substantial energy cost.

Finally, why run slower? Suppose a task has a deadline in 100 milliseconds, but it will only take 50 milliseconds of CPU time when running at full speed to complete. A normal system would run at full speed for 50 milliseconds and then idle for 50

milliseconds (assuming there were no other ready tasks) as in Figure 3.1. During the idle time the CPU can be stopped altogether by putting it into a mode that wakes up upon an interrupt, such as from a periodic clock or from an I/O completion.

Figure 3.1. Different operating rates for the same task

Now, compare this to a system that runs the task at half speed so that it completes just before its deadline. If it can also reduce the voltage by half, then the task will consume 1/4 the energy of the normal system, even taking into account stopping the CPU during the idle time. This is because the same number of cycles is executed in both systems, but the modified system reduces energy use by reducing the operating voltage. Another way to view this is that idle time represents wasted energy, even if the CPU is stopped.

The relation between clock speed, supply voltage, and energy dissipation for Transmeta's Crusoe TM5400 microprocessor as reported in its data sheet [Tiwa96] are shown in Table 3.1. For a program running for time duration of T, its total energy

consumption E is approximately equal to  $E = P_{avg} \times T$ , Where  $P_{avg}$  is the average energy consumed. Researchers have proposed many ways of determining "appropriate" operating clock rate. The basic idea behind these energy saving approaches is to slow down the tasks as much as possible without violating the deadline. This "just-in-time" strategy can be illustrated through a voltage scheduling graph as in Figure 3.2 [Much97].

In a voltage scheduling graph, the X-axis represents time and the Y-axis represents processor speed. The total amount of work for a task is defined by the area of the task "box." For example, task 1 in Figure 3.2 has a total workload of 8,000 cycles. By "stretching" it out all the way to the deadline without change of the area, we are able to decrease the CPU speed from 600MHz down to 400MHz. As a result, 23.4% of total (CPU) energy may be saved on a Crusoe TM5400 processor.

| Frequency<br>(MHz) | Voltage<br>(V) | Relative power<br>(%) |

|--------------------|----------------|-----------------------|

| 700                | 1.65           | 100%                  |

| 600                | 1.60           | 80.6%                 |

| 500                | 1.50           | 59.0%                 |

| 400                | 1.40           | 41.1%                 |

| 300                | 1.25           | 24.6%                 |

| 200                | 1.10           | 12.7%                 |

Table 3.1. The relationship between clock frequencies, supply voltage, and energy dissipation of Transmeta's Crusoe TM5400 microprocessor.

Figure 3.2. Voltage scheduling graph

## 3.1 Power management implementation

There are several ways of achieving energy reduction. In this section, we study the various approaches.

## 3.1.1 Simple shutdown

Energy shutdown to a component is a radical solution that eliminates all sources if energy dissipation, including leakage.

Energy consumption of idle processors can be avoided by energying off the unit. This radical solution requires controllable switches. An advantage of this approach is the wide applicability to all kind of electronic components. A major disadvantage is the wake-up time or the recovery time because the processor operation must be reinitialized.

# 3.1.2 Multiple and variable energy supplies

Dynamic energy management is also applicable to processors that are not idle, but whose performance requirement varies with time. The implementation technology can then be based on the slowdown. The slowdown is achieved by lowering the

voltage supply, such that the machine becomes performance critical.

Dynamically-varying supply voltages may be quantified [Chan96] and thus be restricted to a finite number of values, or may take values in a continuous range. In the former case it is possible to identify a finite number of energy states for the system.

## 3.1.3 OnNow approach

The OnNow approach uses energy-management hardware to put the PC into a low-energy sleep state instead of shutting down completely, so that the system can quickly resume working [Micr04]. While in the sleep state, the PC's processor is not executing code and thus no work is being accomplished for the user. However, events from both hardware devices (such as modem ring or network request) and the real-time clock can be enabled to cause the system to wake up.

Each device in the system has its own energy states, and these are independently managed by the device driver (or other policy owner) while the system is in the working state. The device's policy integrates any particular application's needs with device capabilities and other operating system information to conserve energy without adversely affecting the work that the user is doing.

## **CHAPTER 4**

## **DIRECTED A-CYCLIC GRAPH DAG**

We define a DAG as an a-cyclic graph with nodes representing tasks and edges representing execution precedence between tasks. A weight is associated to each node and edge. The node weight represents the task execution time and the edge weight represents the communication time between connected tasks. This communication time is zero if the tasks are executed on the same processor. Each DAG has a root node which is a node with no incoming edges and a sink node which is a node with no outgoing edges.

Figure 4.1. A sample DAG

The DAG structure occurs in many regular and irregular applications such as Cholesky factorization, LU decomposition, Gaussian elimination, FFT, Laplace transforms, and instruction level parallelism.

Along the lines of [Bask03] a DAG is represented by the tuple G=(V, E, M, T, C, P) where:

- *V* is the set of *n* nodes.

- *E* is the set of *e* edges between the nodes.

- *M* is a set of *m* machines or processors.

- E(n, c) is an edge between nodes n and c.

- T is the set of costs T(n,k), represents the computational time of task n on machine k.

- C is the set of costs C(n,c), which represents the communication cost associated with the edges E(n,c). Since intra-processor communication is insignificant compared to inter-processor communication, C(n,c) is considered to be zero if n and c are executed on the same processor.

- P is the set of costs P(n,k), which presents the consumed power when task n is executed on processor k.

The length of a path is defined as the sum of node and edge weights in that path.

Node n is a *predecessor* of node c if there is a directed edge originating from n and ending at c. In figure 4.1, node 1 is a *predecessor* of nodes 2, 3, 4 and 7.

Likewise, node s is a *successor* of node n if there is a directed edge originating from n and ending at s. From figure 4.1, node 6 is a *successor* of nodes 1, 2, and 3. We

can further define pred(n) as the set of all predecessors of n and succ(n) as the set of all successors of n as an example  $pred(6) = \{1, 2, 3\}$  and  $succ(6) = \{8\}$ .

An *ancestor* of node n is any node c that is contained in pred(n), or any node a, that is also an ancestor of any node c contained in pred(n).

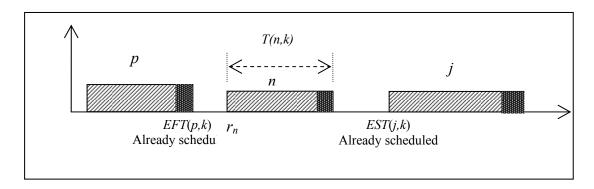

The earliest execution start time of node n on processor k is represented as EST(n,k). Likewise, the earliest execution finish time of node n on processor k is represented as EFT(n,k). EST(n) and EFT(n) represent the earliest start time upon any processor and the earliest finish time upon any processor, respectively.  $R_{nk}$  is defined as the earliest time that processor k will be ready to begin executing task k. We can mathematically define these terms as follows:

$$EST(n, k) = max\{R_{nk}, EFT(c, m) + C(c, n)\}$$

, Where,  $c \in pred(n)$

$EFT(c, m) = EFT(c)$  and  $C(c, n) = 0$  when  $k = m$ ,

$EFT(n, k) = T(n, k) + EST(n, k)$ ,

$EST(n) = min(EST(n, k), k \in M)$ ,

$EFT(n) = min(EFT(n, k), k \in M)$ .

The maximum clause finds the latest time that a predecessor's data will arrive at processor k. If the predecessor finishes earlier on a processor other than k, communication cost must also be included in this time. In other words, the earliest start time of any task n on processor k, EST(n,k) is the maximum of times at which processor k becomes available and the time at which the last message arrives from any of the predecessors of n.

The main goal for any scheduling technique is to minimize the *makespan* of the DAG. The *makespan* is defined as the time at which all nodes finish executing. In our case, the *makespan* will be equal to EFT(y), where y is the exit node in the graph. From Figure 4.1 the *makespan* is EFT(8).

The *critical path (CP)* is the longest path from an entry node to an exit node. The *critical path excluding communication cost (CPEC)* is the longest path from an entry node to an exit node, not including the communication cost of any edge traversed. In our work we assume that each task's mean execution cost across all processors is used to calculate *CP* while each task's minimum execution cost from any processor is used to calculate the *CPEC*.

The *top distance* for a given node is the longest distance from an entry node to the node, excluding the computation cost of the node itself. The *bottom distance* for a given node is the longest distance from the node to an exit node. Again we assume that each task's mean execution cost is used to calculate the *top distance* and *bottom distance*. The bottom distance is also referred to as the *upper rank* or the *blevel*.

The *Decisive Path (DP)* is defined as the *top distance* of a given node plus the *bottom distance* of the node. The *DP* is defined for every node in the DAG. The critical path, *CP*, then becomes the largest *DP* for an exit node.

#### 4.1 Performance

Our algorithms are for scheduling directed acyclic weighted task graph running on a bounded number of heterogeneous processors with the twin objectives of minimizing the amount of energy consumed and minimizing the finish time.

In other words, tasks arrive with given execution time and need to meet certain execution deadlines as well as minimize the consumed energy.

Using simulations, we evaluated the performance of EADAGS and EAGS-D. The first test suite consists of random directed a-cyclic graphs. The input parameters used to generate the graphs were:

- Number of nodes (tasks) in the graph, *n*.

- Shape parameter of the graph,  $\alpha$ . If  $\alpha = 1.0$ , the graph is balanced. A DAG with high parallelism can be generated by selecting  $\alpha >> 1$ . Whereas  $\alpha << 1$  will generate a long DAG with small degree of parallelism.

- Out-degree of a node, *out-degree*, represents the average number of outgoing edges from each node. Each node's *out-degree* is randomly generated from a uniform distribution with mean equal to *out-degree*.

- Communication to Computation ratio, *CCR*. *CCR* is the ratio of the average communication to average computation cost. If a DAG's *CCR* is less than 1, it is a computation-intensive application; if it's CCR is much greater than 1, it is communication-intensive.

- Computation Range,  $\beta$ , represents the range of computation costs on processors. A high  $\beta$  causes significant difference of node's computation costs among processors, whereas a low  $\beta$  means that the expected execution times of a node on any processor are almost equal.

- Processor to node ratio, PNR, represents the availability of processors with

respect to number of nodes. A *PNR* of 100% means the number of processors is equal to the number of nodes.

In generating random DAGs, the parameters were varied as follows:

$$n = \{10, 20, 40, 60, 80, 100, 500, 1000\}$$

$CCR = \{0.1, 0.5, 1, 5, 10\}$

$\alpha = \{0.5, 1, 2\}$

$Out\text{-}degree = \{1, 2, 3, 4, 5, 100\}$

$\beta = \{0.1, 0.25, 0.5, 0.75, 1.0\}$

$PNR = \{25\%, 50\%, 100\%\}$

These values produced 10,800 DAGs, which were repeated for both presented algorithms, EADAGS and EAGS-D.

The second test suite to evaluate the performance of EADAGS and EAGS-D used task graphs of real world problems, specifically Gaussian elimination [Wu90], Molecular dynamic code [Chun92], Sieve of Eratosthenes, and Fast Fourier Transform (FFT). For these problems, the shape of the DAG is fixed and the only parameters we changed were the number of available processors and *CCR*.

Processors were assumed to have three different operating voltage levels and five operating strategies based on the Motorola CMOS 6805 microcontroller, which is rated at 6 MHz at 5.0 Volts, 4.5 MHz at 3.3 Volts, and 3 MHz at 2.2 Volts. First operating voltage was 5V when using this voltage if the processor becomes idle, it shuts down. We will refer to this operating voltage as 5V/off. This level is used for reference only since it has physical limitations. The other two operating voltages are 2V and 3.3V, which slow

the processor during task execution and during processor's idle times.

## **CHAPTER 5**

## SCHEDULING ALGORITHIMS

Many scheduling algorithms for scheduling DAGs in a distributed computing environment have been proposed as has been mentioned in Chapter 2. However, the problem of discovering the schedule that gives the minimum finish time is NP-Complete. Among all these scheduling algorithms, some prove to perform better in term of finish time or *makespan*.

In this work two new scheduling algorithms for scheduling DAGs on distributed computing systems were presented: Energy Aware DAG Scheduling (EADAGS) and Energy Aware Graph Scheduling with Duplication (EAGS-D).

# **5.1 EADAGS algorithm**

A new algorithm for scheduling DAGs on distributed computing systems has been introduced. EADAGS combines Decisive Path Scheduling (DPS) with DVS to minimize both finish time and energy consumption. DPS [Park97], since it is one of the most efficient algorithms, was chosen. The new algorithm is called Energy Aware DAG Scheduling (EADAGS). It consists of two phases. In the first phase, after DPS is run on the DAG to provide a low finish time, the energy consumed is estimated for all

processors. In the second phase, voltage scaling is applied during slack times to reduce energy while maintaining the schedule length.

EADAGS transforms a DAG to one with a single entry node and a single exit node, if not so already. This transformation is accomplished by adding a dummy entry node and/or exit node with zero costs. Next, the top and bottom distances from each node are calculated. The top and bottom distances are calculated using the mean computation value for each node. After building the *DP* for each node, EADAGS begins creating the scheduling queue, *ScheduleQ*, in a top-down fashion starting with the DAGs entry node and traversing down the *CP* (which is the DP of the exit node). Nodes are prioritized based on the lengths of their *DPs*. The priorities are decided as follows: EADAGS puts the *CP* nodes into the *ScheduleQ* in the ascending order of their *top-distances*. A node is added to the queue only if all its predecessors have been added. If not, EADAGS attempts to schedule its predecessors first. The first predecessors added to the queue are those included in the nodes' *DP* other are sorted and added to *ScheduleQ* in increasing *top-distance*.

Next, EADAGS assign tasks in *ScheduleQ* to processors. At each step of the assignment, the selected processor provides the earliest finish time for the task under consideration, taking into account all the communications from the task's parents. If *EFT* of the exit node is larger than the sum of all the computation costs of the nodes on the best processor, EADAGS assigns all nodes to that processor and exits. The time complexity of first phase of EADAGS is  $O(n^2)$ .

Next, EADAGS computes the consumed energy. The total energy consumed when no voltage scaling is used,  $E_I$  is first calculated by the following equations:

$$E_I = T \times \sum_{k \in M} P_1(k)$$

$$P_1(k) = \frac{fV_1^2}{2}$$

where:

- $P_1(k)$  is the amount of power consumed by processor  $k \in M$ ,

- f is the operating frequency of machine k,

- $V_I$  is the operating voltage of machine k,

- *T* is the *makespan*

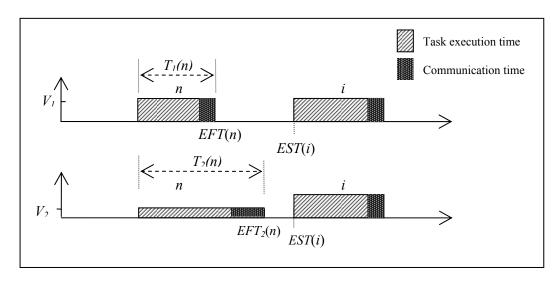

In the second phase of EADAGS, voltage scaling is applied to all processors during their *idle times* by reducing the execution rate to  $f_2$  by lowering the voltage to a predetermined level  $V_2$ . Such voltage scaling is applied to a task only if slowing its execution would not increase the *makespan*. We also reduce the voltage level of processors during all remaining slack times. The total energy consumed after applying voltage scaling is  $E_2 = \sum E_2(k)$  where:

- $E_2(k) = \frac{T_1 f_1 V_1^2 + T_2 f_2 V_2^2}{2}$  represents the energy consumed by processor  $k \in M$  when voltage scaling is used,

- $T_1 = \sum_i T(i) + \sum_{ij} C(i,j)$  is the total task and communication time when operating at  $V_I$ ,

- T(i) is the computation time of task i on the chosen processor,

- C(i, j) is the communication cost between tasks i and j if i and j are not scheduled on the same processor,

- $T_2$  is the total time processor k operates at  $V_2$  (includes idle times during which the processor operates at  $V_2$ ).

A non blocking send protocol has been assumed in which only the sending processor has to process the communication while the receiving processor has a buffer to receive all transmitted data without interrupting its job. The difference between  $E_1$  and  $E_2$  represents the energy that could be saved. The percentage average energy savings =  $\frac{E_1 - E_2}{E_1} \times 100$ . A high level description of EADAGS appears in Table 5.1.

# Table 5.1. EADAGS algorithm

# Let G represent a DAG Let *M* be the set of *m* processors in the system **EADAGS** Transform G to a DAG with a single entry node and a single exit node Compute *DP* of each node $n \in G$ //DP of the exit node is the critical path, CP Fill ScheduleQ with nodes //Starting from the entry node traversing *CP* in increasing *top-distance*. while $ScheduleQ \neq \Phi$ do $i \leftarrow \text{head}(ScheduleO)$ Schedule i on processor $p \in M$ that provides earliest finish time of i. Remove i from ScheduleQ end while if scheduling all nodes on the fastest processor provides a shorter *makespan*, do so and discard prior schedule $T \leftarrow makespan$ Total energy consumed before voltage scaling $E_1 = \frac{fTV_1^2}{2}$ Total energy consumed when employing voltage scaling, $E_2 = ScaledEnergy()$ end EADAGS ScaledEnergy() // Returns the total amount of energy consumption on all processors when voltage scaling has been applied **for** each processor $p \in M$ **do for** each node $n \in G$ scheduled on p **do** //traverse first scheduled to last **if** (executing *n* on scaled voltage fits within the next slack) **then** Scale down the operating voltage during execution of *n* end if end for Energy consumed by processor p = sum of energy consumed by all nodesscheduled on p end for E =Sum of energy consumed by all processors return E end ScaledEnergy

Figure 5.1 lists the notations used by EADAGS and procedures of EADAGS (EADAGS, *AddQ*, *StartTime*, *and ScaledEnergy*).

#### Let

- G represent a DAG

- $y \in G$  be the exit node of G

- M be the set of m processors in the system

- $R_k$  represent the ready time of machine k

- $r_n$  represent the ready time of node n

- f be the frequency of operation

- $s_{ik}$  represent the start time of node i on machine k

- Succ(n) represent the list of all successor nodes of node  $n \in G$

- pred(n) is the list of all predecessors of node  $n \in G$

- ScheduleQ queue of tasks in order of execution

- T(i, k) represent the execution time of node  $i \in G$  on machine k

- C(n, c) represent the communication cost from node n to node c

- EFT(i, k) represent the earliest finish time of node  $i \in G$  on machine k

- EFT(i) represent the scheduled finish time of node  $i \in G$

- $EFT_2(i)$  represent the finish time for node i with the scaled down voltage

- EST(i) represent the scheduled start time of node  $i \in G$

- T represent the makespan of G

- $V_I$  be the voltage of operation

- $V_2$  be the scaled down voltage of operation

- $T_1(n)$  and  $T_2(n)$  represent the execution time for any node  $n \in G$  before and after voltage scaling respectively

- E(k, n) represent the energy consumed by processor k to execute node n

- $\bullet$   $E_I$  represent the total energy consumption before voltage scaling

- $E_2$  is the total energy consumption after scaling down voltage

- $E_1(k)$  and  $E_2(k)$  represent energy consumed by processor  $k \in M$  before and after voltage scaling respectively

Figure 5.1.a. Notations for EADAGS

```

EADAGS

Transform G to a DAG with a single entry node and a single exit node

//O(n^2)

Compute DP for each node n \in G

// DP of the exit node is the critical path, CP

// Fill ScheduleQ with nodes in CP in increasing top-distance.

ScheduleO \leftarrow \Phi

//O(n^2)

for each node n \in CP do

// Traverse in increasing top-distance.

ScheduleQ = addQ(n)

end for

//Schedule nodes in Schedule Q to processors

while Schedule Q \neq \Phi do

//O(n)

Pick the head node i in ScheduleQ

IIO(m)

for each processor k \in M do

s_{ik} = StartTime(i, k)

EFT(i, k) = s_{ik} + T(i, k)

end for

EFT(i) = \min_{k \in M} EFT(i, k)

Schedule i on processor p \in M that gave minimum earliest finish time

Remove i from ScheduleQ

end while

if EFT(y) \ge \min_{k \in M} \sum_{i \in C} T(i, k)

Schedule all nodes on the processor p \in M, which provided the minimum

end if

T \leftarrow EFT(v)

// makespan

E_1 = \frac{fTV_1^2}{2}

E_2=ScaledEnergy()

end EADAGS

```

Figure 5.1.b. *EADAGS* procedure

```

addQ(n)// Adds parents of node n \in G and n to ScheduleQ// Returns ScheduleQfor each parent b of n not visited // in decreasing DPaddQ(b)end forAdd to n to ScheduleQ and mark it visitedreturn ScheduleQend addQ

```

Figure 5.1.c. addQ procedure

```

StartTime (node n, machine k)

// Returns the earliest available start time of node n \in G on machine k \in M

s_{nk} \leftarrow R_k

for each parent b of n do

s_{nk} = \max(s_{nk}, EFT(b) + C(b, n))

end for

return s_{nk}

end StartTime

```

Figure 5.1.d. StartTime procedure

```

ScaledEnergy()

// Returns the total amount of energy consumption after applying voltage scaling

for each processor k \in M do

//O(m)

for each node n \in G scheduled on k do //O(n) from first to last scheduled

T_2(n) = \frac{V_1^2}{V_2^2} \times T_1(n)

EFT_2(n) = s_{nk} + T_2(n)

if (EFT_2(n)+C(n,c) \le min\ EST(c) for each c \in succ(n) then

// if c is scheduled on k, C(n, c) = 0

EFT(n) = EFT_2(n)

//update EFT(n)

Let i be the node scheduled immediately after n on k

// use scaled voltage, see Figure 5.2 E(k, n) = T_2(n) \times V_2^2 + (EST(i) - EFT(n)) \times V_2^2

else

//original voltage for execution and scaled voltage during idle time,

// see Figure 5.2

E(k, n) = T_1(n) \times V_1^2 + (EST(i) - EFT(n)) \times V_2^2

end if

end for

E_2(k) = +E(k, n)

end for

E_2 = \sum_{k \in M} E_2(k)

return E2

end ScaledEnergy

```

Figure 5.1.e. *ScaledEnergy* procedure

Figure 5.2. Timeline for machine *k*

# **5.2 EAGS-D Algorithm**

Energy Aware Graph Scheduling with Duplication (EAGS-D) combines HNPD and dynamic voltage scaling. The Heterogeneous N-Predecessor Duplication (HNPD) algorithm combines the techniques of *insertion-based* list scheduling with multiple *task* duplication to minimize schedule length. The performance of HNPD was proven to outperform two of the best existing heuristics, Heterogeneous Earliest Finish Time (HEFT) and Static Task Duplication Scheduling (STDS), in terms of finish time and the number of processors employed over a wide range of parameters [Bask03]. EAGS-D works as follows: EAGS-D assigns tasks to the best available processor according to the order of tasks in a scheduling queue called *ScheduleQ*. EAGS-D assigns highest priority to critical path nodes (CPN) and then to those predecessors of CPNs that include the CPN in their DP. Among these predecessors it gives higher priority to nodes with higher DP values. This is because the nodes with the higher DP values are likely to be on longer paths. In the order of tasks in *ScheduleQ*, EAGS-D uses *EFT(n)* to select the processor for each task n. As it is an insertion-based algorithm, it calculates ready time of any machine  $k \in M$ ,  $R_k$  to be the earliest idle time slot large enough to execute T(n, k). In other words, it looks for a possible insertion between two already scheduled tasks on the given processor without violating precedence relationships. Once tasks have been assigned to processors, it attempts to duplicate predecessors of the tasks. Predecessors are selected for duplication from most favorite to least and by descending top distance. The goal of duplicating predecessors is to decrease the length of time for which the node is awaiting data by making use of the processor's slack time. Predecessors of node n are duplicated

on processor k, on which node n is scheduled on. If the duplication result in a lower finish time, duplication is retained; otherwise it is discarded. If there is idle time between the recently assigned task n and the preceding task on processor k, EAGS-D attempts to duplicate each predecessor j. If j is not already scheduled on processor k, it is duplicated if EFT(j,k) is less than EFT(j)+C(j,n). The duplication is retained if EFT(n,k) decreases. Otherwise, it is discarded. The same duplication procedure is repeated for each predecessor in order of most favorite to least. After EAGS-D attempts to duplicate each predecessor, it recursively attempts to duplicate the predecessors of any duplicated tasks. Duplication recursively continues until no further duplication is possible.

Then, EAGS-D computes the consumed energy. The total energy consumed when no voltage scaling is used,  $E_1$  is first calculated by the following equations:

$$E_I = T \times \sum_{k \in M} P_1(k)$$

$$P_1(k) = \frac{fV_1^2}{2}$$

where:

- $P_1(k)$  is the amount of power consumed by processor  $k \in M$ ,

- f is the operating frequency of machine k,

- $V_I$  is the operating voltage of machine k,

- T is the makespan

In the second phase of EAGS-D, voltage scaling is applied to all processors during their *idle times* by reducing the execution rate to  $f_2$  by lowering the voltage to a

predetermined level  $V_2$ . Such voltage scaling is applied to a task only if slowing its execution would not increase the *makespan*. We also reduce the voltage level of processors during all remaining slack times. The total energy consumed after applying voltage scaling is  $E_2 = \sum E_2(k)$  where:

- $E_2(k) = \frac{T_1 f_1 V_1^2 + T_2 f_2 V_2^2}{2}$  represents the energy consumed by processor  $k \in M$  when voltage scaling is used,

- $T_1 = \sum_i T(i) + \sum_{ij} C(i, j)$  is the total task and communication time when operating at  $V_I$ ,

- T(i) is the computation time of task i on the chosen processor,

- C(i, j) is the communication cost between tasks i and j if i and j are not scheduled

on the same processor,

- $T_2$  is the total time processor k operates at  $V_2$  (includes idle times during which the processor operates at  $V_2$ ),

A non blocking send protocol has been assumed in which only the sending processor has to process the communication while the receiving processor has a buffer to receive all transmitted data without interrupting its job. The difference between  $E_1$  and  $E_2$  represents the energy that could be saved. The percentage average energy savings =  $\frac{E_1 - E_2}{E_1} \times 100$ . A high level description of EAGS-D appears in Table 5.2.

```

Let G represent a DAG

Let M be the set of m processors in the system

EAGS-D

Transform G to a DAG with a single entry node and a single exit node

Compute DP of each node n \in G

//DP of the exit node is the critical path, CP

Fill ScheduleQ with nodes

//Starting from the entry node traversing CP in increasing top-distance.

while Schedule Q \neq \Phi do

i \leftarrow \text{head}(ScheduleO)

Schedule i on processor p \in M that provides earliest finish time of i.

Remove i from ScheduleQ

Duplicate predecessors of i on p if doing so results in a shorter schedule

//duplicate executions performed within slacks of the schedule of p

end while

if scheduling all nodes on the fastest processor provides a shorter makespan,

do so and discard prior schedule

T \leftarrow makespan

Total energy consumed before voltage scaling E_1 = \frac{fTV_1^2}{2}

Total energy consumed when employing voltage scaling, E_2 = ScaledEnergy()

end EAGS-D

ScaledEnergy()

// Returns the total amount of energy consumption on all processors when voltage scaling

// has been applied

for each processor p \in M do

for each node n \in G scheduled on p do //traverse first scheduled to last

if (executing n on scaled voltage fits within the next slack) then

Scale down the operating voltage during execution of n

end if

end for

Energy consumed by processor p = \text{sum of energy consumed by all nodes}

scheduled on p

E = Sum of energy consumed by all processors

return E

end ScaledEnergy

```

Figure 5.3.a lists the notations used by EAGS-D while Figures 5.3.b, 5.3.c, 5.3.d, 5.3.e, 5.3.f and 5.3.g shows the detailed algorithm procedures: EAGS-D, *AddQ, StartTime, DuplicatePred, Duplicate, and ScaledEnergy* respectively.

#### Let

- G represent a DAG

- $y \in G$  be the exit node of G

- *M* be the set of *m* processors in the system

- $R_k$  represent the ready time of machine k

- $r_n$  represent the ready time of node n

- f be the frequency of operation

- $s_{ik}$  represent the start time of node i on machine k

- Succ(n) represent the list of all successor nodes of node  $n \in G$

- pred(n) is the list of all predecessors of node  $n \in G$

- ScheduleQ queue of tasks in order of execution

- T(i, k) represent the execution time of node  $i \in G$  on machine k

- C(n, c) represent the communication cost from node n to node c

- EFT(i, k) represent the earliest finish time of node  $i \in G$  on machine k

- EFT(i) represent the scheduled finish time of node  $i \in G$

- $EFT_2(i)$  represent the finish time for node i with the scaled down voltage

- EST(i) represent the scheduled start time of node  $i \in G$

- T represent the makespan of G

- $V_1$  be the voltage of operation

- $V_2$  be the scaled down voltage of operation

- $T_1(n)$  and  $T_2(n)$  represent the execution time for any node  $n \in G$  before and after voltage scaling respectively

- E(k, n) represent the energy consumed by processor k to execute node n

- $\bullet$   $E_I$  represent the total energy consumption before voltage scaling

- $E_2$  is the total energy consumption after scaling down voltage

- $E_1(k)$  and  $E_2(k)$  represent energy consumed by processor  $k \in M$  before and after voltage scaling respectively

Figure 5.3.a. EAGS-D notations

```

EAGS-D

Transform G to a DAG with a single entry node and a single exit node

Compute DP for each node n \in G

//O(n^2)

// DP of the exit node is the critical path, CP

// Fill ScheduleQ with nodes in CP in increasing top-distance.

ScheduleQ \leftarrow \Phi

//O(n^2)

for each node n \in CP do

// Traverse in increasing top-distance.

ScheduleQ = addQ(n)

end for

//Schedule nodes in ScheduleQ to processors

while ScheduleQ \neq \Phi do

//O(n)

Pick the head node i in ScheduleQ

for each processor k \in M do

//O(m)

s_{ik} = StartTime(i, k)

EFT(i, k) = s_{ik} + T(i, k)

end for

EFT(i) = \min_{k \in M} EFT(i, k)

Schedule i on processor p \in M that gave minimum earliest finish time

Remove i from ScheduleQ

// Duplicate predecessors of i on p if it results in a shorter schedule

DuplicatePred (i, pred(i), p)

end while

if EFT(y) \ge \min_{k \in M} \sum_{k \in M} T(i,k)

Schedule all nodes on the processor p \in M, which provided the minimum

end if

T \leftarrow EFT(y)

// makespan

E_1 = \frac{fTV_1^2}{2}

E_2=ScaledEnergy()

end EAGS-D

```

Figure 5.3.b. EAGS-D procedure

```

addQ(n)

// Adds parents of node n ∈ G and n to ScheduleQ

// Returns ScheduleQ

for each parent b of n not visited // in decreasing DP

addQ(b)

end for

Add to n to ScheduleQ and mark it visited

return ScheduleQ

end addQ

```

Figure 5.3.c. addQ procedure

Figure 5.3.d. StartTime procedure

```

DuplicatePred (node n, pred(n), machine k)

for each q \in pred(n) // in order from most favorite to least

Duplicate (n, q, k)

if q was duplicated then

DuplicatePred (q, pred(q), k)

end if

end for

end DuplicatePred

```

Figure 5.3.e. *DuplicatePred* procedure

```

Duplicate (node n, node i, machine k)

// Attempts to duplicate node n, a predecessor of node i, on machine k which executes node i

if n has not been scheduled on k then

r_{nk} = StartTime(n, k)

// Attempt to insert node n in the first available slack in the schedule of

Processor k \in M

for each node j already scheduled on k \in M do

//scan from last to first scheduled

if j∉ pred(n) then

if j is the first node scheduled on k then

if EST(j, k) >= r_{nk} + T(n, k) then //see Figure 5.4

S_{nk} = r_{nk}

end if

Let p be the node immediately scheduled prior to j on k

else if (EST(j, k)-EFT(p, k) \ge T(n,k)) and (EFT(p, k) \ge r_{nk}) then

s_{nk} = EFT(p, k)

// see Figure 5.5

end if

EFT(n, k) = s_{nk} + T(n, k)

end if

end for

//If EFT(i) did not decrease due to duplication, discard duplication

if EFT(n,k) \le min_{succ(n)}(EFT(n) + C(n,succ(n)))then

Insert and schedule n on k

Recalculate EFT(i, k)

if EFT(i,k) improves then

Keep n scheduled on k

else

Discard the duplication of node n on k

end if

end if

end if

end Duplicate

```

Figure 5.3.f. *Duplicate* procedure

```

ScaledEnergy()

// Returns the total amount of energy consumption after applying voltage scaling

for each processor k \in M do

//O(m)

for each node n \in G scheduled on k do //O(n) from first to last scheduled

T_2(n) = \frac{{V_1}^2}{{V_2}^2} \times T_1(n)

EFT_2(n) = s_{nk} + T_2(n)

if (EFT_2(n)+C(n,c) \le min\ EST(c) for each c \in succ(n) then

// if c is scheduled on k, C(n, c) = 0

EFT(n) = EFT_2(n)

//update EFT(n)

Let i be the node scheduled immediately after n on k

// use scaled voltage, see Figure 5.6 E(k, n) = T_2(n) \times V_2^2 + (EST(i) - EFT(n)) \times V_2^2

else

//original voltage for execution and scaled voltage during idle time,

// see Figure 5.6

E(k, n) = T_1(n) \times V_1^2 + (EST(i) - EFT(n)) \times V_2^2

end if

end for

E_2(k) = +E(k, n)

end for

E_2 = \sum_{k \in M} E_2(k)

return E2

end ScaledEnergy

```

Figure 5.3.g. *ScaledEnergy* procedure

Figure 5.4. Timeline for machine k (case 1)

Figure 5.5. Timeline for machine k (case 2)

Figure 5.6. Timeline for machine *k*

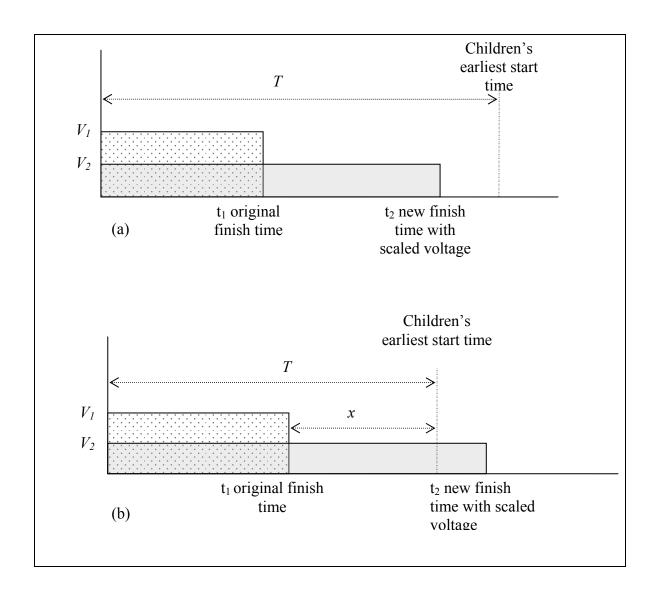

# **5.3 Voltage scaling Strategies**

Executing any task with a slower rate will require longer time to finish. And since we are dealing with DAGs in which tasks are depending on other tasks. Changing the finish time of a task may affect the start time of its predecessors resulting in a change of the schedule *makespan*.

In our algorithm we want to make use of processor's slack time to save energy without changing the *makespan* of the original scheduling algorithms. Processors were assumed to have three different operating voltage levels based on the Motorola CMOS

6805 microcontroller, which is rated at 6 MHz at 5.0 Volts, 4.5 MHz at 3.3 Volts, and 3 MHz at 2.2 Volts. We tested for five different strategies:

- 1. 5V/off: execute tasks with regular voltage level and turn off processors during their idle time. This technique is used for comparison reasons only since turning processors off each time they incur slack time has physical limitations.

- 2. 2V during idle: involves executing tasks with regular execution rate and lowering the processor's voltage level to 2V only during its idle time.

- 3. 3.3V during idle: involves executing tasks with regular execution rate and lowering the processor's voltage level to 3.3V during all its idle time.