# AREA-ARRAY PACKAGE RELIABILITY MODELS FOR NO-CORE PCB ASSEMBLIES IN EXTREME THERMO-MECHANICAL ENVIRONMENTS

Except where reference is made to the work of others, the work described in this thesis is my own work or was done in collaboration with my advisory committee. This thesis does not include proprietary or classified information.

| Ti                                                                      | m Moore                                                            |

|-------------------------------------------------------------------------|--------------------------------------------------------------------|

| Certificate of Approval:                                                |                                                                    |

| Jeffrey C. Suhling Quina Distinguished Professor Mechanical Engineering | Pradeep Lall, Chair Thomas Walter Professor Mechanical Engineering |

| Roy Knight Assistant Professor Mechanical Engineering                   | Joe F. Pittman Interim Dean Graduate School                        |

## AREA-ARRAY PACKAGE RELIABILITY MODELS FOR NO-CORE PCB ASSEMBLIES IN EXTREME THERMO-MECHANICAL ENVIRONMENTS

## Timothy Dale Moore

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirement for the

Degree of

Master of Science

Auburn, Alabama August 4, 2007

# AREA-ARRAY PACKAGE RELIABILITY MODELS FOR NO-CORE PCB ASSEMBLIES IN EXTREME THERMO-MECHANICAL ENVIRONMENTS

| Timothy | Dala | 11.    | _ |

|---------|------|--------|---|

| Limothy | Date | uvioor | C |

| Permission is granted to Auburn University to make copies of this thesis at its discretion, |

|---------------------------------------------------------------------------------------------|

| upon the request of individuals or institutions at their expense. The author reserves all   |

| publication rights.                                                                         |

| Signature of Author | _ |

|---------------------|---|

|                     |   |

|                     |   |

|                     |   |

| Date of Graduation  |   |

## **VITA**

Timothy Dale Moore, son of Mr. Tim and Mrs. Carolyn Moore, was born on January 26, 1982 in Ashland, KY. He graduated in 2005 with a Bachelor of Science in Mechanical Engineering from the University of Louisville's Speed Scientific School in Louisville, KY. During his pursuit of his baccalaureate degree he was hired for three coop internships at United Parcel Service headquarters beginning in 2002. He worked on various aircraft engine optimization, aircraft weight and balance, and aircraft performance projects in the department of Aircraft Performance Engineering. In the pursuit of enhancing his academic qualification he joined the M.S. program at Auburn University in the Department of Mechanical Engineering in Fall 2005. During the M.S. program at Auburn University, he has worked under the guidance of Professor Pradeep Lall, in the Department of Mechanical Engineering as a Graduate Research Assistant in the area of harsh environment electronic packaging reliability.

## THESIS ABSTRACT

## AREA-ARRAY PACKAGE RELIABILITY MODELS FOR NO-CORE PCB ASSEMBLIES IN EXTREME THERMO-MECHANICAL ENVIRONMENTS

## Tim Moore

Master of Science, August 4, 2007 (B.S. Mechanical Engineering, University of Louisville, Louisville, KY, 2005)

## 179 Typed Pages

## Directed by Pradeep Lall

The trends in the electronic packaging industry are to design smaller packages that have higher complexity, and to improve package reliability while reducing costs. These needs in the packaging industry have lead to a newer generation of chip architectures, such as: Chip Scale Packages, Plastic Ball Grid Arrays, and Flip Chips. The ability of these package types to process faster information, and have high degrees of wiring complexity, while taking up minimal space, has made them very appealing to the automotive, space, and military industries. However, despite the increased performance capabilities of these leading-edge package types, their thermo-mechanical reliability is a concern for harsh environment applications.

In this work, risk-management models for reliability prediction of BGA packages on NO-CORE assemblies in harsh environments have been presented. The models presented in this paper provide decision guidance for selection of component packaging technologies. In addition, qualitative parameter interaction effects, which are often ignored in closed-form modeling, have been incorporated in this work. Previous studies have focused on deterministic prediction of reliability. There is need for a turnkey approach for making trade-offs between geometry and materials, and quantitatively evaluating the impact on reliability.

The presented statistics based approach targets a probabilistic life prediction for component wear-out under thermo-mechanical stresses. Models developed have been correlated with experimental data and non-linear finite element models. Factor effects for geometry, materials, and architectures based on statistical models, and FEA models have been developed. Convergence of statistical, failure mechanics, and FEA based model sensitivities with experimental data has been demonstrated. Validation of model predictions with accelerated test data has been presented.

#### ACKNOWLEDGEMENTS

The author acknowledges and extends gratitude for financial support received from Northrop Grumman Corporation. Many thanks are due to the author's advisor, Prof. Pradeep Lall, and other committee members for their invaluable guidance and help during the course of this study.

Deepest gratitude is also due to the author's mother, Carolyn Coffee, for being a constant source of inspiration and motivation, and to friends, Luke Drake, Sameep Gupte, Ganesh Hariharan, and all other colleagues and friends whose names are not mentioned, for their priceless love and support.

Style manual or journal used: <u>Guide to Preparation and Submission of Theses and Dissertations</u>

Computer software used: Microsoft Office 2003, Lab View 6.1, Ansys 9.0,

Minitab 13.1, WinSmith Weibull 3.0

## TABLE OF CONTENTS

| LIST OF FIG | URES                                                  | xiii |

|-------------|-------------------------------------------------------|------|

| LIST OF TAE | BLES                                                  | xix  |

| CHAPTER 1   | INTRODUCTION                                          | 1    |

| 1.1         | Test Parameters                                       | 1    |

| 1.2         | Failure Monitoring                                    | 11   |

| 1.3         | Thermo-Mechanical Reliability                         | 12   |

| 1.4         | Finite Element Modeling                               | 13   |

| 1.5         | Statistical Analysis                                  | 13   |

| CHAPTER 2   | LITERATURE REVIEW                                     | 15   |

| 2.1         | Experimental Techniques.                              | 15   |

| 2.2         | Statistical Analysis                                  | 17   |

| 2.3         | Finite Element Based Numerical Techniques             | 19   |

| 2.4         | Constitutive Behavior of Solder Material              | 20   |

| 2.5         | Objectives and Scope of the Thesis                    | 21   |

| CHAPTER 3   | TEST EQUIPMENT                                        | 23   |

| 3.1         | Experimental Test Equipment                           | 23   |

|             | 3.1.1 Keithley Model 7002 High Density Switch Systems | 23   |

|             | 3.1.2 Keithley 7011-C Quad 1 x 10 Multiplexers        | 25   |

|           | 3.1.3  | Keithley Model 2000 Multimeter | 26 |

|-----------|--------|--------------------------------|----|

|           | 3.1.4  | Fluke 73 Series III Multimeter | 27 |

|           | 3.1.5  | SlimKIC 2000 Thermal Profiler  | 28 |

|           | 3.1.6  | Environmental Chambers         | 29 |

| 3.2       | Lab V  | iew Data Acquisition Program   | 32 |

|           | 3.2.1  | Configuration Files            | 33 |

|           |        | 3.2.1.1 Markstart.txt          | 34 |

|           |        | 3.2.1.2 Rlogset.txt            | 36 |

|           |        | 3.2.1.3 Rtd.txt                | 37 |

|           |        | 3.2.1.4 bBfval.txt             | 38 |

|           |        | 3.2.1.5 bBnameC.txt            | 39 |

|           | 3.2.2  | Data Files                     | 41 |

|           |        | 3.2.2.1 Counta.txt             | 41 |

|           |        | 3.2.2.2 bBfailC.txt            | 42 |

|           |        | 3.2.2.3 bBdataC.txt            | 44 |

|           |        | 3.2.2.4 bBlogC.txt             | 44 |

|           | 3.2.3  | Executing Lab View Software    | 45 |

| 3.3       | Packa  | ge Cross-Sectioning Procedure  | 46 |

| CHAPTER 4 | FINIT  | E ELEMENT ANALYSIS             | 53 |

| 4.1       | Geom   | etry                           | 54 |

| 4.2       | Mater  | ial Properties                 | 57 |

| 4.3       | Finite | Element Modeling Approach      | 58 |

|           | 4.3.1  | Anand Viscoplasticity          | 62 |

|           | 4.3.2   | ANSYS Element Types                         | 63  |

|-----------|---------|---------------------------------------------|-----|

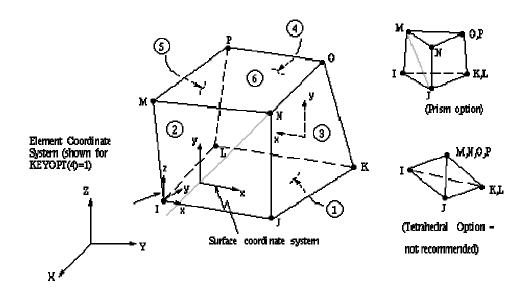

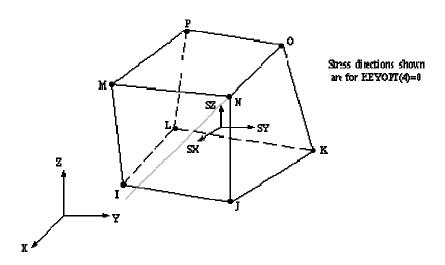

|           |         | 4.3.2.1 SOLID45 Element                     | 63  |

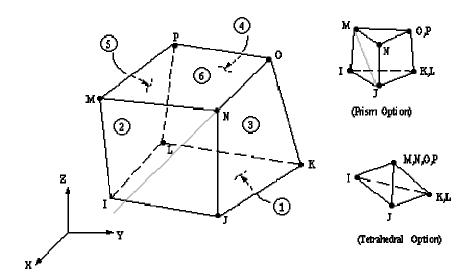

|           |         | 4.3.2.2 VISCO107 Element                    | 64  |

|           | 4.3.3   | Modeling Assumptions                        | 66  |

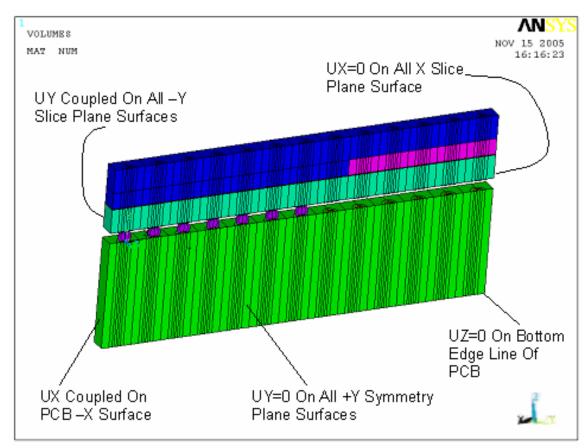

|           | 4.3.4   | Boundary conditions                         | 67  |

| 4.4       | Non-I   | Linear Finite Element Model for 532 I/O BGA | 69  |

| 4.5       | Non-I   | Linear Finite Element Model for 49 I/O BGA  | 76  |

|           | 4.5.1   | Eutectic Solder                             | 79  |

|           | 4.5.2   | SAC305 Solder                               | 86  |

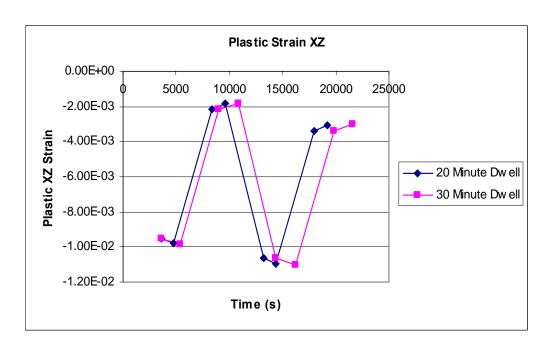

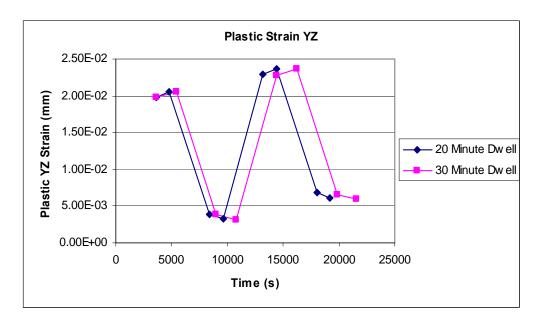

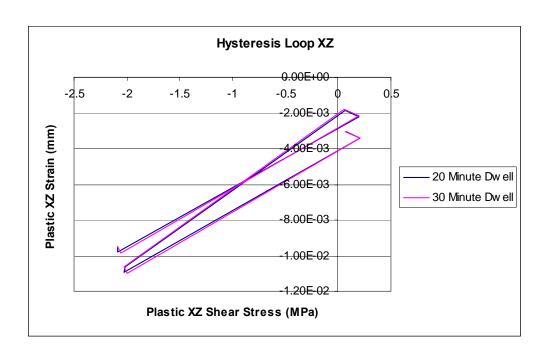

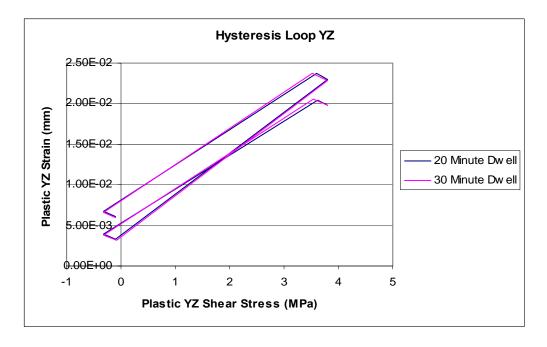

| 4.6       | Time    | History Post Processing of 49 I/O BGA Model | 93  |

|           | 4.6.1   | Eutectic Solder                             | 93  |

|           | 4.6.2   | SAC305 Solder                               | 95  |

| 4.7       | Plastic | c Work Calculation                          | 97  |

|           | 4.7.1   | Eutectic Solder Results                     | 98  |

|           | 4.7.2   | SAC305 Solder Results                       | 99  |

| CHAPTER 5 | STAT    | TISTICAL MODELING                           | 103 |

| 5.1       | Hybri   | d Approach                                  | 103 |

| 5.2       | Mode    | l Library                                   | 105 |

|           | 5.2.1   | Log-Log Model for No Copper Core PCBs       | 106 |

|           | 5.2.2   | Log-Linear Model for No Copper Core PCBs    | 110 |

|           | 5.2.3   | Log-Log Model for No Copper Core PCBs       | 115 |

| 5.3       | Mode    | l Validation                                | 116 |

|           | 5.3.1   | Temperature Cycle Condition                 | 117 |

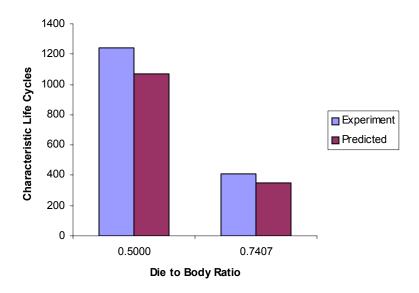

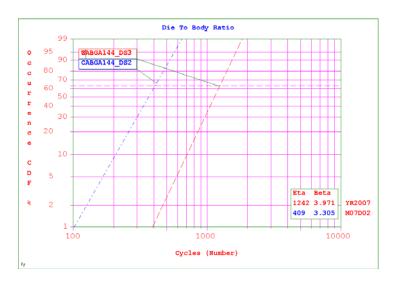

|            | 5.3.2   | Die to Package Ratio          | .118 |

|------------|---------|-------------------------------|------|

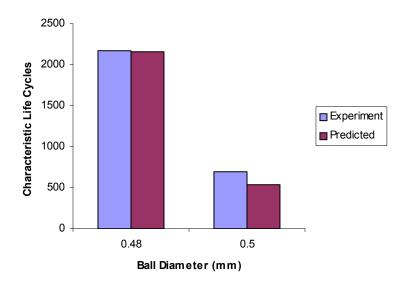

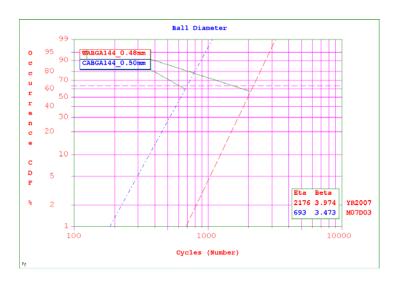

|            | 5.3.3   | Ball Diameter                 | .119 |

|            | 5.3.4   | Model Validation              | .121 |

| CHAPTER 6  | SUMN    | MARY AND CONCLUSIONS          | .124 |

| BIBLIOGRAI | PHY     |                               | .126 |

| APPENDIX A | A – WE  | IBULL PLOTS OF TEST PACKAGES  | .140 |

| APPENDIX E | B – ADI | DITIONAL FINITE ELEMENT PLOTS | .153 |

## LIST OF FIGURES

| 1.1  | CCA's 091-099 (TC2: -55C to 125C). Side A of test board      | 2  |

|------|--------------------------------------------------------------|----|

| 1.2  | CCA's 091-099 (TC2: -55C to 125C). Side B of test board      | 3  |

| 1.3  | CCA's 109-117 (TC2: -55C to 125C). Side A of test board      | 3  |

| 1.4  | CCA's 109-117 (TC2: -55C to 125C). Side B of test board      | 4  |

| 1.5  | CCA's 127-135 (TC2: -55C to 125C). Side A of test board      | 4  |

| 1.6  | CCA's 127-135 (TC2: -55C to 125C). Side B of test board      | 5  |

| 1.7  | CCA's 136-144 (TC3: 3C to 100C). Side A of test board        | 5  |

| 1.8  | CCA's 136-144 (TC3: 3C to 100C). Side B of test board        | 6  |

| 1.9  | CCA's 145-154 (TC4: -20C to 60C). Side A of test board       | 6  |

| 1.10 | CCA's 145-154 (TC4: -20C to 60C). Side B of test board       | 7  |

| 1.11 | Various packages of acceleration test                        | 8  |

| 1.12 | Various packages of acceleration test                        | 8  |

| 1.13 | Various packages of acceleration test                        | 9  |

| 1.14 | TC2 thermal cycling temperature profile                      | 10 |

| 1.15 | TC3 thermal cycling temperature profile                      | 10 |

| 1.16 | TC4 thermal cycling temperature profile                      | 11 |

| 3.1  | Front view of Keithley Model 7002 High Density Switch System | 24 |

| 3.2  | Back view of Keithley Model 7002 High Density Switch System  | 24 |

| 3.3  | Keithley 7011-C multiplexer card                             | 25 |

| 3.4  | Wiring setup of Keithley Model 7002 High Density Switch System | 26 |

|------|----------------------------------------------------------------|----|

| 3.5  | Keithley Model 2000 Multimeter                                 | 27 |

| 3.6  | Fluke 73 Series III Digital Multimeter                         | 28 |

| 3.7  | SlimKIC 2000 thermal profile system                            | 29 |

| 3.8  | Blue M VRC environmental chamber                               | 30 |

| 3.9  | Thermotron S-1.2 Mini-Max environmental chamber                | 31 |

| 3.10 | Tenney Jr. environmental chamber                               | 32 |

| 3.11 | Screenshot of the Lab View data acquisition system software    | 33 |

| 3.12 | Experimental data failure catalog system                       | 46 |

| 3.13 | Example of cross-sectioning cutting scheme                     | 47 |

| 3.14 | The Isomet 1000 wetsaw                                         | 48 |

| 3.15 | Materials used for epoxy coating cross-sectioned samples       | 49 |

| 3.16 | The Ecomet 6 polisher                                          | 50 |

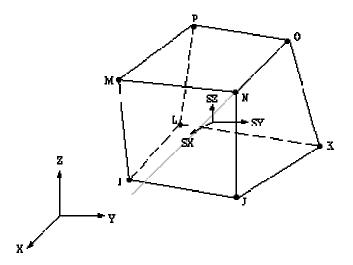

| 4.1  | Diagram of slice model geometry                                | 55 |

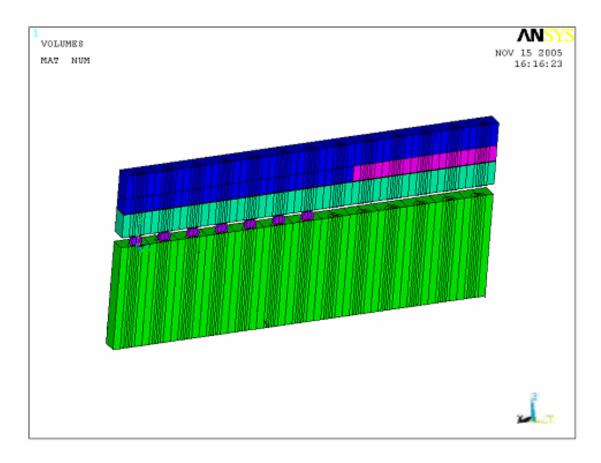

| 4.2  | Isometric view of a slice model                                | 56 |

| 4.3  | SOLID45 3-D Structural Solid                                   | 63 |

| 4.4  | SOLID45 Stress Output                                          | 64 |

| 4.5  | VISCO107 3-D Large Strain Solid                                | 65 |

| 4.6  | VISCO107 Default (No ESYS) Element Coordinate System           | 66 |

| 4.7  | Boundary conditions used for typical slice models              | 68 |

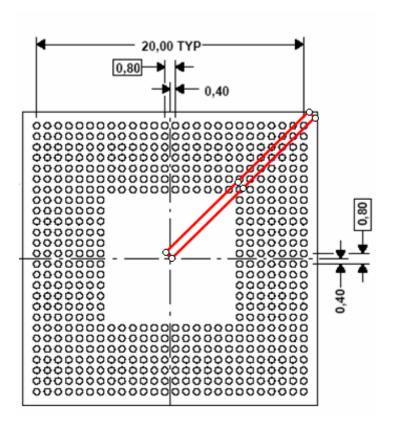

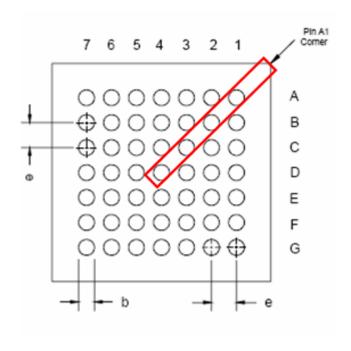

| 4.8  | Footprint of UBGA 532 package                                  | 69 |

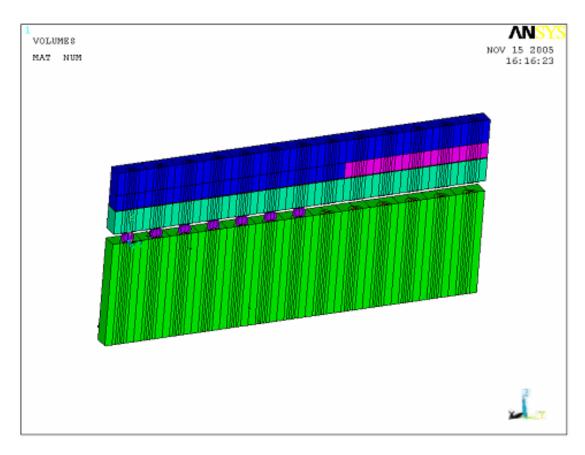

| 4.9  | Isometric volumetric plot of the 532 I/O slice model           | 70 |

| 4.10 | Contour plot of accumulated plastic work on the solder joints  | 71 |

| 4.11 | Contour plot of accumulated plastic work on the critical solder joint          | 72 |

|------|--------------------------------------------------------------------------------|----|

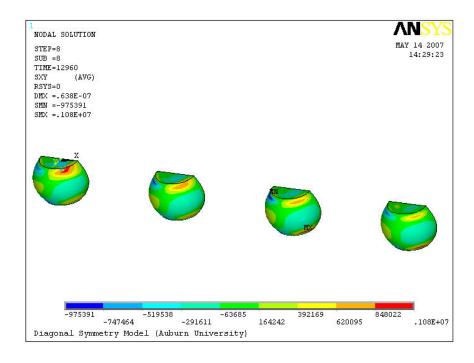

| 4.12 | Plastic shear stress plot results for the XZ plane                             | 73 |

| 4.13 | Plastic shear stress plot results for the YZ plane                             | 73 |

| 4.14 | Plastic shear strain plot results for the XZ plane                             | 74 |

| 4.15 | Plastic shear strain plot results for the YZ plane                             | 74 |

| 4.16 | Hysteresis loop plot results for the XZ plane                                  | 75 |

| 4.17 | Hysteresis loop plot results for the YZ plane                                  | 75 |

| 4.18 | Footprint of UBGA 49 package                                                   | 76 |

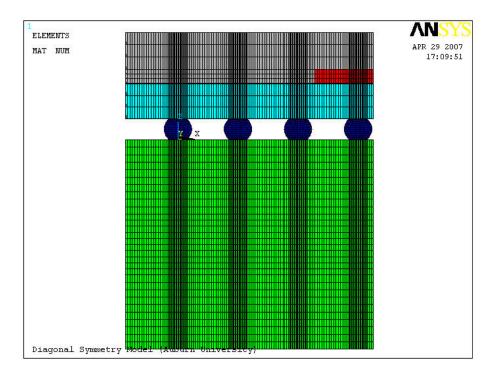

| 4.19 | Front view of UBGA 49 Finite Element Model                                     | 77 |

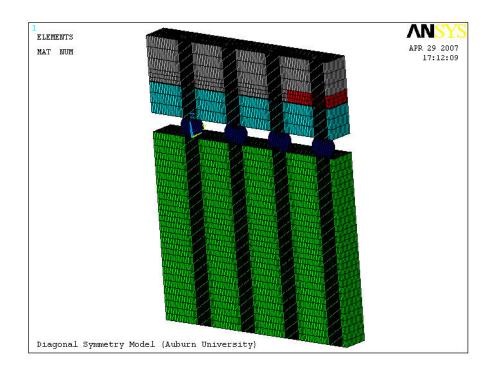

| 4.20 | Isometric view of UBGA 49 Finite Element Model.                                | 78 |

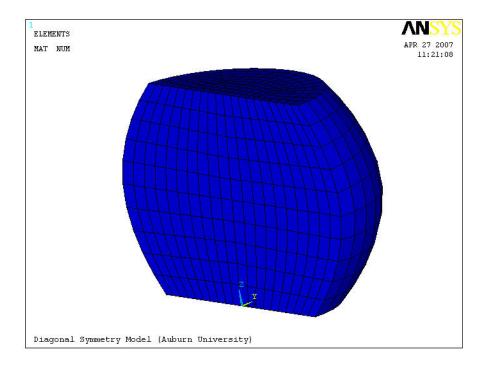

| 4.21 | Isometric view of solder joint                                                 | 78 |

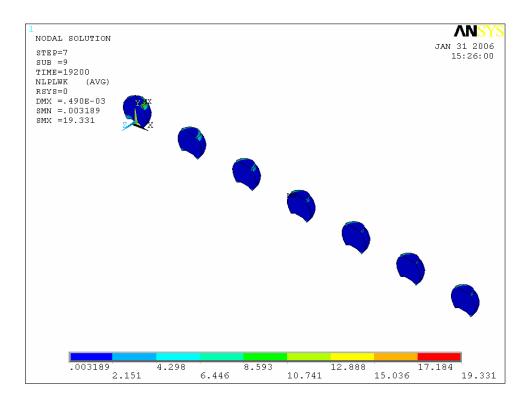

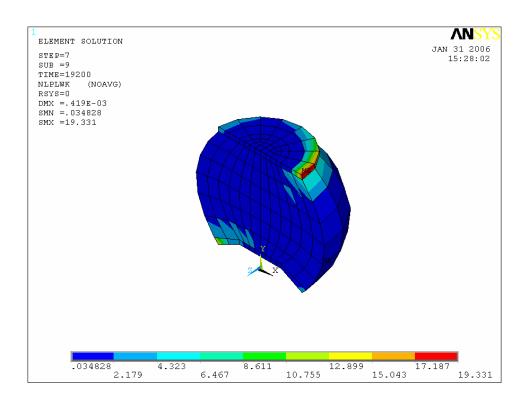

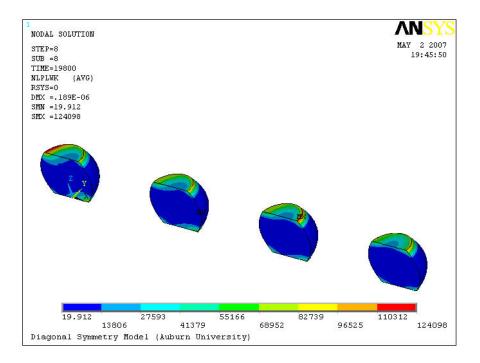

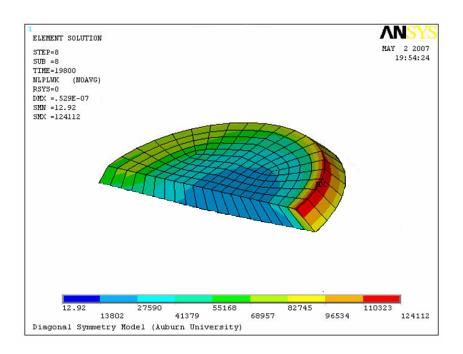

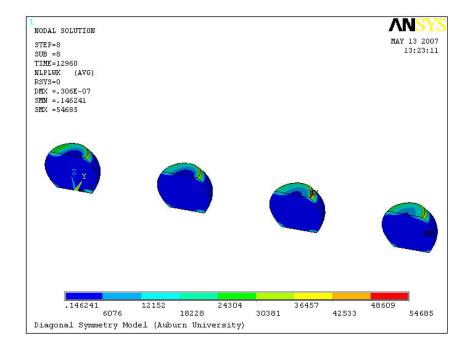

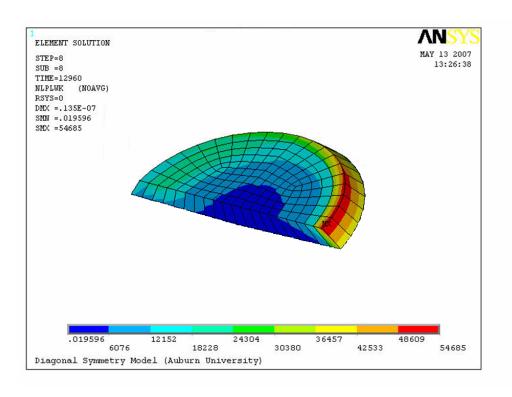

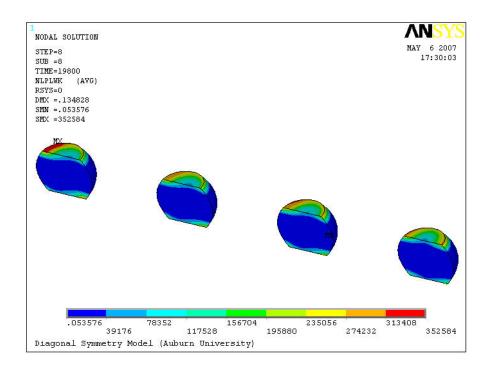

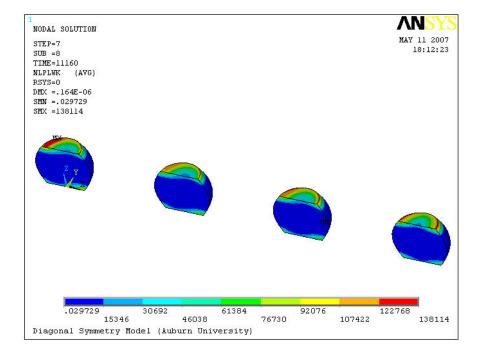

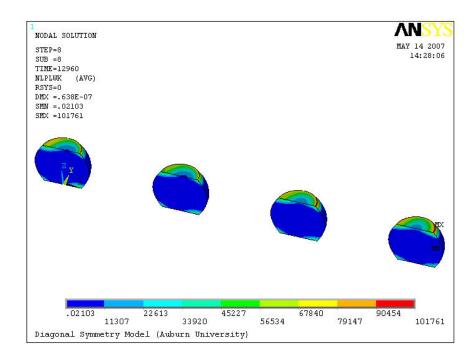

| 4.22 | Plastic work plot of all eutectic solder joints subjected to TC2 condition     | 79 |

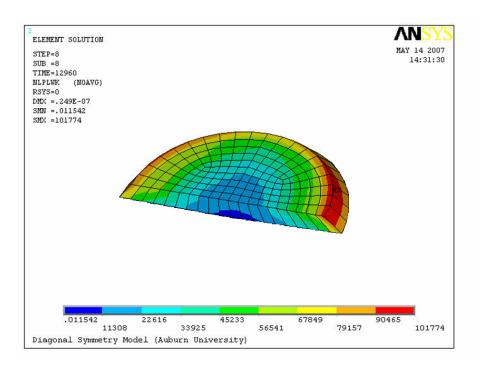

| 4.23 | Plastic work plot of worst eutectic solder joint subjected                     | 80 |

|      | to TC2 condition.                                                              |    |

| 4.24 | Plastic work plot of all eutectic solder joints subjected to TC3 condition     | 80 |

| 4.25 | Plastic work plot of worst eutectic solder joint subjected                     | 81 |

|      | to TC3 condition.                                                              |    |

| 4.26 | Plastic work plot of all eutectic solder joints subjected to TC4 condition     | 81 |

| 4.27 | Plastic work plot of worst eutectic solder joint subjected                     | 82 |

|      | to TC4 condition.                                                              |    |

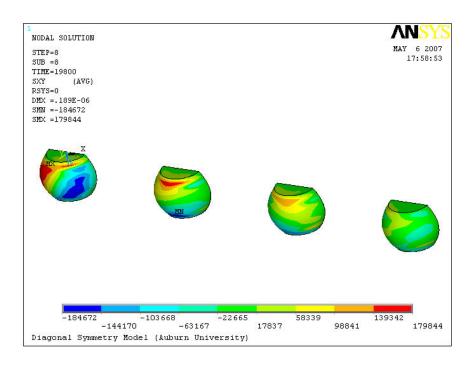

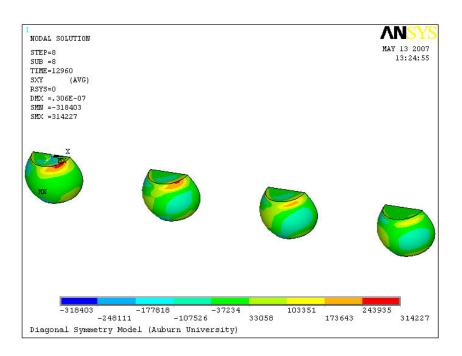

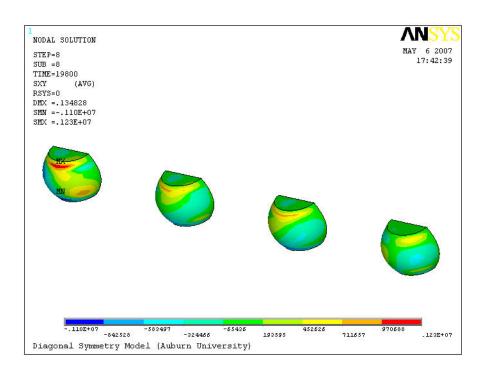

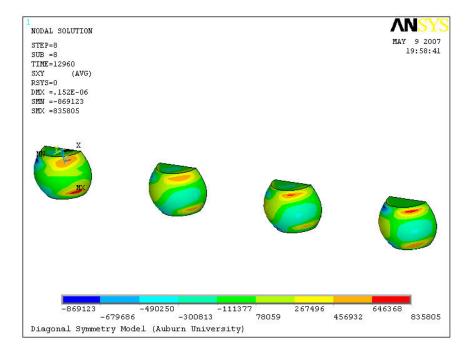

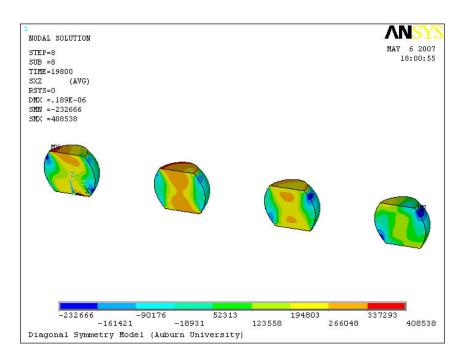

| 4.28 | XY Shear Stress plot of all eutectic solder joints subjected to TC2 condition. | 83 |

| 4.29 | XY Shear Stress plot of all eutectic solder joints subjected to TC3 condition. | 83 |

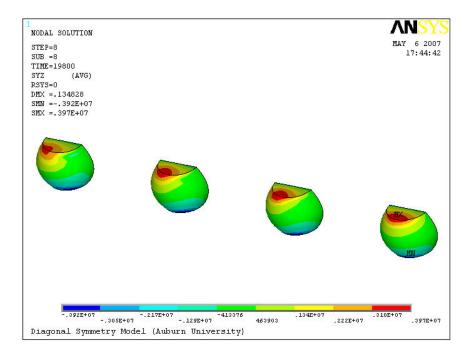

| 4.30 | XY Shear Stress plot of all eutectic solder joints subjected to TC4 condition. | 84 |

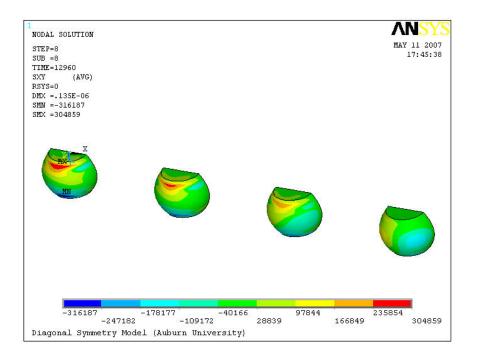

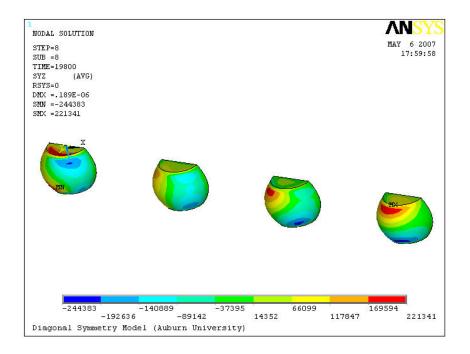

| 4.31 | YZ Shear Stress plot of all eutectic solder joints subjected to TC2 condition84 |

|------|---------------------------------------------------------------------------------|

| 4.32 | YZ Shear Stress plot of all eutectic solder joints subjected to TC3 condition85 |

| 4.33 | YZ Shear Stress plot of all eutectic solder joints subjected to TC4 condition85 |

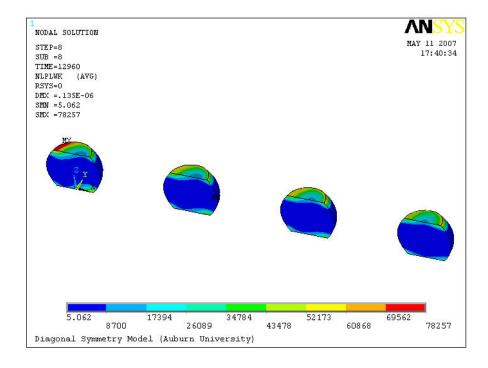

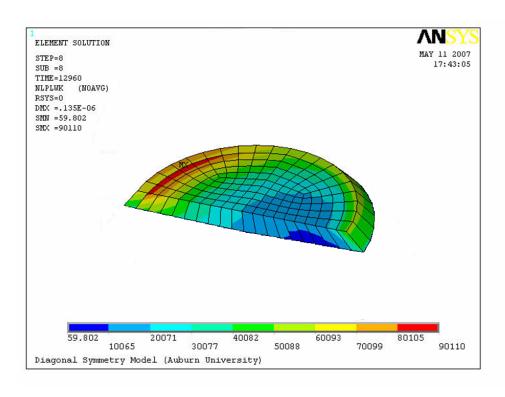

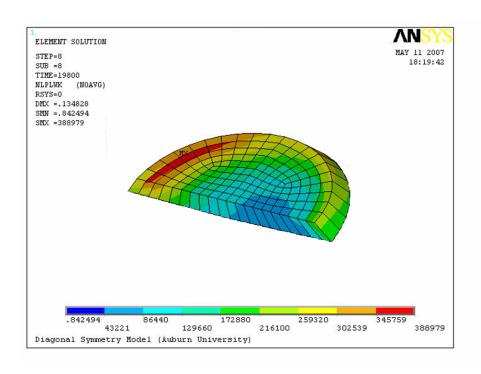

| 4.34 | Plastic work plot of all SAC305 solder joints subjected to TC2 condition86      |

| 4.35 | Plastic work plot of worst SAC305 solder joint subjected                        |

|      | to TC2 condition                                                                |

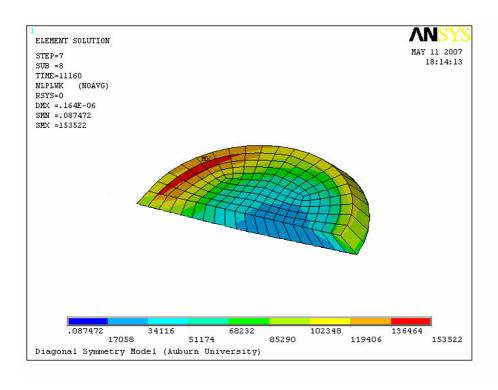

| 4.36 | Plastic work plot of all SAC305 solder joints subjected to TC3 condition87      |

| 4.37 | Plastic work plot of worst SAC305 solder joint subjected                        |

|      | to TC3 condition                                                                |

| 4.38 | Plastic work plot of all SAC305 solder joints subjected to TC4 condition88      |

| 4.39 | Plastic work plot of the most damaged SAC305 solder joint subjected89           |

|      | to TC4 condition                                                                |

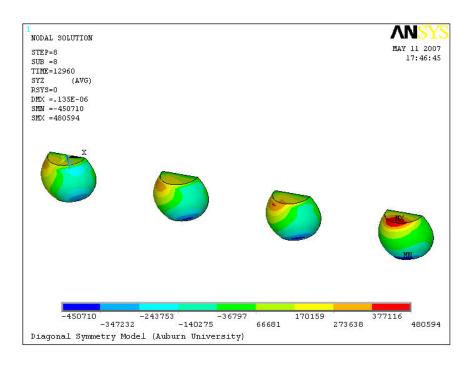

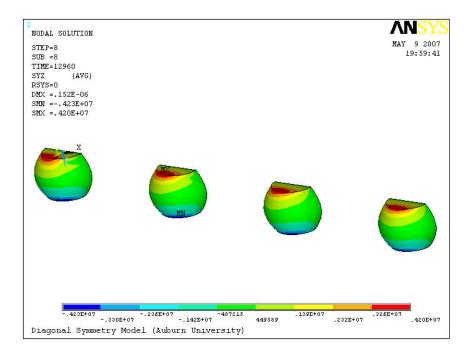

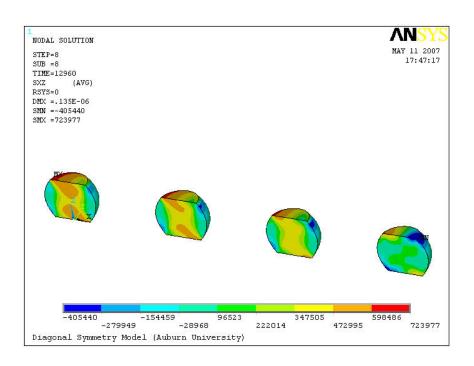

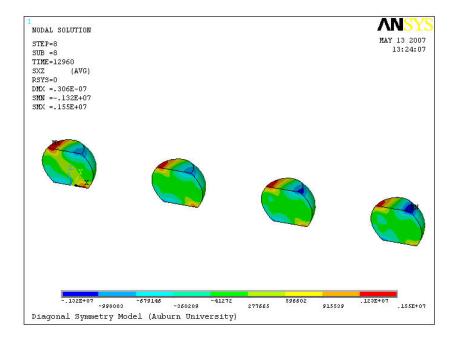

| 4.40 | XY Shear Stress plot of all SAC305 solder joints subjected to TC2 condition90   |

| 4.41 | XY Shear Stress plot of all SAC305 solder joints subjected to TC3 condition90   |

| 4.42 | XY Shear Stress plot of all SAC305 solder joints subjected to TC4 condition91   |

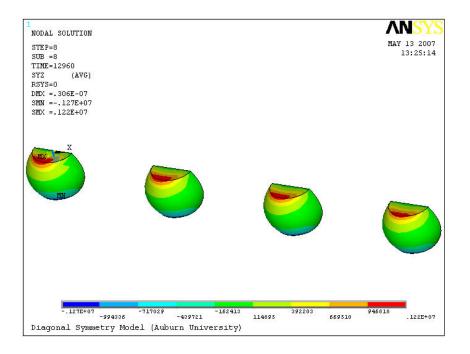

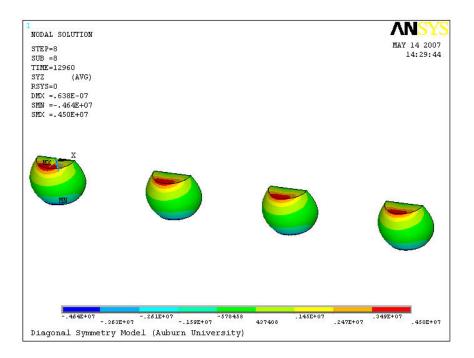

| 4.43 | YZ Shear Stress plot of all SAC305 solder joints subjected to TC2 condition91   |

| 4.44 | YZ Shear Stress plot of all SAC305 solder joints subjected to TC3 condition92   |

| 4.45 | YZ Shear Stress plot of all SAC305 solder joints subjected to TC4 condition92   |

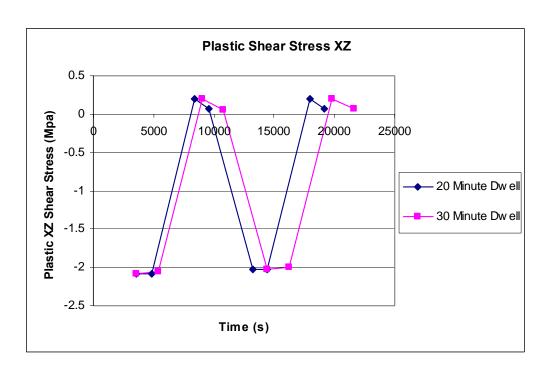

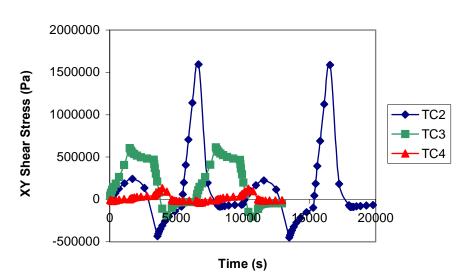

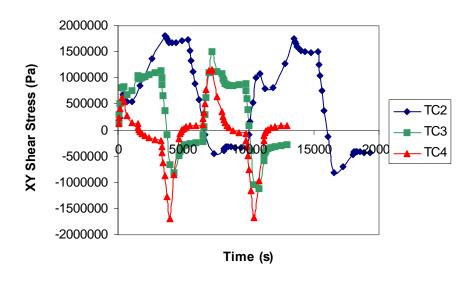

| 4.46 | XY Stress vs. Time plot for eutectic solder                                     |

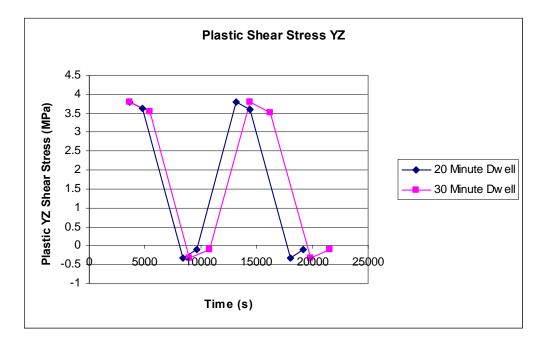

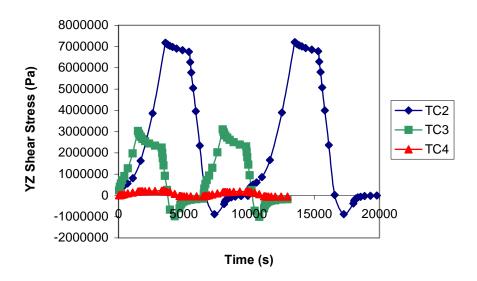

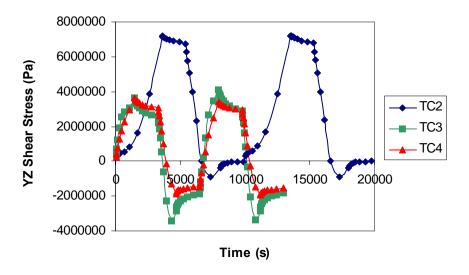

| 4.47 | YZ Stress vs. Time plot for eutectic solder94                                   |

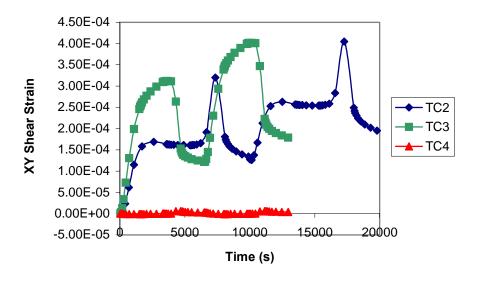

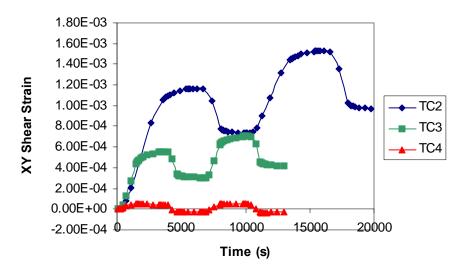

| 4.48 | XY Strain vs. Time plot for eutectic solder94                                   |

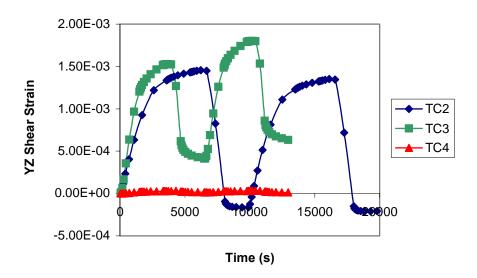

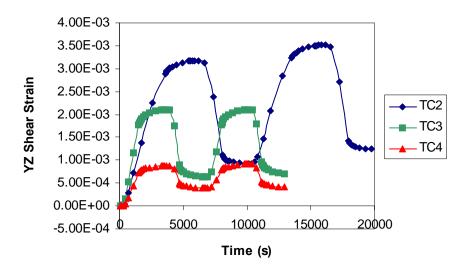

| 4.49 | YZ Strain vs. Time plot for eutectic solder95                                   |

| 4.50 | XY Stress vs. Time plot for SAC305 solder95                                     |

| 4.51 | YZ Stress vs. Time plot for SAC305 solder                                | 96  |

|------|--------------------------------------------------------------------------|-----|

| 4.52 | XY Strain vs. Time plot for SAC305 solder                                | 96  |

| 4.53 | YZ Strain vs. Time plot for SAC305 solder                                | 97  |

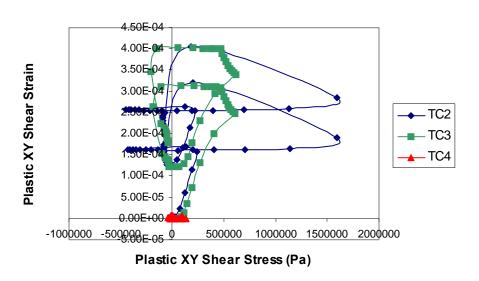

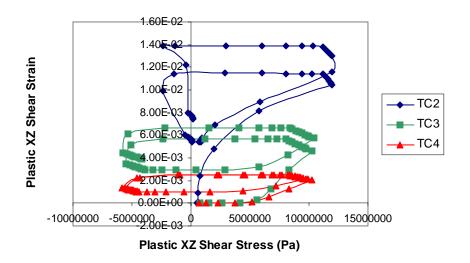

| 4.54 | XY Hysteresis plot of eutectic solder for TC2, TC3, and TC4 conditions   | 98  |

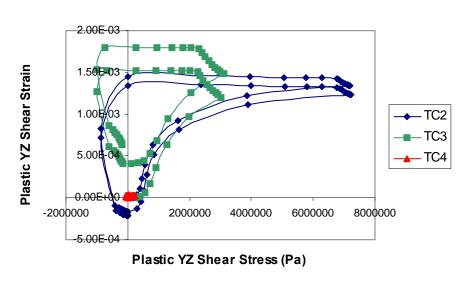

| 4.55 | YZ Hysteresis plot of eutectic solder for TC2, TC3, and TC4 conditions   | 98  |

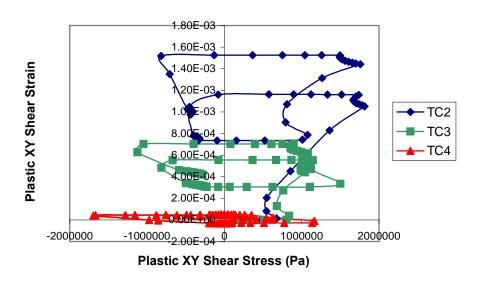

| 4.56 | XY Hysteresis plot of SAC305 solder for TC2, TC3, and TC4 conditions     | 99  |

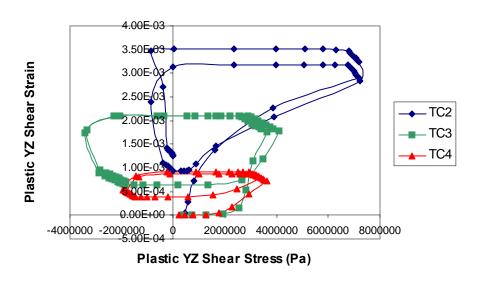

| 4.57 | YZ Hysteresis plot of SAC305 solder for TC2, TC3, and TC4 conditions     | 99  |

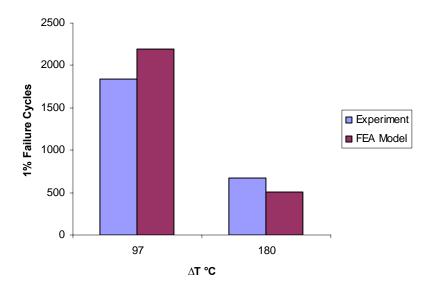

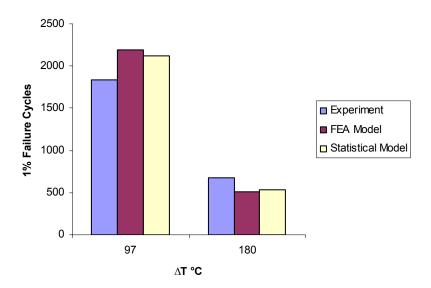

| 4.58 | Correlation between experimental vs. FE predicted N1% failure cycles     | 101 |

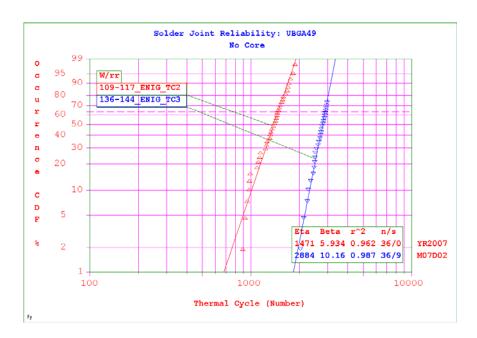

| 4.59 | Weibull distribution for 49 I/O package                                  | 102 |

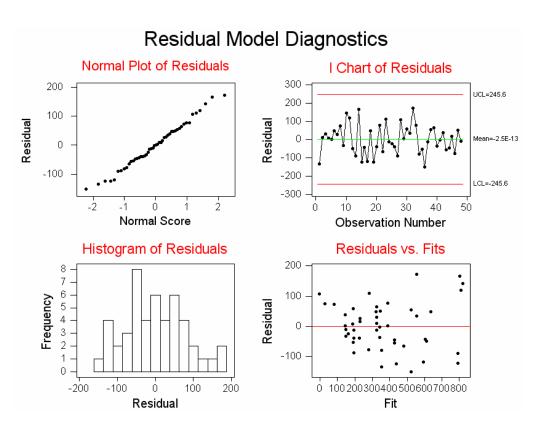

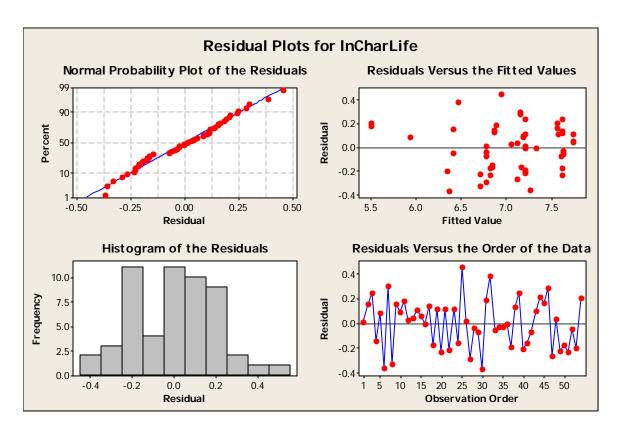

| 5.1  | Residual plots for the statistical model                                 | 108 |

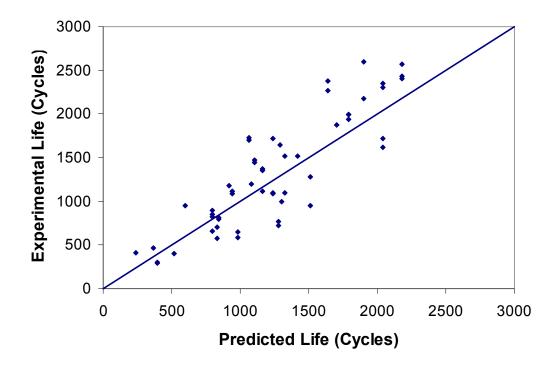

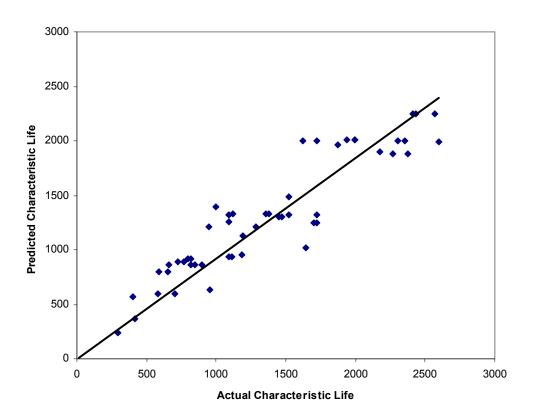

| 5.2  | Actual versus predicted 1% failure cycles plot for modified linear model | 109 |

| 5.3  | Residual plots for the statistical model                                 | 113 |

| 5.4  | Actual versus predicted characteristic life failure cycles plot          | 114 |

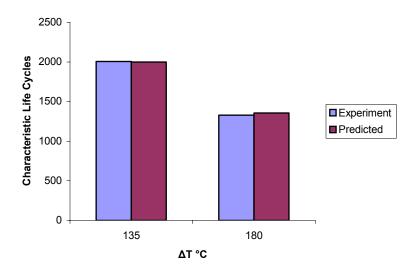

| 5.5  | Effect of temperature cycling range on 196 I/O BGA coupled with          | 117 |

|      | Die Area, Ball Pitch, Ball Diameter, and Die to Body Ratio               |     |

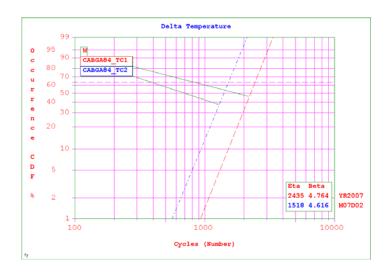

| 5.6  | Weibull plot of packages used for ΔT graph                               | 118 |

| 5.7  | Effect of Die to Body Ratio on 196 I/O BGA coupled with Die Area,        | 119 |

|      | Ball Pitch, Ball Diameter, and $\Delta T$ .                              |     |

| 5.8  | Weibull plot of packages used for Die to Body Ratio graph                | 119 |

| 5.9  | Effect of Ball Diameter on 100 I/O BGA coupled with Package              | 120 |

|      | Pad Area, Ball Pitch, and $\Delta T$ .                                   |     |

| 5.10 | Weibull plot of packages used for Ball Diameter graph                    | 121 |

| 5.11 | Effect of ΔT on thermal reliability of 7mm PBGA package                  | 122 |

| 5.12 | Weibull plot of packages used for correlation graph. | 122 |

|------|------------------------------------------------------|-----|

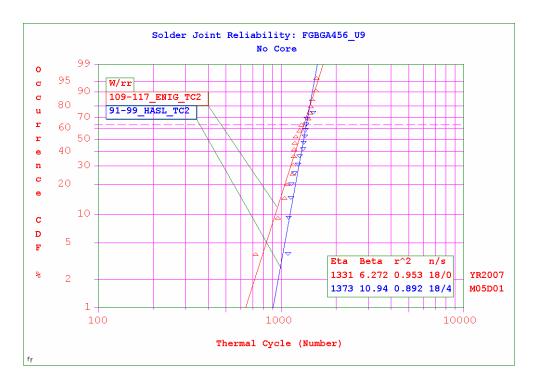

| A.1  | Weibull plot results for FGBGA456                    | 140 |

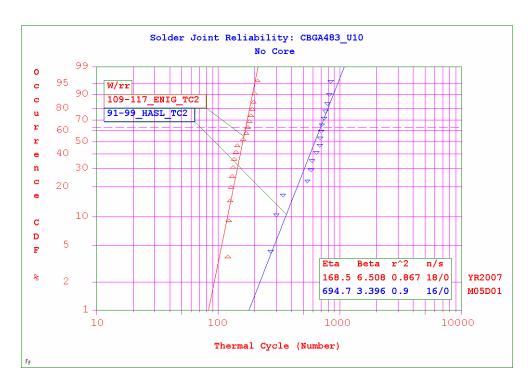

| A.2  | Weibull plot results for CBGA483                     | 141 |

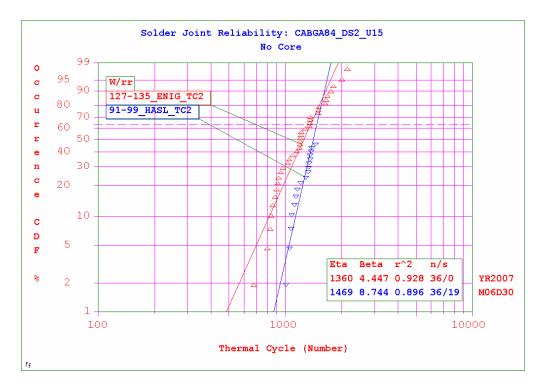

| A.3  | Weibull plot results for CAGA84                      | 141 |

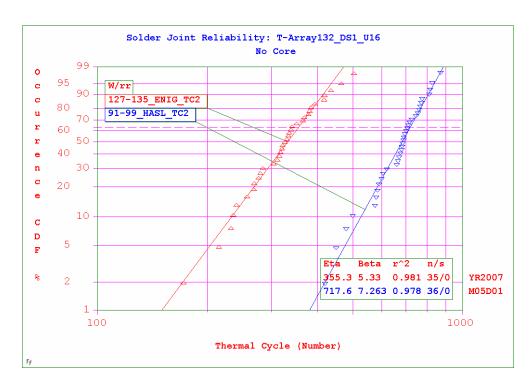

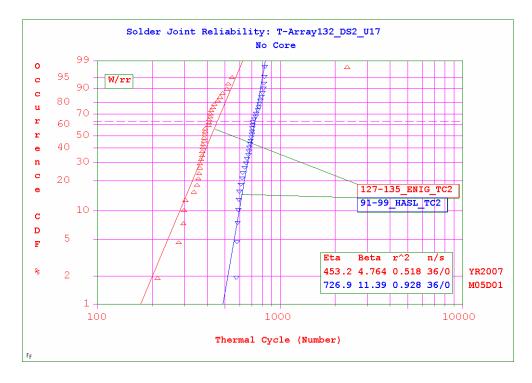

| A.4  | Weibull plot results for T-Array132_DS1              | 142 |

| A.5  | Weibull plot results for T-Array132_DS2              | 142 |

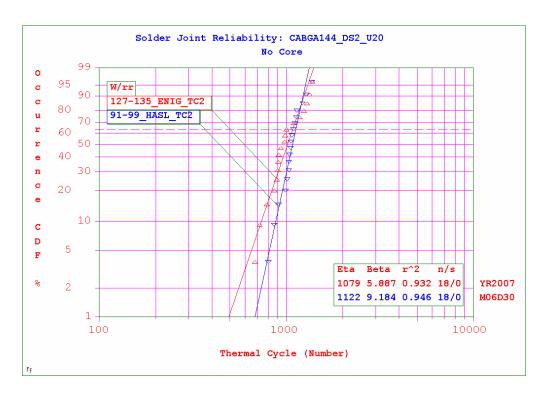

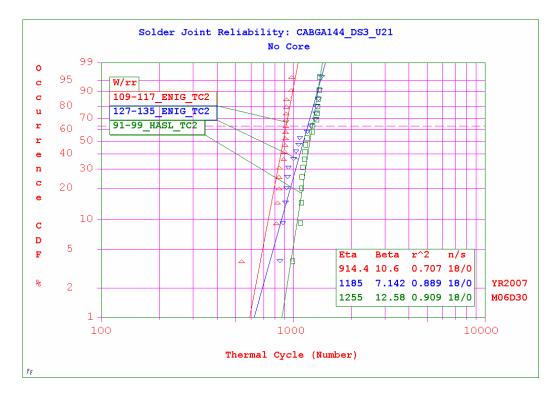

| A.6  | Weibull plot results for CABGA144_DS2                | 143 |

| A.7  | Weibull plot results for CABGA144_DS3                | 143 |

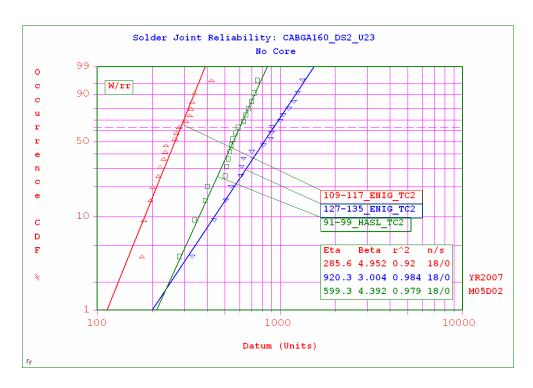

| A.8  | Weibull plot results for CABGA160                    | 144 |

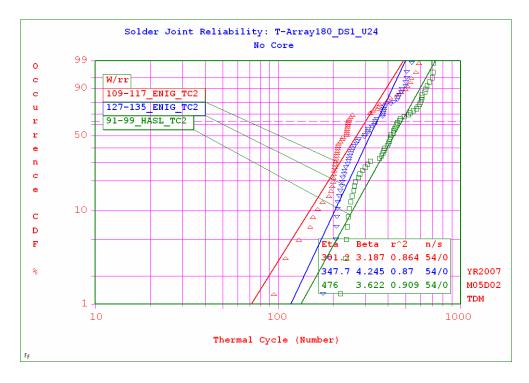

| A.9  | Weibull plot results for T-Array180_DS1              | 144 |

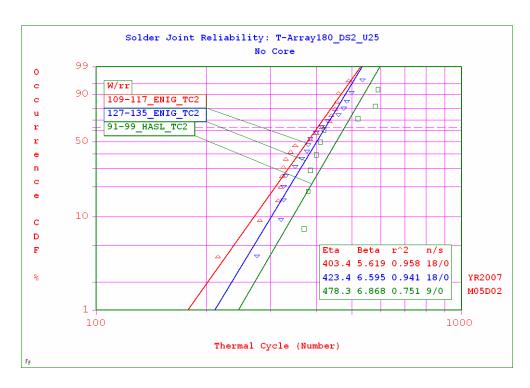

| A.10 | Weibull plot results for T-Array180_DS2              | 145 |

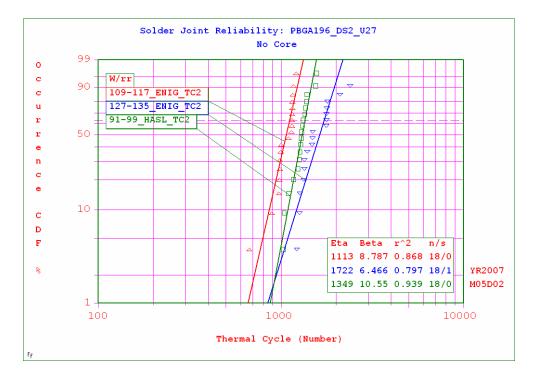

| A.11 | Weibull plot results for PBGA196_DS2                 | 145 |

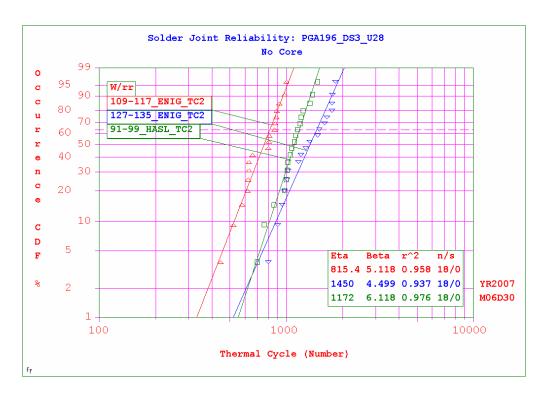

| A.12 | Weibull plot results for PBGA196_DS3                 | 146 |

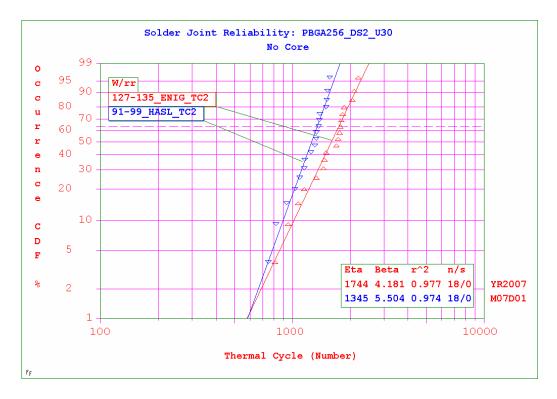

| A.13 | Weibull plot results for PBGA256_DS2                 | 146 |

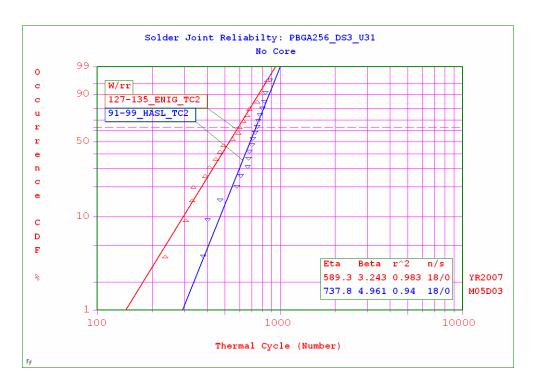

| A.14 | Weibull plot results for PBGA256_DS3                 | 147 |

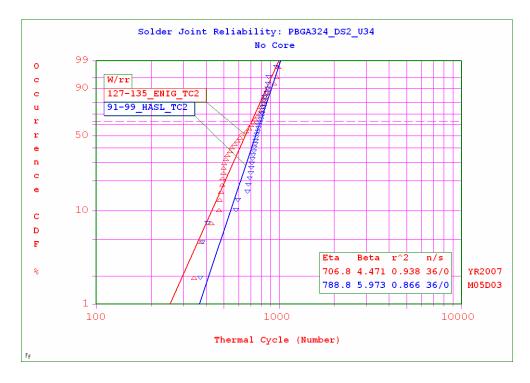

| A.15 | Weibull plot results for PBGA324                     | 147 |

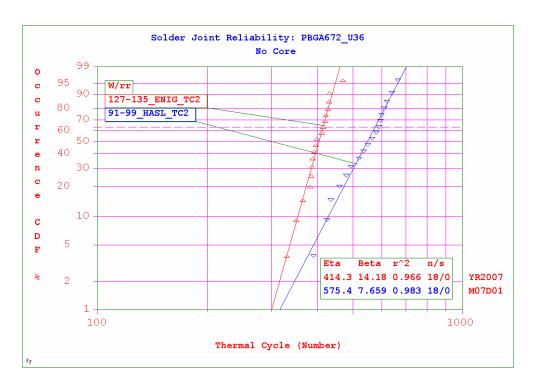

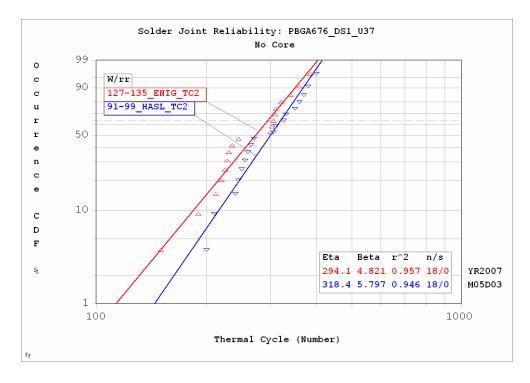

| A.16 | Weibull plot results for PBGA672                     | 148 |

| A.17 | Weibull plot results for PBGA676                     | 148 |

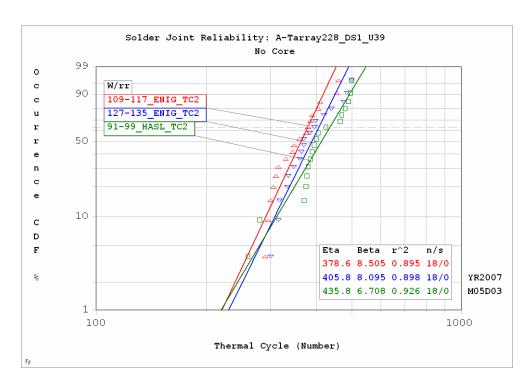

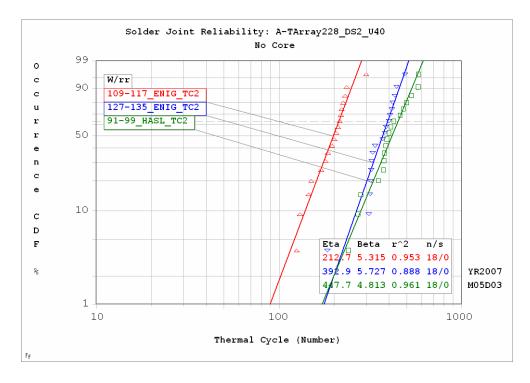

| A.18 | Weibull plot results for A-Tarray228_DS1             | 149 |

| A.19 | Weibull plot results for A-Tarray228_DS2             | 149 |

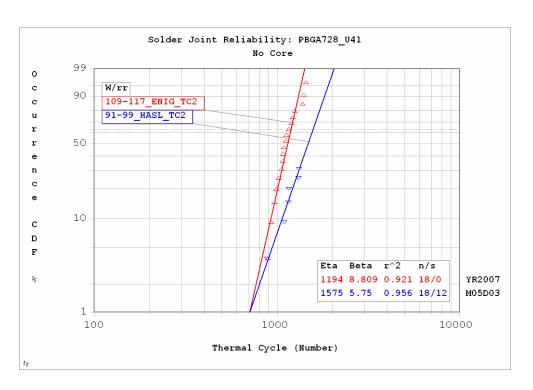

| A.20 | Weibull plot results for PBGA728                     | 150 |

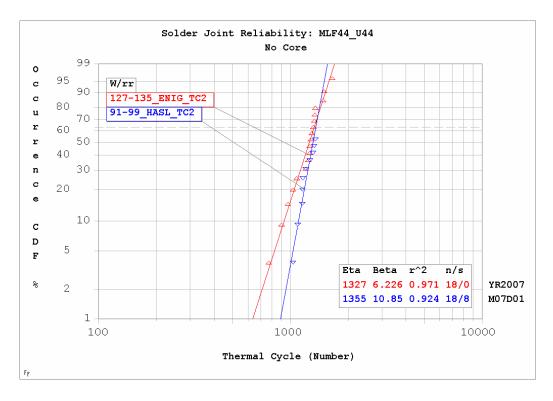

| A.21 | Weibull plot results for MLF44                       | 150 |

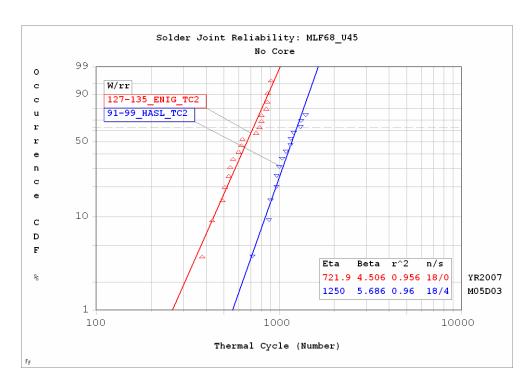

| A.22 | Weibull plot results for MLF68                       | 151 |

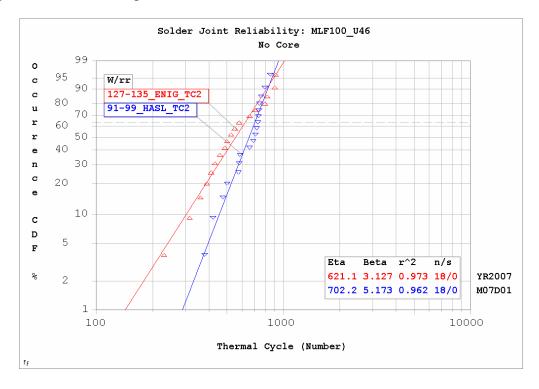

| A.23 | Weibull plot results for MLF100                                               | 151 |

|------|-------------------------------------------------------------------------------|-----|

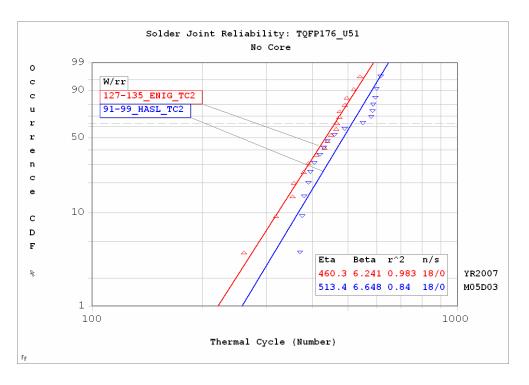

| A.24 | Weibull plot results for TQFP176.                                             | 152 |

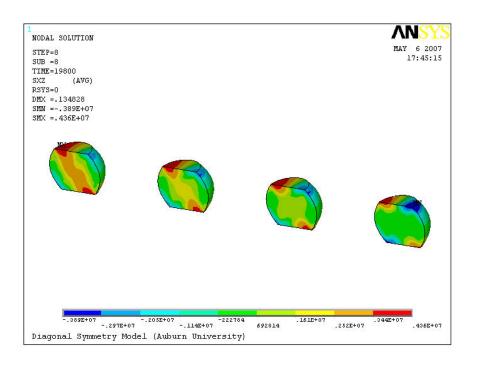

| B.1  | XZ Shear Stress plot of all eutectic solder joints subjected to TC2 condition | 153 |

| B.2  | XZ Shear Stress plot of all eutectic solder joints subjected to TC3 condition | 154 |

| B.3  | XZ Shear Stress plot of all eutectic solder joints subjected to TC4 condition | 154 |

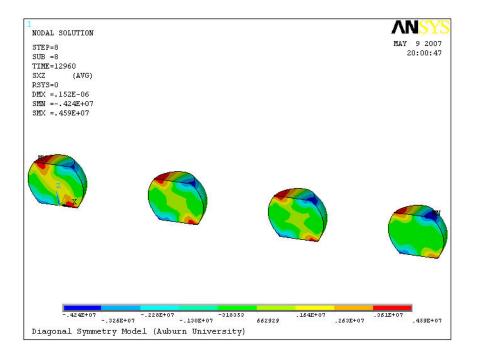

| B.4  | XZ Shear Stress plot of all SAC305 solder joints subjected to TC2             | 155 |

|      | Condition                                                                     |     |

| B.5  | XZ Shear Stress plot of all SAC305 solder joints subjected to TC3             | 155 |

|      | condition                                                                     |     |

| B.6  | XZ Shear Stress plot of all SAC305 solder joints subjected to TC4             | 156 |

|      | condition                                                                     |     |

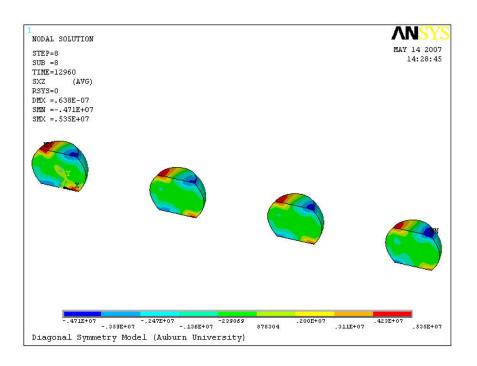

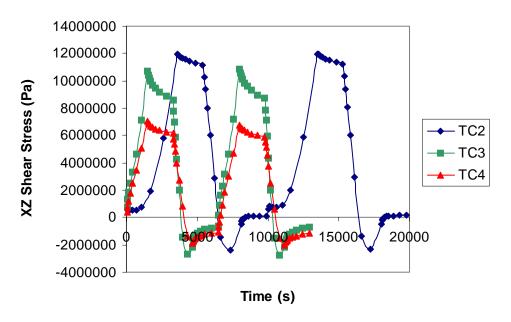

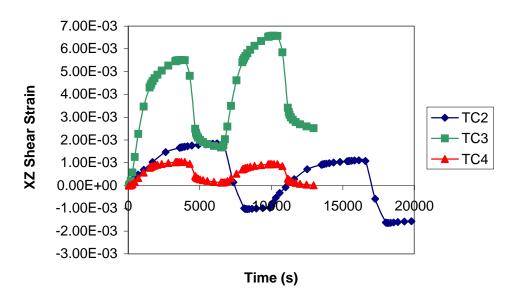

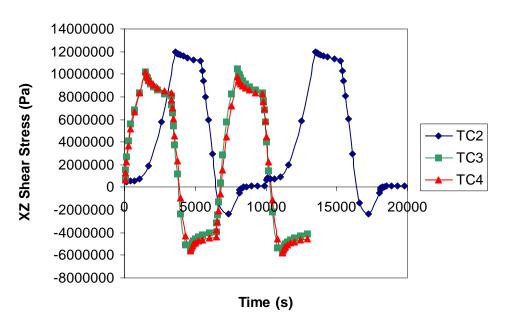

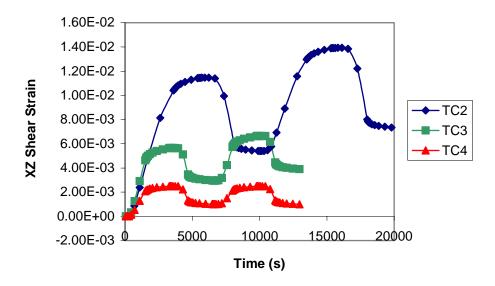

| B.7  | XZ Stress vs. Time plot for eutectic solder                                   | 156 |

| B.8  | XZ Strain vs. Time plot for eutectic solder                                   | 157 |

| B.9  | XZ Stress vs. Time plot for SAC305 solder                                     | 157 |

| B.10 | XZ Strain vs. Time plot for SAC305 solder                                     | 158 |

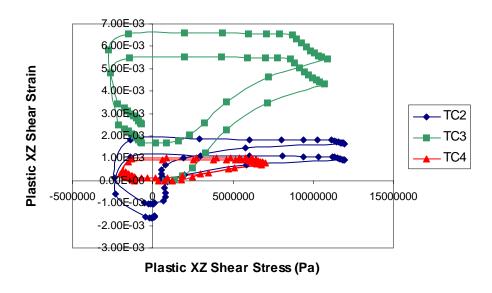

| B.11 | XZ Hysteresis plot of eutectic solder for TC2, TC3, and TC4 conditions        | 158 |

| B.12 | XZ Hysteresis plot of SAC305 solder for TC2, TC3, and TC4 conditions          | 159 |

## LIST OF TABLES

| 1.1 | Temperature conditions of accelerated test                  | 10  |

|-----|-------------------------------------------------------------|-----|

| 1.2 | Typical CTE values for package materials                    | 10  |

| 3.1 | Specifications of the Fluke 73 Series Multimeter            | 28  |

| 3.2 | Specifications of the SlimKIC 2000 Thermal Profiler         | 29  |

| 4.1 | Material Properties Used in Finite Element Model            | 58  |

| 4.2 | Anand's Constants for Solder Alloy                          | 60  |

| 4.3 | Crack Initiation and Propagation Constants                  | 62  |

| 4.4 | Dimensions for 532 I/O BGA package                          | 69  |

| 4.5 | FEA Life Prediction for UBGA49                              | 101 |

| 5.1 | Scope of Accelerated Test Database                          | 104 |

| 5.2 | Multiple Regression Log-Log Model for PBGAs on No-Core PCBs | 107 |

| 5.3 | Multivariate Linear Regression Model For PBGAs              | 111 |

| 5.4 | Multivariate Linear Regression Model For PBGAs              | 116 |

| 5.5 | FEA N1% Life Prediction.                                    | 122 |

| 5.6 | Predicted vs. Actual N1% Failure Data                       | 123 |

#### CHAPTER 1

## INTRODUCTION

Electronic packaging is the process of interconnecting electronic and electromechanical components, devices, and modules between the various layers of the electronic system [Suhling, et.al. 2004]. The package provides protection from the environment, such as protection from moisture, and from external loads and stresses; removes heat from the silicon chip; provides wiring for a power supply to the chip; and provides the wiring for the I/O information to and from the chip. With the growth and advances in the electronic packaging industry, and the trends of packages to become smaller, faster, and have more circuit density, electronics reliability is a critical concern. Damage do to thermal cycling fatigue is a major concern for electronic devices that operate in harsh environments, with the solder joint interconnects being the primary failure component.

## 1.1 Test Parameters

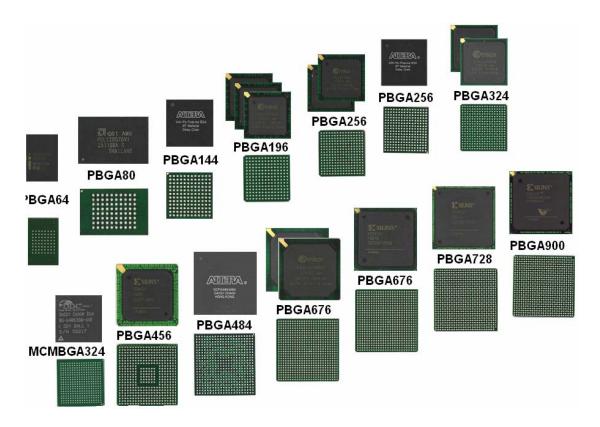

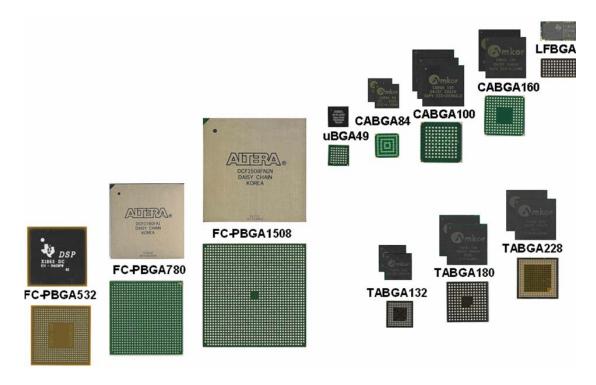

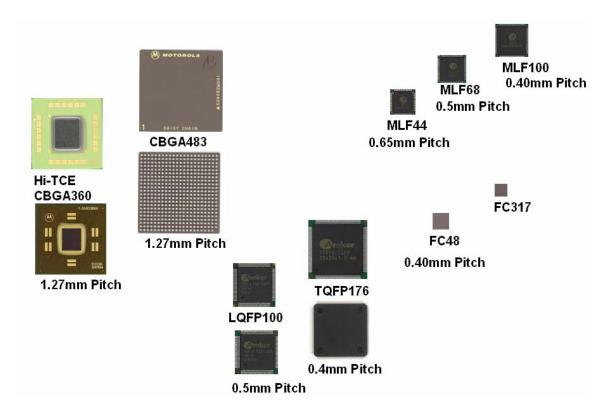

An extensive amount of test packages were monitored in this research, with a multitude of test variables and conditions to consider. Among the package architectures were: Plastic BGAs, Ceramic BGAs, Flex Grid Arrays, CSPs, and Flip Chips, with I/O counts ranging from 49 to 900. Other test variables include: solder alloy (eutectic and

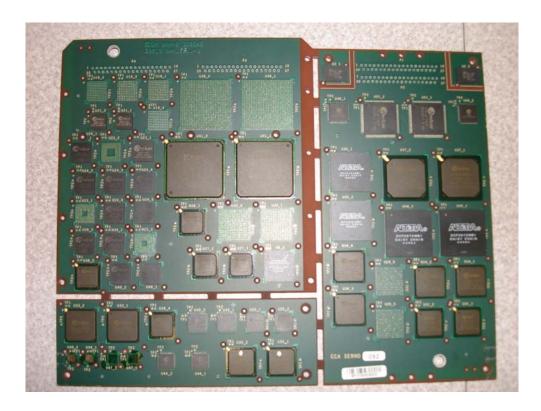

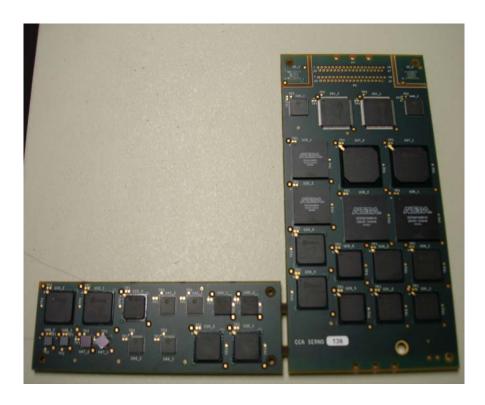

SAC305), PCB with and without a copper core, board surface finish, and four different temperature conditions. For this research, 45 No-Core PCB test boards were monitored (5 groups of 9 boards), with each test board being populated on both sides with packages. Figures 1.1 through 1.10 shows the front and back of a typical test board from each of the five test groups.

Figure 1.1. CCA's 091-099 (TC2: -55C to 125C). Side A of test board.

Figure 1.2. CCA's 091-099 (TC2: -55C to 125C). Side B of test board.

Figure 1.3. CCA's 109-117 (TC2: -55C to 125C). Side A of test board.

Figure 1.4. CCA's 109-117 (TC2: -55C to 125C). Side B of test board.

Figure 1.5. CCA's 127-135 (TC2: -55C to 125C). Side A of test board.

Figure 1.6. CCA's 127-135 (TC2: -55C to 125C). Side B of test board.

Figure 1.7. CCA's 136-144 (TC3: 3C to 100C). Side A of test board.

Figure 1.8. CCA's 136-144 (TC3: 3C to 100C). Side B of test board.

Figure 1.9. CCA's 145-154 (TC4: -20C to 60C). Side A of test board.

Figure 1.10. CCA's 145-154 (TC4: -20C to 60C). Side B of test board.

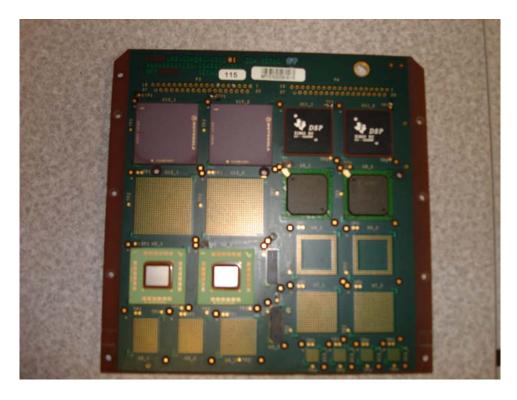

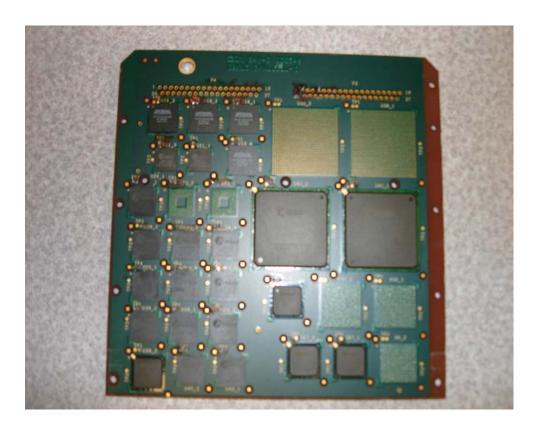

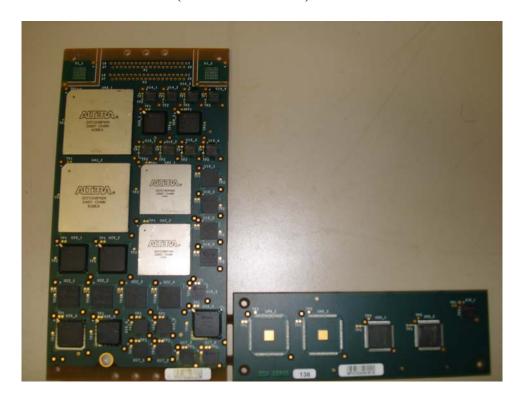

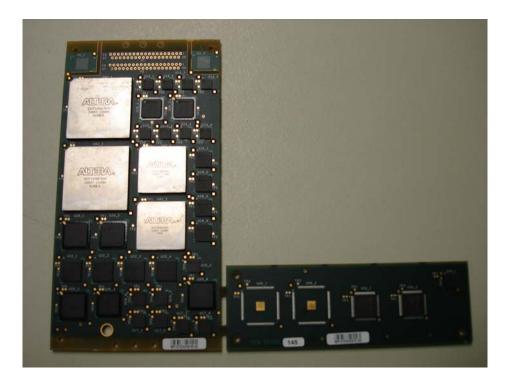

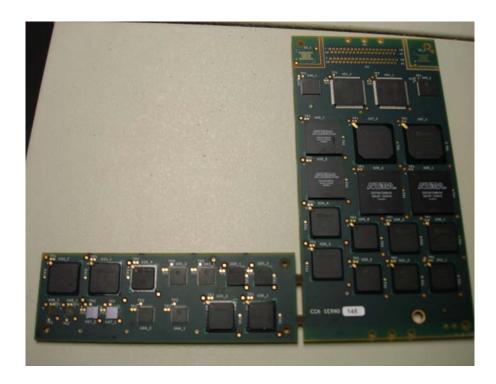

Each of the test boards contained between 61 and 120 packages. The total electronic package count for the scope of the research was approximately 4500 packages. The various types of packages included in this research are shown below in figures 1.11 through 1.13.

Figure 1.11. Various packages of accelerated test.

Figure 1.12. Various packages of accelerated test.

Figure 1.13. Various packages of accelerated test.

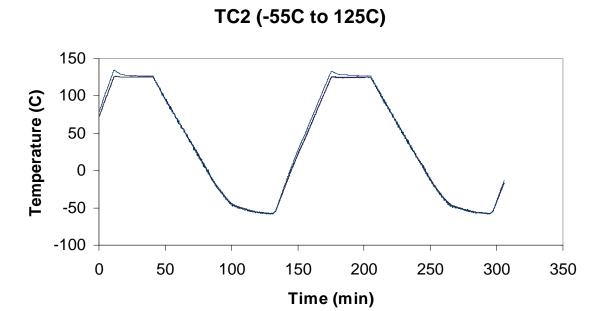

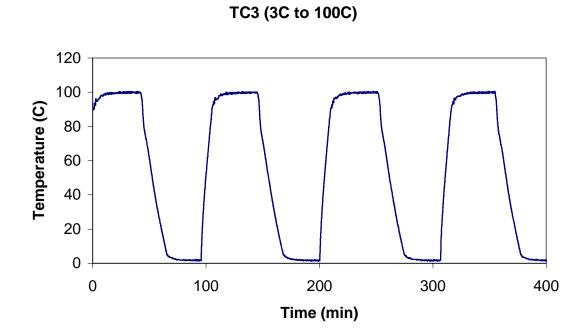

Four different temperature cycling conditions were also applied, three of which were monitored by this research, while the remaining temperature range was monitored by the sponsoring company. The four thermal cycling temperature conditions are shown in Table 1.1.

Table 1.1. Temperature conditions for accelerated test.

|         | Low  | High | Ramp     | Low   | High  |

|---------|------|------|----------|-------|-------|

|         | Temp | Temp | Rate     | Dwell | Dwell |

| Profile | (°C) | (°C) | (°C/min) | (min) | (min) |

| TC1     | -40  | 95   | 3        | 30    | 30    |

| TC2     | -55  | 125  | 3        | 30    | 30    |

| TC3     | 3    | 100  | 3        | 30    | 30    |

| TC4     | -20  | 60   | 3        | 30    | 30    |

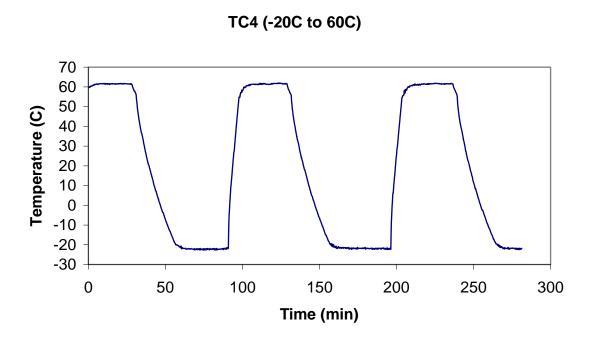

The temperature profiles for TC2, TC3, and TC4 are shown in Figures 1.14, 1.15, and 1.16 respectively.

Figure 1.14. TC2 thermal cycling temperature profile.

Figure 1.15. TC3 thermal cycling temperature profile.

Figure 1.16. TC4 thermal cycling temperature profile.

## 1.2 Failure Monitoring

The reliability of the electronic test packages was monitored by periodically probing the resistivity of the packages, both manually and with data acquisition software, while subjected to thermal cycling temperature environments. The failure monitoring records of certain package types in specific environments allow for algorithms to be developed for use of package reliability and prognostics. By developing accurate life prediction models, significant cost reduction can be achieved by reducing downtime inspections and non-necessary component replacement, as well as reducing the risk of component failure during system operation.

## 1.3 Thermo-mechanical Reliability

Whenever an electronic device is operating, the device will generate heat. With Technology increases in electronic packaging making the IC chips of higher wiring density and increased complexity, the amount of heat generation and subsequent thermal damage is of high concern for the electronic packaging industry. When a device is powered on, which causes heat generation causing the components to heat up, and then powered off, allowing the components to cool back down to their environmental temperatures, a thermal cycle has occurred. Accelerated thermal cycling tests have been performed in this research to simulate the operational life of various components in harsh environments. The thermal cycling of devices leads to thermal fatigue damage, and eventually failure, due to mismatches in coefficients of thermal expansion (CTE) between the different materials in an electronic package. Table 1.2 shows typical values for CTE values among the different materials of an electronic package.

Table 1.2. Typical CTE values for package materials.

| Material                  | CTE (1/K)   |

|---------------------------|-------------|

| Copper Pad                | 16.3E-6     |

| Solder Mask               | 30.0E-6     |

|                           | 12.42E-6    |

| BT Substrate              | (XY)        |

|                           | 57.0E-6 (Z) |

| Die Adhesive              | 52E-6       |

| Silicon Die               | 2.50E-06    |

| Ceramic                   | 7.40E-06    |

| Solder - 62Sn36Pb2Ag      | 24E-6       |

| Solder - 96.5Sn3.0Ag0.5Cu | 25E-6       |

| Mold Compound             | 15E-6       |

|                           | 14.5E-6     |

| PCB                       | (XY)        |

|                           | 67.2E-6 (Z) |

This difference in CTE values causes stresses in the various components, with the most detrimental effects taking place at the interface of two components. The repetitive temperature cycling will accrue thermal plastic fatigue damage, and will lead to failure of the device.

## 1.4 Finite Element Modeling

The FEA (Finite Element Analysis) methodology is a very useful tool in simulating stresses on a device. For the purposes of electronic packaging reliability in this study, finite element analysis uses a physics of failure approach to analyze solder joint fatigue life under thermal cycle loading conditions. The measured amount of thermal fatigue damage that a solder joint accumulates is helpful in life prediction model validation, in which values can be compared to actual experimental values, as well as statistical models that have been developed. FEA analysis can be very useful; however, care must be taken by the user in modeling, meshing, boundary condition selection, and other assumptions in order to yield accurate results.

## 1.5 Statistical Modeling

Multivariate regression analysis has been used to assess the relative influence of parameters on the thermal reliability of electronic packages. Statistical models have been developed for Plastic BGA packages under various temperature environments, solder alloys, and various other package parameters. Parameters investigated for thermal reliability of the BGAs include: die size, die to package ratio, solder ball composition,

solder ball diameter, ball pitch, pad size, and temperature cycle conditions such as delta T and the inverse of mean temperature.

#### **CHAPTER 2**

## LITERATURE REVIEW

The thermo-mechanical fatigue that electronic packages are subjected to is considered to have the most critical effect on their life and reliability. The primary region of the thermal-induced failure occurs in the solder joint. Because of the high mismatch in CTE of the various materials that make up electronic packages, much of the accumulated stress is transferred to the solder joint causing de-lamination or fatigue crack initiation and growth. An abundance of published works exists on the effects of thermal loading and reliability. Numerous test methodologies have also been used to demonstrate results for thermal loading damage effects such as: accelerated thermal cycling tests, failure and damage relationship models, statistical based regression models, and finite element analysis (FEA) models.

## 2.1 Experimental Techniques

Researchers have conducted many types of experimental tests in the past to better understand and address solder joint fatigue life. Examples of such tests are accelerated thermal cycling, thermal shock loading, and vibration testing. These diverse testing procedures have been used by researchers to analyze solder joint fatigue life under different applications.

Syed [1996] conducted thermal fatigue reliability tests of plastic ball grid array packages for four design parameters: ball pitch, substrate thickness, array configuration, and pad size. It was found that thicker BT substrates (0.76 mm), using perimeter array configurations, 0.635 mm pads, and 1.27 mm ball pitch could improve solder joint fatigue life approximately 5X, allowing PBGAs to meet the harsh-environment reliability specifications of the automotive industry.

Suhling, et.al. [2004] presented research on the thermal cycling reliability of lead free solder joints for use in the automotive industry. Four solder compounds were tested: 95.5Sn3.8Ag0.7Cu and three variations of lead free SAC solder that incorporate small additions of bismuth and indium to enhance fatigue resistance. These solder joint compounds were thermally cycled under two test conditions: -40 C to 125 C, and -40 C to 150 C.

Results from this study showed that the eutectic SAC alloy 95.5Sn3.8Ag0.7Cu gave comparable reliability results to standard 63Sn37Pb solder alloy during the -40 C to 125 C temperature condition, but differed greatly, demonstrating much lower reliability relative to the 63Sn37Pb alloy, when subjected to the more harsh -40 C to 150 C temperature range. It was also shown that adding trace amounts of bismuth and indium can enhance the -40 to 150 C thermal cycling fatigue resistance relative to 95.5Sn3.8Ag0.7Cu.

A second set of thermally cycled test samples were cross-sectioned in order to examine crack growth, changes in microstructure, and intermetallic growth at the solder interfaces. It was observed that voiding and spheroidizing was present in all of the lead free alloys, with spheroidizing clearly present after only 500 cycles. This was one proposed explanation for the variations and low beta values seen in the Weibull data.

Another observed difference came from the intermetallic layers. The layers in the two SnAgCuBi alloys and the 95.5Sn3.8Ag0.7Cu alloy were fine (typically around 1-3 mm thick) and continuous, while the SnAgCuIn alloy had rather large (10-20 mm thick) and uneven layers. It was proposed that these variations in the intermetallic layers could be responsible for the differences in harsh temperature reliability of the alloys.

## 2.2 Statistical Analysis

Statistical methods have often been used in research to analyze results of experimental test failure data. Most commonly, the choices of linear regression analysis and Weibull distributions are used. Liu, et al. [2005] conducted thermal reliability tests on anisotropic conductive adhesive (ACA) flip-chip joining technology for electronic packages. In this study, nine types of ACA and one nonconductive film (NCF) were used, totaling nearly 1000 single joints which were subjected to reliability tests of temperature cycling between 40 C and 125 C. A four-parameter Weibull parameter was developed and shown that in optimized conditions, high reliability flip-chip anisotropically conductive adhesive joints on low-cost substrate can be achieved.

Tee, et al. [2006] conducted solder joint reliability tests, comparing five different designs of thermally enhanced ball grid array packages: conduction cooled BGA (C<sup>2</sup>BGA), metal-core BGA, exposed-die land grid array (LGA), slug LGA, and spreader LGA. For this study, the solder joint reliability performances of the thermally enhanced BGAs were benchmarked with the conventional thin-profile fine-pitch ball grid array

(TFBGA). It was found that the C<sup>2</sup>BGA has better solder joint performance compared to conventional TFBGAs, and that solder joint reliability of C<sup>2</sup>BGAs can be enhanced by having smaller die, thinner mold compound and die, thicker substrate, smaller solder ball diameter, and a mold compound with higher CTE and a lower modulus. In his research, Tee also concluded that die-attach and slug-attach materials have little effect on fatigue life, and that thermal solder joints help to reduce the thermal resistance and enhance the solder joint reliability. A good correlation was also found between solder joint fatigue life and package warpage for both TFBGA and C<sup>2</sup>BGA: smaller package warpage leads to longer fatigue life.

Lall, et al. [2005] presented research on prognostics methods developed from statistical analysis from data on leading indicators of failure of electronic packages. Some leading indicators of failure are: micro structural evolution characterized by average phase size and correlated to time and equivalent creep strain rate, and stresses at interface of silicon structures. All predictive models to this point have only been able to predict the life of an electronic package from a known good state starting from a pristine, unused condition. The overall goal of this research was to develop a prognostics model that can predict the remaining useful life of a package based on examination of the current material state and prior stress histories.

The test components for this research include I/O counts in the range of 193 to 388, I/O pitch in the range of 0.8 to 1 mm, and package sizes in the range of 15 to 27 mm. The test board contained two 15 mm BGAs, one 27 mm BGA, and two 16 mm C<sup>2</sup>BGAs. All BGAs had Sn63/Pb37 solder balls, and the substrates used were standard HASL finished high temperature glass epoxy laminate (FR4-06) attached to 2.54-mm-

thick aluminum plate. The thermal cycling test was conducted at a profile from -40 C to 125 C.

It was concluded from experimental data that the rate of change of the phase growth parameter correlates well with several existing macro indicators of damage. A mathematical relationship was found between phase growth rate and time-to-1-percent failure. This allowed the computation of damage, and a forward estimate of residual life.

## 2.3 Finite Element Based Numerical Techniques

The FEA (Finite Element Analysis) methodology is a widely used and valuable instrument in the testing and understanding of solder joint fatigue life and reliability [Seyd 1996, Zahn 2002, Lall, et.al. 2004, Darveuax 2002]. Darveaux, et.al. [1992] conducted accelerated life tests on five types of alloy solder: 62Sn36Pb2Ag, 60Sn40Pb, 96.5Sn3.5Ag, 97.5Pb2.5Sn, and 95Pb5Sn. It was found that the 60Sn40Pb and the 62Sn36Pb2Ag solder alloys accumulate less strain before failure than the 97.5Pb2.5Sn and 96.5Sn3.5Ag alloys, and the 95Pb5Sn solder was the least yielding of all the alloys tested. It was also discovered that all of the test alloys reacted about the same amount under the accelerated thermal cycle conditions; however, under actual use conditions, the 96.5Sn3.5Ag and 97.5Pb2.5Sn solder alloys accumulated significantly less strain.

Zahn [2002] examined the solder joint reliability of same die, stacked, chip scale, ball grid array packages that were subjected to thermal cycling (-40C to 125C). ANSYS finite element analysis software (an industry standard) was used for the study, specifically Anand's Viscoplasticity model for solder plastic strain that combines plasticity and creep phenomenon. Of the two configurations of boards tested (one with

0.1143 mm spacer die with 0.7 mm mold cap and the other having a 0.1397 mm spacer die with a 0.8 mm mold cap), the thinner board configuration was found to have approximately 2X the characteristic life of the thicker board design. This was believed to be a result of the thinner board's greater flexibility, which would lessen the damage of plastic strain on the solder joint.

Novotny, et al. [2005] presented work on improving the reliability and durability of SMD components. Finite element analysis models were simulated to determine time-dependent solder joint fatigue under accelerated temperature cycling conditions (-40 C to 125 C), and to determine the maximum stress deformation in the solder joint during shear. Three types of SMDs were modeled using ANSYS finite element software: SMD 0805, 1206, and 1812. All model analyses were at constant temperature of 100°C.

It was shown that after the comparison of thermo-mechanical stress and shearing, the stress values for shearing were higher than that of thermo-mechanical stress. Of the three SMDs tested, 1812 reported the best reliability, having a predicted lifetime of 20% higher than the other two test configurations.

#### 2.4 Constitutive Behavior of Solder Material

The material properties and behavior of materials is an important facet of modeling parameters, and ultimately, life prediction. Since finite element models require the input of material models and parameters that make up the components of the assembly, developing and classifying constitutive behavior accurately is vital to the modeling process.

A constitutive model is the mathematical representation of the material response to one or more variables [Vandevelde, et.al. 2002]. These constitutive models serve as input into larger computational models for stress analysis to approximate the thermal and mechanical loading a component will experience. Grossmann [1999] presented finding on the activation of deformation mechanisms in Sn62Pb36Ag2 solder alloy. Two deformation phenomenons were observed (Grain Boundary Sliding and Dislocation Climb), each activated by a certain thermal test parameter, and associated to a particular stress-strain curve.

Darveaux, et al. [1992] conducted research on several solder alloys (62Sn36Pb2Ag, 60Sn40Pb, 96.5Sn3.5Ag, 97Pb3Sn and 95Pb5Sn) to collect and compare the stress-strain data. The testing parameters were for shear and tensile loading of the solder joint, over a wide range of strain and temperature rates. Darveaux found in his experiment that all of the data could be fit to the same constitutive model, where only the constant terms of the equation were dependent upon the solder alloy.

Pang, et al. [2004] compared his modified Ramberg-Osgood model to Anand's constitutive model for lead-free solder. His modified version of the Ramberg-Osgood model was derived from the fitted stress strain curves for lead-free (95.5Sn3.8Ag0.7Cu) solder alloy.

### 2.5 Objectives and Scope of the Thesis

The reliability of electronic packages can be analyzed by a physics of failure based and a statistical failure based approach. The research presented here has been done to further understand the reliability of various electronic packages subjected to harsh environments, and to further understand the parameter effects that geometry and materials have on harsh environment package reliability. The field of electronic packages that were tested coved a multitude of variable parameters such as: solder joint diameter, solder joint pitch, package architecture, material properties, temperature conditions for accelerated thermal cycling, and board characteristics. The research presented here uses of physics-of-failure based finite element modeling approach to measure the accumulated strain energy density within components of a package. From these values of strain energy density, fatigue damage equations can be applied to predict the life for ball grid array packages. Also, statistical models were used to identify the critical factors in reliability performance of the tested electronic packages. These critical factors were found from the collection of experimental data, and then quantified through use of regression analysis.

#### **CHAPTER 3**

### **TEST EQUIPMENT**

Given the large scope of the research presented in this work, a multitude of equipment was needed to perform, monitor, and collect useful information from the tests. It would be tedious and superfluous to list all tools, devices, hardware, and software that were needed to complete the research for this thesis; however, the author finds it appropriate to discuss essential equipment that was used to accomplish this research.

## 3.1 Experimental Test Equipment

Several fundamental equipment devices were needed to set up the experimental testing portion of the research. The major components of the data acquisition and testing used for this research were: thermal cycling environmental chambers, high density switching systems, and multiplexer cards, chamber profile calibrating equipment, digital multimeters, and Lab View software.

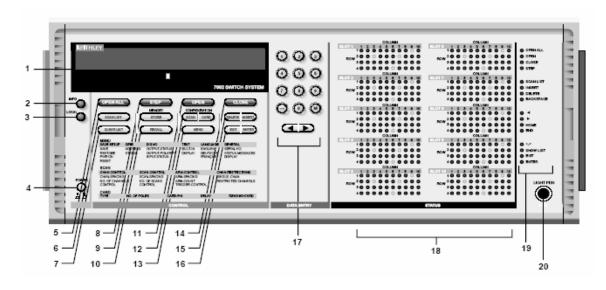

# 3.1.1 Keithley Model 7002 High Density Switch Systems

The switching systems used for this research were Keithley Model 7002 High Density Switch Systems. These switching systems allowed for programmable resistance monitoring of the test boards while cycling in the thermal chamber. The Model 7002

switching system is a ten card system, with 40 channels per card. A front panel and back panel view of this switching system is shown in Figures 3.1 and 3.2 respectively [Keithley 7002 Owner's Manual].

Figure 3.1. Front view of Keithley Model 7002 High Density Switch System.

Figure 3.2. Back view of Keithley Model 7002 High Density Switch System.

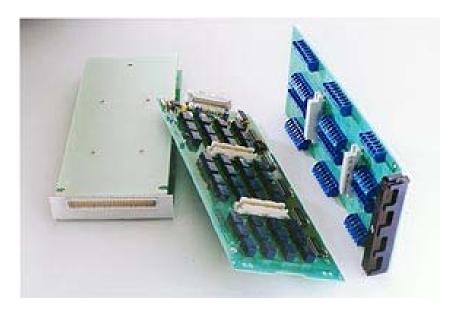

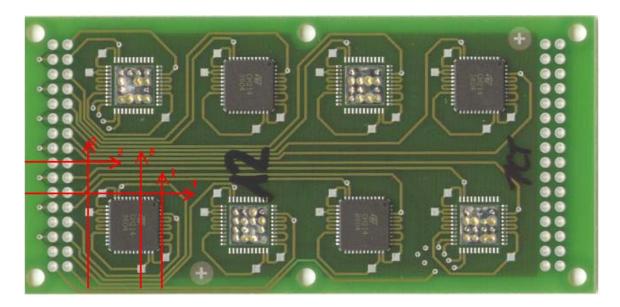

# 3.1.2 Keithley 7011-C Quad 1 x 10 Multiplexers

The cards used within this model switching system were Keithley 7011-C Quad 1 x 10 Multiplexers. The 7011 is a low voltage, two-pole, quad, 1 x 10 multiplexer card [Keithley 7011 Owner's Manual]. These multiplexer cards consist of a multi-pin (mass termination) connector card and a relay card. External test circuit connections to the multiplexer are made through the 96-pin male DIN connector on the connector card. The Keithley 7011-C multiplexer card is shown in Figure 3.3. Figure 3.4 shows an actual test setup of 96-pin ribbon cables connected to the 7011-C multiplexer cards in the back of a Keithley 7002 switch system.

Figure 3.3. Keithley 7011-C multiplexer card.

Figure 3.4. Wiring setup of Keithley Model 7002 High Density Switch System.

# 3.1.3 Keithley Model 2000 Multimeter

The multimeters that were used to measure the test package resistance values were Keithley Model 2000 Multimeters. These 6.5 digit digital multimeters can take fifty triggered rdgs/s over the IEEE-488 bus, with a max speed of 2000 rdgs/s [Keithley 2000 Owner's Manual]. The model 2000 multimeter has a resistance sensitivity of 100  $\mu\Omega$ , and a maximum reading of 120 M $\Omega$ . The Keithley 2000 digital multimeter is shown in Figure 3.5.

Figure 3.5. Keithley Model 2000 Multimeter.

# 3.1.4 Fluke 73 Series III Multimeter

The portable digital multimeters that were used for this research were the Fluke 73 Series III Digital Multimeter. This model multimeter possesses 0.3% basic accuracy with 3200-count resolution. The full statistics are presented in Table 3.1, and a picture is displayed in Figure 3.6.

Table 3.1. Specifications of the Fluke 73 Series Multimeter.

| Fluke Digital Multimeter Specifications |                     |         |  |  |  |  |

|-----------------------------------------|---------------------|---------|--|--|--|--|

| DC Voltage                              | Maximum Voltage:    | 600 V   |  |  |  |  |

|                                         | Basic Accuracy:     | 0.30%   |  |  |  |  |

|                                         | Maximum Resolution: | 0.1 mV  |  |  |  |  |

| AC Voltage                              | Maximum Voltage:    | 600 V   |  |  |  |  |

|                                         | Basic Accuracy:     | 2%      |  |  |  |  |

|                                         | Maximum Resolution: | 1 mV    |  |  |  |  |

| DC Current                              | Maximum Current:    | 10 Amp  |  |  |  |  |

|                                         | Basic Accuracy:     | 1.50%   |  |  |  |  |

|                                         | Maximum Resolution: | 0.01 mA |  |  |  |  |

| AC Current                              | Maximum Current:    | 10 Amp  |  |  |  |  |

|                                         | Basic Accuracy:     | 2.50%   |  |  |  |  |

|                                         | Maximum Resolution: | 0.01 mA |  |  |  |  |

| Resistance                              | Maximum Resistance: | 32 Ω    |  |  |  |  |

|                                         | Basic Accuracy:     | 0.50%   |  |  |  |  |

|                                         | Maximum Resolution: | 0.1 Ω   |  |  |  |  |

Figure 3.6. Fluke 73 Series III Digital Multimeter.

# 3.1.5 SlimKIC 2000 Thermal Profiler

The thermal cycle temperature profile hardware and software used was the SlimKIC 2000. The basic components of the system are shown in Figure 3.7, consisting

of a receiver, data processor, and K type thermocouples. The specifications for the SlimKIC 2000 system are shown in Table 3.2 from the SlimKIC owner's manual.

Table 3.2. Specifications of the SlimKIC 2000 Thermal Profiler.

| SlimKIC Specifications     |                         |  |  |  |  |  |  |

|----------------------------|-------------------------|--|--|--|--|--|--|

| Accuracy                   | ±1.2°C                  |  |  |  |  |  |  |

| Resolution                 | 0.1°C to 0.3°C          |  |  |  |  |  |  |

| Internal Operating Temp.   | 0°C to 105°C            |  |  |  |  |  |  |

| Thermocouple Compatibility | Type K                  |  |  |  |  |  |  |

| Temperature Range          | -150°C to 1050°C        |  |  |  |  |  |  |

| Dimensions                 | 10.5"L x 3.0"W x 0.75"H |  |  |  |  |  |  |

| Power Requirements         | 9V alkaline battery     |  |  |  |  |  |  |

| Thermal Receiver           | 433.92 MHz              |  |  |  |  |  |  |

Figure 3.7. SlimKIC 2000 thermal profile system.

### 3.1.6 Environmental Chambers

Three temperature conditions were monitored by the author; those being TC2 (-55C to 125C), TC3 (3C to 100C), and TC4 (-20C to 60C). An environmental chamber

was needed for each different temperature condition. For the TC2 condition, the Blue M VRC was used. The Blue M, as shown in Figure 3.8.

Figure 3.8. Blue M VRC environmental chamber.

The second thermal cycling chamber employed was the Thermotron S-1.2 Mini-Max, shown in Figure 3.9. This chamber has a maximum temperature range of -73°C to +180°C, with interior chamber dimensions of 40.6cm x 27.9cm x 30.5cm.

Figure 3.9. Thermotron S-1.2 Mini-Max environmental chamber.

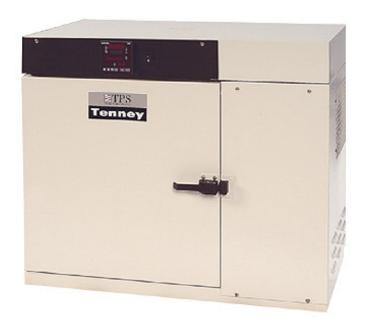

For the TC4 temperature condition, the chamber that was used was the Tenney Jr. bench top thermal chamber, shown in Figure 3.10. The Tenney Jr. chamber has both set point and actual temperature display with  $0.1^{\circ}$ C or  $0.1^{\circ}$ F resolution. The Tenney Jr. also features a control tolerance of  $\pm 0.3^{\circ}$ C after stabilization.

Figure 3.10. Tenney Jr. environmental chamber.

# 3.2 Lab View Data Acquisition Program

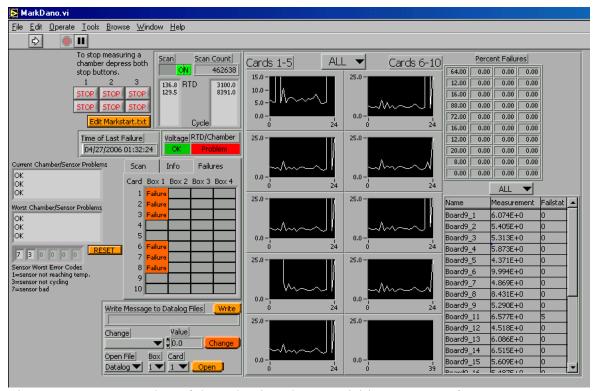

The program used for data acquisition was a Lab View data acquisition program. This program was built to monitor test boards specifically for thermal cycling test environments by monitoring resistivity in packages as the thermal cycle test chamber is cycling. Information about the setup of this software was obtained from a procedural document written by former Auburn University engineering graduate Charles Mitchell. Figure 3.11 displays a screenshot of the Lab View graphical user interface (GUI).

Figure 3.11. Screenshot of the Lab View data acquisition system software.

This program performs by utilizing two types of text files: configuration files and data files.

# 3.2.1 Configuration Files

The configuration text files are manually set up by the user, and are necessary for the program to function correctly. There are six different configuration files, but for the research conducted in this thesis, only five were necessary. The five file were: Markstart.txt, Rlogset.txt, Rtd.txt, bBfval.txt, and bBnameC.txt.

#### 3.2.1.1 Markstart.txt

The first configuration file is titled: <u>Markstart.txt</u>. An example of this file is shown below. The numbers along the left column are not present in the actual file; however, numbered rows allow for easier explanation. It is important to note that on all of the configuration text files, no extra spaces or blank lines must be present after the entered text commands, or the system may not operate correctly.

### Markstart.txt

## Example file:

- 1. Run

- 2. c:\Connector Test

- 3. 1

- 4. 1 0 0

- 5. 5400 0 0

- 6. 1

- 7. 0

- 8. 6.000 4.000

- 9.

- 10. TCgrey/Connector hsgale@eng.auburn.edu;menorris@ieee.org

- 11. 6341

The markstart.txt file is essential for the measurement program to initialize and run. This file is to be placed in the directory: c:\windows\desktop, with a shortcut of the measurement software placed in the Windows Startup folder so it will start when booted. The first line in the Martkstart.txt file is "Run" so the program will initialize and begin taking measurements when the computer is booted. The second line of text displays the directory in which all other configuration files, with the exception of Rlogset.txt, are located. This is also the directory where the data files will be created and store the

measured results. Line three of the text selects the scan speed or integration time in number of power line cycles per measurement (NPLC). This scanning speed is automatically reduced if filters are used, but one is the most adequate. Line four selects the temperature measurement option to be used for the test. Values of (0) through (3) can be entered and represent in order: no temperature sensors, 2-wire resistance of RTDs, 2wire resistance of mechanical switches, and temperature in degrees C using 4-wire RTDs with the 2001 multimeter. Up to three values can be entered, and are tab delimited. The mechanical switch option can be used in place of the temperature sensors. If done, it looks for resistance values below 97 Ohms when the chamber is cold and resistance values above 125 Ohms when the chamber is hot. However, with this setting, the program will not report errors if the switch reaches zero or infinite resistance. Line five lists cycle times for up to three test chambers, and is also tab delimited. This setting is used to determine if the chamber is cycling within the appropriate amount of time. The sixth line lists the switching system number that the temperature sensors (RTDs) are connected to. A value of (0) indicates using the 2000-SCAN with the 2001 multimeter, and values (1) through (4) signify using the first through fourth Keithley 7002 switching system. \*Note: the numbered order of the switching systems refers to the box address number. For checking or changing the box address numbers, refer to the Keithley 7002 operations manual. The seventh line can be either (0) or (1). Choose a value of (1) if one or more bias voltages are to be monitored, otherwise choose (0). Line eight signifies the range of bias voltages that are considered appropriate, with the upper limit first, and then the lower limit separated by a tab. The ninth line decides the type of measurement log setting to be used. A value of (0) results in every data measurement being recorded, (1)

results in data measurements being logged two times per cycle, and (2) will record data measurements every 30 minutes. Line ten gives a name to the test chamber, which is used in e-mail notices and web page status reports. After the chamber name, separated by a tab, e-mail addresses are listed to which error messages will be sent when they arise. Multiple e-mail addresses can be separated by a semicolon. The eleventh line lists the TCP port on the server to which the computer will send information.

## **3.2.1.2 Rlogset.txt**

The next configuration file is Rlogset.txt. An example of this file is shown below.

# Rlogset.txt

# Example File:

| 1.       | 1 | 1 | 1 | 1 |

|----------|---|---|---|---|

| 2.       | 1 | 1 | 1 | 1 |

| 3.       | 1 | 1 | 1 | 1 |

| 4.       | 1 | 1 | 1 | 1 |

| 4.<br>5. | 1 | 1 | 1 | 1 |

| 6.       | 1 | 1 | 1 | 1 |

| 7.       | 1 | 1 | 1 | 1 |

| 8.       | 1 | 1 | 1 | 1 |

| 9.       | 1 | 1 | 1 | 1 |

| 10.      | 1 | 1 | 1 | 1 |

|          |   |   |   |   |

This setup file designates which multiplexer cards in each of the switching systems will have measurement logs recorded for them. It should be noted that the Lab View software is programmed to monitor a maximum of four switching systems. Additional switching systems would require additional computers running the Markdano.dll software.

In this file four columns are present, each representing a Keithley 7002 switching system (in order by box address number from left to right). Also, ten rows are listed, each representing a multiplexer card with the designated switching systems. All columns are tab delimited, and rows are carriage return delimited. Each value within the matrix represents a multiplexer card which the switching system is capable of measuring. An example of how to read this matrix would be: the value in the fifth row and third column represents the fifth multiplexer card in the third switching system. Each value can either be a (1) or a (0), with a (1) designating a measurement log to be recorded for that multiplexer card, and a (0) designating that no measurement log will be recorded for that card. \*Note: It is commonality not to change any of the values in this file, even if only one switching system is being used.

#### 3.2.1.3 Rtd.txt

The next configuration file is the <u>Rtd.txt</u> file. An example of this file is shown below.

### Rtd.txt

Example File:

- 1. 3 40

- 2. 4 40

The Rtd.txt file is responsible for the channel information of the temperature sensors. Each of the two rows assign the number of the multiplexer card that the

temperature sensor is connected to, then a tab, then the channel number that the temperature sensor is connected to for that card. One sensor is listed per line, with two sensors per chamber. Two additional values must be added after the channel number when using 4-wire RTDs, each tab delimited. These third and fourth values represent upper and lower temperature range values of the test respectively. These upper and lower limit values are used to determine if the chamber is cycling properly. The chamber temperature must reach at least 0.4 multiplied by these upper and lower limit values or an error will occur. \*Note: All temperature sensors must be on the same Keithley 7002 switching system or 2000-SCAN system for the software to run properly. \*Note: If the 2000-SCAN system with the 2001-multimeter is used for data measurement, the card number spot in the text file can be disregarded, and only the channel number is used.

## **3.2.1.4** bBfval.txt

The fourth type of configuration file is the <u>bBfval.txt</u> file, which is the failure value file. An example of this file is shown below.

## bBfval.txt (Failure Value File)

### Example File:

- 1. 150 2000 80 1 2. 2000 80 150 1 3. 150 2000 80 1 4. 150 2000 80 1 5. 2000 80 150 1

- 6. 150 2000 80 1

- 7. 150 2000 80 1 8. 150 2000 80 1

- 9. 150 2000 80

This file designates the settings to be used during the measurement scans. The name of the file follows this format: bBfval.txt, where B represents the switching system number (one through four). Each row represents a multiplexer card for that switching system, and can contain up to nine values, which are tab delimited. The first value stands for the upper resistance limit. The other eight values are optional, and are in order as follows: meter range, channels per scan, digital filter, lower limit, meter function, integration time devisor, temperature sensor pair, and close first list. The meter range is typically 1000 to 2000 ohm, depending on the meter used. The channels per scan option defaults to 40, but can be set to 80 allowing a consecutive odd and even numbered multiplexer card with the same scan settings to be scanned together, reducing overall measurement time. The integration time deviser is a division factor number by which the integration time is divided for a scan, reducing the scan time for a test with a large number of channels. The defaults for all of these options are: 100 ohm upper failure limit, 1000 or 2000 ohm meter range (depending on meter used), 40 channels per scan, digital filter off, negative infinity  $(-\infty)$  for lower failure value, 2-wire ohm meter function, integration time divider of 1, first temperature sensor pair (0 indexed), and no close first list.

#### 3.2.1.5 bBnameC.txt

The fifth configuration file is <u>bBnameC.txt</u>. An example of this file is shown below.

# bBnameC.txt (Naming File)

# Example File:

- 1. Board1 1 1

- 2. Board1 2 2

- 3. Board1 3 3

40. Board1 40 40

This file contains channel and test component information of components that are being monitored during thermal testing. The name of the file follows this format: bBnameC.txt, where B is the switching system number (one through four), and C represents the multiplexer card number (one through ten). There needs to be one name file for each multiplexer card that is being scanned. Each row of the file designates a test device or component to be monitored, and is tab delimited. The first value is the name of the component being tested, and can be any name the user desires to identify the component. These component names will be used in the data files to record failures, which will be discussed later. The second value in the row represents the channel number that the device is connected to, on that particular card (C) and switchbox (B). The other two values are optional, and are: upper limit and lower limit. The upper and lower limits are the resistance range values that can be used to determine if the component has failed. When the upper and lower limits are present in this file, they will be used as failure criteria instead of the values in the failure value file. This option is useful when each device has its own separate resistance failure limit requirements.

#### 3.2.2 Data Files

The data files are files that the Lab View program creates automatically when it begins the monitoring process of the experimental test. These files are used to record the various test information. There are four types of data files that the LabView program creates: Count files, Failure Status files, Data files, and Log files.

#### **3.2.2.1** Counta.txt

The first group of data files is the Count files (counta.txt, countb.txt, and scount.txt). Examples of two of these files are shown below. The numbers along the left column are not present in the actual file; however, numbered rows allow for easier explanation.

### Counta.txt

Example file:

#### 1. 388.0

This file, along with the countb.txt file, records the measurement cycle count number of the thermal chamber when the program is monitoring an experiment. These two files are created in the /count subdirectory folder, which the LabView program creates as well. There exists one count file for each temperature sensor in the thermal chamber, and both the counta and countb text files contain only one number, the cycle count number, which automatically starts at zero when the program initiates.

# Scount.txt

# Example file:

### 1. 1128285

The Scount.txt file is similar to the other two count files, except instead of recording the number of thermal cycles that the test has experienced, this file records the total number of scans executed by the measurement software. This file is created in the same directory as the other two count files.

### 3.2.2.2 bBfailC.txt

The second type of data file is the failure status file. An example of this file is shown below.

# bBfailC.txt (Failure Status File)

# Example file:

- 1. 0

- 2. 0

- 3. 0

- 4. 0

- 5. 0

- 6. 0

- 7. 0

- 8. 0

- 9. 0

- 10. 5

- 11. 1

- 12. 1

- 13. 0

- 14. 0

- 15. 0

16. 0 17. 5 18. 0 19. 0 20. 5

This file monitors how many times each test device has been reported as a failure (the number of times each device has been measured to be beyond the allowable range set in either the bBfval.txt file or the bBnameC.txt file). This file is in the format bBfailC.txt, where B is the switching system number, and C designates the multiplexer card number. There is one file created for each multiplexer card being used in the test, and they are found in the /failstat subdirectory. These files contain many rows of numbers, where each row designates a channel number. Every time a device "fails," the value of that channel number increases by one. Once the device is measured to be outside of the set allowable range five times, the test device is considered to have failed, and a record of this is logged in the data file. \*Note: once a channel value has reached five, the value will not increase since the test device is considered to have already failed. The user can manually reset this number.

#### 3.2.2.3 bBdataC.txt

Next is the data file. An example of this text file is shown below.

### bBdataC.txt (Data File)

#### Example File:

| Name | Date       | Time     | Value         | Cycle A | Cycle B | RTD A  | RTD B  | Scan #  | % Failure |

|------|------------|----------|---------------|---------|---------|--------|--------|---------|-----------|

| G19  | 06/06/2006 | 15:39:45 | 99.000000E+36 | 139.5   | 139.5   | 114.55 | 118.09 | 1124125 | 4.76      |

| G5   | 07/05/2006 | 21:46:32 | 2.130781E+3   | 383.0   | 383.0   | 121.10 | 121.06 | 1128163 | 14.29     |

The rows were not numbered in this example file since the rows would have been too wide to properly display. This file records the failure information for each test device. The file has the format bBdataC.txt, where B represents the switching system number, and C stands for the multiplexer card number. These files are saved in the \datalog subdirectory. Each row contains ten values which are all tab delimited. The first four values represent the name, date, time, and measured resistance value at which the test device failed. The fifth and sixth values represent the values of the counta.txt and countb.txt text files respectively at the time of failure. The seventh and eighth values in the row correspond to the temperatures of the tow temperature sensors at the time of failure. The ninth value displays the scount.txt value at the time of failure, and the last column lists the percent failure.

#### **3.2.2.4 bBlogC.txt**

The last data file is the log file. No example file is shown for this file since it can grow very large depending on the type of log file recording preference that was selected

in the markstart.txt configuration file. This file has the format bBlogC.txt, where B represents the switching system number, and C designates the multiplexer card number. This file records the resistance values for every channel on the multiplexer card that is being monitored, as well as information such as: the time, date, temperature sensor values, and cycle count number when the resistance values were logged.

## 3.2.3 Executing Lab View Software

Once all configuration files have been set up to the desired test specifications, the program is now ready to begin monitoring and recording the test data. To begin the program, restart the computer, then immediately power off all switching systems and multimeters. The program is set to automatically begin upon reboot. Now wait until the windows screen appears during the computer reboot process. When the windows screen appears, begin powering on the switching systems in order of their box address number, lowest to highest. For checking or changing the box address numbers, refer to the Keithley 7002 operations manual. Once all switching systems have been powered on, power on the multimeter. All of these devices must be on before the computer is fully rebooted and tries to start the program; else the user must stop the program, and repeat this process. Figure 3.12 shows an excerpt of the experimental data failure record catalog system.

|    | Α     | В | С   | AC      | AD      | AE     | AF      | AG      | AH      | Al       | AJ       | AK       |

|----|-------|---|-----|---------|---------|--------|---------|---------|---------|----------|----------|----------|

| 1  |       |   |     |         |         |        |         |         |         |          |          |          |

| 2  | Date  |   |     | 7/28/06 | 8/21/06 | 9/6/06 | 9/13/06 | 9/21/06 | 9/28/06 | 10/13/06 | 10/19/06 | 10/24/06 |

| 3  | Cycle |   | 151 | 508     | 691     | 822    | 866     | 940     | 1001    | 1123     | 1175     | 1219     |

| 76 | U26_3 |   |     | fail    | fail    | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

| 77 | U26_4 |   |     | 1.8     | 1.1     | 1.1    | 1.1     | 1.1     | 1.2     | 1.2      | 1.2      | 10.4     |

| 78 | U27_1 |   |     | 1.2     | 1.0     | 1.0    | 1.0     | 1.1     | 1.2     | 1.2      | 1.2      | 1.2      |

| 79 | U27_2 |   |     | 1.1     | 1.0     | 1.0    | 1.0     | 1.0     | 1.2     | 1.2      | 1.2      | 1.2      |

| 80 | U28_1 |   |     | 1.1     | 3.9     | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

| 81 | U28_2 |   |     | 1.2     | 1.2     | 1.2    | 1.2     | 1.2     | 1.2     | 1.2      | 1.2      | 1.2      |

| 82 | U29_1 |   |     | fail    | fail    | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

| 83 | U29_2 |   |     | 1.5     | fail    | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

| 84 | U29_3 |   |     | fail    | fail    | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

| 85 | U29_4 |   |     | 1.5     | 1.7     | 4.6    | fail    | fail    | fail    | fail     | fail     | fail     |

| 86 | U29_5 |   |     | 1.2     | 1.2     | 1.2    | 1.2     | 1.2     | 1.4     | 1.4      | 1.4      | 1.4      |

| 87 | U29_6 |   |     | 1.2     | 1.5     | 1.5    | 1.5     | 11.7    | 11.7    | 11.7     | 15.5     | 20.0     |

| 88 | U30_1 |   |     | 1.3     | 1.3     | 1.3    | 1.3     | 8.0     | 8.1     | 8.1      | 8.1      | 8.1      |

| 89 | U30_2 |   |     | 1.2     | 1.2     | 1.2    | 1.2     | 1.3     | 1.3     | 1.3      | 1.3      | 6.5      |

| 90 | U31_1 |   |     | fail    | fail    | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

| 91 | U31_2 |   |     | fail    | fail    | fail   | fail    | fail    | fail    | fail     | fail     | fail     |

Figure 3.12. Experimental data failure record catalog system.

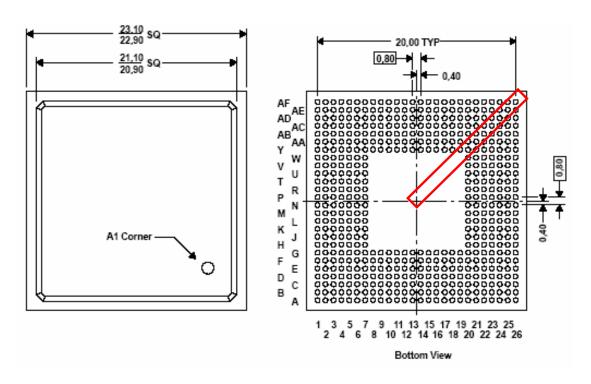

### 3.3 Package Cross-Sectioning Technique

For the finite element based modeling approach previously discussed, proper dimensioning for each of the packages modeled had to be obtained. For some of the electronic packages that were modeled, package cross sectioning had to be done to obtain these component dimensions. Information about the process of cross-sectioning electronic packages was obtained from a procedural document written by former Auburn University engineering graduate Charles Mitchell [2006]. The procedure used for cross sectioning and preparing the package will be discussed in this section.

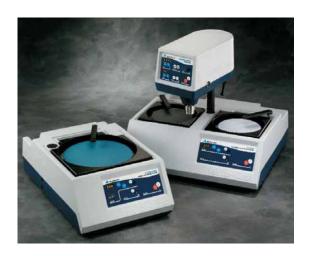

The first step of the cross-sectioning procedure should be to develop a cutting scheme that will give the desired cross section. An example of a cutting scheme is shown

in Figure 3.13; however, each cutting scheme is application specific and should be determined on a case-by-case basis.

Figure 3.13. Example of cross-sectioning cutting scheme.

The cutting procedure is delicate, so care must be taken to make a straight, precise cut. A fine-tipped permanent marker is used to mark the area of interest of the electronic package. Once the mark identifying the location of the cut is made, preparation of the cutting saw must be done to ensure a clean, accurate cut to the package, and to ensure proper care of saw. For cross-section cutting, the Isomet 1000 (Figure 3.14) wet saw was used to make the cuts.

Figure 3.14. The Isomet 1000 wet saw.

In preparing the wet saw for use, the coolant must be checked. If the coolant appears to be clean and at the proper level, then the saw is ready for cross sectioning; however, if the coolant appears dirty or below the proper level, it must be replaced before use. The manufactures' specified coolant ratio is 1 part coolant to 9 parts water (ratio 1:9). Also, the appropriate coolant level is measured to cover the bottom of the saw with 3/8 inch of coolant solution. This ensures heat dissipation of the saw blade generated by cutting the electronic packages, and wets the blade to prevent sawdust or chipping of the package. After the coolant is at the specified level, the saw can be turned on. Dress the saw blade with coolant before starting any package cross sectioning. This is done by setting the saw at 250 rpm and allowing the blade to make two complete revolutions through the coolant. For the cross sections cut in this research, the blade speed was typically set at 200 rpm, but this can be varied to meet the application. After each section cut, label and clean the components. After all cuts have been made, empty and replace the coolant.

Once all cuts have been made, they each must be sealed in epoxy resin so they can be handled and polished. Supplies used for encasing the cross sections are displayed

in Figure 3.15. These supplies consist of epoxy resin, hardener, molds, stabilizing clips, stirs, and a mixing cup. An accurate scale will also be needed to measure the appropriate ratio of epoxy.

Figure 3.15. Materials used for epoxy coating cross-sectioned samples.