# THERMO-MECHANICAL RELIABILITY MODELS FOR LIFE PREDICTION OF BALL GRID ARRAYS ON CU-CORE

# PCBs IN EXTREME ENVIRONMENTS

| Except where reference is made to the work of others, the work desc | ribed in this thes | sis is |

|---------------------------------------------------------------------|--------------------|--------|

| my own or was done in collaboration with my advisory committee.     | This thesis does   | not    |

| include proprietary or classified information.                      |                    |        |

|                                                         | Janothan Luka Duaka |                                                   |

|---------------------------------------------------------|---------------------|---------------------------------------------------|

|                                                         | Jonathan Luke Drake |                                                   |

|                                                         |                     |                                                   |

|                                                         |                     |                                                   |

| Certificate of Approval:                                |                     |                                                   |

|                                                         |                     |                                                   |

|                                                         | _                   |                                                   |

| Jeffrey C. Suhling                                      |                     | Pradeep Lall, Chair                               |

| Quina Distinguished Professor<br>Mechanical Engineering |                     | Thomas Walter Professor<br>Mechanical Engineering |

|                                                         |                     |                                                   |

|                                                         |                     |                                                   |

| Roy W. Knight                                           | -                   | Joe F. Pittman                                    |

| Assistant Professor                                     |                     | Interim Dean                                      |

| Mechanical Engineering                                  |                     | Graduate School                                   |

# THERMO-MECHANICAL RELIABILITY MODELS FOR LIFE PREDICTION OF BALL GRID ARRAYS ON CU-CORE PCBs IN EXTREME ENVIRONMENTS

Jonathan Luke Drake

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama August 4, 2007

# THERMO-MECHANICAL RELIABILITY MODELS FOR LIFE PREDICTION OF BALL GRID ARRAYS ON CU-CORE PCBs IN EXTREME ENVIRONMENTS

| T /1     | T 1   |     | . 1   |     |

|----------|-------|-----|-------|-----|

| Jonathan | Liike | - 1 | )ra   | ke. |

| Jonathan | Lunc  |     | · I U |     |

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions at their expense. The author reserves all publication rights.

| Signature of Author |  |

|---------------------|--|

|                     |  |

|                     |  |

| Date of Graduation  |  |

#### **VITA**

Jonathan Luke Drake, son of Richard and Joe Anne Drake, was born on August 26, 1982 in Phoenix, Arizona. He graduated in May of 2004 with a Bachelor's Degree in Mathematics from East Tennessee State University. After obtaining his Bachelor's Degree, he attended the University of Alabama at Huntsville from May 2004 through August 2005 where he continued his education and completed all of the engineering coursework needed to enter the Master's program in Mechanical Engineering at Auburn University. Since entering the M.S. program at Auburn, he has worked under the guidance of Professor Pradeep Lall, in the Department of Mechanical Engineering as a Graduate Research Assistant in the area of harsh environment electronic packaging reliability. While working under Dr. Lall, he was doing research for Northrop Grumman in Chicago, IL through Auburn University. He has also completed internships at Ford Motor Company in Detroit, MI and Shaw Group Inc. at Browns Ferry Nuclear Plant in Athens, AL.

#### THESIS ABSTRACT

# THERMO-MECHANICAL RELIABILITY MODELS FOR LIFE PREDICTION OF BALL GRID ARRAYS ON CU-CORE

# PCBs IN EXTREME ENVIRONMENTS

Jonathan Luke Drake

Master of Science, August 4, 2007 (B.S. Mathematics East Tennessee State University 2004)

220 Typed Pages

Directed by Dr. Pradeep Lall

In this work, thermo-mechanical models for reliability prediction of BGA packages mounted on Cu-core printed circuit assemblies in harsh environments have been developed. The models have been developed based on thermo-mechanical reliability data acquired on copper-core assemblies in four different thermal cycling conditions. Solder alloys examined include SnPb and SAC alloys. The models presented in this paper provide decisions guidance for smart selection of component packaging technologies and perturbing product designs for minimal risk insertion of new packaging technologies. In addition, qualitative parameter interaction effects, which are often ignored in closed-form modeling, have been incorporated in this work.

Multivariate linear regression and non-linear finite element models have been developed for prediction of geometry and material effects. MLR approach uses the

potentially important variables from stepwise regression. The statistics models are based on accelerated test data acquired as part of this thesis, in harsh environments, while finite-element models are based on damage mechanics and material constitutive behavior. Sensitivity relations for geometry, materials, and architectures based on statistical models, and FEA models have been developed. Convergence of statistical, failure mechanics, and FEA based model sensitivities with experimental data has been demonstrated. Validation of model predictions with accelerated test data has been presented.

## **ACKNOWLEDGEMENTS**

The author acknowledges and extends gratitude for financial support received from Auburn University and Northrop Grumman. Many thanks are due to the author's advisor Prof. Pradeep Lall, and other committee members for their invaluable guidance and help during the course of this study. Deepest gratitude are also due to the author's parents, Richard and Joe Anne Drake, as well as brother Chuck and Sister Lindsey, for their constant support, inspiration, and motivation throughout the program. The author would like to thank all other friends and colleagues whose names are not mentioned, for their priceless love and support.

Style manual or journal used: <u>Guide to Preparation and Submission of Thesis and Dissertations</u>

Computer software used: Microsoft Office 2003, ANSYS<sup>TM</sup> 9.0, MINITAB

# TABLE OF CONTENTS

| LIST OF FIGURES                                 | xiii |

|-------------------------------------------------|------|

| LIST OF TABLES                                  | xix  |

| CHAPTER 1                                       | 1    |

| INTRODUCTION                                    | 1    |

| 1.1 Functions of Electronic Packaging           | 2    |

| 1.2 Evolution of Electronic Packaging           | 4    |

| 1.3 Ball Grid Array Packages                    | 6    |

| 1.4 Design Factors                              | 9    |

| 1.5 Thermo-mechanical Reliability               | 13   |

| CHAPTER 2                                       |      |

| LITERATURE REVIEW                               | 19   |

| 2.1 Experimental Techniques.                    | 20   |

| 2.2 Failure Mechanics Based Analytical Modeling | 22   |

| 2.3 Statistical Modeling                        | 23   |

| 2.4 Finite Element Modeling                     | 25   |

| 2.5 Composition of Solder Alloy                 | 28   |

| 2.6 Objective and Scope of Thesis               | 29   |

| 2.7 Thesis Layout                               | 31   |

# CHAPTER 3

| EXPERIMENTAL SETUP AND DATA ACQUISITION                                | 32 |

|------------------------------------------------------------------------|----|

| 3.1 Test Boards                                                        | 32 |

| 3.2 Chamber Profiles                                                   | 38 |

| 3.3 Data Acquisition                                                   | 42 |

| 3.4 Cross-sectioning.                                                  | 56 |

| CHAPTER 4                                                              |    |

| FAILURE MECHANICS BASED MODELS FOR PBGA PACKAGES                       | 63 |

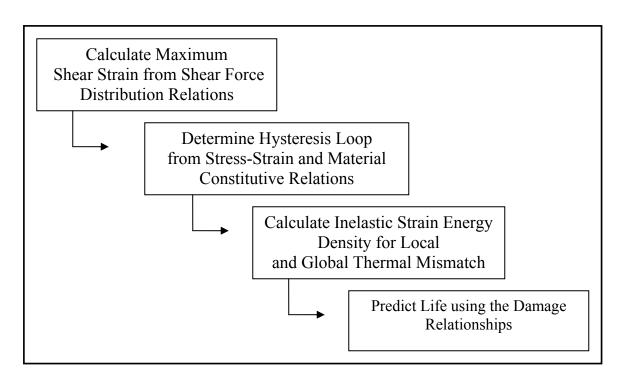

| 4.1 Failure Mechanics Methodology                                      | 64 |

| 4.2 Calculating Maximum Shear Strain                                   | 64 |

| 4.3 Hysteresis Loop Calculation                                        | 67 |

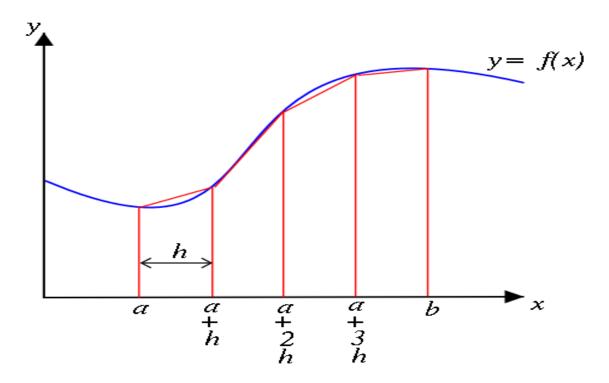

| 4.4 Calculating Inelastic Strain Energy Density                        | 69 |

| CHAPTER 5                                                              |    |

| FEM ANALYSIS OF PBGA PACKAGES                                          | 72 |

| 5.1 Model Description                                                  | 74 |

| 5.2 Geometry                                                           | 74 |

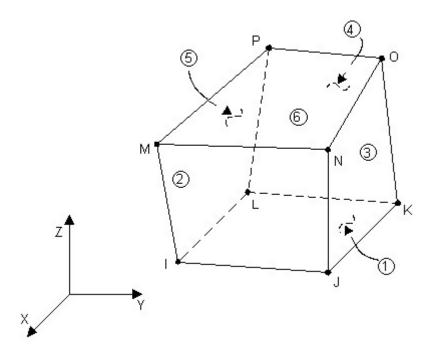

| 5.3 Modeling Elements                                                  | 75 |

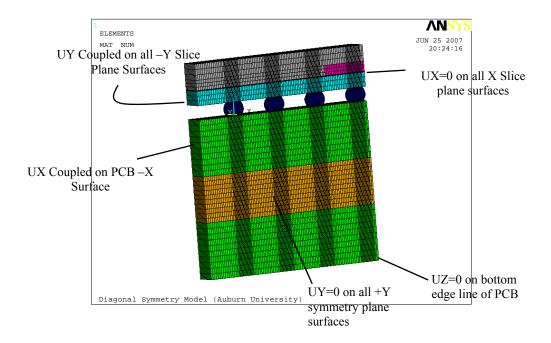

| 5.4 Mesh and Boundary Conditions                                       | 77 |

| 5.5 Material Properties                                                | 79 |

| 5.6 Inelastic Strain Energy Density                                    | 83 |

| 5.7 Using Damage Relationships to Predict Life and Package Reliability | 84 |

| CHAPTER 6                                                              |    |

| FINITE ELEMENT MODELS OF PBGA PACKAGES                                 | 86 |

| 6.1 728 I/O PBGA                                          | 87  |

|-----------------------------------------------------------|-----|

| 6.2 49 I/O PBGA                                           | 99  |

| 6.3 Shear Stress and Plastic Strain Plots for PBGA49      | 113 |

| 6.4 Hysteresis Loops for PBGA49                           | 118 |

| CHAPTER 7                                                 |     |

| STATISTICS BASED CLOSED FORM MODELS FOR PBGA PACKAGES     | 121 |

| 7.1 Perturbation Methodology                              | 122 |

| 7.2 Model Library                                         | 124 |

| 7.3 Linear Models                                         | 125 |

| 7.4 Log-Linear Model-1                                    | 126 |

| 7.4.1 Model Diagnostics of Log-Linear Model-1             | 128 |

| 7.5 Log-Linear Model-2                                    | 131 |

| 7.5.1 Model Diagnostics of Log-Linear Model-2             | 137 |

| 7.6 Correlation of Statistical Model w/ Experimental Data | 140 |

| CHAPTER 8                                                 |     |

| STATISTICAL MODEL VALIDATION FOR PBGA PACKAGES            | 142 |

| 8.1 Model Validation                                      | 142 |

| 8.1.1 Ball Count                                          | 143 |

| 8.1.2 Die to Body Ratio                                   | 145 |

| 8.1.3 Ball Diameter                                       | 149 |

| 8.1.4 Board Finish                                        | 153 |

| 8.1.5 Temperature Cycle Condition (AT)                    | 156 |

| 8.2 Parameter Selection and Packaging Construction Process | 159 |

|------------------------------------------------------------|-----|

| CHAPTER 9                                                  |     |

| LIFE PREDICTION AND FIELD LIFE CORRELATION WITH ATC DATA   | 161 |

| 9.2 Eutectic Solder Life Prediction Models                 | 161 |

| 9.3 Weibull Distribution                                   | 165 |

| 9.4 Crack Growth Correlations and Fatigue Life Predictions | 167 |

| CHAPTER 10                                                 |     |

| SUMMARY AND CONCLUSIONS                                    | 176 |

| REFERENCES                                                 | 181 |

| APPENDIX                                                   | 189 |

# LIST OF FIGURES

| Figure 1.1 Four Main Functions of Electronic Packaging                                            | 3  |

|---------------------------------------------------------------------------------------------------|----|

| Figure 1.2 Evolution of Various Packaging Technologies                                            | 6  |

| Figure 1.3 Cross-Sectional View of typical PBGA on PCB                                            | 7  |

| Figure 1.4 Typical PBGA package with corresponding Coefficients of Thermal Expansion (CTE) values | 14 |

| Figure 1.5 Failure Sites, Modes, and Mechanisms on a Plastic                                      | 14 |

| Figure 1.6 Schematic of CTE Mismatches and Solder                                                 | 18 |

| Figure 3.1 Front Side of Test Boards CCA010-018                                                   | 33 |

| Figure 3.2 Back Side of Test Boards CCA010-018.                                                   | 34 |

| Figure 3.3: Front Side of Test Boards CCA073-081                                                  | 34 |

| Figure 3.4 Back Side of Test Boards CCA 073-081                                                   | 35 |

| Figure 3.5 Front Side of Test Boards CCA 028-036                                                  | 35 |

| Figure 3.6 Back Side of Test Boards CCA 028-036                                                   | 36 |

| Figure 3.7 Front Side of Test Boards CCA 019-027                                                  | 36 |

| Figure 3.8 Back Side of Test Boards CCA 019-027                                                   | 37 |

| Figure 3.9 Slim KIC-II Thermal Profiler and Software                                              | 38 |

| Figure 3.10 TC2 Profile                                                                           | 39 |

| Figure 3.11 Thermal Chamber Used for TC2 Temperature Profile                                      | 39 |

| Figure 3.12 TC3 Profile                                                                           | 40 |

| Figure 3.13 TC4 Profile                                                                   | 41 |

|-------------------------------------------------------------------------------------------|----|

| Figure 3.14 Test Board Holder                                                             | 42 |

| Figure 3.15 Keithley Model 7200 Digital Switching Mainframe                               | 43 |

| Figure 3.16 Keithley 2000 Digital Multimeter                                              | 44 |

| Figure 3.17 Data Acquisition Setup in Dungeon Lab.                                        | 45 |

| Figure 3.18 LabView Software Screen Capture                                               | 46 |

| Figure 3.19 Markstart.txt File Example                                                    | 47 |

| Figure 3.20 Rlogset.txt File Example                                                      | 50 |

| Figure 3.21 Trd.txt Example File.                                                         | 51 |

| Figure 3.22 bBfval.txt File Example.                                                      | 52 |

| Figure 3.23 bBnameC.txt File Example                                                      | 53 |

| Figure 3.24 Test Board Ready for Cross-Sectioning                                         | 57 |

| Figure 3.25 Isomet 1000 Wet Saw                                                           | 58 |

| Figure 3.26 Various Chemicals and Tools used for Cross-Sectioning                         | 58 |

| Figure 3.27 Cross-Sectioning Samples and Polisher                                         | 60 |

| Figure 3.28: Various cross-sections used for package dimensions                           | 62 |

| Figure 4.1 Flow Chart of the Methodology behind failure mechanics based modeling          | 65 |

| Figure 4.2 Example of Calculating the Area Under a Curve Using the Trapezoidal Rule       | 71 |

| Figure 5.1 Eight-noded Hexahedral Isoparametric Element                                   | 76 |

| Figure 5.2 Schematic of Boundary Conditions Applied to PBGA49 Slice Model for Simulations | 78 |

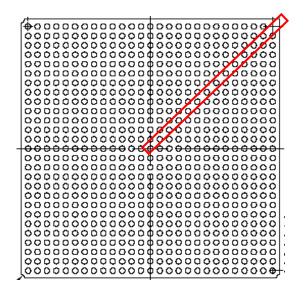

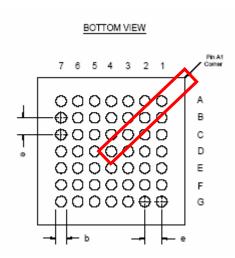

| Figure 6.1 Footprint of 728 I/O PRGA with Diagonal Slice Shown in Red                     | 88 |

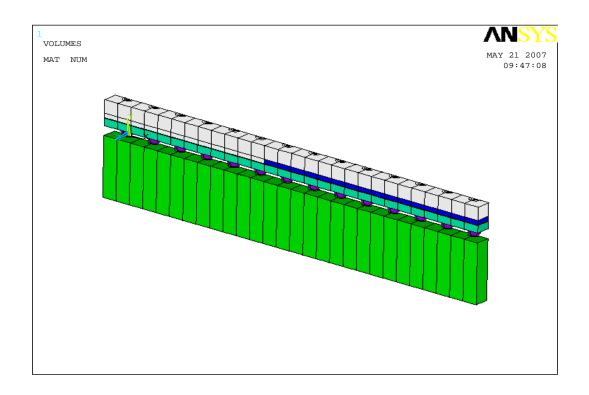

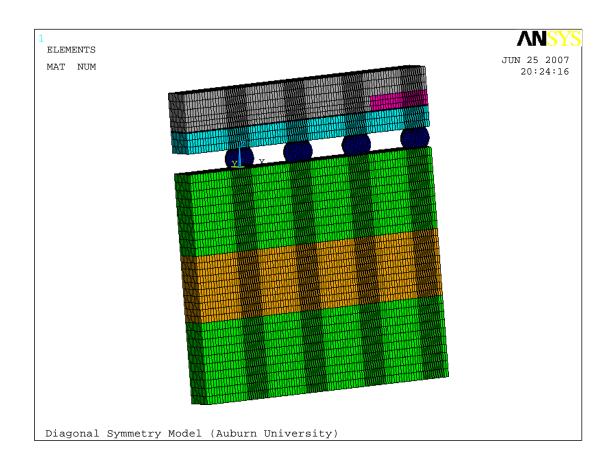

| Figure 6.2 Volumetric View of PBGA 728 Slice Model                                                                                                    | 89  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

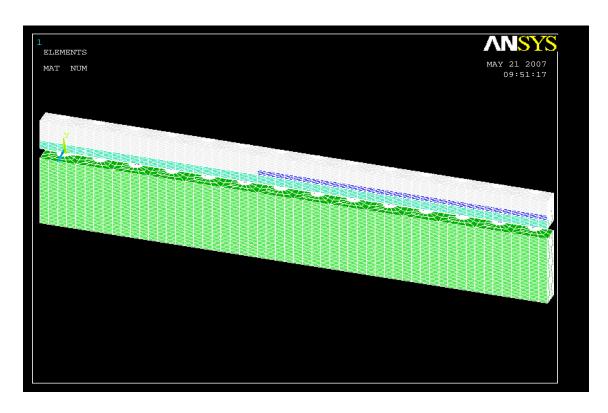

| Figure 6.3 Fully Meshed View of PBGA 728 Slice Model                                                                                                  | 90  |

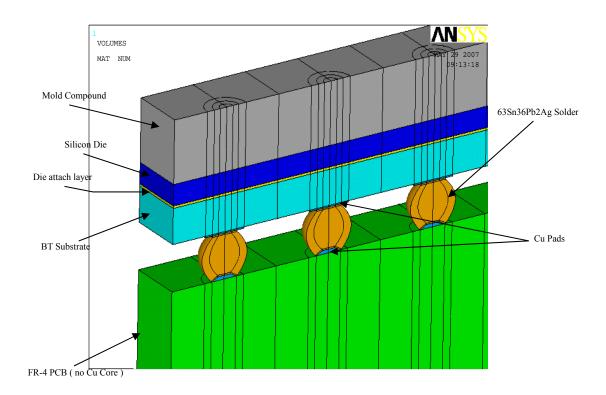

| Figure 6.4 PBGA 728 Schematic Showing Various Layers of the Preliminary Diagonal Slice Model                                                          | 91  |

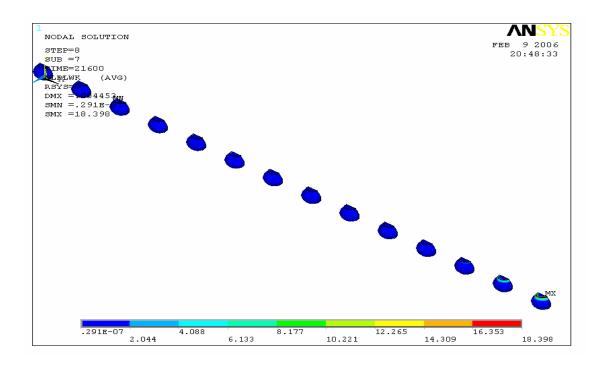

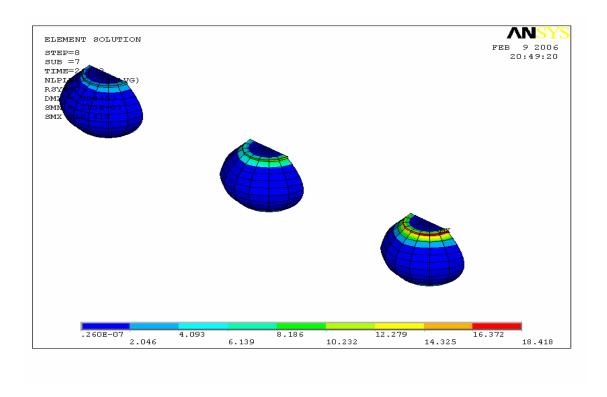

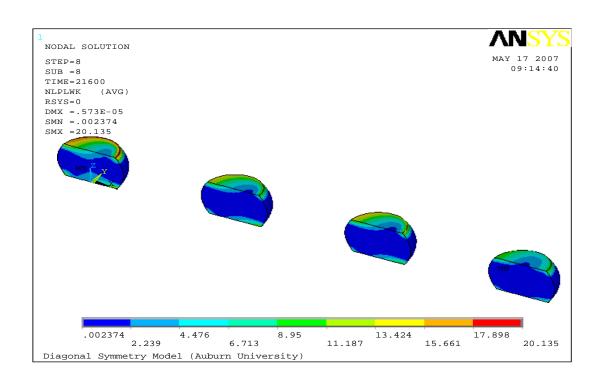

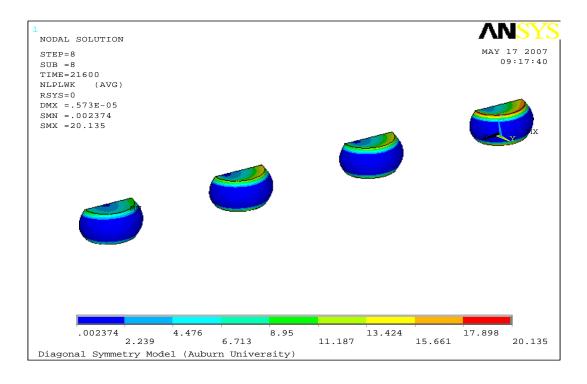

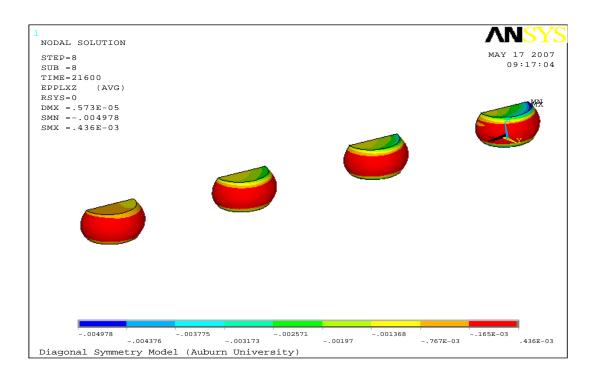

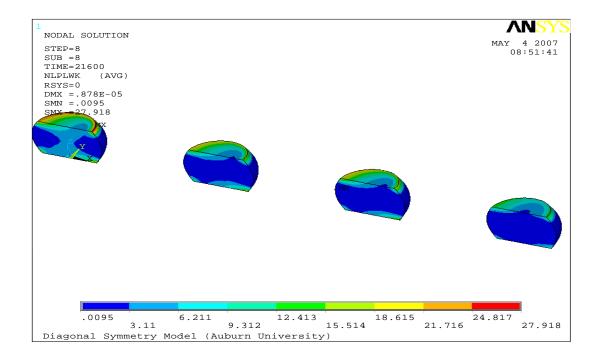

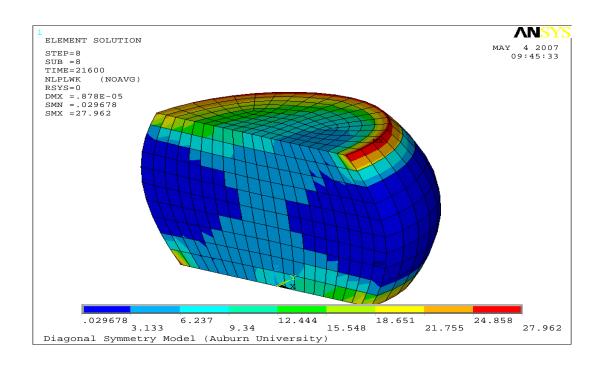

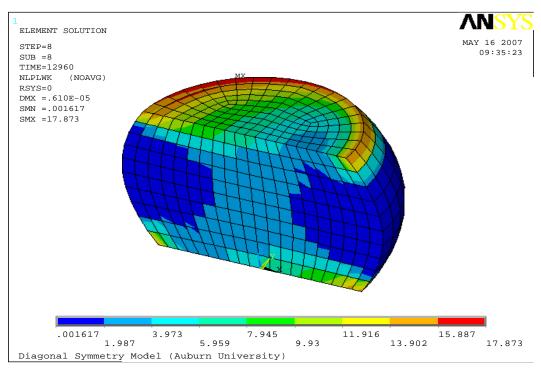

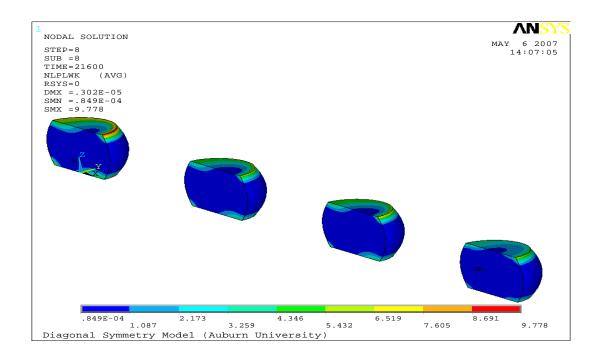

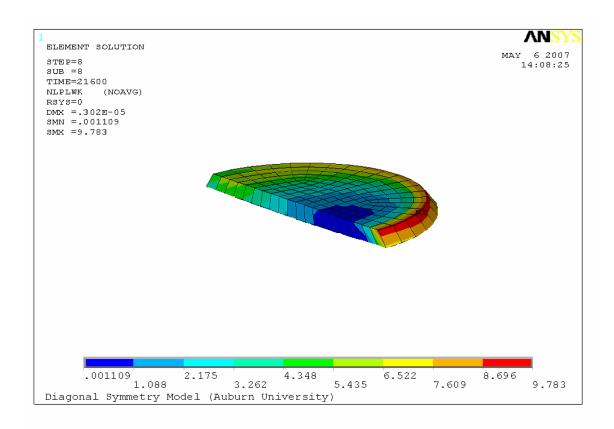

| Figure 6.5 Contour Plots of Accumulated Plastic Work on the Solder Balls                                                                              | 92  |

| Figure 6.6 Close Up of the Last Three Solder Balls Showing the Total Plastic Work of the Solder Ball Which is Furthest From the Center of the Package | 93  |

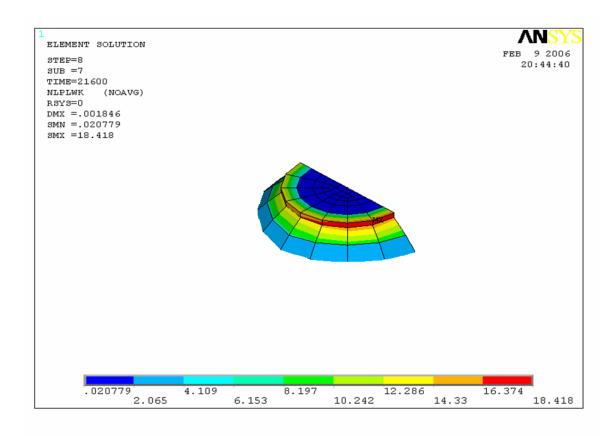

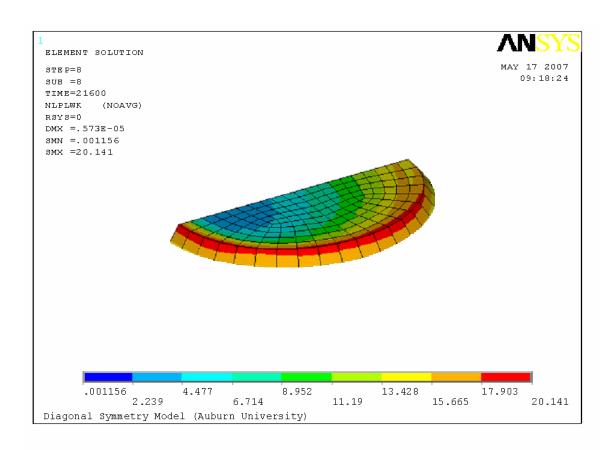

| Figure 6.7 Close up Total Plastic Work Contour Plot of the Furthest Solder Ball (DNP)                                                                 | 94  |

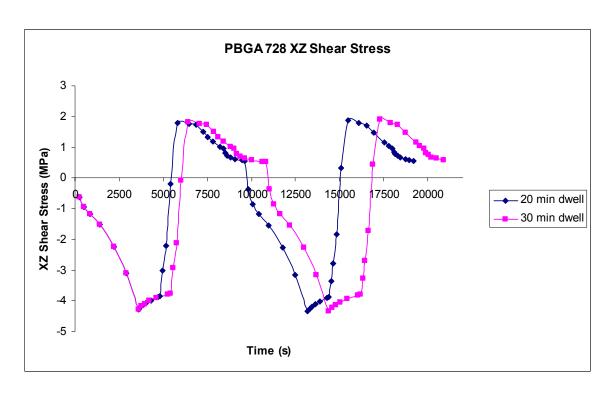

| Figure 6.8 Plot of XZ shear stress with different dwell times                                                                                         | 95  |

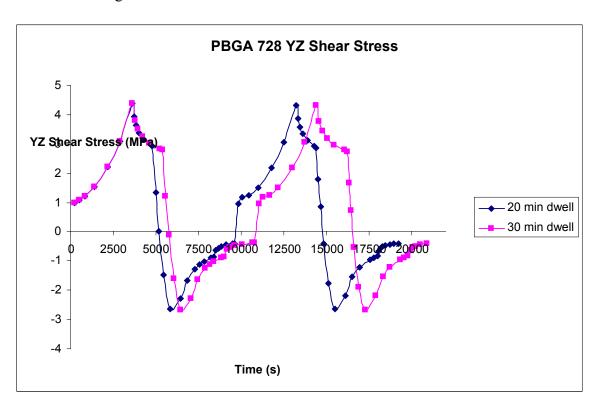

| Figure 6.9 Plot of YZ shear stress with different dwell times                                                                                         | 94  |

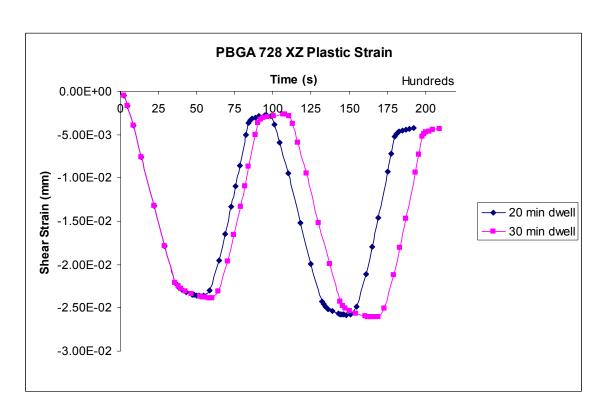

| Figure 6.10 Plot of XZ plastic shear strain with different dwell times                                                                                | 93  |

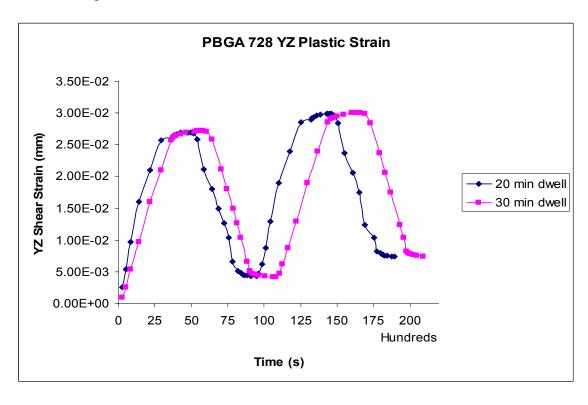

| Figure 6.11 Plot of YZ plastic shear strain with different dwell times                                                                                | 96  |

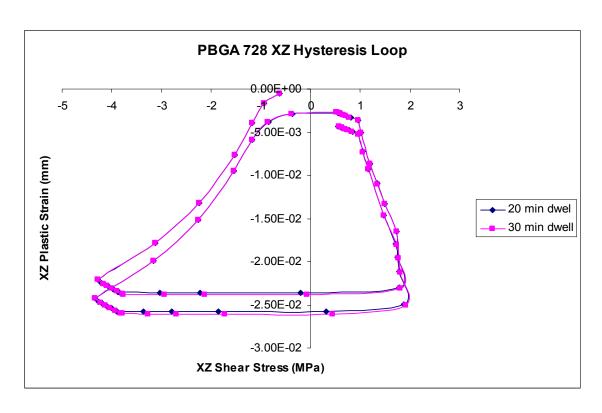

| Figure 6.12 Plot of XZ Hysteresis loop with different dwell times                                                                                     | 97  |

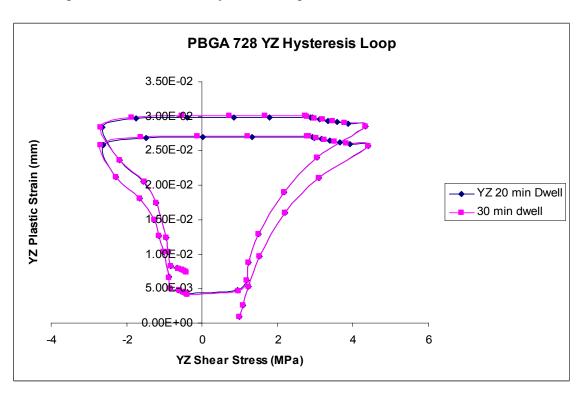

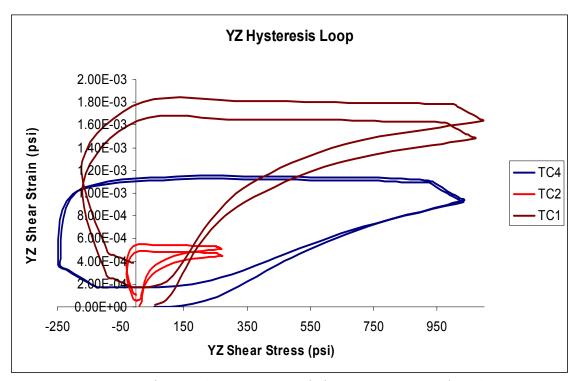

| Figure 6.13 Plot of YZ Hysteresis loop with different dwell times                                                                                     | 97  |

| Figure 6.14 Footprint of 49 I/O PBGA with diagonal slice shown in red                                                                                 | 99  |

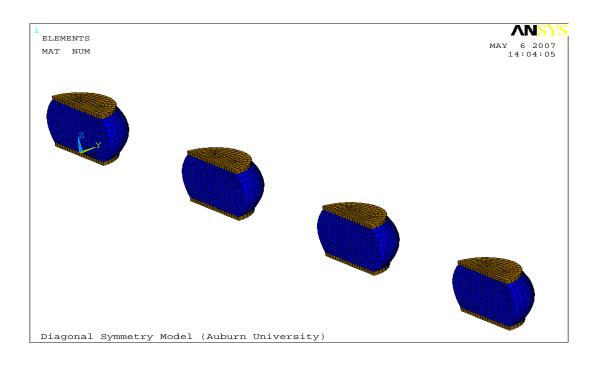

| Figure 6.15 Fully Meshed FEA model of the 49 I/O PBGA                                                                                                 | 101 |

| Figure 6.16 Screen capture showing meshed solder balls and copper pads                                                                                | 102 |

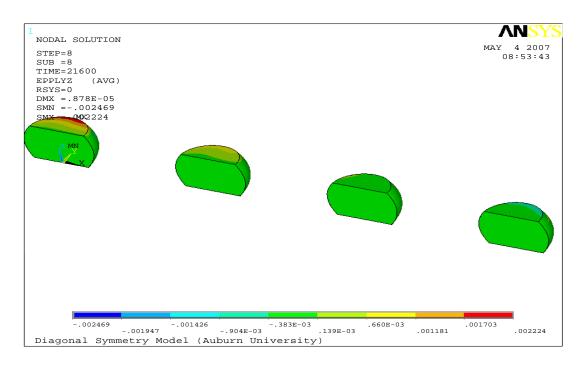

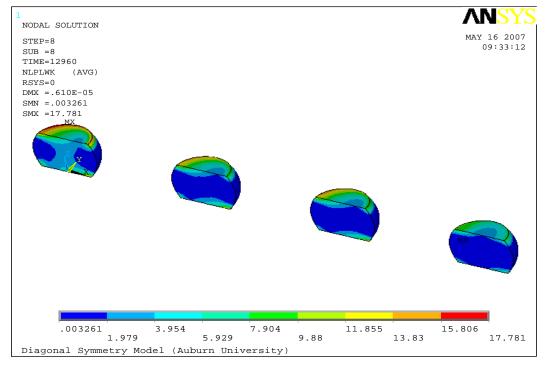

| Figure 6.17 Contour plot of accumulated plastic work of PBGA 49 solder balls (TC1)                                                                    | 103 |

| Figure 6.18 Rotated view of contour plot for accumulated plastic work (TC1)                                                                           | 103 |

| Figure 6.19 Solder ball with maximum accumulated plastic work (TC1)                                                                                   | 104 |

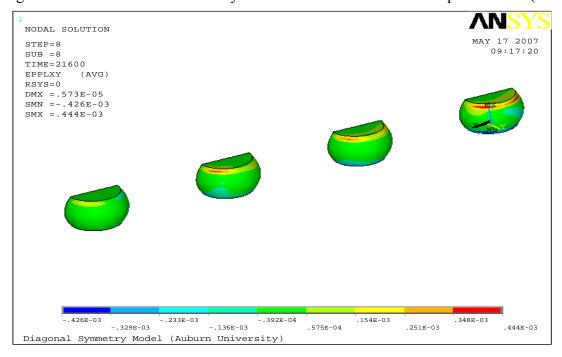

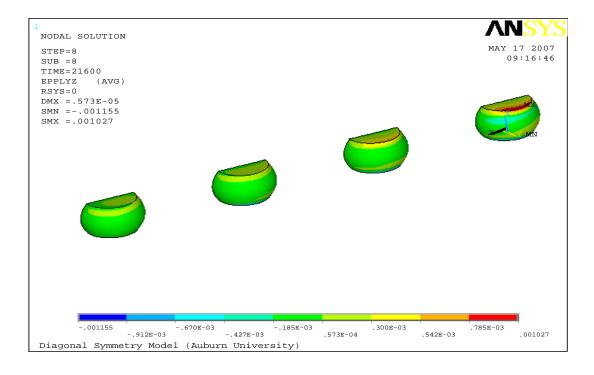

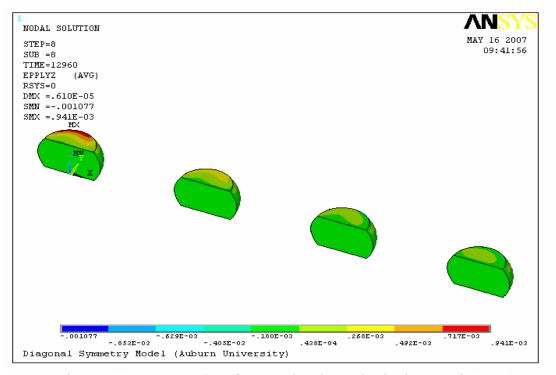

| Figure 6.20 Contour plot of accumulated XY plastic shear strain (TC1)                                                                                 | 104 |

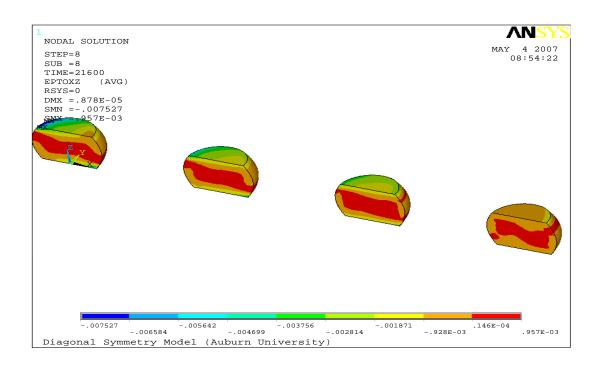

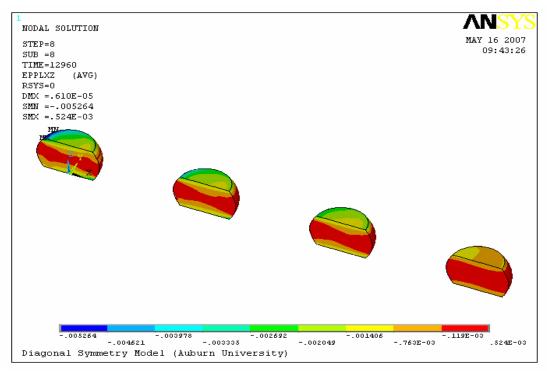

| Figure 6.21 Contour plot of accumulated XZ plastic shear strain (TC1)                                                                                 | 105 |

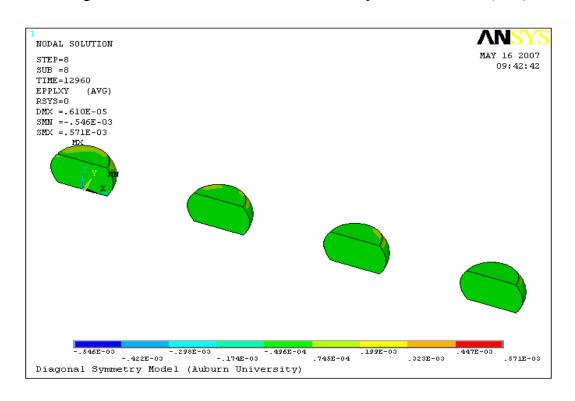

| Figure 6.22 ( | Contour plot of accumulated YZ plastic shear strain (TC1)                            | 105 |

|---------------|--------------------------------------------------------------------------------------|-----|

|               | Contour plot of accumulated plasti work of PBGA 49 solder balls (TC2)                | 106 |

| Figure 6.24 S | Solder ball with maximum accumulated plastic work (TC2)                              | 107 |

| Figure 6.25 ( | Contour plot of accumulated YZ plastic shear strain (TC2)                            | 107 |

| Figure 6.26 ( | Contour plot of accumulated XZ plastic shear strain (TC2)                            | 108 |

|               | Contour plot of accumulated plastic work of PBGA 49 solder balls (TC3)               | 108 |

| Figure 6.28 S | Solder ball with maximum accumulated plastic work (TC3)                              | 109 |

| Figure 6.29 ( | Contour plot of accumulated YZ plastic shear strain (TC3)                            | 109 |

| Figure 6.30 ( | Contour plot of accumulated XZ plastic shear strain (TC3)                            | 110 |

| Figure 6.31 ( | Contour plot of accumulated XY plastic shear strain (TC3)                            | 110 |

|               | Contour plot of accumulated plastic work of PBGA 49 solder balls (TC4)               | 111 |

| Figure 6.33 S | Solder ball with maximum accumulated plastic work (TC4)                              | 112 |

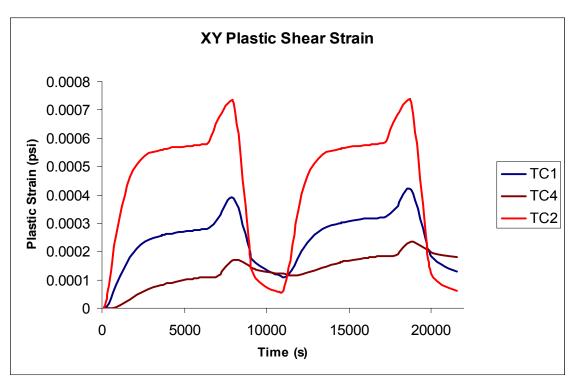

|               | XY plastic shear strain plot of PBGA 49 under TC1, TC2, and TC3 temperature profiles | 114 |

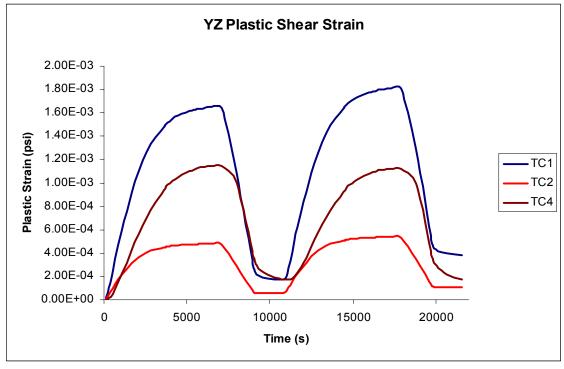

|               | YZ plastic shear strain plot of PBGA 49 under TC1, TC2, and TC3 temperature profiles | 114 |

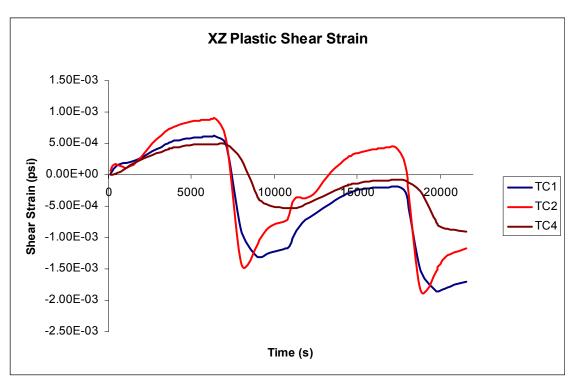

|               | XZ plastic shear strain plot of PBGA 49 under TC1, TC2, and TC3 temperature profiles | 115 |

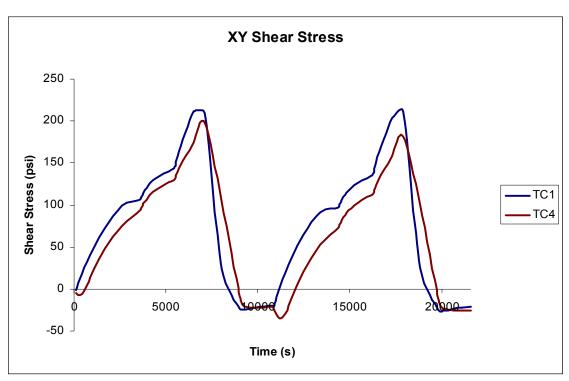

|               | XY Shear stress plots of PBGA 49 under TC1, TC2, and TC3 temperature profiles        | 116 |

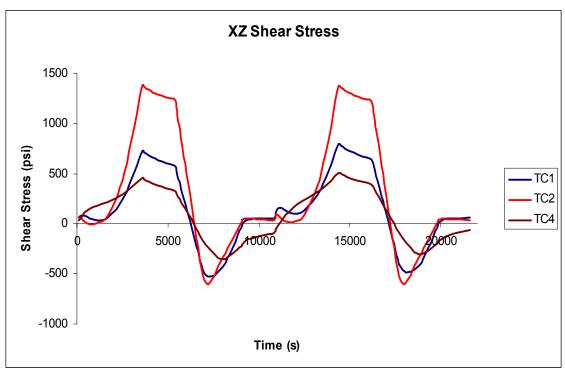

|               | XZ Shear stress plots of PBGA 49 under TC1, TC2, and IC3 temperature profiles        | 116 |

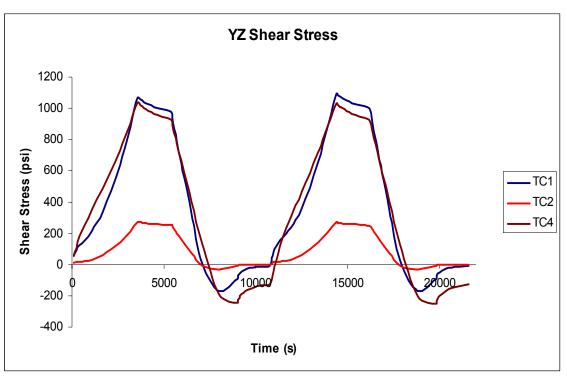

| Τ             | YZ Shear stress plots of PBGA 49 under TC1, TC2, and IC3 temperature profiles        | 117 |

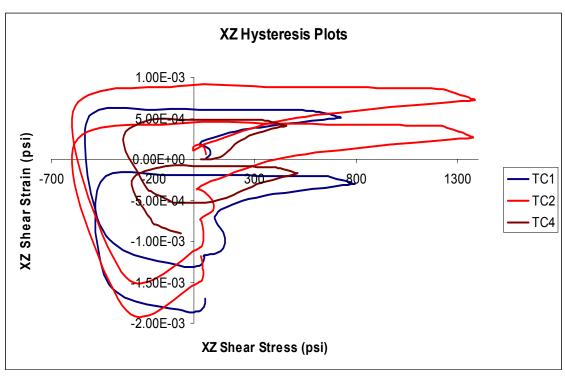

| rigure 6.40 2 | AZ HVSTETESIS DIOTS OF PBUA 49 under TCT, TCZ, and                                   |     |

| TC3 temperature profiles                                                                                                                                      | 119 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.41 YZ Hysteresis loop for TC1, TC2, and TC4                                                                                                          | 120 |

| Figure 7.1 Residual plots for the Log-Log Model-1                                                                                                             | 129 |

| Figure 7.2 Residual plots for the Log-Log Model-2                                                                                                             | 138 |

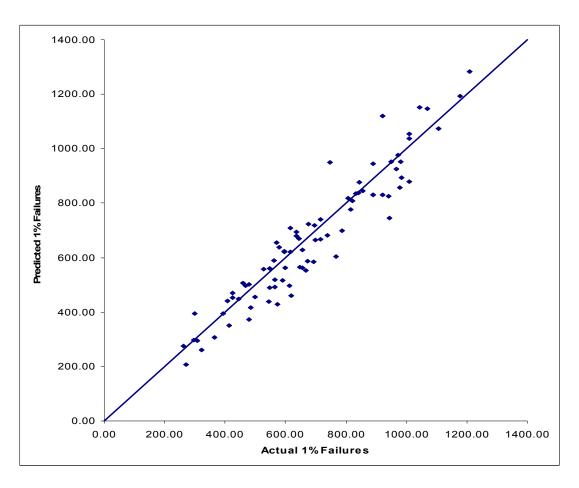

| Figure 7.3 Plot of experimental vs. predicted 1% cycles to failure for the Log-Log Model-2                                                                    | 141 |

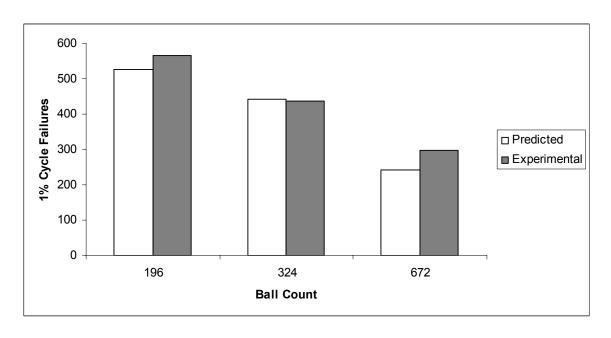

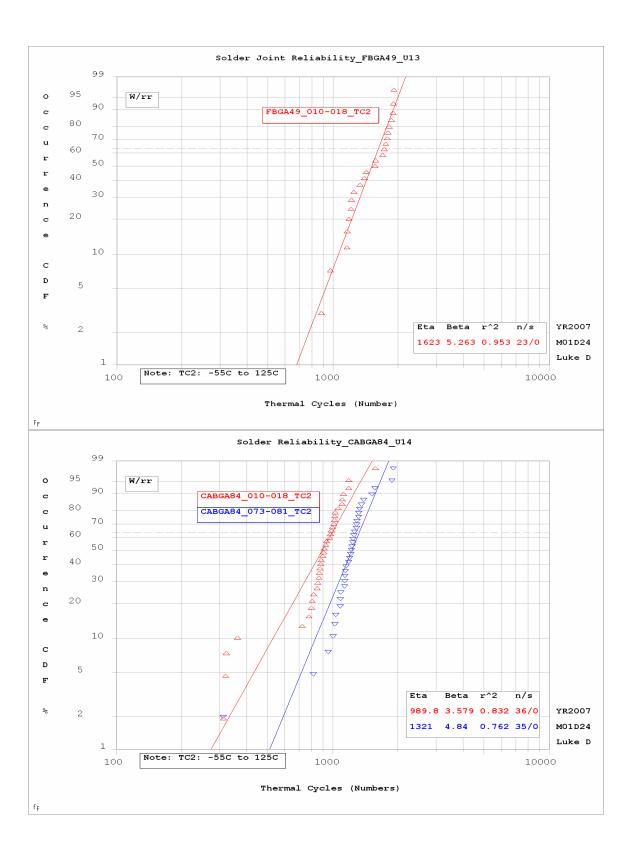

| Figure 8.1 Effect of ball count on thermal reliability of PBGA packages subjected to -55°C to 125°C thermal cycle                                             | 144 |

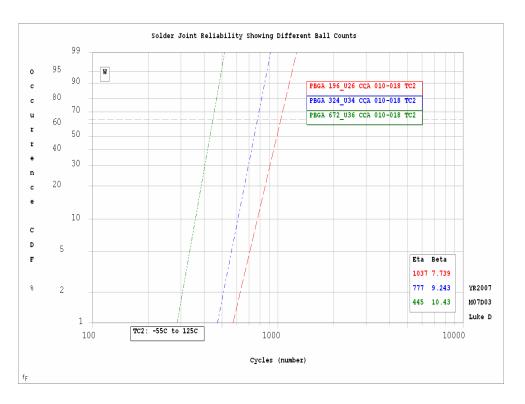

| Figure 8.2 Weibull Distribution showing experimental data correlation with Model predictions                                                                  | 145 |

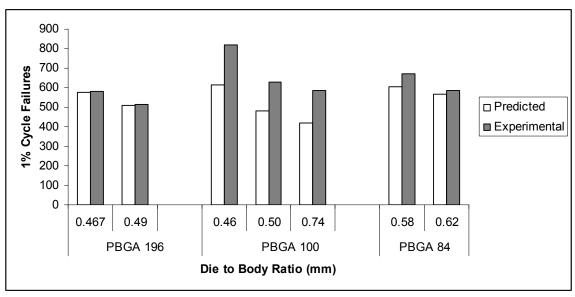

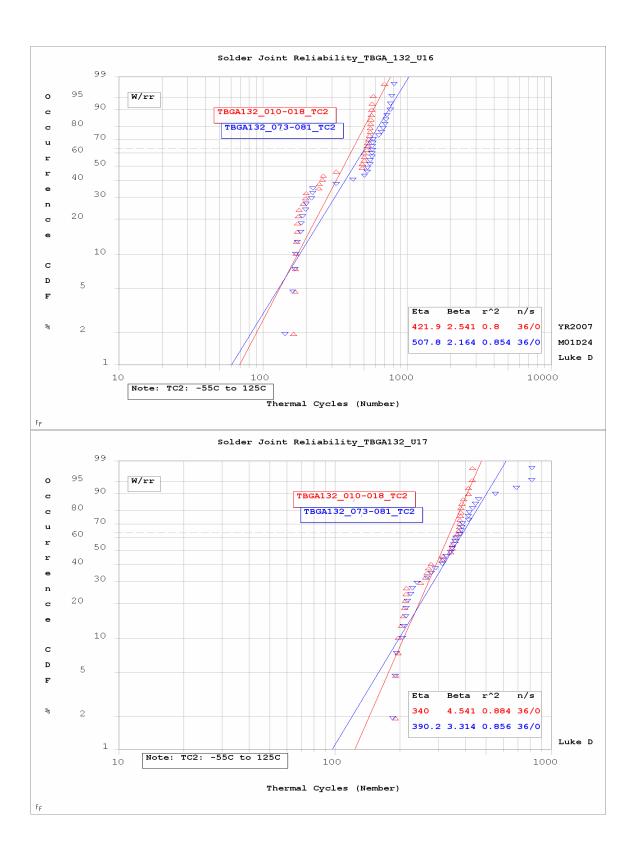

| Figure 8.3 Effect of die-to-body ratio on thermal reliability of PBGA packages subjected to -55°C to 125°C thermal cycle                                      | 147 |

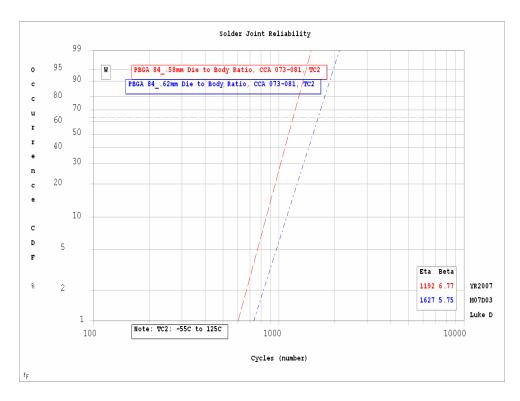

| Figure 8.4 Weibull Distribution of PBGA84 with various die sizes                                                                                              | 148 |

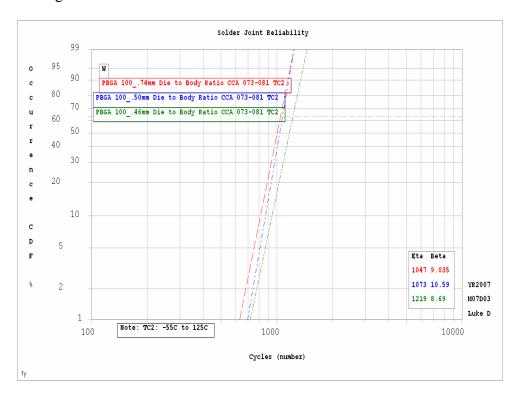

| Figure 8.5 Weibull Distribution of PBGA100 with various die sizes                                                                                             | 148 |

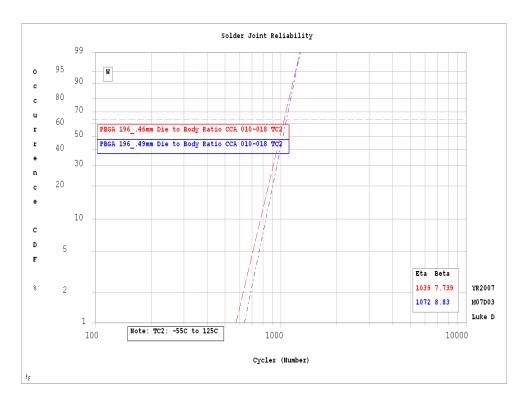

| Figure 8.6 Weibull Distribution of PBGA196 with various die sizes                                                                                             | 149 |

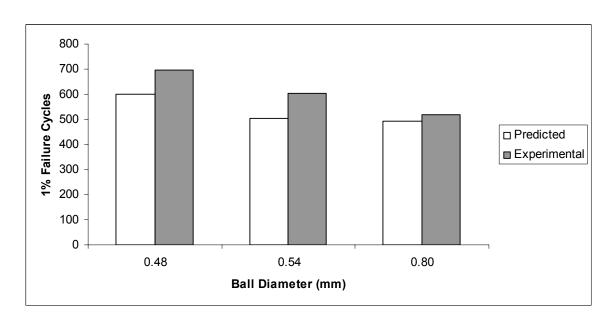

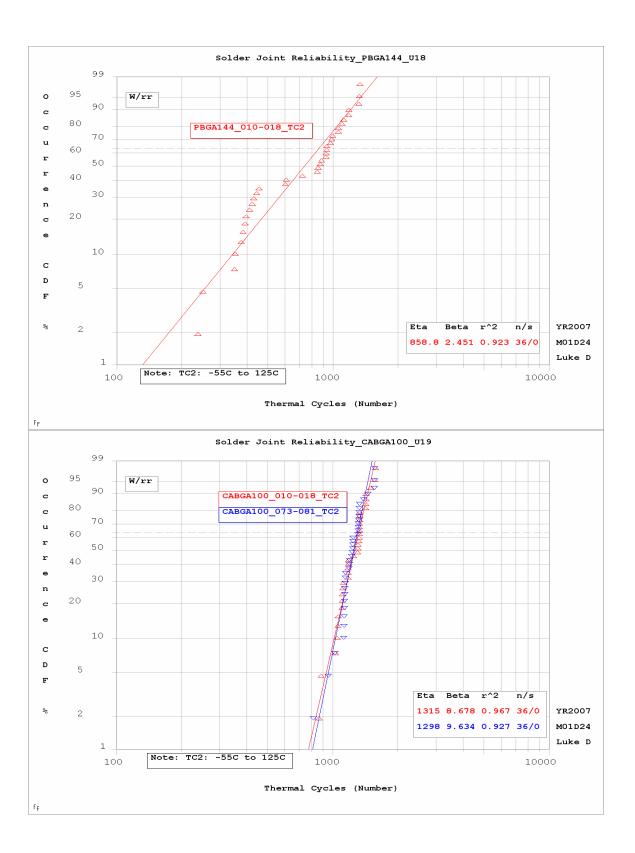

| Figure 8.7 Effect of ball height on thermal reliability of PBGA packages subjected to -55°C to 125°C thermal cycle                                            | 151 |

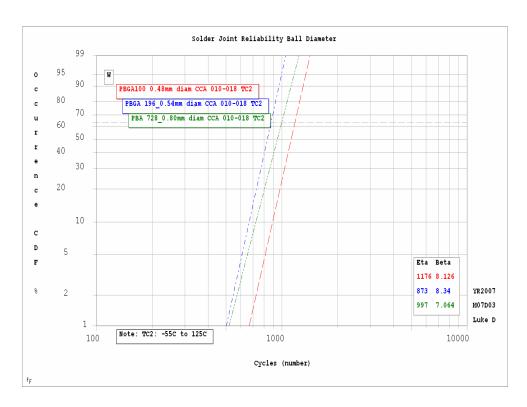

| Figure 8.8 Weibull Distribution for varying solder ball diameters under TC2 thermal cycle                                                                     | 152 |

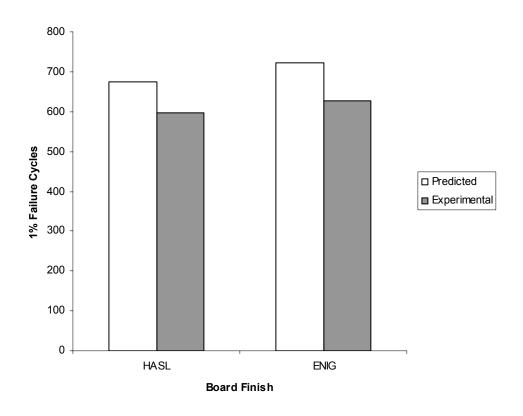

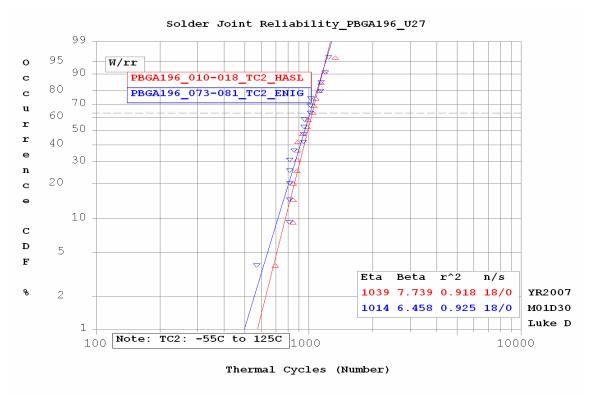

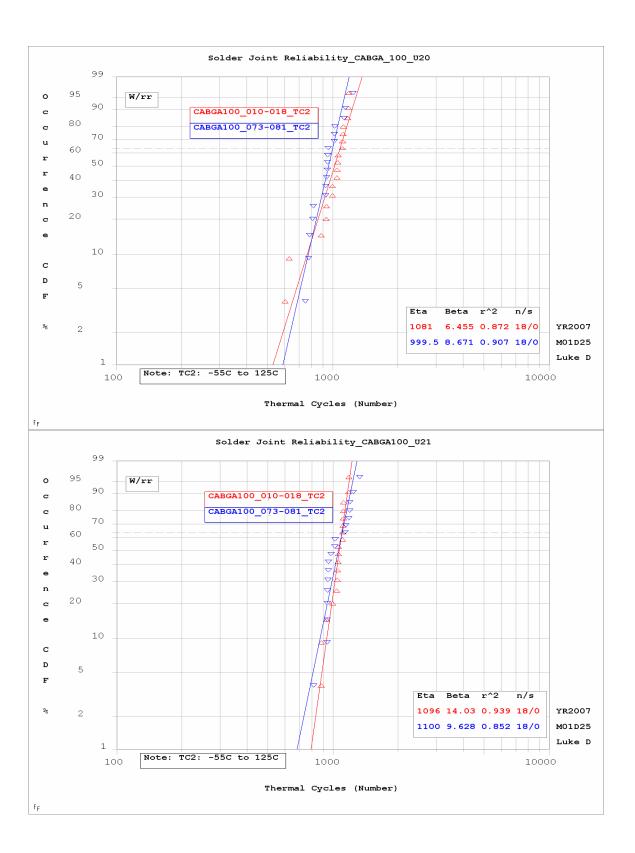

| Figure 8.9 Effect of board finish on thermal reliability of PBGA packages coupled with $\Delta T$ (TC2), ball height, ball count, ball diameter, and die size | 154 |

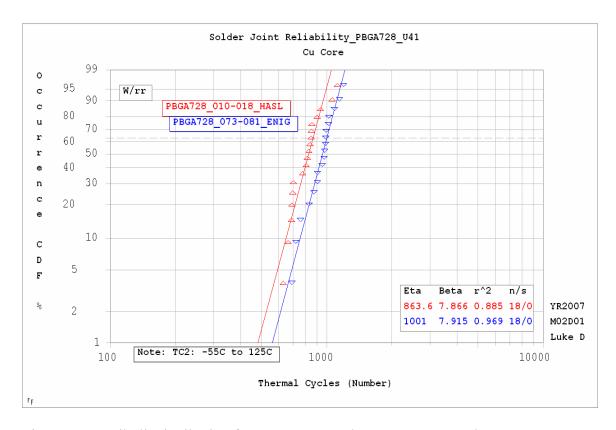

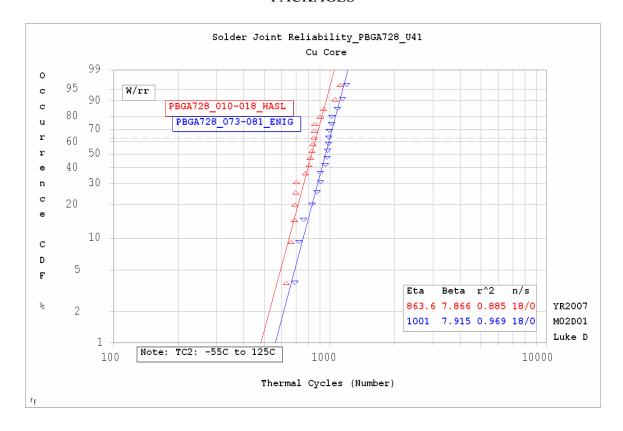

| Figure 8.10 Weibull Plot for validating model with ENIG and HASL Finishes under TC2 temperature profile                                                       | 155 |

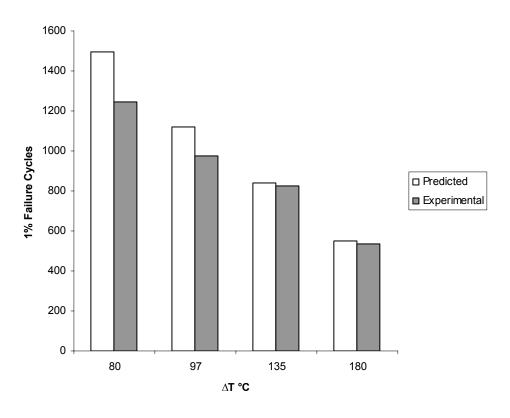

| Figure 8.11 Effect of $\Delta T$ on thermal reliability of PBGA packages                                                                                      | 157 |

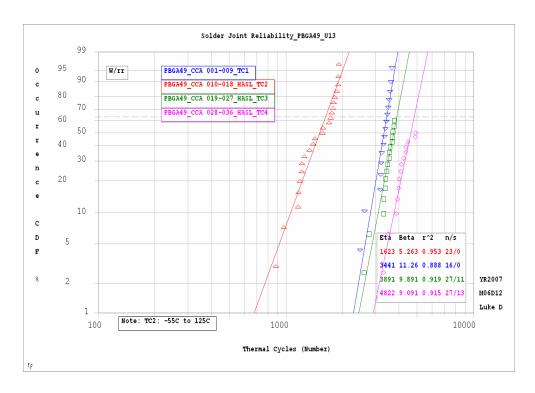

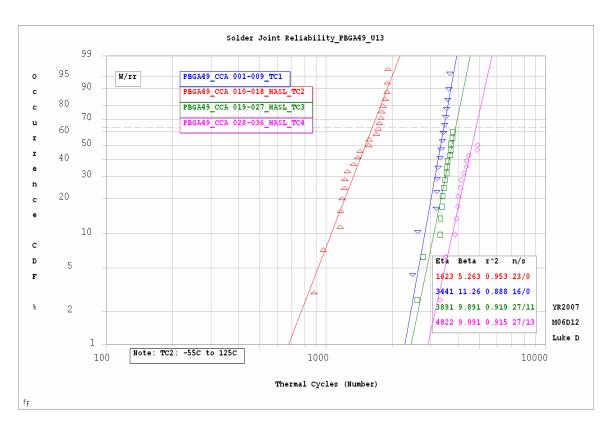

| Figure 8.12 Weibull plot validating model under varying $\Delta T$ thermal conditions                                                                         | 158 |

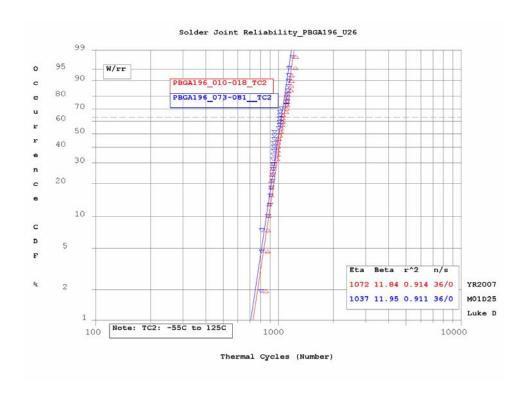

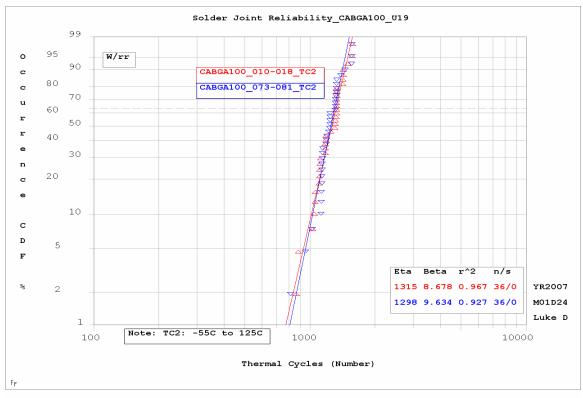

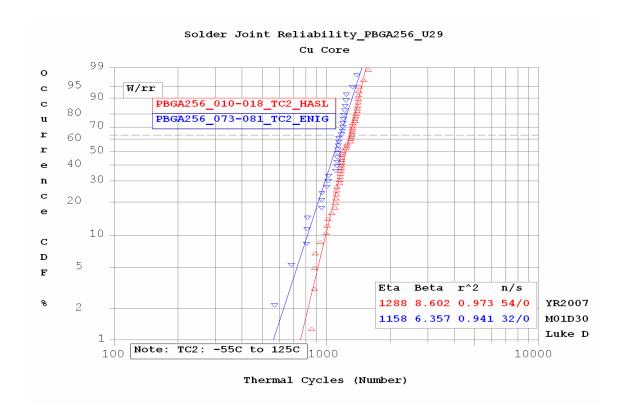

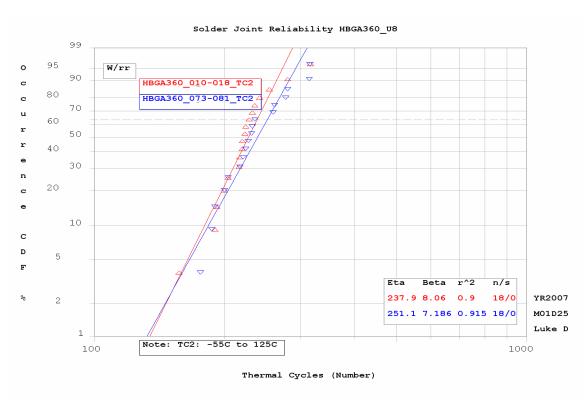

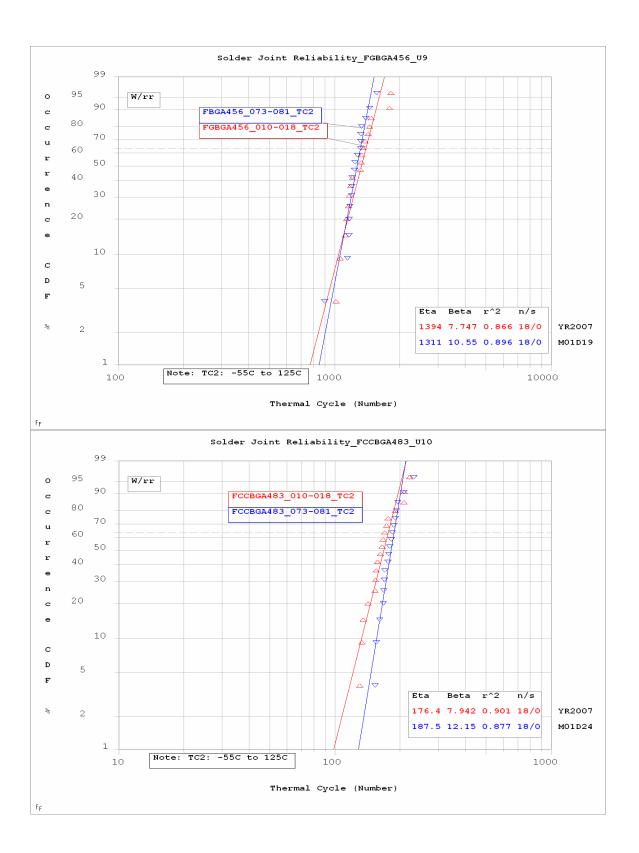

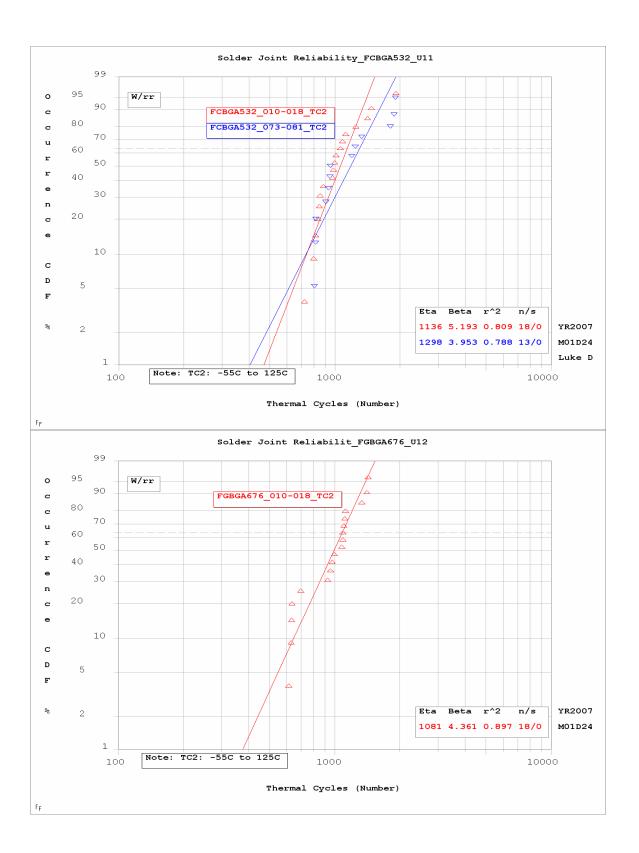

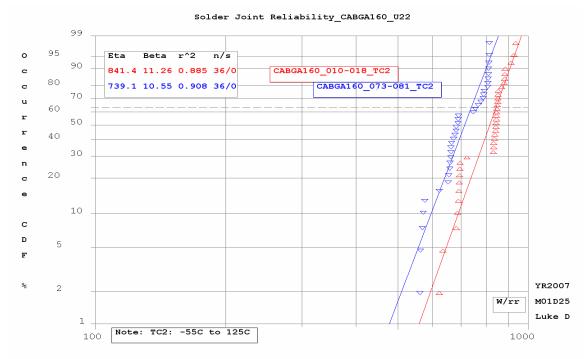

| Figure 9.1 Weibull distribution plot of PBGA 196 with various surface finishes under TC2 temperature profile                                                  | 165 |

| TC1-TC4                                                                                           | 171 |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 9.3 Weibull distribution for PBGA 728 under temperature cycle TC1                          | 172 |

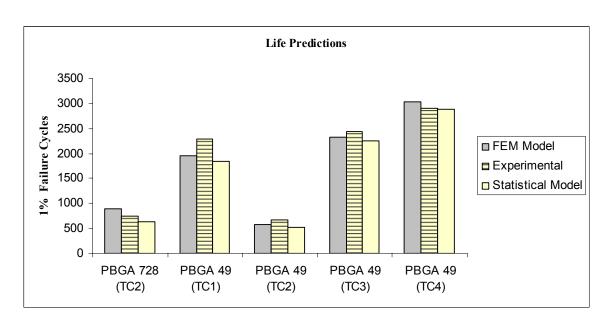

| Figure 9.4 FEM life predictions plotted next to actual experimental data for PBGA 728 and PBGA 49 | 175 |

# LIST OF TABLES

| Table 1.1 Various packaging technologies                                                                                                                                                   | 5                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Table 5.1 Dimensions of fixed parameters used for the finite e                                                                                                                             | element models75       |

| Table 5.2 Linear isotropic material properties                                                                                                                                             | 81                     |

| Table 5.3 Values of the constants of Anand's viscoplastic mod 63Sn46Pb2Ag solder                                                                                                           |                        |

| Table 5.4 Values of the constants of Anand's viscoplastic mod Sn3Ag0.5Cu-lead free solder                                                                                                  |                        |

| Table 5.5 Crack initiation and propagation constants                                                                                                                                       | 85                     |

| Table 6.1 Dimensions of variable parameters for PBGA 728                                                                                                                                   | 88                     |

| Table 6.2 Dimensions of variable parameters for PBG 49                                                                                                                                     | 100                    |

| Table 7.1 Model parameters and analysis of variance for multi-<br>Regression Log-Linear Model-1                                                                                            |                        |

| Table 7.2 Model parameters and analysis of variance for multi-<br>regression Log-Linear Model-2                                                                                            |                        |

| Table 7.3 Pearson's correlation coefficient matrix for the pred of the log-linear model-2                                                                                                  |                        |

| Table 8.1 Sensitivity of package reliability of ball count and c statistical model predictions to actual experimental of                                                                   |                        |

| Table 8.2 Sensitivity of package reliability of die to body ratio statistical model predictions to actual experimental of                                                                  | *                      |

| Table 8.3 Sensitivity of package reliability of ball height and of statistical model predictions to actual experimental of                                                                 |                        |

| Table 8.4 Sensitivity of package reliability of different board to comparison of statistical model predictions to actual Table 8.5 Sensitivity of package reliability of ΔT and comparison | l experimental data154 |

|           | of statistical model predictions to actual experimental data | 157  |

|-----------|--------------------------------------------------------------|------|

| Table 9.  | 1 Damage relationship constants                              | 164  |

| Table 9.2 | 2 FEM Life prediction parameters                             | .173 |

| Table 9.3 | 3 FEM Life prediction results from equations 9.5-9.10        | .173 |

| Table 9.4 | 4 Experimental data and results from ATC testing             | 174  |

#### CHAPTER 1

#### **INTRODUCTION**

Electronics has become the largest industry, surpassing agriculture, automotive, and heavy metal industries [Tummala. et al. 1997]. Over the past three decades, there have been dramatic advances in the area of microelectronics. Today's trend in the electronic packaging industry is to make products that are smaller, faster, and lighter but at the same time they want to make them more reliable, powerful, and affordable. The continuous drive toward high density and low profile integrated circuit (IC) packaging has led to the growing application of ball-grid array (BGA) assemblies. BGA packages with area-array configurations offer many advantages over their predecessors. Smaller footprint, faster signal transmission, lower thermal resistance between the package and the printed circuit board (PCB), and ease of handling are only a few of the advantages that BGAs have over quad flat package (QFP), dual inline packages (DIP), and leadless chip carriers (LCC).

#### 1.1 Functions of Electronic Packaging

In this day of age, almost every electrical device that is used, calculators, cell phones, computers, televisions and ipods, contain numerous forms of electronic packages. Electronic packaging is defined as the art of establishing interconnections between various levels of electronic devices, components, modules and systems. These packages contain various electrical components which include transistors, resistors, capacitors, diodes, as well as other devices. In turn, all of these devices must be interconnected to one another to perform a specific function or multiple functions. The connection of multiple devices to perform a function is called a circuit. As this level of integration increases, these multiple circuit connections are moving towards integrated circuit (IC) chips. Mechanical support and environmental protection are required for the ICs and their interconnections. To function properly, electrical circuits must be supplied with electrical energy, which is consumed and converted into heat. In order for these circuits to operate at their peak performance, they must maintain a certain operating temperature. Thus packaging serves four main functions:

11145 p. 4146 541 45 16 41 111411 14

- Power Distribution

- Heat Dissipation

- Signal Distribution

- Mechanical, chemical, and electromagnetic protection of components and interconnections

These functions are illustrated in figure 1.1 In addition to providing the four functions listed, the package must function at its specified performance level as decided by the requirements of the electronic product of system.

Figure 1.1 Four Main Functions of Electronic Packaging [Tummala 1997]

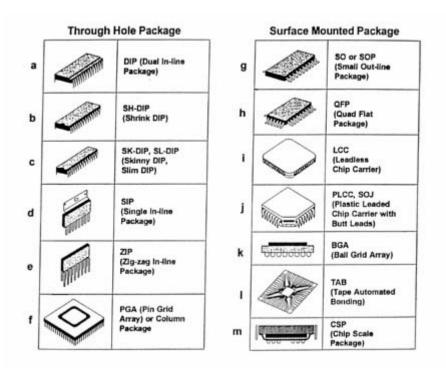

## 1.2 Evolution of Electronic Packaging

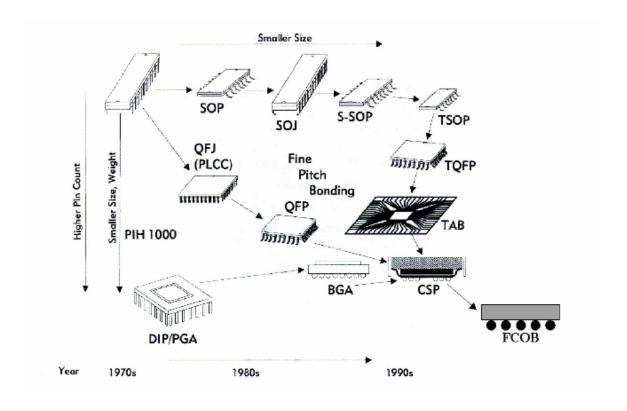

Throughout the past few decades, chip carrier technology has drastically evolved to keep up with the rising demand for higher input/output (I/O) connections per chip, higher I/O density, lower weight, faster signal speed, and lower cost. See Table 1.1 for the various packaging technologies used over the years. The original packaging devices were typically large. In the 1970's most packaging technologies were plated throughhole (PTH) Dual In-Line Packages (DIPs). With DIPs, the I/Os are aligned along each side of the chip carrier in the form of pins, or leads, which were plated with tin and lead (Sn/Pb). In order to create more I/Os, more leads had to be added, which in turn, caused the overall package size to increase dramatically. DIP packages have an upper limit of 64 pins, after which the package simply becomes too large for any practical application. In order to solve this problem and attain higher I/O connections, manufacturers began to build Pin Grid Array (PGA) packages where the I/Os were arranged in an area array underneath the package. PGA packages typically have an upper limit of 200 pins. The Quad Flat Package (QFP) was created as an extension to the small outline package. QFPs have higher I/O connections compared to the small outline packages, but still occupied too much space. However, the main problem with through-hole devices is their size. The trend for manufacturers was to increase density while decreasing the amount of space used on the printed circuit board (PCB).

Table 1.1 Various Packaging Technologies [Tummala 1997]

In the 1980's, through-hole technology began to phase out and a new type of technology, called Surface Mount Technology (SMT) became the main emphasis. With this technology, there was no longer a need to drill holes through the PCB. Instead, the leads from these packages mounted directly to copper plated pads on the surface of the printed circuit board in the form of solder balls. This allowed the width of the leads to become smaller, the spacing, or pitch, between them was drastically decreased, and also allowed a package with the same number of pins as a traditional through-hole device to be significantly smaller in area. Ball Grid Array (BGA) packages are an example of this type of surface mount technology. Figure 1.2 shows the evolution of the various packing technologies.

Figure 1.2 Evolution of Various Packaging Technologies [Tummala 1997]

## 1.3 Ball Grid Array Packages

The IC packaging technology [Suhling, 2003] in the past has evolved from the inline and peripheral array packages such as single inline package (SIP), dual inline package (DIP), plastic leaded chip carrier (PLCC), quad flat package (QFP) or leadless ceramic chip carrier (LCCC) to an area array packaging such as ball grid array (BGA). The BGA is a solution to the problem of producing a miniature package for an integrated circuit with many hundreds of pins. Pin grid arrays, BGAs' predecessors, were being produced with more and more pins which resulted in lowering the pitch between pins.

Creating larger PGAs with more pins seemed like a good idea, until the pitch became

small enough that it began to create soldering issues. Bridging between solder joints during the soldering process became a major concern. BGAs do not have this problem because the solder is factory-applied to the package in the exact volume needed.

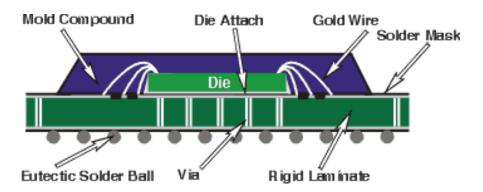

In a typical BGA package, the pins have been replaced by spheres of solder which are applied to the bottom of the package. It is then placed on a PCB which carries copper pads arranged in the same grid pattern that matches the solder balls on the package. The entire assembly is then heated by an infrared heater or in a reflow oven which causes the solder balls to melt. The molten solder balls are held in place by surface tension while the solder cools and solidifies to the printed circuit board. The composition of the solder alloy and the soldering temperature are carefully chosen so that the solder does not completely melt, but stays semi-liquid, allowing each ball to stay separate from its neighbors. Figure 1.3 shows a schematic drawing of a typical PBGA package.

Figure 1.3 Cross-Sectional View of typical PBGA on PCB

Advantages: Ball Grid Arrays allow for a higher number of interconnects in a much more compact space, thus maximizing available space on the PCB. BGAs also allow computerized robots on assembly lines to pickup and move these packages much easier than leaded chips which have very fragile leads. As stated above, one of the main advantages to BGA packages is that during the soldering process, the manufacturers do not have to worry about bridging of solder joints. Another advantage over leaded packages is it lowers the thermal resistance between the package and the printed circuit board. This keeps the chip from overheating by allowing heat that was generated from the integrated circuit inside the package to flow more easily to the PCB. Since the pins and peripheral arrays have been replaced by solder balls, thus creating a shorter electrical conductor, the inductance of the package is also lowered. The short distance between the package and the PCB creates a lower inductance which leads to better electrical performance compared to leaded devices.

<u>Disadvantages</u>: Although, there are many advantages to BGAs compared to leaded chip carriers, there are still a few drawbacks. One of the big disadvantages is that the solder balls can not flex the same way that longer leads can. In previous packages, the mismatch in thermal expansion coefficients between the PCB, the silicon die, the epoxy over-mold, and the Bismaleimide-Triazine substrate, or BT substrate was not as much of an issue as it is in BGAs. With BGAs, the bending and thermal expansion of the PCB is transmitted directly to the package. This, in turn, places great amounts of shear strain on the solder joints and causes them to fracture under high thermal and mechanical stresses, which will be covered more in depth throughout this paper.

However, this problem of mismatched CTEs can be overcome at a cost by matching the mechanical and thermal characteristics of the PCB to those of the silicon die and other materials of the BGA package more closely. Another disadvantage of the BGA is that it is very hard to analyze the package for soldering faults, such as voids or cracks, once the package has been soldered to the PCB.

### 1.4 Design Factors

The trend of electronic products is moving towards further miniaturization and improved performance. Today, manufacturing companies as well as consumers, such as cellular companies, computer, automotive, military, and aerospace companies have many factors determining which type of commercial off the shelf IC package to choose. Not only do they have a wide variety of package architectures to choose from, but they also must decide what the product will be used for, what their budget is, how reliable they want the package to be, as well as how much space they have allotted for the particular application. For instance, a military company may need the package to be sealed off from the elements as well as be capable of handling extreme temperature from -55C all the way up to 125C from one day to the next. Not only would this particular application need a package that has proven its reliability in this temperature extreme, but it would also have to be cost effective as well as use a minimal amount of space. Other applications may require only high reliability, in which the component could be fairly large and weigh twice as much as another product and be less costly. It all depends on the individual's or company's needs.

Cost: One of the most important factors in any industry in this day and age is the ability to design a product and offer it to the consumer at a reasonable price. Over the past few years, there have been many engineering advances in materials used which are all aimed at getting the same performance, but reducing the cost at the same time. If one manufacturer can build PBGAs cheaper than another and still produce around the same performance and reliability numbers as another, that manufacturer is going to prosper and the other, high priced company, will be short lived. Also, certain packages are more expensive than others. Ceramic packages and hermetically sealed packages cost much more than PBGAs and DIPs. Not only are the manufacturers trying to reduce costs, but each particular application must fully research which particular architecture is needed before a decision is made and thousands or even millions of dollars are spent.

Exposure: Electronic packaging is becoming more widely used in various technological applications and thus each particular application requires a different type of protection from environmental, mechanical, and even chemical exposures. Obviously the type of electronic package used in automotive[Lall 2004], aerospace, and military conditions is going to be subjected to much harsher thermal cycling, shock, and vibrations and need better protection from the elements than applications used in personal computers, office equipment, and cellular phones[Sillanpaa 2004].

Size: Aside from cost and exposure, the miniaturization of electronic devices has become the predominant design factor throughout the industry. Cellular phones, personal Global Positioning Satellites (GPS), personal computers, and many other military, aerospace, and automotive applications demand electronic devices to occupy minimal amounts of space. However, the overall size of the product depends on the application which it is used. For instance, and desktop computer, for use at home or in the office, can have larger electronic packages designed to occupy a larger area on the PCB than computer chips and their packaging used underneath the hood of an automobile inside an electronic controller where limited space is available.

Life and Reliability: A product's life, or number of cycles until failure, has become a critical factor for electronic packaging over the past decade. Millions of dollars are being spent each year to design products with higher reliability and increased life. However, from a design perspective, one must choose a product with the correct life span for the application. If the consumer decides to purchase an electronic package with a higher life than the application is needed, the company will be wasting money by purchasing a device with more life than is needed. On the other hand, if the consumer or company purchases a packaging device which has a shorter life span than needed and also begins production of components, premature failures will occur and there will be many unsatisfied customers to deal with.

When selecting which electronic package is right for certain applications, all of these design factors must be analyzed and taken into consideration first. There are many ways to simplify and decide which factors are important and which applications will optimize performance. One way in which this can be done, is to conduct accelerated experimental testing, such as thermal cycling, and to compare the results with actual field tested results. However, this task is very time consuming as well as tedious and costs to conduct the experiment are high as well, which could possibly delay estimated arrival of the product to the public or personal consumer. Another method is to use Finite Element Analysis (FEA) computational simulation to design the product and test it using a computer to build and conduct the analysis of the individual components. This method takes highly trained individuals to conduct and analyze what is needed and can yield false information if used by an untrained individual. No matter which methods a company uses, one must take into consideration that there is a fine balance between these four design factors when deciding which component to use in each individual application.

### 1.5 Thermo-Mechanical Reliability

1.5

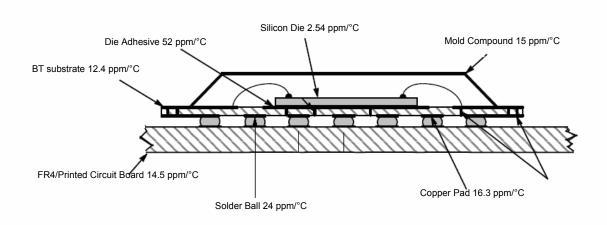

Reliability is defined as the ability of a system or component to perform its required functions under stated conditions for a specified period of time. The operation of any electronic device generates heat and with the increasing device density of the IC chips the amount of heat flux generated by the integrated circuit chips has gone to a level of  $100\text{-}200 \frac{W}{cm^2}$  [Nimkar, et al. 2005]. Each time a device is powered up, the individual components heat up and cool down. This heating and cooling leads to thermal cycling of the electronic components which causes many problems, such as shear deformation, due to the mismatch in coefficients of thermal expansion (CTE) of each material. Figure 1.4 shows the varying CTEs for a typical PBGA package in this research.

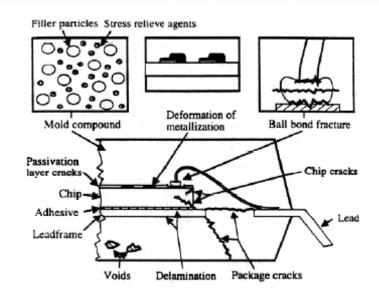

Thermal cycling requirements pose one of the greatest reliability challenges for BGA style packages. Under severe operating conditions or applications that require a high level of reliability, a large number of thermal cycles must be sustained without fracturing solder balls [Galloway, et al 2005]. Since the different packaging components have different coefficients of thermal expansion (CTE), as shown, there is a differential in expansion of varying components. This differential in expansion causes stresses to occur throughout the different components, and over repeated thermal cycling, causes failures to occur throughout the package. These failures in each electronic device can occur in various modes and locations [Viswanadham and Singh 1998], as seen in figure

Figure 1.4 Typical PBGA package with corresponding Coefficients of Thermal Expansion (CTE) values

Figure 1.5 Failure Sites, Modes, and Mechanisms on a Plastic Encapsulated Package [Nguyen 1995]

During the solder joint reflow process, one of the most common failure modes in electronic packaging, known as the 'Popcorn Failure', occurs. A disadvantage of plastic molding compounds is that they are hydrophilic and absorb moisture when exposed to a humid environment [Nguyen, et. al. 1995]. This popcorn-like explosion happens when moisture that is trapped inside the molding compound becomes heated and vaporized during the solder joint reflow process and the only way for it to escape is to expand the molding compound until it cracks and the vapor is released. Ilyas and Roberts [1993] investigated the moisture sensitivity in several surface mount packages that included SOJ, PLCC, TQFP, and PQFP packages. Yip, et al. [1996] studied the moisture induced failures of Ball Grid Array packages such as PBGA and TBGA. They showed that baking the chips at 115°C for sixteen hours essentially removes most of the moisture content from the package, and reduces the possibility of the interfacial delamination and popcorn cracking of the package. By encountering this popcorn cracking, Lee [1996] studied and proposed a new lead frame design for improved reliability of these packages.

The cracking of the silicon die is another failure mode due in part to thermal stresses developed in the chip. These stresses could be caused from either the assembly stage or from the CTE mismatches within the package. Adhesives and molding compounds are the two key components which result in the highest CTE mismatches around the silicon die. From figure 1.4, one can see that the typical coefficient of thermal expansion for the molding compound is 15, the die adhesive is 52, and the silicon die is 2.54. These drastic differences in CTEs account for the majority of the cracks found in the silicon die after thermal cycling.

Edwards, et al. [1987] evaluated shear stresses during thermal cycling and thermal shock tests in the plastic packages and found that the shear stresses are heavily concentrated at the corners and edges of the silicon die. Okikawa [1987] analyzed plastic molded LSI packages subjected to thermal cycling and found that thermal stresses cause passivation film cracks in the package. Lau [1993] also studied and addressed the stresses due to the assembly stage of the package. He studied such aspects as wafer preparation, oxidation, diffusion, metallization, die and wire bonding, encapsulation, and the re-flow and curing processes. Lau [1993] also discussed several problems associated with stress, including package cracking, wire damage, and thin film cracking on the die. Suhling.[1999] measured flip chip die stresses using piezoresistive test die, and Zou [1999] analyzed the die surface stress variation during thermal cycling and thermal aging raliability tests.

Electronic packages are comprised of dissimilar materials which expand and contract at different rates upon heating and cooling. The differential expansion, or thermal mismatch, must be accommodated by the various structural elements of the package. The structural elements that absorb most of this mismatch in expansion coefficients are the leads and solder balls. These stresses developed during the package assembly or due to thermal cycling can lead to interfacial delamination and fracturing which could lead to decreased functionality or failure. Zou, et al. [1998] analyzed the effect of delamination on the die surface stresses and conducted the stress measurements of delaminated and non-delaminated plastic packages.

Clech [2000] studied the CTE mismatches of CSPs and BGAs with 1.27mm pitch using accelerated thermal conditions from -55 to 125°C with 10 to 15°C/min. ramps, 20-minute dwells, and a cycle duration of 68 minutes.

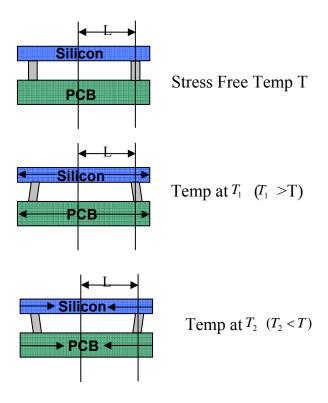

As the trend towards miniaturization continues, the size of the interconnect becomes smaller, and the solder joints become the weakest link in a packages overall reliability. In this study, structural and thermal reliability of ball grid array packages, mainly the shear stresses and strains of critical solder balls, have been investigated using accelerated life testing. Many studies and failure analyses have been conducted [Lall, et al 1997, 2004, 2005, Suhling, et al 2004, Clech 2000, Zbrzezny, et al. 2006, Syed 1996] showing that interconnect failures due to mismatches of CTE during thermal cycling is the most critical mode of failure in leaded and SMT packages such as BGAs. Figure 1.6 shows a schematic of what happens to the solder joints during thermal cycling due to mismatches in CTEs. It shows that at a stress free temperature, the two components, silicon and the PCB, are relaxed. Then, as the temperature increases, the PCB wants to expand at a higher rate since the PCB's CTE is 14.5 ppm/°C and the CTE of the silicon is 2.54 ppm/°C. As the temperature drops, the PCB wants to contract much quicker than the silicon. Looking at the schematic, one can see that the solder joints are having to flex and deform due to the mismatch in CTE between the two materials. Over time, these shear stresses and strains cause the solder joints to become fatigued, then cracks begin to propagate and the package will ultimately fail once a certain number of thermal cycles have been reached.

Figure 1.6 Schematic of CTE Mismatches and Solder Joint Failure due to Thermal Cycling

#### CHAPTER 2

#### LITERATURE REVIEW

It has been recognized that thermal loading is one of the major causes to the failure of electronic devices, especially surface mount packages. Chip delamination, solder joint cracking, and cracking of the silicon chip are only a few of the major problems due to the mismatch of the coefficients of thermal expansion (CTE) in the various layers that make up each individual package. This makes the solder joint reliability analysis one of the most important and focused issue as far as the reliability and life of the electronic packages is concerned [Harper, 2004]. There is a plethora of published literature available addressing solder joint reliability and life prediction. Within these literatures, there is a multitude of methodologies used for the solder joint fatigue life prediction of area array packages. Some of the methodologies used include experimental techniques using accelerated thermal cycling tests and closed form models based on the theory of failure mechanics, finite element analysis, and statistics based multivariate regression analysis.

## 2.1 Experimental Techniques

There are several experimental tests which are performed in order to study the reliability of electronic devices and are designed to operate under certain environmental conditions. Extreme temperatures, high humidity levels, and vibration are a few of the environmental conditions that are tested experimentally. Researchers have applied various test conditions such as the accelerated thermal cycling, thermal shock, HAST (highly accelerated stress test) and vibration tests, to analyze the reliability of the packages for various applications.

Syed [1996] conducted accelerated thermal cycling to determine the effects of four design parameters on the thermal fatigue life of solder joints in automotive underthe-hood environment. The four parameters considered were: substrate thickness, array configuration, ball pitch, and pad size. After conducting the experiment on three BGA configurations, standard, perimeter array, and thicker BT substrate BGA's, he discovered that the CTE mismatch between the board and the package, and the load bearing area of the solder joints are the two main drivers of solder fatigue. For the levels considered in his experiment, the results from the combined design of experiment and validated life prediction model indicated that one could improve the life of the solder joints up to five times by using perimeter array, 0.76mm BT substrate, 0.635mm pads, and 1.27mm pitch.

Lall, et.al [2006] conducted thermal cycling tests, from -40°C to 125°C, to determine the effect of metal-backed boards on the interconnect reliability. In this study 15mm C2BGAs, 27mm BGAs, and 1225 chip resistor solder joints were cross sectioned at every 125cycles to measure crack propagation. It was reported that the addition of metal backing increases the CTE of the substrate and creates potential reliability issues

for many electronic packages. It was shown that the crack propagation rate on metal back boards is approximately 1.7 times faster than nonmetal-backed boards, and that BGAs on metal backed boards exhibit a lower number of cycles-to-crack initiation that packages on nonmetal-backed boards for any inelastic strain energy density.

Darveaux, et.al. [1998, 2000] conducted several board level thermal cycling reliability tests using FBGAs (flex BGA's), TABGAs (tape array BGAs), PBGAs, and μBGA packages. Multiple package and board variables were tested, and it was found that fatigue life increased up to 6X as dies size was reduced. Also shown that for a given die size, fatigue life was up to two times longer for larger packages, and solder joint fatigue life was 20% longer for 0.9mm thick test boards compared to 1.6mm thick test boards. He also showed that there was a 1.6 times greater acceleration factor between thermal cycling profiles of -40°C to 125°C and 0°C to 100°C.

Knight, et.al. [2006] studied the effect of thermal cycling of ball grid array packages on die size, thermal ball, number of perimeter balls, the use of underfills, and printed circuit board heat spreader and thermal via design. He showed that as a result of thermal cycling from -40°C to 125°C, the thermal resistance of the packages with large die size increased significantly, with thermal degradation preceding electrical failure by several hundred cycles. His study also showed that the critical thermal balls cracked before the critical perimeter ball, which is a contradiction in conventional electronic packaging. Normally, the ball furthest from the package's center, the perimeter ball, would crack first, due to the distance to neutral point (DNP) formula. However, in this study, the cracking of the critical thermal ball can be attributed to the fact that the thermal balls were mounted on a relatively thick copper heat spreader. This lead to a mismatch in

CTE of  $\frac{13.8 \times 10^{-6}}{K}$  between the die and the PCB near the thermal balls, where as th mismatch near the perimeter balls was only  $\frac{12 \times 10^{-6}}{K}$ .

#### 2.2 Failure Mechanics Based Analytical Modeling

Clech, et. al [1993] discovered that some predictive tools, like AT&T's Figure of Merit, contained many errors when they were applied to different surface mount packages. After discovering this, he developed a comprehensive surface mount reliability (CSMR) model which was based on the correlations of 28 accelerated tests in the surface mount reliability database and was validated by nine accelerated test data sets. This model uses one-dimensional structural models to estimate solder joint stress/strain hysteresis due to global and local CTE mismatches during thermal cycling. He found that when it was exercised over the entire database, the new model had a correlation coefficient of 0.97 compared to the 0.40 or less for earlier models. The CSMR model was further extended to another Design-for-Reliability Tool, the Solder Reliability Solution (SRS) moded, which was used for the reliability of predictions of leadless ceramic chip carriers (LCCC's) and area array assemblies. He validated the SRS model for a variety of BGA, flip chip, and CSP assemblies as well [Clech, 2000].

Lall, et. al. [2005] used a hybrid approach between failure mechanics based and statistics based methodology to identify critical parameters and their sensitivities on the thermal reliability of certain BGA packages. This study used a combination of Timoshenko beam theory [1925], and its application to tri-material assemblies [Suhir 1990], calculation of time-independent plastic deformation, calculation of stress

relaxation, hysteresis loop calculation [Clech 1996], and life prediction [Darveaux 1992]. Bartelo, et. al. [2004] used failure mechanics methods to study the thermo-mechanical fatigue behaviors of Sn-Ag-Cu solder joints in terms of their Ag content, cooling rate, and ATC test condition. This studied showed that 2.1Sn-0.9Ag-0.9Cu solder joints assembled at a slow cooling rate have the best thermal fatigue life over the high silver content joints for the ATC test of 0°C to 100°C with a 120 minute cycle time.

#### 2.3 Statistical Modeling

Regression analysis and Weibull distribution are the two most common methods of statistical analysis being used by researchers to display trends and analyze failure data in electronic packaging today. Lall, et. al. [2005, 2006] used a combination of statisticsbased and failure-mechanics based methodology to identify the critical parameters and their sensitivity on the thermal reliability of BGA packages. Sensitivities of reliability to design, material, architecture, and environment parameters were developed from both statistical and failure mechanics and then validated with experimental data. Multivariate regression and analysis of variance techniques were used to determine the relative influence of these parameters on thermal reliability. Montgomery, et. al. [2002] used traditional multivariate regression methods to analyze trends in the large amounts of data produced by probe testing following wafer fabrication. Clustering analysis was the preferred method for analyzing this data, however this method of analysis proved useless in this study. Linear regression analysis was also used in this study and they were able to obtain some interpretable results. The method of Classification and Regression Trees (CART), based on a recursive partitioning algorithm, proved to be the model-building

approach that worked best for their data. This study highly recommends using this method when applicable as it was able to explain 91.9% of their data.

Lall, et. al [2006] used statistics-based closed-form models based on multivariate regression, analysis of variance, and principal components to analyze flip-chip assemblies subjected to thermo-mechanical stresses. The study investigated the material properties and the geometric parameters such as die thickness, die size, ball count, ball pitch, bump metallurgy, underfill types, underfill glass transition temperature  $(T_g)$ , solder alloy compostion (SnAgCu, SnPbAg), solder joint height, bump size, and printed circuit board thickness. Model input variables were selected by defining all predictors that were known, and then selecting a subset of predictors to optimize a predefined goodness-of-fit function. The appropriateness of the model was checked by using any one combination of the several of the features of the model, such as linearity, normality, or variance which may be violated. The statistical model methodology provided in this study was validated against the experimental accelerated test failure data from the Center for Advanced Vehicle Electronics (CAVE). This studied showed that there is a direct correlation between what the statistical models predicted and what the experimental data actually showed for each of the geometric parameters and their effects.

## 2.4 Finite Element Modeling

Finite element modeling is an important tool for analyzing complex systems, such as chip-scale packages. FEA (Finite Element Analysis) has been a widely used methodology for solder joint reliability [Darveaux 1996, Syed 2001, Zahn 2000, 2003] analysis and life prediction of various electronic packages. By providing a more thorough understanding of the complex behavior associated with chip-scale packages and their constituent materials, it is possible to create and optimize designs that can take advantage of variable material properties such as CTE and elastic modulus. Moreover, computer simulations of mechanical behavior help to identify design issues early in the design cycle and minimize the number of prototypes needed for tests. Thus, finite element modeling is a cost-effective method for rapidly moving products from concept to production while minimizing risk and increasing understanding of the overall system. FEA is a tool and a technique that should not be ignored if one hopes to keep pace in today's competitive electronics market.

Zahn [2000] used viscoplastic finite element simulation methodologies to predict ball and bump solder joint reliability for a silicon based five-chip multi-chip module package under accelerated temperature cycling conditions of 0°C to 100°C with five minute ramp and dwell times. For this portion of the study, ANSYS sub-modeling methodology was utilized by which global model simulation results were applied as boundary conditions. Further into this study, finite element analysis (FEA) was also used to evaluate the steady-state thermal performance of the multi-chip system. For this model, ANSYS was utilized to create a full-symmetry, three-dimensional FEA model of the 40x40mm, 697 ball 1.0 mm pitch because the structure was not symmetric. Zahn

[2003] also used 3-D slice and symmetry models for the purpose of deriving life prediction equations in order to determine the fatigue response of microelectronic package structures using both eutectic, 63Sn37Pb, and lead-free, 95.5Sn4Ag0.5Cu, solder materials. As a result of this study, it was shown that a combination of minimum true symmetry global modeling and straight slice symmetry global modeling may be the best approach to accurately and efficiently predict accelerated temperature cycling solder fatigue in large microelectronic package structure models such as the 15x15mm 196-lead PBGA and a 35x35mm 388-lead PBGA packages used here.

Pang, et. al. [2001] used finite element analysis to simulate thermal cycle loadings for solder joint reliability in electronic assemblies, namely flip-chip packages. This study was conducted to investigate different methods of implementing thermal cycling analysis, mainly using the dwell creep and full creep methods since there are significant differences between the analysis results for the flip chip solder joint strain responses and the predicted fatigue life of the two methods. A three dimensional slice model of the flip chip on board (FCOB) assembly was created using ANSYS software and used for analysis. After simulation was completed, it showed that the viscoplastic analysis using the 3-D slice model and Darveaux's [2000] model for solder joint fatige life prediction gave even more conservative fatigue life compared to the full creep analysis results observed in a previous study.

Darvaeux [2000] analyzed the effect of simulation methodology on solder joint crack growth correlation and fatigue life prediction using ANSYS 5.6 to run the simulation. Solder joint material was modeled with Anand's viscoplastic constitutive model [Anand 1985, Brown, et al. 1989], which is a standard option in ANSYS. Johnson

[1999] extended Darveaux's approach and implemented it for the finite element simulation of BGA solder joint reliability, Gustafsson et al., [2000] also used finite element modeling for the life prediction of BGA packages.

Lindley, et al. [1995] and Lall, et al. [2003] conducted solder joint reliability study on BGA and CSPs for the automotive underhood application. Yeh, et al. [1996] and Lu, et al. [2000] did parametric analysis of flip chip reliability based on solder joint fatigue modeling, via computer simulation. Time independent plastic behavior [Wiese, et al. 2002] of SnPb and SnAgCu solder alloy has been modeled and it's effect on the FEM (Finite Element Method) simulations of electronic packages.

Lau, et al. [2004] developed a thermal fatigue life prediction equation for lead-free (Sn4.0Ag0.5Cu) bumped WLCSP (wafer level CSP) on lead-free FR-4 PCB with ENIG (electroless nickel-immersion gold) surface finish. FEA simulation based solder joint fatigue life model methodology for both 63Sn37Pb and 95.5Sn4Ag0.5Cu solder alloy has been presented by [Zahn, 2002, 2003, Kim et al. 2003, Schubert et al. 2002]. The effect of underfill on solder strains and susceptibility to delamination in SBGA (Super BGA) was studied [Pyland, et al. 2002] and it was reported that underfill does not always enhance super ball grid arrays.

#### 2.5 Composition of Solder Alloy

Darveaux et.al. [1992] studied various solder compositions, 62Sn36Pb2Ag, 60Sn40Pb, 96.5Sn3.5Ag, 97.5Pb2.5Sn, 95Pb5Sn, in order to determine the effects of grain size and intermetallic compound distribution due to tensile and shear loading with a temperature range between 25°C and 135°C. He observed that the 96.5Sn3.5Ag and 97.5Pb2.5Sn alloys absorbed more strain before the onset of failure than the 60Sn40Pb and 62Sn36Pb2Ag alloys, and that the 95Pb5Sn was the least ductile. He also observed that the thermal cycle simulations indicated that all the alloys tested responded about the same under accelerated test conditions, but the 96.5Sn3.5Ag and 97.5Pb2.5Sn alloys undergo considerably less strain under field use conditions.

Zbrzezny et.al.[2006] studied the effect of different reflow profiles on the reliability of lead-free Sn-3.0 Ag-0.5 Cu (SAC305) ball grid array devices assemble with SnPb eutectic paste. These packages were subjected to 1500 cycles of accelerated thermal cycling with temperature profiles of 0°C to 100°C. The thermo-mechanical testing revealed that assemblies with the mixed alloy, lead-free, assemblies failed much earlier than the SnPb assemblies. It was found that cracks, or fractures, occurred on the board side, between the intermetallic layer and solder. They believe that the interfacial failures resulted from Pb redistribution at the interface and from high tensile stresses that were due to the accelerated thermal cycling.

In the past few years, lead-free solders have received a lot of attention. The National Center for Manufacturing Sciences (NCMS) and the National Electronics Manufacturing Initiative (NEMI) have published multiple year studies on lead free solders. Although it depends strictly on application, there have been many reports of

increased solder joint reliability using lead-free solders, such as SnAgCu, instead of the conventional SnPb solders. Bartelo, et. al. [2004] studied the thermo-mechanical fatigue behaviors of Sn-Ag-Cu solder joints in terms of their Ag content, cooling rate, and ATC test condition. This studied showed that 2.1Sn-0.9Ag-0.9Cu solder joints assembled at a slow cooling rate have the best thermal fatigue life over the high silver content joints for the ATC test of 0°C to 100°C with a 120 minute cycle time.

#### 2.6 Objective and Scope of Thesis

In this thesis, risk-management and decision-support models for reliability prediction of BGA packages in harsh environments have been presented. The models presented in this paper provide decision guidance for smart selection of component packaging technologies and perturbing product designs for minimal risk insertion of new packaging technologies. In addition, qualitative parameter interaction effects, which are often ignored in closed-form modeling, have been incorporated in this work. Previous studies have focused on development of modeling tools at sub-scale or component level. The tools are often available only in an offline manner for decision support and risk assessment of advanced technology programs. There is need for a turn key approach, for making trade-offs between geometry and materials and quantitatively evaluating the impact on reliability.

Multivariate linear regression and robust principal components regression methods were used for developing these models. The first approach uses the potentially important variables from stepwise regression, and the second approach uses the principal components obtained from the eigen values and eigen vectors, for model building.

Principal-component models have been included because of their added ability in addressing multi-collinearity.

The statistics models are based on accelerated test data in harsh environments, while failure mechanics models are based on damage mechanics and material constitutive behavior. Statistical models developed in the present work are based on failure data collected from the published literature and extensive accelerated test reliability database in harsh environments, collected by the author at Auburn University. Sensitivity relations for geometry, materials, and architectures based on statistical models, failure mechanics based closed form models, and FEA models have been developed. Validation of statistical, failure mechanics, and FEA based model sensitivities with experimental data have been demonstrated.

The objective of this research is to develop a fundamental understanding of damage initiation and progression in copper-core electronic assemblies constructed with leaded solder interconnects and development of methodologies for predicting thermal reliability, or N<sub>1%</sub> values, under thermal cycling loads. The fundamental knowledge will be used for development of predictive models and prognostication techniques. Prognostication refers to the ability to determine residual life in deployed electronics without knowledge of prior stress history. Leading indicators of failure will be developed to determine the probability of impending failure in electronics. The research results have wide applicability in extreme environment electronic applications.

# 2.7 Thesis Layout

In Chapter 3, the methods for which the experimental data was acquired, cross-sectioned, and set up are discussed. Chapter 4 talks about the failure mechanics based models and the equations used to develop them for PBGA packages. Chapter 5 deals with finite element modeling steps for PBGA packages while Chapter 6 deals with the specific models that were built and analyzed in this research. Chapter 7 shows the development of statistics based closed form models and Chapter 8 validates them.

Chapter 9 deals with life predictions and field life correlations.

#### CHAPTER 3

## EXPERIMENTAL SETUP AND DATA ACQUISITION

This research was conducted for Northrop Grumman in order to develop a fundamental understanding of damage initiation and progression in copper-core electronic assemblies constructed with leaded solder interconnects and development of methodologies for interrogation of material state under thermal-cycling loads. In this chapter, the accelerated thermal cycling experiment will be explained in great detail. The test boards, the thermal chambers and their temperature profiles, the data acquisition system, the cross-sectioning process, and the microscopes used for taking measurements are all explained.

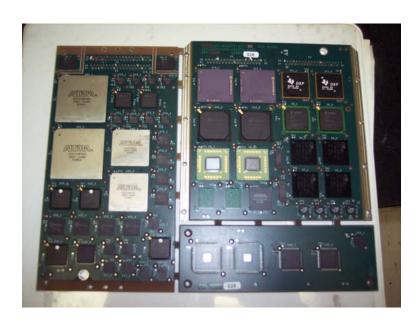

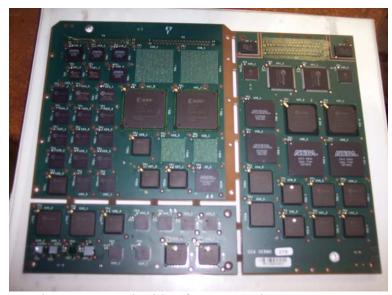

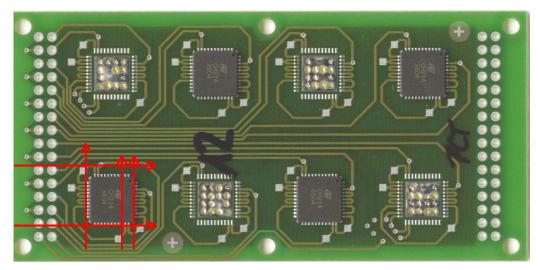

#### 3.1 Test Boards

The test boards were provided by Northrop Grumman and wired up by Auburn University. This experiment utilized 4 sets of 9 copper core test boards each containing electronic packages mounted on the front and rear side of the boards. Figures 3.1-3.6 show the various test boards, CCA073-081, CCA010-018, CCA028-036, and CCA019-027. The test boards used were 254mm x 190.4mm (10in x 7.5in) with various electronic packages on each side. The electronic packages mounted to these test boards were all

BGA's. They contained ceramic ball grid arrays (CBGA), chip array ball grid arrays (CABGA), tape ball grid arrays (TBGA), flex ball grid arrays (FBGA), and primarily PBGA's. The electronic packages ranged from 64 to 900 I/O counts, 0.80 mm to 1.27mm pitch, and package sizes ranging from 5.5mm x 16mm all the way up to 31mm x 31mm.

Figure 3.1 Front Side of Test Boards CCA010-018

Figure 3.2 Back Side of Test Boards CCA010-018

Figure 3.3 Front Side of Test Boards CCA 073-081

Figure 3.4 Back Side of CCA 073-081

Figure 3.5 Front Side of Test Boards CCA 028-036

Figure 3.6 Back Side of Test Boards CCA 028-036

Figure 3.7: Front Side of Test Boards CCA 019-027

Figure 3.8: Back Side of Test Boards CCA 019-027

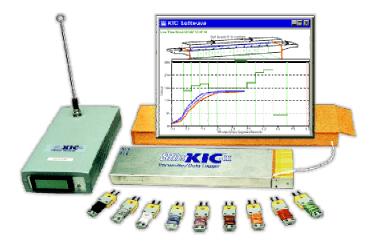

#### 3.2 Chamber Profiles

In order for these tests to be carried out, three thermal chambers were used. Each of the three chambers were to be set up with different temperature profiles, -55°C to 125°C (TC2), 3°C to 100°C (TC3), and -20°C to 60°C (TC4). In order to make sure the thermal chambers' profiles were accurate, a thermal profiler was used. The thermal profiler used for all three chambers was the Slim KIC-II Thermal Profiler by KIC Innovations. (see Figure 3.9). Each chamber contained three thermal couples during the

Figure 3.9: Slim KIC-II Thermal Profiler and Software

profiling. The KIC software allows the user to watch the temperature vs. time plot over the entire thermal cycle.

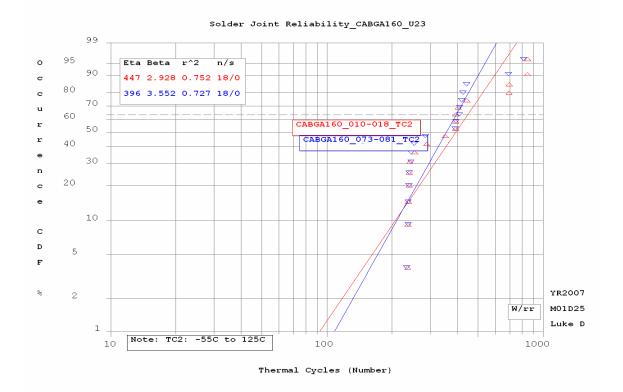

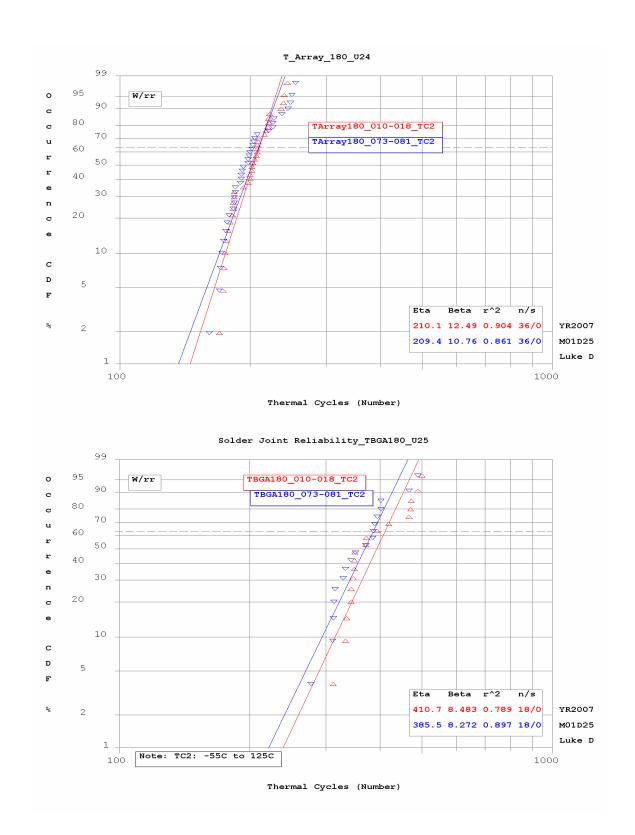

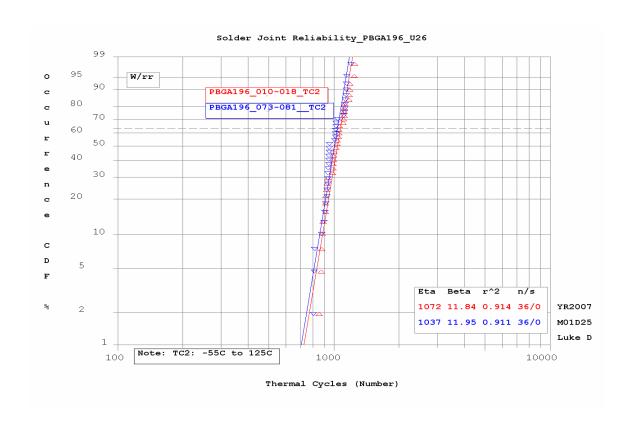

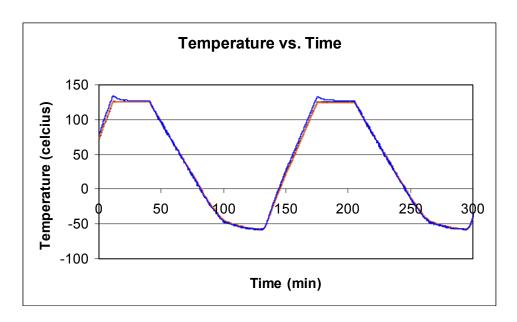

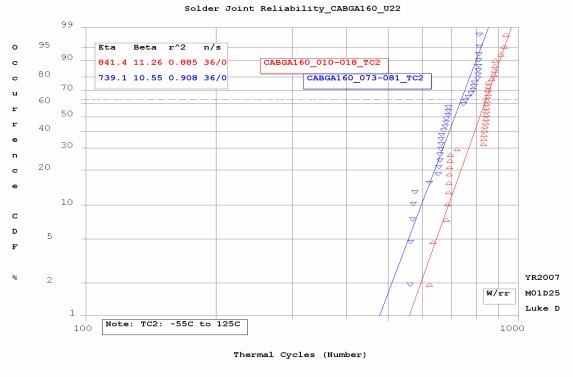

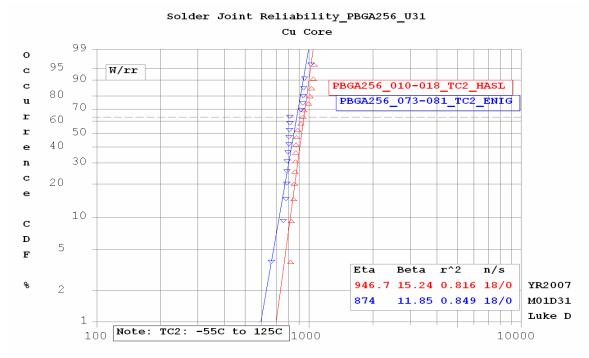

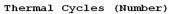

TC2 Thermal Cycle: The thermal profile shown in figure 3.10 has been used for test boards CCA010-018 and CCA 073-081 in order to experimentally determine solder joint reliability in various electronic packages in harsh environments, -55°C to 125°C. This temperature range is used for military and defense companies and is deemed "harsh environment" for electronic packaging. This cycle starts at room temperature (25°C) and

has a 30 minute dwell at the extreme temperatures of -55°C and 125°C and the ramp rate is 3°C/min from the hot extreme to the cold extreme, and 4°C/min. from the cold extreme to the hot. The reason for this difference is that the particular thermal chamber used, Figure 3.11, has a maximum ramp rate of 4°C/min. The total cycle time is 165 minutes.

Figure 3.10: TC2 Profile

Figure 3.11: Thermal Chamber used for TC2 Temperature Profile

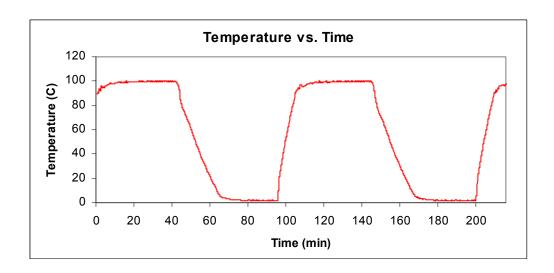

TC3 Thermal Cycle: The thermal profile shown in figure 3.12 has been used for test boards CCACCA-019-027 in order to experimentally determine solder joint reliability in various electronic packages from 3°C to 100°C. This cycle starts at room temperature (25°C) and has a 30 minute dwell at the temperatures of 3°C and 100°C and the ramp rate is 3.2°C/min from the hot extreme to the cold extreme, and 6.5°C/min. from the cold extreme to the hot. The reason for this difference is that the particular thermal chamber used for TC3 and TC4 is much smaller and can ramp up much faster than the larger chamber used for the TC2 temperature conditions.

Figure 3.12: TC3 Profile

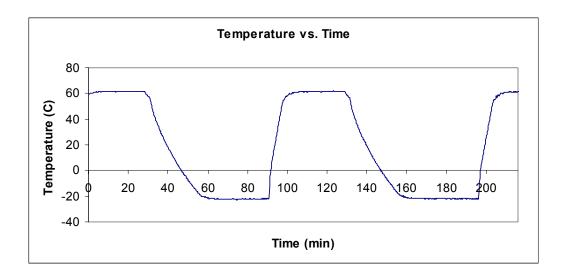

TC4 Thermal Cycle: The thermal profile shown in figure 3.13 has been used for test boards CCACCA-028-036 in order to experimentally determine solder joint reliability in various electronic packages from -20°C to 60°C. This cycle starts at room temperature (25°C) and has a 30 minute dwell at the temperatures of -20°C and 60°C and the ramp rate is 2.6°C/min from the hot extreme to the cold extreme, and 5.3°C/min. from the cold extreme to the hot.

Figure 3.13: TC4 Profile

#### 3.3 Data Acquisition

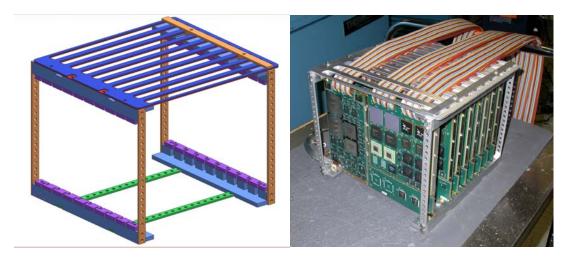

Setup: After each of the chambers have been profiled and set up accordingly, the boards are then placed into their aluminum carriers, as seen in Figure 3.14, which were designed by Northrop Grumman. These carriers allowed each of the test boards to be stood up vertically, as well as maintaining equal distance from each of the other boards.

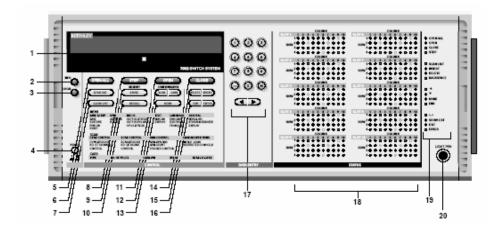

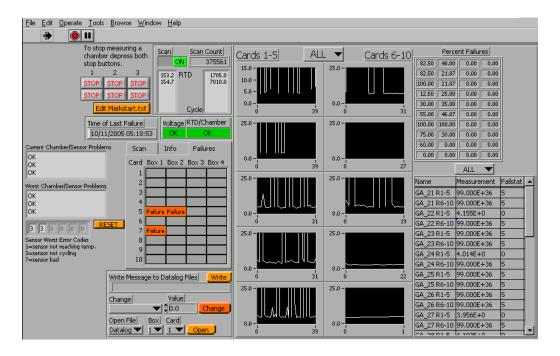

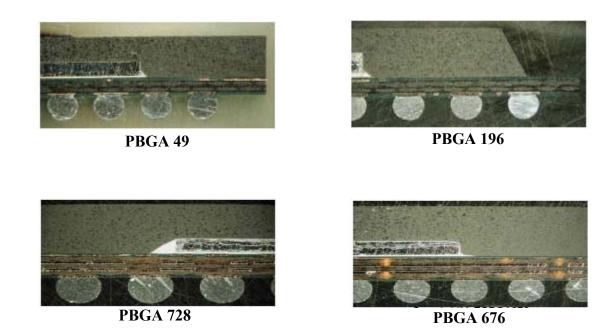

Figure 3.14: Test Board Holders