# On-wafer S-parameter Measurement Using Four-port Technique and $\label{eq:constraint} \text{Intermodulation Linearity of RF CMOS}$

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

| Xiaoyui                             | n Wei                               |

|-------------------------------------|-------------------------------------|

|                                     |                                     |

|                                     |                                     |

| Certificated of approval:           |                                     |

|                                     |                                     |

|                                     |                                     |

| Richard C. Jaeger                   | Guofu Niu, Chair                    |

| Distinguished University Professor  | Alumni Professor                    |

| Electrical and Computer Engineering | Electrical and Computer Engineering |

|                                     |                                     |

|                                     |                                     |

| Fa Foster Dai                       | Stuart Wentworth                    |

| Professor                           | Associate Professor                 |

| Electrical and Computer Engineering | Electrical and Computer Engineering |

|                                     |                                     |

|                                     |                                     |

| George T. Flowers                   |                                     |

| Dean                                |                                     |

| Graduate School                     |                                     |

# On-wafer S-parameter Measurement Using Four-port Technique and $\label{eq:constraint} \text{Intermodulation Linearity of RF CMOS}$

Xiaoyun Wei

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama December 19, 2008

# On-wafer S-parameter Measurement Using Four-port Technique and $\label{eq:constraint} Intermodulation\ Linearity\ of\ RF\ CMOS$

# Xiaoyun Wei

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon request of individuals or institutions and at their expense.

The author reserves all publication rights.

| Signature of Author |  |

|---------------------|--|

| 8                   |  |

|                     |  |

|                     |  |

|                     |  |

|                     |  |

|                     |  |

| Date of Graduation  |  |

## $V_{ITA}$

Xiaoyun Wei, daughter of Xinli Wei and Xinye Wang, spouse of Tong Zhang, was born on December 15<sup>th</sup>, 1978, in Xinxiang, Henan Province, P.R. China. She received her BS degree from Huazhong University of Science and Technology in 2000, majoring in Communication Engineering. She received her MS degree from Huazhong University of Science and Technology in 2003, majoring in Circuit and Signal. In Fall 2004, She was accepted into the Electrical and Computer Engineering Department of Auburn University, Auburn, Alabama, where she has pursued her Ph.D. degree.

### DISSERTATION ABSTRACT

# On-wafer S-parameter Measurement Using Four-port Technique and

### INTERMODULATION LINEARITY OF RF CMOS

# Xiaoyun Wei

Doctor of Philosophy, December 19, 2008 (M.S., Huazhong University of Science and Technology, 2003) (B.S., Huazhong University of Science and Technology, 2000)

## 236 Typed Pages

## Directed by Guofu Niu

Accurate on-wafer characterization of CMOS transistors at extremely high frequencies, e.g. above 60GHz, becomes critical for RFIC designs and CMOS technology development for millimeter wave applications. Traditional two-step error calibration lumps the linear systematic errors as a four-port error adaptor between the perfect VNA receivers and the probe tips, and the distributive on-wafer parasitics as equivalent circuits with shunt and series elements. However, the distributive nature of on-wafer parasitics becomes significant, and the lumped equivalent circuits fail at frequencies above 50GHz.

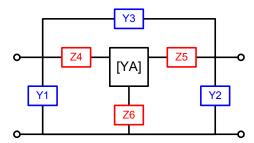

The distributive on-wafer parasitics is essentially a four-port network between the probe tips and the transistor terminals. This dissertation develops two general four-port techniques that can solve the on-wafer parasitics four-port network, and demonstrates their utility on a 0.13µm RF CMOS technology. One is an analytical solution solving

the Y-parameters of the four-port parasitics network. The other one is a numerical solution solving the T-parameters of the four-port parasitics network. Even though the two four-port solutions are developed for on-wafer parasitics de-embedding at the very beginning, the two solutions do not make any reciprocal and symmetric assumptions of the solved four-port network, and can be used for single-step calibration which solves the four-port network between perfect VNA receivers and transistor terminals. In this case, both systematic errors and on-wafer parasitics are included in one four-port network, and can be removed in a single step. With switch error removed, single-step calibration can provide as accurate results as two-step calibration from 2-110GHz.

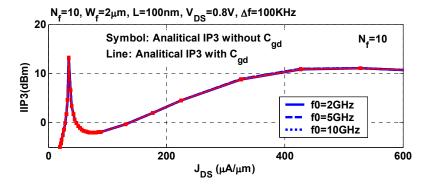

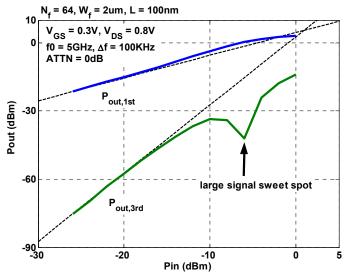

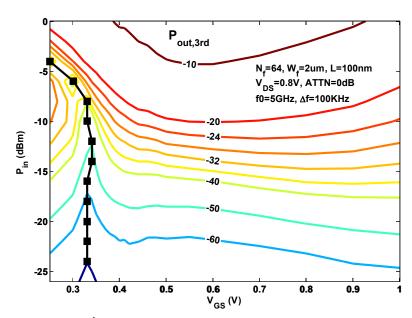

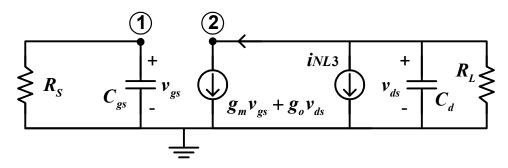

Another topic that draws the attention of RFIC designers is the linearity (nonlinearity) of CMOS transistors. Experimental IP3 results on a 90nm RF CMOS technology are presented at different biasing voltages, different device width, and different fundamental frequencies. To understand the biasing, device width, and frequency dependence of IP3, a complete IP3 expression is developed using Volterra series analysis and nonlinear current source method. The investigation indicates that not only the  $2^{nd}$  and  $3^{rd}$  order nonlinear output conductance but also the cross terms are important for IP3 sweet spot and high  $V_{GS}$  IP3 modeling. Guidelines to identify the IP3 sweet spot for large devices used in RFIC designs are provided.

### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to me supervisor, Dr. Guofu Niu. Without him, this dissertation would not have been possible. His patience and encouragement carried me on through difficult times. I appreciate his vast knowledge and skill in many areas, and his valuable feedback that greatly contributed to this dissertation. I would like to thank the other members of my committee, Dr. Foster Dai, Dr. Stuart M. Wentworth, and Dr. Richard C. Jaeger for the assistance they provided.

Several people deserve special recognition for their contributions to this work. I would like to thank Qingqing Liang for his help with de-embedding techniques. I would like to thank Ying Li for her help with device measurement. I would like to thank Susan Sweeney of IBM Microelectronics for her help with 110GHz S-parameter measurement and noise measurement. I would like to thank Dr. Stewart S. Taylor of Intel Corporation for discussions on device and circuit characterization.

Finally, I am forever indebted to my parents for the support they provided me through my entire life. In particular, I must acknowledge my husband and best friend, Tong Zhang. Without whose love and encouragement, I would not have finished this dissertation.

In conclusion, I recognize that this research would not have been possible without the financial assistance of the Intel Corporation and Vodafone-US foundation. I also would like to thank IBM Microelectronics for fabrication on various technologies.

Style manual or journal used: <u>Transactions of the Institute of Electrical and</u>

Electronics Engineers

Computer software used: <u>The document was prepared using Microsoft Word, The plots were generated using Microsoft Visio and Matlab. The Bibliography was generated using EndNote.</u>

# TABLE OF CONTENTS

| TABLE ( | OF CONTENTS                                                   | IX  |

|---------|---------------------------------------------------------------|-----|

| LIST OF | Figures                                                       | XII |

| LIST OF | Tables                                                        | XIX |

| Снарте  | r 1 Introduction                                              | 1   |

| 1.1     | Scattering parameter measurement                              | 3   |

| 1.2     | Intermodulation linearity measurement                         |     |

| 1.3     | Motivation and objectives                                     |     |

|         | 1.3.1 High-frequency RF CMOS characterization                 |     |

|         | 1.3.2 Four-port network for on-wafer parasitics               |     |

|         | 1.3.3 General four-port solution                              |     |

|         | 1.3.4 Single-step calibration                                 |     |

|         | 1.3.5 Validity of BSIM4 model for nonlinear RF modeling       |     |

|         | 1.3.6 Third order intercept point modeling                    |     |

|         | 1.3.7 Third order intermodulation distortion characterization | 22  |

| 1.4     | Outline of Contributions                                      |     |

| Снарте  | r 2 On-wafer Test Structure                                   | 25  |

| 2.1     | Typical on-wafer transistor test structure                    | 26  |

| 2.2     | Probing pad design considerations                             |     |

| 2.3     | CMOS transistor design considerations                         | 32  |

|         | 2.3.1 Gate pattern and multiplier factor                      |     |

|         | 2.3.2 Gate finger configuration                               |     |

| 2.4     | Summary                                                       |     |

| Снарте  | R 3 ERROR MODELS FOR TWO-PORT S-PARAMETER MEASUREMENT         | 42  |

| 3.1     | Two-port S-parameter measurement                              | 44  |

| 3.2     | Error adaptor concept                                         |     |

| 3.3     | The simplest 8-term error model                               |     |

| 3.4     | The classical 12-term error model                             | 51  |

|         | 3.4.1 Forward mode                                            | 52  |

|         | 3.4.2 Reverse mode                                            | 53  |

|         | 3.4.3 12-term model                                           | 55  |

|         | 3.4.4 SOLT calibration                                        | 58  |

| 3.5     | The most complete 16-term error model                         |     |

| 3.6     | Error adaptor for single-step calibration                     | 66  |

| 3.7     | Summary                                                       | 70  |

| Снарте | R 4 GENERIC ANALYTICAL FOUR-PORT SOLUTION                    | 71  |

|--------|--------------------------------------------------------------|-----|

| 4.1    | Four-port network in Y-parameters                            | 73  |

| 4.2    | General four-port Solution                                   | 74  |

|        | 4.2.1 Relationship between open-short and four-port          | 74  |

|        | 4.2.2 Open-short de-embedded LEFT, RIGHT, and THRU           | 77  |

|        | 4.2.3 Analytical solution of A and B                         |     |

|        | 4.2.4 Summary of general four-port de-embedding              |     |

|        | 4.2.5 Impact of non-ideal load in LEFT and RIGHT             |     |

|        | 4.2.6 Quantifying errors of open-short                       |     |

|        | 4.2.7 Reciprocity and symmetry of the four-port parasitics   |     |

| 4.3    | Reciprocal four-port solution and pad-open-short             |     |

| 4.4    | Summary                                                      |     |

| CHARTE | r 5 Numerical Four-Port Solution                             | 02  |

|        |                                                              |     |

| 5.1    | Four-port parasitic network in T-parameters                  |     |

| 5.2    | SVD based four-port Solution                                 |     |

| 5.3    | Experimental results for on-wafer parasitics de-embedding    |     |

| 5.4    | Reduction of Error Terms and Number of Standards             |     |

|        | 5.4.1 Quantify error terms for four-port on-wafer parasitics |     |

|        | 5.4.2 8-term solution using three on-wafer standards         |     |

| 5.5    | Summary                                                      | 106 |

| Снарте | R 6 SINGLE-STEP CALIBRATION                                  | 107 |

| 6.1    | Analytical four-port single-step calibration                 | 108 |

| 6.2    | Numerical four-port single-step calibration                  |     |

| 6.3    | Impact of switch errors                                      |     |

|        | 6.3.1 Quantify error terms using S-parameters                |     |

| 6.4    | Summary                                                      |     |

| CHADTE | r 7 Validity of BSIM4 model for Nonlinear RF Modeling        | 110 |

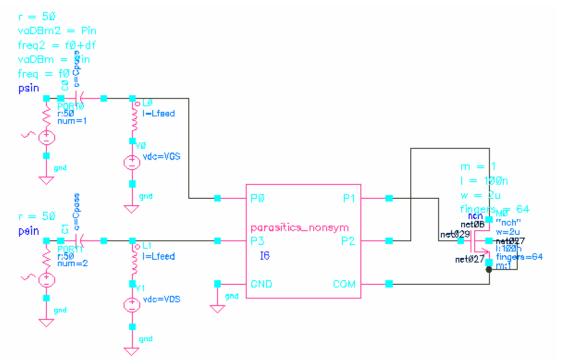

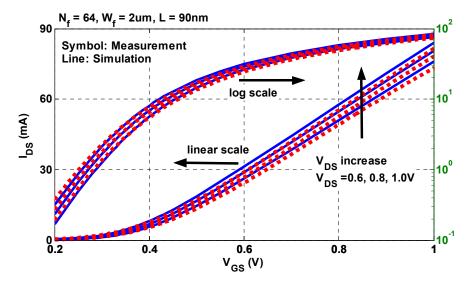

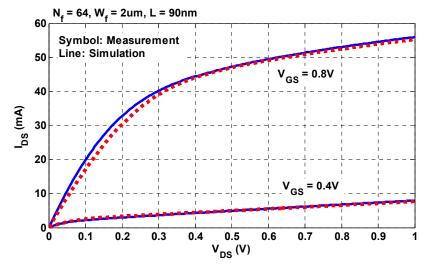

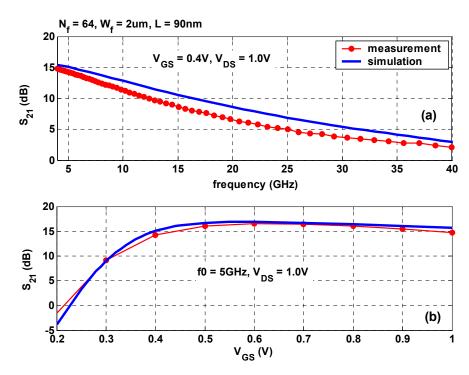

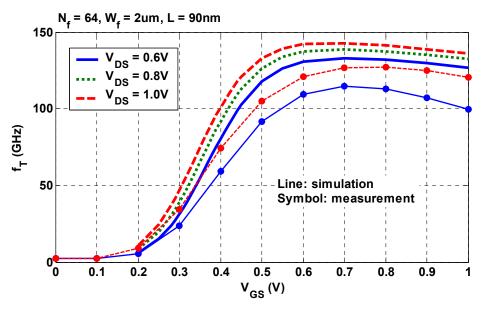

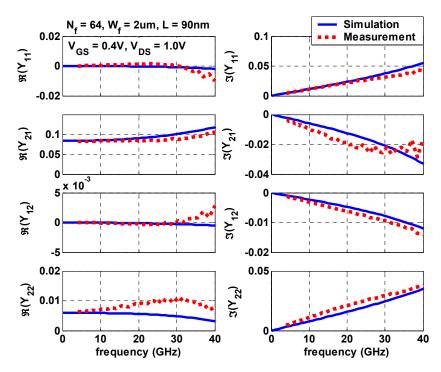

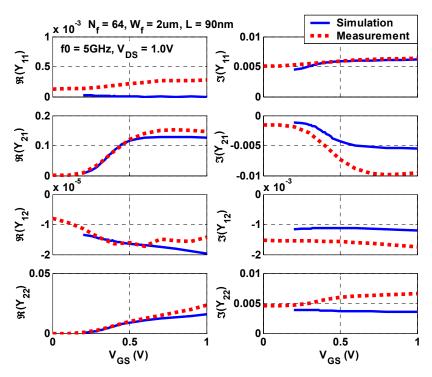

| 7.1    | Linearity measurement and simulation                         |     |

| 7.1    | DC and linear characteristics                                |     |

|        |                                                              |     |

| 7.3    | Nonlinear characteristics                                    |     |

| 7.4    | Summary                                                      | 131 |

| Снарте | R 8 MODELING OF INTERMODULATION LINEARITY                    | 132 |

| 8.1    | First order IP3 theory                                       | 133 |

| 8.2    | Complete IP3 expression                                      | 135 |

|        | 8.2.1 Two dimension nonlinear current source                 |     |

|        | 8.2.2 Input IP3 expression                                   |     |

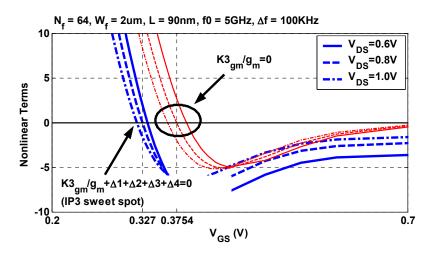

| 8.3    | Impact of the additional terms                               |     |

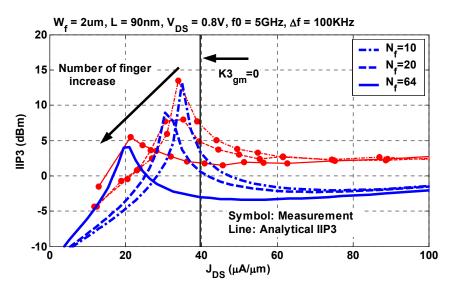

| 8.4    | Device width scaling.                                        |     |

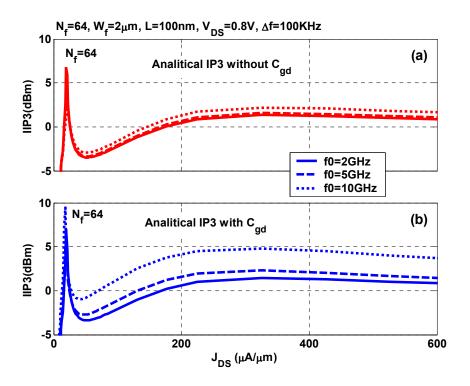

| 8.5    | DIBL effect                                                  |     |

| 8.6    | Summary                                                      |     |

|        | ·                                                            |     |

|        | R 9 CHARACTERIZATION OF RF INTERMODULATION LINEARITY         |     |

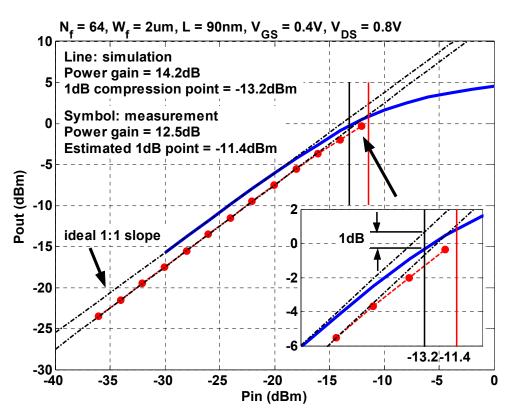

| 9.1    | Power gain measurement                                       | 150 |

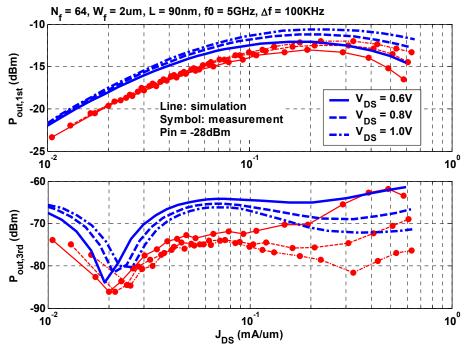

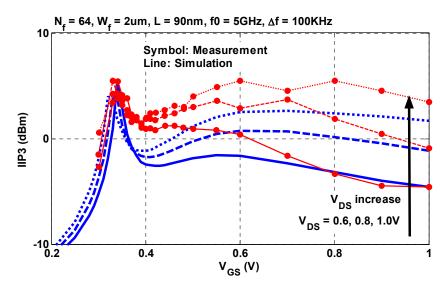

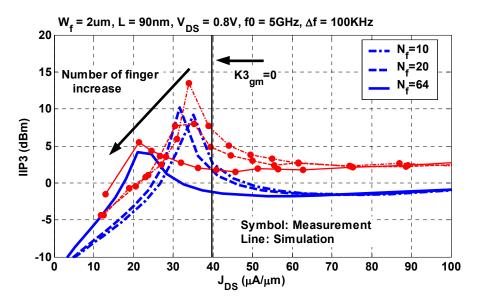

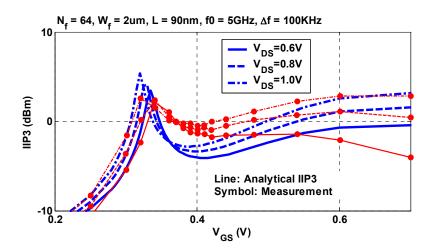

| 9.2.1 Drain voltage dependence       151         9.2.2 Finger number dependence       153         9.2.3 Frequency dependence       154         9.2.4 Large signal linearity       157         9.3 Summary       158         BIBLIOGRAPHY       160         APPENDICES       APPENDIX A ABBREVIATIONS AND SYMBOLS       168         A.1 Abbreviations       168         A.2 Matrix symbols and matrix index       168         A.2 Matrix symbols and matrix index       168         APPENDIX B TWO PORT NETWORK REPRESENTATIONS       170         APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS       172         C.1 Open-Short de-embedding       172         C.2 Pad-open-Short de-embedding       174         C.3 Three-step de-embedding       176         C.4 Transmission line de-embedding       178         APPENDIX D SWITCH ERROR REMOVAL       182         D.1 Switch error removal equations       182         D.2 Step-by-step guide to measure the switch errors       184         APPENDIX E CALIBRATION KIT SETUP       188         APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT       192         APPENDIX G Singularity of Linear Equation Set       196         G.1 Typical calibration standards       196 <tr< th=""><th>9.2</th><th>Linearity Characteristics</th><th>151</th></tr<> | 9.2      | Linearity Characteristics                              | 151 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------|-----|

| 9.2.3 Frequency dependence       154         9.2.4 Large signal linearity       157         9.3 Summary       158         BIBLIOGRAPHY       160         APPENDICES       APPENDICES         APPENDIX A ABBREVIATIONS AND SYMBOLS       168         A.1 Abbreviations       168         A.2 Matrix symbols and matrix index       168         APPENDIX B TWO PORT NETWORK REPRESENTATIONS       170         APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS       172         C.1 Open-Short de-embedding       172         C.2 Pad-open-Short de-embedding       174         C.3 Three-step de-embedding       174         C.4 Transmission line de-embedding       178         APPENDIX D SWITCH ERROR REMOVAL       182         D.1 Switch error removal equations       182         D.2 Step-by-step guide to measure the switch errors       184         APPENDIX E CALIBRATION KIT SETUP       188         APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT       192         APPENDIX G SINGULARITY OF LINEAR EQUATION SET       196         G.1 Typical calibration standards       196         G.2 Singularity of on-wafer standards       196         G.2 Singularity of on-wafer standards       196         G.2 Singularity of                                                                       |          | 9.2.1 Drain voltage dependence                         | 151 |

| 9.2.4 Large signal linearity       157         9.3 Summary       158         BIBLIOGRAPHY       160         APPENDICES       160         APPENDIX A ABBREVIATIONS AND SYMBOLS       168         A.1 Abbreviations       168         A.2 Matrix symbols and matrix index       168         APPENDIX B TWO PORT NETWORK REPRESENTATIONS       170         APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS       172         C.1 Open-Short de-embedding       172         C.2 Pad-open-Short de-embedding       174         C.3 Three-step de-embedding       176         C.4 Transmission line de-embedding       178         APPENDIX D SWITCH ERROR REMOVAL       182         D.1 Switch error removal equations       182         D.2 Step-by-step guide to measure the switch errors       184         APPENDIX E CALIBRATION KIT SETUP       188         APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT       192         APPENDIX G SINGULARITY OF LINEAR EQUATION SET       196         G.1 Typical calibration standards       196         G.2 Singularity of on-wafer standards       197         APPENDIX H ONE-PORT ERROR CORRECTION       201         H.1 Error adaptor for one-port system       202         H.2 Relationshi                                                                       |          |                                                        |     |

| 9.3       Summary       158         BIBLIOGRAPHY       160         APPENDICES       168         A.1       Abbreviations       168         A.2       Matrix symbols and matrix index       168         A.2       Matrix symbols and matrix index       168         APPENDIX B TWO PORT NETWORK REPRESENTATIONS       170         APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS       172         C.1       Open-Short de-embedding       172         C.2       Pad-open-Short de-embedding       172         C.3       Three-step de-embedding       176         C.4       Transmission line de-embedding       178         APPENDIX D SWITCH ERROR REMOVAL       182         D.1       Switch error removal equations       182         D.2       Step-by-step guide to measure the switch errors       184         APPENDIX E CALIBRATION KIT SETUP       188         APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT       192         APPENDIX G SINGULARITY OF LINEAR EQUATION SET       196         G.1       Typical calibration standards       196         G.2       Singularity of on-wafer standards       197         APPENDIX H ONE-PORT ERROR CORRECTION       201         H.1                                                                                                                   |          |                                                        |     |

| BIBLIOGRAPHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                                        |     |

| APPENDICESAPPENDIX A ABBREVIATIONS AND SYMBOLS168<br>A.1 Abbreviations168<br>A.2 Matrix symbols and matrix index168A.2 Matrix symbols and matrix index168APPENDIX B TWO PORT NETWORK REPRESENTATIONS170APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS172<br>C.1 Open-Short de-embedding172<br>C.2 Pad-open-Short de-embedding174<br>C.3 Three-step de-embedding174<br>C.4 Transmission line de-embedding176<br>C.4 Transmission line de-embedding178APPENDIX D SWITCH ERROR REMOVAL182<br>D.1 Switch error removal equations182<br>D.2 Step-by-step guide to measure the switch errors184APPENDIX E CALIBRATION KIT SETUP188APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT192APPENDIX G SINGULARITY OF LINEAR EQUATION SET196<br>G.1 Typical calibration standards196<br>G.2 Singularity of on-wafer standards197APPENDIX H ONE-PORT ERROR CORRECTION201<br>H.1 Error adaptor for one-port system202<br>H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203<br>H.3 A generalized interpretation204<br>APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210<br>J.1 First order kernels211<br>J.2 Second order kernels212<br>J.3 Third order kernels214                                      | 9.3      | Summary                                                | 158 |

| APPENDIX A ABBREVIATIONS AND SYMBOLS168A.1 Abbreviations168A.2 Matrix symbols and matrix index168A.PPENDIX B TWO PORT NETWORK REPRESENTATIONS170APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS172C.1 Open-Short de-embedding172C.2 Pad-open-Short de-embedding174C.3 Three-step de-embedding176C.4 Transmission line de-embedding178APPENDIX D SWITCH ERROR REMOVAL182D.1 Switch error removal equations182D.2 Step-by-step guide to measure the switch errors184APPENDIX E CALIBRATION KIT SETUP188APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT192APPENDIX G SINGULARITY OF LINEAR EQUATION SET196G.1 Typical calibration standards196G.2 Singularity of on-wafer standards197APPENDIX H ONE-PORT ERROR CORRECTION201H.1 Error adaptor for one-port system202H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3 A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1 First order kernels211J.2 Second order kernels212J.3 Third order kernels214                                                                                                                                                                                                                                                   | Bibliog  | RAPHY                                                  | 160 |

| A.1 Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | APPEND   | ICES                                                   |     |

| A.2 Matrix symbols and matrix index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | APPEND   | IX A ABBREVIATIONS AND SYMBOLS                         | 168 |

| APPENDIX B TWO PORT NETWORK REPRESENTATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A.1      | Abbreviations                                          | 168 |

| APPENDIX C REVIEW OF ON-WAFER DE-EMBEDDING METHODS172C.1 Open-Short de-embedding172C.2 Pad-open-Short de-embedding174C.3 Three-step de-embedding176C.4 Transmission line de-embedding178APPENDIX D SWITCH ERROR REMOVAL182D.1 Switch error removal equations182D.2 Step-by-step guide to measure the switch errors184APPENDIX E CALIBRATION KIT SETUP188APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT192APPENDIX G SINGULARITY OF LINEAR EQUATION SET196G.1 Typical calibration standards196G.2 Singularity of on-wafer standards197APPENDIX H ONE-PORT ERROR CORRECTION201H.1 Error adaptor for one-port system202H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3 A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1 First order kernels211J.2 Second order kernels211J.2 Second order kernels212J.3 Third order kernels214                                                                                                                                                                                                                                                                                                                                                                        | A.2      | Matrix symbols and matrix index                        | 168 |

| C.1Open-Short de-embedding172C.2Pad-open-Short de-embedding174C.3Three-step de-embedding176C.4Transmission line de-embedding178APPENDIX D SWITCH ERROR REMOVAL182D.1Switch error removal equations182D.2Step-by-step guide to measure the switch errors184APPENDIX E CALIBRATION KIT SETUP188APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT192APPENDIX G SINGULARITY OF LINEAR EQUATION SET196G.1Typical calibration standards196G.2Singularity of on-wafer standards197APPENDIX H ONE-PORT ERROR CORRECTION201H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                             | APPEND   | IX B TWO PORT NETWORK REPRESENTATIONS                  | 170 |

| C.1Open-Short de-embedding172C.2Pad-open-Short de-embedding174C.3Three-step de-embedding176C.4Transmission line de-embedding178APPENDIX D SWITCH ERROR REMOVAL182D.1Switch error removal equations182D.2Step-by-step guide to measure the switch errors184APPENDIX E CALIBRATION KIT SETUP188APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT192APPENDIX G SINGULARITY OF LINEAR EQUATION SET196G.1Typical calibration standards196G.2Singularity of on-wafer standards197APPENDIX H ONE-PORT ERROR CORRECTION201H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                             | APPEND   | IX C. REVIEW OF ON-WAFER DE-EMBEDDING METHODS          | 172 |

| C.2Pad-open-Short de-embedding174C.3Three-step de-embedding176C.4Transmission line de-embedding178APPENDIX D SWITCH ERROR REMOVAL182D.1Switch error removal equations182D.2Step-by-step guide to measure the switch errors184APPENDIX E CALIBRATION KIT SETUP188APPENDIX G SINGULARITY OF LINEAR EQUATION SET192APPENDIX G SINGULARITY OF LINEAR EQUATION SET196G.1Typical calibration standards196G.2Singularity of on-wafer standards197APPENDIX H ONE-PORT ERROR CORRECTION201H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                        |     |

| C.3 Three-step de-embedding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 1                                                      |     |

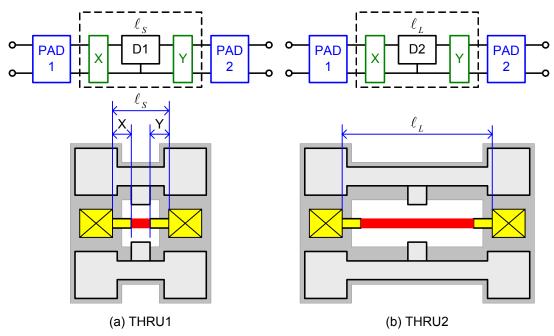

| C.4Transmission line de-embedding178APPENDIX DSWITCH ERROR REMOVAL182D.1Switch error removal equations182D.2Step-by-step guide to measure the switch errors184APPENDIX ECALIBRATION KIT SETUP188APPENDIX FTHE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT192APPENDIX GSINGULARITY OF LINEAR EQUATION SET196G.1Typical calibration standards196G.2Singularity of on-wafer standards197APPENDIX HONE-PORT ERROR CORRECTION201H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX IDERIVATION OF FIRST ORDER INPUT IP3207APPENDIX JDERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                        |     |

| D.1 Switch error removal equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                        |     |

| D.1 Switch error removal equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A DDENID | IV D. SWITCH EDDOD DEMOVAL                             | 192 |

| D.2 Step-by-step guide to measure the switch errors 184  APPENDIX E CALIBRATION KIT SETUP. 188  APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT 192  APPENDIX G SINGULARITY OF LINEAR EQUATION SET 196  G.1 Typical calibration standards 196  G.2 Singularity of on-wafer standards 197  APPENDIX H ONE-PORT ERROR CORRECTION 201  H.1 Error adaptor for one-port system 202  H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203  H.3 A generalized interpretation 204  APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3 207  APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210  J.1 First order kernels 211  J.2 Second order kernels 212  J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                                        |     |

| APPENDIX E CALIBRATION KIT SETUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 1                                                      |     |

| APPENDIX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT 192  APPENDIX G SINGULARITY OF LINEAR EQUATION SET 196 G.1 Typical calibration standards 196 G.2 Singularity of on-wafer standards 197  APPENDIX H ONE-PORT ERROR CORRECTION 201 H.1 Error adaptor for one-port system 202 H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203 H.3 A generalized interpretation 204  APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3 207  APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210 J.1 First order kernels 211 J.2 Second order kernels 212 J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 1 7 10                                                 |     |

| APPENDIX G SINGULARITY OF LINEAR EQUATION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | APPEND   | IX E CALIBRATION KIT SETUP                             | 188 |

| G.1Typical calibration standards196G.2Singularity of on-wafer standards197APPENDIX HONE-PORT ERROR CORRECTION201H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX IDERIVATION OF FIRST ORDER INPUT IP3207APPENDIX JDERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | APPEND   | IX F THE RELATIONSHIP BETWEEN OPEN-SHORT AND FOUR-PORT | 192 |

| G.2 Singularity of on-wafer standards 197  APPENDIX H ONE-PORT ERROR CORRECTION 201 H.1 Error adaptor for one-port system 202 H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203 H.3 A generalized interpretation 204  APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3 207  APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210 J.1 First order kernels 211 J.2 Second order kernels 212 J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | APPEND   | IX G SINGULARITY OF LINEAR EQUATION SET                | 196 |

| APPENDIX H ONE-PORT ERROR CORRECTION 201 H.1 Error adaptor for one-port system 202 H.2 Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203 H.3 A generalized interpretation 204 APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3 207 APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210 J.1 First order kernels 211 J.2 Second order kernels 212 J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                        |     |

| H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | G.2      |                                                        |     |

| H.1Error adaptor for one-port system202H.2Relationship between $\Gamma^M$ and $\Gamma^{DUT}$ 203H.3A generalized interpretation204APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3207APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES210J.1First order kernels211J.2Second order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | APPEND   | IX H ONE-PORT ERROR CORRECTION                         | 201 |

| H.3 A generalized interpretation 204  APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3 207  APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210  J.1 First order kernels 211  J.2 Second order kernels 212  J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                        |     |

| H.3 A generalized interpretation 204  APPENDIX I DERIVATION OF FIRST ORDER INPUT IP3 207  APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210  J.1 First order kernels 211  J.2 Second order kernels 212  J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | H.2      | 1 1 2                                                  |     |

| APPENDIX J DERIVATION OF INPUT IP3 BASED ON VOLTERRA SERIES 210  J.1 First order kernels 211  J.2 Second order kernels 212  J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | H.3      | _                                                      |     |

| J.1First order kernels211J.2Second order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | APPEND   | IX I DERIVATION OF FIRST ORDER INPUT IP3               | 207 |

| J.1First order kernels211J.2Second order kernels212J.3Third order kernels214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Appendi  | IX I DERIVATION OF INDIT IP3 RASED ON VOI TERRA SERIES | 210 |

| J.2 Second order kernels 212 J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                                                        |     |

| J.3 Third order kernels 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                        |     |

| J.4 Input IP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | J.4      |                                                        |     |

# LIST OF FIGURES

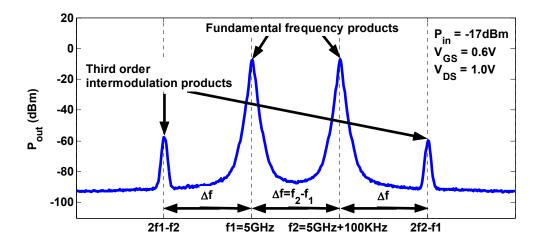

| The power spectrum at the drain of a single transistor under a two-tone excitation, measured by a $50\Omega$ spectrum analyzer.                                                         | 3                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

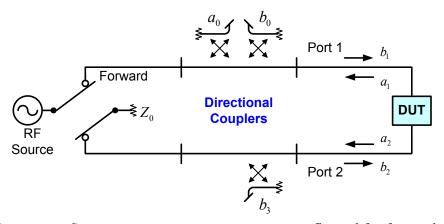

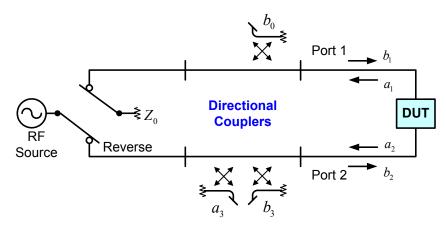

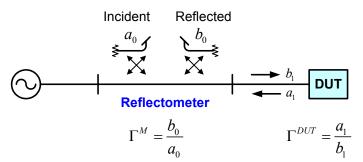

| A typical two-port system for on-wafer S-parameter measurement                                                                                                                          | 4                                                      |

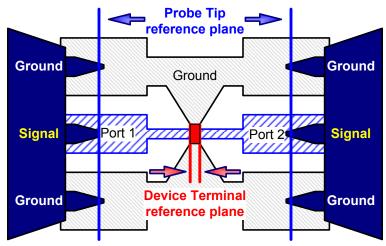

| On-wafer parasitics and reference planes for system error calibration and on-wafer parasitics de-embedding.                                                                             | 5                                                      |

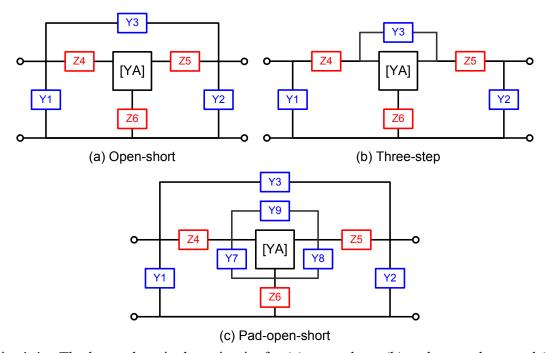

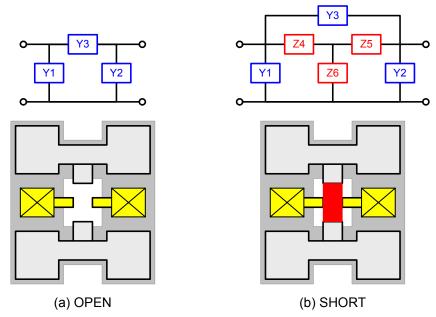

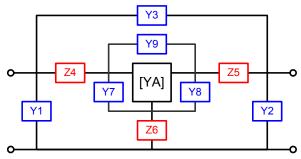

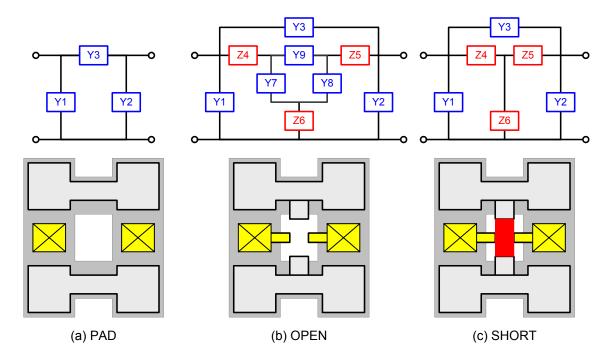

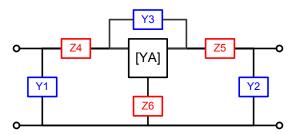

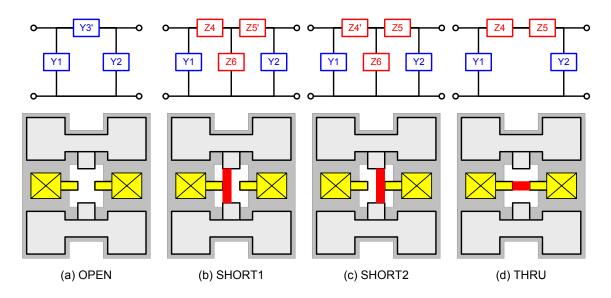

| The lumped equivalent circuits for (a) open-short, (b) pad-open-short, and (c) three-step de-embedding.                                                                                 | 7                                                      |

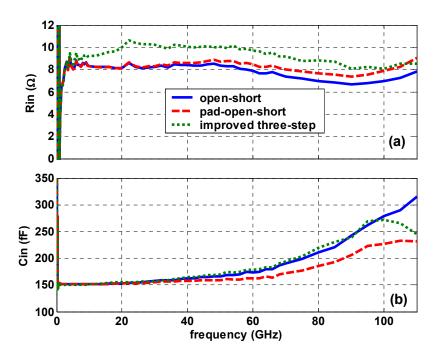

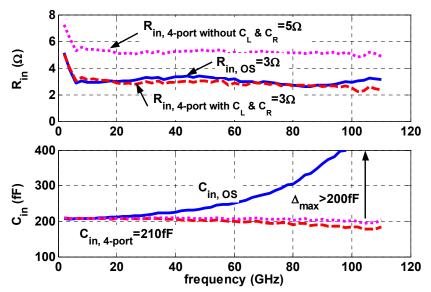

| The equivalent input resistance and capacitance extracted from open-short, pad-open-short, and improved three-step de-embedded results                                                  | 9                                                      |

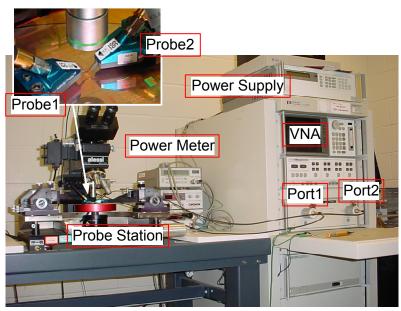

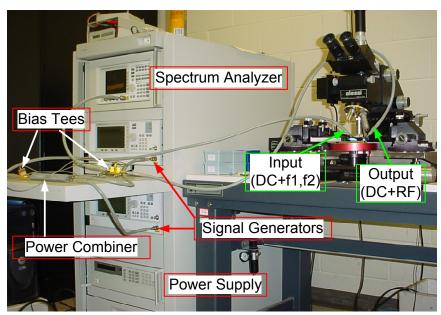

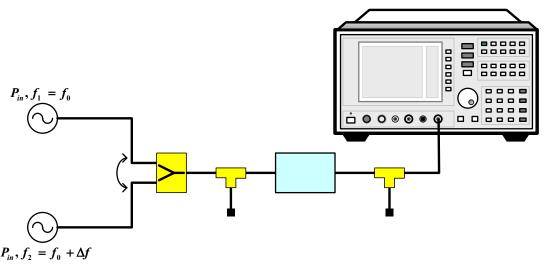

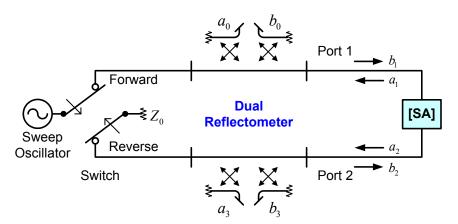

| An on-wafer intermodulation linearity measurement system.                                                                                                                               | . 11                                                   |

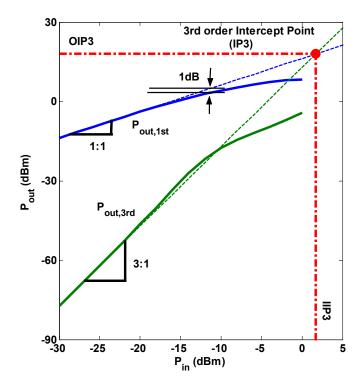

| The fundamental and IM3 output products versus input power for a two-tone excited system.                                                                                               | . 12                                                   |

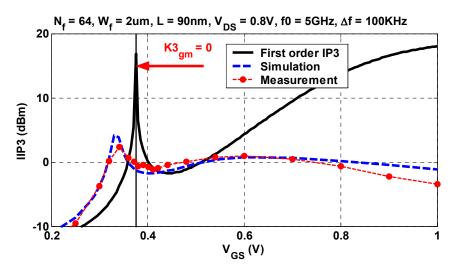

| IIP3 versus $V_{GS}$ from first order IP3 theory, linearity simulation, and two-tone measurement.                                                                                       | . 14                                                   |

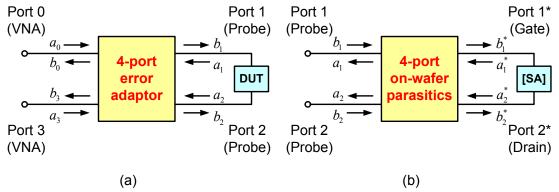

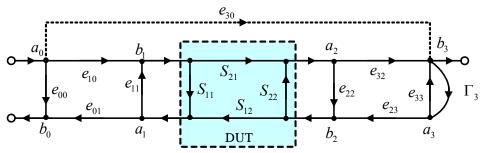

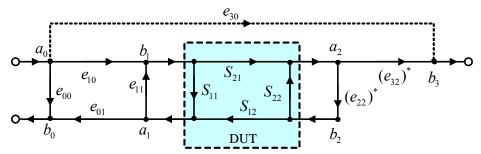

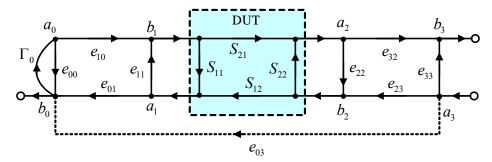

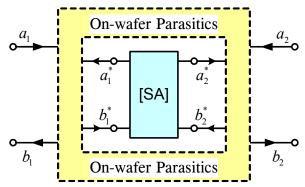

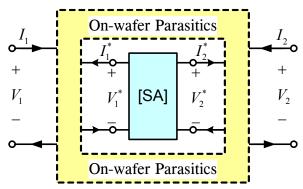

| (a) The four-port network for systematic errors. (b) The four-port network for on-wafer parasitics                                                                                      | . 17                                                   |

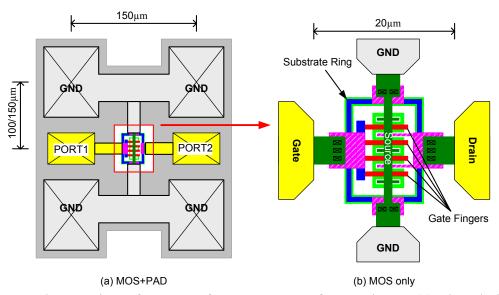

| The top view of an on-wafer test structure for transistors. (a) The whole test structure including probing pads. (b) The MOS transistor under test only. The dimension is not to scale. | . 27                                                   |

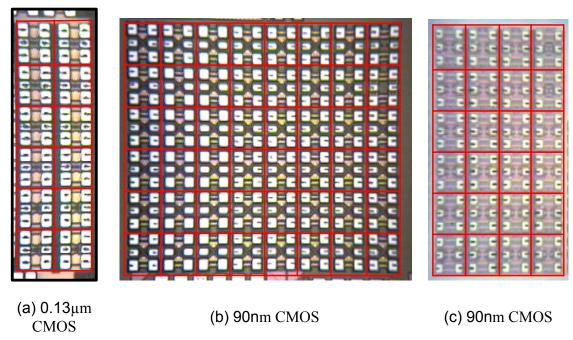

| Chip pictures of the fabricated transistor structures on three RF CMOS technologies. (b) and (c) are fabricated at different foundries                                                  | . 28                                                   |

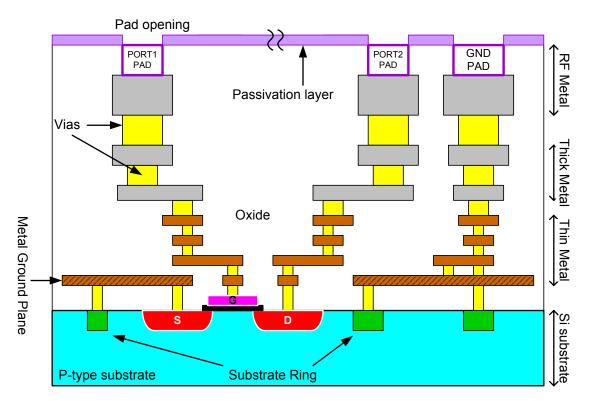

| Cross section view of an advanced RF CMOS technology. The dimension is to scale.                                                                                                        | . 29                                                   |

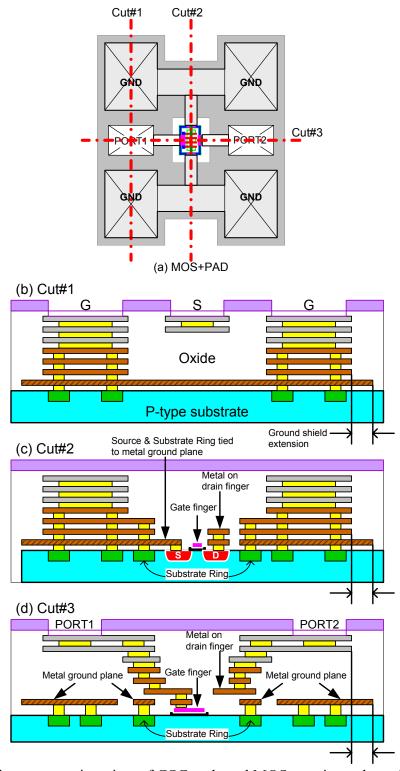

| The cross section view of GSG pads and MOS transistor along three cuts                                                                                                                  | . 31                                                   |

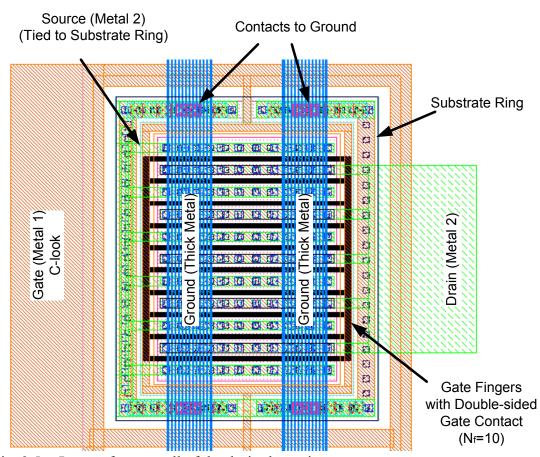

| Layout for one cell of the desired transistor.                                                                                                                                          | . 32                                                   |

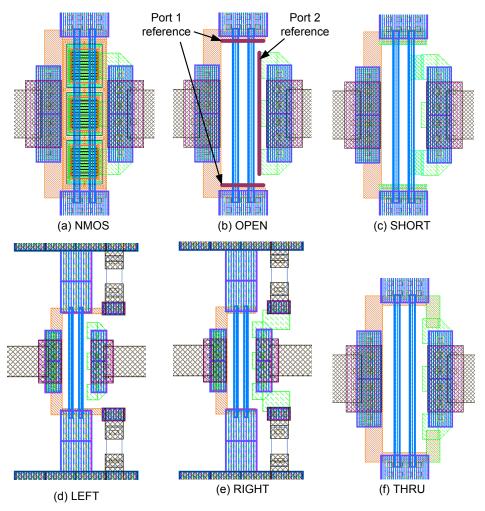

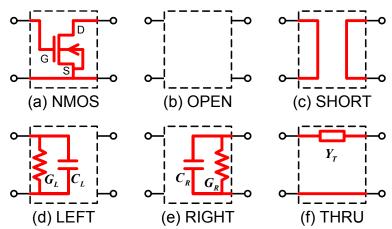

| Layout for the desired transistor, NMOS, and the on-wafer standards, OPEN, SHORT, LEFT, RIGHT and THRU.                                                                                 | . 34                                                   |

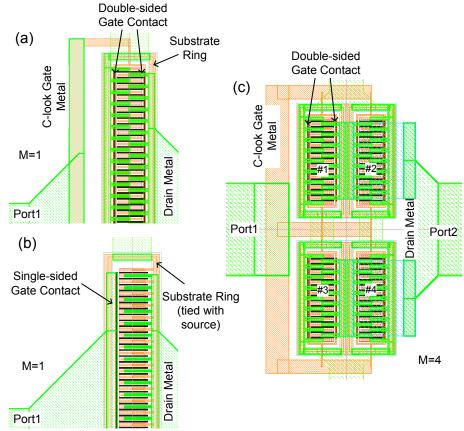

| Layout for NMOS transistors with different gate patterns and multiplier factors.                                                                                                        | . 36                                                   |

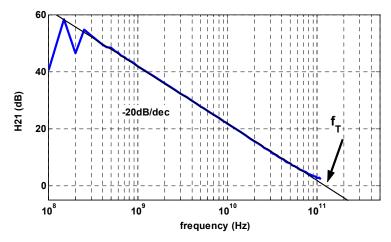

| An example for $f_T$ extraction.                                                                                                                                                        | . 37                                                   |

|                                                                                                                                                                                         | excitation, measured by a $50\Omega$ spectrum analyzer |

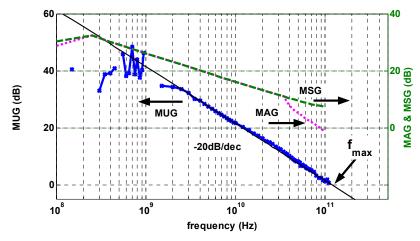

| Fig. 2.9.  | An example for $f_{\text{max}}$ extraction                                                                                                           | . 37 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

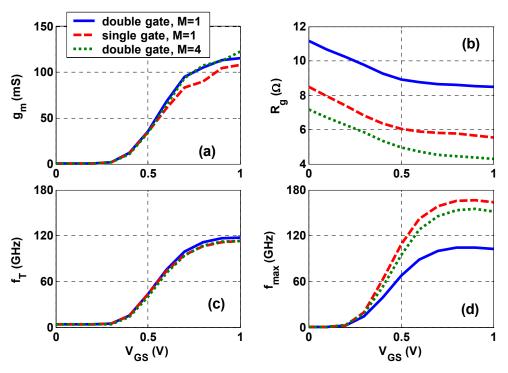

| Fig. 2.10. | Extracted parameters for three NMOS transistors with different gate patterns and multiplier factors.                                                 | . 39 |

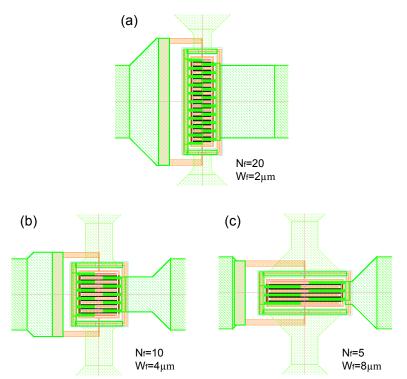

| Fig. 2.11. | Layout for three NMOS transistors with same total channel width but different finger width and finger number. $W_{total}$ =40 $\mu$ m.               | . 40 |

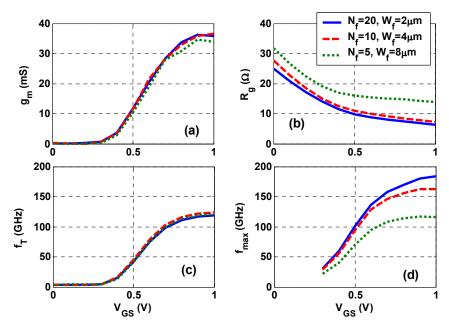

| Fig. 2.12. | Extracted parameters for three NMOS transistors with same total channel width but different finger width and finger number. $W_{total}$ =40 $\mu$ m. | . 41 |

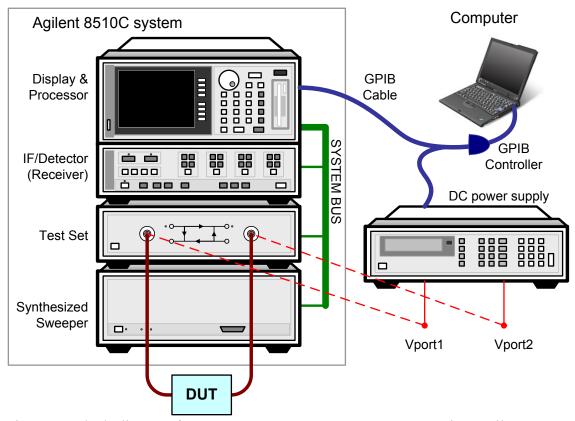

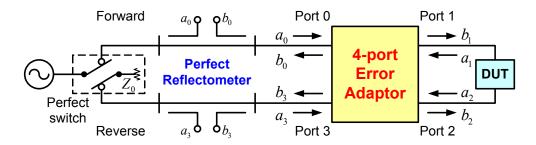

| Fig. 3.1   | Block diagram for two-port S-parameter measurement using Agilent 8510C system.                                                                       | . 45 |

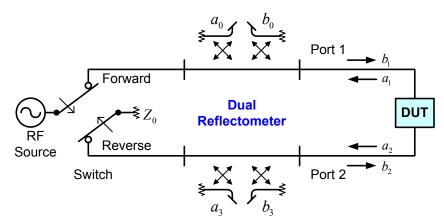

| Fig. 3.2   | A two-port VNA system with four receivers.                                                                                                           | . 46 |

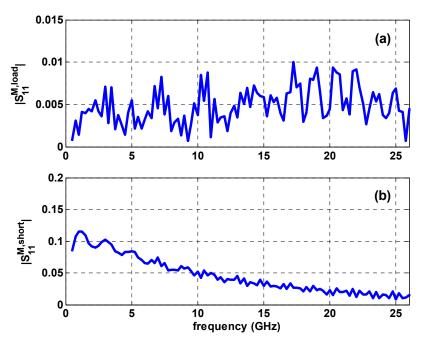

| Fig. 3.3   | The magnitude of the measured $S_{11}$ of an ideal (a) LOAD and (b) SHORT.                                                                           | . 49 |

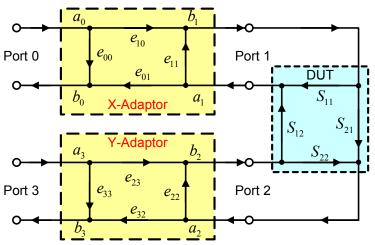

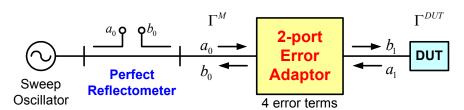

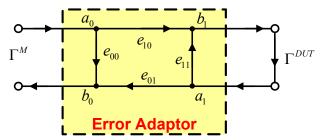

| Fig. 3.4   | The four-port system error adaptor for two-port S-parameter measurement.                                                                             | . 50 |

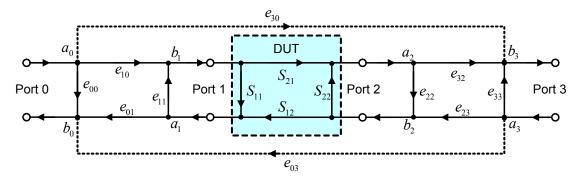

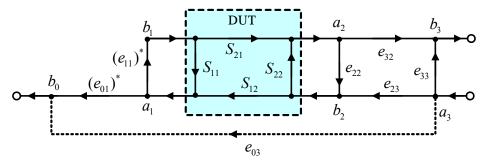

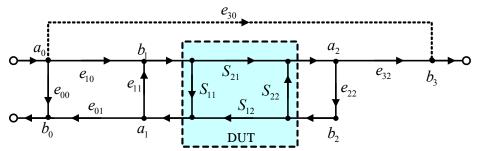

| Fig. 3.5   | Signal flow graph of 8-term error model for a two-port system.                                                                                       | . 51 |

| Fig. 3.6   | The modified 10-term error model with two leakage errors added                                                                                       | . 51 |

| Fig. 3.7   | A two-port S-parameter measurement system configured for forward mode.                                                                               | . 52 |

| Fig. 3.8   | Forward mode signal flow graph for two-port system including non-ideal Z <sub>0</sub> termination.                                                   | . 53 |

| Fig. 3.9   | Simplified forward mode signal flow graph                                                                                                            | . 53 |

| Fig. 3.10  | A two-port S-parameter measurement system configured for reverse mode.                                                                               | . 54 |

| Fig. 3.11  | Reverse mode signal flow graph for two-port system including non-ideal Z <sub>0</sub> termination.                                                   | . 54 |

| Fig. 3.12  | Simplified reverse mode signal flow graph for two-port system.                                                                                       | . 54 |

| Fig. 3.13  | Forward mode signal flow graph for two-port system.                                                                                                  | . 56 |

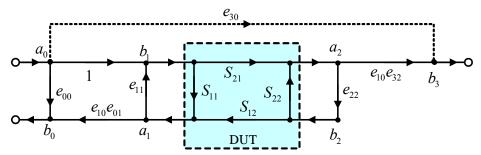

| Fig. 3.14  | Normalized 6-term error model for forward mode                                                                                                       | . 56 |

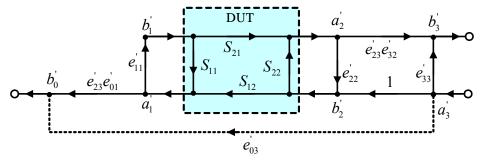

| Fig. 3.15  | Normalized 6-term error model for reverse mode.                                                                                                      | . 57 |

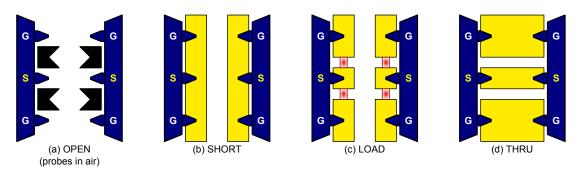

| Fig. 3.16  | (a) OPEN, (b) SHORT, (c) LOAD, and (d) THRU standards for SOLT calibration on Cascade ISS 101-190.                                                   | . 59 |

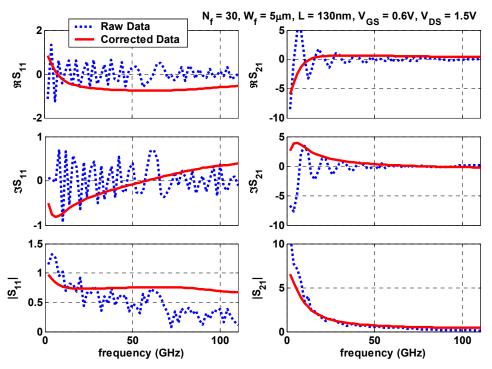

| Fig. 3.17  | Raw and corrected data for $S_{11}$ and $S_{21}$ of a 0.13 $\mu$ m NMOS transistor                                                                   | . 61 |

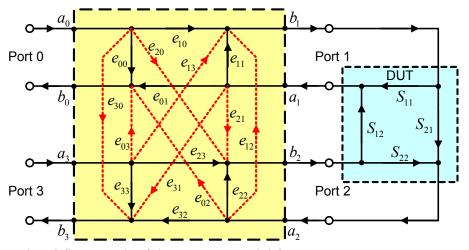

| Fig. 3.18  | Signal flow graph of the 16-term model for a two-port system.                                                                                        | . 62 |

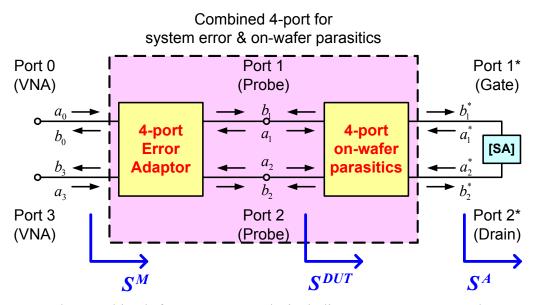

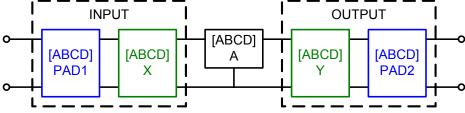

| Fig. 3.19 | The combined four-port network including system errors and on-wafer parasitics.                                                                                                                                                                                       | . 67 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

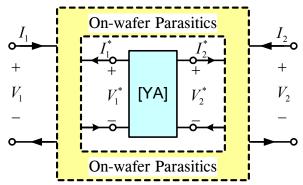

| Fig. 4.1. | Block diagram of the on-wafer parasitics four-port network using I-V representation.                                                                                                                                                                                  | . 73 |

| Fig. 4.2. | The equivalent two-port network of the intrinsic NMOS transistor and the five on-wafer standards OPEN, SHORT, LEFT, RIGHT and THRU.                                                                                                                                   | . 75 |

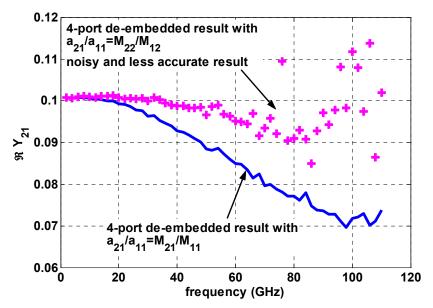

| Fig. 4.3. | The real part of four-port de-embedded $y_{21}$ using different $a_{21}/a_{11}$                                                                                                                                                                                       |      |

|           | choices. The $a_{21}/a_{11}$ defined from $M_{22}/M_{12}$ is clearly nosier, and should not be used.                                                                                                                                                                  | . 82 |

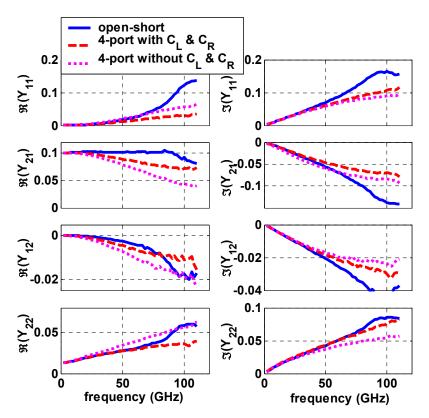

| Fig. 4.4. | The four-port de-embedded transistor Y-parameters with and without including parasitic capacitance in $Y_L$ and $Y_R$ . For comparison, openshort de-embedded results are also plotted. No reciprocal assumptions are made for four-port parasitics de-embedding.     | . 85 |

| Fig. 4.5. | Effective gate resistance and capacitance extracted from four-port de-<br>embedded results with and without parasitic capacitance included in<br>LEFT and RIGHT. Open-short de-embedded results are also shown for<br>comparison. No reciprocal assumptions are made. | . 86 |

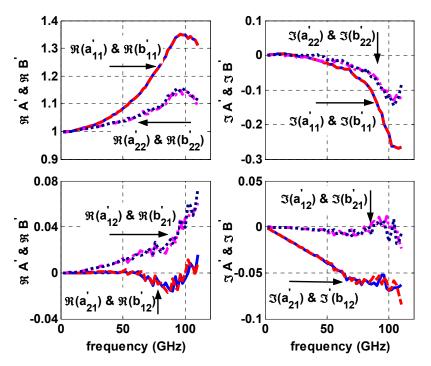

| Fig. 4.6. | The elements of $A'$ and $B'$ versus frequency.                                                                                                                                                                                                                       | . 87 |

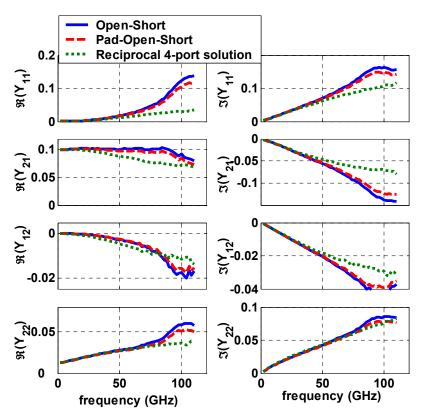

| Fig. 4.7. | Reciprocal four-port de-embedded transistor Y-parameters versus the results using open-short and pad-open-short de-embedding.                                                                                                                                         | . 90 |

| Fig. 5.1  | The four-port error adaptor for on-wafer parasitics in wave representation.                                                                                                                                                                                           | . 93 |

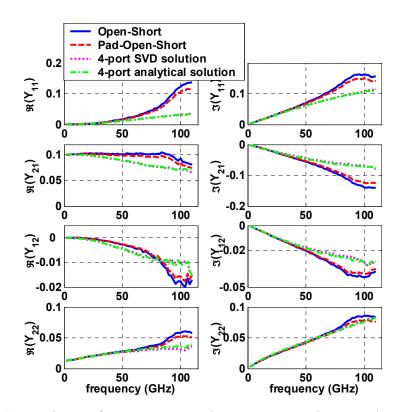

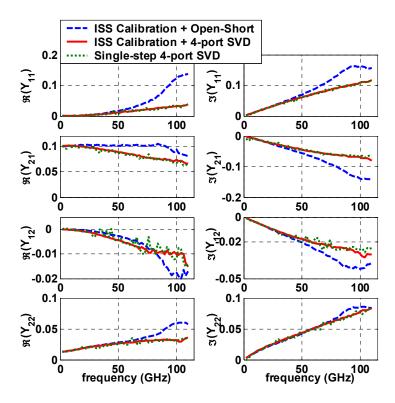

| Fig. 5.2  | Comparison of Y-parameters between open-short, pad-open-short, SVD based numerical four-port solution, and analytical four-port solution.                                                                                                                             | . 98 |

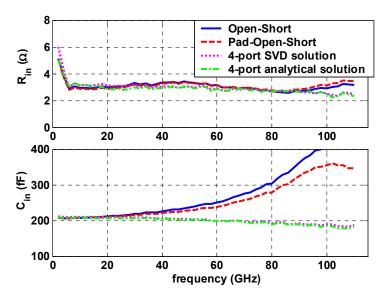

| Fig. 5.3  | Comparison of effective gate resistance and capacitance between open-<br>short, pad-open-short, SVD based four-port solution, and analytical<br>four-port solution.                                                                                                   | . 99 |

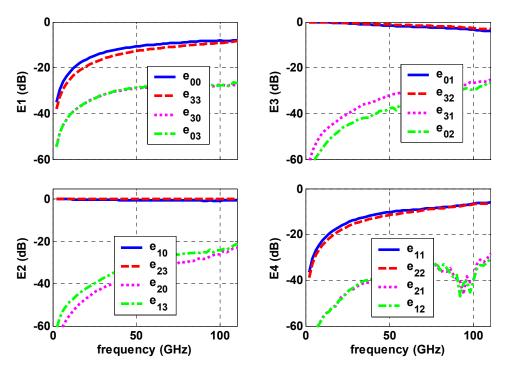

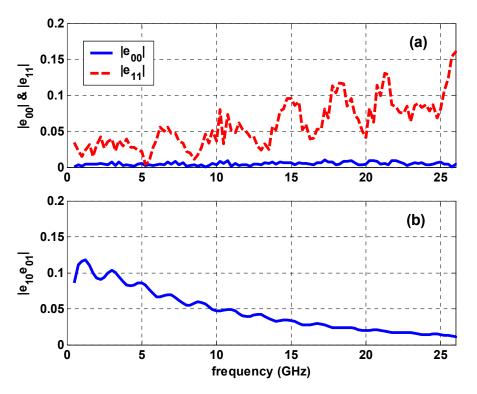

| Fig. 5.4  | The magnitude of the S-parameters for the four-port on-wafer parasitics.                                                                                                                                                                                              | 102  |

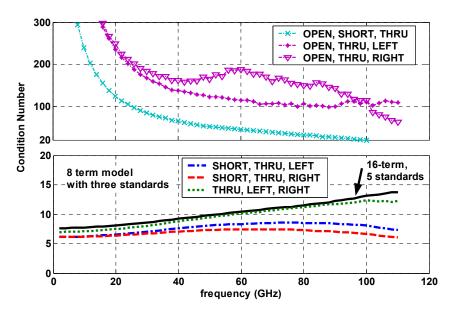

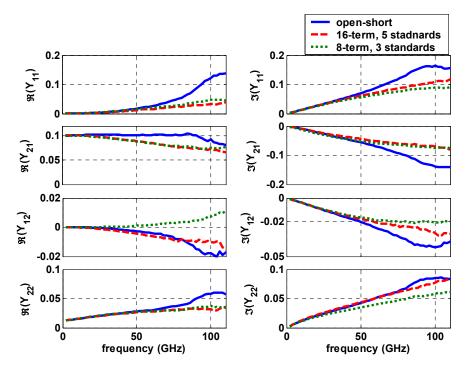

| Fig. 5.5  | Comparison of Y-parameters between open-short, SVD based 16-term solution, and SVD based 8-term solution.                                                                                                                                                             | 105  |

| Fig. 5.6  | Comparison of Y-parameters between open-short, SVD based 16-term solution, and SVD based 8-term solution.                                                                                                                                                             | 105  |

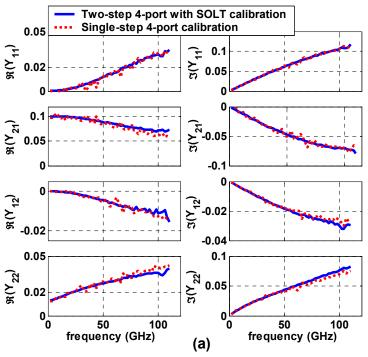

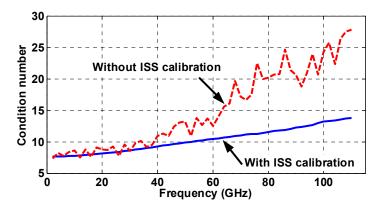

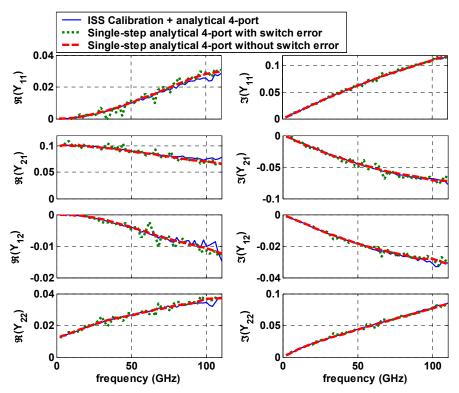

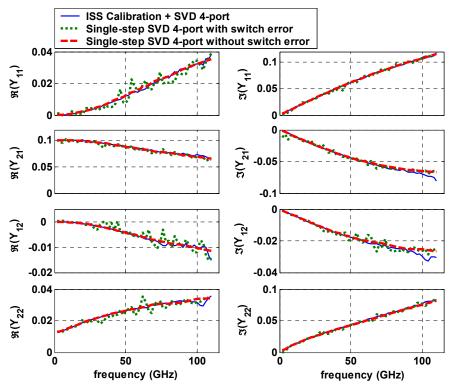

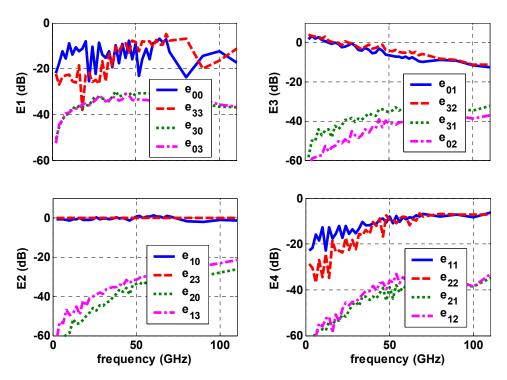

| Fig. 6.1. | Single-step versus two-step four-port using the analytical four-port solution with data measured using a HP 8510XF system from 2 GHz to 110 GHz.                                                                                                                      | 110  |

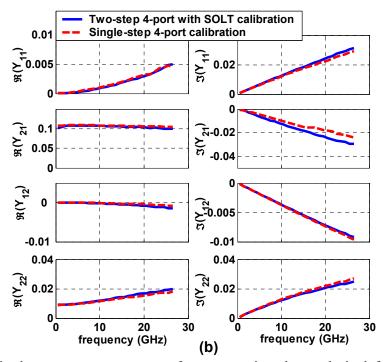

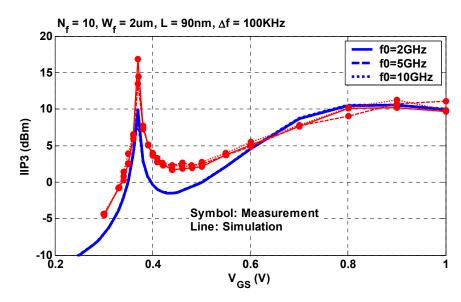

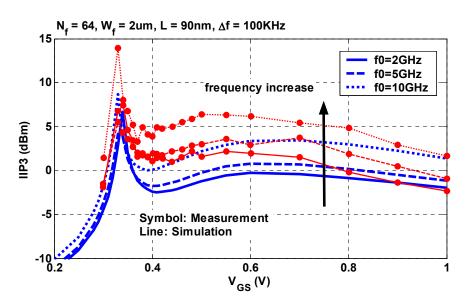

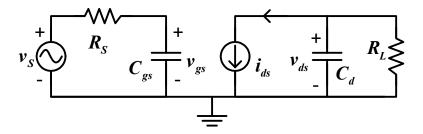

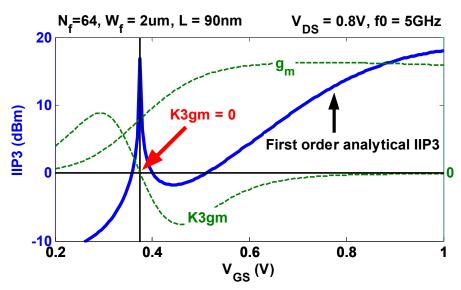

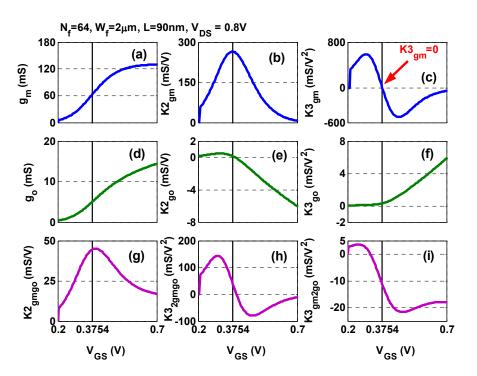

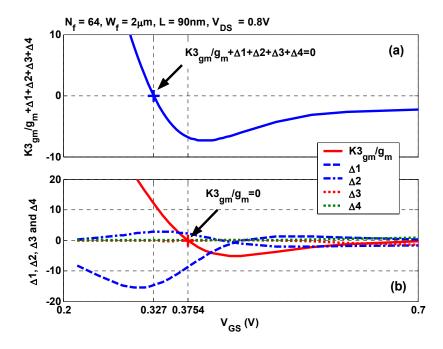

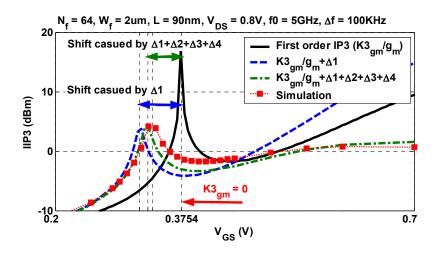

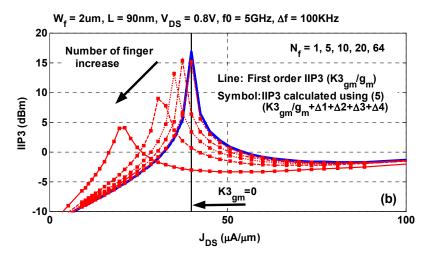

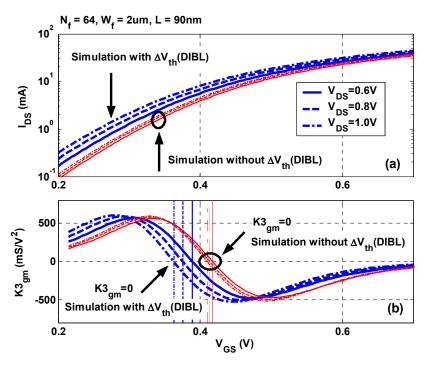

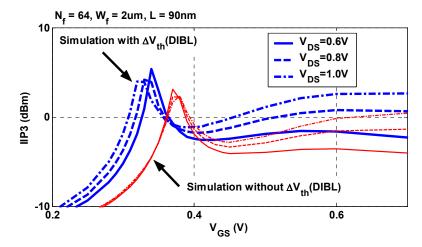

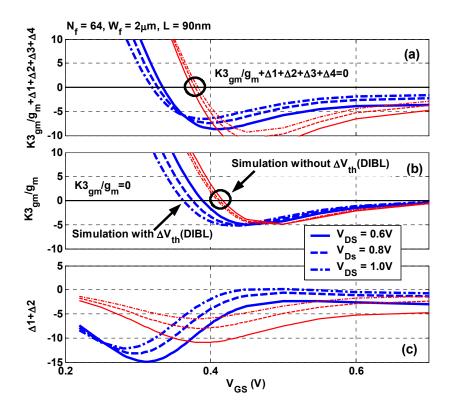

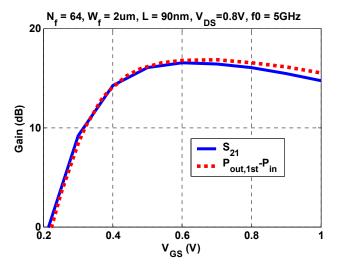

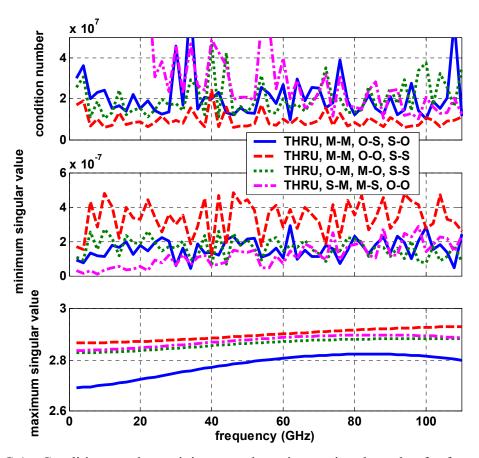

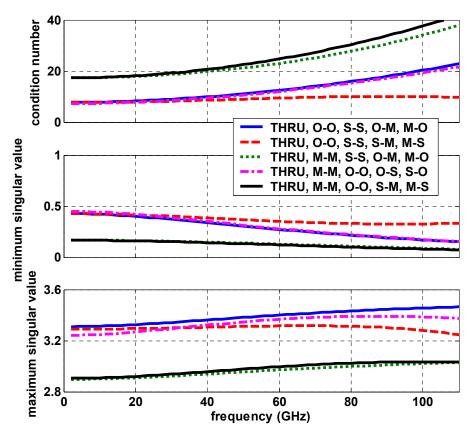

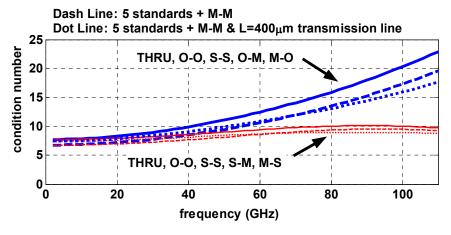

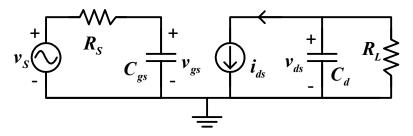

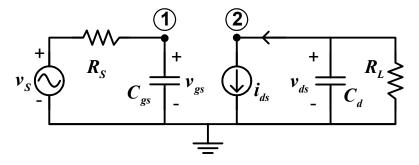

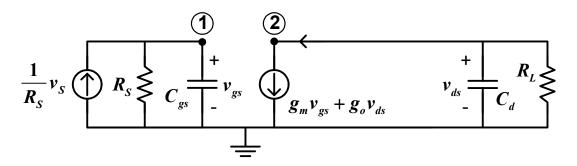

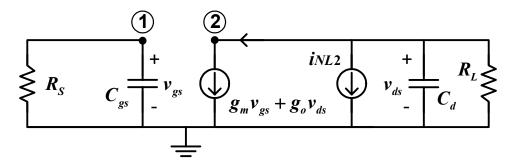

| Fig. 6.2. | Single-step versus two-step four-port using the analytical four-port solution with data measured using a HP 8510C system from 2 GHz to 26.5 GHz                                              | 10 |