# ALTERNATIVE GROWTH AND INTERFACE PASSIVATION TECHNIQUES $\label{eq:formula} FOR~SiO_2~ON~4H\text{-}SiC$

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

| <del></del>              | Xingguang Z       | hu                      |

|--------------------------|-------------------|-------------------------|

| Certificate of Approval: |                   |                         |

|                          |                   |                         |

| Minseo Park              |                   | John R. Williams, Chair |

| Associate Professor      |                   | Professor               |

| Physics                  |                   | Physics                 |

|                          |                   |                         |

| Jianjun Dong             |                   | Yu Lin                  |

| Associate Professor      |                   | Professor               |

| Physics                  |                   | Physics                 |

|                          |                   |                         |

|                          |                   |                         |

|                          |                   |                         |

|                          | George T. Flowers |                         |

|                          | Dean              |                         |

|                          | Graduate School   |                         |

## ALTERNATIVE GROWTH AND INTERFACE PASSIVATION TECHNIQUES $\label{eq:formula} \text{FOR SiO}_2 \text{ ON 4H-SiC}$

Xingguang Zhu

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama December 19, 2008

## ALTERNATIVE GROWTH AND INTERFACE PASSIVATION TECHNIQUES $\label{eq:formula} \text{FOR SiO}_2 \text{ ON 4H-SiC}$

## Xingguang Zhu

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights

| Signature of Author |  |

|---------------------|--|

|                     |  |

|                     |  |

|                     |  |

### **VITA**

Xingguang Zhu, Son of Xi Zhu and Menghua Yang, was born on October 10, 1980, in Suzhou, Jiangsu Province, People's Republic of China. He received a Bachelor of Science degree majoring in Solid State Physics from Physics Department of Nanjing University, Nanjing, P.R.China in July, 2003. He entered the graduate program in Physics Department of Auburn University in August, 2003 and worked as a Graduate Teaching Assistant and later as a Graduate Research Assistant in the Silicon Carbide Research Group under the supervision of Professor John R. Williams. During his graduate study at Auburn, he received a non-thesis Master of Science degree in August, 2005, and also taught the PHYS1500 General Physics I course during the summer semester, 2008. He married Linyun Han in Suzhou, P.R.China on May 28, 2007.

#### DISSERTATION ABSTRACT

## ALTERNATIVE GROWTH AND INTERFACE PASSIVATION TECHNIQUES

FOR SiO<sub>2</sub> ON 4H-SiC

Xingguang Zhu

Doctor of Philosophy, December 19, 2008 (M.Sc., Auburn University, 2005) (B.Sc., Nanjing University, 2003)

256 Typed Pages

Directed by John R. Williams

Silicon Carbide is a novel wide band gap semiconductor material with excellent thermal, chemical and electrical properties. It also shares its natural oxide SiO<sub>2</sub> with Si, which has been widely studied and optimized for decades. These properties make it a perfect candidate for applications in high-temperature, high-power MOS devices. Of over 200 polytypes, 4H-SiC is most commonly used, because it is among the only few commercially available polytypes that are known to be electrically and thermo-dynamically stable for making microelectronic devices. Unfortunately, the performance of such devices is limited by the poor SiO<sub>2</sub>/SiC interface quality after the standard dry O<sub>2</sub> oxidation process. By far, the atomic understanding of the true physical structure and schematic of this interface still remains mystery. After applying most of the conventional

passivation techniques such as NO anneal and H<sub>2</sub> anneal, improvements on the device performances can be clearly observed, however, the results are still far from satisfactory.

In this work, two alternative passivation techniques are applied, in order to obtain better understanding of the interface properties and achieve improved electrical characteristics and higher performance. The first technique is the alumina enhanced oxidation, which by introducing metal impurities via the ceramic alumina during the oxidation, a decreased interface-trap density (D<sub>IT</sub>) and drastic increase in field effect channel mobility can be observed, however, this is also accompanied by a large amount of mobile ions inside the oxide. The results from electrical measurement of the devices as well as the possible cause and effect of those ions on the interface are discussed. Few other passivation techniques are also applied after this process for potential improvement and optimization, and the results are discussed.

Another passivation technique is the nitrogen plasma anneal, which successfully creates atomic nitrogen by microwave induced plasma to achieve an oxygen-free nitridation annealing condition. This helps for further and better understanding of the passivation effect by the sole presence of nitrogen. All the electrical results obtained are discussed in detail and also compared with standard NO results.

#### **ACKNOWLEGEMENTS**

The author would like to express sincere appreciation to Dr. John R. Williams, for all his invaluable advice, guidance, and academic and moral support. His encouragement, knowledge and enthusiasm continuously enlightened and guided him during the entire research work. The author is also very grateful to all the committee members, Dr. Minseo Park, Dr. Jianjun Dong, Dr. Yu Lin and Dr. Guofu Niu for their support, instruction and participation in the evaluating of his work.

In addition, the author is also deeply in debt to Dr. Ayayi, C. Ahyi, for inspiration, collaboration, attention, discussion and help that he kindly provided at all times. Special thanks to Tamara Isaacs-Smith and Max Cichon for their valuable assistance all along, and to Dr. Shurui Wang for her instruction and time during the early part of the work. The author would also like to take this opportunity to thank Zengjun Chen, Mingyu Li, all the collaborators in the research group and the alumni in Physics Department of Auburn University for their help and contributions during the past five years.

Last but not least, the author extends special thanks to his wife Linyun Han for all her patience, understanding and moral support. This dissertation is also dedicated to all his family members and friends.

This work is supported by ARL under contract ARMY-W911NF-07-2-0046 and TARDEC under contract W56H2V-06-C-0228.

| Style manual or journal used: | APA                     | <u></u>                           |

|-------------------------------|-------------------------|-----------------------------------|

|                               |                         |                                   |

|                               |                         |                                   |

| Computer software used: Micr  | osoft® Office Word 20   | 03, Microsoft® Office Excel 2003, |

|                               |                         |                                   |

| Microsoft® Office Powerpoint  | t 2003, Origin® 7.0, SR | RIM 2006, ICS, Labview®           |

## TABLE OF CONTENTS

| LIST OF FIGURES                                                            | xiv |

|----------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                             | XX  |

|                                                                            |     |

| CHAPTER 1 Introduction                                                     | . 1 |

| 1.1 General Introduction                                                   | . 1 |

| 1.2 General Information for SiC                                            | . 5 |

| 1.2.1 Historical Review                                                    | . 5 |

| 1.2.2 Polytypism                                                           | . 7 |

| 1.2.3 Bulk Crystal and Epitaxial Growth                                    | 13  |

| 1.2.4 Physical and Electrical Properties                                   | 18  |

|                                                                            |     |

| CHAPTER 2 Characteristic and Theoretical Parameters for 4H-SiC MOS Devices |     |

|                                                                            | 22  |

| 2.1 MOS Structures                                                         | 22  |

| 2.2 MOS Capacitor                                                          | 23  |

| 2.2.1 General Introduction                                                 | 23  |

| 2.2.2 Operating Modes and Surface Potential under Gate Bias                | 27  |

| 2.2.3 High-Low Frequency Capacitance-Voltage Measurement                   | 34  |

|       | 2.2.4 Non-ideal Characteristic of MOS Capacitor         | 38  |

|-------|---------------------------------------------------------|-----|

| 2.3   | MOSFET                                                  | 60  |

|       | 2.3.1 General Introduction                              | 60  |

|       | 2.3.2 Basic Structure of MOSFET                         | 61  |

|       | 2.3.3 Threshold Voltage V <sub>T</sub>                  | 63  |

|       | 2.3.4 Channel Mobility                                  | 66  |

|       |                                                         |     |

| СНАРТ | TER 3 Equipments and Processes                          | 76  |

| 3.1   | Furnaces                                                | 76  |

| 3.2   | Photolithography                                        | 78  |

| 3.3   | Sputtering System                                       | 80  |

| 3.4   | Lift Off Process                                        | 84  |

| 3.5   | Rapid Annealing System                                  | 85  |

| 3.6   | Reactive Ion Etching (RIE) System                       | 90  |

| 3.7   | Simultaneous High-low Frequency C-V Probe Station       | 96  |

| 3.8   | I-V Probe Station and Measurement                       | 01  |

| 3.9   | MOSFET Mobility Measurement                             | .05 |

|       |                                                         |     |

| СНАРТ | TER 4 Current Oxidation and Passivation Procedures      | .09 |

| 4.1   | General Introduction 1                                  | 11  |

| 4.2   | Standard Dry O <sub>2</sub> Oxidation                   | 13  |

| 4.2   | .1 General Procedure for Standard Dry Oxidation         | 13  |

| 4.2   | .2 Electrical Characteristics of Standard Dry Oxidation | 13  |

| 4.2.  | .3 Summary for Standard Dry Oxidation                                   | 119 |

|-------|-------------------------------------------------------------------------|-----|

| 4.3   | Nitric Oxide (NO) Anneal                                                | 119 |

|       | 4.3.1 General Introduction and Procedure for Standard NO Anneal         | 119 |

|       | 4.3.2 Nitrogen Profile from Standard NO Anneal                          | 120 |

|       | 4.3.3 Electrical Characteristics Following Standard NO Anneal           | 123 |

|       | 4.3.4 Summary for Standard NO Anneal                                    | 130 |

| 4.4   | Hydrogen Passivation                                                    | 133 |

|       | 4.4.1 General Introduction and Procedure for H <sub>2</sub> Anneal      | 133 |

|       | 4.4.2 Electrical Characterizations of Standard H <sub>2</sub> Anneal    | 134 |

|       | 4.4.3 Summary for Standard H <sub>2</sub> Anneal                        | 139 |

|       |                                                                         |     |

| СНАРТ | TER 5 Alumina Enhanced Oxidation (AEO) Process                          | 140 |

| 5.1   | General Introduction                                                    | 140 |

| 5.2   | Characteristics of Oxides Following Alumina Enhanced Oxidation          | 143 |

|       | 5.2.1 Growth Rate                                                       | 143 |

|       | 5.2.2 C-V Characteristics and Interface Trap Density (D <sub>IT</sub> ) | 144 |

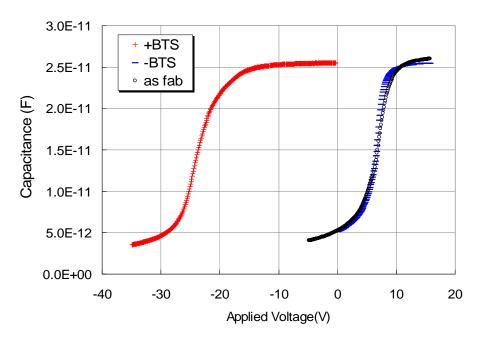

|       | 5.2.3 BTS Measurement and Mobile Ion Concentration                      | 147 |

|       | 5.2.4 Channel Mobility for N-channel MOSFETs                            | 150 |

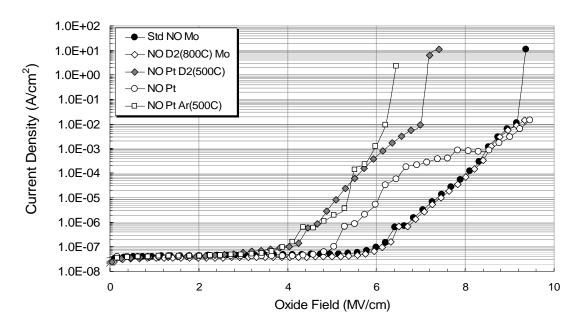

|       | 5.2.5 I-V Characteristics and Breakdown Field                           | 153 |

| 5.3   | Oxidation with Intentional Metal Contamination                          | 155 |

|       | 5.3.1 Introduction                                                      | 155 |

|       | 5.3.2 Oxidation with Different Metal Oxide Compounds                    | 157 |

|       | 5.3.3 Oxidation with Alkali Metal Compounds                             | 159 |

|      | 5.3.4 Summary                                                           | 165   |

|------|-------------------------------------------------------------------------|-------|

| 5.4  | Effect of Other Anneal Methods on Alumina Enhanced Oxidation            | . 166 |

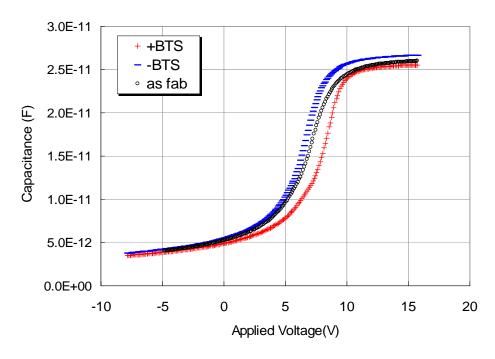

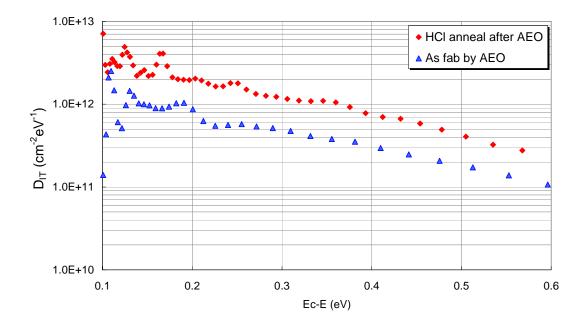

|      | 5.4.1 HCl Anneal on Alumina Enhanced Oxidation                          | . 167 |

|      | 5.4.2 NO Anneal Following Alumina Enhanced Oxidation                    | . 170 |

|      | 5.4.3 Effect on D <sub>IT</sub> of Mobile Ion Removal by +/- BTS on AEO | . 174 |

|      | 5.4.4 Summary for Annealing Methods on Alumina Enhanced Oxidation       | . 178 |

| 5.5  | Conclusion                                                              | 179   |

|      |                                                                         |       |

| CHAP | ΓER 6 Nitrogen Plasma Anneal Process                                    | . 180 |

| 6.1  | General Introduction and Motivation                                     | . 180 |

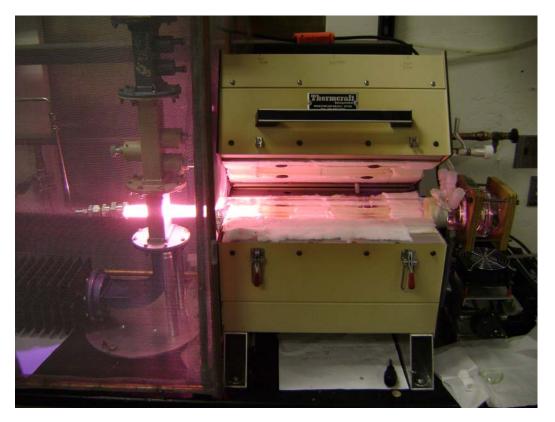

| 6.2  | Nitrogen Plasma Anneal System and Standard Annealing Process            | . 183 |

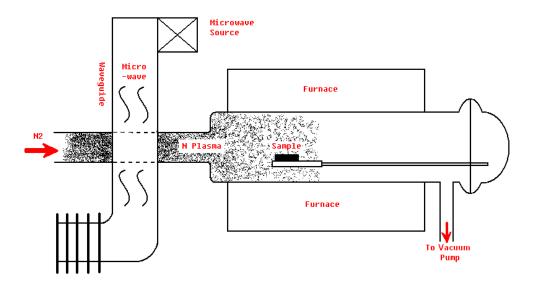

|      | 6.2.1 Plasma Annealing Furnace                                          | . 183 |

|      | 6.2.2 Nitrogen Plasma Anneal Process                                    | . 184 |

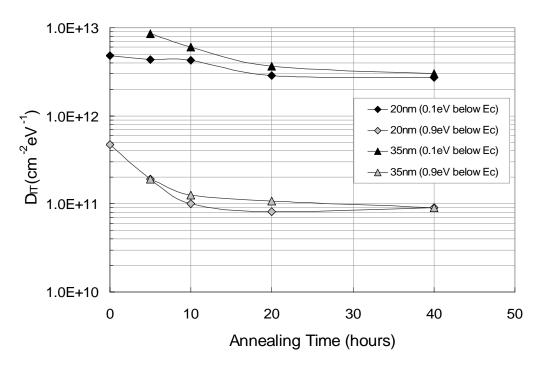

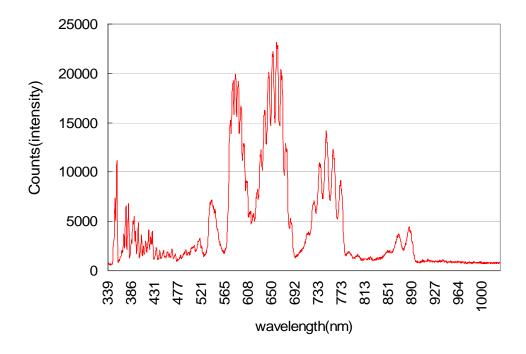

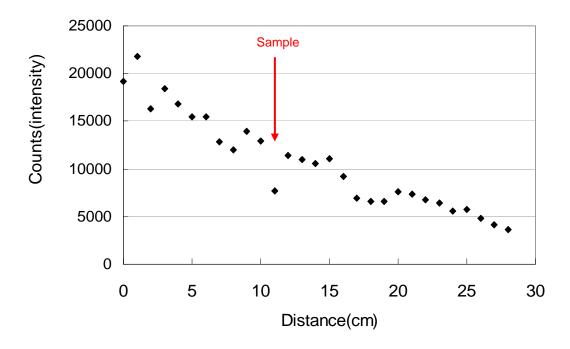

|      | 6.2.3 System Efficiency and Optimization                                | . 187 |

| 6.3  | Electrical Characteristics of Oxides with Nitrogen Plasma Anneal        | . 190 |

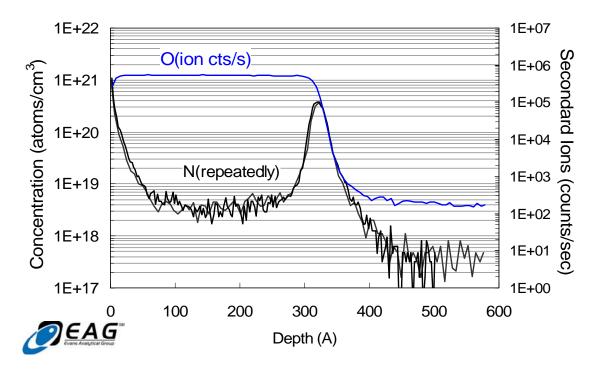

|      | 6.3.1 N Profile by Nitrogen Plasma Anneal                               | . 190 |

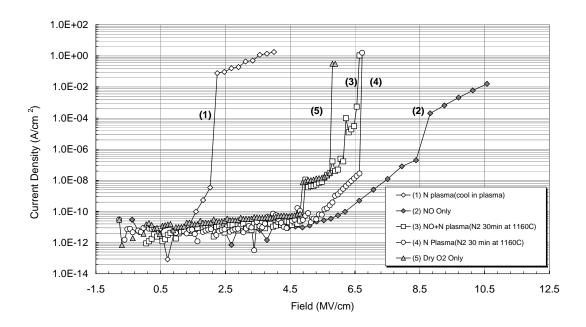

|      | 6.3.2 I-V Characteristics and Breakdown Field                           | . 192 |

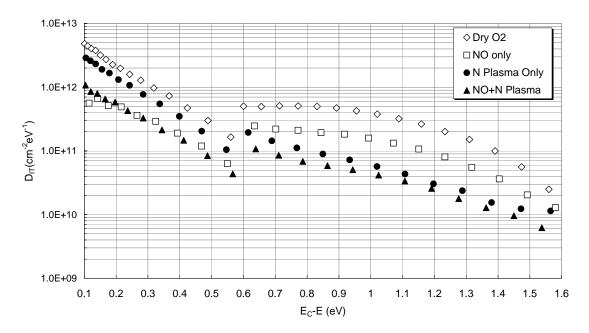

|      | 6.3.3 C-V Characteristics and Interface Trap Density (D <sub>IT</sub> ) | . 194 |

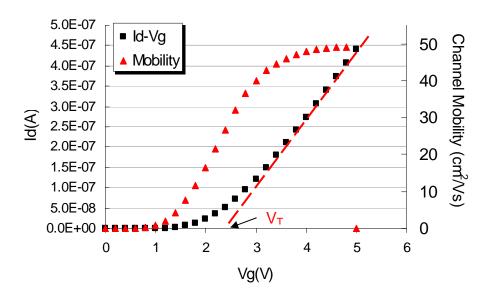

|      | 6.3.4 Channel Mobility for N-channel MOSFETs                            | . 197 |

| 6.4  | Conclusion                                                              | 201   |

|      |                                                                         |       |

| CHAP | ΓER 7 Conclusions and Recommendations for Future work                   | . 202 |

| 7.1  | Conventional Oxidation and Passivation Techniques                       | . 203 |

| 7.2 Alumina Enhanced Oxidation  | 204 |

|---------------------------------|-----|

| 7.2.1 Conclusion and Discussion | 204 |

| 7.2.2 Future Work               | 207 |

| 7.3 Nitrogen Plasma Anneal      | 208 |

| 7.3.1 Conclusion and Discussion | 208 |

| 7.3.2 Future Work               | 210 |

|                                 |     |

| REFERNCES                       | 213 |

| APPENDIX A                      | 226 |

| APPENDIX B                      | 228 |

| APPENDIX C                      | 231 |

## LIST OF FIGURES

| Figure 1.2.1 Tetragonal structure of the SiC crystal                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2.2 Unit cell for different crystal structures of SiC. (a)-cubic; (b)-hexagonal8                                                                                                                             |

| Figure 1.2.3 Stacking sequence for different SiC crystalline polytypes10                                                                                                                                              |

| Figure 2.2.1 Two dimensional diagram for a MOS capacitor                                                                                                                                                              |

| Figure 2.2.2 Energy band diagram of a MOS capacitor on a p-type semiconductor26                                                                                                                                       |

| Figure 2.2.3 Band diagram and corresponding block charge diagrams of p-type ideal MOS capacitor under different static bias condition                                                                                 |

| Figure 2.2.4 Band diagram and corresponding block charge diagrams of n-type ideal MOS capacitor under different static bias condition                                                                                 |

| Figure 2.2.5 Graphical definition of parameters $\phi_S$ and $\phi_F$ on the band diagram34                                                                                                                           |

| Figure 2.2.6 Energy band diagram of real MOS capacitor of $\Phi_M \neq \Phi_S$ under no gate bias ( $V_G$ =0)                                                                                                         |

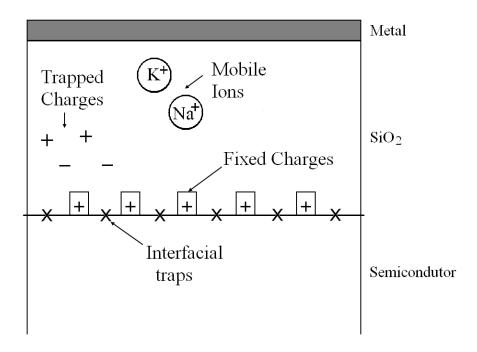

| Figure 2.2.7 Nature and location of different oxide charges in thermally grown SiO <sub>2</sub> 41                                                                                                                    |

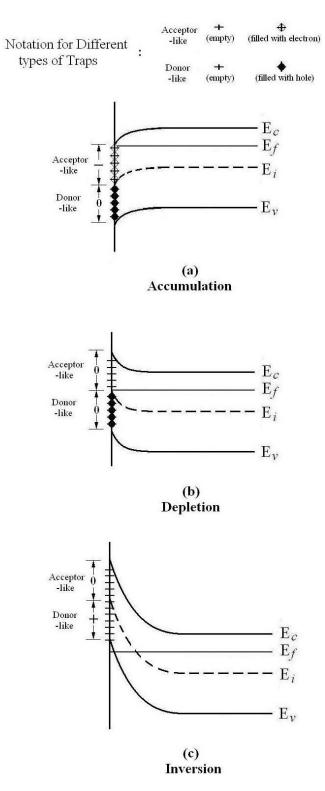

| Figure 2.2.8 Band diagram of the filling of different types of interface traps under (a) accumulation, (b) depletion, (c) inversion for an n-type MOS capacitor48                                                     |

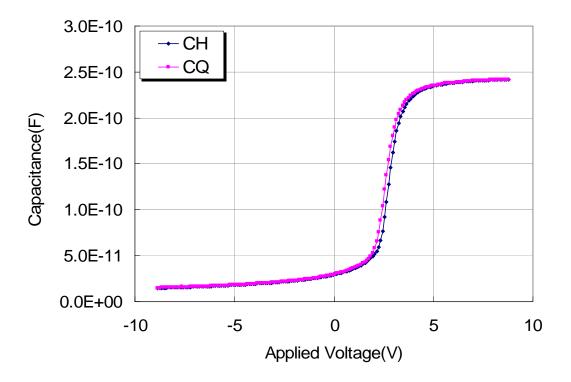

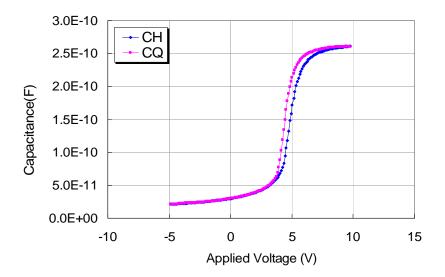

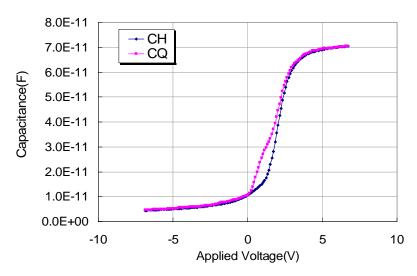

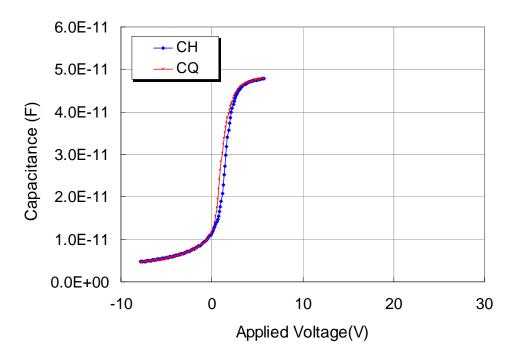

| Figure 2.2.9 Room-temperature (23°C) C-V measurement on an n-4H-SiC MOS capacitor with dry O <sub>2</sub> oxidation followed by standard NO anneal51                                                                  |

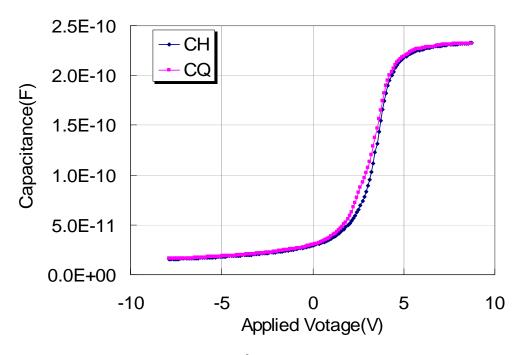

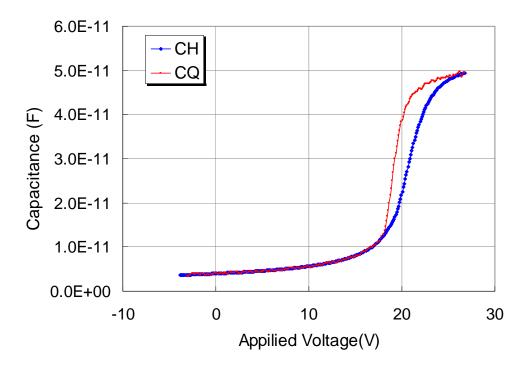

| Figure 2.2.10 High-temperature ( $300^{\circ}$ C) C-V measurement on an n-4H-SiC MOS capacitor with dry O <sub>2</sub> oxidation followed by standard NO passivation anneal52                                         |

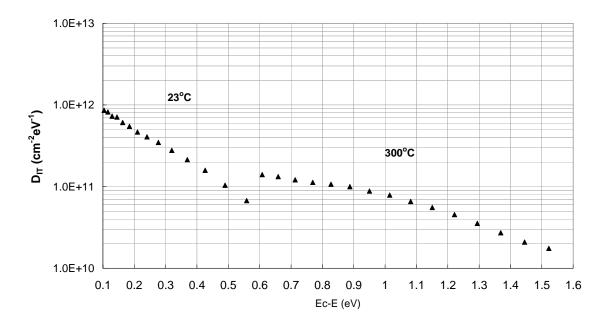

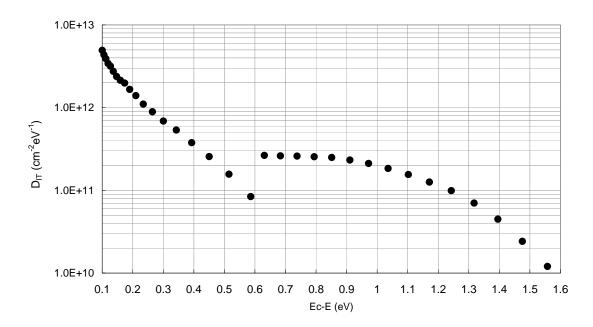

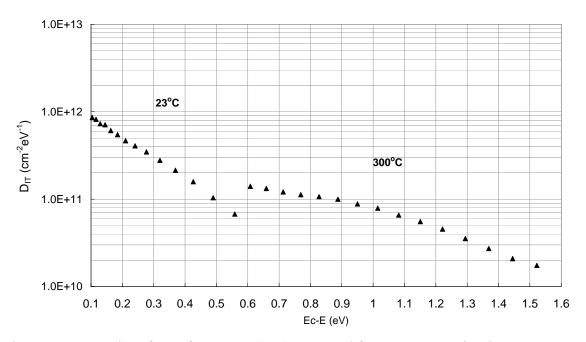

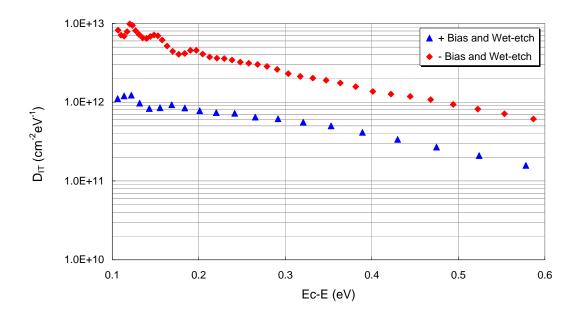

| Figure 2.2.11 The D <sub>IT</sub> extracted from room-temperature (23°C) and high-temperature (300°C) C-V measurements on an n-4H-SiC MOS capacitor with dry O <sub>2</sub> oxidation followed by standard NO anneal. |

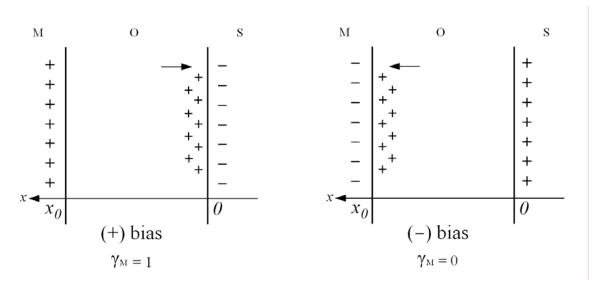

| Figure 2.2.12 Two hypothetical mobile ion distribution inside the oxide layer under (+) and (-) bias-temperature stressing (BTS)                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

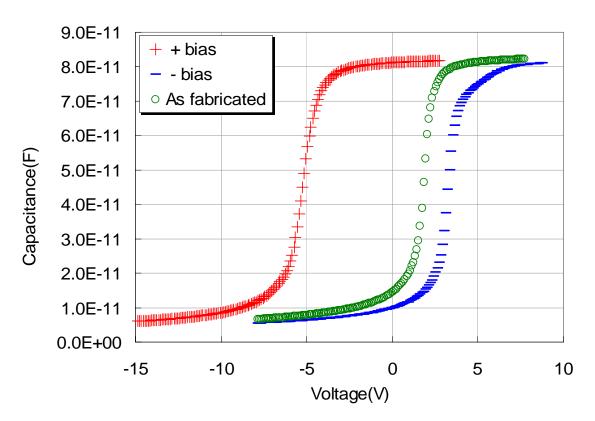

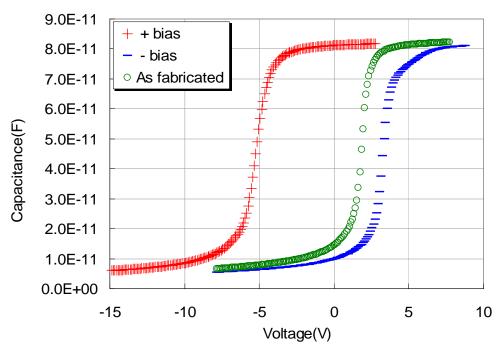

| Figure 2.2.13 BTS result of an n-type 4H-SiC MOS capacitor with oxide grown by alumina enhance oxidation process                                                         |

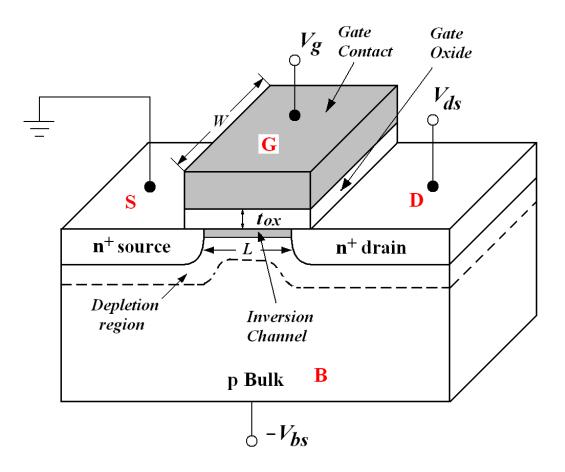

| Figure 2.3.1 Cross-section diagram of an inversion mode, n-channel lateral MOSFET62                                                                                      |

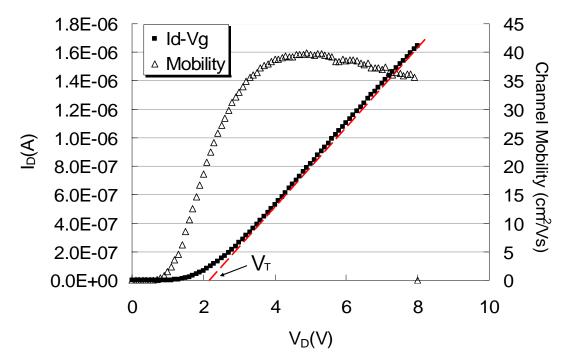

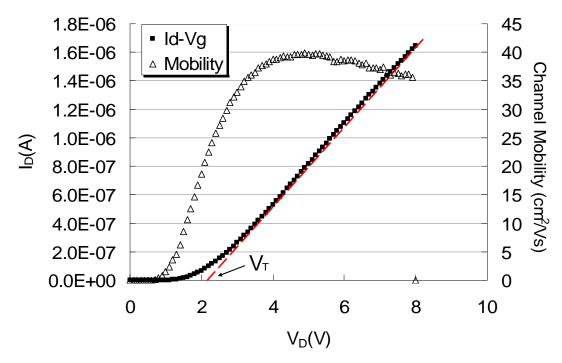

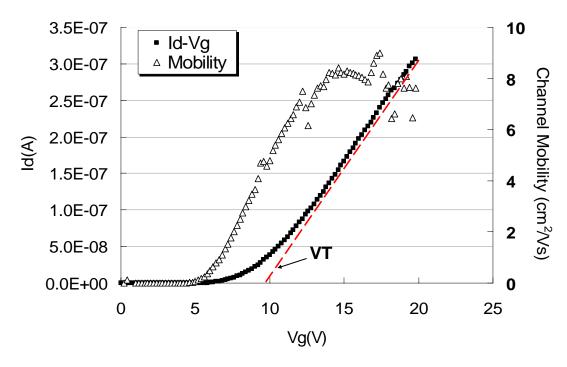

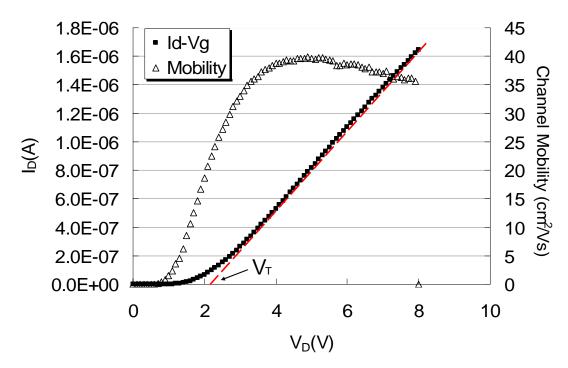

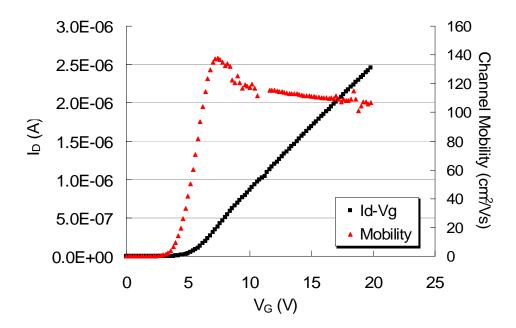

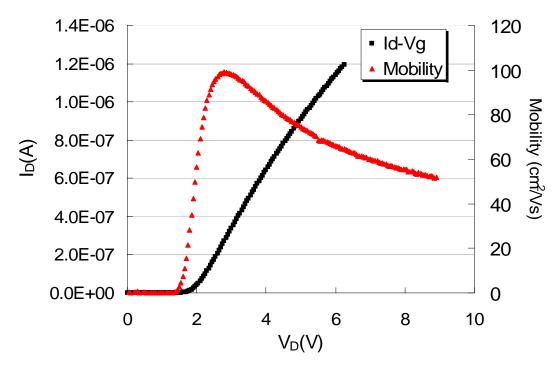

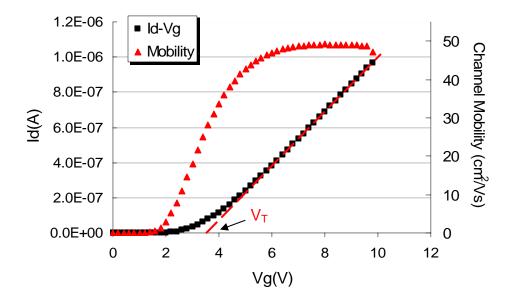

| Figure 2.3.2 $I_D$ - $V_G$ (solid square) and channel mobility (hollow triangle) extracted from a 4H-SiC MOSFET, with gate oxide grown in dry $O_2$ and annealed by NO70 |

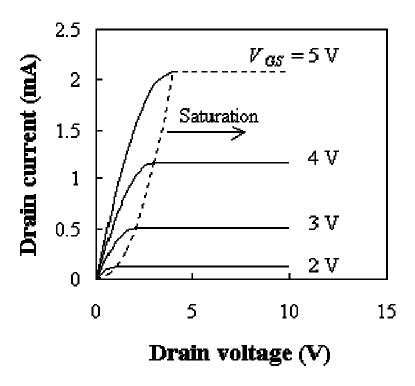

| Figure 2.3.3 Typical I <sub>D</sub> -V <sub>D</sub> behavior of a MOSFET under different V <sub>GS</sub> 73                                                              |

| Figure 3.1.1 Furnace used for standard oxidation and few annealing process77                                                                                             |

| Figure 3.1.2 Furnace used for standard oxidation and few annealing process                                                                                               |

| Figure 3.1.3 Furnaces designated for alumina enhanced oxidation                                                                                                          |

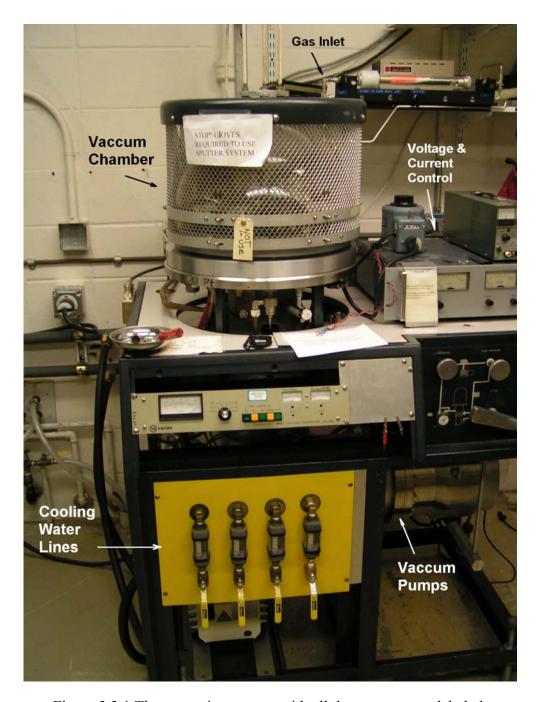

| Figure 3.3.1 The sputtering system with all the components labeled                                                                                                       |

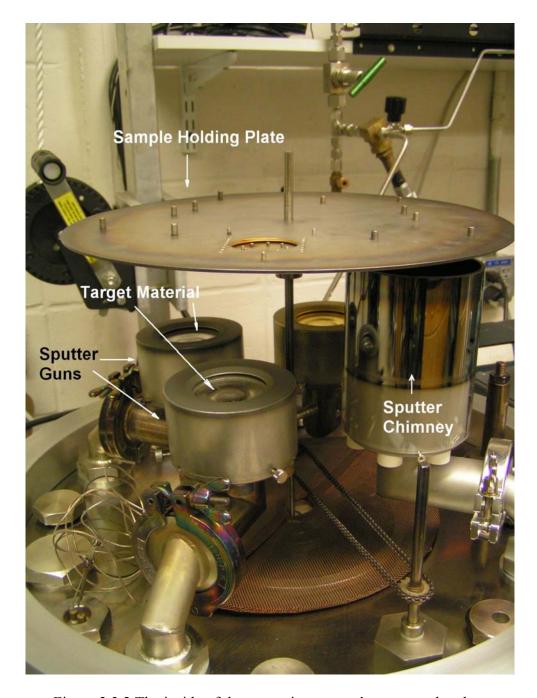

| Figure 3.3.2 The inside of the sputtering system's vacuum chamber                                                                                                        |

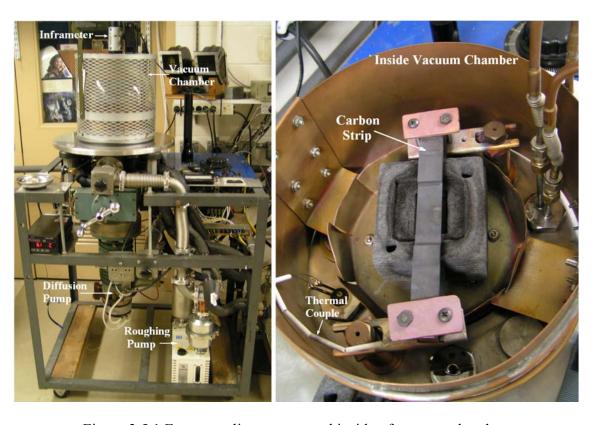

| Figure 3.5.1 Fast annealing system and inside of vacuum chamber                                                                                                          |

| Figure 3.5.2 Circular carbon boxes and carbon foam box used for implant activation87                                                                                     |

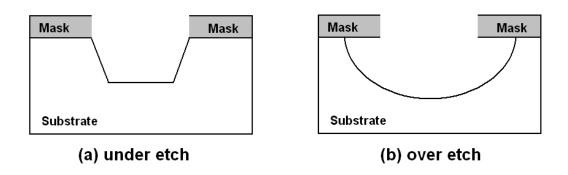

| Figure 3.6.1 Diagram for wet etching: (a) under etching (b) over etching91                                                                                               |

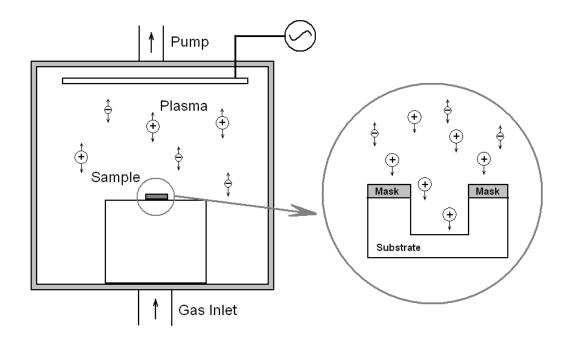

| Figure 3.6.2 Reactive Ion Etching (RIE) system92                                                                                                                         |

| Figure 3.6.3 Diagram of the Vacuum Chamber in the RIE system93                                                                                                           |

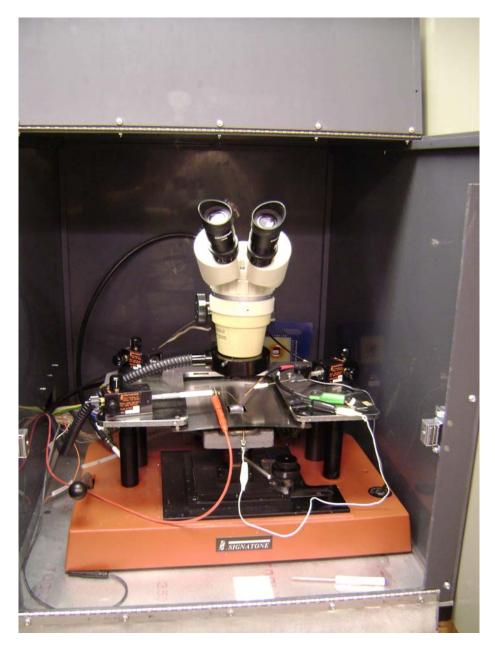

| Figure 3.7.1 Probe Station for room temperature and high temperature C-V measurement.                                                                                    |

| Figure 3.7.2 Keithley CV analyzers and temperature controller for C-V measurement                                                                                        |

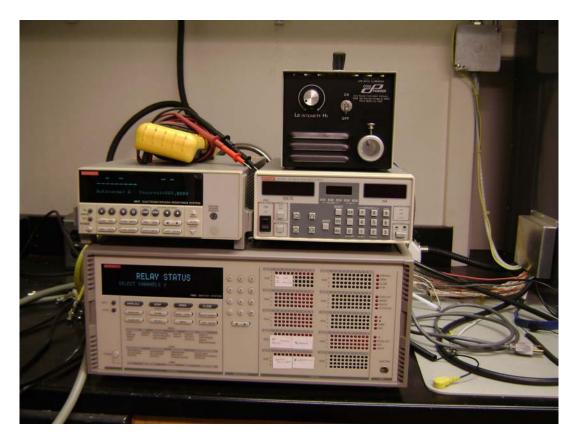

| Figure 3.8.1 Probe station used for I-V measurements                                                                                                                     |

| Figure 3.8.2 Equipments used for I-V measurements                                                                                                                        |

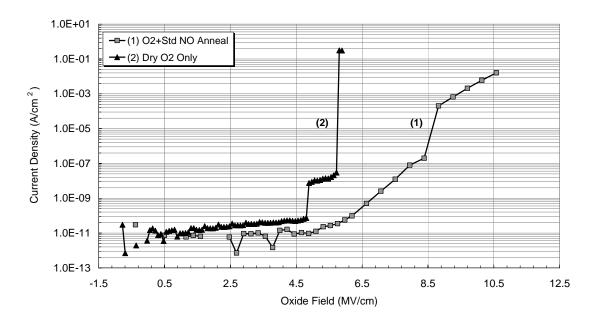

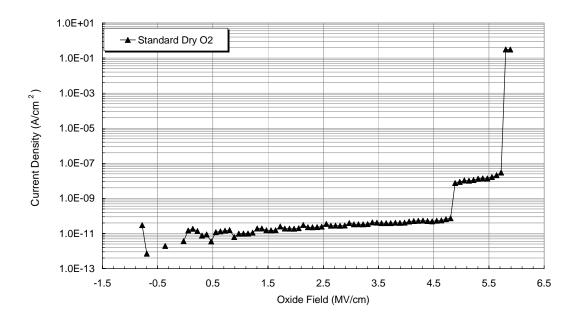

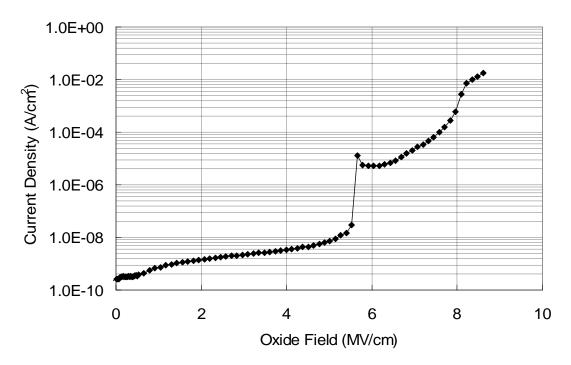

| Figure 3.8.3 I-V characteristic of MOS capacitors with oxide grow with standard dry O <sub>2</sub> and standard dry O <sub>2</sub> +standard NO anneal                   |

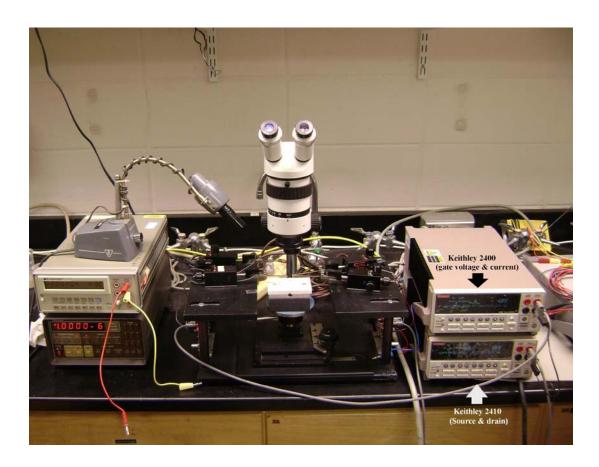

| Figure 3.9.1 Probe station for mobility measurements                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.9.2 Typical $V_T$ , $I_D$ - $V_G$ and channel mobility measured from an n-channel 4H-SiC MOSFET, with gate oxide grown in dry $O_2$ followed by NO anneal108                 |

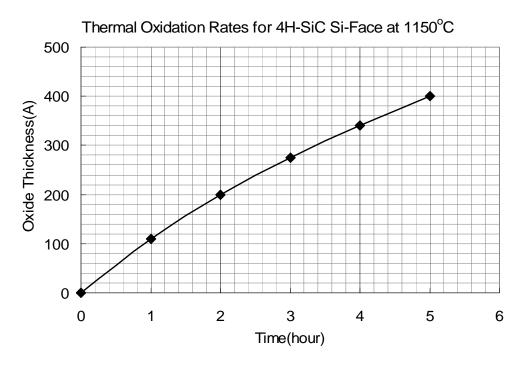

| Figure 4.2.1 Measured growth rate using standard dry O <sub>2</sub> oxidation process112                                                                                              |

| Figure 4.2.2 Room-temperature ( $23^{\circ}$ C) C-V curve for an n-type 4H-SiC MOS capacitor with oxide grown by standard $O_2$ oxidation                                             |

| Figure 4.2.3 High-temperature (300 $^{\circ}$ C) C-V curve for an n-type 4H-SiC MOS capacitor with oxide grown by standard $O_2$ oxidation                                            |

| Figure 4.2.4 Density of Interface-Traps (D <sub>IT</sub> ) extracted from C-V curve in Figure 4.2.2 & Figure 4.2.3                                                                    |

| Figure 4.2.5 Channel mobility $\mu$ of n-channel MOSFET with gate oxide grown under standard dry $O_2$ oxidation                                                                      |

| Figure 4.2.6 I-V characteristic for an MOS capacitor with oxide grown by standard $O_2$                                                                                               |

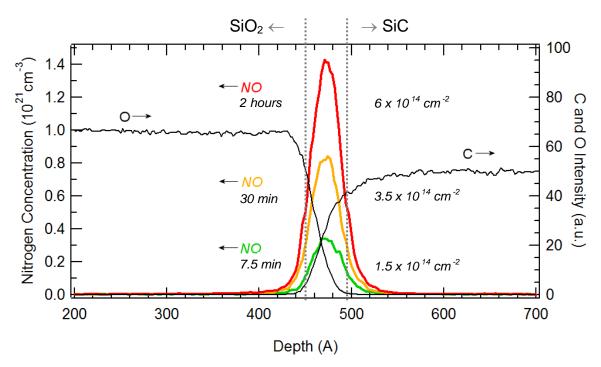

| Figure 4.3.1 SIMS profile of nitrogen concentration at the SiO <sub>2</sub> /SiC interface120                                                                                         |

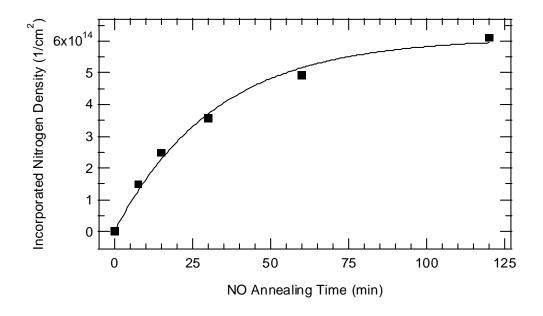

| Figure 4.3.2 Nitrogen concentration at the SiO <sub>2</sub> /SiC interface vs. annealing time122                                                                                      |

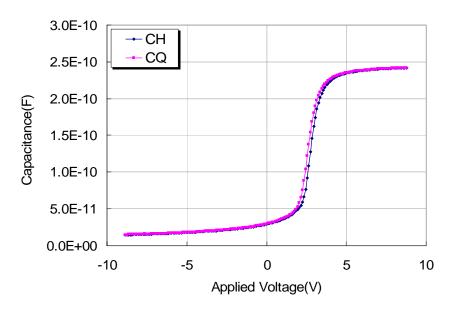

| Figure 4.3.3 Room-temperature ( $23^{\circ}$ C) C-V curve for an n-type 4H-SiC MOS capacitor with oxide grown by standard O <sub>2</sub> oxidation followed by standard NO anneal123  |

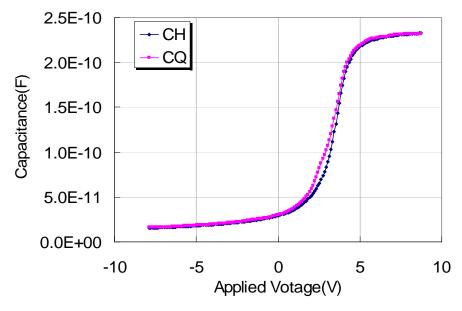

| Figure 4.3.4 High-temperature (300 $^{\circ}$ C) C-V curve for an n-type 4H-SiC MOS capacitor with oxide grown by standard O <sub>2</sub> oxidation followed by standard NO anneal123 |

| Figure 4.3.5 Density of Interface-Traps (D <sub>IT</sub> ) extracted from C-V curve in Figure 4.3.3 & Figure 4.3.4                                                                    |

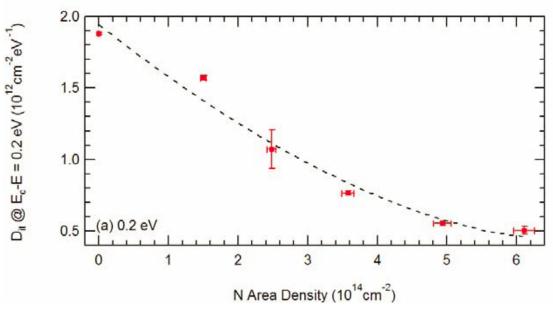

| Figure 4.3.6 D <sub>IT</sub> at 0.2eV below E <sub>C</sub> of different N concentrations at the interface by varying NO annealing time                                                |

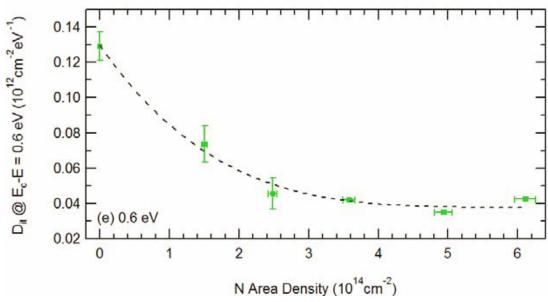

| Figure 4.3.7 D <sub>IT</sub> at 0.6eV below E <sub>C</sub> of different N concentrations at the interface by varying NO annealing time                                                |

| Figure 4.3.8 Channel mobility $\mu$ of n-channel MOSFET with gate oxide grown under standard dry $O_2$ oxidation followed by standard NO anneal                                       |

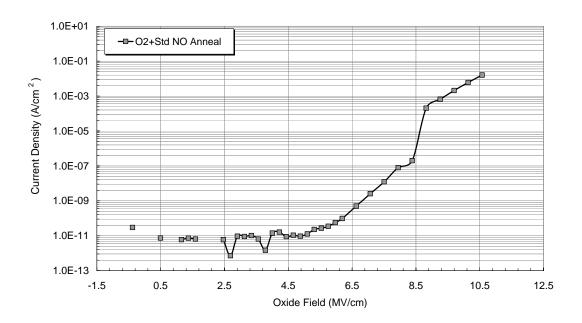

| Figure 4.3.9 I-V characteristic for an MOS capacitor with oxide grown by standard O <sub>2</sub> followed by standard NO anneal |

|---------------------------------------------------------------------------------------------------------------------------------|

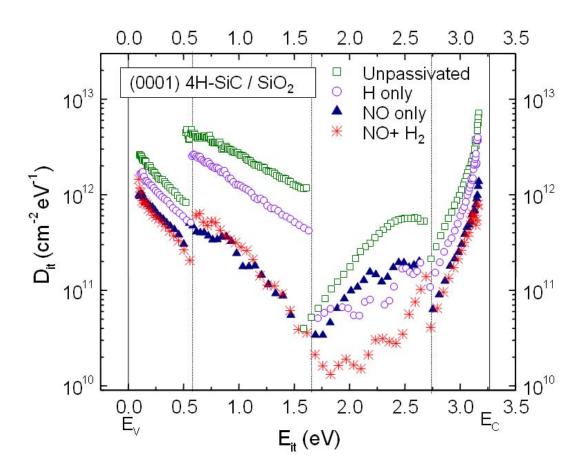

| Figure 4.4.1 The D <sub>IT</sub> of 4H-SiC MOS capacitors with oxides after different passivations.                             |

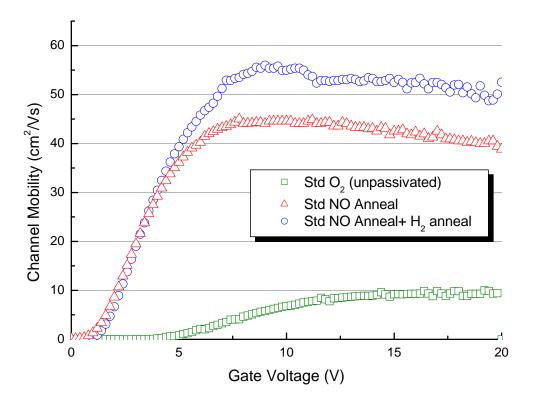

| Figure 4.4.2 Channel mobility $\mu$ of 4H-SiC MOSFET with gate oxides after different passivations                              |

| Figure 4.4.3 I-V characteristic for the MOS capacitor with oxide after different process.                                       |

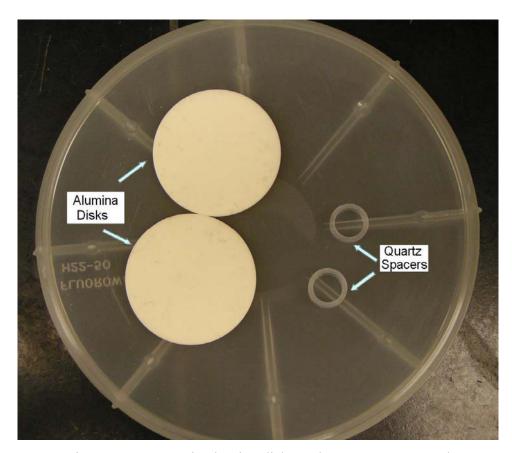

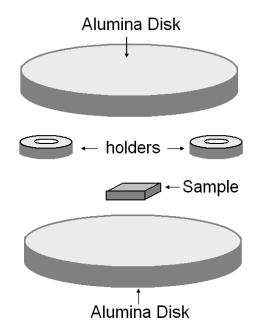

| Figure 5.1.1 Ceramic alumina disks and quartz spacers used                                                                      |

| Figure 5.1.2 Diagram of the sandwich-like set up for alumina enhanced oxidation142                                              |

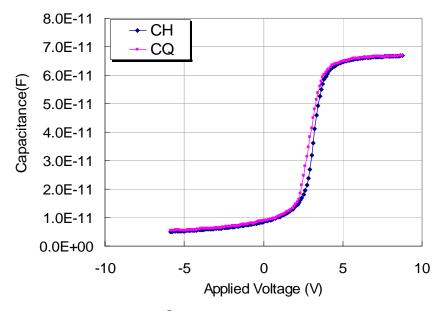

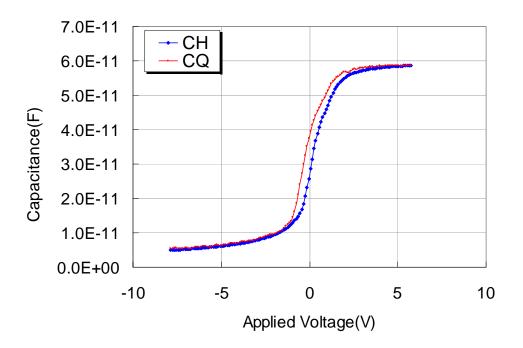

| Figure 5.2.1 Room-temperature (23°C) C-V curve for an n-type 4H-SiC MOS capacitor with oxide grown in the alumina environment   |

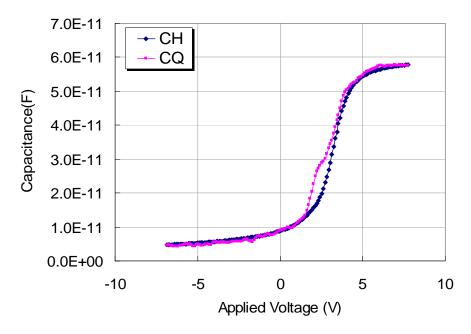

| Figure 5.2.2 High-temperature (300°C) C-V curve for an n-type 4H-SiC MOS capacitor with oxide grown in the alumina environment  |

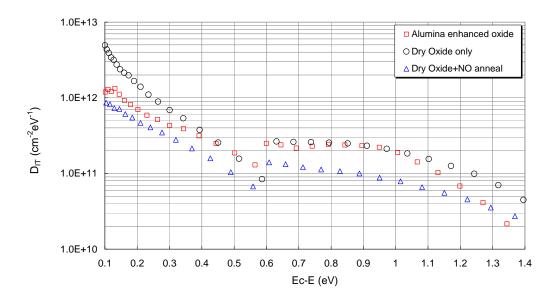

| Figure 5.2.3 Density of Interface-Traps (D <sub>IT</sub> ) extracted from C-V curve in Figure 5.2.1 & Figure 5.2.2              |

| Figure 5.2.4 BTS result for an n-type 4H-SiC MOS capacitor with oxide grown by alumina enhance oxidation process                |

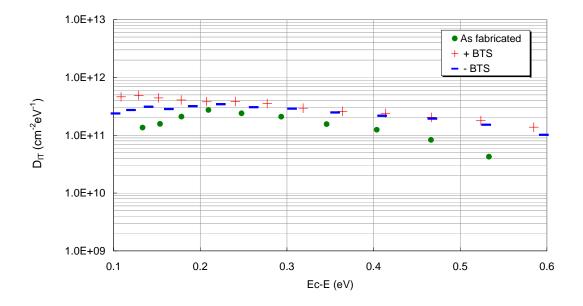

| Figure 5.2.5 D <sub>IT</sub> extracted from the BTS measurements in Figure 5.2.4                                                |

| Figure 5.2.6 Channel mobility $\mu$ of n-channel MOSFET with gate oxide grown under alumina enhanced oxidation process          |

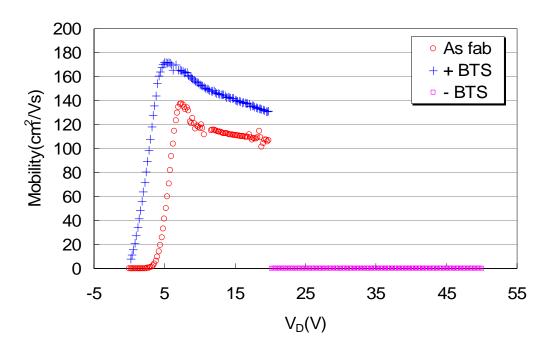

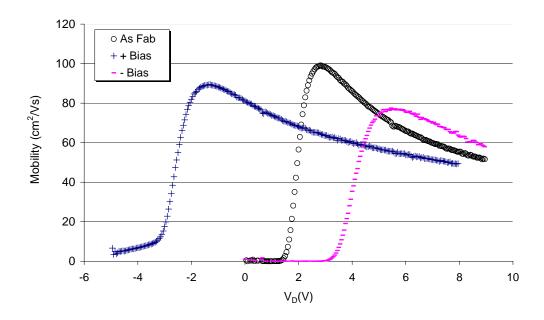

| Figure 5.2.7 Channel mobility behavior after +/- BTS on the device from Figure 5.2.6                                            |

| Figure 5.2.8 I-V characteristic for an MOS capacitor with oxide grown by alumina enhanced oxidation                             |

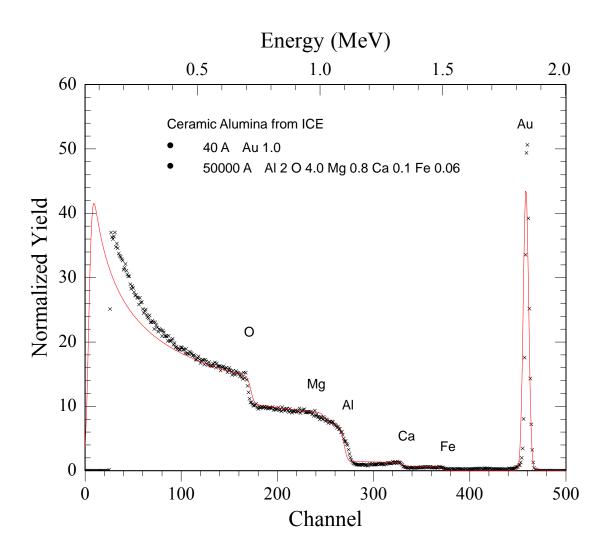

| Figure 5.3.1 Rutherford backscattering (RBS) result for alumina used for this work156                                           |

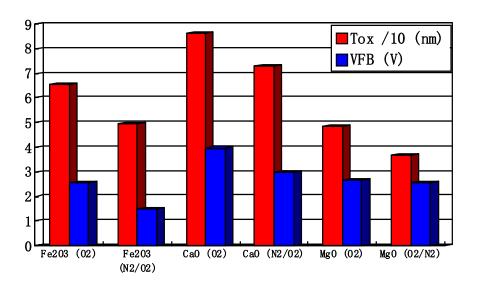

| Figure 5.3.2 Comparison of T <sub>OX</sub> and V <sub>FB</sub> after oxidization with different metal oxides                    |

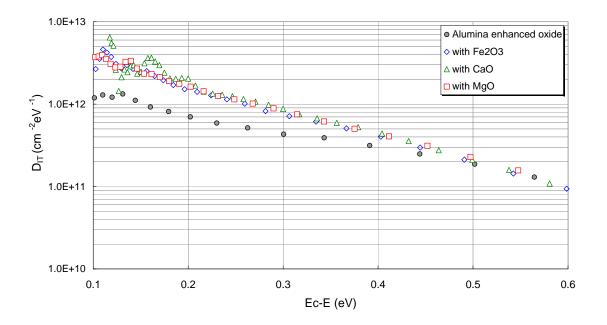

| Figure 5.3.3 D <sub>IT</sub> of sample oxidized in different metal oxide environments158                                        |

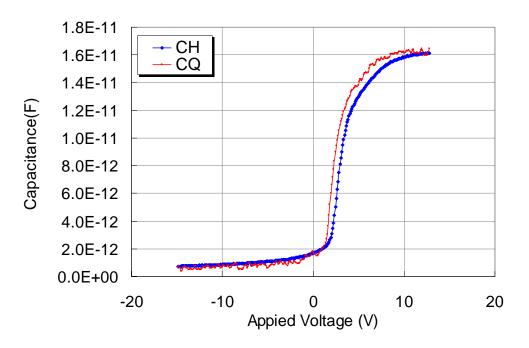

| Figure 5.3.4 C-V curves for sample contaminated with NaCl                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.3.5 C-V curves for sample contaminated with KCl                                                                                                 |

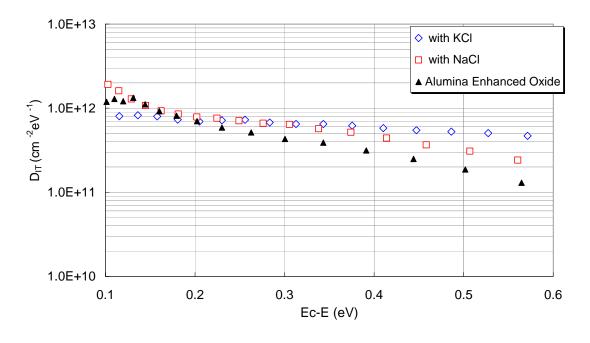

| Figure 5.3.6 $D_{\text{IT}}$ of samples contaminated by NaCl, KCl, and AEO for comparison161                                                             |

| Figure 5.3.7 C-V curves of sample oxidized with Na <sub>2</sub> O <sub>2</sub>                                                                           |

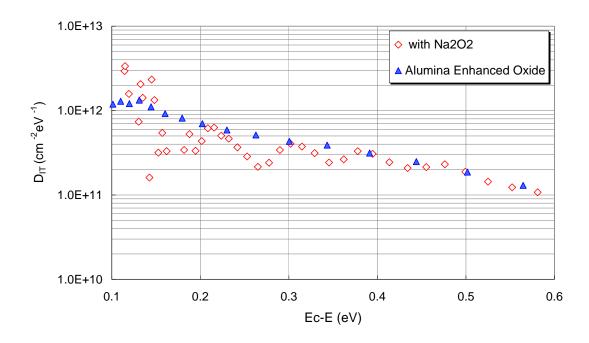

| Figure 5.3.8 D <sub>IT</sub> of sample oxidized with Na <sub>2</sub> O <sub>2</sub> extracted from Figure 5.3.7164                                       |

| Figure 5.4.1 BTS result for sample using alumina enhanced oxidation without HCl anneal                                                                   |

| Figure 5.4.2 BTS result for sample using alumina enhanced oxidation followed by standard HCl anneal                                                      |

| Figure 5.4.3 D <sub>IT</sub> of the samples using alumina enhance oxidation with and without HCl anneal                                                  |

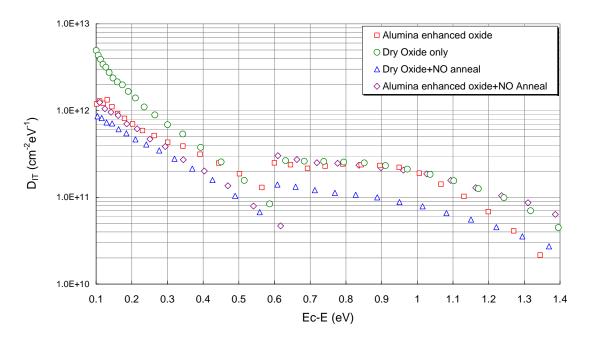

| Figure 5.4.4 D <sub>IT</sub> of oxides with different oxidation and annealing methods171                                                                 |

| Figure 5.4.5 I <sub>D</sub> -V <sub>G</sub> curve and channel mobility from Si-face 4H-SiC MOSFET172                                                     |

| Figure 5.4.6 Channel mobility $\mu$ after +/- BTS on the MOSFET in Figure 5.4.5173                                                                       |

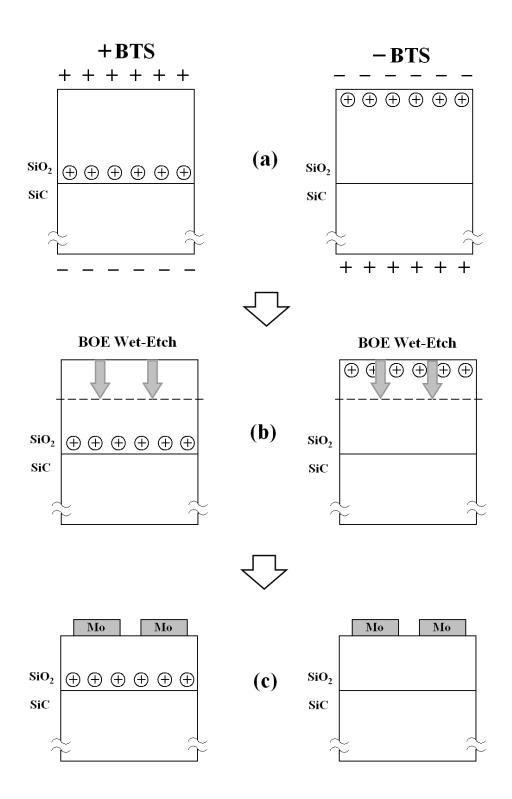

| Figure 5.4.7 Diagram of reposition and removal of mobile ions by +/- BTS and wet-etch                                                                    |

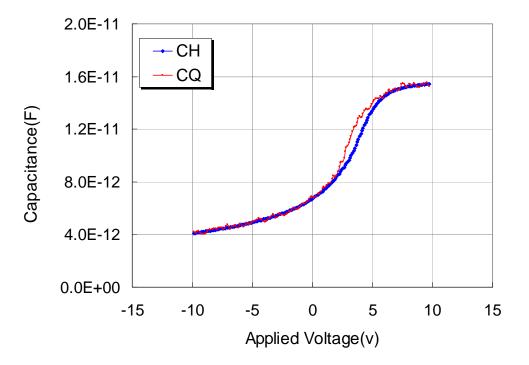

| Figure 5.4.8 C-V characteristic of sample after +BTS and wet etch                                                                                        |

| Figure 5.4.9 C-V characteristic of sample after -BTS and wet etch                                                                                        |

| Figure 5.4.10 D <sub>IT</sub> extracted form C-V curves in Figure 5.4.8 & Figure 5.4.9177                                                                |

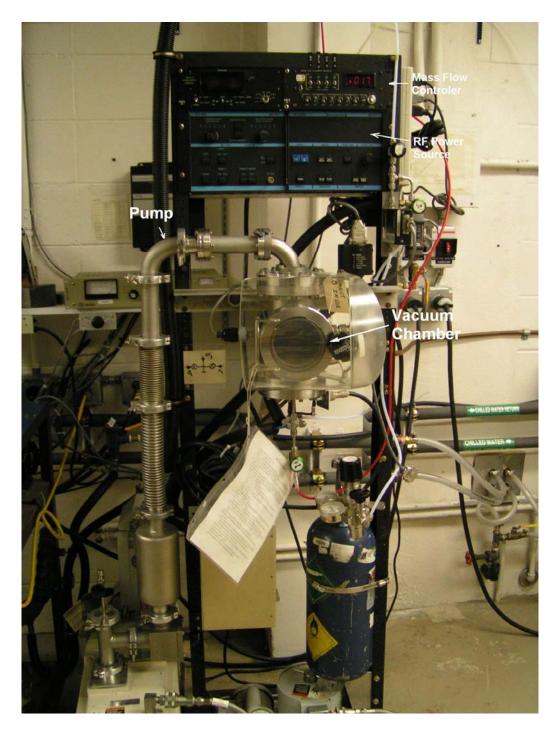

| Figure 6.2.1 The plasma furnace system                                                                                                                   |

| Figure 6.2.2 Schematic diagram of the microwave plasma furnace system185                                                                                 |

| Figure 6.2.3 D <sub>IT</sub> at different energy levels for samples with different oxide thicknesses after the nitrogen plasma anneal vs. annealing time |

| Figure 6.2.4 Optical spectrum of the nitrogen plasma inside the furnace                                                                                  |

| Figure 6.2.5 Intensity of 589 nm peak of the plasma spectrum inside the furnace189                                                                       |

| Figure 6.3.1 SIMS profile of the N concentration inside the N plasma annealed sample.                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.3.2 I-V characteristic of oxides after different annealing process192                                                                                                                                                                                                                                                                                       |

| Figure 6.3.3 D <sub>IT</sub> in the upper half of the 4H-SiC band-gap for different annealing methods: (1) standard dry O <sub>2</sub> oxidation only; (2) NO only: standard post-oxidation NO anneal; (3) N Plasma Only: 20hr N plasma anneal following standard dry oxidation; (4) NO+N Plasma: standard post-oxidation NO anneal followed by 20hr N plasma anneal |

| Figure 6.3.4 Channel mobility $\mu$ of n-channel MOSFET with gate oxide grown by standard dry $O_2$ followed by N plasma anneal                                                                                                                                                                                                                                      |

| Figure 6.3.5 Channel mobility $\mu$ of n-channel MOSFET with gate oxide grown by standard dry $O_2$ followed by standard NO anneal then followed by N plasma anneal.                                                                                                                                                                                                 |

## LIST OF TABLES

| Table 1.2.1. | Mechanical properties of SiC, Si and GaAs                                | . 18 |

|--------------|--------------------------------------------------------------------------|------|

| Table 1.2.2. | Comparison of the electrical properties of SiC, Si and GaAs              | . 19 |

| Table 3.8.1. | Formulas for oxide electric field calculation in accumulation            | 105  |

| Table 5.2.1  | Average growth rate for different oxidation conditions on Si-face 4H-SiC | 145  |

### **CHAPTER 1**

### Introduction

#### 1.1 General Introduction

The silicon-based microelectronic industry has played an essential role in the development of modern technology for the last 50 years. The major reasons that silicon is still the dominant material for most of the electronic devices are the excellent quality of its natural oxide, SiO<sub>2</sub> and the SiO<sub>2</sub>/Si interface. Besides, it is also a great semiconductor material with well-developed processing technology. With the rapid evolution of modern technology, Si can no longer satisfy the demanding requirements for higher power, higher temperature devices due to its own limitations. As a result, a few wide band-gap materials have begun to draw more and more interest in this area. Among them, Silicon Carbide (SiC) is the most developed and the only material that shares the same natural oxide with Si, which enables it to utilize most of the mature fabrication techniques from Si industry, especially for Metal-Oxide-Semiconductor (MOS) electronic devices. In addition, some of its impressive properties also make it superior to others, such as the wide band-gap,

high critical field, low dielectric constant, and high thermal conductivity, make SiC superior to other materials. The details are introduced in the later part of Chapter 1. All of these qualities make SiC a perfect candidate for high power, high temperature electronic devices, especially for power MOS devices, which is the main focus of this work.

The detailed structures and parameters of two MOS devices, MOS capacitor and Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) will be discussed in Chapter 2, along with the characterization and testing of these devices. A few non-ideal characteristic such as work function difference, various oxide charges and mobile ions as well as how they affect the device parameters are also discussed.

Many of the fabrication techniques for these devices do not differ significantly from Si-based devices. The equipments for fabrication and testing as well as some major fabrication processes are introduced in Chapter 3, Discussion of processing techniques will include photolithography, sputtering, rapid thermal annealing, and reactive ion etching. The test equipment will be described in detail including the capacitance-voltage (C-V) system, the current-voltage (I-V) system and the MOSFET mobility measurement system.

MOS devices have a wide range of applications, such as power switching for electric utilities, industrial motor control, hybrid and electric vehicles, as well as other industrial and military applications. Replacing Si-based power devices with SiC devices in these

areas will result in higher efficiency, significant cost reduction, reduced size and weight, simpler system design, and improved reliability and durability.

However, the performance for the SiC MOS devices is hampered by the poor quality of the SiO<sub>2</sub>/SiC interface, which is the major obstacle for the production of SiC based MOS devices currently. The standard dry oxidation yields poor performances in terms of high interface trap density and low effective channel mobility. By applying a few traditional passivation techniques, such as the nitric oxide (NO) anneal and the hydrogen anneal, the performance is raised to a barely acceptable level, but is still far below expectation. Details are further discussed in Chapter 4

The major part of this work consists of studying alternate oxidation and passivation techniques on 4H-SiC MOS devices, which will be discussed in Chapter 5 and 6. In Chapter 5, the main focus is alumina enhanced oxidation (AEO)<sup>2</sup>; basically oxidizing samples with sintered alumina inside the furnace. These samples demonstrate lower interface traps density and drastically increased effective channel mobility. However, a huge number of mobile ions are detected inside the oxide, and it is reported that these ions is quite possibly the major cause for all the improvements to D<sub>IT</sub> and mobility.<sup>94</sup> In this part of study, detailed results after the AEO process will be introduced, followed by the discussion of the possible cause, and the results for other anneal techniques following this AEO process will also be examined.

Chapter 6 is focused on the nitrogen plasma anneal process, which successfully introduces active nitrogen into the oxide through microwave induced plasma in an oxygen free environment. Compared with other nitridation annealing techniques such as NO or N<sub>2</sub>O, This process allows the detailed study of the passivating effect of solely nitrogen on the SiO<sub>2</sub>/SiC interface. And the results indicate that the passivating effects of NO or N<sub>2</sub>O are most likely caused by the presence of nitrogen at the interface. With less amount N at the interface, this anneal efficiently reduces interface trap density (D<sub>IT</sub>), especially near mid-gap and significantly increases effective channel mobility. Besides, this technique allows for more precise control of the amount of N introduced, and is also potentially capable of creating other gaseous plasmas in order to study their effect on the oxide reliability.

Lastly, a summary of all the work is presented in Chapter 7, and a discussion of possible improvements and future work is also offered.

## 1.2 General Information for SiC

### 1.2.1 Historical Review

Silicon Carbide is a compound of silicon and carbon with a 1:1 atomic ratio. The material mostly man made and rarely seen in nature where it is called moissanite - having been first discovered in a meteorite by Moissan in 1893 and named after him in 1905<sup>3</sup>. The first study of SiC was made in 1824 by Jöns Jacob Berzelius<sup>4</sup>, where he mentioned a possible bond between Si and C. It was not long after the invention of the electric smelting furnace by E. H. & A. H. Cowles in 1885<sup>5</sup>, that E.G. Acheson started manufacturing the material which was called Carborundum<sup>6</sup>. The crystalline products Acheson found after the process were found to have a great hardness, refractability and chemical inertness. The invention had a great impact with material produced abrasion and cutting applications for a while.

Years later people also started taking interest in the electronic properties of SiC. The first Light Emitting Diode (LED) made from SiC dates way back in 1907<sup>7</sup>. In 1955, Lely developed a new process for growing high quality crystals<sup>8</sup>. However, interest in SiC waned due to the success and rapid development of Si technology. In 1978, a new procedure for substrate growth using a seeded sublimation process was introduced by by Tairov and Tsvetkov<sup>9</sup>. Their discovery helped refocus attention on SiC technology development. The growth of single crystal SiC on Si was demonstrated by Matsunami et

al<sup>10</sup> in 1981. Shortly thereafter, Cree Research was founded in 1987, and the company has become a leader in SiC growth technology and device development.

Currently, SiC is widely used for applications as both a structural material and a semiconductor material. In addition to being a favorite for abrasives and cutting materials, SiC is also used for heating elements, armor and ceramic membrane and mechanical parts. As a semiconductor material, crystalline SiC has or is being developed for blue light emitting diodes (LED) and high voltage, high temperature power electronics (ultra-fast Schottky diodes and transistors – particularly metal-oxide-semiconductor field effect transistors (MOSFET). Silicon carbide is also used as a substrate for other semiconductor materials such as gallium nitride to take advantage of its wide band gap and good thermal conductivity. Furthermore, well-known limitations set by basic material parameters for Si and the III-V compound semiconductors have further increased interest in SiC. With its excellent physical and electrical properties, especially wide bandgap, SiC is superior to Si for high temperature, high power and radiation-tolerant devices, and device development expanding rapidly, owing to the recent commercial availability of high quality substrates.

Nevertheless, results obtained for SiC MOSFETs to date are still far from satisfactory. Silicon dioxide SiO<sub>2</sub> is SiC's native oxide which is a great advantage considering all of the previous development work over the last 60 years for SiO<sub>2</sub> on Si. However, the poor quality and performance of the SiC/SiO<sub>2</sub> interface has hampered the

development of SiC MOS power transistors. For example, there is a thin transition layer ( $\sim$  1-5nm) that exists between SiO<sub>2</sub> and SiC (compared to an abrupt interface for SiO<sub>2</sub>/Si), an extra carbon as well as other defects contribute to a high interface trap density that lowers channel mobility. Details will be discussed in the later chapters, but at present, efforts are underway worldwide by scientists and engineers to solve these problems. The focus of this dissertation is the improvement of the quality and reliability of the SiO<sub>2</sub> layer and SiC/SiO<sub>2</sub> interface.

## 1.2.2 Polytypism

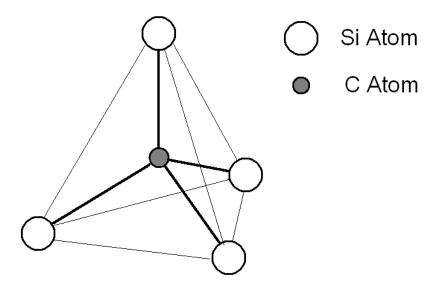

Figure 1.2.1 Tetragonal structure of the SiC crystal.

Silicon carbide occurs with different crystal structures. However, all have the Si-C bond tetragonal structure similar to diamond, with one carbon atom in the center surrounded by four silicon atoms or vice versa, as shown in Figure 1.2.1. The distance between two neighboring silicon or carbon atoms is approximately 3.08 Å for all structures<sup>11</sup>.

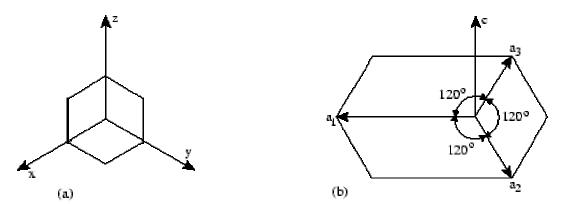

Figure 1.2.2 Unit cell for different crystal structures of SiC: (a)cubic; (b)hexagonal.

Figure 1.2.2 shows the different crystal structures for SiC. For cubic crystals, three Miller indices, h, k, l, are used, which are integers with the same ratio as the reciprocals of the intercepts with the x, y, z axes, respectively. For hexagonal structures four principal axes  $a_1$ ,  $a_2$ ,  $a_3$  and c are commonly used. These three a-axes (with  $120^\circ$  angles between them) are all in the close-packed plane called a-plane, whereas the c-axis is perpendicular to this plane.

One of the most remarkable features of silicon carbide crystal structure is its polytypism. The study of polytypism in crystals began nearly 90 years ago, and the word "polytype" was first used by Baumhauer around 1912<sup>12</sup> in an attempt to describe

materials that crystallize with structural characteristics that differ only along one crystallographic direction. From optical studies, Baumhauer discovered two new crystal structures for silicon carbide in addition to the commonly known 6-layered hexagonal type, both differing in their stacking along the c-axis. Their existence was later confirmed by X-ray diffraction<sup>13</sup>. Several more new polytypes were revealed by morphological and structural studies in the 1940's and 1950's. Schneer<sup>14</sup> called it "polymorphism in one dimension" in order to emphasize that two dimensions of the unit cells of different polytypes are identical, while the third is a variable integral multiple of a common unit. The polytype structures are considered as stacked layers with repeat sequences ranging from 2 layers to many hundreds of layers. For the extreme case of no finite repeat, the polytype can be called a one-dimensionally disordered layer. At present, the number of known SiC polytypes exceedes 200, all with a different stacking sequence of bi-atom layers but without any variation in stoichiometry.

Physical and electrical properties vary distinctively among different polytypes. Therefore, only a few are commonly grown and developed as electronic semiconductors. Among these, the most popular polytypes are cubic SiC (3C), the hexagonal SiC (4H and 6H) and rhombohedral SiC (15R).

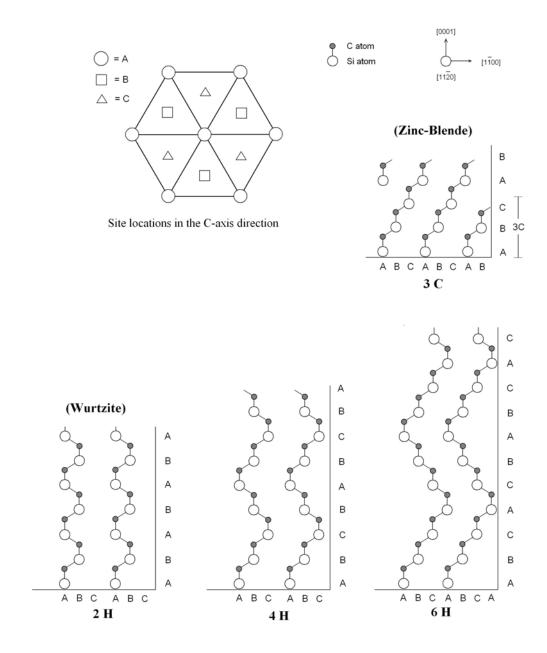

Figure 1.2.3 Stacking sequence for different SiC crystalline polytypes.

The polytypes are mainly characterized by the stacking sequence of bi-atom layers.

This stacking layout can be explained as follows: As shown in the tetragonal structure of Figure 1.2.3 one carbon atom lies at the center of a triangle formed by three adhering

silicon atoms below. The top silicon atom forms a bi-layer with the carbon atom, and has the same projection as the carbon atom. Let us label the locations of the atoms of this hexagonal structure bi-layer as "A" the Figure 1.2.3. The atoms of the next carbon - silicon bi-layer may either occupy a position having its bi-layer projection on "A", the same as the first layer, or on the center of the triangle not covered by the projections of the atoms of the first bi-layer, i.e., "B" and "C" in Figure 1.2.3. Different structures arise as a consequence of the fact that through successive of alterations of tetrahedral layers, a repeating unit is formed. For some polytypes, it is possible to stack up to few hundreds of bi-atom layers without repeating.

Among the most used polytypes, the cubic (a.k.a. zinc-blende) and hexagonal (a.k.a. wurtzite) crystalline structures are most commonly encountered. 3C-SiC is the only known form of SiC with a cubic crystal lattice structure. For this polytype, each bi-atom layer projects into one of those lattice positions labeled A, B and C in Figure 1.2.3. With the stacking sequence ABCABC ... The number 3 refers to the number of layers needed for periodicity, and this arrangement is also referred to as  $\beta$ -SiC.

The rest of the polytypes are hexagonal, and are sometimes referred to as  $\alpha$ -SiC. For the hexagonal structure, the most common polytypes are 2H, 4H, and 6H. 2H-SiC has the bi-layer stacking sequence ABAB ..., and only this type is the simple hexagonal structure (a.k.a. wurtzite). Most of other polytypes are mixtures of the cubic and wurtsite stacking types, and may occur in complex, intermixed forms, yielding a wide range of

ordered structures with large stacking period. The most widely used polytype, 4H-SiC for example, consists of an equal number of cubic and hexagonal bonds with a stacking sequence of ABCB.... Similarly, 6H-SiC is composed of 2/3 cubic bonds and 1/3 hexagonal bonds with a stacking sequence of ABCACB.... The overall symmetry, however, is hexagonal for both polytypes, despite the cubic bonds that present for each. In the same manner, 15R-SiC has a rhombohedral structure which is composed of 3/5 cubic bonds and 2/5 hexagonal bonds.

The stacking sequence can also be better visualized in the way demonstrated in Figure 1.2.3, the stacking of few common polytypes is depicted in the figure. The same A, B, C notation mentioned earlier is used here as well. For all the polytypes, the stacking of the bi-layers is always along *C*-direction. There are some 200 polytypes proven known to exist. As mentioned previously, some polytypes have a stacking period of several hundred double layers, and, in principle, an infinite number of possible stacking variants may exist. However the structures of even the highest period polytypes can be considered as combination sequences of one or more of the smaller period units such as 4H, 6H, 15R, 21R.<sup>15</sup>

Among the large number of polytypes of SiC, only a few are known to be electrically and thermodynamically stable. These are 2H, 3C, 4H, 15R, and 6H which are the forms of SiC currently in use. For different stacking sequences, the physical and chemical properties of these polytypes vary significantly.

## 1.2.3 Bulk Crystal and Epitaxial Growth

The semiconductor electronics industry requires high quality crystals for device fabrication, and SiC wafers are grown at high temperature using a high quality SiC seed sample. Epitaxial growth (from the Greek root "epi = above" and "taxis = in ordered manner") is a replicating thin film growth technique that is subsequently used with a wafer to grow SiC layers specifically tailored for a particular device.

Historically, SiC material has been produced through the Acheson process<sup>6,16</sup> which is still used for production of poly-crysralline SiC that is suitable for grinding and cutting applications. Some of the material produced by the Acheson process is also of adequate quality for electronic grade material growth. This Acheson process uses a mixture of silica, carbon, sawdust and common salt (e.g. 50% silica, 40% coke, 7% sawdust and 3% common salt) heated in an electric furnace to a maximum temperature of approximately 2700°C<sup>17</sup>. Before heating, a graphite and coke mixture is placed in the furnace with the mixture of reactants placed around this mixture. During growth, a pure graphite core layer forms in the center of the mixture, and near the core, useful SiC is found, in the form of threads of crystallites radiating from the core. The size of these crystallites decreases with increasing distance from the core, due to the temperature gradient in the furnace. Further from the core, the SiC is amorphous.

A major improvement to the Acheson process is the non-seeded process developed by Lely in 1955<sup>8</sup>. The Lely process is similar to the Acheson process, and growth takes

place in an Ar ambient at approximately 2500°C. Lely grown material is sometimes used as a substrate for small area epitaxial growth due to the high crystalline quality of these substrates. However, Lely growth is a slow process that yields small substrate platelets with irregular sizes and shapes, and though the crystalline form is normally hexagonal, there is no real polytype control. The purity of the crystals is largely governed by the quality of the starting materials which must be obtained in a high purity form. As a result, of these problems, the non-seeded Lely method has never been considered an important technique for commercial electronic material production.

Tairov and Tsvetkov introduced a modified Lely process in 1978<sup>8</sup> by adding a seed crystal for sublimation growth. Their process has proved most successful, allowing good polytype control during SiC growth. Cree Research Inc. (founded in 1987) has become a leading supplier of SiC wafers grown using the modified Lely technique in which SiC powder is placed inside a cylindrical graphite crucible. The crucible is closed with a graphite lid onto which a seed crystal is attached. The crucible is heated to approximately 2200° C in an induction furnace, normally in Ar at a pressure between 1 and 100 Torr. A temperature gradient is created over the length of the crucible in such a way that the SiC powder at the bottom of the crucible is at a higher temperature than the seed crystal at top. The temperature gradient is typically kept on the order of 20 - 40°C/cm. During growth, the SiC powder sublimes, and the crucible is filled with a vapor mixture of different carbon and silicon compounds (Si<sub>2</sub>C, SiC<sub>2</sub>, Si<sub>2</sub> and Si). Since the seed is coldest part of

the crucible the vapor condenses on the seed and the crystal will start to grow. The growth rate is largely governed by the temperature, pressure and the temperature gradient which determines the diffusion rate of the various species from the source to the seed. It has also been experimentally confirmed that different growth temperatures and seed crystal orientations give rise to different polytypes.<sup>18</sup>

The two most commonly seen defects in bulk SiC material nowadays are Micropipes and Low-Angle Grain Boundaries.

Dislocations and Micropipes: The origin and details of the micropipe formation are still topics of discussion. The first description of the formation of micropipes is F.C. Frank's theory, which states that micropipes are caused by superscrew dislocations that possess a large Burgers vector, several times the unit cell dimension. The high stress along the center core of the screw dislocation causes preferential sublimation during the growth process, which consequently opens a hollow core. These hollow core screw dislocations typically run parallel to the growth direction through the entire SiC boule. The screw dislocation content of micropipes has been observed experimentally by various groups. 20,21

Low-Angle Grain Boundaries: Low-angle boundaries tend to form near the crystal periphery during the growth of large diameter crystals. They appear as void-like linear crystallographic features extending radially inward from the wafer edge and generally follow low-index crystallographic planes. They can sometimes extend through the entire

thickness of the wafer. Despite the fact that the source of these defects is still uncertain, commercial SiC wafers have seen a steady increase in size (now up to 100cm) and steady reductions in the micropipe and grain boundary defect densities.

Compared with Si, dopant species have extremely low diffusion coefficients for SiC (negligible below 1800°C). Therefore, for SiC device fabrication, it is not feasible to achieve doping using diffusion techniques. The main methods currently used are either ion implantation/activation or doping during epitaxial growth. Ion implantation can introduce damage that results in reduced performance; however, one is left with no other choice when selective area doping is required. Another factor is that substrate wafer quality is not comparable to Si. For this reason, almost all the SiC electronic devices nowadays are not fabricated directly on sublimation-grown bulk wafers, but are instead fabricated on thinner, higher quality epitaxial SiC layers that are grown on modified Lely wafer. Well-grown SiC epilayers have improved electrical properties which allow more control and reproducibility. The controlled growth of high quality epilayers is important for high performance SiC devices and the technique can also be used to growth SiC on other substrates (hetero-epitaxy) including sapphire, AlN and Si. 22,23 Only homo-epitaxial growth on SiC substrates is used for high power devices.

There are several techniques available for the epitaxial growth, each with different advantage and disadvantages. Some of the most common techniques (not just for SiC) are chemical vapor deposition (CVD)<sup>24</sup>, low pressure CVD, metalorganic CVD, molecular

beam epitaxy (MBE)<sup>25</sup>, vapor phase epitaxy, liquid-phase epitaxy, hot-wall epitaxy and sublimitation epitaxy.

Many impurities and crystallographic defects found in sublimation-grown SiC wafers do not propagate into SiC homo-epitaxial layers. For example, basal-plane dislocation loops emanating from micropipes and screw dislocations are generally not observed in SiC epilayers. However, some screw dislocations (both micropipes and closed-core screw dislocations) present in commercial c-axis wafers do replicate themselves in the epilayers. Currently, there are many observable defects in the best SiC homo-epilayers. These defects are affected by substrate defects, non-ideal substrate surface finish, surface cleaning, contamination, and/or epitaxial growth conditions. Despite these imperfections, electrical properties are generally much improved with greater device yields and improved performance.

For SiC, n-type dopants are nitrogen and phosphorus, and the common p-type dopants are Al, and B. Typical doping concentrations range from 9E+14 to 1E+19 cm<sup>-3</sup>. For CVD growth, the doping concentration is governed primarily by varying the flow of the dopant gas. Additionally, the "site-competition" doping methodology<sup>26</sup> provides a broader range of doping concentration as well as improved repeatability. This technique is based on the fact that many dopants of SiC will preferentially incorporate into either Si lattice sites (p-type dopants) or C lattice sites (n-type dopants). If epitaxially SiC is grown under a carbon-rich environment, nitrogen incorporation in restricted. Similarly, by

introducing a carbon-deficient environment during growth, the incorporation of nitrogen can be enhanced to form very heavily-doped epilayers for ohmic contacts. The same methods can be applied for p-type dopants which prefer the Si lattice sites.

# 1.2.4 Physical and Electrical Properties

For comparison, the major physical and electrical properties of the common polytypes of SiC along with Si and GaAs are summarized in Tables 1.2.1 and 1.2.2.

Table 1.2.1 Mechanical properties of SiC, Si and GaAs.

|                               | Si   | GaAs    | 3C-SiC | 6H-SiC | 4H-SiC | Diamond |

|-------------------------------|------|---------|--------|--------|--------|---------|

| Lattice a[Å]                  | 5.43 | 5.65    | 4.36   | 3.08   | 3.08   | 3.567   |

| Lattice c[Å]                  | n.a. | n.a.    | n.a.   | 10.05  | 15.12  | n.a.    |

| Bond length [Å]               | 2.35 | 2.45    | 1.89   | 1.89   | 1.89   | 1.54    |

| TEC [10 <sup>-6</sup> /K]     | 2.6  | 5.73    | 3.0    | 4.5    | -      | 0.8     |

| Density [gm/cm <sup>3</sup> ] | 2.3  | 5.3     | 3.2    | 3.2    | 3.2    | 3.5     |

| Ther.cond.[W/cmK]             | 1.5  | 0.46    | 3.2    | 4.9    | 3.7    | 20      |

| Melting point [ OC]           | 1420 | 1240    | 2830   | 2830   | 2830   | 4000    |

| Mohs hardness                 | 7.0  | 5.0~5.5 | 9      | 9      | 9      | 10      |

TEC = thermal expansion coefficient

Table 1.2.2 Comparison of the electrical properties of SiC, Si and GaAs. 27,28,29,30

| 1                                                              | Si              | GaAs    | 4H-SiC                      | 4H-SiC 6H-SiC              |         |

|----------------------------------------------------------------|-----------------|---------|-----------------------------|----------------------------|---------|

| Bandgap energy [eV]                                            | 1.12            | 1.43    | 3.26                        | 3.03                       | 2.4     |

| Relative dielectric constant                                   | 11.9            | 13.1    | 9.7                         | 9.66                       | 9.72    |

| Breakdown Field  E <sub>B</sub> [MV/cm]  (For 1KV operation)   | 0.25            | 0.4     | c-axis:2.2                  | ∥c-axis:2.4<br>⊥c-axis:>1  | >1.5    |

| Thermal Conductivity κ[W/cmK]                                  | 1.5             | 0.5     | 3.0-3.8                     | 3.0-3.8                    | 3.2     |

| Intrinsic Carrier Concentration $n_i$ [cm <sup>-3</sup> ]      | 1.45E+10        | 1.79E+6 | 5E-9                        | 1.6E-6                     | 1.5E-1  |

| Electron Mobility $\mu_n @\ N_D = 10^{16} cm^{-3} \ [cm^2/Vs]$ | 1430            | 8500    | c-axis: 900<br>⊥c-axis: 800 | c-axis: 60<br>⊥c-axis: 400 | 800     |

| Hole Mobility $\mu_p @\ N_A = 10^{16} cm^{-3}\ [cm^2/Vs]$      | 480             | 400     | 115                         | 90                         | 40      |

| Saturated Electron Velocity v[10 <sup>7</sup> cm/s]            | 1               | 1       | 2                           | 2                          | 2.5     |

| Donors & Ionization $Energy \ \Delta E_d [meV]$                | P: 45<br>As: 54 |         | N: 50, 92<br>P: 54, 93      | N: 85, 140<br>P: 80, 110   | N: 50   |

| Acceptors & Ionization $Energy \ \Delta E_a \ [meV]$           | B: 45<br>Al: 67 |         | Al: 200<br>B: 285           | Al: 240<br>B: 300          | Al: 270 |

| 2007 Commercial<br>Wafer Diameter [inches]                     | 12              | 6       | 3                           | 3                          | ?       |

The physical and electronic properties of SiC make it a superior and promising semiconductor material for electronic devices that is applicable for high power / high temperature applications for the following reasons<sup>30</sup>:

- i) SiC's large bandgap energy translates to low intrinsic concentration even at extremely high temperatures. This permits SiC devices to operate at elevated temperatures without suffering from intrinsic conduction effects, resulting in devices that are more stable and reliable during high power / high temperature operation.

- ii) A high breakdown (~x3 Si) electric field allows SiC devices to be smaller with thinner drift regions that contribute significant less drift resistance to the total on-resistance.

- iii) High thermal conductivity provides much faster heat dissipation compared to Si and GaAs, potentially resulting in higher power delivery at higher frequency.

- iv) High saturated electron drift velocity permits SiC devices to operate normally at higher frequencies (RF and microwave).

- v) Small dielectric constant provides low parasitic capacitance and higher operating speed for MOS devices.

- vi) Crystalline SiC is chemically inert, thermally stable (high melting point) with better radiation tolerance which make SiC devices suitable for operation in hostile environments.

Collectively, these properties promise SiC devices that offer tremendous benefits compared to power semiconductors (mostly Si) currently used for industrial and military applications.

#### **CHAPTER 2**

#### **Characteristic and Theoretical Parameters for 4H-SiC MOS Devices**

#### 2.1 MOS Structures

For modern MOS (metal-oxide-semiconductor) device fabrication, the metal layer is commonly replaced by heavily doped polycrystalline silicon for better performance, although the MOS jargon is still used for historical reasons. For more general applications, an insulator layer other than SiO<sub>2</sub> can be used on Si or even some other semiconductor with the nomenclacture metal-insulator-semiconductor (MIS). Although semiconductor technology is evolving rapidly, MOS structures still form the core structure for modern microelectronics circuit design. One of the major advantages of SiC compared with other wide band gap semiconductors is that many circuit design and device structures can be borrowed from Si since the two semiconductors have the same native oxide SiO<sub>2</sub>. In order to take advantage of the situation, one of the major tasks at present is to improve the performance and reliability of SiC-based MOS structures. The performance of these devices is currently limited by SiO<sub>2</sub>/SiC interface quality.

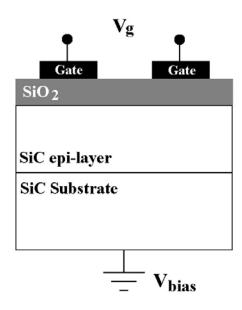

Two MOS device structures have been used for the work described herein - the MOS capacitor and MOSFET (metal-oxide-semiconductor field effect transistor). The two terminal MOS capacitor is the simpler structure. Fabricating the capacitor is straightforward, and essential information related to characteristics and properties of all MOS devices device can be obtained from MOS capacitor studies, especially information about interfacial trap density, transition layer formation and oxide breakdown. MOSFETs on the other hand, are three terminal devices that are more often used in actual circuits. For example, the Si MOSFET-based IC circuit is still the most pervasive technology in semiconductor industry. At present, there are already hundreds of different MOSFET designs available, each tailored for a specific application. However, in this work, we only focus on the simple lateral MOSFET structure in order to determine basic device characteristics such as inversion channel mobility. Lower than expected channel mobility is still one of the major obstacles that limits the performance of 4H-SiC inversion-mode MOSFETs.

#### 2.2 MOS Capacitor

#### 2.2.1 General Introduction

The metal-oxide-semiconductor capacitor (MOS CAP) is the most basic device of all the MOS structures. It has four modes of operation, accumulation, flatband, depletion

and inversion. Studying the MOS capacitor provides important information about the oxide, the oxide-semiconductor interface and even the semiconductor substrate. Also, most MOS CAP parameter relate directly to MOSFET performance, which make the capacitor an important tool for process/quality control. Another major advantage of studying the MOS CAP is the simplicity of the fabrication process for this simple structure. Hence, the MOS CAP is the most popular device for MOS characterization.

Figure 2.2.1 Two dimensional diagram for a MOS capacitor.

Figure 2.2.1 shows the two dimensional diagram for a MOS capacitor. The top circular metal contact is defined by photolithography and metal deposition mentioned in Chapter 1, with circular patterns that have varying radii. On SiC, materials commonly used as gate contacts are molybdenum, aluminum, and highly doped polycrystalline silicon. For the back side contact, a metal forming Ohmic contact is typically used; however, for all the MOS capacitor studies in this work, colloidal silver paint was used to

form a broad area (5mm×5mm minimum) back side contact. Though the backside contact was not annealed, the large area provided a reasonably low MOS capacitor series resistance that was typically  $< 100\Omega$ .

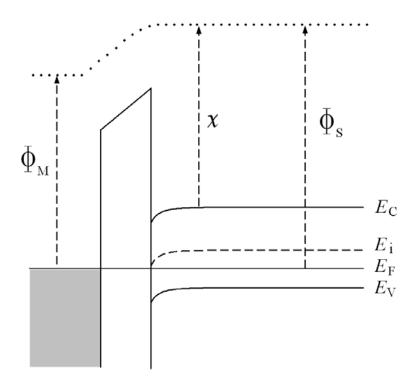

The ideal MOS structure<sup>31</sup> has the following characteristics. (1) the metallic gate is thick enough to be considered at equipotential surface; (2) the oxide is a perfect insulator with no current flowing under all static biasing conditions; (3) there are no charge located at the interface or through the oxide; (4) the substrate is uniformly doped; (5) the semiconductor bulk is thick enough so that a field-free region encountered before reaching the back contact for any gate bias; (6) an Ohmic contact is used for back contact; (7) all the variables can be treated in a one dimensional structure; (8) at equilibrium, the Fermi levels E<sub>F</sub> on metal and semiconductor sides are at the same energy, which also can be expressed as:

$$\Phi_M = \chi + (E_C - E_F)_{\infty}$$

(Eq 2.2.1)

Where  $\Phi_M$  is the metal work function,  $\chi$  is the semiconductor electron affinity, and  $E_C$  and  $E_F$  are the energies of the semiconductor conduction band edge and the Fermi level, respectively (see Figure 2.2.2). In real devices however, while some of the above assumptions hold, others often do not. For example, oxide leakage current and charge at interface and in the oxide are still problems that greatly limit the performance and reliability of SiC MOS devices. Our studies of SiC MOS capacitors are aimed at identifying non-ideal properties and attempting improvements.

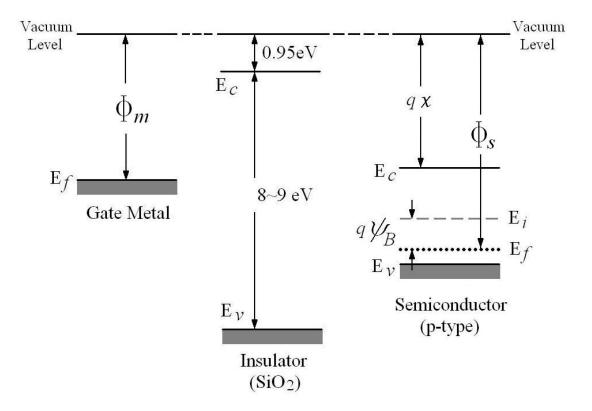

Figure 2.2.2 Energy band diagram of a MOS capacitor on a p-type semiconductor. 32,33

Figure 2.2.2 shows band diagrams for the energy levels of the different components of a p-type MOS capacitor. The reference potential for energy band diagram is usually set at the *Vacuum Level*, which is defined as the energy level of an electron at rest after it is removed from the crystal lattice. On the metal side, the energy difference between the Fermi level and vacuum level is called the *Work Function* of the metal  $\Phi_M$  which varies for different metals. SiO<sub>2</sub> is an insulator with a large energy gap  $E_C$ - $E_V \sim 8$ -9eV. The energy difference between the vacuum level and the oxide conduction band edge is around 0.95eV. Lastly, on the semiconductor side, the energy difference between  $E_C$  and

vacuum level is the *Electron Affinity* ( $\chi$ ) which is the minimum energy necessary to remove an electron with energy  $E_C$  from the semiconductor. For Si,  $\chi$  is 4.05eV while for 4H and 6H-SiC,  $\chi$  is around 3.9eV and 3.65eV, respectively<sup>34</sup>. In other words, the potential barrier between the conduction bands of the semiconductor and the SiO<sub>2</sub> is 4.05eV-0.95eV=3.1eV for Si, while for 4H-SiC, it is 2.7eV. This parameter is important when one considers oxide reliability and electron/hole injection under different bias conditions.

# 2.2.2 Operating Modes and Surface Potential under Gate Bias

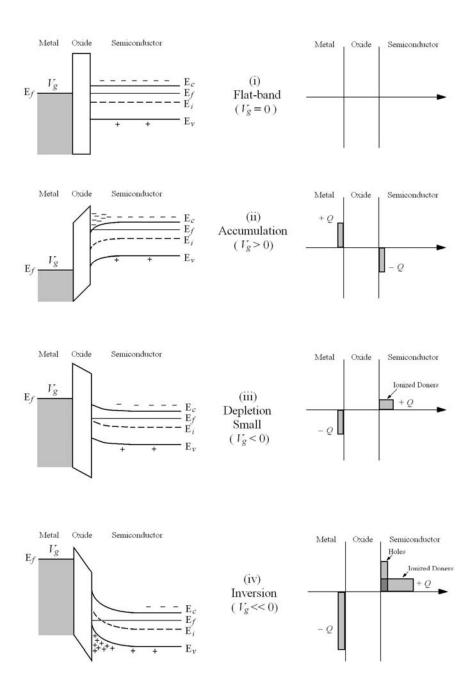

As mentioned previously, when under a gate bias, a typical MOS capacitor will have four operating modes, accumulation, flatband, depletion and inversion. As shown below, Figure 2.2.3 & Figure 2.2.4 are the band diagrams of both p-type and n-type ideal MOS capacitor under different bias conditions. We will discuss the details of the four modes of operation taking the ideal n-type MOS capacitor as an example.

# (a) Energy Band-Diagram (b) Block Charge Diagram Metal Oxide Semiconductor Semiconductor Metal Oxide Flat-band Oxide Metal Semiconductor Metal Oxide Semiconductor (ii) Accumulation $(V_g < 0)$ - Q Metal Oxide Semiconductor Metal Oxide Semiconductor (iii) Depletion Small $(V_g > 0)$ Metal Oxide Semiconductor Metal Oxide Semiconductor Inversion Electrons

Figure 2.2.3 Band diagram and corresponding block charge diagrams of p-type ideal MOS capacitor under different static bias condition. 31,35

### (a) Energy Band-Diagram

### (b) Block Charge Diagram

Figure 2.2.4 Band diagram and corresponding block charge diagrams of n-type ideal MOS capacitor under different static bias condition. 31,35

### i) Flatband

For simplicity, we are assuming the metal work function  $\Phi_M$  and electron affinity  $\chi$  in semiconductor are related following Eq.2.2.1. When there is no applied voltage between the metal and semiconductor, their Fermi levels must to line up, and in the ideal case, their vacuum levels line up as well. All the bands in both the oxide and semiconductor are flat. Hence there is no charge, no field and no current flow. This is called the *flat-band condition*. However, in non-ideal cases, as mentioned in section 2.2.4, the difference between  $\Phi_M$  and  $\Phi_S$ , and the presence of different types of charges at the interface and throughout the oxide layer, require that an initial gate bias voltage be applied to achieve the flat-band condition. This voltage is called the *flat-band voltage*,  $V_{FB}$ .

## ii) Accumulation

Let us take an n-type semiconductor as an example, and consider the situation when a positive gate voltage is applied. The gate bias  $V_G$  lowers the Fermi level  $E_F$  on the metal side relative to  $E_F$  in the semiconductor and causes a positive sloping of the energy bands in both the insulator (SiO<sub>2</sub>) and semiconductor, as shown in Figure 2.2.4(ii). Due to this field, the bands inside the semiconductor will bend downward toward the oxide interface, although the Fermi level will stay flat when there is no current flow. The potential at the semiconductor surface is called the *surface potential*. Because of this bending, the Fermi

level at the surface is much closer to the conduction band than is the Fermi level deep into the bulk. As a result, the electron concentration inside the semiconductor which is given by  $n = n_i \exp[(E_F - E_i)/kT]$ , increases when approaching the oxide/semiconductor interface. This situation, where the majority carrier concentration is greater near the oxide/semiconductor interface than in the bulk of the semiconductor, is called *accumulation*.

Another way to look at this situation is from the block charge diagram. When a gate bias  $V_G>0$  is applied. Positive charges will be induced at the metal/oxide interface. Inside of the bulk semiconductor, negatively charged electrons will be drawn toward the oxide/semiconductor interface by the field. At equilibrium, the charges at both interfaces will reach a charge balance.

## iii) Depletion

Under the same assumptions, consider next a small negative voltage  $V_G$  applied to the gate. The metal Fermi level  $E_F$  rise slightly towards  $E_F$  in the semiconductor, and the energy bands in both the oxide and semiconductor bend with a negative slope, as shown in Figure 2.2.4 (iii). Due to the field induced by the gate voltage, the bands bend upward toward the oxide/semiconductor interface. Since the conduction band at the interface now is farther away from the Fermi level than deeper into the bulk, the majority carrier concentration, in this case the electron concentration, will be lower at the interface than

into the bulk semiconductor. This situation is known as *Depletion*. Similarly from the charge distribution point of view, when gate voltage  $V_G$ <0 is applied, negative charge will be induced on the metal side. As for the semiconductor side, electrons are repelled away from the oxide/semiconductor interface, leaving only positive donor sites. Both electron and hole concentrations at the oxide-semiconductor interface are very low, or *depleted*. This near-interface region is therefore known as the *depletion region*.

#### iv) Inversion

Now consider depletion, but instead with a larger negative gate bias  $V_G$  applied to the metal gate. The bands at the oxide/semiconductor will further bend up, resulting in a wider depletion region and more depletion charge. The bending continues with larger negative bias until the intrinsic level ( $\sim$ mid-gap energy) at the interface becomes higher than the Fermi level, as shown in Figure 2.2.4 (iv). After this point, the semiconductor will behave like p-type material near the oxide/semiconductor interface. In other words, the field is so large that all the electrons are depleted from the interface, and the surface potential is such that it is energetically favorable for holes to populate the conduction band. The positive charge in the semiconductor consists of both the ionized donors and the thermally generated holes driven by the electric field to populate the interface region. Driven by the large applied field instead of doping, the minority carrier concentration at the oxide/semiconductor interface exceeds the bulk majority carrier concentration, and

this situation is referred to as inversion. From the band diagram, this situation happens when 31,36

$$E_i \text{ (surface)} - E_i \text{ (bulk)} = 2[E_F - E_i \text{ (bulk)}]$$

(Eq 2.2.2)

The gate voltage  $V_G$  during the dividing of the depletion and inversion is simply called the depletion-inversion transition point. This equation applies to both n-type and p-type devices. Eq 2.2.2 can also been written as

$$\phi_S = 2\phi_F$$

.... (Eq 2.2.3)

Here,

$$\phi_S = \frac{1}{q} [E_i(bulk) - E_i(surface)]$$

(Eq 2.2.4a)

$$\phi_F = \frac{1}{q} [E_i(bulk) - E_F]$$

(Eq 2.2.4b)

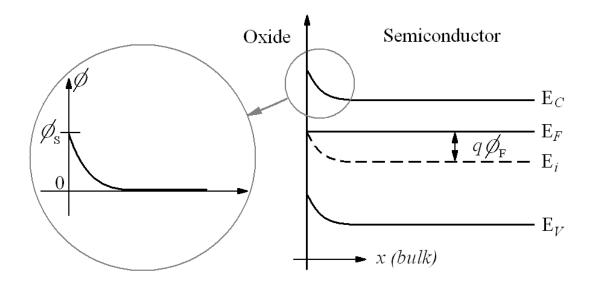

Here,  $\phi_S$  is defined as the potential evaluated at the oxide/semiconductor interface, also known as the surface potential, measured with the potential in the field-free region deep into the substrate as a reference point.  $\phi_F$  is simply defined by Eq 2.2.4b, and it is an important material parameter for determining substrate material type and doping concentration. A graphic depiction of  $\phi_S$  and  $\phi_F$  is shown in Figure 2.2.5.

Figure 2.2.5 Graphical definition of parameters  $\phi_S$  and  $\phi_F$  on the band diagram.

# 2.2.3 High-Low Frequency Capacitance-Voltage Measurement