| (   | OFT FRACE          | DATE I   | DETERMINATION FOR | NANOMETER                 | CMOS VIS | I Cideline |

|-----|--------------------|----------|-------------------|---------------------------|----------|------------|

| - 7 | 70 F.L. P. B B O B | BLATE: I | DETERMINATION FOR | - 1 Λ Λ Ν ( ) Μ Η: T Η: R |          | LUBCHITS   |

| Except where reference is made to the work of others, the work described in this |

|----------------------------------------------------------------------------------|

| thesis is my own or was done in collaboration with my advisory committee.        |

| This thesis does not include proprietary or classified information.              |

|                                   | Fan Wang                          |

|-----------------------------------|-----------------------------------|

|                                   |                                   |

|                                   |                                   |

|                                   |                                   |

|                                   |                                   |

|                                   |                                   |

|                                   |                                   |

|                                   |                                   |

| Certificate of Approval:          |                                   |

|                                   |                                   |

|                                   |                                   |

|                                   |                                   |

| Fa Foster Dai                     | Vishwani D. Agrawal, Chair        |

| Professor                         | James J. Danaher Professor        |

| Electrical & Computer Engineering | Electrical & Computer Engineering |

|                                   |                                   |

|                                   |                                   |

| III . D. W.I.                     |                                   |

| Victor P. Nelson                  | Joe F. Pittman                    |

| Professor                         | Interim Dean                      |

| Electrical & Computer Engineering | Graduate School                   |

# SOFT ERROR RATE DETERMINATION FOR NANOMETER CMOS VLSI CIRCUITS

# Fan Wang

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama May 10, 2008

# SOFT ERROR RATE DETERMINATION FOR NANOMETER CMOS VLSI CIRCUITS

# Fan Wang

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions and at their expense.

The author reserves all publication rights.

-

# $V_{\rm ITA}$

Fan Wang, son of Taiguo Wang and Yuhua Lu, was born on February 2, 1983 in Yunxian, Hubei Province, P. R. China. In 1998, he entered Shiyan No.1 Middle School. He joined Wuhan University of Technology in 2001 and graduated with Bachelor of Engineering degree in Electronic Information Engineering in 2005. In the same year in August he entered the Electrical & Computer Engineering Department at Auburn University, Alabama, for graduate study.

#### Thesis Abstract

SOFT ERROR RATE DETERMINATION FOR NANOMETER CMOS VLSI CIRCUITS

### Fan Wang

Master of Science, May 10, 2008 (B.S., Wuhan University of Technology, 2005)

### 108 Typed Pages

# Directed by Vishwani D. Agrawal

Nanometer CMOS VLSI circuits are highly sensitive to soft errors due to environmental causes such as cosmic radiation and high-energy particles. These errors are random and not related to permanent hardware faults. Their causes may be internal (e.g., interconnect coupling) or external (e.g., cosmic radiation). Nowadays, the term soft errors, also known as Single Event Upsets (SEU), specifically defines radiation errors caused in microelectronic circuits when high energy particles strike at sensitive regions of the silicon devices. The soft error rate (SER) estimation analytically predicts the effects of cosmic radiation and high-energy particle strikes in integrated circuit chips by building SER models. An accurate analysis requires simulation using circuit netlist, device characteristics, manufacturing process and technology parameters, and measurement data on environmental radiation. Experimental SER testing is expensive and analytical approaches are, therefore, beneficial.

We model neutron-induced soft errors using two parameters, namely, occurrence rate and intensity. Our new soft error rate (SER) estimation analysis propagates occurrence rate and intensity as the width of single event transient (SET) pulses, expressed as a probability and a probability density function, respectively, through the circuit. We consider the entire linear energy transfer (LET) range of the background radiation which is available from measurement data specific to the environment and device material. Soft error rates are calculated for ISCAS85 benchmark circuits in the standard units, failure in time (FIT, i.e., failures in 10<sup>9</sup> hours). In comparison to the reported SER analysis results in the literature, our method considers several more relevant factors including sensitive regions, circuit technology, etc., which may influence the SER. Our simulation results for ISCAS85 benchmark circuits show similar trend as other reported work. For example, our soft error rate results for C432 and C499 considering ground-level environment are  $1.18 \times 10^3$  FIT and  $1.41 \times 10^3$  FIT, respectively. Although no measured data are available for logic circuits, SER for  $0.25\mu$  and  $0.13\mu$  1M-bit SRAMs have been reported in the range  $10^4$  to  $10^5$  FIT, and for  $0.25\mu$  1G-bit SRAM around  $4.2 \times 10^3$  FIT. We also discuss the factors that may cause several orders of magnitude difference in our results and certain other logic analysis methods. The CPU time of our analysis is acceptably low. For example, for C1908 circuit with 880 gates, the analysis takes only 1.14 second. The fact that we propagate the error pulse width density information to primary outputs of the logic circuit would allow evaluation of SER reduction schemes such as time or space redundancy.

This thesis also proposes a possible soft error reduction technique by hardware redesign involving circuit board reorientation. The basic idea is that the particles with LET smaller than the critical LET will not be able to cause an error if the angle of incidence is smaller than some critical angle. A proper orientation of hardware circuit boards will possibly reduce the soft error rate.

#### ACKNOWLEDGMENTS

First, I would like to sincerely express my appreciation for my adviser Dr. Vishwani D. Agrawal, for his constant support. Without his patient guidance and encouragement, this work would not be possible. His technical advice made my master's studies a meaningful learning experience. I also want to thank my advisory committee members, Dr. Fa Foster Dai and Dr. Victor P. Nelson for being on my thesis committee and for their invaluable advice on this research.

Appreciation is expressed for all research colleagues at Auburn who have helped me in the course of my research work. I thank Gefu Xu, Yuanlin Lu, Nitin Yogi, Kalyana Kantipudi, Jins Alexander, Khushboo Sheth and Wei Jiang for all the helpful discussions throughout this research and for supplying a refreshing working environment in the department.

Finally, equally important, I acknowledge with gratitude and affection, encouragement and support given by my parents during my graduate study. I also thank all my family members and friends for their support and concern. Special thanks to my wife Jingyun Li, who has always been with me throughout the struggles and challenges of my graduate study at Auburn.

Style manual or journal used Lamport Text: A Document Preparation System by Leslie Lamport together with style know as "aums".

Computer software used The document preparation package TeX (specifically LATEX) together with the departmental style-file aums.sty. The images and plots were generated using Microsoft® Office Visio 2007/SmartDraw6 and Microsoft® Office Excel 2003.

# Table of Contents

| Lis | ST OF                     | FIGURES                                                                                                                                                                                                                                                                               | X                                            |

|-----|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Lis | ST OI                     | F TABLES                                                                                                                                                                                                                                                                              | xii                                          |

| 1   | INTI<br>1.1<br>1.2<br>1.3 | RODUCTION Problem Statement                                                                                                                                                                                                                                                           |                                              |

| 2   | BAC<br>2.1<br>2.2<br>2.3  | What is Soft Error  A Historical Note on Soft Errors  Radiation Environment Overview  2.3.1 Radiation Types  2.3.2 Terrestrial Radiation Environment  How Soft Error Occurs in Silicon  2.4.1 Radiation Mechanisms in Semiconductors                                                  | 8<br>9<br>11<br>11<br>18<br>18               |

|     | 2.5<br>2.6<br>2.7<br>2.8  | 2.4.2 Sensitive Regions in Silicon Devices 2.4.3 Single Event Transient (SET)  An Overview of Soft Error Mitigation Techniques 2.5.1 Prevention Techniques 2.5.2 Recovery Techniques  IBM eServer z990 – A Case Study  Traditional SER Testing Methods  Collected SER Field Test Data | 21<br>22<br>27<br>28<br>29<br>32<br>33<br>37 |

| 3   | PRE 3.1 3.2 3.3           | Figure of Merit Model for Geosynchronous SER                                                                                                                                                                                                                                          | 39<br>39<br>41<br>42                         |

| 4   | ENV<br>4.1                | Gate-Level SET Propagation                                                                                                                                                                                                                                                            | 54                                           |

|    | 4.3 Conclusion                                    | . 63 |

|----|---------------------------------------------------|------|

| 5  | RESULTS COMPARISON AND DISCUSSION                 | 64   |

|    | 5.1 Experimental Results                          | . 64 |

|    | 5.2 Discussion of Results                         | . 65 |

|    | 5.3 Conclusion                                    | . 68 |

| 6  | SOFT ERROR CONSIDERATIONS IN COMPUTER WEB SERVERS | 69   |

|    | 6.1 Soft Error Reduction in Industrial Servers    | . 69 |

|    | 6.2 A Proposed Direction                          | . 71 |

|    | 6.3 Conclusion                                    | . 74 |

| 7  | Conclusion                                        | 76   |

| Ві | BLIOGRAPHY                                        | 78   |

| Aı | PPENDICES                                         | 90   |

| A  | Terms and Definitions                             | 91   |

| В  | Units and Conversion Factors                      | 95   |

# LIST OF FIGURES

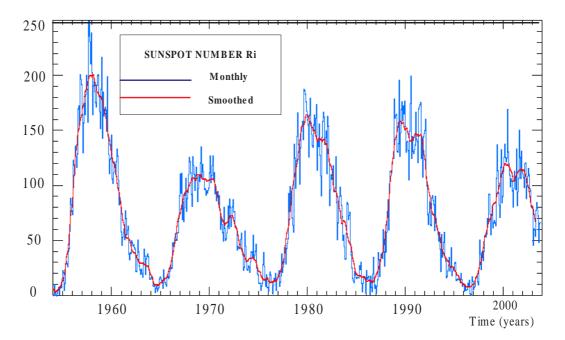

| 2.1  | Sunspot numbers (y-axis) during solar cycles 19 through 23 recorded by Solar Influences Data Center (SIDC) in Belgium [9]                                                                                                         | 17 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

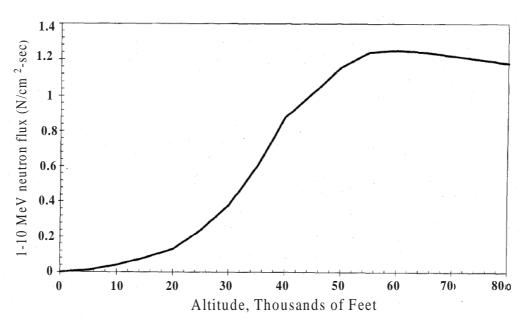

| 2.2  | Neutron flux versus altitude showing peak at about 60,000 ft [139].                                                                                                                                                               | 18 |

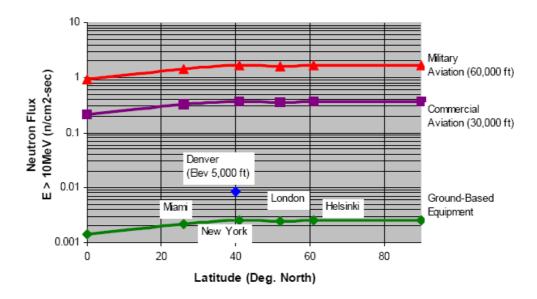

| 2.3  | Neutron flux as a function of altitude and latitude [4]                                                                                                                                                                           | 19 |

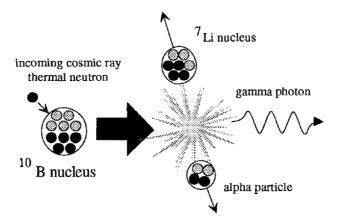

| 2.4  | Fission of $^{10}B$ induced by the capture of a neutron (commonly happened in SRAMs) [26]                                                                                                                                         | 21 |

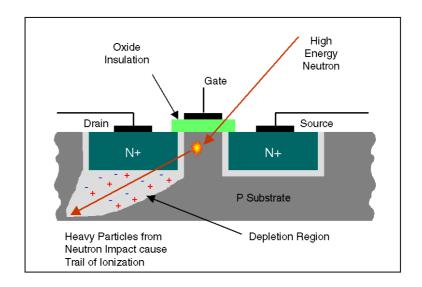

| 2.5  | Interaction of a high energy neutron and a silicon integrated circuit [6].                                                                                                                                                        | 22 |

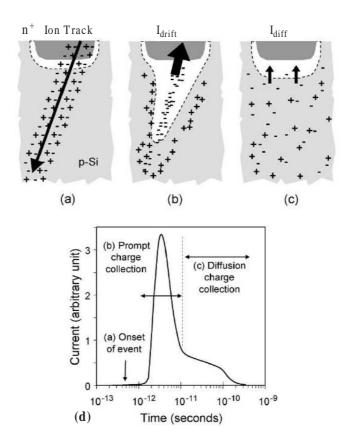

| 2.6  | Schematic representation of charge collection in a silicon junction immediately after (a) an ion strike, (b) prompt (drift) collection, (c) diffusion collection, and (d) the junction current induced as a function of time [29] | 23 |

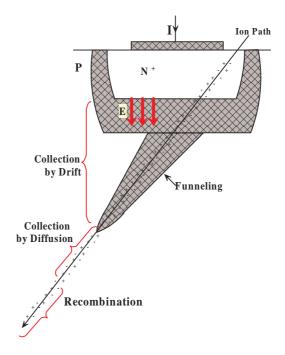

| 2.7  | Schematic of the charge collection mechanism when an ionizing particle strikes an electronic junction [149]                                                                                                                       | 24 |

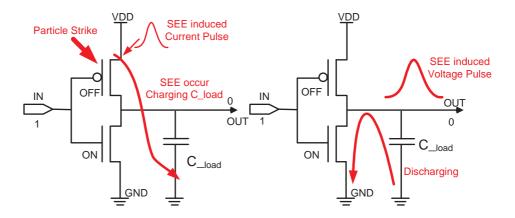

| 2.8  | A schematic view of how SEE-induced current pulse translates into a voltage pulse in a CMOS inverter                                                                                                                              | 27 |

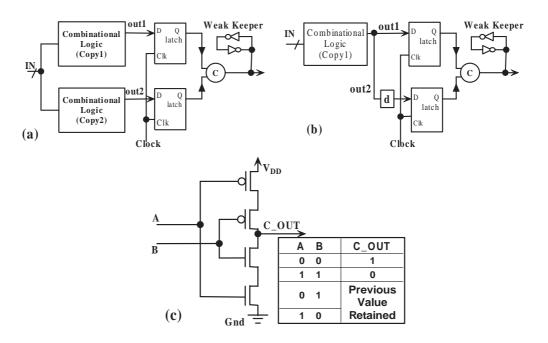

| 2.9  | Error correction using duplication, (a) space redundancy structure, (b) time redundancy structure, and (c) C-element [127]                                                                                                        | 31 |

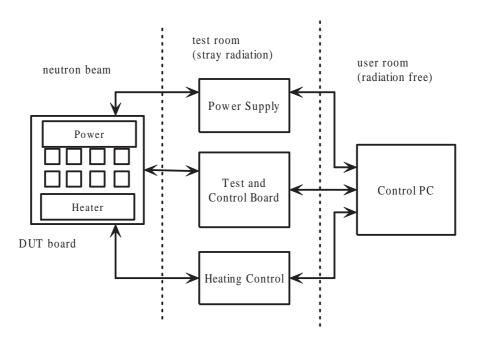

| 2.10 | Typical test setup (hardware) for neutron-accelerated SER testing [86].                                                                                                                                                           | 34 |

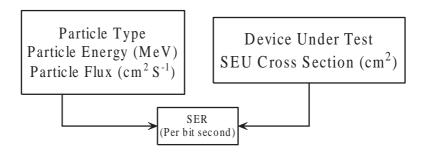

| 2.11 | Traditional SER field test parameters                                                                                                                                                                                             | 36 |

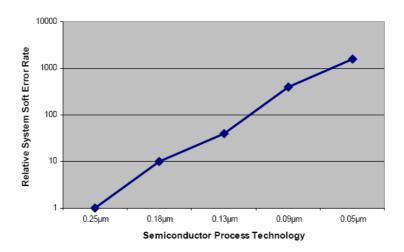

| 2.12 | Soft error rates as a function of IC process technology [7]                                                                                                                                                                       | 37 |

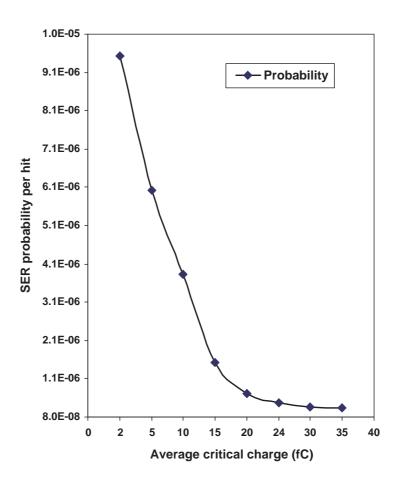

| 4.1  | Probability of soft error for each collision of a 30MeV neutron as a function of the average critical charge for an SRAM chip (from SEMM program [172])                                                                           | 51 |

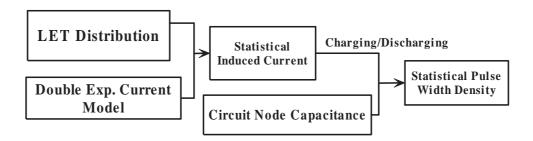

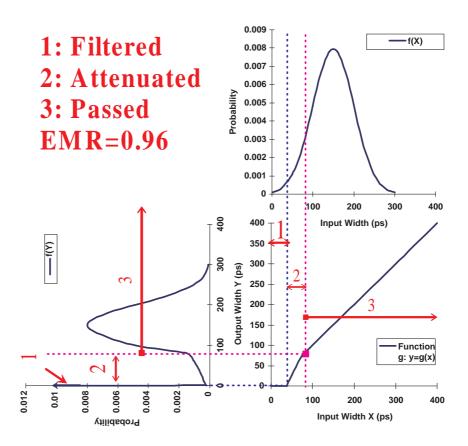

| 4.2 | Transforming statistical neutron energy spectrum to SET width statistics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

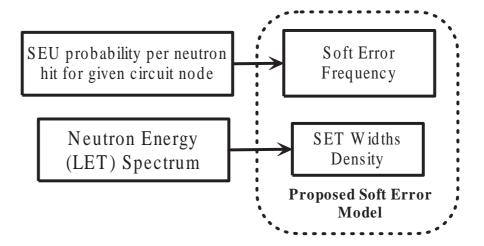

| 4.3 | Proposed probabilistic neutron induced soft error model for logic. $% \left( 1\right) =\left( 1\right) \left( 1\right) $ | 54 |

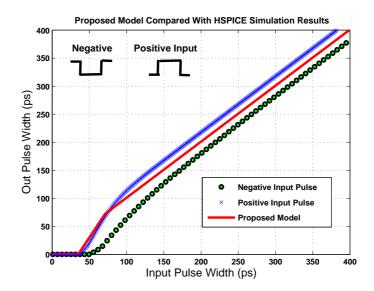

| 4.4 | Comparison of proposed model and HSPICE simulation for CMOS inverter with $10 fF$ load capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58 |

| 4.5 | Pulse width density propagation through a CMOS inverter with $10 fF$ load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59 |

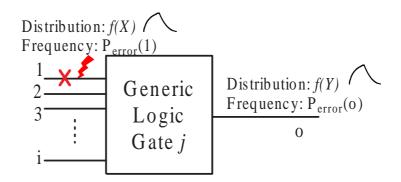

| 4.6 | A generic gate with particle strike on node 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61 |

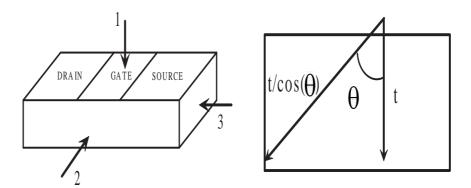

| 6.1 | Three perpendicular orientations for exposing a transistor and particle angle of incidence [158]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74 |

# LIST OF TABLES

| 1.1 | Commodity flash memory reliability requirements (ITRS)                                                       | 2  |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Measured failure rate on SRAM-based FPGA applications due to neutron effects in 130nm technology (Actel) [6] | 10 |

| 2.2 | Projected failure rate on SRAM-based FPGA applications due to neutron effects in 90nm technology (Actel) [6] | 10 |

| 2.3 | Mass, charge and radius of particles of interest in radiation effects [70].                                  | 14 |

| 2.4 | Sample EDAC methods for memory or data devices [106]                                                         | 32 |

| 2.5 | Accelerated testing versus real-time testing [128]                                                           | 35 |

| 2.6 | Recently reported data on soft error rates                                                                   | 38 |

| 4.1 | Output 1 probability calculation for $n$ -input Boolean gates                                                | 60 |

| 4.2 | SER results for ISCAS85 benchmark circuits                                                                   | 62 |

| 4.3 | SER results for inverter chains                                                                              | 62 |

| 5.1 | Experimental results for ISCAS85 benchmark circuits                                                          | 65 |

| 5.2 | Comparison of our work with other SER estimation methods                                                     | 66 |

| 6.1 | Typical server system reliability goals [34].                                                                | 70 |

### Chapter 1

#### Introduction

From the beginning of the recorded history, man has believed in the influence of heavenly bodies on the life on Earth. Machines, electronics included, are considered scientific objects whose fate is controlled by man. So, in spite of the knowledge of the exact date and time of its manufacture, we do not draft a horoscope for a machine. Lately, however, we have started noticing certain behaviors in the state of the art electronic circuits whose causes are traced to be external and to the celestial bodies outside our Earth. The Single Event Upset (SEU) phenomenon, as this non-permanent (i.e., random or soft) error behavior is termed, in digital systems affects the modern nanotechnology electronic devices. We believe SEU will assume greater importance in the future [113]. We begin this introduction with a definition:

"Single Event Upset (SEU): Radiation-induced errors in microelectronic circuits caused when charged particles (usually from the radiation belts or from cosmic rays) lose energy by ionizing the medium through which they pass, leaving behind a wake of electron-hole pairs". · · · NASA Thesaurus [13]

Continuous downscaling of CMOS technologies has resulted in clock frequencies reaching multiples of GHz range, supply voltage decreasing below one volt level and load capacitances of circuit nodes dropping to femtofarads. Consequently, microelectronics systems are more vulnerable to noise sources in the working environment. Nanotechnology therefore makes the meeting of reliability requirements highly challenging. Well-known noise

Table 1.1: Commodity flash memory reliability requirements (ITRS).

|                   | •                     | · ·                 | •                   | \ /                 |

|-------------------|-----------------------|---------------------|---------------------|---------------------|

| Year              | 2007                  | 2010                | 2013                | 2016                |

| Density (megabit) | 1024                  | 2048                | 4096                | 8192                |

| Maximum Data      | 166                   | 200                 | 250                 | 300                 |

| Rate (MHz)        |                       |                     |                     |                     |

| MTTF (hours)      | 4020                  | 4654                | 5388                | 6237                |

| $FIT=10^9/MTTF$   | $2.487 \times 10^{5}$ | $2.149 \times 10^5$ | $1.856 \times 10^5$ | $1.603 \times 10^5$ |

sources include power supply fluctuations, lightning and electrostatic discharge, interconnect coupling capacitance and inductance, and thermal radiation from the galaxy, radio-emitting stars and atmospheric gases. A recent study shows that among the effect of the soft failure sources, hard failure mechanisms exhibit product failure rates on the order of  $1\sim100$  FIT [186] (failures in  $10^9$  hours; see Appendix B for definition of FIT). However, the soft error rate of a low-voltage embedded SRAM can easily be 1000 FIT/Mbit [28]

Electronics applications continue to demand higher reliability levels [79]. The 2002 International Technology Roadmap for Semiconductors (ITRS), in its difficult test challenges report (www.itrs.net/Links/2002Update/2002UpdateTest.pdf), gives the reliability requirements in mean time to failure (MTTF) for commodity flash memory as shown in Table 1.1. We notice that the maximum data rate and density are expected to increase, stressing the reliability requirements. Getting sufficient information on modern microchip reliability, especially with respect to soft errors due to alpha particles or cosmic rays, before the chip is manufactured has become more important for chip designers these days. Most integrated circuits are tested at particle accelerators for their susceptibility to single event effects (SEE). The soft error rate represents the circuit susceptibility and estimating the soft error rate can be typically done by accelerated testing. The purpose

of accelerated life tests is not to expose defects, but to identify and quantify the failures and failure mechanisms which cause products to wear out before the end of their useful life [52]. Unfortunately, accelerated life testing is always time consuming because multiple runs are normally needed to get a sufficient number of samples under test to fail for data to be statistically meaningful. The test time may typically vary from few weeks to few months. The SER results will not be available until almost a year after the first chips start coming out of the fab. This long delay is generally unacceptable. One alternative method is the costly path of testing many more chips with a bigger test facility. Another is to test the chips in a more sensitive state deviated from the nominal conditions, i.e., at reduced voltage. With reduced voltage microchips are more sensitive to radiation. However, low-voltage testing has too many pitfalls to be used with confidence [199, 204].

Soft error is defined as a faulty signal state in a microelectronic circuit caused by charged particles striking at sensitive regions in silicon devices [164]. The soft errors in memories (SRAM and DRAM) were extensively studied at the end of the twentieth century [62]. Because memories have high density of components integrating a large number of storage elements, they are more sensitive to soft errors than logic circuits. Soft error rates in logic and processors are increasing along with the feature downscaling technology trend [73, 105]. In addition, if other circuit noises such as interconnect coupling and ground bounce are considered as soft errors, the logic FIT rate is expected to increase faster and finally the FIT rate in logic is likely to become comparable to the FIT rate in memories [94].

The SER due to high-energy neutrons has been studied in SRAM cells, latches, and logic circuits for feature sizes from 600nm to 50nm. SER per chip for logic circuits is expected to increase by nine orders of magnitude from 1992 to 2011, becoming comparable to the failure rates in unprotected on-chip memories [169].

#### 1.1 Problem Statement

It is very costly to determine the SER of a real chip by accelerated life testing. Experimental results on measurement of neutron flux data at sea level over the past half century have shown a big variance. The neutron flux varies based on the location of the test and time-dependent solar activity [60, 141]. The buildings in which these experiments are located pose another difficulty because different mixtures of concrete will have different shielding affects on cosmic rays. These difficulties can make the measurement of the SER of a SRAM or DRAM vary up to 100X, even when tested at the same location.

Until 2002, there was no comprehensive model to reliably evaluate soft error rate of a device [202]. An accurate prediction of SER needs SER simulation using actual chip circuit models, which include device, process, and technology parameters. Current SER estimation methods are not well developed for logic circuits. Logic circuits, different from memories devices, have specific masking effects on SETs (soft error transients) that depend on the circuit properties. These masking factors are electrical masking, logic masking and temporal masking [133]. Accurate estimation of logic circuit SER continues to be a major challenge as rapid advancement in nanotechnology keeps increasing the circuit sensitivity.

In our SER analysis approach, the inputs to the analysis are (1) circuit characteristics: circuit netlist, technology and node sensitive region data, and (2)background environment data: LET distribution and neutron flux. The output of our analysis is the neutron caused logic circuit soft error rate in standard FIT (failure in time) units.

### 1.2 Contribution of Research

In this research, we model neutron-induced soft errors using two parameters, namely, occurrence rate and intensity. Our soft error rate estimation analysis propagates occurrence rate (expressed as a probability function) and intensity as the width of single event transient (SET) pulse expressed by a probability density function through the logic circuit. We develop an algorithm to compute the SER of a logic circuit based on this soft error model. We consider such issues as circuit technology and the altitude, which may influence the SER results, and use a vector-less statistical approach. We consider the entire linear energy transfer (LET) spectrum of the terrestrial background that is available from measurement data specific to environment and device materials.

Soft error rates are calculated for ISCAS85 benchmark circuits in the standard unit, failures in time (FIT, i.e., failures in  $10^9$  hours). In comparison to the reported SER analysis work by Rao et al. [156], our method considers many more relevant factors, including sensitive regions, circuit technology, etc., which may influence logic SER. Our simulation results for ISCAS85 benchmark circuits differ from those reported by Rao et al. For example, our estimated soft error rates at ground level for C432 and C499 are  $1.18 \times 10^3$  FIT and  $1.41 \times 10^3$  FIT, while Rao et al. reported  $1.73 \times 10^{-5}$  and  $6.26 \times 10^{-5}$ , respectively. We discuss the factors that could have caused several orders

of magnitude difference between these results. Our CPU time is acceptably low. For example, for C1908 with 880 gates our analysis takes just 1.14 seconds on a Sun Fire 280R workstation.

With our novel soft error model, we are able to accurately model electrical masking factors in logic circuits. Also, the error pulse width density information at the primary outputs of the logic circuit allows evaluation of SER reduction schemes such as time redundancy and space redundancy.

An extensive discussion on soft error considerations for contemporary computer web servers is also presented. We propose a possible soft error rate reduction method that considers the cosmic ray striking angle to redesign the circuit board layout in server systems.

Four papers based on the work reported in this thesis have been authored: (1) a tutorial paper that covers broad topics on SEU was presented at the 21st IEEE International Conference on VLSI Design [186], (2) the new soft error model and logic SER estimation algorithm was presented at the 40th IEEE Southeastern Symposium on System Theory [187], (3) the logic SER estimated by our algorithm and that reported in other related work are compared and a detailed discussion is given in a paper presented at 17th IEEE North Atlantic Test Workshop [185], and (4) a manuscript on SER in web servers with a proposal for its reduction is still unpublished.

# 1.3 Thesis Organization

This thesis is organized as follows. In Chapter 2, we provide the basic background on soft errors. Definitions of terms in this field, the mechanisms of how soft errors occur in silicon, and some widely used soft error mitigation techniques are discussed. In Chapter 3, previous soft error rate estimation strategies are broadly discussed. Our attempt is to include the essentials of the existing work related to soft error rate estimation in this chapter. The traditional experimental SER testing methodology is also discussed. In Chapter 4, the novel soft error model is proposed and an algorithm to compute logic SER is developed. In Chapter 5, the new results are compared with those available in the literature. Our extended work that proposes a possible soft error rate reduction method in computer web servers by considering the hardware orientation, is presented in Chapter 6. The thesis is concluded with insights on future work in Chapter 7.

### Chapter 2

#### Background

#### 2.1 What is Soft Error

An electronic circuit, that bears no permanent hardware fault, may display unexplained events resulting in spontaneous single bit changes in the system such that there is no way to repeat such failures. In the computer industry such phenomenon is known as a "soft fail", to differentiate from the "hard or permanent fail", which may be repairable [117, 203]. After observing a soft error, there is no implication that the system hardware is any less reliable than before because the soft fail is completely random. These soft fails may be caused by either well-known electronic noise sources such as a power supply fluctuations, lightning, and electrostatic discharge (ESD) [103], or the thermal radiation from the galaxy, such as radiation-emitting stars and atmospheric gases. A soft or non-permanent fault is a non-destructive fault and falls into two categories [180]:

- Transient faults [38], caused by environmental conditions like temperature, humidity, pressure, voltage, power supply, vibrations, fluctuations, electromagnetic interference, ground loops, cosmic rays and alpha particles.

- Intermittent faults caused by non-environmental conditions like loose connections, aging components, critical timing, power supply noise, resistive or capacitive variations or couplings, and noise in the system.

With advances in design and manufacturing technology, non-environmental conditions may not affect sub-micron semiconductor reliability. However, the errors caused by cosmic rays and alpha particles remain a dominant factor causing errors in electronic systems.

#### 2.2 A Historical Note on Soft Errors

Soft errors have been studied by electrical, aerospace [33], nuclear and radiation engineers for almost half a century. In the period 1954 through 1957 failures in digital electronics were reported during the above-ground nuclear bomb tests. These were originally treated as electronic anomalies in the monitoring equipment because they were random and their cause could not be traced to any hardware fault [199]. Perhaps the first paper concerning the role of cosmic rays on electronics was by Wallmark and Marcus [183]. As quoted in the recent literature [123], these authors predicted that cosmic rays would start upsetting microcircuits due to high energy particle strikes and radiation when feature sizes become small enough. Through 1970s and early 1980s, the effects of radiation received attention and more researchers examined the physics of these phenomena. Also starting around 1950, theories of fault tolerant and self-repairing computing system have been developed due to the increased reliability requirements of critical applications like the space-mission [21, 22, 23, 24, 115, 181].

May and Woods of Intel Corporation [119, 120] determined that intermittent errors were caused by the alpha particles emitted by the radioactive decay of uranium and thorium present just in few parts-per-million levels in package materials. Their papers represent the first public account of radiation-induced upsets in electronic devices at sea level and these errors were referred to as "soft errors". The term soft error was used to differentiate from the repeatable errors traceable to permanent hardware faults.

Table 2.1: Measured failure rate on SRAM-based FPGA applications due to neutron effects in 130nm technology (Actel) [6].

|                                        | Altitude | Neutron    | FPGAs/ | #upsets/              | MTBF    | FIT       |

|----------------------------------------|----------|------------|--------|-----------------------|---------|-----------|

| Application Example                    | (feet)   | Flux       | System | 1M-gate/              | (hours) | (million) |

|                                        |          | (relative) |        | FPGA/day              |         |           |

| (1) Ground-based Communication Network | 5000     | 1          | 512    | $4.19 \times 10^{-4}$ | 112     | 8.92      |

| (2) Civilian Avionics System           | 30,000   | $\sim 40$  | 4      | $1.85 \times 10^{-2}$ | 324     | 3.09      |

| (3) Military Avionics System           | 60,000   | >160       | 16     | $8.33\times10^{-2}$   | 18      | 55.56     |

Table 2.2: Projected failure rate on SRAM-based FPGA applications due to neutron effects in 90nm technology (Actel) [6].

|                                        | Altitude | Neutron    | FPGAs/ | MTBF    | FIT       |

|----------------------------------------|----------|------------|--------|---------|-----------|

| Application Example                    | (feet)   | Flux       | System | (hours) | (million) |

|                                        |          | (relative) |        | , ,     |           |

| (1) Ground-based Communication Network | 5000     | 1          | 512    | 58      | 17.24     |

| (2) Civilian Avionics System           | 30,000   | $\sim 40$  | 4      | 162     | 6.17      |

| (3) Military Avionics System           | 60,000   | >160       | 16     | 9       | 111.11    |

Guenzer and Wolicki [74] reported that the error causing particles came not only from uranium and thorium but that nuclear reactions generated high energy neutrons and protons, which could also cause upsets in circuits. Following the title of their paper, "Single Event Upset of Dynamic RAMs by Neutrons and Protons", the term "SEU" has been in use ever since [74, 123]. In 1979, Ziegler and Lanford from IBM [203] predicted that cosmic rays could result in the same upset phenomenon in digital electronics (not only memories) even at sea level.

Recent Soft Error Rate (SER) testing results for SRAM-based FPGAs from Actel [6] show a significant and growing risk of functional failures due to the corruption of configuration data, especially when the system has higher densities. Table 2.1 and Table 2.2 show measured failure rates for 130nm technology and projected failure rates for 90nm technology, respectively, for different applications without using any error protection. The error rates are shown in units of MTBF (Mean Time Between Failures) and FIT (Failures in Time). The number of upsets per 1 million gates per day increases for cases

(1) through (3) because of the altitude dependent increase in neutron flux density. It is expected that neutron-induced soft errors will get worse by a factor of two as we move from 130nm to 90nm technology. Note that this table ignores alpha particle effects, which are also expected to be significant for nanometer technologies and will further increase the system failure rate.

Radiation induced soft errors have become one of the most important and challenging failure mechanisms in modern electronic devices. SER for commercial chips is controlled to within 100–1000 FIT. Compared to most hard failure mechanisms that produce failure rates on the order of 1–100 FIT, the SER of a low-voltage embedded SRAM can easily be 1000 FIT/Mbit. Therefore, a four-phase approach to deal with them is in progress [162]:

- 1. Methods to protect chips from soft errors (prevention).

- 2. Methods to detect soft errors (testing).

- 3. Methods to estimate the impact of soft errors (assessment).

- 4. Methods to recover from soft errors (recovery).

## 2.3 Radiation Environment Overview

# 2.3.1 Radiation Types

Radiation is kinetic energy in the form of high speed particles and electromagnetic waves. In general, radiation mechanisms can be classified as either ionizing radiation or non-ionizing radiation [89, 174, 175, 176].

- 1. Ionizing radiation is radiation with enough energy, so that during interaction with an atom it can remove tightly bound electrons from their orbits, thus causing the atom to become charged or ionized. Examples are gamma rays and neutrons.

- 2. Non-ionizing radiation is radiation without enough energy to remove tightly bound electrons from their orbits in atoms. Examples are microwaves and visible light.

Common types of radiation include: alpha particles, beta radiation, gamma rys, and X-rays. Neutron particles are also encountered in nuclear power plants, high-altitude flights and are also emitted from some industrial radioactive sources. In some types of atoms, the nucleus is unstable and spontaneously decays into a more stable form after releasing energy as radiation. The major types of radiation are summarized as follows [89]:

Gamma rays and X-rays are short-wavelength photons or electromagnetic radiation.

The two names come from their discoveries at different times. Gamma rays have their origin in nuclear interaction while X-rays originate from electronic or charged-particle collisions. Their interaction mechanisms with matter are identical. The photons are lightly ionizing, highly penetrating, and leave no activity in the irradiated material. Gamma rays have a comparatively higher penetrating power, and it takes a thick sheet of metal such as lead or concrete to attenuate them significantly.

Alpha Particles are the nuclei of helium atoms consisting of 2 protons and 2 neutrons. They have an identical mass as a helium nucleus and a positive charge of 2e, where e is the magnitude of charge on an electron,  $e = 1.6 \times 10^{-19}$  coulomb. They normally have high energy in the MeV range (see Appendix A). They interact strongly with matter and are heavily ionizing. They have low penetrating power and travel in

straight lines. They are easily stopped even by a sheet of paper. A typical alpha particle energy is 5 MeV with a typical range of 50mm in air and  $23\mu$  in silicon.

Beta Particles have the same mass as an electron but they may be either negatively or positively charged. Because they have small mass and charge, they can penetrate matter more easily than alpha particles but are easily deflected. They have high velocity normally approaching that of light. They produce weak ionization. Beta particles are stopped by a sheet of aluminum or plastic such as perspex.

Neutron has the same mass as proton but has no charge, thus it is difficult to deflect. The capture of a neutron can cause the emission of gamma rays. Neutron rays (streams of neutrons) are classified according to their energy as thermal neutrons (energy < 1 eV) [60], intermediate neutrons (1 ev < energy < 100 KeV), and fast neutrons (energy > 100 KeV). Water is an effective shield for neutrons.

**Proton** is the nucleus of a hydrogen atom and carries a positive charge of 1 unit, i.e., +e. The proton has a mass thousands of times that of an electron, and consequently is more difficult to deflect. The proton has a typical range of several centimeters in air, and tens of microns in aluminum at energies in the MeV range.

The particle masses, charges and radii of interest for radiation effects are listed in Table 2.3, derived from experiment data [70].

The ionizing radiation effects in electronics, such as space vehicle electronics, can be separated into two types: total ionizing dose (TID) and single event effects (SEE) [106].

• Total Ionizing Dose (TID) causes long term degradation of electronics through cumulative energy deposited in a material. Effects include parametric failures,

Table 2.3: Mass, charge and radius of particles of interest in radiation effects [70].

| Particle | Mass (kg)               | Charge (C)              | Radius (m)              |

|----------|-------------------------|-------------------------|-------------------------|

| Proton   | $1.672 \times 10^{-27}$ | $1.672 \times 10^{-19}$ | $1.535 \times 10^{-18}$ |

| Neutron  | $1.674 \times 10^{-27}$ | 0                       | $6.317 \times 10^{-18}$ |

| Electron | $9.109 \times 10^{-31}$ | $1.602 \times 10^{-19}$ | $2.817 \times 10^{-15}$ |

variations in device voltage and functional failures. Significant sources of TID exposure in the space environment include trapped electrons, trapped protons, and solar flare protons.

• Single Event Effect (SEE) occurs when a single particle strikes the material and deposits sufficient energy in the device to cause an upset. Here, SEE includes soft errors (SEU, SEFI) and hard errors (SEL, SEB, SEGR<sup>1</sup>).

Parametric and permanent functional failures are the principal failure modes associated with the TID environment. Since TID is a cumulative effect, the total dose tolerances of devices are MTTF (mean time to failure, see Appendix B) numbers, where the time-to-failure is the amount of mission time until the device has encountered enough dose to cause failure [106].

The progression in manufacturing processes to ever deeper sub-micron technologies is increasing the risk from system reliability issues. Due to neutron effects the manufacturers of telecommunications and networking systems are developing qualification tests to identify components that are susceptible to soft errors. The main sources of radiation environment within the interest of avionics and electronics have been listed as follows [50]:

<sup>&</sup>lt;sup>1</sup>for definitions of TID, SEU, SEE, SEL, SEFI and SEGR, see Appendix A

- Trapped Belts: Protons and electrons trapped in the Van Allen<sup>2</sup> belt.

- Heavy ions trapped in the magnetosphere.

- Cosmic ray protons and heavy ions.

- Protons and heavy ions from solar flares.

### 2.3.2 Terrestrial Radiation Environment

When galactic cosmic rays traverse the earth's atmosphere, they collide with atomic nuclei and create cascades of interactions and reaction products like neutrons. Some of these neutrons reach the ground and become a source of single event upsets (SEU) in microelectronics. Neutrons produce SEU only when they collide with the nucleus of an atom in a device or its packaging, causing the nucleus to recoil and release densely ionizing nuclear fragments [72]. The probability of a neutron producing a nuclear recoil and fragments to which a particular device may be sensitive depends on the neutron's kinetic energy.

It has been discovered that cosmic rays impinging on the Earth's atmosphere have almost 90% of the particles as protons, about 9% as helium nuclei (alpha particles) and about 1% as electrons. They are influenced by the Earth's magnetic field and other factors like colliding with atmospheric molecules. The initial particles originating from the outer space (also called "primaries"), have a shower of about 1600 particles

<sup>&</sup>lt;sup>2</sup>The radiation belts are regions of high-energy particles, mainly protons and electrons, held captive by the magnetic influence of the Earth. They have two main sources. A small but very intense "inner belt" (some call it "The Van Allen Belt" because it was discovered in 1958 by James Van Allen of the University of Iowa) lies within 4000 miles or so of the Earth's surface. It mainly consists a high-energy protons (10-50 MeV) and is a by-product of the cosmic radiation, a thin drizzle of very fast protons and nuclei which apparently fill all our galaxy [13].

per square meter per second, with a mean energy of  $\sim$ 7 GeV and an energy spectrum that falls off at the rate of energy<sup>-5/2</sup>. The particles with energies below  $\sim$ 1 GeV are deflected by the earth's magnetic field and do not cause showers. The incident particles are protons, helium ions, and heavier ions [198, 200, 201, 203]. These heavy ions interact like individual nucleons. Ziegler et al. [201] report the incident flux as 87% protons and 13% neutrons from measurement. Almost all of the primaries effectively disappear by altitudes of 20,000m. The secondary particles produced by interaction of the primaries with the gas atoms of the atmosphere include nucleons, electrons and photons. The secondaries are either stopped within the atmosphere from producing further cascades of particles or spontaneously decay into other particles. Finally, the remnants of the cascade strike the earth.

The hit rates of different particle types, such as alpha particles or neutrons, are available from experimental results [72, 203]. It is, however, necessary to note that there are large variations in the documented measured fluxes. These may due to the effects attributed to magnetic latitude, solar cycles, time of day, season, and so on.

The natural radiation levels strongly depend on the activity of the sun and the average solar cycle is eleven years, with approximately four years of solar minimum and seven years of solar maximum shown in Figure 2.1 [9]. Neutrons, created by cosmic ray interactions with  $O_2$  and  $N_2$  in the air, reach a peak flux value at around 60,000 feet. At 30,000 feet the neutron flux is about 1/3 of the peak value and on the ground the neutron flux is 1/400 of its peak value [140] (Figure 2.2). Solar flare protons, together with electrons and alpha particles in smaller quantities, are emitted by the sun periodically during solar storms. These particles with high energy during a solar storm can cause

Figure 2.1: Sunspot numbers (y-axis) during solar cycles 19 through 23 recorded by Solar Influences Data Center (SIDC) in Belgium [9].

significant damage to spacecraft solar arrays [71] and produce SEU in electronics [90, 179]. The particle hit rate  $R_{PH}$  is given by the equation [200].

$$R_{PH} = \int_{E_{n,min}}^{E_{n,max}} F_n(E_n) dE_n \cdot A_t \tag{2.1}$$

where  $F_n(E_n)$  is the altitude and location dependent neutron flux [200] defined between neutron energies  $E_{n,min}$  and  $E_{n,max}$ , and  $A_t$  is the total silicon area of a logic circuit. Figure 2.3 [4] illustrates the neutron flux at a variety of altitudes and latitudes. Note that the flux density is more three times higher in Denver than it is in New York, even though both cities are on approximately the same latitude, but Denver is located at a much higher altitude [6].

Figure 2.2: Neutron flux versus altitude showing peak at about 60,000 ft [139].

In the terrestrial environment, another significant source of ionization in packaged devices is alpha particle coming from the radioactive impurities in the package materials. This radiation mechanism will be discussed in the next section.

# 2.4 How Soft Error Occurs in Silicon

This section discusses the soft errors caused by radiation and particle strikes.

# 2.4.1 Radiation Mechanisms in Semiconductors

Three principal radiation sources cause soft errors in advanced semiconductor devices [30]:

1. Alpha particles are emitted when the nucleus of an unstable isotope decays to a lower energy state. The particles contain kinetic energy in the range of 4 to 9

Figure 2.3: Neutron flux as a function of altitude and latitude [4].

MeV. There are many radioactive isotopes. However, uranium and thorium have the highest activity among naturally occurring materials. In the terrestrial environment, major sources of alpha particles are radioactive impurities such as lead-based isotopes in solder bumps of the flip-chip technology, gold used for bonding wires and lid plating, aluminum in ceramic packages, lead-frame alloys and interconnect metalization [50].

2. High-energy ( > 1 MeV) neutrons from cosmic radiation can induce soft errors in semiconductor devices via secondary ions produced by the neutron reaction with silicon nuclei. Cosmic rays that are of galactic origin react with the Earth's atmosphere to produce complex cascades of secondary particles. Less than 1% of the primary flux reaches ground level and the predominant particles include muons, neutrons, protons, and pions. Because pions and muons are short-lived and proton

and electrons are attenuated by Coulombic interaction with the atmosphere, neutrons are the most likely cosmic radiation sources to cause SEU in deep-submicron semiconductors at the terrestrial altitudes. The neutron flux is dependent on the altitude above the sea level, the density of the neutron flux increases with the altitude.

3. The third significant source of ionizing particles in electronic devices is the secondary radiation produced from the interaction of cosmic ray neutrons and boron [31]. This radiation is induced by low-energy cosmic neutrons, interacting with the isotope boron-10 or <sup>10</sup>B. Boron is extensively used as p-type dopant in silicon and is also specifically used in formation of BPSG (Borophosphosilicate glass) dielectric layer [31]. Boron has two isotopes: <sup>10</sup>B and <sup>11</sup>B of which <sup>10</sup>B is unstable. The reaction scheme is shown in Figure 2.4 [26]. In the <sup>10</sup>B(n, α) Li reaction the lithium nucleus is emitted with a kinetic energy of 0.84 MeV 94% of the time and with 1.014 MeV 6% of the time. The gamma photon has energy of 478 KeV, while the alpha particle is emitted with an energy of 1.47 MeV [26]. This mechanism has recently been found to be the dominant source of soft errors in 0.25μ and 0.18μ SRAMs fabricated with BPSG. Modern microprocessors use highly purified package materials and this radiation mechanism is greatly reduced, leaving the high-energy cosmic rays as the major reason for soft errors.

The SEU due to activation of  $^{10}B$  can be mitigated by removing BPSG material from the process flow. For future deep-submicron DRAM generations a greater suppression of soft error rate is expected for devices made with silicon-on-insulator (SOI) technologies [132].

Figure 2.4: Fission of  $^{10}B$  induced by the capture of a neutron (commonly happened in SRAMs) [26].

# 2.4.2 Sensitive Regions in Silicon Devices