# A Low Power, Low Noise Phase Locked Loop MMIC for Ku- and X-Band Applications

Except where reference is made to the work of others, the work described in this thesis is my own or was done in collaboration with my advisory committee. This thesis does not include proprietary or classified information.

Mark E. Ray

Certificate of Approval:

Stuart Wentworth Associate Professor Electrical and Computer Engineering

Robert Dean Assistant Professor Electrical and Computer Engineering Fa Dai, Chair Professor Electrical and Computer Engineering

Mark Nelms Department Head Electrical and Computer Engineering

George T. Flowers Dean Graduate School

# A Low Power, Low Noise Phase Locked Loop MMIC for Ku- and X-Band Applications

Mark E. Ray

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama May 9, 2009

# A Low Power, Low Noise Phase Locked Loop MMIC for Ku- and X-Band Applications

Mark E. Ray

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights.

Signature of Author

Date of Graduation

Vita

Mark Edward Ray, son of Roger and Lois (Battles) Ray, was born February 12, 1985, in Birmingham, Alabama. He graduated from Trinity Christian Academy, Oxford, Alabama, as co-Valedictorian in 2003. During his Junior and Senior years, he attended Gadsden State Community College in Gadsden, Alabama, becoming the first dual-enrollment student at Trinity Christian Academy. He entered Auburn University as a Sophomore in August, 2003, and he entered the co-operative education program in May, 2004. Mr. Ray worked for the U.S. Army Space and Missile Defense Command on alternating semesters and graduated cum laude with a Bachelor of Electrical Engineering in December, 2007. He entered Graduate School, Auburn University, in January, 2008. He is a Research Assistant for Dr. F. Dai in the field of Integrated Circuit (IC) design. He is married to Christina (Pizano) Ray and has a daughter Kaylee and son Andrew.

### THESIS ABSTRACT

# A Low Power, Low Noise Phase Locked Loop MMIC for Ku- and X-Band Applications

Mark E. Ray

Master of Science, May 9, 2009 (B.S., Auburn University, 2007)

94 Typed Pages

Directed by Fa Dai

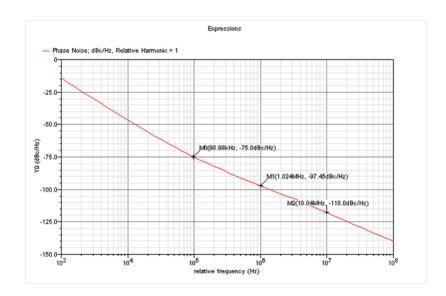

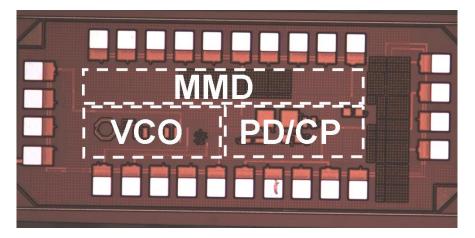

This paper presents the analysis, design, simulation, and test results for a Fractional-N PLL frequency synthesizer. The synthesizer is designed to cover multiple frequency bands, require low power, and have low noise. Detailed analysis is presented on loop dynamics, stability, and noise. All components in the circuit are designed for low noise and low power. For example, The Multi-Modulus Divider (MMD) is implemented such that it has the minimum number of gates and the lowest power consumption. The division ratios can be programmed from 128 to 159 and consumes 11mA under a 2.2V power supply, which corresponds to 59.2% power reduction compared to the prior art.

### Acknowledgments

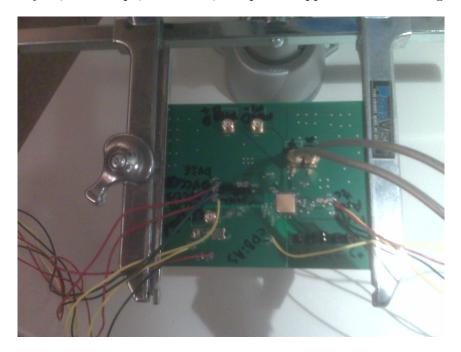

The author would like to thank Dr. Dai for his longsuffering attitude and teacher's heart during this student's learning process. In particular, I would like to thank William Souder for his design of the VCO, Printed Circuit Board, and immense help in all other facets of the design. The author would like to acknowledge Xueyang Geng, Desheng Ma, Yuan Yao, Xuefeng Yu, Zhenqi Chen, Jianjun Yu, and Joseph Cali for their help with the design and testing. I would like to thank Eric Adler, Geoffrey Goldman at U.S. Army Research Laboratory and Pete Kirkland, Rodney Robertson at U.S. Army Space and Missile Defense Command for funding this project, Nat Albritton, Bill Fieselman at Amtec Corporation for business management, and Perry Tapp, Ken Gagnon at Kansas City Plant for fabrication support.

The author would like to thank his wife, Christina, and children for their patience and sacrifice during this time. The author would like to thank his parents, Roger and Lois Ray, who encouraged and facilitated this achievement. A special thanks to Floyd and Kay Battles, Gaines and Barbara Ray, Robbin and Billy Dunn, Randy Barnett, and Keith Adams for their encouragement and support. Style manual or journal used <u>Journal of Approximation Theory (together with the style</u> known as "aums"). Bibliograpy follows van Leunen's *A Handbook for Scholars*.

Computer software used <u>The document preparation package  $T_EX$  (specifically  $\square T_EX$ )</u> together with the departmental style-file aums.sty.

# TABLE OF CONTENTS

| LIST OF FIGURES xi                                                                                                                                                                                                               |                                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| LIST OF TABLES                                                                                                                                                                                                                   | xiv                                                  |  |  |

| 1       INTRODUCTION         1.1       Purpose Statement         1.2       Technology Overview         1.2.1       SiGe HBTs         1.2.2       CMOS Logic and Bipolar Current Mode Logic         1.3       Thesis Organization | 1<br>1<br>3                                          |  |  |

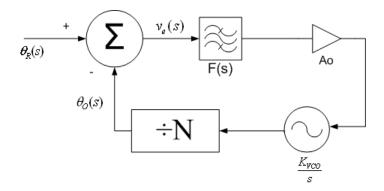

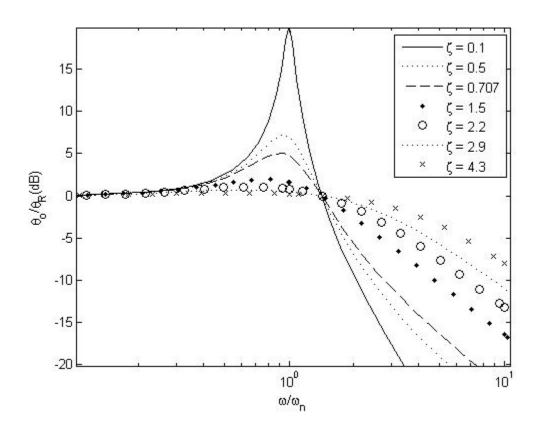

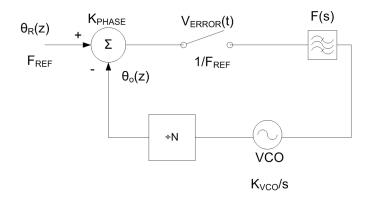

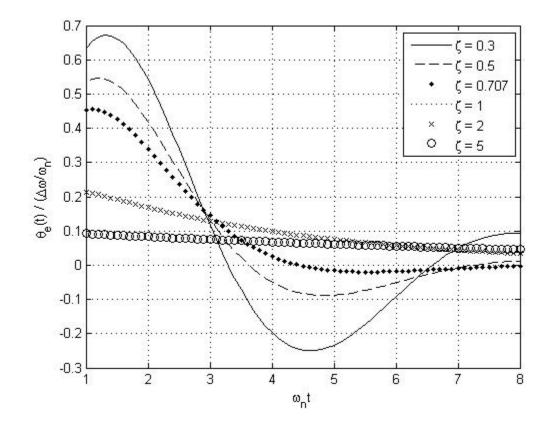

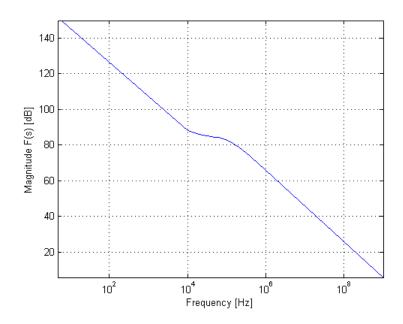

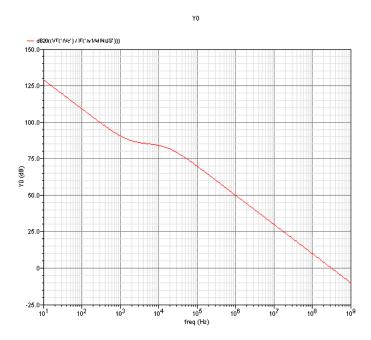

| <ul> <li>2 PLL SYSTEM ANALYSIS</li> <li>2.1 Introduction</li></ul>                                                                                                                                                               | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |

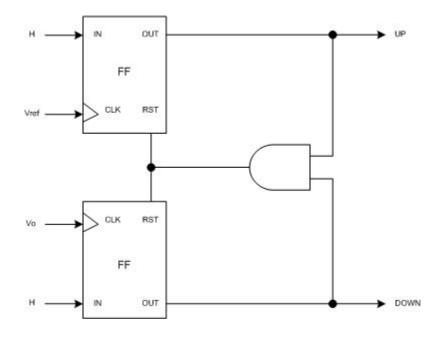

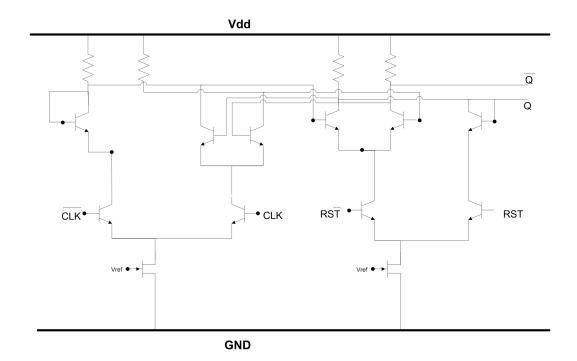

| 3       PHASE FREQUENCY DETECTOR         3.1       Introduction                                                                                                                                                                  | 22<br>25                                             |  |  |

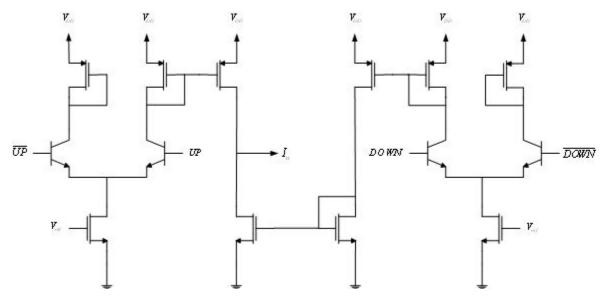

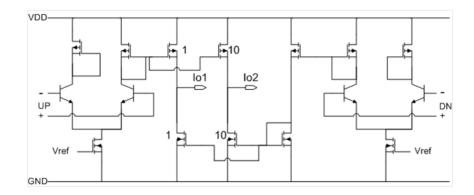

| <ul> <li>4 CHARGE PUMP</li> <li>4.1 Introduction</li></ul>                                                                                                                                                                       |                                                      |  |  |

|   |                  | 4.2.2 Current Source Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                  | 4.2.3 Reference Feedthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                  | 4.2.4 Current Source Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.3              | Differential Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

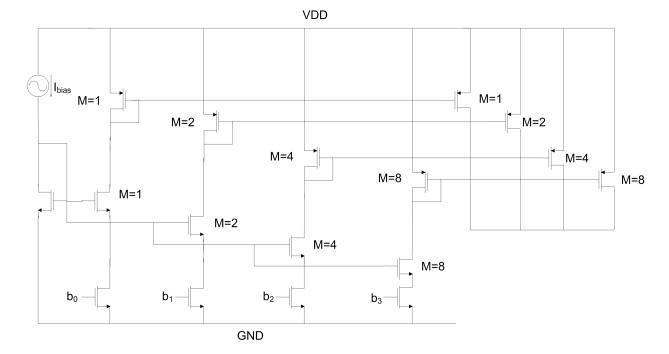

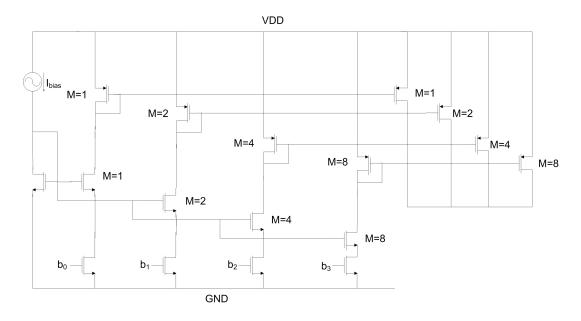

|   | 4.4              | Tunable Current Source    29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 4.5              | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5 | Loc              | 31 april apr |

|   | 5.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

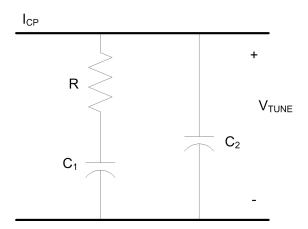

|   | 5.2              | Passive Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

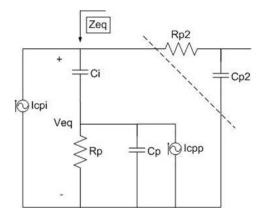

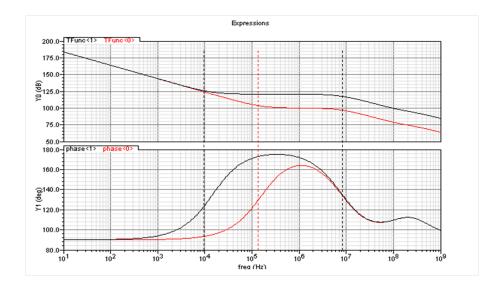

|   | 5.3              | Dual Path Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 5.4              | Simplification of Dual Path Loop Filter Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 5.5              | Tunable Loop Filter    35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 5.6              | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

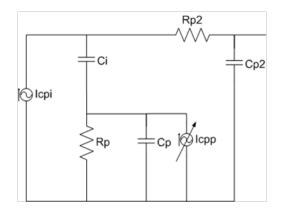

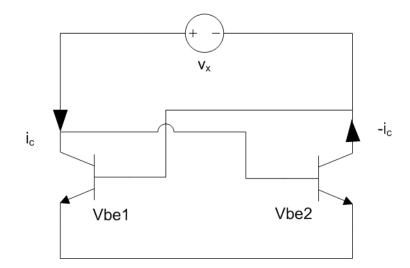

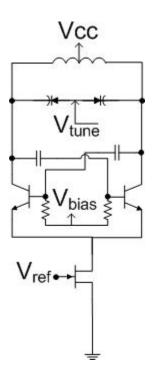

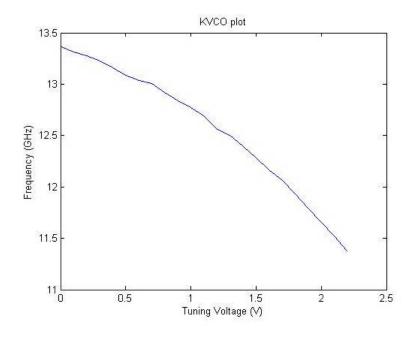

| 6 | Voi              | TAGE CONTROLLED OSCILLATOR 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 6.2              | Negative Gm Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 6.3              | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

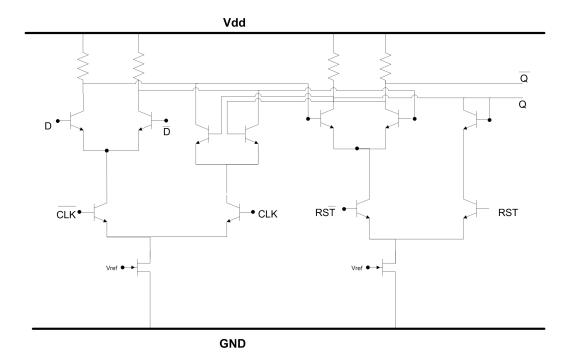

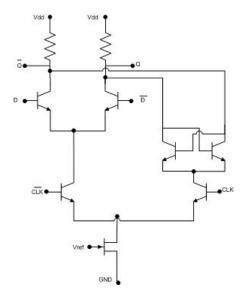

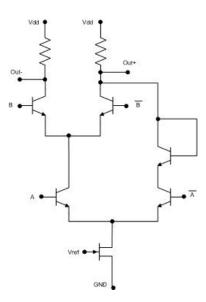

| 7 | Div              | IDER CIRCUIT DESIGN 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| • | 7.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 7.2              | Design Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 7.3              | Divider Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

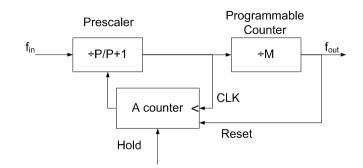

|   |                  | 7.3.1 Dual Modulus Prescaler with Pulse Swallow Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

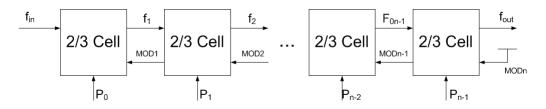

|   |                  | 7.3.2 Vaucher's Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

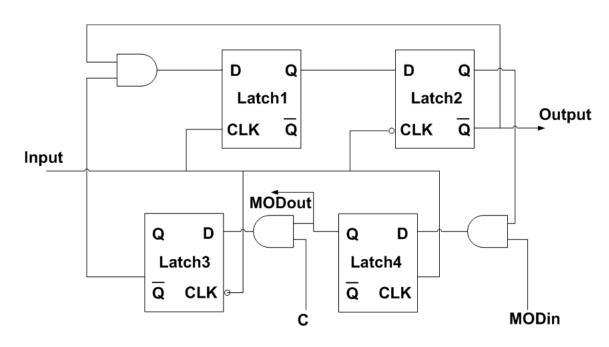

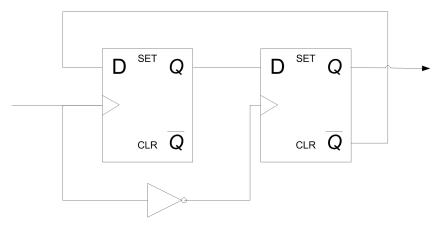

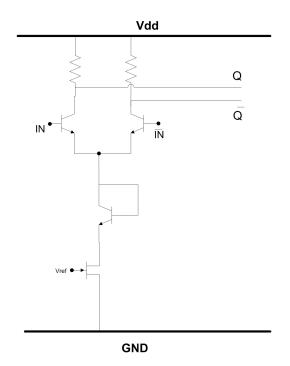

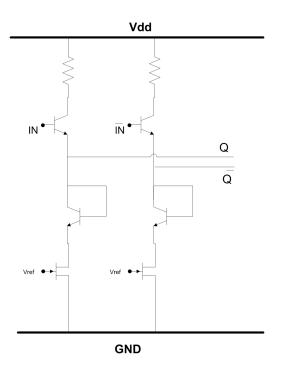

|   |                  | 7.3.3 Designing $P/P+1$ Cells $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

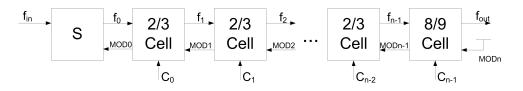

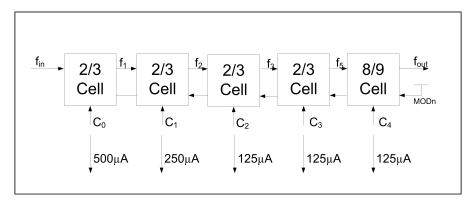

|   |                  | 7.3.4 Multi–Modulus Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

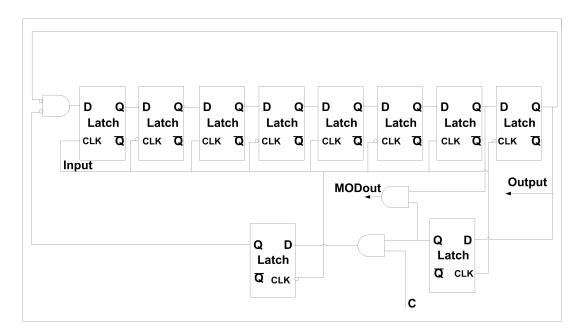

|   | 7.4              | Generic MMD Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

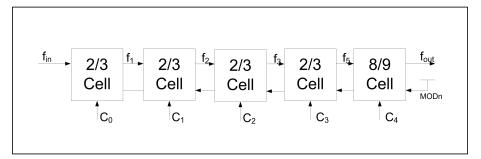

|   |                  | 7.4.1 Example: Design MMD for X-band Radar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

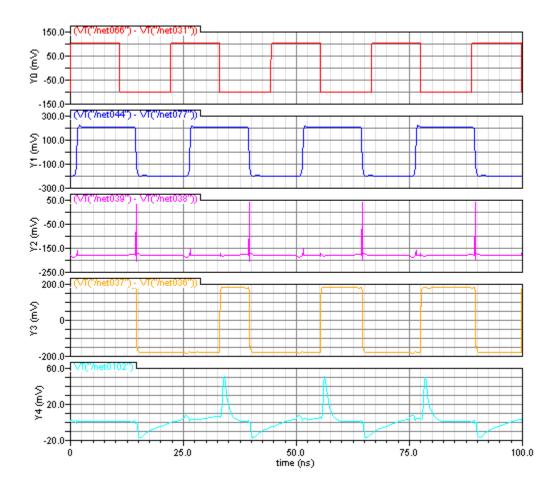

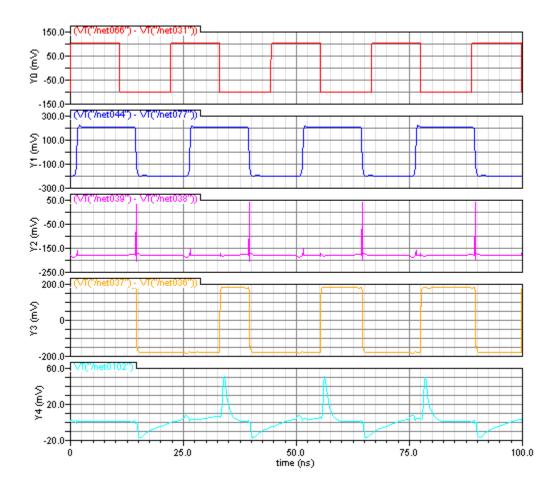

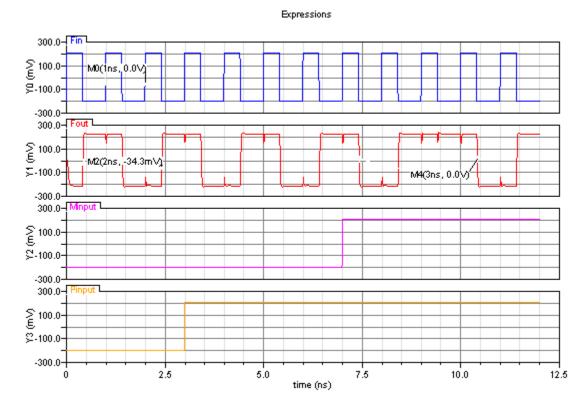

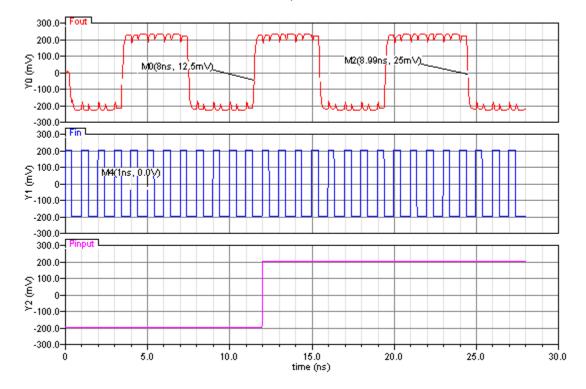

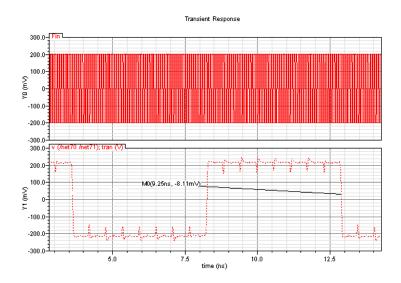

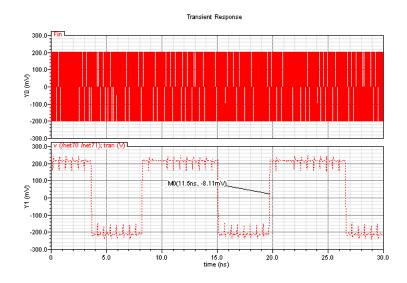

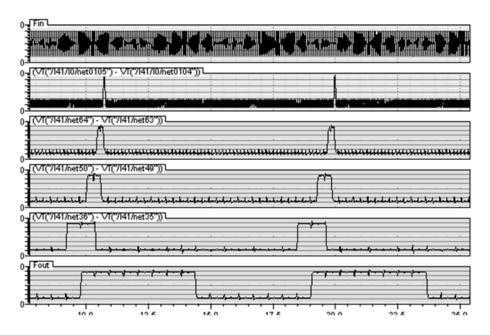

|   |                  | 7.4.2 Design Simulation of MMD in Cadence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 7.5              | Minimizing Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 7.6              | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

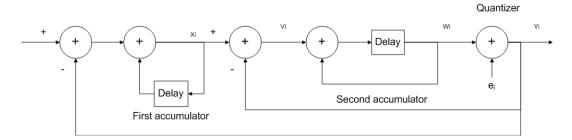

| 8 | $\Sigma \Lambda$ | MODULATION 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0 | 8.1              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 8.2              | Sampling and Quantization Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

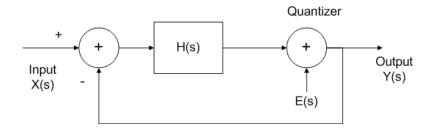

|   | 8.3              | Noise Shaping   57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

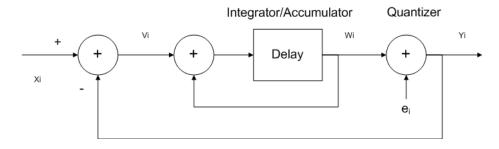

|   | 8.4              | $\Sigma\Delta \text{ Modulator} \qquad 58$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |