HIGH SPEED ROM-LESS DIRECT DIGITAL FREQUENCY SYNTHESIZER

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

Xuefeng Yu

Certificate of Approval:

Richard C. Jaeger Distinguished University Professor Emeritus Electrical and Computer Engineering

Guofu Niu Alumni Professor Electrical and Computer Engineering Fa Foster Dai, Chair Professor Electrical and Computer Engineering

Stuart M. Wentworth Associate Professor Electrical and Computer Engineering

George Flowers Dean Graduate School

## HIGH SPEED ROM-LESS DIRECT DIGITAL FREQUENCY SYNTHESIZER

Xuefeng Yu

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama August 10, 2009

## HIGH SPEED ROM-LESS DIRECT DIGITAL FREQUENCY SYNTHESIZER

Xuefeng Yu

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights.

Signature of Author

Date of Graduation

## DISSERTATION ABSTRACT

### HIGH SPEED ROM-LESS DIRECT DIGITAL FREQUENCY SYNTHESIZER

Xuefeng Yu

Doctor of Philosophy, August 10, 2009 (M.A., Inst. of Semiconductors, CAS, 2003) (B.S., Tsinghua University, 2000)

98 Typed Pages

Directed by Fa Foster Dai

This dissertation presents a complete flow for design and evaluation of high speed direct digital frequency synthesizer (DDS). Though some ultra high speed DDSs have already been reported in the literature, to satisfy the demand of keeping good balance between the power consumption and the high performance of DDS is still quite challenging for the analog designer and is worth to be explored from different perspectives.

As a digital method to direct generating sine or cosine waveforms with specific frequency, DDS does have many merits. DDS has fine frequency tuning step, fast frequency switching speed, precisely controlled output phases. Since there is no feedback loop in a DDS structure, the DDS doesn't suffer the internal loop delay like that in the phase-lockedloop (PLL) synthesizer. One major benefit that makes DDS stand out is that DDS can be directly modulated in the digital domain. It can be incorporated with various kinds modulation schemes to generate modulated signals. By this way, DDS can be served as an important component to build flexible and reconfigurable transmitter in the communication systems. DDS can also generate quadrature phases and multiple phases with ease. Other than sine and cosine waveforms, DDS can be utilized to synthesize arbitrary waveforms. Taking the advantage of well developed Silicon-Germanium (SiGe) process, it is possible to push the envelope of the DDS speed performance as well as keep the moderate budget of power consumption. The standard CMOS technology has also been investigated.

Several DDSs have been implemented with the non-linear digital to analog converters (DAC). The non-linear DAC can directly map the linear phase word into sine or cosine analog output without the assistance of the ROM. By eliminating the ROM, the speed of DDS can be dramatically improved. Due to the code dependent and frequency dependent non-ideal effects from the non-linear DAC, the unwanted harmonics and spurs of the DDS outputs have more significant impacts on the whole systems. In this dissertation, the spurs and harmonics from different sources such as truncation errors, limited DAC amplitude resolutions and non-ideal effects of DAC will be discussed.

During the design, a couple of issues such as clock feed through, clock skew, device matching properties will be addressed. In the layout period, an method that can automatically synthesize the layout of current source matrix block has been developed, which can alleviate the transistor matching problem coming from the fabrication.

The unique structure of a compact periodical waveform generator has also been investigated. In the waveform generator, a ring oscillator has been combined with a weighted non-linear DAC, thus the external clock and internal clock distributing circuits are no longer need. This will provide some benefits for certain on-chip test applications.

#### Acknowledgments

There are many people, throughout my life, provide me the supports in many different ways. Without them, I could not make this far all by myself. First of all, I would like to express my sincere gratitude to my advisor, Dr. Fa Foster Dai. He is more like an important friend to me both in my academic and my personal lives. His invaluable knowledge and wisdom, more than once helped me and guided me to overcome the troubles and difficulties during my study and research.

I would like to take this opportunity to thank my committee members, Dr. Richard Jaeger, Dr. Stuart Wentworth and Dr. Guofu Niu for taking their valuable times to serve in the committee. I would also thank all the professors and staffs in our ECE department. When I have a need, they are always ready to help.

I would express my appreciation to those who helped and made contributions to my research. Among them, the special thanks go to Dayu Yang, Vasanth Kakani, Yuan Yao, Xueyang Geng and Desheng Ma for their cooperations and assistants.

Finally, I want to thank my parents, my wife and my other family members for their unconditional love. They are always on my side, share my joys and sorrows, give me courages and hopes, let me persue my career and let me have a meaningful life. Style manual or journal used <u>Journal of Approximation Theory (together with the style</u> known as "auphd"). Bibliograpy follows van Leunen's *A Handbook for Scholars*.

Computer software used <u>The document preparation package  $T_{E}X$  (specifically  $IAT_{E}X$ )</u> together with the departmental style-file aums.sty.

# TABLE OF CONTENTS

| LI | ST OF                           | FIGURES                                                                                                                    | х                                                                                            |

|----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 1  | INT<br>1.1<br>1.2<br>1.3<br>1.4 | PRODUCTION         Background of DDS         Applications of DDS         Performance specifications of DDS         Outline | $     \begin{array}{c}       1 \\       1 \\       2 \\       4 \\       4     \end{array} $ |

| 2  | SIN                             | GLE PHASE SIGE DDS                                                                                                         | 5                                                                                            |

|    | 2.1                             | Introduction                                                                                                               | 5                                                                                            |

|    | 2.2                             | Ultra-high speed DDS architecture                                                                                          | 6                                                                                            |

|    | 2.3                             | DDS spectra purity                                                                                                         | 10                                                                                           |

|    | 2.4                             | 0                                                                                                                          | 12                                                                                           |

|    |                                 | 1                                                                                                                          | 13                                                                                           |

|    |                                 | 0                                                                                                                          | 16                                                                                           |

|    |                                 |                                                                                                                            | 18                                                                                           |

|    |                                 |                                                                                                                            | 19                                                                                           |

|    | 2.5                             |                                                                                                                            | 22                                                                                           |

|    | 2.6                             | 1                                                                                                                          | 23                                                                                           |

|    | 2.7                             | Conclusion                                                                                                                 | 31                                                                                           |

| 3  | QU                              | ADRATURE PHASES SIGE DDS                                                                                                   | 33                                                                                           |

|    | 3.1                             | Introduction                                                                                                               | 33                                                                                           |

|    | 3.2                             | Direct Modulations in DDS                                                                                                  | 33                                                                                           |

|    | 3.3                             | DDS circuit design                                                                                                         | 37                                                                                           |

|    |                                 | 3.3.1 Quadrature DDS architecture                                                                                          | 37                                                                                           |

|    |                                 | 3.3.2 Pipelined accumulator                                                                                                | 42                                                                                           |

|    |                                 |                                                                                                                            | 44                                                                                           |

|    |                                 | 0                                                                                                                          | 47                                                                                           |

|    |                                 | J.                                                                                                                         | 48                                                                                           |

|    | 3.4                             |                                                                                                                            | 49                                                                                           |

|    | 3.5                             | Conclusion                                                                                                                 | 55                                                                                           |

| 4  | QU                              | ADRATURE PHASES SIGE DDS WITH UP-CONVERSION                                                                                | 59                                                                                           |

| -  | 4.1                             |                                                                                                                            | 59                                                                                           |

|    | 4.2                             |                                                                                                                            | 59                                                                                           |

|    | 4.3                             | 8                                                                                                                          | 64                                                                                           |

|    | 4.4                             |                                                                                                                            | 70                                                                                           |

| 5  | RIN          | G OSCILLATOR BASED PERIODICAL WAVEFORM GENERATOR | 71 |  |  |

|----|--------------|--------------------------------------------------|----|--|--|

|    | 5.1          | Introduction                                     | 71 |  |  |

|    | 5.2          | Waveform generator architectures                 | 72 |  |  |

|    | 5.3          | Circuits of the waveform generator               | 74 |  |  |

|    |              | Experiment results                               |    |  |  |

|    | 5.5          | Conclusion                                       | 81 |  |  |

| 6  | SUN          | AMARY AND FUTURE WORKS                           | 82 |  |  |

|    | 6.1          | Summary of the works                             | 82 |  |  |

|    | 6.2          | Future works                                     | 83 |  |  |

| BI | Bibliography |                                                  |    |  |  |

# LIST OF FIGURES

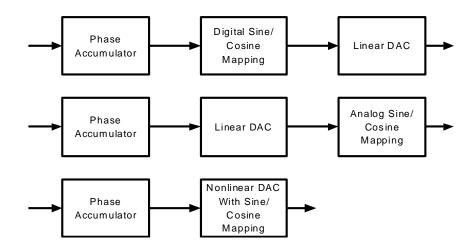

| 2.1  | DDS architectures                                                                                                                                                                                                                                | 7  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

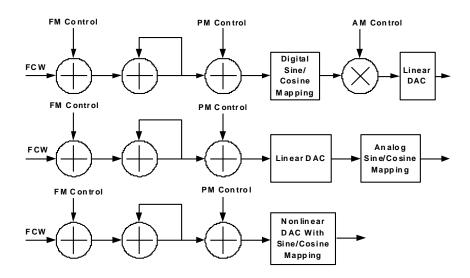

| 2.2  | Digital modulation capability in different DDSs                                                                                                                                                                                                  | 9  |

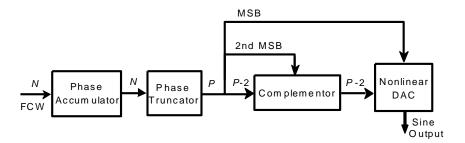

| 2.3  | Conceptual diagram of the ROM-less DDS                                                                                                                                                                                                           | 10 |

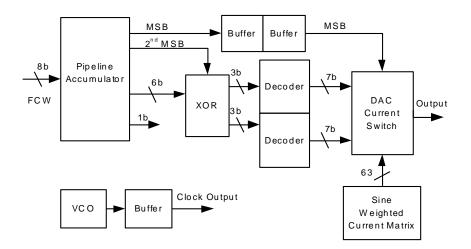

| 2.4  | Block diagram of the implemented DDS MMIC                                                                                                                                                                                                        | 13 |

| 2.5  | NxM generic architecture of a pipelined accumulator                                                                                                                                                                                              | 15 |

| 2.6  | CML full adder circuit                                                                                                                                                                                                                           | 18 |

| 2.7  | Current switch circuit of the nonlinear DAC                                                                                                                                                                                                      | 20 |

| 2.8  | Synchronous switch control circuit of the nonlinear DAC                                                                                                                                                                                          | 21 |

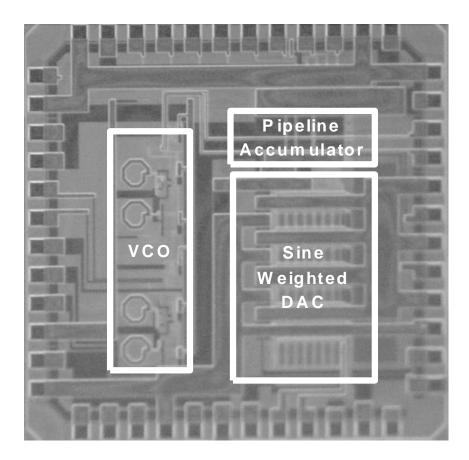

| 2.9  | Die photo of DDS chip                                                                                                                                                                                                                            | 24 |

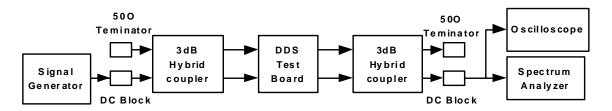

| 2.10 | DDS MMIC test setup                                                                                                                                                                                                                              | 24 |

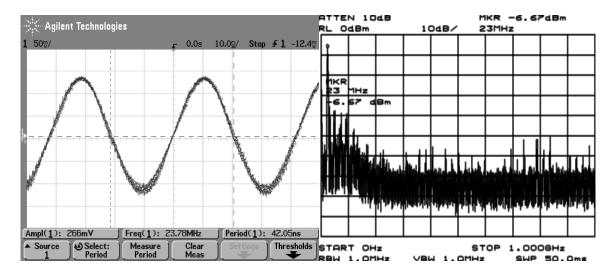

| 2.11 | Measured DDS output waveform (a) and spectrum (b) with a 23.5MHz output (FCW=1) and a clock at 12.021GHz                                                                                                                                         | 27 |

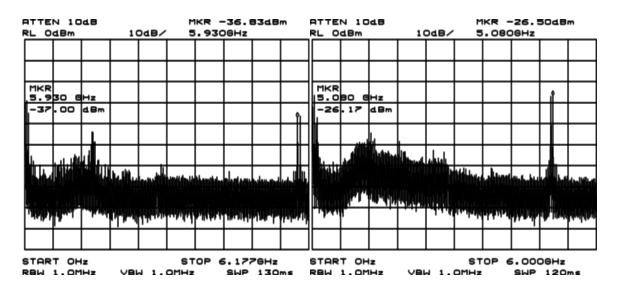

| 2.12 | Measured DDS output spectra at Nyquist rate (FCW=511). (a) The output frequency at 5.930GHz and the image tone at 5.98GHz with a clock at 11.913GHz; (b) The output frequency at 5.04GHz and the image tone at 5.08GHz with a clock at 10.110GHz | 27 |

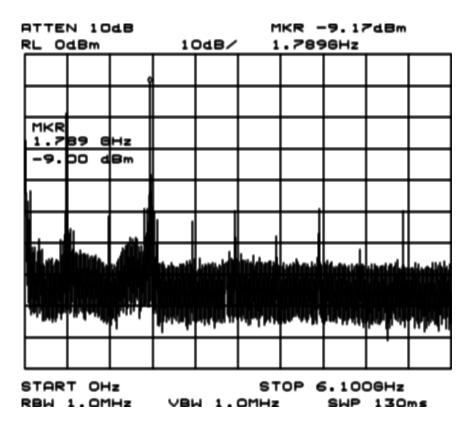

| 2.13 | Measured DDS output spectrum with a 1.7898GHz output and a 9.59GHz clock                                                                                                                                                                         | 28 |

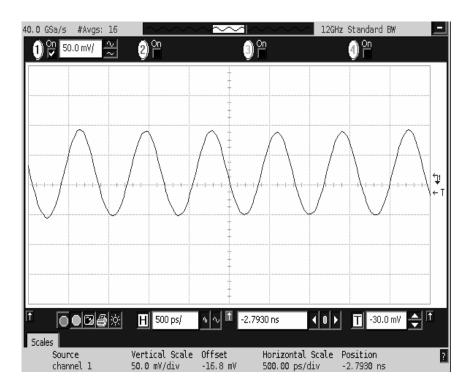

| 2.14 | Measured DDS output waveform with $1.125\mathrm{GHz}$ output and 9GHz clock                                                                                                                                                                      | 29 |

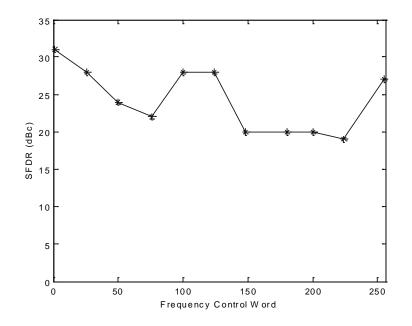

| 2.15 | Measured DDS output SFDR versus frequency control word at -20C ambient temperature                                                                                                                                                               | 30 |

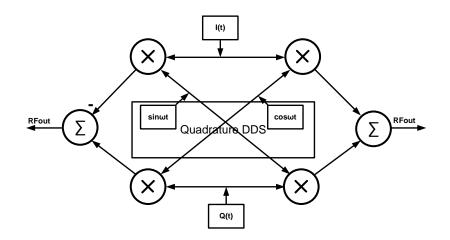

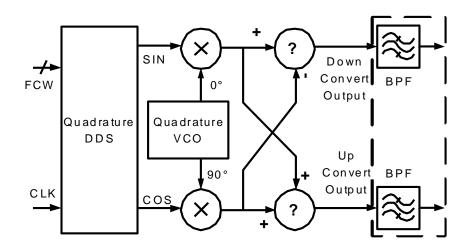

| 3.1  | Direct modulation through a DDS                                                                                                                                                                                                                  | 35 |

| 3.2  | Extend the output frequency range using a quadrature DDS and SSB mixers                        | 36 |

|------|------------------------------------------------------------------------------------------------|----|

| 3.3  | Conceptual drawing of the quadrature DDS RFIC                                                  | 37 |

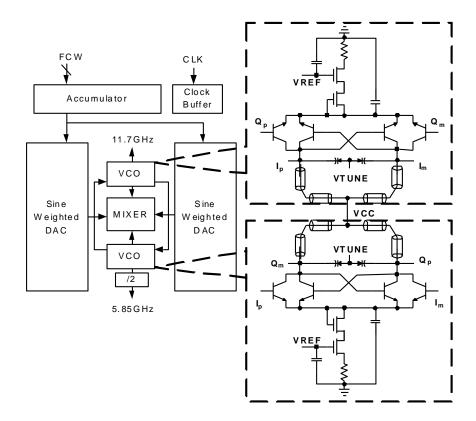

| 3.4  | Detailed block diagram of the qaudarture DDS                                                   | 40 |

| 3.5  | Output sine and cosine waveform depending on the symmetry property of the sine waveform        | 43 |

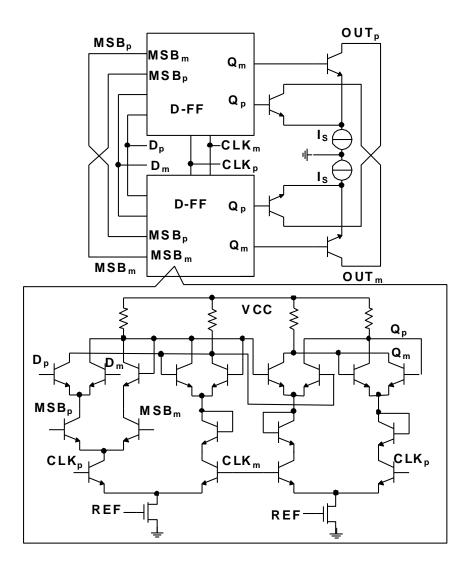

| 3.6  | DAC current switch circuit                                                                     | 45 |

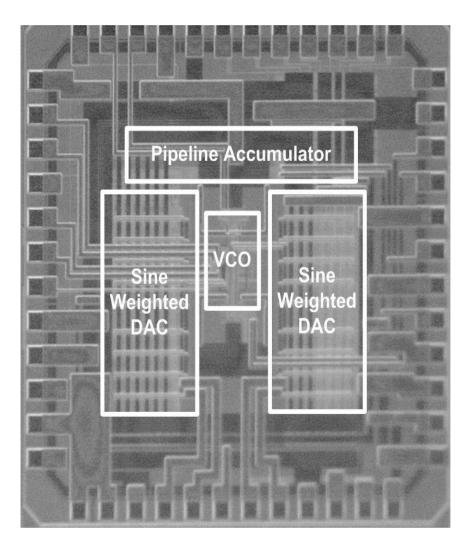

| 3.7  | Die photo of the quadrature DDS MMIC                                                           | 51 |

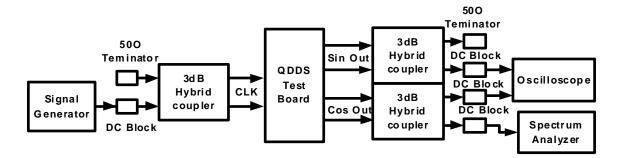

| 3.8  | Test setup of the quadrature DDS RFIC                                                          | 51 |

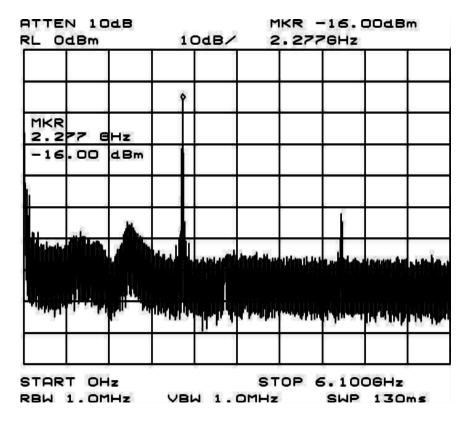

| 3.9  | Measured single phase DDS output spectrum with clock at 9.07 GHz and output at 2.227GHz        | 52 |

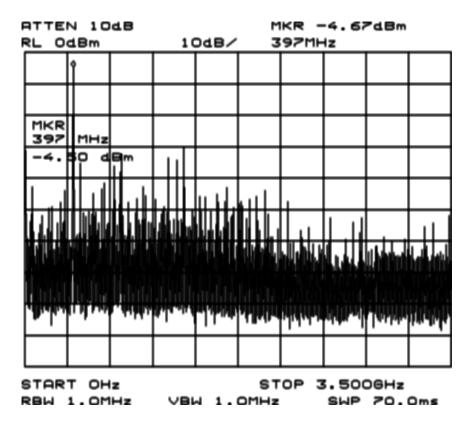

| 3.10 | Measured quadrature phase DDS output spectrum with clock at 5.44 GHz and output at 0.397GHz    | 53 |

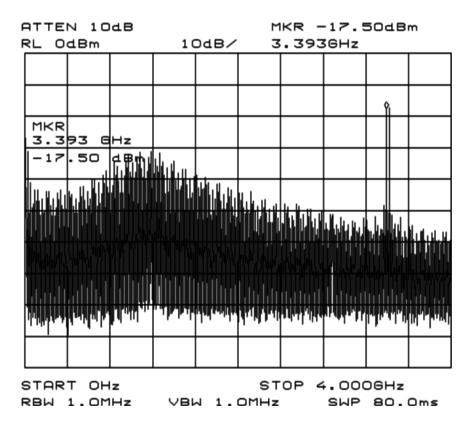

| 3.11 | Measured qaudrature phase DDS output spectrum with clock at 6.815 GHz and output at 3.394GHz   | 55 |

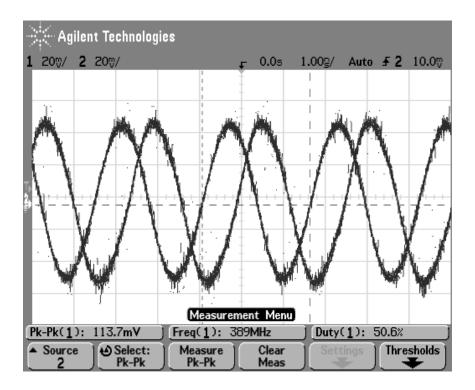

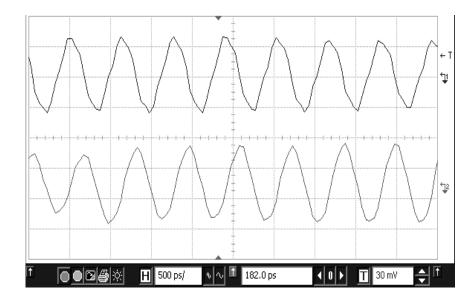

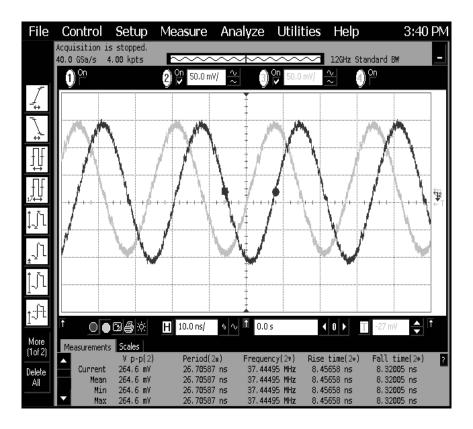

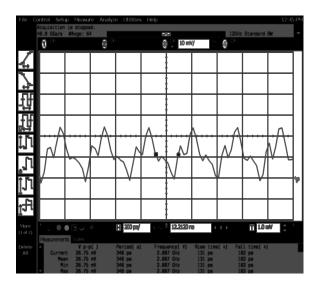

| 3.12 | Measured DDS output waveforms without deglitch filter at 0.389GHz with clock at 6.2GHz         | 56 |

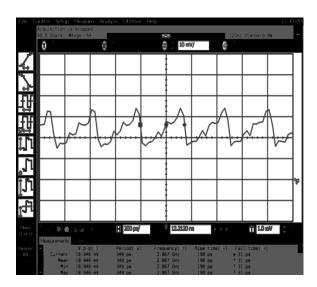

| 3.13 | Measured quadrature DDS output waveforms at $1.58\mathrm{GHz}$ with clock at $6.3\mathrm{GHz}$ | 56 |

| 4.1  | Concept diagram of the frequency synthesizer                                                   | 60 |

| 4.2  | Block diagram with the circuit of quadrature VCO                                               | 61 |

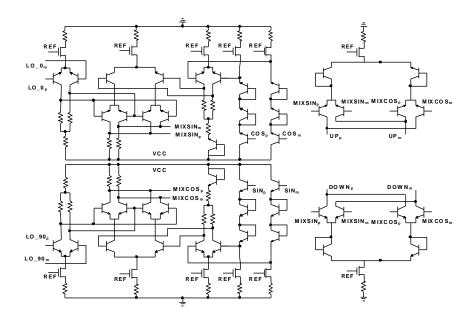

| 4.3  | Circuits of up-convert and down-convert mixers                                                 | 63 |

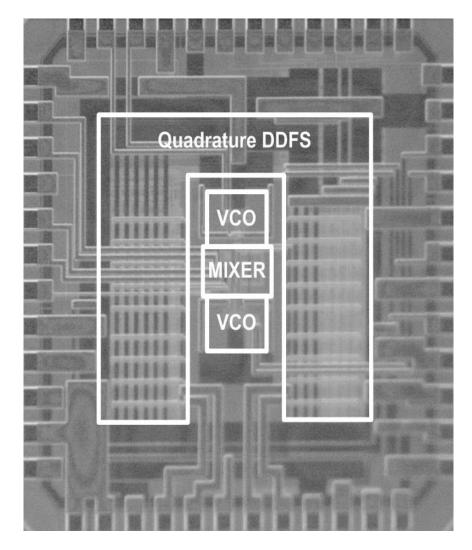

| 4.4  | Frequency synthesizer die photo                                                                | 65 |

| 4.5  | Measured 37MHz output waveforms with a 6.4GHz QDDS                                             | 66 |

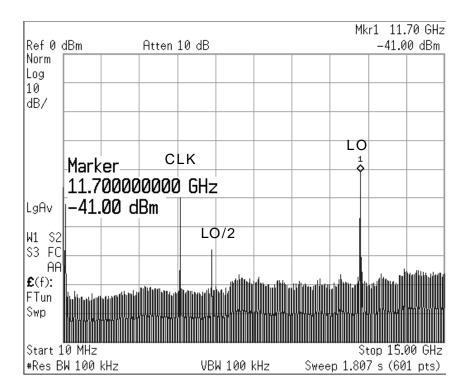

| 4.6  | Measured output spectra of 4.6GHz QDDS clock input and 11.7GHz LO output                       | 67 |

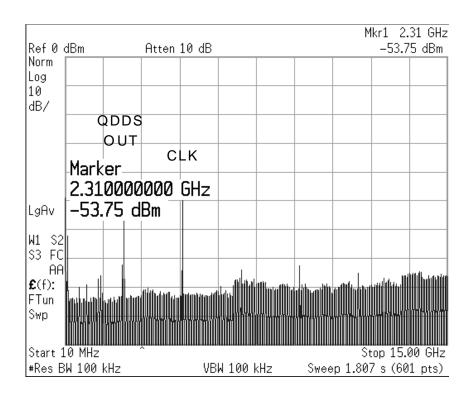

| 4.7  | Measured output spectra of 4.6GHz QDDS clock input and 2.3GHz QDDS output                      | 68 |

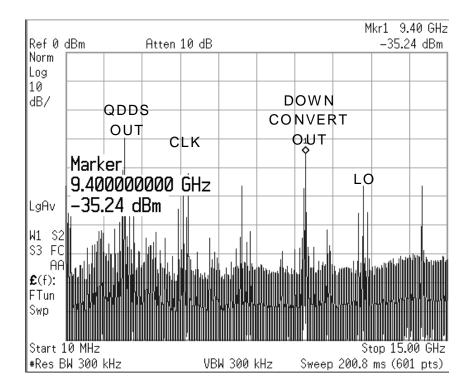

| 4.8  | Measured output down-converted 9.4GHz output                                        | 69 |

|------|-------------------------------------------------------------------------------------|----|

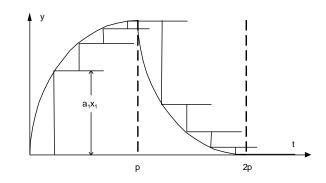

| 5.1  | One cycle of the waveform with constant sampling step $\ldots \ldots \ldots \ldots$ | 72 |

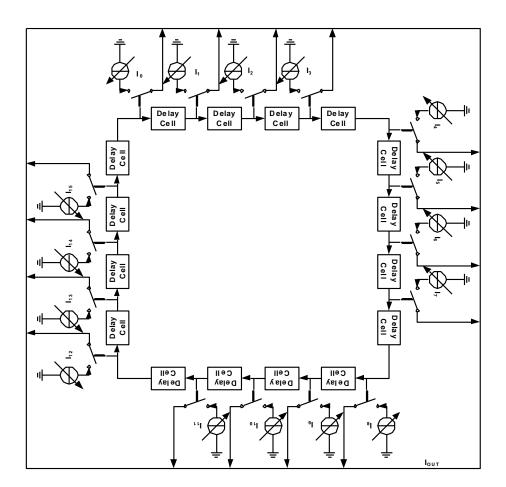

| 5.2  | Block diagram of the ring oscillator waveform generator                             | 73 |

| 5.3  | Simplified circuit of current switch with 3-bit+sign programmable current source    | 75 |

| 5.4  | Die photo of the waveform generator                                                 | 77 |

| 5.5  | Simulated output waveform during data loading                                       | 78 |

| 5.6  | Simulated output sine waveform                                                      | 78 |

| 5.7  | Simulated output waveform during transition                                         | 79 |

| 5.8  | Measured output waveform during data loading                                        | 79 |

| 5.9  | Measured synthesized arbitrary waveform                                             | 80 |

| 5.10 | Measured synthesized arbitrary waveform                                             | 80 |

## Chapter 1

## INTRODUCTION

### 1.1 Background of DDS

High speed frequency synthesizer with fine tuning step and large tuning range is the crucial part in the modern wireless communication. However, the conventional phase locked loop (PLL) based frequency synthesizer can't meet the requirement due to internal loop delay, low resolution and limited tuning range of voltage controlled oscillator (VCO). DDFS provides many advantages including fast frequency switching, fine frequency tuning resolution, continuous-phase switching, and allowing direct phase and frequency modulations in the digital domain.

The traditional DDFS contains the ROM to store sine waveform data and the ROM size is exponentially proportional to the desired phase resolution. The ROM for sine lookup table occupies the majority of the DDFS area and also limits its maximum operation frequency due to the delay through the multi-layer decoders. The simplest method is to reduce the ROM size is based on the quarter-wave symmetry in the sine function and cut the ROM size by a factor of 4. Though many other ROM compression methods have been proposed, such as trigonometric approximation and parabolic approximation [18], the problems indicated above still exist.

A novel approach is to replace the conventional linear DAC that converts digital amplitude words to analog amplitude waveform with a nonlinear one that converts the digital phase word into an analog sine waveform directly [13]. Thus the ROM is completely removed and the performance of the DDFS is improved significantly. As to design the high speed nonlinear DAC, current-steering DAC [15] becomes the ideal candidate which can generate a Nyquist output signal with high accuracy at a high update rate [26].

#### 1.2 Applications of DDS

Integrating a millimeter-wave (mm-wave) frequency synthesizer into a wireless transceiver that can accommodate multiple standards coexisting in communication systems has been a challenging task and attracted great interest in recent years. One conventional approach to cover the frequency bands for different standards is to use a phase-locked loop (PLL) based frequency synthesizer. However, multi-band PLL synthesizers consume large die area and power. Digital synthesis of highly complex wideband waveforms at the highest possible frequency would considerably reduce the size, weight, power and cost of modern communication systems. Recent developments in communication and radar systems are placing increasing demands on low power consumption, high output frequency, fine frequency resolution, fast channel switching and versatile modulation capability for frequency synthesis. These requirements are surpassing the performance capabilities of conventional analog PLL synthesizers. It is difficult for the PLL-based frequency synthesizer to meet these requirements due to internal loop delay, low resolution, modulation problems and the limited tuning range of the voltage-controlled oscillator (VCO). In contrast, a direct digital synthesizer (DDS) generates a digitized waveform at a desired frequency by accumulating the phase word at a higher clock frequency. DDS is a digital technique for frequency synthesis, waveform generation, sensor excitation, and digital modulation/demodulation. Since there is no feedback in a DDS structure, the DDS is capable of extremely fast frequency

switching or hopping at the speed of the clock frequency. A DDS provides various modulation capability and many other advantages, including fine frequency tuning resolution, continuous-phase switching and the ability to provide quadrature signals with accurate I/Q matching. Furthermore, a DDS can generate arbitrary waveforms in the digital domain. The increasing availability of ultra high-speed DACs allows a DDS to operate at mm-wave frequency, providing an attractive alternative solution to conventional analog PLL synthesizers.

Radar systems demand highly accurate control over the output frequencies and phases of the frequency synthesizers in radar transceiver for coherent detection. It is not uncommon that the modern radar systems require frequency synthesizers with low power consumption, high output frequency, fine frequency resolution, fast channel switching and versatile modulation capability. These requirements are surpassing the performance capabilities of conventional analog phase-locked loops (PLL). It is difficult for the conventional PLL-based frequency synthesizer to meet these requirements due to internal loop delay, low resolution, modulation problems and the limited tuning range of the voltage-controlled oscillator (VCO). In contrast, a direct digital synthesizer (DDS) is capable of fast frequency hopping, fine frequency tuning, continuous-phase switching, direct modulation, arbitrary waveform and quadrature signal generations. The advance of technology brings the device operating frequency to a higher level, increases the circuit density and cuts down the manufacture cost. With the improvement of the technology, it becomes feasible to implement a single chip DDS operating at mm-wave frequency at a reasonable cost, replacing the conventional analog PLL synthesizers in radar systems.

#### **1.3** Performance specifications of DDS

One of the most important metric for DDS is the spurious free dynamic range (SFDR). SFDR is defined as the ratio of the RMS amplitude of the carrier frequency (maximum signal components) to the RMS value of their next largest distortion component. SFDR is usually measured in dBc. It can be shown as following

$$SFDR = 20log_{10} \frac{V_{carrier}}{max(V_{spur})}$$

(1.1)

Another useful metric for DDS is the signal-to-noise ratio(SNR). SNR is the ratio of the power of the desired signal to the total power of noise signals, which is always expressed in dB. It can be shown as following

$$SNR = 10log_{10} \frac{P_{carrier}}{\sum P_{spur}}$$

(1.2)

## 1.4 Outline

This dissertation is organized as follows: The first chapter is some basic introduction of the DDS. The second chapter introduces the ultra-high speed single phase DDS design. In the third chapter, the single phase DDS will be extended to quadrature DDS. In chapter four, by adding the internal mixer, the output frequency of a multiple GHz DDS can be moved to a higher frequency. In chapter five, a ring oscillator based periodical waveform generator will be presented. The last chapter is the summary of the whole work and gives some thoughts for the future work.

## Chapter 2

## SINGLE PHASE SIGE DDS

#### 2.1 Introduction

Though CMOS technology can be used to achieve better integration and reduce total cost, heterojunction bipolar transistor (HBT) technology is more favorable in microwave analog circuit design for their high current gain and low device noise in this frequency range. Two major candidates for high speed DDS design are indium phosphide (InP) HBT and silicon germanium (SiGe) HBT technologies. The mobility of the carriers in InP devices is high and the cut off frequency of the device can be well over 300GHz, but the yield of complicated InP designs still is lower than those of other mature technologies. Taking the device performance, manufacture cost and integration density into consideration, SiGe process appears to be a better choice for DDS circuit design.

Radar systems demand highly accurate control over the output frequencies and phases of the frequency synthesizers in radar transceiver for coherent detection. It is not uncommon that the modern radar systems require frequency synthesizers with low power consumption, high output frequency, fine frequency resolution, fast channel switching and versatile modulation capability. These requirements are surpassing the performance capabilities of conventional analog phase-locked loops (PLL). It is difficult for the conventional PLL-based frequency synthesizer to meet these requirements due to internal loop delay, low resolution, modulation problems and the limited tuning range of the voltage-controlled oscillator (VCO). In contrast, a direct digital synthesizer (DDS) is capable of fast frequency hopping, fine frequency tuning, continuous-phase switching, direct modulation, arbitrary waveform and quadrature signal generations. The advance of technology brings the device operating frequency to a higher level, increases the circuit density and cuts down the manufacture cost. With the improvement of the technology, it becomes feasible to implement a single chip DDS operating at mm-wave frequency at a reasonable cost, replacing the conventional analog PLL synthesizers in radar systems.

#### 2.2 Ultra-high speed DDS architecture

A conventional DDS consists of three primary building blocks, a phase accumulator, sine/cosine mapping block, and digital-to-analog converter (DAC), which performs the digital amplitude to analog amplitude conversion [20]. A deglitch filter is normally added off-chip to smooth the waveform by removing the unwanted spectral components. The phase control word (FCW) at the input of the phase accumulator determines the output frequency of the DDS. The sine/cosine block maps the accumulated phase to the sine or cosine amplitude.

Depending on the transfer characteristic of the DAC, a DDS can be characterized in three types, as shown in Fig. 2.1. The first type represents the conventional DDS that has a linear DAC, and the phase-to-amplitude conversion is done in the digital domain using a sine look-up table [20]. The second one also contains a linear DAC, but the sine/cosine conversion is performed in the analog domain by converting an analog triangle waveform to an analog sine waveform [12]. The third type is a ROM-less DDS that combines both the sine/cosine mapping and digital-to-analog conversion in a nonlinear DAC whose current sources are weighted with sine amplitude information [2][13].

Figure 2.1: DDS architectures

The first type of DDS has several variations, depending upon the different mapping methods employed in the phase-to-amplitude look-up table. In the traditional DDS, a sine look-up table is built using a ROM which stores the sine/cosine mapping information. However, the ROM size expands exponentially with phase resolution. The sine ROM lookup table occupies the majority of the DDS area, and also limits its maximum operation frequency due to delay through the phase decoders.

The simplest way to reduce the ROM size is to employ the quarter-wave symmetry of a sine function, reducing the ROM size by a factor of 4. Numerous ROM compression techniques have been proposed, including trigonometric approximation [19][16], parabolic approximation [18], and interpolation [14]. Even though these compression methods partially alleviate the problem, the internal delay caused by retrieving ROM data still restricts the speed of the DDS. Another approach employs series expansions, such as a Taylor expansion or polynomial expansion, to approximate the ideal curve. The coordinate rotating digital computer (CORDIC) method calculates the amplitude directly, based on the projection of a rotating vector in a polar axial system [25]. Both the series expansion and CORDIC approaches require a considerable amount of hardware, and the complexity limits the final speed, so these structures normally appear in DDS implementations below the multiple GHz range. Using improved differential CORDIC [10], the theoretical output of the ROM-based DDS can reach the GHz range, but its performance still needs proof-insilicon. Implementing a GHz ROM simply consumes too large a power and area. Ref. [10] implemented a linear-DAC DDS in 0.25 m CMOS technology with 1.2GHz clock speed. However, it's very difficult, if not presently impossible, to implement a ROM-based DDS with clock frequency beyond 10GHz and amplitude resolution larger than 8 bits.

The second type converts a linear analog triangle waveform to an analog sine waveform. This technique utilizes bipolar differential pairs to perform the conversion task by choosing degenerating resistor values and biasing currents to fit the first two terms of a Taylor expansion. Theoretically, 0.1% total harmonic distortion can be achieved, which corresponds to a 30dB signal-to-noise ratio, or 5 effective bits. Stringent current requirements in the differential pairs limit the usage of this method, particularly when the capacitive load that must be driven varies as a result of different applications. The third type of DDS is a ROM-less DDS with a nonlinear DAC. The first two structures require a linear DAC, while in a ROM-less DDS, the ROM is removed, and a nonlinear DAC serves as the phase-to-amplitude and digital-to-analog converter. The sine weighted DAC eliminates the sine look-up table, which is the speed and area bottleneck for high-speed DDS implementations.

Our design employs the ROM-less structure with a nonlinear current steering DAC. This structure combines the sine/cosine mapping block and the digital amplitude to analog amplitude conversion block, thus significantly improving the speed of the DDS. In the ROM-less DDS design, the current steering DAC structure is an ideal candidate capable of

Figure 2.2: Digital modulation capability in different DDSs

generating a Nyquist output signal with excellent accuracy and high update rate. Digital domain modulation can be easily implemented in a DDS, as illustrated in Fig. 2.2. Frequency modulation (FM), chirp, and phase modulation (PM) can be easily implemented in all three types of DDS. However the first type can implement amplitude modulation (AM) in digital domain prior to the DAC, while the other two can implement AM only in the analog domain. Delta-Sigma modulation can also be added in the DDS to improve the output spectral purity and to reduce the effective number of phase bits [5].

Quadrature rotation can also be implemented in a DDS with quadrature outputs. A quadrature DDS consists of a shared phase accumulator and two DACs with sine and cosine outputs. If linear DACs are used, quadrature rotation can be implemented in digital domain, since digital quadrature waveforms are available at the inputs of the DACs. For a ROM-less DDS, quadrature rotation can only be implemented in analog domain using mixers. A mm-wave quadrature DDS has been implemented in SiGe technology with clock frequency beyond 6GHz [34].

Figure 2.3: Conceptual diagram of the ROM-less DDS

### 2.3 DDS spectra purity

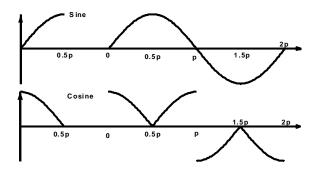

The conceptual block diagram of the ROM-less DDS, employing a nonlinear DAC, is shown in Fig. 2.3. In order to save die area and power, the phase accumulator output is normally truncated. For instance, the output of the phase accumulator is truncated into P bits, according to the signal-to-noise ratio (SNR) requirement of the DDS output. The two MSBs are used to determine the quadrant of the phase accumulator output, according to the quadrant symmetry of the sine wave. The lowest P - 2 bits are fed through the complementor and converted to a sine waveform by the nonlinear DAC. The sinusoidal waveform data are programmed into the current source matrix of the DAC, and the output currents are summed from the DAC output. In the process of discrete phase accumulation and phase word truncation, spurs and quantization noise will be introduced at the DDS output spectrum as discussed below.

The N-bit FCW feeds a phase accumulator that controls the output frequency of the synthesized sine waveform as

$$f_{out} = \frac{FCW}{2^L} f_{clock} \tag{2.1}$$

where fclk is the DDS clock frequency. Thus, the desired output period is given by  $T_0 = \frac{2^N}{FCW}T_{clk}$ . For an N-bit discrete phase accumulator, there is another periodicity, i.e.,  $T_{spur} = \frac{2^N}{GCD(FCW,2^N)}T_{clk}$ , where GCD(a,b) denotes the greatest-common-divisor of a and b. The accumulator repeats its value at the intervals of  $T_{spur}$ , which generates equally spaced spurious tones located at multiples of the frequency

$$f_{spur} = \frac{GCD(FCW, 2^N)}{2^N} f_{clock}$$

(2.2)

When the input frequency word is a power of two, i.e.,  $FCW = 2^i$ , there will be no spurs due to discrete phase accumulation. In this case,  $GCD(FCW, 2^N) = FCW$ , namely, the accumulator output repeats at the same value after every overflow.

The phase truncation process also introduces spurs and quantization noise, which can be modeled as a linear additive noise to the phase of the sinusoidal wave. Phase truncation error is periodic [16]. If the P most significant bits (MSB) of an N-bit phase word are used to address the DAC or lookup table, the truncation resultant spurs are mixed with the DDS output frequency generating spurs at multiples of the frequency

$$f_{spur} = \frac{GCD(FCW, 2^{N-P})}{2^{N-P}} f_{clock}$$

$$\tag{2.3}$$

Note the phase truncation causes errors only when the greatest-common-divisor  $GCD(FCW, 2^N) \leq 2^{N-P}$ . Otherwise, the N - P least-significant bits (LSB) of the phase word vanish and the phase truncation does not cause any error.

In addition to the spurious components, the DDS output waveform will suffer AM distortion due to the finite number of levels that cannot accurately represent the output

waveform. The envelope of the DDS output waveform is modulated by a sine wave with the frequency of

$$f_{envelope} = \frac{2^{N-1} \mod FCW}{2^{N-1}} f_{clock}$$

(2.4)

where AmodB represents the integer residue of A modulo B. If  $2^N modFCW = 0$ , no amplitude modulation will be observed. For a Nyquist output, the frequency of the amplitude modulation becomes

$$f_{envelope} = \frac{2^{N-1} \mod (2^{N-1}-1)}{2^{N-1}} f_{clock} = \frac{1}{2^{N-1}} f_{clock}$$

(2.5)

Therefore, the envelope of the DDS output waveform is modulated by a low frequency signal except when the FCW is an integer power of 2 such that  $2^N \mod FCW = 0$ .

#### 2.4 DDS circuit design

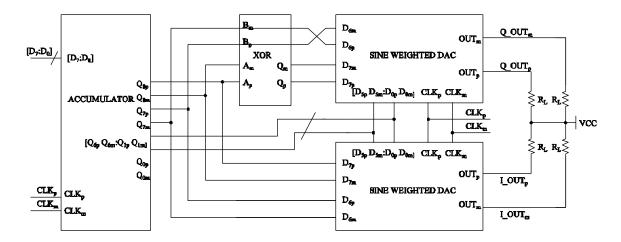

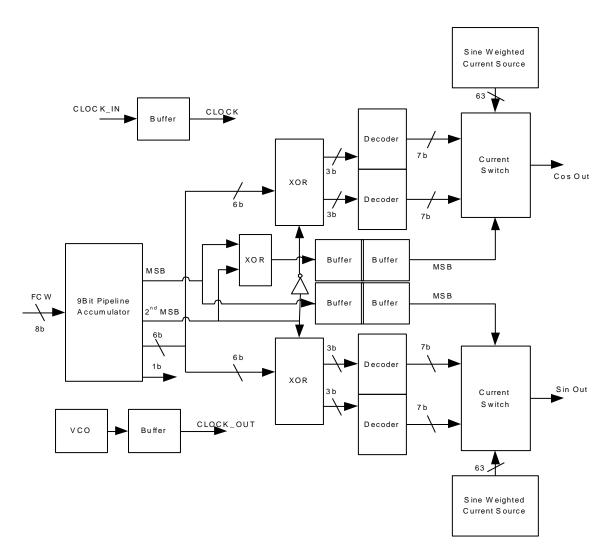

The implemented ultra-high speed DDS MMIC is comprised of a 9-bit pipeline accumulator, and an 8-bit sine-weighted current steering DAC, as shown in Fig. 2.4. Since the output frequency cannot exceed the Nyquist rate, an 8-bit FCW is fed into a 9-bit pipeline accumulator with the MSB of the accumulator input tied to zero. The output of the pipeline accumulator is a 9-bit phase word, whose LSB will be truncated before driving the 8-bit DAC. One bit truncation reduces the size and power consumption of the DAC with minimum spurious penalty. The MSB output of the phase accumulator is used to provide the proper mirroring of the sine waveform about the phase point. The second MSB is used to invert the remaining 6-bits for the second and fourth quadrants of the sine wave prior to the decoding logic. Each column-row decoder has a linear 3:8 operation. The

Figure 2.4: Block diagram of the implemented DDS MMIC

outputs of the column-row decoders go to the switch matrix to control the switches in each cell [15]. The latch and switch matrices contain 64 cells, and each of the cells is comprised of a local decoder, latches, and switch pairs. The current switch outputs are summed at open-collector output nodes. Next, the circuit design of the DDS building blocks will be discussed.

## 2.4.1 Pipelined accumulator

The speed of the DDS is often limited by the speed of the phase accumulator. The speed of the accumulator depends upon the N-bit adder design. The simplest way to construct an N-bit adder is to place N 1-bit adders in a chain starting with a 1-bit half adder followed by (N-1) 1-bit full adders with the carry-in of the full adder connected to the carry-out of the previous bit. This ripple adder topology uses the least hardware, but operates at the slowest speed. The delay of a ripple adder is due to the propagation of the carry bit from the LSB to the MSB. The sum and carry-out of a full adder can be expressed as:

$$SUM = A \oplus B \oplus C_{in}$$

$$C_{out} = A \cdot B + B \cdot C_{in} + C_{in} \cdot A$$

(2.6)

where A and B are the input bits and Cin is the carry in of the adder. The delay of an N-bit ripple adder is given by

$$Delay_{ripple} = (N-1)T_{carry} + T_{sum}$$

$$(2.7)$$

where  $T_{carry}$  is the time for carry generation and is equal to twice the delay of an AND gate. Similarly,  $T_{sum}$  is the time for sum generation in a 1-bit adder and is about twice the delay of an XOR gate.

If the accumulator input is time-invariant, each bit of the input word and the adder output bits can be properly delayed so that a N-bit accumulator can operate at the speed of a 1-bit adder. This type of accumulator, called a pipelined accumulator [7, 11], uses the most hardware, but achieves the fastest speed. Ref. [11] employed the pipeline adder architecture to implement the phase accumulator for a numerically controlled oscillator (NCO).

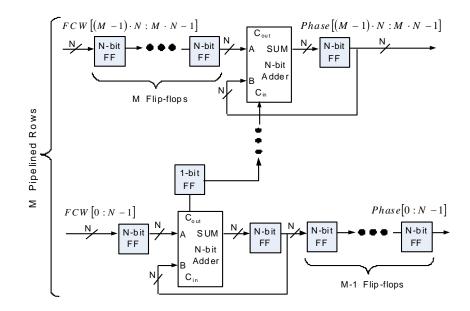

Fig. 2.5 illustrates a generic architecture for an NxM pipelined accumulator with a total of M pipelined rows. Each row has a total of M delay stages placed at the input and output of an N-bit adder. Obviously, an NxM pipelined accumulator has a latency period equal to the propagation delay of M-1 clock cycles. Note that an accumulator needs at least one delay stage even without any pipelined stages. The pipeline accumulator shown allows

Figure 2.5: NxM generic architecture of a pipelined accumulator

the NxM bit accumulator to operate at the speed of an N-bit accumulator, i.e., a speed-up of M times. When the number of adder bits is set to one (N = 1), the 1xM bit accumulator can operate at the same speed as a 1-bit adder. To realize a 9-bit accumulator, we can set N = 1 and M = 9. Then, a 9-bit accumulator will run at the speed of a 1-bit accumulator consisting of a full-adder and a flip-flop.

The pipelined accumulator is used for constant input words and can achieve the maximum operating frequency, whereas an accumulator with a carry look-ahead (CLA) adder can be employed for variable inputs with medium operation frequencies. To achieve the maximum operating speed with a fixed FCW, a pipelined accumulator is used in this design. The total delay of the accumulator is one full adder propagation delay plus one D-flip-flop propagation delay. The MSB of the accumulator input is tied to zero, since the FCW will not exceed half of the clock frequency. The LSB of the pipeline accumulator output is discarded and only its 8 MSB bits are fed to the nonlinear DAC. The flip-flops in the accumulator were designed with a reset signal that can be used to reset the accumulator to zero.

In general, the ripple carry adder has complexity in the order of O(N) and delay proportional to N, where N is the FCW length of the accumulator. The hardware cost of the pipeline accumulator is of the order O(N2). In order to properly trade the area for power, k-bit adders can be used for each pipeline stage as illustrated in Fig. 2.5. We implemented a 1x8 pipelined accumulator in order to achieve the maximum speed. If 2-bit adders are used in each pipeline stage, the critical path delay will not double based on Eq. (7). Thus, the accumulator speed will be greater than half of that of the accumulator using 1-bit pipelined adders.

#### 2.4.2 SiGe CML logic

Previous ultra high speed DDS designs used InP technology in order to take advantage of the high speed InP transistors. However, these InP DDS designs suffer from high power consumption and low yield. This DDS design utilizes a commercial 0.18 m SiGe BiCMOS technology with the HBT peak ft/fmax of 120/100GHz. The digital logic is implemented using current mode logic (CML) cells with differential output swings of 400mV. For a 3level CML circuit, a 3.3V power supply is sufficient to keep all the BJT transistors from saturation. If an NPN transistor operates in saturation mode, its speed is greatly degraded and its parasitic PNP transistor is turned on, causing increased noise coupling through the substrate.

In order to achieve a good balance between speed and power consumption, the bias current is set to 70% of the peak fT current. Further increasing the biasing current doesn't speed up the CML circuit significantly. It's not proper to bias the CML circuits at peak fT current, since any variation of the biasing current may drive the circuit beyond fT current, slowing down the transistors significantly with unnecessarily large power consumption. Although the peak fT current is not a parameter that guarantees the operational speed for different CML circuits with different loads, it's a good indicator for the average speed of the CML logic circuits. The current in a typical three-input CML gate is 0.55mA, which is less than 1/5 of that used in InP DDS designs [21]. This bias current is sufficient to keep the delay of the three level gates below 25ps.

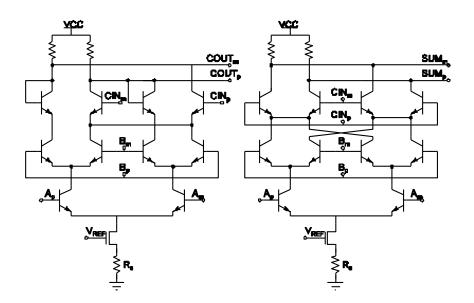

To provide more headroom for bipolar transistor operation, the current source of the CML logic uses an NMOS transistor with degeneration resistor. In this case, the overdrive voltage of the current source MOSFET is around 0.4 0.5V, which is smaller than the head-room required by a bipolar transistor. In order to ensure that all the critical paths have the same delays, the signal paths are designed using symmetrical patterns. Pipelined adder stages are used to achieve the speed that is equivalent to a 1-bit adder. To reduce the logic requirement of the adder, the structures described in [3] are adopted, as shown in Fig. 2.6. The sum and carry-out are implemented using one current tail for low power application. This adder circuit reduces the total number of bipolar transistors in the sum circuit from 14 to 10, and provides a speed improvement of around 15%. The delay of the sum block is estimated to be 30ps, and the carry block is 25ps, with optimized biasing.

The breakdown voltage BVCEO of the NPN transistors in the 0.18 m SiGe BiCMOS technology is approximately 1.8V. With 4-stacked NPNs under a 3.3V supply, each transistor will experience less than 1V voltage cross the C-E junction. In addition, all the circuits

Figure 2.6: CML full adder circuit

are self-biased with no base open, which guarantees safe operation of the transistors without breakdown.

#### 2.4.3 Clock and MSB trees

The most challenging parts of the design are the clock tree and MSB buffer tree designs. To eliminate glitches due to code errors induced by clock skews, clock trees are carefully balanced to ensure synchronization and drive capability. Because the differential clock signals drive every flip-flop cell, and the total number of flip-flops is above 200, synchronization of the clock signals is not a trivial task. With a clock input frequency around 10GHz, the current gain of the transistor degrades to about 10. Thus, the fan-out ratio of a clock buffer is only 3 4, and the depth of the clock buffer chain is at least 6 levels for this design. To fully turn on or turn off the differential pairs, the input differential peak-to-peak voltage swing should be more than  $6V_T + I_E R_E$ , in which  $V_T$  is the thermal voltage and  $I_E$  and  $R_E$  are the emitter current and emitter resistance of the bipolar transistor, respectively. The voltage swing also depends on junction temperature, which can reach above 100C for normal operating conditions. The clock signals at the flip-flop cells should swing no less than 150mV, which is equal to  $6V_T$  at room temperature. Since every switching cell in the DAC has an MSB signal, the total number of gates that the MSB must drive exceeds 120. This MSB signal must also be synchronized with other decoded digital bits. The depth of the buffer chain for the MSB signal is 5 levels. To accomplish all of this, the clock and MSB buffers require careful design, with layout symmetry and balance, in order to ensure synchronization along the clock and MSB distributions.

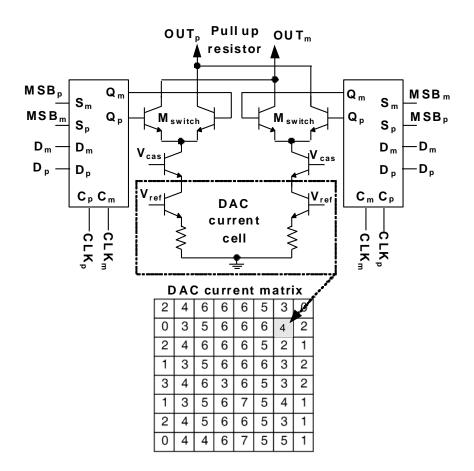

#### 2.4.4 DAC current source and switch

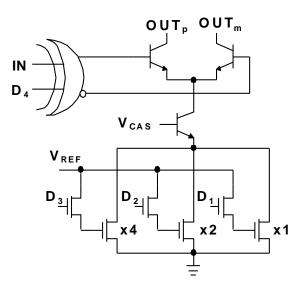

The essential building block of the nonlinear DAC is the sine weighted current source matrix. The unit current of each current source is 0.1mA, which should provide the current switches with enough switching speed when toggling. The largest source current is 0.7mA, which is composed of 7 identical current sources. The table in Fig. 2.7 indicates the number of unit current sources in each sine-weighted current source. The sum of each row is the same, which assures the regularity of the current source array, as well as its compactness.

The current source matrix provides 64 pairs of sine-weighted currents that are summed at the differential current outputs, OUTP and OUTM. The current outputs are converted to differential voltages by a pair of off-chip  $25\Omega$  pull-up resistors. Fig. 2.7 shows that the currents from the cascode current sources are fed to outputs, OUTP and OUTM, by pairs of switches (Mswitch). The MSB controls the selection between different half periods. The current switch contains two differential pairs, with minimum size transistors, and a cascode

Figure 2.7: Current switch circuit of the nonlinear DAC

transistor to isolate the current sources from the switches, and improve the bandwidth of the entire group of switching circuits. The size of the switching transistor pairs is chosen to be minimal in order to achieve the fastest switching speed with minimum power consumption, and to reduce the effect of clock feed-through.

For the current steering DAC, the impedance  $Z_{imp}$  seen at the collectors of the switch transistors of each current cell must be large enough so its impact on the integral nonlinearity (INL) specification of the DAC can be tolerated [23]. However,  $Z_{imp}$  is frequency

Figure 2.8: Synchronous switch control circuit of the nonlinear DAC

dependent. The impedance that is required to obtain a specified resolution is approximately

$$Z_{imp} = \frac{NR_L}{4Q} \tag{2.8}$$

where RL is the load resistance, N represents the total number of unit current sources, and Q is the ratio of the signal to the second harmonic. To obtain 8-bit output resolution,  $Z_{imp}$  should be approximately 500k $\Omega$ . When the frequency increases above 100MHZ, a cascode current source is needed to meet the requirement for  $Z_{imp}$ .

Uncertainty of the switching time of current switches is one of the major causes of glitches at the DAC outputs. To synchronize the switches of the DAC, a D-flip-flop with NAND function is inserted between the MSB control bit and the switch pairs in the DAC. The Sp and Sm are controlled by MSB signal and select either 0 or 180 degree phase, as shown in Fig. 2.8.

Device matching is one of the important factors that affect the static and dynamic performance of the DAC. The matching properties of SiGe HBT bipolar transistors are normally one order of magnitude better than those of MOSFETs with similar feature sizes. To reduce of IR drops and matching errors, one must carefully choose the current source transistor sizes and layout placements, and use wide interconnections. For long interconnections carrying global signals, such as the clock and the MSB phase word, transmission line effects are taken into consideration during the layout. In order to minimize parasitic capacitances and inductances, thick analog metal layers are used for global signal routing.

#### 2.5 Layout

When running at a 10GHz clock rate, layout plays an important role in assuring that the final design meets the expected speed requirement. The current source matrix and the switching matrix are separately laid out and isolated from each other using a deep oxide trench to reduce noise coupling from the digital circuitry to the current sources through the substrate. The output of the DAC is placed close to the output pins to reduce interference from the rest of the circuits. Differential pairs are placed in a symmetrical manner so that the differential signals travel the same distance. In order to make the layout compact and easy to cascade, the CML building blocks were designed to have the same height. Power supply distribution stacks several metal layers to reduce resistance. Cadence Skill language was utilized to generate the connections that form the unit current sources into the sineweighted current sources, in accordance with the given switching sequence. Hence, the INL of the nonlinear DAC, due to symmetrical and gradient errors, is minimized. Two dummy rows and columns have been added around the current source array to avoid edge effects. To minimize the systematic error, introduced by the voltage drop in the ground lines of the current-source transistors, sufficiently wide wires have been used. The clock inputs are differential CML compatible signals, and multiple clock inputs are provided to reduce the parametric inductance resulting from the pins. The maximum delay of the metal wire is about 40ps, and the clock tree is carefully built to ensure an acceptable clock skew.

#### 2.6 Experiment results

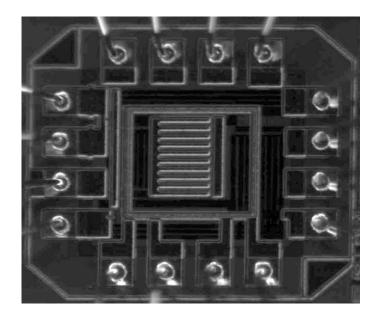

The die photo of the DDS MMIC is shown in Fig. 2.9. This DDS design is quite compact with an active area of 2.3 x 0.7mm2 and a total chip die area of 3 x 3 mm2 including the ESD pads, the layer density filling elements and an 8.2 GHz on-chip VCO that could be used to clock the DDS. The DDS prototypes were packaged using 48 pin ceramic leadless packages. For a frequency range over 10GHz, the PCB test board was developed using a Rogers RO4003 laminate board, which has a loss tangent of less than 0.003 and good temperature stability. To convert the single-ended signal to differential clock inputs, a 180 degree 3dB hybrid coupler is employed at the clock input. For the differential outputs, a second hybrid coupler is inserted into the output path. The test setup diagram is illustrated in Fig. 2.10.

Power consumption of the DDS with the DAC is approximately 1.9W, and the maximum clock frequency as measured is 12.3GHz. With Nyquist output, the DDS achieves a maximum clock frequency of 11.9GHz. The digital and analog parts of a sine-weighted DAC consume 300mA from a 3.3V supply and 35mA from a 4V supply, respectively. The accumulator consumes 250mA of current with a 3.3V supply.

Figure 2.9: Die photo of DDS chip

Figure 2.10: DDS MMIC test setup

Although the power consumption of the SiGe DDS is small compared to other InP DDS, its power density is high due to its small die size. For 1.9W power concentrated on a small die area of 9mm<sup>2</sup>, the power density of the DDS MMIC would exceed 21W/cm<sup>2</sup>, which is a number that normally appears only for high performance processors. The relatively high power density of the DDS MMIC makes it difficult to dissipate the heat when it's packaged. The junction-to-ambient thermal resistance  $\theta_{JA}$  of the 48-pin ceramic package is about 40°C/W with zero air flow. Therefore, the device junction temperature of the DDS MMIC could reach above  $100^{\circ}$ C at the room ambient temperature of  $25^{\circ}$ C with 1.9W power consumption. For this reason, an external fan is used to cool the device during measurements. To further reduce the thermal resistance and maximize heat dissipation, packages with a heat sink can be used. To our knowledge, other InP MMICs [21, 22, 8] were tested on wafer, while this SiGe DDS MMIC was tested as a packaged part. To test the maximum speed, the packaged DDS chips were cooled down to  $-50^{\circ}$ C  $-80^{\circ}$ C such that the junction temperature is around room temperature. This test condition provides a fair comparison between the packaged SiGe DDS MMIC and the wafer-probed InP DDSs. Lowering the junction temperature improves the transistor speed due to increased carrier mobility at lower temperature. Without cooling, the maximum clock speed of the packaged DDS MMIC is measured as 9.6GHz with Nyquist output and 11GHz with FCW = 1 at room ambient temperature. For the 20 tested prototypes, the chip performances are quite consistent. SiGe technology gains advantages of high yield and high performance over the InP technology.

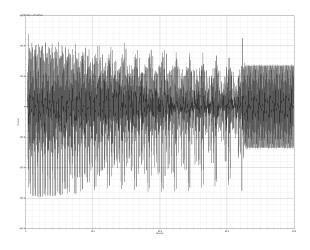

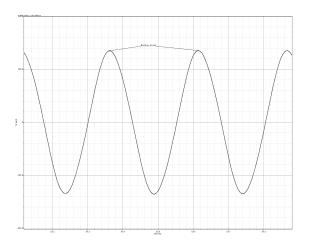

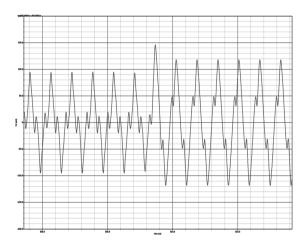

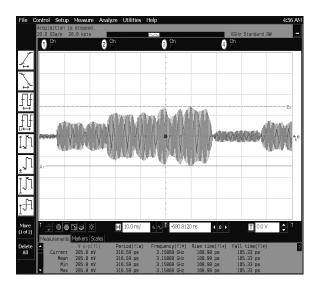

Fig. 2.11,2.12,2.13,2.14 illustrates the measured DDS output spectra and waveforms for different outputs and clock frequencies. The measured spectra were obtained by cooling down the packaged chips so that the device junction temperature approaches the room temperature. Fig. 2.11 presents the 23.5MHz DDS output waveform and spectrum with a 12.021GHz clock input. The time-domain waveform measurements were limited by the digital sampling scope's 500 MHz bandwidth. The measured DDS output power is approximately -6.67 dBm. All measurements were done without calibrating the losses of the cables, the coupler and the PCB tracks. Fig. 2.12 gives the measured DDS output spectra at Nyquist rate, namely, (a) output frequency at 5.930GHz with clock at 11.913GHz; and (b) output frequency at 5.04GHz with clock at 10.110GHz. Fig. 2.12(a) demonstrates the maximum DDS operation frequency of 11.9 GHz at Nyquist output with the SFDR of 22dBc. The measured SFDR of the device, at 5.08 GHz output frequency with a 10.11 GHz clock, is approximately 30dBc in narrow-band as shown in Fig. 2.12(b). For Fig. 2.12(a), the FCW is chosen as 28-1, which is the maximum allowed by an 8-bit FCW input. Thus, the output frequency is set at . The first order image tone mixed by the clock frequency and the DDS output frequency occurs at 11.913GHz-5.93GHz = 5.98GHz, which is 50MHz apart from the output frequency, as shown in Fig. 2.12(a). Operating the DDS at close to Nyquist rate makes it very hard to filter out the image tones. Practically, the DDS output frequency is restricted to be less than 3/8 of the clock frequency. An image tone at 5.08GHz is also observed in Fig. 2.12(b) with a clock at 10.110GHz.

Fig. 2.13 presents the measured DDS output spectrum with a 1.7898GHz output and a 9.59GHz clock. The measured output power of the DDS is -9 dBm, which corresponds to greater than -5dBm power when cable and coupler loss are considered. The input FCW

Figure 2.11: Measured DDS output waveform (a) and spectrum (b) with a 23.5MHz output (FCW=1) and a clock at 12.021GHz

Figure 2.12: Measured DDS output spectra at Nyquist rate (FCW=511). (a) The output frequency at 5.930GHz and the image tone at 5.98GHz with a clock at 11.913GHz; (b) The output frequency at 5.04GHz and the image tone at 5.08GHz with a clock at 10.110GHz

Figure 2.13: Measured DDS output spectrum with a  $1.7898\mathrm{GHz}$  output and a  $9.59\mathrm{GHz}$  clock

equals to 96, so that the GCD(96,29) = 32, which leads to spurs equally spaced with 600 MHz spacing around the fundamental tone when the clock is 9.59GHz.

Fig. 2.14 gives the DDS output waveforms at 1.125GHz with a 9GHz clock. At high temperature, the transistors are slowed down and the DAC current switches are no longer perfectly synchronized due to increased internal delays. Fig. 2.14 demonstrates a clean sinusoidal output waveform with the package measurements at the 9.6GHz clock frequency. Fig. 2.15 illustrates the measured DDS output spurious-free-dynamic-range (SFDR) versus frequency control word with a 4.6GHz clock at ambient temperature of -20 0C. The measured SFDR ranges from 20 to 30 dBc. Compared to the theoretical

Figure 2.14: Measured DDS output waveform with 1.125GHz output and 9GHz clock

analysis, the degradation of the measured SFDR are due to a combination of effects including the wideband matching of the clock and output signals, nonlinearity associated with the nonlinear DAC, and noise coupling from the reference line, the substrate and the power supply.

When compared with the InP DDS in [9], which operates at a 9.2GHz clock frequency, this design achieves similar SFDR performance, yet with much lower power consumption. Most of the InP DDS MMICs were measured using probe stations [21, 22], while this DDS RFIC was tested with packaged parts. Table 1 compares the recently published mm-wave DDS MMIC performances. The designs reported in [21] and [22] used InP technologies with an ft/fmax above 300/300 GHz, which is almost triple those reported here. The InP DDS[9] employs an 8-bit accumulator and an 8-bit DAC and operates at a maximum

Figure 2.15: Measured DDS output SFDR versus frequency control word at -20C ambient temperature

clock frequency of 9.2 GHz with a power consumption of 15 W. On the other hand, this SiGe 9-bit DDS consumes 1.9W with 3.3V power supplies for digital and analog circuits, respectively. The 4V power supply was tied to a pair of pull-up resistors, providing more voltage headroom and output swing for the DAC output stage. The VCO and the DDS are separately powered, and the 1.9W power consumption does not include the power of the VCO.

As shown in Table 2.1, the minimum transistor size in the InP technology is much larger than SiGe technology. Although the current densities required to achieve peak fT frequency in InP and SiGe technologies are similar, the current required to operate the minimum transistor close to a peak fT frequency differs quite a bit, which contributes to the superior power efficiency performance of this SiGe DDS. When compared with the

| Technology                        | InP     | InP      | InP      | InP               | TFAST InP | SiGe                    |

|-----------------------------------|---------|----------|----------|-------------------|-----------|-------------------------|

| fT/fmax [GHz]                     | 137/267 | 300/300  | 300/300  | 180/266           | 406/423   | 120/100                 |

|                                   | [9]     | [21]     | [22]     | [8]               | [8]       | [This work]             |

| Emitter area of minimal size      | 1.5x4   | 0.4x2    | 0.4x2    | $0.5 \mathrm{x2}$ | 0.25 x 1  | 0.2x0.64                |

| transistor [mm2]                  |         |          |          |                   |           |                         |

| Emitter current density at peak   | 1  1.2  | 5        | 5        | -                 | -         | 6                       |

| fT [mA/mm2]                       |         |          |          |                   |           |                         |

| Peak fT current of min size tran- | 7.2     | 4        | 4        | -                 | -         | 0.77                    |

| sistor [mA]                       |         |          |          |                   |           |                         |

| Break down voltage BVceo [V]      | 8       | 4        | 4        | -                 | 5         | 1.8                     |

| Accumulator size [bit]            | 8       | 8        | 8        | 9                 | 9         | 9                       |

| DAC resolution [bit]              | 7       | 7        | 5        | -                 | -         | 8                       |

| Max clock frequency [GHz]         | 9.2     | 13       | 32       | 8                 | 12        | 12.3 cooled             |

| Max clock frequency [GHz]         |         |          |          |                   |           | 9.6 room                |

| SFDR with Nyquist output [dBc]    | 30      | 26.67    | 21.56    | 38                | 30        | 22 @12GHz               |

| Si Dit with Nyquist output [uDe]  |         |          |          |                   |           | 27 @10 GHz              |

| Power consumption [W]             | 15      | 5.42     | 9.45     | 7                 | 8         | 1.9                     |

| Transistors number                | 3000    | 1646     | 1891     | 8695              | 8800      | 9600                    |

| Die size [mm2]                    | 8x5     | 2.7x1.45 | 2.7x1.45 | 4x2               | -         | 3x3 chip                |

|                                   |         |          |          |                   |           | $2.3 \times 0.7$ active |

| FOM [GHz/W]                       | 0.5     | 2.4      | 3.386    | 1.1               | 1.5       | 6.3 cooled              |

|                                   |         |          |          |                   |           | 5.05  room              |

Table 2.1: Ultra-high speed DDS performance comparison

published DDS MMICs, this SiGe DDS achieves the best reported power efficiency FOM of 6.3GHz/W with a much smaller die size of 2.5x0.7mm2.

# 2.7 Conclusion

In this chapter, a 12 GHz direct digital synthesizer (DDS) MMIC with 9-bit phase and 8-bit amplitude resolution has been implemented in a  $0.18\mu$ m SiGe BiCMOS technology. Composed of a 9-bit pipeline accumulator and an 8-bit sine-weighted current steering DAC, the DDS is capable of synthesizing sinusoidal waveforms up to 5.93 GHz. The maximum clock frequency of the DDS MMIC is measured as 11.9 GHz at the Nyquist output and 12.3 GHz at 2.31 GHz output. The spurious free dynamic range (SFDR) of the DDS, measured at Nyquist output with an 11.9 GHz clock, is 22 dBc. The power consumption of the DDS MMIC measured at a 12 GHz clock input is 1.9 W with dual power supplies of 3.3V/4V. The DDS thus achieves a record-high power efficiency figure of merit (FOM) of 6.3 GHz/W. With more than 9600 transistors, the active area of the MMIC is only 2.5 x 0.7mm2. The chip was measured in packaged prototypes using 48-pin ceramic LCC packages.

# Chapter 3

# QUADRATURE PHASES SIGE DDS

## 3.1 Introduction

In wireless transceivers, quadrature clock signals are always required for the modulator and the demodulator. There are several ways to generate the quadrature waveforms that widely adopted in the circuit design. The first is using a divider to divide down the output signal from a local oscillator or external source and the sine and cosine signals natively come out. This requires the output frequency of a local oscillator doubles the carrier frequency. The advantage is that the pulling effect or DC offset coming from the local oscillator can be minimized. Another way is to implement a quadrature VCO which takes more area and consume more power that the single phase VCO. The third approach is by using a polyphase filter to convert single phase signal to quadrature phase outputs. To reduce the phase and amplitude imbalances, multiple stages polyphase filter may required. This will introduce insertion loss and thermal noise. For DDS design, to generate well balanced quadrature waveforms in a large frequency range natively will avoid the problems of the divider method and polyphase method.

### 3.2 Direct Modulations in DDS

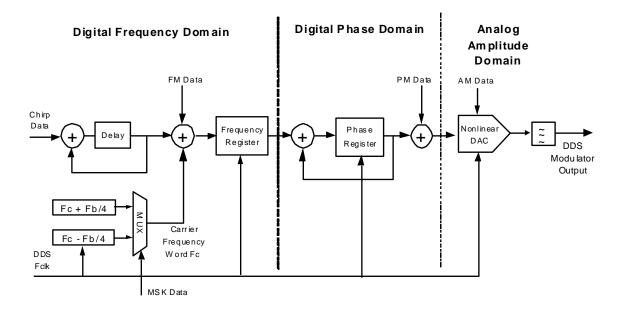

The conceptual diagram in Fig. 3.1 shows the method to implement different types of modulation configurations in a ROM-less DDS employing a nonlinear DAC. The principle of a DDS can be briefly descried as, first integrating the frequency control word into a phase control word, then mapping the phase control word to an amplitude word, finally converting

the amplitude word into an analog signal output. All the frequency, phase and amplitude information are readily available in the DDS data path and can be directly addressed and manipulated, thus the digital modulation can be done without too much extra hardware cost. By directly using digital control words to change the values of registers in the data path of a DDS, the frequency, phase and amplitude of the output waveforms can be precisely controlled. Since all the modulations are done in the digital domain, many disadvantages associated with normal analog modulations can be precluded. The values of the registers in a DDS are updated with a data rate that equals to the input clock frequency, which means that high speed modulated waveforms can be generated. Waveform generation for various modulation schemes is desired for novel radio transmitter architectures. As an example, modern radar systems place ever-increasing demand for affordable low noise signals and high speed waveform generation. With the availability of single chip DDSs working at microwave frequency, digitally generating highly complex wide bandwidth waveforms at the highest possible frequency instead of down near baseband would considerably reduce the transmitter architecture in terms of size, weight and power requirements as well as cost. These waveforms are used for high range resolution radars in sorting targets from clutter with low probability of intercepting communication applications. The modulated waveform generation is a unique feature of the DDS approach. The DDS synthesizer can implement modulations and waveforms such as chirp, step frequency, frequency modulation (FM), frequency shift keying (FSK), minimum shift keying (MSK), phase modulation (PM), amplitude modulation (AM), quadrature amplitude modulation QAM and other hybrid modulations, as illustrated in Fig. 3.1.

Figure 3.1: Direct modulation through a DDS

The typical choice converting the baseband signal from to polar magnitude and phase data to Cartesian I and Q data during the modulation is based on the normal practical consideration. Direct manipulation of magnitude and phase in polar system is expensive and difficult to design and build. The approach of taking DDS into transceiver system to perform the polar modulation task in addition to the normal frequency synthesis is one way to solve this problem that worth further exploring. Since the major parts of a DDS are digital circuits, it's easier to integrate the DDS with baseband circuit and provides a compact solution to the transmitter design.

Sometimes it is expected that the DDS output can cover more frequency range while the typical DDS output frequency ranges from DC to one third of the input clock frequency. When the output frequency closes to the Nyquist output, the frequency of the alias image will come closer to the output frequency, which made it almost impossible to be removed with analog low pass filter. To build low pass filter with steep roll off characteristic at several

Figure 3.2: Extend the output frequency range using a quadrature DDS and SSB mixers GHz will require tremendous effort. A practical solution to extend the output frequency of a DDS to a wider range without incurring the problems of alias images are using single side band (SSB) mixer, as shown in Fig. 3.2.

The local oscillator generates quadrature outputs with relatively fixed output frequency 0, which are mixed with the outputs of a quadrature DDS. Then the mixer outputs are summed and subtracted with each other, so the up-converted cosine waveforms with a frequency of 0+ or 0- are derived. Theoretically the final output should be clean of alias images. However, in practice the DDS output contains harmonics and spurs that significantly deteriorate the purity of desired output waveforms. The imperfections of the mixers due to leakage and second order effects will introduce some other spurs that have negative impacts on the output signals. Even though, the power of the alias image tune is small compare to the fundamental tune, which greatly easies the filter design. Assuming the local oscillator frequency is higher than the output frequency of the quadrature DDS, the above mixing scheme can be used to up convert the DDS output frequency to a higher frequency band.

Figure 3.3: Conceptual drawing of the quadrature DDS RFIC

# 3.3 DDS circuit design

## 3.3.1 Quadrature DDS architecture

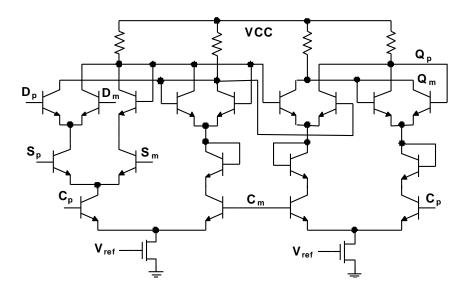

The simplified block diagram of the ROM-less quadrature DDS, employing one 9bit pipeline accumulator and two nonlinear DACs, is shown in Fig. 3.3. Intuitively, by paralleling two single phase DDSs, one with sine output and another with cosine output, and then merging them together, a quadrature DDS can be realized. When performing the merge of two single phase DDSs, the goal is to share the commonly used circuits in both DDSs as much as possible. In this design, the phase accumulator is shared for the two DDSs due to the limitation of the fan-out factors of the digital logic gates at multi GHZ frequency, which leaves very marginal gain when sharing the decoders and other digital blocks inside the DACs.

The main components in a single phase ROM-less DDS are phase accumulator and sine-weighted nonlinear DAC. For a DDS with L-bit frequency control word (FCW) and M-bit phase resolution DAC, the output frequency of the synthesized sine waveform is modulated by the truncation error of the accumulator. The output of the phase accumulator is truncated into M bits to fit the inputs of the nonlinear DAC. Usually the phase resolution of the DAC is much less than the resolution of the phase accumulator, then L-M bits are discarded, which introduces FCW depended spurs. The contribution of phase truncation related spurs to the total spurs and noise of the DDS output is considered to be a dominate factor if the following assumption is valid, that DAC is ideal or close to ideal. However, even for linear DAC, when sampling rate is over multiple GHz and transition of the magnitude is larger comparing to the full scale output, the validity of above assumption is no longer hold. For a nonlinear DAC, the situation is more complicated. It is not an easy task to reach high amplitude resolution with a nonlinear DAC at multiple GHz clock speed. In fact, the ultra high speed nonlinear DACs in the published works at most have 8bit amplitude resolution. The nonlinear DAC approach is still attractive for the microwave DDS design because it provides drastically speed improvement to the ROM based or algorithm based DDS design. To reduce the effect of the amplitude error introduced spurs in an ultra high speed DDS needs to be taking into account during the design. The phase truncation error introduced spurs are already minimized because only one bit of the phase accumulator output has been truncated.

As illustrated in Fig. 3.3, the quadrature DDS RFIC utilizes one 9-bit pipeline accumulator and two nonlinear 8-bit sine-weighted current-steering DACs to simultaneously generate the sine and cosine waveforms. The DDS comprises a 9-bit pipeline accumulator. Since the out frequency cannot exceed the Nyquist rate, an 8-bit FCW is fed into a 9-bit pipeline accumulator with the most significant bit (MSB) of the accumulator input tied to zero internally. Thus, the DDS requires only 8-bit FCW inputs. The output of pipeline accumulator gives a 9-bit phase word. The least-significant-bit (LSB) of the 9-bit phase word is truncation before driving the 8-bit DAC input.