# Reliability of Lead-Free and Advanced Interconnects in Fine Pitch and High I/O Electronics Subjected to Harsh Thermo-Mechanical Environments

by

Robert Bruce Hinshaw III

A thesis submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Master of Science

Auburn, Alabama December 18, 2009

Keywords: Thermo-mechanical, reliability, interconnect, Lead free, electronic packaging

# Approved by

Pradeep Lall, Chair, Thomas Walter Professor of Mechanical Engineering Jeffrey C. Suhling, Quina Distinguished Professor of Mechanical Engineering Roy W. Knight, Assistant Professor of Mechanical Engineering

#### **Abstract**

Industry is moving towards lower cost, increased functionality, and miniaturized electronics placed in ever closer proximity of higher operating temperatures, typical of harsh environments. In this thesis, three aspects of harsh environment thermomechanical reliability of fine-pitch electronics has been studied. (1) Effect of underfills on reliability enhancement of high I/O area-array packages on two board finishes including immersion silver, and Hot Air Solder Level under harsh thermo-mechanical environment. (2) Relative comparison of thermo-mechanical reliability of Sn3Ag0.5Cu, Sn3.5Ag, Sn1Ag0.5Cu, SAC-X, SAC-X-plus has been studied on chip-scale packages under harsh thermo-mechanical environment. (3) Comparison of thermo-mechanical reliability of five interconnect systems including Microperal SOL, Sn3Ag0.5Cu, 90Pb10Sn, 63Sn37Pb, and Copper Column. High-lead packages used in the study are the control group. In each case the reliability models have been developed to validate that the measured response of the experimental assemblies is consistent with the expected inherent trends. Failure analysis of the assemblies has been conducted to understand the failure mechanisms.

## Acknowledgements

The author would like to thank Dr. Pradeep Lall and other committee members for their support and guidance while completing this thesis. The author would also like to thank the Center for Advanced Vehicle and Extreme Environment Electronics (CAVE<sup>3</sup>) for financial support and assistance during the completion of this thesis.

The author would like to thank his parents, brothers, sisters, grandparents, and all other family for their unwavering support. Without any of them this work would have never been completed. The author would like to thank his friends and colleagues who were willing to help along the way including, Chandan Bhat, Darshan Shinde, Prashant Gupta, Sandeep Shantaram, Jordan Roberts, Dhananjay Panchagade, Kaysar Rahim, Madhura Hande and many others. Special thanks are given to Marcus Todd, Mandy Brock, Dan Chadwick, and Jessica Johnsey for always providing me with love, support, and friendship.

# Table of Contents

| Abs  | stract                                             | ii  |

|------|----------------------------------------------------|-----|

| Ack  | knowledgements                                     | iii |

| List | t of Figures                                       | vii |

| List | t of Tables                                        | xiv |

| 1    | Introduction.                                      | 1   |

|      | 1.1 Project Overview.                              | 1   |

|      | 1.2 Packaging Overview                             | 3   |

|      | 1.3 Lead Free Electronics.                         | 5   |

|      | 1.4 Unique Interconnect Designs.                   | 6   |

| 2    | Literature Review.                                 | 8   |

|      | 2.1 General Packaging Architecture.                | 9   |

|      | 2.2 Lead Free Electronics.                         | 11  |

|      | 2.3 Unique Interconnect Information.               | 16  |

| 3    | Unique Architecture BGA Packages                   | 19  |

|      | 3.1 Modeling Techniques and Life Prediction Method | 19  |

|      | 3.2 Modeling and Real World Failure                | 23  |

|      | 3.3 Unique Architecture PBGA Packages              | 26  |

|      | 3.4 BGA 1152                                       | 30  |

|      | 3.4.1 BGA 1152 FEM                                 | 37  |

|   | 3.4.2 BGA 1152 Model Validation   | 48  |

|---|-----------------------------------|-----|

|   | 3.5 PBGA 313                      | 49  |

|   | 3.5.1 PBGA 313 FEM                | 53  |

|   | 3.5.2 PBGA 313 Model Validation   | 59  |

|   | 3.6 PBGA 128                      | 61  |

|   | 3.6.1 PBGA 128 FEM                | 67  |

|   | 3.6.2 PBGA 128 Model Validation.  | 73  |

|   | 3.7 PBGA 256                      | 74  |

|   | 3.7.1 PBGA 256 FEM                | 77  |

|   | 3.7.2 PBGA 256 Model Validation.  | 80  |

|   | 3.8 Package Comparisons           | 82  |

| 4 | Lead Free Electronics             | 88  |

|   | 4.1 Introduction.                 | 88  |

|   | 4.2 Test Vehicle and Setup.       | 94  |

|   | 4.3 Lead Free Reliability Results | 96  |

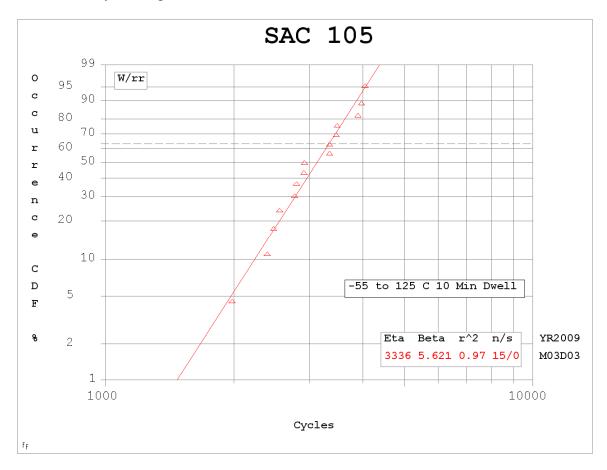

|   | 4.3.1 SAC 105                     | 96  |

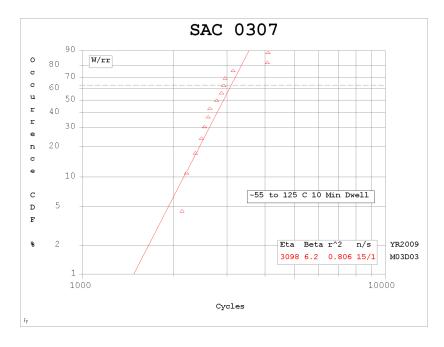

|   | 4.3.2 Sn0.3%Ag0.7%Cu(SAC 0307)    | 99  |

|   | 4.3.3 SAC X                       | 101 |

|   | 4.3.4 SAC X-Plus.                 | 105 |

|   | 4.4 Finite Element Models         | 108 |

|   | 4.4.1 SAC 305 Model               | 110 |

|   | 4.4.2 Sn3.5Ag                     | 114 |

|   | 4.5 Summary                       | 118 |

| 5     | Unique I/O Packages in Harsh Thermal Environments | 120 |

|-------|---------------------------------------------------|-----|

|       | 5.1 Introduction                                  | 120 |

|       | 5.2 Test Vehicle and Setup                        | 123 |

|       | 5.3 SOL Plastic Core I/O                          | 125 |

|       | 5.3.1 SOL Finite Element Model                    | 130 |

|       | 5.4 CCGA                                          | 135 |

|       | 5.4.1 CCGA Finite Element Model                   | 140 |

|       | 5.5 High-lead Interconnect                        | 146 |

|       | 5.5.1 High-lead Finite Element Model              | 151 |

|       | 5.6 SAC 305                                       | 156 |

|       | 5.6.1 SAC 305 Finite Element Model                | 159 |

|       | 5.7 Package Comparison                            | 165 |

| 6     | Summary and Conclusion.                           | 168 |

| Bibli | iography                                          | 170 |

| Appe  | endix                                             | 178 |

|       |                                                   |     |

# List of Figures

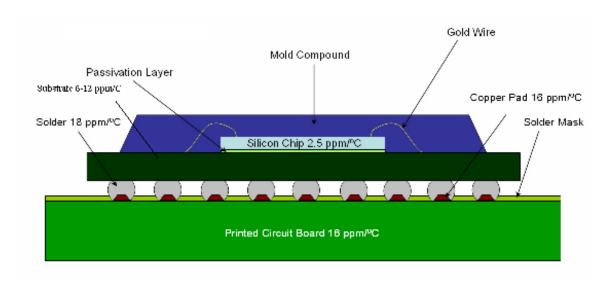

| 1-1  | CTE Electronic package                                     | ۷  |

|------|------------------------------------------------------------|----|

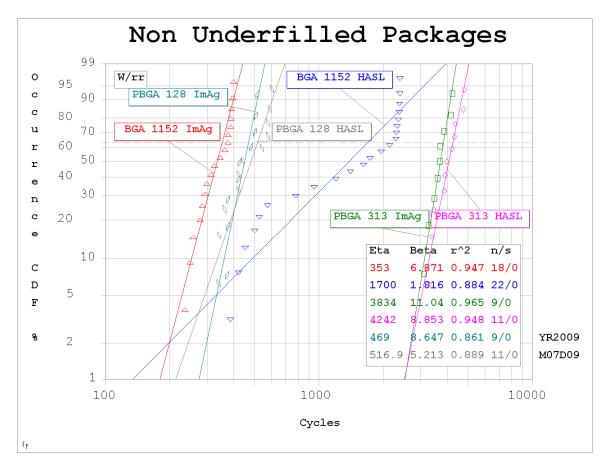

| 3-1  | Solder ball located in the die shadow region               | 20 |

| 3-2  | Solder ball located in the die shadow region               | 20 |

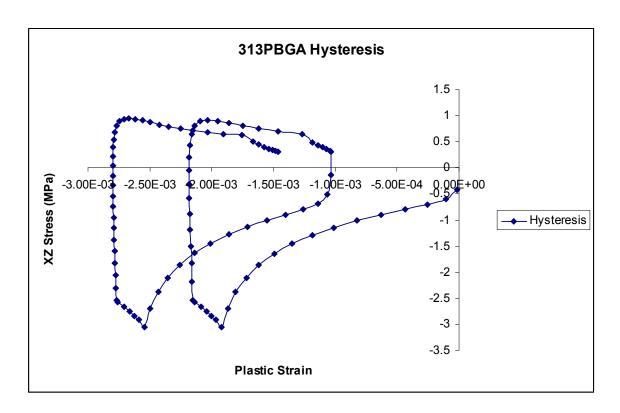

| 3-3  | PBGA 313 Hysteresis loop                                   | 24 |

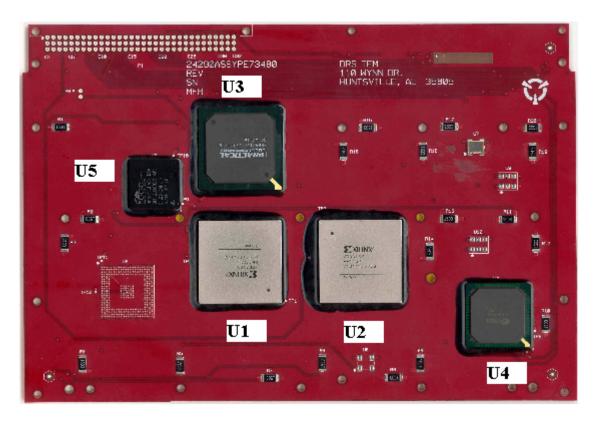

| 3-4  | Test Vehicle with unique I/O packages                      | 28 |

| 3-5  | Unique I/O Thermal Profile                                 | 29 |

| 3-6  | Flip Chip Cross Section                                    | 31 |

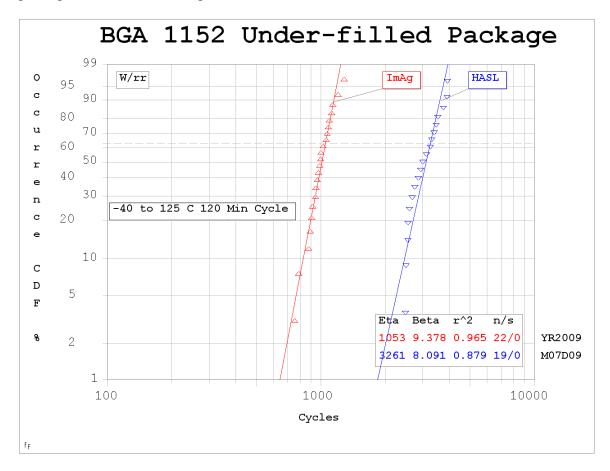

| 3-7  | Weibull plot BGA 1152 ImAg and HASL                        | 33 |

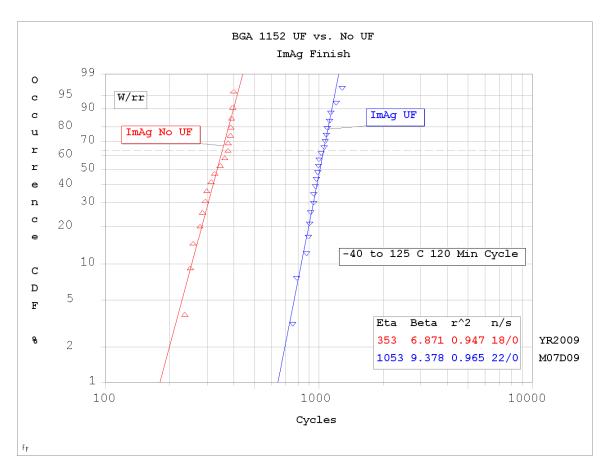

| 3-8  | Weibull plot for underfilled Xilinx packages               | 34 |

| 3-9  | Weibull plot for ImAg finish underfill vs. non underfilled | 35 |

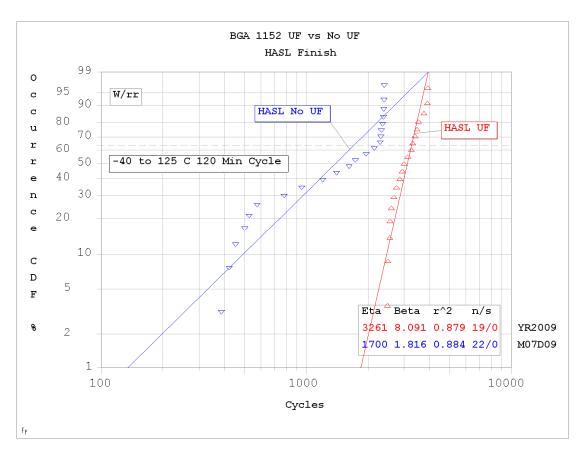

| 3-10 | Weibull plot for HASL finish underfill vs. non underfill   | 36 |

| 3-11 | BGA 1152 Finite Element Model                              | 38 |

| 3-12 | BGA FEM 1152 Failure                                       | 40 |

| 3-13 | Failed ball compared to failed simulation                  | 40 |

| 3-14 | BGA 1152 showing the top layer failure                     | 41 |

| 3-15 | Hysteresis BGA 1152                                        | 41 |

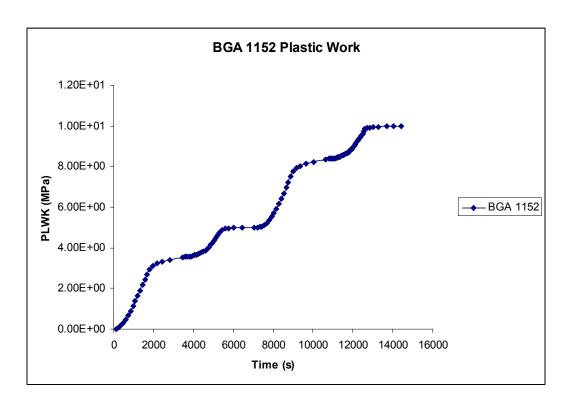

| 3-16 | Plastic Work Plot BGA 1152                                 | 42 |

| 3-17 | Underfilled BGA 1152 package                               | 43 |

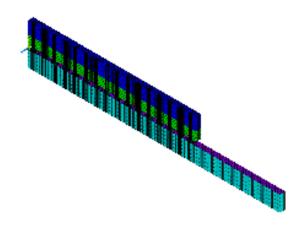

| 3-18 | diagonal view of UF BGA 1152                               | 44 |

| 3-19 | UF BGA 1152 failure in corner ball                 | 45 |

|------|----------------------------------------------------|----|

| 3-20 | diagonal UF solder ball BGA 1152                   | 45 |

| 3-21 | hysteresis loop of UF and non UF BGA 1152          | 46 |

| 3-22 | plastic work of the UF and non UF package BGA 1152 | 47 |

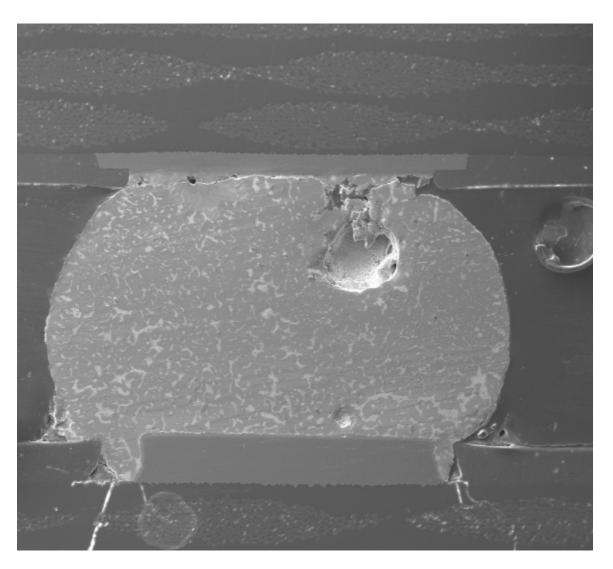

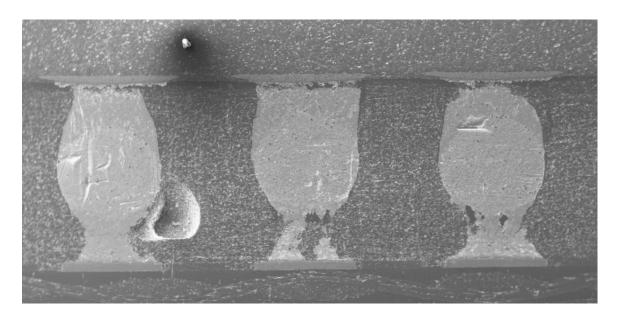

| 3-23 | SEM Cross Section of PBGA 313                      | 51 |

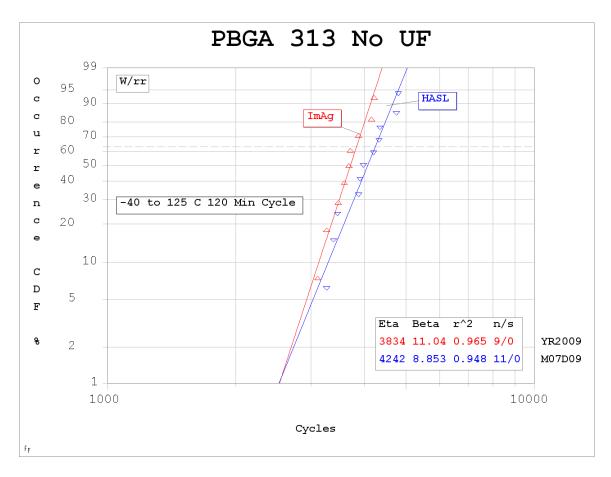

| 3-24 | PBGA 313 non underfilled Weibull plot              | 52 |

| 3-25 | PBGA 313 Failure                                   | 53 |

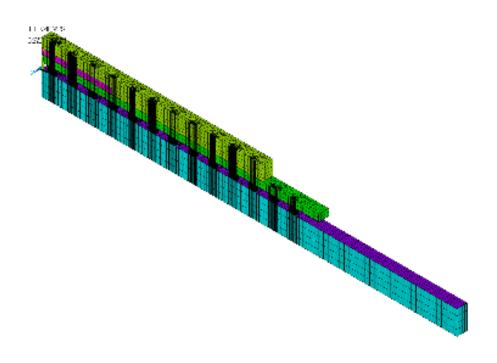

| 3-26 | Diagonal symmetry model PBGA 313                   | 54 |

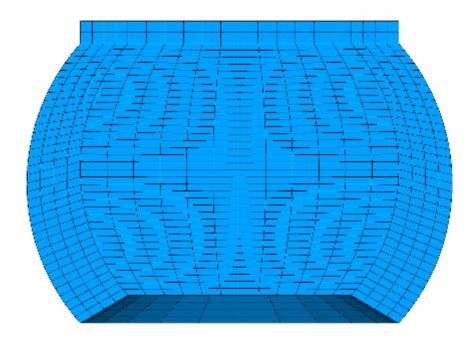

| 3-27 | PBGA 313 FEM Solder Ball                           | 54 |

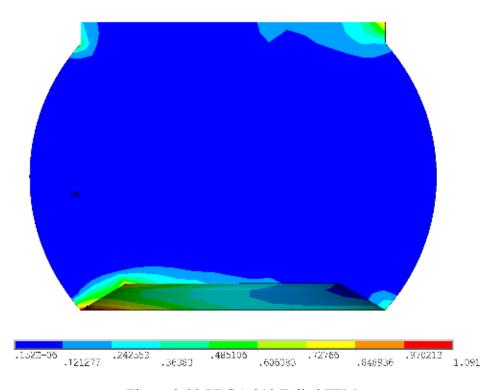

| 3-28 | PBGA 313 Die Shadow Region                         | 56 |

| 3-29 | PBGA 313 Failed Die Shadow Region                  | 56 |

| 3-30 | SEM results showing die shadow failure             | 57 |

| 3-31 | PBGA 313 Die Shadow Failure                        | 58 |

| 3-32 | PBGA 313 Failed FEM                                | 58 |

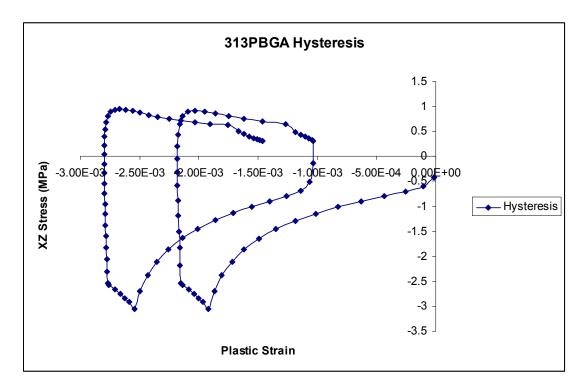

| 3-33 | Hysteresis plot PBGA 313                           | 59 |

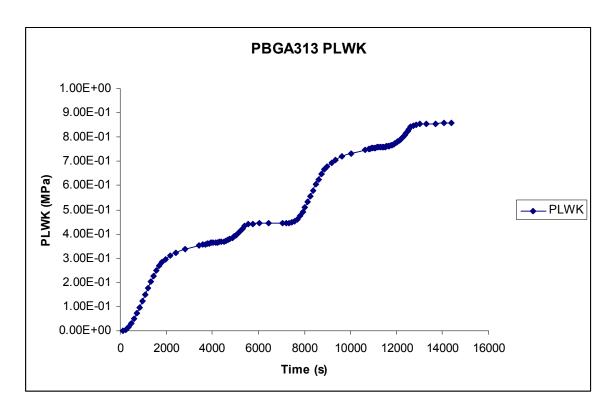

| 3-34 | Plastic work plot PBGA 313                         | 60 |

| 3-35 | CSAM of PBGA 128 package                           | 61 |

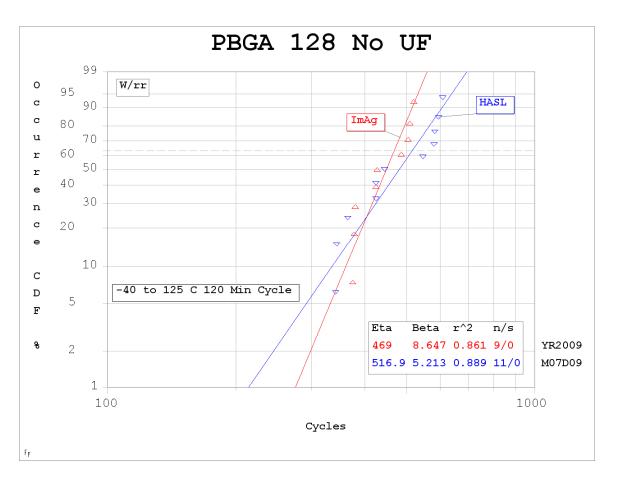

| 3-36 | Weibull plot of PBGA 128                           | 63 |

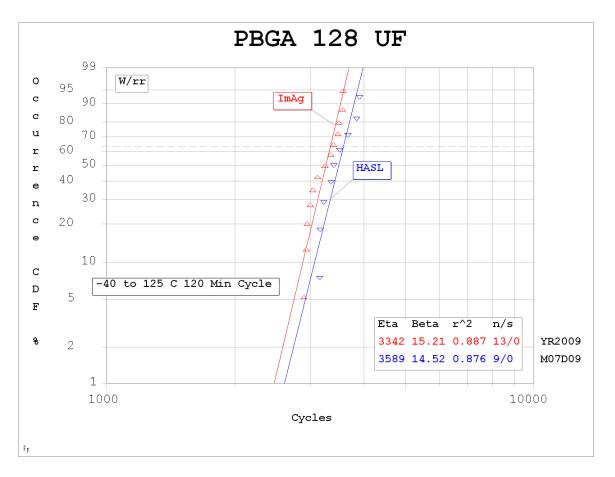

| 3-37 | Underfilled PBGA 128                               | 64 |

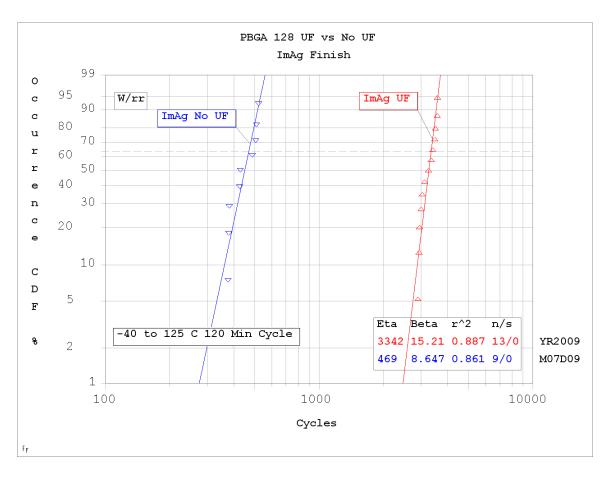

| 3-38 | PBGA 128 ImAg finish underfill and non underfill   | 65 |

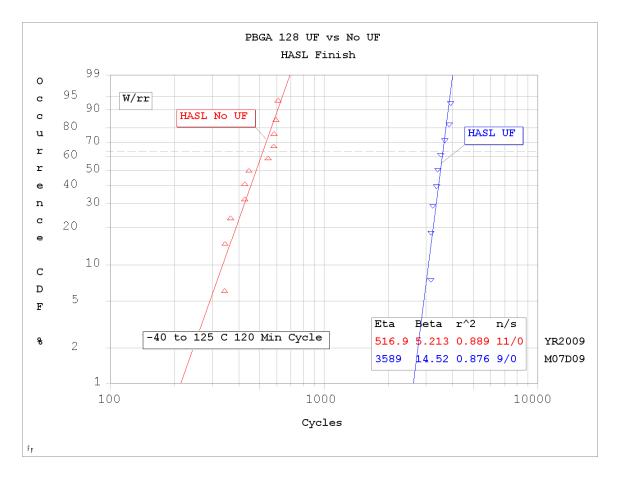

| 3-39 | PBGA 128 HASL finish underfill and non underfill   | 66 |

| 3-40 | Diagonal view PBGA 128 FEM                         | 67 |

| 3-41 | PBGA 128 FEM                                       | 69 |

| 3-42 | PBGA 128 Failure                                     | 69 |

|------|------------------------------------------------------|----|

| 3-43 | Simulation Failure and experimental failure PBGA 128 | 70 |

| 3-44 | Underfilled PBGA 128 Package                         | 70 |

| 3-45 | encapsulated PBGA 128 solder balls                   | 71 |

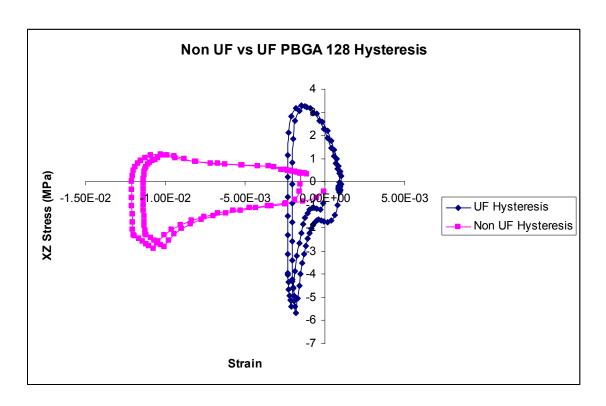

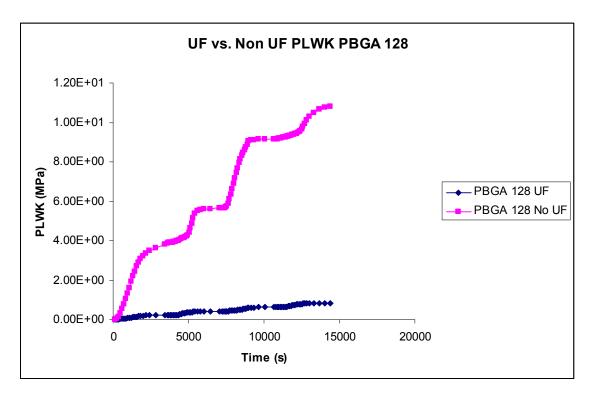

| 3-46 | PBGA 128 UF vs No UF Hysteresis                      | 72 |

| 3-47 | PBGA 128 UF vs No UF Plastic Work                    | 72 |

| 3-48 | PBGA 256 CSAM                                        | 74 |

| 3-49 | Undamaged PBGA 256                                   | 75 |

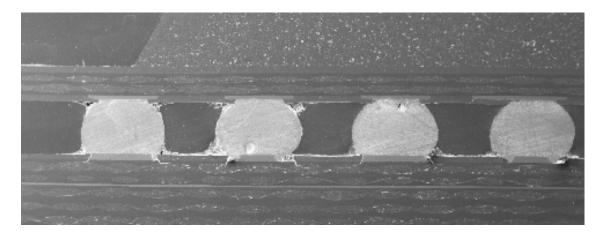

| 3-50 | PBGA 256 Cross Section                               | 76 |

| 3-51 | Cracked Right Most Solder Ball                       | 76 |

| 3-52 | Diagonal View PBGA 256                               | 77 |

| 3-53 | FEM PBGA 256 Solder Ball                             | 78 |

| 3-54 | Failed PBGA 256 FEM solder ball                      | 78 |

| 3-55 | PBGA 256 FEM failed solder balls                     | 79 |

| 3-56 | SEM PBGA 256 Failed Perimeter Ball                   | 79 |

| 3-57 | PBGA 256 Hysteresis Plot                             | 80 |

| 3-58 | PBGA 256 Plastic Work                                | 81 |

| 3-59 | Weibull comparison of boards                         | 82 |

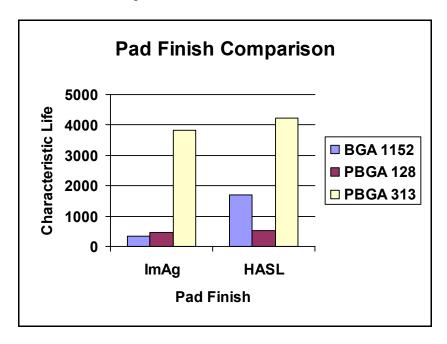

| 3-60 | Comparison of surface finish for all packages        | 83 |

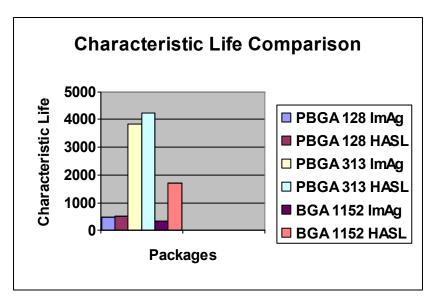

| 3-61 | Package characteristic life comparison               | 84 |

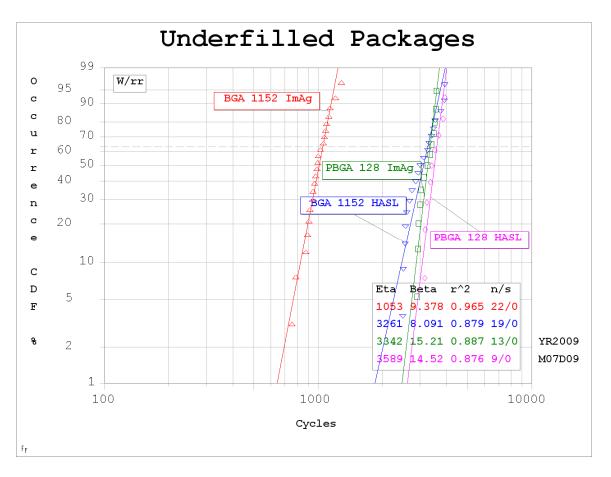

| 3-62 | Comparison of underfilled packages                   | 85 |

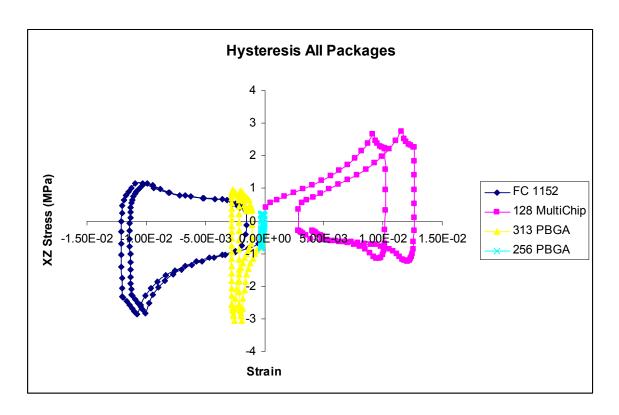

| 3-63 | Non UF Hysteresis Plot                               | 86 |

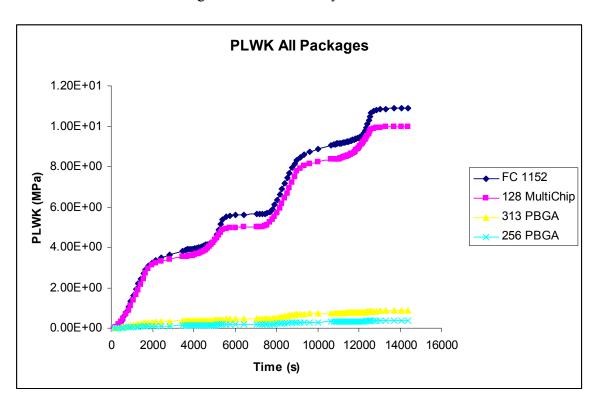

| 3-64 | Non UF Plastic Work Plot                             | 86 |

| 3-65 | PBGA 313 vs PBGA 256 Plastic Work                | 87  |

|------|--------------------------------------------------|-----|

| 4-1  | Thermal profile for lead free experiment         | 94  |

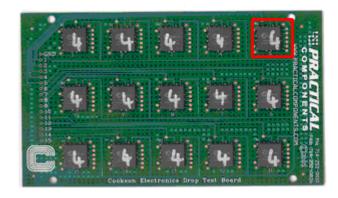

| 4-2  | Lead Free test vehicle                           | 95  |

| 4-3  | SAC 105 Wiebull plot                             | 96  |

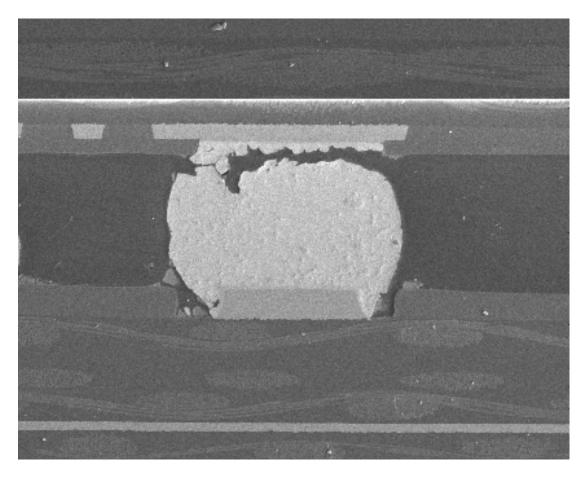

| 4-4  | Sectioned Package                                | 97  |

| 4-5  | Failed Solder Ball in right die shadow           | 97  |

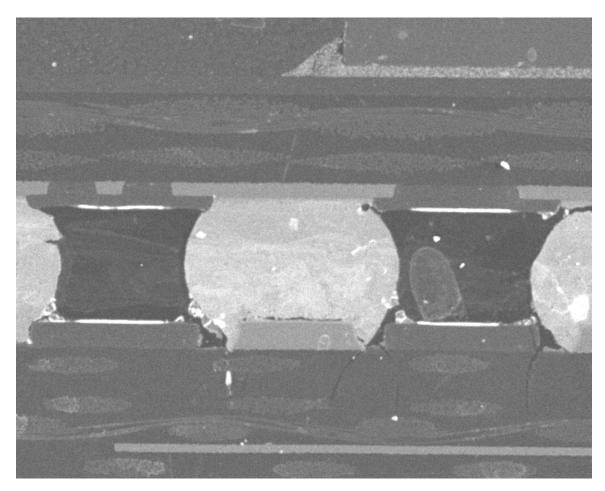

| 4-6  | SAC 105 left die shadow showing board side crack | 98  |

| 4-7  | Blown Up SAC 105 Crack                           | 99  |

| 4-8  | Weibull plot SAC0307                             | 99  |

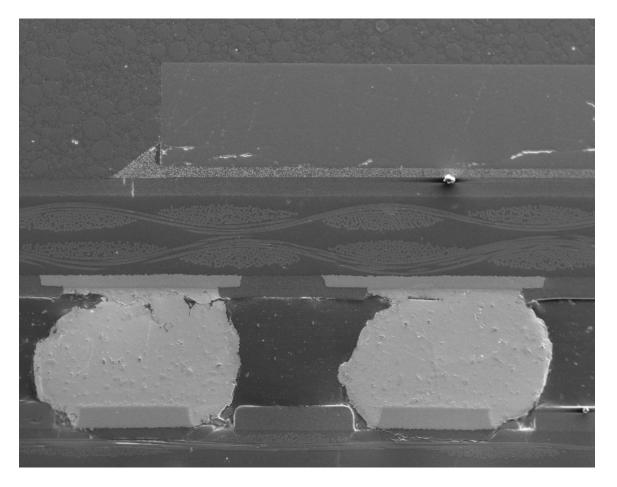

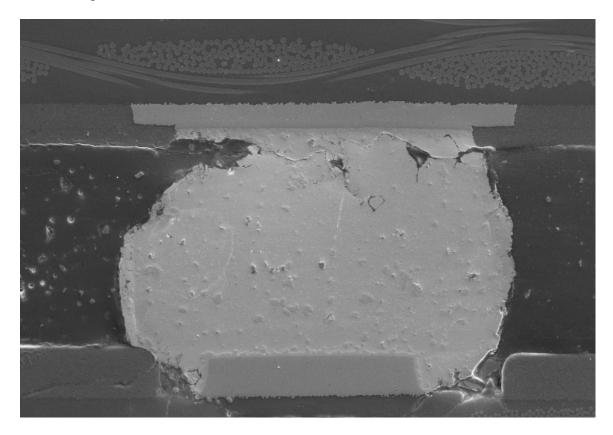

| 4-9  | Failed SAC0307 interconnect                      | 100 |

| 4-10 | Crack in top of SAC 0307 interconnect            | 101 |

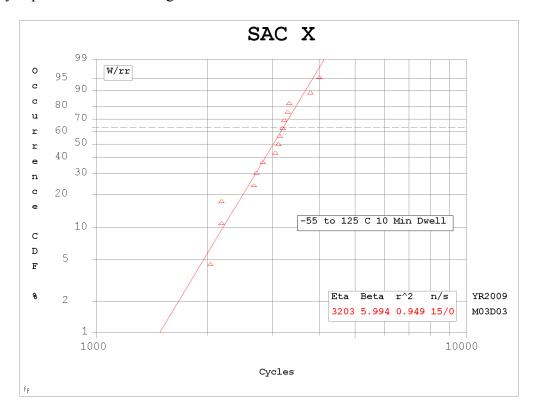

| 4-11 | Weibull plot for SAC X alloy                     | 102 |

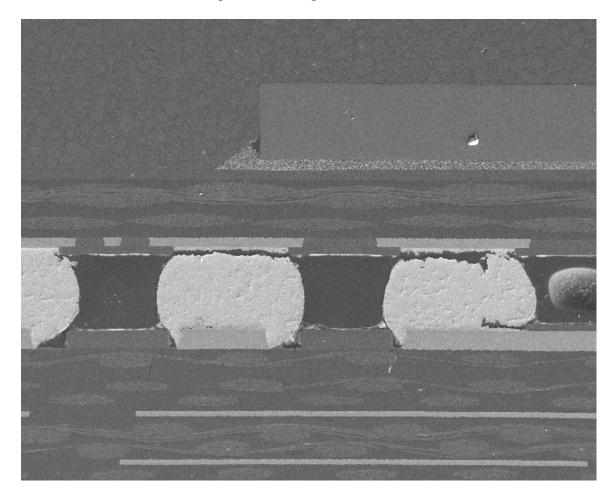

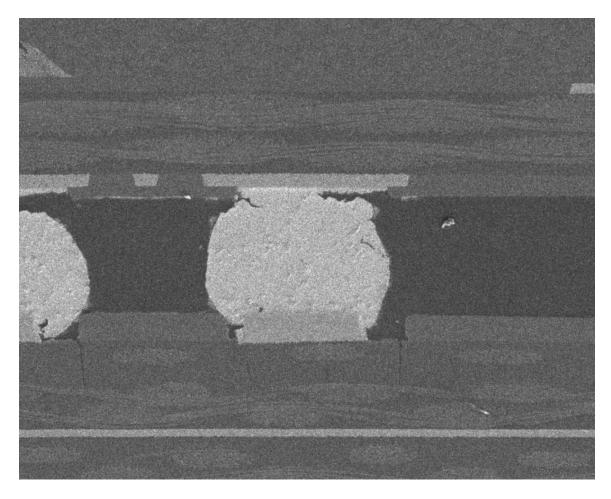

| 4-12 | SAC X Die Shadow failure                         | 103 |

| 4-13 | SAC X Partial Crack                              | 104 |

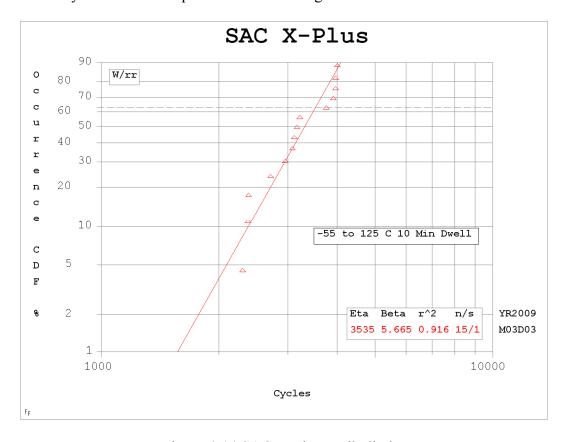

| 4-14 | SAC X-Plus Weibull plot                          | 105 |

| 4-15 | Failed SAC X-Plus Solder Ball                    | 106 |

| 4-16 | SAC X Plus Failed solder ball                    | 107 |

| 4-17 | Diagonal view SAC 305                            | 110 |

| 4-18 | SAC 305 Interconnect                             | 110 |

| 4-19 | SAC 305 FEM Failure                              | 111 |

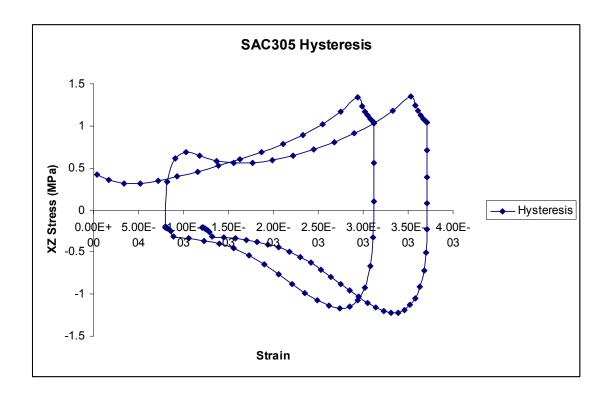

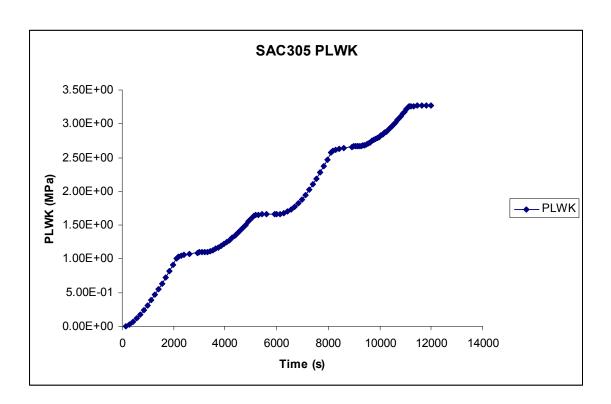

| 4-20 | SAC 305 Hysteresis Loop                          | 112 |

| 4-21 | SAC 305 Plastic Work Plot                        | 112 |

| 4-22 | Sn3.5Ag Finite Element Model                     | 114 |

| 4-23 | Sn3.5Ag Failure Results                    | 115 |

|------|--------------------------------------------|-----|

| 4-24 | Sn3.5Ag Hysteresis Loop                    | 116 |

| 4-25 | Sn3.5Ag Plastic Work                       | 116 |

| 4-26 | Hysteresis Loop Comparison                 | 117 |

| 4-27 | Plastic Work Comparison                    | 118 |

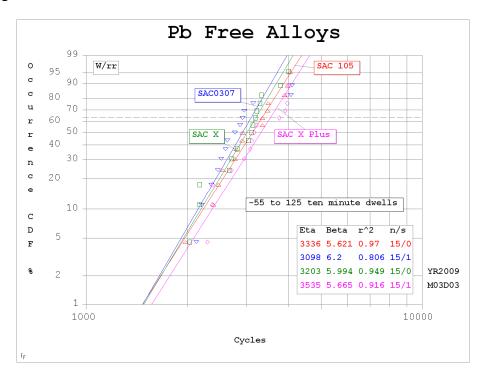

| 4-28 | Lead Free Alloys Comparison                | 119 |

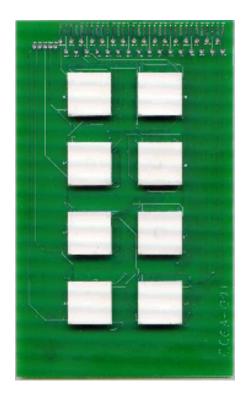

| 5-1  | Unique I/O Test Vehicle                    | 123 |

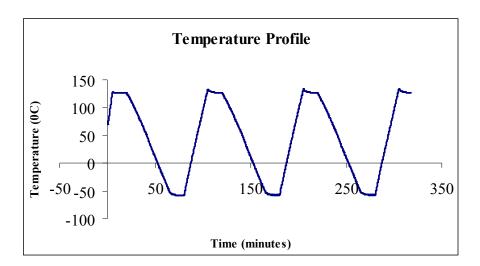

| 5-2  | Thermal Profile Unique I/O Test            | 124 |

| 5-3  | SOL Interconnect                           | 126 |

| 5-4  | Schematic of SOL Interconnect construction | 127 |

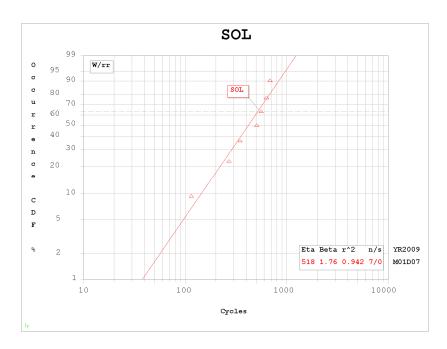

| 5-5  | Weibull Plot SOL I/O                       | 128 |

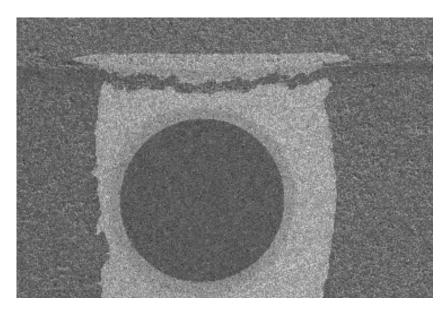

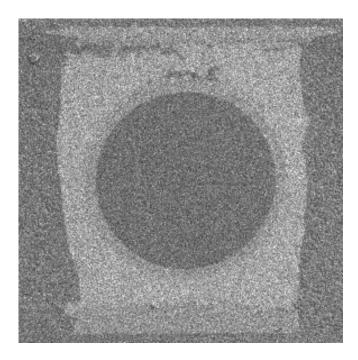

| 5-6  | Failed SOL I/O                             | 128 |

| 5-7  | Top Cracking SOL I/O                       | 129 |

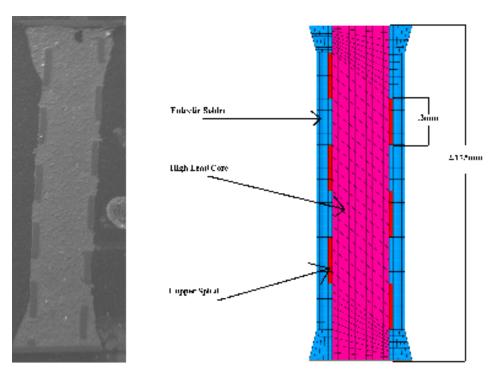

| 5-8  | Diagonal view SOL finite element model     | 131 |

| 5-9  | Finite Element Model SOL I/O               | 131 |

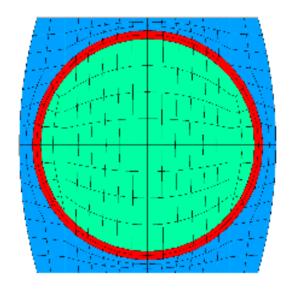

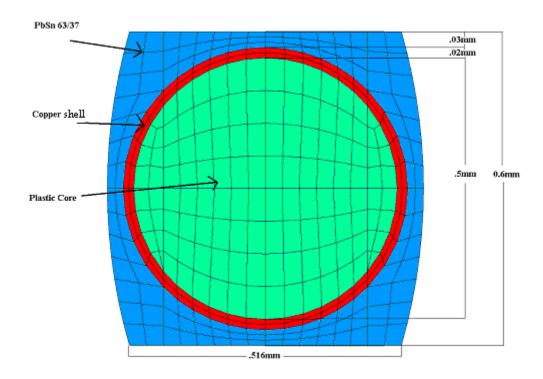

| 5-10 | Dimensioned SOL Finite Element Model       | 132 |

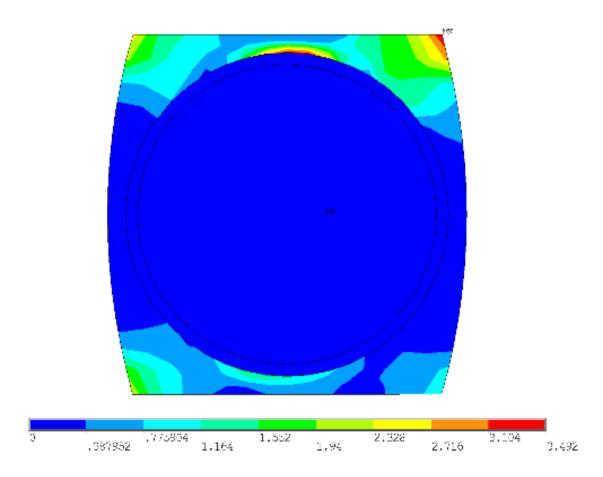

| 5-11 | Failed Finite Element Model SOL I/O        | 133 |

| 5-12 | Hysteresis Loop SOL interconnect           | 134 |

| 5-13 | Plastic Work SOL interconnect              | 134 |

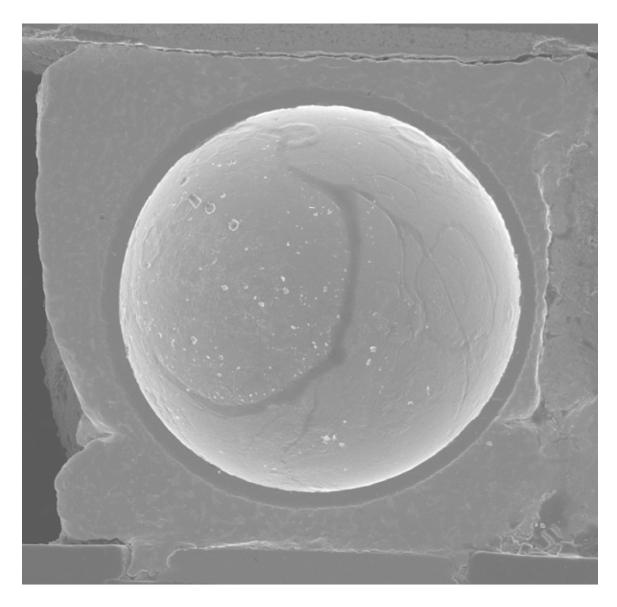

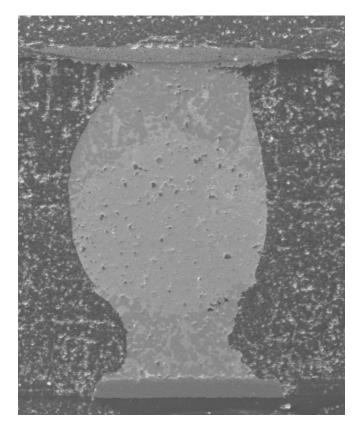

| 5-14 | CCGA Interconnect                          | 136 |

| 5-15 | CCGA I/O Construction                      | 137 |

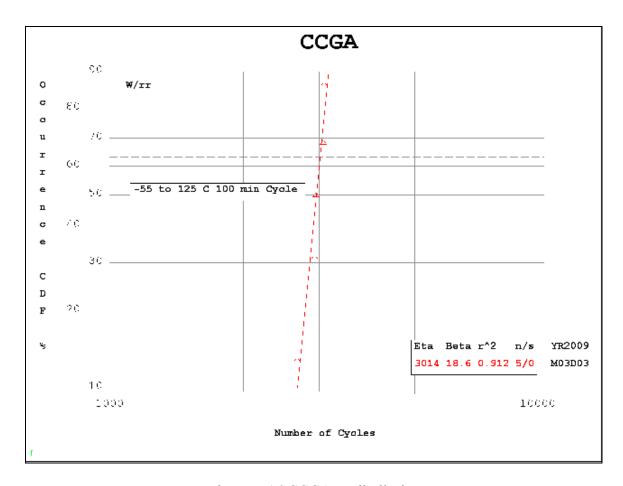

| 5-16 | CCGA Weibull Plot                          | 138 |

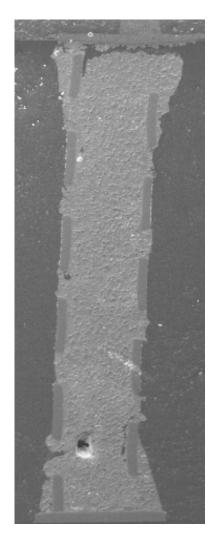

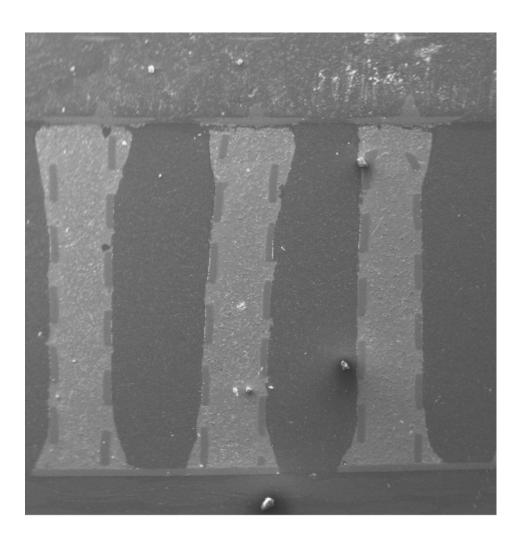

| 5-17 | Failed CCGA SEM                            | 139 |

| 5-18 | Failed CCGA SEM                     | 140 |

|------|-------------------------------------|-----|

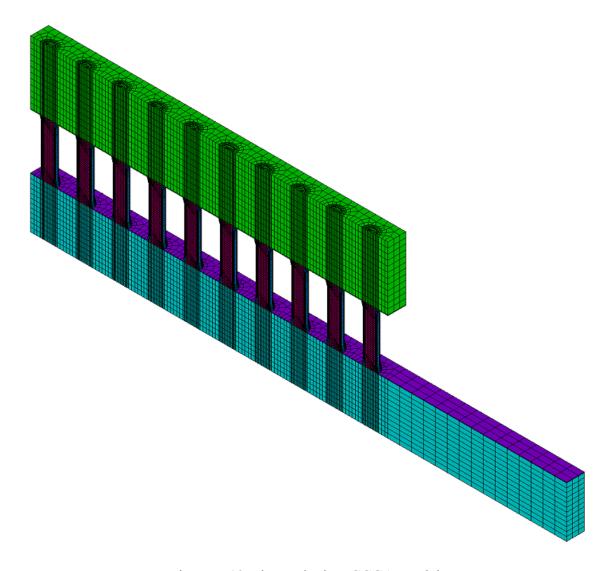

| 5-19 | Diagonal View CCGA Model            | 141 |

| 5-20 | Dimensioned CCGA I/O                | 142 |

| 5-21 | Copper Spiral around high-lead core | 142 |

| 5-22 | Failed CCGA FEM                     | 144 |

| 5-23 | CCGA Hysteresis Plot                | 145 |

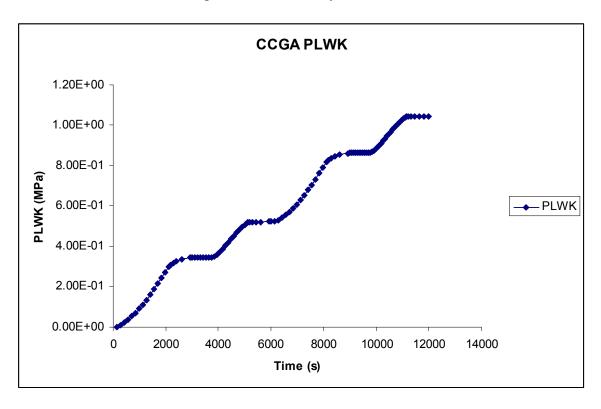

| 5-24 | CCGA Plastic Work Plot              | 145 |

| 5-25 | High-lead Interconnect              | 147 |

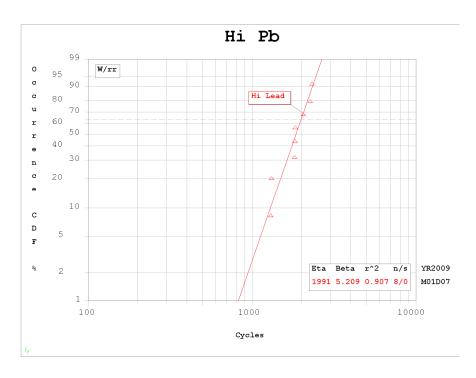

| 5-26 | High-lead Weibull Plot              | 149 |

| 5-27 | SEM Failed High-lead                | 150 |

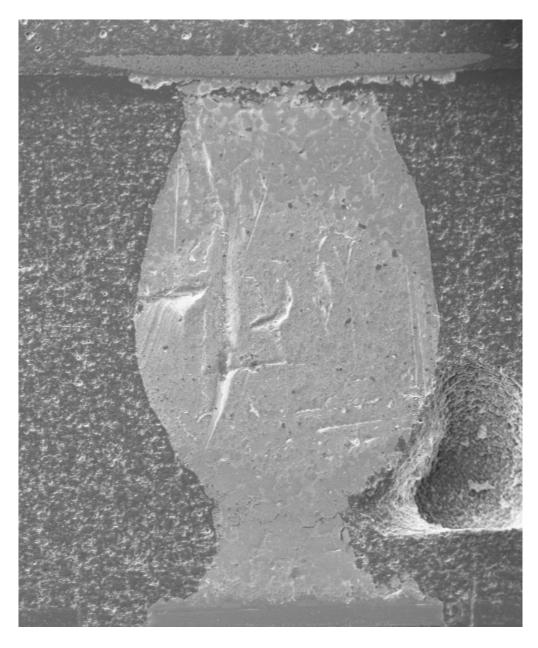

| 5-28 | SEM Failed High-lead interconnects  | 151 |

| 5-29 | High-lead FEM Diagonal View         | 152 |

| 5-30 | High-lead Interconnect              | 152 |

| 5-31 | Failed High-lead FEM                | 153 |

| 5-32 | High-lead Hysteresis Loop           | 154 |

| 5-33 | High-lead Plastic Work              | 155 |

| 5-34 | SAC 305 Weibull Plot                | 157 |

| 5-35 | Failed SAC 305 Interconnect         | 158 |

| 5-36 | Failed SAC 305 interconnect         | 158 |

| 5-37 | Diagonal view SAC 305               | 159 |

| 5-38 | FEM SAC 305 I/O                     | 160 |

| 5-39 | Failed SAC 305 FEM                  | 161 |

| 5-40 | SAC 305 Hysteresis Loop             | 162 |

| 5-41 | SAC 305 Plastic Work                     | 163 |

|------|------------------------------------------|-----|

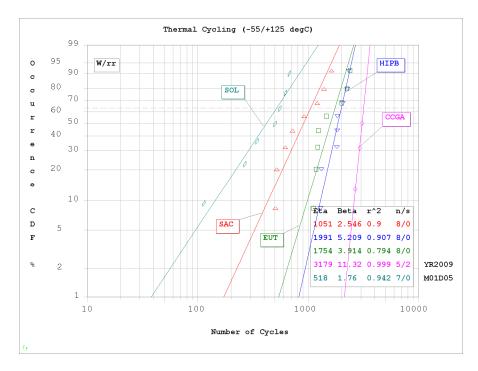

| 5-42 | Weibull Plot Comparison All Packages     | 165 |

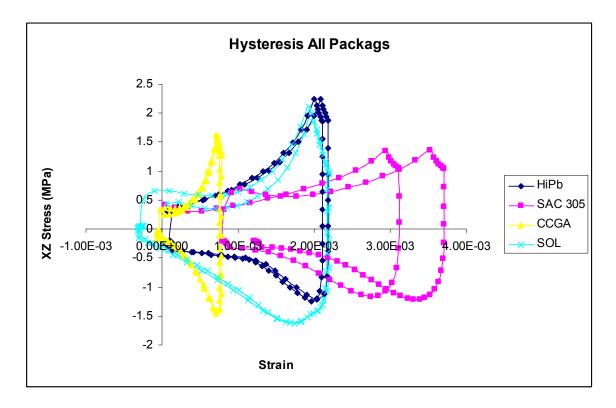

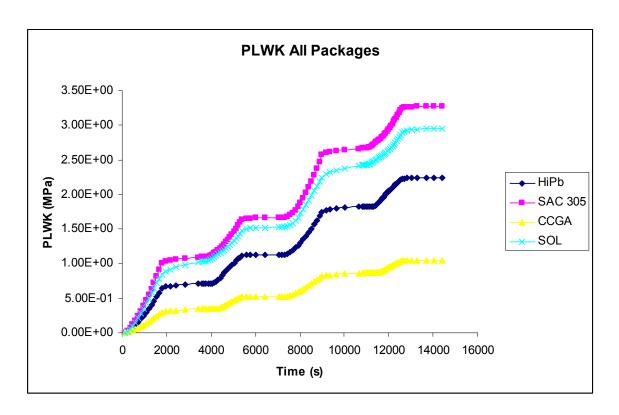

| 5-43 | Comparative Hysteresis Loop All Packages | 166 |

| 5-44 | Plastic Work Comparison of all packages  | 167 |

# List of Tables

| 3-1  | Nine Anand Contants                              | 22 |

|------|--------------------------------------------------|----|

| 3-2  | Package Dimensions for test vehicle              | 28 |

| 3-3  | BGA 1152 Package Dimensions                      | 32 |

| 3-4  | BGA 1152 life comparison                         | 36 |

| 3-5  | Properties of smear plate components             | 37 |

| 3-6  | Smear plate properties used in simulation        | 38 |

| 3-7  | Flip Chip Dimensions                             | 38 |

| 3-8  | Material properties used in BGA 1152 FEM         | 39 |

| 3-9  | 63Sn37Pb Anand constants                         | 39 |

| 3-10 | ME-531 Underfill Properties                      | 43 |

| 3-11 | Experimental vs. Simulation results for BGA 1152 | 49 |

| 3-12 | Dimensions of PBGA 313                           | 49 |

| 3-13 | Material properties PBGA 313                     | 55 |

| 3-14 | PBGA 313 Life Correlation                        | 60 |

| 3-15 | PBGA 128 multichip dimensions                    | 62 |

| 3-16 | PBGA 128 Life Comparisons                        | 67 |

| 3-17 | PBGA 128 material properties                     | 68 |

| 3-18 | Life Correlation PBGA 128                        | 73 |

| 3-19 | PBGA 256 Dimensions                              | 75 |

| 3-20 | PBGA 256 Life Correlation                     | 81  |

|------|-----------------------------------------------|-----|

| 4-1  | Package dimensions Lead Free experiment       | 95  |

| 4-2  | Characteristic life comparison                | 104 |

| 4-3  | Life comparison of all solder alloys          | 108 |

| 4-4  | Anand constants SAC 305                       | 108 |

| 4-5  | Anand constants Sn3.5Ag                       | 109 |

| 4-6  | Material Properties for finite element models | 109 |

| 4-7  | Life Correlation SAC 305                      | 113 |

| 4-8  | Sn3.5Ag Life Correlation                      | 117 |

| 5-1  | Unique I/O Board Dimensions                   | 124 |

| 5-2  | Package Dimensions SOL I/O                    | 127 |

| 5-3  | SOL Finite Element Material Properties        | 130 |

| 5-4  | SOL Life Correlation                          | 135 |

| 5-5  | 5-5 CCGA Dimensions                           | 137 |

| 5-6  | CCGA Material Properties                      | 143 |

| 5-7  | 90Pb10Sn Anand Constants                      | 143 |

| 5-8  | CCGA Characteristic Life                      | 146 |

| 5-9  | Characteristic Life Comparison                | 146 |

| 5-10 | High-lead Dimensions                          | 148 |

| 5-11 | High-lead Material Properties                 | 153 |

| 5-12 | High-lead Life Correlation                    | 155 |

| 5-13 | Package Comparisons                           | 156 |

| 5-14 | SAC 305 Dimensions                            | 157 |

| 5-15 | SAC 305 Material Properties         | 160 |

|------|-------------------------------------|-----|

| 5-16 | SAC 305 Anand Constants             | 161 |

| 5-17 | SAC 305 Life Correlation            | 163 |

| 5-18 | Package Comparison                  | 164 |

| 5-19 | Characteristic Life of all packages | 165 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Project overview

The first project presented involves four different electronic packages of varying geometry and architecture. The first package is a fine pitch high I/O flip chip. The second package is a perimeter array multi chip plastic ball grid array (PBGA) having four chips housed in the package molding. The third package is a full array PBGA. Fourthly, there is a perimeter array PBGA with a smaller die and smaller body. All packages have been subjected to a harsh thermal environment and modeled in ANSYS finite element program. Once the packages were thermal cycled, they were cross sectioned and analyzed so that the failure modes and life predictions made by the finite element model could be validated. With this project, it was hoped that a better understanding of how package parameters, such as pad finish, die size, and underfill can effect the performance of a package in a harsh thermal environment. On top of this, it was also hoped that the finite element models would validate the thermal cycling tests so that computer simulation can one day be reliable enough to replace expensive, actual thermal cycling testing.

The second project involves lead free interconnects. In this project, 6 different lead free alloys are tested. The alloys tested included two low silver content packages Sn1.0%Ag0.5%Cu (SAC 105) and Sn0.3%Ag0.7%Cu; two high silver content packages,

Sn3.5%Ag and Sn3.0%Ag0.5%Cu (SAC 305); and two alloys containing rare earth dopants, Sn0.3%Ag0.7%Cu0.1Bi, called SAC X, and Sn0.2%Ag0.7%Cu0.1%Bi0.1%Ni, called SAC X-Plus. All of the packages were identical with the exception of the solder alloy used as the interconnect. All of the packages were subjected to the same harsh thermal environment, but only two could be created in the ANSYS finite element program due to a lack of information regarding Anand's constants necessary for simulation. While more information has been coming in about lead free alloys, much is still unknown. It is hoped that through this study a life model for lead free alloys can be validated and more information can be gained about how the different lead free alloys hold up in harsh thermal environments so that a clear cut, superior lead free alloy can be identified.

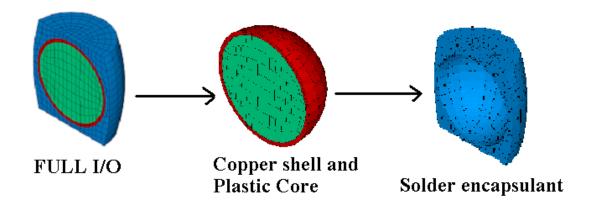

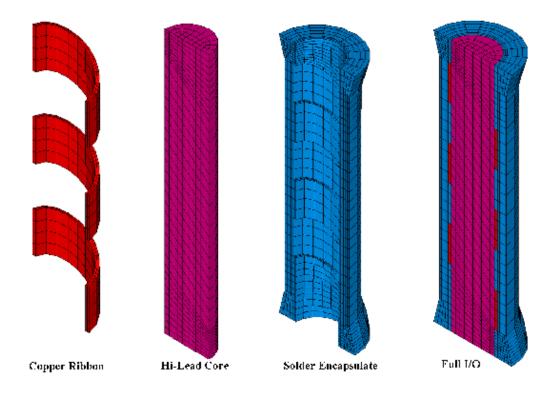

The third project involved ceramic packages with different interconnect architectures and designs. Aside from the standard tin lead eutectic ball, four new and unique interconnects were tested. The first interconnect is called the SOL interconnect. It is a compliant plastic core with a copper shell that has been encased in eutectic solder. The second interconnect presented is a copper reinforced high-lead ceramic grid array (CCGA). The interconnect consists of a high-lead core, spiral wrapped with a copper ribbon, and encased in eutectic tin lead solder. For the third interconnect, a high-lead sphere is wetted with a eutectic bridge. It is thought that the more compliant high-lead sphere will lead to better thermal environment performance. The fourth interconnect is a lead free Sn3.0%Ag0.5%Cu (SAC 305) interconnect. Conflicting reports on SAC 305 thermal reliability have been reported to date. The test in this project offers some conclusive evidence as to how the SAC 305 alloy performs in a harsh thermal

environment. In this project, all packages were subjected to harsh thermal environment testing and modeled in the ANSYS finite element program. The thermal environment was simulated and the finite element model was validated with the actual thermal cycling results. Through this project, it was hoped that a superior interconnect architecture could be discovered to replace and surpass the standard tin lead eutectic solder ball used in most applications today. Also, it was further hoped that the finite element life predictions would be good enough to add growing confidence to simulation models, so that expensive actual thermal testing of the interconnects could be substituted for cheaper computer simulations.

# 1.2 Packaging Overview

In order to understand the ramifications of the tests presented, it is important to have some understanding of electronic packaging. Electronic packaging, according to Suhling, is the art (Based on Science) of establishing interconnections between various levels of electronic devices, components, modules, and systems [Suhling MECH 6310 Notes]. Electronics can be found in nearly every device used today from large vehicles and automobiles to hand held electronic devices. No matter what the application, there is a constant drive to make electronic packages smaller, cheaper, and faster. Because of this, the industry is constantly being driven to test out new designs and improve on older applications. While these new designs may perform optimally from an electronic perspective, they do not always perform that well from a mechanical reliability view point.

Many of these package are subjected to harsh thermal environments, shock/drop loads, or random vibration loads. Today's electronics must withstand harsh environments, and are not just used in benign environments such as the desktop computer in a cubicle. Under thermal cycling load, packages deform due to mismatches in the coefficient of thermal expansion (CTE) found in the different materials of the package. This deformation is taken up by the more compliant solder interconnects. When exposed to repeated thermal cycles, the materials in the package expand and contract at different rates. This cyclic expansion and contraction is a repeated stress on the interconnects and eventually causes their failure by way of low cycle fatigue. Obviously, the longer the fatigue life of the interconnect, the better. Below, in Figure 1-1 an image of an electronic package can be seen demonstrating the different components and their CTE's.

Figure 1-1 CTE Electronic package

The main problem area is usually found in the region where the silicon die meets the substrate. In a plastic package, the substrate has a CTE of 12ppm/°C while the silicon chip has a CTE of 2.5ppm/°C. The stiffer silicon die lowers the effective CTE in the

substrate region, which increases the CTE mismatch between the printed circuit board and the substrate. This increased CTE mismatch causes more stress and deformation in the presence of thermal loads and this stress and deformation is in turn taken up by the second level interconnect, leading to a shortened fatigue life of the interconnect. [Syed 1996]. Cracking most often occurs in the neck of the solder ball where the stress concentration is increased. However, failures can be seen at the lower side of the solder ball as well.

#### 1.3 Lead Free Electronics

Recently there has been a movement in the electronics industry to get rid of the lead found in most interconnects. The eutectic tin lead interconnect, 63Sn37Pb, has been used since the inception of the ball grid array due to it's electrical characteristics, wetabiltiy in soldering, and superior reliability performance. However, some health concerns regarding the amount of lead found in electronic packages has caused a movement against lead free interconnects. Solder alloys composed of tin, silver, and copper have emerged as leading candidates to replace the lead based alloys. There is still much to be learned about the alloys, and testing is still ongoing in order to create a Sn-Ag-Cu (SAC) alloy that is as convenient as the tin lead eutectic. Researchers have experimented with varying the composition of the three SAC components and doping the SAC elements with additional earthen metals such as Nickel and Bismuth. Generally, high silver content alloys hold up better in thermal testing than do the lower silver content packages. The material characteristics of the SAC alloys can be changed by doping, either hardening or softening the alloys and effecting the melting point of the

solder alloys. To date, several life prediction equations have been proposed but an accurate life prediction equation has not been determined. With further finite element modeling and thermal testing, a life prediction model can be determined.

# 1.4 Unique Interconnect Designs

Industry is constantly developing new ways to improve the performance and life of electronic packages. Because the weak point in the package is the solder interconnect new interconnects are often designed and old interconnects are modified. Different interconnects can include solder columns, high-lead spheres with eutectic bridges, and polymer studded interconnects to name a few. In the third project presented, 4 new interconnect designs were created. These new designs include a copper reinforced column grid array; a SOL interconnect, which is a plastic sphere surrounded by a copper ring and encased in eutectic tin lead solder; a lead free Sn3.0%Ag0.5%Cu (SAC 305) interconnect; and a high-lead sphere bridged with eutectic tin lead solder. All of these interconnects were thermal cycled on test boards that had a strip of ceramic with no chip or mold and were connected to FR-4 PCB. The high-lead core interconnects are thought to be more compliant than the stiffer eutectic tin lead solder balls. This increased compliancy should allow the interconnects to deform easier and take on more stress. This should increase the life of the package. The column grid interconnects outperform the standard tin lead eutectic alloys because they have a taller standoff height which reduces the stress found in the interconnect and adds to the compliancy of the interconnect. It was hoped that one of the new designs would greatly improve the life of the package over the standard eutectic solder ball.

All packages were created and simulated in the ANSYS finite element environment. Upon failure of the packages in thermal cycling, they were removed and cross sectioned in order to validate the failure mode shown by the finite element simulation. Good correlation between actual testing failure mode and simulation failure mode was achieved. The package lives were also estimated by way of ANSYS and the simulation lives were matched up with the real thermal testing lives. Again, all of the simulation lives were within 25% error of actual thermal cycle lives.

In sum, the main focus of all the tests is on second level interconnect failure. All of the interconnects are subjected to low cycle fatigue which causes their failure and the failure of the electronic package. The thesis presents data on underfilled packages, packages with different surface finish, packages with different design, new lead free interconnects, newly designed unique interconnects, and finite element simulations. If it can be shown that the finite element simulation closely follows the real world thermal cycling then it may be possible to skip actual thermal cycling, which would save money and time. The thesis presents more information on new lead free alloys, new interconnect designs, and how unique architecture packages hold up against one another.

#### **CHAPTER 2**

#### LITERATURE REVIEW

Electronic packaging started with the dual in line package (DIP). This package consisted of a thin ceramic body housing a chip wired out to a lead frame. This package allowed for more I/O's at the time, but required through hole technology in order to be bonded to the PCB. In the 1970's, the industry created the plastic leaded chip carrier. This package could be surface mounted to the PCB but offered poor reliability due to Jlead connections. From this, the quad flat pack was created which offered a more reliable package due to gull wing leads, which were compliant and didn't fail as easy. As packages evolved, the need for more interconnects became apparent. This need lead to the creation of the pin grid array. In this package, pins were dispensed on the bottom of the package in an area array fashion. These leads, however, gave raise to reliability issues involving the bending of leads and were expensive due to the alloy used in creating the pins. In an attempt to reduce cost and abate pin bending while still allowing for high I/O density and reliability, the ball grid array package was created. In this package, smaller pitch packages with superior reliability and better manufacturing yields were made available. The BGA technology offers high I/O packages that are cheaper, smaller, faster, and more reliable than most other leaded packages.

The major problem with the BGA is the thermal mismatch between components in the package. The BGA featuring an alumina substrate called a ceramic ball grid array

has a ceramic substrate featuring a CTE of 6 °C/ppm while the PCB has a CTE of 13 °C/ppm. This difference in CTE causes the materials in the package to expand and contract at different rates when exposed to thermal loads. This expansion and contraction leads to a cyclic stress or fatigue which is taken up in the second level solder alloy interconnect. The main focus of BGA reliability is trying to reduce the stress on the second level interconnects.

### 2.1 General Packaging Architecture

Many studies have been done involving the reliability of the second level I/O's based on package dimensions. Initially it was thought that the plastic ball grid arrays would not be strong enough to withstand harsh environments such as under the hood of a [Syed 1996] showed that packages designed with perimeter arrays, thicker BT substrates, and an increased pad size can provide packages reliable enough to withstand the under the hood environment. Further studies on reliability have showed that the die size has the greatest impact on reliability [Ghaffarian 2002]. In this study, Ghaffarian showed that the smaller die increases the life of the package. It was also shown that the larger pitched ball grid arrays tend to outperform the fine pitch ball grid arrays. Syed discussed the impact of the die on the package reliability in his 1996 paper [Syed 1996]. In this study, he states that the close proximity of the die increases the effective CTE in the region of the die making it lower. This causes a greater CTE mismatch between the PCB and the package which causes more deformation and stress in the face of a thermal load. The compliant solder ball connections end up taking on the stress and this repeated stress, termed low cycle fatigue, eventually leads to their failure.

Other studies have shown the effect that pad finish and solder mask can have on the interconnections. [Bradley 1995] showed that HASL finish is superior to the immersion nickel based finishes. Oxidation of the nickel through gold layer can lead to poor solderability resulting in a bad connection between the solder ball and copper pad. [Suhling 2002] showed the superiority of HASL pad finish over Palladium based pad finishes in thermal testing on BGA's. It has also been shown that perimeter arrays perform better than the full arrays because the impact of the die is lessened and that a thicker BT substrate also helps abate the CTE mismatch between the die and the PCB [Syed 1996, Ghaffarian 2002]. [Mawer 1999] showed the increased reliability packages have with non solder mask defined copper pads.

The effect of underfill on PBGA's has been the focus of many previous studies. [Elkaday 2004] tests the impact of underfill on the thermal performance of smaller perimeter array packages and shows that the underfill improves the life of the tested packages. [Pyland 2000] shows that a low CTE higher young's modulus underfill improves the reliability of a super BGA, but higher CTE underfills deteriorate the life of the packages. [Qi 2005] tests two different underfills on a smaller full array package. One of the underfills increases reliability while the other underfill did not. An increase in life for PBGA's was seen in [Liji 2002]. [Burnette 2001] presents the effects of six different underfills on different package architectures and determines that having an underfill with a CTE of approximately 15 ppm/°C is optimal for improving life. [Suhling 2002] tests 15,17, and 23 mm packages under the effects of four different underfills and determines that the proper underfill can increase the reliability of a package so that it can be used in an under the hood environment.

In lead free electronics, much work is still being done to understand the deformation and characteristics of lead free interconnects. In particular, an overall superior SAC alloy for replacement of lead based alloys is still being researched.

#### 2.2 Lead Free Electronics

[Zhang 2003] tried to define the overall solder deformation using four major modes over deformation including time independent elastic strain  $\gamma_{el}$ , time independent plastic strain  $\gamma_p$ , time dependent primary strain  $\gamma_{pr}$ , and time dependent secondary strain  $\gamma_{sec}$ . He also defines 4 distinct regions of strain including the Nabarro-Herring creep and superplasticity given by

$$\frac{d\gamma_{scr}}{dt} = A\tau^{n} \exp\left(\frac{-Q}{RT}\right)$$

as well as the climb controlled dislocation and power law breakdown given by

$$\frac{d\gamma_{scr}}{dt} = A' \left[ \sinh(\alpha \tau) \right]^n \exp\left( \frac{-Q}{RT} \right)$$

2.2

He also hypothesizes that the lead free or SAC alloys will perform better in low stress regions where Ag<sub>3</sub>Sn and Cu<sub>6</sub>Sn<sub>5</sub> intermetallics block grain boundary sliding. However, in high stress regions, the deformation is dominated by dislocation climb and glide, as well as matrix diffusion which is better suited for the lead rich particulates commonly found in lead based alloys leading to better lead based reliability in high stress regions. These results have been validated by many reseachers including [Clech 2005] who showed that the SAC alloys underperform the lead based alloys on ceramic packages where the stress is higher. [Schubert 2003] showed that the SAC outperforms the lead based alloy in a more compliant package, such as a PBGA with low CTE mismatch.

Zhang and Syed have separately shown that the point where 63Sn37Pb begins to outperform SAC is temperature dependent. One of the main points regarding lead free testing is that the lead free results are strongly dependent on package type and temperature profile as shown by [Roubaud 2001]. A test performed by Syed involving many different alloy compositions including doping the SAC alloys with earth additives was performed wherein the tin silver alloys underperform the tin silver copper alloys, but again, the results are strongly dependent upon temperature and package type [Syed 2001].

A study involving lead free electronics and polymer stud grid array (PSGA) packages showed that the SAC alloy performance is strongly dependent upon package type with the solder alloys characteristic life doubling when the package architecture changed [Vandevelde 2004]. In a power cycling environment, Young et al. showed that the SAC alloy can outlast the traditional tin lead alloy at low temperatures, but that the tin lead outperforms the lead free alloy at high temperatures in a power cycling test [Young 2008]. In another test, the lead free alloy Sn3.8Ag.7Cu was tested on plastic ball grid array (PBGA), plastic quad flat pack (PQFP), and thin small outlying package (TSSOP) wherein the different failure modes of the solder were demonstrated as well as the solder's performance on different pad finishes [Che 2005].

It has also been shown by many researchers including [Engelmaier 2003] and [Darveaux 2005] that the lead free alloys creep slower than the lead based alloys. In fact, Engelmaier states that the lead free alloys creep up to 100 times slower than the lead based alloys. On top of this, it has been shown by [Schubert 2002] and [Lau 2003] that the SAC alloys have a higher young's modulus when compared to the lead based eutectic alloy. So while the lead free alloys creep slower than the lead based alloys, they are

stiffer and may not hold up as well in a drop shock environment. The creep rate of the lead free alloys is also dependent on silver content as demonstrated by [Zhang 2008], [Darveaux 2008], and [Rooney 2008] wherein they stated that SAC 105 exhibits poorer creep properties than SAC 305. The trade off is that the higher silver content alloys have a higher young's modulus meaning that they are stiff and of little use in shock drop environments [Rooney 2008].

In an effort to create lead free alloys that are both creep resistant and compliant enough so that they may be used in thermal and drop shock applications; rare earth metals have been doped with tin silver copper based alloys to change the mechanical properties of the lead free alloy. [Amagai 2006] reported that the addition of no more than .03 wt % Ni to Sn.3Ag alloy reduces the grain size and IMC thickness. [Rooney 2008] stated that the addition of nickel to high silver content alloys produces a compliant and creep resistant alloy. [Huang 2008] reported similar findings by stating that nickel reduces IMC size and thickness. Huang states that doping SAC 405 with nickel softens so that it is as compliant as SAC 105, but still maintains the creep properties of SAC 305. [Kariya 2004] showed similar findings when he doped SAC 105 with nickel. Kariya states that the alloy becomes stiffer with nickel addition wherein the nickel creates a finer microstructure which gives good mechanical strength and good ductility. Because of this more of the deformation is elastic as opposed to plastic.

Other experiments involving the doping of SAC alloys with Bismuth have been performed by [Kanchanomai 2002] wherein he has shown that the bismuth causes an initial hardening in the alloy so that the stress in the alloy is higher but the plastic strain is lessened. The addition of Bismuth leads to a significant decrease in fatigue life for the

alloy. The bismuth addition has less cracking, but their increased stiffness increases the stress in the alloy. [Kanchanomai 2002] also shows that the addition of bismuth lowers the melting temperature of the alloy but raises the homologous temperature which enhances the occurrence of thermally activated processes such as creep and grain growth. [Zhao 2003] reported similar findings when doping SAC alloys with bismuth when he says that the tensile strength of the alloy increases, but the elongation of the alloy decreases. [Zhao 2003] also says that the optimal amount of bismuth is below 3%. Zhao also shows that the tin rich phase decreases with bismuth addition. Other experiments with Cerium have been performed by [Song 2008] wherein it is reported that Cerium greatly deteriorated the SAC alloy's life span. [Rooney 2008] reported findings where the Cerium increased the strength of the solder joint.

In addition to the creep models presented above in equations 1 and 2 the Anand model as proposed by [Anand 1982] for high temperature metals has also been shown to accurately represent the creep properties of lead free SAC alloys. The equation was modified by brown in his 1989 work [Brown 1989]. The Anand model is a unified creep theory model containing one flow equation and three evolution equations. The flow equation is

$$\frac{d\varepsilon_{p}}{dt} = A \left[ \sinh \left( \frac{\xi \sigma}{s_{o}} \right) \right]^{\frac{1}{m}} \exp \left( \frac{-Q}{kT} \right),$$

2.3

the three evolution equations appear as

$$\frac{ds_o}{dt} = \left\{ h_o \left( |B| \right)^a \frac{B}{|B|} \right\} \frac{d\varepsilon_p}{dt}, \qquad 2.4$$

$$B = 1 - \frac{S_0}{S^*}$$

, 2.5

and

$$s^* = \hat{s} \left[ \frac{d\varepsilon_p}{dt} \exp\left(\frac{Q}{kT}\right) \right]^n$$

2.6

The Anand equations unify both time dependent strain and time independent plastic strain through a common internal stress variable "s". [Rodgers 2005] has proven that the Anand model is valid for SAC finite element simulation by performing stress strain tests on different alloys and simulating the same stress strain test in ANSYS, where the results matched up closely. Anand constants for some of the lead free SAC alloys have been discovered. [Amagai 2002] reported eight of the nine Anand constants necessary for FEM simulation. [Chang 2006] presented Anand constants for SAC 305 that appear to give accurate simulation results. [Chen 2005] presented Anand constants for Sn3.5Ag lead free solder alloy. Though the Anand constants for some of the alloys have been presented, a valid life prediction model for lead free solders is yet to emerge.

Lead based alloys have well established life prediction models. [Darveaux 2000] established 63Sn37Pb eutectic alloy damage relationships correlating crack growth rate with inelastic strain energy density per cycle. These constants were later updated by Lall in his 04 paper [Lall 2004]. Other researchers have presented life models based on coffin manson based equations such as Zhan in his 03 paper [Zhan 2003]. For lead free alloy, [Syed 2004] has proposed a life prediction equation based on creep models making use of the hyperbolic power law breakdown constitutive equation

$$\frac{d\gamma_{scr}}{dt} = A' \left[ \sinh(\alpha \tau) \right]^n \exp\left( \frac{-Q}{RT} \right)$$

2.7

wherein he derives:

$$N_f = (0.0014\omega_{acc})^{-1}$$

2.8

In his 2004 paper Syed also proposed life equations based on many other constitutive equations. As well as lead free solder interconnects, much work is being done to develop interconnects of new geometry and design.

#### 2.3 Unique Interconnect Information

In an attempt to abate the damage found in the second level interconnect new interconnect designs are often proposed. Some examples of uniquely designed interconnects include elastomer interconnects with particle embedding which were tested for thermal reliability in the work proposed by [Liu 2003]. [Chandraskekhar 2003] showed promising results thermal cycling polymer stud grid arrays from -55 to 125 Celsius. [Vandevelde 2004] tested polymer stud grid array packages with SAC and SnPb based solder joints. Multi-copper column interconnects are designed by [Liao 2005] in his work. [Aggarwal 2007] looks at using metal-polymer composites to replace metallic components for packaging interconnects. [Okinaga 2001] shows a 4X reliability of plastic core solder balls over normal tin lead eutectic solder balls. Okinaga proves that the resistivity is not too high and the interconnect is a viable solution for normal solder balls. [Galloway 2005] shows that the polymer core package has a 1.6X life improvement over standard solder balls. Galloway also shows a 10% higher standoff with the interconnect adding to increased reliability. [Movva 2004] demonstrates how the polymer core acts as a strain buffer reducing stress in the rest of the interconnect. Movva also gives the material properties of the polymer core interconnect. [Whalley

2008] established optimal dimensions and material properties in the polymer core interconnect so that the maximum reliability can be achieved. As well as improving the solder ball, efforts have also been made to enhance the column grid array packages.

[Ghaffarian 2006] tests new lead free CCGA designs against plastic ball grid arrays. [Hong 2000] tested solder columns coated in a lead free solder for enhanced connectivity. [Winslow 2005] offers a copper reinforced column in his paper. He shows that the copper ribbon is intended to hold the interconnect together at the normal cracking location. He gives a concise summary of developments in column grid arrays and recent failures and designs. [Perkins 2003] tests a high-lead eutectic tin lead dual alloy column grid array. The failure mode is identified at the location where the high-lead alloy and tin lead eutectic alloy interface. New designs, as seen in [Winslow 2005], hope to abate the failure at the dual alloy interface. The column grid array has an established foundation as being a reliable interconnect as shown in the reliability tests run by [Master 1995] and [Engelmaier 1995].

Another interconnect commonly used on ceramic packages is the high-lead core solder ball. The interconnect has a high-lead sphere that is wetted with a eutectic bridge for connectivity to the component. Within the interconnect, the high-lead sphere is more compliant and takes up the majority of the interconnect strain during thermal loading. Past tests have examined failure mode and strain patterns in high-lead interconnect. [Howieson 2001] tests CBGA dual alloy interconnects and identifies failure modes as well as offering a method for modeling failure of the interconnects. [Farroq 2003] compares SAC CBGA's to dual alloy High-lead etutectic interconnects and shows that the SAC outperforms the dual alloy interconnects. He offers reasoning on why the dual

alloy concept should work. [Hong 1996] gives detailed models on stress in the dual alloy interconnect suggesting that the eutectic alloy has 2X the plastic strain of the 90Pb10Sn alloy. [Interrante 2003] also compares SAC alloys to the dual alloy interconnects and shows the superior reliability of the lead free, SAC, alloys. [Interrante 2003] determines that SAC has twice the fatigue life of the dual alloy CBGA.

#### CHAPTER 3

### UNIQUE ARCHITECTURE BGA PACKAGES

In this chapter, the thermo-mechanical reliability of four different packages of varying architecture and dimensions are presented. The study includes the effects of underfill on different PBGA's and a high I/O flip chip package as well as the effects of pad finish on the lives of the different packages. All of the packages were thermal cycled in a harsh thermal environment and recreated in ANSYS finite element environment for simulation purposes. In depth failure analysis and reliability data is presented in the pages to follow.

#### 3.1 Modeling techniques and life prediction method

All models presented in this paper were modeled using ANSYS V.10.0 finite element program. According to the distance to neutral point formula (DNP)

$$\gamma_{xy} \approx \frac{L(\alpha_{PWB} - \alpha_{CC})\Delta T}{2h}$$

3.1

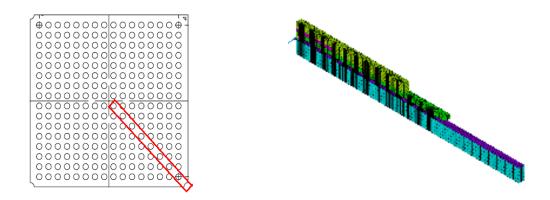

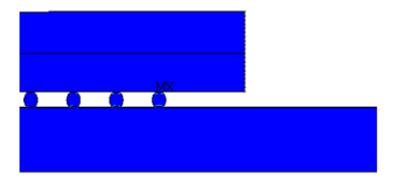

where L is the distance from the neutral point, which is taken as the point in the center of the package; a diagonal slice symmetry model was used for finite element modeling because the worst case, or critical solder ball can be captured in a diagonal slice model of the package. An example of a diagonal slice model is shown below in figure 3-1:

Figure 3-1 Diagonal symmetry model

It should be noted that the corner solder ball will not always be the limiting solder ball. In the presence of a die, the effective CTE is low. This creates a greater CTE mismatch between the package and the printed circuit board. This greater mismatch causes a greater stress which is taken up by the solder ball in the "die shadow" region [Syed 1996]. A finite element model demonstrating the die shadow is shown below:

Figure 3-2 Solder ball located in the die shadow region

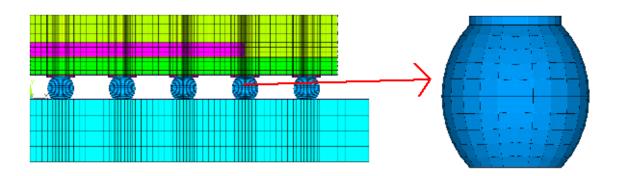

The elements used for modeling were the VISCO107 and eight node SOLID45 brick elements.

Eight node SOLID45 elements were used to model all of the materials in the package except for the solder ball, which was modeled using VISCO107 elements. All of

the materials in the package were modeled as isotropic except for the PCB and the substrate which were modeled as orthotropic. As taken from the ANSYS element library, SOLID45 is used for 3-D modeling of solid structures. It is an eight noded element with  $u_x$ ,  $u_y$ , and  $u_z$  at each node. The element has the capability to model plasticity and creep as well as other deformation features. Body temperature can be put in as a nodal load. The VISCO107 element also has eight nodes with  $u_x$ ,  $u_y$ , and  $u_z$  at each node. The VISCO107 element is used to model rate dependent plasticity. Body temperature can be applied as a body force at each node. For this element, the Anand model is used.

As mentioned in the previous chapter, the Anand equation consists of one flow equation,

$$\frac{d\varepsilon_{p}}{dt} = A \left[ \sinh \left( \frac{\xi \sigma}{s_{o}} \right) \right]^{\frac{1}{m}} \exp \left( \frac{-Q}{kT} \right)$$

3.2

with three evolution equations,

$$\frac{ds_o}{dt} = \left\{ h_o \left( |B| \right)^a \frac{B}{|B|} \right\} \frac{d\varepsilon_p}{dt}$$

3.3

$$B = 1 - \frac{S_0}{S^*}$$

and

$$s^* = \hat{s} \left[ \frac{d\varepsilon_p}{dt} \exp\left(\frac{Q}{kT}\right) \right]^n$$

3.5

The Anand model is a unified equation that unifies rate dependent and rate independent plasticity by an internal state variable "s", the deformation resistance, to describe the averaged isotropic resistance to macroscopic plastic flow [Wilde 2000]. The nine constants required for the Anand equation are seen in table 3-1:

Table 3-1 Nine Anand Contants

| Anand variable       |                                             |

|----------------------|---------------------------------------------|

| s <sub>o</sub> (MPa) | Initial Value of deformation resistance     |

| A(1/sec)             | Pre-exponential factor                      |

| Q/k(1/K)             | Activation energy over boltzmann's constant |

| a                    | Strain rate sentivity of hardening          |

| h <sub>o</sub> (MPa) | Hardening Constant                          |

| ξ                    | Multiplier of stress                        |

| n                    | Stain Rate Sensitivity of Saturation        |

| ŝ (MPa)              | Coefficient of Deformation Resistance       |

| m                    | Strain rate sensitivity of stress           |

In order to obtain the nine constants a series of constant strain rate tests and constant load creep tests must be performed at different temperatures and equations fitted to the generated stress and strain curves. Two things that the Anand equation does not take into effect are the Bauschinger effect and thermal recovery. The Baushinger effect has an impact on the amount of inelastic strain incurred while the material undergoes a cyclic fatigue load. The Baushinger effect must be accounted for when calculating life via a Coffin-Manson power law type of equation [Wilde 2000]. In fact, some researchers have reported error in the fact that Anand doesn't take into account aging, specifically with respect to lead free tin silver copper alloys where aging has a pronounced impact [Vasudevan 2008].

### 3.2 Modeling and real world failure

As mentioned earlier, when the electronic device is used in real world applications, the repeated thermal stresses put on the package cause cyclic fatigue. This cyclic fatigue leads to the eventual failure of the device by way of crack growth through the second level interconnect. The dominating deformation mechanism in the second level interconnect is creep deformation. This creep deformation leads to the generation of plastic work, which is defined by the equation

σĖ 3.6

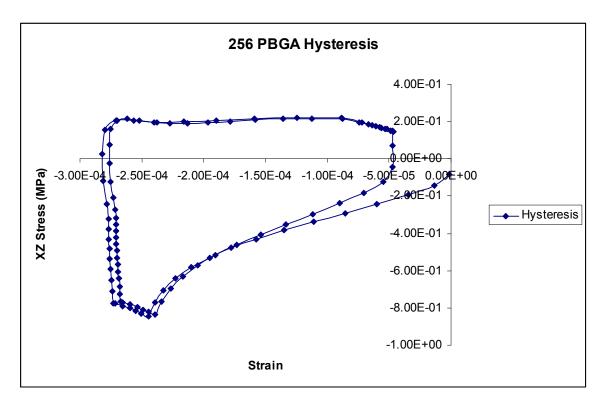

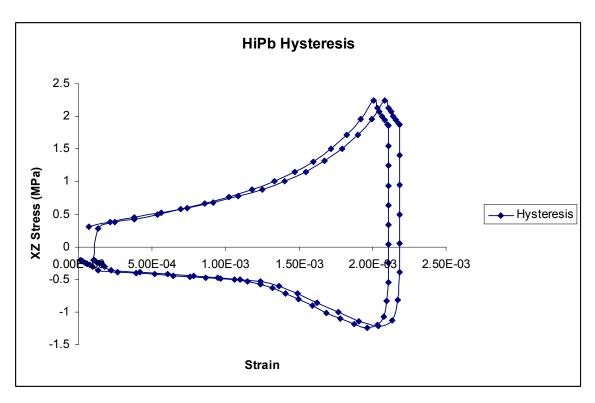

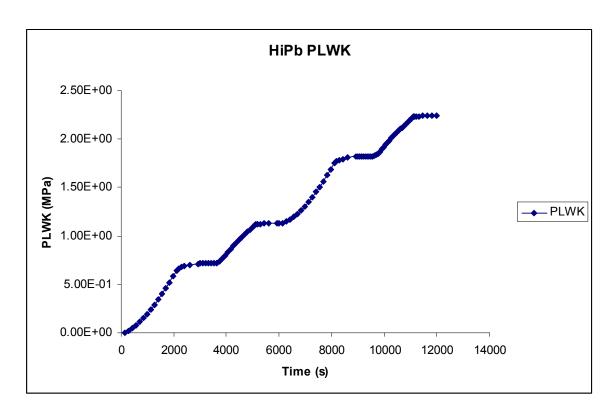

Which is also called the stress power. Essentially, it leads to an increase in energy in the body. The inelastic strain energy is defined as the unrecoverable potential energy of the deforming body. Essentially, this energy is lost when the body deforms plastically. This is why so much effort is put into defining the creep properties of the solder alloys, as will be seen throughout the thesis. When the viscoplastic solder creeps, it has three regions. The first region is the primary, or initial region. Next is the secondary region, and thirdly, the final, or tertiary region. The secondary region is also termed the steady state creep. Steady state creep is the dominant creep mechanism seen in the solder alloy. The tertiary region is the final region before the solder ruptures and fails. In ANSYS, the plastic work is a ready output of the program and is used as a damage parameter. The inelastic strain energy density is represented by the hysteresis plot of the finite element simulation. An example of a hysteresis loop is shown below.

Figure 3-3 PBGA 313 Hysteresis loop

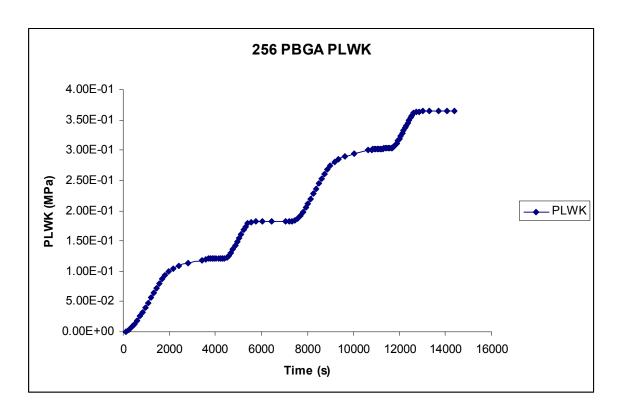

The area enclosed by the curve in the hysteresis loop represents the inelastic strain energy density for the package. When the hysteresis loop stabilizes it can be said that the amount of damage incurred per cycle is constant. This way, only two cycles need to be run in the finite element simulation in order to get a valid damage parameter such as plastic work. Then, the plastic work can be used in the crack growth equations presented in equations 3.8 and 3.9. Essentially, the crack growth is constant per cycle so long as the damage accrued per cycle is constant. If the hysteresis loop has not stabilized after two cycles, then more cycles need to be simulated until the hysteresis loop does finally stabilize. When determining the plastic work of the package from simulation, the plastic work values must be volume averaged over a layer of elements in order to reduce mesh sensitivity according to the formula given by Zhan [Zhan 2003].

$$\Delta W_{\text{ave}} = \frac{\Sigma \Delta W \cdot V}{\Sigma V}$$

Generally, the plastic work is volume averaged over the layer of elements where the damage is maximum and most likely to propagate in real world testing. For example, if the maximum damage is seen in the top of the interconnect, the top layer of elements will be selected for volume averaging. If the bottom layer, at the board side interface, sees maximum damage, then a layer of elements at the copper pad interface on the board side will be selected for volume averaging. The volume selected for averaging the plastic work has a great impact on the simulated life of the package and selection of the right layers should be done wisely.

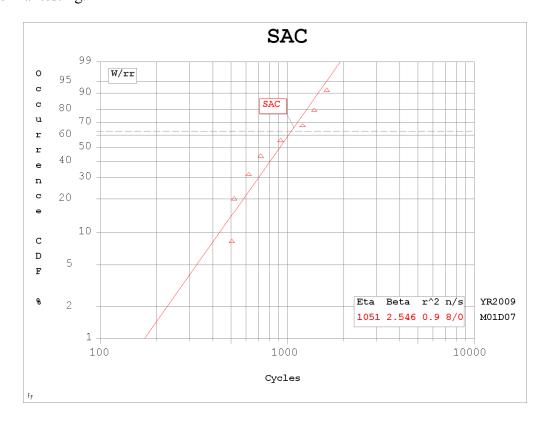

Once the package has a sufficient number of failures, a two parameter Weibull plot can be generated. The Weibull plot gives the number of cycles to a component failure. On the X-axis, the number of cycles to failure is plotted. On the Y-axis, the percentage of the failed population is plotted.  $\beta$  and  $\eta$  are the two constants in the Weibull plot and they represent the slope and the characteristic life of the Weibull plot. The characteristic life is the point where 63.2% of the population has failed. The number of cycles for any percentage of failed components can be found by using

$$N = \eta \left[ \ln \left[ \frac{1}{1 - F(N)} \right] \right]^{\frac{1}{\beta}}$$

3.8

Where F(N) is the percentage of failed parts.

### 3.3 Unique Architecture PBGA packages

In the first experiment, four packages of varying architecture and package type are presented. The first package to be presented is a high I/O flip chip. Secondly, we have a more standard PBGA with a full array and large chip size. Thirdly, we have a perimeter array multi chip module featuring four chips in the mold. All the chips are of varying size. Fourthly, we have a perimeter array PBGA 256 package. Within the four packages everything varies from substrate thickness, die length, die thickness, pitch, solder ball height, I/O count, etc. On top of this, one batch of these packages were underfilled and tested against non underfilled packages. An equal number of packages with ImAg and HASL finish are tested and the reliabilities are plotted against each other. The differences in life due to underfilling and different surface finish are documented in the pages to follow.

Previously, it was thought that PBGA packages would not be able to withstand the harsh under the hood environment. However, it has been proven that the properly designed PBGA can easily meet the extreme environment conditions [Lindley 1995]. Previous studies have shown that packages with larger solder balls and a higher pitch have greater reliability [Syed 1996, Ghaffarian 2002]. Also, many studies have been done on surface finish. In Bradley's paper, he investigates HASL and ImAu packages. He finds that the consistency achieved with an immersion nickel plated pad is desired, but the pad ultimately underperforms the HASL and OPC packages [Bradley 1996]. Studies on solder mask and non solder mask defined pads have shown that NSMD pads provide nearly a 2X increase in life [Mawer 1999]. For our paper, all I/O's are SMD at the package interface, but NSMD on the board side. Out of all of these parameters.

perhaps the most important is die size [Ghaffarian 2002]. Because the die is so stiff, the package has a low effective CTE in the die-substrate region. This thermal mismatch is felt by the compliant solder balls, which deform under the stress. On top of this, the further the balls are away from the neutral point of the package, the quicker they fail. So the combined effect of distance and the low effective CTE due to die/substrate interaction puts an increased amount of stress on the interconnects [Syed 1996]. In this paper, dies of various size and thickness are tested.

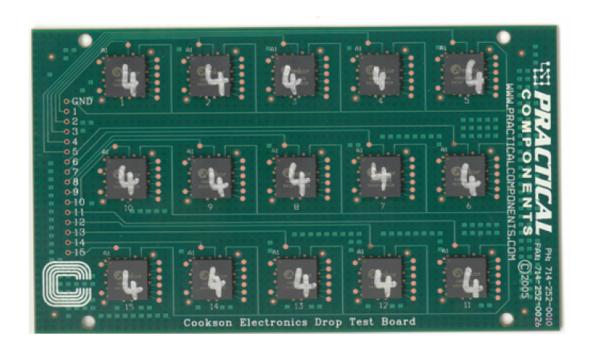

The test vehicle also contains four chips that all have unique designs. Two of the packages on the board are high I/O flip chip. Flip chip packages are unique to standard wire bonded packages in that they can accommodate higher circuit density and provide more I/O's for the chip. Also, they have an area where a heat spreader can be attached providing greater heat transfer from the chip [Matsushima 1998]. 20 high I/O flip chips are tested in this paper. Half are ImAg finished while the other half is HASL finish. The failure results are shown. On top of this, we had a 128 I/O multi-chip package. The package consisted of a perimeter array featuring 4 different chips all of varying size housed in a diallyl phthalate mold. The different die sizes affected the life of the package with the largest chip causing the greatest thermal stress and driving the package to failure. The third package is a standard PBGA while the fourth package is a smaller perimeter array package featuring a smaller die. The test vehicle is shown below in figure 3-4.

Figure 3-4 Test Vehicle Study 1 with unique I/O packages

The dimensions of the packages can be seen below in table 3-2:

Table 3-2 Package Dimensions for test vehicle

| Parameter        | BGA 1152<br>(U1 & U2)          |          | PBGA 313<br>(U3) | PBGA<br>128            | Resistor<br>1503 |

|------------------|--------------------------------|----------|------------------|------------------------|------------------|

|                  | ,                              | <b>\</b> |                  | (U5)                   |                  |

| Length           | 35 mm                          | 27 mm    | 35 mm            | 20.7 mm                | 150 mils         |

| Width            | 35 mm                          | 27 mm    | 35 mm            | 20.7 mm                | 30 mils          |

| Thickness        | 3.2 mm                         | 2.13 mm  | 1.46 mm          | 3.05 mm                | -                |

| I/O              | 1152                           | 256      | 313              | 128                    | -                |

| Pitch            | 1 mm                           | 1.27 mm  | 1.27 mm          | 1 mm                   | -                |

| Ball<br>Diameter | .6 mm                          | .75 mm   | .63 mm           | .56 mm                 | -                |

| Ball<br>Height   | .5 mm                          | .7 mm    | .6 mm            | .56 mm                 | -                |

| Package<br>Type  | Flip Chip<br>Fine Pitch<br>BGA | PBGA     | PBGA             | Multi-<br>Chip<br>PBGA | -                |

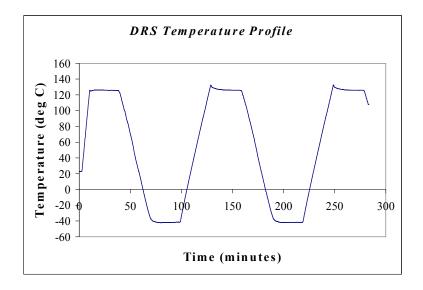

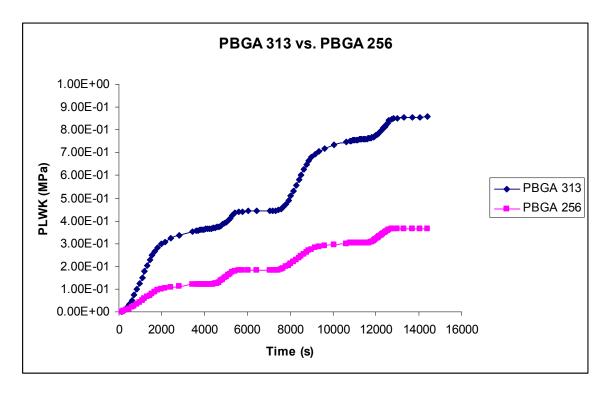

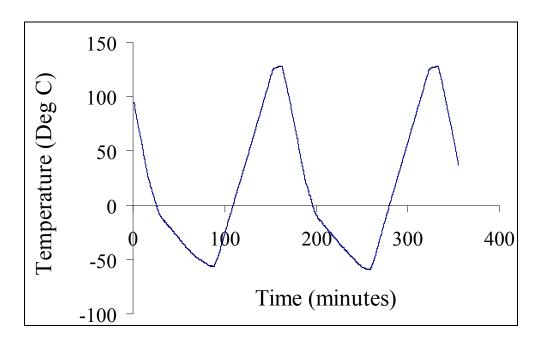

The test was specified as -40 to 125 Celsius with 30 minute dwells and 30 minute ramps at either end giving a 120 minute cycle. The chamber was profiled using Slim Kic software and the temperature plot can be seen below in Figure 3-5:

Figure 3-5 Unique I/O Thermal Profile

For testing purposes, all of the packages were daisy chained. In daisy chaining, all of the interconnects are connected to one another through metallic traces. In this manner an electrical current can be sent through all of the interconnects with the daisy chain providing conductivity. As the package is thermal cycled and damage is accrued in the interconnects, the measured resistance of the current sent through the daisy chain will change. This change in resistance of the signal is used to denote the point of failure in the package. When the resistance is infinite, this indicates an open interconnect where a crack has grown all the way through the interconnect. The resistances of the packages presented were constantly monitored using a switch box and multimeter. The packages were also manually probed to validate failure data. The resistances were recorded via a LABview program. Failure of a package was denoted as a 10% increase in resistance

where the package resistance stayed 10% or higher for the duration of the test. Failure was traced back to the original cycle count where the 10% increase in resistance was initially seen.

Lord Thermoset ME-531 underfill was chosen for the packages. It is a self filleting semiconductor grade epoxy used for the encapsulation of packages. The material properties of the underfill will be seen in the BGA 1152 finite element modeling section of this chapter. The effect of underfill on PBGA's is varying, either increasing or decreasing the life of the packages depending on the material properties of the underfill used. The effects of the underfill as well as some explanation as to underfill effect on packages is given in the package discussions to follow.

#### 3.4 BGA 1152

The first package to be discussed is a high I/O flip chip. Flip chips are commonly used in high end logic devices. The flip chip has a large circuit density, operates at high speed, and generates a large amount of heat. A cross section of a flip chip can be seen below in figure 3-6.

Figure 3-6 Flip Chip Cross Section

From Figure 3-6, the chip is attached to the substrate via flip chip solder bumps. A copper lid is attached to the top of the package and a thin insulating material is put between the copper lid and the chip. This whole assembly is mounted on the PCB with standard size solder balls. Matsushima has shown that the flip chip can accommodate large pitch count packages with improved reliability characteristics [Matsushima 1998]. Li has shown that a higher young's modulus and higher CTE heat spreader will lower warpage in the package. Li also showed that a hi-CTE ceramic substrate is more reliable than a BT substrate. The stress reduction in package reduces with increasing die size and package size. When using a hi-CTE ceramic substrate the corner ball is usually the first to fail because the influence of the die is abated due to the large CTE mismatch between the substrate and PCB [Li 2001]. For the package presented in this test, a ceramic substrate was used. Table 3-3 shows the package dimensions for BGA 1152.

Table 3-3 BGA 1152 Package Dimensions

| Length              | 35 mm   |

|---------------------|---------|

| Width               | 35 mm   |

| I/O                 | 1152    |

| Pitch               | 1 mm    |

| Ball Diameter       | .6 mm   |

| Ball Height         | .5 mm   |

| Substrate Thickness | 1.2 mm  |

| PCB Thickness       | 2.11 mm |

|                     |         |

An equal number of flip chip packages were underfilled and tested as well as an equal number of HASL and ImAg finish packages were tested against each other. The first package is the ImAg finish package. In previous tests involving the reliability of different solder pad finishes, Bradley and Banerji reported that the HASL finished boards outperformed other finishes commonly found in electronic packages. One problem with the HASL finish is that it is difficult to get an even coating, whereas the immersion nickel based finishes can give a smooth and even coating. However, it is thought that the nickel migrates through the porous gold layer and leads to eventual corrosion [Bradley 1996]. Our results showed that the ImAg finish BGA 1152 package greatly underperformed the HASL finish BGA 1152 package. The results can be seen in figure 3-7 below.

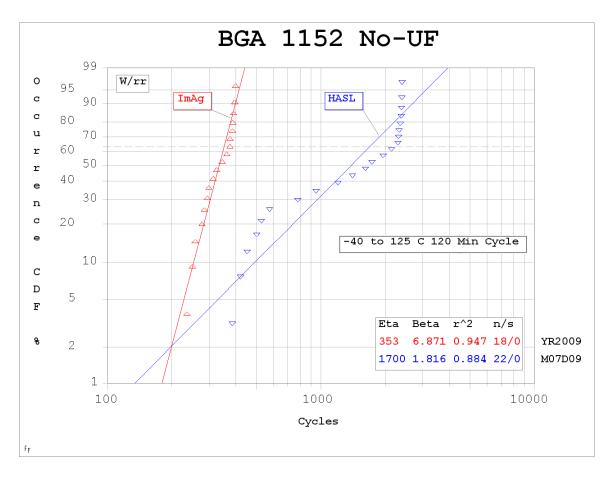

Figure 3-7 Weibull plot BGA 1152 ImAg and HASL

As can be seen from figure 3-7, the HASL board greatly outperforms the ImAg board. The HASL board has a nearly 5X life improvement over the ImAg finish board. This trend seems to be constant throughout all of the unique I/O packages tested, however, none are as pronounced as for the high I/O BGA 1152 flip chip. The HASL finish shown above demonstrates at least two different failure modes as indicated by the change of slope in the failure distribution. The performance of the HASL finish vs. the ImAg finish supports previous findings by Bradley, though the difference is more extreme in the BGA 1152 package.

Secondly, an equal number of the packages were underfilled and thermal cycled under the same temperature profile. The underfill greatly improved the life of the package as can be seen in figure 3-8 below.

Figure 3-8 Weibull plot for underfilled Xilinx packages

The characteristic life greatly improved for both packages, but the HASL still outperformed the ImAg finish by nearly 3X. In this plot, only one failure mode is demonstrated as the failure distributions fall on a linear line with a steep slope. Comparisons of how the different pad finishes performed when underfilled our shown in figure 3-9 and figure 3-10.

Figure 3-9 Weibull plot for ImAg finish underfill vs. non underfilled

Figure 3-10 Weibull plot for HASL finish underfill vs. non underfill

In the ImAg finish, the life improvement was more pronounced with a nearly 3X life improvement due to underfill and in the HASL, it was a 1.7X life improvement. The table below summarizes the characteristic lives of all the BGA 1152 packages.

Table 3-4 BGA 1152 life comparison

| Pad Finish | UF  | (η) Characteristic Life |

|------------|-----|-------------------------|

| ImAg       | No  | 353 cycles              |

| ImAg       | Yes | 1,053 cycles            |

| HASL       | No  | 1,700 cycles            |

| HASL       | Yes | 3,261 cycles            |

# 3.4.1 BGA 1152 FEM

For modeling purposes a smear plate was used to represent the chip, flip chip solder joints, the thin insulating material, and the copper heat lid. A volume averaging technique was used to get the material properties for the smear plate. A rule of mixtures shown below in equations 3.7 and 3.8 was used to get the effective young's modulus and an effective CTE for the smear plate. [Clech 1996].

$$\alpha_{\rm Eff} = \frac{\sum E_i V_i \alpha_i}{\sum E_i V_i}$$

3.7

$$E_{\text{eff}} = \frac{\sum E_i h_i}{\sum h_i}$$

Where h is the thickness of the respective layers, V is the volume of the layers, E is the young's modulus and  $\alpha$  is the coefficient of thermal expansion. The following values were used for the material properties:

Table 3-5 Properties of smear plate components

| Material                 | $\alpha_x(\frac{ppm}{\circ}C)$ | $\alpha_y(\frac{ppm}{^{\circ}C})$ | $\alpha_z(\frac{ppm}{^{\circ}C})$ | E(MPa) |

|--------------------------|--------------------------------|-----------------------------------|-----------------------------------|--------|

|                          |                                |                                   |                                   |        |

| Copper Lid               | 16.3                           | 16.3                              | 16.3                              | 128932 |

|                          |                                |                                   |                                   |        |

| Thin insulating material | 80                             | 80                                | 80                                | 1240   |

|                          |                                |                                   |                                   |        |

| Silicon Die              | 26                             | 26                                | 26                                | 131000 |

|                          |                                |                                   |                                   |        |

| Solder Bumps             | 20                             | 20                                | 20                                | 51000  |

|                          |                                |                                   |                                   |        |

| Underfill                | 38                             | 125                               | 38                                | 6500   |

|                          |                                |                                   |                                   |        |

Using the rule of mixtures shown above, the following dimensions were used for the smear plate:

Table 3-6 Smear plate properties used in simulation

| E(MPA) | $\alpha_x(PPM)$ | $\alpha_y(PPM)$ | $\alpha_z(PPM)$ |

|--------|-----------------|-----------------|-----------------|

| 114357 | 13.3            | 13.6            | 13.3            |

|        |                 |                 |                 |

The dimensions of the smear plate components can be seen below in table 3-7

Table 3-7 Flip Chip Dimensions

| Component    | Thickness (mm) | Length (mm) |

|--------------|----------------|-------------|

| Lid          | .07            | 35          |

| Glue         | .5             | 22          |

| Chip         | .7             | 22          |

| Solder bumps | .05            |             |

| Underfill    | .05            | 22          |

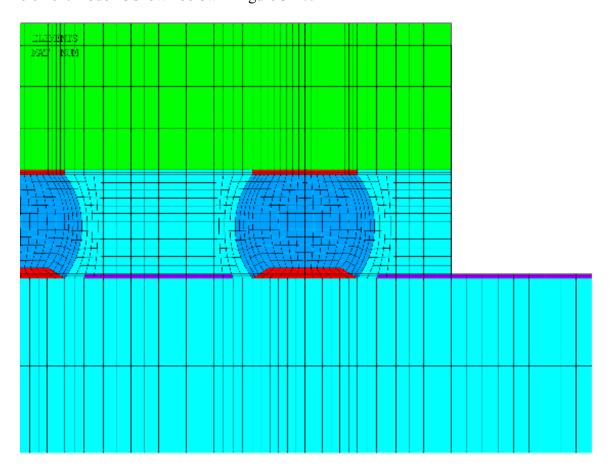

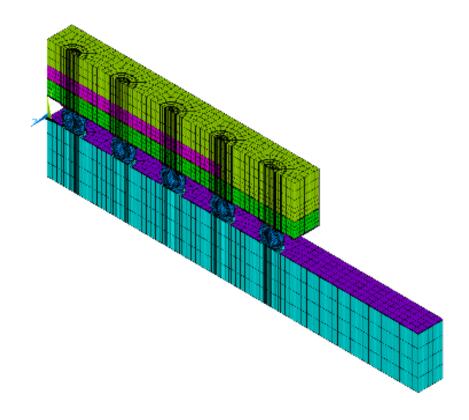

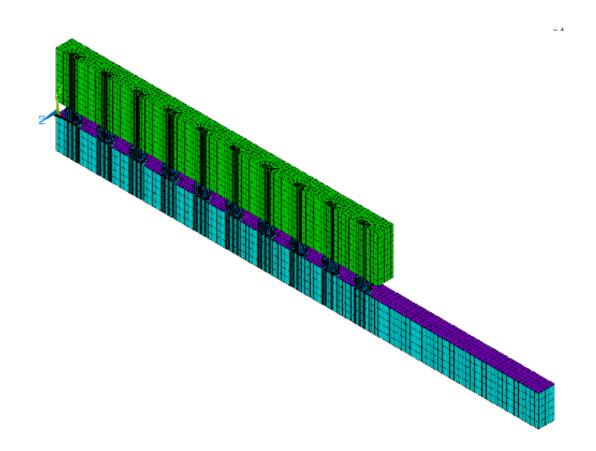

A diagonal view of the finite element model is seen below in figure 3-11

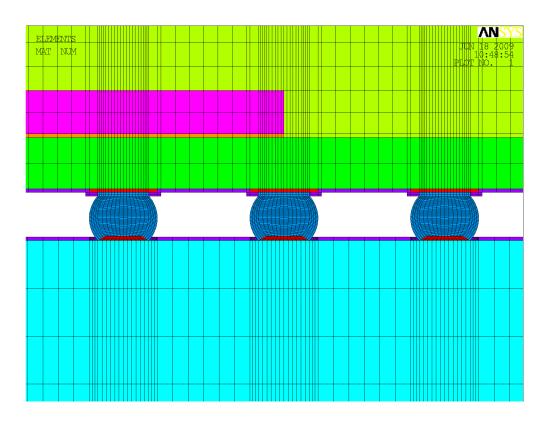

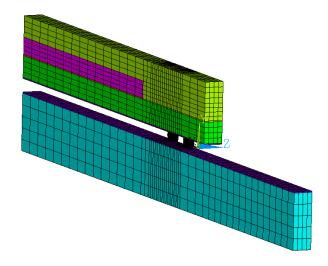

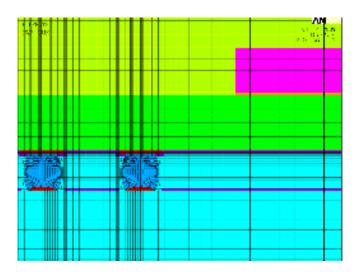

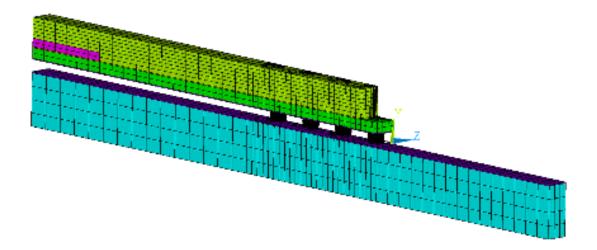

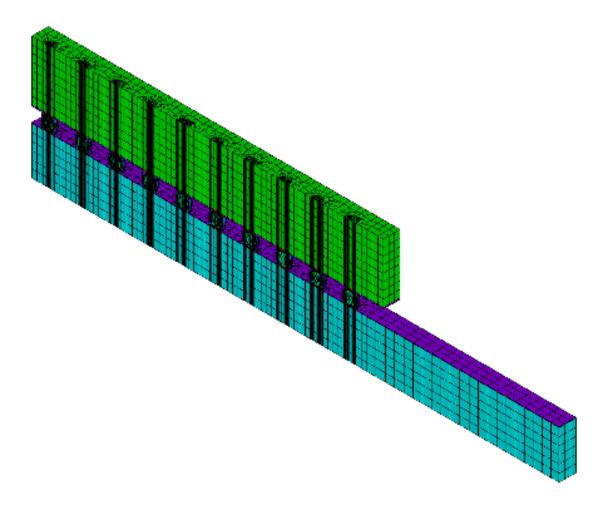

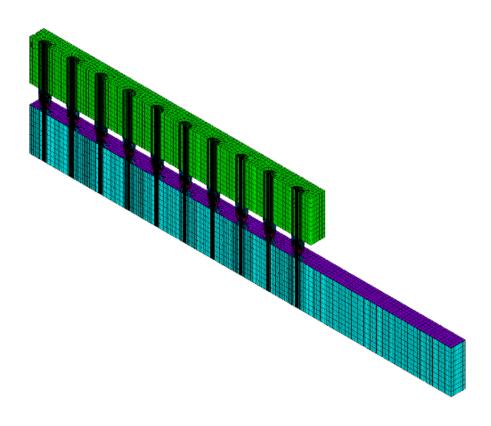

Figure 3-11 BGA 1152 Finite Element Model

A diagonal slice symmetry model of the package was created in order to cut down on simulation time. The solder balls are 63Sn37Pb eutectic tin lead interconnects. A table of the material properties used in the simulation can be seen below.

Table 3-8 Material properties used in BGA 1152 FEM.

| Component         | E GPa        | α ppm/°C       | υ   |

|-------------------|--------------|----------------|-----|

| PCB               | 17(x,z) 7(y) | 15(x,z) 67 (y) | .39 |

| Solder Ball       | 30           | 24             | .35 |

| Ceramic Substrate | 276          | 6.7            | .3  |

| Solder Mask       | 3            | 30             | .3  |

| Copper Pad        | 128          | 16             | .34 |

The Anand constants used for simulation can be seen in the table below

Table 3-9 63Sn37Pb Anand constants [Darveaux 2000]

| 63Sn37Pb Anand constants |                                           |  |

|--------------------------|-------------------------------------------|--|

| $S_o$                    | 12.41 ( <i>MPa</i> )                      |  |

| Q/k                      | 9400 (1/ <sub>K</sub> )                   |  |

| A                        | $4.0e6 \left(\frac{1}{\text{sec}}\right)$ |  |

| 5                        | 1.5                                       |  |

| m                        | .303                                      |  |

| $h_o$                    | 1378.95 (MPa)                             |  |

| n                        | .007                                      |  |

| а                        | 1.3                                       |  |

| ŝ                        | 13.79 ( <i>MPa</i> )                      |  |

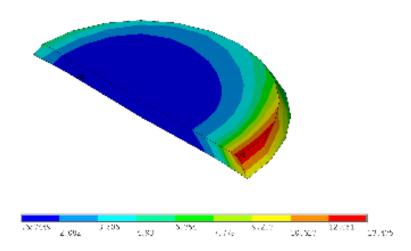

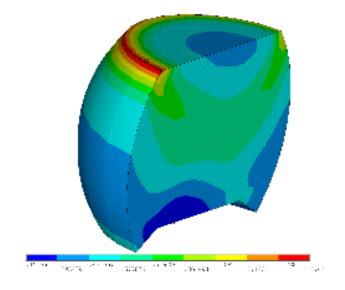

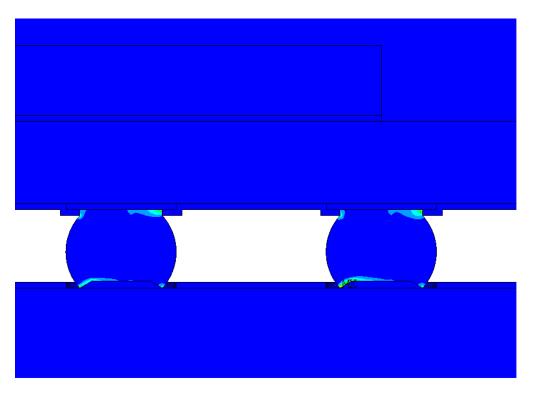

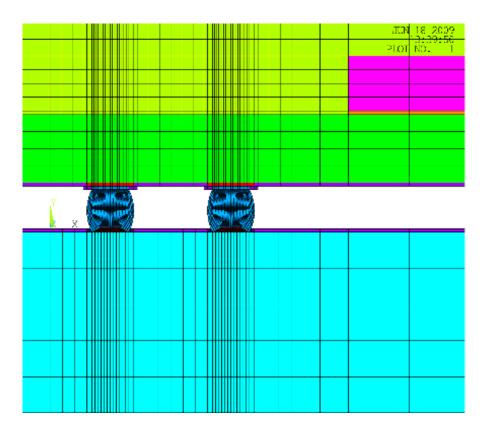

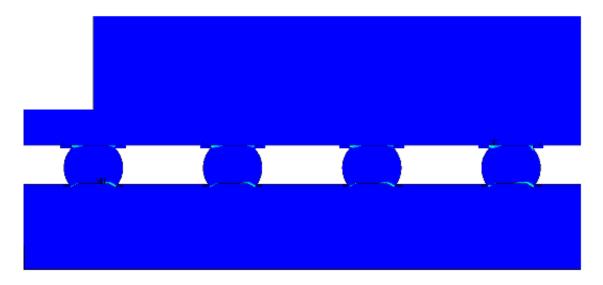

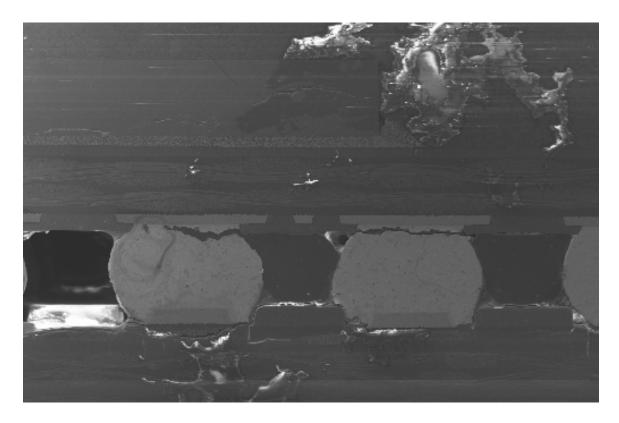

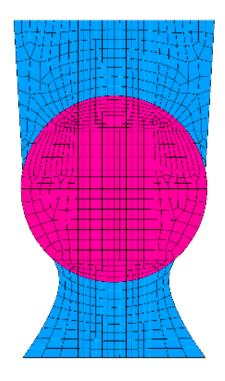

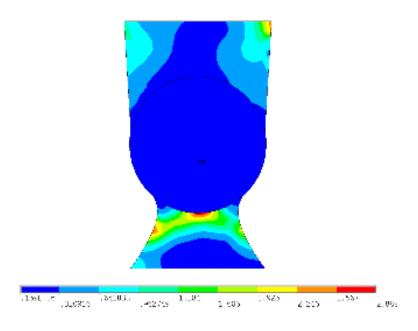

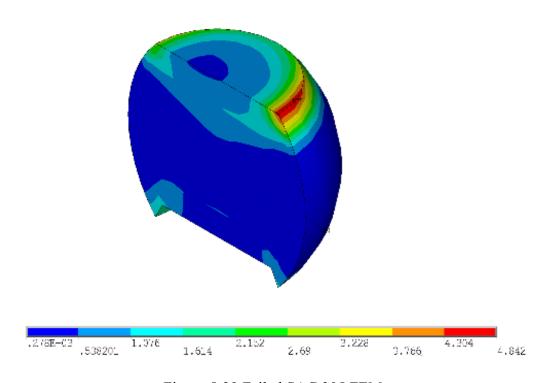

Similarly to the results reported by Li, the corner ball was the first to fail as the effect of the die is abated by the stiffer ceramic substrate [Li 2001]. In figure 3-12 below, the corner ball experienced the most damage.

Figure 3-12 BGA FEM 1152 Failure

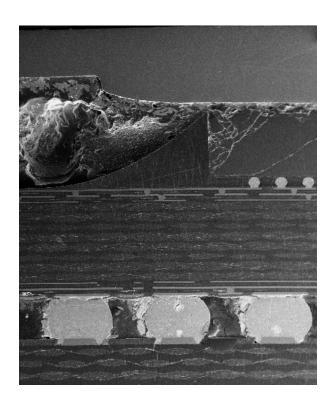

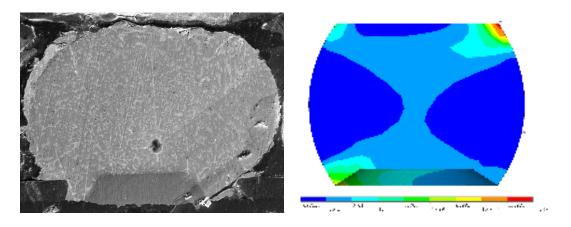

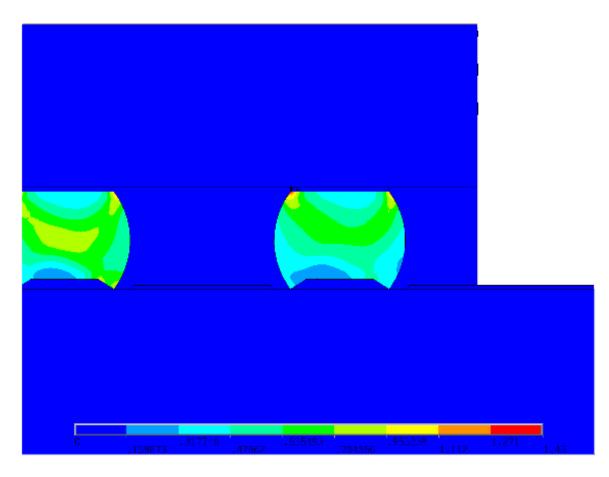

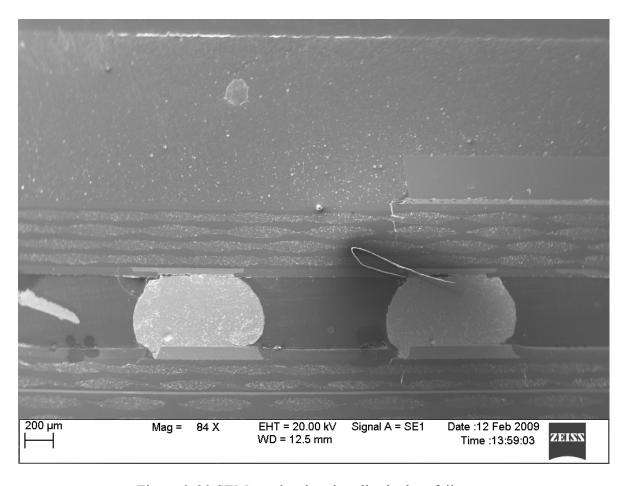

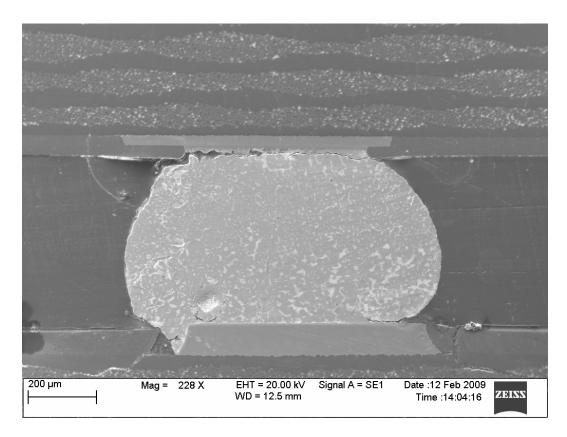

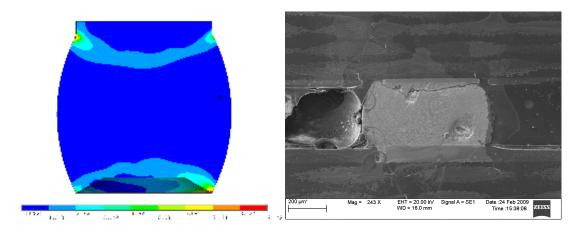

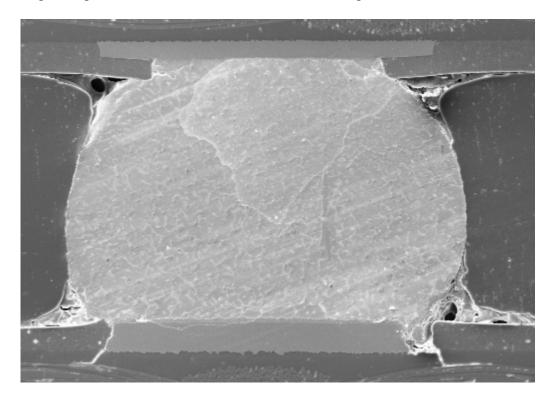

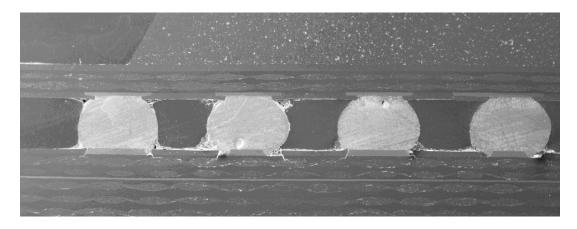

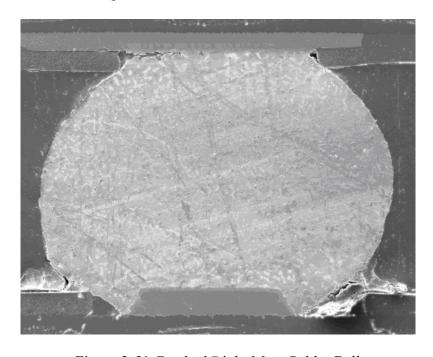

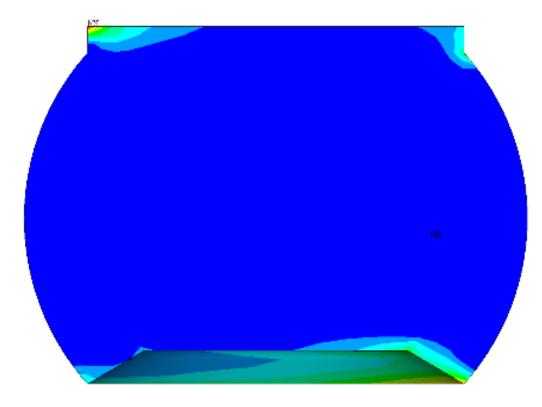

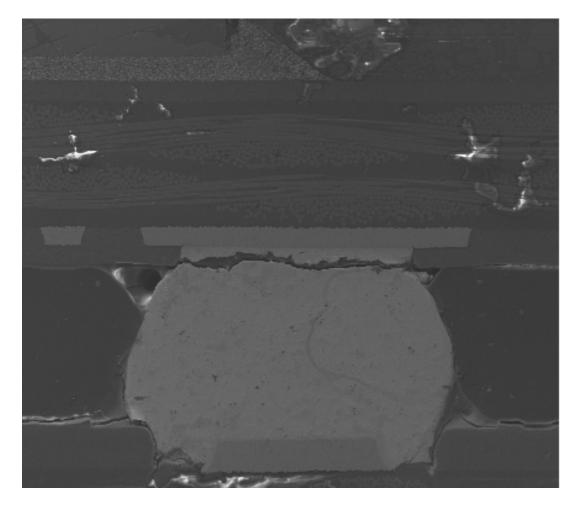

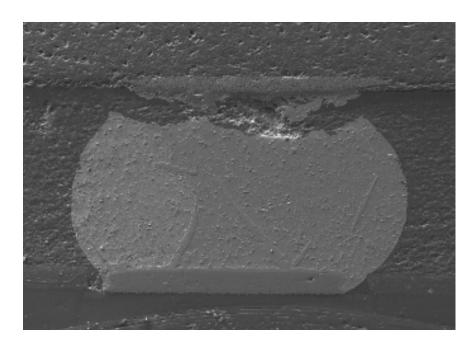

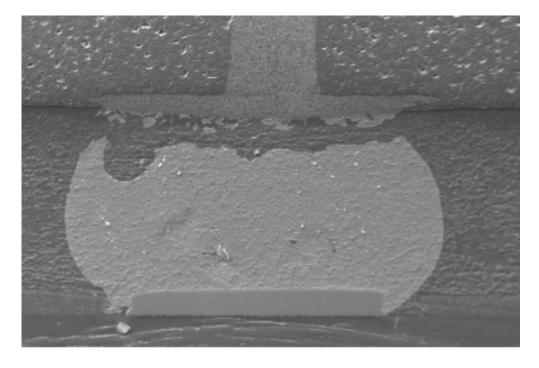

As mentioned above, corner ball failure was expected in this model as the ceramic substrate abates the effect of the die and causes the distance to neutral point formula to come into action, causing the greatest amount of stress in the corner, or furthest, solder ball. Below, an image of the failed solder ball as identified by the ANSYS simulation is placed next to an actual failed ball. Figure 3-13 shows that the crack propagated through the top of the interconnect along the package interface.

Figure 3-13 Failed ball compared to failed simulation

An image of the top layer of the solder ball with maximum damage is shown below in figure 3-14. This is also the layer that was used for plastic work calculation.

Figure 3-14 showing the top layer failure

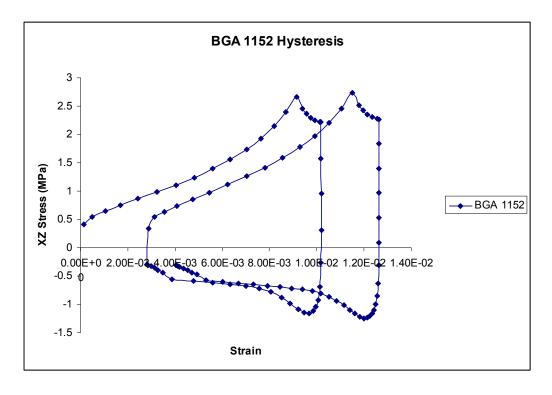

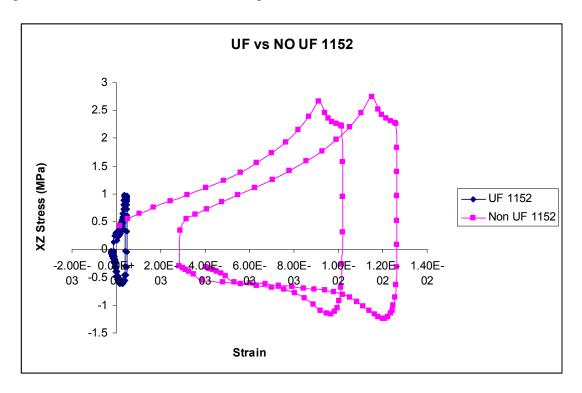

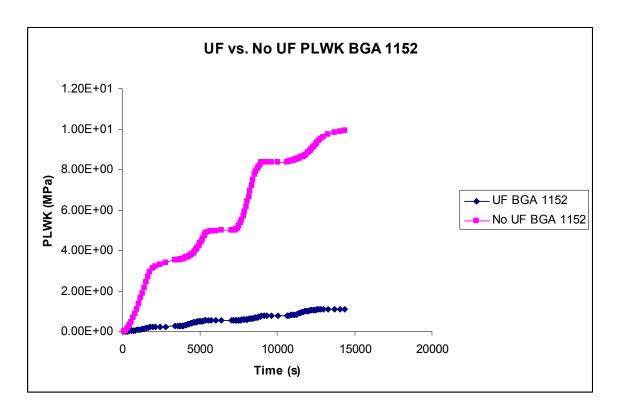

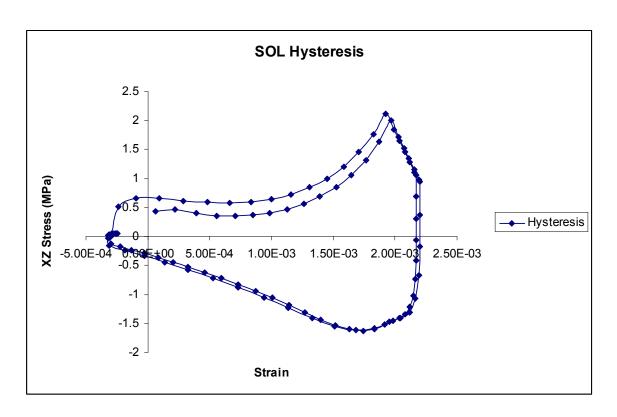

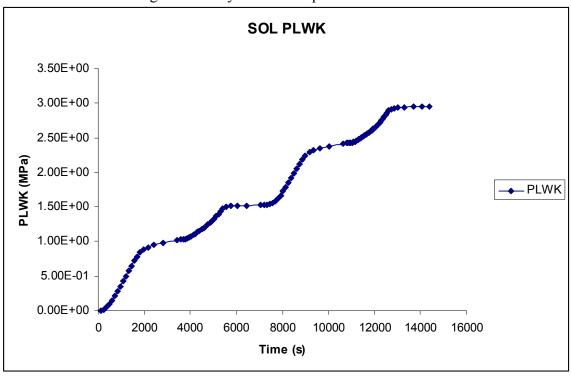

The hysteresis plot and the plastic work plot for the package are shown below in figures 3-15 and 3-16.

Figure 3-15 Hysteresis BGA 1152

Figure 3-16 Plastic Work Plot BGA 1152

Figure 3-15 shows show that the hysteresis loop stabilized after two simulated thermal cycles. The inelastic strain energy is represented by the area enclosed in the hysteresis loop. The plastic work is plotted for the package in Figure 3-16. It approaches ten MPa when the simulation ends.

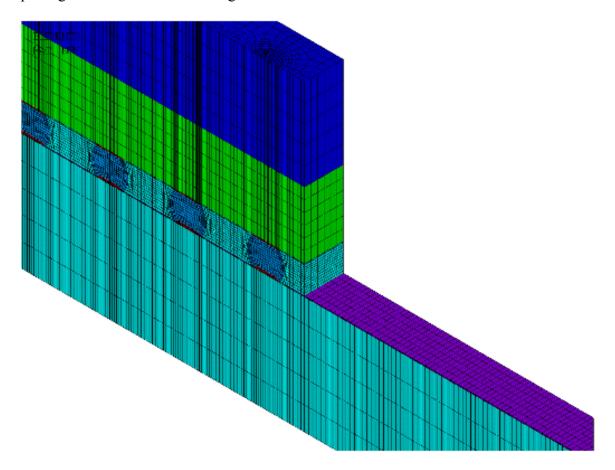

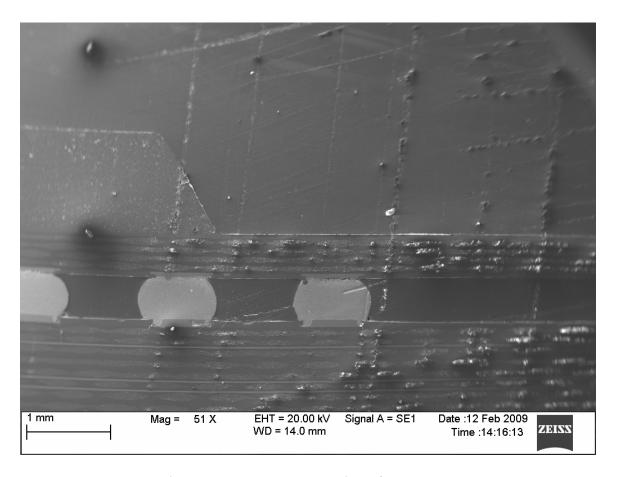

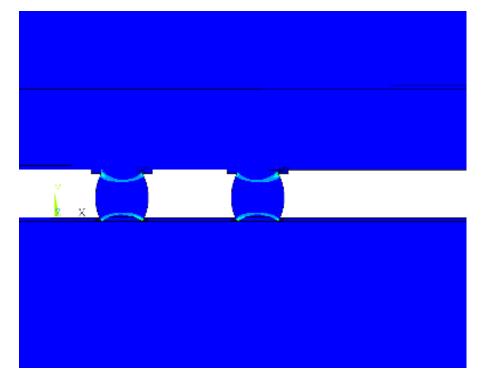

As mentioned previously, the BGA 1152 was underfilled and thermal cycled. Previous tests have shown that the effect of underfill on larger BGA's can be both detrimental and beneficial to the life of the package depending on the material properties of the underfill. Pyland in his 2000 paper shows that higher CTE underfills cause an increase in strain in super BGA's [Pyland 2000]. For smaller packages, the effect of underfill has been shown to increase life [Elkaday 2004, Liji 2002]. In this test, the larger BGA 1152 package was underfilled as were the smaller U3, U4, and U5 packages shown earlier. The results are documented in the pages to follow.

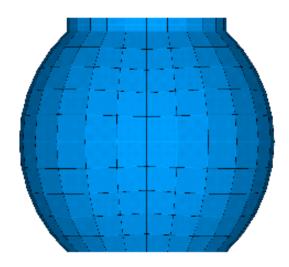

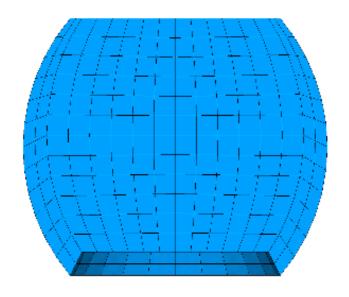

The first underfilled package presented is the BGA 1152 flip chip. An image of the finite element model is shown below in figure 3-17.

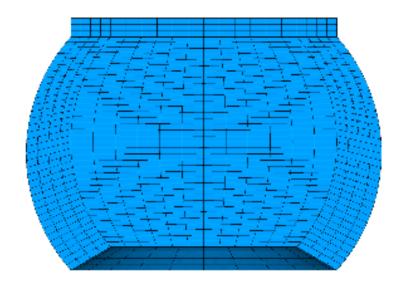

Figure 3-17 Underfilled BGA 1152 package

The sky blue elements encircling the solder ball in Figure 3-17 were elements representing the underfill. The material properties of the underfill can be seen below in Table 3-10

Table 3-10 ME-531 Underfill Properties

| E(MPA) | $\alpha_{x}(PPM)$ | $\alpha_{y}(PPM)$ | $\alpha_z(PPM)$ |

|--------|-------------------|-------------------|-----------------|

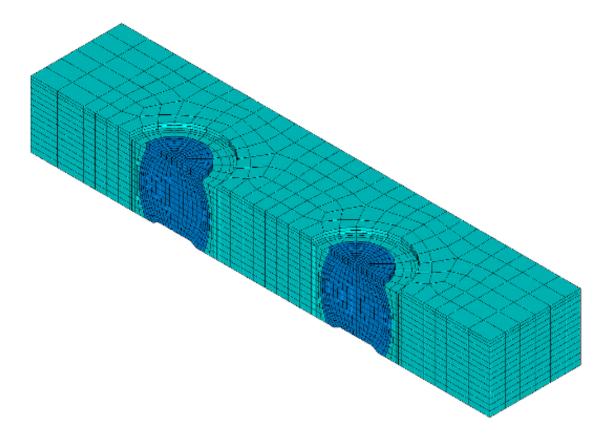

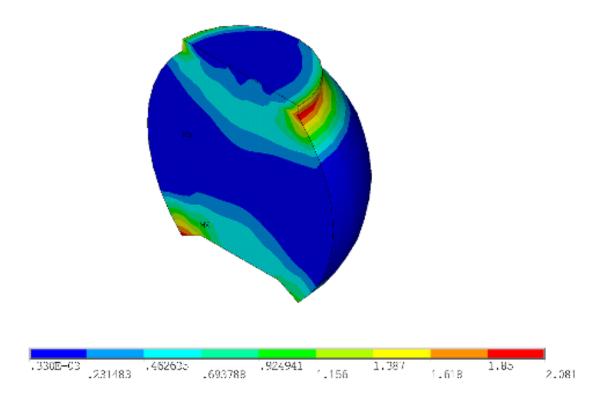

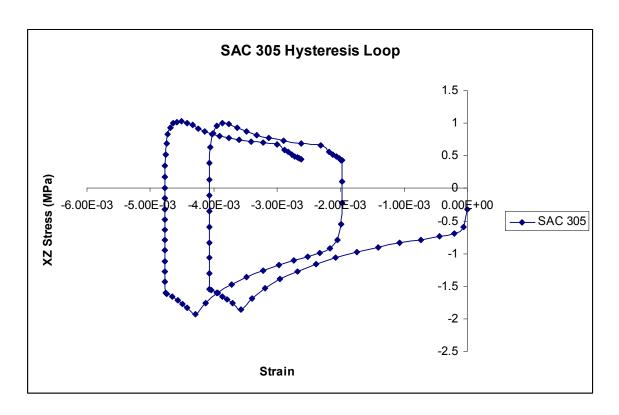

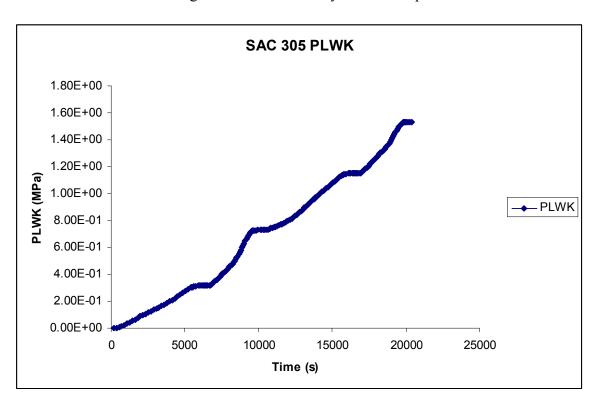

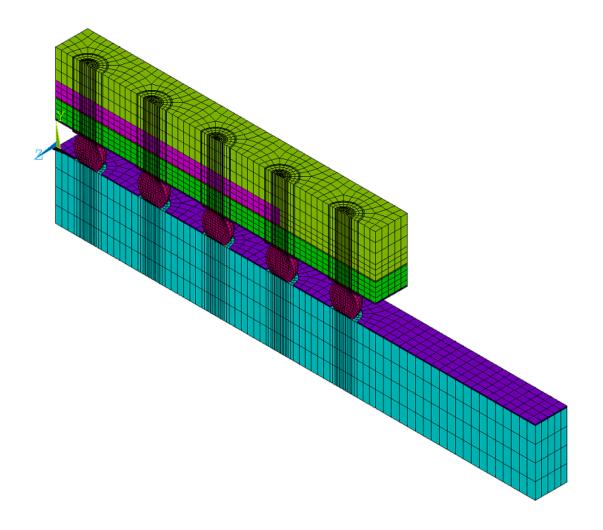

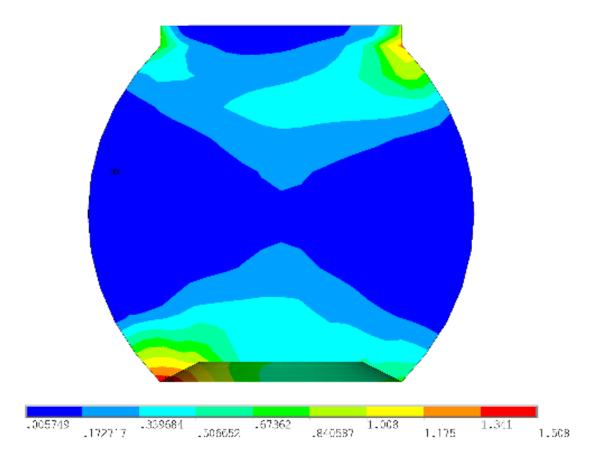

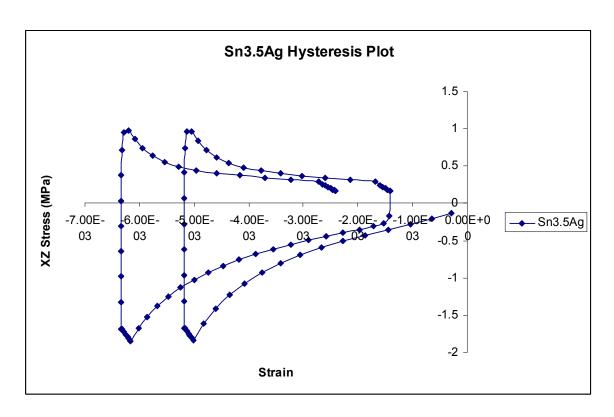

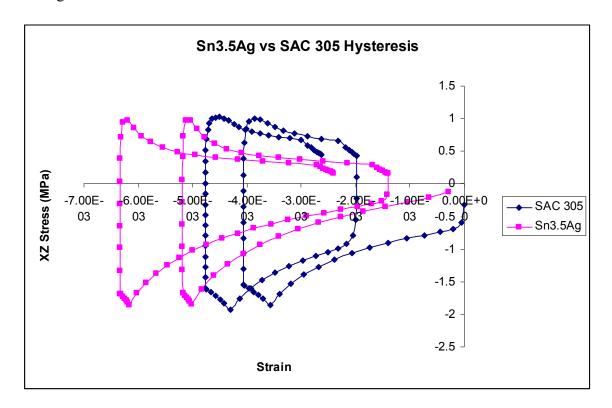

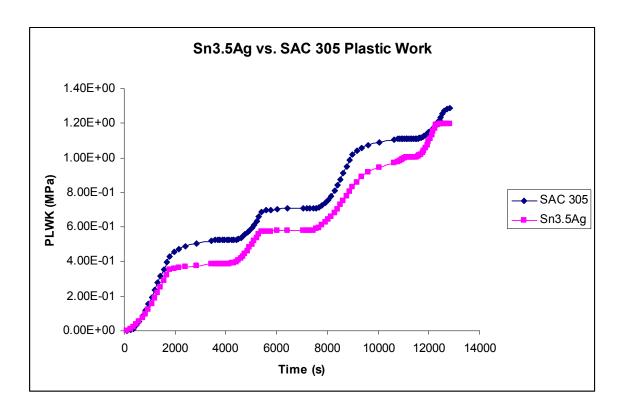

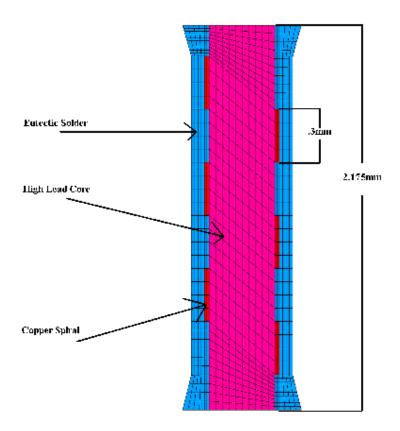

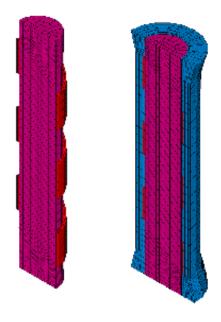

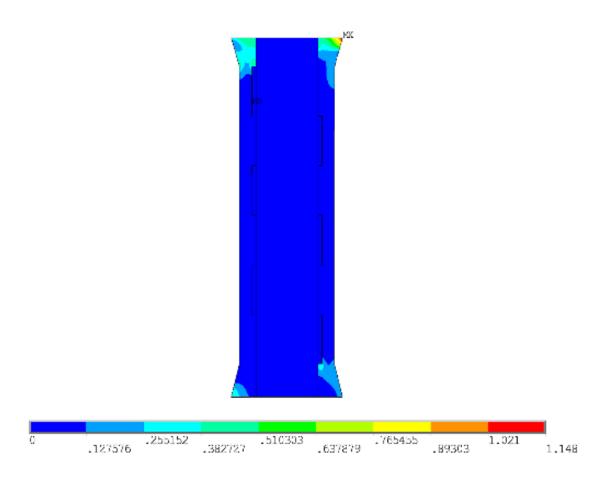

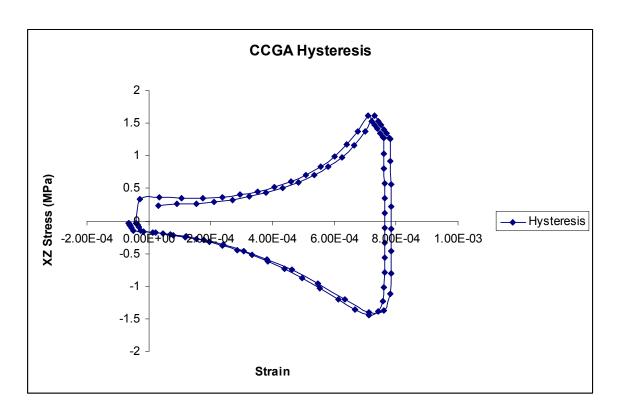

| 6000   | 21                | 21                | 85              |