# Embedded Soft-Core Processor-Based Built-In Self-Test of Field Programmable Gate Arrays

by

**Bradley Fletcher Dutton**

A thesis submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Master of Science

Auburn, Alabama May 14, 2010

Keywords: Built-In Self-Test, Field Programmable Gate Array, Fault Tolerance, Single-Event Upset Detection and Correction

Copyright 2010 by Bradley Fletcher Dutton

# Approved by

Charles E. Stroud, Chair, Professor of Electrical and Computer Engineering Vishwani D. Agrawal, Professor of Electrical and Computer Engineering Victor P. Nelson, Professor of Electrical and Computer Engineering

#### **Abstract**

The exponential growth in the number of transistors on very large scale integration (VLSI) integrated circuits (ICs), coupled with increasing device interface bandwidth and new surface mount and low profile packaging technologies, have made testing of ICs increasingly difficult and costly at all levels of the testing process. Field programmable gate arrays (FPGAs) pose a particularly difficult problem for test engineers due to their programmable nature, overall size and complexity, limited number of inputs/outputs (I/O), and large number and variety of embedded cores. In addition to manufacturing defects, "soft" errors due to single event upsets (SEUs) have become a serious problem because of the increasing size of the configuration memory in FPGAs and shrinking design rules, even in fault-tolerant systems operating at ground level. Building on previous work, this thesis uses built-in self-test (BIST) as a solution to the testing problem for Xilinx Virtex-5 FPGAs. BIST configurations are presented for the configurable logic blocks (CLBs), I/O Tiles, and SEU detection/correction cores in Xilinx Virtex-5 FPGAs. In addition, this thesis presents a novel approach to BIST that uses a soft-core processor configured in the fabric of the device under test to perform reconfiguration of the resources under test, control the BIST execution, and perform fault diagnosis. This approach is particularly useful for in-system testing of FPGAs in fault-tolerant or high-reliability systems because it greatly reduces the amount and complexity of external hardware required for test. To combat the problem of "soft" errors due to SEUs that can occur in the FPGA configuration memory during normal operation, an approach for on-line detection and correction of SEUs in

the configuration memory of Xilinx Virtex-4 and Virtex-5 FPGAs is also presented. While not entirely immune to SEU effects, this approach greatly reduces the probability of an SEU induced failure in the user logic, and no single error from an SEU can cause a complete system failure.

# Acknowledgments

First, I would like to thank Dr. Stroud for three great years of guidance, encouragement, employment, and education. You have taught me most of what I know about being an engineer, and what I appreciate most in hindsight is that you've always challenged me to be the best. I might not have even gone to graduate school if not for you. I also would like to thank the many students that I've had a chance to work with and learn from while in the BIST lab. Lee, Daniel, and Bobby: I learned a lot from you guys and, honestly, the lab was never the same without you (Bobby, you especially: I can't help laughing even as I write this). To the students that came later – Jia, Mary, Brooks, and Joey – thanks for being good friends through thick and thin and for making time spent at work more fun. To Joseph and Jie: for being the best engineers my age that I've ever met, and, therefore, inspiring me to always work a little harder. I would also like especially to thank my mom and dad for always being supportive in everything that I've done. Robbie: for being my best and oldest friend and future business partner (or future landlord, if engineering doesn't work out). And Bo and Samantha, thanks for dragging me out of my room and keeping me up late, regardless of projects or exams, and for teaching me some things that cannot be learned in a classroom.

# Table of Contents

| Abstract                                                                       | ii |

|--------------------------------------------------------------------------------|----|

| Acknowledgments                                                                | iv |

| List of Tables                                                                 | ix |

| List of Figures                                                                | xi |

| List of Abbreviations                                                          | XV |

| Chapter One. Introduction                                                      | 1  |

| 1.1 Overview of Built-In Self-Test                                             | 2  |

| 1.2 Introduction to Field Programmable Gate Arrays (FPGAs)                     | 4  |

| 1.3 Overview of Virtex-5 FPGAs                                                 | 7  |

| 1.4 BIST for FPGAs                                                             | 10 |

| 1.5 Single Event Upsets in FPGAs                                               | 11 |

| 1.6 Verification by Fault Injection                                            | 13 |

| 1.7 Thesis Statement                                                           | 14 |

| 1.8 Thesis Format                                                              | 15 |

| 1.9 References                                                                 | 15 |

| Chapter Two. Built-In Self-Test of Configurable Logic Blocks in Virtex-5 FPGAs | 18 |

| 2.1 Introduction And Background                                                | 18 |

| 2.2 Overview of Virtex-5 CLBs                                                  | 20 |

| 2.3 BIST Approach And Architecture                                             | 22 |

| 2.4 Experimental Results                                                       | 26 |

|   | 2.5 Summary And Conclusions                                                            | 32 |

|---|----------------------------------------------------------------------------------------|----|

|   | 2.6 Acknowledgements                                                                   | 33 |

|   | 2.7 References                                                                         | 34 |

| C | Chapter Three. Built-In Self-Test of Programmable Input/Output Tiles in Virtex-5 FPGAs | 35 |

|   | 3.1 Introduction                                                                       | 35 |

|   | 3.2 Prior Work                                                                         | 37 |

|   | 3.3 Overview of Virtex-5 I/O Tiles                                                     | 38 |

|   | 3.4 Overview of BIST Architecture                                                      | 39 |

|   | 3.5 Configurations for I/O Logic Modes                                                 | 43 |

|   | 3.6 Configurations for I/O SerDes Modes                                                | 43 |

|   | 3.7 Experimental Results                                                               | 45 |

|   | 3.8 BIST for Programmable I/O buffers                                                  | 48 |

|   | 3.9 Conclusions                                                                        | 49 |

|   | 3.10 Acknowledgements                                                                  | 50 |

|   | 3.11 References                                                                        | 50 |

| C | Chapter Four. Built-In Self-Test of SEU Detection Cores in Virtex-4 and Virtex-5 FPGAs | 52 |

|   | 4.1 Introduction                                                                       | 52 |

|   | 4.2 Frame ECC and ICAP Logic                                                           | 54 |

|   | 4.3 Test Algorithm                                                                     |    |

|   | 4.4 BIST Approach                                                                      | 59 |

|   | 4.4.1 Test Pattern Generator                                                           | 60 |

|   | 4.4.2 Output Response Analyzer                                                         | 62 |

|   | 4.4.3 Additional Logic                                                                 |    |

|   | 4.5 Implementation Results                                                             |    |

|   | 4.6 Conclusions                                                                        | 70 |

| 4.7 Acknowledgements                                                              | 70    |

|-----------------------------------------------------------------------------------|-------|

| 4.8 References                                                                    | 71    |

| Chapter Five. Embedded Processor Based Fault Injection and SEU Emulation for FPG. | As 73 |

| 5.1 Introduction and Background                                                   | 73    |

| 5.2 Hard Core Processor Case Study                                                | 75    |

| 5.3 Soft Core Processor Case Study                                                | 79    |

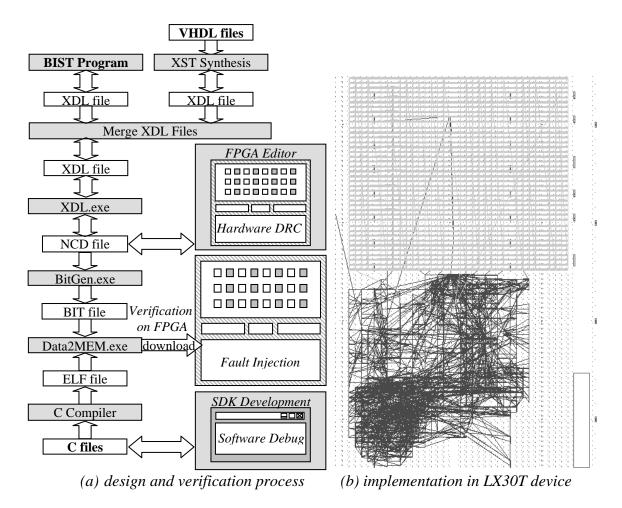

| 5.3.1 Overview of Approach                                                        | 80    |

| 5.3.2 Architecture and Operation                                                  | 85    |

| 5.3.3 Implementation Results                                                      | 88    |

| 5.4 Summary and Conclusions                                                       | 92    |

| 5.5 Acknowledgements                                                              | 92    |

| 5.6 References                                                                    | 93    |

| Chapter Six. Soft-Core Embedded Processor-Based Built-In Self-Test of FPGAs       | 95    |

| 6.1 Introduction                                                                  | 95    |

| 6.2 Background                                                                    | 96    |

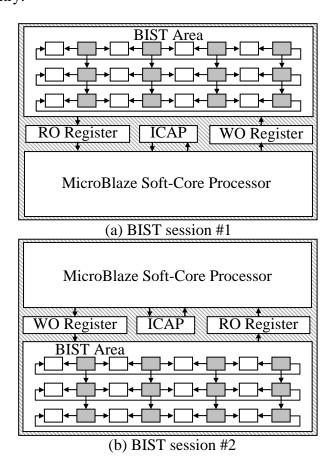

| 6.3 Embedded BIST Architecture                                                    | 100   |

| 6.4 Software Development                                                          | 104   |

| 6.5 Design Flow and Implementation Results                                        | 109   |

| 6.6 Conclusions.                                                                  | 111   |

| 6.7 Acknowledgements                                                              | 111   |

| 6.8 References                                                                    | 112   |

| Chapter Seven. Soft-Core Embedded Processor-Based Built-In Self-Test of FPGAs Ca  | •     |

| 7.1 Introduction                                                                  | 113   |

| 7.2 Background                                                                    | 114   |

| 7.3 Results of Implementation in Virtex-5                                         | 118   |

| 7.4 Future Improvements 123                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------|

| 7.5 Other Applications 124                                                                                                 |

| 7.6 Conclusions                                                                                                            |

| 7.7 Acknowledgements                                                                                                       |

| 7.8 References                                                                                                             |

| Chapter Eight. On-line Single Event Upset Detection and Correction in Field Programmable Gate Array Configuration Memories |

| 8.1 Introduction                                                                                                           |

| 8.2 Background                                                                                                             |

| 8.3 Operation of SEU Detect and Correct                                                                                    |

| 8.4 SEU Detect and Correct Architecture                                                                                    |

| 8.5 Implementation Results                                                                                                 |

| 8.6 Experimental Results                                                                                                   |

| 8.7 Conclusions                                                                                                            |

| 8.8 Acknowledgements                                                                                                       |

| 8.9 References                                                                                                             |

| Chapter Nine. Summary and Conclusions                                                                                      |

| 9.1 Summary of Work                                                                                                        |

| 9.2 Future Work                                                                                                            |

| Bibliography                                                                                                               |

# List of Tables

| Table 2.1: List of acronyms                                       | 20  |

|-------------------------------------------------------------------|-----|

| Table 2.2: SliceL logic BIST configurations                       | 25  |

| Table 2.3: SliceM BIST configurations                             | 26  |

| Table 2.4: CLB BIST totals (17 configurations)                    | 32  |

| Table 3.1: I/O tile BIST totals (15 configurations)               | 48  |

| Table 4.1: Frame ECC codes                                        | 55  |

| Table 4.2: Hamming parity matrix example                          | 57  |

| Table 4.3: ICAP and Frame ECC BIST summary                        | 70  |

| Table 5.1: Embedded fault injection run time analysis for AT94K40 | 78  |

| Table 5.2: Parity bit encoding, where X = don't care              | 87  |

| Table 5.3: Embedded fault list format                             | 87  |

| Table 5.4: Embedded fault injection core resources                | 88  |

| Table 5.5: Fault/SEU injection core I/O descriptions              | 91  |

| Table 6.1: BIST control registers                                 | 103 |

| Table 6.2: Compressed partial reconfiguration data size           | 107 |

| Table 7.1: Test configurations developed for various FPGAs        | 115 |

| Table 8.1: Memory resources in two Virtex-5 FPGAs                 | 130 |

| Table 8.2: Frame ECC error codes [25][26]                         | 135 |

| Table 8.3: Hamming bit error diagnosis [25][26]                   | 143 |

| Table 8.4: SEU controller resource utilization in Virtex-4 devices           | 148 |

|------------------------------------------------------------------------------|-----|

| Table 8.5: SEU controller resource utilization in Virtex-5 devices           | 148 |

| Table 8.6: SEU emulation results                                             | 152 |

| Table 8.7: Approximate number of configuration bits for common resources [5] | 153 |

# List of Figures

| Figure 1.1: Basic BIST architecture [3]                                       | 3  |

|-------------------------------------------------------------------------------|----|

| Figure 1.2: Typical custom ASIC, standard cell ASIC, and FPGA cost vs. volume | 5  |

| Figure 1.3: Typical FPGA architecture [12]                                    | 6  |

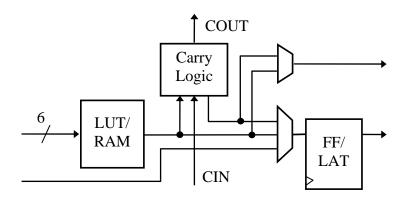

| Figure 1.4: Simplified basic logic element                                    | 7  |

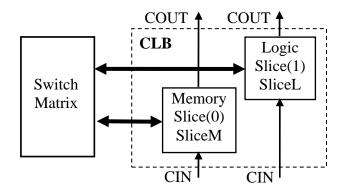

| Figure 1.5: Virtex-5 configurable logic block [15]                            | 8  |

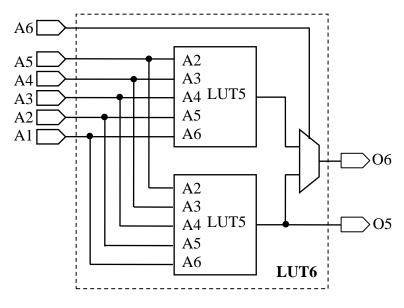

| Figure 1.6: Virtex-5 6-Input LUT [16]                                         | 9  |

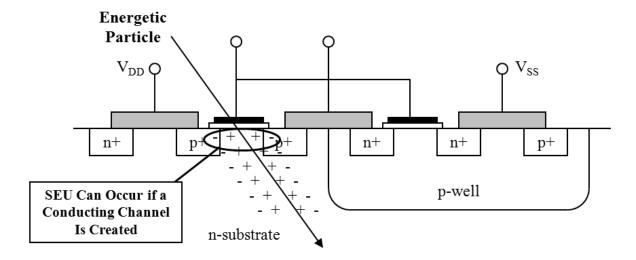

| Figure 1.7: Illustration of a single-event effect in a CMOS inverter          | 12 |

| Figure 2.1: Simplified basic logic element                                    | 21 |

| Figure 2.2: Virtex-5 configurable logic block [11]                            | 21 |

| Figure 2.3: Circular comparison architecture                                  | 23 |

| Figure 2.4: Equivalent ORA architecture                                       | 24 |

| Figure 2.5: SliceL fault coverage (simulation)                                | 29 |

| Figure 2.6: SliceL fault coverage (fault injection)                           | 29 |

| Figure 2.7: SliceM fault coverage (simulation)                                | 30 |

| Figure 2.8: SliceM fault coverage (fault injection)                           | 30 |

| Figure 2.9: Boundary Scan interface test time                                 | 31 |

| Figure 2.10: 32-bit parallel interface test time                              | 31 |

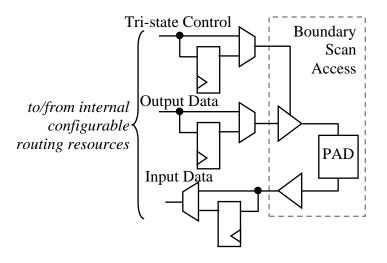

| Figure 3.1: Simplified programmable I/O cell                                  | 37 |

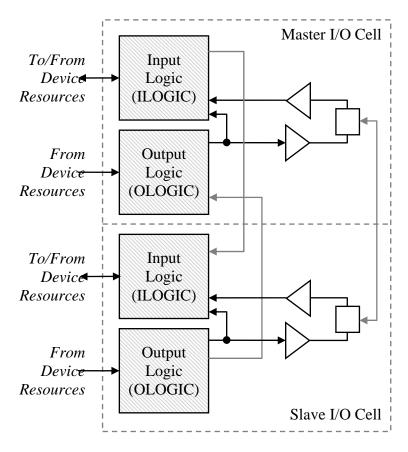

| Figure 3.2: Virtex-5 programmable I/O tile                                    | 38 |

| Figure 3.3: Column oriented circular comparison                                               | 40  |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 3.4: Virtex-5 equivalent ORA architecture                                              | 41  |

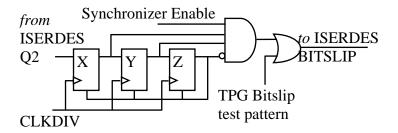

| Figure 3.5: Bitslip synchronizer circuit                                                      | 45  |

| Figure 3.6: 50 MHz Boundary Scan configuration interface test time                            | 47  |

| Figure 3.7: 100 MHz 32-bit parallel configuration interface test time                         | 47  |

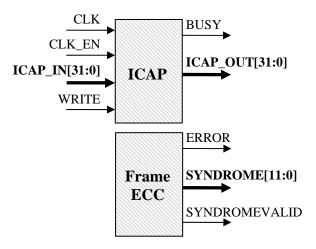

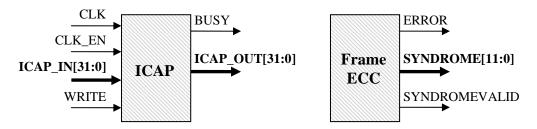

| Figure 4.1: Frame ECC and ICAP primitives                                                     | 56  |

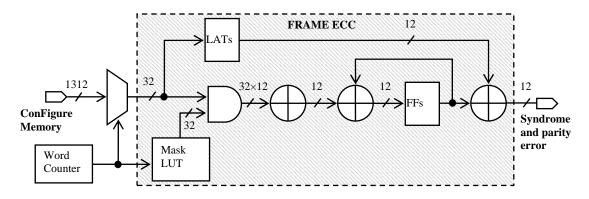

| Figure 4.2: Sequential Hamming bit calculation                                                | 60  |

| Figure 4.3: Test pattern write sequence via ICAP interface                                    | 61  |

| Figure 4.4: Test pattern read sequence via ICAP interface                                     | 61  |

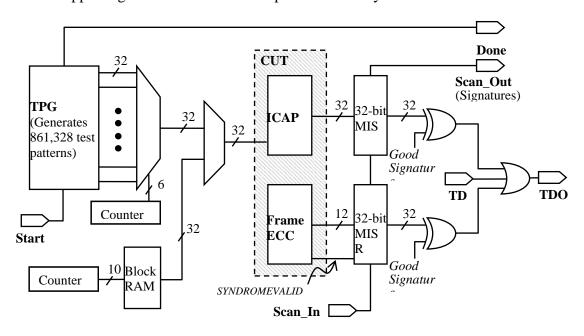

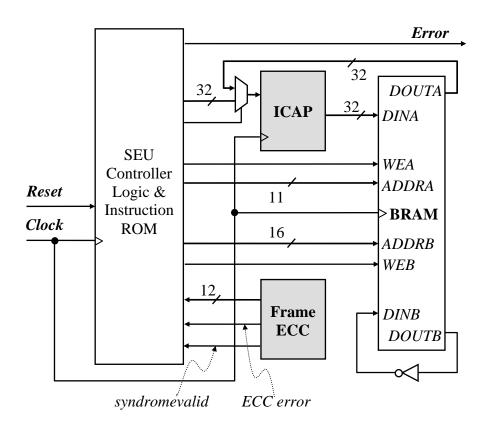

| Figure 4.5: ICAP and Frame ECC BIST architecture.                                             | 65  |

| Figure 4.6: BIST VHDL component declaration.                                                  | 66  |

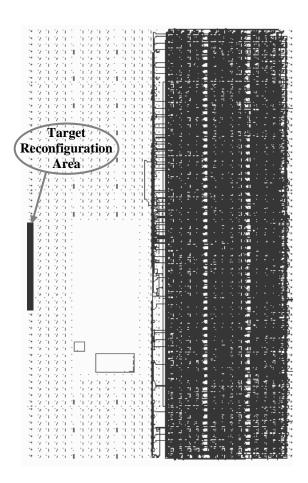

| Figure 4.7: Virtex-4 FX12 with ICAP/Frame ECC BIST                                            | 68  |

| Figure 4.8: Virtex-5 LX20T with ICAP/Frame ECC BIST                                           | 69  |

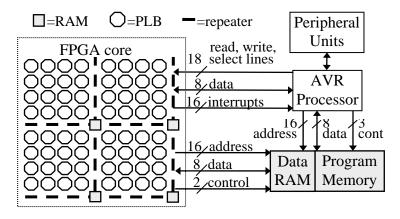

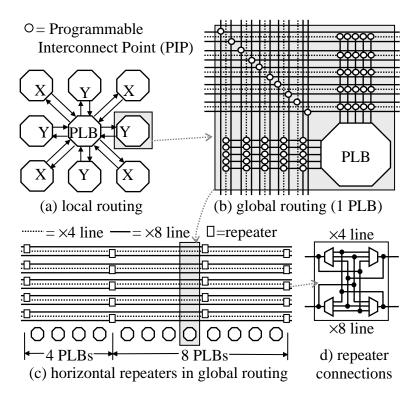

| Figure 5.1: AT94K series SoC architecture                                                     | 76  |

| Figure 5.2: AT94K routing architecture                                                        | 77  |

| Figure 5.3: SliceL simulation stuck-at fault coverage                                         | 83  |

| Figure 5.4: SliceL fault injection stuck-at fault coverage                                    | 83  |

| Figure 5.5: Total CLB test time via Boundary Scan                                             | 84  |

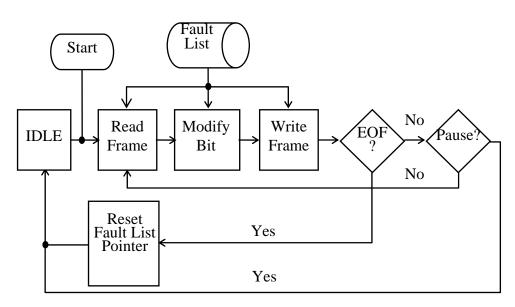

| Figure 5.6: Frame read-modify-write flowchart                                                 | 85  |

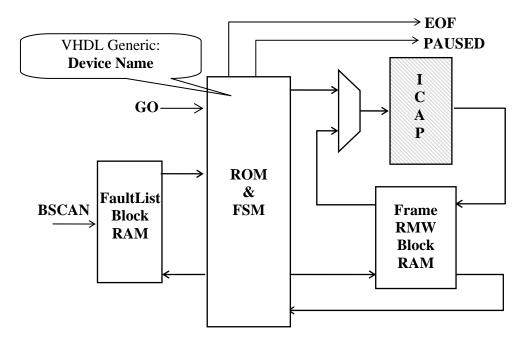

| Figure 5.7: Block diagram of fault injection core                                             | 88  |

| Figure 5.8: Routed embedded fault inject core (right) with half-array of routed CLB BIST (lef | ft) |

| in Virtex-5 LX20T                                                                             | 90  |

| Figure 5.9: Fault inject core component declaration                                           | 91  |

| Figure 6.1: Configurable logic block (CLB) BIST architecture                                   | 97    |

|------------------------------------------------------------------------------------------------|-------|

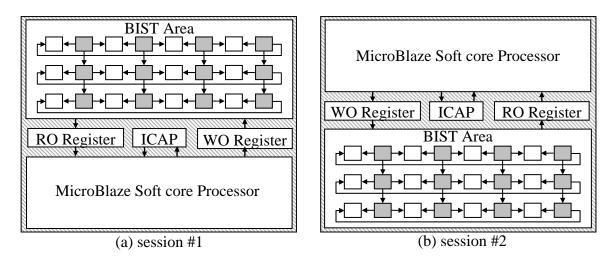

| Figure 6.2: Embedded soft core processor based BIST architecture                               | . 103 |

| Figure 6.3: Embedded processor BIST algorithms                                                 | . 105 |

| Figure 6.4: Compressed BIST partial reconfiguration structure in C                             | . 107 |

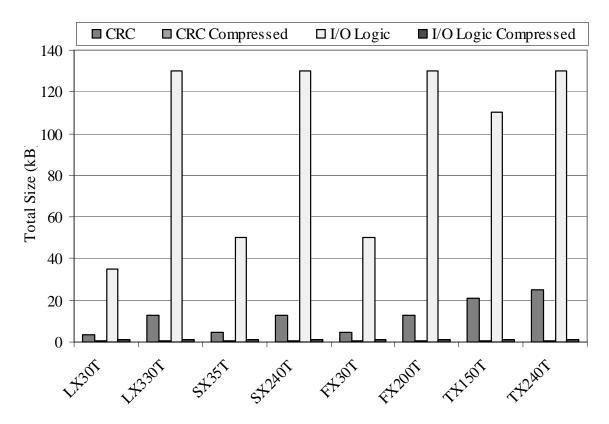

| Figure 6.5: Original reconfiguration file sizes and compressed data structure sizes for one CR | КС    |

| BIST and a set of 5 I/O Logic BIST partial reconfigurations                                    | . 108 |

| Figure 6.6: Embedded processor BIST design implementation                                      | . 110 |

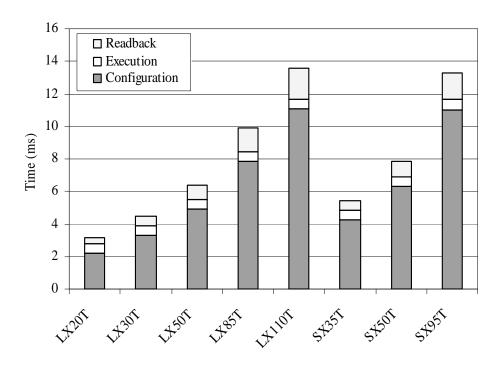

| Figure 7.1: Simplified soft-core processor-based BIST architecture                             | . 117 |

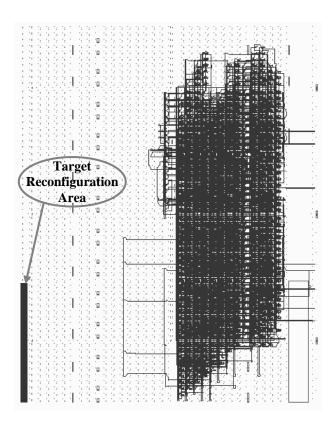

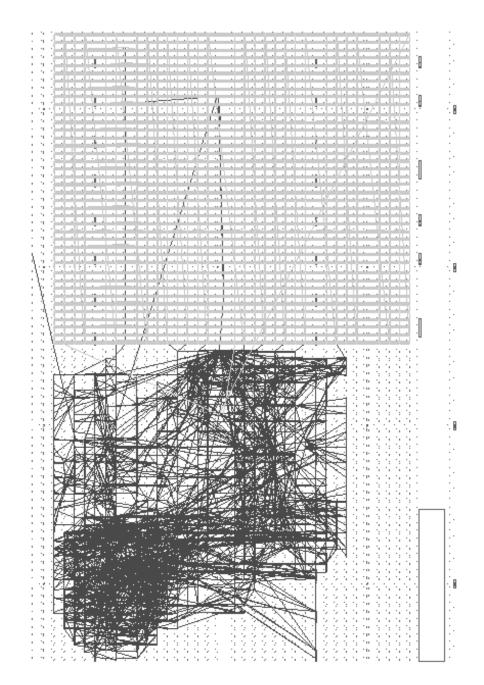

| Figure 7.2: Unrouted embedded processor-based BIST configuration for top configurable log      | gic   |

| blocks (CLB) in Virtex-5 LX30T viewed in FPGA Editor                                           | . 119 |

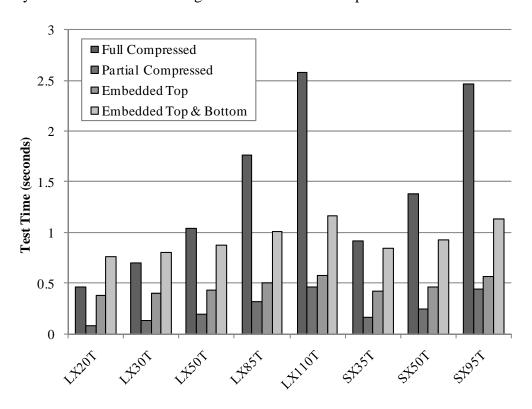

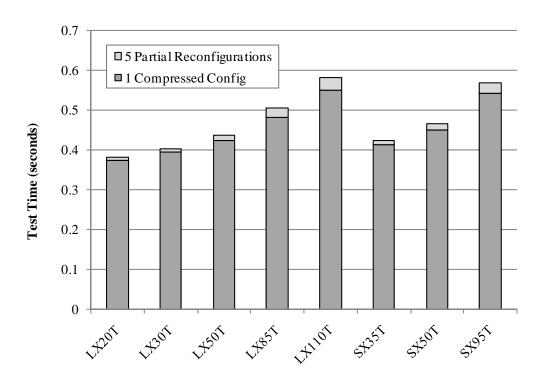

| Figure 7.3: CLB BIST test time for external configuration (full compressed and partial         |       |

| compressed bitstreams) and embedded processor test time                                        | . 120 |

| Figure 7.4: Contribution to embedded processor-based CLB BIST test time by initial external    | 1     |

| configuration and by five internal partial reconfigurations                                    | . 122 |

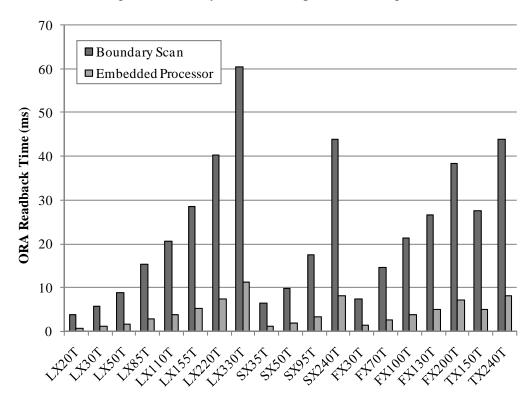

| Figure 7.5: Comparison of CLB BIST ORA read back times with embedded processor-based           |       |

| approach and external Boundary Scan interface                                                  | . 122 |

| Figure 7.6: 32-bit, 100 MHz interface test time for full chip CLB west or east with one full   |       |

| compressed configuration and five partial reconfigurations                                     | . 124 |

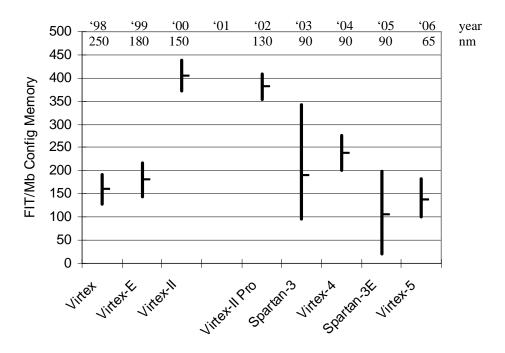

| Figure 8.1: FIT rate (corrected for sea-level New York, NY) versus Xilinx device family, init  | tial  |

| release year, and minimum feature size [6] where the center line represents the nominal value  | Э     |

| and the span of the line represents the upper and lower 95% confidence levels                  | . 131 |

| Figure 8.2: Frame ECC and ICAP primitives                                                      | . 137 |

| Figure 8.3: SELI controller VHDL component declaration                                         | 137   |

| Figure 8.4: SEU controller behavioral pseudocode                       | 139 |

|------------------------------------------------------------------------|-----|

| Figure 8.5: SEU controller block diagram                               | 142 |

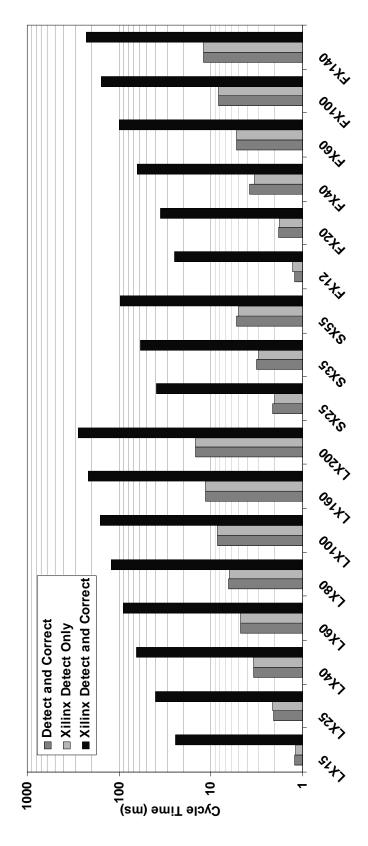

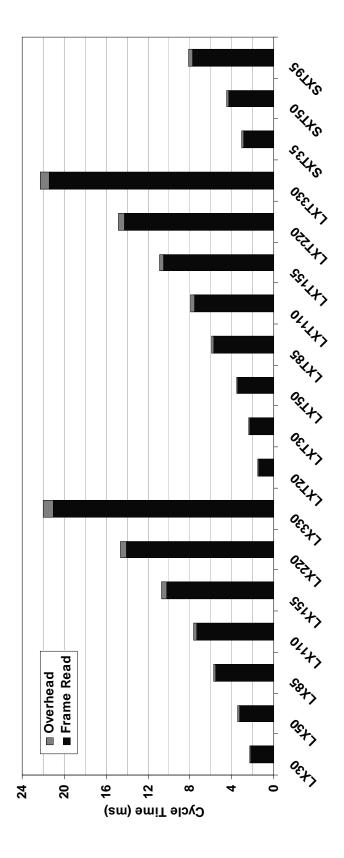

| Figure 8.6: SEU controller LOG cycle time vs. Virtex-4 device          | 140 |

| Figure 8.7: SEU controller cycle time vs. Virtex-5 device              | 147 |

| Figure 8.8: Routed SEU controller implemented in Virtex-5 LX20T device | 150 |

## List of Abbreviations

ATE Automatic Test Equipment

BIST Built-In Self Test

BRAM Block RAM

BSCAN Boundary Scan

BUT Block under Test

CAD Computer-aided Design

CLB Configurable Logic Block

CMOS Complementary Metal-oxide-semiconductor

CUT Circuit under Test

DFT Design for Testability

DSP Digital Signal Processor

DUT Device Under Test

ECC Error Correction Code

FF Flip-flop

FIFO First-in First-out

FPGA Field Programmable Gate Array

FSM Finite State Machine

GUI Graphical User Interface

HDL Hardware Description Language

I/O Input / Output

IC Integrated Circuit

ICAP Internal Configuration Access Port

IP Intellectual Property

LUT Look-up Table

LSB Least Significant Bit

MSB Most Significant Bit

ORA Output Response Analyzer

PIP Programmable Interconnect Point

PLB Programmable Logic Block

RAM Random Access Memory

SERDES Serializer / Deserializer

SEU Single Event Upset

SoC System-on-Chip

SRAM Static Random Access Memory

TCK Test Clock

TDI Test Data In

TDO Test Data Out

TMS Test Mode Select

TPG Test Pattern Generator

VLSI Very Large Scale Integration

# **Chapter One. Introduction**

Moore's law, which predicts a doubling of integrated circuit (IC) transistor density every 18 to 24 months, has been an accurate predictor of the exponential growth in the number of transistors in ICs since it was first observed by Gordon Moore in 1965 [1]. According to the most recent International Technology Roadmap for Semiconductors (ITRS) report, minimum feature size is expected to continue to decrease by a factor of two (*e.g.* transistor density will increase by a factor of two) every two years until 2022 [2]. With very large-scale integration (VLSI) circuits already surpassing the one billion transistor mark in 2008, this report, in accordance with Moore's law, predicts that the number of transistors on a single IC of comparable physical area will exceed 128 billion by 2022.

Increasing transistor count and density and increasing device interface bandwidth, coupled with new surface mount and low profile packaging technologies, have made testing of integrated circuits increasingly difficult and costly at all levels of the testing process [3] [4]. In addition, larger device sizes and smaller feature sizes have increased both the number and type of faults that can occur [4]. Testing embedded resources in VLSI devices is especially difficult because their embedded nature makes them difficult to control and observe from the external chip I/O; furthermore, the number of external I/O is continually decreasing in proportion to the number of transistors on a single die [4]. While the number of I/O has increased by an order of magnitude for most VLSI devices, the number of transistors on a single die increased by more than 4 orders of magnitude over the same time period [4]. (This trend is commonly called Rent's Rule, for E. F. Rent of IBM, who was the first to investigate a relationship between the number

of I/O and the number of internal logic blocks in 1960 [5]). Due to the limited number of external I/O in proportion to the number of transistors on a chip, and without the inclusion of any additional test circuitry, the controllability and observability of most VLSI designs are severely limited during testing.

Another factor affecting testing of VLSI ICs is the cost of automatic test equipment (ATE). While the cost of manufacturing transistors in VLSI circuits has continued to decrease with each new technology node, the cost of testing has increased both in absolute terms and in proportion to overall manufacturing cost. In fact, the cost of testing a single transistor already exceeds its cost of production [3], and due to the ever increasing density and bandwidth of integrated circuits, testing costs will continue to rise. It is expected that by the year 2014, the cost of a leading edge VLSI test machine will exceed twenty million dollars [4]. Consequently, design for testability (DFT) methods, which incorporate additional test circuitry during the design phase to increase circuit controllability and observability during testing, are included in some form in virtually every VLSI design. Two of the most common DFT techniques are scan design and built-in self-test (BIST). Another DFT method, known as Boundary Scan or JTAG (Joint Test Action Group) [6], is usually included to facilitate board-level testing of systems with high pin-count and surface mount components [3] [7]. A recent offshoot of Boundary Scan, IEEE standard 1500-2005 [8], describes a scalable wrapper architecture and control mechanism for testing embedded cores in System-on-Chip (SOC) devices and the interconnect between cores [3]. The primary focus of this thesis will be on BIST as a solution for testing VLSI ICs.

## 1.1 Overview of Built-In Self-Test

BIST was introduced around 1980 as a way to test embedded cores in VLSI devices [4]. The basic idea of BIST is to incorporate extra circuitry and functionality in the device under test

such that the circuit can test itself [3] [4]. This implies that the circuit is capable of generating test patterns and compacting output responses. Therefore, BIST, in contrast to other techniques such as scan design which relies on externally applied test patterns, does not require costly ATE hardware. In addition, many BIST techniques are applicable at every level of the testing process, from wafer-level manufacturing test to board-level and in-system test. Another advantage of some BIST approaches when compared to scan-based test techniques is that patterns can be applied to the circuit under test and the output responses monitored at system speeds, which facilitates the detection of delay and coupling faults [4] [9].

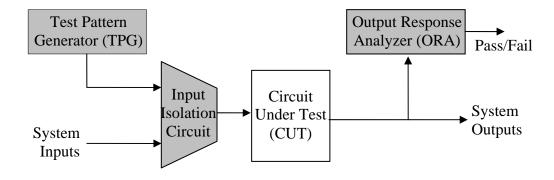

A simple BIST architecture, shown in Figure 1.1, consists of a test pattern generator (TPG), output response analyzer (ORA), circuit under test (CUT), and some additional control circuitry [3] [4]. For system-level use of BIST, input isolation circuitry and a dedicated BIST controller must be included. The BIST controller can be used to initiate the BIST, initialize the CUT, activate the input isolation circuitry, and provide an indication when the test is complete. During off-line tests, the TPG generates a set of test patterns which are applied to the circuit under test (CUT) to sensitize potential fault sites, and the ORA compacts the output response of the CUT. At the conclusion of the test, the results are determined by examination of the ORA contents (generally, by comparison to the fault-free circuit "signature") [4].

Figure 1.1: Basic BIST architecture [3]

There are some costs associated with BIST that must be taken into consideration. In ASICs, BIST requires additional circuitry and functionality that results in area and performance penalties. This additional circuitry is shown in gray in Figure 1.1. Typically, the performance penalty is minimal, amounting to no more than a multiplexer delay in the primary input data path and additional fan-out in the primary output data path of the circuit under test. The area penalty varies depending on the exact BIST architecture used (which is, in turn, usually a function of desired fault coverage and the type of circuit under test). This additional area is disadvantageous because larger chip areas result in fewer chips per wafer, and, therefore, higher cost per chip due to lower yield [4]. Also, some additional I/O pins may be required for activation of the BIST circuitry and results retrieval [4]. The inclusion of BIST also increases the design effort and risk to the project, because, on top of designing the system function, the BIST circuitry must also be designed and verified. However, most case studies have found that the benefits of BIST usually outweigh the costs (including addition design time and overhead) when included in a project [4], and many computer-aided design (CAD) tools now support automatic insertion of preengineered BIST circuitry during the design phase, which reduces the design effort and risk to the project.

## 1.2 Introduction to Field Programmable Gate Arrays (FPGAs)

Field Programmable Gate Arrays (FPGAs) are pre-fabricated semiconductor devices that can be programmed (*i.e.* configured) after manufacturing to perform complex sequential or combinational logic functions. Compared to standard-cell or custom ASIC designs, FPGAs provide lower non-recurring engineering costs and faster time-to-market [10]. The non-recurring engineering costs associated with the design and manufacture of FPGAs are initially absorbed by the manufacturer and are passed to the customer in the form of a higher price-per-part. This cost,

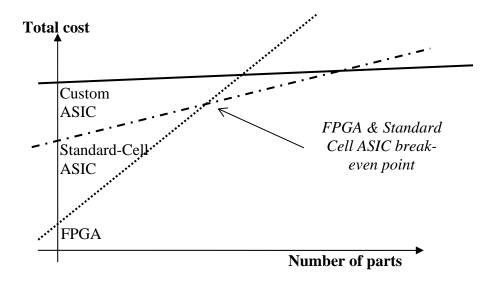

coupled with the cost of the additional logic required for programming of the device, makes the recurring costs of designs with FPGAs higher than those with ASICs. For these reasons, FPGAs are commonly used for rapid prototyping of designs prior to first silicon and in low-volume, highly-specialized digital systems (where the FPGA is used in lieu of an ASIC). An illustration of the total cost (*i.e.* recurring plus non-recurring costs) as a function of volume (number of parts) for a design implemented as a standard-cell ASIC, as a custom ASIC, and in an FPGA is shown in Figure 1.2 [10].

Figure 1.2: Typical custom ASIC, standard cell ASIC, and FPGA cost vs. volume

Due to the programmable nature of FPGAs, area, power and performance penalties are incurred for designs implemented in FPGAs when compared to the same design implemented as an ASIC. For several benchmark circuits implemented in both a 90 nm FPGA and 90 nm standard-cell ASIC, the FPGA implementation required between 18 and 35 times greater silicon area, and the critical path delay of the circuit increased by 3 to 4 times versus the ASIC implementation [11].

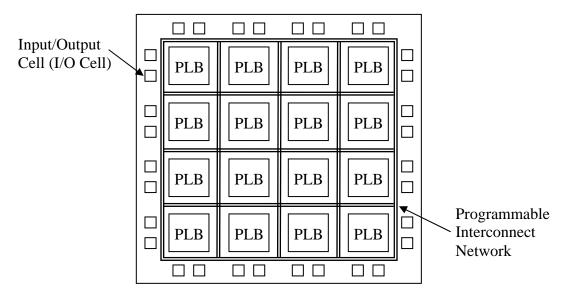

A typical FPGA is composed of an array of programmable logic blocks (PLB) (also called configurable logic blocks, or CLB) and input/output (I/O) cells connected by a

programmable interconnect network, as illustrated in Figure 1.3 [12]. Most modern FPGAs also include "hard" cores such as reduced instruction set computer (RISC) or complex instruction set computer (CISC) processors, digital signal processors (DSPs), random access memories (RAMs), and high-speed serializer/deserializer (SERDES) input/output (I/O) cells. These "hard" cores can perform certain common functions, such as multiply/accumulate or serialization/deserialization, with greater efficiency than can be achieved by implementing the same function in CLBs, which helps to reduce the performance/area penalties when compared with ASICs [11].

Figure 1.3: Typical FPGA architecture [12]

The front-end of the FPGA design process is identical to that for a standard-cell ASIC. However, the post synthesis design flow is much less complex for FPGA implementations. After behavioral simulation and functional verification, computer aided design (CAD) tools (usually supplied by the FPGA manufacturer, but also available through third parties) translate the digital designs in Hardware Description Language (HDL) or schematic form to a device specific netlist which maps the design into the FPGA's configurable logic and programmable routing network.

A configuration bit-file is generated from this netlist and downloaded to the configuration memory of the FPGA to implement the desired user function.

# 1.3 Overview of Virtex-5 FPGAs

This body of work is primarily concerned with Xilinx Virtex-5 FPGAs. Virtex-5 FPGAs are fabricated in a 1.0 V, 65 nm CMOS copper process with 12 metal layers [13]. The number of flip-flops and LUTs in a single Virtex-5 device ranges from 12,480 up to 207,360. As many as 1,200 user I/O are available in the highest pin-count package [13]. The configuration memory in all Virtex-5 devices is a large static random access memory (SRAM), ranging in size from 4.94 Mb (4,935,744 bits) to 82.7 Mb (82,687,488 bits) [14].

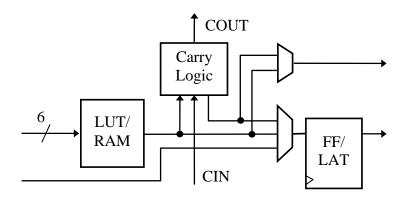

Each CLB in an FPGA consists of one or more basic logic elements. The Virtex-5 basic logic element, illustrated in Figure 1.4, comprises a six-input look-up table (LUT), a configurable flip-flop/latch (FF/LAT), a multiplexor to control the combinational output, and a multiplexor to control the registered output (FF/LAT input) [15].

Figure 1.4: Simplified basic logic element

Additional dedicated carry logic is included to perform special logic and arithmetic functions. In some slices, the LUT can be configured as a small RAM, called a free RAM or LUT RAM, with an independent read and shared write address input. Four such logic elements

are grouped to form a slice, and two slices are grouped to form a complete configurable logic block (CLB), as illustrated in Figure 1.5. The logic blocks are replicated and tiled in columns and rows, as in Figure 1.4, and are connected via programmable switch-boxes to local and global routing resources. Larger devices include more CLBs, but the structure of the CLB is identical across all devices in the FPGA family [15].

Figure 1.5: Virtex-5 configurable logic block [15]

The LUTs in Virtex-5 devices are designed with two outputs each. The primary output can utilize the full 64-bit LUT to implement any six variable Boolean function. The second output can be used to control the carry chain, or both outputs can implement two five variable Boolean functions for five shared inputs. Both outputs can be selected by the multiplexors for the registered or combinatorial CLB output paths. A block diagram of the Virtex-5 6-input LUT is shown in Figure 1.6 [16].

Select slices also support RAM and shift register modes of operation. Each LUT can be configured as a simple 64 x 1-bit or 32 x 2-bit RAM. Dynamic multiplexors in each slice allow for Shannon expansion of the four slice LUTs to form a 256 x 1-bit RAM. Additionally, the four slice LUTs can share address inputs to form a 32 x 8-bit RAM. Each LUT can also form a single 32-bit or two 16-bit shift registers. The four LUTs in the slice can be cascaded to form a 128-bit shift register or can operate in parallel form a 16 x 8-bit shift register in a slice [15] [16].

Figure 1.6: Virtex-5 6-Input LUT [16]

In addition to CLBs, every device in the Virtex-5 family includes DSP and Block RAM "hard" cores. Each DSP core can perform 25 x 18 2's complement multiplication, and includes an adder/subtractor/accumulator block. The DSP can also perform bit-wise logic operations including NOR, OR, AND, NAND, XNOR, and XOR. Up to five pipeline registers may be configured for use in the data path for increased throughput (up to 550 MHz) in high performance applications [17]. Each Block RAM core is 36 Kbit in size, with true dual-port read/write access to each memory element. Each of the read and write ports are configurable, such that the address and data bus widths can vary from 32K x 1-bit to 1K x 72-bit. In addition, the Block RAM can operate in a FIFO mode (with configurable data width and programmable almost-full and almost-empty flags) and/or in an error correction code (ECC) mode [15]. Some devices in the Virtex-5 family also include other "hard" cores such as gigabit transceivers, Ethernet MACs, PCI Express blocks, and/or Power PC processors [13].

#### 1.4 BIST for FPGAs

Testing FPGAs is difficult when compared to testing ASICs because of their programmable nature and overall complexity [9]. Each of the programmable resources must be tested in all modes of operation to achieve high fault coverage. This implies that multiple reconfigurations of the device are required during testing. Because the total test time is usually dominated by the time spent configuring the device under test, the size of FPGA configuration memories is also a factor in testing [9]. FPGAs are, in general, not well-suited for scan-based testing methods. However, the programmable nature of FPGAs allows for the creation of test circuitry in the programmable logic during testing. In addition, the regular structure of FPGAs makes pseudo-exhaustive test methods highly efficient [4] [9] [17] [18] [19].

BIST for FPGAs exploits the re-programmability of FPGAs to create BIST circuitry in the FPGA fabric during manufacturing and system-level off-line testing [4] [9] [17] [18] [19]. The only overhead is the external memory required to store the BIST configurations along with the time required to download and execute the BIST. No area overhead or performance penalties are incurred in the user function because the BIST logic is replaced by the intended system function after testing is complete. The BIST configurations are applicable to all levels of testing because they are independent of the intended system function and require no specialized external test fixture or equipment. Most research and development in BIST for FPGAs has focused on reducing the number of test configurations, reducing the size of test configuration files, and decreasing BIST execution time [4] [7] [8] [23]. Other research has focused on developing BIST techniques for the complex embedded cores included in many modern FPGAs, such as DSPs [24] and RAMs [3] [5]. This thesis presents new BIST approaches for the CLBs, I/O Tiles, and SEU detection cores in Virtex-5 FPGAs.

This thesis also presents a new approach to BIST for FPGAs that utilizes a soft-core processor configured in the fabric of the FPGA under test to execute the BIST sequence, including retrieval and analysis (fault diagnosis) of BIST results and reconfiguration of the FPGA for subsequent BIST configurations. The approach reduces the required number of configurations for BIST of any logic resource to a maximum of four, and by moving the complex BIST controller logic into the FPGA fabric, the external hardware requirements for BIST of FPGAs is greatly reduced. This approach is particularly useful in high-reliability and fault-tolerant applications, especially when fault-diagnosis is required.

# 1.5 Single Event Upsets in FPGAs

BIST is typically targeted at detecting manufacturing defects or "hard" faults that appear during normal operation. However, "soft" errors, known as Single Event Upsets (SEUs), are known to affect the configuration memory and other memory elements of FPGAs during normal operation. These errors are caused when charged particles, such as heavy ions or protons, travel through the FPGA, as illustrated in Figure 1.7 [27]. These particles can alter the state of any static memory element, resulting in an SEU [27] [28] [29]. While SEUs occur more frequently in high radiation environments such as space, they have also been experimentally observed in FPGAs at ground level [28] [29] [30]. Because the configuration memory of an FPGA establishes the overall system function performed by the FPGA, an SEU in the configuration memory can alter the FPGA functionality. This, coupled with the large size of the configuration memory, makes SEUs a significantly greater concern in FPGAs than in typical ASICs [31].

Figure 1.7: Illustration of a single-event effect in a CMOS inverter

Several methods exist to mitigate the effects of SEUs in FPGAs. The most common methods include power cycling, triple modular redundancy, redundant devices, and active configuration memory scrubbing [27]. Power cycling is essentially the simplest form of configuration memory scrubbing, because the entire configuration memory is refreshed (from a radiation hardened memory) each time that power is cycled off and on. When a power cycling mitigation scheme is employed, SEUs can persist in memory elements for a period of time equal to the power-cycling period. This approach is usually sufficient for non-critical applications in low radiation environments [27].

Triple modular redundancy creates three identical copies of the user function in the FPGA fabric and adds majority voters on the inputs to all flip-flops and on all primary outputs of the circuit [32]. This approach is very robust: any single SEU cannot cause the circuit to malfunction, and multiple SEUs must alter the same flip-flop input or primary output in two circuit copies on the same clock cycle in order for the error to propagate. However, the area penalty for any TMR approach is greater than 200% of the original circuit size, which increases system cost and power requirements. Also, circuit performance can be adversely impacted due

to the increased size of the circuit and inclusion of majority voters in critical paths [27]. Duplicating the user function in multiple FPGAs and performing voting on the outputs of the FPGAs in a radiation hardened device is the most robust from of SEU mitigation. However, designing systems with multiple FPGAs is both costly and difficult, and requires special design considerations such that the FPGAs remain synchronized after an SEU is repaired in any one of the devices [27].

Active configuration memory management (also called active configuration memory scrubbing) utilizes error correction code (ECC) stored with configuration data in the configuration memory to actively detect and repair SEUs [14]. The ECC, in conjunction with some additional user-accessible dedicated logic, can be used to detect SEUs in the configuration memory [15]. This approach incurs minimal area overhead, and SEUs persist for only a small window of time. The configuration management hardware may be hosted on an external radiation hardened FPGA, microprocessor, ASIC, or in the FPGA itself. However, in the latter case, the circuitry responsible for the repair of SEUs is also susceptible to SEUs [31]. Therefore, the area of the detection and repair circuitry should be minimized to decrease the probability of an SEU in that logic. An active configuration memory management approach for Xilinx Virtex-4 and Virtex-5 FPGAs that requires no additional external hardware is described in this thesis.

# 1.6 Verification by Fault Injection

During the development of BIST approaches for FPGAs, it is necessary to verify the fault coverage of the BIST configurations. It is difficult to find actual faulty devices and their usefulness is limited due to the fixed nature of the faults. Physical faults can be created by etching the packaged device and creating opens or shorts in routing resources that lie at the top level of interconnect metal for example, but once again the usefulness of these devices is limited.

A more efficient approach is to manipulate the configuration memory bits to emulate physical faults in the device [33] [34] [35] [36]. For example, a stuck-at fault in a look-up table (LUT) bit can be emulated by overwriting the particular configuration memory bit and setting it to the desired stuck-at fault value. SEUs, on the other hand, can be emulated by flipping the value of bits in the configuration memory. Shorts and opens in the interconnect network can be emulated along with almost any fault in the logic resources that can be controlled by configuration memory bits. An approach for the emulation of stuck-at faults and SEUs in the configuration memory of Virtex-4 and Virtex-5 FPGAs is presented in this thesis.

#### 1.7 Thesis Statement

Testing FPGAs is difficult due to their high complexity, the limited observability and controllability of embedded cores, and their programmable nature. Also, the increasing density and large size of the configuration memory has made transient and on-line faults due to SEUs more common and of greater concern, even in fault-tolerant applications that operate at ground level. This work considers both "hard" faults due to manufacturing defects and device ageing as well as transient or "soft" faults induced by SEUs in Virtex-5 FPGAs. Furthermore, this work considers "hard" faults that may affect the detection and correction of SEUs by corrupting the dedicated SEU detection hardware in Virtex-5 FPGAs, and presents BIST approaches for this hardware. Other BIST methods are proposed as a solution to detect "hard" faults and manufacturing defects that can affect the configuration memory and programmable resources in Virtex-5 FPGAs, including the CLBs and I/O Tiles. A novel BIST approach for FPGAs that utilizes a soft-core processor configured in the fabric of the FPGA under test to perform complex functions such as reconfiguration of resources under test and fault diagnosis is also presented. Finally, a method for active detection and correction of temporary or "soft" errors by active

configuration memory management and without the requirement of additional external hardware is presented for Xilinx Virtex-4 and Virtex-5 FPGAs.

#### 1.8 Thesis Format

This thesis is written in "publication format" as suggested by the Auburn University Graduate School *Electronic Thesis and Dissertation Guide*, and consists of conference and journal papers that were published (or accepted for publication) during the course of research conducted by the author while in the graduate program at Auburn University. A majority of the actual research and the writing of all published papers included in this thesis represents the efforts of the primary student author and not collaborators. Each paper is presented "as published", with the exception of an acknowledgments section at the end of each chapter that provides the name, location, and date of publication of the original paper along with any information regarding relevant published papers that do not appear in this thesis. The papers are reformatted to comply with the guidelines set forth by the Graduate School. References are organized as follows: Each chapter in the body of the thesis contains its original list of references (numbered consecutively beginning at 1), such that the chapter may stand-alone and as it appears in the original published paper. In addition, a cumulative bibliography of all references cited in the thesis is included at the end of the thesis.

## 1.9 References

- [1] G. Moore, "Cramming More Components onto Integrated Circuits," *Proc. of the IEEE*, vol. 86, no. 1, pp. 82-85, 1998.

- [2] Semiconductor Industry Association, *International Technology Roadmap for Semiconductors:* 2007 edition, http://public.itrs.net.

- [3] Y. Min and C. Stroud, "Introduction," in *VLSI Test Principles and Architectures*, L-T Wang, C-W Wu, and X. Wen, Eds., San Francisco: Morgan Kaufmann, 2006, pp. 1-33.

- [4] C. Stroud, A Designer's Guide to Built-In Self-Test, Boston: Springer, 2002.

- [5] P. Christie, D. Stroobandt, "The Interpretation and Application of Rent's Rule," *IEEE Trans. on VLSI Systems*, vol. 8, no. 6, pp. 639-648, 2000.

- [6] IEEE Standard Test Access Port and Boundary-Scan Architecture, IEEE Std 1149.1-2001, New York, 2001.

- [7] M. Bushnell and V. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, New York: Springer, 2000.

- [8] IEEE Standard Testability Method for Embedded Core-Based Integrated Circuits, IEEE Std. 1500-2005, New York, 2005.

- [9] L-T Wang, C. Stroud, and N. Touba, *System-on-Chip Test Architectures*, San Francisco: Morgan Kaufmann, 2007.

- [10] M. Smith, Application-Specific Integrated Circuits, Addison-Wesley, 1997.

- [11] I. Kuon and J. Rose, "Measuring the Gap Between FPGAs and ASICs," *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, vol.26, no.2, pp.203-215, 2007

- [12] S. Brown and J. Rose, "FPGA and CPLD architectures: a tutorial," *IEEE Design & Test of Computers*, vol.13, no.2, pp.42-57, 1996

- [13] *Virtex-5 Family Overview*, DS100 (v5.0), Xilinx Inc., 2009.

- [14] Virtex-5 FPGA Configuration User Guide, UG191 (v3.2), Xilinx Inc., 2008.

- [15] *Virtex-5 FPGA User Guide*, UG190 (v 4.2), Xilinx Inc., 2008.

- [16] A. Cosoroaba and F. Rivoallon, "Achieving Higher System Performance with the Virtex-5 Family of FPGAs," Xilinx Inc., San Jose, CA, 2006.

- [17] Virtex-5 FPGA ExtremeDSP Design Considerations: User Guide, UG193 (v3.3), Xilinx Inc., 2009.

- [18] M. Abramovici and C. Stroud, "BIST-based test and diagnosis of FPGA logic blocks," *IEEE Trans. on VLSI Syst.*, vol. 9, no. 1, pp. 159-172, 2001.

- [19] S. Toutounchi and A. Lai, "FPGA test and coverage," *Proc. IEEE Int. Test Conf.*, pp. 599-607, 2002.

- [20] J Sunwoo and C. Stroud, "BIST of Configurable Cores in SoCs Using Embedded Processor Dynamic Reconfiguration," *Proc. Int. SoC Design Conf.*, pp. 174-177, 2005.

- [21] B. Dutton and C. Stroud, "Built-In Self-Test of Configurable Logic Blocks in Virtex-5 FPGAs," *Proc. IEEE Southeastern Symp. on System Theory*, pp. 230-234, 2009.

- [22] B. Dutton and C. Stroud, "Built-In Self-Test of Programmable Input/Output Tiles in Virtex-5 FPGAs," *Proc. IEEE Southeastern Symp. on System Theory*, pp. 235-239, 2009.

- [23] C. Stroud, S. Konala, P. Chen, and M. Abramovici, "Built-in self-test of logic blocks in FPGAs," *Proc. IEEE VLSI Test Symp.*, pp.387-392, 1996.

- [24] M. Pulukuri and C. Stroud, "Built-In Self-Test of Digital Signal Processors in Virtex-4 FPGAs," *Proc. IEEE Southeastern Symp. on System Theory*, pp. 34-38, 2009.

- [25] C. Stroud, S. Garimella and J. Sunwoo, "On-Chip BIST-Based Diagnosis of Embedded Programmable Logic Cores in System-On-Chip Devices," *Proc. ISCA Int. Conf. on Computers and Their Applications*, pp. 308-313, 2005.

- [26] B. Garrison, D. Milton, and C. Stroud, "Built-In Self-Test for Memory Resources in Virtex-4 FPGAs," *Proc. ISCA Int. Conf. on Computers and Their Applications*, pp. 63-68, 2009.

- [27] B. Bridgford, C. Carmichael, and C. Tseng, "Single-Event Upset Mitigation Selection Guide," XAPP987 (v1.0), Xilinx Inc., 2008.

- [28] E. Normand, "Single Event Upset at Ground Level," *IEEE Trans. on Nuclear Science*, vol. 43, pp. 2742-2750, 1996.

- [29] A. Lesea and P. Alfke, "Xilinx FPGAs Overcome the Side Effects of Sub-90 nm Technology," WP256 (v1.0.1), Xilinx Inc., 2007.

- [30] A. Lesea, "Continuing Experiments of Atmospheric Neutron Effects on Deep Submicron Integrated Circuits," WP286 (v1.0), Xilinx Inc., 2008.

- [31] K. Chapman and L. Jones, "SEU Stratagies for Virtex-5 Devices," XAPP864 (v1.0.1), Xilinx Inc., 2009.

- [32] Xilinx TRMTool User Guide: TMRTool Software Version 9.2i, UG156 (v2.2), Xilinx Inc., 2009.

- [33] P. Ellervee, J. Raik, K. Tammemäe and R. Ubar, "Environment for FPGA-based Fault Emulation," *Proc. Estonian Acad. Sci. Eng.*, vol. 12, pp. 323–335, 2006.

- [34] T. Slaughter, C. Stroud, J. Emmert and B. Skaggs, "Fault Injection Emulation for Field Programmable Gate Arrays," *Proc. Int. Society for Optical Eng.*, vol. 4525, pp. 1-9, 2001.

- [35] E. Johnson, M. Caffrey, P. Graham, N. Rollins and M. Wirthlin, "Accelerator Validation of an FPGA SEU Simulator," *IEEE Trans. on Nuclear Sci.*, vol. 50, no. 6, pp. 2147-2157, 2003.

- [36] F. Kastensmidt, L. Carro and R. Reis, *Fault-Tolerance Techniques for SRAM-based FPGAs*, The Netherlands: Springer, 2006.

# Chapter Two. Built-In Self-Test of Configurable Logic Blocks in Virtex-5 FPGAs

A Built-In Self-Test (BIST) approach is presented for the configurable logic blocks (CLBs) in Xilinx Virtex-5 Field Programmable Gate Arrays (FPGAs). A total of 17 configurations were developed to completely test the full functionality of the CLBs, including distributed RAM modes of operation. These configurations cumulatively detect 100% of stuckat faults in every CLB. There is no area overhead or performance penalty and the approach is applicable to all levels of FPGA testing (wafer, package, and in-system). A novel output response analyzer (ORA) design, which is efficiently implemented in FPGAs, provides both an overall single-bit pass/fail result and optimal diagnostic resolution when faults are detected. The implementation of the BIST approach in all Virtex-5 FPGAs and experimental results are discussed.

## 2.1 Introduction And Background

Built-In Self-Test (BIST) for Field Programmable Gate Arrays (FPGAs) is typically targeted at manufacturing defects and operational faults that can appear at any point in the product life-cycle. As a result, BIST for FPGAs employs a defect-oriented test strategy [1]. Ideally, a BIST approach would be applicable to all levels of testing, from manufacturing test to in-system test, and would be entirely independent of the end user function. Additionally, the BIST would achieve maximal stuck-at fault coverage and would be executed at-speed to provide high fault coverage for a variety of fault models. When possible, high diagnostic resolution of detected faults is desired for fault-tolerant applications. This chapter presents a BIST approach

for the configurable logic blocks (CLBs) in Virtex-5 FPGAs that represents the culmination of over 15 years of work in FPGA BIST to address these concerns.

The first BIST for the configurable logic in FPGAs was proposed in [2]. The approach exploits the re-programmability of FPGAs to create BIST circuitry in the FPGA fabric during off-line testing. The only overhead is the external memory required to store the BIST and system function configurations along with the time required to download and execute the BIST. No area overhead or performance penalties are incurred since the BIST logic "disappears" after the test session. Furthermore, the tests are applicable at all levels of testing since they are independent of the system function and require no external test fixture or equipment. The basic idea for the BIST is to configure some of the CLBs as Test Pattern Generators (TPGs) and Output Response Analyzers (ORAs) while configuring other CLBs as blocks under test (BUTs). The BUTs are repeatedly configured until they have been tested in every mode of operation [1]. These tests achieve maximal fault coverage by applying pseudo-exhaustive test patterns such that each sub-circuit of the BUT is exhaustively tested [2].

Several examples of BIST for the CLBs in FPGAs have been published, with each offering some improvement over the previous approach. Reference [3] introduced Boundary Scan as a means of controlling the BIST sequence. Xilinx engineers, in [4], introduced a set of iterative array logic tests with similarities to the approach presented in [2] and [3]. The general BIST approach, which is independent of the CLB array size, can also be adapted for on-line BIST techniques, as discussed in [5]. Previous examples of the implementation of this BIST approach on Xilinx 4000, Spartan, Virtex-I, Spartan-II and Atmel FPGAs are contained in [6], [7], and [8]. Partial reconfiguration was used in [9] to reduce the overall download and test times as well as system down time.

The BIST approach for Virtex-5 FPGAs builds primary on the previous work in [2], [3], [8], and [10]. However, our approach offers an improved ORA architecture and fewer total test configurations. We also improve the accuracy of the fault simulation models and add verification of the configurations on the target device via configuration memory bit fault injection. The remainder of this chapter is organized as follows. Section 2.2 gives an overview of the CLB architecture in Virtex-5 FPGAs. Section 2.3 describes the BIST approach and implementation specific to Virtex-5 FPGAs. Section 2.4 describes the experimental result and verification of the BIST. Section 2.5 summarizes and concludes the chapter.

Table 2.1: List of acronyms

| Acronym | Definition               | Acronym | Definition       |

|---------|--------------------------|---------|------------------|

| CLB     | Configurable Logic Block | BUT     | Block Under Test |

| BIST    | Built-in Self-test       | LUT     | Look-Up Table    |

| ORA     | Output Response Analyzer | SliceL  | Logic Slice      |

| TPG     | Test Pattern Generator   | SliceM  | Memory Slice     |

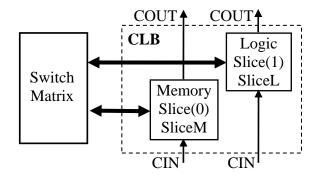

#### 2.2 Overview of Virtex-5 CLBs

The basic Virtex-5 logic element, illustrated in Figure 2.1, is composed of a 6-input lookup table (LUT), a configurable flip-flop/latch, and multiplexers to control the combinational

logic output and the registered output (flip-flop/latch input). Additional dedicated fast carry

logic is included to perform special logic and arithmetic functions. In some slices, the LUT can

be configured as a small RAM, called a distributed RAM or LUT RAM, or as a shift register

[11]. Four such basic logic elements are grouped to form a slice, and two slices are grouped to

form a complete CLB, as shown in Figure 2.2 [11]. Each CLB is connected by a switch matrix

to local and global programmable routing resources. Identical CLBs are tiled in columns and

rows with larger devices including more columns and/or rows of CLBs. Additionally, the

structure of the CLB is identical across all devices in the Virtex-5 family. The 6-input LUTs are

designed with two outputs each. The primary output, O6, can utilize the full 64-bit LUT to implement any 6-variable Boolean function. The secondary output, O5, can be used to initialize the carry chain, or both the O5 and O6 output can implement an independent 5-variable Boolean function for five shared inputs. Either LUT output can be selected by the configuration multiplexers for the registered or combinatorial CLB output paths [11].

Figure 2.1: Simplified basic logic element

Figure 2.2: Virtex-5 configurable logic block [11]

Some slices (specifically the lower slice in every other column of CLBs and both columns to the left of a digital signal processor column) also support RAM and shift register modes of operation. The LUT RAMs in each slice have independent read address inputs and share a set of write address inputs. The independent read inputs facilitate the construction of dual-port RAMs within a slice. Each LUT can be configured as a simple 64×1-bit or 32×2-bit RAM. Dynamically controlled multiplexers in each slice allow the four LUTs to form a 256×1-

bit RAM. Additionally, the four LUTs can share five read address inputs and utilize eight independent data inputs to form a 32×8-bit RAM. Each LUT can also form a single 32-bit or two 16-bit shift registers. The four LUTs can be cascaded to form a 128-bit shift register or can operate in parallel form a 16×8-bit shift register bank [11].

## 2.3 BIST Approach And Architecture

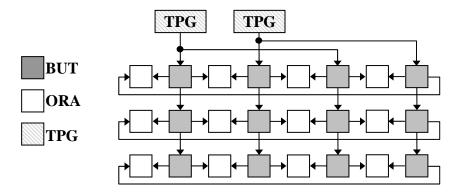

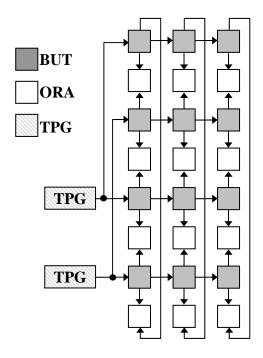

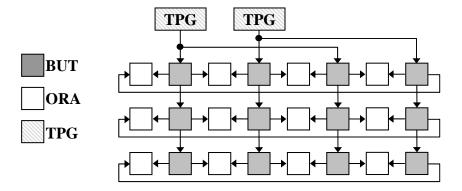

The BIST approach takes advantage of the regular structure of FPGAs by using comparison-based ORAs to compare the outputs of multiple identical BUTs. This detects all faults affecting any combination of BUTs (since all fault-free BUTs must produce the same pattern) so long as all of the BUTs compared by a set of ORAs do not fail identically and at the same time [3]. Since a faulty TPG could cause a faulty BUT to escape detection, multiple identical TPGs are used to drive alternating BUTs. This eliminates the assumption that the TPGs are fault-free because, with multiple identical TPGs, a faulty TPG will cause the outputs of some of the BUTs to disagree, resulting in ORAs reporting failures.

The CLB BIST architectures can be divided into two categories based on the slice mode being tested. The first set of configurations tests every CLB in the FPGA in SliceL (logic) mode of operation. The second set of configurations tests every SliceM. Only those slices which support SliceM (memory) mode are tested during the second set of configurations.

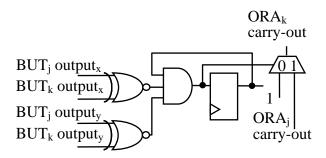

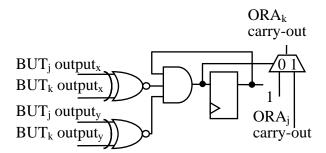

In SliceL BIST architecture, alternating columns of CLBs are configured as ORAs and BUTs, as illustrated in Figure 2.3. The set of BIST configurations is repeated twice with the roles of the CLBs reversed such that every CLB serves both as ORA and as BUT. Two outputs of each BUT are compared by an ORA with the outputs of two adjacent identically configured BUTs in the same row, as shown in Figure 2.4. A mismatch of two identically configured BUT outputs latches a logic 0 in the ORA flip-flop. Otherwise, a logic 1 is retained in the ORA and is

interpreted as a passing result at the end of the test sequence. Traditionally, the results of the BIST are recovered via partial configuration memory readback where the contents of every ORA are retrieved from the configuration memory. However, we use a new ORA design that utilizes the dedicated carry logic in the CLB to form an iterative-OR of the ORA outputs. In each ORA, a passing result of logic 1 selects the Carry-in input, which is the Pass/Fail result of the previous ORA.

Figure 2.3: Circular comparison architecture

The Carry-in input of the first ORA in the iterative-OR chain is connected to Boundary Scan Test Data In (TDI), with the output of the last ORA connected to Test Data Out (TDO). If any ORA in the chain registers a failure, a logic 0 on the output of that ORA will select the logic 1 input of the carry chain multiplexer which translates to a logic 1 on TDO. Otherwise, TDO passes the state of TDI such that by toggling TDI and observing TDO, the integrity of the iterative-OR chain can be verified at the end of the BIST sequence. If the output of the OR chain indicates a failure (TDO is a logic 1 regardless of the state of TDI), the contents of the ORAs can be retrieved via partial configuration memory readback to determine the location(s) of the failing BUT(s). This facilitates the single-bit pass/fail indication for faster test time without sacrificing diagnostic resolution for fault-tolerant applications.

Figure 2.4: Equivalent ORA architecture

In Virtex-5 FPGAs, the carry-in of the bottom CLB and the carry-out of the top CLB in each column are not connected. To continue the carry chain, the carry-out of the top ORA in one column is connected to the D output and is routed to the AX input of the bottom ORA in an adjacent column. The AX input is selected as the carry-chain input in the bottom ORA in each column. In the ORA, each LUT is programmed with the hexadecimal value 0x90090000FFFFFFF. By tying the A6 LUT input to logic 1, the O6 LUT output reads only the upper 32-bits of the LUT which implements the comparison ORA equation shown in Equation 2.1, while the O5 output reads only the lower 32-bits of the LUT (which controls the carry chain multiplexer for the iterative-OR chain).

$$O6 = (\overline{A1 \oplus A2}) \bullet (\overline{A3 \oplus A4}) \bullet A5 \tag{2.1}$$

The architecture of the Virtex-5 CLBs requires a minimum of six configurations to test each of the 6 inputs to the flip-flop input multiplexers, (A-C)FFMUX. The first five of these configurations can also test the 5 inputs to the combinational logic output multiplexers (A-D)OUTMUX. Alternating XOR and XNOR functions in the LUTs detects every LUT stuck-at fault in two BIST configurations. Multiple identical TPGs are implemented in a column of embedded digital signal processors (DSPs) and drive alternating columns of BUTs. This reduces loading on the TPGs in large devices and eliminates the assumption that the TPG is fault-free. The DSPs are configured to accumulate a large prime number placed on the DSP inputs. This

number, 0xCA6691, was shown in [12] to produce an exhaustive sequence of 12-bit test patterns in 2<sup>12</sup> clock cycles with a relatively high number of transitions in the most significant bits of the accumulator output. Virtex-5 CLBs require at least 12 TPG lines for pseudo-exhaustive testing, and, therefore, 4,096 clock cycles for the exhaustive set of test patterns to be produced by the accumulator. Six of the TPG outputs fan out to the inputs of each of the four LUTs. Adjacent LUTs are alternately programmed with XOR and XNOR functions such that adjacent LUTs will produce opposite logic values. Another six TPG lines exercise the AX, BX, CX, DX, CE, and SR slice inputs with pseudo-exhaustive test patterns. A total of 12 SliceL BIST configurations are generated, such that every CLB is a BUT for six configurations and an ORA for another six configurations. A summary of the SliceL BIST configurations is given in Table 2.2.

Table 2.2: SliceL logic BIST configurations

| ConFigure#             | A-D LUTs                                    | FF/Latch                                      | CYINIT           | CLKIINV                                           |

|------------------------|---------------------------------------------|-----------------------------------------------|------------------|---------------------------------------------------|

| #1                     | XOR/XNOR                                    | FF INIT1                                      | #OFF             | CLK                                               |

| #2                     | XNOR/XOR                                    | FF INITO                                      | AX               | CLK                                               |

| #3                     | XOR/XNOR                                    | FF INITO                                      | 0                | CLK                                               |

| #4                     | XNOR/XOR                                    | LAT INIT1                                     | 1                | CLK                                               |

| #5                     | XOR/XNOR                                    | FF INITO                                      | 0                | CLK                                               |

| #6                     | XNOR/XOR                                    | FF INIT1                                      | AX               | CLK B                                             |

| _                      |                                             |                                               | 7 22 2           | · <u>-</u> -                                      |

| ConFigure#             |                                             |                                               |                  | D MUX                                             |

|                        |                                             | MUX                                           | A-               | _                                                 |

| ConFigure#             | A-D FF                                      | MUX<br>O6, O6                                 | A-<br>CY, 0      | D MUX                                             |

| ConFigure#<br>#1       | <b>A-D FF</b> O6, O6,                       | MUX<br>O6, O6<br>O5, O5                       | CY, C<br>XOR, XO | D MUX<br>CY, CY, CY                               |

| ConFigure#<br>#1<br>#2 | A-D FF<br>O6, O6, O<br>O5, O5,              | MUX<br>O6, O6<br>O5, O5<br>CX, DX             | XOR, XO<br>O5, 0 | D MUX<br>CY, CY, CY<br>OR, XOR, XOR               |

| #1<br>#2<br>#3         | A-D FF<br>O6, O6, O<br>O5, O5, O<br>AX, BX, | MUX<br>O6, O6<br>O5, O5<br>CX, DX<br>XOR, XOR | XOR, XO<br>O5, O | D MUX<br>CY, CY, CY<br>OR, XOR, XOR<br>O5, O5, O5 |

Every other CLB column contains a SliceM. In addition, the CLB column to the left of a DSP column contains a SliceM and, in SX devices, the second CLB column to the right of a DSP column contains a SliceM. In columns containing SliceMs, only the bottom slice in each CLB is a SliceM. Therefore, every SliceM can be tested simultaneously since there is at least one SliceL

for every SliceM (located in the same CLB) that can serve as an ORA. The ORAs for the SliceM BIST architecture are the same as those used in the SliceL BIST architecture, including the iterative-OR chain. However, the circular comparison chain is formed along each column containing SliceMs by comparing the outputs of each BUT with the identically configured BUT in an adjacent row. A 2048×18-bit block RAM, effectively configured as a ROM, is used to store deterministic test patterns and, in conjunction with a DSP configured as an address counter, forms a TPG. Multiple identical TPGs are configured to drive alternating rows of BUTs. The SliceM BIST configurations are summarized in Table 2.3. To test the LUT RAMs in single-port modes (configurations #1 and #2), the block RAMs are initialized with the test patterns for a March Y test algorithm. A March Y RAM test requires 8N test patterns, where N is the number of address locations [10] [13]. For the remaining configurations, the block RAMs are initialized with test patterns for a dual-port RAM test algorithm [1] [6].

Table 2.3: SliceM BIST configurations

| ConFigure# | RAM mode | DI1MUX  | WEMUX   | FFMUX    |

|------------|----------|---------|---------|----------|

| #1         | SPRAM64  | DX      | CE      | O6       |

| #2         | SPRAM32  | A-DX    | CE      | O6       |

| #3         | DPRAM32  | DX      | WE      | O5       |

| #4         | SRL32    | MC31    | WE      | MC31     |

| #5         | SRL16    | A-DX    | WE      | O6       |

| ConFigure# | OUTMUX   | WA8used | WA7used | BIST CCs |

| #1         | O6       | 0       | 0       | 2,048    |

| #2         | O6       | #OFF    | #OFF    | 2,048    |

| #3         | O6       | #OFF    | #OFF    | 2,048    |

| #4         | O6       | #OFF    | #OFF    | 2,048    |

| #5         | MC31     | #OFF    | #OFF    | 2,048    |

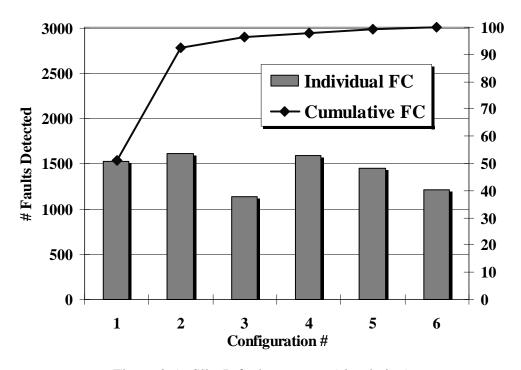

## 2.4 Experimental Results

The BIST configurations were developed using accurate gate-level models of the Virtex-5 CLB. The SliceL and SliceM were modeled separately for fault simulation. For both SliceL

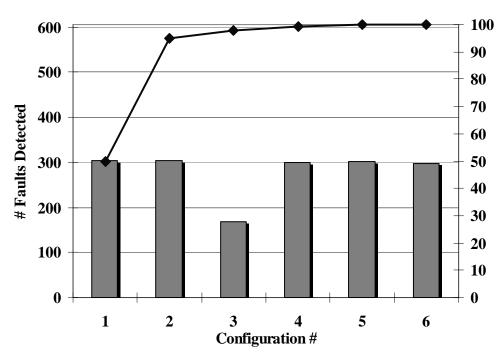

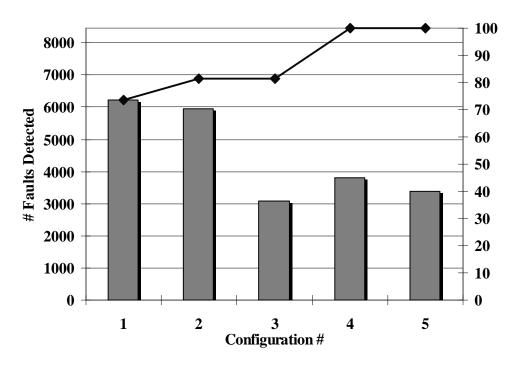

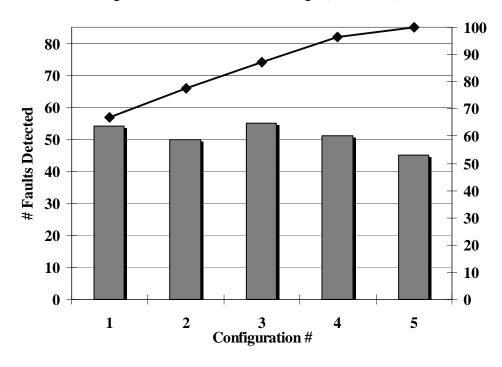

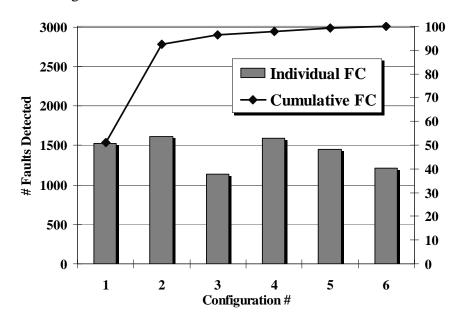

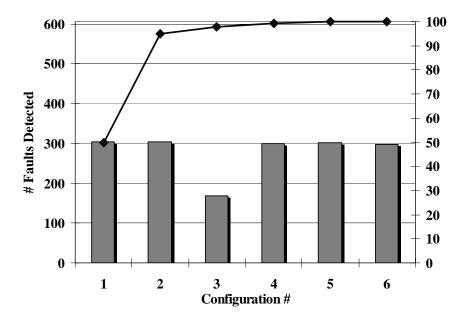

and SliceM, the BIST configurations and their associated fault coverage were first optimized using these gate-level models. The single stuck-at gate-level fault coverage for SliceL and SliceM BIST configurations obtained from fault simulations of these models are summarized in Figure 2.5 and Figure 2.7, respectively.

The BIST configurations were then verified on Virtex-5 LX30T and SX35T devices via configuration memory bit fault injection. Using the fault injection approach, configuration memory bits can be manipulated to emulate physical faults in the FPGA core including shorts and opens in programmable interconnect as well as almost any fault in logic resources controlled by a configuration memory bit. Configuration bits controlling the SliceLs and SliceMs were injected with faults and the BIST configurations were executed with the faulty configuration on the device. The BIST results of the faulty configuration are retrieved via partial configuration memory readback. The fault injection results show that the 17 BIST configurations cumulatively detect every configuration memory bit fault in every CLB. The results of the fault injection for SliceL BIST are shown in Figure 2.6. The similarity of the fault injection results and fault simulation results serve as a good indicator of the accuracy of the gate-level fault models, which include every stuck-at fault in the CLB (including configuration memory bits). Figure 2.7 and Figure 2.8 summarize the fault simulation results and the results of configuration memory bit fault injection, respectively, for the SliceM BIST configurations. It should be noted that three of the SliceM faults are detected by SliceL configurations.

There are two methods by which the results of the BIST sequence can be obtained. First, the single bit pass/fail result can be determined via the TDO output of the ORA iterative-OR chain. However, the location of failing BUTs cannot be determined using this method. Another option is to perform a partial configuration memory readback to determine the contents of each

ORA at the end of the BIST. By this method, the location of the failing BUT(s) can be easily determined with diagnostic resolution of LUT or flip-flop. To minimize test time and achieve maximum fault resolution, a combination of the two methods is used. First, the pass/fail status of the BIST is determined by observing TDO. If TDO presents a logic 1 regardless of the state of TDI, at least one ORA has observed a failure. Partial configuration memory readback can then be used to obtain the locations of the failing ORA(s) and, thereby, determine the location(s) of the faulty BUT(s).

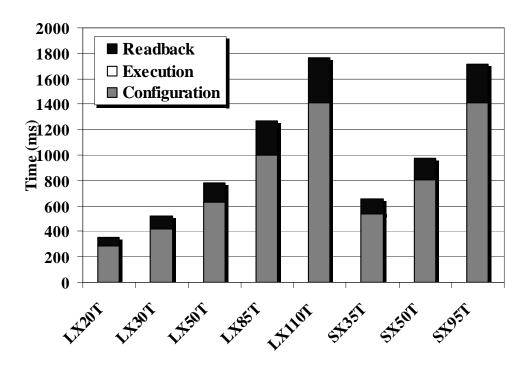

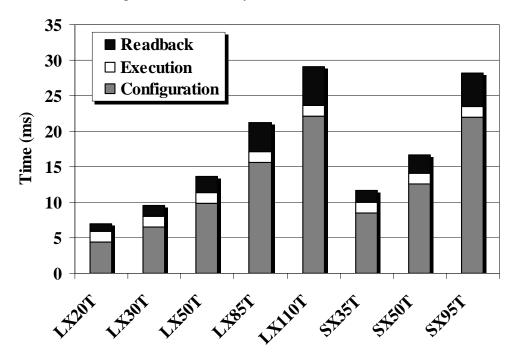

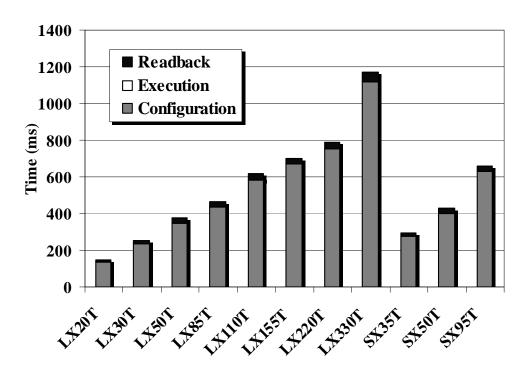

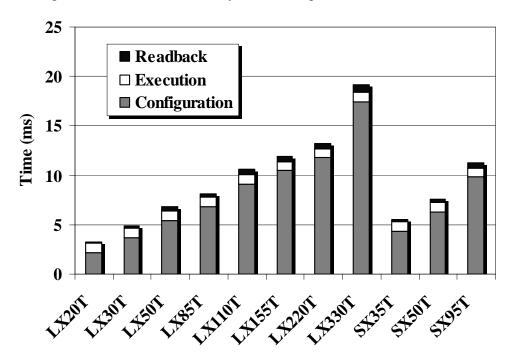

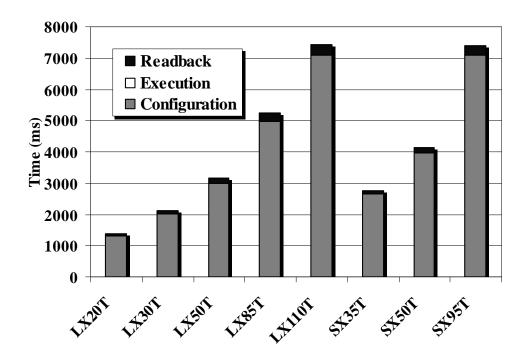

We have developed two C programs that automatically generate the 17 BIST configurations for all Virtex-5 LX, LXT, SXT, and FXT devices. Table 2.4 summarizes the total download file size for the 17 BIST configurations, the maximum BIST clock frequency, and the total number of BIST clock cycles for full chip tests on several Virtex-5 devices. The total full chip test time for serial and parallel configuration interfaces is summarized in Figure 2.9 and Figure 2.10. The calculated test time assumes a 40 MHz BIST clock for all configurations and devices. However, on most devices, the BIST configurations can operate at higher clock frequencies.

Figure 2.5: SliceL fault coverage (simulation)

Figure 2.6: SliceL fault coverage (fault injection)

Figure 2.7: SliceM fault coverage (simulation)

Figure 2.8: SliceM fault coverage (fault injection)

Figure 2.9: Boundary Scan interface test time

Figure 2.10: 32-bit parallel interface test time

In early FPGAs, all LUTs were able to function as small RAMs such that the first BIST configuration applied typically tested the LUTs in the RAM mode of operation. Using this approach, the first BIST configuration was able to detect most faults that could affect the LUT [2]. When combined with a simultaneous test of the flip-flop, the first BIST configuration was able to achieve around 80% fault coverage. A similar characteristic can be observed in the first SliceM BIST configuration in Figure 2.7, which achieves greater than 70% fault coverage. However, current FPGAs, such as Virtex-4 and Virtex-5, limit the number of LUTs that can function as small RAMs. Therefore, two BIST configurations are required (with alternate XOR and XNOR programming) to detect most of the faults in all LUTs. This can be observed in Figure 2.5, where the cumulative fault coverage after the first configuration reaches 51% and after two configurations exceeds 92%.

Table 2.4: CLB BIST totals (17 configurations)

| Device | Total ConFigure<br>Size (kB) | Max. BIST<br>Clock Freq. | BIST CCs |

|--------|------------------------------|--------------------------|----------|

| LX20T  | 1,762                        | 90.7 MHz                 | 59,392   |

| LX30T  | 2,630                        | 74.0 MHz                 | 59,392   |

| LX50T  | 3,930                        | 74.4 MHz                 | 59,392   |

| LX85T  | 6,265                        | 58.2 MHz                 | 59,392   |

| LX110T | 8,837                        | 58.0 MHz                 | 59,392   |

| SX35T  | 3,378                        | 59.2 MHz                 | 59,392   |

| SX50T  | 5,041                        | 61.1 MHz                 | 59,392   |

| SX95T  | 8,818                        | 44.7 MHz                 | 59,392   |

#### 2.5 Summary And Conclusions