### Built-In Self-Test for the Analysis of Mixed-Signal Systems

By

George Joseph Starr

A thesis submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Master of Science

> Auburn, Alabama May 14, 2010

Keywords: Built-In Self-Test, Mixed-Signal, Selective Spectrum Analysis, Multiplier, CORDIC, Test Pattern Generator, Output Response Analyzer

Copyright 2010 by George Joseph Starr

Approved by

Charles E. Stroud, Chair, Professor of Electrical and Computer Engineering Victor P. Nelson, Professor of Electrical and Computer Engineering Foster F. Dai, Professor of Electrical and Computer Engineering

### Abstract

A new Built-In Self-Test technique called Selective Spectrum Analysis has been developed for the measurement of analog characteristics in mixed-signal circuits. This design utilizes digital components to generate and collect analog waveforms to measure both signal strength and phase shift through an analog circuit. These measurements can be used to determine the performance of the analog circuit. However, this design still requires a practical approach to be able to quickly and accurately obtain measurements on-chip.

This thesis proposes improvements to the implementation of this Built-In Self-Test design. These improvements allow for the calculation of the results of these analog measurements on-chip. This thesis also introduces a program to automatically generate the hardware description language model required to fully implement this design in any Application Specific Integrated Circuit or Field Programmable Gate Array.

### Acknowledgements

I would like to thank Dr. Charles Stroud for his constant support and advice throughout my Master's studies. His guidance helped me become a better engineer by teaching me how to logically analyze an unknown behavior and turn it into a known behavior. The knowledge he imparted to me will be invaluable in my future career and for this, I am most grateful. I would also like to thank Dr. Nelson for his instruction in digital design and ASIC fabrication. I would like to thank Dr. Dai for his support in this project and his expertise in the field of analog electronics. I would like to thank these three professors for serving as my committee members. Without their contributions, the work like that presented in this thesis would not be possible.

I would also like to especially acknowledge my colleague Jie Qin whose continued research in Built-In Self-Test acts as a pillar of inspiration to future BIST researchers. I would also like to thank Bradley Dutton and Joseph Cali for their assistance with both the realization of this research and their support throughout my Masters degree. I would also like to thank Mary Pulukuri for her experience in BIST research. I would also like to thank our undergraduate researchers Neil, Alex and Eric for their contributions to my research. Most of all, I would like to thank my wife, Kim, whose constant support, sacrifice and encouragement allowed me realize a dream and pursue graduate school.

iii

## Table of Contents

| Abstract ii                                                          |

|----------------------------------------------------------------------|

| Acknowledgementsiii                                                  |

| List of Figures vi                                                   |

| List of Tables ix                                                    |

| List of Abbreviationsx                                               |

| Introduction1                                                        |

| 1.1 Built-In Self-Test2                                              |

| 1.2 Built-In Self-Test for Analog Components in Mixed-Signal Systems |

| 1.3 Selective Spectrum Analysis                                      |

| 1.4 Thesis Statement7                                                |

| Theory of Operation and Background9                                  |

| 2.1 Analog Characteristics9                                          |

| 2.2 Built-In Self-Test Using Selective Spectrum Analysis13           |

| 2.2.1 Test Pattern Generator15                                       |

| 2.2.2 Output Response Analyzer                                       |

| 2.2.3 Analog Functional Measurements Approach25                      |

| 2.3 Multipliers                                                      |

| 2.4 Coordinate Rotation Digital Computing Algorithm                  |

| 2.5 Thesis Restatement                                               |

| Mixed-Signal Built-In Self-Test Implementation               | 37 |

|--------------------------------------------------------------|----|

| 3.1 Program Generation                                       | 38 |

| 3.1.1 Test Pattern Generator                                 | 42 |

| 3.1.2 Output Response Analyzer                               | 50 |

| 3.2 Built-In Self-Test Test Results                          | 55 |

| In-Circuit Calculations of Analog Characteristics            | 63 |

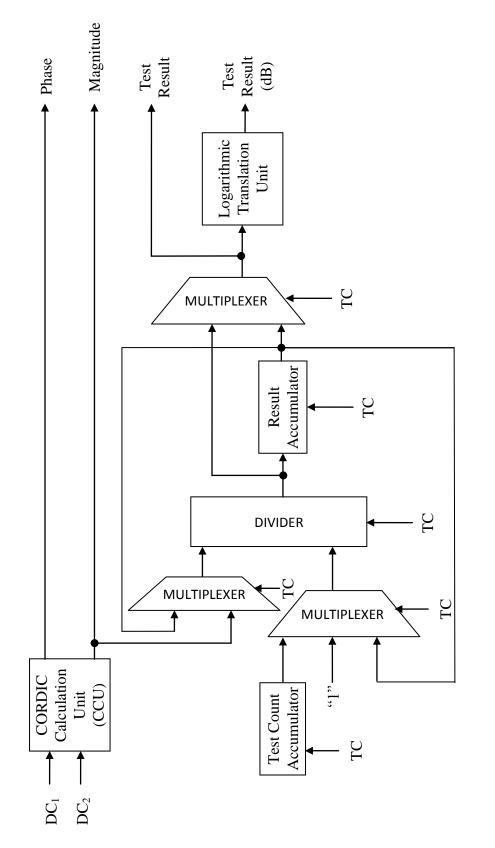

| 4.1 Built-In Self-Test On-Chip Calculation Circuit           | 63 |

| 4.1.1 Coordinate Rotation Digital Computing Calculation Unit | 68 |

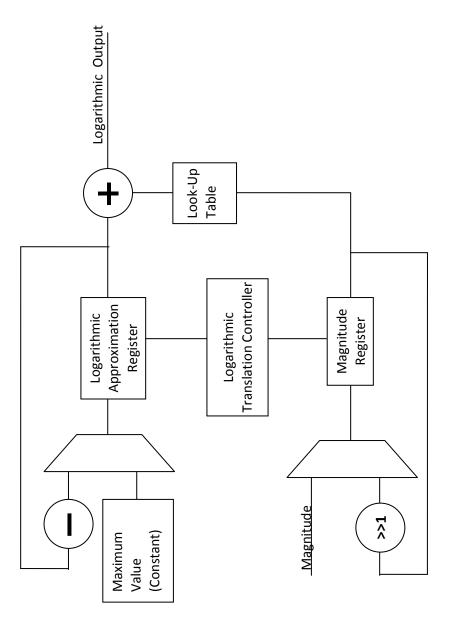

| 4.1.2 Translation of Magnitude Value to Decibels             | 76 |

| 4.2 Built-In Self-Test Implementation Test Results           | 80 |

| Summary and Conclusions                                      | 86 |

| 5.1 Mixed-Signal Built-In Self-Test Improvements             | 86 |

| 5.2 Mixed-Signal Built-In Self-Test Additions                | 88 |

| 5.3 Areas for Future Research and Development                | 89 |

| Bibliography                                                 | 91 |

# List of Figures

| Figure 1-1: Basic BIST Architecture [3]                                                |

|----------------------------------------------------------------------------------------|

| Figure 1-2: DDS-based Analog Test Pattern Generator [17]5                              |

| Figure 1-3: MAC-based Analog Output Response Analyzer Approach                         |

| Figure 2-1: Illustration of Analog Distortion from Two Tone Input [6]10                |

| Figure 2-2: Illustration of Frequency Response Plot Showing the Magnitude Response [8] |

|                                                                                        |

| Figure 2-3: Illustration of SNR, THD, and SINAD Measurement Points in Frequency        |

| Sweep                                                                                  |

| Figure 2-4: Illustration on Mixed-Signal BIST Architecture [11]15                      |

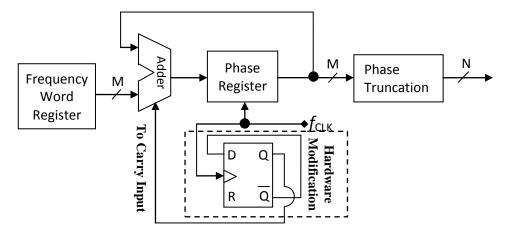

| Figure 2-5: NCO Used in Mixed-Signal BIST Design [4]17                                 |

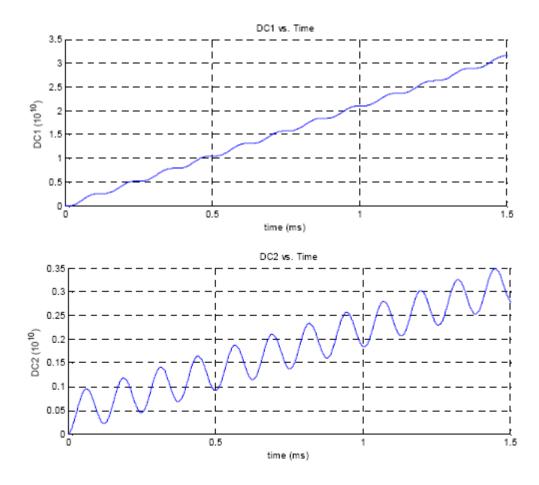

| Figure 2-6: DC <sub>1</sub> and DC2 Versus Time [11]23                                 |

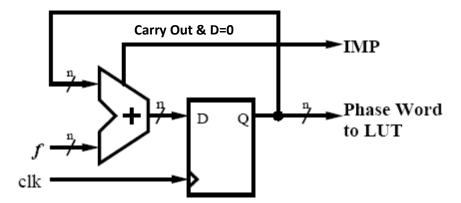

| Figure 2-7: IMP Detection Circuit for Single Tone Measurement [6]24                    |

| Figure 2-8: Illustration of Fundamental Tone Compared to IM3 Tone in IP3 Test [6]27    |

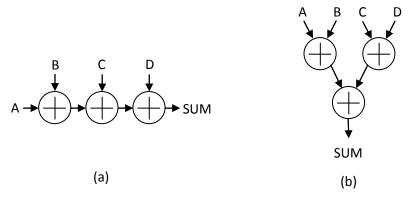

| Figure 2-9: Illustration of Rearranging Partial Product to Decrease Worst Case Path32  |

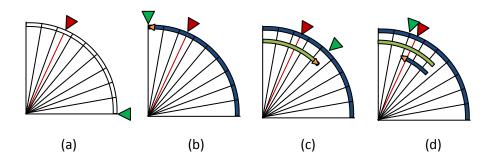

| Figure 2-10: Illustration of CORDIC Rotational Procedure                               |

| Figure 3-1: Screenshot from Automated Program to Generate Mixed-Signal BIST Model,     |

| MSBISTGen.exe                                                                          |

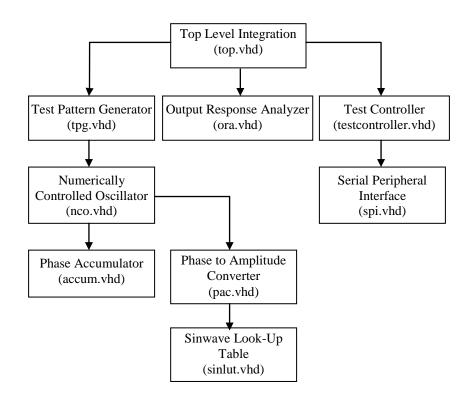

| Figure 3-2: Hierarchical Tree of Files Generated for Mixed-Signal BIST Model41         |

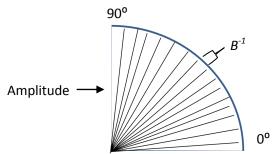

| Figure 3-3: Illustration of Quarter Wave Table45                                       |

| Figure 3-4: Illustration of Repeating Quarter Wave Table to Form Full Wave Table45     |

| Figure 3-5: Illustration of Modified NCO model to include reduced LUT46                  |

|------------------------------------------------------------------------------------------|

| Figure 3-6: Block Diagram of Nicholas Modified Phase Accumulator [17]47                  |

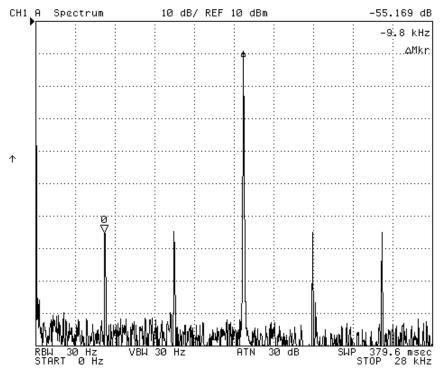

| Figure 3-7: Spurious Free Dynamic Range of 55.169 dBc in a 14.4 kHz Tone Generated       |

| and by the Mixed-Signal BIST Without Nicholas Modified Phase Accumulator49               |

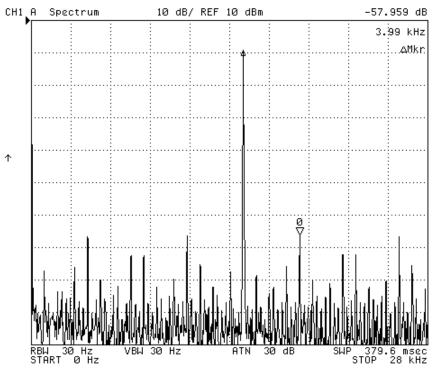

| Figure 3-8: Spurious Free Dynamic Range of 57.959 dBc in a 24.4 kHz Tone Generated       |

| by the Mixed-Signal BIST With Nicholas Modified Phase Accumulator49                      |

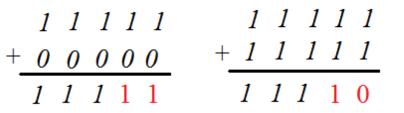

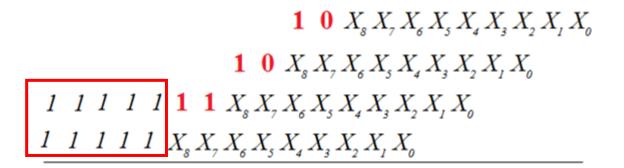

| Figure 3-9: The Logical Addition of the Two's Complement Term with Partial Products.     |

| The First Row Represents the Correction Factor While Each Additional Row Represents      |

| the Partial Products Rows                                                                |

| Figure 3-10: The Two Possible Outcomes for Each Stage of Reduction                       |

| Figure 3-11: The Logical Addition of Offset Term with First Negative Partial Product.    |

| The Highlighted Area Represents the Next Area to Be Reduced                              |

| Figure 3-12: The Logical Addition of Offset Term with Second Negative Partial Product.   |

| The Highlighted Area Represents the Next Area to Be Reduced                              |

| Figure 3-13: The Logical Addition of Offset Term with Third Positive Partial Product.    |

| The Highlighted Area Represents the Next Area to Be Reduced                              |

| Figure 3-14: The Logical Addition of Offset Term with Final Negative Partial Product. 53 |

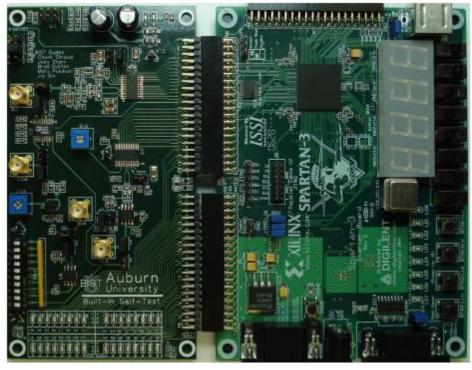

| Figure 3-15: Image of Completed Analog Testing Printed Circuit Board Connected to the    |

| Spartan-3 FPGA56                                                                         |

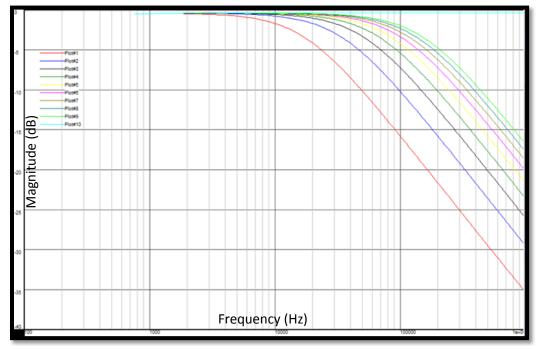

| Figure 3-16: Frequency Response Measurement of the DUT from by the Mixed-Signal          |

| Built-In Self-Test                                                                       |

| Figure 3-17: Linear Response from DUT Measured by the Mixed-Signal BIST59                |

| Figure 3-18: Non-Linear Response from DUT Measured by the Mixed-Signal BIST59            |

| Figure 3-19: Signal to Noise Ratio Measurement from Data Collected from the Mixed-    |

|---------------------------------------------------------------------------------------|

| Signal BIST                                                                           |

| Figure 4-1: Complete In-Circuit Test Calculator Using CORDIC Calculation Unit67       |

| Figure 4-2: CORDIC Relationship on Unit Circle                                        |

| Figure 4-3: Illustration of CORDIC Rotational Procedure Minimizing Y-Axis Value to    |

| Maximize X-axis Value                                                                 |

| Figure 4-4: Illustration of Circular CORDIC Calculation Unit74                        |

| Figure 4-5: Illustration of Logarithmic Translation Unit79                            |

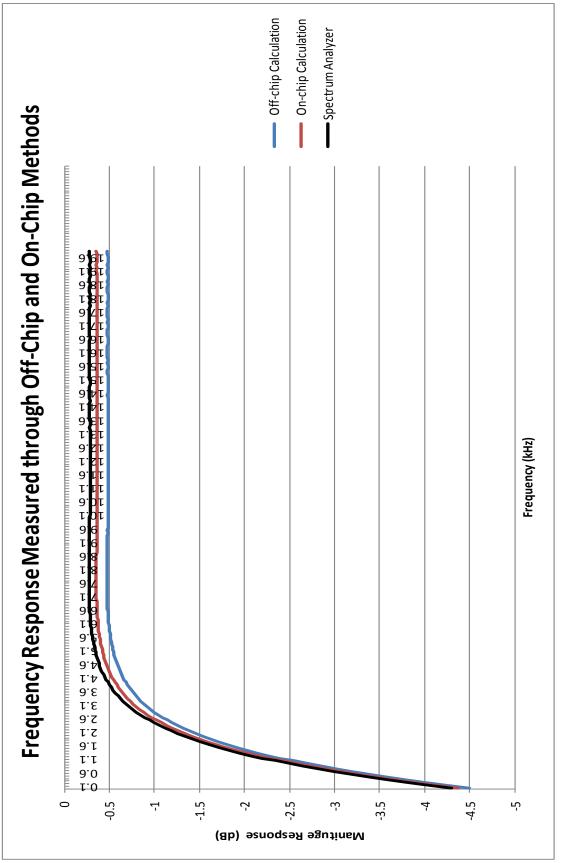

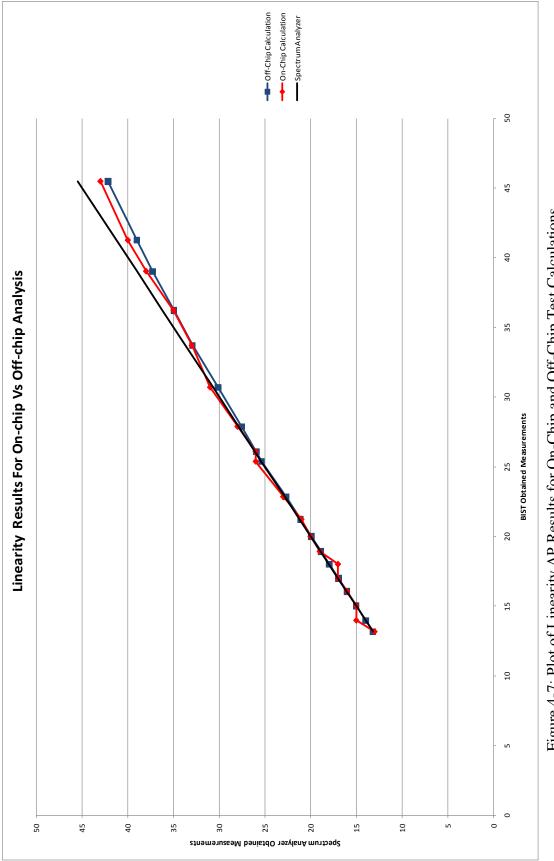

| Figure 4-6: Plot of Frequency Response Using On-Chip and Off-Chip Calculations for    |

| Magnitude                                                                             |

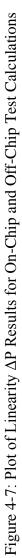

| Figure 4-7: Plot of Linearity ΔP Results for On-Chip and Off-Chip Test Calculations83 |

## List of Tables

| Table 2-1: Relationship Between $\Delta \varphi(\omega)$ and $\Delta \varphi O \omega$ [4]20 |

|----------------------------------------------------------------------------------------------|

| Table 2-2: Booth Recoding Bits Decoded                                                       |

| Table 3-1: Description of Generated Files41                                                  |

| Table 3-2: Decode Top Bits of Quarter Wave Phase Accumulator                                 |

| Table 3-3: Linearity Measurement Comparison of Mixed-Signal BIST Model and                   |

| Spectrum Analyzer60                                                                          |

| Table 3-4: SNR Measurement Comparison of Mixed-Signal BIST Model and Spectrum                |

| Analyzer62                                                                                   |

| Table 4-1: CORDIC Calculation Unit Phase Bits Weight for First Ten Phase Bits73              |

| Table 4-2: Small Value Measurements on the Input of the Logarithmic Translation Unit         |

|                                                                                              |

## List of Abbreviations

| ADC    | Analog to Digital Converter                           |  |

|--------|-------------------------------------------------------|--|

| ASIC   | Application Specific Integrated Circuit               |  |

| ATE    | Automated Test Equipment                              |  |

| BIST   | Built-In Self-Test                                    |  |

| CCU    | Coordinate Rotation Digital Computer Calculation Unit |  |

| CORDIC | Coordinate Rotation Digital Computer                  |  |

| DAC    | Digital to Analog Converter                           |  |

| DDS    | Direct Digital Synthesis                              |  |

| DFT    | Design For Testability                                |  |

| DUT    | Device Under Test                                     |  |

| FFT    | Fast Fourier Transform                                |  |

| GCD    | Greatest Common Denominator                           |  |

| HDL    | Hardware Description Language                         |  |

| IC     | Integrated Circuit                                    |  |

| IIP3   | Input Referred I Third Order Intercept Point          |  |

| IM3    | Third Order Intermodulation                           |  |

| IMD    | Intermodulation Distortion                            |  |

| IMP    | Integer Multiple Period                               |  |

| IP3    | Third Order Intercept Point                           |  |

| LSB    | Least Significant Bit                                 |  |

- LUT Look-Up Table

- MAC Multiplier Accumulator

- MSB Most Significant Bit

- NCO Numerically Controlled Oscillator

- NF Noise Figure

- OIP3 Output Referred Third Order Intercept Point

- ORA Output Response Analyzer

- PAC Phase to Amplitude Converter

- PCB Printed Circuit Board

- SINAD Signal to Noise and Distortion

- SNR Signal to Noise Ratio

- SSA Selective Spectrum Analysis

- THD Total Harmonic Distortion

- TPG Test Pattern Generator

- VHDL Very High Speed Integrated Circuit Hardware Description Language

### Chapter One

### Introduction

The construction of high frequency analog circuits is riddled with difficulties. There are a variety of factors that can determine the quality of an analog Integrated Circuit (IC). These factors can include defects and non-uniform densities in the silicon wafer that cause transistors to operate differently as well as poor design and component choice [1]. Only some of these factors are predictable, therefore there is a need to test the specification of an analog IC to guarantee that it will operate as expected [2].

In digital electronics, there is an expanding field of techniques dedicated to developing self-testing and self-correcting algorithms for digital devices. The most effective of these derived methods is a technique known as Built-In Self-Test, where the testing components are located on-chip, eliminating the need for bulky and expensive test equipment [3]. A mixed-signal Built-In Self-Test approach has been proposed to measure the analog characteristics of a circuit [4]-[12]. This technique utilizes Direct Digital Synthesis (DDS) to generate test patterns and Selective Spectrum Analysis to collect measurement results. Discussed in this thesis are additions and improvements to this Built-In Self-Test (BIST) approach to measure the characteristics of an analog circuit incorporated within a mixed-signal design.

### 1.1 Built-In Self-Test

To keep up with the ever increasing complexity of electronics, the field of circuit testing has had to evolve. Design for Testability (DFT) techniques were developed "to improve the testability of a circuit by including additional circuitry that improves controllability and observability of the circuit under test" [3]. Traditionally, circuits were tested using Automated Testing Equipment (ATE) which would apply a series of inputs to the IC's pins and monitor the output pins for the correct response. This technique of fault testing limits the observable faults to only those that can be directly stimulated from the IC's pins. This shortcoming led to the idea of placing the testing equipment within the silicon device to perform a more thorough and sometimes shorter test sequence [3].

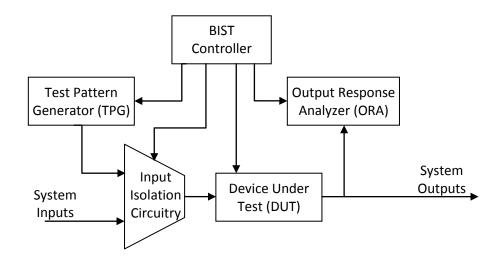

Built-In Self-Test (BIST) is any method for a circuit to test itself to detect faults or invalid responses without the use of external test equipment [3]. The typical BIST architecture contains two essential components used for testing and two additional features used to facilitate testing. The two essential components are the Test Pattern Generator (TPG) and the Output Response Analyzer (ORA). The TPG produces a sequence of test patterns to stimulate the Device Under Test (DUT). The ORA collects the output response of the DUT and translates it into a pass/fail indication [3]. The two secondary components used to facilitate testing are the BIST controller and isolation circuitry. The BIST controller acts to orchestrate the testing procedure by controlling the testing sequence. The isolation circuitry is used to isolate the DUT from the normal inputs so that the TPG can stimulate the DUT with a specific test sequence [3]. This approach is illustrated in Figure 1-1.

2

Figure 1-1: Basic BIST Architecture [3]

### 1.2 Built-In Self-Test for Analog Components in Mixed-Signal Systems

A mixed-signal IC allows developers to combine many different analog and digital systems into one IC. This increases the simplicity of integrating the original design, but the DFT process becomes more difficult. More components are being placed on ICs as the area required for circuit design is shrinking due to improved fabrication techniques, but each added component may require a different DFT technique to verify functionality [1]. These difficulties become even more exaggerated when one considers the introduction of mixed-signal architecture into the IC design. Traditional digital BIST architectures are designed to generate test patterns of distinct ones and zeros to apply to the inputs of the DUT. The output of the circuit is then monitored and compared to the expected digital result [3]. Analog circuits do not operate under such simplified binary principles; therefore a modified approach is required to verify the proper operation of the device.

To perform the test procedure, a TPG is used to produce a series of test patterns that are applied to the DUT. These test patterns are designed to exercise specific aspects of the DUT to test for fault conditions [3]. When testing an analog circuit, the TPG needs to be able to create an analog waveform to test the analog characteristics of a circuit. One method for easily achieving this waveform is a procedure called Direct Digital Synthesis (DDS) [17].

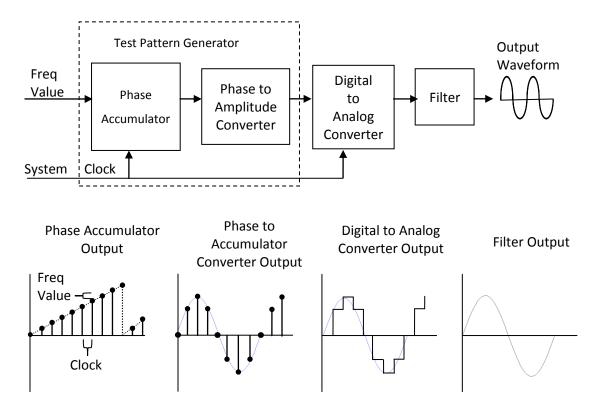

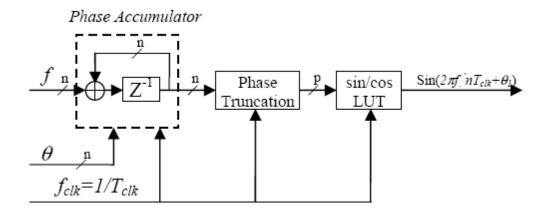

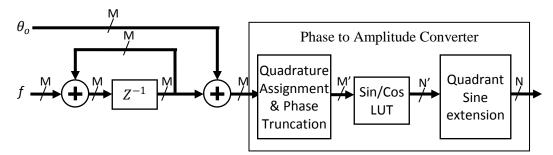

In DDS, a Numerically Controlled Oscillator (NCO) is used in conjunction with a Digital to Analog Converter (DAC) to generate a waveform from a frequency control value and starting phase. The NCO consists of a phase accumulator and a Phase to Amplitude Converter (PAC) [17]. The phase accumulator continuously accumulates the frequency control value at a periodic interval defined by a system clock frequency. This accumulated value is passed to the PAC, which converts the accumulator value to a magnitude value that corresponds to a phase location in the sinusoidal waveform. The output of the PAC is then transmitted to the DAC to generate the analog waveform for testing. Since the phase information is updated every clock cycle, the waveform will appear quantized. An additional filter is needed to smooth this quantized waveform. The illustration in Figure 1-2 shows a visual representation of how a TPG is formed using this method [17]. An illustrated example of the output of each stage is also represented in this figure.

Figure 1-2: DDS-based Analog Test Pattern Generator [17]

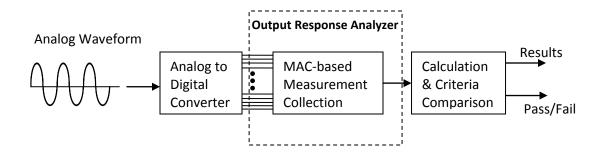

The goal of the ORA is to collect the response from the DUT after it has been stimulated with the output of the TPG. After the response has been collected, it can be interpreted into a pass/fail indicator [3]. For analog BIST measurements however, the results will not be identical with every test. Noise, temperature, humidity, and external electromagnetic radiation sources will affect the performance and response of an analog system [20]. Therefore it becomes necessary to interpret the results and compare these observed measurements to a goal rather than a distinct binary response to determine a pass/fail indicator.

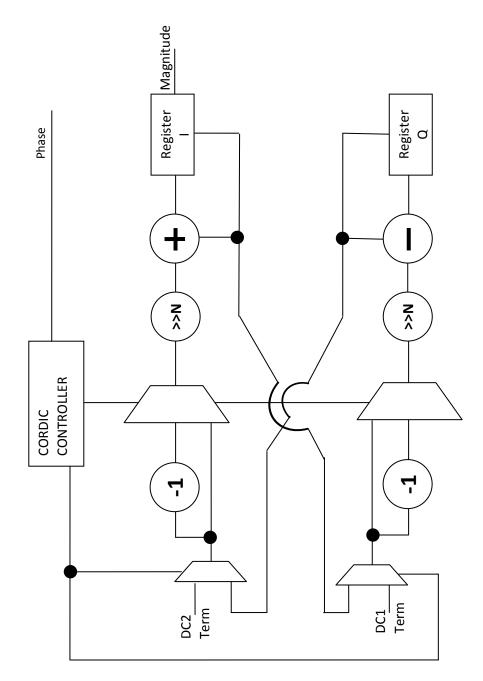

To convert this analog waveform into a digital signal, an Analog to Digital Converter (ADC) can be used. To collect the data points from the digitized input, the ORA implements two multiplier/accumulators (MAC) pairs. These two MACs can be used to extract the in-phase and out-of-phase components of a single frequency within this measured signal [4]. Once this data has been collected, the result can be compared to a set of specifications for that test to generate a pass/fail indicator. This approach to the ORA is illustrated in Figure 1-3.

Figure 1-3: MAC-based Analog Output Response Analyzer Approach

### 1.3 Selective Spectrum Analysis

To perform a test on an analog circuit, a tone must be driven into the circuit and the response measured. To measure this response, a traditional spectrum analysis can be performed by a Fast Fourier Transform (FFT) processor [18]. These FFT engines capture a large amount of data points to perform analysis on a broad frequency spectrum to calculate the phase and magnitude for many distinct frequencies simultaneously using a derivative of the Fourier Transform algorithm [18]. These FFT processors require a large amount of area overhead and power consumption to implement [5]. This is not desirable for a BIST approach where the goal is to use minimal overhead to test.

As an alternative solution, this BIST model applies a different approach to measure the phase and magnitude response of the DUT. Once the analog waveform generated by the TPG has stimulated the DUT, the DUT's response is collected by the ORA. To collect the spectral content, the ORA employs two pairs of MACs to capture and accumulate the results. The MAC acts to filters out a single frequency of interest from the measured response. In this BIST approach, only one frequency can be analyzed at a time, rather than a broad spectrum approach performed by the FFT processor [5]. This allows a circuit with lower area overhead and faster calculation time to be developed. This process of measuring one exclusive frequency at a time is referred to as Selective Spectrum Analysis (SSA).

This SSA approach is not without limitations. To implement this circuit still requires resource overhead to generate tones and collect the DUT response; though the required area is a minimal when compared to that implemented by traditional FFT processors [5]. In addition, the test time to obtain accurate measurements is a function of the frequency words used and how many data points are collected. Therefore, a poor choice in frequency words or performing a test that involves the capturing of multiple frequency points can potentially result in a long test time. This proposed BIST approach includes a mathematical basis for calculating the phase and magnitude from the output of the ORA, but does not include a practical implementation for this design [4][5].

### 1.4 Thesis Statement

The goal of this thesis is to present additions and improvement to the design for the SSA Built-In Self-Test model for mixed-signal systems presented in [4]-[12]. This thesis will present a method for performing common analog tests on-chip. In addition, this thesis will also present improvements to the MAC-based ORA by introducing an improved multiplier design. This thesis will also present a technique for automatically generating the complete hardware descriptive model for multiple platforms of implementation.

7

Chapter 2 will present a detailed overview of the Built-In Self-Test model for mixedsignal systems. Background mathematics and procedures of measurement will also be elaborated upon. Chapter 3 will present the work completed to obtain an automated implementation of the Built-In Self-Test mixed-signal design. This includes improvements in the TPG using minimized NCOs and the ORA using an improved multiplier. Chapter 4 will discuss the improvements to the overall approach with the addition of on-chip interpretation of the ORA measurements. The thesis will be summarized in Chapter 5 and provide suggestions for future areas of research and development.

#### Chapter Two

### Theory of Operation and Background

Complex mixed-signal electronic systems are being extensively developed. Consequently, the increasing cost associated with testing these complex systems has motivated research efforts to explore more efficient testing methodologies. This chapter will present an introduction to Built-In Self-Test using Selective Spectrum Analysis to evaluate the performance of analog devices in mixed-signal systems. This will cover the mechanisms of measurement which are used to collect test information. In addition, a description of previous analog testing techniques will also be presented. This chapter will also cover a brief overview of multiplier architectures and the Coordinate Rotation Digital Computing algorithm as an introduction to improvements to this existing Built-In Self-Test approach. Finally, this chapter concludes with a re-statement of the thesis goals.

### 2.1 Analog Characteristics

In the measurement of electronic circuits, there are key performance parameters that can be used to determine if the circuit has met design specifications. Critical parameters that define an analog circuit include its response to direct stimulus, distortion from the input waveform, and noise within the system. To measure each of these characteristics, the presented mixed-signal BIST model is capable of measuring linearity, frequency response, and a variety of noise measurements for an analog circuit [7].

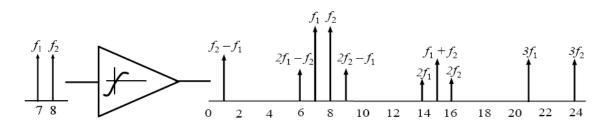

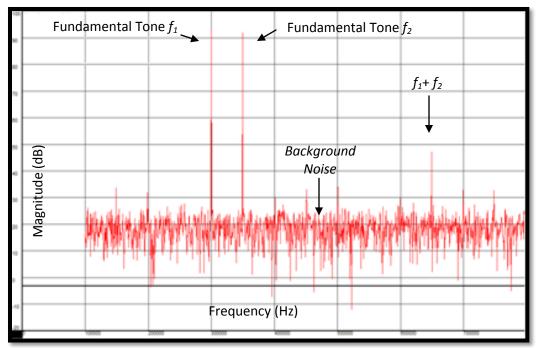

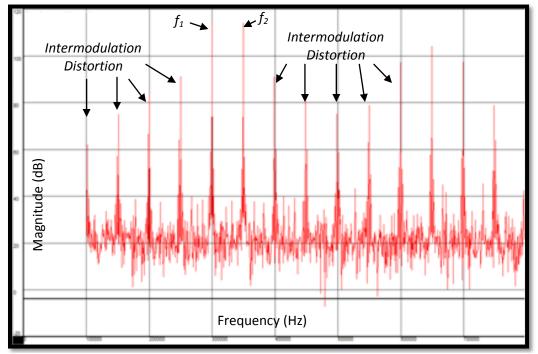

Linearity is a very important characteristic of electronic amplifiers and filters. Linearity refers to the characteristic behavior of a device to have an output which is linearly proportional to the input [20]. This is considered synonymous with having low distortion and preserving the fidelity of analog signals. When two tones are applied to the input of an analog circuit which exhibits a poor linearity response, the output of the circuit experiences Intermodulation Distortion (IMD). This results in the formation of frequencies which are not integer multiple harmonic frequencies of the originally applied two tones [21]. IMD represents a serious hindrance to circuit performance as these unintentionally generated tones may result in signals which prove extremely difficult to filter out by normal means, causing an indeterminate response from the circuit. Illustrated in Figure 2-1 is an example of IMD. Two tones at frequencies 7 and 8 are supplied to an analog amplifier. If this amplifier was linear, the output would contain spectral content at only the two input tones and harmonics. Because this amplifier is nonlinear, the output contains the original frequencies, harmonics of the input tones, and intermodulation between the original frequencies and harmonics tones [6].

Figure 2-1: Illustration of Analog Distortion from Two Tone Input [6]

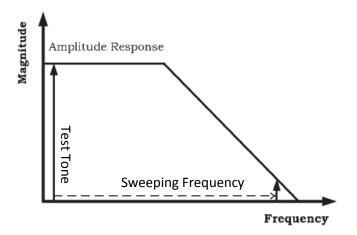

Frequency response is another important measurement when attempting to characterize an analog system [7]. Frequency response can be defined as the comparison between a system's output response and an input signal. Frequency response can be separated into two separate types of measurements: magnitude and phase response. Magnitude response is the difference between the magnitudes of the incident waveform into the device and the magnitude of the output waveform. This is usually expressed graphically against the frequency of that waveform. This is illustrated in Figure 2-2, where the magnitude is recorded as the frequency is swept from low to high. Magnitude response is useful when characterizing the gain delivered by an amplifier or the cutoff point and slope of a filter [8]. Phase response serves an equally important role in characterizing the analog circuit. Phase response measures the phase delay of the output waveform which occurs due to the analog circuit.

Figure 2-2: Illustration of Frequency Response Plot Showing the Magnitude Response [8]

In any electronic circuit, noise plays a considerable factor in determining the quality of the circuit. There are many sources which may generate noise in analog circuits including thermal noise, shot noise, flicker noise, and avalanche noise [20]. This noise appears in tandem with the signal of interest, thus excessive noise increases the difficultly of accurately interpreting the signal. This makes preserving the signal clarity a priority in analog design and testing. To characterize the noise within a system there are two important parameters. The first is the signal to noise ratio (SNR). This measurement is a

direct comparison between the power within the signal of interest and the noise generated by the system [9]. This is defined as

$$SNR = \frac{Signal Power}{Average Noise Power (within specified Bandwidth)}$$

(2-1)

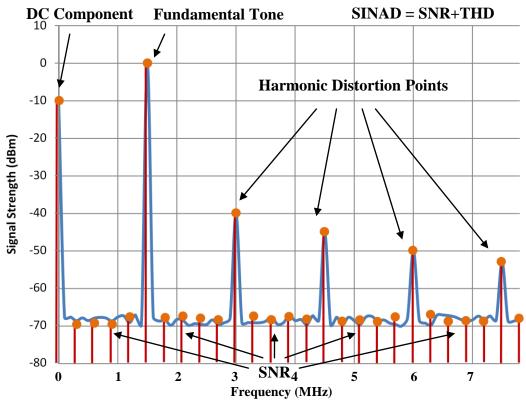

The noise power within an SNR measurement must be defined to a particular bandwidth of interest to contain statistically significant information. SNR can be further subdivided into three equally important measurements based on how the noise power bandwidth is defined. The first subdivision is known as Total Harmonic Distortion (THD) [20]. In a THD measurement, the noise in question is only measured at frequencies where harmonic tones of the original signal exist. This gives a direct comparison between the signal of interest and the generated harmonics of that signal. The next subdivision of noise bandwidth measurement involves measuring only background noise while avoiding all harmonic tones in the measurement. This is how the traditional SNR measurement is performed. The final form of SNR subdivision is known as the Signal to Noise and Distortion (SINAD). The SINAD measurement is a combination of the previous two measurements where both background noise and harmonic distortion are combined as noise and compared to the signal of interest [20]. All three of these noise measurement techniques are illustrated in Figure 2-3. In this illustration each bullet represents a point of measurement.

12

Figure 2-3: Illustration of SNR, THD, and SINAD Measurement Points in Frequency Sweep

The second critical parameter when measuring noise is called the Noise Figure (NF). This parameter is defined as the ratio between the SNR before the influence of the DUT and the SNR after the DUT has processed the signal [9]. This characteristic is important as it represents the degradation of the SNR due to interference within the DUT [20]. The formal definition for NF is shown in Equation 2-2.

$$NF = \frac{SNR_{IN}}{SNR_{OUT}}$$

(2-2)

### 2.2 Built-In Self-Test Using Selective Spectrum Analysis

Analog performance testing is a challenging task even when performed by an experienced engineer with the correct equipment. After the test data is collected, the test results of an analog circuit are then compared to a given set of system specifications to

verify performance [3]. In order to perform a myriad of analog tests such as linearity, frequency response, and noise measurements within a mixed-signal IC, it becomes necessary to implement a BIST approach. This allows for specification testing without the use of expensive and bulky external equipment.

To obtain analog measurements within this application, the BIST needs to collect the frequency spectrum content coming from the DUT. To collect this data, the BIST implements an ORA. Many techniques have been proposed to implement an ORA for analog testing in [21]-[25], but these designs, unfortunately, are incapable of measuring each of the desired analog characteristics of linearity, frequency response, and noise measurements within one unified model. Some designers utilize FFT to perform broad spectrum signal analysis, but the overhead requirements of these techniques limit their utilization in commercial applications [18].

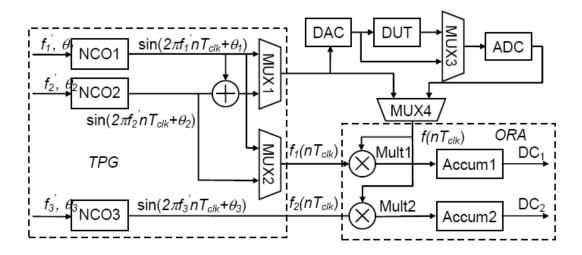

A solution to this overall BIST approach was originally proposed in [6]. Within this design is a digital TPG that is constructed utilizing DDS to generate the tones required for stimulating the DUT and internal reference. The response of the DUT is collected by a digital ORA. To capture these measurements, this ORA will implement two pairs of multipliers/accumulators [4].

14

Figure 2-4: Illustration on Mixed-Signal BIST Architecture [11]

This mixed-signal BIST architecture, illustrated in Figure 2-4, is capable of performing measurements on the DUT depicted in the illustration. In addition, this approach utilizes an analog multiplexer, depicted as MUX3, which allows the DUT to be bypassed and the performance of the remaining system elements to be measured. The BIST method for analog measurement relies primarily on two elements to test an analog DUT. These are the DDS-based TPG and the MAC-based ORA [4].

### 2.2.1 Test Pattern Generator

As shown in Figure 2-4, the DDS-based TPG of is made of three numerically controlled oscillators (NCOs). In this design, each NCO consists of a phase accumulator, phase truncation stage, and phase to amplitude converter. The phase accumulator is capable of accepting both a frequency control word and a starting phase word. In the phase accumulator, the frequency control word, *f*, is continuously accumulated. This acts to control the frequency of the generated waveform. The phase word,  $\theta$ , is used to define a starting offset for the accumulator, which will correspond to a phase offset for the

15

generated waveform. The phase truncation stage removes unused Least Significant Bits (LSBs) and formats the data so that it will properly interact with the PAC. This allows for a large accumulator to accumulate precise phase information but implement the conversion between phase and amplitude with a less precise PAC to reduce area overhead [4]. The PAC design is usually achieved using a Look-Up Table (LUT). The output of the LUT represents the magnitude component of a sinusoidal waveform and can be converted to an analog signal with a DAC or used as a digital reference tone [17]. The resulting waveform and frequency from each NCO are expressed in Equations 2-3 through 2-5.

$$f' = \frac{f \cdot f_{CLK}}{2^N} \tag{2-3}$$

$$\theta' = \frac{\theta * 2\pi}{2^N} \tag{2-4}$$

$$NCO = \sin(2\pi \cdot f' \cdot n \cdot T_{CLK} + \theta')$$

(2-5)

In these equations, the frequency control word and phase control word are represented by f and  $\theta$ , respectively. The size of the phase accumulators in which these control words are accumulated, can be represented as *N*-bits wide. Finally the rate of accumulation can be represented as the system clock frequency,  $f_{\text{CLK}} = 1/T_{\text{CLK}}$ . The accumulator effectively acts to divide  $f_{CLK}$  by  $2^N/f$ , creating the observed frequency and phase of f' and  $\theta'$  [4]. The final waveform output is expressed in Equation 2-5 where variable *n* is equivalent to the number of clock cycles which have elapsed. This NCO design within the TPG of this BIST is illustrated in Figure 2-5.

Figure 2-5: NCO Used in Mixed-Signal BIST Design [4]

In the BIST architecture in Figure 2-4, NCO1 and NCO2 are used to generate the test pattern waveform [4]. Through the multiplexer labeled MUX1, the model is capable of selecting a waveform generated by NCO1 or the combination of NCO1 and NCO2. This allows either a one-tone or two-tone waveform to be generated. The output of this multiplexer is connected to the DAC. By combining the NCOs with the DAC, the DDS model is completed, and it becomes possible to generate one or two-tone analog waveforms. The output of the multiplexer MUX1, which contains the test pattern, is also attached to the input of the ORA by multiplexor MUX4 [4]. This allows the BIST to bypass all analog components and test the functionality of the digital components. To capture each measurement, the ORA requires reference tones. These can be generated from additional NCOs in the TPG [11].

This TPG approach has two disadvantages due to using DDS to generate waveforms. The first problem with using DDS is the generation of image tones around the clock frequency. The lower half of the frequency band, 0Hz to  $f_{CLK}/2$ , contains the tones producible by the DDS, while the upper half of the frequency band,  $f_{CLK}/2$  to  $f_{CLK}$ , contains images of these tones centered around  $f_{CLK}$  [17]. This divides the usable

17

spectrum in which the DDS can generate tones to half the system clock frequency to avoid these image tones. The second disadvantage occurs as the DDS generates tones close to the Nyquist bandwidth of half the clock frequency,  $f_{CLK}/2$ . At this point, the tone generated, f, and the tone's image around the clock,  $f_{CLK} - f$ , will appear very close to each other. This case also results in stronger image tones as quantization effects become more pronounced when the phase accumulator uses larger increments. This results in difficulties distinguishing the tone from the image. To reduce these images, sharp filters are typically applied to remove frequency components at and above  $f_{CLK}/2$ . This reduces the strength of images and quantization noise, but also limits the usable range of the DDS to less than 40 percent of  $f_{CLK}$  [17].

#### 2.2.2 Output Response Analyzer

The second essential element of the mixed-signal BIST approach is the MACbased ORA. Its function is to collect the response signal of the DUT. The ORA operates on the principle of SSA, where the objective is to measure the magnitude and phase of one specific tone.

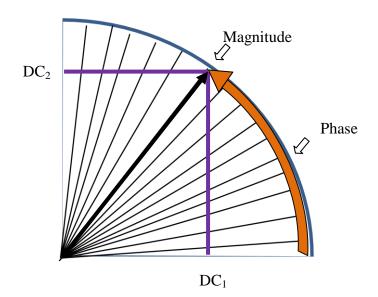

The principles of operation for this ORA are straightforward. The ORA consists of two pairs of MACs. Each multiplier has one input attached to the multiplexer MUX4, which selects the source of the test data as shown in Figure 2-4. When undergoing a test, the waveform being sampled by the ADC can be represented as  $f(nT_{CLK})$  [11]. The second input on each multiplier, signals  $f_1$  and  $f_2$ , connect to a digital NCO which is generating a reference waveform. If signals  $f_1(nT_{CLK})$  and  $f_2(nT_{CLK})$  are set to  $\cos(\omega nT_{CLK})$  and  $\sin(\omega nT_{CLK})$  respectively, then the resulting values of DC<sub>1</sub> and DC<sub>2</sub>, which represent the results of each MAC, are as shown in Equations 2-6 and 2-7 [4].

$$DC_{1}(\omega) = \sum_{n} f(nT_{CLK}) \cdot cos(\omega nT_{CLK})$$

(2-6)

$$DC_{2}(\omega) = \sum_{n} f(nT_{CLK}) \cdot sin(\omega nT_{CLK})$$

(2-7)

Equations 2-6 and 2-7 show that DC<sub>1</sub> and DC<sub>2</sub> each represent the in-phase and out-of-phase components of  $f(nT_{CLK})$  at frequency  $\omega$ . By substituting Equations 2-6 and 2-7 for the in-phase and out-of-phase components of the Fourier transformation equation  $F(\omega)$ , the resulting identity can be obtained [4].

$$F(\omega) = \sum_{n} f(nT_{CLK})e^{-j\omega n T_{CLK}} = DC_1(\omega) - j \cdot DC_2(\omega)$$

(2-8)

Equation 2-8 shows that the frequency content of the sampled waveform can be expressed by the in-phase and out-of-phase components  $DC_1$  and  $DC_2$ , respectively. To selectively examine a single frequency component of the response waveform, the reference tones being mixed with the sampled waveform need to be modified to the desired test frequency in this MAC-based ORA design. To obtain the magnitude and phase of each frequency component, it becomes convenient to express the frequency measurements as shown in Equation 2-9 [4].

$$F(\omega) = DC_1(\omega) - j \cdot DC_2(\omega) = A(\omega)e^{+j\Delta\varphi(\omega)}$$

(2-9)

In this representation of  $F(\omega)$ , the component  $A(\omega)$  represents the magnitude of the measurement for frequency  $\omega$ . The second component  $\Delta \varphi(\omega)$  represents the relative phase delay of the signal of frequency  $\omega$  with respect to the phase of the reference tones. These two parameters,  $A(\omega)$  and  $\Delta \varphi(\omega)$ , are used to determine the results of each of the analog test measurements. The measurement of the relative phase shift can be represented as shown in Equation 2-10 [4].

$$\Delta\varphi(\omega) = \tan^{-1}(\frac{DC_2}{DC_1}) \tag{2-10}$$

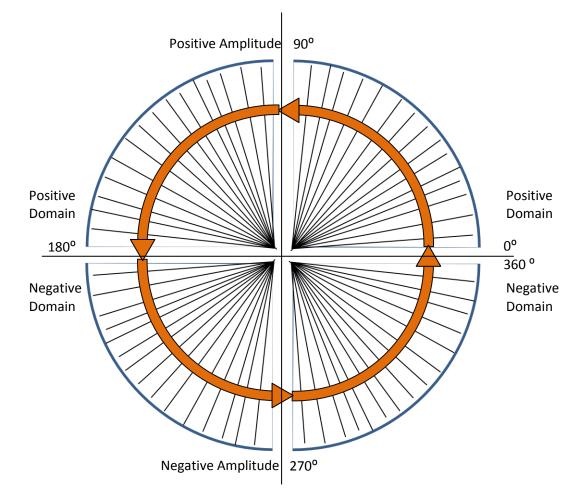

This represents phase measurement only within the limited output of the arctangent range of -90° to +90°. To express the absolute phase shift  $(\Delta \varphi_0(\omega))$ , the magnitude and sign convention of DC<sub>1</sub> and DC<sub>2</sub> must be factored into the measurement. This measurement of absolute phase is summarized in Table 2-1.

Table 2-1: Relationship Between  $\Delta \varphi(\omega)$  and  $\Delta \varphi_0(\omega)$  [4]

|              | DC1 > DC2                                                         | DC1 < DC2                                                         |

|--------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| DC1>0, DC2>0 | $\Delta \varphi(\omega) = \Delta \varphi_0(\omega)$               | $\Delta \varphi(\omega) = 90^{\circ} - \Delta \varphi_0(\omega)$  |

| DC1>0, DC2<0 | $\Delta \varphi(\omega) = 360^{\circ} - \Delta \varphi_0(\omega)$ | $\Delta \varphi(\omega) = 270^{\circ} + \Delta \varphi_0(\omega)$ |

| DC1<0, DC2>0 | $\Delta \varphi(\omega) = 180^{\circ} - \Delta \varphi_0(\omega)$ | $\Delta \varphi(\omega) = 90^{\circ} + \Delta \varphi_0(\omega)$  |

| DC1<0, DC2<0 | $\Delta \varphi(\omega) = 180^{\circ} + \Delta \varphi_0(\omega)$ | $\Delta \varphi(\omega) = 270^{\circ} - \Delta \varphi_0(\omega)$ |

To solve for the  $A(\omega)$  parameter, three approaches are suggested in [4]. The first approach demonstrates that it is possible to adjust the phase of the testing waveform used to stimulate the DUT, such that the DUT response becomes in-phase with the reference tone. If the device is stimulated and the phase shift is measured, the inverse of this phase shift can be applied to the reference source in the TPG. This will shift the in-phase measurement to match the DUT phase response. Therefore the value within the in-phase MAC will directly represent the magnitude of the measurement, while the out-of-phase MAC will contain a value of zero. This magnitude is expressed in Equation 2-11 [4].

$$A(\omega) = F(\omega)e^{-j\Delta\varphi(\omega)}$$

=  $\sum_{n} f(nT_{CLK})e^{j[\omega nT_{CLK} - \Delta\varphi(\omega)]}$

=  $\sum_{n} f(nT_{CLK})\cos(\omega nT_{CLK} - \Delta\varphi(\omega))$  (2-11)

This is very beneficial as there is no calculation circuitry need to directly obtain  $A(\omega)$  from DC<sub>1</sub> and DC<sub>2</sub>. However circuitry would be need to obtain the phase delay and rerun the test with the modified phase to obtain a measurement. This approach would not be valid if measuring noise since the noise phase could change for each subsequent measurement [4].

The second approach to obtaining magnitude relies on factoring the phase out from the observed measurement. If the phase shift of the observed waveform can be obtained, then it can simply be divided out of either the in-phase or out-of-phase component of measurement as shown in Equation 2-12 [4].

$$A(\omega) = \frac{DC_1}{\cos \left[ \Delta \varphi(\omega) \right]} = \frac{DC_2}{\sin \left[ \Delta \varphi(\omega) \right]}$$

(2-12)

Unlike the first approach, this approach does not require the test to be rerun to calculate the magnitude; therefore it can be used to perform noise measurements. However, there is additional hardware required to calculate phase, convert the phase shift through a cosine or sine LUT, and perform the division [4].

There is one common factor between the first two approaches. Both approaches utilize phase shift to calculate magnitude. The third approach does not utilize phase shift to calculate the magnitude, but instead relies on the values of  $DC_1$  and  $DC_2$  directly. The third option presents the most direct method to implement as it only depends on the raw values of  $DC_1$  and  $DC_2$ . This is described in Equation 2-13 [4].

$$A(\omega) = \sqrt{DC_1^2 + DC_2^2}$$

(2-13)

Each of these three options represents a valid method of calculating the magnitude for the SSA response in this MAC-based ORA. Now that the ORA is capable of collecting phase and magnitude utilizing two pairs of MACs, it requires a method for controlling the length of accumulation, N. When the ORA is attempting to accumulate the response of a single tone from the DUT, the accumulator outputs DC<sub>1</sub> and DC<sub>2</sub> are expressed as shown in Equations 2-14 and 2-15 [4].

$$DC_{1}(N) = \sum_{n=1}^{N} A\cos(2\pi f n T_{CLK} + \Delta \varphi) \cdot \cos(2\pi f n T_{CLK})$$

$$= \frac{AN}{2} \cos(\Delta \varphi) + \frac{A}{2} \sum_{n=1}^{N} \cos(4\pi f n T_{CLK} + \Delta \varphi)$$

$$DC_{2}(N) = \sum_{n=1}^{N} A\cos(2\pi f n T_{CLK} + \Delta \varphi) \cdot \sin(2\pi f n T_{CLK})$$

$$= \frac{AN}{2} \sin(\Delta \varphi) + \frac{A}{2} \sum_{n=1}^{N} \sin(4\pi f n T_{CLK} + \Delta \varphi)$$

(2-15)

DC<sub>1</sub> and DC<sub>2</sub> contain the in-phase and out-of-phase components necessary for calculation, represented as  $A \cdot \cos(\Delta \varphi)$  and  $A \cdot \sin(\Delta \varphi)$ , respectively. An additional component of  $\frac{N}{2}$  is factored into the result as a component of accumulation. Because this component exists equally in both DC<sub>1</sub> and DC<sub>2</sub> it can be factored away if the number of accumulation cycles is known. Unfortunately, these terms also contain a summation of cosine and sine which act to skew the correct answer based on when the accumulation is halted. The resulting DC<sub>1</sub> and DC<sub>2</sub> terms will accumulate over time as shown in Figure 2-6 [4].

Figure 2-6: DC<sub>1</sub> and DC2 Versus Time [11]

The slope of each line represents the DC<sub>1</sub> in-phase accumulated value of  $\frac{AN}{2}\cos(\Delta\varphi)$  and the DC<sub>2</sub> out-of-phase accumulated value of  $\frac{AN}{2}\sin(\Delta\varphi)$ . The oscillation in each waveform is a result of the additional erroneous sinusoidal component. In order to obtain the correct measurement, this term must be negated from the calculations. One method for removing this term is to utilize the identity that the summation of all points in the unit circle will equate to zero as shown in Equation 2-16. Therefore, there must be a number of discrete summations *N* of this sinusoidal error factor which result in canceling out this term from both DC<sub>1</sub> and DC<sub>2</sub>.

$$0 = \int_0^{2\pi} cosine(x)\delta x = \int_0^{2\pi} sine(x)\delta x$$

(2-16)

The number of samples *N* which relates to the canceling of this term occurs at the Integer Multiple Period (IMP) of the waveform. This IMP occurs when the waveform crosses the axis after each period. The waveforms are generated using NCOs in the TPG which utilize a phase accumulator. When these accumulators reach their limit and overflow the waveform crosses the origin. The point where the waveform crosses the origin corresponds with an IMP [630]. However, if an overflow occurs and the accumulator contains any value other than zero, then the discrete measured value will contain a measurement past the origin instead of at the origin. The overflow flag of the accumulator as well as the value of zero within the accumulator can be used to signal that an IMP has occurred; a simple circuit can be constructed as shown in Figure 2-7.

Figure 2-7: IMP Detection Circuit for Single Tone Measurement [630]

For tests that require two tones, a slightly modified approach must be taken to obtain the IMP. In a two tone measurement, the results stored in  $DC_1$  and  $DC_2$  contain error based on both the fundamental waveforms and the intermodulation of these waveforms. Therefore the true IMP which will cancel out these terms will occur only when the IMPs of both the fundamental and intermodulation tone occur simultaneously [30].

#### 2.2.3 Analog Functional Measurements Approach

This BIST architecture, utilizing a DDS-based TPG and MAC-based ORA, is capable of performing linearity, frequency response, and noise measurements. These tests allow the performance of the analog circuit to be characterized and compared to design specifications [6]. An overview of how these measurements are conducted within the BIST circuitry is given within this section.

The first of these testable measurements is linearity. The linearity response of a real system is defined by severity of non-linearity, as all real devices inherently contain some degree of non-linearity. The test for linearity involves measuring the Third Order Intercept Point (IP3) under a two tone test input [6]. This product is generated from higher order harmonics of the input tones intermodulating with the original tones to create new frequency content. This is illustrated in the Figure 2-1. Specific points of interest are the frequencies  $2f_{2}$ - $f_1$  and  $2f_1$ - $f_2$ . These represent the two artificially generated products of the IMD which appear closest to the original tones. These two tones in particular are known as the Third Order Intermodulation (IM3) components [4]. The IM3 tones are chosen to define linearity because their proximity to the fundamental tones makes them extremely difficult to filter away. Using these IM3 terms, the Input Referred Intercept Point (IIP3) is defined by Equation 2-17 [4].

$$IIP_{3}[dBm] = \frac{\Delta P[dB]}{2} + P_{in}[dBm]$$

(2-17)

The  $\Delta P$  term represents the difference in power between these IM3 tones and the fundamental tones, and P<sub>in</sub> is the signal power at the input of the device. The intermodulation components of this device can be theoretically calculated using the

Taylor Series approximations. Given that the linearity of interest is that of a non-dynamic input, Taylor Series approximation becomes an ideal representation for nonlinear time-invariant systems. Using the Taylor Series method, the input to analog system, x(t), and the transfer function of the system, y(t), are represented as shown in the following two Equations 2-18 and 2-19 [6].

$$x(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t)$$

(2-18)

$$y(t) = \alpha_0 + \alpha_1 x(t) + \alpha_2 x(t)^2 + \alpha_3 x(t)^3 + \cdots$$

(2-19)

In this case,  $A_1$  and  $A_2$  represent the magnitude of the tones while  $\omega_1$  and  $\omega_2$  represent the two separate frequencies. The symbols  $\alpha_{\#}$  represent the time-invariant coefficients of the Taylor Series expansion [4].

$$y(t) = \frac{1}{2} \alpha_2 (A_1^2 + A_2^2) + \left[ \alpha_1 A_1 + \frac{3}{4} \alpha_3 A_1 (A_1^2 + 2A_2^2) \right] \cos(\omega_1 t) + \left[ \alpha_1 A_2 + \frac{3}{4} \alpha_3 A_2 (2A_1^2 + A_2^2) \right] \cos(\omega_2 t) + \frac{1}{2} \alpha_2 (A_1^2 \cos(2\omega_1 t) + A_2^2 \cos(2\omega_2 t)) + \alpha_2 A_1 A_2 [\cos((\omega_1 + \omega_2)t) + \cos((\omega_1 - \omega_2)t)] + \frac{1}{4} \alpha_3 [A_1^3 \cos(2\omega_1 t) + A_2^3 \cos(2\omega_2 t)] + \frac{3}{4} \alpha_3 \left\{ \begin{array}{c} A_1^2 A_2 [\cos((2\omega_1 + \omega_2)t) + \cos((2\omega_1 - \omega_2)t)] \\+ A_1 A_2^2 [\cos((2\omega_2 + \omega_1)t) + \cos((2\omega_2 - \omega_1)t)] \end{array} \right\}$$

(2-20)

After solving this expression for the component of the fundament term at  $\omega_2$  and the IM3 term at  $2\omega_2 - \omega_1$  and assuming that  $A_1 = A_2$ , then the IIP3 and Output Referred Intercept Point (OIP3) can be obtained from the Taylor Series variables as shown in Equations 2-21 and 2-22 [6].

$$IIP_3 \approx \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \quad , \text{ when } \quad \alpha_1 \gg \frac{9}{4} \alpha_3 A^2 \tag{2-21}$$

$$OIP_3 \approx \alpha_1 IIP_3 \tag{2-22}$$

This technique of measuring linearity relies on the assumption that the test tones and output of the device are relatively small in magnitude such that the device does not become damaged or desensitized [6]. The illustration below in Figure 2-8 shows the relationship between the fundamental tone, IM3 point, and  $\Delta P$ .

Figure 2-8: Illustration of Fundamental Tone Compared to IM3 Tone in IP3 Test [6]

The frequency response is obtained by forcing the TPG to generate a single tone and pass that tone through the DUT. The ORA will then measure the magnitude and phase of the resulting waveform at the frequency of the generated tone. However, this measurement includes the response of not only the DUT, but every component in the measurement path. To negate the effects of the additional components, the test tone is measured a second time. In the second measurement, the DUT is bypassed using an analog multiplexer and the waveform is re-measured. This represents the resulting magnitude and phase from the interaction with all other components within the measurement path. This includes the DAC, smoothing filter, analog multiplexer, and ADC. The resulting difference between these two measurements will represent the frequency response of only the DUT [7]. This procedure can be repeated for different frequencies by sweeping the generated tone and measured tone together. This is illustrated in Figure 2-2. This allows for a measurement of the response over a range of possible frequency values.

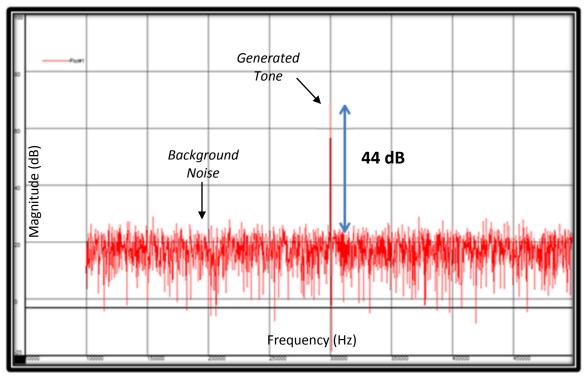

Each noise measurement test begins by forcing the TPG to generate a single tone and passing that waveform through the DUT. The ORA will then calculate a measurement of the signal strength at the fundamental tone [4]. At this point, the test varies based on which of the four noise measurements is being performed. To obtain THD, the ORA will measure the magnitude of harmonic tones which occur at integer frequencies of the fundamental tone, while the TPG continues to generate the fixed fundamental tone. Each of these integer multiple frequencies of the fundamental tone represents a harmonic [20]. The THD can be obtained by taking the ratio of the fundamental tone signal strength to the average of these harmonic noise measurements. To obtain SNR, the ORA will measure the magnitude of frequencies that are not integer multiples of the fundamental tone, while the TPG continues to generate a fixed fundamental tone. This will collect the spectral content of the noise which is not a function of fundamental tone [4]. By averaging these collected noise measurements we obtain the average background noise of the system. The ratio between the signal strength of the fundamental tone and this background noise measurement will be the result of the SNR [20]. The measurement of SINAD, involves the combination of the tests for SNR and THD. Rather than selectively choosing measurement points which contain only a certain type of noise, SINAD selects all measurement points to include in the noise calculation with the exception of the fundamental tone. The SINAD can be obtained by taking the ratio of the fundamental tone signal strength to the average of the noise

measurement points [20]. An illustration of SNR, THD and SINAD can be seen in Figure 2-3.

The NF measurement represents a very important measurement to the device. Measurements of SNR, THD, and SINAD represent the ratio of signal strength to noise strength of the entire measurement path which includes the DAC and ADC. The NF measurement represents the degradation in SNR due to the DUT alone [20]. The NF test represents the longest of the noise tests, because this test requires the SNR to be measured twice. The first SNR measurement is of the DUTs output response. This represents the SNR of the complete path including the DUT. The second SNR measurement involves bypassing the DUT in the measurement path [4]. This can be performed using the analog multiplexor, MUX3, as illustrated in Figure 2-4 to bypass the DUT. By taking the ratio of these two measurements as described in Equation 2-2, the NF can be obtained [24].

## 2.3 Multipliers

Multipliers make up the core of the ORA. A multiplier is a binary circuit which utilizes a combination of logic elements and adder units to implement a multiplication operation on two binary numbers called the multiplier and multiplicand. The basic construction of a multiplier has two parts. The first stage is the generation of the partial products. The second stage is the summation of these partial products to produce the final result [29]. Multipliers are typically differentiated by their implementation of the first stage.

There are many common types of multiplier designs. Array multipliers represent the simplest class of multipliers consisting of a simple array of logical *AND* gates to

generate the partial products and full adders to implement the addition of each partial product row [29]. The fundamental shortcoming of this multiplier is that it is intended for unsigned multiplication. A simple modification is required to transform this multiplier for signed mathematics. By negating the upper most significant bits (MSB) of each partial product and the highest order partial product, the array multiplier is transformed into a Baugh-Wooley multiplier capable of signed multiplication [29]. These two multipliers represent the simplest designs, but both multipliers suffer from long calculation time and high area overhead. These two multipliers have been superseded by an improved multiplier known as the Modified-Booth multiplier.

The Modified-Booth multiplier seeks to reduce the overall size of the multiplier by exploiting patterns in the multiplier and multiplicand inputs to generate half the number of partial products as the Baugh-Wooley multiplier. The Modified-Booth algorithm is based on the fact that a radix-4 multiplier will require half the number of partial product stages as a radix-2. The Booth algorithm examines the contents of the multiplier register input and seeks to reduce the number of partial product rows required by logically combining partial products before they are generated [28]. Within the partial products of a standard signed multiplier, each partial product row can have only one of two possible values. These two values are either the multiplicand or all zeros. The Booth algorithm encodes possible radix-4 combinations in an entity called the Booth recoder [28]. This coded instruction is then applied to these reduced partial products as shown in Table 2-2.

| Multiplier bits |          |                   | Booth Code |    |    | Instruction              |  |  |  |

|-----------------|----------|-------------------|------------|----|----|--------------------------|--|--|--|

| $X_{2N+1}$      | $X_{2N}$ | X <sub>2N-1</sub> | S          | M2 | M1 | Value of Partial Product |  |  |  |

| 0               | 0        | 0                 | 0          | 0  | 0  | Multiplicand x 0         |  |  |  |

| 0               | 0        | 1                 | 0          | 0  | 1  | Multiplicand x 1         |  |  |  |

| 0               | 1        | 0                 | 0          | 0  | 1  | Multiplicand x 1         |  |  |  |

| 0               | 1        | 1                 | 0          | 1  | 0  | Multiplicand x 2         |  |  |  |

| 1               | 0        | 0                 | 1          | 1  | 0  | Multiplicand x -2        |  |  |  |

| 1               | 0        | 1                 | 1          | 0  | 1  | Multiplicand x -1        |  |  |  |

| 1               | 1        | 0                 | 1          | 0  | 1  | Multiplicand x -1        |  |  |  |

| 1               | 1        | 1                 | 1          | 1  | 1  | Multiplicand x -0        |  |  |  |

Table 2-2: Booth Recoding Bits Decoded

The Booth recoder then takes these coded bits, and uses a binary shift and invert operation to reconstruct the partial products. After the Booth algorithm is complete, there are only half the original partial products [28].

The Modified-Booth multiplier modifies the number of partial product bits to improve the performance of the multiplier, but this is not the only method to improve performance. The next technique is known as Wallace tree reduction. The Wallace tree reduction method relies on cleaning up the inefficiency when adding partial product bits to improve calculation speed [28]. In a serial arrangement of accumulation of the partial products, each partial product is serially added to the next partial product after it. This results in *N* partial products consuming *N-1* addition stages. Wallace tree reduction attempts to reduce the long computation time of accumulating these partial products by adding multiple partial product factors together simultaneously rather than sequentially. The Wallace tree reduction method is designed to reduce the number of partial products to two final rows. These two remaining partial products can then be summed together using any number of fast adder approaches [28]. Illustrated in Figure 2-9 is an example of how rearranging partial product addition stages can reduce the calculation time. Figure 2-9 (a) shows a serial summation of products resulting in a worst case path of three adders, but Figure 2-9 (b) rearranges these adders to result in a worst case path of two adders.

Figure 2-9: Illustration of Rearranging Partial Product to Decrease Worst Case Path

## 2.4 Coordinate Rotation Digital Computing Algorithm

The Coordinate Rotation Digital Computer (CORDIC) algorithm is a well known iterative approximation technique to perform various arithmetic operations. The algorithm is very simple to implement in hardware, because it uses only shift-and-add or shift-and-subtract operations to perform vector rotation in a two dimensional plane [29]. By using successive approximation the CORDIC algorithm can approximate the most basic mathematical functions. The most common use of the CORDIC algorithm is in approximating trigonometric functions [28]. The CORDIC algorithm can be broken into three distinct groups. The distinguishing factor of each group is how the CORDIC successive approximation function is implemented [29].

Linear CORDIC – This CORDIC design is capable of expressing linear functions such as multiplication, division, addition, and subtraction. In this method the correction factor that is applied to each successive approximation remains constant. This allows it to be able to express linear operations [28].

- Circular CORDIC This CORDIC design is capable of expressing trigonometric functions which can be expressed around the unit circle. Functions such as sine, cosine, tangent, arctangent, arcsine, arccosine, and square root can be expressed. In this method, the successive approximation is a factor of the arctangent function. This allows for circular functions to be expressed [28].

- Hyperbolic CORDIC This CORDIC design is used for representing hyperbolic, logarithmic, and exponential functions. The hyperbolic CORDIC utilizes an inverse hyperbolic tangent function when performing a successive approximation. This allows for the expression of exponential and logarithmic based operations [28].

The basic operational theory of the CORDIC algorithm is that the CORDIC will approximate a two dimensional vector. To obtain this vector, the CORDIC will start at 0 degrees rotation and attempt to reach a goal of either phase or magnitude. Before each rotation, the CORDIC will be able to measure if it overshot or has not yet reached its goal [29]. Depending on this, it will either add or subtract the next rotation information from the current approximation. Each successive approximation in the circular CORDIC algorithm rotates by:

$$Rotation \ added(N) = \tan^{-1}(2^{-N})$$

(2-23)

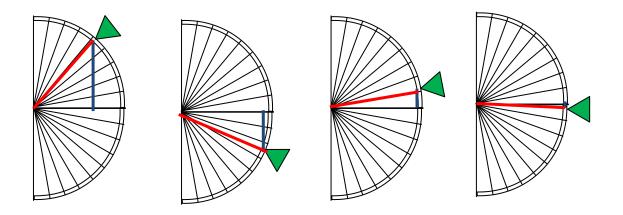

In this estimation, the variable N represents  $N^{th}$  rotation in the series. As evident by this formula, as the number of rotations is increased, the step size of the higher order rotations represents a decreasing amount of change. The illustration in Figure 2-10 represents the CORDIC algorithm attempting to reach a phase of 65 degrees.

Figure 2-10: Illustration of CORDIC Rotational Procedure

In this example, the red arrow illustrates the fixed goal of 65 degrees, while the green represents the current CORDIC estimation. On the first attempt in Figure (a), the CORDIC begins at 0 degrees. The CORDIC is able to ascertain that it has not yet reached the goal of 65 degrees, so it adds the first rotational increment of 90 degrees shown in Figure (b). This estimate overshoots the goal of 65 degrees. Because the CORDIC has passed the goal, it must now take measures to change the direction of the next phase increment. This causes the CORDIC to subtract the next phase rotation of 45 degrees shown in Figure (c). This process is repeated in Figure (d) where it adds the third rotational phase giving it a current phase of 71 degrees. This process will continue to become more accurate as it successively approximates the measurement until a fixed number of rotations has been achieved by the CORDIC.

The CORDIC algorithm for linear, circular, and hyperbolic functions can all be combined into the unified CORDIC model [29]. In the unified CORDIC model, the approach is simplified into one vector V with three components X, Y, and Z. The vector components X and Y represent the projection of the vector V into the two dimensional xyplane. The third component, Z, represents the angle of the vector with respect to the X

axis. For each successive approximation, the value of these components can be expressed as shown in Equation 2-24 [29].

$$V_{i+1} = \begin{cases} x_{i+1} = x_i - m\sigma_i 2^{-S(m,i)} y_i \\ y_{i+1} = y_i + \sigma_i 2^{-S(m,i)} x_i \\ z_{i+1} = z_i - \sigma_i \alpha_{m,i} \end{cases}$$

(2-24)

For each of the three CORDIC models, the CORDIC mode parameter m,

rotational direction  $\sigma_i$ , shift sequence S(m, i), and rotational angle  $\alpha_{m,i}$  used in the definition of the unified CORDIC algorithm can be expressed as shown in Equations 2-25 through 2-28 [29].

$$m = \begin{cases} 0 & \text{For Linear CORDIC} \\ 1 & \text{For Circular CORDIC} \\ -1 & \text{For Hyperbolic CORDIC} \end{cases}$$

(2-25)

$$\sigma_i = \begin{cases} sign(Z_i) & \text{For Linear CORDIC} \\ sign(X_i + Y_i) & \text{For Circular CORDIC} \end{cases}$$

(2-26)

$$S(m,i) = \begin{cases} 0,1,2,3,4,5,\cdots & m=1\\ 1,2,3,4,5,6,\cdots & m=0\\ 1,2,3,4,4,5,\cdots & m=-1 & \text{repeated at } \frac{3^{i+2}-1}{2} \end{cases}$$

(2-27)

$$\alpha_{m,i} = \frac{1}{\sqrt{m}} \arctan\left[\sqrt{m} \cdot 2^{-S(m,i)}\right]$$

(2-28)

Using these equations, the unified CORDIC model can be completely constructed for either the linear, circular, or hyperbolic model. The CORDIC algorithm however has three major disadvantages. The first disadvantage is the speed of calculation. The CORDIC relies on a method of successive approximation. After each pass through the CORDIC calculation, the results become more accurate [29]. Unfortunately, it requires multiple iterations until the output of the CORDIC calculation begins to approximate the correct value within a reasonable margin of accuracy. The second disadvantage also occurs due to the successive approximation. This method will continuously approach the correct value, but never obtain the true value [29]. The third disadvantage in the CORDIC approach appears because of the successive shifting vector rotation. With each rotation, a successively decreasing amount of error is added to the result. This error is based solely on the number of rotations taken to achieve the result. This error can be expressed as shown in Equation 2-29, where *N* represents the number of rotations [28].

$$Error(N) = \prod_{n=0}^{N} \sqrt{(1 + m\sigma_i^2 2^{-2*S(m,i)})}$$

(2-29)

## 2.5 Thesis Restatement

This chapter has presented previous work on mixed-signal BIST using SSA [4]-[12]. This will become the foundation for the topic of this thesis, which includes the implementation of on-chip measurement techniques within the mixed-signal design and the automated generation of this BIST approach.

To achieve these ends, this thesis will focus on the design of the model required to produce these measurements. This thesis will present a new multiplier model which will reduce the size from conventional multipliers as well as increase the speed of calculation. Another goal of this thesis will be to introduce a technique to automatically generate a hardware description language for this mixed-signal BIST design. Finally, this thesis will present a method for calculating on-chip the results of the tests listed in this chapter utilizing a CORDIC based calculation unit.

## Chapter Three

#### Mixed-Signal Built-In Self-Test Implementation

Implementing this mixed-signal Built-In Self-Test design requires the conceptual design to be capable of being expressed in hardware. This is usually achieved using a Hardware Description Language (HDL), which is a language that can be used to express hardware circuit elements for simulation and physical realization of the circuit. One of the most common forms of HDLs is known as Very High Speed Integrated Circuit Hardware Description Language (VHDL). Once this mixed-signal Built-In Self-Test design has been physically implemented from the VHDL, it can then be integrated with the intended analog components and the analog circuit to be tested.

This chapter will discuss the improvements to the implementation of the mixedsignal Built-In Self-Test for analog circuits. The topics covered include automatically generating the hardware descriptive model based on user-defined system performance parameters, producing sinusoidal waveforms in a digital core using a hardware description language which lacks trigonometric operators, and constructing an Output Response Analyzer using an improved multiplier design.

## 3.1 Program Generation

This mixed-signal BIST approach can be utilized in multiple applications; therefore there is a need to develop a method to generalize the model so that it can be implemented to fit multiple instances with differing requirements. In most HDLs, some form of parameterization is possible. This allows for HDL structures to be reconfigured based on the requirements of the application. However, some HDL structures prove too complex to be completely parameterized for all applications. Attempting to parameterize these complex models can result in a hardware description that is too difficult to verify proper operation due to the large number of conditional synthesis statements required to create a universalized model.

This thesis proposes a solution to the potential complexity of parameterizing this mixed-signal BIST approach by implementing a customized program designed to automatically generate the hardware description model given a set of user-defined system parameters. This program, *MSBISTGen.exe*, written in the C programming language is capable of generating the required VHDL models to implement the digital portion of mixed-signal BIST design; this includes the Test Pattern Generator, Output Response Analyzer, and test controller of the BIST design. Given user-defined requirements for the implementation of the design, this C program is also capable of generating the VHDL model to meet these design goals.

The mixed-signal BIST approach described in this thesis can be utilized in many applications, but the components which comprise the hardware model will remain relatively similar within each instance of this BIST model. The design will contain multiple NCOs for the TPG, multipliers and accumulator for the ORA, and multiplexers

to control the datapath as shown in Figure 2-4. However, based on the intended application, priority of the hardware implementation of this BIST design may focus on runtime of the tests, precision of measurements, or area resource consumption. Maximizing these design requirements can be achieved by altering key attributes such as the resolution of the DDS-based TPG or implementation of the Multiplier Accumulator pairs which comprise the ORA. However, by exploiting the fact that the majority of these components remain unchanged between implementations, we can use exact models for these unchanged elements in each design using this mixed-signal BIST. For those components to be altered based on specific system characteristics or other user parameters, the customized program can be used to insert, remove or modify portions of the hardware description to accommodate any changes.

| Mixed-Signal BIST                                                                                                                                                  | Generator                                                                                                                                                                                                                                                                                                            | Program                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device (FPGA/ASIC):<br>Communication:                                                                                                                              |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                  |

| -TPG                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |