# Development of a GPS Software Receiver on an FPGA for Testing Advanced Tracking Algorithms

by

W. Luke Edwards

A thesis submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Master of Science

Auburn, Alabama August 9, 2010

Keywords: GPS, software receiver, FPGA, vector tracking, deep integration

Copyright 2010 by W. Luke Edwards

## Approved by:

John Hung, Co-Chair, Professor of Electrical and Computer Engineering

David Bevly, Co-Chair, Philpot-WestPoint Stevens Associate Professor of Mechanical

Engineering

Victor Nelson, Professor of Electrical and Computer Engineering

#### Abstract

In this thesis, the development of an FPGA-based software GPS receiver with a special focus on advanced tracking algorithms is developed. The particular algorithms of note in this thesis are in a class known as vector tracking algorithms. Vector tracking GPS algorithms boast an increased immunity to interference and jamming and the ability to perform at low signal-to-noise  $(C/N_0)$  ratios. Addition of an inertial device to the vector tracking algorithm is known as deep integration and further boosts these benefits.

A trade study is presented that compares different hardware platforms for an embedded real-time system. An FPGA is chosen based on its ability to combine all of the necessary functions on a single device and its ability to seque a FPGA logic design to an application-specific integrated circuit (ASIC). Implementation details of each different component that constitutes a GPS receiver are given. In the single system, three soft-core microprocessors are synthesized on the FPGA to compute various components of the GPS algorithm, and their interfacing to other custom logic and to each other is described. The operation of each of the custom GPS logic modules is outlined in detail. Hardware resource utilization and computational timing results are also given. This thesis shows that a preliminary design of a real-time embedded GPS receiver capable of vector tracking is feasible, but there are more improvements to be made before deep integration is successful in real time.

## Acknowledgments

I would like to first and foremost give every single ounce of credit to my Heavenly Father, the Lord Jesus Christ. He has been completely faithful to me in this process and throughout my life, and I have done absolutely nothing to deserve His grace in my life. My wife, Kristen, has been wonderful throughout the past two years as I have had to put many long hours into this research and thesis, and I could not have done it without her help and encouragement. I would like to thank my family and friends who have been so supportive, encouraging, and flexible with our strange schedules. I would like to particularly thank Dr. David Bevly for his time, encouragement, and mentoring while I have had the privilege of working under him. The financial support that I have received through Dr. Bevly has been such an incredible blessing, keeping me and my wife from having to take out further student loans. Other members of the GAVLAB have also been instrumental in the progression of this research. Dr. Nelson and Dr. Hung have also always been available for their technical expertise and career decisions, and I owe them both a huge debt of gratitude. I would like to particularly thank Ben Clark for his eagerness and willingness to join this project with me. I have personally never seen someone as driven, intellectual, systematic, and devoted to his friends and his work as I have of Ben. He has been an enormous blessing to me, in and out of work. Brad Dutton has also been an amazing source of knowledge dealing with FPGAs and their implementations. Much of this work would not have been possible without his help.

## Table of Contents

| Abstrac | et                                           | ii  |

|---------|----------------------------------------------|-----|

| Acknow  | rledgments                                   | iii |

| List of | Figures                                      | vii |

| List of | Tables                                       | ix  |

| 1 In    | troduction                                   | 1   |

| 1.1     | Motivation                                   | 1   |

| 1.2     | Vector Tracking and Deep Integration         | 1   |

| 1.3     | Software Receivers                           | 2   |

| 1.4     | Field-Programmable Gate Array                | 2   |

| 1.5     | Contributions and Outline                    | 3   |

| 2 G     | PS Signal Structure                          | 5   |

| 2.1     | Modulation Techniques                        | 5   |

| 2.2     | Transmitted and Received Signals             | 7   |

| 2.3     | C/A Code Details                             | 8   |

|         | 2.3.1 C/A Code Generation                    | 10  |

| 2.4     | Data Bits                                    | 11  |

| 2.5     | Utilization of the GPS Signal                | 14  |

| 3 O     | verview of a Typical GPS Receiver            | 15  |

| 3.1     | RF Front End                                 | 15  |

| 3.2     | Acquisition                                  | 17  |

|         | 3.2.1 Serial Search Acquisition              | 18  |

|         | 3.2.2 Parallel Code Phase Search Acquisition | 20  |

| 3.3     | Signal Tracking                              | 22  |

|   |             | 3.3.1     | Basics of a Phase-Locked Loop               | 22 |

|---|-------------|-----------|---------------------------------------------|----|

|   |             | 3.3.2     | Costas Loop                                 | 23 |

|   |             | 3.3.3     | Basics of a DLL                             | 25 |

|   |             | 3.3.4     | Entire Tracking Loop                        | 27 |

|   | 3.4         | Positio   | on Solution                                 | 27 |

|   |             | 3.4.1     | Calculating Pseudoranges                    | 29 |

|   |             | 3.4.2     | Calculating User Position from Pseudoranges | 30 |

|   |             | 3.4.3     | Determining User Velocity                   | 32 |

|   | <b>3.</b> 5 | Vector    | Tracking and Deep Integration Algorithms    | 33 |

|   |             | 3.5.1     | Traditional Receiver Operation              | 34 |

|   |             | 3.5.2     | Vector Tracking Receiver Operation          | 35 |

|   |             | 3.5.3     | Vector Tracking Algorithm Details           | 36 |

|   |             | 3.5.4     | Predicting Doppler Frequency and Code Phase | 37 |

|   |             | 3.5.5     | Deep Integration                            | 38 |

| 1 | So          | ftware l  | Receiver Platform Trade Study               | 41 |

|   | 4.1         | Microp    | Drocessor                                   | 42 |

|   | 4.2         | Digital   | l Signal Processor                          | 43 |

|   | 4.3         | Field-I   | Programmable Gate Array                     | 43 |

|   |             | 4.3.1     | FPGA as a Real-time Platform                | 44 |

|   |             | 4.3.2     | System on Chip Design                       | 46 |

|   |             | 4.3.3     | Prototyping ASIC Design                     | 47 |

| 5 | $R\epsilon$ | eceiver A | Architecture                                | 48 |

|   | 5.1         | Softwa    | re Architecture                             | 49 |

|   |             | 5.1.1     | Scalar Processor                            | 51 |

|   |             | 5.1.2     | Vector Processor                            | 52 |

|   |             | 5.1.3     | IMU Processor                               | 53 |

|   |             | 5.1.4     | Interprocessor Communication                | 53 |

| 5 <b>.</b> 2 | Hardware Architecture                                |                                                    |    |  |

|--------------|------------------------------------------------------|----------------------------------------------------|----|--|

|              | 5.2.1                                                | Acquisition                                        | 54 |  |

|              | 5.2.2                                                | Scalar Tracking Channels                           | 55 |  |

|              | 5.2.3                                                | Vector Tracking Channels                           | 55 |  |

|              | 5.2.4                                                | GPS Counter                                        | 57 |  |

|              | 5.2.5                                                | PPS Generator                                      | 58 |  |

|              | 5.2.6                                                | Memory Mappings                                    | 58 |  |

|              | 5.2.7                                                | System I/O and Clock Domains                       | 59 |  |

| 6 Co         | mputa                                                | tional Results                                     | 61 |  |

| 6.1          | Hardw                                                | vare Results                                       | 61 |  |

| <b>6.</b> 2  | Softwa                                               | are Results                                        | 62 |  |

| 7 Co         | onclusio                                             | ns and Future Work                                 | 67 |  |

| 7.1          | Conclu                                               | usions based on Computational Results              | 68 |  |

| 7.2          | Propo                                                | sed Low-Cost, High Performance Solution            | 69 |  |

|              | 7.2.1                                                | Separating High Frequency Operations from Baseband | 69 |  |

|              | 7.2.2                                                | Finding a Replacement FPGA                         | 70 |  |

|              | 7.2.3                                                | Replacing Microblazes with an External Processor   | 71 |  |

|              | 7.2.4                                                | Other Potential Replacement Options                | 73 |  |

| 7.3          | Future                                               | e Work                                             | 73 |  |

| Bibliogr     | aphy                                                 |                                                    | 75 |  |

| Append       | Appendix - Software Receiver using Model-based Tools |                                                    |    |  |

## List of Figures

| 2.1           | BPSK Modulation                                                                          | 5  |

|---------------|------------------------------------------------------------------------------------------|----|

| 2.2           | QPSK Modulation                                                                          | 6  |

| 2.3           | Autocorrelation of PRN 1 with no time shift (left) and 500-chip shift (right)            | 9  |

| 2.4           | Cross-correlation of PRN 1 and PRN 2                                                     | 9  |

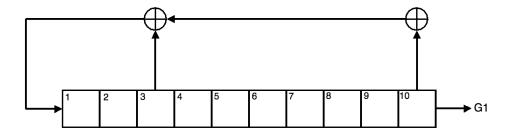

| 2.5           | Shift register generator for G1 $(G1 = 1 + x^3 + x^{10})$                                | 11 |

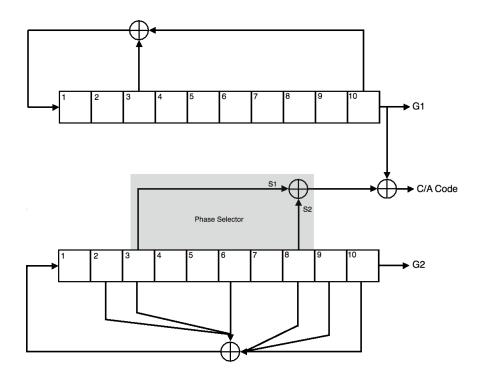

| 2.6           | Entire C/A code generator                                                                | 12 |

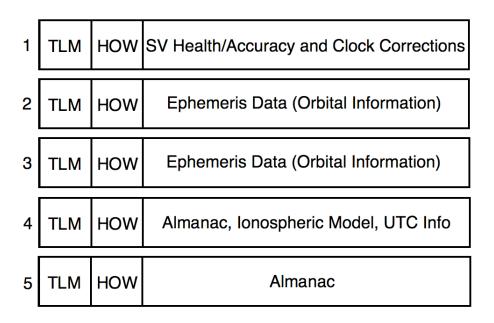

| 2.7           | Navigation Data Message                                                                  | 13 |

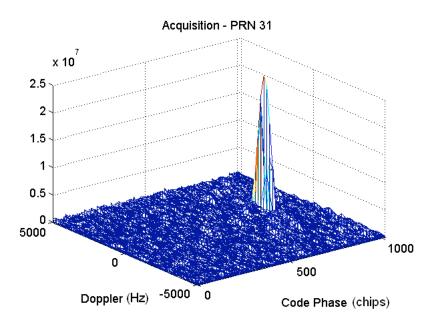

| 3 <b>.</b> 1  | 3D plot of acquisition results                                                           | 18 |

| 3.2           | Serial search acquisition block diagram                                                  | 19 |

| 3.3           | Parallel code phase search acquisition                                                   | 21 |

| 3.4           | Basic PLL block diagram                                                                  | 22 |

| 3.5           | Costas loop block diagram                                                                | 24 |

| 3 <b>.</b> 6  | Basic delay-locked loop block diagram                                                    | 25 |

| 3.7           | Triangular autocorrelation function with early, prompt, and late outputs                 | 26 |

| 3.8           | Combined tracking loop with carrier [blue] and code [green] feedback $\ \ldots \ \ldots$ | 28 |

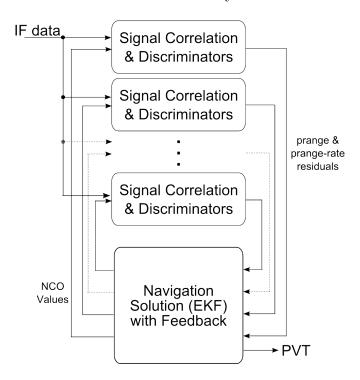

| <b>3.</b> 9   | Block diagram of the traditional receiver scalar tracking loop architecture              | 34 |

| 3.10          | Block diagram of the vector tracking receiver loop architecture                          | 35 |

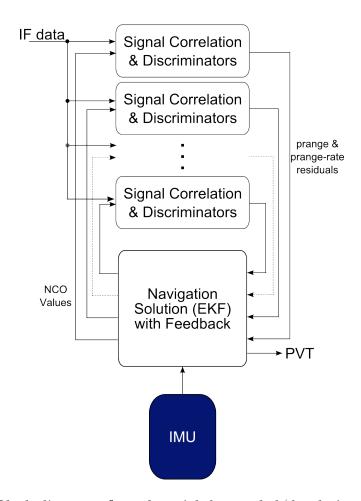

| 3 <b>.</b> 11 | Block diagram of an ultra-tightly coupled/deeply integrated system $\ \ldots \ \ldots$   | 39 |

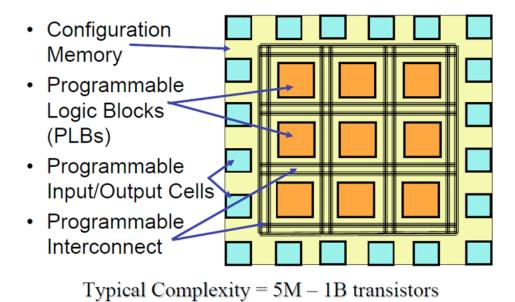

| 4.1           | FPGA overview [44]                                                                       | 44 |

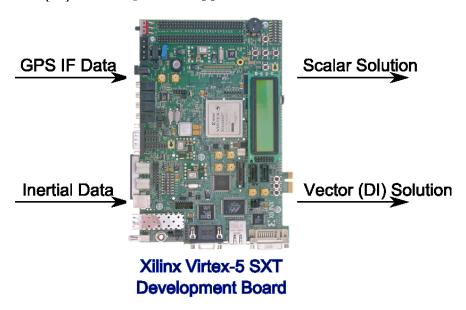

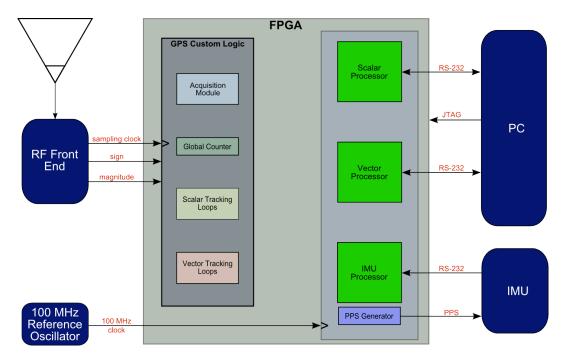

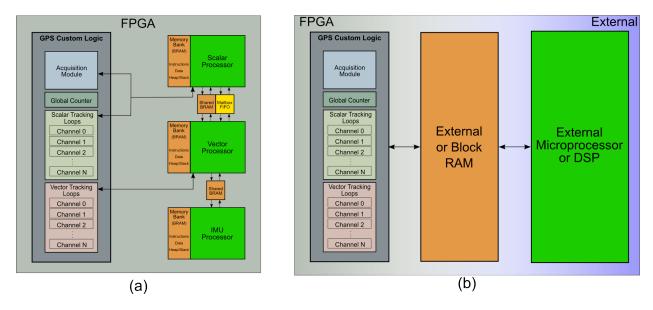

| 5.1           | Proposed hardware solution for combining scalar and vector/deeply integrated GPS/INS     | 48 |

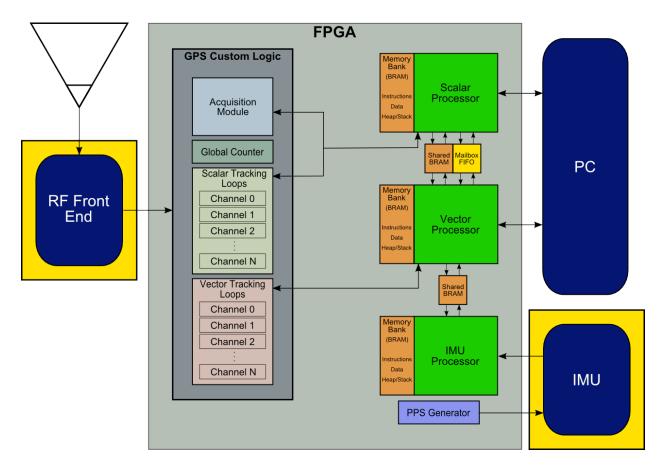

| <b>5.</b> 2  | Block diagram of proposed system                                                                       | 50 |

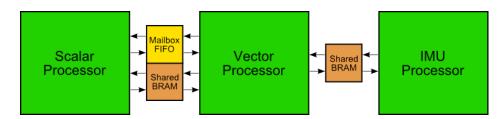

|--------------|--------------------------------------------------------------------------------------------------------|----|

| 5.3          | Block diagram of all processors and their interprocessor communication mechanisms                      | 51 |

| 5.4          | Block diagram of serial acquisition module                                                             | 55 |

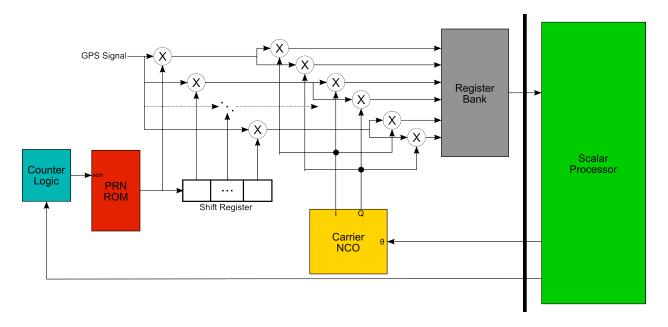

| 5.5          | Block diagram of scalar tracking loop/channel                                                          | 56 |

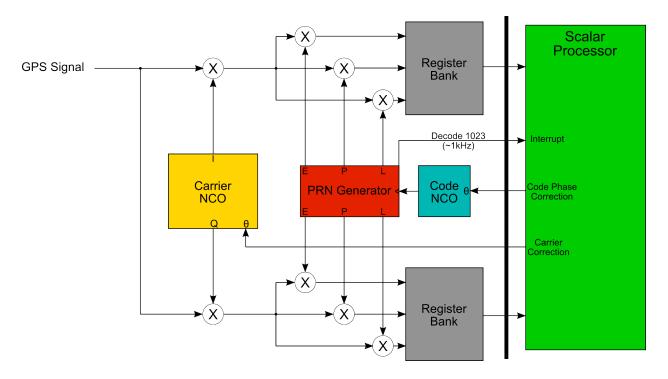

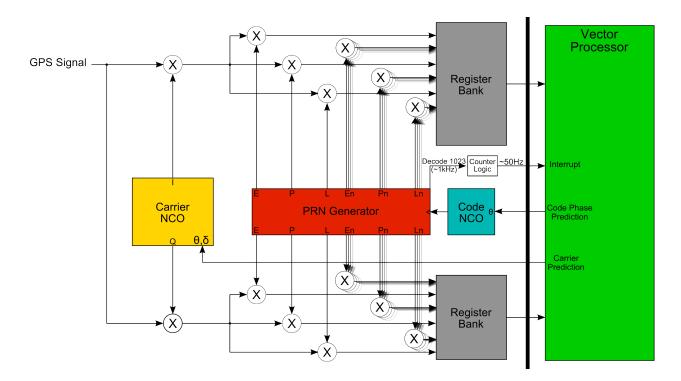

| 5 <b>.</b> 6 | Block diagram of vector tracking channel                                                               | 57 |

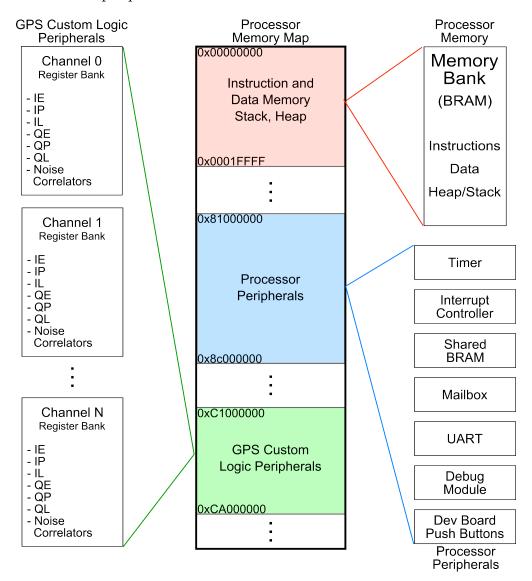

| 5.7          | Memory map for the vector processor                                                                    | 59 |

| <b>5.</b> 8  | Block diagram of the FPGA I/O and clock domains                                                        | 60 |

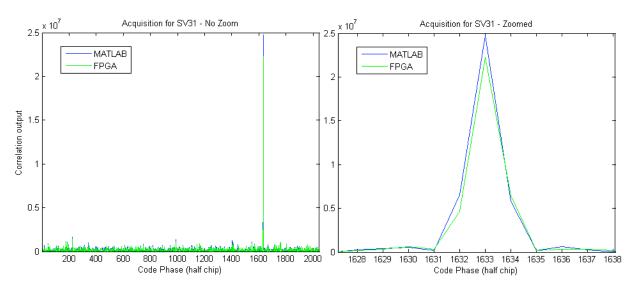

| 6.1          | Serial search acquisition module results in MATLAB and FPGA (using ModelSim)                           | 62 |

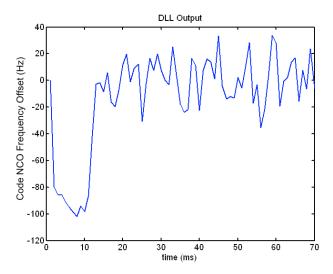

| 6.2          | Scalar processing simulation - delay locked loop output                                                | 63 |

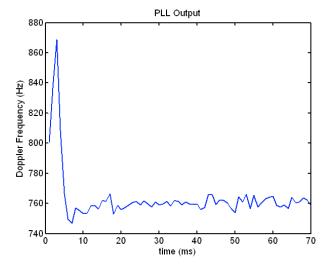

| 6.3          | Scalar processing simulation - phase locked loop output                                                | 63 |

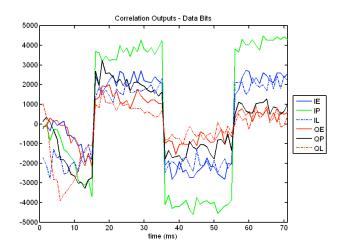

| 6.4          | Scalar processing simulation - correlator outputs                                                      | 64 |

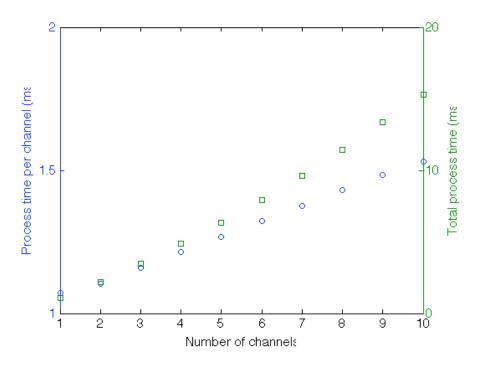

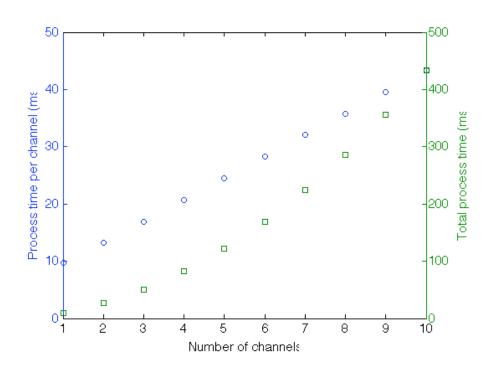

| 6.5          | Graphical representation of (asynchronous) vector tracking timing results                              | 65 |

| 6.6          | Graphical representation of (asynchronous) deep integration timing results $$ .                        | 66 |

| 7.1          | Comparison of (a) fully integrated design as described in thesis versus (b) proposed segregated system | 70 |

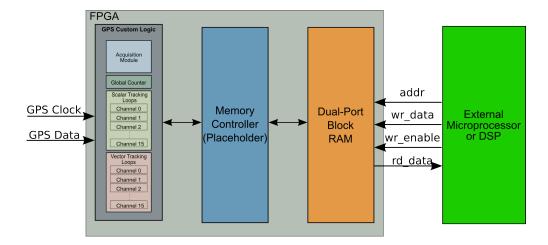

| 7.2          | Block diagram of the proposed hardware changes                                                         | 72 |

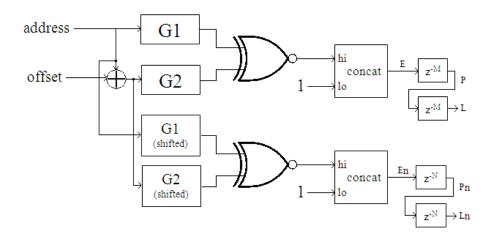

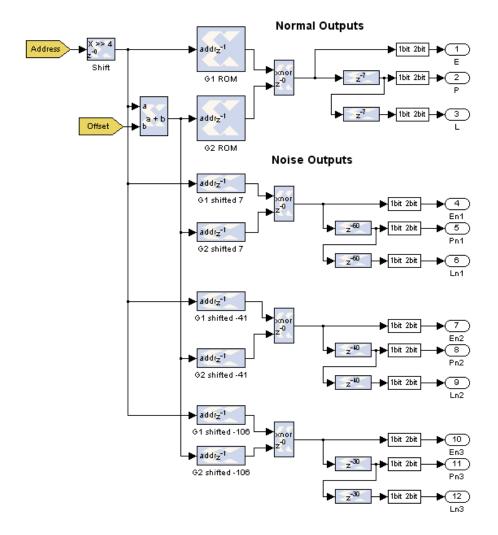

| A.1          | Block diagram of PRN generation for normal and noise correlator banks                                  | 81 |

| A.2          | PRN generation for normal and noise correlator banks using model-based tools                           | 82 |

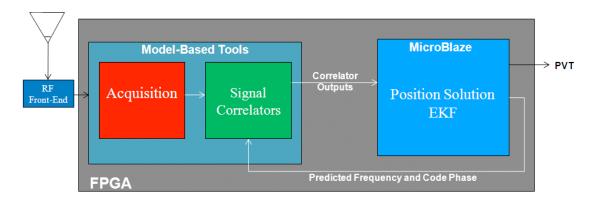

| A.3          | Block diagram of FPGA GPS receiver using model-based tools                                             | 84 |

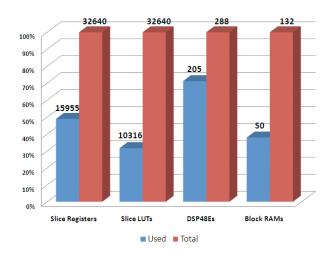

| A.4          | Single vector tracking correlation channel resource usage                                              | 86 |

| A.5          | 8-channel vector tracking receiver resource usage (without acquisition module)                         | 86 |

## List of Tables

| 3.1          | Observed output values on hardware front end                                      | 16 |

|--------------|-----------------------------------------------------------------------------------|----|

| 3.2          | Common Costas loop discriminators [24]                                            | 25 |

| 3 <b>.</b> 3 | Common Code Phase Discriminators [7]                                              | 27 |

| 6 <b>.</b> 1 | Resource utilization for 8-channel system using Virtex-5 SXT50T FPGA $$           | 61 |

| 6.2          | Vector processor real time feasibility analysis using 6-channel receiver baseline | 64 |

| 6 <b>.</b> 3 | Vector tracking (asynchronous) timing results                                     | 65 |

| 6.4          | Deep integration (asynchronous) timing results                                    | 66 |

| A.1          | Functions and sizes of matrices used                                              | 83 |

| A.2          | Resources used for PRN generation using presented technique                       | 85 |

| A.3          | Comparison of time elapsed between FPGA and MATLAB/C implementation               | 88 |

## Chapter 1

#### Introduction

### 1.1 Motivation

Since its inception, the Global Positioning System (GPS) has continued to become more and more ubiquitous. Applications in the commercial sector such as car and marine navigation devices, handheld hiking units, and running watches are commonly used by a number of different people to meet many different needs. Military uses include battlefield logistics, target tracking, and missile guidance. Research is currently being conducted that even uses GPS to guide unmanned vehicles through dangerous territory.

In most of these military applications, there is an undeniable need for a GPS receiver to supply precise, uninterrupted measurements that are immune to jamming. Relaying ground troop position coordinates and precise missile navigation are two notable instances that must be accounted for. GPS is a notably weak signal and is easily occluded by urban canyons and dense foliage. For these reasons and many others, it is important to have a GPS receiver in the field that can withstand these challenging scenarios.

## 1.2 Vector Tracking and Deep Integration

One method to deal with these difficulties is found in vector tracking algorithms. Vector tracking algorithms have been studied for the past two and a half decades [43]. The main advantages of vector tracking include an increased immunity to jamming, an ability to function in low signal-to-noise ratios, and, with inertial aiding, good performance in high dynamics. A GPS receiver that combines a vector tracking algorithm with an inertial measurement unit (IMU) is known as ultra-tight coupling or a deeply integrated (DI) system.

The inertial measurements used in DI systems increase the immunity to receiver dynamics and jamming even further. There has been a good deal of progress in the area of DI systems in the past few decades, but much of this success has been limited to post-processed data or non-embeddable real-time solutions. In order to use these very beneficial algorithms in the field, an embedded GPS receiver that supports vector tracking and deep integration must be designed.

### 1.3 Software Receivers

Since the late 1990s, researchers have studied the power and usefulness of a software-defined GPS receiver [3]. A software-defined GPS receiver, like any other software defined radio, is useful as a testing platform because it can be reconfigured any number of times in any number of ways. Defining the receiver implementation in software also allows explicit control over almost every signal passing through the system. A software platform like this opens up many opportunities to explore new algorithms and to test existing algorithms with little extra effort. Software receivers are normally run on a PC, DSP, or maybe a combination of both. In the past few years, there has been an increased interest in using the field-programmable gate array (FPGA) technology as a real-time software receiver platform [9, 29, 34].

## 1.4 Field-Programmable Gate Array

A field-programmable gate array (FPGA) contains many inherent qualities that make it an ideal platform for achieving this real-time performance. It offers the possibility of high parallelism, speed comparable to an application specific integrated circuit (ASIC), a large number of inputs/outputs (I/O), reprogrammability, and a great deal of design flexibility. An FPGA consists of programmable logic blocks (PLBs), input/output, and interconnects. At any time, an FPGA can be configured to have a specific system function. The system function is determined by activating some or all of the I/O pins, assigning certain logic

functions to the PLBs, and using the interconnects to route information to/from the I/O and PLBs.

An FPGA was chosen as the implementation device for this software receiver because of its practicality as both a testing device and a final product. The main advantage of having an FPGA during testing is the fact that it is reconfigurable. Normally, one or many application-specific integrated circuits (ASICs) are used to build a commercial GPS receiver, but creating an ASIC for a design that needs to be reconfigured and verified multiple times is unrealistic and very costly. In fact, FPGAs are often used as a prototyping platform for designing ASICs. As a practical implementation device, an FPGA is a good choice due to its parallel processing capability, speed, and lack of need for a host PC or separate DSP for co-processing.

#### 1.5 Contributions and Outline

Research in the general area related to this thesis has been mostly limited to seveal different categories. Some work describes the vector tracking and deep integration algorithms themselves [43]. Other research has been performed to compare the validity and performance gain of these algorithms [28, 35, 37]. A few different formulations of the deep integration techniques have been published along with their supposed performance benefits [5, 12]. Software receivers with their application to GPS began to be studied in the late 1990's [3]. There have since been numerous publications describing different GPS software receivers that are used for many different applications [7, 23, 25, 32, 22]. A few researchers have used an FPGA as a standalone hardware platform for a software receiver [34, 39, 13], and some have also used the model-based tools discussed later in this thesis [38, 8]. A very recent paper describes a real-time implementation of a deeply integrated GPS/INS device on a personal computer platform [26].

Besides the published works of the author [16, 17], there are currently no documented attempts of achieving real-time performance of these algorithms on an embedded platform. The goal of this thesis is to discuss the implementation details of a preliminary hardware/software architecture that uses a single FPGA to implement these advanced tracking algorithms. Hardware and software details of a hardware description language-based design will be presented. Timing performance and resource utilization will also be examined. This research is important because real systems which use vector tracking or deep integration are likely to be power, size, and cost-limited. A low-power, small-footprint, and cost-efficient receiver must be designed in order to meet these needs. However, designing embedded devices that meet these needs is complicated in themself, especially when these devices are constrained to real-time performance.

Specific contributions detailed in this thesis are a trade study of different hardware platforms to implement a real-time embedded GPS receiver, a prototype system built using an FPGA, and some preliminary timing and resource utilization results of the prototype system. Chapter 2 provides an overview of the GPS signal structure. Because of the nature of the vector tracking algorithm, the designer cannot take only the position and velocity output of a commercial GPS receiver. Instead, the designer must access the GPS signal immediately after it is sampled by a hardware front end's analog to digital converter (i.e. the bit-level). Chapter 3 describes the hardware and software processes of a typical GPS receiver. Each part of the receiver is duplicated in the proposed hardware platform, so it is important to have an understanding of these functions. Chapter 4 is a trade study of different potential hardware platforms that can be used to implement this embedded real-time receiver with a focus on the chosen platform (FPGA). Chapter 5 describes the prototype system which uses hardware description languages to model its fundamental GPS functions. The prototype uses a 32-bit microprocessor that is synthesized into the FPGA fabric to perform the receiver's baseband functions. This microprocessor is programmed using C and C++. Chapter 6 gives some preliminary timing results and a report of the resource utilization for the prototype. This chapter also summarizes the contributions of this thesis and makes suggestions for future work regarding this research.

## Chapter 2

## GPS Signal Structure

In order to design a full-fledged software GPS receiver, it is necessary to understand the GPS signal structure sent from each satellite vehicle (SV) and received by the user equipment.

## 2.1 Modulation Techniques

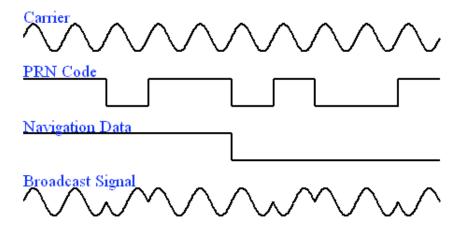

The GPS signal employs a modulation technique called Binary Phase Shift Keying (BPSK), which takes an RF carrier and either leaves it unmodified or reverses the phase of the signal by  $180^{\circ}$  based on a bipolar signal ( $\pm 1$ ) [24]. This effectively means that wherever the bipolar signal changes from a +1 to a -1 or vice versa, the RF carrier reverses its direction. Figure 2.1 shows an example of BPSK modulation with two bipolar signals, PRN code (defined later) and navigation data.

Figure 2.1: BPSK Modulation

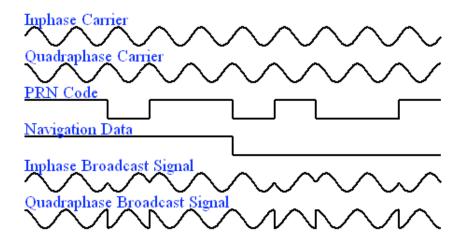

In actuality, the GPS signal uses this same idea in a modulation technique called Quadrature Phase Shift Keying (QPSK). The 180° phase shift modulation is the same, but the difference lies in the fact that QPSK gives two separate outputs - the original modulated carrier (known as the in-phase component) plus another modulated carrier that is 90° out of phase from the first signal (quadra-phase) [24]. These can be thought of as sine and cosine outputs of a waveform generator. Figure 2.2 shows an example of QPSK modulation.

Figure 2.2: QPSK Modulation

The GPS signal structure relies heavily on a modulation technique known as Direct Sequence Spread Spectrum (DSSS). This extends the idea of BPSK by using a high-rate spreading signal known as a Pseudo-random noise (PRN) waveform to spread the signal over a wider bandwidth [30, 24]. Generation and properties of this PRN waveform will be discussed later, but it is important to note that the PRN sequence is periodic and must be known a priori in order to use. Each bit in the PRN sequence is called a chip, and the rate that the code is transmitted is known as the chipping rate. The purpose of DSSS is twofold [24]:

- 1. To make precise ranging possible

- 2. To allow multiple satellites to broadcast on the same frequency using a technique known as code division multiple access (CDMA)

CDMA is especially important to GPS because it allows the receiver to distinguish between the different satellites in view at any particular time [24].

## 2.2 Transmitted and Received Signals

Equation (2.1) gives the signal received by an antenna in a receiver (neglecting transmitted signal power).

$$s(t) = C(t)D(t)cos(2\pi f_{L1}t + \phi_{L1}) + P(Y(t))D(t)sin(2\pi f_{L1}t + \phi_{L1})$$

$$+P(Y(t))D(t)sin(2\pi f_{L2}t + \phi_{L2})$$

(2.1)

Frequencies  $f_{L1}$  and  $f_{L2}$  represent the L1 and L2 carrier frequencies (1575.42MHz and 1227.60MHz, respectively) that are in the dedicated GPS band frequency range [7]. Signals C(t) (coarse acquisition) and P(Y(t)) (precise encrypted) are the aforementioned code spreading waveforms for the civilian and military signals, respectively. Because the GPS receiver designed in this thesis uses only the civilian band signal, the high frequency P(Y) code and L2 bands are filtered out and are no longer considered. After filtering, the data is converted into some intermediate frequency (IF). This process will be discussed in Section 3.1, but it is enough for now to understand that the incoming signal to the software receiver is in the form of Equation (2.2) (again, neglecting signal power) [30].

$$s_i(t) = C(t + \delta_i)D(t + \delta_i)\cos(2\pi(f_{IF} + f_{dopp_i})t + \phi_i)$$

(2.2)

where i represents the ith satellite that is currently in view of the receiver.

The received signal looks very similar to the transmitted signal from each satellite with a few exceptions. The signal is still BPSK-modulated by the C/A code and data bit signals, but the carrier frequency has been downconverted to some intermediate frequency  $(f_{IF})$  and is offset by a Doppler frequency that is unique for each satellite. This Doppler frequency

offset is a function of the relative motion between the user and the particular satellite vehicle in question. This effect is well documented in many communications textbooks and is a very important concept for GPS for determining user velocity [11]. The term  $\phi_i$  is the phase offset between the transmitted and received signal frequencies. The phase of the signal (and therefore the frequency) is usually tracked by a phase-locked loop (PLL) in the receiver hardware [7]. The term  $\delta_i$  is the code phase of the C/A code. This quantifies the time-alignment of the received C/A code and is used for determining precision ranges to each satellite [24].

## 2.3 C/A Code Details

The coarse acquisition (C/A) code is a critical aspect of the GPS signal and must be explored in further detail. It is transmitted only on the L1 frequency at a "chipping rate" of 1.023MHz (each bit in the sequence is called a chip). The C/A code sequence repeats every 1023 chips, which corresponds to a sequence period of 1ms. The purpose of the C/A code is twofold [24]:

- 1. To allow multiple satellites to broadcast on the same carrier frequency

- 2. To acquire precise ranging information to each satellite

As discussed previously, the C/A code BPSK-modulates the GPS signal and is used as a direct sequence spread spectrum (DSSS) signal; that is, one of its purposes is to widen the bandwidth of the received signal. The C/A codes were carefully chosen from a family of pseudo-random noise (PRN) sequences known as Gold codes [19] because of the following two properties:

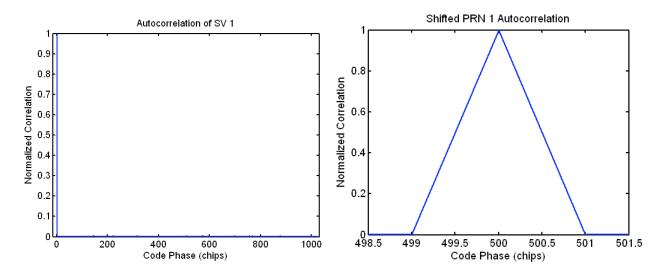

1. Autocorrelation with identical signal only when time-aligned (Figure 2.3) [7]

$$r_{kk}(m) = \sum_{b=0}^{1022} C_k(b) C_k(b+m) \approx 0$$

for  $|\mathbf{m}| \neq 0$

Figure 2.3: Autocorrelation of PRN 1 with no time shift (left) and 500-chip shift (right)

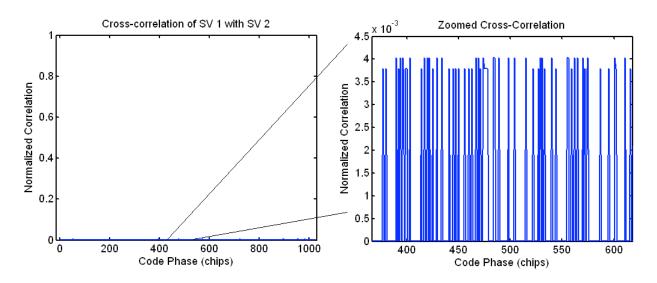

2. Cross-correlation with other Gold codes  $\approx 0$  (Figure 2.4) [7]

$$r_{jk} = \sum_{b=0}^{1022} C_j(b) C_k(b+m) \approx 0$$

for all m

Figure 2.4: Cross-correlation of PRN 1 and PRN 2

This is very important for both of the C/A code purposes mentioned above. First, each of the satellites broadcasts a unique C/A code which is orthogonal to every other satellite's C/A code. Due to this orthogonality, a GPS receiver can determine which satellites are in view of the receiver with near certainty. This process, called signal acquisition, will be outlined in Section 3.2. These Gold code properties (along with DSSS) help to fulfill the second purpose of the C/A code: precise ranging. "De-spreading" the C/A code is accomplished by multiplying the incoming signal by the C/A code in a process called signal tracking that will be described in Section 3.3. When "de-spreading" the C/A code to read off the data bits, the code must be perfectly time aligned; that is, the code phase must be correct between the received signal and the generated replica code [24]. Once the code phase is known, it can be compared to every other visible satellite's code phase to see which satellite is closest to the receiver and compute a position accordingly. This process will be outlined in the position calculation section (Section 3.4).

## 2.3.1 C/A Code Generation

As mentioned before, each satellite's C/A code is unique. However, because they all belong to the same family of Gold codes, they use the same generation scheme. The C/A code generator employs two linear feedback shift registers (LFSRs) called G1 and G2. Each of these shift registers is 10-bits wide and generates a repeating 1023-chip long pattern. The linear feedback portion of G1 and G2 is characterized by the polynomials in Equations (2.3) and (2.4) which correspond to the "tap settings" for that shift register [7].

$$f_{G1}(x) = 1 + x^3 + x^{10} (2.3)$$

$$f_{G2}(x) = 1 + x^2 + x^3 + x^6 + x^8 + x^9 + x^{10}$$

(2.4)

Each of these "taps" is fed into an exclusive-or (XOR) gate which is then fed back into the first position of the shift register. This concept is illustrated for G1 in Figure 2.5.

Figure 2.5: Shift register generator for G1 ( $G1 = 1 + x^3 + x^{10}$ )

Test pattern generation for built-in self test (BIST) platforms use this same technique to generate pseudo-random test patterns [1].

G1 and G2 both output their respective 1023-chip sequences repeatedly, so in order to create unique sequences for each satellite, G2 is shifted by a unique number of chips and then modulo-2 added (using an XOR operation) to G1. This can be done one of two different ways. First, the full 1023-chip G1 and G2 sequences can be generated and then modulo-2 added together, or second, a selection of two different registers called the phase selection can be applied to G2 and then modulo-2 added to G1 [7]. The first option can be chosen when hardware resources can be sacrificed to enjoy simplicity. The second option can be employed when logic space (or program memory) must be conserved, but it comes with a higher degree of complexity. A third option is to generate all of the C/A sequences a priori; this uses the largest amount of resources but requires the least amount of algorithmic complexity. The second option is most commonly done to save resources, and is depicted in Figure 2.6.

### 2.4 Data Bits

As mentioned before, data bits transmitted by each satellite BPSK-modulate the outgoing signal. The purpose of these data bits is to give clock corrections and precise orbital information called ephemeris data which allow a receiver to calculate the satellite's position and velocity at any given time [30, 7, 24]. These data bits are transmitted every 20ms (50Hz)

Figure 2.6: Entire C/A code generator

and each bit begins exactly at the start of a C/A code sequence. A data bit is 20 times longer than the 1ms C/A code sequence.

The data structure is organized into fifty frames with five subframes each. Each of the subframes contains 300 bits organized in ten 30-bit words. Since the data rate is 50Hz, the entire data structure takes 12.5 minutes to complete before cycling through again [7]. Subframes 1, 2, and 3 repeat the same information for all 50 frames. A single frame of the GPS data structure is pictured in Figure 2.7.

Subframe 1 contains satellite clock correction terms (to correct for relativistic effects) and satellite health information [24]. Subframes 2 and 3 contain information regarding that particular satellite's orbital parameters. This is known as the ephemerides or ephemeris data. This includes harmonic data and other orbital parameters that, when processed, yield a very accurate solution of the satellite's position and velocity. Knowing this data with high precision will, in turn, yield a high precision user position. The other two subframes contain information known as almanac data [24]. This holds information about the entire

Figure 2.7: Navigation Data Message

constellation of satellites and rough estimates of where each of them are at a given point in time. This knowledge is often used by GPS receivers to facilitate a warm start, whereby the receiver begins with some knowledge of which satellites will be in view and their approximate locations when the receiver is initially powered on, making it possible to obtain a solution more quickly. This is one method of reducing the time to first fix, or TTFF.

Each subframe begins with a telemetry (TLM) and handover word (HOW). The TLM contains a known 8-bit sequence called the preamble that is used to synchronize the frame data and also to determine which satellite is closest in distance to the receiver [7]. It is because the TLM is repeated every subframe that the GPS receiver does not take 12.5 minutes to initialize. The HOW contains a truncated version of the time of week (TOW) and a few other flags. The time of week is used to measure when particular data frames were sent from the satellite.

## 2.5 Utilization of the GPS Signal

Many of the concepts about the GPS signal structure have been discussed in this chapter. The main purpose of a GPS receiver is to give accurate position and velocity of the user. In order to do this, the GPS signal must be properly processed by the user equipment. In order to demodulate the data bits in each signal, three important signal elements must be known [3, 24].

- 1. Satellites currently in view at the receiver antenna

- 2. Code phase of each C/A code for satellites in view

- 3. Doppler frequencies of each satellite in view

If, for a particular satellite in view, the code phase and Doppler frequencies are tracked perfectly, the data bits in the signal become accessible. Once these data bits are accessible for at least four satellites, a position solution can be calculated. The next chapter outlines the detailed hardware and processing modules of a typical GPS receiver that accomplish the above tasks.

## Chapter 3

## Overview of a Typical GPS Receiver

### 3.1 RF Front End

As mentioned in Section 2.2, the L1 (civilian band) GPS signal is transmitted at a carrier frequency of 1.57542 GHz, but signal processing at such a high frequency is very difficult with current technology [7, 3]. For this reason, a hardware device known as a GPS front end is used to shift the L1 frequency signal down to a more manageable rate. This is accomplished in the front end with a series of filters, downconverters, and an analog-to-digital converter (ADC). The purpose of filtering is to attempt to eliminate all of the unusable portions of the incoming signal. That is, since the usable portion of the signal lies within a particular bandwidth and the antenna is not ideal, the filter selects only that part of the signal that contains GPS data and attenuates the rest [7]. The goal of downconversion is to take the aforementioned high frequency L1 signal and shift it into an intermediate frequency (IF) that can be handled by the ADC. The ADC takes digital samples of the analog signal that will be used by a subsequent processing unit.

The hardware front end provides data and clock signals to whatever component that interfaces it. The clock that is provided is the sampling clock at which the data bits are sampled. The data signals are the digital bits on the output of the ADC, and the width of the data depends on how many bits are used to quantize the data. For this research, 2-bit quantization is used and follows a standard sign and magnitude convention as shown in Table 3.1[40].

Due to the nature of the GPS signal, it is often advantageous to only use one-bit quantization (outputs  $\pm 1$ ) [46]. Even with the signal downconverted to some intermediate frequency, a large amount of signal processing is still required. Using only one bit reduces

Table 3.1: Observed output values on hardware front end

| Sign | Magnitude | Output Value |

|------|-----------|--------------|

| 0    | 0         | +1           |

| 0    | 1         | +3           |

| 1    | 0         | -1           |

| 1    | 1         | -3           |

the incoming data rate by 100%, requires smaller memories, and uses less resources when executing arithmetic operations. However, two-bit quantization gives a higher degree of accuracy for reconstructing the original signal (an effective 1.41dB gain) [42]. This can potentially lead to higher signal integrity and therefore more accurate results.

There are two main hardware front end chips which are popular in the software GPS receiver community. The first and older of the two is the Zarlink GP2010/2015 chip family. This uses 2-bit quantization (sign/magnitude) with an intermediate frequency of 4.309 MHz and a sampling clock of 5.714 MHz [52, 53]. This particular front end is useful for digital signal processors and software receivers that require a low sampling rate. In contrast, one of the more modern front end chips is the SiGe 4110L/4120L. This chip employs 2-bit quantization at an IF of 4.092 MHz and a sampling frequency of 16.3676 MHz, although these values are configurable to suit different applications [40]. The 4110L is touted as a high sensitivity GPS-only device while the 4120L claims to be the world's first GPS/Galileo ready receiver [40]. This research uses the SiGe 4110L as the hardware front end.

It can be noted that any front end chip that uses more than one data bit, such as the SiGe 4110L used in this research, can reduce the signal bandwidth by taking only the sign bit of the quantized data. This effectively reduces the signal from a multi-bit ADC to a one-bit ADC.

## 3.2 Acquisition

Once the high frequency signal has been converted to digital samples by the front end, the software receiver begins the next stage of the process; this stage is called signal acquisition. The purpose of signal acquisition is three-fold [30]:

- 1. Find which satellites are in view from the current GPS antenna position

- 2. Obtain a rough estimate of code phase for observed satellites

- 3. Obtain a rough estimate of Doppler frequency for observed satellites

These rough estimates are used in the subsequent stage of signal processing (tracking). There are many different approaches to finding these rough estimates [7]. First, a serial search over all possible code phases and Dopplers can be performed. This can take the longest amount of time, but has a very low complexity. A second method called a parallel frequency space search acquisition method is also available. This searches all of the frequencies simultaneously (using a Fourier transform) and searches each code phase serially. Because of the Fourier transform, implementation is more complex than the purely serial approach. The third and final option is called parallel code phase search acquisition. This method searches all of the code phases simultaneously by using multiple Fourier transforms, while the Doppler frequencies are searched serially. This approach is much more complicated than the other two, but is the most time-efficient. Due to the resource intensity of this method, much research has been done to mitigate the complexity of these algorithms [15, 39]. The first and third acquisition options will be discussed in this thesis. The second option is not discussed because this method is not typically seen in software receivers; this is perhaps because the frequency resolution is poor compared to the other two methods [7].

The acquisition search space consists of at least 1023 code phases (one for each chip) and several kHz of Doppler offset. For an illustrative purpose, half-chip code phase spacing (totaling 2046 possibilities) and a Doppler bin that spans  $\pm 5000$  Hz from the center (IF)

frequency in increments of 200 Hz is used (for a total of 51 different total Doppler frequency bins) on data collected from a front-end data recorder. Figure 3.1 shows a plot of the entire search space for satellite 31 using the serial search. An obvious peak at a Doppler of +800Hz and code phase of about 820 chips can be seen. The z-axis is the output value of the integrate and dump operation for 1ms of data.

Figure 3.1: 3D plot of acquisition results

## 3.2.1 Serial Search Acquisition

The first acquisition method is known as serial search acquisition [24]. The reason it is called a serial search is because, given no additional information, each possible code phase and Doppler must be independently searched. The code phase is typically searched in half-chip intervals (totaling 1023\*2 = 2046 total code phase bins). The Doppler frequency must be searched in predefined increments around the intermediate frequency. The Doppler search increment spacing is based on expected signal to noise ratio  $(C/N_0)$ , a measure of how much a signal is corrupted by noise); the worse the expected  $C/N_0$ , the smaller the frequency increments that must be searched [24]. Also, the range on either side of the IF that must be searched depends on the expected user dynamics. The higher the receiver dynamics, the

higher the potential Doppler effect [11]. In high dynamic situations, a typical Doppler search increment is about 10kHz around the center frequency. However, for this example, a normal dynamic situation is assumed, and therefore a range of  $\pm 5$  kHz will be used with a 200Hz increment. This corresponds to 51 total Doppler bins  $(2\frac{5000}{200} + 1)$ . Therefore, in order to search every code phase and Doppler possibility sequentially, a total of 2046\*51=104,346 different correlations must be performed.

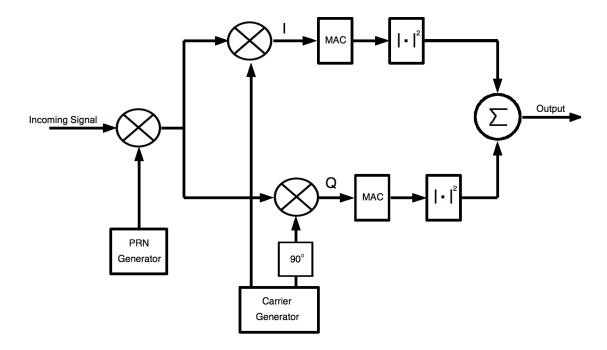

This is a straightforward approach to the signal acquisition problem illustrated in the block diagram found in Figure 3.2. The incoming signal is multiplied by the generated C/A code which is then multiplied by the in-phase and quadra-phase portions of the local oscillator. Over a predetermined period (called the predetection time), the generated signal is integrated by both phases of the oscillator. In order to get an accurate picture of signal strength, both sides are squared and then summed together [7]. At this point, the output is compared to some threshold that determines whether or not a satellite is detected at that code phase and Doppler [24].

Figure 3.2: Serial search acquisition block diagram

If only one of these serial search modules is used, it can take a considerable amount of time to find the correct code phase and Doppler combination. One potential technique to improve acquisition time is to use multiple signal correlators. For example, instead of multiplying a single code phase by a particular Doppler frequency, three different code phases can be used, potentially improving the acquisition speed by three times. Many modern receivers are cited to use thousands of correlators in order to improve signal acquisition time [18]. Another technique that can improve the complexity of the correlators is to use only the sign bit of the incoming signal (1-bit ADC). This requires far fewer hardware resources than a 2-bit multiplier.

Serial search acquisition is mainly used by application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA) GPS devices. This is because the parallel processing capabilities of these types of hardware can easily implement a large array of correlators at relatively little hardware cost. The more advanced parallel code phase search acquisition algorithm is usually done on microcontroller-driven software receivers.

## 3.2.2 Parallel Code Phase Search Acquisition

The parallel code phase search acquisition approach reduces the total search space and computation time as compared to the serial search method, but this comes at the cost of overall complexity [7]. In the serial search, every half-chip must be searched separately, resulting in 2046 total separate code phase bins. As the name suggests, the parallel code phase search acquisition approach searches all of the code phases simultaneously. This effectively means that the number of search iterations is reduced by a factor of 2046, which is a drastic improvement. In the example above, the code phases are completely searched every iteration, and only the 51 Doppler bins must be independently checked. This amounts to a maximum total of 51 different combinations.

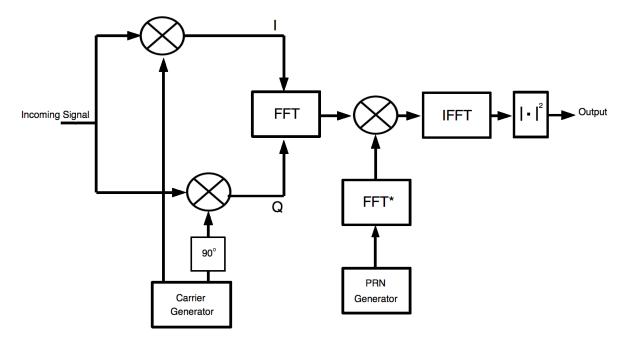

This functionality is made possible by computing this cross-correlation in the frequency domain [7]. Figure 3.3 is a block diagram of this functionality. A fast Fourier transform

(FFT) is used to convert time-domain signals to the frequency domain. This method takes the discrete fast Fourier transform of both the carrier-wiped input (the incoming raw signal modulated by the carrier replica) and the C/A code, conjugates the C/A code branch, and then multiplies the two together. An inverse fast Fourier transform is used to shift the entire system back to the time domain. This method of cross-correlation in the frequency domain is well understood in digital signal processing [31]. Once the system is back to the time domain, the absolute value of the output is squared to get an accurate estimate of signal power. This signal power is compared to a threshold in order to determine if a signal is present at the Doppler being search [24]. The output will peak at the proper code phase that the signal lies within.

Figure 3.3: Parallel code phase search acquisition

Because the fast Fourier transform is a discrete signal processing technique, the size of the FFT is based on the number of samples in the predetection time. In a system with a sample clock of 16.3676 MHz, there are about 16,368 samples per millisecond. In ASIC or FPGA design, the ability to perform a fast Fourier transform on a single 16,368-sample input is very hardware-demanding because there needs to be a large number of hardware multipliers

[31]. This acquisition method requires two fast Fourier transforms, one inverse fast Fourier transform, and other control hardware; therefore it is a very resource intensive approach in these types of hardware. In contrast, this method is very well suited for software receivers that are run on microprocessors. The ability to store large amounts of data in memory and then operate on them sequentially is very beneficial for these types of systems.

## 3.3 Signal Tracking

The purpose of the tracking stage of the GPS receiver is to fine-tune the Doppler frequency and code phase of the incoming signal for a particular satellite [7]. In doing this, the C/A code modulation is removed, the carrier is wiped off, and the data bits become accessible. This information is all that is needed to determine the pseudorange (discussed in Section 3.4) and therefore the user position.

## 3.3.1 Basics of a Phase-Locked Loop

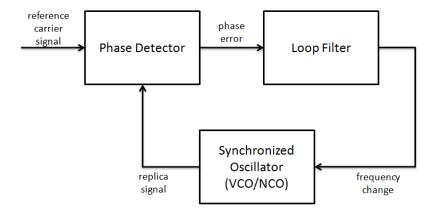

Figure 3.4: Basic PLL block diagram

The phase-locked loop (PLL) shown in Figure 3.4 is the foundation of a tracking loop and includes three basic parts [6]. The first part of the PLL is a synchronized oscillator. This oscillator generates a replica of the system's carrier (or intermediate) frequency based on its inputs. In practice, this oscillator is usually voltage-controlled (taking an analog voltage

as its input) or numerically-controlled (using discrete data points as the input). The next part of the phase-locked loop is the phase detector. This component compares the reference signal with the output coming from the synchronized oscillator. Comparing the two involves multiplying the replica and reference signals together. If the phase and frequency match, the carrier wave is essentially "wiped off" except for a high frequency component (which will be filtered out). This can be seen from the trigonometric product-to-sum identity in Equation (3.1).

$$cos(\theta)cos(\psi) = \frac{1}{2}[cos(\theta - \phi) + cos(\theta + \phi)]$$

(3.1)

At this point, the phase error in the signal has been detected and the high frequency duplicate must be filtered out. This is usually a low-pass filter, taking multiple error signals from the phase discriminator as its input and filtering out the high frequency noise to give a more accurate picture of the error [7]. In practice, this is accomplished by integrating the signal over a certain period of time, amounting to a series of multiply and accumulate operations. Once the signal has been filtered, the outputs are sent to the loop filter. The loop filter, as previously mentioned, converts this error into a form that the synchronized oscillator understands. Based on the phase error, the synchronized oscillator will increase or decrease its frequency to better match the reference. This closes the loop and provides precise frequency information to the navigation processor.

## 3.3.2 Costas Loop

Recall from Section 2.1 that both the ranging codes and the data message use QPSK modulation. This means that anytime the bit changes from a 1 to a 0 (or a 0 to a 1), both sinusoidal signals shift in phase by 180°. If a normal phase-locked loop were used, the synchronized oscillator would suddenly receive information that the signal that it is attempting to replicate suddenly changed by 180°[30]. This would cause very erratic behavior when trying to match the phase.

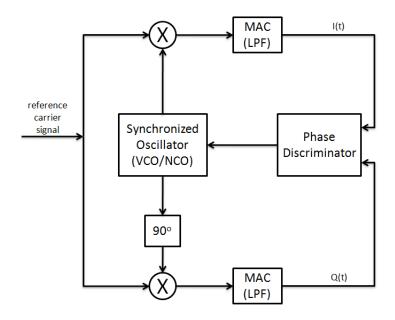

Figure 3.5: Costas loop block diagram

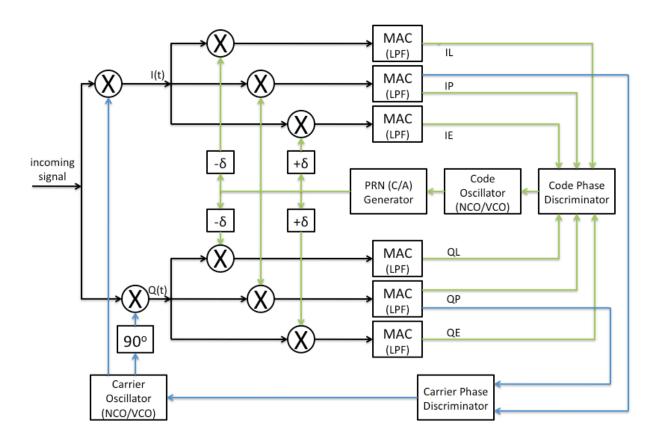

Because of this potential 180° shift, a modified PLL called a Costas loop is used as shown in Figure 3.5. The Costas loop splits the incoming signal into two branches (spaced 90° apart) [6]. The two branches are called the I (in-phase) and Q (quadrature) branches. Each branch contains independent components of a PLL, but they are joined together at the phase discriminator. The carrier replica is multiplied by the reference and then low-pass filtered in both branches. The outputs of each of the low-pass filters in each branch are sent into an advanced loop filter known as the phase discriminator. This part is responsible for calculating the error in phase between the replica and real signal using both branches of the Costas loop. There are a number of different phase discriminators that could be used (see Table 3.2), and each of them has advantages and disadvantages in terms of complexity and accuracy. In practice, the most commonly used discriminator is the 2-quadrant arctangent function [24].

For GPS, a predetection integration period of 1ms to 20ms is used. This means that data is collected and integrated for that length of time. Choosing the integration period depends on how well the signal is currently being tracked. Loosely-locked signals favor the shorter

Table 3.2: Common Costas loop discriminators [24]

| Name                  | Discriminator           | Output Error |

|-----------------------|-------------------------|--------------|

| Classic Analog        | $Q_PI_P$                | $sin(2\phi)$ |

| Decision-directed     | $Q_P sign(I_P)$         | $sin\phi$    |

| Tangent               | $\frac{Q_P}{I_P}$       | $tan\phi$    |

| 2-Quadrant Arctangent | $atan(\frac{Q_P}{I_P})$ | $\phi$       |

predetection integration times so that the filter can react to sharp changes, while tightly tracked signals favor the longer predetection integration times. Once the integration takes place, both branches of the Costas loop send the final result to the arctangent discriminator that was discussed above. The output of the carrier phase discriminator must be converted into a form that the synchronized oscillator understands. This depends on the discriminator output and the type of oscillator that is being used.

## 3.3.3 Basics of a DLL

Figure 3.6: Basic delay-locked loop block diagram

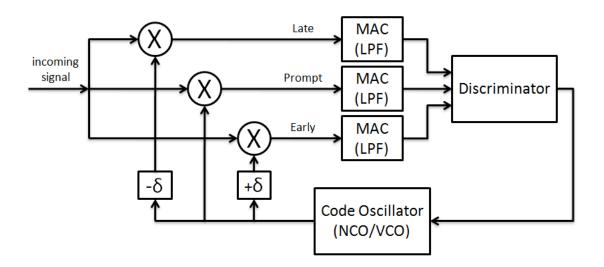

A delay-locked loop, or DLL, is a modified version of a PLL and is used to track the code phase of the C/A code. A picture of a DLL that is used in GPS code tracking loops can be found in Figure 3.6. The DLL operates as follows. First, the received Gold code is split up into three branches - prompt, early, and late. The prompt branch provides the best

estimate of the phase/delay of the Gold code in the received signal. The early branch is spaced  $\delta$  chips in front of the prompt branch, and the late branch is spaced  $\delta$  chips behind the prompt branch. The variable  $\delta$  is called the correlator spacing and carries a typical value of 1/2 chip. These three replicas are created for both the in-phase (I) and quadrature (Q) branches, resulting in a total of six replicas.

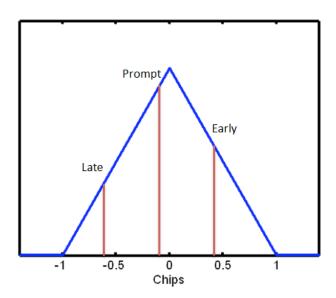

Recall from Section 2.3 that the autocorrelation of the Gold codes is at its maximum when the reference and replica Gold codes are time-aligned. From that center point, the correlation reduces linearly in magnitude until it reaches almost pure noise. This triangular-shaped correlation is illustrated in Figure 3.7. The early, prompt, and late outputs of the DLL are also shown in the figure for purposes of illustration.

Figure 3.7: Triangular autocorrelation function with early, prompt, and late outputs

The DLL, using the six replicas, nominally spaced 1/2 chip apart, serve to track the maximum peak of that triangular-shaped correlation. Because of this triangular shape, the early and late replica must essentially be equal in order for the prompt replica to match up with the correlation peak [7]. There are a number of different types of code phase discriminators that perform this function, and they each have their advantages and disadvantages

in terms of complexity and accuracy. Table 3.3 outlines several of the most commonly used code phase discriminators used in GPS.

Table 3.3: Common Code Phase Discriminators [7]

| Name                        | Type         | Discriminator                                                                 |

|-----------------------------|--------------|-------------------------------------------------------------------------------|

| Early-Late                  | Coherent     | $I_E - I_L$                                                                   |

| Early-Late Power            | Non-Coherent | $(I_E^2 + Q_E^2) - (I_L^2 + Q_E^2)$                                           |

| Normalized Early-Late Power | Non-Coherent | $\frac{(I_E^2 + Q_E^2) - (I_L^2 + Q_E^2)}{(I_E^2 + Q_E^2) + (I_L^2 + Q_E^2)}$ |

| Dot Product                 | Non-Coherent | $I_P(I_E - I_L) + Q_P(Q_E - Q_L)$                                             |

The output of these discriminators must usually be normalized and then converted to a form that controls the rate of the Gold code generator. This rate is controlled by a local oscillator (either NCO or VCO). The DLL follows the same predetection time parameters as discussed in Section 3.3.2.

## 3.3.4 Entire Tracking Loop

For GPS, the carrier-tracking PLL (Costas loop) and code-tracking DLL must be combined into a single structure. This structure has the form of Figure 3.8. Combined, the carrier frequency of the system is tracked in conjunction with the code phase [7]. Keeping a lock on each of these enables the GPS receiver to obtain the data bits needed to calculate GPS position.

## 3.4 Position Solution

After first finding a rough estimate of the Doppler frequency and code phase, the tracking stage makes fine adjustments to those estimates and the final output is the data bits in the signal. Using these data bits and the properties of how they are sent allows a receiver to determine its position and velocity.

Figure 3.8: Combined tracking loop with carrier [blue] and code [green] feedback

## 3.4.1 Calculating Pseudoranges

A pseudorange is the line of sight vector from a satellite to the receiver. The reason that it is known as a "pseudo" range is because a clock bias term is also found in the range measurement [43].

Only a few items within the data message need to be found in order to calculate a correct pseudorange from each satellite. At the beginning of each subframe in the telemetry (TLM) word is what is called a preamble [7]. The preamble is 10001011 (or 01110100 depending on how the data bit polarity is defined). At the rising edge of the first bit of the preamble, the clock reading is captured in a variable called z-count [43]. Each satellite is synchronized with each other to a common GPS time, so the data messages are being transmitted almost simultaneously. This means that the time it takes the signal to reach the user depends on how far away each satellite is from the user. These times can be compared by analyzing the z-count of each satellite [43]. This distance is the pseudorange measurement. A nominal transit time for a signal to reach a user from a satellite is about 68ms (0.068 seconds) [7]. Assume  $i_1$  is the time that the closest satellite has logged its z-count,  $i_2$  is the corresponding time to the next closest SV, and so on. The raw pseudoranges can therefore be calculated by the formulas in Equation (3.2). Note that  $f_S$  is the sampling frequency of the hardware front end (16.3676MHz for the front-end used in this thesis).

$$\rho_{1,raw} = 0.068c$$

$$\rho_{2,raw} = (0.068 + \frac{i_2 - i_1}{f_S})c$$

$$\vdots$$

$$\rho_{N,raw} = (0.068 + \frac{i_N - i_{N-1}}{f_S})c$$

(3.2)

There is also a clock correction factor that comes from the information found in subframe 1. Using this clock correction factor  $T_{corr}$ , the raw pseudoranges can be corrected by Equation (3.3) and then used to compute the user position.

$$\rho_{i,corrected} = \rho_{i,raw} + cT_{i,corr} \tag{3.3}$$

# 3.4.2 Calculating User Position from Pseudoranges

As mentioned, a pseudorange is the estimated geometric range from a user to the satellite plus a clock bias. The pseudorange is represented by Equation (3.4).

$$\rho_i = \sqrt{(x_i - x_u)^2 + (y_i - y_u)^2 + (z_i - z_u)^2} + ct_u + \nu \tag{3.4}$$

In this equation,  $\rho_i$  is the pseudorange from the satellite to the user;  $x_i$ ,  $y_i$ , and  $z_i$  are the satellite *i*'s geometric locations;  $x_u$ ,  $y_u$ , and  $z_u$  is the user's geometric position,  $t_u$  is the receiver clock bias, and  $\nu$  is noise.

The satellite vehicle's x, y, and z positions can be determined by processing the ephemeris in the satellite's data message. Since the receiver does not know its position, an estimated pseudorange (or prediction of the pseudorange, denoted by  $\hat{\rho}$ ) must be calculated as seen in Equation (3.5). In this equation,  $\hat{x}_u$ ,  $\hat{y}_u$ ,  $\hat{z}_u$ , and  $\hat{t}_u$  denote the predicted position and clock bias states of the receiver.

$$\hat{\rho}_i = \hat{r}_i + c\hat{t}_u = \sqrt{(x_i - \hat{x}_u)^2 + (y_i - \hat{y}_u)^2 + (z_i - \hat{z}_u)^2} + c\hat{t}_u$$

(3.5)

A well-known curve-fitting algorithm called least squares is used to determine the user's position [30]. Typically, if no additional information is known, a receiver would begin by guessing a user position, such as  $\{x, y, z\} = \{0, 0, 0\}$  in an earth-centered, earth-fixed (ECEF) coordinate frame - the center of the earth. The least squares algorithm uses this initial position and then identifies the error in the initial guess. This error correction is

applied to the initial guess, and the algorithm is repeated until a very small correction is required. The typical least squares setup holds the form of Equation (3.6):

$$error = H * unknowns$$

(3.6)

In the case of GPS, there are four unknowns: x, y, z, and the clock bias, t. In order to solve for a position, at least four satellites must be tracked. In any case where more than four satellites are being tracked, the system becomes overdetermined and least squares is used to solve for user position and clock bias. The H matrix is the system of linearized pseudorange equations to each satellite, where  $a_{p,N}$  denotes the line of sight unit vector from satellite i to the user in the p direction. The unknowns and H matrix are combined more clearly in Equation (3.7) and the least squares solution is solved in Equation (3.8).

$$\begin{bmatrix} \hat{\rho}_{1} - \rho_{1} \\ \vdots \\ \hat{\rho}_{N} - \rho_{N} \end{bmatrix} = H \begin{bmatrix} \delta \hat{x}_{u} \\ \delta \hat{y}_{u} \\ \delta \hat{z}_{u} \\ \delta \hat{t}_{u} \end{bmatrix} = \begin{bmatrix} \frac{x_{1} - \hat{x}_{u}}{\hat{r}_{1}} & \frac{y_{1} - \hat{y}_{u}}{\hat{r}_{1}} & \frac{z_{1} - \hat{z}_{u}}{\hat{r}_{1}} & -1 \\ \vdots & \vdots & \vdots & \vdots \\ a_{x,i} & a_{y,i} & a_{z,i} & -1 \end{bmatrix} \begin{bmatrix} \delta \hat{x}_{u} \\ \delta \hat{y}_{u} \\ \delta \hat{z}_{u} \\ \delta \hat{t}_{u} \end{bmatrix}$$

(3.7)

$$\begin{bmatrix} \delta \hat{x}_{u} \\ \delta \hat{y}_{u} \\ \delta \hat{z}_{u} \\ \delta \hat{t}_{u} \end{bmatrix} = (H^{T}H)^{-1}H^{T} \begin{bmatrix} \hat{\rho}_{1} - \rho_{1} \\ \vdots \\ \hat{\rho}_{i} - \rho_{i} \end{bmatrix}$$

$$(3.8)$$

Each new pseudorange measurement allows for further user position accuracy and also tracks position and velocity changes for dynamic receivers. Equation (3.9) shows the recursive least squares equation that is run to obtain a new measurement, updating the old measurement with the most current set of data.

$$\begin{bmatrix} \hat{x}_{u,N} \\ \hat{y}_{u,N} \\ \hat{z}_{u,N} \\ \hat{t}_{u,N} \end{bmatrix} = \begin{bmatrix} \hat{x}_{u,N-1} \\ \hat{y}_{u,N-1} \\ \hat{z}_{u,N-1} \\ \hat{t}_{u,N-1} \end{bmatrix} + (H^T H)^{-1} H^T \begin{bmatrix} \hat{\rho}_1 - \rho_1 \\ \vdots \\ \hat{\rho}_i - \rho_i \end{bmatrix}$$

(3.9)

Other more complex methods such as weighted least squares and Kalman filters are used to compute user position instead of least squares, but they shall not be discussed in this thesis.

# 3.4.3 Determining User Velocity

User velocity cannot be determined by taking  $\frac{du}{dt}$  (where du is the change in user position) because the noise in the position measurements is amplified far too much [43]. Instead, user velocity is determined by measuring the Doppler shift on the carrier signal for each satellite or the change in phase with time  $(\frac{d\phi}{dt})$ . Equations (3.10) and (3.11) give the user velocity.

$$d_{i} = \frac{c(f_{dopp} - f_{L1})}{f_{L1}} + \begin{bmatrix} V_{x,i} & V_{y,i} & V_{z,i} \end{bmatrix} \begin{bmatrix} a_{x,i} \\ a_{y,i} \\ a_{z,i} \end{bmatrix}$$

(3.10)

$$\begin{bmatrix} \delta \dot{x}_{u} \\ \delta \dot{y}_{u} \\ \delta \dot{z}_{u} \\ \delta \dot{t}_{u} \end{bmatrix} = (H^{T}H)^{-1}H^{T} \begin{bmatrix} d_{1} \\ \vdots \\ d_{N} \end{bmatrix}$$

$$(3.11)$$

where  $d_i$  is the effect of the Doppler with respect to user position and  $V_{p,i}$  is the satellite velocity in the p-direction. The satellite velocities are obtained from the data message (Section 2.4) by processing the satellite ephemeris data. A pseudorange-rate is directly related to the user velocity and satellite velocities. A pseudorange-rate is the rate of change

of the pseudorange with respect to time. Therefore, there exists a pseudorange-rate for each satellite that is being tracked by the receiver. The pseudorange-rate is the line of sight velocity (including clock terms) of the satellite relative to the user.

## 3.5 Vector Tracking and Deep Integration Algorithms

Vector tracking algorithms designed for use with the global positioning system (GPS) have been studied by the navigation community for the past two and a half decades [5, 12, 20, 26, 28, 33, 35, 43]. The goal of this research is to exploit the advantages that vector tracking offers such as increased immunity to interference and jamming and the ability to perform at low signal-to-noise  $(C/N_0)$  ratios [36]. These advantages increase the reliability and robustness of a normal GPS receiver and have many practical applications in an environment that is typically challenging for normal GPS receivers.

Vector tracking functions by exploiting the general principle by which GPS receivers operate. Typical GPS receivers determine position and velocity by tracking the phases and frequencies of the received signals from available satellites individually [24]. Vector tracking combines the position and velocity determination with the signal tracking for all available satellites into a single step [36]. This combination is usually accomplished with an extended Kalman filter (EKF). Using the estimates from the filter, the phase and frequency of each visible satellite can be predicted for the next iteration of the EKF. Vector tracking loops generally have a greater immunity to receiver dynamics than typical scalar loops, and the additional aiding of inertial sensors bolsters this immunity even further. The fusion of the vector tracking algorithm with inertial sensors is known as Ultra Tightly Coupled (UTC) or Deeply Integrated (DI) systems [33].

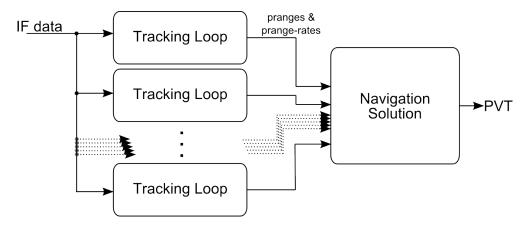

In order to give an accurate description of how vector tracking differs from traditional methods, a traditional GPS receiver must first be discussed. A typical GPS receiver consists of four mostly independent parts as discussed in previous sections. The first part is the radio frequency (RF) front end which mixes the very high frequency satellite signal down

to an intermediate frequency (IF) that can be handled by modern hardware. Second, an acquisition module uses a search algorithm to find which satellites are currently in view and get a rough estimate of their code phase and Doppler frequency. The next step is called tracking, where the estimates of code phase and Doppler frequency for each visible satellite are determined at a much finer resolution. The final step is to take the outputs of each of the tracking loops and compute a position, velocity, and time (PVT) solution. Vector tracking receiver architectures differ from traditional architectures in the tracking and navigation solution steps [36].

## 3.5.1 Traditional Receiver Operation

Traditional GPS receivers utilize scalar tracking loops to track each satellite in view as described in Section 3.3. Scalar loops, as the name implies, treat each loop as a single, independent entity. There is no feedback or sharing of information between any of the scalar tracking loops and no statistical correlation between channels. The outputs of these tracking loops are the pseudorange and pseudorange-rates for each of the satellites. These outputs are used as the input to the navigation solution stage, and using each of these individual measurements, the receiver computes a position. Figure 3.9 is a block diagram of the traditional receiver architecture using scalar tracking loops.

Figure 3.9: Block diagram of the traditional receiver scalar tracking loop architecture

## 3.5.2 Vector Tracking Receiver Operation

Vector tracking receivers take a different approach than traditional receivers. In the vector tracking algorithm, the tracking and navigation solution steps are combined in a single step, usually accomplished by an extended Kalman filter (EKF). Vector tracking, as its name implies, considers all of the satellites in aggregate to obtain a navigation solution [36]. The vector tracking approach that will be considered in this research is a vector delay frequency locked loop (VDFLL) in an unfederated (centralized) architecture. This means that there is one central EKF that predicts both the code phase (pseudorange) and frequency (pseudorange-rate) for each satellite in view. Figure 3.10 is a block diagram of the vector tracking (VDFLL) architecture that is used in this system.

Figure 3.10: Block diagram of the vector tracking receiver loop architecture

Notice that instead of separate tracking loops, the only operation that is done independently is the signal correlation. The outputs of these correlators, after being passed through a discriminator, are the pseudorange and pseudorange-rate residuals. These residuals are the measurements used for the centralized filter. The EKF used in the position state VDFLL

are the errors in the receiver's position, velocity, and time (PVT) rather than the PVT itself, so the actual PVT is managed separately. The error states of the EKF used in this thesis are:

$\begin{array}{c} \delta x \\ \delta \dot{x} \\ \delta \dot{y} \\ \delta \dot{y} \\ \delta z \\ \delta \dot{z} \\ \delta \dot{t} \\ \delta \dot{t} \end{array}$

# 3.5.3 Vector Tracking Algorithm Details

This section outlines some implementation details of the vector tracking implementation used in this thesis. This implementation was originally outlined by Robert Crane from L3 Interstate Communications [12]. It utilizes an extended bank of signal correlators that are positioned around the nulls in the power density function of the C/A code to get an accurate picture of noise power.

Because the vector tracking architecture for this research has been chosen as a VDFLL, where both the code phase and carrier Doppler frequency are predicted, the carrier phase is not locked. Because the carrier phase is not locked, no data bits can be backed out, so the vector tracking receiver must be initialized with a PVT solution, ephemeris data, GPS time, Doppler frequencies, and code phase information.

There are two sets of processes that are performed in the vector tracking algorithm. The first is the extended Kalman filter loop that completes at a rate of 50Hz (20ms period), and the second set of processes yields the data and measurements for each individual satellite.

The second set of processes is mostly unique to vector tracking (denoted by \*) and many are unique to this particular vector tracking formulation by Crane (denoted by \*) [12]. For each satellite, the following operations are performed:

- update satellite position

- get pseudorange and transit time

- populate pertinent rows in C matrix with line of sight unit vectors to current satellite

- predict Doppler frequency\*

- predict code phase\*

- calculate noise variance<sup>\$</sup>

- $\bullet$  get signal amplitude, noise power, and  $C/{N_0}^{\$}$

- calculate measurement covariance matrix R<sup>\$</sup>

- use discriminators to calculate measurements<sup>\$</sup>

Specifics for implementation of the Crane method can be found in [12].

### 3.5.4 Predicting Doppler Frequency and Code Phase

Calculating the Doppler frequency for each satellite is based on the definition of the Doppler effect. First, the velocity of the satellite relative to the receiver is measured using Equation (3.12).

$$LOS_{vel} = a_{x,y,z} \cdot (sv_{vel} - \dot{\hat{x}}) \tag{3.12}$$

Then, the definition of the Doppler effect is used. It is adjusted by the measurement of the receiver clock drift  $(t_d)$  and then shifted from the L1 transmit frequency  $(f_{L1})$  to the

intermediate frequency  $(f_{IF})$ , as shown in Equation (3.13).

$$f_{if+dopp} = \frac{1 - LOS_{vel}}{c + t_d} f_{L1} - f_{L1} + f_{IF}$$

(3.13)

The code phase is predicted by using the fact that all satellites broadcast the preamble of the data message simultaneously. After pseudoranges to the satellites are initially found based on the scalar tracking solution, this range can be converted into a time by multiplying by the sampling period. This is the time difference between the satellite sending the preamble and it being received by the user. Once this time is found, it is compared to the elapsed time that the system actually took based on the previous pseudorange. The difference between these two times is used to adjust the NCO of the PRN generator, and thus the code phase is predicted.

#### 3.5.5 Deep Integration

Most of the research that has been done in the vector tracking field has included measurements from some inertial sensor such as an IMU [35]. A system that combines both vector tracking and an inertial sensor is called ultra-tight coupling or deep integration. The addition of an inertial device increases the receiver's immunity to dynamics by being able to track changes in position and velocity between vector tracking filter updates. Since the vector tracking formulation uses an extended Kalman filter, many of the Doppler and code phase predictions are performed using the time-propagated position. If there is a significant outage in the GPS signal (and thus no measurement update), the predicted position, velocity, and time is propagated forward in time using the designated motion model until it comes back into view. The effects of aiding a receiver with an inertial device to help bridge these outage gaps is well documented [24].

Adding an inertial sensor is not without its complications. If an inertial measurement unit (IMU) is added to the system, there must be several additional states in the navigation

Figure 3.11: Block diagram of an ultra-tightly coupled/deeply integrated system

filter which track the error dynamics of the IMU. Because the update rate of the IMU is typically very fast (~50-800Hz), tracking these parameters can become burdensome on an embedded system. The IMU measurements must also be synchronized in time with the GPS data, as unmodeled errors can be introduced if the two are not synchronized [24]. This synchronization usually involves a one-second timing pulse from the GPS (known as the pulse per second, PPS) and a fairly large amount of memory space to buffer several samples of IMU data so that it can be lined up correctly with the GPS clock.

As mentioned, the addition of an IMU adds numerous states to the central Kalman filter. The 17 states include position, velocity, attitude (roll, pitch, and yaw), gyro biases, accelerator biases, clock bias, and clock drift.

# Chapter 4

### Software Receiver Platform Trade Study

The concept of extending the software defined radio to the GPS industry began in the late 1990's [3]. Software receivers provide several advantages over hardware-only implementations. First and most importantly, software receivers are reconfigurable. They can theoretically be reprogrammed any number of times in any number of ways. This is extremely important in the navigation research community, where developing and testing new algorithms is paramount. The ability to reconfigure a working GPS receiver to incorporate some research interest advances the field far more rapidly than being constrained to third party hardware or software.