# **High Temperature Electronics Packaging Processes and Materials Development**

by

Ping Zheng

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama December 13, 2010

Copyright 2010 by Ping Zheng

Approved by

Robert W Johnson, Chair, Professor of Electrical & Computer Engineering Stuart M. Wentworth, Associate Professor of Electrical & Computer Engineering Robert N Dean, Assistant Professor of Electrical & Computer Engineering Minseo Park, Associate Professor of Physics

#### **Abstract**

Silicon carbide device technology is being developed for power electronics applications for use at high temperatures. In recent studies, SiC based electronics and sensors have also been demonstrated for extended operation at 500 and 600°C, but the level of integration is at a very low level. Silicon on insulator (SOI) technology provides the ability to realize complex electronics functions. SOI rated for 250°C is commercially available and 300°C operation has been demonstrated. To build functional systems operating at high temperatures, packaging technology must be developed to interconnect the SOI and SiC based devices. Key elements of a high temperature packaging technology include the interconnection substrate, die attach and wire bonding. New developments in each of these areas for high temperature operation are discussed in this work.

A system-in-package (SiP) approach has been developed for SOI based devices, using thick film technology on  $Si_3N_4$  ceramic substrates. Eutectic Au-Ge die attach was used with a Ti/Ti:W/Au backside die metallization for  $300^{\circ}$ C operation. Results of die attach reliability based on shear strength are discussed after thermal storage and thermal cycling tests. Wire bonding is a cost-effective and flexible interconnect technology for HTE packaging. SOI die typically have Al wire bond pads that are not compatible with Au thermosonic wire bonding for high temperature applications. A plating process that provides a barrier layer (electroless Ni) and a wire bondable finish (electroless Pd plus immersion Au) over the Al wire bond pads has been

examined. Results of the investigation of Au wire bonding on substrate metallization and die surface metallization are also presented in this dissertation

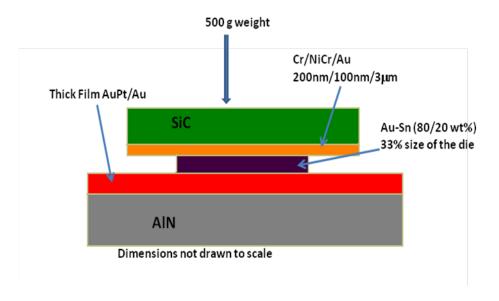

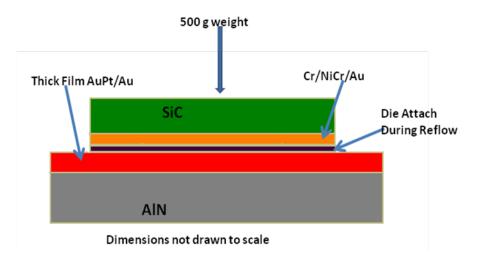

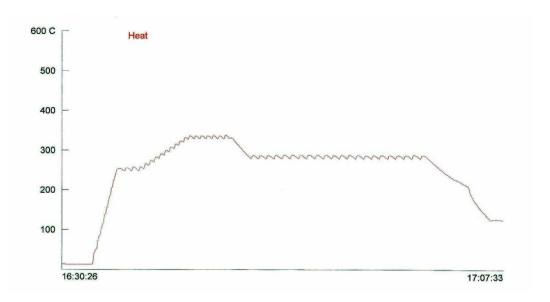

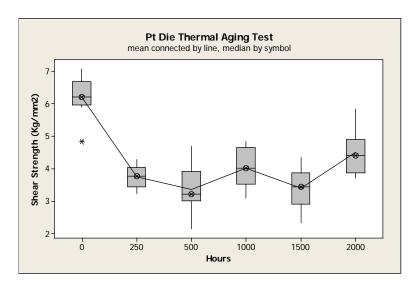

For the SiC based devices applications at 500°C, this project examines off-eutectic Au-Sn as the die attach alloy in the Liquid Phase Transient (LPT) die attach process. Two different approaches that use thick foil Sn-Au-Sn preform and limited volume Au-Sn eutectic preform, have been investigated using. The substrate used in this project was PtAu thick film metallization on AlN substrates. A pure Au thick film layer was printed over the PtAu thick film layer. The SiC backside metallizations evaluated were Ti/TaSi/Pt/Au and Cr/NiCr/Au. Die shear tests were performed after aging at 500°C and after thermal cycling. The shear test results and failure surface analysis are discussed

Hermetic sealing minimizes the intrusion of contamination and allow the circuit mounted inside the package to survive for a longer period of time. Two packaging approaches have been developed in this project: One path was an integrated package that uses a metalized AlN substrate as the package base. A machined AlN cavity lid was sealed to the AlN substrate to create a hermetic cavity for the die. For the second approach, a commercial off the shelf (COTS) Al<sub>2</sub>O<sub>3</sub> package has been evaluated. In this case the metalized AlN substrate with the die attached and wire bonded could be hermetically sealed inside the ceramic package.

# Acknowledgments

I would like to express my appreciation and sincere thanks to my research advisor, Dr. R. Wayne Johnson, who guided and encouraged me throughout my research. His advice and research attitude have provided me with a model for my entire future career. I also wish to thank my advisory committee members, Dr. Robert Dean, Dr. Stuart M. Wentworth, and Dr. Minseo Park for reviewing the dissertation.

Appreciation is also expressed to cooperative support and continual assistance from Michael J. Palmer, John Marcell, Huihua Shu, Rui Zhang, and Phillip Henson throughout the course of this research.

Finally, I would like to thank my husband Joel Hagler, his family and my parents for their continual encouragement and support throughout this work.

# Table of Contents

| Abstract                                                      | ii |

|---------------------------------------------------------------|----|

| Acknowledgments                                               | iv |

| List of Tables                                                | ix |

| List of Figures                                               | X  |

| Chapter 1 Introduction                                        | 1  |

| 1.1High Temperature Electronics (HTE)                         | 1  |

| 1.2 Applications and Benefits of High Temperature Electronics | 1  |

| 1.3 High-Temperature Electronics Technology and Materials     | 3  |

| 1.4 High Temperature Electronics Packaging                    | 5  |

| 1.4.1 Key Elements of HTE Packaging                           | 6  |

| 1.4.2 Substrate Selection                                     | 6  |

| 1.4.3 Die and Substrate Metallization                         | 7  |

| 1.4.4 Die Attach                                              | 8  |

| 1.4.5 Wire Bonding                                            | 9  |

| 1.4.6 Hermetic Sealing                                        | 9  |

| 1.5 Research Outline                                          | 10 |

| Chapter 2 Background                                          | 12 |

| 2.1 Packaging Considerations for HTE                          | 12 |

| 2.2 Thin Film Die Metallization                               | 13 |

|    | 2.2.1 Evaporation and Sputtering                                         | 14 |

|----|--------------------------------------------------------------------------|----|

|    | 2.2.2 Gold Electroplating                                                | 16 |

|    | 2.3 Substrate Technology                                                 | 16 |

|    | 2.4 Die Attach                                                           | 18 |

|    | 2.4.1 General Considerations for HTE Die Attach                          | 18 |

|    | 2.4.2 HTE Die Attach Options                                             | 19 |

|    | 2.4.3 Die Shear Testing                                                  | 22 |

|    | 2.5 Wire Bonding                                                         | 23 |

|    | 2.5.1 Ball Bonding                                                       | 23 |

|    | 2.5.2 Wedge Bonding                                                      | 25 |

|    | 2.5.3 Wire Pull Testing and Bond Shear Testing                           | 26 |

|    | 2.6 Hermetic Sealing                                                     | 28 |

| Ch | napter 3 Packaging for High Temperature Silicon-on-Insulator Electronics | 30 |

|    | 3.1 Introduction                                                         | 30 |

|    | 3.2 Thick Film Si <sub>3</sub> N <sub>4</sub> Substrates                 | 30 |

|    | 3.3 Si Die Backside Metallization                                        | 32 |

|    | 3.4 Die Attach                                                           | 34 |

|    | 3.4.1 Au-Ge Braze                                                        | 34 |

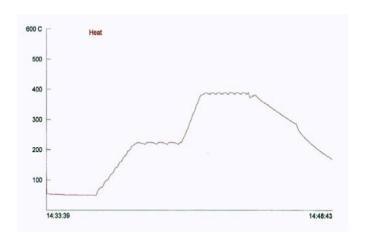

|    | 3.4.2 Au-Ge Brazing Profile                                              | 35 |

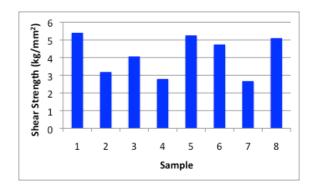

|    | 3.5 Die Attach Reliability Test                                          | 36 |

|    | 3.5.1 High Temperature Thermal Aging Test                                | 36 |

|    | 3.5.2 Thermal Cycle Test                                                 | 42 |

|    | 3.6 Wire Bonding Test                                                    | 45 |

|    | 3.6.1 Wire Bond Pad Metallurgy                                      | 45 |

|----|---------------------------------------------------------------------|----|

|    | 3.6.2 Wire Bond Pull Force Test                                     | 46 |

|    | 3.6.3 Wire Bond Ball Shear Force Test                               | 49 |

|    | 3.6.4 Daisy Chain Electrical Resistance                             | 50 |

|    | 3.7 Summary                                                         | 52 |

| Ch | apter 4 Packaging for High Temperature Silicon Carbide Electronics  | 54 |

|    | 4.1 Introduction                                                    | 54 |

|    | 4.2 Aluminum Nitride Substrate Metallization Fabrication            | 54 |

|    | 4.3 SiC Die Metallization                                           | 58 |

|    | 4.4 Off-eutectic Au-Sn Liquid Phase Transient (LPT) Die Attach      | 59 |

|    | 4.4.1 Background                                                    | 59 |

|    | 4.4.2 Two die attach approaches have been investigated in this work | 60 |

|    | 4.5 High Temperature Thermal Aging Test                             | 65 |

|    | 4.6 Thermal Cycling Test                                            | 70 |

|    | 4.7 Summary                                                         | 78 |

| Ch | apter 5 Hermetic Seal Packages                                      | 80 |

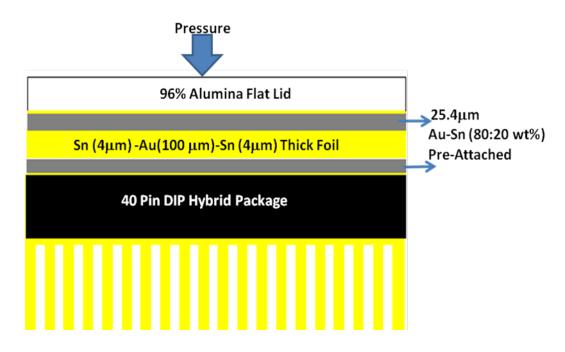

|    | 5.1 Alumina 40 Pin Hybrid Hermetic Seal Package                     | 81 |

|    | 5.1.1 Alumina 40 Pin Hybrid Package                                 | 81 |

|    | 5.1.2 Au-Sn Pre-Attach                                              | 82 |

|    | 5.1.3 Off-Eutectic Sn-Au-Sn TLP Lid Seal Process                    | 84 |

|    | 5.14 Leak Testing                                                   | 87 |

|    | 5.2 AlN Integrated Package Hermetic Seal                            | 87 |

|    | 5.2.1 AlN Cavity Lid Fabrication                                    | 88 |

| 5.2.2 AlN Package Base Fabrication                                    | 89 |

|-----------------------------------------------------------------------|----|

| 5.2.3 Off-Eutectic TLP Lid Attach                                     | 94 |

| 5.3 Discussion                                                        | 94 |

| 5.4 Conclusion                                                        | 95 |

| Chapter 6 Conclusion and Future work Recommendation                   | 96 |

| 6.1 Packaging for High Temperature SOI Devices                        | 96 |

| 6.2 Packaging for High Temperature SiC Based Devices                  | 96 |

| 6.3 Off-Eutectic Sn-Au-Sn TLP Lid Seal Process for Hermetic Packaging | 97 |

| 6.4 Recommendations for Future Work                                   | 97 |

| References                                                            | 98 |

# List of Tables

| Table 1.1 Applications area and Parameters for High Temperature Electronics                                                             | 2  |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1.2 Key Physical & Electronic Properties of Semiconductor Material                                                                | 3  |

| Table 1.3 Typical Properties of Ceramic Substrates                                                                                      | 7  |

| Table 2.1 Melting Points of Common solder and Braze Alloy Materials                                                                     | 20 |

| Table 3.1 Thermal Cycle Die Shear Results                                                                                               | 44 |

| Table 3.2 Wire Bonding Parameters                                                                                                       | 52 |

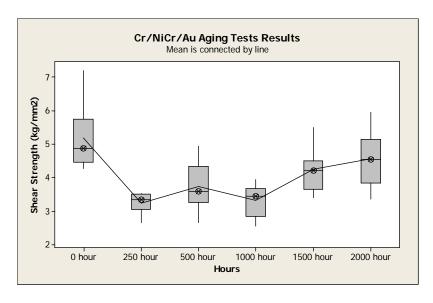

| Table 4.1 Cr/NiCr/Au Die with Limited Volume AuSn Eutectic Die Attach 60 Shear Strength (kg/mm²) as a Function of Storage Time at 500°C | 67 |

| Table 4.2 (a) AES Analysis of Fracture Surface Element for Off-eutectic Au-Sn Die Attach                                                | 69 |

| Table 4.2 (b) AES Analysis of Fracture Surface Element Limited Volume Au-Sn Die Atta                                                    | 70 |

| Table 4.3 Pt Die with Off-Eutectic Die Attach Thermal Cycle Shear Results                                                               | 71 |

| Table 4.4 Cr/NiCr/Au Die with Off-Eutectic Sn-Au-Sn Die Attach Thermal Cycle Shear Results                                              | 72 |

| Table 4.5 Cr/NiCr/Au Die with Limited Volume Eutectic Au-Sn Die Attach Thermal Cycle Shear Results                                      | 77 |

# List of Figures

| Figure 1.1 the Illustration of Key Elements of a Package                                               | 6  |

|--------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 Typical system of e-beam evaporation of materials                                           | 15 |

| Figure 2.2 Typical Plasma Sputtering System                                                            | 16 |

| Figure 2.3 Schematic Illustration of TLP bonding process                                               | 22 |

| Figure 2.4 Test Set-up for Die Attach Shear Testing                                                    | 23 |

| Figure 2.5 (a) Typical Au Wire Ball Bonding Sequence                                                   | 24 |

| Figure 2.6 (a) Ultrasonic Wedge Bonding Sequence                                                       | 26 |

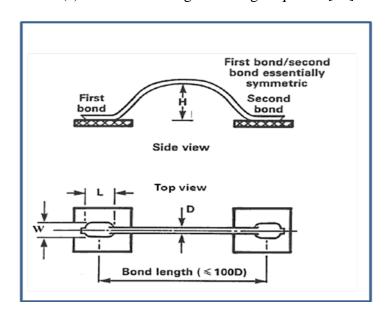

| Figure 2.6 (b) Schematic Illustration of the Geometry of Wedge Bonding                                 | 26 |

| Figure 2.7 (a) Typical Geometrical Configuration and Pull Test Failure Modes for Wire Pull Test        | 27 |

| Figure 2.7 (b) Typical Geometrical Configuration and Position of Chisel for Bond Shear Test            | 28 |

| Figure 3.1 (a) Thick Film Metalized Si <sub>3</sub> N <sub>4</sub> Substrate Wire Bond Test Pattern    | 31 |

| Figure 3.1 (b) Thick Film Metalized Si <sub>3</sub> N <sub>4</sub> Substrate Close-up of Wire Bond Pad | 32 |

| Figure 3.2 Cross Section of Fired Thick Film Au Conductor on Si <sub>3</sub> N <sub>4</sub> Substrate  | 32 |

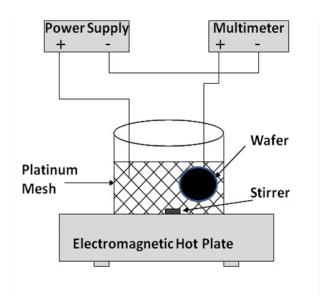

| Figure 3.3 Schematics of Gold Electroplating Setup                                                     | 34 |

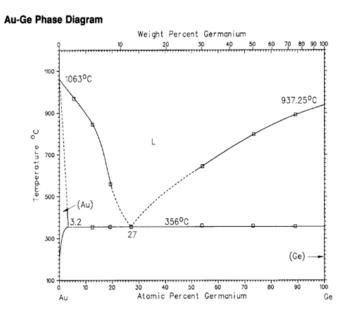

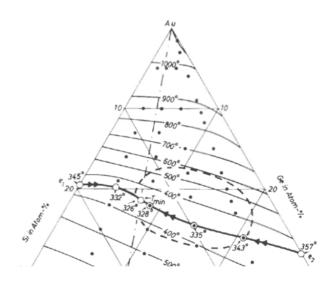

| Figure 3.4 Gold-Germanium phase diagram                                                                | 35 |

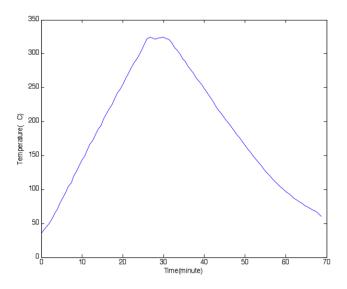

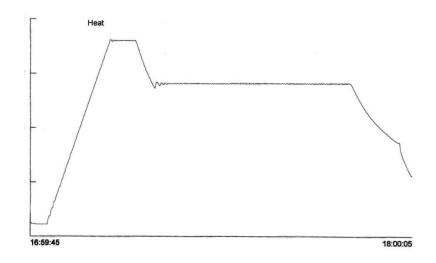

| Figure 3.5 Au-Ge SST Bonding Profile                                                                   | 35 |

| Figure 3.6 Distributions of Initial Die Shear Strengths                                                | 36 |

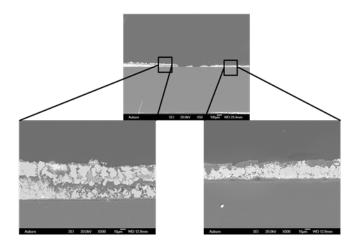

| Figure 3.7 Cross Section of Die Attach As-Assembled                                                    | 37 |

| Figure 3.8 ( | Cross Section of a High Die Shear Strength Substrate Showing Au Thick Film3                                                            | 8  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|              | Cross Section of a Die Shear Strength Substrate Showing Failure at Chick Film to Engineered Surface Layer Interface under the Die      | 8  |

| Figure 3.10  | Wetting of 9 AuGe Preforms to Substrate as a Function of Time at Peak Temp3                                                            | 9  |

| Figure 3.11  | Die Shear as a Function of Storage Time at 325°C                                                                                       | 0  |

| Figure 3.12  | Cross Section Micrograph of Die Attach after 3000 Hours at 325°C4                                                                      | .1 |

| Figure 3.13  | Au-rich Region of Au-Ge-Si Phase Diagram                                                                                               | .1 |

| Figure 3.14  | Cross Section of Substrate after Die Shear Test following 3000 Hours Storage at 325°C                                                  | 2  |

| Figure 3.15  | Cross Section of Wire Bond Test Die after 3000 Hours at 320°C4                                                                         | -2 |

| Figure 3.16  | Thermal Cycle Profile                                                                                                                  | .3 |

| Figure 3.17  | Cross Section of Substrate after Shear Test Following 1000 Thermal Cycles4                                                             | 4  |

| Figure 3.18  | Micrograph (left side) of Crack at the Perimeter of the Thick Film Au and Au-Ge Interface After 1500 Thermal Cycles Prior to Die Shear | 5  |

| Figure 3.19  | Electroless Ni/Electroless Pd/Immersion Au Wire Bond Pads                                                                              | 6  |

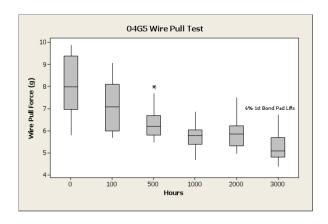

| Figure 3.20  | Pull Force as a Function of Aging Time at 320°C for 5.8µmNi/200nmPd/22nmAu Die                                                         | .7 |

| Figure 3.21  | Pull Force as a Function of Aging Time at 320°C for 5.8µmNi/400nmPd/19nmAu Die                                                         | 8  |

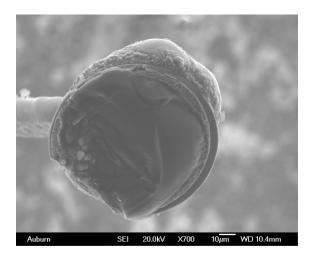

| Figure 3.22  | Scanning Electron Micrograph of Lifted Ball Bond Illustrating Cratering of the Si Pad after 3000 Hours of Aging at 320°C               | 8  |

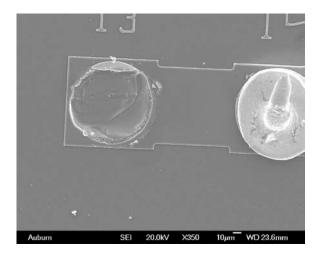

| Figure 3.23  | Scanning Electron Micrograph of Cratered Si Pad after 3000 Hours of Aging at 320°C                                                     | 8  |

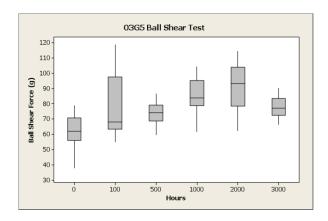

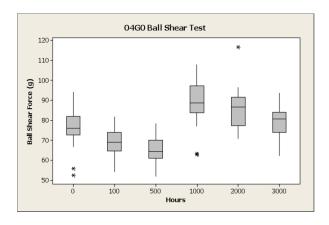

| Figure 3.24  | Ball Shear Force as a Function of Aging Time at 320°C for 5.8µmNi/200nmPd/22nmAu Die4                                                  | 9  |

| Figure 3.25  | Ball Shear Force as a Function of Aging Time at 320°C for 5.8umNi/400nmPd/19nmAu Die                                                   | .9 |

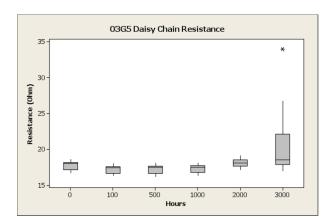

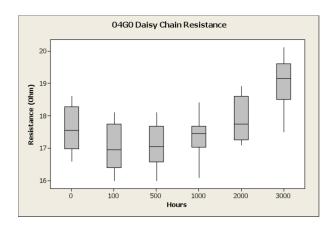

| Figure 3.26 Daisy Chain Resistance as a Function of Aging Time at 320°C for 5.8μmNi/200nmPd/22nmAu Die                                              | 50 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.27 Daisy Chain Resistance as a Function of Aging Time at 320°C for 5.8μmNi/200nmPd/19nmAu Die                                              | 51 |

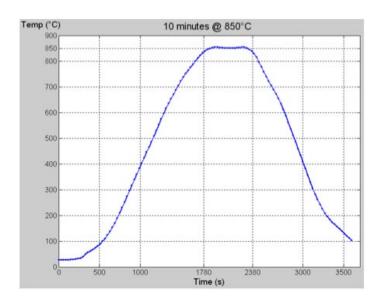

| Figure 4.1 Belt Oven Firing Profile with Peak Temperature of 850°C                                                                                  | 55 |

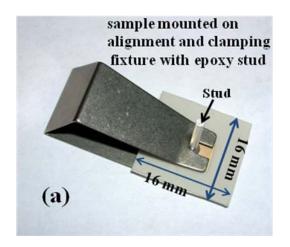

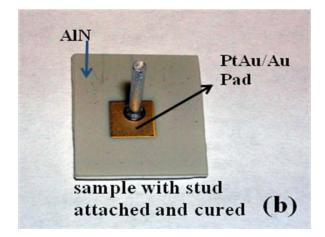

| Figure 4.2 (a) Sample Mounted on an Alignment and Clamping Fixture                                                                                  | 56 |

| Figure 4.2 (b) Sample with an Epoxy Stud Attached                                                                                                   | 56 |

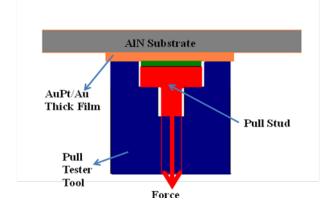

| Figure 4.3 Schematic Side View of Stud Pull Test Setup                                                                                              | 56 |

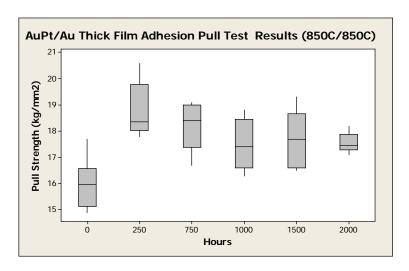

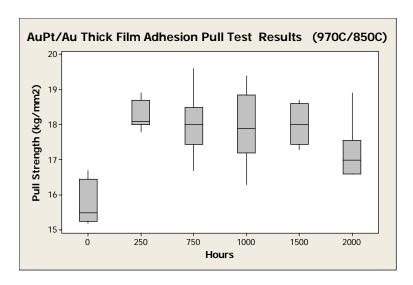

| Figure 4.4 Thick Film Adhesion Pull Test Results as a Function of Storage Time at 500°C: Both Thick Film Layers Fired with 850°C Profile            | 57 |

| Figure 4.5 Thick Film Adhesion Pull Test Results as a Function of Storage Time at 500°C: PtAu Fired with 970°C Profile, Au Fired with 850°C Profile | 58 |

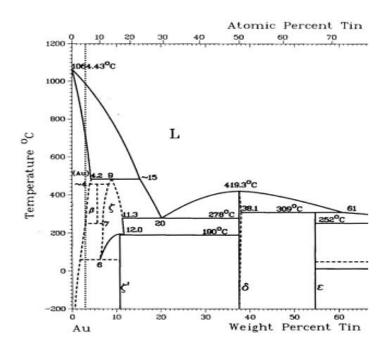

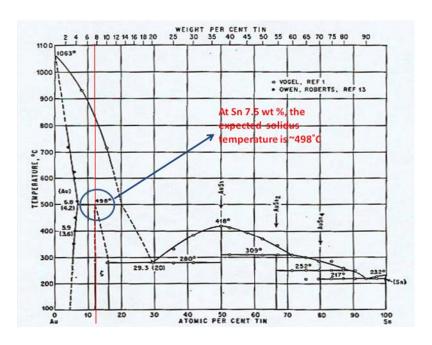

| Figure 4.6 Au-Sn Phase Diagram                                                                                                                      | 60 |

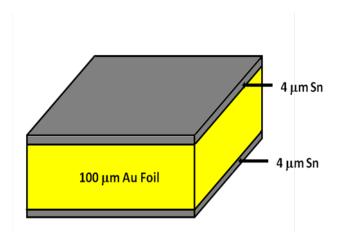

| Figure 4.7 Sn-Au-Sn Off-eutectic Thick Foil Sketch                                                                                                  | 61 |

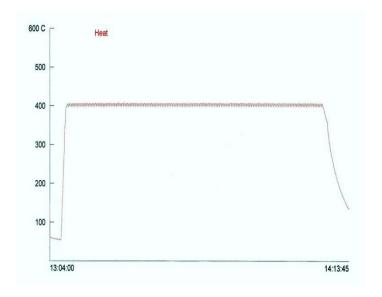

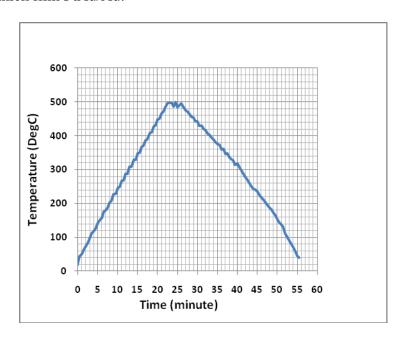

| Figure 4.8 Off-eutectic Sn-Au-Sn SST Bonding Profile                                                                                                | 62 |

| Figure 4.9 (a) Limited Volume Au-Sn Die Bonding Sketch before Brazing                                                                               | 63 |

| Figure 4.9 (b) Limited Volume Au-Sn Die Bonding Sketch During Reflow                                                                                | 64 |

| Figure 4.10 Limited Volume Eutectic Au-Sn (80/20 wt%) SST Bonding Profile                                                                           | 65 |

| Figure 4.11 Ti/TaSi <sub>2</sub> /Pt/Au Die Assembled with Off-Eutectic Sn-Au-Sn Shear Strength as a Function of Storage Time at 500°C              | 66 |

| Figure 4.12 Cr/NiCr/Au Die Assembled with Off-Eutectic Sn-Au-Sn<br>Shear Strength as a Function of Storage Time at 500°C                            | 66 |

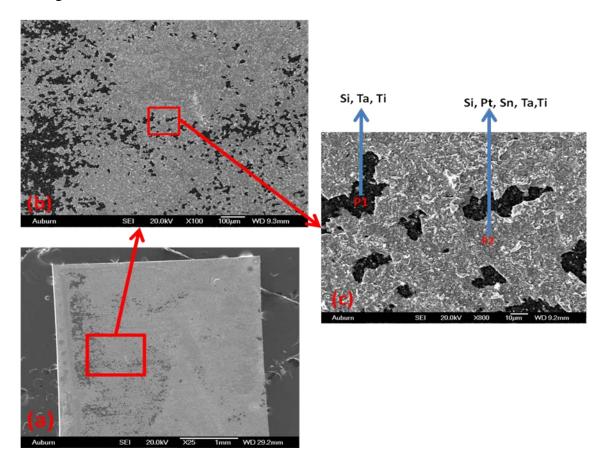

| Figure 4.13 (a) Scanning Electron Micrograph of Pt Die Fracture Surface with Sn-Au-Sn Die Attach after 2000 Hours at 500°C                          | 68 |

| Figure 4.13 (b) Close-up View of the Frame in Figure 4.13 (a)                                                                                       | 68 |

| Figure 4.13 (c) Close-up View of the Frame in Figure 4.13 (b)                                                                                       | 68 |

| Figure 4.14 Thermal Cycle Profile                                                                                                                   | 70 |

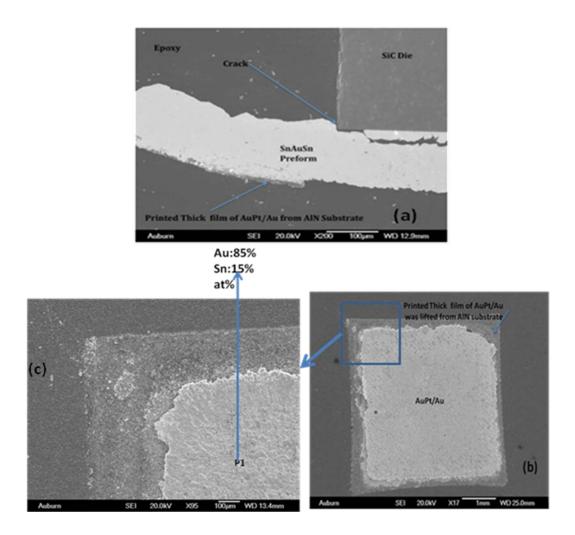

| Figure 4.15 Cross Section Micrograph of a Pt Die with an Off-Eutectic Sn-Au-Sn Preform after 300 cycles from 35°C to 500°C                    | 72 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.16 (a) Cross Section Micrograph of a Cr/NiCr/Au Die with an Off-Eutectic Sn-Au-Sn Preform after 500 Cycles from 35°C to 500°C        | 74 |

| Figure 4.16 (b) SEM Picture of the Sheared AlN Substrate Fracture Surface after 500 cycles from 35°C to 500°C                                 | 74 |

| Figure 4.16 (c) a Close-up View of the Frame in Figure 4.13 (b)                                                                               | 74 |

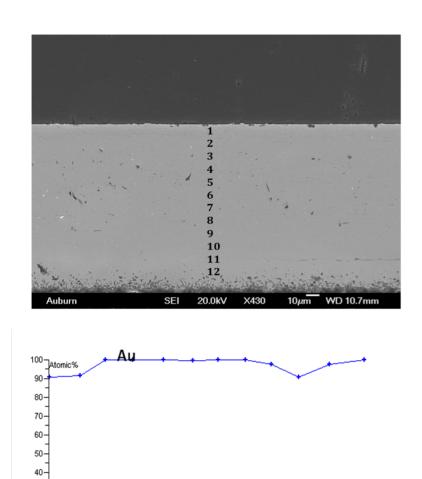

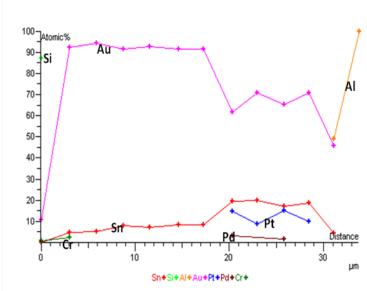

| Figure 4.17 Elemental Analysis Across the Bond Layer of the As-assembled Cr/NiCr/Au Test Sample with Off-eutectic Sn-Au-Sn Die Attach         | 75 |

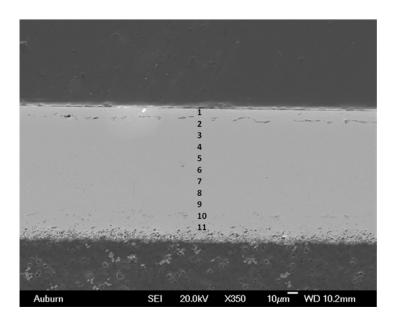

| Figure 4.18 Line Profile of Cr/NiCr/Au Die with Off-Eutectic Sn-Au-Sn Die Attach after 25 Hours at 500°C                                      | 76 |

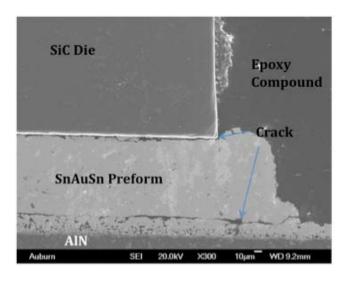

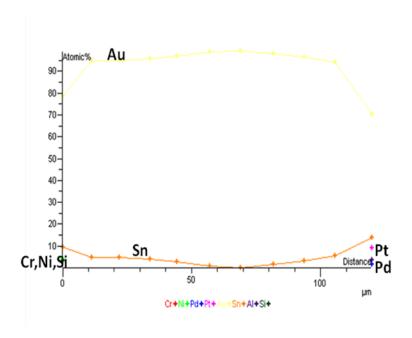

| Figure 4.19 Cross Section Micrograph of the Cr/NiCr/Au Die with Limited Volume Eutectic AuSn Die Attach after 500 cycles from 35°C to 500°C   | 77 |

| Figure 4.20 Elemental Analysis across the Bond Layer of the As-assembled Cr/NiCr/Au Test Sample with Limited Volume Eutectic Au-Sn Die Attach | 78 |

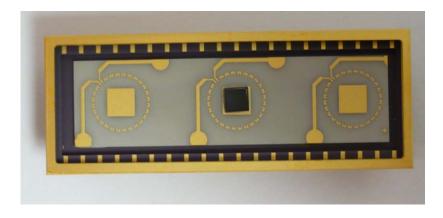

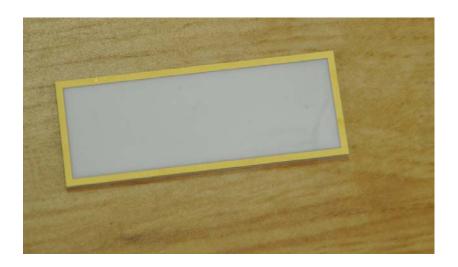

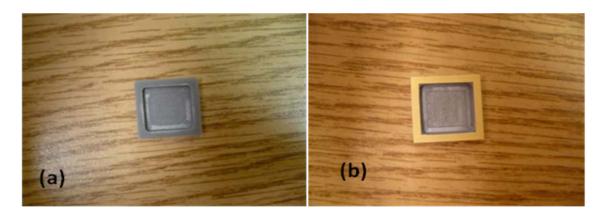

| Figure 5.1 COTS Ceramic 40 Pin DIP Packag                                                                                                     | 81 |

| Figure 5.2 Metalized AlN Substrate Attached in COTS Ceramic 40 Pin Package                                                                    | 81 |

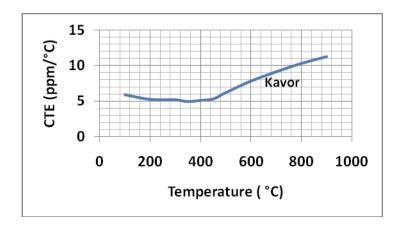

| Figure 5.3 Coefficient of Thermal Expansion for Kovar® as a Function of Temperature                                                           | 82 |

| Figure 5.4 96% Alumina Flat Lid with Mo-Mn/Ni/Au Metallization                                                                                | 83 |

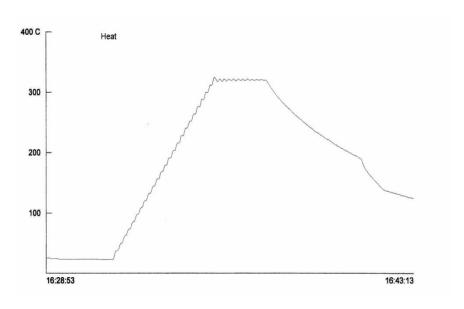

| Figure 5.5 Eutectic AuSn Preform Ring Pre-Attach Profile                                                                                      | 84 |

| Figure 5.6 Schematic Side view of 40 Pin Package Lid Attach                                                                                   | 85 |

| Figure 5.7 Off-Eutectic SnAuSn Thick Foil TLP Lid Sealing Profile Ceramic DIP Package Sealed with Ceramic Flat Lid                            | 85 |

| Figure 5.8 Picture of 40 Pin Package Hermetically Sealed with Metalized Flat Lid                                                              | 86 |

| Figure 5.9 Au-Sn Phase Diagram                                                                                                                | 87 |

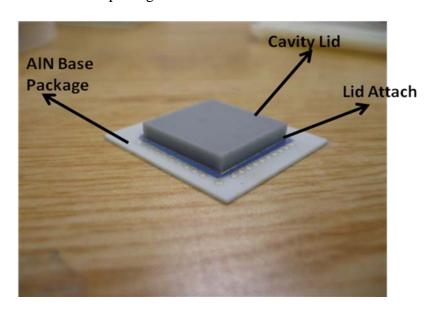

| Figure 5.10 Key Elements in an AlN Integrated Package                                                                                         | 88 |

| Figure 5.11 (a) Machined AlN cavity lid before metallization and (b) Perimeter of the AlN lid was metalized with thick film PtAu/Au | 89 |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

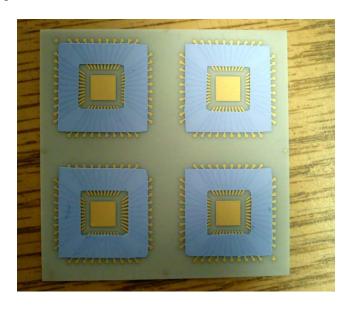

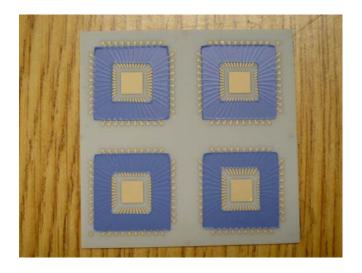

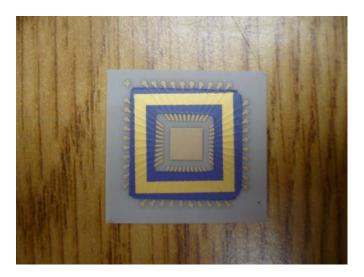

| Figure 5.12 (a) AlN substrate metalized with AuPt thick film and (b) AlN with Au thick film over AuPt                               | 89 |

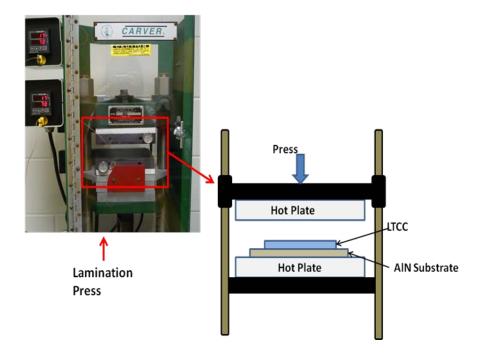

| Figure 5.13 Figure Scheme of the Lamination Process for the LTCC Tape                                                               | 90 |

| Figure 5.14 LTCC Frame Laminated on Metalized AlN Substrate before Firing                                                           | 91 |

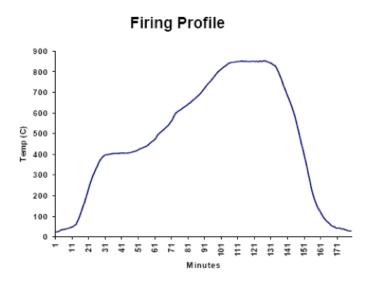

| Figure 5.15 LTCC Tape Firing Profile                                                                                                | 91 |

| Figure 5.16 LTCC Tape Frame Laminated on Metalized AlN Substrate after firing process                                               | 92 |

| Figure 5.17 AlN Base Package with Au Seal Ring on LTCC Tape                                                                         | 93 |

| Figure 5.18 Schematic Side-view of AlN Integrated Package                                                                           | 95 |

#### CHAPTER 1 INTRODUCTION

# 1.1High Temperature Electronics (HTE)

"High temperature electronics" (HTE), a term subject to various interpretations, is conventionally taken to mean electronics operation at temperatures beyond the MIL-STD-883 method 1011 range whose upper limit is 125°C. However, in various fields there are demands for electronics that must operate at much higher temperatures.

# 1.2 Applications and Benefits of High Temperature Electronics

Existing and envisioned needs for high temperature electronics derive from various industry and government programs. For example, applications for on-engine aircraft sensors can require operating temperatures in excess of 500°C. Surface temperatures are 485°C on Venus, electronics for probing and analyzing the surface of Venus must be capable of operating at such high temperatures for days or even months. The primary applications for HTE encompass automotive, aerospace, deep-well drilling, nuclear power generation and space. Table 1.1 lists a number of high-temperature applications and summarizes their temperature operating times, and other requirements [1].

Table 1.1 Applications area and Parameters for High Temperature Electronics. [1]

| Application        | Temperature     | Minimum Duration    | Duty                   | Other Environmental  |

|--------------------|-----------------|---------------------|------------------------|----------------------|

|                    | (°C)            | (hours, unless      |                        | Factors              |

|                    |                 | otherwise indicated |                        |                      |

| Well-logging-gas   | 150 to 300      | Few hours-years     | Intermittent/cyclical, | Temperature cycling, |

| & oil (down-hole)  |                 |                     | or continuous          | chemicals, pressure, |

| instrumentation    |                 |                     |                        | mechanical stress,   |

|                    |                 |                     |                        | possibly radiation   |

| Well-logging-      | 150 to 400      | Few-100             | Intermittent/cyclical  | Temperature cycling  |

| geothermal         |                 |                     |                        | chemicals, pressure, |

|                    |                 |                     |                        | mechanical stress    |

| Aircraft systems-  | 300 to 500      | 1000                | Intermittent/cyclical  | Temperature cycling, |

| on engines &       |                 |                     |                        | vibration, stress,   |

| smart transducers  | <b>7</b> 00 100 | 100                 |                        | fuel/oil/chemicals   |

| Aircraft engine R  | 500 to 600      | 100                 | Intermittent/cyclical  | Temperature cycling, |

| & D                |                 |                     | (one-shot acceptable)  | shock/vibration      |

| Automobiles        | 150 to 250      | 8000 operating, 10  | Intermittent/cyclical  | Temperature cycling, |

|                    | (700)           | years "shelf"       |                        | vibration,           |

|                    |                 |                     |                        | fuel/oil/chemicals,  |

|                    |                 |                     |                        | rough handling       |

| Fossil-fuel energy | 400 to 500      | Months-years        | Continuous             | Radiation            |

| plants             |                 |                     |                        |                      |

| Nuclear reactors   | 200 to 450      | Months-years        | Continuous             | Radiation            |

| Space Exploration  | 125 to 485      | Month - years       | Intermittent/cyclical, | Temperature cycling  |

|                    |                 |                     | or continuous          | chemicals, pressure, |

In HTE applications, the need for HTE arises from either "a high temperature environment" or "difficulties in disposing of the heat dissipation", sometimes both. Thermal protection systems such as dewars (vacuum-insulated vessel) and phase change materials may be used to protect conventional temperature range electronics operating in high temperature environments for limited periods of time. For longer duration applications, complex thermal management systems such as fluid cooling are used to maintain the electronics at lower temperatures. In both cases, this adds weight, bulk, cost, complexity, and maintenance issues while introducing additional failure points. These burdens may be less acceptable or less practical compared to using HTE electronics which can withstand the temperature of the environments. The ability to operate electronics at the ambient temperature will simplify the

electronics system and enable the use of electronics in some applications where it is not possible today. [2]

#### 1.3 High-Temperature Electronics Technology and Material

Silicon and GaAs are two commonly used semiconductor materials, which have found many applications in modern electronics. However, both with relative low band-gap (the energy difference between the conduction band minimum and valence band maximum) are clearly outperformed by wide band-gap semiconductors, (SiC, GaN etc.) for use at high temperatures. SiC, which has the potential to operate above 500°C, is by far the most developed among all wide band-gap semiconductors due to the availability of high quality SiC substrates and the progress in epitaxial growth technologies. It has a wide variety of poly-types, but only 4H-SiC and 6H-SiC are commercially available. Recently, SiC has been recognized as a good candidate material for high temperature, radiation resistant, short wavelength optoelectronic and high-power/high-frequency electronic devices. Table1.2 shows the key properties of SiC in comparison to Si and GaAs [3].

Table 1.2 Key Physical & Electronic Properties of Semiconductor Materials [3]

|                                                  | 4H-SiC  | 6H-SiC  | GaAs    | Si      |

|--------------------------------------------------|---------|---------|---------|---------|

| Bandgap Energy (eV)                              | 3.26    | 3.03    | 1.43    | 1.12    |

| Breakdown Electric Field                         | 2.2E+06 | 2.4E+06 | 3.0E+05 | 2.5E+05 |

| [V/cm (for 1000 V operation)]                    |         |         |         |         |

| Thermal Conductivity                             | 3.0-3.8 | 3.0-3.8 | 0.5     | 1.5     |

| (W/cm · K @ RT)                                  |         |         |         |         |

| Saturation Electron Drift Velocity               | 2.0E+07 | 2.0E+07 | 1.0E+07 | 1.0E+07 |

| [cm/sec (@ E $\ge 2 \times 10^5 \text{ V/cm}$ )] |         |         |         |         |

The properties that make SiC an attractive semiconductor material for these applications are [3,4,5]:

• Wide energy band-gap. Electronic devices formed in SiC can operate at extremely

high temperatures without suffering from intrinsic conduction effects because of the wide energy band-gap. Also, this property allows for unique optoelectronic applications, that include blue light emitting diodes and UV photo-detectors

- High thermal conductivity. Heat will flow more readily through SiC than other semiconductor materials. This property enables SiC devices to operate at extremely high power levels and still dissipate the large amounts of excess heat generated. Additionally, high thermal conductivity is also beneficial in maximum device packaging density.

- High breakdown electrical field. SiC can withstand a voltage gradient (or electric

field) without undergoing avalanche breakdown. This property enables the fabrication

of very high-voltage, high-power devices such as diodes, power transistors, power

thyristors and surge suppressors, as well as high power microwave devices. High

break down electric field also allows for increased isolation between devices and

higher packing densities.

- High saturated drift velocity. Due to the high saturated electron drift velocity of SiC,

SiC devices can operate at high frequencies (RF and microwave).

Silicon carbide device technology is being developed for power electronics applications for use at high temperatures [5, 6, 7]. In recent studies, SiC based electronics and sensors have also been demonstrated for extended operation at 500 and 600°C. However, level of integration is at a very low level. In addition, for realization of high-power applications, SiC-based power switches are not yet commercially available [8, 9, 10, 11].

For efficient and effective integration of wide bandgap power devices into the power electronic modules, silicon on insulator (SOI) based integrated circuits are needed to interface

them with the control units. SOI technology provides the ability to realize complex electronics functions for high temperature applications. In high-temperature electronics, junction leakage is a major concern. Bulk complementary metal-oxide-semiconductor (CMOS) processes suffer from significant leakage current which contributes to higher junction temperature compared to the ambient. In SOI devices and circuits, the active device area is restricted to a Si layer of small thickness, perfectly isolated by the buried and field oxide. Buried insulator layer in SOI structure provides dielectric isolation, greatly reducing the leakage path associated with the drain and the source p-n junction diodes, which enables higher temperature operation. The threshold voltage variation with temperature is smaller in SOI devices than in bulk devices. SOI also provides improved latch-up immunity, which ultimately increases the reliability of the circuit operation at higher temperature [1, 12]. These make SOI-based circuits capable of operating successfully in the 200°C-300°C temperature range which is well above the range of conventional bulk siliconbased devices. It has been shown that the leakage current remains manageable in SOI until at 300°C [1, 12]. At elevated temperatures, SOI devices and circuits clearly outperform comparable bulk silicon. SOI rated for 250°C [13, 14] is commercially available and 300°C operation has been demonstrated [15, 16]. Power electronics for 200-300°C applications will combine SOI for control and SiC power devices [17]. SOI will be the primary technology for low power digital, mixed signal and analog electronics at temperature < 300°C. To build functional systems operating at high temperatures, packaging technology must be developed to interconnect the SOI and SiC based devices.

# 1.4 High Temperature Electronics Packaging

Devices capable of functioning in high temperature environments need robust and reliable packaging to sustain operation throughout its entire designed lifetime cycle.

Additionally, to build any functional systems, multiple devices including passives must be interconnected. Without parallel developments in packaging technology, the advances in HTE technology will be hindered. Therefore, packaging and interconnections for these devices are important requirements for realizing any practical HTE systems. This work addresses packaging for the SOI electronic devices applications at 300°C and SiC devices applications up to 500°C.

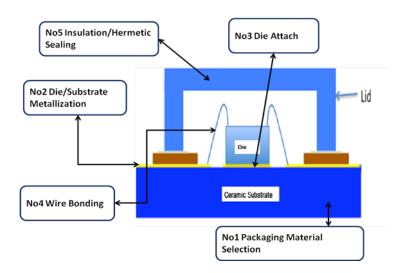

#### 1.4.1 Key Elements of HTE Packaging

The key elements in realizing HTE packaging technology are (1)substrate materials selection; (2) die and substrate metallization; (3)die attach; (4)wire bonding; and (5)hermetic sealing. Figure 1.1 is the illustration of key elements of a HTE package.

Figure 1.1 the Illustration of Key Elements of a Package

# 1.4.2 Substrate Selection

Unlike organic based packaging, metalized ceramic substrates have the potential for use at extreme high temperature. Aluminum oxide  $(Al_2O_3)$  is the most commonly used ceramic substrate and a wide variety of  $Al_2O_3$  packages are commercially available. However, the coefficient of thermal expansion (CTE) of  $Al_2O_3$  (CTE = 6.5ppm/ $^{\circ}$ C) is relatively high compared to that of SiC (CTE = 4.2ppm/ $^{\circ}$ C). With a potential thermal cycle range from room temperature

to 500°C and this CTE mis-match, the strain on interfaces such as the die attach is significant and will limit the number of thermal cycles to failure. Aluminum nitride (AlN) has excellent high temperature stability, high thermal conductivity and a coefficient thermal expansion (CTE) (CTE=4.4 ppm/°C) closely matching that of SiC, which provides a ideal packaging platform for SiC based high temperature electronics. For Si die (CTE = 2.9ppm/°C) [18], silicon nitride (Si<sub>3</sub>N<sub>4</sub>) provides the best CTE match. Si<sub>3</sub>N<sub>4</sub> also has higher mechanical strength and fracture toughness than Al<sub>2</sub>O<sub>3</sub> and AlN. For these reasons, AlN is being investigated for SiC device packaging and Si<sub>3</sub>N<sub>4</sub> is being investigated for SOI device packaging in this research. The typical properties of these ceramics substrates are presented in Table 1.3[19]

Table 1.3 Typical Properties of Ceramic Substrates [19]

|                                                                   | Al <sub>2</sub> O <sub>3</sub> (96%) | AlN                  | $Si_3N_4$            |

|-------------------------------------------------------------------|--------------------------------------|----------------------|----------------------|

| Flexural Strength (MPa)                                           | 350                                  | 220                  | 610                  |

| Coefficient of Thermal Expansion 40-400°C (x10 <sup>-6</sup> /°C) |                                      | 4.6                  | 2.6                  |

|                                                                   |                                      |                      |                      |

| Thermal Conductivity @ RT (W/m K)                                 | 24                                   | 150                  | 20                   |

| Volume Resistivity (W-cm)                                         |                                      |                      |                      |

| 20°C                                                              | $>10^{14}$ $10^{10}$                 | $>10^{14}$ $10^{10}$ | $>10^{14}$ $10^{12}$ |

| 300°C                                                             | $10^{10}$                            | $10^{10}$            | $10^{12}$            |

| Dielectric Constant @ 1MHz                                        | 9.4                                  | 9.6                  | 8.6                  |

| Dielectric loss angle @1MHz (x10 <sup>-4</sup> )                  | 4                                    | 19                   | 3                    |

|                                                                   |                                      |                      |                      |

#### 1.4.3 Die and Substrate Metallization

A basic metallization scheme for a semiconductor die used in HTE technology consists a contacting layer (either Ohmic or Schottky contact), a diffusion barrier layer and a cap layer for interconnection [20]. For the die attach process success, the die backside metallization must have good adhesion and low contact resistance. The contacting layer must be made of a material that is thermodynamically stable in contact with the semiconductor/oxide, otherwise the electrically active interface thus formed cannot be stable; The barrier layer is a critical part of the

metallization and must have high resistance to oxidation and inter-diffusion because its function is to impart thermal stability to the system; The cap layer, in general, Au, must have good wettability with the die attach material in order to obtain a void-free bond joint [20]. In this dissertation, Ti/Ti:W/Au was evaluated as SOI backside die metallization for 300°C operation. For 500°C operation, the SiC backside metallization evaluated were Ti/TaSi/Pt/Au and Cr/NiCr/Au.

The ceramic substrate metallization provides a base for the die attachment and electrical interconnections for the systems. The substrate metallization intended for high temperature operation must resist surface oxidation and migration while maintaining good adhesion to the substrate [21, 22]. In this work, thick film technology is used to metalize the ceramics: Au and Pt/Au conductive metal pastes were deposited in patterns defined by screen printing onto a ceramic substrate and fired using a high temperature profile (peak temperature 850°C). During the firing process, the inorganic binder molecules in the metal paste migrate to the metal/substrate interface and form reactive binding chains.

#### 1.4.4 Die Attach

Die attach is the process of attaching the chip to the substrate or the semiconductor package. It is a fundamental element of any packaging approach. Commonly, there are two common die attach processes, adhesive die attach and eutectic die attach. For high temperature applications, Au based alloys have been proposed as promising die attach materials for high-temperature device packaging because of their good compatibility with the die and substrate metallization, excellent electrical conductivity, thermal conductivity and corrosion resistance. In this dissertation, eutectic Au-Ge (88/12 wt%) preforms have been investigated as die attach material for SOI die packaging for 300°C operation, and a liquid transient phase die attach

bonding process using Au-Sn (80/20 wt%) preform or off eutectic Sn-Au-Sn thick foil were developed for SiC devices at 500°C operation.

#### 1.4.5 Wire Bonding

Wire bonding is an electrical interconnection technique using thin wires and a combination of heat, pressure and/or ultrasonic energy, where the two metallic materials (wire and pad surface) are brought into intimate contact. [23] It is generally considered the most cost-effective and flexible interconnect technology, and is used to assemble the vast majority of semiconductor packages [24]. Commonly aluminum or gold wires are used for wire bonding, but when the operation temperature is increased to more than 200 °C, Al becomes weak. On the other hand, Au possesses much higher strength at high temperature than Al. In addition, Al and Au are incompatible because Au reacts with Al, forming brittle intermetallics at high temperature. The reaction accelerates with increasing temperature and Kirkendall voids are created if gold-aluminum diffusion is excessive, which will lower the physical and mechanical properties of the bond [25, 26]. In this study, the bonding process was investigated and the suitable process parameters were identified for 1mil diameter Au wire and Al/Ni/Pd/Au die wire bond pads on SOI using thermo-sonic wire bonding for 320°C applications.

# 1.4.6 Hermetic Sealing

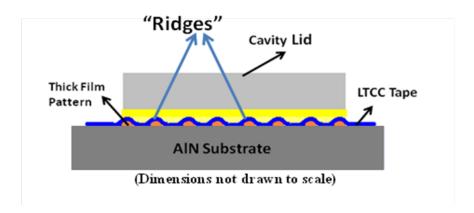

Hermetic sealing protects the electronic devices from mechanical damage and intrusion of the atmosphere contaminants. One of the hermetic packaging schemes that have received most use for high temperature is multilayer ceramic packages [27, 28]. Two types of approaches were investigated in this project for hermetic sealing: LTCC (low temperature co-fired ceramic) AlN packages and commercially available 40pin hybrid Al<sub>2</sub>O<sub>3</sub> packages with a metalized Al<sub>2</sub>O<sub>3</sub> lid. Key features of the LTCC AlN packages construction evaluated in this project were metalized

AlN substrate, the LTCC frame, screen printed thick film Au seal ring and machined AlN cavity lid.

#### 1.5 Research Outline

The goal of the project was to develop the assembly materials and processes for packaging SiC and SOI electronics, which will be used in high temperature environments. In Chapter 2, material properties and device technology related to HTE are briefly discussed. Key issues in packaging of HTE are reviewed in Chapter 2, including: substrates technologies, die thin film metallization, die attach materials and processing, wire bonding, and hermetic lid sealing.

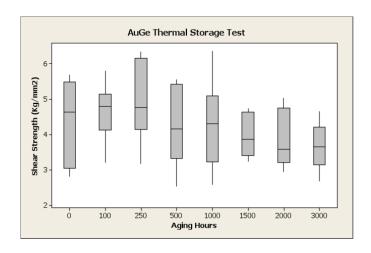

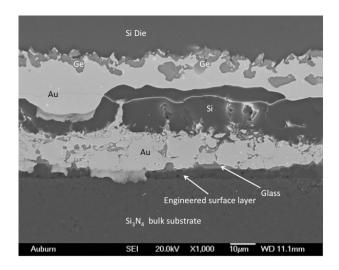

Chapter 3 describes an investigation of eutectic Au-Ge die attach for the Silicon-on-insulator (SOI) die packaging for applications at 300°C, including substrates technology, die metallization, die attach bonding process. Results of die attach reliability based on shear strength are discussed after thermal storage and thermal cycling tests. Results of the investigation of Au wire bonding on substrate metallization and die metallization are also presented in chapter 3, including wire bonding parameters, bond-ability and reliability based on pull and shear strength tests. Failure analysis after reliability testing was also performed.

Chapter 4 presents details of the Au-Sn liquid transient phase (LTP) die attach technology for SiC packaging at 500°C operation, which includes die attach materials, suitable brazing processes, SiC die and AlN substrate metallization preparation. Chapter 4 also reports the mechanical strength and investigations of the braze joint during high temperature storage and thermal cycling tests. Failure analyses after reliability testing are presented.

Chapter 5 reports the details of hermetic lid sealing processes for HTE ceramic packages, including AlN substrate metallization, LTCC AlN package preparation, and lid sealing profiles. Results of the gross leak testing were also included.

#### CHAPTER 2 BACKGROUND

This chapter presents the background information related to the topics that will be covered in this dissertation. Packaging considerations for HTE are reviewed. Key issues in HTE packaging will also be discussed in this chapter including: die thin film metallization, substrate technologies, die attach materials and processing, wire bonding, and hermetic lid sealing.

# 2.1 Packaging Considerations for HTE

In the selection of proper packaging and interconnection materials for high temperature applications, the critical issues that must be considered are [29,30, 31]:

- A. Thermo-mechanical compatibility: Coefficient of Thermal Expansion (CTE) mismatches between the die and the substrate as well as between the different packaging components will cause stresses during assembly and during operation. With higher operating temperatures, the temperature span (ΔT) associated with the thermal cycle increases, resulting in higher stress/strain on materials with mismatched CTEs. The higher stress/strain levels will lead to a lower number of thermal cycles to failure. Therefore, the thermal expansion mismatch between the die, the substrate, and other packaging components should be small at all temperatures to minimize thermal stresses.

- B. Thermal conductivity: Poor thermal conductivities can mean poor ability to dissipate heat and cause excessive temperature differences between parts of the circuit. Therefore, substrate, metallization, and die attach thermal conductivity must be maximized. The fact that the thermal conductivity of packaging materials decreases with increasing

- temperature must be considered, and thermal designs must be based on materials at the highest operating temperature expected for the system.

- C. Electrical properties: With increasing operating temperature, the electrical conductivity of metal decreases, and the voltage blocking capability/insulation resistance of the dielectrics decreases as well. These factors must be considered in simulations of system performance at elevated temperatures.

- D. Chemical compatibility: Inter-diffusion in metals can cause Kirkendall voiding due to the differential diffusion rates of one metal into another. Many metal couples can form intermetallic compounds, which are often brittle and have different properties from those of the individual metal. Oxidation of metals will reduce material electrical conductivity. Moreover, excessive oxidation can lead to structural/mechanical failure. Therefore, die attach and wire bonding materials, as well as die and substrate metallization should have good oxidation resistance, minimum inter-diffusion and inter-metallic formation.

- E. Hermeticity: Hermetic seal prevents gases and liquids from entering the package cavity where the die is mounted. For high temperature and harsh environment packaging, the package should have atmospheric integrity to protect the die from environmental elements.

#### 2.2 Thin Film Die Metallization

Multilayer thin film metallization compatible with HTE packaging and interconnecting techniques (wire bonding and die attach) are commonly used for die metallization (The term "thin film" here refers more to the manner in which the film is deposited as opposed to the actual thickness of the films.). As it has been stated in the introduction chapter, the basic metallization scheme consists of three layers: (1) the bottom layer provides adhesion to the die and serves as

Ohmic or Schottky contact if required; (2) the middle layer acts as a diffusion barrier between the contact layer and the cap layer; and (3) the cap layer is the interconnection layer. An effective chip metallization should provide the following features [32]:

- Good adhesion to the wafer passivation and the contact (Ohmic or Schottky)

- Low contact resistance

- An effective diffusion barrier

- A metal stack that is compatible with wire bonding and braze metallurgy

- High temperature reliability

# 2.2.1 Evaporation and Sputtering

Thermal evaporation and sputtering are the two most important physical vapor deposition (PVD) methods employed for depositing multilayer metal thin films. The main principle is to convert the source material (target) into vapor by sputtering or evaporation. The vapor passes across a region of low pressure from its source to the substrate and subsequently condenses on substrate surfaces to form the thin films [33,34,35,36].

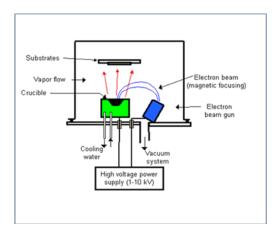

In thermal evaporation, the conversion into vapor phase is achieved by applying heat to the source material. High vacuum is required in the evaporation method to allow the atoms/molecules to evaporate freely in the chamber. There are two widely used evaporation technologies: electron-beam evaporation (E-beam) and resistive evaporation. In electron beam evaporation, a high kinetic energy beam of electrons is aimed at the target for evaporation. Upon impact, the high kinetic energy is converted into thermal energy, heating up and evaporating the target material. Resistive heating uses a big current passing through the resistor (the target material is put or attached to the resistor) to generate high temperature, converting the target material into vapor state. Traditionally the resistors are made by W(Tm=3380°C),

Ta(Tm=2980°C) or Mo(Tm=2630°C) which have a high melting temperature. A schematic diagram of a typical system for e-beam evaporation [35] is shown in the Figure 2.1.

Figure 2.1 Typical system of e-beam evaporation of materials [35]

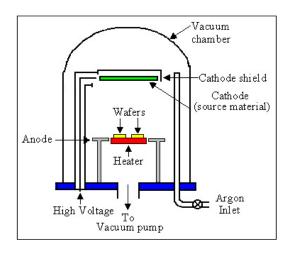

Sputtering is performed in a vacuum chamber filled with noble gas, commonly Argon. The source material to be deposited (target) is negatively charged as the cathode. By adding a high voltage DC or RF power source, the argon will enter a plasma state and Ar<sup>+</sup> will move toward the cathode with high speed. The high-energy impact of the ions induces atoms at the surface of the target to be ejected or sputtered. These sputtered atoms will then form a thin film coating on the substrate after condensing [35,37]. Since the source atoms are released by impinging high-energy ions, sputtering thin film metallization deposition uses much lower temperature than evaporation. Figure 2.2 is a schematic diagram of plasma sputtering deposition system [37]

2.2 Typical Plasma Sputtering System [37]

# 2.2.2 Gold Electroplating

Gold is the most common conductor material used in thin film metallization, because of the ease of wire and die bonding and the high resistance of the gold to oxidation and corrosion. In the thin film technology, it is a common practice to sputter a very thin layer of gold which is only a few hundred Å (or less) to a few thousand Å and to build up the thickness of gold film by electroplating. This is considerably more economical and results in much less target usage [34]. The details of gold electroplating process used in this research will be discussed in chapter 3 & 4. 2.3 Substrate Technology

Substrates provide electrical interconnection between various active and passive elements, mechanical supports for the components and a path for heat removal from the devices. Organic substrates due to their relatively low glass transition point  $(T_g)$  and decomposition temperatures are not suitable for temperature in excess of 250°C. Ceramics offer the greatest potential for high temperature packaging and interconnection technology. Commonly used substrate materials include aluminum oxide  $(Al_2O_3)$ , aluminum nitride (AlN), and silicon nitride  $(Si_3N_4)$ . The typical properties of these ceramics substrates are presented in Table 1.3 in the first Chapter, (section 1.4.2) Depending on the materials' properties, compatibility, and packaging

requirements, there are three basic technologies that can be used to form metallurgy on ceramic substrate: thick film technology; thin film technology, copper metallization technology.

Screen printing of thick film paste is among the earliest methods employed to form metallization on ceramic substrates. The metallization process sequentially consists of screen printing, drying and firing. Thick film paste materials are usually composed of (1) fine metal (such as gold) powder, (2) inorganic binder (such as metal oxides), and (3) organic vehicle (solvent and polymer). Screen printing is the first step in this technique: thick film paste is pushed through a patterned mesh screen onto the ceramics with thickness control [38]. During the following drying process (2<sup>nd</sup> step) at 150 °C, the solvent portion of the organic vehicle evaporates and the paste becomes a semi-solid phase mixture of metal powder, polymer and binder. In the following firing process the polymer decomposes, and the inorganic binder molecules migrate to the metal/substrate (e.g. Au/ceramic) interface and form reactive binding compounds. The binder may also be a glass that mechanically interlocks with the substrate. Precious metal thick-film metallization (on ceramic substrates) have been used for hybridpackaging conventional (room temperature to 150 °C) electronics. In this project, Au and Pt based thick film materials, which are processed at high temperatures (850 °C), have been used to produce metalized ceramic substrate for high temperature operation [39]. Screen printing is also used to deposit refractory metals, typically molybdenum or tungsten to ceramics. These require very high temperature firing in H<sub>2</sub>. Gold and nickel can be post-plated on top of the refractory metal thick film to allow components mounting and wire bonding.

In thin film technology, multilayer thin film conductor materials are deposited by vacuum deposition (such as sputtering and evaporation as described in section 2.2.1), after which fine-line patterns can be produced on the ceramic substrate by photo-lithograph and etching, which is

suited for high density interconnection and high frequency application. But due to inter-diffusion at elevated temperatures, multilayer composite metallurgy leads to reliability issues. Effective diffusion barriers are a limiting factor in the use of thin films at high temperature [30, 34].

Thick and thin film technologies are limited in their ability to handle large currents. Copper metallization technologies provide considerable advantages when packaging high power circuits. There are three basic technologies available: direct bond copper (DBC), active metal braze (AMB), and various methods of plating copper directly to the ceramic [34]. The thick layer of copper is capable of handling large currents without excessive voltage drops and heat generation, and also allows the heat to spread rapidly outwards from the devices.

#### 2.4 Die Attach

#### 2.4.1 General Considerations for HTE Die Attach

Die attach provides mechanical, electrical and thermal connection between the SiC die and the substrate. The ideal die attach materials for HTE packaging should have the following properties [21, 29,32]:

- Good adhesion to the die and the substrate.

- Good corrosion resistance.

- High thermal conductivity, so that heat dissipated from the devices and the thermal expansion difference between the die and the substrate can be minimized.

- An appropriate processing temperature and good thermal stability to fit into the die bonding process.

- Self-resilience to provide good stress relaxation behavior so that induced internal stress is reduced to low levels.

#### 2.4.2 HTE Die Attach Options

Attachment of the die (chip) to the substrate with conductive polymeric adhesives is a commonly used method for conventional temperature ranges. These die attach materials have the advantages of low processing temperature and relatively low cost, however, they are not suitable for applications above 250°C due to their relative low decomposition temperature [30, 40]. Epoxies are typically limited to a maximum continuous operating temperature of 150°C-200°C. Silver-filled polyimide has been used long term to 250°C-275°C. Unfilled polyimide has much higher glass transition and decomposition temperature, but much lower thermal conductivity than metal-filled versions, which is important in dissipating heat from the die to keep junction temperature lower for high temperature electronic systems [41].

For higher operating temperature ranges, there are generally three options for HTE die attachment: soldering, brazing and transient liquid bonding. The selection of bonding materials and/or process will depend on the compatibility with the terminal metallization of the die and the operating temperature requirements.

Solders are conventionally metal alloys, coming in the form of either a solder paste amenable to screen printing or a preform (sheet) [30, 42, 43]. Soldering is a process in which die and substrate are bonded together by melting and flowing the solder alloy into the joint. Solders based on Au and Ag are often called "hard solder, whereas solders based on Pb, Sn and In are called "soft solder". The terms soft and hard are taken to mean the mechanical behavior of the alloy. Hard materials have higher strength and lower elasticity than soft materials; they also exhibit less stress relaxation from thermal cycling to high temperatures. For instance, gold based alloys such as Au/Sn, Au/Ge, and Au/Si can offer high mechanical strength, but they do not provide good stress relief. Consequently, matching the CTE of the die and substrate becomes an

increasingly crucial design criterion as the die size and the operating temperature increase. There is no fundamental difference between brazing and soldering. According to the usual metallurgical definition, soldering and brazing are distinguished by the melting point of the filler metal. Typically, filler melting below 400C are considered solders and those above are considered brazes. To prevent oxidation, brazing is normally conducted in an inert gas or in a vacuum [30, 42,43]. The melting points of several high temperature solders and brazes are given in Table 2.1 [44,45,46].

Table 2.1 Melting Points of Common solder and Braze Alloy Materials [44,45,46]

| Alloy Composition (WT%)        | Solidus (°C)   | Liquidus |

|--------------------------------|----------------|----------|

|                                |                | (°C)     |

| Sn 63, Pb 37                   | 183 (eutectic) |          |

| Sn 95, Pb 5                    | 235            | 240      |

| Pb 92.5, Sn 5, Ag 2.5          | 280 (eutectic) |          |

| Au 80, Sn 20                   | 280 (eutectic) |          |

| Pb 92, In 5, Ag 3              | 300            | 310      |

| Pb 95, Sn 5                    | 310            | 314      |

| Au 88, Ge 12                   | 361(eutectic)  |          |

| Au96.76, Si 3.24               | 363 (eutectic) |          |

| Au 82, In 18                   | 451            | 485      |

| Ag 45, Au 38, Ge 17            | 525 (eutectic) |          |

| Ag 50, Cd 18, Zn 16.5, Cu 15.5 | 625            | 635      |

| Ag 78, Cu28                    | 780 (eutectic) |          |

| Au 82, Ni 18                   | 950 (eutectic) |          |

# Liquid Transient Bonding (LTB) [30,47]

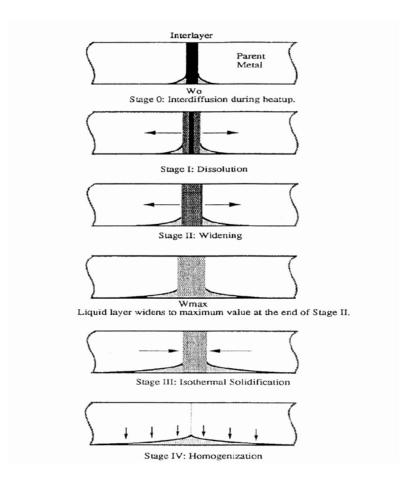

Transient-liquid-phase (TLP) bonding is a material joining process that can produce a high quality bond at the interface of the parts to be joined with no remnant of the bonding agent. The four discrete stages of the TLP bonding process are (1) heating, (2) dissolution and widening, (3) isothermal solidification, and (4) homogenization [48]. A schematic illustration of the process, shown in Figure 2.3 [49,50], indicates that by placing a thin interlayer of an alloying metal containing a melting point depressant (MPD) between the two pieces of parent metal to be

joined and heating the entire assembly, a liquid interlayer is formed. The liquid may form because the melting point of the interlayer has been exceeded, or because reaction with the parent metal results in a low melting liquid alloy. The liquid then fills voids formed by unevenness of the mating surfaces and can sometimes dissolve residual surface contamination. With time the MPD diffuses into the parent metal resulting in isothermal solidification. Upon cooling there remains no trace of the liquid phase, and ideally the joint becomes indistinguishable from other grain boundaries.

The interlayer rich in a melting point depressant can be provided by foils, electroplated, sputter coats, or any other process that deposits a thin film on the surfaces that need to be bonded. The two most important stages in terms of joint quality are the isothermal solidification and the homogenization stages; coincidently, it is also these stages that require the longest time for completion since they are controlled by solute diffusion in the solid. [51] In systems with a low solubility limit, the isothermal solidification stage becomes longer. Conversely, in some systems with a high solubility limit, the homogenization stage requires longer time for completion. The major advantage of TLP bonding is that it is an isothermal process, the thermal stresses formed between the die and substrate are minimal. When TLP is possible, it generally produce joints of excellent stength and high reliability.

Figure 2.3 Schematic Illustration of TLP bonding process [49]

# 2.4.3 Die Shear Testing

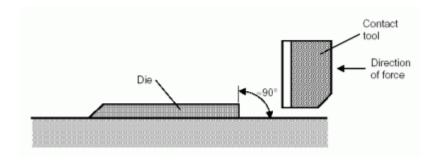

Die shear testing is a widely used process to determine the strength of adhesion of a die to the substrate. The purpose of die shear testing is to assess quality of the die-attach process as well as the integrity of the bonding materials used in the process. A typical die shear tester consists of: (a) a mechanism that applies the correct load to the die, (b) a die contact tool which applies the force uniformly from one end of the edge to the other, (c) provisions to ensure that the die contact tool is perpendicular to the die attach plane, in the mean time, the die edge and contact tool are aligned in parallel to each other [36]. During testing, the shearing arm moves the contact tool horizontally against the die, subjecting the die to a stress that is parallel to the plane of die attach substrate, resulting in a shearing stress between: 1) the die-die attach material

interface; and 2) the die attach material-substrate interface. The force needed to shear a die off its pad, known as the die shear force, is then measured by the shear tester. A typical test set-up for die attach shear testing is shown in Figure 2.4[52].

Figure 2.4 Test Set-up for Die Attach Shear Testing [52]

### 2.5 Wire Bonding

Wire bonding is a process used to make the electrical connections from the bond pads on the top surface of the die to the substrate or a lead frame, from package terminals to substrate, or from one point on the substrate to another. Wire pull test and bond (ball) shear test are the two most universally accepted methods for monitoring the quality of the wire bonding operation. A critical factor that must be considered when operating at elevated temperatures is the material interactions between the wire and the pad to which it is being bonded, because of the brittle intermetallic phases that could form.

There are two basic forms of wire bonding: ball bond (Figure 2.5) and wedge bond (Figure 2.6). Depending on bonding agent (heat and ultrasonic energy), the bonding process can be defined to three major processes: thermo-compression bonding (T/C), ultrasonic bonding (U/S), and thermo-sonic bonding (T/S) [53].

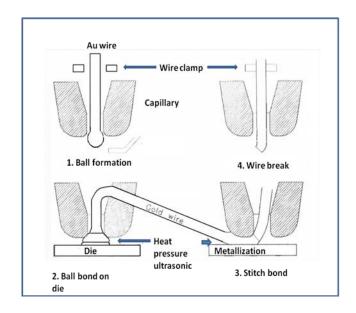

### 2.5.1 Ball Bonding

During ball bonding, a free air ball (FAB) is first formed by melting a small portion of the wire extending beneath the capillary through an electric arc called electronic flame-off (EFO). The FAB is then pressed to the bonding pad on the die, and adequate amounts of pressure, heat, and ultrasonic forces are applied to the ball for a specific amount of time, forming the initial metallurgical weld between the ball and the bond pad. The capillary is then raised and repositioned over the second bond site on the substrate; a precisely shaped wire connection called a wire loop is thus created. Deforming the wire against the bonding pad makes the second bond (stitch bond). Then the wire clamp closes, and the capillary ascends once again breaking the wire just above the wedge, an exact wire length is left for the EFO to form a new ball to begin bonding the next bonding cycle [53,54,55]. Ball bonding is generally used in thermocompression (T/C) or thermo-sonic bonding (T/S) process and this technique is used extensively for Gold wire bonding. However, Ball bonding is not recommended for Aluminum wire because Al wire doesn't form a uniform FAB during flame-off unless an inert gas is used. Figure 2.5 (a) shows the typical Au wire ball bonding sequence and (b) is schematic representations of the geometry of a ball bonding [34,56].

2.5 (a) Typical Au Wire Ball Bonding Sequence [34]

Figure 2.5 (b) Illustration of the Geometry of Ball Bonding [56]

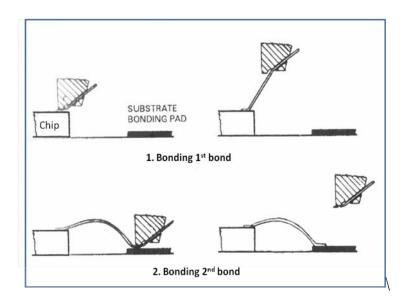

## 2.5.2 Wedge Bonding

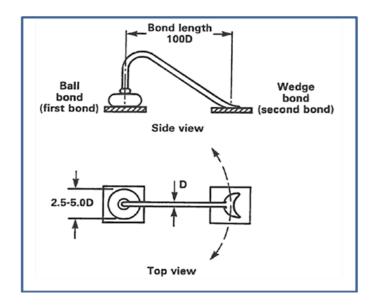

Wedge bonding is named based on the shape of its bonding tool. In this technique, the wire is fed at an angle usually 30-60° from the horizontal bonding surface through a hole in the back of a bonding wedge. By lowering the bonding wedge onto the bond pad, the wire is pinned against the pad surface and an U/S or T/S bond is performed. Next, the wedge rises and executes a motion to create a desired loop shape. At the second bond location, the wedge descends, making a second bond. The wire is then broken off by clamping and movement of the wire [54, 55, 56]. Wedge bonding technique can be used for both aluminum wire and gold wire bonding applications. The principle difference between the two processes is that the aluminum wire can be bonded in an ultrasonic bonding process at room temperature, whereas gold wire wedge bonding is performed through a thermo-sonic bonding process with heating up to at least 150°C. Figure 2.6 (a) shows the Al wire ultrasonic wedge bonding sequence and (b) is schematic representations of the geometry of ultrasonic wedge bonding [34, 56].

2.6 (a) Ultrasonic Wedge Bonding Sequence [34]

Figure 2.6 (b) Schematic Illustration of the Geometry of Wedge Bonding [57]

# 2.5.3 Wire Pull Testing and Bond Shear Testing

Wire pull testing requires special equipment commonly referred to as a wire pull tester (or bond pull tester), which consists of two major parts: 1) a mechanism for applying the upward pulling force on the wire using a tool known as a pull hook; and 2) a calibrated instrument for measuring the pulling force at which the wire eventually breaks. This breaking force is usually

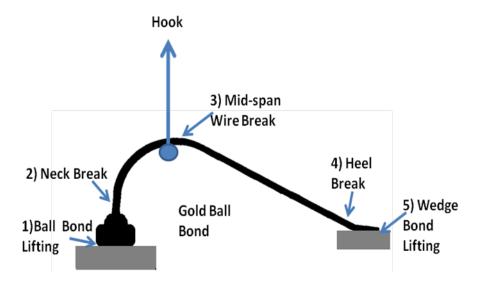

recorded by wire pull tester in grams-force [36, 53, 55]. Aside from the bond strength reading, the operator must also record the bond failure mode. Failure mode in this context refers to one of the following: 1) first bond (ball bond) lifting; 2) neck break; 3) mid-span wire break; 4) heel break; and 5) second bond (wedge bond) lifting. First or second bond lifting is unacceptable and should prompt the process owner to investigate why such a failure mode occurred. Figure 2.7(a) shows the schematic illustration and pull test failure modes of a typical wire pull test.

Figure 2.7 (a) Typical Geometrical Configuration and Pull Test Failure Modes for Wire Pull Test [54]

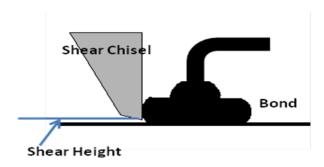

A bond shear tester is needed to perform the bond shear test [36,53]. This equipment consists of a sample holder, a shearing arm with a chisel-shaped tool at the end, and an instrument for measuring the shear strength of the bond. Initially, the shearing tool is positioned beside the ball bond to be tested. The shearing arm then moves the tool horizontally against the ball, in effect pushing the ball off its bond pad. The force needed to shear a ball off its pad, known as the bond shear force, is then measured by the ball shear tester. During bond shear testing, the shear height is an important variable, and it must be set high enough to avoid

dragging on the substrate surface but low enough to produce a shear load rather than a rolling force. The schematic illustration of bond shear test is shown in Figure 2.7 (b).

Figure 2.7 (b) Typical Geometrical Configuration and Position of Chisel for Bond Shear Test [54]

## 2.6 Hermetic Sealing

Hermetic sealing minimizes the intrusion of contamination and allow the circuit mounted inside the package to survive for a longer period of time. In practice, "hermetic" is defined not in the absolute sense of the word but rather in meeting a finite helium leak rate below a specified standard rate. For added reliability, a hermetic package is sealed in either a benign environment, generally nitrogen, or in vacuum [34, 41].

Ceramic packages and metal packages are two common types of hermetic packages[34,41]. Kovar<sup>®</sup> metal packages [58] which are fabricated primarily from F-15 alloy (known as Kovar<sup>®</sup> alloy) have glass to metal feed-throughs and are widely used to hermetically seal hybrid circuit with low I/O counts. They can provide a close match in CTE between glass and the F-15 alloy, but the CTE varies significantly as a function of temperature, which can cause high stress during cycling. Kovar<sup>®</sup> packages may be Au-plated or Ni-plated and sealed with similarly plated Kovar<sup>®</sup> lids [58]. Most ceramic packages used today are produced from cofired alumina, either by HTCC (high temperature co-fired ceramic) or LTCC (low temperature

co-fired ceramic) [31,34,41]. Leads are then brazed to the package body. The metalized areas of the package are electroplated (usually nickel followed by gold). LTCC packages are gaining prominence because of the ability to co-fire with low resistivity Au, Ag and Cu at relatively low temperature, and the flexibility and ease with which packages integrated with substrates can be designed and fabricated [58]. Further benefit of LTCC packages includes that the CTEs can be tailored to closely match Si and GaAs devices. Ceramic packages can be sealed with a flat lid metalized around the periphery of the seal area by soldering, usually with Au-Sn (80/20 wt%) alloy (eutectic T<sub>m</sub>=280°C). For higher operating temperature, Au-Sn TLP sealing is an option [30,41]. Sealing with a low-melt-point glass is less expensive but this method is also less reliable because the glass seal is susceptible to mechanical and thermal stress; Welding can provide the highest temperature capability, but the technique requires a seal ring to be brazed to the ceramic. At temperature above 400°C, it is challenging to find reliable materials for the brazes and a compatible seal ring [59].

# CHAPTER 3 PACKAGING FOR HIGH TEMPERTURE SILICON-ON-INSULATOR ELECTRONICS

### 3.1 Introduction

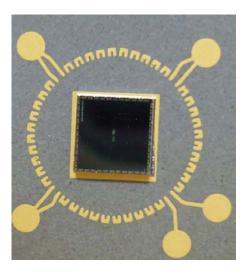

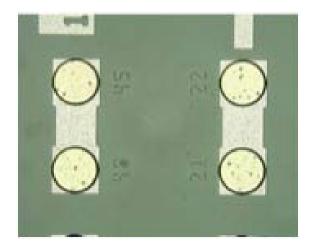

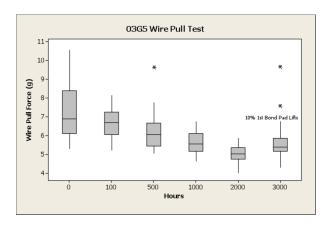

Silicon-on-insulator (SOI) integrated circuits have been demonstrated for use at temperatures up to 300°C. However, to build functional electronics, multiple devices must be interconnected to provide the desired functionality. A system-in-package (SiP) approach has been developed using thick film technology on Si<sub>3</sub>N<sub>4</sub> ceramic substrates in this project. Eutectic Au-Ge die attach was used with a Ti/Ti:W/Au backside die metallization for 300°C operation. Results of die attach reliability based on shear strength are discussed after thermal storage and thermal cycling tests. Wire bonding is a cost-effective and flexible interconnect technology for HTE packaging [60]. SOI die typically have Al wire bond pads that are not compatible with Au thermosonic wire bonding for high temperature applications. A plating process that provides a barrier layer (electroless Ni) and a wire bondable finish (electroless Pd/immersion Au.) over the Al wire bond pads has been examined. Results of the investigation of Au wire bonding on substrate metallization and die surface metallization are also presented in this chapter.

### 3.2 Thick Film Si<sub>3</sub>N<sub>4</sub> Substrates

Fabrication of a thick film module begins with the substrate. For Si die, silicon nitride  $(Si_3N_4)$  provides the best CTE match.  $Si_3N_4$  also has a higher flexural strength than  $Al_2O_3$  and AlN, which is important in measure-while-drilling (MWD) applications. For these reasons,  $Si_3N_4$  is being investigated for SOI die packaging.

Thick film materials have not been developed specifically for  $Si_3N_4$  ceramic substrates. An early attempt to use a standard thick film conductor material developed for AlN yielded poor adhesion of the thick film Au metallization to the  $Si_3N_4$  substrate [61].

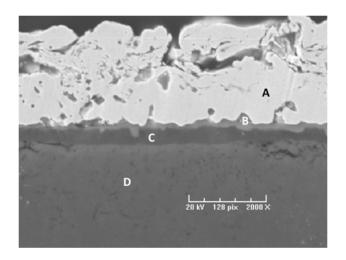

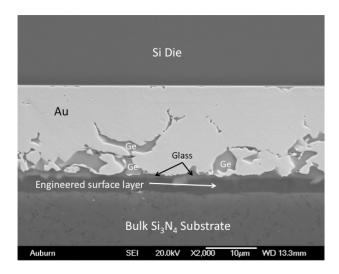

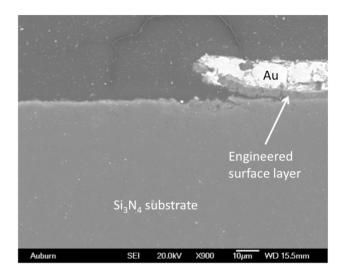

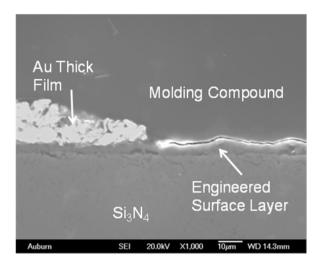

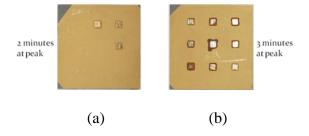

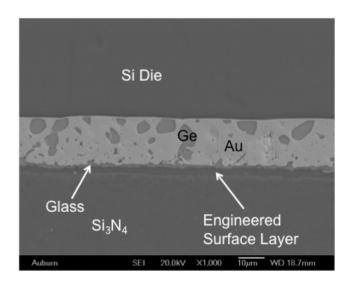

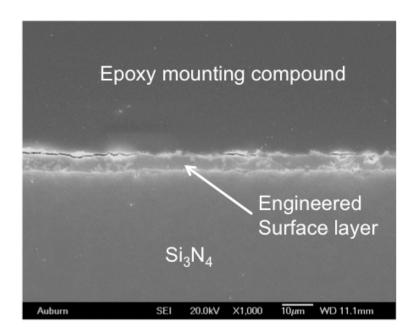

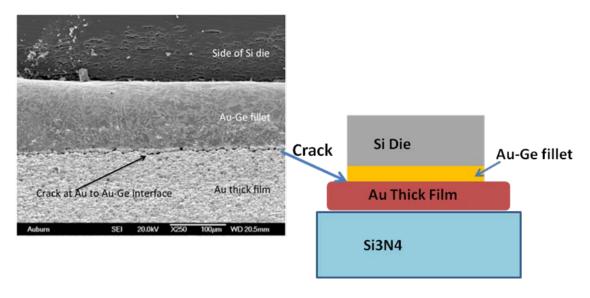

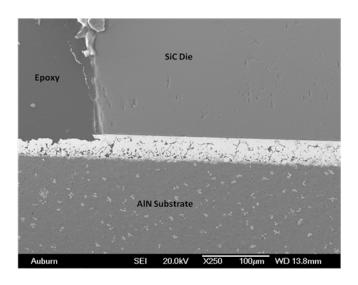

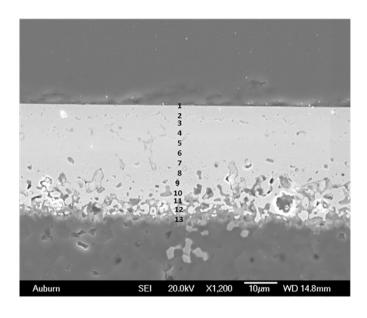

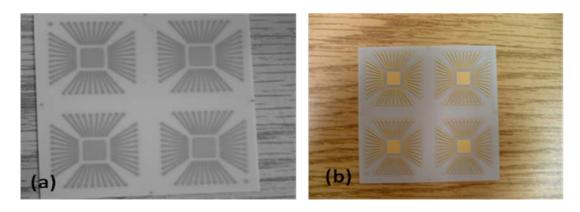

Sienna Technologies, Inc. (Woodinville, WA) has recently developed a first generation thick film Au for  $Si_3N_4$  including paste chemistry control and surface engineering that yields excellent metallization adhesion. Figure 3.1 shows an Au metalized  $Si_3N_4$  substrate. A cross section of the metalized substrate is shown in Figure 3.2. The glass adhesion layer (B) of the thick film conductor can be clearly seen. The engineered surface layer (C) on the surface of the  $Si_3N_4$  substrate is seen below the thick film glass adhesion layer. Sienna Technologies, Inc. fabricated substrates for the die attach (high temperature aging and thermal cycling) and wire bond experiments.

Figure 3.1(a)

Figure 3.1 (b) Figure 3.1 Thick Film Metalized  $Si_3N_4$  Substrate. (a) wire bond test pattern, (b) close-up of wire bond pad

Figure 3.2 Cross Section of Fired Thick Film Au Conductor on  $Si_3N_4$  Substrate, A = Sintered Au, B = Thick Film Glass Adhesion Layer, C = Engineered Surface Layer, D = Bulk  $Si_3N_4$ .

### 3.3 Si Die Backside Metallization

Au-Ge has been shown to be incompatible with Ni/Au plated on direct bond copper (DBC) for high temperature applications due to the formation of Ni-Ge intermetallics [62]. To avoid any potential issue with Ni-Ge intermetallics, the Si test die backside metallization used in this experiment was: Ti/Ti:W(10:90wt%)/Au. The deposited thin film layer thicknesses were: