# EXPLORING THE INTEGRATION OF MODEL-BASED FORMAL METHODS INTO SOFTWARE DESIGN EDUCATION

Except where reference is made to the work of others, the work described in this thesis is my own or was done in collaboration with my advisory committee. This thesis does not include proprietary or classified information.

| S                                                                           | Shuo Wang                                                                          |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Certificate of Approval:                                                    |                                                                                    |

| John Hamilton Associate Professor Computer Science and Software Engineering | Levent Yilmaz, Chair Assistant Professor Computer Science and Software Engineering |

| Dean Hendrix Associate Professor Computer Science and Software Engineering  | Stephen L. McFarland Acting Dean Graduate School                                   |

# EXPLORING THE INTEGRATION OF MODEL-BASED FORMAL METHODS INTO SOFTWARE DESIGN EDUCATION

Shuo Wang

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements of the

Degree of

Master of Science

Auburn, Alabama December 16, 2005

# EXPLORING THE INTEGRATION OF MODEL-BASED FORMAL METHODS INTO SOFTWARE DESIGN EDUCATION

| Shuo Wa                                                                                                           | ang                                       |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Permission is granted to Auburn University to r<br>upon request of individuals or institutions and<br>publication | at their expense. The author reserves all |

|                                                                                                                   | Signature of Author                       |

|                                                                                                                   | Date of Graduation                        |

# **VITA**

Shuo Wang, son of Linfu Wang and Suran Guo, was born in October 1979 in Tianjin, the People's Republic of China. He entered Georgia Institute of Technology in 1998 and received a Bachelor of Science degree in College of Computing in December 2002. Mr. Wang entered Graduate School at Auburn University in August, 2003.

#### THESIS ABSTRACT

# EXPLORING THE INTEGRATION OF MODEL-BASED FORMAL METHODS INTO SOFTWARE DESIGN EDUCATION

#### Shuo Wang

Master of Science, December 16, 2005 (B.S., Georgia Institute of Technology, December 2002)

## 105 Typed Pages

Directed by Dr. Levent Yilmaz

Proper design analysis is indispensable to assure quality and reduce emergent cost due to faulty software. Teaching proper design verification skills early during the pedagogical development of a software engineer is crucial, as much analysis is the only tractable way of resolving software problems early when they are easy to fix. Besides, fundamental component of any engineering discipline, including software engineering, is the use of formal and sound techniques that facilitate analysis of artifacts produced by students. Yet, the impact of formal methods in software engineering practice, as well as education, is minuscule. The fundamental reasons why formal methods are not effectively utilized are attributed to (1) the impedance mismatch between the underlying mathematical underpinning of formal methods and students' semi-formal, if not informal,

view of the design problem and (2) the lack of tool support for seamless and transparent integration of formal methods into software design education. This thesis suggests a strategy and tool support to improvement attainment of software design verification skills. The strategy illustrates how selective and pragmatic application of model-based verification methods can be used in software design education via tools that aim to bridge the gap between students' semi-formal design world-view and the formalism underlying formal methods.

# **ACKNOWLEDGEMENT**

I would like express sincerely appreciation to Dr. Levent Yilmaz for his guidance, insight, and encouragement throughout the research to help me succeed.

I would also like to thank the rest of my thesis committee members, Dr. John Hamilton and Dr. Dean Hendrix for their valuable suggestions and comments.

Last but not least, I would like to thank my family and friends for their understanding, motivation and support.

Style manual or journal used: <u>Journal of SAMPE</u>

Computer software used: Microsoft Word

# TABLE OF CONTENTS

| List of Figures                                                                      | xi   |

|--------------------------------------------------------------------------------------|------|

| List of Tables                                                                       | xiii |

| 1 Introduction                                                                       | 1    |

| 1.1 The Need for Integration of Formal Methods into Software Design Education        | 1    |

| 1.2 The Challenges in Integrating Formal Methods into Software Design Education      | 3    |

| 1.3 Research Objective                                                               | 6    |

| 2 Literature Review                                                                  | 8    |

| 2.1 Formal Methods                                                                   | 8    |

| 2.2 Model Checking                                                                   | 10   |

| 2.2.1 The Advantages and Disadvantages of Model Checking                             | 11   |

| 2.2.2 Symbolic Model Checking and Partial Order Reduction                            | 12   |

| 2.2.3 Using Temporal Logic for Model Checking                                        | 14   |

| 2.2.4 Existing Model Checking Tools                                                  | 18   |

| 2.3 The Role of Formal Methods in Software Design Education                          | 19   |

| 2.3.1 Formal Methods as Part of an Engineering Curriculum                            | 21   |

| 2.3.2 Common Formal Methods used in Software Engineering Education                   | 25   |

| 3 A Practical Strategy for Integrating Model Checking into Software Design Education | 29   |

| 3.1 Using UML Models as Input Design Models                                          | 30   |

| 3.2 Substituting Temporal Logic with Specification Templates                         | 31   |

| 3.3 Three Incremental Steps to Realize the BMA                                       | 36   |

| 4 Architectural Design of the Behavioral Model Analyzer                             | 37 |

|-------------------------------------------------------------------------------------|----|

| 4.1 Architectural Design of the Semi-Automated BMA                                  | 42 |

| 4.2 Architectural Design of the Automated BMA                                       | 42 |

| 4.3 The Architectural Design of the Advanced Visualizer                             | 45 |

| 5 The Verification Process Using the Behavioral Model Analyzer                      | 48 |

| 5.1 Converting UML Statecharts to PROMELA Model Description Language                | 48 |

| 5.2 Augmenting State Variables to the Design Model                                  | 50 |

| 5.3 Specification Templates                                                         | 51 |

| 5.4 Deriving Specification Templates from UML Sequence Diagrams                     | 52 |

| 5.5 Visualizing Model Checking Results                                              | 57 |

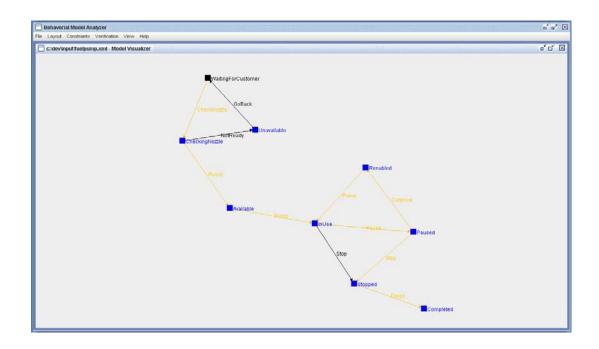

| 5.6 Visualizing the Reachability Graph                                              | 58 |

| 5.7 Visualization of the Specification Finite State Machine                         | 61 |

| 6 Implementation and Case Study                                                     | 64 |

| 6.1 Implementation                                                                  | 64 |

| 6.2 Case Study                                                                      | 64 |

| 6.2.1 Scenario Description                                                          | 65 |

| 6.2.2 Model Checking Using Supplied Specification Templates                         | 67 |

| 6.2.3 Model Checking Using Derived Specification Templates                          | 77 |

| 6.2.4 Visualizing the Specification Finite State Machine and the Reachability Graph | 81 |

| 7 Conclusions                                                                       | 83 |

| 7.1 The Limitations of the BMA                                                      | 83 |

| 7.2 Future Work                                                                     | 85 |

| 7.3 Conclusion                                                                      | 86 |

| Deferences                                                                          | 97 |

# LIST OF FIGURES

| Figure 1 Scopes of specification templates                    | 32 |

|---------------------------------------------------------------|----|

| Figure 2 Specification templates in hierarchical order        | 33 |

| Figure 3 Three subsystems of the BMA                          | 37 |

| Figure 4 Static structure of the Semi-Automated BMA           | 39 |

| Figure 5 Sequence diagram of the Semi-Automated BMA           | 40 |

| Figure 6 UML Deployment diagram of the Semi-Automated BMA     | 41 |

| Figure 7 Static structure of the Automated BMA                | 42 |

| Figure 8 UML Sequence diagram of the Automated BMA            | 43 |

| Figure 9 UML Deployment diagram of the Automated BMA          | 44 |

| Figure 10 Static structure of the Advanced Visualizer         | 45 |

| Figure 11 UML Sequence diagram for the Advanced Visualizer    | 46 |

| Figure 12 UML Deployment diagram for the Advanced Visualizer  | 47 |

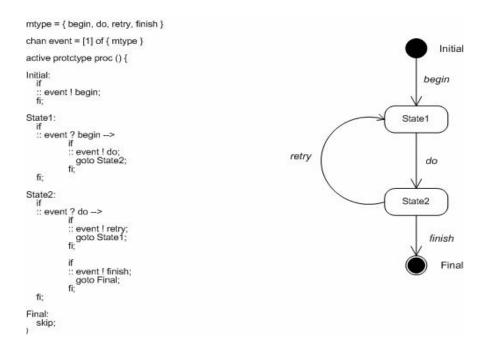

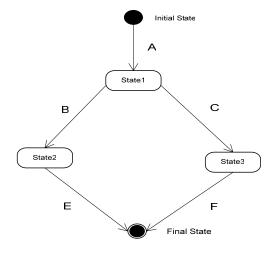

| Figure 13 A simple finite state machine and its PROMELA model | 48 |

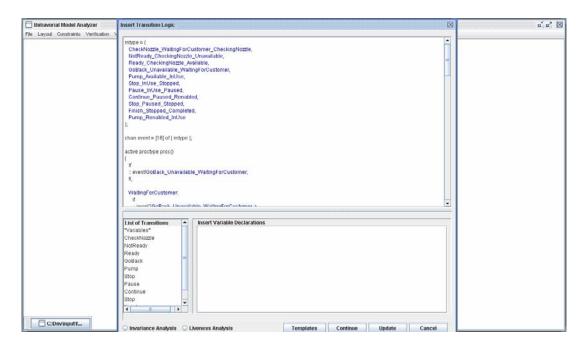

| Figure 14 Defining state variables in the BMA                 | 49 |

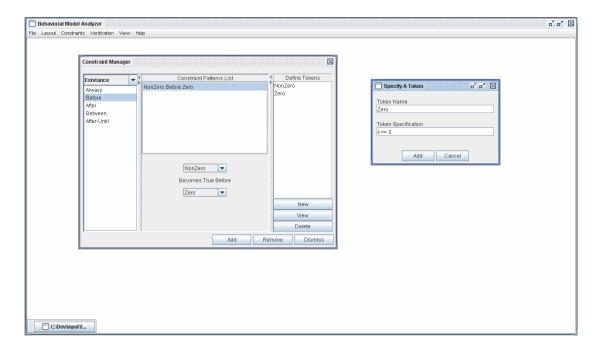

| Figure 15 Defining specification templates in the BMA         | 52 |

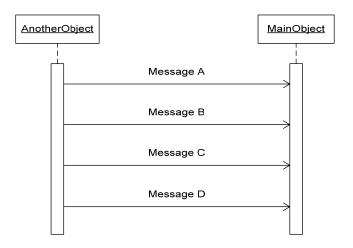

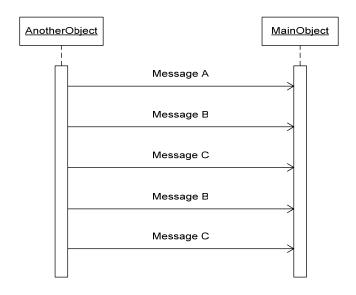

| Figure 16 A simple UML sequence diagram                       | 54 |

| Figure 17 Another UML sequence diagram as an example          | 55 |

| Figure 18 Confirming the derived templates                    | 56 |

| Figure 19 An unreachable path                                 | 56 |

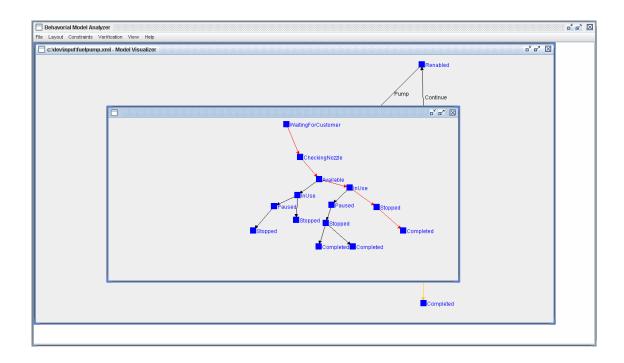

| Figure 20 Visualizing model checking results in the BMA       | 58 |

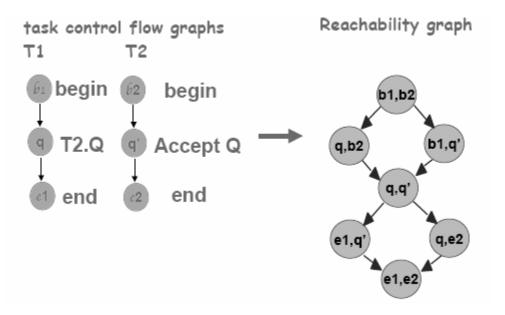

| Figure 21 A simple reachability graph                                   | 59 |

|-------------------------------------------------------------------------|----|

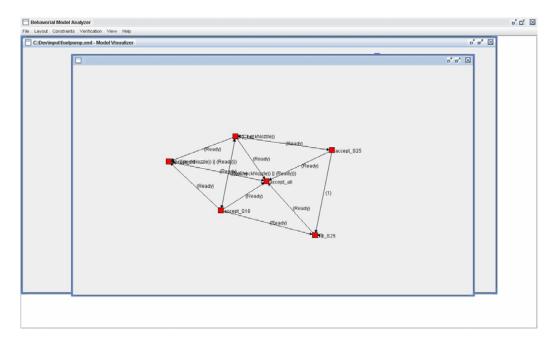

| Figure 22 The reachability graph produced by the BMA                    | 61 |

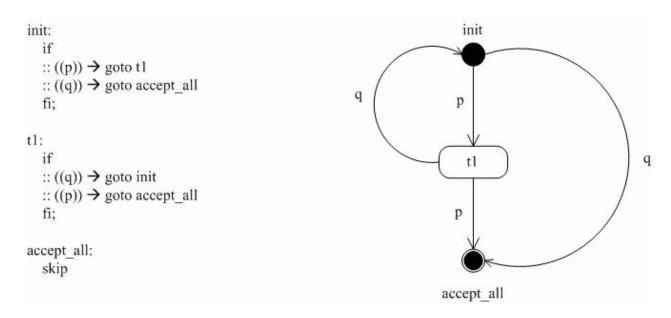

| Figure 23 A simple specification text file and its Visualization        | 62 |

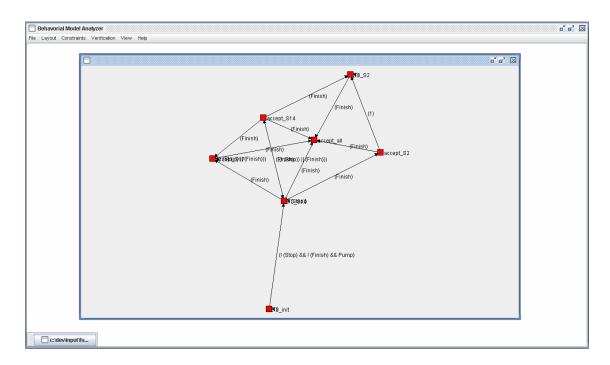

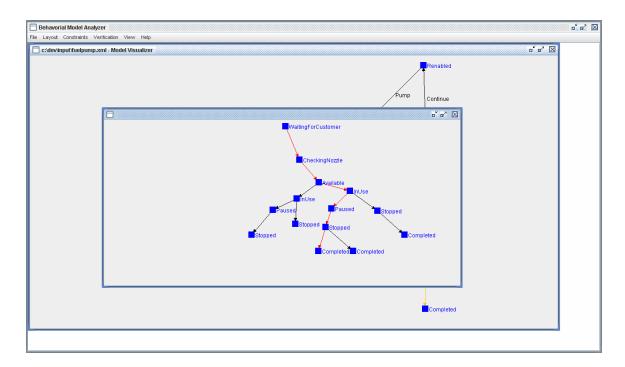

| Figure 24 The specification finite state machine visualized by the BMA  | 63 |

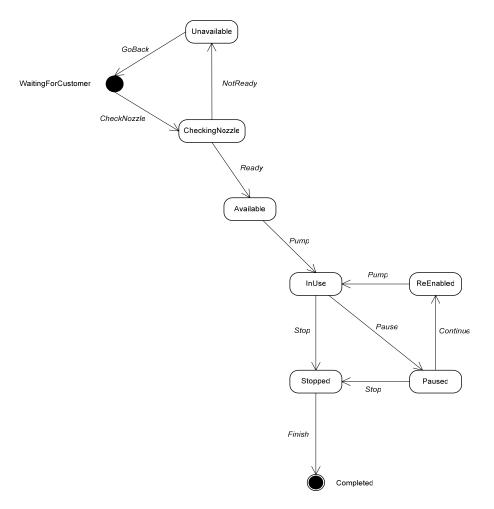

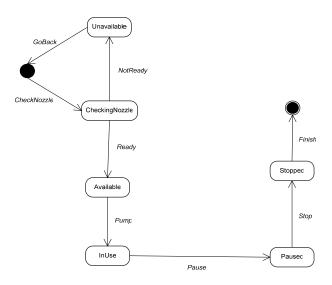

| Figure 25 Statechart diagram of the gas pump model                      | 66 |

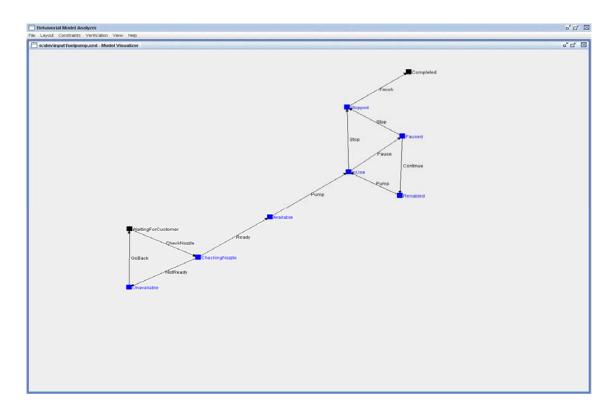

| Figure 26 Visualization of the UML statechart model                     | 66 |

| Figure 27 Interface for state variables in the BMA                      | 67 |

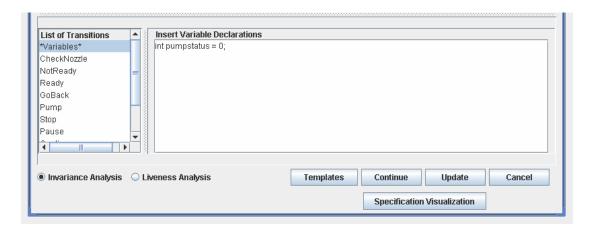

| Figure 28_Initializing a state variable                                 | 68 |

| Figure 29_Assigning values for the states                               | 69 |

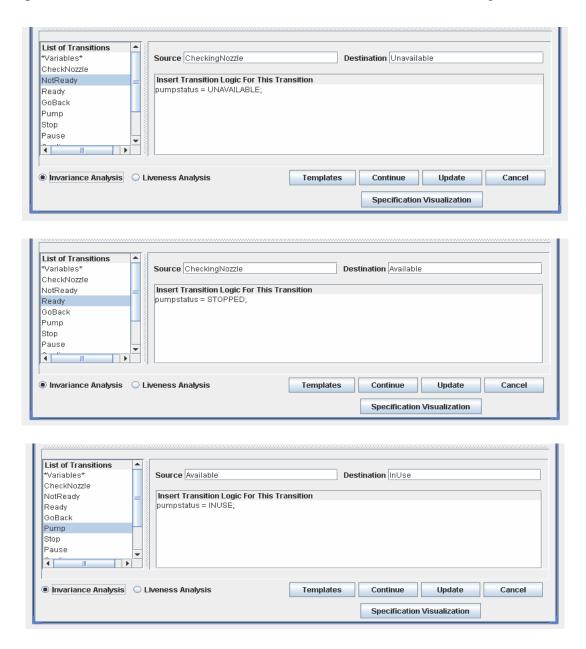

| Figure 30_Assigning transitional logic to different transitional events | 71 |

| Figure 31 Specifying specification templates in the BMA                 | 72 |

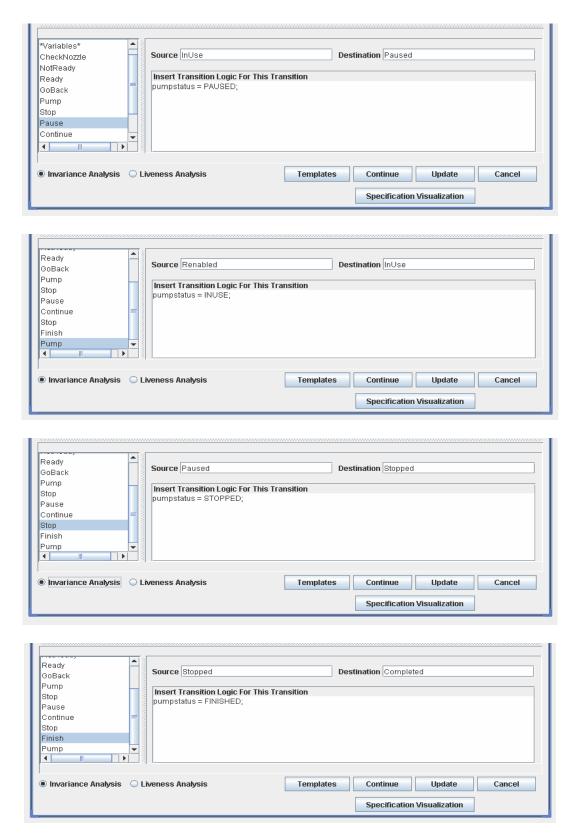

| Figure 32_Declaration of propositions during template specification     | 73 |

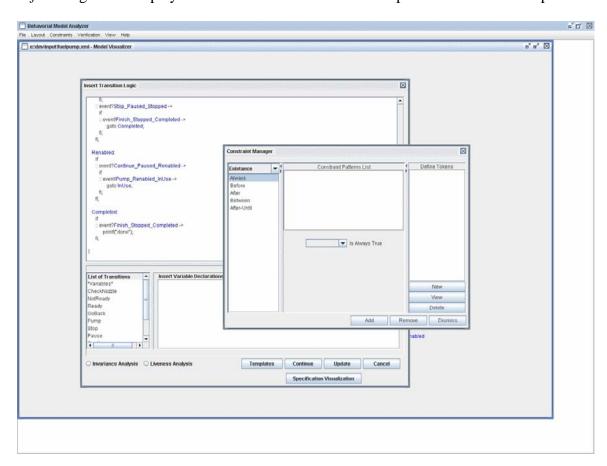

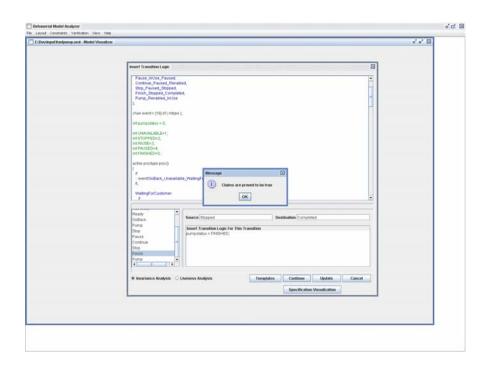

| Figure 33 No error is found during model checking                       | 73 |

| Figure 34 Defining the second specification template                    | 74 |

| Figure 35 Error detected in model checking                              | 75 |

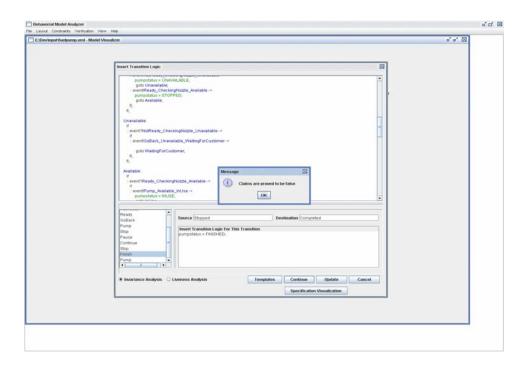

| Figure 36_Error trace displayed by the BMA                              | 76 |

| Figure 37 A model conforms to the specification                         | 76 |

| Figure 38 The UML sequence diagram for the case study                   | 77 |

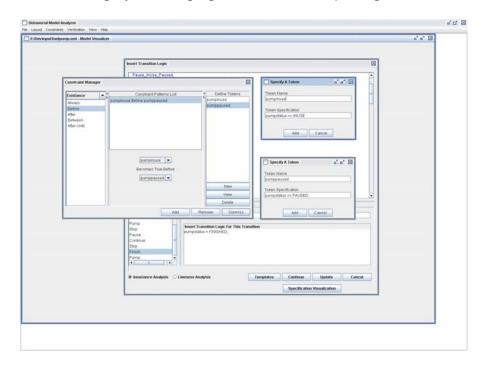

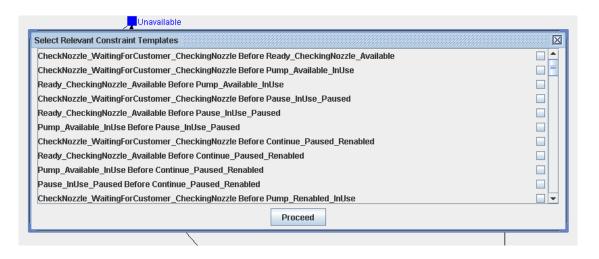

| Figure 39 The list of specification templates derived by the BMA        | 78 |

| Figure 40 The design model does not violate the specification           | 79 |

| Figure 41 The specification finite state machine                        | 80 |

| Figure 42 The reachability graph                                        | 81 |

# LIST OF TABLES

| Table 1 | Temporal | Logic | Specifications | for the existence templates |

|---------|----------|-------|----------------|-----------------------------|

|---------|----------|-------|----------------|-----------------------------|

#### 1. INTRODUCTION

As modern systems are increasingly becoming reliant upon computing technologies, software that powers these platforms is emerging as a vital component for today's technology infrastructure. A study performed by the National Institute of Standards and Technology (NIST) reveals that erroneous and inefficient software products cost U.S. economy \$59.5 billion annually in failed missions and lost productivity [42]. Clearly, the need for reliable software systems is critical as such systems are becoming pervasive in our lives. With the continuing growth of using software-intensive technology products, it will be even more important to attain higher levels of reliability and assurance. Various software verification methods have been introduced and applied [8] through software development stages to detect and eliminate errors as early as possible. Concomitantly, in academia, there has been considerable interest in developing more effective software design and verification techniques [1] and teaching them to new generation of software engineers [28].

1.1 The Need for Integration of Formal Methods into Software Design Education

The principle methods for complex system verification include simulation [8], testing [42], deductive verification [8], and model checking [6]. Simulation and testing both involve conducting experiments before deploying the system in the field. While simulation is performed using an abstraction (i.e. model) of the system, testing is performed on the actual product. In both cases, they usually involve providing certain

inputs to the system or the system model and observing the corresponding outputs. These methods are common and cost-effective ways to find many errors. However, checking all possible interactions among all building blocks of the system using simulation and testing techniques is computationally intractable.

Deductive verification [8] refers to the use of axioms and proofs to prove the correctness of the software systems and usually applied in the verification of mission critical systems. Proofs were first constructed by hand and eventually software tools were built to facilitate the effort. Although deductive reasoning is widely recognized and accepted by computer scientists, the process is rather time consuming and can only be performed by experts who have proper education and experience in logical reasoning.

Model checking is a technique for formally verifying finite state concurrent systems based on formal methods [7]. Formal methods, mathematically based techniques that provide a framework to specify, define, and verify systems, can effectively reveal ambiguity, incompleteness, and inconsistency within complex systems. Use of formal methods does not automatically guarantee correctness. However, when used appropriately, these techniques have proven themselves to result in software products with higher levels of quality [9]. In model checking, specified systems are modeled as finite-state machines and its expected properties and behaviors are specified in temporal logic, and the process of verification can be performed automatically. The procedure normally uses an exhaustive search of the state space of the system to determine if some specification is true or not. While model checking has become increasingly popular in the industry, other formal methods have received relatively little attention. The introduction

of formal methods, as a set of engineering disciplines and practices, into software design education has at least a two-fold benefit to the students [28]. First, it bridges the gap between theories in computer science and emerging industry practices. Second, it provides students valuable and pragmatic skills in the formal modeling and analysis of complex software systems that are beyond the scope of conventional informal verification methodologies.

# 1.2 The Challenges in Integrating Formal Methods into Software Design Education

The emerging trend of model-driven development [14] and model-driven architecture [30] suggests significant benefits when integrating model-based verification techniques into software design education. By learning the engineering discipline of applying these techniques to facilitate the development, analysis, and verification of software, students will grasp the significance of formal methods and gain valuable skills and experience in software design and modeling [28]. Strategies of integrating formal methods in the form of model-based verification into software design education have been difficult. Many academic institutions either completely avoid teaching formal methods or teach them in an isolated manner, with emphasis on notations rather than its underlying principles [15]. Carnegie Mellon University [15] has successfully integrated formal methods throughout its software engineering graduate program, but their approach cannot easily be adapted into undergraduate software design curriculum because undergraduate students do not possess the requisite skills to understand and apply formal methods. For these students, it is beneficial to participate in courses designed specifically toward them, such as courses that provide exposure to model checking without having students to burden themselves

with high requirements in advanced background in mathematics. Concomitantly, new software tools should be developed to facilitate learning the pragmatic use of formal methods and to fill the gap between learning and practice to help the students accomplish following goals [47]:

- to use formal methods without getting into the quagmire of theoretical details

- to avoid steep learning curves about the syntax of a specific formal method by using alternative generic high-level constraint patterns to analyze designs

- to collaboratively analyze inconsistencies and design conflicts at least semiformal reasoning within the realm of the actual industrial software development process

Using today's technology, students must rely on existing model checking tools to assist their learning experience. There are indeed capable model checking tools available, such as SMV [29] and SPIN [18]; yet, they share a common problem for a typical undergraduate student: These tools are difficult to learn and difficult to use, despite many accolades they have won from the industry, they are not designed for education purposes, and the learning curve is enormous, considering the range of functionalities they provide. Both model checkers are command-line applications requiring the user to memorize the meaning of all of their run-time parameters and options. In order to perform model checking, the software model which serves as an input to the model checkers need to be encoded using a separate but complex notation, almost as if the user is learning a new programming language. But perhaps the most serious problem of all, the model checkers do not facilitate the understanding or the learning of model checking by hiding the model

checking processes from their users. No information is conveyed back to the users until the end, when model checking has been completed and lines of cryptic text-based results are dumped on the screen. To a typical undergraduate software engineering student, these text-based results probably make little sense.

The origin of the steep learning curve of the existing model checking tools can be traced back to almost twenty years ago when these tools were still in their infant stage of development. Computing at the time was a lot different than today. Computers were not only bulky and slow, but also extremely expensive. Computing resources were scarce and precious. As a result, most computer applications are written using structured programming languages in the most cost-effective manner to boast their performance. In order to do so, other aspects of the software, such as usability and maintainability, had been sacrificed. When building a software application to solve a particular problem, as long as the problem is solved within a reasonable amount of time and using a reasonable amount of computing resources, one could care less of how does the application solve the problem. As time has progressed and technology has been improved, modern computer platforms with the computation power one could only dream of just a few years ago have become accessible at much lower costs. The availability of high performance computing platforms has triggered a paradigm shift in the computing society regarding how to write software. Much more emphasis has been given to the learnability, flexibility, and robustness of the software instead of its crude performance, and the structured programming approach has been gradually shifted out and replaced by the object-oriented programming approach for the same purpose. It is quite ironic during the same period of

time formal methods have gained acceptability in the industry and even some popularity when dealing with the verification of mission critical hardware systems [4]. This success has quickly led the application of the same approach on the verification of software systems. Model checking tools have become more robust, powerful, and feature-rich, and have a lot of potential to offer in the campaign against hidden software design flaws. However, it is built on top of an aging foundation. It is rather difficult to integrate these legacy tools directly with today's software design methodology being taught in undergraduate level classrooms.

#### 1.3 Research Objective

Given the challenging obstacle of merging formal methods into software design education, the goal of this research is to enable the methodology of teaching formal methods in undergraduate level software design curricula, without having the students to be burdened by the vast amount of theoretical details and mathematical logic required to understand formal methods. This objective can be realized by developing a tool that integrates model checking into current software design methodology being taught in undergraduate software design courses. The design of this tool addresses the difficulties of teaching formal methods to undergraduate students in general, as well as the shortcomings of existing model checking tools for educational purposes. This tool abstracts unnecessary theoretical details away from its users while emphasizing flexible interaction with during the model checking process. As a result, the students may not only gain a novel verification technique to validate their software design in a quick and effective manner, but also attain fresh insights on how model checking works.

The thesis is organized as follows. Chapter 2 reviews the related work in formal methods, model checking and the integration of formal methods into software design education. Chapter 3 lays out the general strategy on how to realize the research objectives. Chapter 4 provides the conceptual design of the tool, and chapter 5 addresses finer design details related to components of the tool. Chapter 6 describes the implementation details of the tool and provides a case study to demonstrate its utility and effectiveness. Finally, in chapter 7 we conclude by discussing the benefits and limitations of the tool as well as future work to extend our research.

#### 2. LITERATURE REVIEW

In meeting the challenge of software products' growing complexity, a major goal of software engineering is to enable the construction of reliable software systems [16]. The use of formal improves reliability by revealing inconsistencies, ambiguities, and incompleteness hidden in the system design [43]. As a result, a set of software engineering techniques and practices for software verification and testing based on formal methods, known as model-based verification, has been codified and adopted [16].

#### 2.1 Formal Methods

Modeling and verification techniques employed by model-based verification involve the application of a formal methodology. A formal method in software development is defined as "a method that provides a formal language for describing a software artifact (e.g. specifications, designs, code) such that formal proofs are possible, in principle, about properties of the artifact [43]." In this formal methodology, essential models of a software system are created using a formalism, which is a collection of principles and practices that are built upon well-defined language of expression and inference and meaning assigned to the symbols of the language [9], and then analyzed and compared against its expected behaviors. Formal specification is the use of notations derived from formal logic to describe [26]

• the assumptions about the world in which a system will operate,

- the requirements that the system is to achieve, and

- the design to accomplish those requirements.

Essentially, a real system is represented, as a rule, in the form of labeled transition system (LTS) [26]. LTS is an oriented graph whose nodes are associated with the states of the system, and edges of this graph that connects the nodes, labeled by symbols of performed actions, are used for representation of the transition-action relation in the system. When the system starts, some state called initial is selected in the set of states of the LTS, and a sequence of transition-actions in the LTS is called its run or trace. The totality of all possible traces in the LTS is called the language of the system. An LTS is called finite if the sets of its states and transitions are finite, and infinite if otherwise. In formal specification, the basic types of properties that are usually specified include behavior properties over time, working characteristics, and internal structure. The behavioral properties are most important. Examples of such behavioral properties include safety and liveness properties, and they can be expressed in logic languages, such as temporal logic.

On the other hand, formal verification is the use of proof methods from formal logic to [26]

- analyze specifications for certain forms of consistency and completeness,

- prove that the design will satisfy the requirements, given the assumptions, and

- prove that a more detailed design implements a more abstract one

Two well established approaches to formal verification are model checking [8] and theorem proving [9]. Theorem proving, proposed by Burstall [5], Kröger [25] and Pneuli

[34], is a technique by which both the system and its desired properties are expressed in the form of mathematical logic. This logic is given by a formal system which defines a set of axioms and a set of inference rules. Theorem proving is the process of finding a proof of a property from the axioms of the system, and it is increasingly being used today in the mechanical verification of safety-critical properties of hardware and software designs [8]. The theorem proving tools consists of powerful collections of inference steps that can be used to reduce a proof goal to simpler sub-goals that can discharged automatically by the primitive proof steps of the prover. Given a property and a model, the prover is either able to verify the property by completing the proof or given back scenarios in which the property is violated. The advantage of theorem proving is that it can deal directly with infinite state spaces by relying on techniques such as structural induction to prove over infinite domains. Therefore, it is not limited by size of the state space. Large systems cannot be verified by a model checker for the same reason, but they can still by verified by the theorem prover. Unfortunately, theorem proving requires considerable amount of technical expertise. As a result, the process is often slow and error prone.

# 2.2 Model Checking

Model checking relies on building a finite model of a system and checking that a desired property is holding in the model [9]. It involves an exhaustive state space search which is guaranteed to terminate. During the search process, the model and the property are fed to a model checker and the model checker determines whether the system model satisfies the property. The result is either a claim that the property is true or a sequence of states

from some initial state that violates the property, also known as a counterexample. Model checking can be applied to analyze specifications of software systems. Because checking whether a single model satisfies a formula is much easier than proving the validity of a formula for all models, model checking can be implemented fairly efficiently [8].

## 2.2.1 The Advantages and Disadvantages of Model Checking

Applying model checking to a design consists of several tasks: modeling [8], specification [8], and verification [39]. Modeling refers the conversion of a design into a formalism accepted by a model checking tool. In some cases, this is a straightforward compilation task. In other cases, owing to limitations on time and memory, modeling a particular design may require the use of abstraction to eliminate irrelevant or unimportant details. Before verification, it is necessary to state the properties that the design must satisfy. This specification is usually given in some logical formalism, such as temporal logic, which is able to assert the behavior of the system as it evolves over time. Although model checking provides means for checking a model of a design satisfies a given specification, it is impossible to determine whether the given specification covers all the properties that the system should satisfy. With modeling and specification in proper order, verification can take place. In theory, model checkers can perform verification automatically, given a model and a specification. However in practice, it often involves human assistance [8]. An example is the analysis of the verification results. In case of a negative result, the user is often provided with an error trace serving as a counterexample for the supplied property, which can be used to track down the exact location of the design fault. False negatives result from incorrect modeling of the system or incorrect

specification Erroneous results or premature termination of verification can also emerge due to the size of model. In this case, it is necessary to decompose the model into finegrain sub-models or change some parameters of the model checking tool.

Compared to theorem proving, model checking is relatively easy, systematic, and fast [8]. Model checking can be used to check partial specifications and provide valuable feedback about a system's correctness even if the system has not been completely specified. Model checker can produce counterexamples that reflect the errors in design, which can be invaluable for debugging. It is preferable to theorem proving, or deductive reasoning, whenever it can be applied. However, there will always be critical applications in which theorem proving is necessary for complete verification. There have been new research directions that attempt to integrate deductive verification and model checking to maximize benefits offered by both [36]. The main disadvantage of model checking is state explosion problem, as mentioned earlier. Many efforts have been invested to resolve the problem, such as McMillan's symbolic model checking [29]. Other approaches such as partial order reduction [33], localization reduction [22], and semantic minimization [13], are all designed to remove redundant states from a system model.

# 2.2.2 Symbolic Model Checking and Partial Order Reduction

In the original implementation of model checking algorithm, transition relations were represented explicitly by adjacency lists [8]. For a software system with small number of states and processes, the approach was quite practical. As the system model becomes more complex, the model checker simply could not handle the growing number of states. Since a model checker replies on an internal global state transition graph to keep track of

the states and transitions during model checking, McMillan [29], in 1987, realized that by using a symbolic representation for the state transition graph, much larger systems could be verified. The new symbolic representation was based on Bryant's ordered binary decision diagrams (OBDDs) [3]. OBDDs provide a canonical form for Boolean formulas that is usually much more compact than conjunctive or disjunctive normal form, and very efficient algorithms have been developed in order to manipulate them. In this implicit representation, each state is encoded by an assignment of Boolean values to the set of state variables associated with the model. The transition relation can be expressed as a Boolean formula in terms of two sets of variables, one set encoding the old state and the other encoding the new. This formula is then represented by a binary decision diagram. The model checking algorithm is based on computing fix points of predicated transformers that are obtained from the transition relation. The fix points are sets of states that represent various temporal properties of the system. In the new implementations, both the predicate transformers and the fix points are represented with OBDDs. Thus, it is possible to avoid explicitly constructing the state graph of the system.

Besides symbolic model checking, partial order reduction is another popular technique designed to combat the state explosion phenomenon [33]. This technique exploits the independence of concurrently executed events. Two events are independent of each other when executing them in either order results in the same global outcome. A common model for representing concurrent software is the interleaving model, in which all of the events in a single execution are arranged in a linear order called an interleaving sequence. Concurrently executed events appear arbitrarily ordered with respect to one another. As a result, all possible interleaving of such events are normally considered and

causing an extremely large state space. The partial order reduction technique makes it possible to decrease the number of interleaving sequences that must be considered. Thus, the number of states that are needed for model checking is reduced. Under the partial order reduction technique, when a specification cannot distinguish between two interleaving sequences that differ only by the order in which concurrently executed events are taken, it is sufficient to analyze only one of them.

#### 2.2.3 Using Temporal Logic for Model Checking

Temporal logic is a formalism for describing sequences of transitions between states in a reactive system and has been proven to be useful for specifying concurrent systems, as they can describe the ordering of events in time without introducing time explicitly [8]. In temporal logic model checking, finite state machine models software or hardware system and a property specified as a formula in a certain temporal logic are given. The goal is to determine whether the system satisfies the formula. Since time is not considered explicitly, instead, a formula might specify that *eventually* some designated state is reached, or that an error state is *never* entered. Properties like *eventually* or *never* are specified using special temporal operators and these operators can be combined with Boolean connectives or nested arbitrarily.

CTL\* is a powerful logic used for model checking as well as foundation for other logics [8]. Conceptually, CTL\* formulas describe properties of computation trees. The tree is formed by designating a state in a Kripke structure [8] as the initial state and then unwinding the structure into an infinite tree with the designated state as the root. The computation tree shows all of the possible executions starting from the initial state. The

logic formulas are composed of path quantifiers and temporal operators. The path quantifiers are used to describe the branching structure in the computation tree, and there are two of such quantifiers: A for all computation paths, and E for some computation path. These quantifiers are employed in a particular state to specify either paths starting from this state or some of the paths starting from this state contain certain properties. The temporal operators are used to describe properties of a path through the tree. There are five basic operators [8]:

- $X next \ time$ , which requires a property to hold in the second state of the path.

- F eventually or in the future, which requires a property to hold at some state on the path.

- G always or globally, which requires a property to hold at every state on the path.

- U until, which requires the second property to hold at some state on the path,

and the first property to hold at every proceeding state in the path.

- R release, which requires the second property to hold along the path up and

including the first state where the first property holds. However, the first property

is not required to hold eventually.

There are two useful sub-logics based on CTL\* [8]. One is branching-time logic called Computation Tree Logic (CTL) [7]. The other is linear-time logic called Linear Temporal Logic (LTL) [7]. CTL is a restricted subset of CTL\* in which each of the temporal operators X, F, G, U, R must be immediately preceded by a path quantifier,

resulting ten basic CTL operators:

- AX and EX

- AF and EF

- AG and EG

- AU and EU

- AR and ER

Examples of some typical CTL formulas include the following:

- AG safe: All reachable states are safe.

- AG AF stable: The system is stable infinitely often.

- AG (request → AF response): A request is always a response sometime in the future.

- AG EF restart: It is possible to restart the system in any reachable state

Formally, a finite state machine  $\langle Q, R, I \rangle$  consists of a set of states Q, a state transition relation  $R \subseteq Q \times Q$ , and a set of initial state  $I \subseteq Q$ . A path is an infinite sequence of states such that each consecutive pair of states is in R. The set of states Q is often encoded by a set of state variables, such that each state corresponds to some value for the variables and no distinct states correspond to the same value. Basic on this foundation, a proposition is defined as any Boolean combination of predicates on the state variables. A formula is a proposition, a Boolean combination of formulas, or the combination of a temporal operator and a formula [8]. Each formula is evaluated at some state q. A proposition

holds at q if q satisfies the proposition. The operator A means "for all paths starting at q", E means "for some path starting at q", G means "for every state along the path", and F means "for some state along the path". Therefore, AG safe holds at q is every state (G) along every path (A) starting at q satisfies the proposition safe. The system satisfies a formula if the formula holds at all initial states. If not, a model checker typically attempts to find a counterexample. For instance, if the formula AG safe is false, a counterexample is a finite path starting at some initial state and ending at a state that is not safe.

In explicit model-checking techniques, the truth value of a CTL formula is determined in a graph-theoretic manner by traversing the state diagram, with time complexity linear in the size of the state space and in the length of the formula [7]. Using symbolic model checking techniques, instead of visiting individual states as in conventional state space search, symbolic model checkers visit a set of states at a time [4, 28]. A state set can be represented by a predicate on the state variables such that a state is in the set if and only if the predicate is true at the state. When the state space is finite, we can assume that the state variables are Boolean and there are only finitely many of them. A predicate on these variables is simply a Boolean function, which can be represented by reduced ordered binary decision diagrams (OBDDs) [3]. An OBDD resembles a binary decision tree, except that isomorphic sub-trees must be combined resulting a directed acyclic graph. In addition, each path can contain a variable at most once, and must comply with a fixed linear order of the variables.

Linear Temporal Logic (LTL) is an extension of propositional logic to include discrete time information [8]. Formulas are interpreted as referring to events along an infinite path of time points. LTL formulas are built inductively from its set of atomic propositions. These atomic propositions and their operators are given below, and p and q are some states or events occurring in the path of time points:

| • | And | $p \wedge q$ |

|---|-----|--------------|

|   |     |              |

•

$$Or$$

$p \vee q$

One can model LTL by assigning to each natural number a set of true atomic propositions. The operators then define requirements on those propositions. The formula for the proposition "And" means that states p and q must both be true. "Or" means that either state p is true, or state q is true. "Not" means that state p is false. Atomic propositions "Next", "Always", "Eventually", "Until" and "Release" have same meanings from CTL\*, where they have been originated.

### 2.2.4 Existing Model Checking Tools

There are tools available that facilitate the checking of expected model based system behavior and properties of concurrent programs under different fairness assumptions. SMV [29], the Symbolic Model Verifier, is a popular model-checking system first developed by McMillan in 1993. It uses the OBDD-based symbolic model checking

algorithm to perform verification and takes a finite state machine as the model of the system, expressed in its own input language, and properties of the system, expressed in CTL formula. The system model is often decomposed into a series of modules and each can be instantiated multiple times. A SMV module can be composed either synchronously, which means all modules perform an action concurrently at a time period, or using interleaving, which means exactly one module performs an action at a time period. The state transitions in the model can be either deterministic or nondeterministic. The state transitions in the model can be specified explicitly in terms of Boolean relations or implicitly as a set of parallel assignment statements. When performing model checking, a breadth-first searching procedure with fixed-point algorithms is used to check the satisfaction of the finite state machines against the expected properties.

An alternative model checking system is called SPIN [18], which uses explicit state enumeration and partial order reduction during model checking. It was developed at Bell Laboratories by Gerard Holzmann and Doron Peled, and primarily used for verifying asynchronous software systems such as communication protocols. It can check a system model for deadlocks or unreachable code or determines if it satisfies a particular property composed by LTL specification. The input language to describe the system model, called PROMELA [18], an acronym for Process Meta-Language, was developed by Gerard Holzmann. It uses syntactic constructs similar to several other programming languages, such as C. The basic building blocks of SPIN models are asynchronous processes, buffered and un-buffered message channels, synchronizing statements, and structured data. Unlike SMV, SPIN uses partial order reduction to limit the state space explosion problem to optimize the process of model checking.

#### 2.3 The Role of Formal Methods in Software Design Education

Formal methods involve the use of discrete mathematics and mathematical logic in the study and practice of computer science and software engineering [1]. From its beginning, computing was regarded as an abstract, mathematical science. Pioneers like Turing, Church, and von Neumann used mathematics to establish the essence and boundaries of the computing discipline. Although computing technology is crucial in software engineering education and practice, the underpinnings are mathematical in nature and computing does deal with purely logical processes [30]. Students often resist the use of mathematics in the study of computing, usually for the following reasons:

- Students may lack the proper preparation or motivation.

- Many have neither an understanding of nor appreciation for the role of mathematics, or more explicitly, formal methods, in computing [31].

- Some feel intimidated or even fearful of the level of mathematical knowledge and capability required.

As the term software engineer becomes a popular title for software developers, there is little evidence to show that the practice of software design and engineering compares with the rigor and discipline that is required for practice in other engineering fields [32]. So the question seems to be whether software engineering programs should follow the traditional engineering approach to professional education. Quality problems arise from incomplete and imprecise requirements, specification, shoddy designs with poor documentation, and almost sole reliance on testing for software quality assurance, and there is increasing interest in the use of formal methods for specification and design [1].

With the explosive growth of software, the Internet, and electronic commerce, formal methods become a practical approach for achieving higher confidence in today and tomorrow's infrastructure system [1].

## 2.3.1 Formal Methods as Part of an Engineering Curriculum

Formal methods improve software reliability by providing mathematical frameworks to define, specify, and verify complex software systems. However, the majority of software engineering curricula have a low level of emphasis on formal methods [1]. This is partly due to a lack of interest on the part of the software industry, but much of the responsibility must be attributed to the state of the curriculum and course design. The computing education community has adopted a curriculum strategy of dividing curricula elements into areas of theory and practice. This causes both faculty and students to view the theory of computing as separate and distinct from the practice of computing. As a result, there are theorists who are viewed as the mathematical elite and practitioners with little respect for the applicability of formal methods to their work. This mindset inhibits the use and integration of formal methods into software development process, and ultimately, into software design and engineering education. Because of this, there is little guidance and support available to faculty, who would like to introduce formal methods into their software engineering courses.

The scope and scale of software projects today are increasing dramatically, along with shorter release cycles, and traditional software quality assurance methodologies are facing more challenges in attempting to meet quality standards [16]. Equipped with formal methods to address the complexity, model checking provides software engineers

fresh insights on how to debug, verify, and validate designs. With the success of model checking and other formal approaches for software verification are attracting attentions, trying to integrate them into software design education has lead to following observations [28]:

- The theoretic foundations of model checking involve mathematical logic.

- The engineering principles and processes used for implementing model checking provide excellent training for students to solve complicated design and analysis problems.

- The skills and knowledge that students acquire from the course provide them with alternative approaches to solve problems in many important software engineering areas.

Strategies of integrating formal methods in the form of model-based verification into software design education have been difficult. Generally there are three strategies [15]. The first approach avoids teaching formal methods altogether and considers formal methods are impractical and mature enough to be beneficial in software engineering practices. The appropriateness of this argument for the general software engineering education is debatable. The second approach is to devote a specific course which emphasizes formal verification of source code using a number of formal methods, such as VDM [21] or Z [40]. The students are expected to learn about the methods, and then they are expected to apply the formal skills to software development activities. This approach involves broad coverage of a variety of formal methods that provide students with a larger scope of exposure, but may not enable them to be proficient in any specific

approach. Furthermore, the methods tend to be taught in an isolated manner with emphasis in notations rather than its underlying principles. This isolated exposure generally prohibits students to apply such approaches in software engineering practices. Finally, the third approach is invented to redesign the curriculum so that formal methods are integrated throughout the entire curriculum [15]. Carnegie Mellon University [15], as an example, redesigned its software engineering graduate program to promote better understanding to formal models of software systems. This approach offers many benefits to the students as they incorporate finite state modeling and temporal logic for model checking interactive aspects of system. More specifically, the curriculum integrated with formal methods enables the analysis of software development products such as delivered code, specifications, designs, documentation, prototypes, and test suites. It also treats both static and dynamic analyses, such as type checking, verification, testing, performance analysis, hazard analysis, reverse engineering, and program slicing.

Although a novel strategy, the approach adopted at Carnegie Mellon is difficult to apply at the undergraduate level, as it assumes that students in the curriculum have already had exposure to advanced logic, discrete and combinatorial mathematics that facilitate the attainment of the requisite skills to understand and apply formal methods. Although many graduate students who have strong background in mathematics indeed possess such skills; many undergraduate students with comparatively limited background in advanced mathematics, a course delivery strategy that revolves around formal methods can be overwhelming for two reasons:

- The impedance mismatch between the underlying mathematical underpinning of formal methods and students' semi-formal, if not informal, view of the design problem and

- The lack of tool support in the seamless integration of formal methods into software design education

Considering the difficulties of teaching formal methods to undergraduate students, software tools should encourage learning by abstracting required material into relatively simple paradigms that novice users can easily learn and manage [9]. However, most tools, used to support the learning and the teaching of formal methods, are developed for practitioners, rather than for educators or learners. Some desired properties of tools that are attractive to this group of users include [9]:

- Ease of Use: Tools should be easy to use and their output should be easily interpreted by novice users.

- Ease of Learning: Tools should provide a starting point for writing formal specifications for users who would not otherwise write them. The knowledge requirement of formal methods on the users should be kept minimal.

- Focused Analysis: Tools should be good at analyzing at least one aspect of the system well.

- Early Payback: Tools should provide significant benefits almost as soon as the users start to use them.

- Incremental Gain for Incremental Effort: Tools should provide users increased benefits as the users are getting more adept or are putting more effort into writing specifications.

- Efficiency: Tools should make efficient use of users' time, and the amount of time used by the tool should be proportional to the extensiveness of the analysis.

- Integrated Use: Tools should work in conjunction with other common programming languages and techniques and should be integrated with traditional software development tools. Users should not have to look into another new methodology in order to receive benefits.

- Evolutionary Development: Tools should allow partial specification and analysis

of selected aspects of a system.

- Orientation toward Error Detection: Tools should be optimized to find errors rather than confirming correctness.

Going one step further, rather than building a single tool, "meta-tools" can be built to automatically produce tools that are customized toward a particular problem domain [38], formal notation [10], or logic [17, 24]. It is also important for a tool to make the user aware its strengths, limitations, modeling assumptions, ease of integration with other tools, and start-up costs.

#### 2.3.2 Common Formal Methods used in Software Engineering Education

The education of formal methods in a classroom environment often revolves around a particular technique. As a result, specific formal techniques have become foundations for

certain curricula aimed to provide exposure of formal methods to students, due to their popularity in the industry. The most popular formal techniques are VDM [21] and the Z notation [40].

VDM is a model-oriented formal method based on a denotational semantic setting, intended to support stepwise refinement of abstract models into concrete implementations [21]. The method includes a formal specification language, VDM-SL [21], which supports various forms of abstraction. Representational abstraction is supported by data modeling facilities. These facilities are based on six mathematical data-structuring mechanisms: sets, sequences, maps, composite objects, Cartesian products and unions. At a lower level, the language provides various numeric types, Booleans, tokens and enumeration types. By using the data-structuring mechanism and the basic data types, compound data types can be formed with a specific mathematical structure, and these compound data types are denoted as domains. Sub-typing is supported by attaching domain invariants to domain definitions. Operational abstraction is supported by both functional abstraction and relational abstraction: the former by means of function specification and the latter by operation specification. Both functions and operations may be specified implicitly using pre and post conditions, or explicitly using applicative constructs to specify functions and imperative constructs to specify operations. Operations have direct access to a collection of global objects: the state of the specification. The state is constructed as a composite object and built from labeled components. A VDM specification typically consists of a state description augmented with invariant and initialization predicates, a collection of domain definitions augmented with invariants, a collection of constant definitions, a collection of operations and a collection of functions. An initial specification is usually kept as abstract as possible. Then the initial specification can be further developed and refined using two techniques: data reification, which addresses the refinements of state elements, and operation modeling, which addresses the refinements of the functions and operations. Data reification involves the transition from abstract to concrete data types, and a justification of this transition. Choosing a more concrete data model implies a redefinition of all operations and functions on the original model in terms of the new model, a process called operation modeling. Central to data reification is the notion of adequacy, expressed through two functions on the abstract and concrete domains, the abstraction-function and the retrieve-function. The abstraction-function maps abstract values onto concrete values; the retrieve-function does the opposite, mapping concrete values onto abstract values. The final step within the development is the transition of a low-level specification into the chosen programming language.

The Z notation is based upon set theory and mathematical logic [44]. The set theory used includes standard set operators, set comprehensions, Cartesian products, and power sets. The mathematical logic is a first-order predicate calculus. Together they make up the mathematical objects in Z. These objects and their properties can be collected in schemas, which are patterns of declaration and constraint. The schema language can be used to describe the state of a systems, and conditions in which that state may change. It can also be used to describe system properties, and to reason about possible refinements of a design. A characteristic feature of Z is the use of types. Every object in the mathematical language has a unique type, represented as a maximal set in the current specification. This notion of types suggests that an algorithm can be written to check the

type of every object in the specification. Another important feature of Z is the use of natural language. In Z, mathematics is used to state the problem, to discover solutions, and to prove the chosen design meets the specification. Natural language is used to relate the mathematics to objects in the real world. This task is often partly achieved by the judicious naming of variables and additional comments in the specification. Z also supports the concept of refinement. A system can be developed by constructing a model of a design, using simple mathematical data types to identify the desired behavior. This description can be further refined later by constructing another model which respects the design decisions made, and yet is closer to implementation. This process of refinement can be continued until executable code is produced.

In summary, both VDM the Z notation are mathematical languages with powerful structuring mechanisms capable of producing formal specifications, and both require immense requisite skills in mathematical logic to be understood and used effectively. As a result, their user group is largely limited to seasoned professionals who have grasped the underlying principle over years of experience [43].

# 3. A PRACTICAL STRATEGY FOR INTEGRATING MODEL CHECKING INTO SOFTWARE DESIGN EDUCATION

The goal of the research is to integrate formal methods into current software design methodology being taught in undergraduate software design courses. This objective is realized by building a tool called the Behavioral Model Analyzer (referred as the BMA in the rest of the thesis). The BMA aims to address the difficulties of teaching formal methods to undergraduate students, as well as the shortcomings of existing model checking tools for educational purposes. The operation of the BMA can broadly be described in the following manner. It accepts as input a software design model (i.e., statechart) and a property specifying how the model is required to behave. The BMA then performs model checking using the model and the property to display the results back to the modeler. Although this description hardly differs from the operation of any other model checking tool, the BMA places emphasis on the following features that are not present in other model checkers:

- The input software design models are UML models, which are commonly used in software design, rather than tool-specific model description languages which modelers have little exposure.

- The properties defining the required behaviors of the models can either be supplied or derived in the form of abstract and user-friendly specification

- templates rather than temporal logic, thus eliminating the requisite mathematical skills involved in formal methods.

- The results of model checking are shown using graph visualization rather than cryptic text, so that students can have better grasps on where problems are detected and how to fix them.

# 3.1 Using UML Models as Input Design Models

Unified Modeling Language (UML) [2, 19, 38], is a general-purpose visual modeling language that is used to specify, visualize, construct, and document the artifacts of a software system and is capable of capturing information about the static structure and dynamic behavior of the system. The static structure defines the collection of discrete objects that make up the system and the dynamic behavior defines the history of objects over time and the communication among objects to accomplish goals. Software tools can provide code generators from UML into a variety of programming languages, as well as reverse engineered models from existing programs. UML is not a highly formal language designed for the theorem proving, but rather a modeling language for discrete systems. These reasons, coupled with the increasing popularity of object-oriented methodology, made UML ubiquitous in both the industry and the academia [2, 38].

Although UML offers a variety of diagrams to model different perspectives of a software system, we are interested of using the state machine view, modeled by a statechart diagram, to represent an input design model, since the state machine view describes the dynamic behavior of objects over time by modeling the lifecycles of objects of each class [2, 19, 38]. A state machine is a graph of states and transitions and it is

attached to a class and describes the response of an instance of the class to events that it receives. Events represent the kinds of changes that an object can detect – the receipt of calls or explicit signals from one object to another, a change in certain values, or the passage of time. Anything that can affect an object can be characterized as an event. A state is a set of object values for a given class that have the same qualitative response to events that occur; therefore it describes a period of time during the life of an object of a class. In the state machine, a set of states is connected by transitions. A transition leaving a state and entering into another state defines the response of an object to the occurrence of an event.

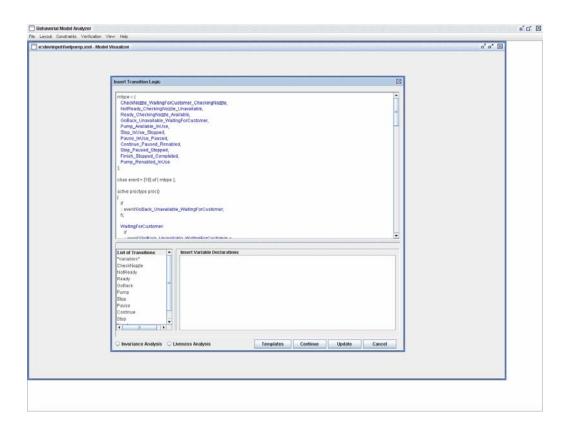

To facilitate model checking of UML statecharts, the BMA translates input models into an intermediate format defined in terms of PROMELA language. This is similar in principle to the translation of UML models into code skeletons within the Model-Driven Architecture initiative [30]. PROMELA is an acronym for Process Meta-Language [18], which is a model description language for the model checker SPIN [18]. The BMA uses SPIN to perform model checking by translating abstract and user-friendly inputs from the modeler into tool-specific inputs for SPIN, and visualizing text-based model checking output in the form of graphs. As a result, UML statecharts need to be translated into PROMELA before the model checking process.

#### 3.2 Substituting Temporal Logic with Specification Templates

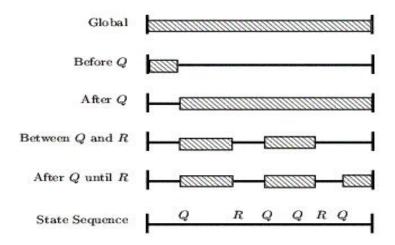

In model checking, a property (i.e., required behavior) of the model is specified using temporal logic. The steep learning curve for the mathematical skills required to use temporal logic is one of the core reasons why formal methods have been almost absent in undergraduate design education. It is imperative for the BMA to circumvent this obstacle. As a result, the BMA uses the notion of specification templates [12] to describe the required property of the model. A specification template is a generalized description of a commonly occurring requirement on the permissible state sequences in a finite-state model of a system, and it describes the essential structure of some aspect of the system's intended behavior. The specification templates are generalized in a hierarchical structure in terms of their scopes for formal specification and verification. The scope of a template is the extent of program execution over which the template must hold. It is determined by specifying a starting and an ending state for the template. Therefore the scope consists of all states beginning with the starting state and up to but not including the ending state. There are five different scopes (Figure 1) [12]:

- *Global* the entire program execution

- Before the execution up to a given state

- After the execution after a given state

- Between any part of the execution from one given state to another

- After-Until just like Between but the designated part of the execution continues

even if the second state does not occur

Figure 1 Scopes of specification templates

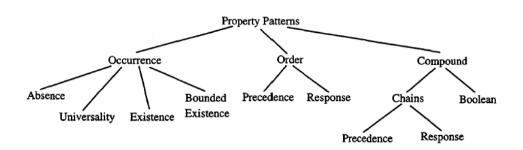

Each template can be translated into its corresponding temporal logic formula by the BMA. When working with a specification template, only states required by the particular template need to be supplied by the modeler in terms of simple mathematical logic. Some common specification templates are listed as follows (Figure 2) [12]:

Figure 2 Specification templates in hierarchical order

# Occurrence Templates include

- *Absence* A given state or event does not occur within a scope. This template is also known as *Never*.

- Existence A given state or event must occur within a scope. This template is also known as Future or Eventuality.

- Bounded Existence A given state or event must occur k times within a scope.

• *Universality* – A given state or event occurs throughout a scope. This template is also known as *Globally*, *Always* and *Henceforth*.

## Ordering Templates include

- Precedence A state or event P must always be preceded by a state or event Q within a scope.

- Response A state or event P must always be followed by a state or event Q within a scope. This template is also known as Follows and Leads-to.

#### Compound Templates include

- Chain Precedence A sequence of states or events  $P_1$ , ...,  $P_n$  must always be preceded by a sequence of states or events  $Q_1$ , ...,  $Q_m$ .

- Chain Response A sequence of states or events  $P_1$ , ...,  $P_n$  must always be followed by a sequence of states or events  $Q_1$ , ...,  $Q_m$ .

- Boolean Combinations Sometimes we want to generalize the templates to allow for sets of states to describe scopes and properties. Some times this is straightforward and sometimes disjunctions and conjunctions of state or event descriptions can yield incorrect specifications when substituted into templates. These templates outline how Boolean combinations can be applied in different case.

Each of the hierarchical specification templates has its corresponding temporal logic specified, and the BMA translates these templates into temporal logic. The model checker SPIN can perform model checking using the translated temporal logic as input. Table 1 provides the temporal logic specifications for the *Existence* Templates.

| Specification Scope | Temporal Logic Specification  |

|---------------------|-------------------------------|

| Globally            | <>(P)                         |

| Before R            | !R W (P & !R)                 |

| After Q             | [](!Q)   <>(Q & <>P))         |

| Between Q and R     | [](Q & !R -> (!R W (P & !R))) |

| After Q until R     | [](Q & !R -> (!R U (P & !R))) |

Table 1 Temporal logic specifications for the *existence* templates

In the table, P, Q, and R are events and the column *specification scope* indicates the scope where event P is true. The temporal operators in the temporal logic specifications have the following semantics:

- Eventually <>

- *Always* []

- Negation !

- Or

- *And* &

- Implies →

- *Until* U

- Strong Until W

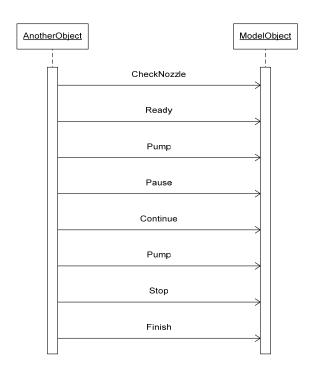

Using the temporal logic for the specification templates as a foundation, the BMA can automatically derive the specification templates from UML sequence diagrams [2, 38], if they are included in the input design model, thus avoiding the necessity of having the modeler to input the required behavioral property of the design model. A sequence

diagram specifies a set of messages arranged in time sequence to depict a scenario or the behavioral sequence of a use case. Each message on a sequence diagram corresponds to an operation on a class or an event trigger on a transition in a state machine. Since each specification template involves with the occurrence of one or more states or events present based on different scopes, it is possible to derive these specification templates by detecting the order of occurrence of the events in the sequence diagram.

#### 3.3 Three Incremental Steps to Realize the BMA

The features of the BMA are implemented using three incremental steps. The first step includes the translation of UML statechart models for the purpose of model checking, the construction of the specification template input interface so that a modeler can supply the required behavioral property for the design model without the intricate details involving formal methods, and a graph visualization shows the counterexample, as a sequence of states, which violates the required property. The second step incorporates the capability to automatically recognize and derive the behavioral properties, in the form of specification templates, from the UML sequence diagrams. The third and final step adds the capability to visualize the specification finite state machine generated from the required behavioral properties before model checking. This visualization offers two benefits to the modelers. First, it provides detailed awareness and representation of the specification templates to the modeler. When deriving these templates from the UML sequence diagrams, it is unlikely the modeler knows the derived templates ahead of time. Second, since the BMA emphasizes learning formal methods through interaction, the detailed representation of specification templates in the form of graphs provides the modeler better intuitive grasp of the required behavior.

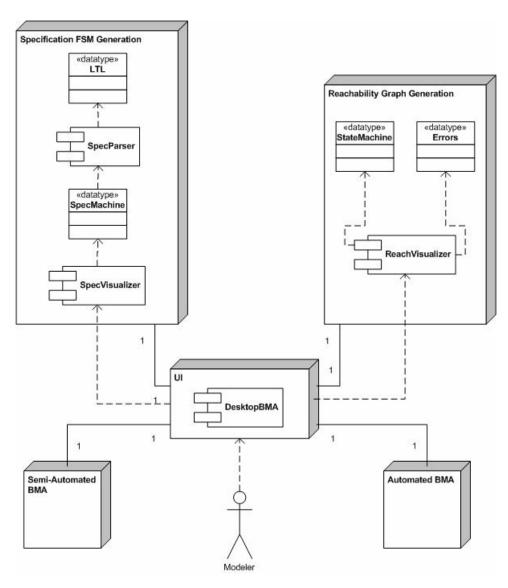

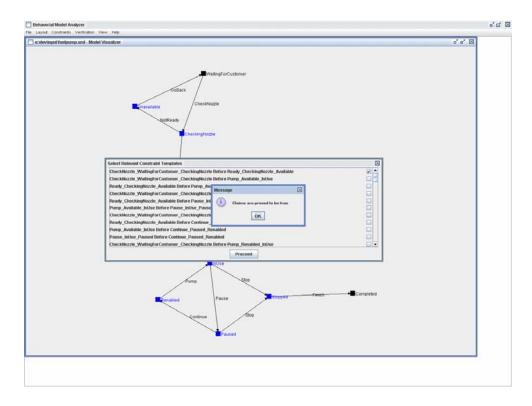

#### 4. ARCHITECTURAL DESIGN OF THE BEHAVIORAL MODEL ANALYZER

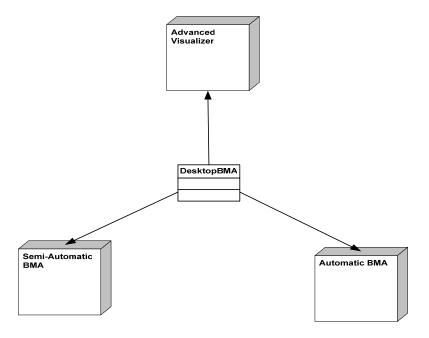

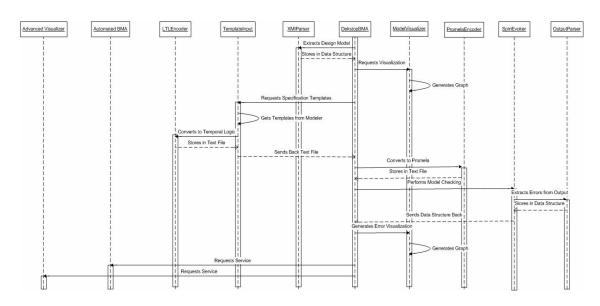

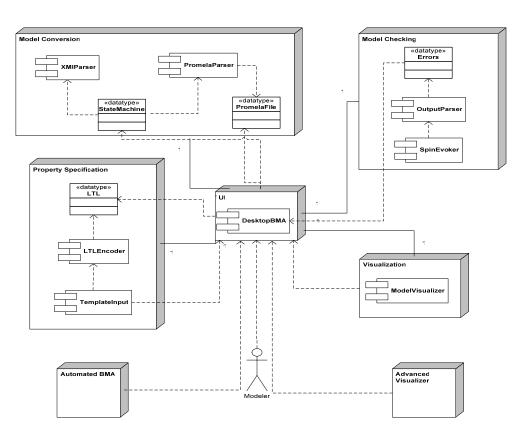

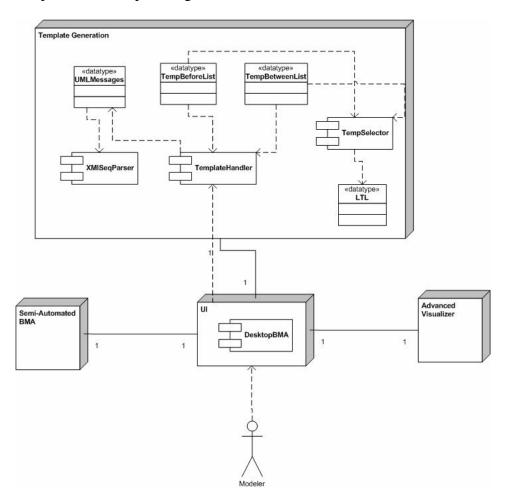

The development strategy described in chapter 3 has outlined the required functions of the BMA. The architectural design of the BMA follows this strategy to form the functional components of the application. This goal of this chapter is to provide the design details at the component level in three phases to reflect distinct functions performed in each of one of the phases. The architectural design for the BMA can be divided into three subsystems as shown in Figure 3: the *Semi-Automated BMA*, the *Automated BMA*, and the *Advanced Visualizer*. The *DesktopBMA* is the front-end UI component of the entire application.

Figure 3 Three subsystems of the BMA

The *Semi-Automated BMA* fulfills Phase I requirements of the BMA. In this subsystem, model information from the UML statecharts, exported in XMI, are extracted and translated into PROMELA design models described by the PROMELA model description language. Specification templates are obtained from the modeler and translated into temporal logic. Model checking is then performed using the PROMELA model and behavioral constraints defined in terms of temporal logic. The results of model checking are visualized in an interactive and informative manner.

The *Automated BMA* fulfills Phase II requirements of the BMA. In this subsystem, messages in the UML sequence diagrams are examined and specification templates are derived based on the order of occurrence of these messages without intervention from the modeler.

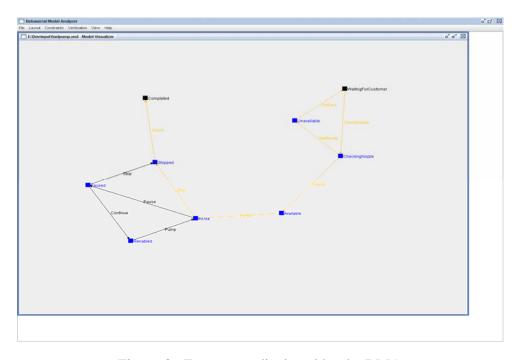

The Advanced Visualizer fulfills Phase III requirements of the BMA. In this subsystem, the reachability graph of the states in the design model is generated. If errors are detected during model checking, an error trace is also shown to indicate the execution path of the error. The specification finite state machine is also generated from the specification templates either supplied by the modeler or derived from the UML sequence diagrams.

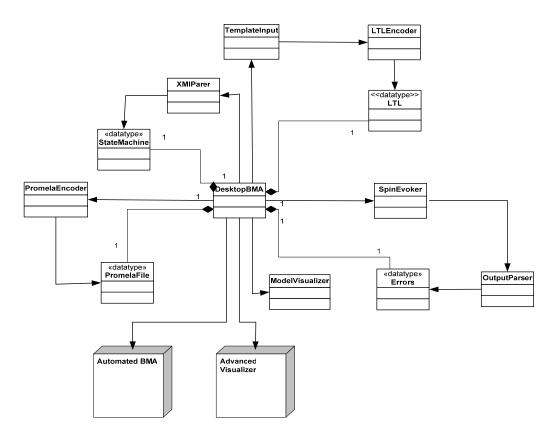

#### 4.1 Architectural Design of the Semi-Automated BMA

The architectural design of the *Semi-Automated BMA* consists of eight functional components as shown in Figure 4: *DesktopBMA*, *XMIParser*, *TemplateInput*, *LTLEncoder*, *PromelaParser*, *SpinEvoker*, *OutputParser*, and *ModelVisualizer*. These components provide the following functions to perform model checking and display the

#### results:

- 1. Convert UML statecharts to PROMELA model description language

- 2. Obtain specification templates and translate them into temporal logic

- 3. Perform model checking

- 4. Graphically display the errors detected during model checking

Figure 4 Static structure of the Semi-Automated BMA

The BMA is enacted when the *DestopBMA* initializes. This component contains functions to call other components to execute the work request by using interactive user interface widgets. Using these widgets, a UML design model is converted into PROMELA language; specification templates regarding the design model are supplied; and the model checking process is launched to find potential errors. When a UML input

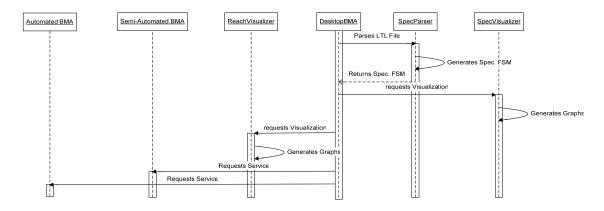

model has been chosen, the detailed structure information of the input model is extracted by the *XMIParser* and stored in a data structure called *StateMachine*. Afterwards, the graph visualization of the input model is generated by the *ModelVisualizer*. The model information stored in the *StateMachine* data structure is converted into PROMELA language and stored in a text file by the *PromelaEncoder*. Meanwhile, specialized user interface elements provided by the *TemplateInput* enable constraint templates to be supplied, and these templates are converted into temporal logic by the *LTLEncoder* and saved into a temporal text file. Once the design model and the specification templates are converted into PROMELA and temporal logic, respectively, the model checker is evoked by the *SpinEvoker* to perform model checking. Error information is extracted from the text-based model checking results by the *OutputParser* and saved into a data structure called *Errors*. Using this data structure, a colored trace linking the problematic states in the existing visualization is generated by the *ModelVisualizer*. The interactions among the components are specified in terms of the UML sequence diagram shown in Figure 5.

Figure 5 Sequence diagram of the Semi-Automated BMA

The deployment diagram shown in Figure 6 provides the physical view of the components grouped by their functions. The components in this system can be grouped into five subsystems. The subsystem *UI* contains the *BMADesktop*. Besides being the user interface, it facilitates communication among other components. The *Property Specification* handles the process of converting supplied specification templates to temporal logic and contains the *TemplateInput*, *LTLEncoder*, and the text file that includes the converted temporal logic from the specification templates. The *Model Checking* component performs model checking and retrieves the raw results from the model checker. It contains the *SpinEvoker*, *OutputParser*, and the data structure containing the errors found during model checking. Finally, the *Visualization* provides the results of model checking using graphs.

Figure 6 UML Deployment diagram of the Semi-Automated BMA

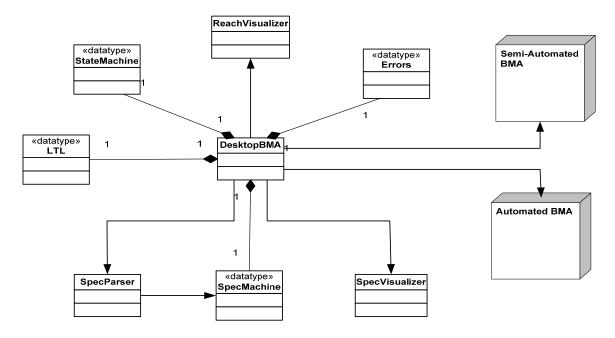

# 4.2 Architectural Design of the Automated BMA

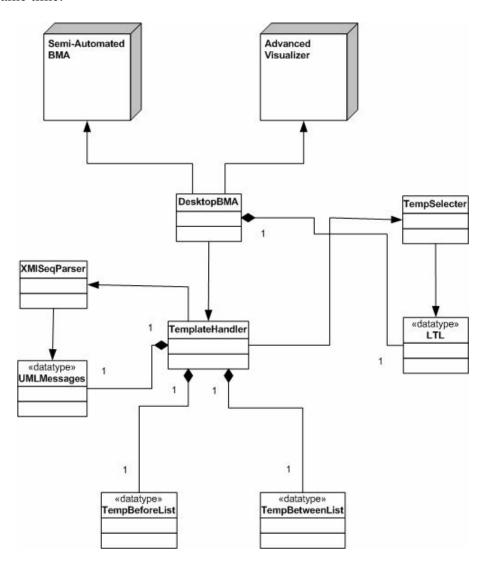

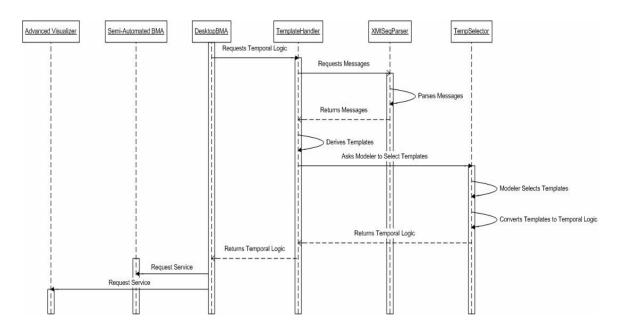

The architectural design of the *Automated BMA* consists of four major components as shown in Figure 7: *DesktopBMA*, *TemplateHandler*, *XMISeqParser*, and *TempSelector*. These components facilitate the derivation of specification templates from the UML sequence diagram. When using the BMA, the specification templates can either be directly supplied or automatically derived from the UML sequence diagram, but not both at the same time.

Figure 7 Static structure of the Automated BMA

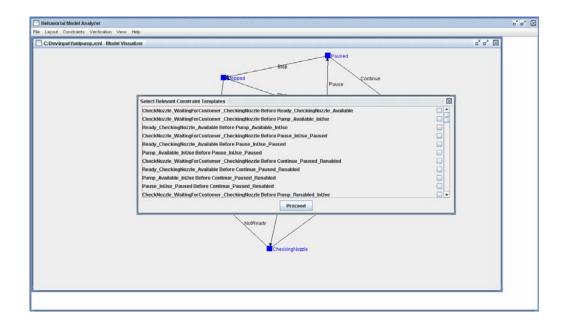

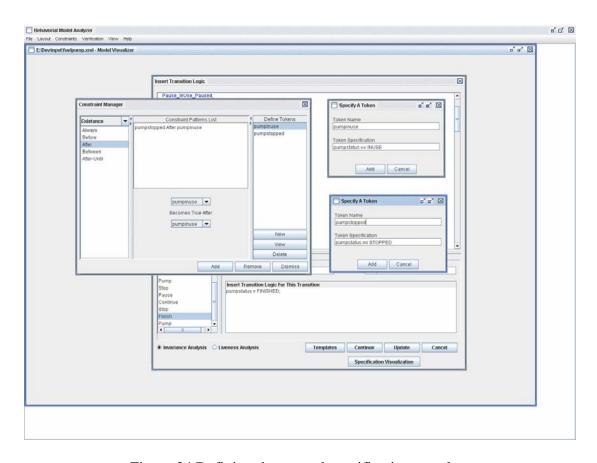

The process of deriving specification templates starts when the messages in the UML sequence diagrams are extracted by the *XMISeqParser* and stored in a data structure named *UMLMessages*. Then the list of messages in the data structure is examined and relevant specification templates are derived by the *TemplateHandler*. Since the BMA is a prototype application, only the recognition of the *before* and the *between* occurrence templates defined by Dwyer et al [12] is implemented to demonstrate the effectiveness of our strategy. The recognized templates are saved into the data structures *TempBeforeList* and *TempBetweenList*, respectively. The list of recognized templates are shown to the modeler by the *TempSelector*, and the modeler needs to check off the particular ones to use as properties for the design model to perform model checking. Afterwards, the selected templates are converted into temporal logic and saved in a text file by the *TempSelector*. The interactions among the components are described in terms of the UML sequence diagram shown in Figure 8.

Figure 8 UML Sequence diagram of the Automated BMA

The deployment diagram shown in Figure 9 provides the physical view of the components in this system based on their functions. It contains two subsystems. The *UI* subsystem contains the *DesktopBMA*, which is the user interface. The rest of the components are all grouped under the *Template Generation*. This subsystem performs the extraction of the messages from the UML sequence diagrams, the derivation of specification templates based on their order of occurrence, and the conversion of the derived templates into temporal logic.

Figure 9 UML Deployment diagram of the Automated BMA