## A Novel Through-Silicon-Via (TSV) Fabrication Method

by

#### Emir Adanur

A thesis submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Master of Science

Auburn, Alabama August 6, 2011

Keywords: Through-Silicon-Via, TSV, MEMS, ADE Process

Copyright 2011 by Emir Adanur

## Approved by

Robert N. Dean, Chair, Associate Professor of Electrical and Computer Engineering Thomas Baginski, Professor of Electrical and Computer Engineering Thaddeus Roppel, Associate Professor of Electrical and Computer Engineering

#### **Abstract**

The Through Silicon Via (TSV) is expected to be the future of 3-D chip stacking technology for electronic devices. The structure of the TSV interconnect is developed by first etching deep vias into the surface of a wafer, and later filling those vias with a desired metal. Currently, copper based TSVs are the most cost effective mass producible TSVs. Vias filled with copper provide the interconnect "through" the wafer, once both the top and the bottom of the vias are exposed. This provides a solid robust interconnect isolated and protected by the wafer. It also provides the interconnect using much less volume, while reducing the need for a majority of the packaging associated with modern microelectronic packages. Copper based TSVs were produced in this work using two methods, the ADE method and the blind-via method. The ADE method introduces a unique process that is potentially compatible with post-microelectronic manufacturing. The fabricated TSVs from both methods were cross-sectioned for analysis, which revealed successful formation of solid copper TSVs.

# **Acknowledgments**

I first would like to thank God, for without his support none of this would be possible. I would like to thank Dr. Robert N. Dean for his guidance, expertise, and support throughout my studies and this work. I would like to thank Dr. Thomas Baginski and Dr. Thaddeus Roppel for their support in joining my committee. I also would like to thank Charles Ellis and Michael Palmer for their knowledge and support in the lab. I would like to thank AEgis Technologies for funding the work and Eric Tuck and Derek Strembicke for their collaboration efforts in making this successful. I would like to thank Colin Stevens and Shakib Morshed for their help in the lab. I would also like to thank my professors and the department for their support. I finally would like to thank my family for their encouragement, love and support throughout my studies.

# **Table of Contents**

| List of Tabl | esviii                         |

|--------------|--------------------------------|

| List of Figu | resix                          |

| List of Abb  | reviationsxiii                 |

| Chapter 1:   | Introduction                   |

| Chapter 2:   | Literature Review              |

| 2.1 W        | afers                          |

| 2.2 Cl       | eaning                         |

| 2.3 W        | et Etching                     |

| 2.4 Pri      | mer4                           |

| 2.4.1        | Primer Materials4              |

| 2.4.2        | Primer Application Methods     |

| 2.5 Ph       | otoresist (PR)5                |

| 2.6 Etc      | ching6                         |

| 2.6.1        | Mechanical Drilling            |

| 2.6.2        | Chemical Etching               |

| 2.6.3        | Electrical Discharge Machining |

| 2.6.4        | Powder Blasting                |

| 2.6.5        | Laser Cutting and Ablation     |

| 2.6.6        | Deep Reactive Ion Etching      |

| 2  | 2.7   | See  | d Layer Deposition                                               | 9  |

|----|-------|------|------------------------------------------------------------------|----|

| 2  | 2.8   | Fill | Material                                                         | 9  |

| 2  | 2.9   | Ele  | ctroplating                                                      | 10 |

| 2  | 2.10  | T    | SV Applications                                                  | 12 |

| Ch | apter | 3:   | Materials, Equipment and Processes.                              | 16 |

| 3  | 3.1   | Ma   | terials and Chemicals                                            | 16 |

|    | 3.1.  | 1    | Silicon Wafers                                                   | 16 |

|    | 3.1.  | 2    | HMDS                                                             | 16 |

|    | 3.1.  | 3    | Photoresist                                                      | 18 |

|    | 3.1.  | 4    | Photolithography Masks                                           | 19 |

|    | 3.1.  | 5    | Photoresist Developer                                            | 20 |

|    | 3.1.  | 6    | Electroplating Chemicals                                         | 20 |

| 3  | 3.2   | Equ  | ipment                                                           | 22 |

|    | 3.2.  | 1    | Spin Rinse Dryer – STI Semitool ST 240 Wafer Spin Rinse Dryer    | 22 |

|    | 3.2.  | 2    | Ultrasonic Cleaner: Branson 5510 Tabletop Ultrasonic Cleaner     | 23 |

|    | 3.2.  | 3    | HMDS Coating Chamber                                             | 24 |

|    | 3.2.  | 4    | Photoresist Spinner                                              | 25 |

|    | 3.2.  | 5    | Hotplate                                                         | 26 |

|    | 3.2.  | 6    | Karl Suss MA/BA6 Contact Aligner                                 | 27 |

|    | 3.2.  | 7    | Matrix Oxygen Plasma Asher                                       | 28 |

|    | 3.2.  | 8    | Inductively Coupled Plasma (ICP) Deep Reactive Ion Etcher (DRIE) | 30 |

|    | 3.2.  | 9    | Horizontal Oxidation and Diffusion Furnace                       | 31 |

|    | 3.2.  | 10   | Electron Beam Evaporation and Sputtering System                  | 31 |

| 3.2.    | .11  | Profilometer: Tencor Alpha Step 200 Profilometer   | 33 |

|---------|------|----------------------------------------------------|----|

| 3.2.    | .12  | Scanning Electron Microscope                       | 34 |

| 3.2.    | .13  | Pre-Wet System and Vacuum Pump                     | 35 |

| 3.2.    | .14  | Beaker Copper Electroplating Bath                  | 36 |

| 3.2.    | .15  | Custom Copper Electroplating Bath                  | 36 |

| 3.2.    | .16  | Dicing Saw: Disco Automatic Dicing Saw (DAD 3220)  | 40 |

| Chapter | 4:   | ADE Process Design, Fabrication, and Results       | 42 |

| 4.1     | AD   | E Process                                          | 42 |

| 4.2     | AD   | E Process Design                                   | 42 |

| 4.2.    | .1   | TSV Wafer Design                                   | 43 |

| 4.2     | .2   | Backing Wafer Design                               | 44 |

| 4.2     | .3   | Wafer Assembly Design                              | 45 |

| 4.3     | AD   | E Process Fabrication                              | 46 |

| 4.3     | .1   | TSV Wafer Fabrication                              | 46 |

| 4.3     | .2   | Backing Wafer Fabrication                          | 49 |

| 4.3.    | .3   | Wafer Assembly Fabrication                         | 50 |

| 4.4     | AD   | E Process Results                                  | 58 |

| Chapter | 5:   | Blind-Via Process Design, Fabrication, and Results | 60 |

| 5.1     | Blin | nd-Via Process Design                              | 60 |

| 5.2     | Blin | nd-Via Process Fabrication                         | 68 |

| 5.3     | Blin | nd-Via Process Results                             | 78 |

| 5.4     | PR   | Bubbling                                           | 81 |

| 5.5     | Ma   | sk Cleaning                                        | 82 |

| 5.6 Via Etc.  | hing Sidewall Characteristics of Low Power vs. High Power etching | 83  |

|---------------|-------------------------------------------------------------------|-----|

| 5.7 Chambe    | er Conditioning                                                   | 84  |

| 5.8 Seed La   | ayer Coverage                                                     | 85  |

| 5.9 Via Tap   | pering                                                            | 86  |

| 5.10 Wafe     | r Pre-Wetting                                                     | 87  |

| Chapter 6: Co | nclusion and Recommendations for Future work                      | 90  |

| Bibliography  |                                                                   | 92  |

| Appendix A    | ADE Process TSV Traveler                                          | 96  |

| Appendix B I  | Blind-Via TSV Traveler                                            | 107 |

| Appendix C N  | Mask Aligner Settings                                             | 115 |

| Appendix D V  | Via Low Power Etch, DRIE Settings                                 | 116 |

| Appendix E    | Via High Power Etch, DRIE Settings                                | 119 |

| Appendix F    | Via Widen Etch, DRIE (STEP 2) Settings [57]                       | 122 |

| Appendix G V  | Via Widen Etch, DRIE (STEP 3) Settings [57]                       | 125 |

| Appendix H I  | DRIE Cleaning                                                     | 128 |

| Appendix I Ox | idation Settings                                                  | 131 |

| Appendix J H  | E-beam settings                                                   | 132 |

# List of Tables

| Table 1: Resistivity, Cost, and Volumetric Coefficients for TSV Fill Candidates | 10  |

|---------------------------------------------------------------------------------|-----|

| Table 2: Electroplating Chemistry for ADE Process                               | 20  |

| Table 3: TSV Plating Chemical Summary                                           | 22  |

| Table 4: Photoresist Spinner Parameters                                         | 26  |

| Table 5: Softbake Schedule AZ 9245                                              | 27  |

| Table 6: Softbake Schedule AZ P4620                                             | 27  |

| Table 7: Softbake Schedule                                                      | 62  |

| Table 8: Exposure Schedule                                                      | 63  |

| Table 9: RCA Clean                                                              | 97  |

| Table 10: RCA Clean                                                             | 104 |

| Table 11: RCA Clean                                                             | 108 |

| Table 12: Oxidation Settings                                                    | 131 |

| Table 13: E-beam Details                                                        | 132 |

| Table 14: E-beam Layer Samples                                                  | 132 |

# List of Figures

| Figure 1: HMDS Chemical Structure                                       | 17 |

|-------------------------------------------------------------------------|----|

| Figure 2: HMDS Coming Into Contact With An Oxidized Silicon Surface     | 17 |

| Figure 3: HMDS Chemically Bonding With the Oxidized Silicon Surface     | 18 |

| Figure 4: HMDS Bonding Complete                                         | 18 |

| Figure 5: Photolithography Mask                                         | 19 |

| Figure 6: Spin Rinse Dryer – STI Semitool ST 240 Wafer Spin Rinse Dryer | 23 |

| Figure 7: Ultrasonic Cleaner: Branson 5510 Tabletop Ultrasonic Cleaner  | 24 |

| Figure 8: HMDS Coating Chamber                                          | 25 |

| Figure 9: Photoresist Spinner                                           | 26 |

| Figure 10: Hotplate                                                     | 27 |

| Figure 11: Karl Suss MA/BA6 Contact Aligner                             | 28 |

| Figure 12: Matrix Oxygen Plasma Asher                                   | 29 |

| Figure 13: ICP DRIE                                                     | 30 |

| Figure 14: Oxidation Furnace                                            | 31 |

| Figure 15: Electron Beam Evaporation and Sputtering System              | 32 |

| Figure 16: Profilometer: Tencor Alpha Step 200 Profilometer             | 33 |

| Figure 17: Scanning Electron Microscope                                 | 34 |

| Figure 18: Pre-Wet System and Vacuum Pump                               | 35 |

| Figure 19: Beaker Copper Electroplating Bath                            | 36 |

| Figure 20: Copper Plating Bath                               | 37 |

|--------------------------------------------------------------|----|

| Figure 21: Sheer Plate Mixer                                 | 38 |

| Figure 22: Pure Copper Source                                | 38 |

| Figure 23: SPM Assembly Side View                            | 39 |

| Figure 24: SPM Assembly Top View                             | 39 |

| Figure 25: ADE Process Bath Set-Up                           | 40 |

| Figure 26: Dicing Saw: Disco Automatic Dicing Saw (DAD 3220) | 41 |

| Figure 27: Detailed Design Using The ADE Process             | 43 |

| Figure 28: TSV Wafer Design                                  | 44 |

| Figure 29: Backing Wafer Design                              | 45 |

| Figure 30: Wafer Assembly Design                             | 46 |

| Figure 31: Wafer CMP                                         | 48 |

| Figure 32: Wafer Feature Details, Post-CMP                   | 48 |

| Figure 33: Backing Wafer                                     | 49 |

| Figure 34: Copper Foil Tape                                  | 50 |

| Figure 35: UV Sealed Wafer Assembly (Front)                  | 51 |

| Figure 36: UV Sealed Wafer Assembly (Back)                   | 51 |

| Figure 37: Sample Dicing Tape Incision                       | 51 |

| Figure 38: Varying TSV Overburden                            | 52 |

| Figure 39: Complete Electroplating In Beaker                 | 53 |

| Figure 40: ADE Process Set-up                                | 54 |

| Figure 41: TSV Verification                                  | 55 |

| Figure 42: Wafer Assembly                                    | 56 |

| Figure 43: Wafer Assembly After UV Tape Removal                        | 56 |

|------------------------------------------------------------------------|----|

| Figure 44: Acetone Removal of Sacrificial PR Removal                   | 57 |

| Figure 45: Wafer quarter Post-PR Removal (front)                       | 57 |

| Figure 46: Wafer Quarter Post-PR Removal (back)                        | 57 |

| Figure 47: Beaker Plating Result (1 of 2)                              | 58 |

| Figure 48: Beaker Plating Result (2 of 2)                              | 58 |

| Figure 49: Sheer Plate Mixing Results (1 of 2)                         | 59 |

| Figure 50: Sheer Plate Mixing Results (2 of 2)                         | 59 |

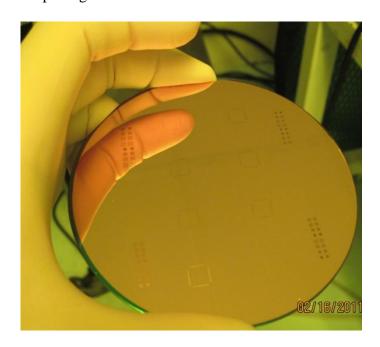

| Figure 51: Silicon Wafer                                               | 60 |

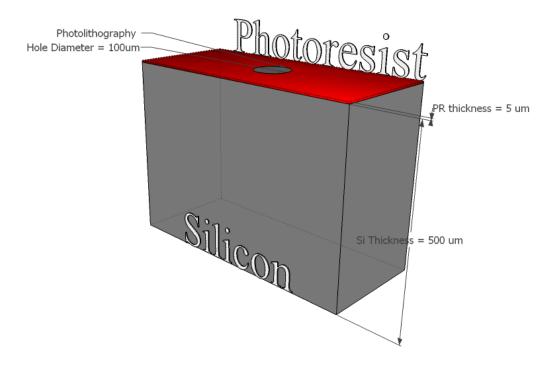

| Figure 52: Photoresist                                                 | 61 |

| Figure 53: Photoresist Development                                     | 62 |

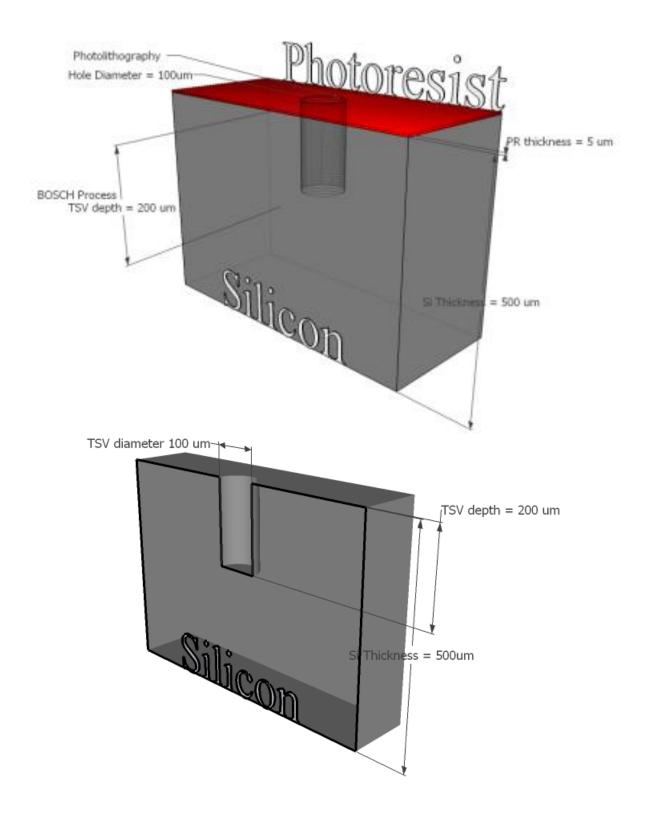

| Figure 54: DRIE (BOSCH <sup>TM</sup> Process)                          | 64 |

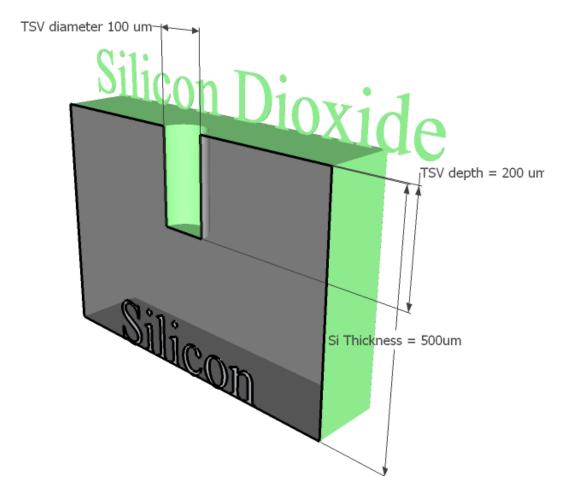

| Figure 55: Oxidation                                                   | 65 |

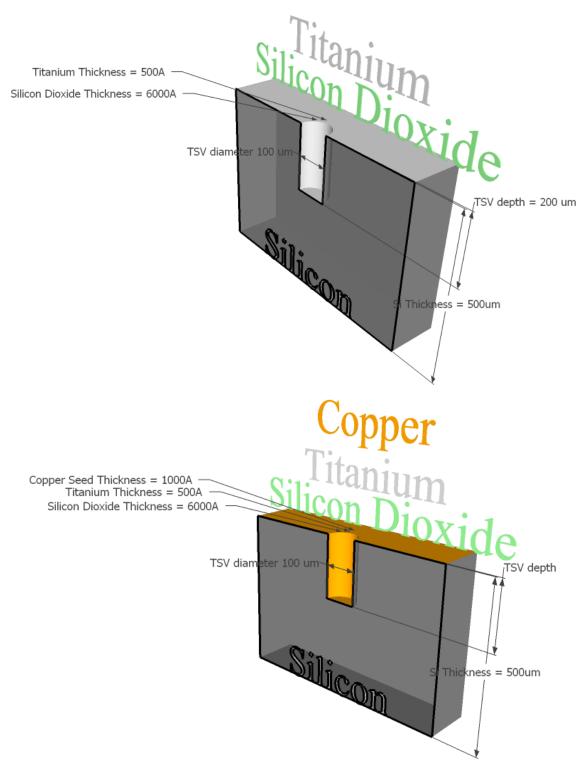

| Figure 56: Copper Seed Layer                                           | 67 |

| Figure 57: Copper Plating                                              | 68 |

| Figure 58: Wafer Mask In Contact Aligner                               | 69 |

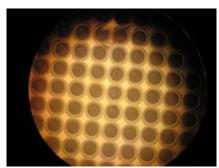

| Figure 59: PR Post-Development Inspection.                             | 70 |

| Figure 60: Descummed PR Wafer                                          | 71 |

| Figure 61: BOSCH Process Anisotropic Etch                              | 72 |

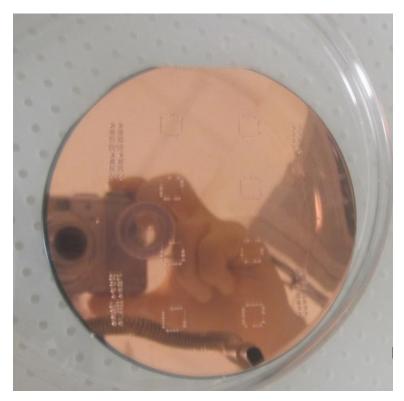

| Figure 62: Wafer Post-Copper Deposition                                | 73 |

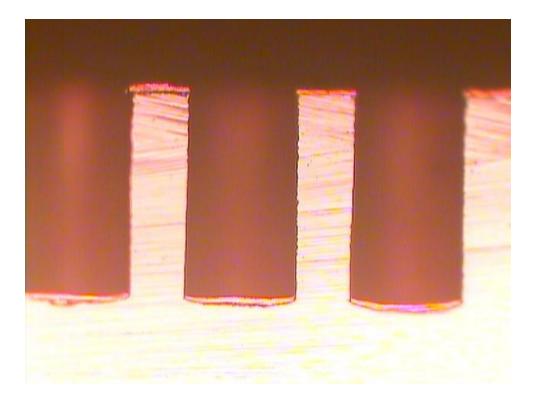

| Figure 63: Wafer Cross-Section Post-E-Beam Deposition (Edge Focus)     | 73 |

| Figure 64: Wafer Cross-Section Post-E-Beam Deposition (Sidewall Focus) | 74 |

| Figure 65: Wafer Secured In Wafer Holder Post-Pre-Wet                  | 75 |

| Figure 66: Wafer Removal For Inspection                                                | 76   |

|----------------------------------------------------------------------------------------|------|

| Figure 67: Wafer Removal For Inspection, Surface Oxidation.                            | 76   |

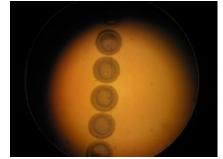

| Figure 68: Via Inspection.                                                             | 77   |

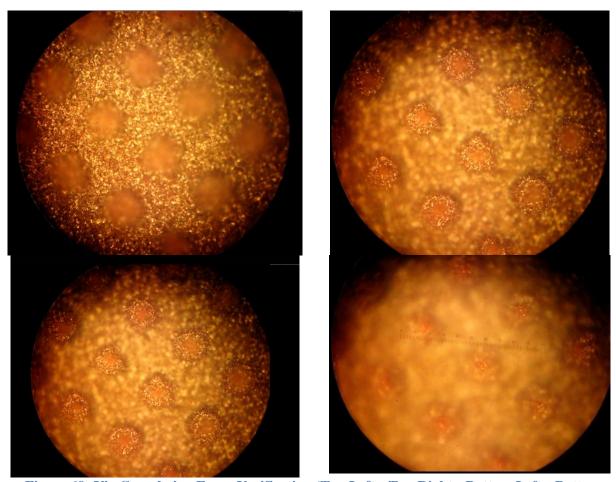

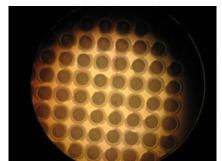

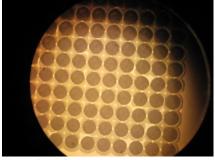

| Figure 69: Via Completion Focus Verification (Top Left->Top Right->Bottom Left->Bottom |      |

| Right)                                                                                 | 77   |

| Figure 70: Via Conformal Filling Verified (Left Half of Wafer)                         | 78   |

| Figure 71: Via Conformal Filling Verified (Right Half of Wafer)                        | 79   |

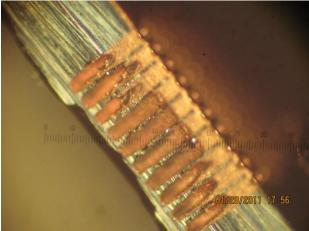

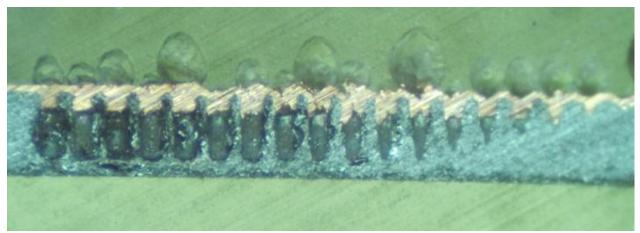

| Figure 72: TSV Cross-Section                                                           | 80   |

| Figure 73: Conformal Via Fill                                                          | 80   |

| Figure 74: PR Bubbling on Edge of Wafer (1 of 2)                                       | 81   |

| Figure 75: PR Bubbling on Edge of Wafer (2 of 2)                                       | 82   |

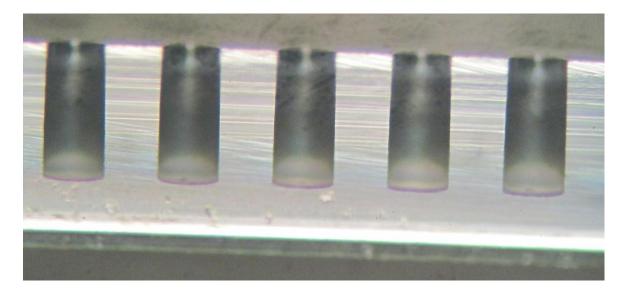

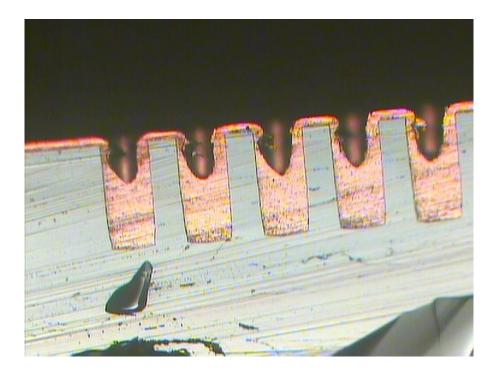

| Figure 76: 12W Deep Striations                                                         | 83   |

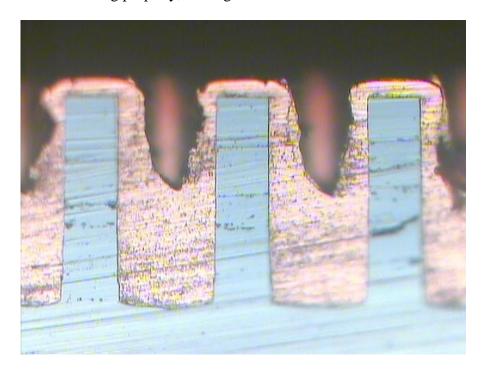

| Figure 77: 18W Smoother Shallow Striations                                             | 84   |

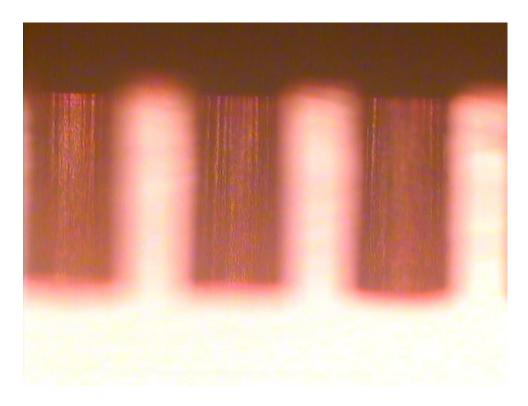

| Figure 78: E-beam Deposition of Seed Layer                                             | 85   |

| Figure 79: Irregular Via Widening                                                      | 86   |

| Figure 80: Narrow Spacing After Via Widening                                           | 86   |

| Figure 81: Excessive Via Widening                                                      | 87   |

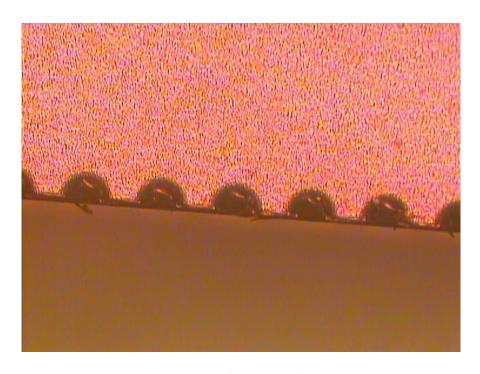

| Figure 82: Poor Via Pre-Wet Results                                                    | 88   |

| Figure 83: Air Evacuating Vias Under Vacuum in IPA                                     | 89   |

| Figure 84: Fully Pre-Wet Wafer (Darkened Via Openings)                                 | . 89 |

#### List of Abbreviations

AU Auburn University

TSV Through-Silicon-Via

MEMS Microelectromechanical Systems

DRIE Deep Reactive Ion Etching

HMDS Hexamethyldisilazane

DI De-Ionized

CMP Chemical Mechanical Polishing

DRIE Deep Reactive Ion Etching

STS Surface Technology Systems

ASE Advanced Silicon Etcher

CTE Coefficient of Thermal Expansion

AMNSTC Alabama Micro/Nano Science and Technology Center

PR Photoresist

PVA Polyvinyl Alcohol

## **Chapter 1: Introduction**

As the package size of modern microelectronics rapidly shrinks, Moore's law begins to accurately describe the limitation on the amount of technology that can fit on an integrated circuit. The development of single electron transistors such as the SketchSET; however, have given us a glimpse towards the end of transistor scaling [1]. As the end of Moore's law approaches, a more recent approach emerges, called "More than Moore". This new trend attempts to improve systems by reducing the package size of devices. This ultimately delivers a higher component density. This transitions the electronic world from a classical multichip module, in which multiple chips were used for different functions, to a system on chip (SOC) model which integrates everything into a single chip. Production of such a chip, however, can be difficult with current conventional approaches.

One of the main limiting factors in package size comes from a chip's interconnects. Modern technology heavily uses wire bonds, which may take little material volume but as a result of their use they waste much more 3-D space. This is because nothing can come in contact with them, forcing them to be spatially separated from the chip and each other. Additionally, they have to be electrically isolated using more material. The leading alternative to wire bonds is the utilization of Through-Silicon-Vias (TSVs). TSVs are interconnects that pass through a wafer or chip allowing for an electrical connection through the substrate. This technology is beginning to be commercially utilized in many different devices, and it shows a promising future in many prospective applications including cameras [2], video cameras [3], and DRAM [4].

As TSVs ease their way into modern devices, the number of potential benefits and the effectiveness of these interconnects are surfacing. The benefits TSVs introduce are numerous. To begin with, a TSV can be customized to fit many different design specifications from dimensions

to materials to the location of the TSVs. They drastically reduce the routing length in comparison with wire bonds. A TSV's reduced length can increase speed and improve the performance of a circuit. Their mechanical robustness and isolation within the wafer make them ideal long term interconnects for a wide variety of applications.

With the demand for TSVs growing, this research is intended to propose a detailed procedure for an existing TSV development method as well as introduce a new method. A detailed description of those methods, along with experimental results, will be discussed. Problems that arose during the fabrication and how they were handled will also be analyzed.

# **Chapter 2: Literature Review**

This chapter will focus on different methods that have been used to develop TSVs. It will discuss different materials, processes and technologies that can be utilized during the TSV microfabrication process. It will also review previous published work related to TSVs

#### 2.1 Wafers

There are many different types of semiconductor wafers, including silicon, gallium arsenide, and gallium phosphide [5]. Silicon wafers are heavily used in industry since they are readily available and relatively inexpensive compared to Gallium based wafers. The leading alternative is gallium arsenide (GaAs), which is far more expensive but more ideally suited for microelectronic processing, and is considered toxic due to the presence of Arsenic. Although GaAs circuits can operate much faster due to GaAs's intrinsic electrical properties[6], the cost and possible safety concerns removed it from consideration for this project. Thus, in this paper, wafers are assumed to be made of silicon.

#### 2.2 Cleaning

In any micro fabrication process, maintaining a clean wafer is essential. According to some sources, over fifty percent of IC yield losses are a direct result of micro-contamination [7]. This section will describe different methods that can be used throughout the fabrication process to maintain a clean wafer.

#### 2.3 Wet Etching

Piranha etch is solution mixture of sulfuric acid ( $H_2SO_4$ , 98%) and hydrogen peroxide ( $H_2O_2$ , 30%) and is used to remove organics from a wafer. One ratio that can be used is 4:1 ( $H_2O_2$ : $H_2SO_4$ ) [7]. An HF (hydrofluoric acid) etch will etch through silicon dioxide as the acidity will form silanol bonds with the oxide on the wafer surface. The fluorine will form SiF<sub>4</sub>

gas which is soluble in water yielding H<sub>2</sub>SiF<sub>6</sub> [8]. This removes all oxides on the wafer surface making it hydrophobic. Nitric acid can be added to HF in order to enhance the etching properties [9]. Another method is known as the RCA Standard Clean. It is composed of two separate bath solutions. The first, known as RCA standard clean 1 (or SC-1) is a mixture of 5:1:1 H<sub>2</sub>O: H<sub>2</sub>O<sub>2</sub>: NH<sub>4</sub>OH and is carried out for 10 minutes at 75-80°C. The second solution is known as the RCA standard clean 2 (or SC-2), which is used for the same duration and temperature as SC-1 but is composed of 6:1:1 H<sub>2</sub>O: H<sub>2</sub>O<sub>2</sub>: HCl. The solution is formulated not to aggressively attack Si or SiO<sub>2</sub> [10]. Tetramethyl ammonium hydroxide (TMAH, (CH<sub>3</sub>)<sub>4</sub>NOH) has been introduced as a silicon etch [11]. Although, the TMAH solution requires many other solutions including surfactants, pH regulators and complexing agents. Of all the different types of etching solutions listed here, the RCA standard clean's trusted method along with the HF's effective cleaning were the deciding factors in integrating them into the blank wafer cleaning process for this research.

#### 2.4 Primer

A primer is used as an adhesion promoter so that the PR may adhere well to the silicon wafer's surface. There are different primer materials and methods of application.

#### 2.4.1 Primer Materials

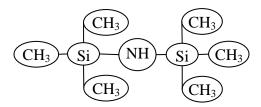

There are many choices for wafer primer. For silicon, the main three choices are: (CH<sub>3</sub>)<sub>3</sub>SiNHSi(CH<sub>3</sub>)<sub>3</sub> 1,1,1,3,3,3-hexamethyldisilizane (HMDS), C<sub>6</sub>H<sub>5</sub>SiCl<sub>3</sub> Phenyltrichlorosilane or trichlorophenylsilane (TCPS), and (CH<sub>3</sub>)<sub>3</sub>SiNCH<sub>3</sub>COSi(CH<sub>3</sub>)<sub>3</sub> bistrimethylsilylacetamide (BSA). In the case of gallium arsenide (GaAs) wafers, Monazoline C, Trichlorobenzene, and Xylene are more desirable primers due to GaAs wafer's polar surface. For the purpose of this research, we will focus on the silicon wafer primers. Of the three silicon primers, it can be seen from the chemical equation that TCPS contains chlorine which is toxic

and corrosive; this primer also requires a hard bake of 200°C for 30 minutes [12]. BSA had little material resources available. The Hazardous Materials Identification System (HMIS® ranking chemicals from 0 minimal hazard to 4 severe hazard) rating on the HMDS sheets were used to compare safety [13], [14], [15]. TCPS and BSA were ranked a 3, and HMDS was ranked a 2. HMDS was chosen as the PR primer due to TCPS and BSA's health concern, the TCPS requiring a long hard bake, and the BSA resources being difficult to obtain.

## **2.4.2 Primer Application Methods**

There are two main methods for HMDS priming. The first is called spin priming, and is performed by dripping a small amount of primer on the wafer and spinning the wafer to propel excess primer of the surface and to evaporate any remaining solution. This can only be done one wafer at a time. The second method is Vapor priming, and can be performed on multiple wafers at the same time while yielding good uniformity. Thus, being the preferred method for industry, it was chosen as the selected method for primer application for this project.

#### 2.5 Photoresist (PR)

There are many different types of resist that can be used to mask a wafer. There are photosensitive liquid resists that are poured onto a spinning wafer, which removes excess resist and thins the resist down to a desired thickness. This process gives the user good control over formation of the resist on the wafer's surface. Dry film PRs are also becoming popular as they boast advantages such as protection of vias, wafer back-side protection, high etching selectivity (100:1), and also allowing the chemical processing for copper traces and vias.[16]. In comparison to spin-on liquids, they do not exhibit an edge-bead deformity which is the collection of PR on ridges or the edge of the wafer. Although there are some added benefits to the dry film

approach, its added benefit has no profound effect on TSV processing. The AMNSTC's experience using spin-on resists made it a more controlled variable in process development.

## 2.6 Etching

The etching process forms the via in any TSV procedure. There are three critical parameters that are used to analyze an etching process. The first parameter is feature size, which can be considered the width of the via since it is the smallest feature of the etch. The second parameter is an expansion of feature size, which is the aspect ratio of the etch. This gives us a comparison of the vertical sidewall height to the width of the etch. The last parameter is the sidewall surface roughness which needs to be smooth in order to allow for a better TSV.

## 2.6.1 Mechanical Drilling

Mechanical drilling is the same for micro scale as it is in macro scale. It uses a bit which is smaller than the hole being drilled, and is made from a strong enough material to withstand the forces associated with drilling (i.e. cemented carbide)[17]. Mechanical drilling can have an aspect ratio >10, although the feature size must be greater than 300μm, and the roughness is considered "average" [18]. The average sidewall roughness is due to the drill bit's non-uniformity and possibly micro-deformations developed due to drilling forces/abrasion. Although, the aspect ratio and roughness may be workable into a TSV procedure, the feature size is too large to be commercially viable.

#### 2.6.2 Chemical Etching

Chemical Etching is a slight improvement over mechanical drilling for feature size. It allows for a reduced minimum feature size of 150 µm, but it is limited by an aspect ratio of roughly 1. The sidewall roughness is more uniform than mechanical drilling [18]. Wet etching is usually cheap, fast, and has limited damaging effects on the wafer; however, it is very isotropic

and would be very difficult to control in making high aspect ratio and high quality through silicon vias[19]. Thus, even with the improvements workable into a TSV procedure, the feature size needs to be competitive with wire bond technology in order for there to be enough benefit to use it in a TSV procedure.

## 2.6.3 Electrical Discharge Machining

Although Electrical Discharge Machining is a technology generally used to cut metals, it has recently been tested on silicon. Since the silicon is softer than most metals, the speed of machining silicon is faster, while exposing the electrode to less wear [20]. This technology is a further improvement in both aspect ratio (roughly 15) and minimum feature size (>50µm). The sidewall roughness is poorer than chemical etching, but roughly equal with mechanical drilling [18]. However, the minimum feature size and aspect ratios are big enough improvements over mechanical drilling and chemical etching to make it a better choice

## 2.6.4 Powder Blasting

Powder Blasting is another approach for etching wafers. It uses a photosensitive elastomer as a protection layer around the via. Then using 9-29μm diameter Al<sub>2</sub>O<sub>3</sub> particles bombarding the silicon wafer at 90m/s, it begins to etch the silicon through the mask. The minimum feature size that can be obtained is roughly equal to electrical discharge machining (>50μm), but yields a poorer aspect ratio (~3-5) than mechanical drilling and electrical discharge machining. The sidewall roughness is the poorest of all etching discussed in this article [18]. The poor sidewall characteristics and aspect ratio make this an undesirable etching process for TSVs.

#### 2.6.5 Laser Cutting and Ablation

Both laser processes were maskless but required a PVA layer on the wafer surface to prevent the ejected material from contaminating the wafer. Laser cutting was experimented with

in the same comparison study using an ND:YAG laser whose wavelength of 1064nm. It was pulsed for a duration of 0.2ms on a spot size ranging from 30-100μm. A high-pressure gas flow removed the molten silicon. This produced a better minimum feature size (>30μm), but not as good surface characterization as laser ablation [18].

Laser ablation was experimented with in the same comparison study using an ND:YAG laser whose wavelength of 355nm and pulsed for a duration of 30ns on a spot size ranging from 10-30µm. This yielded a high power density beam (108~1010 W/cm2), which evaporated the silicon instead of melting it. The results yielded a better aspect ratio (>20) and minimum feature size (>10µm) than the previously described techniques. The sidewall characterization was the same as mechanical drilling and electrical discharge machining [18]. The sidewall characterization and lack of equipment prevented this research from pursuing this option. Although, it should be mentioned that laser methods can be significantly faster than DRIE (roughly 25 times according to some research)[21]. This may soon compete with the Deep Reactive Ion Etching in that it is much faster and can also be used to dice a substrate. However, it should also be noted that laser etching is performed one via at a time, and if there are many vias, this process may actually take longer.

## 2.6.6 Deep Reactive Ion Etching

DRIE was also compared in the same study using  $SF_6/O_2$  chemistry, using PECVD oxide as the masking layer. The result of the DRIE yielded the best aspect ratio (>20), minimum feature size (>5 $\mu$ m), and acceptable roughness [18]. This direct comparison proved that DRIE was still the best process for making vias. In addition to the standard BOSCH process for DRIE, a newer and higher aspect ratio method called the S.H.A.R.P. process has emerged from Alcatel

for the DRIE [22]. The BOSCH and S.H.A.R.P. processes made DRIE the most functional technology for etching silicon.

## 2.7 Seed Layer Deposition

Most research has been employing the standard E-beam/CVD approach for depositing a copper seed layer for TSVs [23][24][25]. DC sputtering was another approach used to line vias with a copper seed layer [26]. Those who used the E-beam and sputtering mechanisms also tended to taper the via's sidewalls before deposition. This was performed in order to obtain proper coating on the via's sidewalls. One research group worked with Metalorganic Chemical Vapor Deposition (MOCVD) and had a very conformal seed deposition on high aspect ratio (16:1) vias. This MOCVD approach allowed for sidewalls perpendicular to the surface while depositing a very conformal thin layer of copper [27].

#### 2.8 Fill Material

Many fill materials can be used to fill TSVs. The need will come from the wide range of devices used in a wide variety of conditions. One study showed a detailed look at the stresses caused by CTE differences at extreme temperatures, and showed a more pronounced effect on device lifespan as TSV size increases. In addition, the study commented on the idea that the standard fill material being used today (copper) does not have a suitable coefficient of thermal expansion match with silicon. [28] Further investigation found that there are many conductors that can be used for this purpose. Cost, resistivity and wafer compatibility were the main considerations. Wafer compatibility referred to the volumetric coefficient of expansion,  $\beta$ . This aspect of the materials should be taken into long-term consideration, since over time, the expansion and contraction of the plated metal may have detrimental effects on the lifetime of the device. Finding a material to fill the vias that best matches the volumetric coefficient of

expansion of silicon may produce a higher yield for long-term, extreme temperature, and high current density devices. For the context of this paper, the low resistivity and cost of copper, as well as its use in commercial devices, were the deciding factors in pursuing copper as the fill material. A variety of possible plating materials are listed and compared in Table 1.

Table 1: Resistivity, Cost, and Volumetric Coefficients for TSV Fill Candidates

| Material | Resistivity Ω·cm at 20°C [29] | Cost (\$/lb) [30] | Volumetric Coefficient of Expansion [31] |

|----------|-------------------------------|-------------------|------------------------------------------|

| Copper   | $1.68 \times 10^{-8}$         | 3.99              | $5.1 \times 10^{-5}$                     |

| Silver   | $1.59 \times 10^{-8}$         | 561.16            | $5.4 \times 10^{-5}$                     |

| Gold     | $2.44 \times 10^{-8}$         | 21,746.66         | $4.2 \times 10^{-5}$                     |

| Tungsten | $5.6 \times 10^{-8}$          | 15.00             | $1.35 \times 10^{-5}$                    |

| Silicon  |                               |                   | $.9 \times 10^{-5}$                      |

## 2.9 Electroplating

There are several methods for electroplating. The base of all the mechanisms involves a circuit connection connecting the cathode target to the negative terminal of the power supply and the anode to the positive\_terminal of the power supply and connecting the two in series through a solution. The solution is generally a copper sulfate based solution. The solution is composed of sulfuric acid and copper sulfate, which may contain traces of metal impurities. The sulfuric acid has three main functions. The first is to prevent the hydrolysis of water found in the solution. The second function is to decrease resistivity. This reduces the overall power required for the plating as well as reduces the formation of rough deposits when higher currents are obtained. It also decreases copper ion concentration, but it doesn't inhibit the supply of copper ions. The cathode (negative, or target wafer) uses the simple reaction:

$$Cu^{2+} + 2e^{-} \rightarrow Cu$$

to take the aqueous copper and form solid copper with the acceptance of two electrons. The reverse occurs at the anode (positive, or source) in order to continually replenish the solution with copper ions:

$$Cu - 2e^{-} \rightarrow Cu^{2+}$$

Ideally the sulfuric acid is not needed; however, since copper can be either Cu2+ or Cu+, the copper anode may give off Cu+ ions via the following reaction:

$$Cu - e^{-} \rightarrow Cu^{+}$$

The Cu+ ions would ideally plate the target with less current, but it tends to oxidize via oxygen found in solution from exposure to air or through non-degassed DI water through the following reaction:

$$Cu_2SO_4 + H_2SO_4 + O \rightarrow 2CuSO_4 + H_2O$$

Summarized:

$$2Cu^{+} + 2H^{+} + O \implies 2Cu^{2+} + H_{2}O$$

The Cu+ ions also tend to form a solid Cu sludge residue on the source copper's surface as well as expelling it into solution through the reaction:

$$Cu_2SO_4 \rightarrow CuSO_4 + Cu$$

Summarized:

$$2Cu^+ = Cu^{2+} + Cu$$

There are three ways to avoid these problems. The first is periodic solution preplacement with water and sulfuric acid to maintain balance. The second approach includes using nodes containing small amounts of lead. Or finally, the solution can completely be replaced [32].

Two common problems with electroplating blind-via TSVs include voids, seams, and platting overburden. To combat these two causes for error, many researchers have employed

different techniques, but most use a variety of chemical additives. The first additive in combating voids is the addition of an accelerator. This chemical accelerates the copper deposition rate. If only this were used, then void formation would still not be inhibited since the rapid copper deposition would cause the via to neck off (or bottle off) much faster. Thus, a leveler is added to deactivate the accelerated plating along the neck of the via. This inhibits the void from sealing off. If only these two chemicals were used then the vias would fill conformally but would have excessive overburden on the surface of the wafer. Thus another additive that can be used is what is called suppressor, which inhibits the copper deposition. It is a long polymer that tends to coat the wide open surfaces to create a "blocking" layer to inhibit copper overburden on the surface [33].

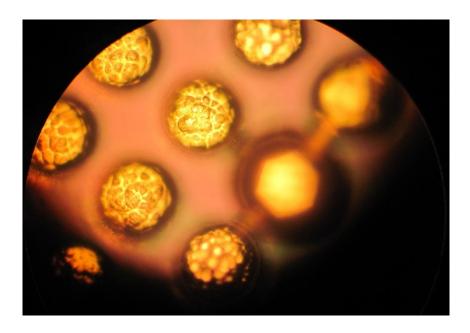

In addition to chemistry issues, one study showed the negative side effects of directional fluid flow over TSVs during plating [34]. This need for even solution flow over the wafer's surface has been met in several different ways. Some researchers employ a shower head jet nozzle spraying towards the wafer in solution in order to achieve coating in the depths of vias [35]. The use of a ShearPlate<sup>TM</sup> mixer (by Nexx Systems) has also been proven to be very beneficial in achieving conformal copper coating. In addition the same research has proven that smoother denser plating can be achieved by using a reduced current [36].

### 2.10 TSV Applications

TSVs boast a wide range of benefits including: low power consumption, short connections, higher density, better heat dissipation, reduced RC delays, and low impedance [37]. The application of these benefits yields the much desired effects in the products we use every day. The following is a discussion on TSV applications.

There has been much research in recent years in regard to TSVs. Modest capacitance reduction can be achieved with the replacement of long wires or wire bonds with shorter TSVs. This greatly enhances performance and power efficiency of devices. While Through Silicon Stacking (TSS) produces reduced form factor (allowing miniaturization), reducing the overall volume of the device. This reduction has been experienced by different sources [38] [39], A sideeffect of miniaturization is the difficulty associated with routing, thus copper redistribution layers can be plated in order to connect TSVs on different parts of a wafer. This allows TSVs to have an x-y dimension routing capability. [40]. Hermetic sealing is at times an industry requirement for some applications such as MEMS accelerometers and gyroscopes. TSVs are compatible with these hermetically sealed packages [41]. TSVs can also be coaxial if necessary, and do not need to be simple copper (or other fill material). Analysis and modeling has been performed on this type of structure [42]. One of the key applications and research has been its effective use in stacked devices such as memory and RAM. A 3-D solid state drive has been designed, employing TSVs to show significant improvement [43]. Another research group developed a DDR3 DRAM with copper TSVs. They were able to reduce standby power by 50% and the active power by 25% when compared with QDP packages. Additionally, the TSV design increased the I/O speeds to 1.5Gb/s. [44].

In addition to this research, many companies are implementing TSVs in different RAM modules. Elpida Memory, Inc., for example, has recently begun sample shipments of its 1GB DDR3 SDRAM (x32) based TSV technology consuming very low power [45]. Samsung, however, tops this with its 8GB advanced Green DDR3 DRAM module. Samsung is able to reduce power by nearly 40% with this technology. They state that even with the 30% reduction in memory slots for next generation servers, TSV technology will overcome this by increasing

density by more than 50%. [4]. The excessively high density bandwidth of TSVs was also used as an advantage in TSV research carried out by Georgia Tech in order to improve memory fetch times, which merely stacking main memory on processors could not achieve [46].

Toshiba took the TSV technology into cameras by applying them down to the pixel level by attaching each pixel directly to a dedicated application specific integrated circuit (ASIC) through a TSV. ST Microelectronics has also utilized TSVs in ultra-small 2 megapixel system on chip image sensors with a built-in image signal processor [47]. This was used in an image sensor that was developed for mobile phones. [48][2]. Medigus also made the world's smallest medical video camera, only 0.99mm in diameter. [3].

Micron is also using this technology in what they call Osmium<sup>TM</sup> Packaging Technology. It takes advantage of TSVs (which they call TWIs or Through Wafer Interconnects) as the interconnect for this new technology in order to eliminate wire bonds from hindering the device's electrical performance. [49]. Tessera Technologies had one of the first Through-Silicon-Via solutions it called SHELLCASE MVP wafer-level chip-scale packaging (WLCSP), which now licenses for others to utilize TSVs in developing thinner, faster, and what it claims cheaper devices [50]. Silex Microsystems also offers its own version of Through Silicon Vias called Sil-Via®, but interestingly offers what it calls Met-Cap<sup>TM</sup> which is a Metal Via Wafer Level packaging that actually contains a cavity up to the surface of the wafer. It says it can be used as a capping feature in addition to being used to store passive devices [51]. This is a small variety of the many TSV manufacturers.

As industry pushes TSV manufacturing into the mainstream, software companies such as Cadence have jumped on board to develop technology allowing for the easy testing of TSV implemented 3D stacked ICs [52]. Mentor Graphics Corporation is also beginning to follow up

with its Calibre physical verification/extraction tool and its Tessent IC test solution to allow for TSV compatible test and verifications [53].

With the advantages of TSVs, it is apparent why so many companies are flocking toward TSV implementation.

## **Chapter 3: Materials, Equipment and Processes**

The following sections describe in detail the materials, equipment and processes used throughout the research in this document. In addition to research, all the materials, equipment, and processes used in this research were located the Alabama Micro Nano Science and Technology Center (AMNSTC) facilities. The facilities contain a 4000 square foot Class-100 clean room in addition to several auxiliary laboratories. The laboratory is fully equipped with standard microelectronic fabrication equipment.

#### 3.1 Materials and Chemicals

This section describes in detail the materials and chemicals used in this research.

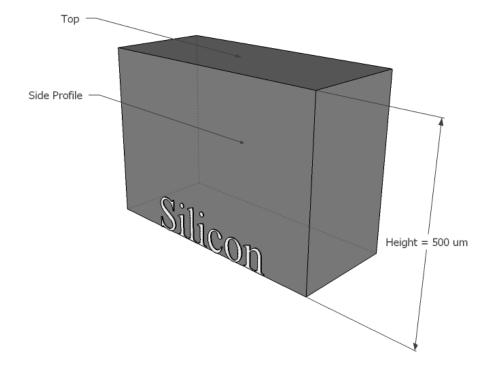

#### 3.1.1 Silicon Wafers

Silicon wafers (to be called wafers) are the first design decision of any device. There are many different orientations that can be chosen. The processes described in this work are orientation independent and thus any orientation is compatible. Thus, arbitrary (100) and (111) (for backing wafers) orientations were chosen.

#### 3.1.2 HMDS

Photolithography is a critical process during microfabrication. PR's adhesion to the wafer's surface is a critical step in this process. In order to assure quality PR adhesion to a wafer's surface, a primer, such as HMDS, must be coated on the wafer surface prior to PR application. This is necessary because even with the oxide strip during the RCA clean, the silicon wafer naturally develops a thin layer of oxide when exposed to atmosphere. In addition to the PR not adhering well to oxide, the oxide adsorbs water from the air through hydrogen bonds. Thus water may be absorbed by the oxide if a primer is not used, and the presence of water prior to PR application makes it difficult for the PR to adhere to the silicon wafer's surface.

The primer chosen for this research was Hexamethyldisilizane (HMDS). It works by exploiting the presence of silicon dioxide, on which it will chemically bond with the oxide and leave a surface which is readily adhesive to PR. This can be seen by closer examination of the HMDS structure. The chemical formula for HMDS is:

$$C_6H_{19}NSi_2$$

The chemical structure is shown Figure 1 below.

**Figure 1: HMDS Chemical Structure**

The chemical reaction is:

$$2(=Si - OH) + (CH_3)_3SiNHSi(CH_3) \rightarrow 2(=Si - O - Si - (CH_3)_3) + NH_3[54]$$

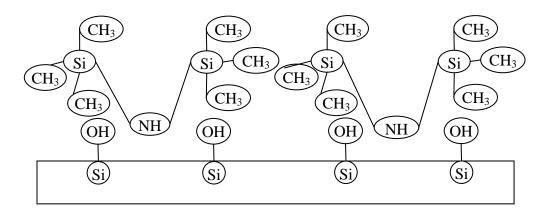

Using the equation, the following 3 images show how HMDS interacts with the oxidized silicon surface in order to bind to it and leave binding sites for the PR. First the NH from within the HMDS structure approaches the silicon wafer as shown in Figure 2.

Figure 2: HMDS Coming Into Contact With An Oxidized Silicon Surface

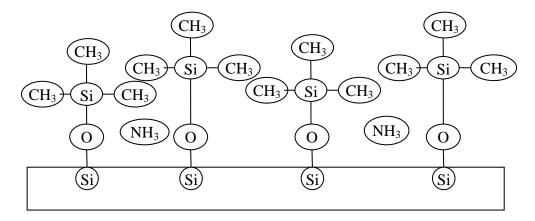

The HMDS then chemically bonds with the oxidized surface by stripping the oxygen atoms of hydrogen and forming NH<sub>3</sub> (ammonia).

Figure 3: HMDS Chemically Bonding With the Oxidized Silicon Surface

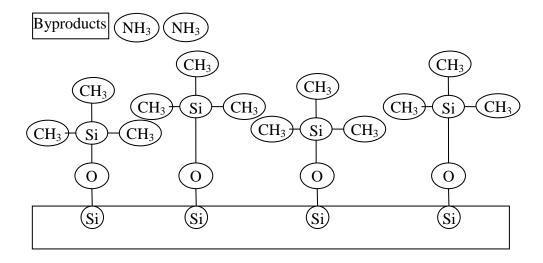

The ammonia gas is then released as byproducts leaving the HMDS chemically bonded with oxide bonded on the Silicon's surface (Figure 4). PR will now readily adhere to the primer applied surface.

**Figure 4: HMDS Bonding Complete**

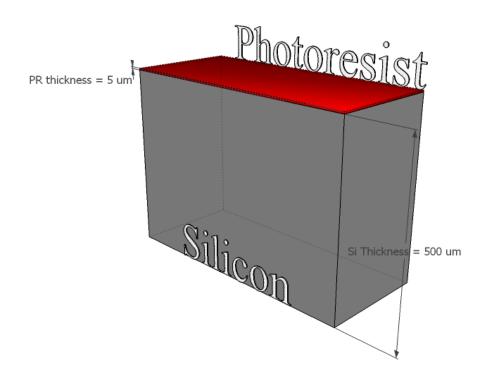

#### 3.1.3 Photoresist

Two different photoresists were used in this research. The first was photoresist AZ P4620, which was chosen for its approximately 70:1 etching selectivity with Si when used in a DRIE. In

addition to this, it was chosen for its maximum spin on thickness of up to 24µm, which allowed for wafer etching down to any depth in the wafer. It is a positive photoresist which means areas exposed to UV radiation will be developed away. The second photoresist, AZ 9245, was chosen for its ability to brush up deformities in the photolithography process of the AZ P4620 and also used for temporary wafer to wafer bonding for full wafer etching. If a wafer was not backed with another wafer, there would be a gas up leak once the DRIE etching penetrated the entire depth of the wafer. These photoresists will be referred to as "PR" along with their name (AZ P4620 and AZ 9245).

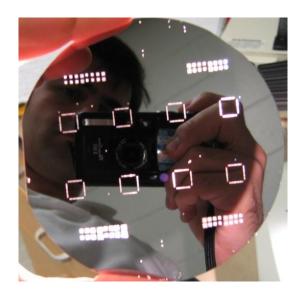

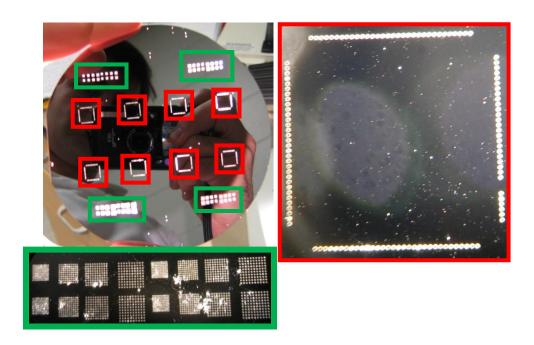

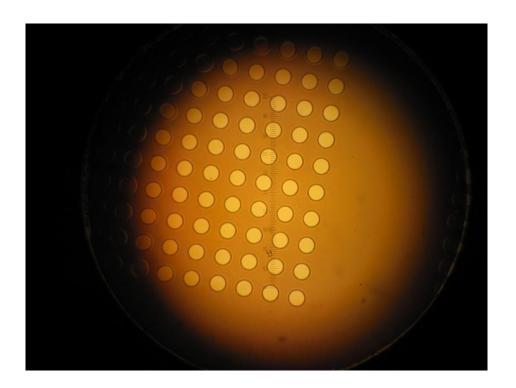

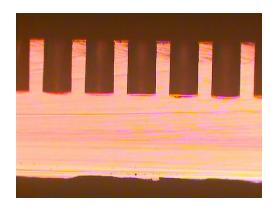

## 3.1.4 Photolithography Masks

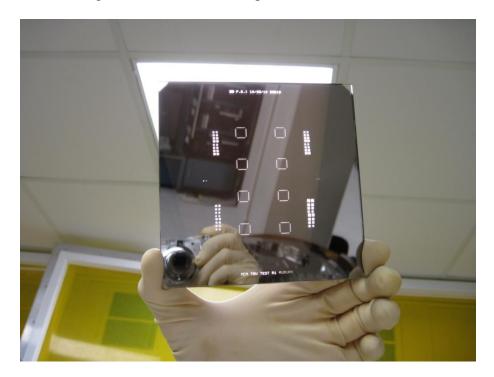

The photolithography mask used in this work (referred to as "mask") was made from chrome on glass. The mask is shown in Figure 5. The eight squares in the center of the mask contain 100μm circle diameters along their perimeters. The four sets of grids on the left and right of the squares are 10x10 grids of circles containing via dimension of 60, 70, 80, and 100μm.

Figure 5: Photolithography Mask

## 3.1.5 Photoresist Developer

Once a PR coated wafer is exposed through a mask, it is developed in a developer solution. In this research, the only developer used was AZ 400K, which is a clear colorless solution. It is a potassium based buffered developer, is said to produce high contrast on thick film photoresists such as AZ P4620 and AZ 9245 photoresists. The developer was used in a 2:1 mixture of DI water (200mL) and AZ 400K (100mL). The wafers were developed for 1 minute, and then rinsed with DI water and N<sub>2</sub> air dried by hand.

# **3.1.6** Electroplating Chemicals

There were 2 types of solution chemistries for the electroplating in this research. The first solution was used for the ADE process and the second was used for the blind-via process.

The ADE process chemistry consisted of a solution from Enthone Chemicals known as "Part A", because of its general use with multiple additives for blind-via chemistries. In the ADE process, only part A was used because we did not need the additives for suppression (detailed in the blind-via portion of this section). The details of part A can be found in Table 2, and was the sole ingredient.

**Table 2: Electroplating Chemistry for ADE Process**

| PART | Manufacturer | Manufacturer Part        | Technical      | Use    | Ratio | %    |

|------|--------------|--------------------------|----------------|--------|-------|------|

|      |              | Number                   | description    |        |       |      |

| A    | Enthone, Inc | Microfab DVF-            | Copper Sulfate | Copper | 3.5L  | 100% |

|      |              | 200 TSV Sulfate  Make Up | Solution       | source |       |      |

The electroplating chemistry for the blind-via TSV was also from Enthone Chemicals.

The chemistry contained four solutions, each with its own added benefit to the plating process.

Part A is a majority of the solution (98.519%) and is used as the source for copper ions in solution. These positive cations will neutralize on the negative copper wafer's surface, neutralizing the ions into solid, stable metal. Gradually this will plate the TSV on any copper surface. Since some TSVs can be very deep, a solution called "part B" is added to be 0.495% of the solution. This is known as the accelerator, since it accelerates the ions/solution into the bottoms of the TSVs. This allows for the solution to continually circulate into the depths of the TSV, allowing all copper surfaces to be plated. Another problem associated with plating is the overburden of plating on the wafer's planar surface. For this problem, a solution referred to as "part C" or the primary suppressor (referred to as the suppressor) is added as 0.617% of the solution. It is a solution containing larger molecules with position themselves on open easily accessible areas such as the wafer surface, suppressing excess plating. The final concern addressed with the chemistry is the ready availability of negative charge along the perimeter of the TSV opening the wafer, which has a tendency to result in excess plating around the "neck" of the via. This "necking off' leads to the sudden sealing of the via's opening, and results in voids within the center of the TSV. This problem requires the introduction of a new solution called "part D" or the secondary suppressor solution (to be called the leveler). It is added as 0.369% of the solution. It is a polar chemical that prevents the excessively charged wafer surface and the higher charged via openings from plating too quickly. It slows any plating in these areas by removing any plated copper. Since the rate of deposition is faster than the removal, only limited plating occurs (but no degradation). A summary of the plating chemistry can be found in Table 3.

**Table 3: TSV Plating Chemical Summary**

| PART | Manufacturer | Manufacturer Part | Technical      | Use         | Ratio  | %       |

|------|--------------|-------------------|----------------|-------------|--------|---------|

|      |              | Number            | description    |             |        |         |

| A    | Enthone, Inc | Microfab DVF-     | Copper Sulfate | Copper      | 3.5L   | 98.519% |

|      |              | 200 TSV Sulfate   | Solution       | source      |        |         |

|      |              | Make Up           |                |             |        |         |

| В    | Enthone, Inc | MICROFAB DVF      | Accelerator    | Accelerator | 17.6mL | 0.495%  |

|      |              | 200-B Sulfuric    |                |             |        |         |

|      |              | acid              |                |             |        |         |

| C    | Enthone, Inc | COMPOUND          | Primary        | Suppressor  | 21.9mL | 0.617%  |

|      |              | C94510            | Suppressor     |             |        |         |

|      |              | MICROFAB DVF      |                |             |        |         |

|      |              | 200-C 1,2-        |                |             |        |         |

|      |              | Ethanediol        |                |             |        |         |

| D    | Enthone, Inc | MICROFAB DVF      | Secondary      | Leveler     | 13.1mL | 0.369%  |

|      |              | 200-D             | Suppressor     |             |        |         |

## 3.2 Equipment

In this section, the detailed descriptions of each piece of equipment used in order to undertake this research are presented. A short reference name/descriptor is given for each tool to be referred to throughout this document.

## 3.2.1 Spin Rinse Dryer – STI Semitool ST 240 Wafer Spin Rinse Dryer

The STI Semitool ST 240 Wafer Spin Rinse Dryer (Figure 6) is used throughout the fabrication process to keep a clean wafer surface. The spin rinse dryer contains a wafer boat used to hold 4in wafers, which are locked into place before the spin rinse dry begins. There are two phases: a spin-rinse phase and a spin-dry phase. During the spin-rinse phase, the wafers begin to spin while DI water is sprayed on the surfaces of the wafers. The DI water removes any debris and contamination while the rotation propels the debris-collected water off the wafer's surfaces to a drain. This spin-rinse phase has adjustable time and rotation parameters. For this research, the time was fixed to 90 seconds and the rotation speed was fixed to 500 rpm. The drying phase immediately follows. In this phase, the wafers spin while heated nitrogen air is blown to dry the

wafers. The force of the nitrogen gas removes larger droplets of water from the surface while the heat from the nitrogen gas dries the wafers on a micro-scale. This step also has the same adjustable time and rotation parameters. For this research, the time was fixed to 120 seconds and the rotation speed was fixed to 2500 rpm. Together these two steps ensure a streak-free, clean wafer surface. This procedure will be referred to as a "spin-rinse-dry".

Figure 6: Spin Rinse Dryer – STI Semitool ST 240 Wafer Spin Rinse Dryer

## 3.2.2 Ultrasonic Cleaner: Branson 5510 Tabletop Ultrasonic Cleaner

The 2.5 gallon tank is filled to the operating level with water. The sample to be cleaned is then placed in a pyrex bowl and the bowl is filled with a cleaning solution (acetone, IPA, etc...). The machine is turned on and the 40kHz ultrasonic frequency vibrates the sample through the solutions. This is used for a variety of tasks including vibrating away any debris from deep vias or simply quick removal of photoresist from a wafer's surface. This will be referred to as an "ultrasonic clean".

Figure 7: Ultrasonic Cleaner: Branson 5510 Tabletop Ultrasonic Cleaner

# 3.2.3 HMDS Coating Chamber

The HMDS chamber (Figure 8) is used to coat/bond HMDS, an adhesion promoter for photoresist, to a wafer's surface. The wafers are placed face-up in a wafer boat, which is placed in the chamber with a small quantity of HMDS poured into the basin. The wafers are placed face up in order to avoid contact with the surface of the wafer's edges. The volatile HMDS then fills the chamber and bonds to the wafer's oxidized surface, allowing future photoresist to adhere well to the wafer's surface. This will be referred to as an "HMDS coat".

**Figure 8: HMDS Coating Chamber**

# 3.2.4 Photoresist Spinner

A photoresist spinner (Figure 9), manufactured by Cost Effective Equipment, ensured proper PR coating on the wafer's surface. It was capable of coating 4-6 inch wafers. It allowed precise and accurate control of the PR's thickness as well even uniformity. This was accomplished by controlling the parameters listed in Table 4. The spin speed (0 to 6000rpm) controlled the thickness of the PR, with shorter spin time coating a thicker PR. The time (0 to 999sec) and to a lesser extent ramp acceleration (0~30,000rpm/sec) controlled the uniformity of the PR coat. Longer time and slower ramp acceleration providing the best uniformity. This will be referred to as a "PR spin" and the parameters will be listed as "a spin speed of A rpm and a ramp acceleration of B rpm/s for C seconds".

**Table 4: Photoresist Spinner Parameters**

| Parameter    | Control                    | Effect     |

|--------------|----------------------------|------------|

| SPIN SPEED   | The top speed (in rpm)     | Thickness  |

|              | desired for the given      |            |

|              | "TIME".                    |            |

| RAMP         | Rate increase from 0 to    | Uniformity |

| ACCELERATION | "SPIN SPEED" in rpm/s.     |            |

| TIME         | Total time of the spinning | Uniformity |

|              | in seconds.                |            |

**Figure 9: Photoresist Spinner**

# 3.2.5 Hotplate

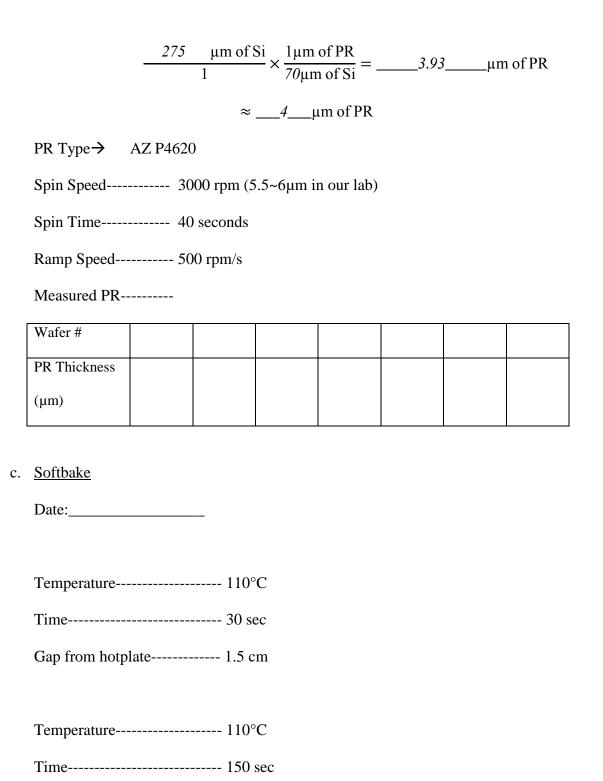

Following a PR application, a wafer is heated on a hotplate (Figure 10), this is called a softbake, to remove solvents and gases trapped in the PR. For AZ9245 photoresist, the softbake schedule is shown in Table 5. As for AZ P4620, the softbake schedule is shown in Table 6.

Figure 10: Hotplate

Table 5: Softbake Schedule AZ 9245

| Duration (seconds) | Temperature (°C) | Wafer separation from |

|--------------------|------------------|-----------------------|

|                    |                  | hotplate surface (cm) |

| 30                 | 110              | 1.5                   |

| 150                | 110              | 0                     |

Table 6: Softbake Schedule AZ P4620

| Duration (seconds) | Temperature (°C) | Wafer separation from |

|--------------------|------------------|-----------------------|

|                    |                  | hotplate surface (cm) |

| 150                | 110              | 0                     |

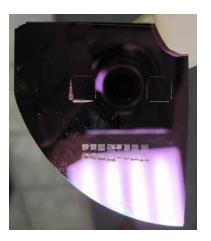

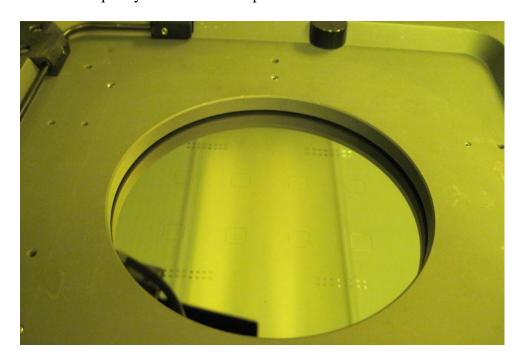

# 3.2.6 Karl Suss MA/BA6 Contact Aligner

The Karl Suss MA/BA6 Contact Aligner (Figure 11) brings a PR coated wafer into contact with a photolithography mask, and exposes UV light through the mask onto the wafer. The UV light comes from a mercury lamp. The machine is capable of processing wafers from 50mm to 150mm in diameter. It has three contact modes: Proximity, Soft and Hard. For this

work, the "hard" option was used in order to ensure maximum resolution. This means the mask will be in direct contact with the wafer, minimizing spacing and maximizing resolution. The optical resolution of the exposure device is 0.4µm, and the wavelength range of the lamp is 350-450nm. This will be referred to as the "exposure" procedure.

Figure 11: Karl Suss MA/BA6 Contact Aligner

## 3.2.7 Matrix Oxygen Plasma Asher

The Matrix Oxygen Plasma Asher (Figure 12) is used to remove organic/PR residue. The asher uses oxygen plasma, a heated chuck (0-190°C), high pressure (3-5 torr), and high RF power (0-500W) to remove any PR whether it is hardened by etching or simply difficult to remove. The oxygen plasma reacts with any organics (including PR) to form an ash that is

vacuum pumped from the system (hence "plasma asher"). For the purposes of this research, the chuck was not heated. The machine accepts both 4 and 5 inch wafers for processing. The tool effectively removes PR, but may also oxidize any exposed metal. It can also be used to descum (partially etch thin layers) of PR; however, a short time duration is desired. In this work, the asher was used to descum wafers immediately prior to etching, since the PR used for etching has a 70:1 etching ratio, even a small amount of PR residue could change the depth of vias containing PR residue. It was also used to completely remove any remaining PR or residue before wafers were copper coated in the E-beam system. The asher program used is called "PR\_STRIP". The only modified parameter was time of exposure which was 14 seconds for descum and 5 minutes for wafer cleaning. This was performed using 300W RF at a 4~5 Torr pressure with oxygen flowing at 31% of the rated 100sccm flow. The wafer was not heated since it had PR on it. The two processes will be referred to as descum and wafer clean.

Figure 12: Matrix Oxygen Plasma Asher

### 3.2.8 Inductively Coupled Plasma (ICP) Deep Reactive Ion Etcher (DRIE)

The Advanced Silicon Etcher manufactured by Surface Technologies Systems, Inc. shown in Figure 13 is an Inductively Coupled Plasma Deep Reactive Ion Etcher (to be referred to as DRIE). It utilizes the Bosch process using multiple, alternating cycles of passivation using C<sub>4</sub>F<sub>8</sub> plasma and etching using SF<sub>6</sub>/O<sub>2</sub>. The machine has an RF induction coil which forms the plasma. This machine utilizes the BOSCH process to develop a nearly straight vertical anisotropic etch. There were three programs used on this machine that allowed for all the etching required in this work. They will be referred to as the "Via Low Power Etch" APPENDIX D, "Via High Power Etch" APPENDIX E, "Via Widen Etch Step 1" APPENDIX F and "Via Widen Etch Step 2" APPENDIX G. The difference between the low and high power via etch is the platen power (power applied to the plate that holds the wafer while processing).

Figure 13: ICP DRIE

#### 3.2.9 Horizontal Oxidation and Diffusion Furnace

The oxidation furnace (Figure 14) is used to grow oxide in a controlled manner. It does this by controlling the temperature within the furnace as well as the flow of gases: nitrogen, oxygen, and hydrogen. The nitrogen flow is used to keep the furnace dry as well as clean (purging other gases). The oxygen is used to grow pure silicon dioxide (SiO<sub>2</sub>), this is called dry oxidation. The introduction of hydrogen allows for more rapid, thicker silicon dioxide growth, but it is lower quality. This is called wet oxidation. The oxidation in this TSV research was performed via wet oxidation. The oxidation schedule used is shown in Appendix I.

**Figure 14: Oxidation Furnace**

#### 3.2.10 Electron Beam Evaporation and Sputtering System

The Mark 50 electron beam chamber (Figure 15) made by CHA is used to deposit metals in thin layers. It can deposit the metal layers very precisely with high accuracy. It does so by

rotating the wafers to be deposited on a hemisphere carousel facing down towards the metal source. The metal source is in a crucible which is targeted with an electron beam guided toward the crucible with a magnetic field. The entire system is under high vacuum while the process is running. A three minute argon ion cleaning of the samples was performed prior to any deposition. The machine was used to deposit three metals for the various TSV processes: chrome, titanium, and copper. It will be referred to as "E-beam deposition of" a given metal at a given thickness in angstroms (Å).

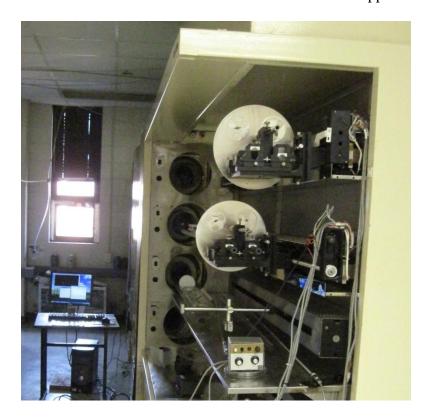

Figure 15: Electron Beam Evaporation and Sputtering System

## 3.2.11 Profilometer: Tencor Alpha Step 200 Profilometer

The profilometer is a non-destructive way to take step measurements. It is accomplsihed using contact measurement of a diamond-tipped stylus. The tip is attached to an arm which moves the tip along the surface of the measured material. The profilometer measures the surface topology by measuring the arm's vertical deflection as the tip moves along the surface. It has a vertical range of  $\pm 160 \mu m$  with a 5nm resolution. It can be used to measure step heights, etch depths, coating thicknesses, and surface roughness.

Figure 16: Profilometer: Tencor Alpha Step 200 Profilometer

#### **3.2.12 Scanning Electron Microscope**

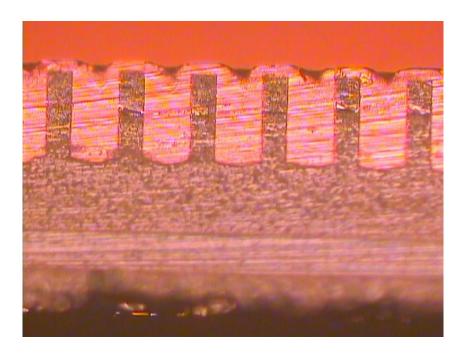

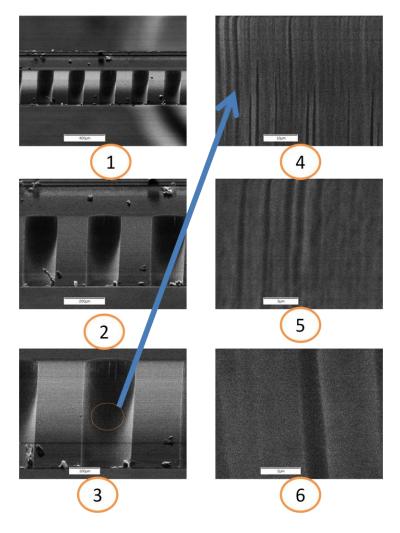

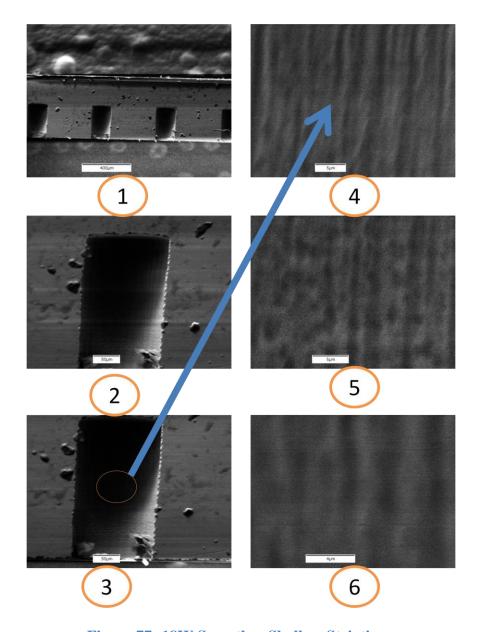

A scanning electron microscope (Figure 17) was used in this research to analyze sidewall surface roughness. The machine works by emitting an electron beam from a tungsten coil filament that acts as a cathode. The sample is placed in a holder (anode) which is grounded to attract the electrons, which accelerate toward the sample in the holder. As the electrons approach the sample, they pass through a magnetic field which guides the beam through apertures to focus it on the sample. As the electrons hit the sample's surface, many deflections occur including cathodoluminescence, auger electrons, primary backscattered electrons, secondary electrons and x-rays. The SEM used in this research measures secondary electron deflections to produce the high quality images. Horizontal lines in the images from the SEM are a result of charging and are not actually present in the sample. This will be used to determine sidewall smoothness.

**Figure 17: Scanning Electron Microscope**

### 3.2.13 Pre-Wet System and Vacuum Pump

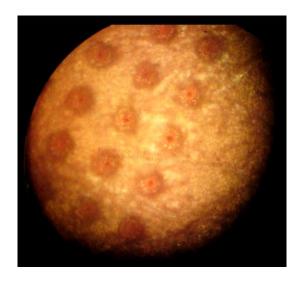

The chamber shown in (Figure 18) is the pre-wet system used to pre-wet the vias prior to electroplating. Since the electroplating process is a wet chemical process, it requires proper pre-wetting, which is the introduction of fluid into the vias before plating. This ensures that the entire via will plate in solution. The pre-wet is accomplished by placing the wafer to be plated in an empty petri dish. From here the wafers were pre-wet in two ways. In the first method, the petri-dish was filled with IPA and the vacuum pump was turned on. In the second method, the vacuum pump was turned on first before the dish was filled with IPA (without breaking the vacuum seal through a valve in the top of the chamber). The second method was more effective, as it removes all the air from the chamber and the insides of the vias instead of attempting to force the air out of the vias through the IPA in the petri dish. IPA was selected since it has a low surface tension. Therefore the low surface tension IPA rushes to fill the voids within the vias when air is evacuated. A rubber mallet was used to agitate the solution using mechanical shocks through the chamber. This entire process will be referred to as a "pre-wet" (either IPA first or vacuum first).

Figure 18: Pre-Wet System and Vacuum Pump

### 3.2.14 Beaker Copper Electroplating Bath

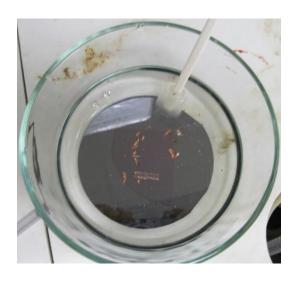

Initially plating was completed in a beaker set up as shown in Figure 19. The setup consisted of a current source to control and measure the applied current between the copper source and the tape assembly. The beaker is filled with Enthone Chemical's Microfab DVF-200 TSV Sulfate Solution to fully submerse the target and copper source. A magnetic spinner is used to stir the solution during plating.

Figure 19: Beaker Copper Electroplating Bath

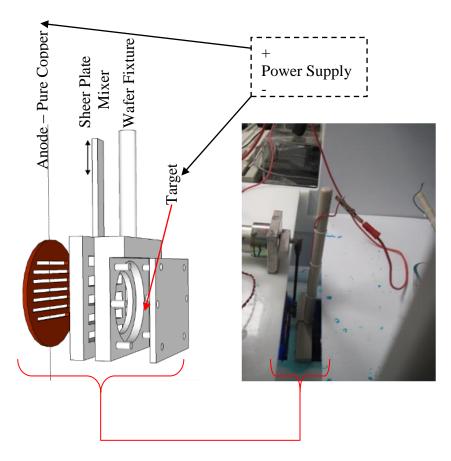

#### 3.2.15 Custom Copper Electroplating Bath

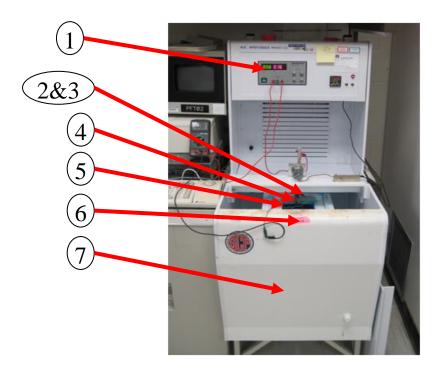

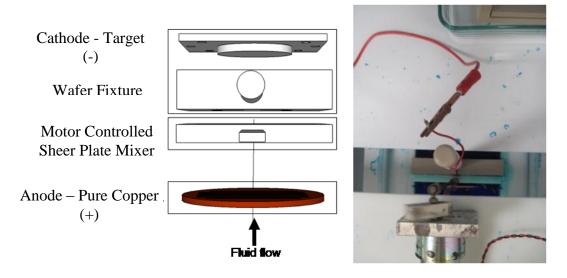

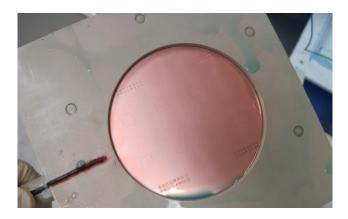

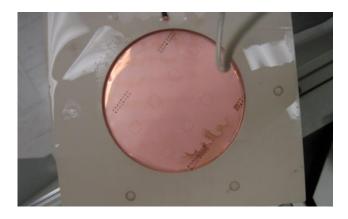

The copper plating bath (Figure 20) is a custom designed copper electroplating bath. The problems with the beaker electroplating bath (such as non-uniformity and via necking off) prompted the design this custom bath. This bath was design for plating blind vias.

Figure 20: Copper Plating Bath

The main components of the copper plating bath include:

- 1. The Adjustable Current Source steadily supplying a set current.

- 2. The plating target (cathode, wafer with Ti/Cu surface).

- 3. A wafer fixture to hold the copper coated face of the wafer pointing towards the copper source. The fixture has a water proof seal to protect the connectors used to connect to the anode's surface.

- 4. A Sheer-Plate-Mixer (SPM) for moving waves of the plating chemistry on the wafer's surface constantly (refreshing it). The SPM moves up and down at 6 Hz. There are laterally cut sections that allow fluid to freely flow through the SPM.

Figure 21: Sheer Plate Mixer

5. The metal source (Cu anode), which has vertical cuts to allow fluid flow from the pump through the source.

**Figure 22: Pure Copper Source**

- 6. The plating chemistry described earlier.

- 7. The filter/pump which pumps/filters the solution continuously.

Figure 23: SPM Assembly Side View

Figure 24: SPM Assembly Top View

Once the wafers are placed in the assembly and connected in the solution, the current supply is turned on and the current is ramped to the desired level to allow conformal plating/filling. This will be referred to as electroplating.

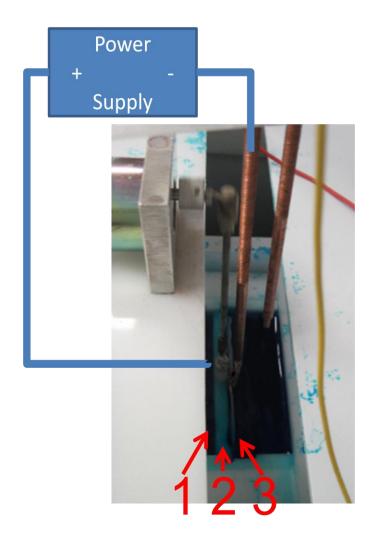

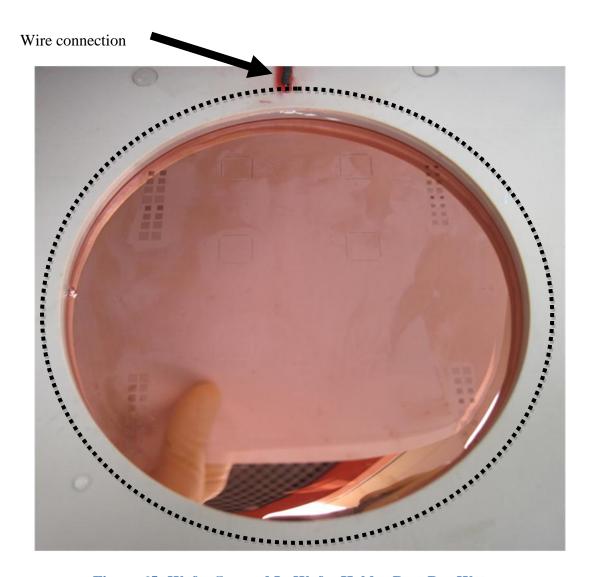

Since the ADE process is not a blind via process, the setup was slightly modified for electroplating using this process. The modification came in the form of a conductive wafer clip attached to the end of a conductive copper rod to connect to the tape used in the ADE process (Figure 25).

Figure 25: ADE Process Bath Set-Up

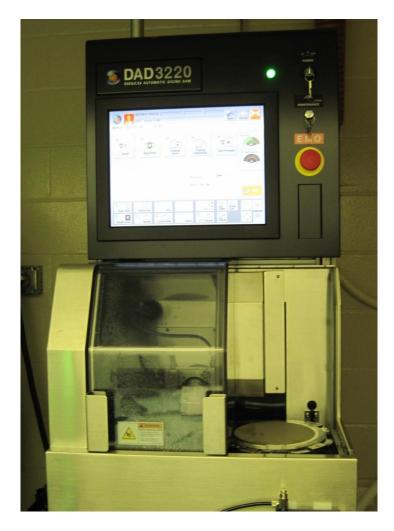

## 3.2.16 Dicing Saw: Disco Automatic Dicing Saw (DAD 3220)

This compact dicing saw was used to dice wafers into sections before using them for electroplating. It was also used to cut through the center of structures and obtain smooth sidewalls. This was done in order to produce high quality side profile images, as well as test for voids in the TSVs.

Figure 26: Dicing Saw: Disco Automatic Dicing Saw (DAD 3220)

# **Chapter 4: ADE Process Design, Fabrication, and Results**

Two Methods were used to develop the TSVs. The first was the ADE process and is detailed in this section. The section begins with a more theoretical design, followed by the actual fabrication used, and finally a discussion of the results.

#### 4.1 ADE Process

The ADE (Adhesive, DRIE, Electroplated) Process is a process that utilizes UV dicing tape to seal a wafer assembly. This sealed wafer assembly allows for copper plating from a backing wafer's seed layer through the vias of the TSV wafer. The detailed design and fabrication of this wafer is described in this section.

## 4.2 ADE Process Design

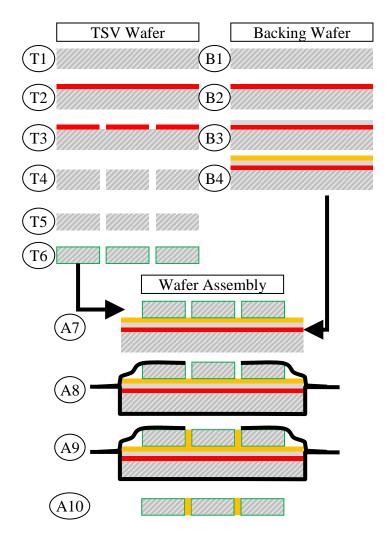

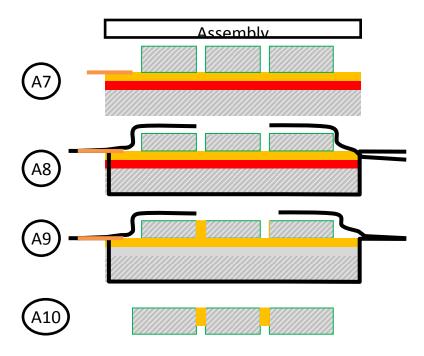

The wafer design consisted of 3 main parts (Figure 27). The first two parts are the fabrication and preparation of the TSV and Backing wafers. These two wafers can be processed in parallel. The two are then sealed into one assembly, using UV removable adhesive tape, and copper plated to fill the vias. The next three sections describe these parts in more detail.

Figure 27: Detailed Design Using The ADE Process

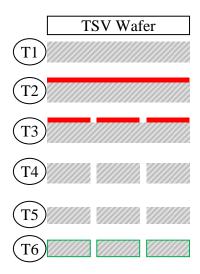

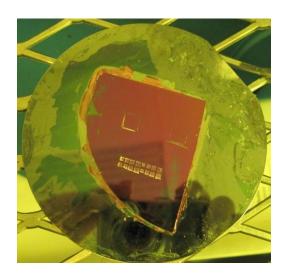

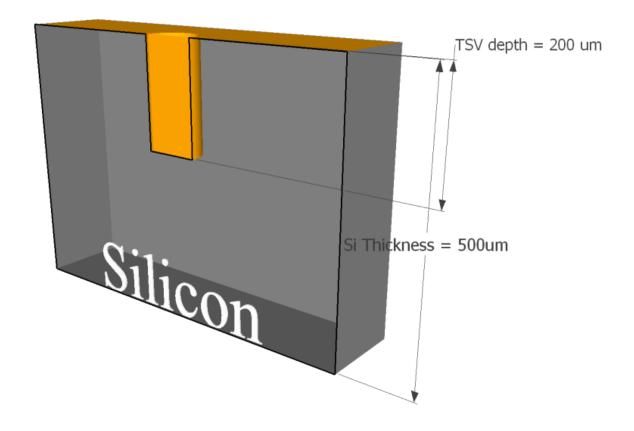

# 4.2.1 TSV Wafer Design

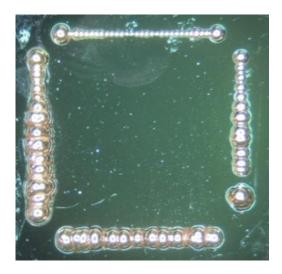

The first part of the design consisted of fabricating the TSV wafer; a diagram of the process is shown in Figure 28. The first step was selecting a wafer. Any wafer thickness could have been used but the application called for using 100mm diameter, 350µm thick silicon wafers (Figure 28-T1). The wafers were then cleaned and deposited with PR (Figure 28-T2). This PR was then exposed and developed to reveal the TSV pattern (varying grids of 10x10 circles maximum 100µm diameter, 30µm spacing edge to edge) (Figure 28-T3). The DRIE was then used to etch the vias down through the entire depth (350µm) of the wafer (Figure 28-T4). The

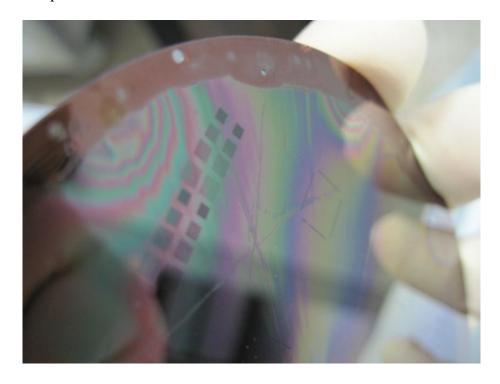

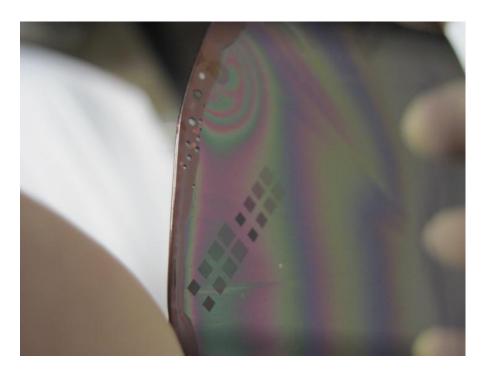

wafers were then thinned using a backgrind and polish (Figure 28-T5). The backgrind and polish (CMP) step is not necessary in all applications, but this application required the thinning down of the wafer to 225µm. The wafer was then oxidized in order to prevent any electrical shorting between TSVs through the substrate (Figure 28-T6).

Figure 28: TSV Wafer Design

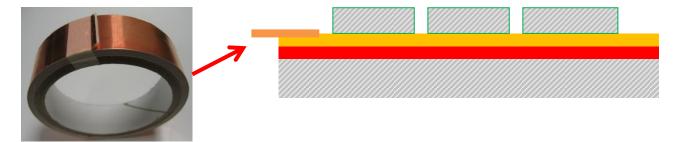

### 4.2.2 Backing Wafer Design

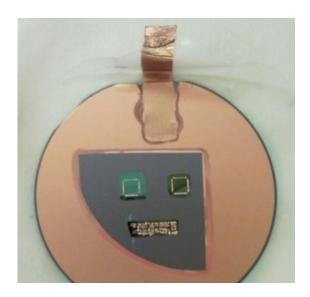

The backing wafer was the second part of the assembly. The fabrication process began the same way as the TSV wafer, by cleaning a blank wafer (Figure 29-B1) and preparing/spinning on of PR (Figure 29-B2); however, the PR was not exposed or developed. The seed layer deposition was performed using an electron beam evaporation system. 250Å of chromium (Figure 29-B3) and 2,500Å of copper (Figure 29-B4), which were sequentially deposited without breaking vacuum. This completed the backing wafer's preparation. The backing wafer, along with the TSV wafer, was then ready to be joined in the assembly.

Figure 29: Backing Wafer Design

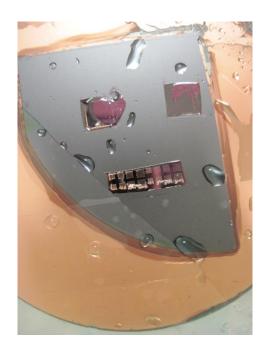

### 4.2.3 Wafer Assembly Design

The assembly began by stacking the TSV wafer on top of the copper surface of the backing wafer. A strip of electrically conductive adhesive copper foil tape was used to form an electrical connection from the backing wafer's copper layer through the tape assembly (Figure 30-A7). This way an electrode could be connected to it while it remained isolated in the plating solution. The assembly was then sealed using clear UV-removable adhesive tape. Openings were cut into the clear tape in order to expose the vias with copper at the base (Figure 30-A8). The wafers were then plated in a copper sulfate based TSV solution, with no added organics (Figure 30-A9). Once plating was completed, the UV tape was exposed to UV light and removed, leaving the plated wafer attached to the backing wafer through the PR. The remaining assembly was dipped in acetone to release the TSV wafer from the backing wafer by removing the sacrificial PR layer.

Figure 30: Wafer Assembly Design

#### 4.3 ADE Process Fabrication

The procedure described in the design was followed as a guideline throughout the ADE process fabrication. Wafers were also quartered in order to get more trial results from a single wafer which would have very similar features since they were from the same wafer.

#### 4.3.1 TSV Wafer Fabrication

The cleaning of these wafers was essential. The cleaning was performed using the RCA cleaning process to remove any organic, oxide, and metal contaminants. A spin-rinse dry was the final step in preparing the wafers for photolithography (Figure 28-T1). Once cleansed, the wafers were dehydration baked for 20 minutes. Since the TSV wafer was to be DRIE'd using a PR masking layer, a primer (HMDS) was coated to ensure PR adhesion during the aggressive DRIE process. The PR used was AZ P4620, which was a thick positive PR capable of spinning on at a thickness of up to 24µm. During Deep Reactive Ion Etching (DRIE) this PR had approximately a 70:1 etching selectivity with silicon. Once the PR was coated on the wafer, it was soft baked at

110°C for 2.5 minutes. Here it was essential to allow the wafer time to properly outgas in order to avoid deformities during exposure, development and etching. The outgassing allows any trapped gasses to release or solvents to evaporate from the PR. Once outgassed, the wafers were exposed to UV light in a contact mask aligner through a mask. The mask was composed of 10x10 grids of circles ranging in diameter with a maximum of 100μm. The pitch separating the circles was dependent on the via width with the maximum being 30μm. Once exposed, the wafer was developed in the 2:1 H<sub>2</sub>0:AZ400K developer solution for 1 minute

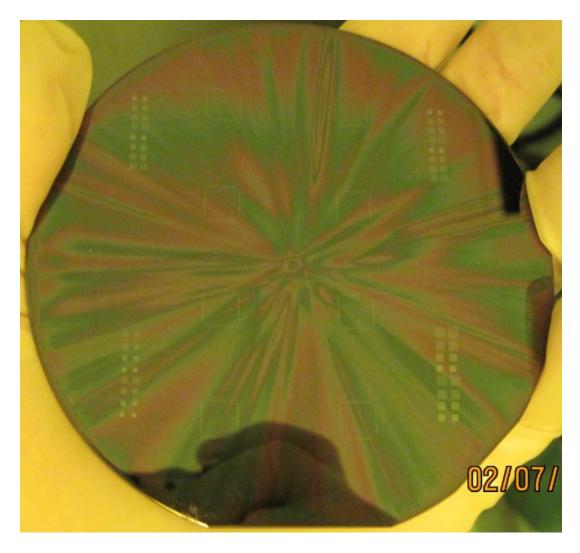

The wafer was then ready for the Inductively Coupled Plasma Deep Reactive Ion Etcher (ICPDRIE). The machine uses octafluoro-cyclobutane ( $C_4F_8$ ) as the passivation gas and a mixture of sulfur hexafluoride / oxygen ( $SF_6/O_2$ ) as the etching gas. The fluorine from the  $SF_6$  provides the etching gas while the oxygen removes the passivation. These gasses were used in the BOSCH<sup>TM</sup> process in order to develop high aspect ratio vias. The etching program used is described in Appendix E . Once etched, the remaining PR on the surface was removed using acetone and a spin-rinse-dry. The wafer was then descumed to ensure via cleanliness. The wafers were then shipped to Aptek Industries for wafer CMP. The wafers were CMP processed down to the desired thickness of 225 $\mu$ m.

Figure 31: Wafer CMP

Figure 32: Wafer Feature Details, Post-CMP

This CMP step would be omitted if there were electronic patterns already on the wafer. The wafers were cleaned again using the modified RCA process before oxidation. Silicon dioxide was thermally grown in an oxidation furnace to allow for a conformal  $SiO_2$  growth on all surfaces of the wafer including the via's sidewalls. A two hour  $H_2/O_2$  oxidation at  $1000^{\circ}C$

yielded a  $6000\text{\AA}$  thick layer of silicon dioxide (detailed oxidation settings found in Appendix I ). This completed the TSV wafer.

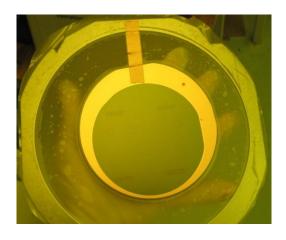

#### **4.3.2** Backing Wafer Fabrication