#### Vernier Ring Time-to-Digital Converter Based Digital Phase Locked Loop

by

Jianjun Yu

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama December 12, 2011

Keywords: Vernier, Time-to-Digital Converter, Digital Phase-Locked Loop

Copyright 2011 by Jianjun Yu

Approved by

Fa Dai, Chair, Professor of Electrical and Computer Engineering Guofu Niu, Professor of Electrical and Computer Engineering Bogdan Wilamowski, Professor of Electrical and Computer Engineering Stuart Wentworth, Associate Professor of Electrical and Computer Engineering

#### **Abstract**

Digital phase-locked loops (DPLLs) recently are widely explored for wireless communication applications. Time-to-digital converter(TDC)-based DPLLs feature a high degree of integration, easy calibration and high programmability, and the DPLL can be easily scaled down to the deep-submicron CMOS process with less area and improved performance. Replacing the function of a phase detector and charge pump used in a conventional PLL, the TDC measures the phase error between the reference signal and the feedback signal in the time domain and directly outputs the phase errors in a digital format that can be processed by an on-chip digital loop filter. Due to the use of a programmable digital loop filter, the loop dynamics of a DPLL can be programmed on the fly and thus can achieve fast settling time and low phase noise simultaneously. The on-chip digital loop filter can provide accurate loop dynamics that are less sensitive to process, voltage and temperature (PVT) variations and more immune to the supply and substrate noise. In addition, the area of the DPLL can be reduced by eliminating large capacitors used in analog loop filters.

TDC is a critical building block of the DPLL. Similar to other sampling circuits, a TDC inevitably generates quantization noise while digitizing the input phase error or time interval. This quantization noise associated with the finite TDC resolution limits the in-band noise of a TDC-based DPLL. On the other hand, it's desired for a TDC to have a large detectable range in order to be able to respond to large phase error during the pull-in of a phase locking process, especially in the low output frequency DPLL.

In this research, a novel 8-ps resolution Vernier ring TDC and a 16-ps resolution 3-D Vernier ring TDC were invented and designed to achieve both the fine resolution and large detectable range. The state-of-art TDC design was also used in the on-chip jitter measurement. The 3.6GHz digital phase locked loop based on the Vernier ring TDC was designed and analyzed. The detailed circuit design and performance analysis are extensively discussed in the dissertation. The simulation and measured results of these circuits are also presented to verify the proposed designs.

#### Acknowledgments

I would like to gratefully and sincerely thank Dr. Fa Dai for his support, guidance and understanding during my study and research at Auburn University in the past four and a half years. His mentorship was paramount in providing me the valuable research opportunity and guiding me toward the invention of the magical design of Vernier ring TDC.

I also would like to thank my committee members, Dr. Bogdan Wilamowski, Dr. Guofu Niu and Dr. Stuart Wentworth for their guidance and assistance not only in my study of their classes, but also in my research. Their generous support is critical to the accomplishment of my research work. I am grateful to Dr. Richard C. Jaeger and Dr. David Irwin for their terrific comments and valuable help in the revision of my publications.

I would like to say thanks to all my team mates in RFIC Design and Test Lab at Auburn University, which include Xuefeng Yu, Yuan Yao, Zhenqi Chen, Xueyang Geng, Desheng Ma, Jie Qin, Yuehai Jin, Joseph Cali, Mark Ray, Bill Souder, Michael Pukish, Feng Zhao, Xin Jin, Zachary Hubbard and Siyu Yang. I have great pleasure in working with you in the numerous research tasks. The discussion and cooperation with you always enlightened me in my work.

Last but not least, this dissertation is dedicated to my family, including my father Daihong Peng, my mother Yimei Yu, my bother Jianping Peng, my sister Qinwei Peng and especially my beloved wife Tao Liu. Without your support and encouragement, I can not finish this work.

### Table of Contents

| Abstract  |          |                                                      | ii   |

|-----------|----------|------------------------------------------------------|------|

| Acknow    | ledgmer  | nts                                                  | iv   |

| List of T | ables    |                                                      | viii |

| List of F | igures   |                                                      | ix   |

| List of A | bbrevia  | itions                                               | xiii |

| Chapter   | 1 Introd | luction                                              | 1    |

| 1.1       | Back     | ground and motivation                                | 1    |

| 1.2       | Orga     | nization of dissertation                             | 2    |

| Chapter   | 2 Overv  | view of Time-to-Digital Converter                    | 5    |

| 2.1       | Intro    | duction                                              | 5    |

| 2.2       | Time     | e-to-digital converter for digital phase locked loop | 9    |

| Chapter   | 3 Verni  | er Ring TDC                                          | 11   |

| 3.1       | Conc     | cept of Vernier ring TDC                             | 11   |

| 3.2       | Circu    | uit implementation of Vernier ring TDC               | 17   |

|           | 3.2.1    | Pre-logic unit                                       | 17   |

|           | 3.2.2    | Arbiter, edge detector and control logic             | 18   |

|           | 3.2.3    | Thermometer-to-binary encoder                        | 25   |

|           | 3.2.4    | Counters and design redundancy                       | 27   |

|           | 3.2.5    | Delay stage                                          | 30   |

| 3.3       | Test setup and measurement results                                       | 34 |

|-----------|--------------------------------------------------------------------------|----|

| 3.4       | Summary of Vernier ring TDC                                              | 40 |

| Chapter 4 | 3-dimensional Vernier Ring TDC                                           | 41 |

| 4.1       | Concept of 3-dimensional Vernier ring TDC                                | 41 |

| 4.2       | Circuit implementation of 3-dimensional Vernier ring TDC                 | 43 |

|           | 4.2.1 3-D Vernier ring TDC core                                          | 44 |

|           | 4.2.2 Circuits of the main building blocks                               | 49 |

|           | 4.2.3 Chip information and measurement results                           | 52 |

| Chapter 5 | On-Chip Jitter Measurement Using Vernier Ring TDC                        | 55 |

| 5.1       | Introduction of on-chip jitter measurement                               | 55 |

| 5.2       | Jitter measurement using Vernier ring TDC                                | 57 |

| 5.3       | DPLL with built-in jitter measurement                                    | 59 |

| 5.4       | Jitter test results                                                      | 60 |

| 5.5       | Summary                                                                  | 62 |

| Chapter 6 | VCO with Digitally Controlled Artificial Dielectric.                     | 64 |

| 6.1       | Introduction of artificial dielectric                                    | 64 |

| 6.2       | Colpitts VCO with digitally controlled artificial dielectric             | 66 |

| 6.3       | Circuit design of the VCO                                                | 68 |

| 6.4       | Chip fabrication and measured results.                                   | 70 |

| 6.5       | Summary                                                                  | 74 |

| Chapter 7 | Vernier Ring TDC and Other Building Blocks for Digital Phase Locked Loop | 76 |

| 7.1       | Overview of digital phase locked loop                                    | 76 |

| 7.2       | System analysis of the digital phase locked loop                         | 77 |

| 7.3       | TDC     | for digital phase locked loop   | 80 |

|-----------|---------|---------------------------------|----|

| 7.4       | Other   | r building blocks design        | 83 |

|           | 7.4.1   | Digital IIR filter              | 83 |

|           | 7.4.2   | Digitally controlled oscillator | 86 |

| Chapter 8 | 8 Concl | usion                           | 88 |

| 8.1       | Sum     | mary of dissertation            | 88 |

| 8.2       | Conc    | clusion and future work         | 90 |

| Referenc  | es      |                                 | 92 |

### List of Tables

| Table 1 Performance Summary and Comparison of Vernier ring TDCs | . 40 |

|-----------------------------------------------------------------|------|

| Table 2 Performance Comparison of VCOs                          | . 74 |

# List of Figures

| Fig.2.1 Delay line based TDC                                                                                     | 6        |

|------------------------------------------------------------------------------------------------------------------|----------|

| Fig.2.2 Vernier delay line TDC.                                                                                  | 6        |

| Fig.2.3 (a) time difference amplifier (b) gated ring oscillator with multi-path inputs to the inverter           | 7        |

| Fig.2.4 Fractional DPLL with multi-modulus divider.                                                              | 10       |

| Fig.2.5 Divider-less DPLL with DCO.                                                                              | 10       |

| Fig.3.1 Conceptual view of Vernier delay line TDC.                                                               | 11       |

| Fig.3.2 Block diagram of the VRTDC core with 15 stages.                                                          | 12       |

| Fig.3.3 Illustration of the VRTDC operation at (a) first lap, and (b) second lap                                 | 13       |

| Fig.3.4 Block diagram of the VRTDC system.                                                                       | 14       |

| Fig.3.5 Timing diagram of VRTDC                                                                                  | 15       |

| Fig.3.6 Simplified circuits of the pre-logic unit.                                                               | 18       |

| Fig.3.7 Simplified circuits of arbiter A and B                                                                   | 19       |

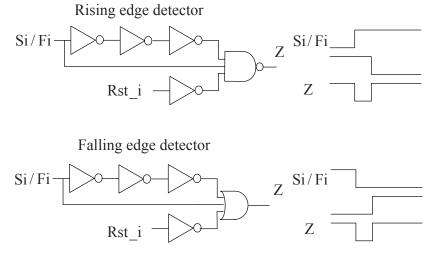

| Fig.3.8 Simplified circuits of rising/falling edge detector                                                      | 19       |

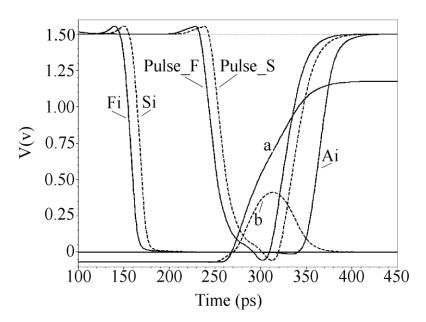

| Fig.3.9 Transient simulation of arbiter B with the time interval between Si and Fi setting as 2ps                |          |

| Fig.3.10 Dependence of arbiter delay on the time interval between two input signals                              | 21       |

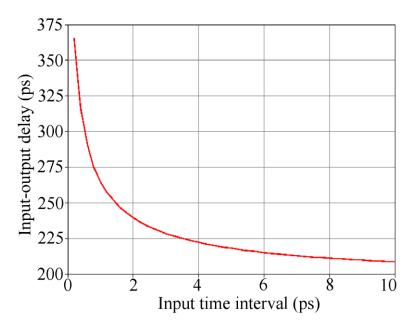

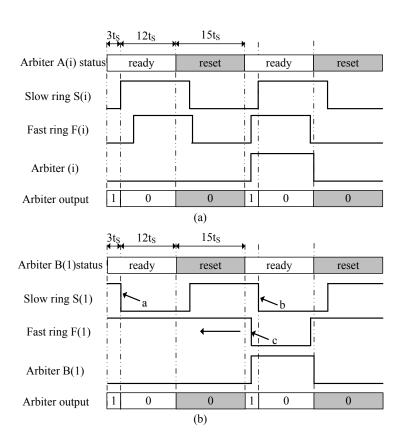

| Fig.3.11 Illustration of (a) the operating cycle of arbiter A and (b) unexpected "01" transition at arbiter B(1) | on<br>22 |

| Fig.3.12 Block diagram of correction circuit                                                                     | 23       |

| Fig. 3.13 Block diagram of thermal-to-binary encoder                                                             | 25       |

| Fig.3.14  | Timing diagram showing that register bank filters out the fake "01" at the falling edges.                                                                                                                                               | 25 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.3.15  | (a)The circuit of small phase error detector(SPED), (b,c) timing diagram of B1 and B2, (d,e) characteristics of SPED without and with overlap. (Horizontal axis indicates the time interval by which the lag signal leads or lags S15). | 28 |

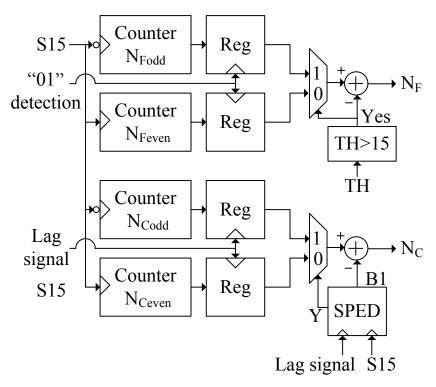

| Fig.3.16  | Counter design for redundancy.                                                                                                                                                                                                          | 29 |

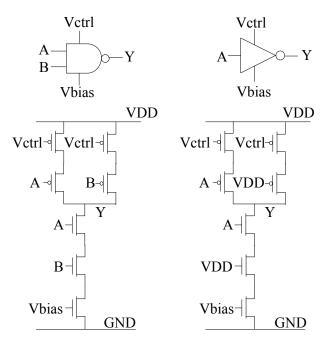

| Fig.3.17  | Simplified circuits of NAND and inverter.                                                                                                                                                                                               | 30 |

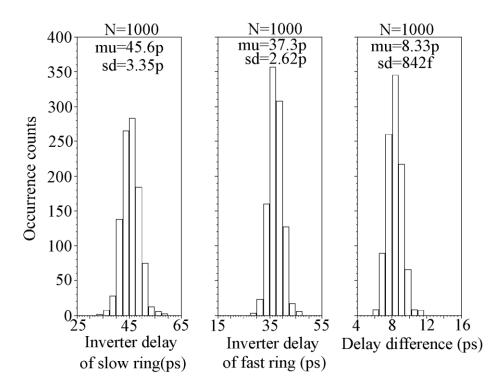

| Fig.3.18  | Dependence of the inverter delay and delay difference on the process variation                                                                                                                                                          | 31 |

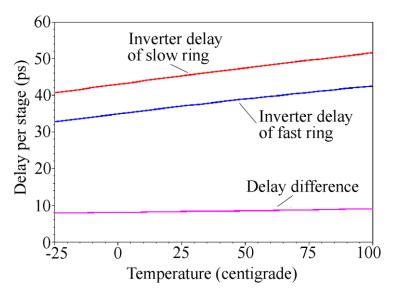

| Fig.3.19  | Dependence of the inverter delay and delay difference on the temperature.                                                                                                                                                               | 32 |

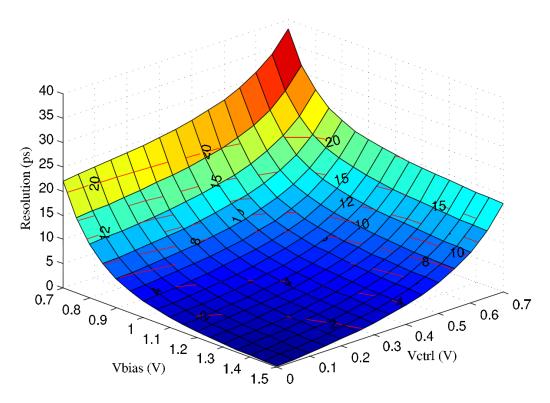

| Fig.3.20  | Dependence of resolution on Vbias and Vctrl.                                                                                                                                                                                            | 34 |

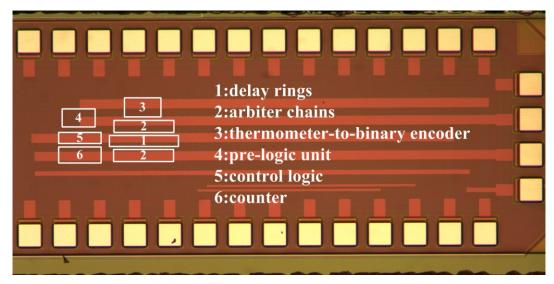

| Fig.3.21  | Die photo of the 12-bit Vernier ring TDC in 0.13um CMOS technology                                                                                                                                                                      | 35 |

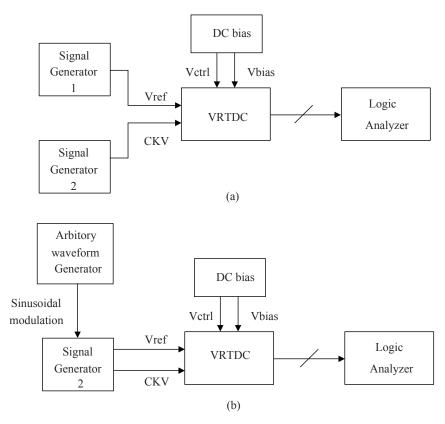

| Fig.3.22  | (a) Time interval ramp test setup (b) sinusoidal modulation of time interval                                                                                                                                                            | 36 |

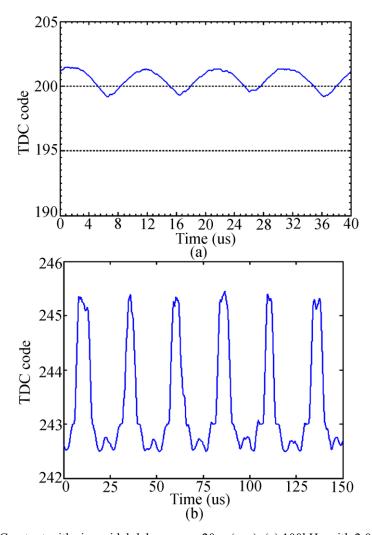

| Fig.3.23  | Measured TDC output with sinusoidal delay sweep 20 ps(p-p), (a) 100kHz with 2.05ns fixed delay and (b) 40kHz with 1.95ns fixed delay                                                                                                    | 37 |

| Fig.3.24  | The power spectrum of TDC output in Fig.23 (b)                                                                                                                                                                                          | 38 |

| Fig.3.25  | Measured TDC output after median filter with 30X averaging                                                                                                                                                                              | 39 |

| Fig.3.26  | Measured TDC code distributions at 4 constant delays.                                                                                                                                                                                   | 39 |

| Fig.4.1   | Conceptual view of 3-D Vernier delay-space                                                                                                                                                                                              | 42 |

| Fig.4.2   | Block diagram of the proposed Vernier ring TDC core                                                                                                                                                                                     | 45 |

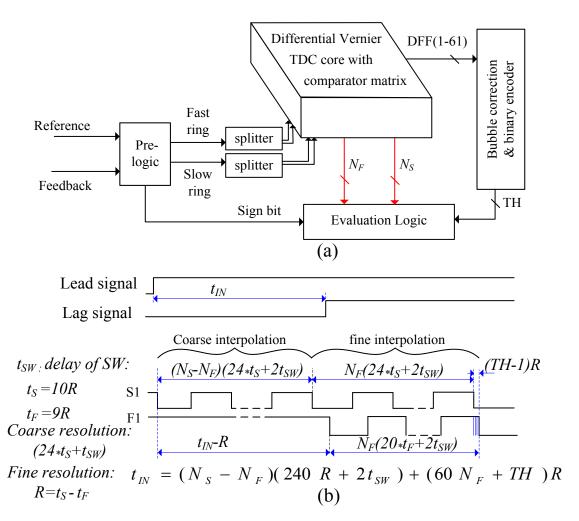

| Fig.4.3 ( | (a) Block and (b) timing diagrams of the proposed TDC chip.                                                                                                                                                                             | 48 |

| Fig.4.4   | Block diagram of the proposed Vernier ring TDC core                                                                                                                                                                                     | 50 |

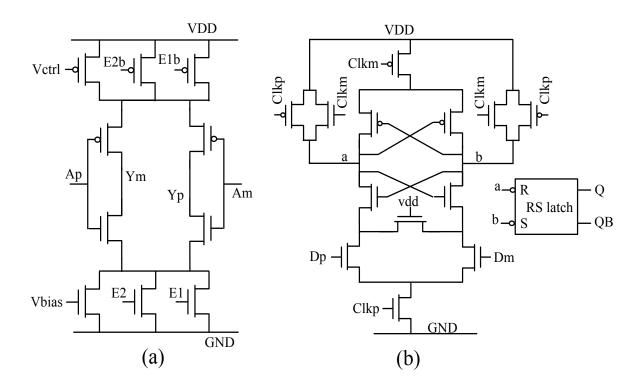

| Fig.4.5   | Circuits of (a) delay stage and (b) differential DFF                                                                                                                                                                                    | 51 |

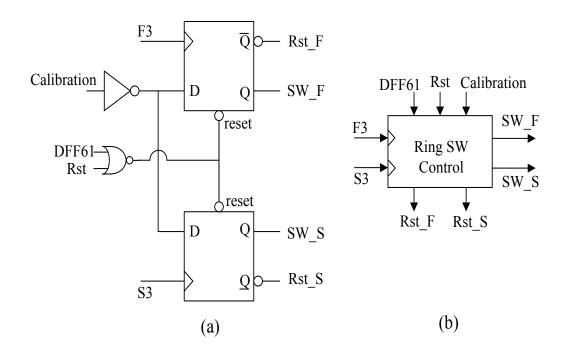

| Fig.4.6   | (a)Simplified circuit and (b)symbol of ring switch control unit                                                                                                                                                                         | 52 |

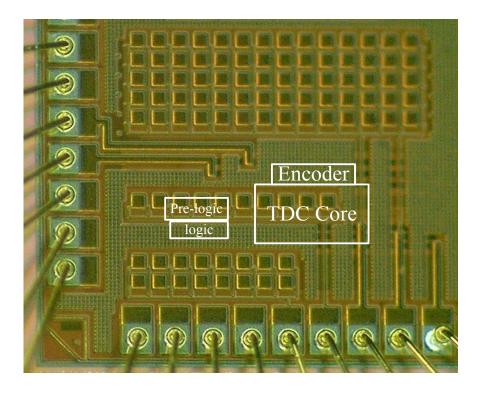

| Fig.4.7   | Chip photo of the proposed TDC                                                                                                                                                                                                          | 52 |

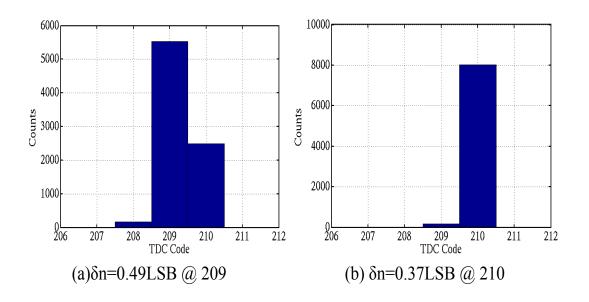

| Fig.4.8   | Measured TDC output code distribution.                                                                                                                                                                                                  | 53 |

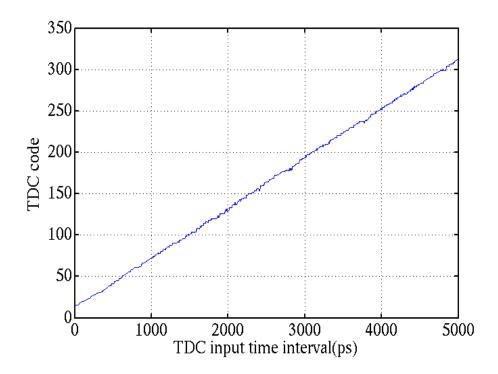

| Fig 4 9 1 | Measured TDC characteristics of 3-D Vernier ring TDC                                                                                                                                                                                    | 54 |

| Fig.5.1 | Block diagram of jitter measurement using Vernier ring TDC.                                                                                       | 57 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.5.2 | Block diagram of the DPLL.                                                                                                                        | 59 |

| Fig.5.3 | Block diagram of jitter testing setup.                                                                                                            | 61 |

| Fig.5.4 | (a)Transient waveform and (b) histogram of TDC output when measuring a predefined 20ps peak-to-peak jitter with a DC offset phase error of 2.05ns | 62 |

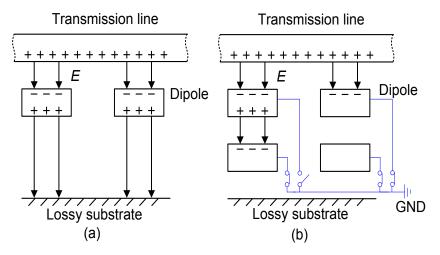

| Fig.6.1 | (a) Conventional artificial dielectrics, and (b) proposed multi-layer digitally controlled artificial dielectrics.                                | 64 |

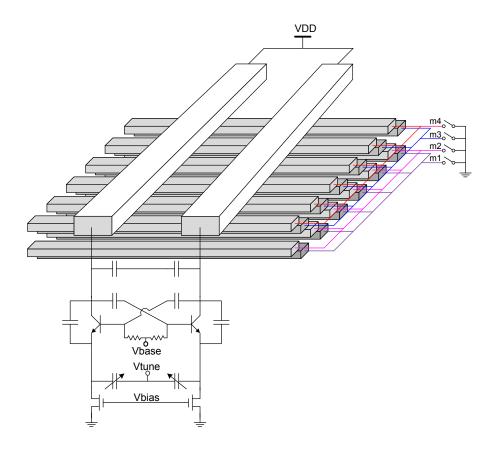

| Fig.6.2 | Differential Colpitts VCO with digital controlled artificial dielectric                                                                           | 67 |

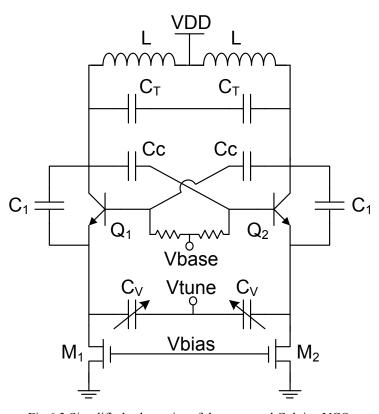

| Fig.6.3 | Simplified schematics of the proposed Colpitts VCO.                                                                                               | 68 |

| Fig.6.4 | Cross-sectional view of the proposed RF transmission line with underlying artificial dielectric.                                                  | 69 |

| Fig.6.5 | Die photo of the Colpitts VCO MMIC.                                                                                                               | 70 |

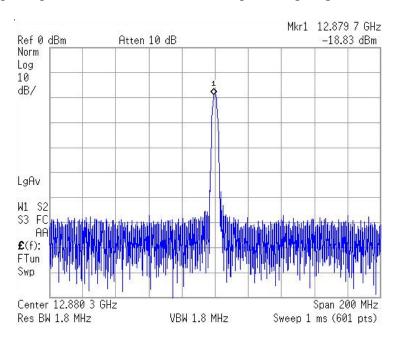

| Fig.6.6 | The measured power spectrum of the proposed VCO.                                                                                                  | 71 |

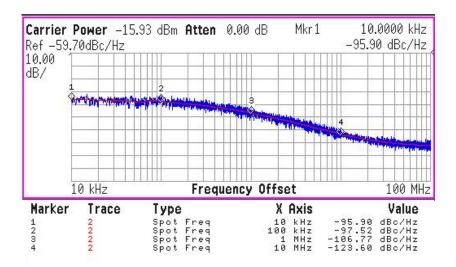

| Fig.6.7 | The measured phase noise of the proposed VCO.                                                                                                     | 72 |

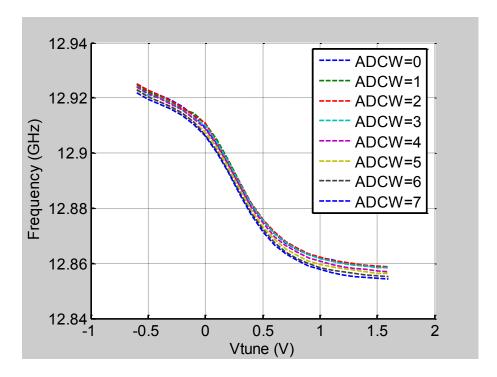

| Fig.6.8 | The measured VCO output frequency vs. tuning voltage with digital controlled artificial dielectric.                                               | 73 |

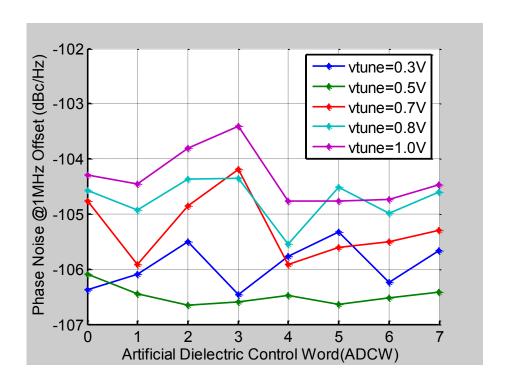

| Fig.6.9 | The measured phase noise @ 1MHz offset vs. artificial dielectric control word under various tuning voltages of varactor                           | 74 |

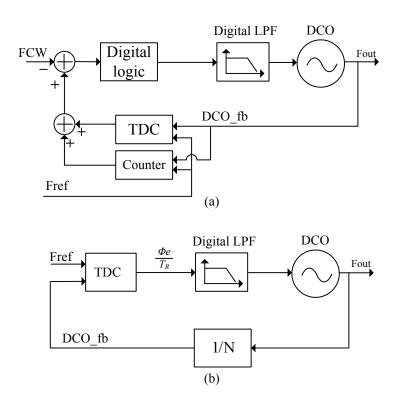

| Fig.7.1 | Simplified block diagram of (a) divider-less DPLL and (b) divider-assisted DPLL                                                                   | 77 |

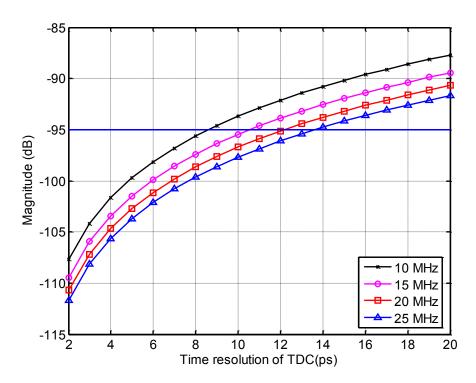

| Fig.7.2 | Estimated in-band PN due to TDC quantization vs. time resolution                                                                                  | 78 |

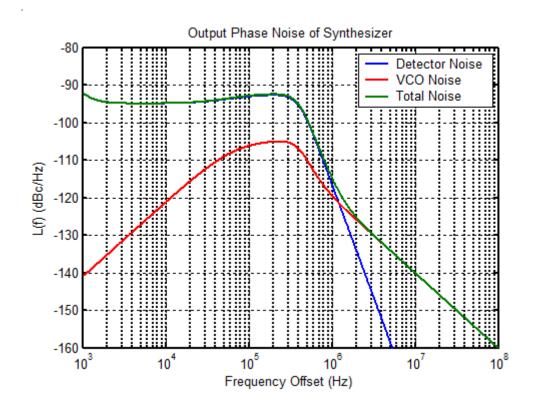

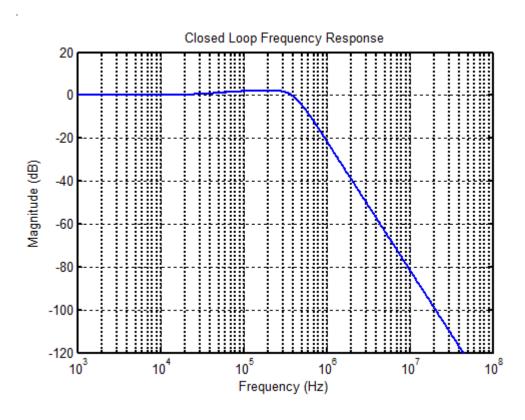

| Fig.7.3 | Simulated phase noise spectrum of DPLL                                                                                                            | 79 |

| Fig.7.4 | Simulated transfer curve of DPLL                                                                                                                  | 79 |

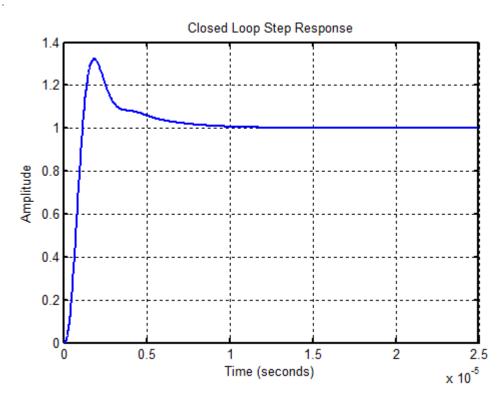

| Fig.7.5 | Simulated step response of DPLL                                                                                                                   | 80 |

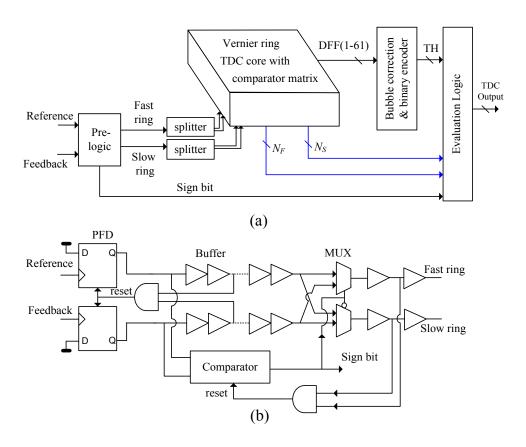

| Fig.7.6 | (a) Block diagram of the Vernier ring TDC and (b) schematic of the PFD embedded pre-log unit for DPLL applications                                | 81 |

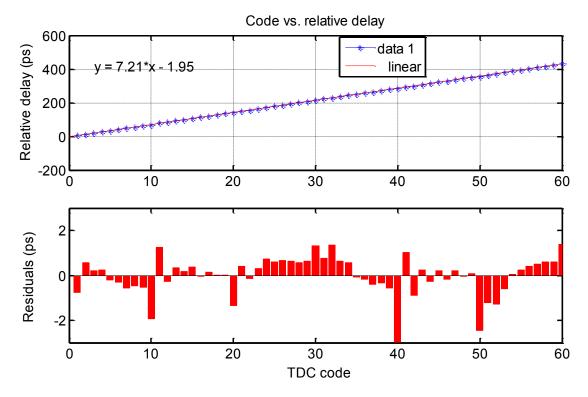

| Fig.7.7 | Simulated quantization code vs. relative delay of the Vernier ring TDC with comparator matrix                                                     | 82 |

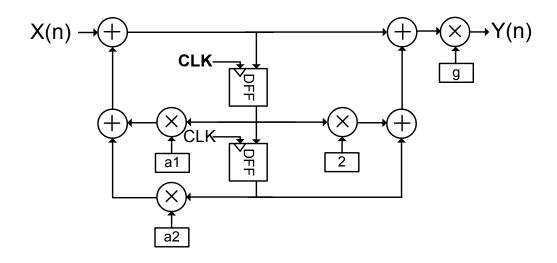

| Fig.7.8 Simplified diagram of the 2nd-order IIR filter                      | 84 |

|-----------------------------------------------------------------------------|----|

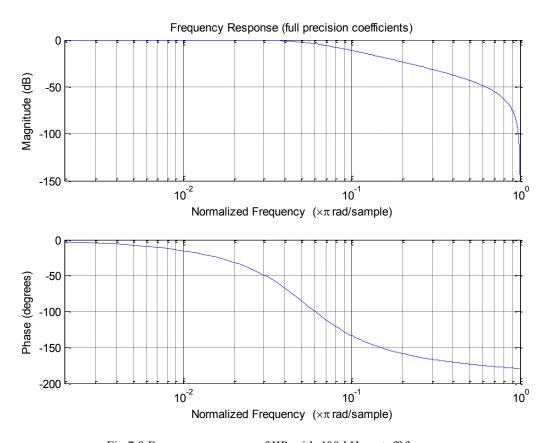

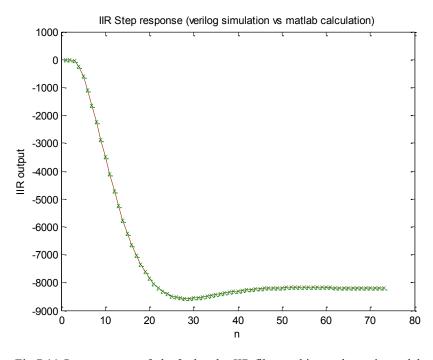

| Fig.7.9 Frequency response of IIR with 400 kHz cutoff frequency             | 84 |

| Fig.7.10 Zeros and poles of IIR with 400 kHz cutoff frequency               | 85 |

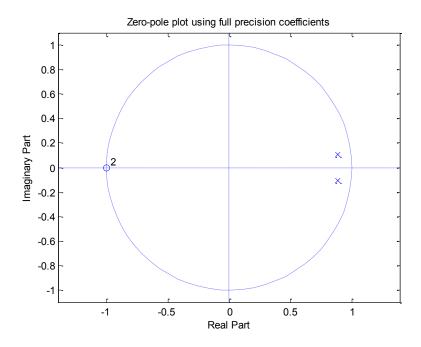

| Fig.7.11 Step response of the 2nd-order IIR filter and its mathematic model | 85 |

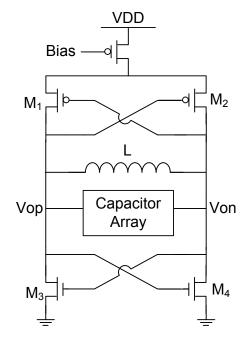

| Fig.7.12 Simplified diagram of the capacitor array                          | 87 |

| Fig.7.13 Simplified schematic of the DCO.                                   | 87 |

#### List of Abbreviations

BiCMOS Bipolar and Complementary Metal-Oxide-Semiconductor

BIST Build-In-Self-Test

CMOS Complementary Metal-Oxide-Semiconductor

DCO Digitally Controlled Oscillator

FOM Figure of Merit

DPLL Digital Phase Locked Loop

DNL Differential Non-Linearity

GRO Gated Ring Oscillator

IIR Infinite Impulse Response

INL Integral Non-Linearity

LIDAR Light Detection And Ranging

LSB Least Significant Bit

LPF Low Pass Filter

MSB Most Significant Bit

TDC Time-to-digital Converter

TOF Time-of-flight

VRTDC Vernier Ring Time-to-digital Converter

### **Chapter 1 Introduction**

#### 1.1 Background and motivation

Time-to-digital converters (TDCs) are used to measure the time interval between two events by a small quantization step that is called the time resolution. High resolution TDCs have become increasingly popular for time-of-flight (TOF) measurement for applications such as clock data recovery, test instrumentation, light detection and ranging (LIDAR) and all digital phase-locked loop (DPLL). Time resolution, detectable range, measurement time, power consumption and die area are most important concerns in TDC designs. Similar to any other analog to digital converter, the quantization step is the major parameter of TDC that determines the system performance in all the applications stated above. In the standard CMOS technology, the basic logic gates, like inverters and buffers, are often used to generate a small amount of delay (time resolution) for time interval measurement. Time resolution of a single delay line based TDC thus suffers from process, voltage and temperature (PVT) variations. On another hand, the detectable range specifies the maximum time interval a TDC can measure. The requirements of a large detectable range and a fine resolution often conflict with each other in TDC designs. The proposed novel N-dimensional Vernier TDC is intended to provide an efficient solution to address this issue.

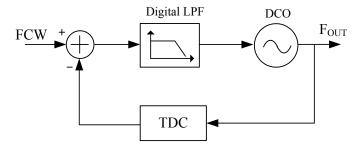

TDC is a critical building block for emerging DPLL applications [1][2]. TDC-based DPLLs feature a high degree of integration, easy calibration and high programmability. A DPLL can be

easily scaled down to the deep-submicron CMOS process with less area and improved performance. Replacing the function of a phase detector and charge pump used in a conventional PLL, a TDC measures the phase error between the reference signal and the feedback signal in time domain and directly outputs the phase errors in digital format that can be processed by an on-chip digital loop filter. Due to the use of a programmable digital loop filter, the loop dynamics of a DPLL can be programmed on the fly and thus can achieve fast settling time and low phase noise simultaneously. An on-chip digital loop filter can provide accurate loop dynamics that are less sensitive to PVT variations and are more immune to the supply and substrate noise. In addition, the area of the DPLL can be reduced by eliminating large capacitors used in analog loop filters, making loop filter integratable. Similar to any sample circuits, a TDC inevitably generates quantization noise while digitizing the input phase error or time interval. This quantization noise associated with the finite TDC resolution limits the in-band noise of a TDC-based DPLL. In another words, the finer the TDC resolution is, the better the in-band phase noise the DPLL can achieve. On the other hand, it's desired for a TDC to have a large detectable range in order to be able to respond to large phase error during the pull-in of a phase locking process. DPLLs can be divided into two categories: divider-assisted DPLL and divider-less DPLL. Large range TDC is required in divider-assisted DPLL. The TDC in divider-less DPLL uses the DCO period as the coarse quantization resolution which is not stable and has a large variance compared to the fine resolution of TDC. In addition, more number of TDC bits is required in the divider-less DPLL with a larger DCO period, namely a larger coarse resolution. However, conventional delay-line based TDCs entail the use of an extra hardware to extend its range of operation [2], which requires large area and high power consumption.

#### 1.2 Organization of dissertation

In this dissertation, a new idea of N-dimensional Vernier TDC is proposed to improve both time resolution and detectable range. The organization of the dissertation is as follows:

Chapter 2 gives the overview of the various existing time-to-digital converter (TDC) architectures. Although there are many ways to quantize the input time interval, the digital inverter is still an appealing delay element to build a TDC due to its digital-intensive design approach, easy implementation and compatibility to most technology. The conventional delay line TDC, time-amplifier based TDC and gated ring oscillator based TDC are all introduced in this chapter. The Vernier structure is an attractive way to obtain a fine resolution TDC.

Chapter 3 discusses the novel Vernier ring TDC which achieved a fine resolution of 8 picosecond with a large resolution of 13 bits. The die area and power consumption are improved by placing the delay cells in a ring format. The detailed circuit design along with the simulation and measured data are presented in this chapter.

Chapter 4 presents a novel 3-dimensional Vernier ring TDC which further improved the power consumption and die area by introducing the comparator matrix which is the key element to build a 2-dimensional delay plane. The measured data shows that a time resolution of 16.5ps and 8-bit detectable range were obtained in this design.

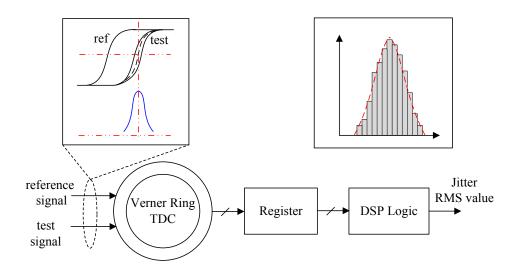

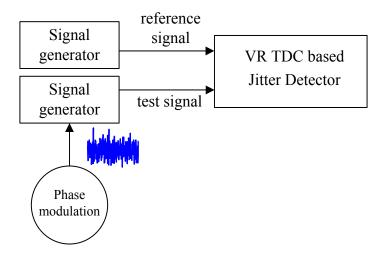

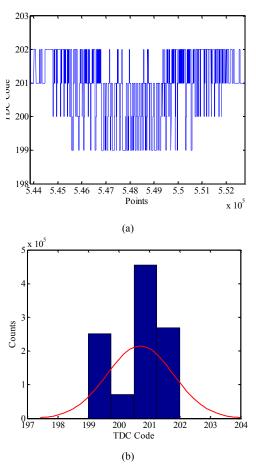

Chapter 5 introduces the application of Vernier ring time-to-digital converter to the on-chip jitter measurement. The Vernier TDC was tested by inputting a clock signal with a small amount of jitter modulated by a noise source. The Gaussian distribution of the digitized code was obtained at the TDC outputs and the standard variation of that distribution indicates the rms value of the input jitter.

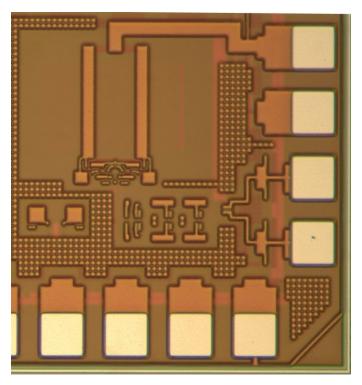

Chapter 6 explores the design of 12GHz Colpitts VCO using artificial dielectrics to add the shielding of LC tank to the lossy substrate and improve the phase noise performance with the optimized combination of the artificial dielectrics control code.

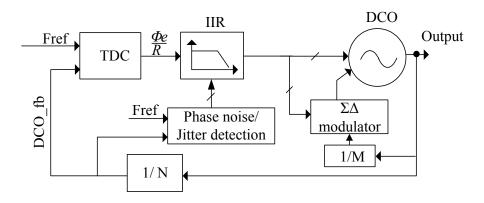

Chapter 7 shows the dedicated Vernier ring TDC for DPLL and other building blocks such as digital filter and digitally controlled oscillator. The impact of the TDC resolution to the DPLL inband noise has been analyzed.

Chapter 8 summarizes the research work mentioned above and presents the future work on the TDC and DPLL.

## **Chapter 2 Overview of Time-to-Digital Converter**

#### 2.1 Introduction

In the past, a large amount of TDC topologies have been explored to reduce time resolution and to extend detectable range while keeping the power and area cost at a reasonable level [1-16]. The proposed TDC was evolved from a so-called Vernier ruler concept as explained below.

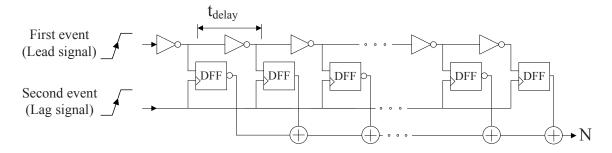

An inverter-chain based TDC was implemented in the first DPLL chip for a blue-tooth radio application [3]. Ever since, a variety of TDC architectures have been proposed with improved resolution and detectable range [1-16]. Although there are many ways to digitize the input time interval, the digital inverter-delay-line is still an appealing structure due to its digital-intensive design approach [4]. Fig.2.1 shows the conventional inverter-delay-line based TDC. Its time resolution is the propagation delay of each individual inverter stage, while its detectable range is proportional to the number of delay stages used. Its measured time interval can be expressed as  $N^*T_{delay}$ , where  $T_{delay}$  is the time resolution of the TDC and N is the number of stages used. Consequently, achieving fine resolution contradicts the goal of achieving large detectable range, since a TDC with finer resolution would require more delay cells in order to achieve the same detectable range. Moreover, both the time resolution and the detectable range of the TDC are very sensitive to PVT variation, which directly affects the accuracy of the measurement and thus degrades the phase noise of a DPLL that employs such kind of TDC.

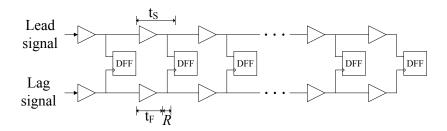

A Vernier delay line is well known for its fine time resolution [5]. Fig.2.2 illustrates a simplified Vernier inverter delay line TDC that employs two inverter/buffer chains with different delays of  $T_s$  and  $T_F$ , respectively. Time resolution of the Vernier TDC now becomes the delay difference of two delay lines, namely,  $T_s - T_F$ . Note that the resolution is greatly improved by using two delay lines. In addition, Vernier delay line architecture can tolerate first order PVT variation if the two delay lines are well matched. Nevertheless the Vernier delay line TDC struggles with reduced efficiency in measuring large time intervals for the same reason mentioned above.

Fig.2.1 Delay line based TDC

Fig.2.2Vernier delay line TDC.

Recently several topologies have been reported to shrink the TDC time resolution to several picoseconds. The two-step TDC uses a delay-line TDC as a coarse TDC and a Vernier delay-line TDC as a fine TDC to achieve fine resolution and large detectable range [6][7]. As shown in Fig.2.3(a), a time amplifier based TDC improves the resolution and detectable range by

amplifying the time residue left in a coarse TDC before quantizing it using a fine TDC [8]. A multipath gated ring oscillator (GRO) structure (Fig.2.3(b)) was proposed to improve the TDC resolution to 6ps in a 0.13µm technology [9]. This GRO-based TDC also achieves first order quantization noise shaping by holding the phase of the oscillator output between measurements. This GRO based TDC achieves a detectable range of 11 bits with up to 21mW power consumption and an area of 0.04 mm<sup>2</sup>. A local passive interpolation TDC employs a differential delay line to obtain a coarse delay. It then interpolates this delay with a resister voltage divider and achieves a sub-gate-delay of 4.7ps [10]. The parallel scaled delay line structure provides an alternative approach for resolution improvement. A two-level interpolation TDC with this parallel structure achieved a time resolution of 12.2ps in a 0.35um CMOS technology [11]. A pulse shrinking delay element based TDC was reported with a sub-gate-delay resolution [12]. A 1 ps-resolution jitter-measurement macro was implemented recently with two-step hierarchical Vernier delay line structure [13].

Fig. 2.3 (a) time difference amplifier (b) gated ring oscillator with multi-path inputs to the inverter

A 2-dimensional Vernier TDC was reported with a time resolution of 4.8 ps [14]. This TDC places the two Vernier delay lines in two mutually perpendicular directions and a plurality of comparators in a matrix comparing the delays between taps in the two delay lines. The number of the delay stages used in this 2-dimensional structure is almost the square root of what is required in a conventional Vernier delay line TDC for the same detectable range. As a result, the power consumption was reduced due to less toggles of two propagating signals through delay stages. However, the 2-dimensional structure still struggles with the area cost in the applications where the large detectable range is needed, since the number of delay stages and comparators monotonically increase when detectable range increases.

We proposed a Vernier Ring TDC (VRTDC) that leverages the time difference between two rings of delay cells to achieve a time resolution of 8ps [15][16]. Unlike the conventional Vernier TDC, this novel TDC places the Vernier delay cells in a ring format such that the delay chains can be reused for measuring large time intervals. The reuse of Vernier delay cells in a ring configuration achieves fine resolution and large detectable range simultaneously with small area and low power consumption. In the Vernier ring architecture, detectable range can be increased to any large number without causing extra cost in area, as long as the counter has enough space to hold the output data. Compared with other structures mentioned above, less power will be consumed in the measurement of a large time interval due to its build-in coarse-fine two-level interpolation scheme. In this design, a large detectable range of 12 bits has been achieved with a small area of 0.26 mm<sup>2</sup>.

The novel structure of Vernier ring TDC proposed here has been further improved in the power consumption and die area by conceiving a new set of Vernier ring TDC structures. This novel

idea of constructing a 3-dimensional up to N-dimensional delay space is presented for the first time after our patent application filed in Jan. 2010 [17]. The idea is intended to build a highly efficient TDC with several pico-second resolution and a large dynamic range, which will fuel the improvement in many TDC applications such as frequency synthesis, time interval measurement and light detection and ranging (LIDAR).

#### 2.2 Time-to-digital converter for digital phase locked loop

DPLL has recently emerged as an attractive alternative to the traditional analog PLL for many applications. Recent results demonstrate that digital frequency synthesizers have good noise performance comparable to that achieved by analog PLLs [4]. Compared to direct digital synthesizers that can offer a high output frequency with fine frequency resolution, fast frequency switching and versatile modulations [8][18][19][20][21], DPLL is characterized with superior spectrum purity at RF frequency and less power consumption. DPLLs have the potential to replace analog PLLs used in wireless transceivers [4][22][23][24].

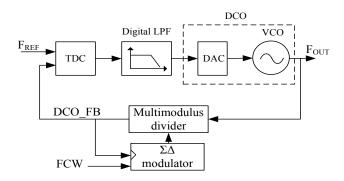

In transition from analog PLL to digital PLL, phase-frequency detector and charge pump were replaced by a TDC, which quantizes the phase error between the reference clock and feedback clock. Consequently, digital loop filter and digital controlled oscillator are substitutes for their analog counterparts. A fractional DPLL was implemented with DAC and VCO instead of DCO to achieve low phase noise [32]. This hybrid VCO structure leverages a switched capacitor array for frequency band selection and an analog varactor for fine tuning and has become a popular choice in many recent DPLLs due to their ability to achieve a wide tuning range with excellent phase noise. Similar to the analog fractional-N PLL, a multi-modulus divider with sigma-delta modulator in the feedback path was employed to generate fractional divide ratio as shown in

Fig.2.4. Many DPLLs use the divider-less topology [33][34], which are further simplified by replacing the combination of DAC and VCO with a DCO as shown in Fig.2.5. The output frequency is tuned by switching on and off capacitors in the LC tank controlled by a digital control word. Compared to analog PLL, additional quantization noise coming from the DCO and the TDC degrade the output spectral purity. A Sigma-Delta modulator can be used at the input of the DCO to dither and shape DCO quantization noise to high frequency band where it can be rejected by the low pass characteristics of the close loop.

Fig.2.4 Fractional DPLL with multi-modulus divider.

Fig.2.5 Divider-less DPLL with DCO.

## **Chapter 3 Vernier Ring TDC**

#### 3.1 Concept of Vernier ring TDC

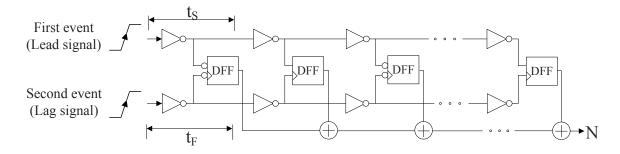

The proposed Vernier ring time-to-digital converter evolves from the conventional Vernier delay line TDC (Fig.3.1). Inverters or buffers were used as the delay stages to build the Vernier delay line TDC in a standard digital process. Connecting the outputs of the last delay cells of a Vernier delay line TDC to the inputs of the first pair of delay cells constructs a novel Vernier ring TDC (VRTDC). An odd number of delay cells (15 stages in this design) are used to form the rings. A NAND gate replaces an inverter as the first delay stage is used to input the signals under test. The rising edge of a signal to be measured can be fed into the delay ring through one of the inputs of the NAND gate. The pair of NAND cells in the two rings have the same delay difference as that of the inverter pairs in the two rings. Note that there are some subtle things that must be accounted for in order to construct a fully functional TDC using the proposed Vernier rings.

Fig.3.1 Conceptual view of Vernier delay line TDC.

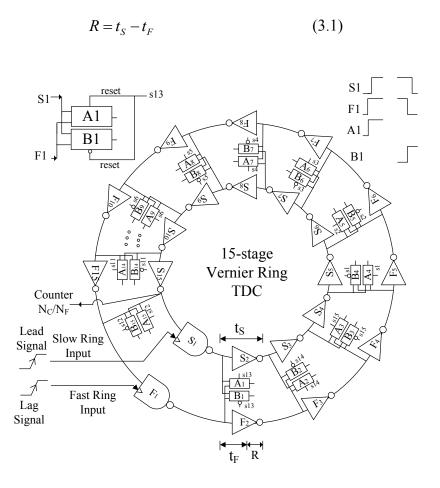

Fig.3.2 illustrates the concept of the proposed VRTDC core. Two rings of inverters with

slightly different delays are used to measure the input time interval. The VRTDC core consists of two chains of arbiters, which operate in odd laps and even laps, respectively. Recall that the VRTDC contains odd number of delay cells. Thus, a rising edge becomes a falling edge after one lap of propagation along the ring. The two types of arbiters are placed alternatively along the rings to compare the rising or falling edges, respectively. The VRTDC core consists of a fast ring with smaller delay, a slow ring with larger delay and 30 arbiters as shown in Fig.2. Each ring has 15 stages of inverters with delays adjustable by external bias voltages. The propagation delay of the inverters in fast and slow rings are set to  $t_F$  and  $t_S$ , respectively. Thus the time resolution of the proposed TDC is given by

Fig.3.2 Block diagram of the VRTDC core with 15 stages.

Fig.3.3 illustrates the operation of the proposed VRTDC in two successive laps, i.e., the first lap and the second lap. Two arbiter chains (shown in Fig.3.2) work alternatively during the

Fig.3.3 Illustration of the VRTDC operation at (a) first lap, and (b) second lap

measurement. To help understand the operation of the proposed VRTDC, we separate the whole VRTDC core into two Vernier delay rings shown in Fig.3.3. Each ring consists of two rings of inverters and one arbiter chain. Fig.3.3 (a) depicts the operation of VRTDC in the first lap. Initially, slow ring and fast ring inputs are pulled down to ground (GND) before measurement starts. Two rings are latched to a stable state, where both inverter S15 and F15 output logic "1". In the first lap, the rising edges of the lead and lag signals are fed into two NAND gates to start their propagations along the fast and slow rings, respectively. Lead signal propagates to S2 after an inverter delay of  $t_S$ . Lag signal propagates to F2 after an inverter delay of  $t_F$ . Arbiter B1 compares two falling edges at S1 and F1, while the arbiter A2 compares the rising edges at S2

and F2. B1 and A2 will be reset when lead signal propagates to S13 and S14, respectively. Fig.3.3 (b) shows the operation of Vernier ring at the second lap. Both slow and fast ring inputs are set to logic "1" after two signals are fed into the Vernier ring until the lag signal catches up the lead signal. Setting the inputs of the rings to "1" enables two signals to propagate through the delay cells in the rings over and over again, allowing reuse of the hardware. Note that S1 and F1 toggle to logic "1" in the second lap, namely, a falling edge in the first lap becomes a rising edge in next lap. Thus, arbiter needs to compare rising edges at S1 and F1 as well as the falling edges at S2 and F2. Hence another set of arbiters are needed to work in the second lap and the following even number of laps. This novel Vernier ring TDC is constructed by combining two set of delay rings and arbiters as illustrated in Fig.3.2.

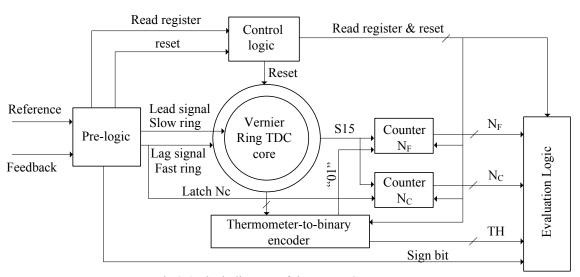

Fig.3.4 Block diagram of the VRTDC system

Fig.3.4 shows the overall architecture of the proposed 12-bit VRTDC system. The IC chip is composed of the VRTDC core, pre-logic, control logic, thermometer decoder, a 6-bit fine counter ( $N_F$ ) and a 6-bit coarse counter ( $N_C$ ). The reference signal and oscillator feedback signal in a DPLL are fed into the pre-logic cell, where an arbiter judges whether the reference leads the feedback or vice versa and determines the sign bit of the TDC output. As shown in Fig.3.4, the

lead signal is steered to the slow ring by the output of the arbiter, while the lag signal is fed into the fast ring. The lag signal chases the lead signal along the ring and eventually passes it after a certain amount of propagation.

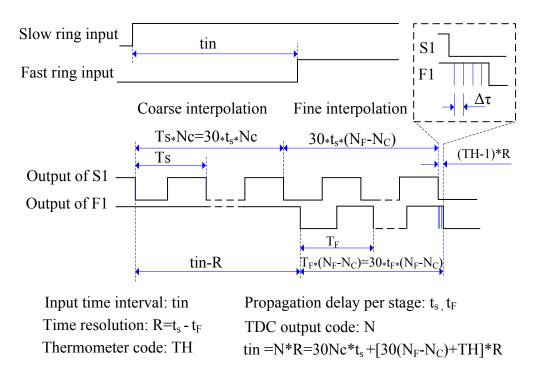

Fig.3.5 Timing diagram of VRTDC

The outputs of 30 arbiters are combined into a 30-bit thermometer code "TH" and are translated into a 5-bit binary code by a thermometer-to-binary encoder. TH records the location (number of delay cells) where the lag signal passes the lead signal. The fine counter ( $N_F$ ) records the number of laps (odd and even) that the lead signal has propagated before the lag signal catches up the lead signal. The coarse counter ( $N_C$ ) records the number of laps that the lead signal has propagated before the lag signal arrives at the input of the TDC. Therefore the total amount of delay N consists of four elements: the sign bit, the coarse counter value  $N_C$ , the fine counter value  $N_F$  and the thermometer code TH, as shown in the timing diagram of Fig.3.5. Before the lag signal enters the proposed TDC, only one signal propagates along the slow ring.

Hence, the TDC operates in its coarse measurement mode, where it interpolates the input time interval with a coarse resolution of  $30 \cdot t_s$ . This coarse interpolation mode improves the power and area efficiency, and the measurement time as well. Once the lag signal enters the ring, the TDC automatically switches to its fine measurement mode using the Vernier principal, where the TDC interpolates the residue of the time interval under test with a fine resolution of  $R = t_s - t_F$  till the lag signal catches up the lead signal. Counter  $N_F$  is used to assist the counting of the number of fine interpolations due to the limited bit count of thermometer code. The dynamic resolution adjustment of the proposed TDC differs from the *prior art* TDC architectures, where a fixed resolution were employed. Even with the conventional two-step approach, additional hardware is needed to achieve coarse and fine resolutions. The final output code of the proposed TDC, which is the digital representation of the measured time interval, is thus given by

$$N = \pm 30(N_F - N_C) + TH + 30N_C t_S / R$$

(3.2)

where TDC resolution is given by  $R = t_S - t_F$  and the polarity of N, i.e., the sign bit of the TDC output, is determined by the pre-logic as described above. This sign bit can be used to program the polarity of the phase error in a DPLL implementation. The detectable range is determined by the interpolation ratio  $t_S/R$  for a given number of bits of the coarse and fine counters because the fine interpolation code should be equal or less than the coarse resolution, namely  $30(N_F - N_C) + TH \le 30t_S/R$ . The detectable range is given by the following equations:

$$|N| \ge 30N_C t_S / R = 30[N_E - (N_E - N_C)]t_S / R$$

(3.3)

$$\max(|N|) \ge 30[2^6 - 1 - (N_F - N_C)]t_S / R \ge 30[63 - t_S / R]t_S / R \tag{3.4}$$

Therefore the detectable range varies with the interpolation ratio. For instance the maximum code is larger than 12 bits for the ratio  $t_S/R = 4$  since max(|N|)  $\geq 30*[63-4]*4 = 7080 > 2^{12}$ . It is theoretically possible that the detectable range can achieve 13 bits when the ratio is set to 8.

#### 3.2 Circuit implementation of Vernier ring TDC

In this section, we discuss the detailed circuit implementation of the proposed VRTDC. We present the circuits of the pre-logic unit, two types of arbiters with edge detectors, the thermometer-to-binary encoder, and two delay stages. We also explain the operation of arbiters and the correction circuit for "01" detection.

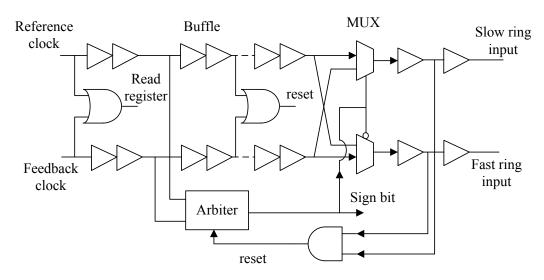

#### 3.2.1 Pre-logic unit

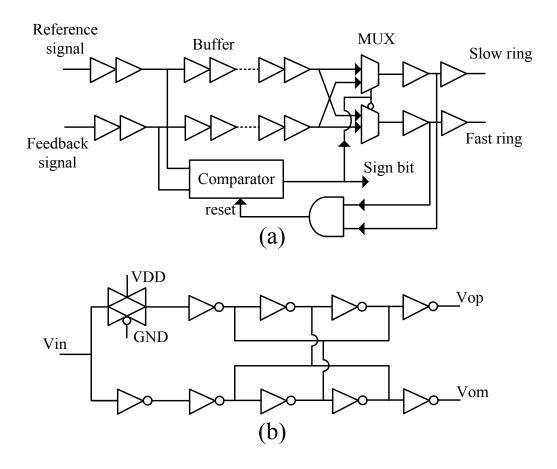

The pre-logic unit, arbiter and delay stage are the critical building blocks of the Vernier ring TDC. The reference signal may lead or lag the oscillator feedback signal in DPLL applications. Since the two rings of inverters in the Vernier ring TDC core have different propagation delays, the lead signal should be steered to the slow ring, while the lag signal goes to the fast ring. Otherwise, the lag signal will never catch up with the lead signal and the VRTDC will not work. Therefore, the pre-logic unit is essential to the VRTDC implementation. Reference signal and the oscillator feedback signal in a DPLL are first fed into the pre-logic cell. The pre-logic unit consists of an arbiter, two symmetrical delay chains, a multiplexer (MUX) and a reset path, as shown in Fig.3.6. The delay of buffer lines inserted between the input of the arbiter and MUX has sufficient delay to allow the MUX to swich the propagation path before two signals arrive. The arbiter is reset after both lead and lag signals pass by. The output of the sign bit will be "0" when the arbiter judges that the reference signal leads the feedback signal. Otherwise the sign bit is "1". This sign bit and other bits of VRTDC output will be combined into a signed value

representing the positive and negative phase error in the DPLL application. The first arriving signal is used to synchronize the entire VRTDC as a global clock. Two OR gates are employed to generate the "read" and "reset" signal to control the registers where the previous measurement results are stored. The arbiters and other registers associated with the last measurement are reset as well.

Fig.3.6 Simplified circuits of the pre-logic unit

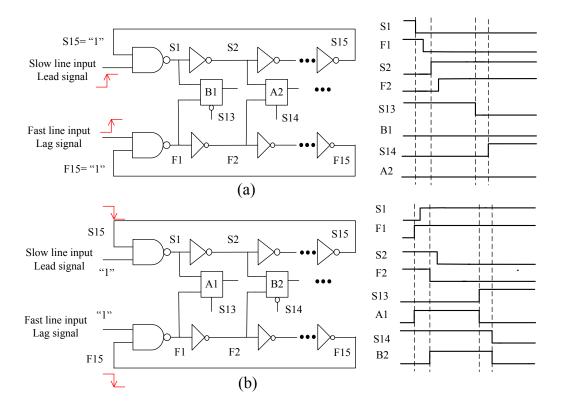

#### 3.2.2 Arbiter, edge detector and control logic

Similar to the operation of a Vernier delay line TDC, a comparator is needed at every stage to compare the arriving sequence of two signals propagating through the slow ring/line and fast ring/line, respectively. A D-flip-flop is often used to build this type of comparators. However, the clock propagation and data propagation paths in the conventional DFF normally do not match well such that there will be a large time offset in the DFFs characteristics [8]. This time offset is subject to the PVT variations from stage to stage and will cause a shift in the TDC output result. Therefore, an alternate arbiter architecture with symmetric topology was used in this VRTDC,

where the clock path and data path match well so that the comparison is less sensitive to the PVT variation.

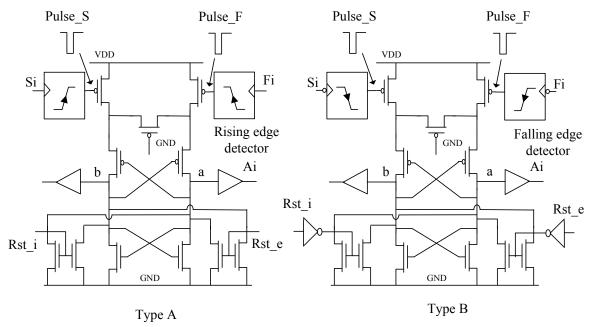

Fig.3.7 Simplified circuits of arbiter A and B

Fig.3.8 Simplified circuits of rising/falling edge detector

Fig.3.7 shows the schematics of arbiters used in the proposed VRTDC. Arbiter A and B are triggered by rising and falling edges, respectively. Both arbiters consist of a pair of edge detectors, two sets of reset circuits and a core comparator. They are reset by the signal applied to  $Rst_i$  every other lap during the propagation of the lead signal in the slow ring. The reset signal coming from the control logic will reset all the arbiters through the port  $Rst_i$  before a new measurement starts. As shown in Fig.3.8, the edge detector in both arbiters outputs a narrow negative pulse to set the arbiters and then release the control to the reset signals. The arbiter outputs "0" when the signal in the slow ring arrives first at Si, namely, the lag signal has not caught up to the lead signal yet. The arbiter outputs "1" when the signal in the fast ring arrives first at Fi, namely, the lag signal catches up to the lead signal. The first transition from zero to one at the arbiter output will be detected and used to latch the fine counter.

Fig. 3.9 Transient simulation of arbiter B with the time interval between Si and Fi setting as 2ps

Fig.3.9 shows the transient simulation of arbiter B when the time interval between Si and Fi is set to 10ps. Pulse\_F and Pulse\_S start the core comparator by pulling both node a and node b to

"1" so that the positive feedback loop works then the comparator settles to a stable state. In this simulation, node a settles to a higher voltage than node b which is around three fourths of VDD, representing that the signal at Fi arrives first. A set of buffers are necessary to boost the voltage to VDD. Ai is the output of the arbiter. The input-output delay of the arbiter is critical to the TDC. This delay has a dependence on the time interval between two input signals, as shown in Fig.3.10. The arbiter delay increases dramatically when the time interval shrinks to less 1ps. The maximum delay of 369ps shown in Fig.3.10 is obtained at a time interval of 0.2ps. The arbiter delay eventually settles to around 200ps as the time interval increases.

Fig.3.10 Dependence of arbiter delay on the time interval between two input signals

The arbiter needs to be reset before the next comparison starts. The reset signal comes from the output of the delay stage in the slow ring three stages ahead of the current one. Thus the arbiter is ready for comparison in a half period of the slow ring and is reset in another half period. There is always a current leakage path from VDD to ground for conventional arbiters without an edge detector during the reset half period [14], and this current leakage will waste power. In this

design, two types of edge detectors shut off this current leakage path in arbiters A and B. Two types of edge detectors will block the input edge when any reset signal is applied to  $Rst_i$ . The edge detectors also make the arbiter into a genuine edge-triggered device and distinguish the arbiter A from arbiter B. The narrow negative pulse can reduce the probability of overlap of negative pulse triggered by the lag signal at Fi and reset signal in an arbiter operating cycle so that it also reduces the probability of occurrence of current leakage path. In another word, the narrower the negative pulse can be, the less dynamic power will be consumed. However the narrow negative pulse must be wide enough to set the arbiter. The width of the negative pulse can be easily adjusted through the delay of the inverter chain in the edge detector.

Fig. 3.11 Illustration of (a) the operating cycle of arbiter A and (b) unexpected "01" transition at arbiter B(1)

Fig.3.11 (a) shows the operating cycle of arbiter A. The first half cycle is a ready cycle in which the arbiter is ready to receive input signals and judge the arriving timing sequence of them. The following half cycle is the reset cycle, in which the arbiter is reset to zero and the input signals are screened as well. As indicated in the figure, the arbiter will output zero when the rising edge of F(i) occurs in "0" zone and output one when it occurs in "1" zone. The process of the lag signal chasing the lead signal in the two rings can be viewed as the rising edge/falling edge of F(i) getting closer and closer to the edge of S(i) and eventually passing it. Each half period has a length of  $15*t_S$ , in which the "1" zone and "0" zone have lengths of  $3*t_S$  and  $12*t_S$ , respectively.

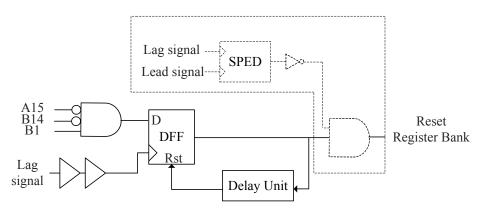

Fig.3.12 Block diagram of correction circuit

As shown in Fig.11 (b), an unexpected "01" transition is likely to occur at B(1) only when the lag signal happens to appear in the "1" zone during its first lap of propagation. Edge  $\mathbf{c}$  is supposed to be compared with edge a by the arbiter B(1). Unfortunately this arbiter has been reset after it was set to zero by edge a. Therefore the edge is going to be compared with the next falling edge b at  $F_1$ . Arbiter B(1) and the following few arbiters will be set to "1". Moreover, arbiter A15 and B14 have been set to "0" before lag signal propagates in the fast ring. A "001" transition will be erroneously detected at the least significant bit of thermometer code. The

VRTDC would have mistakenly judged that the lag signal had caught up with the lead signal without proper error detection and correction circuits. This correction circuit will screen the "001" detection signal and keep edge c of the lag signal chasing edge a till the next catch-up happens. Fig.3.12 illustrates the block diagram of the correction circuit. The properly delayed lag signal will sample  $\overline{B}_{14}\overline{A}_{15}B_1$  as soon as it is fed into the slow fast ring. Correction circuit will reset the register bank in the thermometer-to-binary encoder if the erroneous "001" code is detected. This reset signal will remain effective untill edge c in Fig.3.11(b) enters the reset area of arbiter.

As shown in Fig.3.10, the arbiter in pre-logic unit can resolve as tiny as 0.2ps time interval between two input signals, which should be digitized as "zero" time interval in the TDC output code. This arbiter should have very little chance of erronous switching when the two input signals are so close due to phase noise. In that case the lead signal will be fed into the fast ring and set first a few arbiters to zero before its edge enters the reset zone as the edge c shown in Fig.3.11(b). Similarly the correction circuit in Fig.3.12 also works since the  $\overline{B}_{14}\overline{A}_{15}B_1 = 1$  is sampled by the lag signal. The lead signal will run away from the lag signal until it overpasses the lag signal the second time. Thus the measured result is  $Ts - tin \approx Ts$ , which will cause a spur in the TDC output and will be filtered out by the low pass filter in DPLL applications. As shown in Fig.3.12, an amendments can be made to the correction circuit to disable the reset of the register bank with an extra small phase error detector (SPED) when input time interval is very small. SPED will be introduced in Section III D.

Control logic in this design coordinates the entire system to work continually. Apart from the correction circuit decribed above, the control logic also sets up the timing for the read, reset and

output of the measurement results in the pipeline mode. It consists of correction logic, several delay lines and clock trees.

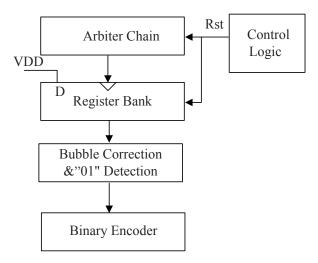

# 3.2.3 Thermometer-to-binary encoder

Fig.3.13 Block diagram of thermal-to-binary encoder

Fig.3.14 Timing diagram showing that register bank filters out the fake "01" at the falling edges.

As shown in Fig.3.13, the thermometer-to-binary encoder consists of a register bank, a bubble correction, a "01" detection circuit and a binary encoder. The outputs of the two arbiter chains are combined to form a 30-bit thermometer code. They are then converted to a 5-bit binary code for further processing by the evaluation unit. The outputs of the arbiters are periodical pulses with the same period as the fast ring after the lag signal catches up with the lead signal. The first "01" transition in the thermometer code will be detected by the "01" detection circuit. However there are many fake "01" transitions shown in Fig.3.14 at the falling edge of the arbiter outputs which have to be removed from the output of the VRTDC. A register bank is designed to filter out those falling edges of the arbiter outputs, thus eliminating the fake "01" transitions in the thermometer code. The register bank also stores the outputs of arbiters and partly eliminates the leakage problem in the arbiters, which often screws up the measurement in many low frequency applications. In addition, the proposed arbiters are reset every other lap at a frequency of several mega-hertz during the chasing process and device leakage should be negligible during the reset interval determined by the total delay of the slow ring. The arbiter outputs will not be monitored after the first "01" is detected, which means the device leakage does not limit the minimum operating frequency of the TDC. The two rings can be stopped when two external inputs of Vernier rings are reset to "0" after the catch-up. As mentioned before, the two rings need to be stopped when the measurement is finished. The ring can be stopped without causing extra propagating edges if the external input of NAND gate is reset during the period that another input to this NAND gate is "0". The stop sequence of two rings is not of concern in this design since the arbiter outputs are screened by the register bank after the catch-up. However, the stop of two rings will be properly delayed to allow the correction circuit in Fig.3.12 to complete the detection.

Bubble correction is also necessary for the encoding. "Bubble" means that it is possible to have an "...00010111..." pattern in the thermometer code due to the delay mismatch in the each arbiter or a disturbance in the circuit causing the arbiter to take more time to settle. The bubble could occur when the single stage delay of the fast and slow rings is occasionally reversed as well as the time interval input to this delay pairs is less than the reversed delay difference of this pair of stages. Therefore the "...00010111..." pattern is most likely to occur in the vicinity where the real "01" transition happens. Similar to the bubble correction circuit in ADCs, the bubble correction is helpful to get rid of the errors in the thermometer code in VRTDC and relax the demand of matching in the arbiter and interconnecting wire layout. In order to simplify the design, a "001" detection circuit is used in this design. The "001"detector can suppress the bubbles in the thermometer code to some extent.

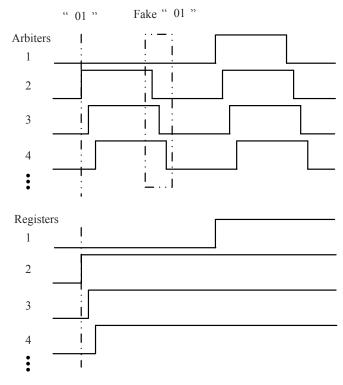

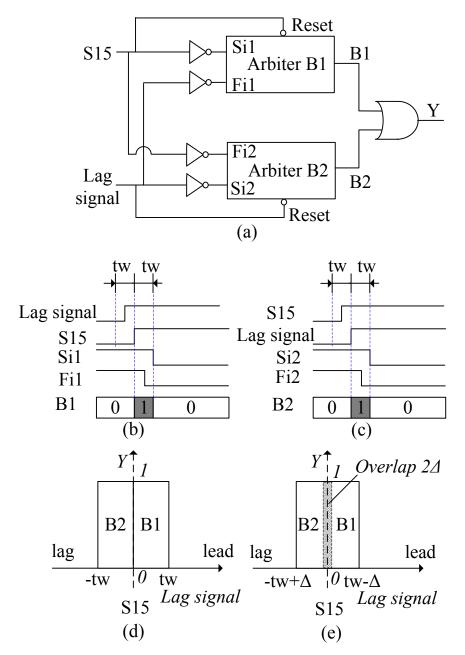

#### 3.2.4 Counters and design redundancy

Fig.3.15 shows the small phase error detector (SPED) which outputs "1" if the time interval between two input signals is smaller than  $t_W$ . SPED consists of two arbiters with crossed inputs of lag signal and S15. Fig.3. 15 (b) and (c) illustrate the timing diagram of SPED, in which the Si1, Fi2 and Si2, Fi1 are inversely replicated, with a delay of  $t_W$ , of S15 and the lag signal, respectively. B1 will output "1" only if the Fi1 appears in the "1" zone of B1 and B2 will output "1" only if Fi2 appears in the "1" zone of B2. As a result, Y is set to "1" only when the lag signal shows up in a small vicinity of S15 as shown in Fig.3.15 (d). Area B1 and B2 are adjacent assuming the four inverters ideally have equal delay. Fig.3.15 (e) shows a slight overlap of B1 and B2 achieved by a small decrease of propagation delay  $\Delta$  in the inverters in Fi1 and Fi2 input paths. At least one arbiter outputs "1" when the erroneous switching occurs due to the tiny time

interval between *S15* and lag signal. The overlap in the characteristics adds the redundancy to the design.

Fig.3.15 (a)The circuit of small phase error detector(SPED), (b,c) timing diagram of B1 and B2, (d,e) characteristics of SPED without and with overlap. (Horizontal axis indicates the time interval by which the lag signal leads or lags S15).

Fig.3.16 Counter design for redundancy

The counters  $N_C$  and  $N_F$  are triggered by the node S15 in the Vernier ring as shown in Fig.3.2 and Fig.3.4. The missing-code may occur due to the propagation delay difference between Vernier ring to thermometer-to-binary encoder and Vernier ring to two counters, as well as delay difference between node S15 to coarse counter  $N_C$  and the lag signal to  $N_C$ . These delay differences vary with input time intervals and are not easy to match. Two set of counters ( $N_C$  and  $N_F$ ) have been used to tackle the missing code problem

Fig.3.16 shows the circuit diagram of the counters.  $N_{Ceven}$  and  $N_{Codd}$ , triggered by the rising and falling edges of S15, are used to count the number of even and odd laps that the lead signal has propagated before the lag signal's entry into the Vernier ring.  $N_{Ceven}$  will be selected by SPED when the lag signal is not close to the S15. Otherwise the  $N_{Codd}$  minus B1 will be the result of  $N_{Codd}$  will be set to "1" only when the lag signal leads S15 by a small time interval and  $N_{Codd}$  is

larger than  $N_C$  by "1". Similarly,  $N_{Feven}$  will be selected when catch-up happens in the odd laps; otherwise  $N_{Codd}$  minus "1" will be the output of  $N_F$ . Counting all outputs of arbiters will be simple but consumes much more power than the presented double sets of counters with redundancy.

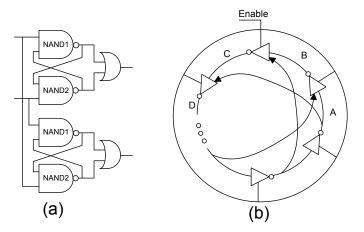

# 3.2.5 Delay stage

The design of delay stages is crucial to the performance of the VRTDC. Two identical rings are employed in this design to prevent the process variation from affecting the tiny difference in the propagation delay. In order to achieve a programmable delay difference, two different sets of bias voltages and control voltages are applied to the delay stages in the fast and slow rings, respectively. As shown in Fig.3.17, the NAND and inverter also have the same topology in each ring to reduce the variation of the time resolution due to the difference in circuit topology. This delay difference between two identical rings can cancel the first order PVT variation. The simulation results shown in Fig.3.18 and Fig.3.19 verified this cancellation.

Fig.3.17 Simplified circuits of NAND and inverter.

Fig.3.18 Dependence of the inverter delay and delay difference on the process variation.

Fig.3.18 shows the dependence of the inverter delay and delay difference on the temperature. The propagation delays of the inverters in the slow and fast ring exhibit temperature coefficients of  $0.094~ps/^{\circ}C$  and  $0.08~ps/^{\circ}C$ , respectively. The temperature coefficient of the delay difference between two inverters is reduced to  $0.014~ps/^{\circ}C$ , which is only one sixth of that of the single inverter delay.

Fig.3.19 Dependence of the inverter delay and delay difference on the temperature.

Fig.3.19 illustrates the monte carlo analysis of the dependence of the inverter delay and delay difference on the process vialation. These two delays and delay difference are subject to Gaussian variations. The propagation delay of inverters in the slow and fast rings has a standard deviation of 3.35ps and 2.62ps, respectively. The standard deviation of the delay difference reduces to 0.84ps, which is only one third of that of both inverter delays. As known, Vernier TDC gains advantages over single-delay-line based TDC for its improved resolution and immunity to device mismatch. To first order accuracy, the mismatches between the Vernier delay chains are cancelled. In our design, the delay difference is obtained through different bias voltages applied to the two delay stages. These delay stages are designed with the same structure and the parameters. Therefore the process variations between two delay stages are correlated assuming the two stages are well matched and close enough in the layout. When two variations are totally independent, the delay difference variance can be calculated with the equation  $\sqrt{\alpha^2 + \beta^2}$ , where  $\alpha$  and  $\beta$  are the standard variation of two delays. The Monte Carlo analysis

justified that the standard variation of delay difference is much smaller than that of each stage delay due to symmetry.

The mismatch of delay pair is accumulated as INL from the beginning of the delay line. INL is dependent on the variance of element delay and the length of delay line [11]. Recycling delay line can be considered to shrink the length to reduce the INL, since the INL is viewed as zero at the end of line. Reduced INL can be easily verified in the case that the frequency of two delay rings is calibrated by DLL. The delay error caused by random noise, for instance jitter and power supply noise, will be accumulated as that in the conventional delay line TDC. However, the Vernier structure can cancel out the first order mismatch and common mode noise.

The identical delay stages using different bias voltages in Vernier rings are intended to compensate the PVT variations. For testing purpose, we brought tuning voltages *Vetrl* and *Vbias* off-chip for tunability. However, this approach suffers from noise coupling through the tuning voltages. The measured resolution was also largely degraded by the jitter performance of the test equipment. The bias condition that leads to a 2ps resolution in simulations obtains an 8ps resolution in measurement. In addition to noises from test equipment, PCB and package the resolution degradation is also affected by the loading effect of parasitic capacitances. In the measurement, the fine resolution smaller than 8 ps can be tuned with a higer *Vbias* close to *VDD* and a lower *Vctrl* approaching *GND* according to Fig.3.20. However the performance under those conditions is more sensitive to noise coupling from power supply and ground.

Fig.3.20 Dependence of resolution on Vbias and Vctrl.

# 3.3 Test setup and measurement results

The prototype of the VRTDC shown in the die photo Fig.3.21 was fabricated in 0.13μm CMOS technology. The chip has an area of 1x2mm² including the ESD pads and layer density filling elements. The VRTDC circuit occupies an area of only 0.75 x 0.35 mm². The VRTDC core has an area of 0.05mm². The other parts of the VRTDC occupy a large portion of the circuit area for testing purpose. The area of the VRTDC can be further shrunk when embedded in a DPLL chip. The entire TDC chip consumes 7.5mW from a 1.5V power supply while operating at 15 MSPS. The TDC prototypes were packaged using 44 pin LCC packages and the PCB test board was developed using FR402 laminate material, which has a loss tangent of 0.015 at 1GHz.

Fig.3.21 Die photo of the 12-bit Vernier ring TDC in 0.13um CMOS technology.

The test setup consists of two pulse generators, an arbitrary waveform generator, an Agilent logic analyzer and a PCB test board. Two types of test setup are employed to obtain the TDC transfer curve and sinusoidal delay sweep response. Fig.3.22(a) shows the test setup for measurement of the TDC transfer curve with a time interval ramp generated by two signals with a slight frequency difference at 15MHz. A logic analyzer was used to collect TDC outputs continually and display the output code for adjustment of control and bias voltage. In the test, an input time interval ramp is subject to the jitter and frequency stability of the signal source, the power supply noise and noise coupled from the PCB board and other environmental noise sources. Fig.3.22(b) illustrates a sinusoidally time-varying phase difference generated by the sinusoidal modulation in one channel. An Agilent 33220A 20MHz arbitrary waveform generator was used to provide the modulating signal of interest. The other channel was set with a fixed output delay.

Fig.3.22 (a) Time interval ramp test setup (b) sinusoidal modulation of time interval.

Fig.3.23 (a) shows the TDC output measured with two inputs that have a fixed phase difference of 2.05ns plus a sinusoidally time-varying phase difference of 20ps peak-to-peak. The signal generator shown in Fig.3.22(b) outputs a clock of 15MHz at two channels. The output delay in one channel is modulated by a 100kHz sinusoidal signal. The other channel has a constant delay of 2.05ns. Sixty sequentially measured output codes were averaged to obtain the TDC output in the time domain. The measured TDC output correctly follows the input sinusoidal phase sweep when the time resolution was set to 10.2ps.

Fig.3.23 (b) shows the measured results of a fixed phase difference of 1.95ns plus a 40kHz 20 ps (p-p) sinusoidal delay sweep. The measured TDC output curve swings from 242.6 to 245.2 at a frequency of 40kHz and demonstrates that the TDC works well at a time resolution of 7.6ps, which was achieved by adjusting the delay difference between the two rings. The spurs in

Fig.3.23 are due to the harmonics of the distorted modulation signal generated by the arbitrary waveform generator or the nonlinearity of the delay modulation

Fig.3.23 Measured TDC output with sinusoidal delay sweep 20 ps(p-p), (a) 100kHz with 2.05ns fixed delay and (b) 40kHz with 1.95ns fixed delay.

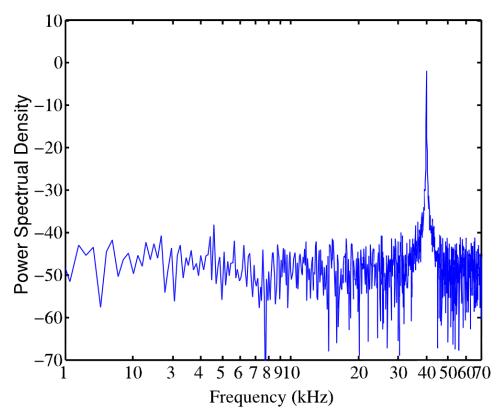

Fig.3.24 shows the measured power spectrum of the TDC output corresponding to the conditions used in Fig.3.23 (b). It demonstrates that the TDC output correctly follows the input time interval with its spectral energy concentrated at a single-tone frequency of 40 kHz, which is exactly the input phase-modulation frequency.

Fig.3.24 The power spectrum of TDC output in Fig.23 (b).

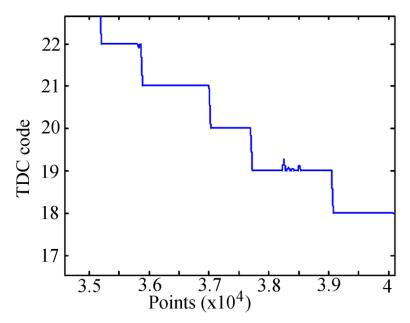

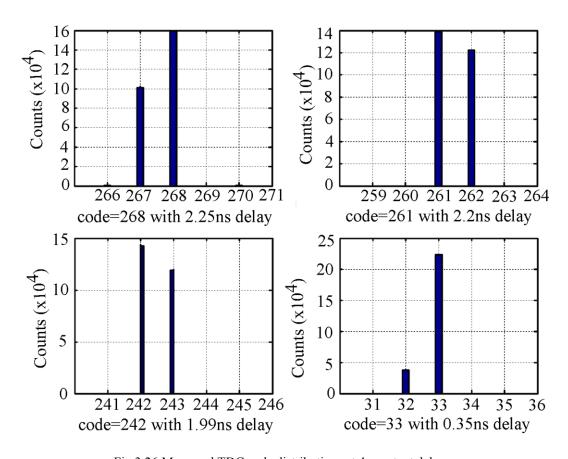

Fig.3.25 shows the measured TDC output after a median filter with 30x averaging. Two input signals with 2Hz frequency difference at 15MHz are applied to generate a ramp of time interval for the measurement of the TDC transfer curve. The input time interval, namely the period difference between two input signals, will increase or decrease 8.9fs every single pulse. The slope of the transfer curve indicates an average measured time resolution of 8ps. The measured time resolution of 8ps was limited by the available test equipment and test setup. Noise coupling from PCB/power supply and the frequency variation of the signal generators can affect the TDC test. The simulated TDC performance achieves better than 2ps resolution. Fig.3.26 gives the measured code distribution with a constant input time interval. It indicates that the standard deviation of the TDC output is less than 1-LSB for 256,000 tests.

Fig.3.25 Measured TDC output after median filter with 30X averaging.

Fig.3.26 Measured TDC code distributions at 4 constant delays.

# 3.4 Summary of Vernier ring TDC

This dissertation presented a novel TDC architecture that places the Vernier delay cells in a ring format such that the delay chains can be reused for measuring large time intervals. The reuse of Vernier delay cells in a ring configuration achieves fine resolution and large detectable range simultaneously with small area and low power consumption. The proposed Vernier ring TDC, featuring 12-bit measuring range and 8-ps resolution, was implemented in a 0.13 µm CMOS technology. The core of the TDC circuit occupies an area of only 0.75 x 0.35 mm<sup>2</sup>. The entire TDC chip consumes 7.5mW from a 1.5V power supply with operation frequency of 15 MSPS. Finally, Table I summarizes the performance comparison between the proposed work and recently reported TDCs.

Table 1 Performance Summary and Comparison of Vernier Ring TDCs.

| Reference             | [7]   | [8]  | [9]    | [10] | [11] | [4]  | This work |

|-----------------------|-------|------|--------|------|------|------|-----------|

| Sample Rate (MS/s)    | 130   | 10   | 50     | 180  | 5    | 26   | 15        |

| Time resolution (ps)  | 24    | 1.25 | 6      | 4.7  | 12.2 | 20   | 8         |

| Measuring range (bit) | 8     | 9    | 11     | 7    | 14   | 5    | 12        |

| Power Supply (V)      | 3-3.6 | 1    | 1.5    | 1.2  | 3.3  | 1.3  | 1.5       |

| Power (mW)            | <50   | 3    | 2.2-21 | 3.6  | 40   | 6.9  | 7.5       |

| Technology(nm)        | 350   | 90   | 130    | 90   | 350  | 90   | 130       |

| Area (mm2)            | 0.6   | 0.6  | 0.04   | 0.02 | 7.5  | 0.01 | 0.26      |

# **Chapter 4 3-dimensional Vernier Ring TDC**

### 4.1 Concept of 3-dimensional Vernier ring TDC

Time resolution, detectable range, measurement time, power consumption and die area are most important concerns in TDC designs for all-digital phase-locked loop applications. Shrinking the time resolution has fueled the exploration of various TDC architectures recently [8][15][18]. Time-amplifier based two-step TDC amplifies the time residue and then quantizes it with a delay-line based coarse TDC [8]. Various Vernier TDCs have been implemented with fine resolutions. However, they all struggled with low efficiency, long testing time and high power consumption for measuring large time intervals. Recently a 2D Vernier structure was developed to reduce the number of delay stages required by linear TDCs [18]. Vernier ring TDC re-uses the hardware by placing the delay stages in a ring format and thus extends the detectable range without compromising the resolution [15]. To further improve the Vernier ring TDC (VR-TDC), This dissertation presents a 3-dimensional Vernier ring TDC that re-uses two delay rings and a comparator matrix. The proposed TDC greatly improves the measurement time, efficiency and power consumption. Moreover, it can achieve large detectable range without compromising the resolution.

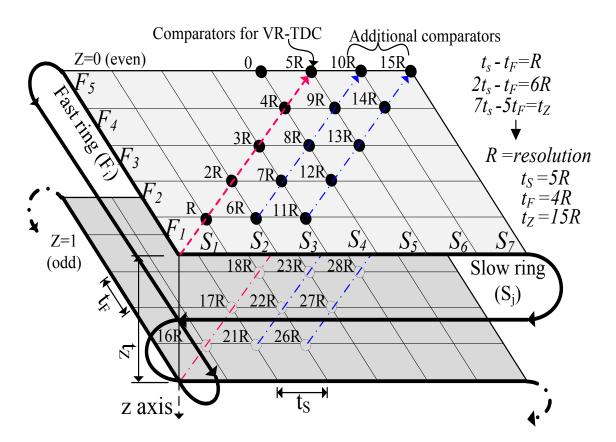

To explain the concept of the proposed 3-D Vernier ring TDC, Fig.4.1 illustrates a delay-space that is composed of a slow-ring with 7 slow delay stages, a fast-ring with 5 fast delay stages and Z planes formed by comparator matrix. As shown, two delay axes with a comparator matrix form

a 2-D delay plane. While the delay plane can be extended to a 3-D delay space by adding more 2-D delay planes, we implemented the 3-D space by connecting the Venier delay chains to form Vernier delay rings and reusing comparator matrix. The propagation delay per stage in the slow and fast rings are  $t_s$  and  $t_F$  respectively. The exemplary 3-dimensional Vernier ring TDC evolves from a 5-stage VR-TDC [3] by extending the slow-ring to 7-stages and adding two comparator columns to the right-side of the existing comparator line (labeled with red) to form a 2-dimensional comparator matrix. The 2D placement of the comparator array extends the detectable range from 5R to 15R comparing to conventional Vernier TDC, where  $R = t_s - t_F$  is TDC time resolution.

Fig.4.1 Conceptual view of 3-D Vernier delay-space

Assuming two input signals start their propagations from the origin on the plane Z=0 along two rings. The 2D comparator array compares the edges of two signals in fast- and slow-rings every lap. If the lag signal propagating along the fast-ring doesn't catch up with the lead signal propagating along the slow-ring after one lap of propagation, i.e., the input time interval is larger than 15R, the race goes into the 2nd lap with re-use of the delay rings and the comparators. In this scenario, the race in the 2nd lap is represented in the delay-space using another plane denoted Z=1, where the detectable range goes from 16R to 30R. The re-use of hardware will continue until the catch occurs and the delay-space can theoretically contain any number of planes. Similar to Vernier ring TDC, a large time interval is first interpolated with coarse resolution, i.e., the period of slow-ring prior to the arrival of the lag signal at TDC input. After lag signal arrives, the residue of the coarse interpolation will be automatically quantized with a fine resolution, which is the delay difference between fast- and slow-stages. Thus, the maximum detectable range of the proposed TDC can be infinitely large without sacrificing the fine resolution. The delay difference detected by a comparator located at (i, j, z) in delay-space is given by

$$D(i, j, z) = j \cdot t_S - i \cdot t_F + z \cdot (7t_S - 5t_F) = i \cdot R + (j - i)t_S + z \cdot t_Z$$

(4.1)

where i, j, z are the coordinates in exemplary delay-space. R is the minimum time interval and  $t_z = 7t_s - 5t_F = 15R$  is the maximum time interval detected by the comparator array on the same Z-plane. The delay difference in all Z-planes becomes a monotonic function without overlap when  $2t_S - t_F = 6R$  and  $7t_S - 5t_F = 15R$ .

# 4.2 Circuit implementation of 3-dimensional Vernier ring TDC

# 4.2.1 3-D Vernier ring TDC core

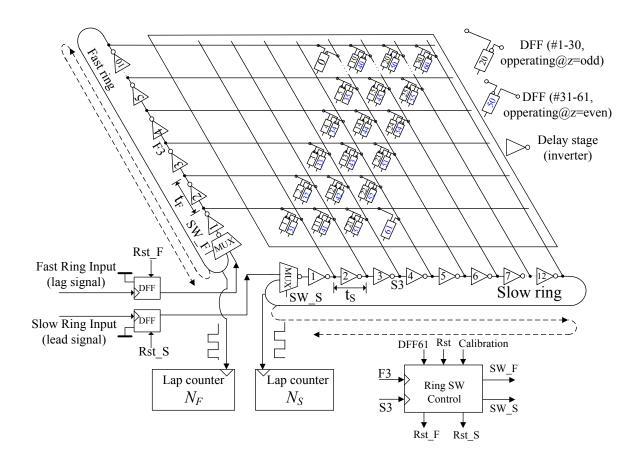

Based on the concept proposed above, we implemented a novel Vernier ring TDC chip that contains 10 fast stages, 12 slow stages, two MUXs and 62 DFF comparators, as shown in Fig.4.2. DFF1 to DFF30 works in the odd laps while DFF31 to DFF61 operates in the even laps since output of each delay stage toggles between rising and falling edges when two signals are propagating in two rings lap by lap. The implemented Vernier TDC chip can detect a minimum time interval of R that is set by the delay difference of two Vernier rings and can be programmed to a very small delay. Without increasing the delay stages and comparators, this TDC can measure very large time intervals as long as the counters have sufficient number of bits to hold the data. Unlike the conventional Vernier TDC that requires large testing time to measure large time interval, the measurement time for the proposed 3-dimensional Vernier ring TDC has been reduced. For instance, the time taken to measure the time interval of 30R requires only propagating 12 delay stages instead of 30 stages needed by a conventional Vernier TDC.

Fig.4.2 Block diagram of the proposed Vernier ring TDC core