# Informed Prefetching in Distributed Multi-Level Storage Systems

by

Maen Mahmoud Al Assaf

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama December 12, 2011

Keywords: informed prefetching, pipelining, parallel storage systems, multi-level storage systems

Copyright 2011 by Maen Mahmoud Al Assaf

Approved by

Xiao Qin, Chair, Associate Professor of Computer Science and Software Engineering David Umphress, Associate Professor of Computer Science and Software Engineering Wei-Shinn Ku, Assistant Professor of Computer Science and Software Engineering

# Abstract

In this dissertation, we present pipelined prefetching mechanisms that use applicationdisclosed access patterns to prefetch hinted blocks in multi-level storage systems. The fundamental concept in our approach is to split an informed prefetching process into a set of independent prefetching steps among multiple storage levels (e.g., main memory, solid state disks, and hard disk drives). In the first part of this study, we show that a prefetching pipeline across multiple storage levels is an viable and effective technique for allocating file buffers at the multiple-level storage devices. Our approaches (a.k.a., iPipe and IPO) extends previous ideas of informed prefetching in two ways: (1) our approach reduces applications' I/O stalls by keeping hinted data in caches residing in the main memory, solid state disks, and hard drives; (2) we propose a pipelined prefetching scheme in which multiple informed prefetching mechanisms semi-dependently work to fetch blocks from low-level (slow) to high-level (fast) storage devices. Our iPipe and IPO strategies integrated with the pipelining mechanism significantly reduce overall I/O access time in multiple-level storage systems. Next, we propose a third prefetching scheme called IPODS that aims to maximize the benefit of informed prefetches as well as to hide network latencies in a distributed storage systems. Finally, we develop a simulator to evaluate the performance of the proposed informed prefetching schemes in the context of multiple-level storage systems. We implement a prototype to validate the accuracy of the simulator. Our results show that our iPipe improves system performance by 56% in most informed prefetching cases, IPO and IPODS improve system performance by 56% and 6% respectively in informed prefetching critical cases across a wide range of real-world I/O traces.

## Acknowledgments

I owe my gratitude to all the people who have made this work possible and who supported me during my stay at Auburn University.

I would like to express my deepest gratitude to my advisor, Dr. Xiao Qin. I was indeed fortunate to be his student. He educated me and gave me support, experience, encouragement, and guidance. He taught me good research methodologies, team work, and writing skills. He also did his best to help me when I face obstacles. Without his help and support, this work would not have been possible. I really hope to be a good advisor like Dr. Qin for my future students.

I am grateful and thankful for Dr. David Umphress who reviewed my proposal and dissertation. He alerted me to many important points concerning good writing skills and research. I am pleased to be his student.

I would like to express my sincere thanks for Dr. Wei-shinn Ku for reviewing my proposal and dissertation. Dr. Ku indeed supported me in my research and guided me on the right track. I am really grateful and thankful for him.

I would also like to acknowledge Dr. Guofu Niu from the Department of Electrical and Computer Engineering at Auburn University for reviewing my dissertation and supporting my research. I really thank him very much.

This work was discussed with my colleagues in Dr. Xiao Qin's research group. I would like to mention in particular Xiaojun Ruan, Shu Yin, Yun Tian, Zhiyang Ding, James Majors , Jiong Xie, Yixian Yang, Ji Zhang, Joshua Lewis, and Jianguo Lu. I really thank them very much. I am indebted to the University of Jordan who sponsored me during my stay in the United States. In particular, I would like to thank my colleagues in King Abdullah II School of IT for their support and advise.

Most importantly, I thank my family who encouraged me to continue my Ph.D education. Without their patience and love, this work would not have been possible. I dedicate this dissertation to them.

# Table of Contents

| Abstra  | act        |                                                                          | ii |

|---------|------------|--------------------------------------------------------------------------|----|

| Ackno   | wledgmei   | ntsi                                                                     | ii |

| List of | Figures    |                                                                          | х  |

| List of | Tables     |                                                                          | v  |

| 1 In    | ntroducti  | on                                                                       | 1  |

| 1.1     | Proble     | m Statement                                                              | 1  |

|         | 1.1.1      | Informed Prefetching for Multiple-Level Storage Systems                  | 2  |

|         | 1.1.2      | Prefetching in Multi-Level Storage Systems with Limited I/O Bandwidth $$ | 3  |

|         | 1.1.3      | Informed Prefetching for Distributed Multi-level Storage Systems         | 3  |

| 1.2     | Motiva     | tions                                                                    | 4  |

|         | 1.2.1      | Motivation 1: the growing needs of multi-level storage systems. $\ldots$ | 4  |

|         | 1.2.2      | Motivation 2: the I/O access hints offered by applications               | 4  |

|         | 1.2.3      | Motivation 3: multiple prefetching mechanisms perform in parallel.       | 5  |

| 1.3     | Contri     | butions                                                                  | 6  |

| 1.4     | Dissert    | tation Organization                                                      | 7  |

| 2 L     | literature | Review & Current Work                                                    | 8  |

| 2.1     | Storag     | e systems current work                                                   | 8  |

|         | 2.1.1      | Multi-level storage systems                                              | 8  |

|         | 2.1.2      | Solid State Disks and Hard Drives                                        | 0  |

|         | 2.1.3      | Parallel Storage Systems                                                 | 1  |

|         | 2.1.4      | Distributed Storage Systems                                              | 2  |

| 2.2     | Prefete    | ching 1                                                                  | 3  |

|         | 2.2.1      | Two Types of Prefetching                                                 | 3  |

|   |     | 2.2.2   | Informed Prefetching                                                                            | 14 |

|---|-----|---------|-------------------------------------------------------------------------------------------------|----|

|   |     | 2.2.3   | Predictive Prefetching                                                                          | 15 |

|   |     | 2.2.4   | Prefetching in multi-level storage systems                                                      | 16 |

|   |     | 2.2.5   | Prefetching in Distributed and Parallel Storage Systems                                         | 17 |

|   | 2.3 | Summ    | ery                                                                                             | 18 |

| 3 | As  | sumptio | ons and Parameters Validations                                                                  | 20 |

|   | 3.1 | System  | n Assumptions                                                                                   | 20 |

|   |     | 3.1.1   | Demand Misses                                                                                   | 20 |

|   |     | 3.1.2   | Informed Caching                                                                                | 21 |

|   |     | 3.1.3   | Bandwidth Limitations                                                                           | 22 |

|   |     | 3.1.4   | I/O Bandwidth Sharing                                                                           | 22 |

|   |     | 3.1.5   | Life Time of Solid State Disk (SSD)                                                             | 23 |

|   | 3.2 | Assum   | ptions on Prefetching and Pipelining                                                            | 23 |

|   |     | 3.2.1   | Initial Data Allocation                                                                         | 23 |

|   |     | 3.2.2   | A Pipeline for Data Transfers                                                                   | 24 |

|   |     | 3.2.3   | Writes and Data Consistency                                                                     | 25 |

|   |     | 3.2.4   | Pipelining Depth                                                                                | 26 |

|   |     | 3.2.5   | Block Size                                                                                      | 26 |

|   |     | 3.2.6   | LASR Traces                                                                                     | 26 |

|   | 3.3 | Valida  | tions $\ldots$ | 27 |

|   |     | 3.3.1   | Overview                                                                                        | 27 |

|   |     | 3.3.2   | System Setup                                                                                    | 28 |

|   |     | 3.3.3   | Proof of the Concept                                                                            | 29 |

|   |     | 3.3.4   | Block Size                                                                                      | 31 |

|   |     | 3.3.5   | Model $T_{cpu} + T_{hit} + T_{driver}$                                                          | 31 |

|   |     | 3.3.6   | System Parameters validation                                                                    | 35 |

|   |     | 3.3.7   | Limited Parallel I/O Bandwidth                                                                  | 36 |

|   | 3.4 | Summ    | ary                                                                                               | 39 |

|---|-----|---------|---------------------------------------------------------------------------------------------------|----|

| 4 | iP  | ipe: An | Pipelined and Informed Prefetching for Multi-Level Storage Systems .                              | 41 |

|   | 4.1 | Overv   | iew                                                                                               | 41 |

|   | 4.2 | Motiva  | ations and Objectives                                                                             | 41 |

|   | 4.3 | Desigr  | n Issues in iPipe                                                                                 | 42 |

|   |     | 4.3.1   | Architecture of iPipe                                                                             | 43 |

|   |     | 4.3.2   | Assumptions                                                                                       | 45 |

|   | 4.4 | The iI  | Pipe Algorithm                                                                                    | 46 |

|   |     | 4.4.1   | Stalls and Disk Read Latencies                                                                    | 46 |

|   |     | 4.4.2   | Prefetching Horizon                                                                               | 48 |

|   |     | 4.4.3   | The Pstart and Pdepth Algorithms                                                                  | 48 |

|   |     | 4.4.4   | Stalls, Elapsed Time, Prefetching Horizon, and Prefetching Benefit $% \mathcal{T}_{\mathrm{A}}$ . | 53 |

|   |     | 4.4.5   | The iPipe Algorithm                                                                               | 57 |

|   | 4.5 | Perfor  | mance Evaluation                                                                                  | 58 |

|   |     | 4.5.1   | System Setup                                                                                      | 58 |

|   |     | 4.5.2   | Preliminary Results                                                                               | 59 |

|   |     | 4.5.3   | Validated Performance Evaluation                                                                  | 67 |

|   | 4.6 | Summ    | ary                                                                                               | 73 |

| 5 | IP  | O: Info | rmed Prefetching Optimization in Multi-level Storage Systems                                      | 74 |

|   | 5.1 | Overv   | iew                                                                                               | 74 |

|   | 5.2 | Motiva  | ations and Objectives                                                                             | 74 |

|   | 5.3 | Desigr  | n Issues in IPO                                                                                   | 75 |

|   |     | 5.3.1   | Architecture of IPO                                                                               | 76 |

|   |     | 5.3.2   | Assumptions                                                                                       | 79 |

|   | 5.4 | The II  | PO Algorithm                                                                                      | 79 |

|   |     | 5.4.1   | Definitions                                                                                       | 79 |

|   |     | 5.4.2   | The Pstart and Pnext Algorithms                                                                   | 81 |

|   |     | 5.4.3   | The IPO Algorithm                                                                                                               |

|---|-----|---------|---------------------------------------------------------------------------------------------------------------------------------|

|   | 5.5 | Perform | mance Evaluation                                                                                                                |

|   |     | 5.5.1   | Simulation Environment                                                                                                          |

|   |     | 5.5.2   | Elapsed Time Improvement                                                                                                        |

|   |     | 5.5.3   | Bandwidth Utilization                                                                                                           |

|   |     | 5.5.4   | Increasing the $Max_{BW}$ Value $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $ 91                     |

|   | 5.6 | Summ    | ary                                                                                                                             |

| 6 | IP  | ODS: Ii | nformed Prefetching in Distributed Multi-level Storage Systems 94                                                               |

|   | 6.1 | Overvi  | ew                                                                                                                              |

|   | 6.2 | Motiva  | ations and Objectives                                                                                                           |

|   | 6.3 | IPODS   | S Design Issues                                                                                                                 |

|   |     | 6.3.1   | The IPODS Architecture                                                                                                          |

|   |     | 6.3.2   | Assumptions                                                                                                                     |

|   | 6.4 | The IF  | PODS Algorithm                                                                                                                  |

|   |     | 6.4.1   | Definitions                                                                                                                     |

|   |     | 6.4.2   | The IPODS Algorithm                                                                                                             |

|   | 6.5 | Perform | mance Evaluation                                                                                                                |

|   |     | 6.5.1   | Simulation Environment                                                                                                          |

|   |     | 6.5.2   | Improving Elapsed Time                                                                                                          |

|   | 6.6 | Summ    | ary                                                                                                                             |

| 7 | Pr  | ototype | Development $\dots \dots \dots$ |

|   |     | 7.0.1   | Objectives                                                                                                                      |

|   |     | 7.0.2   | System Setup                                                                                                                    |

|   |     | 7.0.3   | Design Issues of the Prototypes                                                                                                 |

|   |     | 7.0.4   | Validation Process                                                                                                              |

|   | 7.1 | Protot  | ypes                                                                                                                            |

|   |     | 7.1.1   | The iPipe Prototype 108                                                                                                         |

|    |        | 7.1.2    | The IPO Prototype                                                    | 115 |

|----|--------|----------|----------------------------------------------------------------------|-----|

|    |        | 7.1.3    | The IPODS Prototype                                                  | 119 |

|    | 7.2    | Summ     | ary                                                                  | 120 |

| 8  | Сс     | onclusio | ns & Future Work                                                     | 123 |

|    | 8.1    | Main     | Contributions                                                        | 123 |

|    |        | 8.1.1    | iPipe: An Pipelined and Informed Prefetching                         | 124 |

|    |        | 8.1.2    | IPO: Informed Prefetching Optimization                               | 125 |

|    |        | 8.1.3    | IPODS: Pipelined Prefetching in Distributed/Parallel Storage Systems | 126 |

|    |        | 8.1.4    | Prototypes for iPipe, IPO, and IPODS                                 | 126 |

|    | 8.2    | Future   | e Work                                                               | 127 |

|    |        | 8.2.1    | Data Migration                                                       | 127 |

|    |        | 8.2.2    | The Cost-Benefit Model                                               | 128 |

|    |        | 8.2.3    | Write Performance                                                    | 128 |

|    |        | 8.2.4    | Most Recently Used Policy                                            | 129 |

|    |        | 8.2.5    | Extending Storage Hierarchy                                          | 129 |

|    |        | 8.2.6    | Caching and Benchmarking                                             | 130 |

|    |        | 8.2.7    | Various Solid State Disks                                            | 130 |

|    |        | 8.2.8    | Block Sizes                                                          | 130 |

|    |        | 8.2.9    | Fast Networks for Distributed Storage Systems                        | 131 |

| Bi | bliogr | aphy     |                                                                      | 132 |

# List of Figures

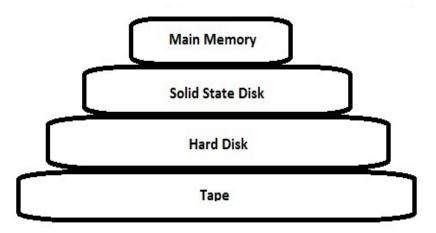

| 2.1  | Multi-level storage system that consists of different storage devices with various speed performance.                                                                                                                                                                                                                                                                                                                                                                                                       | 9  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

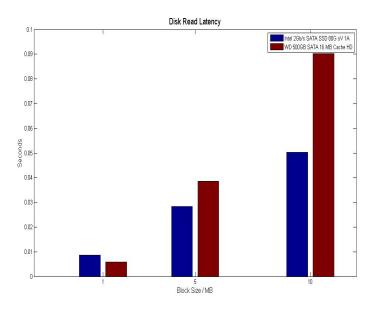

| 3.1  | Read Latency of HDDs and SDDs. When block size is 10 MB, SSD has better read performance than HDD                                                                                                                                                                                                                                                                                                                                                                                                           | 30 |

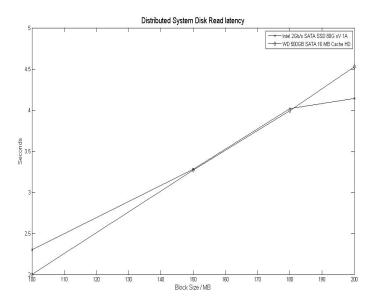

| 3.2  | Read Latency of accessing a remote HDD and SDD through the LAN network connection. In this distributed system setting, SSD has better read performance than HDD when block size is 200 MB                                                                                                                                                                                                                                                                                                                   | 30 |

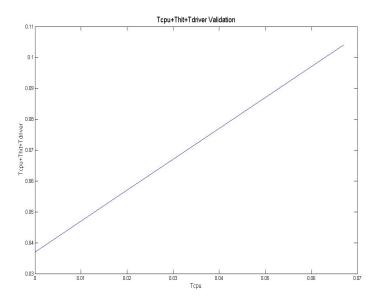

| 3.3  | $(T_{cpu}) + (T_{hit}) + (T_{driver})$ values range from 0.037- 0.104 seconds. We will consider the smallest value.                                                                                                                                                                                                                                                                                                                                                                                         | 35 |

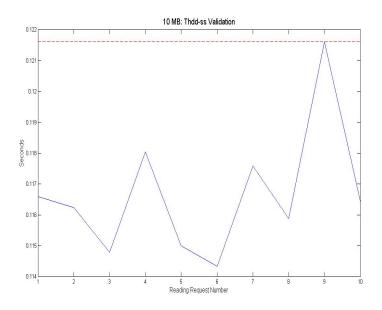

| 3.4  | 10 MB: Estimated $T_{hdd-ss}$ is 0.122 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

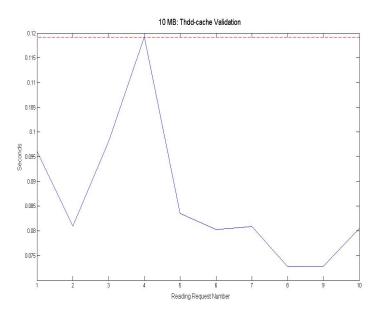

| 3.5  | 10 MB: Estimated $T_{hdd-cache}$ is 0.12 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37 |

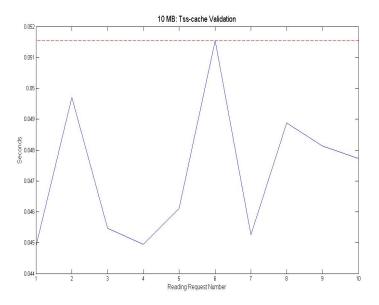

| 3.6  | 10 MB: Estimated $T_{ss-cache}$ is 0.052 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37 |

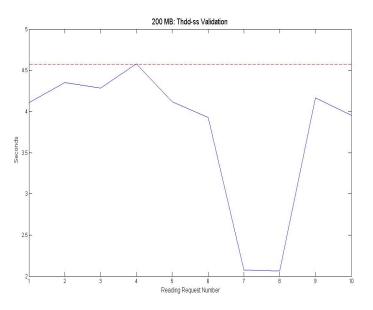

| 3.7  | 200 MB: Estimated $T_{hdd-ss}$ is 4.5 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38 |

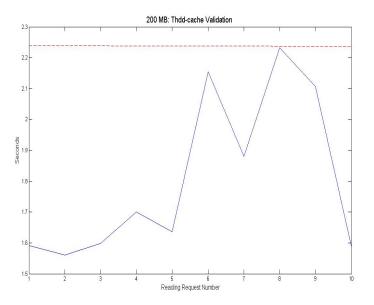

| 3.8  | 200 MB: Estimated $T_{hdd-cache}$ is 2.3 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38 |

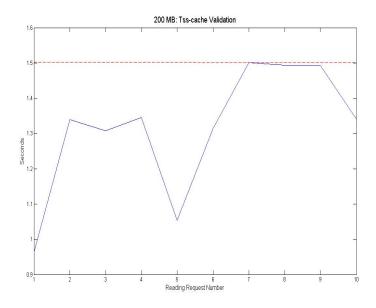

| 3.9  | 200 MB: Estimated $T_{ss-cache}$ is 1.5 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

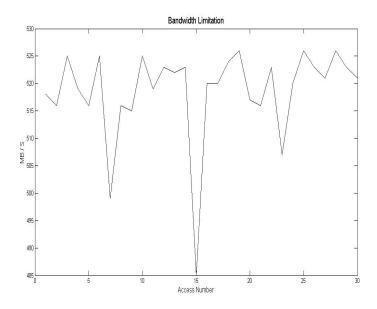

| 3.10 | Limited Parallel I/O Bandwidth. Concurrent read requests are noticeably affected by the limited parallel I/O bandwidth.                                                                                                                                                                                                                                                                                                                                                                                     | 40 |

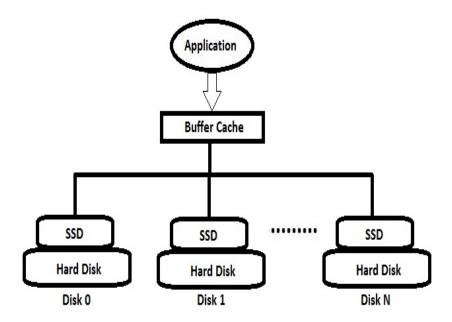

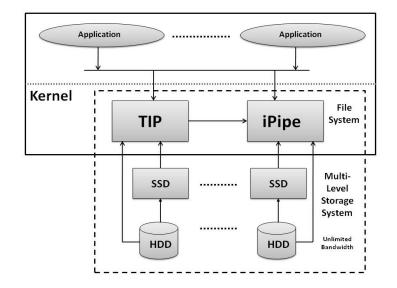

| 4.1  | iPipe system hardware architecture. Consists of an array of multi-level disks                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

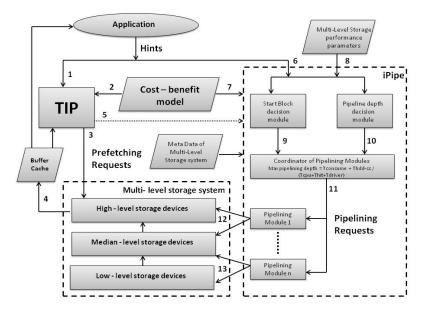

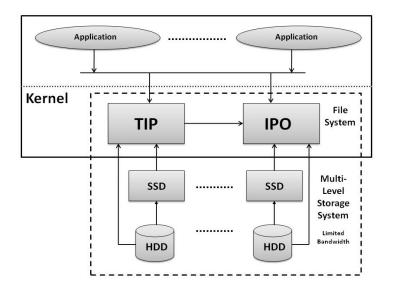

| 4.2  | High-level design of the iPipe software architecture for a multi-level storage system. The multi-level storage system consists of two levels - SSDs and HDDs                                                                                                                                                                                                                                                                                                                                                | 44 |

| 4.3  | Detailed design of the iPipe software architecture for a three-level storage system.<br>An application provides hints to both TIP and iPipe. The system performance<br>parameters are passed to iPipe to calculate the pipelining starting block and<br>depth. iPipe keeps fetching hinted data blocks to the highest level. Since the<br>storage system's bandwidth is high enough, iPipe is able to fetch most of the<br>hinted blocks. TIP uses a cost benefit model to determine the number of prefetch |    |

buffers. Hinted data blocks are fetched from the storage system to the buffer cache. 45

| 4.4  | Average stall when using iPipe and a fixed number of buffers for pipelined<br>prefetching. $T_{hdd-cache} = 5$ , $T_{hdd-ss} = 8$ , $T_{ss-cache} = 4$ , $X_{cache} = 3$ . The first<br>stall is 5 time units. Before the first hinted block is fetched from HDD into SSD,<br>the application stalls for $T_{stall-hdd}(X_{cache}) = T_{hdd-cache} - 3(T_{cpu} + T_{hit} + T_{driver})$<br>= 2 time units every 3 accesses. When hinted blocks are retrieved in the SSD,<br>the application stalls for $T_{stall-ss}(X_{cache}) = T_{hdd-cache} - 3(T_{cpu} + T_{hit} + T_{driver}) =$<br>1 every 3 accesses | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | Average stall when using a fixed number of buffers for pipelined prefetching.<br>$T_{hdd-cache} = 5$ , $X_{cache} = 3$ . The first stall is for 5 time units, because all data<br>blocks are read from the HDD. The application stalls for $T_{stall-hdd}(X_{cache}) = T_{hdd-cache} - 3(T_{cpu} + T_{hit} + T_{driver}) = 2$ time units every 3 accesses                                                                                                                                                                                                                                                    | 56 |

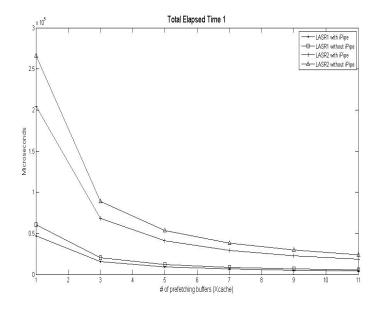

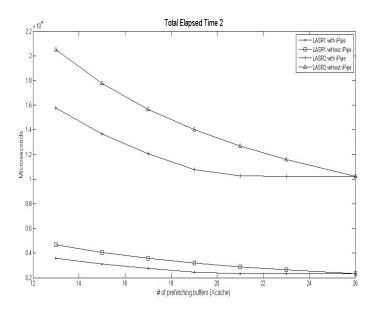

| 4.6  | Total elapsed time when the number of prefetching buffers is set from 1 to 11.<br>iPipe reduces the elapsed time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61 |

| 4.7  | Total elapsed time when the number of prefetching buffers is set from 13 to 26. iPipe reduces the elapsed time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62 |

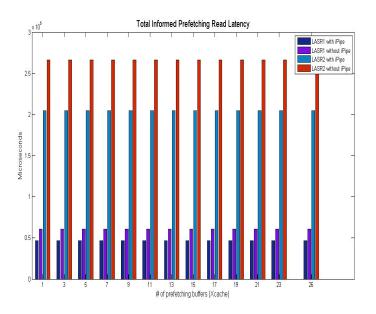

| 4.8  | Total informed prefetching read latency. iPipe reduces the read latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62 |

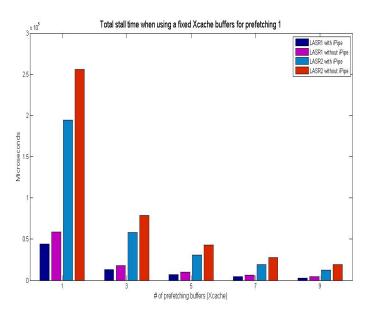

| 4.9  | Total stall time when the number of prefetching buffers is set from 1 to 9. iPipe reduces the stall time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

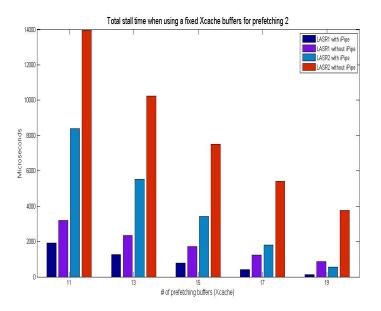

| 4.10 | Total stall time when the number of prefetching buffers is set from 11 to 19. iPipe reduces the stall time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64 |

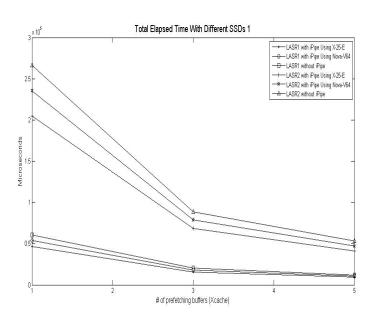

| 4.11 | Total elapsed time when the number of prefetching buffers is set from 1 to 5. iPipe reduces the elapsed time in both Nova-V64 and Intel X25-E SSDs. Elapsed time is less when Intel X25-E SSD is tested because it is faster than Nova-V64 SSD                                                                                                                                                                                                                                                                                                                                                               | 65 |

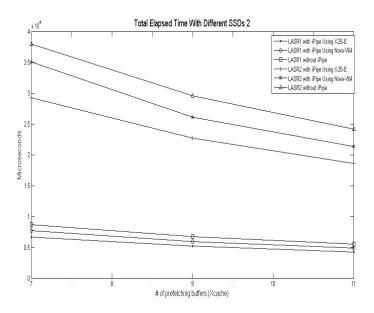

| 4.12 | Total elapsed time when the number of prefetching buffers is set from 7 to 11.<br>iPipe reduces the elapsed time in both Nova-V64 and Intel X25-E SSDs. Elapsed<br>time is less when Intel X25-E SSD is tested because it is faster than Nova-V64<br>SSD                                                                                                                                                                                                                                                                                                                                                     | 66 |

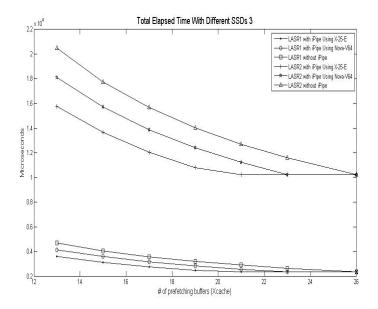

| 4.13 | Total elapsed time when the number of prefetching buffers is set from 13 to 26.<br>iPipe reduces the elapsed time in both Nova-V64 and Intel X25-E SSDs. Elapsed<br>time is less when Intel X25-E SSD is tested because it is faster than Nova-V64<br>SSD                                                                                                                                                                                                                                                                                                                                                    | 66 |

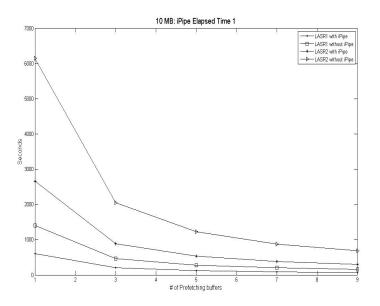

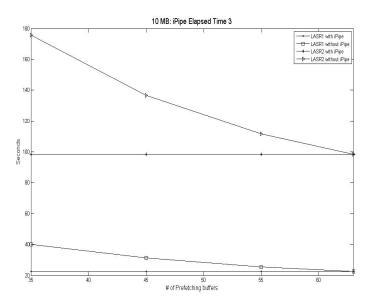

| 4.14 | Block size = 10 MB. Total elapsed time when the number of buffers is set from 1 to 9. iPipe reduces the elapsed time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69 |

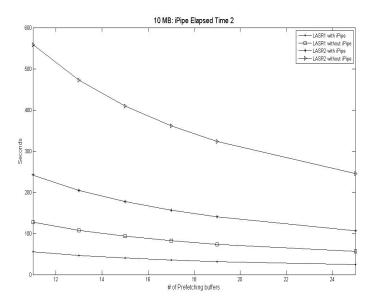

| 4.15 | Block size = 10 MB. Total elapsed time when the number of buffers is set from 11 to 25. iPipe reduces the elapsed time. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69 |

| 4.16 | Block size = 10 MB. Total elapsed time when the number of buffers is set from 35 to 63. iPipe reduces the elapsed time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

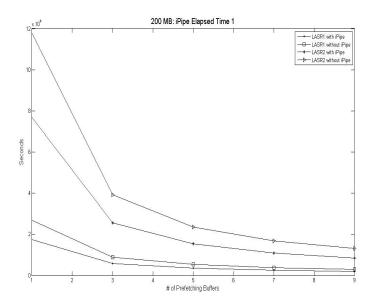

| 4.17 | Block size = 200 MB. Total elapsed time when the number of buffers is set from 1 to 9. iPipe reduces the elapsed time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

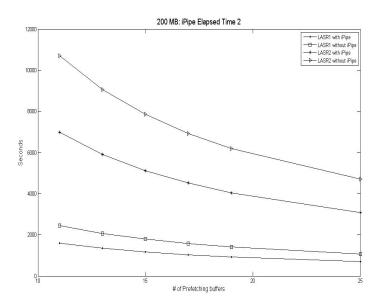

| 4.18 | Block size = 200 MB. Total elapsed time when the number of buffers is set from 11 to 25. iPipe reduces the elapsed time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

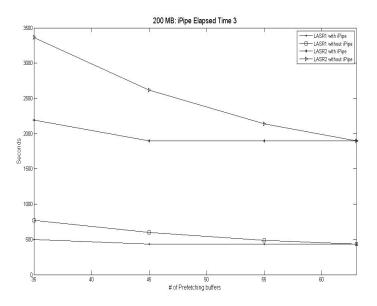

| 4.19 | Block size = 200 MB. Total elapsed time when the number of buffers is set from 35 to 63. iPipe reduces the elapsed time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

| 5.1  | High-level design of IPO software architecture. The multi-level storage system consists of an array of two levels of SSDs and HDDs with limited bandwidth and scalability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78 |

| 5.2  | Detailed design of IPO software architecture for a three-level storage system. The application provides hints on future I/O accesses. IPO determines the appropriate hinted blocks to be fetched. IPO keeps prefetching a particular number (depends on available bandwidth) of hinted blocks to the uppermost level. The upper-level prefetcher (i.e., TIP) uses the cost/benefit model to determine the number of prefetching buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78 |

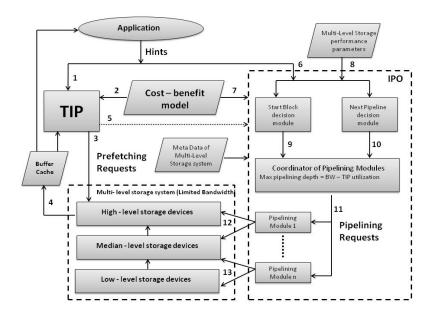

| 5.3  | Average stalls when using IPO and a fixed number of buffers for parallel prefetch-<br>ing in the buffer cache. The maximum number $(Max_{BW})$ of read requests is 5.<br>Informed prefetching buffers = 2, and the rest 3 spaces of the bandwidth are used<br>for pipelined prefetching. $T_{hdd-cache} = 5$ , $T_{hdd-ss} = 8$ , $T_{ss-cache} = 4$ , and $X_{cache} =$<br>2. The first accesses stall for 5 time units. Before IPO fetches hinted blocks from<br>HDD to SSD, the application stalls for $T_{stall-hdd}(X_{cache}) = T_{hdd-cache} - 3(T_{cpu} + T_{hit} + T_{driver}) = 2$ time units every 3 accesses. IPO continues to fetch 3 hinted<br>blocks each time from HDD. When a prefetched block is consumed from SSD, a<br>new pipelined prefetching request is initiated by IPO. When IPO is employed,<br>stalls time becomes 40 and elapsed time is 76 time units | 84 |

| 5.4  | Continue Figure 5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85 |

| 5.5  | Average stalls when using a fixed number of buffers for parallel prefetching in<br>buffer cache. $T_{hdd-cache} = 5$ , and $X_{cache} = 2$ . The first accesses stall for 5 time<br>units. All data is read from HDD. The application stalls for $T_{stall-hdd}(X_{cache})$<br>$= T_{hdd-cache} - 3(T_{cpu} + T_{hit} + T_{driver}) = 2$ time units every 3 accesses. In the<br>non-IPO case, stalls time is 45 and elapsed time is 81                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86 |

| 5.6  | Continue Figure 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87 |

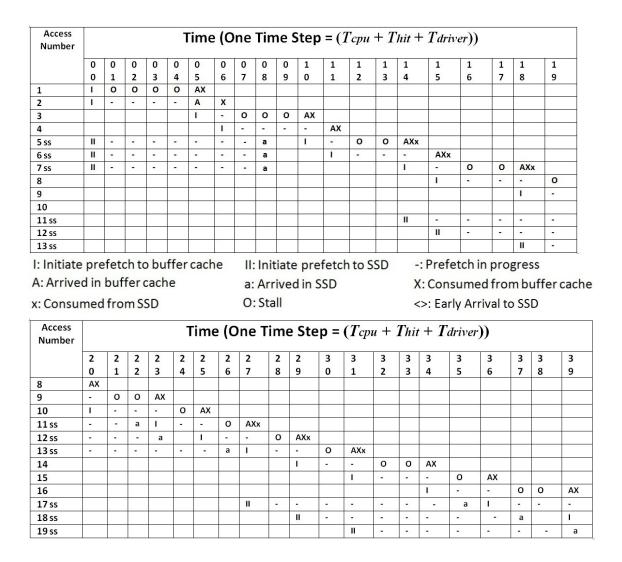

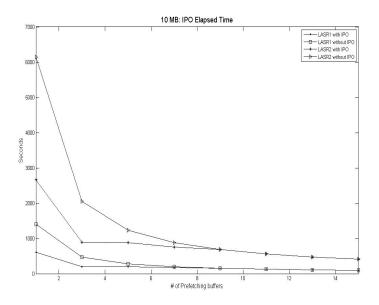

| 5.7  | IPO reduces application elapsed time. 10 MB block size. Total elapsed time when using 1 to 15 prefetching buffers. $Max_{BW} = 15. \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89 |

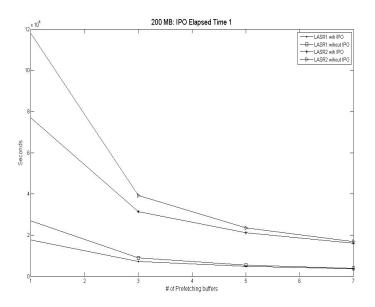

| 5.8  | IPO reduces application elapsed time. 200 MB block size. Total elapsed time when using 1 to 7 prefetching buffers. $Max_{BW} = 15. \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                          | 90  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

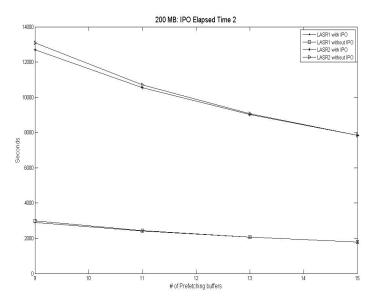

| 5.9  | IPO reduces application elapsed time. 200 MB block size. Total elapsed time when using 9 to 15 prefetching buffers. $Max_{BW} = 15. \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                       | 90  |

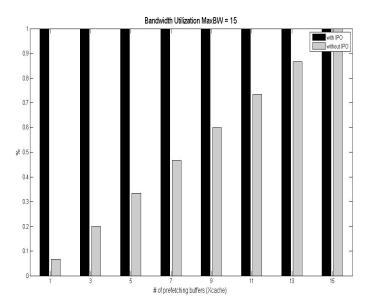

| 5.10 | Bandwidth utilization when $X_{cahce}$ is varied from 1 to 15 in both IPO and non-IPO cases. IPO fully utilizes the bandwidth                                                                                                                                                                                                                                                                                                                            | 91  |

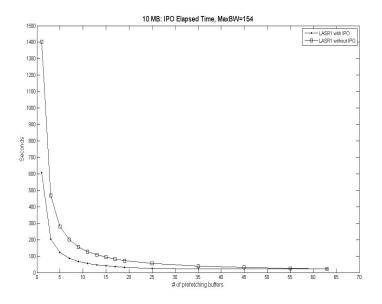

| 5.11 | IPO reduces the elapsed time. Total elapsed time when the $X_{cahce}$ value is increased from 1 to 63. $Max_{BW}$ is set to 154                                                                                                                                                                                                                                                                                                                          | 92  |

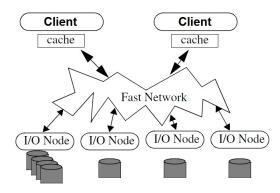

| 6.1  | The architecture of a distributed parallel storage system. Several distributed clients and storage nodes are connected by a network. T.Madhyastha; G. Gibson; C. Faloutsos: Informed prefetching of collective input/output requests, Proceedings of the 1999 ACM/IEEE conference on Supercomputing (CDROM), Portland, Oregon, 1999.                                                                                                                     | 95  |

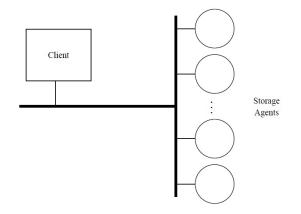

| 6.2  | [71] Another architecture of a distributed parallel storage system. Several dis-<br>tributed clients and storage nodes are connected by a network. Luis Cabrera<br>, Darrell D.E. Long: SWIFT: USING DISTRIBUTED DISK STRIPING TO<br>PROVIDE HIGH I/O DATA RATES, University of California at Santa Cruz,<br>Santa Cruz, CA, 1991                                                                                                                        | 96  |

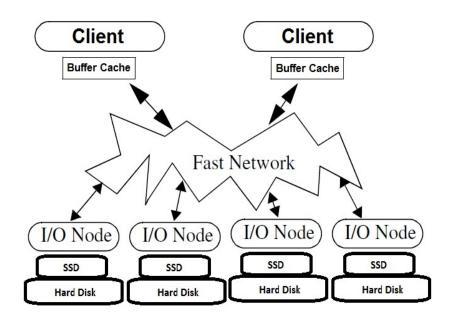

| 6.3  | Distributed/Parallel Multi-level Storage System: The system shows several dis-<br>tributed storage nodes and clients connected by a network. Each I/O stor-<br>age node consists of a two-level storage device containing both SSD and HDD.<br>T.Madhyastha; G. Gibson; C. Faloutsos: Informed prefetching of collective in-<br>put/output requests, Proceedings of the 1999 ACM/IEEE conference on Super-<br>computing (CDROM), Portland, Oregon, 1999. | 98  |

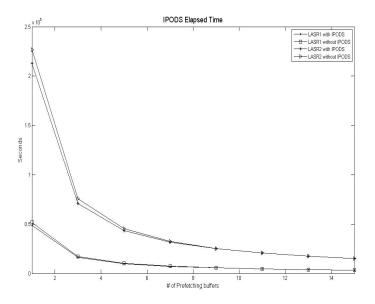

| 6.4  | Total elapsed time when the number of prefetching buffers is varied from 1 to 15. $Max_{BW} = 15$ . IPODS reduces the elapsed time                                                                                                                                                                                                                                                                                                                       | 104 |

# List of Tables

| 3.1 | I/O bandwidth measured using the Ramspeed benchmark                                                                                                                                                                                                                                                                                                                  | 33  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | The number of informed prefetching requests issued to HDDs when the LASR1 and LASR2 traces are evaluated.                                                                                                                                                                                                                                                            | 60  |

| 4.2 | Service time is reduced when one extra buffer is added for prefetching                                                                                                                                                                                                                                                                                               | 61  |

| 4.3 | Prefetching Horizon $P(T_{cpu})$ equals 26 data blocks distance while iPipe is not used. $P(T_{cpu})$ drops to 20 data blocks distance when iPipe is used                                                                                                                                                                                                            | 63  |

| 4.4 | Total stall time when the number of prefetching buffers is set from 21 to 26. iPipe reduces the stall time.                                                                                                                                                                                                                                                          | 65  |

| 4.5 | Data block size = $10$ MB. The position of the first data block to be prefetched.                                                                                                                                                                                                                                                                                    | 72  |

| 4.6 | Data block size = 10 MB. The depth of the pipelined prefetching when using dif-<br>ferent $X_{cahce}$ values. Small depth is needed when few $X_{cahce}$ buffers are used. The<br>maximum depth = 91. iPipe needs to assign the maximum depth for pipelined<br>prefetching starting from $X_{cahce} = 35$ , because the reading stalls from SSD at<br>that point = 0 | 72  |

| 4.7 | Data block size = $200$ MB. The position of the first data block to be prefetched.                                                                                                                                                                                                                                                                                   | 73  |

| 4.8 | Data block size = 200 MB. The depth of the pipelined prefetching when using different $X_{cahce}$ values. Small depth is needed when few $X_{cahce}$ buffers are used. The maximum depth = 163. iPipe needs to assign the maximum depth for pipelined prefetching starting from $X_{cahce} = 45$ , because the reading stalls from SSD at that point = 0             | 73  |

| 7.1 | Total elapsed time measured in seconds when the iPipe prototype is tested. The number of prefetching buffers is set to a range between 1 to 63. The block size is 10 MB.                                                                                                                                                                                             | 111 |

| 7.2 | Total elapsed time measured in seconds when the LASR traces are replayed by the iPipe prototype. The number of prefetching buffers is set to a range between 1 to 63. The block size is 10 MB                                                                                                                                                                        | 111 |

| 7.3 | Total elapsed time measured in seconds when the iPipe simulator is tested. The number of prefetching buffers is set to a range between 1 to 63. The block size is 10 MB.                                                                                                                                                                                             | 112 |

| 7.4  | Comparison between iPipe's simulation results and the prototyping results. Total elapsed time measured in seconds when the LASR traces are replayed by the iPipe simulator and prototype. The block size is 10 MB. | 112 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.5  | Total elapsed time measured in seconds when the iPipe prototype is tested. The number of prefetching buffers is set to a range between 1 to 63. The block size is 200 MB                                           | 113 |

| 7.6  | Total elapsed time measured in seconds when the LASR traces are replayed by the iPipe prototype. The number of prefetching buffers is set to a range between 1 to 63. The block size is 200 MB                     | 113 |

| 7.7  | Total elapsed time measured in seconds when the iPipe simulator is tested. The number of prefetching buffers is set to a range between 1 to 63. The block size is 200 MB                                           | 114 |

| 7.8  | Comparison between iPipe's simulation results and the prototyping results. Total elapsed time measured in seconds when the LASR traces are replayed by the iPipe simulator and prototype. The block size is 200 MB | 114 |

| 7.9  | Total elapsed time measured in seconds when the IPO prototype is tested. The number of prefetching buffers is set to a range between 1 to 15. The block size is 10 MB.                                             | 116 |

| 7.10 | Total elapsed time measured in seconds when the LASR traces are replayed by the IPO prototype. The number of prefetching buffers is set to a range between 1 to 15. The block size is 10 MB                        | 116 |

| 7.11 | Total elapsed time measured in seconds when the IPO simulator is tested. The number of prefetching buffers is set to a range between 1 to 15. The block size is 10 MB.                                             | 116 |

| 7.12 | Comparison between IPO's simulation results and the prototyping results. Total elapsed time measured in seconds when the LASR traces are replayed by the iPipe simulator and prototype. The block size is 10 MB    | 117 |

| 7.13 | Total elapsed time measured in seconds when the IPO prototype is tested. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB                                             | 117 |

| 7.14 | Total elapsed time measured in seconds when the LASR traces are replayed by the IPO prototype. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB.                      | 117 |

| 7.15 | Total elapsed time measured in seconds when the IPO simulator is tested. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB                                             | 118 |

| 7.16 | Comparison between IPO's simulation results and the prototyping results. Total elapsed time measured in seconds when the LASR traces are replayed by the iPipe simulator and prototype. The block size is 200 MB | 118 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.17 | Total elapsed time measured in seconds when the IPODS prototype is tested. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB                                         | 120 |

| 7.18 | Total elapsed time measured in seconds when the LASR traces are replayed by the IPODS prototype. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB                   | 120 |

| 7.19 | Total elapsed time measured in seconds when the LASR traces are replayed by the IPODS simulator. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB                   | 121 |

| 7.20 | Total elapsed time measured in seconds when the IPODS simulator is tested. The number of prefetching buffers is set to a range between 1 to 15. The block size is 200 MB                                         | 121 |

# Chapter 1

## Introduction

To solve the I/O bottleneck problem (see [81]) in large-scale computing systems, researchers have proposed a wide range of prefetching techniques for preloading data from disks into the main memory prior to the data accesses. Existing prefetching techniques can be categorized into two camps - predictive prefetching and informed prefetching. Predictive prefetching schemes predict future I/O access patterns based on historical I/O accesses of applications [2], whereas informed prefetching techniques make preloading decisions based on applications' future access hints [1]. In this dissertation study, we will focus on informed prefetching schemes and investigate performance impact of informed prefetching on multiple level storage systems. Well-known predictive prefetching solutions are summarized in Section 2.2.

The chapter is organized as follows. The first section describes the problem statement of this dissertation study. In the second section, we illustrate the important motivations for our new proposed informed prefetching approaches. Next, the second section outlines the main contributions of this study. Finally, the last section specifies the organization of the dissertation.

### 1.1 Problem Statement

As the performance gap between processors and I/O subsystems increases rapidly, disk performance becomes a serious bottleneck for large-scale computing systems supporting dataintensive applications [32]. Recent studies show that informed prefetching can bridge the performance gap between the CPU and I/O; for example, an informed prefetching algorithm called TIP proposed by Patterson *et al.* aims to improve performance of I/O-intensive applications by applying cost-benefit analysis to allocate buffers for both prefetching and caching [1]. TIP's cost-benefit analysis is possible, because TIP estimates the impact of alternative buffer allocations on application execution time.

This dissertation research is inspired by the TIP approach [1]. Follows are three main challenges to be addressed our study:

- 1. informed prefetching for multiple-level storage systems,

- 2. prefetching in multi-level storage systems with limited I/O bandwidth, and

- 3. informed prefetching for distributed multi-level storage systems.

## 1.1.1 Informed Prefetching for Multiple-Level Storage Systems

When disk arrays are employed, the TIP algorithm improves the quality of parallel prefetching through accurately eliminating I/O stalls. In Patterson's approach, the informed caching and prefetching algorithm assigns a portion of buffer space used for demand caching (LRU) and the rest of the buffer to store hinted blocks prefetched from disks [1]. This buffer allocation process is guided by a cost-benefit model. When data accessing time increases due to high disk load, I/O stall time goes up and creates an increasing benefit of assigning additional buffers for hinted blocks. When parallel disk subsystems are extended into multiple-level storage systems [52] [23], a hierarchy of multiple storage devices increases data access latency if the data are residing in a lower level of the systems. To shorten long data transfer latency, popular data or future accessed data may be stored in the upper level of the storage systems.

Traditional informed prefetching schemes can hide the latency of accessing storage systems by invoking disk I/O parallelisms and fetching data based on application-disclosed hints. We will show that building an informed prefetching pipeline can significantly improve the I/O performance of multi-level storage systems. We will illustrate how to use application hints to initiate prefetching among multiple storage levels like main memory, solid state disks, and hard disk drives. The centerpiece of our approach is a pipeline in which we split the informed prefetching process into a set of independent prefetching steps among the multiple storage levels. In particular, we will demonstrate how to integrate this pipeline with informed prefetching and caching to manage file buffers at various storage levels.

#### 1.1.2 Prefetching in Multi-Level Storage Systems with Limited I/O Bandwidth

I/O-intensive applications can disclose hints about their future I/O accesses and these hints can be used to guide prefetching mechanisms in making accurate prefetching decisions. Existing informed prefetching algorithms rely on the assumption that parallel disks offer enough I/O bandwidth for prefetching without encountering I/O congestion. Under such an assumption, an informed prefetching mechanism can prefetch a large number of data blocks in parallel; Unfortunately, our preliminary results show that real-world storage systems may not have unlimited I/O bandwidth; this observation is especially true for small-scale storage systems. We addressed this issue by developing an informed prefetching algorithm (see Chapter 5) in a multiple-level storage system where disk devices offer limited I/O bandwidth. Our informed prefetching solution is practical, because it does not rely on the assumption that storage systems provide unlimited I/O bandwidth.

#### 1.1.3 Informed Prefetching for Distributed Multi-level Storage Systems

To further extend our prefetching approaches (see Chapters 4 and 5), we developed an informed prefetching algorithm (see Chapter 6) tailored for distributed multi-level storage systems, each of which consists of a group of multi-level storage servers. In a distributed storage system, large disk access latency due to network delays can be hidden by informed prefetching. We will demonstrate that a pipeline mechanism can be used to efficiently prefetch data blocks from a low-level storage device to a up-level storage device before moving the data blocks to the clients.

#### **1.2** Motivations

The following key factors motivated us to investigate pipelined informed prefetching:

- 1. the growing needs of multi-level storage systems,

- 2. the I/O access hints offered by applications, and

- 3. the possibility of multiple prefetching mechanisms working in parallel.

#### 1.2.1 Motivation 1: the growing needs of multi-level storage systems.

Multi-level storage systems have been widely employed in data centers supporting service-based applications such as multimedia streaming and scientific computing. For example, popular data are fetched and cached in an upper-level server while massive amounts of unpopular data are placed in lower-level storage servers. Overall performance of I/Ointensive applications can be improved by increasing the I/O performance of multi-level storage systems. Existing studies (see, for example, [19] and [9]) suggest that new prefetching and caching techniques are needed to boost the I/O performance of multi-level storage systems. Since prefetching must be performed at each storage level to hide I/O latencies, prefetching mechanisms at multi-level need to coordinate in order to achieve high prefetching efficiency.

## 1.2.2 Motivation 2: the I/O access hints offered by applications.

The second factor motivating our informed prefetching for multi-level storage systems is that largely predictable I/O access patterns can be disclosed by applications as hints. I/O access hints are used by prefetching mechanisms to invoke asynchronous I/O accesses to fetch data to upper-level storage like the main memory and solid state disks.

Informed prefetching in multi-level storage systems is challenging for two main reasons. First, hints must be processed at different storage levels in different manners. For example, an upper-level prefetching mechanism takes hints and makes conservative prefetching decisions for upper-level storage with small capacity; a lower-level prefetching mechanism is aggressive in order to effectively use large lower-level storage as a staging area. Second, at each storage level, an informed prefetching manager must balance cache space against prefetching space. Informed prefetching mechanisms at multiple levels should coordinate to manage caches across multiple levels of storage devices.

Prefetching and caching issues in multi-level storage systems have been investigated in existing studies [19] [9]. However, to our best knowledge no research has incorporated informed prefetching mechanisms into a multi-level storage system.

# 1.2.3 Motivation 3: multiple prefetching mechanisms perform in parallel.

Multiple informed prefetching mechanisms can independently fetch blocks from lowerlevel to upper-level storage devices. These prefetching mechanisms can work in parallel, because multiple prefetching operations can be simultaneously processed by the upper-level and lower-level prefetching mechanisms. Such storage parallelisms make it possible to implement a prefetching pipeline, where the informed prefetching processes are separated into a set of distinct prefetching steps among multiple storage levels.

When data blocks have to be cached in all of the storage levels, significant I/O delays are incurred by prefetching data from the lowest-level to the highest-level of storage. We show that a pipelined prefetching approach can increase prefetching throughput, which is defined as the number of blocks prefetched from the lowest storage level to the highest storage level.

We will focus on read-intensive applications, because read performance of applications is poor when the data to be accessed are residing in the lower-level storage subsystems. Write performance in multi-level storage systems is not as critical as read performance, since applications can write data to upper-level storage devices (e.g., write-behind buffer) before moving data from the upper-level to the lower-level storage.

# 1.3 Contributions

The following list summarizes the major research contributions made in this dissertation study:

- To reduce I/O delays in multi-level storage systems, we propose new informed prefetching approaches to coordinating multiple prefetching mechanisms in the form of a pipeline. The three informed prefetching algorithms developed in this study are called iPipe (see Chapter 4), IPO (see Chapter 5), and IPODS (see Chapter 6). We show that with our prefetching pipeline in place, multiple prefetching operations can be processed in parallel by both upper-level and lower-level prefetching mechanisms.

- We apply a novel cost-benefit model to estimate the value of prefetching or caching a block at a specific storage level in a multi-level storage system. The cost-benefit model is used by prefetching mechanisms deployed in multiple storage levels to improve buffer usage at all storage levels. We describe how we employed the model in our prefetching algorithms in Chapters 4-6.

- We developed a simulated multiple-level storage system, in which the three prefetching algorithms are implemented. Simulation results show that our prefetching mechanism powered by a data fetching pipeline reduces applications' stall and execution times. Simulation results also indicate that our approaches can reduce prefetching distance (a.k.a., prefetching horizon).

- We implemented a prototype to validate our simulator for multi-level storage systems. Like the simulator, the prototype contains the implementation of all the three proposed informed prefetching algorithms. We conducted an experiment using the prototype, showing that our prefetching solutions can reduce disk read latency in distributed multi-level storage system, an environment in which data are stored in different nodes that are connected by a network. Prefetching time will increase because of network

and server latencies. Pipelining can only reduce the disk read latency as a part of the total prefetching time.

#### 1.4 Dissertation Organization

The rest of the dissertation is organized as follows:

Chapter 2 describes the cutting-edge-research in multi-level storage systems as well as informed and predictive prefetching techniques.

Chapter 3 explains the assumptions made in this dissertation, shows the proof of concept, and validates system parameters used throughout this dissertation.

Chapter 4, outlines the system architecture, algorithm Design, and performance evaluation for our iPipe solution that assumes enough storage system's bandwidth.

Chapter 5, outlines our IPO solution that performs pipelining in a limited bandwidth storage system. The chapter discusses the system architecture, algorithm Design, and the performance evaluation.

Chapter 6 outlines IPODS solution which implements IPO in distributed multi-levels storage systems.

Chapter 7 discuss our solutions' prototyping results.

Finally, Chapter 8 provides a summary of this dissertation study with a list of directions for future research.

## Chapter 2

## Literature Review & Current Work

Previous researchers have suggested that application-disclosed hints can be used by prefetching mechanisms to dramatically improve I/O performance. To our best knowledge, however, ours is the first study to focus on informed prefetching in multi-level storage systems, the first to consider how to apply the cost-benefit model in a multi-level prefetching system, the first to construct a pipeline to coordinate multiple prefetching mechanisms in a multi-level storage system, and the first to offer a systematic performance evaluation of informed prefetching in multi-level hybrid storage systems.

In this Chapter, we will discuss closely related work in both storage systems in general and prefetching in particular.

# 2.1 Storage systems current work

We will begin this subsection by describing multiple-level storage systems (see Section 2.1.1). Then, we will compare solid state disks with traditional hard disk drives (see Section 2.1.2). Next, we introduce new techniques in parallel storage systems (see Section 2.1.3). Finally, we will discuss related work in distributed storage systems (see Section 2.2).

## 2.1.1 Multi-level storage systems

A multi-level storage system consists of a hierarchy of heterogeneous storage devices that differ in their hardware, speed, size, and other specifications [87]. Multilevel storage systems provides cost-effective solutions for large-scale data centers without significantly affecting I/O response times. The I/O performance of a multi-level storage system depends on data placement of the system. Ideally, a high-level storage device should store two types of data:

Figure 2.1: Multi-level storage system that consists of different storage devices with various speed performance.

(1) popular data that are frequently accessed and (2) data that are likely to be access in the not-too-distant future.

Typical storage devices in a modern multi-level storage system include main memory, solid state disks, hard disks, and magnetic tape subsystems (see, for example, [23]). Figure 2.1 shows a 4-level storage system, which is a straightforward extension of a traditional 2-level storage system with main memory and hard drives.

Multi-level storage systems and caches share similar advantages. A multi-level cache system contains a hierarchy of more cache levels [33]. Previous studies show that there is a maximum benefit of having a single level cache [21] [22]. Making tradeoff between cache latency and hit rate is a challenge, because large caches inevitably have high hit rates with long latency. To achieve a good tradeoff between hit rate and latency, researchers proposed multiple-level caches, where small, fast caches (i.e., upper level caches) are backed up by large, slow caches (lower level caches).

Similar to multi-level caches, multi-level storage systems [18] [19] [20] first check their upper-level storage devices. If data items are not in the upper level storage, the next storage level is checked. This process is repeated until the required information is retrieved.

In a multi-level storage system, data can be moved from one particular level to another by data migration processes. The decision of migrating data blocks from one level to another is based on the data's metadata (e.g., popularity and pass access patterns). Data migration based on popularity or predictions is a good example of the important metadata used by data migration modules [38], [34], [36]. When a multi-level storage system migrates data to upper levels based on popularity or predicted access patterns, the migrated data will be accessed by clients in a fast way thanks to reduced access delays [37].

#### 2.1.2 Solid State Disks and Hard Drives

Compared to traditional hard drives (HDD), solid state disks (SSD) show better data read performance. Tuma provides comparisons between a wide range of SSDs and HDDs; detailed comparisons can be found in [85]. Tuma's results show that SSDs have better random read-performance than HDDs. For example, reading 4- KB blocks from a seagate HDD achieves a throughput of 0.70 MB/s; whereas reading the same data blocks from Msystems Model FDD 3.5" Flash SSD can obtain a throughput of 4.3 MB/s. Rizvi and Chung compares SLC with MLC-flash SSDs with HDDs; the findings show that SSDs offer better I/O throughput than HDDs [86]. Therefore, solid state disks are becoming increasingly popular in the support of large-scale multimedia systems requiring high I/O bandwidth. Researchers can obtain the specifications of various HDD and SDD products from vendors (e.g., [94] [93] [92] [90]). The product data sheets clearly indicate that SDDs outperform HDDs in term of reads. For example, WD Caviar Green has approximately a maximum read bandwidth of 190 MB/s, assuming that the WD's SSDs are connected with SATA 1.5 Gb/s (1.5 Gb/s is approximately equal to 190 MB/s). On the other hand, Nova Series V64 solid-state drive can achieve a high read bandwidth of 215 MB/s, which is higher than that of WD's SSDs. Different SSD products vary in their I/O performance. For example, Intel's X25-E Extreme SATA SSDs - with a read bandwidth of 250 MB/s - is better than Nova Series V64 SSDs. Many SSD and HDD products distinguish themselves from each other in terms of I/O performance, size, cost, and other aspects. In general, SDDs have good I/O performance and a high price whereas HDDs offer high storage capacity at low cost. As such,

J. No built a hybrid file system using both SSDs and HDDs, thereby taking the advantages of two different types of storage devices [56].

#### 2.1.3 Parallel Storage Systems

Parallel storage systems are commonly deployed in supercomputers [1] [23] [63]. A parallel storage system consist of redundant storage devices offering high I/O performance and bandwidth [51] [60]. Disk arrays are important components in parallel storage systems.