## HIGH TEMPERATURE HIGH POWER SIC DEVICES PACKAGING PROCESSES AND MATERIALS DEVELOPMENT

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee.

This dissertation does not include proprietary or classified information.

| Cai W                                                                | Vang                                                                                |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Certificate of Approval:                                             |                                                                                     |

| Thomas A. Baginski Professor Electrical and Computer Engineering     | R. Wayne Johnson, Chair<br>Ginn Professor<br>Electrical and Computer<br>Engineering |

| Victor P. Nelson<br>Professor<br>Electrical and Computer Engineering | Thaddeus A. Roppel<br>Associate Professor<br>Electrical and Computer<br>Engineering |

| Stephen L. McFarla<br>Dean                                           | nd                                                                                  |

Graduate School

# HIGH TEMPERATURE HIGH POWER SIC DEVICES PACKAGING PROCESSES AND MATERIALS DEVELOPMENT

Cai Wang

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama August 7, 2006

## HIGH TEMPERATURE HIGH POWER SIC DEVICES PACKAGING PROCESSES AND MATERIALS DEVELOPMENT

| $\alpha$ . | ***    |

|------------|--------|

| ('21       | Wang   |

| Car        | vv anz |

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon the request of individuals or institutions at their expense. The author reserves all publication rights.

| Signature of Author |

|---------------------|

| _                   |

|                     |

|                     |

| Date of Graduation  |

## **VITA**

Cai Wang, son of Hanping Wang and Saier Chang, was born August 6, 1970, in Jiangsu, China. He attended Tsinghua University in Beijing, China, and graduated with a bachelor of Material Science and Engineering in July of 1993. He entered Graduate School at Auburn University in March 2000. He received Master degree of Electrical and Computer Engineering in 2003. He then continued his education in the Ph.D. program in the Department of Electrical and Computer Engineering of Auburn University.

## DISSERTATION ABSTRACT

## HIGH TEMPERATURE HIGH POWER SIC DEVICES PACKAGING PROCESSES

### AND MATERIALS DEVELOPMENT

Cai Wang

Doctor of Philosophy, August 7, 2006 (M.S., Auburn University, 2003) (B.S., Tsinghua University, 1993)

160 Typed Pages

Directed by R. Wayne Johnson

Silicon power devices have reached their theoretical limits in terms of higher temperature and higher power operation by virtue of the physical properties of the material. SiC has been identified as a material with the potential to replace Si devices because of its superior material advantages. However, there is a lack of reliable packaging techniques and materials for SiC, in particular die attach, wire bonding and die passivation that can survive temperature as high as 500°C.

Based on the high melting point of Au-In alloy (81/19 wt%), it was evaluated as a potential high temperature die attach material using a transient liquid phase bonding process in this study. Thermal cycle test results over the temperature range from 35°C to

V

400°C and high temperature storage at 450°C results are presented. Vertical cracks developed in the die attach on Mo tabs during the thermal cycling tests and indium segregated to the defects (voids and cracks) during the high temperature storage and thermal cycling tests. This segregation appeared to negatively impact the reliability of the die attach.

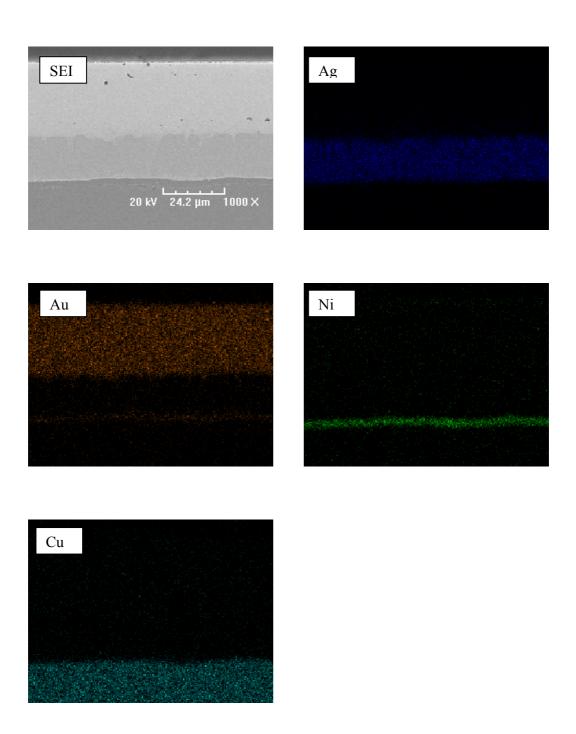

The 6μm of nickel or nickel phosphorous commonly used as a barrier layer in conventional ceramic substrate metallization did not prevent Cu diffusion to the surface at a temperature of 450°C. A multi-layer nickel phosphorous structure was found to serve as a good barrier to prevent Cu diffusion for high temperature applications.

The bondability and reliability of large diameter (250µm) gold and platinum wire using thermosonic wedge bonding was investigated. High temperature storage results at 350°C for wire bonds on the substrate metallization and 300°C for die metallizations are presented. A simplified FEMA 2D model was used to understand the effects of bond force and die metallization structure on the failure modes, SiO<sub>2</sub> cracking and SiC cratering. The results matched the experimental results very well. This work demonstrated the effects of wire and pad stack metallurgy on bond reliability.

Polyimide PI2611has been evaluated as a passivation coating material. The results were promising at 300°C; however, higher temperature tests have shown rapid decomposition of the polyimide.

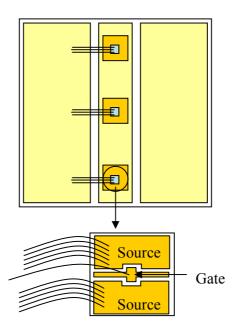

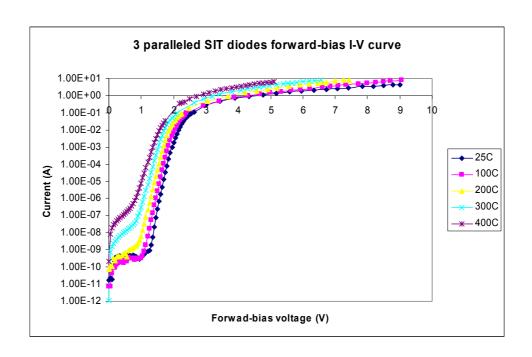

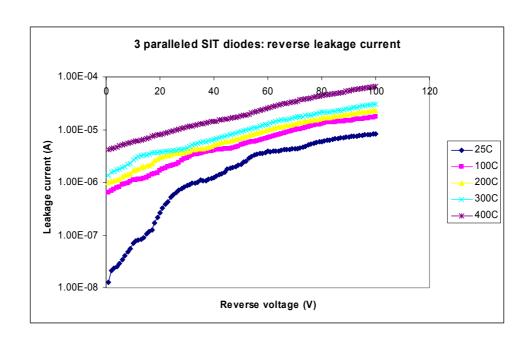

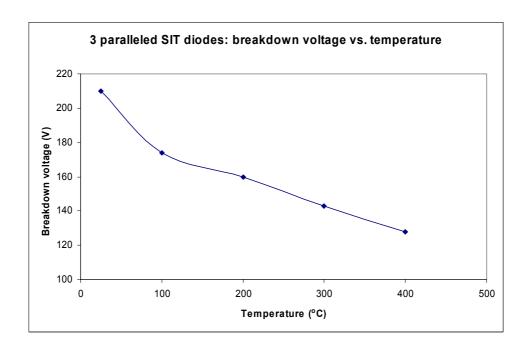

In this work, electrical characteristics of VJFET and SIT diode modules were measured over the temperature range from 25°C to 400°C to demonstrate the feasibility of paralleling SiC power VJFETs to develop Si IGBT replacements. Paralleled VJFETs formed an equivalent switch of much greater current than the single VJFET, and showed

a positive temperature coefficient of on-resistance. The paralleled SIT diodes resulted in a lower cut-on voltage than the single SIT diode, and the leakage current of the paralleled SIT diodes was less than 70  $\mu$ A when  $V_{ds}=100$  V at 400°C, validating the impressive blocking performance of the SIT diode at extreme temperatures.

## **ACKNOWLEDGEMENTS**

The author would like to express his appreciation and sincere thanks to his advisor, Dr. R. Wayne Johnson, for all the support, guidance and encouragement in performing this research. Also thanks to Dr. Thaddeus A. Roppel, Dr. Thomas A Baginski, Dr. Victor P. Nelson, and Dr. John R. Williams for help in reviewing the dissertation.

He would also like to thank the cooperative support from Dr. Yi Liu, his project coworker, and the valuable help from Mr. Mike Palmer, Dr. Michael J. Bozack, Dr. Hyacinth S. Gale, Guoyun Tian, John Marcell throughout the course of his research.

Finally, the author would also like to express my profound gratitude to my wife, Yurun Cang, my daughters, Sienna Wang and Sophia Wang, and my parents for their encouragement and support throughout this work.

Style manual or journal used: <u>IEEE Transaction on Components and Packaging Technology.</u>

Computer software used:  $\underline{\text{Microsoft Office 2003}}$

## TABLE OF CONTENTS

| LIST OF FIGURES                                 | xiii |

|-------------------------------------------------|------|

| LIST OF TABLES                                  | xvii |

| CHAPTER 1 INTRODUCTION                          | 1    |

| CHAPTER 2 BACKGROUND                            | 8    |

| 2.1 SiC Properties                              | 10   |

| 2.2 Thin Film SiC Die Metallization             | 12   |

| 2.3 Substrate and Substrate Metallization.      | 18   |

| 2.4 Die Attach                                  | 22   |

| 2.5 Wire Bonding                                | 27   |

| 2.6 Polyimide                                   | 34   |

| CHAPTER 3 SiC DIE ATTACH CHARACTERATION         | 37   |

| 3.1 Transient Liquid Phase Bonding Process      | 37   |

| 3.2 Thick Gold Die Specimen Preparation         | 40   |

| 3.2.1 SiC Die Metallization Fabrication         | 40   |

| 3.2.2 Substrate Metallization Fabrication       | 41   |

| 3.2.3 TLP Process of Thick Gold Die Attach      | 42   |

| 3.2.4 High Temperature Storage Test             | 45   |

| 3.3 Thick Silver Substrate Specimen Preparation | 47   |

| 3.3.1 SiC Die Metallization Fabrication         | 47   |

| 3.2.2 Substrate Metallization Fabrication                                             | 47  |

|---------------------------------------------------------------------------------------|-----|

| 3.3.3 TLP Process of Thin Gold Die Attach on Thick Silver Substrate                   | 49  |

| 3.3.4 High Temperature Storage Test                                                   | 54  |

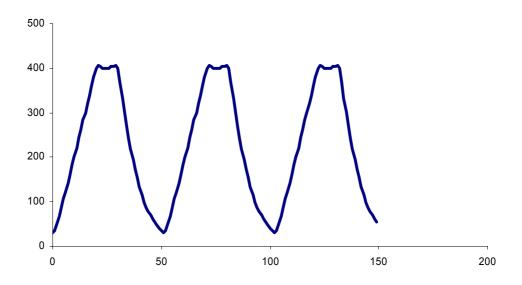

| 3.3.5 Thermal Cycling Test                                                            | 56  |

| 3.4 Thermal Cycling Tests of Thin Au Die Bonding on Mo Tab                            | 60  |

| 3.5 Substrate Metallization Barrier Material Evaluation                               | 68  |

| 3.6 Summary                                                                           | 72  |

| CHAPTER 4 LARGE DIAMETER WIRE BONDING ON SIC SUBSTRATE AND                            | )   |

| DIE METALLIZATIONS                                                                    | 75  |

| 4.1 Large Diameter Wire Bondability of Substrate Metallization                        | 75  |

| 4.1.1 Wire Bond Test Substrate and Bonding Wires                                      | 75  |

| 4.1.2 Bonding Parameters and Bond Criteria                                            | 76  |

| 4.1.3 Optimization of Wire Bond Parameters                                            | 80  |

| 4.1.4 Accelerated Aging Testing                                                       | 83  |

| 4.2 Large Diameter Wire Bondability of SiC Die Metallizations over SiO <sub>2</sub>   | 85  |

| 4.2.1 Wire Bond Test Die Metallization and Bonding Wires                              | 85  |

| 4.2.2 Wire Bond Parameters                                                            | 86  |

| 4.2.3 Accelerated Aging Testing                                                       | 86  |

| 4.2.4 Failure Analysis                                                                | 91  |

| 4.3 Large Diameter Wire Bondability of SiC Die Metallization without SiO <sub>2</sub> | 104 |

| 4.3.1 Wire Bond Test Die Metallization and Bonding Wire                               | 104 |

| 4.4 Summary                                                                           | 106 |

| CHAPTER 5 POLYIMIDE BREAKDOWN TEST                                         | 108 |

|----------------------------------------------------------------------------|-----|

| 5.1 Polyimide Test Sample Fabrication and Experiment Set-up                | 108 |

| 5.2 Experiment Results                                                     | 111 |

| CHAPTER 6 SiC VJFET DEVICES OPERATING at EXTREME                           |     |

| TEMPERATURES                                                               | 114 |

| 6.1 Introduction                                                           | 114 |

| 6.2 Performance of SiC VJFETs at Extreme Temperatures                      | 120 |

| 6.2.1 VJFET Packaging Process                                              | 120 |

| 6.2.2 DC Characterization of Paralleled VJFETs                             | 123 |

| 6.3 Performance of SIT Diode Operating at Extreme Temperatures             | 127 |

| 6.3.1 SIT Diode                                                            | 127 |

| 6.3.2 SIT Diodes Packaging Process                                         | 128 |

| 6.3.2 DC Characterization of Paralleled SIT Diodes                         | 129 |

| 6.4 Summary                                                                | 133 |

| CHAPTER 7 CONCLUSON                                                        | 134 |

| 7.1 Transient Liquid Phase Bonding Process                                 | 134 |

| 7.2 Barrier Material Evaluation                                            | 134 |

| 7.3 Large Diameter Wire Bonding                                            | 135 |

| 7.4 High Temperature, High Power Passivation                               | 136 |

| 7.5 4H-SiC VJFETs Devices Operated at Extreme Temperatures                 | 136 |

| 7.6 Recommendations for Packaging sic High Power, High Temperature Devices | 137 |

| 7.7 Recommendations for Future Work                                        | 137 |

| BIBLIOGRAPHY                                                               | 138 |

## LIST OF FIGURES

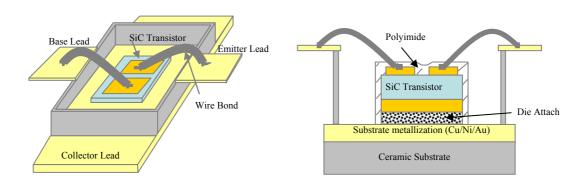

| Figure 1.1 SiC power transistor device structure                              | 2  |

|-------------------------------------------------------------------------------|----|

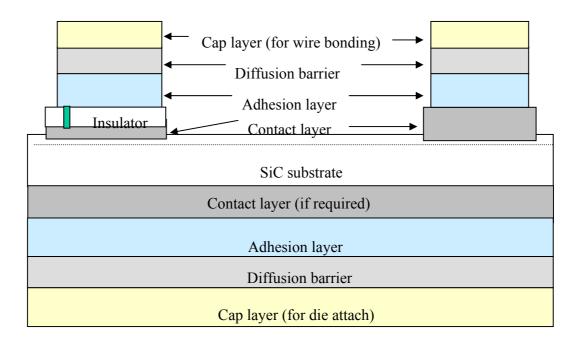

| Figure 2.1Typical composite contact on SiC bipolar transistor [14]            | 13 |

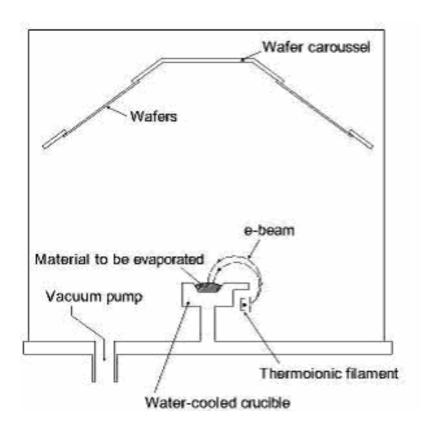

| Figure 2.2 Typical system of e-beam evaporation of materials [16]             | 16 |

| Figure 2.3 Typical DC sputtering system [16]                                  | 17 |

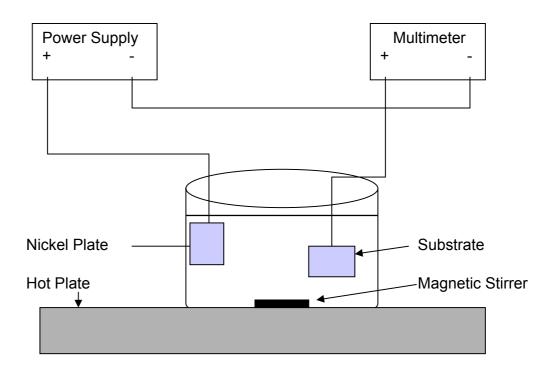

| Figure 2.4 Typical nickel electroplating setup [20]                           | 20 |

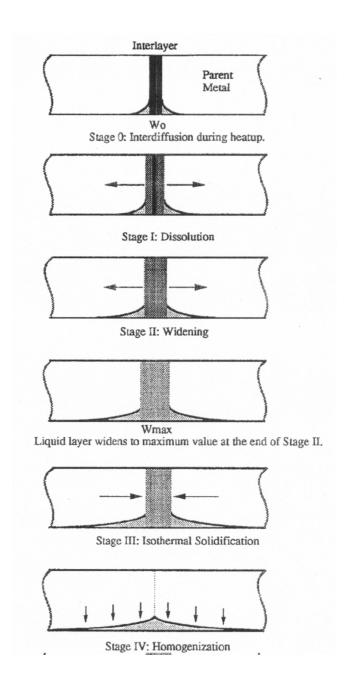

| Figure 2.5 Four stages of TLP bonding process [31]                            | 26 |

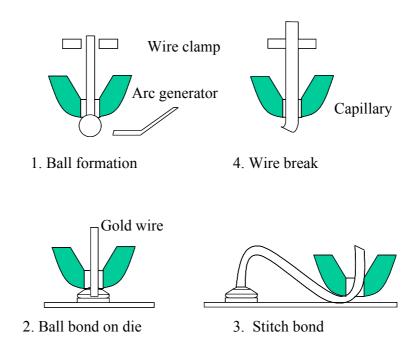

| Figure 2.6 Thermosonic bonding of gold wire [36]                              | 28 |

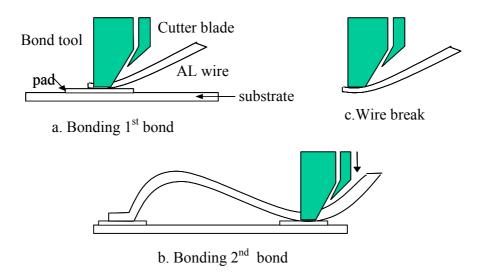

| Figure 2.7 Aluminum ultrasonic wedge bonding [37]                             | 30 |

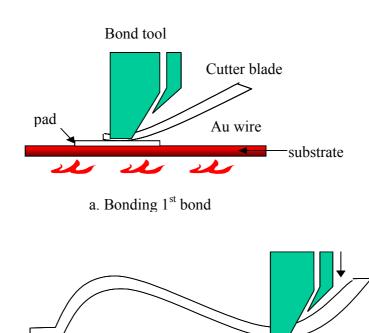

| Figure 2.8 Gold wire thermosonic wedge bonding                                | 31 |

| Figure 2.9 Pull test [37]                                                     | 32 |

| Figure 2.10 Bond heel definition [38]                                         | 33 |

| Figure 2.11 Shear test [37]                                                   | 34 |

| Figure 2.12 Synthesis of polyimide [40]                                       | 35 |

| Figure 3.1Gold-Indium phase diagram [43]                                      | 37 |

| Figure 3.2 Calculation schematic for thickness of added Au                    | 38 |

| Figure 3.3 Thick Au die TLP bonding sketch                                    | 40 |

| Figure 3.4 Thick Au die TLP bonding profile                                   | 43 |

| Figure 3.5 EDX spot analysis of the as-built sample (TLP temperature @ 525°C) | 44 |

| Figure 3.6 SEM image of the as-built sample(TLP temperature @ 550°C)          | 44 |

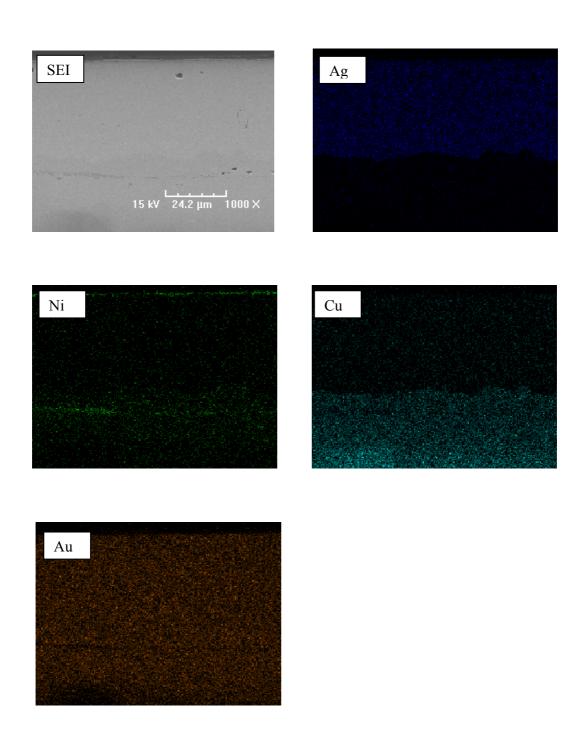

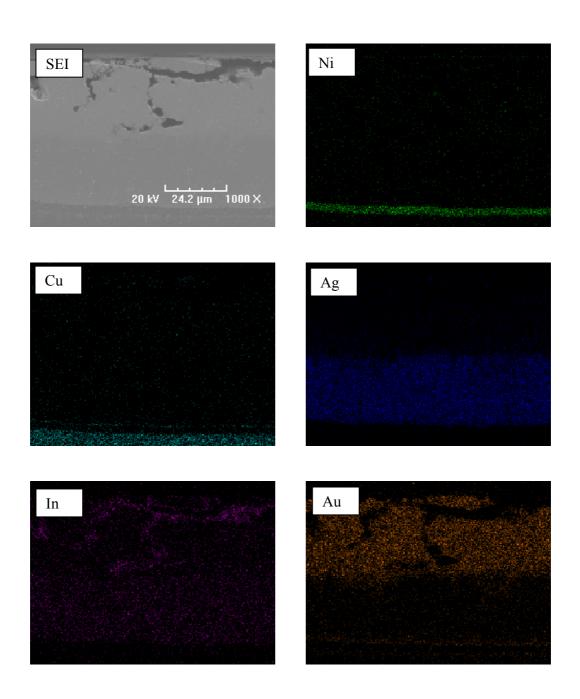

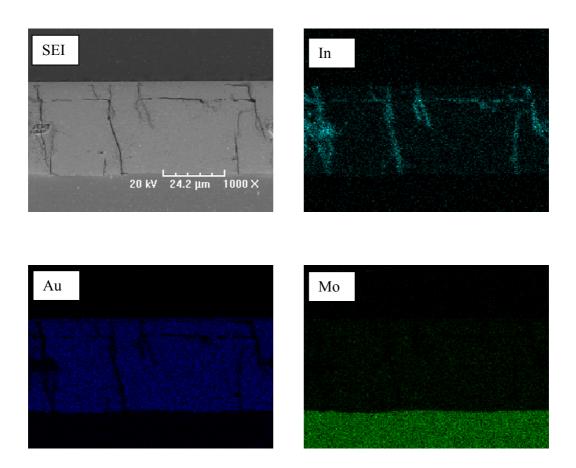

| Figure 3.7 EDX element dot maps of the AuIn sample after 1000 hour aging               | 46 |

|----------------------------------------------------------------------------------------|----|

| Figure 3.8 Silver electroplating setup [49]                                            | 48 |

| Figure 3.9 Thin Au die TLP bonding sketch                                              | 50 |

| Figure 3.10 Thin Au die TLP bonding profile                                            | 51 |

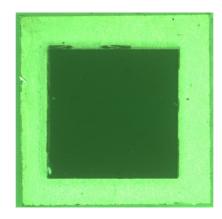

| Figure 3.11 X-ray picture of as-brazed thin gold die sample                            | 51 |

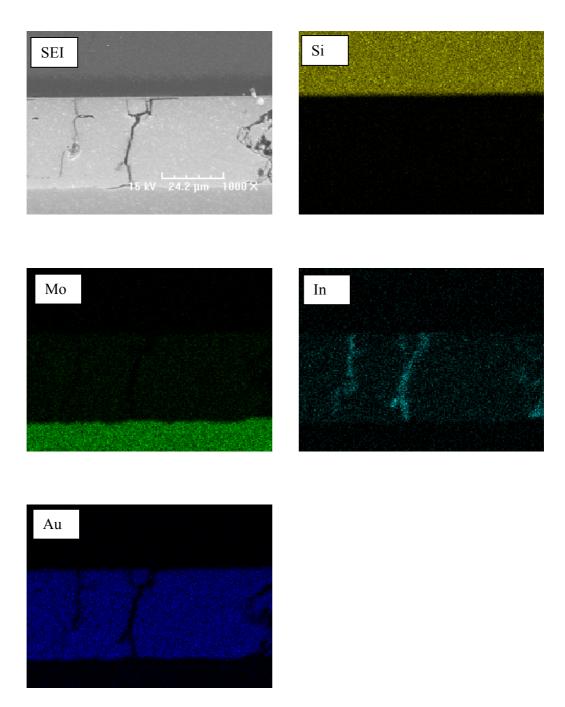

| Figure 3.12 EDX element dot maps for as-built thin Au die sample                       | 53 |

| Figure 3.13 EDX element dot maps for thin Au die sample after 2000 hour aging          | 55 |

| Figure 3.14 Thermal cycle test profile                                                 | 56 |

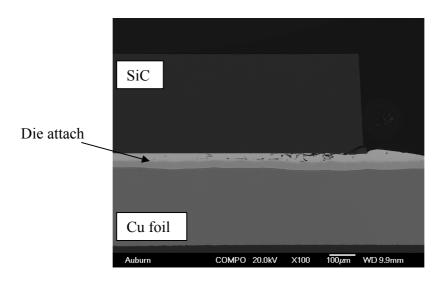

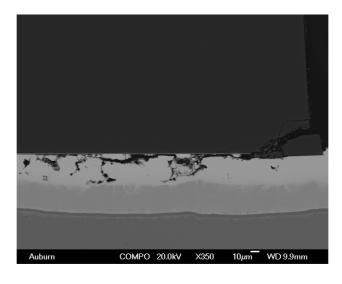

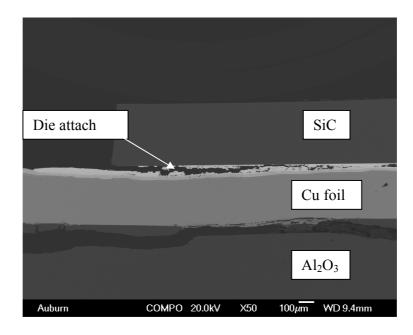

| Figure 3.15 Cross-section picture for thin Au die on thick Ag sample after 120 cycles. | 57 |

| Figure 3.16 EDX element dot maps for thin Au die on thick Ag sample after 120          |    |

| cycles                                                                                 | 58 |

| Figure 3.17 Cross-section picture of thin Au die on thick Ag sample after 300 cycles   | 59 |

| Figure 3.18 Thin Au die bonding on Mo tab sketch                                       | 60 |

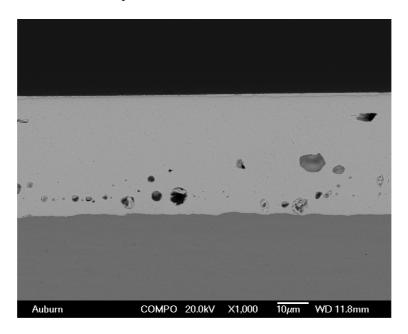

| Figure 3.19 SEM image for as-built sample of thin Au die bonding on Mo tab             | 61 |

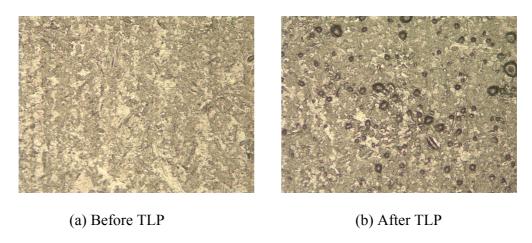

| Figure 3.20 Bare Mo tab before and after TLP process.                                  | 61 |

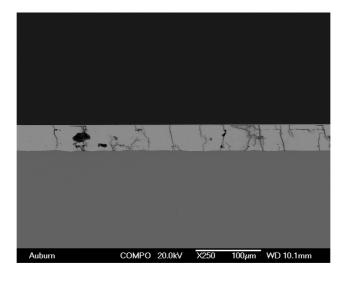

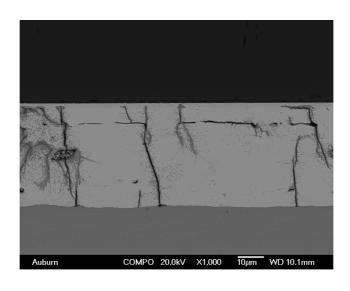

| Figure 3.21 Cross-section of sample after 120 cycles                                   | 63 |

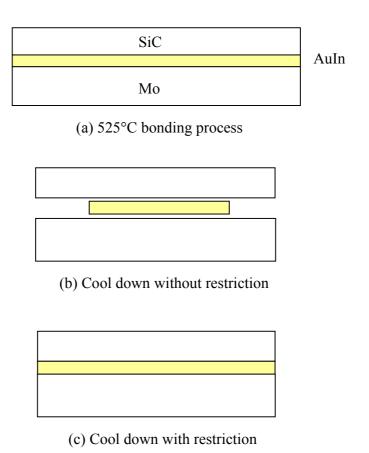

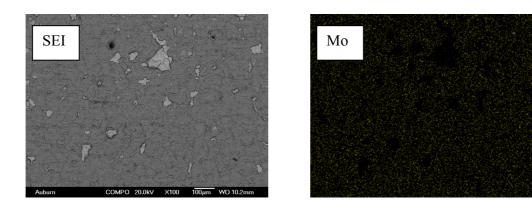

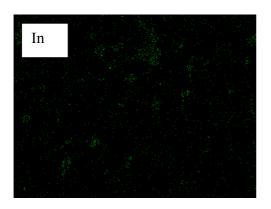

| Figure 3.22 EDX element dot maps for sample after 120 cycles                           | 64 |

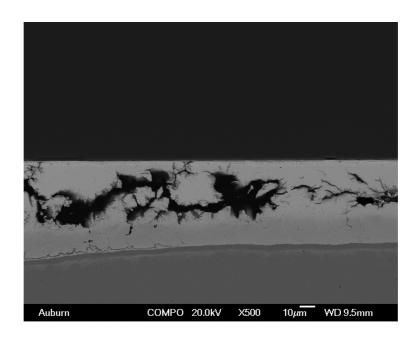

| Figure 3.23 Die attach thermal expansion in the TLP bonding process                    | 65 |

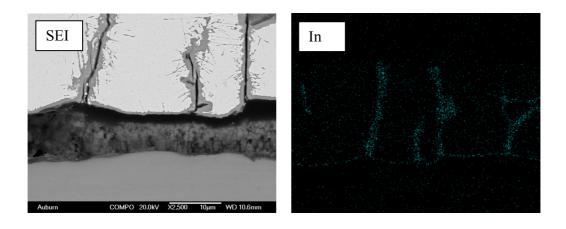

| Figure 3.24 Cross-section picture with EDX In dot map for sample after 1200 cycles     | 66 |

| Figure 3.25 Cross-section of sample after 2880 cycles                                  | 67 |

| Figure 3.26 SEM image of fell off substrate after 2880 cycles                          | 68 |

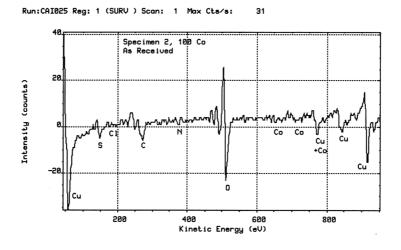

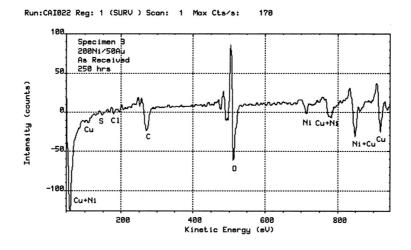

| Figure 3.27 2.5µm Co/ Au after 500 hours at 450°C                                      | 70 |

| Figure 3.28 5μm Ni/1.25μm Au after 250 hours at 450°C                                  | 70 |

| Figure 3.29 5μm Ni/2.5μm Au after 1000 hours at 450°C                                      | 71  |

|--------------------------------------------------------------------------------------------|-----|

| Figure 3.30 Co-Ni/ Au after 500 hours at 450°C                                             | 71  |

| Figure 3.31 Multilayer Ni-P after 2000 hour at 450°C                                       | 72  |

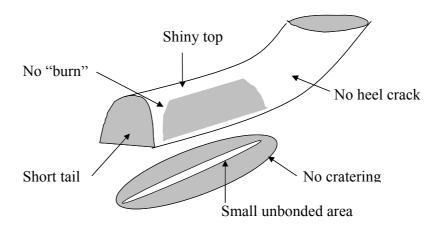

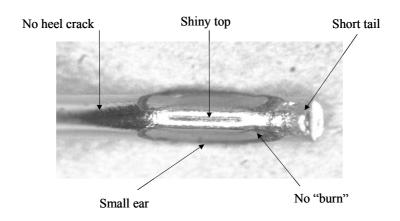

| Figure 4.1 Before and after bonding [37]                                                   | 76  |

| Figure 4.2 Perfect bond [37]                                                               | 79  |

| Figure 4.3 Real bond                                                                       | 80  |

| Figure 4.4 Main effects plot for means based on shear strength                             | 82  |

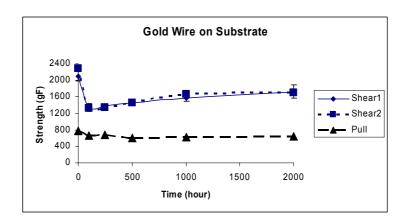

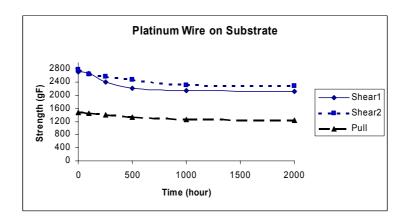

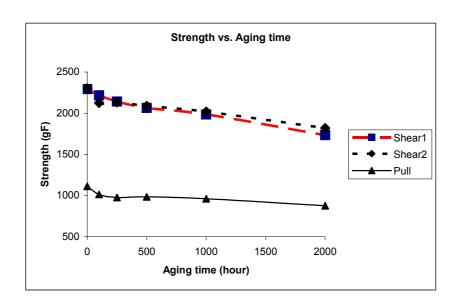

| Figure 4.5 Average pull/shear strength of gold wire on substrate metallization             | 84  |

| Figure 4.6 Average pull/shear strength of platinum wire on substrate metallization         | 84  |

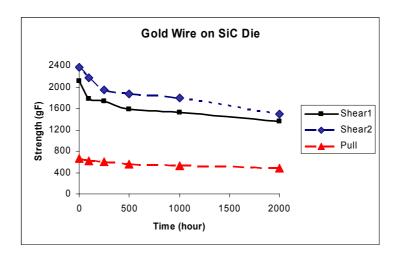

| Figure 4.7 Average pull/shear strength of Au wire on Ti/TiW/Au metallization               | 87  |

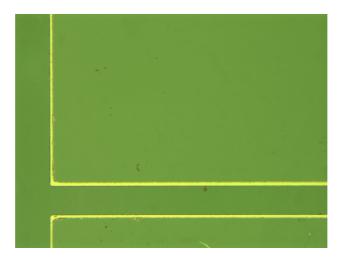

| Figure 4.8 SiO <sub>2</sub> under Ti/Pt/Au without and with wire bond after 200 hour aging | 90  |

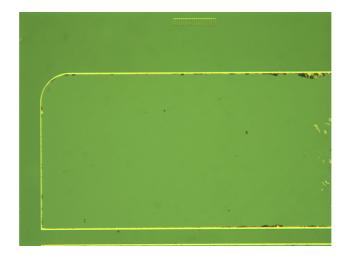

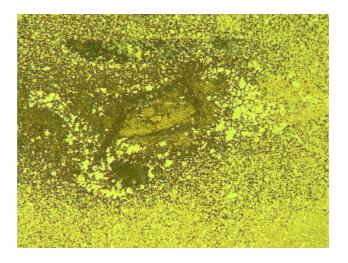

| Figure 4.9 Picture of SiC damage under Ti/Pt/Au metallization with Pt wire bond            | 91  |

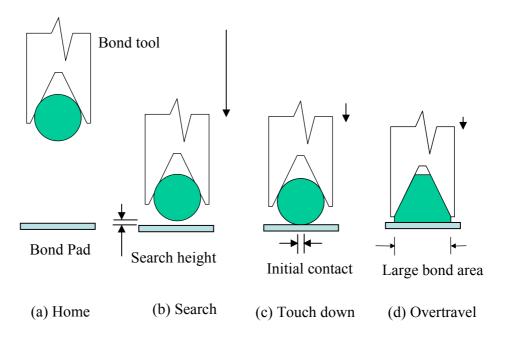

| Figure 4.10 Bond head movement [37]                                                        | 94  |

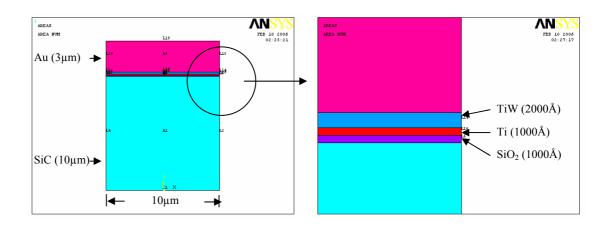

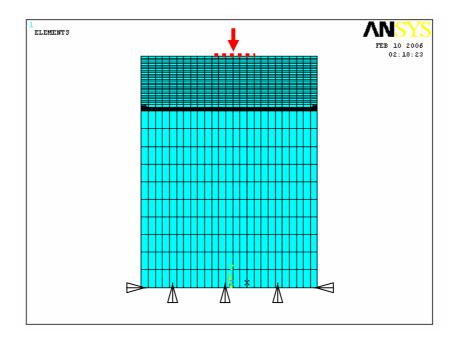

| Figure 4.11 Bond pad metallization 2D model                                                | 98  |

| Figure 4.12 Pad metallization mesh and load                                                | 98  |

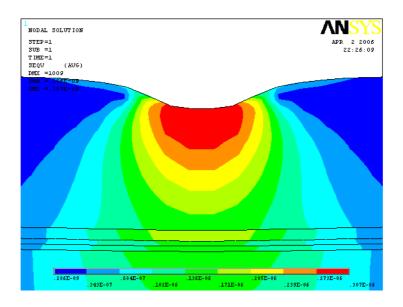

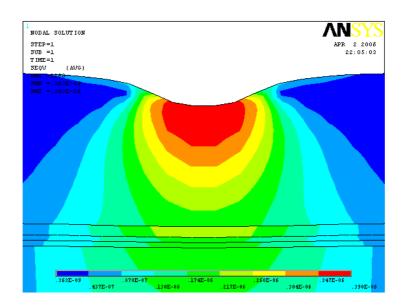

| Figure 4.13 Von Mises stress in Ti/TiW/Au metallization for Au wire bonding                | 99  |

| Figure 4.14 Von Mises strain in Ti/TiW/Au metallization for Au wire bonding                | 99  |

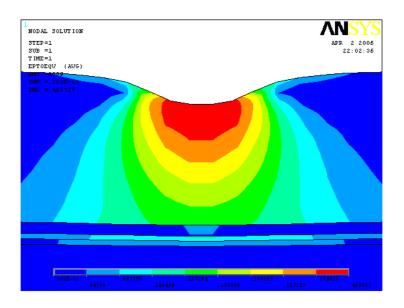

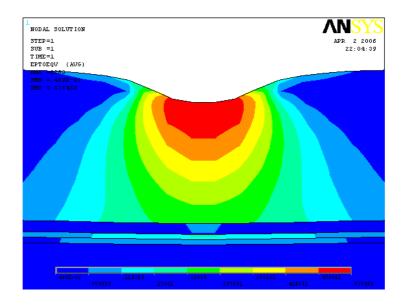

| Figure 4.15 Von Mises stress in Ti/Pt/Au metallization for Au wire bonding                 | 100 |

| Figure 4.16 Von Mises strain in Ti/Pt/Au metallization for Au wire bonding                 | 100 |

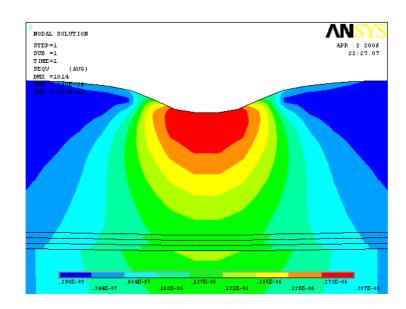

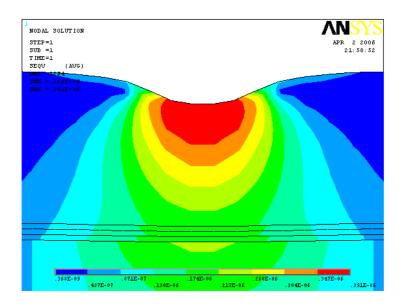

| Figure 4.17 Von Mises stress in Ti/TiW/Au metallization for Pt wire bonding                | 101 |

| Figure 4.18 Von Mises strain in Ti/TiW/Au metallization for Pt wire bonding                | 101 |

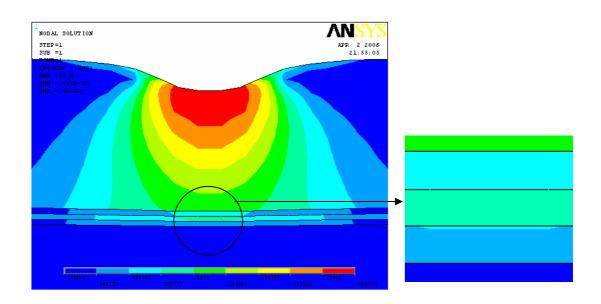

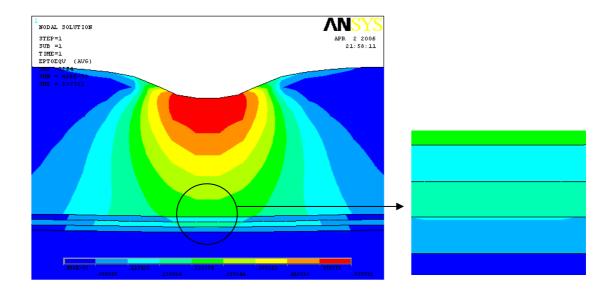

| Figure 4.19 Von Mises stress in Ti/Pt/Au metallization for Pt wire bonding                 | 102 |

| Figure 4.20 Von Mises strain in Ti/Pt/Au metallization for Pt wire bonding                 | 102 |

| Figure 4.21 Average shear/pull strength of gold wire bonds on Ta-Si-N 92%)/Pt-N/ |     |

|----------------------------------------------------------------------------------|-----|

| Au                                                                               | 106 |

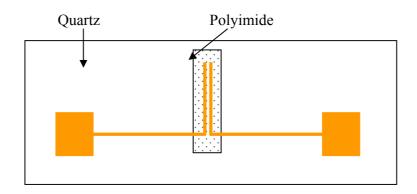

| Figure 5.1 Polyimide breakdown testing sample pattern                            | 110 |

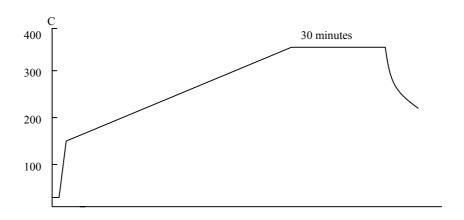

| Figure 5.2 Polyimide PI2611 curing profile                                       | 110 |

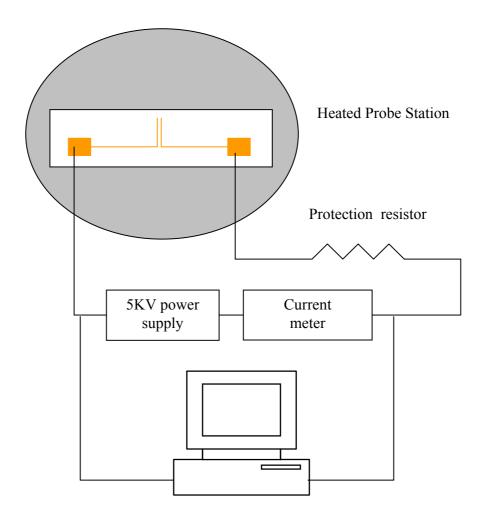

| Figure 5.3 Polyimide breakdown measurement circuit schematic                     | 111 |

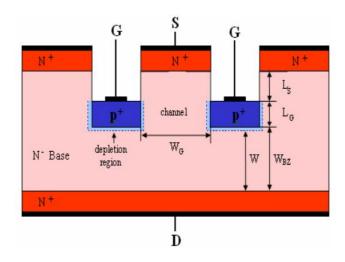

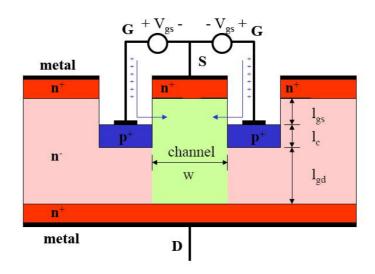

| Figure 6.1 Cross-sectional view of a SiC VJEFT [60]                              | 116 |

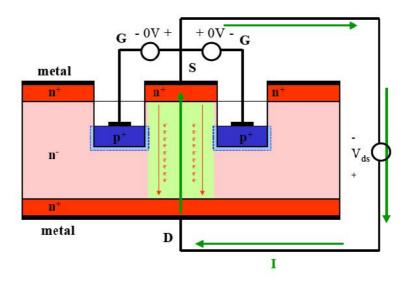

| Figure 6.2 VJFET in unipolar mode [60]                                           | 117 |

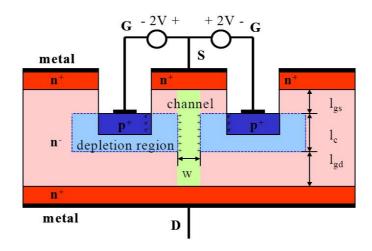

| Figure 6.3 Variation of width of depletion region [60]                           | 117 |

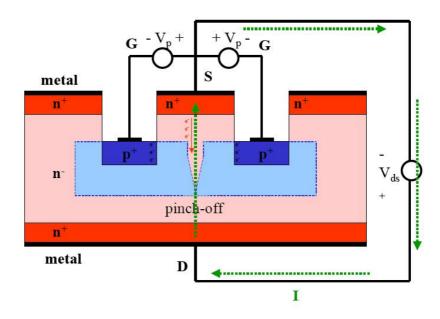

| Figure 6.4 Pinch-off condition in the JFET [60]                                  | 118 |

| Figure 6.5 JFET operating in the bipolar mode [60]                               | 119 |

| Figure 6.6 Ag-Cu brazing profile.                                                | 121 |

| Figure 6.7 Substrate structure for VJFET package                                 | 122 |

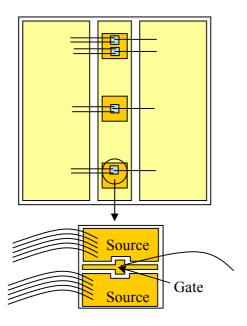

| Figure 6.8 Paralleled VJFET package structure                                    | 123 |

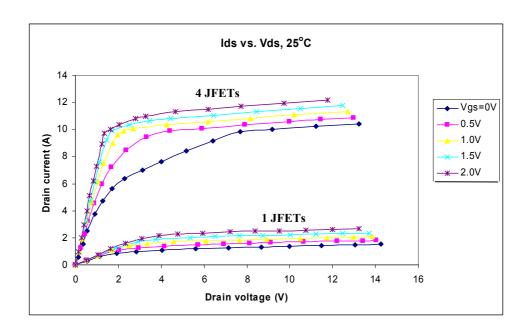

| Figure 6.9 Forward characteristics of the paralleled VJFETs and single VJFET     | 124 |

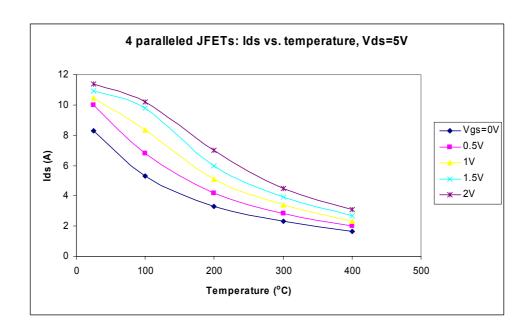

| Figure 6.10 Drain current as a function of temperature for paralleled VJFETs     | 125 |

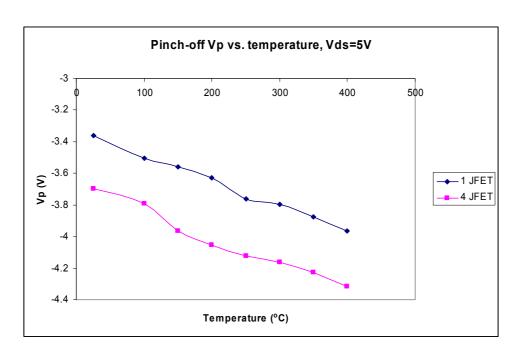

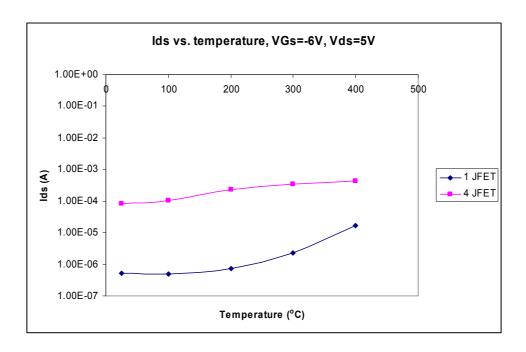

| Figure 6.11 $V_p$ vs. temperature for the paralleled VJFETs and single JFET      | 126 |

| Figure 6.12 $I_{ds}$ vs. temperature for the paralleled VJFETs and single VJFET  | 126 |

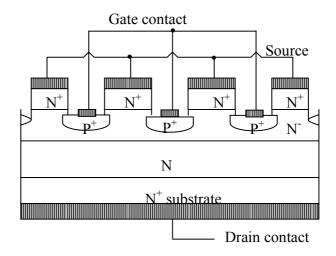

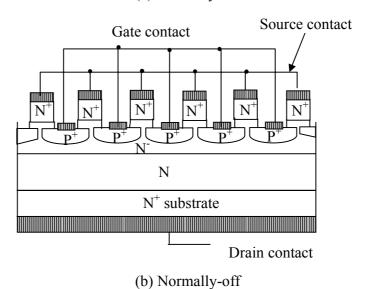

| Figure 6.13 "Normally-on" and "normally-off" VJFET                               | 128 |

| Figure 6.14 Paralleled SIT diodes package structure.                             | 129 |

| Figure 6.15 Forward characteristics for the single SIT diode                     | 130 |

| Figure 6.16 Forward characteristics for the paralleled SIT diode                 | 131 |

| Figure 6.17 Reverse characteristics for the paralleled SIT diodes                | 132 |

| Figure 6.18 Breakdown voltage for the paralleled SIT diodes                      | 132 |

## LIST OF TABLES

| Table 2.1 Key properties of semiconductor materials [13]                            | 11  |

|-------------------------------------------------------------------------------------|-----|

| Table 2.2 High temperature substrate properties [17]                                | 18  |

| Table 2.3 Conductive adhesive properties [26]                                       | 23  |

| Table 2.4 Some common solder materials for die attach [28]                          | 24  |

| Table 3.1 Thick Au Die shear strength as a function of aging time (unit: kg-f)      | 45  |

| Table 3.2 Die shear strength (unit: kg-f) as a function of thermal cycling numbers3 | 62  |

| Table 3.3 Substrate metallization structure                                         | 69  |

| Table 4.1 Control factors and levels for DOE of wire bonding parameters             | 81  |

| Table 4.2 Taguchi 3k factorial design for wire bonding DOE                          | 81  |

| Table 4.3 ANOVA for wire bond shear strength                                        | 82  |

| Table 4.4 Optimal wire bonding parameters for thick gold substrate                  | 83  |

| Table 4.5 Optimal wire bonding parameters for die metallizations                    | 86  |

| Table 4.6 Materials properties at 225/250°C [52][53][54][55]                        | 96  |

| Table 4.7 Comparison between FEMA simulation and testing results                    | 103 |

| Table 5.1 Polyimide breakdown test results                                          | 113 |

#### **CHAPTER 1 INTRODUCTION**

There is a growing demand for cost effective high power, high temperature semiconductor devices to support the latest advancements in aerospace, automotive, and high power electronics systems. The goal of power electronics is to transfer power from an electrical source to an electrical load in a highly efficient, highly reliable and cost-effective way. Power electronics packages provide mechanical support, device protection, cooling and electrical connection and isolation. Controlling and reducing power loss from packaging materials in the package is becoming increasingly important [1].

High power devices usually operate at high current densities, high internal electric fields and, consequently, high temperatures. High operating temperatures can result from either the ambient environment, dissipated power or a combination of both. For applications at temperatures above 300°C, it is very challenging to use conventional semiconductor electronics because they are generally limited to operating temperatures below 250°C due to the limitations imposed by their material properties and traditional packaging technology [2].

The use of silicon carbide device technology opens the door for electronic circuits operating at 350°C and higher. SiC has long been viewed as a potentially useful semiconductor for high temperature applications. SiC-based electronics and sensors have been demonstrated to operate at temperatures up to 600°C, thereby offering the promise

of direct insertion into high temperature environments without the need for cooling. However, the lack of reliable device packaging methodologies for this operating environment has so far largely prevented the application of these devices[3][4][5][6].

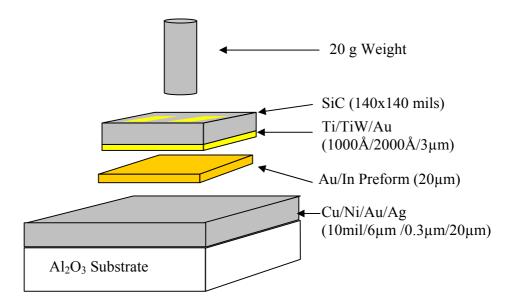

Figure 1.1 shows the structure of a potential SiC power transistor package. The thick metallization on the ceramic substrate is typically a thick layer of copper, covered by a thick coating of nickel that serves as a barrier layer, capped by an electroplated gold layer, which functions as the die attaching or wire bonding metallization. The power SiC transistor is attached to the gold metallization, typically using a soldering or brazing process. Then, wires are thermosonically wedge bonded from the pads on the power die to the lead frame or substrate metallization. Finally, a passivation layer is applied and cured to provide high voltage insulation.

Figure 1.1 SiC power transistor device structure

The SiC power transistor is expected to be capable of functioning in harsh environments and needs an appropriate package in order to sustain operation throughout the entire planned life cycle. In the absence of robust and reliable packaging, this device

is useless if it cannot perform its designed functions and survive the harsh environments. In order to realize the potential of the SiC transistor for high temperature applications, appropriate high temperature packaging technologies must therefore be developed [7].

The key processes and materials that need to be developed for the SiC transistor device package include:

Die attach. For power SiC transistor devices used in high temperature applications, the die attach must produce a joint between the die and substrate, which must have a higher melting point than the operating temperature, and have good electrical and thermal conductivity. The material selection of SiC die backside metallization, substrate metallization, and die attach material is very important to the bonding process success.

Typically, SiC die backside metallization requires three metallization layers for high temperature applications: the ohmic or Schottky contact, the diffusion/oxidation barrier layer and the cap layer. For die attach process success, the die backside metallization must have good adhesion; the cap layer, in general, Au, must have good wettability with the die attach material in order to obtain a void-free bond joint; and the barrier layer must have high resistance to oxidation and inter-diffusion in order to keep the contact resistance consistent for device performance.

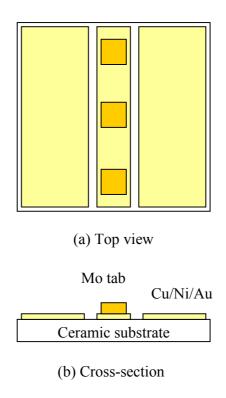

The ceramic substrate metallization provides a base for the die attachment of the power device. The conventional substrate metallization, Cu/Ni/Au on alumina ceramic, was used in this research. Cu provides high electrical current and thermal conducting paths from the power device to the outside circuit, Ni

functions as a barrier layer to prevent Cu diffusion, and Au provides good wettability with the die attach material in order to obtain a void-free bond joint.

Au based alloys are the ideal die attach materials due to their good adhesion to the die and substrate metallization, high electrical and thermal conductivity, and good corrosion resistance. In this dissertation, a transient liquid phase bonding method using gold-indium (81/19 wt%) preforms was developed for the die attach process. Either excess Au plated on the die backside metallization SiC/Ni<sub>2</sub>Si/Ti/TiW/Au or Ag plated on the substrate metallization was used to change the Au-In preform composition, thus leading to an increased solidus temperature. Die attach reliability testing and failure analysis were also performed.

Wire bonding. Large diameter wire bonding is the most widely used method to make electrical connections from the power device to its package because large diameter wire provides high current carrying capability. Large diameter aluminum wire bonding is used with Si power devices, but at high temperatures the mechanical strength of the Al decreases significantly. Also, Al is incompatible with the Au wire bond pads due to intermetallic formation and Kirkendall voiding at high temperatures [5]. Large diameter gold and platinum wire appear to offer good alternatives to Al wire for high temperature applications because they have no incompatible issues with the Au wire bond pads and provide high current capability, and both Au and Pt are highly corrosion resistant to air and harsh environments. The main disadvantages of large diameter wire bonding, especially for Pt wire, are the high bonding force or high ultrasonic energy required for the

bonding process, which have significant impact on the layers underneath the die bonding pads. In the worst case, the SiC may be damaged. For the substrate bonding pads, the high bonding force or ultrasonic energy has less impact because of the thickness of the substrate metallization compared to the thin die metallization. A thermosonic wedge bonding method was developed to bond the large diameter (250µm) Au and Pt wires used in this dissertation. The wire bondability and reliability of conventional substrate metallization Cu/Ni/Au and three die metallizations (SiC/Ni<sub>2</sub>Si/SiO<sub>2</sub>/Ti/Pt/Au, SiC/Ni<sub>2</sub>Si/SiO<sub>2</sub>/Ti/TiW/Au and SiC/Ni<sub>2</sub>Si/TaSi-(2%)/Pt-N/Au) were evaluated in this study.

High temperature passivation. Devices operating at high power conditions may also be exposed to high voltages, and as a result high voltage breakdown may occur between adjacent electrical connections and/or between high voltage electrical connections and the surrounding air. This issue is particularly important as the breakdown voltage of air decreases with increasing temperature. With the die contact pads exposed to air, leakage current through the air or at the die surface will increase with increasing temperature. An effective dielectric passivation coating must therefore be applied to ensure reliable package operation.

Polyimides have both higher insulation resistances and higher breakdown voltages than air at high temperatures, so they can be used as a passivation layer to decrease the leakage current and increase the breakdown voltage between adjacent ohmnic contact pads. This research evaluated the reliability of one

polyimide material (PI2611) as a passivation layer for high temperature applications.

The primary goal of the project was to develop assembly materials and processes for SiC power electronic components that can be used in extreme environments. In Chapter 2, the properties, processing and device technology related to SiC are briefly reviewed and some key issues in packaging of power electronics are discussed, including SiC properties, SiC die thin film metallization, substrate and substrate metallization, die attach materials and processes, wire bonding, and high voltage passivation coatings.

Chapter 3 describes an investigation of the Au-In die attach using a transient liquid phase bonding process, including die metallization, substrate metallization, the die attach bonding process, reliability based on shear strength tests and the cross-section microstructure of the die joint. Failure analysis after reliability testing was performed. In addition, a variety of barrier materials for copper diffusion in the substrate metallization stack was evaluated for high temperature applications.

Chapter 4 reports the results of an investigation of large diameter gold and platinum wire bonding on substrate metallization and die metallizations, including the wire bonding process itself, bondability and reliability based on pull and shear strength tests. A simplified FEMA 2D model was used to understand the failure mode observed.

In Chapter 5, the results of electrical breakdown tests of PI2611 polyimide are presented. This chapter includes a study of the polyimide application and curing process, breakdown tests and reliability tests.

In chapter 6, electrical characteristics of VJFET and SIT diode modules were measured over the temperature range from 25°C to 400°C to demonstrate the feasibility of paralleling SiC power VJFETs to develop Si IGBT replacements for use in electric vehicles.

Chapter 7 summarizes the results and findings of this dissertation. Topics for future work are also discussed.

### **CHAPTER 2 BACKGROUND**

This chapter provides background information related to the topics that will be discussed in this dissertation. SiC properties, thin film die metallization, thick substrate metallization, wire bonding, die attach, and the properties and applications of polyimide passivation coatings are discussed.

Power devices capable of functioning in harsh environments need an appropriate package in order to sustain operation throughout their entire planned life cycle. In order to realize the potential of high temperature electronics, appropriate high temperature packaging technologies must therefore be developed [8]. The basic elements of the SiC transistor device package include: 1) the substrate; 2) the SiC die attach materials; 3) wire bonding; and 4) insulation materials.

For high power devices that will be used in high temperature and harsh environment applications, the most critical issues to be considered are[7][8][9]: 1) current carrying capability, which requires thick substrate metallization and large diameter wire bonds; 2) high voltages, which requires a suitable insulation material with high stability at high temperatures; 3) the mitigation of thermal stresses caused by the thermal expansion mismatches (CTE) between the devices and the various packaging elements, including substrates; 4) resistance to the fatigue brought about by thermal cycling during service; 5) the provision for appropriate heat removal to maintain the temperatures at safe

operating levels; and 6) resistance to high temperature effects such as those induced by diffusion, intermetallic formation, creep and decomposition. Material properties can significantly impact how well the package can meet these stringent requirements. Therefore, the package design is, to a great extent, influenced by the available materials.

The following material properties must be considered during the process of selecting proper materials for high temperature, high power devices for use in harsh environment applications [7][8][9][10][10]:

- Electrical conductivity: For power electronics, thick copper metallization is

required to provide the high current carrying capability. Thick copper

metallization on ceramic substrates can be achieved by direct bond copper (DBC),

copper electroplating onto an adhesion layer or by reactive brazing a copper foil

to the ceramic.

- Thermomechanical compatibility: Thermal expansion differences between the die and the substrate, as well as between the different packaging components, can produce stress during assembly as well as during operation that can result in the failure of the package or the device. The coefficient of thermal expansion (CTE) mismatch between the die, substrate, and other packaging components should be as small as possible at all temperatures to minimize thermal stresses.

- Fatigue resistance: the SiC package should have good fatigue resistance in order to withstand cyclic stresses due to exposures to high and low temperature extremes.

- Thermal conductivity: If the die temperature exceeds the safe operating temperature, the device will fail prematurely. Therefore, the system's thermal

resistance must be minimized. The substrate metallization and die attach joint thermal conductivity must also be maximized. The fact that the thermal conductivity of packaging materials decreases with increasing temperature must be considered.

• Chemical stability: Wire bonding materials should have good corrosion resistance in harsh environments, and be compatible with Au wire bond pads. Die and substrate metallizations should limit inter-diffusion and oxidation for long term stability at assembly and service temperatures. The insulating materials should have high temperature stability without suffering problems due to decomposition.

### 2.1 SIC PROPERTIES

Historically, germanium was one of the first semiconductors to be used. However, it was rapidly supplanted by silicon, which today is the most important semiconductor material. Silicon has a wider bandgap energy than germanium, allowing it to be used in higher temperature applications. Thermal oxidation of silicon forms a stable insulating oxide, giving silicon significant processing advantages over germanium during the fabrication of ICs. In addition to silicon, GaAs is commonly encountered today in optoelectronic applications, including light-emitting diodes (LEDs), lasers, and photo detectors. However, the superior physical and electronic properties of SiC make it the foremost semiconductor material for short wavelength optoelectronic, high temperature, radiation resistant, and high-power/high-frequency electronic devices [2][12]. The key properties of SiC compared to other semiconductor materials are shown in Table 2.1 [13].

Table 2.1 Key properties of semiconductor materials [13]

|                                                       | Si       | GaAs     | 4H-SiC   | 6H-SiC   |

|-------------------------------------------------------|----------|----------|----------|----------|

| Band Gap (eV)                                         | 1.12     | 1.43     | 3.26     | 3.03     |

| Breakdown Electric Field (V/cm for 1000V Operation)   | 2.50E+05 | 3.00E+05 | 1.00E+06 | 1.00E+06 |

| Thermal Conductivity (W/cm-<br>K@ R.T)                | 1.5      | 0.5      | 3.38     | 3.38     |

| Saturation Electron Drift Velocity (cm/s@E>2x105V/cm) | 1.00E+07 | 1.00E+07 | 2.00E+07 | 2.00E+07 |

SiC has many polytypes, but 6H and 4H (H=hexagonal) are the two most commonly used. SiC offers unique electrical and thermophysical properties compared to Si and GaAs, which include [13]:

- Wide energy bandgap. With bandgaps of only 1.12eV for Si and 1.43eV for GaAs, both become intrinsic and lose their pn junction characteristics at 200~350°C, depending on their doping concentrations. Leakage currents also become a challenge, requiring silicon-on-insulator technology as temperatures approach 200°C. With a bandgap over 3eV, electronic devices formed in SiC can operate at extremely high temperatures without suffering from intrinsic conduction effects. Also, this property allows SiC to emit and detect short wavelength light, which makes the fabrication of blue light emitting diodes and nearly solar blind UV photodetectors possible.

- High breakdown electrical field. SiC can withstand a voltage gradient (or electric field) over eight times greater than either Si or GaAs without undergoing avalanche breakdown. This high breakdown electric field enables the fabrication of very high-voltage, high-power devices such as diodes,

power transistors, power thyristors and surge suppressors, as well as high power microwave devices. Additionally, it allows the devices to be placed very close together, providing high device packing density for integrated circuits.

- High thermal conductivity. SiC is an excellent thermal conductor. Heat will flow more readily through SiC than other semiconductor materials, and at room temperature, SiC even has a higher thermal conductivity than many metals. This property enables SiC devices to operate at extremely high power levels and still dissipate the large amounts of excess heat generated.

- High saturated electron velocity. SiC devices can operate at high frequencies

(RF and microwave) because of its high saturation electron drift velocity.

Collectively, these properties allow SiC devices to offer tremendous benefits over other available semiconductor devices for a large number of industrial and military applications, such as geothermal well logging and instrumentation, distributed controls for aircraft, and power electronics for more electric aircraft, ships and combat vehicles.

#### 2.2 THIN FILM SIC DIE METALLIZATION

Composite (multi-layer) contacts that are compatible with the techniques and procedures used for packaging (wire bonding and die attach) are used for high temperature, high power devices [1]. A typical composite contact is shown in Figure 2.1

[14]. The simplest composite contact requires three metallization layers: 1) the ohmic or Schottky contact; 2) the diffusion/oxidation barrier layer and 3) the cap layer [1][14].

Figure 2.1Typical composite contact on SiC bipolar transistor [14]

An ohmic contact must have symmetric current-voltage (I-V) characteristics, with the lowest possible specific contact resistance. A Schottky contact is a metal-semiconductor contact with asymmetric I-V characteristics. It should be able to turn on at low forward voltages, and the reverse leakage current should be as low as possible. The diffusion/oxidation barrier layer must have metal-like conduction while preventing, or at least slowing, the intermixing of stack layers as well as preventing oxidation of the contact, which can lead to increased contact resistance. Because of the non-ideality of the barrier layer, it may be necessary to introduce other layers (e.g., a suitable adhesion layer) in the metallization stack. Finally, the cap layer must be suitable for packaging through wire bonding or die attach [14].

When a metallized SiC die in a package is exposed to a harsh environment (generally a high ambient temperature) during the packaging process and during its service life at high temperature, several things can happen [7][8][9][10]:

- The reactivity of the metal with its substrate may increase. This reactivity could

be limited to inter-diffusion or it could lead to a chemical reaction, resulting in

new compound formation.

- The electrical resistance of the metal stack may increase due to: 1) oxygen diffusion in the composite metallization and consequent oxidation of the contacts;

2) the intermixing/diffusion between different layers; or 3) grain growth even if there is no significant inter-diffusion or reaction with the surroundings. This reduction in conductivity can cause additional heat generation, and can also contribute to increased time delays and a loss of performance in high-speed applications.

- Electromigration induced by flowing current may be enhanced due to increased self-diffusion. Electromigration can lead to failures by forming open or short circuits.

- The difference between the coefficient of thermal expansion (CTE) of the metallization and that of the die may increase with increasing temperature. CTE mismatches cause thermal stresses that often lead to delamination.

The reactivity of the metal, electromigration, grain growth, and hillock growth are influenced by the self-diffusion in the metal and between the metal and its surroundings. Diffusion in metals is related to the melting point and the crystallinity of the metal; the

higher the melting point, the lower the diffusivity. As a rule of thumb [7], the melting temperature of the metal should be at least 1.5 times higher than the operating temperature in order to prevent diffusion-related problems such as creep and electromigration. Also, an effective diffusion barrier layer in the stack can prevent or hinder oxidation and inter-diffusion problems.

Therefore, an effective die metallization for high temperature applications should possess the following features:

- High oxidation and inter-diffusion resistance;

- Good adhesion to the wafer passivation layer and contact (ohmic or Schottky);

- Low contact resistance;

- Low thermal stress;

- High compatibility with the packaging process (wire bonding and die attachment); and

- High temperature stability.

Evaporation and sputtering are the two most used technologies for thin film metallization deposition. In the evaporation process, the substrate is placed inside a vacuum chamber, in which a block (source) of the material to be deposited is also located. The source material is then heated to the point where it starts to boil and evaporate. Vacuum is required to allow the molecules to evaporate freely in the chamber, and they subsequently condense on all surfaces [15]. This principle is the same for all evaporation technologies, only the method used to heat (evaporate) the source material differs. There are two popular evaporation technologies, e-beam evaporation and resistive

evaporation. In e-beam evaporation, an electron beam is aimed at the source material causing local heating and evaporation. In resistive evaporation, a tungsten boat, containing the source material, is heated electrically with a high current to make the material evaporate. Many materials are restrictive in terms of what evaporation method can be used (i.e. aluminum is quite difficult to evaporate using resistive heating), which typically relates to the phase transition properties of that material [15]. A schematic diagram of a typical system for e-beam evaporation [16] is shown in the Figure 2.2.

Figure 2.2 Typical system of e-beam evaporation of materials [16]

Sputtering is a technology in which the material is released from the source at much lower temperature than evaporation. The substrate is placed in a vacuum chamber with the source material, called a target, and an inert gas (such as argon) is introduced at low pressure. A gas plasma is struck using a DC or RF power source, causing the gas to become ionized. The ions are accelerated towards the surface of the target, causing atoms of the source material to break off from the target in vapor form and condense on all surfaces including the substrate. The basic principle of sputtering is the same for all sputtering technologies. The differences typically relate to the manner in which the ion bombardment of the target is realized. A schematic diagram of a typical DC sputtering system is shown in the Figure 2.3 [16].

Figure 2.3 Typical DC sputtering system [16]

#### 2.3 SUBSTRATE AND SUBSTRATE METALLIZATION

Ceramic substrates have been successfully used for SiC packaging and typical properties are presented in Table 2.2 [17]. Alumina (Al<sub>2</sub>O<sub>3</sub>) has been used to package high temperature SiC based amplifiers [5]. These circuits used screen-printed thick film metallization. However, this technology will not provide the current carrying capability required for power applications. Ceramic substrates with thick copper metallization are used for power devices because the thick copper provides both high current capability and high thermal conductivity. Thick copper can be achieved by direct bond copper (DBC), copper electroplating onto an adhesion layer or by reactive brazing a copper foil directly to the ceramic [5]. However, how to overcome the CTE mismatch between the copper (16 ppm/°C) and the ceramic is a significant challenge.

Table 2.2 High temperature substrate properties [17]

|                                           | 96% Al <sub>2</sub> O <sub>3</sub> | AlN     | Si <sub>3</sub> N <sub>4</sub> |

|-------------------------------------------|------------------------------------|---------|--------------------------------|

| Flexural Strength (MPa)                   | 400                                | 345     | 700                            |

| Fracture Toughness (MPa•m1/2)             | 3.85-3.95                          | 2.79    | 6.50                           |

| Thermal Conductivity (W/m-K@ R.T)         | 26                                 | 140-220 | 60                             |

| Coefficient of thermal expansion (ppm/°C) | 7.4                                | 4.40    | 2.70                           |

Aluminum nitride (AlN) appears to be an ideal candidate for packaging SiC devices for high temperature applications due to its high thermal conductivity (140-220  $W \bullet m^{-1} \bullet k^{-1}$ ), a CTE (4.4 ppm/°C) that closely matches that of 4H-SiC (4.2~4.68 ppm/°C)

[18], environmental stability and chemical inertness at high temperature. However, when used in conjunction with thick copper, aluminum nitride is prone to fracture during thermal cycling due to its low flexural strength and poor fracture toughness.

Silicon nitride has an intermediate thermal conductivity, but the highest mechanical strength and fracture toughness. The poorer thermal performance of the silicon nitride substrate can be improved through the use of thick copper metallization. The CTE of  $Si_3N_4$  is lower than that of SiC and AlN.

Although alumina has the lowest thermal conductivity, and intermediate fracture toughness, Al<sub>2</sub>O<sub>3</sub> based ceramics are popular as substrates because of their availability, low cost, and good electrical properties. The poorer thermal performance can be improved through the use of thick copper metallization.

Copper metallized ceramic substrates ( $Si_3N_4$ , AlN and  $Al_2O_3$ ) can be supplied with a standard Ni/Au surface finish. Typically 5-6 $\mu$ m Ni is electrolessly plated or electrolytically plated over the copper foil, and then a thin layer of gold ( $0.1\sim0.5\mu$ m) is plated on top of the Ni to prevent Ni oxidation.

Nickel provides good corrosion protection by creating a physical barrier between the corrosive environment and the underlying copper [19]. For traditional temperature ranges, Ni/Au functions as a good barrier for preventing copper oxidation and diffusion. However, the solubility of Ni into Au and Au into Ni increases with increasing temperature. Furthermore, copper and nickel are soluble in each other, and the copper will continue to diffuse to the surface and oxidize in air.

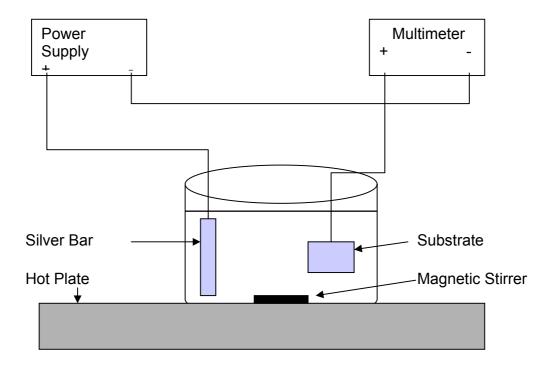

A schematic diagram of a typical nickel electroplating setup is shown in the Figure 2.4 [19]. The substrate is placed into a solution of nickel salts and connected to an

electrical circuit, forming the cathode of the circuit, while the nickel plate forms the anode. When an electrical current is passed through the circuit, nickel ions in the solution are attracted to the cathode. The cathode releases electrons to neutralize the nickel ions, resulting in a layer of nickel deposited on the cathode [20].

Figure 2.4 Typical nickel electroplating setup [20]

There are three main types of electroplated nickel coatings: bright nickel electroplating (Watts nickel), sulfamate nickel electroplating, and chloride nickel [20]. Watts nickel is deposited from a nickel sulfate bath. Watts nickel normally yields a brighter finish than other methods since the Watts bath contains a grain refiner to improve the quality of the deposit. The brightener in the Watts bath levels the deposit, yielding a smoother surface than that of the underlying part. However, these brighteners

may also lead to problems with soldering and brazing, and this should be considered when selecting a finish for various applications. Sulfamate nickel is deposited from a nickel sulfamate bath, and is the most widely used electrolytic nickel. It is often used as a final plating layer and also as an underlayer for precious metals. Sulfamate nickel is a pure deposit that allows soldering and brazing during later assembly steps. Sulfamate nickel deposits can be much more formable than bright nickel deposits because sulfamate nickel has little to no tensile stress in the deposit and very good ductility. The chloride nickel can be plated thick with low pitting, however, it is sometimes less pure and the mechanical properties of the deposit are not as good as those from the Watts bath [20].

Electroless nickel plating is an autocatalytic process and does not use externally applied electric current to produce the deposit. The electroless process deposits a uniform coating of metal, regardless of the shape of the part or its surface irregularities. It therefore overcomes one of the major drawbacks of electroplating, namely the variation in plating thickness that results from variations in current density caused by the geometry of the plated part and its relationship to the plating anode. An electroless plating solution produces a deposit wherever it contacts a properly prepared surface, without the need for conforming anodes and complicated setup. Since the chemical bath maintains a uniform deposition rate, the deposit thickness can be precisely controlled simply by controlling the immersion time [21].

There are three main types of electroless nickel coatings: nickel-phosphorus, nickel-boron and poly alloys. Nickel-phosphorus is generally used for engineering applications. In the most widely used electroless technique, nickel is deposited by the catalytic reduction of nickel ions with sodium hypophosphite in acid baths at a pH of 4.9

and at a temperature of 88°C. The deposit typically contains 3 to 13 wt% phosphorus, depending on the chemical composition of the solution and the operating conditions. The phosphorus content significantly influences the nickel's chemical and physical properties in both the as-plated and after-heat-treatment conditions. High phosphorus nickel is recommended where superior corrosion resistance is desired. Uses include various components in the electronics industry, oil and gas, printing, aerospace, and the chemical processing industries. The narrow melting range of the deposit makes it suitable for certain welding and brazing applications [21].

One of the drawbacks to electroless phosphorus nickel is the slow speed at which the plated layer is developed. The speed restriction of this technique typically precludes it from being used in continuous plating processes [22].

Recent developments in electroplating chemistry have lead to the introduction of an electroplated phosphorous nickel technique, which not only enhances the deposition rate of the phosphorous nickel alloy, but also allows for the selective placement of this deposit in a continuous plating process [23][24].

## 2.4 DIE ATTACH

Die attach is the process of attaching the silicon carbide transistor onto the substrate. For high temperature SiC transistor devices, the die attach material must have a melting or decomposition point that is well above the operating temperature in order to provide mechanical attachment, good thermal conductivity, and good electrical conductivity for the device operation. There are four bonding options for the SiC

transistor die attach: conductive adhesive bonding, soldering, brazing, and transient liquid phase bonding.

Conductive adhesive bonding is a material jointing process in which an electrically conductive adhesive is dispensed between two facing surfaces, and cured to produce an adhesive bond. An electrically conductive adhesive is made by incorporating conductive particles such as silver, nickel, or gold into the adhesive formulation. These particles carry electrical current through the adhesive. The most popular filler material is silver due to its moderate cost and superior conductivity [25]. Table 2.3 presents typical conductive compositions and properties [26]. Electrically conductive adhesives are not suitable for use above 250°C. Electrically conductive adhesives also have higher resistance than solders and brazes, which limits their use in high current applications.

Table 2.3 Conductive adhesive properties [26]

| Basic<br>Resin | Filling<br>materials | Configuration of Particles | Glass<br>transition<br>temperature | Operating temperature | Curing conditions |

|----------------|----------------------|----------------------------|------------------------------------|-----------------------|-------------------|

| Epoxy          | Ag                   | Flakes                     | 90°C                               | -65~150°C 0           | 1hr/130°C         |

| Epoxy          | Ag-plated Cu         | Flakes                     | N/A                                | 20~160°C              | 30min/125°C       |

| Epoxy          | Ni                   | other                      | N/A                                | -50~150°C             | 2hr/65°C          |

| Silicone       | Ag-plated Cu         | Flakes/ball                | -55°C                              | -55~125°C             | 168hr/25°C        |

| Silicone       | Ag                   | Flakes                     | N/A                                | -50~200°C             | 1hr/150°C         |

| Polyimide      | Ag                   | Flakes                     | 249°C                              | 20~250°C              | 1hr/140°C         |

Soldering is a method to bond the die to the substrate using an alloy of low melting point (solder) below 427°C. These solders are typically lead- and tin-based alloys. The solder can be introduced as a solder paste, or solder preform between the die and the substrate. The assembly is heated until the solder melts and bonds the two

surfaces under a protective atmosphere (forming gas or N<sub>2</sub>) [27]. After the solder cools down, a solid connection is established. A controlled temperature profile is required to define the liquidus/solidus transition. A range of commonly used solders is given in Table 2.4 [28]. Soldering is not suitable for the SiC power transistor die attach because all the solder liquidus temperatures are much less than the potential application temperature.

Table 2.4 Some common solder materials for die attach [28]

| Alloy                    | Solidus<br>(°C) | Liquidus<br>(°C) |

|--------------------------|-----------------|------------------|

| 95% Pb, 5% Sn            | 310             | 314              |

| 80% Au, 20% Sn           | 280 (eutectic)  |                  |

| 63% Sn 37% Pb            | 183 (eutectic)  |                  |

| 65% Sn, 25% Ag, 10% Sn   | 233             | 233              |

| 95% Sn, 5% Sb            | 235             | 240              |

| 1% Sn, 97.5% Pb, 1.5% Ag | 309             | 309              |

| 75% Pb, 25% In           | 240             | 260              |

| 50% Pb, 50% In           | 180             | 209              |

| 62% Sn, 36% Pb, 2% Ag    | 179 (eutectic)  |                  |

Brazing is a bonding process in which the filler metal has a melting point higher than 427°C but lower than that of the materials being joined. To prevent oxidation, brazing is normally conducted in an inert gas or in a vacuum. At its liquid temperature, the molten filler metal interacts with a thin layer of the base metal, cooling to form an exceptionally strong, sealed joint due to grain structure interaction [29].

In actual practice, most brazing alloys melt at temperatures well above 427°C, and most solders at temperatures well below 427°C [30]. For brazing process under 600°C, the Au-In alloy (81/19 wt%), which has a melting point of 487°C, is the most commonly

used brazing alloy. Most of brazing alloys based on silver have melting points above 600°C.

Transient liquid phase (TLP) bonding is a jointing process that has been applied to many metallic systems throughout the ages, and yet it still holds promise as a technique for joining in aerospace and semiconductor applications. The TLP process produces a strong, interface-free joint with no remnant of the bonding agent. schematic illustration of the process, shown in Figure 2.5 [31], indicates that by placing a thin interlayer of an alloying metal containing a melting point depressant (MPD) between the two pieces of parent metal to be joined and heating the entire assembly, a liquid interlayer is formed. The liquid may form because the melting point of the interlayer has been exceeded, or because reaction with the parent metal results in a low melting liquid alloy. The liquid then fills voids formed by unevenness of the mating surfaces and can sometimes dissolve residual surface contamination. With time the MPD diffuses into the parent metal resulting in isothermal solidification. Upon cooling there remains no trace of the liquid phase, and ideally the joint becomes indistinguishable from other grain boundaries. The formation of a thin liquid interlayer eliminates the need for a high bonding or clamping force. The interlayer can be provided by foils, electroplated, sputter coats, or any other process that deposits a thin film on the surfaces that need to be bonded [32].

Figure 2.5 Four stages of TLP bonding process [31]

The TLP process is not limited to binary eutectics, but can be applied to any system where the parent metal or alloy will form a relatively low melting temperature

phase and has solubility for the MPD. The concept can also be applied to other systems whereby a chemical or other driving force inherently leads to solid state equilibrium.

In summary, the advantages of transient liquid phase bonding are as follows [33]:

- Transient liquid phase bonding is an isothermal process, so there are minimal thermal stresses formed between the die and substrate, thus avoiding the risk of cracking or fracture.

- During transient liquid phase bonding, oxides on the surface of the substrate are

either dissolved by the liquid interlayer or reduced by subjecting the substrate to

high-temperature vacuum exposure. Thus, transient liquid phase bonding is

normally tolerant to the presence of oxide layers on the surface of the substrate

and die, and can be applied to a wider range of materials.

- There are fewer geometrical restrictions on the materials to be bonded because no pressure or scrubbing is required.

- The use of high vacuum environment reduces the amount of air trapped in the joint, therefore fewer or no voids are formed after transient liquid phase bonding.

### 2.5 WIRE BONDING

Wire bonding is the most widely used method for making electrical connections from a semiconductor chip to its package [33]. There are basically two forms of wire bonds, wedge bonds and ball bonds. There are three wire bonding methods that are commonly used: thermocompression, thermosonic, and ultrasonic bonding. Thermocompression bonding requires a high-force on a surface with a high temperature

around 300°C to form a bond [35]. Thermosonic ball bonding combines the thermocompression bonding with the use of ultrasonic vibration to produce strong bonds at low stage temperatures of around 100°C to 240°C. Due to the lower stage temperature of thermosonic ball bonding it has largely replaced thermocompression bonding in the industry. Figure 2.6 shows the thermosonic ball bonding steps [36].

Figure 2.6 Thermosonic bonding of gold wire [36]

Usually, gold wire is used in thermosonic ball bonding because of the ease with which it forms a uniform ball when melted. The gold wire protruding from the capillary is melted by an electric arc to form a ball. This process is called "flame off". The capillary with the ball lowers to the first bonding site, where pressure, ultrasonic energy and temperature are applied to form the bond. The capillary then rises off the surface with

the wire flowing out to form a loop. Once the loop has been formed, the capillary lowers to the second bond site. Pressure, ultrasonic energy and temperature are again applied to form the second bond, which is generally called the stitch bond. Once the stitch bond is made, the capillary rises to a pre-determined height with the wire clamps open to pull wire through the capillary. The wire clamps are then shut as the capillary continues to move up, breaking the wire behind the stitch bond and thus producing a wire tail used to form the next ball [37].

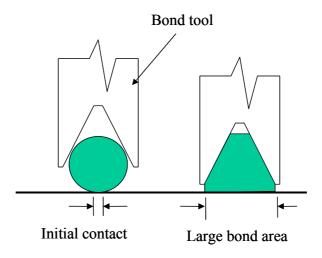

Thermosonic ball bonding cannot be easily used with aluminum wire because aluminum wire does not form a uniform ball during flame off unless an inert cover gas is used. This led to the development of a second type of wire bonding for aluminum wire, namely ultrasonic wedge bonding. Ultrasonic wedge bonding applies a combination of pressure and ultrasonic vibration of the bonding tool to form a bond. The ultrasonic wedge bonding process starts by feeding aluminum wire through a bond tool. This bond tool then moves to the first bond site, where ultrasonic vibration (20-60 KHz) and pressure is used to form the bond. The bond tool then rises and moves to the second bond site. Once the second bond is made, the bond tool rises and a cutter is applied to the aluminum wire which causes the wire to break behind the second bond. Figure 2.7 shows the steps used in ultrasonic wedge bonding [37]. Ultrasonic wedge bonding is slower than thermosonic ball bonding because the second bond must be directly behind the first bond in order to maintain proper wire alignment through the bonding tool. To accommodate wire bonds that are at different angles to each other, either the bond tool or the substrate must be rotated. The time needed to perform this rotation limits the rate of bond formations.

Figure 2.7 Aluminum ultrasonic wedge bonding [37]

Large diameter aluminum wire bonding is used with Si power devices to provide high current carrying capability. However, high temperature annealing increases the grain size in the wire, reducing the wire's strength and fatigue resistance. Also, Al is incompatible with the Au wire bond pads due to intermetallic formation and Kirkendall voiding at high temperatures [5].

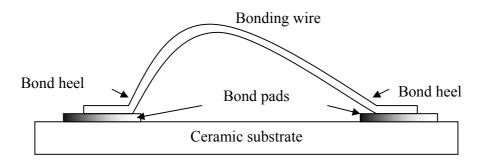

Large diameter gold and platinum wire are alternatives to Al wire for high temperature applications because both have high current capability, excellent corrosion resistance to air and harsh environments at high temperature and no incompatible issues with the Au wire bond pads. Pt also has high mechanical strength at high temperatures. Large diameter Au and Pt ultrasonic wedge bonding requires a heated stage and can appropriately be called thermosonic wedge bonding. Figure 2.8 shows the steps used in thermosonic wedge bonding.

b. Bonding 2<sup>nd</sup> bond

c. Wire break

Figure 2.8 Gold wire thermosonic wedge bonding

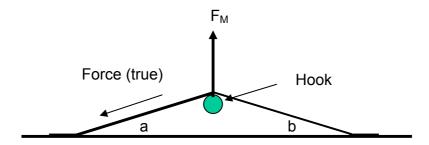

One of the most common ways to determine wire bond strength is destructive pull testing. Destructive pull testing places a hook under the wire between the two bonds and pulls upward along a line centered and perpendicular to the base line running between the bonds until the wire breaks, either at one of the bond sites or in the span itself. Figure 2.9 shows the placement of the hook for pull testing [37].

Force (true) =

$$\frac{F_{M}}{2 \sin a}$$

Figure 2.9 Pull test [37]

The force applied to each bond is equal if a = b and has the value:

Force (true) =

$$F_M/2\sin a$$

(2.1)

where Force (true) is the actual force applied to the bond through the wire;  $F_M$  is the gage reading; and a is the angle between the baseline and the wire when both angles a and b are equal [37].

Note that raising the height of the loop yields higher breaking load values, as measured by the pull test machine. Thus, angle becomes an important factor that must be recorded if this data is to be used in comparisons. Any changes in loop height or angle will affect the gage reading.

The amount of force required to break the wire in grams-force (g-f) and the failure mode are recorded for each wire tested. The typical failure mode for a wire that has a good bond is in the middle of the loop. The worst type of failure for wire bonding is a bond lift, which occurs when the bond peels off the pad to which it has been bonded

during destructive pull testing. This type of failure indicates that the bond formed was not sufficiently strong. The most common failure for a wire bond occurs at the heel of the bond. Figure 2.10 shows the bond heel definition [38].

Figure 2.10 Bond heel definition [38]

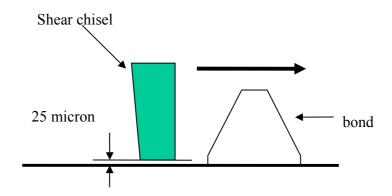

Wire bond shear testing is routinely used for large diameter aluminum wedge bonds. The shear tester pushes a chisel against the side of a bond until it gives way. The shear height is an important variable, and it must be set high enough to avoid dragging on the substrate surface but low enough to produce a shear load rather than a rolling force. For most large wire bonds, 25µm is a reasonable working height. Figure 2.11 illustrates the shear test process [37].

Figure 2.11 Shear test [37]

## 2.6 POLYIMIDE

Devices operating under high power conditions may also be exposed to high voltages, and as a result high voltage breakdown may occur between adjacent electrical connections and/or between high voltage electrical connections and the surrounding air. To prevent this, an effective dielectric passivation coating must be applied to ensure reliable package operation [39].

Polyimide films are amber in color and highly transparent, being formed by the condensation reactions of aromatic dianhydrides with aliphatic or aromatic diamines. The synthesis includes two steps [40]: the synthesis of the polyamic acid, followed by thermal imidization. The synthesis of Dupont PI2611 polyimide is shown as Figure 2.12. Here, S-Biphenyldianhyride (BPDA) is mixed with a solution of P-phenylenediamine (PPD), generating an intermediate, polyamic acid. The intermediate acid is then heated to produce cyclodehydration in the imidization stage. Interaction between adjacent imide

and benzene rings results in a rigid backbone structure and causes spontaneous molecular orientation during thermal imidization.

Figure 2.12 Synthesis of polyimide [40]

Polyimide

This kind of polyimide has a rodlike structure with a backbone composed of rigid cyclic elements. This stiff structure exhibits an exceptional combination of high thermal stability (>500°C), a very low lateral CTE (coefficient of thermal expansion) of 3ppm/°C, good mechanical toughness (6.6GPa), good chemical corrosion resistance, excellent

dielectric properties (dielectric constant 2.9 (out of plane)) and relatively low moisture uptake (0.8%) [41] compared to most other organic or polymeric materials. Because of its high degree of ductility and inherently low CTE, PI2611 polyimide can be readily implemented into a variety of microelectronics applications.

In the fabrication of microelectronic devices, polyimide coatings can be applied to the substrate by spin, draw, spray, extrusion, roller, dip and drop coating automatically or manually, depending on the dimensions, the shape of the part or its surface irregularities, and then thermally cured into a smooth, rigid, intractable polymeric film or structural layer. For optimal adhesion to silicon, oxides, and most metals, adhesion promoters are required [42].

# CHAPTER 3 SIC DIE ATTACH CHARACTERATION

# 3.1 TRANSIENT LIQUID PHASE BONDING PROCESS

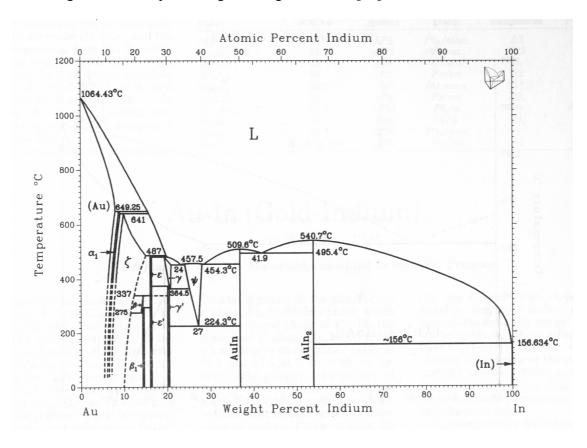

In this research, AuIn alloy (81/19 wt%) preform (size: 130mil x 130mil) manufactured by Williams Advanced Materials was selected as the interlayer of metal for the transient liquid phase bonding for die attach. In this case, the indium acted as the MPD. Figure 3.1 is the phase diagram for gold-indium [43].

Figure 3.1Gold-Indium phase diagram [43]

From the Au-In phase diagram, if the concentration of indium changes from 19% to less than 12 wt%, the alloy solidus temperature will increase to 550°C. Thick gold on the SiC die backside provided a source of gold to lower the concentration of indium to less than 12 wt% in this work. Figure 3.2 shows the schematic for calculation of the thickness of the Au required on the SiC die.

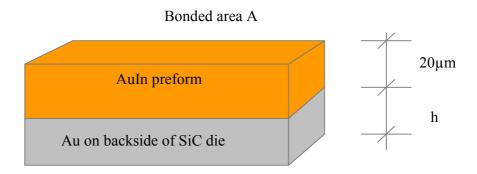

Figure 3.2 Calculation schematic for thickness of added Au

To lower the concentration of indium to 12 wt%, the thickness of the Au layer on the SiC die was calculated from Equation (3.1) to be  $9\mu m$ . Hence, a thickness of  $10\mu m$  Au was selected for the SiC die metallization cap layer.

$$W_{ln}\% = \frac{\rho_{Auln} * A * 19\% * 20}{\rho_{Auln} * A * 28 + \rho_{Au} * A * h}$$

(3.1)

In Equations (3.1):

A: Bonded area

h: Thickness of Au or Ag

$\rho_{AuIn}$ : Density of eutectic AuIn, 14.72 mg/cm<sup>3</sup>

$\rho_{Au}$ : Density of Au, 19.3 mg/cm<sup>3</sup>

Thick silver was studied as an alternative metal to gold due to its moderate cost, superior conductivity, and high solubility of indium at high temperature. The diffusion coefficient of indium in silver  $D=0.41 \exp(-40630/RT) \operatorname{cm}^2/\sec[44]$ , and gold in silver  $D=0.26 \exp (-45500/RT) \text{ cm}^2/\text{sec}$  [45] at 500~720°C. When the temperature increases above 487°C, the preform melts to form a liquid phase. Indium and gold both diffuse into the silver, but indium diffuses in silver much quicker than gold at high temperature. For example, at the temperature of 510°C, the diffusion coefficient of indium in silver is about 1.97x10<sup>-12</sup> cm<sup>2</sup>/sec which is much more than that of gold in silver, 5.49x10<sup>-14</sup> cm<sup>2</sup>/sec, resulting in reduction of the concentration of the indium in the liquid phase. Therefore, thick silver on the ceramic substrate side acted as a sink for indium in the second approach to lower the concentration of indium. The second approach differs from the first in that the gold-silver-indium ternary alloys form in the joint due to the indium and gold diffusion into the silver and silver dissolved by the melt. The melting point of the bond joint will depend on the gold-silver-indium ternary alloy composition and structure. However, the thickness of the added silver, the alloy composition and the melting point of the bond joint could not be predicted because there is no Au-Ag-In ternary phase diagram available in this field. In this research, a thickness of 20µm silver was selected as the substrate metallization cap layer.

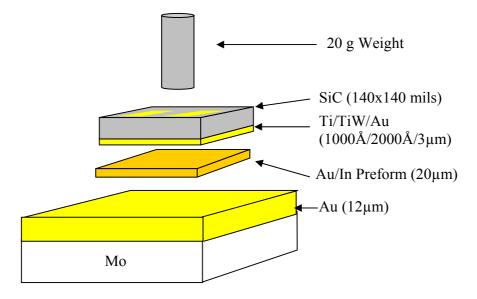

## 3.2 THICK GOLD DIE SPECIMEN PREPARATION

In the first approach, the AuIn preform was sandwiched between the SiC die and substrate. The preforms were supplied with dimensions of 3.3mm x 3.3mm x 0.020mm. The properties of AuIn preform include a melting point of of 487°C, density of 14.72 mg/cm<sup>3</sup>, thermal coefficient of expansion (CTE) of 14.7 ppm/K at 25°C, and tensile strength of 33700 psi at 25°C [47]. Figure 3.3 shows the sandwich structure. This assembly is referred to as the thick Au die-to-thin Au substrate construction.

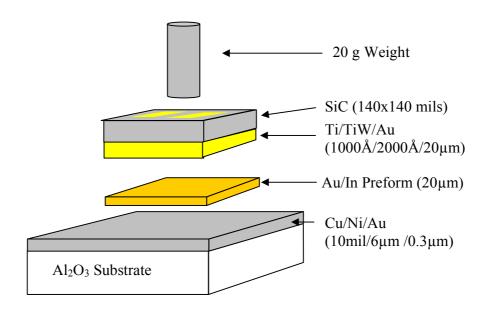

Figure 3.3 Thick Au die TLP bonding sketch

# 3.2.1 SiC Die Metallization Fabrication

A metallization stack, Ti/TiW/Au (thickness:  $1000\text{Å}/2000\text{Å}/20\mu\text{m}$ ), deposited on an n-type 4H-SiC wafer provided by Cree Inc., was used as the die metallization for the

liquid transient phase bonding process. The SiC wafer metallization fabrication process was as follows:

- Pre-Clean SiC wafer in organic and inorganic solution.

- High vacuum sputter the Ni (thickness < 800 Å) on the SiC wafer.

- Anneal at 900°C for 1 minute in a high vacuum chamber to form Ni<sub>2</sub>Si as ohmic contact.

- High vacuum sputter each of the Ti, TiW and Au (2000Å) layers in turn without breaking the vacuum.

- Electroplate Au to a thickness of 20μm.

- Dice the wafer to the experimental size (140x140 mils).

The inclusion of a pure Ti film improves adhesion to the device contacts (Ni<sub>2</sub>Si, an ohmic contact), reducing the interfacial oxide layer and improving the step coverage. The TiW (10/90 wt%) film usually consists of columnar grains of tungsten without any free Ti phase [46]. The titanium is in solid solution, with some tungsten atoms distributed at the grain boundaries. The distribution of titanium is important for improving the barrier properties of TiW. The Au film protects the underlying layer TiW from oxidation and serves as a die bonding wettable surface.

## 3.2.2 Substrate Metallization Fabrication

A thick metallization, Cu/ Ni/ Au (thickness:  $250\mu m/6\mu m$  /0.3 $\mu m$ ), deposited on 96% Al<sub>2</sub>O<sub>3</sub> provided by Stellar Industries Corp was used as the substrate metallization. The substrate metallization fabrication process was as follows:

- Put 10mil Cu foil on Al<sub>2</sub>O<sub>3</sub> ceramic, heat to 1065°C to 1085°C to form a CuO and Al<sub>2</sub>O<sub>3</sub> joint.

- Electroplate 6µm Ni on DBC Cu.

- Immersion plate 0.3µm Au on Ni.

- Dice the substrate to the experimental size (200x200 mils).

The direct bond copper provides high electrical and thermal conductivity, and high mechanical strength due to the strong joint between Cu and Al<sub>2</sub>O<sub>3</sub>. Nickel acts as the barrier layer to prevent Cu diffusion and oxidation. The Au film protects the underlying layer Ni from oxidation and serves as a die bonding wettable surface.

#### 3.2.3 TLP Process of Thick Gold Die Attach

From the Au-In phase diagram shown in Figure 3.1, when the temperature increases above 487°C, the preform melts to form a liquid phase. Indium in the liquid zone diffuses into the gold on the SiC die and substrate, and the gold on the die and substrate diffuses into the liquid zone, resulting in reduction of the concentration of the indium in the liquid phase. Upon cooling a strong joint is produced. And because of the reduction of the concentration of the indium in the joint, the solidus temperature of the bond joint will be higher than 487°C.

The TLP bonding process was performed in a SST 3150 high vacuum furnace. The components were assembled within a graphite block, which was heated under vacuum by passing a high current through it. Inside the fixture were placed successively the substrate, a graphite slip with cavities for the preform and die, an AuIn preform, and the die. The samples were compressed with a 20g weight.

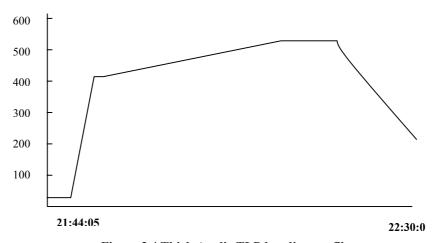

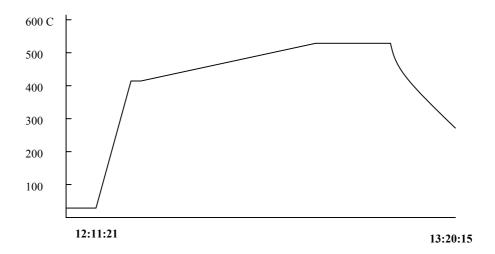

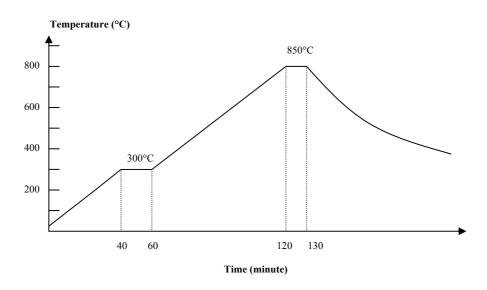

The bonding profile for the thick Au die is shown in Figure 3.4. It included a 2 minute soak at 420°C to bake out residual moisture and then 25 minutes ramping from 420°C to 525°C, followed by a soak at 525°C for 15 minutes.

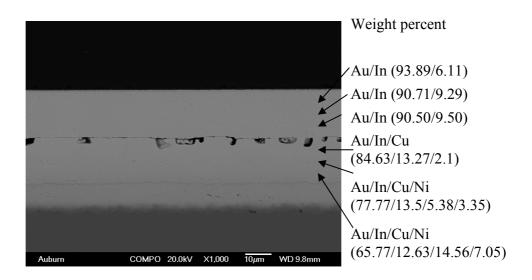

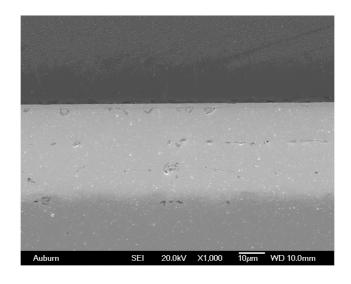

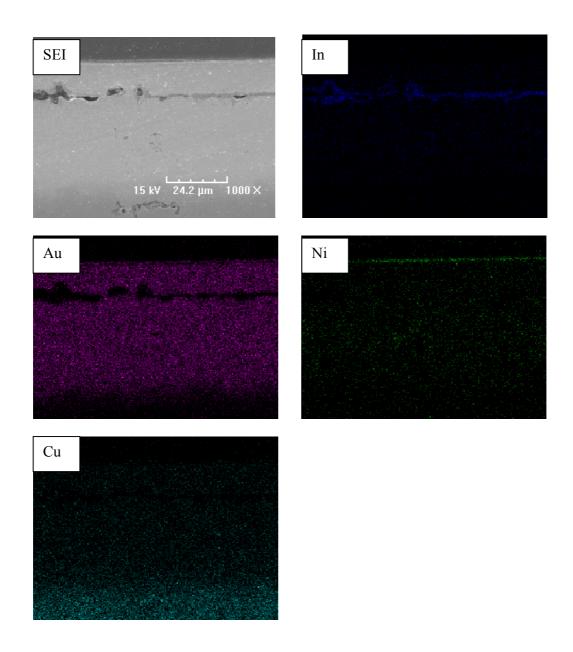

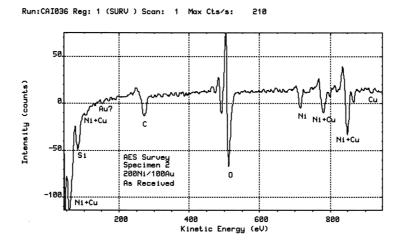

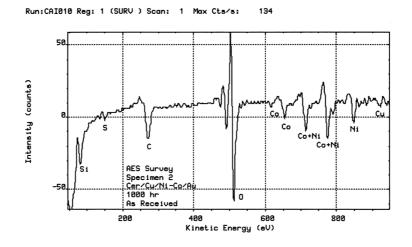

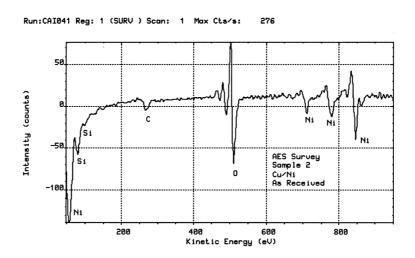

Figure 3.4 Thick Au die TLP bonding profile