## BUILT-IN SELF-TEST OF LOGIC RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS USING PARTIAL RECONFIGURATION

Except where reference is made to the work of others, the work described in this thesis is

| my own or was done in collaboration with my advisory committee. This thesis does no include proprietary or classified information. |                                     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|

|                                                                                                                                    |                                     |  |  |  |

| Sachin                                                                                                                             | Dhingra                             |  |  |  |

|                                                                                                                                    |                                     |  |  |  |

|                                                                                                                                    |                                     |  |  |  |

| Certificate of Approval:                                                                                                           |                                     |  |  |  |

|                                                                                                                                    |                                     |  |  |  |

| Victor P. Nelson                                                                                                                   | Charles E. Stroud, Chair            |  |  |  |

| Professor                                                                                                                          | Professor                           |  |  |  |

| Electrical and Computer Engineering                                                                                                | Electrical and Computer Engineering |  |  |  |

|                                                                                                                                    |                                     |  |  |  |

| Vishwani D. Agrawal                                                                                                                | Stephen L. McFarland                |  |  |  |

| Professor                                                                                                                          | Acting Dean                         |  |  |  |

| Electrical and Computer Engineering                                                                                                | Graduate School                     |  |  |  |

Electrical and Computer Engineering

## BUILT-IN SELF-TEST OF LOGIC RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS USING PARTIAL RECONFIGURATION

### Sachin Dhingra

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama August 7, 2006

## BUILT-IN SELF-TEST OF LOGIC RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS USING PARTIAL RECONFIGURATION

| α 1 .   | T 1           | •    |             |

|---------|---------------|------|-------------|

| Sachin  | I)h           | 1110 | rra         |

| Saciiii | $\nu_{\rm H}$ | 1116 | <b>41 U</b> |

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions and at their expense.

The author reserves all publication rights.

| Signature of Author |

|---------------------|

|                     |

| Date of Graduation  |

#### VITA

Sachin Dhingra, son of Baldev Raj and Anita Dhingra, was born on May 31, 1982 in Chandigarh, India. He graduated with a Bachelor of Engineering degree in Electronics and Telecommunications Engineering in May 2003 from Maharashtra Institute of Technology, University of Pune, India. After completion of his undergraduate degree, he joined Electronic Projects Management, Canada as a Senior Test Technician in November 2003. He entered the graduate program at Auburn University in August 2004. While in pursuit of his Master of Science degree at Auburn University, he worked under the guidance of Dr. Charles E. Stroud as a graduate student research assistant in the Electrical and Computer Engineering Department.

#### THESIS ABSTRACT

# BUILT-IN SELF-TEST OF LOGIC RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS USING PARTIAL RECONFIGURATION

#### Sachin Dhingra

Master of Science, August 7, 2006 (B.E, University of Pune, India, 2003)

97 Typed Pages

Directed by Charles E. Stroud

Field Programmable Gate Arrays (FPGAs) are programmable logic devices that can be used to implement virtually any digital circuit design. Built-In Self-Test (BIST) is a testing approach that enables the device to test itself without any external test equipment. The re-programmability feature of the FPGAs makes BIST a very attractive approach for testing FPGAs because it eliminates any area or performance degradation associated with BIST.

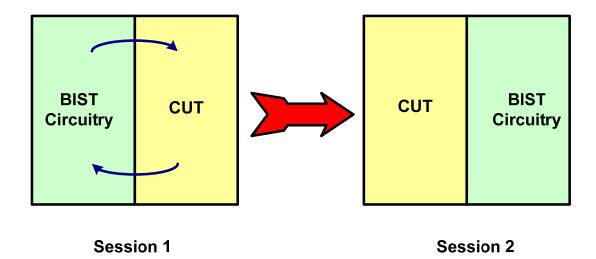

Traditional BIST for FPGAs suffers from long test times and large memory storage requirements due to the slow configuration download speeds and the large number of test configurations required to test the FPGAs. The work presented in this thesis implements testing of logic resources of Xilinx Virtex/Spartan-II and Virtex-4 FPGAs with focus on reduction of test time and memory storage requirements using

techniques like dynamic partial reconfiguration and partial configuration memory readback.

The total number of configurations required to completely test the logic resources are 28 for Virtex/Spartan-II FPGAs and 24 for Virtex-4 FPGAs. A speed-up of 5.1 times and 12.9 times in test time was achieved for Logic BIST for Virtex/Spartan-II and Virtex-4 FPGAs respectively, using dynamic partial reconfiguration and partial configuration memory readback. A reduction in configuration memory storage requirements was also achieved using partial reconfiguration; this reduction was 3.2 times and 5.3 times for Virtex/Spartan-II and Virtex-4 FPGAs respectively.

#### **ACKNOWLEDGMENTS**

I am indebted to Dr. Stroud for his support and advice throughout my research at Auburn University. I would also like to thank Dr. Nelson and Dr. Agrawal for being on my graduate committee and for their contribution to my thesis. I would like to acknowledge my research colleagues Daniel, John, Jonathan, Lee, Srinivas, and Sudheer for their help and inspirational discussions during my research. Finally, I would like to express my deepest gratitude to my parents and my brother whose love and encouragement is inspiring me to achieve my goals.

Style manual or journal used: <u>IEEE (Institute of Electrical and Electronic Engineers)</u> Journal style

Computer software used: Microsoft® Word® 2003, Microsoft® Excel® 2003,

Microsoft® Visio® 2003

## TABLE OF CONTENTS

| LIST OF | FIGURES                                                  | xi   |

|---------|----------------------------------------------------------|------|

| LIST OF | TABLES                                                   | xiii |

| LIST OF | ACRONYMS                                                 | xiv  |

|         |                                                          |      |

|         | ΓER ONE: Introduction                                    |      |

| 1.1     | Field Programmable Gate Arrays (FPGAs)                   |      |

| 1.2     | Testing and BIST                                         |      |

| 1.3     | FPGA BIST                                                |      |

| 1.4     | Xilinx FPGAs                                             |      |

| 1.5     | Thesis Statement                                         | 7    |

| CHAP    | ΓER TWO: Background                                      | 9    |

| 2.1     | =                                                        |      |

| 2.      | 1.1 Configuration Memory                                 | 10   |

| 2.      | 1.2 Programmable interconnects, IOBs, Memory and DSP     |      |

| 2.      | 1.3 Programmable Logic Resources                         | 12   |

| 2.2     | Virtex/Spartan-II Architecture                           |      |

| 2.3     | Virtex-4 Architecture                                    | 18   |

| 2.4     | FPGA Configuration                                       | 23   |

| 2.4     | 4.1 Configuration Interface                              | 24   |

| 2.4     | 4.2 Configuration Process                                |      |

|         | 4.3 Configuration Memory Readback                        |      |

| 2.5     | Prior Work in FPGA Testing                               |      |

| 2.6     | General BIST Architectures                               |      |

| 2.7     | BIST for Logic Resources of an FPGA                      |      |

|         | 7.1 BIST Architecture                                    |      |

|         | 7.2 Test Pattern Generation and Output Response Analysis |      |

|         | 7.3 Configuration Schemes                                |      |

| 2.      | 7.4 Results Retrieval                                    |      |

| 2.8     | Restatement of Thesis Goals                              | 36   |

| CHAP    | ΓER THREE: Logic BIST for Virtex/Spartan II              | 38   |

| 3.1     | Introduction                                             |      |

| 3.2     | Virtex/Spartan-II PLB Architecture                       |      |

| 3.3    | BIST Architecture                               | 39 |

|--------|-------------------------------------------------|----|

| 3.4    | Partial Reconfiguration                         | 43 |

| 3.5    | Partial Configuration Memory Readback           | 45 |

| 3.6    | Logic BIST Configurations for Virtex/Spartan-II |    |

| 3.6.   | Fault Model and Fault Coverage                  |    |

| 3.6.   |                                                 |    |

| 3.7    | Logic BIST Configuration Generation Process     |    |

| 3.8    | Methods for Application of BIST                 |    |

| 3.9    | Results                                         |    |

| 3.10   | Summary                                         |    |

|        | •                                               |    |

| CHAPT  | ER FOUR: Logic BIST for Virtex-4                | 55 |

| 4.1    | Introduction                                    | 55 |

| 4.2    | Virtex-4 Architecture                           | 55 |

| 4.3    | BIST Architecture                               | 56 |

| 4.4    | Logic BIST Configurations for Virtex-4          | 61 |

| 4.4.   | Fault Model and Fault Coverage                  | 61 |

| 4.4.   | 2 Configuration Details                         | 62 |

| 4.5    | Timing Analysis                                 | 67 |

| 4.6    | Logic BIST Configuration Generation Process     | 68 |

| 4.7    | Methods for Application of BIST                 |    |

| 4.8    | Results                                         | 71 |

| 4.9    | Summary                                         | 73 |

| CHAPT  | ER FIVE: Summary and Conclusions                | 75 |

| 5.1    | Thesis Summary and Main Contributions           |    |

| 5.2    | Application to Embedded Processors              |    |

| 5.3    | Areas for Future Research and Development       |    |

| ٥.5    | Areas for 1 didic research and Development      | 70 |

| REFERE | ENCES                                           | 79 |

## LIST OF FIGURES

| Figure 1.1 FPGA Architecture                                               | 3  |

|----------------------------------------------------------------------------|----|

| Figure 1.2 Basic BIST Architecture [6]                                     | 4  |

| Figure 1.3 BIST in FPGAs                                                   | 6  |

| Figure 2.1 Configuration Memory Element                                    | 10 |

| Figure 2.2 Typical PLB Slice of a Xilinx FPGA                              | 13 |

| Figure 2.3 Virtex/Spartan-II Architecture                                  | 15 |

| Figure 2.4 PLB of a Xilinx Virtex series FPGA                              | 16 |

| Figure 2.5 Virtex/Spartan-II PLB Slice [8]                                 | 17 |

| Figure 2.6 Configuration memory structure of Virtex FPGAs                  | 18 |

| Figure 2.7 Virtex-4 Architecture                                           | 19 |

| Figure 2.8 Diagram of a Xilinx Virtex-4 series FPGA PLB.                   | 20 |

| Figure 2.9 Virtex-4 SliceL [10]                                            | 21 |

| Figure 2.10 Virtex-4 SliceM [10]                                           | 22 |

| Figure 2.11 Boundary Scan Architecture                                     | 25 |

| Figure 2.12 On-line BIST [6]                                               | 30 |

| Figure 2.13 BIST Architecture to test Logic Resources [3]                  | 32 |

| Figure 2.14 Output Response Analyzer                                       | 34 |

| Figure 3.1 Logic BIST Architecture for Virtex/Spartan-II FPGAs             | 41 |

| Figure 3.2 Output Response Analyzers                                       | 42 |

| Figure 3.3 Fault Coverage of a Virtex FPGA PLB slice                       | 47 |

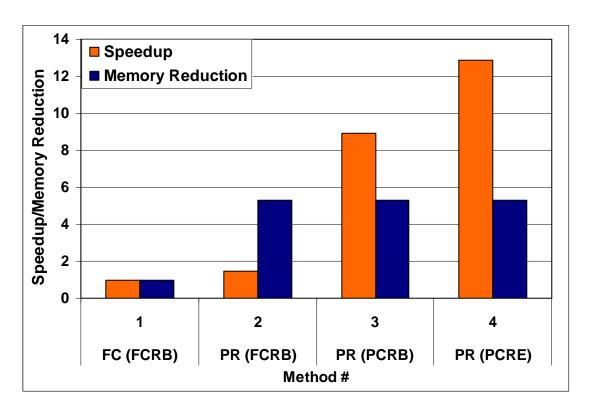

| Figure 3.4 Test time speed-up and reduction in memory storage requirements | 52 |

| Figure 4.1 Logic BIST Architecture for Virtex-4 FPGAs                      | 57 |

| Figure 4.2 ORAs in a Single PLB slice                                      | 58 |

| Figure 4.3 Fault Coverage of a Virtex-4 PLB.                               | 62 |

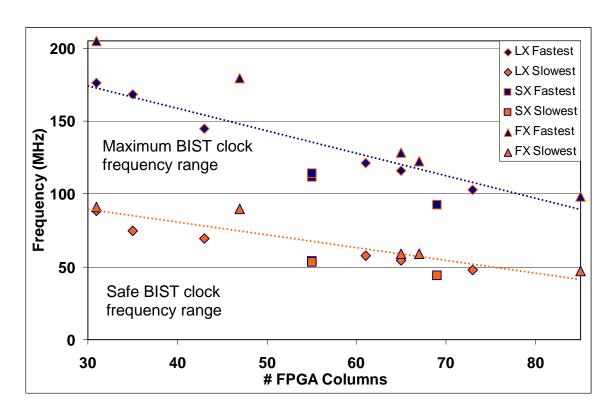

| Figure 4.4 Maximum BIST clock frequency vs. Device size                    | 68 |

| Figure 4.5 BIST Architecture in Virtex-4 FX FPGAs                          | 70 |

## LIST OF TABLES

| Table 2.1 | Resources available in different FPGA families [8] [12] [9]      | 14 |

|-----------|------------------------------------------------------------------|----|

| Table 3.1 | Configuration Details                                            | 48 |

| Table 3.2 | Methods used for Logic BIST                                      | 51 |

| Table 3.3 | Speed-up vs. Device Size.                                        | 53 |

| Table 4.1 | Configuration Details                                            | 63 |

| Table 4.2 | Methods used for Logic BIST                                      | 71 |

| Table 4.3 | Comparison of test time speed-up and reduction in memory storage |    |

| requireme | nts of Virtex/Spartan-II and Virtex-4 FPGAs                      | 73 |

#### LIST OF ACRONYMS

BIST Built-In Self Test

BSCAN Boundary SCAN

BUILT BUILT TO A

**BUT** Block Under Test

**CPLD** Complex Programmable Logic Device

**CRC** Cyclic Redundancy Check

CUT Circuit Under Test

DLL Delay Locked Loop

DSP Digital Signal Processor

FAR Frame Address Register

**FDR** Frame Data Register

**FPGA** Field Programmable Gate Array

GSR Global Set/Reset

IC Integrated Circuit

ID IdentificationI/O Input Output

IOB Input Output BufferIP Intellectual Property

**LFSR** Linear Feedback Shift Register

**LUT** Look-Up Table

NCD Native Circuit Design

**ORA** Output Response Analyzer

PIP Programmable Interconnect Point

PLB Programmable Logic Block

**PROM** Programmable Read Only Memory

**RAM** Random Access Memory

**ROM** Read Only Memory

**SRAM** Static Random Access Memory

TCK Test Clock

**TDI** Test Data Input

**TDO** Test Data Output

**TMS** Test Mode Select

**TPG** Test Pattern Generator

**VLSI** Very Large Scale Integration

**XDL** Xilinx Design Language

#### **CHAPTER ONE**

#### Introduction

Rapid advances in semiconductor processing technologies have allowed transistor densities to double every two years; this phenomenon has led to new opportunities in Very Large Scale Integration (VLSI) design and new challenges in design verification and testing [1]. The growing complexity of design has made programmable logic devices like Field Programmable Gate Arrays (FPGAs) and Complex Programmable Logic Devices (CPLDs) some of the leading products in the semiconductor industry, as they provide an easy way to implement and verify complex digital designs.

Every innovation in Integrated Circuit (IC) design is accompanied by new challenges in testing. The test systems accordingly are becoming faster, more complex and hence more expensive. Cost and time are two of the most important factors that govern the development of any kind of test system. Built-In Self-Test (BIST) is one technique which reduces the cost and time overheads involved in external test systems. It is a technique that places a device's testing function within the device itself [6].

#### 1.1 Field Programmable Gate Arrays (FPGAs)

FPGAs are programmable logic devices that can be configured or programmed to perform tasks specific to any digital application. The FPGAs gained popularity due to

their flexibility and short time-to-market, making them ideal for prototyping systems and low volume products. The design to be implemented in an FPGA is converted to a string of bits called the configuration file using tools provided by the FPGA manufacturer. The configuration file is used to program the memory elements inside the FPGA that control the functionality of the programmable components of the FPGA to implement the required design [2]. Traditionally, the entire configuration memory of an FPGA is rewritten with configuration data if the design needs to be modified; this is called full reconfiguration. Current FPGAs have the ability to be configured partially such that only the section of the configuration memory that changes due to the design modifications is rewritten with new configuration data. This configuration technique is known as partial reconfiguration [13] [14].

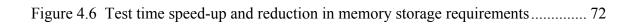

An FPGA typically consists of an array of Programmable Logic Blocks (PLBs), programmable interconnect network, Input/Output Buffers (IOBs) and embedded cores like memory blocks. The PLBs form the logic resources of an FPGA and usually consist of look-up tables, flip-flops and multiplexers. The programmable interconnect network is comprised of wire segments and programmable switches that connect or disconnect the wire segments. PLBs can be configured and connected to each other using the programmable interconnect network to implement virtually any combinational or sequential circuit. The IOBs are used to interface the circuit to the outside world [13]. A current trend in FPGAs is to embed pre-designed Intellectual Property (IP) cores into the FPGA. These IP cores include memory blocks like Random Access Memories (RAMs) and Digital Signal Processor (DSP) blocks to improve application-specific performance. Figure 1.1 shows the architecture of a typical FPGA.

Figure 1.1 FPGA Architecture

### 1.2 Testing and BIST

A quality product can be delivered only if it has been tested thoroughly. Testing is done to ensure fault-free operation of a circuit. In order to test any circuit, a mechanism is needed to apply a set of input stimuli to the Circuit Under Test (CUT) and another

mechanism is required to analyze or compare the output response with the response of a known good circuit to determine whether the circuit is fault-free or faulty [5].

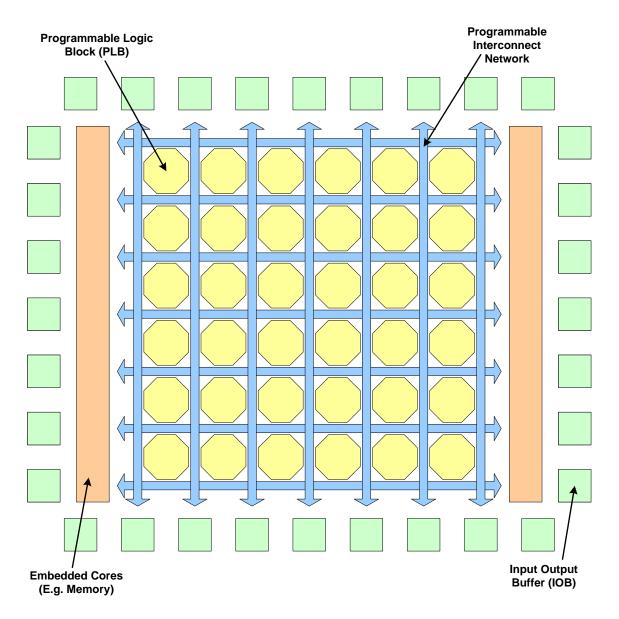

The input stimuli in case of external test systems are applied and the output response is analyzed or compared externally. In case of BIST, the test system is integrated within the system itself; the input stimuli are applied and the output response is analyzed internally within the system. The BIST technique involves addition of extra circuitry to an existing design. There are many variations in BIST depending on the CUT, but they all have a common purpose, which is to generate test patterns and analyze the output responses of the CUT [6]. A typical implementation of BIST consists of a Test Pattern Generator (TPG) for the CUT, input isolation circuitry for isolation of the primary inputs of the CUT during testing, an Output Response Analyzer (ORA) for verification of proper operation of the CUT, and control circuitry for execution of the test procedure as shown in Figure 1.2.

Figure 1.2 Basic BIST Architecture [6]

The external test approach is best suited for circuits that allow access to all the I/O pins for testing. Over the past two to three decades, the number of I/O pins on most very

large scale integration devices has increased by an order of magnitude while the number of transistors has increased by as much as four orders of magnitude [6]. This has resulted in reduced accessibility of the ICs; making external test systems more complicated and expensive. BIST on the other hand is much simpler and inexpensive, as external test equipment is absent. Moreover, BIST techniques can be used at any level of testing ranging from manufacturing level testing to system level testing. Major drawbacks of the BIST technique are additional design requirements, area overhead and performance penalty [6]. The drawbacks of BIST are easily compensated by the advantages it offers. BIST has been successfully implemented in many digital logic designs and finds special use in testing of FPGAs.

#### 1.3 FPGA BIST

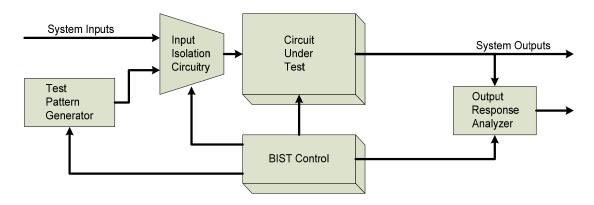

The growing popularity of FPGAs in the VLSI industry has fueled research on new methodologies for testing these FPGAs. The re-programmability of FPGAs makes them harder to test as compared to regular structures. This is due to the fact that the FPGA can be operated and connected in many ways internally; as a result, it must be configured multiple times in order to be tested completely. But, due to the in-system re-programmability of the FPGAs, they can be configured to test themselves [6]. The idea is to program the BIST circuitry in a part of the FPGA and treat the rest of the FPGA as the CUT. Once the CUT is completely tested, a reversal of roles takes place, as the part of the FPGA used for BIST circuitry now becomes the CUT and vice versa. This process is illustrated in Figure 1.3.

Figure 1.3 BIST in FPGAs

The BIST circuit can be designed in a number of ways to provide high resolution diagnostics for the FPGA, opening the door for fault-tolerant systems which was previously not possible with external test systems [3]. Moreover, BIST implemented in FPGAs does not suffer from any kind of area or performance overhead compared to conventional BIST techniques, as the BIST circuitry can be easily replaced by reprogramming the FPGA with the system function after test [3].

Considerable work has been done in the area of BIST for FPGAs. Depending on the resources to be tested, some of the PLBs of an FPGA are configured as Test Pattern Generators and Output Response Analyzers, forming the BIST circuitry which tests the targeted resources in the FPGA [7]. An FPGA is reconfigured repetitively for testing and, as a result, a major portion of the time required to test the FPGAs is spent re-configuring them, i.e. downloading BIST configuration data into the FPGA.

The majority of an FPGA is comprised of routing and logic resources [15]. So not surprisingly, most of the research and development work done in the area of BIST for

FPGAs has been for its logic and routing resources [3] [7] [17] [20] [23] [27]. A generic approach cannot be used to completely test an FPGA since different fault models and test techniques are used to test logic and routing resources. The work presented in this thesis focuses on BIST for programmable logic resources only. Although considerable work has been done in the area of BIST for logic resources of an FPGA, the BIST technique for the testing logic resources presented in this thesis is most influenced by work described in [3] and [7]. A BIST approach for testing the PLBs of ORCA series FPGAs was presented along with a procedure for diagnosis and location of faulty PLBs in [3]. The BIST technique presented in [3] was extended to Xilinx XC4000 and Spartan series FPGAs to completely test their logic and routing resources in [7].

#### 1.4 Xilinx FPGAs

The FPGAs used for the work presented in this thesis are Xilinx Virtex/Spartan-II and Virtex-4 FPGAs. Virtex/Spartan-II family of FPGA devices consist of primarily an array of PLBs, IOBs and memory blocks as shown in Figure 1.1 [8]. The Virtex-4 family of FPGAs combine a traditional FPGA with embedded processors, multipliers and high speed I/O interfaces in one package [9]. The architectural and operational features of these FPGAs can be exploited for implementation of BIST to speed-up the test time and also reduce the amount of memory required to store all the test configurations [16].

#### 1.5 Thesis Statement

The research work presented in this thesis, primarily focuses on ways to improve BIST implementation for programmable logic resources of FPGAs. This involves

reduction in test time, improvement in diagnostic resolution and reduction in memory storage requirements for BIST configurations. This work builds upon the previous work done in the area described in [3] [7] [18] [19] [29], extending to newer FPGA device families using techniques like partial reconfiguration and partial configuration memory readback. The target devices for this research are the Xilinx Virtex/Spartan-II and Virtex-4 family of devices. Configurations for BIST for programmable logic of Virtex/Spartan-II series FPGAs are developed along with methods to improve the test time. In case of the Virtex-4 family of devices, a set of BIST configurations for PLBs is developed and using architectural and operational features, further improvement in test time and reduction in configuration memory storage requirements is achieved.

The thesis is organized as follows: Chapter 2 describes the previous work done in the area of BIST for programmable logic resources and elaborates upon the architectures of Virtex/Spartan-II and Virtex-4 FPGAs. Implementation and experimental results of BIST for programmable logic resources in the Virtex/Spartan-II family of FPGAs is described in Chapter 3. Chapter 4 presents the implementation of BIST for programmable logic resources in the Virtex-4 FPGAs along with experimental results. Chapter 5 concludes the thesis with suggestions for future work and a discussion regarding the potential use of an embedded processor to assist in BIST.

### **CHAPTER TWO**

#### **Background**

This chapter covers the background knowledge required to understand the research work presented in the following chapters. It begins with an overview of the architectures and configuration process of the Virtex/Spartan-II and Virtex-4 FPGAs used for the work presented in this thesis. This is followed by a discussion of prior work done in FPGA testing and BIST for testing the programmable logic resources of an FPGA. The chapter concludes with a restatement of the thesis goals.

#### 2.1 FPGA Architectures

A typical FPGA consists of an array of PLBs, programmable interconnects, IOBs and RAM cores. The PLB array is interleaved with RAM cores and IOBs are arranged on the periphery as shown in Figure 1.1. Newer FPGAs have additional embedded cores like DSP cores, embedded microprocessors, and high-speed I/O interface for better system performance [13]. A design can be programmed into the FPGA by writing data to the configuration memory of the FPGA. The configuration memory then defines the function of the various programmable components of an FPGA. The following sub-sections describe the major components of Xilinx Virtex/Spartan-II and Virtex-4 series FPGAs.

#### 2.1.1 Configuration Memory

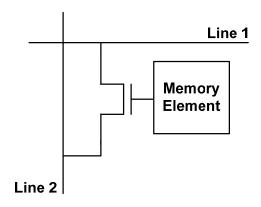

All programmable devices have some kind of memory elements which connect or break connections in a programmable device to establish the desired functionality. Figure 2.1 illustrates a memory element that determines the connection between two lines [2].

Figure 2.1 Configuration Memory Element

A memory element can be an anti-fuse, a floating-gate transistor, as in Read-Only Memory (ROM)/Flash memory, or a Static RAM (SRAM) cell. Most modern FPGAs use SRAM based memory elements which can be reprogrammed quickly in-system [2]. Xilinx Virtex/Spartan-II and Virtex-4 FPGAs are SRAM based, the drawback being volatile configuration memory. This means that the FPGA needs to be configured with the desired system function every time it is powered up, as the configuration memory elements lose their data on loss of power [11]. The configuration memory is spread across the entire device and is organized into smaller addressable segments called frames in the case of Xilinx devices. The size of the configuration memory varies depending on the size of the FPGA [11].

#### 2.1.2 Programmable Interconnects, IOBs, Memory and DSP

All components in the FPGAs are connected using some type of routing resources; as a result the programmable interconnect network forms the biggest part of an FPGA [10]. The programmable interconnect network consists of wire segments that are connected or disconnected using Programmable Interconnect Points (PIPs), these PIPs are essentially switches controlled by configuration memory bits. A collection of these PIPs form a switch-matrix that is used in conjunction with wire segments to connect to various components of the FPGA like PLBs and RAMs. The routing resources of an FPGA are organized in a hierarchical manner that includes local, I/O, dedicated and global routing resources. Local routing resources include internal wire segments of a component for direct connections between adjacent components and switch matrices. I/O routing resources connect the internal components of the FPGA to the IOBs. Dedicated routing resources are used to implement high speed buses for better performance. Global routing consists of buffered nets used to route high-fanout signals like clock and reset [8]

Over the years memory cores have become an integral part of the FPGA, as any kind of modern digital design requires storage capability. The memory cores, also known as BlockRAMs in Xilinx FPGAs, can be configured to operate in different modes depending on the data width and the size of the memory required. The BlockRAM in Xilinx FPGAs is a dual-port RAM that has two ports that can read and write to the memory simultaneously. To connect the FPGAs to the outside world, IOBs are provided which can be configured to be compatible with different IO standards, drive capabilities

and speeds [10]. Newer FPGAs have specialized DSP cores to implement high performance digital signal processing functions, these DSP cores typically consist of dedicated multipliers, adders and accumulators [10].

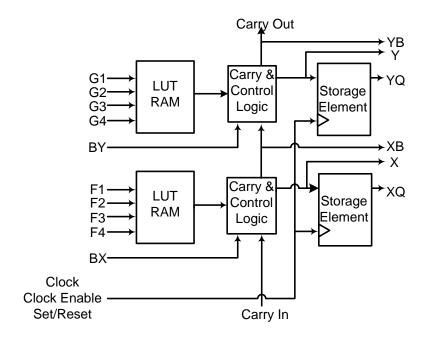

#### 2.1.3 Programmable Logic Resources

The PLBs of Xilinx FPGAs are divided into smaller units of logic called *slices*. Each slice typically consists of a pair of logic cells, where a logic cell is comprised of a Look-Up Table (LUT), a storage element, some carry logic circuitry and multiplexers. Figure 2.2 illustrates a typical PLB slice of a Xilinx FPGAs. The LUT in Xilinx FPGAs can also be used to implement a shift register or a small RAM (16-bit for a 4-input LUT); these small RAMs are called distributed RAMs or Look-Up Table RAMs (LUT RAMs). Virtex/Spartan-II FPGAs have two identical slices per PLB [8] [12], whereas a Virtex-4 PLB consists of two different kind of slices, named SliceL and SliceM. The LUTs in SliceM can be used to implement LUT RAMs or shift registers, whereas LUTs in SliceL do not have this feature [10]. A Virtex-4 PLB consists of two SliceLs and two SliceMs for a total of four slices.

Figure 2.2 Typical PLB Slice of a Xilinx FPGA

Table 2.1 shows the various resources available in Virtex/Spartan-II and Virtex-4 families of FPGAs. Although Spartan-II and Virtex are separate families of FPGAs, Spartan-II is essentially derived from the Virtex architecture with fewer features and lower performance for lower cost. The Virtex-4 family of FPGAs is sub-divided into three sub-families:

- LX: for logic applications (higher logic resources)

- SX: for DSP applications (higher DSP resources)

- FX: for embedded applications (embedded processor, Rocket IO and Ethernet cores)

Table 2.1 Resources available in different FPGA families [8] [12] [9]

| Resource               | Spartan-II | Virtex    | Virtex-4 LX | Virtex-4 SX | Virtex-4 FX |

|------------------------|------------|-----------|-------------|-------------|-------------|

| Largest PLB            |            |           |             |             |             |

| Array Size             | 28 x 42    | 64 x 96   | 192 x 116   | 128 x 48    | 192 x 84    |

| (Rows x Columns)       |            |           |             |             |             |

| PLBs                   | 1,176      | 6,144     | 22,272      | 6,144       | 16,128      |

| Logic slices           | 2,352      | 12,288    | 89,088      | 24,576      | 64,152      |

| <b>Distributed RAM</b> | 74 Kbits   | 384 Kbits | 1,392 Kbits | 384 Kbits   | 987 Kbits   |

| BlockRAMs              | 56 Kbits   | 184 Kbits | 6,048 Kbits | 5,760 Kbits | 9,936 Kbits |

| I/O pins               | 284        | 512       | 960         | 640         | 896         |

| DSP cores              | -          | -         | 96          | 512         | 192         |

#### 2.2 Virtex/Spartan-II Architecture

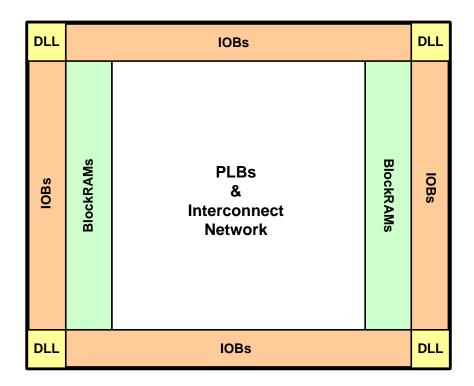

The architecture of a Virtex/Spartan-II FPGA is shown in Figure 2.3. An array of PLBs and associated routing resources is at the core of the FPGA. A column of BlockRAMs is placed at the east and west edges of the PLB array. The IOBs and the Delay Locked Loops (DLL) for clocks are located at the periphery of the FPGA. The BlockRAMs and PLBs are surrounded by additional routing resources, primarily used to connect the internal resources of the FPGA to the I/O pins of the FPGA.

Figure 2.3 Virtex/Spartan-II Architecture

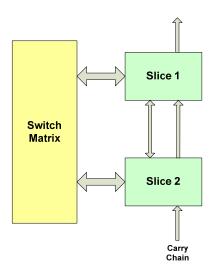

A Virtex/Spartan-II PLB consists of a pair of identical slices which are connected to a switch matrix as illustrated in Figure 2.4. The switch matrix is responsible for routing the signals in and out of the PLB. These PLBs also feature a carry chain that spans the entire column of PLBs. Each PLB slice has dedicated circuitry associated with the carry chain to implement fast arithmetic functions like an adder using look-ahead carry.

Figure 2.4 PLB of a Xilinx Virtex series FPGA

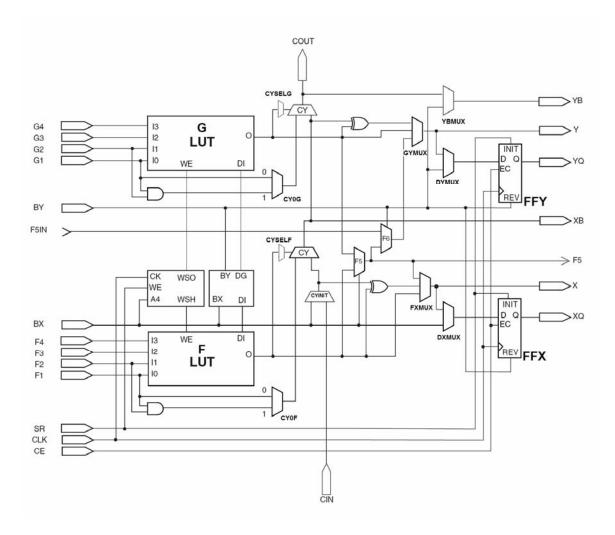

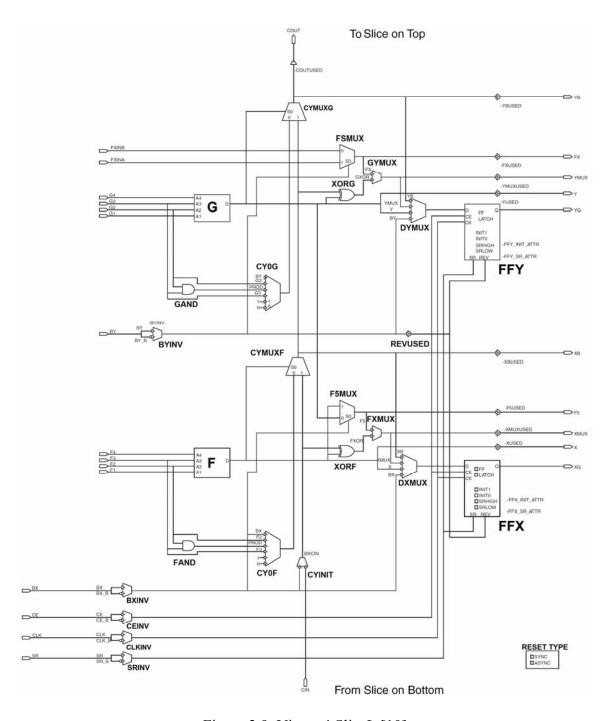

The internal architecture of a Virtex/Spartan-II PLB slice is illustrated in Figure 2.5. A single LUT of a Virtex/Spartan-II PLB can be used to implement any 4-input combinational logic function. It can also operate as a 16x1-bit RAM. Two LUTs of a PLB can be combined to form single-port 32x1-bit, 16x2-bit or a dual-port 16x1-bit RAM. The storage element can be operated either as a positive or negative edge-triggered flip-flop or as an active low or an active high level-sensitive latch. Storage elements have control signals including set/reset and clock-enable that are shared by all storage elements within a slice [8]. All four LUTs of the PLB can be combined using control logic and multiplexers provided in the PLB slices to implement any combinational logic function of up to six inputs. The PLBs feature dedicated logic like XOR gates and AND gates in order to implement fast arithmetic logic.[8].

Figure 2.5 Virtex/Spartan-II PLB Slice [8]

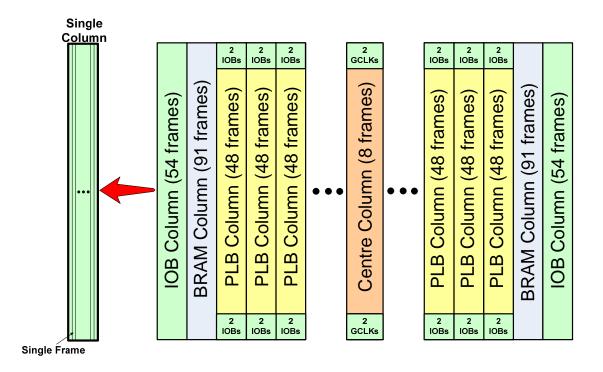

The configuration memory of Virtex/Spartan-II FPGAs is divided into frames. The number frames per column of PLBs and associated routing is fixed at 48 frames as shown in Figure 2.6. The frame size varies from 12 words of 32 bits each for the smallest device to 39 words for the largest device in the Virtex family, depending on the number of PLB rows in the FPGA. The IOB frames are on the edges of the FPGA followed by the BlockRAM frames. The PLB frames also have some IOB configuration data at the

start and end of the frame. The Centre column consists of frame data for global clocks [32].

Figure 2.6 Configuration memory structure of Virtex FPGAs

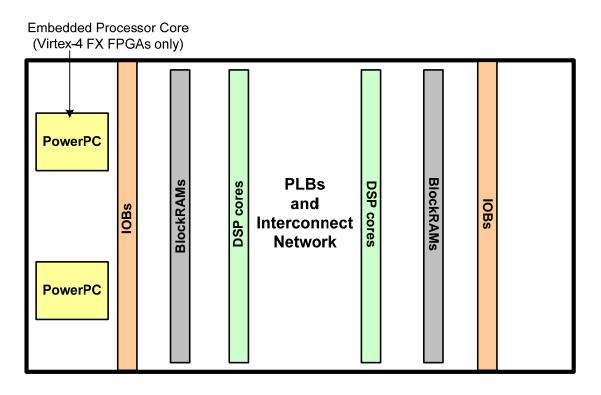

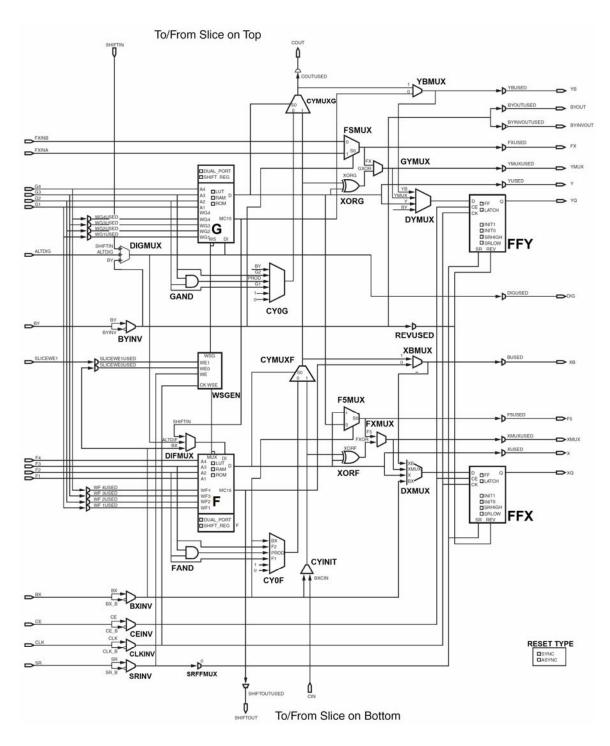

#### 2.3 Virtex-4 Architecture

The architecture of Virtex-4 FPGAs is different from Virtex/Spartan-II FPGAs, as illustrated in Figure 2.7. The PLBs and routing resources are spread across the entire FPGA. The I/O buffers are arranged in columns inside the FPGA, unlike Virtex/Spartan-II FPGAs that have IOBs only on the edges of the FPGA. Columns of BlockRAMs and DSP cores are interleaved with columns of PLBs. Virtex-4 FPGAs have up to 12 columns of BlockRAMs and 8 columns of DSP cores. The Virtex-4 FX family also features up to two embedded PowerPC cores.

Figure 2.7 Virtex-4 Architecture

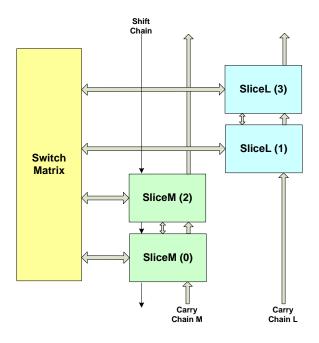

The PLB of a Virtex-4 FPGA is comprised of four slices, two SliceLs and two SliceMs as shown in Figure 2.8. All four slices are interconnected and similar slices are placed together in a column. Both pairs of slices have an independent carry chain spanning the entire column. The LUTs of SliceM also feature a Shift Register and a RAM mode of operation, consequently SliceMs feature a shift chain that can be used to combine SliceMs in single or multiple PLBs to form a long shift register [10].

Figure 2.8 Diagram of a Xilinx Virtex-4 series FPGA PLB

The slices in Virtex-4 feature two 4-input LUTs, denoted F and G, two storage elements, carry logic, multiplexers and some arithmetic gates. The LUTs can be used as a 4-input LUT, up to a 16-bit shift register (SliceM only) or a 16-bit LUT RAM (SliceM only). The storage elements can be configured as positive or negative edge-triggered flip-flops or active high or active low level-sensitive latches with clock-enable control capability. They can be initialized to high or low value after download and set/reset synchronously or asynchronously during operation. Multiplexers present in the slices are used to cascade LUTs in multiple slices or PLBs to form up to 64x1 LUT RAM in a single PLB or a 64-bit shift register using a single PLB (multiple PLBs can be cascaded to form larger shift registers). A PLB has two carry chains that are directed vertically upwards, the carry chain logic in the slices is used to implement look-ahead carry functions. A pair of AND and XOR gates are provided in a slice as dedicated arithmetic

gates for efficient utilization of the logic resources [10]. The internal architectures of Virtex-4 SliceL and SliceM are illustrated in Figures 2.9 and 2.10, respectively.

Figure 2.9 Virtex-4 SliceL [10]

Figure 2.10 Virtex-4 SliceM [10]

The Configuration memory of a Virtex-4 FPGA is divided into frames of fixed size of 41 words of 32 bits each. These frames span a fixed number of rows of an FPGA column, unlike Virtex/Spartan-II frames that span the entire column. Frames are grouped together to form blocks based on the resources defined by them, like PLBs or BlockRAMs [11].

## 2.4 FPGA Configuration

A design is typically synthesized and converted to a configuration file or a bitstream that is downloaded into the FPGA to implement the required design [2]. Several interfaces are available to configure the FPGAs including Boundary Scan, dedicated serial interface and dedicated parallel interface [11]. As the FPGA devices grow bigger, the configuration file or bitstream size also grows. This leads to a longer time required to download a design.

Partial reconfiguration is a technique used to reduce the time required to reconfigure an FPGA. Once a full configuration for a design has been downloaded to the FPGA, minor changes in the design result in small changes in the bitstream. So instead of downloading the full bitstream, only parts of the bitstream that change are downloaded using partial reconfiguration [29]. In case of Xilinx FPGAs, a frame is the smallest unit of configuration memory that can be changed. One of the features of the newer FPGAs is dynamic partial reconfiguration. This feature allows the user to retain the flip-flop contents of the PLBs and IOBs during reconfiguration. Unused parts of FPGAs are reconfigured while the FPGA is operational with the system function [14].

## 2.4.1 Configuration Interface

There are three main configuration interfaces available in Xilinx FPGAs [11]. They are:

- 1. Master/Slave Serial interface

- 2. Master/Slave Parallel (SelectMAP) interface

### 3. Boundary Scan interface

The source of clock used for configuration determines whether the interface is in master mode or slave mode. If the source for generation of the configuration clock is external to the FPGA then the configuration mode is in slave mode. In master mode the configuration clock is generated internally by the FPGA. The configuration interface to be used for Xilinx FPGAs is determined by the value set on three mode pins of the FPGA [11].

One bit is downloaded to the FPGA per clock cycle when the serial interface is used. In case of the SelectMAP interface, configuration data is downloaded in parallel. The configuration data can be both downloaded to the FPGA or read back from the FPGA using the SelectMAP interface. The SelectMAP interface is capable of reading or writing 8 or 32 bits per clock cycle in parallel, greatly reducing the configuration download time as compared to the serial interface [11]. The third interface is known as Boundary Scan [5] [30]. It was originally developed to test the integrity of the connections between devices on a printed circuit board. Xilinx FPGAs make additional use of the Boundary Scan interface to download to or read back from the FPGA configuration memory [11].

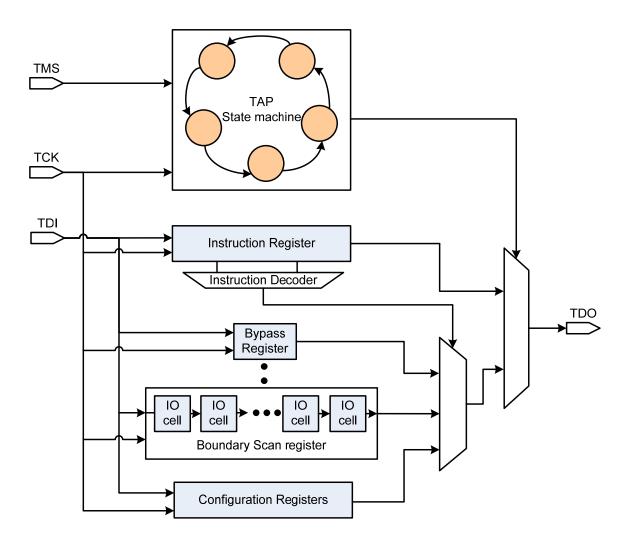

The Boundary Scan interface consists of a 4-pin Test Access Port (TAP), TAP controller, instruction register and decoder, bypass register and Boundary Scan register as shown in Figure 2.11.

Figure 2.11 Boundary Scan Architecture

The TAP controller consists of a finite state machine that is controlled by four TAP pins, namely TCK (Test Clock), TMS (Test Mode Select), TDI (Test Data In) and TDO (Test Data Out). Depending on the state of the TAP controller, instructions or data

can be loaded into the Boundary Scan interface registers. All the IOBs are interconnected to form a Boundary Scan register in test mode and test vectors are loaded to the IOBs using TDI. Similarly TDO is used to read out the test results from the IOBs. The bypass register is a single bit register used to put the device in bypass mode to access other devices connected in the Boundary Scan chain. The instruction register and decoder are used to execute the Boundary Scan test instructions [11]. Most of the current FPGAs allow configuration download using the Boundary Scan interface. Xilinx FPGAs implement Boundary Scan instructions that allow both configuration memory download and readback by using configuration registers, like the frame data register and frame address register. The configuration memory can be written using a CFGIN command and read back using a CFGOUT command [11].

Xilinx also provides user access to the FPGA core from the Boundary Scan interface via Boundary SCAN (BSCAN) modules in the FPGA. These user access modules can be used to create internal Boundary Scan chains to implement user-defined functions in an FPGA. The BSCAN modules have to be activated using Boundary Scan commands before they can be used to perform a user function. All BSCAN modules source the clock from the TCK pin in the Boundary Scan interface and the clock for a given BSCAN module is enabled only when it is activated. BSCAN modules also consist of output pins that indicate the status of the Boundary Scan interface [11] [32] [33].

### 2.4.2 Configuration Process

The configuration of a Xilinx FPGA is a multi-stage process. Before the download of configuration data, the FPGA is initialized, which involves synchronization

of the configuration interface logic of the FPGA with the configuration data to be downloaded. It may also include clearing of the configuration memory. A Cyclic Redundancy Check (CRC) is performed on the configuration data to check for errors while data is downloaded to the configuration memory. The final step is known as the startup sequence, it is a multi-step process that includes activation/de-activation of global signals like global set/reset (GSR), global write-enable for all the RAMs and flip-flops in the FPGA and global tri-state enable for all the IOBs [11].

For full configuration, all the frames in the FPGA are written with configuration data, whereas for partial reconfiguration only the frames that change are rewritten. The configuration process is similar for both methods except for the initialization. The configuration memory is not cleared during initialization of the FPGA using partial reconfiguration. During configuration download, the frame address register (FAR) is written with the address of the frame to be written and 32-bit words of configuration data are written to the specified frame in the configuration memory via the frame data register (FDR) [11].

## 2.4.3 Configuration Memory Readback

Xilinx FPGAs allow the user to read back contents of the complete configuration memory of the FPGA. This can be used to verify the configuration bits downloaded into the FPGA. Instead of full configuration memory readback, parts of the configuration memory can also be read back; this procedure is known as partial configuration memory readback [14]. A frame is the smallest unit of configuration memory that can be read using partial configuration memory readback. For reading a frame, the frame address is

written in the FAR and the configuration data is read out from the FDR using an external interface like SelectMAP or Boundary Scan [33]. Xilinx FPGAs are also capable of capturing the contents of the BlockRAMs and flip-flops of the FPGA during configuration memory readback [11]. In the case of Xilinx FPGAs, a CAPTURE module needs to be instantiated in the design in order to perform configuration memory readback [11] [33].

## 2.5 Prior Work in FPGA Testing

This section lists some of the work previously done in the area of FPGA testing. Major work related to testing of logic resources of an FPGA is presented in [3] [7] [16] [17] [18] [21] [22] [23] [24] [28]. Stroud et al. present a method to evaluate the number of configurations required to test all the logic resources of an FPGA in [21]. The most comprehensive works in testing of programmable logic resources using a BIST approach were presented in [3] [7]. Reference [7] extends the work done in [3], which was done using Lucent's ORCA series FPGAs to Xilinx 4000 series FPGAs. Reference [3] also describes an algorithm called MULTICELLO that can be used for diagnosis of faulty PLBs in FPGAs. The work done in [3] and [7] laid the basis for the work presented in this thesis.

Ideas were derived from work done in [17] [18] [19] to improve the BIST approach to test logic resources for better diagnostic resolution and faster test times. Abramovici et al. introduced a new concept of self-testing areas that are used to implement BIST in small unused areas of the FPGA, while the rest of the FPGA is operational with the system function in [17] [18]. This work inspired the use of dynamic

partial reconfiguration to achieve test time speedup. A technique to test embedded cores of SoCs that include regular structures like RAM and multiplier cores, using the FPGA core, is explained in [19]. This work introduced the concept of circular comparison that results in higher diagnostic resolution.

Reference [28] by Wang et al. presents an alternative technique to test logic resources using BIST. A non-BIST based approach to test an FPGA that uses an external Programmable Read Only Memory (PROM) to store the test configurations and test vectors is presented in [22] by Huang et al. Reference [23] introduces another technique to externally test the logic resources of Xilinx 3000, 4000 and 5000 series FPGAs.

References [7] [16] [17] [18] [20] [22] [24] [25] [26] [27] present some of the work done in the area of FPGA interconnect testing. Reference [20] expands upon the BIST technique used in [17] and [18] to test FPGA interconnects. Renovell et al. [25] and Wang et al. [27] present techniques to externally test the interconnects of an FPGA. A BIST approach to test the interconnects of an FPGA using small BIST structures known as BISTERs is presented in [26] by Harris et al. Renovell et al. describe a technique to test the Xilinx FPGAs by dividing the FPGA into separate arrays of logic and interconnects and LUT RAMs in [24].

References [16] and [19] describe comprehensive work done in testing all the resources of the FPGAs, including the embedded cores of FPGAs like RAMs and multipliers. Stroud et al. presented a case study that uses Atmel's FPGA based SoCs to present the implementation of BIST to completely test the logic, interconnect and memory resources of an FPGA [16].

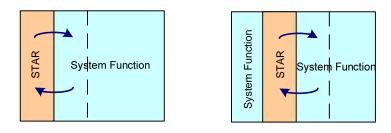

### 2.6 General BIST Architectures

There are two primary approaches for testing an FPGA using BIST. One approach is to configure the complete FPGA with BIST circuitry to test itself and replace it with the original system function after the device has been tested; this method is known as off-line testing since the system function of the FPGA is halted to test the FPGA [6] [3]. This scheme is discussed in detail in the next section. The other option is to keep the system operational while testing unused portions of the FPGA by configuring them as Self Testing AReas (STARs). These STARs are moved around the FPGA using dynamic partial reconfiguration of the FPGA as shown in Figure 2.12. This scheme is called online testing because the system is on-line or operational even when the device is being tested [17] [18].

Figure 2.12 On-line BIST [6]

## 2.7 BIST for Logic Resources of an FPGA

This thesis deals only with off-line testing of programmable logic resources, hence the CUT in this case is the array of PLBs in the FPGA. BIST for testing logic resources from here on shall be referred to as **Logic BIST**.

#### 2.7.1 BIST Architecture

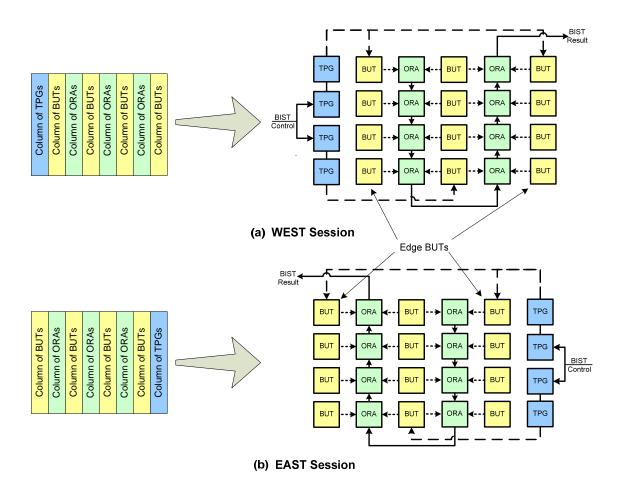

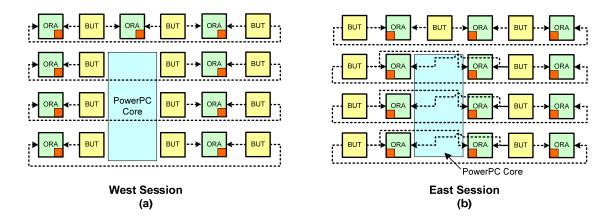

BIST circuitry comprises Test Pattern Generators (TPGs) and Output Response Analyzers (ORAs). The TPGs generate the test patterns required to test the PLBs. The ORAs essentially compare the outputs of two identically configured PLBs under test, also called Blocks Under Test (BUTs), and record any mismatch due to a fault. Since PLBs are required to implement the BIST circuitry, all logic resources of an FPGA cannot be tested simultaneously. If half of the PLBs can be configured as BUTs, then only two test sessions are required to completely test all the PLBs. So, in the first session half of the PLBs are configured as Blocks Under Test (BUTs) and the rest are configured as TPGs and ORAs. In the second session they are swapped, i.e. the PLBs that were BUTs in first session now become TPGs and ORAs and vice versa, as illustrated in Figure 2.13 [3][7]. The two test sessions are called West and East sessions depending on the location of the TPGs, shown in Figure 2.13 (a) and (b) respectively. This scheme shows a column based arrangement of BUTs, TPGs and ORAs, but it can also be row based and the two test sessions are then called North and South sessions [3].

The BUTs are located in alternate columns of the FPGA with an ORA column sandwiched between every two columns of the BUTs such that they compare the outputs of the BUTs in the neighboring columns. The ORAs latch any mismatch between the BUT outputs being compared as a result of a fault. The fault can be associated with either of the two BUTs compared by the ORA. The ORAs are connected in a scan chain as illustrated in Figure 2.13. The BIST results can be shifted out after the BUTs have been tested using the scan chain [3]. To completely test the PLBs, they are reconfigured and tested in different modes of operation while keeping the BIST architecture untouched. A

test phase is a configuration that tests a PLB in a single mode of operation. A group of test phases that test a PLB in all of it's modes of operation form a test session [3]. The PLBs are also tested in their LUT RAM mode of operation which tests the logic in the PLBs associated with LUT RAMs [7] [37]. BIST results of faulty devices can then be analyzed using MULTICELLO [3] to determine the exact location of the faulty PLB.

Figure 2.13 BIST Architecture to test Logic Resources [3]

It can be noticed from Figure 2.13 that BUTs in the edge columns of the BIST architecture suffer from lower diagnostic resolution, as they are compared by only one

ORA, whereas the rest of the BUTs are compared by two ORAs. Reference [19] introduces a circular comparison technique that allows the comparison of every BUT by two ORAs, thereby increasing the diagnostic resolution.

## 2.7.2 Test Pattern Generation and Output Response Analysis

As the number of inputs of a PLB is small, exhaustive test vectors can be used to test them. A simple counter or a linear feedback shift register (LFSR) can be implemented as a TPG using very few PLBs to generate exhaustive test vectors [5] [6]. An LFSR is more commonly used because it can generate pseudo-random patterns and utilizes fewer gates as compared to a counter [6].

Two identical TPGs drive alternate columns of BUTs in the FPGA such that every ORA compares the output response of BUTs that receive input patterns from two different TPGs. This ensures that even if one of the PLBs used as a TPG is faulty, the ORAs record a mismatch as both the TPGs generate different test patterns. Hence, using two TPGs improves fault detection because if a single faulty TPG was driving all BUTs, the ORAs would have never recorded a mismatch [3]. TPG loading is an issue in this BIST architecture, since a large number of BUTs are connected to a single TPG. The large loading on a TPG output limits the maximum operating frequency of the BIST architecture. Solutions proposed are to either use drivers for TPG signals or split the FPGA into smaller sections with independent pairs of TPGs that are tested in parallel [7]. Both the schemes limit TPG loading without increasing the number of configurations.

The comparison based approach has better fault detection capability compared to signature analysis, as the response of the BUTs is not compacted. Instead it is compared,

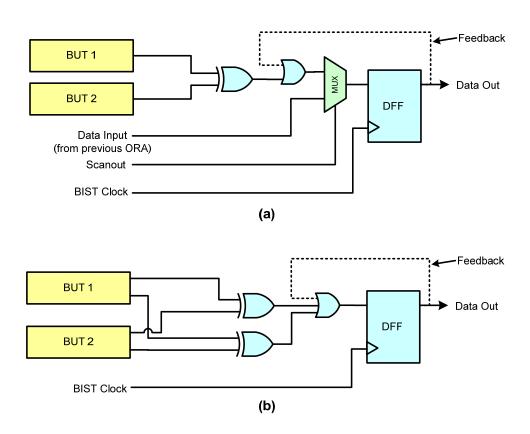

so unless there are equivalent faults in certain extremely rare cases the faults are guaranteed to be detected [3]. A comparison based ORA is illustrated in Figure 2.14 (a). It uses an XOR gate to detect any mismatch and the feedback from the flip-flop to the OR gate latches a '1' into the flip-flop in case of a mismatch. The multiplexer is used to form a scan chain of ORAs in order to scan out the BIST results after every test phase [3]. A good circuit is represented by a '0' and a fault is indicated by a '1' stored in the ORA flip-flop. Configuration memory readback can be used instead of using a scan chain to retrieve BIST results. Figure 2.14 (b) shows the ORA without the scan chain logic used in this case [7].

Figure 2.14 Output Response Analyzer

## 2.7.3 Configuration Schemes

The BIST approach described in the initial work [3] [7] uses complete reconfiguration of an FPGA to switch between test phases. Full reconfiguration is highly time consuming and in the case of Logic BIST, only the BUT configurations change from one test phase to the next for a given test session. The use of partial reconfiguration to reconfigure only the BUTs of the FPGA, to operate in a different mode of operation for a given test session, was proposed in [29]. Partial reconfiguration reduces the memory required to store the test configurations and leads to faster test times, since less configuration data is downloaded into the FPGA per test phase.

#### 2.7.4 Results Retrieval

After execution of a test phase the BIST results have to be read out of the ORAs in the FPGA. As described in [3], the ORAs form a scan chain and the BIST results can be shifted out using the *Scanout* signal shown in Figure 2.14 (a). The data input of the ORA at the tail of the scan chain is tied to a '1', so there is a trail of ones at the end of the BIST results scanned out which serves as an indicator for the end of the scan chain and serves as a check for correct operation of the ORAs.

Most FPGAs have the ability to capture the contents of flip-flops in the PLBs during configuration memory readback. This feature can be used to retrieve the BIST results captured in the flip-flops of PLBs configured as ORAs by reading back the configuration memory. Although configuration memory readback increases the testing time per test phase it reduces the total number of test configurations and improves the diagnostic resolution [7]. Due to the limited resources of some FPGA PLBs, not all outputs of a

BUT can be observed in a single configuration, therefore there are multiple configurations for every test phase. If configuration memory readback is used then the scan chain to retrieve BIST results can eliminated from the ORA, making extra logic resources available in the PLBs to be used as ORAs. The extra logic resources in the ORAs make it possible in some FPGAs to compare all the BUT outputs in a single configuration for a test phase. Figure 2.14 (b) illustrates the ORA without the scan chain logic that is capable of comparing more BUT outputs and also has fewer control signals than the ORA with the scan chain logic.

#### 2.8 Restatement of Thesis Goals

A significant amount of work has been done in the area of Logic BIST for FPGAs. As the technology advances and the feature sizes shrink, FPGAs grow larger in size and feature many more capabilities, compared to their predecessors. The testing time increases as the size of the FPGA grows, so new methods and architectural features have to be used in order to keep the test times and the memory storage requirements to a minimum.

The work presented in this thesis builds upon the work previously done in [3] [7] [19] [29] and introduces some new techniques to implement Logic BIST for newer FPGA devices. As the majority of the time required for testing FPGAs using BIST is spent on their reconfiguration, emphasis is put on techniques like partial reconfiguration and partial configuration memory readback to reduce the test time and configuration memory storage requirements for Logic BIST. This chapter introduced the basic concepts and overview of the previous work done, required to understand the work presented in

the following chapters. Chapter 3 presents the implementation of Logic BIST on Virtex/Spartan II series FPGAs, along with the use of partial reconfiguration and partial configuration memory readback to achieve speedup in test time and reduction in memory storage requirements. Chapter 4 presents the implementation of Logic BIST for Virtex-4 FPGAs. The Logic BIST architecture was modified for Virtex-4 to achieve better diagnostic resolution. In both cases, the PLB slices were modeled and, based on the resultant fault simulations, Logic BIST configurations were developed to test the PLBs. Chapter 5 concludes with a summary and suggestions for future improvements along with a discussion regarding the use of an embedded processor for BIST.

## CHAPTER THREE

# Logic BIST for Virtex/Spartan II

## 3.1 Introduction

This chapter discusses the implementation of Logic BIST for Xilinx Virtex and Spartan-II FPGAs. The details regarding the Logic BIST architecture and test configurations are described along with the fault coverage of the logic resources. The methods to achieve speed-up in test time and reduction in memory storage requirements are also discussed. These methods include techniques like partial reconfiguration and partial configuration memory readback, which reduce the configuration download time and BIST results retrieval time, respectively. The experimental results of all the methods employed are presented with a summary and analysis of the results to conclude the chapter. The work presented in this chapter is primarily the work presented in [31] with some additional details.

## 3.2 Virtex/Spartan-II PLB Architecture

An overview of the Virtex/Spartan-II FPGA architecture was presented in Chapter 2. In this chapter, additional details regarding the internals of the PLB are provided. Figure 2.8 shows the block diagram of a PLB slice of a Virtex/Spartan-II FPGA [8]. It consists of two 4-input LUTs, F and G, that can also function as 16-bit LUT RAMs or

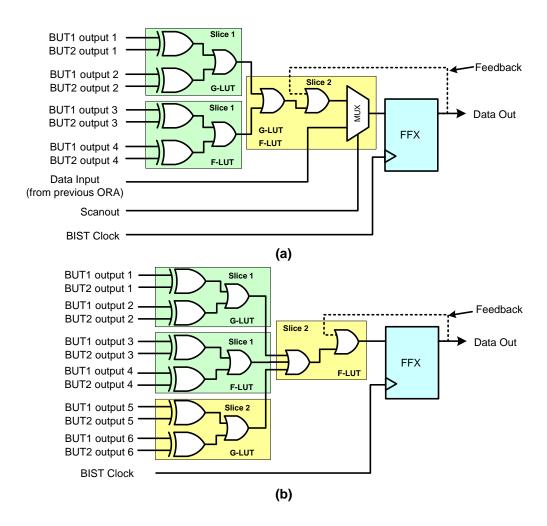

16-bit shift registers. For the RAM or shift-register modes of operation, additional circuitry is provided to generate the write enable signals. Two AND and two XOR gates are provided in each PLB slice to efficiently implement arithmetic functions. Multiplexers CY and input CIN are used to implement the carry chain logic. A slice has two storage elements, FFX and FFY, which can be used either as flip-flops or as latches to implement sequential circuits. Multiplexers DXMUX and DYMUX are provided to choose the data input for the storage elements FFX and FFY, respectively. Multiplexers F5 and F6 are used to combine LUTs to implement combinational logic functions with five or six inputs using a single PLB [8].

#### 3.3 BIST Architecture

Logic BIST for Virtex/Spartan-II builds upon previous work done on Lucent's ORCA and Xilinx 4000 series FPGAs, as described in [3] and [7], respectively. The BIST approach is very similar to those described in [3] and [7], as illustrated in Figure 2.13. It is modified with focus on partial reconfiguration and partial configuration memory readback.

The BIST architecture can be either row-oriented or column-oriented, but column-oriented BIST architecture emerges as the more efficient BIST implementation for Virtex/Spartan-II FPGAs for three major reasons. Firstly, the carry chain implemented between the PLBs is implemented vertically upwards within each column, so in order to test logic resources associated with the carry chain the BIST architecture has to be column-oriented. Secondly, dedicated local routing is available for making direct connections between horizontally adjacent PLBs [8]. Therefore it is easier to make

BUT to ORA connections across rows in a column-oriented BIST architecture without any routing issues. Lastly, the structure of the configuration memory is also column-oriented. As mentioned earlier, configuration memory is comprised of frames and it takes multiple frames to configure a column of PLBs and their associated routing in an FPGA, as illustrated in the Figure 2.6. A column-oriented BIST architecture aids in reducing the number of frames to be written using partial reconfiguration and read using partial configuration memory readback for retrieval of BIST results.

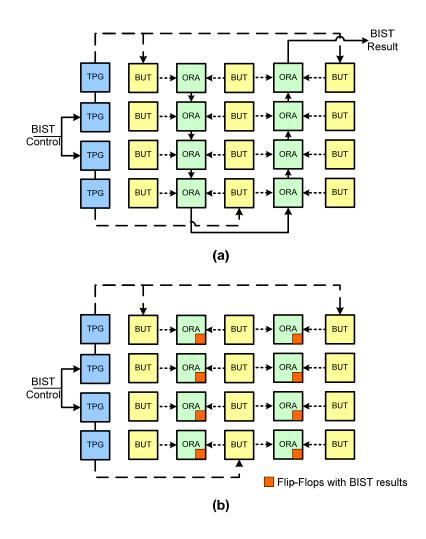

Figure 3.1 illustrates the architecture of Logic BIST for Virtex/Spartan-II FPGAs. Two identical TPGs are restricted to one column of the FPGA and alternate columns are configured as ORAs and BUTs. The TPG is a 12-bit LFSR that generates pseudo-exhaustive test vectors, providing identical vectors to both the slices of each PLB configured as a BUT. Each TPG provides identical input patterns to alternate BUT columns, which improves fault detection in case of a faulty TPG [3]. The ORAs compare the outputs from the two neighboring BUTs that get identical test patterns from two different TPGs. BIST results after testing are either scanned out or captured in the configuration memory. Figure 3.1 (a) shows the ORAs connected in a scan chain that allows scanning out of BIST results. Figure 3.1 (b) illustrates the architecture in which the BIST results are captured in the configuration memory and retrieved using configuration memory readback.

Figure 3.1 Logic BIST Architecture for Virtex/Spartan-II FPGAs

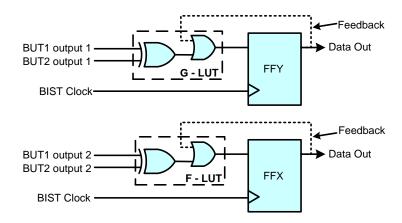

Two *test sessions* are required to test all the logic resources. BUTs in each test session are configured in different modes of operation in order to be tested completely; these configurations are called *test phases*. In a PLB only 12 out of the 16 outputs can be observed, as four outputs related to carry and multiplexer logic cannot be routed out of the PLB. The limited logic resources of a PLB allow a maximum of five BUT outputs to be observed by an ORA in a single configuration. Therefore a set of test phases has to be repeated three times, each time looking at a different set of four BUT outputs for a total

of twelve BUT outputs as shown in Figure 3.2 (a). This set of test phases is called a *slice test set*. To retrieve the BIST results, if readback is used instead of implementing a scan chain of ORAs, the ORA can be modified to compare six BUT outputs in a single configuration as shown in Figure 3.2 (b), where the logic resources of an ORA previously used for scan chain implementation are now used for comparing more BUT outputs. As a result the number of slice test sets can be reduced from three to two, where one slice is tested in each slice test set.

Figure 3.2 Output Response Analyzers

The Boundary Scan interface was used for the implementation of Logic BIST. The frame address register is written with the address of the frame to be written or read and 32-bit words of configuration data are written to or read from the frame data register, depending on the operation being performed. Xilinx provides two user access registers in Virtex/Spartan-II FPGAs that can be used by invoking a Boundary Scan module (BSCAN\_VIRTEX). For Logic BIST, user access register 1 was used to source the BIST clock for BUTs, TPGs and ORAs from the Boundary Scan interface and user access register 2 was used to generate a reset signal for all the TPGs and ORAs.

There are two test sessions: East and West, each testing half of the PLBs. To completely test a PLB, except for the case when it is configured as LUT RAM, a total of seven different test configurations of a PLB are required. Therefore the total number of Logic BIST configurations depends on the method used for BIST results retrieval.

- Scan chain method: 2 sessions x 7 phases x 3 slice test sets = 42 configurations

- Readback method: 2 sessions x 7 phases x 2 slice test sets = **28** configurations

## 3.4 Partial Reconfiguration

Using partial reconfiguration, only BUT configurations are changed in a given test session. Most of the 48 frames of a PLB column are associated with routing resources rather than BUT configurations. So, in order to reconfigure the BUTs, a small number of frames per PLB column in only the columns of BUTs have to be rewritten with new configuration data. After the first test configuration is downloaded for a test session, the rest of the configurations can be partial reconfigurations.

The sequence in which the test configurations are applied is crucial for keeping the partial reconfigurations small, as discussed in [29]. Since multiple slice test sets are required for each test phase, three scenarios were investigated regarding the sequence of configurations to be applied:

- **Scenario 1.** For a given test session, the configuration of both the slices is kept fixed but the BUT outputs compared by the ORAs are changed. Therefore each test phase consists of two or three slice test sets, depending on the BIST results retrieval technique used.

- **Scenario 2.** For a given test session, the BUT outputs compared by the ORAs are kept fixed and the configurations of both PLB slices are changed. Therefore each slice test set consists of seven test phases.

- **Scenario 3.** For a given test session, the BUT outputs compared by the ORAs are kept fixed and the configuration of only the slice whose outputs are being compared is changed, while maintaining the first configuration in the other slice. Therefore each slice test set consists of seven test phases and each test session has two or three slice test sets depending on the BIST results retrieval method used.

Partial reconfiguration is not effective in reducing the configuration file size when routing changes from one configuration to the next, as frames related to interconnects comprise the majority of the total number of frames in the FPGA. Consequently, the third scenario turns out to be most effective [29]. The sequence in which the test phases are applied can also be optimized to reduce the difference between consecutive test configurations, thereby reducing the partial reconfiguration file size.

## 3.5 Partial Configuration Memory Readback

Partial configuration memory readback can be used instead of using full configuration memory readback or scan chain to retrieve BIST results. Full configuration memory readback reduces the number of slice test sets from three to two but it takes the amount of time comparable to full configuration. On the other hand, scan chain implementation only requires a few clock cycles (equal to the number of ORAs) to retrieve BIST results, making it faster by a few orders of magnitude. This gap is greatly reduced by using partial configuration memory readback. The ORAs are designed such that the BIST results are stored in a single flip-flop of a PLB. This allows the BIST results to be captured in only one frame per ORA column. So, a total of (M/2)-1 frames are read back to retrieve BIST results, where M is the total number of PLB columns of the FPGA.

The configuration bit generation tool provided by Xilinx is used to obtain a logic allocation file. This file provides the information regarding the location of the configuration memory bits that contain the data captured from the PLB flip-flops. The location of each ORA flip-flop is defined in terms of the frame address and an offset within the frame.

## 3.6 Logic BIST Configurations for Virtex/Spartan-II

The following subsections present the details regarding the implementation of Logic BIST for Virtex/Spartan-II FPGAs.

## 3.6.1 Fault Model and Fault Coverage

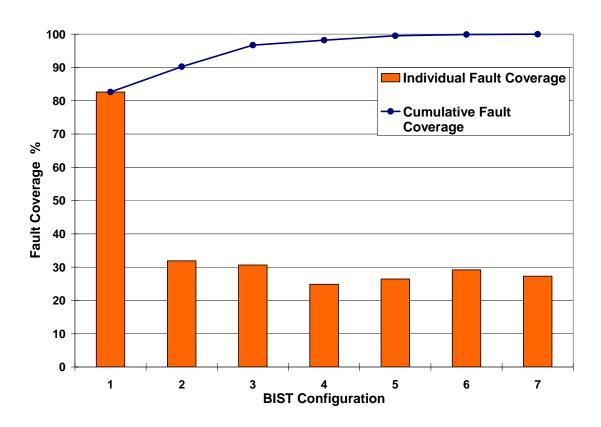

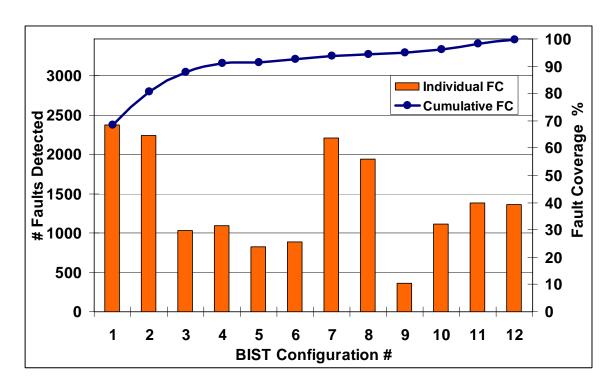

The PLB of a Virtex/Spartan-II FPGA consists of 2 identical slices, so a single slice was modeled instead of modeling the entire PLB for fault simulations. The gate level stuck-at fault model was considered for fault coverage. The logic in the slice related to the RAM mode of operation of the LUTs was not considered, as faults in that logic would get detected by a LUT RAM test presented in [37]. The storage elements of the PLB were not tested in the asynchronous mode of operation, the reason for which is discussed in the Section 3.6.2. A total of seven configurations are required to completely test the PLB, not including the LUT RAMs and related logic. Cumulative fault coverage was evaluated by simulating the complete fault list for the first test configuration and then the list of undetected faults is used as the fault list for simulation of successive test configurations. Individual fault coverage of each test configurations. Both cumulative and individual fault coverage are shown in Figure 3.3.

Figure 3.3 Fault Coverage of a Virtex FPGA PLB slice

## 3.6.2 Configuration Details

The details of the seven configurations of a Virtex Slice are summarized in Table 3.1. Some BUTs were diagnosed as faulty during Logic BIST when asynchronous reset was used; the cause for this was attributed to timing skew in the TPG output signals controlling the reset signal to the flip-flops, which introduced an uncertainty regarding the value stored in the storage elements of the BUTs. This issue remained unresolved during development for Virtex/Spartan-II FPGAs, but it was later resolved for Virtex-4, which is discussed in Section 4.4.2.

Table 3.1 Configuration Details

| Slice              |          | Configuration     |              |                 |              |              |               |               |  |

|--------------------|----------|-------------------|--------------|-----------------|--------------|--------------|---------------|---------------|--|

| Component          |          | 1                 | 2            | 3               | 4            | 5            | 6             | 7             |  |

| LUT<br>F/G         | LUT      | 0000              | xnor<br>/xor | xor<br>/xnor    | xnor<br>/xor | xor<br>/xnor | xnor<br>/xor  | xor<br>/xnor  |  |

|                    | MODE     | shift<br>register | lut          | lut             | lut          | lut          | lut           | lut           |  |

| FF<br>X/Y          | MODE     | ff                | ff           | latch           | latch        | latch        | ff            | ff            |  |

|                    | X INIT   | 0                 | 1            | 0               | 1            | 1            | 0             | 1             |  |

|                    | Y INIT   | 0                 | 1            | 0               | 1            | 1            | 0             | 1             |  |

|                    | RESET    | sync              | sync         | async           | async        | async        | sync          | async         |  |

| CY0G /<br>CY0F     |          | prod              | g1/f1        | prod            | 0            | 1            | 1             | 1             |  |

| CYSELG /<br>CYSELF |          | g/f               | g/f          | 1               | g/f          | g/f          | 1             | 1             |  |

| GYMUX /<br>FXMUX   |          | g/f               | f6/f5        | gxor<br>/fxor   | f6/f5        | f6/f5        | gxor<br>/fxor | gxor<br>/fxor |  |

| DYMUX /<br>DXMUX   |          | I1                | 10           | I1              | I1           | I1           | I0/I1         | 10            |  |

| YBMUX              |          | I1                | I1           | I1              | 10           | I1           | 10            | 10            |  |

| BY / BX            |          | byinv<br>/bxinv   | by<br>/bx    | byinv<br>/bxinv | 0            | 1            | by<br>/bx     | by<br>/bx     |  |

|                    | SR       |                   | sr           | sr              | sr           | 1            | 0             | 1             |  |

| (                  | CE       |                   | 1            | ce              | 0            | 1            | 1             | 1             |  |

| CLK                |          | clk               | clkinv       | clk             | clkinv       | clk          | clkinv        | clk           |  |

| CY                 | CYINIT   |                   | bx           | cin             | cin          | cin          | cin           | cin           |  |

| Breakpoints        |          |                   |              |                 |              |              |               |               |  |

| Cout               |          | on                | on           | on              | on           | off          | on            | on            |  |

| Y                  |          | on                | on           | on              | on           | off          | on            | on            |  |

| XB                 |          | on                | on           | on              | on           | off          | on            | on            |  |

| F5                 |          | on                | on           | on              | on           | off          | on            | on            |  |

| X                  |          | on                | on           | on              | on           | off          | on            | on            |  |

|                    | REV USED |                   | on           | on              | on           | off          | off           | on            |  |

| SR                 |          | on                | on           | on              | on           | off          | on            | on            |  |

## 3.7 Logic BIST Configuration Generation Process

Two programs were developed to generate all the test configurations, referred to as the template generation program and the template modification program. The design is described in Xilinx Design Language (XDL), a netlist format used by Xilinx. The template generation program generates a template file depending on the session and the slice test set, where the BUTs are configured with Configuration 1 as summarized in Table 3.1. The template file generated does not contain routing information as it simplifies configuration file generation process. The template is converted from XDL format to a Native Circuit Description (NCD) format that can be used by Xilinx CAD tools for routing the design. The template is routed using Xilinx routing tools and converted back to XDL format. The template modification program uses the routed template configuration file and modifies only the BUT configurations while keeping the routing fixed to generate all the other BIST configuration files. This approach results in generation of small partial reconfiguration files as the routing structure remains fixed for all test phases of a slice test set. The routed configuration files are used to generate the configuration bitstreams that are downloaded to the FPGA.

The Xilinx routing tools try to swap input pins of the LUTs and modify the LUT values to improve routability of the design. This is undesirable for the template modification program as it assumes the routing of the template file to be without modification of the LUT contents. Xilinx routing tools are prevented from swapping the LUT inputs by configuring the LUTs as shift registers in the first configuration. It can also be done by setting a 'no pin swap' option in FPGA Editor (a design editing tool by Xilinx) for routing a design.

## 3.8 Methods for Application of BIST

In this section, the methods used to speed up test time and reduce the configuration storage requirements for Logic BIST are described. The following are the various configuration download methods used:

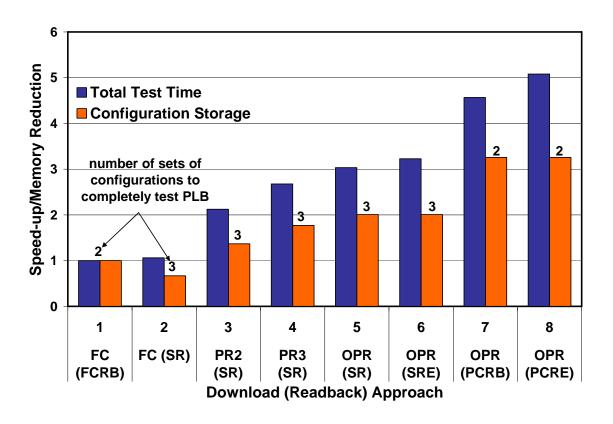

FC - Full Configuration; partial reconfiguration is not used and all the test configurations downloaded to the FPGA are full configurations.