# Modeling and Optimization of Parallel Matrix-based Computations on GPU

by

# Andrew White

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama May 5, 2013

Keywords: GPU, matrix-based computations, parallelization procedure, execution metrics

Copyright 2013 by Andrew White

Approved by

Soo-Young Lee, Chair, Professor of Electrical and Computer Engineering Victor Nelson, Professor of Electrical and Computer Engineering Chwan-Hwa Wu, Professor of Electrical and Computer Engineering

#### Abstract

As graphics processing units (GPUs) are continually being utilized as coprocessors, the demand for optimally utilizing them for various applications continues to grow. This work narrows the gap between programmers and minimum execution time for matrix-based computations on a GPU. To minimize execution time, computation and communication time<sup>1</sup> must be considered. For computation, the placement of data in GPU memory significantly affects computation time and therefore is considered. Various matrix-based computation patterns are examined with respect to the layout of GPU memory. A computation pattern refers to the order in which each GPU thread computes a result. From examination of computation patterns, an optimized computation pattern, a pattern which reduces computation time, is derived. After the optimized computation pattern is derived, the access pattern to GPU memory, or order in which data is accessed, is considered. From the optimized access pattern, fine-tuning is performed to the GPU code such as minimization of index calculations and loop unrolling to further reduce computation time and resource allocation. After fine-tuning, input parameters which yield the minimum computation time for a matrix-based computation on the GPU are derived. Input parameters are defined as the dimensions of the grid and blocks assigned for execution on the GPU. Execution metrics are formulated, as functions of the input parameters, to represent the executional behavior of the GPU. The execution metrics are utilized to derive the optimal input parameters which are input parameters that yield the minimum computation time.

<sup>&</sup>lt;sup>1</sup>In this work, computation time refers to the amount of time required for the GPU to execute a given computation. Communication time refers to the amount of time required for a CPU to GPU or a GPU to CPU data transfer.

The matrix-based computations considered are matrix-vector multiplication (Mv), matrix-matrix multiplication (MM), convolution, and the conjugate gradient method. A parallelization procedure is developed to minimize execution time by deriving the optimal placement of data, optimized computation pattern, optimized access pattern, and optimal input parameters. Each step of the procedure is developed through analysis of Mv and MM. The procedure includes an accurate communication model and estimates for CPU and GPU data transfers. With accurate estimates for communication and computation times, partitioning computation for CPU and GPU execution is performed to minimize execution time. Convolution and conjugate gradient are utilized to verify the validity of the procedure. Therefore, the overall goal of this work is to develop a parallelization procedure which minimizes execution time of matrix-based computations executing on the GPU.

#### Acknowledgments

First, I would like to thank God for blessing me with the opportunity to complete this work. Countless prayers from family, friends and myself enabled me to finish this dissertation. I would like to thank my wife, Abigail, who has always been supportive through the many years. Her dedication is truly inspiring. My family, particularly my parents, Bob and Ann, provided financial assistance and emotional support which none of this would be possible without. The lengthy phone calls about this work with my father also provided an outside perspective for improvement and I am sincerely grateful.

I would like to thank the entire Department of Electrical Engineering at Auburn University. Specifically, I would like to acknowledge my advisor, Dr. Soo-Young Lee, for always being supportive. This work would not have been possible without his constant help and guidance. Through countless meetings, emails, and phone calls, Dr. Lee always believed we could finish this work and went above and beyond expectations of an advisor.

I would also like to acknowledge Dr. Victor Nelson and Dr. Chwan-Hwa Wu for their thorough review of this work as well as availability to discuss any problems encountered along the way. Lastly, Dr. Amnon Meir, the outside reader of this work, provided quick and helpful revisions for completion. It was always a pleasure meeting with these professors and I truly appreciate the help.

Lastly, I would like to acknowledge the graduate students with whom I have shared an office for many years at Auburn. It was always enjoyable and relaxing to discuss life, and of course work, with Dr. Chris Wilson over lunch. I also appreciate the conversations with Siwei Wang and Praveen Venkataramani which provided me a wider understanding of the rest of the world and some social interaction in an otherwise non-social environment.

# Table of Contents

| Abstract   |                              | ii  |

|------------|------------------------------|-----|

| Acknowle   | edgmentsi                    | iv  |

| List of Fi | igures                       | iii |

| List of Ta | ables                        | ïV  |

| 1 Intr     | oduction                     | 1   |

| 1.1        | Problem Definition           | 1   |

| 1.2        | Review                       | 2   |

| 1.3        | Motivation                   | 6   |

| 1.4        | Objectives                   | 7   |

| 1.5        | Organization                 | 8   |

| 2 GP       | U, CUDA and Terms            | 9   |

| 2.1        | GPU History                  | 9   |

| 2.2        | GPU Architecture             | 10  |

| 2.3        | GPU Performance              | 13  |

| 2.4        | CUDA Environment             | 14  |

| 2.5        | Terms                        | L5  |

| 3 Mod      | deling                       | 18  |

| 3.1        | Global Memory Layout         | 19  |

|            | 3.1.1 Partition Camping      | 19  |

| 3.2        | Shared Memory Layout         | 22  |

|            | 3.2.1 Bank Conflicts         | 23  |

| 3.3        | Execution Metrics            | 24  |

| •          | 3.3.1 Global Memory Accesses | 26  |

|   |     | 3.3.2     | Active Threads           | 29 |

|---|-----|-----------|--------------------------|----|

|   |     | 3.3.3     | Fragmented Threads       | 30 |

|   |     | 3.3.4     | Global Memory Partitions | 31 |

|   | 3.4 | Comm      | nunication Time          | 31 |

|   |     | 3.4.1     | CPU-GPU                  | 32 |

|   |     | 3.4.2     | GPU-CPU                  | 33 |

|   | 3.5 | Comp      | utation Time             | 34 |

|   |     | 3.5.1     | CPU                      | 35 |

|   |     | 3.5.2     | GPU                      | 39 |

| 4 | Pa  | ralleliza | ation Procedure          | 41 |

|   | 4.1 | Placen    | ment of Data             | 44 |

|   |     | 4.1.1     | Mv                       | 46 |

|   |     | 4.1.2     | MM                       | 52 |

|   | 4.2 | Comp      | utation Patterns         | 55 |

|   |     | 4.2.1     | Mv                       | 56 |

|   |     | 4.2.2     | MM                       | 60 |

|   | 4.3 | Access    | s Patterns               | 66 |

|   |     | 4.3.1     | Mv                       | 67 |

|   |     | 4.3.2     | MM                       | 72 |

|   | 4.4 | Fine-t    | uning                    | 75 |

|   |     | 4.4.1     | Mv                       | 77 |

|   |     | 4.4.2     | MM                       | 79 |

|   | 4.5 | Input     | Parameters               | 82 |

|   |     | 4.5.1     | Mv                       | 84 |

|   |     | 4.5.2     | MM                       | 89 |

|   |     | 4.5.3     | GPU Computation Summary  | 95 |

|   | 4.6 | Comp      | utation Partitioning     | 07 |

|    |        | 4.6.1   | Mv                       |

|----|--------|---------|--------------------------|

|    |        | 4.6.2   | MM                       |

| 5  | Pe     | rformar | nce Analysis             |

|    | 5.1    | Convo   | lution                   |

|    |        | 5.1.1   | Placement of Data        |

|    |        | 5.1.2   | Computation Patterns     |

|    |        | 5.1.3   | Access Patterns          |

|    |        | 5.1.4   | Fine-tuning              |

|    |        | 5.1.5   | Input Parameters         |

|    |        | 5.1.6   | Computation Partitioning |

|    | 5.2    | Conjug  | gate Gradient            |

| 6  | Со     | nclusio | n                        |

| Bi | bliogr | aphy.   |                          |

# List of Figures

| 2.1 | Architecture of the T10 GPU                                                                                                                                                          | 11 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Memory organization of the T10 GPU                                                                                                                                                   | 12 |

| 2.3 | A square block of size 64                                                                                                                                                            | 15 |

| 2.4 | Partitioning of a square block of size 64 into warps                                                                                                                                 | 16 |

| 2.5 | Partitioning of a square block of size 64 into half-warps                                                                                                                            | 17 |

| 3.1 | Global memory connection of the T10 GPU. Memory is divided into 8 equal-sized partitions. Each address represents 256 bytes                                                          | 19 |

| 3.2 | An example of partition camping occurring: global memory accesses by 2 HWs to 2 partitions.                                                                                          | 20 |

| 3.3 | An example of partition camping not occurring: global memory accesses by 2 HWs to 2 partitions                                                                                       | 20 |

| 3.4 | Shared memory layout in the T10 GPU. Memory is divided into 16 equal-sized partitions. Each column is 4 bytes wide                                                                   | 22 |

| 3.5 | Threads within a HW accessing 16 shared memory banks. No bank conflicts occur.                                                                                                       | 22 |

| 3.6 | Threads within a HW accessing one shared memory bank. 16 bank conflicts occur.                                                                                                       | 23 |

| 3.7 | Modeling MM with input parameters: average percent difference between the maximum and minimum computation time $(ms)$ of a group defined by $n$ and a subset of the input parameters | 25 |

|     | bubber of the input parameters                                                                                                                                                       | 40 |

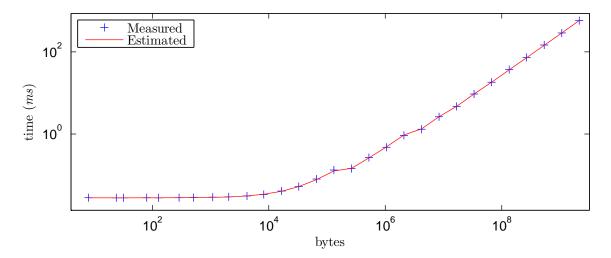

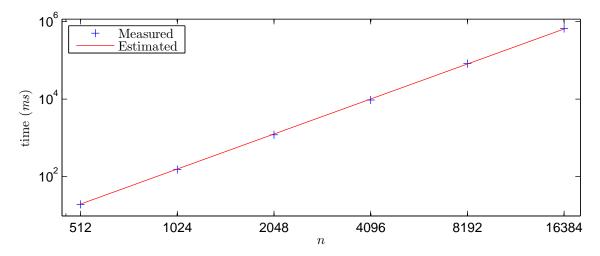

| 3.8  | Comparison of measured and estimated CPU to GPU communication time $(ms)$ on the T10 GPU                                                                                                                           | 33 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

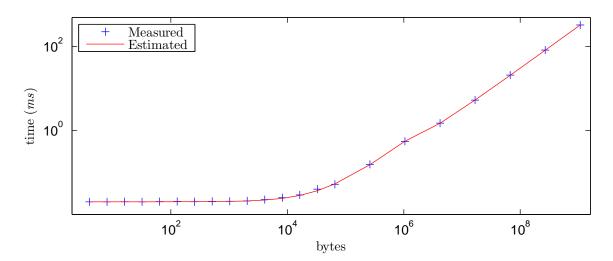

| 3.9  | Comparison of measured and estimated GPU to CPU communication time $(ms)$ on the T10 GPU                                                                                                                           | 34 |

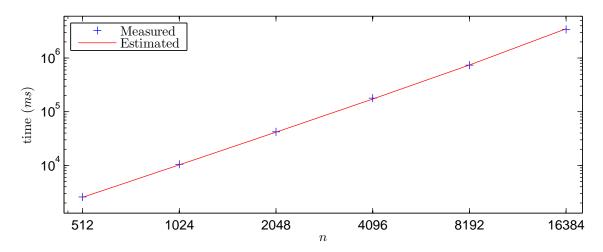

| 3.10 | Comparison of measured and estimated computation time $(ms)$ for the optimized BLAS implementation of Mv on the CPU                                                                                                | 36 |

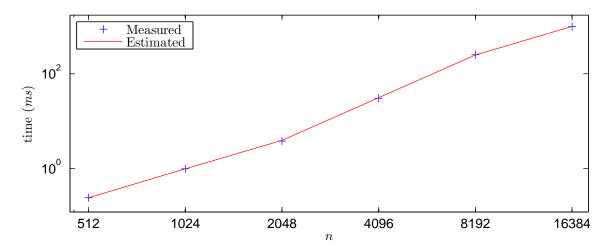

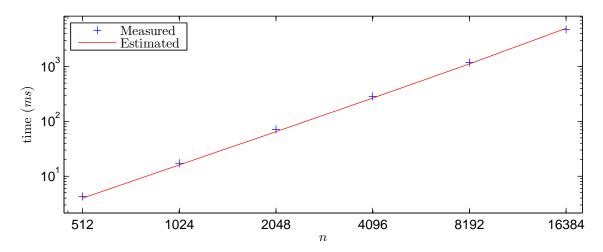

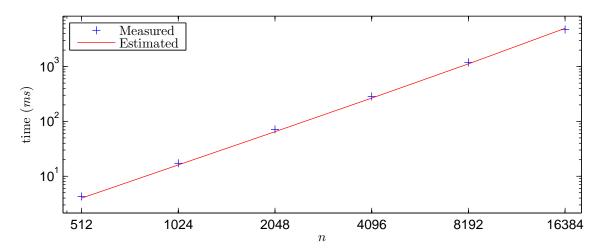

| 3.11 | Comparison of measured and estimated computation time $(ms)$ for the optimized BLAS implementation of MM on the CPU                                                                                                | 37 |

| 3.12 | Comparison of measured and estimated computation time $(ms)$ for the non-optimized C implementation of convolution on the CPU. $FS=3.$                                                                             | 38 |

| 3.13 | Comparison of measured and estimated computation time $(ms)$ for the non-optimized C implementation of convolution on the CPU. $FS$ =63                                                                            | 38 |

| 3.14 | Comparison of measured and estimated computation time $(ms)$ for the non-optimized C implementation of convolution on the CPU. $FS$ =513                                                                           | 39 |

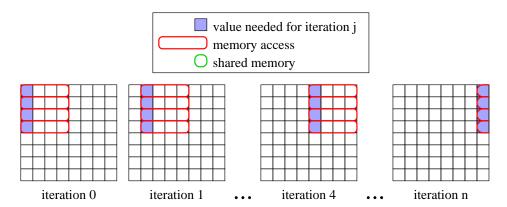

| 4.1  | Example of a HW, consisting of 4 threads, accessing <b>A</b> in each iteration of Mv.  Each memory transaction is 4 bytes. The accesses to <b>A</b> are uncoalesced and 4 accesses are required for each iteration | 49 |

| 4.2  | Example of a HW, consisting of 4 threads, accessing <b>A</b> in each iteration of Mv utilizing shared memory. Each memory transaction is 4 bytes. The accesses to                                                  |    |

|      | ${\bf A}$ are coalesced and 4 accesses are required every $4^{th}$ iteration                                                                                                                                       | 50 |

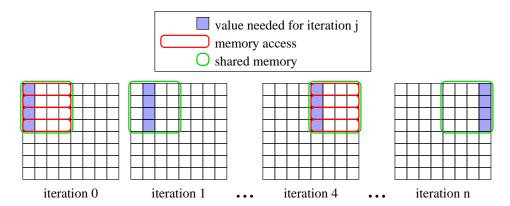

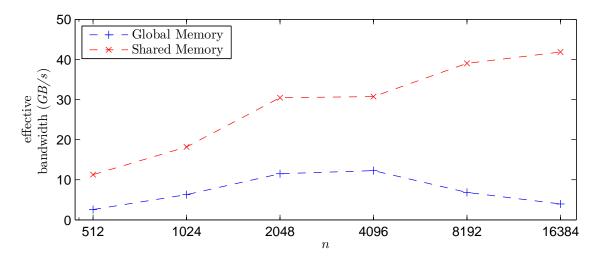

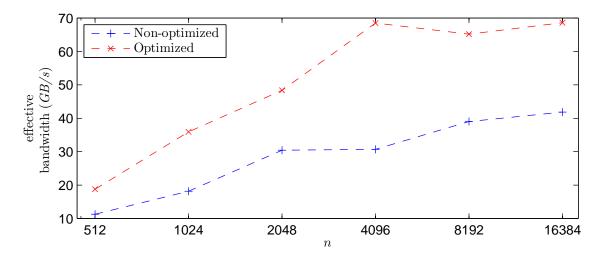

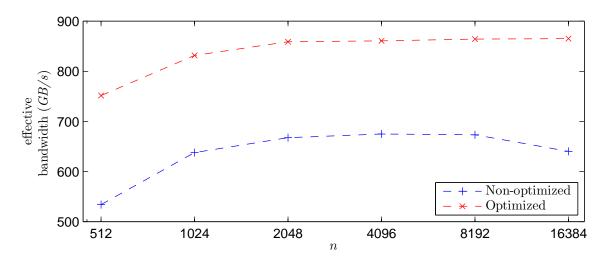

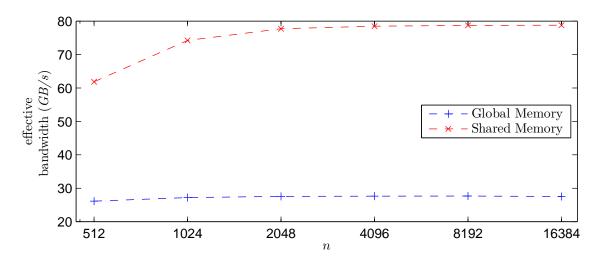

| 4.3  | Comparison of GPU memories: Maximum effective bandwidth $(GB/s)$ for Mv on the T10 GPU                                                                                                                             | 52 |

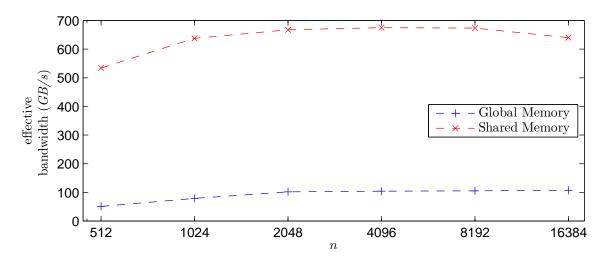

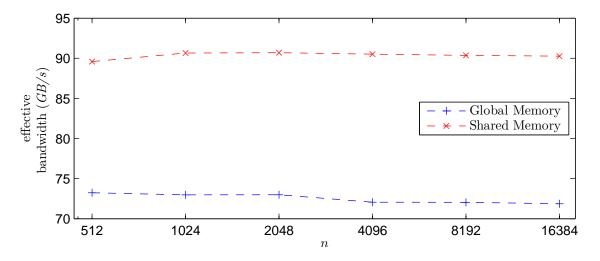

| 4.4  | Comparison of GPU memories: Maximum effective bandwidth $(GB/s)$ for MM               |    |

|------|---------------------------------------------------------------------------------------|----|

|      | on the T10 GPU                                                                        | 55 |

| 4.5  | Computation patterns: two computation patterns for Mv for computing multiple          |    |

|      | $C_j$ s                                                                               | 56 |

| 4.6  | Average computation time $(ms)$ varying the number of total threads for Mv on         |    |

|      | the T10 GPU                                                                           | 57 |

| 4.7  | Comparison of computation patterns: Maximum effective bandwidth $(GB/s)$ for          |    |

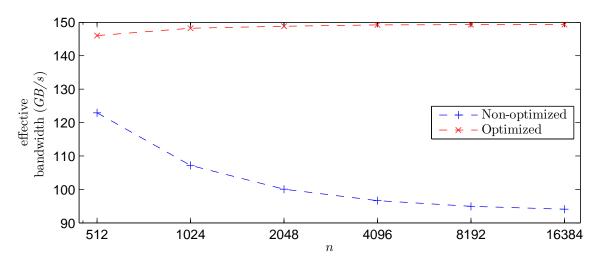

|      | Mv on the T10 GPU                                                                     | 59 |

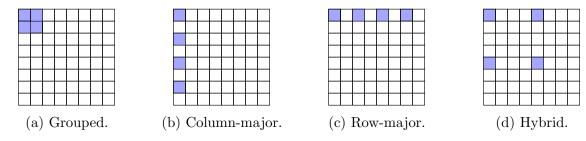

| 4.8  | Computation patterns: four computation patterns for MM for computing multi-           |    |

|      | ple $C_{ij}$ s                                                                        | 60 |

| 4.9  | Computation patterns: hybrid computation patterns for MM for computing mul-           |    |

|      | tiple $C_{ij}$ s                                                                      | 62 |

| 4.10 | Comparison of computation patterns: Maximum effective bandwidth $(GB/s)$ for          |    |

|      | MM on the T10 GPU                                                                     | 66 |

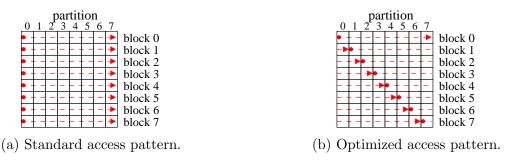

| 4.11 | Access patterns: example of block-level access patterns to ${\bf A}$ for matrix-based |    |

|      | computations. Each column is one partition of global memory. Each row is 512          |    |

|      | values of type float                                                                  | 67 |

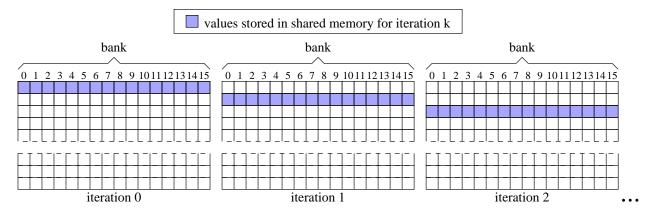

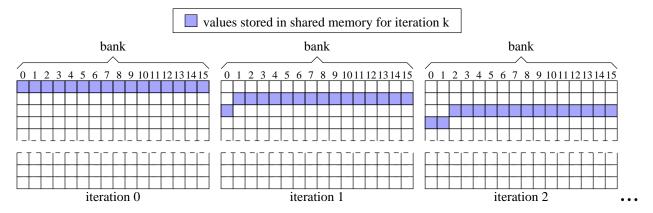

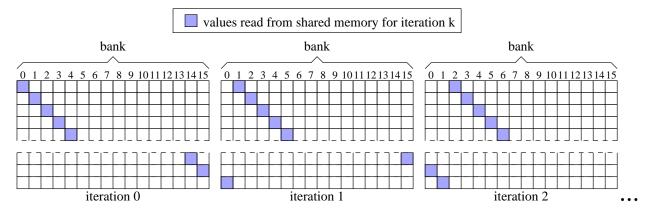

| 4.12 | Example of loading ${\bf A}$ into shared memory for the shared memory implementation  |    |

|      | of Mv utilizing the optimized computation pattern but not the optimized access        |    |

|      | pattern. No bank conflicts occur. $dBlk.x = 16.$                                      | 69 |

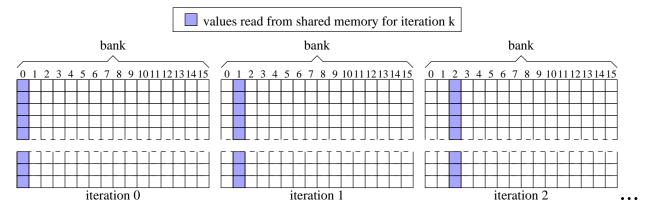

| 4.13 | Example of reading shared memory for the shared memory implementation of              |    |

|      | Mv utilizing the optimized computation pattern but not the optimized access           |    |

|      | pattern. Bank conflicts occur. $dBlk.x = 16$                                          | 70 |

| 4.14 | Example of loading <b>A</b> into shared memory for the shared memory implementation    |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | of Mv utilizing the optimized computation and access pattern. No bank conflicts        |     |

|      | occur. $dBlk.x = 16.$                                                                  | 70  |

| 4.15 | Example of reading shared memory for the shared memory implementation of               |     |

|      | Mv utilizing the optimized computation and access pattern. No bank conflicts           |     |

|      | occur. $dBlk.x = 16.$                                                                  | 71  |

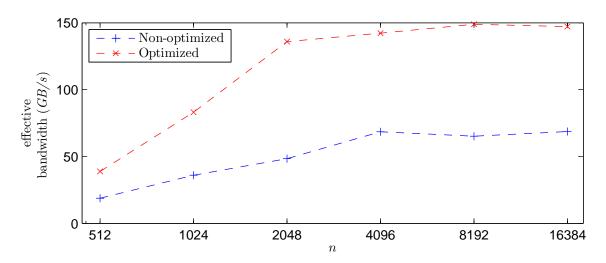

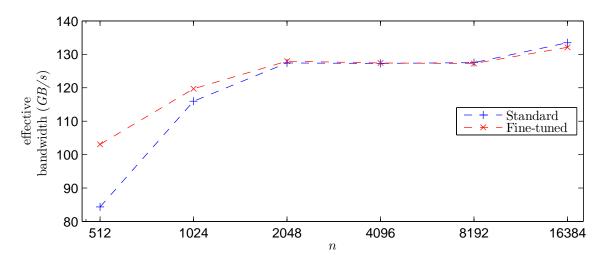

| 4.16 | Comparison of access patterns: Maximum effective bandwidth $(\mathit{GB/s})$ for Mv on |     |

|      | the T10 GPU                                                                            | 71  |

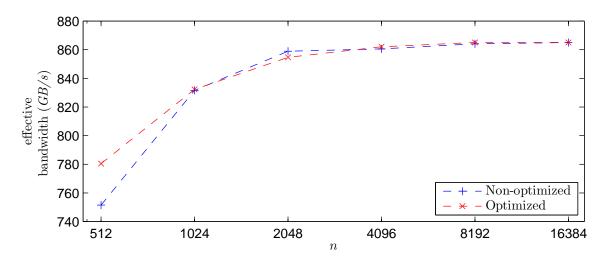

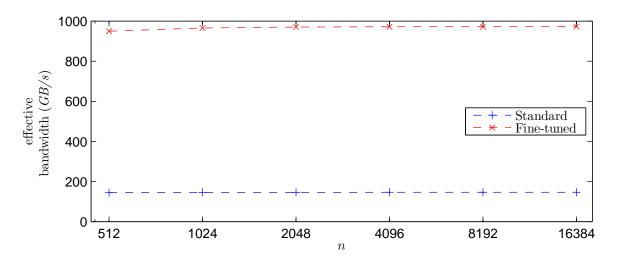

| 4.17 | Comparison of access patterns: Maximum effective bandwidth $(GB/s)$ for MM             |     |

|      | on the T10 GPU                                                                         | 74  |

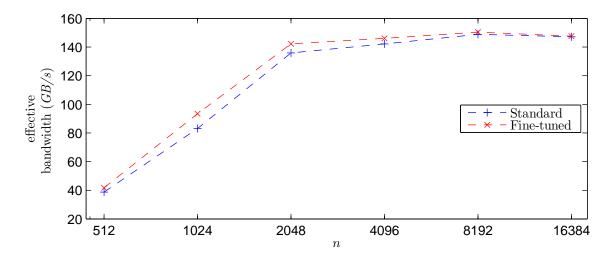

| 4.18 | Comparison of fine-tuning: Maximum bandwidth $(GB/s)$ for Mv on the T10 GPU.           | 79  |

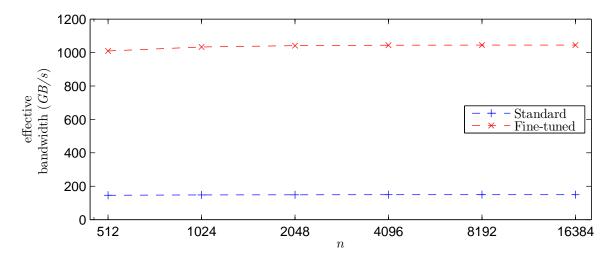

| 4.19 | Comparison of fine-tuning: Maximum effective bandwidth $(GB/s)$ for MM on              |     |

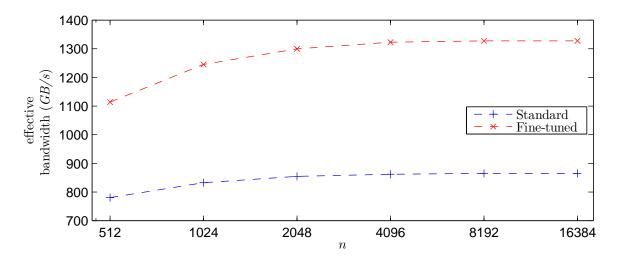

|      | the T10 GPU                                                                            | 82  |

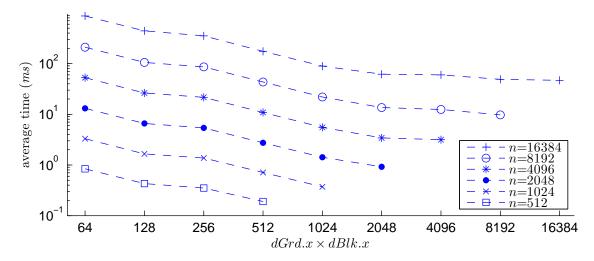

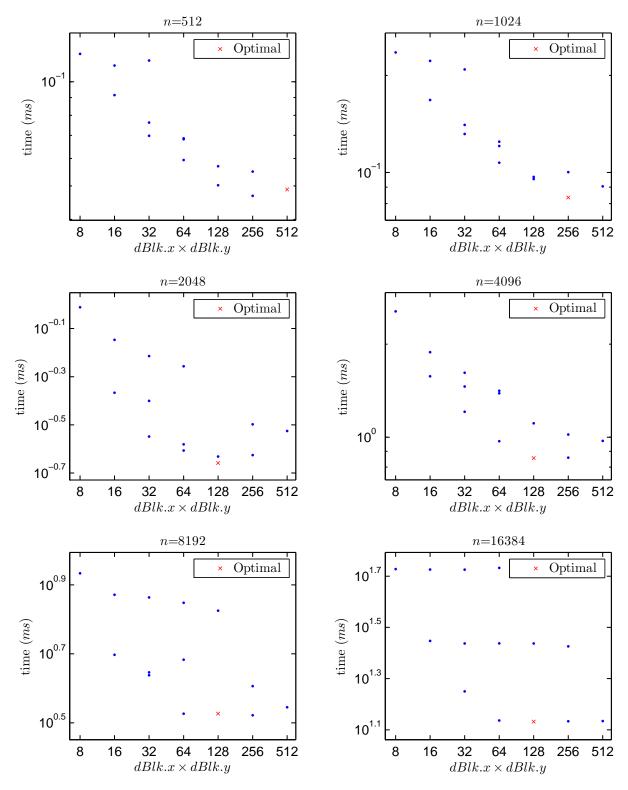

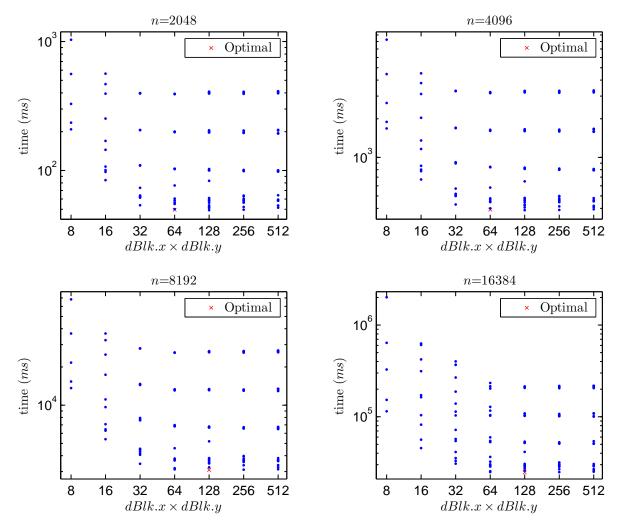

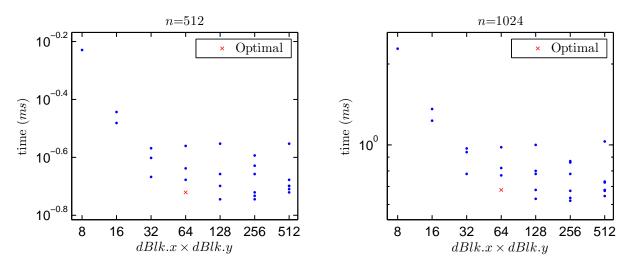

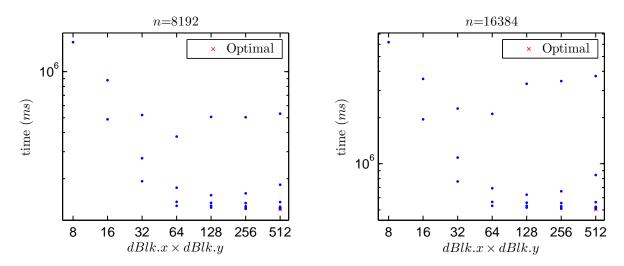

| 4.20 | Comparison of input parameters: Computation time $(ms)$ of all input parameters        |     |

|      | for Mv on the T10 GPU                                                                  | 88  |

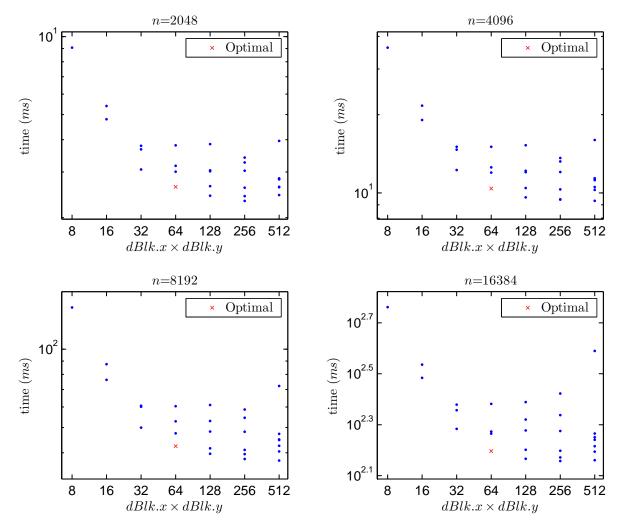

| 4.21 | Comparison of input parameters: Computation time $(ms)$ of all input parameters        |     |

|      | for MM on the T10 GPU                                                                  | 94  |

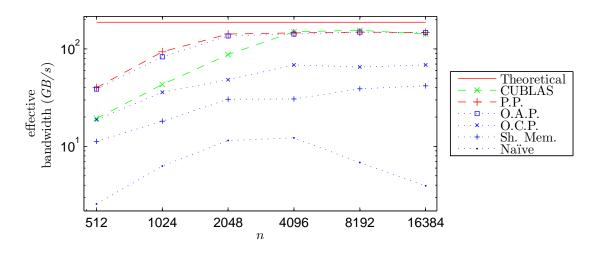

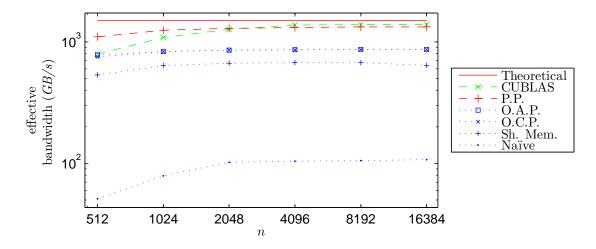

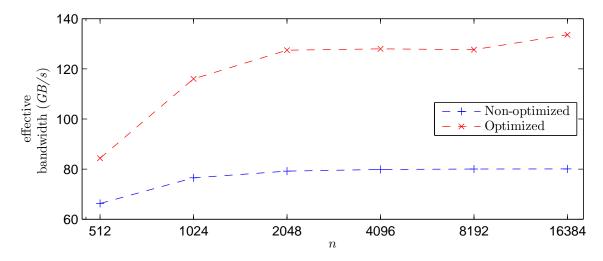

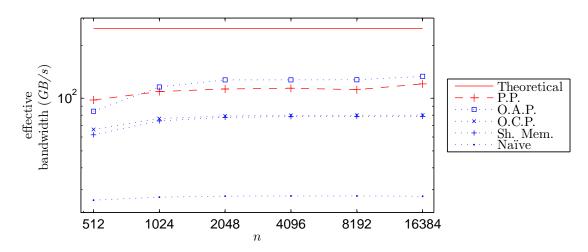

| 4.22 | Comparison of effective bandwidth $(GB/s)$ for Mv on the T10 GPU                       | 95  |

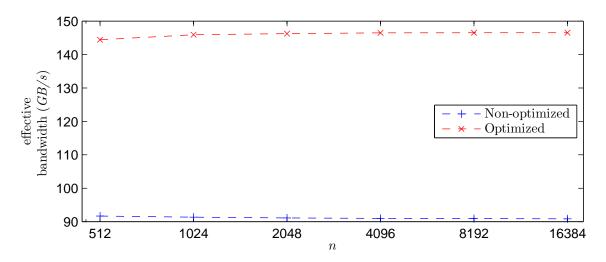

| 4.23 | Comparison of effective bandwidth $(GB/s)$ for MM on the T10 GPU                       | 96  |

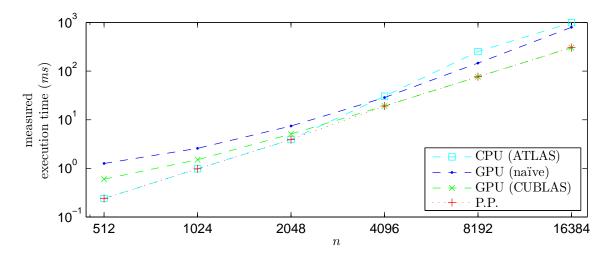

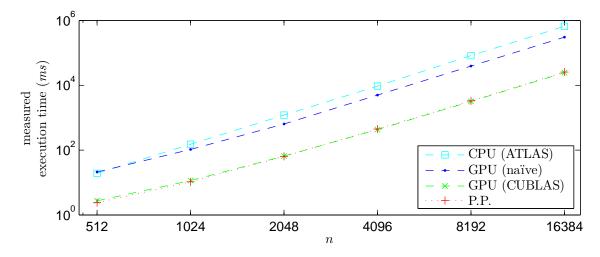

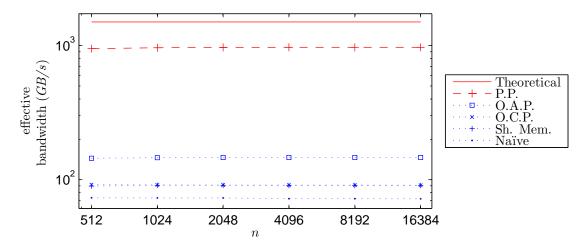

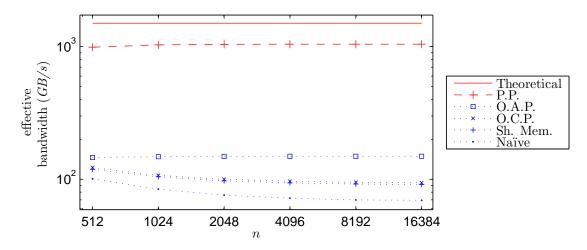

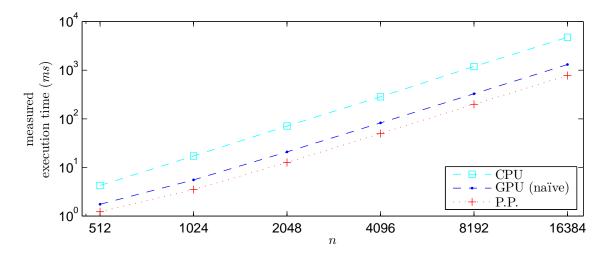

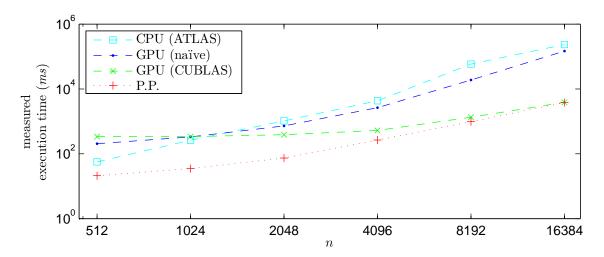

| 4.24 | Comparison of execution time $(ms)$ for Mv on the T10 GPU                              | 99  |

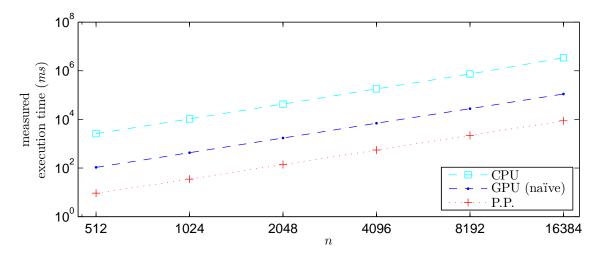

| 4.25 | Comparison of execution time $(ms)$ for MM on the T10 GPU                              | 101 |

| 5.1  | Comparison of GPU memories: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS=3$                         | )8 |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | Comparison of GPU memories: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =63                       | )8 |

| 5.3  | Comparison of GPU memories: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =513                      | )9 |

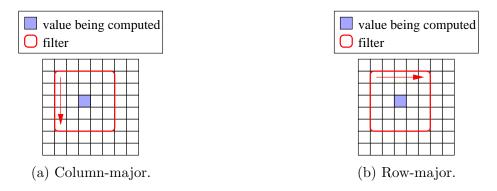

| 5.4  | Computation patterns: two computation patterns for convolution                                                                  | 10 |

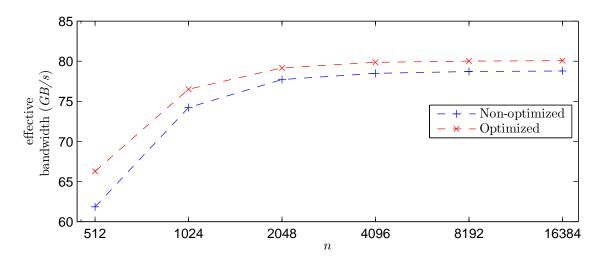

| 5.5  | Comparison of computation patterns: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS=3$                 | 14 |

| 5.6  | Comparison of computation patterns: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =63               | 14 |

| 5.7  | Comparison of computation patterns: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =513              | 15 |

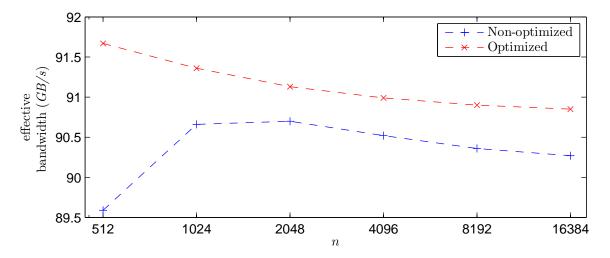

| 5.8  | Access patterns: example of a 3x3 filter, <b>B</b> , stored in global memory. Each row of a partition is 4 values of type float | 16 |

| 5.9  | Comparison of access patterns: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =3                     | 18 |

| 5.10 | Comparison of access patterns: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =63                    | 19 |

| 5.11 | Comparison of access patterns: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =513                   | 19 |

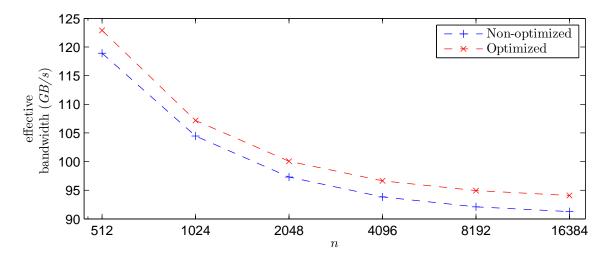

| 5.12 | Comparison of fine-tuning: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS=3$                    |

|------|---------------------------------------------------------------------------------------------------------------------------|

| 5.13 | Comparison of fine-tuning: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =63                  |

| 5.14 | Comparison of fine-tuning: Maximum effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =513                 |

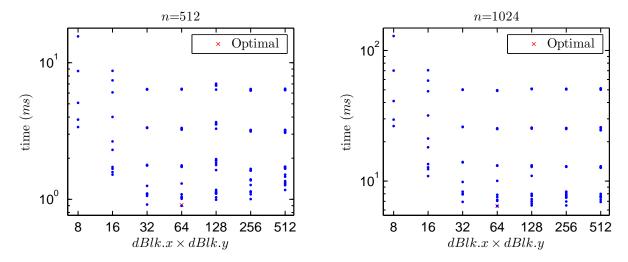

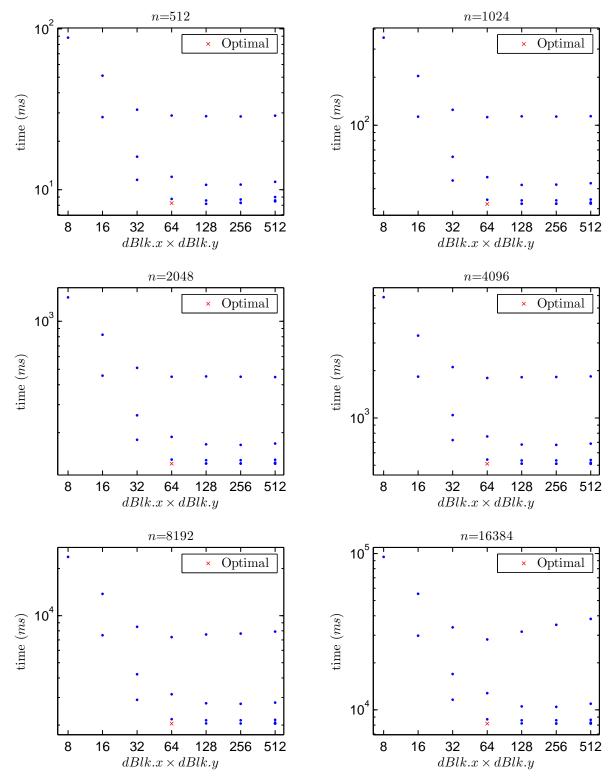

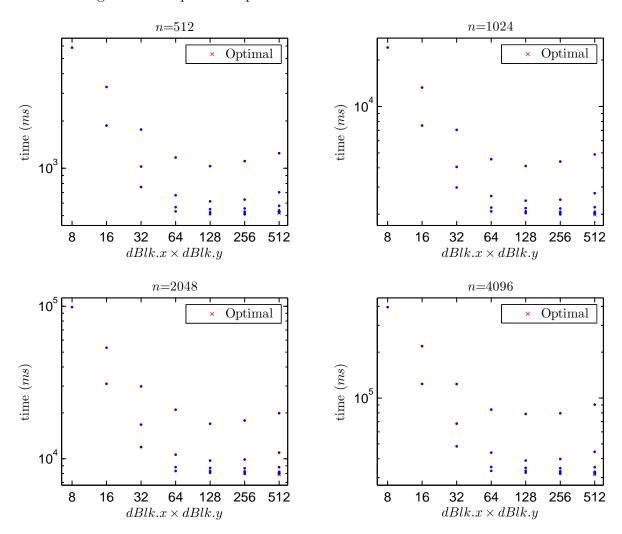

| 5.15 | Comparison of input parameters: Computation time $(ms)$ of all input parameters for convolution on the T10 GPU. $FS=3.$   |

| 5.16 | Comparison of input parameters: Computation time $(ms)$ of all input parameters for convolution on the T10 GPU. $FS$ =63  |

| 5.17 | Comparison of input parameters: Computation time $(ms)$ of all input parameters for convolution on the T10 GPU. $FS$ =513 |

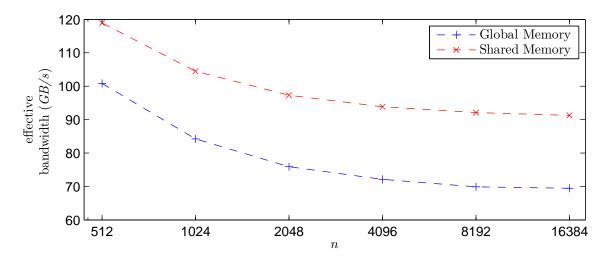

| 5.18 | Comparison of effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS=3.$                                        |

| 5.19 | Comparison of effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS$ =63                                       |

| 5.20 | Comparison of effective bandwidth $(GB/s)$ for convolution on the T10 GPU. $FS=513$                                       |

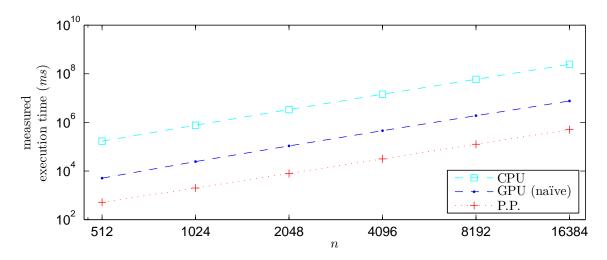

| 5.21 | Comparison of execution time $(ms)$ for convolution on the T10 GPU. $FS = 3$ 136                                          |

| 5.22 | Comparison of execution time $(ms)$ for convolution on the T10 GPU. $FS = 63$ 137                                         |

| 5.23 | Comparison of execution time $(ms)$ for convolution on the T10 GPU. $FS = 513138$                                         |

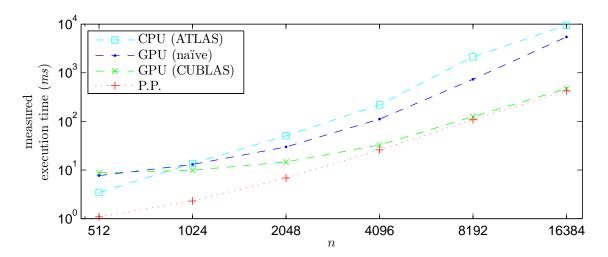

| 5.24 | Comparison of execution time $(ms)$ for 8 iterations of the conjugate gradient   |

|------|----------------------------------------------------------------------------------|

|      | method on the T10 GPU                                                            |

| 5.25 | Comparison of execution time $(ms)$ for 256 iterations of the conjugate gradient |

|      | method on the T10 GPU                                                            |

# List of Tables

| 3.1 | Measured results of executing Listing 3.1 which demonstrate the effect of partition |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | camping on the T10 GPU. $v$ is the number of values each thread summed              | 21 |

| 3.2 | Measured results of executing Listing 3.2 which demonstrates the effect of bank     |    |

|     | conflicts on the T10 GPU. $v$ is the number of values summed by each thread         | 24 |

## Chapter 1

#### Introduction

#### 1.1 Problem Definition

As the market for massively multithreaded architectures continues to grow, so does the development of general-purpose graphics processing unit (GPGPU) applications. Many programming models such as NVIDIA's compute unified device architecture (CUDA) try to ease the gap between programmers and GPUs. While much research has been done in optimizing written GPU applications, little has been done to bridge the gap between programmers and minimum execution time for matrix-based computations on a GPU. Therefore, a parallelization procedure is necessary to provide programmers a guide to achieve minimum execution time for matrix-based computations on a GPU.

To develop a parallelization procedure, it is necessary to consider computation and communication time. Accurate estimates for computation and communication time are necessary to minimize execution time. To assist in modeling GPU computation time, the layout of GPU memory must be examined for various matrix-based computation patterns. Therefore, it is necessary to determine in which type of GPU memory data is placed. After the placement of data is determined, the order in which threads executing on the GPU compute results, the computation pattern, is considered. Therefore, a computation pattern which reduces the computation time with respect to the layout of GPU memory for matrix-based computations must be derived. After deriving the optimized computation pattern, it is necessary to derive an optimized access pattern to GPU memory since the order in which threads access memory affects computation time. Utilizing the optimized access pattern, the code must be fine-tuned to reduce computation and resource allocation. From the fine-tuned code, it is necessary to derive the input parameters for the GPU computation which yield

the minimum computation time. To derive optimal input parameters, an accurate model of the computational behavior of the GPU is required. Since modeling GPU computation using input parameters is insufficient, execution metrics must be formulated as functions of the input parameters to model the behavior. From the execution metrics, optimal input parameters must then be derived which yield the minimum computation time for matrix-based computations.

Communication estimates between the CPU and GPU are also necessary to develop a parallelization procedure which minimizes execution time. Accurate communication estimates, in addition to accurate computation estimates, are necessary to determine which computations are performed by the CPU and GPU to minimize execution time.

Therefore, a parallelization procedure which minimizes execution time of matrix-based computations on the GPU must consider the placement of data, computation patterns, access patterns, input parameters, communication time, and computation partitioning.

#### 1.2 Review

In early GPU research, Fatahalian and others performed a study of matrix-matrix multiplication on GPU architectures [1]. It was shown at the time that GPUs suffer from memory bandwidth limitations which has later been expounded upon by many research groups. At that time, work showed that CPUs were better candidates for applications that feature data reuse such as matrix-matrix multiplication. Since then, GPU architecture has evolved creating an increasing atmosphere for GPUs being utilized as coprocessors.

Shortly after 2004, work began on automatically tuning matrix-matrix multiplication for GPUs [2]. However, results proved that automatic tuning of GPU programs severely reduced performance. After that, a Microsoft research group proposed a system to program GPUs [3]. Results proved that CPUs were several times faster than GPUs at executing computations such as Mv. After that, research began to focus on modeling GPU performance [4]. At the

time, results showed accurate estimations of GPU computation time. However, the advent of CUDA and CUDA-enabled devices obsoleted this work.

Researchers at the Georgia Institute of Technology attempted to predict GPU performance in very fine detail by examining the PTX code (NVIDIA assembly code equivalent) to determine the number of computation and memory access cycles and using these to determine the GPU computation time [5,6]. This work was utilized to predict the optimal number of active cores for the GPU and to disable some of the cores to reduce energy consumption [7]. Although the work provides a detailed algorithm to count the number of instructions from PTX code, this can be a tedious job to calculate the cycles and predict the result. Analysis at a higher level allows a more general approach and can reduce the time required to yield a minimum execution time. In addition, while the predictions for older model GPUs such as the FX5600 are mostly accurate, the behavior of the predicted time on newer GPUs, such as 200-series architectures, is not the same as the behavior of the measured time. Moreover, the work provided a static approach to predicting the computation time but left optimizations up to the programmer. Most importantly, the layout of the global memory in the GPU was not considered which largely affects the computation time for matrix-based computations on GPUs.

Researchers at the International Institute of Information Technology in Hyderabad, India focused on explaining the behavior of current NVIDIA GPUs and worked on developing a model to illustrate the performance of an NVIDIA GPU [8]. Their work focused on creating a simulator for the GPU in the future which would aid in writing optimized applications. However, their research, as stated in publications, does not aim to provide a procedure to programmers which minimizes execution time for GPU applications.

Researchers at the Center for Reliable and High-Performance Computing at the University of Illinois at Urbana-Champaign have also spent time researching GPUs and their performance [9–13]. The work is a discussion of balancing shared resource usage to achieve high performance on the GeForce 8800 [9]. They focused on generating enough threads to

hide memory latency, choosing applications with a high percentage of floating point operations such as MM, and reducing the number of global memory accesses. They use this example to show that shared memory is useful for reducing redundant loads and thus reducing the pressure on memory bandwidth. In addition, some of their research focuses on resource utilization by the kernel such as shared memory, registers and occupancy [10, 11]. Similar to previous work, PTX code is examined for modeling computation time. The research focused on minimizing the number of trials necessary to find optimal input parameters rather than deriving them. In addition, the research did not consider the layout of global memory or access pattern and thus does not work well for memory-bound problems such as many matrix-based computations.

In addition to the previous work mentioned, the group at the Center for Reliable and High-Performance Computing at the University of Illinois at Urbana-Champaign developed a program called CUDA-lite [14]. This was developed to be an enhancement to CUDA that automates the task of selecting the appropriate memory to use and the coding of data transfers between memories. The tool was written to coalesce memory accesses which was a roadblock to GPU performance at the time. However, NVIDIA continues to relax the requirements to achieve coalesced read/writes with every SDK released so there is a dwindling need for a programmer to use an automated compiler to handle such a task. In addition, requiring programmers to learn other tools in addition to CUDA creates an additional burden. Regardless, it should be assumed that programmers understand the basic concepts of the memory hierarchy and thus do not need additional tools to optimize the access patterns if some basic guidelines are followed when writing applications. Lastly, this work does not consider the global memory layout and can produce poor results in such cases as utilizing shared memory to coalesce accesses.

The most recent research by this group includes an adaptive performance modeling tool [12] and a CUDA application survey [13]. In [13], a survey is performed of different

applications and the suitability of CUDA-enabled GPUs. While this provides a useful summary of the architecture and how the GPU operates, along with analysis as to why certain applications are optimal, it does not satisfy the need for a procedure to minimize computation time. In [12], a compiler-based approach is utilized to estimate GPU computation time. They, too, analyzed the effects on computation time from utilizing various GPU memories. While this was a major step in automatic selection of optimal applications, it does not provide a procedure which yields optimal GPU code and derivation of input parameters that yield the minimum computation time.

With the release of CUDA, NVIDIA released CUBLAS [15], an optimized implementation of the BLAS [16] routines for GPUs. However, source for CUBLAS is closed and little work is published on how each routine is implemented. Alternatively, MAGMA [17] released an optimized implementation of the BLAS routines similar to LAPACK [18] for GPUs. Several works [19–34] provide insights into optimized GPU applications. However, the research aims to provide users optimized BLAS routines rather than provide programmers a procedure for optimizing GPU computations and minimizing execution time.

Other work [35–48] also focuses on optimizing individual computations, such as Mv or MM, but is limited to specific implementations or ignores certain aspects of the GPU such as memory layout.

Lastly, work has been performed that highlights the programming experiences with CUDA as well as the architectures of GPUs [49–52]. [49] provides a summary of research done with different applications on GPUs utilizing CUDA. The work highlights the benefits of CUDA as well as what is necessary to make applications suitable for a GPU, such as exposing sufficient amounts of fine-grained parallelism to occupy the device, ability to block computation, efficiency of data-parallel programs without thread divergence and finally, usage of shared memory. [51] focuses on the architecture of Tesla GPUs and how it has evolved over the last decade from fixed-function graphics pipelines to programmable processors with computing power greater than multi-core CPUs. One of the newest GPU architectures,

Fermi, is outlined in [52], which also discusses the demand for increasing GPU capabilities and the future of GPUs. The research shows the benefit of co-processing architectures (such as CUDA) and explains the reason the market for these architectures and their usability will continue to grow. Because of this expanding market, research is needed to provide users with a procedure for achieving the minimum execution time.

#### 1.3 Motivation

With the development of environments such as CUDA, GPUs are increasingly becoming a viable option for parallel processing. With the increased interest in utilizing the GPU as a coprocessor, it is necessary that programmers be able to write applications for this platform without the need to fully understand the underlying architecture of the GPUs. Often, GPU manufacturers do not disclose certain aspects of the hardware, or sometimes even the software, to maintain a competitive advantage. Therefore, researchers are constantly testing and analyzing the new generations of GPUs to understand how to fully utilize them. It is necessary to provide programmers a procedure for minimizing the execution time while also providing a logical reasoning.

Previous research does not provide programmers a parallelization procedure for matrix-based computations which yields minimum execution time. More specifically, previous research does not account for the layout of GPU global memory or the access pattern to that memory, which is determined by the code, and thus, optimized access patterns are not derived to minimize computation time. In addition, previous research does not consider the computation pattern by the executing threads, which affects computation time. Therefore, optimized computation patterns are not derived to achieve the minimum time. In previous research, input parameters are determined through testing the application, and thus, optimal input parameters are not derived for various computations to yield the minimum computation time. Therefore, it is necessary to develop a parallelization procedure for matrix-based

computations executing on a GPU which minimizes execution time by considering the placement of data, computation patterns, access patterns, input parameters, communication time, and computation partitioning.

# 1.4 Objectives

Since the primary goal of this work is to develop a procedure which yields the minimum execution time for matrix-based computations on a GPU, the objectives are to

- examine the layout of GPU memory,

- formulate execution metrics to accurately represent the computational behavior of the GPU,

- model and estimate CPU to GPU and GPU to CPU communication time,

- model and estimate CPU and GPU computation time,

- determine the optimal placement of data in GPU memory,

- analyze computation patterns for GPUs and derive the optimized computation pattern,

- derive the optimized access pattern for GPU memory,

- fine-tune code to minimize computation and resource allocation,

- from the execution metrics, derive the optimal input parameters for the GPU,

- determine the optimal partitioning of computation between the CPU and GPU,

- verify these objectives by comparing the procedure with several matrix-based computations.

This is accomplished with consideration to grid and block partitioning, data arrangement and partitioning, code arrangement and data transfers. Therefore, the intellectual contribution

of this work is a parallelization procedure which minimizes execution time for matrix-based computations on a GPU.

# 1.5 Organization

Chapter 2 is an introduction to GPUs, CUDA and terms utilized in this work. An examination of the layout of GPU memory and the formulation of execution metrics to accurately represent the computational behavior of the GPU are presented in Chapter 3. In addition, modeling communication and computation times is presented in Chapter 3. From the layout of GPU memory and formulation of execution metrics, the parallelization procedure to minimize execution time for matrix-based computations executing on a GPU is developed in Chapter 4. The parallelization procedure considers the placement of data, computation patterns, access patterns, fine-tuning, input parameters, communication, and computation partitioning. The procedure is developed through and applied to Mv and MM in Chapter 4. Results are included to illustrate the impact on time for each step of the procedure. In Chapter 5, the procedure is applied to convolution and the conjugate gradient method. The application of the procedure to convolution is shown. Results illustrate the performance of the procedure applied to convolution and the conjugate gradient method. Chapter 6 is a summary and conclusion of the presented work.

## Chapter 2

# GPU, CUDA and Terms

This chapter includes a brief history of GPUs, a comparison of CPU and GPU architectures, and the performance of GPUs. Following is a summary of CUDA, the NVIDIA GPU programming environment, and lastly, terms are introduced.

# 2.1 GPU History

As GPUs continue to become low-cost, parallel processing architectures, additional programmers will turn to these architectures to minimize execution time. Therefore, there is an increasing need for optimizing applications written for GPUs. While much work has been done by NVIDIA and other researchers using the CUDA environment to explain the impact of different application parameters, much information is not public knowledge about how GPUs function. Therefore, it is necessary to expand upon the previous research into optimizing applications, and develop a procedure for minimizing execution time to ease future programmers into writing efficient CUDA applications for GPUs.

Over the last 30 years, GPU architecture has evolved to a massively parallel design. In the 1980s, GPUs were large expensive systems that typically cost in the range of \$50,000 and were capable of processing 50 million pixels per second. By the 1990s, GPU costs decreased significantly, causing them to be more widespread as they were deployed in small workstations as PC accelerators. During this time, graphics APIs such as DirectX became popular and programmers began utilizing the fixed-functions to perform other tasks. In the 2000s, GPUs dropped in price to the \$100 range and became available on every computer. Those GPUs were capable of processing 1 billion pixels per second. More importantly, those GPUs became programmable for general purpose computing using such languages as CUDA and Open CL.

This advancement in graphics performance has been driven by the market demand for high-quality, real-time graphics in computer applications, namely the gaming industry. The result is that, over time, graphics architecture has changed from being a simple pipeline for drawing wire-frame diagrams to a highly parallel computing chip [53] [52] [51].

In order to fully utilize today's chips and maximize performance, GPU algorithms need several key components: access to data with minimal bank conflicts, SIMD parallelism and many arithmetic computations. GPU algorithms are best suited for computationally intensive applications that require little inter-process communication and include but are not limited to physical modeling, computational engineering, matrix algebra, convolution, correlation and sorting. Therefore, matrix-based computations are ideally suited for GPUs.

#### 2.2 GPU Architecture

GPUs, as opposed to CPUs, are not well-suited for all algorithms due to their architecture. CPUs are designed for optimal sequential performance and application performance increases with increasing clock frequencies. However, the rate at which clock speeds increase is beginning to slow. Because of the importance of sequential performance, CPU cores include the full x86 instruction set with complex branching. In addition CPUs have large cache memories to decrease instruction and data latencies for applications. The larger cache memories and the need for complex control logic forces designers to use less of the available silicon for ALUs. On the other hand, GPUs are designed for optimal parallel performance. While GPU clock speeds are slower than CPU speeds, the application performance increases with the number of cores. The lack of large cache memories and complex control logic decreases the sequential performance in comparison to CPUs but allows designers to implement more ALUs on the available silicon thus increasing the numeric computing capability. Lastly, since GPUs are designed with a focus on parallelism, their structure includes many smaller cores than CPUs.

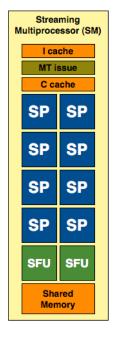

The NVIDIA GPU<sup>1</sup> architecture is a collection of streaming multiprocessors (SMs) with each SM having a number of cores or streaming processors (SPs). The control logic and instruction cache for all SPs within an SM are shared as illustrated in Figure 2.1a. This work utilizes the Tesla T10 (T10) GPU which is built on the NVIDIA 200-series architecture. The T10 architecture has a total of 30 SMs with each SM having 8 SPs. A newer architecture, Fermi, includes only 16 SMs but each SM has 32 SPs. In both architectures, each SP consists of an ALU and FPU as illustrated in Figure 2.1b. The 200-series architecture has a 24-bit ALU while the Fermi architecture includes a 32-bit ALU. However, the 200-series architecture is capable of 32-bit precision arithmetic through the use of multiple arithmetic instructions.

- (a) Streaming Multiprocessor.

- (b) Streaming Processor.

Figure 2.1: Architecture of the T10 GPU. Source: http://www.anandtech.com/show/2549/2

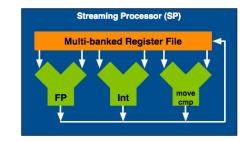

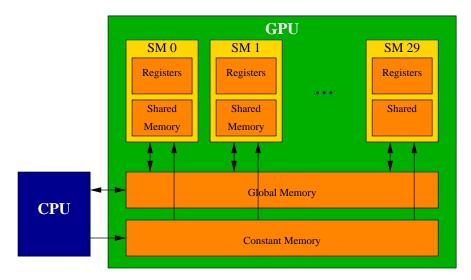

In current GPU systems, the GPU and CPU have a separate memory space with a GPU consisting of three separate types of memory: global, constant and shared. Figure 2.2 depicts the organization of GPU memory. Global and constant memory are accessible by all

<sup>&</sup>lt;sup>1</sup>From this point forward, GPU refers to an NVIDIA GPU.

Figure 2.2: Memory organization of the T10 GPU.

SPs while shared memory is partitioned for each SM. Therefore, each SP in the same SM can share data through the shared memory. However, SPs from one SM cannot share data with SPs from a different SM. Global memory is the slowest memory available on the GPU and is 4GB in size for the Tesla T10 GPU. It is utilized as a transfer medium for the host (CPU) to the device (GPU) or for the device to the host. The GPU can read and write to the global memory while the CPU can copy memory to or from the global memory. Global memory is persistent through kernel calls while constant and shared are not. A CUDA application can transfer data from the system memory at 4GB/s and at the same time upload data to the system memory at 4GB/s. Constant memory is much faster and smaller than the global memory and is only 64KB in size on the Tesla T10. However, the GPU cannot write to constant memory therefore it is simply used to transfer constant data from the CPU to the GPU. Shared memory is also faster and smaller than global memory and can be written to and read from by the GPU. There are 16KB of shared memory per SM for the Tesla T10. However, shared memory cannot be accessed by the CPU therefore it is typically used as a scratch-pad memory for each SP. All computational results generated by the GPU must be stored in global memory to be accessible by the CPU. In some applications, shared memory can also be used for sharing data amongst SPs in the same SM. In addition to the three types of memory, each thread has access to registers and local memory<sup>2</sup> both of which are read/write. The shared memory can be read/written by all threads in the same SM. However, threads from different SMs cannot access the same shared memory while the constant memory can be read by any thread. The global memory can be read/written by any thread.

#### 2.3 GPU Performance

Because of differences in architecture, GPUs have continually outperformed CPUs in terms of floating-point operations per second. "As of 2009, the ratio between many-core GPUs and multicore CPUs for peak floating-point calculation throughput is about 10 to 1" [53]. The fundamental difference in the design of CPUs versus GPUs has created this large increase in performance in terms of FLOPS.

While the CPU is designed to optimize sequential performance, GPUs are designed to optimize parallel instructions throughput. Therefore, GPUs need thousands of threads executing in parallel to achieve full efficiency where a CPU may only need a few. However, each thread of a GPU is lightweight in comparison and requires little overhead to create. The NVIDIA 200-series architecture supports 1024 threads per SM for a total of 30720 threads running in parallel for the entire chip. In addition, new generations of hardware, such as the Fermi, support even more threads running concurrently. Today's Tesla C1060, currently sold by NVIDIA, includes one Tesla T10 processor built on the 200-series architecture. The T10 includes 240 cores, each with a clock speed of 1.33GHz and is connected to 4GB of DRAM. The C1060 fits in a standard PCIe dual slot and consumes around 160 watts of power. Because of these low-cost, low-power GPUs, massively parallel applications are quickly being ported for GPGPU use.

To date, more than 200 million GPUs have been deployed, providing economical parallel processing around the globe. GPGPU hardware is currently being used in a variety of

$<sup>^{2}</sup>$ Local memory is a subsection of global memory used to store variables when the maximum amount of registers is exceeded.

applications, including MRI products. In the past, typical parallel processing research was focused on using large clusters but actual clinical MRI machines needed to be much smaller than that. Because of this, groups such as the National Institutes of Health (NIH) would not fund parallel processing research since it was considered to be limited to large cluster-based machines. However, current MRI machine manufacturers ship MRI products with GPUs and the NIH funds research using GPUs as coprocessors [53].

Previously, a large drawback of GPGPU applications was the necessary programming. In the past, programmers had to learn to program the GPUs using drivers and assembly language. These languages also did not include many useful general computing instructions like integer or bit operations since they were not implemented at the time. In addition, a lack of communication between any of the processors in the GPU was limited making any data sharing difficult. While this is still somewhat of a limitation, it has been greatly improved, since the original design, through CUDA.

#### 2.4 CUDA Environment

Since GPUs were starting to be used as massively parallel processors, NVIDIA developed a programming interface to utilize them known as CUDA. CUDA stands for Compute Unified Device Architecture and is based on the C/C++ language. It enables programmers to write applications in either C or C++ to utilize the GPU as a massively parallel co-processor. In addition, since MATLAB version 2010b, there is support for m-files to use the CUDA environment allowing access for computation on the GPU. CUDA provides constructs for memory transfers between the CPU and GPU for sharing data. It is based on an SPMD programming style which executes the same program on multiple parts of the data. This is different than SIMD since the processing units do not have to be executing the same instruction at the same time. In the CUDA programming environment, there is a host which is the CPU and a device which is the GPU. The NVIDIA CUDA programming language is a large reason more and more industries are looking at GPUs as portable parallel processing

systems. The CUDA extension of the C programming language has enabled all programmers to create parallel applications without any special hardware or software knowledge beyond C. However, knowledge of the underlying architecture to achieve high speedups has inhibited typical programmers from using GPUs as coprocessors.

#### 2.5 Terms

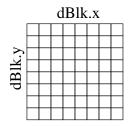

Using CUDA, a C/C++ program consists of host code, code written to execute on the CPU, and device code, code written to execute on the GPU. Device code is divided into individual functions known as kernels. To compile kernels, NVIDIA provides a C compiler known as NVCC. It separates the host and device code and only performs compilation on the device code while using the gcc for the host code. In addition, NVIDIA provides a low-level programming language, parallel thread execution, PTX, similar to assembly language for writing kernels without exposing any of the underlying instruction set. Kernels can be written for any computational operation involving the GPU and are similar to functions in C. They are executed using a specified number of threads. Since the GPU is an SPMD structure, all threads execute the same code on different portions of data and each thread has an identifier known as the thread index. Thread identifiers are used for control logic and data access. A collection of threads is a block, as shown in Figure 2.3. A block can be partitioned in 1, 2, or 3-dimensions. The number of threads in the x- and y-dimension of each block is defined by dBlk.x and dBlk.y, respectively. Threads in the same block

Figure 2.3: A square block of size 64.

can cooperate through atomic operations and synchronization. However, threads in separate

blocks cannot since there is no guarantee to which SM a block is assigned. Each block also has an identifier similar to a thread, known as the block index. The collection of blocks is considered the grid and can be partitioned in 1 or 2-dimensions. The number of blocks in the x- and y-dimension of the grid is defined by dGrd.x and dGrd.y, respectively. Each kernel call can define different grid and block sizes and dimensions but these cannot be changed dynamically during kernel execution.

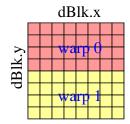

In the T10 processor, each grid can have a maximum of 65,536 blocks in each dimension and each block can have a maximum of 512 threads yielding a maximum total of 2<sup>41</sup> threads. The dimensions of a grid and block determine the total number of threads operating in the GPU, so each need to be chosen to ensure the GPU is fully occupied. Since blocks can execute in any order with respect to other blocks, CUDA applications are very scalable which allows applications to adapt to new hardware without changing any of the existing code. However, architecture changes that often accompany new hardware can cause issues with scalability. Once the partitioning for the grid and blocks is determined, the scheduler organizes threads into groups of 32 known as warps as shown in Figure 2.4. Since warps

Figure 2.4: Partitioning of a square block of size 64 into warps.

waiting for long-latency operations such as intensive arithmetic operations or memory access are not selected for execution, this provides a type of latency hiding. While those warps are waiting for their operations to finish executing, other warps that are not waiting are scheduled to execute. This type of zero-overhead thread scheduling ensures that the maximum instruction throughput is realized. This is one major reason GPUs do not dedicate as much chip area to cache memories and branch prediction mechanisms as CPUs, thus allowing for many more ALUs to fit in the same size of silicon.

A warp is divided into *half-warps* (HWs), a group of 16 threads in row-major order as shown in Figure 2.5. Memory accesses are issued at the HW level. The number of HWs

Figure 2.5: Partitioning of a square block of size 64 into half-warps.

is defined by the dimensions of the grid and blocks, *input parameters*, which are specified by the programmer. The four input parameters are defined as dGrd.x, dGrd.y, dBlk.x, and dBlk.y. dGrd.x and dGrd.y are the dimensions of the grid in the x and y-dimensions, respectively. dBlk.x and dBlk.y are the dimensions of each block in the x and y-dimensions, respectively. Lastly, the focus of this work is on matrix-based computations. All matrices are assumed to be square and n is used to denote the width or height of a square matrix.

## Chapter 3

## Modeling

Developing a parallelization procedure to minimize execution time requires an accurate model of communication and computation times. Several modeling techniques, including fine-grain, vector-based, and table-based modeling, were initially applied to model GPU computational behavior. Fine-grain modeling was performed by measuring computation times for arithmetic operations and extrapolating for larger computations. Vector-based modeling was performed by measuring computation times for vector-based arithmetic operations such as a dot product and extrapolating for larger computations. Lastly, table-based modeling was performed by measuring computation time for various numbers of blocks and threads and extrapolating for other input parameters. However, none of these techniques provided reasonable models of the GPU computational behavior, partly due to the layout of the GPU's memory.

Therefore, this chapter includes an examination of the layout of GPU memory and the formulation of execution metrics to accurately represent the computational behavior of the GPU. Section 3.1 is an examination of the layout of global memory on the GPU. Included in this section are the effects on computation time from the layout. Section 3.2 is an examination of the layout of shared memory and the effects on computation time. The beginning of Section 3.3 provides reasoning for utilizing execution metrics to model GPU computational behavior. Instead of utilizing input parameters to model behavior, execution metrics are formulated as functions of the input parameters for modeling. Section 3.4 is a model and estimation of CPU to GPU and GPU to CPU communication time. Results are included to prove the validity of the estimation. CPU computation time is estimated in Section 3.5 through curve-fitting measured data and results are included in the section.

# 3.1 Global Memory Layout

One reason the aforementioned modeling techniques for GPU computational behavior yield inaccurate models is the layout of global memory on the GPU. Due to the layout of global memory, a problem referred to as *partition camping* exists. Partition camping has been defined by NVIDIA [54], although its effects on various applications have not been studied until recently [55] [56] [57].

# 3.1.1 Partition Camping

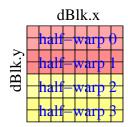

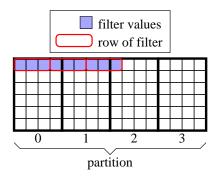

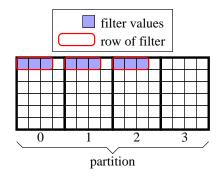

A description of the GPU architecture is necessary to understand partition camping. The global memory on an 8-series and 200-series GPU is divided into 6 and 8 partitions, respectively. On both GPU architectures, each partition is 256-bytes wide. All partitions are connected to a memory controller allowing access by all SMs as depicted in Figure 3.1. Data

Figure 3.1: Global memory connection of the T10 GPU. Memory is divided into 8 equal-sized partitions. Each address represents 256 bytes.

is stored in row-major order and each address in the figure occupies one row of a partition.

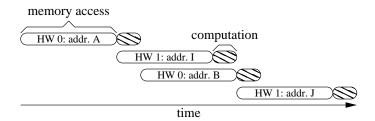

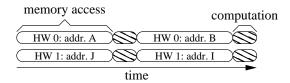

Accesses to global memory partitions are performed at the HW level. Therefore, partition camping occurs when multiple HWs attempt to access the same partition, but not necessarily the same address, at a given time. Figure 3.2 illustrates partition camping occurring when two HWs access two consecutive partitions where Figure 3.1 depicts in which partition each address resides. Since addresses A and I are in the same partition, HW 1

Figure 3.2: An example of partition camping occurring: global memory accesses by 2 HWs to 2 partitions.

must wait, until HW 0 finishes accessing address A, to access address I. The same occurs for the second accesses to addresses B and J. Therefore, partition camping occurs and the memory accesses are serialized.

Figure 3.3 illustrates the access of two partitions by two HWs which eliminates partition camping. For the first access, HW 0 accesses address A which resides in partition 0 and HW

Figure 3.3: An example of partition camping not occurring: global memory accesses by 2 HWs to 2 partitions.

1 accesses address J in partition 1. Partition camping does not occur since the accesses by each HW occur in different partitions. Similarly, for the second access, each HW accesses different partitions and partition camping does not occur. Figures 3.2 and 3.3 demonstrate the theoretical effects on computation time due to partition camping on a GPU such that minimizing partition camping should be performed to minimize computation time.

#### **Effects**

For most GPU computations, thousands of HWs are executing at a given time. To minimize partition camping, and thus the computation time, it is necessary that HWs utilize all partitions of global memory. In addition, it is necessary that the HWs be evenly distributed to the partitions.

The code in Listing 3.1 is a portion of a kernel tested to measure the effects of utilizing a varying number of partitions.

```

1 int offset = floor(BlkIdx / BlksPerPart) * 64;

2 for(j = 0; j < v; j++)

3 temp += A[j * 512 + offset + threadIdx.y];</pre>

```

Listing 3.1: Code to test the effects of partition camping.

Line 1 calculates which partition of global memory each block accesses by utilizing a linear block index, BlkIdx, and the number of assigned blocks per partition, BlksPerPart. The fraction of the two is multiplied by 64 since each value is stored as a float and a partition is 256 bytes wide on a 200-series GPU. The length of a vector in the matrix that is summed is represented by v. Adding the thread index in the y-dimension, threadIdx.y, minimizes the possible effect of memory request merging [58] [59].

The computation time and effective bandwidth, from executing the code in Listing 3.1 on the T10 GPU, are given in Table 3.1<sup>1</sup>. Each time was measured using a square block of 256 threads and 120 blocks to yield a maximum occupancy for each SM. Since threads are assigned to warps in row-major order, each thread in a HW sums identical values. However, each HW in a block computes different sums. The bandwidth decreases linearly as the

|       | number of partitions |      |      |       |

|-------|----------------------|------|------|-------|

| v     | 8                    | 4    | 2    | 1     |

| 512   | 0.4                  | 0.9  | 1.7  | 3.4   |

| 1024  | 0.9                  | 1.7  | 3.4  | 6.7   |

| 2048  | 1.7                  | 3.4  | 6.8  | 13.5  |

| 4096  | 3.3                  | 6.8  | 13.5 | 26.9  |

| 8192  | 6.8                  | 13.4 | 26.5 | 53.8  |

| 16384 | 13.7                 | 26.5 | 52.3 | 107.5 |

|       | number of partitions |      |      |     |

|-------|----------------------|------|------|-----|

| v     | 8                    | 4    | 2    | 1   |

| 512   | 69.4                 | 34.4 | 17.2 | 8.7 |

| 1024  | 68.4                 | 34.6 | 17.2 | 8.7 |

| 2048  | 69.9                 | 34.5 | 17.2 | 8.7 |

| 4096  | 71.7                 | 34.4 | 17.4 | 8.7 |

| 8192  | 69.6                 | 35.1 | 17.7 | 8.7 |

| 16384 | 68.5                 | 35.4 | 17.9 | 8.7 |

(b) Effective bandwidth (GB/s).

Table 3.1: Measured results of executing Listing 3.1 which demonstrate the effect of partition camping on the T10 GPU. v is the number of values each thread summed.

number of partitions utilized decreases, due to partition camping. Since the number of HWs remains constant in the tests, using less partitions increases partition camping which

<sup>(</sup>a) Measured computation time (ms).

<sup>&</sup>lt;sup>1</sup>These results suggest memory request merging mentioned in [58] and [59] does not occur.

increases the computation time. For MM, all partitions are utilized at some point when  $n^2 \ge 512$ , where n is the height or width of a square matrix. However, the order in which HWs access each partition varies depending on the computation pattern, which is determined by how the code is written. Therefore, partition camping and the effects are considered in the parallelization procedure.

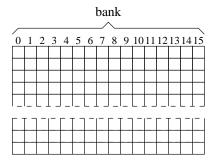

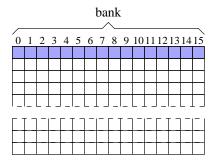

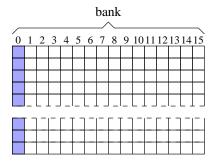

# 3.2 Shared Memory Layout

Shared memory is divided into equal-sized banks for GPUs. For the T10 GPU, there are 16 banks as depicted in Figure 3.4. Each bank consists of 256 rows, 4 bytes wide, and all banks can be accessed simultaneously. Bank conflicts occur at the thread level. If all

Figure 3.4: Shared memory layout in the T10 GPU. Memory is divided into 16 equal-sized partitions. Each column is 4 bytes wide.

threads within a HW access different banks, as illustrated in Figure 3.5, no bank conflicts occur and only one access is necessary.

Figure 3.5: Threads within a HW accessing 16 shared memory banks. No bank conflicts occur.

## 3.2.1 Bank Conflicts

If two or more addresses of a memory access to shared memory fall into the same memory bank, a bank conflict occurs. Since memory accesses are issued at the HW level, threads within a HW accessing differing addresses in the same bank cause bank conflicts and the accesses are serialized. In Figure 3.6, all threads within a HW access different rows of shared memory but the same column. Since the column resides in the same shared memory bank,

Figure 3.6: Threads within a HW accessing one shared memory bank. 16 bank conflicts occur.

16 bank conflicts occur. Therefore, 16 accesses to shared memory are issued to service the HW. However, the T10 GPU supports shared memory broadcasting. Therefore, if threads within a HW access the same address in shared memory, no bank conflicts occur.

## Effects

The portion of the kernel utilized to test the effects of bank conflicts is depicted in Listing 3.2.

```

1    __shared__ float As[dBlkx][dBlky];

2    int offset = blockIdx.x % 8 * 64;

3    int soffset = threadIdx.x % Banks;

4    for(j = 0; j < v; j++) {

As[threadIdx.y][threadIdx.x] = d_A[j * 512 + offset + threadIdx.y];

temp += As[threadIdx.x][soffset];

7    }</pre>

```

Listing 3.2: Code to test the effects of bank conflicts.

The number of banks each HW accesses is defined by *Banks*. In Line 3, *soffset* is calculated to specify which column of shared memory is accessed and therefore, the number of bank conflicts is fixed. *blockIdx.x* and *threadIdx.x* are the indices of each block and thread in the x-dimension, respectively.

Table 3.2 shows the effect on computation time due to bank conflicts. Similar to the

|       | number of banks |      |      |      |      |  |  |

|-------|-----------------|------|------|------|------|--|--|

| v     | 16              | 8    | 4    | 2    | 1    |  |  |

| 512   | 0.5             | 0.5  | 0.6  | 0.9  | 1.5  |  |  |

| 1024  | 0.9             | 1.0  | 1.3  | 1.8  | 2.9  |  |  |

| 2048  | 1.7             | 1.9  | 2.5  | 3.6  | 5.8  |  |  |

| 4096  | 3.4             | 3.8  | 5.0  | 7.2  | 11.5 |  |  |

| 8192  | 6.6             | 7.6  | 9.9  | 14.3 | 23.0 |  |  |

| 16384 | 12.9            | 15.1 | 19.6 | 28.5 | 46.0 |  |  |

|       | number of banks |      |      |      |      |  |  |

|-------|-----------------|------|------|------|------|--|--|

| v     | 16              | 8    | 4    | 2    | 1    |  |  |

| 512   | 65.1            | 58.6 | 45.8 | 31.8 | 19.9 |  |  |

| 1024  | 66.6            | 60.4 | 46.5 | 32.2 | 20.1 |  |  |

| 2048  | 67.7            | 61.4 | 47.1 | 32.6 | 20.2 |  |  |

| 4096  | 69.1            | 61.7 | 47.3 | 32.7 | 20.3 |  |  |

| 8192  | 71.2            | 61.9 | 47.6 | 32.8 | 20.4 |  |  |

| 16384 | 72.4            | 62.1 | 47.7 | 32.9 | 20.4 |  |  |

Table 3.2: Measured results of executing Listing 3.2 which demonstrates the effect of bank conflicts on the T10 GPU. v is the number of values summed by each thread.

effects of partition camping in global memory, shared memory bank conflicts significantly affect computation time. As the number of banks increases, the number of bank conflicts decreases as does the computation time. Although the change in computation time is not linearly proportional to the number of banks utilized, the effects of bank conflicts are clearly illustrated. Therefore, bank conflicts and the effects are considered in the parallelization procedure.

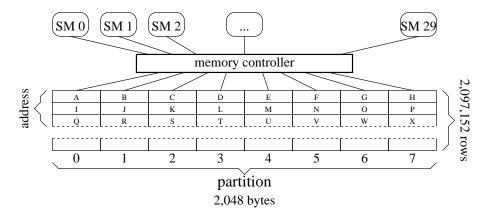

## 3.3 Execution Metrics

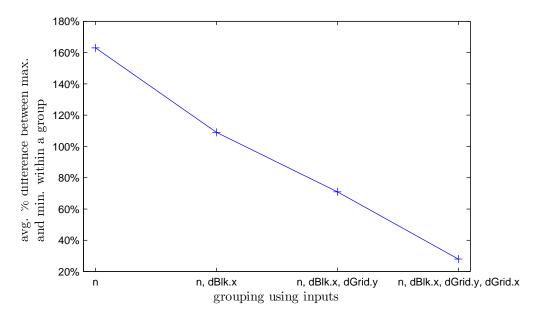

In this section, execution metrics are formulated to represent computational behavior of the GPU to assist in modeling. Figure 3.7 shows the necessity for execution metrics, as input parameters, the dimensions of the grid and blocks, do not accurately model computational behavior. Initially, all measured computation times of MM utilizing varying input parameters are grouped by n. The average percent difference between the maximum and minimum time within a group is shown. Grouping by n yields an average difference of

<sup>(</sup>a) Computation time (ms).

<sup>(</sup>b) Effective bandwidth (GB/s).

163% between the maximum and minimum time of a group. Next, all measured computation times utilizing varying input parameters are grouped by n and dBlk.x. The average percentage difference is 109 between the maximum and minimum of a group. The order of the groupings is determined by the input parameter which yields the smallest average percent difference between the maximum and minimum time of a group. Continuing until 3 of the 4 input parameters are exhausted for grouping yields an average percent difference of 28. Therefore, modeling the computational behavior of the GPU is inaccurate utilizing input parameters. Because of this, execution metrics are formulated as functions of input parameters to accurately represent computational behavior.

Figure 3.7: Modeling MM with input parameters: average percent difference between the maximum and minimum computation time (ms) of a group defined by n and a subset of the input parameters.

Four input parameters, dGrd.x, dGrd.y, dBlk.x and dBlk.y, and the size of each matrix, n, are used to formulate the execution metrics. Input parameters and n are assumed to be powers of two in this work. The product of the four input parameters yields the total number

of threads assigned for execution on the GPU<sup>2</sup> as

Thds<sup>total</sup><sub>GPU</sub> =

$$dGrd.x \times dGrd.y \times dBlk.x \times dBlk.y$$

. (3.1)

The execution metrics can be formulated for any matrix-based computation. However, in this work, the focus of the execution metrics pertains to Mv, MM, and convolution.

## 3.3.1 Global Memory Accesses

Thds $_{GPU}^{total}$  is used to formulate an execution metric for representing the number of global memory accesses. The number of memory accesses significantly affects the computation time for matrix-based computations since the time is largely dependent on memory access latency.

In general, for matrix-based computations, all matrices reside in global memory and portions of matrices may reside in shared memory. For MM, there are  $2n^3$  values read from global memory, although consecutive reads from threads in the same block can be combined. The number of writes to global memory for MM is  $n^2$  and consecutive writes from threads in the same block can be combined. Therefore, the amount of time for writing to global memory for MM is significantly less than the amount of time for reading from global memory. This is similar for other matrix-based computations such as Mv and 2D convolution. Therefore, the number of writes to global memory is ignored in this work.

Memory accesses are issued at the HW level and the GPU combines consecutive thread accesses within a HW into one access, known as coalescing. The memory access is issued as either a 32-, 64- or 128-byte memory transaction. Therefore, the number of reads is the sum of 32B, 64B and 128B transactions.

$$\mathrm{Gld}=\mathrm{Gld}_{32B}+\mathrm{Gld}_{64B}+\mathrm{Gld}_{128B}.$$

<sup>&</sup>lt;sup>2</sup>The notation used in Equation (3.1) is used throughout this work. The unit being defined, threads (Thds) or blocks (Blks), is specified first. The superscript represents the type of unit being defined, total (total), active (active) or fragmented (frag.). The subscript represents the execution unit being defined, GPU (GPU) or SM (SM).

Initially, each transaction is considered a 128B access by the GPU's memory controller and is reduced if possible. If the threads in a HW access between 9 and 16 consecutive and aligned memory locations of float or integer value, only one 64B memory transaction is issued. If the HW accesses less than 9 consecutive memory locations of float or integer value, one 32B memory transaction is issued. If the HW accesses memory locations which are not consecutive and 128B aligned, multiple 32B and/or 64B memory transactions are issued until all threads in the HW have been serviced. Since each HW is a group of 16 threads, the number of HWs that execute on the GPU is defined as

$$HWs^{\#} = \frac{Thds_{GPU}^{total}}{16}.$$

The equation assumes there are at least 16 threads in a block.

From the input parameters, and considering coalescing, the number of 32B and 64B reads for matrix-based computations can be formulated<sup>3</sup>.

For a naïve implementation of Mv utilizing only global memory,  $thread_j$ , to compute  $c_j$  where  $\mathbf{c} = \mathbf{A} \times \mathbf{b}$ , computes  $row_j \cdot \mathbf{b}$  where  $row_j$  is one row of  $\mathbf{A}$ . Therefore, the neighboring thread,  $thread_{j+1}$ , computes  $row_{j+1} \cdot \mathbf{b}$ . If  $dBlk.x \geq 16$ , each HW accesses 16 values of  $\mathbf{A}$  and 1 value of  $\mathbf{b}$ . Since 1 value of  $\mathbf{b}$  is accessed, a 32B transaction is issued. The 16 values of  $\mathbf{A}$  reside in differing rows of  $\mathbf{A}$ , and therefore the accesses are uncoalesced and require 16 32B transactions. This is repeated for each HW n times. Therefore, the number of 32B transactions for this implementation of Mv is

Gld<sub>32B</sub> =

$$\begin{cases} \frac{(dBlk.x + 1)n^2}{dBlk.x} & \text{if } dBlk.x \le 8\\ \frac{17n^2}{16} & \text{if } dBlk.x \ge 16. \end{cases}$$

(3.2)

This equation assumes only global memory is utilized for Mv. The equation is modified for varying memories as shown in Section 4.1.

$<sup>^{3}128</sup>B$  reads do not exist in matrix-based computations when using values of type int or float.

For a naïve implementation of MM utilizing only global memory, to compute  $C_{ij}$  where  $C=A\times B$ ,  $thread_{ij}$  accesses  $row_i$  and  $col_j$ . If dBlk.x > 1, the neighboring thread,  $thread_{i(j+1)}$ , accesses  $row_i$  and  $col_{j+1}$ . Since both threads are in the same HW, then if  $dBlk.x \ge 16$ ,  $n \ 32B$  transactions are issued to read  $row_i$  and  $n \ 64B$  transactions to read  $col_j...col_{j+15}$ . However, if  $dBlk.x \le 8$ , then only 32B transactions are issued. Therefore, the total number of reads performed to global memory is defined as

Gld<sub>32B</sub> =

$$\begin{cases} \frac{n^3}{dBlk.x} + \frac{n^3}{16} & \text{if } dBlk.x \le 8\\ \frac{n^3}{16} & \text{if } dBlk.x \ge 16 \end{cases}$$

(3.3)

$$Gld_{64B} = \frac{n^3}{16}$$

if  $dBlk.x \ge 16$ . (3.4)

These equations assume only global memory is utilized for MM. The equations are modified for varying memories as shown in Section 4.1. Assuming  $dBlk.x \ge 16$ , half of the reads are 32B transactions and half are 64B. Since memory access latency to constant and shared memory is much shorter than global, the number of accesses performed to constant and shared memory is ignored in this work as it has an insignificant impact on computation time.

For a naïve implementation of 2D convolution<sup>4</sup>,  $thread_{ij}$  computes  $C_{ij}$  where  $\mathbf{C} = \mathbf{A} * \mathbf{B}$ . In image processing,  $\mathbf{A}$  is an image and  $\mathbf{B}$  is a *filter*. Therefore,  $\mathbf{C}$  is the result of applying a filter to an image and  $C_{ij}$  is one pixel of the resulting image. In this work, all filters,  $\mathbf{B}$ , are assumed to be square. Therefore, the size, height or width, of a filter is represented by FS. For a naïve implementation of convolution utilizing only global memory, to compute  $C_{ij}$ ,  $thread_{ij}$  accesses  $FS^2$  values of  $\mathbf{A}$  and  $\mathbf{B}$ . Since each thread within a HW accesses the same value of  $\mathbf{B}$  in each iteration of computation, the number of 32B transactions for accessing  $\mathbf{B}$  is defined only by FS. If  $dBlk.x \geq 16$ , neighboring threads within a HW access neighboring values of  $\mathbf{A}$  and therefore the accesses are coalesced into one 64B transaction. However, if

<sup>&</sup>lt;sup>4</sup>From this point forward, convolution refers to 2D convolution of two matrices where  $\mathbf{C} = \mathbf{A} * \mathbf{B}$ .

$dBlk.x \le 8$ , no 64B transactions occur and the number of 32B transactions is dependent on FS and dBlk.x. Therefore, the number of global memory accesses is approximately<sup>5</sup>

$$Gld_{32B} = \begin{cases} \frac{n^2 F S^2}{16} \left( 1 + \frac{16}{dBlk.x} \right) & \text{if } dBlk.x \le 8\\ \frac{n^2 F S^2}{16} & \text{if } dBlk.x \ge 16 \end{cases}$$

(3.5)

$$Gld_{64B} = \frac{n^2 F S^2}{16}$$

if  $dBlk.x \ge 16$ . (3.6)

These equations assume only global memory is utilized for convolution. The equations are modified for varying memories as shown in Section 5.1.1. The number of accesses performed to shared memory is ignored in this work as it has an insignificant impact on computation time. In addition to formulating the amount of reads to global memory, it is necessary to formulate the amount of threads executing in parallel on the GPU.

## 3.3.2 Active Threads

The number of threads executing at a given time on a GPU, or the number of active threads, is defined by Threads $_{GPU}^{active}$ . To formulate the number of active threads, it is necessary to formulate the number of active blocks per SM, Blks $_{SM}^{active}$ . Blks $_{SM}^{active}$  is dependent on the number of registers used per block (RegsPerBlk), amount of shared memory used per block (SMemPerBlk), maximum amount of blocks allowable, and maximum amount of threads allowable. The number of registers used per thread is dependent on the compiler and determined after compilation. The amount of shared memory used per block is defined by the kernel and determined after compilation.

The maximum number of blocks and threads that can be active varies depending on the GPU. The T10 GPU consists of 30 SMs and each SM can have a maximum of 8 blocks or 1024 threads. Assuming there are more blocks assigned for execution than SMs,  $dGrd.x \times dGrd.y > 0$

<sup>&</sup>lt;sup>5</sup>Due to boundary checking, not all reads are issued.

30, Blks $_{SM}^{active}$  is formulated as

$$Blks_{SM}^{active} = \min\left(\left\lfloor \frac{16384}{RegsPerBlk} \right\rfloor, \left\lfloor \frac{16384}{SMemPerBlk} \right\rfloor, 8, \frac{1024}{dBlk.x \times dBlk.y} \right). \tag{3.7}$$

Therefore, from Equation (3.7), the number of active blocks on the GPU at a given time is

$$Blks_{GPU}^{active} = min \left(30 \times Blks_{SM}^{active}, dGrd.x \times dGrd.y\right). \tag{3.8}$$

The number of active threads on the GPU is formulated as the product of Equation (3.8) and the number of threads per block. Therefore,

Thds<sup>active</sup><sub>GPU</sub> = Blks<sup>active</sup><sub>GPU</sub> ×

$$dBlk.x \times dBlk.y$$

. (3.9)

### 3.3.3 Fragmented Threads