## Characterization of Die Stress in Microprocessor Packaging Due to Mechanical, Thermal, and Power Loading

by

Jordan Christopher Roberts

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama August 2, 2014

Keywords: piezoresistive stress sensor, test chip, die stress, heat sink clamping, thermal cycling, power cycling

Copyright 2014 by Jordan Christopher Roberts

Approved by

Jeffrey C. Suhling, Co-Chair, Quina Distinguished Professor and Chair of Mechanical Engineering Richard C. Jaeger, Co-Chair, Professor Emeritus of Electrical Engineering Roy W. Knight, Assistant Professor of Mechanical Engineering Robert N. Dean, Associate Professor of Electrical Engineering

#### Abstract

Microprocessor packaging in modern workstations and servers often consists of one or more large flip chip die that are mounted to a high performance ceramic chip carrier. The final assembly configuration features a complex stack up of flip chip area array solder interconnects, underfill, ceramic substrate, lid, heat sink, thermal interface materials, second level ceramic ball grid array (CBGA) solder joints, organic printed circuit board, etc., so that a very complicated set of mechanical loads is transmitted to the microprocessor chip. Several trends in the evolution of this packaging architecture have exacerbated die stress levels including the transition to larger die, high CTE ceramic substrates, lead free solder joints, higher levels of power generation, and larger heat sinks with increased clamping forces. Die stress effects are of concern due to several reasons including degradation of silicon device performance (mobility/speed), damage that can occur to the copper/low-k dielectric top level interconnect layers, and potential mechanical failure of the silicon in extreme cases.

In this work, test chips containing piezoresistive stress sensors have been used to measure the buildup of mechanical stresses in a microprocessor die after various steps of the flip chip CBGA assembly process. (111) silicon test chips were used to measure the complete threedimensional stress state at each sensor site being monitored by the data acquisition hardware. Special test fixtures were developed to eliminate any additional stresses due to clamping effects. The developed normal stresses are compressive (triaxial compression) across the die surface, with significant in-plane and out-of-plane (interfacial) shear stresses also present at the die corners. The compressive stresses increase with each assembly step (flip chip solder joint reflow, underfill dispense and cure, and lid attachment).

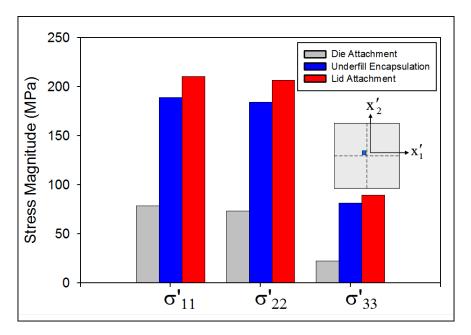

The experimental observations from this study show clearly that large area array flip chip die are subjected to relatively large compressive in-plane normal stresses after solder reflow. It was also observed that the majority of the die compressive stress is accumulated during the underfilling assembly step. Typical increases in the stress magnitude were on the order of 300% (relative to the stresses due to solder joint reflow only). As a general "rule of thumb," approximately two-thirds (66%) of the final die stress magnitudes were observed to be developed during the underfill dispense and cure, with the second largest contribution coming from the die attachment, and the smallest contribution coming from lid attachment.

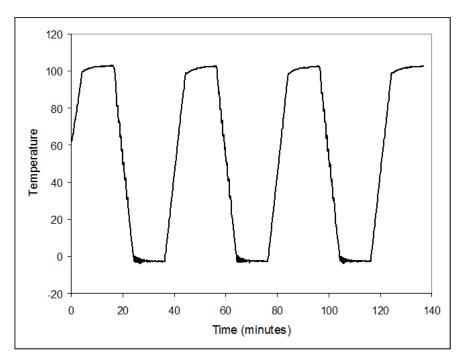

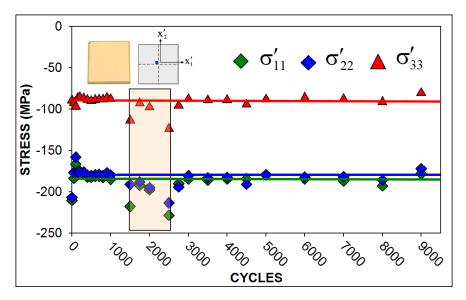

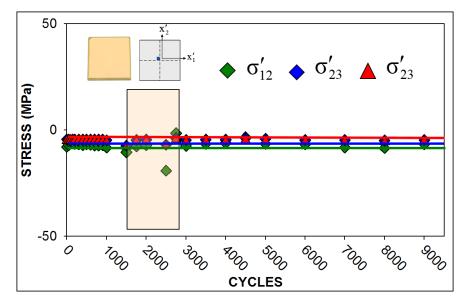

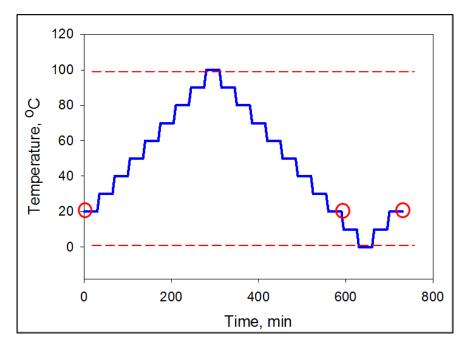

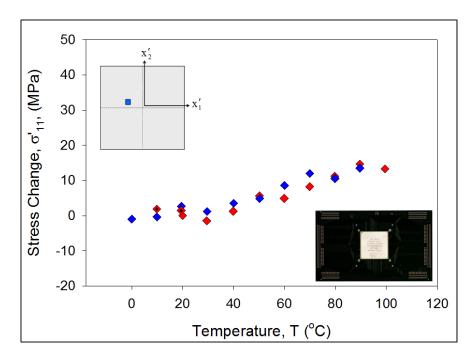

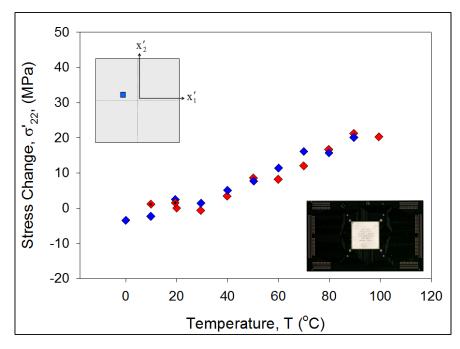

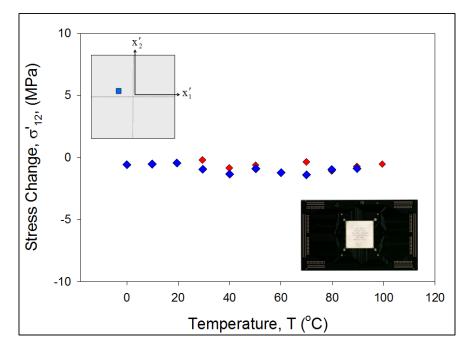

A unique package carrier was developed to allow measurement of the die stresses in the FC-CBGA components during thermal and power cycling without inducing any additional mechanical loadings. Initial experiments consisted of measuring the die stress levels while the components were subjected to slow (quasi-static) temperature changes from 0 to 100 °C. In later testing, long term thermal cycling of selected parts was performed from 0 to 100 °C (40 minute cycle, 10 minute ramps and dwells) for up to 9000 cycles. After various durations of cycling, the sensor resistances at critical locations on the die device surface (e.g. die center and die corners) were recorded. From the resistance data, the stresses at each site were calculated and plotted versus time. Finally, thermal and power cycling of selected parts was performed, and in-situ measurements of the transient die stress variations were performed. Power cycling was implemented by exciting on-chip heaters on the test chips with various power levels. During the thermal/power cycling, sensor resistances at critical locations on the die device surface (e.g. die center and die corners) were recorded continuously. From the resistance data, the stresses at each site were cycling was implemented by exciting on-chip heaters on the test chips with various power levels. During the thermal/power cycling, sensor resistances at critical locations on the die device surface (e.g. die center and die corners) were recorded continuously. From the resistance data, the stresses at each site were calculated and plotted versus time.

The experimental test chip stress measurements were correlated with finite element simulations of the packaging process. A sequential modeling approach was used to predict the build-up of compressive stress. The method used incorporates precise thermal histories of the packaging process, element creation, and nonlinear temperature and time dependent material properties. With suitable detail in the models, excellent correlation has been obtained with the sensor data throughout all packaging processes. Finally, CBGAs with the stress sensing chips were soldered to organic PCB test boards. A simulated heat sink mechanical loading was applied, and the stresses were measured as a function of the clamping force. Compressive stress increases of up to 60 MPa were observed for a 1000 N applied clamping force. The experimental test chip stress measurements were correlated with finite element simulations of the clamping process. Excellent correlation has been obtained between the predicted and measured stress changes occurring during simulated heat sink clamping.

#### Acknowledgments

I would like to thank my savior, Jesus Christ for grace in times of need, including the completion of this dissertation. I would also like to express my sincere gratitude to my mother for her love, encouragement, and patience among so many other good things. I would also like to thank my father for his encouragement and the values he instilled in me before his passing.

I truly appreciate the guidance, hard work, and patience of my advisor, Dr. Jeffrey C. Suhling throughout my graduate career. Many thanks go my co-advisor Dr. Richard C. Jaeger for his technical insight and support of my graduate research. Thanks are extended to Dr. Roy W. Knight for serving on my committee, giving insight for this dissertation, and very timely advice in several teaching matters. I would also like to thank Dr. Robert N. Dean for his service on my committee, and Dr. Michael Hamilton for serving as the University Reader of this dissertation.

Many thanks go to Mr. John Marcell for countless acts of assistance, friendship, and advice. I sincerely appreciate Mr. Mike Palmer for his friendship as well as supporting the development and manufacture of almost every assembly in this work. Thanks go to Safina Hussain for help with designing test boards, and Dr. Mohammad Motalab for finite element simulation results. A special thanks to all lab mates, past and present, and too many to name, for friendship and encouragement.

## Table of Contents

| Abstract                                                   | ii   |

|------------------------------------------------------------|------|

| Acknowledgments                                            | v    |

| List of Figures                                            | Х    |

| List of Tables                                             | xxi  |

| Nomenclature                                               | xxii |

| 1 Introduction                                             | 1    |

| 1.1 Area Array Components in Microprocessor Packaging      | 1    |

| 2 Literature Review                                        | 5    |

| 2.1 Introduction and Review of Electronic Packaging Issues | 5    |

| 2.1.1 Historical Packaging Issues                          | 5    |

| 2.1.2 High-End Microprocessor Issues                       | 6    |

| 2.2 Stress Determination in Electronic Packaging           | 7    |

| 2.2.1 Experimental Methods                                 | 7    |

| 2.2.2 Interferometric Techniques                           | 7    |

| 2.2.3 Semiconductor Test Chips                             | 8    |

| 2.2.4 Numerical Methods                                    | 11   |

| 2.3 Correlation of Experimental and Numerical Methods      | 13   |

| 2.4 Heat Sink Clamping                                     | 14   |

| 2.5 Thermal Cycling                                        | 15   |

| 2.6 Power Cycling of IC Components                         | 17   |

| 3 Review of Piezoresistive Theory                          | 20   |

| 3.1 General Resistance Change Equations                    | 20   |

| 3.2 Piezoresistivity in the (111) Silicon Plane            | 25   |

| 4 | (11) | 11) Silio | con Test Chips                                                    | 27 |

|---|------|-----------|-------------------------------------------------------------------|----|

|   | 4.1  | Rosett    | te and Test Chip Designs                                          | 27 |

|   |      | 4.1.1     | Optimized Eight-Element Rosette                                   | 27 |

|   |      | 4.1.2     | Area Array Stress Test Chip                                       | 31 |

|   | 4.2  | Test C    | Chip Calibration                                                  | 39 |

|   |      | 4.2.1     | Introduction                                                      | 39 |

|   |      | 4.2.2     | Four-Point Bending Calibration                                    | 39 |

|   |      | 4.2.3     | Hydrostatic Calibration and TCR Measurement                       | 40 |

|   | 4.3  | Resist    | ance Measurement Procedure                                        | 46 |

|   |      | 4.3.1     | Introduction                                                      | 46 |

|   |      | 4.3.2     | Resistance Measurements                                           | 48 |

|   |      | 4.3.3     | Test Measurement Equipment                                        | 48 |

| 5 | Di   | e Stress  | ses Due to Assembly                                               | 56 |

|   | 5.1  | CLGA      | A Package and Assembly Procedure                                  | 56 |

|   |      | 5.1.1     | Measurement Methodology                                           | 61 |

|   | 5.2  | Exper     | imental Stress Characterization of Packaging Induced Die Stresses | 66 |

|   |      | 5.2.1     | Die Stress Due to Solder Reflow                                   | 66 |

|   |      | 5.2.2     | Die Stress Due to First Level Underfill                           | 68 |

|   |      | 5.2.3     | Die Stress Due to Lid Attachment                                  | 70 |

|   |      | 5.2.4     | Summary of Packaging Induced Die Stresses                         | 73 |

|   | 5.3  | Nume      | rical Evaluation of Packaging Induced Die Stresses                | 77 |

|   |      | 5.3.1     | Multipoint Constraints                                            | 77 |

|   |      | 5.3.2     | Material Constitutive Models                                      | 77 |

|   |      | 5.3.3     | Stress Build-up During Assembly Processes                         | 80 |

|   |      | 5.3.4     | Solder Joint Reflow                                               | 81 |

|   |      | 5.3.5     | Underfill Curing Process                                          | 82 |

|   |      | 5.3.6     | Lid Attachment Process                                            | 87 |

|   |     | 5.3.7    | Correlation with Experimental Measurements                                | 90   |

|---|-----|----------|---------------------------------------------------------------------------|------|

| 6 | Di  | e Stress | ses Due to Thermal Exposures                                              | 95   |

|   | 6.1 | Tempe    | erature Dependent Die Stresses                                            | 95   |

|   |     | 6.1.1    | Numerical Predictions of Temperature Dependent Die Stresses               | 108  |

|   | 6.2 | Die St   | resses Due to Thermal Cycling                                             | 111  |

|   |     | 6.2.1    | Numerical Prediction of Die Stresses Due to Thermal Cycling $\ . \ . \ .$ | 125  |

|   | 6.3 | In-Situ  | ı Die Stress Measurements During Thermal Cycling                          | 127  |

|   |     | 6.3.1    | Numerical Predictions for Transient Die Stresses During Thermal Cy-       |      |

|   |     |          | cling                                                                     | 128  |

| 7 | Te  | emperat  | ure and Stress Effects Due to Power Dissipation                           | 129  |

|   | 7.1 | In-Situ  | 1 Temperature Determination                                               | 129  |

|   | 7.2 | Tempe    | erature Change due to Power Dissipation                                   | 131  |

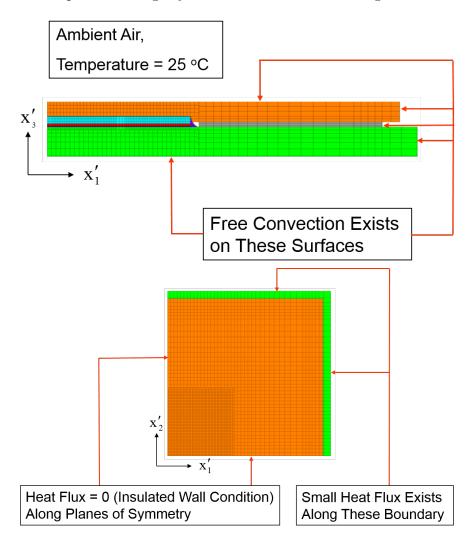

|   |     | 7.2.1    | Numerical Predictions of Temperature Change due to Power Dissipation      | n134 |

|   | 7.3 | Exper    | imental and Numerical Evaluation of Power Cycling                         | 135  |

| 8 | Se  | cond Le  | evel Assembly of Ceramic Ball Grid Array Packages                         | 139  |

|   | 8.1 | Second   | d Level Assembly Test Board                                               | 139  |

|   | 8.2 | Ceram    | nic Ball Grid Array Packages                                              | 143  |

|   | 8.3 | Second   | d Level Assembly Equipment and Techniques                                 | 143  |

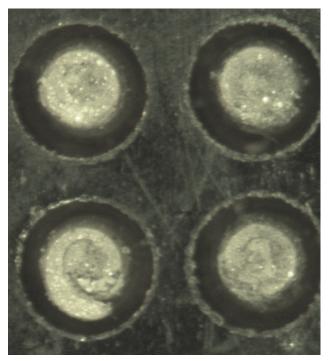

|   |     | 8.3.1    | Assembly Verification                                                     | 146  |

|   | 8.4 | Tempe    | erature Dependent Die Stresses in CBGA on Laminate Assemblies             | 151  |

| 9 | Di  | e Stress | ses Due to Heat Sink Clamping                                             | 159  |

|   | 9.1 | Introd   | uction                                                                    | 159  |

|   | 9.2 | Exper    | imental Characterization of Die Stresses due to Heat Sink Clamping .      | 160  |

|   |     | 9.2.1    | CBGA on Test Board Assemblies                                             | 160  |

|   |     | 9.2.2    | CLGA in Socket Assemblies                                                 | 172  |

|   |     | 9.2.3    | Comparison of CBGA and CLGA Clamping Response                             | 176  |

|   | 9.3 | Nume     | rical Simulation of CBGA Die Stresses due to Heat Sink Clamping           | 182  |

| 10 | Summary and Conclusions                                                    | 186 |

|----|----------------------------------------------------------------------------|-----|

|    | 10.1 Summary                                                               | 186 |

|    | 10.2 Conclusions                                                           | 190 |

| Bi | bliography                                                                 | 216 |

| Ap | opendices                                                                  | 217 |

| А  | Calculation of Die Stresses using Alternative Stress-Free Reference States | 218 |

# List of Figures

| 1.1  | Architecture for a High Performance Flip Chip Microprocessor                                                  | 2  |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Filamentary Silicon Conductor                                                                                 | 21 |

| 3.2  | (111) Silicon Wafer $\ldots$ | 26 |

| 4.1  | Optimized Eight-Element Rosette                                                                               | 28 |

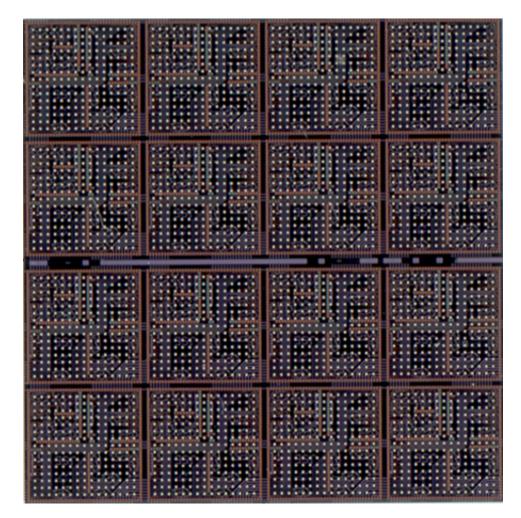

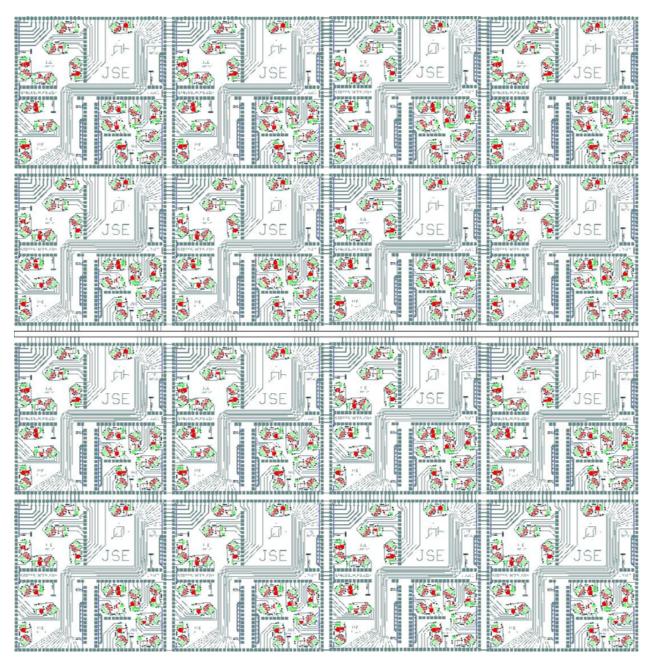

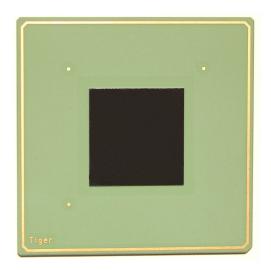

| 4.2  | Area Array Flip Chip Stress Test Chip                                                                         | 32 |

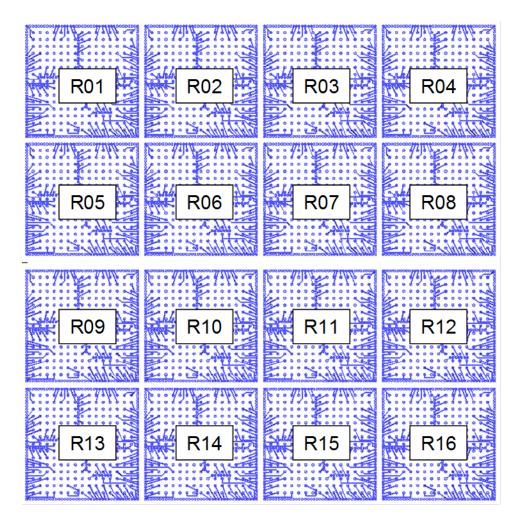

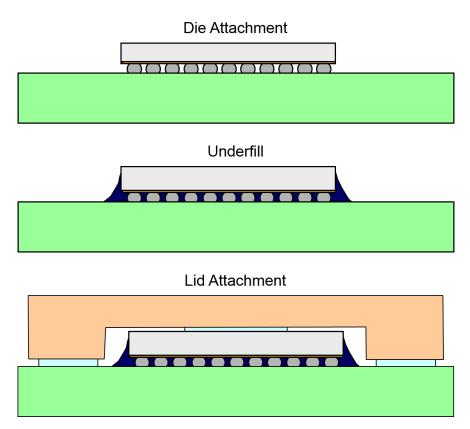

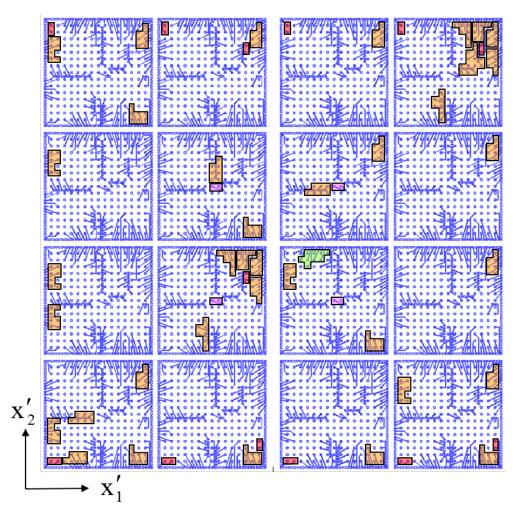

| 4.3  | Array of Identical 5 x 5 mm Regions                                                                           | 33 |

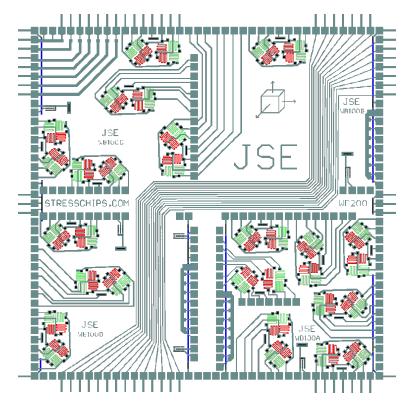

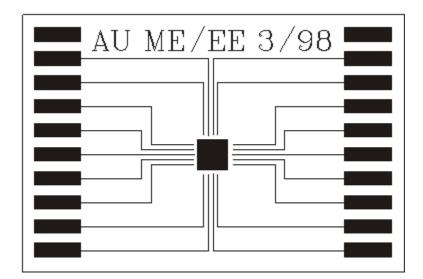

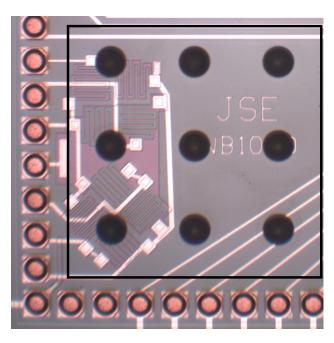

| 4.4  | Wirebond Stress Test Chip (JSE WB200)                                                                         | 34 |

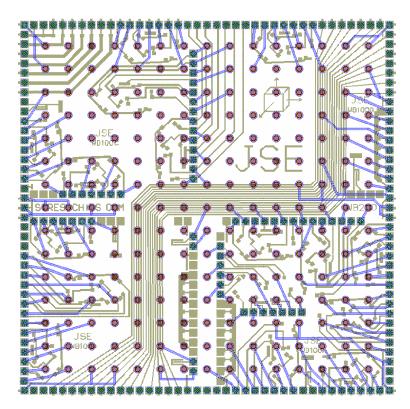

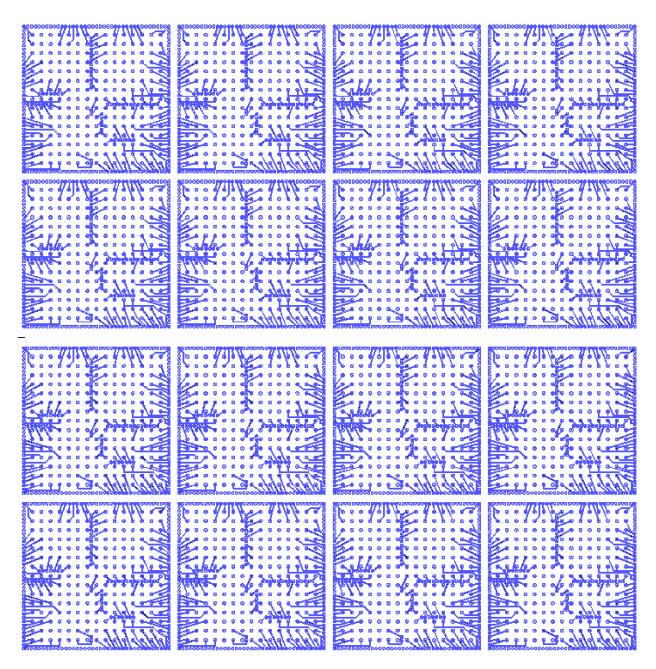

| 4.5  | Redistribution Pattern on each 5 x 5 mm Region                                                                | 35 |

| 4.6  | 20 x 20 mm Test Chip Before Redistribution                                                                    | 36 |

| 4.7  | Redistribution Pattern on each 5 x 5 mm Region                                                                | 37 |

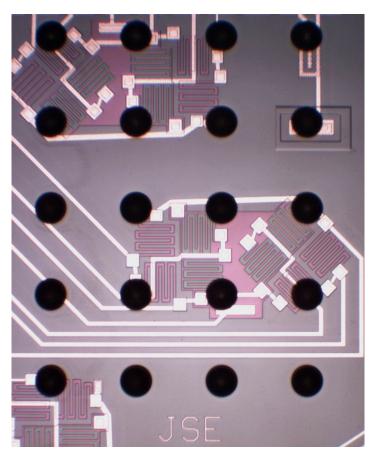

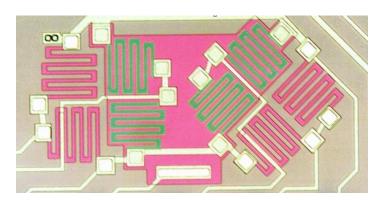

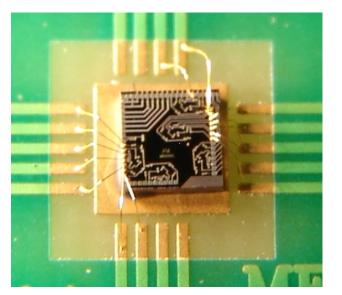

| 4.8  | Photograph of Sensor Rosettes                                                                                 | 38 |

| 4.9  | Close-Up Photograph of a Fabricated Rosette                                                                   | 38 |

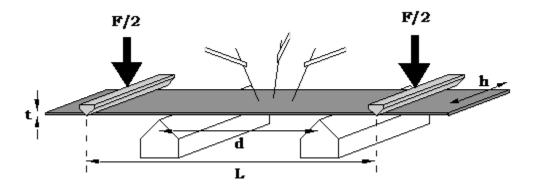

| 4.10 | Four-Point Bending Geometry                                                                                   | 39 |

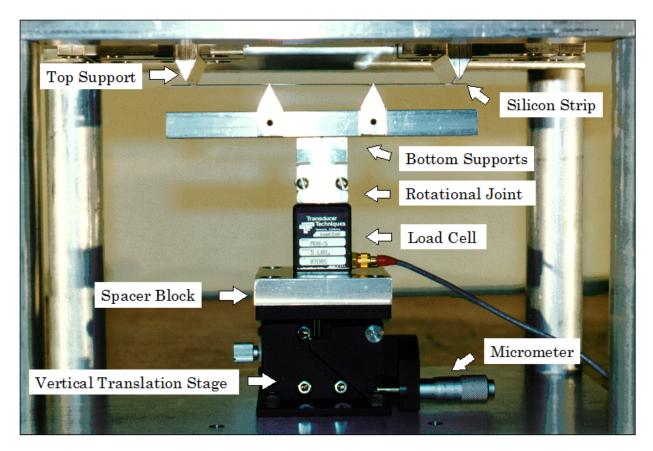

| 4.11 | Four-Point Bending Fixture                                                                                    | 41 |

| 4.12 | Hydrostatic Pressure Vessel                                                                                   | 43 |

| 4.13 | Schematic of Hydrostatic PCB                                | 43 |

|------|-------------------------------------------------------------|----|

| 4.14 | Wire-Bonded WB100 Die for TCR and Hydrostatic Tests         | 44 |

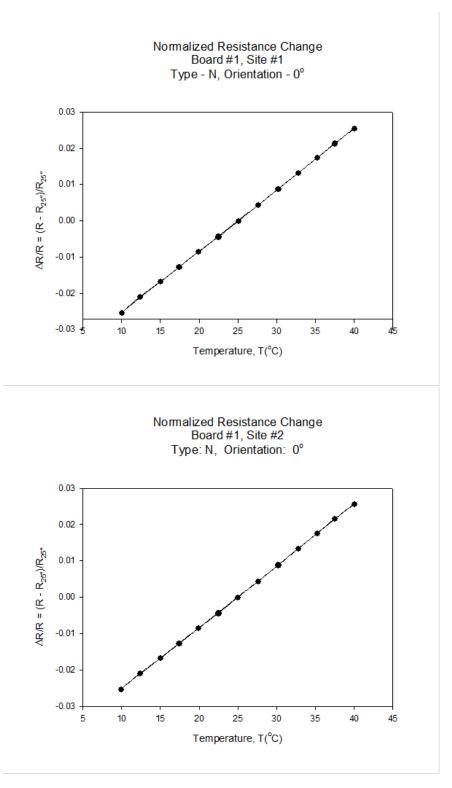

| 4.15 | Typical TCR Data                                            | 45 |

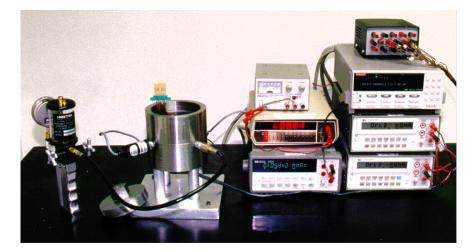

| 4.16 | Hydrostatic Test Setup                                      | 46 |

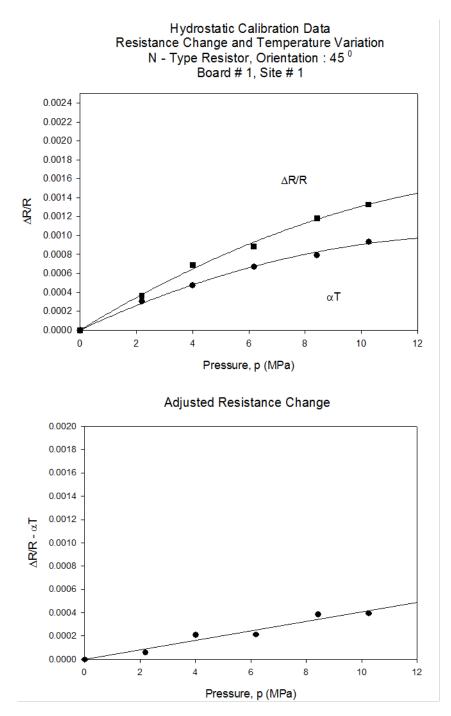

| 4.17 | Typical Hydrostatic Test Results                            | 47 |

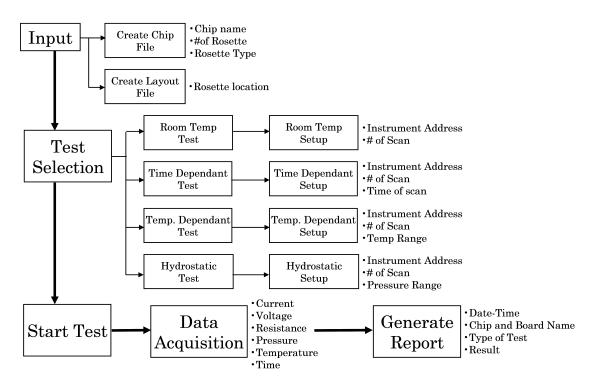

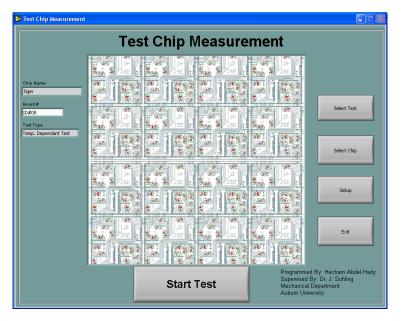

| 4.18 | Test Chip Software Logic                                    | 50 |

| 4.19 | Test Chip Measurement Software Interface                    | 51 |

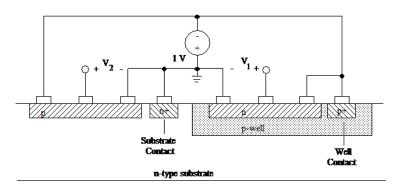

| 4.20 | Proper Biasing of Sensors                                   | 51 |

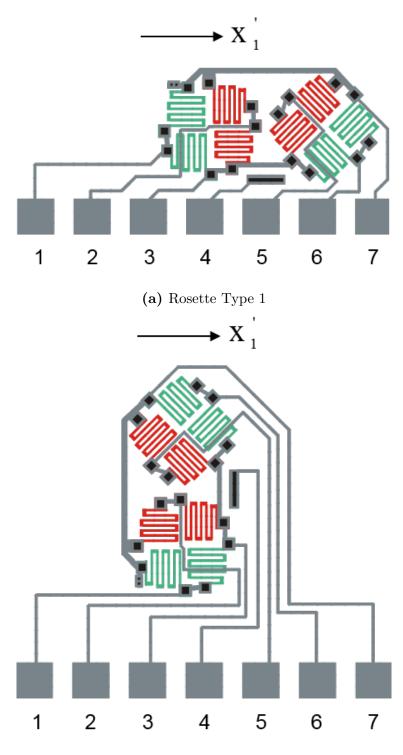

| 4.21 | Rosette Types 1 and 2                                       | 52 |

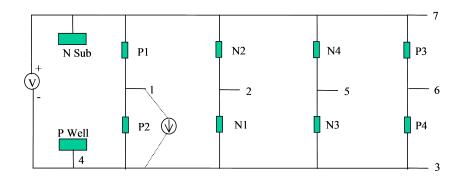

| 4.22 | Typical Wiring Diagram of Sensors used in JSE-WB Test Chips | 53 |

| 4.23 | Bias for Resistance Measurements, Upper Arm of Half Bridge  | 55 |

| 4.24 | Bias for Resistance Measurements, Lower Arm of Half Bridge  | 55 |

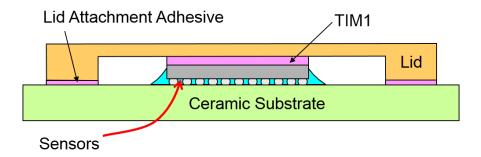

| 5.1  | Schematic of Typical Microprocessor Architecture            | 56 |

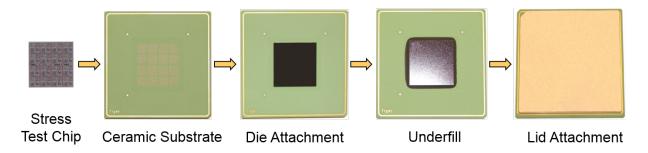

| 5.2  | CLGA Packaging Process Steps                                | 57 |

| 5.3  | Schematics: CLGA Assembly Process                           | 57 |

| 5.4  | Active Pads on the Packaged Test Chips                      | 59 |

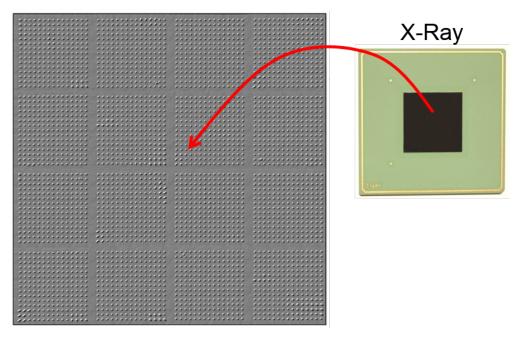

| 5.5  | X-Ray Verification of Solder Bumps                          | 60 |

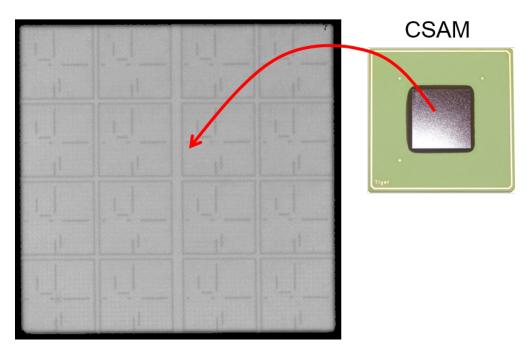

| 5.6  | CSAM Verification of Die-Underfill Interface                | 60 |

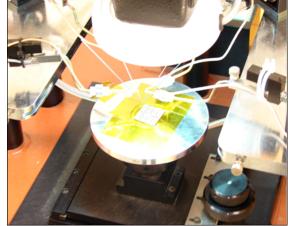

| 5.7  | Measurement with Manual Probe Station                                                              | 62 |

|------|----------------------------------------------------------------------------------------------------|----|

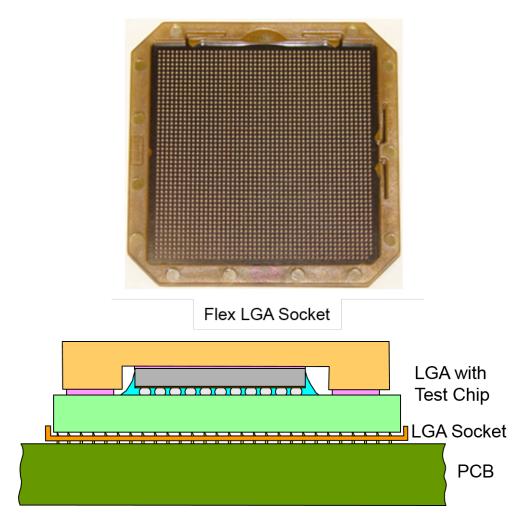

| 5.8  | Electrical Connection via Flex LGA Socket                                                          | 63 |

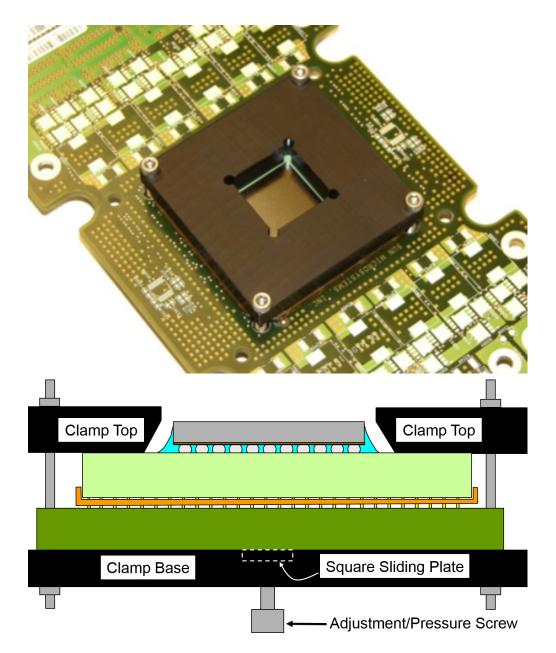

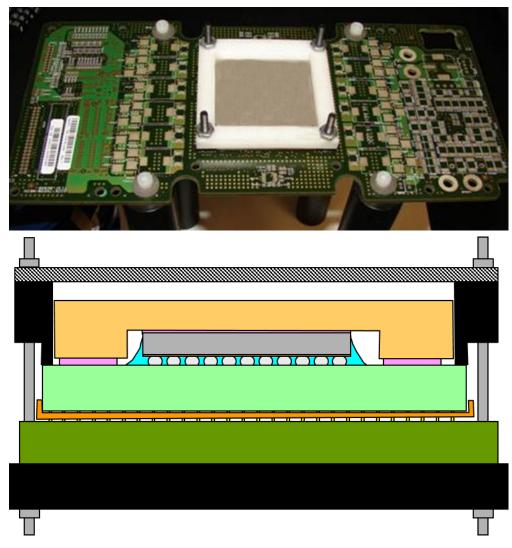

| 5.9  | Clamping Fixture for Ceramic LGA (After Solder Reflow and Underfill Steps) $% \mathcal{L}^{(1)}$ . | 64 |

| 5.10 | Clamping Fixture for CLGA (Lid Attachment Step)                                                    | 65 |

| 5.11 | Data Acquisition System                                                                            | 65 |

| 5.12 | Typical Package After Die Attachment                                                               | 67 |

| 5.13 | Stresses Due to Die Attachment                                                                     | 67 |

| 5.14 | Typical Package After Underfill Dispense and Cure                                                  | 68 |

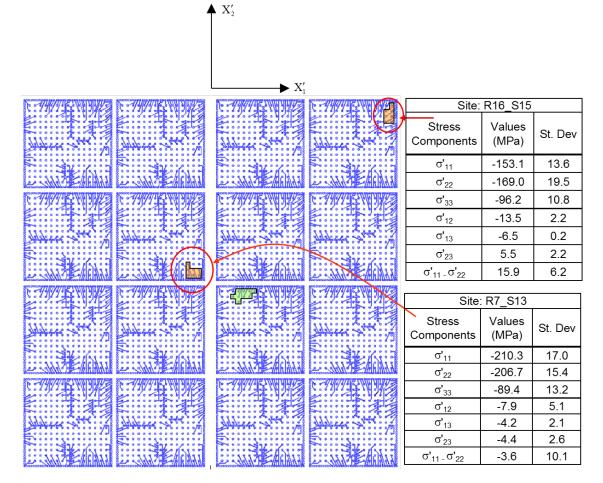

| 5.15 | Stresses After Underfill Dispense and Cure                                                         | 69 |

| 5.16 | Typical Package After Lid Attachment                                                               | 70 |

| 5.17 | Schematic of Typical Package After Lid Attachment                                                  | 70 |

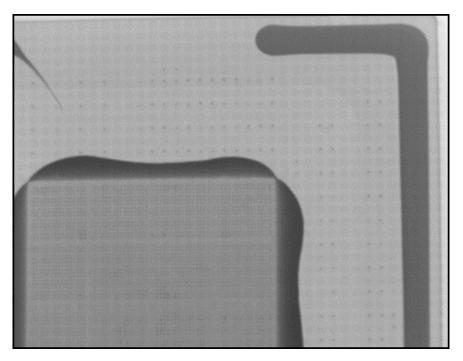

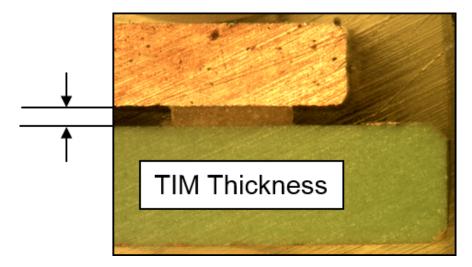

| 5.18 | X-ray of TIM1 Layer and Lid Adhesive                                                               | 71 |

| 5.19 | Cross Section Showing Lid Adhesive Thickness                                                       | 71 |

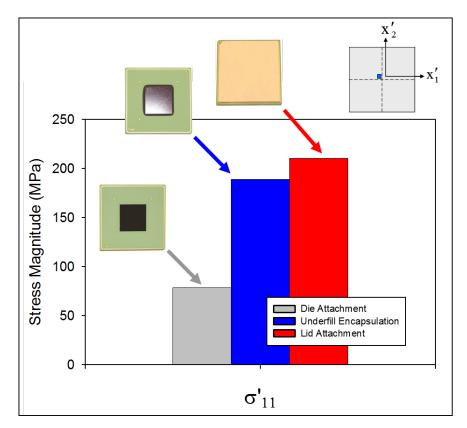

| 5.20 | Stresses After Lid Attachment                                                                      | 72 |

| 5.21 | Evolution of Die Stress at the Center of the Chip (Compressive Horizontal Normal                   |    |

|      | Stress)                                                                                            | 74 |

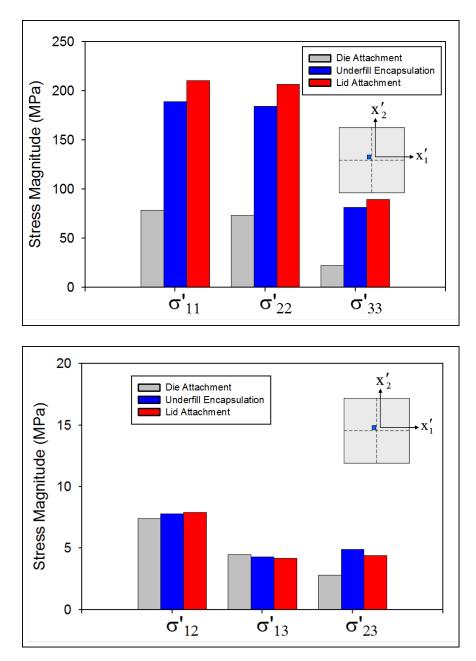

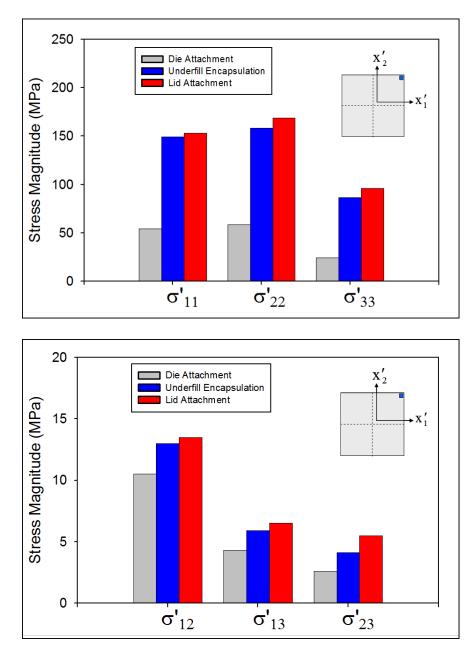

| 5.22 | Evolution of the Six Die Stress Components at the Center of the Chip $\ \ .\ .\ .$ .               | 75 |

| 5.23 | Evolution of the Six Die Stress Components at the Corner of the Chip $\ \ldots \ \ldots$           | 76 |

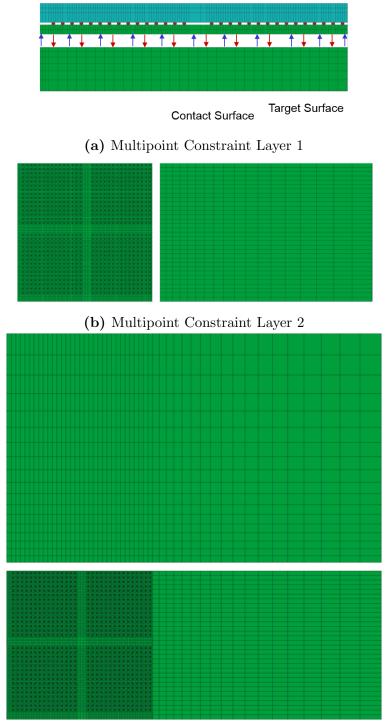

| 5.24 | Multipoint Constraint Layers                                                                       | 78 |

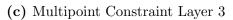

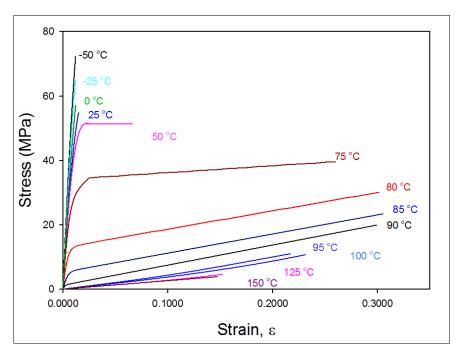

| 5.25 | Stress Strain Behavior of HiTCE Substrate                                                  | 79 |

|------|--------------------------------------------------------------------------------------------|----|

| 5.26 | Stress Strain Behavior of First Level Underfill                                            | 80 |

| 5.27 | Quarter Model of Die Attachment                                                            | 81 |

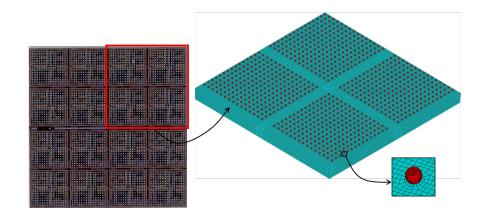

| 5.28 | Silicon and Solder Bump Detail of Quarter Model                                            | 82 |

| 5.29 | Die Stress Buildup During Cooldown After Solder Joint Reflow                               | 83 |

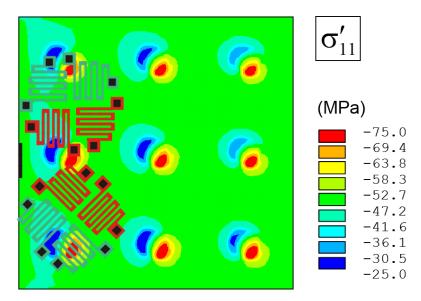

| 5.30 | In-plane Normal Stress Distribution After Die Attachment                                   | 83 |

| 5.31 | In-plane Normal Stress Distribution After Die Attachment                                   | 84 |

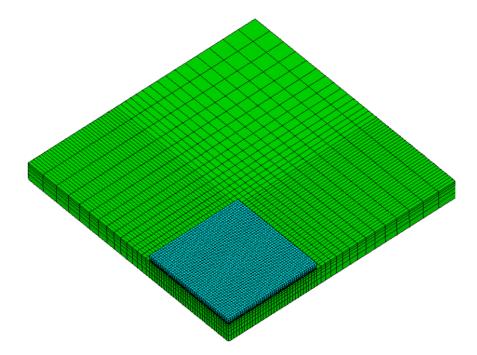

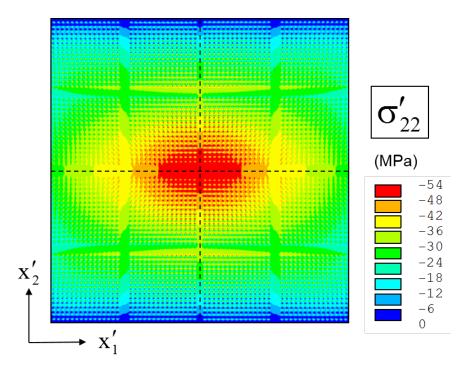

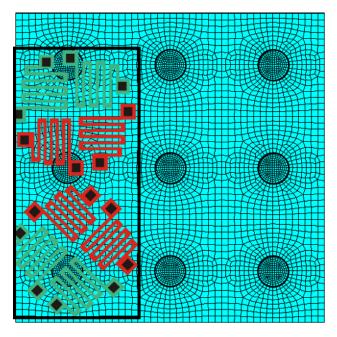

| 5.32 | Quarter Symmetry Mesh for Underfill Cure Model with Detail                                 | 85 |

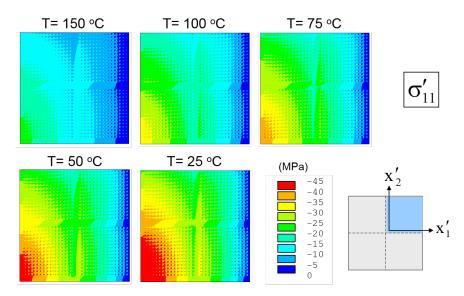

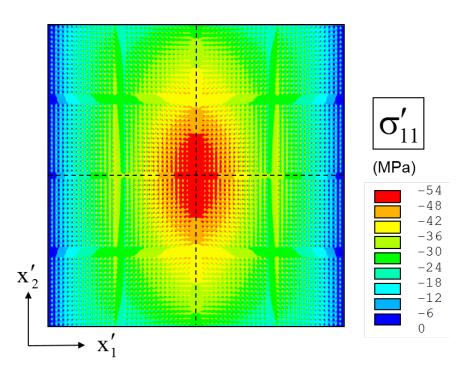

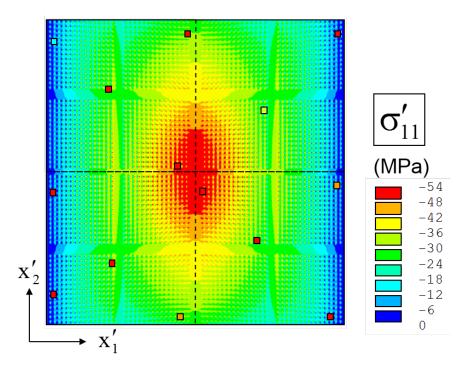

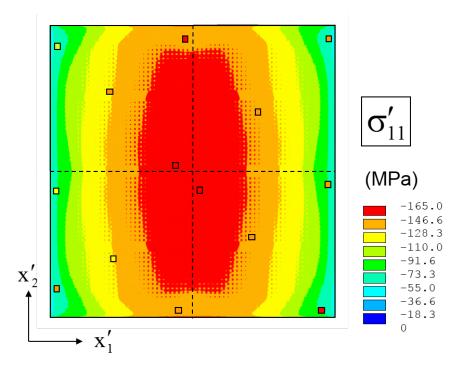

| 5.33 | In-plane Normal Stress Distribution After Underfill Cure                                   | 86 |

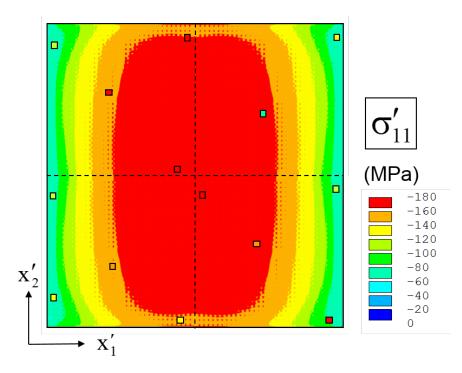

| 5.34 | In-plane Normal Stress Distribution After Underfill Cure                                   | 87 |

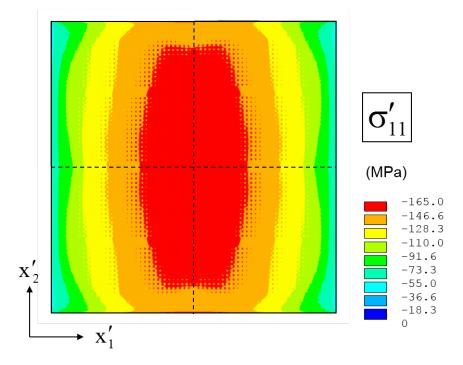

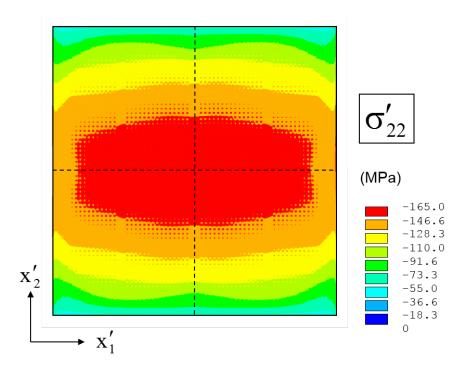

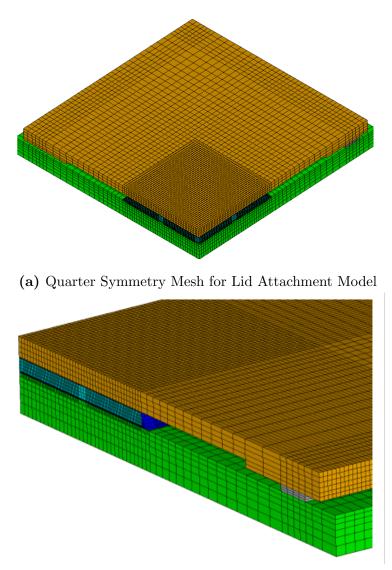

| 5.35 | Quarter Symmetry Mesh for Lid Attachment Model with Detail                                 | 88 |

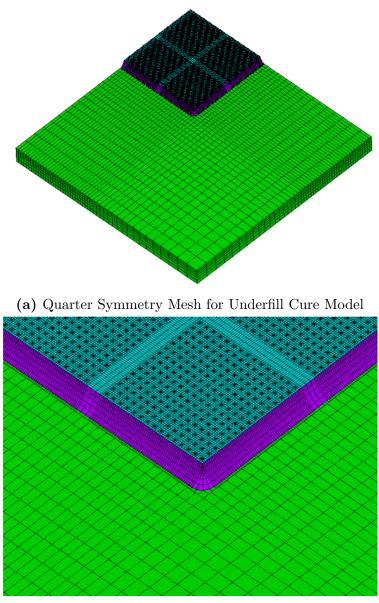

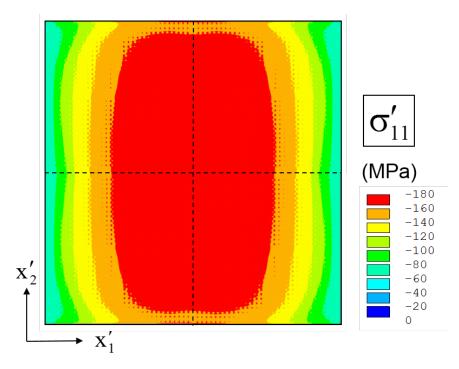

| 5.36 | In-plane Normal Stress Distribution After Lid Attachment                                   | 89 |

| 5.37 | In-plane Normal Stress Distribution After Lid Attachment                                   | 90 |

| 5.38 | Correlation of FEA Predictions with Sensor Data (Solder Joint Reflow)                      | 92 |

| 5.39 | Correlation of FEA Predictions with Sensor Data (Underfill Cure)                           | 92 |

| 5.40 | Correlation of FEA Predictions with Sensor Data (Lid Attachment)                           | 93 |

| 5.41 | Micrograph of Rosette with Mesh Outline (Solder Joint Reflow) $\ \ldots \ \ldots \ \ldots$ | 93 |

| 5.42 | Finite Element Mesh with Rosette Superimposed (Solder Joint Reflow)                        | 94 |

| 5.43 | Stress Gradients near Solder Bumps (Solder Joint Reflow)          | 94  |

|------|-------------------------------------------------------------------|-----|

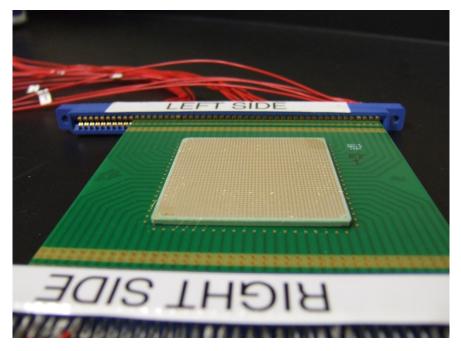

| 6.1  | Wirebonded CLGA Test Assembly                                     | 97  |

| 6.2  | CLGA Temperature Test Board                                       | 98  |

| 6.3  | Wirebond Stitching on CLGA Lands                                  | 98  |

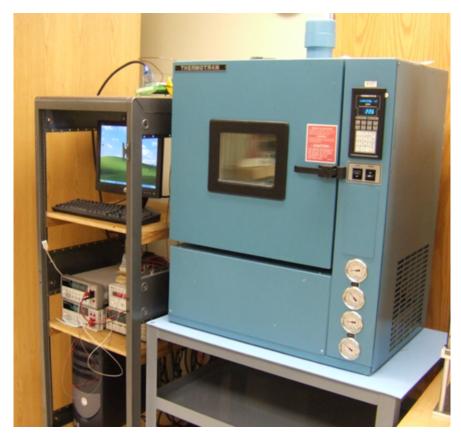

| 6.4  | Thermal Chamber and DAQ                                           | 99  |

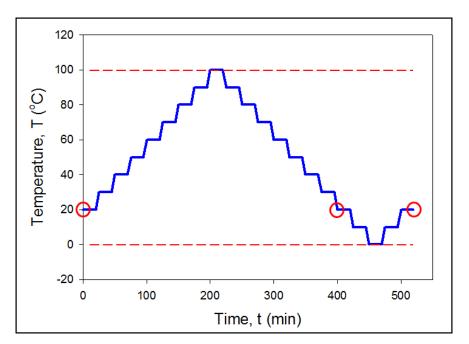

| 6.5  | Thermal Profile for Temperature Dependent Stress Testing          | 99  |

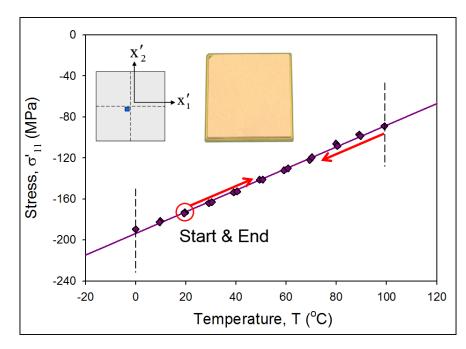

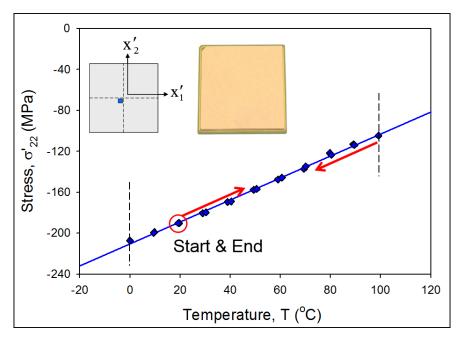

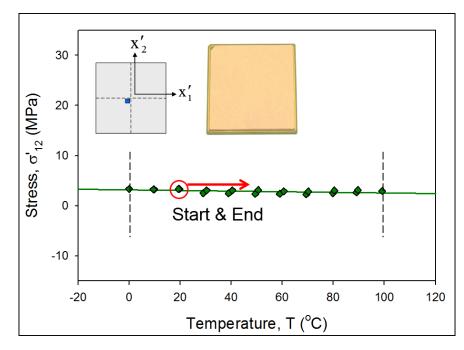

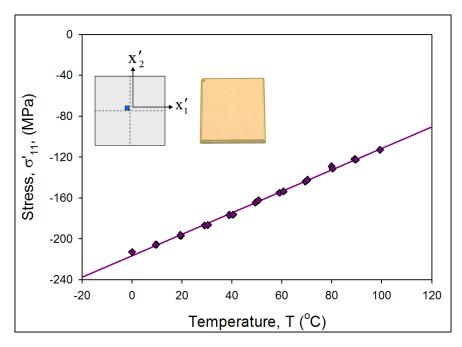

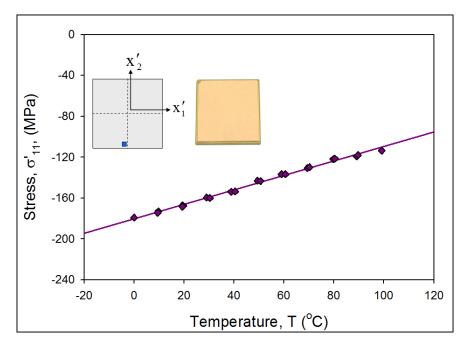

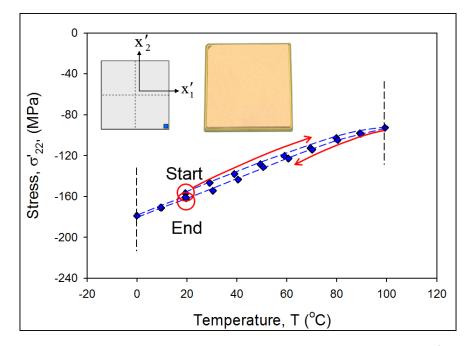

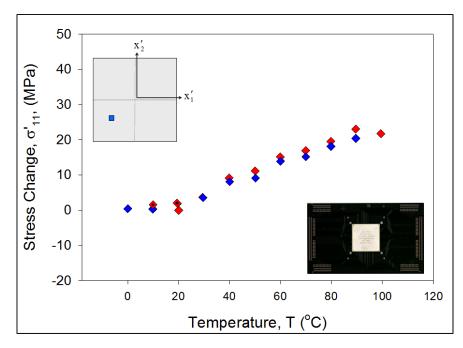

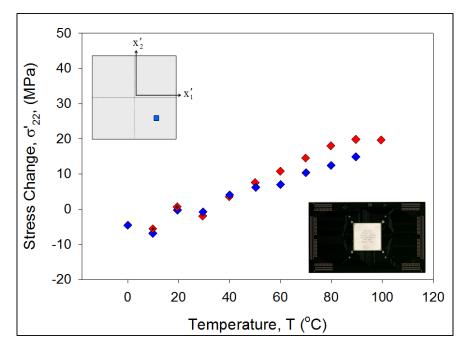

| 6.6  | Variation of In-Plane Normal Stress with Temperature (Die Center) | 100 |

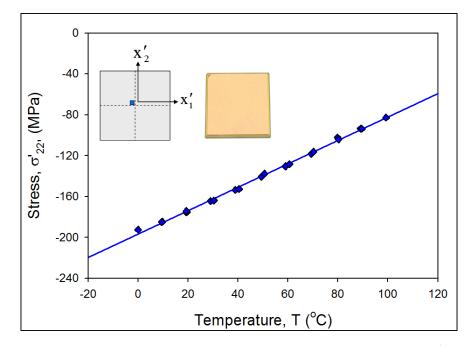

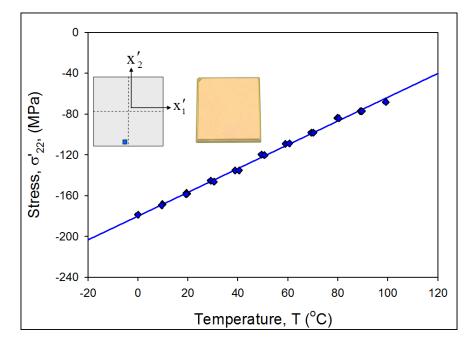

| 6.7  | Variation of In-Plane Normal Stress with Temperature (Die Center) | 101 |

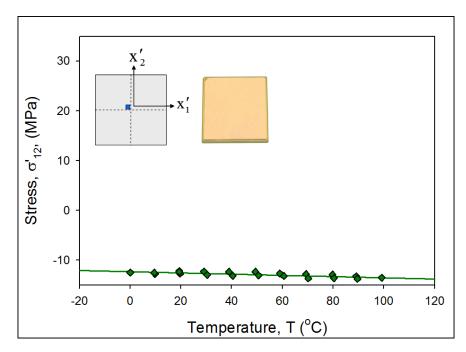

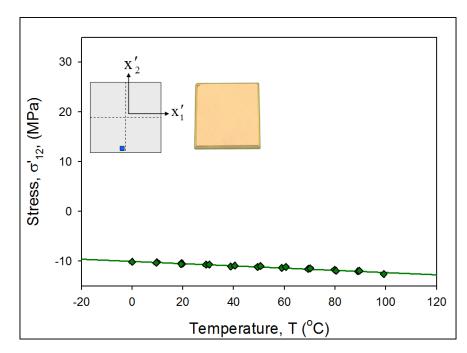

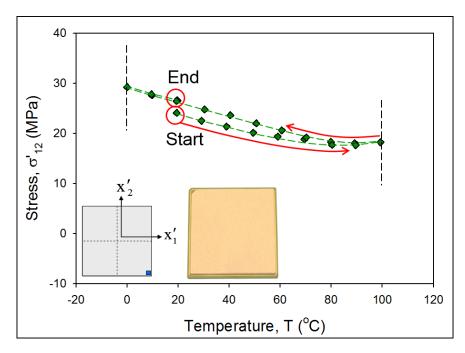

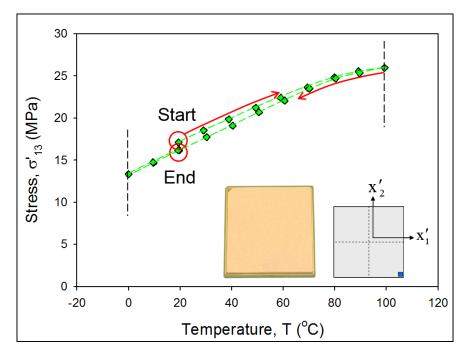

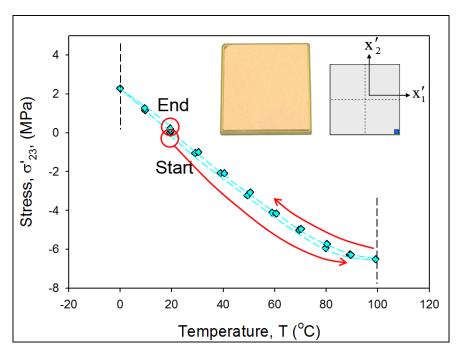

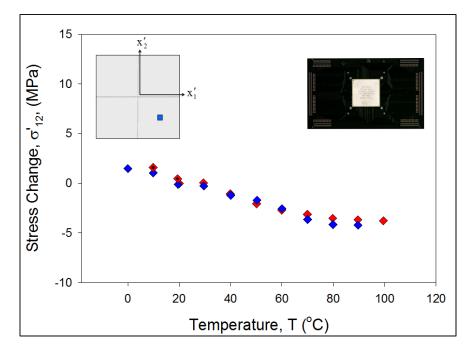

| 6.8  | Variation of In-Plane Shear Stress with Temperature (Die Center)  | 101 |

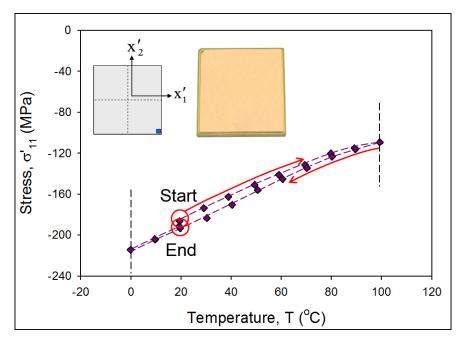

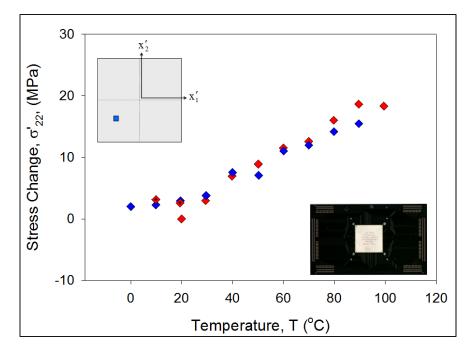

| 6.9  | Variation of In-Plane Normal Stress with Temperature (Die Center) | 102 |

| 6.10 | Variation of In-Plane Normal Stress with Temperature (Die Center) | 102 |

| 6.11 | Variation of In-Plane Shear Stress with Temperature (Die Center)  | 103 |

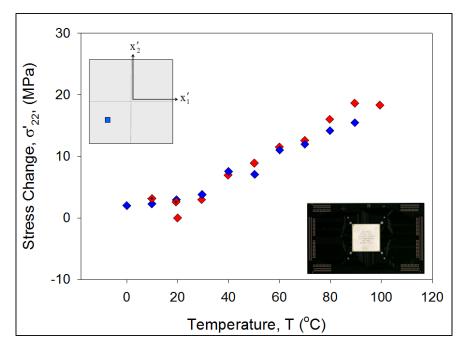

| 6.12 | Variation of In-Plane Normal Stress with Temperature (Die Edge)   | 104 |

| 6.13 | Variation of In-Plane Normal Stress with Temperature (Die Edge)   | 104 |

| 6.14 | Variation of In-Plane Shear Stress with Temperature (Die Edge)    | 105 |

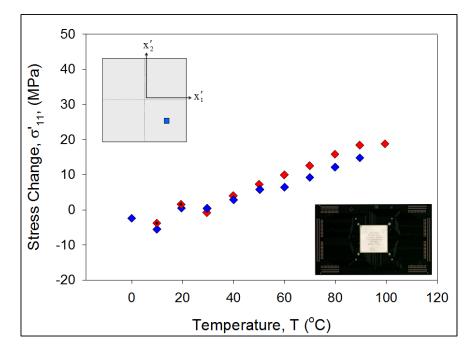

| 6.15 | Variation of In-Plane Normal Stress with Temperature (Die Corner) | 106 |

| 6.16 | Variation of In-Plane Normal Stress with Temperature (Die Corner) | 106 |

| 6.17 | Variation of In-Plane Shear Stress with Temperature (Die Corner)  | 107 |

| 6.18 Variation of Out-of-Plane Shear Stress with Temperature (Die Corner) 107                  |

|------------------------------------------------------------------------------------------------|

| 6.19 Variation of Out-of-Plane Shear Stress with Temperature (Die Corner) 108                  |

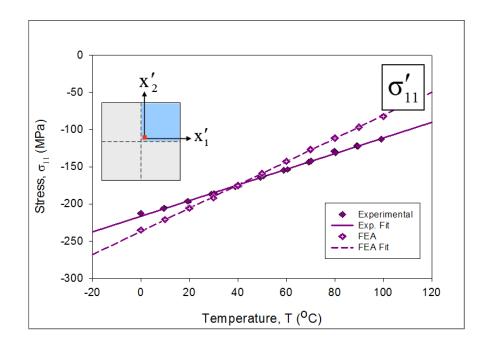

| 6.20 FEA Correlation of In-Plane Normal Stress with Temperature (Die Center) $$ $109$          |

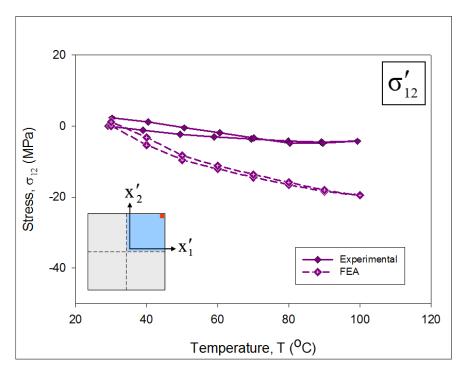

| 6.21 FEA Correlation of In-Plane Shear Stress with Temperature (Die Corner) $~\ldots~~110$     |

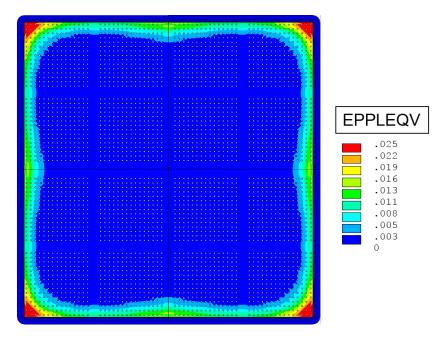

| 6.22 FEA Prediction of Equivalent Plastic Strain in Underfill                                  |

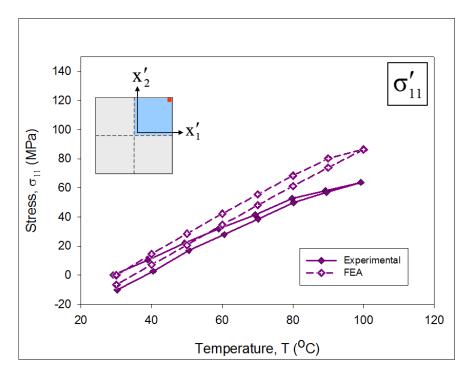

| 6.23 FEA Correlation of In-Plane Normal Stress with Temperature<br>(Die Corner) 111            |

| 6.24 Blue M ETC-16 Environmental Chamber used for Thermal Cycling 112                          |

| 6.25 Thermal Cycling Profile (40 Minute Cycle)                                                 |

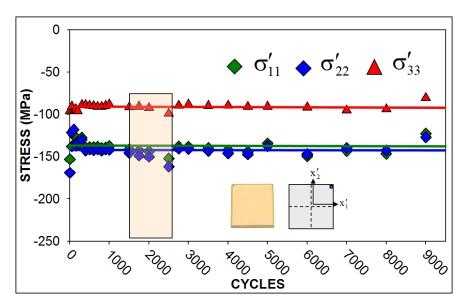

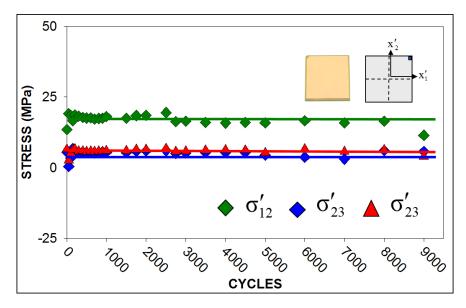

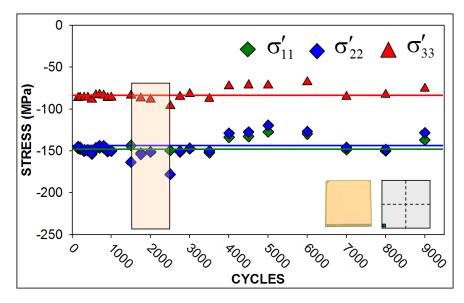

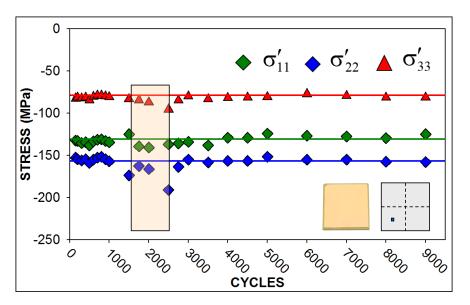

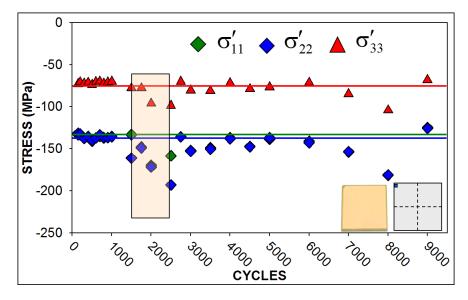

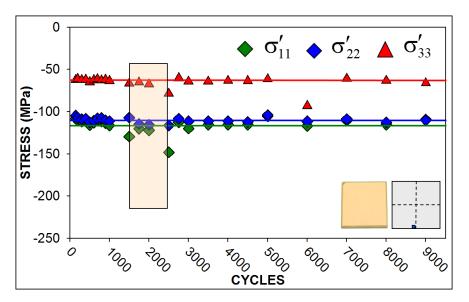

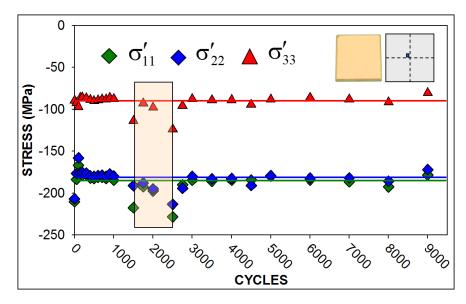

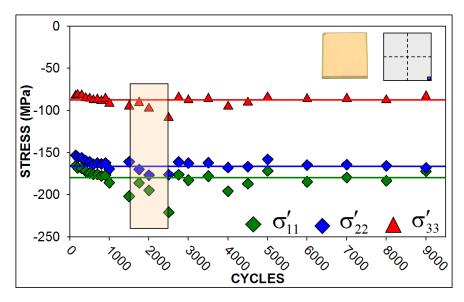

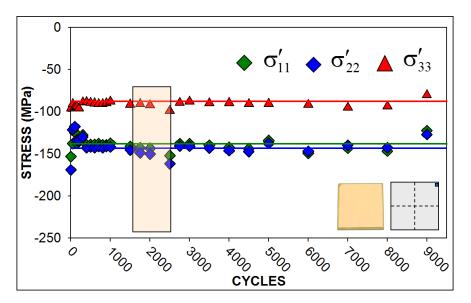

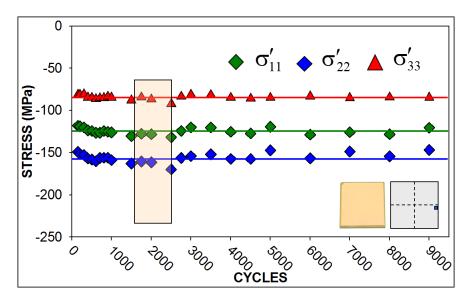

| 6.26 Variation of the Average Normal Stresses with Thermal Cycling (Die Center) $$ . $$ 114 $$ |

| 6.27 Variation of the Average Shear Stresses with Thermal Cycling (Die Center) $$ . $$ . $114$ |

| 6.28 New and Old CLGA Socket                                                                   |

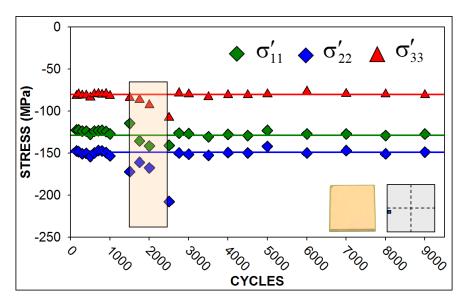

| 6.29 Variation of the Average Normal Stresses with Thermal Cycling (Die Corner) $$ . $$ 117 $$ |

| 6.30 Variation of the Average Shear Stresses with Thermal Cycling (Die Corner) $$ 117          |

|                                                                                                |

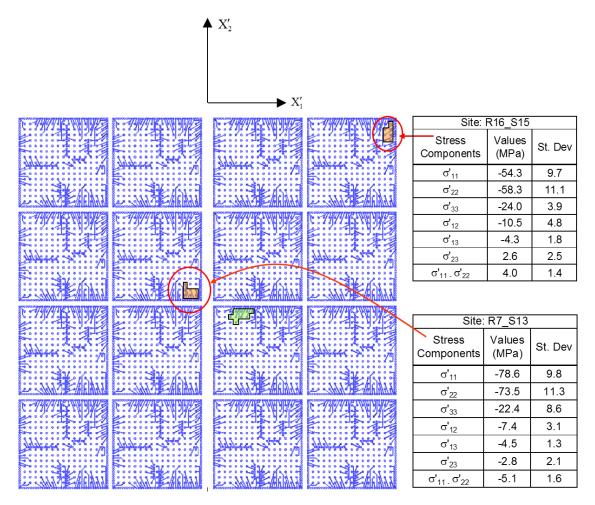

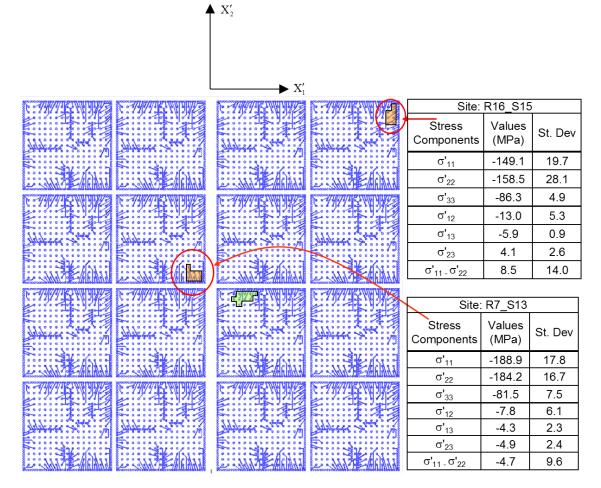

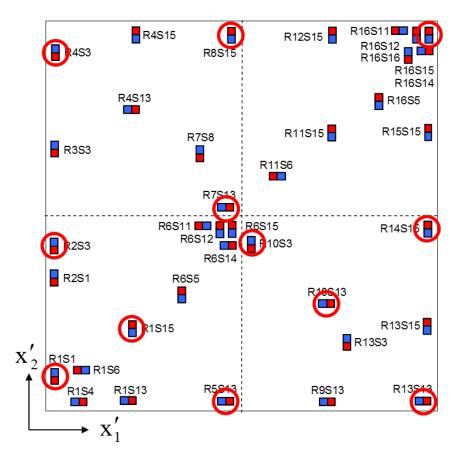

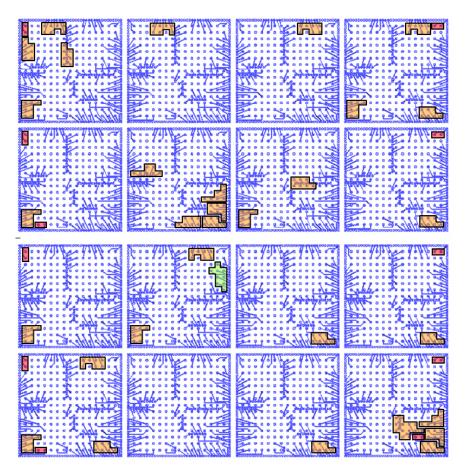

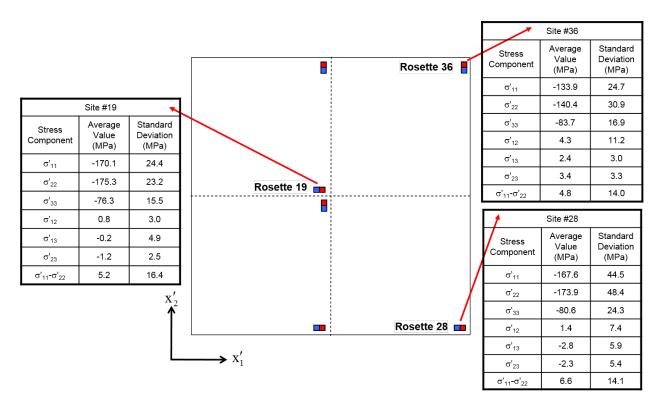

| 6.31 Test Chip Rosette Sites for Stress Measurement                                            |

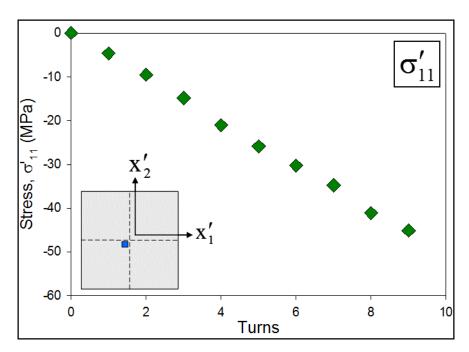

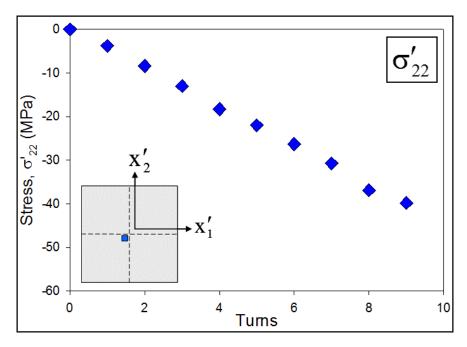

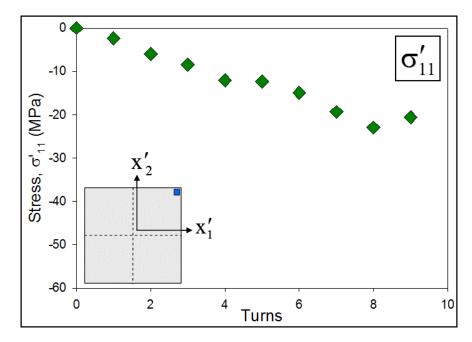

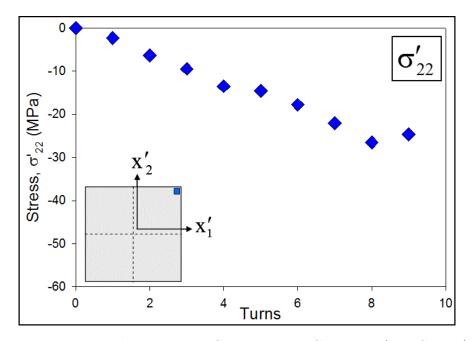

| <ul> <li>6.31 Test Chip Rosette Sites for Stress Measurement</li></ul>                         |

|                                                                                                |

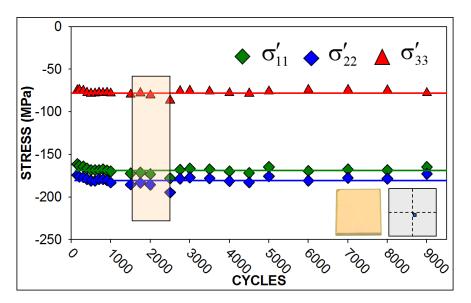

| 6.32 Variation of the Average Normal Stresses with Thermal Cycling                             |

| 6.36 | Variation of the Average Normal Stresses with Thermal Cycling                           | 121 |

|------|-----------------------------------------------------------------------------------------|-----|

| 6.37 | Variation of the Average Normal Stresses with Thermal Cycling                           | 121 |

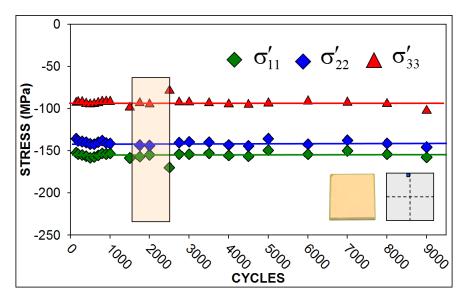

| 6.38 | Variation of the Average Normal Stresses with Thermal Cycling                           | 122 |

| 6.39 | Variation of the Average Normal Stresses with Thermal Cycling                           | 122 |

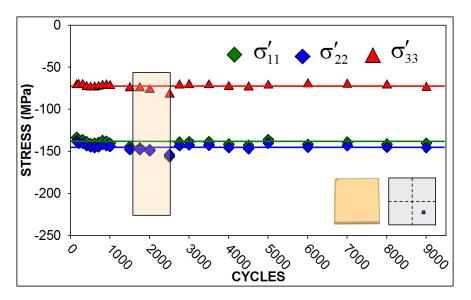

| 6.40 | Variation of the Average Normal Stresses with Thermal Cycling                           | 123 |

| 6.41 | Variation of the Average Normal Stresses with Thermal Cycling                           | 123 |

| 6.42 | Variation of the Average Normal Stresses with Thermal Cycling                           | 124 |

| 6.43 | Variation of the Average Normal Stresses with Thermal Cycling                           | 124 |

| 6.44 | Variation of Normal Stress at the Die Center with Thermal Cycling (Finite Element)      | 125 |

| 6.45 | Variation of Normal Stress at the Die Corner with Thermal Cycling (Finite Ele-<br>ment) | 126 |

| 6.46 | Variation of In-Plane Shear Stress at the Die Corner with Thermal Cycling (Finite       |     |

|      | Element)                                                                                | 126 |

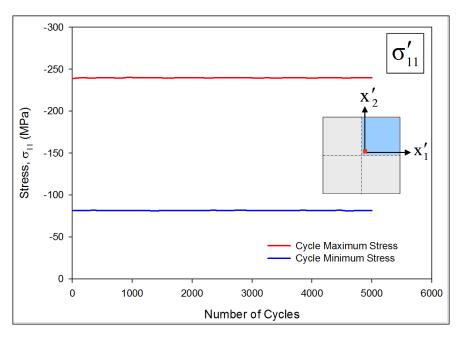

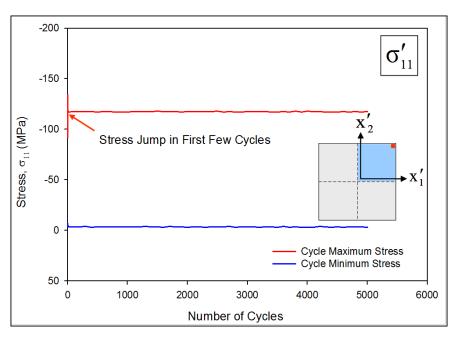

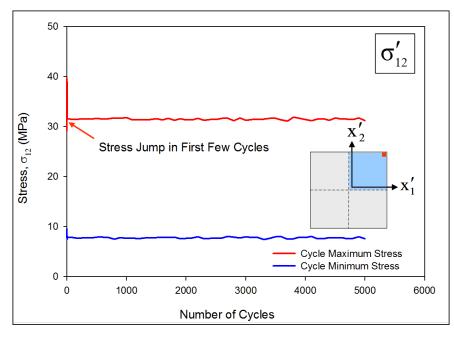

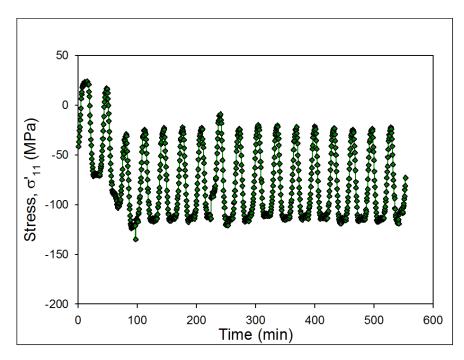

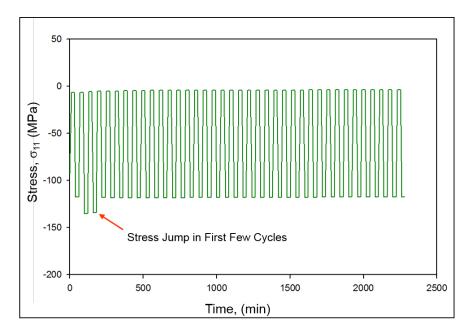

| 6.47 | Normal Die Stress During Thermal Cycling                                                | 127 |

| 6.48 | In-Plane Normal Die Stress Variation During Thermal Cycling(Finite Element)             | 128 |

| 7.1  | Temperature Calibration of Sensor Rosette                                               | 131 |

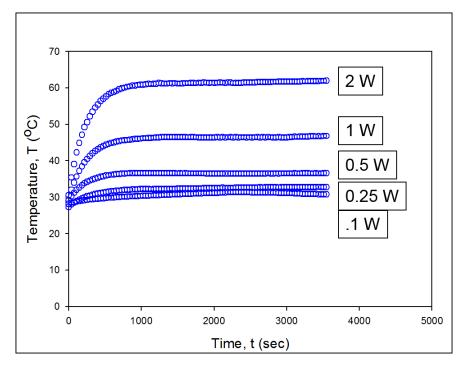

| 7.2  | Die Surface Temperature vs. Time for On-Chip Power Dissipation                          | 132 |

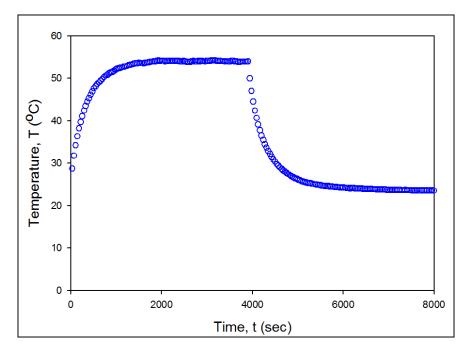

| 7.3  | Die Surface Temperature vs. Power Dissipation                                           | 133 |

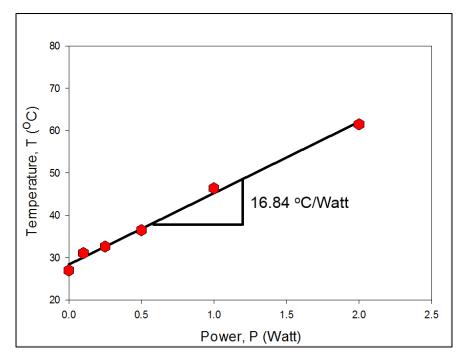

| 7.4  | Die Surface Temperature vs. Time for On-Chip Power Dissipation                          | 133 |

| 7.5  | Thermal Boundary Conditions of Power Dissipation FEA Model                  | 134 |

|------|-----------------------------------------------------------------------------|-----|

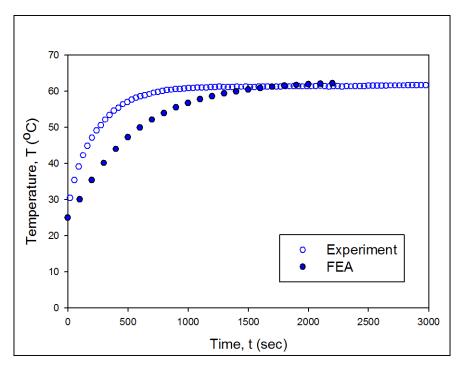

| 7.6  | FEA and Experimental Transient Die Surface Temperatures                     | 135 |

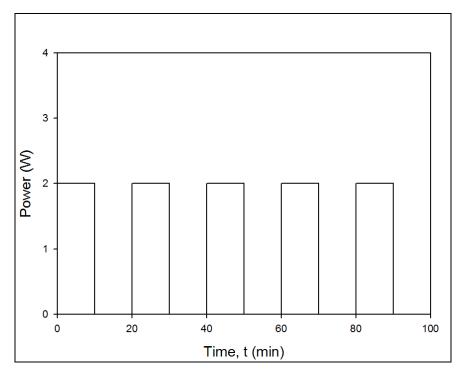

| 7.7  | Square Wave Power Cycle                                                     | 136 |

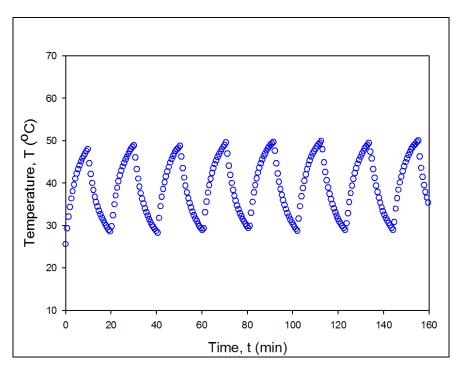

| 7.8  | Measured Transient Die Surface Temperature Variation during Power Cycling . | 137 |

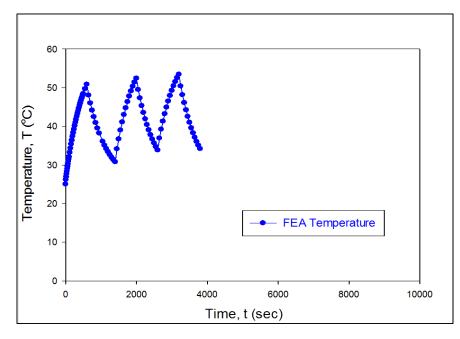

| 7.9  | Transient Die Surface Temperature Variation during Power Cycling (FEA)      | 137 |

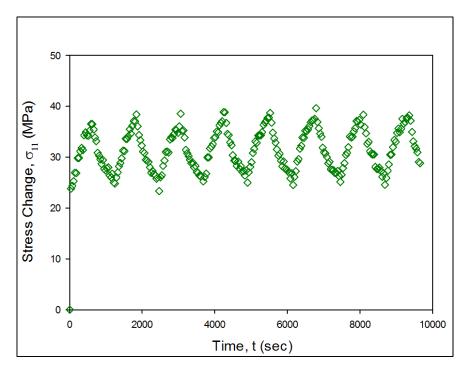

| 7.10 | Measured Transient Die Stress Variation during Power Cycling                | 138 |

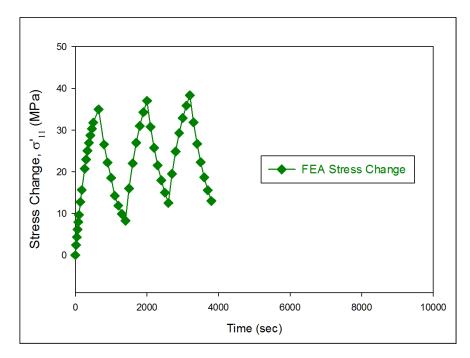

| 7.11 | Transient Die Stress Variation during Power Cycling (FEA)                   | 138 |

| 8.1  | Rosettes, ID, and Buried Layer Heater Access Points                         | 140 |

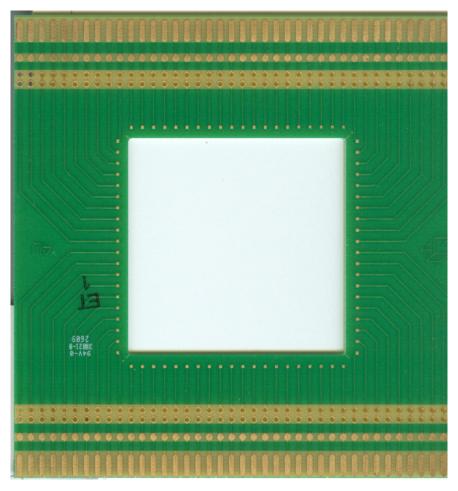

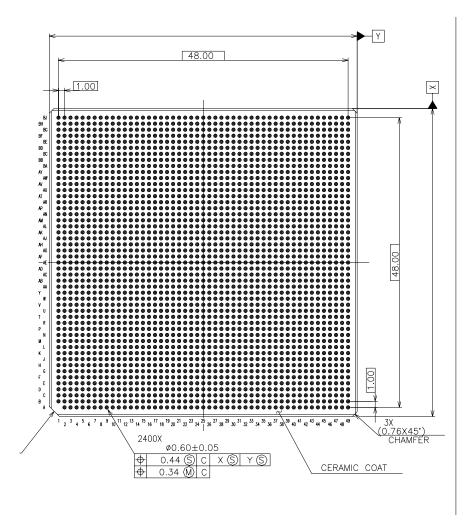

| 8.2  | Pattern and Spacing of LGA Pads                                             | 141 |

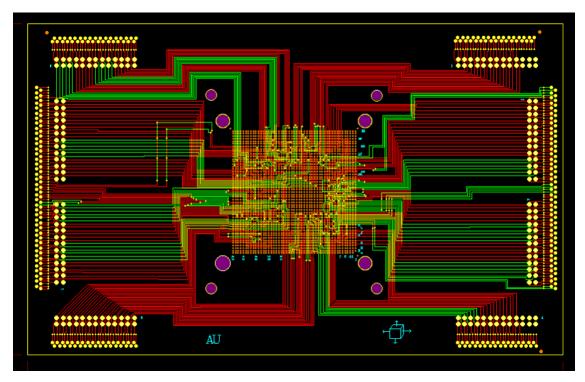

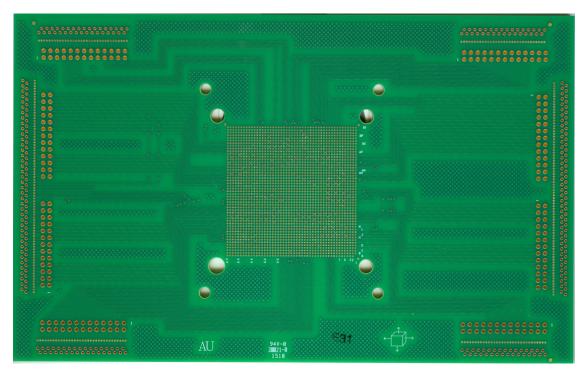

| 8.3  | Second Level Test Board Routing Design                                      | 142 |

| 8.4  | Second Level Test Board Photograph                                          | 142 |

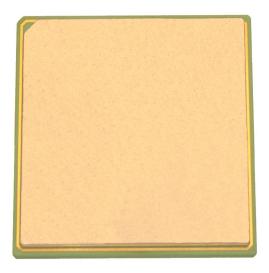

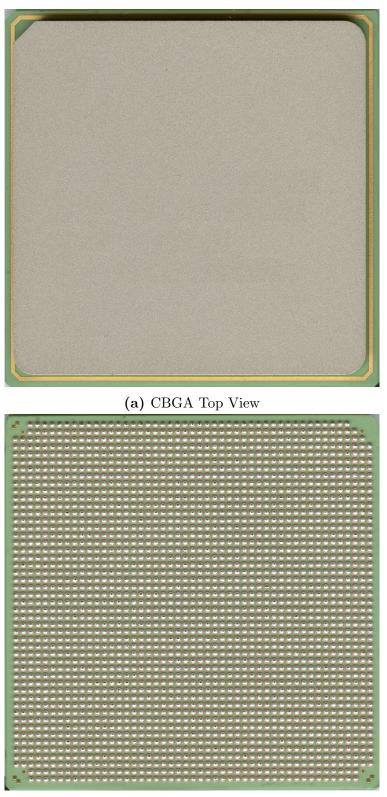

| 8.5  | Assembled Ceramic Ball Grid Array for Second Level Assembly Study           | 144 |

| 8.6  | Schematic of CBGA Package Measurement                                       | 145 |

| 8.7  | Stresses After CBGA Ball Attachment                                         | 145 |

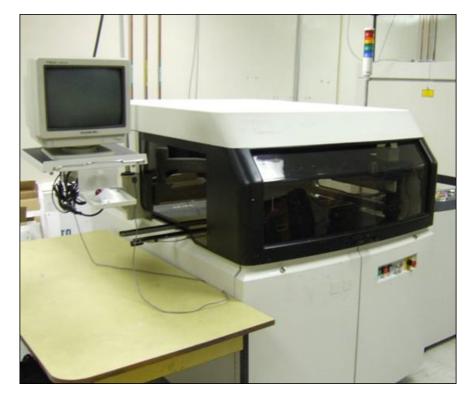

| 8.8  | MPM AP25 Solder Stencil Screen Printer                                      | 146 |

| 8.9  | Semiconductor Equipment Corporation 4150 Placement Machine                  | 147 |

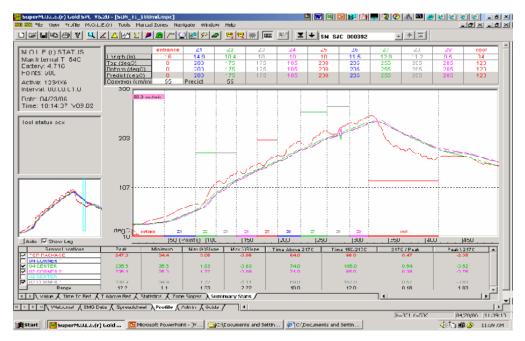

| 8.10 | Heller 1800EXL Reflow Oven                                                  | 147 |

| 8.11 | Initial Reflow Profile for Second Level Assembly                            | 149 |

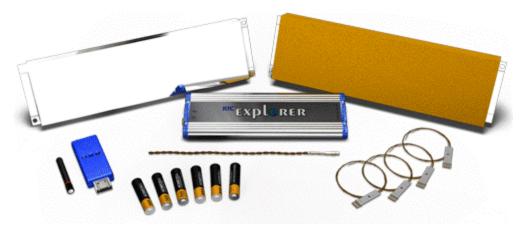

| 8.12 | KIC Explorer Thermal Profiling System                                  | 149 |

|------|------------------------------------------------------------------------|-----|

| 8.13 | Second Level Interconnects after Bad Reflow Profile                    | 149 |

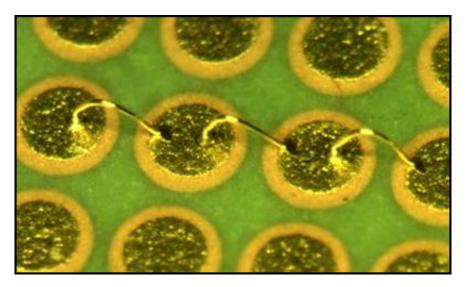

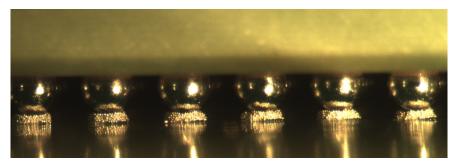

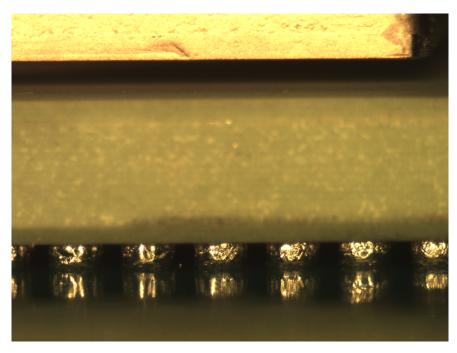

| 8.14 | Second Level Interconnects after Good Reflow Profile                   | 150 |

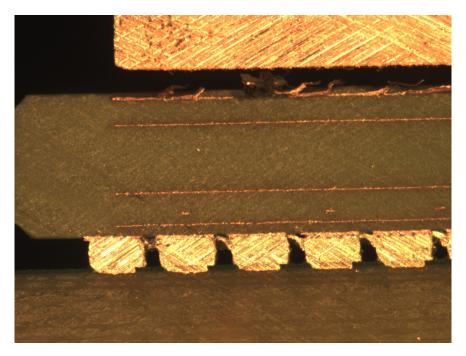

| 8.15 | Cross Section of CBGA Second Level Assembly                            | 150 |

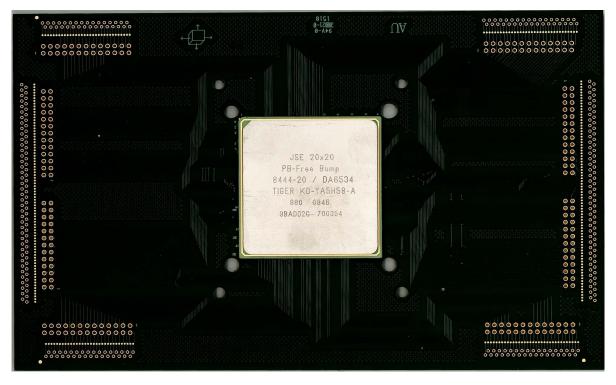

| 8.16 | CBGA Assembled with Second Level Interconnects                         | 151 |

| 8.17 | Thermal Chamber and DAQ                                                | 152 |

| 8.18 | Thermal Profile for Temperature Dependent Stress Testing               | 153 |

| 8.19 | Variation of In-Plane Normal Stress with Temperature (Near Die Center) | 154 |

| 8.20 | Variation of In-Plane Normal Stress with Temperature (Near Die Center) | 155 |

| 8.21 | Variation of In-Plane Shear Stress with Temperature (Near Die Center)  | 155 |

| 8.22 | Variation of In-Plane Normal Stress with Temperature                   | 156 |

| 8.23 | Variation of In-Plane Normal Stress with Temperature                   | 156 |

| 8.24 | Variation of In-Plane Shear Stress with Temperature                    | 157 |

| 8.25 | Variation of In-Plane Normal Stress with Temperature                   | 157 |

| 8.26 | Variation of In-Plane Normal Stress with Temperature                   | 158 |

| 8.27 | Variation of In-Plane Shear Stress with Temperature                    | 158 |

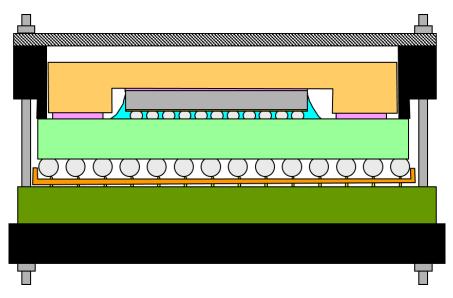

| 9.1  | CBGA Heat Sink Clamping Geometry                                       | 159 |

| 9.2  | Pre-Assembled Test Board for Clamping Experiments                      | 161 |

| 9.3  | Clamping Fixture Provided by Test Sponsor                          | 163 |

|------|--------------------------------------------------------------------|-----|

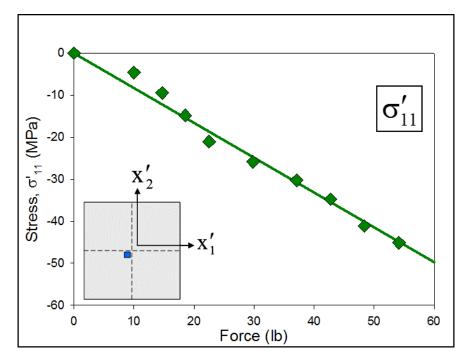

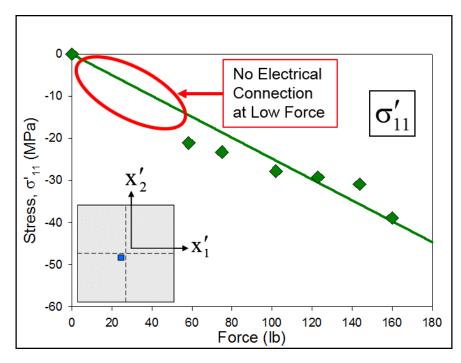

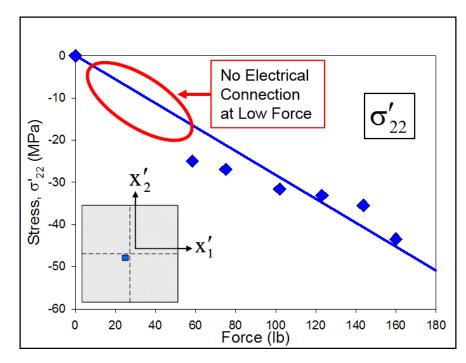

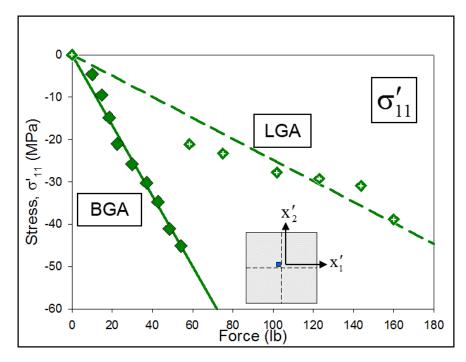

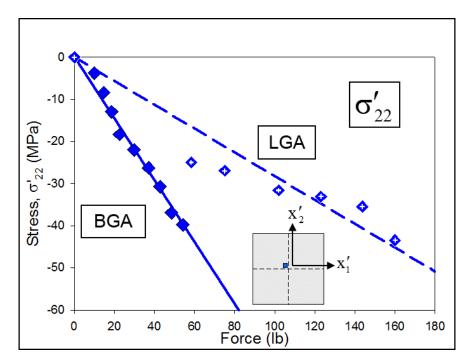

| 9.4  | In-plane Normal Stress Due to Clamping (Die Center)                | 163 |

| 9.5  | In-plane Normal Stress Due to Clamping (Die Center)                | 164 |

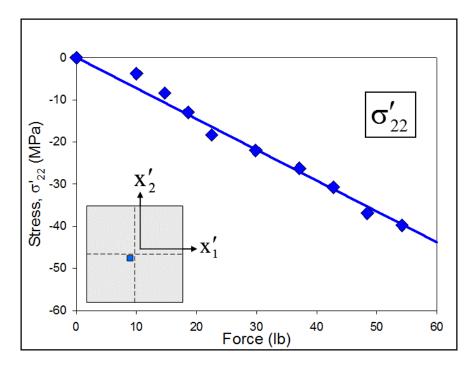

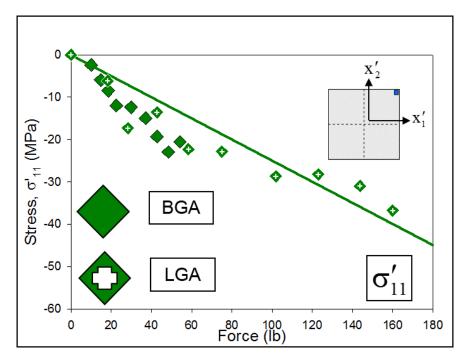

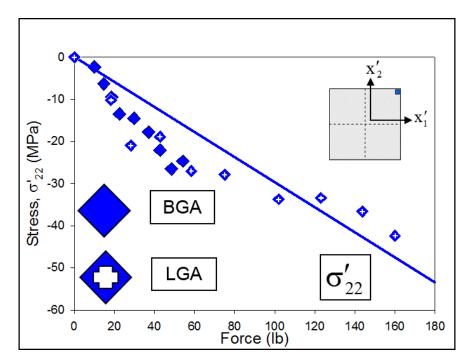

| 9.6  | In-plane Normal Stress Due to Clamping (Die Corner)                | 164 |

| 9.7  | In-plane Normal Stress Due to Clamping (Die Corner)                | 165 |

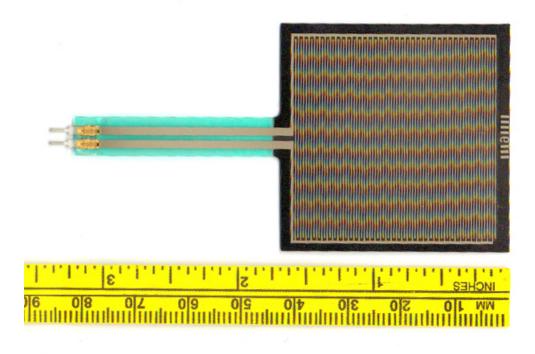

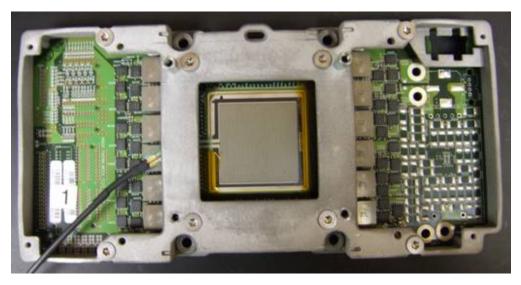

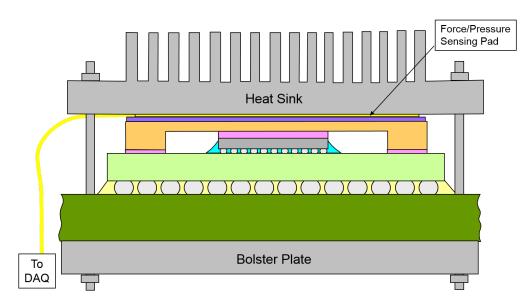

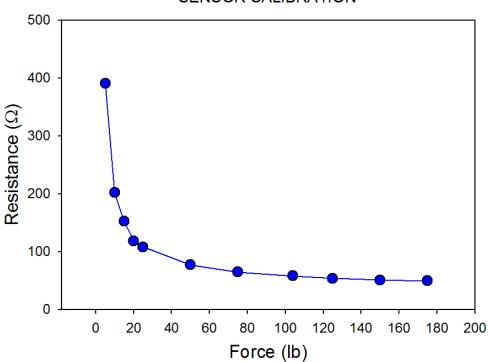

| 9.8  | Thin Resistive Force Sensor                                        | 166 |

| 9.9  | Thin Resistive Force Sensor in Clamping Fixture                    | 166 |

| 9.10 | Schematic of Resistive Force Sensor in Clamping Fixture            | 167 |

| 9.11 | Resistive Force Sensor Calibration                                 | 167 |

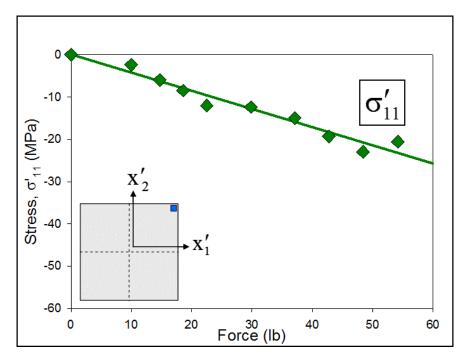

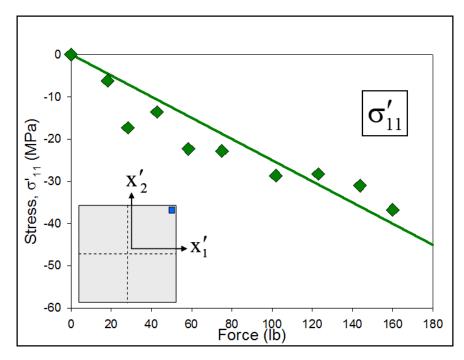

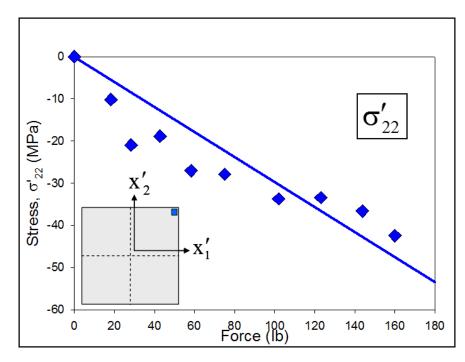

| 9.12 | In-Plane Normal Stress Due to Clamping (Die Center)                | 168 |

| 9.13 | In-Plane Normal Stress Due to Clamping (Die Center)                | 168 |

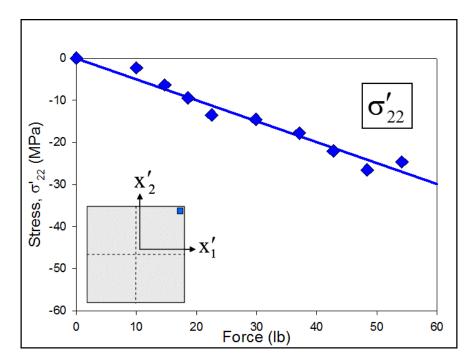

| 9.14 | In-Plane Normal Stress Due to Clamping (Die Corner)                | 169 |

| 9.15 | In-Plane Normal Stress Due to Clamping (Die Corner)                | 169 |

| 9.16 | Simulated Heat Sink Clamping Fixture (First Edition)               | 171 |

| 9.17 | Second Iteration Clamping Fixture with Instrumentation             | 172 |

| 9.18 | In-Plane Normal Stress Due to Clamping (Die Center, Single Sample) | 173 |

| 9.19 | In-Plane Normal Stress Due to Clamping (Die Center, Single Sample) | 173 |

| 9.20 | Average In-Plane Normal Stress Due to Clamping (Die Center)        | 174 |

| 9.21 Average In-Plane Normal Stress Due to Clamping (Die Center)                                   |

|----------------------------------------------------------------------------------------------------|

| 9.22 Average In-Plane Normal Stress Due to Clamping (Die Corner)                                   |

| 9.23 Average In-Plane Normal Stress Due to Clamping (Die Corner)                                   |

| 9.24 Schematic of CLGA Clamping Fixture                                                            |

| 9.25 Average In-Plane Normal Stress Due to CLGA Clamping (Die Center) 177                          |

| 9.26 Average In-Plane Normal Stress Due to CLGA Clamping (Die Center) 177                          |

| 9.27 Average In-Plane Normal Stress Due to CLGA Clamping (Die Corner) 178                          |

| 9.28 Average In-Plane Normal Stress Due to CLGA Clamping (Die Corner) 178                          |

| 9.29 Comparison of In-Plane Normal Stress at Die Center (CBGA vs. CLGA) 180                        |

| 9.30 Comparison of In-Plane Normal Stress at Die Center (CBGA vs. CLGA) 180                        |

| 9.31 Comparison of In-Plane Normal Stress at Die Corner (CBGA vs. CLGA) 181                        |

| 9.32 Comparison of In-Plane Normal Stress at Die Corner (CBGA vs. CLGA) 181                        |

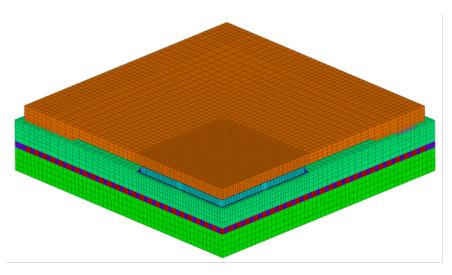

| 9.33 Quarter Model of CBGA and Second Level Solder Balls with Underfill 183                        |

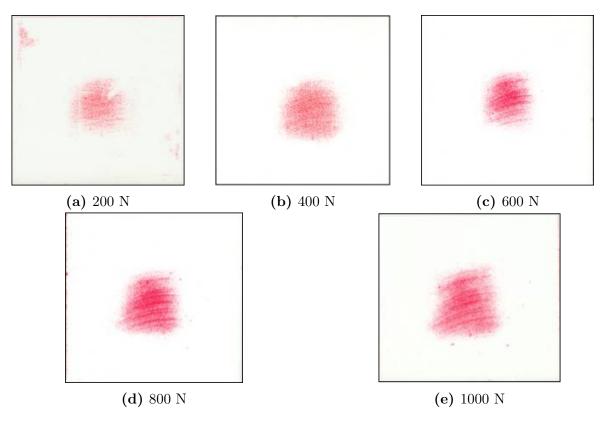

| 9.34 Pressure Map of Applied Load on Heat Spreader                                                 |

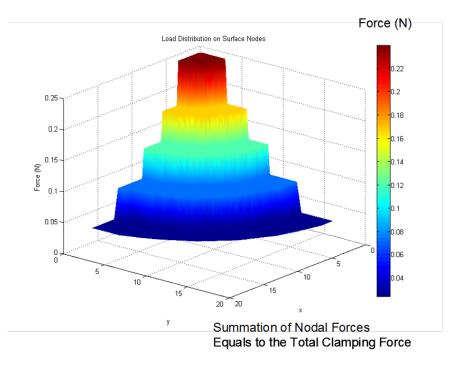

| 9.35 Nonuniform Pressure Used in Simulation of Clamping Measurements 184                           |

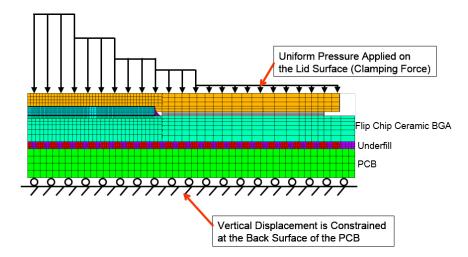

| 9.36 Loading and Boundary Conditions for Clamping Finite Element Model 185                         |

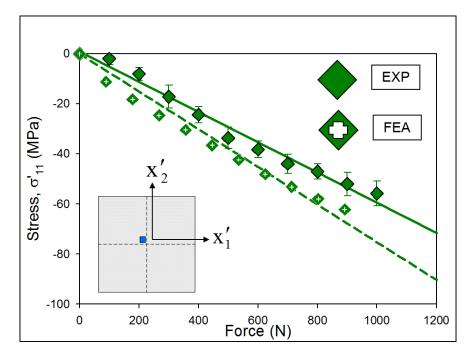

| 9.37 Experimental and FEA Results for In-plane Normal Stress $\sigma_{11}'$ (Die Center) $~$ . 185 |

| A.1 Normal Stresses Due to Assembly at Die Center                                                  |

## List of Tables

| 4.1 | Average Piezoresistive Coefficients                                               | 40  |

|-----|-----------------------------------------------------------------------------------|-----|

| 4.2 | Bonding Pad and Scanner Card Connections                                          | 54  |

| 5.1 | Anand Constants for Modeling of SAC Solder                                        | 79  |

| A.1 | Stress Change Due to Underfill (Subtraction Method)                               | 219 |

| A.2 | Stress Change Due to Underfill (Alternate Reference Method)                       | 220 |

| A.3 | Stress Change Due to Lid Attachment (Subtraction Method)                          | 220 |

| A.4 | Stress Change Due to Lid Attachment (Alternate Reference Method) $\ . \ . \ .$    | 221 |

| A.5 | Stress Change Due to Underfill Cure & Lid Attachment (Subtraction Method) .       | 221 |

| A.6 | Stress Change Due to Underfill Cure & Lid Attachment (Alternate Reference Method) | 221 |

#### Nomenclature

## Acronyms

- AlSiC Aluminum Silicon Carbide

- ALT accelerated life testing

- BGA ball grid array

- CBGA ceramic ball grid array

- CCGA ceramic column grid array

- CLGA ceramic land grid array

- CMOS complementary metal-oxide-semiconductor

- CSAM c-mode scanning acoustic microscopy

- CSP chip scale package

- CTE coefficient of thermal expansion

- DAQ data acquisition system

- DIMM dual in-line memory module

- DNP distance to neutral point

- ENIG electroless nickel immersion gold

- FC-CBGA flip chip ball grid array

- FC-CBGA flip chip ceramic ball grid array

FC-PBGA flip chip plastic ball grid array

- FEA finite element analysis

- FET field-effect transistor

- FIFI far infrared Fizeau interferometry

- GPIB general purpose interface bus

- HiTCE high temperature coefficient of expansion

- ILD interlayer dielectric

- LEAP laboratory for electronics assembly and packaging

- LGA land grid array

- LTCC low temperature cofired ceramic

- MPC multipoint constraint

- PBGA plastic ball grid array

- PCB printed circuit board

- PGA pin grid array

- PLGA plastic land grid array

- PTH plated through hole

- RTD resistance temperature detector

- SAC tin silver copper solder

- SHS simulated heat sink

- SMES shadow moiré with enhanced sensitivity

- SOP system-on-package

- TCR temperature coefficient of resistance

- TEFCBGA thermally enhanced flip chip ball grid array

- TIM1 first level thermal interface material

- TIM2 second level thermal interface material

- TIM thermal interface material

- WB wire bond

## English letter symbols

- $B_i$  Piezoresistive coefficient

- *l* direction cosine

- m direction cosine

- n direction cosine

- R resistance,  $\Omega$

- T temperature, K

- t time, s

## Greek letter symbols

- $\delta_{ij}$  Kronecker Delta,

- $\Delta\sigma$  stress change

- $\pi$  resistivity tensor,

- $\rho$  resistivity, kg/m<sup>3</sup>

- $\bar{\rho}$  isotropic unstressed resistivity

- $\sigma$  stress, MPa

- $\theta$  angle

# Superscripts

- *n* n-type

- p p-type

## Subscripts

| DA  | die attach |

|-----|------------|

| L   | lower arm  |

| lid | lid attach |

| ref | reference  |

| U   | upper arm  |

|     |            |

UF underfill

#### Chapter 1

#### Introduction

#### 1.1 Area Array Components in Microprocessor Packaging

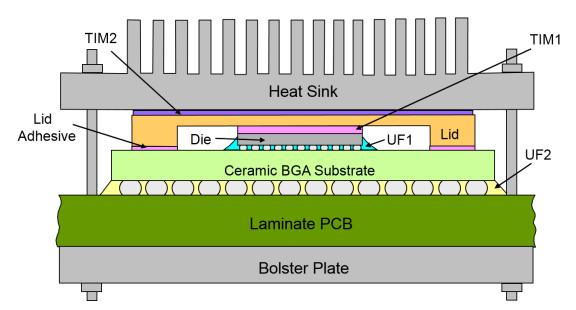

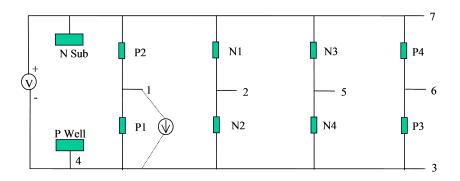

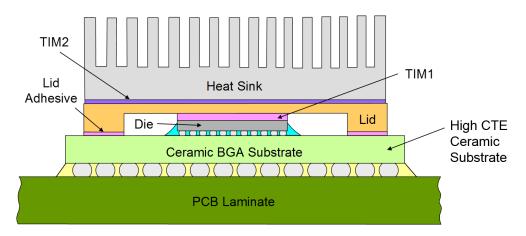

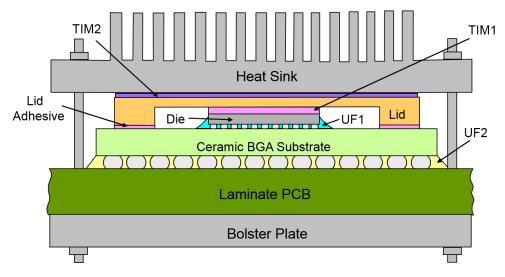

Area array microprocessor packages are at the heart of high-end workstations and servers. A typical package may consist of at least one large flip chip die attached to a high density ceramic chip carrier. Figure 1.1 illustrates the typical configuration of a server microprocessor mounted on a motherboard and topped with an air-cooled heat sink. With the need for ever increasing computing power and increased interconnect density, the first level, chip-to-substrate interconnections have transitioned to full area arrays of lead free solder bumps. Die size has also increased significantly. While older alumina ceramic substrate technology allowed better reliability performance due to the the close matching of the coefficients of thermal expansion of alumina and silicon, manufacturers are currently using "high CTE" (HiTCE) glass ceramic materials [1–7].

The thermal expansion coefficients of the HiTCE ceramics are closer to the CTE of the typical organic printed circuit board to which they are mounted, increasing second level interconnect reliability in many cases. However, matching of the thermal expansion coefficients of the second level comes at the cost of increasing the dissimilarity in the CTE values of the die and ceramic, resulting in lower reliability of the first level of interconnections. High CTE ceramics have found their place mostly due to their lower stiffness (70 - 80 GPa) and lower co-firing temperatures, which allows the use of copper conductors as opposed to lower performance tungsten conductors used with alumina ceramic substrates.

A glass-filled epoxy commonly known as underfill, found between the die and substrate, is another component of a typical microprocessor package. A metal (copper or AlSiC) lid, or heat spreader, tops the silicon die and is mechanically connected to the substrate and die by a thermal interface material (TIM1). Figure 1.1 shows the ceramic substrate mechanically and electrically connected to a large printed circuit board (PCB) with second level solder balls, with the remaining volume under the substrate filled with a second level underfill. In this configuration, the chip and substrate assembly is referred to as a Ceramic Ball Grid Array (CBGA), due to the inclusion of an additional set of second level solder interconnects to the substrate. The chip and substrate assembly can also be used as a Land Grid Array (LGA), and be connected to the PCB with a socket and associated mechanical connections. In both cases, a heat sink is clamped to the entire assembly and bonded with a second Thermal Interface Material (TIM2).

Figure 1.1: Architecture for a High Performance Flip Chip Microprocessor

This complex architecture and others under development transmit a complicated set of mechanical loads to the microprocessor chip. Along with the change to higher CTE substrates, the use of stiff lead free solders along with ever increasing die sizes have increased die stress levels. Although necessary to ensure good heat transfer, mechanical clamping of associated heat sinks adds to die stress issues. Microprocessors are also dissipating more power with each generation of new designs. The amount of power dissipation along with the cyclical nature of the power usage of microprocessors further exacerbates analysis of package reliability. The various mechanical, thermal, and power loadings associated with a typical package affect the stresses in the die, which can degrade silicon device performance (mobility/speed) and damage critical copper/low-k dielectric chip interconnect layers.

On-chip piezoresistive stress sensors represent a unique approach for characterizing stresses in silicon die embedded within a complicated packaging architecture such as that described above. Die stress measurements in flip chip assemblies have been performed by several investigators using test chips [8–14]. Variations of the (100) silicon Sandia ATC04 test die have been used to examine device side die stresses and compare stress levels with different underfills [8–10]. In previous flip chip studies, the mechanical stresses present on the backside (top side) [11] and the device side (bottom side) [12–14] of the die at each stage of the flip chip assembly process were investigated. In these investigations, (111) silicon test chips were used that were able to measure all of the die stress components including the interfacial shear stresses. Die stress variations were observed during underfill curing, and the room temperature die stresses in the final cured assemblies have been compared for several different underfill encapsulants.

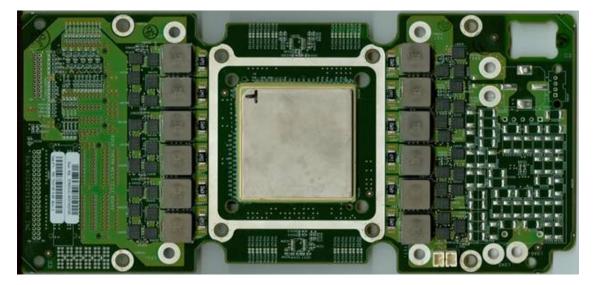

In this work, test chips using piezoresistive sensors were used to measure die stresses in microprocessor packages caused by various stages of assembly as well as mechanical, thermal, and electrical loading. Use of (111) test chips allowed measurement of the complete three-dimensional state of stress at sensor locations across the entire die. The 20 x 20 mm test chips were attached to high CTE ceramic chip carriers with a full array of 3600 lead free solder bumps. Prior to assembly, each bare test chip was manually probed to measure initial resistances of each selected sensor. The test die were then assembled by solder reflow attachment to ceramic substrates, applying and curing a first level undefill, and adding a thermal adhesive (TIM1) and heat spreader. The chosen sensor resistances were measured again after each assembly step in order to characterize stresses induced by each step. The build-up of the die stresses was found to be monotonically increasing, and the relative severity of each assembly step was judged and compared. The assemblies were then used to characterize the stresses induced by temperature change and thermal cycling using a novel package carrier. Several assemblies were also used in the characterization of die stresses due to power dissipation in the die and initial power cycling experiments. A separate set of additional test die were measured at the bare die state and again after application of second level solder interconnects, and reflow to large laminate printed circuit boards.

#### Chapter 2

#### Literature Review

#### 2.1 Introduction and Review of Electronic Packaging Issues

From the inception of the integrated circuit, chips have increasingly become faster, more powerful, and contained more transistors while actual feature sizes continue to shrink. These trends in IC technology have created reliability issues across all platforms, and especially in high-end computing and server applications. Each assembled chip and associated packaging contains a myriad of materials, each with, in some cases, drastic differences in mechanical and thermal properties. Some materials exhibit isotropic mechanical behavior with little or no dependence on temperature, while others are anisotropic, rate and temperature dependent. The coefficient of thermal expansion, or CTE, has been demonstrated to be one of, if not the largest contributor to package stress generation and failure. Given the relationship between mechanical stress and failure, an obvious need arises for the characterization of stress levels caused not only by manufacturing, but by the use of electronic packages.

#### 2.1.1 Historical Packaging Issues

Dale and Oldfield [15] described die attachment, wire bonding, and encapsulation as sources of stress in electronic packaging. They found that several contributors to manufacturing induced stresses including oxidation, diffusion, metallization, and wafer processing. Lau [16] concurred with these findings and additionally cited the effects of various surface mounting processes and die bending during assembly. Lau also related stresses to wire bond damage, die passivation cracking, and package cracking. Several investigators have examined the effects of temperature on package stresses. Lesk, et al. [17], and Edwards, et al. [18] looked at metal shift and damage due to thermally induced stresses. Reference [17] also considered the issues related to packages with large die. Inayoshi, et al. [19] also studied the effect of stress on the passivation layer of silicon die. Van Kessel, et al. [20] studied the effects of manufacturing processes, including die attachment on stresses as well as the large effect of stresses on packages with certain die surface finishes. Nishimura and co-authors [21, 22] demonstrated that while cracks in packages can be induced by thermal cycling, the cracks also have a large effect on die stress levels. Additionally, encapsulants may pose other problems in encapsulated packages.

#### 2.1.2 High-End Microprocessor Issues

Several investigations have been performed on the thermal-mechanical reliability of the second level CBGA solder joints when using high CTE ceramic substrates. Pendse, et al. [2] demonstrated order of magnitude type improvements in the thermal cycling reliability using both thermal cycling tests and finite element simulations. Dai, et al. [3] and Pan and co-workers [4] have examined the effects on reliability of 52.5 x 52.5 mm CBGAs (2533 I/O) with various solder alloys (SnPb and SAC), ceramic substrate thicknesses, lid configurations, and lid materials (AlSiC compositions). Their results suggest that reliability is increased significantly when using the SAC solder alloy, a lid-less configuration (not practical if a heat sink is needed), and a lid material with lower SiC content. The ceramic substrate thickness had little effect on reliability due to the fact that the new ceramic materials are more compliant (lower stiffness) than traditional alumina compositions, as well as they provide a better CTE match between the ceramic substrate and PCB laminate.

Enhanced solder joint reliability has also been demonstrated for 42.5 x 42.5 mm and 45 x 45 mm CBGAs [5, 6], and for Ceramic Column Grid Arrays (CCGAs) [5, 7] when using the higher CTE ceramic substrates. Xu, et al. [23] have explored the heat transfer characteristics and air cooling limits of the packaging configuration in the previous chapter (Figure 1.1). Using finite element simulations, Tosaya et al. [6] have predicted a 2X increase in the die normal stress levels for a flip chip mounted on a high CTE ceramic carrier (relative

to the analogous configuration on an alumina carrier). In addition, the stresses at the die to underfill interface were significantly higher with the high CTE ceramic carrier, complicating underfill selection and raising concerns relative to damage of fragile Interlayer Dielectric (ILD) layers.

#### 2.2 Stress Determination in Electronic Packaging

Integrated circuit package failures have existed since their inception, and numbers of investigators have employed diverse methods to characterize, measure, and otherwise understand stress levels in IC packages. Suhir [24, 25] drew parallels between bimetal thermostats and interfacial stresses in electronic packages. Using this understanding, an analytical approach using beam theory was developed. Tay and co-workers [26–28] modeled delamination during reflow using an analytical approach and correlated modeling results with experiments.

The complex geometries of electronic packages have historically limited the use of accurate analytical methods. Well known and often used reliability models such as Coffin-Manson equation and the Distance to Neutral Point (DNP) approach are crude, being based on simplified approaches with extensive assumptions. The limited effectiveness of these analytical models has led to increased use of experimental methods, especially when correlated with some form of simulation such as finite element analysis (FEA).

#### 2.2.1 Experimental Methods

#### 2.2.2 Interferometric Techniques

Moiré interferometry is a useful tool for experimental measurement of displacements of an object. Classical moiré methods capture the in-plane deformations of a body and allow for extraction of strain data in the plane. Shadow Moiré methods are invaluable for measurements of out-of-plane warpage and other out-of-plane displacement. Han and Guo [29], Bastawros and Voloshin [30], and Liu, et al. [31] have used moiré methods to measure thermally induced deformations in electronic packages. Hartsough, et al. [32] used a combination of Twyman-Green Interferfometry and shadow moiré techniques to study warpage of non-conventional packages caused by reflow and assembly processes. Huang and co-workers [33] employed shadow moiré along with strain gages to study warpage and curvature of printed circuit boards with DIMM memory chip sockets during reflow and correlated FEM simulation results. Powell and Ume [34] developed a warpage measurement system to study packages during convective solder reflow. Verma, et al. [35] employed shadow moiré with enhanced sensitivity (SMES) along with far infrared Fizeau interferometry (FIFI) to study warpage of plastic ball grid array (PBGA) packages during thermal cycling. Wang and Hassell [36] used phase-stepping shadow moiré to study thermally induced warpage in BGA packages and substrates. Zhong, et al. [37] discussed methods of extracting highresolution data from moiré images used in warpage measurement.

#### 2.2.3 Semiconductor Test Chips

Silicon is a piezoresistive material which exhibits a change in resistivity upon application of a mechanical stress. This feature has led to the development of silicon stress sensing integrated circuit chips. In the 1950s, the concept of using piezoresistive semiconductors as tools to measure stress and strain was introduced by Smith [38]. Later, the temperature dependencies of the piezoresistive coefficients of silicon, as well as germanium, were studied by Tufte and Stetzer [39], as well as Suhling, et al. [40, 41]. The nonlinear nature of the piezoresistive effect was discussed by Yamada and co-workers [42], while the piezoresistive coefficients were represented graphically by Kanda [43]. A full discussion of semiconductor strain gages was given by Dally and Riley [44]. The detailed theory of silicon piezoresistive sensors was derived by Bittle, et al. [45, 46], while Kang [47] expanded and applied this theory to various wafer planes for silicon and silicon carbide.

In the use of piezoresistive silicon stress sensors, the need for calibration of the piezoresistive coefficients of the silicon chip is widely accepted. Traditionally, some form of four-point bending method is used for calibration. This method has been discussed in detail by Beaty, et al. [48], Bittle, et al. [45, 46], Suhling, et al. [40, 41], Jaeger, et al. [49–52], and van Gestel [53]. A method of calibration employing application of a hydrostatic state of stress to a chip in a pressure vessel was devised by Kang, et al. [54]. The four-point bending and hydrostatic methods are performed on sliced silicon wafer strips and diced silicon chips, respectively. Cordes [55] and Suhling, et al. [56] have alternatively devised a calibration technique applied at the wafer level. Lwo, et al. [57–59] also discussed the design and fabrication of stress sensors, and designed and fabricated a calibration apparatus.

Piezoresistive stress sensors have been used by many researchers to study die stress levels in electronic packages. In early work, Edwards, et al. [18], Groothuis, et al. [60], and van Kessel, et al. [20] used chips fabricated from (100) silicon wafers to examine small packages. These early test chips contained two-element sensor rosettes, with the sensors oriented at 0 and 90 degrees to the wafer flat. Early work was aimed at material evaluation, reliability testing, and process control. Later, Gee, et al. [61] used four element rosettes to map stresses during thermal cycling. Van Gestel and co-workers [62] also used these same chips to study dual inline packages.

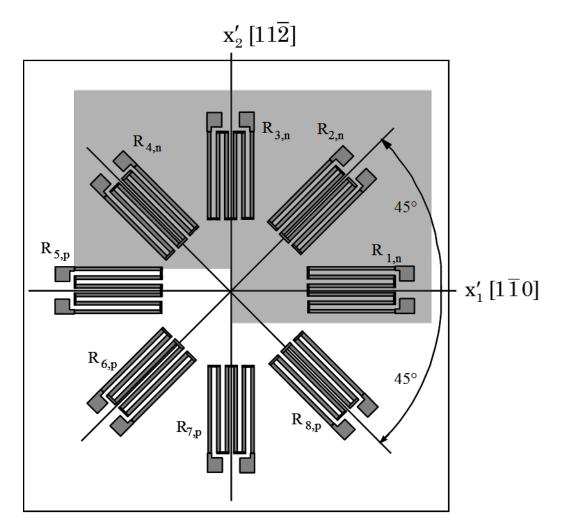

Miura, et al. [63-65] also used (100) chips to study die stresses in dual inline packages. The chips used in their study employed sensors fabricated with both n-type and p-type doping, where the n-type sensors were oriented at 0° and 90°, and the p-type sensors were oriented at  $\pm 45^{\circ}$ . This chip was notable, as it was the first test chip able to measure outof-plane normal stresses on the die. Zou, et al. [66-68] also used (100), four element test chips. The chips used the same sensor orientations as the Miura chips, but the doping of the sensor pairs was reversed. The Sandia ATC-04, a (100) silicon test chip, was used to study die mounted on ceramic substrates by Sweet [69]. The Sandia chip used a sensor rosette with eight resistors, including four n-type sensors at orientations of 0°,  $\pm 45^{\circ}$ , and 90°, and four p-type sensors of the same orientations. The third generation of Sandia test chips has also been studied [70]. Bossche, et al. [71, 72] and Lo, et al. [73, 74] designed, fabricated, and calibrated stress sensing chips with similar capabilities to prior studies. Mayer [75, 76] has also developed piezoresistive test structures, mainly to study the effects of thermosonic wire bonding.

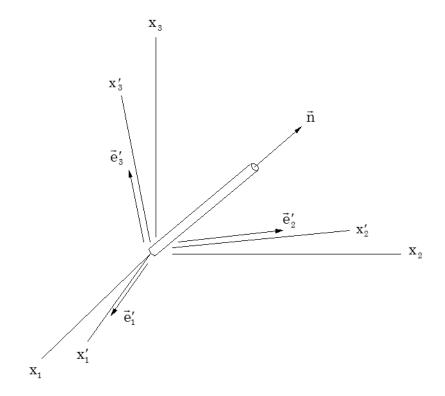

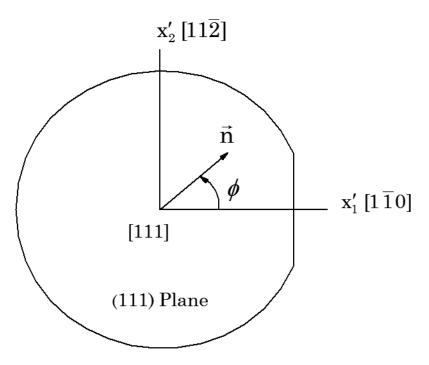

Suhling and his co-workers [77–81] have demonstrated the advantages of stress sensors fabricated from (111) silicon wafers as opposed to (100) wafers. When optimized, rosettes on (111) silicon can measure the complete state of stress at a point. In addition, optimized (111) rosettes can measure four temperature compensated stress components, as opposed to (100) rosettes, which can measure two temperature compensated stress components. Suhling, et al. [78, 80] used these advantages to be the first to measure the complete state of stress at a point on the surface of a die with test chips designated BMW-1. This chip used an eight sensor rosette containing n-type and p-type sensors oriented at 0°,  $\pm 45^{\circ}$ , and 90°, with respect to the wafer flat. The BMW-1 chips were mounted to organic substrates, and then used to measure stress in chip on board packages at room temperature. These studies were the first to measure out-of-plane shear stresses at the interface of the die and encapsulant. Zou, et al. [66–68] used a second iteration of the BMW chip to measure stresses in different packages. Schwizer, et al. [82, 83] described a new test chip package that uses a flip chip micro sensor, capable of measuring forces on solder balls in three directions.

Jaeger, et al. [84–88] and others [89–91] have utilized other silicon devices such as transistors and van der Pauw structures to develop stress sensor chip technology. In these studies, relationships between applied mechanical stress and transistor performance were developed. Mian [92] developed and used van der Pauw structures to characterize stress. Mayer, et al. [93] also used test chips with MOS technology.

Piezoresistive stress sensors have also been used to characterize stress levels during and after different stages of package assembly. Stresses due to die attachment and encapsulation were studied by Natarajan, et al. [94] using chips fabricated from n-doped (100) silicon wafers. Integrated piezoresistive stress sensors were also employed by Bjorneklett, et al. [95] to measure stress induced by die attachment. Ducos, et al. [96] measured stress levels during package assembly in-situ. Evans and co-workers [97] measured the resistances of sensors on chips assembled into various ball grid array packages. Rahim [98] measured stress levels on both sides of a flip chip die during each stage of assembly. Peterson, et al. [8, 99] used test chips to study flip chip ball grid array packages. Zou and co-workers [100] also used test chips to evaluate die attachment adhesives in ceramic Pin Grid Array (PGA) packages. Palaniappan, et al. [9, 10] used test chips to study curing parameters of flip chip assemblies.

It should be noted that use of piezoresistive stress sensors requires foreknowledge of errors expected in their calibration and use. Aside from error in any data acquisition system or the physical wiring of a test setup, there are several ways inappropriate use or calibration may affect results. A discussion of optimized rosette design has been given by Suhling, et al. [78], and a complete discussion of design and calibration errors was presented by Jaeger and co-workers [52, 101, 102].

#### 2.2.4 Numerical Methods

While experimental methods have given great insight to stress and reliability issues in electronic packaging, in many cases they are expensive and time consuming. Some methods are destructive and do not allow further testing of samples that were carefully prepared with substantial cost. In an effort to to decrease expenditures related to experimental methods, numerical methods have gained widespread popularity in industry and research. The finite element method (FEM) and finite element analysis (FEA) are powerful tools that can decrease time to market, eliminating experimental costs. Finite element analysis allows modelers to implement the wide variety of geometric, material, and environmental conditions seen by IC packages.

In early work, FEA techniques were used to study the effects of different materials and geometry on dual inline packages by Groothuis, et al. [60], and Pendse [103]. Kelly, et al. [104, 105] studied thermal stresses in plastic packages numerically. Van Gestel [62] used simulation techniques to study delamination in plastic packages. Sweet, et al. [70, 106] used a viscoplastic material model in a study of die surface stresses. Bailey, et al. [107] used a one-eighth model to simulate the reliability of perimeter bumped flip chip on laminate assemblies.

Gektin and Bar-Cohen [108] used finite element simulations to study the effects of underfill on the reliability of flip chip assemblies. Chen, et al. [109] modeled the effects of underfill filler particles on the interfacial stresses in flip chip assemblies. Chen, et al. [110] numerically investigated die stresses in over-molded flip chip, chip scale packages (CSP). Hong and Su [111] also studied the effects of overmolding, but in plastic ball grid array (PBGA) chip scale packages using using a popular technique called slice modeling. A slice model only uses geometry of approximately one solder ball width in the linear region from the center of the die to the corner ball. This technique is popular due to small computational time and the fact that historically, the critical solder ball(s) in reliability testing is found along this diagonal.

Chen, et al. [112] used a visco-plastic model to study flip chip on flex substrate assemblies. Chung, et al. [113] modeled stresses in second level interconnects of flip chip CSP packages. Fan and coworkers [114] modeled the effects of temperature cycling on undefill delamination and cracking. Similarly, Gao, et al. [115] analyzed the effect of underfill delamination on flip chip reliability. Guo and Zhao [116] modeled die stresses and package warpage in flip chip ball grid array assemblies. Jhou [117] modeled thermally induced stresses and deformations in several geometries including copper post and copper pillar interconnects. Kpobie, et al. [118] used an FEA technique called sub-modeling to predict stresses and displacements in flip chip assemblies with a large array of fine pitch interconnects.

Ma, et al. [119] uses the Anand model for lead-free solder to study the reliability of thermally enhanced flip chip ball grid array (TEFCBGA) packages. Pang and Chong [120] used both one-eighth and slice models to study the reliability of flip chip on board assemblies. Tsai, et al. [121] and Tzeng, et al. [122] simulated the warpage and package stresses during assembly and thermal cycling of FCBGA packages. Tsai, et al. [123] also modeled the effect of underfill selection and Tzeng, et al. [124] predicted the effects of different solder bump geometries. Ernst and coworkers [125] modeled the effects of underfill material models on the effects of underfill cure on residual package stress. Davoine, et al. [126] modeled the effects of pitch on residual stresses due to reflow for flip chip packages.

### 2.3 Correlation of Experimental and Numerical Methods

While models have advantages over some experimental methods in cost and time, numerical analysis is truly a prediction tool, and is only as good as the given input. Many times bad input or bad assumptions lead to incorrect finite element predictions for the mechanical system. For this reason, researchers have relied on correlation of numerical methods with experimental data. Skipor, et al. [127] used moiré interferometry to measure displacements of two different packages, then measured stresses in the packages with test chips, and compared both sets of data with finite element predictions. Ducos, et al. [96] also correlated their results with FEA data. Slattery, et al. [128] used both piezoresistive stress chips and finite element analysis to characterize stress levels in packages. Chen, et al. [129] studied the effects of underfill in two types of packages with the use of two-dimensional finite element analysis and experimental techniques. Analytical, numerical, and experimental results were also correlated in the work of Peterson, et al. [8]. Zou [66, 68, 100] related test chip stress data from PGA and chip on board packages to finite element simulations. More recently, Rahim [98] showed graphical correlation between measured die stress levels at various stages of assembly and the corresponding predictions from FEA models, and also investigated stress effects over large temperature ranges with both finite element models and piezoresistive test chips [13]. Chen [130] mapped die stress levels using CMOS stress sensors and also graphically showed agreement with finite element data.

Hong, et al. [111] correlated models of thermally induced stress with reliability data from thermal cycling. Ma, et al. [119] related numerical results of the failure mode of TEFCBGA packages to thermal cycling data and destructive failure analysis. Ouimet and coworkers [131] used acoustic microscopy, warpage measurements, and thermal performance testing to validate models of a large dual flip chip plastic land grid array (PLGA). Shen, et al. [132] combined the use of piezoresistive stress sensors and finite element models to better understand die stresses relative to solder ball location. Son, et al. [133] combined traditional moiré, phase-shifted moiré, contact resistance measurements and finite element simulations to study fine pitch lead free flip chip on organic assemblies. Tsai and co-workers [134, 135] also correlated their finite element simulation of plastic ball grid array thermal warpage to moiré results. Guo and Zhao [116] correlated warpage and stress data in flip chip packages to finite element simulations. Fan, et al. [114] correlated models of the effects of temperature cycling on undefill delamination and cracking with course finite element models. Jhou, et al. [117] not only modeled thermally induced stresses and deformations in several geometries including copper post and copper pillar interconnects, but compared simulation with both analytical solutions and moiré data.

## 2.4 Heat Sink Clamping

The use of thermal heat sinks to draw heat away from the working die is commonplace in computing. It is effective method for removing heat from the die surface and improving the life performance of the overall product. The use of heat sinks does bring about several issues related to reliability and the mechanical effects on the assembly, specifically the die. Eyman and Kromann [136] investigated the effects of several types of clip on and adhesive attached heat sinks on reliability of plastic ball grid array (PBGA) componenets using several methods including thermal cycle reliability testing, drop testing, and heat sink shear testing. Zhu, et al. [137] studied the effects of the mechanical interplay between clamping force and thermal expansion during thermal cycling on the reliability of BGA packages. Lopez and co-workers [138] used Monte Carlo simulations to probabilistically determine the loading on the package for clamped CLGA assemblies.

Chen, et al. [139] measured the force acting on the die due to heat sink clamping. In one part of the study, forces acting on the package were quantified as a function of various mounting schemes and fastener torque levels. Three-dimensional finite element models were used to predict the stress distributions in both the TIM1 layer and solder interconnects. Garner, et al. [140] and Bhatti, et al. [141] studied the effects of simulated heat sink loading on the reliability on FCBGA components using experimental reliability tests along with finite element simulations. Quinones and Babiarz [142] looked at effects of heat sink application on the reliability of chip scale packaging. Ben-Achour and Bar-Cohen [143] studied die displacement and stress under the presence of heat sink loading using finite element models as well as thermal reliability testing. Chiu, et al. [144] quantified the effects of compressive heat sink loading on board level reliability (BLR) and assembly collapse using experimental and numerical methods. Most of the literature related to heat sink clamping is focused on reliability of the interconnects on the package or thermal performance. Very few studies specifically investigated the effects of heat sink clamping on the die.

## 2.5 Thermal Cycling

Accelerated life testing (ALT) is a popular method of qualifying electronic components. ALT is normally performed using thermal cycling, where the test assemblies are subjected to harsh changes in temperature over a much shorter period of time than expected in field exposures of the parts. The range of temperature is also often much greater than the true application environment. The goal is to then use the ALT data to predict/estimate the reliability. This process also allows the determination of various characteristics of the packaging architecture during its life cycle, i.e. critical locations, failure modes, stress levels, etc. Subjecting a component to high stress levels not only allows for the study of failures during a life cycle, it also enables reduction of the time required to make design improvements, component choices, and material selections.

Much of the literature is related to reliability studies more than stress effects on the package. Sherry, et al. [145] thermally cycled leadless ceramic chip carriers (LCCC) on FR4 using three different thermal profiles, from -20 to 130 °C, -20 to 80 °C, and 30 to 80 °C,

and correlated finite element models to the results. Lodge and Pedder [146] cycled dielectric ceramic on silicon test chip structures for up to 2000 thermal cycles over a range of -55 to 125 °C. Suryanarayana, et al. [147] studied the effects of different encapsulants on the thermal cycling reliability of flip chip on ceramic substrate assemblies subjected to 0 to 100 °C and -55 to 125 °C testing. Various temperature profiles were used by Clementi, et al. [148] to investigate different encapsulant materials for flip chip on ceramic components, including -40 to 65 °C, 0 to 100 °C, 10 to 100 °C, -55 to 125 °C, as well as a cryogenic to room temperature cycle of -200 to 25 °C. Parts in the tests from 0 and 10 to 100 °C were cycled a minimum of 10,000 times.

Master, et al. [149] used thermal cycling tests from both 0 to 100 °C and -55 to 125 °C to quantify the reliability of ceramic column grid array (CCGA) packages as well as ceramic ball grid array (CBGA) packages. The bulk of their study looked at the CCGA packages and the effects of interconnect pitch, substrate rework, and flux type (rosin vs. no-clean) on interconnect reliability. Similar treatment was given to the AMD K6 flip chip die [150]. As part of a study on organic flip chip substrates, Petefish and co-workers [151] cycled flip chip components on organic substrates from -55 to 125 °C for a minimum of 1000 cycles. Mercado and Sarihan [152] performed a parametric reliability study to determine the effects of substrate thickness, solder composition, interconnect array design, underfill selection and solder interconnect height on reliability of CBGA components. Mercado, et al. [153, 154] later studied the effects of thermal cycling on the copper/low-k interconnects found in both PBGA and CBGA packages. Di Giacomo, et al. [155] studied the effects of cycling rate on the reliability of CBGA packages. Newman, et al. [156] tested various chip scale package (CSP) devices on the same laminate test board over the range of 0 to 100 °C.

Shinotani and co-workers [157] used thermal cycling from -55 to 125 °C to aid in material selection of substrates for system-on-package (SOP) components. Spraul, et al. [158] cycled flip chip components on low temperature cofired ceramic (LTCC) substrates from -40 to 125 °C and from -40 to 85 °C. Jen and coworkers [159] compared finite element simulations

to thermal cycling results for both flip chip plastic ball grid array (FC-PBGA) and flip chip ceramic ball grid array (FC-CBGA) components. Yan and co-workers [160] compared thermal shock results to finite element simulations for a unique double bump interconnect for flip chip assembly.

While several researchers have applied accelerate life testing techniques to flip chip packages, including many with ceramic substrates, only a few limited studies have been performed on geometries and materials that are directly related to this dissertation. Zhang, et al. [161] first studied the applicability of different lead free solder joint acceleration factor models of several geometries. A plastic ball grid array geometry and a ceramic ball grid array geometry were studied using three thermal cycles. The flip chip ceramic ball grid array investigated matches the geometry in Figure 1.1 and that found in the remainder of this work. The FC-CBGA was simulated and tested using thermal cycles of 0 to 100 °C, 25 to 85 °C, and a mini-cycle of 75 to 85 °C. Zhang [162] later carried out an experimental and numerical study of the flip chip ceramic ball grid array found in this study. He was primarily concerned with the reliability of the second level solder ball interconnects, but his work was valuable in further understanding the geometry seen later in the current study, as the basic package contained the same geometry and material set.

# 2.6 Power Cycling of IC Components

Thermal cycling accelerated life testing aims to gain better understanding of the mechanical behavior of electronic packages while reducing time needed to see failures representative of those seen in field use. In thermal cycling, the temperature source is external to the chip itself, which is the true heat source in working microprocessors. Power cycling of IC components aims to gain a similar understanding of the interactions seen in thermal cycling, and more importantly the actual use of the package.

In relatively early studies, Munikoti and Dhar [163, 164] used daisy chained plated through holes (PTH) to provide internal ohmic heating to evaluate the reliability of plated through holes and interconnects on printed circuit boards. Later, Hong [165] studied the behavior of 119-ball plastic ball grid array packages under power loads of 0 to 3 Watts with a frequency of 2 cycles per hour, and showed a sawtooth wave type transient temperature response. Hong, et al. [166] also numerically and experimentally evaluated the reliability of 25 mm flip chip ceramic ball grid array packages in close proximity to each other. A power cycle of 0 to 5 Watts at 3 cycles per hour was chosen for the study, and the effects of airflow on the transient temperature response of the packages was reported. Ham and co-authors [167] worked to understand the fundamental differences between thermal cycling and power cycling by measuring deformations with moiré techniques and performing simulations for both scenarios. They found that while shear strains in the solder interconnects were similar in both cases, the normal deformations were fundamentally different, with the bending in power cycling tests found to be opposite that found in thermal cycling tests.

Syed [168] used peltier junctions attached to plastic ball grid array packages on laminate substrates to carry out power cycling experiments in order to alleviate the need for thermal test die. Using transient thermal analysis, the resulting temperature profile was correlated with finite element simulations. Towashiraporn and co-workers [169, 170] also used a peltier junction heater to provide heat dissipation, measuring the thermal response of the chip scale package with infrared thermography, and correlated their findings with finite element simulations. The work aimed to compare the effects of power cycling and thermal cycling on the same package, but admittedly the thermal profiles of the two tests were very different. Rodgers, et al. [171] also thermal and power cycled BGA packages, but instead of comparing the effects, combined them. Transient thermal response measured by both infrared thermography and on-package diodes correlated very will to predicted temperature from a transient thermal finite element model.

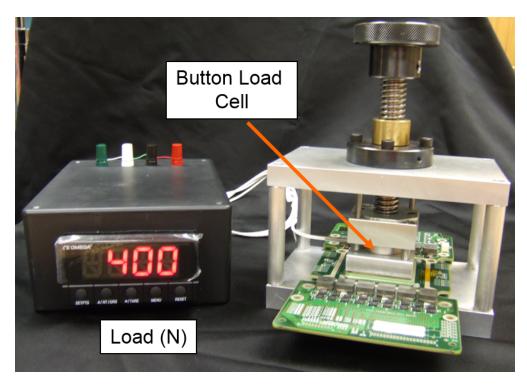

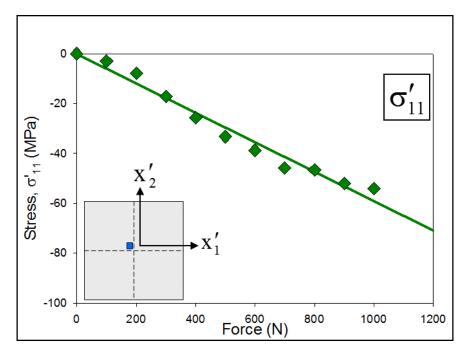

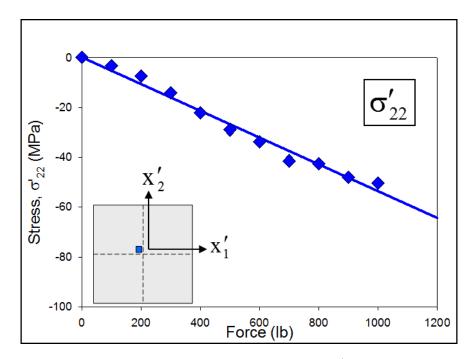

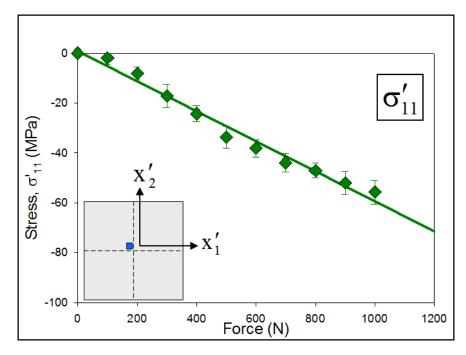

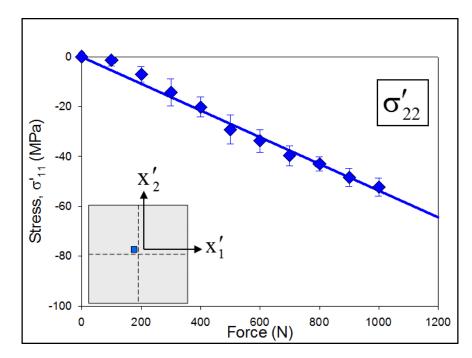

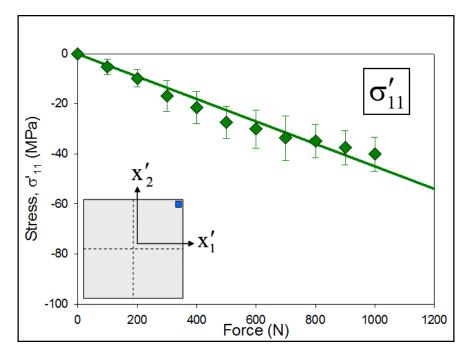

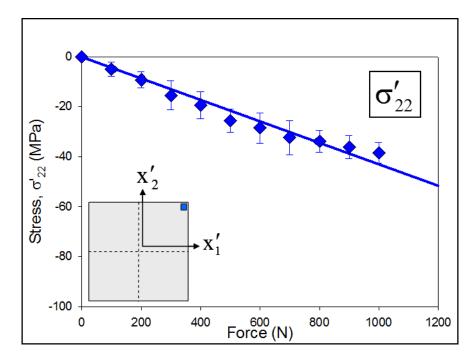

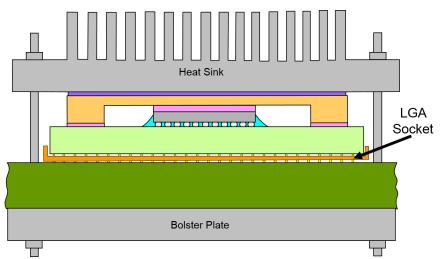

Mawer and co-workers [172] also thermal and power cycled components, using flip chip plastic ball grid array components on laminate substrates. In both cases, the assemblies were cycled from room temperature to 125 °C, with die temperature monitored by an integral RTD stucture on the die. In this study the power cycled components exhibited a greater characteristic life, but it is noted that the thermal profiles of both tests did not match. Liu and Irving [173] focused on electromigration and thermal-mechanical failure in their power cycling study. Small die bumped to lead frames were subjected to one Watt of power for two minutes, followed by two minutes of no power dissipation. Transient temperature and stress profiles were also modeled for the solder ball interconnects. Similarly, Ahmed and Park [174] measured the effects of a 3 Watt, 16 second power cycle on flip chip ceramic ball grid array packages, correlating results from transient computational fluid dynamic and structural finite element simulations.