## Novel Interface Trap Passivation and Channel Counter-doping for 4H-SiC MOSFETs

by

Aaron Lee Modic

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama May 9, 2015

Keywords: MOSFET, Silicon carbide, counter-doping, passivation

Copyright 2015 by Aaron Lee Modic

## Approved by

Sarit Dhar, Chair, Assistant Professor of Physics

John R. Williams, Professor Emeritus of Physics

Minseo Park, Professor of Physics

Leonard C. Feldman, Distinguished Professor of Physics and Astronomy

and Materials Science and Engineering

Michael C. Hamilton, Assistant Professor of Electrical Engineering

Guofu Nui, Alumni Professor of Electrical Engineering

#### **Abstract**

4H-Silicon carbide (4H-SiC) is the most promising wide band gap semiconductor for next generation high power and high temperature metal-oxide-semiconductor field-effect transistors (MOSFETs). However, the channel mobility for as-grown oxide 4H-SiC is poor due to the high density of electronic traps near the SiO<sub>2</sub>/4H-SiC interface. Nitric oxide (NO) post oxidation anneal increased 4H-SiC MOSFET mobility and allowed for commercially available devices. However, there is a limit to the amount of nitrogen that can passivate the electronic interface traps from nitric oxide passivation due to competing nitridation and oxidation reactions.

In the first part of this work, nitrogen plasma passivation, nitridation without oxidation, is explored as an alternative passivation process. Nitrogen plasma passivation is demonstrated to obtain a 50% increase in nitrogen coverage compared to standard NO. However the maximum field-effect mobility remains similar to NO. Explanations for this discrepancy are discussed.

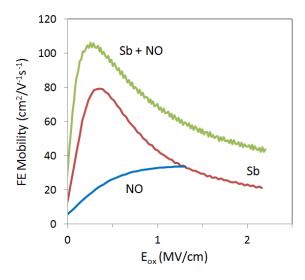

Recent publications reported that nitrogen and phosphorus both passivate interface traps and counter-dope. To further examine these observations, the effects of antimony and arsenic at the interface were studied in this work. Antimony and arsenic are both in the same periodic column as nitrogen and phosphorus, but little is known about whether antimony and arsenic passivate electronic traps. Peak mobilities using several counter-doping processes are presented (110cm² V-¹ s-¹ for counter-doping combined with nitric oxide annealing). Evidence is also presented demonstrating that antimony does not passivate interface traps, thus improved field-effect mobility results from antimony are strictly from counter-doping effects.

### Acknowledgments

Thank you to everyone who has helped and encouraged me to come this far: Prof. John R. Williams and Prof. Sarit Dhar for accepting me into the SiC semiconductor group, aiding me with experiments, and furthering my knowledge of SiC; Dr. Tamara Isaacs-Smith and Prof. Ayayi C. Ahyi for all of the time spent teaching me how to use the equipment, answering questions, and always having time to help; Prof. Dallas Morisette, Dr. Gang Liu, Dr. Yi Xu, and Prof. Leonard C. Feldman for their contribution to this work; Victor A. Crainich who taught me how to organize a research notebook and laboratory; Dr. James L. Blackshire for teaching me how to use modeling software and how to create experiments; Prof. Gregory A. Kozlowski for giving me the opportunity to learn and develop my own nanoscience experiments; Prof. Peter J. Collings for giving me my first taste of experimental research; Prof. Michael "Doc" R. Brown for his encouragement and advice to attend Auburn University; Prof. Carl Grossman for being my advisor at Swarthmore College; my Graduate Committee members for taking the time to read and critique this dissertation (twice); and finally, the biggest thank you goes to the two people without whom I would not even be here, let alone complete this dissertation, my parents, Rob Modic and Allyn Modic. I could not have accomplished this without your help and encouragement throughout my entire life.

# **Table of Contents**

| Abstract                                                      | ii  |

|---------------------------------------------------------------|-----|

| Acknowledgments                                               | iii |

| List of Tables                                                | ix  |

| List of Figures                                               | X   |

| List of Abbreviations                                         | xiv |

| Chapter 1. Introduction                                       | 1   |

| 1.1 Power electronics and wide band gap semiconductors        | 1   |

| 1.2 Silicon carbide field-effect device comparison to silicon | 5   |

| 1.2.1 Critical field and lower on-resistance                  | 5   |

| 1.2.2. Temperature dependence of leakage current              | 9   |

| 1.2.3 Switching frequency                                     | 11  |

| 1.2.4 Cooling requirements                                    | 11  |

| 1.3 SiC hurdles                                               | 12  |

| 1.4 SiC passivation processes                                       | 14 |

|---------------------------------------------------------------------|----|

| 1.5 Counter-doping                                                  | 16 |

| 1.4 SiC passivation processes.  1.5 Counter-doping.  1.6 References | 16 |

| Chapter 2. MOS systems physics and characterization                 | 23 |

| 2.1 MOS fundamentals                                                | 23 |

| 2.1.1 Hole accumulation                                             | 25 |

| 2.1.2 Flat-band condition                                           | 27 |

| 2.1.3 Depletion                                                     | 28 |

| 2.1.4 Inversion                                                     | 29 |

| 2.2 Practical MOS capacitor                                         | 30 |

| 2.2.1 Interface traps                                               | 32 |

| 2.2.2 Mobile ions                                                   | 35 |

| 2.2.3 Oxide trapped charges and fixed oxide charges                 | 36 |

| 2.3 High-low capacitance-voltage characterization                   | 37 |

| 2.3.1 Oxide thickness                                               | 41 |

| 2.4 Lateral MOSFETs                                                 | 42 |

| 2.5 Inversion channel mobility                                      | 43 |

| 2.6 Scattering mechanisms                                           | 44 |

| 2.6.1 Coulomb scattering                                            | 45 |

| 2.6.2 Surface roughness scattering                                  | 47 |

| V                                                                   |    |

| 2.6.3 Phonon scattering                                          | 47 |

|------------------------------------------------------------------|----|

| 2.7 Universal mobility in Si MOSFETs                             | 48 |

| 2.8 Field-effect mobility                                        | 50 |

| 2.9 Counter-doping of MOSFETs                                    | 52 |

| 2.9.1 P-n junction physics                                       | 52 |

| 2.9.2 Counter-doping                                             | 54 |

| 2.9.3 Nitrogen and phosphorus counter-doping                     | 56 |

| 2.10 Vertical power MOSFETs                                      | 58 |

| 2.11 References                                                  | 59 |

| Chapter 3. Nitrogen plasma passivation                           | 64 |

| 3.1 Introduction                                                 | 64 |

| 3.2 Previous attempts                                            | 66 |

| 3.3 Experimental Procedure                                       | 68 |

| 3.4 Initial nitrogen plasma passivation results                  | 70 |

| 3.5 Nitrogen plasma optimization                                 | 72 |

| 3.5.1 Microwave power calibration                                | 73 |

| 3.5.2 Temperature calibration                                    | 74 |

| 3.5.3 Pressure calibration                                       | 77 |

| 3.6 Oxide quality using modified nitrogen plasma process         | 78 |

| 3.6.1 Attempts to improve six-hour nitrogen plasma MOS capacitor | 79 |

|   | 3.6.2 Attempts to shorten production process                      | 80  |

|---|-------------------------------------------------------------------|-----|

|   | 3.7 N <sub>it</sub> , nitrogen coverage and field-effect mobility | 81  |

|   | 3.8 Nitrogen fast traps                                           | 88  |

|   | 3.9 Conclusions                                                   | 92  |

|   | 3.10 References                                                   | 93  |

| C | hapter 4: Counter-doping with heavy dopants Sb and As             | 96  |

|   | 4.1 Introduction                                                  | 96  |

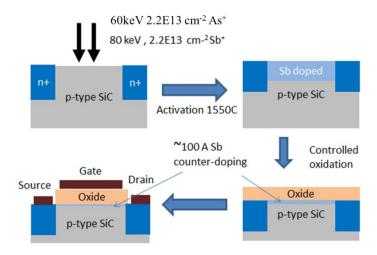

|   | 4.2 Antimony and arsenic MOSFET process                           | 99  |

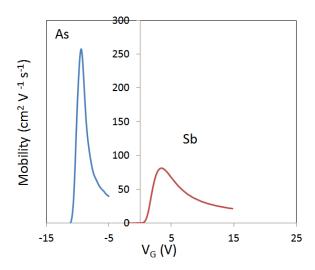

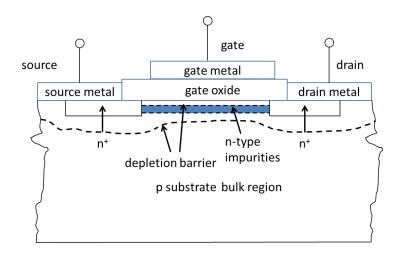

|   | 4.3. Results and discussion                                       | 101 |

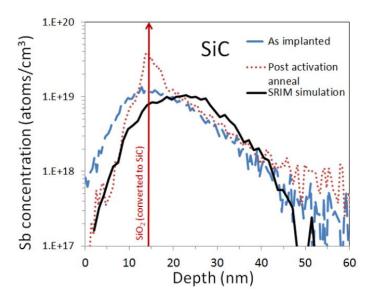

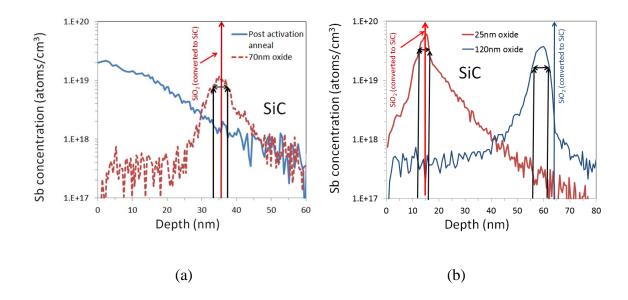

|   | 4.3.1 Secondary ion mass spectrometry                             | 103 |

|   | 4.3.2 Implantation model and SIMS results                         | 104 |

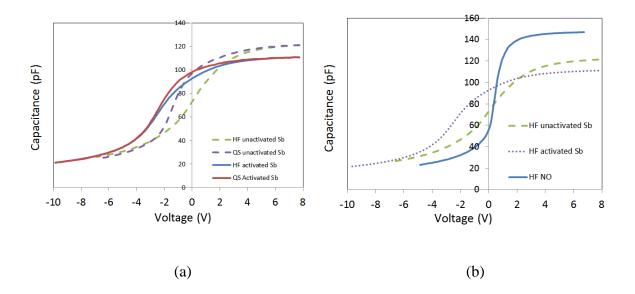

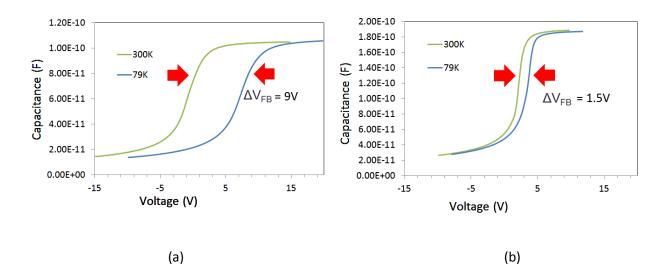

|   | 4.4 Antimony high-low capacitance-voltage characterization        | 109 |

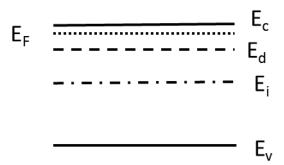

|   | 4.5 Antimony acts only as a counter-dopant                        | 111 |

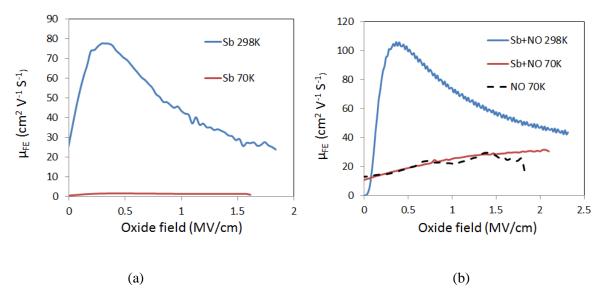

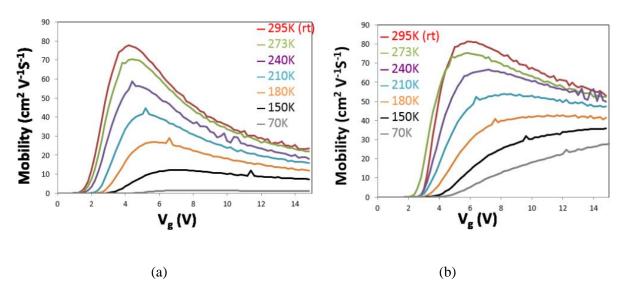

|   | 4.5.1 Low temperature mobility                                    | 111 |

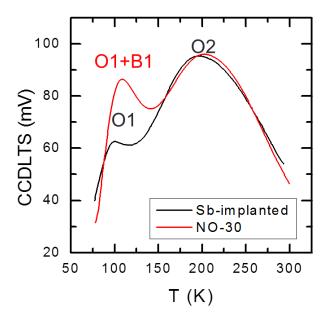

|   | 4.5.2 Constant capacitance deep-level transient spectroscopy      | 114 |

|   | 4.5.3 Low temperature C-V                                         | 116 |

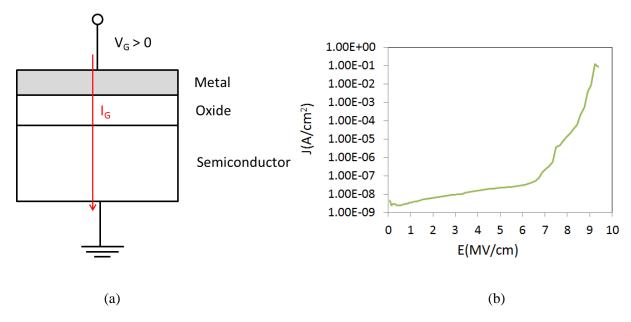

|   | 4.6 Antimony implanted MOS capacitor breakdown field              | 117 |

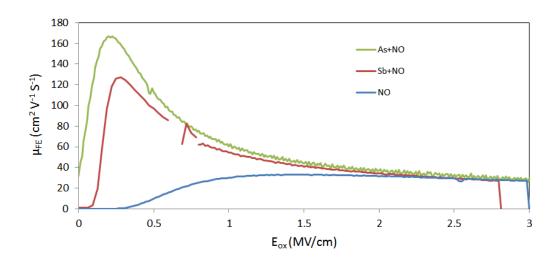

|   | 4.7 MOSFET field-effect mobility                                  | 118 |

|   | 4.7.1 Coulomb scattering mobility                                 | 120 |

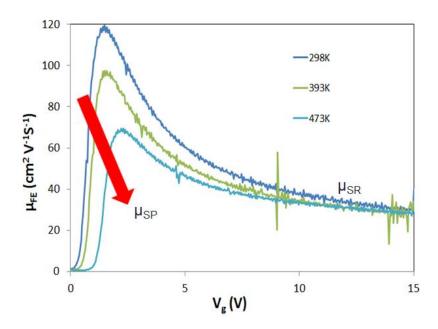

|   | 4.7.2 Phonon mobility                                             | 122 |

| 4.7.3 Surface roughness mobility and universal mobility            | 123 |

|--------------------------------------------------------------------|-----|

| 4.8 Conclusion                                                     | 124 |

| 4.9 References                                                     | 125 |

| Chapter 5. Conclusions                                             | 129 |

| 5.1 References                                                     | 130 |

| Appendix A. Device cleaning process                                | 132 |

| Appendix B. Sample oxidation                                       | 133 |

| Appendix C. Plasma furnace operation                               | 135 |

| Appendix D. LPCVD deposited oxide procedure                        | 137 |

| Appendix E. Mask aligner and spinner procedure                     | 138 |

| Appendix F. Sputter system procedure                               | 139 |

| Appendix G. Reactive ion etch procedure                            | 140 |

| Appendix H. Ohmic anneal furnace procedure                         | 141 |

| Appendix I. Carbon cap procedure                                   | 142 |

| Appendix J. Activation anneal procedure                            | 143 |

| Appendix K. Capacitance-Voltage measurement procedure and settings | 144 |

| Appendix L. Nitrogen plasma recombination                          | 145 |

| I. 1 References                                                    | 146 |

# List of Tables

| Table 1-1. Table of several key intrinsic properties among Si, 4H-SiC, and 6H-SiC        | . 7 |

|------------------------------------------------------------------------------------------|-----|

| Table 3-1. Position number and distance for monochromator along nitrogen plasma furnace7 | 72  |

| Table 3-2. Comparison of nitrogen coverage for the various processes studied             | 84  |

| Table 3-3. Oxide thickness, threshold voltage, and peak field-effect mobility comparison | 87  |

| Table 3-4. Oxide thickness and effective charge for various processes                    | 88  |

| Table 4-1. Calculated antimony and location based on SIMS results                        | Э8  |

| Table 4-2. Threshold voltage for standard NO, Sb-only, and Sb+NO processes               | 20  |

# List of Figures

| Figure 1-1. Band gap comparison of 4H-SiC, 6H-SiC, and Si                                                |

|----------------------------------------------------------------------------------------------------------|

| Figure 1-2. Stacking layer for 4H-SiC.                                                                   |

| Figure 1-3. 4H-SiC crystal lattice structure                                                             |

| Figure 1-4. Energy band diagrams of silicon and 4H-SiC                                                   |

| Figure 1-5. Specific on-resistance of Si and SiC MOSFET.                                                 |

| Figure 1-6. Creation of electron-hole pair.                                                              |

| Figure 1-7. Qualitative plot of D <sub>it</sub> and band gap energy level for Si and 4H-SiC              |

| Figure 2-1. Simple diagram of a MOS capacitor                                                            |

| Figure 2-2. Space-charge density in a semiconductor compared to surface potential                        |

| Figure 2-3. Space-charge diagram, band bending diagram and device diagram for MOS system in accumulation |

| Figure 2-4. Space-charge diagram, band bending diagram and device diagram for MOS system in flat-band    |

| Figure 2-5. Space-charge diagram, band bending diagram and device diagram for MOS system in depletion    |

| Figure 2-6. Space-charge diagram, band bending diagram and device diagram for MOS system in inversion    |

| Figure 2-7. Types of charges derived from thermally oxidized silicon                                     |

| Figure 2-8. Energy diagram of acceptor interface traps and donor interface traps                         |

| Figure 2-9. Energy diagram of interface-trap system                                                      |

| Figure 2-10. Interface traps in a MOS system                                                            | 35    |

|---------------------------------------------------------------------------------------------------------|-------|

| Figure 2-11. Diagram of a hi-lo C-V measurement                                                         | 37    |

| Figure 2-12. Simplified MOS capacitor and circuit diagram                                               | 38    |

| Figure 2-13. Band diagram of hi-lo C-V method                                                           | 40    |

| Figure 2-14. Lateral MOSFET diagram                                                                     | 43    |

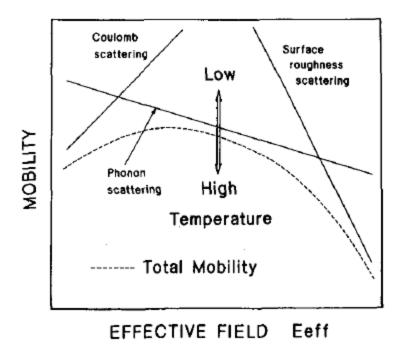

| Figure 2-15. Inversion channel scattering mechanisms and their effect on total mobility                 | 45    |

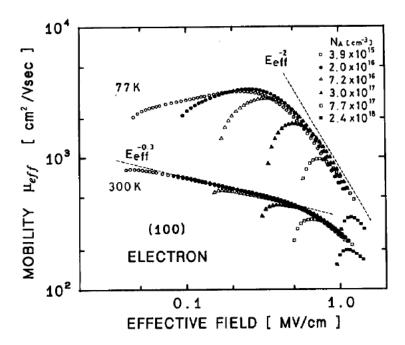

| Figure 2-16. Diagram of universal mobility behavior across a range of substrate acceptor concentrations | 49    |

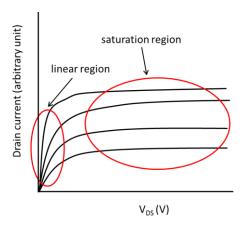

| Figure 2-17. Comparison of drain current to the source-to-drain voltage                                 | 51    |

| Figure 2-18. Creation of a p-n junction                                                                 | 53    |

| Figure 2-19. Band bending near the interface for standard MOS and p-n junction                          | 53    |

| Figure 2-20. Space-charge diagrams for standard and counter-doped MOSFET                                | 55    |

| Figure 2-21. Scanning capacitance microscopy diagram and carrier concentration                          | 57    |

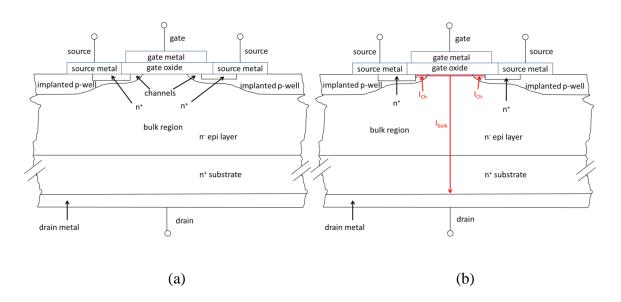

| Figure 2-22. n-DMOSFET diagram                                                                          | 58    |

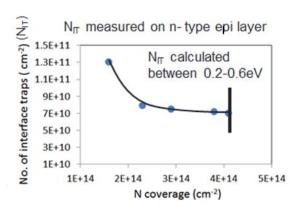

| Figure 3-1. N <sub>it</sub> and nitrogen coverage for NO passivation plot                               | 64    |

| Figure 3-2. N <sub>it</sub> and maximum field effect mobility plot                                      | 65    |

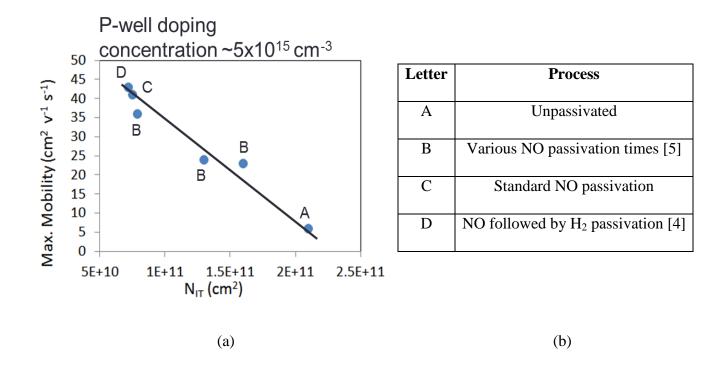

| Figure 3-3. Hi-lo C-V for 8h nitrogen plasma passivation MOS capacitor                                  | 70    |

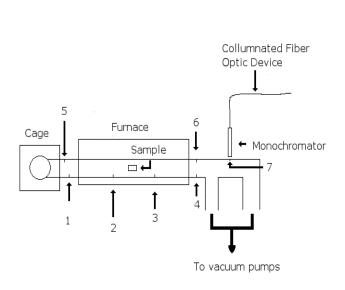

| Figure 3-4. Monochromator positions along nitrogen plasma furnace diagram                               | 72    |

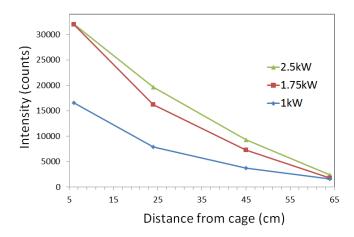

| Figure 3-5. I <sub>580</sub> and microwave power plot                                                   | 74    |

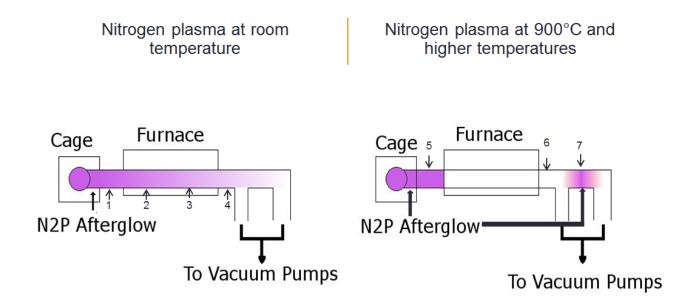

| Figure 3-6. Qualitative diagram of viewed nitrogen recombination afterglow                              | 75    |

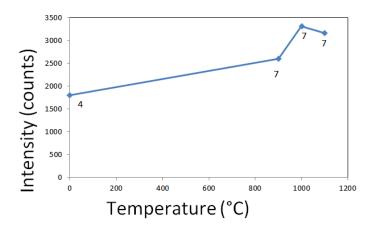

| Figure 3-7. Nitrogen plasma afterglow intensity and temperature plot                                    | 76    |

| Figure 3-8. Hi-lo C-V for 6h nitrogen plasma passivation at 900°C                                       | 77    |

| Figure 3-9. I-V characterization for varied durations of nitrogen plasma passivation                    | 78    |

| Figure 3-10. Breakdown field strength of 6h nitrogen plasma MOS capacitors with varied of               | oxide |

| recovery durations                                                                                                          | 80    |

|-----------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 3-11. D <sub>it</sub> plots for different nitrogen plasma recovery anneal processes                                  | 81    |

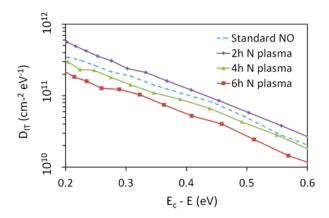

| Figure 3-12. Time-dependent study of D <sub>it</sub> compared to nitrogen plasma duration                                   | 82    |

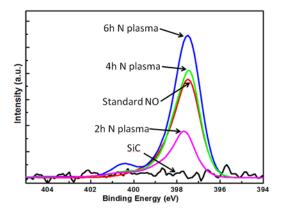

| Figure 3-13. XPS profile of N1s nitrogen after oxide etch                                                                   | 83    |

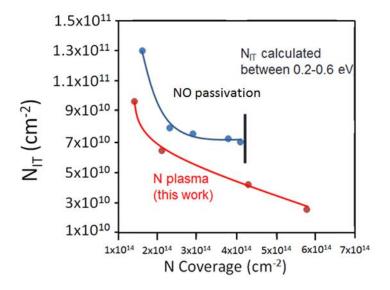

| Figure 3-14. Comparison of nitrogen plasma and NO nitrogen coverage to calculated N <sub>it</sub>                           | 86    |

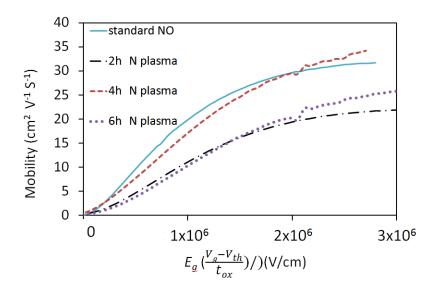

| Figure 3-15. Normalized field-effect mobility for various MOSFET processes                                                  | 87    |

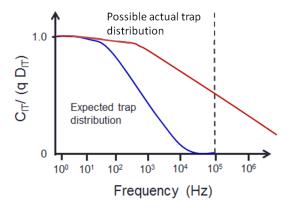

| Figure 3-16. Expected vs. actual trap distribution with fast traps                                                          | 89    |

| Figure 3-17. Quantifiable quasi-static and high frequency compared to ideal high frequency                                  | 90    |

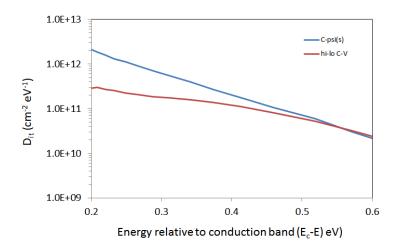

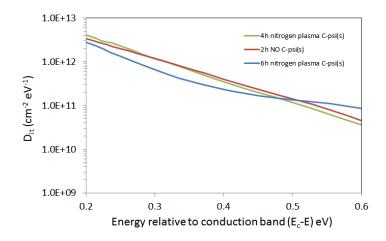

| Figure 3-18. C-Ψ <sub>s</sub> and hi-lo C-V characterization of a 6h nitrogen plasma MOSFET                                 | 91    |

| Figure 3-19. C- $\Psi_s$ comparison of 2h NO, 4h nitrogen plasma, and 6h nitrogen plasma $D_{it}$                           | 91    |

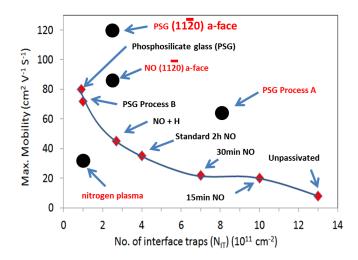

| Figure 4-1. Representation plot demonstrating scaling relationship between N <sub>it</sub> and maximu field-effect mobility |       |

| Figure 4-2. Implanted-antimony MOSFET process flowchart                                                                     | . 100 |

| Figure 4-3. Arsenic and antimony mobility plot                                                                              | . 101 |

| Figure 4-4. Buried channel MOSFET diagram                                                                                   | . 102 |

| Figure 4-5. Modeled antimony profile compared to SIMS antimony profile                                                      | . 105 |

| Figure 4-6. SIMS antimony profile for different oxidation depths                                                            | . 106 |

| Figure 4-7. Hi-lo C-V of activated and unactivated antimony MOS capacitors                                                  | . 110 |

| Figure 4-8. Band diagram of dopant freeze-out in semiconductor                                                              | . 113 |

| Figure 4-9. Low temperature field-effect mobilities                                                                         | . 113 |

| Figure 4-10. CCDLTS of antimony with NO passivation and NO passivation                                                      | . 116 |

| Figure 4-11. Low temperature hi-lo C-V of Sb-only and NO MOS capacitors                                                     | . 117 |

| Figure 4-12. I-V diagram and plot for antimony implanted devices                                                            | . 118 |

| Figure 4-13. Field-effect mobilities of NO, Sb-only, and Sb+NO MOSFETs                                                      | . 119 |

| Figure 4-14. Low temperature field-effect mobilities of Sb-only and Sb+NO MOSF | ETs 121 |

|--------------------------------------------------------------------------------|---------|

| Figure 4-15. High temperature field-effect mobilities                          | 122     |

| Figure 4-16. Mobility comparison of various MOSFET processes                   | 123     |

### List of Abbreviations

As Arsenic

BOE Buffered oxide etch

$C-\Psi_s$  Capacitance-surface potential

CCDLTS Constant-capacitance deep-level transient spectroscopy

Cs Cesium

D<sub>it</sub> Density of interface traps

DI Demineralized

DLTS Deep-level transient spectroscopy

DMOSFET Double-implanted metal-oxide-semiconductor field-effect transistor

Hi-lo C-V Simultaneous high-low capacitance-voltage

Intensity of 580.4nm wavelength

LPCVD Low-pressure chemical vapor deposition

Mo Molybdenum

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field-effect transistor

N<sub>it</sub> Number of interface traps

NO Nitric oxide

POA Post-oxidation anneal

PSG Phosphosilicate glass

RCA Radio Corporation of America

Sb Antimony

SCM Scanning capacitance microscopy

SiC Silicon carbide

SIMS Secondary ion mass spectroscopy

SRIM Stopping and range of ions in matter

TCE Trichloroethylene

TEOS Tetraethylorthosilicate

WBG Wide bang gap

XPS X-ray photoelectron spectroscopy

## **Chapter 1. Introduction**

### 1.1 Power electronics and wide band gap semiconductors

Power electronics encompasses a vast array of solid-state electronic devices that control electrical energy. Approximately 30% of energy used in the United States passes through at least one power electronics device at some point between generation and consumption [1]. Forecasts by researchers at Oak Ridge National Laboratory expect this percentage to grow to 80% by 2030 [1]. Power electronics are found in many everyday appliances: cell phones, computers, automobiles, motors, air conditioning/heating units, and power line transformers. They are critical in converting solar, wind, and hydro energy into electricity.

As power electronics becomes more and more important for society, higher efficiency devices are becoming increasingly important because they are both environmentally friendly and cost effective. Increasing the efficiency of power electronics in cars has significant advantages. Lux Research Inc. found that a 20% increase in power savings translates to \$6000 or more savings in battery costs for the new Tesla Model S electric car [2]. More efficient power electronics can also reduce up to 90% of power loss during AC-to-DC and DC-to-AC conversions [3].

Most early power electronics devices have been silicon-based technologies. However, silicon technology is approaching the theoretical limits for maximum operating temperature, miniaturization, and switching frequency. In addition, silicon's low thermal conductivity limits heat transfer, making it necessary for cooling system implementation.

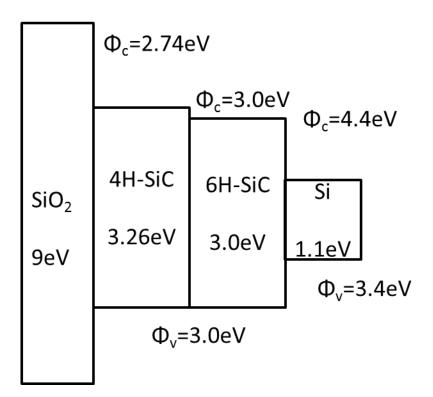

Power electronics devices can be made more efficient when silicon is replaced with wide band gap (WBG) semiconductors such as GaN, SiC, or diamond. The intrinsic properties of WBG semiconductors are superior to current silicon-based power electronics devices. Compared to other WBG semiconductors, silicon carbide (SiC) has the advantage that, like silicon, it can grow a native oxide [4]. Not only is SiO<sub>2</sub> a very good insulating oxide, but band alignments between SiO<sub>2</sub> and SiC are suitable for metal-oxide-semiconductor (MOS) devices (Figure 1-1). Furthermore, for commercial manufacturing, many silicon foundries can be readily converted for SiC device processing [5].

**Figure 1-1**. Band gap comparison of 4H-SiC, 6H-SiC, and silicon [6-7].  $\Phi_C$  is the potential difference between the bottom of the semiconductor conduction band and the bottom of the SiO<sub>2</sub> conduction band.  $\Phi_V$  is the potential difference between the top of the semiconductor valence band and the top of the SiO<sub>2</sub> valence band.

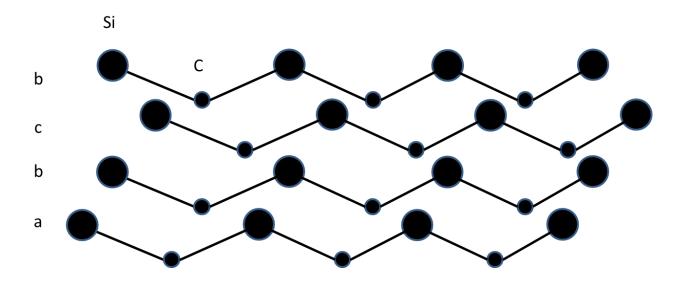

Silicon carbide has more than a hundred poly-types, but only three are commercially viable at this point. SiC crystals grow in layers, and as these layers stack upon each other, they form certain patterns. The poly-type nomenclature is derived from these patterns. The three commercially viable poly-types are 4H, 6H, and 3C. The letters H and C designate the shape of the crystalline structure: H for hexagonal; C for cubic. The poly-types are denoted by a number indicating how many layers are stacked before repeating. An example of this can be seen in Figure 1-2 is a 4H stacking order, as can be seen by the a-b-c-b stacking pattern.

Figure 1-2. Stacking layer pattern for 4H-SiC.

4H-SiC was selected for this study because it has the largest band gap among the three poly-types and the highest bulk electron mobility. 6H-SiC has a higher anisotropy in mobility making it less favorable than 4H for vertical power devices (Mobility will be further discussed in Chapter 2). For these reasons, 4H-SiC is the best candidate for SiC-based power electronics.

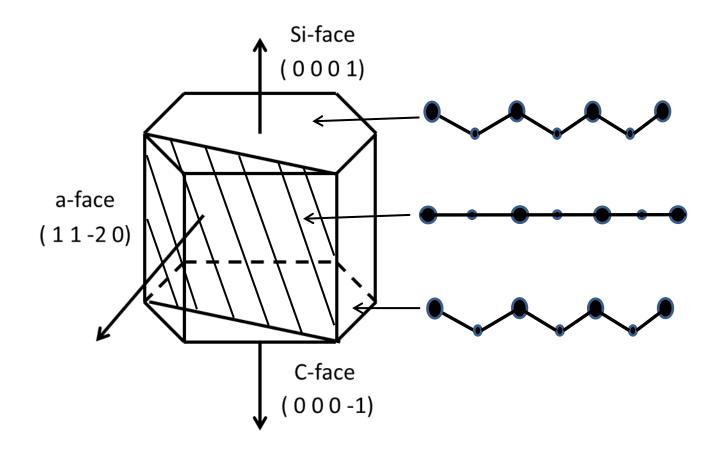

The hexagonal structure for 4H-SiC is shown in Figure 1-3. The stacked layers, shown in Figure 1-2, create a layer of silicon across the top and a layer of carbon across the bottom.

This study used the (0001) Si- terminated crystal face of 4H-SiC. The C-face is not as desirable due to a lower oxide breakdown field compared to the Si-face and immaturity in epitaxial growth [8]. The a-face has alternating silicon and carbon atoms across the surface. The a-face was not used in this study, however previous results from several a-face experiments are part of the foundation for this study as described in Chapter 4.

**Figure 1-3**. 4H-SiC crystal lattice structure.

## 1.2 Silicon carbide field-effect device comparison to silicon

Field-effect devices using silicon carbide (SiC) have the following advantages over silicon:

- Higher critical field and lower on-resistance

- Less current leakage at a higher temperature

- Higher switching frequency

- Less cooling

#### 1.2.1 Critical field and lower on-resistance

A device with a larger critical field ( $E_{CR}$ ) can be made proportionally thinner. The critical field determines the largest electric field a semiconductor can withstand before breakdown. Breakdown occurs when the electric field is large enough that a sufficient number of carrier electrons can ionize atoms by impact [9-10]. Each of these newly generated electrons creates more carrier electrons by colliding with atoms, creating a chain reaction of carrier electron generation known as avalanche breakdown. During avalanche breakdown, the secondary carrier electrons generated by electron-atom collisions must have large enough kinetic energies to generate further carrier electrons upon impact. The critical field equations for Si and 4H-SiC are [10-13]

$$E_{CR}, Si\left(\frac{V}{cm}\right) = \frac{4 \times 10^5}{1 - \frac{1}{3}log\left(\frac{N_D}{10^{16}}\right)}$$

(1.1)

$$E_{CR}, 4H - SiC\left(\frac{V}{cm}\right) = \frac{2.49 \times 10^6}{1 - \frac{1}{4}\log\left(\frac{N_D}{10^{16}}\right)}$$

(1.2)

where  $N_D$  is the doping density of the semiconductor. The critical field of 4H-SiC is nearly an order of magnitude larger than silicon. This increase in the critical field is due to the larger energy band gap of 4H-SiC (Table 1-1, page 7).

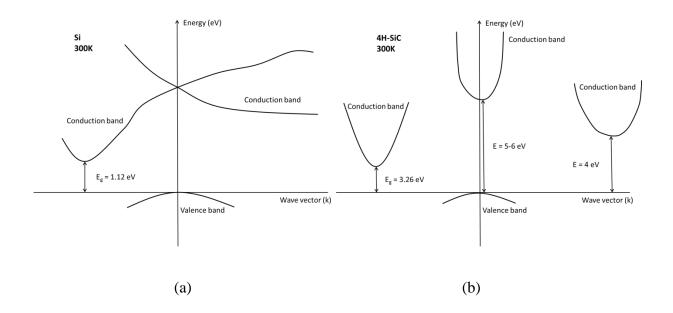

**Figure 1-4**. Energy band diagrams of silicon (a) and 4H-SiC (b) at room temperature [14]. Wave vector is inversely proportional to wavelength. Band energies in silicon are continuous, while band energies in 4H-SiC are discontinuous.

Within the crystalline electronic structure of a semiconductor, the band gap is an energy region in which no electronic states exist. This region is between the highest point of the valence band and the lowest point of the conduction band (Figure 1-4). Electrons need a specific minimum amount of energy to move from the valence band to the conduction band. The band gap for 4H-SiC is three times as large as silicon (Table 1-1), so the energy needed for impact

ionization is larger. Also, due to the discontinuous energy spectrum in 4H-SiC (Figure 1-4), the ballistic transport model of ionization is not valid [13-14]. In 4H-SiC, the electrons can reach the conduction band only through phonon collisions and quantum tunneling.

| Property                                                             | Si   | 4H-SiC | 6H-SiC                      |

|----------------------------------------------------------------------|------|--------|-----------------------------|

| Band Gap (eV)                                                        | 1.12 | 3.26   | 3.0                         |

| Electron Mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 1400 | 900    | 400 ⊥ c-axis<br>80 ∥ c-axis |

| Hole Mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )     | 600  | 100    | 90                          |

| Critical Field (MV/cm)                                               | 0.3  | 3      | 3.2                         |

| Thermal Conductivity (W cm <sup>-1</sup> K <sup>-1</sup> )           | 1.5  | 4.9    | 4.9                         |

| Saturation Drift Velocity (10 <sup>7</sup> cm/s)                     | 1    | 2.7    | 2                           |

| Dielectric Constant $\varepsilon_S$ (F/cm)                           | 11.8 | 10     | 10                          |

**Table 1-1.** Table of several key intrinsic properties for Si, 4H-SiC, and 6H-SiC. [15-17]

The wider band gap of SiC compared to silicon allows a significant increase in the blocking voltage of SiC power devices. The equation for blocking voltage ( $V_{BI}$ ) is [11]

$$V_{Bl} = \frac{\varepsilon_S E_{CR}^2}{2qN_D} \tag{1.3}$$

where  $\varepsilon_s$  is the dielectric constant,  $E_{CR}$  is the critical field, q is the charge and  $N_D$  is the doping density.  $V_{Bl}$  varies with respect to the square of the critical field, so for the same doping density, SiC blocks 30-60 times the voltage as silicon. SiC power devices can also block voltages beyond the range available for silicon power devices, since the specific on-resistance (resistance per unit area) for silicon power devices with larger blocking voltages becomes too large to be feasible [15].

The specific on-resistance is the measured resistance across the closed path of the power device. Power devices with lower specific on-resistances are more efficient. The specific on-resistance ( $R_{ON,sp}$ ) equation is

$$R_{ONsp} = \frac{4V_{Bl}^2}{\varepsilon_s \mu_n E_g^3} \tag{1.4}$$

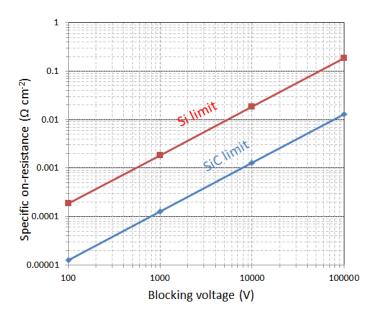

where  $V_{Bl}$  is the blocking voltage,  $\varepsilon_s$  is the dielectric constant,  $\mu_n$  is the electron mobility, and  $E_g$  is the band gap energy [11, 18].  $E_g$  for SiC is nearly three times greater than silicon, implying the  $R_{ON,sp}$  for SiC will be nearly one-tenth that of silicon devices across a wide range of blocking voltages (Figure 1-5).

**Figure 1-5.** Specific on-resistance of silicon metal-oxide-semiconductor field-effect transistor (MOSFET) and SiC MOSFET compared to blocking voltage [11-13]. SiC specific on-resistance is nearly an order of magnitude less than silicon.

### 1.2.2. Temperature dependence of leakage current

Leakage current is the unintentional flow of current across a semiconductor device. Small amounts of leakage current increase power consumption of the device while sufficiently large amounts of leakage current can cause device failure. In metal-oxide-semiconductor (MOS) devices, one of the primary components of leakage current is subthreshold leakage (I<sub>sub</sub>): current leakage across the device when the applied gate voltage is below the threshold voltage (i.e. when the device is off) [19-21]. I<sub>sub</sub> is caused by minority carrier generation [19-20]. Minority carriers have the opposite charge of the majority carriers. In n-doped semiconductors, majority carriers are electrons, and minority carriers are holes.

Minority carriers are generated either by quantum tunneling of electrons across the semiconductor band gap or by impact ionization [22]. Both of these processes create an electron-hole pair (Figure 1-6). Quantum tunneling is a quantum-mechanical event. Unlike classical

mechanics, in quantum mechanics, particles do not stop at the edge of a boundary. If the boundary width is short enough, the particle can tunnel through the boundary and appear on the other side. Applying the concept of tunneling to minority carrier generation, electrons in the valence band have a probability of tunneling through the band gap and into the conduction band. The probability of an electron tunneling through the band gap increases as the energy of the electron increases. The energy can be gained either from thermal energy or photon absorption. Impact ionization occurs when an electron with sufficient kinetic energy collides with a lattice atom and knocks a valence electron into the conduction band.

**Figure 1.6.** Creation of electron-hole pair.

When a semiconductor's temperature rises, the average kinetic energy of its electrons increases. These energized electrons in the valence band gain sufficient energy to jump the band gap and enter the conduction band. Also, as the temperature rises, the average kinetic energy of the carrier electrons increases, increasing the number of electrons available for impact ionization. When the temperature rises to a critical level, both of these electron-hole generation processes generate enough minority carriers to cause either a significant increase in power consumption or a complete device failure. For silicon power metal-oxide-semiconductor field-effect transistors (MOSFETs), the temperature limit is 150°C [18]. However, for SiC, the theoretical temperature

limit can approach 600°C because the wider band gap requires electrons to have a much larger amount of energy to jump across it [18]. Although the theoretical temperature limit for SiC is much larger than silicon, current packaging techniques restrict both silicon and SiC devices to around 150°C operational temperature.

#### 1.2.3 Switching frequency

The maximum switching frequency is mainly limited by the power dissipation during switching and gate charging [23]. Power dissipation can be decreased by decreasing the specific on-resistance. In addition, switching frequency is also affected by drift velocity. The drift velocity is the average velocity that electrons travel inside the semiconductor. A higher drift velocity for SiC (Table 1-1) implies that SiC power devices can operate at faster switching speeds than silicon devices [17-18].

## 1.2.4 Cooling requirements

Cooling systems are required to disperse the large amounts of heat generated in silicon power devices. The heat is generated from power dissipated in the semiconductor during operation (specific on-resistance and switching loss), leakage current, and environmental conditions. Silicon power devices can only function properly at temperatures less than 150°C, so cooling systems, either forced air or liquid cooling, are required to maintain an appropriate temperature [24]. Silicon also has a relatively poor thermal conductivity compared to SiC, so silicon power devices require a more complex cooling system design. These cooling systems add extra weight, size, and complexity [24].

SiC power devices do not need the extensive cooling systems required by silicon power devices. SiC power devices have about 10 times lower specific on-resistance compared to silicon and have less power dissipation from switching losses. Leakage current is also less in SiC power devices since SiC does not generate as many minority carriers compared to silicon. In addition, the thermal conductivity of SiC is three times larger than silicon (Table 1-1), so SiC can dissipate heat quicker than silicon. All of these advantages of SiC compared to silicon imply that cooling systems for SiC devices can be lighter, smaller and less complex.

#### 1.3 SiC hurdles

While the intrinsic properties of SiC make it very appealing for next generation power MOSFETs, there are hurdles preventing SiC from achieving wide-spread use. Before SiC MOSFETs achieve commercial viability, three critical challenges must be met: increasing channel mobility, improving stability, and establishing a better defined threshold voltage.

SiC MOSFETs using only a thermally grown oxide have mobilities less than  $10 \text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  [25]. Comparing this experimental mobility to the bulk electron mobility in Table 1-1,  $\sim 900 \text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , it can be seen there is much room for improvement.

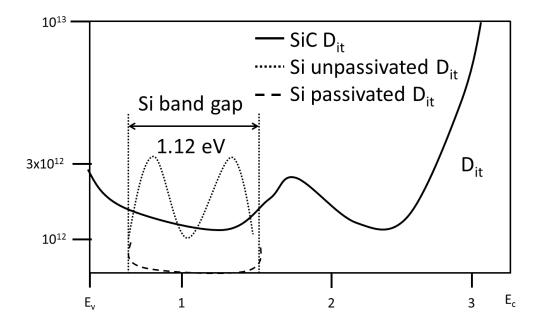

Low mobility in SiC MOSFETs operating below 1500V is primarily caused by the high resistance experienced in the channel. This high resistance is caused by the very high density of interface traps ( $D_{it}$ ) that are formed at the SiC/SiO<sub>2</sub> interface, two to three orders of magnitude larger than found at the Si/SiO<sub>2</sub> interface [26-27].

Interface traps can form when there is a Si or C deficiency. While there is no unanimity on which atom is vacant [28-31], evidence has shown that near interface oxide traps are reduced

through nitric oxide (NO) passivation (discussed below) [32-33]. Defects create electron traps with the majority having energies located near the conduction band edge [34].

**Figure 1-7**. Qualitative plot of  $D_{it}$  vs. 4H-SiC band gap energy level. Si band gap and  $D_{it}$  are shown for comparison with SiC.

Figure 1-7 is a qualitative diagram representing the  $D_{it}$  with the corresponding energy level in the SiC bandgap. This large concentration of interface traps decreases the maximum channel mobility in n-channel MOSFETs. Carrier electrons fill these traps before contributing to the mobility. After these electron traps are filled, they cause an additional reduction to channel mobility since they become Coulomb scattering sites (explained further in Chapter 2.6.1). By passivating these interface traps with another atom, the expected mobility of SiC MOSFETs should increase.

This mobility hindrance is not limited solely to SiC. Early development of Si-based MOSFETs also confronted poor mobility due to near interface traps (Figure 1-7 "Si unpassivated

$D_{it}$ "). These traps were Si dangling bonds produced during oxidation, and the traps were passivated with hydrogen (Figure 1-7 "Si passivated  $D_{it}$ "). However, hydrogen passivation on SiC MOSFETs only slightly reduced  $D_{it}$ , indicating that the interface traps in SiC are different than those found in silicon [35].

## 1.4 SiC passivation processes

Nitrogen passivation of the SiC MOSFET Dit was originally discovered to improve the electrical performance of 6H-SiC [36]. Soon after, nitrogen passivation showed improved electrical performance of 4H-SiC MOSFETs [37-38]. Today, standard industry nitrogen passivation is performed by a post oxidation anneal in nitric oxide (NO) gas for two hours at 1175°C. This temperature decomposes NO into its basic elements (N and O), which then move to the SiC/SiO<sub>2</sub> interface and interact at the defect sites. Nitrogen is believed to take the place of the vacant atom, passivating the electron trap [32-33]. The oxygen atom also interacts at the interface via oxidation to consume SiC, creating additional oxide [39]. The additional oxidation drives the SiC/SiO<sub>2</sub> interface deeper into the material, creating a new interface which requires more nitrogen to passivate. Because of these competing passivation and oxidation reactions, the nitrogen saturation point for the NO passivation process is about 5x10<sup>14</sup> cm<sup>2</sup> [39]. NO passivated samples have been found to be highly stable and reliable, allowing for commercially viable device production. Later, another method combined NO passivation with hydrogen passivation, surpassing the mobility benchmark established by NO passivation. However, the combination process produced an oxide breakdown field much lower than standard NO passivated devices (5MV/cm compared to 7-8MV/cm) [40].

Recent studies of the NO passivation process show a correlation between the nitrogen coverage at the  $SiC/SiO_2$  interface, the number of  $SiC/SiO_2$  interface traps  $(N_{it})$ , and mobility [41].  $N_{it}$  is the total number of interface traps across an energy range. It is obtained by integrating the  $D_{it}$  across an energy range, normally 0.2-0.6 eV below the conduction band for 4H-SiC. In essence, there appears to be scaling between increasing nitrogen coverage at the interface, decreasing the  $N_{it}$ , and increasing the peak mobility. Therefore, it is expected that a process that produces greater nitrogen coverage at the interface should decrease  $N_{it}$  and increase peak mobility. To verify this expectation, a study was conducted using a nitrogen plasma process. Chapter 3 has a discussion of this process and results.

Another process for SiC MOSFET passivation uses phosphorus (P). Using  $POCl_3$ , Okamoto, et. al. first demonstrated 4H-SiC MOSFETs with much lower  $D_{it}$  at energies 0.2eV or greater below the conduction band edge [42]. These phosphorus passivated MOSFETs had greater mobility compared to NO (peak mobility  $80\text{cm}^2$  V $^{-1}$  s $^{-1}$ ) [42]. However, a drawback of phosphorus passivation is that the phosphorus reacts with the oxide, transforming it from a standard thermally-grown oxide (SiO<sub>2</sub>) into phosphosilicate glass (PSG). PSG is a polar substance, and recent studies of the stability and reliability of phosphorus passivated devices show that PSG has very poor stability at higher temperatures and stronger applied fields [43]. Electric dipoles in the PSG align with the applied electric field, which radically changes the threshold voltage (V<sub>T</sub>) of the MOSFET (8V or higher V<sub>T</sub> shift) [43]. When the gate is unbiased, due to the relaxation of the aligned dipoles, the threshold voltage will return to its pre-biased state. This voltage shifting makes the device unstable.

However, there is evidence that modifying the phosphorus passivation process can minimize the voltage shift of the PSG. This modified process, developed at Auburn University,

begins with a thin, thermally grown oxide that undergoes the phosphorus passivation process. Next, the device is capped with a much thicker deposited oxide formed using a tetra-ethyl-oxy-silicate precursor [44]. Deal and Snow estimated the thickness ratio of PSG to standard oxide needed to mitigate the polar effects of PSG [45]. The devices are more stable and retain a high mobility  $(60-70\text{cm}^2\text{ V}^{-1}\text{ s}^{-1})$  [44].

### 1.5 Counter-doping

Recent studies of phosphorus passivation revealed that phosphorus acts as a counter-dopant and passivating agent [46]. Further research into nitrogen passivation revealed that nitrogen also counter-dopes in addition to its role as a passivating agent [47]. Since nitrogen and phosphorus both counter-dope and passivate interface traps, the question may be raised, "How much of the improved mobility is a result of passivation and how much is from counter-doping?"

The first step to addressing this question is to differentiate the effects interface trap passivation and counter-doping have on MOSFET mobility. Since antimony and arsenic are in the same periodic column as nitrogen and phosphorus, they should have similar chemical behavior. However, their larger atomic size compared to nitrogen or phosphorus may help to differentiate between the effects of passivation and counter-doping for improved mobility. The question is further addressed in Chapters 4 and 5.

#### 1.6 References

[1] L. M. Tolbert, T. J. King, B. Ozpineci, J. B. Campbell, G. Muralidharan, D. T. Rizy, A. S. Sabau, H. Zhang, W. Zhang, Y. Xu, H. F. Huq, and H. Liu, "Power Electronics for Distributed

- Energy Systems and Transmission and Distribution Applications," ORNL, UT-Battelle, LLC. for the U.S. Department of Energy (2005).

- [2] Lux Research, Inc. "Silicon carbide power electronics can slash \$6000 from cost of Tesla Model S" http://www.luxresearchinc.com/news-and-events/press-releases/read/silicon-carbide-power-electronics-can-slash-6000-cost-tesla (2014).

- [3] "Wide Bandgap Semiconductors: Pursuing the Promise," Advanced Manufacturing Office, U. S. Department of Energy (2013).

- [4] R. W. Kee, K. M. Geib, C. W. Wilmsen, and D. K. Ferry, "Interface characteristics of thermal SiO<sub>2</sub> on SiC," *J. Vac. Sci. Technol.*, Vol. 15, No. 4 (1978) pp. 1520-1523.

- [5] F. Amy and P. Soukiassian, "Silicon carbide surface oxidation," *NSRRC surface and thin films highlights* (2003) pp 64-67.

- [6] A. Alkauskas, P. Broqvist, F. Devynck, and A. Pasquarello, "Band offsets at semiconductor-oxide interfaces from hybrid density functional calculations," *Physical Review Lett.*, Vol. 101, No. 10 (2008).

- [7] V. V. Afanas'ev, M. Bassler, G. Pensl, M. J. Schulz and E. Stein von Kamienski, "Band offsets and electronic structure of SiC/SiO<sub>2</sub> interfaces," *J. Appl. Phys.*, Vol. 79 (1996) pp. 3108.

- [8] Z. Chen, A. C. Ahyi, X. Zhu, M. Li, T. Isaacs-Smith, J. R. Williams, and L. C. Feldman, "MOS characteristics of C-face 4H-SiC," *Journ. of Electron. Materials*, Vol. 39, No. 5 (2010) pp. 526-529.

- [9] J. Lutz, H. Schlangenotto, U. Scheuermann, R. D. Doncker, *Semiconductor Power Devices: Physics, Characteristics, Reliability*, Springer Science & Business Media (2011).

- [10] W. Mönch, "On the Physics of Avalanche Breakdown in Semiconductors," *Phys. Stat. Sol. B*, Vol. 89, No. 9 (1969) pp. 9-48.

- [11] J. A. Cooper, Jr., Development of SiC Power MOSFETs with Low On-Resistance for Military and Commercial Applications, Office of Naval Research (2003) pp.1-6.

- [12] S. M. Sze, *Physics of Semiconductor Devices*, 2<sup>nd</sup> Edition, John Wiley & Son (1981).

- [13] A. O. Konstantinov, Q. Wahab, N. Nordell and U. Lindefelt, "Ionization rates and critical fields in 4H silicon carbide," *App. Phys. Lett.*, Vol. 71, No. 1 (1997) pp. 90-92.

- [14] NSM Archive Silicon Carbide (SiC), http://www.ioffe.rssi.ru

- [15] Rhom Semiconductor, SiC Power and Devices Modules, Application Note, Issue June 2013.

- [16] G. L. Harris, *Properties of SiC*, EMIS Datareviews Series, No. 13, INSPEC, IEE, UK, 1995.

- [17] J. L. Hudgins, G. S. Simin, E. Santi, and M. A. Khan, "An assessment of wide bandgap semiconductors for power devices," *IEEE Transactions on Power Electron.*, Vol. 18, No. 3 (2003) pp. 907-914.

- [18] B. Ozpineci and L. M. Tolbert, "Comparison of wide-bandgap semiconductors for power electronics applications," Oak Ridge National Laboratory, ORNL/TM-2003/257 (2003) pp. 10.

- [19] F. Fallah and M. Pedram, "Standby and Active Leakage Current Control and Minimization in CMOS VLSI Circuits," *IEICE Trans. Electron. (Special Section on Low-Power LSI and Low-Power IP)*, Vol. 88, No. 4 (2005) pp. 509-519.

- [20] S. K. Singh, B. K. Kaushik, D. S. Chauhan, and S. Kumar, "Reduction of Subthreshold Leakage Current in MOS Transistors," *World Applied Sciences Journal*, Vol. 25, No. 3 (2013) pp. 446-450.

- [21] B. H. Calhoun, *Circuit Techniques for Subthreshold Leakage Reduction in a Deep Sub-Micron Process*, Master's Thesis, Massachusetts Institute of Technology (2002).

- [22] B. V. Zeghbroeck, *Principles of Electronic Devices* (2011).

- [23] Z. J. Shen, D. N. Okada, F. Lin, S. Anderson, and X. Cheng, "Lateral Power MOSFET for Megahertz-Frequency, High-Density DC/DC Converters," *IEEE Transactions on Power Electron.*, Vol. 21, No. 1 (2006) pp. 11-17.

- [24] S. S. Kang, "Advanced Cooling for Power Electronics," *International Conference on Integrated Power Electronics Systems CIPS*, Nuremberg, Germany (2012).

- [25] K. Ueno, R. Asai, T. Tsuji, "4H-SiC MOSFET's utilizing the H<sub>2</sub> surface cleaning technique," *IEEE Electron. Device Lett.*, Vol. 19, No. 7 (1998) pp. 244-246.

- [26] N. S. Saks, S. S. Mani, and A. K. Agarwal, "Interface trap profile near the band edges at the 4H-SiC/SiO<sub>2</sub> interface," *Appl. Phys. Lett.*, Vol. 76, (2000) pp 2250.

- [27] G. Chung, C. C. Tin, J. R. Williams, K. McDonald, M. D. Ventra, R. K. Chanana, S. T. Pantelides, L. C. Feldman, and R. A. Weller, "Effects of anneals in ammonia on the interface trap density near the band edges in 4H-silicon carbide metal-oxide-semiconductor capacitors," *Appl. Phys. Lett.*, Vol. 77, No. 22 (2000) pp. 3601-3603.

- [28] C. J. Cochrane, P. M. Lenahan, and A. J. Lelis, "Identification of a silicon vacancy as an important defect in 4H SiC metal oxide semiconducting field effect transistor using spin dependent recombination," *Appl. Phys. Lett.*, Vol. 100 (2012) pp. 023509-023509-3.

- [29] E. Pipel, J. Woltersdorf, H. Ö. Óladsson, and E. Ö. Sveinbjörnsson, "Interfaces between 4H-SiC and SiO2: Microstructure, nanochemistry, and near-interface traps," *Jour. Appl. Phys.*, Vol. 97 (2005) pp. 034302-034302-8.

- [30] D.P. Ettisserry, S. Salemi, N. Goldsman, S. Potbhare, A. Akturk, A. Lelis, "Identification and quantification of 4H-SiC (0001)/SiO2 interface defects by combining density functional and device simulations," Simulation of Semiconductor Processes and Devices (SISPAD), 2013

International Conference, Glasgow (2013) pp. 396-399.

- [31] C. X. Zhang, E. X. Zhang, D. M. Fleetwood, R. D. Schrimpf, S. Dhar, S-H. Ryu, X. Shen, S. T. Pantelides, "Origins of low-frequency noise and interface traps in 4H-SiC MOSFETs," *IEEE Electron. Dev. Lett.*, Vol. 34, No. 1 (2013) pp. 117-119.

- [32] X. D. Chen, S. Dhar, T. Isaacs-Smith, J. R. Williams, L. C. Feldman, and P. Mooney, "Electronic capture and emission properties of interface states in thermally oxidized and NO-annealed SiO<sub>2</sub>/4H-SiC," *Jour. Appl. Phys.*, Vol. 103 (2008) pp. 033701-033701-7.

- [33] A. F. Basile and P. Mooney, "Modeling of high-frequency capacitance-voltage characteristics to quantify trap distributions near SiO2/SiC interfaces," *Jour. Appl. Phys.*, Vol. 111 (2012) pp. 094509-094509-13.

- [34] P. Deák, J. M. Knaup, T. Hornos, C. Thill, A. Gali, and T. Frauenheim, "The mechanism of defect creation and passivation at the SiC/SiO<sub>2</sub> interface," *J. Phys D: Appl. Phys.*, Vol. 40 (2007) pp. 6242-6253.

- [35] E. G. Stein von Kamienski, C. Leonhard, S. Scharnholz, A. Gölz, and H. Kurz, "Passivation of interface traps in MOS-devices on n- and p-type 6H-SiC," *Diamond and related materials*, Vol. 6 (1997) pp. 1497-1499.

- [36] H-F. Li, S. Dimitrijev, H. B. Harrison, and D. Sweatman, "Interfacial characteristics of N<sub>2</sub>O and NO nitride SiO<sub>2</sub> grown on SiC by rapid thermal processing," *Appl. Phys. Lett.*, Vol. 70, No. 15 (1997) pp. 2028-2030.

- [37] G.Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, M. D. Ventra, S. T. Pantelides, L. C. Feldman, and R. A. Weller, "Effect of nitric oxide annealing on the interface trap densities near the band edges in the 4H polytype of silicon carbide," *Appl. Phys. Lett.*, Vol. 76, No. 13 (2000) pp. 1713-1715.

- [38] G.Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, R. K. Chanana, R. A. Weller, S. T. Pantelides, L. C. Feldman, O. W. Holland, M. K. Das, and J. W. Palmour, "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron. Device Lett.*, Vol. 22, No. 4 (2001) pp. 176-178.

- [39] S. Dhar, L. C. Feldman, K-C. Chang, Y. Cao, L. M. Porter, J. Bentley, and J. R. Williams, "Nitridation anisotropy in SiO<sub>2</sub> 4H-SiC," *Jour. Appl. Phys.*, Vol. 97, No. 7 (2005) pp. 074902-074902-5.

- [40] S. Dhar, S. Wang, A. C. Ahyi, T. Isaacs-Smith, S. T. Pantelides, J. R. Williams, and L. C. Feldman, "Nitrogen and Hydrogen Induced Trap Passivation at the SiO2/4H-SiC Interface," *Materials Science Forums*, Vols. 527-529 (2006) pp. 949-954.

- [41] J. Rozen, S. Dhar, M. E. Zvanut, J. R. Williams, and L. C. Feldman, "Density of interface states, electron traps, and hole traps as a function of the nitrogen density in SiO<sub>2</sub> on SiC," *Jour. Appl. Phys.*, Vol. 105 (2009) pp. 124506-124506-11.

- [42] D. Okamoto, H. Yano, K. Hirata, T. Hatayama, and T. Fuyuki, "Improved inversion channel mobility in 4H-SiC MOSFETs on Si face utilizing phosphorus-doped gate oxide," *IEEE Electron. Dev. Lett.*, Vol. 31, No. 7 (2010) pp. 710-712.

- [43] Y. K. Sharma, A. C. Ahyi, T. Isaacs-Smith, X. Shen, S. T. Pantelides, X. Zhu, L. C. Feldman, J. Rozen, and J. R. Williams, "Phosphorus passivation of the SiO<sub>2</sub>/4H-SiC interface," *Solid-State Electronics*, Vol. 68 (2012) pp. 103-107.

- [44] Y. K. Sharma, A. C. Ahyi, T. Isaacs-Smith, A. Modic, M. Park, Y. Xu, E. L. Garfunkel, S. Dhar, L. C. Feldman, and J. R. Williams, "High-mobility stable 4H-SiC MOSFETs using a thin PSG interfacial passivation layer," *IEEE Electron Device Lett.* Vol. 34, No. 2 (2013) pp. 175-177.

- [45] E. H. Snow and B. E. Deal, "Polarization phenomena and other properties of phosphosilicate glass films on silicon," *J. Electrochem. Soc.*, Vol. 113, No. 3 (1966) pp. 263-269.

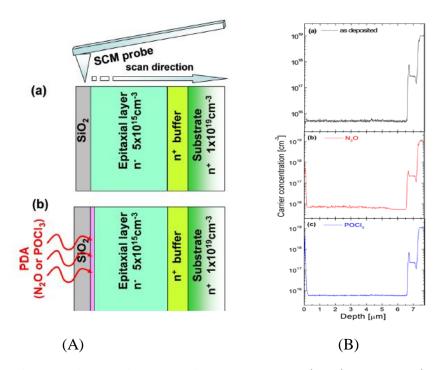

- [46] G. Liu, A. C. Ahyi, Y. Xu, T. Isaacs-Smith, Y. K. Sharma, J. R. Williams, L. C. Feldman, and S. Dhar, "Enhanced Inversion Mobility on 4H-SiC (1120) Using Phosphorus and Nitrogen Interface Passivation," *IEEE Electron Device Lett.*, Vol. 34, No. 2 (2013) pp. 181–183.

- [47] P. Fiorenza, F. Giannazzo, M. Vivona, A. La Magna, F. Roccaforte, "SiO<sub>2</sub>/4H-SiC interface doping during post-deposition-annealing of the oxide in N<sub>2</sub>O or POCl<sub>3</sub>," *Appl. Phys. Lett.* Vol. 103 (2013) pp. 153508-143508-3.

#### Chapter 2. MOS systems physics and characterization

The metal-oxide-semiconductor (MOS) system is directly related to most silicon planar devices and integrated circuits [1]. Thus, this chapter introduces the metal-oxide-semiconductor capacitor (MOS capacitor) and the four distinct regimes defined by the relationship between the semiconductor surface potential ( $\Psi_s$ ) and the semiconductor space-charge density ( $Q_s$ ) at the oxide-semiconductor interface. The role of interface traps for MOS capacitors is explained, and the simultaneous high-low capacitance-voltage (hi-lo C-V) technique for measuring the number and density of interface traps is described.

Lateral metal-oxide-semiconductor field-effect transistors (lateral MOSFETs) are introduced because these MOSFETs were used in experiments, described in Chapters 3 and 4, to understand and improve SiC MOSFET inversion channel mobility. Inversion channel mobility and the three scattering mechanisms that affect the inversion channel are discussed. All mobility measurements in this study were field-effect mobility measurements, and the concept of field-effect mobility is addressed. A basic introduction to universal mobility lays the foundation for one of the results discussed in Chapter 4. This study also examines counter-doping to improve lateral MOSFET field-effect mobility, and a discussion of p-n junction physics and counter-doping is included. A discussion of the vertical power MOSFET concludes this chapter.

## 2.1 MOS fundamentals

In an ideal metal-semiconductor system under equilibrium, the Fermi levels ( $E_{fs}$  for the semiconductor Fermi level and  $E_{fm}$  for the metal Fermi level) are equalized by electron transfer from the material with the higher Fermi level to the material with the lower Fermi level.

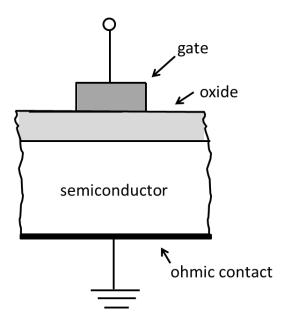

However, in the case of an ideal MOS capacitor (Figure 2-1), the oxide prevents the transfer of charge. The accumulation of electrons and holes at the metal-oxide and oxide-semiconductor interfaces creates a surface potential ( $\Psi_s$ ) at these interfaces. These surface potentials create a potential gradient across the oxide.

Figure 2-1 Simple diagram of a MOS capacitor.

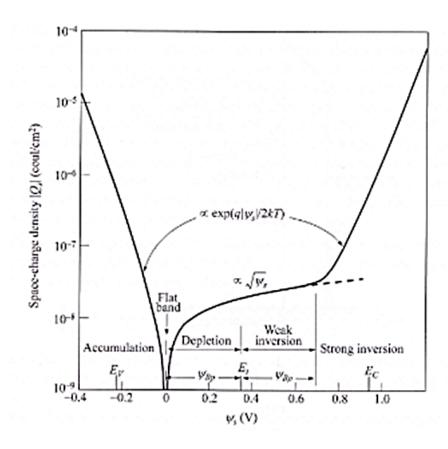

The surface potential at the oxide-semiconductor interface determines the regime of the semiconductor. Changing the surface potential (normally by applying a voltage on the metal (gate voltage)) allows the semiconductor to move to different regimes. To explain the effect of a changing surface potential (a result of changing gate voltage) of the MOS capacitor, p-type silicon with an aluminum gate is considered (Figure 2-2). For negative  $\Psi_s$ , the space-charge density ( $Q_s$ ) is positive, while positive  $\Psi_s$  corresponds to a negative  $Q_s$ . The space-charge density is the density and type of charge (positive or negative) at distances across a MOS system. Based upon the functions describing the rate of change between  $\Psi_s$  and  $Q_s$  (Figure 2-2), the MOS

system has four distinct surface potential regimes: (1) Hole accumulation (2) Flat-band (3)

Depletion (4) Inversion. The discussion below is restricted to n-channel MOSFETs with a p-type body, but the same discussion can be extended to p-channel devices [2].

**Figure 2-2.** Space-charge density  $(Q_s)$  variation in a semiconductor compared to surface potential  $(\Psi_s)$  for p-type silicon at room temperature [1]. (Permission received from John Wiley & Sons, Inc., S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*,  $3^{rd}$  edition, © 2007)

#### 2.1.1 Hole accumulation

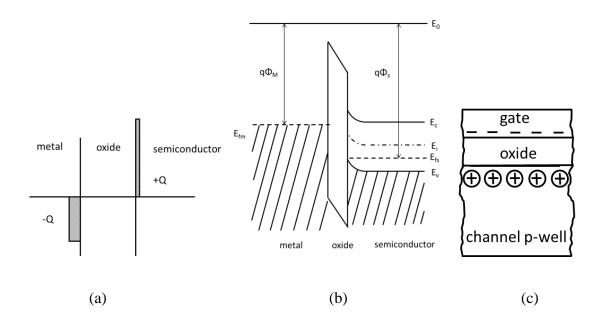

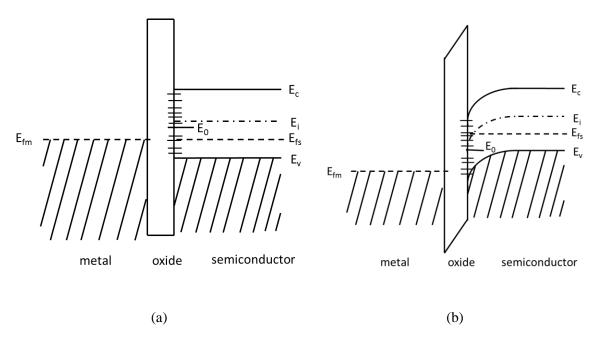

When a large negative bias is applied to the gate, electrons (-Q) collect at the metal-oxide interface and holes (+Q) collect at the oxide-semiconductor interface (Figure 2-3(a)). The electron build up at the metal-oxide interface raises the metal Fermi level closer to the vacuum energy level ( $E_0$ ) which is the energy required for an electron to be free from a material (Figure

2-3(b)). Since the oxide prevents current from flowing in the semiconductor, the semiconductor Fermi level does not change at deep distances in the semiconductor. However, near the oxide-semiconductor interface, the semiconductor energy bands bend upward because the Fermi level must be continuous across the entire MOS system. The energy levels of the oxide are also bent due to the electric field in the oxide so that the oxide Fermi level connects the metal Fermi level and the semiconductor Fermi level.

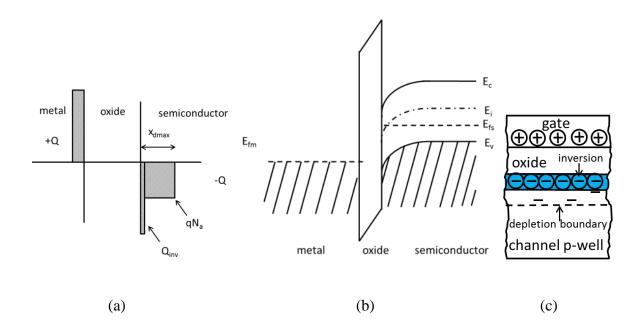

**Figure 2-3**. Space-charge diagram (a), band diagram (b), and device diagram (c) for a MOS system in accumulation.

The buildup of negative charge at the metal-oxide surface increases the hole density at the surface until the hole density is greater than the acceptor density (Figure 2-3(c)). This condition is called accumulation. As the gate voltage decreases further into accumulation, the surface hole space-charge density increases exponentially as shown in Fig. 2-2.

# 2.1.2 Flat-band condition

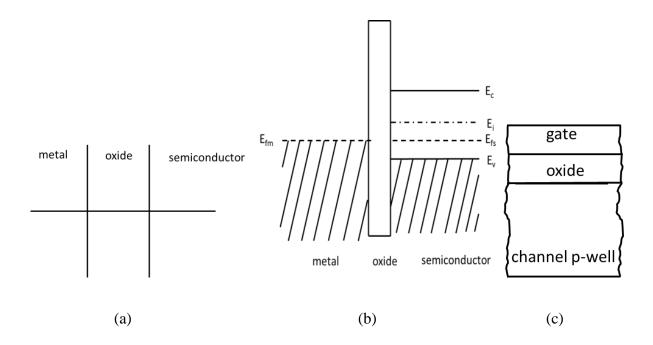

From deep accumulation, as the gate voltage is made less negative, the charges that have accumulated on both sides of the oxide decrease until none remain (Figure 2-4(a)). The point at which there are no accumulated charges on either side of the oxide is important because at this point the metal Fermi level equals the semiconductor Fermi level, and consequently the oxide and semiconductor bands are flat (Figure 2-4(b)).

**Figure 2-4**. Space-charge diagram (a), band diagram (b), and device diagram (c) for a MOS system in flat-band.

For an ideal MOS system, the voltage necessary to reach the point where all of the bands are flat is known as the flat band voltage and defined as

$$V_{FB}^0 = \Phi_M - \Phi_S = \Phi_{MS} \tag{2.1}$$

where  $V_{FB}^0$  is the flat band voltage,  $\Phi_{\rm M}$  is the metal work function, and  $\Phi_{\rm S}$  is the semiconductor work function. The work function is the minimum amount of energy required to remove an electron from a material.

The flat band voltage is an important characterization for two reasons: (1) it influences the threshold voltage for a MOSFET, as discussed later; (2) the difference between the ideal and the experimental flat-band voltages is a measure of defects and trap-related fixed charges located in the oxide as well as near the oxide-semiconductor interface [1]. The experimental flat-band voltage is typically extracted from capacitance-voltage (C-V) measurements by determining the gate voltage at which the device capacitance is equal to flat-band capacitance ( $C_{FB}$ ).

# 2.1.3 Depletion

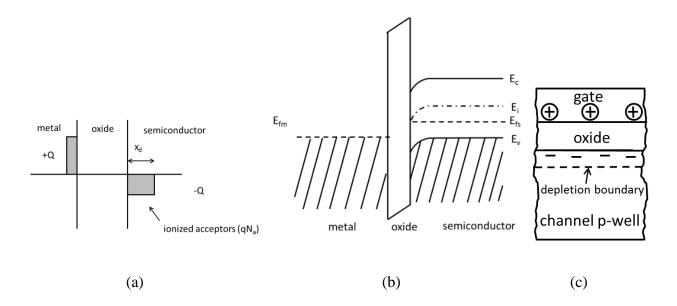

As the gate voltage increases past the flat band voltage, positive charge builds up at the metal-oxide interface. This positive charge causes holes to move away from the oxide-semiconductor interface, leaving behind the negative-charged acceptor core ions (Figure 2-5(a)).

The positive charge at the metal-oxide interface increases the metal work function, which lowers the metal Fermi level below the semiconductor Fermi level (Figure 2-5(b)). The difference between the metal Fermi level and the semiconductor Fermi level causes the semiconductor bands to bend near the oxide-semiconductor interface, and the electric field in the oxide causes the oxide bands to bend, similar to what occurs in the accumulation regime. However, because the electric field and charge build up are opposite to what occurs in the accumulation regime, the bands bend in the opposite direction.

Since the space-charge potential must be equal on both sides of the oxide, the negative charge in the semiconductor is manifested by the depletion of holes (the majority carrier in ptype semiconductors) at the surface region and the negative-charged acceptor core ions which are left behind (Figure 2-5(c)). As higher gate voltage is applied, the depletion region expands, and the negative space charge continues to increase ( $x_d$  Figure 2-5(a)).

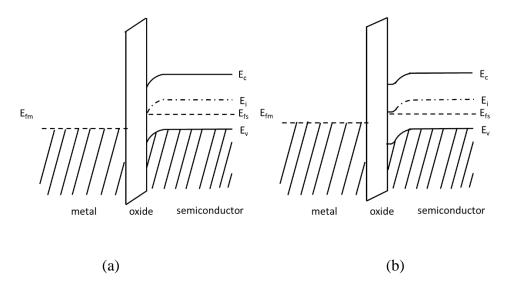

**Figure 2-5**. Space-charge diagram (a), band diagram (b), and device diagram (c) for a MOS system in depletion.

#### 2.1.4 Inversion

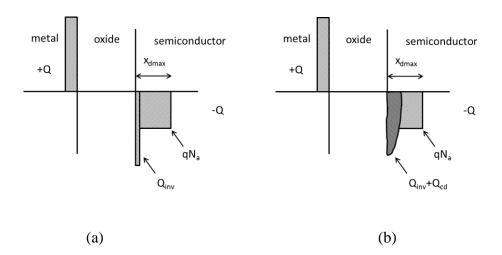

As the gate voltage increases, the depletion region continues to expand until the maximum depletion width is reached ( $x_{dmax}$  Figure 2-6(a)). The maximum depletion width is such that the generation of electrons exceeds recombination at the surface, causing the formation of a minority-carrier (electrons in this case) conducting channel, commonly known as the inversion channel ( $Q_{inv}$  Figure 2-6(a)). Under this condition, the intrinsic Fermi level ( $E_i$ ) crosses

the semiconductor Fermi level ( $E_{fs}$ ), bringing the conduction band edge ( $E_c$ ) closer to the Fermi level than to the valance band edge ( $E_v$ ) (Figure 2-6(b)).

This condition is called inversion because the surface has more electrons than holes (Figure 2-6(c)), even though the semiconductor was doped with p-type acceptor dopants. These negative charges "invert" the p-type material at the surface. Because the minority carriers will continue to increase exponentially as the gate voltage increases (Figure 2-2), the depletion width will no longer increase.

**Figure 2-6**. Space-charge diagram (a), band diagram (b), and device diagram (c) for a MOS system in inversion.

# 2.2 Practical MOS capacitor

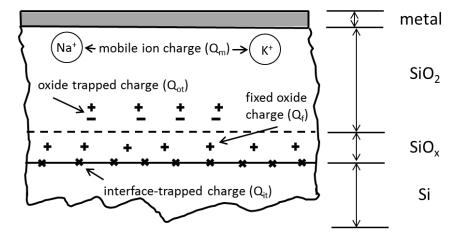

Thermal oxidation of silicon does not leave a clear-cut separation between the silicon crystal and the oxide. The chemical composition of thermally oxidized silicon consists of the

silicon crystal, a monolayer of  $SiO_x$  (incompletely oxidized silicon), a thin strained region of  $SiO_2$  (due to imperfect lattice matching between  $SiO_2$  and silicon), and strain-free amorphous  $SiO_2$  [1] (Figure 2-7). The non-ideal layer of  $SiO_x$  and the strained  $SiO_2$  at the oxide-semiconductor interface, along with other non-ideal conditions (i.e. real-world conditions) give rise to oxide charges and interface traps that affect the MOS system. The flat band voltage ( $V_{FB}$ ) of a non-ideal metal-oxide-semiconductor capacitor (MOS capacitor) is derived from

$$V_{FB} = \Phi_{MS} - \frac{Q_i}{C_{ox}} - \frac{1}{\varepsilon_{ox}} \int_0^{t_{ox}} \rho_{ox}(x) dx$$

(2.2)

where  $\Phi_{MS}$  is the metal-semiconductor work function,  $Q_i$  is the interface charge,  $C_{ox}$  is the oxide capacitance,  $\epsilon_{ox}$  is the oxide dielectric constant, and  $\rho_{ox}$  is the oxide charge density.

**Figure 2-7.** Types of charges derived from thermally oxidized silicon [1].

Figure 2-7 shows the basic classifications of interface traps and oxide charges [1]: interface-trap charges  $(Q_{it})$ ; mobile ion charges  $(Q_m)$ ; fixed oxide charges  $(Q_f)$ ; and oxide trapped charges  $(Q_{ot})$ .

# 2.2.1 Interface traps

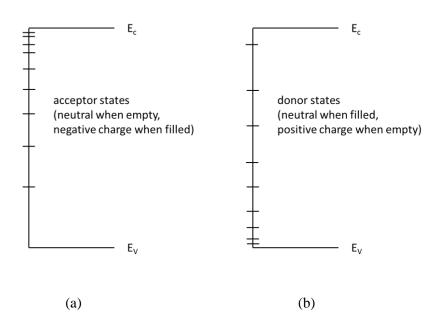

Interface traps ( $Q_{it}$ ) are located at the oxide-semiconductor interface and have energy states that exist within the forbidden band gap of the semiconductor [1]. In silicon MOS systems, these traps can be produced by excess silicon or oxygen, dangling silicon bonds, or impurities [1]. Interruption of the lattice structure at the interface allows these traps to exist within the band gap [1]. The presence of these traps at the  $Si/SiO_2$  interface can be as high as  $10^{15}$  atoms cm<sup>-2</sup> (though hydrogen annealing reduces the density of interface traps to  $10^{10}$  atoms cm<sup>-2</sup>) [1]. Interface traps can be either acceptors (Figure 2-8 (a)) or donors (Figure 2-8 (b)).

Figure 2-8. Energy diagram of acceptor interface traps (a) and donor interface traps (b).

The occupancy of these traps follows the Fermi-Dirac distribution function, so the probability of donor states being occupied is [1]

$$F_{SD}(E_t) = \frac{1}{1 + \frac{1}{g_D} \exp[(E_F - E_t)/(kT)]}$$

(2.3)

and the probability of acceptor states being occupied is

$$F_{SA}(E_t) = \frac{1}{1 + \frac{1}{g_A} exp[(E_t - E_F)/(kT)]}$$

(2.4)

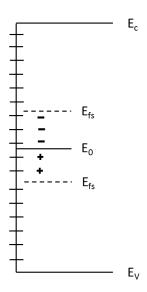

where  $E_t$  is the interface trap energy,  $E_F$  is the Fermi level energy, and the degeneracy of the ground-state is represented by  $g_D$  which equals 2 for the donor traps and  $g_A$  which equals 4 for acceptor traps [1]. A convenient interpretation of the interface traps is to sum all of the traps into an equivalent density of interface traps  $(D_{it})$  and determine the energy level at which the total charge contribution is zero  $(E_0)$  (Figure 2-9) [1]. Above  $E_0$ , the interface trap states are acceptor types, and below  $E_0$ , the interface trap states are donor types. The interface traps are also assumed to be filled if the trap energy state is below the semiconductor Fermi level, and empty if the trap energy state is above the semiconductor Fermi level [1]. Therefore, if the semiconductor Fermi level is above  $E_0$ , the interface traps will contribute a net negative charge, while if the semiconductor Fermi level is below  $E_0$ , the interface traps will contribute a net positive charge.

Figure 2-9. Energy diagram of an interface-trap system consisting of both acceptor and donor traps.

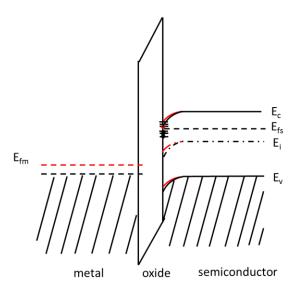

Referring back to Chapter 2.1.1-2.1.4, an applied gate voltage causes the semiconductor energy bands to raise or lower (band bending) near the oxide-semiconductor interface. The applied gate voltage also raises or lowers the trap energy level along with the semiconductor energy bands. Thus, as the applied gate voltage is changed, the number of interface traps below/above the semiconductor Fermi level also change. Applying the interface-trap system in Figure 2-9 to a MOS system, at the flat-band regime, the semiconductor Fermi level is below E<sub>0</sub>, so the net charge of the interface traps is positive (Figure 2-10(a)). However, once the semiconductor is brought into the inversion regime, the semiconductor energy bands and the interface trap energies have lowered. In this regime, the semiconductor Fermi level is above some of the acceptor traps, so the interface traps contribute a net negative charge (Figure 2-10(b)).

Figure 2-10. Interface traps in a MOS system at the flat-band regime (a) and in the inversion regime (b).

Interface-trap energy levels are distributed across the entire semiconductor band gap.

Therefore, using the assumptions made in the interface-trap system seen in Figure 2-9, the density of the interface traps can be characterized by [1]

$$D_{it} = \frac{1}{q} \frac{dQ_{it}}{dE} \tag{2.5}$$

Equation 2.5 is the concept used to experimentally determine D<sub>it</sub> in MOS systems (Chapter 2.3).

# 2.2.2 Mobile ions

Mobile ions  $(Q_m)$  are usually metallic ions, such as sodium or potassium, that enter the oxide during oxidation or later during MOS system fabrication since practical MOS processing

cannot be perfectly clean. At room temperature, these ions are fixed, but at biased, high-temperature conditions, these ions become mobile. Mobile ions cause stability issues with MOS systems. Under negative-biased high-temperature conditions, mobile ions migrate to the metal-oxide interface of the MOS system. This concentration of ions at the metal-oxide interface increases the flat-band voltage [3]. However, if the MOS system is switched to a positive-bias at high temperatures, these ions will flow into the oxide and congregate near the oxide-semiconductor interface. These positive charges in the oxide reduce the flat-band voltage [3]. In other words, mobile ions can cause a MOS system operating under bias at high temperatures to have different flat-band voltages depending on the direction of a gate voltage sweep, creating instability in the MOS system.

# 2.2.3 Oxide trapped charges and fixed oxide charges

Oxide trapped charges ( $Q_{ot}$ ) are dispersed throughout the oxide. Their creation is associated with several different methods, such as X-ray radiation or hot-electron injection [1]. Fixed oxide charges ( $Q_f$ ) are located near the oxide-semiconductor interface. Unlike mobile ions, fixed oxide charges are immobile under applied electric fields. There has been much investigation into the creation of these charges, with one of the more recent proposals suggesting that the value of  $Q_f$  is determined by the number of interstitial silicon atoms near the oxide-silicon interface [4]. These interstitials are formed during the processes of silicon interstitial generation and recombination at the oxide-silicon interface [4].

## 2.3 High-low capacitance-voltage characterization

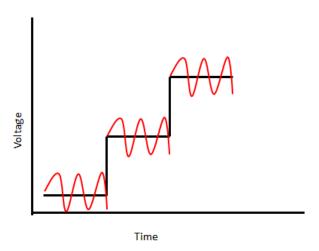

High-low capacitance-voltage characterization (hi-lo C-V) is a technique that obtains data by measuring the capacitance from a small amplitude high-frequency and low-frequency AC input centered around the DC steady state voltage applied to the gate in MOS devices (Figure 2-11). This technique is used to determine several characterization factors. One of the most important characterizations is the density of electron traps near the oxide-semiconductor interface. The density of these interface traps (D<sub>it</sub>) is important in semiconductor processing, since a greater density of interface traps means there is more Coulomb scattering and reduced reliability. While there are several other methods to calculate the D<sub>it</sub> of MOS devices, each with their own strengths and limitations, this section will focus solely on the simultaneous hi-lo C-V characterization method used in the experiments described in Chapters 3 and 4.

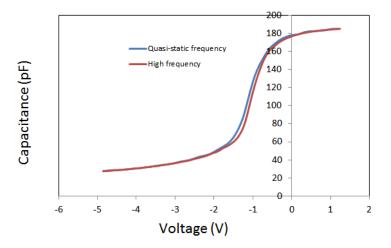

**Figure 2-11**. Diagram of a hi-lo C-V measurement. The black line represents the DC voltage; the red lines are the AC bias.

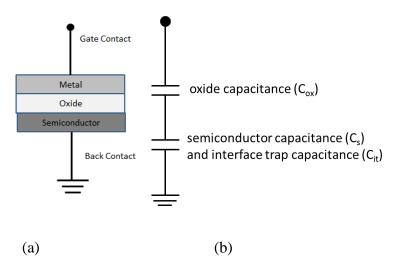

The total capacitance of a MOS device is

$$\frac{1}{C_{tot}} = \frac{1}{C_{ox}} + \frac{1}{C_{it} + C_s} \tag{2.6}$$

where  $C_{tot}$  is the total capacitance,  $C_{ox}$  is the oxide capacitance,  $C_{it}$  is the interface trap capacitance, and  $C_s$  is the semiconductor capacitance [5].  $C_{ox}$  and  $C_s$  are capacitors in series (Figure 2-12).

**Figure 2-12.** Simplified MOS device diagram (a) and circuit diagram (b). The oxide and semiconductor are capacitors in series.

Capacitance can be defined as the ratio of change in charge to the change in potential:

$$C \equiv \frac{\Delta Q}{\Delta V} \tag{2.7}$$

When  $C_{ox}$  and  $C_{s}$  are known, the  $C_{it}$  can be calculated from a measured  $C_{tot}$ . In taking hi-lo C-V measurements, the high frequency must be high enough to prevent electron traps from responding to the AC frequency, and the low frequency must be low enough for all traps to respond to the AC frequency. The total capacitance for the high frequency can be written as

$$\frac{1}{C_{tot}^{HF}} = \frac{1}{C_{ox}} + \frac{1}{C_s} \tag{2.8}$$

and the total capacitance for the low frequency can be written as

$$\frac{1}{C_{tot}^{QS}} = \frac{1}{C_{ox}} + \frac{1}{C_{it} + C_s} \tag{2.9}$$

Also, in Equation 2.7, if  $\Delta Q$  is replaced with  $D_{it}$ , then the  $C_{it}$  can be written as

$$C_{it} = q D_{it} (2.10)$$

since the capacitance associated with the interface traps is the electron charge multiplied by the density of the traps. The hi-lo C-V method usually starts in accumulation and then sweeps the voltage downward toward depletion. In accumulation, all of the electron traps are filled, since the conduction band edge is below the Fermi level. As the DC voltage slowly decreases, the metal Fermi level increases, which begins to bend the semiconductor bands upward. The AC voltage oscillates around each stopping point of the DC voltage (Figure 2-13). The high frequency is too rapid for electrons to respond by moving into and out of the traps with the change in voltage. However, the electrons do respond to the low frequency and move into and out of the traps as the

AC voltage oscillates. The difference between the electron being in the trap and out of the trap creates a difference in the charge Q, so the capacitance is larger for the low frequency than for the high frequency. This extra capacitance from the electron in the trap is the  $C_{it}$ . Since the  $C_{it}$  is based only around one specific energy level, as determined by the DC voltage, a  $D_{it}$  can be extracted from the  $C_{it}$ .

**Figure 2-13.** Band diagram of hi-lo C-V method. The black lines represent the steady state DC current. The red lines represent a small gate voltage change from the AC current. The red dot represents a filled trap in the DC voltage, but emptied from the low frequency AC voltage. The change from the trap being filled to empty contributes to the  $C_{it}$ .

Solving Equation 2.9 for D<sub>it</sub> yields

$$D_{it} = \frac{C_{ox}}{q} \left( \frac{C_{tot}^{QS}}{C_{ox} - C_{tot}^{QS}} \right) - \frac{C_s}{q}$$

(2.11)

Using Equation 2.8 to solve for C<sub>s</sub>:

$$C_s = \frac{C_{ox}C_{tot}^{HF}}{C_{ox} - C_{tot}^{HF}} \tag{2.12}$$

Substituting the equation for C<sub>s</sub> into Equation 2.11 results in the standard D<sub>it</sub> equation [5-8]:

$$D_{it} = \frac{C_{ox}}{q} \left( \frac{C_{tot}^{QS}}{C_{ox} - C_{tot}^{QS}} - \frac{C_{tot}^{HF}}{C_{ox} - C_{tot}^{HF}} \right)$$

(2.13)

This equation is only valid if none of the electron traps respond to the high frequency during measurement. If electron traps respond to the high frequency, then the semiconductor capacitance in Equation 2.8 becomes larger. This increase in the semiconductor capacitance increases the total high frequency capacitance. If the total high frequency capacitance increases, then the difference between the quasi-static total capacitance and the high frequency total capacitance is reduced. This underestimates the  $D_{it}$  value obtained from Equation 2.13.

#### 2.3.1 Oxide thickness

Hi-lo C-V offers a nondestructive way to measure the oxide thickness. The oxide thickness is calculated from the equation

$$t_{ox} = \frac{A\varepsilon_{ox}}{C_{ox}} \tag{2.14}$$

where  $t_{ox}$  is the oxide thickness, A is the area of the device,  $\varepsilon_{ox}$  is the oxide dielectric constant, and  $C_{ox}$  is the oxide capacitance. The oxide capacitance is extracted from the total capacitance

from the high frequency measurement (Equation 2.8). When the device is in strong accumulation, the contribution from the semiconductor capacitance is negligible. Therefore, a close approximation to the oxide thickness can be obtained as oxide capacitance is equal to total capacitance [6].

#### 2.4 Lateral MOSFETs

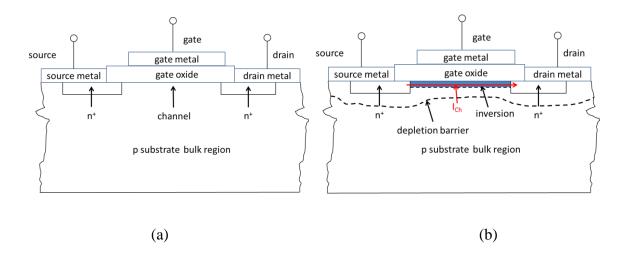

Lateral MOSFETs (Figure 2-14) are MOSFETs with long channels and are commonly used for audio amplification [9]. These MOSFETs are lightly doped (~5x10<sup>15</sup> cm<sup>-3</sup>) p-substrate SiC with highly n-doped (1x10<sup>20</sup> cm<sup>-3</sup>) regions for the source and drain. When the applied gate voltage is below the threshold voltage (Figure 2-14(a)), little leakage current occurs and the device is considered to be "off." The n-p-n junction between the source and drain blocks current as long as the gate voltage is below threshold. When the gate voltage is below threshold and a large positive voltage is applied to the source, a depletion region forms at the n-p junction as the electrons in the n-type region flow toward the source, and the holes in the p-type region flow away from the source. If a large negative voltage is applied to the source, a depletion region forms at the p-n junction. The threshold voltage (V<sub>TH</sub>) is when the MOSFET turns on (inversion). Once the threshold voltage is reached, inversion occurs in the channel and current flows (Figure 2-14(b)).

**Figure 2-14**. Lateral MOSFET diagram in off mode (a). Channel forms under gate oxide during inversion (b).

### 2.5 Inversion channel mobility

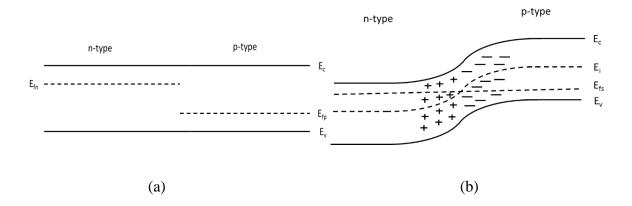

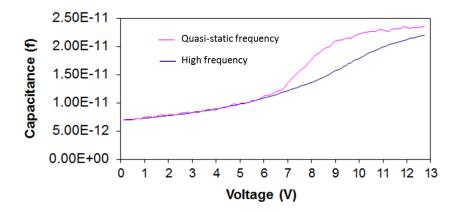

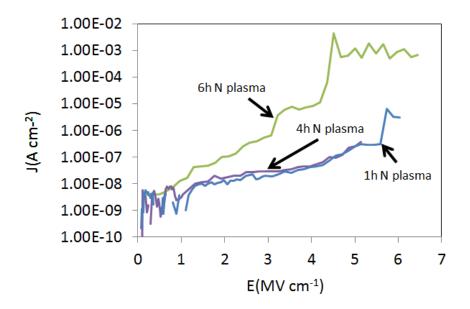

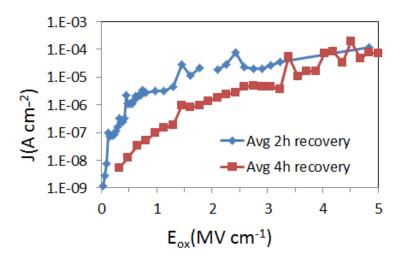

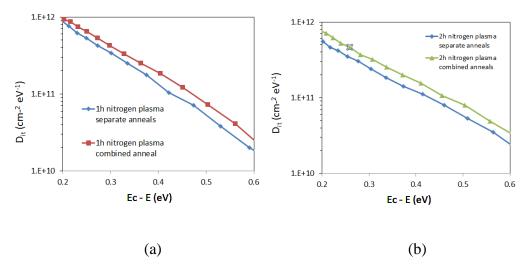

For n-MOSFETs, the inversion channel mobility is the mobility measured through the channel region after inversion has occurred. High mobility devices are efficient because during operation fewer electrons are scattered which reduces power dissipation.