# **Design and Implementation of Digital Current Mode Control**

by

Siyu He

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama May 10, 2015

Key words: Current mode control, Digital implementation, Switch-mode power supplies Analog Control, Small-signal modeling

Copyright 2015 by Siyu He

Approved by

Robert Mark Nelms, Chair, Professor of Electrical Engineering

John York Hung, Professor of Electrical Engineering

Steve Mark Halpin, Alabama Power Company Distinguished Professor Electrical Engineering

Victor Peter Nelson, Professor of Electrical Engineering

#### **Abstract**

Presented in this dissertation are three digital control methods of current mode control for switch-mode power supplies. Both the current and voltage loop are implemented on the digital processor. Digital versions of peak current mode control (predictive current mode control), average current mode control and I<sup>2</sup> average current mode control are proposed and investigated in sequence. Issues of noise filtering, high frequency analog-to-digital (ADC) sampling and digital PWM modulations are discussed.

Since the peak current mode control (PCM) finds wide application in low-to-medium power DC-DC converters, the digital predictive current mode control is first presented in this dissertation which is the equivalent digital version of PCM. The control law is derived based on the steady state operation of analog PCM control, which only needs one sample per cycle to estimate the current peak signal. The small-signal model is developed and verified by measurements from an AP300 network analyzer. Because of the common configuration for the digital current mode control methods, the small-signal model developed for predictive current mode control can be used as a basis for other digital current mode control.

Then, three digital implementations of average current mode control are discussed which are the basis for the digital I<sup>2</sup> average current mode control in the later chapter. The advantages and disadvantages of each implementation are compared. The modification of the small-signal model for predictive current mode control is developed to predict the frequency response of digital average current mode control.

I<sup>2</sup> average current mode control was proposed in 2013, a small-signal modeling for an analog implemented I<sup>2</sup> average current mode is presented. This small-signal model successfully predicts the "sub-harmonic" oscillation when the duty cycle is close, or greater than 0.5. By paralleling the current loops of peak current mode and average current mode, the digital I<sup>2</sup> average current mode control is designed using predictive current mode control and digital average current mode control.

A TMS320F2812 DSP controlled boost converter is built to serve as a prototype to experimentally demonstrate the feasibility of these digital current mode control technique.

# Acknowledgments

I would like to thank my advisor, Dr. R. Mark Nelms for his patient guidance. The most precious thing I learned from him is the attitude toward research, open to different opinions and always prepared for the future. Without his guidance, this dissertation would not have been possible.

I also appreciate my committee members: Dr. John Y. Hung, Dr. S. Mark Halpin and Dr. Victor P. Nelson for their help and valuable suggestions.

I am very grateful to my parents, Gujia He and Yuanhua Cao, who have been encouraging and supporting me to pursue my goal.

# TABLE OF CONTENTS

| Abstract         |                                                 | ii   |

|------------------|-------------------------------------------------|------|

| Acknowledgem     | ients                                           | iv   |

| List of Figures. |                                                 | ix   |

| List of Tables   |                                                 | xiii |

| CHAPTER 1.       | Introduction                                    | 1    |

| 1-1.             | Basic Concept of Current-Mode Control           | 1    |

| 1-2.             | Digital control power converters                | 4    |

| 1-3.             | Organization of the Dissertation                | 7    |

| CHAPTER 2.       | Predictive current mode control                 | 8    |

| 2-1.             | Introduction to Predictive Current Mode Control | 8    |

| 2-2.             | Development of the predictive control method    | 10   |

| 2-3.             | Stability Analysis                              | 13   |

| 2-4.             | Extension to other converters                   | 15   |

| 2-5.             | Simulation and Experimental Results             | 16   |

| 2-6.             | Experimental Results                            | 19   |

| 2-7.    | Conclusion                                                  | 26 |

|---------|-------------------------------------------------------------|----|

| CHAPTER | 3. Modeling of Predictive Control                           | 27 |

| 3-1.    | Introduction                                                | 27 |

| 3-2.    | Review of small-signal model of analog current mode control | 28 |

| 3-3.    | Proposed Small-Signal Model                                 | 30 |

| 3-3-1   | Modulator gain                                              | 30 |

| 3-3-2   | Effect of digital controller                                | 32 |

| 3-4.    | Small-signal characteristics                                | 33 |

| 3-5.    | Experimental Verification                                   | 35 |

| 3-6.    | Conclusion                                                  | 39 |

| CHAPTER | 4. Digital Average Current Mode Control                     | 41 |

| 4-1.    | Introduction                                                | 41 |

| 4-2.    | Digital Average Current Designs and Performance             | 42 |

| 4-2-1.  | Geometric Design                                            | 43 |

| 4-2-2.  | Low-pass Filter Design                                      | 45 |

| 4-2-3.  | Slope Midpoint Design                                       | 47 |

| 4-3.    | Compensator Design                                          | 50 |

| 4-4.    | Experimental Results                                        | 52 |

| 4-5.    | Conclusion                                                  | 54 |

| СНАРТЕР | 5 I <sup>2</sup> average current mode control               | 62 |

| 5-1 | •      | Introduction                                           | 62 |

|-----|--------|--------------------------------------------------------|----|

| 5-2 | ·.     | I <sup>2</sup> Average Current Mode Control            | 64 |

| 5-3 |        | Small Signal Modeling                                  | 66 |

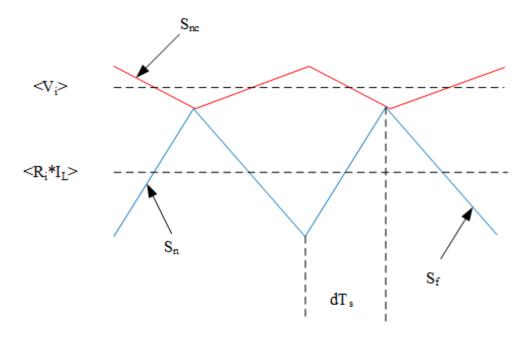

|     | 5-3-1. | Modulator Gain                                         | 68 |

|     | 5-3-2. | Sampling Gain                                          | 71 |

|     | 5-3-3. | Feedback and Feed-forward Gain                         | 72 |

| 5-4 | ·.     | Transfer Function Characteristics                      | 74 |

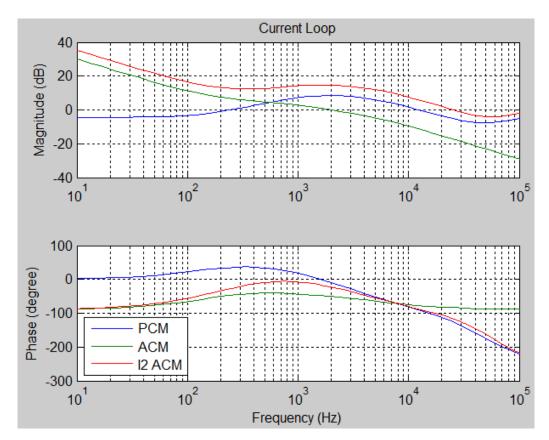

|     | 5-4-1. | Current Loop Gain                                      | 76 |

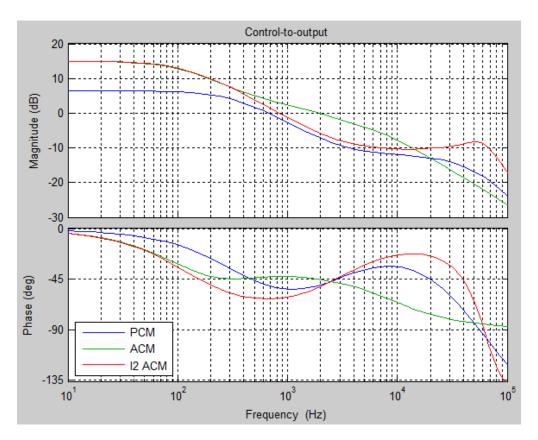

|     | 5-4-2. | Control-to-output Voltage                              | 77 |

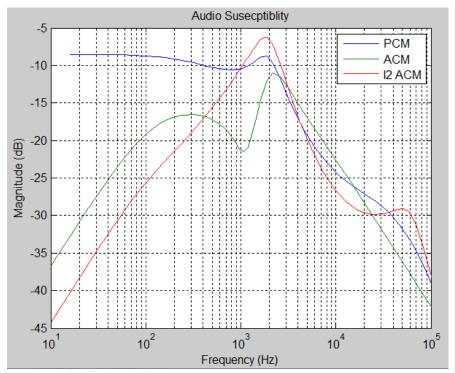

|     | 5-4-3. | Audio Susceptibility                                   | 77 |

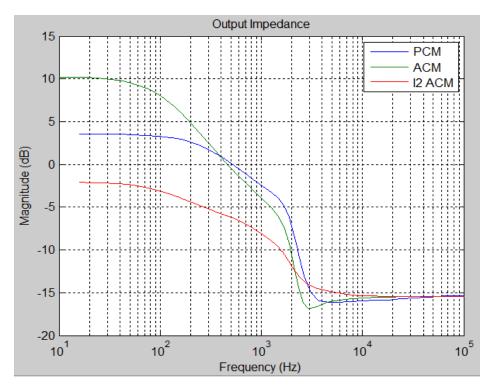

|     | 5-4-4. | Output Impedance                                       | 78 |

|     | 5-4-5. | Stability                                              | 79 |

| 5-5 |        | Simulation and Experimental Verification               | 81 |

|     | 5-5-1. | Simulation Results                                     | 81 |

|     | 5-5-2. | Experimental Results                                   | 85 |

| 5-6 | j.     | Conclusion                                             | 86 |

| СН  | IAPTER | 6. Digital I <sup>2</sup> average current mode control | 92 |

| 6-1 |        | Introduction                                           | 92 |

| 6-2 | ·.     | Digital I <sup>2</sup> Average Current Mode Control    | 94 |

|     | 6-2-1. | Current Loop Compensator                               | 95 |

| 6-2-   | 2. Modulator                                   | 96  |

|--------|------------------------------------------------|-----|

| 6-3.   | Small-Signal Model and Design Guideline        | 98  |

| 6-3-   | -1. Current Loop Compensator                   | 100 |

| 6-3-   | 2. Voltage Loop Compensator                    | 100 |

| 6-4.   | Simulation and Experimental Results            | 101 |

| 6-4-   | 1. Simulation Results                          | 101 |

| 6-4-   | -2. Experimental Results                       | 105 |

| 6-5.   | Small-Signal Model Verification                | 106 |

| 6-6.   | Conclusion                                     | 106 |

| CHAPT  | ER 7. Conclusions and Suggests for Future Work | 111 |

| BIBLIO | GRAPHY                                         | 116 |

# LIST OF FIGURES

| Figure 1.1 Concept of voltage mode control                                                     | 1             |

|------------------------------------------------------------------------------------------------|---------------|

| Figure 1.2 Concept of current mode control                                                     | 2             |

| Figure 1.3 Circuit diagram of peak current mode control                                        | 3             |

| Figure 1.4 Circuit diagram of average current mode control                                     | 4             |

| Figure 2.1 Diagram of peak current mode controlled boost converter                             | 8             |

| Figure 2.2 Diagram of a new predictive current control scheme                                  | 10            |

| Figure 2.3 Inductor current waveform of boost converter in CCM                                 | 11            |

| Figure 2.4 Perturbation in the n <sup>th</sup> cycle                                           | 13            |

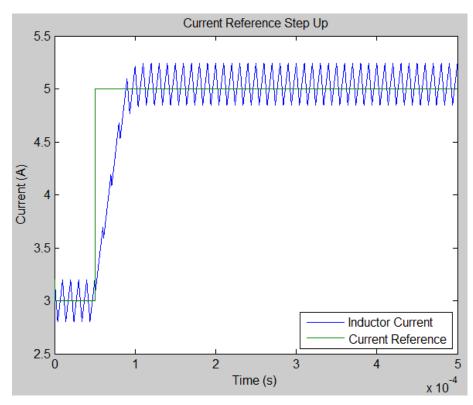

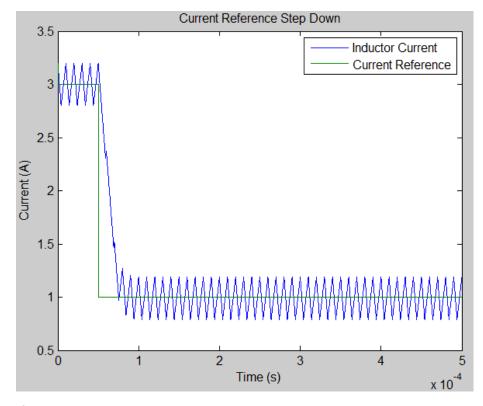

| Figure 2.5 Simulated transient response due to a step up in the current reference              | 17            |

| Figure 2.6 Simulated transient response due to a step down in the current reference            | 17            |

| Figure 2.7 Simulated current response for a change in inductance value with current commanup   | -             |

| Figure 2.8 Simulated current response for a change in inductance value with current commandown | nd step<br>18 |

| Figure 2.10 Inductor current response due to a current reference step down                     |               |

| Figure 2.11 Closed loop inductor current transient for a load step up                          | 23            |

| Figure 2.12 Closed loop inductor current transient for a load step down                        | 23            |

| Figure 2.13 Output transient response for a 11 V input voltage                                 | 24            |

| Figure 2.14 Output transient response for a 15 V input voltage                                 | 25            |

| Figure 2.15 Output transient response for a 14 V input voltage                                 | 25            |

| Figure 3.1 Small-signal model for current mode control                                     | . 29      |

|--------------------------------------------------------------------------------------------|-----------|

| Figure 3.2 Block diagram representation of equation (3-1)                                  | . 30      |

| Figure 3.3 Small-signal representation of equation (3-1)                                   | . 30      |

| Figure 3.4 Small-signal model of the sample and hold process in a digital controller       | . 32      |

| Figure 3.5 Small-signal model for predictive current mode control                          | . 33      |

| Figure 3.6 Voltage loop gain designed by the trial and error method                        | . 37      |

| Figure 3.7 Voltage loop gain of the technique proposed in [22]                             | 40        |

| Figure 3.8 Voltage loop gain of the technique described in Chapter 2                       | 40        |

| Figure 4.1 A boost converter showing potential current measurement point                   | 42        |

| Figure 4.2 Inductor current waveform in CCM and corresponding program execution scheme .   | 43        |

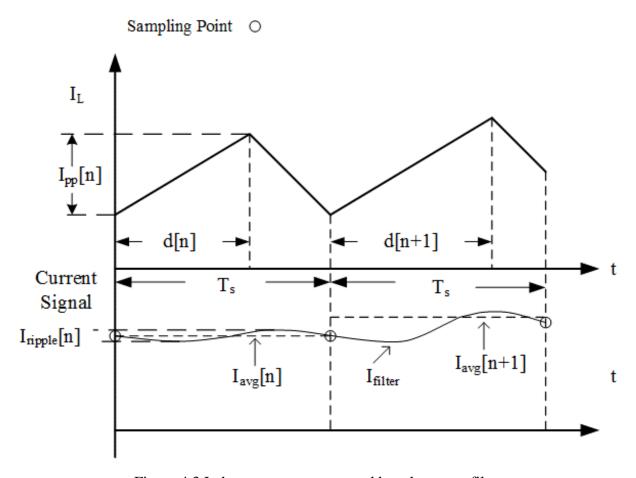

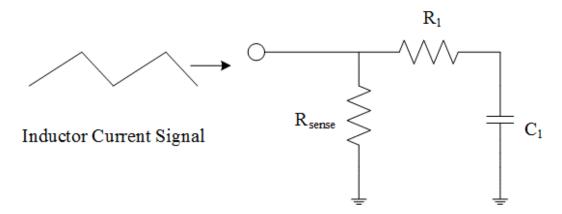

| Figure 4.3 Inductor current processed by a low-pass filter                                 | 45        |

| Figure 4.4 RC low-pass filter to extract the average current signal                        | 46        |

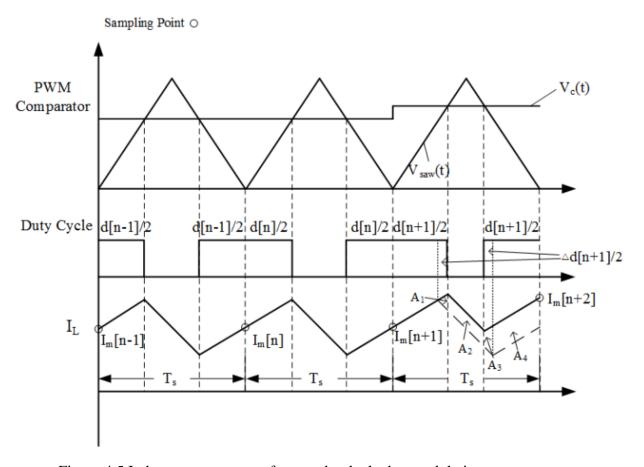

| Figure 4.5 Inductor current waveform under dual edge modulation                            | 48        |

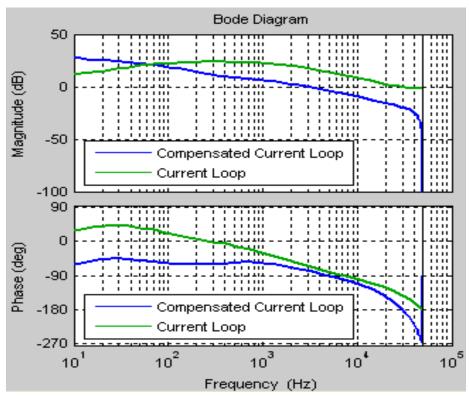

| Figure 4.6 Small-signal model for digital average current mode control                     | 50        |

| Figure 4.7 Frequency response of compensated and uncompensated current loop                | . 55      |

| Figure 4.8 Frequency response of compensated voltage loop and the proposed model           | . 55      |

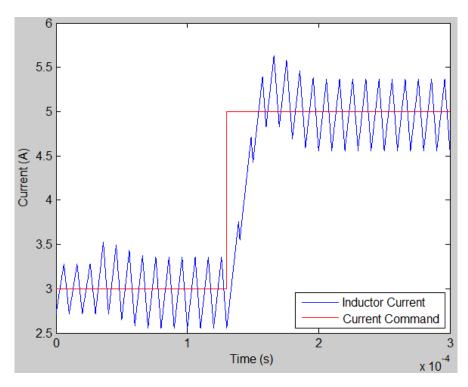

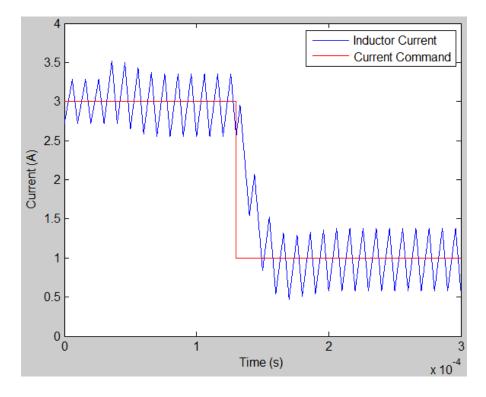

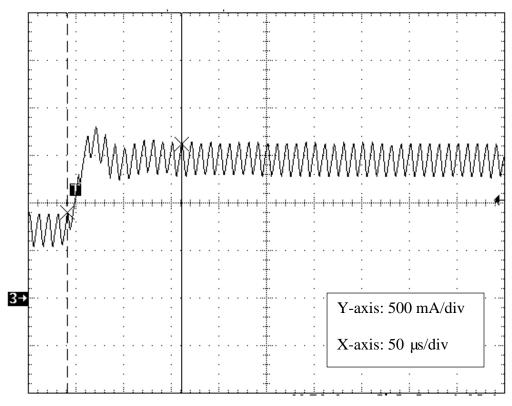

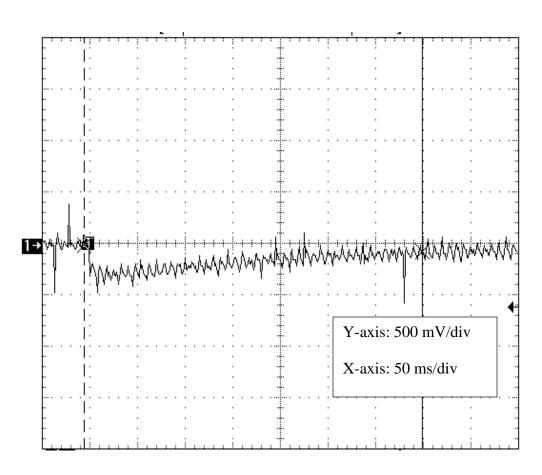

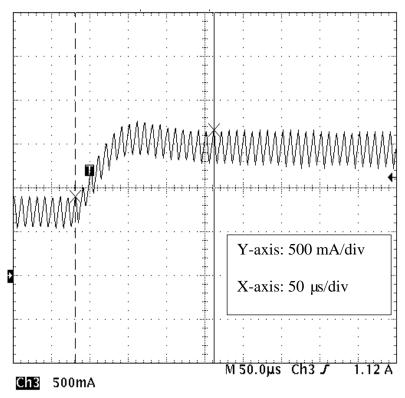

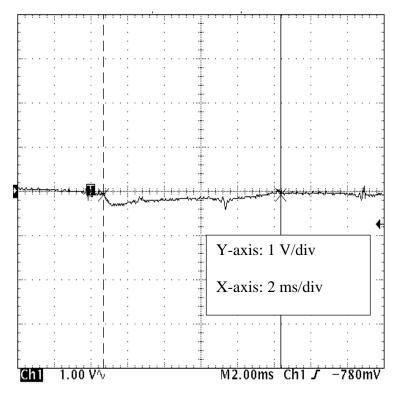

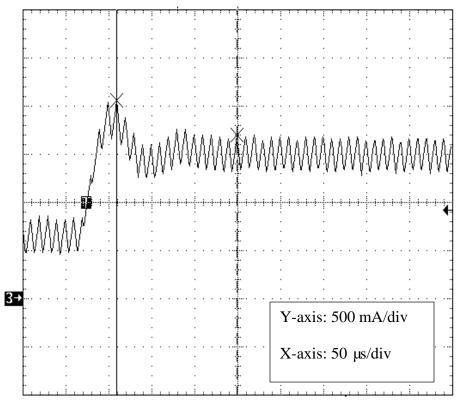

| Figure 4.9 Dynamic performance of the geometric design with current command step up        | . 56      |

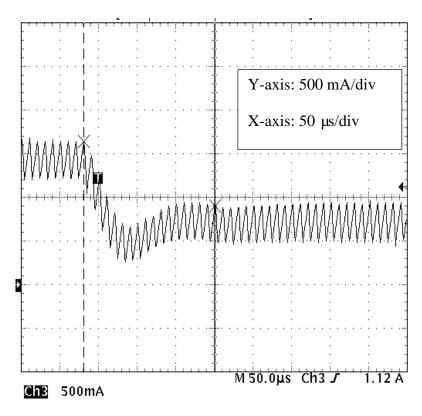

| Figure 4.10 Dynamic performance of the geometric design with current command step down     | 56        |

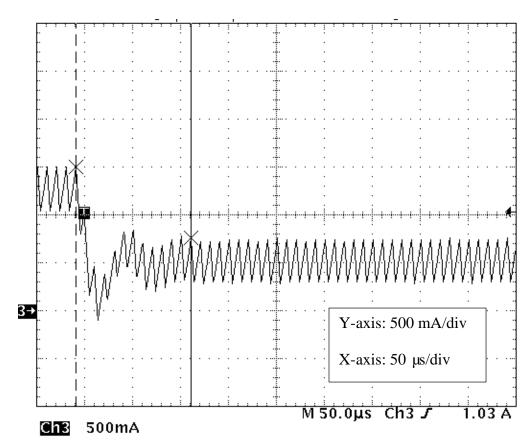

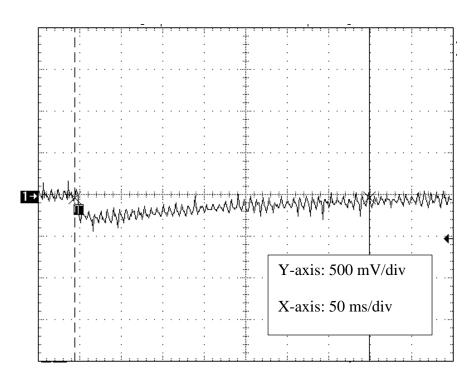

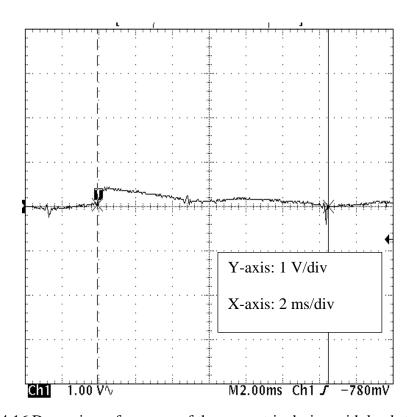

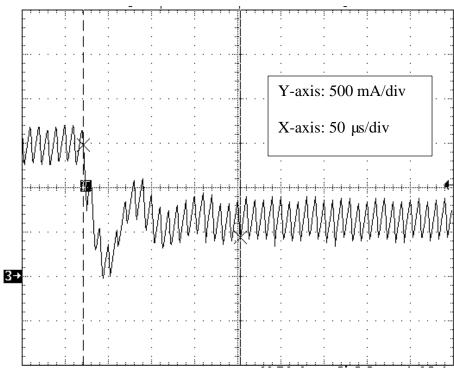

| Figure 4.11 Dynamic performance of the low-pass filter design with current command step up | 57        |

| Figure 4.12 Dynamic performance of the low-pass filter design with current command step do |           |

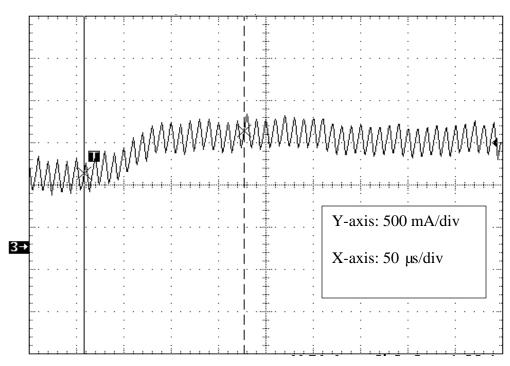

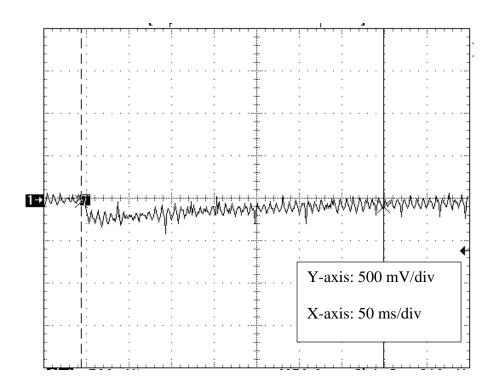

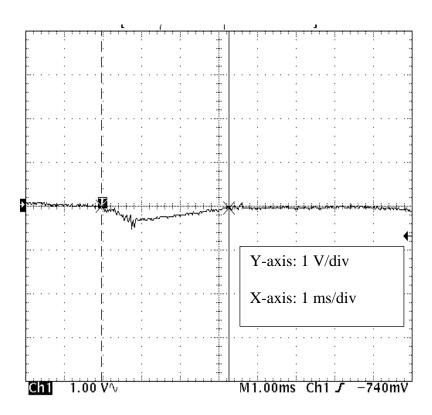

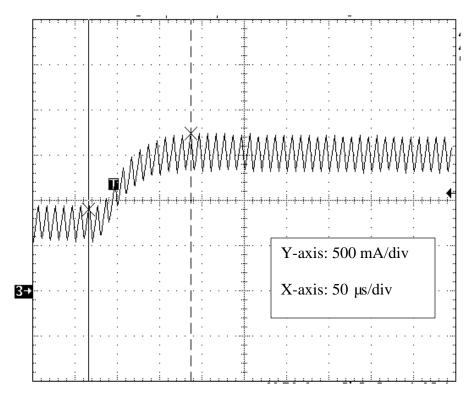

| Figure 4.13 Dynamic performance of the slope midpoint design with current command step up  | 57<br>58c |

| Figure 4.14 Dynamic performance of the slope midpoint design with current command step do  |           |

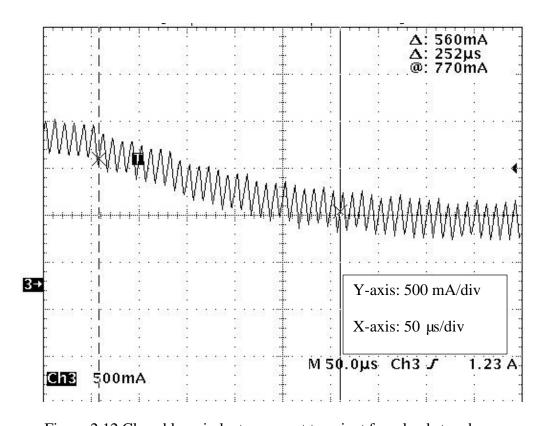

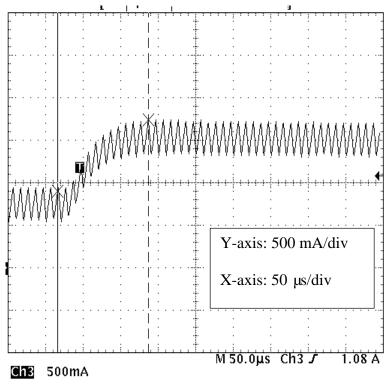

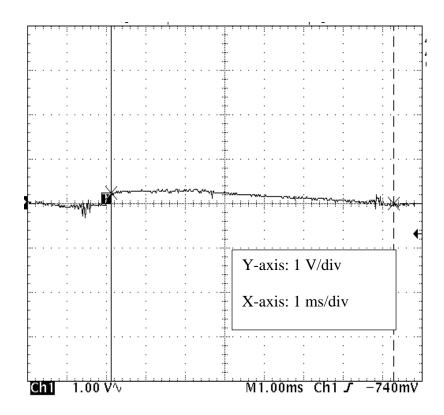

| Figure 4.15 Dynamic performance of the geometric design with load step up                  |           |

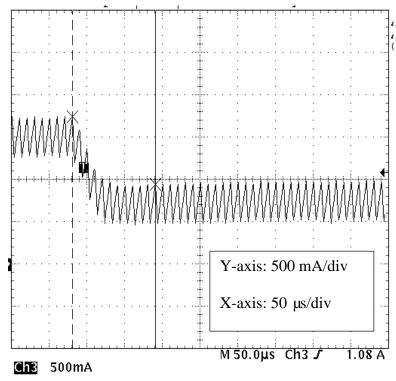

| Figure 4.16 Dynamic performance of the geometric design with load step down            | 59 |

|----------------------------------------------------------------------------------------|----|

| Figure 4.17 Dynamic performance of the low-pass filter design with load step up        | 60 |

| Figure 4.18 Dynamic performance of the low-pass filter design with load step down      | 60 |

| Figure 4.19 Dynamic performance of the slope midpoint design with load step up         | 61 |

| Figure 4.20 . Dynamic performance of the slope midpoint design with load step down     | 61 |

| Figure 5.1 I <sup>2</sup> average current mode control                                 | 64 |

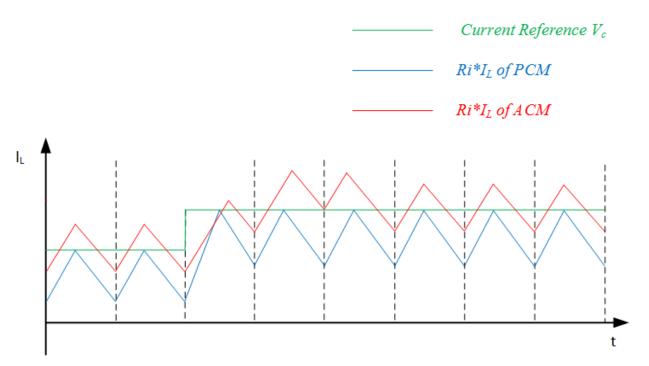

| Figure 5.2 Current waveforms for I <sup>2</sup> ACM control current                    | 65 |

| Figure 5.3 waveforms for ACM and PCM control                                           | 66 |

| Figure 5.4 Small-signal model for I <sup>2</sup> ACM control                           | 67 |

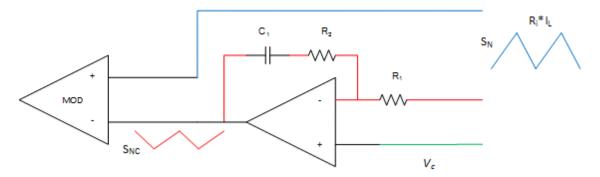

| Figure 5.5 Current compensator and modulator                                           | 68 |

| Figure 5.6 Current waveforms for modulator                                             | 69 |

| Figure 5.7 Current loop transfer functions                                             | 75 |

| Figure 5.8 Control-to-output transfer functions                                        | 76 |

| Figure 5.9 Comparison of audio susceptibility                                          | 77 |

| Figure 5.10 Comparison of output impedance                                             | 79 |

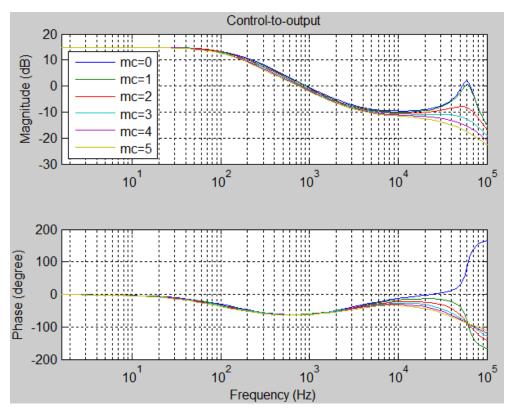

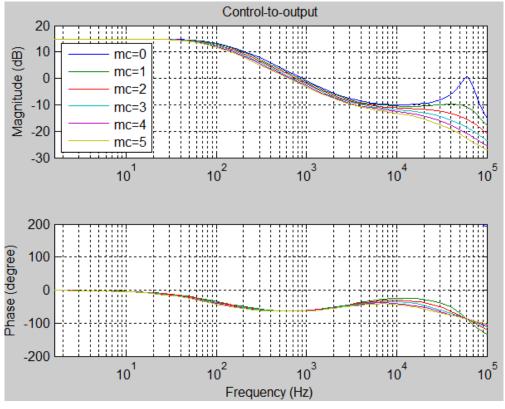

| Figure 5.11 Control-to-output voltage for different m <sub>c</sub> for a 3 V output    | 80 |

| Figure 5.12 Control-to-output voltage for different mc for a 2 V output                | 80 |

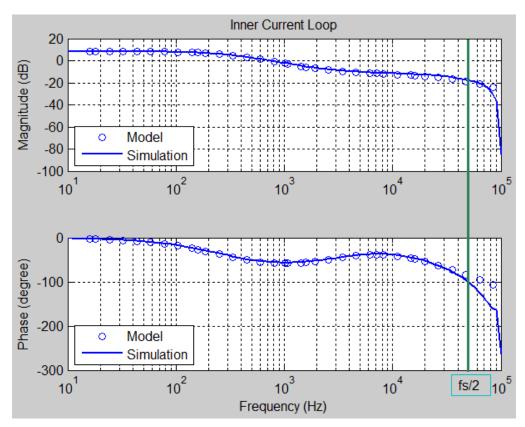

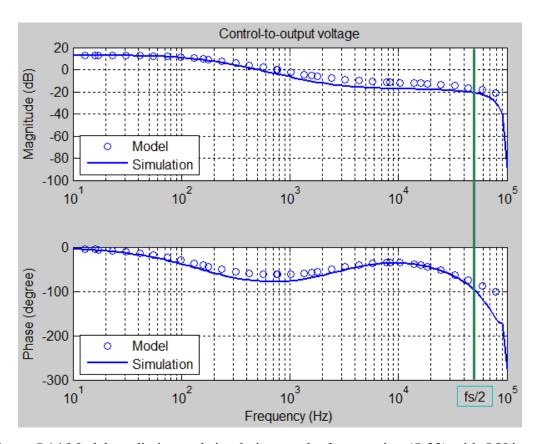

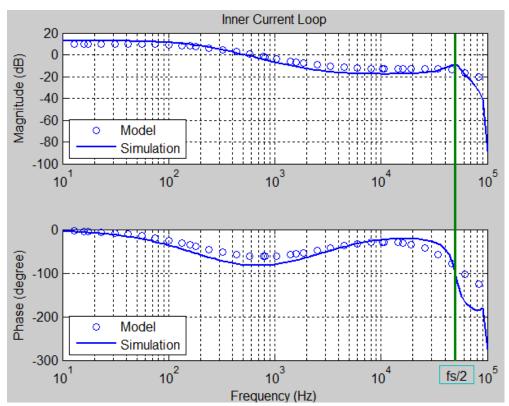

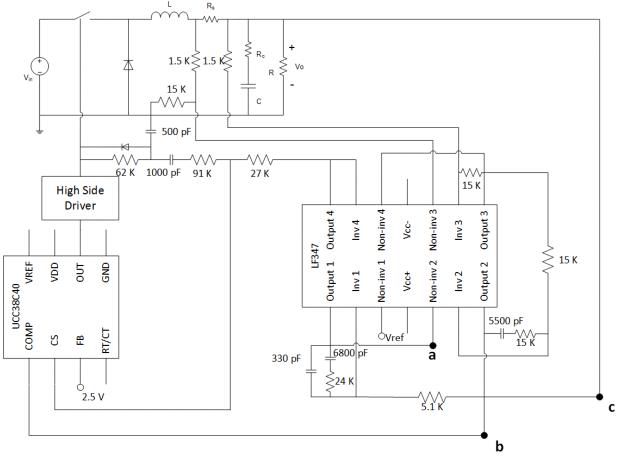

| Figure 5.13 Model prediction and simulation results for equation (5-27) with 5 V input | 82 |

| Figure 5.14 Model prediction and simulation result for equation (5-22) with 5 V input  | 83 |

| Figure 5.15 Model prediction and simulation result for (5-27) with a 6 V input         | 84 |

| Figure 5.16 Model prediction and simulation result for (5-22) with a 6 V input         | 84 |

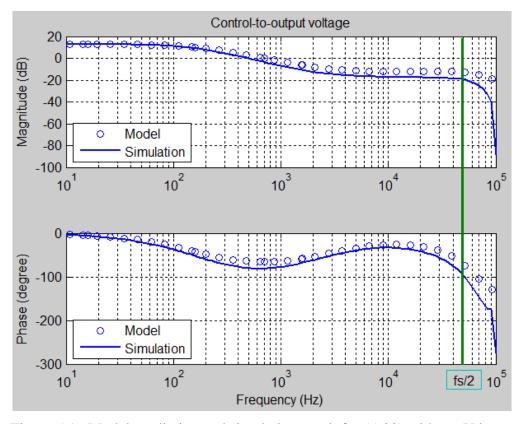

| Figure 5.17 Schematic of the buck converter prototype                                  | 85 |

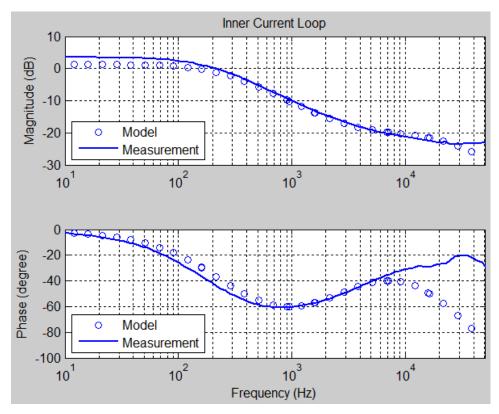

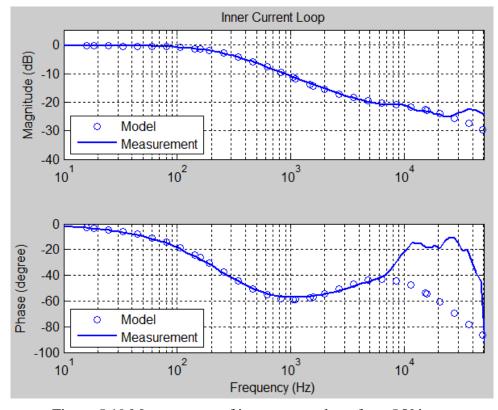

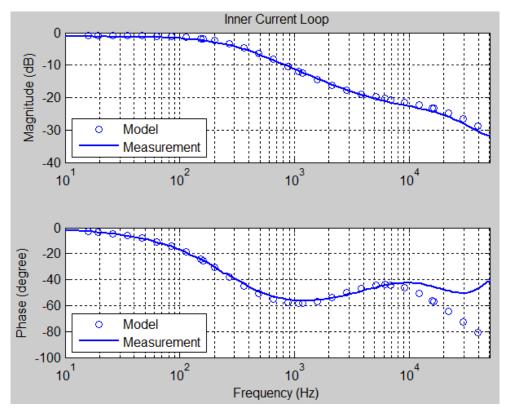

| Figure 5.18 Measurement of inner current loop for a 3.3 V input                        | 88 |

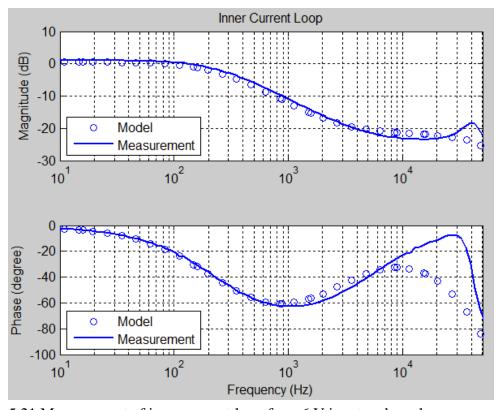

| Figure 5.19 Measurement of inner current loop for a 5 V input                                                         |

|-----------------------------------------------------------------------------------------------------------------------|

| Figure 5.20 Measurement of inner current loop for a 6 V input                                                         |

| Figure 5.21 Measurement of inner current loop for a 6 V input and no slope compensation 89                            |

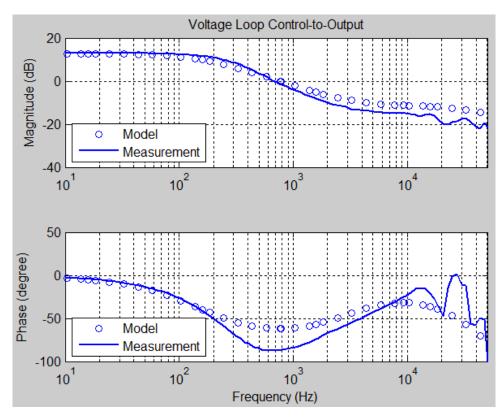

| Figure 5.22 Measurement of control-to-output voltage for a 3.3 V input                                                |

| Figure 5.23 Measurement of control-to-output voltage for a 5 V input                                                  |

| Figure 5.24 Measurement of control-to-output voltage for a 6 V input                                                  |

| Figure 5.25 Measurement of control-to-output voltage for a 6 V input and no slope compensation                        |

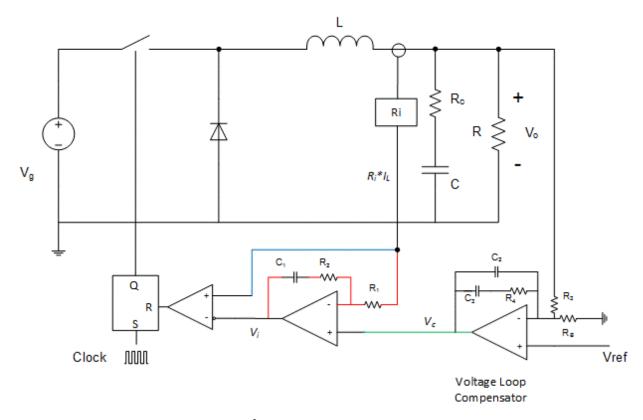

| Figure 6.1 I <sup>2</sup> average current mode controlled boost converter                                             |

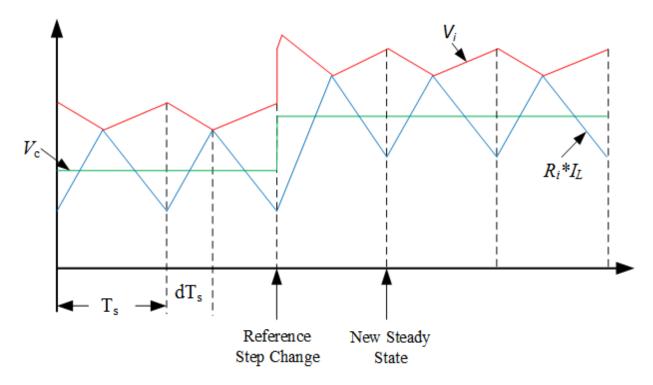

| Figure 6.2 Current waveforms for analog I <sup>2</sup> control                                                        |

| Figure 6.3 Perturbation in digital I <sup>2</sup> control signal                                                      |

| Figure 6.4 Small-signal model of digital I <sup>2</sup> current mode control                                          |

| Figure 6.5 Sub-harmonic oscillation of digital I <sup>2</sup> current control                                         |

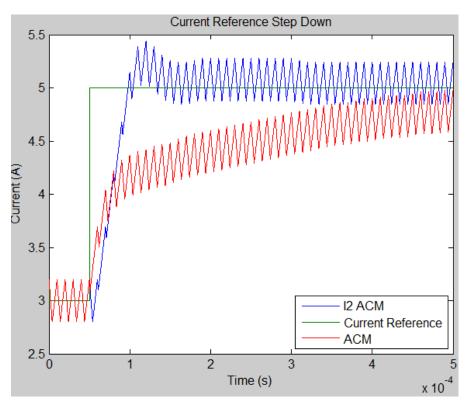

| Figure $6.6  \mathrm{I}^2$ current loop transient response of reference step up without calculation delay $103$       |

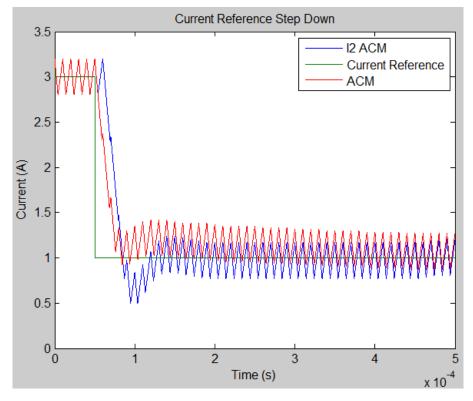

| Figure $6.7  I^2$ current loop transient response of reference step down without calculation delay $103$              |

| Figure 6.8 Comparison of current loop transient response for reference step up                                        |

| Figure 6.9 Comparison of current loop transient response for reference step down                                      |

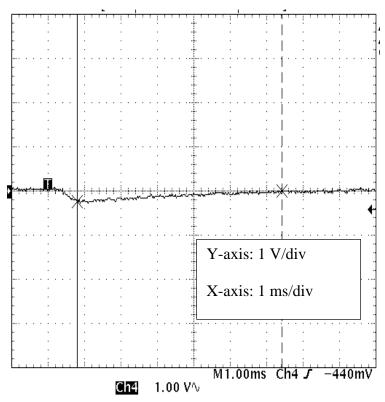

| Figure 6.10 Experimental results of $I^2$ current loop transient response for a reference step up . 108               |

| Figure 6.11 Experimental results of I <sup>2</sup> current loop transient response for a reference step down          |

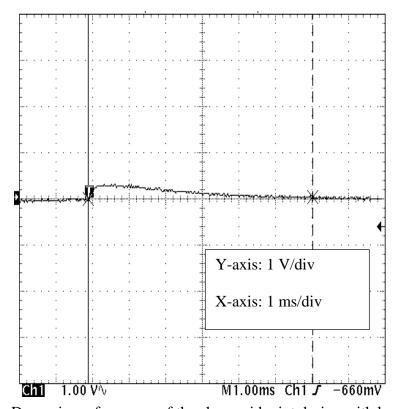

| Figure 6.12 Comparison of ACM current loop transient response for a reference step up 109                             |

| Figure 6.13 Experimental results of I <sup>2</sup> output voltage transient response for a load step up 109           |

| Figure 6.14 Measurement Experimental results of I <sup>2</sup> output voltage transient response for a load step down |

# List of Tables

| Table 2-1 Predictive Duty Ratio For Three Basic Converters                | 16                |

|---------------------------------------------------------------------------|-------------------|

| Table 2-2 Sensitivity and Compensation of Input Voltage Variation         | 21                |

| Table 3-1 Parameters for the Prototype Converter                          | 36                |

| Table 3-2 Parameters for Compensator Design                               | 37                |

| Table 4-1 Parameters Value Used in (4-15)                                 | 51                |

| Table 4-2 Parameters Value Used in (4-16)                                 | 52                |

| Table 5-1 Feedforward Gain and Feedback Gain as a Representation of $Kf'$ | and <i>Kr'</i> 74 |

| Table 5-2 Circuit Parameters for the Prototype Converter                  | 74                |

| Table 6-1 Modulator Gain for Basic Topologies                             | 98                |

| Table 6-2 Parameters Used in the Compensators                             | 102               |

#### CHAPTER 1. INTRODUCTION

The switch-mode converters have been widely used as power supplies in applications ranging from milliwatt on-chip power management to megawatt converters for power utility applications. Traditional switch-mode power supplies (SMPS) are controlled purely by analog circuitry. The rapid advances in power semiconductor and digital VLSI technology have improved the computation capability of digital processors and reduced unit cost. Furthermore, digital control offers the advantage to modify a design through software updates without touching the printed circuit board (PCB). Therefore, digital control techniques for SMPS are gaining more interest and applications.

## 1-1. Basic Concept of Current-Mode Control

The study on control techniques for SMPS began about five decades ago [1], since it provides higher efficiency, smaller size, less weight and larger voltage operation range than linear power supplies. However, the control of SMPS is far more complicated due to its nonlinear

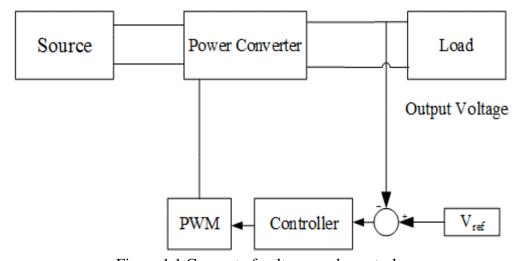

Figure 1.1 Concept of voltage mode control

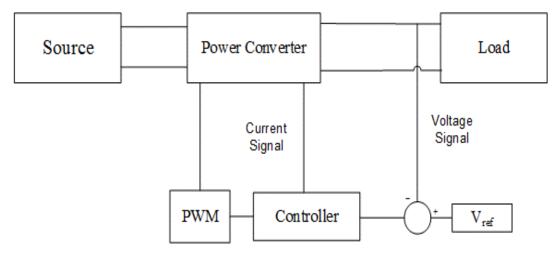

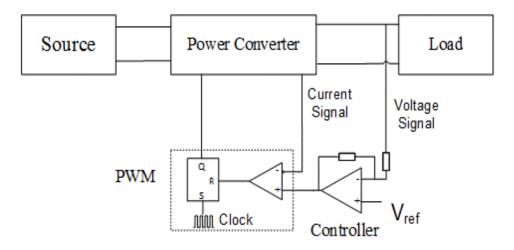

Figure 1.2 Concept of current mode control

operation. The first successful control method is called "voltage mode control" (VMC) or "voltage mode programming", since the control signal is only related to the difference between the converter output voltage and the reference voltage, as shown in Figure 1.1. The converter output voltage is sensed and compared with a reference; the error signal is then processed by the controller. The pulse-width-modulator (PWM) compares the output of the controller and a sawtooth waveform; the result is the "duty cycle" (ratio of switch ON-time to the total time period) for the transistor. If the sawtooth waveform is of constant frequency, the PWM signal turns on the switch in the power converter at the same constant frequency. By this control technique, the output voltage is regulated and tracking the voltage reference. From the control perspective, the system controls only one system state, the output voltage. Thus, the internal state which is the inductor current is ignored. It has little capability of protecting over current and fails to shape the input current as required for power factor correction (PFC).

Later in 1970's, another technique was proposed using both output voltage and inductor current which is called current mode control (CMC) or current programmed control [2][3], as shown in Figure 1.2. However, until the early 1980s, integrated circuits (ICs) were based on voltage mode control due to the complexity of adding a current controller. The CMC power

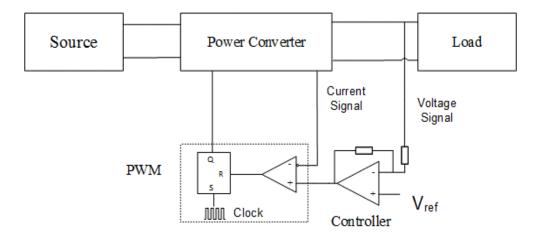

Figure 1.3 Circuit diagram of peak current mode control

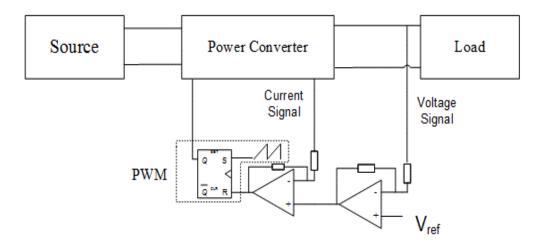

converter is typically a two-loop control system: an inner current loop and an outer voltage loop. The inductor current signal is sensed as the main control state and compared with the output of the voltage loop controller by a PWM comparator, which yields the PWM duty cycle. By using different features of the inductor current, CMC can be classified as: peak current mode control (PCM), valley current mode control (VCM) or average current mode control (ACM). For these methods, the outer voltage loop produces the current reference for the inner current loop by comparing the voltage reference and a signal proportional to the output voltage. The current loop causes the inductor current to track the current reference. PCM is widely used in the low-to-medium power converters. As shown in Figure 1.3, the PWM goes high at the beginning of every switching cycle and goes low when the current signal reaches the output of the controller. Shown in Figure 1.4, ACM is applied in applications which requires precise control of the current. The major difference with PCM is that ACM employs an extra controller in the current loop, which is designated as the current controller. The duty cycle is determined by the intersection of the current controller output and the sawtooth waveform.

Although the control circuit of CMC is more complicated than that of VMC, CMC has advantages such as lower audio-susceptibility, faster dynamic response and over current protection

Figure 1.4 Concept of average current mode control

[4]. Besides, CMC makes the inductor work as a current source, thus reducing the system order and simplifies the compensation network [5]. Hence, CMC is widely used in many high-performance applications. Furthermore, it is still an active research area today [6].

#### 1-2. Digital control power converters

Over the last three decades, digital controllers, such as the digital signal processors (DSP's), have been extensively employed in complex applications such as motor drives and three-phase utility interfaces [7]. Despite the high cost, the DSP provides a much easier solution for complicated mathematical computations. Therefore, digital control units were mainly used in high power and high cost application. The rapid development of semiconductor technology has reduced the price of digital processors tremendously. A vast amount of research has been conducted on applying digital control on high frequency low power SMPS since the 1990's [8]. The early experiments were performed based on the VMC, which has one control loop and only requires sampling the converter's output voltage. Digital voltage mode control (DVMC) turns out to be very successful and is utilized in distributed power management.

In the mid 1990's, Unitrode (part of Texas Instruments, Inc. today) marketed the famous PWM IC chips UC38XX series, which drove the application of CMC power converters became a

standard analog design for low power converters (up to kilowatts). However, the digital application of CMC is far less mature than that of VMC. CMC needs to sense the fast changing inductor current (same as switching frequency) and may use the instantaneous value to determine switching action, which is not an easy task for a digital controller. Since the pure digital current mode control (DCMC) implementation requires a high speed analog-to-digital converters (ADCs) and a high frequency system clock for sampling to reproduce continuous signals from discrete time signals and sufficient computational power for both the voltage loop and current loop calculation. In the early 2000's, a hybrid control method was proposed which used both analog and digital control for CMC [9]. The fast changing current loop was controlled by an analog chip, the slow outer voltage loop was handled by an inexpensive digital controller. At the same time, advance processor made it possible to estimate current by software calculation [10]. Later on, more and more sophisticated control techniques were investigated [11]. As a specific application of digital control, ASICs for power electronics tend to be another way to improve the performance of digitally-controlled power converters [12].

Although the analog versus digital control debate for DC-DC converters has intensified as digital control of power converters becomes an attractive area for both academic research and industrial application, it is necessary to understand the advantages and disadvantages of digital control and analog control [13][14].

The common listed advantages for analog control are:

- simplicity

- wider bandwidth

- finer sensing resolution

- fast processing

• low cost

The common listed disadvantages for analog control are:

- fixed and simple function

- less flexibility

- susceptibility to noise and age

- a large amount of discrete components

The common listed advantages of digital control include:

- programmability

- accuracy, reliability

- better noise immunity

- less susceptibility to aging

- versatile function

The common listed disadvantages of digital control include:

- noise generation

- sampling and quantization error

- delay in updating and signal processing

- higher cost

In this dissertation, three digital CMC techniques are proposed and the corresponding DSP based implementations are presented - predictive current model [15], digital average current mode control (DACM) [16] and digital I<sup>2</sup> average current mode control [18]. The pros and cons of each technique are analyzed thoroughly. Furthermore, small-signal models for each control technique are proposed and verified by frequency response measurements [17][19].

## 1-3. Organization of the Dissertation

This dissertation is organized as follow:

Chapter 2 illustrates the design of a proposed predictive current mode control and its DSP implementation.

Chapter 3 presents a small-signal model for the predictive technique introduced in Chapter 2. This model can also be applied to other predictive methods which are developed under the same condition. It also establishes a basic model form for other digital current mode control methods. Modifications on this model are used to model the digital average current mode control in Chapter 4 and digital I<sup>2</sup> average current mode control in Chapter 6.

In Chapter 4, digital average current mode control is discussed. Three different implementations for calculating the average current are introduced. The comparison of the three techniques are performed based on transient response, accuracy and program complexity. The small-signal model from Chapter 3 is modified to develop a model for these schemes. The efficacy of this model is checked by frequency response measurement.

Chapter 5 introduces the I<sup>2</sup> average current mode control which was first reported in 2013.

A small-signal model is developed for this control technique by analyzing the control system loop by loop. The result is verified by both simulation and measurement.

Chapter 6 demonstrates a digital implementation of the I<sup>2</sup> average current mode control, which only requires one sampling per switching period to determine the PWM duty cycle. The small-signal model is also developed and verified by the measurement.

Chapter 7 presents conclusions and suggestions for future work.

#### CHAPTER 2. PREDICTIVE CURRENT MODE CONTROL

In this chapter, a digital predictive current mode control technique is proposed. It utilizes a signal based on the average inductor current, which is created by a low-pass filter. The advantages of the proposed technique are immunity to switching noise, fast dynamic response and ease of programming. The derivation of the control law is presented and its stability discussed. It is also shown that the exact value of the input voltage and the converter inductance are not necessary to design a stable controller. The performance of this control method has been verified through simulation and experimental measurements.

#### 2-1. Introduction to Predictive Current Mode Control

Because of the fast transient response and simple compensation network needed for peak current mode control (PCM), as shown in the Figure 2.1, it becomes the first consideration for many power supply designers. Digital control units provide unrivalled flexibility to implement complex control schemes. Since the PCM needs to use the instantaneous signal of the peak current

Figure 2.1 Diagram of peak current mode controlled boost converter

to determine the switching action, it increases circuit complexity for the digital controller to reproduce the instantaneous signal from discrete time signals. As a purely digital control technique, predictive current mode control [20][23], which can be taken as a digital variation of peak current mode control, has been studied intensively because of its fast dynamic performance and ease of programming. Some approaches for predictive current mode control have utilized the duty ratio from the previous switching period [20][21], while others are based on a steady-state duty ratio Dss [10][22][23]. In these schemes, a signal proportional to the instantaneous inductor current is sampled. Thus, the controller is sensitive to the noise picked up by an analog-to-digital converter. The approach presented here is a predictive current control implementation for the continuous current mode (CCM) based on a signal proportional to the average inductor current, which is sampled instead of the instantaneous inductor current. It is demonstrated that the sampling of the input voltage is not necessary, which saves sampling and computation time, thus allowing operation at higher frequency.

This chapter is organized as follows. The proposed predictive current mode control is first introduced for the boost converter in Section 2-1. Stability analysis of the predictive control technique is discussed in Section 2-3. In addition, the impact of not sampling the input voltage and of having an inaccurate inductance value are described. The extension of the control law to the three basic dc-dc converters is presented in Section 2-4. Simulation and experimental results in Section 2-5 demonstrate the performance of the proposed control method.

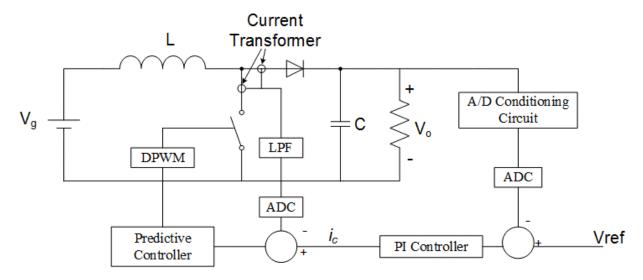

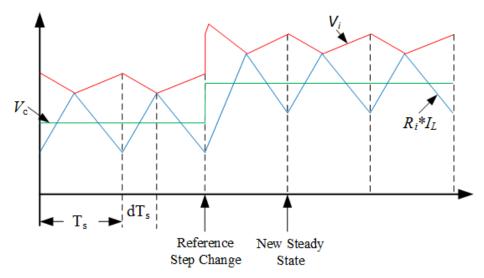

Figure 2.2 Diagram of a new predictive current control scheme

## 2-2. Development of the predictive control method

The proposed control method is developed in this section using the basic boost converter as shown in Figure 2.2, where DPWM indicates digital pulse width modulator, LPF – low pass filter and ADC – the analog-to-digital converter. Thus, all results presented in this section are based on the boost topology. As illustrated in this diagram, two current transformers are used one in series with the active switch and the other in series with the diode to recover the inductor current and eliminate saturation problems [24]. The outputs of these transformers are connected to a low-pass filter to remove current ripple and produce a signal proportional to the average value of the inductor current. In the same manner as other current control techniques, two control loops – an inner current loop and an outer voltage loop – are utilized here. From this point on,  $i_c$  indicates the current command signal, which is the output of the voltage control loop. The letter n is utilized to indicate the corresponding signal sampled or applied in the  $n^{th}$  switching period.  $D_{ss}$  is the duty ratio in steady state and  $D_{ss}$  equals  $1-D_{ss}$ . The variable d[n] is the duty ratio for the  $n^{th}$  switching period.

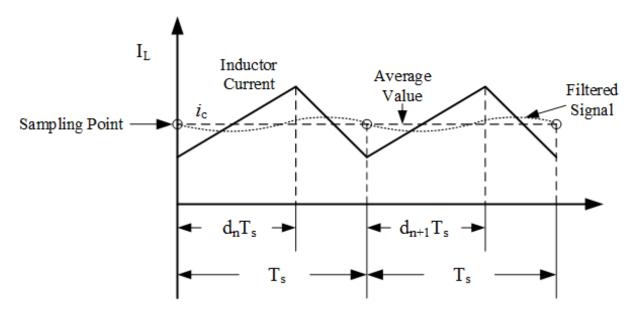

Figure 2.3 Inductor current waveform of boost converter in CCM

The goal of the proposed control algorithm is to ensure that the average inductor current in CCM follows the reference i<sub>c</sub>. The controller samples the average inductor current and output voltage at the beginning of each switching period and computes the duty ratio for the next switching period based on these values. It will be shown later that the input voltage does not need to be sampled as is required for other predictive schemes.

To begin with, assume that the sampled average inductor current signal is very close to the real average value of the last switching period, and the input and output voltage are constant within a switching period (due to their slow variations compared with a switching period). Without loss of generality, the inductor current waveform for a boost converter, shown in Figure 2.3, is used to illustrate the approach. In steady state, the average inductor current of the  $n^{th}$  and  $(n+1)^{th}$  cycles,  $\langle I[n] \rangle$  and  $\langle I[n+1] \rangle$ , satisfies the formula

$$< I[n+1] > = < I[n] > + (V_g - D'_{ss}V_o)\frac{T_s}{L}$$

(2-1)

Under steady-state conditions,

$$< I[n+1] > = < I[n] > = i_c$$

(2-2)

and

$$V_g = D'_{ss} \cdot V_o \tag{2-3}$$

Perturb the waveform for the n<sup>th</sup> period so that the average value is not equal to current reference. In order to make the average inductor current at the  $(n+1)^{th}$  period still track the desired current signal and reduce the tracking error, the desired duty ratio can be calculated by replacing  $< I[n+1] >= i_c$  and using the sample of the average inductor current of the n<sup>th</sup> cycle as:

$$i_c = \langle I[n] \rangle + (V_g - d'[n+1] \cdot V_o) \frac{T_s}{L}$$

(2-4)

so that

$$d'[n+1] = D'_{ss} + (\langle I[n] \rangle - i_c) \frac{L}{T_c \cdot V_o}$$

(2-5)

or

$$d[n+1] = D_{ss} + (i_c - \langle I[n] \rangle) \frac{L}{T_s \cdot V_o}$$

(2-6)

It should be noted that (2-1) and (2-2) are derived from the waveform in steady state, thus they are an approximation for the transient case. By applying the control law of (2-5) or (2-6), the average inductor current of the (n+1)<sup>th</sup> cycle does not equal the current reference, but the average value for this cycle will be very close to the desired current. The difference in increment between real average inductor current and sensed current is calculated later.

As a comparison, both predictive current mode control and peak current mode control adjust the duty ratio of the PWM signal to make the inductor current track the current reference. Therefore, the predictive current mode control can be treated as a digital implementation of peak current mode control. The predictive controller used in the current loop amplifies the error between the sampled value and the current reference by the gain of  $L/(T_s \cdot V_o)$ , and predicts the control

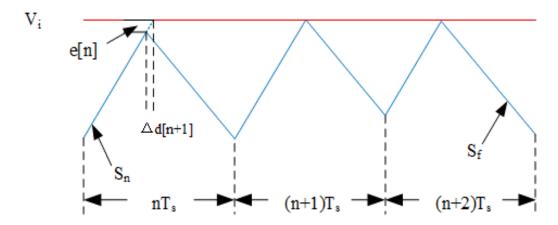

Figure 2.4 Perturbation in the n<sup>th</sup> cycle

effort based on this value. Therefore, the predictive controller functions as a proportional controller.

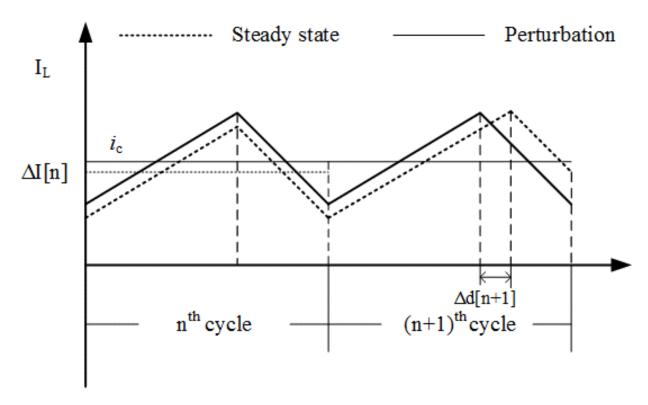

## 2-3. Stability Analysis

The stability properties of the predictive control can be examined with reference to the waveform of Figure 2.4. Suppose the predictive scheme is implemented using Trailing Edge Modulation [1]. The variation in the duty ratio of the (n+1)<sup>th</sup> cycle makes the valley current at the beginning of the period deviate from that at the end of the same period. The area under the (n+1)<sup>th</sup> cycle inductor current waveform is related to the average inductor current by a second order expression involving the duty ratio. Let's use a simple method to illustrate stability. Due to the small signal condition, it is fair to assume that the mid-point of the rising slope is the average value for this cycle. Assume that the converter is operating in steady state and an exaggerated perturbation happens in the n<sup>th</sup> cycle as shown in Figure 2.4. The perturbed waveform of the n<sup>th</sup>

cycle is shown by the dashed line. As a result, no corresponding duty ratio variation occurs, which means  $d[n] = D_{ss}$ . The error created in the average inductor current is

$$\Delta I[n] = I_c - \langle I[n] \rangle \tag{2-7}$$

Using (2-6) to calculate the duty ratio for the  $(n+1)^{th}$  cycle, the next duty ratio d[n+1] and resultant average current are

$$d[n+1] = D_{ss} + \Delta I[n] \cdot \frac{L}{T_s \cdot V_o}$$

(2-8)

$$\langle I[n+1] \rangle = \langle I[n] \rangle + \frac{1}{2} \cdot \Delta I[n] \cdot \frac{L}{T_s \cdot V_o} \cdot \frac{Vin \cdot T_s}{L}$$

(2-9)

In equation (2-9), the first term  $\langle I[n] \rangle$  is due to the term  $D_{ss}$  in (2-8). If there is no variation in duty ratio in the nth cycle, the  $(n+1)^{th}$  cycle will retain the same average current. The second term is calculated under the assumption that the mid-point of the rising slope of the inductor current waveform is still the average value. Combining equations (2-7) and (2-9) to derive the error of  $(n+1)^{th}$  cycle with respect to current command  $i_c$  yields,

$$\Delta I[n+1] = i_c - \langle I[n+1] \rangle = \frac{(1+D_{ss})}{2} \cdot \Delta I[n]$$

(2-10)

Since  $D_{ss}$  is always less than 1 for a switch-mode power supply, the error in the average current will decay to a negligible value. The current error extended to the following cycles can written as

$$\Delta I[n+k] = \left(\frac{1+D_{SS}}{2}\right)^k \cdot \Delta I[n]$$

(2-11)

Equation (2-11) indicates that the speed at which the current error decays is higher with a lower D<sub>ss</sub>. The reason that decaying speed of perturbation in each cycle is related to the duty ratio in steady state is that the duty ratio is used in the prediction of the duty ratio for the next cycle. If the disturbance in the inductor current does not satisfy the small signal assumption, the voltage loop will change the current command i<sub>c</sub>.

From the analysis above, one can conclude that the input voltage  $V_g$  and the inductance L have little effect on stability. Since  $D_{ss}$  is always less than 1, the inductor current error will become very small. Therefore, it is acceptable to replace the input voltage by the steady-state duty ratio, which results in reducing the time delay from the ADC because the input voltage does not have to be sampled. The inductance L does not appear in (2-11). Therefore, an error in the inductance value would only affect the number of periods required to reach steady state, but not the stability of the current loop.

It should be noted that the average inductor current of the (n+1)<sup>th</sup> cycle does not equal the current reference, as revealed by (2-10). By applying the resultant duty ratio in the (n+1)<sup>th</sup> cycle, the average current value for this cycle will be very close to the desired current. Furthermore, the method presented does not suffer sub-harmonics and eliminates the need for external slope compensation as required in peak current mode control operating under Trailing Edge Modulation with duty ratios greater than 0.5 [25].

#### 2-4. Extension to other converters

The derivation of the proposed predictive current mode control is easy to extend to other topologies. For convenience, the rising slope of the inductor current is denoted as m<sub>1</sub>, the falling slope as -m<sub>2</sub>, the duty ratio of the n<sup>th</sup> switching period as d[n], and T<sub>s</sub> stands for the switching period. In steady state,

$$< I[n+1] > = < I[n] > +m_1 \cdot D \cdot T_s - m_2 \cdot (1-D) \cdot T_s$$

(2-12)

Replace the average inductor current of the  $(n+1)^{th}$  cycle by the current reference, and D by the desired duty ratio for the  $n^{th}$  period d[n].

$$i_c = \langle I[n] \rangle + m_1 d[n] T_s - m_2 (1 - d[n]) T_s$$

(2-13)

Rearranging the formula above yields

$$d[n] = \frac{m_2}{m_1 + m_2} + \frac{i_c - \langle I[n] \rangle}{(m_1 + m_2)T_S}$$

(2-14)

Under steady state and the small perturbation assumption, the equations below are valid for all basic converters (buck, boost, and buck-boost) operating in CCM.

$$D_{ss} = \frac{m_2}{m_1 + m_2} \tag{2-15}$$

$$d_n = D_{ss} + \frac{i_c - \langle I[n] \rangle}{(m_1 + m_2)T_s}$$

(2-16)

The results for three basic converters, buck, boost and buck-boost, are given in Table 2-1. As can be seen, the duty ratio predictions for basic dc-dc converters are very similar - only the gain of the current error varies with topology.

Table 2-1 Predictive Duty Ratio For Three Basic Converters

| Buck       | $d[n+1] = D_{ss} + (Ic - \langle I[n] \rangle) \cdot \frac{L}{Ts \cdot Vin}$           |

|------------|----------------------------------------------------------------------------------------|

| Boost      | $d[n+1] = D_{ss} + (Ic - \langle I[n] \rangle) \cdot \frac{L}{Ts \cdot Vo}$            |

| Buck-Boost | $d[n+1] = D_{ss} + (Ic - \langle I[n] \rangle) \cdot \frac{L}{Ts \cdot (V_{in} + Vo)}$ |

## 2-5. Simulation and Experimental Results

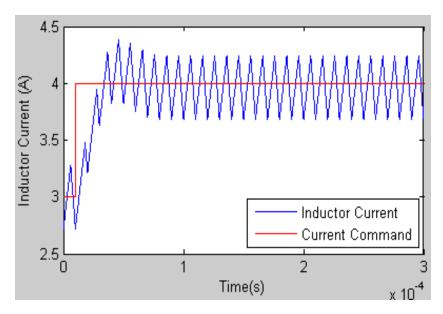

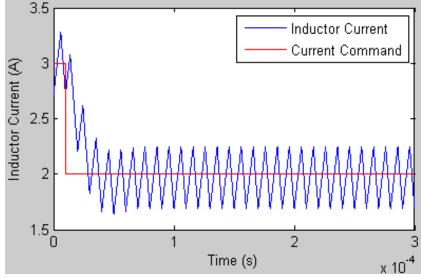

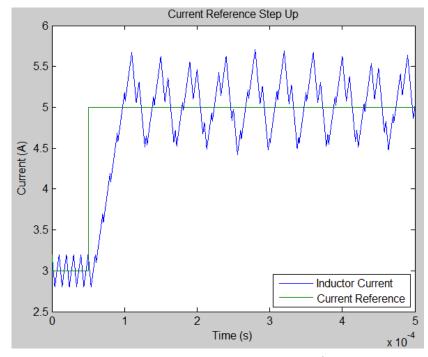

The proposed algorithm has been tested by simulating a boost converter with the following circuit parameters in MATLAB: input voltage = 12 V, output voltage = 30 V, L = 128 µH which forces the converter to operate in continuous conduction mode, and switching frequency = 100 kHz. The duty ratio was limited to the range of 0.1 to 0.9 in each switching cycle. Shown in Figure 2.5 and Figure 2.6 are simulation results for a change in the current command. Both the input and output voltages were held constant during the changes. These results demonstrate that the proposed predictive current control technique has a fast dynamic response and is stable. The simulation

results shown in Figure 2.7 and Figure 2.8 verify that the proposed control law has good immunity to an error in the inductance value. In Figure 2.7, the inductance was reduced to 70% of its original value at 50 µs and a current reference step up occurred at 150 µs. In Figure 2.8, the change in inductance happens at the same time, with the current reference stepped down at 150 µs. It can be seen that the inductor current reaches the new operating point in 3 cycles after the change in inductance. Although the control law was based on an inaccurate inductance value, the inductor current responses to current command change are still fast and stable.

Figure 2.5 Simulated transient response due to a step up in the current reference

Figure 2.6 Simulated transient response due to a step down in the current reference

Figure 2.7 Simulated current response for a change in inductance value with current command step up

Figure 2.8 Simulated current response for a change in inductance value with current command step down

Figure 2.9 Inductor current response due to a current reference step up

## 2-6. Experimental Results

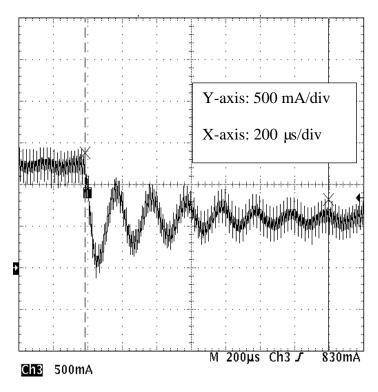

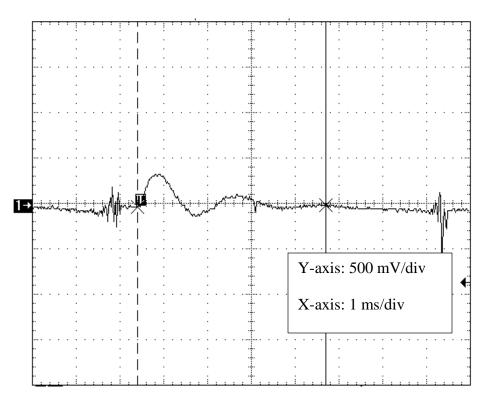

The performance of the proposed predictive control scheme was also investigated experimentally. The scheme was implemented on a TMS320F2812 TI DSP chip, which has an on-board 12-bit ADC and 16-bit digital pulse width modulators (DPWMs). The converter's load resistance was 120  $\Omega$ , and its output capacitance was 220  $\mu$ F which reduces the output voltage ripple below 0.5 V. The output voltage loop employed a discretized integral lead-lag compensator to compute the current reference signal. Figure 2.9 and Figure 2.10 show the inductor current response to a step change in the current reference with the voltage loop open. The current reference was changed from 0.75A to 1.5 A for Figure 2.9 and then returned to 0.75 A for Figure 2.10. It should be noted that the actual inductance in the circuit was 182  $\mu$ H, as measured by an AP300

Figure 2.10 Inductor current response due to a current reference step down

network analyzer while the control scheme was designed based on an inductance of 128 µH. The approximate 30% inductance error was utilized to verify the robustness of the proposed scheme to inductance value.

The overshoot and oscillation during the transient are mainly caused by: 1) the delays introduced by the Digital-Pulse-Width-Modulator (Zero Order Hold) and the computation time between sampling and the duty ratio update, and 2) the predictive controller works like a proportional gain related to the inductance value. As can be seen from the figures above, although the predictive control law was based on an inaccurate inductance value, the inductor current reached the new reference in about 7 cycles. Thus, the predictive current mode control has fast dynamic response, and its transient behavior was not impacted by the inaccurate inductance value.

Another experiment was set up to examine the sensitivity of the control law to variations in the input voltage. The nominal 12 V input voltage was varied from 6 V to 20 V, while the output voltage was held constant at 30 V. In Table 2-2, the values of input voltage, current error (difference between current reference and measured average inductor current), input variation with respect to the output voltage ( $\Delta V_g/V_o$ ) and the second term of equation (2-6) were collected. The third column indicates the difference between  $D_{ss}$  in equation (2-6) for an input voltage of 12 V and the input voltage shown in the first column of this table.

Table 2-2 Sensitivity and Compensation of Input Voltage Variation

| Input (V) | Current Error | $\Delta V_{g}/V_{o}$ | $(i_c - \langle I[n] \rangle) \cdot L/(T_s \cdot Vo)$ |

|-----------|---------------|----------------------|-------------------------------------------------------|

| 6         | 0.3848289     | -0.2                 | 0.194193677                                           |

| 8         | 0.3374241     | -0.13333333          | 0.143967627                                           |

| 10        | 0.1470242     | -0.06666667          | 0.06273033                                            |

| 12        | 0.0102516     | 0                    | 0.004374016                                           |

| 14        | -0.1955281    | 0.066666667          | -0.083425329                                          |

| 16        | -0.3432706    | 0.133333333          | -0.146462134                                          |

| 18        | -0.4896741    | 0.2                  | -0.208927632                                          |

| 20        | -0.6203613    | 0.266666667          | -0.264687509                                          |

To keep the output voltage constant, the outer voltage loop adjusted the current reference feeding into the predictive controller to maintain the output current constant. Comparing the 3rd and 4th columns in Table 2-2, the change in the current reference ic due to the input variation cancels out the error in the steady state duty ratio. The voltage loop and predictive current loop worked together to compensate the error in the estimation of input voltage and steady state duty

ratio. Therefore, sampling of the input voltage was not necessary for this predictive control scheme.

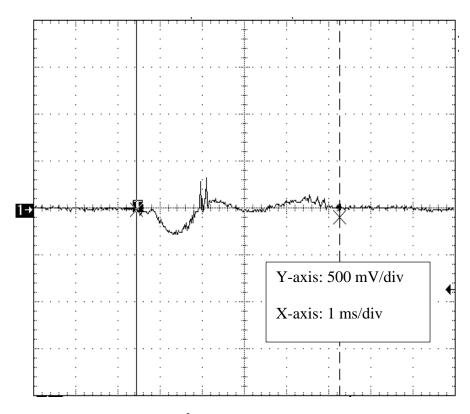

The experimental results for a load change are given in Figure 2.11 and Figure 2.12. With the voltage loop closed, the load resistance was changed from  $120 \Omega$  to  $50 \Omega$  and then back to  $120 \Omega$ . The inductor current gradually increased/decreased and tracked the current reference signal. It should be noted that this test is not consistent with the small signal assumption. With the voltage loop closed, the response of the converter was primarily determined by the dynamics of the voltage loop. The compensator for the voltage loop is given in (2-17)

$$G_c(s) = \frac{k_c}{s} \frac{(1+s/\omega_z)}{(1+s/\omega_p)}$$

(2-17)

where  $k_c$  is the gain,  $\omega_z$  indicates the low frequency zero and  $\omega_p$  the high frequency pole. The integrator in this compensator yielded zero DC error in steady state, but also slows down the transient response. The zero and pole were placed to retain sufficient phase margin. The bilinear transformation was utilized to convert the transfer function of (2-17) into a discrete difference representation for the software implementation as shown below.

$$G_c(z) = \frac{T_S}{2} \frac{k_c \omega_p}{\omega_z} \frac{(\omega_z T_S + 2)z^2 + 2\omega_z T_S z + (\omega_z T_S - 2)}{(\omega_p T_S + 2)z^2 - 4z - (\omega_z T_S - 2)}$$

(2-18)

Figure 2.11 Closed loop inductor current transient for a load step up

Figure 2.12 Closed loop inductor current transient for a load step down

To demonstrate robustness against variations in the input voltage, the output voltage transient response was measured for different input voltages for a load change. The input voltage was varied from 10 V to 16 V, in steps of 1 V, and the corresponding transients were recorded. The voltage transient for all input voltages was similar, and the output voltage returned to its nominal value. Shown in Figure 2.13, Figure 2.14 and Figure 2.15 are the results for input voltages of 11 V, 12 V and 14 V, respectively. It can be concluded that the controller is effective for this range of input voltages. Variations in the input voltage only affect the speed of the transient response. It should be mentioned that the controller would become unstable if the input voltage is far above or below the nominal input. A large difference in input voltage from its nominal value diminishes the phase margin of the control loop, which can cause oscillation.

Figure 2.13 Output transient response for a 11 V input voltage

Figure 2.14 Output transient response for a 15 V input voltage

Figure 2.15 Output transient response for a 14 V input voltage

### 2-7. Conclusion

A new predictive current control scheme was introduced in which the duty ratio for the next switching period is calculated based on the average inductor current. A low-pass filter is utilized in the current loop to filter out most of the switching noise and provide a clean average current signal to a digital controller. The control law is easy to derive, just requiring basic understanding of the inductor waveform in CCM and is easy to implement on a DSP chip. The proposed scheme can be easily extended to all basic dc-dc converter topologies. The response of the inner current loop is very fast. Compared to other predictive current control schemes, it was shown that it is not necessary to sample the input voltage of the converter. An insensitivity to the converter inductance value was also discussed. Both simulation and experimental results have demonstrated the effectiveness of this control scheme. The control law is insensitive to the variation of input voltage and is suitable for power factor correction (PFC) applications.

### CHAPTER 3. MODELING OF PREDICTIVE CONTROL

As introduced in the Chapter 2, predictive current mode control is a promising digital current mode control technique. It has the advantages of fast transient response without knowledge of the exact value of the input voltage and inductance in the power converter. Control laws are based on an understanding of the inductor current waveform, thus providing flexibility in programming and implementation. However, only a few papers have been written about developing small-signal models for predictive current controllers. It is important to have a small-signal model to optimize the controller performance. In this chapter, a small-signal s-domain model for predictive current mode control is proposed. This small-signal model is applied to two different predictive controller systems. The frequency response of the systems are compared with experimental measurements obtained with an AP300 network analyzer.

### 3-1. Introduction

As discussed in Chapter 2, predictive current mode control, which can be treated as a pure digital implementation of peak current mode control, provides fast transient response and ease of design. For analog implementation, design changes could require component changes as well as modification of the printed circuit board layout. In comparison, digital control offers the capability to modify a design through software updates. Sophisticated control schemes are difficult to implement in analog, but can be realized through software [26]. Modeling of digital control is far more complicated than analog and still requires intensive exploration. A correct model can provide insight into the circuit operation and thus save engineers much work.

Predictive current mode control is one of the promising digital current mode control techniques which has been investigated by several researchers [10][22][23][25]. The proposed control algorithms use the sampled inductor current and are derived from an analysis of the typical inductor current waveform in a DC-DC converter operating in the continuous conduction mode (CCM). Stability analysis of these predictive schemes has been performed for different modulation methods (peak, average, valley current). However, a survey of the literature reveals very few investigations into small-signal models for predictive schemes [27]. These models are needed to design the compensator for the outer voltage loop to optimize converter performance. Described in this chapter is a small-signal model for a predictive control scheme for the control of DC-DC converters operating in CCM. The efficacy of this model is verified through measurements on a prototype converter.

## 3-2. Review of small-signal model of analog current mode control

Small signal models for analog current-mode control have been studied for over three decades [28] [29]. The more accurate models are third order in nature for both peak and average current-mode controllers [4][30][31][32]. Since these models are widely accepted by practicing engineers, let's briefly review them.

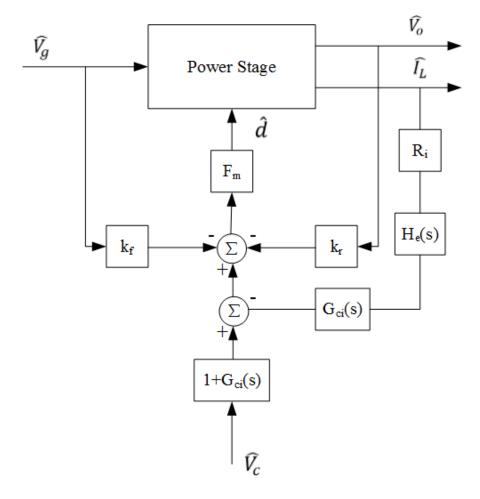

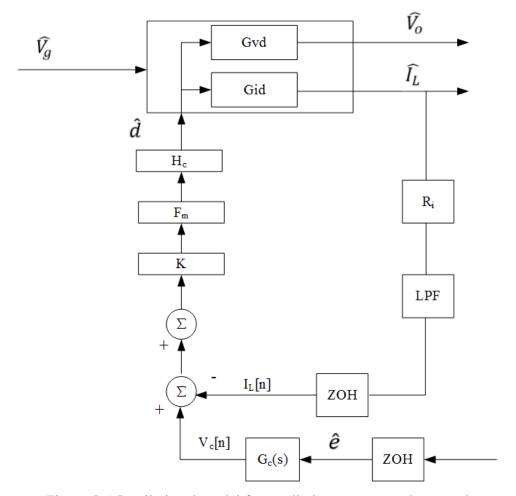

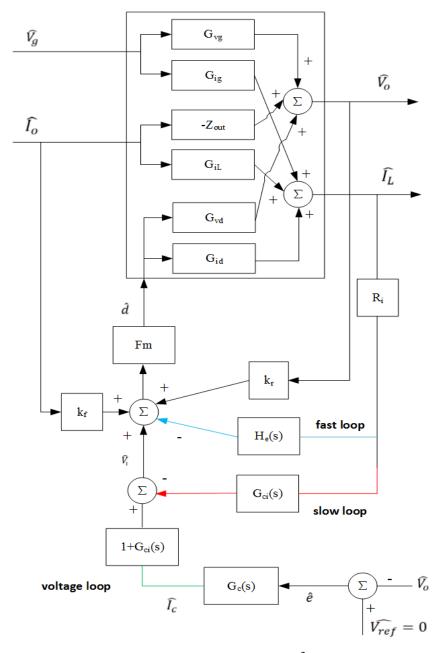

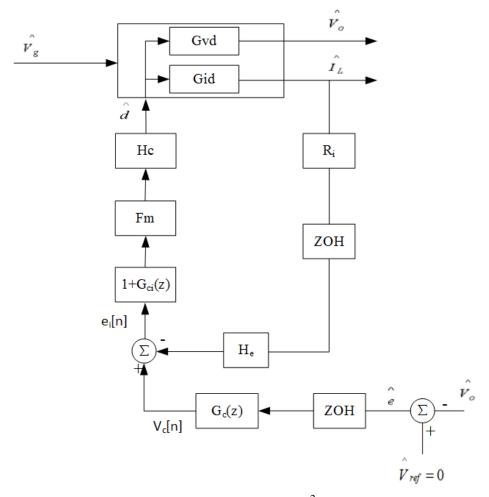

Shown in Figure 3.1 is a small-signal model for both peak and average current mode control. It should be noted that the blocks in this diagram have different values for the different control methods. This diagram can be utilized to reveal common points for both current control techniques. The gain  $k_f$  is the feed-forward gain from the input voltage, the gain  $k_r$  is the feedback gain from the output voltage,  $F_m$  is the modulator gain,  $H_e(s)$  is the sampling effect,  $G_{ci}(s)$  is the compensator in the current loop,  $R_i$  is the sampling gain of the current loop,  $V_c$  is the output of the

Figure 3.1 Small-signal model for current mode control

voltage loop regulator,  $V_g$  is the input voltage,  $V_o$  is the power converter output voltage, and  $I_L$  is the inductor current.

These values of the blocks in the Figure 3.1 are different, depending on whether peak or average current mode control is implemented. In [31], it was questioned whether to include the sampling effect H<sub>e</sub>(s) in the current loop for average current mode control. And for peak current mode control, the two blocks with G<sub>ci</sub>(s) can be ignored, because there is no such compensator in the current loop. In conclusion, different current mode controllers have the same general configuration as shown in Figure 3.1 with some corresponding variations. The small-signal model for digital predictive current mode control should have the same basic configuration as that of

Figure 3.2 Block diagram representation of equation (3-1)

Figure 3.3 Small-signal representation of equation (3-1)

analog current mode control methods. However, because the digital compensators used in both the voltage and the current loop are implemented in software, while the compensators in analog control are implemented in hardware, the corresponding digital blocks are positioned at different places.

## 3-3. Proposed Small-Signal Model

## 3-3-1 Modulator gain

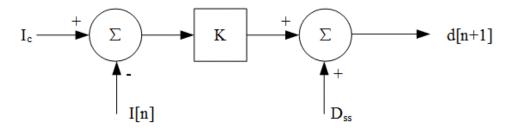

By studying the predictive current mode control methods operating in CCM introduced in [10][22][23][25], it can be observed that most of the methods for predicting the next duty ratio have the form of

$$d[n+1] = D_{ss} + (I_c - I[n]) \cdot K$$

(3-1)

where d[n+1] is the desired duty ratio for the  $(n+1)^{th}$  switching period,  $D_{ss}$  is the duty ratio in steady state,  $I_c$  is the current command from the voltage loop, I[n] is the sampled inductor current of the  $n^{th}$  cycle, K is a linear gain derived from analysis of the converter current waveform. The duty ratio derivation for more than one switching period delay can be based on (3-1). A block diagram

to illustrate (3-1) is given in Figure 3.2. As can be seen in this figure, the control algorithm in the current loop can be treated as a proportional controller, which amplifies the difference between the current command and sampled current. The variable  $D_{ss}$  helps the controller find the desired steady-state operating point. The controller performs better during startup when  $D_{ss}$  is close to the desired steady-state duty cycle.

For power converters with a wide input voltage range or when D<sub>ss</sub> is not near the desired value, the voltage loop compensator will adjust the current command, thus building up the current error signal to cancel out the error in Dss. This can be verified by simply changing the input voltage of a DC-DC converter or the value of Dss used in a digital control unit which deviates the real steady state duty ratio; the output voltage will still be well-regulated due to the voltage loop compensation. Another issue is that proportional controllers suffer steady-state error, which can be caused by inductor current sampling, error in Dss, and truncation. As long as the output voltage is held constant, these errors will remain in the controller to cancel out other errors and maintain the correct duty ratio. The advantage of the predictive current method is that it is not sensitive to the linear error in current sampling or deviation in D<sub>ss</sub> from the real steady-state duty ratio. The disadvantage is that error will exist between the sampled inductor current and the current command, since there is no integral term used in the current loop controller. Additionally, Dss is a constant and does not affect the transient response after the converter has reached steady state. As such, this variable will disappear from the small-signal model. The modified small-signal model for the current controller is shown in Figure 3.3. The notation "^" indicates the variable is a smaller signal which is much smaller in magnitude than the steady state value.

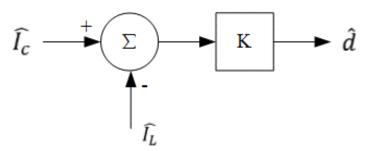

Figure 3.4 Small-signal model of the sample and hold process in a digital controller

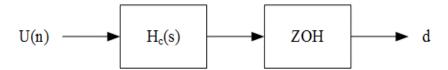

# 3-3-2 Effect of digital controller

A digital controller contains an analog-to-digital converter and a digital pulse width modulation (DPWM) module. The ADC can be represented as a ZOH (zero order hold) in series with a delay module, which models the update delay between the end of conversion and the update of the PWM output based on the sampled data. In addition to the delay in ADC, there are delays in the processes of calculation and output update. All these delays can be modelled by a single delay module, which accounts for the total signal delay in the digital controller. The small-signal model for these elements can be represented as shown in Figure 3.4. In this figure, U(n) represents the output of the modulation module F<sub>m</sub>, which modulates the duty ratio. H<sub>c</sub>(s) accounts for the update delay of the duty ratio [33],

$$H_c(s) = e^{-s \cdot T_d} \tag{3-2}$$

where  $T_d$  is the delay time, which could be more than 1 switching period. The s-domain model for a zero order hold can be written as [34]

$$ZOH = \frac{1 - e^{-s \cdot n \cdot T_s}}{s} \tag{3-3}$$

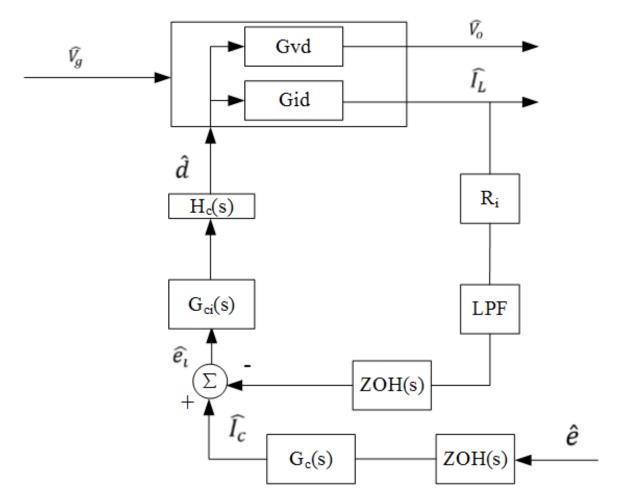

where n is the number of cycles delay and  $T_s$  is the switching period of the power converter. However, for digital current mode control, both voltage and current signals are sampled. The ADC (analog to digital conversion) happens twice in the control loop. Therefore, the block diagram shown in Figure 3.4 could be placed separately. As shown in the Figure 3.5, the ZOH represents

Figure 3.5 Small-signal model for predictive current mode control

where ADC occurs, which is located between the converter's analog variables and digital compensators in the processor.  $H_c(s)$  is located between the modulation module and power stage, which groups the delays in the ADC and DPWM.

# 3-4. Small-signal characteristics

Inserting the small-signal model for the current loop and sample and hold circuit into Figure 3.1 yields the small-signal model for predictive current mode control shown in Figure 3.5, where the block LPF represents the low-pass filter used for inductor current sampling. The bandwidth of the LPF could be set high to reduce switching noise. In this case, it can be ignored in the frequency response calculations if the system bandwidth is much lower than the cutoff

frequency of the filter. Or, it could be a circuit with a lower bandwidth used to produce a signal proportional to the average current. In Figure 3.5, the gain  $G_{vd}$  is the duty cycle-to output transfer function, and  $G_{id}$  is the duty cycle-to-inductor current transfer function. The sampling effect  $H_e(s)$  was not observed in this experiment, so it is ignored here. The feed-forward gain  $k_f$  and the feedback gain  $k_f$  from [4] and [32] are not included here, because the digital controller only samples the instantaneous value of the inductor current and does not use the current slope to determine the duty ratio as in an analog controller. Therefore, the effects of input voltage and output voltage on inductor current slope should not be considered. The modulator gain  $F_m$  is 1 here [33]. Therefore, the inner current loop can be expressed as

$$T_i = K \cdot F_m \cdot H_c \cdot ZOH \cdot G_{id} \cdot R_i \cdot LPF \tag{3-4}$$

It is not unusual for the power converter to have a stable output voltage, while the inductor current can exhibit low frequency oscillations. Under certain operating conditions, this frequency of oscillation can be one-half the switching frequency. The expression in (3-4) can be utilized to predict these low frequency oscillations. In addition, the stability of the loop can be examined by checking the phase margin of T<sub>i</sub>. For most cases, the current loop has a large bandwidth with a small phase margin. The gain K should be selected to keep the phase margin positive.

The control-to-output transfer function can be written as

$$\frac{\widehat{V_o}}{\widehat{V_c}} = \frac{K \cdot F_m \cdot H_c \cdot ZOH \cdot G_{vd}}{1 + T_i}$$

(3-5)

It should be noted that the delay H<sub>c</sub> and the zero order hold ZOH appear in both the numerator and denominator of (3-5). Once the transfer function in (3-5) is known for a power converter, it would be easy to design the voltage loop regulator by the K factor [35] method. A type II compensator was selected because it provides the necessary amount of phase boost required to increase the phase margin to stabilize the loop. This compensator has the form

$$G_c(s) = \frac{k_c}{s} \cdot \frac{(1+s/\omega_z)}{(1+s/\omega_p)}$$

(3-6)

Because a digital control unit can only process discrete signals, the compensator in (3-6) is transformed to the z domain using the Bilinear transformation. The equivalent discrete controller can be expressed as

$$G_c(z) = \frac{T_S}{2} \frac{k_c \omega_p}{\omega_z} \frac{(\omega_z T_S + 2)z^2 + 2\omega_z T_S z + (\omega_z T_S - 2)}{(\omega_p T_S + 2)z^2 - 4z - (\omega_z T_S - 2)}$$

(3-7)

where  $k_c$  is the gain,  $\omega_z$  indicates the low frequency zero and  $\omega_p$  the high frequency pole. The compensator in (3-6) is designed first in the s-domain and then transformed to the z-domain as shown in (3-7) for implementation in a digital controller. It should be pointed out that all s-to-z transformations, including the Bilinear, are approximations. It was reported in [36] that some transformations can give more accurate discrete time equivalents for the continuous time model, and the transformation methods could be selected based on some certain properties of power converters. It is important to plot the frequency response of the z-domain function in (3-7) using software such as MATLAB to compare with measured values obtained from a network analyzer.

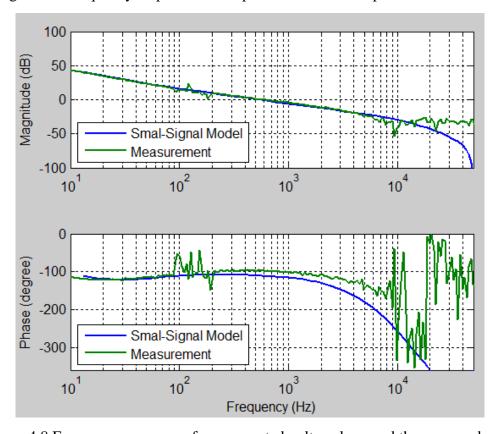

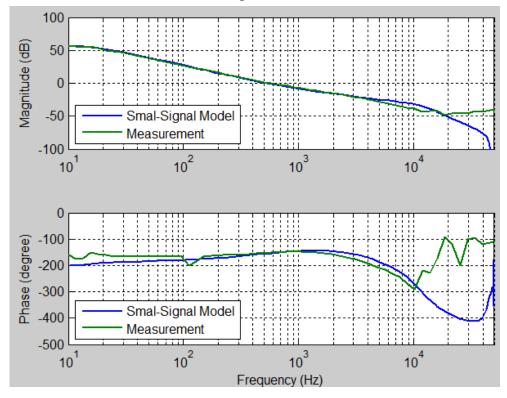

### 3-5. Experimental Verification

The same boost converter in Chapter 2 was used to demonstrate the accuracy of the proposed model for predictive current mode control. The parameters for the prototype are shown in Table 3-1. To maximize the accuracy of the proposed model, the values of the circuit elements (inductor, output capacitor and their corresponding equivalent series resistances (esr), were determined using an AP300 network analyzer from Ridley Engineering. The controller implementation was based on a 32-bit fix-point DSP TMS320F2812. All closed-loop system frequency response measurements were obtained using an AP300 network analyzer.

Table 3-1 Parameters for the Prototype Converter

| Input             | 12 V  | Inductor      | 185 μH   |

|-------------------|-------|---------------|----------|

| Output            | 30 V  | Capacitor     | 206 μF   |

| Sampling Resistor | 1 Ω   | Capacitor esr | 26.42 mΩ |

| Load              | 119 Ω | Ts            | 10 µs    |

To check the accuracy of the proposed model, a voltage loop regulator was designed to stabilize the voltage loop so that the frequency response could obtained. One method to design a PI regulator for the voltage loop is to utilize trial and error without knowledge of the model of the control system. One of the widely adopted two-step trial and error methods is summarized as: (1) use a single proportional gain in the voltage regulator, then decrease this gain until the output voltage and inductor current are stable while ignoring the steady state error and (2) adopt a very small integral gain together with the proportional gain acquired in step (1), then reduce the integral gain until the output voltage and inductor current are stable. By this method, the resulting PI regulator has a fairly small mid-band gain and a low frequency zero which has characteristics of low cross-over frequency and small disturbance rejection in the frequency range of interest. The reason is that converters with a right-half plane zero (boost and buck-boost) limit the proportional gain when there is no zero boosting the open loop phase shift as in step (1), since the current loop normally has large bandwidth and little phase margin due to a right half plane (RHP) zero. The Euler transformation of the PI controller designed by the trial and error method is

$$I_c[n] = I_c[n-1] + (k_p + k_i \cdot T_s) \cdot e[n] - k_p \cdot e[n-1]$$

(3-8)

where  $k_P$  is the proportional gain picked in step (1),  $k_I$  the integral gain picked in step (2),  $T_s$  the switching period, and  $I_c[n]$  the output of voltage loop compensator in the  $n^{th}$  cycle.

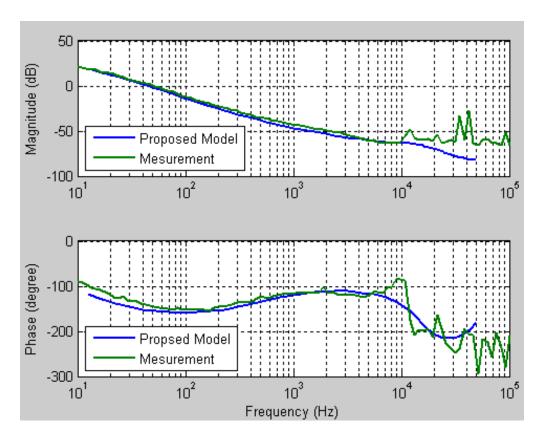

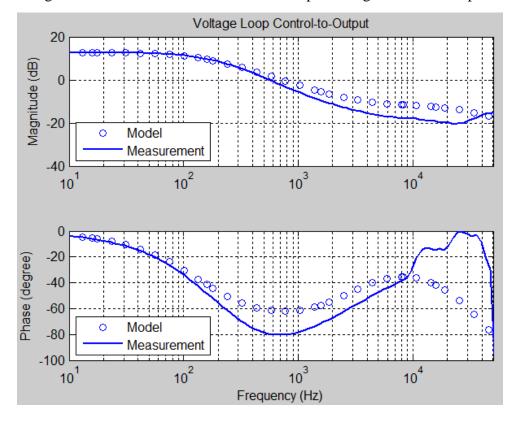

Figure 3.6 Voltage loop gain designed by the trial and error method

The PI controller based on the trial and error method was implemented on the DSP. The measured voltage loop frequency response and the proposed model are shown in Figure 3.6. It can be seen that the magnitude plots match very well up to 10 kHz. Beyond that frequency, the converter gain is so low that the measurements are unreliable due to noise in the system. The small-signal model provides a reasonable estimate of the phase up to approximately 7 kHz. The compensator parameters used in this design is shown in Table 3-2.

Table 3-2 Parameters for Compensator Design

| Trial and Error | Value  | K Method   | Value |

|-----------------|--------|------------|-------|

| kı              | 0.016  | kc         | 375   |

| kР              | 0.0155 | $\omega_p$ | 8000  |

|                 |        | ωz         | 100   |

Now that the accuracy of the proposed model has been confirmed, it was utilized to optimize the design of the voltage loop compensator to further verify the small-signal model. A voltage loop regulator with a larger bandwidth and higher DC gain was designed. Using the K factor method and setting the desired crossover frequency at 1 kHz, a new voltage loop compensator shown by (3-6) was applied with the parameters collected in Table 3-2. The corresponding discrete time regulator developed is

$$I_c[n] = 1.923I_c[n-1] - 0.9231I_c[n-2] + 0.1443e[n]$$

$$+0.0001442e[n-1] - 0.1442e[n-2]$$

(3-9)

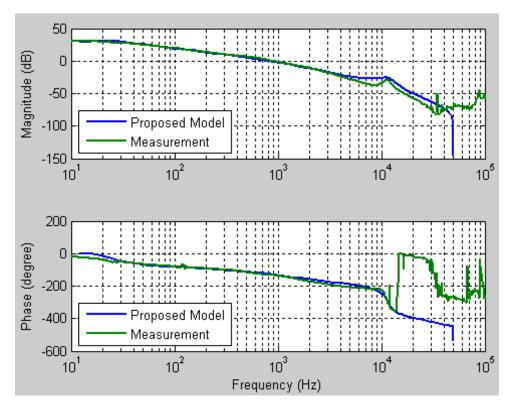

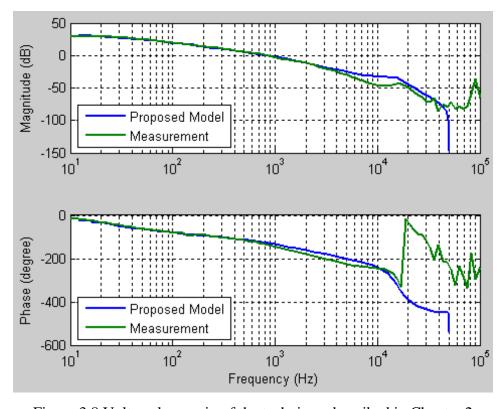

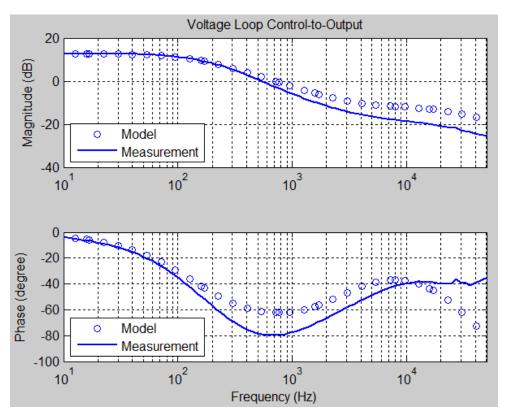

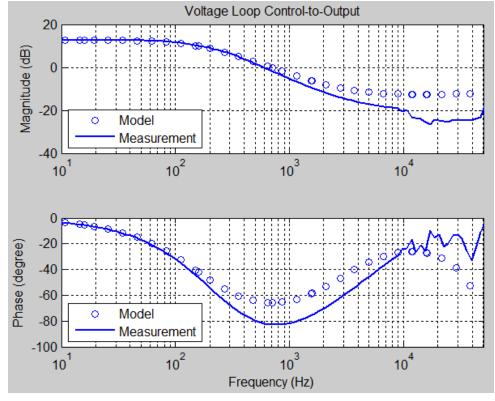

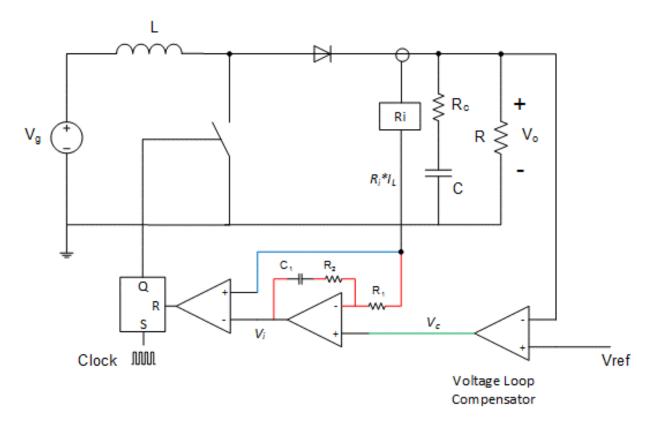

Using this compensator, two different predictive current mode schemes were implemented on the DSP chip, and the frequency responses were measured using an AP300 network analyzer. The first method, proposed by Ferdowsi [22], utilizes the geometrical relationships between the inductor valley current and the current command from voltage loop regulator. It has been claimed that this method has very fast transient response with no overshoot/undershoot during the transient. The second method utilizes the average current in a predictive scheme, as described in Chapter 2. The difference between the two methods is that the first one subtracts the steady state ripple current value from the current command to determine the corresponding valley current command. Then the desired duty ratio is calculated using the sampled inductor valley current and valley current command. The measured frequency response for the first method is given in Figure 3.7 while that for the second method is given in Figure 3.8. For both methods, the model provides a very good prediction for the magnitude of the voltage loop transfer function. In the phase plots, the calculated and measured values are close until approximately 10 kHz. The network analyzer produces phase angles only in the range of -360° to 0°, which explains the abrupt phase change in these figures.

The two methods were programmed with an update delay equal to one switching period, which means the  $T_d$  in (3-2) is 10  $\mu$ s and n in (3-3) is 1. The magnitude peak between 10-11 kHz is caused by the delay  $H_c$ . In addition,  $H_c$  also affects the phase delay at high frequency, which is important for power converters designed with a high crossover frequency.

### 3-6. Conclusion

A small-signal model for predictive current mode control in CCM has been developed. The validity of this model has been confirmed through measurements on a prototype converter which was controlled by two different voltage loop compensators and two distinct predictive current controllers. It has been shown that it is reasonable to model the predictive current controller as a single proportional gain. The delay function H<sub>c</sub> and a zero order hold ZOH formed by the ADC and DPWM modules in a digital control unit should be considered in the loop gain. Expressions for the current loop and control-to-output transfer functions were derived based on the proposed model. Measurements with a network analyzer indicate that this model is useful in the design of the voltage loop regulator for a predictive current control technique.

Figure 3.7 Voltage loop gain of the technique proposed in [22]

Figure 3.8 Voltage loop gain of the technique described in Chapter 2

## CHAPTER 4. DIGITAL AVERAGE CURRENT MODE CONTROL

In this chapter, three different implementations for digital average current mode control for DC-DC converters operating in the continuous conduction mode are presented. These techniques are the basis for the digital I<sup>2</sup> average current mode control, which can be treated as a combination of peak current mode control with average current mode control and will be introduced in Chapter 5 and Chapter 6. The advantages and disadvantages of each implementation are described. Design procedures for the both the voltage and current loops are presented. Using a boost converter prototype, the dynamic performance of all three implementations has been evaluated and is presented here.

## 4-1. Introduction

Average current mode control has been widely used in applications where the current needs to be strictly controlled, such as an LED driver, a battery charger or power factor correction. This type of control provides improved noise immunity and the elimination of slope compensation required for peak current control [37] [38]. In comparison to an analog controller, a digital controller offers better programmability and more flexibility [33]. The combination of a digital controller and average current mode control is an excellent solution for Li-Ion battery charging [39], as it requires both constant current and constant voltage operation. In the current control stage of the charging process, the digital controller samples the current signal, calculates a current reference, and then adjusts the PWM control signal to supply the commanded current to the battery.

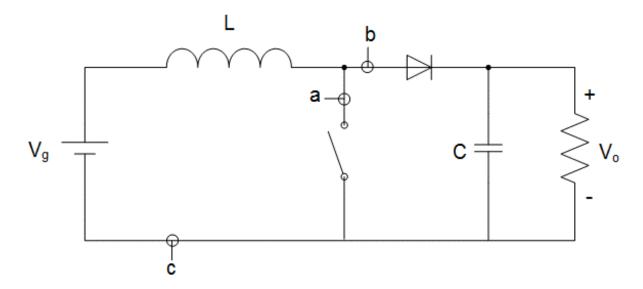

Figure 4.1 A boost converter showing potential current measurement point

When the charging process transitions to the voltage stage, the digital controller adjusts the current command by sampling the output voltage and comparing it to a voltage reference command.

Average current mode control requires sampling the inductor current in the converter. Three potential points for measuring the inductor current are marked on the boost converter shown in Figure 4.1. By measuring at point a, in series with the active switch, the rising part of the inductor current can be obtained. At point b, in series with the diode, the falling part of the inductor current can be measured. Measuring the current at point c, which is the inductor current, allows the full waveform to be sampled. Current sampling techniques are discussed in the next section followed by a discussion of compensator designs. Experimental results are included to illustrate the performance of these techniques.

# 4-2. Digital Average Current Designs and Performance

In this section, three current sampling techniques aimed at obtaining the average inductor current are introduced: geometric, low-pass filter, and slope midpoint. Each is discussed in detail, and corresponding advantages and disadvantages are analyzed.

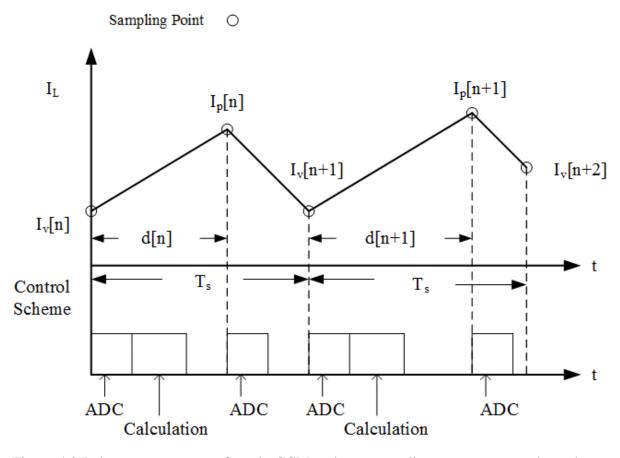

Figure 4.2 Inductor current waveform in CCM and corresponding program execution scheme

# 4-2-1. Geometric Design

This method utilizes the common shape of the inductor current in the continuous conduction mode. The average inductor current can be calculated by dividing the area enclosed by the waveform and the time axis in a switching cycle by the switching period. Then the required duty ratio is computed to make the average inductor current track a current reference  $I_c$ .

For the inductor current waveform shown in Figure 4.2, the area under the curve can be divided into two parts at the peak point, leaving two right trapezoids. Assume that the valley current and peak current of the  $n^{th}$  cycle are  $I_v[n]$  and  $I_p[n]$ , respectively. The average current for the  $n^{th}$  cycle <I[n]> can be expressed as

$$< I[n] > = \frac{1}{T_s} \left[ \frac{(l_v[n] + l_p[n])d[n]}{2} T_s + \frac{(l_v[n+1] + l_p[n])(1 - d[n])}{2} T_s \right]$$

(4-1)

where d[n] is the duty ratio for the n<sup>th</sup> cycle. Rearranging the terms in (4-1) yields,

$$< I[n] > \frac{l_v[n] \cdot d[n] + l_p[n] + l_v[n+1] \cdot (1 - d[n])}{2}$$

(4-2)