### Analog Computation of a High Frequency Exactly Solvable Chaotic Communication System Using State Variable Networks

by

Aubrey Nathan Beal

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama August 1, 2015

Keywords: Analog Computing, Chaotic Oscillator, Chaos Communication

Copyright 2014 by Aubrey Nathan Beal

Approved by

Dr. Robert N. Dean, Chair, Associate Professor of Electrical and Computer Engineering Dr. Lloyd S. Riggs, Professor of Electrical and Computer Engineering

Dr. Bogdan M. Wilamowski, Professor of Electrical and Computer Engineering

Dr. Michael C. Hamilton, Assistant Professor of Electrical and Computer Engineering

Dr. Ned J. Corron, Adjunct Assistant Professor of Physics, University of Alabama in Huntsville

#### Abstract

The design of a high frequency, chaotic oscillator and linear matched filter has been shown as a viable means of electronic communication. Although many chaotic systems are noted for complex or unpredictable behavior, a class of chaotic oscillators may be constructed by imposing elementary, iterated maps with unstable, linear oscillations. These simple hybrid systems exhibit closed-form solutions that allow expressions of the system's symbolic dynamics. Previously, these exact solvable systems have been implemented at low frequencies (~100Hz-10kHz). This work considers the design, simulation, fabrication and testing of these systems at higher frequencies (~10kHz-2MHz). These designs contribute a frequency increase that effectively provides new applications for chaotic systems such as low probability of intercept radar and communications using linear matched filters and well defined symbolic dynamics. A treatment of theory, modeling, simulation and implementation is provided.

#### Acknowledgments

I would like to deeply thank my advisor Dr. Robert N. Dean for his guidance, patience and encouragement throughout my studies and research. His support has nurtured an opportunity in higher education that I would have never found otherwise.

My sincere gratitude and respect are extended to the members of my committee: Dr. Lloyd S. Riggs, Dr. Bogdan M. Wilamowski, Dr. Michael C. Hamilton and Dr. Ned J. Corron. Each of these individuals has taught me invaluable merit in persistence, academic study and personal character. Their thoughtful and engaging conversations will stay with me for a long time.

Most critically, I thank my wife, Anna Beal, my family and my friends for their understanding and willingness to endure my pursuit of a doctoral degree. Without this support network, my goals in academia would would be far out of reach.

### Table of Contents

| Abstract                                                | ii   |

|---------------------------------------------------------|------|

| Acknowledgments                                         | iii  |

| List of Figures                                         | vii  |

| List of Tables                                          | ciii |

| 1 Introduction                                          | 1    |

| 1.0.1 Organization of Material                          | 2    |

| 2 Background                                            | 3    |

| 2.1 Exact Solvable Chaos                                | 3    |

| 2.2 The Iterated Shift Map                              | 3    |

| 2.3 Exact Solvable Shift-band Chaos                     | 5    |

| 2.4 Analytic Solution for Shift-band Chaos              | 10   |

| 2.5 Symbolic Dynamics for the Shift-band                | 16   |

| 2.6 Control of Chaotic Systems                          | 18   |

| 2.7 Shift-Band Linear Solution                          | 19   |

| 2.8 Spectral Content of Shift-Band Oscillations         | 20   |

| 2.9 Linear Matched Filters                              | 20   |

| 2.10 Shift-band Linear Matched Filter                   | 25   |

| 2.11 Overview of Exactly Solvable Communications System | 26   |

| 2.12 Ergodic Properties of Exact Solvable Chaos         | 29   |

| 3 Subsystem Circuit Design and Simulation               | 33   |

| 3.1 System Overview                                     | 33   |

| 3.2 Stable and Unstable RLC Tank Circuits               | 34   |

| 3.2.1 Operational Amplifier -RLC Synthesis              | 38   |

| 3.3<br>3.4<br>3.5<br>3.6<br>4.1 | 3.3.1<br>3.3.2<br>Zero (<br>3.4.1<br>3.4.2<br>Guard<br>3.5.1<br>3.5.2<br>Delay<br>3.6.1<br>3.6.2                                   | n Function                                                                    | 58<br>58<br>59                               |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------|

| 3.5<br>3.6<br>- S               | 3.3.2<br>Zero (<br>3.4.1<br>3.4.2<br>Guard<br>3.5.1<br>3.5.2<br>Delay<br>3.6.1<br>3.6.2                                            | Opamp & Comparator Thresholding                                               | 52<br>53<br>56<br>58<br>58<br>59<br>60<br>61 |

| 3.5<br>3.6<br>- S               | Zero (<br>3.4.1<br>3.4.2<br>Guard<br>3.5.1<br>3.5.2<br>Delay<br>3.6.1<br>3.6.2                                                     | Crossing Detector                                                             | 53<br>56<br>58<br>58<br>59<br>60<br>61       |

| 3.5<br>3.6<br>- S               | <ul> <li>3.4.1</li> <li>3.4.2</li> <li>Guard</li> <li>3.5.1</li> <li>3.5.2</li> <li>Delay</li> <li>3.6.1</li> <li>3.6.2</li> </ul> | Simple Hysteresis                                                             | 53<br>56<br>58<br>59<br>60<br>61             |

| 3.6<br>- S                      | <ul> <li>3.4.2</li> <li>Guard</li> <li>3.5.1</li> <li>3.5.2</li> <li>Delay</li> <li>3.6.1</li> <li>3.6.2</li> </ul>                | Schmitt Trigger Topology                                                      | 56<br>58<br>59<br>60<br>61                   |

| 3.6<br>- S                      | Guard<br>3.5.1<br>3.5.2<br>Delay<br>3.6.1<br>3.6.2                                                                                 | Circuit                                                                       |                                              |

| 3.6<br>- S                      | 3.5.1<br>3.5.2<br>Delay<br>3.6.1<br>3.6.2                                                                                          | Sample & Hold                                                                 | 58<br>59<br>60<br>61                         |

| S                               | 3.5.2<br>Delay<br>3.6.1<br>3.6.2                                                                                                   | Latches, D-Flip Flops & Latched Comparators            Conversion Based Delay | 59<br>60<br>61                               |

| S                               | Delay<br>3.6.1<br>3.6.2                                                                                                            | Conversion Based Delay                                                        | 60<br>61                                     |

| S                               | 3.6.1<br>3.6.2                                                                                                                     | Conversion Based Delay                                                        | 61                                           |

|                                 | 3.6.2                                                                                                                              | v                                                                             |                                              |

|                                 |                                                                                                                                    | All Pass Filter                                                               | 61                                           |

|                                 |                                                                                                                                    |                                                                               | 01                                           |

| 4.1                             | ystem D                                                                                                                            | esign and Simulation                                                          | 70                                           |

|                                 | Opam                                                                                                                               | p Synthesized System                                                          | 71                                           |

|                                 | 4.1.1                                                                                                                              | Opamp Synthesized Transmitter Circuit                                         | 71                                           |

|                                 | 4.1.2                                                                                                                              | Opamp Synthesized Receiver Circuit                                            | 76                                           |

| 4.2                             | OTA S                                                                                                                              | Synthesized System                                                            | 78                                           |

|                                 | 4.2.1                                                                                                                              | OTA Synthesized Transmitter Circuit                                           | 78                                           |

|                                 | 4.2.2                                                                                                                              | Chaotic Transmitter with AMIS $0.5\mu m$ Process OTAs                         | 80                                           |

| Н                               | ardware                                                                                                                            | Implementation & Results                                                      | 86                                           |

| 5.1                             | Opam                                                                                                                               | p-based Transmitter Prototype                                                 | 86                                           |

| 5.2                             | Opam                                                                                                                               | p-based Transmitter Proof of Concept                                          | 88                                           |

| 5.3                             | All-pa                                                                                                                             | ss Delay of Exact Solvable Chaos                                              | 92                                           |

| C                               | onclusio                                                                                                                           | n                                                                             | 94                                           |

| Υ F                             | uture W                                                                                                                            | ork                                                                           | 95                                           |

| Ap | openc | dice | es.  |     |      |      |     |     | • |  |  |   | • | <br> | • | • | • | • | • | • |       |   | • | • |  | <br>• | • | 100 |

|----|-------|------|------|-----|------|------|-----|-----|---|--|--|---|---|------|---|---|---|---|---|---|-------|---|---|---|--|-------|---|-----|

| А  | SI    | PIC  | CE M | [OI | DEL  | .S . |     |     | • |  |  |   | • |      |   | • | • |   | • |   | <br>• |   | • |   |  |       |   | 101 |

|    | A.1   | А    | MIS  | 0.5 | 5 µr | n P  | roc | ess |   |  |  | • | • |      |   | • | • |   | • | • | <br>• | • |   |   |  |       |   | 101 |

# List of Figures

| 2.1  | Plot of iterated shift-map                                                                                                             | 4  |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Function block diagram of exact solvable shift band chaotic system                                                                     | 6  |

| 2.3  | Time series data for solution $u(t)$ of shift band chaotic system in SIMULINK<br>with $\beta = 0.81 \cdot \ln 2$ and $\omega = 2\pi$ . | 7  |

| 2.4  | Time series data for $s(t)$ of shift band chaotic system in SIMULINK                                                                   | 7  |

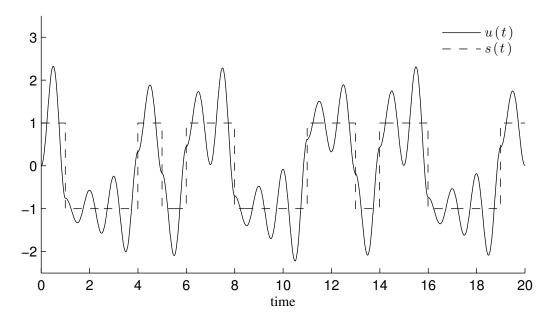

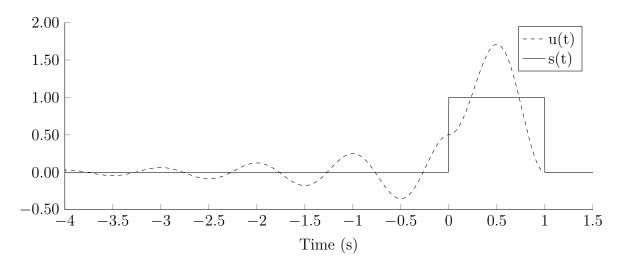

| 2.5  | Time series data for solutions $u(t)$ and $s(t)$ of shift band chaotic system in SIMULINK overlain.                                    | 8  |

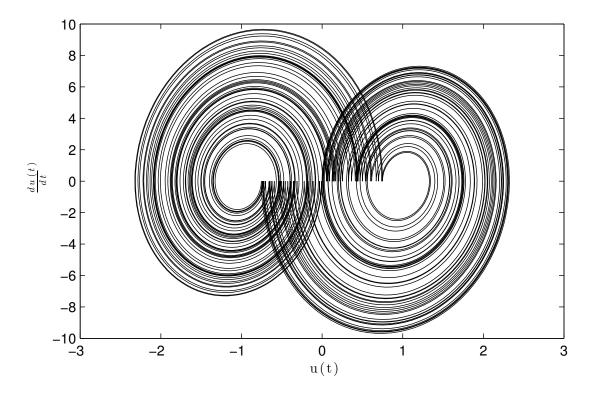

| 2.6  | Phase space data for shift band chaotic system in SIMULINK with $\beta = 0.81 \cdot \ln 2$<br>and $\omega = 2\pi$                      | 9  |

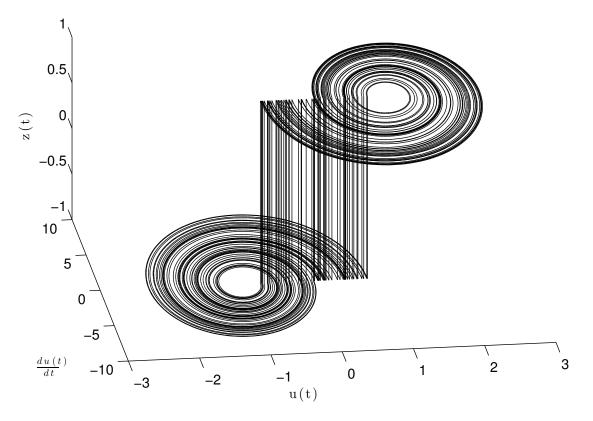

| 2.7  | 3D Phase space data for shift band chaotic system in SIMULINK                                                                          | 10 |

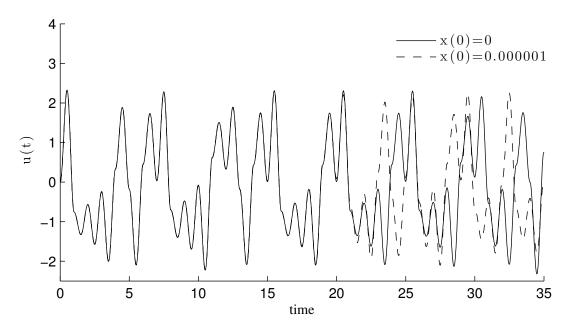

| 2.8  | Time series divergence of shift map chaotic system due to small change in initial condition.                                           | 11 |

| 2.9  | Basis pulse for synthesizing chaos via linear superposition with $\beta = \ln(2)$                                                      | 20 |

| 2.10 | Basis pulse for synthesizing chaos via linear superposition with $\beta = \ln(2)$                                                      | 21 |

| 2.11 | Function block diagram of matched filter for the basis pulse of the exact solvable shift-band chaotic system.                          | 27 |

| 2.12 | Overview of exactly solvable chaotic communications system.                                                                            | 28 |

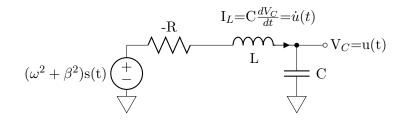

| 3.1  | Lumped element circuit realization of unstable, linear portion of the exactly solvable chaotic system                         | 35 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

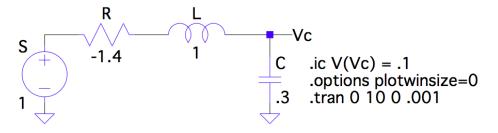

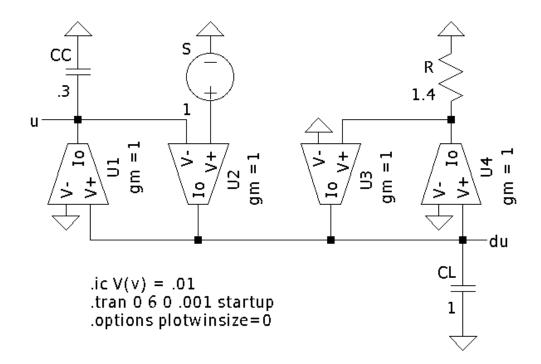

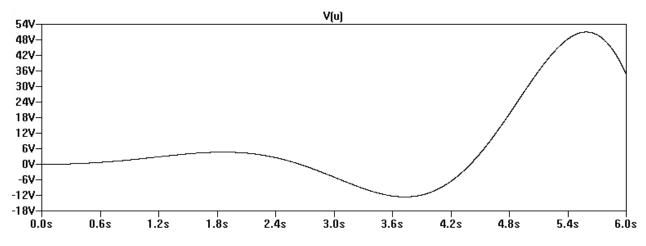

| 3.2  | LTSPICE IV simulation schematic of unstable -RLC network with $R = -1.4\Omega$ ,<br>C = .3F and $L = 1H$ .                    | 36 |

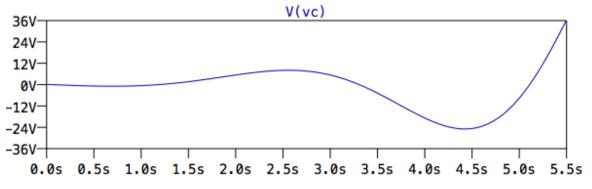

| 3.3  | LTSPICE IV simulation result of unstable -RLC network with $R = -1.4\Omega$ , $C = .3F$ and $L = 1H$ .                        | 36 |

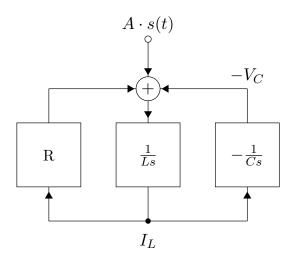

| 3.4  | State variables for unstable -RLC tank circuit synthesized using integrators in a ladder network                              | 37 |

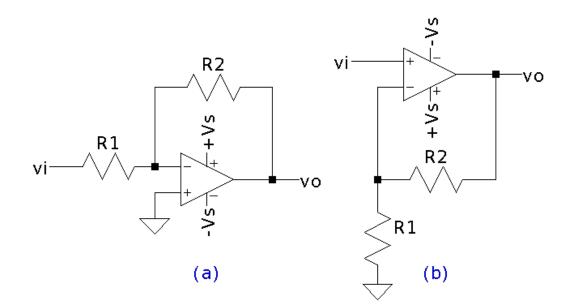

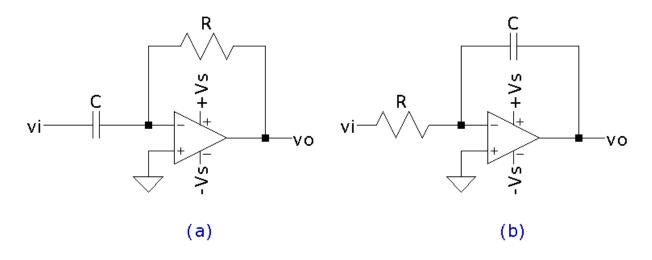

| 3.5  | (a) Inverting amplifier topology using operational amplifier (b) Non-inverting amplifier topology using operational amplifier | 38 |

| 3.6  | (a) Differentiator topology using operational amplifier (b) Integrator topology using operational amplifier                   | 39 |

| 3.7  | -RLC network realized using operational amplifier ladder filter techniques                                                    | 41 |

| 3.8  | Waveform of opamp ladder filter synthesized -RLC network simulation schematic for LTSPICEIV                                   | 41 |

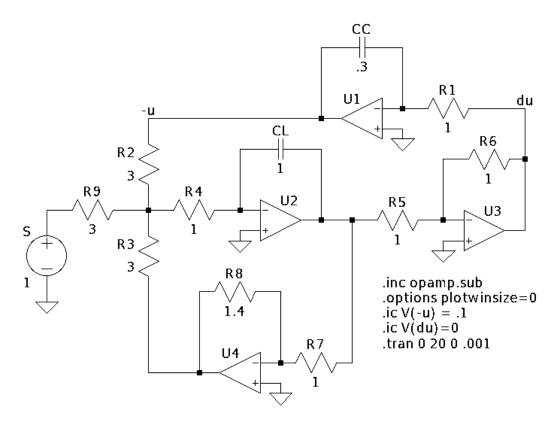

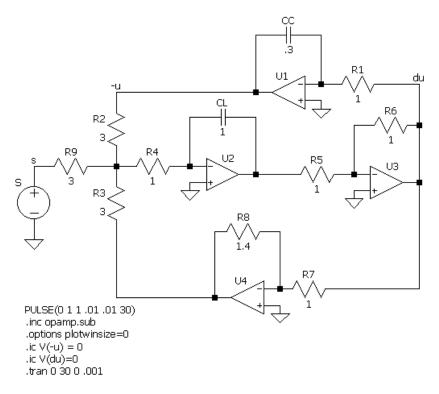

| 3.9  | Opamp ladder filter synthesized -RLC network simulation schematic for LTSPI-<br>CEIV                                          | 42 |

| 3.10 | Opamp Ladder filter synthesized RLC network simulation schematic for LTSPI-<br>CEIV                                           | 43 |

| 3.11 | Waveform for opamp ladder filter synthesized RLC network simulation schematic for LTSPICEIV                                   | 44 |

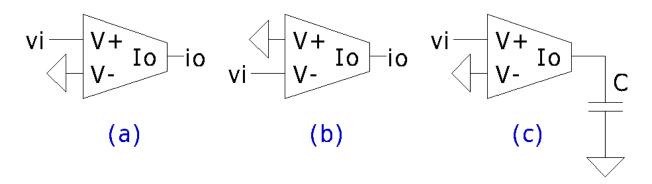

| 3.12 | (a) Non inverting amplifier topology using OTA (b) Inverting amplifier topology |    |

|------|---------------------------------------------------------------------------------|----|

|      | using OTA (c) No inverting integrator topology using OTA                        | 45 |

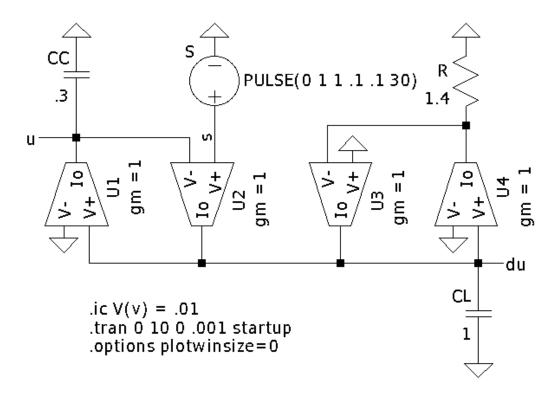

| 3.13 | LTSPICEIV simulation schematic for OTA implementation of unstable -RLC          |    |

|      | network                                                                         | 46 |

| 3.14 | LTSPICEIV simulation waveform for OTA implementation of unstable -RLC           |    |

|      | network                                                                         | 47 |

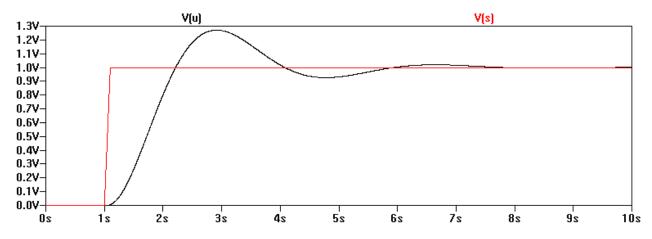

| 3.15 | LTSPICEIV simulation schematic for OTA implementation of stable RLC network     | 47 |

| 3.16 | LTSPICEIV simulation waveform for OTA implementation of stable RLC network      | 48 |

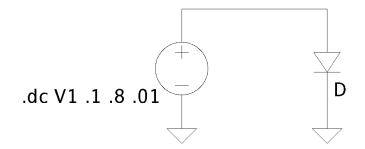

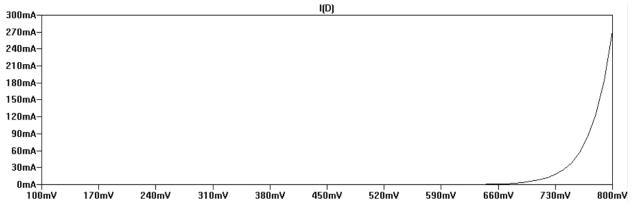

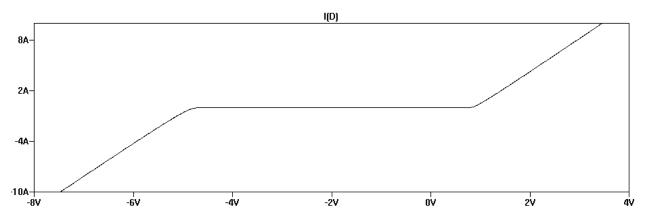

| 3.17 | Schematic for SPICE simulation of forward biased diode with $V_D = V1$          | 49 |

| 3.18 | SPICE simulation of I-V relationship of a forward-biased diode                  | 50 |

| 3.19 | SPICE simulation of I-V relationship of a forward-biased diode                  | 50 |

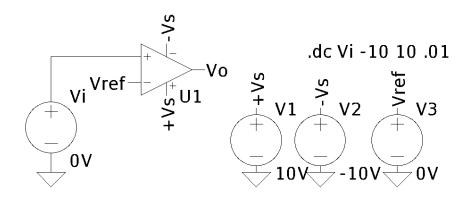

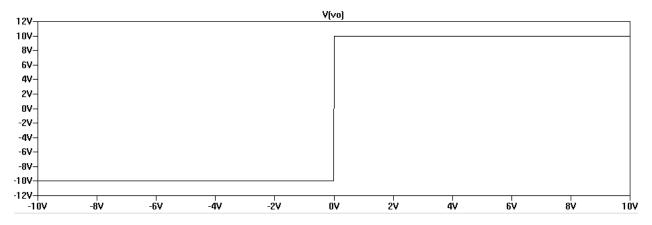

| 3.20 | Simulation schematic for opamp used as a comparator in LTSPICEIV                | 52 |

| 3.21 | Simulation results for opamp used as a comparator in LTSPICEIV                  | 53 |

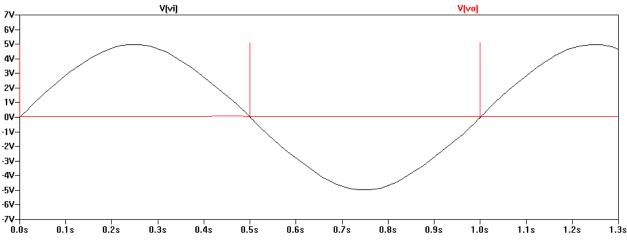

| 3.22 | Simulation results for ideal zero crossing detector in LTSPICEIV                | 54 |

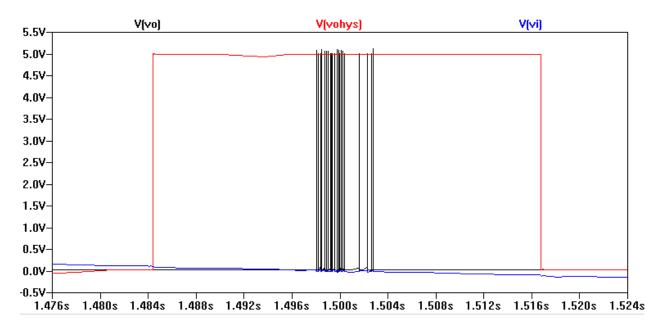

| 3.23 | Zoomed view of simulation results for zero crossing detector comparison in LT-  |    |

|      | SPICE IV when 100mV of random white noise is introduced. $\ldots$               | 55 |

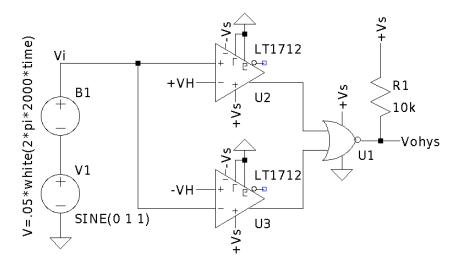

| 3.24 | Simulation results for opamp used as a comparator in LTSPICEIV                  | 55 |

| 3.25 | Simulation results for opamp used as a comparator in LTSPICEIV                  | 56 |

| 3.26 | Guard circuit using sample and hold function block.                             | 59 |

| 3.27 | Latch based circuits to implement the guard condition digitally: (a) integrated                                                                     |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | D latch (b)D latch using AND & OR gates (c) D latch using NAND gates (d)                                                                            |    |

|      | latched comparator as guard circuit.                                                                                                                | 60 |

| 3.28 | Signal delay scheme utilizing an ADC, timed storage in a $\mu C$ and a DAC. $~$                                                                     | 61 |

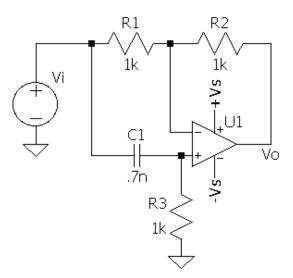

| 3.29 | Circuit schematic for a single all-pass delay cell                                                                                                  | 62 |

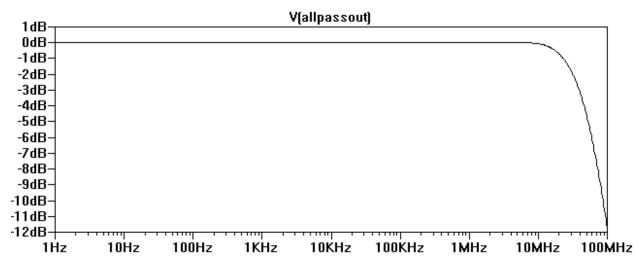

| 3.30 | Output magnitude of a single all-pass delay cell as a function of frequency                                                                         | 64 |

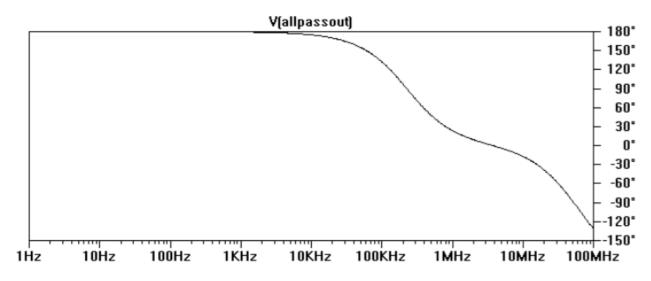

| 3.31 | Output phase of a single all-pass delay cell as a function of frequency                                                                             | 64 |

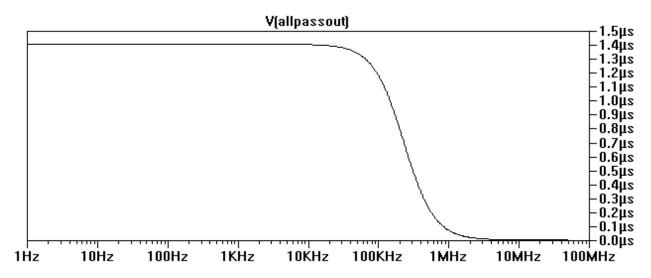

| 3.32 | Group delay of a single all-pass delay cell as a function of frequency. $\ . \ . \ .$                                                               | 66 |

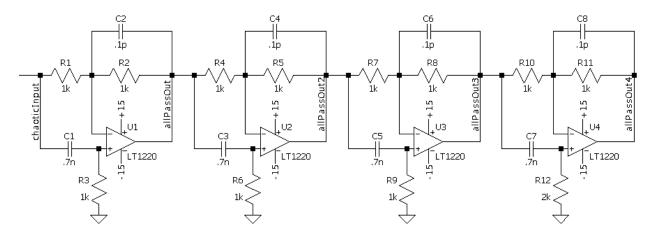

| 3.33 | Schematic of 4 cascaded all-pass delay stages used to increase total effective signal                                                               |    |

|      | delay                                                                                                                                               | 66 |

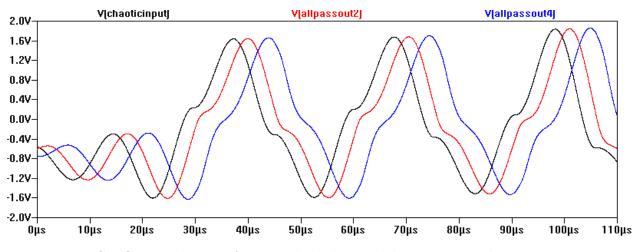

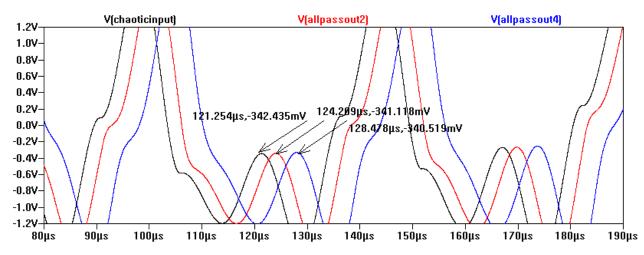

| 3.34 | SPICE simulation of 4 cascaded all-pass delay stages as shown in Figure 3.33. $% \left( {{{\rm{B}}} \right) = 0.0000000000000000000000000000000000$ | 67 |

| 3.35 | Zoomed view of LTSPICE simulation of 4 cascaded all-pass delay stages as shown                                                                      |    |

|      | in Figure 3.33                                                                                                                                      | 68 |

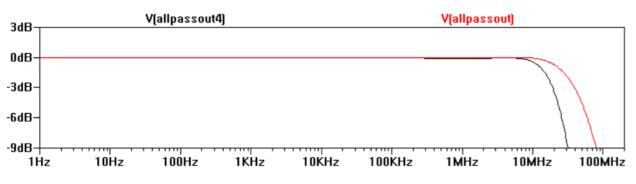

| 3.36 | Output magnitude comparison of a single all-pass delay cell and 4 cascaded delay                                                                    |    |

|      | cells as a function of frequency.                                                                                                                   | 69 |

| 4.1  | Detailed overview of exact solvable chaotic system with identified subsystem com-                                                                   |    |

|      | ponents                                                                                                                                             | 70 |

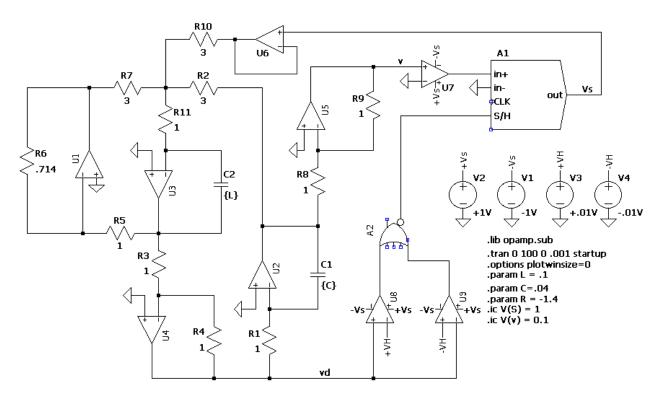

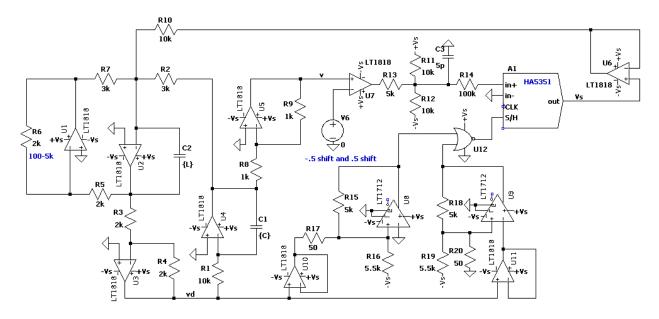

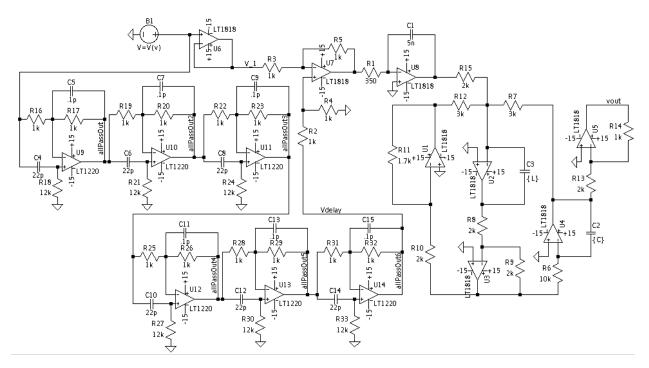

| 4.2  | LTSPICE simulation schematic of op amp synthesized transmitter circuit. $\ . \ .$                                                                   | 72 |

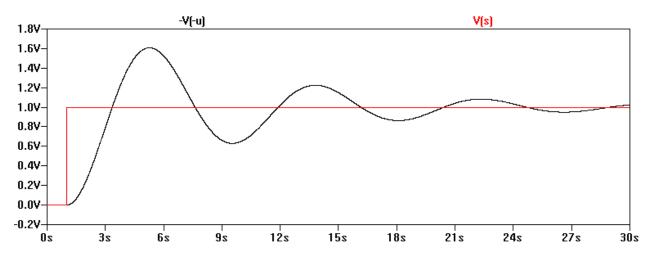

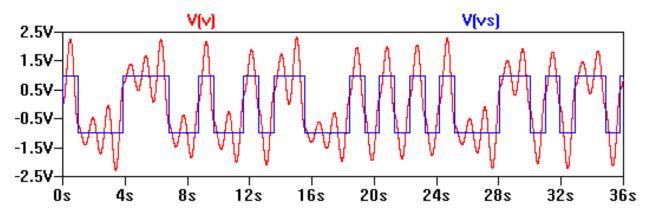

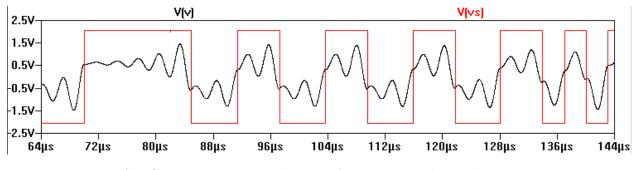

| 4.3  | LTSPICE time-series simulation of op amp synthesized transmitter circuit                                                                            | 72 |

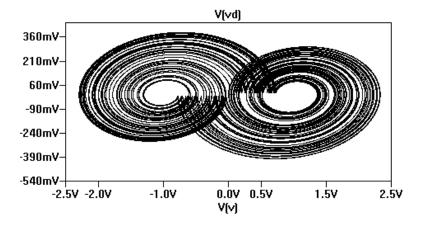

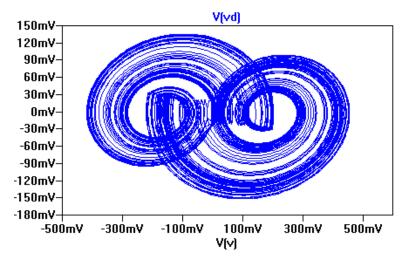

| 4.4  | LTSPICE phase space simulation of op amp synthesized transmitter circuit                                                                            | 73 |

| 4.5  | LTSPICE simulation schematic of the scaled op amp synthesized transmitter                                                                                                                                   |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | circuit                                                                                                                                                                                                     | 74 |

| 4.6  | LTSPICE time-series simulation of op amp synthesized transmitter circuit                                                                                                                                    | 74 |

| 4.7  | LTSPICE phase space simulation of scaled op amp synthesized transmitter circuit.                                                                                                                            | 75 |

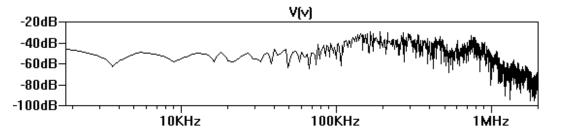

| 4.8  | LTSPICE FFT simulation of scaled op amp synthesized transmitter circuit                                                                                                                                     | 75 |

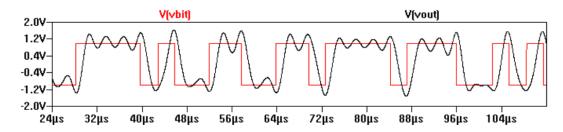

| 4.9  | LTSPICE simulation schematic for the linear matched filter corresponding to the basis pulse of the chaotic oscillator. Values used were $C3 = C_L = 700pF$ and $C2 = C_C = 10pF$ .                          | 76 |

| 4.10 | SPICE simulation results for the linear matched filter corresponding to the basis                                                                                                                           |    |

|      | pulse of the chaotic oscillator shown if Figure 4.9.                                                                                                                                                        | 78 |

| 4.11 | Simplified schematic of chaotic oscillator using ideal OTAs                                                                                                                                                 | 79 |

| 4.12 | Simulated time series waveform of the circuit provided by Figure 4.11                                                                                                                                       | 80 |

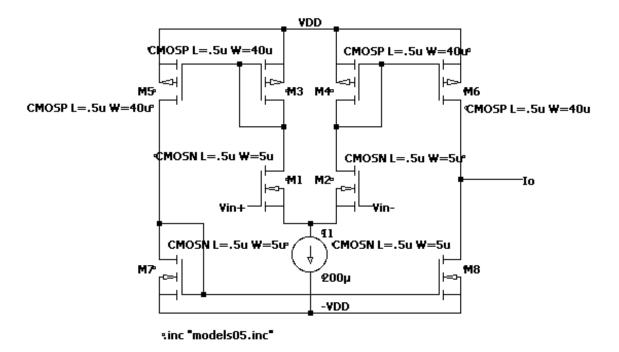

| 4.13 | Transistor level schematic for an AMIS 0.5 $\mu m$ process OTA                                                                                                                                              | 81 |

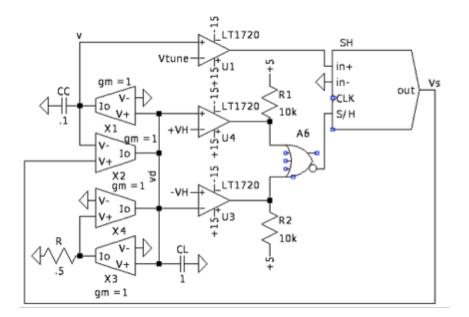

| 4.14 | SPICE simulation showing how the transconductance $G_m$ of the network in Figure 4.13 changes in respect to signal frequency provided at its input. A single ended supply was used with a 9V supply source. | 83 |

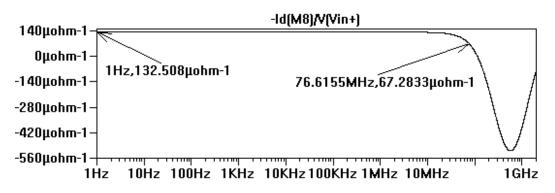

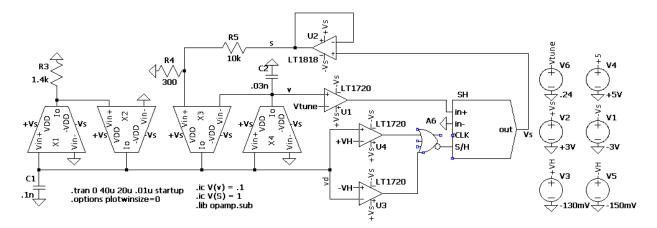

| 4.15 | Chaotic transmitter simulation schematic for using AMIS 0.5 $\mu m$ process OTAs and off-the-shelf folding and guard circuit components.                                                                    | 84 |

| 4.16 | SPICE simulation showing chaotic time series data produced by the circuit in Figure 4.15.                                                                                                                   | 84 |

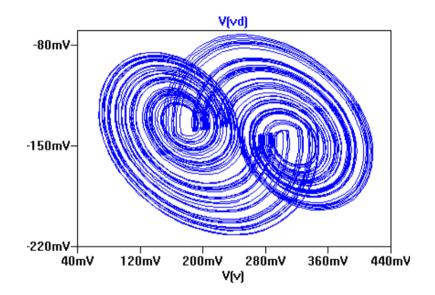

| 4.17 | SPICE simulation showing phase space data produced by the circuit in Figure 4.15.                                                                                                                           | 85 |

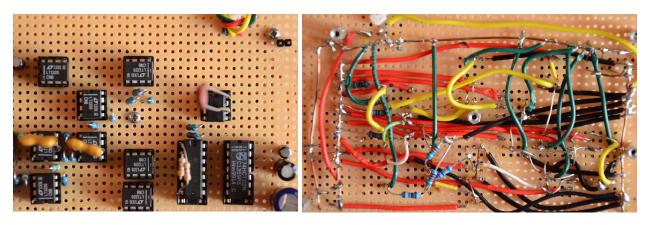

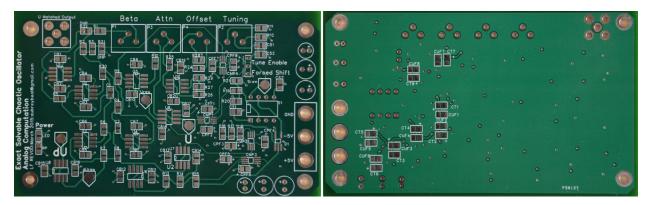

| 5.1 | Low frequency prototype of chaotic oscillator – LEFT: top side of prototype –        |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | RIGHT: bottom side of prototype                                                      | 87 |

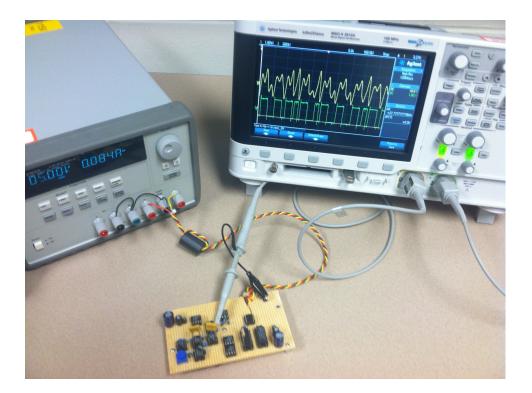

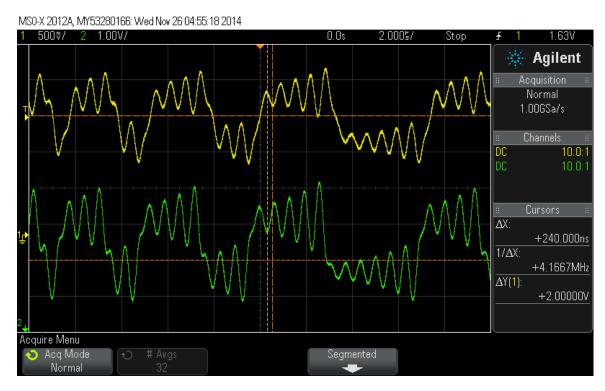

| 5.2 | Testing of the LF chaotic transmitter prototype                                      | 87 |

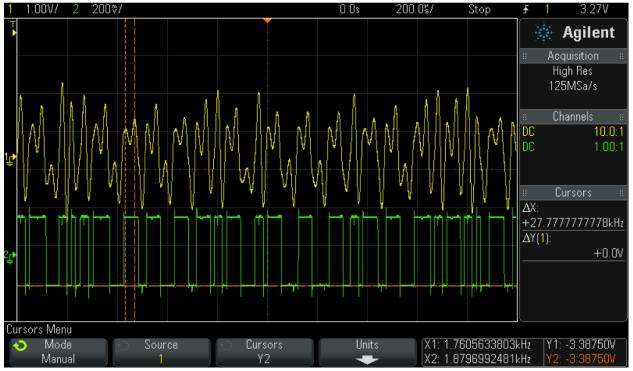

| 5.3 | Testing results of the LF chaotic transmitter prototype. (Yellow) Continuous         |    |

|     | voltage signal $V_v = u(t)$ . (Green) Discrete switching function $V_S = s(t)$       | 88 |

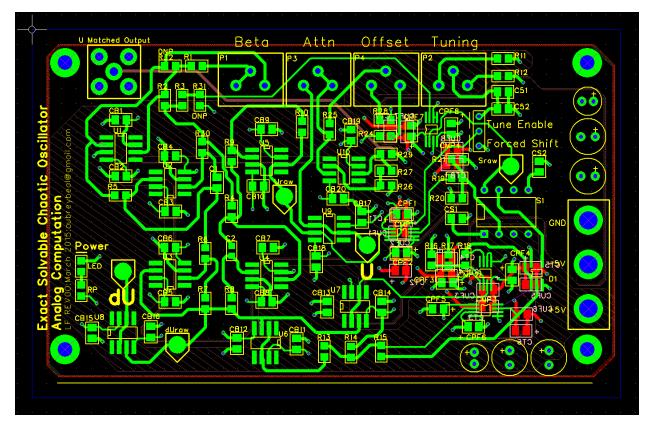

| 5.4 | CAD screen capture depicting the Rev 0 four layer PCB design of the chaotic          |    |

|     | transmitter circuit.                                                                 | 89 |

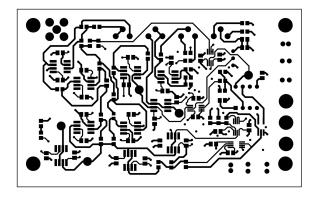

| 5.5 | Top and bottom layers of chaotic transmitter PCB                                     | 90 |

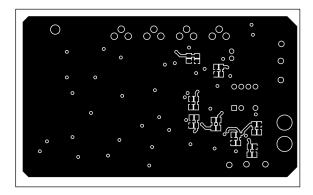

| 5.6 | Middle layers of chaotic transmitter PCB                                             | 91 |

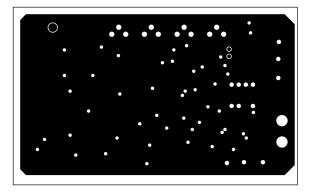

| 5.7 | Unpopulated chaotic transmitter PCB                                                  | 92 |

| 5.8 | Completed PCB showing fully populated circuit.                                       | 92 |

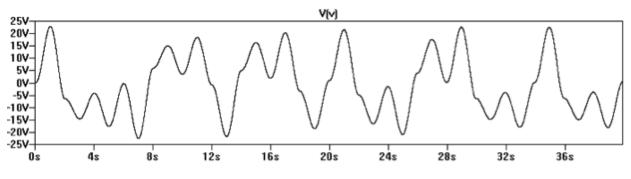

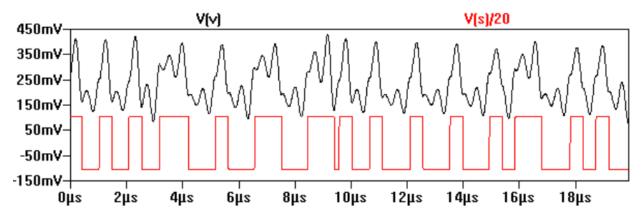

| 5.9 | Testing results for a single delay cell using op amp based all-pass filter used as a |    |

|     | delay for a chaotic voltage signal                                                   | 93 |

## List of Tables

| 3.1 | Table displaying the input/output relationship of a D-flip flop as it applies to the |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | guard condition.                                                                     | 60 |

#### Chapter 1

#### Introduction

A simple, high frequency (HF), mixed signal chaotic oscillator has been realized in hardware. This oscillator topology exhibits many innate advantages of both linear and nonlinear systems due to its closed form solution. Novel low frequency (LF) oscillators (700Hz-2kHz) exhibiting solvable, chaotic behavior have been previously proposed, however, the generation of low frequency signals has limited applicability in fields such as Communications.

These limitations motivate the development of similarly solvable, chaotic oscillators that operate in HF bands ( $\sim 1$ MHz). The nonlinear dynamics of such chaotic systems provide interesting and exclusive, real world advantages to engineering applications. These inherent benefits include synchronicity, the spreading of spectral components, truly random number generation and the capacity for securely encoding information through the means of small perturbation techniques known as Ott, Grebogi and Yorke (OGY) control to achieve Hayes type chaos communications.

Furthermore, it has been shown that symbolic information encoded with oscillators of this topology may be extracted accurately and elegantly through means of a simple, linear matched filter for optimal performance in the presence of additive gaussian white noise (AGWN). Unfortunately, implementation problems involving extreme frequency dependence of negative impedance converter circuits complicate the system's symbolic dynamics.

This work provides the analog computation of such systems using linear analog filter synthesis techniques in order to mitigate the non ideal component issues. The result is a HF electrical system with high fidelity dynamics in respect to the intended set of nonlinear differential equations. This behavior was verified in hardware through a LF prototype using operational amplifiers (opamps). Finally, a HF system design utilizing operational transconductance amplifiers (OTAs) was verified through SPICE simulation and a clear path to an application specific integrated circuit (ASIC) was provided.

#### 1.0.1 Organization of Material

The material in this manuscript is offered in 6 distinct section. After this brief introduction, Chapter 2 offers a background of exact solvable chaos as well as previous work related to the topic. Chapter 3 focuses on modeling and designing each subsystem needed to realize the exact solvable chaotic system transmitter and receiver. In most cases several circuit realizations are offered with a short discussion of alternate designs and trade-offs. The system in its entirety is examined in Chapter 4. The communication is implemented fully using operational amplifiers, and partially using operational transconductance amplifiers. Chapter 5 addresses hardware implementation and results as well as errors. Finally, Chapter 6 offers a conclusion to the work and provides suggestions for extending these endeavors.

#### Chapter 2

#### Background

#### 2.1 Exact Solvable Chaos

Counterintuitively, complex behavior may often arise from simple systems or rule sets. Although complicated system dynamics are found in examples of sophisticated functions, the interconnectivity of variables contributes to significant complexity. In an effort to construct a complex system from simple functions, consider the dynamics of an elementary iterated map imposed upon a simple basis function such as a linear 2<sup>nd</sup> order differential equation. This chapter reviews a detailed analysis of this concept revealing that from simple functions (such as a binary shift or a set of piecewise linear conditions), second order oscillations may be conditioned to exhibit chaotic behavior without prohibiting a closed-form solution.

More precisely, noninvertible dynamics characterized by a chaotic semi-flow may be observed in a low-dimensional equation that includes a discontinuous, nonlinear term. A chaotic set of continuous-time waveforms is then defined using linear differential equations. This linear system is not chaotic, but a family of linear systems may be distinguished with solutions which collectively constitute a chaotic set. This chaotic set provides an analytic solution for the resultant nonlinear differential equation.[17]

#### 2.2 The Iterated Shift Map

As an introductory example of a simple iterated map, consider the iteration:

$$x_{n+1} = 2x_n \operatorname{mod}(1) \tag{2.1}$$

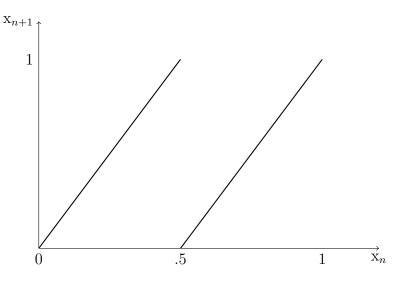

Figure 2.1: Plot of iterated shift-map

This iterated map will be referred to as the shift map but may be addressed in other literature as the Bernoulli shift map, bit-shift map, doubling map or sawtooth map. Figure 2.1 shows this map's symmetric behavior as it undergoes iteration. Consider initial conditions for this map as some binary decimal

$$x_0 = 0.a_1 a_2 a_3 \dots = \sum_{j=1}^{\infty} 2^{-j} a_j, \qquad (2.2)$$

where  $a_j$  is represented by either 0 or 1. This map iterates the initial condition by setting the first decimal place equal to 0 and multiplying the result by 2. This doubling results in a left bit shift, i.e. the decimal place will move to the right giving  $x_1 = 0.a_2a_3a_4...$  and  $x_2 = 0.a_3a_4a_5...$  [24] It is clear that changes to very precise digits that occupy spaces far to the right of the decimal have little impact on early iteration values. These digits are gradually shifted into more dominant positions in a doubling fashion. This behavior provides evidence of the map's sensitivity to initial conditions.

Ott compares this kneading mechanism to a map on a circle by suggesting the modulo 1 function acts upon x as if it were an angle variable. [24] One revolution around this circle corresponds to x increasing from 0 to 1. Expanding this concept, the shift map may be thought of as a *strech-twist-fold* operation. The circumference of the circle is first uniformly

stretched to twice its initial length. This newly stretched circle is then twisted to construct a figure 8 shape that has upper and lower lobes equal to the original circumference. Finally, this figure 8 shape is combined by folding the upper lobe down on the lower lobe such that the two circles are pressed together. The progression of this operation satisfies the necessary stretching and folding needed to produce chaotic dynamics.

#### 2.3 Exact Solvable Shift-band Chaos

Chaos may be synthesized in the iterated shift map by means of a linear second order differential equation. [17] The result is a chaotic semi-flow possessing a return map that is a chaotic shift map. This system is realized by driving linear differential equations to define a low-dimensional chaotic set of continuous-time waveforms. These waveforms are exact analytic solutions to a chaotic, nonlinear differential equation. Exact symbolic dynamics for this system are observed due to these closed form, exact solutions. Interestingly, it may be shown that this system's Poincaré return map is conjugate to a shift-map as shown in Figure 2.1, thus providing an exact symbolic representation of the continuous-time waveform with a one-sided shift dynamic. [17]

Consider the linear, ordinary differential equation

$$\ddot{x} - 2\beta \dot{x} + (\omega^2 + \beta^2)(x) = (\omega^2 + \beta^2)s(t)$$

(2.3)

with initial conditions  $x(0) = x_0$  and  $\dot{x}(0) = y_0$ , where  $0 < \beta \leq \ln 2$  and  $\omega = 2\pi$  as a hybrid system. A binary waveform s(t) provides a conditional switching event or guard condition. This discrete signal may be loosely considered as a random square wave that provides a scaled, forcing function f(x) to the system  $\ddot{x} - 2\beta \dot{x} + (\omega^2 + \beta^2)(x) = f(x)$ . The unscaled, binary forcing is provided provisionally by the signum function, sgn(x), and is defined as

$$s(t) = \begin{cases} 1 & : u(t) \ge 0 \\ -1 & : u(t) < 0 \end{cases}$$

Note that the 2<sup>nd</sup> order system has a negative damping factor that cause the sinusoid to grow exponentially. As the system satisfies  $\dot{u}(t) = 0$ , the signum function is applied to u(t) and s takes the value of sgn(u). This value is held as the waveform resets and continues to grow until the next guard condition is satisfied, at which time the guard condition is reevaluated.

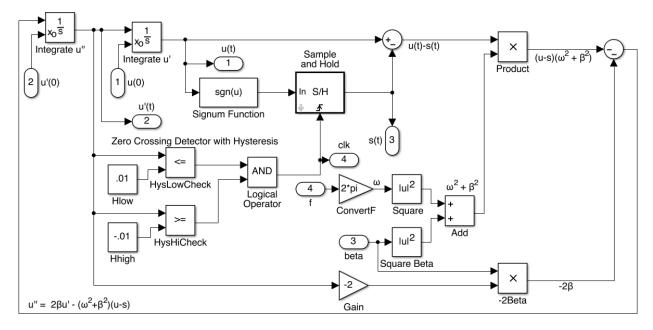

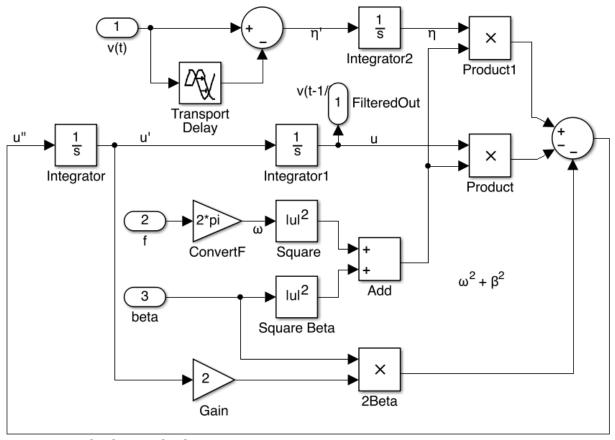

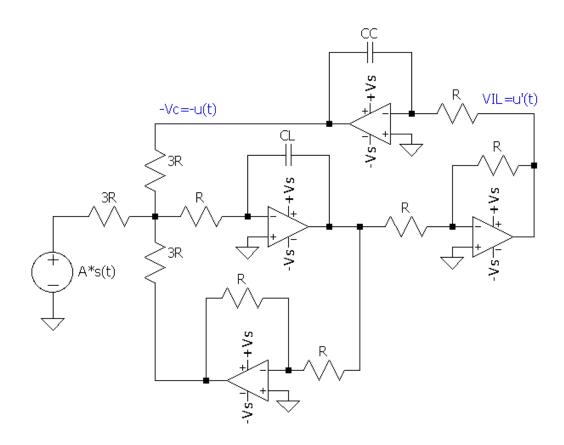

A function block diagram for a SIMULINK simulation of this system, as shown in Figure 2.11, provides a clear visualization of the simple continuous and discrete systems interconnected to give complex behavior.

Figure 2.2: Function block diagram of exact solvable shift band chaotic system.

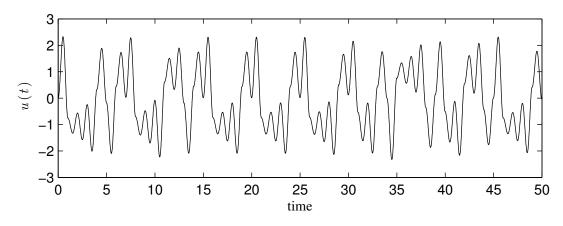

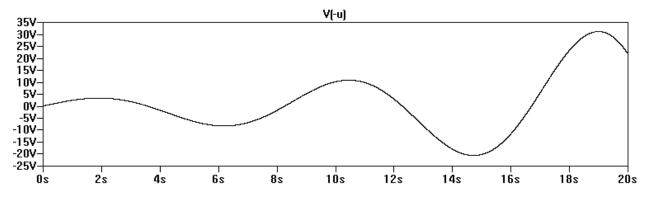

The resulting time series waveforms indicate the predicted growing  $2^{nd}$  order sinusoidal solution. Occasionally, the guard condition is met and resets the exponential growth of the sinusoid about a new equilibrium point that is governed by the signum function. This behavior is illustrated by Figure 2.3

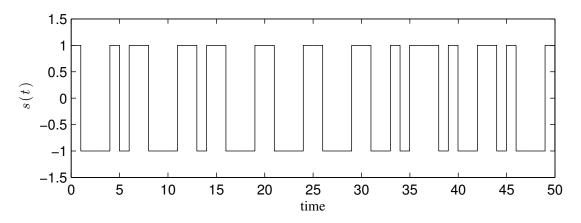

A bit stream is created by the unstable equilibrium points presented by the guard condition and is shown in Figure 2.4. This sequence has an exact solution given by the system's symbolic dynamics. Furthermore, if this bitstream is evaluated from a free running system beyond the precision of the initial conditions u(0) and  $\dot{u}(0)$ , the bitstream is truly

Figure 2.3: Time series data for solution u(t) of shift band chaotic system in SIMULINK with  $\beta = 0.81 \cdot \ln 2$  and  $\omega = 2\pi$ .

random (assuming that its initial condition is an irrational number). A treatment from first principles that considers this system as a true random number generator (TRNG) is given in a later section dealing with ergodic properties of these types of oscillators.

Figure 2.4: Time series data for s(t) of shift band chaotic system in SIMULINK.

The relation of the resulting bitstream s(t) to the solution u(t) is clearly depicted when the two signals are overlain as shown in Figure 2.5. The bitstream ultimately is a forcing function that is scaled to match the system's resonant frequency and damping factor. This forcing function provides one of two singular points for the solution u(t) and is continually evaluated by the guard condition.

When considering one-dimensional maps, chaotic systems must have both stretching and folding mechanisms. [24] In the case of the shift band system, the exponential growth of u(t)

Figure 2.5: Time series data for solutions u(t) and s(t) of shift band chaotic system in SIMULINK overlain.

provides the stretching functionality and the guard condition gives the required folding. The resulting system gives thick solution bands in the phase space diagram that are characteristic to chaotic systems as shown in Figure 2.6.

These solution bands indicate trajectories of the basis function as it is continuously presented one of two singular points. Viewing the phase-space as a function of s(t) clearly reveals that this system has a three dimensional phase space and satisfies Strogatz's classification of chaos. [28]. This is shown by Figure 2.7. This third degree of freedom allows nearby trajectories to diverge exponentially (positive Lyapunov exponent). Continuous systems in a 2-dimensional phase space cannot exhibit this type of divergence. [28]

This chaotic system provides exponential divergence of nearby trajectories (characterized by a positive Lyapunov exponent i.e. the term  $\beta$ ) and trajectory boundedness (achieved from threshold limiting). This type of divergence is the precise type of phenomena famously described by Lorenz. [1] A small change in the system's initial condition was simulated and the resulting time series data is given in Figure 2.8.

Figure 2.6: Phase space data for shift band chaotic system in SIMULINK with  $\beta = 0.81 \cdot \ln 2$ and  $\omega = 2\pi$ .

This characteristic of sensitivity to initial conditions must be carefully considered when designing a communication system. The precision of these initial conditions greatly affects the symbolic dynamics used to construct the system's coding function. This topic is considered out of scope as this work focuses in constructing hardware for chaotic transmitter and receiver circuits and not in controlling them to known symbol sequences.

Even so, it should be noted that these systems must be controlled timely as to stay within anticipated behavior. If the system is controlled after it has diverged from the known coding function, errors will occur. Furthermore, controlling these systems with a mapping that stresses initial condition precision limits may cause problems.

Similarly, the characteristic of trajectory boundedness must be considered carefully such that the practical electronic realization of these systems doesn't cause latching to supply rails. It has been shown that when considering the switching times, the continuous state

Figure 2.7: 3D Phase space data for shift band chaotic system in SIMULINK.

u(t) is guaranteed to be between the equilibrium points imposed by the switching event  $f(x) = (\omega^2 + \beta^2)s(t)$  for  $\beta \le \ln 2$ . This ensures that the system is bounded. [18]

#### 2.4 Analytic Solution for Shift-band Chaos

Recalling the hybrid system  $\ddot{u} - 2\beta\dot{u} + \omega_0^2[u-s] = 0$  where  $s(t) = sgn(u(t))|_{\dot{u}=0}$ ,  $\omega_0^2 = \omega^2 + \beta^2$ ,  $\omega^2$  and  $\beta^2$  are fixed parameters and  $0 < \beta \leq \ln 2$ , a general solution may be obtained analytically.[18] First, if the forcing function is ignored, the characteristic equation for the now homogeneous, linear, ordinary differential equation is

$$\lambda^2 - 2\beta\lambda + \omega_0^2 = 0. \tag{2.4}$$

Solving for the resulting eigenvalues by using the quadratic formula gives

Figure 2.8: Time series divergence of shift map chaotic system due to small change in initial condition.

$$\lambda_{1,2} = \frac{2\beta \pm \sqrt{(-2\beta)^2 - 4\omega_0^2}}{2} = \beta \pm j\omega$$

(2.5)

The general solution may be expressed of the form

$$u(t) = U \cdot e^{\lambda_{1,2}t} = C_1 e^{\lambda_1 t} + C_2 e^{\lambda_2 t}.$$

(2.6)

This gives a general solution to the system that may be expressed as

$$u(t) = C_1 e^{(\beta + j\omega)t} + C_2 e^{(\beta - j\omega)t} = Y e^{\beta t} e^{\pm j\omega t}.$$

(2.7)

It is useful to recall Euler's formula  $e^{jx} = \cos(x) + j\sin(x)$ . Applying this relationship gives the general solution

$$u(t) = e^{\beta t} \left[ C_1 \cos(\omega t) \pm j C_2 \sin(\omega t) \right].$$

(2.8)

In the case of linearly independent solutions to homogeneous ODEs, the linear sum, i.e. the real and imaginary parts, are taken independently to satisfy the ODE. This gives

$$u(t) = e^{\beta t} \left[ A\cos(\omega t) + B\sin(\omega t) \right].$$

(2.9)

If  $\dot{u}(t)$  is expressed, a system of equations involving u(0) and  $\dot{u}(0)$  may be produced in order to solve for the constants A and B. In an effort to reinforce undergraduate Calculus topics, the derivative of u(t) may be found by simply applying the product rule,  $(f \cdot g)' = f' \cdot g + f \cdot g'$ . This gives

$$\dot{u} = \beta e^{\beta t} A\cos(\omega t) - A\omega e^{\beta t} \sin(\omega t) + \beta e^{\beta t} B\sin(\omega t) + e^{\beta t} B\omega \cos(\omega t)$$

(2.10)

Creating a system of equations to find the constants A and B gives

$$u(0) = A \tag{2.11}$$

and

$$\dot{u}(0) = A\beta + B\omega = u_0\beta + B\omega.$$

(2.12)

Finally, solving for B gives the expression

$$B = \frac{\dot{u}(0)}{\omega} - \frac{u_0\beta}{\omega} \tag{2.13}$$

The solution may now be written as

$$u(t) = e^{\beta t} \left[ u_0 \cos(\omega t) + \left[ \frac{\dot{u}(0)}{\omega} - \frac{u_0 \beta}{\omega} \right] \sin(\omega t) \right].$$

(2.14)

Recalling the restriction  $\dot{u}(0) = 0$  gives

$$u(t) = e^{\beta t} \left[ u_0 \cos(\omega t) - \frac{u_0 \beta}{\omega} \sin(\omega t) \right] = u_0 e^{\beta t} \left[ \cos(\omega t) - \frac{\beta}{\omega} \sin(\omega t) \right].$$

(2.15)

In order to consider the result of the forcing function applied by the guard condition, this result may be elaborated to produce a general solution for the non-homogeneous case. This solution consists of the homogeneous solution  $u_h(t)$  and the particular solution  $u_p(t)$ such that  $u(t) = u_h(t) + u_p(t)$ . The homogeneous solution is expressed by Equation 2.15. To find the particular solution, it may be assumed that  $u_p(t)$  is of the same form as the forcing function, which is some constant  $C = s_0$ . This gives

$$u_p(t) = C. (2.16)$$

By differentiation,  $\dot{u}_p(t) = 0$  and  $\ddot{u}_p(t) = 0$ . Applying this to the original ODE gives  $0 - 0 + \omega_0^2(C - s) = 0$  or  $C = s_0$ . Combining the general solution and the particular solution such that  $u(t) = u_h(t) + u_p(t)$  gives

$$u(t) = s_0 + \left[u_0 - s_0\right] e^{\beta t} \left[\cos(\omega t) - \frac{\beta}{\omega} \sin(\omega t)\right].$$

(2.17)

Recall the restriction  $|u_0| < 1$ . In order to keep this restriction and simultaneously account for the particular solution  $u_p(t) = s_0$ , the homogeneous solution  $u_h(t)$  is modified such that  $u_h(t) = [u_0 - s_0]e^{\beta t} [\cos(\omega t) - \frac{\beta}{\omega}\sin(\omega t)].$

This general solution may be differentiated – i.e. recall Equation 2.12 with substituted constants A and B

$$\dot{u} = (u_0 - s_0)e^{\beta t}[\beta\cos(\omega t) - \omega\sin(\omega t) - \beta\frac{\beta}{\omega}\sin(\omega t) - \frac{\beta}{\omega}\omega\cos(\omega t)]$$

$$= (u_0 - s_0)e^{\beta t}[(-\omega + \beta\frac{\beta}{\omega})\sin(\omega t)]$$

$$\dot{u} = -(u_0 - s_0)e^{\beta t} \left(\frac{\omega^2 + \beta^2}{\omega}\right) \sin(\omega t)$$

(2.18)

This expression may be evaluated at zero crossings to investigate instances at which the guard condition is met. Because  $\omega = 2\pi$ , these zero crossings expressed by  $\dot{u} = 0$  occur when  $\sin(2\pi t) = 0$ . The first instance of where the guard condition is met occurs when t = 1/2.

Consider this system with the initial conditions  $u(0) = u_0$ ,  $\dot{u}(0) = 0$  and  $s(0) = s_0$  with the restriction  $|u(0)| \le 1$  and allow  $s_0 = sgn(u_0)$ .

Uninterestingly, when  $|u_0| = 1$  the system's solution is it's singular points  $u(t) = u_0$  and  $s(t) = s_0$ . However, in the case of  $|u_0| < 1$ , the solution is

$$u(t) = s_0 + \left[u_0 - s_0\right] e^{\beta t} \left[\cos(\omega t) - \frac{\beta}{\omega}\sin(\omega t)\right]$$

(2.19)

between switching conditions, i.e. while s(t) is constant. Evaluating the derivative described previously such that the guard condition is met gives

$$\dot{u}(t) = -(u_0 - s_0)e^{\beta t} \left(\frac{\omega^2 + \beta^2}{\omega}\right) \sin(\omega t) = 0.$$

(2.20)

For analytical purposes, recognize that  $\omega = 2\pi$ . The guard condition will be met periodically as described by setting  $\dot{u}(t) = 0$ . This occurs when  $\sin(2\pi t) = 0$  or in the fashion of  $t = \frac{n}{2}$ for integers n = 1, 2, 3, 4... The guard condition is first met as t = 1/2 giving

$$u\left(\frac{1}{2}\right) = s_0 - \left[|u_0| - s_0\right]e^{\frac{\beta}{2}} = s_0\left[1 + (1 - |u_0|)e^{\frac{\beta}{2}}\right].$$

(2.21)

Because  $|u_0| < 1$ , the magnitude of the equilibrium point  $s_0$  is too great to undergo a sign change. Therefore, it may be shown that  $sgn(u(1/2)) = s_0$  and the discrete state does not undergo a switching event. The first trigger of the guard condition results in no change and the solution for u(t) may be followed until the guard condition is next satisfied. The second triggering of the guard condition may be found at t = 1. The solution u(t) may be described at this point by

$$u(1) = u_1 = s_0 + [u_0 - s_0]e^\beta = e^\beta u_0 - (e^\beta - 1)s_0.$$

(2.22)

It may be shown that  $|u(1)| \leq 1$  because  $|u_0| \leq 1$ . At this point in the analysis, uncertainty arises. Because the sign  $s_1 = sgn(u_1)$  depends explicitly on  $u_0$ , a transition in the discrete state may occur. Generally, Equation 2.19 is reliably valid on the interval  $0 \leq t < 1$  for all  $|u_0| \leq 1$ . [18]

Further analysis of the system for  $t \ge 1$  requires consideration of the hybrid system complete with switching events for  $u(1) = u_1$ ,  $\dot{u}(1) = 0$ , and  $s(1) = s_1$ . The initial conditions will keep the similar restrictions  $u_1 \le 1$  and  $s_1 = sgn(u_1)$ . A new problem is posed with similarity to the previous problem. This allows for a time-shifted analysis. This translation will be further denoted by incrementing subscripts. For the first interval  $1 \le t < 2$  the solution is

$$u(t) = s_1 + [u_1 - s_1]e^{\beta(t-1)} [\cos(\omega t) - \frac{\beta}{\omega}\sin(\omega t)].$$

(2.23)

Similar analysis over this interval results with

$$u(2) = u_2 = e^{\beta} u_1 - (e^{\beta} - 1)s_1 \tag{2.24}$$

where

$$s_2 = sgn(u_2). \tag{2.25}$$

Once more, it may be shown that  $|u_2| \leq 1$  giving yet another time-shifted extension to express a solution for a new interval.

For the general case, this solution approach may be continually repeated for the interval  $n \le t < n + 1$ . The solution over this arbitrary interval is

$$u(t) = s_n + \left[u_n - s_n\right] e^{\beta(t-n)} \left[\cos(\omega t) - \frac{\beta}{\omega}\sin(\omega t)\right].$$

(2.26)

The returns at potential transition times satisfy the iterated relation

$$u_{n+1} = e^{\beta}u_n - (e^{\beta} - 1)s_n \tag{2.27}$$

with

$$s_{n+1} = sgn(u_{n+1}). (2.28)$$

This analytic process shows that for given initial conditions,  $u_0$  and  $s_0$ , this hybrid dynamical system may be exactly calculated using a known solution for all intervals  $t \ge 0$ . [18]

The resulting iterated relation is a form of the iterated shift map. The map is closed on the interval  $|u_n| \leq 1$  and piecewise linear with a constant slope of  $e^{\beta} > 1$ . The slope of this map is positive indicating that the map has positive entropy. Because this system is a source of entropy it is chaotic. Furthermore, the continuous state of the system may be sampled at regular times to obtain a Poincaré return map for the continuos-time dynamics of the system. It follows that the hybrid system is also chaotic with a Lyapunov exponent  $\lambda = \beta$ . [18]This map may be used to describe symbols related to  $s_n = \pm 1$  as  $u_n$  is iterated relative to partition defined at zero.

#### 2.5 Symbolic Dynamics for the Shift-band

The symbols described by partitioning the aforementioned iterated map gives a means to fully describe the continuous-time hybrid system dynamics. This is done by forming a description of the system's symbolic dynamics. Although, symbolic dynamics is considered outside the scope of this work – for completeness, a brief description is offered. It is recommended that source[18] be reviewed. The initial condition and recurrence relation formed by the analytic solution yield

$$u_n = e^{n\beta} \bigg\{ u_0 - (1 - e^{-\beta}) \sum_{i=0}^{n-1} s_i e^{-i\beta} \bigg\}.$$

(2.29)

This equation may be inverted to gain an expression that is terms of future iterates. This inversion gives

$$u_0 = e^{-n\beta}u_n + (1 - e^{-\beta})\sum_{i=0}^{n-1} s_i e^{-i\beta}$$

(2.30)

for all n > 0. Because  $u_n$  is bounded, a given initial condition may be expressed exclusively in terms of future symbols  $\{s_i : 0 \le i < \infty\}$  by taking the limit as  $n \to \infty$ . This yields

$$u_0 = (1 - e^{-\beta}) \sum_{i=0}^{\infty} s_{i+n} e^{-i\beta}.$$

(2.31)

This representation shows that the symbolic dynamics are characterized by a one-sided shift. These symbols form the symbolic dynamics for the chaotic map.[18] Considering the integer portion of continuous-time n = [t], the continuous-time waveform may be described in terms of current and future symbols by

$$u(t) = s_n + \left\{ -s_n + (1 - e^{-\beta}) \sum_{i=0}^{\infty} s_{i+n} e^{-i\beta} \right\} \cdot e^{\beta(t-n)} \left( \cos(\omega t) - \frac{\beta}{\omega} \sin(\omega t) \right).$$

(2.32)

Using this solution, subsequent waveforms may be established for an initial condition at any integer time by temporally translating this expression such that t = 0. This specifies an analytic relationship such that symbol sequences may be communicated using predetermined initial conditions.

#### 2.6 Control of Chaotic Systems

The characteristic of sensitivity to initial conditions intuitively seems to subvert the useful control of chaotic systems. However, this is not the case. Small perturbation techniques may be used to steer the phase space orbit of a chaotic system to a desired trajectory. [43] [44] In terms of symbolic dynamics, sequences of future symbols correspond to desired trajectories and are used to define the otherwise ambiguous precision of initial conditions. For the shift-band oscillator, encoding symbols for targeted trajectories using many bits efficiently satisfies small perturbations. These small control signals increasingly influence the system as time progresses by the shifting operation inherit to the iterated shift map. There is a trade-off, however, with latency of newly presented information and using such small control signals. [43]

Chaos control mechanisms are not considered in this work, although, for completeness the concept of chaos control is briefly provided. At the heart of a successful communication system is some sort of controller that imposing information. Generally, a coding function may be obtained by iterating through the initial conditions of the chaotic oscillator. A mapping of these initial conditions may be used to create a representation of symbols. This mapping may be imposed by a chaotic control technique. For the system presented, chaotic control techniques such as Hayes type control [47], OGY small perturbation techniques [45] and forms of dynamic limiting [43] may be employed. These techniques are closely detailed in Reference [43] and Reference [44].

Interestingly, subsequent design of the shift band chaotic oscillator may be thought of as an analog computer. This is a slight shift in electronic design philosophy that views the system as an analog computation of the exactly solvable shift band oscillator. Although less mathematically elegant, this analog computation allows for conventional analog computation techniques to be used for the control of this system. It is expected that this approach may have limited applicability at very high frequencies.

#### 2.7 Shift-Band Linear Solution

A complete description of the system may be found by evaluating the solution due to an initial condition at a series of discrete time stages, n, such that  $t = t_n$ ,  $u(t_n) = u_n$ ,  $\frac{du}{dt}(t_n) = 0$ , and  $s(t_n) = s_n$  where  $s_n = sgn(u_n)$ . Considering the closed-form analytic expression that describes the continuous-time solution for u(t) and a particular symbol,  $s_m$ , a powerful representation of u(t) may be found in the linear convolution

$$u(t) = \sum_{m=-\infty}^{\infty} s_m \cdot P(t - t_n - m), \qquad (2.33)$$

where P(t) is the analytic solution found for the linear,  $2^{nd}$  order basis function,

$$P(t) = \begin{cases} (1 - e^{-\beta})e^{\beta t} \left(\cos(\omega t) - \frac{\beta}{\omega}\sin(\omega t)\right), & t < 0\\ 1 - e^{-\beta(t-1)} \left(\cos(\omega t) - \frac{\beta}{\omega}\sin(\omega t)\right), & 0 \le t < 1\\ 0, & t \ge 1. \end{cases}$$

The discrete signal, s(t), may be written as the linear convolution

$$s(t) = \sum_{m=-\infty}^{\infty} s_m \cdot \phi(t - t_n - m)$$

(2.34)

where

$$\phi = \begin{cases} 0, & t < 0 \\ 1, & 0 \le t < 1 \\ 0, & t \ge 1. \end{cases}$$

The waveforms that constitute the basis pulse and state change are shown in Figure 2.9. These dynamics are best described as a fixed basis pulse, P(t), centered at time  $t = t_n + m$ that is modulated by a binary symbol,  $s_m$ . [43] Information is presented in the form of this binary symbol modulation.

Figure 2.9: Basis pulse for synthesizing chaos via linear superposition with  $\beta = \ln(2)$

#### 2.8 Spectral Content of Shift-Band Oscillations

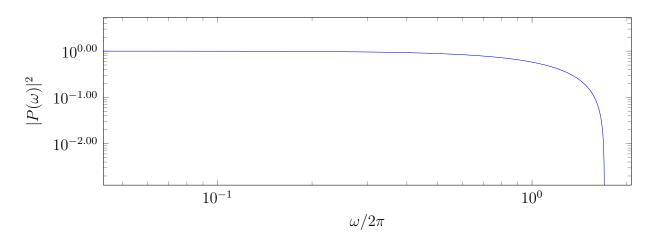

Given that the solution, u(t), may be expressed as a linear convolution in the timedomain, spectral properties may be observed by transforming this expression into the frequency domain. Considering the Fourier transform of the basis pulse, P(t),

$$P(\omega) = \int_{-\infty}^{\infty} P(t)e^{j\omega t}dt = \frac{e^{-j\omega}}{-j\omega} \cdot \frac{\omega_0^2 + \beta^2}{\omega_0^2 + (\beta + j\omega)^2}$$

(2.35)

where  $j = \sqrt{-1}$  and  $\omega_0$  is the fundamental frequency of the basis pulse representing the system's informational bit rate. [43] Figure 2.10 shows that this type of system occupies a wide bandwidth. It may be shown that the extended spectral content of this system is characterized by zeros at its bit rate and subsequent harmonics. [18]

#### 2.9 Linear Matched Filters

When considering receiver models for detection or communication, a received signal consists of some intended transmission corrupted by environmental noise. If no a priori information is known about the noise that envelops this transmission, a reasonable first approximation of this noise may be found by modeling it as additive Gaussian white noise

Figure 2.10: Basis pulse for synthesizing chaos via linear superposition with  $\beta = \ln(2)$

(AGWN). Thus, an important task arises. Given a receiver network input, x(t), seek some network with an impulse response, h(t), such that a desired transmission may be optimally obtained in the presence of AGWN, w(t).

To begin, consider the input of the receiver as

$$x(t) = g(t) + w(t) \qquad 0 \le t \le T$$

(2.36)

where T is arbitrary observation interval and g(t) is some arbitrarily shaped transmission pulse.[15] It is assumed that w(t) is a stochastic noise process of zero mean and power spectral density  $N_o/2$ . It is further assumed that the receiver has knowledge of the shape of the transmitted waveform.

In order to optimize this filter design by maximizing the detection of the transmitted signal, g(t) by minimizing the effects of noise w(t), consider a linear matched filter with the output y(t) such that

$$y(t) = g_o(t) + n(t)$$

(2.37)

where  $g_o(t)$  is produced by the signal component of input x(t) and n(t) is produced by the noise component of x(t). Ultimately, the instantaneous power in the output signal  $g_o(t)$ ,

measured at time t = T must be maximized when compared to the average power of the output noise n(t). This may be expressed as the peak pulse signal-to-noise ratio

$$\eta = \frac{|g_o(T)|^2}{\mathbf{E}|n^2(t)|} \tag{2.38}$$

where  $|g_o(T)|^2$  is the instantaneous power provided by the output signal, and  $\mathbf{E}|n^2(t)|$  is the statistical expectation of the average output noise power. This expression gives a signal-to-noise ratio in terms of power that may be maximized for some filter input's impulse h(t).

Defining the Fourier transform of g(t) as G(f) and h(t) as H(f), the output signal may be expressed as  $G_o(f) = H(f)G(f)$ . Taking the inverse Fourier transform of the output signal gives the time-domain representation

$$g_o(t) = \int_{-\infty}^{\infty} H(f)G(f)e^{j2\pi ft}df.$$

(2.39)

Ignoring the presence of noise, the output of the filter may be sampled at t = T to give

$$|g_o(T)|^2 = \left| \int_{-\infty}^{\infty} H(f)G(f)e^{j2\pi fT}df \right|^2.$$

(2.40)

Similarly, ignoring the presence of the transmitted signal, the power spectral density of the output noise may be expressed as

$$S_N(f) = \frac{N_0}{2} |H(f)|^2.$$

(2.41)

This expression assumes that the power spectral density of the output noise, n(t), is equal to the power spectral density of the input noise, w(t), with the impulse response of the filter, H(f), imposed upon it. The average power of the noise, n(t), seen at the output of the filter is expressed by

$$\mathbf{E}[n^{2}(t)] = \int_{-\infty}^{\infty} S_{N}(f) df = \frac{N_{0}}{2} \int_{-\infty}^{\infty} |H(f)|^{2} df.$$

(2.42)

The expressions for the independent contributions to the power seen at the output of the filter, Equation 2.40 and Equation 2.42, may be substituted into Equation 2.38 to give

$$\eta = \frac{\left| \int_{-\infty}^{\infty} H(f)G(f)e^{j2\pi fT}df \right|^2}{\frac{N_0}{2} \int_{-\infty}^{\infty} |H(f)|^2 df}.$$

(2.43)

With this expression, the signal-to-noise ratio is now in terms of an input signal G(f) and the response of some linear matched filter H(f). This ratio gives a relation to which an optimization problem may be solved. It is desired to find the filter response, H(f), in order maximize the signal-to-noise ratio,  $\eta$ , if an arbitrary signal, G(f), is presented as in input.

To obtain a solution, Schwarz's inequality may be applied to the numerator. [14] Schwarz's inequality states that if two complex functions  $\phi_1(x)$  and  $\phi_2(x)$  in the real variable x satisfy

$$\int_{-\infty}^{\infty} |\phi_1(x)|^2 dx < \infty \tag{2.44}$$

and

$$\int_{-\infty}^{\infty} |\phi_2(x)|^2 dx < \infty \tag{2.45}$$

then the expression

$$\left| \int_{-\infty}^{\infty} \phi_1(x)\phi_2(x)dx \right|^2 \le \int_{-\infty}^{\infty} |\phi_1(x)|^2 dx \int_{-\infty}^{\infty} |\phi_2(x)|^2 dx$$

(2.46)

if and only if

$$\phi_1 = k\phi_2^*(x) \tag{2.47}$$

where k is an arbitrary constant, and  $\phi_2^*$  represents the complex conjugate of  $\phi_2$ .

Recognizing that the terms in the numerator of Equation 2.43 are finite, the impulse response may be set as  $H(f) = \phi_1(x)$  and  $G(f)\exp(j2\pi fT) = \phi_2(x)$ . Applying Schwarz's inequality to the numerator of Equation 2.43 gives

$$\left| \int_{-\infty}^{\infty} H(f)G(f)e^{j2\pi fT}df \right|^{2} \leq \int_{-\infty}^{\infty} |H(f)|^{2}df \int_{-\infty}^{\infty} |G(f)|^{2}df.$$

(2.48)

Substituting this result into Equation 2.43 gives a new relation for the signal-to-noise ratio,

$$\eta \le \frac{\int_{-\infty}^{\infty} |H(f)|^2 df \int_{-\infty}^{\infty} |G(f)|^2 df}{\frac{N_0}{2} \int_{-\infty}^{\infty} |H(f)|^2 df} = \frac{2}{N_0} \int_{-\infty}^{\infty} |G(f)|^2 df,$$

(2.49)

that describes a maximum signal-to-noise ratio exclusively dependent on the input, G(f). As a result, the maximum signal-to-noise ratio,  $\eta_{\text{max}}$ , may be obtained when the conditions of the inequality are met. More formally,

$$\eta_{max} = \frac{2}{N_0} \int_{-\infty}^{\infty} |G(f)|^2 df$$

(2.50)

for an optimally matched filter response  $H_{opt}(f)$  if the following condition is met

$$H_{\rm opt}(f) = kG^*(f)e^{-j2\pi fT}$$

(2.51)

where k is an arbitrary magnitude scaling factor and  $G^*(f)$  is the complex conjugate of the input signal G(f). Succinctly stated, the transfer function for the optimally matched filter is identical to the complex conjugate of the input signal with the exception of magnitude scaling and a term that represents a linear time shift, T.

This time shift is explicitly shown by transforming these results into the time-domain. Taking the inverse Fourier transform of  $H_{opt}(f)$  gives

$$h_{\rm opt}(t) = k \int_{-\infty}^{\infty} G^*(f) e^{-j2\pi f(T-t)df}.$$

(2.52)

If it is assumed that g(t) is a real signal, taking the complex conjugate gives  $G^*(f) = G(-f)$ . The result is

$$h_{\rm opt}(t) = kg(T-t).$$

(2.53)

This result concludes with a powerful and elegant statement that the presence of any physical waveform, g(t), may be optimally detected when considering corruption due to AGWN by simply selecting a filter with an impulse response that is a time-reversed, timedelayed version of the input with a magnitude scaling factor k. [15] A linear time-invariant filter defined using this approach is referred to a matched filter. [14] It may be carefully noted that the only assumption made about the input noise is that w(t) is white, stationary, zero mean, and has power spectral density of  $N_0/2$ .

Design advantages arise when considering matched filters because the impulse response of the optimal filter is uniquely defined by a known input pulse signal, g(t), with the exception of magnitude scaling and time delay. Ultimately, the peak pulse signal-to-noise ratio of a matched filter only depends on the ratio of signal energy to the power spectral density of the white noise at the filter input. [14]

## 2.10 Shift-band Linear Matched Filter

Despite the characteristics of chaotic systems to behave in a seemingly random, noiselike manner – this specific chaotic system may be optimally detected in the presence of AGWN. Because chaos is synthesized by a known basis function, P(t), a linear matched filter may be constructed for its detection. As previously derived, a matched filter may be constructed for any physical signal by constructing a filter with an impulse response that is a time-reversed and delayed version of the desired input signal. [14] [18]

Let  $\rho(t) = P(-t)$  that satisfies

$$\ddot{\rho} + 2\beta\dot{\rho} + \omega_0^2 \rho = \omega_0^2 h(t), \qquad (2.54)$$

where  $\omega_0^2 = \omega^2 + \beta^2$  and

$$h(t) = \begin{cases} 1, & -1 \le t < 0\\ 0, & \text{otherwise.} \end{cases}$$

It is assumed that h(t) is a square pulse of unit duration and amplitude. If h(t) is differentiated it may be shown that

$$\dot{h}(t) = \delta(t+1) - \delta(t), \qquad (2.55)$$

where the Dirac delta function,  $\delta(t)$ , is an impulse with unit area. [18] This gives a timereversed basis function serves as the impulse response of the linear matched filter

$$\dot{\eta} = v(t+1) - v(t), \tag{2.56}$$

$$\ddot{\xi} + 2\beta\dot{\xi} + \omega_0^2\xi = \omega_0^2\eta(t),$$

(2.57)

where v(t) is the filter's input,  $\eta(t)$  is an intermediate state, and  $\xi$  is the filter's output. Equation 2.56 and Equation 2.57 construct the matched filter for the basis pulse. [18]A functional diagram for the matched filter of the basis pulse is shown by the SIMULINK simulation schematic provided by Figure 2.11

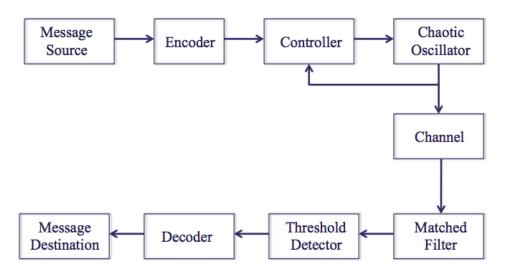

# 2.11 Overview of Exactly Solvable Communications System

Viewing these background concepts as interacting components in a chaotic communication system drives the design methodology throughout this work. A high-level function block diagram of a chaotic communications system is shown in Figure 2.12. The realization

$u''=-2\beta u'-(\omega^2+\beta^2)u+(\omega^2+\beta^2)\eta$

Figure 2.11: Function block diagram of matched filter for the basis pulse of the exact solvable shift-band chaotic system.

of each subsystem in Figure 2.12 leads to successful communication by means of encoding and decoding information in a chaotic oscillator over some communications channel.

First, considering some information such as the text "*I'm picking up good vibrations*" may be converted into binary data using ASCII, unicode or any binary character encoding scheme. This binary code is then presented to the inverse coding function of a particular chaotic oscillator. This inverse coding function translates the intended binary signal into representative initial conditions that are imposed upon the chaotic oscillator. These initial conditions may be elegantly imposed using small perturbation techniques or controlled with a more heavy handed technique as the rapid analog computation of consecutive initial conditions.

Figure 2.12: Overview of exactly solvable chaotic communications system.

As these initial conditions progressively steer trajectories of the chaotic oscillator, the resulting waveform may be up-converted or directly presented to a communication channel. These oscillations are transmitted over this channel and are subjected to channel bandwidth limitations and various forms of noise. The resulting transmission may be down-converted or directly received by a linear matched filter.

The output of the linear matched filter may be used to extract information by thresholding (or other methods) in the form of a chaotic bitstream. This bitstream may be decoded by using the chaotic oscillator's coding function that defines the initial condition from which a particular symbol sequence provides. With this information a the binary character encoding scheme may be obtained and translated to the text "*I'm picking up good vibrations*" as the communicated message at the final stage of the receiver.

More detailed descriptions of coding functions and chaos communications may be found in [43], [47], and [48]. The primary efforts involved in this work concentrated on the electronic design of a controllable chaotic oscillator and linear matched filter. These efforts stemmed from the motivations of fundamental frequency increase and the possibility of monolithically integrating an exact solvable chaotic oscillator and linear matched filter.

### 2.12 Ergodic Properties of Exact Solvable Chaos

Because this system is topologically conjugate to the iterated shift map, or Bernoulli map, the system dynamics may be analyzed using well defined ergodic theory developed for one dimensional maps. This system is a reliable entropy source because possible solution trajectories that compromise the system's randomness is of zero measure. [20] Chaotic trajectories are theoretically ensured and motivations to obtain the entropy and statistical properties produced by the dynamical system may be pursued. Ergodic theory is used to analyze the probability distribution function (PDF) of dynamical systems. The PDF for such systems is often referred to as the system's invariant measure or natural measure.

If this map is given enough iterations, the resulting solution trajectory will orbit arbitrarily close to every point on its defined interval. Ideally, the solution trajectories tracing these points would be uniformly distributed to ensure a fair coin flip. This means that no orbit within a given solution is favored over a long enough time duration. All solution trajectories are equally typical. [20] Furthermore, the entropy of this system may be defined from first principles.

Although the Bernoulli map is deterministic, the symbols generated by the map may be Markovian if the correct partition is chosen by considering the critical point of the map. Given a chaotic, one-dimensional, piecewise-linear Markov map, the system's invariant density may be computed by obtaining the kneading matrix K and applying the Boyarsky-Gora method. [21] Ultimately, the system's entropy may be found using the Shannon formula and the invariant density.

Consider the Bernoulli shift map  $x_{n+1} = f(x_n)$  partitioned in two sets on the [-1, 1]interval. The sets  $\rho_1 = [-1, 0)$  and  $\rho_2 = [0, 1]$  span the domain of  $f(x_n)$  with a piecewise discontinuity at  $x_n = 0$ . These partitions correspond to the binary symbols A and B. The partition is denoted as  $\beta = \{\rho_1, \rho_2\}$  and the union of the boundaries between the regions of  $\beta$ are denoted by  $B(\beta)$ . Verifying that the map  $f(x_n)$  is Markov of order 1 [22]; the boundaries  $B(\beta)$  are invariant of the map dynamics, i.e.  $x_{n+1} = f[B(\beta)] \subseteq B(\beta)$ . It is easily verified that indeed  $x_{n+1}$  is a subset of the union of the boundaries between regions of  $\beta$ .

The kneading matrix K for f is a  $2 \ge 2$  matrix because the partition contains two sets.

$$K_{i,j} = pr[x_{n+1} \in \rho_j | x_n \in \rho_i] \tag{2.58}$$

Each element  $K_{i,j}$  represents the conditional probability of the next mapped point appearing in partition set j, given that it is currently located in partition set i. These elements are computed by

$$K_{i,j} = \frac{\mu[\rho_i \cap f^{-1}(\rho_i)]}{\mu[\rho_i]}$$

(2.59)

where the  $\mu$  operator is the measure of a set with non-integer dimension known as the standard Lebesque measure. Considering  $f^{-1}(\rho_1) = [-1, -\frac{1}{2}) \cup (0, \frac{1}{2})$  and  $f^{-1}(\rho_2) = [-\frac{1}{2}, 1] \cup [\frac{1}{2}, 1]$ , the first element of K may be computed as

$$K_{11} = \frac{\mu[(-1,-1/2)]}{\mu[(-1,0)]} = \frac{1/2}{1} = \frac{1}{2}.$$

These calculations may be extended to obtain the kneading matrix

$$K = \begin{bmatrix} K_{11} & K_{12} \\ K_{21} & K_{22} \end{bmatrix} = \begin{bmatrix} \frac{1}{2} & \frac{1}{2} \\ \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(2.60)

Assuming that a randomly chosen initial condition is characterized by a uniform PDF over the partition  $\beta$ :

$$p_0(x) = \alpha \gamma_{\rho 1}(x) + (1 - \alpha) \gamma_{\rho 2}(x)$$

(2.61)

where  $\gamma_{\rho j}(x)$  is the characteristic function for the partition set  $\rho_j$  and  $0 \le \alpha \le 1$ . The PDF evaluates the initial condition's membership to one of the two partitions.

The Frobenius-Perron (F-B) operator is used to describe the time evolution of densities in phase space. These densities may be described ergodically by taking the fixed point of the Frobenius-Perron equation

$$\rho_{n+1}(x) = \int_0^1 dy \delta[x - F(y)] \rho_n(y)$$

(2.62)

which gives

$$\rho(x) = \int_0^1 \delta[x - F(y)]\rho(y)$$

(2.63)

as the resulting invariant measure for the system. For the next iteration of the mapping, the F-B operator creates a description of partition membership for  $p_1$  when applied to  $p_0$ . When considering  $\rho(x) = \frac{1}{2}[\gamma_{\rho 1}(x) + \gamma_{\rho 2}(x)]$ , the resulting invariant density is

$$\rho(y) = \frac{1}{2} \left[ \rho\left(\frac{y}{2}\right) + \rho\left(1 - \frac{y}{2}\right) \right]$$

(2.64)

A uniform invariant density is shown over the [-1, 1] interval with the probability of each symbol A and B being  $\frac{1}{2}$ . More formally,

$$\rho_A = \int_{x \in A} \rho(x) dx = \rho_B = \int_{x \in B} \rho(x) dx = \frac{1}{2}$$

(2.65)

verifies that the Bernoulli shift map ensures a fair coin flip. This satisfies that the PDF is uniform by  $\rho(x) = \frac{1}{n}$  for n = 2 symbols. This has been computed equivalently by many both for the case of Markov maps [21] as well as the more general case where Markovian properties are not assumed.[23]

The entropy for this map is described using the formula for the Shannon entropy  $H_s$ :

$$H_s = \sum_{i=1}^{r} p_i \ln(1/p_i)$$

(2.66)

where it is defined that  $p \ln(1/p) \equiv 0$  if p = 0 and  $p_i$  is the probability of symbol *i* appearing in a stream of symbols. This information entropy describes the degree of surprise a system is capable of providing. For the Bernoulli map with two full shifts, the Shannon entropy is described by the most uncertain case for which each symbol is equally probable, i.e.  $p_i = 1/r$ for i = 1, 2, ...r. [24]

This gives  $H_s = \ln(r)$  which yields  $H_s = \ln(2) = 0.693$ . For the case of the hybrid dynamical system, the entropy is given directly be its Lyapunov exponent  $\beta = \ln(2).[18]$ This theoretically verifies the system as an entropy source that produces two symbols A and B analogous to a perfect coin flip.

# Chapter 3

# Subsystem Circuit Design and Simulation

# 3.1 System Overview

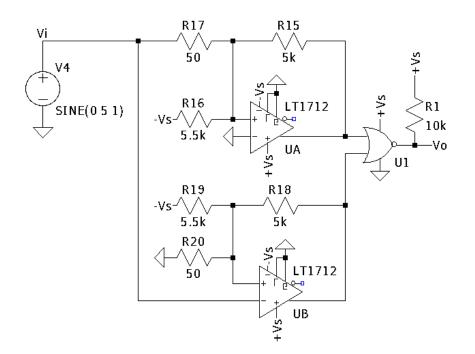

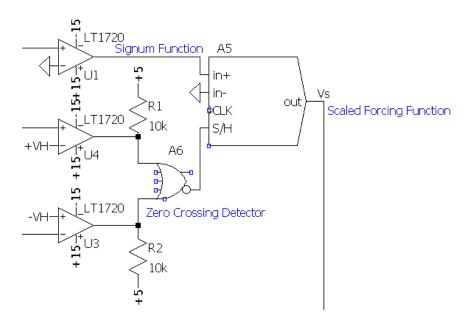

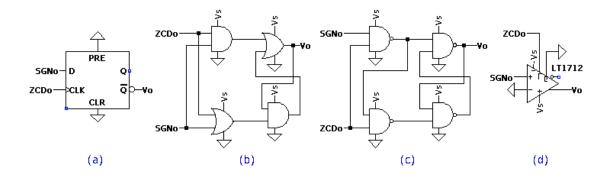

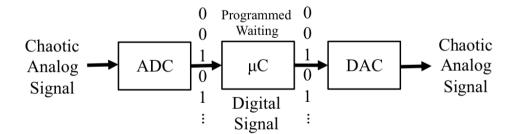

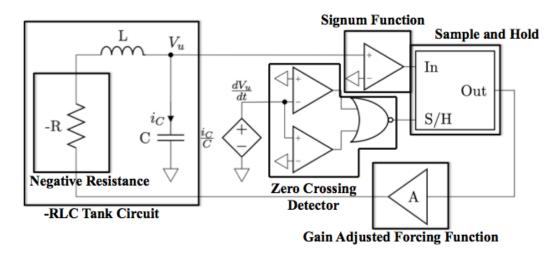

Consider the design of this chaotic communications system with two major components; a transmitter and a receiver. The transmitter must be designed such that given an initial condition, it accurately reproduces a predetermined bit sequence as defined by the system's symbolic dynamics. This is a careful conversion of a continuous input signal, sampled at discrete time intervals that corresponds to an output bitstream to a predefined coding function. From a design perspective, this is an analog computation of a series of clocked initial conditions. Although, the coding function and symbolic dynamics are of great importance to the overall communications system, it will be assumed that these dynamics are known a priori and implemented using OGY type control techniques [45] or conventional analog computational approaches [49].

Essentially, the transmitter may be considered an analog computer implementing the desired differential equations. From a subsystem point of view, this computer consists of a few components that contribute to an unstable stretching mechanism that interacts with a guarded folding mechanism. The interdependence of these components give the necessary conditions for chaos:

- 1. Unstable RLC network (stretching mechanism)

- 2. Signum function (guard mechanism)

- 3. Zero crossing detector (trigger for guard mechanism)

- 4. Sample & Hold (conditional folding mechanism)

Similarly, the receiver constructs a linear matched filter for the transmitter's basis pulse allowing for optimal detection in the presence of additive gaussian white noise (AGWN). This matched filter is comprised of the following subsystems:

- 1. Carefully paired RLC network

- 2. Wideband delay

- 3. Integration function

- 4. Summing function

This chapter's focus entails the design and simulation of these subsystems such that each component may be systematically integrated with relative ease. A systematic approach grants universality to many electronic implementations of nonlinear systems by providing a methodology complete with basic, process independent building blocks. These basic building blocks include integrators built from opamps or OTAs, thresholding decisions, logic functions and simple delay circuits. Complex interconnections and systems of equations may be easily and reliably realized using well researched and documented techniques common in Microelectronics, Analog Computing, Hybrid Computing and Filter Synthesis. Using these techniques gives reliable integration when considering non ideal effects such as temperature fluctuations, noise, power supply rejection, fabrication dependent errors and other well researched and mitigated topics.

### 3.2 Stable and Unstable RLC Tank Circuits

The linear portion of the transmitter and receiver systems may be synthesized using standard ladder filter synthesis techniques [27]. This method contrasts General Impedance Converter (GIC) and Negative Impedance Converter (NIC) topologies that may bottleneck or distort some systems when frequency scaling is needed. [19] It should be noted that filter synthesis techniques may inadvertently implement GIC topologies in some cases. These cases, generally, do not provide frequency or distortion bottlenecks, however, careful consideration should be given. First, consider the unstable, linear portion of the system between switching events. For this special case, the switching event s(t) may be considered as a constant forcing function. This gives

$$\ddot{u} - 2\beta \dot{u} + (\omega^2 + \beta^2)(u - s(t)) = 0$$

(3.1)