# **Experimental Investigation of a Liquid Immersion Cooled Electronics Module using Two- Phase Heat Transfer for Thermal Management**

by

Joshua Lyn Gess

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama December 12, 2015

Keywords: liquid immersion cooling, electronics thermal management, two-phase heat transfer, boiling, dielectric fluid, data center, surface enhancement

Copyright 2015 by Joshua Lyn Gess

#### Approved by

Sushil H. Bhavnani, Chair, Professor of Mechanical Engineering Roy W. Knight, Assistant Professor of Mechanical Engineering Jeyhoon M. Khodadadi, Professor of Mechanical Engineering Brian S. Thurow, Associate Professor of Aerospace Engineering

#### **Abstract**

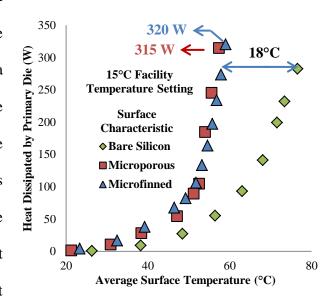

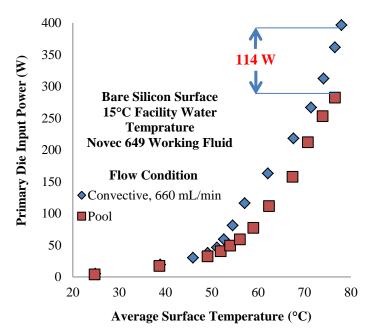

As society's demand for constant connectivity to one another grows, both from an economic and social perspective, the requirements on high performance data centers throughout the world will as well. The expeditious transfer of data over reliable and efficient networks is as much a problem that must be addressed from a thermal management perspective as it is from a computer science one. The speed at which data is transferred is directly related to the amount and density of heat that a processing element emits. System reliability is tied to the operating temperature at which these high performance computing devices are maintained. The need for energy efficiency of any design will only continue to grow as worldwide consumption increases in the face of dwindling global power resources. With these macro-scale issues in mind, the current study proposes a thermal management solution for near and far-term high performance electronic devices which addresses all three of these concerns. The proposed system is a small form factor, power dense cartridge which houses heated elements meant to simulate the heat output of electronic components typically found in servers or other high performance computing systems. These elements are immersed in a low boiling point dielectric fluid where, when powered to an adequate heat flux, cools the devices through two-phase heat transfer. The combination of latent and convective heat transfer from boiling results in incredibly high heat transfer coefficients, translating to lower operating temperatures and greater system reliability. In allowing the heated elements to boil in a pool of dielectric fluid, power dissipations of over 300 W have been achieved at an operating temperature of 77°C using the bare silicon surface.

By introducing boiling surface enhancements, microporous and microfinned surfaces, operating temperatures at the maximum power dissipation decrease by roughly 18°C. By pumping dielectric fluid through the cartridge, power dissipations over 700 W have been achieved at a surface temperature of only 71°C. At this latter power dissipation, the cartridge, which is only 300 mm x 150 mm x 38 mm (L x W x H), has eight times the volumetric power dissipation capabilities of a similar system that uses air cooling techniques. Particle Image Velocimetry (PIV) measurements, both in the single and two-phase, have been taken to ascertain flow distribution characteristics as well as assist in the development of ways in which to divert flow over critical areas of interest within a densely packed electronics enclosure.

#### Acknowledgements

To my wife and son, thank you so much for your love and support. I couldn't have done this without you. To my grandfather, thank you for making me the person I am today. I wouldn't have had the spirit and the stamina to complete this work without the values you instilled in me. To my committee members, who combined have taught me in over half of my classes at Auburn, thank you for your guidance not only in this document but also in helping to shape how I approach the lab and the classroom. To all of the friends and family who have supported me over the years, I have drawn strength from each and every one of you. Thank you for helping me to reach this point. Thank you to Dr. Bar-Cohen, who started me on this path many years ago. I would have never thought that I was even remotely capable of doing this without your belief in me and words of encouragement. Finally, to Dr. Sushil Bhavnani, thank you for being a great advisor, educating me on how to be a researcher, and challenging me every step of the way. You have impacted my life in ways that extend well beyond the research I've done. I will always be grateful for the opportunities you have given and the faith you had in me to complete this.

# **Table of Contents**

| Abstract                                                               | ii   |

|------------------------------------------------------------------------|------|

| Acknowledgements                                                       | iv   |

| List of Figures                                                        | viii |

| List of Tables                                                         | xiv  |

| List of Symbols                                                        | XV   |

| Chapter 1: Introduction                                                | 1    |

| Chapter 2: Literature Review                                           | 13   |

| 2.1 Genesis of Liquid Cooling in the Data Center                       | 13   |

| 2.2 Boiling Heat Transfer Performance Historical Studies               | 20   |

| 2.3 Introduction of Condensation Limitations in Liquid Filled Modules  | 25   |

| 2.4 Novel Electronics Cooling System Studies                           | 28   |

| 2.5 Interface Resistances and Surface Enhancement Possibilities        | 30   |

| 2.6 Embedded Thermal Management Solutions                              | 34   |

| 2.7 Coolant Flow Modeling and Visualization Techniques                 | 37   |

| Chapter 3: Experimental Facility                                       | 42   |

| 3.1 Electronics Cartridge Assembly Design Motivations and Construction | 42   |

| 3.2 Flow Delivery and Monitoring Subsystems                            | 52   |

| 3.3 Surface Enhancement Details                                       | 55     |

|-----------------------------------------------------------------------|--------|

| 3.4 PIV Setup and Execution                                           | 58     |

| 3.5 Coolant Distribution Options and Modifications                    | 62     |

| Chapter 4: Pool Boiling Results and Discussion                        | 64     |

| 4.1 Bare Silicon Pool Boiling Thermal Performance and Fundamental Tr  | ends64 |

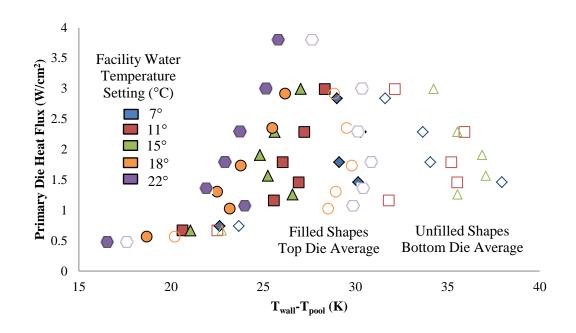

| 4.2 Pool Boiling Working Fluid Comparison                             | 70     |

| 4.3 Bare Silicon Facility Water Temperature Variation Effects         | 71     |

| 4.4 Surface Enhancement Thermal Performance Benefits                  | 75     |

| 4.5 Surface Enhancement Facility Water Temperature Variation Effects. | 77     |

| 4.6 Condensive Limit Trends and Modelling Attempt                     | 82     |

| 4.7 Module Level Thermal Resistance Plateaus                          | 93     |

| 4.8 Passive Element Integration Effects                               | 98     |

| 4.9 Two-Phase PIV Visualizations and Analysis                         | 100    |

| Chapter 5: Flow Boiling Results and Discussion                        | 109    |

| 5.1 Flow Boiling Thermal Performance Benefits and Fundamental Trend   | ls 109 |

| 5.2 Dielectric Fluid Flow Rate Variation and Subcooling Effects       | 111    |

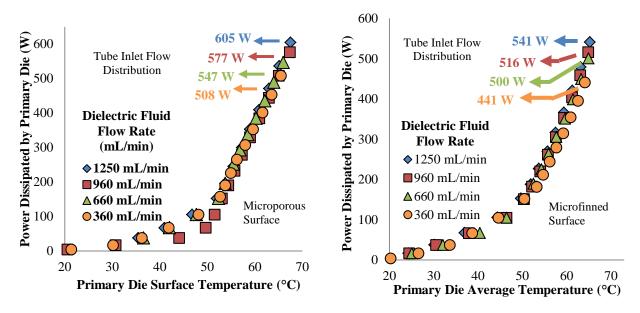

| 5.3 Surface Enhancement Tube Inlet Flow Distribution Trends           | 120    |

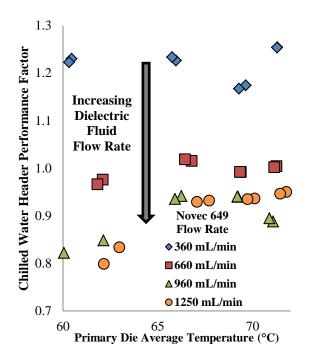

| 5.4 Chilled Water Header Impact                                       | 126    |

| 5.5 Flow Distributor Impact and Fundamental Trends                    | 135    |

| 5 6 Passive Element Effect on Flow Boiling Thermal Performance        | 142    |

| 5.6.1 Flow Guide Integration Effects on Flow Boiling Performance      | 143 |

|-----------------------------------------------------------------------|-----|

| 5.6.2 Maximum Power Dissipation Recorded                              | 150 |

| 5.7 Single Phase PIV Analysis                                         | 151 |

| Chapter 6: Conclusions                                                | 157 |

| Bibliography                                                          | 164 |

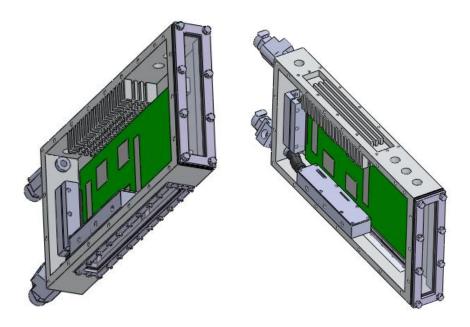

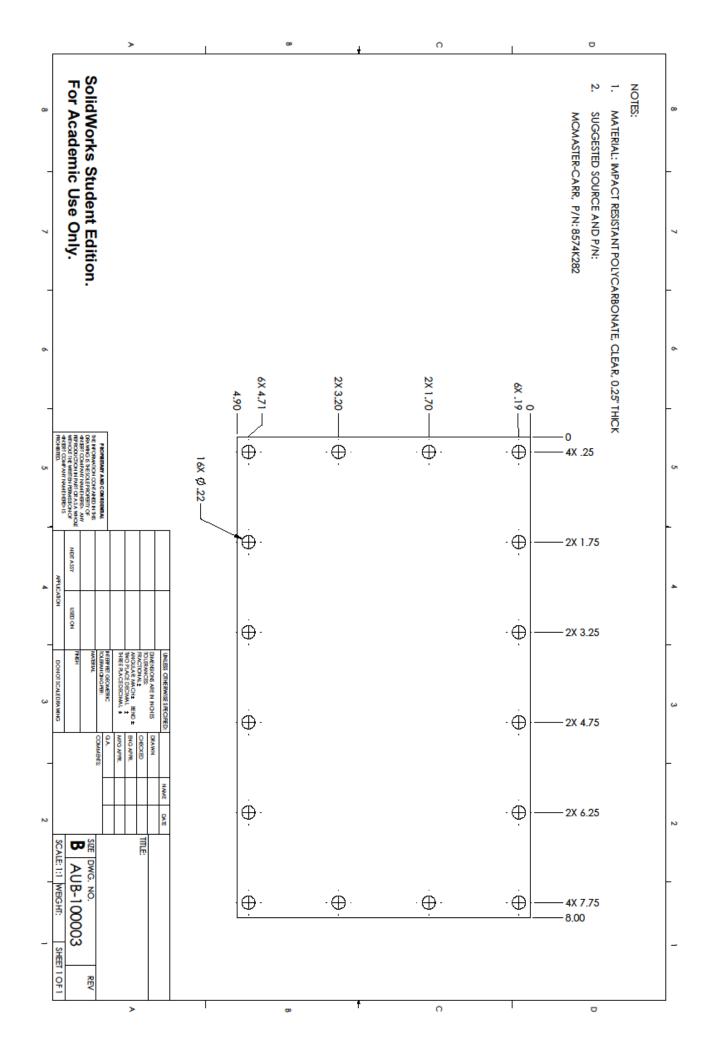

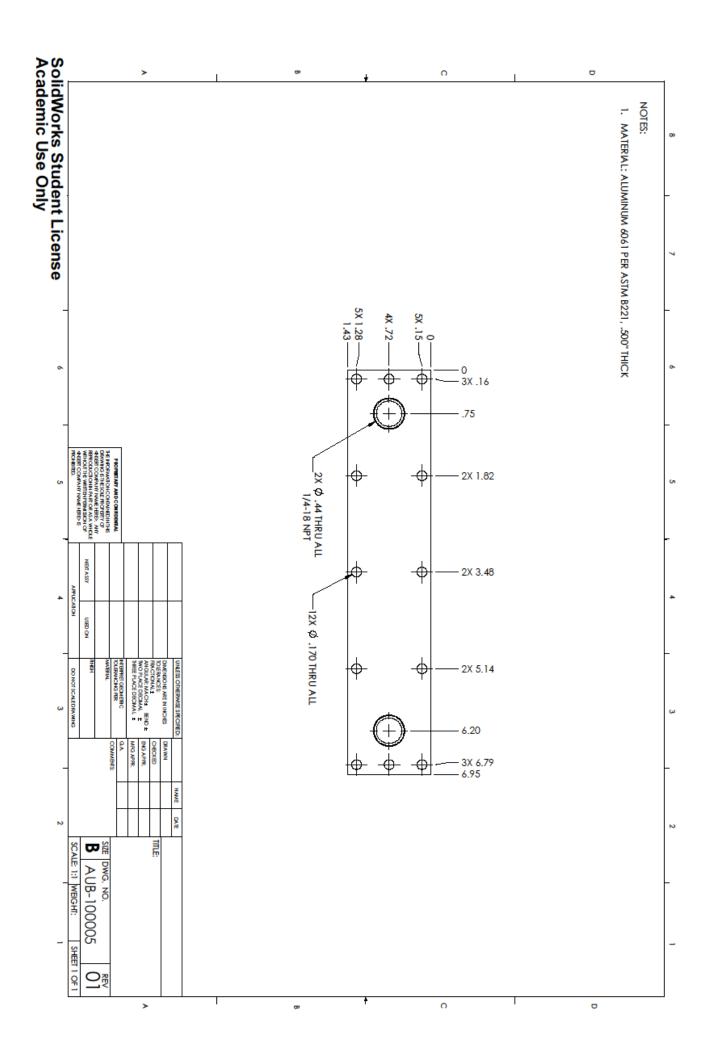

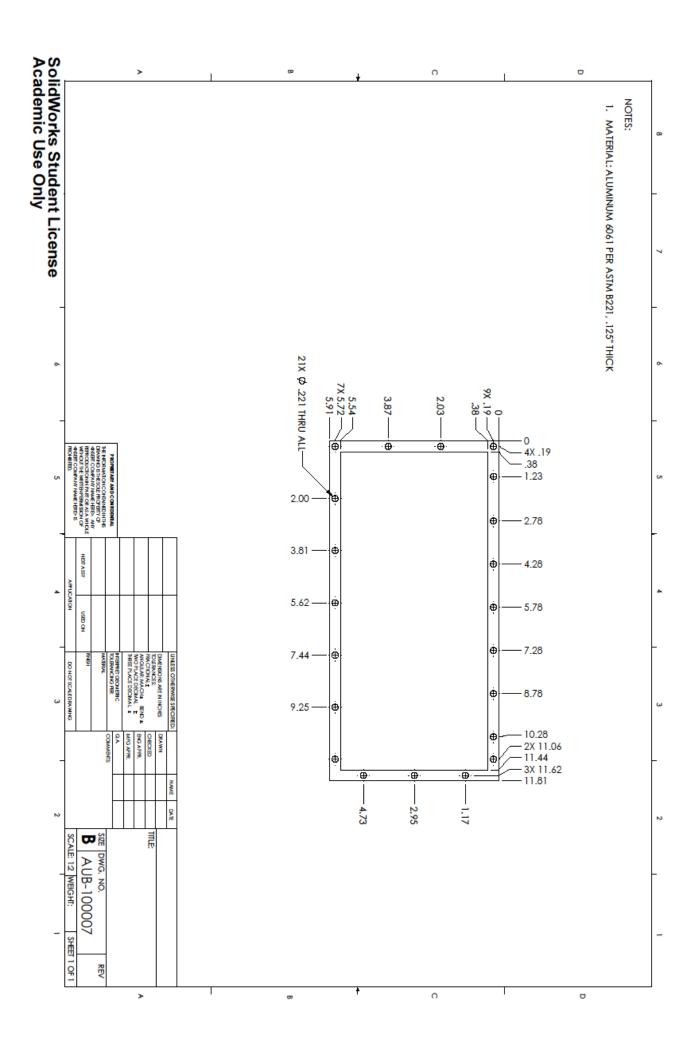

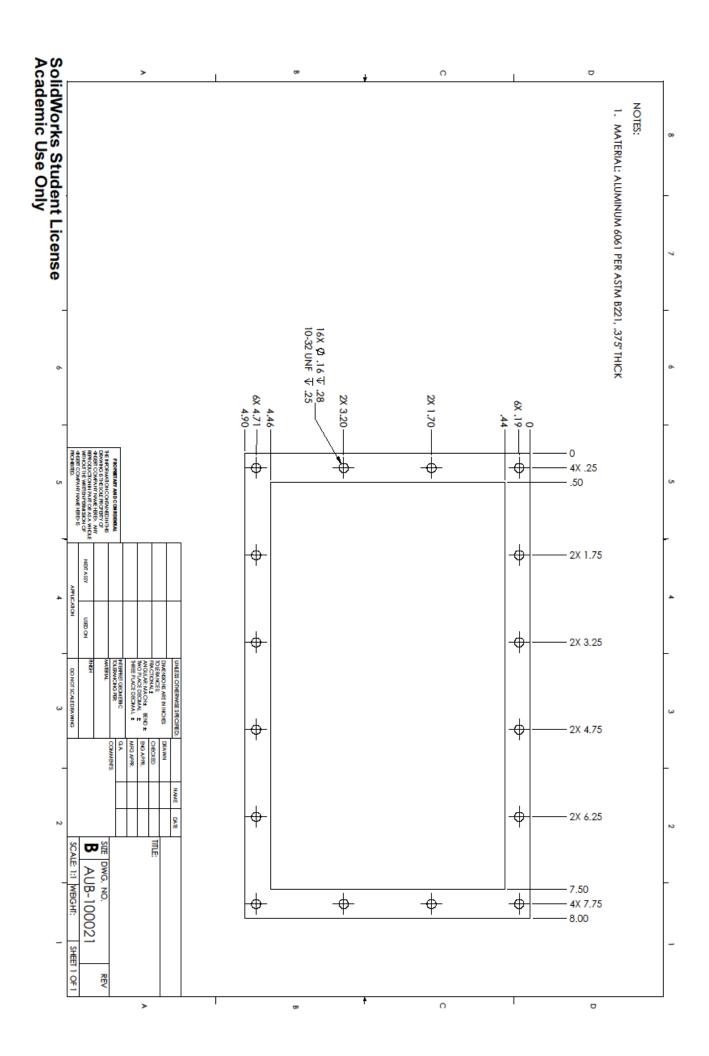

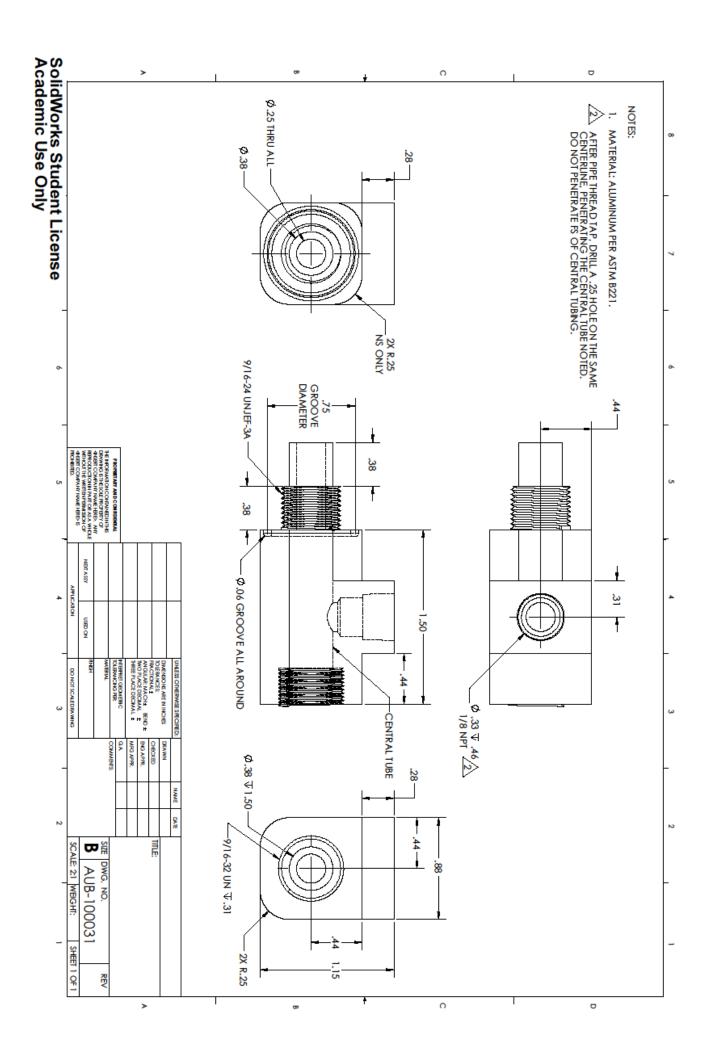

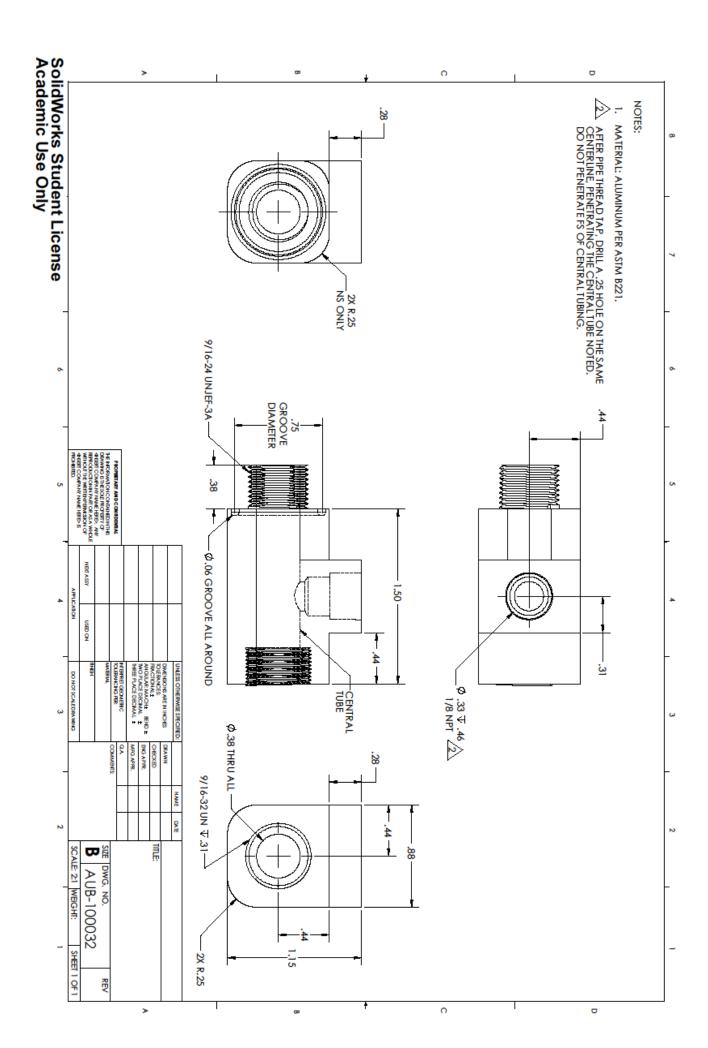

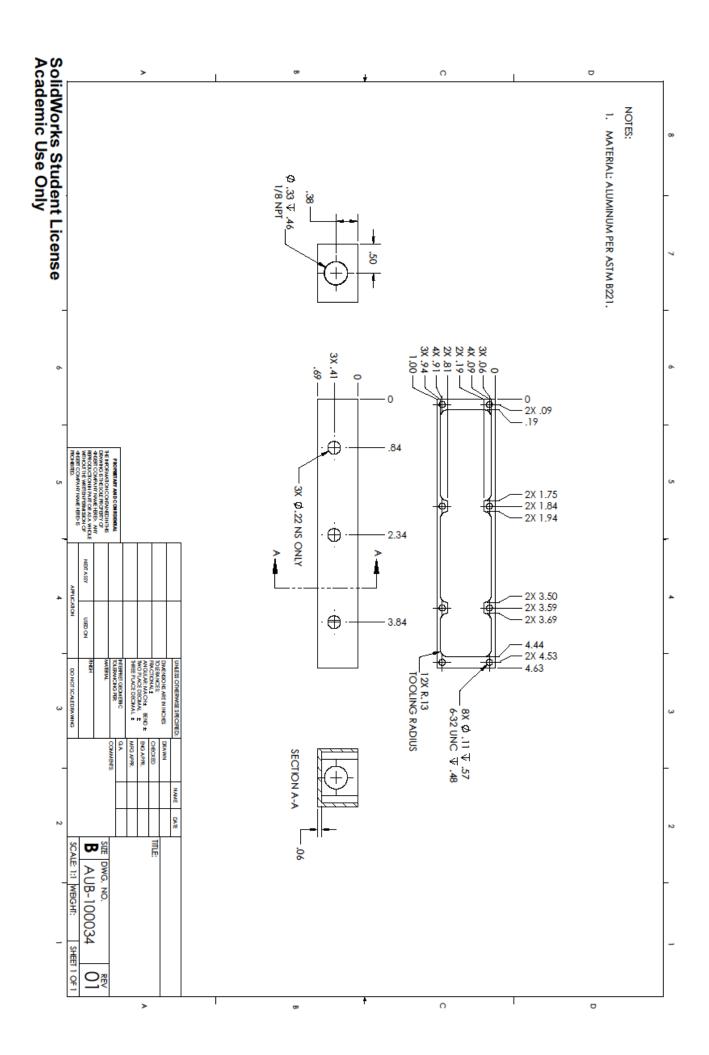

| Appendix I: Mechanical Assembly and Construction Drawings             | 181 |

| Appendix II: Microporous Surface Enhancement Fabrication Instructions | 195 |

| Appendix III: Sample Calculations                                     | 197 |

| Appendix IV: Calibration                                              | 209 |

| Appendix V: Uncertainty Analysis                                      | 215 |

| Appendix VI: Data Acquisition                                         | 223 |

# **List of Figures**

| Figure 1 – B2C Ecommerce transactions 2012-2017 [3]                        | 2  |

|----------------------------------------------------------------------------|----|

| Figure 2 – B2B Ecommerce breakdown [3]                                     | 2  |

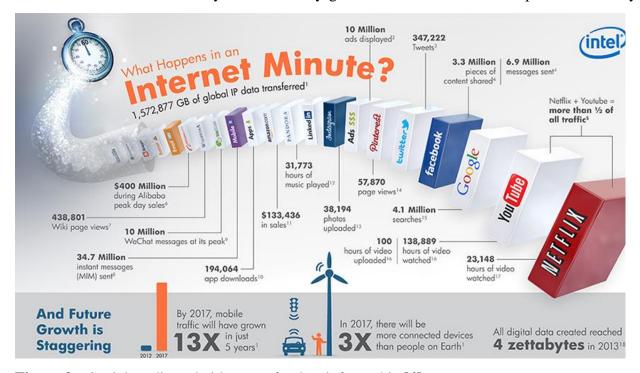

| Figure 3 – Social media and video transfer data infographic [4]            | 3  |

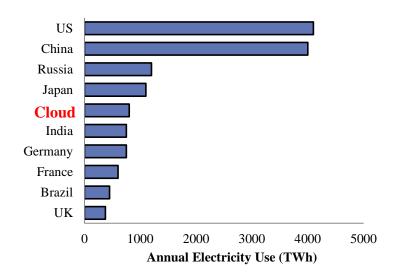

| Figure 4 – Cloud power consumption vs. industrialized nations [5]          | 4  |

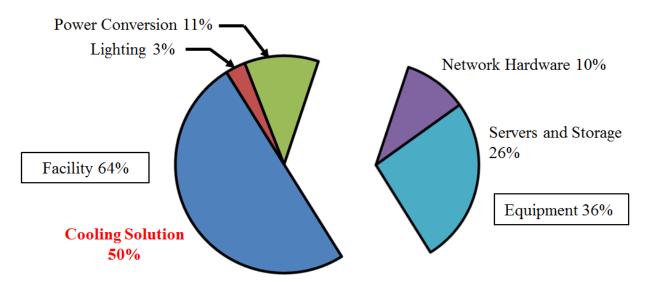

| Figure 5 – ICT infrastructure power consumption breakdown [5]              | 4  |

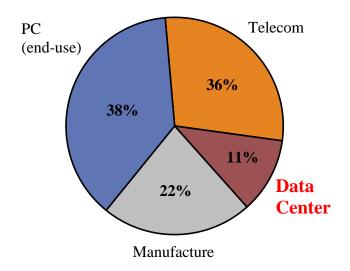

| Figure 6 – Data center power consumption breakdown [8]                     | 6  |

| Figure 8 – OBI Installation Example                                        | 7  |

| Figure 7 – Typical Iceotope Installation                                   | 7  |

| Figure 9 – Google's reduction in data center PUE [14]                      | 8  |

| Figure 10 – Case Study PUE Benchmarks                                      | 10 |

| Figure 11 – Cooling method heat transfer coefficient comparison chart [24] | 12 |

| Figure 12 – High performance electronics heat flux rise timeline [30]      | 14 |

| Figure 13 – IBM TCM details [32] [33]                                      | 15 |

| Figure 14 – Air gap contact resistance with traditional TIM's [34]         | 16 |

| Figure 15 – Schematic of Cray-2 supercomputer cooling system [36]          | 18 |

| Figure 16 – Sample 1986 high performance processing motherboard            | 19 |

| Figure 17 – Pool boiling curve trends and regimes [40]                     | 20 |

| Figure 18 – Liquid/Vapor Column CHF Model [47]                             | 23 |

| Figure 19 – Condensive limit of Freon-113 trends [55]                      | 25 |

| Figure 20 – Trends of LFM angle of inclination on maximum performance [55] | 27 |

| Figure 21 – IBM two-phase immersion cooling module example [59]                 | 29 |

|---------------------------------------------------------------------------------|----|

| Figure 22- Nature inspired boiling enhancement surface [78]                     | 33 |

| Figure 23 – Simplified 2.5D IC schematic                                        | 34 |

| Figure 24 – Simplified schematic of 3D IC structure [79]                        | 36 |

| Figure 25 – PIV measurements of air flow in a data center [90]                  | 37 |

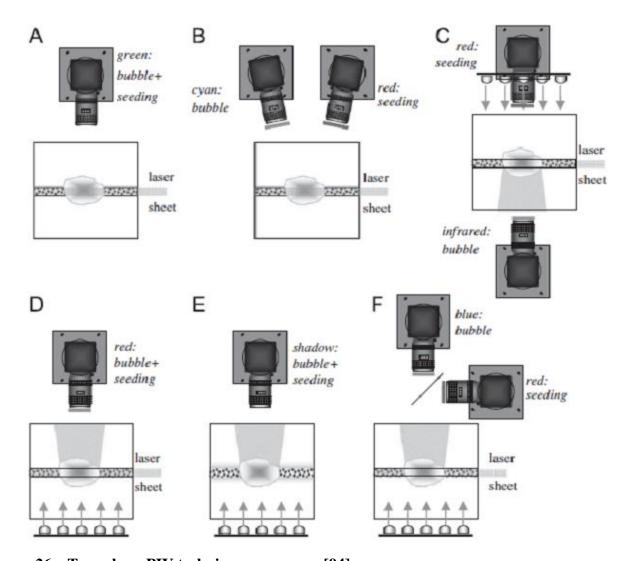

| Figure 26 – Two-phase PIV techniques summary [94]                               | 39 |

| Figure 27 – Two-phase PIV shadowgraphy and fluorescence technique [95]          | 40 |

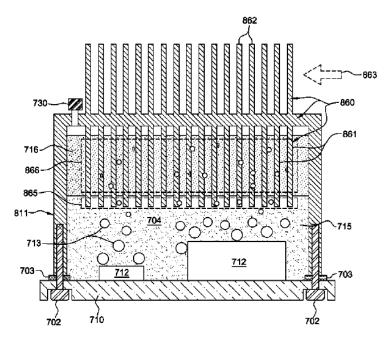

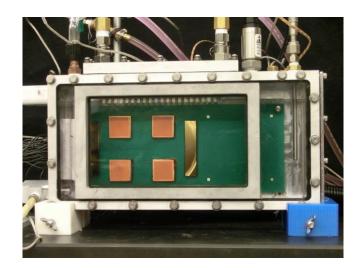

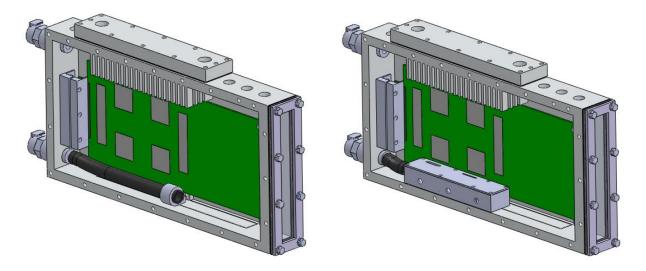

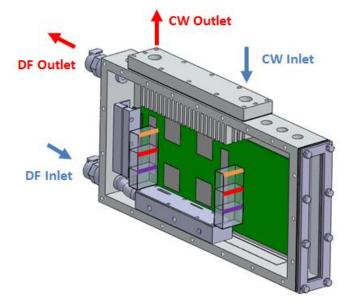

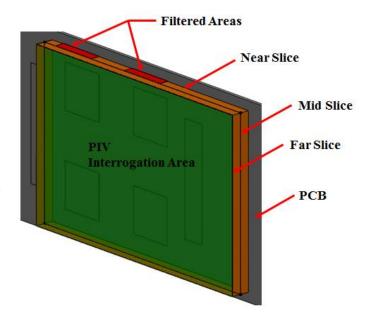

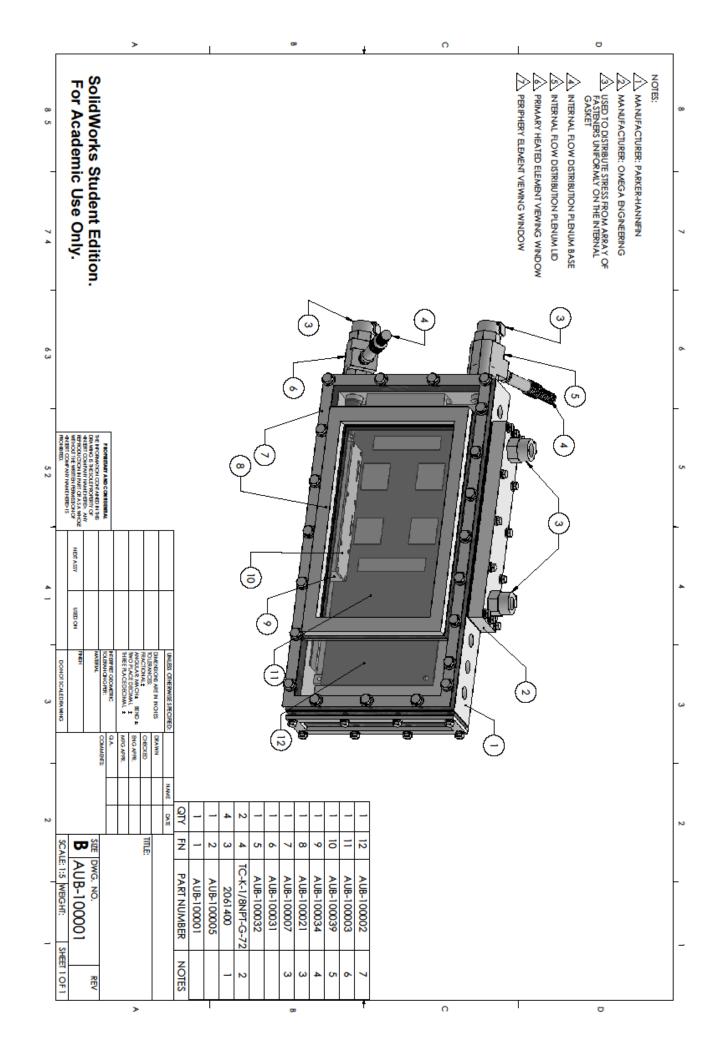

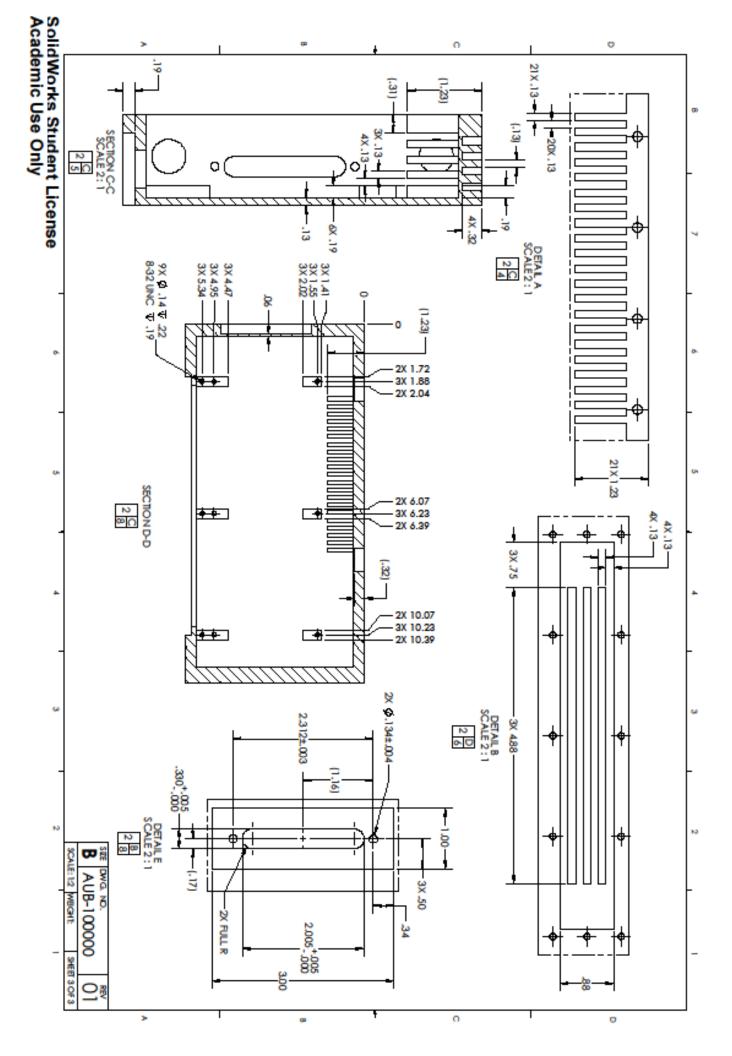

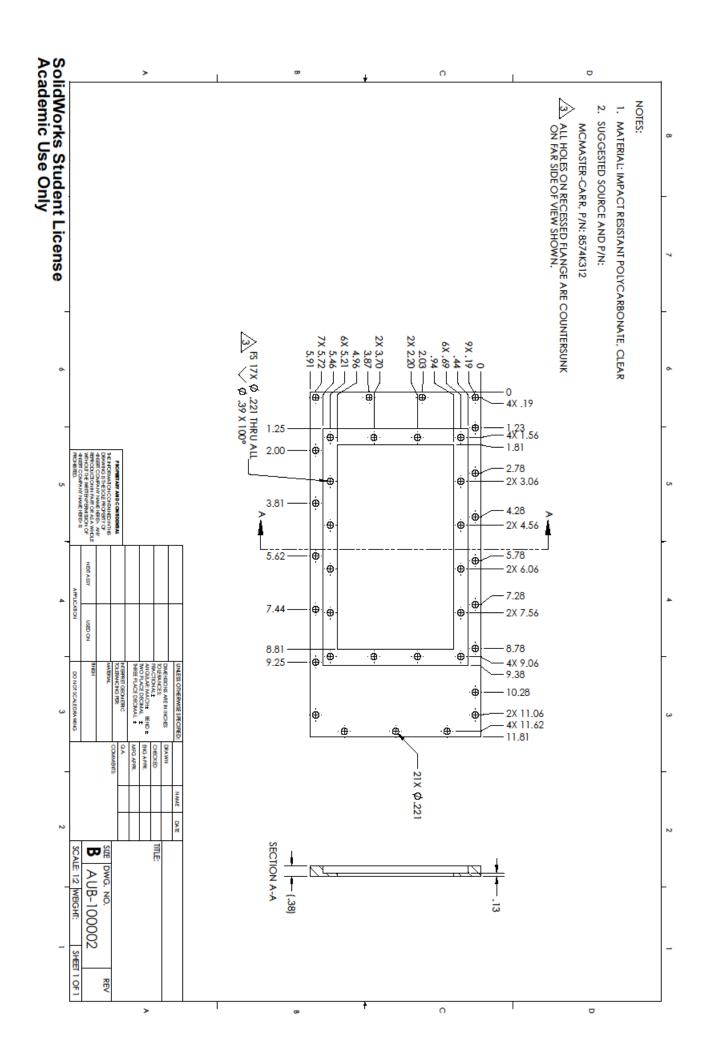

| Figure 28 – Electronics Cartridge Assembly                                      | 42 |

| Figure 29 – Condenser fin and external coolant channel images                   | 44 |

| Figure 30 – Graham condenser heat gain analysis                                 | 46 |

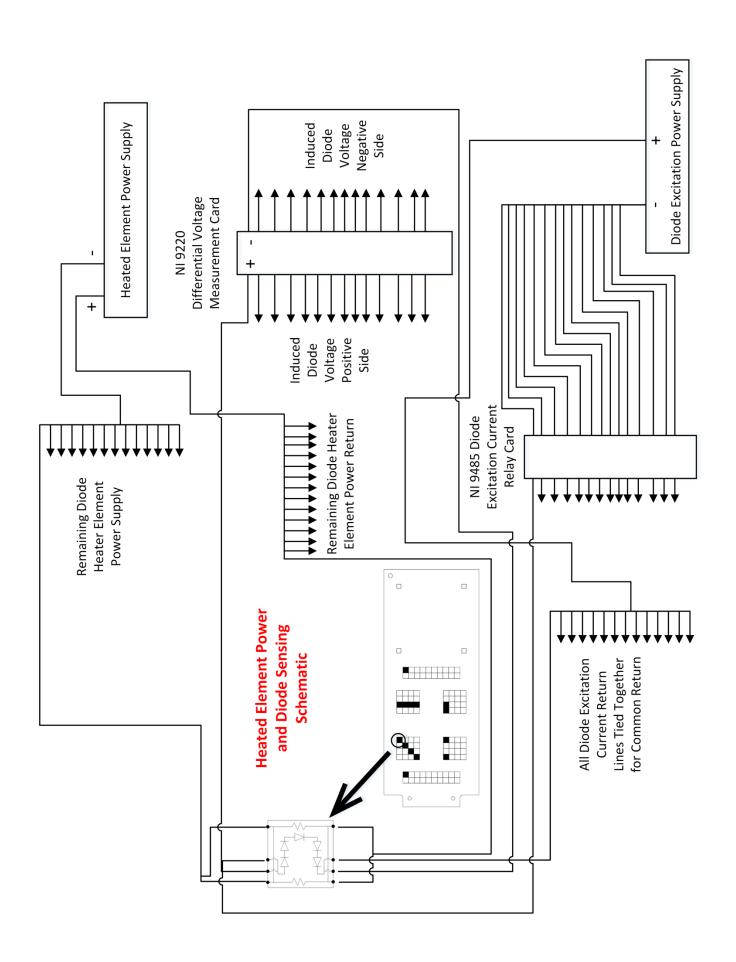

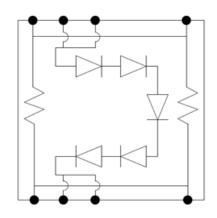

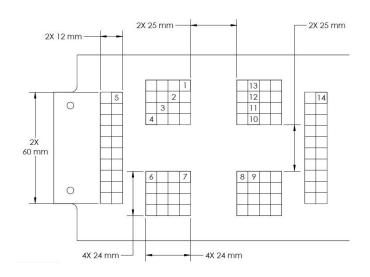

| Figure 31 – Thermal test cell circuit diagram                                   | 49 |

| Figure 32 – PCB schematic and thermal test cell layout                          | 49 |

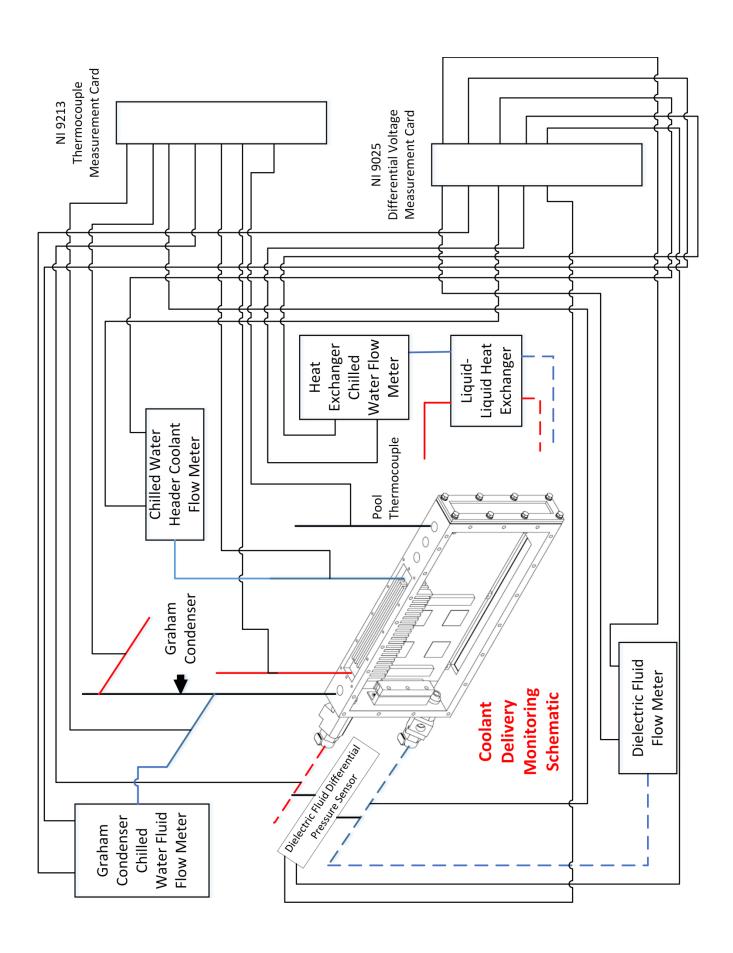

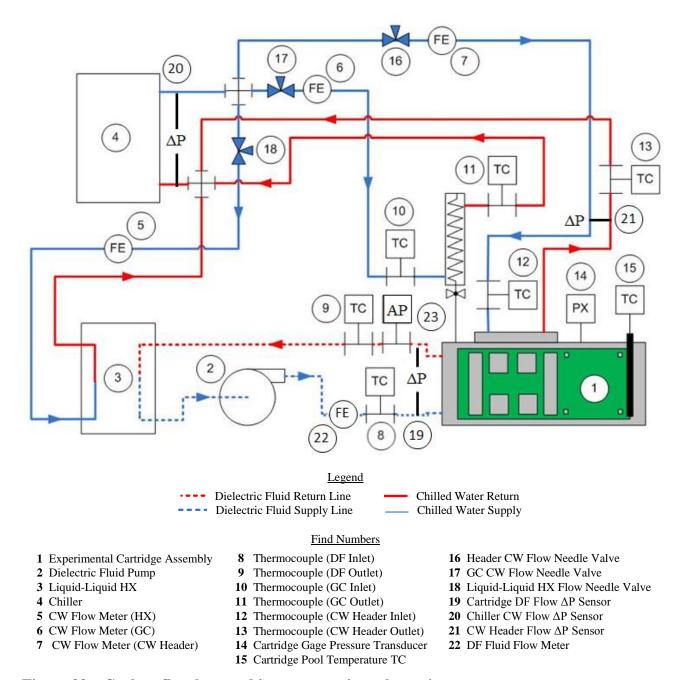

| Figure 33 – Coolant flow loop and instrumentation schematic                     | 53 |

| Figure 34 – Two-phase surface enhancement images                                | 55 |

| Figure 35 – Microfinned surface CHF benefit                                     | 57 |

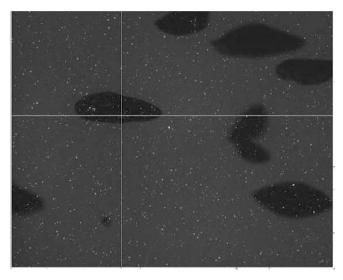

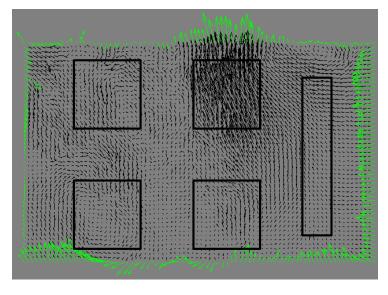

| Figure 36 – Sample raw PIV image                                                | 58 |

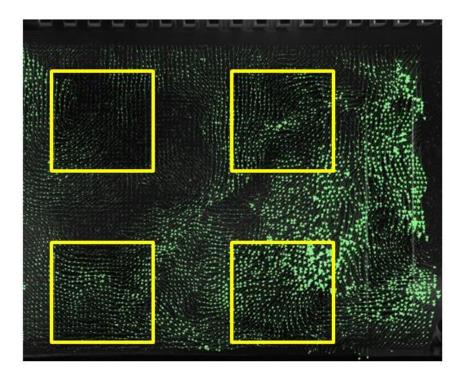

| Figure 37 – Sample PIV vector map                                               | 59 |

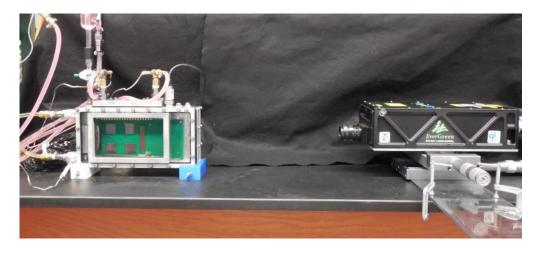

| Figure 38 – PIV laser orientation relative to cartridge assembly                | 60 |

| Figure 39 – Two primary dielectric fluid flow distribution methods assessed     | 62 |

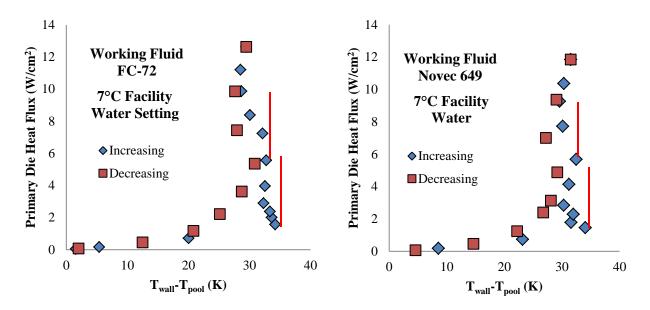

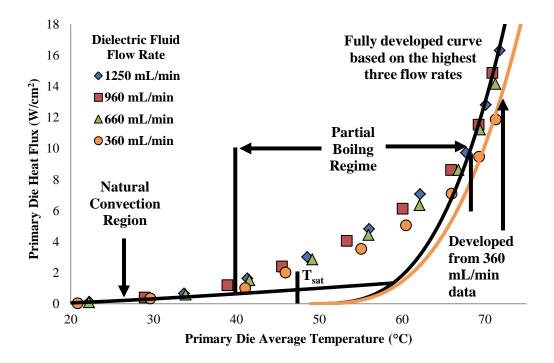

| Figure 40 – Primary die heat flux fluid and incipience phenomenon               | 66 |

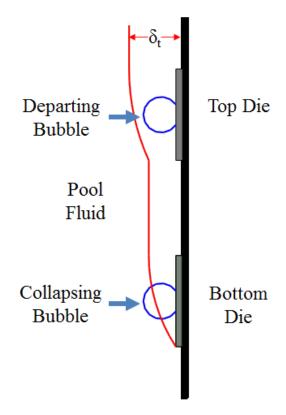

| Figure 41 – Hsu model explanation schematic for cartridge incipience phenomenon | 67 |

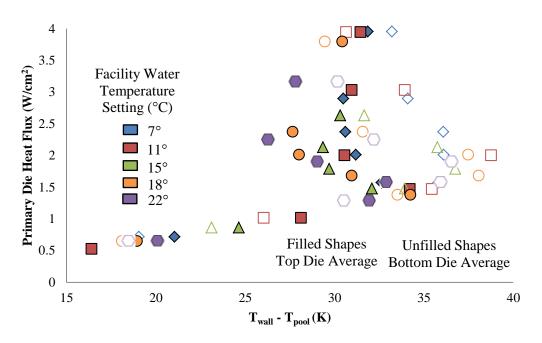

| Figure 42 – Bottom vs. top die pool boiling comparison for FC-72                | 69 |

| Figure 43 - Bottom vs. top die pool boiling comparison for Novec 649            | 69 |

| Figure 44 – Working fluid operating temperature comparison                                              |

|---------------------------------------------------------------------------------------------------------|

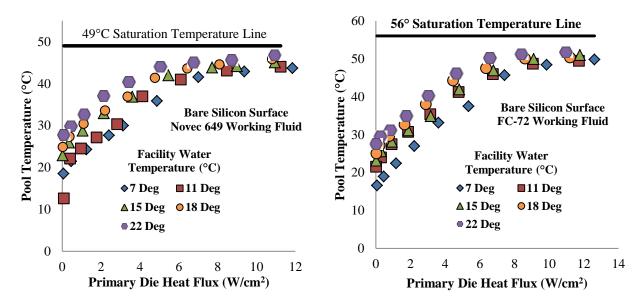

| Figure 45 – Bare Silicon Pool Temperature Variations                                                    |

| Figure 46 – Novec 649 bare silicon boiling curves over various facility water settings                  |

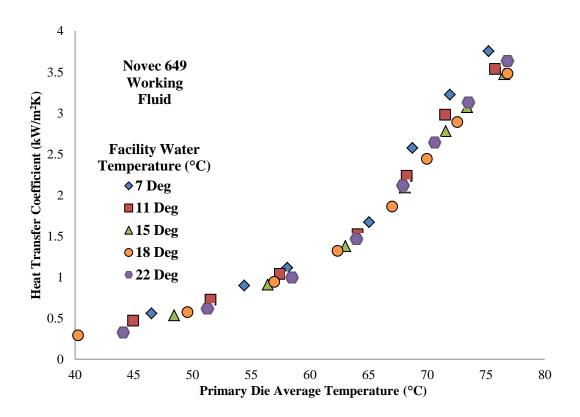

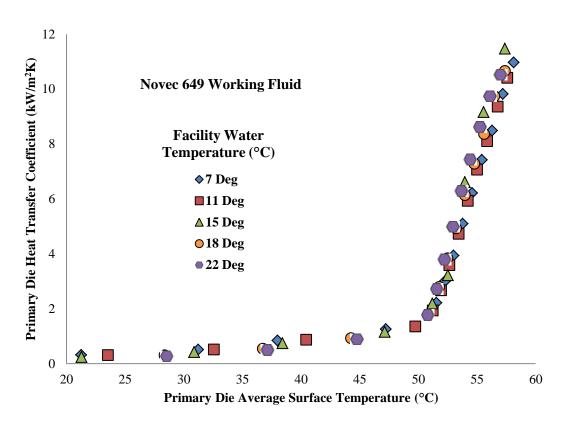

| Figure 47 – Novec 649 bare silicon HTC data over various facility water settings                        |

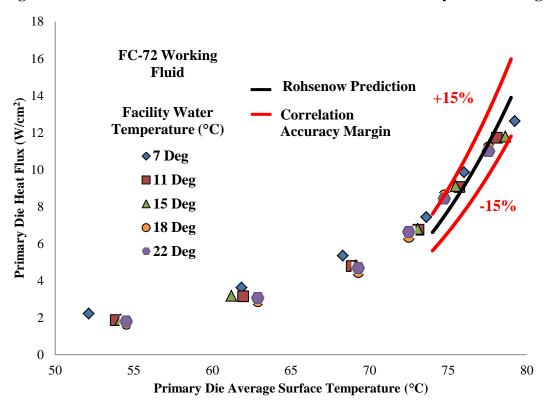

| Figure 48 – FC-72 bare silicon boiling curves over various facility water settings                      |

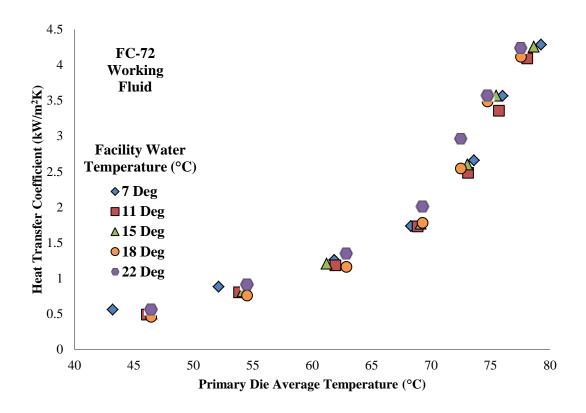

| Figure 49 – FC-72 bare silicon HTC data over various facility water settings                            |

| Figure 50 – Surface enhancement power dissipation and operating temperature improvements. 75            |

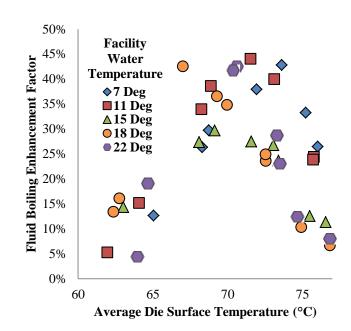

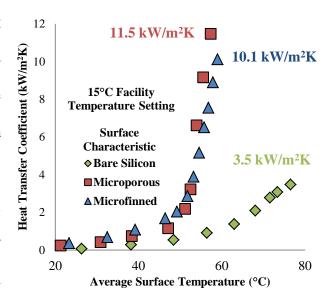

| Figure 51 – Surface enhancement heat transfer coefficient improvement                                   |

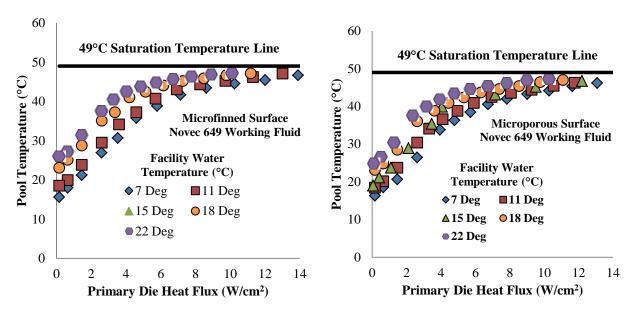

| Figure 52 – Surface Enhancement Pool Temperature Variation                                              |

| Figure 53 – Microporous surface boiling curves over various facility water settings                     |

| Figure 54 – Microfinned surface boiling curves over various facility water settings                     |

| Figure 55 – Microporous HTC data over various facility water settings                                   |

| Figure 56 – Microfinned HTC data over various facility water settings                                   |

| Figure 57 – Condensive limit appearance across all conducted pool tests                                 |

| Figure 58 - Thermal resistance network for estimating the condenser base temperature                    |

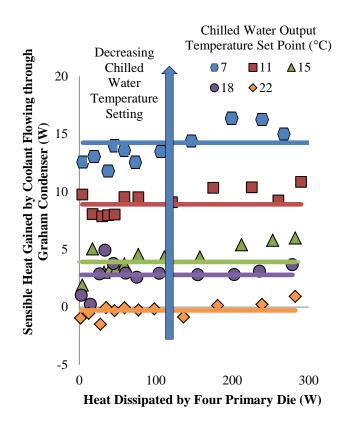

| Figure 59 – Sensible heat gained by the chilled water header under pool conditions                      |

| Figure 60 – Actual CW header heat gain versus theoretical condensive limit expectations 88              |

| Figure 61 – Single theoretical condensive limit line for two different working fluids [55] 90           |

| Figure 62 – FC-72 module level thermal resistance results for the bare silicon surface                  |

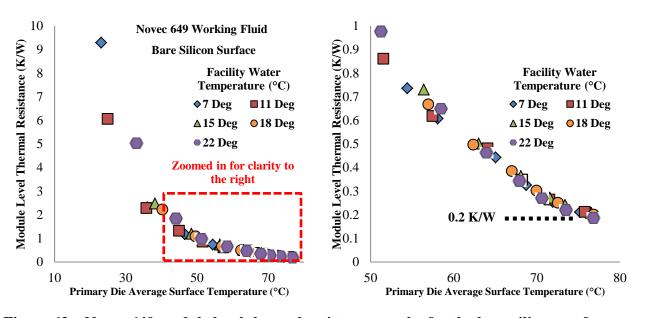

| Figure 63 – Novec 649 module level thermal resistance results for the bare silicon surface 94           |

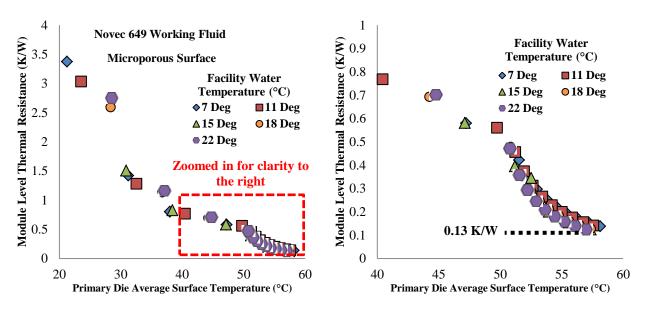

| Figure 64 – Novec 649 module level thermal resistance results for the microporous surface 95            |

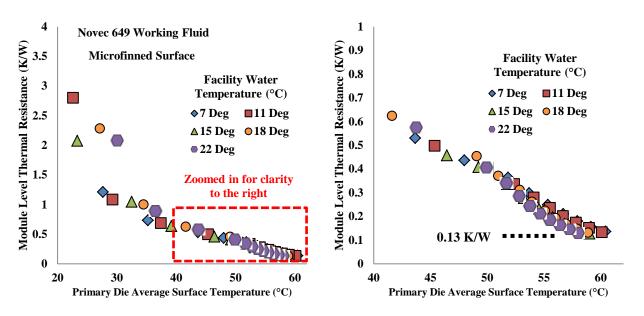

| Figure 65 – Novec 649 module level thermal resistance results for the microfinned surface 95            |

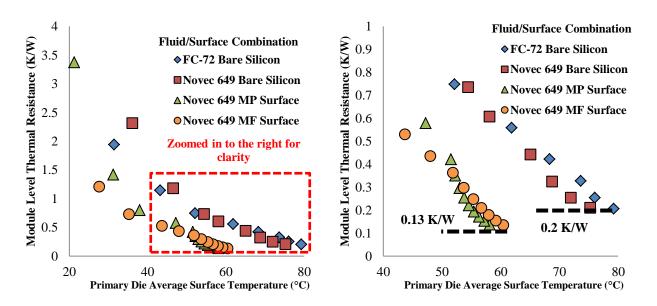

| Figure 66 – Final module level thermal resistance comparison with 7°C Facility Wate Temperature Setting |

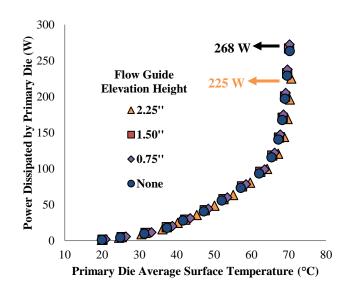

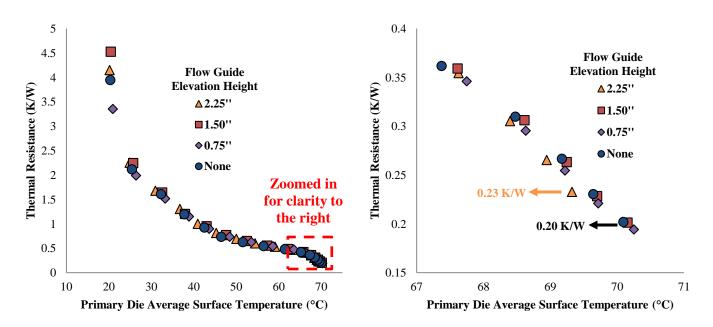

| Figure 67 – Maximum flow guide impact on peak thermal performance                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 68 – Passive Element Integration Details                                                                                                           |

| Figure 69 – Module level thermal resistance performance across the various flow guides integrated                                                         |

| Figure 70 – Vectors highlighted for two-phase PIV analysis                                                                                                |

| Figure 71 – Control surface definition for two-phase PIV analysis                                                                                         |

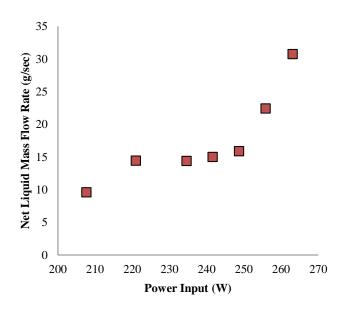

| Figure 72 – Quenching fluid mass flow rate variation as a function of input power 103                                                                     |

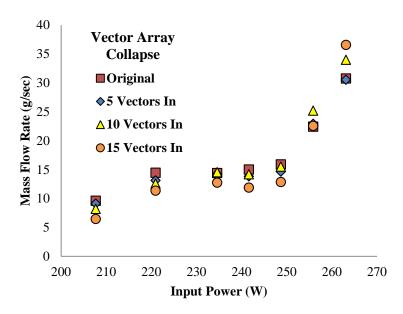

| Figure 73 – Vector collapse liquid mass flow rate control surface analysis results                                                                        |

| Figure 74 – Vector array reduction illustrations for control surface analysis justification 105                                                           |

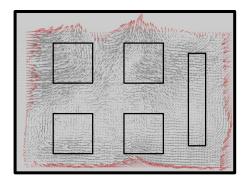

| Figure 75 – Discretized flow map showing how quenching fluid enters the area surrounding the boiling elements                                             |

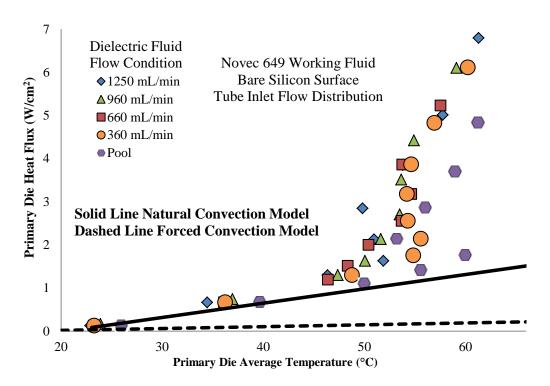

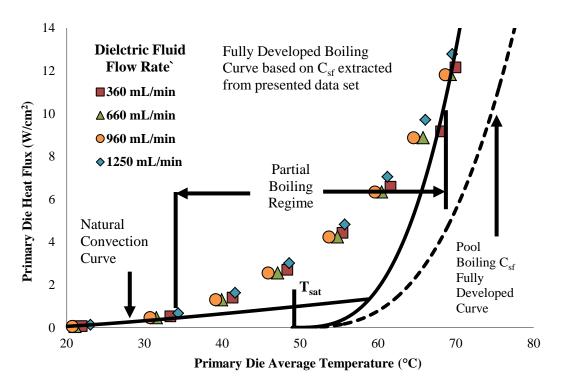

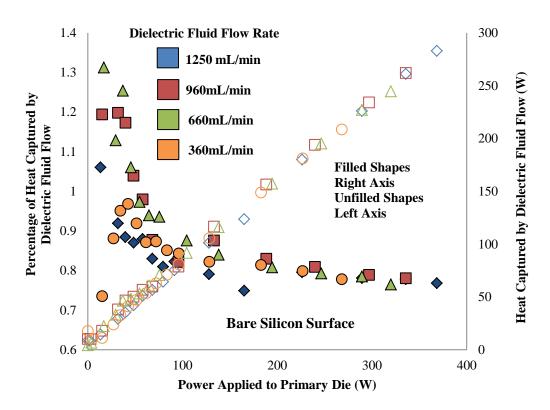

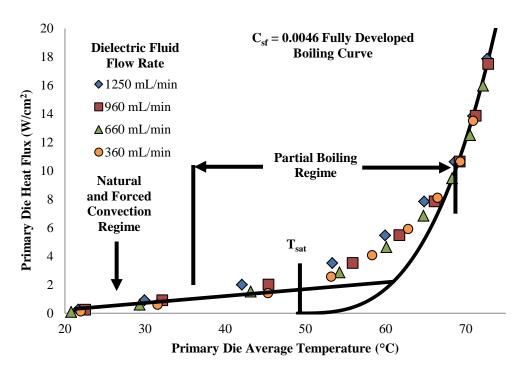

| Figure 76 – Basic flow boiling introduction enhancement results                                                                                           |

| Figure 77 – Bare Silicon Tube Inlet Flow Distribution Boiling Incipience Variations                                                                       |

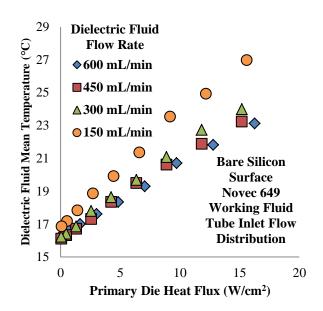

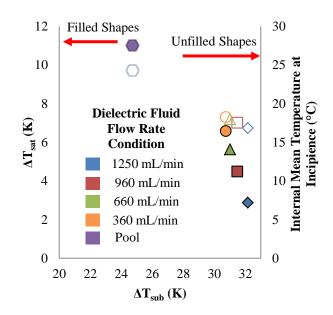

| Figure 78 – Influence of increasing dielectric fluid flow rate on internal mean temperature for the tube inlet flow distribution design                   |

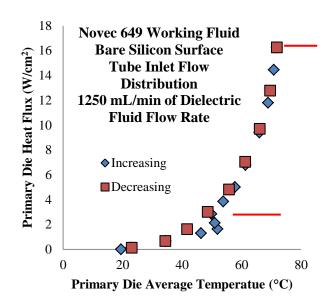

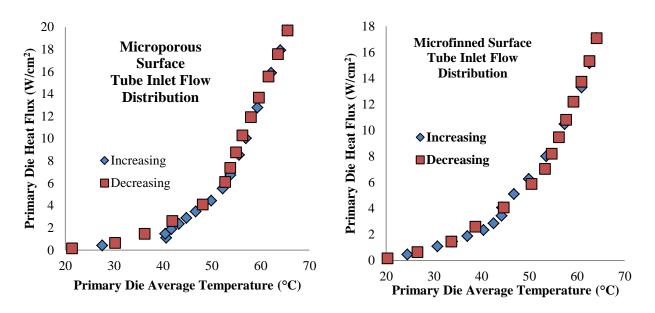

| Figure 79 – Increasing and decreasing heat flux comparison of tube inlet flow condition 116                                                               |

| Figure 80 – Temperature overshoot dependence on dielectric fluid flow rate for the tube inlet design                                                      |

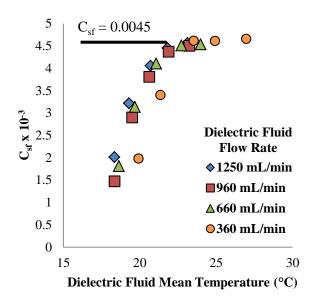

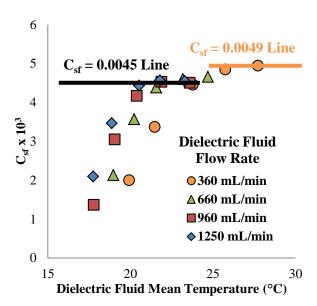

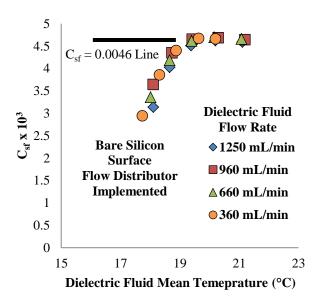

| Figure 81 – C <sub>sf</sub> convergence in flow boiling for bare silicon surface and the tube inlet flow distribution                                     |

| Figure 82 – Fundamental breakdown on subcooled flow boiling regimes [104] 117                                                                             |

| Figure 83 – Subcooled flow boiling curve for the bare silicon surface and the tube inlet distribution                                                     |

| Figure 84 – Illustration of subcooling effects on boiling performance [109] 119                                                                           |

| Figure 85 – Lack of temperature overshoot for both surface enhancements                                                                                   |

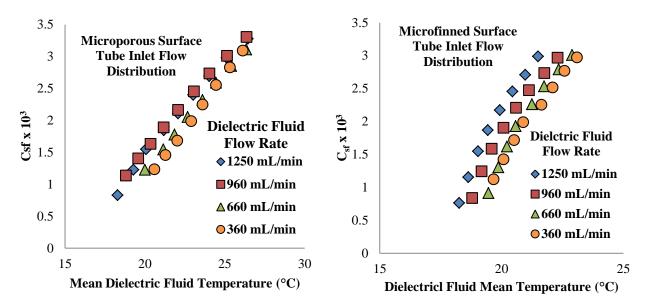

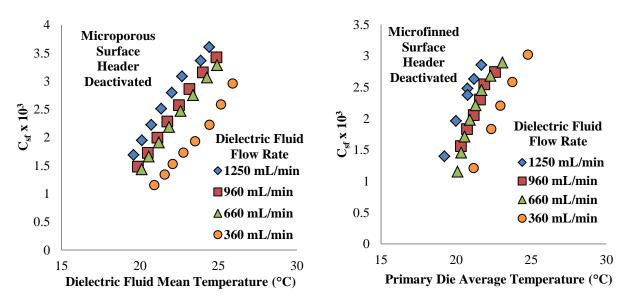

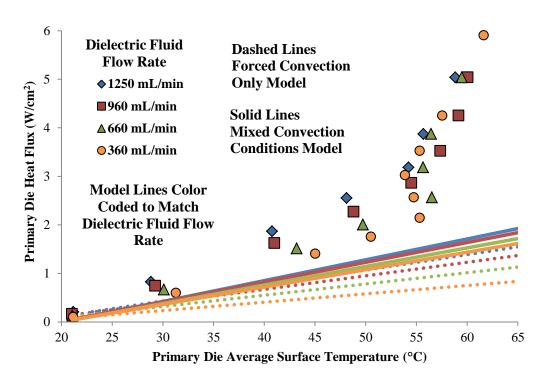

| Figure 86 – C <sub>sf</sub> values leading up to maximum heat fluxes attained in subcooled flow boiling with the tube inlet flow distribution integrated. |

| -             | Decreasing heat flux runs for both surface enhancements with the tube inlet flow distribution                                         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 89 –   | Bare silicon chilled water header performance factor                                                                                  |

|               | C <sub>sf</sub> convergence in flow boiling for bare silicon surface and the chilled water header deactivated                         |

| Figure 90 – 1 | Dielectric fluid sensible heat gain analysis with the chilled water header deactivated 129                                            |

| _             | Subcooled flow boiling curve for the bare silicon surface and chilled water header deactivated                                        |

|               | C <sub>sf</sub> values leading up to maximum heat fluxes attained in subcooled flow boiling with the chilled water header deactivated |

| _             | Increasing heat flux runs for both surface enhancements with the chilled water header deactivated                                     |

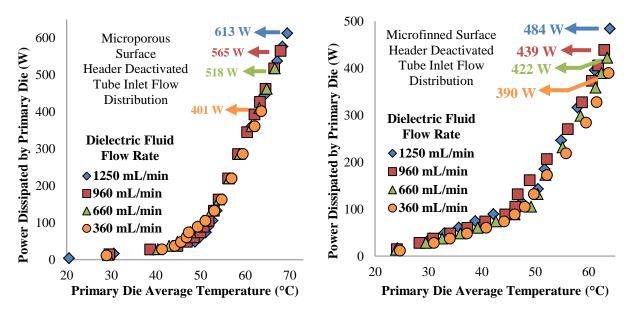

| _             | - Microporous surface enhancement factor illustrating potential benefits of chilled water header                                      |

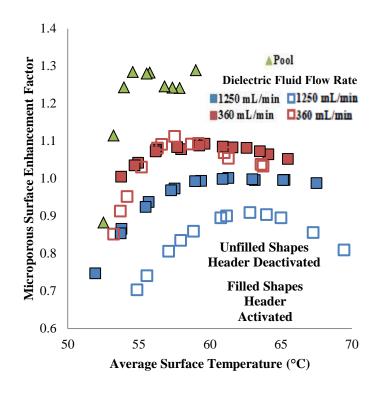

| -             | Combined free and forced convection trend with the flow distributor implemented on the bare silicon surface                           |

|               | - C <sub>sf</sub> convergence for flow boiling with the bare silicon surface and the flow distributor implemented                     |

| •             | - Decreasing heat flux data for the bare silicon surface and the flow distributor implemented                                         |

| -             | - Decreasing heat flux data for the microporous surface with the flow distributor implemented                                         |

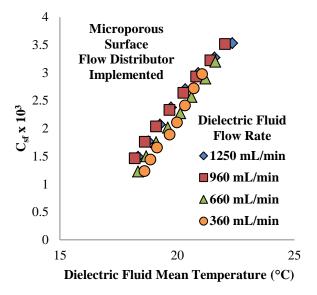

| Figure 99 –   | $C_{\rm sf}$ variation for the microporous surface with the flow distributor integrated 140                                           |

| Figure 100 -  | - Flow distributor performance from a thermal resistance perspective                                                                  |

| •             | - Decreasing heat flux data for the bare silicon surface as flow guide elevation height is varied                                     |

| Figure 102 -  | - $C_{\rm sf}$ variation over different flow guide designs with the bare silicon surface 144                                          |

| •             | $ C_{\rm sf}$ variation with the maximum flow guide implemented over various dielectric fluid flow rate runs                          |

| Figure 104   | <ul> <li>Decreasing heat flux data for the bare silicon surface with the maximum flow guide integrated over various dielectric fluid flow rate runs.</li> </ul> |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 105   | - Pressure drop across the cartridge with the maximum flow guide implemented under flow boiling across the bare silicon surface                                 |

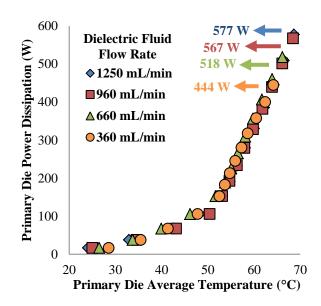

| Figure 106   | – Maximum power dissipation recorded by the experimental facility                                                                                               |

| Figure 107   | - Highlighted vector set used for single phase PIV analysis 151                                                                                                 |

| Figure 109   | - Resolution of vector set over each of the four primary die for single phase PIV analysis                                                                      |

| Figure 108   | - Resolution of the mass flow rate near the four primary die for single phase PIV analysis                                                                      |

| Figure 110 - | - Sample PIV vector sets from the tube inlet (left) and flow distributor (right) designs 153                                                                    |

| Figure 111   | - Flow distributor effectiveness at delivering fluid to the four primary elements over the tube inlet design                                                    |

| Figure 112   | - Sample PIV images of the flow distributor (right) and that of tallest flow guide implemented (left)                                                           |

| Figure 113   | - Tallest flow guide effectiveness at delivering fluid to the four primary elements over the flow distributor design                                            |

# **List of Tables**

| Table 1 - Surface Temperature Measurement Locations                                                                    |

|------------------------------------------------------------------------------------------------------------------------|

| Table 2 – Bare Die Pool Boiling Thermal Performance Summary                                                            |

| Table 3 – Saturated Fluid Properties for FC-72 and Novec 649                                                           |

| Table 4 – Surface Enhancement Pool Boiling Thermal Performance Summary                                                 |

| Table 5 – Summary of thermal resistances used for pool boiling condensive limit model 84                               |

| Table 6 – Tube Inlet Distribution Design Flow Boiling Thermal Performance Summary 121                                  |

| Table 7 – Tube Inlet Distribution and Header Deactivated Flow Boiling Thermal Performance Summary                      |

| Table 8 – Flow Distributor Design Flow Boiling Thermal Performance Summary                                             |

| Table 9 – Passive Element Integration Flow Boiling Thermal Performance Summary 143                                     |

| Table 10 – Ideal pumping power required to deliver fluid through the cartridge with the maximum flow guide implemented |

## **List of Symbols**

- a channel width (m)

- b channel height (m)

- A surface area (m<sup>2</sup>)

- $c_p$  solid specific heat  $(J/kg \cdot K)$

- $C_{pl}$  liquid specific heat  $(J/(kg \cdot K))$

- C<sub>sf</sub> Rohsenow correlation surface factor constant

- d diameter

- e thermal effusivity  $(J/(m^2 \cdot K \cdot \sec^{1/2}))$

- g gravitational acceleration constant (m/sec<sup>2</sup>)

- h heat transfer coefficient  $(W/(m^2 \cdot K))$

- $h_{lv}$  latent heat of vaporization (J/kg)

- $k \qquad \quad \text{thermal conductivity } (W/(m\!\cdot\! K))$

- L length (m)

$L_{heater}$  length of heated element (m)

- N number of fins

- q heat transfer (W)

- q" heat flux (W/m<sup>2</sup>)

- $\overline{Nu}_L$  average Nusselt number over the length of the heater

- P<sub>1</sub> liquid pressure (Pa)

- Pr Prandtl Number

- $Ra_L$  Rayleigh Number at the trailing edge of the heater

- T temperature (K)

## **Subscripts**

b base property

CHF Critical Heat Flux

c condenser property

conv convective property

f fin property

F forced convection related

Gr Graetz number

h heater property

i liquid-vapor interface property

l liquid state property

m mean

mod modified

N natural convection related

p particle property

rad radiative property

s surface property

sat saturation property

tot total

v vapor state property

w heated wall surface property

$\infty$  ambient property

#### **Greek Symbols**

α channel aspect ratio (b/a)

$\Delta$  change in property

$\delta_t$  thermal boundary layer

ε emissivity

- ρ density (kg/m<sup>3</sup>)

- μ dynamic viscosity (kg·m/sec)

- v kinematic viscosity (m<sup>2</sup>/sec)

- η efficiency

- $\sigma_{SB}$  Stefan-Boltzman constant

- $\sigma$  surface tension (N/m)

- τ time constant (sec)

#### **Chapter 1: Introduction**

Technological breakthroughs have governed society's ability to share ideas and conduct trade throughout our history. From the navigational advancements that brought the first pioneers across the Atlantic, to the first use of the transatlantic telegraph cable in 1858, and on to the development of the internet, people have strived to develop ways in which to communicate and do business with one another faster and more efficiently. With the previously mentioned historical progression, data transfer speeds have accelerated from taking many men and many months to deliver a message via boat, to delivering information over the cloud in a matter of seconds. Clearly these discoveries have broken down cultural and economic barriers in a time frame that once seemed unfathomable.

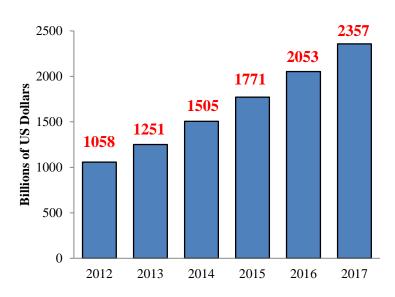

The desire to exchange information more expeditiously continues today in the form of society's need for constant connectivity to various social networking platforms and the conduction of vital commercial transactions and data storage within cloud based computing. Ecommerce is a giant pecuniary industry representing roughly six trillion dollars of global transactions in 2013 [1] which, according to recent data published by the International Monetary Fund (IMF), is larger than the GDP of all countries save China and the United States [2]. Ecommerce transactions can be broken down into two categories, Business to Consumer (B2C) and Business to Business (B2B). The former represents general online shopping purchases while the latter represents industry transactions such as raw material, equipment, new construction purchases, etc. These categories are indicators of the growth and relevance of data processing

requirements that successful companies will require to be impactful players in a fast-paced and competitive global economy. Figure projects significant growth in the coming years within the B2C sector, topping over two trillion dollars by next year [3]. As for the B<sub>2</sub>B division

Figure 1 – B2C Ecommerce transactions 2012-2017 [3]

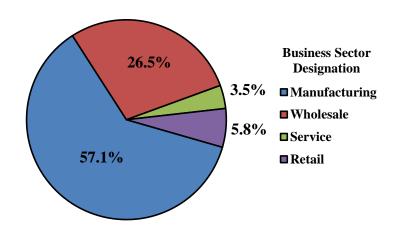

Ecommerce, Figure 2 shows the breakdown of the relative importance for various sectors within commercial transactions.

Notice that over half of this division goes to manufacturing, a cornerstone of a strong economy.

Figure 2 – B2B Ecommerce breakdown [3]

This indicates the importance of

data transfer not just to the success of individual commercial entities but also to the development and prominence of national economies. As more money is transferred over online and cloud based computing, the requirements for faster and more efficient means by which to process the data will grow as well.

As mentioned previously, this need will not be solely based on economics. Cultural mandates for constant connectivity will stress information transfer equipment to new levels. The

primary forms of this strain will come from streaming video transfer services along with the continued explosive growth of social media outlets. An interesting infographic published by Intel©, presented as Figure 3, illustrates the enormous amount of data transferred in any given minute over the internet as well as how this data is distributed [4]. From Figure 3 it is evident that data hungry streaming video transfer accounts for the majority of traffic with Netflix© and Youtube©. The social media giants Facebook© and Twitter© are not that far behind in terms of the amount of information they transfer at any given moment. The most important takeaway

Figure 3 – Social media and video transfer data infographic [4]

from Figure 3 however is that while this demand is currently staggering, it is only expected to grow tremendously in the coming years as more devices become connected and society expects that these devices bring them up to the second information on a growing number of fronts. This information can be as far reaching as providing instant vehicular diagnostics and driving patterns for traffic control or monitoring human vitals to help people live a healthier lifestyle. All of

these data logging initiatives can make society be more functional efficient. and but whatever information is transferred monitored will need to be stored and processed in some fashion. Therefore, it is to be expected that tomorrow's data center demands will grow as people become more connected, socially both and economically.

Figure 4 – Cloud power consumption vs. industrialized nations [5]

Note: Cloud consumption here includes telecommunications infrastructure, but not the entire ICT ecosystem

This growth in demand is most evident in the enormous power consumption that data centers presently command as well as in its recent and projected growth. Global Information-Communications-Technologies

(ICT) infrastructure, a good measure of cloud based computing systems, is said to consume 1,500 TWh of energy, a number that approaches 10% of the world's total electricity generation [5]. At an assumed average American residential energy consumption value of 10,000 kWh, this number

Figure 5 – ICT infrastructure power consumption breakdown [5]

represents roughly 150 million households. From a financial standpoint, at an assumed dollar/kWh value of ten cents, this number represents roughly 150 billion dollars. As shown in Figure 4, cloud based computing consumes more electricity than several industrialized countries including India and the UK [5]. The distribution of energy going to cloud based computing is shown as Figure 5. While the manufacture of the equipment, telecom equipment in the field used to distribute the data as well as the power drawn by the end-users equipment consume a great deal of the energy, the data center itself is power hungry coming in at slightly over 10% [5]. The problem that thermal and packaging engineers face in the near future is that these numbers have increased in recent years and only show signs of rising further. Data center power numbers rose 7% from 2012 to 2013, going from 38 GW to 40 GW [6]. Compounding this problem is the fact that the planet has dwindling energy resources in a time when global energy consumption is significantly on the rise. In 2010, global energy consumption was 153 PWh and projections to 2020 are 185 PWh and even higher in 2040 at 240 PWh [7]. This represents a 21% increase over the next decade and a 57% increase over the next thirty years in electricity demand. Of the power going to the data center, roughly half of it is dedicated to the cooling solution implemented as shown in Figure 6 [8]. Due to the increases in demands on these systems in tandem with a growing global energy crisis, it is incumbent upon engineers to find better and more efficient designs for future systems.

Figure 6 – Data center power consumption breakdown [8]

With such a significant portion of the data center's power draw going to the thermal management solution employed, this is an area where packaging and thermal engineers can make a significant impact. The purpose of this study is to illustrate the effectiveness of a modular small form factor two-phase liquid immersion cooled solution for future data center applications as well as promote new experimental techniques meant to enhance and ensure consistent performance from such a system. While there are still lingering fears within the data center design community about using liquid cooling, even dielectrics, in such close proximity to electronics, the industry has recently studied and implemented a variety of liquid immersion cooled solutions with marked success. Systems similar to that proposed within this study have already been implemented in the industry. Iceotope™ installed a modular Line Replaceable Unit (LRU) system at a company called PSNC© in Poland, reporting a 40.8% reduction in power requirements when compared to a traditional air cooling method [9]. This solution is a single phase natural convection method where buoyancy drives the fluid movement and heat transfer within the cartridge and overall rack assembly. An image showing the Iceotope solution is

provided as Figure 8. A modular two-phase liquid cooling approach very similar to that proposed within this study where the fluid is pumped through the cartridge has also been proposed [10], forming the foundation for LiquidCool Solutions© product line. Green Revolution Cooling (GRC) and Intel© reported a 90% reduction in data center thermal management

Figure 8 – Typical Iceotope Installation

energy consumption using a single phase liquid immersion cooling approach with mineral oil as the working fluid [11]. This is an Open Bath Immersion (OBI) approach where many complete server boards are immersed in large baths of cooling fluid. A sample image of a GRC installation is provided as Figure 7. A two-phase OBI approach at a Bitcoin mining farm in

Hong Kong reported a Power Usage Effectiveness (PUE) of 1.02 [12]. PUE is a common Figure of Merit (FOM) for data centers as it is the ratio of the power drawn by the data center and the processing power yielded by the data center. An ideal PUE value would be one, where every watt of power delivered to the data center was

**Figure 7 – OBI Installation Example**

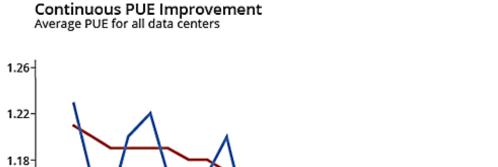

used solely for processing, i.e. no overhead power consumption for operations. Building on the success of the Hong Kong installation, a team of 3M and SGI are currently building a data center using the same method in the United States [13]. The importance of PUE cannot be understated as Google©, a major player in the data center industry, not only tracks and reports the value for all of their data centers but has also made a concerted effort to reduce it year by year as shown in Figure 9 [14].

1.141.10

2008 2009 2010 2011 2012 2013 2014

Trailing twelve-month (TTM) PUE Quarterly PUE

Figure 9 – Google's reduction in data center PUE [14]

PUE

The flexibility of forcing fluid through the liquid filled cartridge as opposed to using pool boiling as the sole means of heat transfer is explored in this study. While this study focuses on using low boiling point dielectrics as the working fluid, forced convection methods in liquid filled enclosures with mineral oil has already been studied. Most notably, the work of Eiland *et al* [15] reported a partial PUE (pPUE) of 1.06. This pPUE only takes into account the energy required to deliver the heat into the working fluid and does not take into account the energy required to exhaust the heat from the working fluid into the ambient environment. A total PUE

would be slightly higher once one decided upon a method of extracting the heat from the working fluid. There are a number of state of the art air cooled facilities that are achieving incredible PUE numbers, although not as low as liquid cooled systems. State of the art data centers at Google and Facebook have achieved PUE's of 1.12 [14] and 1.08 [16] respectively. An American Society of Heating, Refrigeration and Air Conditioning Engineers (ASHRAE) innovation award was given to a 7.2 MW data center for Oracle© in West Jordan, UT. Like the Google and Facebook systems, this facility brings in outdoor air to cool servers from the dryer and more moderate temperature surroundings in West Jordan to reduce air conditioning costs, resulting in a PUE of 1.25 [17]. Care and additional design considerations must be taken into account for these types of facilities as air that is too dry can cause a static discharge on the electronics within the data center. Typically, the precaution taken to prevent this failure is an inline humidifier for the incoming air to control moisture content appropriately. The PUE numbers presented for all of these solutions are even more impressive when compared to the current Environmental Protection Agency's (EPA) current best practice value of 1.50 for data centers [18]. A summary bar chart of the PUE case studies presented is shown as Figure 10 highlighting the primarily liquid cooled solutions and their efficiency advantages over more traditional air cooled systems. Even indirect liquid cooling systems, with the working fluid flowing through a thermally attached cold plate, has been shown to reduce facility power requirements by as much as 45% over air cooling methods [19]. The current study builds on elements of liquid cooling solutions already implemented to show how two-phase heat transfer can achieve higher power dissipations in a smaller form factor with lower operating temperatures which promotes cost savings, better reliability and lower system level thermal resistances.

Figure 10 – Case Study PUE Benchmarks

The main factor driving higher operating temperatures is the consumer demand that electronics be constructed in more tightly packaged systems. The classic argument for this

$$q = h * A * (T_s - T_{\infty}) \tag{1}$$

$$q'' = h * \Delta T \tag{2}$$

relationship uses the terms found in Newton's law of cooling with all terms shown in Equation 1 or with some terms compressed in Equation 2. While there is debate as to whether the failure rate of a processor truly doubles with every 10°C increase in operating temperature, it is generally accepted that increased operating temperatures do have some deleterious effect on system reliability [20] [21]. Therefore, the aim of the thermal engineer is to keep this value as low as possible to keep reliability as high as possible. The amount of heat transfer is directly proportional to the amount of processing taking place within the device, so limiting this to reduce the surface temperature would not be advantageous from a performance perspective. Decreasing the ambient temperature would require additional air conditioning costs so oftentimes reducing this term is not feasible. Increasing the area would reduce the surface temperatures but goes against consumer expectations for smaller systems. The most direct way to increase reliability of the system is to increase the heat transfer coefficient. Oftentimes, the thermal engineer is faced with the problem of a varying heat flux so the same argument with the reference of Equation 2 is

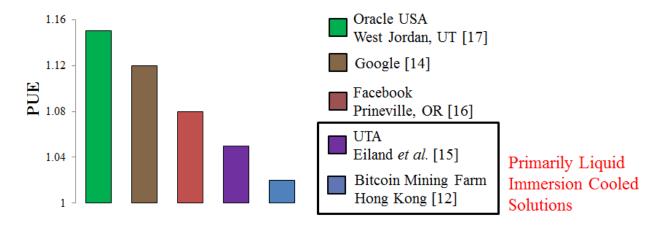

presented. With the desire to have increased processing, or increased heat transfer, with a smaller footprint, or less area, the heat flux must increase. From Equation 2, in order to increase the reliability in a fixed ambient temperature environment, the driving temperature difference,  $\Delta T$ , must decrease. To accommodate this desired decrease in temperature with the expected rise in heat flux, again the heat transfer coefficient must go up. Unfortunately for the thermal design engineer, heat fluxes for high performance electronics are projected to rise significantly in the coming years. Heat fluxes as high as 250 W/cm<sup>2</sup> [22] are projected in the near term while those near 1000 W/cm<sup>2</sup> are expected within the next decade [23]. Fortunately however, two-phase heat transfer offers several orders of magnitude increases in heat transfer coefficients over more traditional forced convection air cooling methods as illustrated by Figure 11 [24]. Industrial examples have already shown significant increases in efficiency using liquid immersion cooling techniques and the increases in heat transfer coefficients when two-phase heat transfer is added provides a two-pronged attack at cutting operating costs. Even more cost savings can be realized in the construction of a liquid cooled data center as piping and plumbing installation is much easier and cost effective than routing large air ducts. Installation of a traditional air cooled thermal management system can account for as much as 43% of initial construction cost [25].

Figure 11 – Cooling method heat transfer coefficient comparison chart [24]

With the current trend of high performance processing equipment attaining heat fluxes that will undoubtedly overwhelm traditional air cooling methods, a fundamental understanding of liquid cooling with these systems is critical for the future as the industry will continue its matriculation to the consistent application of this thermal management solution. The experimentation and analysis conducted within this study will help to answer the questions sure to arise as this solution gains a stronger foothold in the industry.

#### **Chapter 2: Literature Review**

There have been a number of fundamental and application oriented studies conducted within the thermal science and fluid mechanics community over the last several decades regarding the use of two-phase heat transfer, liquid immersion cooling, and flow visualizations using Particle Image Velocimetry (PIV) techniques that are of particular pertinence to the current study. This chapter seeks to provide some historical perspective on why the problems currently facing thermal and packaging engineers of high performance electronics are present along with highlighting a number of examples in the literature that have influenced the motivations behind the current study.

## 2.1 Genesis of Liquid Cooling in the Data Center

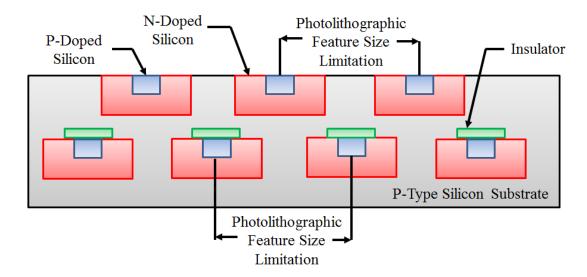

The advancements in microelectronic fabrication techniques over the last several decades brought about the necessity for integration of more effective thermal management solutions in high performance computing equipment. The spacing between transistors on an Integrated Circuit (IC) is critical as interconnect length is a main driver of processing speeds. Conventional IC construction involves a number of photolithographic steps that build transistor networks on silicon wafers. The rule of thumb is that economically feasible and commercially producible transistor spacings are limited to the wavelength of the light used for photolithography. The seemingly prescient Dr. Gordon E. Moore stated that the number of transistors on a chip would double every 10 years [26], essentially predicting the advancements of microelectronics fabrication. Until recently this statement had been proven consistently correct and remarkably

accurate. Current limitations with microelectronics fabrication techniques have led to the slowing of transistor density growth resulting in a slight deviation from Moore's Law [27]. The current feature length for state of the art commercially available chips is 14 nm with plans to have 10 nm systems available by 2017 [28], representing a giant leap back on the track set forth by Moore's Law. The consequence for the thermal engineer with the decrease in feature size and

increase in transistor density the amount of power generated in a given area will increase with the predictions of Moore's Law. Given that Dr. Moore himself has recently claimed that adherence to his law will continue for at least another ten years [29], thermal engineers will continue to face growing

challenges as heat fluxes for

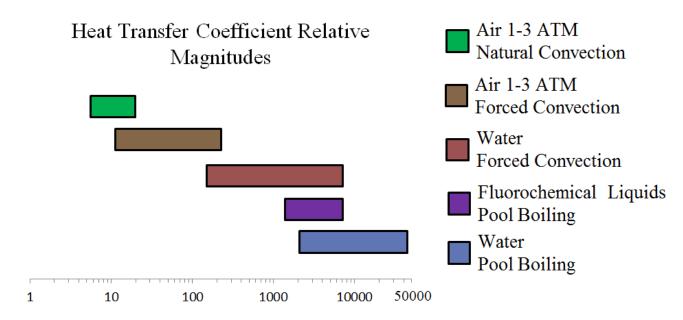

Figure 12 – High performance electronics heat flux rise timeline [30]

high performance computing equipment will begin to overwhelm conventional cooling techniques.

The necessity for implementation of liquid cooling in the data center to face these thermal challenges has happened before. Prior to the implementation of the more efficient Complementary Metal Oxide Semiconductor (CMOS) transistor in the early 1990's, bipolar

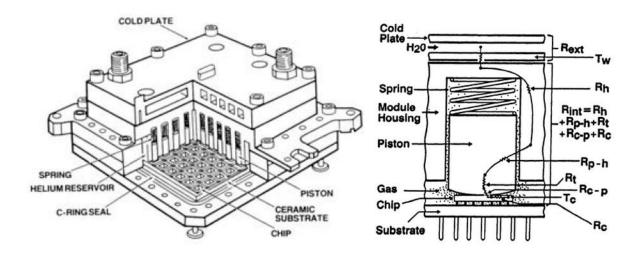

transistors were the primary switching elements used in IC fabrication. The rise of the heat flux associated with the use of bipolar transistors along with the dramatic reduction realized when the switch to CMOS took place is illustrated in Figure 12 [30]. A number of computing systems that represented significant leaps forward in performance are highlighted on Figure 12 as well. One of the first attempts at bringing liquid into the data center was made with the introduction of the Thermal Conduction Module (TCM) integrated onto the IBM® 3081 computing system in 1982 [31]. A schematic of this device is presented as Figure 13 showing a cutaway view on the left

**Figure 13 – IBM TCM details [32] [33]**

[32] and a zoomed in detail of the pistons [33] used to maintain more direct thermal contact with processing elements. One of the motivations behind the design of this module is to reduce the thermal resistance experienced by the heat flow emanating from the transistor junction to the cooling medium. Thermal Interface Materials (TIMs) are a critical point of increased resistance to heat flow out of the chip into the ambient along with a potentially detrimental junction for increased thermal stresses due to Coefficient of Thermal Expansion (CTE) mismatches between the materials in the chip to heat sink stack-up. When a heat sink is attached to a processor chip with a conventional grease TIM, heat flows primarily through the channels where the heat sink

and the chip are connected by the adhesive. These channels are generated by the peaks and valleys formed during the curing process of the grease. While these connections offer conduction paths, the gaps are filled with comparatively insulative gas gaps which add to the thermal resistance substantially. These peaks and valleys are illustrated by Figure 14 [34]. When the amount of thermal expansion of a TIM differs from that of the expansion experienced by the silicon of an IC, stress and strain is imposed on the processing element resulting in the potential for failure or decreased reliability. The use of springs in IBM's TCM is an attempt to alleviate the stresses induced by CTE mismatch as well as provide a superior heat flow path via

springs as well as through the surrounding helium gas encapsulated by the module. Low pressure helium sealed within the

conduction through the metallic

conductivity than the atmospheric

module has a higher thermal Figure 14 - Air gap contact resistance with traditional TIM's [34]

air captured in a traditional grease TIM. The combination of these two heat flow path enhancements provide improved heat extraction to the chilled water flowing in the cold plate that sits on top of the module. As an example, a 1 in<sup>2</sup> IC that has a heat sink attached to it with a typical thermal grease can experience a resistance of up to 6.5 K/W at the adhesive interface alone [34]. With a high end thermal grease this value can be reduced to 1.3 K/W [34] but it should be noted that this is not the overall chip to ambient thermal resistance as it does not take into account the junction to case thermal resistance experienced in the encapsulating material surrounding the chip, that experienced via conduction through the heat sink, or that experienced

during the convective removal of heat away from the heat sink surface. IBM's TCM boasts an overall chip to ambient thermal resistance of 4 K/W [35] with a 90 x 90 array of smaller processing elements resulting in an overall heat generation of 300 W [31]. While the omission of the thermal resistance experienced by a traditional grease may have been removed and the piston design of the TCM yielded optimal pressure and thermal contact to the processing elements embedded within, this value is an order of magnitude higher than the chip to ambient thermal resistances yielded by the current study. By immersing the electronic component within the cooling medium itself, not only are the manufacturing complexities associated with attaching heat sinks, TIMs, cold plates, heat spreaders, etc. to processing elements taken away, but the chip to ambient thermal resistance is also reduced drastically by ejecting the heat directly into the coolant. While the TCM was significant for its time, immersion cooling techniques remove the thermal resistances introduced with intricate cold plate style designs or traditional heat sink attachment approaches. Less thermal resistance results in lower operating temperatures for equivalent processing power, increasing the reliability of the system as well. The point at which the TCM was introduced in the heat flux rise timeline shown in Figure 12 is interesting in that it came at a time when heat fluxes from high performance computing equipment was at roughly 2.5 W/cm<sup>2</sup>. Liquid had to be introduced into the data center to effectively manage this heat flux and is also the point at which two-phase heat transfer is initiated for the dielectric fluids used within the current study. This highlights the natural progression, and possible inevitability, towards introducing liquid into the data center as systems become increasingly more compact and power dense.

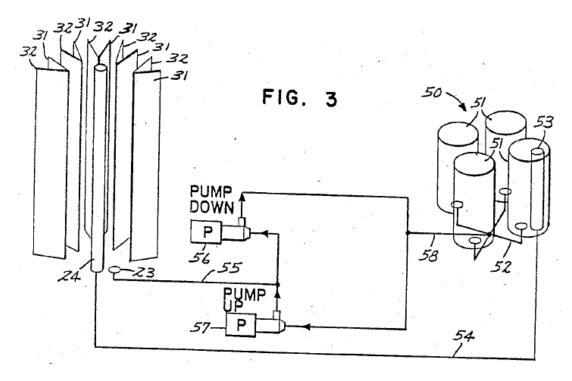

Another historical system that emphasizes the important and growing role of two-phase liquid immersion cooling techniques in the industry is the Cray-2 liquid supercomputer [36]. A schematic from the patent filed in 1982 is provided as Figure 15. The patent touches on another issue that two-phase liquid immersion cooling is suited to handle, namely the rise in volumetric heat dissipations. For example, it is possible to achieve significantly high base heat transfer coefficients within optimally spaced vertically oriented plate fins on a heat sink, nearly 190 W/m<sup>2</sup>K as shown by Bar-Cohen *et al* [37]. However, this heat transfer coefficient would be attained for fins that are 675 mm (2.2 feet) tall, prohibitive for most electronics cooling

Figure 15 – Schematic of Cray-2 supercomputer cooling system [36]

The radial array of processing boards shown on the left accept the dielectric fluid coolant delivered via the pumps shown in the middle which has been subcooled by the reservoirs shown on the right. These reservoirs also act as the point at which heat is extracted from the system to ambient.

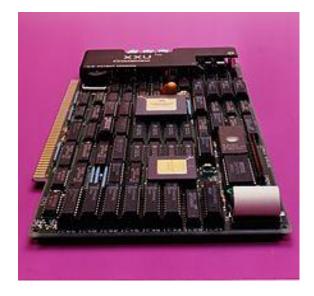

applications. During this time, high performance processing packages could be as small as 4 in x 8 in x 1 in (102 mm x 204 mm x 25.4 mm) dissipating 600 W of heat [36]. An example of the form factor and layout of such a board is provided as Figure 16. From a heat flux perspective this translates to a value of 2.93 W/cm², again in the proximity of the value that drove the design behind the previously mentioned TCM. Current high performance processors are above this heat flux with Intel's top of the line processor producing a value of 6.92 W/cm² from a reported Thermal Design Power (TDP) of 155 W [38]. Given that heat flux history is repeating itself as suggested by Figure 12 this provides further evidence that liquid cooling must find its way into the data center in some capacity moving forward. The 600 W board level power dissipation translates to a volumetric heat dissipation of 1.13 W/cm³ for the motherboard only. This value exceeds even current state of the art air cooling capabilities as the top of the line HP Proliant Gen8 server has a volumetric power density of 0.051 W/cm³ [39]. The design reported that incoming fluid temperatures were 70°F (21°C) while the outgoing temperature was 90°F (32°C) which kept the maximum temperature of any chip within the system at 130°F (54°C) at a flow

rate translating to 1 in/sec across the circuit board [36]. The Cray-2 approach also includes many boards in a single bath of fluid, adding complexity to the maintainability of the system should only one of the boards within the array of modules fail. The LRU approach proposed by the current study allows for the potential of hot-swapping modules in case of single failure.

Even with the maintainability issues, this **Figure 16 – Sample 1986 high performance processing motherboard**

approach and technology was far-reaching for its time. It came at a moment in the evolution of high performance electronics when more aggressive thermal management solutions were necessary, not unlike the current situation in this field.

### 2.2 Boiling Heat Transfer Performance Historical Studies

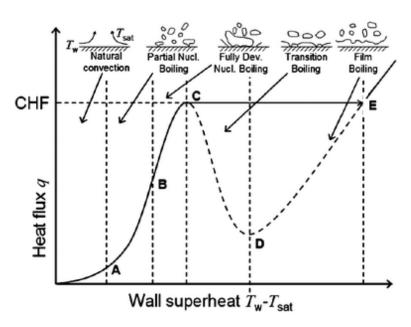

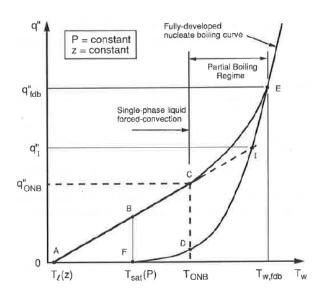

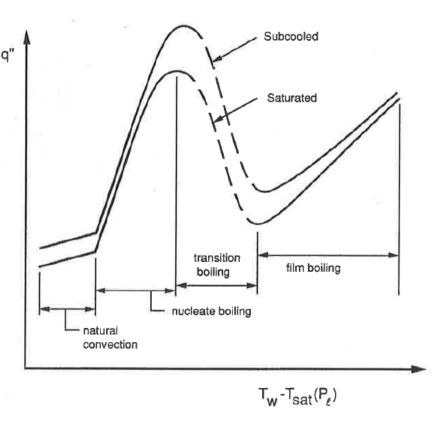

The fundamental phenomena governing the two-phase heat transfer that allows the power densities of high performance electronics to be reliably maintained at a suitable operating temperature have been studied in depth. The classic work that begins to characterize the various regimes within pool boiling was conducted by Nukiyama [40]. By supplying current to nichrome, nickel, platinum, iron and fuse wires of known resistance, constant heat flux experiments were conducted to gather portions of the traditional boiling curve shown in Figure 17. For an immersion cooling system of high performance computing equipment, the first regime, leading up to point A on Figure 17, where natural convection dominates is typically of little consequence as heat fluxes of these systems are large enough to initiate boiling with many

of the low saturation temperature dielectric liquids used as working fluids in these applications. The benefits of immersion cooling for lower power elements on a computing board can be realized beyond what air cooling can offer. For example, assuming a moderate

heat flux of 1 W/cm<sup>2</sup> and using Figure 17 – Pool boiling curve trends and regimes [40]

$$\overline{Nu}_{L} = \left\{ 0.825 + \frac{0.387 * Ra_{L}^{1/6}}{\left[1 + \left(\frac{0.492}{Pr}\right)^{9/16}\right]^{8/27}} \right\}^{2}$$

(3)

the work of Churchill and Chu [41] for free convection on a vertical plate shown as Equation 3, the 1 in<sup>2</sup> element used in the current study is predicted to have a surface temperature of 56°C with an average heat transfer coefficient of 323 W/m<sup>2</sup>K with Novec 649 as the working fluid at an ambient temperature of 25°C. Although boiling would have developed at some sites on the surface at this temperature given that the atmospheric saturation temperature for Novec 649 is 49°C, this heat transfer coefficient and surface temperature match well with the experimental results yielded through pool boiling from a bare silicon surface. The same conditions with air as the cooling medium yield an average heat transfer coefficient of 13.7 W/m<sup>2</sup>K with a surface temperature of 753°C. The latter value shows why heat spreaders, sinks and other extended surfaces are necessary to cool computing equipment in traditional air cooled systems.

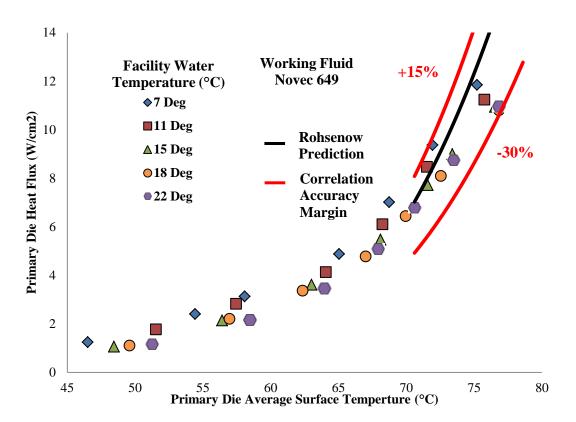

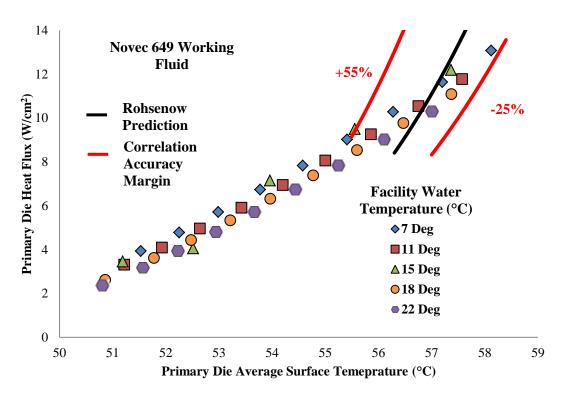

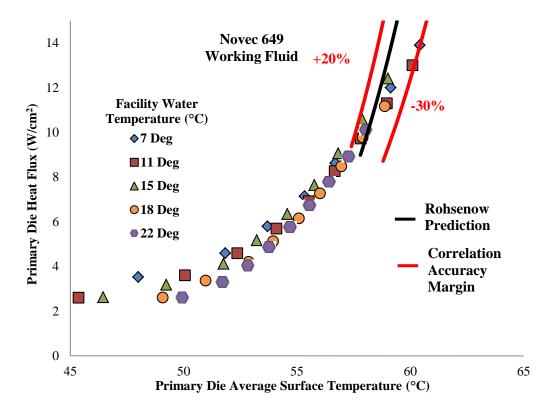

The area of most interest to the current study is the fully developed nucleate boiling regime, the area between points B and C on Figure 17. The behavior in this regime can be predicted by the well-known Rohsenow semi-empirical correlation [54] shown as Equation 4. For the purposes of the dielectric fluids used in the current study the values of the constants s and r are 0.33 and 1.7 respectively in Equation 4. Interestingly, the seemingly complex equation stems from the assumption that there exists a bubble Nusselt number,  $Nu_b$ , that takes the fundamental form of a convective relation, namely  $Nu_b = A * Re_b^m * Pr_l^n$ . With the appropriate selection of a bubble Reynolds number and a bubble length scale, the fluid properties take the

$$\frac{q''}{\mu_l * h_{lv}} * \left[ \frac{\sigma}{g * (\rho_l - \rho_v)} \right]^{\frac{1}{2}} = \left( \frac{1}{C_{sf}} \right)^{\frac{1}{r}} * Pr_l^{-\left(\frac{S}{r}\right)} * \left[ \frac{C_{pl} * [T_w - T_{sat}(P_l)]}{h_{lv}} \right]^{\frac{1}{r}}$$

(4)

form of those shown in Equation 4. The empirical portion comes into play with the selection of the r,s and  $C_{sf}$  values. With an adequately determined  $C_{sf}$  values, accepted error with this correlation can be in the range of  $\pm$  40%.

The point at which the temperature jumps significantly as heat flux is increased, from the point C to point E on Figure 17, is generally referred to as the Critical Heat Flux (CHF). In a typical electronics system, this results in a catastrophic failure of the system as conventional attachment materials cannot withstand the orders of magnitude temperature increase that coincides with this event. Using the work of Lubin [42] to get the convective heat transfer coefficient in the post-CHF film boiling regime shown as Equation 5, the heat transfer coefficient contribution from radiation shown by Equation 6, the simplification of their contributions to the total heat transfer coefficients proposed by Bromley [43] shown as Equation 7, and Newton's Law of Cooling Equation shown previously as Equation 1, the maximum temperature of the heated element used in the current study at the beginning of film boiling,

$$h_{conv} = \left[ \frac{k_v * g * \rho_v * (\rho_l - \rho_v) * h_{lv}}{4 * \mu_v * (T_w - T_{sat}) * L_{heater}} \right]^{1/4}$$

(5)

$$h_{rad} = \frac{\sigma_{SB} * (T_w^2 + T_{sat}^2) * (T_w + T_{sat})}{\frac{1}{\varepsilon_i} + \frac{1}{\varepsilon_w} - 1}$$

(6)

$$h = h_{conv} + \left(\frac{3}{4}\right) * h_{rad} \tag{7}$$

marked as point E on Figure 17, was found to be 338°C. Conventional electronic equipment attach materials such as solder and indium have melting points of 183°C and 157°C respectively, both sufficiently below the temperature experienced by the heated surface after the CHF event. Given that this event should be avoided in most practical situations, extensive studies have been conducted to quantify the point at which it is reached along with ways in which to predict its

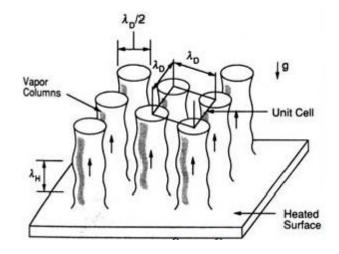

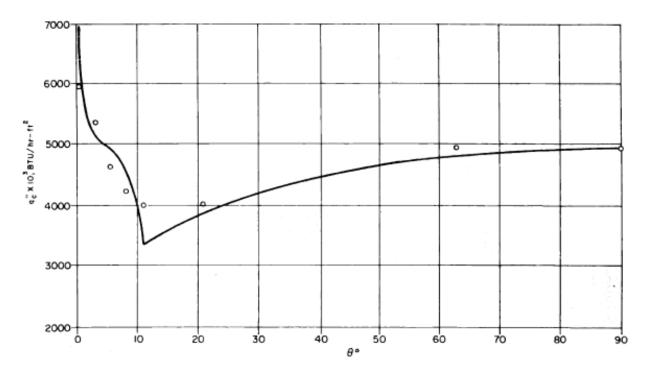

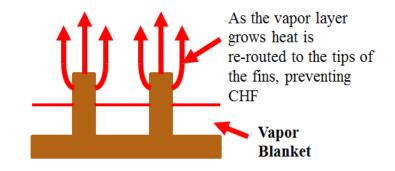

occurrence. Kutateladze [44] and Zuber [45] both independently came to the same equation for predicting CHF, shown as Equation 8. The governing theory for both of their models is that at some point the velocity of the rising vapor becomes so great that the drag induced on the neighboring quenching fluid column completely blocks the liquid's return to the heated surface. A figure to provide clarity to this phenomenon is provided as Figure 18 [46]. By proposing a cross-hatched pattern of columns as Zuber did, the spacing between them was the Taylor wavelength multiplied by the square root of two. Lienhard and Dhir [47] modified this calculation by adjusting the critical spacing to the Taylor wavelength, as would be the case in a uniform square grid array, leading to an adjustment of the CHF model. The resulting Lienhard and Dhir CHF equation substitutes a 0.149 for the 0.131 coefficient shown in Equation 8.

$$q''_{CHF} = 0.131 * \rho_v * h_{lv} * \left[ \frac{g * (\rho_l - \rho_v) * \sigma}{\rho_v^2} \right]^{1/4}$$

(8)

The theory behind these correlations is limited to horizontal surfaces. Howard and Mudawar [48] executed a visualization study on vapor lift off from heaters at various angles. They

for CHF to three different regions. The regions of interest were an upward facing region (between 0 and 60 degrees), a near vertical region (60 to 165 degrees), and a downward facing region (>165 degrees). In the near vertical region, of interest to the

proposed to apply a different model

Figure 18 – Liquid/Vapor Column CHF Model [47]

current study as the heated elements are aligned vertically within the module, interfacial wavy vapor layer instabilities with the neighboring liquid region were dominant as the bubbles lifted off from the heated surface. Further refinement of the CHF predictive model was proposed by Arik and Bar-Cohen [49] in the form of the Thermal Management of Electronics (TME) CHF correlation. This lengthy and detailed correlation takes into account the thermal effusivity of the heater material along with its dimensions to account for the spreading of heat to more effectively quenched areas at the heat fluxes leading up to the CHF event. Thermal effusivity, e, is a measure of the material's ability to exchange thermal energy with its surroundings and is defined by the square root of the product of its thermal conductivity and volumetric heat capacity, or  $(k \cdot p \cdot c_p)^{1/2}$ . This heat spreading could allow for the more effectively quenched areas to carry some of the heat load before the catastrophic vapor blanketing event can occur. The heat fluxes leading up to CHF are also characterized by a leveling off of the heat transfer coefficient as experimentally documented by Sridhar [50]

The area of the boiling curve between the points marked C and D on Figure 17 is known as the transition regime and is accessible with temperature varied experiments, such as the quenching of a highly conducting rod or sphere. The nature of this curve is hard to predict given the precision of temperature control required, although a number of researchers have tried. Berenson [51] was the first to discover this region and quantify the heat flux and temperature trends that characterize it. Witte and Lienhard [52] claimed a hysteresis exists in this region due to the mechanisms driving the departure from nucleate boiling, the point marked as C on Figure 17, when temperature is increased versus departure from the minimum heat flux, the point marked as D on Figure 17, when temperature is decreased. They claimed that the phenomenon driving this "jump" between the two sub-regions was the difference in the advancing versus

receding contact angle during these two events. Conversely, Hohl *et al* [53] showed no hysteresis in this region when FC-72 was used, one of the fluids used in the current study. Although the debate still exists as to the influence of contact angle on this region, it is generally of little consequence for the study of immersion cooled electronics as these systems are typically characterized as heat flux controlled, making this region of the boiling curve not accessible.

Figure 19 – Condensive limit of Freon-113 trends [55]

# 2.3 Introduction of Condensation Limitations in Liquid Filled Modules

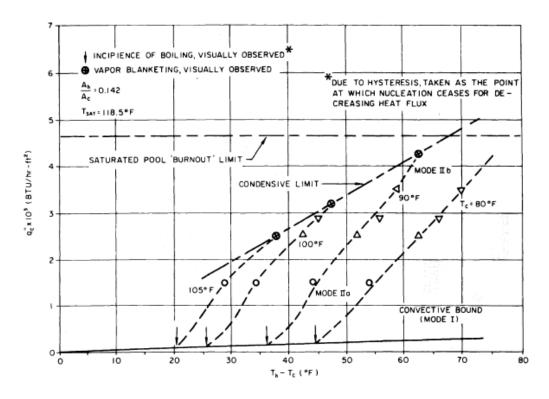

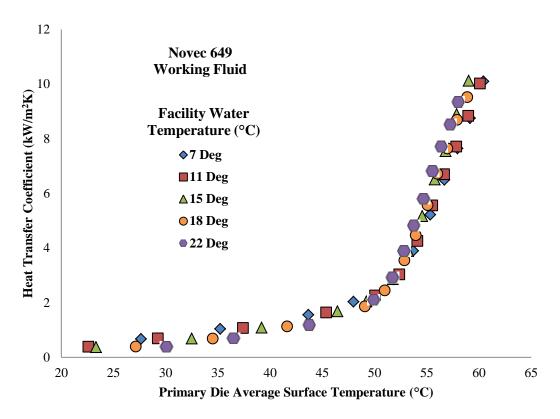

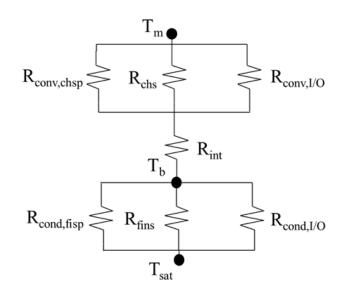

While the available CHF correlations are useful as an estimate for the potential performance of a two-phase immersion cooled electronics enclosure, there is often another and more limiting factor associated with the extraction of the heat out of the module itself. This is referred to as the condensive limit and was first explored in a Liquid Filled Module (LFM) application by Markowitz [55]. Using a flat horizontal plate for condensation heat transfer

extraction from the module above 0.25" diameter heaters submerged in either water or Freon-113, the limitations of an LFM below the generally accepted CHF value was explored. By plotting the variation in heat flux at the heater versus the driving temperature difference between the heater surface and condensive plate, a clear trend can be seen as to the variation of the burnout heat flux as the condensive plate temperature is varied. This trend is shown by the dashed line in Figure 19 with Freon-113 as the working fluid. As noted in the study of Markowitz, one of the primary factors in the determination of whether an LFM will be condensation limited is the heated area to condensive area ratio, or  $A_h/A_c$ . For the data shown in

Figure 20 – Trends of LFM angle of inclination on maximum performance [55]

Figure 19, this ratio is 0.142 while for the current study it is 0.078. The latter number is assuming that all of the vertically oriented pin fins and flat area below the chilled water header used for extracting the heat from the module is completely active in the heat transfer process, as would be the case in the horizontally oriented condenser used in the work of Markowitz. The degree of activity and efficiency of the vertically oriented pin fins is an issue addressed in the current study, specifically in an attempt to model this upper limit behavior. The relative activity and contribution of the condenser surface is based on a number of factors. Markowitz showed that by tilting the LFM at various angles, the boiling activity within allowed for the liquid-vapor

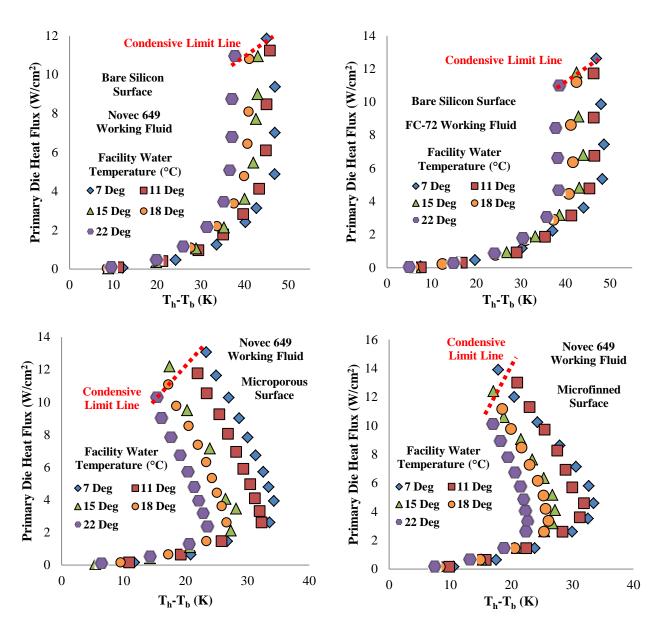

$$h_{m,mod} = \frac{k_l}{L_{fin}} * (0.943) * \left(\frac{\rho_l * (\rho_l - \rho_v) * g * h'_{lv} * L_{fin}^3}{\mu_l * k_l * (T_{sat} - T_b) * \eta_{fin}}\right)^{1/4}$$

(9)

$$h'_{lv} = h_{lv} * (1 + 0.68 * Ja)$$

(10)

$$q_{tot,fin} = N * A_{fin} * \eta_{fin} * h_{m,mod} * (T_{sat} - T_b)$$

$$\tag{11}$$

interface to interact with the condensive film on the condenser wall in addition to immersing a portion of the surface in the coolant thus modifying the overall performance of the system. The effects are competing in that the sloshing can clean the condensate surface allowing for a new film to be generated thus enhancing heat transfer, while immersing a portion of the condenser surface effectively insulates it relative to the condensation heat transfer coefficients experienced on the exposed surfaces. This overall effect is shown in the maximum heat transfer rate achieved at various angles with a 40°F driving temperature difference between the heater and condenser plate with water as the working fluid, shown as Figure 20. Another contributing factor to the performance of the condenser, which is particularly important for the current study, is the fin efficiency of the extended surfaces used there. Iyengar [56] proposed modifying the classic Nusselt [57] laminar film condensation equation for a vertical plate by placing the fin efficiency in the denominator as shown in Equation 9 taking into account the modified latent heat relations proposed by Rohsenow [58] shown as Equation 10. This modified heat transfer coefficient can then be used in the traditional way of calculating heat transfer from a series of fins as shown in Equation 11. The unmodified heat transfer coefficient calculated from the Nusselt laminar film condensation vertical plate equation is used in the determination of the individual fin efficiency. The effect of sloshing and the relative contribution of the vertical fins used as the condenser for the liquid immersion module proposed in the current study will play an important role in modeling the expected behavior of the system.

## 2.4 Novel Electronics Cooling System Studies

There have been a number of recent achievements and studies with a focus in electronics cooling that have advanced the science, both in terms of power dissipations achieved as well as more reliable operating temperatures manifesting in the form of heat transfer coefficient

improvement. In a similar approach to the current study although in a slightly larger form factor, Campbell et al [59] explored the use of chilled water maintained condenser fins to extract the heat from boiling surfaces oriented horizontally and vertically. This study also explored the potential of using a more conductive and immiscible fluid with low boiling point dielectrics such as those used in the current study in the condenser space to enhance heat transfer in this area. A schematic of the proposed solution is shown as Figure 21. This is just one of a number of patents proposed by IBM in this area. Campbell et al [60] proposed a LRU rack system where vapor from a collection of modules was captured in a single heat exchanger for condensation and subsequent return back to each individual system under pool boiling conditions. The use of intricate heat sinks at both the heated and condensing surface of a two-phase immersion cooled electronics module was explored by Campbell [61]. While these are primarily pool boiling devices, a system that utilized flow boiling where a Liquid Pumped Cooling (LPC) and Vapor Compression Cooling (VCC) system could be used interchangeably was proposed by

Marcinichen et al [62]. This study explored the potential of also recovering energy from the cooling loop to be used as power for other devices within the data center. With the already low PUE's possible with the use of two-phase cooling immersion methods shown **Figure** 10, in energy recovery methods could bring about

Figure 21 – IBM two-phase immersion cooling module example [59]

the possibility of a PUE less than one. An exergetic analysis of an ionic-liquid based absorption chiller to utilize waste heat generated by processing chips in a data center was conducted by Kim and Gonzalez [63]. The analysis yielded an Exergetic Coefficients of Performance (ECOP) of 1.05 for the best case scenario showing the potential for this technology to capture and utilize cooling energy that would otherwise be wasted. It should be noted that this exergetic analysis represents the ideal energy conversion scenario, so there are other irreversibilities and inefficiencies that would have to be accounted for in a practical installation. The results from the study however indicate the feasibility of such a system, and research such as this will grow ever more important as data center power consumption grows while global energy sources dwindle. Chi et al [64] reported energy savings with the integration of Iceotope's solution, similar to the LRU approach proposed in the current study except that fluid is kept in the single phase, over liquid cooled solutions that utilize rear-door liquid-air heat exchangers on the server's racks, a common practice amongst water-cooled cold plate computing solutions. The air/liquid hybrid approach yielded a partial PUE value of 1.48 while that of the direct liquid immersion cooled solution was only 1.14, a 23% reduction in energy savings with the understanding that the partial PUE does not take into account the energy required to exhaust the heat from the server room itself.

### 2.5 Interface Resistances and Surface Enhancement Possibilities

Thermal performance improvements are available with the use of additional heat extraction infrastructure within the electronics module. Ujerah *et al* [65] explored the use of Carbon Nano-Tubes (CNT's) grown on a bare silicon surface for two-phase heat transfer. In this study, heat fluxes of 11 W/cm<sup>2</sup> with FC-72 as the working fluid were attained with boiling from the bare silicon surface, but the introduction of CNT's increased the maximum heat flux to 15

W/cm<sup>2</sup>, a 35% improvement. While there are improvements to be had with the integration of this surface, design considerations for the volatility of boiling damaging the thin and fragile CNTs must be taken into account along with the cost of these materials. Currently, a 1 cm x 1 cm square of Multi-Walled CNT (MWCNT) from Sigma-Aldrich (Part Number: 687804-1EA) costs approximately \$1000. Given that the footprint of an Intel Xeon processor is 5.2 cm x 4.5 cm [38], the integration of this surface enhancement for a typical high performance processor may be prohibitively costly. While the potential of using CNTs as a TIM for systems requiring a lower thermal resistance heat sink or spreader attachment method have been explored by Peacock [66], studies directed at overcoming the reliability deteriorating CTE mismatches that exist between TIMs and chip packages using Liquid Metal Alloys (LMAs) have been conducted as well. Roy et al [67] have tested various LMAs reporting a specific thermal resistance range of 0.005 cm<sup>2</sup>K/W to 0.065 cm<sup>2</sup>K/W. These values when applied to a 1 in<sup>2</sup> (6.45 cm<sup>2</sup>) heated surface like that used in the current study translates to a range of thermal resistances of 0.42 to 0.03 K/W. Martin and van Kessel [68] at IBM conducted a study of LMA TIMs where the specific thermal resistance steadily rose from a minimum value of 2 mm<sup>2</sup>K/W to 7 mm<sup>2</sup>K/W as the thickness of the material used was varied from 10µm to 200µm. Campbell and Tuma [69] explored the added benefits of using a Boiling Enhancement Coating (BEC) similar to the microporous structure used in the current study. Through numerical analysis and experimental input, they concluded that the use of this surface to initiate two-phase heat transfer in the otherwise single-phase water cooled P575 supercomputer would produce improved thermal management of the high density processing elements contained within. Tuma [70] also showed how this same microporous coating could surpass the performance of several aftermarket heat pipes and thermosyphons. The study reported heat transfer coefficients nearing 90 kW/m<sup>2</sup>K with

the use of this surface and, with its integration on to the aftermarket products, drove system to fluid specific thermal resistances down to as low as 0.12 cm<sup>2</sup>K/W. With this same surface, Moreno et al [71] yielded a 50% increase in CHF and 430% increase in heat transfer coefficients over a bare surface using a HFC-245fa refrigerant as the working fluid under pool boiling Using a patented Aluminum/Devcon Brushable Ceramic/Methyl-Ethyl-Keytone conditions. (ABM) coating application technique [72], Rainey and You [73] showed how microfinned structures could have their two-phase heat transfer performance enhanced even further. With a microscale heat sink using 8 mm tall fins, the CHF was taken from 91.7 W/cm<sup>2</sup> to 129.4 W/cm<sup>2</sup> in FC-72 when the structure was coated with the previously mentioned patented method, resulting in a maximum heat transfer coefficient of 17.5 kW/m<sup>2</sup>K based on the entire heat sink surface area. The effects of adding more nucleation sites to microfins by placing mesh and porous plate structures on top of them was explored by Pastuszko and Strak [74]. It was found best to not place structures on top of the fins for fluids with low surface tension, like FC-72 and Novec 649. For this design scenario maximum heat transfer coefficients of 8 kW/m<sup>2</sup>K and 3.5 kW/m<sup>2</sup>K were reported for FC-72 and Novec 649 respectively, near the values yielded in the current study for similar microfinned structures. Diamond particle coated chips were used in the work of Arik et al [75] to explore the effects of significant subcooling and pressure variations on microporous surfaces. Heat fluxes between 19.4 W/cm<sup>2</sup> and 47 W/cm<sup>2</sup> were yielded for minimal subcooling under atmospheric conditions and 71K subcooling under 3 atm of pressure respectively. The average CHF enhancement factor over the bare surface condition achieved across all subcooling and pressure conditions tested was 1.6, illustrating again the improvement potential possible when microstructures are integrated. The effect of surface enhancement geometry, specifically thickness and porosity, were studied by El-Genk and Ali [76]. They used

electrochemical an creating process for microscale copper dendrites. these As initially structures are very fragile, a second step added to provide strengthening the

surface. This second step

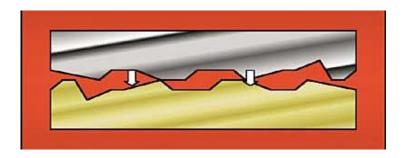

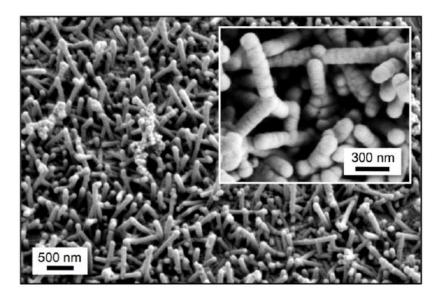

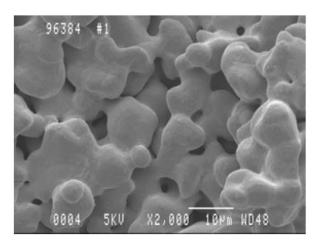

Figure 22- Nature inspired boiling enhancement surface [78]

resulted in rounded cavities which reduced porosity and increased the wetted surface area resulting in the recording of very high CHF's and nucleate boiling heat transfer coefficients, on the order of 27 W/cm² and 135 kW/m²K respectively at superheats as low as 2K. In a study of pool boiling with porous graphite structures as the surface enhancement and FC-72 as the working fluid, El-Genk [77] achieved a maximum nucleate boiling heat transfer coefficient of 34 kW/m²K and a CHF of 30 W/cm². Incredibly intricate and unique structures can be inspired by regularly occurring structures in nature. Using a nickel plating process on the Tobacco Mosaic Virus (TMV), the surface structure shown in Figure 22 can be grown on bare and microstructured surfaces yielding significant CHF and heat transfer coefficients. Pool boiling heat transfer performance for this surface enhancement was explored by Rahman and McCarthy [78]. Values reported in the study were as high as 247 W/cm² for CHF and 74 kW/m²K, much higher than those in the current study as the current work uses much simpler surface enhancements.

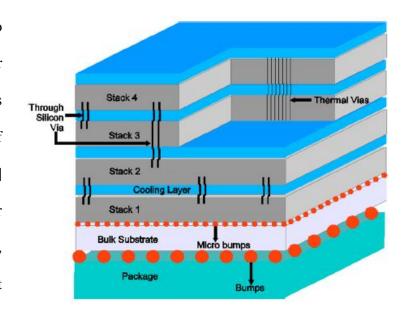

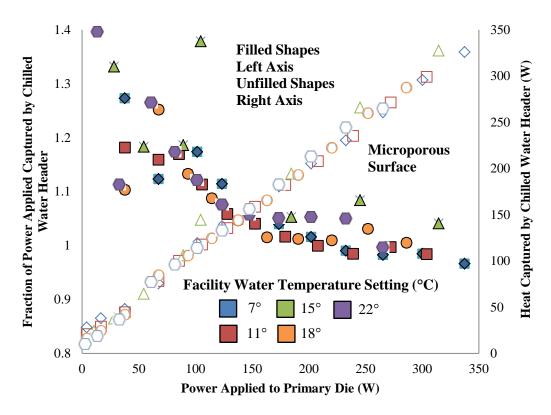

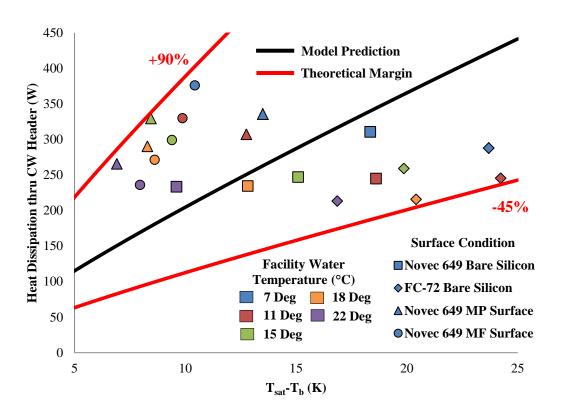

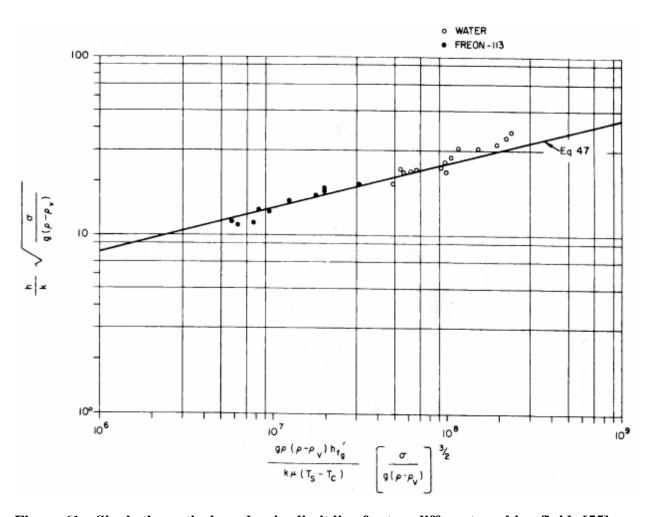

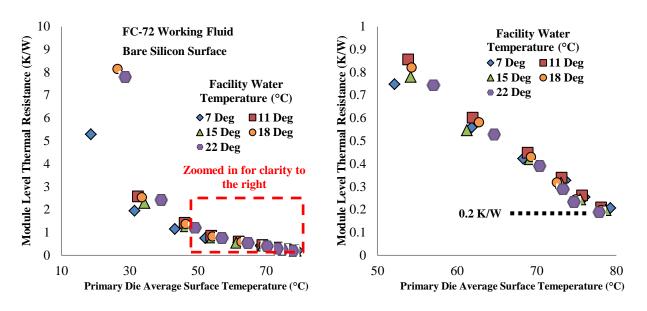

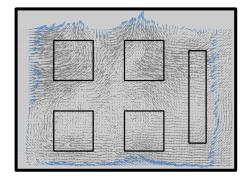

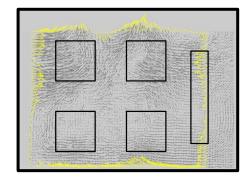

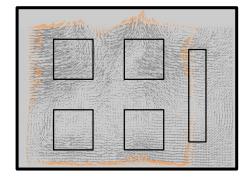

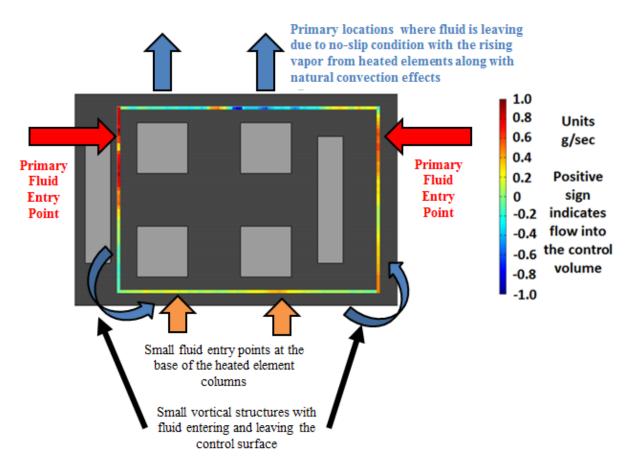

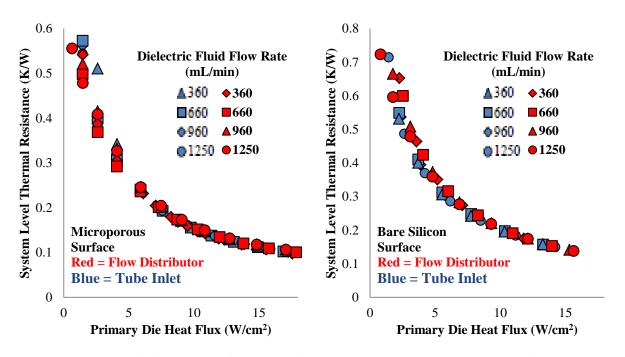

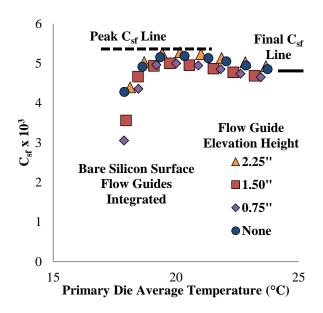

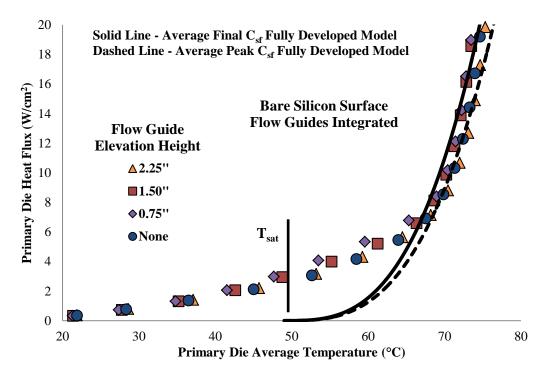

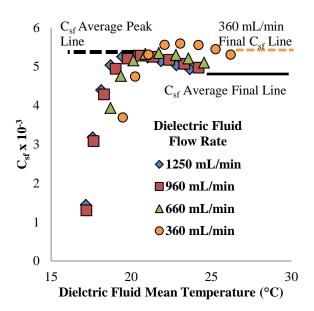

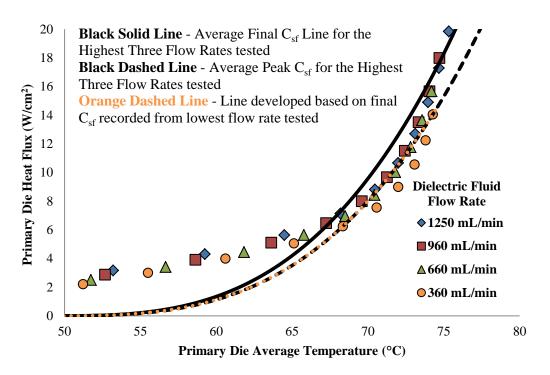

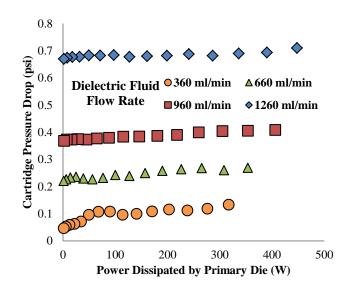

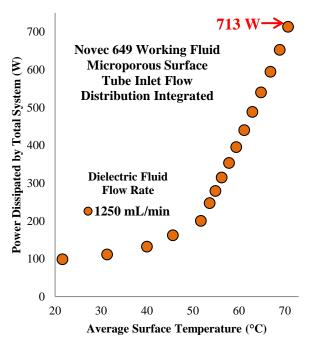

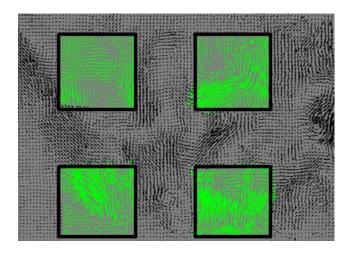

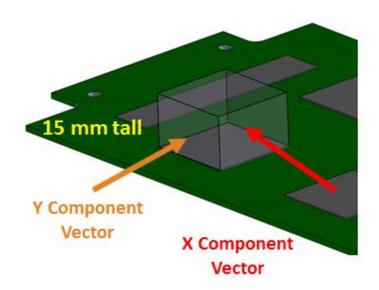

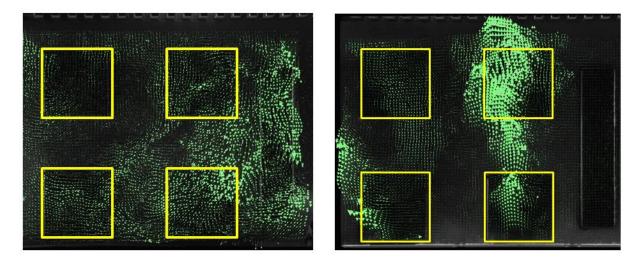

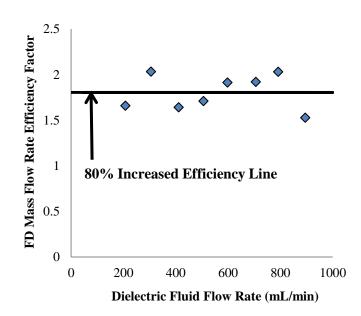

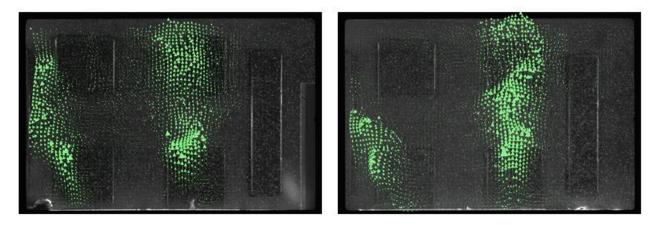

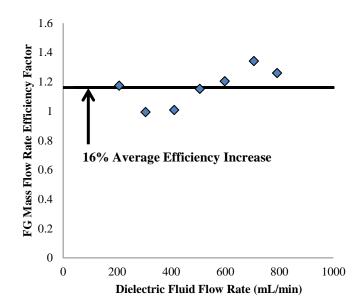

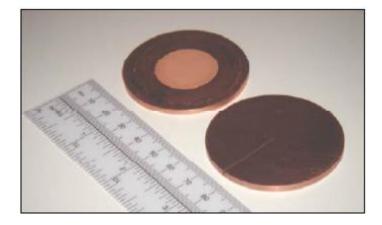

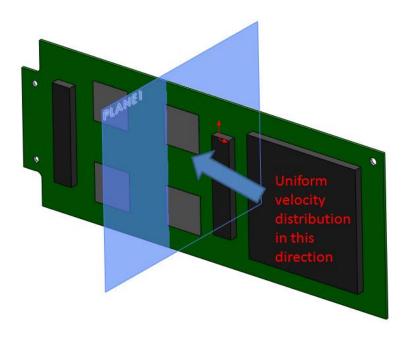

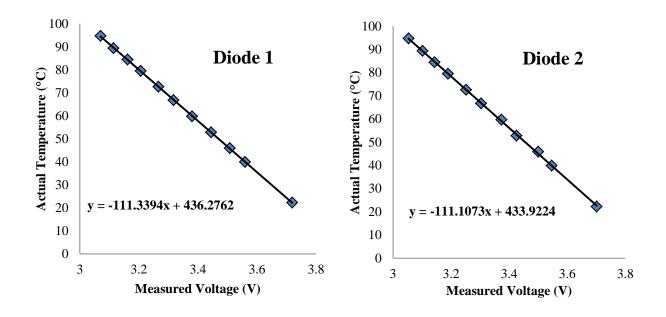

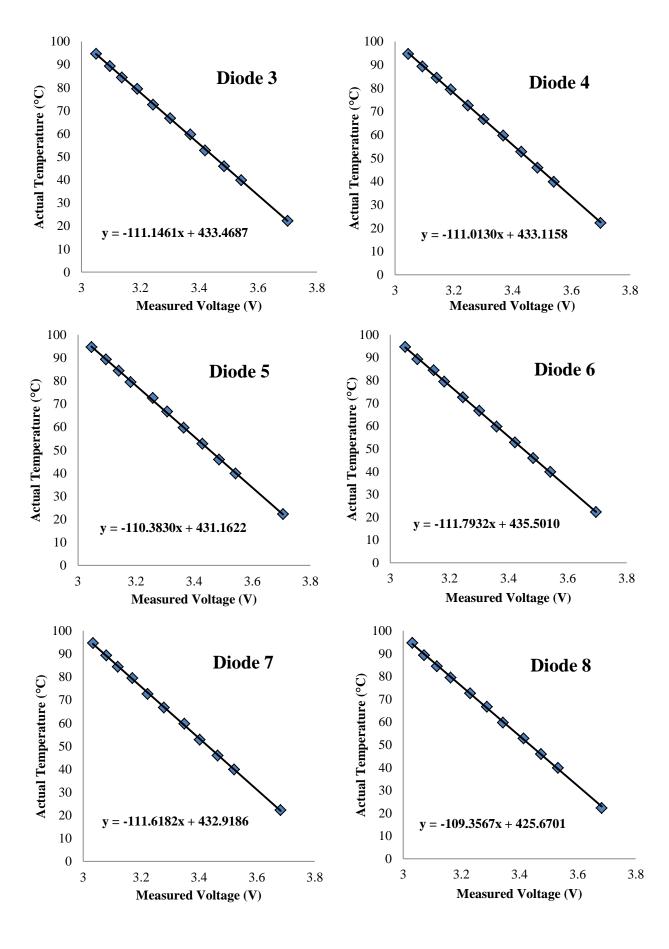

### 2.6 Embedded Thermal Management Solutions