# ALGORITHMS FOR TASK SCHEDULING IN HETEROGENEOUS COMPUTING ENVIRONMENTS

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

|                                                                                 | Prashanth C. Sai Ranga                                                                         |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Certificate of Approval:                                                        |                                                                                                |

| Homer W. Carlisle Associate Professor Computer Science and Software Engineering | Sanjeev Baskiyar, Chair<br>Associate Professor<br>Computer Science and Software<br>Engineering |

| Yu Wang<br>Assistant Professor<br>Computer Science and Software<br>Engineering  | Joe F. Pittman Interim Dean Graduate School                                                    |

## ALGORITHMS FOR TASK SCHEDULING IN HETEROGENEOUS COMPUTING ENVIRONMENTS

Prashanth C. Sai Ranga

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama December 15, 2006

## ALGORITHMS FOR TASK SCHEDULING IN HETEROGENEOUS COMPUTING ENVIRONMENTS

Prashanth C. Sai Ranga

Permission is granted to Auburn University to make copies of this dissertation at its discretion, upon request of individuals or institutions and at their expense. The author reserves all publication rights.

| Signature of Author |

|---------------------|

|                     |

|                     |

| Date of Graduation  |

#### DISSERTATION ABSTRACT

### ALGORITHMS FOR TASK SCHEDULING IN HETEROGENEOUS

#### **COMPUTING ENVIRONMENTS**

Prashanth C. Sai Ranga

Doctor of Philosophy, Dec 15,2006 (M.S., University of Texas at Dallas, Dec, 2001) (B.E., Bangalore University, India, Aug 1998)

136 Typed pages

Directed by Sanjeev Baskiyar

Current heterogeneous meta-computing systems, such as computational clusters and grids offer a low cost alternative to supercomputers. In addition they are highly scalable and flexible. They consist of a host of diverse computational devices which collaborate via a high speed network and may execute high-performance applications. Many high-performance applications are an aggregate of modules. Efficient scheduling of such applications on meta-computing systems is critical to meeting deadlines. In this dissertation, we introduce three new algorithms, the Heterogeneous Critical Node First (HCNF) algorithm, the Heterogeneous Largest Task First (HLTF) algorithm and the Earliest Finish Time with Dispatch Time (EFT-DT) algorithm. HCNF is used to schedule

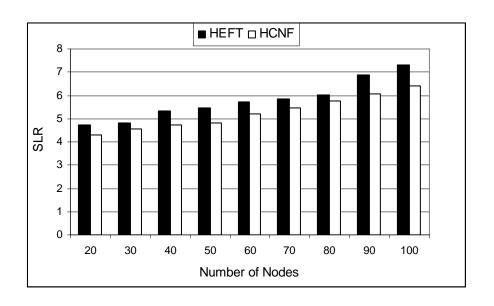

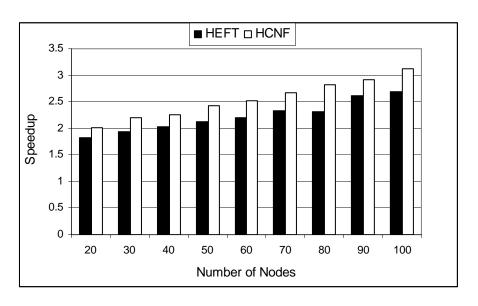

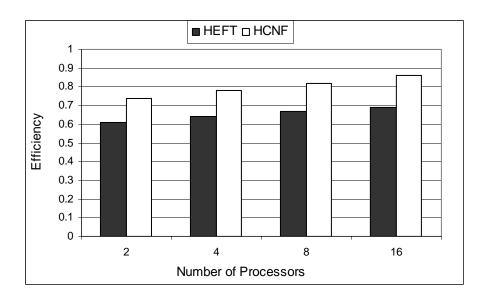

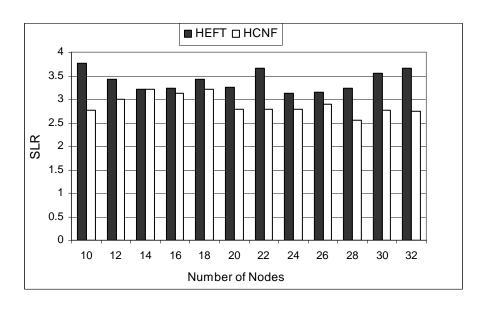

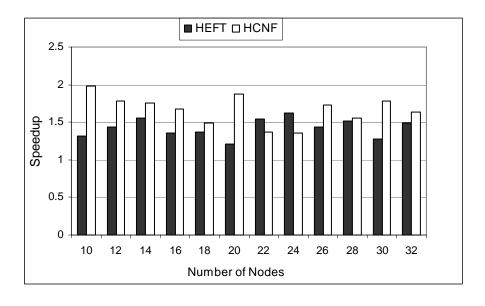

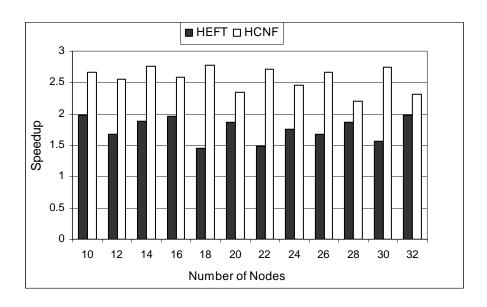

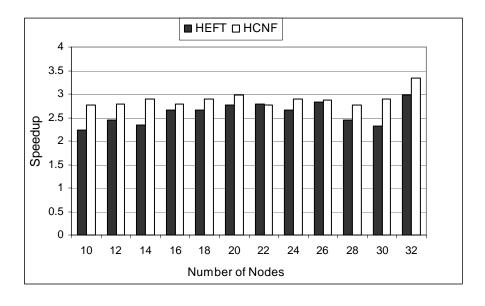

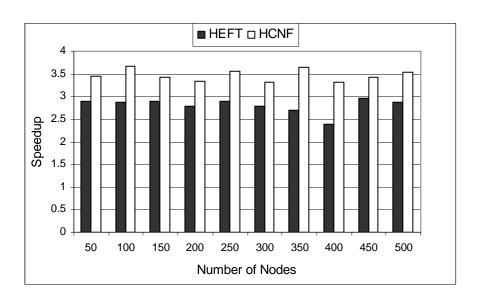

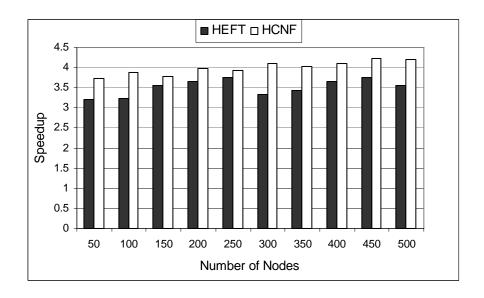

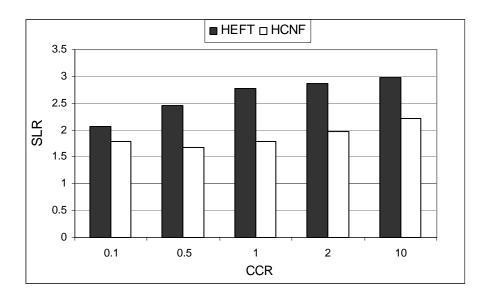

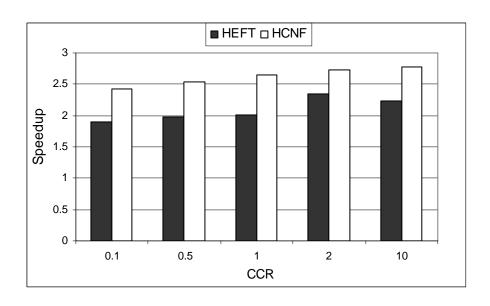

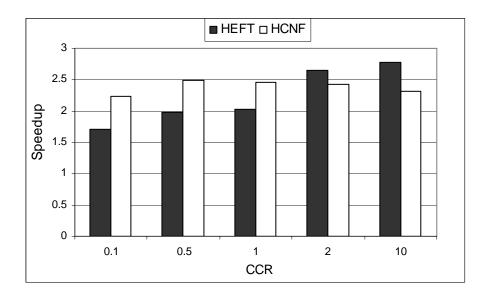

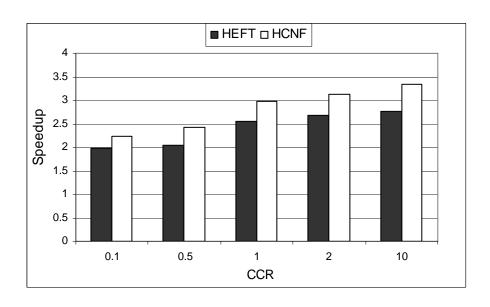

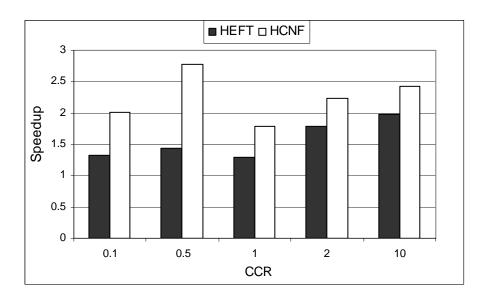

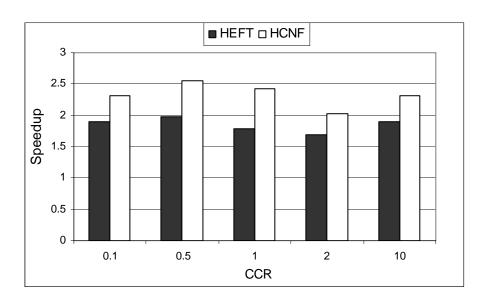

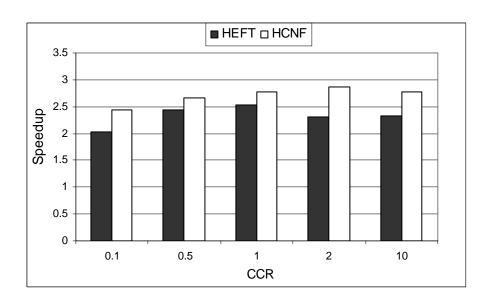

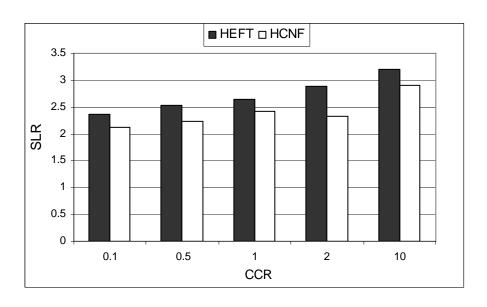

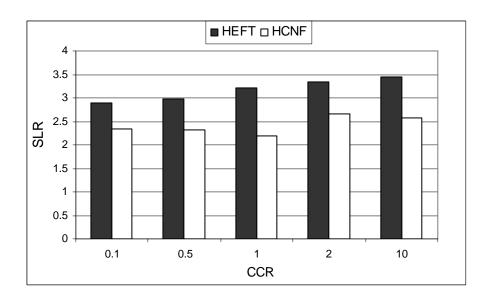

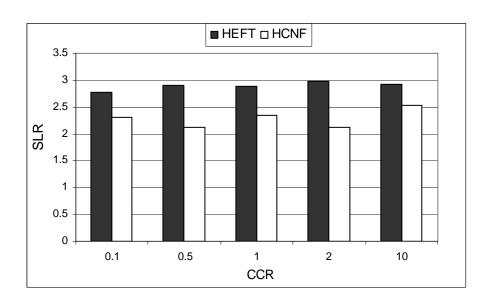

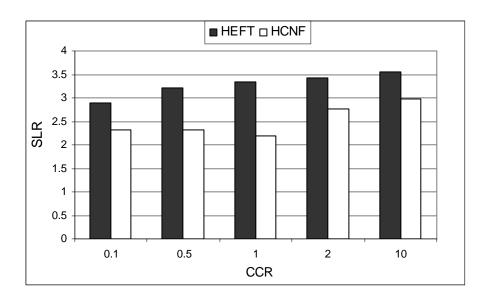

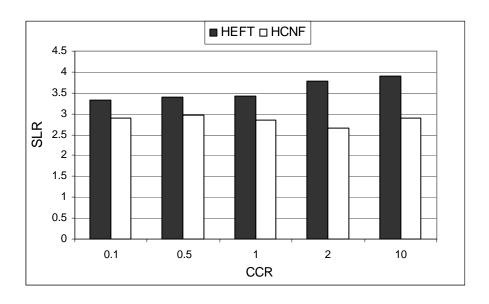

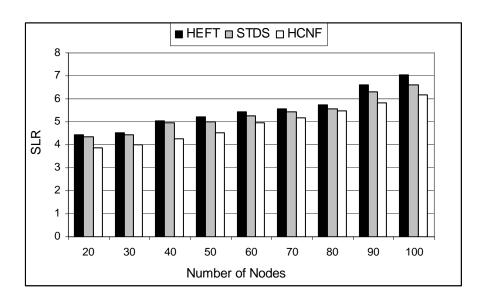

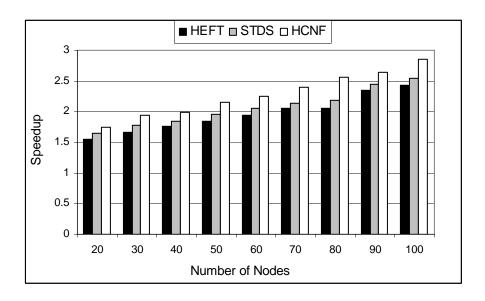

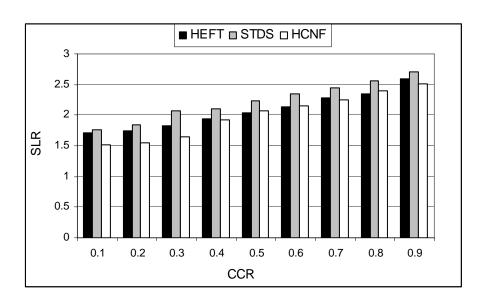

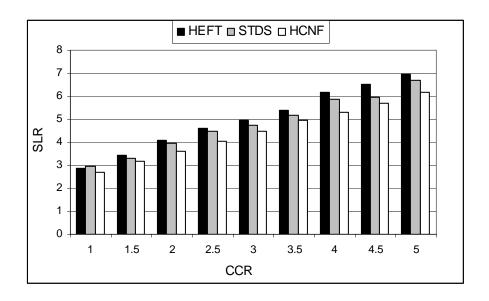

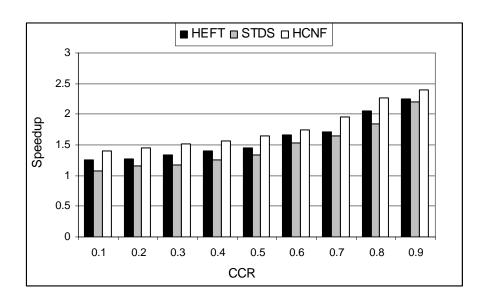

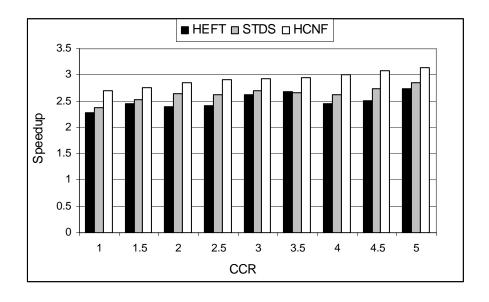

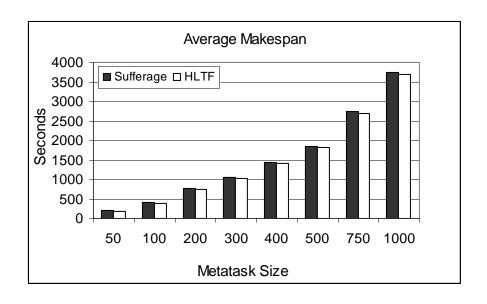

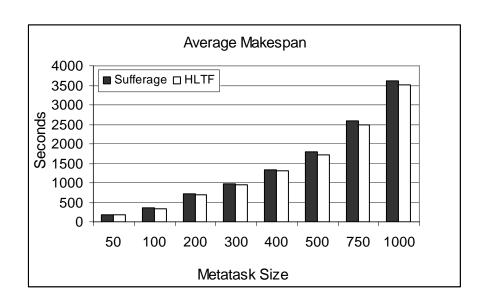

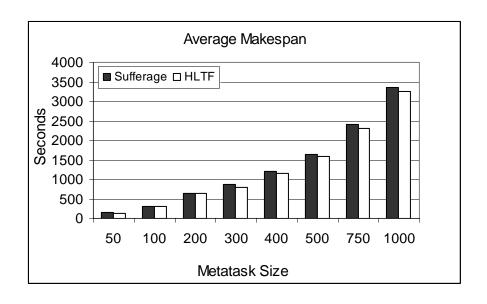

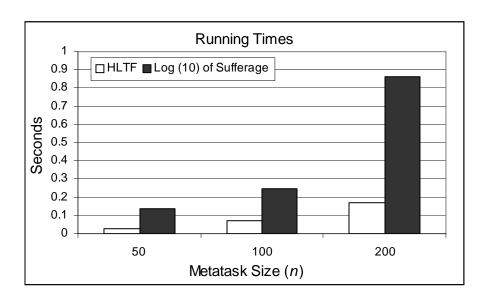

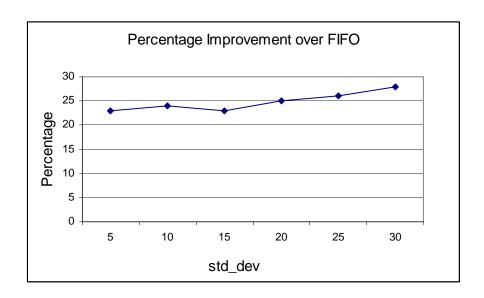

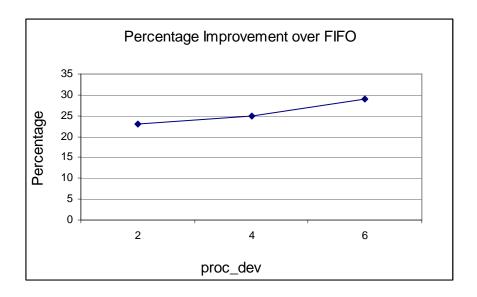

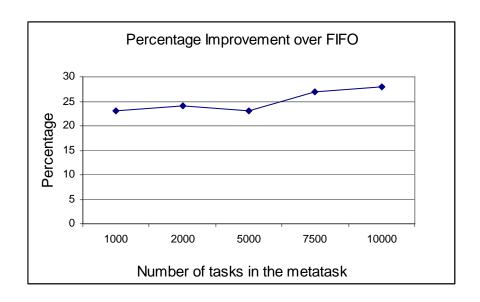

parallel applications of forms represented by directed acyclic graphs onto networks of workstations to minimize their finish times. We compared the performance of HCNF with those of the Heterogeneous Earliest Finish Time (HEFT) and Scalable Task Duplication based Scheduling (STDS) algorithms. In terms of Schedule Length Ratio (SLR) and speedup, HCNF outperformed HEFT on average by 13% and 18% respectively. HCNF outperformed STDS in terms of SLR and speedup on an average by 8% and 12% respectively. The HLTF algorithm is used to schedule a set of independent tasks onto a network of heterogeneous processors to minimize finish time. We compared the performance of HLTF with that of the Sufferage algorithm. In terms of makespan, HLTF outperformed Sufferage on average by 4.5 %, with a tenth run-time. The EFT-DT algorithm schedules a set of independent tasks onto a network of heterogeneous processors to minimize finish time when considering dispatch times of tasks. We compared the performance of EFT-DT with that of a First in First out (FIFO) schedule. In terms of minimizing makespan, on average EFT-DT outperformed FIFO by 30%.

#### **ACKNOWLEDGMENTS**

The author is highly indebted to his advisor, Dr. Sanjeev Baskiyar, for his clear vision, encouragement, persistent guidance and stimulating technical inputs. His patience, understanding and support are deeply appreciated. Thanks to Dr. Homer Carlisle and Dr. Yu Wang, for their review and comments on this research work. Their invaluable time spent on serving on my graduate committee is sincerely appreciated. Special thanks to Mr. Victor Beibighauser, Mr. Basil Manly and Mr. Ron Moody of South University, Montgomery, for their concern, understanding and co-operation. Finally, the author would like to thank his parents, sister and bother-in-law for their constant support and encouragement.

Style manual or journal used: <u>IEEE Transactions on Parallel and Distributed Systems</u>

Computer software used: Microsoft Word, Adobe PDF

### TABLE OF CONTENTS

| LIST OF FI | GURES  |                                                                                                               | X           |

|------------|--------|---------------------------------------------------------------------------------------------------------------|-------------|

| LIST OF TA | ABLES  |                                                                                                               | xiii        |

| CHAPTER    | 1 INTE | RODUCTION                                                                                                     | 1           |

| 1.1        | Moti   | vation                                                                                                        | 1           |

| 1.2        | Clust  | er Computing                                                                                                  | 1<br>5<br>7 |

| 1.3        | Grid   | Computing                                                                                                     | 7           |

| 1.4        | Task   | Scheduling in Heterogeneous Computing Environments                                                            | 10          |

| 1.5        | NP-C   | Complete Problems                                                                                             | 14          |

| 1.6        | Resea  | arch Objectives and Outline                                                                                   | 15          |

| CHAPTER 2  | 2 LITE | RATURE REVIEW                                                                                                 | 16          |

| 2.1        |        | duling a Parallel Application Represented by a Directed clic Graph onto a Network of Heterogeneous Processors |             |

|            | •      | inimize the Make-Span                                                                                         | 16          |

|            | 2.1.1  | Directed Acyclic Graphs                                                                                       | 16          |

|            | 2.1.2  | Problem Statement                                                                                             | 17          |

|            | 2.1.3  | The Best Imaginary Level Algorithm                                                                            | 19          |

|            | 2.1.4  | The Generalized Dynamic Level Algorithm                                                                       | 21          |

|            | 2.1.5  | The Levelized Min-Time Algorithm                                                                              | 24          |

|            | 2.1.6  | The Heterogeneous Earliest Finish Time Algorithm                                                              | 26          |

|            | 2.1.7  | The Critical Path on Processor Algorithm                                                                      | 27          |

|            | 2.1.8  | The Fast Critical Path Algorithm                                                                              | 30          |

|            | 2.1.9  | The Fast Load Balancing Algorithm                                                                             | 32          |

|            | 2.1.10 | The Hybrid Re-mapper Algorithm                                                                                | 34          |

|            | 2.1.11 | Performance Comparison                                                                                        | 36          |

| 2.2        | Sche   | duling a Parallel Application Represented by a Set of                                                         |             |

|            |        | pendent Tasks onto a Network of Heterogeneous                                                                 |             |

|            | -      | essors to Minimize the Make-Span                                                                              | 38          |

|            | 2.2.1  | Problem Statement                                                                                             | 38          |

|            | 2.2.2  | The Min-Max and the Max-Min Algorithm                                                                         | 38          |

|            | 2.2.3  | The Sufferage Algorithm                                                                                       | 40          |

| CHAPTER :  | 3 THE  | HETEROGENEOUS CRITICAL NODE FIRST                                                                             |             |

|            | ALG    | ORITHM                                                                                                        | 43          |

| 3.1 Motivation                                                               | 43  |

|------------------------------------------------------------------------------|-----|

| 3.2 The HCNF Algorithm                                                       | 44  |

| 3.3 Running Trace                                                            | 46  |

| 3.4 Simulation Study                                                         | 54  |

| 3.4.1 Performance Parameters                                                 | 54  |

| 3.4.2 Randomly Generated Graphs                                              | 55  |

| 3.4.3 Gaussian Elimination Graphs                                            | 56  |

| 3.4.4 Benchmark Graphs                                                       | 57  |

| 3.4.5 Parametric Random Graph Generator                                      | 73  |

| 3.5 Conclusion                                                               | 79  |

| CHAPTER 4 THE HETERGOENEOUS LARGEST TASK FIRST                               |     |

| ALGORITHM                                                                    | 80  |

| 4.1 Motivation                                                               | 80  |

| 4.2 The HLTF Algorithm                                                       | 81  |

| 4.3 Theoretical Non-Equivalence of Sufferage and HLTF                        | 83  |

| 4.4 Simulation Study                                                         | 87  |

| 4.4.1 Comparison of Make-span                                                | 88  |

| 4.4.2 Comparison of Running Times                                            | 88  |

| CHAPTER 5 SCHEDULING INDEPENDENT TASKS WITH                                  |     |

| DISPATCH TIMES                                                               | 95  |

| 5.1 Motivation                                                               | 95  |

|                                                                              | 96  |

| <ul><li>5.2 The EFT-DT Algorithm</li><li>5.3 Example Run of EFT-DT</li></ul> | 90  |

| 1                                                                            | 99  |

| 5.4 Simulation Study                                                         | 99  |

| CHAPTER 6 CONCLUSION                                                         | 113 |

| BIBLIOGRAPHY                                                                 | 116 |

### LIST OF FIGURES

| 1.1  | Architecture of Cluster Computing Systems             | 6  |

|------|-------------------------------------------------------|----|

| 1.2  | Grid Architecture                                     | 8  |

| 2.1  | A sample DAG $G_I$                                    | 17 |

| 2.2  | The BIL algorithm                                     | 21 |

| 2.3  | The GDL algorithm                                     | 23 |

| 2.4  | The LMT algorithm                                     | 25 |

| 2.5  | The HEFT algorithm                                    | 27 |

| 2.6  | The CPOP algorithm                                    | 29 |

| 2.7  | The FCP algorithm                                     | 31 |

| 2.8  | The FLB algorithm                                     | 33 |

| 2.9  | The Hybrid Re-mapper algorithm                        | 35 |

| 2.10 | The Min-Min algorithm                                 | 37 |

| 2.11 | The Sufferage algorithm                               | 38 |

| 3.1  | The HCNF algorithm                                    | 39 |

| 3.2  | Sample DAG $(G_I)$                                    | 40 |

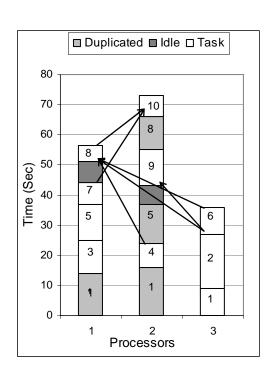

| 3.4  | Gantt chart for $G_I$                                 | 41 |

| 3.5  | HCNF running trace-step 1                             | 42 |

| 3.6  | HCNF running trace-step 2                             | 42 |

| 3.7  | HCNF running trace-step 3                             | 42 |

| 3.8  | HCNF running trace-step 4                             | 43 |

| 3.9  | HCNF running trace-step 5                             | 43 |

| 3.10 | HCNF running trace-step 6                             | 43 |

| 3.11 | HCNF running trace-step 7                             | 44 |

| 3.12 | HCNF running trace-step 8                             | 45 |

| 3.13 | HCNF running trace-step 9                             | 45 |

| 3.14 | HCNF running trace-step10                             | 45 |

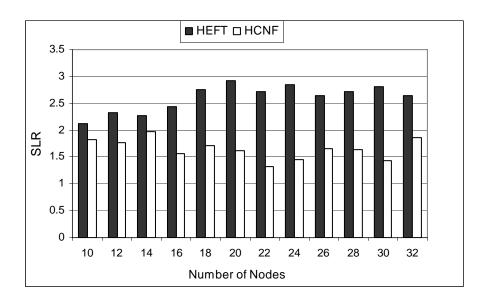

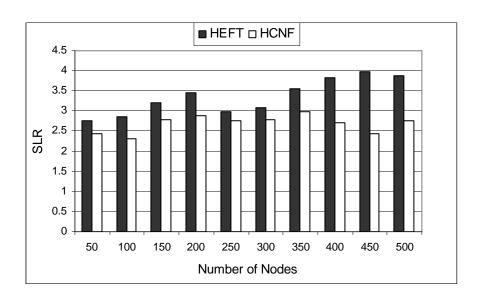

| 3.15 | Random graphs-Average SLR vs. number of nodes         | 46 |

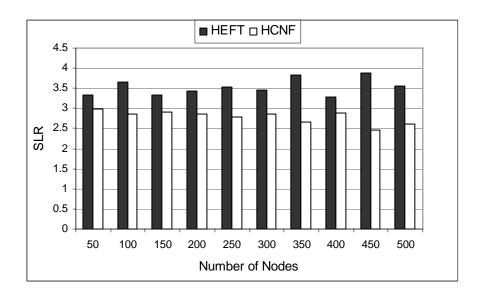

| 3.16 | Random graphs-Average speedup vs. number of nodes     | 46 |

| 3.17 | Random graphs-Average SLR vs. CCR (0.1 to 1)          | 47 |

| 3.18 | Random graphs-Average SLR vs. CCR (1 to 5)            | 48 |

| 3.19 | Random graphs-Average speedup vs. CCR (0.1 to 1)      | 48 |

| 3.20 | Random graphs-Average speedup vs. CCR (1 to 5)        | 48 |

| 3.21 | Gaussian Elimination-Average SLR vs. matrix size      | 49 |

| 3.22 | Gaussian Elimination-Efficiency vs. no. of processors | 50 |

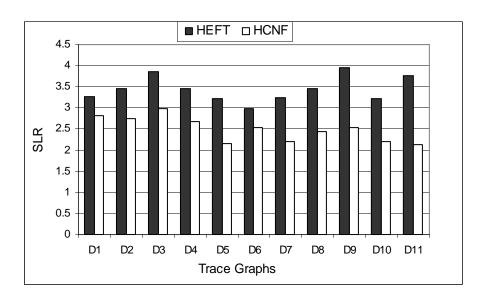

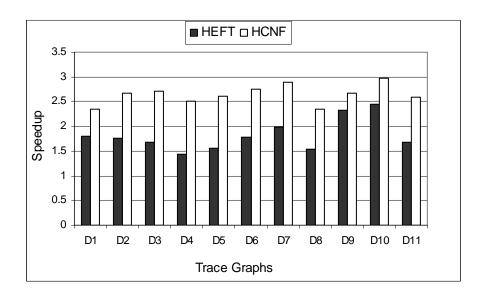

| 3.23 | Trace Graphs-SLR                                       | 51 |

|------|--------------------------------------------------------|----|

| 3.24 | Trace Graphs-Speedup                                   | 52 |

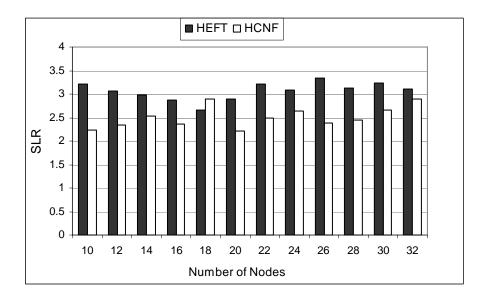

| 3.25 | RGBOS SLR ( $CCR = 0.1$ )                              | 52 |

| 3.26 | RGBOS SLR ( $CCR = 1.0$ )                              | 53 |

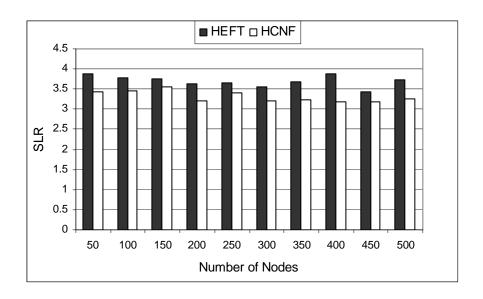

| 3.27 | RGBOS SLR ( $CCR = 10.0$ )                             | 53 |

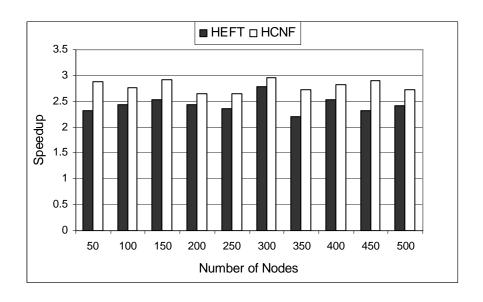

| 3.28 | RGBOS Speedup ( $CCR = 0.1$ )                          | 54 |

| 3.29 | RGBOS Speedup (CCR = 1.0)                              | 54 |

| 3.30 | RGBOS Speedup (CCR = 10.0)                             | 55 |

| 3.31 | RGPOS SLR ( $CCR = 0.1$ )                              | 56 |

| 3.32 | RGPOS SLR ( $CCR = 1.0$ )                              | 56 |

| 3.33 | RGPOS SLR ( $CCR = 10.0$ )                             | 57 |

| 3.34 | RGPOS Speedup ( $CCR = 0.1$ )                          | 57 |

| 3.35 | RGPOS Speedup ( $CCR = 1.0$ )                          | 58 |

| 3.36 | RGPOS Speedup ( $CCR = 10.0$ )                         | 58 |

| 3.37 | Fast Fourier Transform- SLR vs. CCR                    | 59 |

| 3.38 | Fast Fourier Transform- Speedup vs. CCR                | 59 |

| 3.39 | Cholesky Factorization- Speedup vs. CCR                | 60 |

| 3.40 | Gaussian Elimination- Speedup vs. CCR                  | 60 |

| 3.41 | Laplace Transform- Speedup vs. CCR                     | 61 |

| 3.42 | LU Decomposition- Speedup vs. CCR                      | 61 |

| 3.43 | MVA- Speedup vs. CCR                                   | 62 |

| 3.44 | Cholesky- SLR vs CCR                                   | 62 |

| 3.45 | Gaussian Elimination- SLR vs.CCR                       | 63 |

| 3.46 | Laplace Transform- SLR vs.CCR                          | 63 |

| 3.47 | LU Decomposition- SLR vs. CCR                          | 64 |

| 3.48 | MVA- SLR vs. CCR                                       | 64 |

| 3.49 | Parametric random graphs - SLR vs. number of nodes     | 67 |

| 3.50 | Parametric random graphs - Speedup vs. number of nodes | 67 |

| 3.51 | Parametric random graphs-SLR vs. CCR (0.1 to 0.9)      | 68 |

| 3.52 | Parametric random graphs-SLR vs. CCR (1.0 to 5.0)      | 68 |

| 3.53 | Parametric random graphs-Speedup vs. CCR (0.1 to 0.9)  | 69 |

| 3.54 | Parametric random graphs-Speedup vs. CCR (1.0 to 5.0)  | 69 |

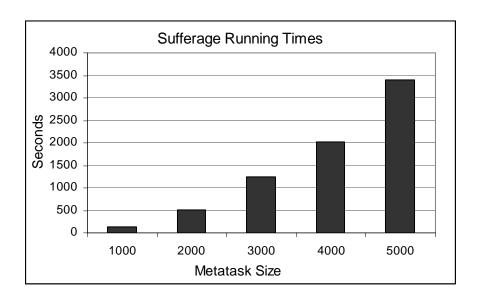

| 4.1  | Running times of the Sufferage Algorithm               | 70 |

| 4.2  | HLTF Algorithm                                         | 72 |

| 4.3  | The Sufferage algorithm                                | 74 |

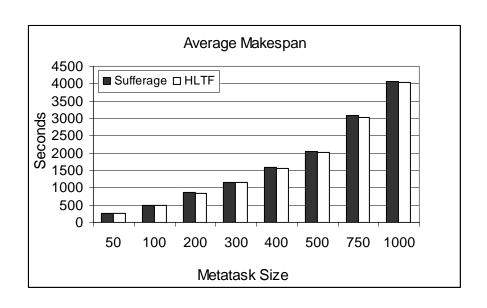

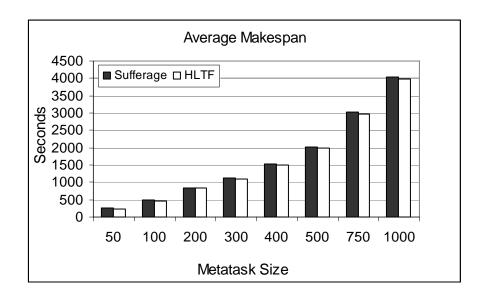

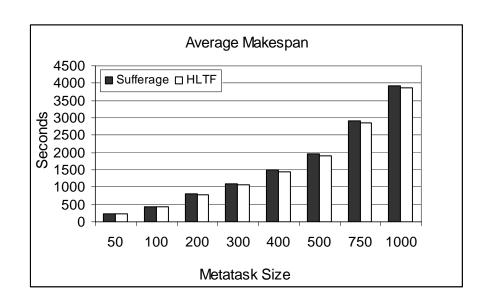

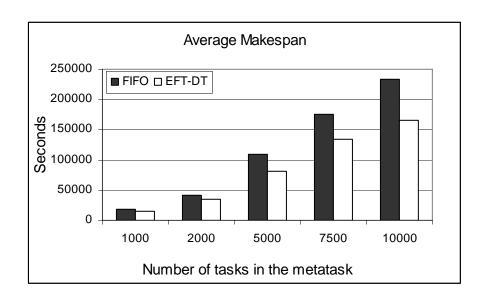

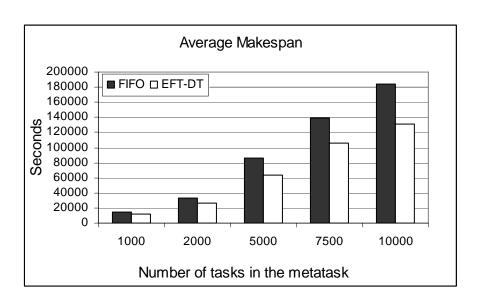

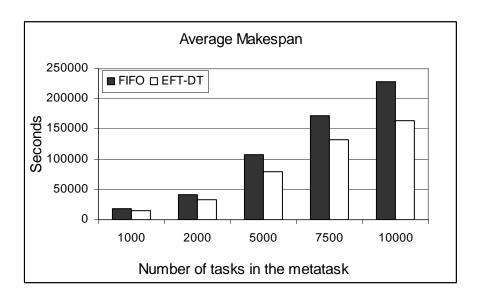

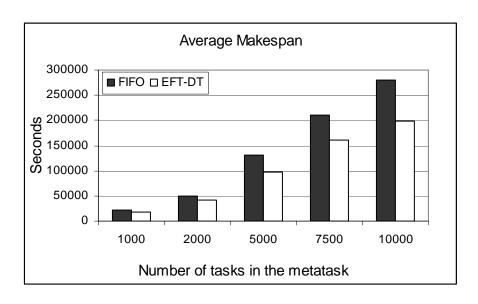

| 4.4  | Average Makespan of Metatasks <i>std_dev</i> =5        | 76 |

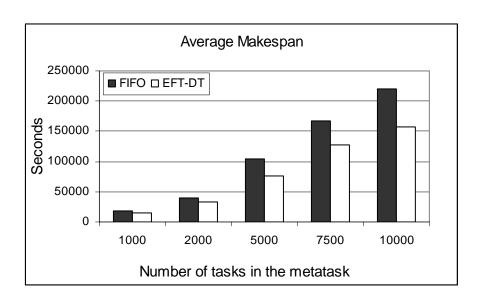

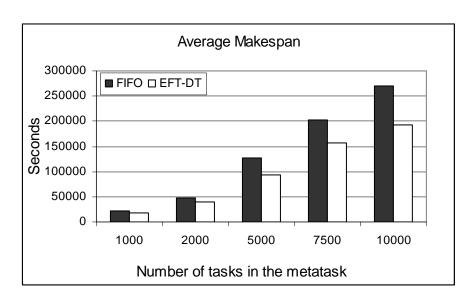

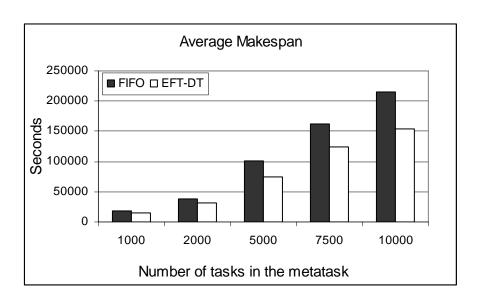

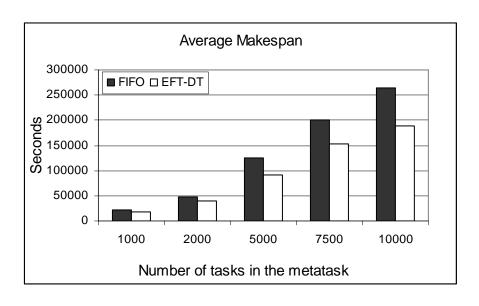

| 4.5  | Average Makespan of Metatasks <i>std_dev</i> =10       | 78 |

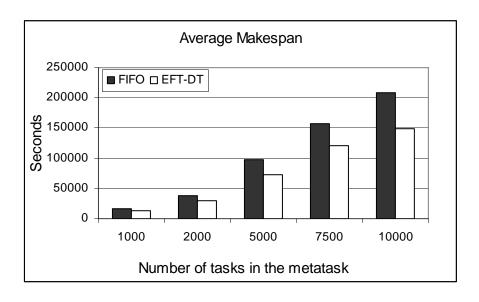

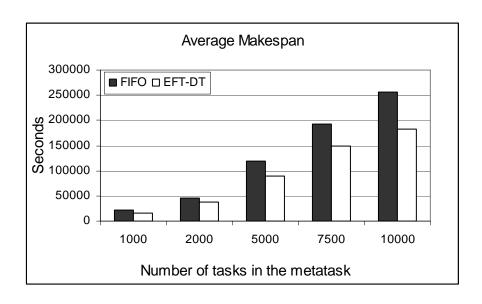

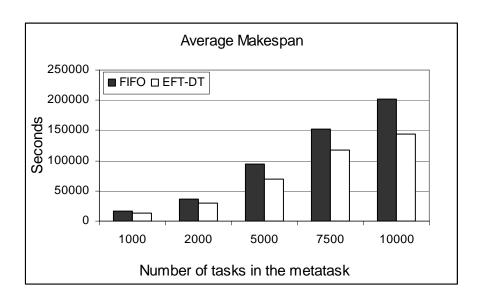

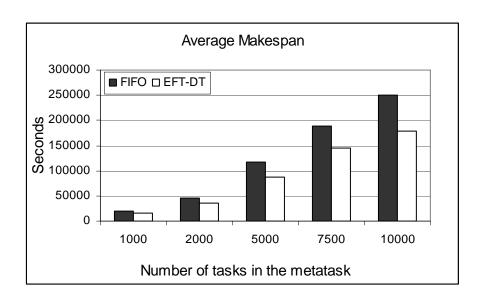

| 4.6  | Average Makespan of Metatasks <i>std_dev</i> =15       | 80 |

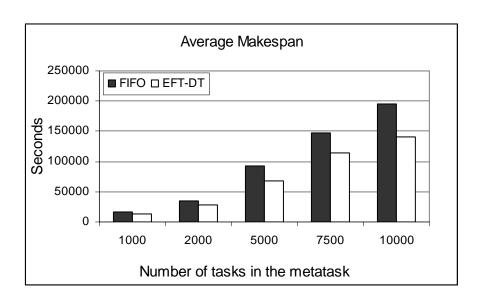

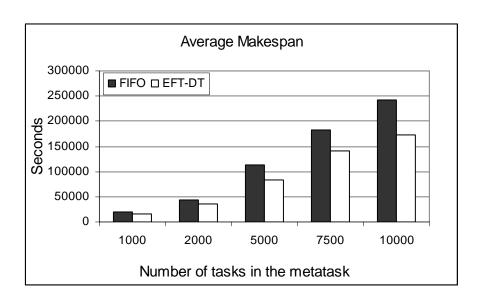

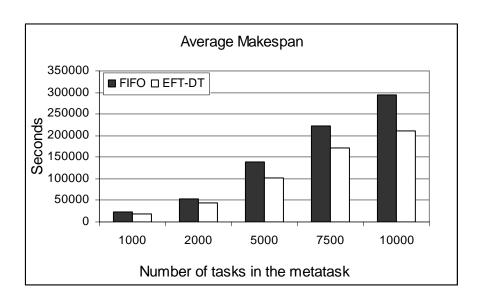

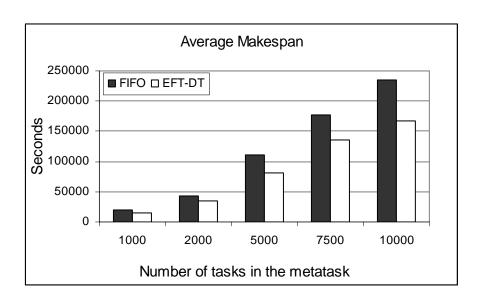

| 4.7  | Average Makespan of Metatasks std_dev=20               | 82 |

| 4.8  | Average Makespan of Metatasks <i>std dev</i> =25       | 84 |

| 4.9  | Average Makespan of Metatasks <i>std_dev</i> =30 | 85  |

|------|--------------------------------------------------|-----|

| 4.10 | Running Times $\{n = 50,100,200\}$               | 87  |

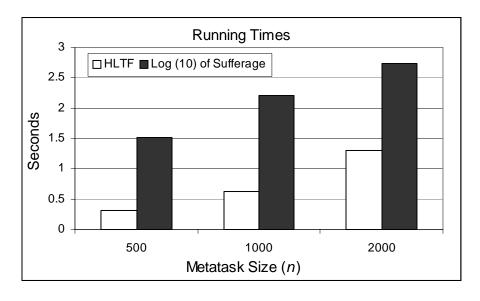

| 4.10 | Running Times $\{n = 500, 1000, 2000\}$          | 87  |

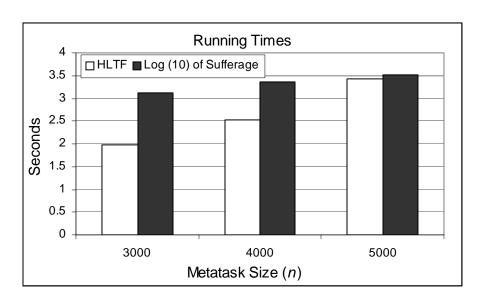

| 4.11 | Running Times $\{n = 3000, 4000, 5000\}$         | 90  |

| 5.1  | The EFT-DT Algorithm                             | 94  |

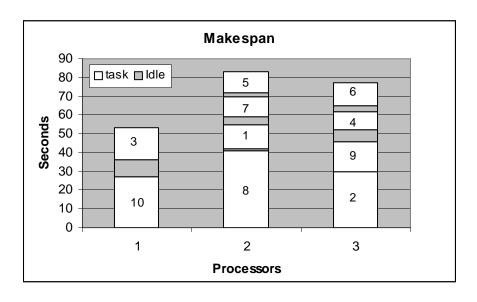

| 5.2  | Gantt Chart for the Meta-Task                    | 96  |

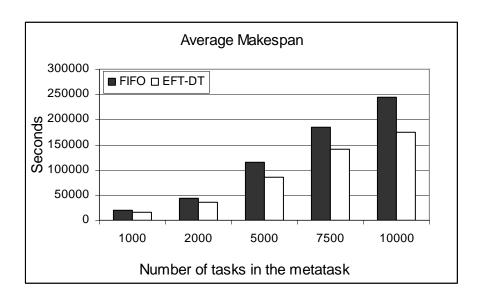

| 5.3  | Average Makespan- std_dev=5, proc_dev=2          | 98  |

| 5.4  | Average Makespan- std_dev=10, proc_dev=2         | 99  |

| 5.5  | Average Makespan- std_dev=15, proc_dev=2         | 99  |

| 5.6  | Average Makespan- std_dev=20, proc_dev=2         | 100 |

| 5.7  | Average Makespan- std_dev=25, proc_dev=2         | 100 |

| 5.8  | Average Makespan- std_dev=30, proc_dev=2         | 101 |

| 5.9  | Average Makespan- std_dev=5, proc_dev=4          | 101 |

| 5.10 | Average Makespan- std_dev=10, proc_dev=4         | 102 |

| 5.11 | Average Makespan- std_dev=15, proc_dev=4         | 102 |

| 5.12 | Average Makespan- std_dev=20, proc_dev=4         | 103 |

| 5.13 | Average Makespan- std_dev=25, proc_dev=4         | 103 |

| 5.14 | Average Makespan- std_dev=30, proc_dev=4         | 104 |

| 5.15 | Average Makespan- std_dev=5, proc_dev=6          | 104 |

| 5.16 | Average Makespan- std_dev=10, proc_dev=6         | 105 |

| 5.17 | Average Makespan- std_dev=15, proc_dev=6         | 105 |

| 5.18 | Average Makespan- std_dev=20, proc_dev=6         | 106 |

| 5.19 | Average Makespan- std_dev=25, proc_dev=6         | 106 |

| 5.20 | Average Makespan- std dev=30, proc dev=6         | 107 |

### LIST OF TABLES

| 2.1  | Table of values for $G_I$                                           | 18 |

|------|---------------------------------------------------------------------|----|

| 2.2  | Definition of terms used in BIL                                     | 20 |

| 2.3  | Definition of terms used in GDL                                     | 22 |

| 2.4  | Definition of terms used in LMT                                     | 24 |

| 2.5  | Definition of terms used in HEFT                                    | 27 |

| 2.6  | Definition of terms used in CPOP                                    | 28 |

| 2.7  | Definition of terms used in FCP                                     | 30 |

| 2.8  | Definition of terms used in FLB                                     | 32 |

| 2.9  | Definition of terms used in Hybrid Re-mapper                        | 34 |

| 2.10 | Performance Comparison                                              | 38 |

| 2.11 | Definition of terms used in Min-Min                                 | 40 |

| 2.12 | Definition of terms used in Sufferage                               | 42 |

| 3.1  | HCNF-definition of terms                                            | 55 |

| 3.2  | Task execution times of $G_I$ on three different processors         | 58 |

| 3.3  | Run-time values for $G_I$                                           | 60 |

| 3.4  | Trace graph details                                                 | 64 |

| 4.1  | Definition of Terms used in Sufferage and HLTF                      | 81 |

| 4.2  | Theoretical Nonequivalence of the Sufferage and the HLTF Algorithms | 83 |

| 5.1  | EFT-DT Algorithm –Defnition of Terms                                | 93 |

| 5.2  | A sample metatask                                                   | 95 |

| 5.3  | Meta-task Dispatch Times                                            | 95 |

#### **CHAPTER 1**

#### INTRODUCTION

This chapter provides an introduction to our research work and discusses a few relevant topics. Section 1.1 discusses our research motivation. Section 1.2 describes the architecture of cluster computing systems. Section 1.3 describes the architecture of grid computing systems. Section 1.4 provides an overview of task scheduling in heterogeneous computing systems. Section 1.5 provides an introduction to NP-complete problems and Section 1.6 discusses the organization of this dissertation.

#### 1.1 Motivation

Information Technology has revolutionized the way we share and use information. The IT revolution has witnessed a myriad number of applications with a wide range of objectives which include: small personal computer based applications like the calculator program, medium-sized applications like the Microsoft Word, large-sized applications like the Computer Aided Design software and very-large sized applications like the Weather Forecasting application. Some of these programs can run efficiently on a normal personal computer and some may need a more powerful workstation. However, there are applications like Weather Forecasting, Earthquake Analysis, Particle Simulation and a host of other engineering and scientific applications that require computing

capabilities beyond that of personal computers or workstations. They are called "High-Performance Applications".

How do we run these high-performance applications efficiently, given the fact that sequential computers (PCs, workstations) are too slow to handle them? There are three ways to improve efficiency [1]: work harder, work smarter or get help. In this context, working harder refers to increasing the speed of sequential uni-processor computers. In the last two decades, microprocessor speed has on an average doubled once in 18 months. Today's microprocessor chip is faster than the mainframes of yesteryears, owing to the phenomenal advances in Very Large Scale Integration (VLSI) technology. Even though this trend is expected to continue in the future, microprocessor speed is severely limited by the laws of physics and thermodynamics [2]. There is very high probability that it will eventually hit a plateau in the near future.

Working smarter refers to designing efficient algorithms and programming environments to deal with high-performance applications. By working smarter, we can definitely improve the overall efficiency, but will not be able to overcome the speed bottleneck of sequential computers.

Getting help refers to involving multiple processors to solve the problem. The idea of multiple processors working together simultaneously to run an application is called "Parallel Processing." Most of the applications consist of thousands of modules or sub-programs that may or may not interact with each other depending on the nature of the application. In either case, there are usually a number of modules that are independent of one another and could run simultaneously on different processors. The parallel nature of many applications is what makes parallel processing very appealing. In other words, if

applications were to be one large sequential module, parallel processing would not be feasible.

Parallel processing has captivated researchers for a long time. The initial trend in parallel processing was to create tightly coupled multi-processor systems with shared memory, running proprietary software. These systems were generally referred to as "Supercomputers". Supercomputers were extremely fast and expensive. In the 1960s Seymour Cray created the world's first commercial supercomputer the CDC 6600. Other companies like IBM, Digital and Texas Instruments created their own proprietary versions of supercomputers. The 70s and the 80s witnessed major companies and research labs across the word vie with one another to create the world's fastest super computer. Even though the trend continues to this day, parallel processing has slowly drifted away from supercomputing for a number of reasons. Supercomputers are extremely expensive systems that run on proprietary technology. Since they run on proprietary technology, they offer less flexibility with respect to developing software solutions to execute high performance applications. Since supercomputers are very expensive to lease/purchase and maintain, it is beyond the reach of many organizations to deploy them. Also in view of today's technological growth, it is important for systems to be readily scalable. Owing to factors like proprietary hardware and software technologies, most of the supercomputers are not readily scalable. To summarize, supercomputers have a very high cost/performance factor.

The very high cost/performance factor made them unattractive to a number of organizations. Most organizations (business, academic, military etc) were interested in high performance computing but were seeking systems with low cost/performance factor,

which could not be offered by supercomputers. In the meantime, PCs and workstations became extremely powerful and significant advances were made in networking technologies. Researchers began to explore the possibility of connecting low cost PCs with a high-speed network to mimic the functioning of a supercomputer albeit with a low cost/performance factor.

Extensive research has been carried out to create high performance systems by connecting PCs/workstations with a high-speed network. Most of the research was focused on creating viable parallel programming environments, developing high-speed network protocols and devising effective scheduling algorithms. Initially, the PCs/workstations had uniform hardware characteristics and thus the systems were termed "Homogeneous." However due to rapid advances in PC technology, computers and other hardware items had to be continuously upgraded and it was no longer the case that all the machines had identical hardware characteristics. This led to the notion of "Heterogeneous Systems" where individual PCs/workstations in a network could have different hardware characteristics. Researchers today focus on creating a high-performance system with a low cost/performance factor using a Heterogeneous Network of Workstations (NOWs).

So, what goes into creating a viable high performance computing system with a low cost/performance ratio out of a NOW given the fact that we have powerful workstations and very high-speed networks? Firstly, an efficient run-time environment must be provided for high-performance applications. Extensive research has been done in this area and has led to the creation of efficient technologies like the Message Passing Interface (MPI) [2] and the Parallel Virtual Machine (PVM) [2]. Secondly, in order to be able to provide a low cost/performance ratio, these systems must optimize the overall

execution time (or turnaround time) of high-performance applications. This requires efficient scheduling of the sub-tasks of high-performance applications onto the individual machines of a NOW. The sub-tasks of a parallel application may either be independent or may have precedence constraints. In either case, the problem of scheduling these subtasks to optimize the overall execution time of an application is a well-known NP Complete problem [3].

The focus of our research is to devise efficient scheduling algorithms for scheduling parallel applications represented by independent tasks as well as tasks with precedence constraints onto heterogeneous computing systems to minimize the overall execution time. We strongly believe that efficient task scheduling is the most important factor in creating a low-cost high-performance computing system. We now discuss the architectures of two very popular heterogeneous computing systems, the Cluster and the Grid.

#### 1.2 Cluster Computing

A cluster is a heterogeneous parallel computing system which consists of several stand alone systems that are interconnected to function as an integrated computing resource. A cluster generally refers to two of more computers interconnected via a local area network. A cluster of computers can appear as a single system to users and applications. It provides a low-cost alternative to supercomputers with a relatively reasonable performance.

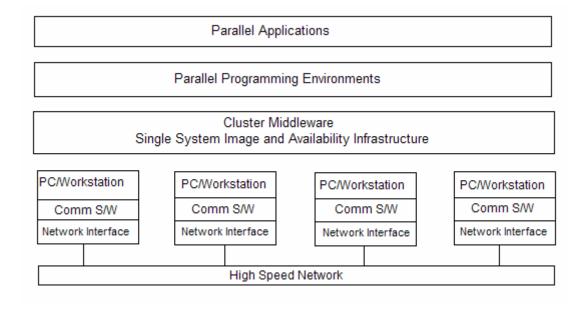

Figure 1.1 describes the architecture and the main components of a cluster computing system [2]. The individual nodes of a cluster could be PCs or high speed

workstations connected through a high-speed network. The network interface hardware acts as a communication processor and is responsible for transmitting and receiving packets of data between cluster nodes. The cluster communication software provides a means for fast and reliable data communication among cluster nodes and to the outside world. Clusters often use communication protocols such as "Active Messages" [2] for fast communication among their nodes. They usually bypass the operating system and remove the critical communication overhead normally involved by providing a direct user-level access to the network interface.

Figure 1.1 Architecture of Cluster-Computing Systems

The cluster nodes can either work as individual computers or can work collectively as an integrated computing resource. The cluster middleware is responsible for offering an illusion of a unified system image (Single System Image) and Availability

out of a collection of independent but interconnected computers. Parallel programming environments offer portable, efficient, and easy-to-use tools for development of applications. They include message passing libraries, debuggers, and profilers. Clusters also run resource management and scheduling software such as LSF (Load Sharing Facility) and CODINE (Computing in Distributed Networked Environments) [2]. The individual nodes of a cluster can have different hardware characteristics and new nodes can be seamlessly integrated into existing clusters thus making them easily scalable. Clusters make use of these hardware and software resources to execute high performance applications and typically provide a very low cost/performance ratio.

#### 1.3 Grid Computing

The massive growth of the Internet in the recent years has encouraged many scientists to explore the possibility of harnessing idle CPU clock cycles and other unutilized computational resources spread across the Internet. The idea was to harness idle CPU cycles and other computational resources and provide a unified computational resource to those in need of high-performance computation. This led to the notion of "Grid Computing".

The concept of grid computing is similar to that of "Electrical Grids." In electrical grids, power generation stations in different geographical locations are integrated to provide a unified power resource for consumers to plug into on demand. In the same fashion, computational grids allow users to plug into a virtual unified resource for their computational needs.

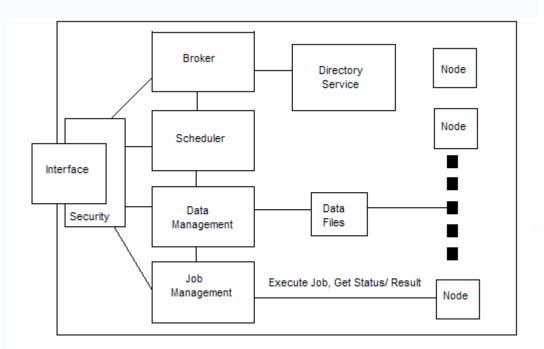

**1.3.1 Architecture of a Grid Computing System** Grid systems are highly complex and comprise of a host of integrated hardware and software features as illustrated in Figure 1.2. The following sub-sections describe the major components of a grid.

**Figure 1.2 Grid Architecture**

#### **1.3.1.1 Interface**

Grid systems are designed to shield their internal complexities from users. User interfaces can come in many forms and can be application specific. Typically grid interfaces are similar to web portals. A grid portal provides an interface to launch applications which would use its resources and services. Through this interface, users see the grid as a virtual computing resource.

#### **1.3.1.2 Security**

Security is a critical issue in grid computing. A grid environment should consist of mechanisms to provide security, which includes authentication, authorization, data encryption etc. Most of the grid implementations include an Open SSL [4] implementation. They also provide a single sign-on mechanism, so that once a user is authenticated, a proxy certificate is created and used while performing actions within the grid.

#### 1.3.1.3 Broker

A grid system typically consists of a diverse range of resources spread across the internet. When a user desires to launch an application through the portal, depending on the application and other parameters provided by the user, the system needs to identify and appropriate the resources to use. This task is accomplished by the grid broker system. The broker makes use of the services provided by the Grid Information Service (GIS) which is also known as the Monitoring and Discovery Service (MDS). It provides information about the available resources within the grid and their status. Upon identifying available resources, the broker needs to choose the most viable resource based on the requirements of the user. Resource brokering is a major research topic in grid computing and forms the focus of what is known as "G-Commerce".

#### **1.3.1.4 Scheduler**

Applications requiring services of a grid could be one large module or could consist of several independent modules with or without data dependencies. Depending on the nature of the application, the scheduler must be able to effectively map the

application or its components onto the best available resource. Most of the grid schedulers use different algorithms to deal with different cases. Grid schedulers have a number of algorithms to choose from depending on scheduling parameters and user requirements. However, the most common criteria for schedulers is to minimize the turnaround time of an application.

#### 1.3.1.5 Data Management

Scheduling high performance applications onto grids constantly requires movement of data files from one node to another. The grid environment should provide a reliable and a secure means for data exchange. The Data Management component of the grid system commonly uses the Grid Access to Secondary Storage (GASS) [4] component to move data files across the grid. The GASS incorporates the GridFTP, which is protocol built over the standard FTP in the TCP/IP protocol suite. The GridFTP protocol adds a layer of encryption and other security features on top of the standard FTP protocol.

#### 1.3.1.6 Job Management

This component includes the core set of services that perform the actual work in a grid environment. It provides service to actually launch a job on a particular resource, check its status, and retrieve results when it is complete. The component is also responsible for ensuring fault tolerance.

#### 1.4 Overview of Task Scheduling in Heterogeneous Computing Environments

There are a number of reasons why scheduling programs or the tasks that comprise the programs is important. For users it is important that the programs they wish to run are executed as quickly as possible (faster turnaround times). On the other hand the owners of computing resources would ideally wish to optimize their machine utilization. These two objectives, faster turnaround times and optimal resource utilization, are not always complementary. Owners are not usually willing to let a single user utilize all their resources (especially in grid systems), and users are not usually willing to wait an arbitrarily long time before they are allowed access to particular resources. Scheduling, from both points of view, is the process by which both the users and the owners achieve a satisfactory quality of service.

#### 1.4.1 Scheduling Strategies

There are different approaches to the selection of processors onto which sub-tasks of a program would be placed for execution. In the static model, each sub-task is assigned to a processor before the execution of a program commences. In the dynamic scheduling model, sub-tasks are assigned to different processors in run-time. In the Hybrid scheduling model, a combination of both static and dynamic scheduling strategies is used.

#### 1.4.1.1 Static Scheduling

In the static model, all sub-tasks of a program are assigned once to a processing element. An estimate of the cost of computation can be made a priori. Heuristic models for static task scheduling are discussed in Chapter 2. One of the main benefits of the

static model is that it is easier to implement from a scheduling and mapping point of view. Since the mapping of tasks is fixed a priori, it is easy to monitor the progress of computation. Likewise, estimating the cost of jobs is simplified. Processors can give estimates of the time that will be spent processing the sub-tasks. On completion of the program they can be instructed to supply the precise time that was spent in processing. This facilitates updating of actual running costs and could be used in making performance estimates for new programs. The Static Scheduling model has a few drawbacks. The model is based on an approximate estimation of processor execution times and inter-processor communication times. The actual execution time of a program may often vary from the estimated execution time and sometimes may result in a poorly generate schedule. This model also does not consider node and network failures

#### 1.4.1.2 Dynamic Scheduling

Dynamic scheduling operates on two levels: the local scheduling strategy, and a load distribution strategy. The load distribution strategy determines how tasks would be placed on remote machines. It uses an information policy to determine the kind of information that needs to be collected from each machine, the frequency at which it needs to be collected and also the frequency at which it needs to be exchanged among different machines. In a traditional dynamic scheduling model, the sub-tasks of an application are assigned to processors based on whether they can provide an adequate quality of service. The meaning of quality of service is dependent on the application. Quality of service could mean whether an upper bound could be placed on the time a task needs to wait before it can start its execution; the minimum time under which the task can complete its

execution without interruption and the relative speed of the processor as compared to other processors in the system. If a processor is assigned too many tasks, it may invoke a transfer policy to check to see if it needs to transfer tasks to other nodes and if so, to which ones? The transfer of tasks could be sender initiated or receiver initiated. In the later case, a processor that is lightly loaded will voluntarily advertise to offer its services to heavily loaded nodes.

The main advantage of dynamic scheduling over static scheduling is that the scheduling system need not be aware of the run-time behavior of the application before execution. Dynamic scheduling is particularly useful in systems where the goal is to optimize processor utilization as opposed to minimizing the turnaround times. Dynamic scheduling is also more efficient and fault tolerant when compared to static scheduling.

#### 1.4.1.3 Hybrid Static-Dynamic Scheduling

Static scheduling algorithms are easy to implement and usually have a low schedule generating cost. However, since static scheduling is based on estimated execution costs, it may not always produce the best schedules. On the other hand, dynamic scheduling uses run-time information in the scheduling process and generates better schedules. But dynamic scheduling suffers from very high running costs and may be prohibitively expensive while trying to schedule very large applications with tens and thousands of sub-tasks. Since both the scheduling techniques have their own advantages, researchers have tried to combine them to create a hybrid scheduling technique. Usually in hybrid scheduling, the initial schedule is obtained using static scheduling and the sub-

tasks are mapped onto the respective processors. However, after the execution commences, the processors use run-time information to check and see if the tasks could be mapped to better processors to yield a better a makespan. The running cost of a hybrid scheduling algorithm is greater than the static scheduling algorithms, but is significantly lower than the dynamic only scheduling algorithms.

#### 1.5 NP-complete Problems

Computational problems can be broadly classified into two categories, tractable problems and intractable problems [3]. Tractable problems are the ones whose worst case running time or time complexity is smaller than  $O(n^k)$ , where n is the input size of the problem and k is a constant. These problems are also known as "Polynomial Time Problems" since they can be executed in polynomial time. The Intractable problems are ones that cannot be executed in polynomial time. They take super-polynomial times to execute.

However, there is a class of problems whose status is unknown to this day. These problems are known as the "NP-complete problems". For these problems, no polynomial time solution has yet been discovered, nor has anyone been able to solve them with a super-polynomial lower bound [3]. Many computer scientists believe that NP-complete problems are intractable. This is mainly because there has been no success in devising a polynomial time solution to any of the existing NP-complete problems so far and if a polynomial time solution is devised for one NP-complete problem, mathematically a polynomial time solution can be devised for all NP-complete problems.

Algorithm designers need to understand the basics and importance of NP-complete problems. If designers can prove that a problem is NP-complete, then there is a good chance that the problem is intractable. If a problem is intractable, it would be better to design an approximation algorithm instead of a perfect algorithm.

The task scheduling problems that form the focus of this dissertation are well known NP-complete problems [3]. We devise approximation algorithms or heuristics to deal with various cases of the task-scheduling problem, which forms the focus of this research.

#### 1.6 Research Objectives

In this dissertation, we intend to propose new algorithms for scheduling tasks in heterogeneous computing systems. In Section 2 we provide a comprehensive literature review on the existing work in the area of task scheduling in heterogeneous computing systems. In Section 3, we propose a new algorithm called the Heterogeneous Critical Node First (HCNF) to schedule a parallel application modeled by a Directed Acyclic Graph (DAG) onto a network of heterogeneous processing elements. In Section 4, we propose a new low-complexity algorithm called the Heterogeneous Largest Task First (HLTF) to schedule independent tasks of a meta-task onto a network of heterogeneous processors. In Section 5, we propose a new algorithm called the Earliest Finish Time with Dispatch Time (EFT-DT) to schedule a set of independent tasks of a meta-task onto a network of heterogeneous processors while also considering the dispatch times. In Section 6, we provide the concluding remarks and also make suggestions for future research in this area.

#### **CHAPTER 2**

#### LIERATURE REVIEW

Among the problems related to task scheduling in heterogeneous computing environments, scheduling a parallel application represented by a directed acyclic graph (DAG) to minimize the overall execution time (makespan) and scheduling a parallel application represented by a meta-task (set of independent tasks) to minimize the makespan are the most important and often researched ones. This section defines the two problems and surveys related research work.

# 2.1 Scheduling Parallel Applications Represented by Directed Acyclic Graphs onto Heterogeneous Computing Systems to Minimize the Makespan

Many parallel applications consist of sub-tasks with precedence constraints and can be modeled by directed acyclic graphs. This section discusses the problem of scheduling a parallel application represented by a DAG onto a network of heterogeneous processors to minimize its makespan and reviews related research work

#### 2.1.1 Directed Acyclic Graphs

A DAG is represented by  $G = \{V, E, W, C\}$ . V is the set of n nodes:  $\{n_1, n_2, n_3, n_4, ...\}$ . E is the set of directed edges of the form  $(n_i, n_i)$  which represents an edge directed from

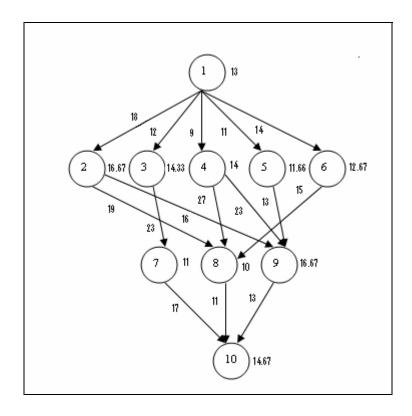

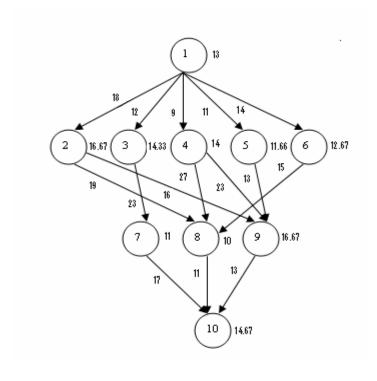

node  $n_i$  to  $n_i$ . W is the set of node weights of the form  $w_i$ , where  $w_i$  denotes the weight of node  $n_i$ . C is the set of edge weights of the form  $c_{i,j}$ , where  $c_{i,j}$  denotes the weight of the edge  $(n_i, n_i)$ . A DAG is a graph without a cycle (A directed path from a node onto itself). The set of nodes in a DAG which have an edge directed towards a node  $n_i$  are called its predecessor nodes and are denoted by  $PRED(n_i)$ . Likewise, the set of nodes which have a directed edge from a node  $n_i$  are called its *successor nodes* and are denoted by  $SUCC(n_i)$ . Nodes in a DAG that do not have a predecessor are called *start nodes* and nodes that do not have a successor are called *exit nodes*.  $blevel(n_i)$  is the bottom level of  $n_i$  and is length of the longest path from  $n_i$  to any exit node including the weight of  $n_i$ . The length of a path in a DAG is the sum of its node and edge weights.  $tlevel(n_i)$  is the is the top level of  $n_i$  and is the length of the longest path from a start node to node  $n_i$  excluding the weight of  $n_i$ . The longest path in a DAG is called the *critical path*. A DAG may have multiple critical paths. A sample DAG is illustrated in Figure 2.1. The node weights are to the right of each node and the edge weights are to the left of each edge. Table 2.1 provides the table of values for the sample DAG.

#### 2.1.2 Problem Statement

The objective is to schedule a parallel application represented by a DAG onto a network of heterogeneous processors to minimize its overall execution time. Nodeweights in a DAG represent average execution times of nodes over all the processors in the target execution system. Edges represent precedence constraints between nodes. An edge  $(n_i, n_i)$  indicates that node  $n_i$  cannot start execution until  $n_i$  completes execution and

receives all the required data from it. Edge-weights represent the time required to transfer the required data.

**Figure 2.1** A sample DAG,  $G_I$

**Table 2.1** Table of values for  $G_1$

| $n_i$ | $PRED(n_i)$ | $SUCC(n_i)$ | $tlevel(n_i)$ | $blevel(n_i)$ |

|-------|-------------|-------------|---------------|---------------|

| 1     | {null}      | {2,3,4,5,6} | 0             | 108.01        |

| 2     | {1}         | {8,9}       | 31            | 77.01         |

| 3     | {1}         | {7}         | 25            | 80            |

| 4     | {1}         | {8,9}       | 22            | 81.34         |

| 5     | {1}         | {9}         | 24            | 69            |

| 6     | {1}         | {8}         | 27            | 63.34         |

| 7     | {3}         | {10}        | 62.33         | 42.67         |

| 8     | {2,4,6}     | {10}        | 66.67         | 35.67         |

| 9     | {2,4,5}     | {10}        | 67.67         | 44.34         |

| 10    | {7,8,9}     | {null}      | 97.34         | 14.67         |

The target execution system consists of a finite number of heterogeneous processors connected with a high speed network. Communication among processors is assumed to be contention-less. Computation and communication is assumed to take place simultaneously. Node-execution is assumed to be non-preemptive; meaning nodes once scheduled on a processor cannot be removed (or preempted) and scheduled on other processors. If a DAG has multiple start nodes, a dummy start node with a zero node weight is added. Zero weight communication edges are then added from the dummy start node to the multiple start nodes. Likewise, if a DAG has multiple exit nodes, a dummy exit node is added. The make-span of a DAG is the time difference between the commencement of execution of the start node and the completion of execution of the exit node. The heterogeneous DAG scheduling problem is NP-complete [28] and can be formally defined as: To schedule the nodes of a DAG representing a parallel application onto a network of heterogeneous processors such that all the data precedence constraints are satisfied and the overall execution time of the DAG is minimized. The following sections survey existing research related to this problem.

#### 2.1.3 The Best Imaginary Level Algorithm

The Best Imaginary Level (BIL) algorithm [22] assigns node-priorities based on the *best imaginary level* of each node. At each scheduling step, a free node with the highest priority is selected and mapped onto a processor based on a criterion. Table 2.2 defines the terms used in BIL and Figure 2.2 lists the algorithm.

$BIL(n_i, p_j)$  is the best imaginary level of node  $n_i$  on processor  $p_j$ . It is the length of the longest path in the DAG beginning with  $n_i$  assuming it is mapped onto  $p_j$ , and is recursively defined as:

$$BIL(n_i, p_j) = w_{i, j} + \max_{n_k \in Succ(n_i)} [\min(BIL(n_i, p_j), \min_{p \neq j} (BIL(n_i, p_p) + c_{i, p}))].$$

BIL of a node is adjusted to its basic imaginary make-span (BIM) as follows:

$$BIM(n_i, p_j) = BIL(n_i, p_j) + T \_Available[j].$$

Table 2.2 Definition of terms used in BIL

| Term                   | Definition                                                                                                             |

|------------------------|------------------------------------------------------------------------------------------------------------------------|

|                        |                                                                                                                        |

| N                      | $= \{n_1, n_2, n_3, n_4, n_5, n_6\} // \text{Set of nodes in the DAG},  N  = n$                                        |

| P                      | = $\{p_1, p_2, p_3, p_4, p_5, p_6\}$ //Set of processors, $ P  = m$                                                    |

| $W_{i,j}$              | Time required to execute $n_i$ on $p_j$                                                                                |

| $c_{i,j}$              | Time required to transfer all the requisite data from $n_i$ to $n_j$ when they are scheduled on different processors   |

| $BIL(n_i, p_j)$        | $= w_{i, j} + \max_{n_k \in Succ(n_i)} \left[ \min(BIL(n_k, p_j), \min_{j \neq l} (BIL(n_i, p_l) + c_{i, k})) \right]$ |

| $T_A$ vailable $[p_j]$ | Time at which processor $p_j$ completes the execution of all the nodes previously assigned to it                       |

| $BIM(n_i, p_j)$        | $= BIL(n_i, p_j) + T \_Avaialble[p_j]$                                                                                 |

| k                      | Number of free nodes at a scheduling step                                                                              |

| $BIM*(n_i, p_j)$       | $=BIM(n_i, p_j) + w_{i,j} \times \max(k/m-1,0)$                                                                        |

If k is the number of free nodes (those nodes whose predecessors have completed execution) at a scheduling step, the priority of a free node is the  $k^{th}$  smallest BIM value. If the  $k^{th}$  smallest BIM value is undefined, the largest finite BIM value becomes its priority. If two or more nodes have the same priority, ties are broken randomly. At each scheduling step, the free node with the highest priority is selected for mapping. If k is greater than the number of processors, node execution times become more important than the communication overhead. On the contrary, if k is less than the number of available processors, node execution times become less important. The BIM value for the selected node is revised to incorporate this factor as follows:

$$BIM*(n_i, p_j) = BIM(n_i, p_j) + w_{i,j} \times \max(k/m-1,0)$$

.

The processor which provides the highest revised BIM value for the node is selected. If more than one processor provides the same revised BIM value, the processor that maximizes the sum of the revised BIM values of all the other nodes is selected. The time complexity of the algorithm is  $O(n^2 + m \log m)$ .

#### 2.1.4 The Generalized Dynamic Level Algorithm

The Generalized Dynamic Level (GDL) Algorithm [28] assigns node-priorities based on their *generalized dynamic levels*. A number of factors are incorporated in the calculation of the generalized dynamic level and are explained next. The definition of terms used in GDL is listed in Table 2.3 and the algorithm is listed in Figure 2.3.

```

BIL Algorithm

ReadyTaskList \leftarrow Start node

While ReadyTaskList NOT empty

k \leftarrow |ReadyTaskList| // Number of free nodes

For all n_i in ReadyTaskList and p_i in P

Compute BIM(n_i, p_i)

End For

Priority of n_i \leftarrow k^{th} smallest BIM value, or the largest finite

BIM value if the k^{th} smallest value is undefined

n_t \leftarrow node in ReadyTaskList with the highest priority

For all p_i in P

Compute BIM*(n_t, p_i)//Revised BIM

End For

p_{fav} \leftarrow The processor that provides the highest revised BIM value

for n_t

Map n_t on p_{fav}

ReadyTaskList \leftarrow ReadyTaskList - n_t + Free nodes(if any)

End While

End BIL

```

Figure 2.2 The BIL algorithm

$SL(n_i)$  is the static level of a node  $n_i$  and is the largest sum of the median execution times of all the nodes from node  $n_i$  to an exit node along any path in the DAG.  $DL(n_i,p_j) = SL(n_i) - EST(n_i, p_j) + \Delta(n_i, p_j)$  is the Dynamic Level (DL) of a node  $n_i$  on processor  $p_j$ . It indicates how well the node and the processor are matched for execution. Even though  $DL(n_i,p_j)$  indicates how well  $n_i$  and  $p_j$  are matched, it does not indicate how well the descendents of  $n_i$  are matched with  $p_j$ .  $D(n_j)$  is the descendent of node  $n_i$  to which  $n_i$  passes the maximum data.  $F(n_i,D(n_i),p_j) = d(n_i,D(n_i)) + min_{k\neq j} E(D(n_i),p_k)$  is defined to indicate how quickly  $D(n_i)$  can be completed on a processor other than  $p_j$ , if node  $n_i$  is

executed on processor  $p_j$ . The Descendent Consideration (DC) term is defined as:  $DC(n_i, p_j) = w*(D(n_i)) - min \{ E(D(n_i), p_j), F(n_i, D(n_i), p_j) \}$

Table 2.3 Definition of terms used in GDL

| Term                | Definition                                                                                                               |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| N                   | = $\{n_1, n_2, n_3, n_4, n_5, n_6\}$ //Set of nodes in the DAG, $ N =n$                                                  |  |  |  |  |

| P                   | = $\{p_1, p_2, p_3, p_4, p_5, p_6\}$ //Set of processors, $ P  = m$                                                      |  |  |  |  |

| $w_{i,j}$           | Execution time of node $n_i$ on $p_j$                                                                                    |  |  |  |  |

| $c_{i,j}$           | Data transfer time from node $n_i$ to $n_j$                                                                              |  |  |  |  |

| $w^*(n_i)$          | Median execution time of $n_i$ over all the processors                                                                   |  |  |  |  |

| $SL(n_i)$           | largest sum of the median execution times of all the nodes from node $n_i$ to an exit node along any path in the DAG     |  |  |  |  |

| $\Delta(n_i, p_j)$  | $= w^*(n_i) - w_{i,j}$                                                                                                   |  |  |  |  |

| $EST(n_i, p_j)$     | Earliest start time of $n_i$ on $p_j$                                                                                    |  |  |  |  |

| $DL(n_i, p_j)$      | $= SL(n_i) - EST(n_i, p_j) + \Delta(n_i, p_j)$                                                                           |  |  |  |  |

| $D(n_j)$            | Descendent node of node $n_i$ to which $n_i$ passes the maximum data                                                     |  |  |  |  |

| $d(n_i,D(n_i))$     | Time required to transfer data from $n_i$ to $D(n_i)$                                                                    |  |  |  |  |

| $E(D(n_i),p_k)$     | Time required to execute $D(n_i)$ on processor $p_k$                                                                     |  |  |  |  |

| $F(n_i,D(n_i),p_j)$ | $= d(n_i, D(n_i)) + \min_{k \neq j} E(D(n_i), p_k)$                                                                      |  |  |  |  |

| $DC(n_i, p_j)$      | $= w^*(D(n_i)) - min \{ E(D(n_i), p_j), F(n_i, D(n_i), p_j) \}$                                                          |  |  |  |  |

| $C(n_i)$            | = $DL(n_i, p_{pref}) - max_{k \neq pref}DL(n_i, p_k)$ (pref is the processor on which node $n_i$ obtains the maximum DL) |  |  |  |  |

| $GDL(n_i, p_j)$     | $= DL(n_i, p_j) + DC(n_i, p_j) + C(n_i)$                                                                                 |  |  |  |  |

```

GDL Algorithm

For all n_i in N

Compute SL(n_i)

End For

ReadyTaskList \leftarrow Start Node

While ReadyTaskList is NOT NULL do

For all n_i in ReadyTaskList and p_j in P

Compute DL(n_i, p_j)

Compute DC(n_i, p_j)

Compute C(n_i)

GDL(n_i, p_j) \leftarrow DL(n_i, p_j) + DC(n_i, p_j) + C(n_i)

End For

Select the node-processor pair with the maximum GDL

Update ReadyTaskList

End While

End GDL

```

Figure 2.3 The GDL algorithm

The preferred processor of a node is the processor which maximizes its dynamic level (DL). The cost of not scheduling a node on its preferred processor is defined as follows.  $C(n_i) = DL(n_i, p_{pref}) - max_{k \neq i} DL(n_i, p_k) \quad (p_{pref} \text{ is the preferred processor})$

The combination of DL, the Descendent Consideration (DC) term and the cost incurred in not scheduling a node on its preferred processor is used to define the Generalized Dynamic Level (GDL) of a node as:  $GDL(n_i, p_j) = DL(n_i, p_j) + DC(n_i, p_j) + C(n_j)$ .

At each scheduling step, the algorithm selects among the free nodes, the node and the processor with the maximum GDL. The time complexity is  $O(n^2 + m \log m)$ .

# 2.1.5 The Levelized Min Time Algorithm

In the Levelized Min Time (LMT) algorithm [16], the input DAG is divided into k levels using the following rules. The levels are numbered 0 to k-1. All the nodes in a level

**Table 2.4** Definition of terms used in LMT

| Term                   | Definition                                                                                                           |  |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| N                      | $= \{n_1, n_2, n_3, n_4, n_5, n_6\}$ //Set of nodes in the DAG, $n= N $                                              |  |  |  |  |

| P                      | = $\{p_1, p_2, p_3, p_4, p_5, p_6\}$ //Set of processors, $m= P $                                                    |  |  |  |  |

| k                      | Number of levels in the DAG                                                                                          |  |  |  |  |

| $W_{i,j}$              | Time required to execute $n_i$ on $p_j$                                                                              |  |  |  |  |

| $c_{i,j}$              | Time required to transfer all the requisite data from $n_i$ to $n_j$ when they are scheduled on different processors |  |  |  |  |

| $T_A$ vailable $[p_j]$ | Time at which processor $p_j$ completes the execution of all the nodes previously assigned to it                     |  |  |  |  |

| $EST(n_i, p_j)$        | $Max(T_Available[j], max_{n_m \in pred(n_i)} EFT(n_m, p_k) + c_{m,i}))$                                              |  |  |  |  |

| $EFT(n_i, p_j)$        | $= w_{i,j} + EST(n_i, p_j)$                                                                                          |  |  |  |  |

are independent of each other. Level 0 contains the start nodes and level k-l contains the exit nodes. For any level j, where 0 < j < k-l, nodes in level j can have incident edges from any of the nodes in levels 0 thru j+l. Additionally, there must be at least one node in level j with an edge incident from a node in level j+l. LMT maps the nodes one level at a time starting from level 0. If the number of nodes at a given level is more than the number of processors in the target system, the smallest nodes (based on the average computation times) are merged until the number of nodes equals the number of

processors. Nodes are then sorted by the descending order of their average computations times. At each scheduling, the largest node is mapped onto the processor that provides its minimum finish time. Table 2.4 defines the terms used in LMT and Figure 2.4 lists the algorithm.

```

LMT Algorithm

Divide the input DAG into k levels (level \theta to level k-l)

For levels 0 thru k-1 do

num \leftarrow number of nodes in the current level

If num > m

Merge the smallest nodes in the current level until num=m

ReadyTaskList \leftarrow Nodes in the current level sorted in the

descending order of average node weights

While ReadyTaskList is NOT NULL do

n_i \leftarrow First node in the ReadyTaskList

For all p_i in P

Compute EST(n_i, p_i)

EFT(n_i, p_i) \leftarrow w_{i,i} + EST(n_i, p_i)

End For

Map node n_i on processor p_i which provides its least EFT

Update T Available [p_i]

Update ReadyTaskList

End While

End For

End LMT

```

**Figure 2.4** The LMT algorithm

#### 2.1.6 The Heterogeneous Earliest Finish Time Algorithm

The Heterogeneous Earliest Finish Time (HEFT) algorithm [30] assigns node - priorities based on the bottom level (*blevel*) of each node. The *blevel* of a node is the

length of the longest path in the DAG from the node to the exit node. The length of a path in a DAG is the sum of the node and edge weights that constitute the path. At each scheduling step, a node with the highest priority is assigned to a processor that minimizes its finish time. The definition of terms used in HEFT in listed in Table 2.5 and the algorithm is listed in Figure 2.5. As a first step, HEFT traverses the DAG in a top down fashion and computes the *blevels* of all the nodes. At each scheduling step, a node with the highest *blevel* is selected for mapping. Ties are broken randomly

$EST(n_i, p_j)$  is the earliest start time of a node  $n_i$  on a processor  $p_j$  and is defined as:  $EST(n_i, p_j) = Max(T_Available[p_j], \max_{n_m \in pred(n_i)} EFT(n_m, p_k) + c_{m,i})$ ). It is the maximum of a) the time at which processor  $p_j$  becomes free or b) The time at which node  $n_i$  receives all the required data from its predecessor nodes after the completion of their exeuction.  $EFT(n_i, p_j)$  is the Earliest Finish Time of a node  $n_i$  on a processor  $p_j$  and is defined as:  $EFT(n_i, p_j) = EST(n_i, p_j) + w_{i,j}$ . HEFT computes the EFTs of the selected node on all the processors and selects the processor that provides the minimum EFT. The time complexity is  $O(n^2 m)$ .

#### 2.1.7 The Critical Path on Processor Algorithm

The critical path is the longest path in a DAG. The length of the critical path gives the lower bound on the overall execution time of the DAG [30]. Minimizing the length of the critical path would aid minimizing the overall execution time of a DAG [30]. The Critical Path on Processor (CPOP) algorithm [30] is a variant of the HEFT algorithm and is from the same authors [30]. CPOP adopts a different mapping strategy for the critical path nodes and the non-critical path nodes.

Table 2.5 Definition of terms used in HEFT

| Term                      | Definition                                                                                                           |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                           |                                                                                                                      |  |  |  |  |

| N                         | $= \{n_1, n_2, n_3, n_4, n_5, n_6\}$ //Set of nodes in the DAG, $n= N $                                              |  |  |  |  |

| P                         | = $\{p_1, p_2, p_3, p_4, p_5, p_6,\}$ //Set of processors, $m =  P $                                                 |  |  |  |  |

| $W_{i,j}$                 | Time required to execute $n_i$ on $p_j$                                                                              |  |  |  |  |

| $c_{i,j}$                 | Time required to transfer all the requisite data from $n_i$ to $n_j$ when they are scheduled on different processors |  |  |  |  |

| priority(n <sub>i</sub> ) | $= blevel(n_i)$                                                                                                      |  |  |  |  |

| $T_A$ vailable $[p_j]$    | Time at which processor $p_j$ completes the execution of all the nodes previously assigned to it                     |  |  |  |  |

| $EST(n_i, p_j)$           | $Max(T\_Available[j], \max_{n_m \in pred(n_i)} EFT(n_m, p_k) + c_{m,i}))$                                            |  |  |  |  |

| $EFT(n_i, p_j)$           | $= w_{i,j} + EST(n_i, p_j)$                                                                                          |  |  |  |  |

```

HEFT Algorithm

For all n_i in N

Compute blevel(n_i)

End For

ReadyTaskList \leftarrow Start Node

While ReadyTaskList is NOT NULL do

n_i \leftarrow node in the ReadyTaskList with the maximum blevel

For all p_j in P

Compute EST(n_i, p_j)

EFT(n_i, p_j) \leftarrow w_{i,j} + EST(n_i, p_j)

End For

Map node n_i on processor p_j which provides its least EFT

Update T_Available[p_j] and ReadyTaskList

End While

End HEFT

```

Figure 2.5 The HEFT Algorithm

Table 2.6 Definition of terms used in CPOP

| Term                      | Definition                                                                                                           |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| N                         | = $\{n_1, n_2, n_3, n_4, n_5, n_6\}$ //Set of nodes in the DAG, $n= N $                                              |  |  |  |  |

| P                         | = $\{p_1, p_2, p_3, p_4, p_5, p_6\}$ //Set of processors, $m= P $                                                    |  |  |  |  |

| $W_{i,j}$                 | Time required to execute $n_i$ on $p_j$                                                                              |  |  |  |  |

| ${\cal C}_{i,j}$          | Time required to transfer all the requisite data from $n_i$ to $n_j$ when they are scheduled on different processors |  |  |  |  |

| priority(n <sub>i</sub> ) | $= tlevel(n_i) + blevel(n_i)$                                                                                        |  |  |  |  |

| CP processor              | $p_j \in P$ which minimizes $\sum_{n_i \in CP} w_{i,j} //CP$ is the critical path                                    |  |  |  |  |

| $T_A$ vailable $[p_j]$    | Time at which processor $p_j$ completes the execution of all the nodes previously assigned to it                     |  |  |  |  |

| $EST(n_i, p_j)$           | $Max(T_Available[p_j], \max_{n_m \in pred(n_i)} EFT(n_m, p_k) + c_{m,i}))$                                           |  |  |  |  |

| $EFT(n_i, p_j)$           | $= w_{i,j} + EST(n_i, p_j)$                                                                                          |  |  |  |  |

CPOP traverses the DAG in a top down fashion to compute the *tlevels* and *blevels* of all the nodes. It identifies the critical path/s and marks the critical path nodes. The priority of each node is the sum of its *tlevel* and *blevel*. At each scheduling step, a free task with the highest priority is selected for mapping. Ties (if any) are broken randomly.

A *CP* processor is defined as the processor that minimizes the overall execution time of the critical path assuming all the critical path nodes are mapped onto it. If the selected node is a critical path node, it is mapped onto the *CP* processor. Else, it is

mapped onto a processor that minimizes its *EFT* (like the HEFT algorithm). The time complexity is  $O(n^2 m)$ .

```

CPOP Algorithm

For all n_i in N

Compute tlevel(n_i) and blevel(n_i)

Identify the critical path/s and mark the critical path nodes

priority(n_i) \leftarrow tlevel(n_i) + blevel(n_i)

End For

ReadyTaskList \leftarrow Start\ Node

While ReadyTaskList is NOT NULL do

n_i \leftarrow node in the ReadyTaskList with the maximum priority

If n_i \in \text{critical path}

Map n_i on the CP processor

Else

For all p_i in P

Compute EST(n_i, p_i)

EFT(n_i, p_j) \leftarrow w_{i,j} + EST(n_i, p_j)

End For

Map node n_i on processor p_i which provides its least EFT

End If

Update T Available[p<sub>i</sub>]

Update ReadyTaskList

End While

End CPOP

```

**Figure 2.6** The CPOP algorithm

#### 2.1.8 The Fast Critical Path Algorithm

There are three steps involved in a typical static DAG scheduling algorithm: computation of node priorities, node selection, and processor selection. These steps contribute to the overall time complexity of the algorithm. The Fast Critical Path (FCP)

algorithm [24] tries to reduce the overall time complexity by reducing the complexity of the node selection and the processor selection steps.

**Table 2.7** Definition of terms used in FCP

| Term                      | Definition                                                                                                           |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| N                         | $= \{n_1, n_2, n_3, n_4, n_5, n_6\}$ //Set of nodes in the DAG, $n= N $                                              |  |  |  |  |

| P                         | = $\{p_1, p_2, p_3, p_4, p_5, p_6\}$ //Set of processors, $m= P $                                                    |  |  |  |  |

| e                         | Number of edges in the DAG                                                                                           |  |  |  |  |

| $W_{i,j}$                 | Time required to execute $n_i$ on $p_j$                                                                              |  |  |  |  |

| priority(n <sub>i</sub> ) | $= blevel(n_i)$                                                                                                      |  |  |  |  |

| $C_{i,j}$                 | Time required to transfer all the requisite data from $n_i$ to $n_j$ when they are scheduled on different processors |  |  |  |  |

| $T_A$ vailable $[p_j]$    | Time at which processor $p_j$ completes the execution of all the nodes previously assigned to it                     |  |  |  |  |

| $EST(n_i, p_j)$           | $Max(T_Available[j], max_{n_m \in pred(n_i)} EFT(n_m, p_k) + c_{m,i}))$                                              |  |  |  |  |

| $EFT(n_i, p_j)$           | $= w_{i,j} + EST(n_i, p_j)$                                                                                          |  |  |  |  |

**Node Selection:** FCP tries to reduce the complexity of the node selection process by restricting the size of the *ReadyTaskList* to *m* (The number of processors in the target execution system). Additional free nodes (if any) are stored in a *FIFO* queue. Node priorities are based on their *blevels*. At each scheduling step, a node with the highest priority is selected for mapping. By restricting the size of the *ReadyTaskList* to *m*, the time complexity of the node selection process would be *O(n log m)*.

**Processor Selection:** The complexity of the processor selection step is reduced by restricting the choice to just two processors: the first processor that becomes free and the *enabling processor* (The processor which is the last to send a data item to a node). The authors [24] prove that the EFT of a node is always minimized by one of these two processors. The time complexity of the processor selection step would be reduced to O(nlogm+e). Of the two processors, the one which provides the least EFT for the selected node is chosen. The overall time complexity of FCP is O(nlogm+e).

```

FCP Algorithm

For all n_i in N

Compute tlevel(n_i)

priority(n_i) \leftarrow blevel(n_i)

End For

ReadyTaskList \leftarrow Start\ Node

AdditionalTaskList \leftarrow NULL //FIFO Queue

While ReadyTaskList is NOT NULL do

n_i \leftarrow node in the ReadyTaskList with the maximum priority

p_I \leftarrow First processor in P to become free

P_2 \leftarrow Enabling processor of n_i

Compute EST(n_i, p_i)

EFT(n_i, p_1) \leftarrow EST(n_i, p_1) + w_{i,1}

Compute EST(n_i, p_2)

EFT(n_i, p_1) \leftarrow EST(n_i, p_2) + w_{i,2}

Map node n_i on processor p_i which provides its least EFT

Update T Available [p_i]

Update ReadyTaskList

Update Additional TaskList (If applicable)

End While

End FCP

```

Figure 2.7 The FCP algorithm

### 2.1.9 The Fast Load Balancing Algorithm

The Fast Load Balancing (FLB) algorithm [24] is a variant of the FCP algorithm. The node selection complexity is reduced by limiting the number of nodes in the *ReadyTaskList* to *m* (number of processors). Additional free nodes, if any, are added to a *FIFO* list. As was discussed in previous section, the earliest start time for a node can be obtained on either the first processor to become free or a task's enabling processor. For each node in the *ReadyTaskList*, the earliest start time of the node on the first processor to become free and the node's enabling processor is calculated. Among the free nodes, the node with the minimum earliest start time is selected and mapped onto the corresponding processor. The overall time complexity of FLB is *O(nlogm+e)*.

Table 2.8 Definition of terms used in FLB

| Term                      | Definition                                                                                                           |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| N                         | $= \{n_1, n_2, n_3, n_4, n_5, n_6\}$ //Set of nodes in the DAG, $n= N $                                              |  |  |  |

| P                         | = $\{p_1, p_2, p_3, p_4, p_5, p_6\}$ //Set of processors, $m= P $                                                    |  |  |  |

| $W_{i,j}$                 | Time required to execute $n_i$ on $p_j$                                                                              |  |  |  |

| priority(n <sub>i</sub> ) | $= blevel(n_i)$                                                                                                      |  |  |  |

| $C_{i,j}$                 | Time required to transfer all the requisite data from $n_i$ to $n_j$ when they are scheduled on different processors |  |  |  |

| $T_A$ vailable $[p_j]$    | Time at which processor $p_j$ completes the execution of all the nodes previously assigned to it                     |  |  |  |

| $EST(n_i, p_j)$           | $Max(T_Available[j], max_{n_m \in pred(n_i)} EFT(n_m, p_k) + c_{m,i}))$                                              |  |  |  |