## DIE STRESS CHARACTERIZATION AND INTERFACE DELAMINATION STUDY

## IN FLIP CHIP ON LAMINATE ASSEMBLIES

Except where reference is made to the work of others, the work described in this dissertation is my own or was done in collaboration with my advisory committee. This dissertation does not include proprietary or classified information.

Md. Sayed Kaysar Rahim

Certificate of Approval:

Richard C. Jaeger, Co-Chair Distinguished University Professor Electrical and Computer Engineering Jeffrey C. Suhling, Co-Chair Quina Distinguished Professor Mechanical Engineering

Pradeep Lall Associate Professor Mechanical Engineering Roy W. Knight, Assistant Professor Mechanical Engineering

Stephen L. McFarland Acting Dean Graduate School

# DIE STRESS CHARACTERIZATION AND INTERFACE DELAMINATION STUDY IN FLIP CHIP ON LAMINATE ASSEMBLIES

Md. Sayed Kaysar Rahim

A Dissertation

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Doctor of Philosophy

Auburn, Alabama

August 8, 2005

# DIE STRESS CHARACTERIZATION AND INTERFACE DELAMINATION STUDY IN FLIP CHIP ON LAMINATE ASSEMBLIES

Md. Sayed Kaysar Rahim

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon request of individuals or institutions and their expense. The author reserves all publication rights.

Signature of Author

Date of Graduation

VITA

Md. Kaysar. Rahim, son of Md. Abdur Rahim and Shamima Akhtar, was born on January 1, 1972, in Rajshahi, Rajshahi Province, Bangladesh. He graduated from Rajshahi University School and College in 1989. He went to Bangladesh University of Engineering and Technology, and graduated with the degree of Bachelor of Mechanical Engineering in July of 1996. After his graduation, he joined the faculty of the Mechanical Engineering Department of Bangladesh Institute of Technology, and performed his teaching and research duties in the area of structural design, and experimental mechanics. He started his graduate studies in the Mechanical Engineering Department, Auburn University, Alabama, in September 1998.

#### DISSERTATION ABSTRACT

## DIE STRESS CHARACTERIZATION AND INTERFACE DELAMINATION STUDY

IN FLIP CHIP ON LAMINATE ASSEMBLIES

Md. Sayed Kaysar Rahim

Doctor of Philosophy, August 8, 2005 (M.S., Auburn University, 2004) (B. S., Bangladesh University of Engineering And Technology, 1996)

292 Typed Pages

Directed by Jeffrey C. Suhling and Richard C. Jaeger

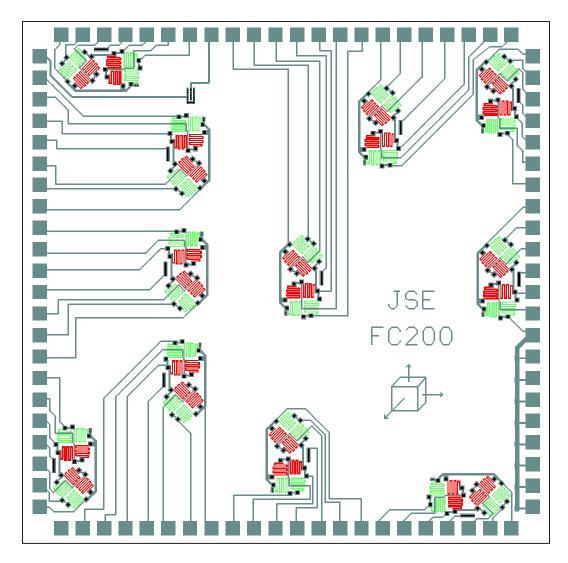

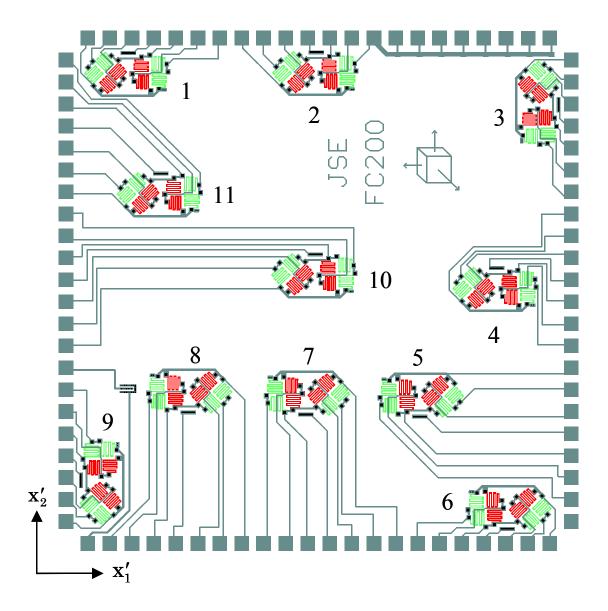

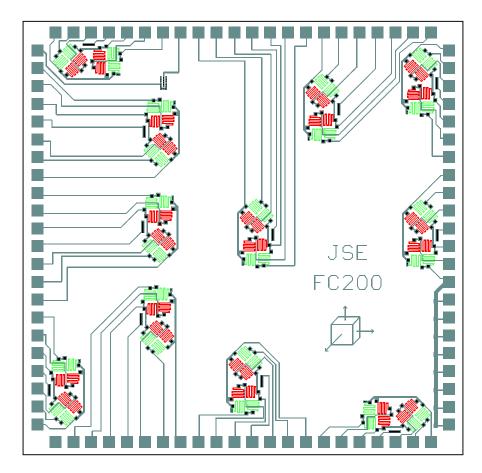

Thermo-mechanical reliability of flip chip on laminate packaging is a major concern when the assemblies are exposed to harsh operating environments such as space or automotive underhood applications. In this study, structural and thermal reliability of flip chip packages have been investigated during the assembly process and accelerated life testing using piezoresistive stress sensing test chips. Both 5 x 5 mm (FC200) and 10 x 10 mm (FC400) test chips fabricated on (111) silicon were utilized to characterize the complete die stress state on the device side of the chip in flip chip on laminate assemblies. The FC200 chip includes 11 eight-element sensor rosettes, a diode for temperature measurement, an eight-bit fuse style chip ID, and contains 200  $\mu$ m (8 mil)

pitch perimeter solder bumps. The FC400 chip includes 19 stress sensor rosettes, 2 diodes for temperature measurement, a 10-bit fuse style chip ID, an embedded full coverage heater for heat transfer or power cycling experiments, and also contains 200  $\mu$ m pitch perimeter solder bumps.

This flip chip study is divided into four parts. In the first part of this work, transient die stress measurements have been made during underfill cure, and the room temperature die stresses in final cured assemblies have been compared for several different underfill encapsulants. The experimental stress measurements in the flip chip samples were then correlated with finite element predictions for the tested configurations. It is well known that underfill has significant impact on flip chip package reliability. To investigate the effects of underfill on thermo-mechanical behavior of flip chip packages, three different underfill materials were used in this study. A total of 75 flip chip test boards (1 die size x 3 underfills x 25 samples per combination) were assembled at the CAVE SMT Line at Auburn University. In each assembly, the three-dimensional die surface stresses have been recorded during underfill cure, and after underfill cure (room temperature).

In the second part of this work, the silicon die stresses occurring in flip chip assemblies have been characterized and modeled at extremely low temperatures. Stress measurements have been made down to -180 °C using test chips incorporating piezoresistive sensor rosettes. The obtained stress measurement data have been correlated with the predictions of nonlinear finite element models. A microtester has been used to characterize the stress-strain behavior of the solder and underfill encapsulant from -180 to 150 °C to aid in this modeling effort.

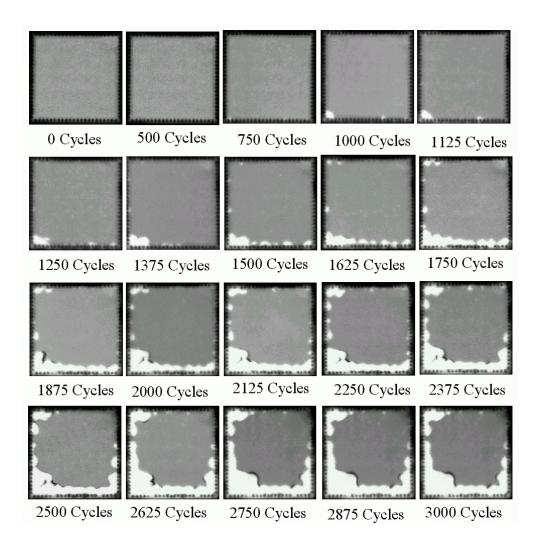

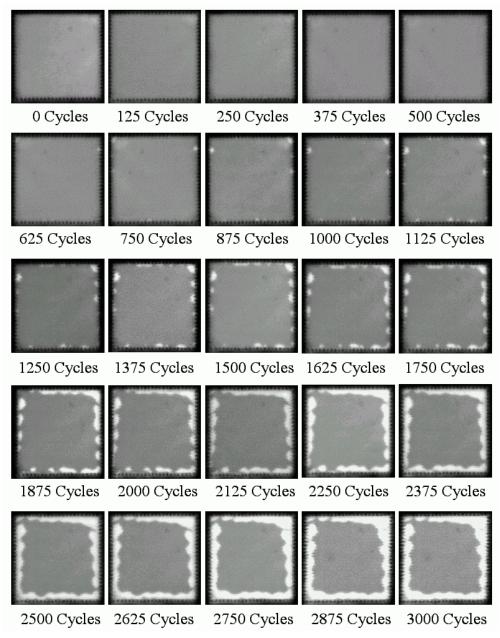

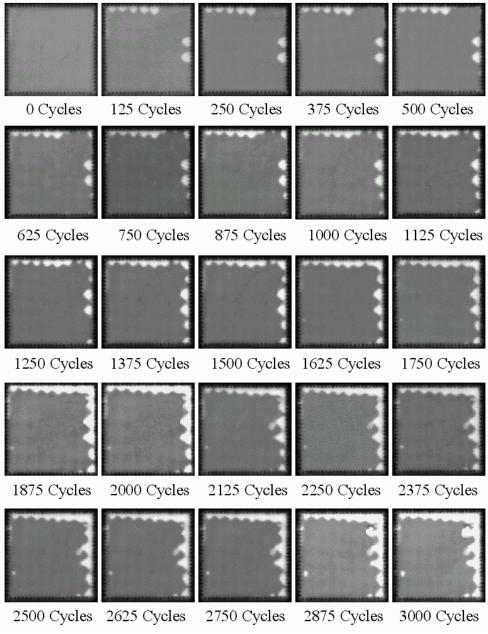

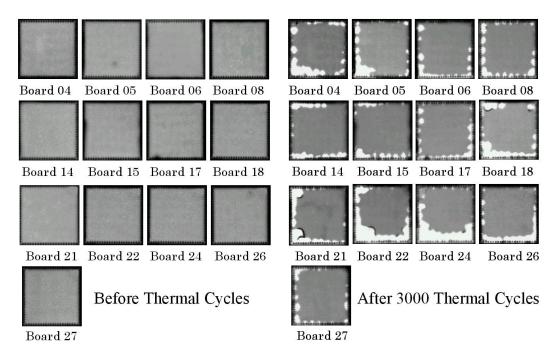

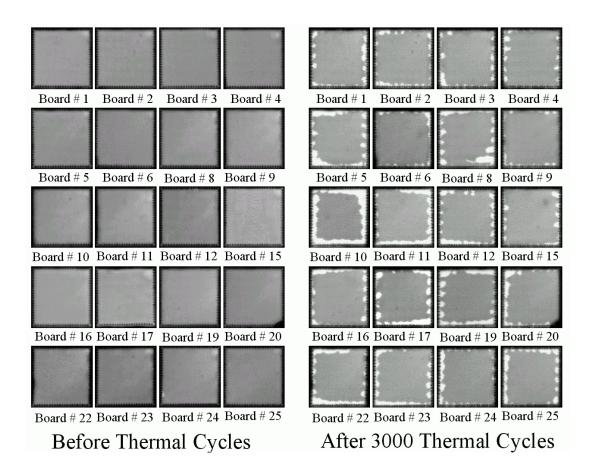

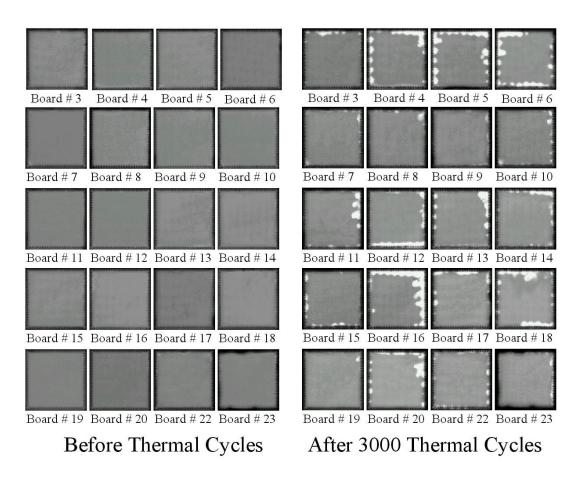

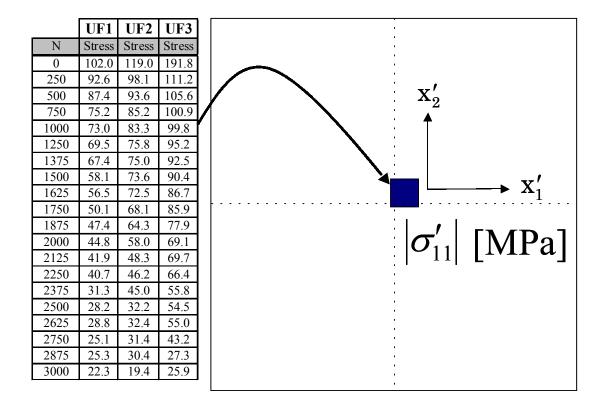

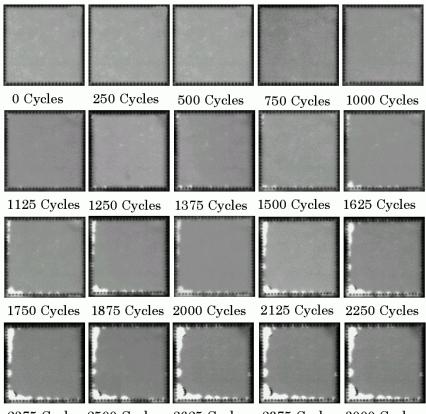

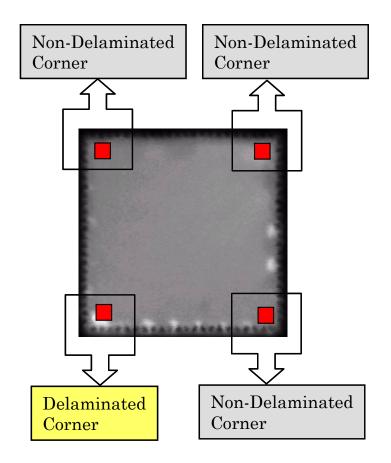

In the third part of this work, the stress variations occurring during thermal cycling from -40 to +125 °C have been characterized. These measurements have been correlated with the delaminations occurring at the die passivation to underfill interface measured using C-mode Scanning Acoustic Microscopy (C-SAM). With this approach, the stress distributions across the chip, and the stress variations at particular locations at the die to underfill interface have been interrogated for the entire life of the flip chip assembly. In order to correlate the stress changes at the sensor sites with delamination onset and propagation, CSAM evaluation of the test assemblies was performed after every 125 thermal cycles.

A total of 75 flip chip assemblies with 3 different underfills have been evaluated. For each assembly, the complete histories of three-dimensional die surface stresses and delamination propagation have been recorded versus the number of thermal cycles. The stress histories that lead to delamination initiation for each underfill encapsulant, and the variation of the stresses that occur before and during delamination propagation have been identified. The progressions of stress and delamination have been mapped across the entire surface of the die, and a series of stress/delamination videos have been produced. One of the most important discoveries is that the shear stresses occurring at the corners of flip chip die have been demonstrated to be a suitable proxy for prognostic determination of future delamination initiations and growth. Thus, shear stress sensors have great potential as health-monitoring devices in flip chip packaging.

In the fourth and final part of this work, die stress characterization was performed in flip chip assemblies utilizing a new low expansion coefficient laminate material. The new substrate material is a hybrid laminate formed using a combination of standard glass fiber reinforced resin outer layers (FR-4), with a carbon fiber reinforced resin core layer. The carbon fiber based central core (STABLCOR) features both high stiffness and high thermal conductivity, as well as near zero thermal expansion coefficient. Because of the extremely low expansion coefficient of the carbon fiber core and the bonded nature of the laminate, the surface CTE of the hybrid laminate PCB stack-up is typically in the range of 2.0-4.0 ppm/°C over the temperature range of -55 to 150 °C, which is much lower than the typical 13.0-20.0 ppm/°C seen with standard FR-4 based laminates. In addition, the high stiffness of the carbon fiber based core can help reduce PCB warpage issues, as well as vastly improve the net heat conduction characteristics of the PCB substrate

FC200 and FC400 flip chip test die were packaged on the low expansion laminates, and the die surface stresses were measured throughout the assembly process. Die stress measurements have been made during underfill cure, and at room temperature after final assembly. The results have been compared to those from analogous FR-406 substrate assemblies. Significant stress reductions have been observed when using the low expansion coefficient laminate.

#### ACKNOWLEDGEMENTS

The author would like to thank his advisor Dr. Jeffrey C. Suhling and co-advisor Dr Richard C. Jaeger for their directions, patience and encouragement. The author also wishes to acknowledge the financial support of the NSF Center for Advanced Vehicle Electronics (CAVE), the NASA Center for Space Power and Advance Electronics (CSPAE), and the Alabama Microelectronics Science and Technology Center (AMSTC).

The author would like to thank all of his friends for their support and understanding. Finally, many thanks go to his parents Md. Abdur Rahim, and Shamima Akhtar, and his one sister and brother for their love as a family. Style manual or journal used <u>Guide to Preparation and Submission of Theses and</u> Dissertations Computer software used Microsoft Office 2003, Adobe Photoshop, Solid Edge, Patran,

ANSYS, MathCAD, Visual Basic, LabView and Sigma Plot

# TABLE OF CONTENTS

| Lis | st of Figures                                             | xiv |

|-----|-----------------------------------------------------------|-----|

| Lis | List of Tables                                            |     |

| 1.  | INTRODUCTION                                              | 1   |

| 2.  | LITERATURE REVIEW                                         | 13  |

| 3.  | REVIEW OF PIEZORESISTIVE THEORY                           | 33  |

|     | 3.1. General Resistance Change Equations                  | 33  |

|     | 3.2. Resistance Change Equations for Silicon Wafer Planes | 37  |

| 4.  | (111) SILICON TEST CHIPS                                  | 44  |

|     | 4.1. JSE (111) Silicon Test Chips (FC200)                 | 44  |

|     | 4.1.1 Optimized Eight-Element Rosette                     |     |

|     | 4.1.2 FC200 Silicon Test Chip                             |     |

|     | 4.2. Calibration Results for FC200 and FC400 Test Chips   | 54  |

|     | 4.2.1 Four-Point Bending Tests                            |     |

|     | 4.2.2 Hydrostatics Tests                                  |     |

|     | 4.2.3 TCR Measurements                                    |     |

|     | 4.2.4 Hydrostatic Test Procedure                          |     |

|     | 4.3. Test Chip Application Procedure                      | 66  |

|     | 4.3.1 Resistance Measurements                             |     |

| 5. | DIE STRESS CHARACTERIZATION IN FLIP CHIP ON LAMINATE<br>ASSEMBLIES            | 80  |

|----|-------------------------------------------------------------------------------|-----|

|    | 5.1. Introduction                                                             | 80  |

|    | 5.2. Stress Equations for Test Chips Characterizations                        | 88  |

|    | 5.3. Stress Test Chips                                                        | 91  |

|    | 5.4. Test Board Assembly                                                      | 94  |

|    | 5.5. Flip Chip Stress Measurements                                            | 104 |

|    | 5.5.1 Stress Variation During Underfill Cure                                  |     |

|    | 5.5.2 Stresses After Underfill Encapsulation                                  |     |

|    | 5.6. Finite Element Correlations                                              | 124 |

|    | 5.7. Die Stress Variation with Temperature (-40 to +150 °C)                   | 137 |

|    | 5.8. Summary                                                                  | 139 |

| 6. | MEASUREMENT OF ELECTRONIC PACKAGING MATERIAL                                  |     |

|    | BEHAVIOR AND FLIP CHIP DIE STRESSES AT EXTREME LOW<br>TEMPERATURES            | 144 |

|    | 6.1. Introduction                                                             | 144 |

|    | 6.2. Packaging Technologies and Test Chips                                    | 148 |

|    | 6.3. Test Results (-180 to +150 °C)                                           | 158 |

|    | 6.4. Finite Element Simulations and Low Temperature Material Characterization | 164 |

|    | 6.5. Summary                                                                  | 176 |

| 7. | FUNDAMENTALS OF DELAMINATION INITIATION AND GROWTH<br>IN FLIP CHIP ASSEMBLIES | 177 |

|    | 7.1. Introduction                                                             | 177 |

|    | 7.2. Stress Test Chips                                                        | 181 |

|    | 7.3. Test Board Assembly                                                      | 183 |

|    | 7.4. Flip Chip Stress Measurements                                            | 187 |

|    | 7.5. Thern   | nal Cycling Experiments                                                | 187 |

|----|--------------|------------------------------------------------------------------------|-----|

|    | 7.5.1        | Interface Delamination Initiation and Growth                           |     |

|    | 7.5.2        | Stress Variation During Thermal Cycling                                |     |

|    | 7.5.3        | Leading Indicators-of-Failure                                          |     |

|    | 7.6. Sumn    | nary                                                                   | 219 |

| 8. |              | PANSION PCB FOR MINIMIZING DIE STRESSES<br>CHIP ON LAMINATE ASSEMBLIES | 225 |

|    | 8.1. Introd  | luction                                                                | 225 |

|    | 8.2. Packa   | iging Technology and Test Chips                                        | 228 |

|    | 8.3. Comp    | parison of Test Results with FR4 Flip Chip Assembly                    | 231 |

|    | 8.3.1        | Stress Variation During Underfill Cure                                 |     |

|    | 8.3.2        | Stresses After Underfill Encapsulation                                 |     |

|    | 8.3.3        | Temperature Dependent Stress Measurements                              |     |

|    | 8.4. Sumn    | nary                                                                   | 244 |

| 9. | SUMMAR       | RY AND CONCLUSION                                                      | 246 |

| BI | BIBLIOGRAPHY |                                                                        | 252 |

# LIST OF FIGURES

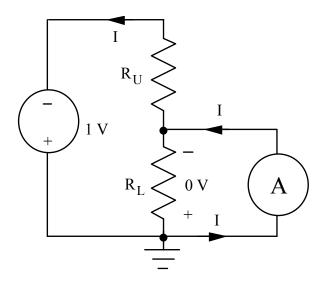

| Figure 1.1: Piezoresistive Sensor Concept                                                                                 | 4  |

|---------------------------------------------------------------------------------------------------------------------------|----|

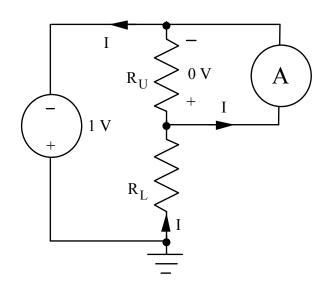

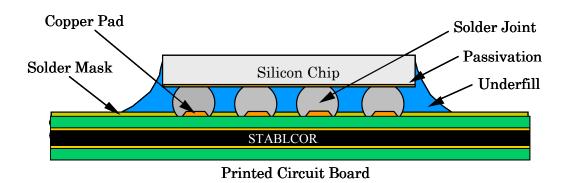

| Figure 1.2: Typical Cross-Section of a Flip Chip Package                                                                  | 8  |

| Figure 3.1: Filamentary Silicon Conductor                                                                                 | 34 |

| Figure 3.2: (100) Silicon Wafer                                                                                           | 38 |

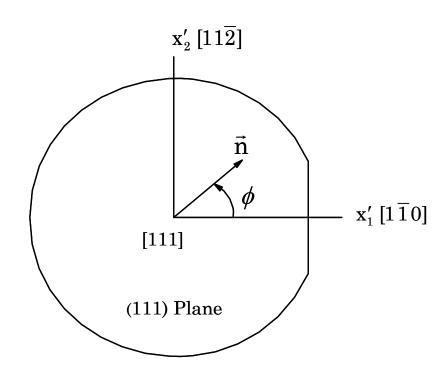

| Figure 3.3: (111) Silicon Wafer                                                                                           | 41 |

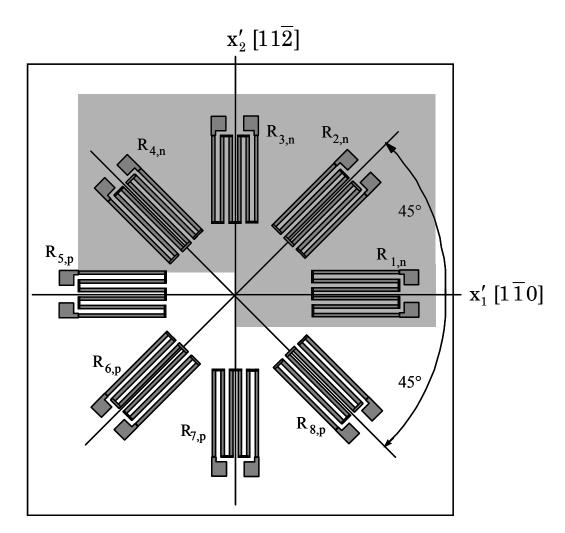

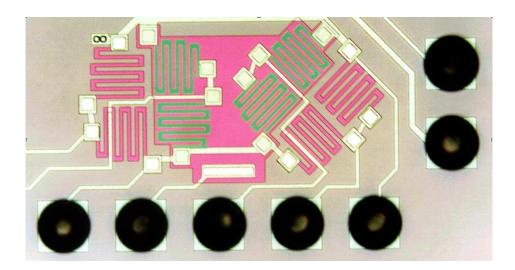

| Figure 4.1: Optimized Eight-Element Rosette                                                                               | 45 |

| Figure 4.2: Calibration Methods to Obtain Piezoresistive Coefficients                                                     | 50 |

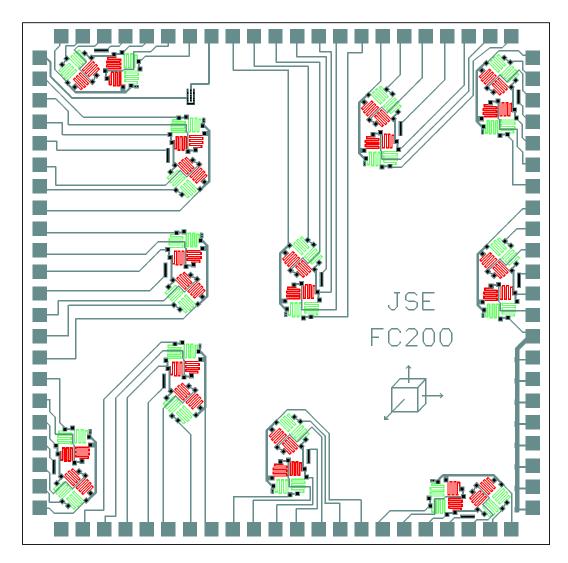

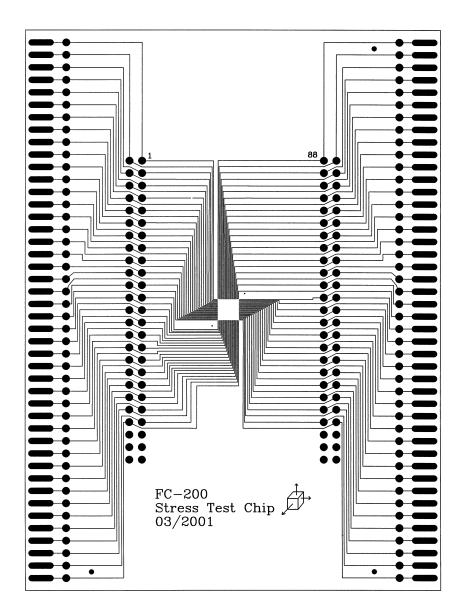

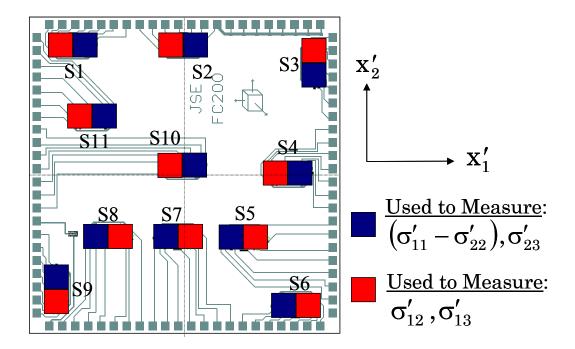

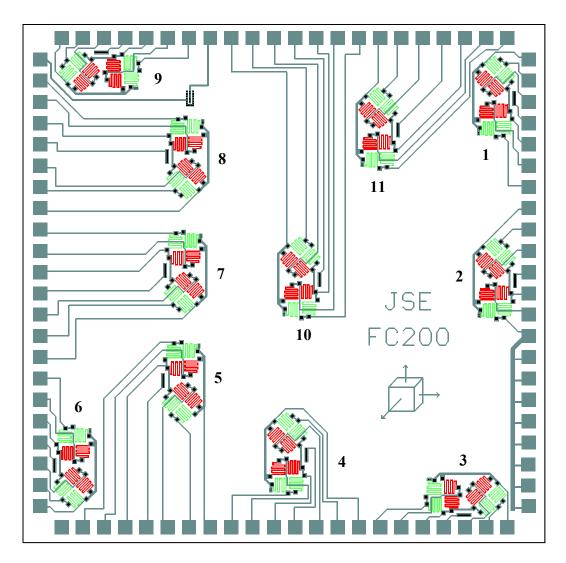

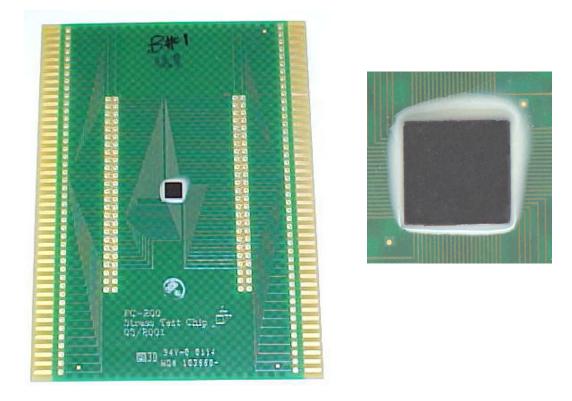

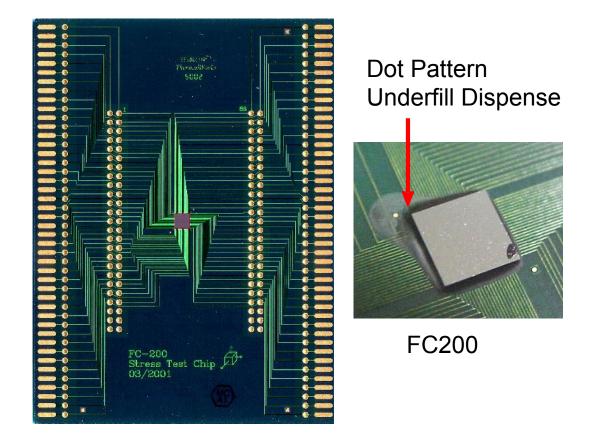

| Figure 4.3: FC200 Flip Chip Test Die (5 x 5 mm)                                                                           | 52 |

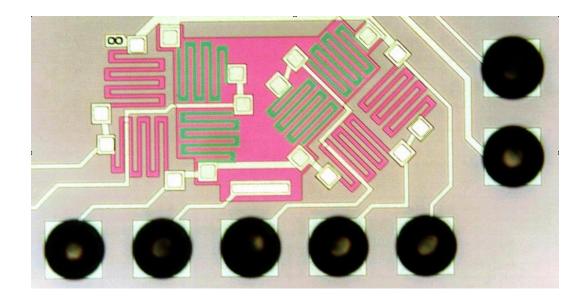

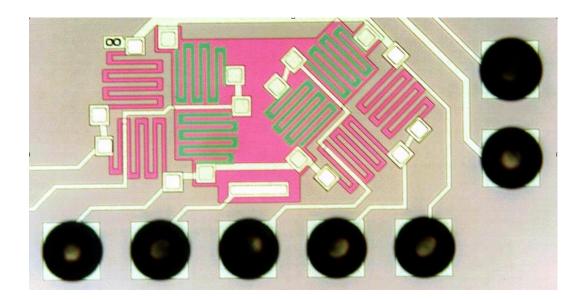

| Figure 4.4: Photograph of FC200 Sensor Rosette                                                                            | 53 |

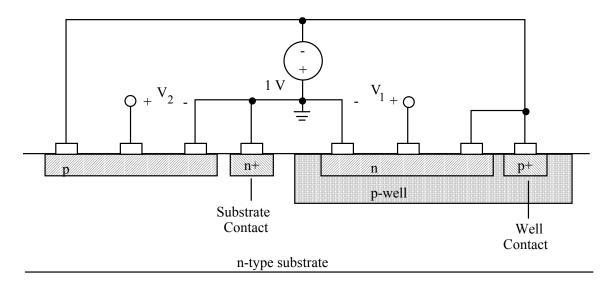

| Figure 4.5: Cross Sectional Schematic of FC200 Resistors                                                                  | 53 |

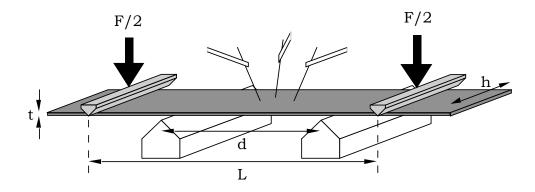

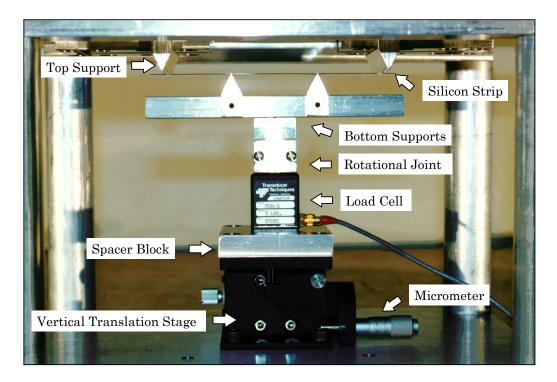

| Figure 4.6: Four Point Bending Loading Fixture                                                                            | 55 |

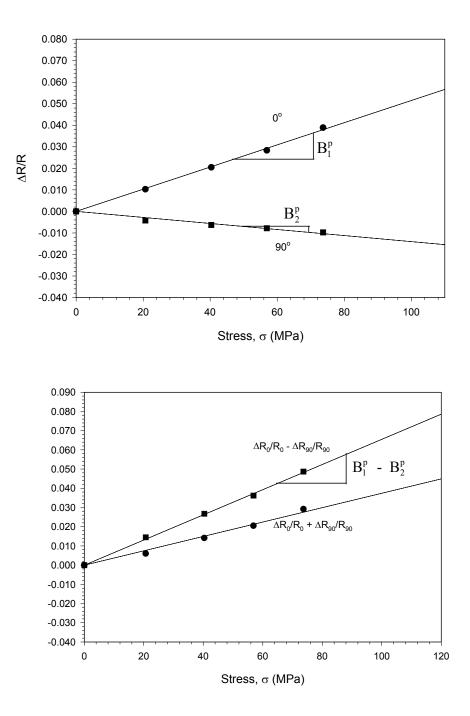

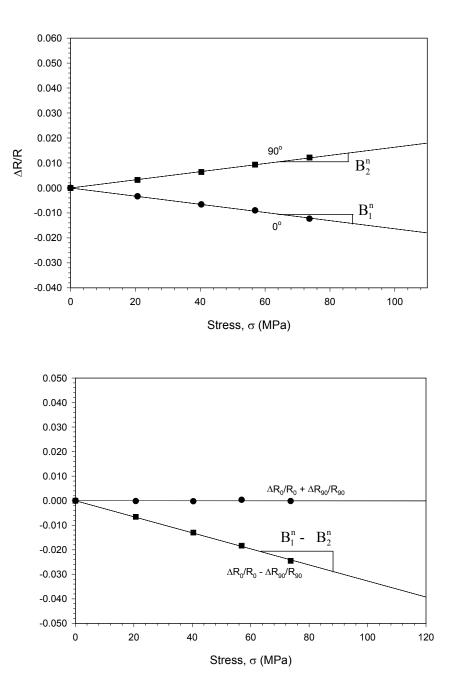

| Figure 4.7: Typical Normalized Resistance Change vs. Uniaxial Stress Data<br>for the FC200/FC400 Flip Chip p-Type sensors | 57 |

| Figure 4.8: Typical Normalized Resistance Change vs. Uniaxial Stress Data<br>for the FC200/FC400 Flip Chip n-Type sensors | 58 |

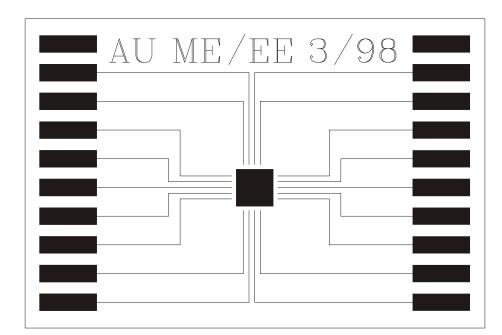

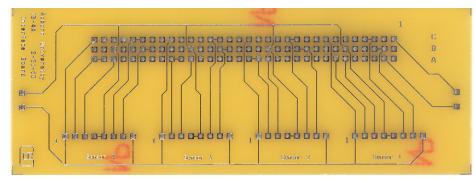

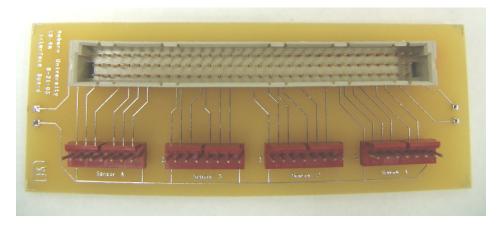

| Figure 4.9: TCR and Hydrostatic Printed Circuit Board                                                                     | 61 |

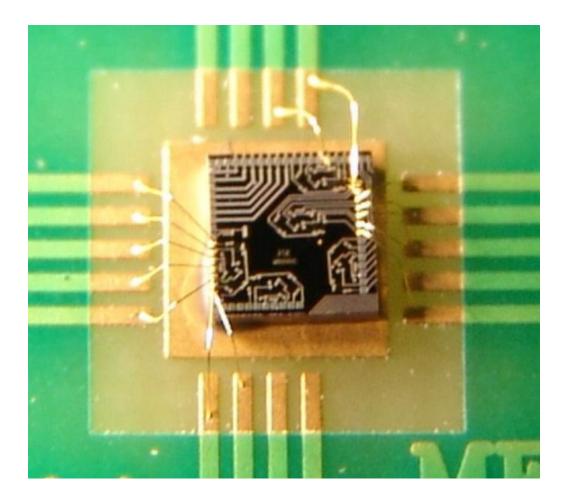

| Figure 4.10: Wire-Bonded Die for TCR and Hydrostatic Tests                                                                | 63 |

| Figure 4.11: Hydrostatic Test Setup                                                                                       | 64 |

| Figure 4.12: Hydrostatic Pressure Vessel                                                                                  | 65 |

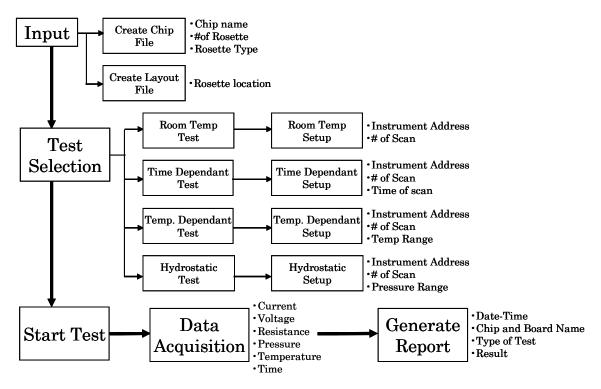

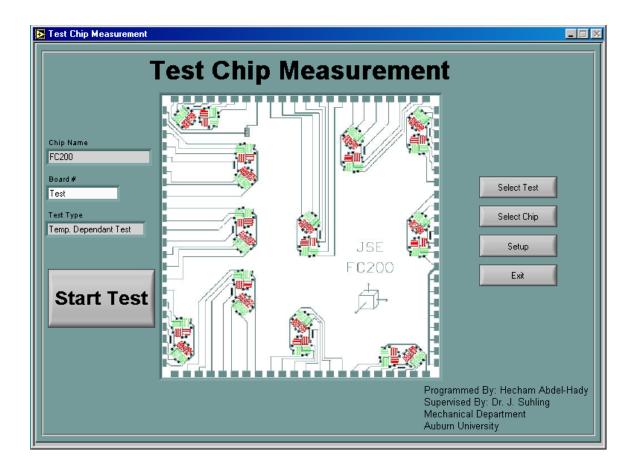

| Figure 4.13: Labview Program Logic for Test Chips Measurement                                                             | 68 |

| Figure 4.14: Labview Program Interface for Test Chips Measurement                             | 69  |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 4.15: Interface Board and Junction Box for Test Chips Measurement                      | 72  |

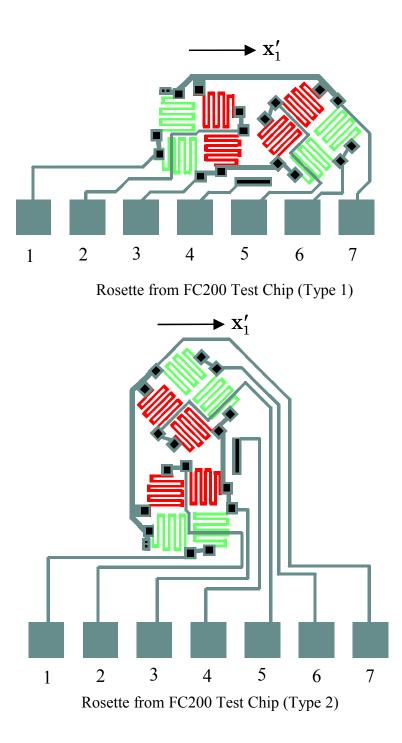

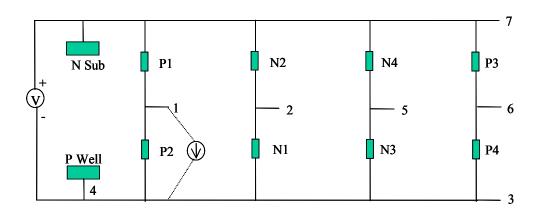

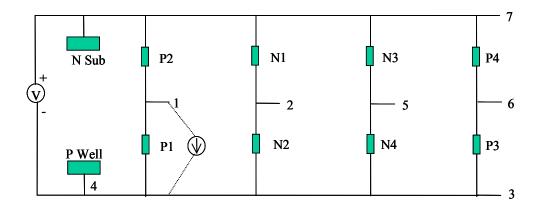

| Figure 4.16: Rosette Types 1 and 2 (Horizontal and Vertical)                                  | 73  |

| Figure 4.17: Measurement Rosette Numbering on<br>a 200 x 200 mil FC200 Test Chip              | 74  |

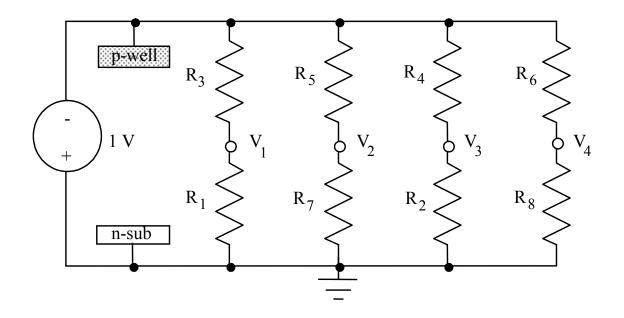

| Figure 4.18: Typical Resistance Measurement Wiring Diagram for<br>the FC200 Test Chip Rosette | 75  |

| Figure 4.19: Bias for Half Bridge Resistance Measurements                                     | 78  |

| Figure 4.20: Bias for Resistance Measurements (Upper Arm of Half-Bridge)                      | 78  |

| Figure 4.21: Bias for Resistance Measurements (Low Arm of Half-Bridge)                        | 79  |

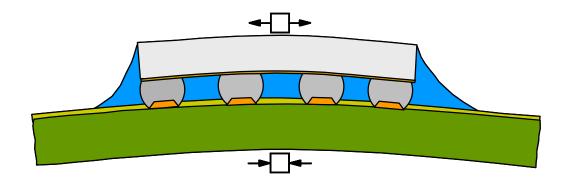

| Figure 5.1: Typical Cross-Section of a Flip Chip Package                                      | 81  |

| Figure 5.2: Shearing of Solder Bumps During Temperature Cycling                               | 82  |

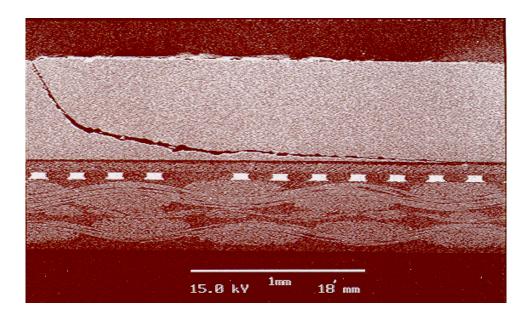

| Figure 5.3: Solder Joint Failure in a Flip Chip Packages<br>Due to Llarge Shear Strains       | 82  |

| Figure 5.4: Underfill/Die Interface Delamination and Solder Joint Fatigue Failure             | 84  |

| Figure 5.5: Bending of a Flip Chip Assembly                                                   | 85  |

| Figure 5.6: Die Cracking                                                                      | 85  |

| Figure 5.7: FC200 Flip Chip Test Die (5 x 5 mm)                                               | 92  |

| Figure 5.8: Photograph of FC200 Sensor Rosette                                                | 93  |

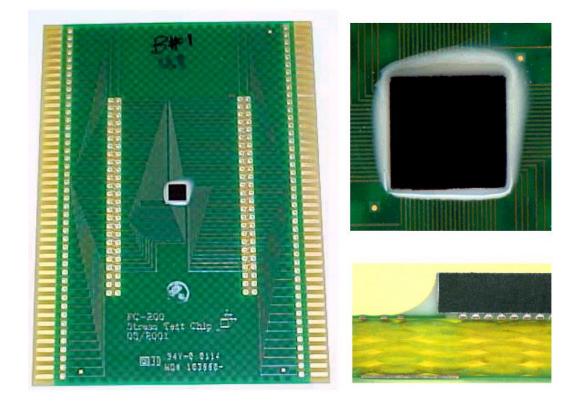

| Figure 5.9: PCB Design Layout for FC200 Flip Chip Assembly                                    | 96  |

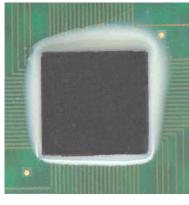

| Figure 5.10: Photos of an Assembled Test Board and Test Chip                                  | 97  |

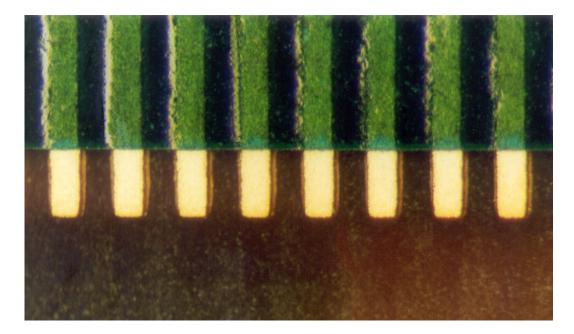

| Figure 5.11: Finger Soldermask Design                                                         | 98  |

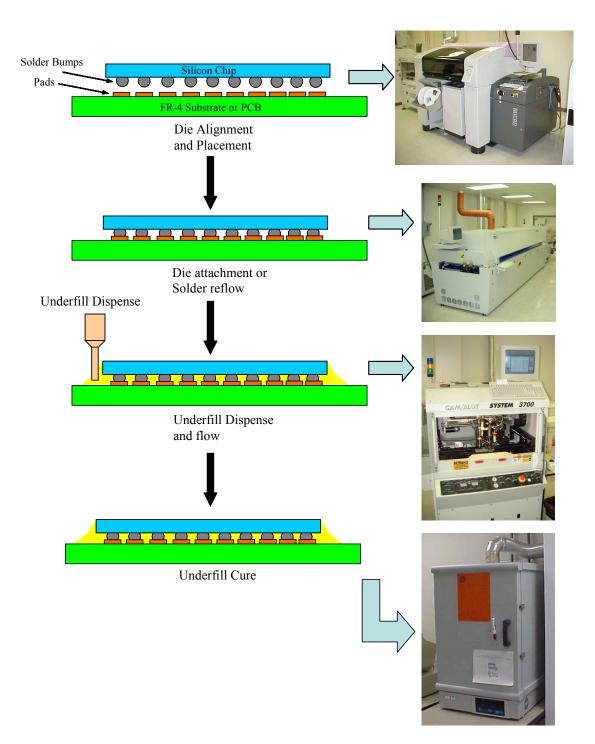

| Figure 5.12: The Flip Chip Assembly and Underfilling Process Steps                            | 99  |

| Figure 5.13: Flip Chip Assembly with Different Underfills                                     | 101 |

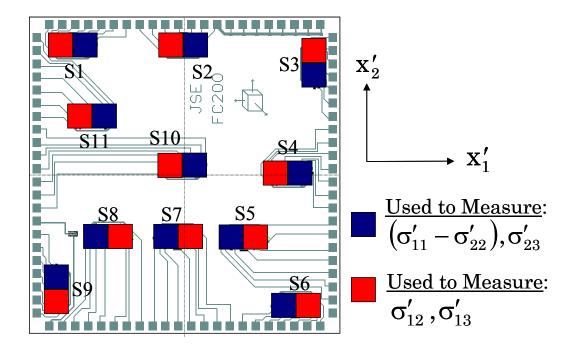

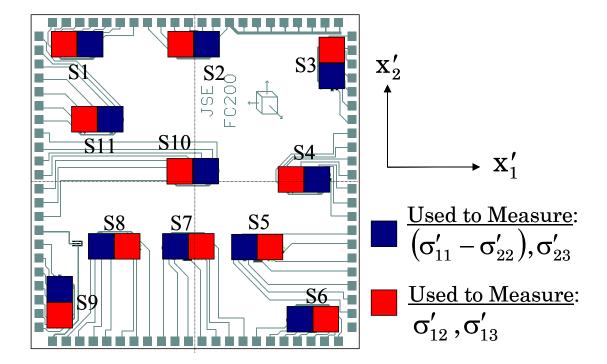

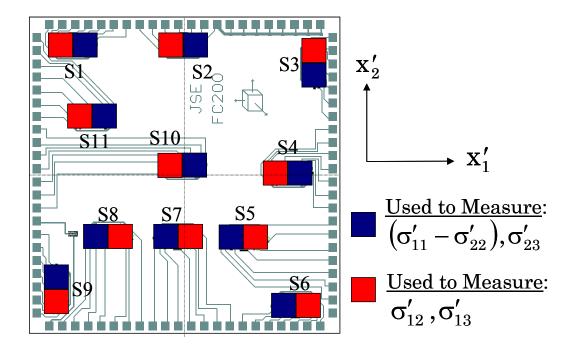

| Figure 5.14: Rosette Sites for Stress Measurement                                             | 103 |

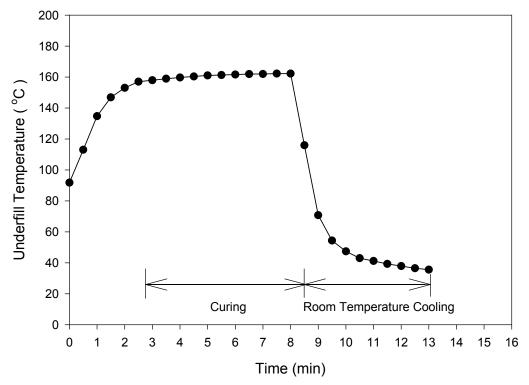

| Figure 5.15: Underfill Temperature Variation with Time in the Cure Oven xv                    | 105 |

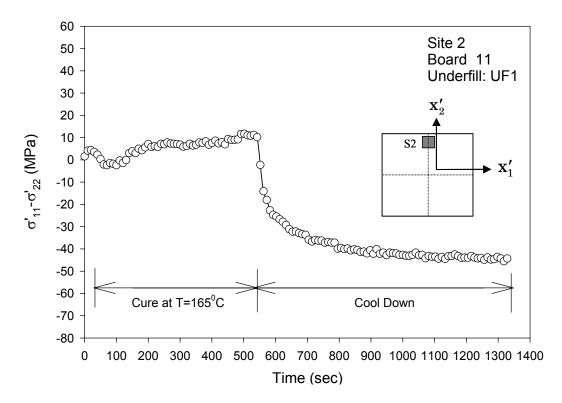

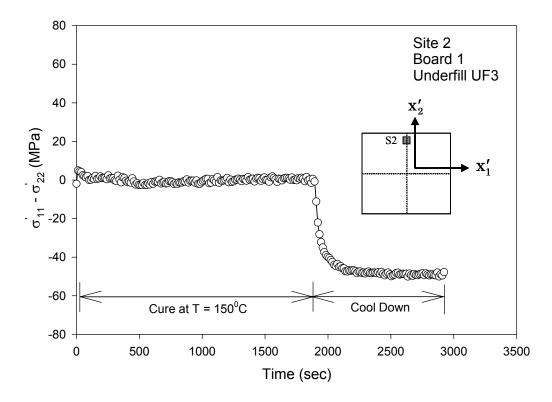

| Figure 5.16: Typical Normal Stress Variation During Underfill Cure                                                                         | 106 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

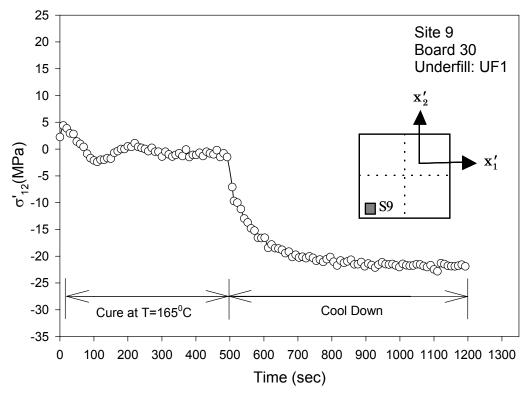

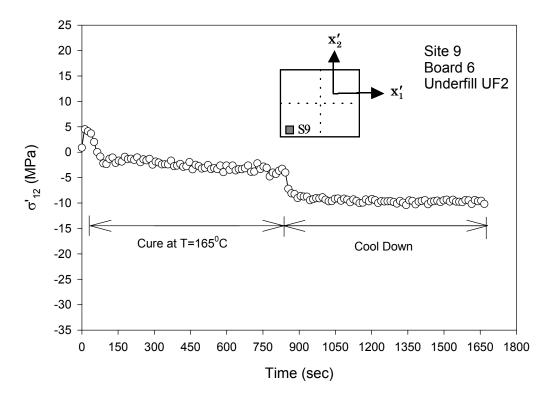

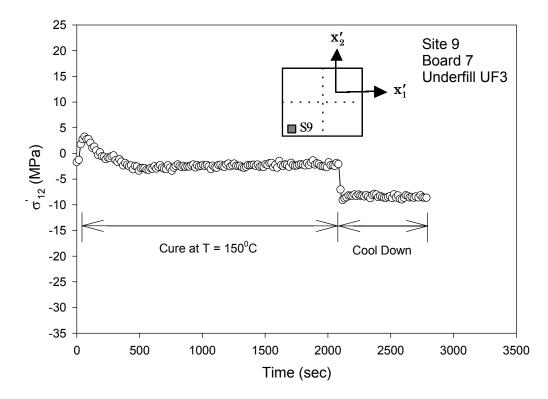

| Figure 5.17: Typical In-Plane Shear Stress Variation During Underfill Cure                                                                 | 107 |

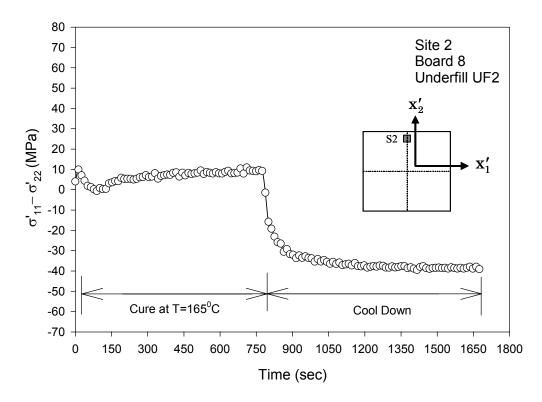

| Figure 5.18: Typical Normal Stress Variation During Underfill Cure<br>for Underfill UF2                                                    | 110 |

| Figure 5.19: Typical Normal Stress Variation During Underfill Cure<br>for Underfill UF3                                                    | 110 |

| Figure 5.20: In-Plane Shear Stress Variation During Underfill Cure<br>for Underfill UF2                                                    | 111 |

| Figure 5.21: In-Plane Shear Stress Variation During Underfill Cure<br>for Underfill UF3                                                    | 111 |

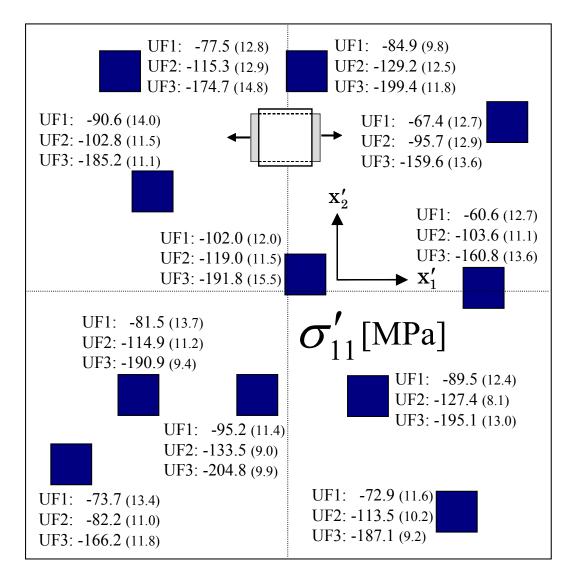

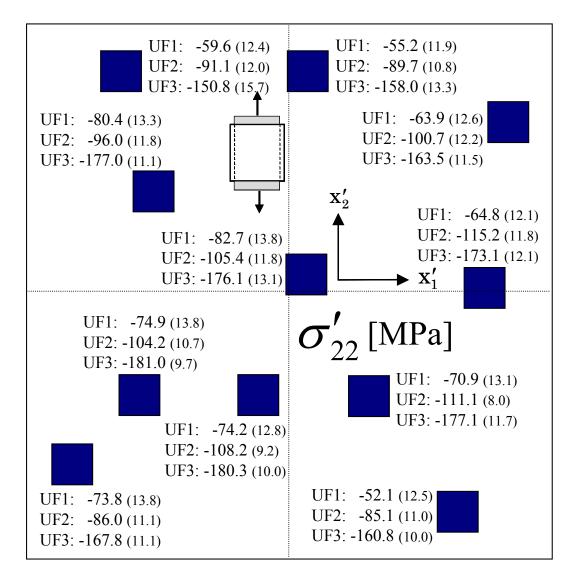

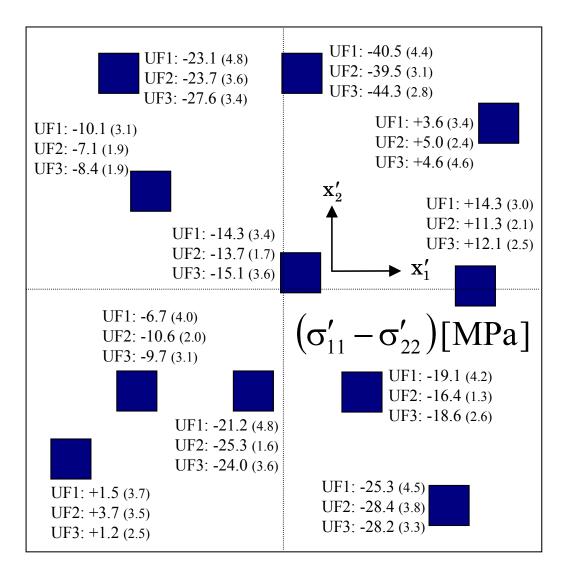

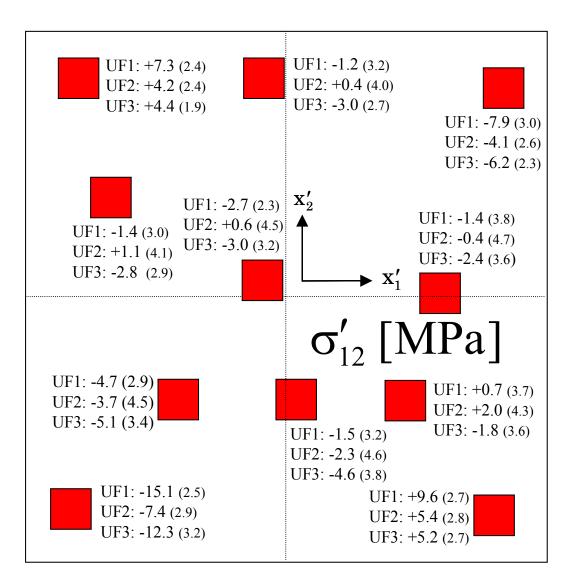

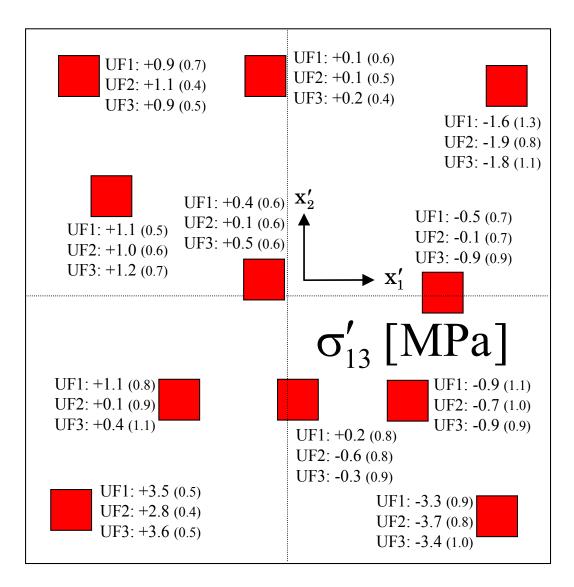

| Figure 5.22: Average Stresses after Underfill Cure                                                                                         | 113 |

| Figure 5.23: Average Stresses after Underfill Cure                                                                                         | 114 |

| Figure 5.24: Average Stresses after Underfill Cure                                                                                         | 115 |

| Figure 5.25: Average Stresses after Underfill Cure                                                                                         | 116 |

| Figure 5.26: Average Stresses after Underfill Cure                                                                                         | 117 |

| Figure 5.27: Average Stresses after Underfill Cure                                                                                         | 118 |

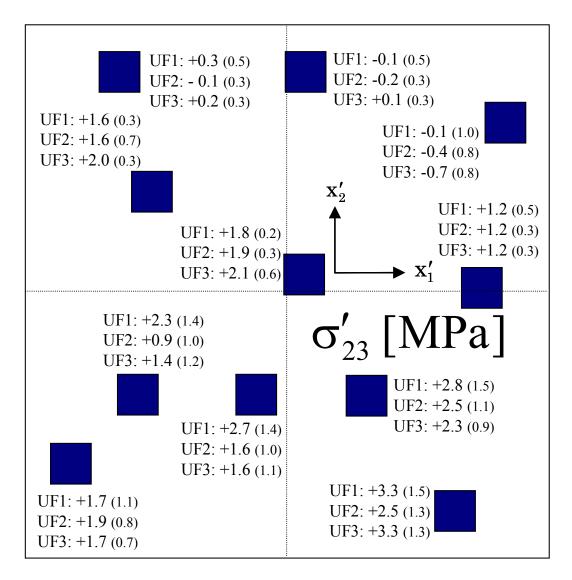

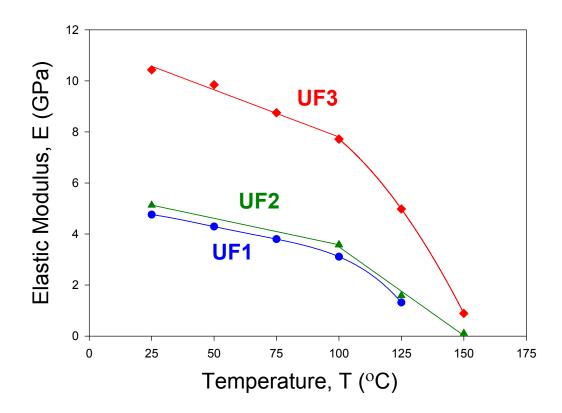

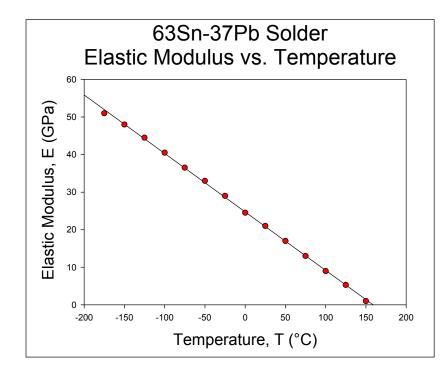

| Figure 5.28: Elastic Modulus vs. Temperature                                                                                               | 119 |

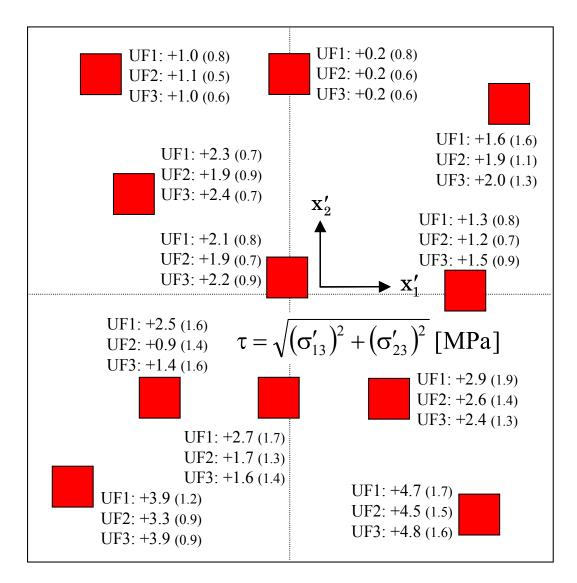

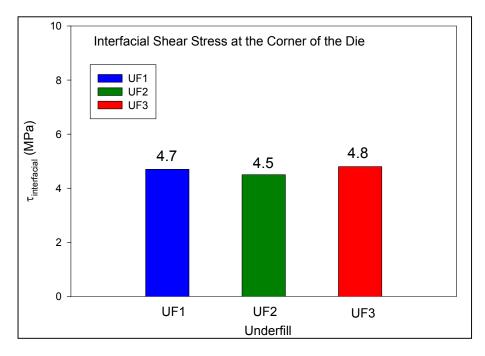

| Figure 5.29: Average Interfacial Stresses after Underfill Cure                                                                             | 122 |

| Figure 5.30: Cross-Section Along Outside Row of Solder Balls Showing<br>Non-Uniform Underfill Fillet (Dispense Corner is on the Left Side) | 123 |

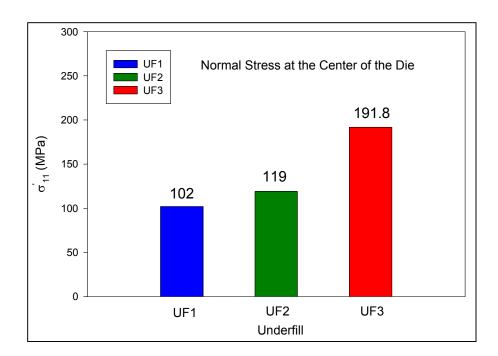

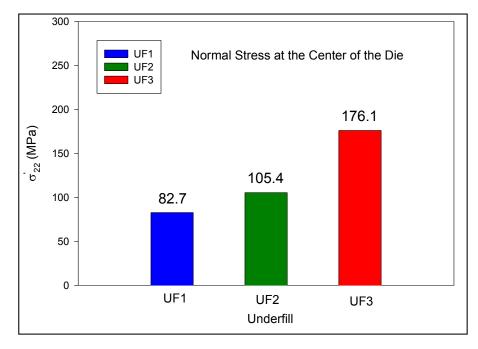

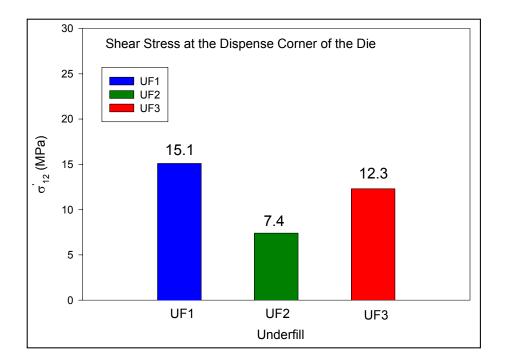

| Figure 5.31: Comparison of Normal Stresses at the Die Center<br>for the Three Underfills                                                   | 125 |

| Figure 5.32: Comparison of Shear Stresses at the Die Dispense Corner<br>for the Three Underfills                                           | 126 |

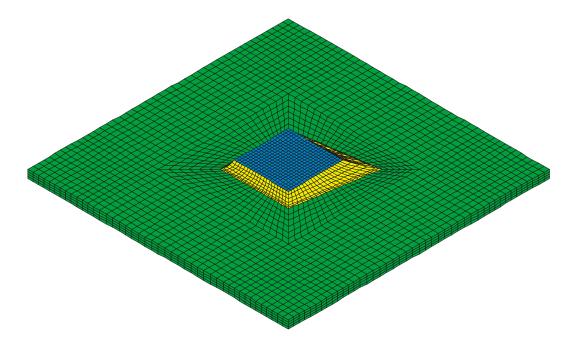

| Figure 5.33: Finite Element Mesh (UF1)                                                                                                     | 128 |

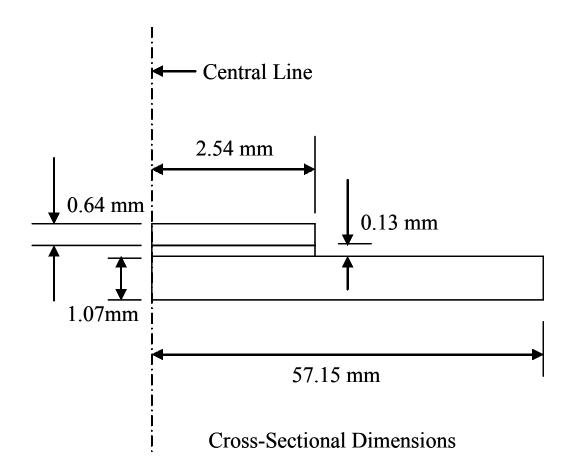

| Figure 5.34: Dimensions of the Flip Chip on Laminate Assemblies                                                                            | 129 |

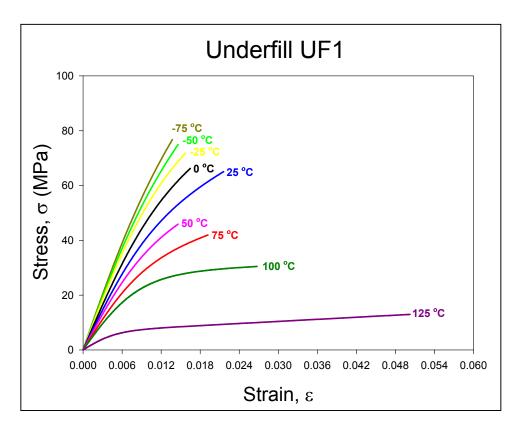

| Figure 5.35: Underfill UF1 Stress-Strain Curves (-175 to +150 °C) [144]                                       | 130 |

|---------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.36: Packaging Material Properties for FEM Simulations                                                | 130 |

| Figure 5.37: Correlation of Test Chip Measurements with Finite<br>Element Simulations (UF1)                   | 131 |

| Figure 5.38: Correlation of Test Chip Measurements with Finite<br>Element Simulations (UF1)                   | 132 |

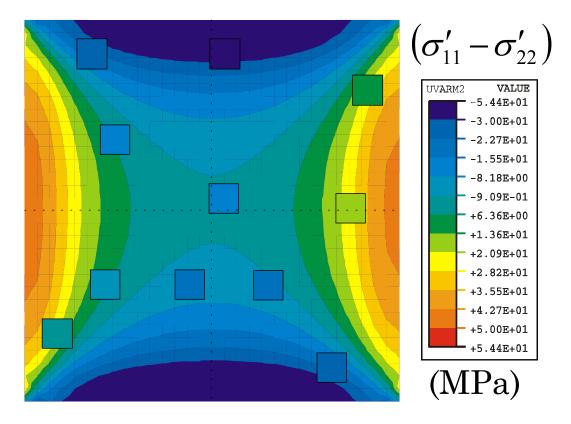

| Figure 5.39: Correlation of Test Chip Measurements with Finite<br>Element Simulations (UF1)                   | 133 |

| Figure 5.40: Correlation of Test Chip Measurements with Finite<br>Element Simulations (UF1)                   | 134 |

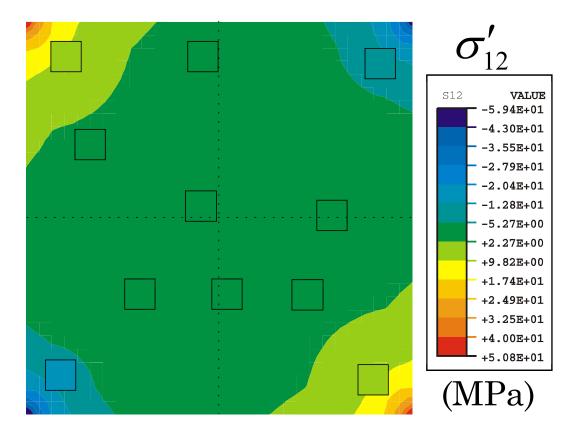

| Figure 5.41: Numerical Prediction of the In-Plane Shear Stress Distributions<br>Along the Four Chip Diagonals | 136 |

| Figure 5.42: Correlation of the In-Plane Shear Stresses                                                       | 136 |

| Figure 5.43: Die Normal Stress vs. Temperature (Underfill UF1)                                                | 138 |

| Figure 5.44: Die Shear Stress vs. Temperature (Underfill UF1)                                                 | 138 |

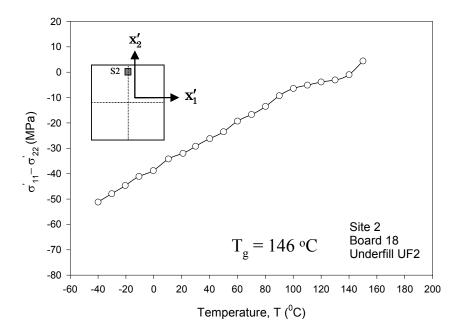

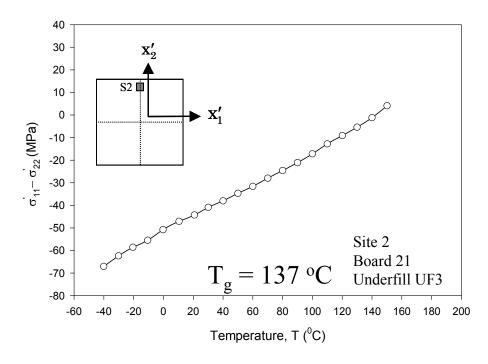

| Figure 5.45: Die Normal Stress vs. Temperature (Underfill UF2)                                                | 140 |

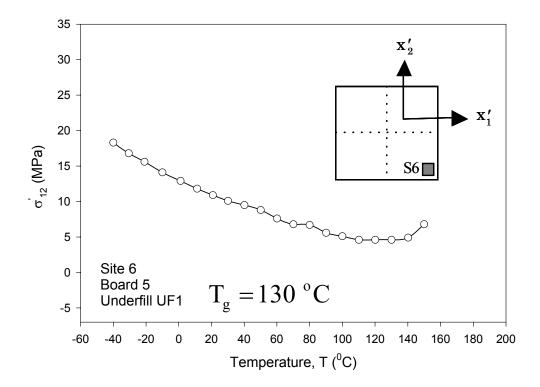

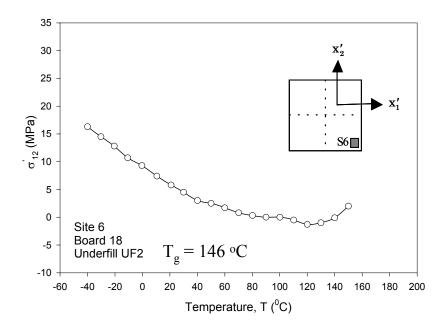

| Figure 5.46: Die Shear Stress vs. Temperature (Underfill UF2)                                                 | 140 |

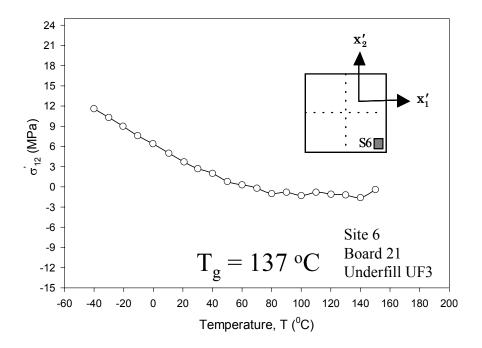

| Figure 5.47: Die Normal Stress vs. Temperature (Underfill UF3)                                                | 141 |

| Figure 5.48: Die Shear Stress vs. Temperature (Underfill UF3)                                                 | 141 |

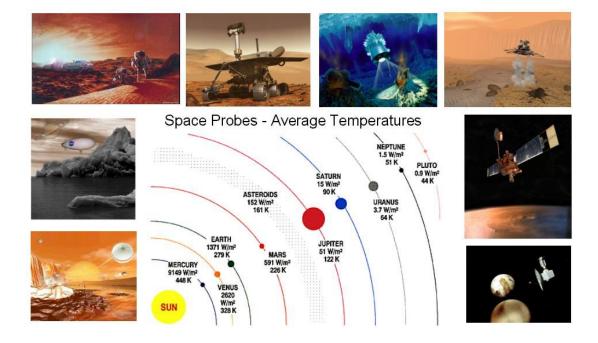

| Figure 6.1: Typical Harsh Environment Electronics Temperature Ranges                                          | 145 |

| Figure 6.2: Temperature Extremes for Planetary Missions                                                       | 146 |

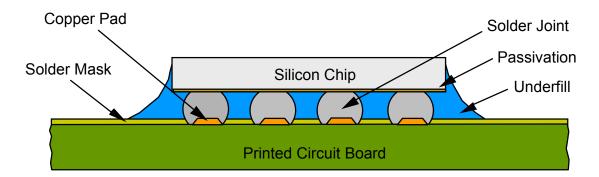

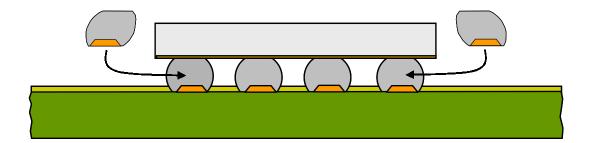

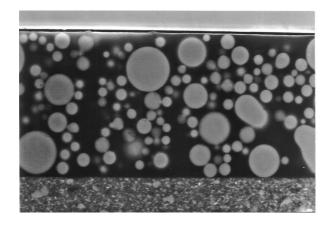

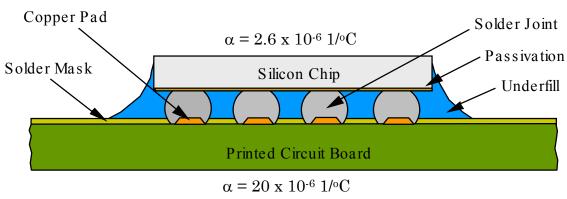

| Figure 6.3: Chip on Board Assembly (Flip Chip)                                                                | 149 |

| Figure 6.4: Test Chip with Piezoresistive Sensors                                                             | 151 |

| Figure 6.5: Eight Element Piezoresistive Sensor Rosette                                                       | 152 |

| Figure 6.6: Flip Chip Assembly Incorporating Stress Test Chip                                                 | 155 |

| Figure 6.7: Rosette Sites for Stress Measurement                                                              | 157 |

|                                                                                                               |     |

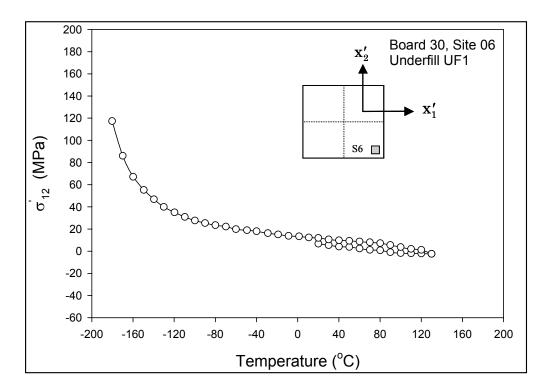

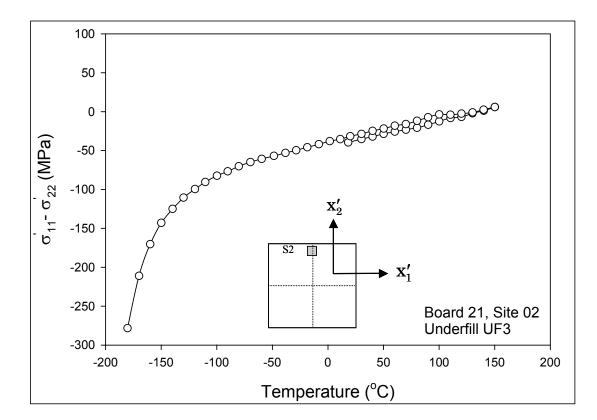

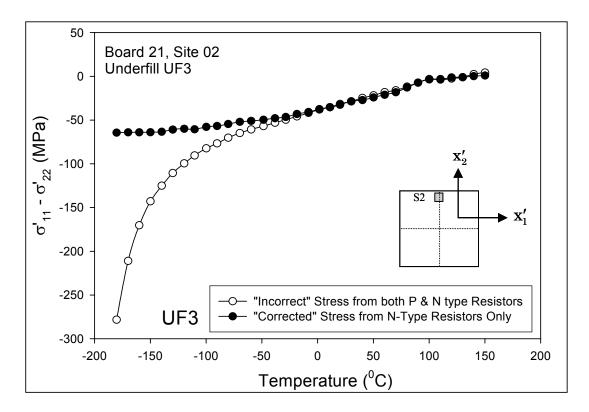

| Figure 6.8: Measured Die Stress Variation with Temperature                                                     | 159 |

|----------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.9: Measured Die Stress Variation with Temperature                                                     | 160 |

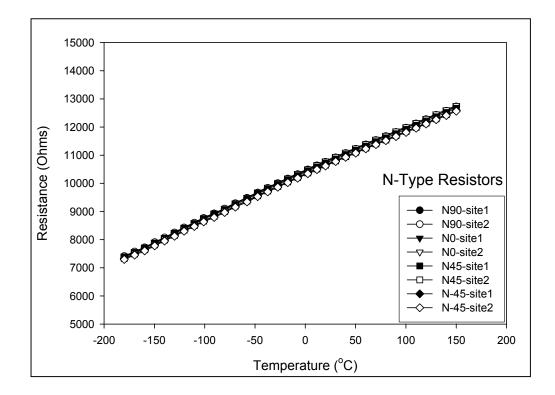

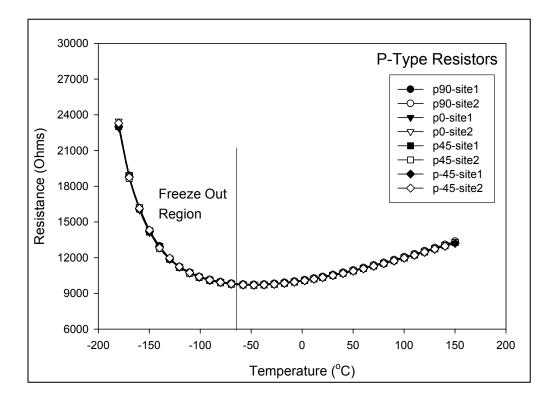

| Figure 6.10: Resistance vs. Temperature for the Resistor Sensors<br>(Stress Free Conditions)                   | 162 |

| Figure 6.11: Resistance vs. Temperature for the Resistor Sensors<br>(Stress Free Conditions)                   | 163 |

| Figure 6.12: Corrected Measurements of the Die Stress Variation<br>with Temperature                            | 165 |

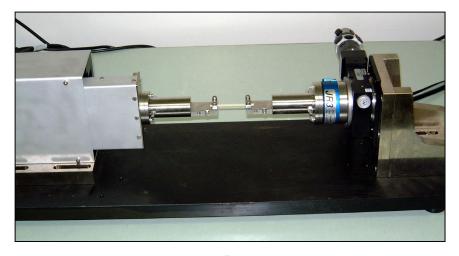

| Figure 6.13: Microtester and Associated Environmental Chamber                                                  | 166 |

| Figure 6.14: Test Specimens: Underfill Encapsulant and Solder                                                  | 168 |

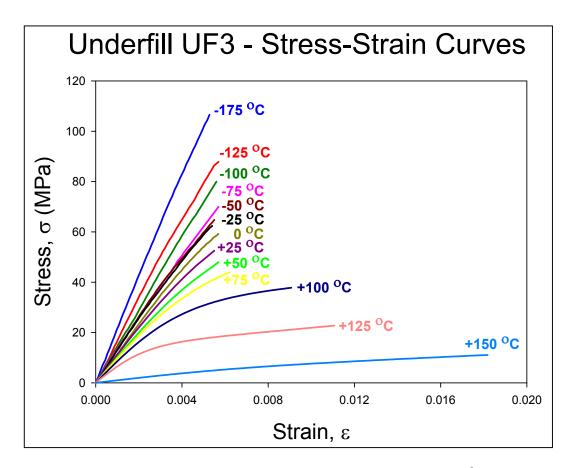

| Figure 6.15: Underfill Stress-Strain Curves (-175 to +150 °C)                                                  | 169 |

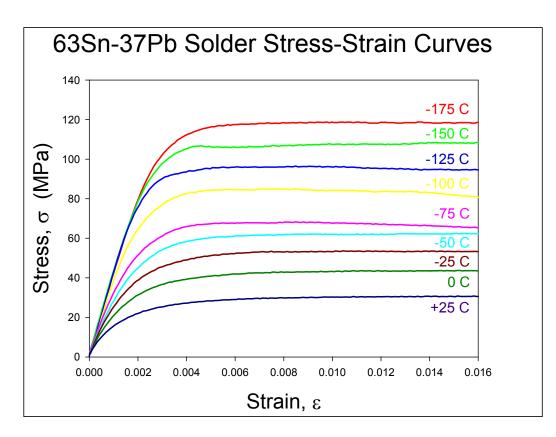

| Figure 6.16: Solder Stress-Strain Curves (-175 to +25 °C)                                                      | 170 |

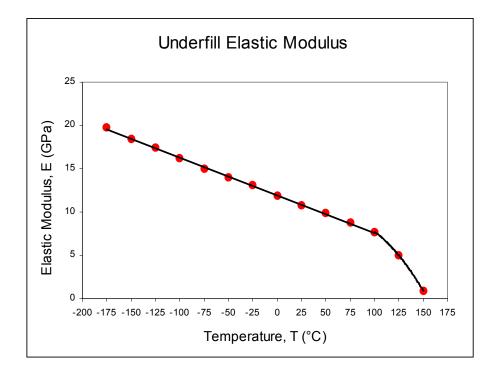

| Figure 6.17: Elastic Modulus vs. Temperature for Underfill (-175 to +150 °C)                                   | 171 |

| Figure 6.18: Elastic Modulus vs. Temperature for Solder (-175 to +150 °C)                                      | 171 |

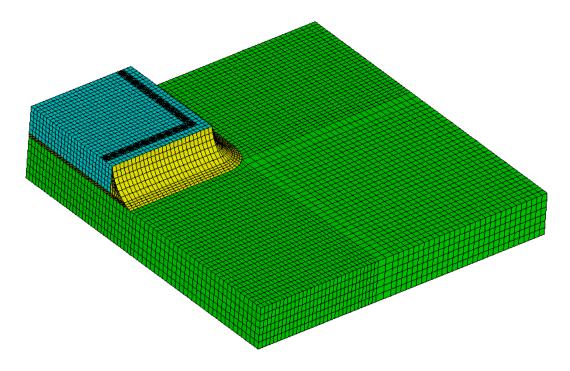

| Figure 6.19: Finite Element Mesh for the Flip Chip Test Assembly                                               | 173 |

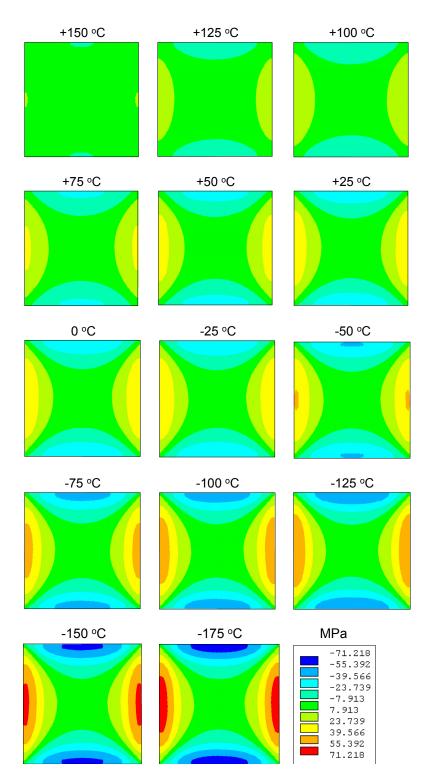

| Figure 6.20: Finite Element Predictions for the Normal Stress<br>Difference Contours at Various Temperatures   | 174 |

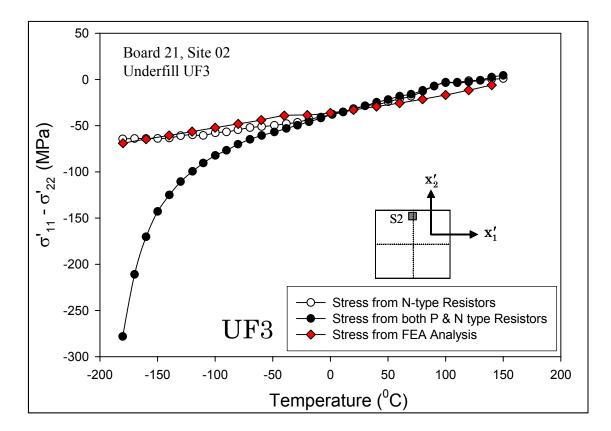

| Figure 6.21: Correlation between Finite Element Predictions<br>and Experimental Data                           | 175 |

| Figure 7.1: FC200 Flip Chip Test Die (5 x 5 mm)                                                                | 182 |

| Figure 7.2: Photos of an Assembled Test Board and Test Chip                                                    | 184 |

| Figure 7.3: Rosette Sites for Stress Measurement                                                               | 186 |

| Figure 7.4: Temperature Profile for Thermal Cycling                                                            | 189 |

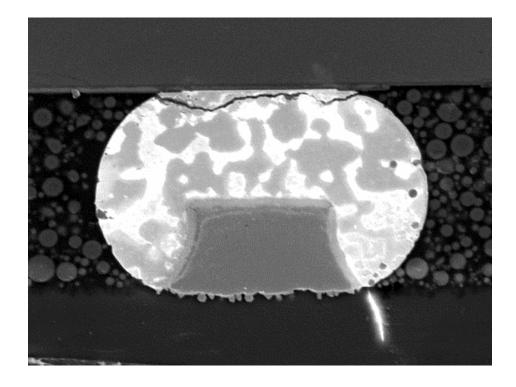

| Figure 7.5: Typical CSAM Image of the Underfill to Die<br>Interface in a Flip Chip Assembly                    | 190 |

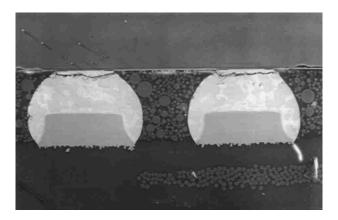

| Figure 7.6: Typical Delamination History for a Single Flip<br>Chip Assembly (Underfill UF1, Board 22)<br>xviii | 192 |

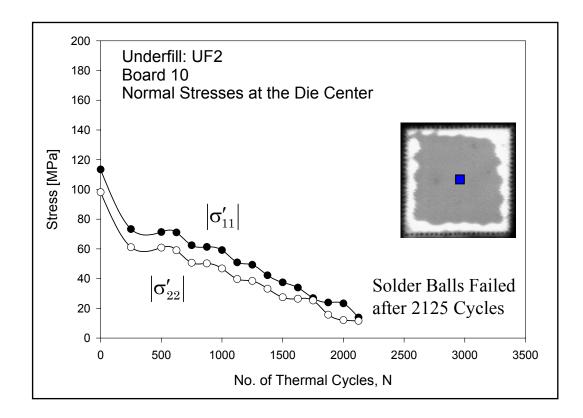

| Figure 7.7: Typical Delamination History for a Single Flip<br>Chip Assembly (Underfill UF2, Board 10) | 193 |

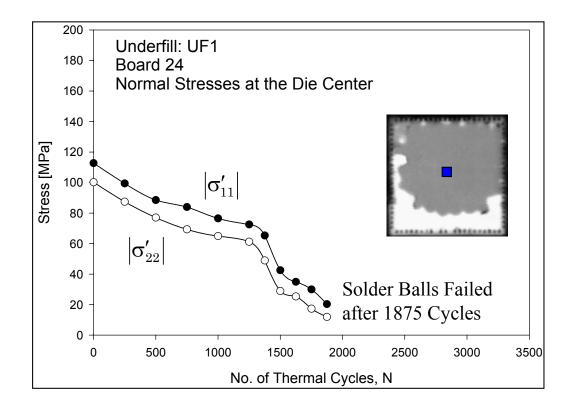

|-------------------------------------------------------------------------------------------------------|-----|

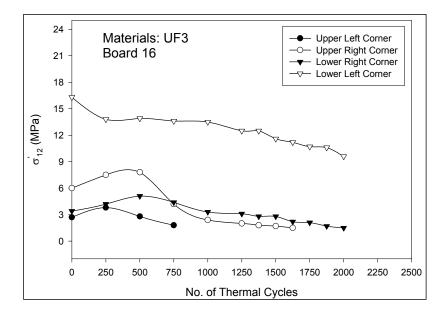

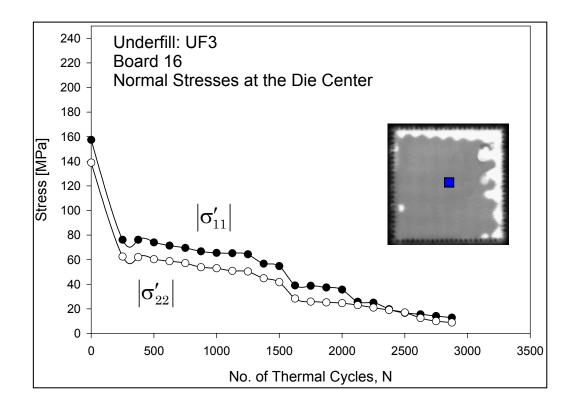

| Figure 7.8: Typical Delamination History for a Single Flip<br>Chip Assembly (Underfill UF3, Board 16) | 194 |

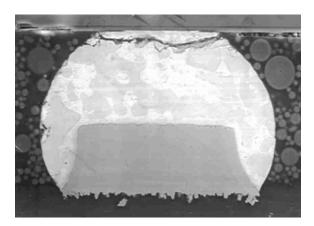

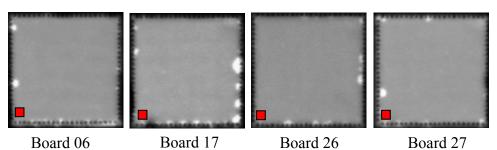

| Figure 7.9: Initial and Final CSAM Images for the Flip<br>Chip Assemblies with Underfill UF1          | 195 |

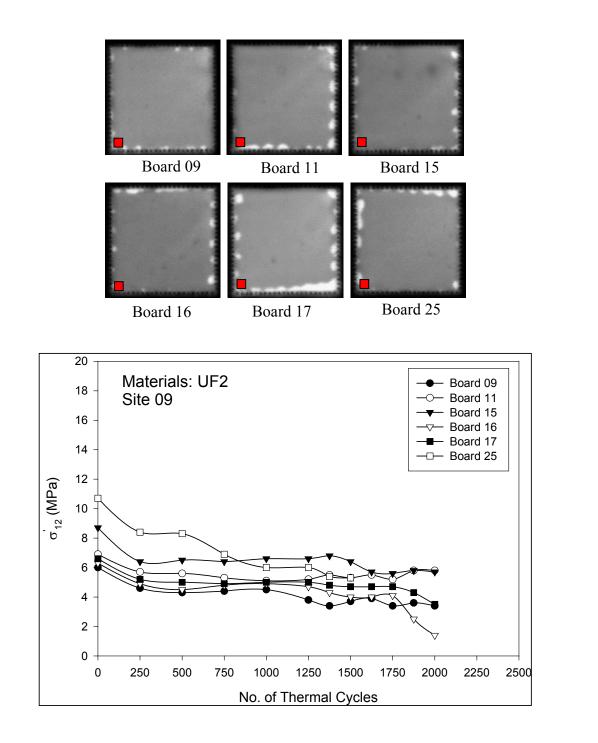

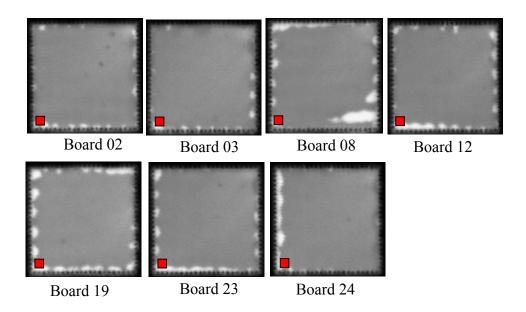

| Figure 7.10: Initial and Final CSAM Images for the Flip<br>Chip Assemblies with Underfill UF2         | 196 |

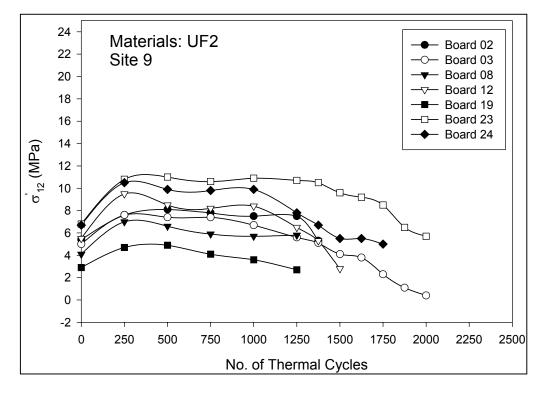

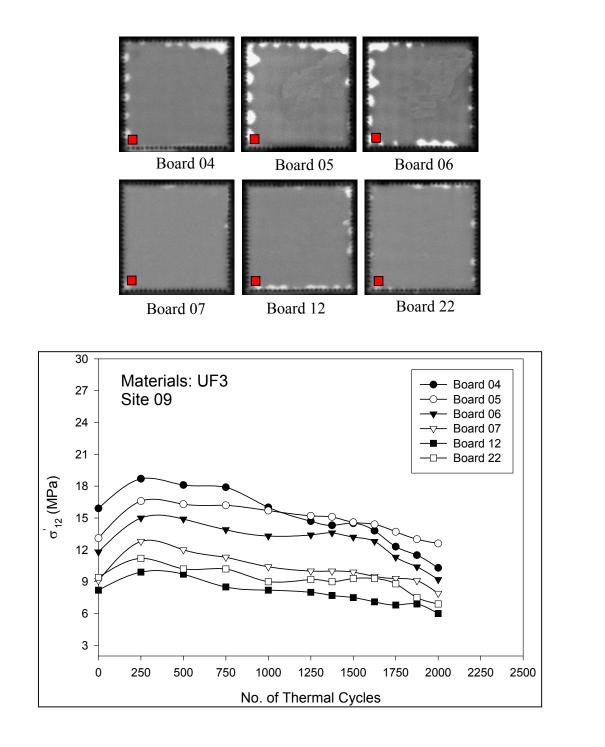

| Figure 7.11: Initial and Final CSAM Images for the Flip<br>Chip Assemblies with Underfill UF3         | 197 |

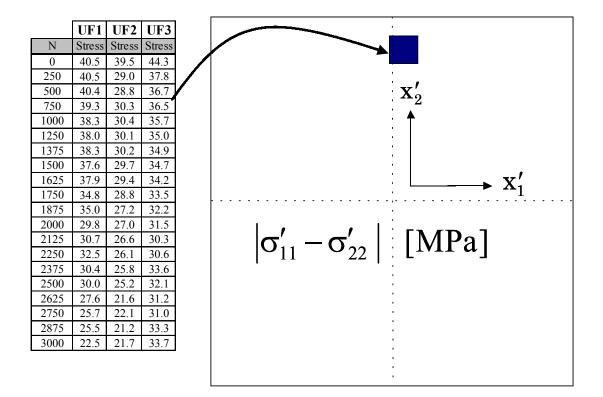

| Figure 7.12: Average Stress Variation with Thermal Cycling                                            | 200 |

| Figure 7.13: Average Stress Variation with Thermal Cycling                                            | 201 |

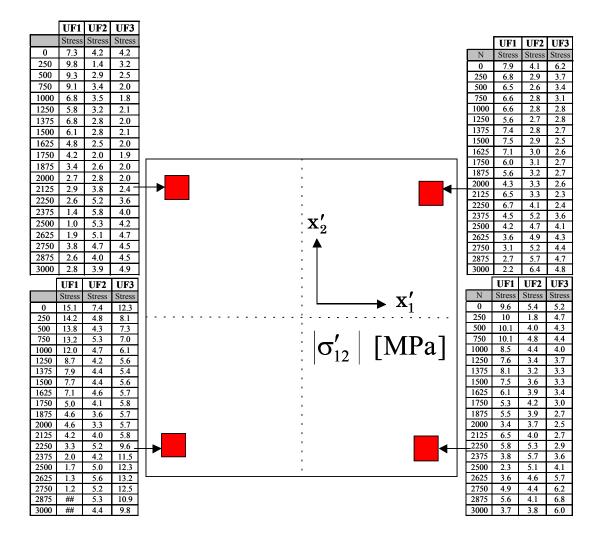

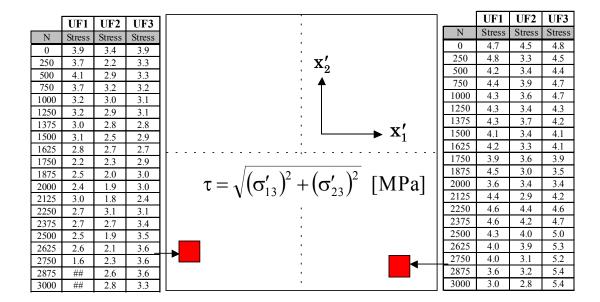

| Figure 7.14: Average Stress Variation with Thermal Cycling                                            | 202 |

| Figure 7.15: Average Stress Variation with Thermal Cycling                                            | 203 |

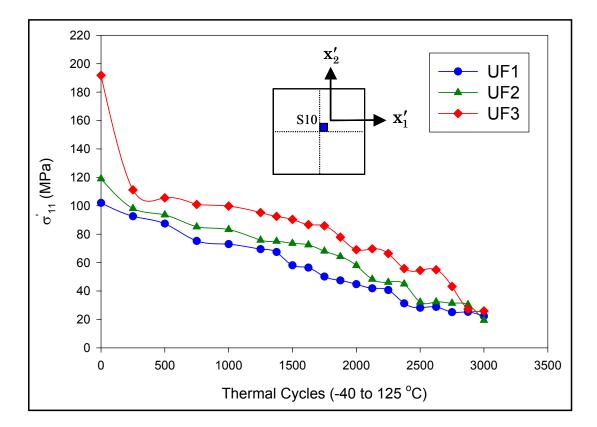

| Figure 7.16: Normal Stress Variation with Thermal Cycling                                             | 205 |

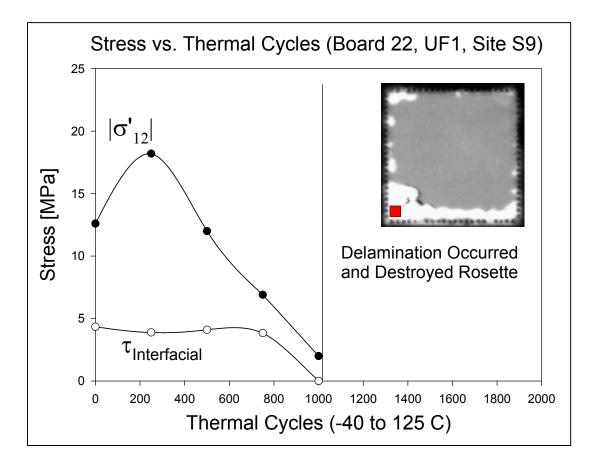

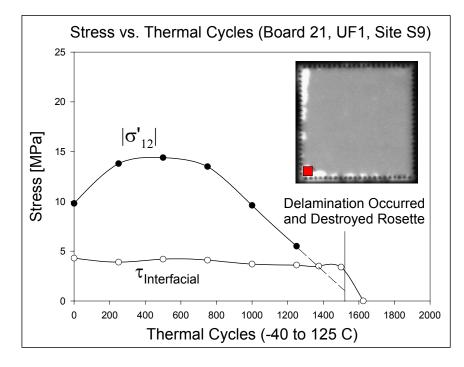

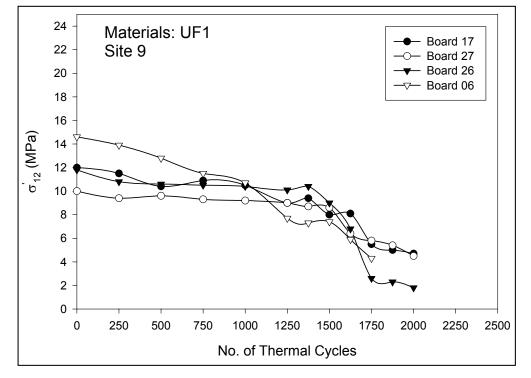

| Figure 7.17: Stress History at Site S9 (Lower Left Corner)                                            | 207 |

| Figure 7.18: Stress History at Site S9 (Lower Left Corner)                                            | 209 |

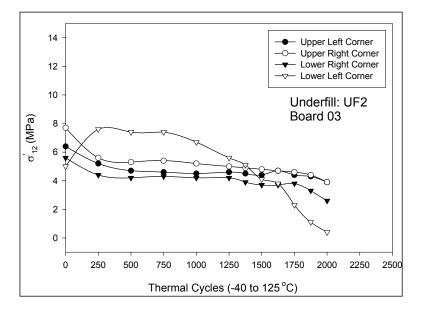

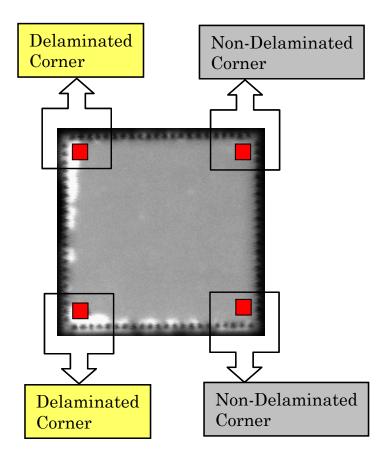

| Figure 7.19: Corner Delamination Status (UF2, Board 3)                                                | 210 |

| Figure 7.20: Stress Histories at Corner Sites (UF2, Board 3)                                          | 210 |

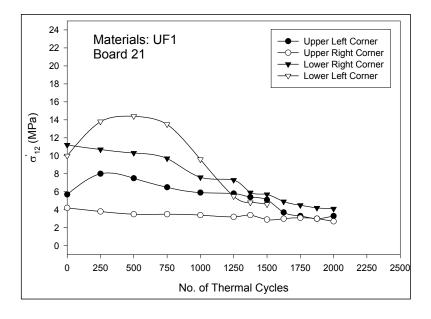

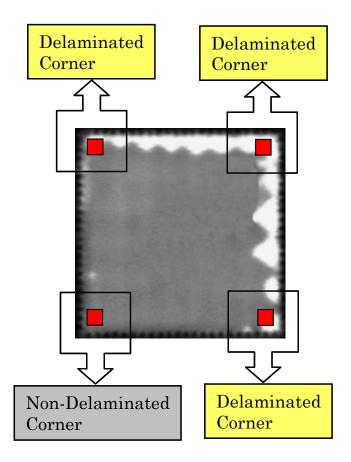

| Figure 7.21: Corner Delamination Status (UF1, Board 21)                                               | 211 |

| Figure 7.22: Stress Histories at Corner Sites (UF1, Board 21)                                         | 211 |

| Figure 7.23: Corner Delamination Status (UF3, Board 16)                                               | 212 |

| Figure 7.24: Stress Histories at Corner Sites (UF1, Board 16)                                         | 212 |

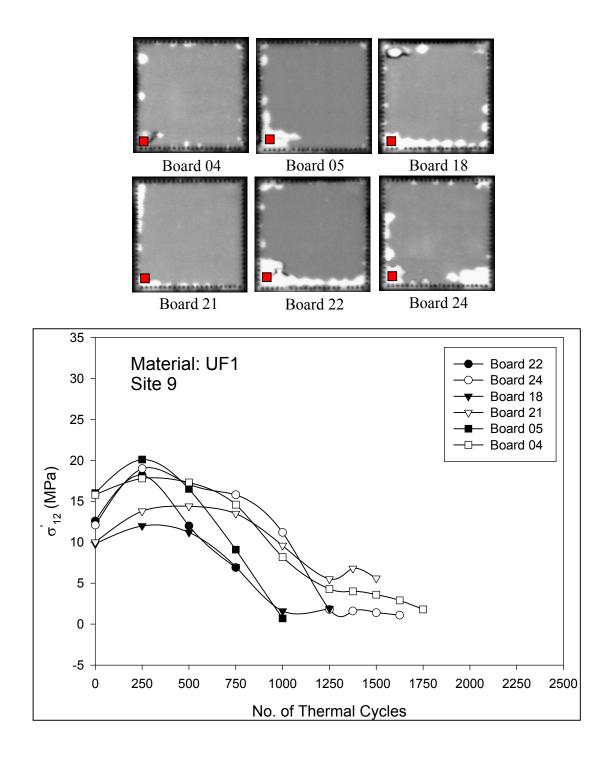

| Figure 7.25: Stress Variation at Non-Delaminated Corners (Underfill UF1)                              | 213 |

| Figure 7.26: Stress Variation at Delaminated Corners (Underfill UF1)                                  | 214 |

| Figure 7.27: Stress Variation at Non-Delaminated Corners (Underfill UF2)                                                                      | 215 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 7.28: Stress Variation at Delaminated Corners (Underfill UF2)                                                                          | 216 |

| Figure 7.29: Stress Variation at Non-Delaminated Corners (Underfill UF3)                                                                      | 217 |

| Figure 7.30: Stress Variation at Delaminated Corners (Underfill UF3)                                                                          | 218 |

| Figure 7.31: Typical Normal Stress History at the Center of the Die<br>in An Example Flip Chip Assembly (Underfill UF2)                       | 220 |

| Figure 7.32: Typical Normal Stress History at the Center of the Die<br>in An Example Flip Chip Assembly (Underfill UF1)                       | 221 |

| Figure 7.33: Typical Normal Stress History at the Center of the Die in<br>An Example Flip Chip Assembly (Underfill UF3)                       | 222 |

| Figure 8.1: Example Hybrid PCB Laminate Incorporating Low<br>CTE Carbon Fiber Based Core (STABLCOR)                                           | 227 |

| Figure 8.2: Flip Chip Assembly on Low CTE<br>Carbon Fiber Based Core (STABLCOR)                                                               | 229 |

| Figure 8.3: STABLCOR Flip Chip Assembly Incorporating Stress Test Chip                                                                        | 230 |

| Figure 8.4: Rosette Sites for Stress Measurement                                                                                              | 232 |

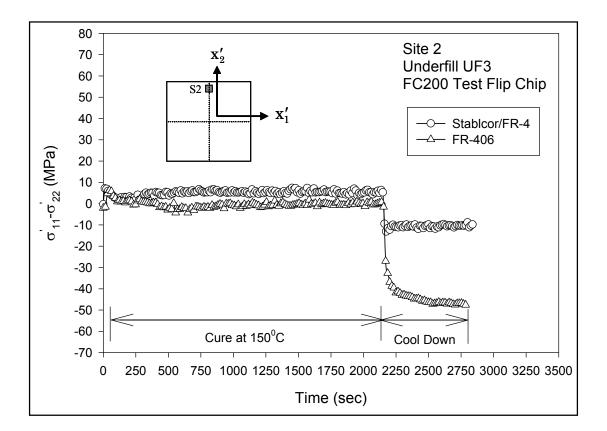

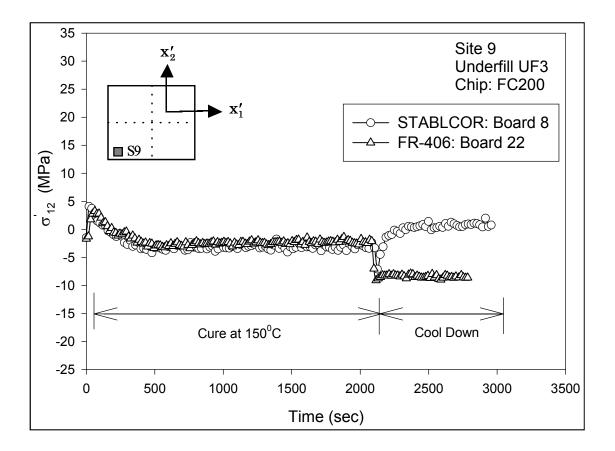

| Figure 8.5: In-Plane Normal Stress Difference Variation During Underfill Cure for<br>Different Substrate Configurations (FR-406 and STABLCOR) | 233 |

| Figure 8.6: In-Plane Shear Stress Variation During Underfill Cure for<br>Different Substrate Configurations (FR-406 and STABLCOR)             | 234 |

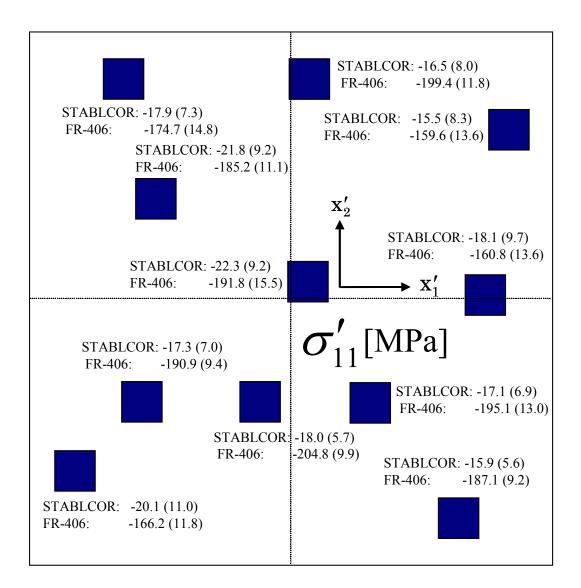

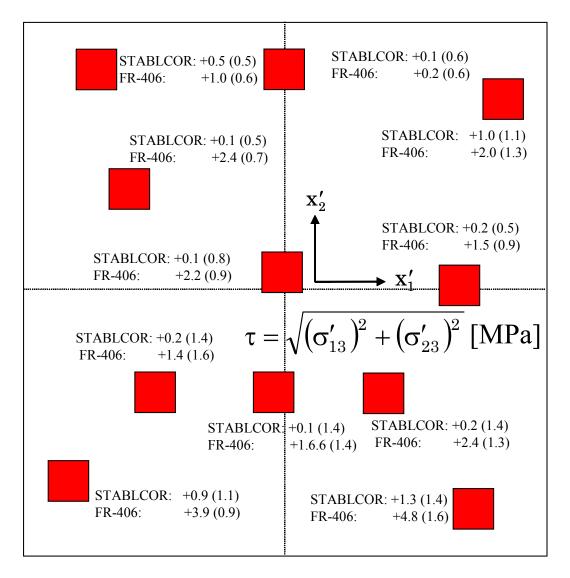

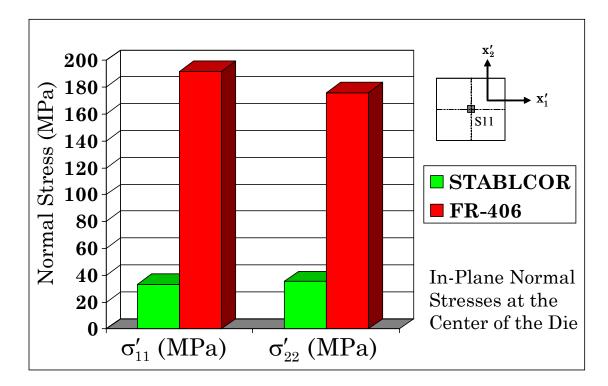

| Figure 8.7: Average In-Plane Normal Stress After Cure for Different Substrate<br>Configurations (FR-406 and STABLCOR)                         | 236 |

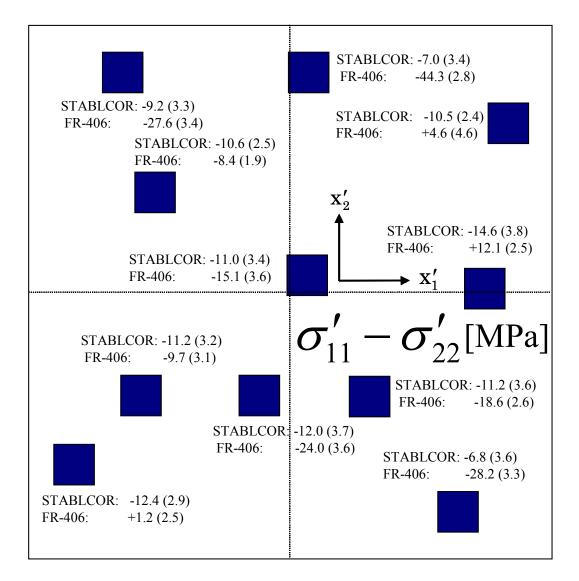

| Figure 8.8: Average In-Plane Normal Stress Difference After Cure for Different Substrate Configurations (FR-406 and STABLCOR)                 | 237 |

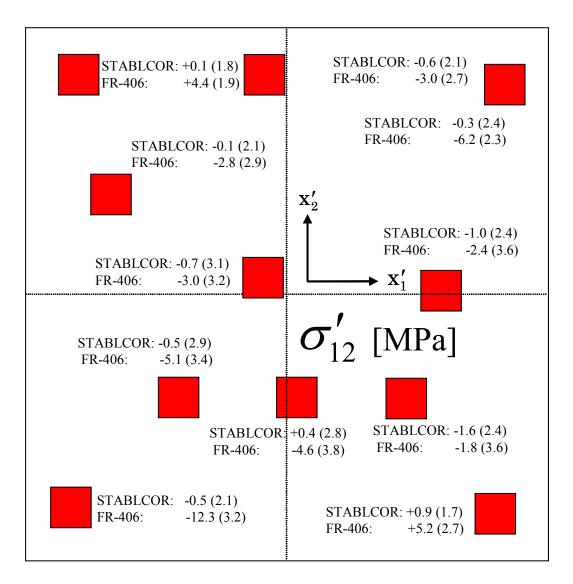

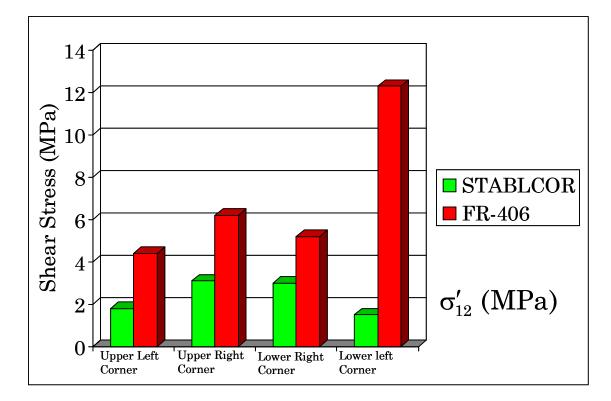

| Figure 8.9: Average In-Plane Shear Stress After Cure for Different<br>Substrate Configurations (FR-406 and STABLCOR)                          | 238 |

| Figure 8.10: Average Interfacial Shear Stress After Cure for Different<br>Substrate Configurations (FR-406 and STABLCOR)                      | 239 |

| Figure 8.11: Comparison of Average In-Plane Normal Stress for<br>Different Substrate Configurations (FR-406 and STABLCOR)                                  | 240 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 8.12: Comparison of Average In-Plane Shear Stress for Different Substrate<br>Configurations (FR-406 and STABLCOR)                                   | 241 |

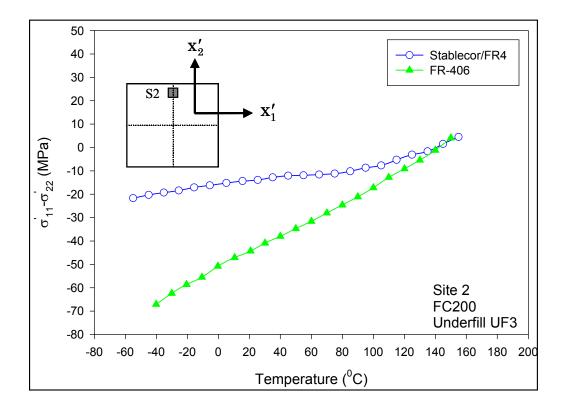

| Figure 8.13: Comparison of In-Plane Normal Stress Difference Variation<br>with Temperature for Different Substrate Configurations<br>(FR-406 and STABLCOR) | 242 |

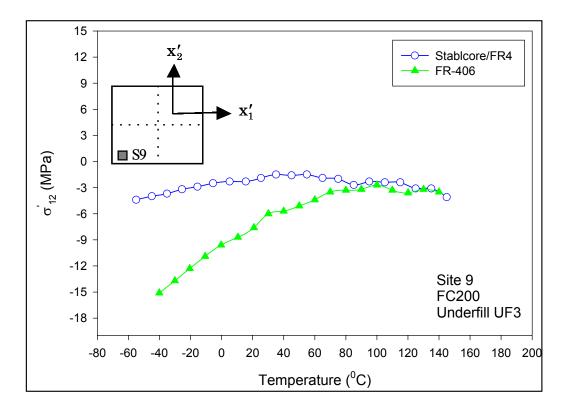

| Figure 8.14: Comparison of In-Plane Shear Stress Variation with<br>Temperature for Different Substrate Configurations                                      |     |

| (FR-406 and STABLCOR)                                                                                                                                      | 243 |

# LIST OF TABLES

| Table 4.1: Four Point Bending Calibration Results<br>for the FC200/FC400 p-Type Sensors  | 56  |

|------------------------------------------------------------------------------------------|-----|

| Table 4.2: Four Point Bending Calibration Results<br>for the FC200/FC400 n-Type Sensors  | 56  |

| Table 4.3: All Six Calibrated Piezoresistive Coefficients                                | 62  |

| Table 4.4: Connection between Bonding Pads and Channels in<br>a Bank of One Scanner Card | 76  |

| Table 5.1: Calibrated Piezoresistive Coefficients                                        | 94  |

| Table 5.2: Underfill Properties (Vendor Specified)                                       | 102 |

| Table 8.1: Laminate Types for Test Boards                                                | 228 |

### CHAPTER 1

### INTRODUCTION

Structural reliability of integrated circuit (IC) chips in electronic packages continues to be a major concern due to ever-increasing die size, circuit densities, power dissipation, operating temperatures, and the use of a wide range of low-cost packaging materials. Stress related problems are prevalent in every stage of semiconductor manufacturing. When a semiconductor wafer undergoes fabrication processes, it is stressed due to the coefficient of thermal expansion mismatches between the silicon substrate and the deposited thin film layers. Localized stresses also occur due to discontinuities in these films. In addition to these wafer level stresses, assembly and packaging materials. These stresses can affect the quality and reliability of the assembled components. Such stresses arise due to several reasons including coefficient of thermal expansion mismatches, geometrical discontinuities, cyclical and random thermal loadings and handling during assemblies operations.

Typical IC packages are comprised of a variety of materials ranging from brittle materials (e.g. silicon) to ductile materials (e.g. solder). All of these materials expand and contract at different rates and have different elastic moduli. When such assemblages of materials are heated or cooled, the coefficient of thermal expansion mismatches lead to

thermal stresses. A silicon chip has a very uneven surface on a microscopic level after it has gone through the wafer fabrication process. In addition, local amplifications in stress can result from stress raisers such as sharp edges on the die, lead fingers, and die pad, or voids in the molding compound or die attach material. Typical reliability tests for IC packages involve thermal cycling them between hot and cold extreme temperatures. These cyclical temperature excursions can lead to delaminations and/or fatigue. Moreover, whenever devices on the chip are powered on and off, the associated ohmic heating and subsequent cooling produces additional thermal loading of the package. These cyclic and random thermal loadings are unavoidable, and the design of the packages must be optimized so that these stresses can be minimized. Mishandling or misprocessing during assembly can produce unacceptable peak stresses. Examples are improper wafer dicing, local unbonded areas in die attachment operations, and excessive pressure or ultrasonic energy applied during wire bonding. The stresses in this category can be managed by optimizing of assembly processes. Although each assembly step is potentially a stress producing operation, most of the stresses in the semiconductor chip are induced during die attachment (bonding) and during encapsulation such as the molding of plastic packages or underfilling of flip chip on laminate assemblies.

The microelectronics industry continues to seek higher density packaging and more chip complexity. This results in larger chips but smaller packages, so that the die is becoming a larger portion of the total package volume. Thus, mechanical stress levels in the silicon die continue to increase as the chip becomes a more significant structural element in the package. Also, the area array solder bump interconnection schemes used in Direct Chip Attach (DCA) can put non-uniform loads across the die. These stress distributions can change rapidly over small length scales.

Stress analyses of electronic packages and their components have been performed using analytical, numerical, and experimental methods. Analytical investigations have been primarily concerned with finding closed-form elasticity solutions for layered structures, while numerical studies have typically considered finite element solutions for sophisticated package geometries. Experimental approaches have included the use of test chips incorporating piezoresistive stress sensors (semiconductor strain gages), and the use of optical techniques such as holographic interferometry, moiré interferometry, and photoelasticity.

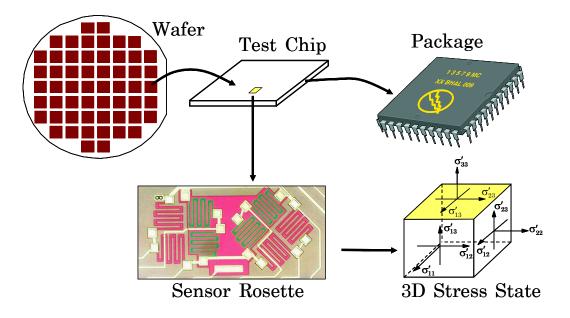

Piezoresistive stress sensors are a powerful tool for experimental structural analysis of electronic packages. Figure 1.1 illustrates the basic application concepts. The structures of interest are semiconductor (e. g. silicon) chips that are incorporated into electronic packages. The sensors are resistors that are conveniently fabricated into the surface of the die using current microelectronic technology. The sensors are not mounted on the chips. Rather, they are an integral part of the structure (chip) to be analyzed by the way of the fabrication process. The stresses in the chip produce resistance changes in the sensors (due to the piezoresistive effect) that can be measured. Therefore, the sensors are capable of providing non-intrusive measurements of surface stress states on a chip even within encapsulated packages (where they are embedded sensors). If the piezoresistive sensors are calibrated over a wide temperature range, thermally induced stresses can be measured. Finally, a full-field mapping of the stress distribution over the surface of a die can be obtained using specially designed test chips, which incorporate an array of sensor rosettes.

Figure 1.1 – Piezoresistive Sensor Concept

Prior publications on stress sensing test chips have included sensor rosettes with up to eight resistors. Using n-type and p-type sensors at various orientations, several or all the stress components on the die surface can be measured. By monitoring packaging stresses using stress sensing test chips, a variety of accomplishments have been achieved. For instance, test chips have been used to provide a better understanding of the shear stress failure mechanisms in encapsulated packages. In addition, thermal stresses due to die attachment, molding, and temperature variation have been characterized. The effects of die size and package configuration on the stresses after molding have also been quantified for various package pin counts. Piezoresistive measurements have allowed molding compound materials to be evaluated with respect to their thermal-induced stress levels. Also, the effects of thermal cycling and delamination at the chip/encapsulant interface can be explored using test chips. Recently, thermal stress measurements of epoxy underfilled flip-chip on board devices were reported, and the effects of the curing conditions of the underfill were investigated. Details of these studies are discussed in the subsequent chapter (literature review).

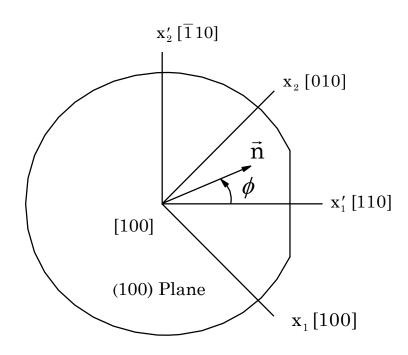

Theoretical analysis has established that properly designed sensor rosettes on the (111) silicon wafer plane have several advantages relative to sensors fabricated using standard (100) silicon. In particular, optimized rosettes on (111) silicon can be used to measure the complete state of stress (six stress components) at a point on the top surface of the die, while optimized rosettes on (100) silicon can measure at most four stress components. Also, optimized sensors on (111) silicon offer the unique capability of measuring four temperatures compensated combined stress components, while those on (100) silicon can only be used to measure two temperature compensated quantities.

Furthermore, it has been established that the (111) plane offers the opportunity to measure the highest number of stress components in a temperature compensated manner. This is particularly important, given the large thermally induced errors, which can often be found in stress sensor data. The four stress components, which can be measured in a temperature compensated manner using (111) silicon sensors, are the three shear stress components and the difference of the in-plane normal stress components. Details of these theoretical considerations are reviewed in chapter 3.

In this work, (111) silicon test chips containing an array of optimized piezoresistive stress sensor rosettes have been successfully applied within flip chip packaging configurations. Calibrated and characterized stress test chips were flip chip bonded on laminate substrate, and then the post packaging resistances of the sensors were recorded. These packaging resistances were monitored at room temperature, as a function of temperature excursion, and during long term packaging reliability qualification tests (thermal cycling). The stresses on the die surface were calculated using the measured resistance changes and the appropriate theoretical equations. For comparison purposes, three-dimensional nonlinear finite element simulations of the flip chip packages were also performed, and the stress predictions were correlated with the experimental test chip data.

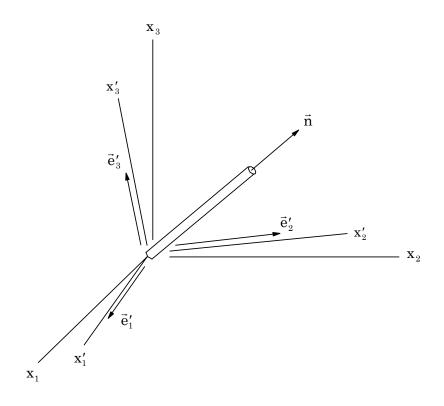

In the early chapters of this thesis, silicon piezoresistive theory has been reviewed to allow for understanding of the equations utilized for stress calculation on the die surface. General resistance change equations have been expressed in the unprimed crystallographic system, and in an arbitrarily rotated primed coordinate system. The ensuing resistance change equations for (111) silicon wafer planes were then extracted. The (111) silicon test chips used in this study contain sensors rosettes with p-type and n-type sensor sets, each with resistor elements making angles of  $\phi = 0, \pm 45, 90^{\circ}$  with respect to  $x'_1$ -axis perpendicular to the wafer flat. For the (111) silicon case, this eight-element dual polarity rosette has been optimized to measure all six-stress components (four in a temperature compensated manner). This is a particularly important attribute, given the large errors which can be introduced into non-temperature compensated stress sensor data when the temperature change T is not precisely known. The four measurable temperature compensated stress components are  $(\sigma'_{11} - \sigma'_{22}), \sigma'_{12}, \sigma'_{13}, \sigma'_{23}$ .

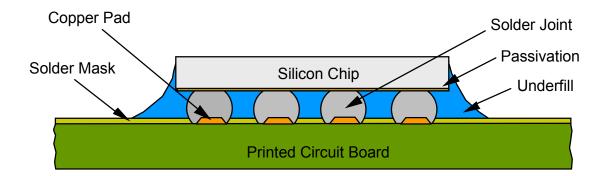

In this work, an extensive study on thermo-mechanical evaluation of flip chip packages has been performed. The use of flip chip technology is increasing with the demands for high-density packaging and electronics miniaturization. It is an attractive solution for many system designs, including digital watches, cellular phones, disk drives, and personal digital assistants, which are constrained by size, I/O density, electrical performance (e.g., signal speed), reliability, or cost. Flip chip technology offers high I/O density on a small footprint with fast signal processes, due to the short electrical interconnect length. Flip chip assembly refers to a method by which a solder bumped bare integrated circuit (IC) die is attached, face down, directly to a substrate (ceramic, silicon, or laminate). A schematic of a flip chip on laminate assembly is shown in Figure 1.2. This attachment method eliminates the need for conventional first level IC packaging. Die that are to be used as flip chips leave the wafer fabrication and are maintained in wafer form until the bumping operations are complete. By batch processing wafers, millions of I/O can be bumped at once, in contrast to wire bonds, which are generated one I/O at a time. It is important to note that flip chips have been used by IBM in electronic systems since the 1960's. Widespread use of flip chip as a

Figure 1.2 - Typical Cross-Section of a Flip Chip Package

surface mount alternative has been slow to develop due to the multi-million dollar investment in capital equipment required to bump wafers using traditional bumping techniques (i.e. vapor deposition, photolithography, electroplating, etc.). Over the past decade, many advances have been made towards generating low cost flip chip on laminate solutions.

Thermo-mechanical reliability of flip chip on laminate packaging is a major concern when the assemblies are exposed to harsh operating environments such as space or automotive underhood applications. In this study, structural and thermal reliability of flip chip packages have been investigated during the assembly process and accelerated life testing using piezoresistive stress sensing test chips. Both 5 x 5 mm (FC200) and 10 x 10 mm (FC400) test chips fabricated on (111) silicon were utilized to characterize the complete die stress state on the device side of the chip in flip chip on laminate assemblies. The FC200 chip includes 11 eight-element sensor rosettes, a diode for temperature measurement, an eight-bit fuse style chip ID, and contains 200  $\mu$ m (8 mil) pitch perimeter solder bumps. The FC400 chip includes 19 stress sensor rosettes, 2 diodes for temperature measurement, a 10-bit fuse style chip ID, an embedded full coverage heater for heat transfer or power cycling experiments, and also contains 200  $\mu$ m pitch perimeter solder bumps.

This flip chip study is divided into four parts. In the first part of this work, transient die stress measurements have been made during underfill cure, and the room temperature die stresses in final cured assemblies have been compared for several different underfill encapsulants. The experimental stress measurements in the flip chip samples were then correlated with finite element predictions for the tested configurations.

It is well known that underfill has significant impact on flip chip package reliability. To investigate the effects of underfill on thermo-mechanical behavior of flip chip packages, three different underfill materials were used in this study. A total of 75 flip chip test boards (1 die size x 3 underfills x 25 samples per combination) were assembled at the CAVE SMT Line at Auburn University. In each assembly, the three-dimensional die surface stresses have been recorded during underfill cure, and after underfill cure (room temperature).

In the second part of this work, the silicon die stresses occurring in flip chip assemblies have been characterized and modeled at extremely low temperatures. Stress measurements have been made down to -180 °C using test chips incorporating piezoresistive sensor rosettes. The obtained stress measurement data have been correlated with the predictions of nonlinear finite element models. A microtester has been used to characterize the stress-strain behavior of the solder and underfill encapsulant from -180 to 150 °C to aid in this modeling effort.

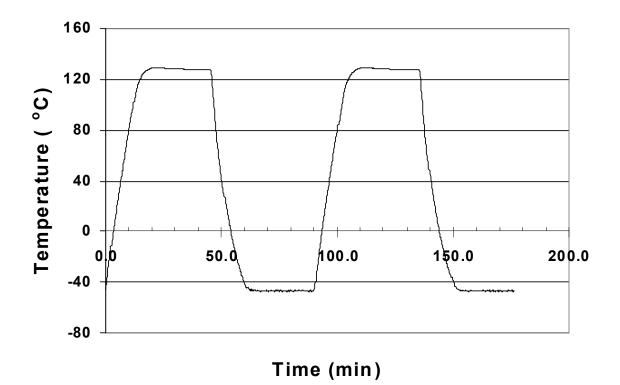

In the third part of this work, the stress variations occurring during thermal cycling from -40 to +125 °C have been characterized. These measurements have been correlated with the delaminations occurring at the die passivation to underfill interface measured using C-mode Scanning Acoustic Microscopy (C-SAM). With this approach, the stress distributions across the chip, and the stress variations at particular locations at the die to underfill interface have been interrogated for the entire life of the flip chip assembly. In order to correlate the stress changes at the sensor sites with delamination onset and propagation, CSAM evaluation of the test assemblies was performed after every 125 thermal cycles.

A total of 75 flip chip assemblies with 3 different underfills have been evaluated. For each assembly, the complete histories of three-dimensional die surface stresses and delamination propagation have been recorded versus the number of thermal cycles. The stress histories that lead to delamination initiation for each underfill encapsulant, and the variation of the stresses that occur before and during delamination propagation have been identified. The progressions of stress and delamination have been mapped across the entire surface of the die, and a series of stress/delamination videos have been produced. One of the most important discoveries is that the shear stresses occurring at the corners of flip chip die have been demonstrated to be a suitable proxy for prognostic determination of future delamination initiations and growth. Thus, shear stress sensors have great potential as health-monitoring devices in flip chip packaging.

In the fourth and final part of this work, die stress characterization was performed in flip chip assemblies utilizing a new low expansion coefficient laminate material. The new substrate material is a hybrid laminate formed using a combination of standard glass fiber reinforced resin outer layers (FR-4), with a carbon fiber reinforced resin core layer. The carbon fiber based central core (STABLCOR) features both high stiffness and high thermal conductivity, as well as near zero thermal expansion coefficient. Because of the extremely low expansion coefficient of the carbon fiber core and the bonded nature of the laminate, the surface CTE of the hybrid laminate PCB stack-up is typically in the range of 2.0-4.0 ppm/°C over the temperature range of -55 to 150 °C, which is much lower than the typical 13.0-20.0 ppm/°C seen with standard FR-4 based laminates. In addition, the high stiffness of the carbon fiber based core can help reduce PCB warpage issues, as well as vastly improve the net heat conduction characteristics of the PCB substrate FC200 and FC400 flip chip test die were packaged on the low expansion laminates, and the die surface stresses were measured throughout the assembly process. Die stress measurements have been made during underfill cure, and at room temperature after final assembly. The results have been compared to those from analogous FR-406 substrate assemblies. Significant stress reductions have been observed when using the low expansion coefficient laminate.

### CHAPTER 2

#### LITERATURE REVIEW

Structural reliability of electronic packages has become an increasing concern for a variety of reasons including the advent of higher integrated circuit densities, power density levels, and operating temperatures. Electronic packaging typically involves several thermal and mechanical processes and also many different kinds of materials. As electronic packages are comprised of dissimilar materials, the assembly and operation reliability issues are often present due to the coefficient of thermal expansion (CTE) mismatch between these materials. Due to the CTE mismatch, mechanical stresses are usually built in at virtually every stage of manufacture or during application. These stresses may cause degradation of device characteristics and failure of the interconnections, cracking of the die or package, etc. Thus, die stress evaluation is a major concern for insuring reliability of packages.

Dale and Oldfield [1] addressed stress generation in packaging processes such as wafer preparation, oxidation, diffusion, metalization, die and wire bonding, encapsulation, and curing. Lau [2] has discussed several problems associated with stress, including package cracking, wire damage, and thin film cracking on the die. Stress generation mechanisms were also discussed with respect to die attachment, encapsulation, surface mounting processes, and bending during application. Nguyen [3] has presented current reliability issues involved with typical postmold IC packages. One of the four major concerns is stress. Issues such as stress mechanisms and measurement were reviewed. Mechanical and electrical failures due to induced thermal stresses have been documented since the 1970's. Within a plastic package, out-of-plane shear stresses act on the chip surface with the traction direction toward the center of the chip, causing deformation of the die metalization. With chips coated with passivation glass, these deformations can cause passivation cracking. Microcracks in the plastic encapsulant or delamination at the die-encapsulant interface promote metal deformation, since they reduce the restrictions on plastic movement at the chip surface [4-8]. Isagawa, et al. [4] observed the deformation of aluminum metalization during thermal shock tests of plastic packages. The deformations were related to encapsulant properties, chip size, test temperature range, etc. Thomas [5] performed thermal cycling on molded packages containing unpassivated test chips. Lundström and Gustafsson [6], Lesk, et al. [7], and Edwards, et al. [8] also described metal shift or damage during thermal shock or thermal cycling tests.

Shear stresses are heavily concentrated at the corners and edges of the silicon die, and can result in thin film brittle passivation cracking or interlayer dielectric film cracking [9-15]. Okikawa, et al. [9-10] and Shirley, et al. [11] presented studies of thin film cracks due to thermal stresses. Foehringer, et al. [12] described a model that explained the interactions among the key variables related to thin film cracking. The effort to model the failure rate as a function of environmental stress severity was done by Blish and Vaney [13]. A special test chip was designed by Gee, et al. [14] to detect thin film cracking in PLCC packages with various pin counts, die sizes, thermal cycling numbers, etc. Inayoshi [15] demonstrated that stresses could disrupt the chip passivation, permitting moisture to penetrate through to the underlying aluminum metalization causing corrosion.

Delamination at the chip-encapsulant interface is believed to be the result of critical shear stresses on the die surface, and usually occurs during reliability tests, such as temperature cycling and Highly Accelerated Stress Testing (HAST). The delamination typically starts at the corners of the silicon die, and proceeds toward the chip center [16-23]. Nishimura, et al. [16] confirmed the delamination at the die-encapsulant interface using ultrasonic inspection techniques. Doorselaer, et al. [17] revealed the relation between electrical failures and delamination. Moore, et al. [18-20] applied C-SAM (C-Mode Scanning Acoustic Microscopy) technique to inspect delamination and cracks in IC packages. The evaluations were performed with various molding compounds, lead frame finishes, and die surface conditions. A comparison of delamination effects between temperature cycling and HAST tests was carried out by van Gestel, et al. [21-22]. Delaminations at the chip-encapsulant interface of 240 pin QFP packages were also found by Zou, et al. [23] even before reliability tests. Interfacial adhesion is one of the key factors to achieve delamination free packaging. Nguyen, et al. [24-26], conducted evaluations of various interfaces in plastic packages.

The occurrence of microcracks in the encapsulant is another serious reliability issue with plastic packages. The microcracks usually initiate at the chip edges, then propagate into the encapsulant at roughly a 135° angle from the chip surface [5].

Nishimura, et al. [16, 27] performed thermal cycling between –55 and 150 °C on Dual Inline Packages. Package cracking was observed as a function of the number of temperature cycles for different encapsulant and lead frame materials. The presence of microcracks in the encapsulant dramatically changes the stress distribution in a package. A tentative model was proposed by Schroen, et al. [28] to describe the stress relief and oscillation measurements during temperature cycling tests. The stresses causing the cracks are so high that may cut through silica filler particle [7]. To avoid high stress, suggestions such as development of plastic encapsulant with low CTE, low elasticity modulus, high strength, optimized plastic curing processes, and prevention of moisture absorption, have been proposed or practiced [28-31].

Large residual stresses introduced during packaging procedures, especially die attachment and encapsulation steps, can also cause die cracks. Since silicon is an extremely brittle material, minor surface flaws can act as crack starters in the presence of tensile stresses [32, 33]. Improper dicing of silicon wafers is another contributor to die cracking [1].

Electronic characteristic changes occur in IC chips due to mechanical stresses introduced by packaging processes. The resistivity of diffused resistor shifts due to piezoresistive effects so that piezoresistive stress sensors can be developed [34-36]. Other device characteristics shifts were also experimentally studied, or observed in actual plastic packaged devices [37-50]. Using the relations between MOS drain current change and the applied mechanical stress, stress sensors based on piezoresistive field effect transistors (PIFET's) and bipolar transistors were proposed and designed [43-50]. In addition, Mian, et al. have studied the sensitivity of the resistance of Van der Pauw structures to applied stress [51-52]. Frutt, et al. [53] have discussed techniques for minimization of the piezoresistive effect for integrated p-type implanted resistors.

To understand the stress developed in plastic packages during packaging processes, reliability tests, and actual applications, researchers have performed stress analyses using analytical, numerical, and experimental methodologies. Suhir [54-57] and Liew, et al. [58] suggested analytical methods for evaluation of the interfacial stresses in bimetal thermostats based on elementary beam (or long-and-narrow plate) theory. Tay, et al. [59-61] discussed the mechanics of interfacial delamination, and presented analytical methods to describe moisture-induced delamination growth during solder reflow. These analytical models were correlated with experimental observations to help understand failure mechanisms. Miura, et al. [62] also discussed the temperature distribution in the IC plastic package during solder reflow process.

Finite element simulations provide useful insight into the stress distributions produced in plastic packages during die attachment, encapsulation, and reliability tests. Various package configurations, packaging material combinations, and conditions related to package processes and reliability tests can be investigated by means of finite element methods [63-76]. In early finite element modeling, Groothuis, et al. [63] and Pendse [64] displayed the effects of material choices and structure changes on stress variation within a DIP package. Kelly, et al. [65-68] demonstrated how thermal stresses are developed within a plastic package, and suggested innovations in processes such as a side buffer of soft material, etc. Mertol [69] studied the thermal stresses in a high pin count PQFPs.

In two-dimensional finite element simulations of plastic packages, plane strain analyses would be more suitable for prismatic bodies (DIPs and SOPs), while packages with square features (PLCC, PQFP) could be represented by coaxial rings using axissymmetric analyses [3]. Van Gestel, et al. [70] used three layers of special interface elements to simulate delamination behavior when plastic packages were subjected thermal cycling. Sweet, et al. [71], applied a linear viscoplastic model to predict die surface stresses. Effects of various delamination conditions to die surface stress distributions were also evaluated. Liu, et al. [72-73] built finite element models to predict thermal deformation and delamination in PQFP's and made comparison with moiré interferometry testing data. Yeung, et al. [74] and Park, et al. [75] used finite element analysis to evaluate the thermal residual stress in a PQFP assuming viscoelastic stress-strain behavior of the molding compounds.

Analytical solutions are difficult to achieve for complex packaging configurations. Although the finite element method (FEM) is a reliable modeling tool to predict stress distributions within packages, the computational results have to be verified by experimental analysis. In addition, finite element simulations are limited by the availability of packaging material properties, accurate understanding of packaging processes, and other assumptions and approximations. Thus, it is desirable to develop experimental stress analysis methods for electronic packages. Bastawros, et al. [76], Han and Guo [77], and Liu, et al. [72-73] to measure thermal deformations within packages applied moiré interferometry. Shadow moiré methods were effective in evaluating the

warpage of packages [78-79]. Some other testing and measurement techniques were reviewed by Guo and Sarihan [80].

The piezoresistive effect is caused by the change of resistivity of semiconductors as a function of applied stresses. Smith [81] first proposed to use the piezoresistive behavior of semiconductors for stress and strain measurements. Since then, Tufte and Stezer [82] and Suhling, et al. [83-84] have investigated the temperature dependence of piezoresistive coefficients of silicon or germanium. Kanda [85] represented the piezoresistive coefficients graphically. Yamada, et al. [86] addressed the nonlinearity of the piezoresistive effect. Dally and Riley [87] discussed the properties and performance characteristics of semiconductor strain gauges. Bittle, et al. [35, 88] derived the detailed theory for silicon piezoresistive sensors, and Kang [89] developed piezoresistive theory for silicon on various wafer planes and for silicon carbide.

Piezoresistive sensors are a powerful tool for experimental structural analysis of electronic packages. The sensors are resistors that are conveniently fabricated into the surface of the die using current microelectronic technology, and are capable of providing non-intrusive measurements of surface stress state on a chip even within encapsulated packages [90-93]. A comprehensive review of piezoresistive sensor issues has been given by Sweet [34].

Several investigators have used stress test chips based on piezoresistive sensors to examine die stresses in plastic encapsulated packages. In early studies, Edwards and co-workers [8, 28, 94-95], Groothuis, et al. [63], and van Kessel, et al. [32] used (100) silicon test chips based on 0-90 two-element sensor rosettes to examine stresses in small

pin count packages. Resistance changes of sensors during thermal cycling and pressure cooker environment tests were compared [28]. Die stress studies were utilized to direct the selection of packaging materials and the control of packaging processes [94-95]. The mechanism of structure failures were also investigated [32, 42, 63].

Gee and co-workers [96-98] have mapped die surface stress distributions using (111) test chips containing an array of four element  $0-\pm45-90^{\circ}$  sensor rosettes. In these studies, tests were also performed to understand the effects of package geometrical parameters and thermal cycling on the die stress levels. Further investigations with these chips were performed on 40 pin Dual in-Line packages (DIPs) by van Gestel and co-workers [99-100]. In addition, Lead frames and molding compounds were studied by Lundström, et al. [6] using a (111) silicon test chip with p-type four-element rosettes. Temperature dependent stress state measurements after die attachment and encapsulation were examined by Natarajan, et al. using n-type (100) silicon test chips [101].

Miura, et al. [36, 39, 102-105] have used (100) test chips incorporating fourelement dual-polarity rosettes (0-90° n-type resistors and  $\pm 45°$  p-type resistors) to characterize thermally-induced die stresses in DIPs. Their sensor rosette design was the first capable of measuring the out-of-plane normal stress perpendicular to the die surface. In one of these studies, the effects of internal structure on plastic packaging reliability were explored [104]. The level of die stress was studied as a function of temperature changes and thermal cycling test [36]. Delamination at the interface of die/encapsulant was also correlated to varied stress magnitudes [39]. Zou, et al. [106] have recently used (100) test chips based on a similar rosette with reversed doping polarities (0-90° p-type resistors and  $\pm 45^{\circ}$  n-type resistors) to characterize the stresses in plastic leaded chip carrier (PLCC) packages that were encapsulated using several different molding compounds. Sweet and co-workers [34, 71, 107-109] have used the (100) silicon Sandia ATC-04 test chip to investigate liquid encapsulation of integrated circuit die mounted directly on ceramic substrates, and to study 160 pin quad flat packs (QFP's). The ATC-04 contains a multiplexed array of sensor rosettes. Each dual-polarity rosette contains eight resistors (0- $\pm 45^{\circ}$ -90° orientations for both p-type and n-type resistors). An improved third generation version of the Sandia test chip has recently been designed and prototyped [110]

Other experimental studies using test chips with piezoresistive stress sensors can be found in the literature [111-123]. Skipor, et al. [111] compared both stress measurements using test chips and displacement measurements using moiré interferometry with FEM calculations for 64 pin TQFP and 68 pin PLCC packages. Lo, et al. [112-113] and Bossche, et al. [114-115] described the design, fabrication, and calibration of their own stress test chips. Ducos, et al. [116] presented the in-situ stress measurements during package assembly. Nysaether, et al. [117-118] examined the thermally induced stresses in glob-on-top pressure sensor samples. Rey, et al. [119] associated creep of the solder joints in leaded components with stress measurements in the silicon die. They used experimental data together with the FEM simulations to find a mathematical model for creep in the solder. Palmer, et al. [120] attempted to measure the stress variation during plastic package molding. Sensor resistance measurements for test chips assembled into TBGA, MBGA, and ViperBGA<sup>TM</sup> packages were made by Thomas, et al. [121]. The die stresses induced in TO220 packages using different mold compounds has been investigated using test chips by Caruso, et al. [122]. Another test chip for studing packaging induced stress has been developed by Jia, et al. [123].

Mayer, et al. [124-126] have measured in-situ transient stresses during ball bonding using integrated piezoresistive microsensors. In their studies, the devices were fabricated using a commercial CMOS process, exploiting p plus diffusion as the piezoresistive sensing material. The resistors were fabricated with the commercial 2  $\mu$ m CMOS process alp2lv of EM Microelectronic-Marin SA, Switzerland. The NMOS source/drain diffusion with a sheet resistance of approximately 21  $\Omega$  was used for the resistors [126]. The design and fabrication process of piezoresistive sensors for packaging stress measurements were also discussed by Lwo, et al. [127-128]. In these studies, test chips with both p-type and n-type piezoresistive stress sensors, as well as a heat source, were designed, and then manufactured by a commercialized foundry so that the uniformity of the test chips was expected. Both temperature and stress calibrations were performed through a special designed MQFP (Metal Quad Flat Package) and fourpoint bending (4PB) structure, respectively.

Stresses developed on the silicon surface due to encapsulation and molding process have also been discussed in several other publications [129-136]. van den Bogert, et al. [129] have analyzed a bilayer beam structure to determine the relationship between the material properties of the molding compound and the generated thermal stresses. Three commercial molding compounds were studied. The stress levels were determined by the thermal expansion difference between the molding compound and silicon, the moduli, and the amount of relaxation that occurs during the experiment due to the viscoelastic nature of the molding compound. Kitoh, et al. [130] measured the internal stresses produced in three cylinder models simulating the structures of epoxy resin encapsulated electronic components by using strain gages. The mechanism of stress generation was very different between an open type structure that has one surface of the resin free, and a closed type that does not. Slattery, et al. [131] described the use of finite-element techniques and piezoresistive strain sensors to determine package stress levels. The effect of delaminations at the interfaces of the package materials was also discussed, and the scanning acoustic microscope was introduced as a complimentary tool to identify stress-related defects in plastic packages. Mei, et al. [132] developed a nonlinear finite element model for predicting the deformation, stress, and fracture behavior of delaminated plastic packages induced by mechanical and hygro-thermal loads. The model consists of a sequentially coupled hygro-thermo-mechanical analysis considering moisture absorption, evaporation and interface contact and fracture analysis. Mixed mode fracture modes were discussed.

An analysis of environment induced stresses in silicon sensors has been performed by Voloshin, et al. [133-134]. In these studies, an experimental technique, Digital Image Analysis Enhanced Moiré Interferometry (DIAEMI), was used to measure the in-situ outof-plane displacements of the die due to the die-attachment process. This information was related to the residual stresses in the die. Several test die, with and without coating, were prepared and two different bonding materials, "low-stress" and "high-stress", were used for analysis of the induced stresses. The initial and final (after die-attach) surface contour patterns of the die were observed and recorded. Out-of-plane displacements of the die were obtained and induced stresses were calculated by a hybrid finite element method.

Bjorneklett, et al. [135] measured the stress induced during the chip attachment process using integrated piezoresistive strain sensors on test chips. The stress was found to be different for different adhesives. The effect of temperature cycling (i.e., stress cycling) was investigated by measuring the thermal resistance between chip and substrate. An increasing thermal resistance that strongly depends on the mismatch in thermal expansion was found. The wear-out mechanisms were crack growth and detachment. Alpern, et al. [136] used Scanning Acoustic Microscopy (SAM) to evaluate the degradation of adhesion on a blown up sample, i.e., a Si-beam coated only on the passivated side with the molding compound under consideration.

In recent applications of piezoresistive stress sensors, mechanical stresses in epoxy underfilled flip-chip on board packages were studied [137-147]. In-situ flip-chip assembly mechanical stress measurements using piezoresistive test chip were first reported by Peterson and co-workers [137]. In that work, die stresses were evaluated for several underfill materials. Nysaether, et al. [138] and Palaniappan, et al. [139] investigated the impact of curing parameters on the die stresses induced in flip-chip assembly processes. In reference [138], stress measurements were presented as a function of temperature when the underfill was cured at temperatures of 85 °C, 120 °C, and 150 °C. In reference [139], the residual die stresses were found to be strongly dependent on several underfill properties including CTE, storage modulus,  $T_g$ , and ultimately the underfill cure process. Palaniappan, et al. [140-141] reported on the effects of the choice of encapsulation material on the stresses during underfill cure and also made preliminary stress measurements during thermal cycling.

Measurement of die stresses in flip chip on laminate assemblies was performed by Rahim, et al. [142-144]. In these flip chip studies, the authors have investigated the mechanical stresses present on the backside (top side) [142] and the device side (bottom side) [143-144] of the die at each stage of the flip chip assembly process. The die stresse variations were observed during underfill curing, and the room temperature die stresses in the final cured assemblies have been compared for several different underfill encapsulants. Finally, stress variations have been monitored in the assembled flip chip die as the test boards were subjected to slow temperature changes from -40 to +150 °C. Schwizer, et al. [145], reported on the latest member of a test chip family for packaging process characterization, containing a novel flip-chip microsensor that can measure forces in all three directions, acting on each of its solder balls.

Several researchers have studied the effect of thermomechanical properties of underfill and underfill technology on flip chip packages reliability [146-156]. Qi, et al. [146] examined the manufacturing steps required for flip chip on laminate assembly and the impact of these new materials on production cycle time. Adhesion testing, liquid-toliquid thermal shock, and thermal cycling have been used to examine the reliability of the underfilled flip chip on laminate. New underfill materials provided a cost-effective option for flip chip-on-laminate applications. Wang, et al. [147] have compared different types of reworkable underfill formulations as well as the methodologies for developing such materials. Furthermore, generic concepts for new underfilling processes including noflow, molding, and wafer-level were introduced. Okura, et al. [148] have investigated the effect of thermo-mechanical properties of underfill, such as coefficient of thermal expansion (CTE) and stiffness (Young's modulus), on reliability of flip chip on board (FCOB) assemblies under thermal cycling stresses.

Luo, et al. [149] used the three-liquid-probe method to investigate the surface properties of solder mask and different passivation materials including benzocyclobutene (BCB), polyimide (PI), silicon oxide (SiO<sub>2</sub>), and silicon nitride (Si<sub>3</sub>N<sub>4</sub>). Dai, et al. [150] characterized underfill materials for flip chip packages. Chen, et al. [151] have investigated the effects of underfill on thermo-mechanical behavior of two types of flip chip packages with different bumping size and stand-off height under thermal cycling. Both experimental testing and two-dimensional finite element simulations were used. Viscoelasticity of the underfill and viscoplasticity of the solder were considered in the simulations.

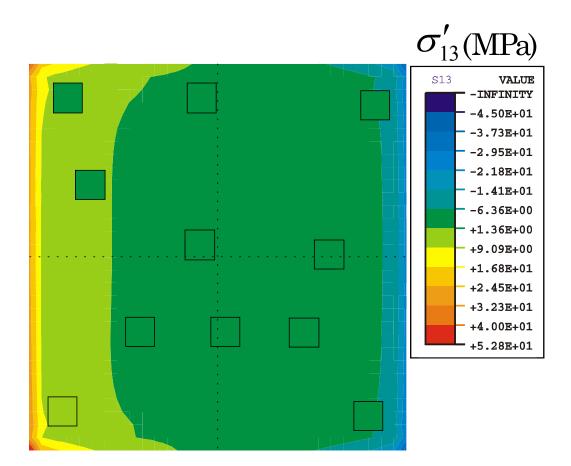

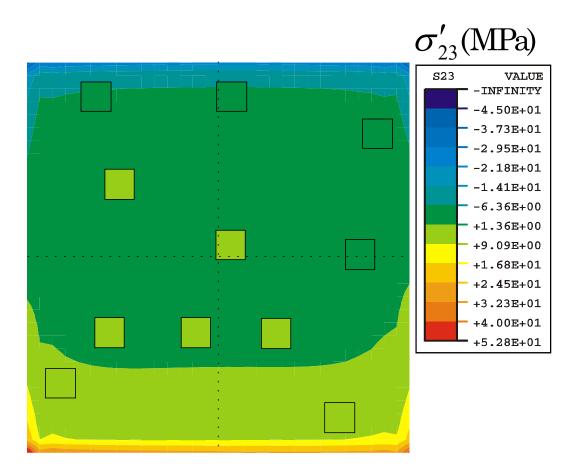

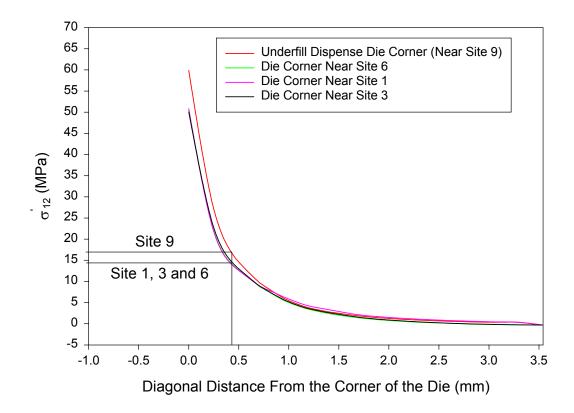

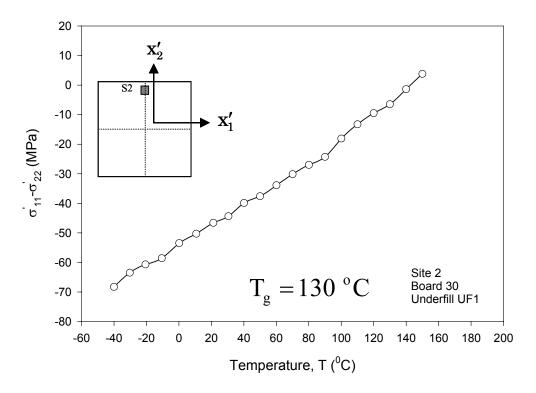

Ernst, et al. [152-153] have studied the effect of curing induced residual stresses on flip chip failure. In their studies, cure-dependent material parameters were determined using experimental data from unit-step relaxation tests performed during cure. Yang and co-workers [154-155] have studied and investigated the effects of cure-dependant underfill properties on flip chip failures. In these studies, a cure-dependent viscoelastic constitutive relation was applied to describe the curing process of epoxy underfill in flip chip on board (FCOB) assemblies. The chemical shrinkage of the epoxy underfill during the curing process was applied via incremental initial strains. Thus, the stress and strain build-up, caused by the simultaneous increase in stiffness and shrinkage during the curing process, were simulated. Islam, et al. [156] have characterized the stress-strain curves and elastic modulus of underfill as a function of temperature by uniaxial testing using a microscale tension-torsion testing machine.