#### Silicon Carbide/Aluminum Oxide Field-Effect Transistors

by

Isanka Udayani Jayawardhena

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama Aug 8, 2020

Keywords: Interface trap density, MOS Physics, MOSFET mobility, surface treatments, Silicon dioxide, CCDLTS

Copyright 2020 by Isanka Udayani Jayawardhena

## Approved by

Sarit Dhar, Chair, Associate Professor of Physics

Ayayi C. Ahyi, Chair, Associate Research Professor of Physics

Minseo Park, Professor of Physics

Marcelo A. Kuroda, Assistant Professor of Physics

Michael Gramlich, Assistant Professor of Physics

Leonard C. Feldman, Distinguished Professor Emeritus of Physics and Astronomy,

Material Science and Engineering, Rutgers University

Willis E. Hames, Professor of Geology

#### Abstract

4H-Silicon Carbide is a wide band gap semiconductor with attractive physical properties for high power, high-frequency devices, and electronics that operate under harsh environments that are not accessible to conventional silicon devices. A significant challenge in 4H-SiC metal oxide semiconductor field-effect transistors (MOSFETs) is the poor channel conductance due to the trapping of carriers by high-density of near-interface traps at the 4H-SiC/SiO<sub>2</sub> interface. Many trap passivation methods have been researched as a solution and currently, nitridation of the interface via processes such as nitric oxide (NO) annealing is the most reliable approach. The nitrided SiO<sub>2</sub>/4H-SiC interfaces are still far from ideal and alternate approaches are desirable. One such approach is the deposition of high-k dielectrics which has added advantages over conventional SiO<sub>2</sub>. Among these alternative dielectrics, atomic layer deposition (ALD) of Al<sub>2</sub>O<sub>3</sub> has shown promising results in the literature. The focus of this thesis is the study of ALD Al<sub>2</sub>O<sub>3</sub>/4H-SiC interfaces using systematic process variations, device fabrication and electrical characterization. Among the electrical characterization methods used to evaluate interface trap densities (D<sub>it</sub>), constant capacitance deep level transient spectroscopy (CCDLTS) is a method capable of differentiating trap types in MOS devices. Two signature near interface oxide traps named O1 and O2 are typically detected for the SiO<sub>2</sub>/4H-SiC interfaces by CCDLTS. In this work, for the first time, it was found that such traps are absent in Al<sub>2</sub>O<sub>3</sub>/4H-SiC interfaces formed on the Hterminated 4H-SiC surface. This strongly indicates that the O1 and O2 traps are inherent to SiO<sub>2</sub>/4H-SiC interfaces. This result motivated further investigation where a systematic study of the effect of 4H-SiC surface treatments prior to the deposition of Al<sub>2</sub>O<sub>3</sub> by ALD was conducted. This is the first comprehensive study where Al<sub>2</sub>O<sub>3</sub>/4H-SiC MOSFETs were fabricated to analyze the dependence of the channel mobility on the surface treatments. Among the studied surface

treatments, H2 annealing at high temperature prior to ALD was found to result in reduced Dit and impressive channel mobility along with improved stability for the Al<sub>2</sub>O<sub>3</sub>/4H-SiC MOS devices. The most likely reason for this is that H<sub>2</sub> annealing results in a Si-H terminated 4H-SiC surface, which in turn leads to a more uniform nucleation of the ALD Al<sub>2</sub>O<sub>3</sub> thin film, resulting in a better SiC/Al<sub>2</sub>O<sub>3</sub> interface. In addition, it was also found that similar to SiO<sub>2</sub>/4H-SiC, nitridation of the Al<sub>2</sub>O<sub>3</sub>/4H-SiC interface results in trap passivation and possible surface doping by N. In this work, interfacial nitridation was carried out by performing sacrificial oxidation of SiC in NO. This results in a sub-nm thick SiON layer on top of SiC and subsequent H<sub>2</sub> annealing of this surface prior to Al<sub>2</sub>O<sub>3</sub> deposition leads to further improvements. Al<sub>2</sub>O<sub>3</sub>/4H-SiC MOSFETs fabricated with this process resulted in peak field-effect mobility of 52 cm<sup>2</sup>/Vs which is 2x higher channel electron mobility compared to conventional nitrided SiO<sub>2</sub>/4H-SiC MOSFETs. The channel mobility results in this work are very encouraging for the application of ALD Al<sub>2</sub>O<sub>3</sub> on SiC from the point of view from channel conductance. However, it was observed that the large dielectric leakage currents associated with the defects in the bulk of the ALD thin films is the biggest challenge that need to be overcome. In this work, it was conclusively demonstrated that 4H-SiC surface treatments prior to ALD are key to the optimization of MOS interfaces using deposited dielectrics. The Hydrogen and Nitrogen based surface treatments developed in this work can be applied to other deposited dielectrics in the future as well.

#### Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor Professor Sarit Dhar for being the best mentor I could ask for. His tremendous enthusiasm for science and consistent motivation guided me enormously to grow continuously throughout these years in my Ph.D. study. I greatly appreciate his patience, guidance, knowledge, and excellent leadership. I appreciate his efforts and how effectively he influenced me to be a better researcher by understanding my traits.

I am greatly thankful to Prof. Ayayi C. Ahyi for being helpful at any point in the research experience, as well for all the enlightening discussions on research strategies. Mrs. Tamara Isaacs Smith and Mr. Max Cichon deserve a great appreciation for the assistance in experimental setups and constant support to find a way to overcome a challenge. I am thankful for Mr. Drew Sellers and colleagues in the Electrical Engineering department for sharing resources which were critical for my research success. My sincere gratitude for Prof. Marcelo Kuroda, Prof. Minseo Park, Prof. Jianjun Dong, Prof. Allen Landers, Prof. Edward Thomas, Prof. Yu Lin, Prof. David A. Maurer, and Dr. Kimberly Mulligan for their support throughout my Ph.D. life.

I appreciate and am thankful for all my committee members, Dr. Sarit Dhar (advisor), Dr. Ayayi C. Ahyi, Dr. Minseo Park, Dr. Marcelo A. Kuroda, Dr. Michael Gramlich, Dr. Leonard Feldman, and Dr. Willis Hames (university reader) for agreeing to evaluate my work and all their suggestions for improvements.

Special thanks go to Prof. Dallas Morisette, Dr. Koushik Ramadoss, and Dr. Rahul Ramamurthy from Purdue University for the incredible support during my experiments and encouraging discussions. I am very grateful for all the suggestions and support I received from Prof. Leonard Feldman, Dr. Ryan Thorpe and colleagues at Rutgers University.

Sincere gratitude to my group members, Dr. Asanka Jayawardena, Dr. Yongju Zheng, Dr. Chunkun Jiao, Mr. Benjamin Schoenek, Mr. Suman Das, and Mr. Arka Sardar for their friendships and all their invaluable support. Sincere gratitude to my colleagues Dr. Kosala Yapabandara, Dr. Min Khanal, Dr. Burcu Ozden, Mr. Sunil Uprety, Mr. Mohamad Menati, Dr. Paul Sanders, Dr. Taylor Hall, Ms. Eleanor Williamson, Ms. Lu Wang and Mr. Jonathan Heath for your selfless support and intellectual discussions.

I am thankful for all the great teachers who taught me throughout my life for making me a better person. I would like to extend great gratitude towards my precious friends and family for being there for me.

Last, but not least I would like to thank my parents R. M. Jayawardhena, Vijitha Ariyasiri for all their endless sacrifices and unconditional love. I am dedicating this thesis to you two. My sincere gratitude for my caring sister, Isurika for believing in me and motivating me especially on the darkest days. I am indebted towards my loving husband, Shanike for his incredible patience, sacrifices, understanding, and encouragement throughout this time. You all made this possible.

This work has been financially supported by the Auburn University, II-VI Foundation Block-Gift Program, and US Army Research Lab.

# Table of Contents

| Abstract                                                                                              | ii |

|-------------------------------------------------------------------------------------------------------|----|

| Acknowledgments                                                                                       | iv |

| List of Tables                                                                                        | X  |

| List of Figures                                                                                       | xi |

| Chapter 1. Introduction                                                                               | 1  |

| 1.1. Wide band gap semiconductors and power electronics                                               | 2  |

| 1.2. Properties of SiC                                                                                | 5  |

| 1.2.1. Crystal structure                                                                              | 5  |

| 1.2.2. Electrical properties                                                                          | 7  |

| 1.2.3. SiC bulk and epitaxial growth                                                                  | 8  |

| 1.3. Dielectrics                                                                                      | 10 |

| 1.3.1. SiO <sub>2</sub> for 4H-SiC MOSFETs                                                            | 10 |

| 1.3.2. Replacing SiO <sub>2</sub> with alternative high-k dielectrics: Al <sub>2</sub> O <sub>3</sub> | 13 |

| 1.3.3. Status of MOSFET mobilities of 4H-SiC with SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> | 14 |

| 1.3.4. Atomic layer deposition of Al <sub>2</sub> O <sub>3</sub>                                      | 16 |

| 1.4. The motivation of the dissertation work                                                          | 18 |

| 1.4.1. CCDLTS analysis of SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> 4H-SiC MOS devices      | 18 |

| 1.4.2. Study of 4H-SiC surface treatments on MOSFETs with deposited Al <sub>2</sub> O <sub>3</sub>    | 19 |

| 1.5. Thesis Outline                                                                                   | 20 |

| References                                                                                            | 21 |

| Chapter 2. Fundamentals of MOS device physics and characterization                                    | 31 |

| 2.1 MOS Fundamentals                                                                                  | 31 |

|      | 2.1.1. MOS capacitor-ideal structure and electrostatics                                                                    | 31 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

|      | 2.1.2. n-channel lateral MOSFET                                                                                            | 40 |

|      | 2.1.3. MOSFET mobility                                                                                                     | 43 |

|      | 2.1.4. Mobility limiting mechanisms                                                                                        | 47 |

|      | 2.2. Interface trap characterization.                                                                                      | 49 |

|      | 2.2.1. Interface trap fundamentals                                                                                         | 49 |

|      | 2.2.2. Simultaneous high-low frequency capacitance-voltage method                                                          | 51 |

|      | 2.2.3. C-ψ <sub>S</sub> method                                                                                             | 53 |

|      | 2.2.4. Gray-Brown technique                                                                                                | 54 |

|      | 2.2.5. Constant capacitance deep level transient spectroscopy (CCDLTS)                                                     | 55 |

|      | 2.3. Physical Analysis                                                                                                     | 60 |

|      | 2.3.1. Optical Microscopy                                                                                                  | 60 |

|      | 2.3.2. Digital Microscopy                                                                                                  | 61 |

|      | 2.3.3. Atomic Force Microscopy                                                                                             | 61 |

|      | 2.3.4. X-ray photoelectron spectroscopy (XPS)                                                                              | 62 |

|      | 2.4. Summary                                                                                                               | 64 |

| Ref  | Perences                                                                                                                   | 65 |

| Cha  | apter 3. Nature of 4H-SiC interface traps in SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> MOS devices: A comparison | l  |

| usiı | ng CCDLTS                                                                                                                  | 68 |

|      | 3.1. Introduction                                                                                                          | 68 |

|      | 3.2. Effect of passivation of SiO <sub>2</sub> /4H-SiC interfaces                                                          | 71 |

|      | 3.3. Effect of wafer orientation with nitrided SiO <sub>2</sub> /4H-SiC                                                    | 77 |

|      | 3.4. Effect of epitaxial layer doping on nitrided SiO <sub>2</sub> /4H-SiC                                                 | 86 |

| 3.5. Absence of O1/O2 traps in H-terminated Al <sub>2</sub> O <sub>3</sub> /4H-SiC                   | 90  |

|------------------------------------------------------------------------------------------------------|-----|

| 3.6. Summary                                                                                         | 93  |

| References                                                                                           | 95  |

| Chapter 4. Effect of 4H-SiC surface treatments on Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOS devices | 99  |

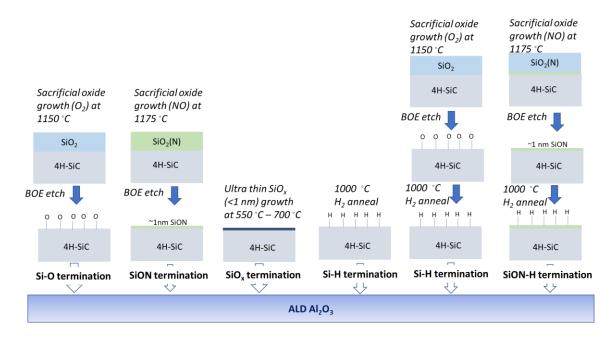

| 4.1. Different surface treatments on (0001) 4H-SiC                                                   | 99  |

| 4.1.1. Sacrificial oxidation in O <sub>2</sub>                                                       | 100 |

| 4.1.2. Sacrificial oxidation in NO                                                                   | 102 |

| 4.1.3. Insertion of ultra-thin oxide between 4H-SiC and Al <sub>2</sub> O <sub>3</sub>               | 108 |

| 4.1.4. H <sub>2</sub> annealing                                                                      | 110 |

| 4.2. Experimental details of fabricated Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOS capacitors        | 115 |

| 4.3. Band Alignments of ALD Al <sub>2</sub> O <sub>3</sub> deposited on 4H-SiC                       | 117 |

| 4.4. CV based trap characteristics of Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOS capacitors          | 119 |

| 4.4.1. Effective interface charge density calculations                                               | 119 |

| 4.4.2. Simultaneous high-low CV analysis                                                             | 121 |

| 4.5. Device stability                                                                                | 126 |

| 4.6. Dielectric leakage measurements                                                                 | 128 |

| 4.7. Effect of post-deposition annealing                                                             | 129 |

| 4.8. Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOSFET fabrication methods and process modifications     | 132 |

| 4.9. Effect of 4H-SiC surface treatments on MOSFET Field-effect mobility                             | 134 |

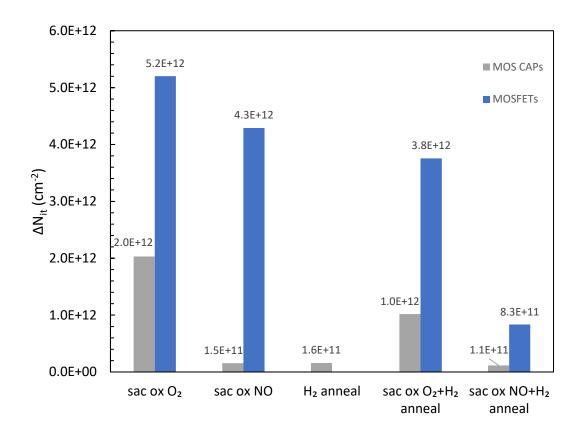

| 4.10. Trap analysis in MOSFETs using Gray-Brown method                                               | 136 |

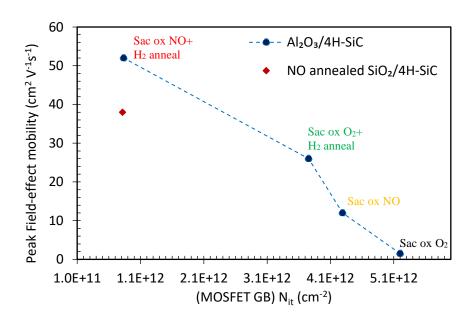

| 4.11. MOSFET Field-effect mobility versus interface trap densities relationship                      | 139 |

| 4.12. Summary                                                                                        | 141 |

| References                                                                                           | 144 |

| Chapter 5. Conclusions and future work         | 149 |

|------------------------------------------------|-----|

| 5.1. Conclusion                                | 149 |

| 5.2. Future work                               | 151 |

| Appendix A: Sample cleaning                    | 154 |

| Appendix B: Thermal Oxidation and NO annealing | 156 |

| Appendix C: Photolithography                   | 157 |

| Appendix D: DC Sputtering                      | 158 |

| Appendix E: Al evaporation                     | 160 |

| Appendix F: Reactive Ion Etching (RIE)         | 161 |

| Appendix G: Ohmic contact anneal               | 163 |

# List of Tables

| Table 1.1: Comparison of properties of several wide bandgap semiconductor materials 3                            |

|------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Table of physical properties of major SiC polytypes) compared to Si                                   |

| Table 1.3: Some recently reported (0001) 4H-SiC MOSFET channel mobilities prepared with                          |

| different approaches of dielectrics                                                                              |

| Table 3.1: MOS capacitors fabricated with different passivation methods                                          |

| Table 3.2: O1, O2 trap activation energies with standard deviation over several devices, capture                 |

| cross-sections and trap densities obtained by CCDLTS for MOS capacitors fabricated with                          |

| different passivation methods compared to dry oxidation                                                          |

| Table 3.3: Sample matrix for n-type 4H-SiC MOS capacitors fabricated on Si-, C-, and a- face                     |

| wafers with and without nitridation                                                                              |

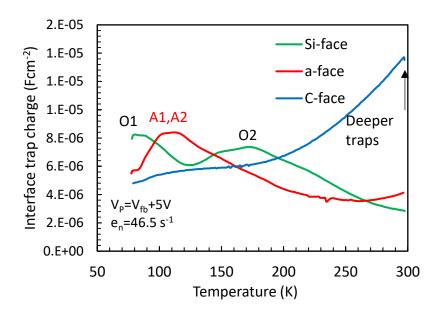

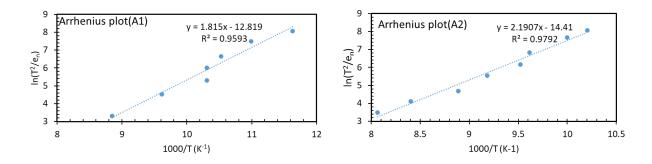

| Table 3.4: Traps types, activation energies, cross-section areas and trap densities detected by                  |

| CCDLTS for different wafer orientations of 4H-SiC/SiO <sub>2</sub> MOS capacitors with 2 hr NO                   |

| annealing                                                                                                        |

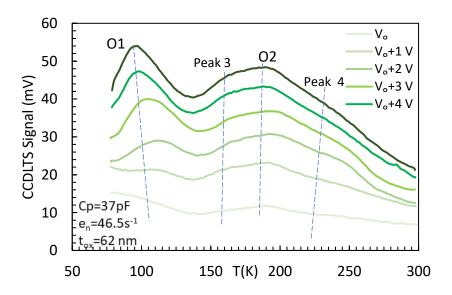

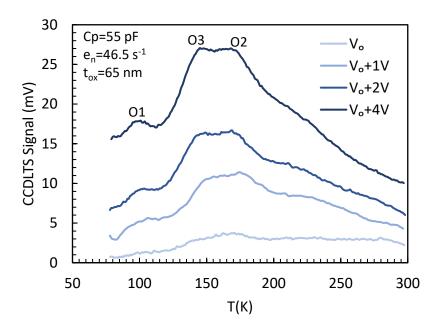

| Table 3.5: Traps, cross-section areas and trap densities detected by CCDLTS for NO annealed                      |

| SiO <sub>2</sub> / (0001) 4H-SiC MOS capacitors doped with nitrogen                                              |

| Table 4.1: 4H-SiC surface treatments prior to ALD Al <sub>2</sub> O <sub>3</sub>                                 |

| Table 4.2: Thin oxide growth conditions and thicknesses (XPS thickness measured using $Si^{2+}$ , $3^+$ ,        |

| $4^+$ intensities and $\lambda = 3.7$ nm) [Unpublished, Courtesy: Dr. Ryan Thorpe (RU)]                          |

| Table 4.3: Peak field-effect mobilities and threshold voltages of Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOSFETS |

| prepared with different treatments measured at 298 K and 77 K                                                    |

# List of Figures

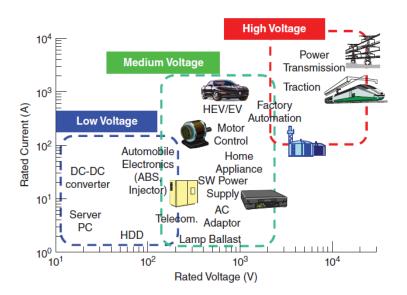

| Figure 1.1: Power device application in general areas                                                              | . 2 |

|--------------------------------------------------------------------------------------------------------------------|-----|

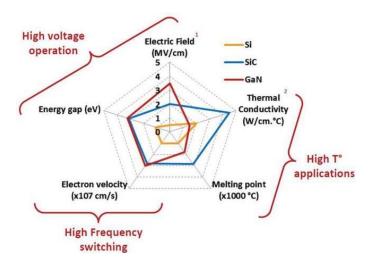

| Figure 1.2: Comparison of figures of merit of Si, SiC, and GaN                                                     | . 3 |

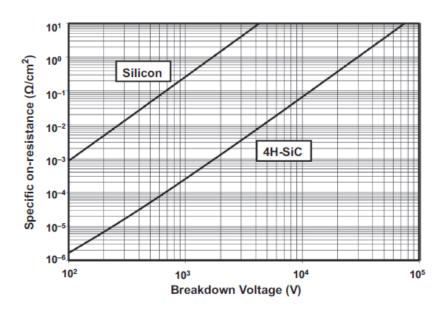

| Figure 1.3: Ideal specific on-resistance for SiC compared to Si                                                    | 4   |

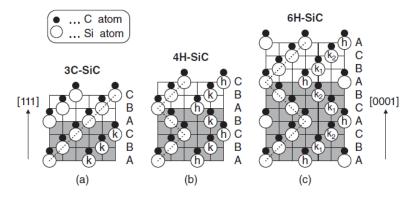

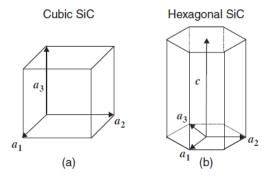

| Figure 1.4: Schematic structures of (a) 3C-SiC, (b) 4H-SiC and (c) 6H-SiC polytypes                                | . 5 |

| Figure 1.5: Primitive cells and fundamental translation vectors of (a) cubic (b) hexagonal SiC                     |     |

|                                                                                                                    | . 6 |

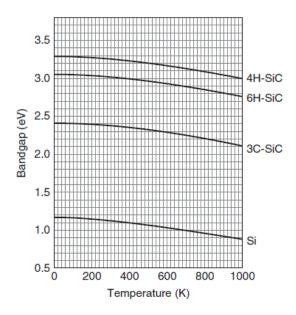

| Figure 1.6: Temperature dependence of bandgap for SiC polytypes                                                    | . 7 |

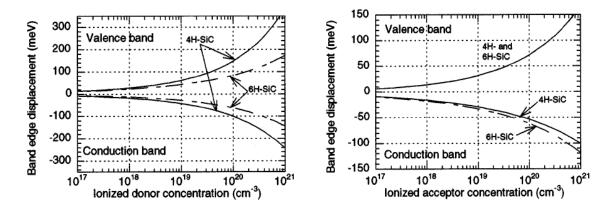

| Figure 1.7: Conduction and valence band displacements for n-type and p-type SiC                                    | 8   |

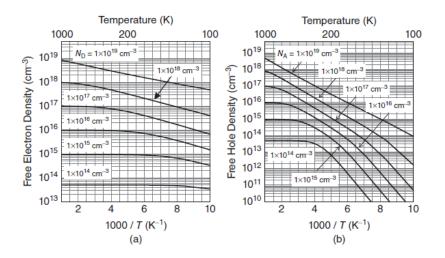

| Figure 1.8: Arrhenius plots of the free carrier density of nitrogen-doped (left) and aluminum-                     |     |

| doped (right) 4H-SiC                                                                                               | 8   |

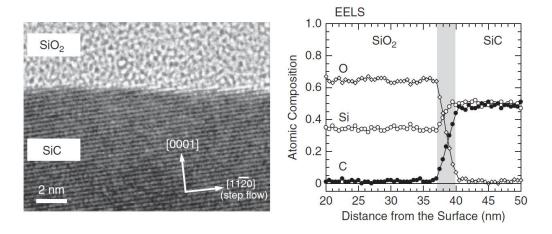

| Figure 1.9: Typical cross-sectional TEM image (left) and Si, O, and C signals in EELS                              |     |

| measurements on (0001) 4H-SiC with thermal oxide grown at 1300 °C                                                  | l 1 |

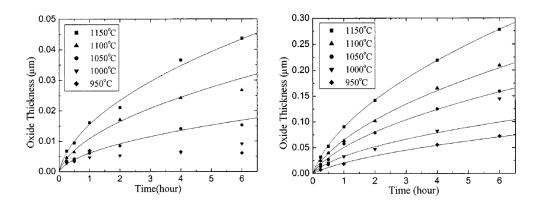

| Figure 1.10: Oxidation thickness as a function of temperature and time for (0001) Si-terminate                     | d   |

| (left) and (000-1) C terminated (right) 4H-SiC                                                                     | l 1 |

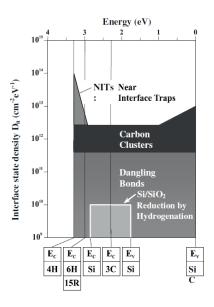

| Figure 1.11: Schematic representation of the density of states at the SiC/SiO <sub>2</sub> interface of            |     |

| different SiC polytypes1                                                                                           | 12  |

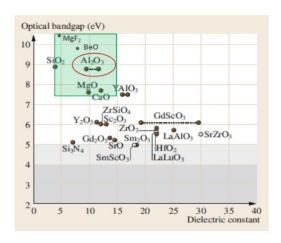

| Figure 1.12: Adapted plot of dielectric constant vs. optical bandgaps of alternative dielectrics 1                 | 14  |

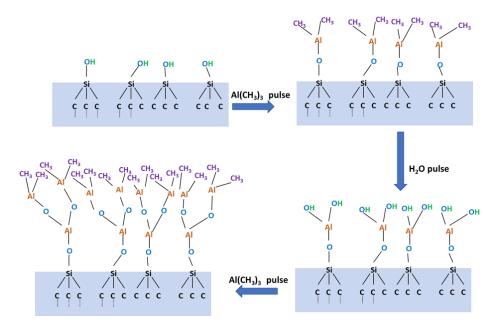

| Figure 1.13: Atomic layer deposition of Al <sub>2</sub> O <sub>3</sub> with TMA and H <sub>2</sub> O as precursors | 18  |

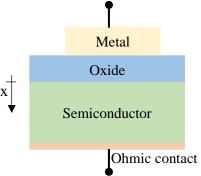

| Figure 2.1: MOS capacitor structure                                                                                | 32  |

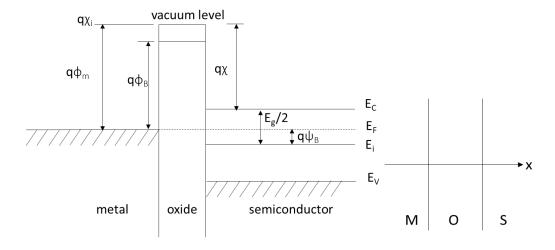

| Figure 2.2: Energy band diagram of the ideal n-MOS capacitor at flat band condition at $V_G$ =0                    |     |

| (left). Block charge diagram of MOS system at flat-band condition (right)                                          | 33  |

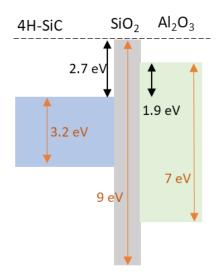

| Figure 2.3: Band alignment diagram for the 4H-SiC. SiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub>             | 33  |

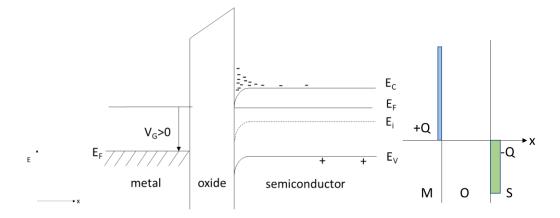

| Figure 2.4: Energy band diagram of n-MOS system at accumulation (left). Block charge diagram          |

|-------------------------------------------------------------------------------------------------------|

| of MOS system at accumulation (right)                                                                 |

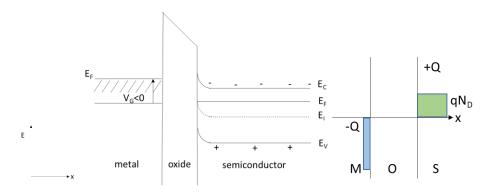

| Figure 2.5: Energy band diagram of n-MOS system at depletion (left). Block charge diagram of          |

| MOS system at depletion (right)                                                                       |

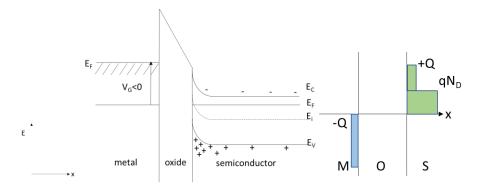

| Figure 2.6: Energy band diagram of n-MOS system at inversion (left). Block charge diagram of          |

| MOS system at inversion (right)                                                                       |

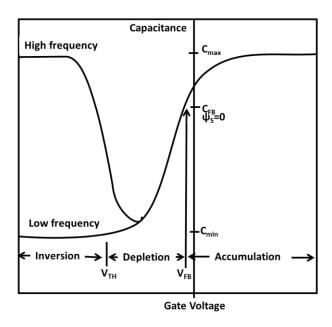

| Figure 2.7: Capacitance versus voltage diagram for a n-type MOS capacitor                             |

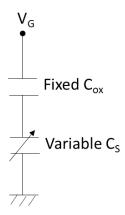

| Figure 2.8: Equivalent circuit for the overall capacitance of the MOS system                          |

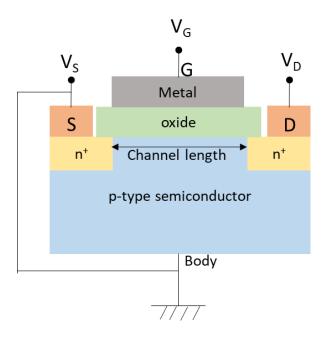

| Figure 2.9: Schematic diagram of an n-channel MOSFET                                                  |

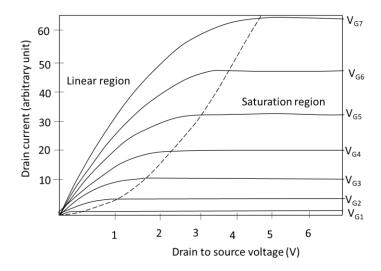

| Figure 2.10: Drain characteristics of a MOSFET                                                        |

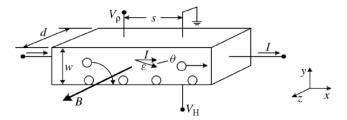

| Figure 2.11: Schematic of Hall measurement setup for a p-type semiconductor                           |

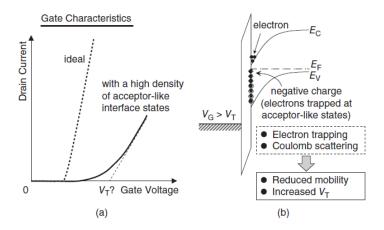

| Figure 2.12: Effect of interface trap densities in channel mobility and threshold voltage. (a)        |

| Degradation of gate characteristics due to a high density of interface states, (b) major limiting     |

| factors of channel mobility in 4H-SiC MOSFETs47                                                       |

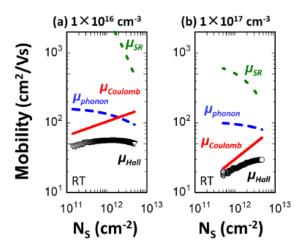

| Figure 2.13: Dominant limiting factors of inversion layer mobility in Si-face 4H-SiC was found        |

| to be mainly Coulomb and phonon scatterings                                                           |

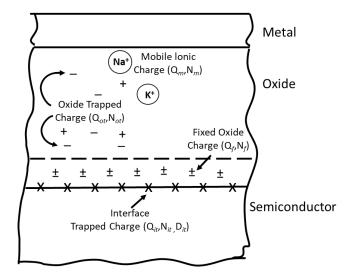

| Figure 2.14: Various oxide charges in the MOS system                                                  |

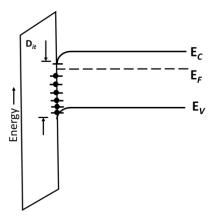

| Figure 2.15: Energy levels at the oxide/semiconductor interface showing $D_{it}$ within the forbidden |

| energy gap for n-type MOS device at accumulation. Lines with balls indicate filled interface          |

| traps and hollow lines represent unoccupied traps                                                     |

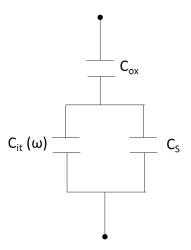

| Figure 2.16: Equivalent circuit for overall capacitance with interface traps response                 |

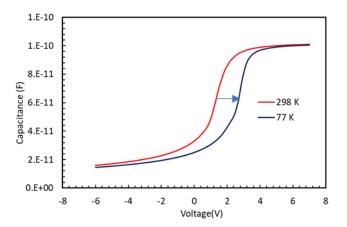

| Figure 2.17:1 MHz frequency CV curves obtained at 298 K and 77 K for NO annealed $SiO_2/4H$ -         |

| SiC MOS capacitor                                                                                     |

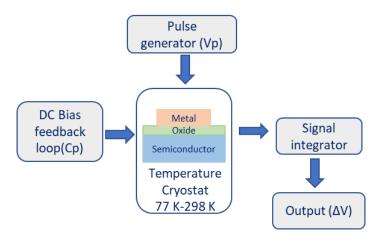

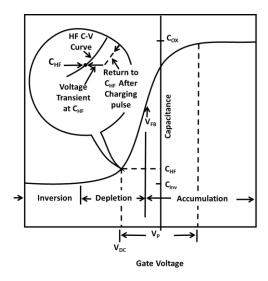

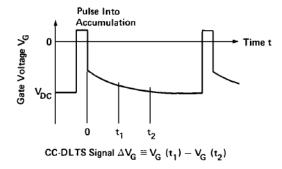

| Figure 2.18: Schematic of the basic CCDLTS setup                                                                     | 56  |

|----------------------------------------------------------------------------------------------------------------------|-----|

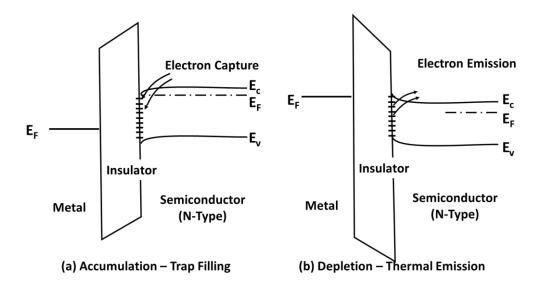

| Figure 2.19: Energy band diagram for n-type MOS device for (a) trap filling at accumulation (                        | (b) |

| trap emission at depletion bias                                                                                      | 57  |

| Figure 2.20: High-frequency CV characteristics of the MOS capacitor for pulsing during                               |     |

| CCDLTS measurement                                                                                                   | 58  |

| Figure 2.21: CCDLTS measurement during thermal emission of interface traps                                           | 58  |

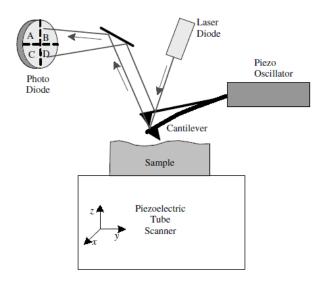

| Figure 2.22: Schematic of the main components of AFM                                                                 | 62  |

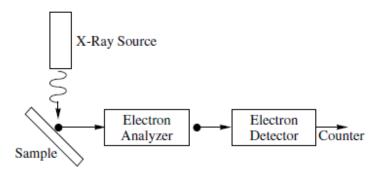

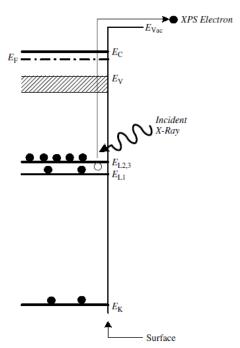

| Figure 2.23: Schematic of XPS measurement                                                                            | 63  |

| Figure 2.24: Electronic processes in XPS                                                                             | 64  |

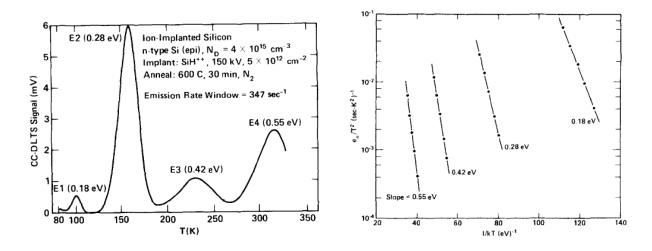

| Figure 3.1: CCDLTS spectrum for Si Schottky-barrier diode (left). Arrhenius analysis of the fe                       | ou  |

| peaks in the CCDLTS spectrum (right)                                                                                 | 69  |

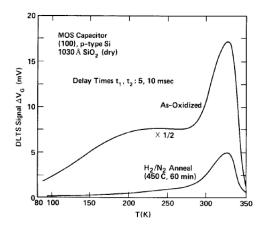

| Figure 3.2: CCDLTS spectrum for as oxidized and annealed Si MOS capacitors                                           | 70  |

| Figure 3.3: a) CCDLTS spectra for emission rate of 465 s <sup>-1</sup> for as SiO <sub>2</sub> /4H-SiC MOS capacito. | rs  |

| with different NO anneal durations (constant capacitance 35 pF, and filling voltage of 16 V).                        | b)  |

| Arrhenius plots for O1 and O2 peaks for the 4H-30 sample                                                             | 70  |

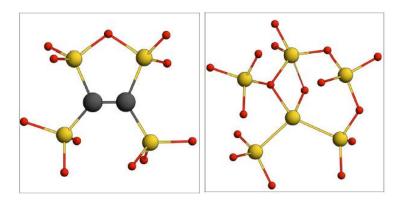

| Figure 3.4: Carbon dimers substituted for O dimers in SiO <sub>2</sub> (suggested to be O1) in left.                 |     |

| Interstitial Si in SiO <sub>2</sub> (suggested to be O2) in right. Si: larger yellow, O: smaller red, C: black       |     |

| spheres                                                                                                              | 71  |

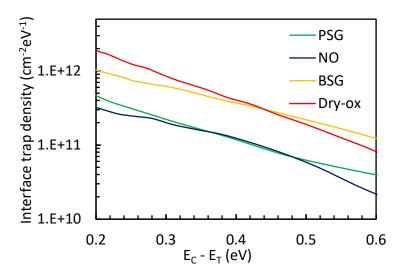

| Figure 3.5: D <sub>it</sub> extracted by simultaneous high-low capacitance-voltage method for MOS                    |     |

| capacitors with different post oxidation annealing conditions                                                        | 74  |

| Figure 3.6: CCDLTS for samples with different passivation methods compared to dry oxidation                          | on. |

| Inset shows magnified CCDLTS spectra for NO, PSG and BSG samples                                                     | 75  |

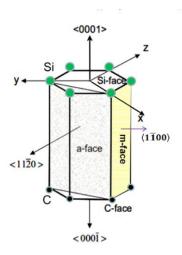

| Figure 3.7: Crystal faces in 4H-SiC. The Si-face is terminated by Si atoms and C-face by C-                              |

|--------------------------------------------------------------------------------------------------------------------------|

| atoms. A-face and m-face have equal number of Si and C atoms. (Si-large green balls, C-small                             |

| black balls)                                                                                                             |

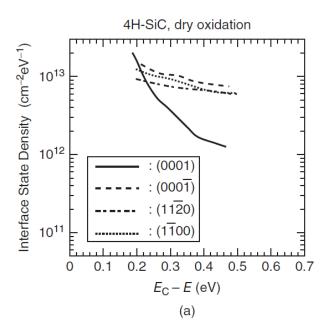

| Figure 3.8: Interface state densities obtained by simultaneous high-low CV method for n-type                             |

| 4H-SiC MOS capacitors prepared under dry oxidation using different wafer orientations 78                                 |

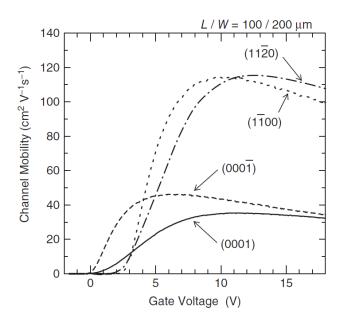

| Figure 3.9: Field-effect mobility as a function of the gate voltage of n-channel MOSFETs                                 |

| fabricated on 4H-SiC (0001), (000-1), (11-20), and (1-100) with NO annealed $SiO_2$ 79                                   |

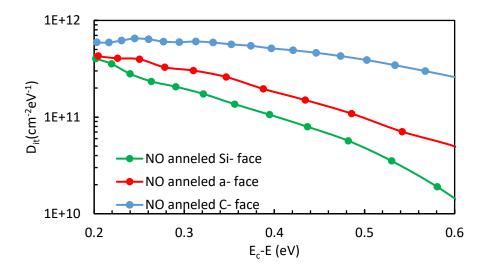

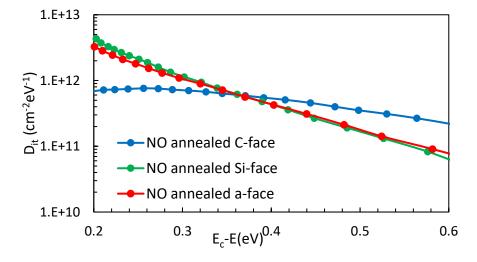

| Figure 3.10: Interface state densities obtained by simultaneous high-low CV method for 2 hr NO                           |

| annealed n-type 4H-SiC MOS capacitors with different wafer orientations                                                  |

| Figure 3.11: Interface state densities obtained by C- $\psi_s$ method for 2 hr NO annealed n-type 4H-                    |

| SiC MOS capacitors with different wafer orientations                                                                     |

| Figure 3.12: CCDLTS spectra for different filling voltages for NO annealed $SiO_2/4H$ -SiC MOS                           |

| capacitors fabricated on a-face 4H-SiC                                                                                   |

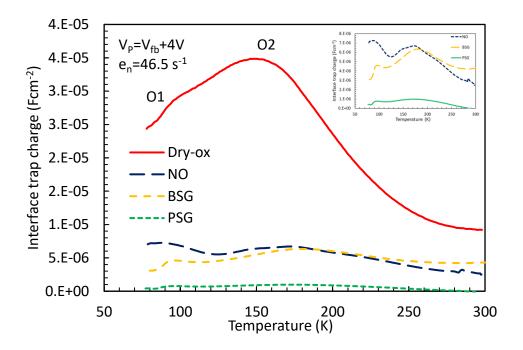

| Figure 3.13: CCDLTS analysis for NO annealed SiO <sub>2</sub> /4H-SiC MOS capacitors fabricated on                       |

| different 4H-SiC wafer orientations for $V_p=V_{fb}+4\ V$ and electron emission rate $(e_n)$ of 46.5 s <sup>-1</sup> .83 |

| Figure 3.14: Arrhenius plots for A1 (left) and A2(right) peaks detected by CCDLTS analysis NC                            |

| annealed SiO <sub>2</sub> /4H-SiC MOS capacitors fabricated on a-face 4H-SiC for $V_p = V_{fb} + 5 \text{ V}$            |

| 84                                                                                                                       |

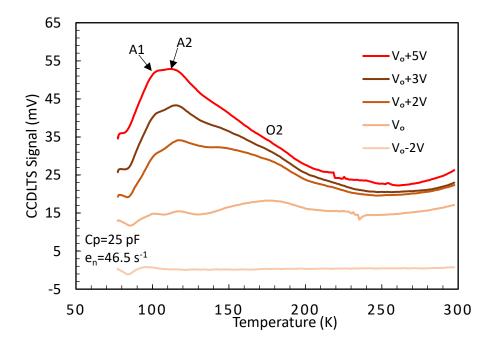

| Figure 3.15: Series of CCDLTS spectra taken with increasing trap filling pulse voltages (V <sub>P</sub> ) in             |

| the temperature range 77 K-298 K on the NO annealed (1175 $^{\circ}$ C for 2hrs) SiO <sub>2</sub> /(0001) 4H-SiC         |

| doped with nitrogen at $\sim 2 \times 10^{16}$ cm <sup>-3</sup>                                                          |

| Figure 3.16: Series of CCDLTS spectra taken with increasing trap filling pulse voltages (V <sub>P</sub> ) in                        |

|-------------------------------------------------------------------------------------------------------------------------------------|

| the temperature range 77 K-298 K on the NO annealed $SiO_2/$ (0001)4H-SiC doped with nitrogen                                       |

| at $\sim 10^{17} \text{ cm}^{-3}$                                                                                                   |

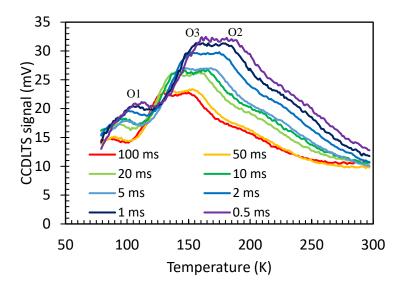

| Figure 3.17: Series of CCDLTS spectra taken for different initial delays in the temperature range                                   |

| 77 K-298 K for $V_p = V_{fb} + 4$ V on the NO annealed $SiO_2/(0001)$ 4H-SiC doped with nitrogen at                                 |

| $\sim 10^{17} \text{ cm}^{-3}$ keeping constant capacitance at 55 pF, $t_{ox}$ =65 nm                                               |

| Figure 3.18: Arrhenius analysis of O1, O2 and O3 traps for $V_p=V_{fb}+4V$ on the NO annealed                                       |

| SiO <sub>2</sub> / (0001)4H-SiC doped with nitrogen at $\sim 10^{17}$ cm <sup>-3</sup> for $C_p$ =55 pF and $V_p$ = $V_{fb}$ +4 $V$ |

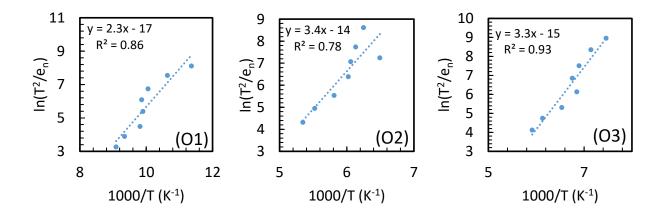

| Figure 3.19: D <sub>it</sub> extracted by simultaneous high-low method (High-low) and C- $\psi_s$ method for NO                     |

| annealed $SiO_2$ / (0001) 4H-SiC MOS capacitors doped with different nitrogen concentrations.                                       |

| 90                                                                                                                                  |

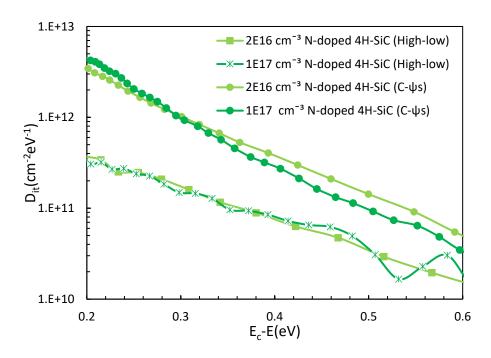

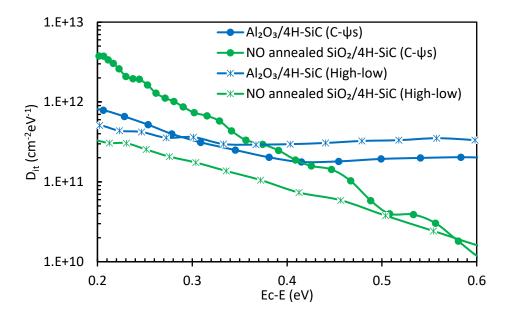

| Figure 3.20: $D_{it}$ extracted by simultaneous high-low method (High-low) and $C$ - $\psi_s$ method for H-                         |

| etched and H <sub>2</sub> annealed Al <sub>2</sub>                                                                                  |

| O <sub>3</sub> /4H-SiC MOS capacitor compared to NO annealed SiO <sub>2</sub> /(0001) 4H-SiC MOS capacitors                         |

| fabricated on ~10 <sup>17</sup> cm <sup>-3</sup> n-doped 4H-SiC91                                                                   |

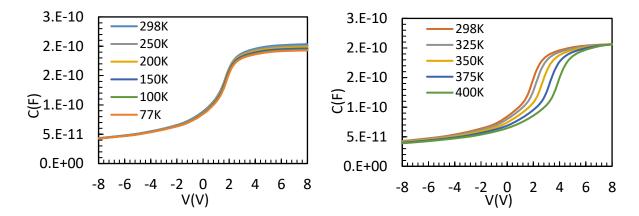

| Figure 3.21: 1 MHz capacitance-voltage (CV) measurements performed from 77 K- 400 K                                                 |

| region                                                                                                                              |

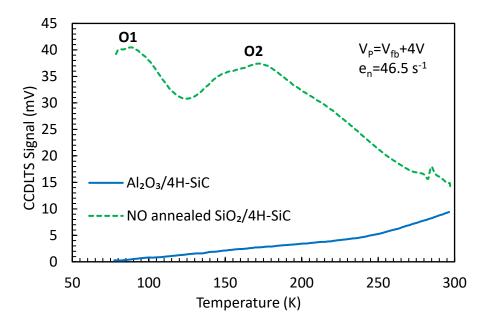

| Figure 3.22: CCDLTS for 4H-SiC capacitors with ALD Al <sub>2</sub> O <sub>3</sub> and NO annealed SiO <sub>2</sub> as gate          |

| dielectric. The ALD was performed after H <sub>2</sub> etch and H <sub>2</sub> annealing of the 4H-SiC93                            |

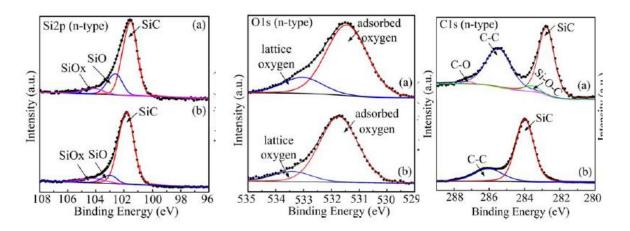

| Figure 4.1: XPS analysis of Si2p, O1s and C1s spectrum of p-type (0001) 4H-SiC surfaces (a)                                         |

| before and (b) after the sacrificial oxidation                                                                                      |

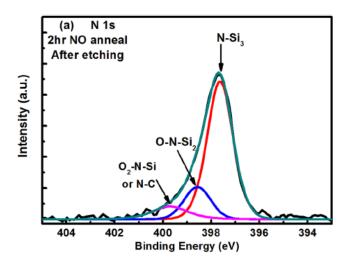

| Figure 4.2: Nitrogen-1s spectrum with possible peak assignments                                                                     |

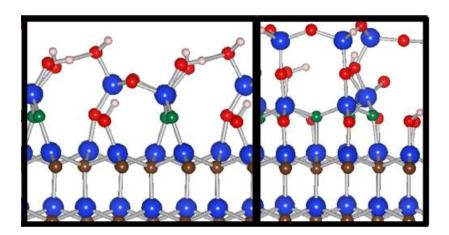

| Figure 4.3: Models (Model 2:left, Model 3:right) for SiC/Oxynitride interfaces (before etching)                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| with Si (blue), C (brown), N (green), O (red), and hydrogen (white)                                                                            |

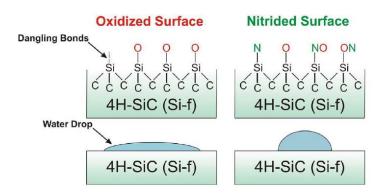

| Figure 4.4: Representation of an oxidized (hydrophilic) and a nitrided (hydrophobic) SiC (Si-                                                  |

| face) surface and their effects on a water drop                                                                                                |

| Figure 4.5: Schematic of SiO <sub>2</sub> /4H-SiC stacks formed with gate dielectric deposition or oxidation                                   |

| followed by nitridation, and by N2-conditioning approach followed by the gate dielectric                                                       |

| deposition. The bottom drawings are corresponding to atomic configurations previously                                                          |

| proposed                                                                                                                                       |

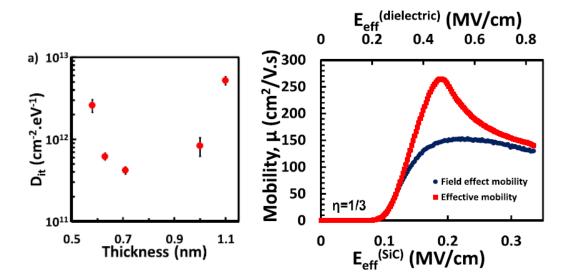

| Figure 4.6: Variation of $D_{it}$ with $SiO_2$ interlayer thickness (a) $D_{it}$ extracted at $E-E_v=0.2$ eV, for                              |

| each capacitor as a function of the measured oxide thickness. (b) D <sub>it</sub> for the MOS capacitor                                        |

| corresponding to 0.7 nm SiO <sub>2</sub> structure                                                                                             |

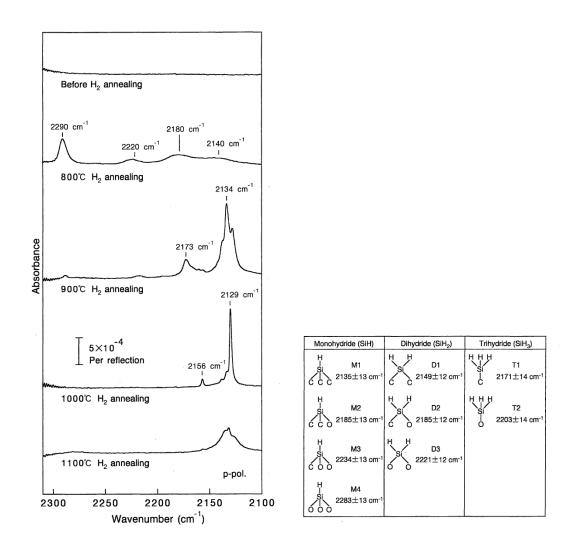

| Figure 4.7: Si-H stretching vibrations from the 6H-SiC (0001) on- axis surfaces before and after                                               |

| H <sub>2</sub> annealing in the temperature range of 800-1000°C for p-polarized light (left). Calculated                                       |

| frequency of the Si-H stretching vibrations (right)                                                                                            |

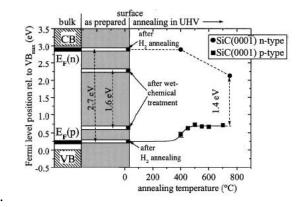

| Figure 4.8: Surface Fermi level positions of p-type SiC (0001) and n-type SiC (0001) as a                                                      |

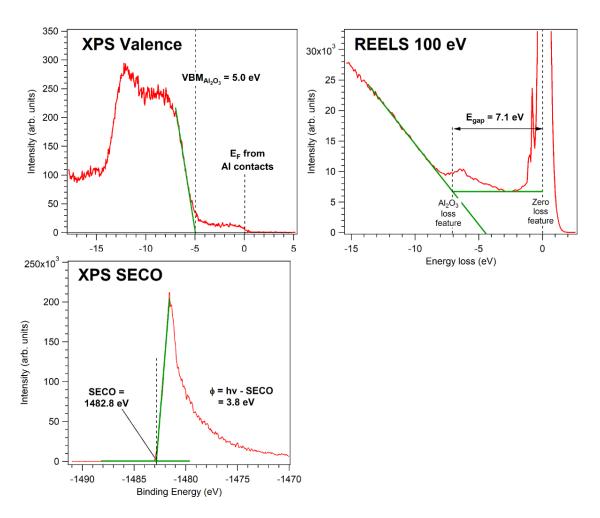

| function of surface preparation and annealing temperature                                                                                      |

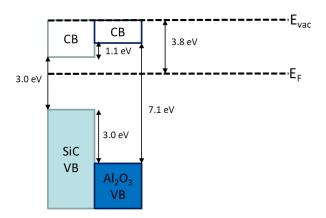

| Figure 4.9: XPS and REELS measured for H <sub>2</sub> annealed 4H-SiC/Al <sub>2</sub> O <sub>3</sub> sample. [Unpublished,                     |

| Courtesy: Dr. Ryan Thorpe (RU)]                                                                                                                |

| Figure 4.10: Energy band diagram for 4H-SiC/Al <sub>2</sub> O <sub>3</sub> sample with sacrificial oxidation in O <sub>2</sub> +H <sub>2</sub> |

| annealing treatment prior to ALD. [Unpublished, Courtesy: Dr. Ryan Thorpe (RU)]119                                                             |

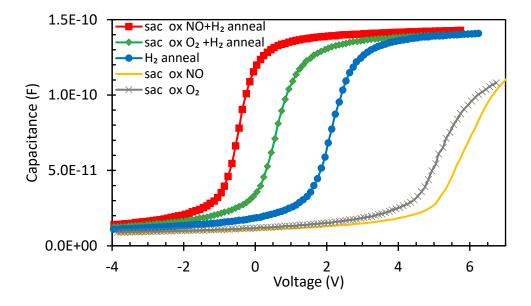

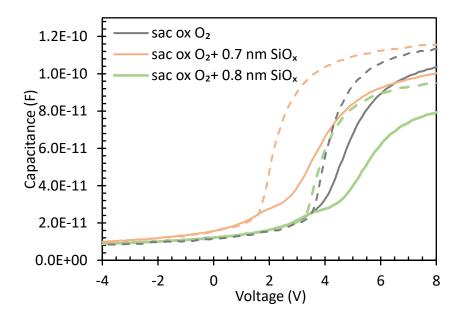

| Figure 4.11: 100 kHz capacitance-voltage (CV) measurements for capacitors prepared under                                                       |

| different 4H-SiC surface treatments                                                                                                            |

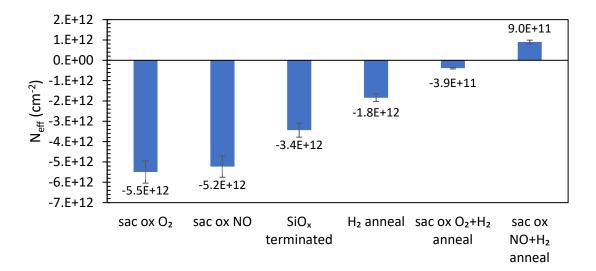

| Figure 4.12: Effective residual charge densities (N <sub>eff</sub> ) in oxide for Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOS capacitors |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| fabricated under different surface treatments                                                                                           |

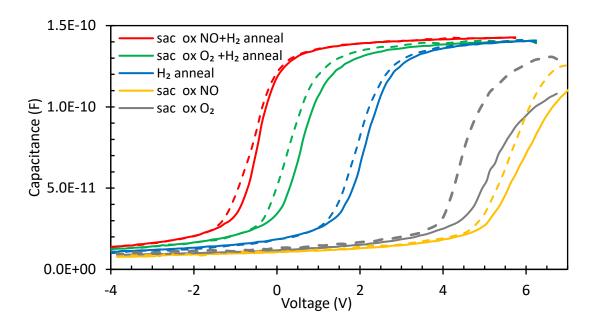

| Figure 4.13: High-low CV measurements for capacitors (t <sub>ox</sub> =33 nm) prepared under different                                  |

| 4H-SiC surface treatments (CH-100 kHz high-frequency capacitance, CQ- Quasistatic                                                       |

| capacitance)                                                                                                                            |

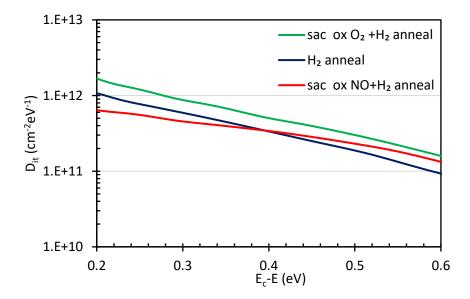

| Figure 4.14: $D_{it}$ extracted from high-low CV measurements for capacitors ( $t_{ox}$ =33 nm) prepared                                |

| under different 4H-SiC surface treatments                                                                                               |

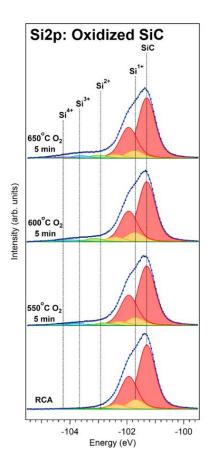

| Figure 4.15: XPS spectrum for samples with grown SiO <sub>x</sub> thin oxide under different conditions.                                |

| [Unpublished, Courtesy: Dr. Ryan Thorpe (RU)]                                                                                           |

| Figure 4.16: High-low CV measurements for capacitors (t <sub>ox</sub> =40 nm) prepared by inserting a thin                              |

| $SiO_x$ layer compared to sacrificial oxidation only sample (CH-100 kHz high-frequency                                                  |

| capacitance, CQ- Quasistatic capacitance).                                                                                              |

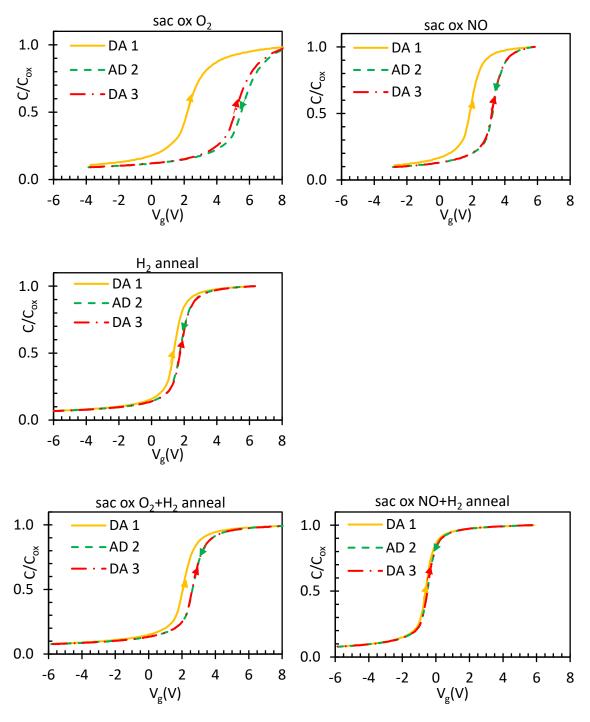

| Figure 4.17: CV hysteresis obtained from Gray-Brown technique for Al2O3/4H-SiC MOS                                                      |

| capacitors fabricated under different surface treatments where DA 1: depletion to accumulation                                          |

| sweep 1, AD 2: accumulation to depletion sweep 2, DA 3: depletion to accumulation sweep 127                                             |

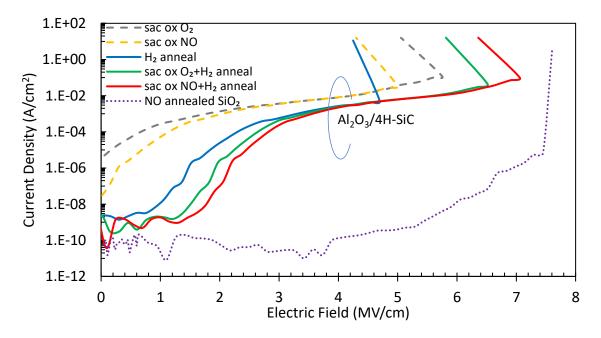

| Figure 4.18: IV measurements performed on Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOS capacitors prepared with                           |

| different surface treatments. 2 hr NO annealed SiO <sub>2</sub> /4H-SiC MOS capacitor IV data is for                                    |

| reference purpose. 128                                                                                                                  |

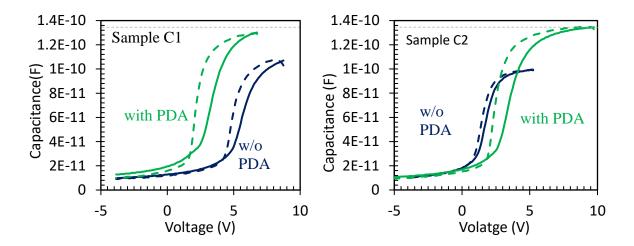

| Figure 4.19: Effect of Post deposition anneal (PDA) on sacrificial oxidized in O <sub>2</sub> (left) and                                |

| sacrificial oxidized in $O_2+H_2$ annealed (right) 4H-SiC/40 nm $Al_2O_3$ MOS capacitors by                                             |

| simultaneous high-low CV measurements where dotted lines represent adjusted quasistatic CV                                              |

| and solid lines represent adjusted 100 kHz high-frequency CV                                                                            |

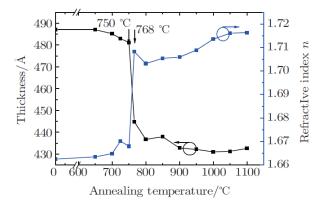

| Figure 4.20: Phase change of $Al_2O_3$ from amorphous to crystalline ( $\gamma$ ) by high temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| annealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

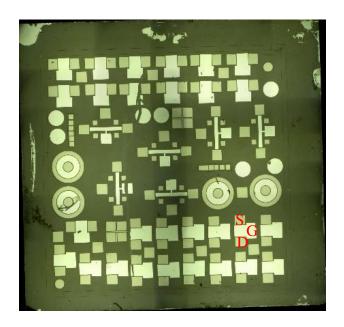

| Figure 4.21: Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOSFET sample top view after fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

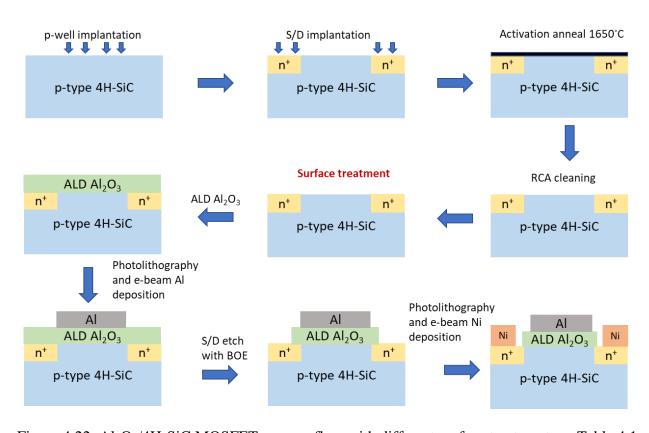

| Figure 4.22: Al $_2O_3$ / 4H-SiC MOSFET process flow with different surface treatments as in Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

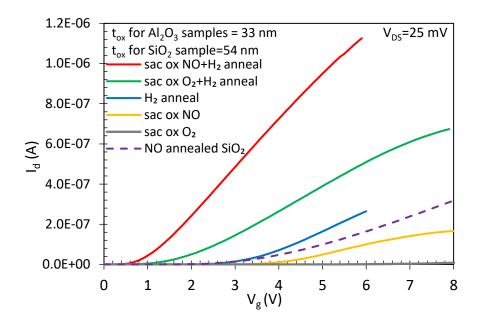

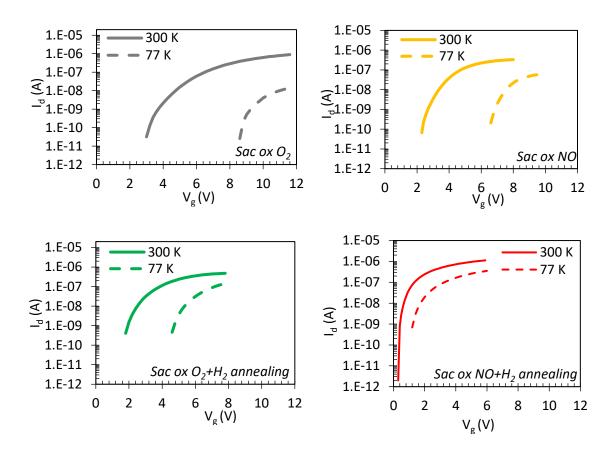

| Figure 4.23: I <sub>d</sub> -V <sub>g</sub> for Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOSFETs prepared with different surface treatments are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| compared with standard 2hr NO annealed SiO <sub>2</sub> /4H-SiC MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

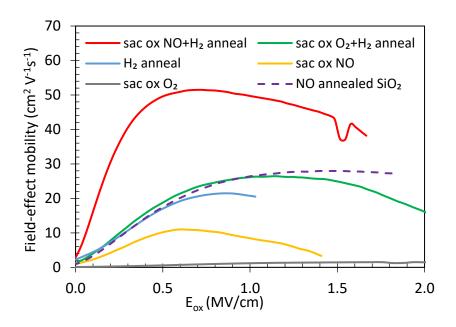

| Figure 4.24: Field-effect mobilities for Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOSFETs prepared with different surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| treatments are compared with standard 2hr NO annealed SiO <sub>2</sub> /4H-SiC MOSFET135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 4.25: $I_d$ - $V_g$ for $Al_2O_3/4H$ -SiC MOSFETs prepared with different surface treatments at 298 $I_d$ - $I_$ |

| K (solid lines) and 77 K (dotted lines)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

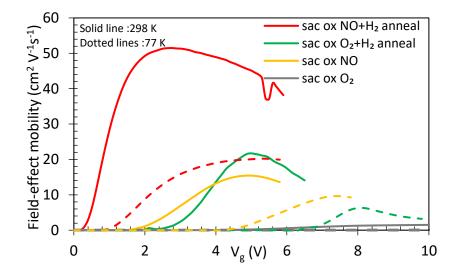

| Figure 4.26: Field-effect mobilities for Al <sub>2</sub> O <sub>3</sub> /4H-SiC MOSFETs prepared with different surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| treatments are compared at 298 K and 77 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |