# Alternative Techniques for Built-In Self-Test of Field Programmable ${\it Gate \ Arrays}$

| Except where reference is made to the work of others, the work described in this | thesis |

|----------------------------------------------------------------------------------|--------|

| is my own or was done in collaboration with my advisory committee. This thesis   | s does |

| not include proprietary or classified information.                               |        |

| Aditya                              | Newalkar                            |

|-------------------------------------|-------------------------------------|

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

|                                     |                                     |

| Certificate of Approval:            |                                     |

| TT                                  |                                     |

|                                     |                                     |

|                                     |                                     |

| Victor P. Nelson                    | Charles E. Stroud, Chair,           |

| Professor                           | Professor                           |

| Electrical and Computer Engineering | Electrical and Computer Engineering |

|                                     |                                     |

|                                     | <u></u>                             |

| Foster Dai                          | Stephen L. McFarland                |

| Associate Professor                 | Acting Dean, Graduate School        |

| Electrical and Computer Engineering |                                     |

# ALTERNATIVE TECHNIQUES FOR BUILT-IN SELF-TEST OF FIELD PROGRAMMABLE GATE ARRAYS

Aditya Newalkar

A Thesis

Submitted to

the Graduate Faculty of

Auburn University

in Partial Fulfillment of the

Requirements for the

Degree of

Master of Science

Auburn, Alabama August 8, 2005

#

| Aditya | News | lkar |

|--------|------|------|

| Aunya  | newa | ınaı |

Permission is granted to Auburn University to make copies of this thesis at its discretion, upon the request of individuals or institutions and at their expense. The author reserves all publication rights.

|               | Signa | ature of Author |             |

|---------------|-------|-----------------|-------------|

|               |       |                 |             |

|               |       |                 |             |

|               | Date  |                 |             |

|               |       |                 |             |

| Copy sent to: |       |                 |             |

| Name          |       |                 | <u>Date</u> |

# VITA

Aditya Newalkar, son of Anil and Sugandha Newalkar was born on April 17, 1979, in Mumbai, India. He graduated with Bachelor of Engineering degree in Electronics Engineering from Mumbai University in December 2000. What started as a student project at Indian Institute of Technology (IIT), Powai, Mumbai in year 1999 grew into valuable two year research experience for him after graduating from Mumbai University. While in pursuit of his Master of Science degree at Auburn University, he received guidance of Dr. Charles Stroud in the Electrical and Computer Engineering department. He worked as an intern in Medtronic Navigation in Louisville, CO.

#### Thesis Abstract

ALTERNATIVE TECHNIQUES FOR BUILT-IN SELF-TEST OF FIELD PROGRAMMABLE

GATE ARRAYS

Aditya Newalkar

Master of Science, August 8, 2005 (B.E., Mumbai University, 2000)

174 Typed Pages

Directed by Charles E. Stroud

In the Built-In Self-Test method of testing the logic and interconnect resources of the Field Programmable Gate Arrays (FPGAs), configuration time and time to retrieve of the test results dominates the duration of the test. The techniques presented in this thesis offer reduction in the configuration time and result retrieval time for the Built-In Self-Test using partial reconfiguration and partial configuration memory readback. Though the work has been done targeting Xilinx Virtex-I and Spartan-II FPGAs, the method is general enough to be applied on any FPGA featuring Partial Run Time Reconfiguration (PRTR). We also evaluate the Computer Aided Design (CAD) tools that are mainly used for partial reconfiguration, for their usefulness in generating test configurations for the programmable interconnect and logic resources of an FPGA using the Built-In Self-Test method.

# ACKNOWLEDGMENTS

The author would like to thank Dr. Charles Stroud for giving him insight on the subject of Built-In Self-Test for FPGAs. The author admires his relentless pursuit for quality and is thankful for his patience. Special thanks to author's family, Anil, Sugandha, Bhau Newalkar and Siddharth Tambe for their unconditional love, support and continuous encouragement. The author thanks all friends from Auburn for making his time enjoyable. Finally, principles by which Mohandas Gandhi lived his life give author strength and inspiration.

Style manual or journal used <u>Journal of Approximation Theory (together with the</u> style known as "aums"). Bibliograpy follows van Leunen's *A Handbook for Scholars*.

Computer software used <u>The document preparation package TFX (specifically LATEX)</u> together with the departmental style-file aums.sty.

# Table of Contents

| Lı  | ST OI | F TABL  | ES                                                            | X   |

|-----|-------|---------|---------------------------------------------------------------|-----|

| Lı  | ST OI | F FIGUI | RES                                                           | xii |

| 1   | Inti  | RODUCT  | ΓΙΟΝ                                                          | 1   |

|     | 1.1   | FPGA    | A Architecture                                                | 1   |

|     |       | 1.1.1   | Programmable Logic Blocks                                     | 1   |

|     |       | 1.1.2   | Programmable Interconnection Network                          | 3   |

|     |       | 1.1.3   | Programmable I/O Cells                                        | 4   |

|     | 1.2   | Flow o  | of Design with FPGAs                                          |     |

|     | 1.3   | Advar   | ntages of FPGAs                                               | 5   |

|     | 1.4   | Recon   | figurable Computing                                           | 6   |

|     |       | 1.4.1   | Dynamic Reconfiguration                                       |     |

|     |       | 1.4.2   | Static Reconfiguration                                        | 8   |

|     |       | 1.4.3   | Partial Reconfiguration                                       | 8   |

|     | 1.5   | Testin  | g of FPGAs                                                    | Ć   |

|     | 1.6   | Built-  | In Self Test                                                  | 10  |

|     |       | 1.6.1   | BIST for FPGAs                                                | 10  |

|     | 1.7   | Thesis  | s Statement                                                   | 12  |

| 2   | Rev   | TEW O   | F PARTIAL RECONFIGURATION AND BIST                            | 14  |

|     | 2.1   |         | tecture of Virtex-I and Spartan-II FPGAs                      | 14  |

|     |       | 2.1.1   | PLB Architecture                                              | 14  |

|     |       | 2.1.2   | Interconnect Architecture                                     | 17  |

|     |       | 2.1.3   | Block RAMs                                                    | 20  |

| 2.2 |       |         | guration of the FPGA                                          | 20  |

|     |       | 2.2.1   | SelectMAP Mode                                                | 21  |

|     |       | 2.2.2   | Boundary Scan Mode                                            | 21  |

|     |       | 2.2.3   | Start-up Sequence                                             | 23  |

|     | 2.3   | Config  | guration Memory Architecture of Virtex-I and Spartan-II FPGAs | 23  |

|     |       | 2.3.1   | Addressing                                                    | 24  |

|     |       | 2.3.2   | Frame Organization                                            | 27  |

|     |       | 2.3.3   | Configuration Registers                                       | 28  |

|     |       | 2.3.4   | Full Reconfiguration Bitstream                                | 32  |

|     | 2.4   | Readb   | 9                                                             | 33  |

|     | . =   | 2.4.1   | Readback Verification                                         | 33  |

|     |       | 2.4.2   | Readback Capture                                              | 33  |

|     |       | 2 4 3   | Readback Operations                                           | 34  |

|   | 2.5 | Partial Reconfiguration                                             | 35  |

|---|-----|---------------------------------------------------------------------|-----|

|   |     | 2.5.1 Partial Reconfiguration without Shutdown Sequence             | 35  |

|   |     | 2.5.2 Partial Reconfiguration with Shutdown Sequence                | 36  |

|   |     | 2.5.3 BitGen                                                        | 36  |

|   |     | 2.5.4 JBits                                                         | 37  |

|   | 2.6 | BIST for FPGAs                                                      | 48  |

|   |     | 2.6.1 Logic BIST                                                    | 48  |

|   |     | 2.6.2 Interconnect BIST                                             | 50  |

|   |     | 2.6.3 BIST for Xilinx FPGAs                                         | 54  |

|   |     | 2.6.4 Using JBits API to Generate Interconnect BIST Configurations  | 57  |

|   | 2.7 | Thesis Statement                                                    | 59  |

| 3 | Par | TIAL RECONFIGURATION AND READBACK FOR LOGIC BIST                    | 61  |

|   | 3.1 | Floorplan of Logic BIST to Aid Partial Reconfiguration              | 62  |

|   | 3.2 | Generating Partial Reconfiguration Files                            | 63  |

|   | J   | 3.2.1 Using BitGen                                                  | 64  |

|   | 3.3 | Generating a Test Plan for Logic BIST                               | 66  |

|   | 3.4 | Experimental Results for Logic BIST                                 | 73  |

|   | 3.5 | Partial Configuration Memory Readback to Retrieve the BIST Results  | 76  |

|   |     | 3.5.1 Commands for Partial Configuration Memory Readback            | 80  |

|   | 3.6 | Summary                                                             | 81  |

| 4 | CEN | NERATING ROUTING BIST CONFIGURATIONS USING JBITS                    | 83  |

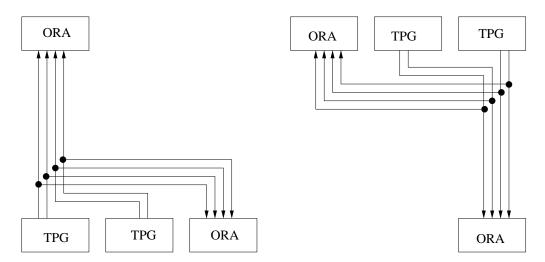

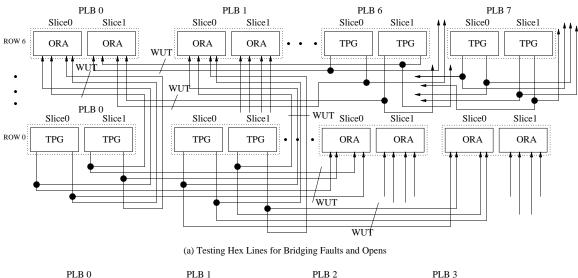

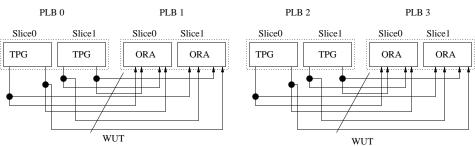

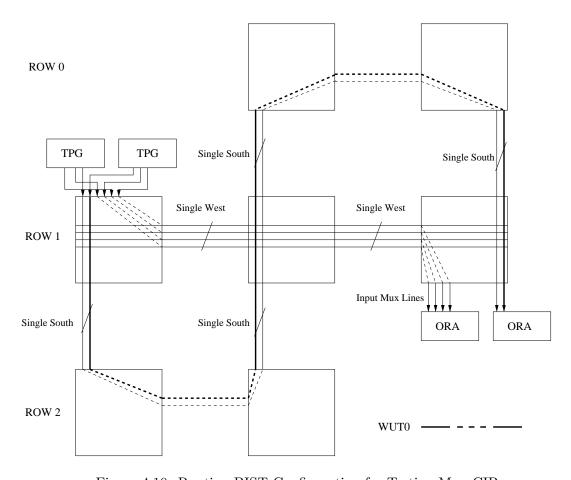

| 4 | 4.1 | Overview of Routing BIST Architecture                               | 84  |

|   | 4.1 | 4.1.1 Testing the Interconnects in Parallel                         | 86  |

|   | 4.2 | The Routing BIST RTPCores                                           | 87  |

|   | 7.2 | 4.2.1 Configuring the TPG                                           | 91  |

|   |     | 4.2.2 Configuring the ORA                                           | 92  |

|   |     | 4.2.3 Routing the WUTs                                              | 93  |

|   |     | 4.2.4 Populating the PLB Array                                      | 94  |

|   |     | 4.2.5 Generating the XDL File                                       | 98  |

|   | 4.3 | Experimental Results of Routing BIST                                | 98  |

|   |     | 4.3.1 Partial Reconfiguration and Routing BIST                      | 102 |

|   |     | 4.3.2 Test Phase Sequence                                           | 104 |

|   | 4.4 | Calculation of the Total Number of Interconnect BIST Configurations |     |

|   |     | Required                                                            | 106 |

|   |     | 4.4.1 Hex Interconnects                                             | 107 |

|   |     | 4.4.2 Single Interconnects                                          | 108 |

|   |     | 4.4.3 Switch Box CIPs                                               | 108 |

|   |     | 4.4.4 MUX CIPs                                                      |     |

|   | 4.5 | Generating Configurations for Switch-Box CIPs                       |     |

|   | 16  | Conclusion                                                          | 199 |

| 5 Summery and Future Work                           | 123 |

|-----------------------------------------------------|-----|

| Bibliography                                        | 127 |

| Appendices                                          | 132 |

| A STEPS IN WRITING PARENT RTPCORE                   | 133 |

| B STEPS IN WRITING CHILD RTPCORES                   | 138 |

| C Complete Program Source                           | 140 |

| D COMPLETE LIST OF CONNECTIONS BETWEEN THE MUX CIPS | 158 |

# LIST OF TABLES

| 2.1  | Virtex TAP Controller Pins                                                                   | 22 |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2  | Constants Used in the Address Calculation [Xil03d]                                           | 26 |

| 2.3  | Variables Used for Address Calculation [Xil03d]                                              | 26 |

| 2.4  | Calculating the Location of the LUT RAM Bit in Virtex-I Bitstream [Xil03d]                   | 27 |

| 2.5  | Equations for Calculating PLB FF Location in the Bitstream $[Xil03d]$                        | 27 |

| 2.6  | PLB Column Frame Organization                                                                | 27 |

| 2.7  | Configuration Registers [Xil03d]                                                             | 29 |

| 2.8  | Command Header Format [Xil02d] $\dots$                                                       | 29 |

| 2.9  | Configuration Commands and their Usage [Xil03d] [Xil04]                                      | 30 |

| 2.10 | Readback Commands Required to Perform Readback on PLB Configuration                          | 34 |

| 2.11 | Classes Used for Bit Level Manipulation of PLB Elements [Xil01d] $\ \ldots \ \ldots$         | 42 |

| 2.12 | Classes Used for Bit Level Manipulation of Switch Box ${\it CIPs}[{\it Xil01d}]$             | 43 |

| 2.13 | Classes Used for Bit Level Manipulation of Output MUX ${\it CIPs}[{\it Xil01d}]$             | 44 |

| 2.14 | Classes Used for Bit Level Manipulation of input MUX ${\it CIPs}[{\it Xil01d}]$              | 44 |

| 2.15 | Model of Interconnect Resources in the Package com.xilinx.JRoute2.Virtex.ResourceDB [Xil01d] | 45 |

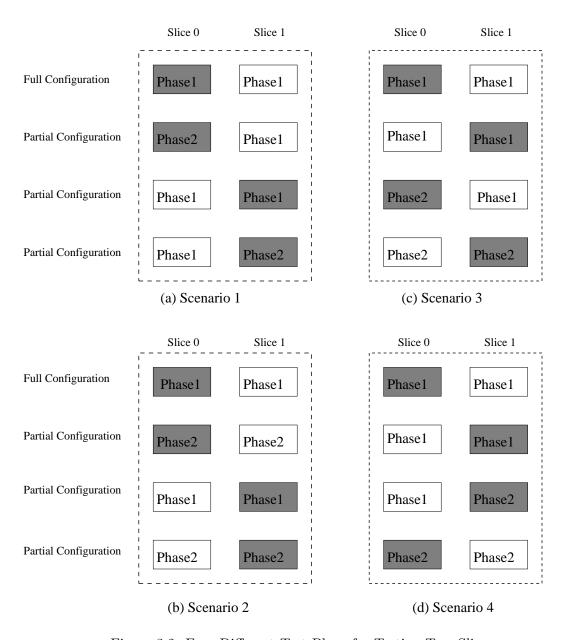

| 3.1  | Command Listing for Scenario 1                                                               | 70 |

| 3.2  | Command Listing for Scenario 2                                                               | 71 |

| 3.3  | Command Listing for Scenario 3                                                               | 72 |

| 3.4  | Command Listing for Scenario 4                                                      |

|------|-------------------------------------------------------------------------------------|

| 3.5  | Partial Frames                                                                      |

| 3.6  | Partial Frames                                                                      |

| 3.7  | Sizes of Partial Bitstreams vs. Full Bitstreams                                     |

| 3.8  | Comparison of Boundary Scan Access Method and Partial Configuration Memory Readback |

| 3.9  | Bitstream for Partial Configuration Memory Readback                                 |

| 4.1  | Connectivity between Output Multiplexers and Interconnects 87                       |

| 4.2  | Input and Output ports of TPGCounterCore                                            |

| 4.3  | Input and Output Ports of ORACore                                                   |

| 4.4  | Command Line Arguments Available for the JBits Program 99                           |

| 4.5  | Possible Values of the Command Line Arguments                                       |

| 4.6  | Command Listing for Generating Partial Bitstreams for Routing BIST $103$            |

| 4.7  | Sizes of Partial Bitstreams vs. Full Bitstreams                                     |

| 4.8  | Routing BIST and Test Phase Sequence                                                |

| 4.9  | Mapping of the CIPs in Various JBits Classes [Xil01d]                               |

| 4.10 | MUX CIPs in Virtex-I Architecture and their Functions $[Xil01d]$ 119                |

| 4.11 | MUX CIP Groups Tested in Parallel                                                   |

| 4.12 | Testing MUX CIPs for Stuck-On and Stuck-Off Faults [SWHA98] 120                     |

| C.1  | Input and Output ports of LUT5                                                      |

| D.1  | Mux CIPs Mux28to1 and Connecting Single Interconnects                               |

| D.2  | MUX CIPs Mux16to1 and Connecting Interconnects                                      |

# LIST OF FIGURES

| 1.1  | General Architecture of FPGA                                                        | 2  |

|------|-------------------------------------------------------------------------------------|----|

| 1.2  | Typical Architecture of PLB [Str02]                                                 | 3  |

| 1.3  | Typical CIP Structure                                                               | 4  |

| 1.4  | Spatial Vs. Temporal Computing [DeH00]                                              | 7  |

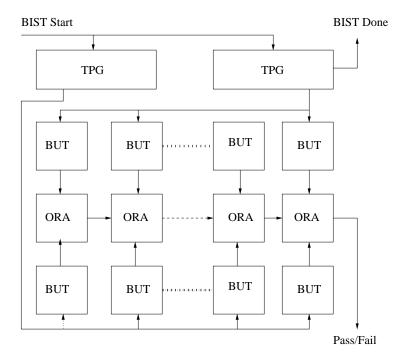

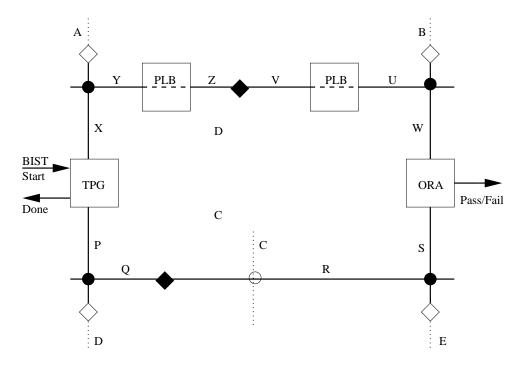

| 1.5  | BIST for FPGA $[AS01]$                                                              | 11 |

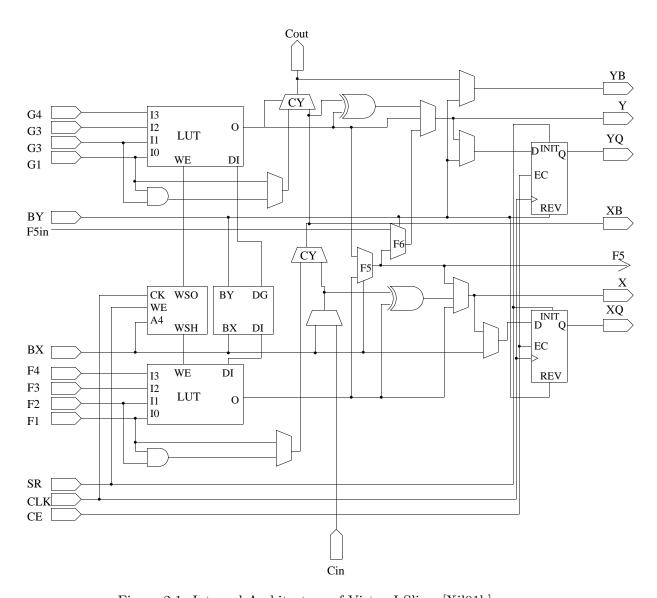

| 2.1  | Internal Architecture of Virtex-I Slice $[Xil01b]$                                  | 16 |

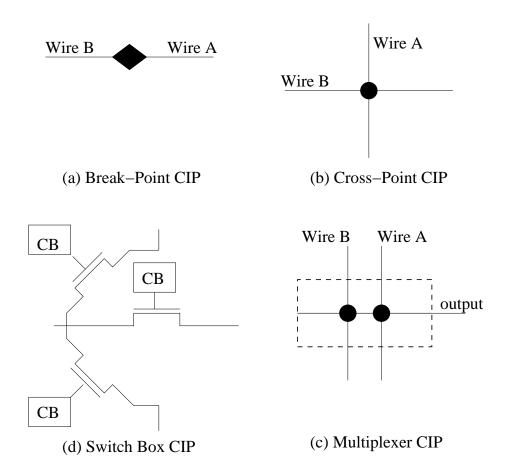

| 2.2  | Different Types of CIPs Found in FPGA $[SWHA98]$ $[FH03]$                           | 18 |

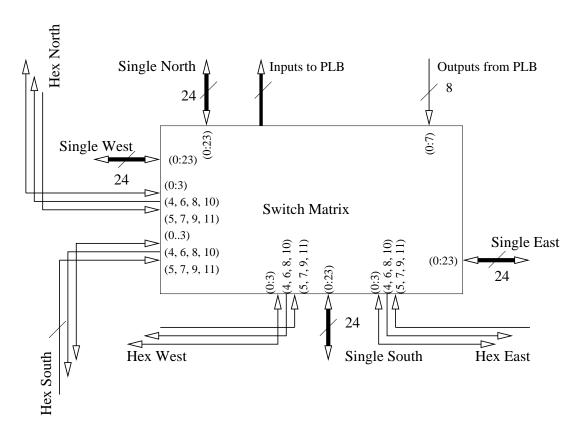

| 2.3  | Switch Box CIP and Xilinx Interconnect Architecture                                 | 19 |

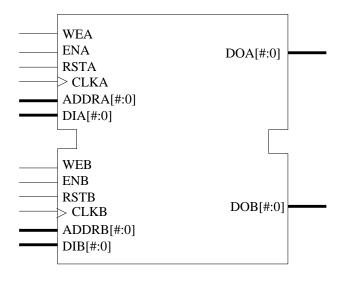

| 2.4  | Block RAM in Virtex-I and Spartan-II FPGAs                                          | 20 |

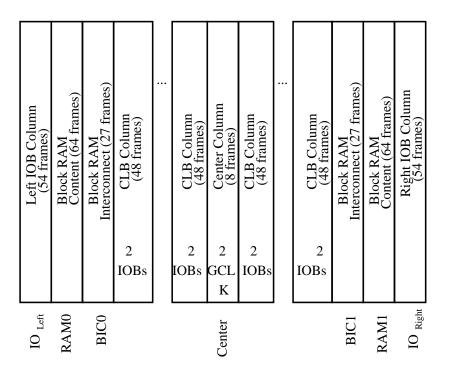

| 2.5  | Xilinx Virtex-I and Spartan-II Addressing Scheme [Xil03d] $\ \ \ldots \ \ \ldots$   | 25 |

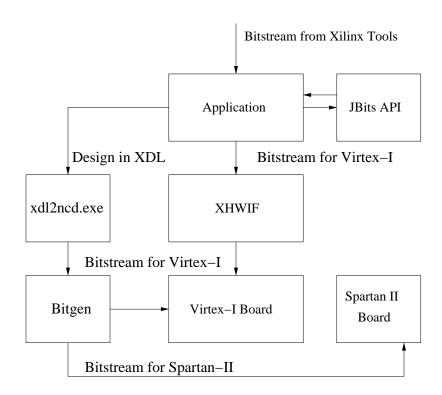

| 2.6  | Design Flow of the Application with JBits                                           | 38 |

| 2.7  | JBits Program for Manual Routing                                                    | 47 |

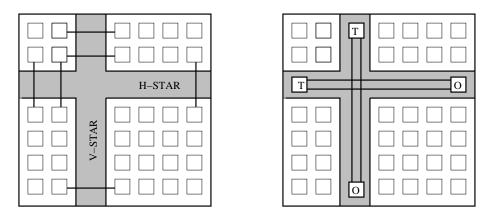

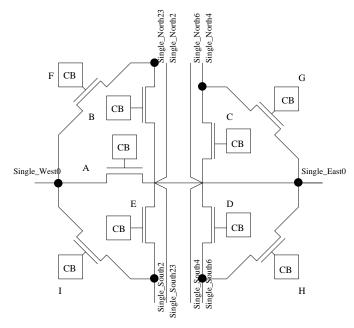

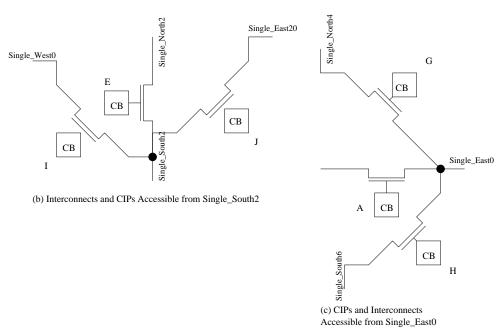

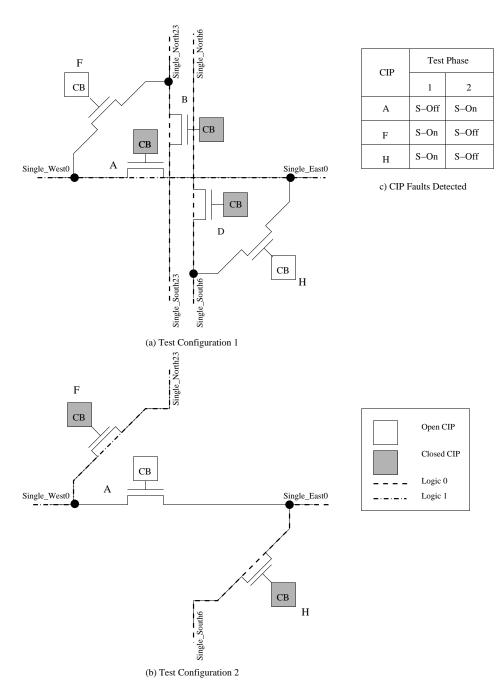

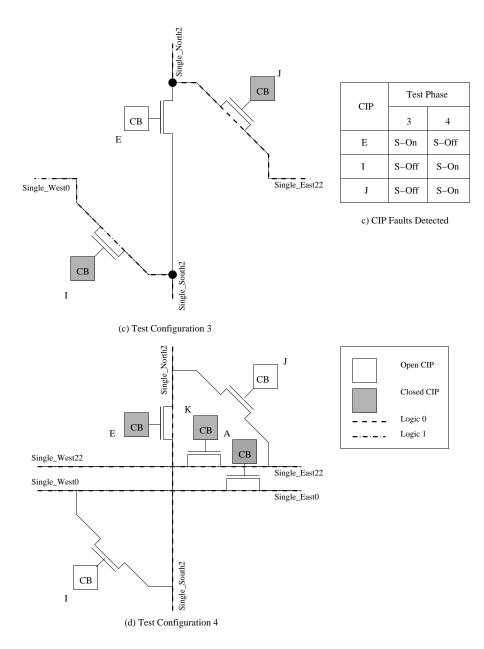

| 2.8  | BIST for FPGA Interconnect Resources [SWHA98]                                       | 51 |

| 2.9  | FPGA Floorplan for Online Interconnect Testing [AES01] $\ \ldots \ \ldots \ \ldots$ | 53 |

| 2.10 | FPGA Floorplan with "Galaxy" BIST [SNLA02]                                          | 54 |

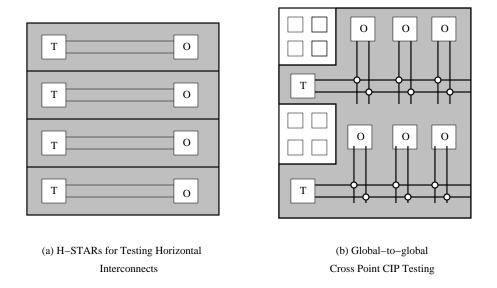

| 2.11 | Complete Testing of Switch Boxes [SWHA98]                                           | 56 |

| 2.12 | Scan Cell Interfacing with IEEE 1149.1 [HGWS99]                                     | 58 |

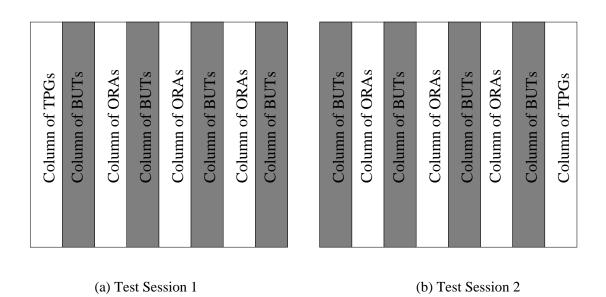

| 3.1  | Floorplan for BIST Test Session                                                     | 63 |

| 3.2  | Four Different Test Plans for Testing Two Slices                                    | 69 |

| 4.1  | Horizontal and Vertical Interconnect Resources Tested for Shorts and Opens          | 85 |

| 4.2  | Hex and Single Wires Tested for Shorts and Opens                        |

|------|-------------------------------------------------------------------------|

| 4.3  | Configuration of Comparator-Based ORA                                   |

| 4.4  | JBits Program for Routing the WUTs                                      |

| 4.5  | Boundary Condition for Populating PLB Array in Vertical Direction 97    |

| 4.6  | Switch Box CIP and Xilinx Interconnect Architecture                     |

| 4.7  | Sections of Switch Box CIP                                              |

| 4.8  | Test Configurations Needed to Completely Test Switch Box CIPs 113       |

| 4.9  | Test Configurations Continued                                           |

| 4.10 | Routing BIST Configuration for Testing Mux CIPs                         |

| 4.11 | Testing MUX CIPs in Parallel [RPFZ99]                                   |

| 4.12 | Problem of Undetected Faults Due to Invisible Logic in MUX [AS01] $118$ |

| A.1  | JBits Program for Instantiating a Counter core                          |

| A.2  | JBits Program Continued                                                 |

| C.1  | Configuration of LUT5 RTPCore                                           |

| C.2  | JBits Program for User Interaction and Populating the PLB Array 145 $$  |

| C.3  | JBits Program Continued                                                 |

| C.4  | JBits Program Continued                                                 |

| C.5  | JBits Program Continued                                                 |

| C.6  | JBits Program Continued                                                 |

| C.7  | JBits Program Continued                                                 |

| C.8  | JBits Program Continued                                                 |

| C.9  | JBits Program Continued                                                 |

| C.10 | JBits Program Continued                                                 |

| C.11 JBits Program Continued | 52 |

|------------------------------|----|

| C.12 JBits Program Continued | 53 |

| C.13 JBits Program Continued | 54 |

| C.14 JBits Program Continued | 55 |

| C.15 JBits Program Continued | 56 |

| C.16 JBits Program Continued | 57 |

# Chapter 1

#### INTRODUCTION

Field programmable gate arrays (FPGAs) have evolved from simple programmable logic devices (PLDs) like programmable array logic (PALs) and programmable logic arrays (PLAs). These early devices were used in digital design as glue logic. As the need of the digital system designers grew from simple decoders to more complicated designs like protocol resolvers, multiple PLDs were connected through a programmable routing architecture to form the FPGA [BR96]. This architecture gives the user the ability to program the interconnects to realize various types of complex digital designs. Due to their size and programmability, testing modern FPGAs has become a complex and time consuming task.

# 1.1 FPGA Architecture

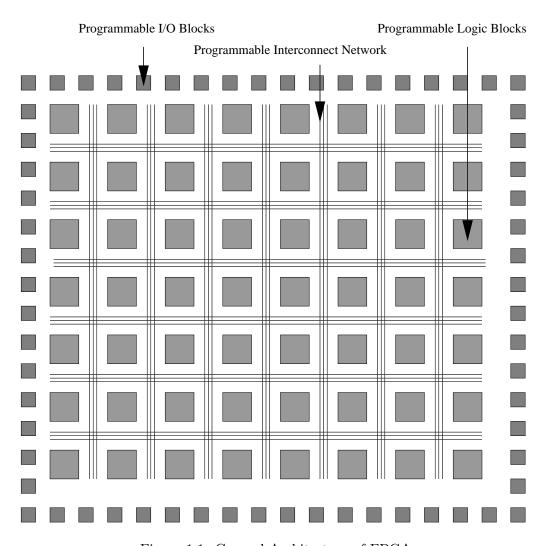

The Figure 1.1 shows the general architecture of a typical FPGA. The FPGA consists of uncommitted resources of an  $N \times M$  array of programmable logic blocks (PLBs), programmable input and output (I/O) cells, a programmable interconnection network, and a configuration memory to program the device.

# 1.1.1 Programmable Logic Blocks

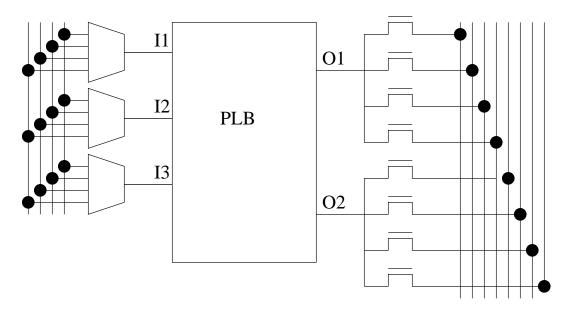

The PLBs of most FPGAs contain multiplexers, *look up tables* (LUTs) and flipflops. An important characteristic of a PLB is its *functionality*, defined as the number of different boolean functions that it can implement [BFRV92]. The elements in the

Figure 1.1: General Architecture of FPGA

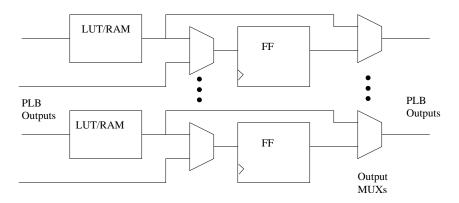

Figure 1.2: Typical Architecture of PLB [Str02]

PLB architecture can be programmed to function in different modes of operation. The LUT can be used either in a LUT mode of operation or random access memory (RAM) mode of operation. In the LUT mode, the element can implement combinational logic functions of multiple inputs (typically 3 to 4). In the RAM mode of operation, the PLB can logically be configured to behave either as a synchronous or asynchronous, single port or dual port RAM. The flip-flops can be configured in latch mode or edge-triggered mode, with asynchronous or synchronous preset/clear, and programmable clock enable. The multiplexers can be selected to connect the LUT outputs to the flip-flops or to bypass the flip-flops [Str02]. Thus the PLB contains the functionality to implement any combinational or sequential logic functions using the logic resources in the architecture as shown in the Figure 1.2. The mode of operation for each element is selected when the device is programmed or configured.

# 1.1.2 Programmable Interconnection Network

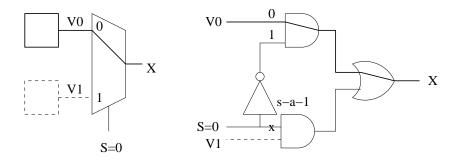

The programmable interconnect network in an FPGA, also called its routing architecture [BFRV92], consists of segments of wires of various lengths and programmable

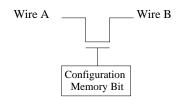

Figure 1.3: Typical CIP Structure

switches. There are global routing resources and local routing resources. Global routing resources facilitate the routing of the signals between the PLBs that are separated by other PLBs. Local routing resources facilitate the routing between PLBs that are next to each other in the array [SNLA02]. The connections are made via configurable interconnect points (CIPs), also referred to as programmable interconnect points (PIPs). A CIP consists of a transmission gate controlled by configuration memory bit. As shown in the Figure 1.3, the connection between the wire segments A and B is made or broken depending upon the logic value of the configuration memory bit [Str02].

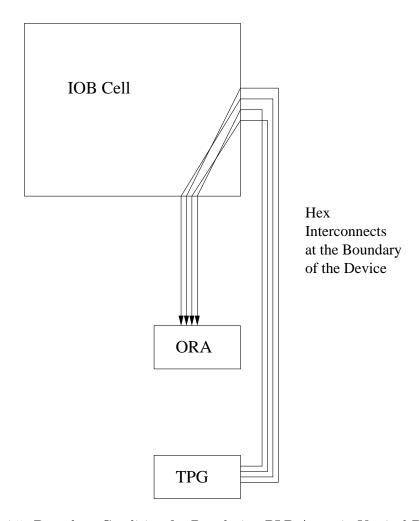

# 1.1.3 Programmable I/O Cells

Most of the I/O pins of the FPGA can be configured in input, output or bidirectional mode of operation. The I/O cells can also be programmed as registered or latched I/Os depending on the design. The I/O cells support TTL as well as CMOS I/O standards thereby eliminating need for the voltage shifters for interfacing [Lat02] [Xil01b].

# 1.2 Flow of Design with FPGAs

The circuit designer typically implements the design in a hardware description language (HDL) and synthesizes the circuit description with the help of one or more computer aided design (CAD) tools. The CAD tools generate a bitstream file that contains programming instructions and data to establish the application specific system functionality of the various programmable resources of the device like PLBs, routing architecture and I/O blocks. This bitstream file is then loaded into the FPGA chip using one of the configuration interfaces provided for the FPGA [Jay01]. The process of loading a design-specific bitstream into one or more FPGAs to define the functional operation of the PLBs, the interconnect resources and I/O blocks is known as configuring or downloading the bitstream to the device [Xil99]. The significance of the FPGA design lies in the fact that static random access memory (SRAM) based FPGAs can be reconfigured an unlimited number of times, implementing a different design each time. In order to implement a different design simply requires overwriting the previous configuration loaded into the SRAM with a new bitstream through the configuration interfaces provided by the FPGA manufacturer [Xil99].

#### 1.3 Advantages of FPGAs

FPGAs provide a low cost solution to low volume products where user programmability is needed at the deployment time. *Application specific integrated circuits* (ASICs) edge out FPGAs in high volume products in terms of unit costs and performance parameters, which are significantly better than FPGAs. The reason for significant difference in performance parameters is that the flexibility provided by the programmability in FPGAs is at the cost of substantial signal delays and area overhead introduced by the programming circuitry [AR94]. However, FPGAs offer some advantages over ASICs including:

- Low cost solution for low volume applications,

- Low non-recurring engineering (NRE) costs, and

- Rapid prototyping [Mil94].

# 1.4 Reconfigurable Computing

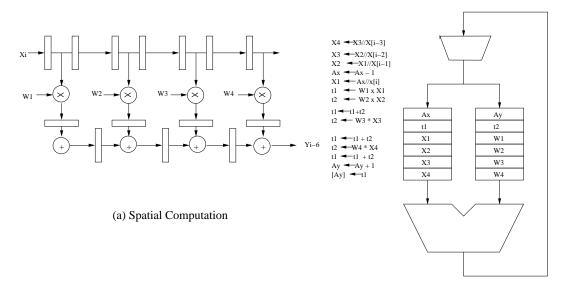

Traditionally, software is considered to be a component that is flexible, relatively slow and inefficient compared to hardware. The hardware is perceived to be customized to the problem and faster compared to the software [DW99]. Hardware can be designed to execute functions concurrently. Therefore, at any given time there are multiple computing elements actively performing their functions. This is referred to as spatial computing. In a conventional processor, instructions are executed serially using memory or registers to store the program variables. This is called temporal computing. Figure 1.4 shows examples of spatial and temporal computing. A conventional digital signal processor (DSP) would take multiple instruction cycles to execute a filter algorithm (Figure 1.4(b)), while the spatial implementation of the same filter in an FPGA gives a new result every cycle in a pipelined fashion, thus higher throughput is observed (Figure 1.4(a)) [DeH00]. The idea of reconfigurable computing tries to bring together best of both worlds. Reconfigurable computing relies on devices, like FPGAs, that are user programmable an unlimited number of times. The more generalized resources or structures like LUTs, flip-flops, and SRAMs, that are provided in an FPGA, can be configured to

(b) Temporal Computation

Figure 1.4: Spatial Vs. Temporal Computing [DeH00]

execute the functions spatially. The process of reconfiguration gives the ability to load different functions in the FPGA serially in time, taking advantage of temporal computing [DeH00] [DW99]. Because of this inherent parallelism in the FPGA architecture, these devices frequently show an order of magnitude higher performance than a general purpose processor [DeH00][CHW00][GSB+00] [DW99].

# 1.4.1 Dynamic Reconfiguration

Dynamic or runtime reconfiguration is a process where the reconfigurable unit is configured without interrupting the configured system function [ESSA00]. The reason for such an arrangement might be that the design is partitioned into many small parts, either too large or too many to fit in the FPGA simultaneously. These partitions of the original design can be loaded into the FPGA without interrupting the function of other

partition(s) already loaded into the FPGA. An external agent like a microprocessor may be used to control which partition(s) is(are) loaded and in what order [ESSA00].

# 1.4.2 Static Reconfiguration

Static or compile time reconfiguration is an idea that can be defined as an inverse of dynamic reconfiguration, where the reconfigurable unit is configured while it is idle or inactive. Most FPGAs are capable of reading the configuration data from an *electrically erasable programmable read-only memory* (EEPROM) when the power is turned on [Xil99]. This is referred to as power-on configuration. This is an example of static reconfiguration.

# 1.4.3 Partial Reconfiguration

Complete reconfiguration of an FPGA chip can be an onerous process [HLS98]. The configuration time varies depending on the size of the bitstream to be loaded into the FPGA. This delay could be unacceptable in high performance systems, which are expected to be reconfigured many times to execute the system function. If the circuit implemented in one configuration is not significantly different from the one implemented in the next configuration, the configuration time can be reduced if the next configuration bitstream were to contain only the programming instructions and data for the programmable resources of the FPGA that are configured differently from the previous configuration. The size of the partial reconfiguration bitstream is now reduced as it contains only the difference between the prior full configuration and the subsequent reconfiguration [HLS98]. The problem in implementing such a scheme is that the FPGAs should have architectural support for configuring only part of their programmable resources,

referred to as partial reconfiguration. For the applications that need to reconfigure only part of their logic depending on the circumstances, this raises an exciting possibility of gaining significant time advantage. Fault-tolerant applications are one example of such applications that benefit from partially reconfigurable architectures [ESSA00].

# 1.5 Testing of FPGAs

Commercially available FPGAs have reached gate counts of 8 million, feature banks of RAMs, hundreds of user I/Os and are capable of running at clock speeds of 400 MHz [Xil02e]. Such high performance FPGA-based systems, when subjected to aging and environment (temperature, humidity, vibration, cosmic rays and  $\alpha$ -rays) are vulnerable to faults [ESSA00]. Therefore having a good FPGA testing method is ever more essential.

Testing of FPGAs poses a different set of challenges than ASICs. The challenge is to test PLBs as well as interconnect resources in all possible modes of operation. It is an important consideration for safety-critical applications because if the test methodology tests only the normal mode of operation for a given system function, when the FPGA is reconfigured to implement different system function, the latent faults may take over and hamper the system function [AS01] [SS99]. Testing the PLBs and interconnect in all possible modes of operation is advantageous for the fault-tolerant applications to identify if any particular mode of PLB operation is faulty so it can be used in one of the other fault-free modes. The testing method is required to detect single and multiple faults in PLBs and interconnects. Meeting this requisite entails selection of a method that is capable of in-system testing. Ideally, the testing method should not introduce any overhead of area and delay penalties [AS01]. Diagnostics provided by the test method

should enable the user to identify and locate the defective module for fault-tolerant applications [SNLA02].

# 1.6 Built-In Self Test

Built-In Self Test (BIST) is a design-for-testability (DFT) approach in which testing (test pattern generation, application and output response analysis) is accomplished through built-in hardware features [AKS93]. In other words, the BIST circuitry is part of the hardware that it tests. One of the advantages of BIST includes the capability of in-system testing without the need of external test equipment.

For ASIC testing, BIST has area overhead and delay penalties. However, when viewed in the context of FPGAs, BIST offers a unique advantage over the external or internal dedicated BIST circuitry: SRAM based FPGAs are reconfigurable and are capable of implementing any given design. While testing, the FPGA may be configured as a BIST circuit, the tests are run and the results are obtained. If the device passes the test, it can be reconfigured to implement the desired system function. If one or more faults are detected and identified, the system function can be reconfigured to avoid the fault(s) for fault-tolerant applications. Thus, the BIST circuit would "disappear" in the reconfiguration process after testing of the device is complete. Therefore, it can be said that testability is achieved without any area or performance penalties [AS01].

# 1.6.1 BIST for FPGAs

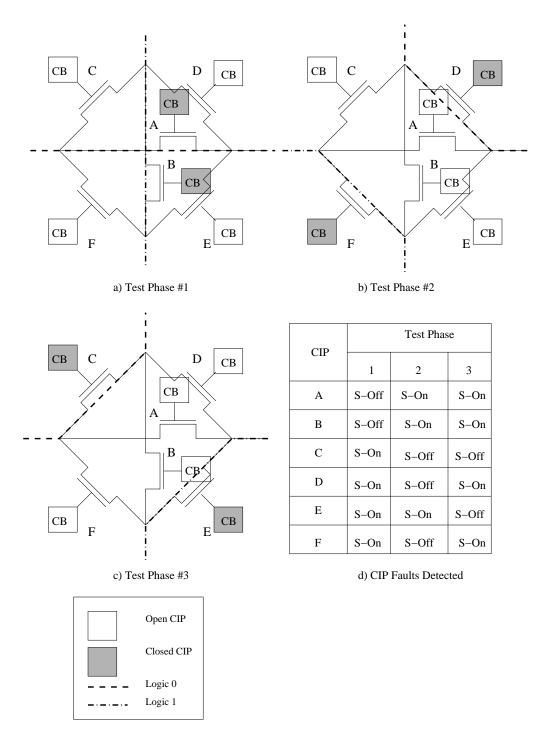

An example of the structure of BIST for FPGAs is as follows: a group of PLBs are configured as test pattern generators (TPGs), blocks under test (BUTs) and output

Figure 1.5: BIST for FPGA [AS01]

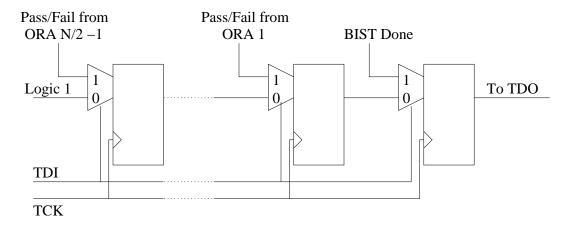

response analyzers (ORAs) as illustrated in Figure 1.5. The TPGs generate test patterns that are applied as inputs to the BUTs. All BUTs are configured and tested in identical modes of operation. The outputs of the identically programmed BUTs for a set of test patterns generated by TPGs are compared by the output response analyzers (ORAs) giving a single Pass/Fail indication at the end of the BIST sequence depending on whether a mismatch in the BUT outputs was observed [SCKA96] [SKCA96] [AES01] [SNLA02] [AS01]. The structure of TPGs can be as simple as a N-bit counter or a linear feedback shift register (LFSR) [Str02]. ORAs consist of comparators with a latch to retain any mismatch observed by the comparison.

The problem with BIST in regards to PLB and interconnect testing is that the FPGA needs to be reconfigured many times, each time testing a different mode of operation. For example, to completely test programmable logic in Xilinx 4000 and Spartan

series FPGAs, 24 BIST configurations are needed, while to completely test interconnects it takes 206 configurations [SLS03]. Therefore, with BIST for FPGAs, testing all modes of operation of the FPGA requires a large number of time consuming reconfigurations and thus poses a problem for high performance systems which cannot afford to spend system down time in lengthy BIST configuration.

# 1.7 Thesis Statement

Since some FPGA architectures are capable of partial reconfiguration to speed-up the reconfiguration process, the work presented in this thesis focuses on optimizing the BIST method for FPGA testing using partial reconfiguration. Chapter 2 presents more details about the full reconfiguration and partial reconfiguration facility offered by the new Xilinx FPGA families like Spartan-II, Spartan-III, Virtex and Virtex-II. In Chapter 2 reviews CAD tools used for partial reconfiguration. It presents details about the boundary scan interface, used to partially reconfigure these FPGAs. It provides details about the current state-of-art BIST method for testing PLBs as well as interconnect resources in FPGAs. Chapter 3 describes how the partial reconfiguration can be used for logic BIST of Xilinx Spartan-II, Spartan-III, Virtex and Virtex-II FPGAs and presents results from actual BIST of PLBs in Spartan-II and Virtex devices to illustrate the improvements obtained with partial reconfiguration. Chapter 4 explores a technique to generate interconnect BIST configurations using Java application programmer's interface library, JBits. The chapter also describes the experiments performed to generate partial interconnect BIST configurations and the effects of partial reconfiguration on the size of the routing BIST configurations. Chapter 4 also includes estimates of the number of BIST configurations required to test the routing resources in Virtex I and Spartan

II FPGAs and considers partial reconfiguration for routing BIST. Finally, Chapter 5 presents the summary and conclusions as well as suggestions for the future research and development. While this thesis will focus on Xilinx FPGAs, it is important to emphasize that these techniques can be applied to any FPGA that supports partial reconfiguration.

#### Chapter 2

# REVIEW OF PARTIAL RECONFIGURATION AND BIST

This chapter begins with a review of the operation and architecture of Xilinx FPGAs. The configuration memory architectures of Virtex-I and Spartan-II families are then reviewed. These two FPGAs have nearly identical architectures and will be the target of this research. The differences between partial reconfiguration and full reconfiguration are discussed along with the CAD tools used to generate partial reconfiguration viz. BitGen and JBits. Finally, a description of how BIST methods are applied to test programmable logic and interconnect of FPGAs is given. In this section, we review the prior work done using JBits to automatically generate interconnect BIST configurations.

# 2.1 Architecture of Virtex-I and Spartan-II FPGAs

The PLB and interconnect architecture of Xilinx Virtex-I and Spartan-II is similar. Therefore, unless specified, whenever reference is made towards Virtex-I architecture it is assumed that it applies to Spartan-II.

# 2.1.1 PLB Architecture

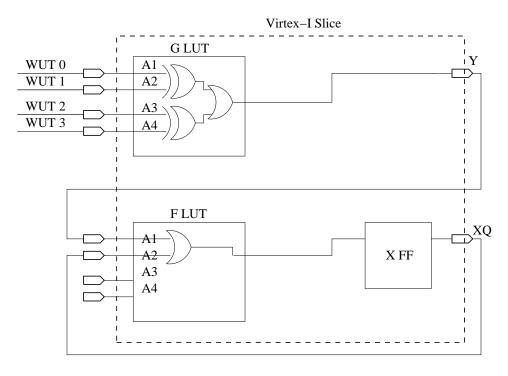

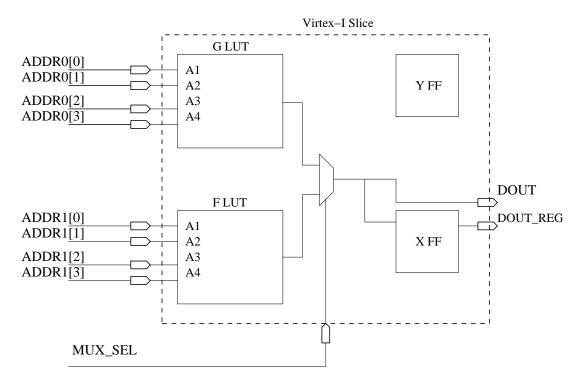

The unit logic cell in the PLB, consists of a 4-input LUT, a flip-flop, and additional dedicated logic. A *slice* consists of two of these unit logic cells. There are two identical slices in a PLB [Xil01b]. The internals of a single Virtex-I slice are shown in Figure 2.1.

# Look-Up Table

Each logic cell in the PLB features a 4-input LUT. The LUT can be used in the LUT mode, in a RAM mode or in a shift register mode of operation. In the LUT mode of operation, it acts as a 4-input combinational logic function generator. In the RAM mode of operation, Virtex-I and Spartan-II contain support for implementing 16x1 synchronous RAM or combining two LUTs in a slice to implement 32x1 or 16x2 synchronous RAM. The LUT can also implement up to a 16-bit shift register in the shift register mode of operation [Xil01b].

# Flip-Flops

The flip-flops can be configured as edge-triggered flip-flops or level-sensitive latches, can be set or reset synchronously or asynchronously, and contain a clock enable signal. The signals used to set or reset the flip-flops are shared by both the flip-flops within the slice. A global reset signal initializes the storage elements [Xil01b]. The value with which the flip-flops are initialized is specified by a specific bit in the configuration bitstream. The input signals can be applied at the input of the flip-flop through the LUT or directly, bypassing the LUT.

# **Additional Logic**

The dedicated carry logic is used to implement the carry chains found in wide adders and counters. In order to realize the wide adders and counters, the carry logic takes carry input from the previous stages [Xil01b]. A dedicated multiplexer CY, illustrated in Figure 2.1, is utilized to implement wide arithmetic logic functions [Xil03c].

Figure 2.1: Internal Architecture of Virtex-I Slice [Xil01b]

Using multiplexer F5 in Figure 2.1, either of the outputs of the LUTs can be selected. Thus implementing a 5-input function generator, a 4:1 multiplexer, or selected functions of up to nine inputs [Xil01b]. The F6 multiplexer, on the other hand, facilitates implementation of any 6-input function, an 8:1 multiplexer, or selected functions of up to 19 inputs [Xil01b].

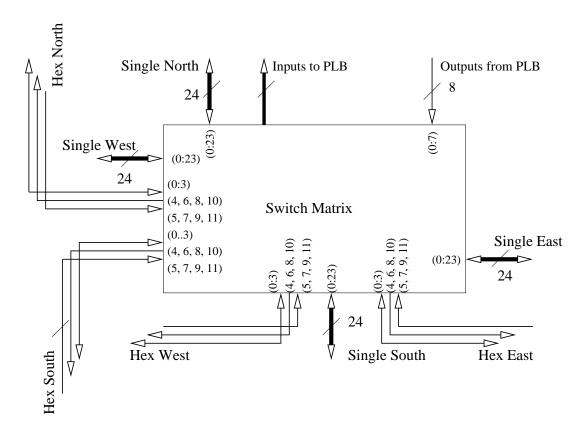

#### 2.1.2 Interconnect Architecture

CIPs are the programmable switches used to make connections in the global and local routing resources and the PLBs. There are three basic types of CIPs that can be found in the FPGA interconnect network: cross-point CIP, break-point CIP and multiplexer CIP, as illustrated in Figure 2.2. The cross-point CIP connects or disconnects the connection between a wire segment in the horizontal plane and a wire segment in the vertical plane, depending on the value loaded in the configuration memory bit. The state of the memory bit controlling the break-point CIP determines if the two segments in the same plane would be connected [SWHA98]. The Xilinx FPGAs feature a switch box CIP or global routing matrix as referred in the literature from Xilinx [Xil01b]. The switch box CIP comprises an array of break-point CIPs that can be programmed to provide a variety of connections in horizontal and vertical routing resources as well as the PLB inputs and outputs as shown in Figure 2.2(d) [Xil01b]. The multiplexer or MUX CIP controls connection to the common interconnect from one of the k possible connections. There are k configuration memory bits associated with a MUX CIP. The complete set of switch box CIPs has 24 Single wires emerging from its four sides that allow connection between the four neighboring switch box CIPs. The Single lines or x1 lines are part of the local interconnects and provide signal connectivity between the

Figure 2.2: Different Types of CIPs Found in FPGA [SWHA98] [FH03]

adjacent PLBs. A total of 12 buffered Hex wires at each of the four sides drive the signal to switch box CIP that is six PLBs away. The Hex lines or the x6 lines span between the PLBs separated by five PLBs and are part of global interconnect resources. A total of 12 Long wire segments provide connectivity across the horizontal width and vertical length of the chip [Xil01b]. The Long wires often carry signals to multiple PLBs and span all the PLBs in horizontal or vertical direction. The switch box featured in Virtex-I and Spartan-II architecture along with the Hex and Single interconnects, is shown in the Figure 2.3.

Figure 2.3: Switch Box CIP and Xilinx Interconnect Architecture

Figure 2.4: Block RAM in Virtex-I and Spartan-II FPGAs

# 2.1.3 Block RAMs

Large memory blocks are provided in the architecture and are referred to as block RAMs. These block RAMs are located along the two outside columns of the PLB array and each memory block RAM occupies the same height as that of 4 PLBs. Thus a PLB array 64 PLBs high will have 16 memory block RAMs in each outer column and thus 32 total block RAMs. The block RAM is, as illustrated in Figure 2.4, a synchronous, dual port memory and has a total capacity of 4096 bits. The width of data and address bus is configurable and can be set as per the design requirement.

# 2.2 Configuration of the FPGA

Typically the bitstream can be downloaded bit serially or byte-wide, i.e. one bit or one byte of configuration data is written into the configuration memory each clock cycle. How the bitstream is loaded into the FPGA depends upon the *configuration mode*. The configuration mode can be selected by setting particular logic levels at the mode-select

pins of the FPGA. Different configuration modes offer different capabilities e.g. speed of configuration, partially reconfiguration etc. Different sequences of events may also take place in different configuration modes. Thus selecting the mode of configuration is an important design decision. Virtex-I and Spartan-II FPGAs support eight different modes of configuration. The partial reconfiguration support is available in selectMAP and boundary scan modes of configuration [Xil02c].

# 2.2.1 SelectMAP Mode

In the selectMAP mode, one byte of the bitstream is written every clock cycle into the configuration data bus interface (pins D[0:7]). To load a given configuration, selectMAP takes the least time among all the configuration modes available [Xil01b]. First the configuration memory is cleared. The configuration control circuitry senses the mode pins and the mode of configuration is determined to be selectMAP. The bitstream is them loaded byte-by-byte on every rising edge of the configuration clock. To ensure the veracity of the bitstream, a cyclic redundancy check (CRC) check is performed at the end. If the CRC checksum loaded is different from the internally calculated CRC, the configuration sequence is aborted. Otherwise the normal Startup-Sequence is commenced as will be discussed in subsection 2.2.3 [Xil02d].

# 2.2.2 Boundary Scan Mode

In the boundary scan mode, one bit of the bitstream is written into the test access port (TAP) of the FPGA each clock cycle. The IEEE 1149.1 test access port and boundary scan architecture is an IEEE standard for in-system testing [IEE90]. The boundary scan has a four wire interface as shown in Table 2.1. All FPGAs from Xilinx support

boundary scan mode of configuration and contain all the mandatory elements in the IEEE 1149.1 standard: the TAP controller, the instruction register, the instruction decoder, the boundary scan register, and the bypass register [Xil01b] [Xil02e] [Xil03b] [Xil03a].

Table 2.1: Virtex TAP Controller Pins

| TDI | Test Data In     |

|-----|------------------|

| TDO | Test Data Out    |

| TMS | Test Mode Select |

| TCK | Test Clock       |

The TAP controller is a 16-state finite state machine. The logic value of the TMS pin at the rising edge of TCK determines the next state of the TAP controller. The data can be shifted into the data registers by selecting the data register scan sequence or the instruction register by selecting the instruction scan sequence.

The Virtex-I and Spartan-II devices implement all the mandatory commands as well as additional commands to the IEEE 1149.1 standard. These additional commands allow read and write access to the configuration memory. The boundary scan interfaces provide two user defined serial interfaces to the core of the FPGA. In order to use them, the interfaces must be incorporated in the design. The user defined serial interfaces are active after the configuration is completed and may be accessed using special instructions to the TAP controller [Xil02b] [Xil02a] [Xil].

The configuration control circuitry senses the mode pins and mode of configuration is determined to be boundary scan. The CFG\_IN instruction is loaded into the instruction register to allow write access to the configuration memory. The bitstream is then loaded bit serially using the boundary scan interface. If the CRC is determined to be correct then the JSTART instruction is loaded in the instruction register which will initiate the Start-up Sequence [Xil02b] [Xil02a].

### 2.2.3 Start-up Sequence

After the bitstream is completely and successfully written into the configuration memory, the *Start-up Sequencer* state machine in the FPGA initiates the *Start-up Sequence*. Start-up is the transition from the configuration mode to normal operational mode of the FPGA [Xil02d]. The Start-up Sequence includes activation of global reset for initialization of the device. Xilinx provides a CAD tool, called BitGen, to control the Start-up Sequence according to the options set by the user. The subsection 2.5.3 gives an overview of this tool.

### 2.3 Configuration Memory Architecture of Virtex-I and Spartan-II FPGAs

The configuration memory of Xilinx Virtex-I FPGAs is divided into sections called frames. A frame contains configuration data for each section of the device, extending vertically from top to the bottom of the device. Multiple configuration frames clubbed together form a column [Xil02d]. The columns can belong to one of the following types:

**Center:** The center column contains the configuration for the four global clock pins and routing in the center of the device.

Configurable Logic Blocks: The PLBs are sometimes also referred to as configurable logic blocks (CLBs). This type of column contains the configuration for all the PLBs and routing in that column, along with two I/O blocks (IOBs) at the top and bottom of the column.

**IOB:** The IOB columns contain the configuration for all the IOBs on the left and right edges of the device.

**Block RAM Interconnect:** These columns contain the configuration for all interconnect of the block RAMs of the device.

Block RAM Content: These columns contain the initial data contents with which the block RAMs will be pre-loaded during configuration [Xil03d].

A frame is the smallest unit of reconfiguration. The least data that needs to be written into the configuration memory, in order to configure a portion of FPGA, is one frame. The length of the frame increases with the dimensions of PLB array to account for the increase in programmable logic and routing resources in the array. The length of the frame is written into a dedicated internal register in the full configuration process. As the FPGA is fully configured at least once before the partial reconfiguration, it is not necessary to write frame length for the partial reconfiguration [Xil02d].

### 2.3.1 Addressing

The configuration memory address space is divided into RAM blocks and PLB blocks. The RAM block contains the block RAM content columns. The PLB blocks include the Center, PLB, IOB and block RAM interconnect columns. These blocks are then further divided into major and minor addresses where each configuration column has a unique major address and each frame has a unique minor address within its column [Xil03d]. For the Virtex-I family, the following addressing scheme is in place for the configuration memory as shown in Figure 2.5 (which also includes the number of frames in each column):

- the address '0' is assigned to the center column,

- the even major addresses of PLB column are on the left side of the device,

Figure 2.5: Xilinx Virtex-I and Spartan-II Addressing Scheme [Xil03d]

- the higher even major addresses are assigned to left IOB columns,

- the left block RAM interconnect columns mark the end of even major addresses,

- the address '1' is assigned to the PLB column at the right side of the center column

- the odd major addresses of PLB column are on the right side of the device,

- the higher odd major addresses are assigned to right IOB columns, and

- the right block RAM interconnect columns mark the end of the PLB address block.

The major and minor addresses for any slice or LUT bit in any row/column can be easily calculated, by inserting the values of the constants in the Table 2.2 and Table 2.3, in the formulae given in Table 2.4 and Table 2.5.

Table 2.2: Constants Used in the Address Calculation [Xil03d]

| Term      | Definition                                                           |  |

|-----------|----------------------------------------------------------------------|--|

| Chip_Cols | Number of PLB columns on the Virtex device.                          |  |

| Chip_Rows | Number of PLB rows on the Virtex-I device.                           |  |

| Chip_Rams | Number of block RAM columns on the Virtex-I device RAM Space         |  |

|           | Spacing of block RAM columns (in terms of PLB columns).              |  |

| FL        | Number of 32-bit words in the frame.                                 |  |

| RW        | 1 for Read, 0 for Write.                                             |  |

| CLB_Col   | Column number of the desired PLB.                                    |  |

| CLB_Row   | Row number of the desired PLB.                                       |  |

| Slice     | 0 or 1.                                                              |  |

| FG        | 0 for the F-LUT, 1 for the G-LUT.                                    |  |

| lut_bit   | The desired bit from the given LUT. Bits in the LUT are indexed from |  |

|           | 0 to 15.                                                             |  |

| XY        | 0 for the X Flip-Flop, 1 for the Y Flip-Flop.                        |  |

| RAM_Col   | Column number of the desired block RAM.                              |  |

| RAM_Row   | Row number of the desired block RAM.                                 |  |

| ram_bit   | The desired bit from the given block RAM. Bits are indexed from 0 to |  |

|           | 4095.                                                                |  |

Table 2.3: Variables Used for Address Calculation [Xil03d]

| MJA           | Frame Major Address.                                                   |  |

|---------------|------------------------------------------------------------------------|--|

| MNA           | Frame Minor Address.                                                   |  |

| $fm_st_wd$    | The index of the word within a full configuration segment that corre-  |  |

|               | sponds to the starting word of the desired frame. A full configuration |  |

|               | segment is defined as the following: 1) for PLB/IOB, all PLB, IOB,     |  |

|               | and RAM interconnect frames beginning at MJA=0, MNA=0 and 2)           |  |

|               | for block RAM, all RAM content frames for the given RAM column.        |  |

|               | Words are numbered starting at 0.                                      |  |

| fm_wd         | The index of the 32-bit word within a frame that contains the desired  |  |

|               | bit. Words in a frame are numbered starting at 0.                      |  |

| fm_wd_bit_idx | The bit index of the desired bit within frame word fm_wd. Words are    |  |

|               | indexed in big-endian style, with bit 31 on the left and bit 0 on the  |  |

|               | right.                                                                 |  |

| fm_bit_idx    | Bit index within a frame of the desired bit. Numbered starting with    |  |

|               | 0 as the left-most (first) bit. Bit numbering within a frame continues |  |

|               | across all the words in the frame.                                     |  |

Table 2.4: Calculating the Location of the LUT RAM Bit in Virtex-I Bitstream [Xil03d]

| MJA           | if (CLB_Col $\leq$ Chip_Cols $\div$ 2),                                                                 |

|---------------|---------------------------------------------------------------------------------------------------------|

|               | then Chip_Cols - CLB_Col $\times$ 2 + 2                                                                 |

|               | else 2 × CLB_Col - Chip_Cols - 1                                                                        |

| MNA           | $lut\_bit + 32 - Slice \times (2 \times lut\_bit + 17)$                                                 |

| fm_bit_idx    | $3 + 18 \times \text{CLB\_Row} - \text{FG} + \text{RW} \times 32$                                       |

| fm_st_wd      | $\mathrm{FL} \times (8 + (\mathrm{MJA} - 1) \times 48 + \mathrm{MNA}) + \mathrm{RW} \times \mathrm{FL}$ |

| fm_wd         | $floor(fm\_bit\_idx \div 32)$                                                                           |

| fm_wd_bit_idx | $31 + 32 \times \text{fm\_wd} - \text{fm\_bit\_idx}$                                                    |

Table 2.5: Equations for Calculating PLB FF Location in the Bitstream [Xil03d]

|               | e i                                                        |

|---------------|------------------------------------------------------------|

| MJA           | if (CLB_Col $\leq$ Chip_Cols $\div$ 2)                     |

|               | then Chip_Cols - CLB_Col $\times$ 2 + 2                    |

|               | else 2 × CLB_Col - Chip_Cols - 1                           |

| MNA           | Slice $\times$ (12 $\times$ XY - 43) - 6 $\times$ XY + 45  |

| fm_bit_idx    | $(18 \times \text{CLB\_Row}) + 1 + (32 \times \text{RW})$  |

| fm_st_wd      | $FL \times (8 + (MJA - 1) \times 48 + MNA) + RW \times FL$ |

| fm_wd         | $floor(fm\_bit\_idx \div 32)$                              |

| fm_wd_bit_idx | $31 + 32 \times \text{fm\_wd} - \text{fm\_bit\_idx}$       |

## 2.3.2 Frame Organization

The frame can be viewed as being vertically superimposed on the device, with the beginning of the frame at the top of the device. As shown in Table 2.6, the first 18 bits control the two IOBs at the top of the column. The subsequent groups of 18 bits are allocated for each PLB row. Finally the last 18 bits control the two IOBs at the bottom of the PLB column. The frame data is then padded with '0's to make it an integral multiple of 32-bit words [Xil03d].

Table 2.6: PLB Column Frame Organization

| I | Top 2 IOBs | PLB R1 | PLB R2 | <br>PLB Rn | Bottom 2 IOBs |

|---|------------|--------|--------|------------|---------------|

|   | 18         | 18     | 18     | <br>18     | 18            |

### 2.3.3 Configuration Registers

The Virtex-I FPGAs provide configuration registers to control the configuration process. The configuration architecture defines eleven 32-bit configuration registers, summarized in Table 2.7. To configure the FPGA, commands are written into these configuration registers followed by the data frames containing the configuration data, which are then loaded into the configuration memory of the FPGA [Xil02d].

The configuration register where the commands are to be written is selected by a 32-bit word called *command header format* (Table 2.8) or *Type-I header*. The field *word count* in the command header format, gives the number of words to be written in the subsequent write sequence. With the command header alone, 2048 32-bit words can be written. The configuration architecture also defines the *large block count header extension format* also known as *Type-II header format*, that supports larger write sequences [Xil02d].

## Command Register (CMD)

The state of the configuration state machine, the Frame Data Register (FDR), and some of the global signals are determined by the command loaded in the command register. The commands are executed each time a new value is loaded into the Frame Address Register (FAR) [Xil03d]. The commands and their functions are summarized in Table 2.9.

## Configuration Option Register (COR)

The bits in the Configuration Option Register (COR) determine the behavior of specific signals used during configuration and the Start-up Sequence. The fifteenth bit

Table 2.7: Configuration Registers [Xil03d]

|                               |     | Ion registers [Anosu]                      |

|-------------------------------|-----|--------------------------------------------|

| Register Name                 | R/W | Function                                   |

| Command (CMD)                 | R/W | Controls the operation of the configura-   |

|                               |     | tion state machine.                        |

| Configuration Option (COR)    | R/W | Sets various options for events that take  |

|                               |     | place in the configuration and behavior of |

|                               |     | the device after configuration.            |

| Control (CTL)                 | R/W | Sets the preferences for the behavior of   |

|                               | ,   | the device after the configuration.        |

| Cyclic Redundancy Check (CRC) | R/W | Used while configuring the device to load  |

|                               | ,   | CRC checksum that is verified against the  |

|                               |     | internally counted one.                    |

| Frame Address (FAR)           | R/W | Used to load the frame address of the en-  |

|                               | ,   | suing frame data. For PLB data, this is    |

|                               |     | automatically incremented after a com-     |

|                               |     | plete frame is loaded. For block RAM       |

|                               |     | data the frame address has to be incre-    |

|                               |     | mented manually.                           |

| Frame Data Input (FDRI)       | W   | Writing the configuration data into the    |

|                               |     | configuration memory.                      |

| Frame Data Output (FDRO)      | R   | Reading the configuration data and         |

|                               |     | states of registers, flip-flops and LUTs   |

|                               |     | from the configuration memory.             |

| Frame Length (FLR)            | R/W | Determines the size of the frame in 32-bit |

|                               | ,   | words.                                     |

| Legacy Output (LOUT)          | W   | For daisy chaining the bitstream of legacy |

| _ , ,                         |     | devices.                                   |

| Mask (MASK)                   | R/W | Mask register for writes to CTL register.  |

| Status (STAT)                 | R   | Loaded with current values of various      |

|                               |     | control and status signals.                |

|                               |     |                                            |

Table 2.8: Command Header Format [Xil02d]

| Type  | Write/Read | Destination Register Address | Byte Address | Word Count   |

|-------|------------|------------------------------|--------------|--------------|

|       |            |                              |              | 32-bit Words |

| 31:29 | 28:27      | 26:13                        | 12:11        | 10:0         |

| 001   | 10/01      | xxxxxxxxxxxx                 | XX           | XXXXXXXXXX   |

Table 2.9: Configuration Commands and their Usage [Xil03d] [Xil04]

|         |      | Domiguration Commands and their Usage [Anood] [Ano4]                |  |

|---------|------|---------------------------------------------------------------------|--|

| Command | Code | Description                                                         |  |

| WCFG    | 1    | Write Configuration Data: Used prior to writing configuration       |  |

|         |      | data to the FDRI. It takes the internal configuration state ma-     |  |

|         |      | chine through a sequence of states that control the shifting of the |  |

|         |      | FDR and the writing of the configuration memory.                    |  |

| LFRM    | 3    | Last Frame: This command is loaded prior to writing the last        |  |

|         |      | (pad) data frame if the GHIGH_B signal was asserted. This com-      |  |

|         |      | mand is not necessary if the GHIGH_B signal was not asserted.       |  |

|         |      | This allows overlap of the last frame write with the release of the |  |

|         |      | GHIGH_B signal.                                                     |  |

| RCFG    | 4    | Read Configuration Data: Used prior to reading frame data from      |  |

|         |      | the Frame Data Output (FDRO). Similar to the WCFG com-              |  |

|         |      | mand in its effect on the Frame Data Register (FDR).                |  |

| START   | 5    | Begin Start-up Sequence: Starts the Start-up Sequence. This         |  |

|         |      | command is also used to start a shutdown sequence prior to par-     |  |

|         |      | tial reconfiguration. The Start-up Sequence begins with the next    |  |

|         |      | successful CRC check.                                               |  |

| RCAP    | 6    | Reset Capture: Used when performing capture in single-shot          |  |

|         |      | mode. This command must be used to reset the capture signal if      |  |

|         |      | single-shot capture has been selected.                              |  |

| RCRC    | 7    | Reset CRC: Used to reset CRC register.                              |  |

| AGHIGH  | 8    | Assert GHIGH_B Signal: Used prior to reconfiguration to pre-        |  |

|         |      | vent contention while writing new configuration data. All PLB       |  |

|         |      | outputs and signals are forced to a one.                            |  |

| SWITCH  | 9    | Switch CCLK Frequency: Used to change the frequency of the          |  |

|         |      | Master CCLK.                                                        |  |

|         |      |                                                                     |  |

of this register is reset by the "SHUTDOWN" command, used for shutting down the FPGA for partial reconfiguration. The "START" command sets this bit to value '1', initiating the Start-up Sequence [Xil03d]. The BitGen tool, which is used to generate the configuration file for the device, provides options to set/reset bits in this register.

# Cyclic Redundancy Check (CRC)

The Cyclic Redundancy Check (CRC) register provides a means of checking for transmission errors in the bitstream. A 16-bit CRC checksum is calculated every time data is written into specific registers using the following polynomial:

$$\text{CRC-16} = X^{16} + X^{15} + X^2 + 1$$

[Xil02d]

The CRC register is used to store the checksum. In complete reconfiguration, CRC check is performed twice by loading a pre-calculated CRC block-check value. The second CRC checksum is calculated with the data of the last frame. A non-zero resulting value indicates error in transmission, therefore, configuration is aborted.

## Frame Address Register (FAR)

The Frame Address Register contains the address of the frame being loaded. The address is partitioned into block type (PLB or RAM block), major address, and minor address. The minor address is auto-incremented each time a complete data frame is loaded and major address is auto-incremented if the last frame for the PLB column is completely loaded. For RAM blocks the major address needs to be loaded separately [Xil03d].

## Frame Data Input Register (FDRI)

The Frame Data Input Register is used to specify the size of the configuration data in words that would be written to the configuration memory. Type-I or Type-II headers are used depending on how large the data is. The FDRI is used to hold this header information [Xil03d].

### Frame Length Register (FLR)

The length of the frame without the pad word is set in terms of 32-bit words in this register. As the devices grow in the array size, the frame length increases to incorporate the configuration data of increased routing and logic resources [Xil03d].

# 2.3.4 Full Reconfiguration Bitstream

The commands in the bitstream for full reconfiguration of a Virtex-I device can be divided into 3 command sets. The first command set initializes the internal configuration logic for loading the data frames. A default value is assigned to the CRC register. The frame length is set in Frame Length Register (FLR). The Configuration Option Register (COR) is loaded with the value that would specify the desired behavior of the device after the configuration. The SWITCH command is loaded into the CMD register to change the configuration clock frequency to the clock frequency specified in the COR.

The second command set writes the configuration data frames. The command, WCFG (Write Configuration), is loaded into the CMD register. This, among other things, activates the circuitry that writes the data loaded into the FDRI into the configuration memory cells. The data word count is specified in command word of Type 1 or if the data word count is too large, the command word of Type 2 follows command word of Type 1. Typically three large frame sets are loaded containing the PLB configuration, the block RAM configuration and the last frame data. At the end of the third frame set, the CRC checksum is loaded into the CRC register. The Last Frame command (LFRM) is loaded into the CMD register indicating to the configuration circuitry that the following frame set will be the last frame.

The third command set triggers the Start-up Sequence with the START command and completes the CRC checking and activates the FPGA.

### 2.4 Readback

Readback is the process of reading data from the configuration memory [Xil02d]. Readback can be utilized to compare the stored configuration against the actual bit-stream, as well as to read the current state of all internal PLB and IOB registers, LUTs operating in RAM mode and block RAM values. The former is known as readback verification and latter is referred to as readback capture. Both verification and capture can be done in one readback sequence.

### 2.4.1 Readback Verification

Readback verification can be obtained without any changes in the configuration memory, through selectMAP and boundary scan mode [Xil02d]. This readback data can then be verified against a *bitmap file* generated by the BitGen tool when run with "readback" option enabled for each design.

### 2.4.2 Readback Capture

In order to examine the state of the internal logic resources, the readback capture capability must be enabled. An additional readback capture option allows a single capture or multiple captures after the device is configured. When asserted, the register states are captured in unused space in the configuration memory on the rising edge of the clock signal [Xil] [Xil02d].

Table 2.10: Readback Commands Required to Perform Readback on PLB Configuration

| Synchronization word                 | AA99 5566h |

|--------------------------------------|------------|

| Packet Header: Write to FAR Register | 3000 2001h |

| Packet Data: Starting frame Address  | 0000 0000h |

| Packet Header: Write to CMD Register | 3000 8001h |

| Packet Data: RCFG                    | 0000 0004h |

| Packet Header: Read from FDRO        | 2800 6000h |

| Packet Header Type 2: Data Words     | 48- —-h    |

The logic allocation file provided by BitGen indicates the absolute position of the flip-flop bits in the complete readback file. This information will prove to be important while retrieving BIST results, as will be discussed in Chapter 3.

### 2.4.3 Readback Operations

Readback is performed by reading a data packet from the Frame Data Output Register (FDRO) register. There are three types of data packets to be read (one for PLB configuration with capture data and two for block RAMs). The commands needed to be given in order to accomplish this are summarized in Table 2.10.

The complete configuration memory readback is initiated by writing the starting frame address of (0000 0000)h in the FAR register. The number of words to be read for full readback capture is function of the size of the device, e.g. for an XCV100 the number of 32-bit readback words would be 22,554 [Xil02d].

The bits in the readback bitstream indicate three types of information 1) configuration data, 2) captured data and 3) pad bytes. The pad bytes align the frame data to a 32-bit word boundary. It can be noted that readback bitstream does not contain any CRC check information.

### 2.5 Partial Reconfiguration

The sequence of events taking place while partially reconfiguring the device is considerably different than that of full reconfiguration. For partial reconfiguration, it is required that device be fully configured once and that the configuration interface be active after the full configuration is complete. That is to say, the I/O pins used for selectMAP mode of reconfiguration would retain their configuration function [Xil02d]. The boundary scan mode is a permanent interface and is always present [Xil03d].

The bitstream performing partial reconfiguration of any logic resource of the FPGA, henceforth simply referred to as a partial bitstream, contains the major and minor addresses of the frame containing the configuration data for that resource. The major and minor addresses of the frame are calculated using formulae given in Table 2.4 and Table 2.5 [Xil03d]. The partial bitstream contains instructions to write the address to the FAR register. The ensuing instructions load the FDRI register with the number of words to be written into the configuration memory. After these instructions, the frame data follows. There are two ways in which the FPGA can be partially reconfigured: with or without shutdown [Xil02c].

# 2.5.1 Partial Reconfiguration without Shutdown Sequence

If the device is not shut down, the functions implemented in the parts of the FPGA not affected by partial reconfiguration may continue to work without interruption. The logic changes in the PLB or routing take place once the corresponding frame gets completely written into the device. This mode would be used for operations such as online testing and fault-tolerance [AES01].

### 2.5.2 Partial Reconfiguration with Shutdown Sequence

If the device is shut down, then parts of the FPGA not affected by partial reconfiguration would stop executing the configured function. At the start of the Shutdown Sequence, the dummy word (FFFF FFFF)h and the synchronization word (AA99 5566)h are written. The dummy word provides the clock cycles necessary to initialize the configuration logic. The synchronization word is used to align the bitstream on the 32-bit-word boundary [Xil04]. The Shutdown bit is set in the COR register. The START command is then loaded into the CMD register to start the Shutdown Sequence. The CRC value is reset. As the Shutdown Sequence requires all the other logic in the device to be disabled, the clock to all sequential logic is disabled. The AGHIGH command is then loaded into the CMD register to prevent contention on the internal signals while writing the new data. As the GHIGH B signal is asserted due to the AGHIGH command, the LFRM command is written into the CMD register. This allows writing the Last Frame packet as GHIGH B signal is released [Xil03d].

#### 2.5.3 BitGen

BitGen is a command line tool that converts the netlist file in Xilinx native format (.ncd file) into a configuration bitstream file. The FPGA can then be configured with this bitstream. This tool gives a number of options to control the tasks, in and after the Start-up Sequence, for the design implemented. These tasks include: the timing of the start-up signals, clock rate to be used for the configuration, signal assignment of some of the I/O pins used during configuration once the configuration is over, etc. The BitGen options are set as per the design being implemented. BitGen also gives options for generating a partial reconfiguration bitstream that contains only the difference between

the .ncd file, and the old bitstream. The use of BitGen for partial reconfiguration during BIST will be discussed in more detail in Chapter 3.

#### 2.5.4 JBits

JBits is a set of Java classes which provide an Application Program Interface (API) into the Xilinx XC4000, Virtex-I, Virtex-II series FPGA bitstreams [GLS99]. The JBits API facilitates writing applications that would modify the bitstream on-the-fly, configure and readback from the FPGA configuration memories [Xil01a]. The API gives the programmer gate level access to the FPGA and the Java programming language allows a programmer to create many layers of abstraction. JBits can therefore be used to write custom CAD tools featuring dynamic partial reconfiguration or traditional CAD tools to produce place-and-route for the FPGA families supported [Xil01a].

The simplest of the applications that can be built with JBits API would take the bitstream generated by BitGen as input and configure an FPGA board with it. More advanced applications contain circuit designs specified with the JBits API calls and generate the output in Xilinx Design Language (XDL) which defines the netlist in symbolic format along with the bitstream. The design flow with JBits API is illustrated in Figure 2.6.