#### **Novel Approaches for Microelectronics Security and Test**

by

### Ziqi Zhou

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama August 7, 2021

Keywords: Hardware Security, Piracy, Logic Locking, Obfuscation, Design-for-Security, Tampering, Hardware Trojan, Magnetic Skyrmion, Fault Modeling.

Copyright 2021 by Ziqi Zhou

### Approved by

Ujjwal Guin, Chair, Assistant Professor, Electrical and Computer Engineering Vishwani D. Agrawal, Professor Emeritus, Electrical and Computer Engineering Adit D. Singh, Godbold Chair Professor, Electrical and Computer Engineering Peng Li, Assistant Professor, Electrical and Computer Engineering Shubhra (Santu) Karmakar, Reader, Assistant Professor, Computer Science and Software Eng.

#### **Abstract**

Due to the globalization in semiconductor industry, the cost of maintaining a foundry is enormous. Hence, most integrated circuit (IC) design houses have become fabless. Typically, a design house acquires multiple third party intellectual property (IP) cores for a system on a chip (SoC) and sends a contract to a foundry/fab for manufacturing and test. The global supply chain of semiconductor design, manufacture, and test opens up a Pandora's box of harmful threats. These can be overproduction or counterfeiting of ICs, piracy of intellectual property (IP), or insertion of hardware Trojans. To prevent these threats, researchers have proposed solutions that include hardware metering, logic locking, IP watermarking, and split manufacturing to address threats.

Logic locking is a widely studied design-for-security (DFS) measure. It protects the IP by inserting logic gates in the design to allow it to become completely functional only when a secret key is programmed in. The inserted logic commonly consists of XOR/XNOR gates, multiplexers (MUXs) or look-up tables (LUTs). The existing logic locking can be disabled using the existing state-of-art methods that include Boolean satisfiability (SAT) based attacks, probing, and tampering attacks. One can obtain the secret key from a functional chip and then unlock any number of locked ones as the secret key is same for every chip.

In this dissertation, we are the first to propose a new secure logic locking method by implementing a design-for-security (DFS) architecture. We modify the scan cell such that it can be set to hold its previous state. To accomplish this the output of the flip-flop (FF) is fed back to its input through a multiplexer (MUX). The proposed infrastructure can prevent the adversary from obtaining the key by accessing the scan chains. Our modification does not affect the testability of the chip during the normal manufacturing flow, which may include the test before activation, post-silicon validation, and debug. Moreover, the proposed secure cell can disable scan dump after functional activation. The proposed design is resistant to various known attacks at a cost lower than 1% area overhead.

Besides the design-for-security (DFS) architecture, we also propose a novel attack that can break any logic locking techniques that rely on stored secret key. This proposed Tampering Attack on

Any Key-based Logic Locked Circuit *TAAL* inserts a malicious hardware Trojan in the netlist, which, when activated, leaks the secret key to an adversary. The attack approach is to tamper with the locked netlist in order to extract the secret key information. The untrusted foundry can extract the netlist of a design from the layout/mask information, which makes it feasible to implement such a hardware Trojan with the adversary's knowledge. Three types of *TAAL* attacks are proposed for extracting the secret key through hardware Trojans placed at various locations in the netlist. Models for both combinational and sequential hardware Trojans are introduced such that they would evade manufacturing tests. An adversary only needs to choose one hardware Trojan out of a large set of possible Trojans to launch the proposed attack.

Given the above-mentioned Trojan attacks, a method to detect this tampering is necessary. In this dissertation, we devise tests that would detect a Trojan in a manufactured chip. Based on the two parts of a Trojan, namely, a trigger derived as a Boolean function of any set of signals and a payload (typically, an XOR gate) inserted on a signal line, we develop a test generation model. A single-line trigger combined with a single payload line gives a set of  $2K \times (K-1)$  Trojans in this model for a circuit with K signal lines. Tests for these are shown to be the vectors that detect "conditional stuck-at" faults, for which we give a test generation algorithm using standard Automatic Test Pattern Generation (ATPG) tools. This procedure allows us to define and measure a Trojan coverage metric for tests. Results show scalability of these tests, besides being more effective in detecting real Trojans than N-detect stuck-at test vectors or random vectors.

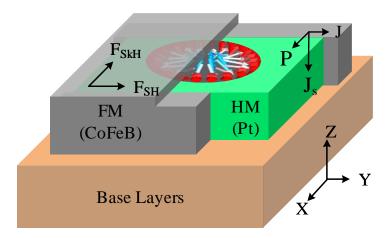

Considering the previous hardware Trojan detection methods, we realize that the fault modeling can both benefit manufacturing tests and hardware Trojan detection. We develop a fault modeling methodology to generate test patterns to detect defects in Skyrmion circuit, which is an emerging technology. We examine breaks, extra material, etching blemishes, bridges in nanotrack interconnects, etc., forming a set of 19 technology-specific defects in the skyrmion gate structures. We believe we are the first to characterize such defects using magnetic simulation. Simulator  $MuMax^3$  is used to exhaustively simulate all gates, and each defect is mapped onto an analyzable fault model using the principle of fault equivalence. Experiments on benchmark circuits demonstrate that tests for all nanotrack breaks can be found using the available ATPG and simulation tools. Some defects are classified as technology-specific defects. For example,

a bridge between two nanotracks results in simultaneous AND and OR functions on respective nanotracks. This dissertation presents the test generation results for the Skyrmion versions of benchmark circuits for defects that can be expressed as a single stuck-at faults.

This dissertation provides a comprehensive overview of attackers and their attack choices. The proposed DFS structure can provide sufficient security to resist SAT-based attacks, and the proposed hardware Trojan detection method can effectively detect potential risks in the circuit. For emerging technologies, a technology-specific defect to logic-fault modeling approach of testing is proposed. The proposed future work provides definitive paths into new directions for the research community.

#### Acknowledgments

I would like to express my heartfelt gratitude to Dr. Ujjwal Guin, my graduate advisor, for his encouragement and guidance during my time at Auburn University. His encouragement and guidance paved the way for my successful research projects and thesis completion. I would like to express my gratitude to Dr. Vishwani Agrawal for his experience and insight into research. This dissertation would not have been possible without his constant support and guidance. Also, special thanks to Dr. Adit Singh for his great help and efforts. I would like to thank Dr. Peng Li for leading me into a new field of scientific research, and helping me achieve results in this field. I would also like to thank Dr. Karmaker for being my university reader providing me with valuable comments and kind support. I want to extend my gratitude to the committee members again for their time, support, and advice toward my research and thesis preparation. Thanks to all of my labmates and colleagues for the valuable information I acquired during my course and study work. The lab exercises and brainstorming sessions taught me a lot about my field of study, and I owe much gratitude to them. Finally, I would like to thank my parents and friends for their unwavering support during my academic career.

## Contents

| Ał | ostrac                                                                        | t        |                                                                | ii  |  |  |  |  |

|----|-------------------------------------------------------------------------------|----------|----------------------------------------------------------------|-----|--|--|--|--|

| Αc | cknow                                                                         | ledgme   | nts                                                            | V   |  |  |  |  |

| Li | st of A                                                                       | Abbrevia | ations                                                         | xii |  |  |  |  |

| 1  | Intr                                                                          | oduction | n                                                              | 1   |  |  |  |  |

|    | 1.1                                                                           | Motiv    | ration                                                         | 2   |  |  |  |  |

|    | 1.2                                                                           | Contr    | ibutions                                                       | 2   |  |  |  |  |

|    | 1.3                                                                           | Organ    | nization of this Dissertation                                  | 3   |  |  |  |  |

| 2  | Bacl                                                                          | kground  | and Prior Work                                                 | 5   |  |  |  |  |

|    | 2.1                                                                           | Logic    | Locking                                                        | 5   |  |  |  |  |

|    | 2.2                                                                           | Hardy    | vare Trojan                                                    | 8   |  |  |  |  |

| 3  | A Design-for-Security Architecture to Prevent IP Piracy and IC Overproduction |          |                                                                |     |  |  |  |  |

|    | 3.1                                                                           | The R    | elated Work                                                    | 11  |  |  |  |  |

|    | 3.2                                                                           | Attack   | ss on Existing Logic Obfuscation Techniques                    | 14  |  |  |  |  |

|    |                                                                               | 3.2.1    | Brute-Force Attack Based on Logic Cones                        | 15  |  |  |  |  |

|    |                                                                               | 3.2.2    | Greedy Attacks on Logic Cones                                  | 17  |  |  |  |  |

|    | 3.3                                                                           | Descri   | ption of the Proposed Design-for-Security (DFS) Implementation | 20  |  |  |  |  |

|    |                                                                               | 3.3.1    | Requirements of DFS Implementation                             | 20  |  |  |  |  |

|    |                                                                               | 3.3.2    | Proposed Design-for-Security (DFS) Architecture                | 21  |  |  |  |  |

|    | 3.4                                                                           | Propos   | sed Flow for Enabling Trust in IC Manufacturing and Test       | 26  |  |  |  |  |

|   | 3.5 | Results and Analysis |                                                       |    |  |  |  |  |  |

|---|-----|----------------------|-------------------------------------------------------|----|--|--|--|--|--|

|   |     | 3.5.1                | Security Analysis                                     | 29 |  |  |  |  |  |

|   |     | 3.5.2                | Area Overhead Analysis                                | 30 |  |  |  |  |  |

|   |     | 3.5.3                | Simulation Results                                    | 31 |  |  |  |  |  |

|   | 3.6 | Summ                 | ary                                                   | 32 |  |  |  |  |  |

| 4 | TAA | .L: Tam              | pering Attack on Any Key-Based Logic Locked Circuits  | 34 |  |  |  |  |  |

|   | 4.1 | Propos               | sed TAAL Attack for Extracting Secret Keys            | 36 |  |  |  |  |  |

|   |     | 4.1.1                | Adversarial Model                                     | 37 |  |  |  |  |  |

|   |     | 4.1.2                | T1 Type TAAL Attack                                   | 37 |  |  |  |  |  |

|   |     | 4.1.3                | T2 Type TAAL Attack                                   | 38 |  |  |  |  |  |

|   |     | 4.1.4                | T3 Type TAAL Attack                                   | 39 |  |  |  |  |  |

|   | 4.2 | Design               | ning Hardware Trojans for TAAL Attacks                | 41 |  |  |  |  |  |

|   |     | 4.2.1                | Design of a Combinational Hardware Trojan             | 42 |  |  |  |  |  |

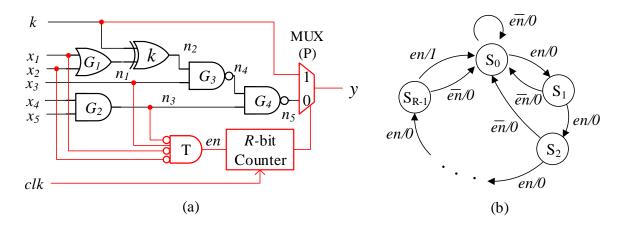

|   |     | 4.2.2                | Design of a Sequential Hardware Trojan                | 45 |  |  |  |  |  |

|   |     | 4.2.3                | Design of an Analog/RF Trojan                         | 47 |  |  |  |  |  |

|   | 4.3 | Analys               | sis                                                   | 48 |  |  |  |  |  |

|   |     | 4.3.1                | Complexity Analysis                                   | 48 |  |  |  |  |  |

|   |     | 4.3.2                | Overhead Analysis                                     | 50 |  |  |  |  |  |

|   | 4.4 | Future               | Research Direction for Secure Logic Locking           | 54 |  |  |  |  |  |

|   | 4.5 | Summ                 | ary                                                   | 56 |  |  |  |  |  |

| 5 | Mod | leling ar            | nd Test Generation for Combinational Hardware Trojans | 58 |  |  |  |  |  |

|   | 5.1 | Model                | ing a Hardware Trojan                                 | 59 |  |  |  |  |  |

|   |     | 5.1.1                | Hardware Trojan Model                                 | 60 |  |  |  |  |  |

|   |     | 5.1.2                | Finding All Type- <i>n</i> Trojans                    | 63 |  |  |  |  |  |

|   | 5.2 | Test G               | eneration for Type- <i>n</i> Trojans                  | 65 |  |  |  |  |  |

|    |        | 5.2.1     | Conditional SAF Pattern (CSP-1 or CSP) Generation         | 65 |

|----|--------|-----------|-----------------------------------------------------------|----|

|    |        | 5.2.2     | An Example: Circuit of Figure 5.2                         | 67 |

|    | 5.3    | Bench     | mark Circuits                                             | 67 |

|    | 5.4    | Summ      | ary                                                       | 69 |

| 6  | Defe   | ect Char  | acterization and Testing of Skyrmion-Based Logic Circuits | 70 |

|    | 6.1    | How S     | kyrmion Works?                                            | 71 |

|    |        | 6.1.1     | Skyrmion Motion in Nanotrack                              | 71 |

|    |        | 6.1.2     | Micromagnetic Simulation Platform                         | 73 |

|    |        | 6.1.3     | Skyrmion Logic Gates                                      | 73 |

|    | 6.2    | Defect    | Characterization                                          | 76 |

|    |        | 6.2.1     | Interconnect Faults                                       | 76 |

|    |        | 6.2.2     | Technology-Specific Defects in Gates                      | 77 |

|    | 6.3    | Fault N   | Modeling                                                  | 81 |

|    | 6.4    | Test Pa   | attern Generation                                         | 82 |

|    | 6.5    | Result    | s and Discussion                                          | 84 |

|    | 6.6    | Summ      | ary                                                       | 85 |

| 7  | Con    | clusion a | and Future Work                                           | 87 |

|    | 7.1    | Conclu    | usion of Dissertation                                     | 87 |

|    | 7.2    | Future    | Work                                                      | 88 |

|    |        | 7.2.1     | Hardware Trojan Detection                                 | 88 |

|    |        | 7.2.2     | Emerging Technologies                                     | 89 |

| Bi | bliogr | aphy      |                                                           | 90 |

## List of Figures

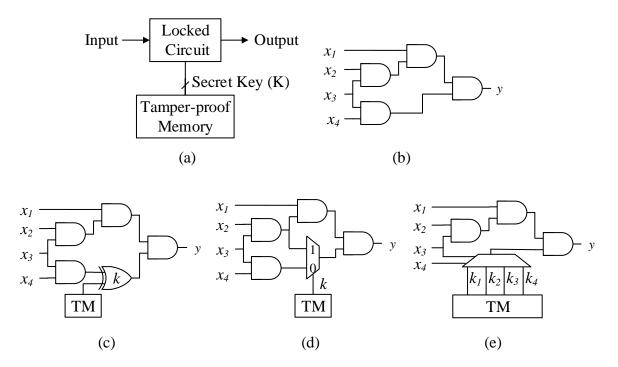

| 2.1 | Different logic locking techniques. (a) A locked circuit, where the secret key $(K)$ is programmed in a tamper-proof memory $(TM)$ . (b) Original circuit. (c) XOR-based locking [1]. (d) MUX-based locking [2,3]. (e) LUT-based locking [4].                                                                                                                | 6  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

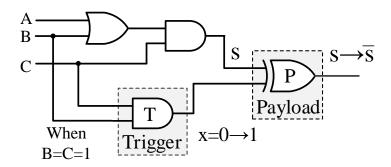

| 2.2 | A Hardware Trojan                                                                                                                                                                                                                                                                                                                                            | 9  |

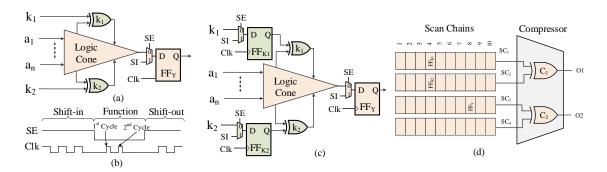

| 3.1 | Prior obfuscation approaches and their vulnerabilities. (a) Techniques proposed in [1], [5]. (b) Timing diagram for manufacturing tests. (c) Technique proposed in [6]. (d) Attacks in [6]                                                                                                                                                                   | 13 |

| 3.2 | An example of a scan inserted sequential circuit                                                                                                                                                                                                                                                                                                             | 16 |

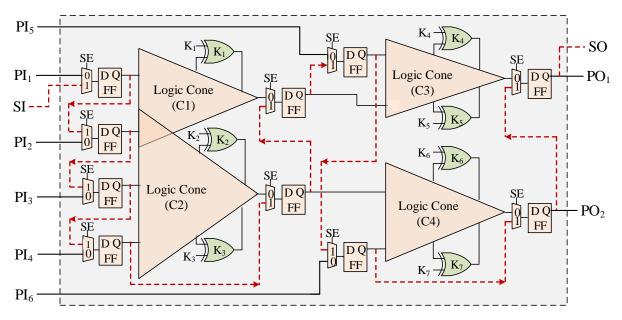

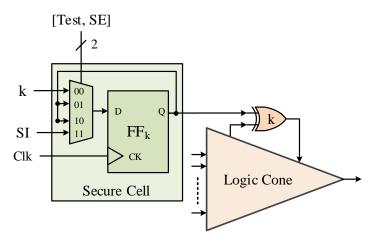

| 3.3 | Proposed secure cell architecture                                                                                                                                                                                                                                                                                                                            | 22 |

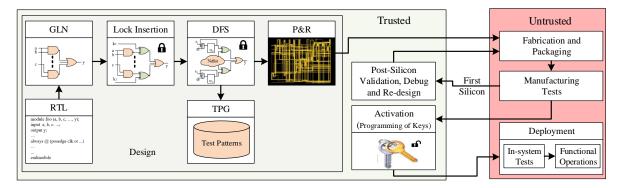

| 3.4 | Proposed flow for enabling trust in IC manufacturing and test                                                                                                                                                                                                                                                                                                | 23 |

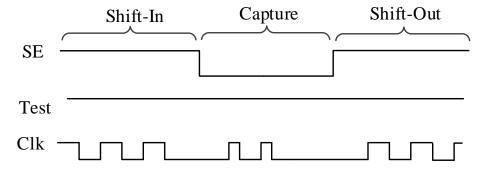

| 3.5 | Timing diagram for manufacturing tests (delay tests)                                                                                                                                                                                                                                                                                                         | 23 |

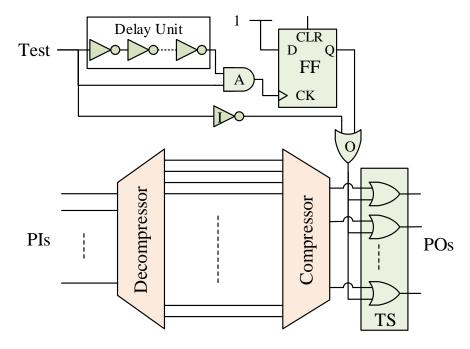

| 3.6 | Proposed architecture to restrict scan data access                                                                                                                                                                                                                                                                                                           | 25 |

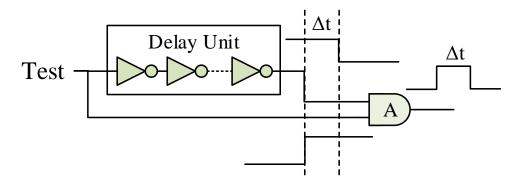

| 3.7 | Pulse generator module for detecting a positive transition at $Test$ pin                                                                                                                                                                                                                                                                                     | 25 |

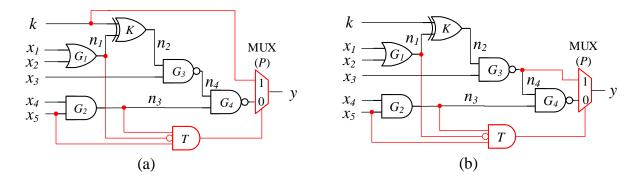

| 4.1 | (a) <i>T1 type TAAL attack</i> , where a <i>Type-3</i> combinational Trojan is inserted for key extraction directly from the connection between key gate and tamper-proof memory, (b) <i>T2 type TAAL attack</i> , where a <i>Type-3</i> combinational Trojan is inserted for the secret key extraction                                                      | 38 |

| 4.2 | T3 Type TAAL attacks. (a) Original netlist with $k_2$ inserted to prevent the propagation of $k_1$ , (b) T3 type TAAL attack with a Type-3 combinational Trojan with payload as multiplexer (MUX) and (c) T3 type TAAL attack with a Type-3 combinational Trojan with payload as OR gate                                                                     | 40 |

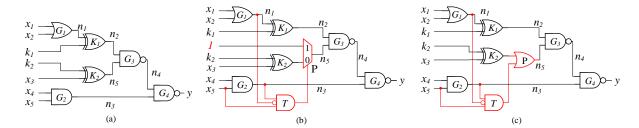

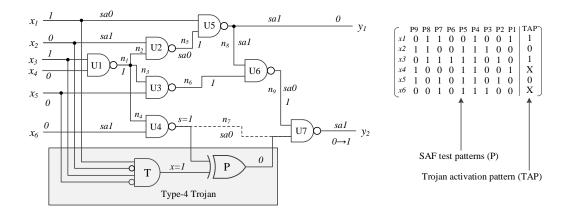

| 4.3 | Design for a combinational hardware Trojan that evades manufacturing tests. (a) A combinational circuit with a <i>Type-4</i> Trojan. (b) Stuck-at fault (SAF) test patterns for manufacturing tests. The hardware Trojan activation pattern ( <i>HTAP</i> ) is $[x_1 \ x_2 \ x_3 \ x_4 \ x_5] = [0\ 0\ 1\ 1\ 0]$ while treating the key input as unknown (X) | 43 |

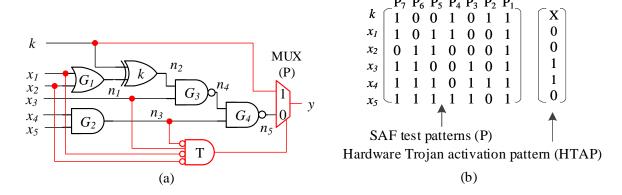

| 4.4 | (a) The netlist of a sequential Trojan with a <i>R-bit</i> counter, (b) The finite state machine (FSM) of the counter used in a sequential Trojan                                                                                                                                                                                                            | 46 |

| 5.1 | A model for a combinational hardware Trojan                                                                                                                                                                                                                                                                                                                  | 59 |

| 5.2 | An 18-line $(K=18)$ combinational circuit with Type-4 Trojan $(n_7 x_1, \overline{x_2}, x_3, \overline{x_5})$ . For Trojan activation pattern (TAP) 101000, logic states of lines and detectable SAFs are marked on the circuit        | 61 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1 | Nanotrack structure for skyrmion movement.                                                                                                                                                                                             | 72 |

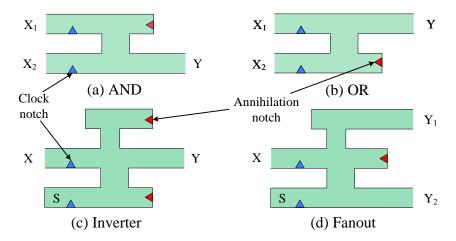

| 6.2 | Structure of skyrmion gates. (a) AND gate (b) OR gate (c) Inverter, and (d) Fanout.                                                                                                                                                    | 74 |

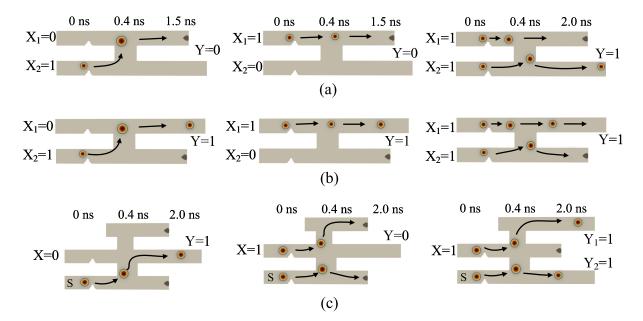

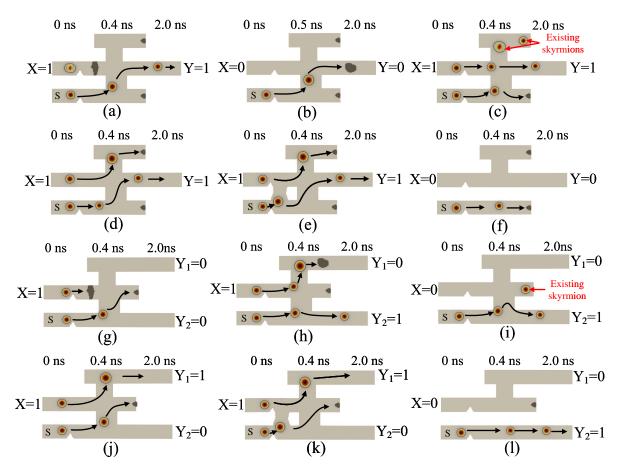

| 6.3 | Simulation of skyrmion gates: (a) AND, (b) OR, and (c) Inverter and fanout                                                                                                                                                             | 75 |

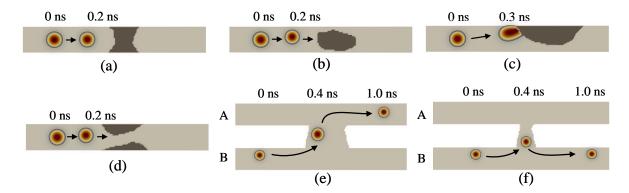

| 6.4 | Simulation of interconnect defects: (a) break, (b) void, (c) and (d) etching blemishes, (e) wide bridge, and (f) narrow bridge. Defects (a) through (d) map onto stuck-at faults, (e) causes a bridging fault, and (f) causes no fault | 76 |

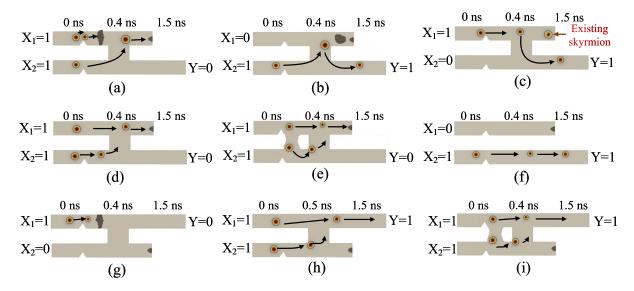

| 6.5 | Some technology-specific defects in skyrmion gates. AND gate - (a) through (f), OR gate - (g), (h) and (i)                                                                                                                             | 78 |

| 6.6 | Technology-specific defects in skyrmion inverter and fanout gates                                                                                                                                                                      | 79 |

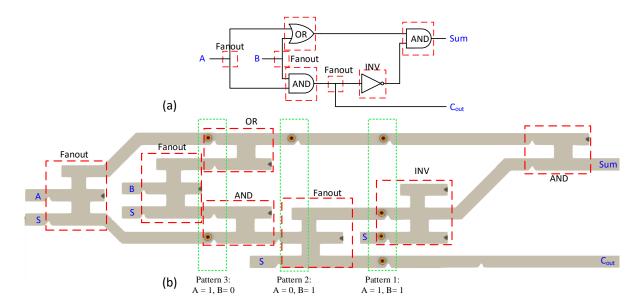

| 6.7 | Skyrmion circuit design for a half adder                                                                                                                                                                                               | 85 |

# List of Tables

| 3.1 | Percentage of cones (PC) in IWLS benchmarks                                                                             | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Greedy attacks on small cones                                                                                           | 19 |

| 3.3 | Greedy attacks on large cones                                                                                           | 19 |

| 3.4 | Modes of operation                                                                                                      | 22 |

| 3.5 | Test Metrics Comparison - Test Coverage                                                                                 | 31 |

| 3.6 | Test Metrics Comparison - Pattern Count                                                                                 | 32 |

| 4.1 | Circuit parameters                                                                                                      | 48 |

| 4.2 | Number of hardware Trojans for launching TAAL attacks                                                                   | 49 |

| 4.3 | Area overhead for ITC'99 benchmark circuits                                                                             | 52 |

| 4.4 | Power overhead for benchmark circuits                                                                                   | 53 |

| 5.1 | Modeled Hardware Trojans in Circuit of Figure 5.2                                                                       | 63 |

| 5.2 | HT Test Coverage (%) of Valid Trojans $(V_n)$                                                                           | 68 |

| 6.1 | Wide interconnect bridge of Figure 6.4(e)                                                                               | 77 |

| 6.2 | Exhaustive simulation of skyrmion-based gates with defects                                                              | 81 |

| 6.3 | Skyrmion gate defect mapping onto single stuck-at faults in AND $(Y = X_1 X_2)$ and OR $(Y = X_1 + X_2)$ logic gates    | 82 |

| 6.4 | Skyrmion gate defect mapping onto single stuck-at faults in inverter $(Y = \overline{X})$ and fanout $((Y_1, Y_2) = X)$ | 83 |

| 6.5 | Testing stuck-at faults in CMOS and Skyrmion circuits                                                                   | 84 |

### List of Abbreviations

3PIP Third-Party Intellectual Property

AE Attacker's Effort

ATPG Automatic Test Pattern Generation

BEOL Back End of Line

CSP Conditional SAF Pattern

CSP Conditional Stuck-at Fault Pattern

DFS Design-for-Security

DIP Distinguishing Input Pattern

DMI Dzyaloshinskii-Moriya Interaction

EDA Electronic Design Automation

FEOL Front End of Line

FF Flip-Flop

FIB Focused Ion Beam

FM Ferromagnetic

GDSII Graphic Database System II

GLN Gate Level Netlist

HM Heavy Metal

HT Hardware Trojan

HTAP Hardware Trojan Activation Pattern

IC Integrated Circuit

IP Intellectual Property

LUT Lookup Table

MTJ Magnetic Tunnel Junction

MUX Multiplexer

NVM Non-volatile Memory

OASIS Open Artwork System Interchange Standard

P&R Place and Route

PC Percentage of Cones

PI Primary Input

PO Primary Output

PUF Physically Unclonable Function

RE Reverse Engineering

RTL Register-Transfer Level

SAF Stuck-at Fault

SAT Boolean Satisfiability

SC Secure Cell

SE Scan Enable

SEM Scanning Electron Microscope

SI Scan In

SoC System on-chip

SOT Spin Orbit Torque

SSA Single Stuck-at

STT Spin Transfer Torque

TAP Trojan Activation Pattern

TM Tamper-proof Memory

TS Test Suppressor

VCMA Voltage Controlled Magnetic Anisotropy

### Chapter 1

#### Introduction

Due to the continuing trend of device scaling and the resulting increase in the complexity of the fabrication process, most (SoCs) design companies no longer maintain their own manufacturing units, commonly known as foundries or fabs. The cost of building and maintaining such foundries is reported to be more than several billion dollars [7]. This high cost has forced many design companies to become fabless and adopt a horizontal semiconductor integration model, where the SoC designers contract foundries and assemblies for production. In parallel, the continuous trend of device scaling has enabled designers to compact the design of SoCs and reduce the overall area and cost. As the complexity of modern SoCs is growing exponentially, design of a complete system by a single SoC designer becomes impossible. Instead of designing the whole SoC from scratch, reuse of pre-designed blocks has become a popular solution adopted by the semiconductor industry. SoC designers generally use various third-party intellectual properties (3PIPs) to limit the research and development (R&D) expenses, which may also cause a trust issue from the 3PIPs. The globalization of the semiconductor industry and outsourcing of the design and manufacturing of integrated circuits (ICs) cause IP piracy and IC overproduction to become major threats because of the untrusted entities [8–16].

To prevent IP piracy and IC overproduction, different solutions have been proposed over the years and obfuscation or locking of a circuit netlist was introduced as a viable solution [1,6,17–19]. Logic locking aims to hide the functionality of an IP by inserting additional logic elements into the original design. The intentionally added additional lock elements usually include XOR gates, MUXes, or lookup tables (LUT). No matter what method a designer uses to lock the circuit, without applying the correct secret key, the actual function of the original circuit will be hidden. Attackers cannot analyze the structure of the circuit through the locked netlist and thus cannot

copy or modify the circuit design. Once the correct key value is programmed into the chip in a secure environment, the correct output of the locked chip will be generated. The confidentiality of the secret key is indispensable for the security of the lock design, as it is the only barrier to prevent the piracy of the IP. The secret key is stored in tamper-proof non-volatile memory (NVM) to prevent an adversary from accessing it using physical means.

#### 1.1 Motivation

Logic locking has become a prominent method to address the threats incurred from untrusted manufacturing. However, recently a Boolean Satisfiability (SAT)-based attack [20] has demonstrated an effective way of extracting the secret key through iteration of distinguishing input patterns (DIPs). Due to the robustness and efficiency of SAT-based attacks, the latest logic locking research work mainly focused on defending against SAT-based attacks. At the same time, different physical attacks [21–24] have also shown effectiveness in breaking a secure locking technique. These attacks become feasible as an untrusted foundry has the ability to obtain all the layout information since it has access to the GDSII or OASIS file [25]. An untrusted foundry can also initiate a tampering attack through malicious modification by inserting a hardware Trojan without the designers' knowledge. Because the secret key is stored in non-volatile memory (NVM), and connections are made from the NVM to the key gates, the secret key will directly leak the to adversary once the hardware Trojan is activated. Following this motivation, we have proposed a series of methods to prevent IP piracy and IC overproduction.

#### 1.2 Contributions

• A novel design-for-security (DFS) architecture to prevent IP piracy and IC overproduction is proposed. This DFS architecture can achieve complete protection against the state-of-art attacks without modifying the existing IC manufacturing and test flow, only with the cost of a small area overhead. The proposed DFS architecture allows full scan-based structural manufacturing tests for the unlocked design. The unlocked design can be tested with complete functional and structural tests in a secure environment with the secret key.

- A novel tampering attack based on malicious modification of any key-based locked circuit is proposed. The proposed attack is based on implanting a hardware Trojan into the original design to obtain the secret key from any existing logic locking circuit.

- Models for a combinational hardware Trojan and a sequential hardware Trojan have been presented. The model of combinational hardware Trojan is named Type-n Trojan, where n is the number of Trojan's trigger inputs. The model of sequential Trojan is constructed on the basis of combinational hardware Trojan, with an additional state element added in the design as a counter. The Trojan is activated when the activation signal is applied r times.

- A hardware Trojan detection technique based on conditional stuck-at fault patterns (CSP) is proposed. The conditional stuck-at fault test pattern generation starts with Type-1 Trojan. With a reasonable test length, all Type-1 Trojans can be detected. The same test patterns can also be used to detect a large percentage of higher-order hardware Trojans.

- A defect characterization method is proposed for an emerging technology: skyrmion-based logic circuits. The defects are mapped onto an analyzable fault model. Each defect is represented by either a technology-independent single stuck-at fault or a technology-dependent fault. A test pattern generation method is then proposed based on the available EDA tools.

### 1.3 Organization of this Dissertation

The rest of this dissertation is organized as follows:

- Chapter 2 introduces the basic concept of logic locking and summarizes the state-of-art in this field. The related attack methods on logic locking are presented. In addition, the background of the hardware Trojan is introduced in this chapter.

- Chapter 3 introduces our design-for-security (DFS) architecture to prevent the aforementioned attacks by obfuscating a netlist. The proposed design is resistant to various known attacks including the well-known SAT-based attack. Importantly, the proposed design does not limit the testability of the chip during the normal manufacturing flow in any way, including the post-silicon validation and debug.

- Chapter 4 proposes a new hardware Trojan based attack method on the SAT-resilient design.

According to our analysis, even if the locked circuit provides sufficient security protection

- against SAT-based attacks, a malicious foundry can be a feasible attacker who would unlock any number of chips and sell overproduced and defective parts.

- Chapter 5 extends the modeling and test generation for combinational hardware Trojans which appeared in Chapter 4. A Trojan may be added to the verified netlist without the knowledge of the designer or user causing unexpected malfunction or data theft when the device is in use. For this new type of hardware Trojan attack, especially the Trojan mentioned in Chapter 4, a method that can effectively detect this type of Trojan is urgently needed. In this chapter, we introduce a Trojan detection method that would detect a Trojan in a manufactured chip.

- Chapter 6 introduces the defect characterization and testing of skyrmion-based logic circuits based on fault modeling. According to the Trojan detection method proposed in Chapter 5, it appears that fault modeling not only adds efficiency to testing, but also plays a critical role in HT detection. Thus, fault modeling has a wider application. In this chapter, we advance fault modeling beyond the conventional CMOS circuits, to a most recent emerging technology.

- Chapter 7 is the conclusion of this dissertation, which also outlines the possible future work. Hardware security has played an important and significant role in CMOS devices and will continue to do so for emerging technologies, especially when the traditional semiconductor device size is approaching the physical limit. We end this chapter with a list of some future research directions.

#### Chapter 2

### Background and Prior Work

In this chapter, we discuss fundamentals essential for understanding the core concepts in this thesis. We give a background of logic locking and the existing attack methods. Previous research on hardware Trojans is also summarized.

### 2.1 Logic Locking

Logic locking is a widely accepted protection technology against IP Piracy and IC Overproduction. Logic locking modifies the original design by adding additional key gates to the netlist, thereby generating circuits that rely on key functions. The challenges for protecting a circuit against hardware security threats have been the driving force for developing different techniques to limit the amount of circuit information that can be recovered by an adversary. Logic locking has emerged as a field of significant interest from researchers, as it can provide complete protection against IC overproduction and IP piracy [1, 6, 17–19].

The objective of logic locking is to obfuscate the inner details of the circuit and make it infeasible for an adversary to reconstruct the original netlist. Logic Locking hides the circuit's functionality by inserting additional logic gates into the original design, which are termed *key gates*. In addition to the original inputs, the locked circuit needs secret key inputs to key gates from on-chip tamper-proof memory (see Figure 2.1(a) for details). The correct functionality of the design is obtained when the key inputs receive the proper secret key value. Applying an invalid key to the key gates would result in incorrect functionality of the locked design. Note that for a securely locked circuit, the design details cannot be recovered using reverse engineering.

Figure 2.1: Different logic locking techniques. (a) A locked circuit, where the secret key (K) is programmed in a tamper-proof memory (TM). (b) Original circuit. (c) XOR-based locking [1]. (d) MUX-based locking [2,3]. (e) LUT-based locking [4].

Different logic locking methods were devised over the years and can be categorized into three different categories. First, XOR-based logic locking, shown in Figure 2.1(c), has received much attention due to its simplicity. In this technique, a set of XOR or XNOR gates are inserted as key gates [1,5,6,26–30]. The secret key is stored in tamper-proof memory (TM), and connections are made from TM to the key gates. Second, in the MUX-based logic locking technique [2,3], multiplexers (MUX) are inserted so that one of its input is correct, which is the actual net of the circuit. The other input of the MUX is incorrect, which is a dummy net randomly selected from the netlist. This technique is shown in Figure 2.1(d). The select signal of the MUX is associated with the key bit from the tamper-proof memory. The correct signal goes through the MUX upon applying a valid key value; otherwise, the incorrect signal propagates in the netlist. Third, in LUT-based logic locking, [4, 31, 32], shown in Figure 2.1(e), a look-up table with several key inputs is used to lock the netlist. The LUTs replace a combinational logic in the design, making it difficult to predict the output as it depends on several different key values.

The research community has proposed several attacks to exploit the security vulnerability on a logic locked circuit. Subramanyan et al. [20] first showed that a locked circuit could be broken using Boolean Satisfiability (SAT) analysis. The SAT attack algorithm, attributed as an oracle-guided attack, requires a locked netlist, which can be recovered using reverse engineering and a functional chip with a valid key stored/programmed in its tamper-proof memory. In this attack, an adversary can query an activated chip and observe the response. Note that the SAT attack requires access to the internal nodes of the circuit through the scan chains, which is common in today's netlist for implementing Design-for-Testability (DFT) [33]. The SAT attack works iteratively to eliminate incorrect key values from the key space using distinguishing input patterns (DIPs). A DIP is defined as an input pattern for which two sets of hypothesis keys produce complementary results. By comparing these with the output of an unlocked chip, one set of hypothesis keys is discarded. The SAT attack works efficiently as it discards multiple hypothesis keys in one iteration.

Thereafter, researchers have focused on improving and developing locking techniques to be resilient against the SAT attack. Subsequent work in this direction involved Anti-SAT [26], SAR-Lock [27], SFLL [30], design-for-security (DFS) architecture [6, 28, 29]. However, Subramanyan et al. has shown that SFLL can be defeated through FALL attack [34]. The attack is built on three primary steps, namely, structural analysis, functional analysis, and key confirmation. The structural analysis is performed to identify the gates that are the output of the cube stripping function in SFLL. After identification of these candidate gates, the functional analysis targets the property of cube stripping functions, which results in a set of potential key values. Finally, the key confirmation algorithm identifies the correct key from the set of potential key values.

As the SAT-attack is based on the availability of accessing the internal states of a circuit through the scan chains, Guin et al. proposed placing multiple flip-flops capturing signals controlled by different key bits at the same level of the parallel scan chains, which were used in the current test compression methodologies [6]. However, a vulnerability existed in this design, when an adversary performs multi-cycle tests, such as delay tests (transition delay faults and path delay faults) [33]. This leads to the necessity for developing a new design-for-security (DFS) architecture to prevent leaking of the key during any manufacturing tests [28, 29]. This design prevents scanning out the internal states after a chip is being activated, and the keys are programmed/stored in the circuit.

Apart from SAT-based attacks, probing attacks [21,35] have also shown serious threats to the security of logic locking, where an attacker makes contact with the probes at signal wires in order to extract sensitive information, mainly, the secret key. With the help of a focused ion beam (FIB), a powerful circuit editing tool that can mill and deposit material with nanoscale precision, an attacker can circumvent protection mechanisms and reach wires carrying sensitive information. However, the countermeasures reflect the complexity of shield-structure and nanopyramid structures as the defense, making it difficult to perform these attacks [36,37]. Recently, Zhang et al. proposed an oracle-less attack to extract the key from locked circuits [38]. The notion of this attack is to compare the locked and unlocked instances of repeated Boolean functions in the netlist to predict the key. A solution was proposed to countermeasure the attack as well.

#### 2.2 Hardware Trojan

Ensuring the security of integrated circuits becomes a major challenge due to the globalization of the semiconductor industry. Majority of system-on-chip design companies outsource their production across the world to fabrication units (fabs or foundries) due to a massive cost (several billion dollars [7]) for building and maintaining such foundries. This creates the threat of *hardware Trojans* (HT), which is a leading security concern for government and industry [9, 39–45]. A hardware Trojan is a malicious altercation to the original design to modify its functionality such that an adversary can gain control of the system. An adversary may insert a hardware Trojan into a design to interrupt its normal operation in the field. The Trojan would act like a "silicon time bomb" [41]. It can also create a backdoor in a secure system to give access to critical system functionality or leak secret information to an adversary.

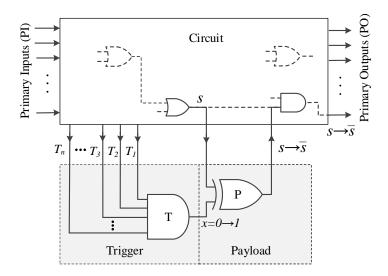

The hardware Trojan generally consists of two parts, the trigger and payload, as shown in Figure 2.2. The trigger can activate hardware Trojan when it meets certain activation conditions. The input of the trigger can come directly from the primary input (PI) or from the internal nodes of the circuit. Although shown here as an AND gate, triggers can be any logical function. When the Trojan is activated, for example, when the input B and C are both 1 AND gate output will also change from 0 to 1, it transfers the payload to the circuit by modifying its function. A two

Figure 2.2: A Hardware Trojan.

input XOR gate with inputs from the trigger and a node in the circuit, can be used for this purpose. The output of the payload is brought back to the circuit.

Researchers have proposed numerous techniques to detect and prevent HTs. These techniques are broadly classified into two groups, namely, solutions targeted for the detection of HTs, and solutions designed for preventing an adversary to insert an HT in a design. The detection methods for HTs can further be classified into logic testing [46–50], and side-channel analysis [51–56]. Prevention methods can be grouped into design-for-trust measures [57–60] and split manufacturing [61,62].

The overall aim is to detect HTs in chips manufactured in an untrusted environment and, thus, prevent Trojan infected devices from getting into the electronics supply chain. Logic testing can be used to detect these Trojans, where we apply stimuli to primary inputs (PIs) and observe responses at primary outputs (POs) [43, 46, 48–50]. Detection of an HT occurs when there is a mismatch between the observed and expected responses. Such detection of an HT through logic testing does not have any impact on the process and environmental variations. On the other hand, the side-channel analysis uses physical characteristics such as power [63], temperature [64], delay [65], and radiation [66] to detect the HT. Side-channel detection methods primarily rely on the availability of Trojan-free golden circuits, which may not be available in reality. Moreover, process and environmental variations may mask the side channel leakage, if the Trojan circuitry is small. Despite significant research performed on HT, we still lack methods for modeling and test generation to detect them.

In this chapter, we provided the background knowledge on logic locking, including the state-ofart techniques and existing attack methods of targeting the mentioned locking techniques. Additionally, the background of hardware Trojans is studied to understand how an adversary can implement malicious altercation to the original circuitry without the knowledge of the designer or user.

#### Chapter 3

#### A Design-for-Security Architecture to Prevent IP Piracy and IC Overproduction

In the last chapter, we observed that the existing logic locking technology cannot ensure complete safety of the circuit, especially when the SAT-based attack is a possibility. In this chapter, we will show how a proposed design-for-security architecture protects the circuit against IP piracy and IC overproduction.

#### 3.1 The Related Work

The continuous trend of device scaling has enabled designers to fit more and more functionality on an SoC to reduce overall area and cost of a system. As the complexity of modern SoCs grows exponentially, it is virtually impossible to design a complete system by a SoC designer alone. Therefore, the semiconductor industry has shifted gears to the concept of design reuse rather than designing the whole SoC from scratch. In parallel, the increased complexity of the fabrication process has resulted in a majority of SoC designers to no longer maintain a fabrication unit (foundry or fab) of their own. Building and maintaining such fabs for modern SoCs are reported to cost more than several billions of dollars and increasing as technology further scales [7]. Given the increasing cost, the semiconductor business has largely shifted to a contract foundry business model (horizontal business model) over the past two decades. However, the lack of transparency and the resulting lack of trust may lead to the following vulnerabilities:

• *IC Overproduction*. An untrusted foundry/assembly can produce more number of unauthorized chips [1,4,6,18,19,67–70], and can make illegitimately larger profits by selling them in the market as no R&D cost is incurred during production. Moreover, they can also practically overbuild chips at zero cost by manipulating the yield information [6,71–73].

- Out-of-Specification/Defective ICs from Manufacturing. Due to the imperfect manufacturing and assembly processes, foundry/assembly discards defective chips and sends defect free chips to the market. In a trusted environment, these defective chips are always scrapped. However, an untrusted entity in the production process (a rogue employee) can source these rejected defective chips to the grey market [6]. The application of these chips in a critical infrastructure can cause significant damage.

- *IP Piracy and Reverse Engineering*. An untrusted foundry or its rogue employee can pirate the details of an SoC (e.g., test patterns, mask information, etc.) to a competitor company or make one or more illegitimate copies of the original IPs [70,74–76]. The design details of an SoC can be reconstructed from the musk information by reverse engineering, which ultimately help to make cloned ICs [77,78]. An untrusted foundry can also add some extra features to the SoC to introduce a backdoor or a hardware Trojan into these clone chips.

IC metering aims to prevent all the aforementioned attacks by attempting to give the control over the IC manufacturing to the SoC designer [1,4,6,18,19,67–69,79]. These approaches can be either passive or active. Passive approaches register all new authorized ICs by incorporating physically unclonable functions (PUFs) [80–84] in each copy and then storing their challenge-response pairs in a secure database. Later, any suspect ICs taken from the market can be checked for proper registration. Active metering approaches are designed to automatically lock each new IC that is manufactured by a foundry until it is unlocked (activated) by the authorized SoC designers. Active metering can be efficiently implemented through logic obfuscation. This is a technique where a design is transformed to a different one to obfuscate the inner details of the original design [1, 2, 4, 5, 76, 85]. Only on the application of a programmed secret key can make the transformation reversed, thus preserving the original functionality. Roy et al. first proposed to obfuscate a netlist by using a set of XOR/XNOR gates which can only be unlocked by using a key [1]. Unfortunately, this design is not resistant to reverse engineering (RE) as the key controlled gates are directly related to their key bits (XOR and XNOR gates indicate 0 and 1 at the key location, respectively) and vulnerable to key sensitization attacks [5].

The solutions to prevent key discovery proposed by Rajendran et al. [5] appear to adequately address the above issues. However, Subramanyan et al. have shown that the key in an activated

Figure 3.1: Prior obfuscation approaches and their vulnerabilities. (a) Techniques proposed in [1], [5]. (b) Timing diagram for manufacturing tests. (c) Technique proposed in [6]. (d) Attacks in [6].

circuit can always be exposed using scan based manufacturing tests through SAT-based analysis [20]. The SAT-based analysis algorithm [20] finds the correct key by ruling out incorrect ones iteratively, by using distinguishing input scan test patterns (DIP). For simplicity, the logic cone schematic is shown in Figure 3.1(a) is obfuscated by two key bits,  $k_1$  and  $k_2$ . Here, a logic cone is a combinational logic unit that represents a Boolean function, and generally bordered by flip-flops and input/output ports. Assume that this cone produces different outputs for  $k_1 = 0$  and  $k_1 = 1$  for some input pattern  $[a_1a_2 \dots a_n]$ . Then by observing the correct response from an activated working chip, the correct key  $(k_1 = 0 \text{ or } 1)$  can be determined. Guin et al. [6,73] proposed placing multiple flip-flops capturing signals controlled by different key bits (shown in Figure 3.1(d)) at the same level of the parallel scan chains used in current test compression methodologies [86,87], thereby exploiting the output compression architecture to address SAT-based attacks. Figure 3.1(d) shows the architecture, where the keys  $(k_1 \text{ and } k_2)$  are placed at the same level (location 4) in scan-chain 1 and 2  $(SC_1 \text{ and } SC_2)$ . It appears impossible to perform SAT-based attacks that discover both  $k_1$  and  $k_2$ , as an adversary cannot access individual scan cells from the compressed output  $O_1$ . One cannot determine the key bits  $k_1$  and  $k_2$ , as they are equally likely in the key.

A vulnerability still remains with this design in view of advances in SAT-based formal tools that can support analysis over multiple sequential clock cycles. The key may be exposed to the adversary through multi-cycle tests, such as delay tests to detect transition delay faults and path delay faults [33]. During these tests, the circuit response is captured multiple times (typically 2 for timing tests), which is shown in Figure 3.1(b). In the first clock cycle, the key bits  $k_1$  and  $k_2$  are captured at  $FF_{k1}$  and  $FF_{k2}$ . Now, this key information is captured in the second clock cycle at

$FF_Y$  (see Figure 3.1(c)) which can be located in a different scan chain (location 8 in  $SC_3$ ). Thus, an adversary can perform a multi-cycle attack using a SAT-based approach. So even if the designer attempts to obscure the capture of key  $FF_{k1}$  and  $FF_{k2}$  at the end of the first cycle, an attacker can capture two or more clock cycles  $(FF_Y)$  to perform a SAT-based analysis.

A greater challenge occurs when the designer places the key gates uniformly in an SoC. This is often necessary to obfuscate the netlist to hide most of its functionality. An attacker does not necessarily perform the SAT-based attacks to extract the key when they are distributed throughout the netlist. An adversary can simply search the entire key space (brute-force) to find out the key. In Section 3.2.1, a brute-force attack will be demonstrated to find the key. However, brute-force attacks can be unfeasible when the keys are placed in larger cones (e.g., 128 inputs). An improved version of brute-force attack (greedy attack) can help an adversary to find the key by using a small number of random patterns (see Section 3.2.2 for details). Towards addressing these vulnerabilities, this project focuses on designing an obfuscated circuit such that it can withstand SAT-based, brute-force, and greedy attacks.

#### 3.2 Attacks on Existing Logic Obfuscation Techniques

Modern electronic designs are sequential in nature and consist of combinational logic and memory elements. The outputs of a sequential circuit depend both on the inputs and its internal state. Generating test vectors to test a sequential circuit is extremely challenging as it is required to initialize the internal state before applying a pattern and then carry the response to the primary output [33]. This leads to adopt scan design, where controllability and observability are provided for the memory elements (flip-flops). The basic idea of scan is to convert the sequential circuit to its combinational equivalent. Each combinational block can be tested simultaneously through the scan chains. It is now very relevant to analyze the security of the obfuscated sequential circuits. In this section, two different attacks that can partially (fully) recover the obfuscation key for sequential circuits have been presented.

#### 3.2.1 Brute-Force Attack Based on Logic Cones

For the uniform obfuscation of a netlist, it is required to distribute the key throughout the netlist such that the circuit produces incorrect result most of the time. This can create a new vulnerability that an adversary can estimate the key by using exhaustive search when a key gate is placed in a smaller cone. This kind of attack based on logic cones is named as a brute-force attack, which was first introduced by Lee et al. [3]. Brute-force attack is useful for evaluating the security strength of an obfuscated design.

Brute-force attacks can be performed through the scan chains, which are inserted in a design to provide manufacturing test support [33]. This converts a sequential design to its combinational equivalent and contains hundreds/thousands of cones with varying input sizes. If a key gate is placed in a cone with smaller number of inputs, an adversary can perform an exhaustive search to estimate the key value. In order to get a better understanding of brute-force attack, it is necessary to analyze attacker's effort (AE), which can be defined as the total number of trials to estimate the key. In this attack scenario, an adversary tries all possible combinations of key and input values of a cone, and observes the output of the locked circuit. For a correct key, the output must be equal to the output of that cone of an unlocked functional IC (oracle).

Let us assume a cone with n logic inputs, and m key inputs. Here,  $X = \{x_1, x_2, \dots, x_{2^n}\} \in \{\{0, 1\}^n\}$  represents all inputs patterns,  $K = \{k_1, k_2, \dots, k_{2^m}\} \in \{\{0, 1\}^m\}$  denotes all possible keys. Now, the input/output relations of the cone is represented by a function F, such that Y = F(X). Similarly, for an obfuscated cone, it becomes Y = F(X, K). For an unlocked circuit  $F(x) = F(x, k_O) \ \forall x \in X$ , where  $k_O$  is the obfuscation key. A brute-force attack verifies for every  $k_j \in K$  if

$$F(x, k_O) \stackrel{?}{=} F(x, k_i) \,\forall x \in X \tag{3.1}$$

The hypothesis key,  $k_j$  becomes the obfuscation key,  $k_O$  if Equation 3.1 holds. Here, the attacker's effort (AE) becomes  $O(2^{n+m})$  for a logic cone. Let us now study the case, where the keys are uniformly distributed across the design. The m-bit obfuscation key is distributed into r cones, where  $i^{th}$  cone receives  $m_i$ -bit key, and  $\sum_{i=1}^r (m_i) = m$ . The attacker's effort  $(AE_i)$  for cone i becomes  $O(2^{n_i+m_i})$ . The overall attacker's effort will be  $AE = max(AE_i)$  as all the cones

Figure 3.2: An example of a scan inserted sequential circuit.

can be tested simultaneously through the scan chains (see details in McCluskey's verification test paper [88]).

A short example will be presented to illustrate the complexity of this attack. Figure 3.2 shows a sequential circuit, where 7 key gates are placed. It is assumed that the circuit contains four logic cones, namely, C1, C2, C3, and C4, where C1 and C2 have one overlapping input. The circuit has 6 inputs and 2 outputs. For simplicity, assume that it contains one scan chain (highlighted with red broken line). To find the correct key, an adversary will try all possible combinations. Thus, the attacker's effort for C1  $(AE_1)$  will be  $2^3$ . Similarly, AE for cones C2, C3, and C4 will be  $AE_2 = 2^5$ ,  $AE_3 = 2^4$ , and  $AE_4 = 2^4$ , respectively. It is interesting to note that an adversary can apply brute-force to all the cones simultaneously by shifting the appropriate patterns through the scan chain. The number of such scan shift operations (the overall attacker's effort) is the  $max(A_i) = 2^5$ , which is much smaller than the exhaustive key search  $(2^{6+7})$  to find 7-bit obfuscation key. However, an adversary can find some key bits much quickly if they are placed in a smaller cone (e.g., C1).

In summary, an adversary can perform brute-force attacks on all cones simultaneously through scan chains to estimate the complete m-bit key. However, he/she can find a part of key if those keys are placed in a small cone. The strength of the obfuscation depends only on the cone size, rather than the total number of bits in the obfuscation key and the primary inputs of a complete

Table 3.1: Percentage of cones (PC) in IWLS benchmarks.

| Bench-<br>mark | #<br>Gates | PC ≤ 16 | 16 <pc<br>≤ 32</pc<br> | 32 <pc<br>≤ 64</pc<br> | 64 <pc<br>≤ 128</pc<br> | PC<br>>128 |

|----------------|------------|---------|------------------------|------------------------|-------------------------|------------|

| S35932         | 16,065     | 100.00% | 0.00%                  | 0.00%                  | 0.00%                   | 0.00%      |

| S38584         | 19,253     | 78.49%  | 19.88%                 | 1.64%                  | 0.00%                   | 0.00%      |

| S38417         | 22.179     | 58.33%  | 16.25%                 | 9.42%                  | 16.00%                  | 0.00%      |

| b17            | 37,117     | 11.06%  | 4.36%                  | 11.76%                 | 22.43%                  | 50.39%     |

| b18            | 92,048     | 6.97%   | 5.04%                  | 12.91%                 | 14.60%                  | 60.47%     |

| b19            | 174,157    | 6.80%   | 5.14%                  | 12.59%                 | 14.55%                  | 60.92%     |

*netlist*. It is thus necessary for a system designer to place all the keys in cones with sufficiently large number of inputs, such that a brute-force attack is infeasible.

The simulations were performed against IWLS benchmarks [89] to analyze the number of cones that can be targeted for brute-force attacks. Table 3.1 shows the cone analysis for six different benchmarks. Based on this table, it can be found that the cone size in the netlist varies from a few inputs up to hundreds of inputs. For a small benchmark (e.g., S35932) all cones have less than 16 inputs. For benchmark S38584, percentage of cones (PC) with less than 16 inputs is 78.49% and PC with less than 64 is 100%. For these smaller benchmarks, an adversary can simulate all input and key combinations to find out the obfuscation key. As mentioned before the objective of an SoC designer is to place the key gates uniformly to have a higher obfuscation impact. Each cone may have very few key gates. For larger benchmarks (e.g., b19), PC with less that 16 inputs is 6.8%, whereas PC with less than 32 inputs, and greater than 16 inputs is 5.14%. Thus, an adversary can find few key bits if the keys are uniformly distributed across the circuit. However, an SoC designer can place the keys in larger cones to prevent the attack.

#### 3.2.2 Greedy Attacks on Logic Cones

Brute-force is an efficient approach to obtain the key value especially when the cone size is small. However, when the size of the cone becomes larger, the brute-force attack may not be feasible as the attacker's effort remains exponential complexity with the number of inputs. In this

section, a new attack is proposed that can greatly reduces AE for a circuit. This method of attack is referred as greedy attack.

Instead of applying every input combinations, an adversary greedily selects a few patterns to recover the secret key.

In greedy attack, an adversary simulates a cone with few random patterns. Then the same patterns are applied to the same cone of an unlocked chip (oracle) to receive the correct response. If the comparison fails, it is guaranteed that the hypothesis key used during simulation is not the obfuscation key. The greedy attacks iterates all possible key combinations to rule out all hypothesis keys. Note that number of key bits are very small for uniform obfuscation. This is a probabilistic attack and it cannot guarantee to find the obfuscation key. However, the experimental results show that a hypothesis key with few random patterns can be ruled out in most cases.

**Greedy attack:** The hypothesis key,  $k_j$  is not the obfuscation key if:

$$\exists x \in X^P : F(x, k_i) \neq F(x, k_O)$$

(3.2)

$X^P$  is the set of p randomly selected patterns. The complexity of greedy attack is  $O(p \times 2^{m_i}) \approx O(p)$ , where  $m_i$  (can be very small, e.g., 1) is the key size of the  $i^{th}$  cone. This attack is feasible when a designer uniformly distributes the keys in their design to have a greater impact of obfuscation.

To validate this attack, the experiment is performed by using Synopsys Design Compiler [90], and VCS [91] on few IWLS 2005 [89] benchmarks. A wrong key of different sizes (1-bit, 2-bit, 4-bit, and 8-bit) can be found by using only 10k random input patterns for a small cone size (see Table 3.2) and 200k random patterns for large cones (see Table 3.3). A Perl script extracts few cones from benchmarks b17, b18 and b19, and uses VCS to perform the simulation.

Table 3.2 shows the simulation results for few small cones (less than 128 bits) from the ITC'99 benchmarks. Ten thousand random patterns have been applied to observe the responses. Six different cones (C1-C6) are randomly selected to perform the greedy attack. Column 1 represents

Table 3.2: Greedy attacks on small cones.

| Key      | Cone   | The Number of Get 1 in 10000 Patterns |     |      |      |      |      |  |

|----------|--------|---------------------------------------|-----|------|------|------|------|--|

| Size     | Size   | C1                                    | C2  | C3   | C4   | C5   | C6   |  |

| 1        | 44-56  | 208                                   | 11  | 272  | 2031 | 898  | 87   |  |

| 1        | 94-106 | 101                                   | 57  | 1742 | 3    | 28   | 15   |  |

| 2        | 44-56  | 886                                   | 321 | 461  | 1760 | 329  | 98   |  |

| 2        | 94-106 | 633                                   | 391 | 29   | 65   | 182  | 59   |  |

| 4        | 44-56  | 2715                                  | 327 | 402  | 911  | 946  | 5    |  |

| <b>T</b> | 94-106 | 236                                   | 417 | 62   | 106  | 31   | 169  |  |

| 8        | 44-56  | 1958                                  | 293 | 2162 | 414  | 1391 | 1269 |  |

|          | 94-106 | 520                                   | 377 | 3354 | 378  | 64   | 292  |  |

Table 3.3: Greedy attacks on large cones.

| Key  | Key Cone |           | The Number of Getting 1 in 200000 Patterns |      |       |      |           |  |  |

|------|----------|-----------|--------------------------------------------|------|-------|------|-----------|--|--|

| Size | Size     | <b>C1</b> | C2                                         | С3   | C4    | C5   | <b>C6</b> |  |  |

| 1    | 144-156  | 2         | 3                                          | 412  | 3     | 3    | 6         |  |  |

| 1    | 194-206  | 6         | 14                                         | 19   | 7096  | 7    | 9         |  |  |

| 2    | 144-156  | 5         | 3                                          | 5    | 25    | 1    | 6         |  |  |

| 2    | 194-206  | 2         | 1686                                       | 6    | 131   | 17   | 13        |  |  |

| 4    | 144-156  | 13        | 2                                          | 6    | 12623 | 5    | 3         |  |  |

| 7    | 194-206  | 2         | 4                                          | 11   | 30    | 221  | 906       |  |  |

| 8    | 144-156  | 13        | 4                                          | 1511 | 11    | 3    | 13        |  |  |

| O    | 194-206  | 7         | 632                                        | 12   | 2726  | 1573 | 3408      |  |  |

the number of key gates that are placed in these cones. Column 2 represents cone size. A cone is selected as mentioned in the range. Rest of the columns show the number of times Equation 3.2 are satisfied. Form the table, it is clear that almost all the cones produce incorrect results most of the cases.

Table 3.3 shows the greedy attack on large cones. The larger cones require more random patterns to find a mismatch that satisfies Equation 3.2. When 200k random patterns are applied it generally takes less than a minute to apply all these patterns to perform the attack, assuming the simulation is performed in HP Z840 Workstation with Intel<sup>®</sup> Xeon<sup>®</sup> E5-2620 v3 (2.4 GHz/6 cores) processor

and 64 GB of RAM. In majority of the cases, the adversary finds an incorrect key effectively in few minutes.

In summary, existing logic obfuscation techniques suffer from three different - brute-force, greedy and SAT-based - attacks. Our objective is to design an obfuscation technique that can effectively circumvent all these attacks. Alternatively, one can state that they require a design solution that prevents access to the response of a logic cone through scan chains. Without an oracle, an adversary cannot compare the simulation results with the oracle and perform such attacks.

## 3.3 Description of the Proposed Design-for-Security (DFS) Implementation

#### 3.3.1 Requirements of DFS Implementation

This section provides an in-depth analysis for all the requirements for successfully preventing IC overproduction, manufacturing rejection, and IP piracy.

Attack resistance. The netlist must be designed in such a way that the chip never leaks the key (either during tests or normal functions), which makes the design resistant to various known attacks [5, 20, 28, 92, 93]. Finding of a key must satisfy NP completeness, and the key must be kept long enough such that brute-force attacks become impractical. In addition, the key must be resistant to reverse engineering (RE) attack, where an attacker must not find the key by looking at the circuit netlist. Direct mapping of the key bits to XOR or XNOR gates are prohibited.

**Uniform distribution of the key.** The key gates need to be placed uniformly to a design to obfuscate its significant part. As the modern designs are sequential in nature, care needs to be taken to place a key gate. It can be subjected to brute-force attacks (see Section 3.2.1). It can also be vulnerable to greedy attacks (see Section 3.2.2) irrespective of the size of the cone. In addition, any cones are subjected to SAT-based attacks. The obfuscation scheme must address all these attacks.

**Structural test capability without the key.** Allowing structural tests before the activation is one of the key requirements for preventing the overproduction of chips. It is necessary to add capability which permit a foundry or assembly to perform structural tests right after manufacturing

and discard the defective chips. One can argue that tests can be performed at the SoC designer's site. However, it requires additional test setup for the SoC designers, which they may not have. In addition, it is not wise to send chips to the SoC designers without tests which requires addition transportation. However, the greater challenge is that the foundry cannot stabilize the process unless they monitor the outcome. Thus, it is absolutely required that the tests have to be performed at the manufacturing site.

**Post-silicon validation and debug capability.** The circuits must be modified in such a way that it does not impact the post-silicon validation and debug, where the chips generally run at-speed and scan-dumps may be required to obtain high observability of internal nodes.

Full in-system test capability. The obfuscated circuit must support in-system test capability. It is absolutely necessary that a chip does not leak key information to its primary outputs (POs) while it is in functional mode. In this mode, a set of functional test vectors is required to test a design. While testing it is required that each module (IPs) to be initialized to the desired state. Setting that state of a complex industrial circuit through primary inputs becomes a major challenge and could potentially take millions of clock cycles [94]. Thus, test engineers often shift the state through existing design-for-test (DFT) structure [95]. It is thus required that keys do not impose any limitation to this hybrid testing.

#### 3.3.2 Proposed Design-for-Security (DFS) Architecture

The objective in designing the new DFS architecture is to prevent the key getting exposed during manufacturing tests. As mentioned in Section 3.3.1 that if the key information is captured during a test, it will eventually be exposed to the primary outputs of a working (unlocked) chip and an adversary can effectively retrieve the key.

Figure 3.3 shows the proposed secure cell (SC) architecture used for design-for-security. The scan cell is modified in such a way that it can hold its previous state. The output of  $FF_k$  is fed back to the its input through a multiplexer (MUX). As the MUX has four inputs, One additional *Test* pin is needed for the MUX control. Depending on the value of Test and SE pins, a particular

Figure 3.3: Proposed secure cell architecture.

Table 3.4: Modes of operation.

| Test | SE | Mode  | Description                                                               |

|------|----|-------|---------------------------------------------------------------------------|

| 0    | 0  | M0    | The chip is in functional mode. The secure cell applies key to the logic. |

| 0    | 1  | M1    | The secure cell holds its previous value.                                 |

| 1    | 0  | 1V1 1 | The rest of the circuit is in functional/shift mode depending on the SE.  |

| 1    | 1  | M2    | The SC becomes scan cell and it becomes a part of the scan chain.         |

input is selected. The key bit (k), and scan in (SI) are connected to the first and the fourth inputs of the MUX, respectively. The output of  $FF_k$  is connected to the second and third inputs, which provides the capability to hold its previous state.

The SC operates in three different modes based on Test and SE, which is shown in Table 3.4. In mode M0,  $FF_k$  captures the key k, which represents the normal functionality of the unlocked chip. The chip will be operated in this mode while it is in the field. In mode M1, the secure cell continues to hold its previous state. This mode provides test and debug capability without letting the key to be exposed as  $FF_k$  continues to hold its previous state. Thus, no key information is captured in M1. Note that the rest of the circuit becomes functional mode when SE=0 and scan mode (shift-in or shift-out) when SE=1. Finally, SC becomes the scan cell at mode M2 and  $FF_k$  becomes a part of a scan chain.

**Manufacturing test.** The implementation of manufacturing tests using our proposed secure cell does not require any additional modifications in the existing test infrastructure. Note that the key is

Figure 3.4: Proposed flow for enabling trust in IC manufacturing and test.

Figure 3.5: Timing diagram for manufacturing tests (delay tests).

not programmed at this stage (see Figure 3.4). It is required to keep Test pin active high (logic 1) during the test. During the scan shift-in phase, the secure cells (SCs) become a part of a scan chain  $(\{Test, SE\} = \{1, 1\} = M2)$  and receive values generated by the ATPG tool. As the key gate (k) (see Figure 3.3) is directly reachable from the SI.

As shown in the timing diagram of Figure 3.5, during the test response capture, the rest of the circuit becomes functional while the SCs hold their current state (( $\{Test, SE\} = \{1, 0\} = M1$ ). No key bits are captured in the SCs as they continue to hold the states received during scan shift-in phase. This helps us to eliminate all the attacks completely. Finally, the captured functional responses are shifted out through the scan chain ( $\{Test, SE\} = \{1, 1\} = M2$ ).

**Post-silicon debug and validation.** Complex modern designs can suffer from subtle logic and electrical design bugs that escape design verification and are only discovered in first silicon. This necessitates support for post silicon validation, and if a bug is discovered, its diagnosis followed by design changes to correct the problem. Post silicon debug is extremely challenging, and at a minimum requires both a fully functional test (on the activated design) as well as extensive scan

test support. This extent of intrusive testing of the fully functional circuit can make it vulnerable to key discovery through SAT-based attacks or other formal tools. Therefore such full testing is only allowed in a secure design environment, with the key again applied through the scan chain, even if it is already programmed.

Full scan tests on the fully functional circuit are performed in mode M1 (Table 3.4). Recall that in this mode, with the scan enable low (functional mode), the programmed key bits are not captured in the secure cells from where they are presented to the logic; instead, the SCs are designed to hold and retain their current value. Thus, if the key bits are shifted into the SCs during the scan shift in M2, and the scan enable (SE) is then lowered to the functional mode (M1), the scanned in key bits will be retained in the SCs ensuring unlocked functional operation as long as the scan enable stays low. Single or multi-cycle tests can be performed and the results shifted out (M2).

Functional Tests. The functional test can only be performed after the activation of the chips. Mode M0 supports functional tests. Functional patterns are applied to the primary inputs (PIs) of a chip and the responses are collected at the primary outputs (POs). It is required to initialize the finite state machine of a design before actual tests are performed, and sometimes could lead to millions of clock cycles [94]. Test engineers often shift this initialization state through existing scan architecture. Mode M2 can be used to shift this state to the design and then it is switched to mode M0.